# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

# Investigation into Low Power and Reliable System-on-Chip Design

by Rishad Ahmed Shafik

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the

Faculty of Engineering, Science and Medicine School of Electronics and Computer Science

June 2010

#### UNIVERSITY OF SOUTHAMPTON

#### SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

# Investigation into Low Power and Reliable System-on-Chip Design ${\it ABSTRACT}$

#### Rishad Ahmed Shafik

It is likely that the demand for multiprocessor system-on-chip (MPSoC) with low power consumption and high reliability in the presence of soft errors will continue to increase. However, low power and reliable MPSoC design is challenging due to conflicting trade-off between power minimisation and reliability objectives. This thesis is concerned with the development and validation of techniques to facilitate effective design of low power and reliable MPSoCs. Special emphasis is placed upon system-level design techniques for MPSoCs with voltage scaling enabled processors highlighting the trade-offs between performance, power consumption and reliability.

An important aspect in the system-level design is to validate reliability in the presence of soft errors through simulation technique. The first part of the thesis addresses the development of a SystemC fault injection simulator based on a novel fault injection technique. Using MPEG-2 decoder and other examples, it is shown that the simulator benefits from minimum design intrusion and high fault representation. The simulator is used throughout the thesis to facilitate the study of reliability of MPSoC.

On-chip communication architecture plays a vital role in determining the performance and reliability of MPSoCs. The second part of the thesis focuses on comparative study between two types of on-chip communication architectures: network-on-chip (NoC) and advanced microprocessor bus architecture (AMBA). The comparisons are carried out using real application traffic based on MPEG-2 video decoder demonstrating the trade-off between performance and reliability.

The third part of the thesis concentrates on low power and reliable system-level design techniques. Two new techniques are presented, which are capable of generating optimised designs in terms of low power consumption and reliability. The first technique demonstrates a power minimisation technique through appropriate voltage scaling of the MPSoC cores, such that real-time constraints are met and reliability is maintained at acceptable-level. The second technique deals with joint optimisation of power minimisation and reliability improvement for time-constrained MPSoCs. Extensive experiments are conducted for these two new techniques using different applications, including MPEG-2 video decoder. It is shown that the proposed techniques give significant power reduction and reliability improvement compared to existing techniques.

# Contents

| Li | st of | Acronyms                                                    | ζi |

|----|-------|-------------------------------------------------------------|----|

| Li | st of | Symbols                                                     | V  |

| A  | ckno  | wledgements xv                                              | ii |

| 1  | Intr  | roduction                                                   | 1  |

|    | 1.1   | Motivations and Scope of the Thesis                         | 1  |

|    | 1.2   | Thesis Overview and Contributions                           | 3  |

| 2  | Bac   | kground and Previous Works                                  | 6  |

|    | 2.1   | Multiprocessor System-on-Chip                               | 6  |

|    |       | 2.1.1 Advanced Microprocessor Bus Architecture              | 7  |

|    |       | 2.1.2 Network-on-Chip                                       | 9  |

|    | 2.2   | Low Power Design                                            | 4  |

|    | 2.3   | Reliability and Fault Injection                             | 5  |

|    | 2.4   | System-Level Modelling and Design                           | 7  |

|    |       | 2.4.1 System-level Modelling and Simulation using SystemC 1 | 7  |

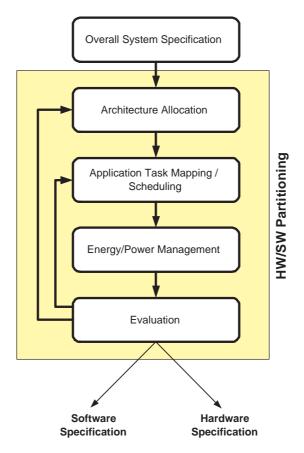

|    |       | 2.4.2 Hardware/Software Co-design                           | 9  |

|    |       | 2.4.2.1 Architecture Allocation                             | 0  |

|    |       | 2.4.2.2 Application Task Mapping and Scheduling 2           | 0  |

|    | 2.5   | Previous Works                                              | 0  |

|    | 2.6   | Concluding Remarks                                          | 2  |

| 3  | Sys   | temC Fault Injection Simulator 2                            | 3  |

|    | 3.1   | Related Works                                               | 4  |

|    |       | 3.1.1 Saboteurs                                             | 4  |

|    |       | 3.1.2 Mutants                                               | 6  |

|    |       | 3.1.3 Emulation Techniques                                  | 8  |

|    |       | 3.1.4 Simulation Command                                    | 9  |

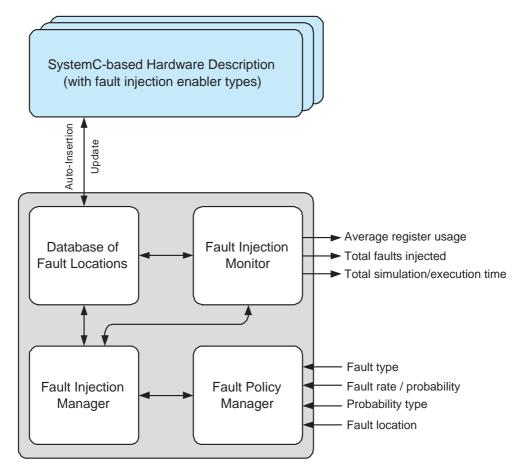

|    | 3.2   | Fault Injection Simulator                                   | 9  |

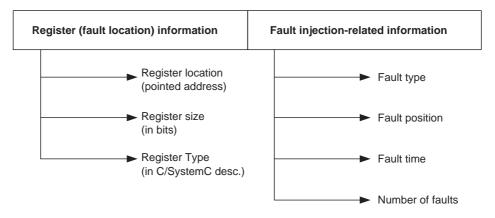

|    |       | 3.2.1 Fault Locations Database                              | 0  |

|    |       | 3.2.2 Fault Policy Manager                                  | 3  |

|    |       | 3.2.3 Fault Injection Manager                               | 6  |

|    |       | 3.2.4 Fault Injection Monitor                               | 0  |

|    | 3.3   | Comparison of Fault Injection Techniques                    | 1  |

|    |       | 3.3.1 Comparison 1: Simplicity and Intrusiveness 4          | 1  |

*CONTENTS* iii

|          |     | 3.3.2  | Comparison 2: Fault Representation and Capabilities            | 4   |

|----------|-----|--------|----------------------------------------------------------------|-----|

|          |     | 3.3.3  | Comparison 3: Simulation Time                                  |     |

|          |     | 3.3.4  | Summary of Comparisons                                         | 4'  |

|          | 3.4 | MPEC   | G-2 Decoder Case Study                                         |     |

|          | 3.5 | Concl  | uding Remarks                                                  | 5   |

| 4        | On- | Chip ( | Communication Architecture Comparative Analysis                | 53  |

|          | 4.1 | Relate | ed Works                                                       | 5   |

|          | 4.2 | Design | a Space                                                        | 50  |

|          |     | 4.2.1  | MPEG-2 Video Decoder Cores                                     |     |

|          |     | 4.2.2  | Shared-bus AMBA Design                                         |     |

|          |     | 4.2.3  | Network-on-Chip Design                                         |     |

|          | 4.3 | Simula | ation Setup and Comparisons                                    | 65  |

|          |     | 4.3.1  | Simulation Environment and Test Cases                          | 65  |

|          |     | 4.3.2  | Performance Metrics                                            | 6   |

|          |     |        | 4.3.2.1 Concurrency                                            | 60  |

|          |     |        | 4.3.2.2 Core Efficiency                                        | 68  |

|          |     |        | 4.3.2.3 Channel Latency                                        | 7   |

|          |     |        | 4.3.2.4 Bandwidth                                              | 75  |

|          | 4.4 | Comp   | arative Application Performance                                | 73  |

|          |     | 4.4.1  | Per Macroblock Decoding Time                                   | 73  |

|          |     | 4.4.2  | Operating Clock Frequency                                      | 7   |

|          |     | 4.4.3  | Impact of Architecture Allocation                              |     |

|          | 4.5 |        | arative Reliability Analysis                                   |     |

|          |     | 4.5.1  | Fault Injection Model                                          |     |

|          |     | 4.5.2  | Impact of SEUs Injected                                        |     |

|          |     |        | 4.5.2.1 SEUs Experienced During Computation                    |     |

|          |     |        | 4.5.2.2 SEUs Experienced During Communication                  |     |

|          |     |        | 4.5.2.3 Impact of SEUs at Application-Level                    |     |

|          |     | 4.5.3  | Impact of Architecture Allocation                              |     |

|          | 4.6 | Concl  | uding Remarks                                                  | 92  |

| <b>5</b> | Vol | _      | caling Technique for Power Minimisation                        | 93  |

|          | 5.1 |        | ed Works                                                       |     |

|          | 5.2 | Prelin | ninaries                                                       | 90  |

|          |     | 5.2.1  | Application and Architecture                                   |     |

|          |     | 5.2.2  | Voltage Scaling                                                |     |

|          |     | 5.2.3  | Fault Injection Model                                          |     |

|          |     | 5.2.4  | Application-level Correctness                                  |     |

|          | 5.3 | Motiv  |                                                                |     |

|          | 5.4 |        | sed Voltage Scaling Technique                                  |     |

|          |     | 5.4.1  | Problem Formulation                                            |     |

|          |     | 5.4.2  | Power Minimisation                                             |     |

|          |     | 5.4.3  | Application-level Correctness and Voltage Scaling Relationship |     |

|          | 5.5 | -      | imental Results                                                |     |

|          | 5.6 | Applio | cation Task Mapping and Architecture Allocation                | 11' |

*CONTENTS* iv

|              | 5.7<br>5.8                      | 5.6.1 Application Task Mapping                             | 121<br>126 |  |  |  |

|--------------|---------------------------------|------------------------------------------------------------|------------|--|--|--|

| 6            | Soft                            |                                                            | 130        |  |  |  |

| U            | 6.1                             | Related Works                                              |            |  |  |  |

|              | 6.2                             | System Model                                               |            |  |  |  |

|              | 0.2                             | 6.2.1 Architecture Model                                   |            |  |  |  |

|              |                                 | 6.2.2 Application Model                                    |            |  |  |  |

|              |                                 | 6.2.3 Fault Injection Model                                |            |  |  |  |

|              | 6.3                             | Impact of Task Mapping on Reliability                      |            |  |  |  |

|              | 6.4                             | Proposed Design Optimisation                               |            |  |  |  |

|              |                                 | 6.4.1 Power Minimisation                                   |            |  |  |  |

|              |                                 | 6.4.2 Soft Error-Aware Application Task Mapping            | 143        |  |  |  |

|              |                                 | 6.4.3 Iterative Assessment                                 |            |  |  |  |

|              | 6.5                             | Experimental Results                                       | 149        |  |  |  |

|              | 6.6                             | Architecture Allocation                                    | 156        |  |  |  |

|              | 6.7                             | Concluding Remarks                                         | 161        |  |  |  |

| 7            | Conclusions and Future Work 162 |                                                            |            |  |  |  |

|              | 7.1                             | Summary and Research Contributions                         | 162        |  |  |  |

|              | 7.2                             | Future Research Directions                                 |            |  |  |  |

|              |                                 | 7.2.1 Soft Error-Aware Leakage Power Minimisation          | 164        |  |  |  |

|              |                                 | 7.2.2 Online Soft Error-Aware Design Optimisation          | 165        |  |  |  |

| A            | MP                              | EG-2 Video Decoder                                         | 166        |  |  |  |

|              | A.1                             |                                                            | 166        |  |  |  |

|              |                                 | A.1.1 Frame Formats                                        |            |  |  |  |

|              |                                 | A.1.2 Decoding Rates                                       |            |  |  |  |

|              |                                 | A.1.3 MPEG Fidelity                                        | 169        |  |  |  |

|              | A.2                             | MPEG-2 Video Decoder Implementation                        | 170        |  |  |  |

| В            | Sim                             | ulation Tools Used                                         | 173        |  |  |  |

|              | B.1                             | NIRGAM: NoC Interconnect Routing and Application Modelling |            |  |  |  |

|              | B.2                             | MPARM                                                      |            |  |  |  |

|              | B.3                             | Adaptive Simulated Annealing Tool                          |            |  |  |  |

|              | B.4                             |                                                            |            |  |  |  |

| $\mathbf{C}$ | Ran                             | adom Task and Resource Graphs                              | 177        |  |  |  |

| _            | C.1                             |                                                            |            |  |  |  |

|              | C.2                             |                                                            |            |  |  |  |

|              | _                               | Other Example Task Graphs                                  |            |  |  |  |

# List of Figures

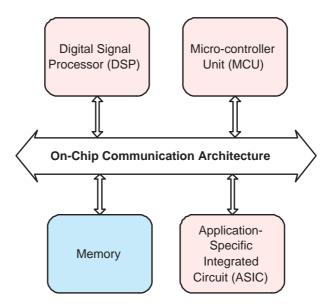

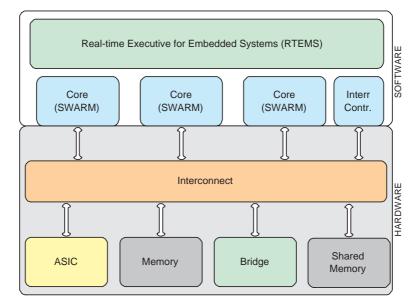

| 2.1        | An example MPSoC showing different components and on-chip communication architecture                                                                  | 7  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

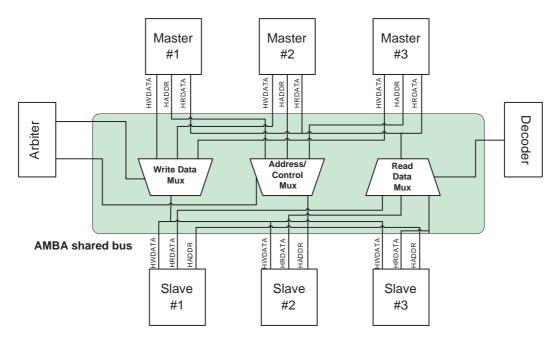

| 2.2        | Block diagram of AMBA AHB central multiplexing scheme connecting                                                                                      | 1  |

|            | arbiter, decoder, masters and slaves                                                                                                                  | 8  |

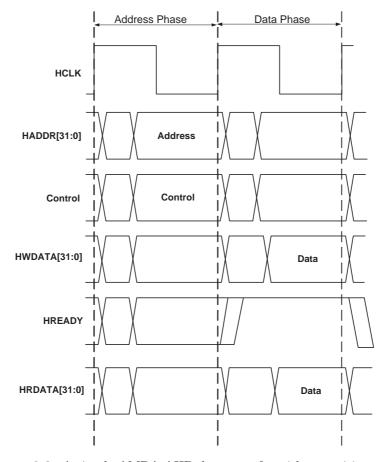

| 2.3        | A simple AMBA AHB data transfer without waiting states                                                                                                | 9  |

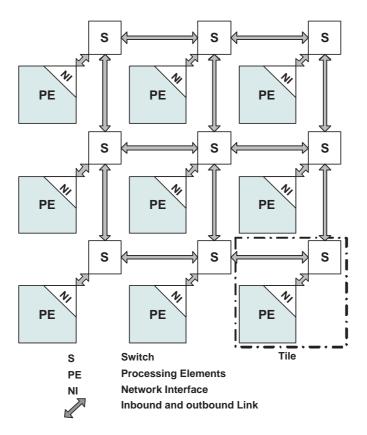

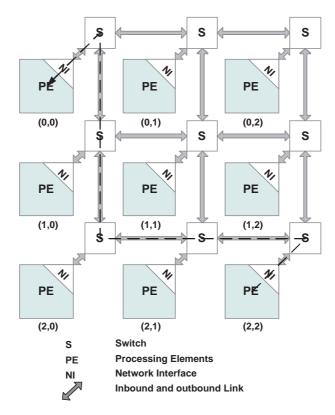

| 2.4        | A $(3 \times 3)$ NoC architecture with CLICHE or mesh-based topology                                                                                  | 10 |

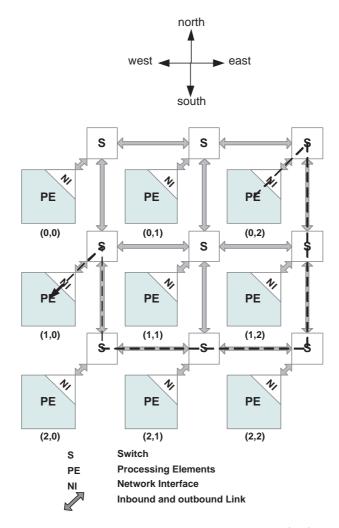

| 2.5        | An example of XY routing between node $(2,2)$ to node $(0,0)$ in a $(3 \times 3)$ mesh-based NoC                                                      | 12 |

| 2.6        | An example of odd-even routing between node $(0,2)$ to node $(1,0)$ in a $(3 \times 3)$ mesh-based NoC                                                | 13 |

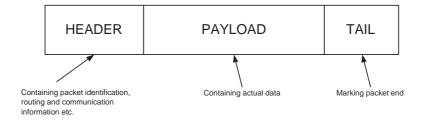

| 2.7        | A general structure of NoC packet with different components                                                                                           | 13 |

| 2.8        | Different packet communication techniques: (a) store and forward, (b) virtual cut through, and (c) wormhole packet communication technique .          | 14 |

| 2.9        | An example SystemC model of a 1-bit adder                                                                                                             | 18 |

| 2.10       | Flowchart of hardware/software co-design                                                                                                              | 19 |

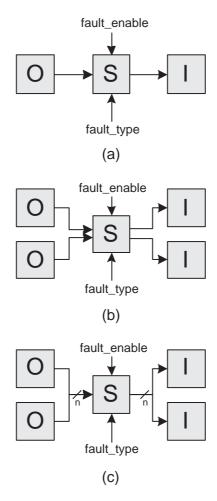

| 3.1        | Different types of saboteurs (unidirectional only): (a) Serial simple sabo-                                                                           |    |

|            | teur, (b) Serial complex saboteur, and (c) Parallel saboteur                                                                                          | 25 |

| 3.2        | An example SystemC template of a serial simple saboteur (Figure 3.1(a))                                                                               | 26 |

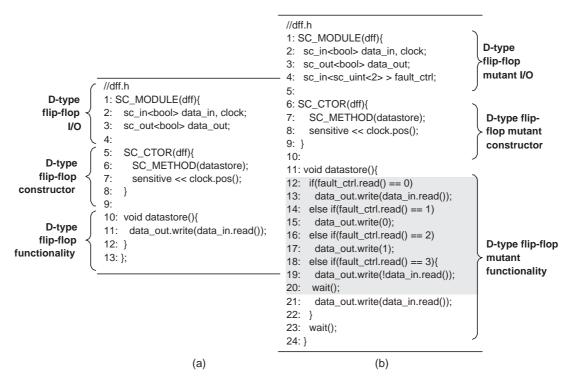

| 3.3        | Example of mutant based fault injection: (a) an original D-type flip-flop in SystemC, (b) a mutant D-type flip-flop in SystemC                        | 27 |

| 3.4        | Example of modification of design description using emulation technique: (a) fault-free (before emulation) design description, and (b) faulty (after  | 20 |

| 0.5        | emulation) design description                                                                                                                         | 28 |

| 3.5<br>3.6 | Block diagram of the proposed SystemC fault injection simulator SystemC definition of (a) Reg <pri>primitive type&gt; as a replacement of prim-</pri> | 30 |

|            | itive types, (b) IntReg <n> as replacement of SystemC sc_int<n> type</n></n>                                                                          | 00 |

| 0.7        | for enabling fault injection                                                                                                                          | 32 |

| 3.7        | Organisation of each record within the fault locations database                                                                                       | 32 |

| 3.8        | SystemC model of the fault policy manager, FIPolicy showing main functions                                                                            | 35 |

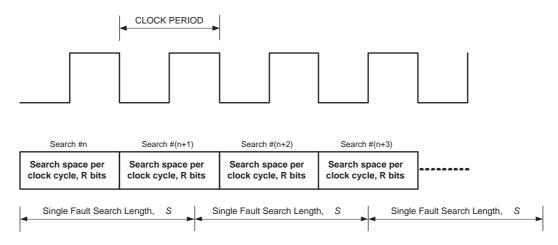

| 3.9        | Fault injection mechanism using sampling between time and register space                                                                              | 36 |

| 3.10       | SystemC model of the fault injection manager showing main functions                                                                                   | 37 |

| 3.11       | Example illustration of the fault injection technique employed in the pro-                                                                            | 91 |

| 0.11       | posed fault injection simulator: (a) a synchronous SystemC 8-bit counter                                                                              |    |

|            | module, and (b) a synchronous SystemC 8-bit counter module using the                                                                                  |    |

|            | technique employed in proposed fault injection simulator                                                                                              | 42 |

LIST OF FIGURES vi

| 3.12 | Example of fault injection in synchronous 8-bit counter design using (a) saboteurs, (b) mutant, and (c) simulation command based approach                                                                  | 43 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

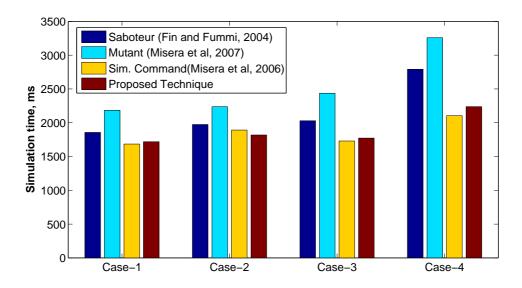

| 3.13 | Comparison of simulation speed for fault simulation techniques                                                                                                                                             | 46 |

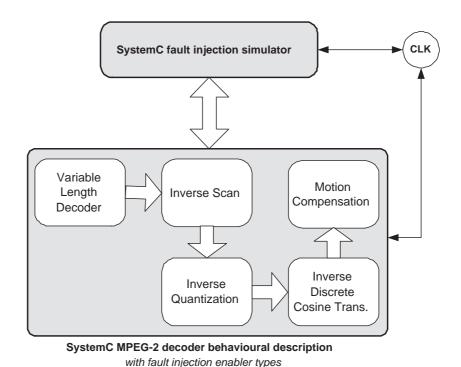

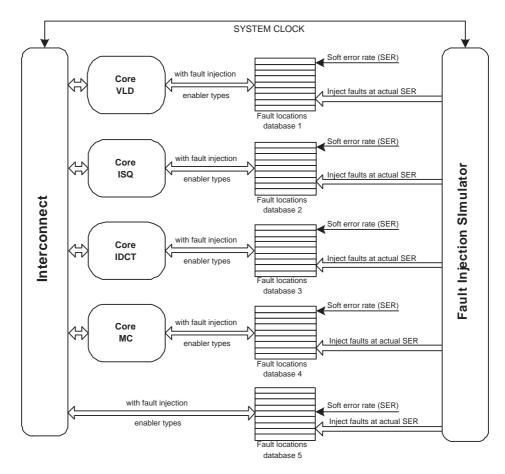

| 3.14 | MPEG-2 video decoder setup for fault injection                                                                                                                                                             | 48 |

| 3.15 | Example description of inverse discrete cosine transformation (IDCT) functions in the MPEG-2 decoder highlighting the modifications for enabling fault injection in the proposed fault injection simulator | 49 |

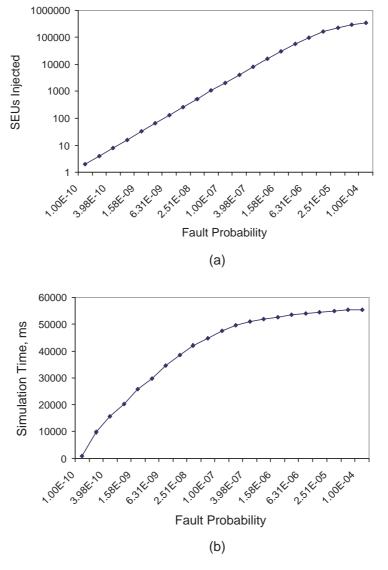

| 3.16 | (a) Total number of faults injected for varying fault probabilities, and (b) simulation times (in ms) for varying fault probabilities of the MPEG-2 video decoder fault injection setup                    | 50 |

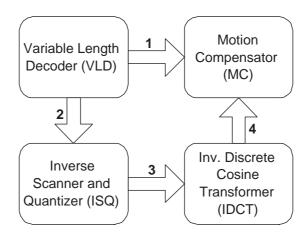

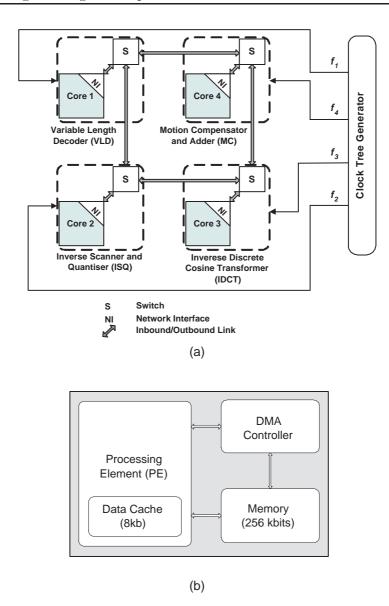

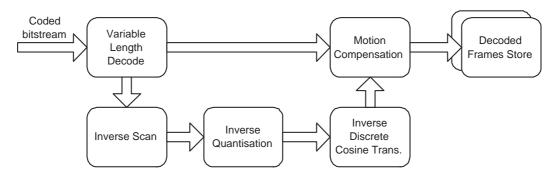

| 4.1  | Block diagram of MPEG-2 video decoder                                                                                                                                                                      | 57 |

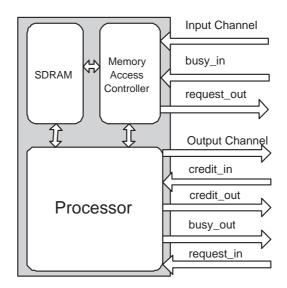

| 4.2  | Simplified block diagram of a processing core used in the MPEG-2 video decoder (Figure 4.1)                                                                                                                | 58 |

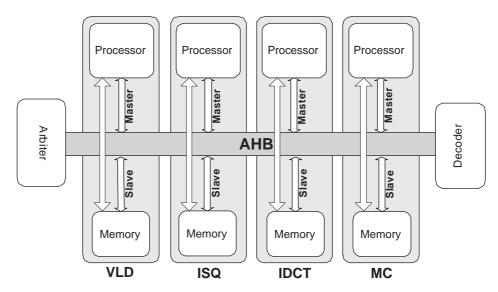

| 4.3  | Block diagram of shared-bus AMBA with MPEG cores used for comparison                                                                                                                                       | 58 |

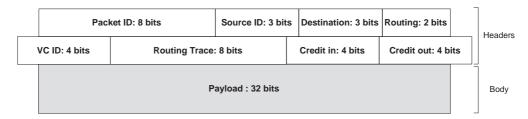

| 4.4  | Packet structure used in mesh-based NoC architecture used for comparison                                                                                                                                   | 59 |

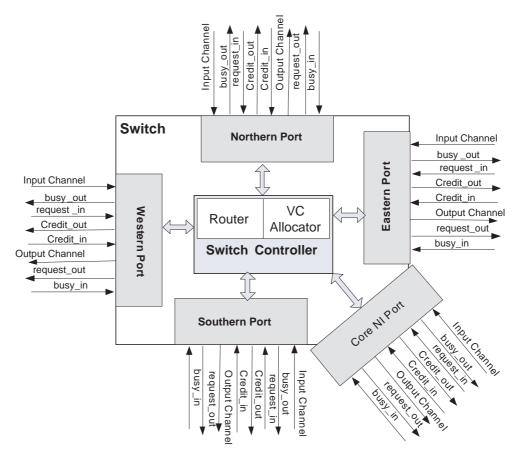

| 4.5  | Switch structure for mesh-topology NoC used for comparison                                                                                                                                                 | 60 |

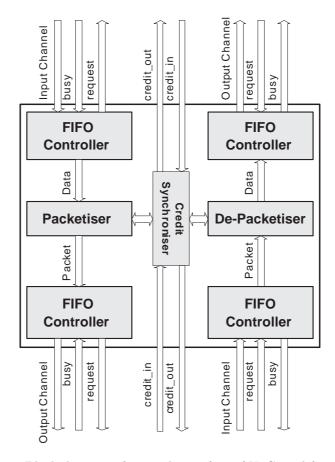

| 4.6  | Block diagram of network interface of NoC used for comparison                                                                                                                                              | 61 |

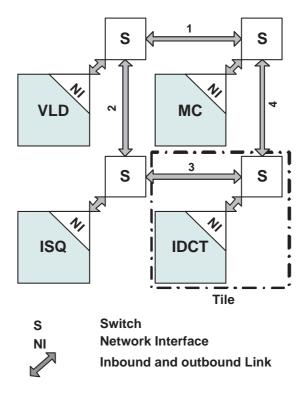

| 4.7  | Block diagram of mesh-based $(2 \times 2)$ NoC with MPEG-2 video decoder cores (Figure 4.1) used for comparison                                                                                            | 62 |

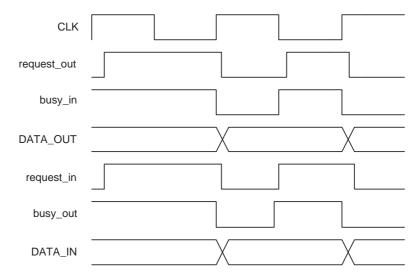

| 4.8  | Cycle-accurate write and read transactions in NoC used for comparison .                                                                                                                                    | 65 |

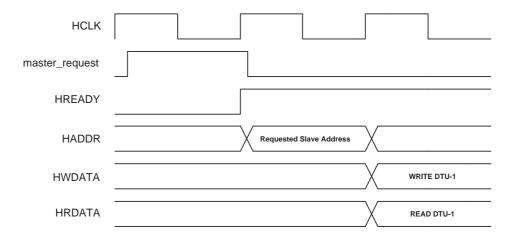

| 4.9  | Cycle-accurate write and read transactions in AMBA used for comparison                                                                                                                                     | 65 |

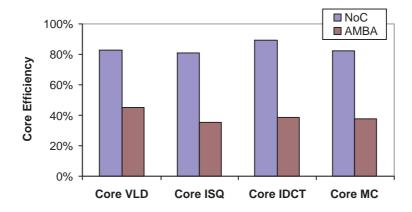

| 4.10 | Average core efficiencies ( $\sigma$ ) of AMBA and NoC MPEG-2 video decoder (Figure 4.1)                                                                                                                   | 71 |

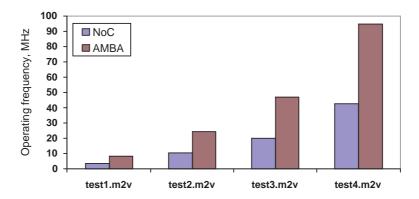

| 4.11 | Required clock frequency of NoC and AMBA for decoding different test video bitstreams (Table 4.1) at specified frame rate                                                                                  | 75 |

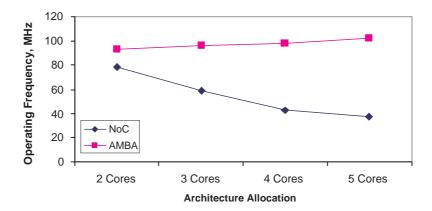

| 4.12 | Operating clock frequencies of AMBA and NoC (in MHz) for decoding test4.m2v with different architecture allocations                                                                                        | 78 |

| 4.13 | Fault injection setup used for comparative reliability analyses between AMBA and NoC on-chip communication architecture                                                                                    | 80 |

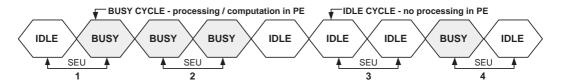

| 111  | Manifestation of SEUs during computation cycles of a processing core                                                                                                                                       | 81 |

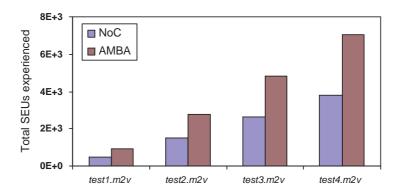

|      | Comparative $\mathcal{F}_{comp}$ in AMBA- and NoC-based decoders for an arbitrary                                                                                                                          | 01 |

|      | SER of $10^{-9}$                                                                                                                                                                                           | 83 |

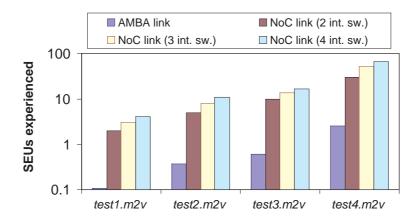

|      | Comparative $\mathcal{F}_{comm}$ in interconnects of AMBA- and NoC- decoders for an arbitrary SER of $10^{-9}$                                                                                             | 86 |

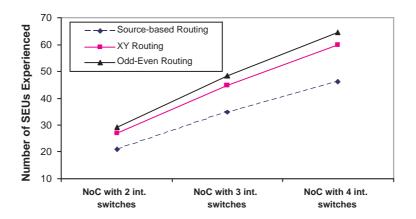

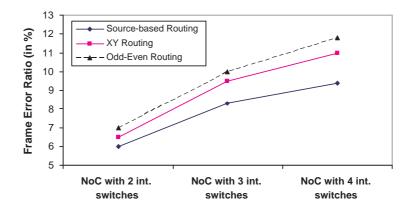

| 4.17 | Impact of choice of routing algorithm on $\mathcal{F}_{comm}$ in NoC interconnects, while decoding $test4.m2v$                                                                                             | 86 |

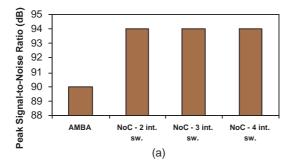

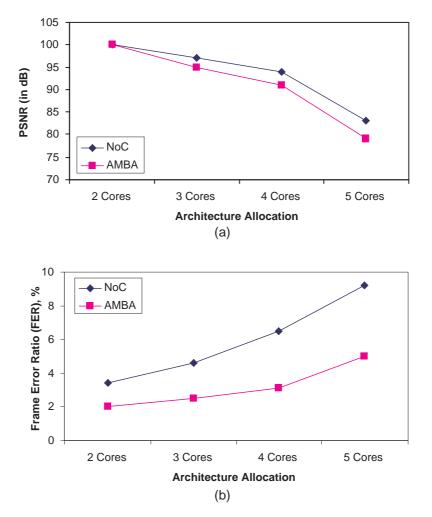

| 4.18 | (a) Comparative PSNRs of AMBA- and NoC-based decoders, while decoding <i>test4.m2v</i> , (b) comparative FERs of AMBA- (Figure 4.3) and NoC-                                                               |    |

|      | based decoders (Figure 4.7), while decoding $test4.m2v$                                                                                                                                                    | 88 |

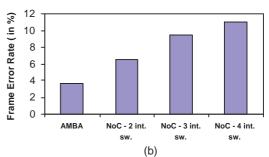

| 4.19 | Impact of choice of routing algorithm on the FER of NoC-based decoder, while decoding $test4.m2v$                                                                                                          | 89 |

| 4.20 |                                                                                                                                                                                                            |    |

|      | while decoding $test4.m2v$                                                                                                                                                                                 | 91 |

LIST OF FIGURES vii

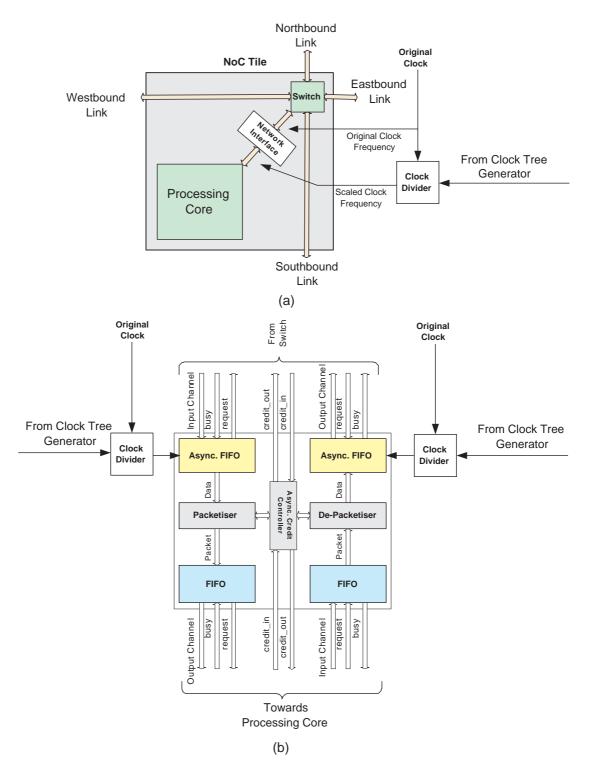

| 5.1 | (a) An MPEG-2 video decoder MPSoC architecture based on two-dimension<br>mesh-based NoC using four processing cores with support for voltage scal-<br>ing, and (b) block diagram of a processing core within the NoC tile used                                                                                                                                    | nal   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | in this work                                                                                                                                                                                                                                                                                                                                                      | . 97  |

| 5.2 | (a) Block diagram of the voltage scaling arrangements used in the NoC tile, and (b) block diagram of the NoC network interface (NI) with asynchronous FIFO buffer and interface between different clock frequencies to                                                                                                                                            |       |

|     | enable synchronised communication between the NI ends                                                                                                                                                                                                                                                                                                             | . 99  |

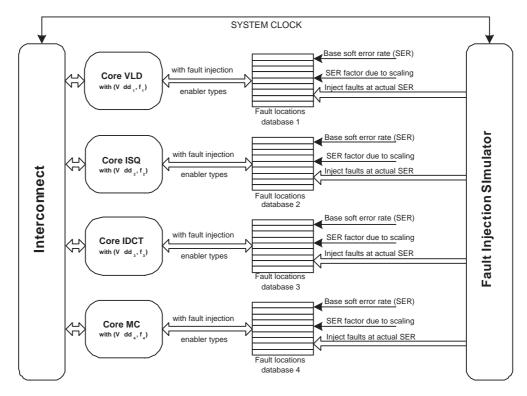

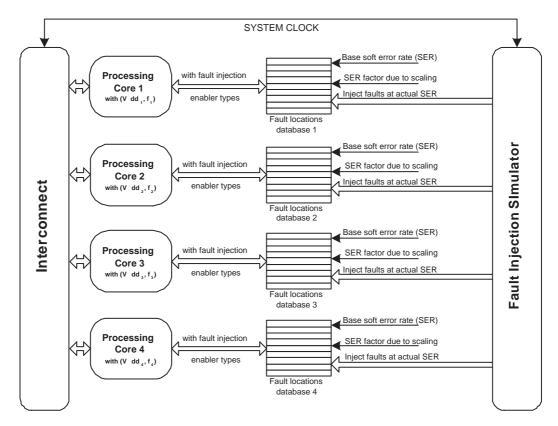

| 5.3 | Fault injection setup for MPSoC decoder with four processing cores (Figure 5.1)                                                                                                                                                                                                                                                                                   | . 101 |

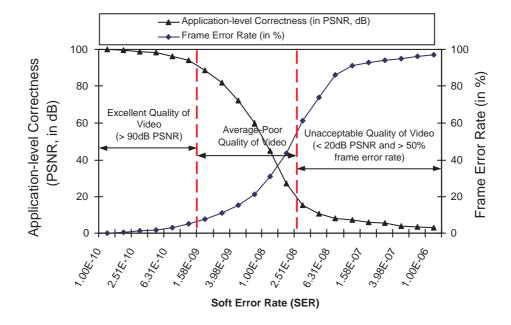

| 5.4 | Application-level correctness in terms of PSNR (in dB) and frame error rate (in $\%$ ) of decoded frames of $tennis$ video sequence (Table 5.1)                                                                                                                                                                                                                   | . 102 |

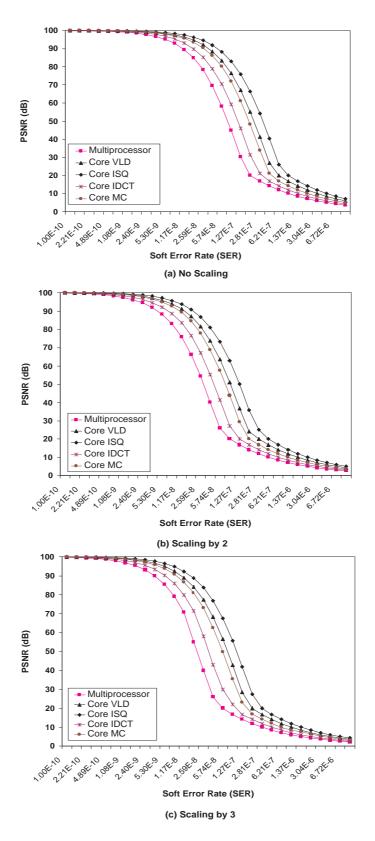

| 5.5 | Application sensitivity (in terms of PSNR, in dB) of processing cores and multiprocessor MPEG-2 video decoder with varying base soft error rate, $\lambda_0$ , with (a) no voltage scaling, (b) voltage scaling by 2, and (c) voltage scaling by 3                                                                                                                | . 110 |

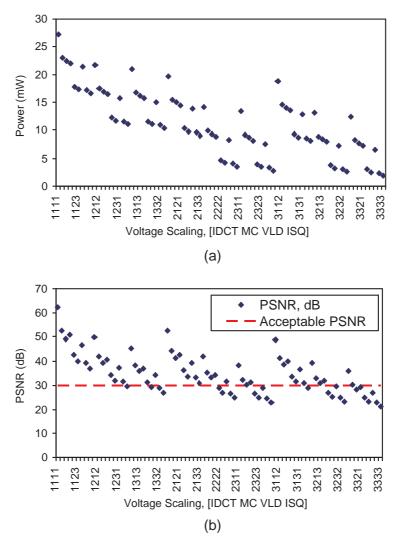

| 5.6 | (a) Power consumption $(P, \text{ in mW})$ for different voltage scaling options using $tennis$ video sequence at soft error rate (SER) of $3.98 \times 10^{-8}$ , and (b) PSNR values $(\Omega, \text{ in dB})$ for different voltage scaling options using                                                                                                      |       |

|     | tennis video sequence at soft error rate (SER) of $3.98 \times 10^{-8}$                                                                                                                                                                                                                                                                                           |       |

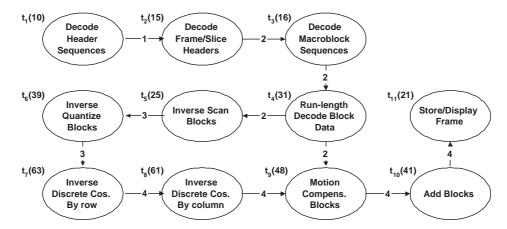

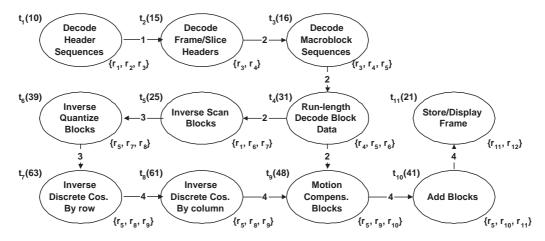

| 5.7 | Task graph of MPEG-2 video decoder (Figure 5.1(a)) with eleven tasks                                                                                                                                                                                                                                                                                              | . 117 |

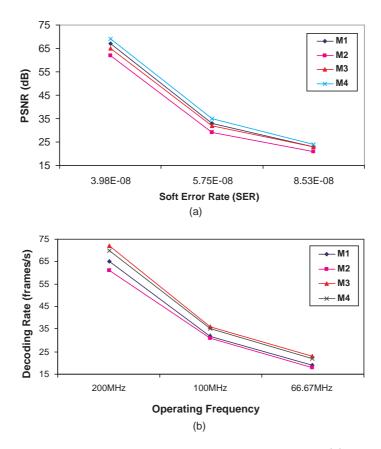

| 5.8 | Impact of different application task mappings on (a) application-level correctness and (b) decoding rates of the MPEG-2 video decoder                                                                                                                                                                                                                             | 110   |

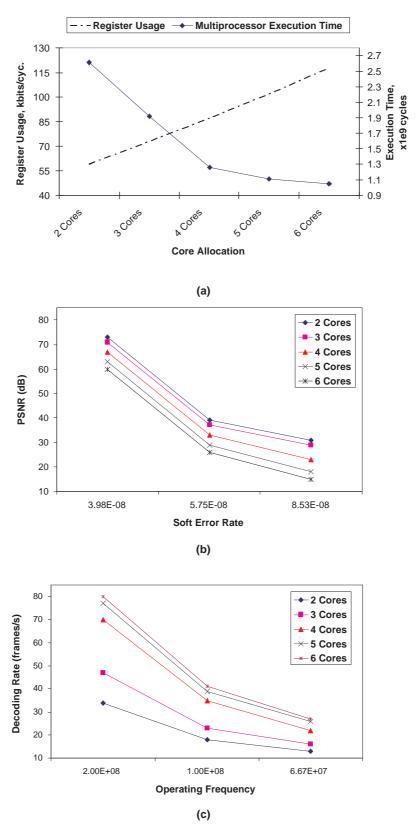

| 5.9 | (a) Multiprocessor execution time and register usage for different architecture allocations, (b) PSNRs for different architecture allocations at different SERs, and (c) Decoding rates of different architecture alloca-                                                                                                                                         |       |

|     | tions at different operational frequencies                                                                                                                                                                                                                                                                                                                        | . 122 |

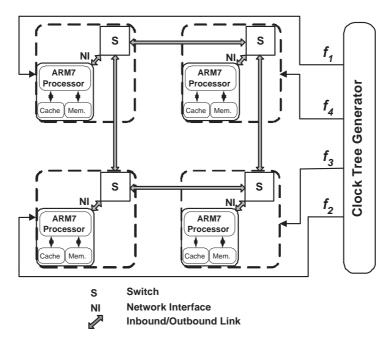

| 6.1 | MPSoC architecture with four processing cores and power minimisation support through clock tree generator                                                                                                                                                                                                                                                         | . 133 |

| 6.2 | MPEG-2 video decoder task graph with eleven tasks and associated register resources                                                                                                                                                                                                                                                                               |       |

| 6.3 | Fault injection setup for MPSoC architecture with four processing cores                                                                                                                                                                                                                                                                                           | . 137 |

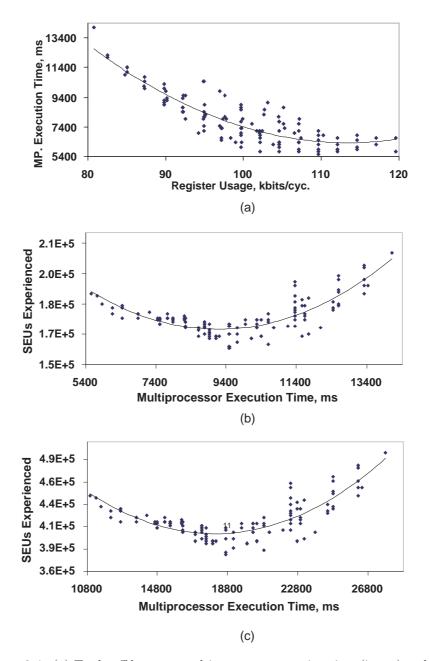

| 6.4 | (a) Trade-off between multiprocessor execution time (in ms) and register usage (in kbits/cycle), (b) SEUs experienced and multiprocessor execution time (in ms) when no scaling is used for MPSoC cores, and (c) SEUs experienced and execution time when MPSoC cores are scaled by 2; all for different task mappings of MPEG decoder with four processing cores |       |

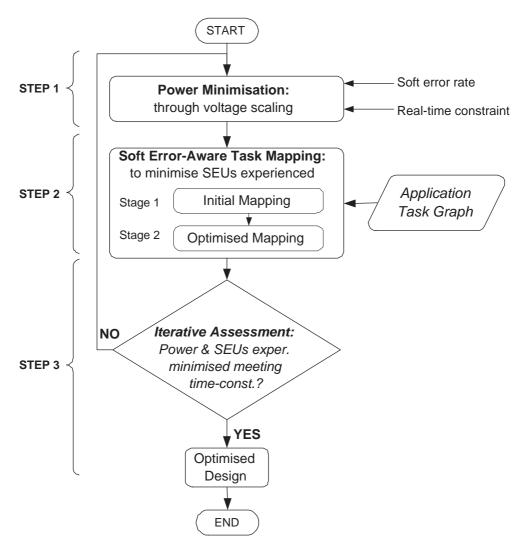

| 6.5 | Flowchart of the proposed design optimisation                                                                                                                                                                                                                                                                                                                     | . 141 |

| 6.6 | (a) Voltage scaling algorithm used for power minimisation, (b) example of voltage scaling coefficients for four processing cores using voltage scaling                                                                                                                                                                                                            |       |

|     | algorithm shown in (a)                                                                                                                                                                                                                                                                                                                                            |       |

| 6.7 | Initial soft error-aware mapping algorithm, InitialSEAMapping                                                                                                                                                                                                                                                                                                     |       |

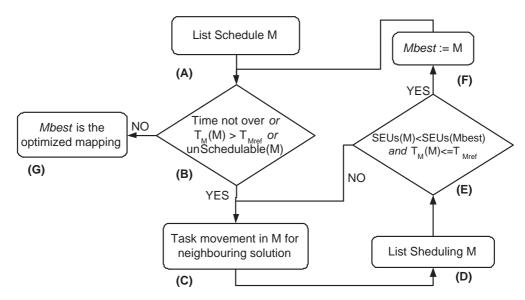

| 6.8 | Flowchart of optimised mapping, Optimised Mapping                                                                                                                                                                                                                                                                                                                 | . 144 |

LIST OF FIGURES viii

| 6.9  | Example illustration of the soft error-aware application task mapping (a) example application task graph, (b) sets of registers and their sizes, (c)                                                                                        |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | register usage of different tasks of the application, (d-f) initial soft error-<br>aware application task mapping ( <i>InitialSEAMapping</i> , Figure 6.7) steps,<br>and (g) optimised mapping ( <i>OptimisedMapping</i> , Figure 6.8) step | 146  |

| 6.10 | Example iterative assessment for design optimisation using MPEG-2 video                                                                                                                                                                     | 110  |

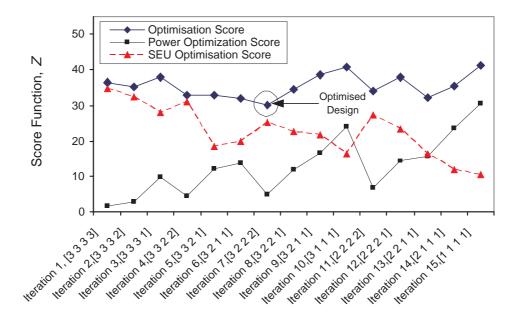

| 0.20 | decoder with four processing cores                                                                                                                                                                                                          | 149  |

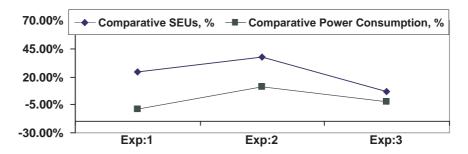

| 6.11 |                                                                                                                                                                                                                                             |      |

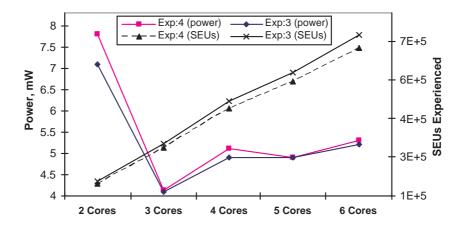

| 6.12 | Comparison of power consumption (P, in mW) and SEUs experienced                                                                                                                                                                             |      |

|      | $(\Gamma)$ between Exp:3 and Exp:4 for different random task graphs                                                                                                                                                                         | 155  |

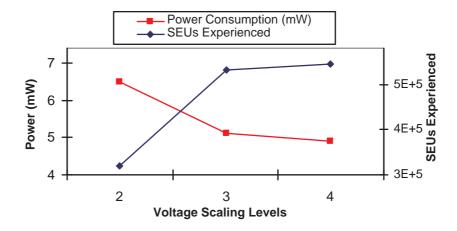

| 6.13 | Power consumption $(P, \text{ in mW})$ and SEUs experienced $(\Gamma)$ for different                                                                                                                                                        |      |

|      | scaling levels using the proposed design optimisation technique                                                                                                                                                                             | 156  |

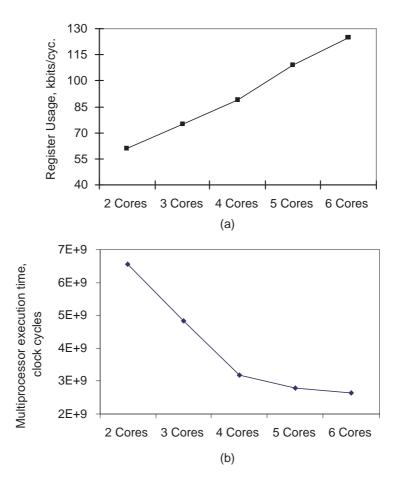

| 6.14 | (a) Register usage $(R, \text{ in kbits/cycle})$ , and (b) multiprocessor execution time $(T_M, \text{ in clock cycles})$ of the MPEG-2 decoder MPSoC for different                                                                         |      |

|      | architecture allocations                                                                                                                                                                                                                    | 158  |

| 6.15 | Comparison of power consumption $(P, \text{ in mW})$ and SEUs experienced                                                                                                                                                                   |      |

|      | $(\Gamma)$ between Exp:3 and Exp:4 for different architecture allocations using                                                                                                                                                             | 1.01 |

|      | random task graph of 60 tasks                                                                                                                                                                                                               | 161  |

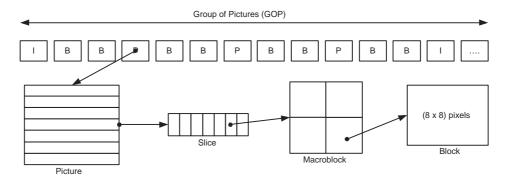

| A.1  | Simplified MPEG-2 video decoding process                                                                                                                                                                                                    | 166  |

| A.2  | Hierarchical video data structure used in MPEG-2 video                                                                                                                                                                                      |      |

| A.3  | Example SystemC prototype class for MPEG variable length decoder                                                                                                                                                                            |      |

|      | (VLD) core used in Chapter 4                                                                                                                                                                                                                | 171  |

| A.4  | Sample of MPARM initialiser class for defining MPEG-2 video decoder                                                                                                                                                                         |      |

|      | tasks highlighting task mapping to processing cores, used in Chapter $5$ .                                                                                                                                                                  | 172  |

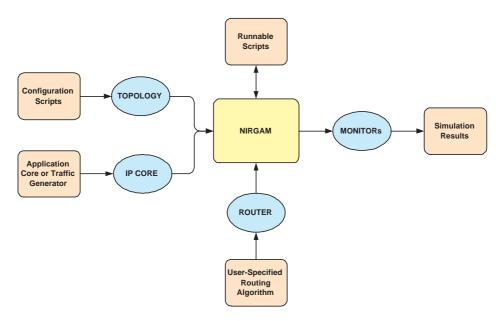

| B.1  | Simplified block diagram of NIRGAM NoC simulator                                                                                                                                                                                            | 174  |

| B.2  | Simplified block diagram of MPARM hardware/software codesign                                                                                                                                                                                |      |

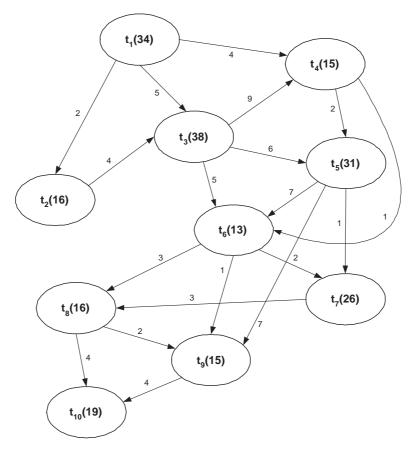

| C.1  | Example task graph description with 10 tasks without resource mapping                                                                                                                                                                       | 178  |

| C.2  | Example task graph with 10 tasks without resource mapping showing                                                                                                                                                                           |      |

|      | computational tasks as nodes and communication tasks as edges                                                                                                                                                                               |      |

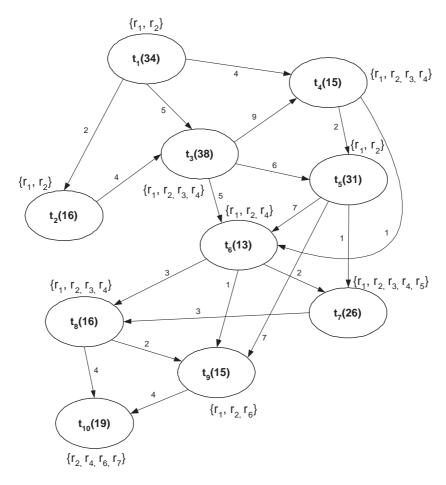

| C.3  | Example task graph description with 10 tasks with resource mapping                                                                                                                                                                          | 180  |

| C.4  | Example task graph with 10 tasks with resource mapping showing computational tasks as nodes, communication tasks as edges and register                                                                                                      |      |

|      | resources with each task                                                                                                                                                                                                                    |      |

| C.5  | Example task graph description with 20 tasks with resource mapping                                                                                                                                                                          |      |

| C.6  | Example task graph description with 40 tasks with resource mapping                                                                                                                                                                          | 182  |

# List of Tables

| 3.1        | Original variable/signal types and corresponding fault injection enabler types used in the fault injection simulator                                                           | 31 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2        | Different fault types and injection techniques used in the fault injection                                                                                                     | 38 |

| 3.3        | MPEG-2 video decoder setup with input in the fault policy manager and                                                                                                          | 50 |

| 4.1        | Test video bitstreams used for comparisons between AMBA and NoC                                                                                                                | 65 |

| 4.2<br>4.3 | Core concurrency of NoC and AMBA for different video bitstreams Execution and non-processing times (in clock cycles) of processing cores                                       | 67 |

| 4.3        |                                                                                                                                                                                | 70 |

| 4.4        | · /                                                                                                                                                                            | 74 |

| 4.5        | Task distribution of MPEG-2 video decoder among cores for different architecture allocations                                                                                   | 76 |

| 4.6        | Impact of architecture allocation on the multiprocessor execution time                                                                                                         |    |

| 4.7        | $(T_M)$ and per macroblock decoding time $(T_{MB})$                                                                                                                            | 77 |

| 4.0        | usage $(R_i)$ of processing cores in AMBA- and NoC-based decoders                                                                                                              | 82 |

| 4.8        | Inter-core data transaction units (DTUs) of the MPEG-2 video decoder (Figure 4.1) for decoding different video bitstreams (Table 4.1)                                          | 85 |

| 4.9        | Impact of architecture allocation on the reliability in terms of number of SEUs experienced during computation $(\mathcal{F}_{comp})$ and communication $(\mathcal{F}_{comm})$ | 90 |

| 5.1        | Test video sequences used for experimental purposes (Section 5.5)                                                                                                              | 98 |

| 5.2        | Operating frequency, $f$ and supply voltage, $V_{dd}$ , for different scaling options for ARM7TDMI processor                                                                   | 00 |

| 5.3        | Power consumption (in mW) and PSNRs (in dB) for different voltage scaling options at $\lambda = 3.98 \times 10^{-8}$                                                           | 03 |

| 5.4        | Execution time and register usages of the processing cores of the MPEG-2 video decoder with four processing cores (Figure 5.1(a))                                              | 08 |

| 5.5        | Application-level correctness and power minimisation trade-off using tennis video sequence                                                                                     |    |

| 5.6        | Application-level correctness and power minimisation trade-off using other video sequences                                                                                     |    |

| 5.7        | Application-level correctness and power minimisation trade-off using num-                                                                                                      | 10 |

|            | ber of voltage scaling levels of $S=2$                                                                                                                                         | 16 |

LIST OF TABLES

| 5.8  | Power consumption (in mW), PSNRs and decoding rates of the MPEG-2 video decoder (Figure $5.1(a)$ ) using the proposed voltage scaling with dif-     |       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | ferent levels of acceptable application-level correctness (in terms of PSNR, dB)                                                                    | . 116 |

| 5.9  | Different task mappings, register usages and execution times for MPSoC decoder using four cores                                                     | . 118 |

| 5.10 | Impact of decoder task mapping on the power minimisation using the proposed voltage scaling technique                                               | . 120 |

| 5.11 |                                                                                                                                                     |       |

| 5.12 | Power consumption (in mW), PSNRs (in dB) and decoding rates (in frames/s) for different architecture allocations using the proposed power           | . 120 |

| F 10 | minimisation technique                                                                                                                              | . 125 |

| 5.13 | Power consumption $(P, \text{ in mW})$ and the overall SERs $(\lambda)$ for different synthetic applications for different architecture allocations | . 128 |

| 6.1  | Operating frequency, $f$ , and supply voltage, $V_{dd}$ , for different voltage scaling of ARM7TDMI processor                                       | . 134 |

| 6.2  | Register usage of MPEG-2 video decoder tasks (Figure 6.2) and their approximate sizes                                                               |       |

| 6.3  | Comparison of soft error-unaware and the proposed soft error-aware optimisations using MPEG decoder MPSoC with four cores                           | . 151 |

| 6.4  | Power consumption $(P)$ , register usage $(R)$ and SEUs experienced $(\Gamma)$ for different applications using Exp:4                               |       |

| 6.5  | Task distribution of MPEG-2 video decoder (Figure 6.2) among cores for different architecture allocations using the optimised task mapping in the   | . 101 |

| 6.6  | proposed design optimisation technique (Figure 6.5) Power consumption $(P, \text{ in mW})$ and SEUs experienced $(\Gamma, \times 10^5)$ for         | . 157 |

| 0.0  | different applications and different architecture allocations $\dots \dots$                                                                         | . 160 |

| Δ 1  | Different frame formats used in MPEC-2 video decoder                                                                                                | 160   |

# Declaration of Authorship

I, Rishad Ahmed Shafik, declare that the thesis entitled

#### Investigation into Low Power and Reliable System-on-Chip Design

and the work presented in it are my own and has been generated by me as the result of my own original research. I confirm that:

- 1. This work was done during the period of candidature of the intended qualification at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this has been clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself or jointly with others, I have made clear exactly what was done by others and what have been contributed by myself;

- 7. Parts of this work have been published as listed in page 3, Section 1.2 (Chapter 1).

| Signed: |  |  |  |

|---------|--|--|--|

| Date:   |  |  |  |

## List of Acronyms

ABB Adaptive base bias

AHB Advanced high-performance bus

AMBA Advanced microprocessor bus architecture

APB Advanced peripheral bus

ASA Adaptive simulated annealing

ASB Advanced system bus

ASIC Application-specific integrated circuit

AXI Advanced extensible interface

BILP Binary integer linear programming

CIF Common intermediate format

CLICHE Chip-level integration of communicating heterogeneous elements

DCT Discrete cosine transformation

DRAM Dynamic random access memory

DSP Digital signal processor

DTU Data transaction unit

DUT Device under test

DVS Dynamic voltage scaling

EDA Electronic design automation

ESL Electronic system-level

FER Frame error ratio/rate

FI Fault injection

FIFO First-in first-out

FIR Fault injection rate

FIT Fault injection time

LIST OF ACRONYMS

xiii

FLIT Flow control unit

FPGA Field programmable gate array

HDL Hardware description language

HW Hardware

HW/SW Hardware / software

IDCT Inverse discrete cosine transformation

ILP Integer linear programming

ISQ Inverse scan and quantisation

MC Motion Compensation

MCU Microcontroller unit

MPARM Multiprocessor ARM

MPEG Moving picture experts group

MPSoC Multiprocessor system-on-chip

MTBF Mean-time-between-failure

MTTF Mean-time-to-failure

NI Network interface

NoC Network-on-chip

NTSC National television system committee

OSCI Open SystemC initiative

P2P Point-to-Point

PAL Phase alternating line

PE Processing element

PSNR Peak signal-to-noise ratio

QCIF Quarter common intermediate format

RAM Random access memory

RHEL Red Hat Enterprise Linux

RTEMS Real-time executive for embedded systems

RTOS Real-time operating system

RTL Register transfer level

SA Simulated Annealing

SER Soft error rate

SEU Single-event upset

SoC System-on-chip

SRAM Static random access memory

SW Software

VLD Variable length decoder

VLSI Very large scale integration

### List of Symbols

$t_j$

$T_A$

$T_E$

$d^{j,k}$ Communication cost between j-th and k-th task, in clock cycles CNumber of processing cores in MPSoC architecture DDegree of concurrency of cores  $D_r$ MPEG decoding rate, frames per second  $D_{rated}$  Specified MPEG frame rate, frames per second Operating clock frequency, in MHz Effective multiprocessor frequency, in MHz  $f_{eff}$ GTask graph with a set of computational and communication tasks Number of MPEG frames in a video sequence MNNumber of tasks in a task graph KNumber of switches between communicating NoC cores LNumber of pixels in an MPEG frame  $L_{ch}$ Channel latency, in clock cycles PPower consumption, in mW Fault probability per bit  $p_B$ Dynamic power consumption, in mW  $P_{dun}$ Leakage power consumption, in mW  $P_{leak}$ Register usage of j-th task in a task graph, in bits per cycle  $r_i$  $R_i$ Register usage of *i*-th processing core, in bits per cycle ROverall register usage of an MPSoC, in bits per cycle SNumber of scaling levels in a voltage scaling-enabled system

Computational cost of j-th task, in clock cycles

Total application time, in clock cycles

Processor execution time, in clock cycles

LIST OF SYMBOLS xvi

- $T_M$  Multiprocessor execution time, in clock cycles

- $T_{NP}$  Non-processing time in a core, in clock cycles

- $T_P$  Processing time in a core, in clock cycles

- $T_{MB}$  Per macroblock execution time

- $T_i^{I-I}$  Idle-idle transition times of *i*-th processing core of an MPSoC, in clock cycles

- $T_i$  Execution time of *i*-th processing core of an MPSoC, in clock cycles

- $V_{dd}$  Operating supply voltage, in volts

- Z Optimisation score function

- $Z_P$  Optimisation score function for power

- $Z_{\Gamma}$  Optimisation score function for SEUs experienced

- $\alpha_i$  Activity factor of *i*-th processing core within an MPSoC

- $\mathcal{E}$  Set of communication edges in a task graph

- $\mathcal{F}$  Total number of SEUs experienced by computation cores and communication interconnects

- $\mathcal{F}_{comp}$  Number of SEUs experienced during computation

- $\mathcal{F}_{comm}$  Number of SEUs experienced during communication

- $\Gamma$  Number of SEUs experienced

- $\lambda$  Soft error rate after scaling, in SEUs per bit per cycle

- $\lambda$  Base soft error rate before scaling, in SEUs per bit per cycle

- $\mathcal{N}$  Number of data transaction units for inter-core communication within an application

- $\mathcal{M}$  Number of inter-core communication links within the MPSoC

- $\Omega$  Application-level correctness

- $\mathcal{V}$  Set of computational nodes in a task graph

- $\rho$  Ratio of register usage  $(R_i)$  of a processing core to the overall register usage (R) of an MPSoC

- $\sigma$  Core efficiency of a processing core within an MPSoC

- $\tau$  Duration of a bit upset for transient faults, in cycles

#### Acknowledgements

I would like to express my sincere gratitude to my supervisor, *Professor Bashir M. Al-Hashimi*, for the privilege of working under his supervision. I am deeply indebted to him for his constant support and guidance throughout this research. His comments and suggestions at different phases of work and related writings has been extra-ordinary. The intellectual freedom, encouragements and the time-to-time nudging in the right direction from his side have made my time very useful and productive. I also gratefully acknowledge and appreciate the valuable advice and encouragement I received from *Professor Eric Rogers*. His comments and feedback at different stages of PhD have been truly enlightening. *Dr. Jeff Reeve* deserves profound appreciation for his constructive comments during nine-month, MPhil/PhD transfer and PhD examinations.

Given this opportunity, I would like to thank Professor Sandip Kundu (University of Massachusetts, Amherst, USA) and Professor Krishnendu Chakrabarty (Duke University, USA) for their very useful feedback regarding this work. Their insightful comments and suggestions helped me address the different challenges more efficiently. I have also received useful suggestions about my work from colleagues in the research group, Dr. Paul Rosinger, Dr. Alireza Ejlali and Dr. Saqib Khursheed. Lavina Jain merits a worthy mention for her untiring efforts to develop the NIRGAM simulator, which has been used in this research. I am truly grateful to all of them. I am also thankful to my fellow mates in the lab, Amit, Mustafa, Simon, Sheng, Shida and Jatin to name a few, for the help, knowledge and encouragement I received from them over the years. Part of my work has been funded by Engineering and Physical Sciences Research Council (EPSRC) and I am indebted to them.

To my parents, I owe my deepest appreciation and admiration. Throughout my life, they have encouraged me in everything I ever wanted to do. Even at great hardship to themselves, they made sure I had every opportunity they could possibly give me. My brothers, *Sadrul* and *Rafique*, have also been outstanding with their support from time-to-time. I hope that my accomplishments will make all of them proud. Last, but not the least, I would like to thank my wife, *Sonia*, whole-heartedly for her enormous patience, emotional support and inspiration.

to my parents.....

### Chapter 1

### Introduction

Over the last decade, the popularity of portable electronic devices has increased significantly. These devices are realised by interconnecting various system components into a single integrated circuit, called system-on-chip (SoC). The methodology of component interconnection in an SoC is defined by an on-chip communication architecture. Development of efficient on-chip communication architecture is a crucial design issue as it greatly influences the underlying performance of an SoC. Since most of these devices are battery-powered, low power consumption is a prime design objective to extend battery life. Recently, reliability is emerging as another design requirement to operate in the presence of soft errors (i.e. transient faults caused by radiation and harsh operating environment). However, low power consumption and reliability are conflicting design objectives as power minimisation techniques cause substantial increase in the number of soft errors. Hence, design of low power and reliable SoCs is a complex and challenging task. To produce optimised designs, appropriate design flows are needed. This thesis addresses the above challenges through investigation into design and development of efficient, low power and reliable SoCs. The remainder of this chapter is organised as follows. Section 1.1 underlines the motivations of the research carried out in this thesis and Section 1.2 presents an overview of the thesis and its contributions.

#### 1.1 Motivations and Scope of the Thesis

Embedded systems are making their way into more and more devices, from hand-held gadgets to household appliances, and from mobile devices to cars. The current trend is that this growth will continue and the market is expected to experience a three-fold rise in the demand from 2009 to 2014 [1]. This growing demand has led the designers to reduce cost and improve system performance through integration of more functionality into a single chip. The continued increase in device integration has become possible due

to CMOS transistor scaling and miniaturisation described by the Moore's Law [2, 3].

Traditionally, embedded systems are designed with single-processor chips. To accommodate more functionality with increased complexity of applications, multiprocessor system-on-chip (MPSoC) is emerging as a popular embedded systems platform. MP-SoC consists of multiple processing elements on a single piece of silicon, each with specific functionality reflecting the need of the expected application domain. The inclusion of multiple processing elements in MPSoCs has a number of benefits, including parallel processing, low clock speed and low power consumption [4]. However, the design of the current and future MPSoCs presents a number of challenges [5]. A core issue in the design of MPSoCs is on-chip communication architecture, which affects the performance of the system [6]. Also, since a vast majority of today's embedded systems are battery powered, a prime design objective is to minimise power consumption to extend battery life of these systems. However, power minimisation is reported to cause exponential increase in the number of soft errors, particularly that of single-event upsets (SEUs) caused by cosmic or electromagnetic radiation [7, 8, 9]. The existence of these errors highlighting the impact of technology scaling and operating environments has been investigated in a number of academic [10] and industrial studies [11, 12]. Therefore, reliability of MP-SoCs in the presence of soft errors is an emerging design challenge in addition to high performance and low power consumption requirements. A number of design approaches have been proposed by researchers over the years addressing various issues related to low power and reliable design of MPSoCs, such as [13, 14, 15, 16].<sup>1</sup>

This research addresses the following challenges in the design of efficient, low power and reliable MPSoCs:

1. To date there has been good progress in developing efficient on-chip communication architectures. Advanced microprocessor bus architecture (AMBA) is today's dominant, industrial standard on-chip communication architecture [17]. AMBA enables multiple processing elements to be incorporated in an MPSoC through shared communication bus architecture [18]. Network-on-Chip (NoC) is an emerging paradigm for on-chip communication architecture in MPSoCs. It enables multiprocessing through integration and spatial multiplexing of communication interconnects among processing elements [19]. Over the years a number of studies have been carried out showing comparisons between AMBA and NoC in terms of performance, power and area, such as [20, 21, 22]. However, most of these studies are based on synthetic applications (random task graphs). Also, with reliability as an emerging design challenge, no study has been reported so far showing the impact of AMBA and NoC based on-chip communication architectures on MP-SoC reliability. To understand the benefits and shortcomings of AMBA and NoC in terms of performance and reliability and to facilitate development of efficient

<sup>&</sup>lt;sup>1</sup>A review of related previous works carried out is presented in Section 2.5, Chapter 2).

- on-chip communication architecture, further investigations are needed using real application traffic.

- 2. There is growing interest in evaluating the impact of soft errors on MPSoCs at application-level rather than architectural-level. Such evaluation at application-level, often known as application-level correctness, has been reported to enable low-cost fault-tolerant design techniques, particularly in multimedia applications [23, 24]. To achieve low-cost power reduction the impact of system-level power minimisation on application-level correctness needs to be investigated. Currently no such study exists that address the relationship between system-level power minimisation and application-level correctness. Such relationship can be effectively employed to reduce power consumption, whilst maintaining acceptable application-level correctness and meeting the real-time performance constraints.

- 3. Traditionally, low power and reliable MPSoC design is carried out through power-aware fault tolerance techniques considering low power and reliability as two separate objectives. To find effective design optimisation technique with low power and improved reliability as a joint objective, further studies are needed to understand the reliability of applications, particularly from system- and application-level design perspective. Application task mapping is one such design step of applications, which is concerned with distribution of computational and communication tasks among available resources in an MPSoC. Currently there is no study into the impact of the application task mapping on the reliability of application in the presence of soft errors. Such investigation is expected to facilitate soft error-aware design optimisation technique for MPSoCs such that both power minimisation and reliability improvement can be achieved at the same time.

- 4. To study the above challenges using simulation technique, appropriate tools for profiling power, performance and reliability need to be employed. A number of academic and industrial simulation tools have been developed so far that can effectively profile performance and power, such as MPARM [21], NIRGAM [25] and PrimeTime [26]. However, currently there is a lack of effective fault injection simulators based on system-level specification language, such as SystemC, offering high fault representation and minimum design intrusion.

#### 1.2 Thesis Overview and Contributions

This thesis presents novel and effective techniques for the design of low power and reliable MPSoCs. An overview of the following chapters highlighting their contributions follows. In Chapter 2, the fundamental concepts used in this work are introduced and a brief review of related previous works is presented (further reviews of related works

are presented in each of the following chapters). Chapter 3 presents a prototype fault injection simulator using a novel fault injection technique. The fault injection is carried out through simulation command approach using SystemC description of the device under test. Comparisons with recently reported SystemC fault injection techniques show that the proposed fault simulator benefits from high fault representation, fast simulation speed and flexibility with different fault types and probabilities. The simulator is validated using an MPEG-2 video decoder and other examples. Chapter 4 highlights comparative performance and reliability analysis between traditional advanced microprocessor bus architecture (AMBA) and emerging network-on-chip (NoC) architecture using real application traffic based on MPEG-2 video decoder. The comparisons are carried out using SystemC cycle-accurate realistic simulations and fault injection experiments employing the fault injection simulator presented in Chapter 3. It is shown that NoC outperforms AMBA in terms of application performance. Furthermore, comparative reliability analyses between the two on-chip communication architectures show that NoC outperforms AMBA in terms of the number of soft errors experienced due to less execution time in NoC.

Chapter 5 outlines the relationship between application-level correctness and systemlevel power management using voltage scaling technique. Using this relationship, a voltage scaling technique is proposed to generate designs that are optimised in terms of power consumption, while providing acceptable application-level correctness and realtime performance. The effectiveness of the proposed technique is evaluated using an MPEG2 video decoder and synthetic application examples. Using peak signal-to-noise ratio (PSNR) as an application-level correctness metric for MPEG-2 decoder it is shown that the proposed voltage scaling technique can significantly reduce power consumption, while maintaining acceptable application-level correctness and meeting real-time performance constraint. Furthermore, the impact of application task mapping (distribution of application tasks among processing cores in an MPSoC) and architecture allocation (choice of number of processing cores in an MPSoC) is investigated on the trade-offs between the application-level correctness and power consumption. Chapter 6 examines the impact of application task mapping on system reliability in the presence of singleevent upsets (SEUs). Based on this study, a novel soft error-aware design optimisation technique is proposed using joint power minimisation and reliability improvement. The power minimisation is carried out using voltage scaling technique and reliability improvement is achieved using application task mapping. The aim is to minimise the number of SEUs experienced by an MPSoC application, while providing low power consumption under a real-time constraint. To evaluate the effectiveness of the proposed design optimisation, different experiments are carried out using a number of applications, including MPEG-2 video decoder and random task graphs. Chapter 7 presents a summary of the thesis along with future and worthy research areas to improve power minimisation and reliability of MPSoCs. The details of the application and simulation models used in the

thesis are described in Appendices A, B and C.

The following peer-reviewed publications have been generated from the research work carried out in this thesis:

- **Shafik, R. A.** and Al-Hashimi, B. M. (In Press) Reliability Analysis of On-Chip Communication Architectures: An MPEG-2 Decoder Case Study. *Elsevier Journal of Embedded Hardware Design (MICPRO)*.

- Shafik, R. A., Al-Hashimi, B. M. and Chakrabarty, K. (2010) Soft Error-Aware Design Optimization of Low Power and Time-Constrained Embedded Systems. In: *International Conference on Design, Automation and Test in Europe (DATE)*, 2010, Dresden, Germany, pp.1462-1467.

- **Shafik, R. A.**, Al-Hashimi, B. M., Kundu, S. and Ejlali, A. (2009) Soft Error-Aware Voltage Scaling Technique for Power Minimization in Application-Specific MPSoC. *ASP Journal of Low Power Electronics (JOLPE)*, vol. 5, no. 2, pp. 145-156.

- Shafik, R. A. and Al-Hashimi, B. M. (2009) Comparative Reliability Analysis between AMBA and Network-on-Chip: An MPEG-2 Case Study. In: *International System-on-Chip Conference (SOCC)*, 9-11 September, 2009, Belfast, Northern Ireland, pp. 247-250.

- **Shafik, R. A.**, Rosinger, P. and Al-Hashimi, B. M. (2008) SystemC-based Fault Injection Technique with Improved Fault Representation. In: *European Test Symposium* (ETS), May 25-28, Italy.

- **Shafik, R. A.**, Rosinger, P. and Al-Hashimi, B. (2008) SystemC-based Minimum Intrusive Fault Injection Technique with Improved Fault Representation. In: *International On-line Test Symposium (IOLTS)*, 7-9 July, 2008, Rhodes, Greece. pp. 99-104.

- **Shafik, R. A.**, Rosinger, P. and Al-Hashimi, B. M. (2008) MPEG-based Performance Comparison between Network-on-Chip and AMBA MPSoC. In: *IEEE Design and Diagnostics of Electronic Circuits and Systems (DDECS)*, 16-18 April, 2008, Bratislava, Slovakia. pp. 98-103.

The following publication is currently under preparation:

**Shafik, R. A.**, Al-Hashimi, B. M. and Chakrabarty, K. (under preparation) Design Optimization of Low Power, Reliable and Time-Constrained Embedded Systems. to be submitted to *IEEE Transactions on Very Large Scale Integration Circuits (TVLSI)*.

### Chapter 2

## Background and Previous Works

This chapter introduces the fundamental concepts involved in this thesis and presents a review of the previous works. The remainder of this chapter is organised as follows. Section 2.1 introduces MPSoC platform and different on-chip communication architectures. Section 2.2 presents the principles of low power design and Section 2.3 introduces reliability and fault injection techniques. Section 2.4 describes the system-level design techniques. Finally, Section 2.5 gives a review of the previous works relevant to the presented research.

#### 2.1 Multiprocessor System-on-Chip

To accommodate more functionality meeting the needs of increased complexity of applications, multiprocessor system-on-chip (MPSoC) is emerging as a popular embedded systems platform [5]. MPSoC contains multiple processing elements on a single piece of silicon, each with an assigned task to define an expected application domain. The inclusion of multiple processing elements in MPSoCs has a number of benefits, including parallel processing, low clock speed and low power consumption [4]. Figure 2.1 shows an MPSoC with two processors, viz. digital signal processor (DSP) and microcontroller unit (MCU), a memory and an application-specific integrated circuit (ASIC). The interconnection of these components within the MPSoC is controlled by on-chip communication architecture. Since on-chip communication architecture defines how inter-component communication takes place, it greatly influences the underlying performance of the system. Currently, there are three major on-chip communication architectures for MP-SoCs: point-to-point (P2P), on-chip bus and network-on-chip (NoC). The P2P on-chip communication architecture lays out dedicated interconnects between each communicating component within an MPSoC. Such interconnection results in poor scalability and as such P2P architectures are generally not suited for MPSoCs [6]. The advanced

Figure 2.1: An example MPSoC showing different components and on-chip communication architecture

microprocessor bus architecture (AMBA) is a dominant, industrial standard on-chip bus architecture for today's MPSoCs, which offers good connectivity and scalability. Network-on-chip is an emerging on-chip communication architecture for the present and future MPSoCs. In the following, AMBA and NoC are briefly introduced.

#### 2.1.1 Advanced Microprocessor Bus Architecture

The advanced microprocessor bus architecture (AMBA) protocol [27] is an open standard, on-chip bus specification that details a strategy for the interconnection and management of functional blocks of a system-on-chip (SoC). AMBA uses a set of signals connected with all other communicating modules, called bus, as the main interconnection unit. Four distinct buses are defined within the AMBA specification [27]: a) the advanced high-performance bus (AHB), b) the advanced system bus (ASB), c) the advanced peripheral bus (APB), and recently specified d) advanced extensible interface (AXI). In this work, AMBA AHB has been chosen as the shared-bus architecture due to its high performance and high clock-frequency [18].

The AMBA AHB bus protocol is designed to be used with a central multiplexor interconnection scheme among various components, including masters (e.g. processing elements, microcontrollers) and slaves (e.g. memory, peripherals). Figure 2.2 shows a block diagram of the interconnection scheme used in AMBA. Using such scheme all bus masters drive out the address (HADDR) and control signals (Read: RD, Write: WR) to the address/control multiplexor indicating the transfer they wish to perform. The arbiter determines which master has its address from address/control multiplexor and routes the control signals (Read: RD, Write: WR) to all slaves. Each of the master

FIGURE 2.2: Block diagram of AMBA AHB central multiplexing scheme connecting arbiter, decoder, masters and slaves

HWDATA interface (for write data interface) is connected to the slaves through AMBA write data multiplexor. Similarly, the HRDATA interfaces (for read data interface) from slaves is connected to the masters through a read data multiplexor. A central decoder is required to control the read data multiplexor and select the appropriate signals from the slave that is involved in the transfer (Figure 2.2).