# MOOSE: A Physically Based Compact DC Model of SOI LDMOSFETs for Analogue Circuit Simulation

Nele V. T. D'Halleweyn, James Benson, William Redman-White, *Member, IEEE*, Ketan Mistry, and Maarten Swanenberg

Abstract-In this paper, we present a compact model for silicon-on-insulator (SOI) laterally double diffused (LD) MOSFETs. The model is complete insofar as it uses no subcircuits, and is intended to predict device operation in all regions of bias. The device current is described by two main equations handling the MOS channel and the drift region, both of which are smooth and continuous in all operating regimes. Attention is also given to the modeling of inversion at the back oxide to ensure correct behavior is predicted for a source follower in power control applications ("high side operation"). A surface-potential-based formulation is used for the inversion/accumulation channel giving smooth transitions between different regions of operation, and care has been taken to ensure all expressions are smooth and infinitely differentiable to achieve the best possible convergence performance. Self (and coupled) heating effects exert a major influence over the behavior of power SOI devices, and these issues are incorporated in the model core in a consistent fashion. The model has been installed in a commercial SPICE-type circuit simulator and evaluated against individual devices and complete circuits fabricated in an industrial smart power SOI process. Accuracy is significantly improved with respect to the existing LDMOS models, and convergence behavior in switching and linear circuit simulations is comparable with industry standard models of this complexity.

*Index Terms*—Analogue circuits, compact models, laterally double diffused (LD) MOSFET, MOS devices, silicon-on-insulator technology, simulation.

# I. INTRODUCTION

S THE scaling down of smart power ICs is gaining in importance, silicon-on-insulator (SOI) technology is becoming more attractive. Compared with a bulk technology, SOI offers a far better isolation scheme [1] leading to improved circuit density, and exhibits a significantly lower on-resistance for source-high conditions [2].

Manuscript received November 20, 2002; revised December 12, 2003. This paper was recommended by Associate Editor S. Saxena.

- N. V. T. D'Halleweyn was with the Microelectronics Centre, Department of Electronics and Computer Science, University of Southampton SO17 1BJ, UK. She is now with Arnold en Siedsma, 2018 Antwerp, Belgium.

- J. Benson was with the Microelectronics Centre, Department of Electronics and Computer Science, University of Southampton SO17 1BJ, United Kingdom. He is now with the Advanced Technology Institute, University of Surrey, Guildford GU2 7XH, UK (e-mail: j.benson@eim.surrey.ac.uk).

- W. Redman-White is with the Microelectronics Centre, Department of Electronics and Computer Science, University of Southampton SO17 1BJ, UK.

- K. Mistry was with the Microelectronics Centre, Department of Electronics and Computer Science, University of Southampton SO17 1BJ, UK. He is now with the Department of Electronic and Electrical Engineering, University College Dublin, Dublin, Ireland.

- M. Swanenberg is with Philips Semiconductors, 6534 AE Nijmegen, The Netherlands.

Digital Object Identifier 10.1109/TCAD.2004.835125

The LDMOS transistor is one of the key devices in high voltage (HV) ICs, and a good model is indispensable in order to perform accurate circuit design. Some subcircuit models for bulk and SOI LDMOS devices are available, but, when certain specific aspects of device behavior become critical, they are not always sufficient. Moreover, they also suffer from a higher degree of complexity, compared with a compact model and, hence, an increase in computation time and a more complex parameter extraction procedure. The need for an accurate, robust compact model is therefore apparent.

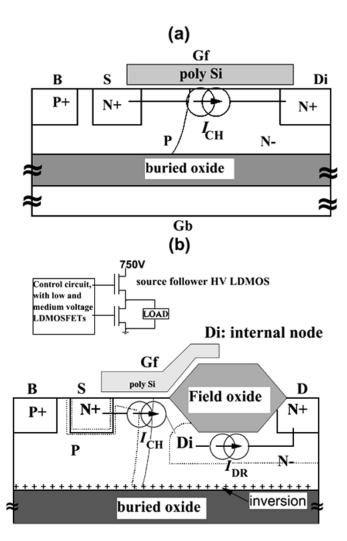

In the general class of SOI LDMOS devices with a constant doping profile in the drift region, two different structures can be distinguished, each designed for a different range of drain voltages. The first type does not contain a field oxide, and the thin gate oxide extends over the drift region all the way to the drain. This device is illustrated in Fig. 1(a) and will be referred to as the low voltage (LV) SOI LDMOS. In the second type, a thicker oxide (field oxide) is grown on the drift region to bend back the equipotential lines and reduce the fringing fields at the edge of the polysilicon gate. This construction is shown in Fig. 1(b) and will be referred to as the medium voltage (MV) LDMOS. Note that the model can also be used for the offset drain structure, being the MV structure with the thickness of the field oxide being zero. HV LDMOS transistors often have a graded doping profile in the drift region to fullfill the conditions of the RESURF principle [3], [4], or use superjunction techniques [5]. At present, these HV devices are very technology dependent, and it would be difficult to develop one general model for this type of device; this task is left for a succeeding research project.

Compact models for SOI LDMOS transistors have received much attention in the literature [6]–[10]. The main difference between SOI and bulk structures is to be found in the drift region; for SOI, the lightly doped drift region rests on a thick oxide, while, in a bulk device, it sits on top of a *P*-type substrate. The modeling of the MOS channel part with the doping gradient in the inversion channel is similar for both technologies. The vertical and lateral bulk DMOS models from the University of Florida [6]–[9] take this lateral doping gradient in the channel into account, albeit only partly. In the Motorola LDMOS model [10] this gradient can be accounted for by partitioning the channel into regions of constant doping, and thus creating more internal nodes; this is accurate, but increases the computation time considerably.

Our model aims to describe in particular LV and MV SOI LDMOS transistors, which have a constant doping concentration in the drift region. Particular emphasis has been placed on

Fig. 1. Definition of the dc currents: (a) LV LDMOS and (b) MV LDMOS working under high side conditions.

the behavior and circuit-level modeling issues related to highside drive applications, and on the self- and mutual heating. For the N-type LDMOS, high-side operation increases the on-resistance and demands specific modeling effort. To describe accurately the behavior of the MV SOI LDMOS, we use two current equations, both of which are smooth and continuous in all regions of operation. These two current expressions have been matched consistently with the help of limiting procedures and an accurate prediction of the internal node voltage. MOOSE can be made to converge more quickly than a compound subcircuit model, since the internal node voltage is set automatically to some reasonable initial estimate, calculated within the model.

Although it is not intended to be the main focus of this paper, a comparison between the two types of models was made by constructing subcircuit models and comparing their performance with the MOOSE compact model when running single device and test circuit simulations [11]. That subcircuit models are subject to a higher risk of convergence failure was indeed confirmed. Furthermore, the subcircuit models were found to be somewhat limited in the types of physical effects that could be modeled. For instance, accurate modeling of self-heating effects was not possible, unless a separate thermal node was added to each device model. Charge modeling was also problematic. Additionally, more parameters were required, and these tended to be less physical than in a compact model, and more difficult to extract. Despite these drawbacks, the subcircuit models still managed to provide good agreement with DC measurements, and reasonable matching for transient and AC results. The issue of poor convergence speed could not however be resolved using these models; we now turn our attention to the development of our compact model.

In Section II, we develop the first current expression  $(I_{CH})$ , which describes the LV LDMOS part, including the drift region under the thin gate oxide. The formulation for the current under the thin gate oxide is surface potential based, and models both the drift and diffusion currents in all operating regions. Care has been taken to use only continuous and infinitely differentiable expressions. Furthermore, the model ensures a smooth transition between subthreshold and strong inversion and between triode and saturation. Both the lateral doping gradient in the channel and the overlap of the thin gate oxide over the drift region are accounted for in a compact and physical manner.

In Section III, we explain the second expression  $(I_{DR})$ , which models the drift region under the field oxide and includes highside behavior. By using both the potential in the drift region and the surface potential at the surface of the buried oxide, we ensure a purely physical prediction of the unique high-side behavior observed in the SOI LDMOS. Fig. 1 illustrates where  $I_{\rm CH}$  and  $I_{\rm DR}$  are applicable in the LV and MV SOI LDMOS structures.

The MOOSE model combines an electrical model with a thermal network to model self- and coupled heating effects in a consistent manner. In Section IV, the implementation of the internal thermal netlist is discussed.

The model has been implemented in the SPICE circuit simulator and careful formulation and coding has led to a very robust SOI LDMOS model, which converges easily without the frequent need for node setting commands. The model has been thoroughly evaluated, both qualitatively, using a set of simulations based on the SEMATECH tests [12], and quantitatively, verifying single device characteristics against measurements for different geometries. Some key results are presented in Section V.

## II. CURRENT UNDER THIN-GATE OXIDE $(I_{CH})$

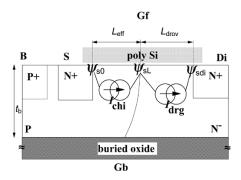

To derive  $I_{\rm CH}$ , we define first the surface potentials with respect to the P-body (B), in all regions of operation. The different symbols used in this section are defined in Fig. 2. We consider three regimes, these being strong inversion, subthreshold, and saturation. Using a logarithmic smoothing function to join the various components, we arrive at the following expression [13]:

$$\psi_{s0} = \phi_t \ln \left( 1 + \frac{\exp\left(\frac{\psi_{si0}}{\phi_t}\right)}{1 + \exp\left(\frac{\psi_{si0} - \psi_{ss0}}{\phi_t}\right)} \right)$$

$$\psi_{sL} = \phi_t \ln \left( 1 + \frac{\exp\left(\frac{\psi_{siL}}{\phi_t}\right)}{1 + \exp\left(\frac{\psi_{siL} - \psi_{sLsatf}}{\phi_t}\right)} \right)$$

(2)

$$\psi_{sL} = \phi_t \ln \left( 1 + \frac{\exp\left(\frac{\psi_{siL}}{\phi_t}\right)}{1 + \exp\left(\frac{\psi_{siL} - \psi_{sLsatf}}{\phi_t}\right)} \right)$$

(2)

$$\psi_{\text{sdi}} = V_{\text{DiB}} + \phi_{\text{bid}} \tag{3}$$

Fig. 2. Symbols used for the calculation of  $I_{CH}$ .

where  $\phi_t$  is a smoothing parameter equal to the thermal voltage,  $\phi_{\rm t} = (kT/q)$ . The expression for  $\psi_{\rm sLsatf}$  is developed in Section II-D. It is shown that  $\psi_{sLsatf} = \psi_{ss0}$  in the subthreshold region and  $\psi_{\mathrm{sLsatf}} = \psi_{\mathrm{sLsat}}$  in the saturation regime. For more details about the physical background, refer to [14].

#### A. Inversion-Channel Current

Using standard assumptions for MOSFETs [14], the inversion-channel current can be expressed using the classic chargesheet model [15]. Using the electron continuity equation [16] and neglecting recombination and generation currents yields

$$I_{\text{chi}} = \frac{W}{L_{\text{eff}}} \left( -\int_{\psi_{s0}}^{\psi_{\text{sL}}} \mu_{s}(y) q_{\text{cinv}}(y) \cdot d\psi_{s} + \phi_{t} \int_{q_{0}}^{q_{\text{L}}} \mu_{s}(y) \cdot dq_{\text{cinv}} \right)$$

(4)

where  $q_{\rm cinv}(y)$  is the channel charge density,  $\psi_{\rm s}$  the surface potential at position  $y, \mu_s(y)$  the surface mobility, and  $L_{\text{eff}}$  the effective length of the channel, defined by the length of the underdiffusion of the P-well minus the underdiffusion of the  $N^+$ source well ( $L_{\text{eff}} = L - L_{\text{D}}$ ).  $q_{\text{cinv}}$  is denoted by  $q_0$  at y = 0and by  $q_L$  at  $y = L_{\text{eff}}$ .

The mobility is initially assumed to be constant along the channel. Using the depletion approximation, which assumes that the depletion region under the gate is free of mobile carriers [17], the inversion channel charge can be obtained as

$$q_{\text{cinv}}(\psi_{s}, y) = -C_{\text{of}} \cdot (V_{g} - \psi_{s} - \gamma(y)\sqrt{\psi_{s}})$$

(5)

with  $V_{\rm g} = V_{\rm GfB} - V_{\rm FB}^{\rm f}$ ,  $C_{\rm of}$  the thin-gate oxide capacitance per unit area, and the body factor  $\gamma(y)$  is given by  $(\sqrt{2q\,\epsilon_{\rm si}N_{\rm A}(y)})/(C_{\rm of}).$

In order to get an analytic closed-form expression for the saturation voltage when including high field effects (see Section II-D), the body charge is linearized using a Taylor expansion for the square root term [18]

$$q_{\rm b} = C_{\rm of} \gamma \sqrt{\psi_{\rm s}}$$

$$\cong C_{\rm of} \gamma \cdot \left( \sqrt{\psi_{\rm s0}} + \delta \cdot (\psi_{\rm s} - \psi_{\rm s0}) \right)$$

(6)

$$(7)$$

$$\cong C_{\rm of}\gamma \cdot \left(\sqrt{\psi_{\rm s0}} + \delta \cdot (\psi_{\rm s} - \psi_{\rm s0})\right) \tag{7}$$

with  $\delta = (1)/(2\sqrt{1+\psi_{s0}})$ .

The LDMOS has a nonuniformly doped channel region, starting at the end of the  $N^+$  source diffusion and ending where the P-implant equals the N-type background doping. Thus, the doping concentration along the channel has a maximum near the source  $(N_A(0) = N_{As})$  and decreases sharply toward the drain  $(N_{\rm A}(L_{\rm eff})=N_{\rm Ad})$ . The lateral doping gradient in the channel  $(k_{N_A})$  is brought in by means of  $\gamma(y)$ , which is a function of  $N_A(y)$  and thus of the position y along the channel. In order to perform the integration of (4),  $q_{\rm cinv}$  is needed in terms of  $\psi_s$  only, or in other words, we have to transform  $\gamma(y)$ to  $\gamma(\psi_s)$ . This can only be done under certain assumptions, which are set out below.

The doping profile is assumed to be exponential  $(N_A =$  $N_{\rm As} \exp(-k_{\rm N_A}(y)/(L_{\rm eff})))$  [9], [8] and hence

$$\gamma(y) = \gamma_0 \exp\left(-\frac{k_{\text{N}_A}y}{2L_{\text{eff}}}\right) \cong \gamma_0 \cdot \left(1 - \frac{k_{\text{N}_A}y}{2L_{\text{eff}}}\right)$$

(8)

with  $\gamma_0 = (\sqrt{2q\epsilon_{\rm si}N_{\rm As}})/(C_{\rm of})$ . To transform  $\gamma(y)$  into  $\gamma(\psi_{\rm s}), \psi_{\rm s}$  is assumed to be a linear function of y, i.e.,

$$\psi_{\rm s} = \psi_{\rm s0} + \frac{y}{L_{\rm off}} (\psi_{\rm sL} - \psi_{\rm st0}).$$

(9)

This yields

$$\gamma(\psi_{\rm s}) = \gamma_0 \cdot \left(1 - \frac{k_{\rm NA}}{2(\psi_{\rm sL} - \psi_{\rm s0})} (\psi_{\rm s} - \psi_{\rm s0})\right).$$

(10)

In a standard MOSFET with a constant doping in the channel, the linearity of  $\psi_s$  with y is accurate for low drain biases, but deteriorates toward higher drain biases. However, a decreasing doping concentration in the channel causes a reduced field effect, giving a reasonable linearity for higher drain biases. This has been confirmed using ATLAS simulations [11]. Furthermore, the MOS part of the LDMOS never reaches very deep saturation because the main part of the applied voltage drops over the drift region.

Using (10) and (7), the inversion channel density can be expressed as a function of  $\psi_s$  only. Substituting this expression into (4) results in a closed-form continuous equation, which can be used for the inversion-channel current in all regions of operation

$$I_{\text{chi}} = \beta \cdot \left( g \cdot (\psi_{\text{sL}}^2 - \psi_{\text{s0}}^2) + f \cdot (\psi_{\text{sL}} - \psi_{\text{s0}}) \right) \tag{11}$$

with

$$\beta = \frac{W}{L_{\text{eff}}} \mu_{\text{s}} C_{\text{of}} \tag{12}$$

$$g = -\frac{1}{2}\eta_{\rm s} + \gamma_0 \delta \cdot \left(\frac{1}{6}k_{\rm N_A} - \frac{1}{2}\right) \tag{13}$$

$$f = f_1 + f_2 \tag{14}$$

$$f_1 = V_{\rm g} - \gamma_0 \sqrt{\psi_{\rm s0}} \left( 1 - \frac{k_{\rm N_A}}{4} \right) + \left( 1 - \frac{k_{\rm N_A}}{3} \right) \gamma_0 \delta \psi_{\rm s0}$$

(15)

$$f_2 = \phi_{\rm t} \cdot \left( \eta_{\rm s} + \gamma_0 \delta - \frac{1}{2} \gamma_0 k_{\rm N_A} \delta \right) \tag{16}$$

where  $\eta_s$  accounts for the influence of the fast surface states at the silicon-oxide interface [16]. Note that  $\beta$  can be recognized as the inversion layer gain factor.

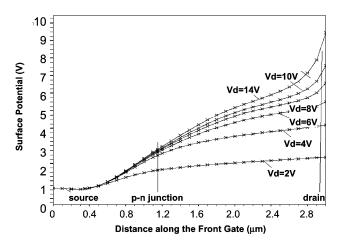

Fig. 3. ATLAS simulation of the depletion layers and the surface potential under the front gate ( $V_{\rm GfB}=4$  V).

#### B. Accumulation/Drift Current Under Thin Gate Oxide

In linear region operation, an accumulation layer exists in the drift region under the thin oxide, and this has a significant impact on device behavior. In bulk and SOI compact models published so far [7], [9], [19] this effect is neglected, or else an additional current source is added [10], slowing down convergence. In this work, we handle the issue analytically without introducing an extra node.

Since the length of this part of the drift region  $(L_{\rm drov})$  is typically comparable with the channel length, we assume that the channel current saturates before the accumulation layer starts to disappear at the drain, and ATLAS [20] simulations confirm the validity of this approach (Fig. 3). Further, when looking at the measured output characteristics of an LV LDMOS (see Fig. 8), it can be observed that the current saturates before  $V_{\rm DiS}$  reaches  $V_{\rm GfS}-V_{\rm FB}^{\rm fdr}$ .

Neglecting the diffusion current and assuming that the surface is completely accumulated, the current in the drift region under the front gate can be expressed by [21]

$$I_{\rm drg} = -\frac{W}{L_{\rm drov}} \int_{\psi_{\rm sL}}^{\psi_{\rm sdi}} \left( \mu_{\rm dr} q_{\rm b}^{\rm dr} + \mu_{\rm acc} q_{\rm cacc} \right) \cdot d\psi_{\rm s}. \tag{17}$$

where  $\mu_{\rm dr}$  is the low field mobility in the drift region,  $\mu_{\rm acc}$  is the surface mobility in the accumulation region, and  $q_{\rm b}^{\rm dr}$  is the free bulk charge density in the  $N^-$  region, and  $q_{\rm cacc}$  the surface accumulation charge density:

$$q_{\rm b}^{\rm dr} = q N_{\rm D} t_{\rm b} f_{\rm v},\tag{18}$$

$$q_{\text{cacc}} = C_{\text{of}} \cdot \left( \left( V_{\text{GfB}} - V_{\text{FB}}^{\text{f}} \right) - \psi_{\text{s}} \right) \tag{19}$$

where  $N_{\rm D}$  is the doping concentration in the drift region and  $f_{\rm v}$  is a fitting parameter taking into account the fact that the current flow is partially vertical. This is due to the current flow lines being longer than  $L_{\rm drov}$ , especially when  $L_{\rm drov}$  is of the same order as the silicon film thickness  $t_{\rm b}$ . When  $L_{\rm drov}$  is considerably larger than  $t_{\rm b}$  this factor should approach one.

To ensure zero model current when  $V_{\rm DiS}=0$ , we use  $\psi_{\rm sdi}=V_{\rm DiS}+\psi_{\rm si0}$  instead of  $V_{\rm DiB}+\phi_{\rm bid}$ . The difference between

$\phi_{\rm bid}=\phi_{\rm F}+\phi_{\rm Fdr}$  and  $2\phi_{\rm F}$  is usually negligible (<0.1 V), because, considered on a logarithmic scale, the doping concentrations of the P-body and the  $N^-$  drift region are comparable.

After integration of (17) we obtain

$$I_{\rm drg} = h_1 \cdot (V_{\rm DiS} + \psi_{\rm si0} - \psi_{\rm sL}) + h_2 \cdot ((V_{\rm DiS} + \psi_{\rm si0})^2 - \psi_{\rm sL}^2)$$

(20)

with

$$h_1 = \frac{f_{\rm v}}{R_{\rm ON}} + \beta_{\rm acc} \cdot \left(V_{\rm GfB} - V_{\rm FB}^{\rm f} + (\psi_{\rm si0} - V_{\rm SB})\right) \tag{21}$$

$$h_2 = -\frac{1}{2}\beta_{\rm acc} \tag{22}$$

$$\beta_{\rm acc} = \frac{\bar{W}}{L_{\rm drov}} \mu_{\rm acc} C_{\rm of} \tag{23}$$

$$R_{\rm ON} = \left(\frac{W}{L_{\rm drov}} \mu_{\rm dr} q N_{\rm D} t_{\rm b}\right)^{-1}.$$

(24)

This expression completely describes the drift current under the thin gate oxide with a second order equation in the surface potentials  $\psi_{\rm sL}$  and  $\psi_{\rm sdi}.$  Note that  $R_{\rm ON}$  can be recognized as the ON-resistance of the drift region under the thin gate oxide under zero bias conditions, and  $\beta_{\rm acc}$  is the accumulation layer gain factor.

# C. Solving for Surface Potential at the End of the Inversion Channel

Having obtained expression for the inversion-layer channel current  $(I_{\rm chi})$  and the drift current under the thin-gate oxide  $(I_{\rm drg})$ , an analytical expression for the surface potential at the P-N junction  $(\psi_{\rm sL})$  can be derived. To find  $\psi_{\rm sL}$  when the channel is in strong inversion  $(\psi_{\rm s0}=\psi_{\rm si0},\psi_{\rm sL}=\psi_{\rm siL}^*)$ , (11) is equated to (20),  $I_{\rm drg}=I_{\rm chi}$  and yields  $\psi_{\rm siL}^*$  as a function of the known surface potentials  $\psi_{\rm si0}$  and  $\psi_{\rm sdi}$

$$\psi_{\rm siL}^* = \frac{-\frac{B}{2} + \sqrt{\frac{B^2}{4} - AC^*}}{A} \tag{25}$$

with

$$A = g + G \tag{26}$$

$$B = f + F \tag{27}$$

$$C^* = -(g\psi_{si0}^2 + f\psi_{si0}) - F \cdot (V_{DiS} + \psi_{si0}) - G \cdot (V_{DiS} + \psi_{si0})^2$$

(28)

$$G = -\frac{\beta_{\text{acc}}}{2\beta} \tag{29}$$

$$F = \frac{f_{\rm v}}{\beta R_{\rm ON}} + \frac{\beta_{\rm acc}}{\beta} \left( V_{\rm GfB} - V_{\rm FB}^{\rm f} + (\psi_{\rm si0} - V_{\rm SB}) \right). \tag{30}$$

#### D. Inclusion of High Field Effects

1) Vertical Field Mobility Reduction: Using the linearized expression for the body and the channel charge densities [(7) and (5)], the transverse electric field becomes [22]

$$\xi_{x} = -\frac{\zeta C_{\text{of}}}{\epsilon_{\text{si}}} \left\{ V_{\text{g}} - \psi_{\text{s}} - \gamma_{\text{m}} \cdot \left( 1 - \frac{1}{\zeta} \right) \left( \sqrt{\psi_{\text{s0}}} + \delta \right) \right\}$$

$$\cdot (\psi_{\text{s}} - \psi_{\text{s0}})$$

(31)

where  $\zeta$  is an empirical parameter, taking on the value (1/2) for electrons and (1/3) for holes, and a mean value for the body factor has been defined as  $\gamma_{\rm m} = (\gamma_0 + \gamma_{\rm L})/(2)$ .

Averaging  $\xi_{\rm x}$  over the length of the device and using this average in the expression for the effective mobility for an N-type device (assuming classical diffuse scattering at the Si-SiO<sub>2</sub> surface) yields

$\mu_{\text{xeff}}$

$$= \frac{\mu_{\rm s}}{1 + \theta \cdot \left(V_{\rm g} + \gamma_{\rm m} \cdot \left(\sqrt{\psi_{\rm s0}} - \delta \psi_{\rm s0}\right) - (1 - \gamma_{\rm m} \delta) \frac{\psi_{\rm s0} + \psi_{\rm sL}}{2}\right)}$$

(32)

with  $\theta$  the vertical field mobility coefficient. Note that it is important to include the linearized root terms in HV devices because the doping concentration of the P-body is often higher than for standard CMOS, leading to a higher body factor and hence an increased importance of these terms.

2) Carrier-Velocity Saturation: When the longitudinal field  $\xi_{\rm v}$  increases, the carrier velocity increases proportionally to the field strength, until eventually reaching the saturation velocity  $v_{\rm sat}$ . The critical field for which this happens is given by  $\xi_{\rm c}\cong$  $(v_{\rm sat})/(\mu_{\rm s})$ . This effect is modeled as [14]

$$\mu_{\text{yeff}} = \frac{\mu_{\text{S}}}{1 + \frac{\mu_{\text{s}}}{v_{\text{sat}}} \frac{\psi_{\text{sL}} - \psi_{\text{s0}}}{L_{\text{eff}}}}.$$

(33)

3) Combined Mobility Model: The two high-field effects give rise to (34), which is shown at the bottom of the page for the high-field effective mobility.

In [6], it is claimed that velocity saturation in LDMOS transistors occurs at the source side because the doping concentration is highest there, but this is not proven. The position of the lateral field maximum also depends on the applied biases and, on whether velocity saturation occurs before channel pinch-off, i.e., for very short channel length devices, the onset position will probably move along the channel. For long channel devices, pinch-off generally happens before velocity saturation, and velocity saturation takes place at the internal drain junction, where the lateral field is highest. Considering the above arguments, characterizing saturation by electron velocity saturation at a fixed position [6] is questionable. To find the saturation-surface potential at  $y=L_{\rm eff}$  , we search for the value of  $\psi_{\rm sL}$ for which the channel current reaches a maximum and avoid the problem of the peak position of the lateral field

$$\frac{\partial I_{\text{chi}}}{\partial \psi_{\text{sL}}} \bigg|_{\psi_{\text{sL}} = \psi_{\text{sL,sat}}} = 0.$$

(35)

If we consider only the drift part of the channel current, which means neglecting  $f_2$  in (14), we find

$$\psi_{\text{sLsat}} = \psi_{\text{s0}} + \frac{\psi}{S} \tag{36}$$

with

$$S = \frac{1}{2} + \frac{1}{2} \sqrt{1 + \frac{2\psi M_{\text{mob}}}{1 + \theta \cdot (V_{\text{g}} - \psi_{\text{s0}}) + \theta \gamma_{\text{m}} \sqrt{\psi_{\text{s0}}}}}$$

(37)

$$M_{\rm mob} = -\frac{\theta}{2} + \frac{1}{L_{\rm eff}\xi_c} + \theta\gamma_{\rm m}\frac{\delta}{2}$$

(38)

$$\psi = -\psi_{s0} - \frac{f_1}{2a}.\tag{39}$$

Let us now have a closer look at the expression for  $\psi$

$$\psi = -\psi_{s0} - \frac{f_1}{2q} \tag{40}$$

$$= \frac{V_{g} - \eta_{s}\psi_{s0} - \gamma_{0}\sqrt{\psi_{s0}}\left(1 - \frac{k_{N_{A}}}{4}\right)}{2g}$$

$$= \frac{\frac{q_{0}}{C_{of}} + \gamma_{0}\sqrt{\psi_{s0}}\frac{k_{N_{A}}}{4}}{2g}.$$

(41)

$$=\frac{\frac{q_0}{C_{\text{of}}} + \gamma_0 \sqrt{\psi_{\text{s0}}} \frac{k_{\text{NA}}}{4}}{2q}.$$

(42)

In the strong inversion case, the term  $\gamma_0\sqrt{\psi_{\rm s0}}(k_{

m N_A})/(4)$  can be neglected, compared with  $(q_0)/(C_{\rm of})$ . On the other hand, in the subthreshold case,  $q_0$  is zero, and neglecting the abovementioned term means  $\psi = 0$ . So, under subthreshold conditions, we find  $\psi_{\rm sLsat} = \psi_{\rm s0} = \psi_{\rm ss0}$ , which is what we want. Rewriting (36) without that term gives the final expression for the saturation surface potential at  $y = L_{\text{eff}}$

$$\psi_{\text{sLsatf}} = \psi_{\text{s0}} + \frac{V_{\text{g}} - \eta_{\text{s}}\psi_{\text{s0}} - \gamma_{0}\sqrt{\psi_{\text{s0}}}}{2aS}.$$

(43)

#### E. Calculation of the Saturation Voltage

In the previous section, the saturation surface potential at  $y = L_{\rm eff}(\psi_{\rm sLsatf})$  was calculated. To calculate the drain saturation voltage,  $V_{\rm dsat}$ , we look for  $V_{\rm DiS}=V_{\rm dsat}$  for which  $I_{\rm chi}(\psi_{\rm sLsatf}) = I_{\rm drg}(\psi_{\rm sLsatf}, V_{\rm DiS})$ . This results in

$$V_{\text{dsat}} = \frac{1}{G} \left( -\frac{F}{2} + \sqrt{R_{\text{s}}} \right) - \psi_{\text{s}0} \tag{44}$$

$$R_{\rm s} = \frac{F^2}{4} + G \cdot \left( g \cdot \left( \psi_{\rm sLsatf}^2 - \psi_{\rm s0}^2 \right) + f \cdot \left( \psi_{\rm sLsatf} - \psi_{\rm s0} \right) + \psi_{\rm sLsatf} \cdot \left( G \psi_{\rm sLsatf} + F \right) \right)$$

(45)

and F and G as defined by (30) and (29).

To attain a smooth transition from triode into saturation region a smoothing function is invoked to limit  $V_{DiS}$  to  $V_{dsat}$  [23]:

$$V_{\rm DiSn} = \frac{V_{\rm DiS}V_{\rm dsat}}{\left((V_{\rm DiS})^{2m} + (V_{\rm dsat})^{2m}\right)^{1/2m}}$$

(46)

with m an empirical parameter, which can take integer values only. For a short channel MOSFET, m=2 gives a good fit. For longer channel lengths, larger values of m must be used.

$$\mu_{\text{eff}} = \frac{\mu_{\text{s}}}{1 + \theta \cdot \left\{ V_{\text{g}} - \frac{\psi_{\text{sL}} + \psi_{\text{s0}}}{2} + \gamma_{\text{m}} \left( \sqrt{\psi_{\text{s0}}} + \frac{\delta}{2} (\psi_{\text{sL}} - \psi_{\text{s0}}) \right) \right\} + \frac{\mu_{\text{s}}}{v_{\text{sat}}} \frac{\psi_{\text{sL}} - \psi_{\text{s0}}}{L_{\text{eff}}}}$$

(34)

#### F. Total Current Expression

All the different aspects of the current under the thin-gate oxide studied in the previous sections can now be joined to give the final formulation as seen in (47), located at the bottom of the page with  $\psi_{\rm s0}$  and  $\psi_{\rm sL}$  given by (1) and (2). The expression for  $\psi_{\rm siL}$  is identical to  $\psi_{\rm siL}^*$  (25), with the difference that  $V_{\rm DiS}$  is replaced by  $V_{\rm DiSn}$  to include the saturation effects.

#### G. Auxiliary Model

The model also includes short and narrow channel effects, the channel-length modulation (CLM) effect, the DIBL effect, the parasitic bipolar effect, and impact ionization; these are all implemented in the same way as for standard SOI MOSFETs [14]. A couple of points need to be made however.

First, the CLM and DIBL effects in LDMOS transistors are much smaller than in a standard MOSFET because a large part of the drain voltage drops over the drift region. However, for low gate biases, it is important to take the CLM into account because it determines the value of the output conductance in the saturation regime.

Second, in LDMOS technology, it is common to place the body contact parallel with the source contact. This can lead to a relatively high body resistance, which is formed by the pinched region underneath the source junction. This body resistance, together with the impact ionization back gate current, can switch on the lateral parasitic bipolar transistor (BJT), and this can determine the safe operating area of the LV and MV LDMOS [24]. The safe-operating area is reduced further by self-heating; when the device heats up, the effective body source voltage necessary to trigger the parasitic BJT becomes smaller. Furthermore, because the BJT has a positive temperature dependent factor in the expression for the collector current, this effect can lead to early failure of the device.

#### III. DRIFT CURRENT UNDER THE FIELD OXIDE

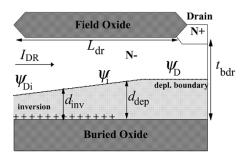

The current flow in the drift region is illustrated in Fig. 4. When the back gate voltage is negative, the surface at the buried oxide can be partially (as illustrated in Fig. 4) or fully inverted, depending on the channel potential  $\psi$ .

## A. Intrinsic Drift Current

Neglecting the diffusion contribution, the current can be written as in a depletion-type MOSFET with the back gate acting as the gate terminal [21]

$$I_{\rm DR0} = \frac{W}{L_{\rm dr}} \mu_{\rm dr} q N_{\rm D} \int_{\psi_{\rm Di}}^{\psi_{\rm D}} (t_{\rm bdr} - d(\psi)) \cdot d\psi \qquad (48)$$

where  $d(\psi)$  is the depletion layer thickness extending from the buried oxide into the silicon, and  $t_{\rm bdr}$  the silicon thickness under the field oxide. Refer to Fig. 4 for the channel potentials  $\psi_{\rm Di}$  and

Fig. 4. Current flow in the drift region under high side conditions.

$\psi_{\rm D}$ . In this section, all potentials are defined with respect to the neutral bulk potential minus  $\phi_{\rm bid}$ .

We consider two definitions for the depletion-layer thickness, before and after inversion. Before inversion this is given by [21]

$$d_{\rm dep} \cong \frac{C_{\rm ob}}{qN_{\rm D}}(-V_{\rm gb} + \psi) \tag{49}$$

with  $V_{\rm gb} = V_{\rm GbB} - V_{\rm FB}^{\rm bdr}$ , and  $C_{\rm ob}$  the buried oxide capacitance per unit area. In standard depletion-type MOSFET devices, the possibility of surface inversion is usually excluded for practical devices. However, when an LDMOS is working under high side conditions, the formation of an inversion layer is crucial to limit the further increase in ON-resistance. If the surface at the buried oxide is inverted, the depletion layer thickness  $d_{\rm inv}$  can be expressed as

$$d_{\rm inv} = \sqrt{\frac{2\epsilon_{\rm si}(2\phi_{\rm Fdr} + \psi)}{qN_{\rm D}}}$$

(50)

using the depletion-layer approximation from [17], and where the inversion surface potential is approximated as  $2\phi_{\rm Fdr}+\psi.$  To obtain closed-form analytical expressions for the saturation potentials in the next section, the square root of the surface potential is linearly approximated with a Taylor approximation around  $2\phi_{\rm Fdr}$

$$d_{\rm inv} \cong \sqrt{\frac{2\epsilon_{\rm si}}{qN_{\rm D}}} (\sqrt{2\phi_{\rm Fdr}} + \delta_{\rm dr}\psi)$$

(51)

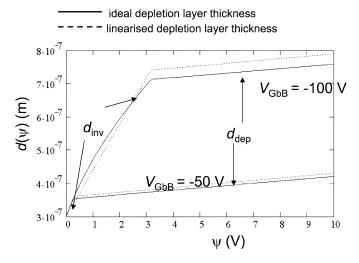

with  $\delta_{\rm dr}=(1)/(2\sqrt{1+2\phi_{\rm Fdr}})$ . In Fig. 5, the linearized and ideal depletion layer thicknesses  $d_{\rm dep}$  and  $d_{\rm inv}$  are compared for typical parameters. Very good agreement is obtained for low values of  $\psi$  and  $V_{\rm GbB}$ . For higher values, the deviation increases, but remains below 5%.

Using the linearized formulations for  $d(\psi)$  the integral in (48) can be rewritten as

$$\int_{\psi_{\text{Di}}}^{\psi_{\text{D}}} (t_{\text{bdr}} - d(\psi)) \cdot d\psi = t_{\text{bdr}} \cdot (\psi_{\text{D}} - \psi_{\text{Di}})$$

$$- \int_{\psi_{\text{Di}}}^{\psi_{\text{i}}} d_{\text{inv}}(\psi) \cdot d\psi - \int_{\psi_{\text{i}}}^{\psi_{\text{D}}} d_{\text{dep}}(\psi) \cdot d\psi \quad (52)$$

$$I_{\text{CH0}} = \frac{\beta}{1 + \theta \cdot \left\{ V_{\text{g}} - \frac{\psi_{\text{sL}} + \psi_{\text{s0}}}{2} + \gamma_{\text{m}} \cdot \left( \sqrt{\psi_{\text{s0}}} + \frac{\delta}{2} (\psi_{\text{sL}} - \psi_{\text{s0}}) \right) \right\} + \frac{\mu_{\text{s}}}{v_{\text{sat}}} \frac{\psi_{\text{sL}} - \psi_{\text{s0}}}{L_{\text{eff}}}} \cdot \left( g \cdot \left( \psi_{\text{sL}}^2 - \psi_{\text{s0}}^2 \right) + f \cdot (\psi_{\text{sL}} - \psi_{\text{s0}}) \right)$$

(47)

Fig. 5. Comparison of the linearized (dotted line) and ideal (full line) formulation of the depletion layer thickness:  $d(\psi)$  versus  $\psi$  for  $V_{\rm GbB}=-50$  V and -100 V.

where  $\psi_i$  is the potential at the end of the inversion layer as denoted in Fig. 4. This potential can be calculated from  $d_{\rm inv}(\psi_i) = d_{\rm dep}(\psi_i)$

$$\psi_{\rm i} = \frac{\gamma^{\rm bdr} \sqrt{2\phi_{\rm Fdr}} + V_{\rm gb}}{1 - \gamma^{\rm bdr} \delta_{\rm dr}}$$

(53)

with  $\gamma^{\rm bdr}=(\sqrt{2\epsilon_{\rm si}qN_{\rm D}})/(C_{\rm ob})$  being the back gate-body factor in the drift region. The potentials at the internal drain node and at the drain can be expressed in terms of the nodal voltages using  $\psi_{\rm Di}=V_{\rm DiB}$  and  $\psi_{\rm D}=V_{\rm DB}$ . Substituting (49), (51), and (53) into (52) results in

$$I_{\rm DR0} = \frac{1}{R_{\rm ON}^{\rm dr}} \left\{ V_{\rm DB} - V_{\rm DiB} - \frac{1}{V_{\rm Pdep}} (\gamma^{\rm bdr} H_{1t} + H_{2t}) \right\}$$

(54)

with

$$R_{\rm ON}^{\rm dr} = \frac{L_{\rm dr}}{W\mu_{\rm dr}qN_{\rm D}t_{\rm bdr}}$$

(55)

$$V_{\text{Pdep}} = \frac{qN_{\text{D}}t_{\text{bdr}}}{C_{\text{ch}}} \tag{56}$$

$$H_{1t} = \left( (V_{\text{DBf0}} - V_{\text{DiB}}) \sqrt{2\phi_{\text{Fdr}}} + \frac{\delta_{\text{dr}}}{2} \left( V_{\text{DBf0}}^2 - V_{\text{DiB}}^2 \right) \right)$$

(57)

$$H_{2t} = \frac{1}{2} \left( (-V_{gb} + V_{DB})^2 - (-V_{gb} + V_{DBf0})^2 \right)$$

(58)

and  $V_{\rm DBf0} = \min(V_{\rm DB}, \max(V_{\rm DiB}, \psi_{\rm i}))$ . The "min" and "max" functions describe a smooth and continuous minimum and maximum respectively. Note that  $R_{\rm ON}^{\rm dr}$  can be recognized as the ON-resistance of the drift region under zero bias conditions.  $V_{\rm Pdep}$  is the pinch-off voltage when the back surface is not inverted and  $V_{\rm gb} = 0$ .

#### B. Saturation by Pinch-Off

The maximum value for the depletion layer thickness is  $t_{\rm bdr}$ . Assume here that  $V_{\rm DB} > V_{\rm DiB}$ ; otherwise  $V_{\rm DB}$  and  $V_{\rm DiB}$  need only be swapped in the current equation. The pinch-off voltage  $V_{\rm Psat}$  can be found by equating  $d_{\rm dep}$  to  $t_{\rm bdr}$  if  $V_{\rm DiB} > \psi_{\rm i}$  (no inversion at the buried oxide), and  $d_{\rm inv}$  to  $t_{\rm bdr}$  in the inverse case. It can be shown [11] that  $V_{\rm Psat}$  is given by the maximum of

$$V_{\text{Psatdep}} = V_{\text{gb}} + V_{\text{Pdep}},$$

(59)

and

$$V_{\text{Psatinv}} = \frac{V_{\text{Pdep}} - \gamma^{\text{bdr}} \sqrt{2\phi_{\text{Fdr}}}}{\delta \gamma^{\text{bdr}}}.$$

(60)

To include saturation by pinch-off in the drift current expression,  $V_{\rm DiB}$  and  $V_{\rm DB}$  have to be limited smoothly [11] to  $V_{\rm Psat}$ .

# C. Velocity Saturation

For high drain biases the high field velocity saturation effects must be taken into account. Therefore, the low-field mobility  $\mu_{\rm dr}$  is replaced with [25]

$$\mu_{\text{dreff}} = \frac{\mu_{\text{dr}}}{1 + \theta_{3\text{dr}}(V_{\text{DB}} - V_{\text{DiB}})} \tag{61}$$

with  $\theta_{3dr} = (\mu_{dr})/(v_{satdr}L_{dr})$ , where  $v_{satdr}$  is the drift saturation velocity.

To calculate the saturation potential, we solve

$$\frac{\partial I_{\text{DR0}}}{\partial V_{\text{DB}}}\bigg|_{V_{\text{DB}}=V_{\text{out}}} = 0.$$

(62)

It can be proven [11] that the solution which is valid for all bias situations is shown in (63) at the bottom of the page with

$$V_{\text{DiB}}^{\text{e}} = \max\left(\min(V_{\text{DiBs}}, \psi_{i}), \psi_{i} - \sqrt{\frac{2}{\theta_{\text{2dr}}} \operatorname{pos}(V_{\text{Psatinv}} - \psi_{i})}\right)$$

(64)

where

$$\max(x, y, \epsilon) = x - 0.5((x - y) - \sqrt{(x - y)^2 + 4\epsilon^2})$$

(65)

$$\min(x, y, \epsilon) = x - 0.5((x - y) + \sqrt{(x - y)^2 + 4\epsilon^2})$$

(66)

with  $\epsilon$  being a fitting parameter. Here,  $V_{\rm DDi}$  is limited to  $V_{\rm sat}$  –  $V_{\rm DiB}$ .

#### IV. MODELLING HEATING EFFECTS

Self-heating effects are a well-known complicating factor for high-power dissipation levels in DMOS [26]–[28] and other HV devices [29]. In a SOI technology, the thermal resistance is much higher than in its bulk counterpart, especially for HV devices where the buried oxide layer can be reasonably thick.

$$V_{\text{sat}} = V_{\text{DiBs}} - \frac{1}{\theta_{\text{3dr}}} + \sqrt{\frac{1}{\theta_{\text{3dr}}^2} - 2\frac{V_{\text{DiBs}}}{\theta_{\text{3dr}}} + 2\frac{V_{\text{Psat}}}{\theta_{\text{3dr}}} + (\psi_{\text{i}} - V_{\text{DiB}}^{\text{e}})^2 (1 - \gamma^{\text{bdr}} \delta_{\text{dr}})}$$

(63)

The finite thermal capacitance prevents the device temperature from following the device power instantaneously, and so it is important to consider self-heating as a dynamic effect both in large and small signal terms [30]–[32]. The increase of the output conductance with frequency due to the thermal time constant (typically in the range of 100 kHz–1 MHz) is of extreme importance for analogue designers, since the output conductance determines the gain of any amplifier.

In ultrathin RESURF SOI LDMOS structures, the distribution of the heat generation in the drift region will be highly nonuniform, but will be reasonably constant in thicker SOI LDMOS devices [33], [34]. In compact models two-dimensional (2-D) heat-flow analysis [35] is too complicated, and it is usually preferred [14], [36] to assume thermal equilibrium and use an average temperature rise  $\Delta T$ .

A separate circuit is used to model the thermal behavior of a device [37], [38], consisting of a thermal resistance  $(R_{\rm T})$  and a thermal capacitance  $(C_{\rm T})$ . Only one time constant has been embedded in the model, but if more are needed [39], a higher order network can be added externally. The thermal node can also be connected to a thermal interconnection network for the simulation of static and dynamic thermal coupling between devices.

In the case of a first order thermal circuit, the simulated temperature rise is obtained from

$$P = \frac{\Delta T}{R_{\rm T}} + C_{\rm T} \frac{d(\Delta T)}{dt}.$$

(67)

The dissipated power in the SOI LDMOS is given by

$$P = I_{\rm CH} V_{\rm DiS} + I_{\rm DR} V_{\rm DDi}$$

(68)

from which the simulated temperature rise can be determined via (67). To find the small-signal equivalent, the thermal dissipation must be differentiated with respect to  $\Delta T, V_{\rm DiB}, V_{\rm GfB}, V_{\rm GbB}, V_{\rm DB}$ , and  $V_{\rm SB}$ , just as with all the other electrical current expressions in the compact model. The temperature rise is treated as another voltage for which SPICE has to solve, and the local device temperature rise is available to circuit designers as a terminal voltage. Thermal dependence of model parameters is also included [14].

#### V. VALIDATION

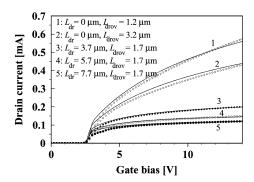

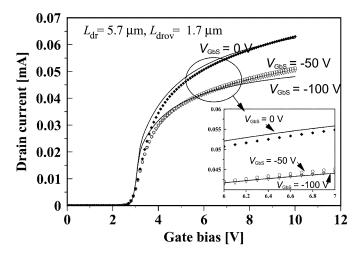

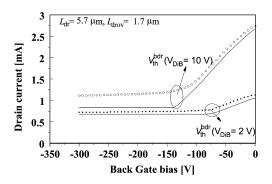

Test chips were fabricated using a commercial HV SOI process containing single LV and MV LDMOS structures with different geometries. In this section, the measured data from the single devices are presented compared with MOOSE simulations. LV LDMOS devices with two different overlap lengths ( $L_{\rm drov}=1.2~\mu{\rm m}$  and  $L_{\rm drov}=3.2~\mu{\rm m}$ , with  $L_{\rm dr}=0~\mu{\rm m}$ ) and MV LDMOS devices with three different drift lengths ( $L_{\rm dr}=3.7~\mu{\rm m}$ ,  $L_{\rm dr}=5.7~\mu{\rm m}$ , and  $L_{\rm dr}=7.7~\mu{\rm m}$ , with  $L_{\rm drov}=1.7~\mu{\rm m}$ ) were selected for study and represent a comprehensive range of geometries. Other relevant process details are: front gate oxide thickness  $t_{\rm of}=60~{\rm nm}$ , back gate oxide thickness  $t_{\rm ob}=3~\mu{\rm m}$ , silicon film thickness  $t_{\rm b}=1.5~\mu{\rm m}$ , silicon thickness under field oxide  $t_{\rm bdr}=1~\mu{\rm m}$ , and maximum doping concentration  $N_{\rm As}=10^{17}/{\rm cm}^3$ .

Fig. 6. Measured (markers) and simulated (full line) drain current in the linear region for different geometries and  $V_{\rm DS}=0.1$  V.

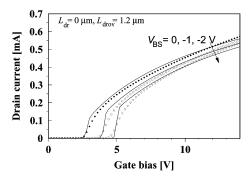

Fig. 7. Measured (markers) and simulated (full line) drain current in the linear region  $V_{\rm BS}=0$ , -1, -2 V, and  $V_{\rm DS}=0.1$  V.

The parameter extraction procedure used is very similar to the one used in compound models [40], although less parameters are required, which eases the optimization procedure.

# A. Linear Characteristics

The linear characteristic for different geometries is shown in Fig. 6. As can be seen, the MOOSE model matches the measured data very well in almost all regions.

Curves 1 and 2 show the drain-current decrease with increasing  $L_{\rm drov}$ , and curves 3–5 show the current decrease with increasing  $L_{\rm dr}$ . The match is very good for gate voltages more than 2 V above the threshold voltage but just above the threshold, the model slightly overestimates the measured current.

Fig. 7 shows the linear characteristic for different body voltages. Similar agreement is observed. The reason for overestimation in the simulated current has its origin in the approximation for the body factor employed in (10). Just above the threshold, the body factor is not exactly a linear function of the surface potential; the lower threshold at the drain end of the channel causes the inversion at the source end to be considerably less than at the drain end, and hence the main part of the drain voltage will drop over the source end of the inversion layer, becoming almost constant toward the point where  $y=L_{\rm eff}$ . Because of the assumption that  $\gamma$  is a linear function of  $\psi_{\rm s}$ , the inversion charge in the intergral of (4) will be overestimated just above the threshold for values between  $\psi_{\rm s0}$  and  $\psi_{\rm sL}$ , explaining the slightly overestimated current.

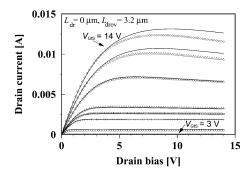

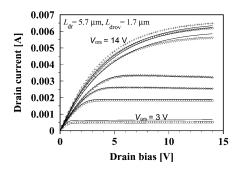

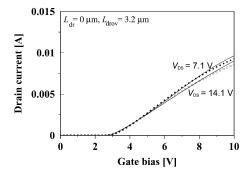

Fig. 8. LV LDMOS with  $L_{\rm drov}=3.2~\mu{\rm m}$ ; measured (markers) and simulated (full line) current vs.  $V_{\rm DS}$  for  $V_{\rm GfS}=3.5~{\rm V},4.5~{\rm V},5~{\rm V},5.5~{\rm V},8~{\rm V},11~{\rm V},$  and  $14~{\rm V}.$

Fig. 9. MV LDMOS with  $L_{\rm drov}=1.7~\mu{\rm m}$  and  $L_{\rm dr}=5.8~\mu{\rm m}$ ; measured (markers) and simulated (full line) current versus  $V_{\rm DS}$  for  $V_{\rm GFS}=3.5~{\rm V}, 4.5~{\rm V}, 5.5~{\rm V}, 8~{\rm V}, 11~{\rm V},$  and 14 V.

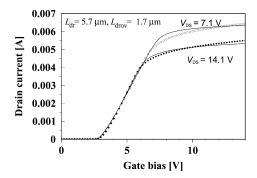

Fig. 10. LV LDMOS with  $L_{

m drov}=3.2~\mu{

m m}$ ; measured (markers) and simulated (full line) current versus  $V_{

m GfS}$  for  $V_{

m DS}=7.1~{

m V}$  and  $V_{

m DS}=14.1~{

m V}$ .

#### B. Output Characteristics

Output characteristics for the LV and MV LDMOS are shown in Figs. 8 and 9, respectively. In almost all cases, the model yields a good match with the measured data. The onset of saturation is well predicted, proving that pinch-off and saturation effects in the drift region are well modeled. For the LV LDMOS, the drain-saturation current keeps increasing with the gate bias, while for the MV LDMOS the drift region limits the current much more noticeably. The model predicts well the decrease in current due to self-heating, which can lead to a negative output resistance in some bias situations.

This is also shown in Figs. 10 and 11. Self-heating is very noticeable in these curves because, above a certain gate voltage, the curves cross each other, leading to a higher current for the lower drain bias.

Fig. 11. MV LDMOS with  $L_{\rm drov}=1.7~\mu{\rm m}$  and  $L_{\rm dr}=5.8~\mu{\rm m}$ ; measured (markers) and simulated (full line) current versus  $V_{\rm GfS}$  for  $V_{\rm DS}=7.1~{\rm V}$  and  $V_{\rm DS}=14.1~{\rm V}$ .

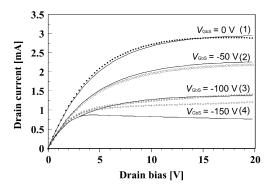

Fig. 12. Measured (markers) and simulated (full line) current for  $V_{\rm GfS}=10$  V and  $V_{\rm GbS}=0$  V, -50 V, -100 V, and -150 V.

#### C. High-Side Behavior

Fig. 12 shows the device operated under high-side conditions. We observe a current decrease with increasingly negative back gate bias (i.e., substrate bias), but when inversion is established, the back gate voltage no longer influences the drain current. Good agreement is found between the simulated and measured data for curves 1–3. However, measured curve 4 has a positive slope, while the simulated curve 4 has saturated and has a negative slope; this latter effect is due to self-heating and is masked prior to current saturation. One would expect the current for measured curve 4 to also have saturated due to pinch-off of the drift region, so that the current decreases with increasing  $V_{\rm DS}$ . In reality, 2-D effects in the drift region may change the field distribution when  $V_{\rm DS}$  is increased, or else enhanced CLM may occur with increasing back gate bias, thus delaying saturation and keeping the slope of the curve positive.

Fig. 13 shows the influence of a negative back gate on the linear characteristic. As explained in Section V-A, the simulated current just above the threshold slightly overestimates the real current, but the decrease in current due to a negative back gate bias shows good agreement with the measurements. In Fig. 14 we have plotted the current vs. the back gate bias for a fixed front gate bias and two different drain biases. As explained in the previous paragraph, the simulated saturation current is too low for very negative back gate biases. The plot illustrates nicely the decrease in current with increasingly negative back gate bias until the drain voltage-dependent back gate threshold voltage of

Fig. 13. MV LDMOS with  $L_{\rm drov}=1.7~\mu{\rm m}$  and  $L_{\rm dr}=5.8~\mu{\rm m}$ ; measured (markers) and simulated (full line) current vs.  $V_{\rm GfS}$  for  $V_{\rm DS}=0.1~{\rm V}$  and  $V_{\rm GbS}=0~{\rm V}, -50~{\rm V}, -100~{\rm V}.$

Fig. 14. MV LDMOS with  $L_{\rm drov}=1.7~\mu{\rm m}$  and  $L_{\rm dr}=5.8~\mu{\rm m}$ ; measured (markers) and simulated (full line) current versus  $V_{\rm GbS}$ ;  $V_{\rm GfS}=10~{\rm V}$ ;  $V_{\rm DS}=2~{\rm V}$ , and  $V_{\rm DS}=10~{\rm V}$ .

the drift region is reached  $(V_{\rm th}^{\rm bdr})$ , at which point the current stays constant.

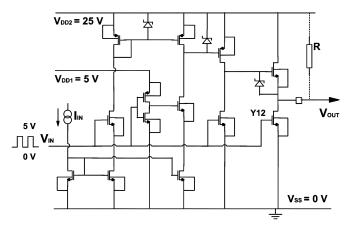

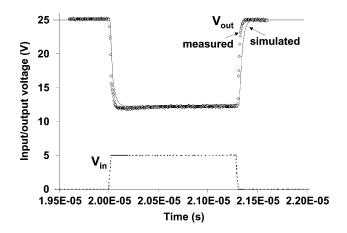

# D. Circuit Simulation Performance: Switching-Power Circuit

In this section, the influence of self-heating on some circuit blocks has been investigated and further insights about the compact model are set out. Obviously, the MOOSE model also includes a full charge description [41], but to observe space restrictions, we will concentrate on the dc aspects of the circuit.

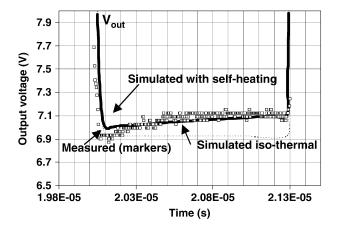

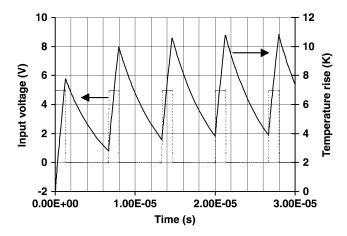

The circuit consists of a simplified horizontal line-driver circuit for plasma displays as shown in Fig. 15. To investigate the self-heating behavior of the circuit, a load resistor was added between the output and the positive supply (see dotted lines in Fig. 15). The output voltage does not go all the way back to 0 V when Y12 is switched on, but reduces to a value determined by Y12 and the load resistor. The measured and simulated results for the MV circuit when  $R = 120 \Omega$  are shown in Fig. 16. Due to self-heating the temperature of Y12 increases with time when it is on. This reduces the current in Y12 and results in a slight rise in the output voltage. In Fig. 17, the output voltage is plotted in detail and one can clearly observe the positive slope. In the same figure, the output voltage is simulated with and without self-heating; it is clear that including self-heating correctly predicts the positive slope while the isothermal result shows a constant value for  $V_{\rm out}$ . Fig. 18 shows the simulated temperature

Fig. 15. Circuit schematic for a switching power block.

Fig. 16. Simulated (full line) and measured (markers) output voltage of a plasma display driver switching circuit with a resistive load ( $R=73~\Omega$ ) to the positive supply voltage (LV circuit).

Fig. 17. Detail of the measured (markers) and simulated (with (full line) and without (dotted line) self-heating) positive slope from the switching circuit in Fig. 15.

rise of Y12 during the transient simulation, and for a frequency of 150 kHz and a duty cycle of 20%, a temperature rise of 10 K is observed. Measuring the circuit at higher frequencies with a

Fig. 18. Simulated temperature rise of the output transistor Y12 in Fig. 15 when  $R\,=\,73~\Omega.$

higher duty cycle can lead to very high temperatures with the possibility of destroying the circuit.

#### VI. CONCLUSION

In this paper, the MOOSE SOI LDMOS dc model was set out. Expressions for the current under the thin gate oxide and under the field oxide were carefully derived, keeping the model approach as physical as possible. The assumptions made were considered critically and verified where necessary.

First, an expression for the current under the thin-gate oxide was developed, describing the current in terms of the surface potentials, whilst taking into account the lateral doping gradient and the overlap of the gate over the  $N^-$  drift region. Next, an expression for the current under the field oxide was developed. The impact on the current of the thickness of the depletion layer at the buried oxide was studied rigorously, leading to a good prediction of the unique high-side behavior.

The model simulations match the measured characteristics well for a wide range of geometries, with self-heating effects being accounted for. The accuracy of the MOOSE model has been thoroughly evaluated and compared with measurements from single devices, and the usefulness in practical situations has been demonstrated by comparison with a complete circuit.

#### REFERENCES

- E. Arnold, "Silicon-on-insulator devices for high voltage and power IC applications," J. Electrochem. Soc., vol. 141, no. 7, pp. 1983–1988, 1994.

- [2] E. Arnold and S. Merchant, "Comparison of junction-isolated and SOI high-voltage devices operating in the source-follower mode," in *Proc.* IEEE Int. Symp. Power Semiconductor Devices ICs, 1992, pp. 242–243.

- [3] S. Merchant, E. Arnold, H. Baumgart, S. Mukherjee, H. Pein, and R. Pinker, "Realization of high breakdown voltage (>700 V) in thin SOI devices," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1991, pp. 31–35.

- [4] S. Merchant, E. Arnold, H. Baumgart, R. Egloff, T. Levatic, S. Mukherjee, and H. Pein, "Dependance on breakdown voltage on drift length and buried oxide thickness in SOI RESURF LDMOS transistors," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1993, pp. 124–128.

- [5] L. Lorenz, G. Deboy, A. Knapp, and M. Marz, "COOLMOS™—A new milestone in high voltage power MOS," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1999, pp. 3–10.

- [6] Y.-S. Kim and J. G. Fossum, "Physical DMOST modeling for high-voltage IC CAD," *IEEE Trans. Electron Devices*, vol. 37, pp. 797–803, Mar. 1990.

- [7] Y.-S. Kim, J. G. Fossum, and R. K. Williams, "New physical insight and models for high-voltage LDMOST IC CAD," *IEEE Trans. Electron Devices*, vol. 38, pp. 1641–1649, July 1991.

- [8] C.-Y. Tsai, D. E. Burk, and K. D. T. Ngo, "Physical modeling of the power VDMOST for computer-aided design of integrated circuits," *IEEE Trans. Electron Devices*, vol. 44, pp. 472–479, Mar. 1997.

- [9] Y. Chung and D. E. Burk, "A physically based DMOS transistor model implemented in SPICE for advanced power IC TCAD," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1995, pp. 340–345.

- [10] J. Victory, C. C. McAndrew, R. Thoma, K. Joardar, M. Kniffin, S. Merchant, and D. Moncoqut, "A physically-based compact model for LDMOS transistors," in *Proc. Int. Conf. Simulation Semiconductor Process Devices*, 1998, pp. 271–274.

- [11] N. D'Halleweyn, "Modeling and characterization of silicon-on-insulator lateral double diffused MOSFET's for analogue circuit modeling," Ph.D. dissertation, Dept. Electron. Comput. Sci., Univ. Southampton, UK. Dec. 2001.

- [12] (1995) Technology computer-aided design (TCAD) roadmap: A supplement to the national roadmap for semiconductors. Sematech Technology Transfer 95012696A-TR. [Online]. Available: http://www.sematech.org/public

- [13] R. van Langevelde, "A compact MOSFET model for distortion analysis in analog circuit design," Ph.D. dissertation, Philips Research, Tech. Univ. Eindhoven, The Netherlands, Nov. 1998.

- [14] M. S. L. Lee, B. M. Tenbroek, W. Redman-White, J. Benson, and M. Uren, "A physically based compact model of partially depleted SOI MOSFETs for analogue circuit simulation," *IEEE J. Solid-State Circuits*, vol. 36, pp. 110–121, Jan. 2001.

- [15] J. R. Brews, "A charge sheet model of the MOSFET," *Solid-State Electron.*, vol. 21, pp. 345–355, 1978.

- [16] N. Arora, "MOSFET Models for VLSI Circuit Simulation," in Computational Microelectronics. Vienna, Austria: Springer-Verlag, 1993.

- [17] Y. P. Tsividis, Operation and Modeling of the MOST. New York: Mc-Graw-Hill, 1987.

- [18] M. R. Spiegel and J. Liu, Mathematical Handbook of Formulas and Tables. New York: McGraw-Hill, 1999.

- [19] C. M. Liu, F. C. Shone, and J. B. Kuo, "A closed-form physical back-gate-bias dependent quasisaturation model for SOI lateral DMOS devices with self-heating for circuit simulation," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1995, pp. 321–324.

- [20] ATLAS, V 4.0, Device Simulation Software. Santa Clara, CA: SIL-VACO International, 1996.

- [21] H. C. de Graaff and F. M. Klaassen, Compact Transistor Modeling for Circuit Design. Vienna, Austria: Springer-Verlag, 1990.

- [22] A. G. Sabnis and J. T. Clemens, "Characterization of the electron mobility in the inverted (100) Si surface," in *Proc. Int. Electron Device Meeting*, 1979, pp. 18–21.

- [23] K. Joardar, K. K. Gullapalli, C. McAndrew, M. E. Burnham, and A. Wild, "An improved MOSFET model for circuit simulation," *IEEE Trans. Electron Devices*, vol. 45, pp. 134–148, Jan. 1998.

- [24] B. H. Krabbenborg and J. A. van der Pol, "Robustness of LDMOS power transistors in SOI-BCD processes and derivation of design rules using thermal simulation," in *Proc. IEEE Int. Symp. Power Semiconductor De*vices ICs, 2001, pp. 157–160.

- [25] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1981.

- [26] M. D. Pocha and R. W. Dutton, "A computer-aided design model for high-voltage double diffused MOS (DMOS) transistors," *IEEE J. Solid-State Circuits*, vol. 11, pp. 718–724, Oct. 1976.

- [27] R. Kraus, P. Turkes, and H. J. Mattausch, "Modeling the self-heating of power devices.," in *Proc. IEEE Int. Symp. Power Semiconductor Devices* ICs, 1992, pp. 124–129.

- [28] H. Neubrand, R. Constapel, R. Boot, M. Fullmann, and A. Boose, "Thermal behavior of lateral power devices on SOI substrates," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1994, pp. 123–127.

- [29] D. Sharma, J. Gautier, and G. Merckel, "Negative dynamic resistance in MOS devices," *IEEE J. Solid-State Circuits*, vol. 13, pp. 378–380, June 1978.

- [30] A. L. Caviglia and A. A. Iliades, "Linear dynamic self-heating in SOI MOSFETs," *IEEE Electron Device Lett.*, vol. 14, pp. 133–135, Mar. 1993.

- [31] B. M. Tenbroek, W. Redman-White, M. J. Uren, M. S. L. Lee, and M. C. L. Ward, "Identification of thermal and electrical time constants in SOI MOSFET's from small-signal measurements," in *Proc. Eur. Solid-State Device Res. Conf.*, Sept. 1993, pp. 189–192.

- [32] B. M. Tenbroek, "Characterization and parameter extraction of silicon-on-insulator MOSFET's for analogue circuit modeling," Ph.D. dissertation, Dept. Electron. Comput. Sci., Univ. Southampton, UK, 1997.

- [33] Y.-K. Leung, A. K. Paul, K. E. Goodson, J. D. Plummer, and S. S. Wong, "Heating mechanisms of LDMOS and LIGBT in ultrathin SOI," *IEEE Trans. Electron Devices*, vol. 18, pp. 414–416, Sept. 1997.

- [34] A. K. Paul, Y. K. Leung, J. D. Plummer, S. S. Wong, S. C. Kuehne, V. S. K. Huang, and C. T. Nhuyen, "High voltage LDMOS transistors in sub-micron SOI films," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 1996, pp. 89–92.

- [35] G. Watchutka, "Rigorous thermodynamic treatment of heat generation and conduction in semiconductor device modeling," *IEEE Trans. Com*puter-Aided Design, vol. 9, pp. 1141–1149, Nov. 1990.

- [36] L. J. McDaid, S. Hall, P. H. Mellor, W. Ecclestone, and J. C. Alderman, "Physical origin of negative differential resistance in SOI transistors," *Electron. Lett.*, vol. 25, no. 13, pp. 827–828, 1989.

- [37] M. S. L. Lee, W. Redman-White, B. M. Tenbroek, and M. Robinson, "Modeling of thin film SOI devices for circuit simulation including perinstance dynamic self-heating effects," in *Proc. IEEE Int. SOI Conf.*, Oct. 1993, pp. 150–151.

- [38] J. Bielefeld, G. Pelz, H. B. Abel, and G. Zimmer, "Dynamic SPICE-simulation of the electrothermal behavior of SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 42, pp. 1968–1974, Oct. 1995.

- [39] A. Ammous, S. Ghedira, B. Allard, H. Morel, and D. Renault, "Choosing a thermal model for electrothermal simulation of power semiconductor devices," *IEEE Trans. Electron Devices*, vol. 14, pp. 300–307, Feb. 1999.

- [40] N. D'Halleweyn, M. Swanenberg, J. Benson, and W. Redman-White, "A circuit simulation model for SOI LDMOS transistors, with accurate high-side behavior," in *Proc. ISDRS*, 1999, pp. 195–199.

- [41] N. V. D'Halleweyn, L. F. Tiemeyer, J. Benson, and W. Redman-White, "Charge model for SOI LDMOST with lateral doping gradient," in *Proc. IEEE Int. Symp. Power Semiconductor Devices ICs*, 2001.

William Redman-White (M'85) received the B.Sc. degree from Exeter University, Exeter, UK, in 1974 and the M.Sc. and Ph.D. degrees from Southampton University, Southampton , UK, in 1980 and 1983, respectively.

From 1974 to 1978, he was with Post Office Telecommunications, working on PCM systems. In 1979, he became a Research Fellow at Southampton University, and joined its academic staff in 1983. While maintaining a continuing academic activity, he has worked extensively in the semiconductor industry. From 1984 to 1990, he was a Part-Time Design Consultant for GEC Research, London, UK, working on silicon-on-sapphire design amongst other things. During 1989 he was with Motorola, Switzerland, and since 1990, he has been with Philips Semiconductors, Southampton, UK, where he is an Analogue Design Consultant for advanced consumer IC projects. His research interests are centred on analogue and mixed signal-design issues, spanning data conversion, filtering, circuit design for space environments and charaterization and modeling of SOI CMOS.

Dr. Redman-White is a Member of the IEE.

Nele V. T. D'Halleweyn was born in Gent, Belgium, in 1974. She received the electrical engineering degree from the Université Catholique de Louvain-la-Neuve, Louvain, Belgium, in 1997, and the Ph.D. degree from the University of Southampton, Southampton, UK, in 2002.

In 2000, she was with Philips Semiconductors, Nijmegen, The Netherlands working in the Device Modeling Group. She is currently with Arnold and Siedsma, Belgium as a patent attorney.

**Ketan Mistry** received the M.Eng. degree in electronic engineering from the University of Newcastle upon Tyne, UK, in 1999. He is currently pursuing the Ph.D. degree in microelectronic circuit design at the University of Southampton, Southampton, UK.

He was with Philips Research Laboratories, Eindhoven, The Netherlands, where he designed frequency dividers for the IEEE802.11a transceiver. He is now with the Electronic and Electrical Engineering Department, University College Dublin, Dublin, Ireland, where he is working on a project

investigating the nonlinear dynamics of various communication circuits and systems.

**James Benson** received the B.Sc. degree in physics from Leicester University, Leicester, UK, in 1994 and the M.Sc. degree in semiconductor science and technology from Imperial College, London, UK, in 1995.

From 1995 to 1997, he was with Philips Semiconductors, Southampton, UK. Between 1997 and 2003, he was a Researcher in the Microelectronics Group, Electronics and Computer Science Department, University of Southampton, Southampton, UK. Since 2003, he has been with the Advanced Technology Institute, University of Surrey, UK,

where he is investigating models to predict the effects of biaxial lattice strain on dopant diffusion in silicon. His research interests include the modeling and characterization of silicon-on-insulator MOSFETs, with particular emphasis on developing advanced high-field mobility models.

Mr. Benson is a Member of the Institute of Physics.

**Maarten Swanenberg**, photograph and biography not available at the time of publication.