University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

**Novel Chalcogenide Optoelectronic and

Nanophotonic Information Storage and

Processing Devices**

by

Behrad Gholipour

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Physical and Applied Sciences

Optoelectronics Research Centre

May 2012

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL AND APPLIED SCIENCES

OPTOELECTRONICS RESEARCH CENTRE

Doctor of Philosophy

by Behrad Gholipour

This project is focused on the application of new electronic and optical materials. In particular it involves examining the use of chalcogenide thin films as phase change and ion conducting glasses for emerging optoelectronic applications. The ability of this group of materials to easily change their state from glass to crystal has meant that they have been widely used in CD's and DVDs. However, their ability to also conduct electrons and ions, promises novel solutions for next generation logic and memory devices which will take us in the short term beyond the limits of the silicon chip and, into the world of neuromorphic cognitive computing (computers that think and adapt). Additionally, this reversible change in the structure of these thin films allows their utilisation in ultra-high speed optical and optoelectronic switches to power the internet and future computers.

Three main goals are pursued within this research. First, next generation phase change (PCRAM) and nano-ionic resistive (ReRAM) memory is pursued for faster, non-volatile high density data storage. Secondly, the design of novel processing elements like next generation logic gates enabling neuromorphic cognitive processing and data storage in one structure based on material properties. Finally, the integration of phase change thin films with metamaterial arrays to produce electro-optic and all optical switches for future photonic computers and communication networks.

## Statement of Authorship

Declaration of Authorship I, Behrad Gholipour, declare that the thesis entitled 'Novel chalcogenide optoelectronic and nanophotonic information storage and processing devices' and the work presented in it are my own. I confirm that:

- this work was done wholly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given; With the exception of such quotation, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as shown in the List of Publications;

Signed: ..... Date: .....

## List of Publications

1. Characterization of supercooled liquid  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  and its crystallization by ultra-fast-heating calorimetry, J. Orava, A. L. Greer, B. Gholipour, D. W. Hewak and C. E. Smith, *Nature Materials*, 11, 279283, 2012.

2. Crystallization Study of the  $\text{Cu}_2\text{ZnSnS}_4$  Chalcogenide Material for Solar Applications, F. Al-Saab, B. Gholipour, C. C. Huang, D. W. Hewak, A. Anastopoulos and B. Hayden, PV-SAT, Northumbria University, United Kingdom, 8, 2–4, April 2012.

3. Laser-induced forward transfer of thermoelectric materials on polymer and glass substrates, M. Feinaeugle, C. Sones, E. Koukharenko, B. Gholipour, D. W. Hewak and R. Eason, E-prints conference, Basle, Switzerland, 2012.

4. Laser Induced Forward Transfer-printing of pre-machined crystalline magneto-optic garnet discs, C. L. Sones, M. Feinaugle, B. Gholipour and R. Eason, Cleo 2012, San Jose, CA, United States, 6–11, May 2012.

5. Non-volatile bi-directional all-optical switching in chalcogenide glass metamaterials, B. Gholipour, J. Zhang, K. F. MacDonald, D. W. Hewak and N. I. Zheludev, Cleo 2012, San Jose, CA, United States, 6–11, May 2012.

6. Deposition of elements for a thermoelectric generator via laser-induced forward transfer, M. Feinaeugle, C. L. Sones, E. Koukharenko, B. Gholipour, D. W. Hewak and R. W. Eason, Cleo 2012, San Jose, CA, United States, 6–11, May 2012.

7. Laser-induced forward transfer as a method for manufacturing elements for a thermoelectric energy harvester, M. Feinaeugle, C. L. Sones, E. Koukharenko, B. Gholipour, D. W. Hewak and R. W. Eason, E-MRS 2012, Strasbourg, France, 14–18, May 2012.

8. Laser assisted fabrication of chalcogenide glass microspheres on a planar waveguide device, V. Leonard, B. Gholipour, K. Khan and D. W. Hewak, ISNOG 2012, San melo, France, 1–5, July 2012.

9. Fabrication and aero dynamic levitation of chalcogenide glass spheres, K. Khan, T. Farmer, B. Gholipour, V. Leonard, D. Hewak, and A. C. Barnes, ISNOG 2012, San melo, France, 1–5, July 2012.

10. Non-volatile bi-directional all-optical switching in chalcogenide glass metamaterials (Poster), B. Gholipour, J. Zhang, K. F. MacDonald, D. W. Hewak, and N. I. Zheludev, SPIE Photonics Europe, Brussels, Belgium, 16 - 19, April 2012.

11. Metamaterial All-Optical Switch of Nanoscale Thickness, B. Gholipour, J. Zhang, K. F. Macdonald, D. W. Hewak and N. I. Zheludev (In preparation).

12. Sulphide nanowires for ultra low power thermally stable phase change memory applications, B. Gholipour, C. C. Huang and D. W. Hewak (In preparation).

13. High throughput nanowires: The search for the perfect memory material, B. Gholipour, F. Al Saab, A. Anastasopoulos, B. Hayden and D. W. Hewak (In preparation).

14. Deposition and characterization of CVD grown Ge-Sb thin film device for phase change memory application, C. C. Huang, B. Gholipour, K. Knight, J. Y. Ou, and D. W. Hewak, (Accepted, *Advances in optoelectronics*).

15. Electrical phase change of CVD Ge-Sb-Te thinfilm device, C. C. Huang, B. Gholipour, J. Y. Ou, K. Knight and D. W. Hewak, *Electronics Letters*, 47, 288–289, 2011.

16. Thermally Stable, Low Current Consuming Gallium and Germanium Chalcogenides for Consumer and Automotive Memory Applications (Invited talk), D. W. Hewak, C. C. Huang, B. Gholipour and K. Knight, S. Guerin and B. Hayden, E/PCOS 2011, Zurich, Switzerland, September 2011.

17. Non-volatile bi-directional all-optical switching in chalcogenide glass metamaterials, B. Gholipour, J. Zhang, K. F. MacDonald, D. W. Hewak and N. I. Zheludev, *Nano-meta*, 2012.

18. Scalability and thermal stability of low current consuming, nanowire phase change memory cells for high density commercial applications, B. Gholipour, D. W. Hewak, C. C. Huang, A. Anastasopoulos, F. Al Saab, S. Guerin, B. Hayden and G. Purdy, E/PCOS 2011, Zurich, Switzerland (Contributed poster).

19. Chalcogenide Phase Change Materials in Active Plasmonic and Metamaterial Technologies, B. Gholipour, J. Zhang, F. Al-Saab, A. Anastasopoulos, K. F. MacDonald, B. Hayden, D. Hewak and N. I. Zheludev, SAIT Global Research Outreach Scheme, October 2011.

20. Fabrication of thin film solar cell materials by APCVD, C. C. Huang, F. Al-Saab, B. Gholipour and D. W. Hewak, Low Carbon Earth Summit, Dalian, China, Oct. 19–26, 2011.

21. Metamaterial electro-optic switch of nanoscale thickness, Z. L. Samson, K. F. MacDonald, F. De Angelis, B. Gholipour, K. Knight, C. C. Huang, E. Di Fabrizio, D. W. Hewak and N. I. Zheludev, *Applied Physics Letters*, 96, 143–105, 2010.

22. Chalcogenide phase change materials for nanoscale switching, D. W. Hewak, Z. L. Samson, B. Gholipour, K. Knight, C. C. Huang, S. Li, K. F. MacDonald and N. I. Zheludev, *Photonics North 2010*, Niagara Falls Canada, 1–3, June 2010.

23. Chalcogenide plasmonic metamaterial switches, Z. L. Samson, J. Zhang, G. Adamo, T. Uchino, B. Gholipour, K. Knight, C. C. Huang, F. De Angelis, K. F. MacDonald, P. Ashburn, E. Di Fabrizio, D. W. Hewak and N. I. Zheludev, SPIE Optics and Photonics 2010, San Diego, 1–5, August 2010.

24. Advances in nonlinear and switchable photonic metamaterials (SPP5)(Invited), K. F. MacDonald, M. Ren, J. Zhang, B. Gholipour, N. Papasimakis, A. E. Nikolaenko, Z. X. Shen, D. Hewak and N. I. Zheludev, Busan, S. Korea, 15–20, May 2010.

25. Active photonic metamaterials, Z.L. Samson, B. Gholipour, F. De Angelis, S. Li, K. J. Knight, J. Zhang, T. Uchino, C. C. Huang, K. F. MacDonald, P. Ashburn, E. Di Fabrizio, D. W. Hewak and N. I. Zheludev, 8th Electro-Optics and infrared Conference Shrivenham UK, 7–9, July 2010.

26. Active chalcogenide glass photonics and electro-optics for the midinfrared, D. W. Hewak, C. C. Huang, K. J. Knight, B. Gholipour, S. Li, Z. L. Samson, K. F. MacDonald, N. I. Zheludev, 8th Electro-Optics and Infrared Conference Shrivenham UK, 7–9, July 2010.

27. Phase change Gallium and Germanium Chalcogenides for optical, Electronic and Plasmonic Switching, D. W. Hewak, C. C. Huang, B. Gholipour, K. Knight, S. Li, Z. L. Samson, K. F. Macdonald, S. C. Yen, C. D. Shiue and D. P. Tsai, F. De Angelis and E. Di Fabrizio, S. Guerin and B. Hayden, E/PCOS 2010, Milan, Italy, 2010.

28. Chalcogenides for the future: Beyond the silicon chip, B. Gholipour, UK EPSRC ICT Pioneers, London, United Kingdom, March 2010.

29. Solar cells for the dark, B. Gholipour and D. W. Hewak, Set for Britain 2010, London, United Kingdom, March 2010.

# Contents

|                                                           |             |

|-----------------------------------------------------------|-------------|

| <b>Statement of Authorship</b>                            | <b>v</b>    |

| <b>List of Publications</b>                               | <b>vii</b>  |

| <b>Nomenclature</b>                                       | <b>xvii</b> |

| <b>Acknowledgements</b>                                   | <b>xxi</b>  |

| <b>1 Introduction</b>                                     | <b>1</b>    |

| 1.1 Project aim . . . . .                                 | 11          |

| 1.2 Thesis synopsis . . . . .                             | 13          |

| <b>2 Chalcogenide Phase Change</b>                        | <b>17</b>   |

| 2.1 Materials . . . . .                                   | 17          |

| 2.1.1 Glassy amorphous semiconductor thin films . . . . . | 17          |

| 2.1.2 Chalcogenides . . . . .                             | 18          |

| 2.2 Phase change . . . . .                                | 19          |

| 2.2.1 Glass formation . . . . .                           | 19          |

| 2.2.2 Crystallisation . . . . .                           | 20          |

| 2.2.3 Phase change alloys . . . . .                       | 21          |

| 2.2.3.1 Germanium antimony telluride (GeSbTe) . . . . .   | 21          |

| 2.2.3.2 Germanium antimony (GeSb) . . . . .               | 24          |

| 2.2.3.3 Gallium lanthanum sulphide (GaLaS) . . . . .      | 25          |

| 2.3 Applications . . . . .                                | 26          |

| <b>3 Tools and Techniques</b>                             | <b>27</b>   |

| 3.1 Device fabrication . . . . .                          | 27          |

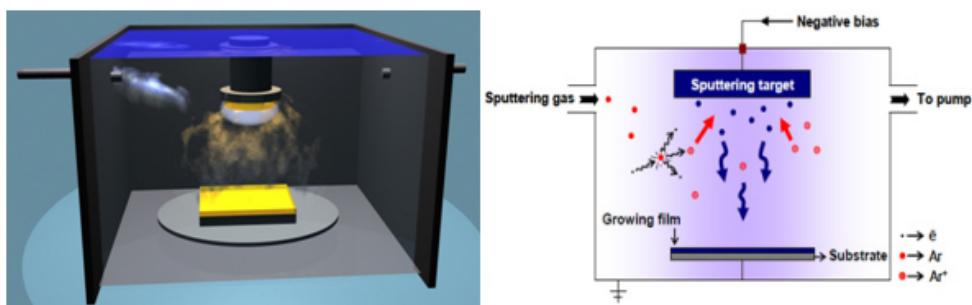

| 3.1.1 Sputtering . . . . .                                | 28          |

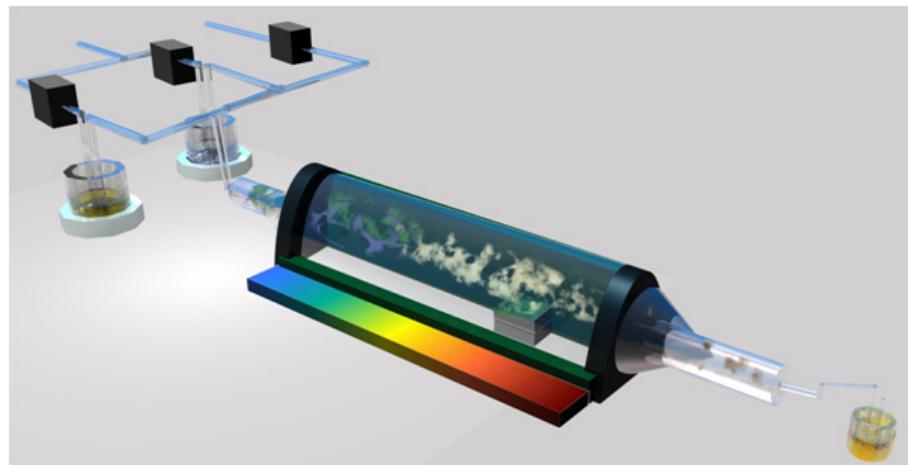

| 3.1.2 Chemical vapour deposition (CVD) . . . . .          | 30          |

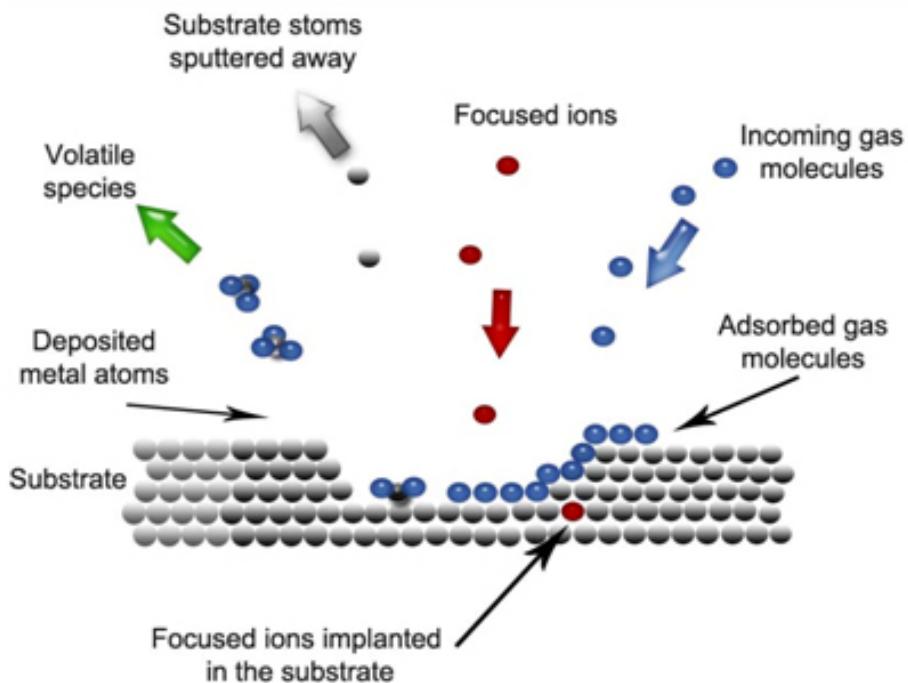

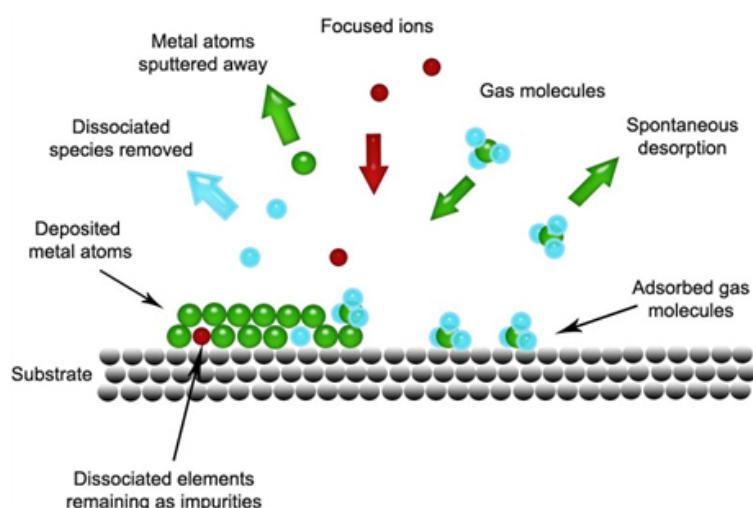

| 3.1.3 Focused ion beam milling and deposition . . . . .   | 31          |

| 3.1.4 Physical vapour deposition (PVD) . . . . .          | 33          |

| 3.1.4.1 High throughput synthesis . . . . .               | 33          |

| 3.1.5 E-beam evaporation . . . . .                        | 35          |

| 3.1.6 Photolithography . . . . .                          | 35          |

| 3.1.6.1 Resist spinning . . . . .                         | 36          |

| 3.1.6.2 Exposure . . . . .                                | 36          |

| 3.1.6.3 Development . . . . .                             | 37          |

| 3.1.7 Etching . . . . .                                   | 37          |

---

|           |                                      |           |

|-----------|--------------------------------------|-----------|

| 3.1.7.1   | Reactive ion etching                 | 38        |

| 3.2       | Characterisation                     | 40        |

| 3.2.1     | Scanning electron microscopy         | 40        |

| 3.2.2     | Energy dispersive x-ray spectroscopy | 41        |

| 3.2.3     | Infrared spectrophotometry           | 42        |

| 3.3       | Elevated temperature measurements    | 43        |

| 3.3.1     | Differential scanning calorimetry    | 45        |

| <b>4</b>  | <b>Data Storage</b>                  | <b>47</b> |

| 4.1       | Background                           | 47        |

| 4.1.1     | Electrical phase change              | 47        |

| 4.1.1.1   | Electrical switching parameters      | 49        |

| 4.1.2     | Electrical phase change devices      | 50        |

| 4.1.2.1   | Materials                            | 50        |

| 4.1.3     | Sulphide phase change devices        | 52        |

| 4.1.3.1   | Structure                            | 53        |

| 4.2       | Motivation                           | 56        |

| 4.3       | Micron scale devices                 | 59        |

| 4.4       | Thin film devices                    | 59        |

| 4.4.1     | Modelling                            | 60        |

| 4.4.1.1   | Nanowire modelling                   | 62        |

| 4.4.2     | GeSb nanowire PCRAM                  | 63        |

| 4.4.2.1   | GeSb thin film                       | 63        |

| 4.4.2.2   | GeSb nanowire                        | 63        |

| 4.4.3     | GaLaS nanowire PCRAM                 | 64        |

| 4.4.3.1   | GaLaS thin film                      | 64        |

| 4.4.3.2   | GaLaS nanowire                       | 67        |

| 4.4.3.2.1 | Contact fabrication                  | 67        |

| 4.4.3.2.2 | Nanowire fabrication                 | 67        |

| 4.4.3.2.3 | Capping layer fabrication            | 68        |

| 4.4.4     | GeSbTe nanowire PCRAM                | 68        |

| 4.4.4.1   | GeSbTe thin film                     | 69        |

| 4.4.4.2   | GeSbTe nanowire                      | 71        |

| 4.4.4.3   | High throughput depositions          | 71        |

| 4.4.4.4   | High throughput PC-NW chip           | 73        |

| 4.5       | Characterization                     | 74        |

| 4.5.1     | Electrical characterization          | 74        |

| 4.5.2     | Thermal stability measurements       | 78        |

| 4.6       | Results and discussion               | 79        |

| 4.6.1     | Nanowire memory cells                | 79        |

| 4.6.1.1   | Electrical characterization          | 79        |

| 4.6.1.1.1 | GeSb nanowire                        | 79        |

| 4.6.1.1.2 | GeSbTe nanowire                      | 83        |

| 4.6.1.1.3 | GaLaS nanowire                       | 84        |

| 4.6.1.1.4 | Comparison                           | 85        |

| 4.6.2     | NW PCRAM composition optimization    | 87        |

| 4.6.3     | Elevated temperature operation       | 88        |

---

|           |                                                   |            |

|-----------|---------------------------------------------------|------------|

| 4.7       | Summary                                           | 90         |

| <b>5</b>  | <b>Information Processing Devices</b>             | <b>91</b>  |

| 5.1       | Background                                        | 91         |

| 5.1.1     | Logic gates                                       | 91         |

| 5.1.1.1   | Processors                                        | 92         |

| 5.1.1.2   | Resistive memory                                  | 94         |

| 5.1.1.3   | Neuromorphic computing                            | 95         |

| 5.1.1.3.1 | Cognitive behaviour                               | 95         |

| 5.1.1.3.2 | Memristive behaviour                              | 96         |

| 5.2       | Motivation                                        | 100        |

| 5.3       | Fabrication                                       | 100        |

| 5.3.1     | Cognitive switching                               | 101        |

| 5.3.1.1   | Electronic cognitive switch                       | 101        |

| 5.3.2     | Memristive devices                                | 101        |

| 5.3.3     | Logic gates                                       | 102        |

| 5.3.3.1   | Electronic gates                                  | 102        |

| 5.3.3.2   | Optoelectronic gates                              | 104        |

| 5.4       | Characterization                                  | 104        |

| 5.4.1     | Electronic logic gates                            | 104        |

| 5.4.2     | Electrical cognitive switching setup              | 105        |

| 5.4.3     | Memristive switching setup                        | 106        |

| 5.4.4     | Optoelectronic gate setup                         | 107        |

| 5.5       | Results and discussion                            | 107        |

| 5.5.1     | Electronic logic gates                            | 107        |

| 5.5.2     | Optoelectronic logic gates                        | 108        |

| 5.5.3     | Cognitive behaviour                               | 110        |

| 5.5.3.1   | Electronic                                        | 110        |

| 5.5.3.2   | Optical cognitive switching                       | 111        |

| 5.5.4     | Memristive/RRAM behaviour                         | 113        |

| 5.6       | Summary                                           | 118        |

| <b>6</b>  | <b>Metamaterial Phase Change Optical Switches</b> | <b>119</b> |

| 6.1       | Background                                        | 119        |

| 6.1.1     | Metamaterials                                     | 119        |

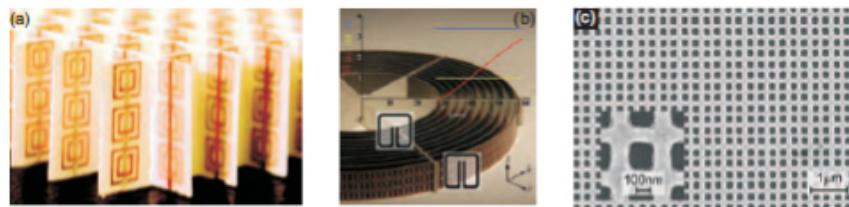

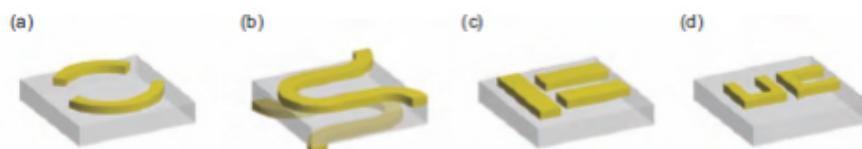

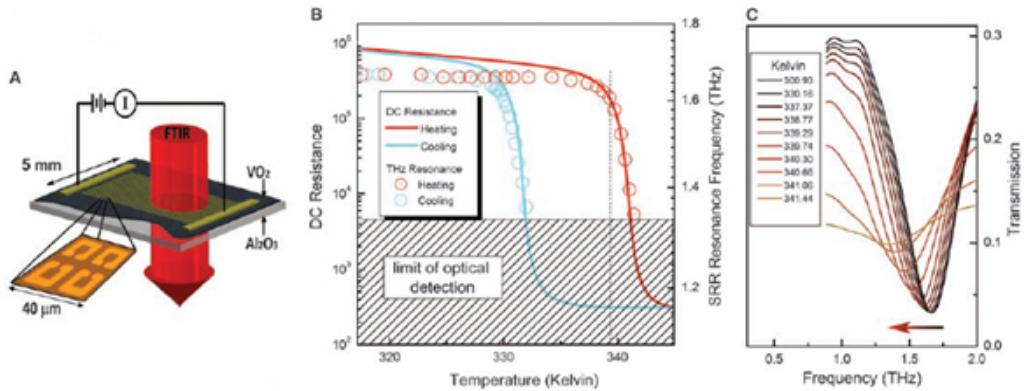

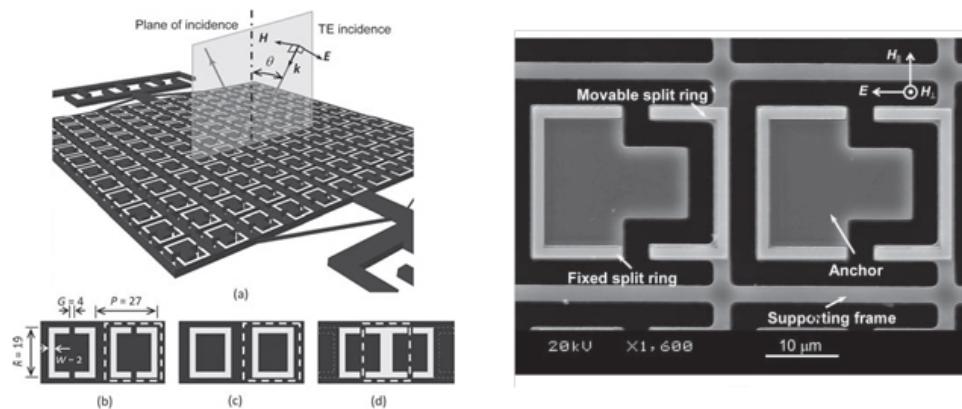

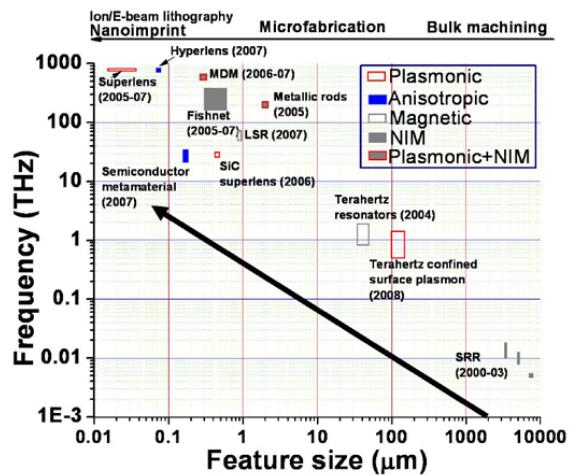

| 6.1.1.1   | Switchable metamaterials                          | 122        |

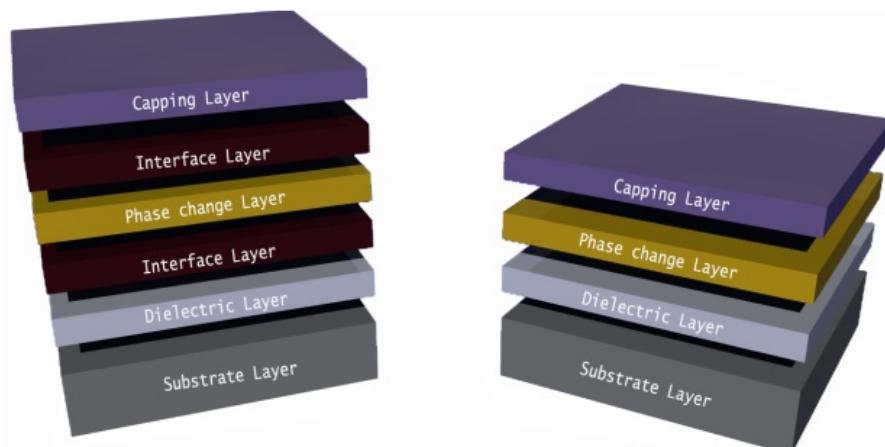

| 6.1.2     | Optical phase change devices                      | 127        |

| 6.2       | Motivation                                        | 130        |

| 6.3       | Metamaterial design                               | 131        |

| 6.4       | Modelling                                         | 133        |

| 6.4.1     | Large area crystallisation microribbons           | 133        |

| 6.4.2     | Hybrid metamaterial device                        | 134        |

| 6.4.3     | Metamaterial integration modelling                | 134        |

| 6.5       | Fabrication                                       | 136        |

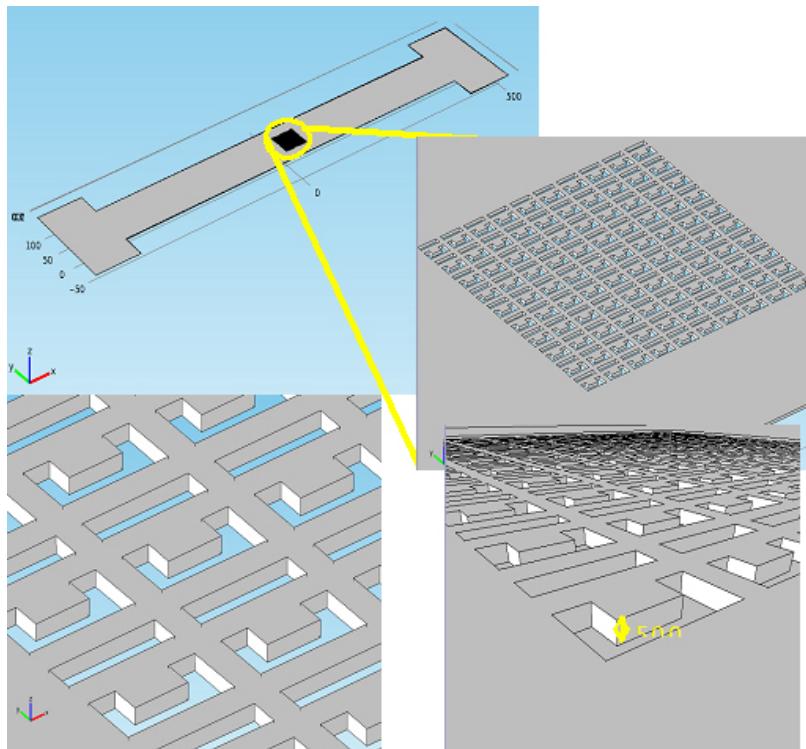

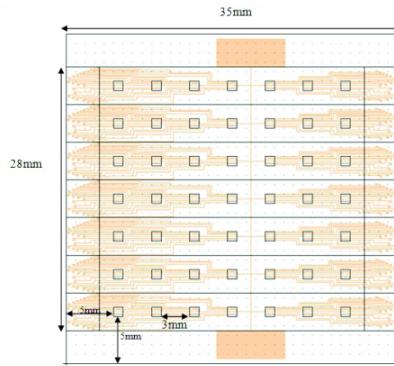

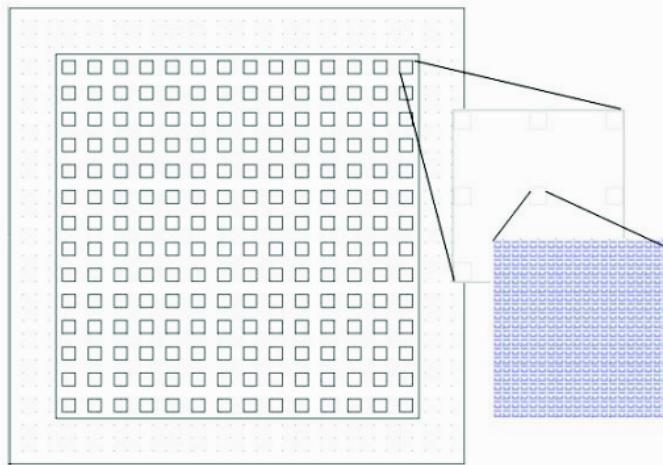

| 6.5.1     | High throughput mask                              | 136        |

| 6.5.1.1   | Fabrication processes                             | 137        |

| 6.5.1.1.1 | High throughput chip fabrication                  | 137        |

---

|                     |                                                |            |

|---------------------|------------------------------------------------|------------|

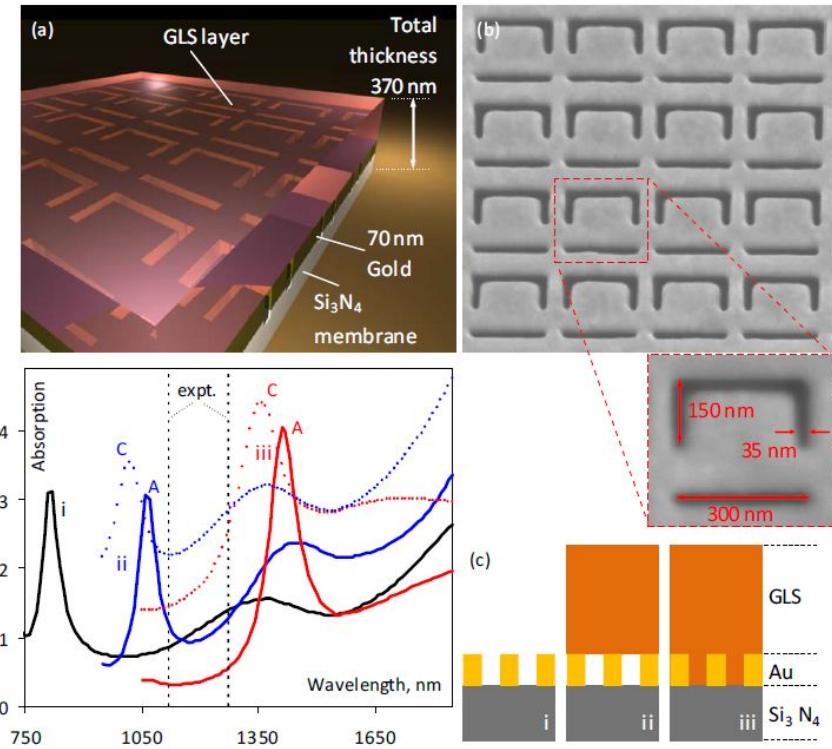

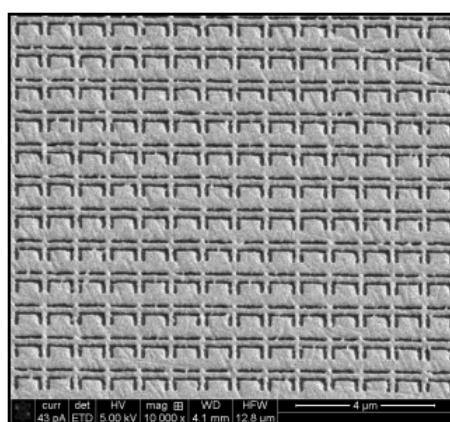

| 6.5.2               | GeSbTe metamaterial optical switches           | 139        |

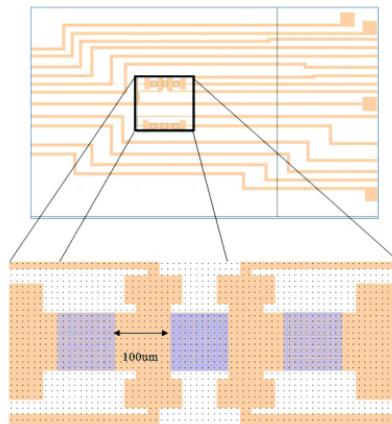

| 6.5.2.1             | Design                                         | 139        |

| 6.5.2.2             | Fabrication process (FIB and sputtering)       | 141        |

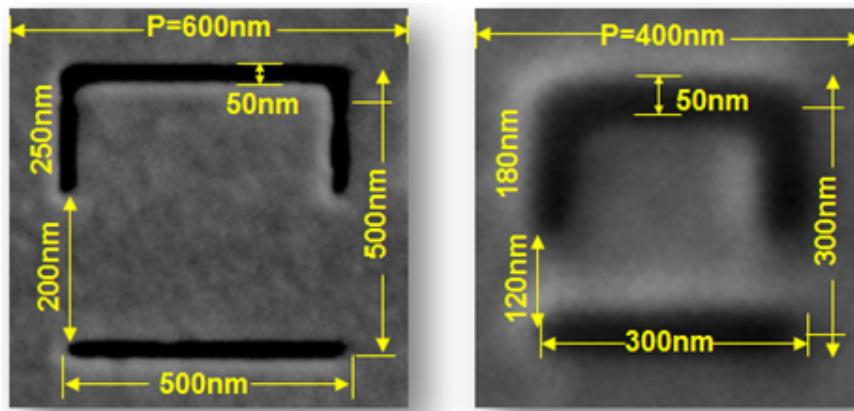

| 6.5.2.3             | Structural optimisation                        | 144        |

| 6.6                 | Characterisation                               | 147        |

| 6.6.1               | Metamaterial heater switching setup            | 147        |

| 6.6.2               | Metamaterial optical switching                 | 147        |

| 6.6.2.1             | Rastor setup                                   | 147        |

| 6.6.2.2             | Single pulse large area switching              | 148        |

| 6.7                 | Results and discussion                         | 149        |

| 6.7.1               | Large area crystallisation tests               | 149        |

| 6.7.1.1             | All optical GeSbTe metamaterial switches       | 154        |

| 6.8                 | Summary                                        | 159        |

| <b>7</b>            | <b>Conclusions</b>                             | <b>161</b> |

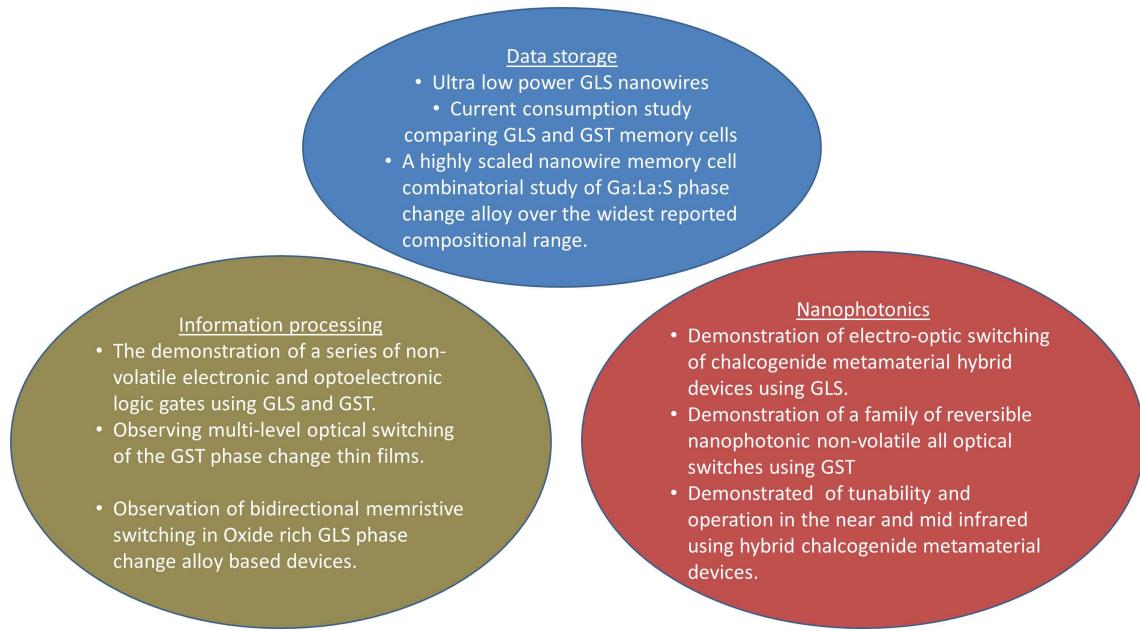

| 7.1                 | Conclusion                                     | 161        |

| 7.1.1               | Data storage                                   | 161        |

| 7.1.2               | Information processing                         | 163        |

| 7.1.3               | Nanophotonics                                  | 163        |

| 7.2                 | Future work                                    | 164        |

| 7.2.1               | Memristive work                                | 164        |

| 7.2.2               | Phase change memory                            | 166        |

| 7.2.2.1             | NWs with e-beam lithography                    | 167        |

| 7.2.2.2             | NW by VLS technique                            | 168        |

| 7.2.3               | Metamaterial logic devices (Radial structures) | 169        |

| <b>A</b>            | <b>Optoelectronic reconfigurable logic</b>     | <b>171</b> |

| <b>B</b>            | <b>Oxide rich GLS resistive switching</b>      | <b>173</b> |

| <b>Bibliography</b> |                                                | <b>177</b> |

# List of Figures

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

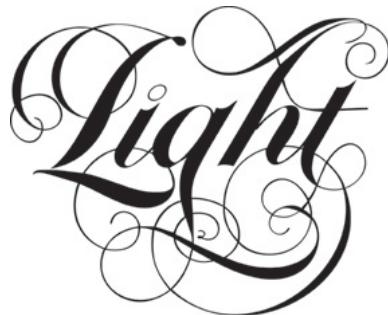

| 1.1 | Top: shows the conventional (left) and future computer architectures (right) which can be achieved through non volatile fast reliable memory [Adapted from (1)]. Bottom: the schematic representation of SRAM (left) and DRAM (right) . . . . .                                                                                                                                                                                                                                                                              | 2 |

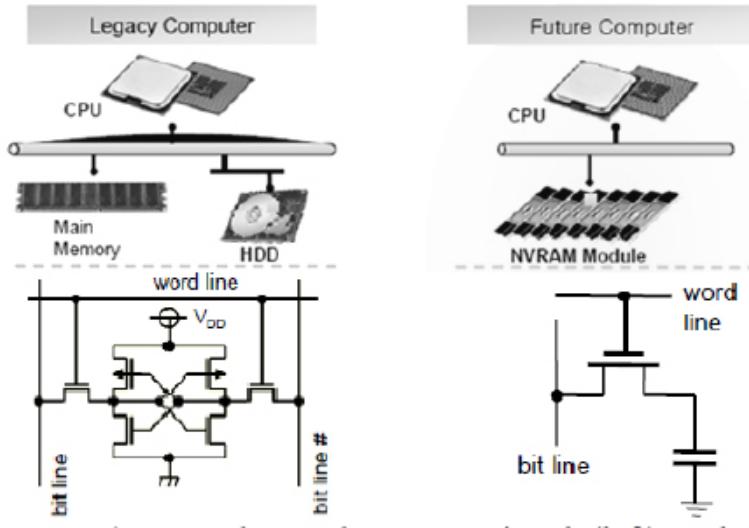

| 1.2 | The simplified structure of the floating gate Flash architecture showing the 1 and 0 bit representation [Redrawn from (2)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                          | 3 |

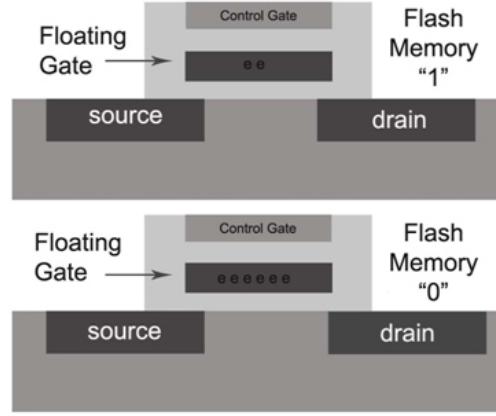

| 1.3 | Scaling limitation of Flash memory [Reprinted from (2)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

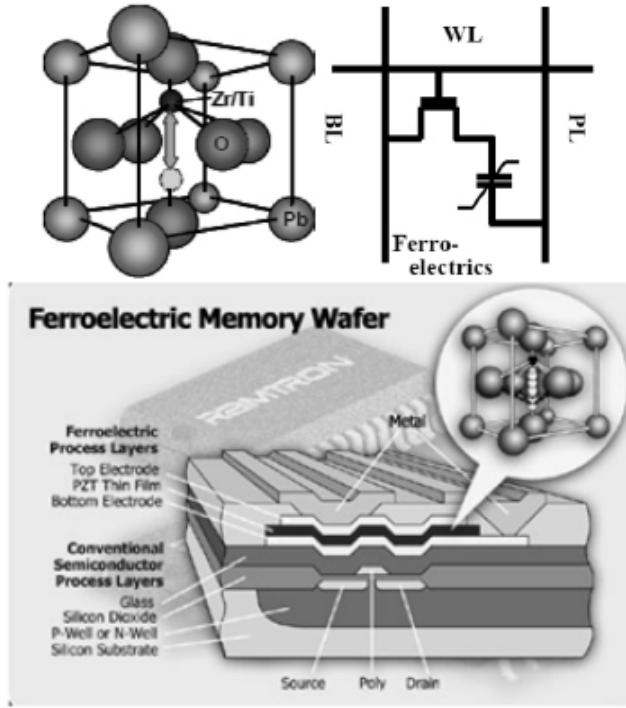

| 1.4 | Top: Representation of crystal structure of FRAM ferroelectric atom showing the movement of the central atom for data representation (right) along with the schematic model of the 1T1C FRAM cell (left) adapted from [Reprinted from (3)]. Bottom: Representation of the fabricated FRAM structure produced by Ramtron Inc. Showing the two electrodes on either side of the ferroelectric layer that controls the electric field responsible for adjusting the position of the central atom. [Reprinted from (4)]. . . . . | 4 |

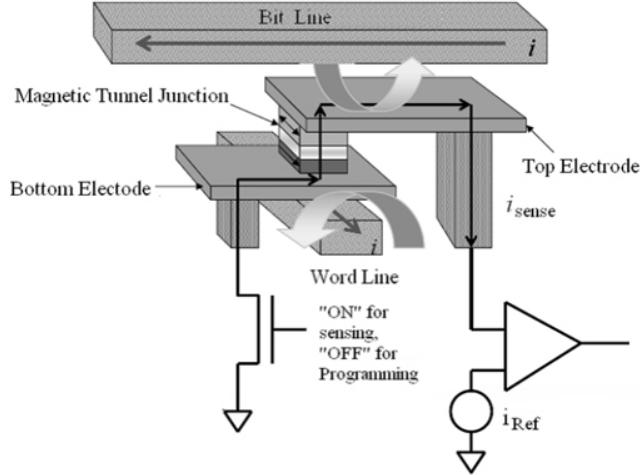

| 1.5 | The structure of the MTJ MRAM cell showing the fixed and dynamic layers as well as the flow of the electrons and data path through the memory architecture and operational circuitry. [Reprinted from (5)] . . .                                                                                                                                                                                                                                                                                                             | 5 |

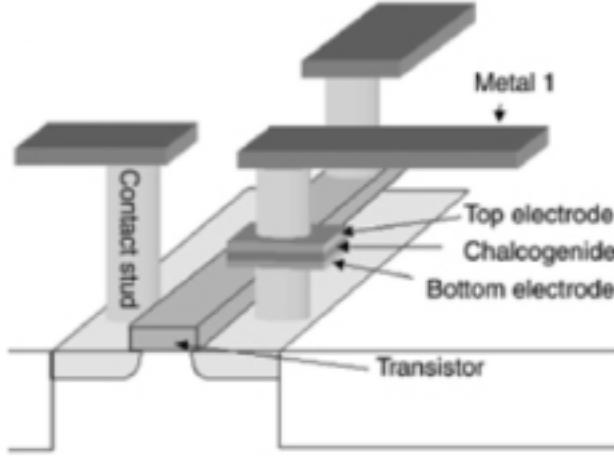

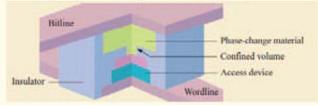

| 1.6 | The conventional chalcogenide based phase change memory architecture with the electrodes that supply the energy needed for phase change and ultimately data storage. As the phase of the material changes the change in resistivity shifts the threshold voltage of the transistor that is connected to the electrodes, thus data is stored [Reprinted from (6)]. . . . .                                                                                                                                                    | 5 |

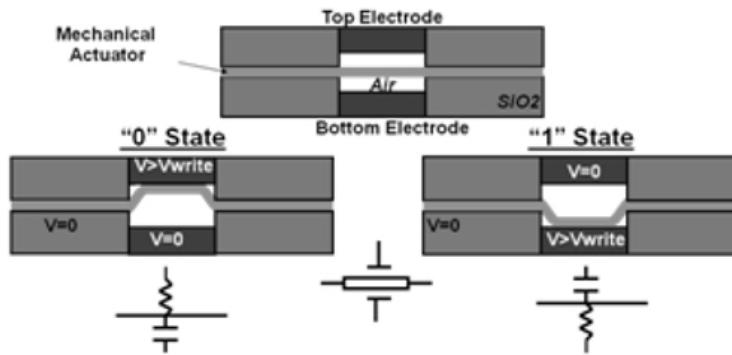

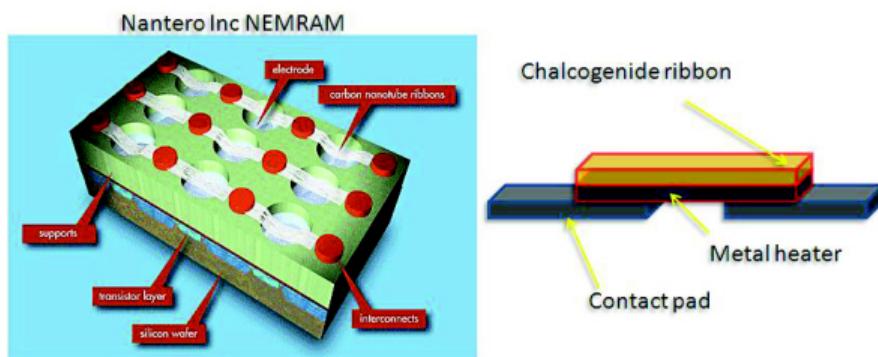

| 1.7 | The NEMRAM structure showing the actuation of the floating actuator based on the field applied by the electrodes. Depending on the position of the actuator the threshold voltage of the transistor will be different as a different level of electrostatic control is observed over the channel [Reprinted from (7)]. . . . .                                                                                                                                                                                               | 6 |

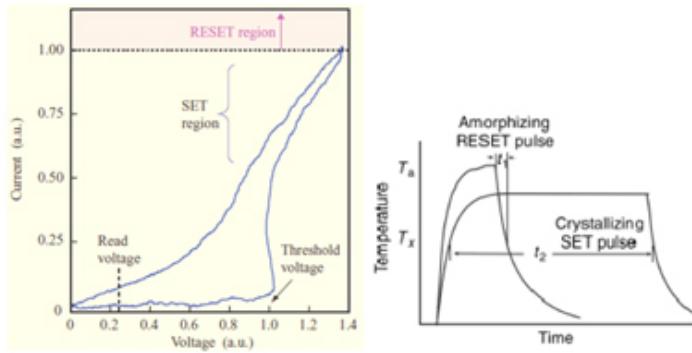

| 1.8 | The I-V characteristic of a typical PRAM showing the relatively high current needed for resetting the bits (left) [Reprinted from (20)] as well as, The relatively long current pulse needed for erasing the PRAM device is shown (right), both show the need for reducing the power consumption of the devices at lower scales.[Reprinted from (8)] . . . . .                                                                                                                                                               | 7 |

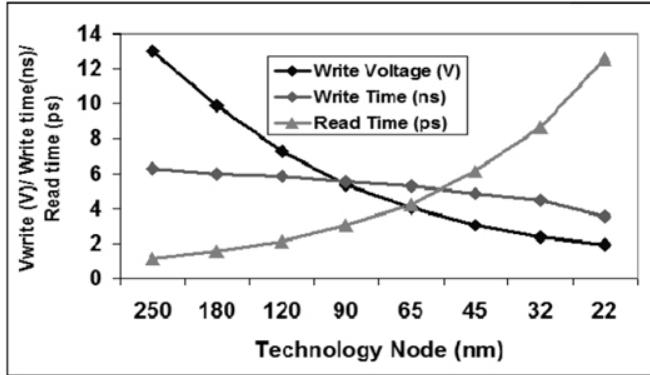

| 1.9 | Showing the progression of the NEMRAM as nodes are scaled down to much smaller scales. Showing the trade off between speed and read times as the technology is scaled further. Although the lower energy needed for smaller scales is a promising feature for the future development. Data is based on simulations [Reprinted from (7)]. . . . .                                                                                                                                                                             | 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

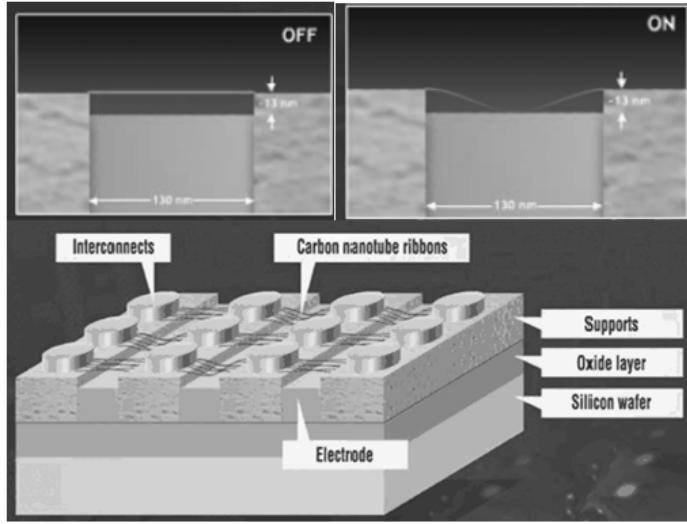

| 1.10 Top: The data representation of the carbon nanotube based NEMRAM produced by Nantero, taking advantage of the same actuating concept of NEMRAM but the nanotubes are bent through applying a current to them. Bottom: The array of the implemented architecture showing the electrodes used for actuation as well the nanotube ribbons connected to the device using the interconnects shown [Reprinted from (9)]. . . . . | 9  |

| 1.11 The demonstrated industrial distribution of FRAM by Ramtron showing limited distribution to a number of specific industries, where high costs are acceptable [Reprinted from (4)]. . . . .                                                                                                                                                                                                                                 | 10 |

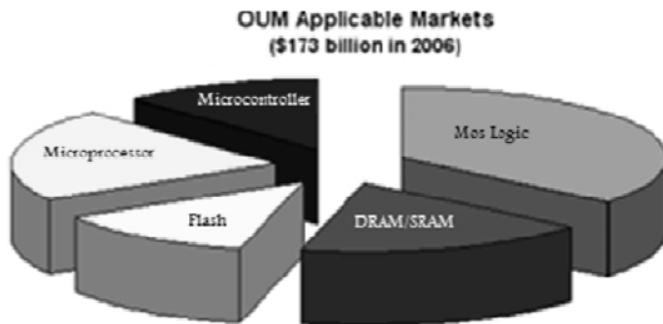

| 1.12 Intel predicted market for their PRAM variant OUM which effectively shows the great potential for the successful non-volatile memory not just for PRAM but for the successfully commercialized future non volatile memory [Adapted from (10)]. . . . .                                                                                                                                                                     | 10 |

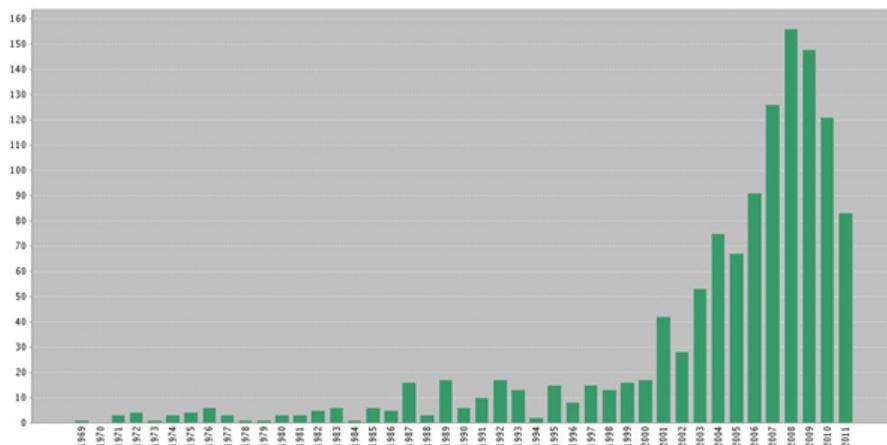

| 1.13 “Chalcogenides” +”phase change” -Published items per year (as presented in Web of Sciences) . . . . .                                                                                                                                                                                                                                                                                                                      | 12 |

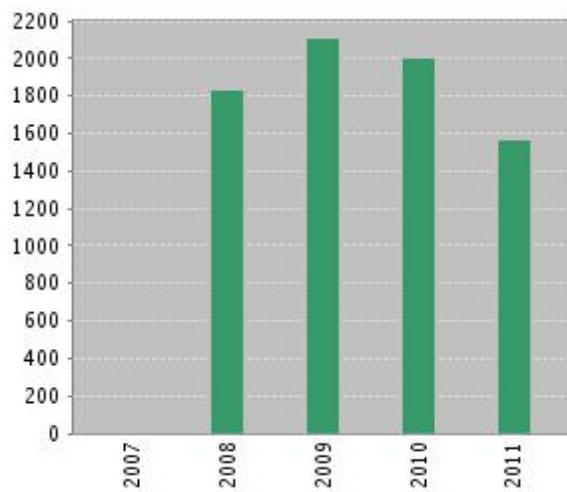

| 1.14 published items per year - “Metamaterials”, (as presented in Web of Sciences). . . . .                                                                                                                                                                                                                                                                                                                                     | 12 |

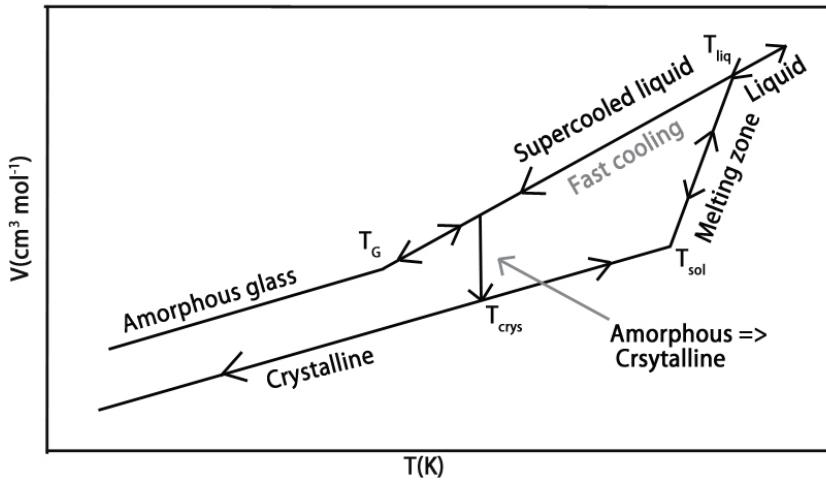

| 2.1 Dynamics of crystalline to super-cooled liquid transition. . . . .                                                                                                                                                                                                                                                                                                                                                          | 20 |

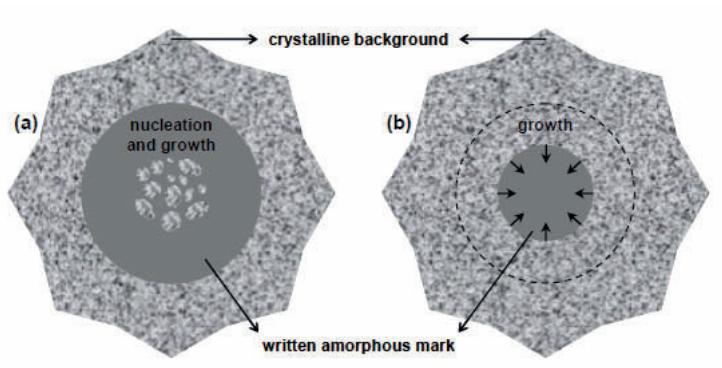

| 2.2 Nucleation driven crystallisation versus growth driven crystallisation [Reprinted from (11)]. . . . .                                                                                                                                                                                                                                                                                                                       | 21 |

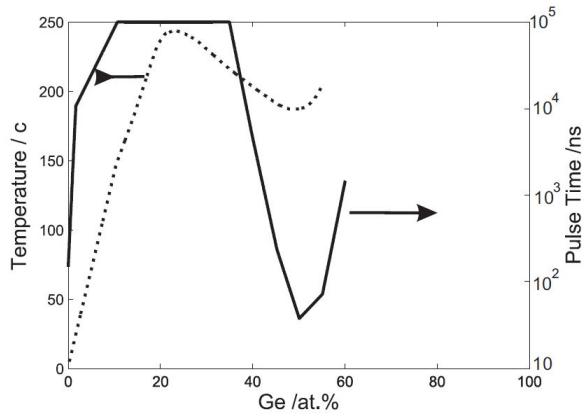

| 2.3 Ge-Te crystallisation time as a function of composition [Reprinted from (12)]. . . . .                                                                                                                                                                                                                                                                                                                                      | 22 |

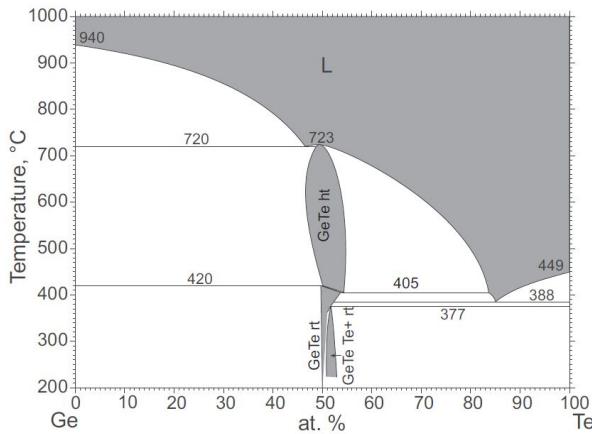

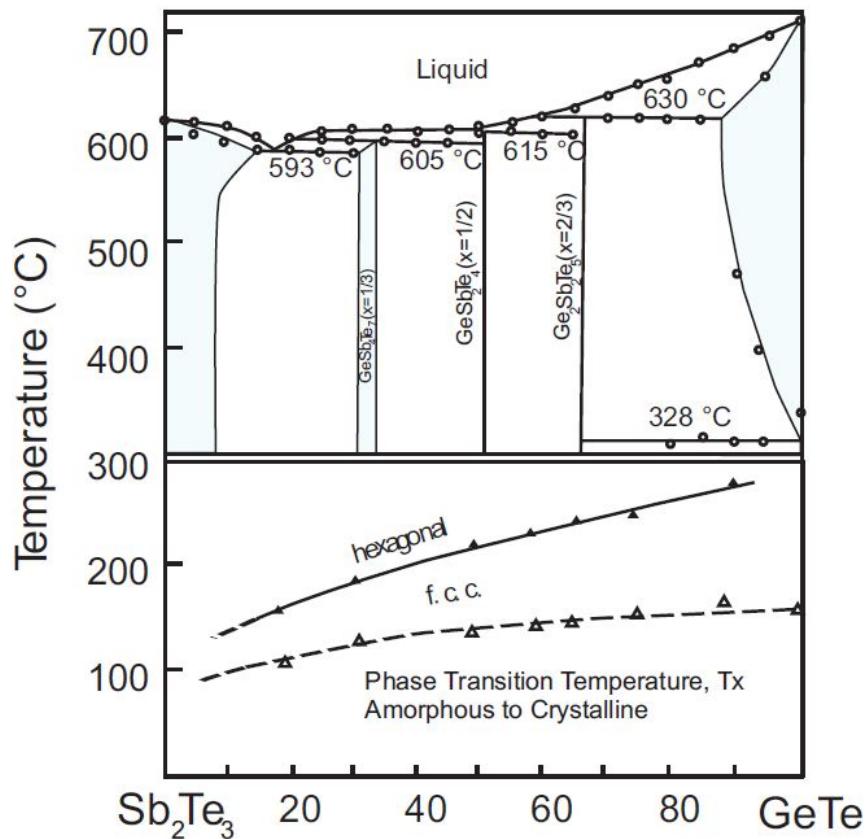

| 2.4 Phase diagrams for Ge-Te [Reprinted from (13)]. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 23 |

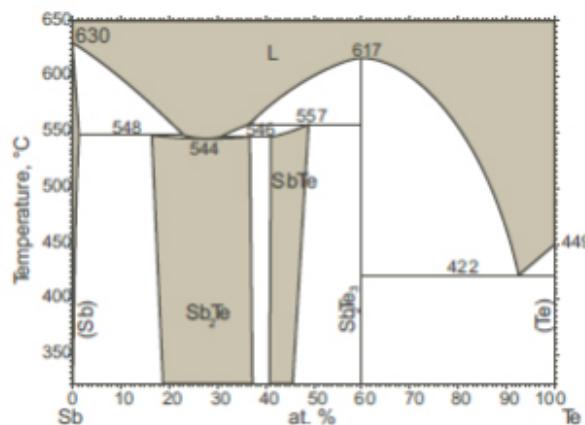

| 2.5 Phase diagrams for Sb-Te [Reprinted from (13)]. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 23 |

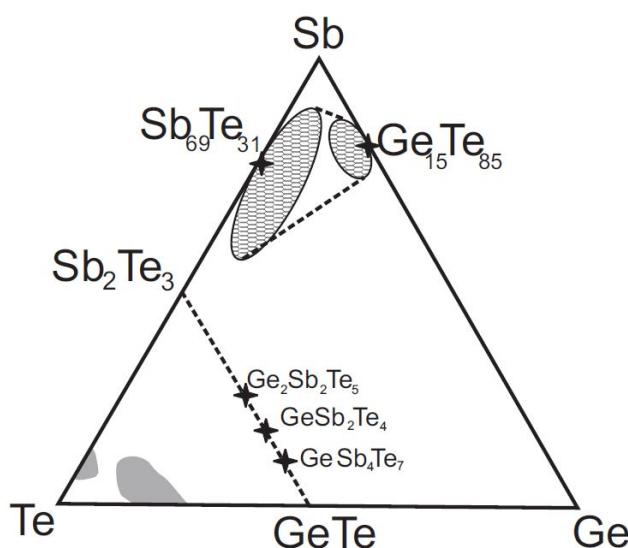

| 2.6 Ternary of GeSbTe. The pseudo binary line, the amorphous bulk and the fast growth compositional areas are indicated [Reprinted from (13)]. . . .                                                                                                                                                                                                                                                                            | 24 |

| 3.1 A typical sputtering system [Reprinted from (11)]. . . . .                                                                                                                                                                                                                                                                                                                                                                  | 28 |

| 3.2 Schematic diagram of the CVD system used for the deposition of GeSb as designed and built by Kevin Huang. . . . .                                                                                                                                                                                                                                                                                                           | 31 |

| 3.3 Schematic diagram of the ion beam milling process [Redrawn from (14)] .                                                                                                                                                                                                                                                                                                                                                     | 32 |

| 3.4 Schematic diagram of the electron/ion beam deposition process [Redrawn from (14)] . . . . .                                                                                                                                                                                                                                                                                                                                 | 32 |

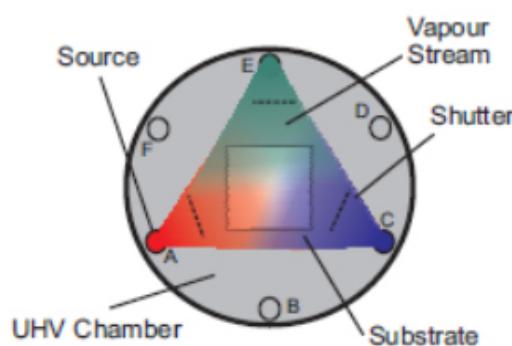

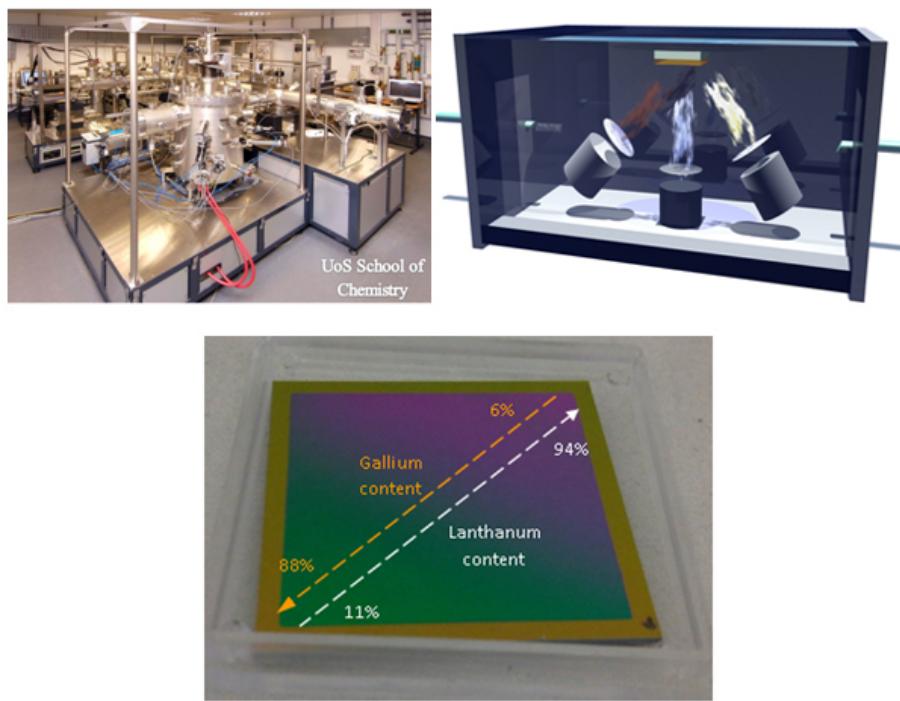

| 3.5 A schematic showing how composition varying thin films have been synthesised . . . . .                                                                                                                                                                                                                                                                                                                                      | 33 |

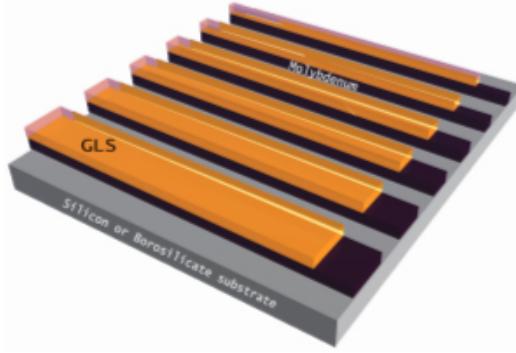

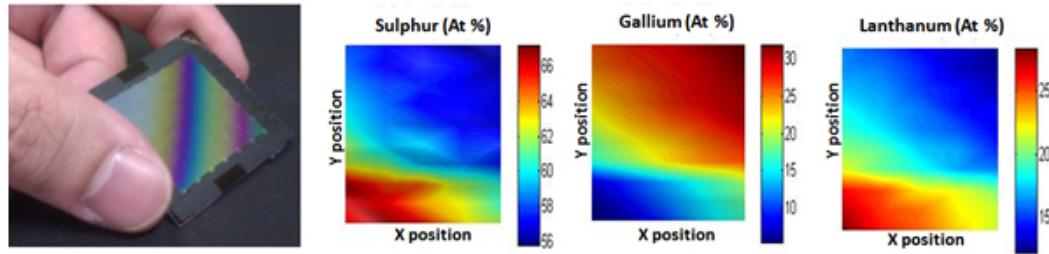

| 3.6 Compositional gradient GLS sample prepared by high throughput physical vapour deposition . . . . .                                                                                                                                                                                                                                                                                                                          | 34 |

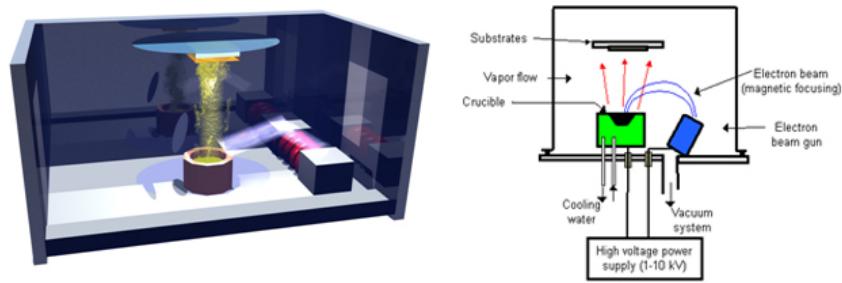

| 3.7 Schematic view of the electron beam evaporation system used predominantly for the deposition of thin films of gold. . . . .                                                                                                                                                                                                                                                                                                 | 35 |

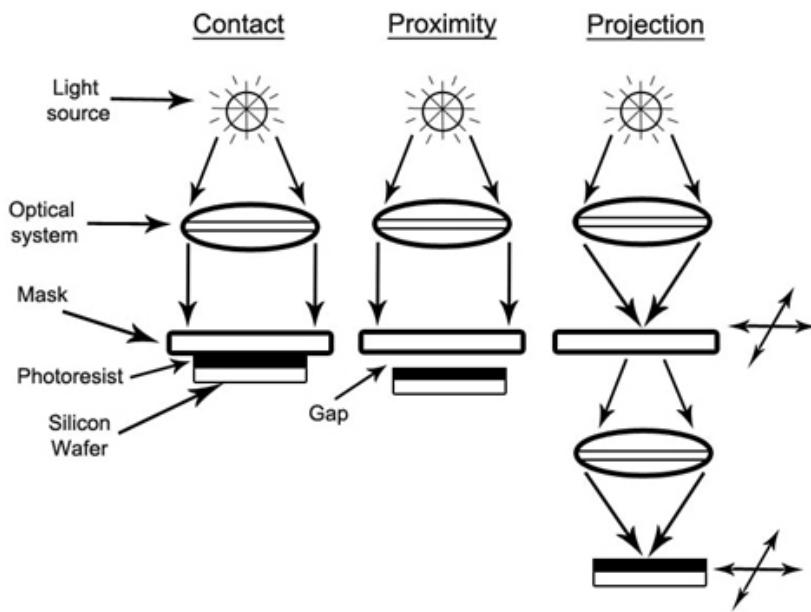

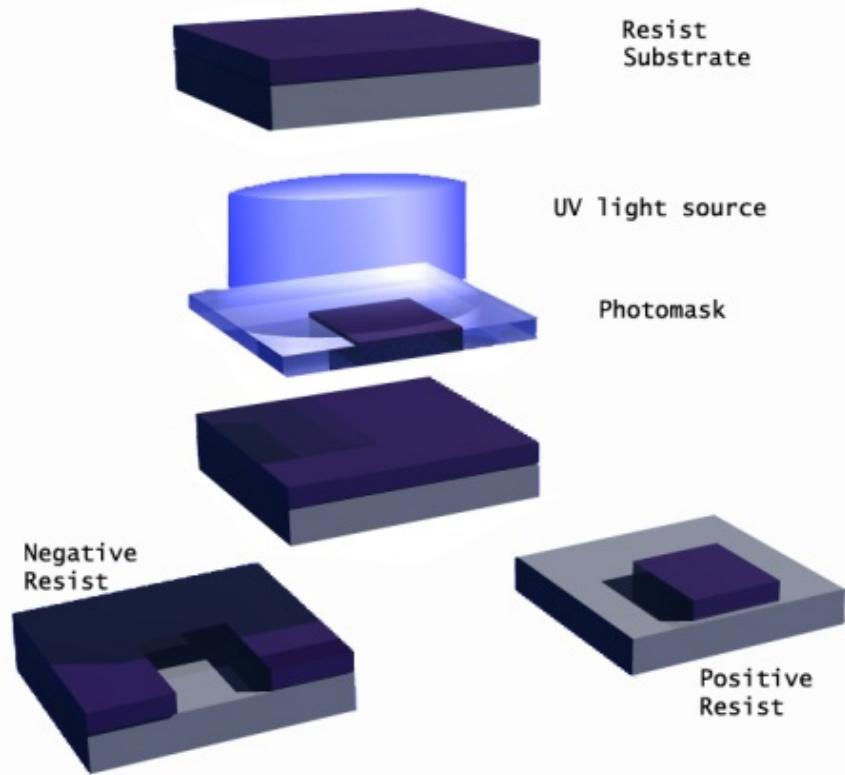

| 3.8 Different modes of projection in UV photolithography [Reprinted from (14)]                                                                                                                                                                                                                                                                                                                                                  | 36 |

| 3.9 Simplified process diagram for the photolithography technique. . . . .                                                                                                                                                                                                                                                                                                                                                      | 37 |

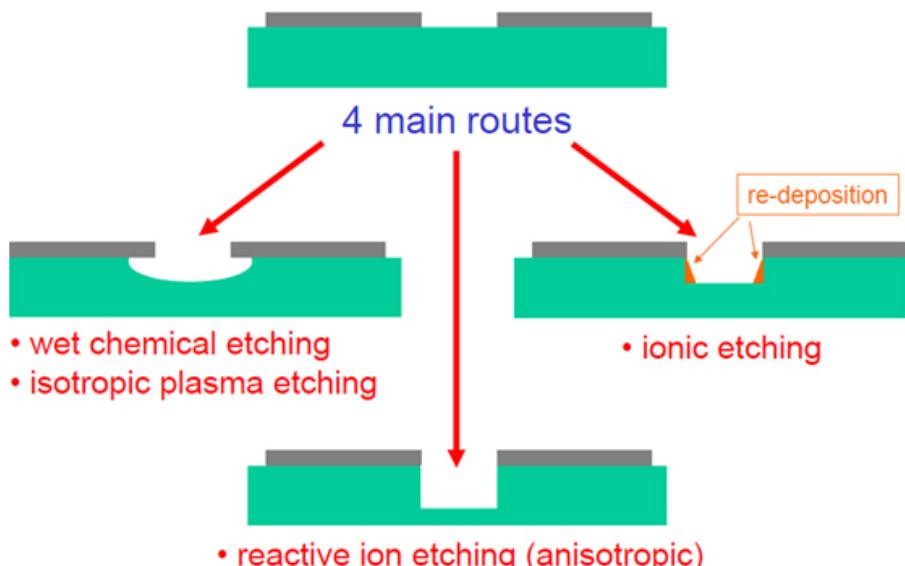

| 3.10 Different types of wet and dry etching each exhibiting different etch profiles, as a result each type of etching process has its own specific applications and one must choose the type of etch very carefully [Reprinted from (15)]. . . . .                                                                                                                                                                              | 38 |

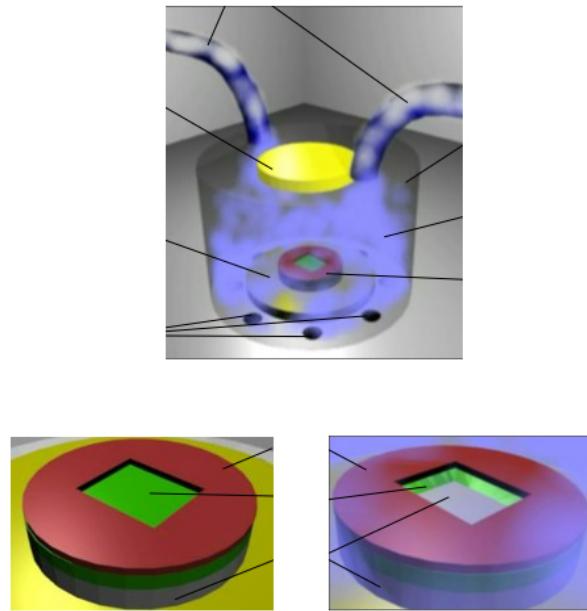

| 3.11 Simple model of reactive ion etching [Reprinted from (15)]. . . . .                                                                                                                                                                                                                                                                                                                                                        | 39 |

|                                                                                                                                                                                                                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

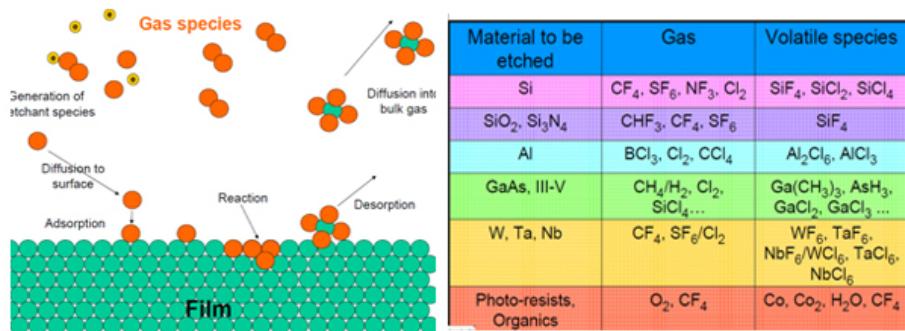

| 3.12 (left) Reactive ion etching, showing the interaction of species with sample surface. (right) Common materials with the respective plasma gas capable of etching these materials, along with the volatile species which are created in the chamber in order to etch the surface of the material [Reprinted from (15)]. . . . . | 39 |

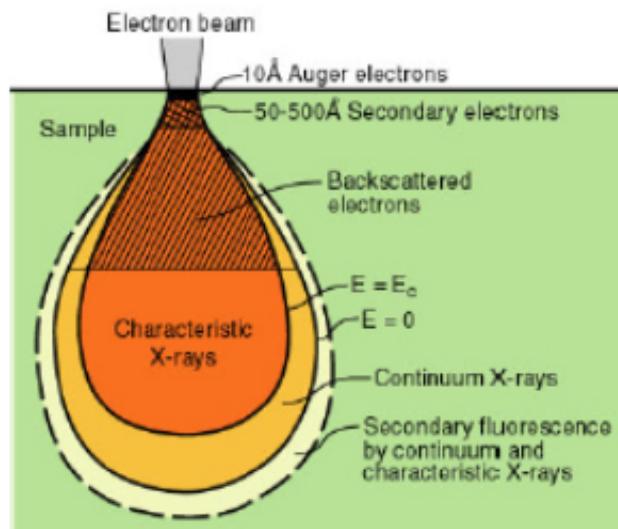

| 3.13 Interaction volume showing the regions of various electron-specimen interactions [Reprinted from (16)]. . . . .                                                                                                                                                                                                               | 41 |

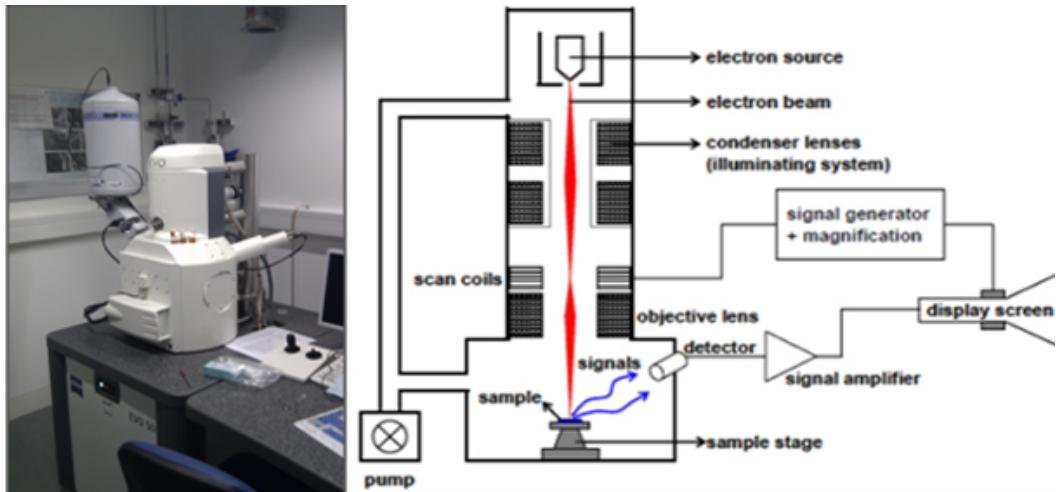

| 3.14 (left) The ORC Scanning electron microscope facility. (right) Schematic diagram of a typical scanning electron microscope [Reprinted from (16)]. . . . .                                                                                                                                                                      | 42 |

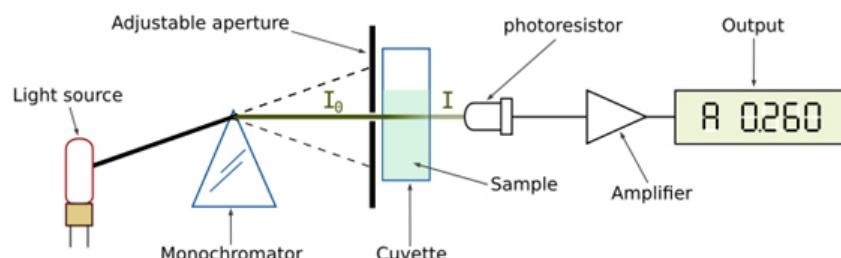

| 3.15 schematic diagram of an infrared spectrophotometer. . . . .                                                                                                                                                                                                                                                                   | 43 |

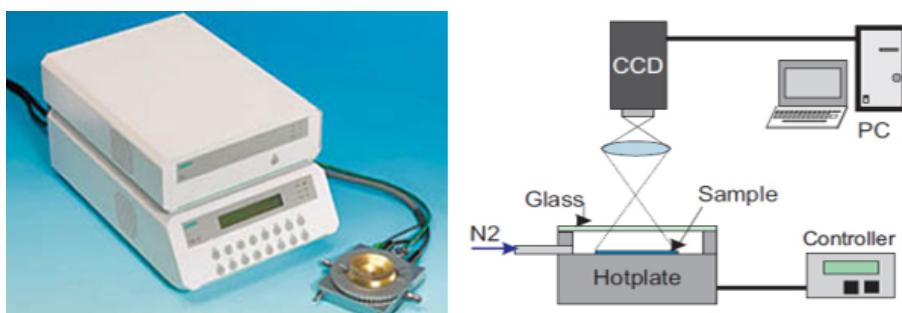

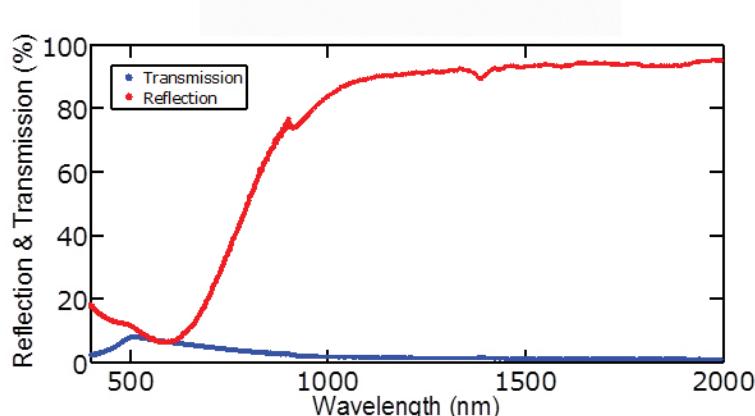

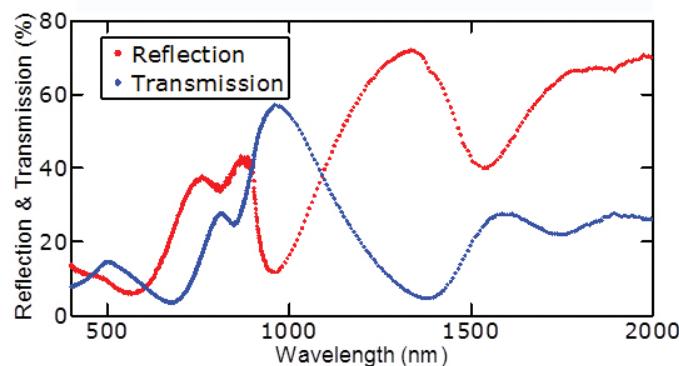

| 3.16 (left) CRAIC microspectrophotometer for NIR measurements. (right) Jasco micro spectrophotometer for Mid IR measurements. . . . .                                                                                                                                                                                              | 44 |

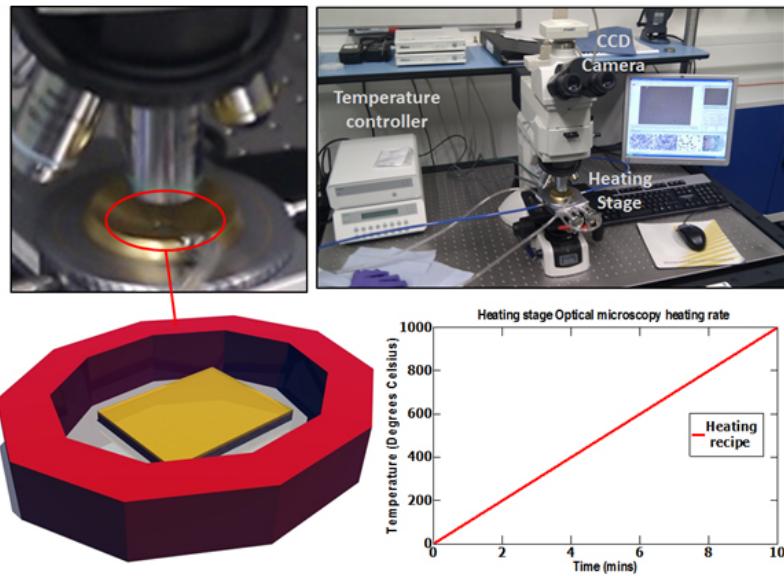

| 3.17 Heating stage enabling thermal optical microscopy. . . . .                                                                                                                                                                                                                                                                    | 44 |

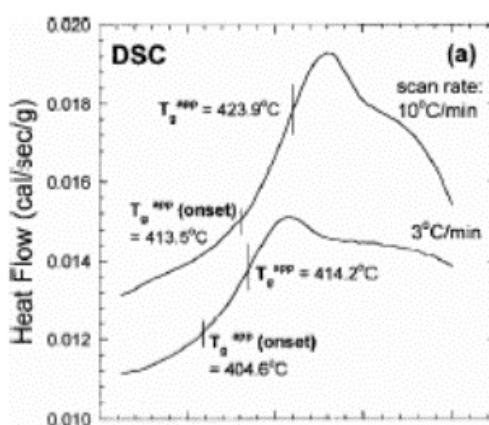

| 3.18 DSC curve showing glass transition,crystallisation and melting points as observed from such a measurement [Reprinted from (17)]. . . . .                                                                                                                                                                                      | 45 |

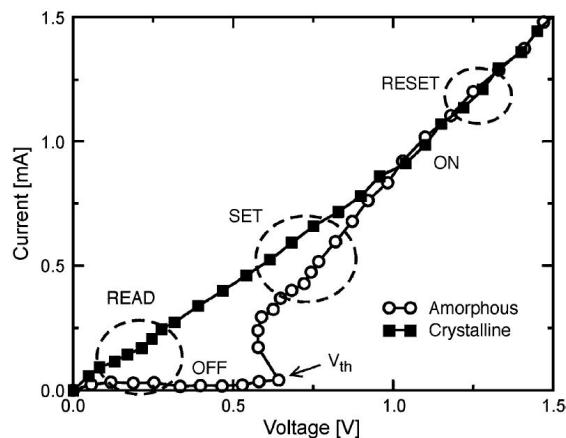

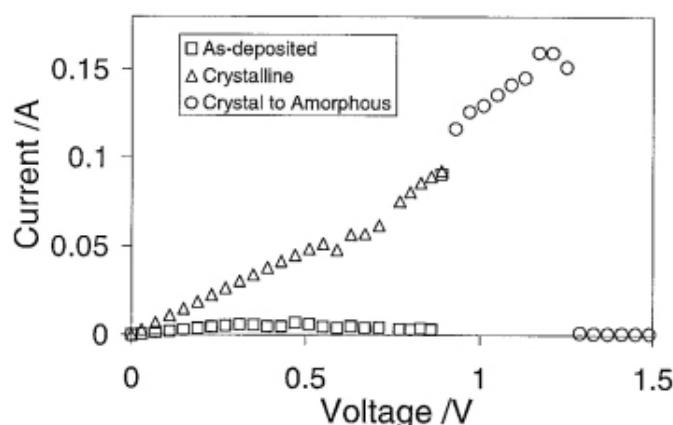

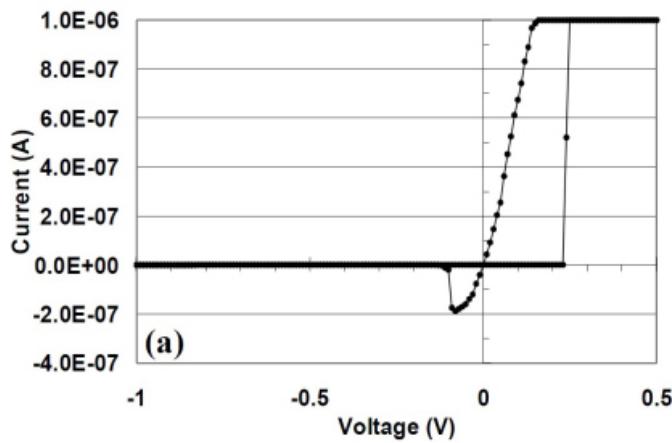

| 4.1 Typical I-V Characteristics of an OUM cell [Reprinted from (18)]. . . . .                                                                                                                                                                                                                                                      | 49 |

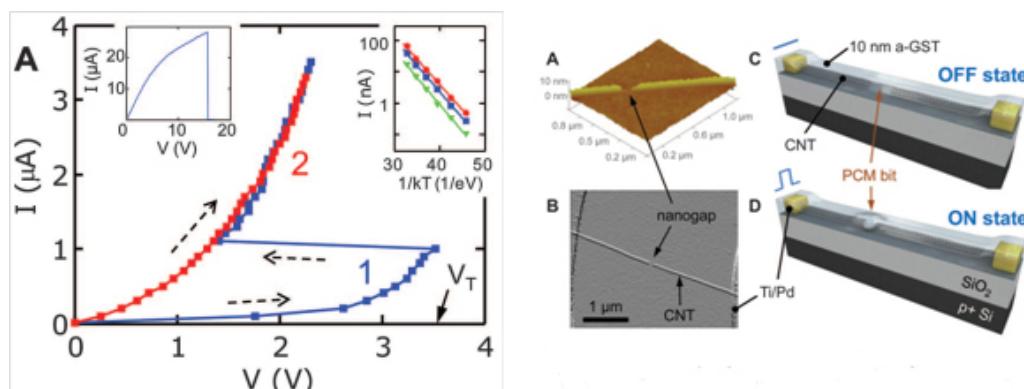

| 4.2 Carbon nanotubes as electrodes has been demonstrated as a means of achieving low current consumption devices [Reprinted from (19)]. . . . .                                                                                                                                                                                    | 50 |

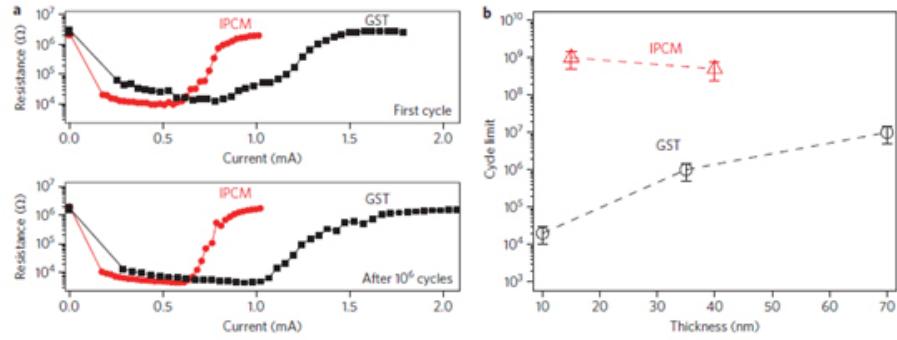

| 4.3 phase change memory concept known as iPCM exhibiting high stability and low power consumption [Reprinted from (20)]. . . . .                                                                                                                                                                                                   | 51 |

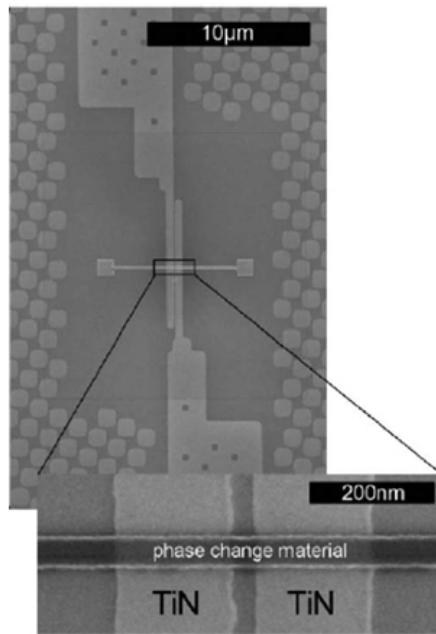

| 4.4 SEM picture of the demonstrated ultra thin GeSb phase change bridge memory cell [Reprinted from (21)] . . . . .                                                                                                                                                                                                                | 51 |

| 4.5 I-V characteristics of the previously demonstrated GaLaS:Cu phase change cell [Reprinted from (13)]. . . . .                                                                                                                                                                                                                   | 52 |

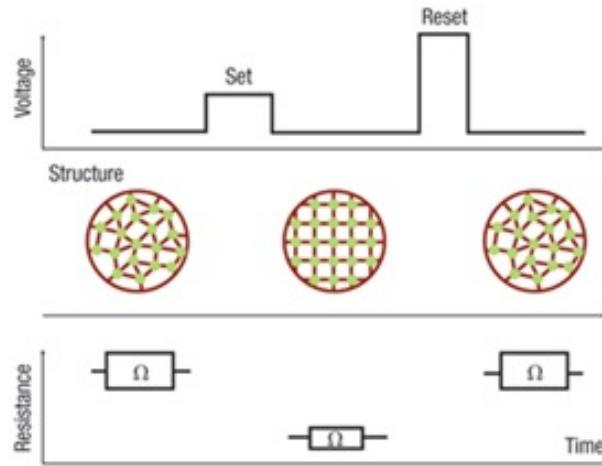

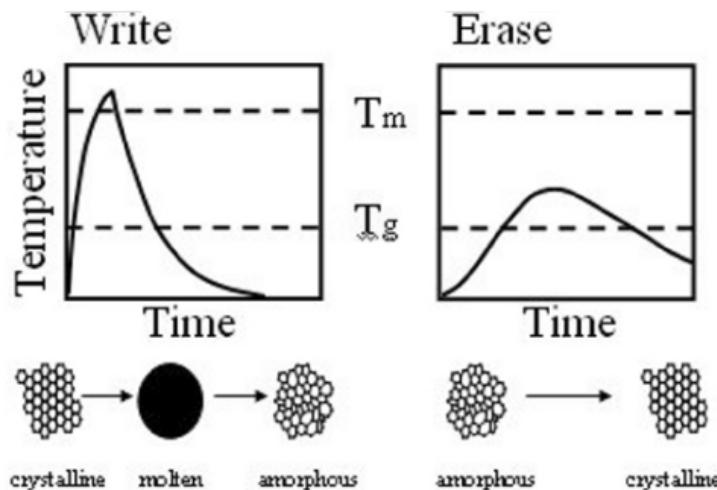

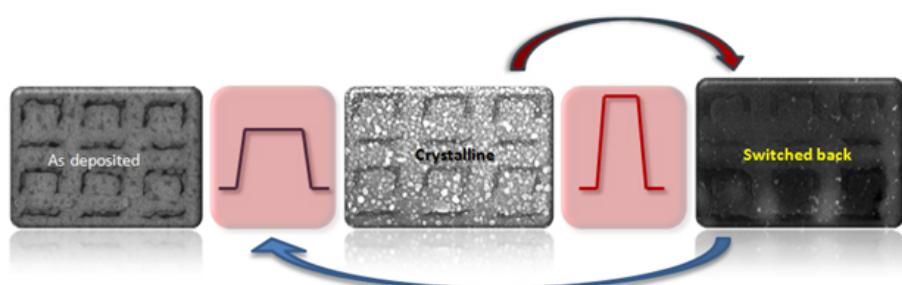

| 4.6 Set and reset pulses allow the controlled reversible phase change of the material from a high resistance amorphous state to a low resistance crystalline state [Reprinted from (22)]. . . . .                                                                                                                                  | 54 |

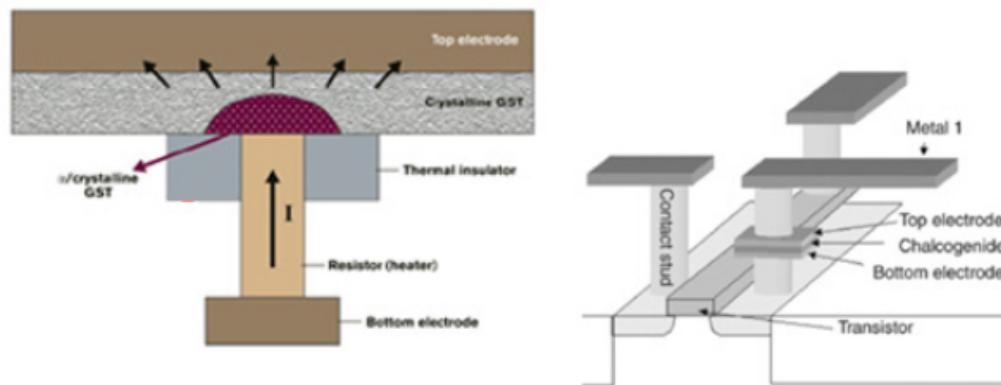

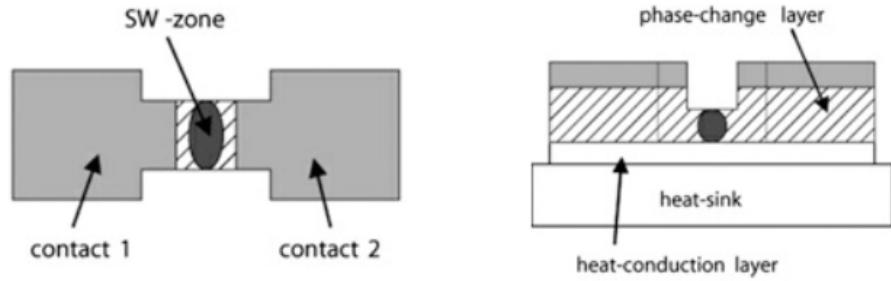

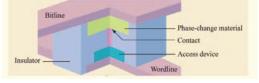

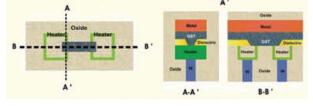

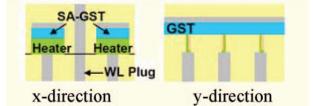

| 4.7 Typical schematic of a Mushroom cell design and integration into a wider PCRAM [Reprinted from (23)]. . . . .                                                                                                                                                                                                                  | 54 |

| 4.8 Typical diagram of a lateral phase change memory cell [Reprinted from (24)]. . . . .                                                                                                                                                                                                                                           | 55 |

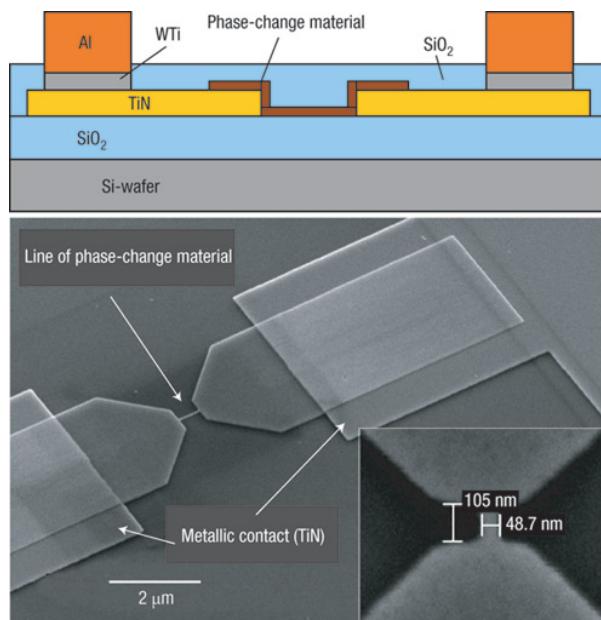

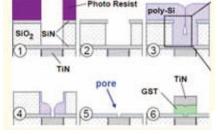

| 4.9 Schematic plot of the line structure (top) and SEM images of the structure after fabrication (bottom) [Reprinted from (25)]. . . . .                                                                                                                                                                                           | 55 |

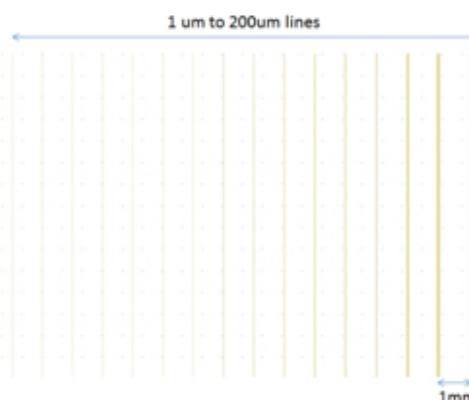

| 4.10 Lines used for electrodes with varying widths between $1\mu$ and $200\mu\text{m}$ . . . . .                                                                                                                                                                                                                                   | 60 |

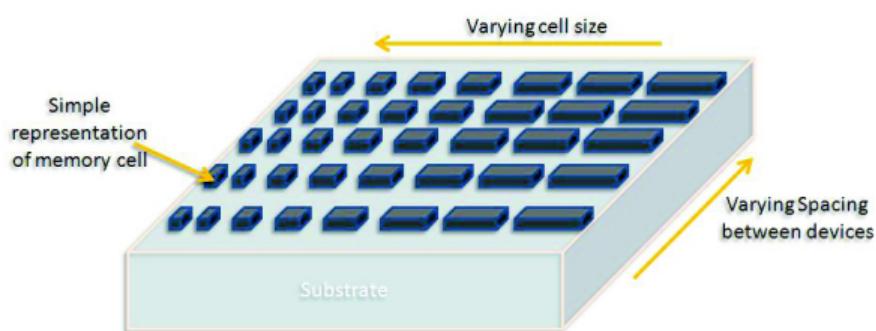

| 4.11 Simple diagram of final device with varying cell sizes. . . . .                                                                                                                                                                                                                                                               | 61 |

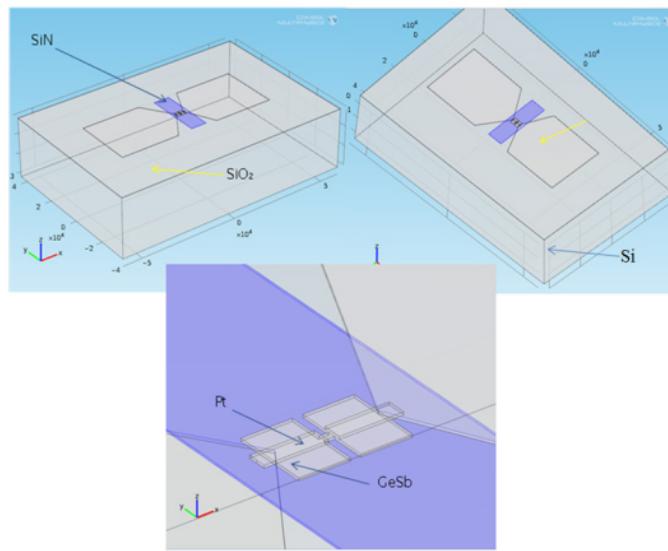

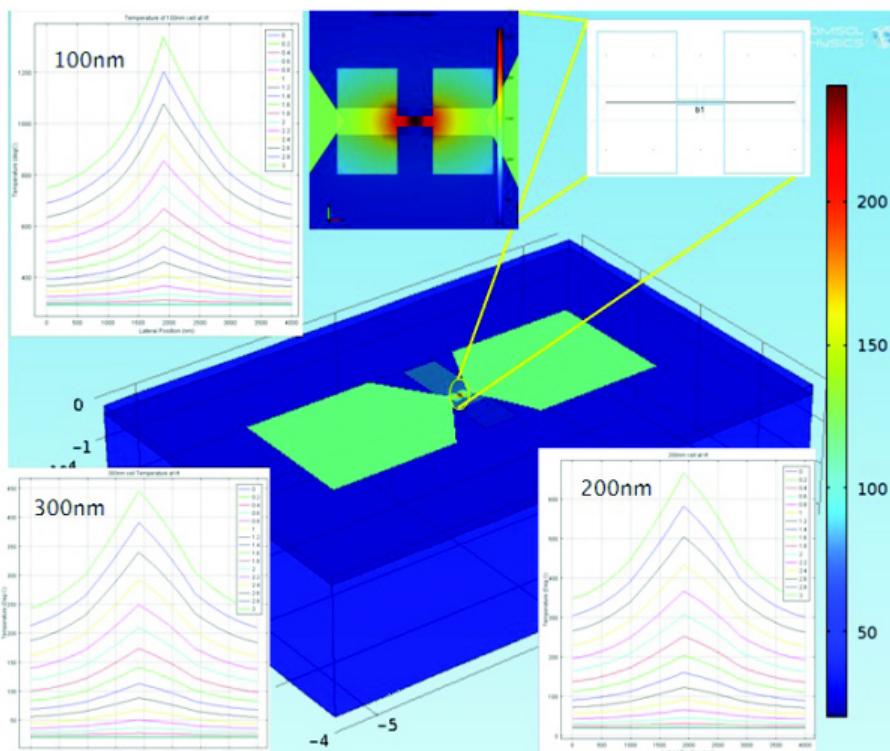

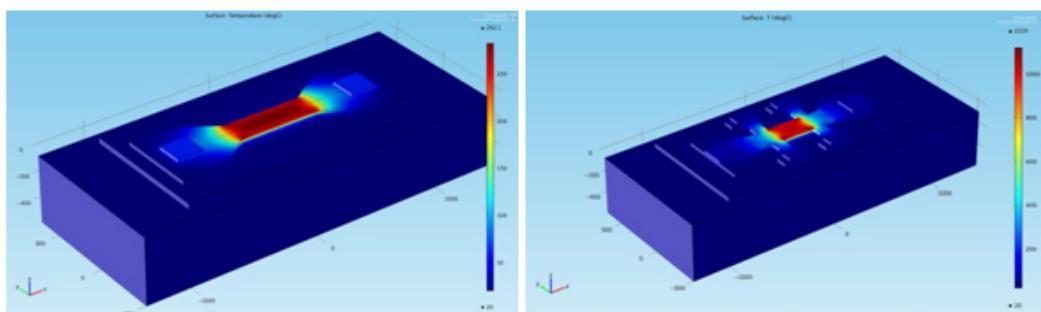

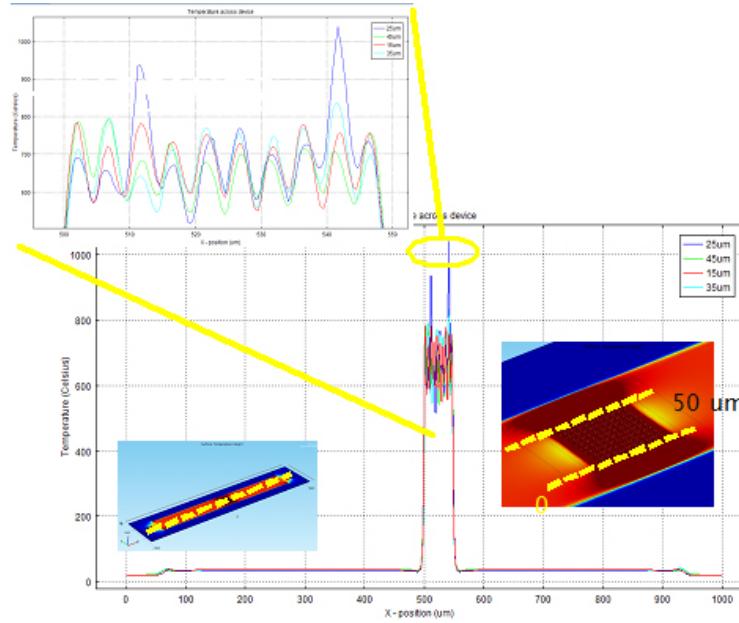

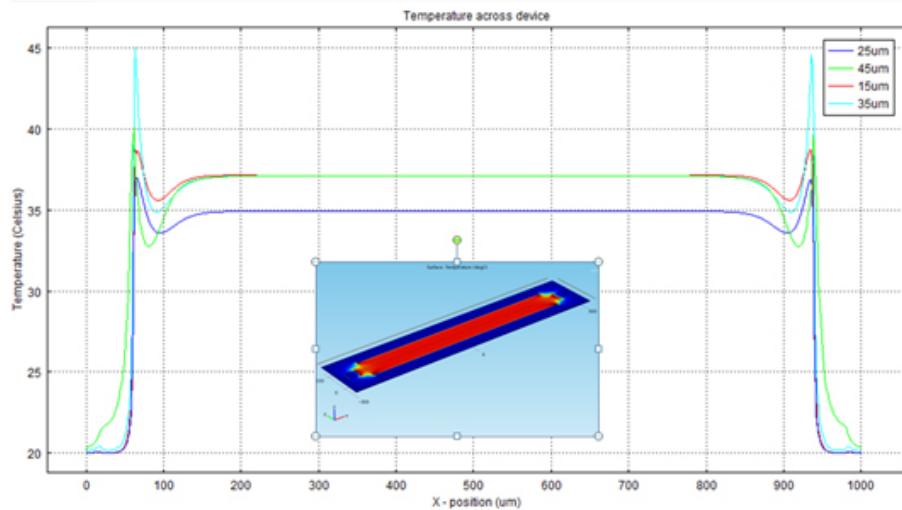

| 4.12 Overview of the multiphysics model made for the GeSb nanowire cells. . . . .                                                                                                                                                                                                                                                  | 61 |

| 4.13 The multiphysics model and temperature gradient across the nanowire device simulated across the length of the memory cell. . . . .                                                                                                                                                                                            | 62 |

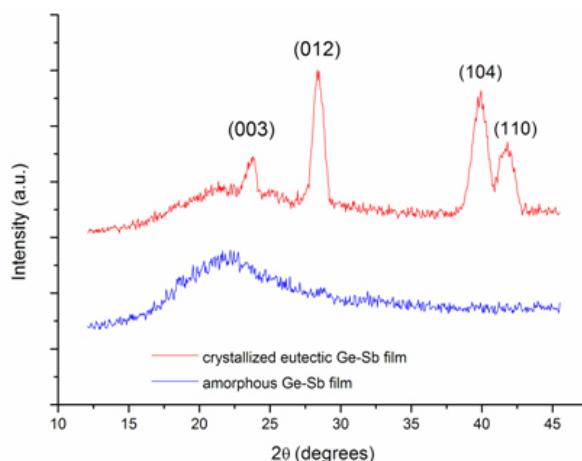

| 4.14 XRD spectra of amorphous and crystalline CVD grown eutectic Ge:Sb, measurement taken by Dr C. C. Huang. . . . .                                                                                                                                                                                                               | 63 |

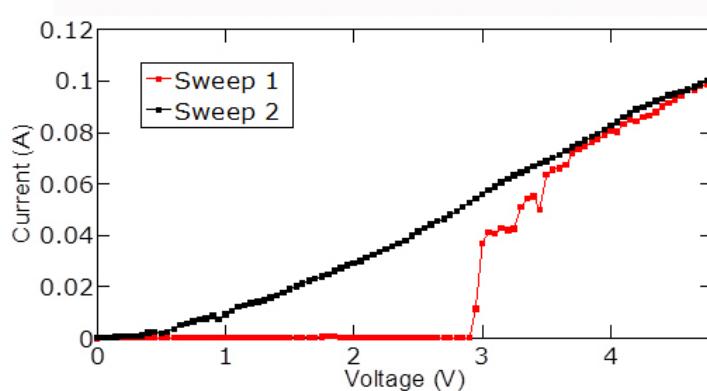

| 4.15 Typical current-voltage characteristics of a Ge:Sb thin film microheater device. . . . .                                                                                                                                                                                                                                      | 64 |

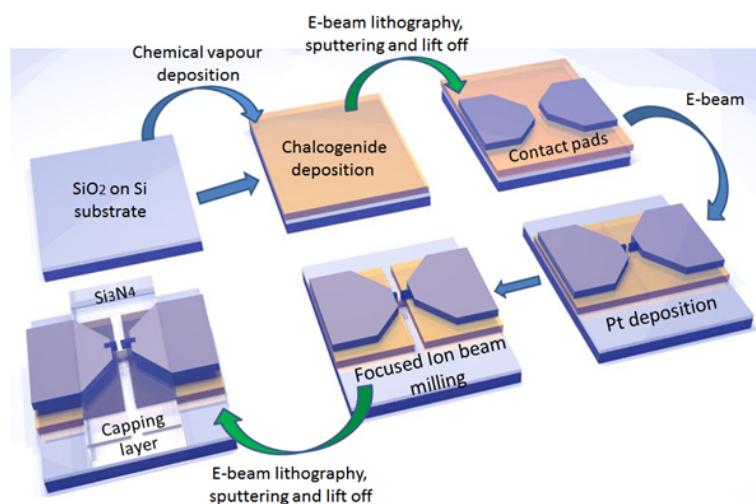

| 4.16 Process flow diagram showing the fabrication process used for the production of GeSb nanowires. . . . .                                                                                                                                                                                                                       | 64 |

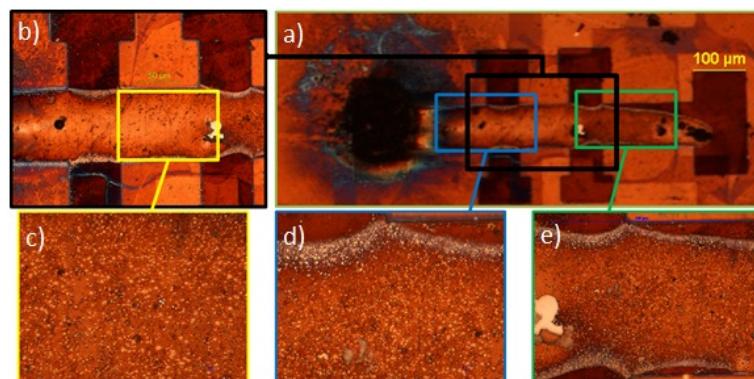

| 4.17 Microscopy images of GeSb nanowire memory cells. . . . .                                                                                                                                                                                                                                                                      | 65 |

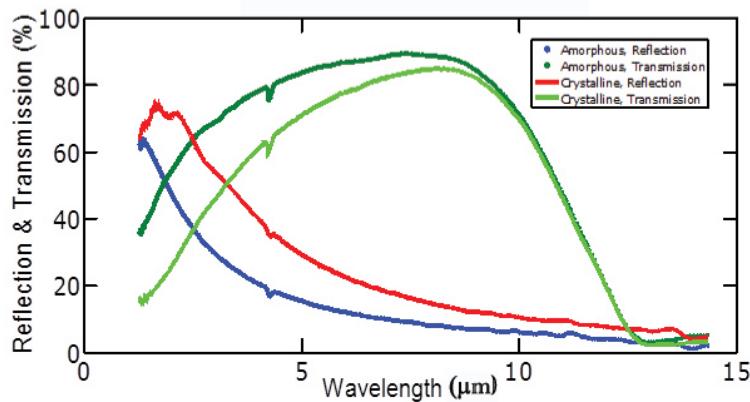

| 4.18 Thermo-optical microscopy of crystallisation and melting characteristics of thin film chalcogenide films. . . . .                                                                                                                                                                                                             | 66 |

|      |                                                                                                                                                                                                                                                            |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.19 | Typical current voltage characteristics of GaLaS thin film microheater devices. . . . .                                                                                                                                                                    | 66 |

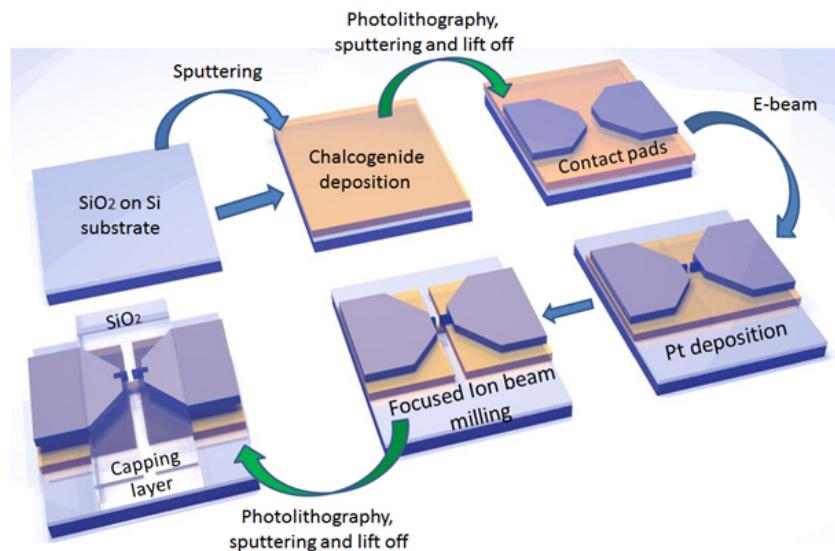

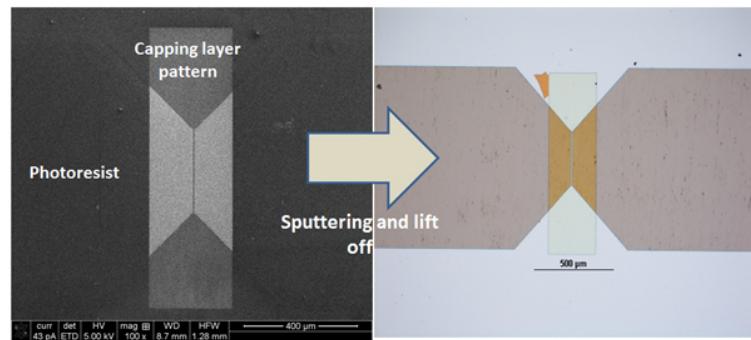

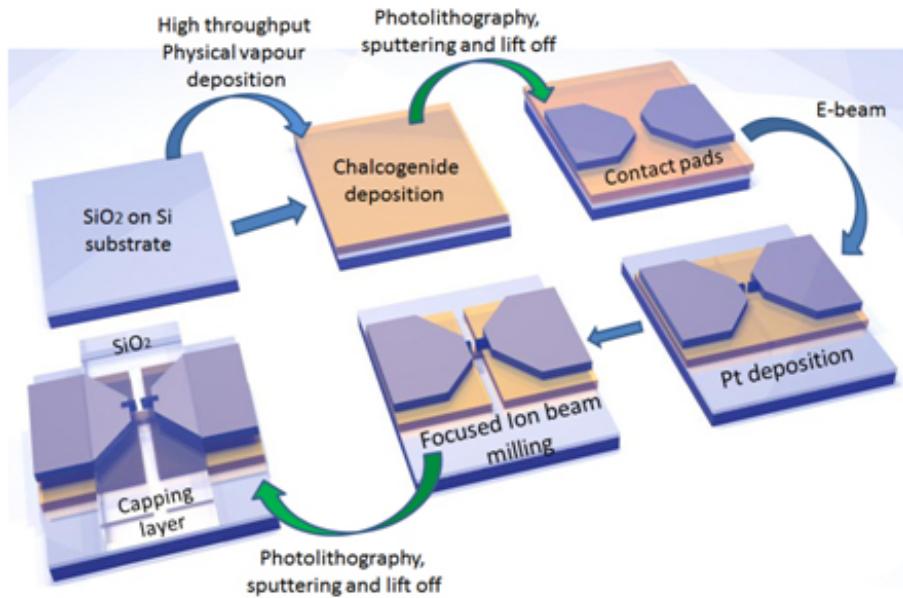

| 4.20 | Process flow diagram showing the fabrication process used for the production of GaLaS nanowires. . . . .                                                                                                                                                   | 67 |

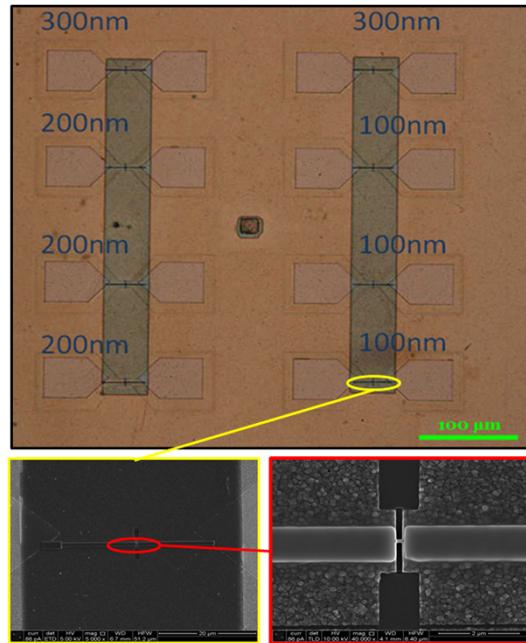

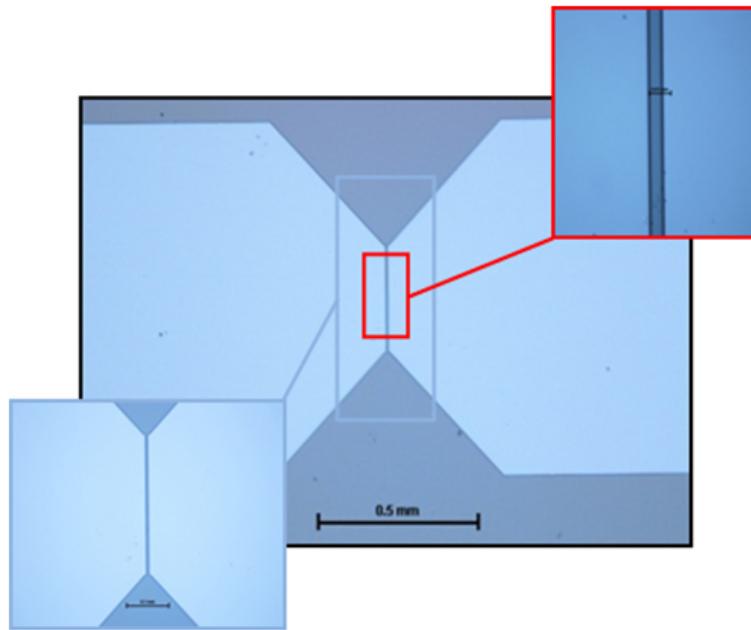

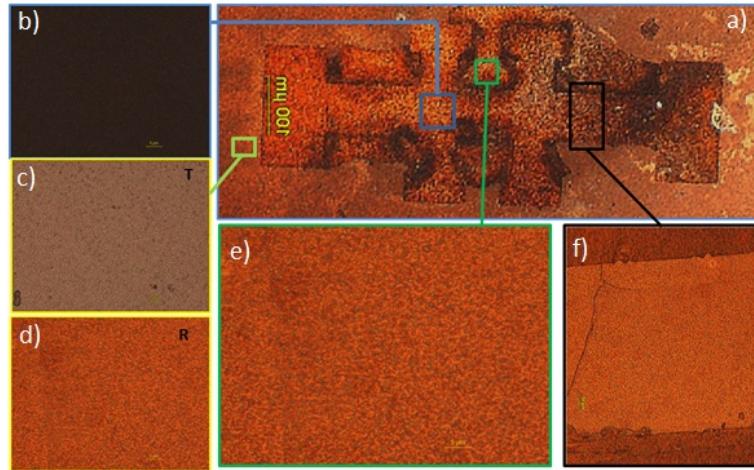

| 4.21 | Optical microscopy images of contact pads fabricated using photolithography, sputtering and the lift-off technique. . . . .                                                                                                                                | 68 |

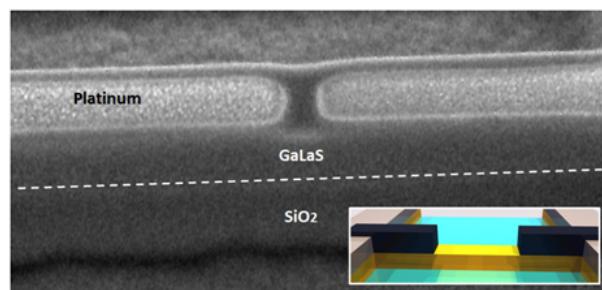

| 4.22 | Scanning electron microscope (SEM) image of GaLaS memory cell formed from two platinum electrodes spaced apart. The chalcogenide layer has been milled away to form the nanowire cell. . . . .                                                             | 68 |

| 4.23 | Fabrication of the capping layer of the memory cells using photolithography, sputtering and lift-off technique, followed by an ashing step to remove any residue photoresist on the sample surface. . . . .                                                | 69 |

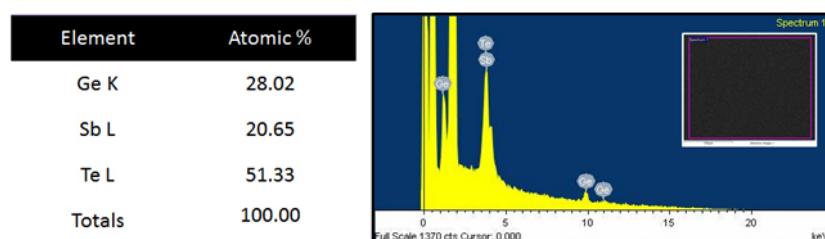

| 4.24 | Energy dispersive X-ray of sputtered 100nm GeSbTe thin film. . . . .                                                                                                                                                                                       | 69 |

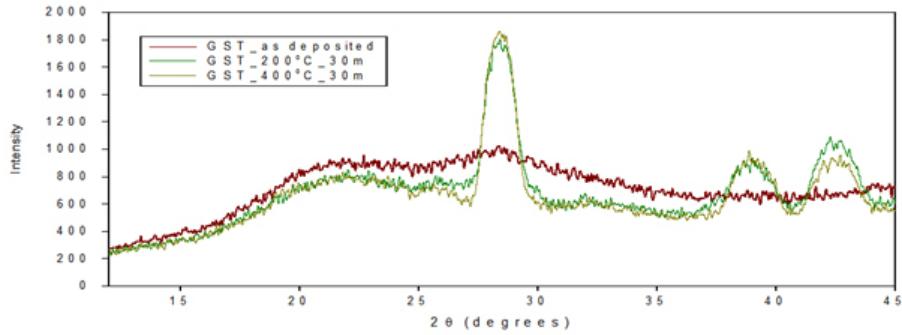

| 4.25 | XRD spectra of GeSbTe thin film with different annealing temperatures. .                                                                                                                                                                                   | 70 |

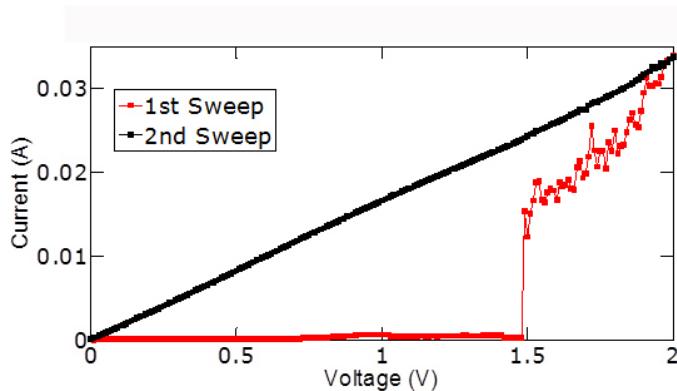

| 4.26 | Typical current-voltage characteristics of GeSbTe thin film microheater device. . . . .                                                                                                                                                                    | 70 |

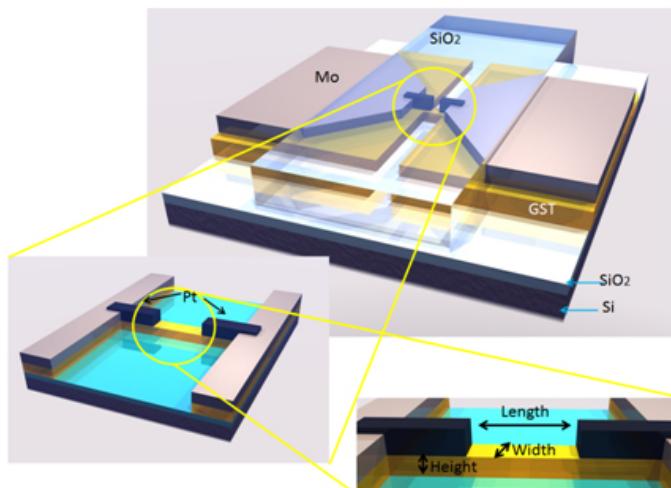

| 4.27 | model of the GeSbTe and GaLaS NW memory cells. . . . .                                                                                                                                                                                                     | 70 |

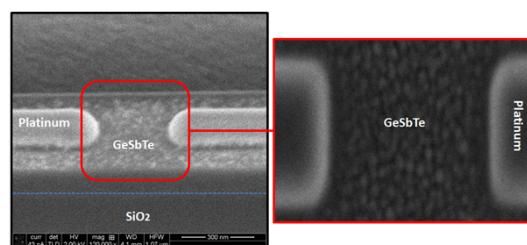

| 4.28 | Scanning electron microscope (SEM) image of GeSbTe memory cell formed from two platinum electrodes spaced 375 nm apart. The chalcogenide layer has been milled away to form the nanowire cell. . . . .                                                     | 71 |

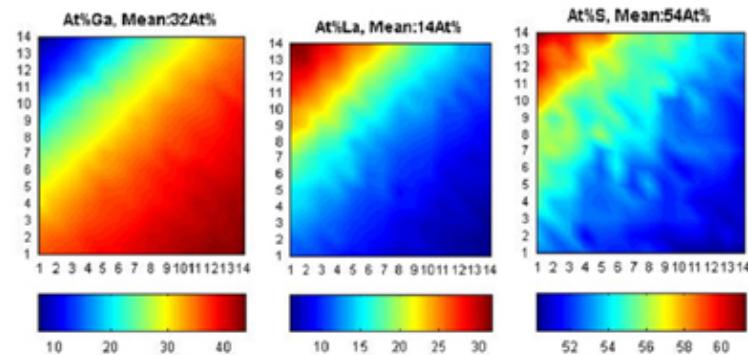

| 4.29 | Energy dispersive xray across a 35 x 35 mm sample deposited with the compositional gradient of the ternary family of GaLaS. . . . .                                                                                                                        | 72 |

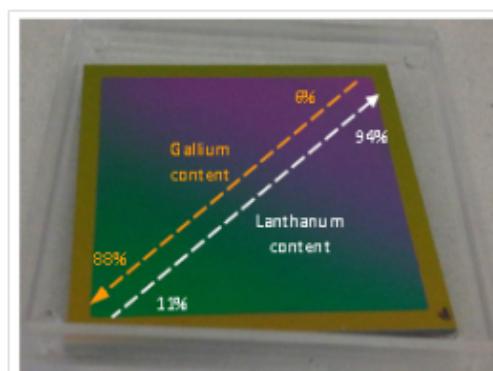

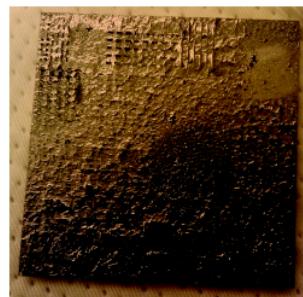

| 4.30 | Compositional gradient GaLaS sample prepared by high throughput physical vapour deposition. . . . .                                                                                                                                                        | 72 |

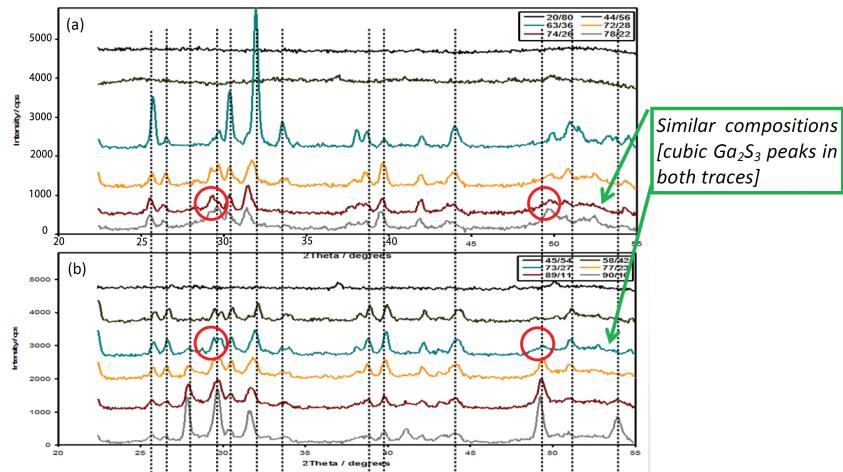

| 4.31 | XRD of GaLaS samples (a)deposited at 200°C using native sulphur in PVD chamber annealed to 650°C. (b) deposited at 200°C using a sulphur cracking k-cell annealed to 700°C. . . . .                                                                        | 73 |

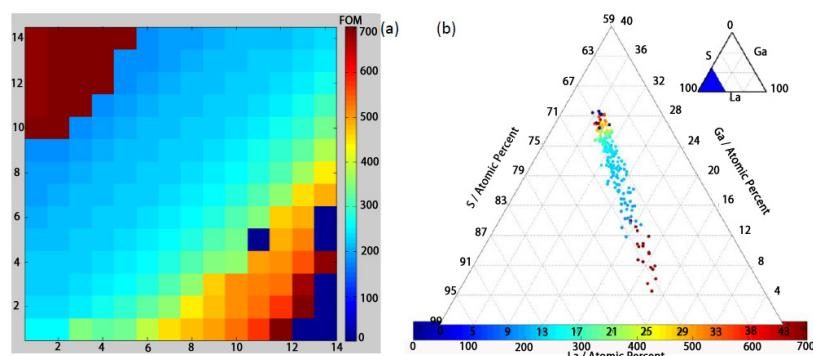

| 4.32 | Crystallisation temperature of GaLaS (a) as a function of position across a compositional gradient samples varying from lanthanum sulphide top left to gallium sulphide bottom right. (b) translated to a ternary composition plot. . . . .                | 73 |

| 4.33 | Process flow diagram showing the fabrication process used for the production of nanowires across compositional gradient thin film. . . . .                                                                                                                 | 74 |

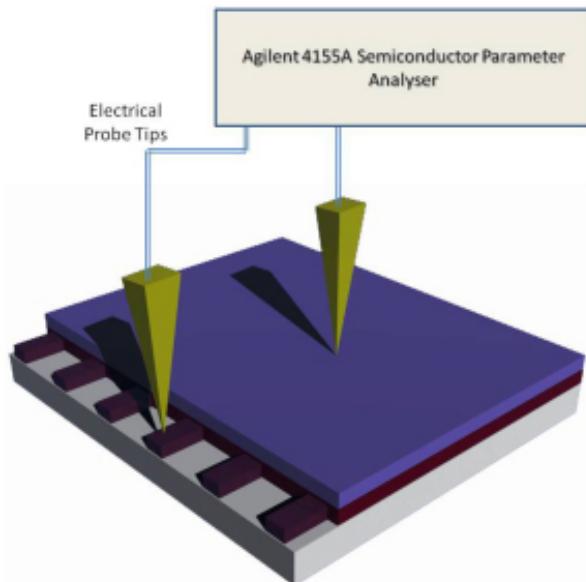

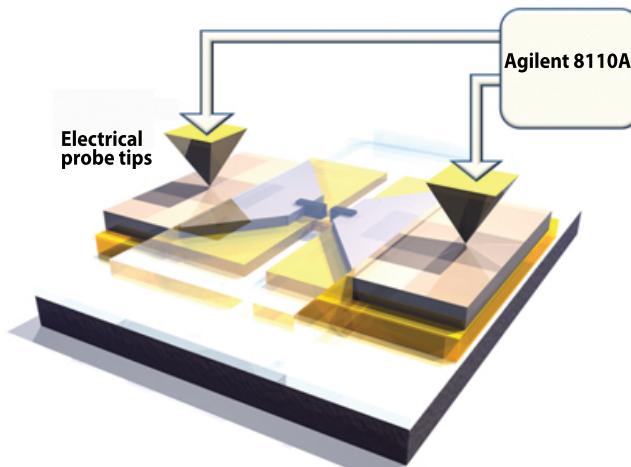

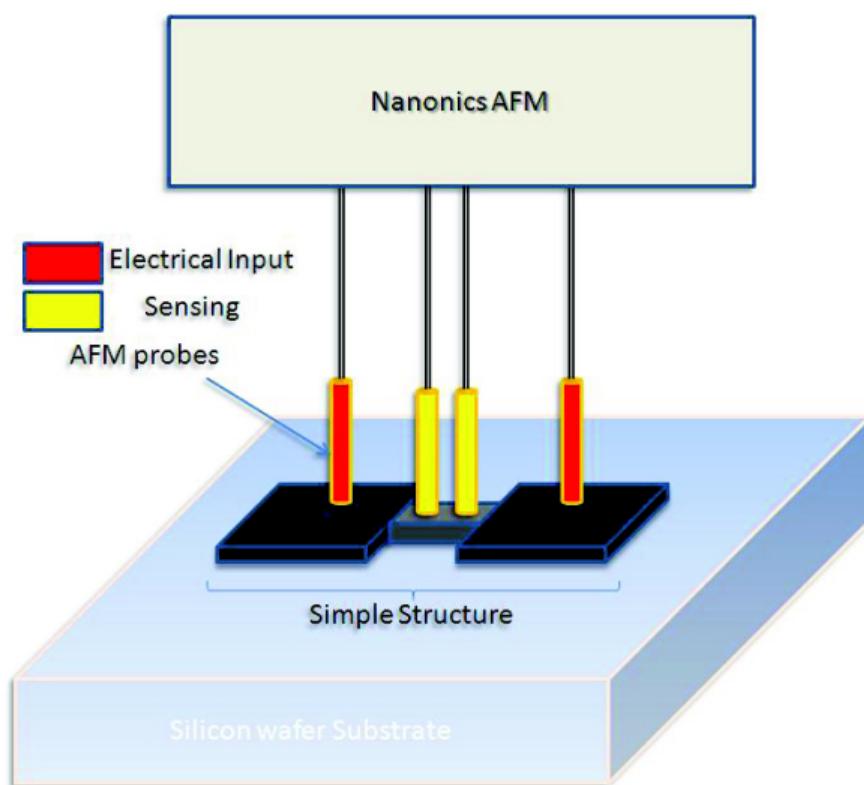

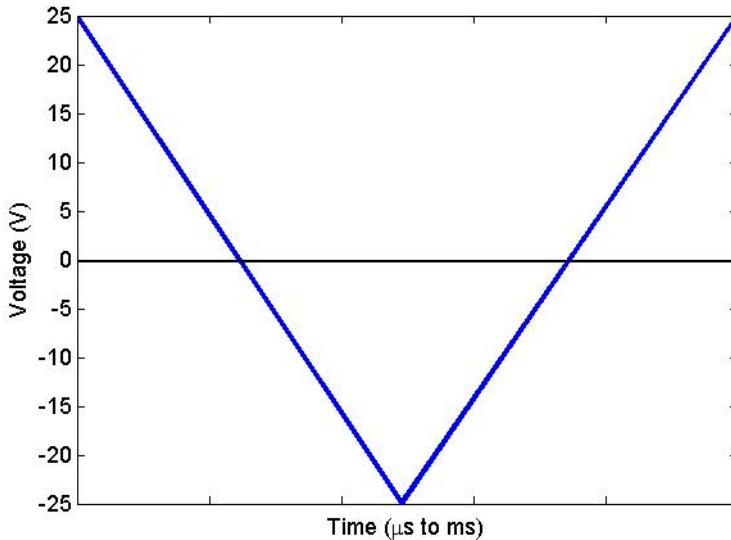

| 4.34 | Experimental setup used for the electrical sweep measurements. . . . .                                                                                                                                                                                     | 75 |

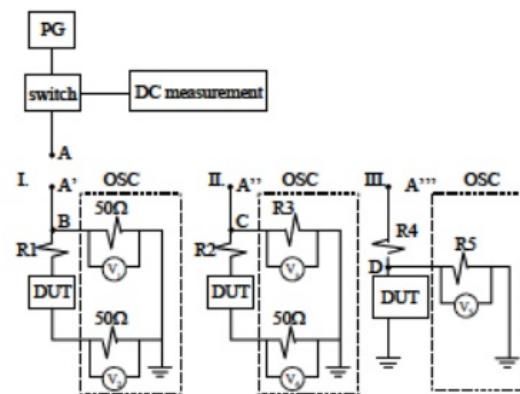

| 4.35 | Typical configurations of a memory cell testing setup [Reprinted from (17)].                                                                                                                                                                               | 75 |

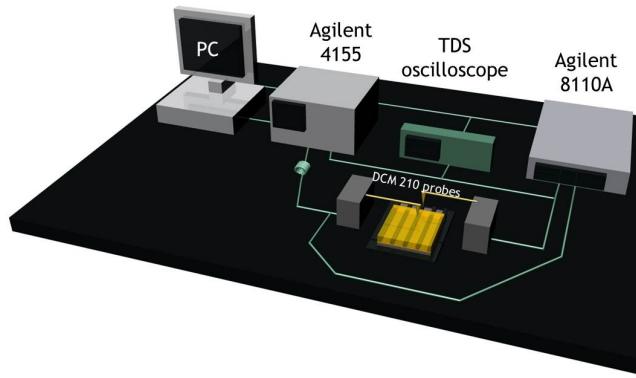

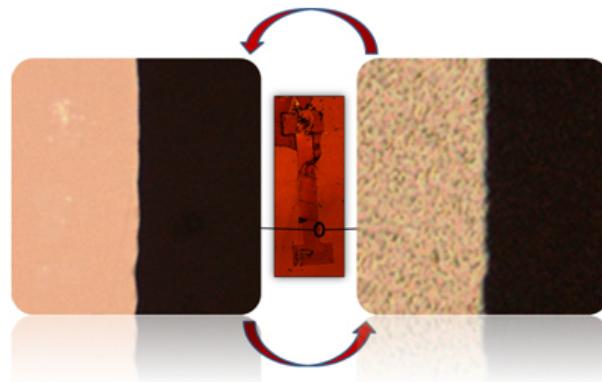

| 4.36 | Experimental setup used for the dual pulse switching measurements. . .                                                                                                                                                                                     | 76 |

| 4.37 | Simple setup used for characterising the phase change nanowire memory cells. . . . .                                                                                                                                                                       | 76 |

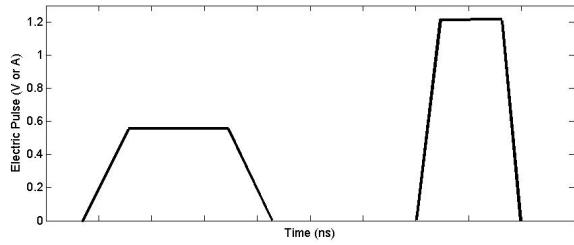

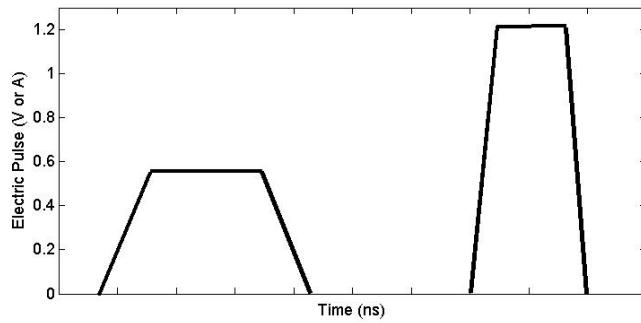

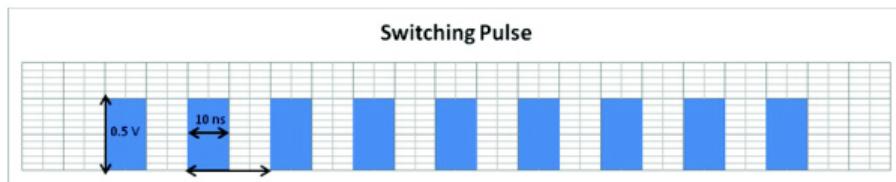

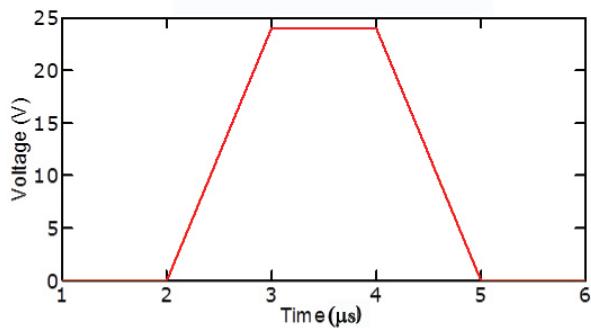

| 4.38 | Two pulses are provided to allow switching between the two states of the phase change layer. . . . .                                                                                                                                                       | 77 |

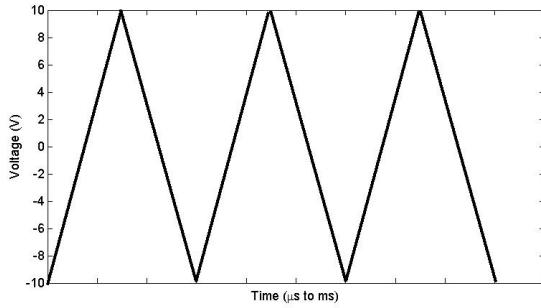

| 4.39 | The two sweep mechanisms used to switch the phase change layer. The current sweep is limited to 0.1A on the Agilent 4155C and to 1A on the Keithley 238 and the voltage sweep is limited to 25V on the Agilent 4155C and 110V on the Keithley 238. . . . . | 77 |

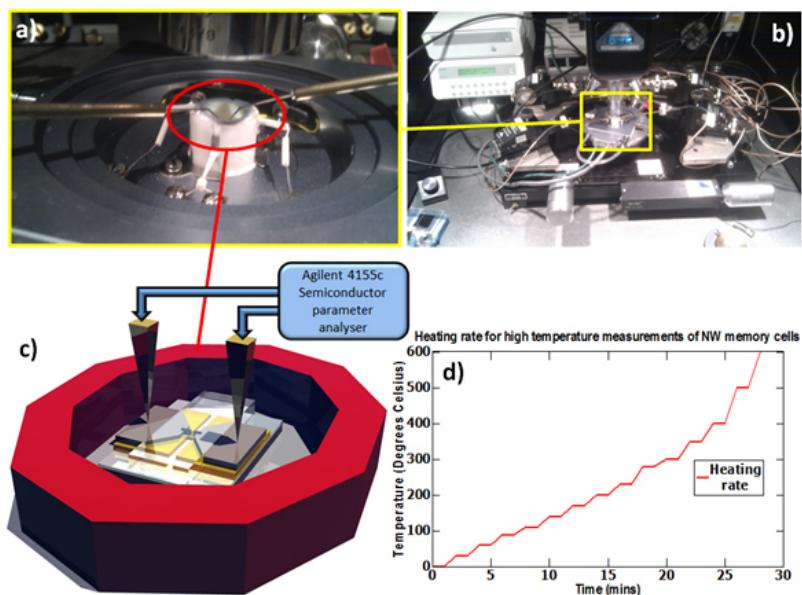

| 4.40 | Experimental setup used to obtain current voltage characteristics of the memory cells across different device temperatures. . . . .                                                                                                                        | 78 |

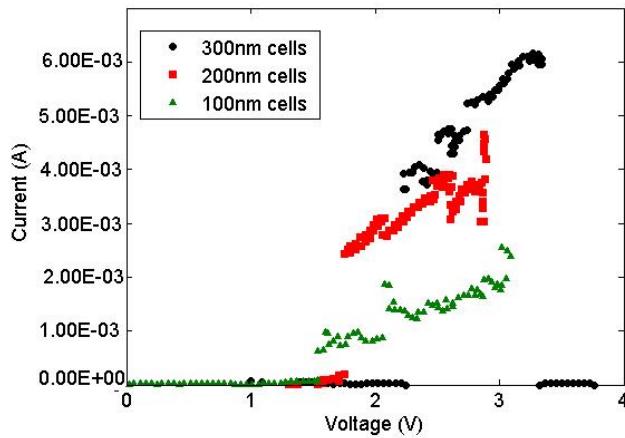

| 4.41 | The current-voltage characteristics of the nanowire memory cells with different effective cell sizes. . . . .                                                                                                                                              | 80 |

---

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

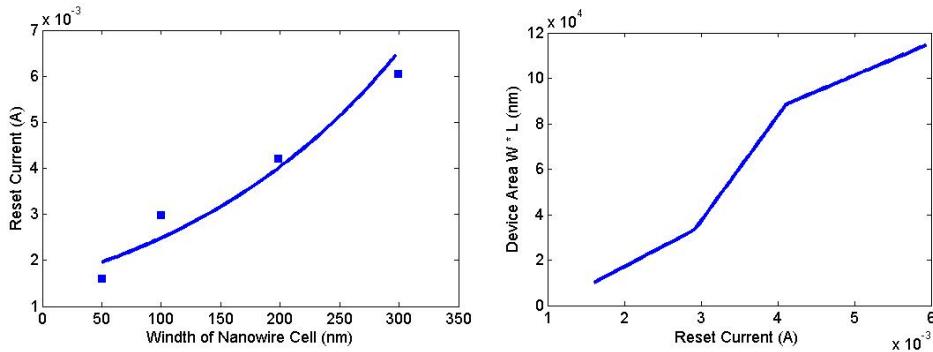

| 4.42 (left) The reset current measured across the different nanowire memory cells with different widths (right) The reset current measured across the different nanowire memory cells with different areas. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

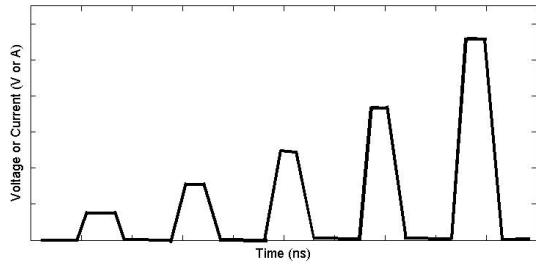

| 4.43 Incremental electrical pulses used to arrive at a single pulse switching speed used for the memory cells. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81 |

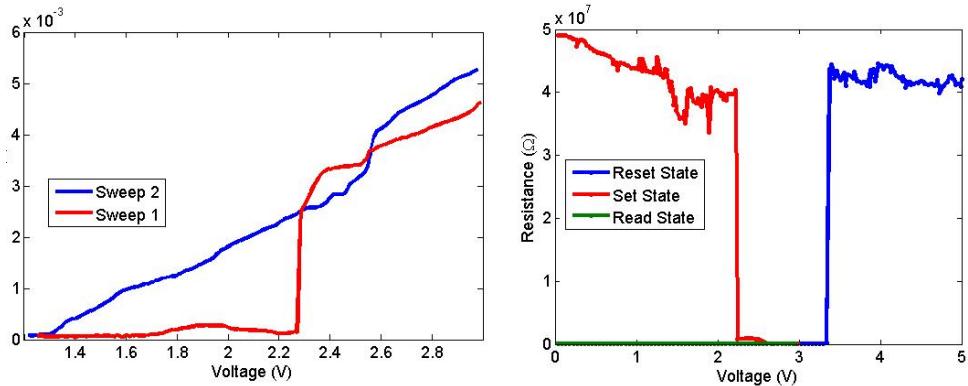

| 4.44 (left) Current-voltage characteristics of a 200nm memory cell recorded simultaneously whilst attempting pulse switching of the device.(right) Resistance - Voltage characteristics of a GeSb nanowire cell, showing a Ron/Roff ratio of the order of $10^3\Omega$ . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81 |

| 4.45 (left) Current-Voltage characteristics of Ion beam deposited nanowire memory cells. They all show a lack of a threshold voltage with a much lower resistance ratio between on and off state.(right) Current-voltage characteristics of the gallium contaminated device as a result of ion beam induced deposition. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82 |

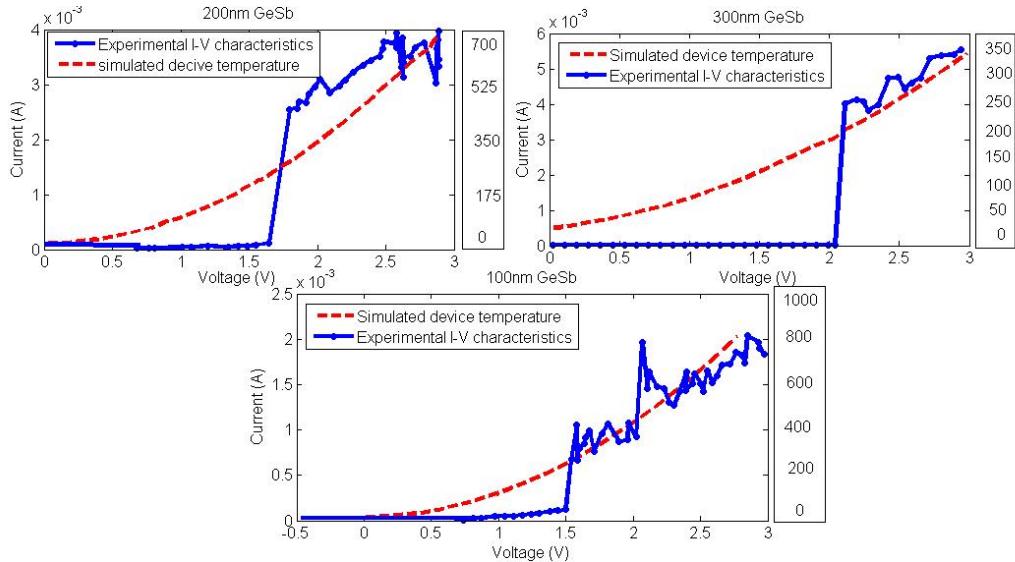

| 4.46 The current-voltage characteristics and corresponding modelled device temperatures for different nanowire cell sizes. It can be observed that at the onset of the threshold voltage where the experimental results show a change from a high resistance amorphous state to a low resistance crystalline state, the modelled device temperature indicates that the hot zone of the chalcogenide nanowire should be reaching temperatures very close to the crystallisation temperature, this reaffirms our understanding that phase change is responsible for the on/off switching observed in these memory cells. . . . .                                                                                                                                                                                                                                                                                                                                                                                       | 82 |

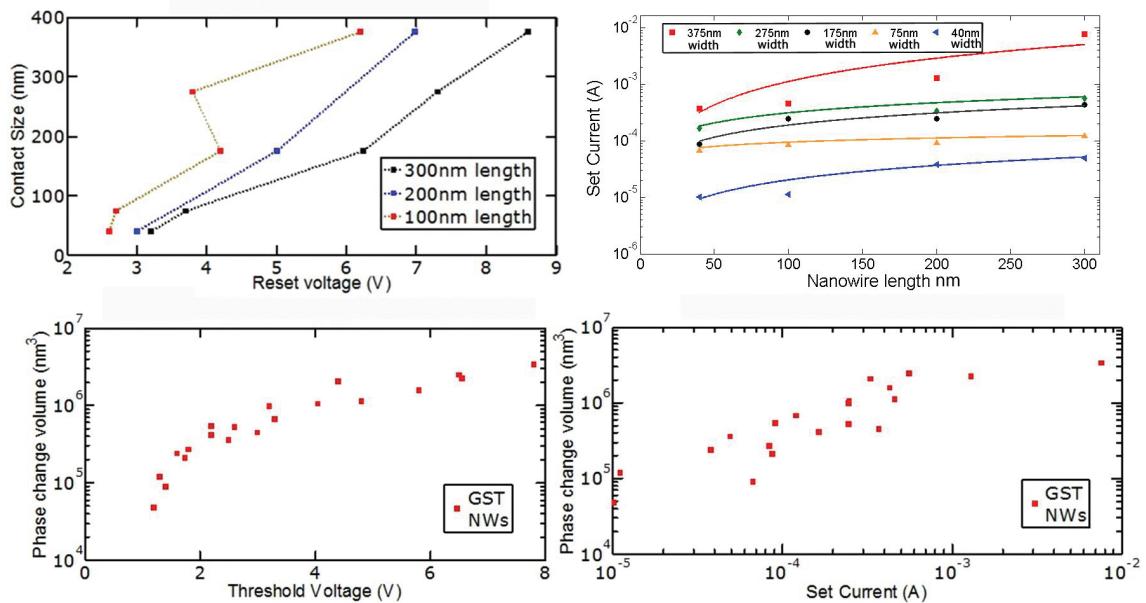

| 4.47 Scaling of the GeSbTe memory cells has been accompanied by a study of the effect of scaling on the different memory parameters of these devices (top left) Reduction of the voltage required to reset the device with decreasing contact size is seen (top right) The shorter the length of the nanowire phase change active area, the lower the current required to set the device to a low resistance state, the reduction in the width of the nanowires shows a much more pronounced and direct effect on the reduction in current consumption, as current localisation is directly related to the width of the nanowires, as a result of the greater change in phase change volume in width scaling (bottom left and bottom right) The reduction in the volume of the phase change material, brings about a lower power requirement as less energy is needed to phase switch the memory cells. As a result, the reduction in both threshold voltages and set currents can be clearly observed here. . . . . | 83 |

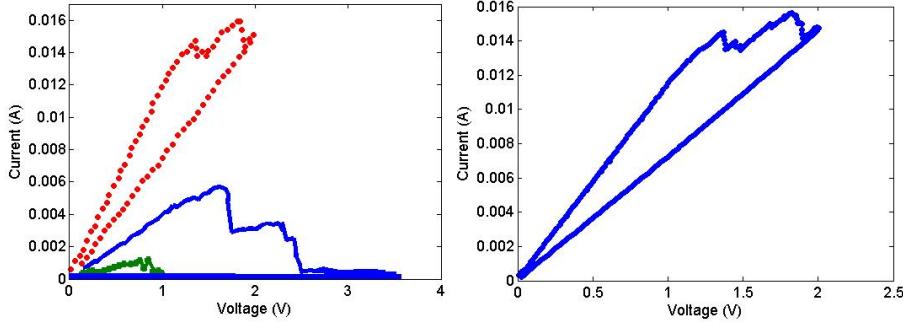

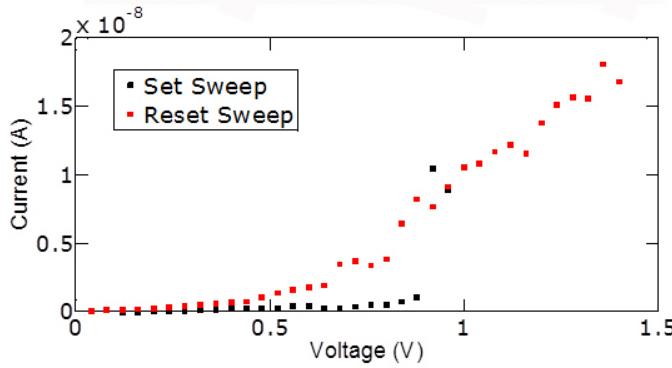

| 4.48 Smallest current consumption observed within the GaLaS NW memory cells. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84 |

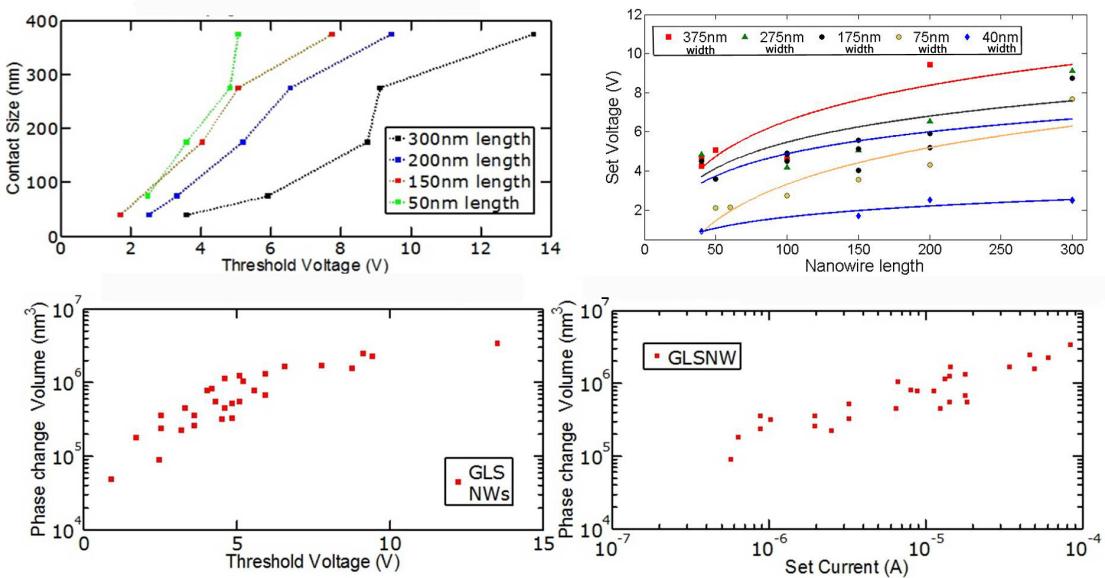

| 4.49 (left) Reset voltage of GaLaS NWs with decreasing volume of phase change material.(right) Reset current of GaLaS NWs with decreasing volume of phase change materials. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84 |

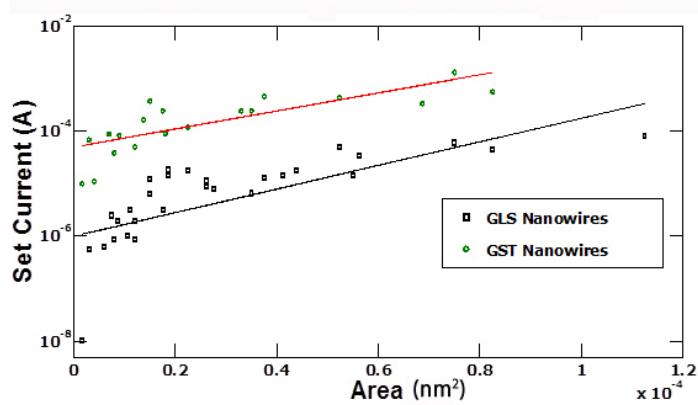

| 4.50 Set current of NW memory cells with decreasing effective area. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85 |

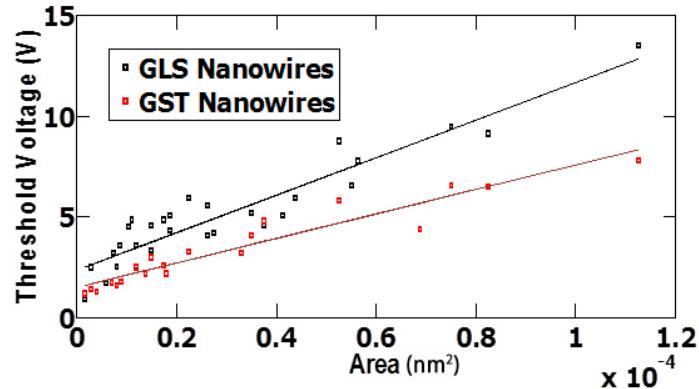

| 4.51 Threshold voltage of NW memory cells with decreasing effective area. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85 |

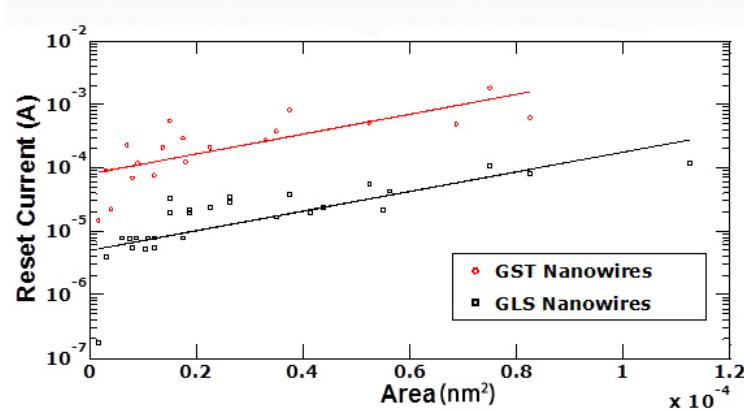

| 4.52 Reset current of NW memory cells with decreasing effective area. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

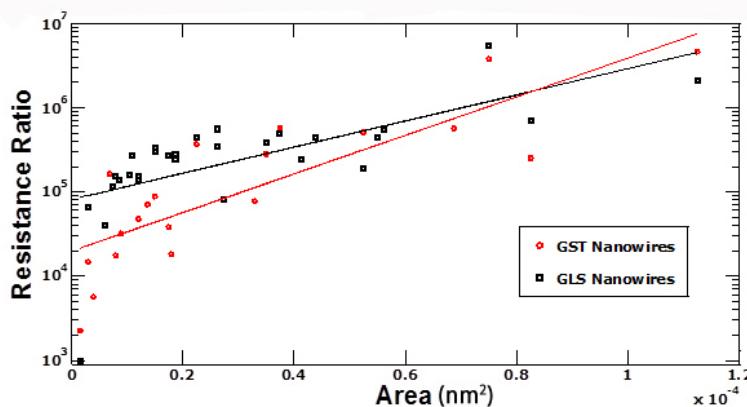

| 4.53 Resistance ratio of NW memory cells with decreasing effective area of the memory cell. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86 |

| 4.54 Energy dispersive X-ray of nanowires across compositional gradient. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87 |

---

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

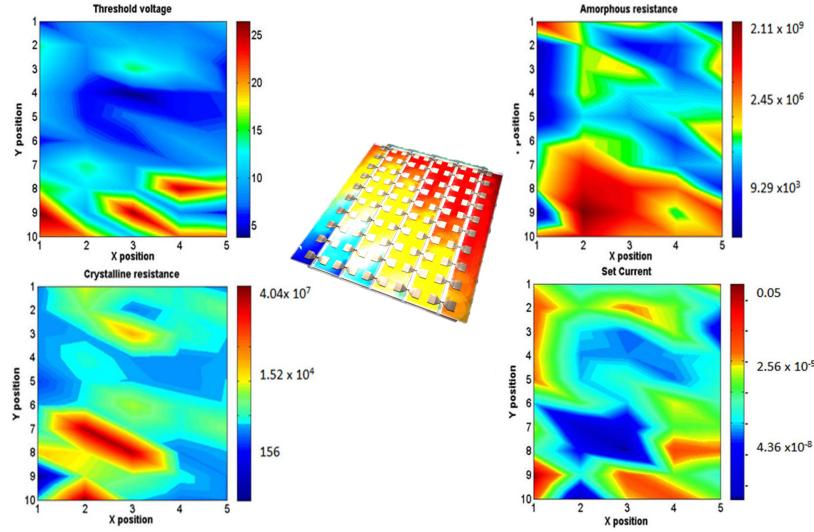

| 4.55 | Memory attributes of GaLaS nanowires across a compositional gradient chip. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88  |

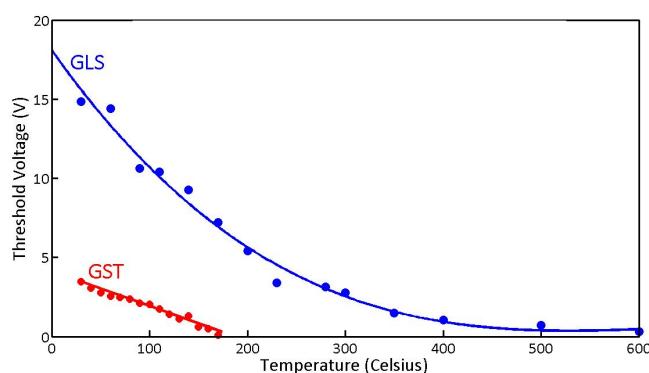

| 4.56 | Observation of switching and threshold voltage change with increasing device temperature. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89  |

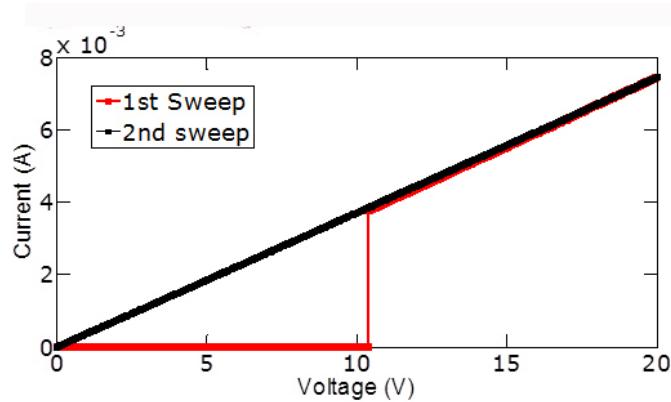

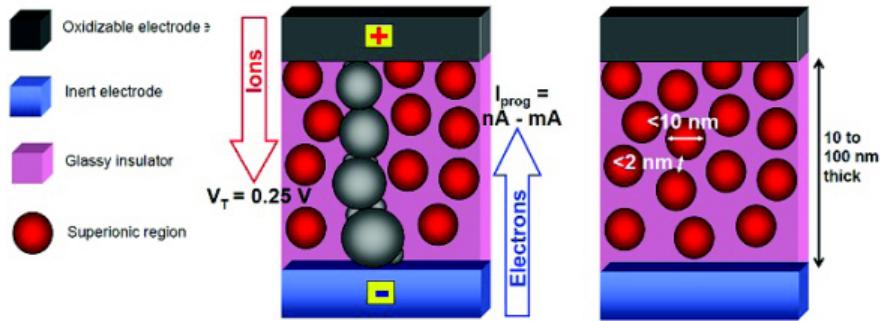

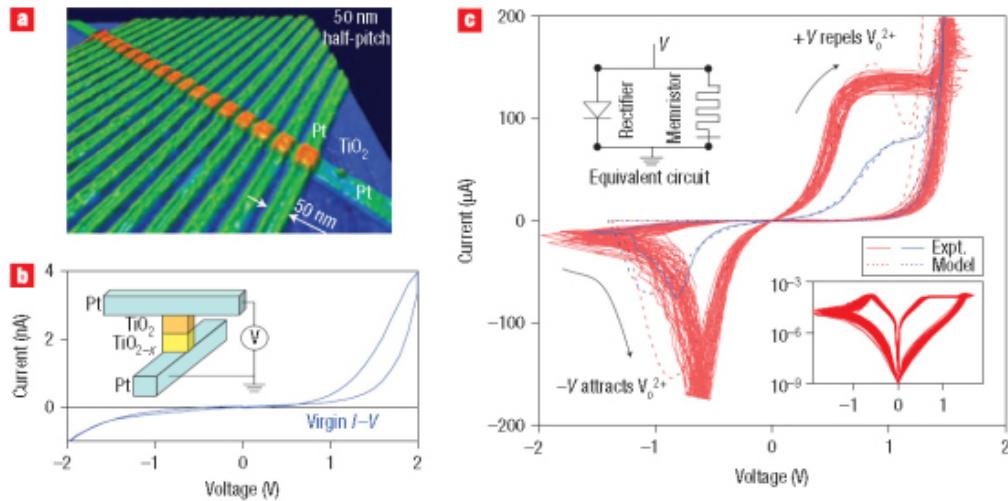

| 5.1  | Representation of ionic movement across the RRAM structure as a function of electrical input [Reprinted from (26; 27)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                         | 94  |

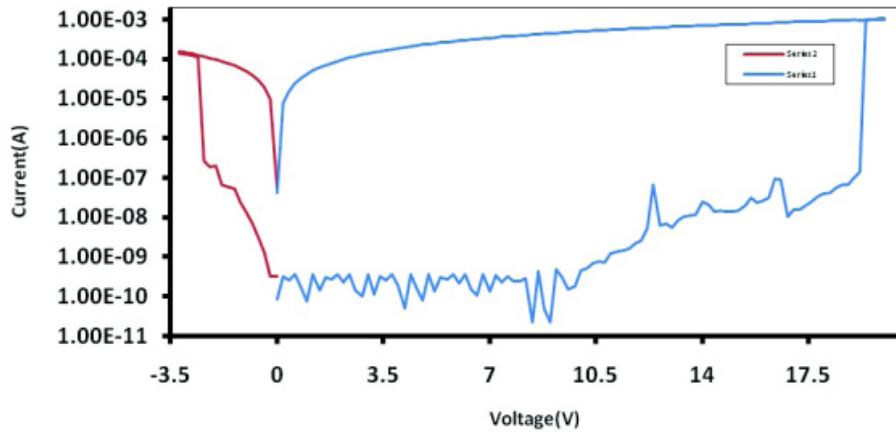

| 5.2  | Typical current-voltage characteristics of a solid electrolyte RRAM device [Reprinted from (26; 27)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                           | 95  |

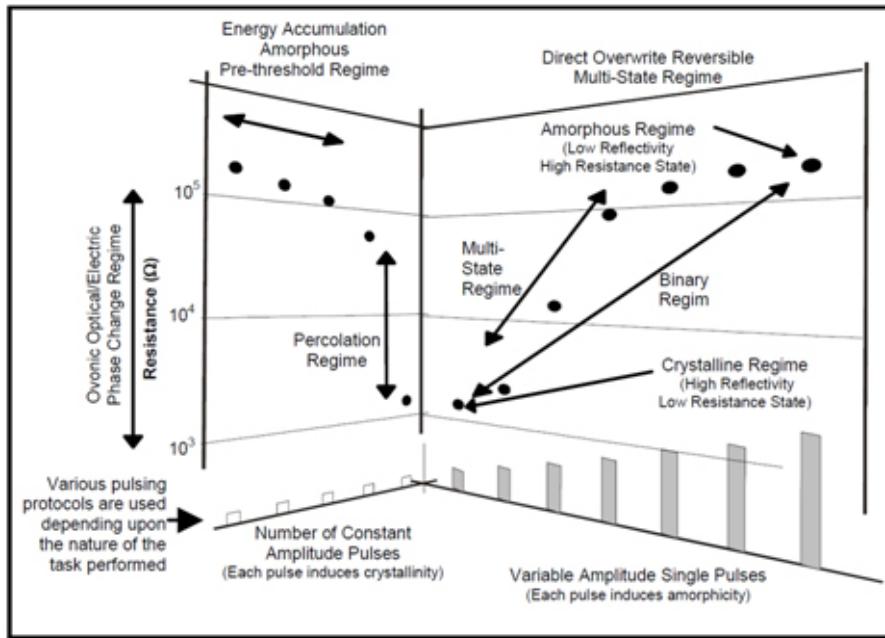

| 5.3  | Representation of a typical characteristics of the cognitive behaviour within chalcogenides [Reprinted from (28)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                              | 96  |

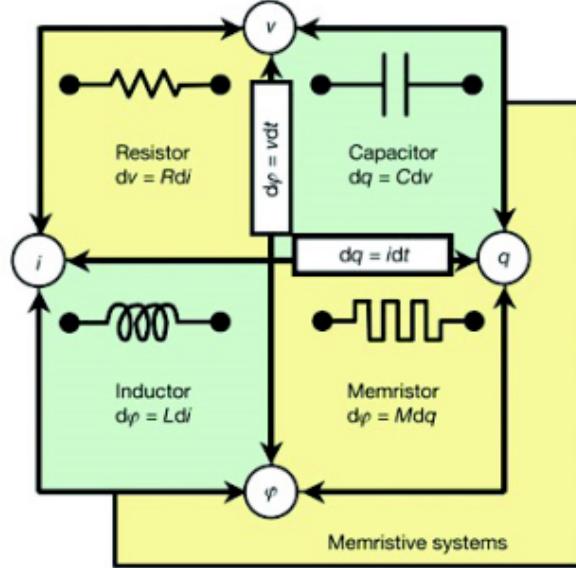

| 5.4  | The four fundamental circuit elements in electronics [Reprinted from (29)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97  |

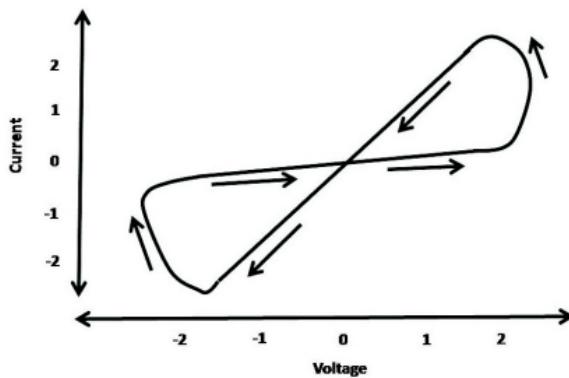

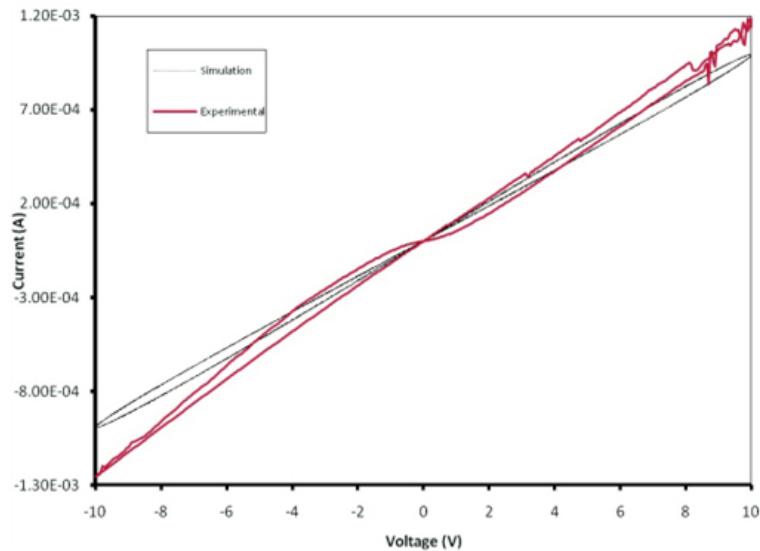

| 5.5  | Typical current-voltage characteristics of a memristor given a generic AC signal [Redrawn from (30)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                           | 97  |

| 5.6  | Schematic and typical current-voltage characteristics of a HP memristor [Reprinted from (31)]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98  |

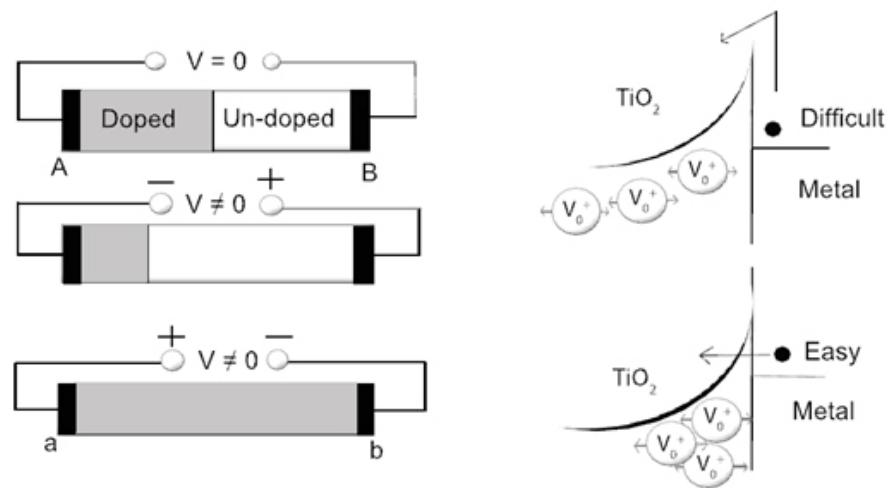

| 5.7  | Ionic conduction mechanism in a titanium oxide based memristor. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

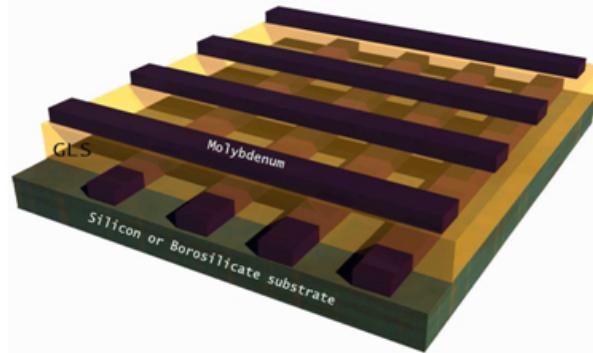

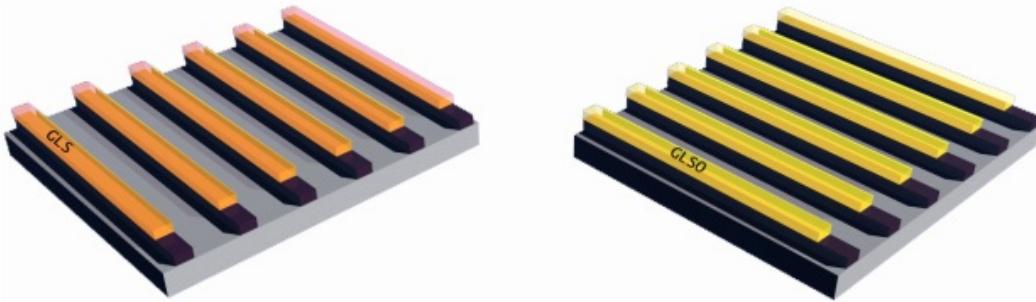

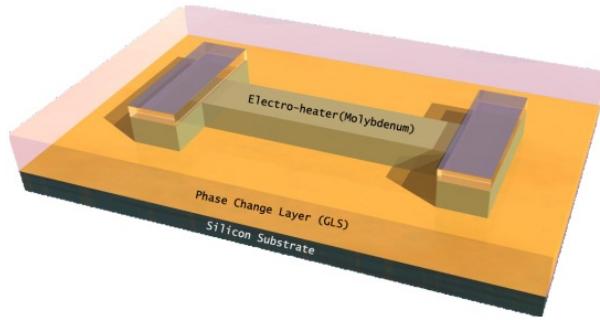

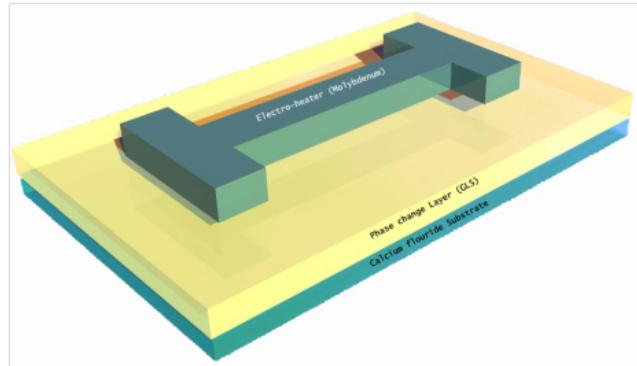

| 5.8  | Representation of cross array cells used for cognitive switching, with molybdenum electrodes and a GaLaS active layer in between. . . . .                                                                                                                                                                                                                                                                                                                                                                                               | 101 |

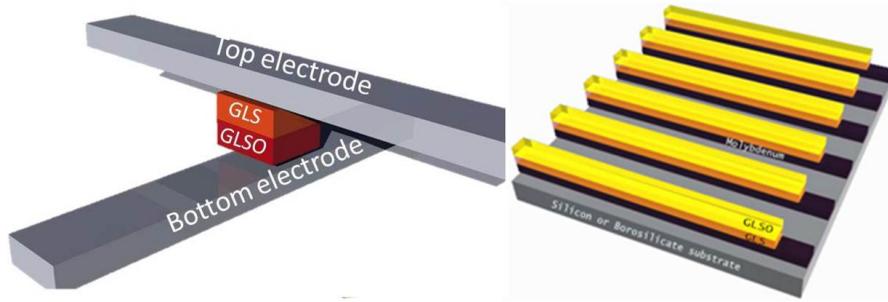

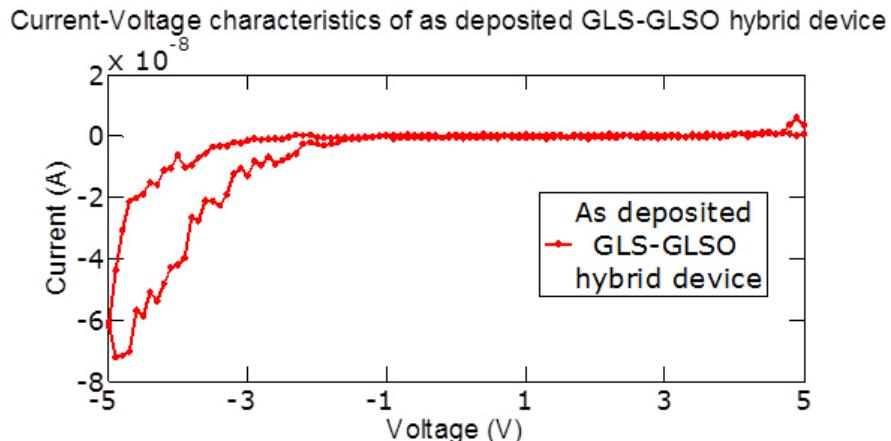

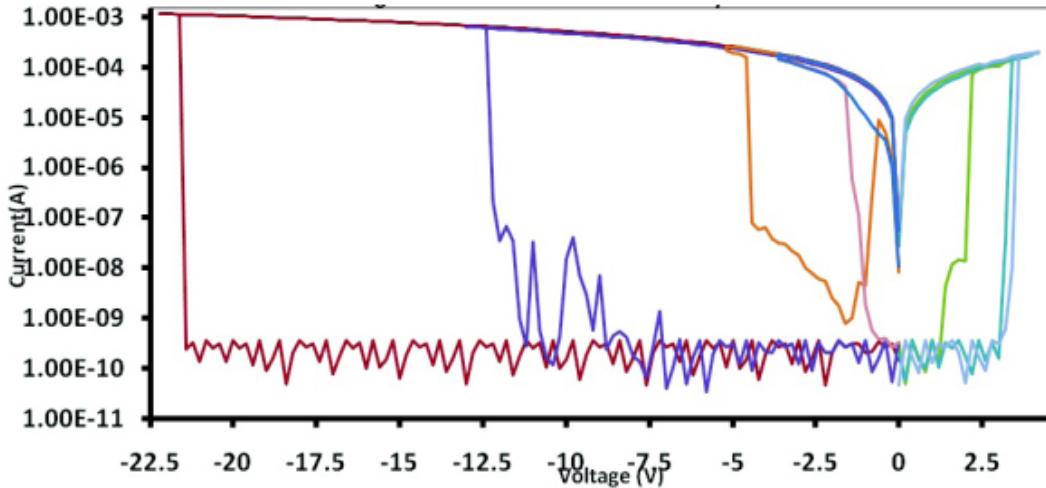

| 5.9  | Molybdenum-GaLaS-GaLaSO- hybrid Test Sample used for memristive/RRAM switching. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102 |

| 5.10 | Pure GaLaS and GaLaSO control samples fabricated with molybdenum bottom electrodes. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102 |

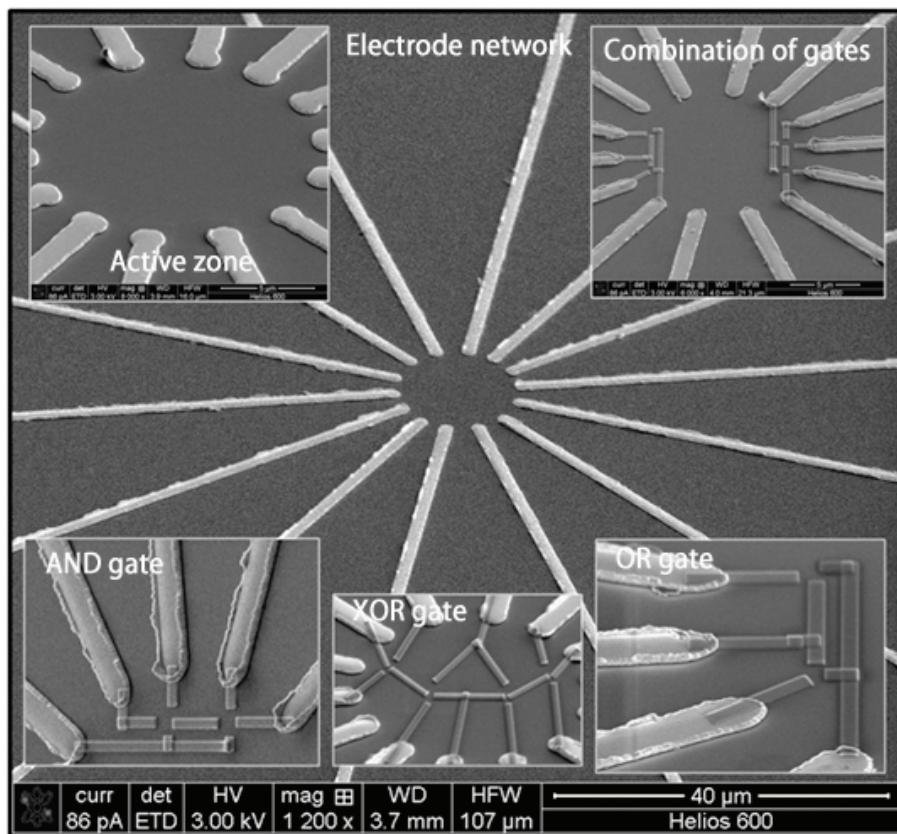

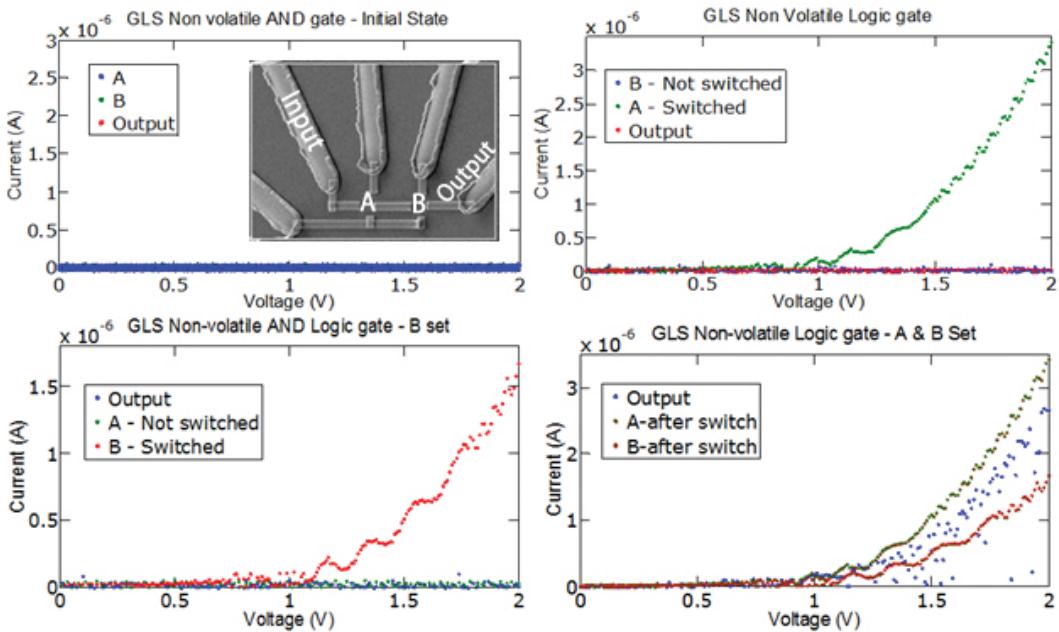

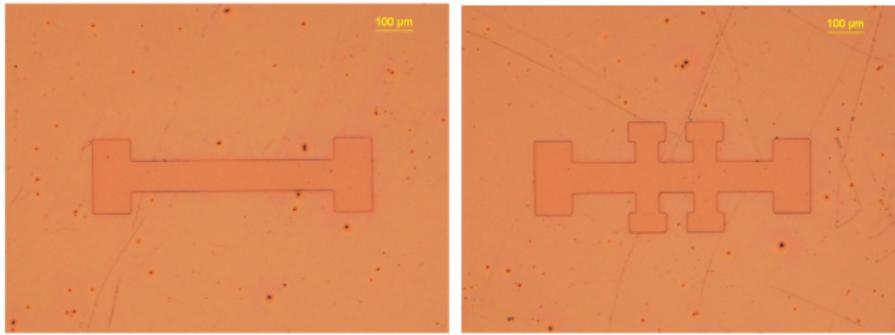

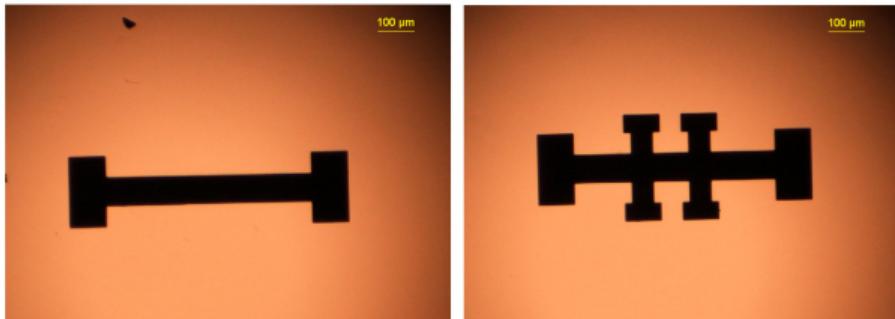

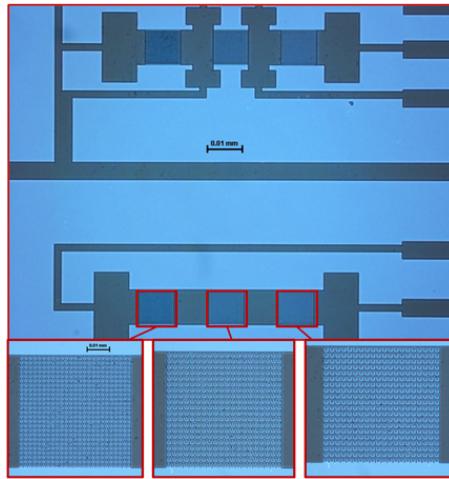

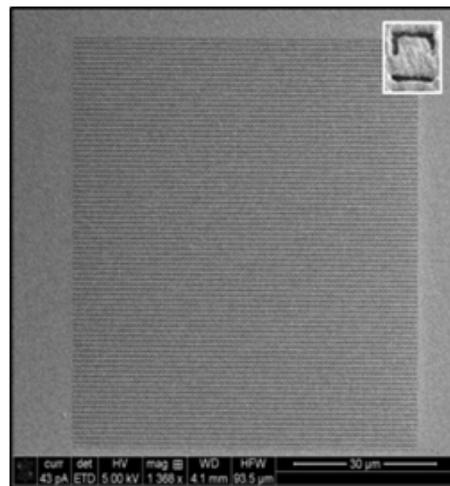

| 5.11 | Scanning electron microscopy images of fabricated electronic logic gates before final sputtering of the chalcogenide and capping layers. The nanogaps between the nanowires deposited provide the switchable area in the final devices. . . . .                                                                                                                                                                                                                                                                                         | 103 |

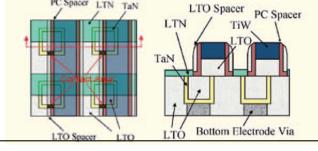

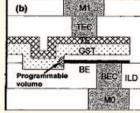

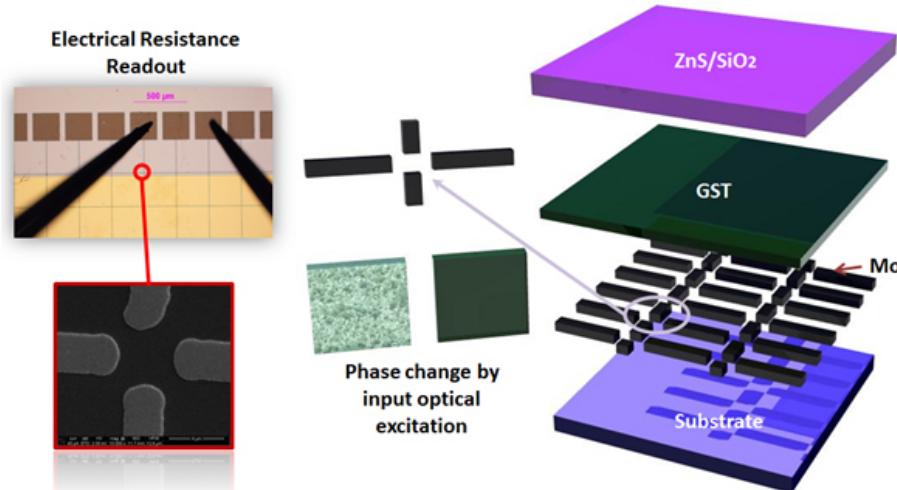

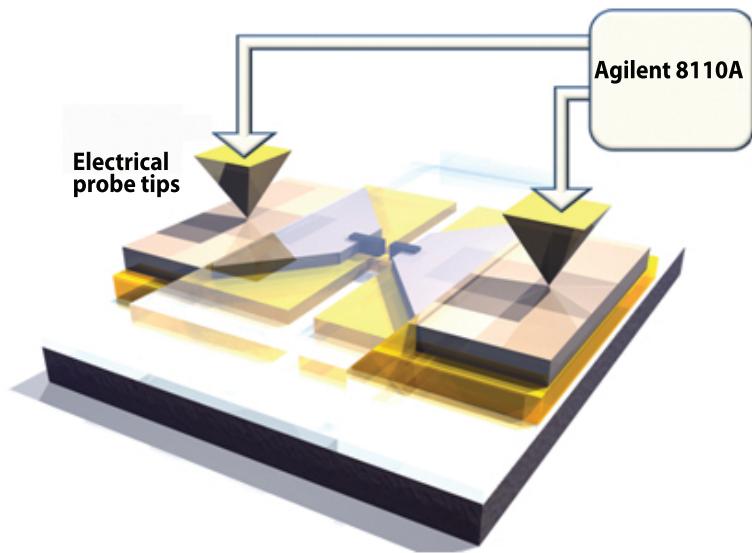

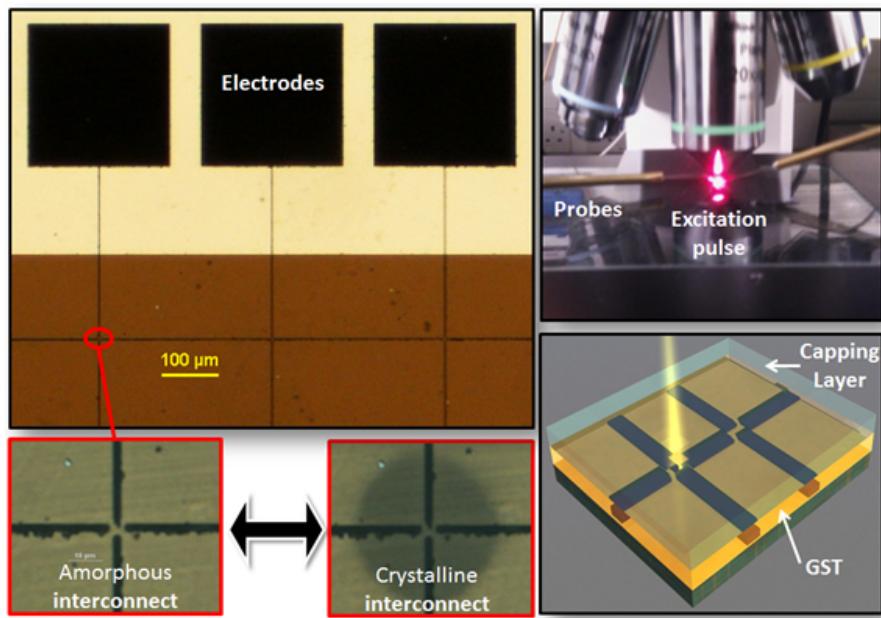

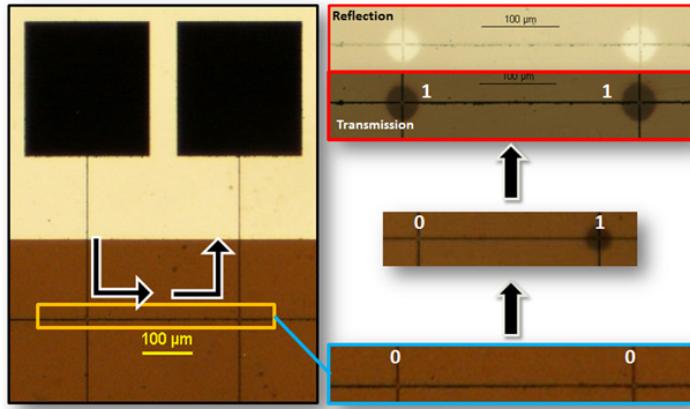

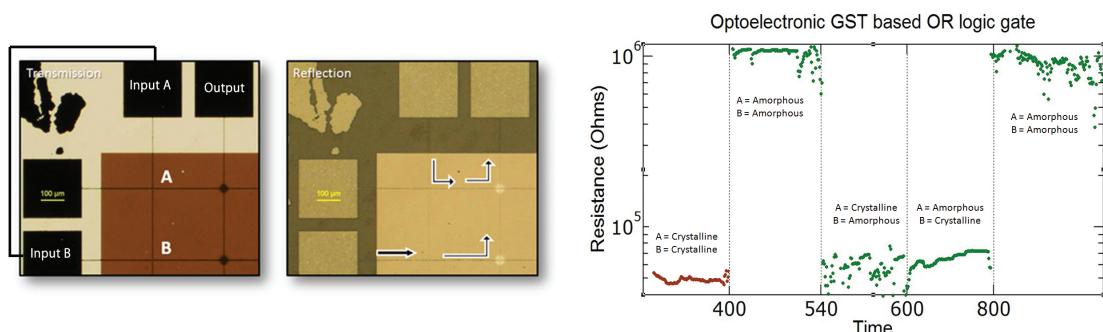

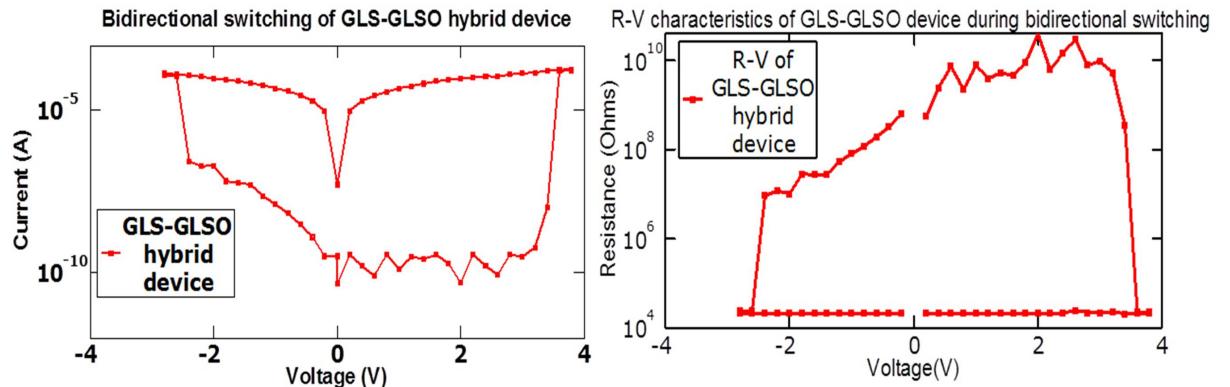

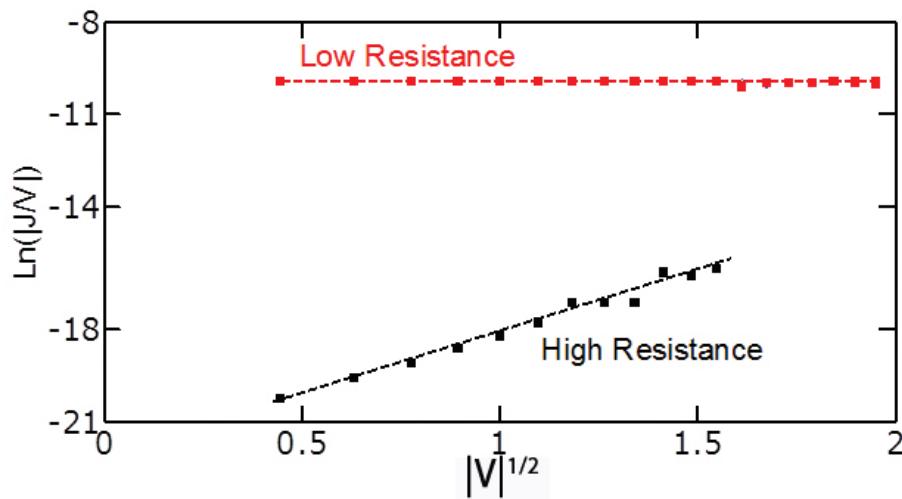

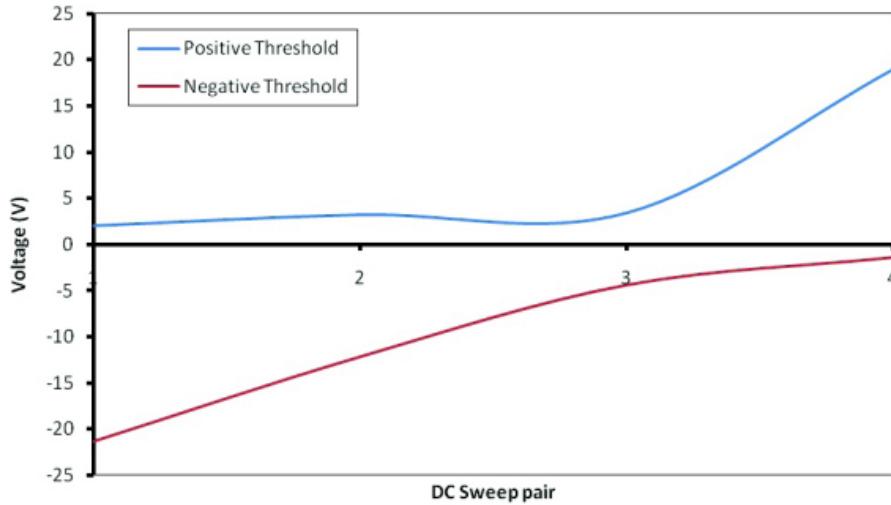

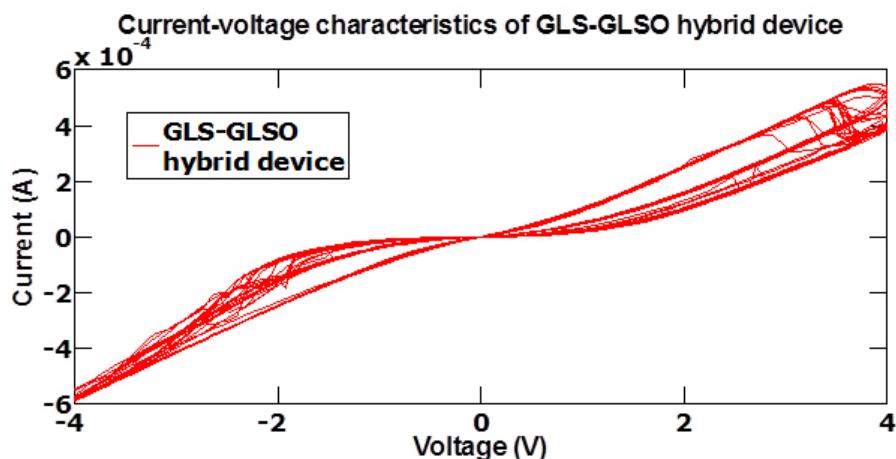

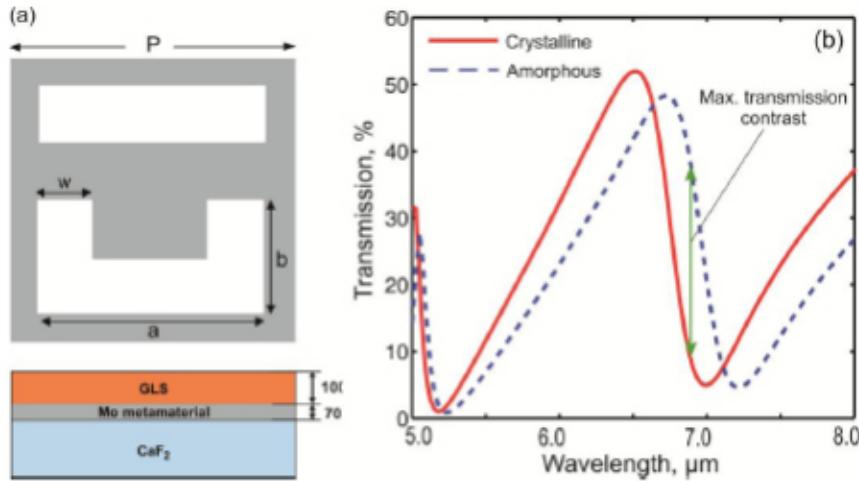

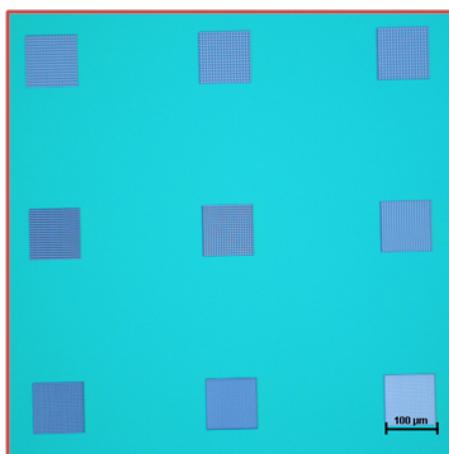

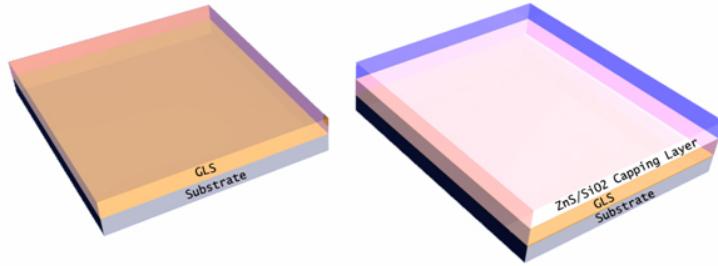

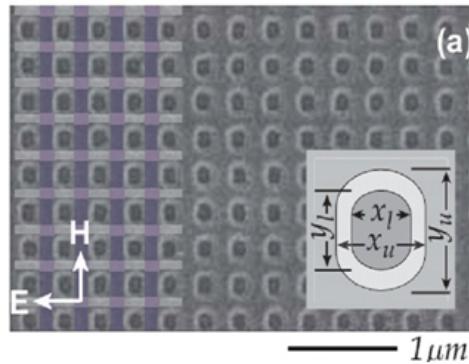

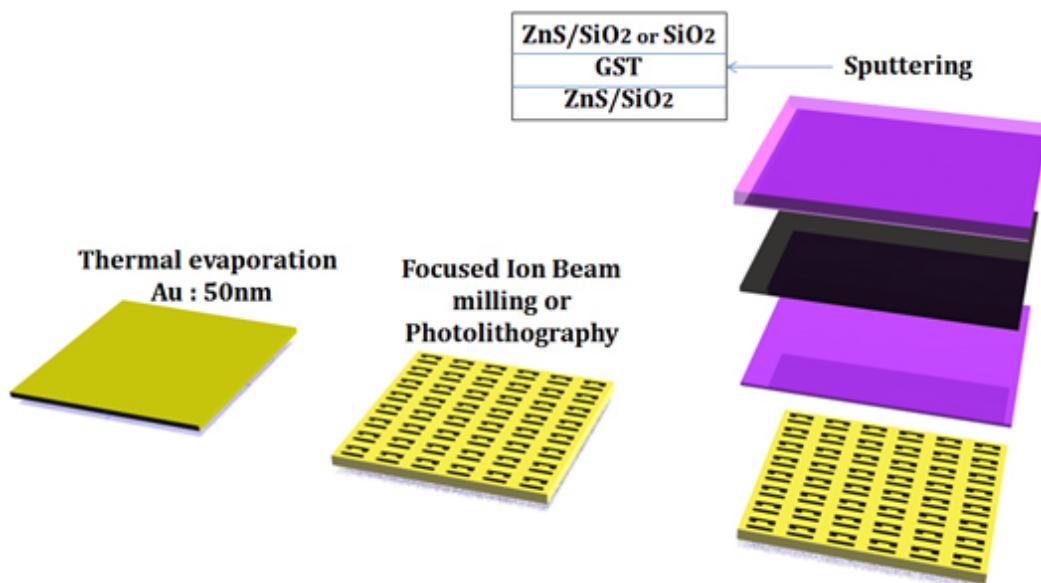

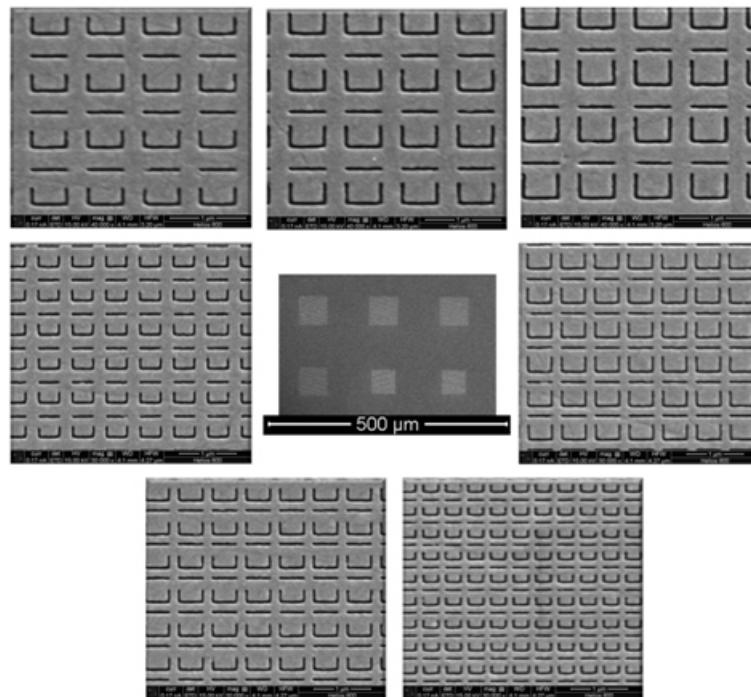

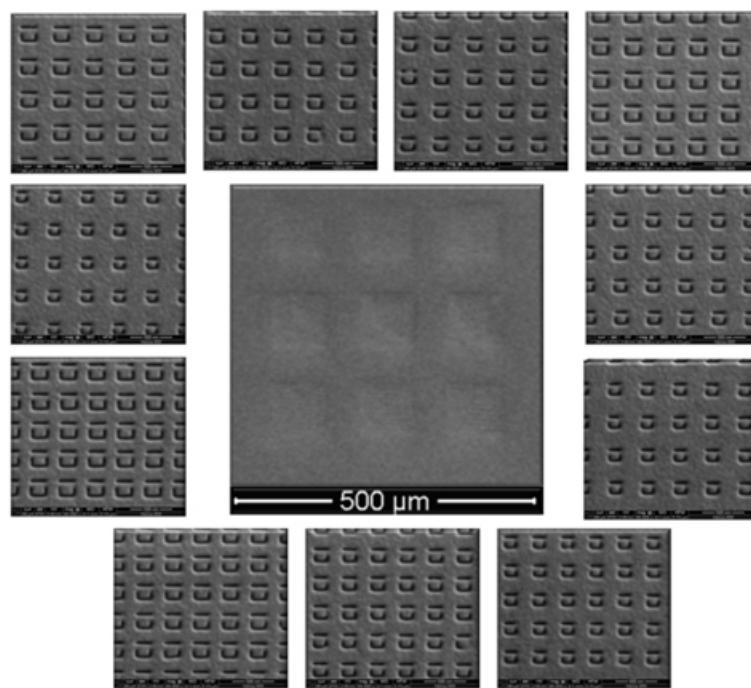

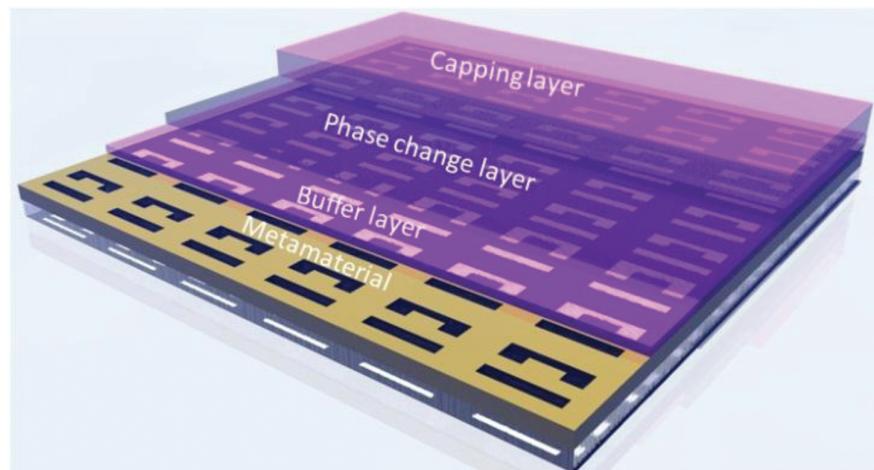

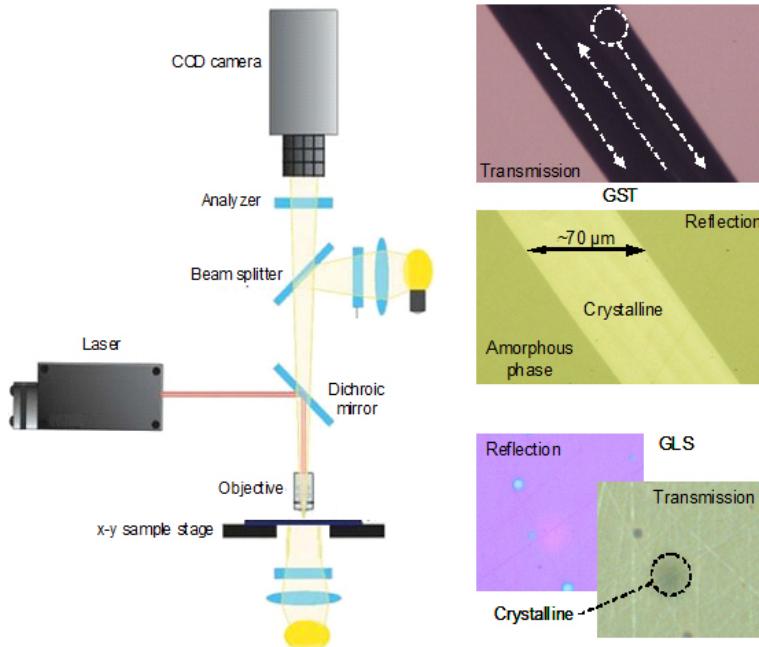

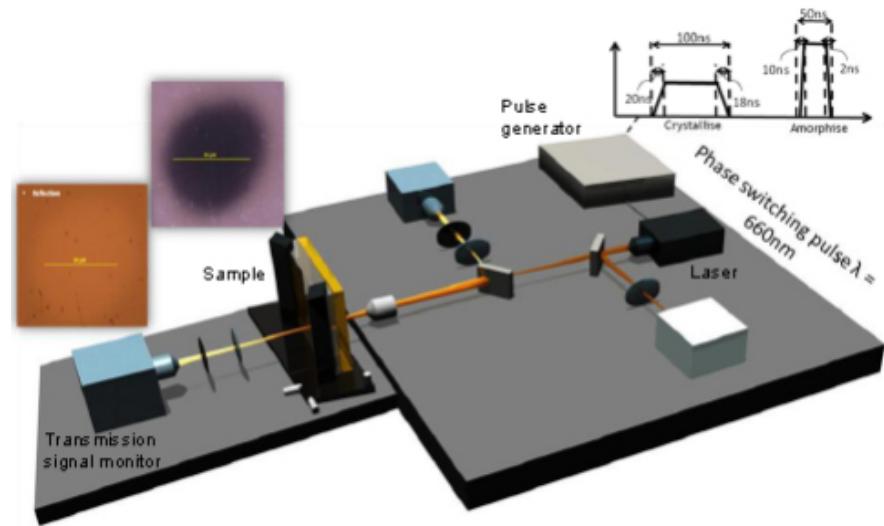

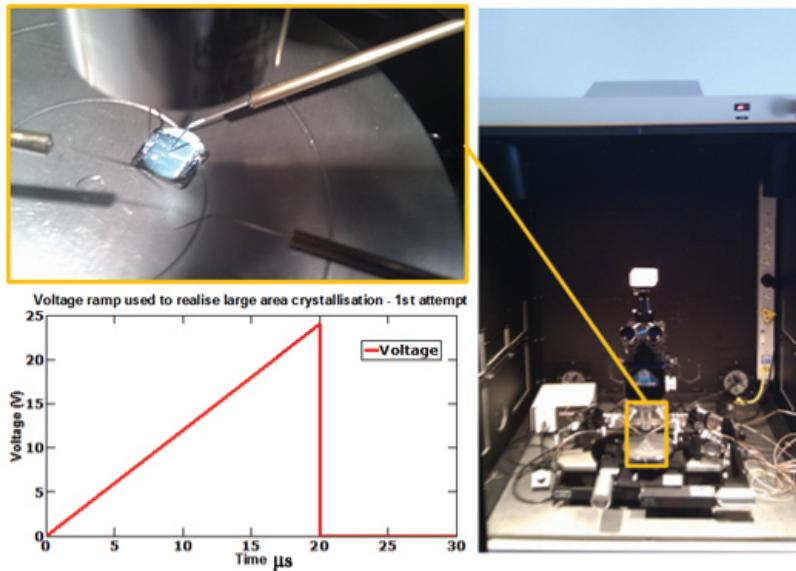

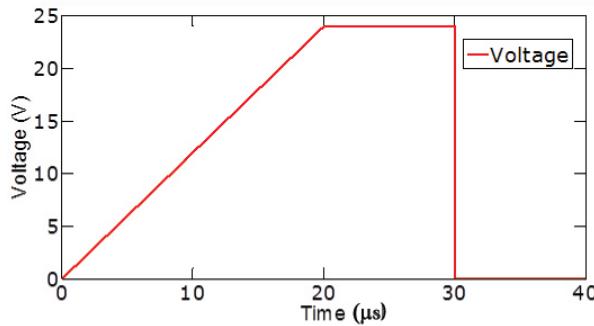

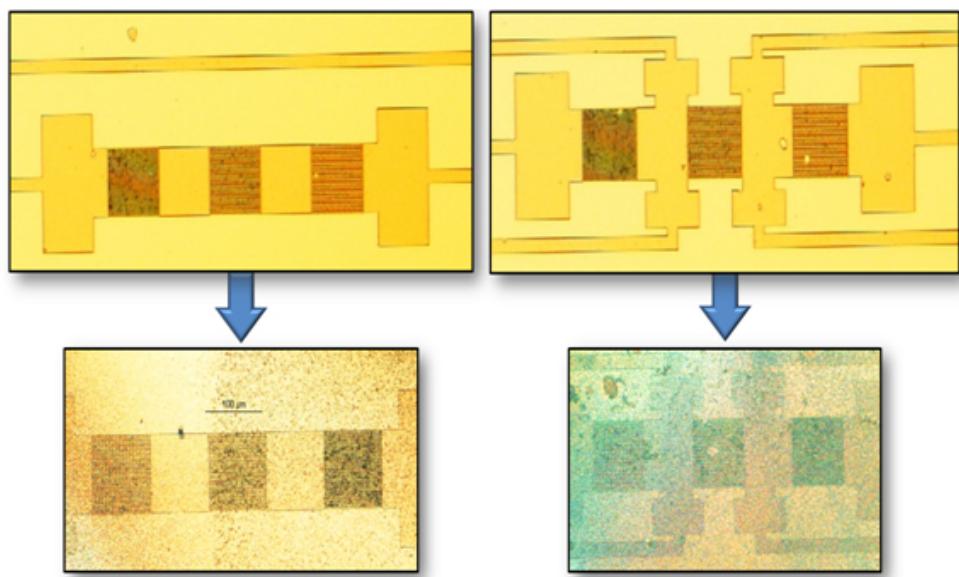

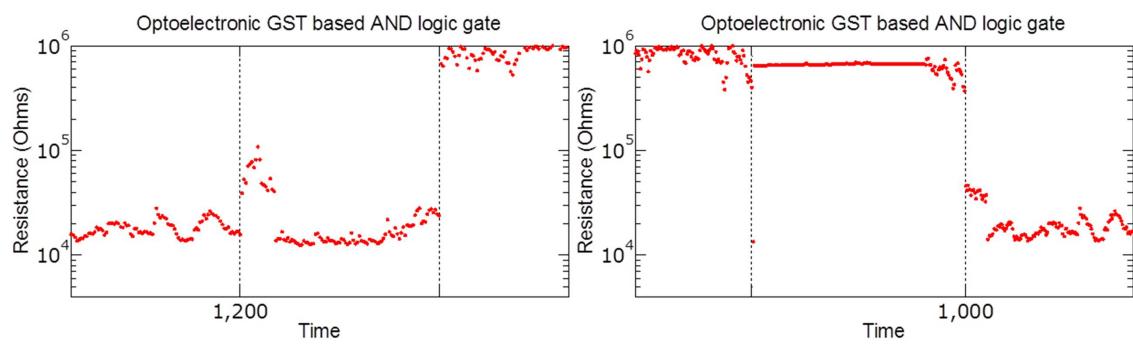

| 5.12 | (top left) optical microscopy image of the optoelectronic logic gates during characterisation with electrical probes visible on contact pads. (bottom left) scanning electron microscopy of nanogaps in the programmable array which act as optoelectronic switches on the application of optical phase transition pulses. (right) Model of the structure of the optoelectronic gates showing the electrodes in a programmable array architecture with a phase change GeSbTe layer and ZnS/SiO <sub>2</sub> capping the device. . . . . | 104 |

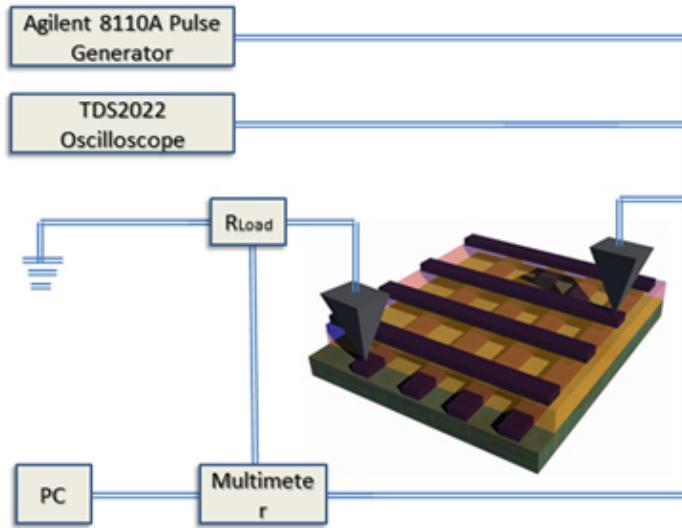

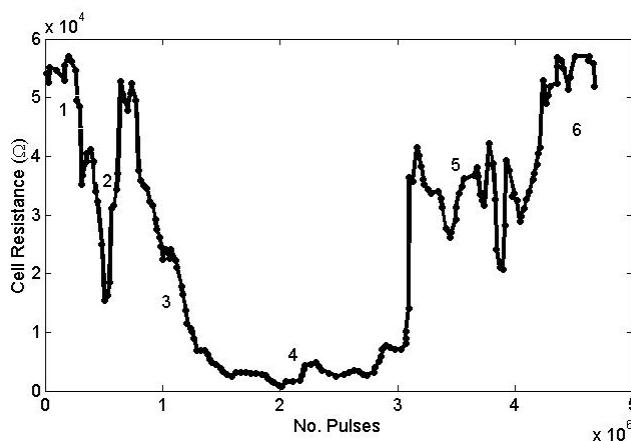

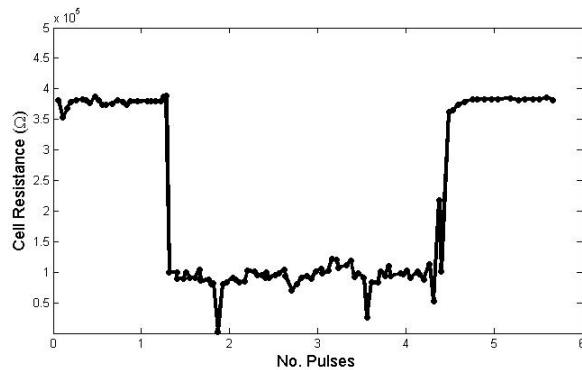

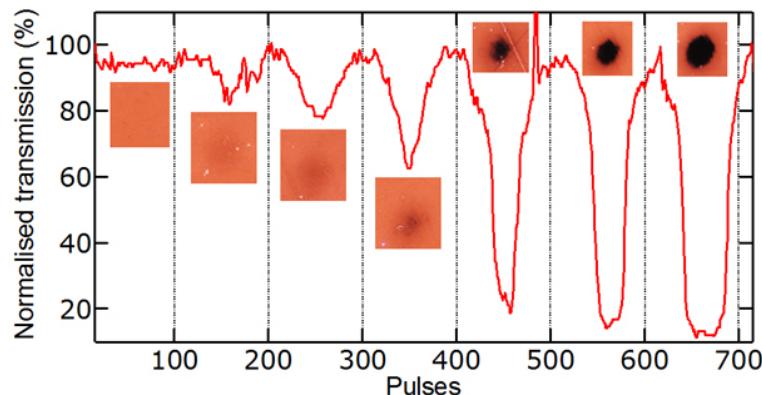

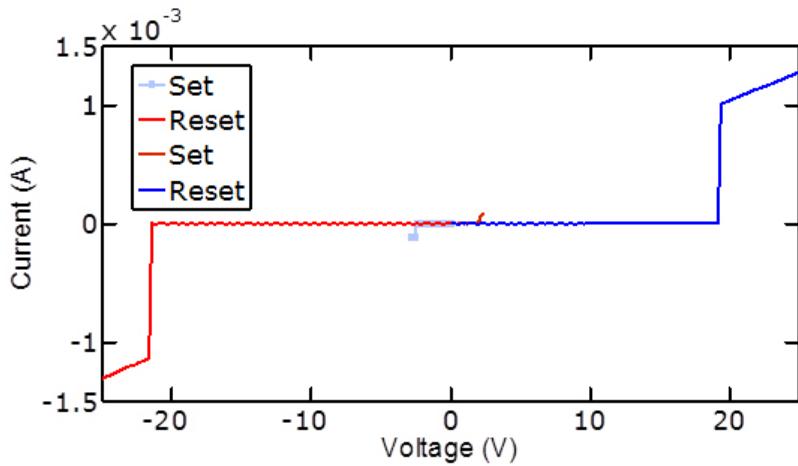

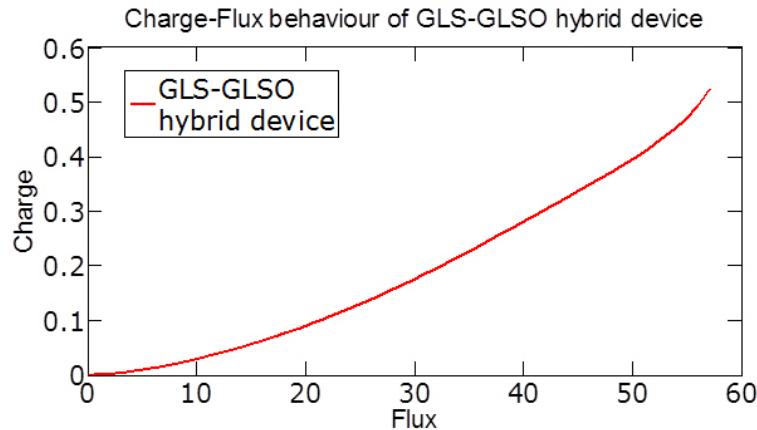

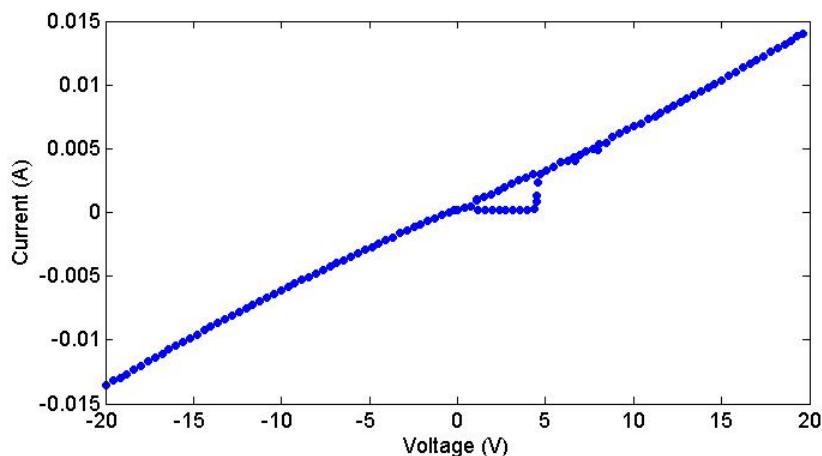

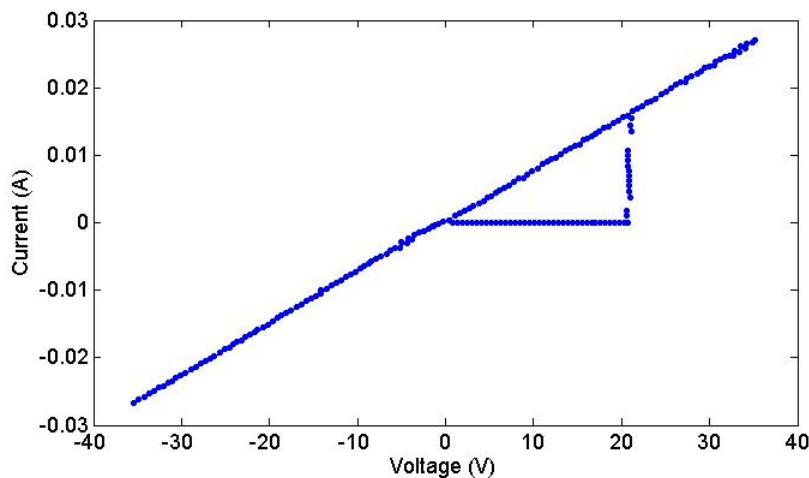

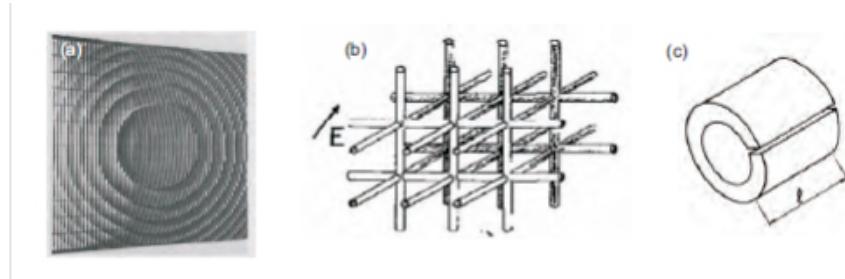

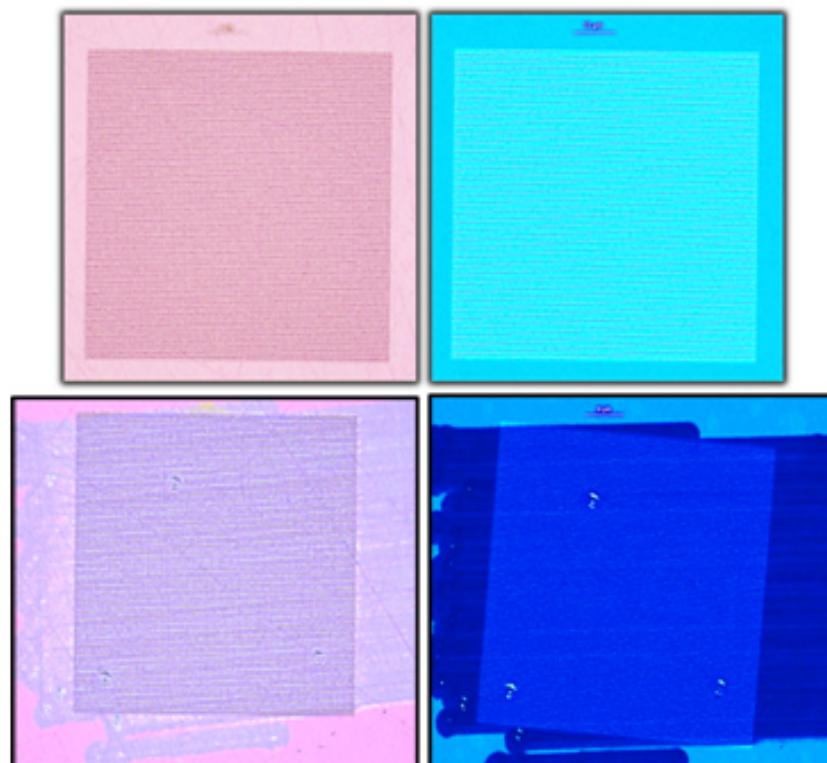

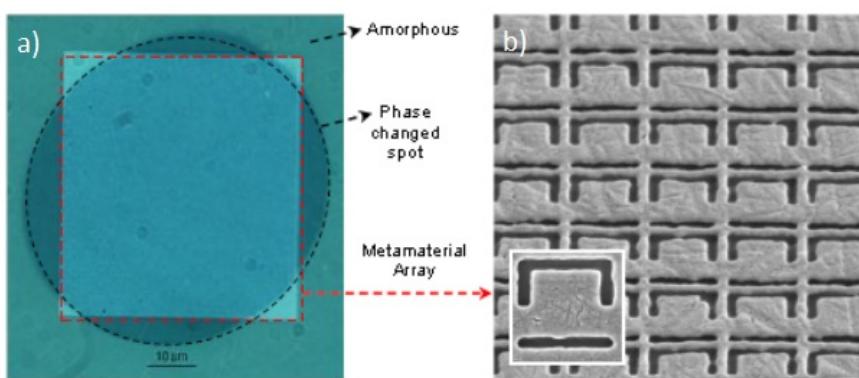

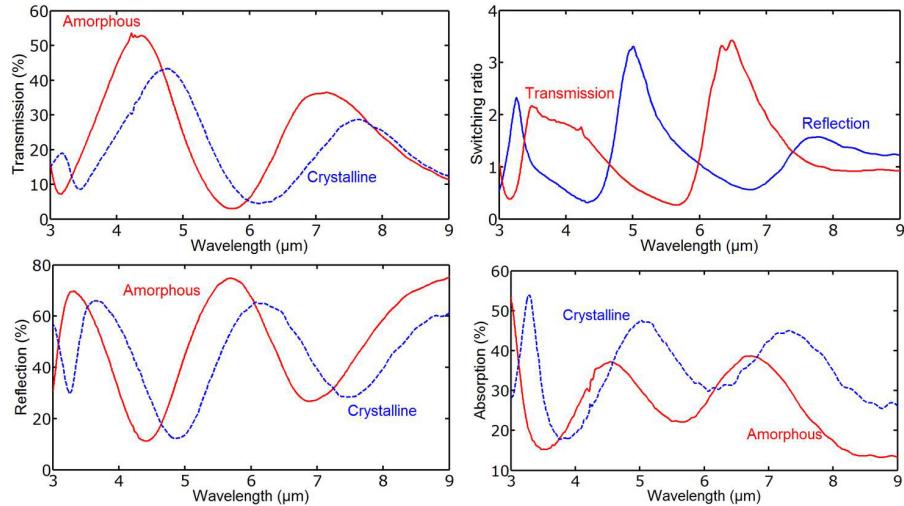

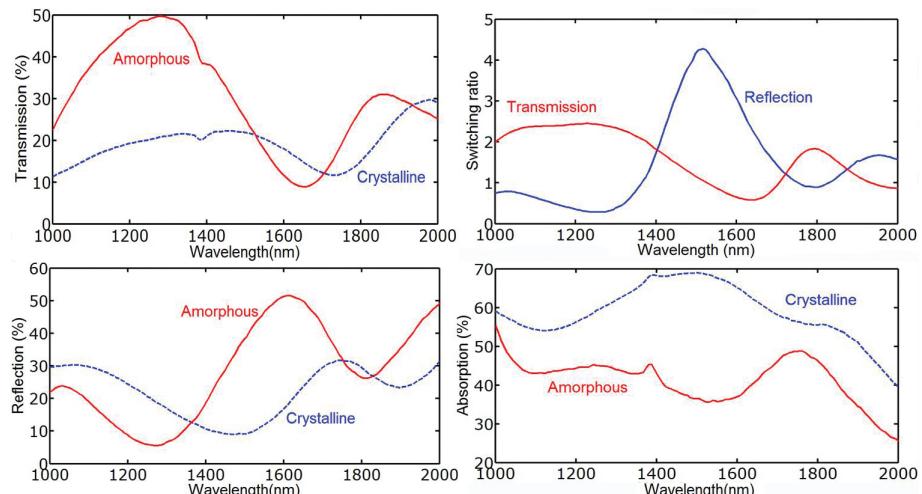

| 5.13 | Experimental setup used for the dual pulse switching measurements. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105 |