University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

**System Level Performance and Yield

Optimisation for Analogue Integrated

Circuits**

by

Sawal Hamid Md Ali

A thesis submitted for the degree of

**Doctor of Philosophy**

in the

Faculty of Engineering, Science and Mathematics

School of Electronics and Computer Science

November 2009

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

by Sawal Hamid Md Ali

Advances in silicon technology over the last decade have led to increased integration of analogue and digital functional blocks onto the same single chip. In such a mixed signal environment, the analogue circuits must use the same process technology as their digital neighbours. With reducing transistor sizes, the impact of process variations on analogue design has become prominent and can lead to circuit performance falling below specification and hence reducing the yield.

This thesis explores the methodology and algorithms for an analogue integrated circuit automation tool that optimizes performance and yield. The trade-offs between performance and yield are analysed using a combination of an evolutionary algorithm and Monte Carlo simulation. Through the integration of yield parameter into the optimisation process, the trade off between the performance functions can be better treated that able to produce a higher yield. The results obtained from the performance and variation exploration are modelled behaviourally using a Verilog-A language. The model has been verified with transistor level simulation and a silicon prototype.

For a large analogue system, the circuit is commonly broken down into its constituent sub-blocks, a process known as hierarchical design. The use of hierarchical-based design and optimisation simplifies the design task and accelerates the design flow by encouraging design reuse.

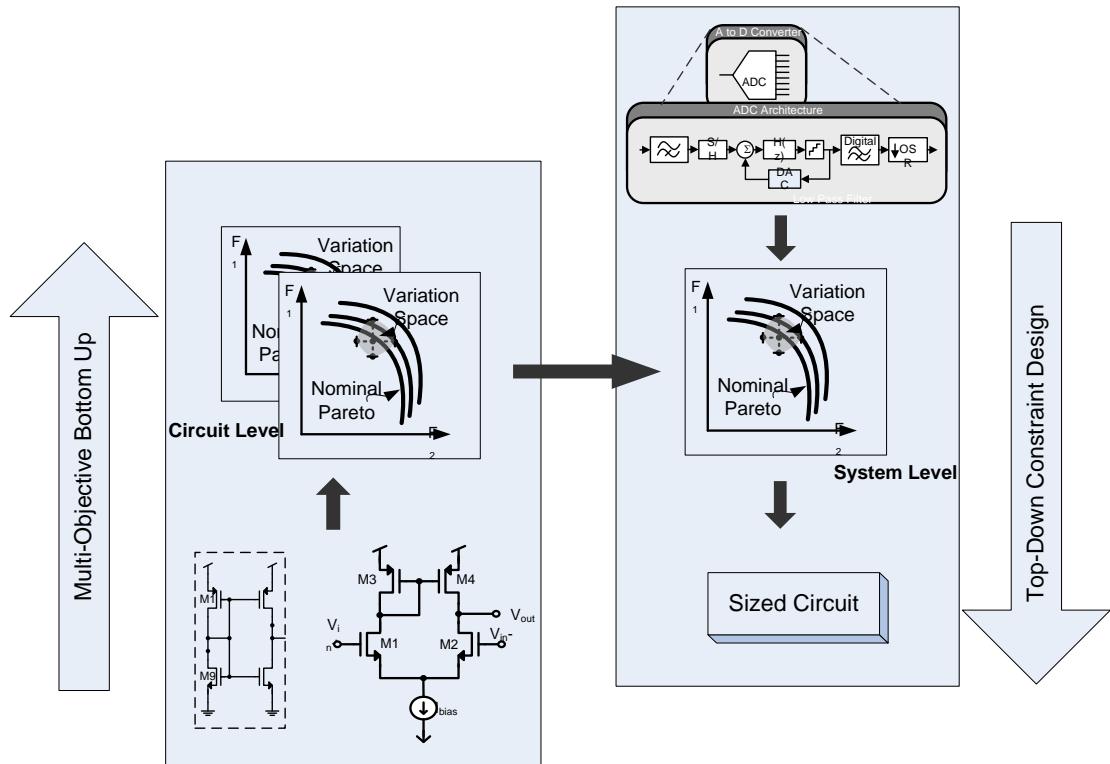

A new approach for system level yield optimisation using a hierarchical-based design is proposed and developed. The approach combines Multi-Objective Bottom Up (MUBU) modelling technique to model the circuit performance and variation and Top Down Constraint Design (TDCD) technique for the complete system level design. The proposed method has been used to design a 7<sup>th</sup> order low pass filter and a charge pump phase locked loop system. The results have been verified with transistor level simulations and suggest that an accurate system level performance and yield prediction can be achieved with the proposed methodology.

## DECLARATION OF AUTHORSHIP

I, Sawal Hamid Md Ali, declare that the thesis entitled System Level Performance and Yield Optimisation for Analogue Integrated Circuits and the work presented in it are my own. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as:

- Sawal Ali, R. Wilcock and P.R. Wilson, "Improved performance and variation modelling for hierarchical-based optimisation of analogue integrated circuits", *Design, Automation and Test in Europe (DATE) 2009, Nice, France*.

- Sawal Ali, R. Wilcock, P.R. Wilson and A.D. Brown, "A new approach for combining yield and performance in behavioural model for analogue integrated circuits", *Design, Automation and Test in Europe (DATE) 2008, March 3-7, Munich*.

Signed: .....

Date: .....

# Acknowledgements

Alhamdulillah, I thank to Allah for giving me a good health and the opportunity to continue my life and finish my study successfully.

I wish to express my sincere gratitude to my supervisor, Dr. Peter R. Wilson for providing the opportunity to carry out this study, and for guidance and support. I am deeply indebted to Dr. Reuben Wilcock for his valuable suggestion and active cooperation and having been a part of every single stage of my thesis, from inception to completion.

I wish to extend my warmest thank to all the staff in the Electronics System Devices Group, School of Electronics and Computer Science who have helped me in my work throughout my study.

Collective and individual acknowledgments are also owed to my colleagues at ESD group whose present somehow perpetually refreshed, helpful and memorable especially to Noohul Basheer, Abu Bakar, Sankalp Modi, Karthik Badam, Arash Ahmadi, Biswajit Misra, Li Ke, John Goodwin, Julian Bailey, for giving me such a pleasant time and valuable advice.

I convey my special acknowledgements to the National University of Malaysia (UKM), Ministry of Higher Education of Malaysia and Malaysian government for the financial support given to me and my family. I gratefully thank Tun Dr. Mahathir Mohamad, the ex-prime minister of Malaysia for being a role model for hard working person and for all his encouragements towards hardworking ethics.

My sincere thanks are given to my parents, Md Ali bin Daud and Sabura abd Karim for their inseparable support and prayers. I would like to offer my greatest appreciation to my wife Siti Anom and my little prince and princess, Syafique Azra'ei and Syra Arisha for being understanding and always stand by me with love and prayers. Thank you very much for letting me do this "geek" thing and I'm glad we're travelling together through this journey called life! I love all of you.

# List of Contents

|                  |                                                                                 |           |

|------------------|---------------------------------------------------------------------------------|-----------|

| <b>Chapter 1</b> | <b>Introduction</b>                                                             | <b>1</b>  |

| 1.1              | Integrated Circuits                                                             | 1         |

| 1.2              | Challenges in analogue design                                                   | 3         |

| 1.3              | Project motivation and goal                                                     | 4         |

| 1.4              | Project Scope                                                                   | 5         |

| 1.4.1            | Introduction                                                                    | 5         |

| 1.4.2            | Structure of the Project                                                        | 5         |

| 1.4.3            | Project Hypotheses                                                              | 8         |

| 1.5              | Thesis Structure                                                                | 8         |

| 1.5.1            | Chapter 1 : Introduction                                                        | 9         |

| 1.5.2            | Chapter 2 : Review of Analogue circuit Design and Statistical Design Techniques | 9         |

| 1.5.3            | Chapter 3 : Review of Simulation & Modelling                                    | 9         |

| 1.5.4            | Chapter 4 : Yield Optimised Design                                              | 9         |

| 1.5.5            | Chapter 5 : Performance and Variation Modelling                                 | 10        |

| 1.5.6            | Chapter 6 : Hierarchical-based Design Optimisation                              | 10        |

| 1.5.7            | Chapter 7 : Mixed Signal System Level Application                               | 10        |

| 1.5.8            | Chapter 8 : Conclusion and Future Work.                                         | 10        |

| <b>Chapter 2</b> | <b>Review of Analogue Circuit Design and Optimisation</b>                       | <b>11</b> |

| 2.1              | Introduction                                                                    | 11        |

| 2.2              | Automatic Circuit Sizing                                                        | 14        |

| 2.2.1            | Knowledge-Based Design                                                          | 14        |

|                  | IDAC                                                                            | 15        |

|                  | OASYS                                                                           | 15        |

|                  | BLADES                                                                          | 16        |

| 2.2.2            | Optimization-based Circuit Sizing                                               | 17        |

|                  | Equation-based Optimisation                                                     | 18        |

|                  | OPASYN                                                                          | 19        |

|                  | Maulik                                                                          | 19        |

|                  | GPCAD                                                                           | 20        |

|                  | Simulation-based Optimisation                                                   | 20        |

|                  | DELIGHT.SPICE                                                                   | 21        |

|                  | FRIDGE                                                                          | 22        |

|                  | ASTRX/OBLX                                                                      | 22        |

|                  | ANACONDA and MAELSTROM                                                          | 23        |

| 2.4              | Optimization Technique                                                          | 25        |

| 2.4.1            | Direct Search Optimisation                                                      | 25        |

|                  | Tabulation Method                                                               | 25        |

|                  | Sequential Method                                                               | 26        |

|                  | Linear Method                                                                   | 26        |

| 2.4.2            | Gradient-search Optimisation                                                    | 27        |

|                  |                                                       |           |

|------------------|-------------------------------------------------------|-----------|

|                  | Steepest Descent Method                               | 27        |

|                  | Newton's Method                                       | 28        |

| 2.4.3            | Simulated Annealing                                   | 29        |

| 2.4.4            | Genetic Algorithm                                     | 30        |

| 2.4.5            | Multi Objective Optimization                          | 33        |

|                  | Weighted-based GA                                     | 34        |

|                  | Non-dominated Sorting GA-II                           | 34        |

| 2.5              | Statistical fluctuations in integrated circuit        | 36        |

| 2.6              | Parametric Yield Maximization                         | 37        |

| 2.7              | Variation Analysis                                    | 40        |

| 2.7.1            | Worst Case Analysis                                   | 40        |

| 2.7.2            | Simplicial Approximation                              | 41        |

| 2.7.3            | Monte Carlo Method                                    | 42        |

| 2.8              | Variation-aware Design                                | 42        |

| 2.8.1            | Direct Method                                         | 43        |

| 2.8.2            | Indirect Method                                       | 44        |

| 2.9              | Integrated Yield Optimization in Circuit Synthesis    | 45        |

| 2.9.1            | ASTRX/OBLX Extension                                  | 46        |

| 2.9.2            | Simultaneous Yield and Robustness Optimization        | 46        |

| 2.10             | Summary                                               | 47        |

| <b>Chapter 3</b> | <b>Review of Circuit Simulation and Modelling</b>     | <b>48</b> |

| 3.1              | Introduction                                          | 48        |

| 3.2              | Analogue Circuit Simulation                           | 49        |

| 3.2.1            | Circuit Netlist                                       | 49        |

| 3.2.2            | Types of Analysis                                     | 50        |

|                  | DC Analysis                                           | 51        |

|                  | AC Analysis                                           | 51        |

|                  | Transient Analysis                                    | 52        |

| 3.3              | Modelling Theory                                      | 53        |

| 3.3.1            | Definition of a Model                                 | 53        |

| 3.3.2            | Device Modelling                                      | 54        |

|                  | MOS Level 1, 2 and 3                                  | 54        |

|                  | BSIM Model                                            | 54        |

| 3.3.3            | Hardware Description Language (HDL) modelling         | 55        |

| 3.4              | Summary                                               | 57        |

| <b>Chapter 4</b> | <b>Yield Optimised Design</b>                         | <b>58</b> |

| 4.1              | Introduction                                          | 58        |

| 4.2              | Integrated yield optimised model                      | 59        |

| 4.3              | Design Example for Yield Optimised Model              | 61        |

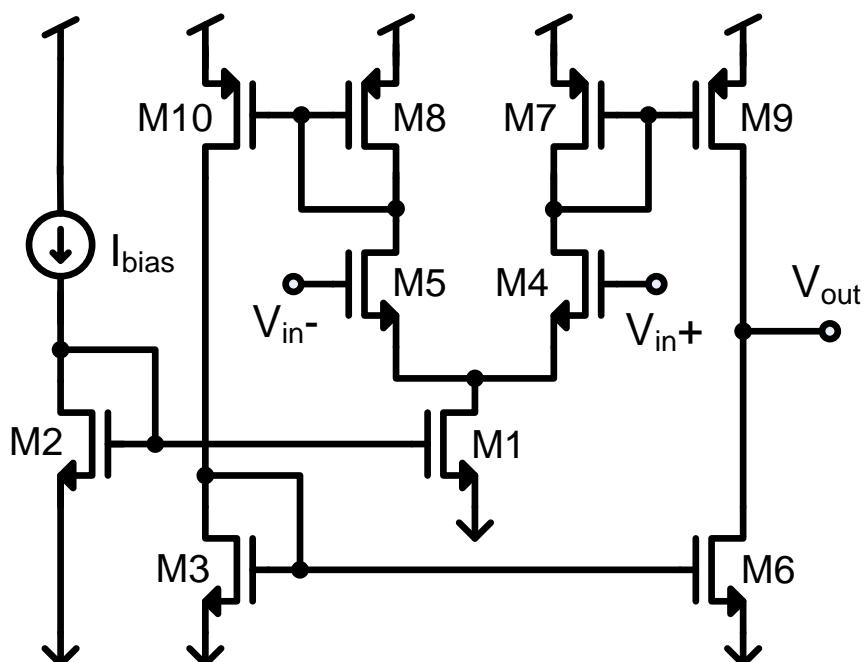

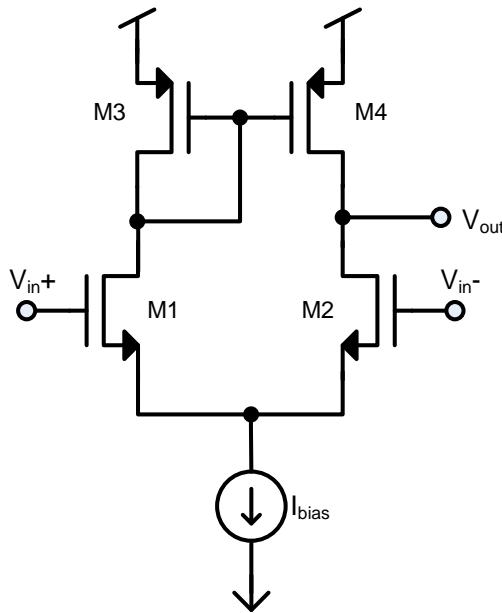

| 4.3.1            | OTA design and objective functions                    | 61        |

| 4.3.2            | Comparison With Design Centring Approach              | 65        |

| 4.4              | Improved yield optimised algorithm                    | 66        |

| 4.5              | Design Example for Improved Yield Optimised Algorithm | 68        |

| 4.5.1            | Pareto front and feasible region                      | 68        |

|                                                                    |            |

|--------------------------------------------------------------------|------------|

| 4.5.2 Monte Carlo simulation                                       | 70         |

| 4.5.3 Comparison with NeoCircuit Optimisation Tool                 | 72         |

| 4.6 Summary                                                        | 74         |

| <b>Chapter 5 Performance and Variation Modelling</b>               | <b>75</b>  |

| 5.1 Introduction                                                   | 75         |

| 5.2 Pareto-front modelling                                         | 76         |

| 5.2.1 Pareto-front modelling – performance                         | 77         |

| 5.2.2 Pareto-front modelling – variation                           | 78         |

| 5.2.3 Interpolation from a lookup table                            | 78         |

| Linear Spline                                                      | 80         |

| Quadratic Spline                                                   | 80         |

| Cubic Spline                                                       | 81         |

| 5.3 Modelling Example                                              | 82         |

| 5.3.1 Performance and Variation Model                              | 83         |

| 5.3.2 Table Model function implementation                          | 85         |

| 5.3.3 Interpolation example                                        | 88         |

| 5.3.4 Model Verification                                           | 89         |

| 5.3.5 Topology Comparison                                          | 91         |

| 5.3.6 Summary of Example                                           | 91         |

| 5.4 Application Example                                            | 92         |

| 5.4.1 System level design                                          | 92         |

| 5.4.2 Silicon Prototype                                            | 95         |

| 5.5 Summary                                                        | 97         |

| <b>Chapter 6 Hierarchical-based design optimisation</b>            | <b>98</b>  |

| 6.1 Introduction                                                   | 98         |

| 6.2 Hierarchical-based design                                      | 99         |

| 6.3 Hierarchical-based Design Methodology                          | 100        |

| 6.3.1 Bottom-Up Methodology                                        | 100        |

| 6.3.2 Top-down Constraint-Driven Methodology (TDCD)                | 101        |

| 6.3.3 Feasibility Modelling Bottom-up (FMBU) + TDCD                | 101        |

| 6.3.4 Multi Objective Bottom-up Methodology (MUBU)                 | 102        |

| 6.4 Multi Objective Bottom Up (MUBU) + TDCD Architecture           | 103        |

| 6.5 Design Example: 7 <sup>th</sup> order elliptic low pass filter | 105        |

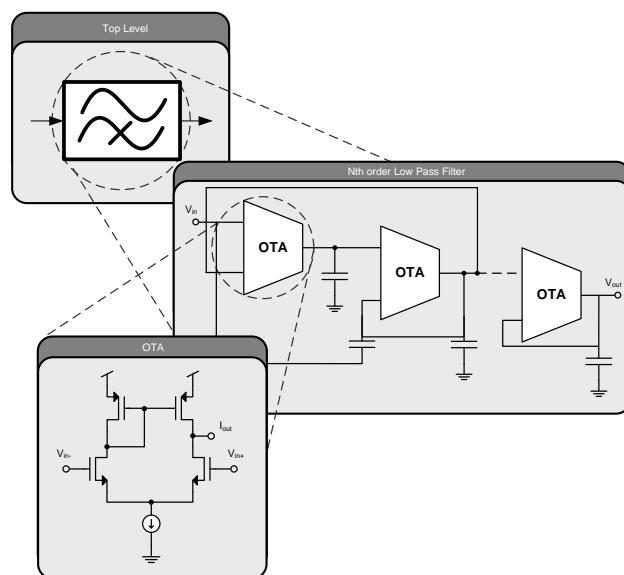

| 6.5.1 Circuit Decomposition                                        | 105        |

| 6.5.2 Design Initialisation                                        | 106        |

| 6.5.3 Optimisation                                                 | 107        |

| 6.5.4 Performance and Variation Model                              | 107        |

| 6.5.5 Behavioural Description                                      | 109        |

| 6.5.6 System level optimisation                                    | 115        |

| 6.7 Summary                                                        | 118        |

| <b>Chapter 7 Mixed-signal System Level Application</b>             | <b>120</b> |

| 7.1 Introduction                                                   | 120        |

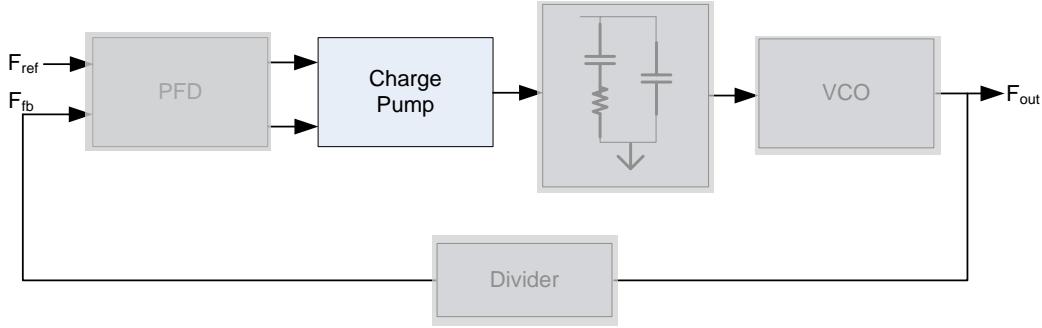

| 7.2 PLL system                                                     | 122        |

---

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| 7.2.1 Phase Frequency Detector                                            | 122        |

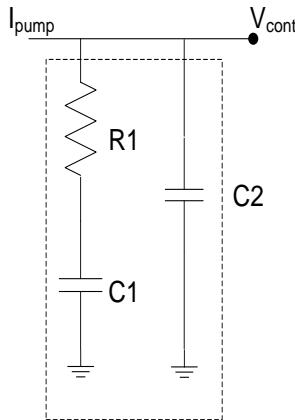

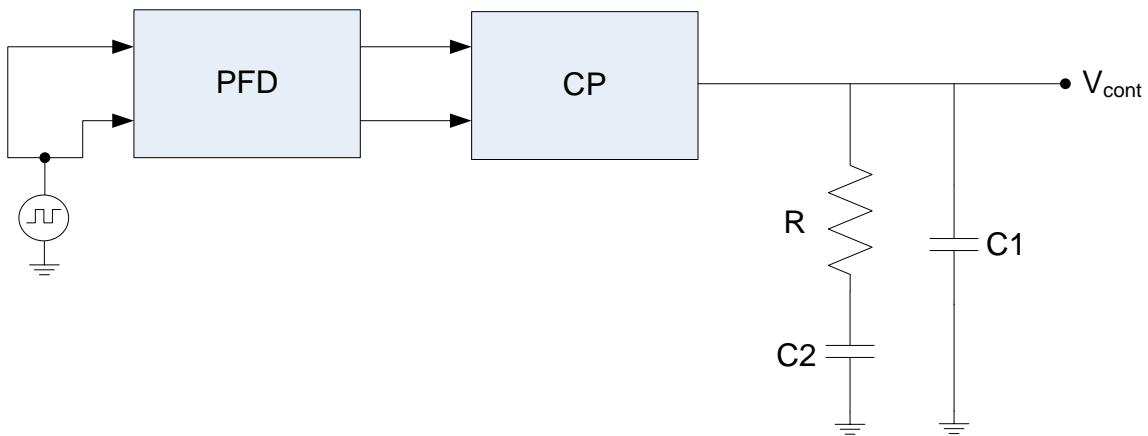

| 7.2.2 Charge Pump and Loop Filter                                         | 124        |

| 7.2.3 Voltage Controlled Oscillators                                      | 125        |

| 7.3 PLL System Performances                                               | 126        |

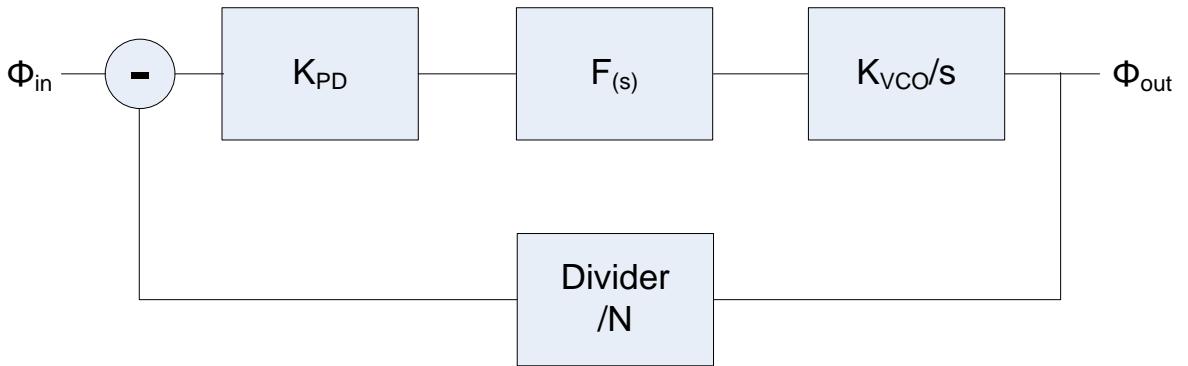

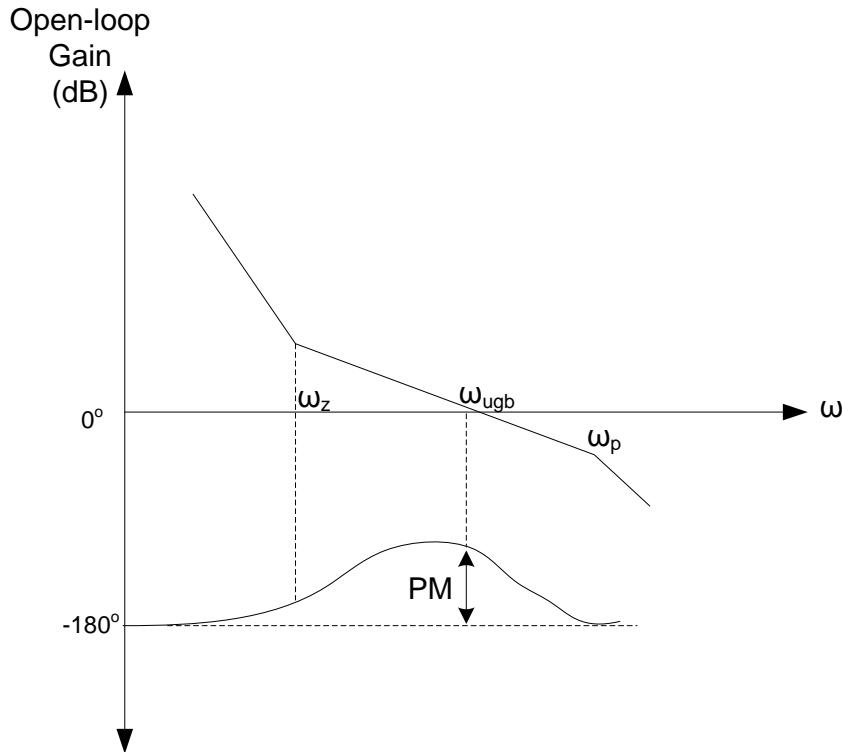

| 7.3.1 PLL transfer function                                               | 127        |

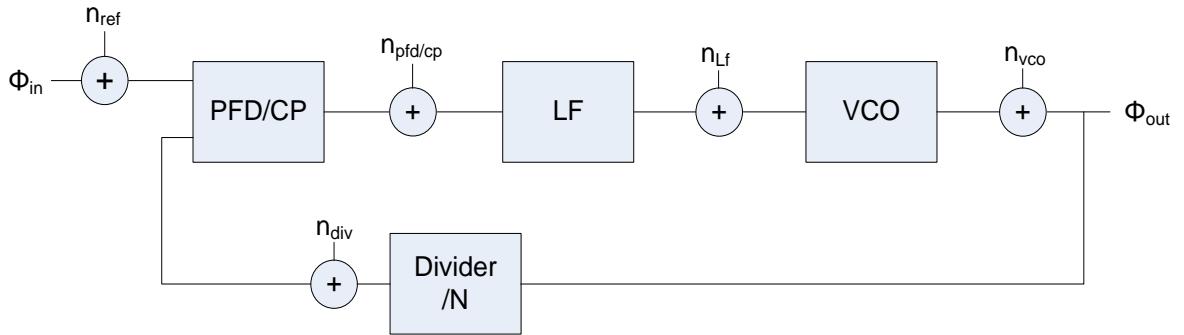

| 7.3.2 PLL phase noise                                                     | 130        |

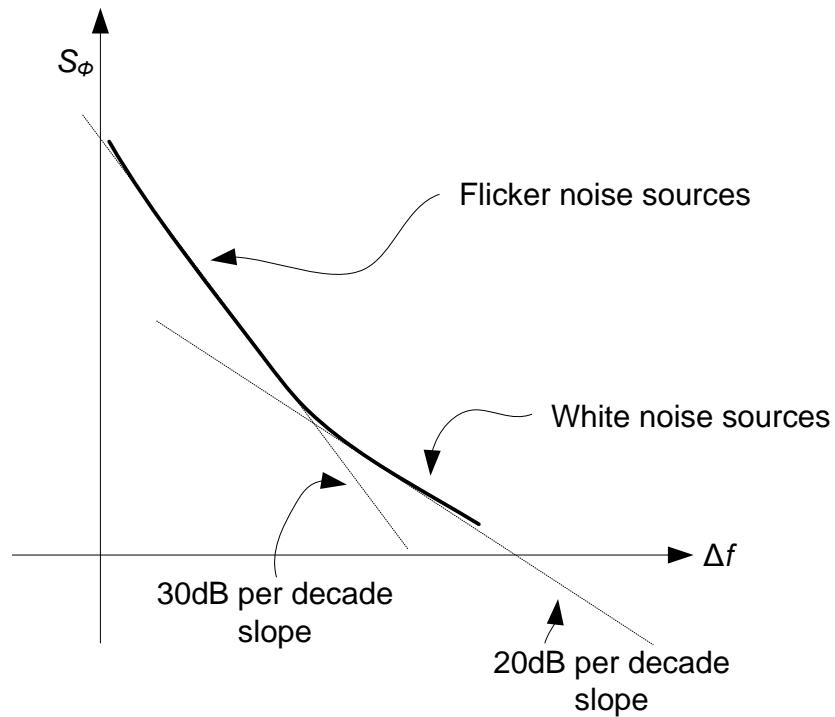

| 7.3.3 Extracting individual phase noise contribution                      | 131        |

| VCO Noise                                                                 | 131        |

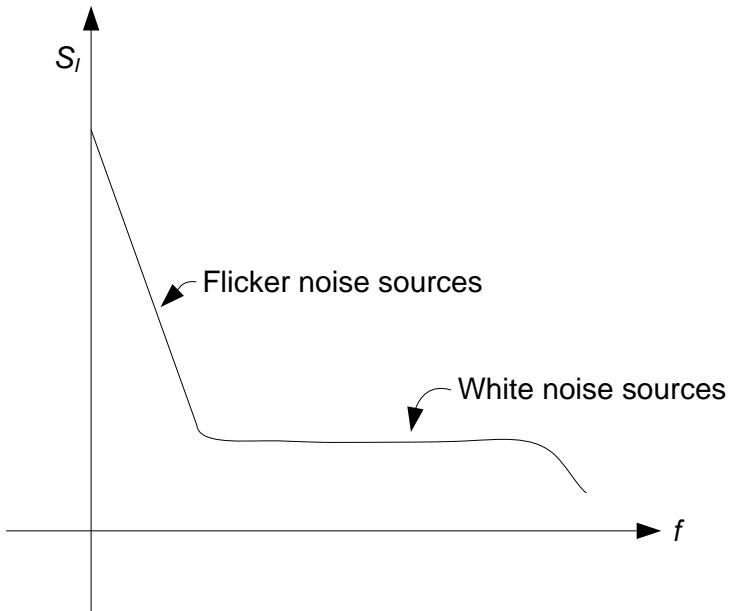

| PFD/CP and loop filter noise                                              | 132        |

| 7.3.4 Behavioural Modelling of Noise Sources                              | 133        |

| 7.4 Design Example                                                        | 136        |

| 7.4.1 Charge Pump (CP) performance and variation model                    | 137        |

| 7.4.2 Voltage-controlled Oscillator (VCO) performance and variation model | 142        |

| 7.4.3 PLL System Level Design                                             | 150        |

| 7.4.4 Design Summary                                                      | 158        |

| 7.5 Summary                                                               | 160        |

| <b>Chapter 8 Conclusions and Future Work</b>                              | <b>161</b> |

| 8.1 Conclusion                                                            | 161        |

| 8.2 Accuracy, generality and limitations of the method                    | 163        |

| 8.3 Project Objectives Achieved                                           | 164        |

| 8.4 Contribution                                                          | 166        |

| 8.4.1 Specific Contribution                                               | 166        |

| 8.4.2 Publications                                                        | 167        |

| 8.5 Future Work                                                           | 167        |

| 8.5.1 Topological Automation                                              | 167        |

| 8.5.2 Hybrid Analytical and Simulation-based Approach                     | 167        |

| 8.5.3 Parallel Optimisation                                               | 168        |

| <b>Publications</b>                                                       | <b>169</b> |

| <b>Reference</b>                                                          | <b>171</b> |

| <b>Appendix A Spice Model Listings</b>                                    | <b>181</b> |

| <b>Appendix B Algorithm Model Listings</b>                                | <b>195</b> |

| <b>Appendix C Verilog-A Model Listings</b>                                | <b>206</b> |

# List of Figures

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Figure 1.1 : Transistor complexity's trend – Moore's Law                | 2  |

| Figure 1.2 : Project structure                                          | 7  |

| Figure 2.1 : Typical design flow for analogue IC design                 | 13 |

| Figure 2.2 : Optimisation-based design                                  | 17 |

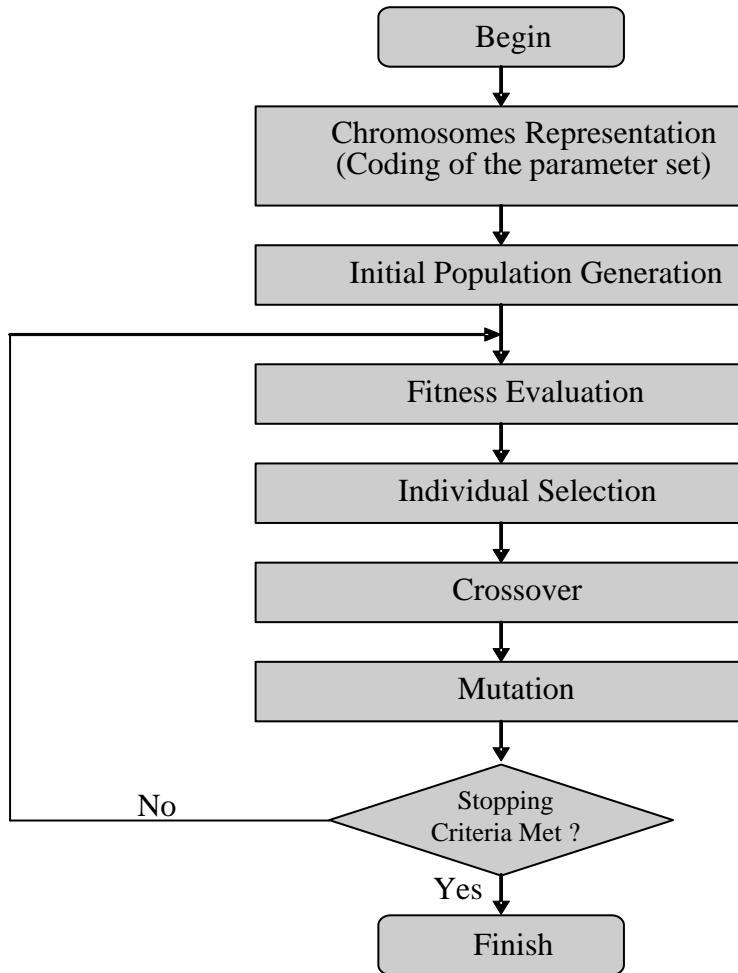

| Figure 2.3 : Flowchart of Genetic Algorithm                             | 31 |

| Figure 2.4 : Example of genetic algorithm report                        | 32 |

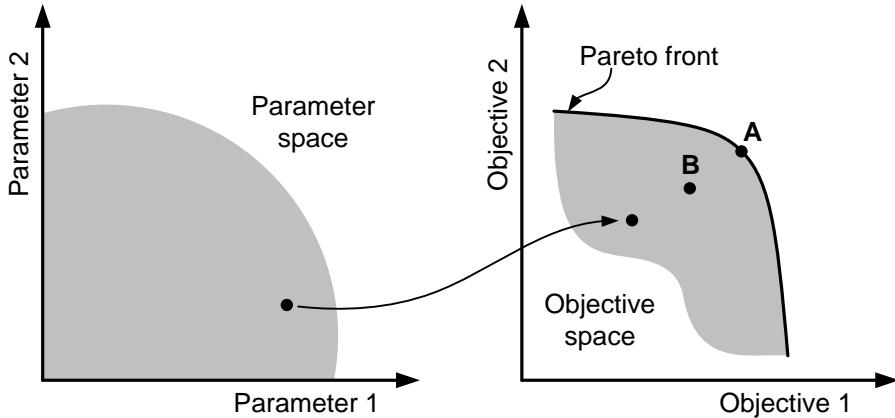

| Figure 2.5 : Relationship between parameter space and objective space   | 34 |

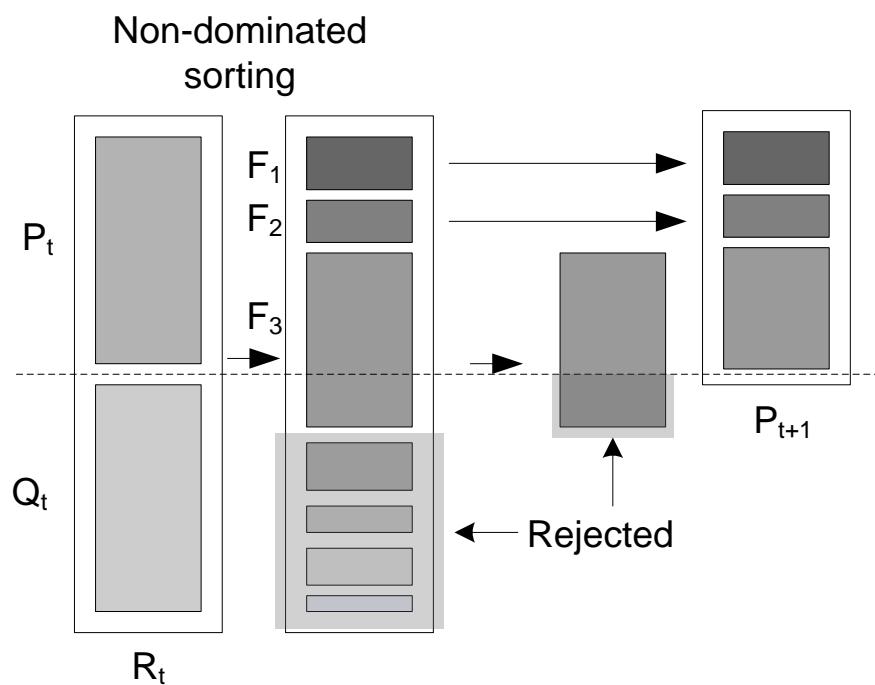

| Figure 2.6 : NSGA-II Procedure                                          | 35 |

| Figure 2.7 : NSGA-II Algorithm                                          | 36 |

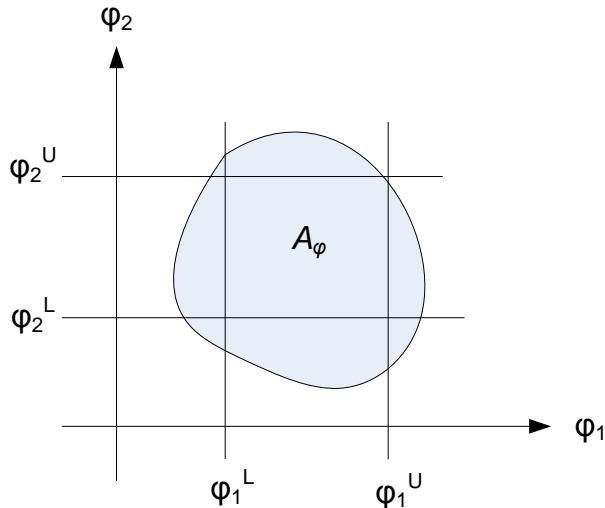

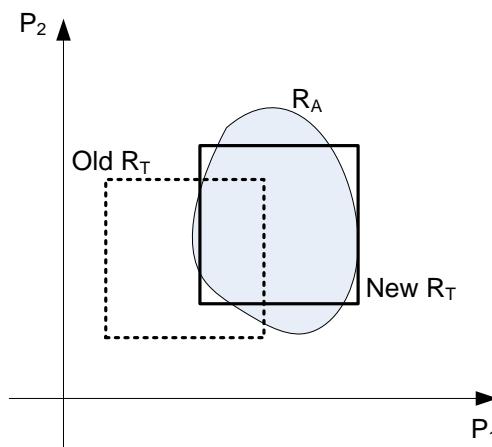

| Figure 2.8 : Acceptability region in performacne space                  | 38 |

| Figure 2.9 : Design centring to maximise yield                          | 45 |

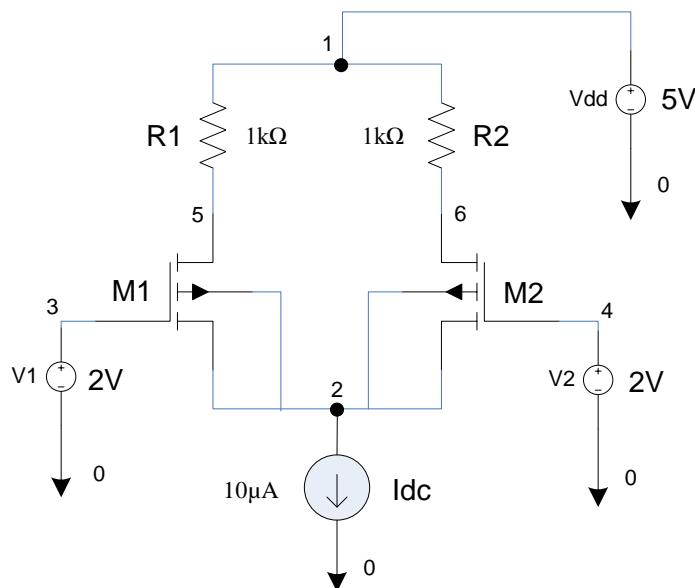

| Figure 3.1 : Circuit diagram for differential pair                      | 49 |

| Figure 3.2 : Netlist for differential pair                              | 50 |

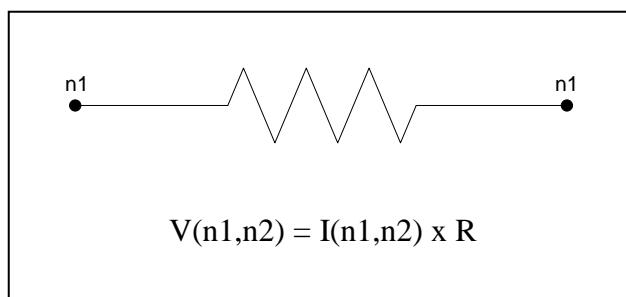

| Figure 3.3 : Resistor model                                             | 53 |

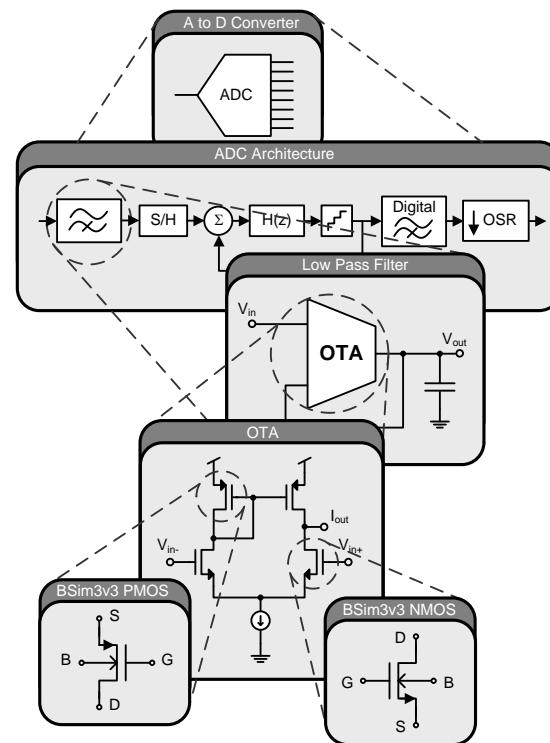

| Figure 3.4 : Typical hierarchy level in analogue circuit design         | 56 |

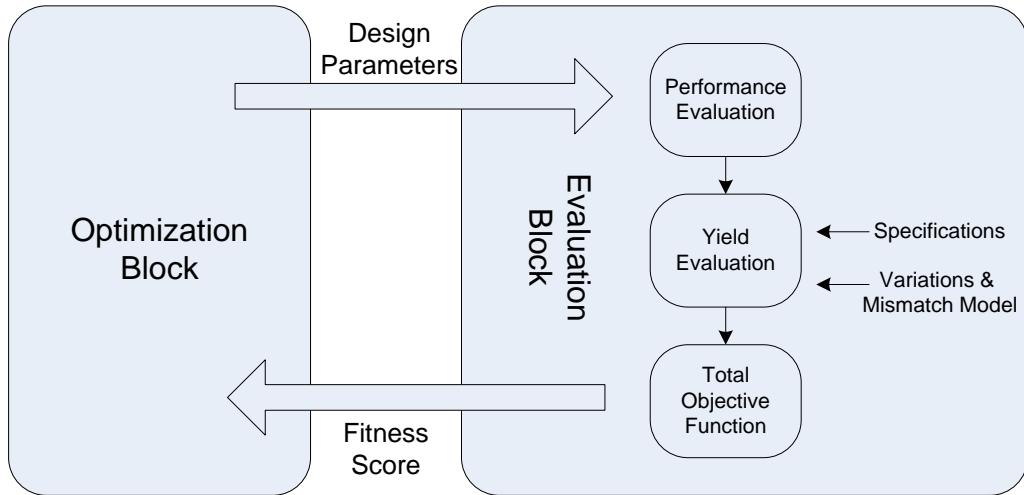

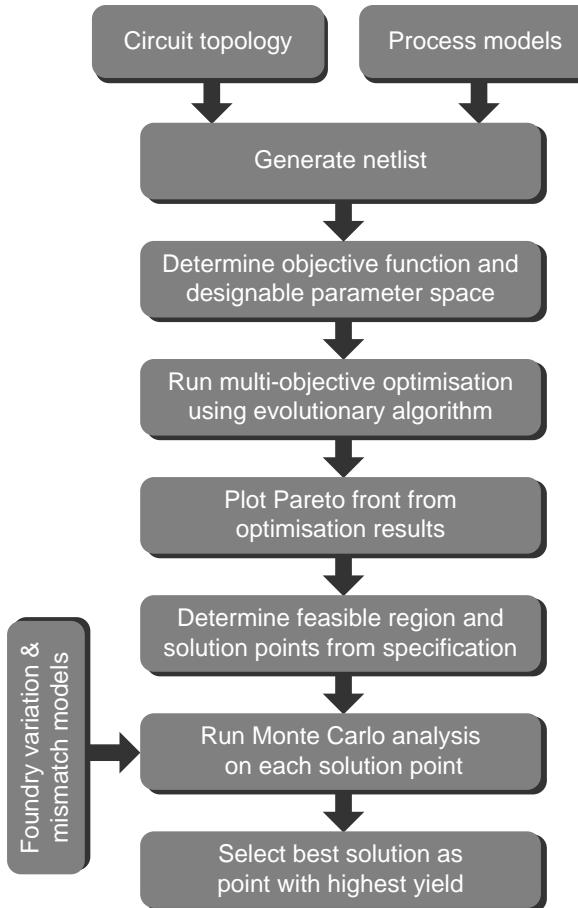

| Figure 4.1 : Integrated yield optimised model                           | 60 |

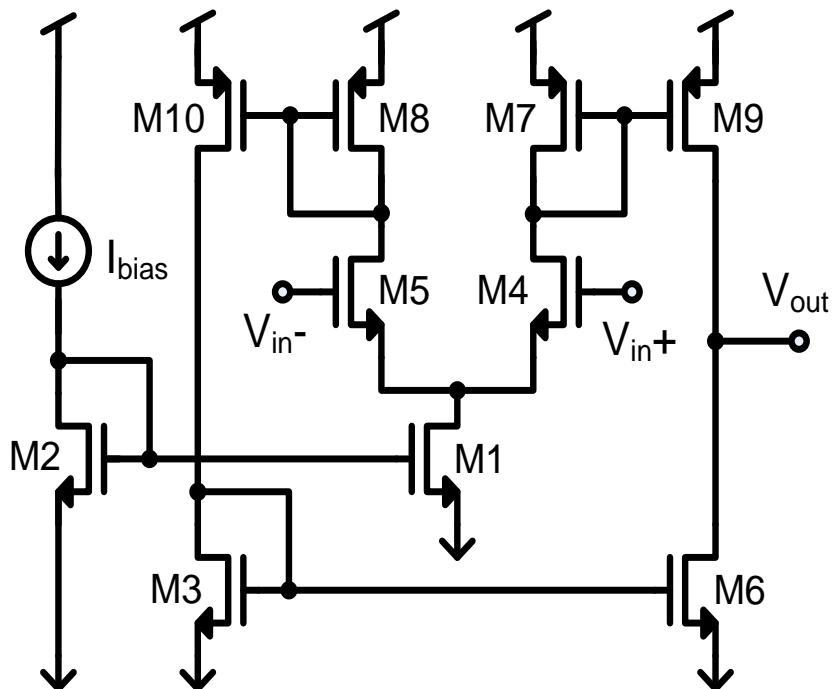

| Figure 4.2 : Symmetrical OTA topology                                   | 61 |

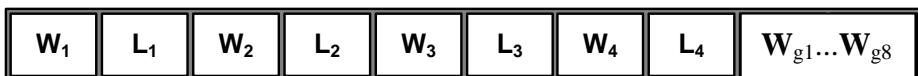

| Figure 4.3 : GA string                                                  | 63 |

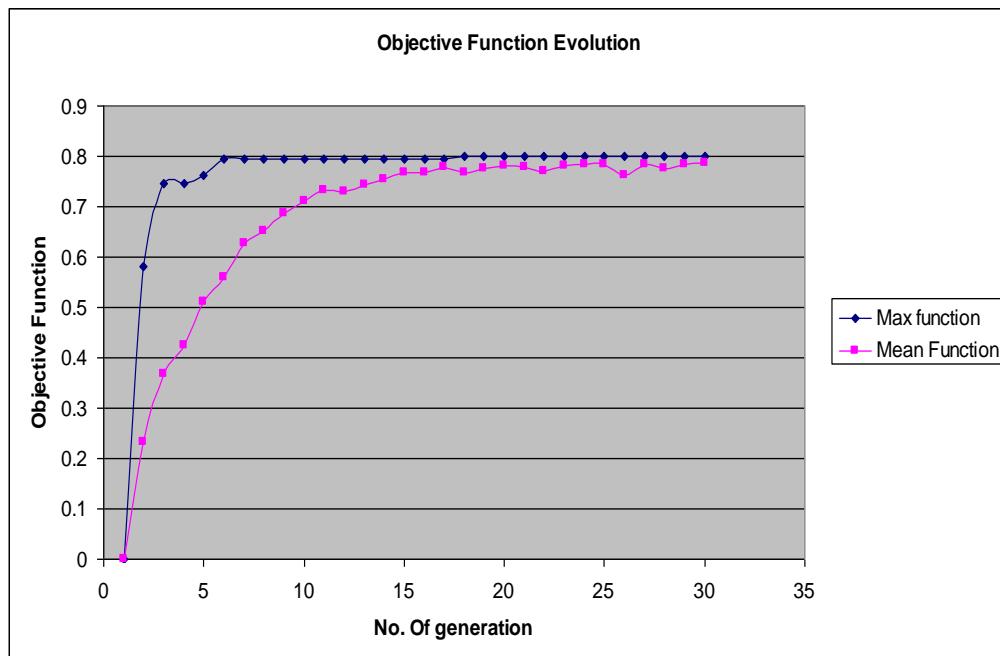

| Figure 4.4 : Convergence criteria                                       | 64 |

| Figure 4.5 : Yield targeted algorithm                                   | 67 |

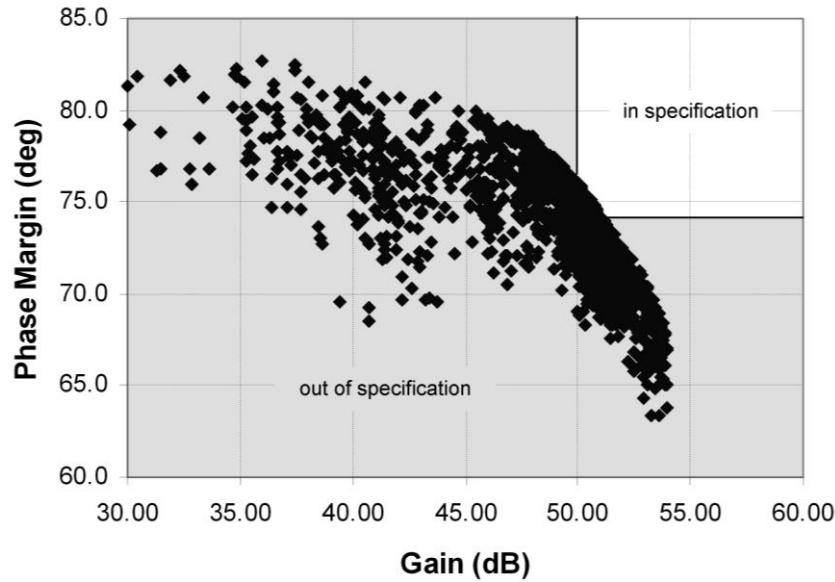

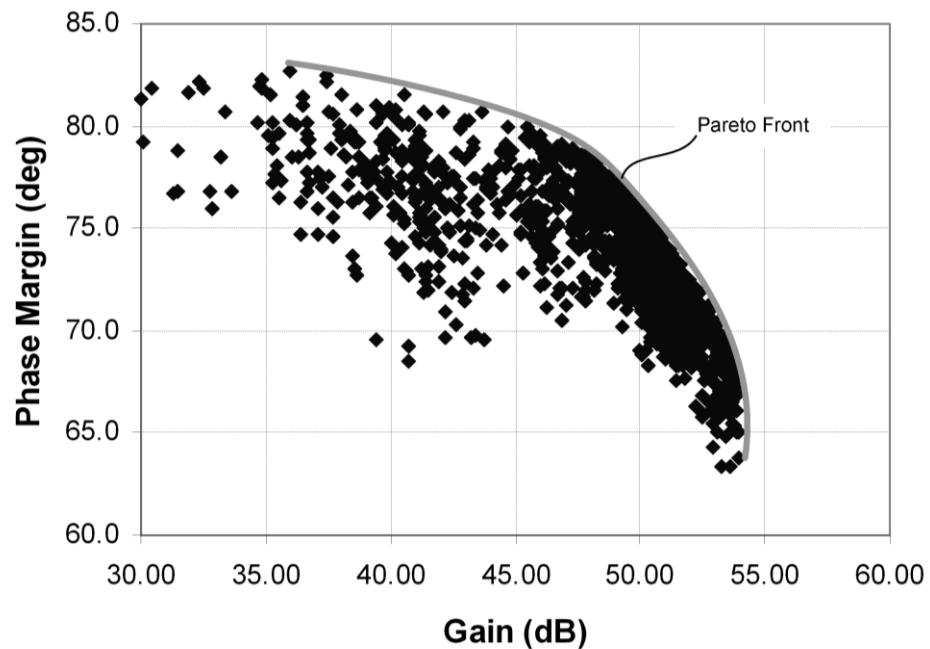

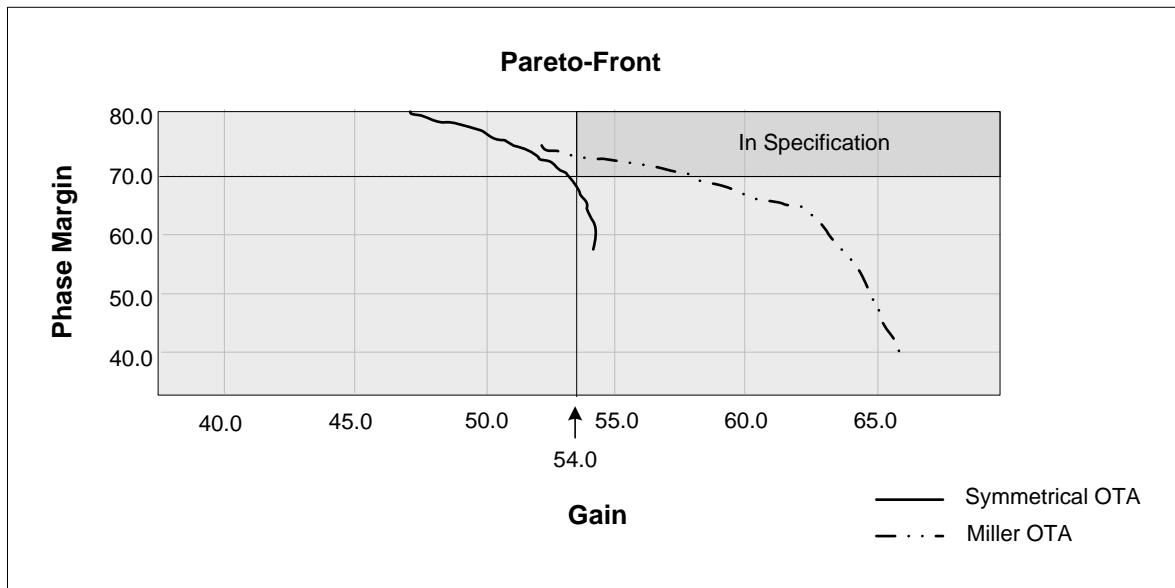

| Figure 4.6 : Objective space and Pareto-front                           | 69 |

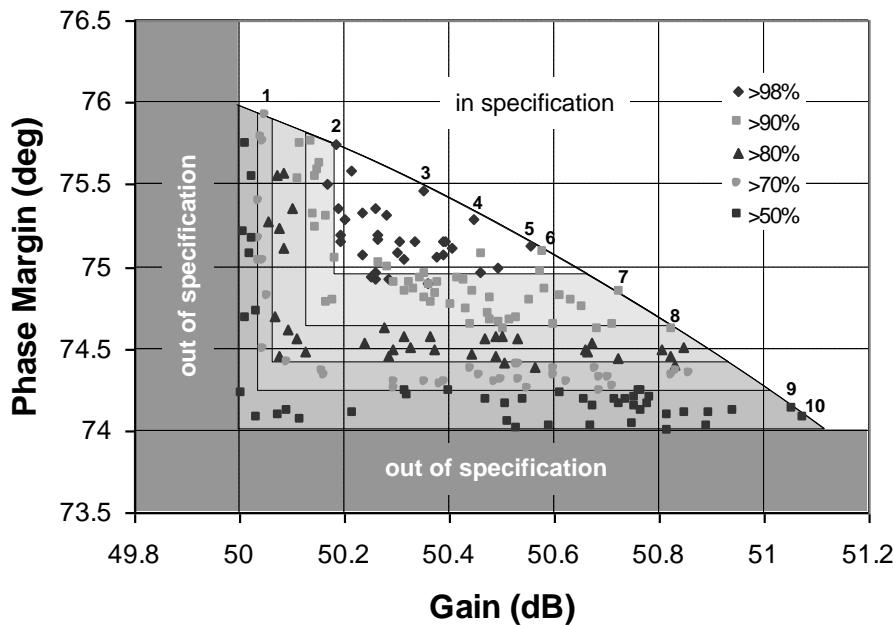

| Figure 4.7 : Detail view of feasible region                             | 69 |

| Figure 4.8 : Process variation parameters                               | 70 |

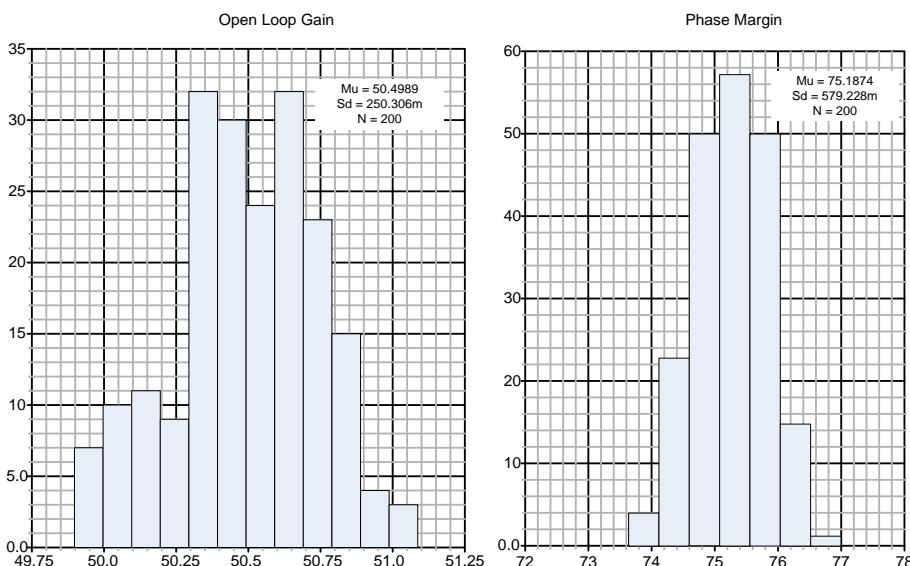

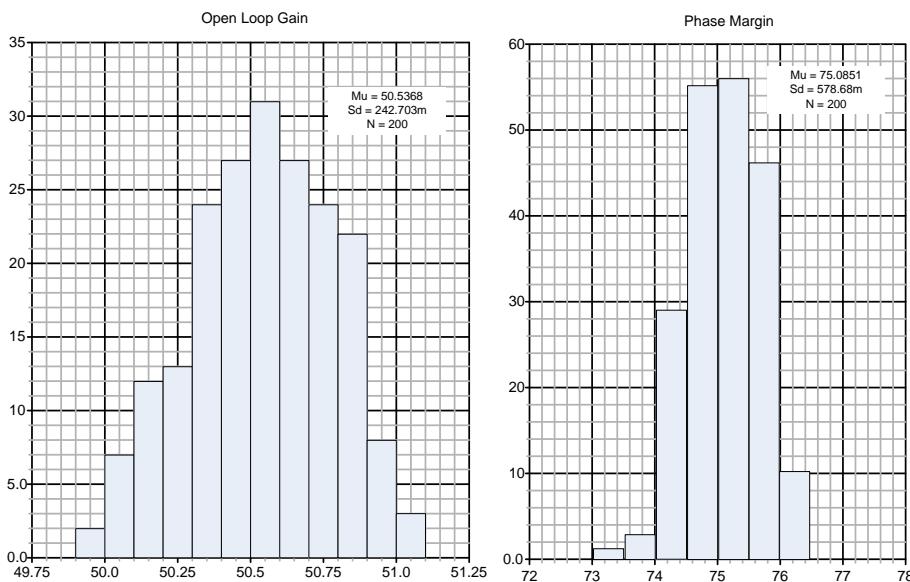

| Figure 4.9 : Monte Carlo histogram for gain and phase margin            | 73 |

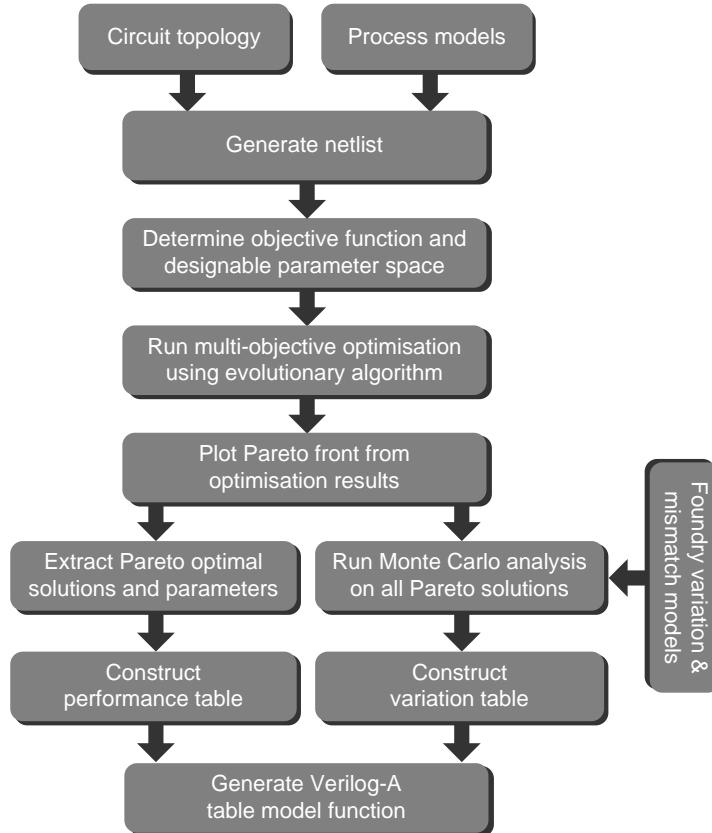

| Figure 5.1 : Performance and variation's model development flow         | 77 |

| Figure 5.2 : Symmetrical OTA topology                                   | 82 |

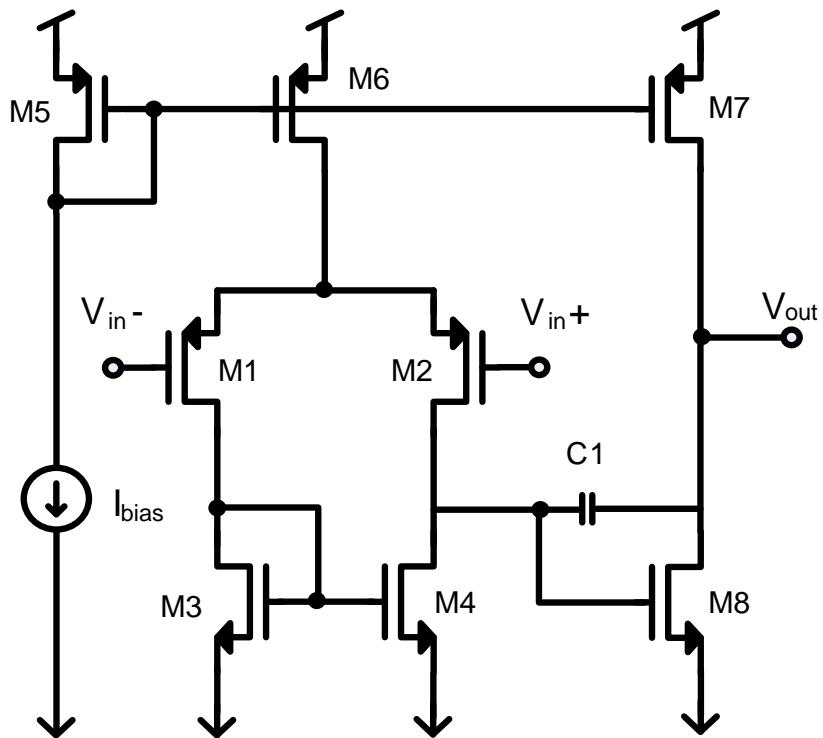

| Figure 5.3 : Miller OTA topology                                        | 83 |

| Figure 5.4 : Symmetrical OTA Pareto plot                                | 84 |

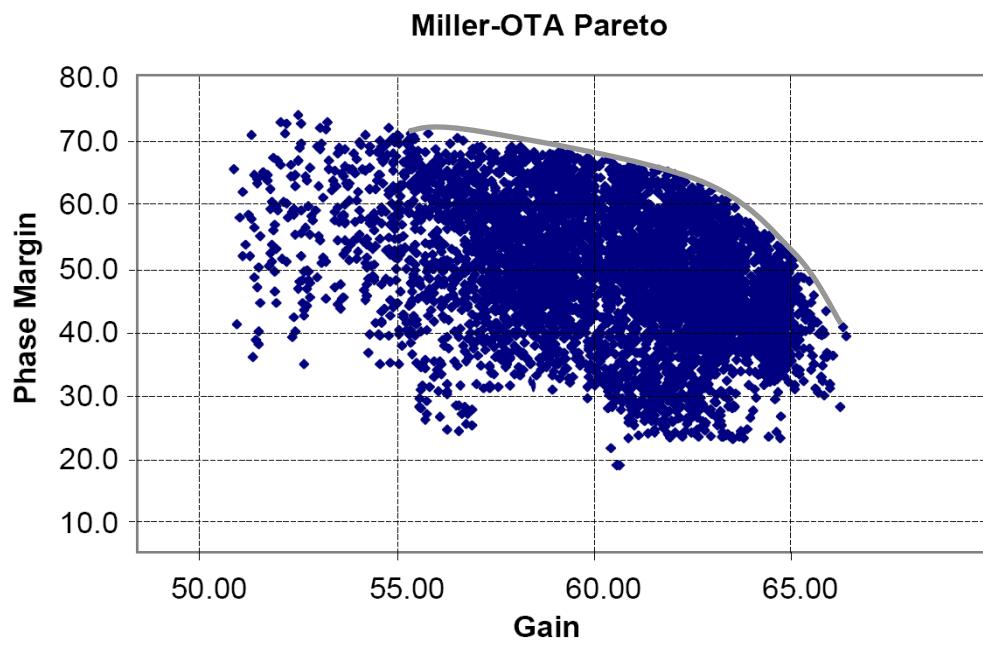

| Figure 5.5 : Miller OTA Pareto plot                                     | 84 |

| Figure 5.6 : Table model file for OTA performance model                 | 87 |

| Figure 5.7 : Table model file for gain and phase margin variation model | 87 |

---

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| Figure 5.8 : Verilog-A model for OTA performance and variation lookup table | 87  |

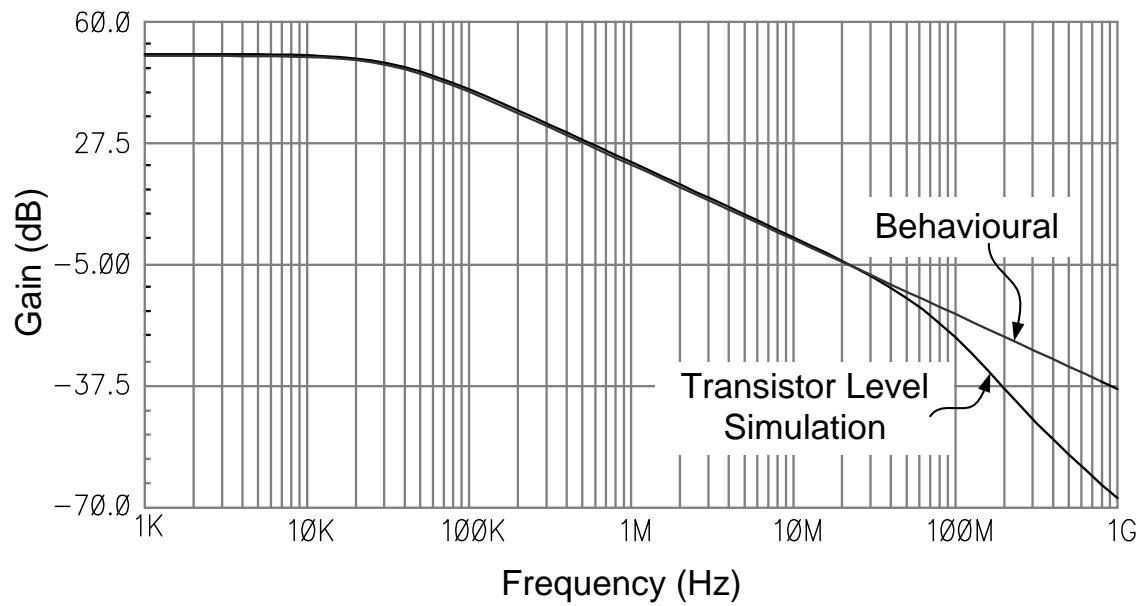

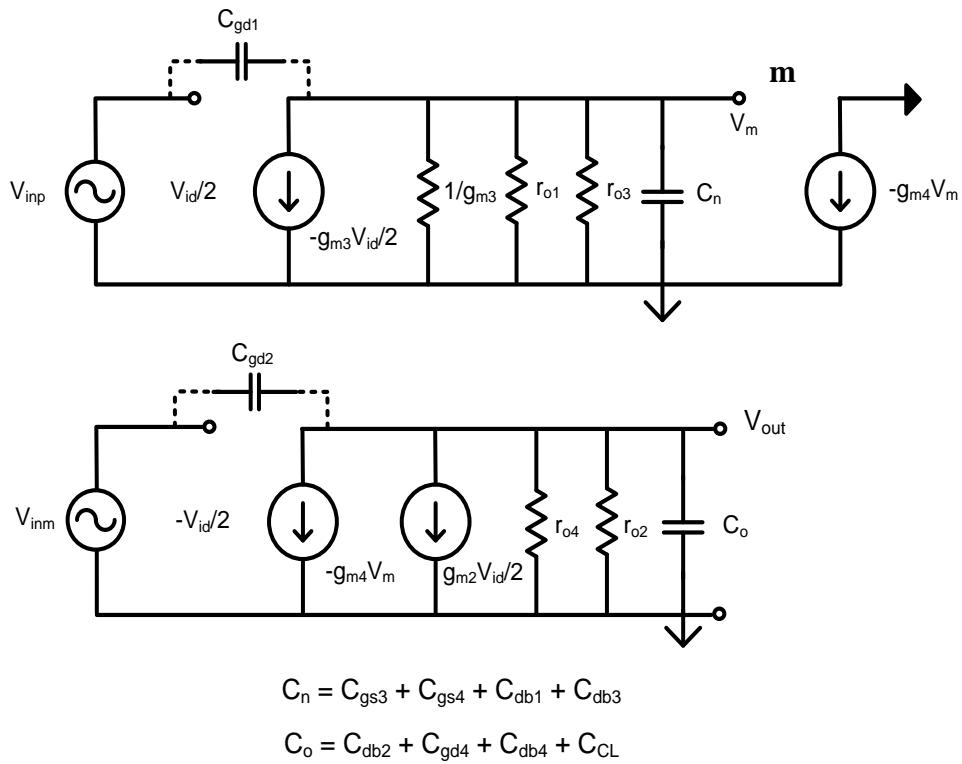

| Figure 5.9 : Behavioural and transistor level simulation comparison         | 90  |

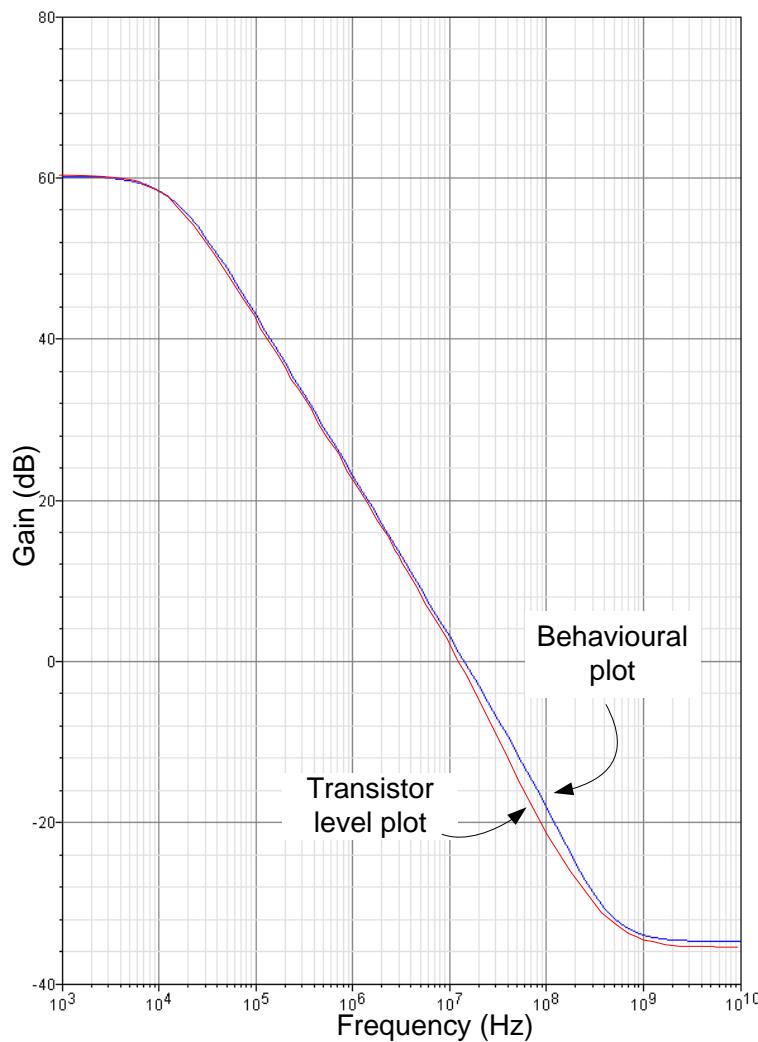

| Figure 5.10 : Open loop gain comparison for Miller-OTA                      | 90  |

| Figure 5.11: Pareto comparison between topology                             | 91  |

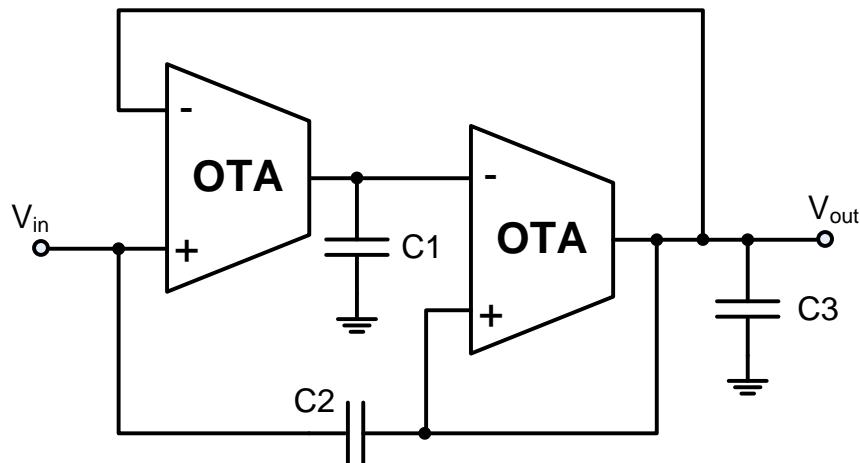

| Figure 5.12 : 2 <sup>nd</sup> order lowpass filter topology                 | 93  |

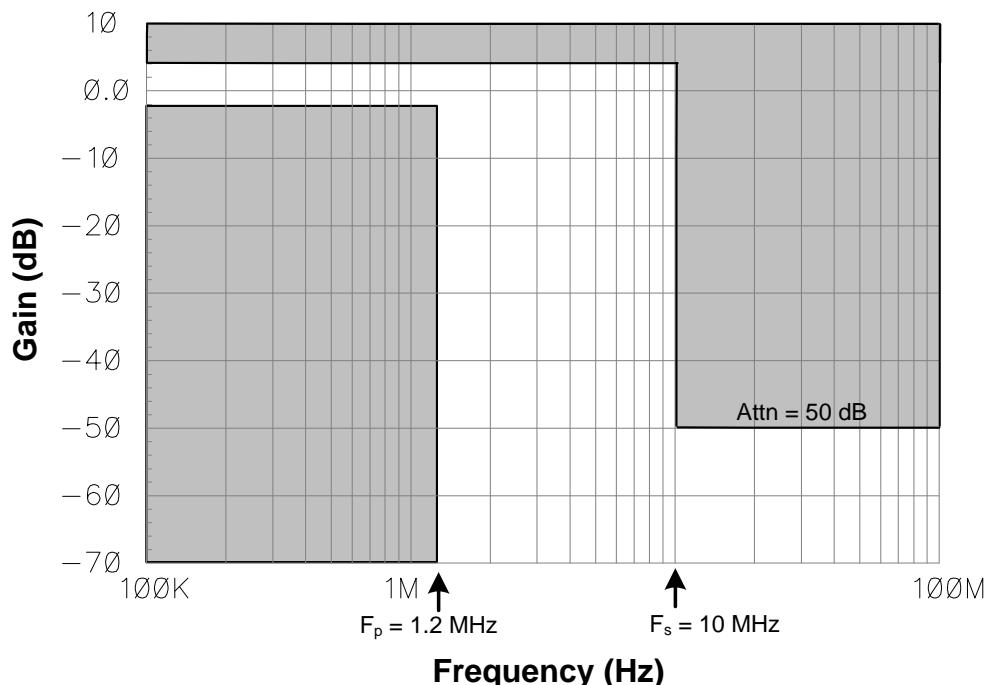

| Figure 5.13 : Filter specification                                          | 93  |

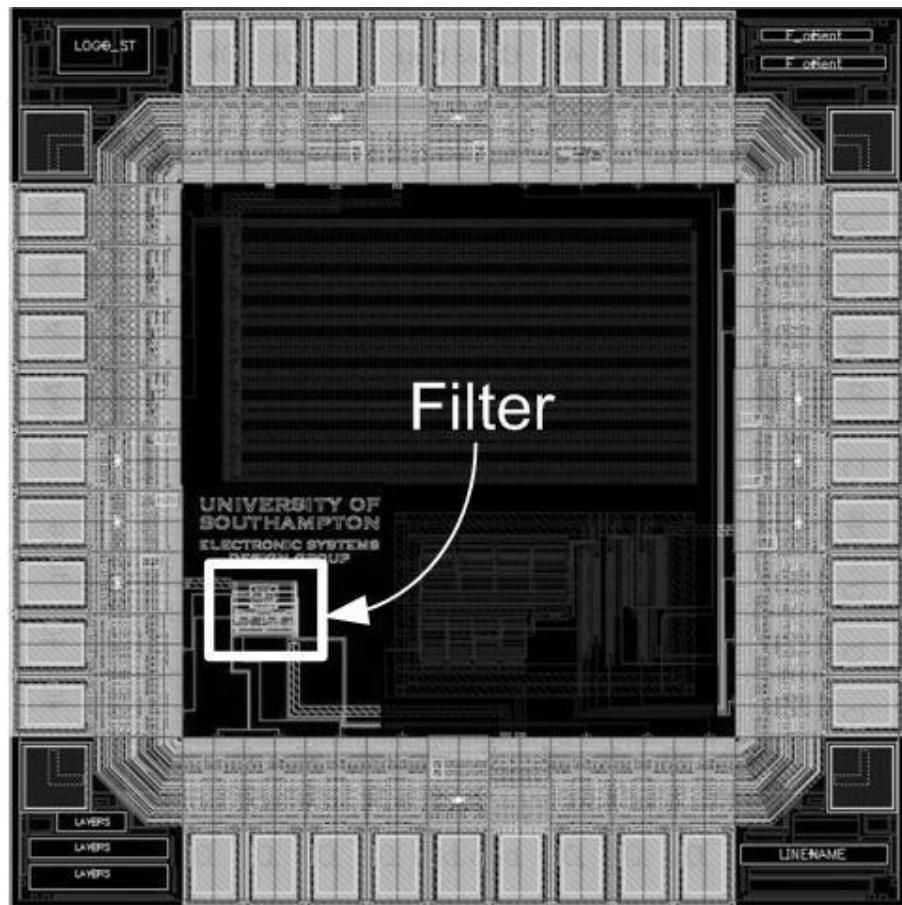

| Figure 5.14 : Layout view of silicon prototype                              | 95  |

| Figure 5.15 : Testboard snapshot                                            | 96  |

| Figure 5.16 : Chip measurement result                                       | 96  |

| Figure 6.1 : Hierarchy design methodology                                   | 100 |

| Figure 6.2 : Multi Objective Bottom Up hierarchical methodology             | 102 |

| Figure 6.3 : MUBU + TDCD architecture                                       | 104 |

| Figure 6.4 : Circuit decomposition                                          | 105 |

| Figure 6.5 : Single stage OTA topology                                      | 106 |

| Figure 6.6 : GA string for the design example                               | 107 |

| Figure 6.7 : Verilog-A table model function                                 | 108 |

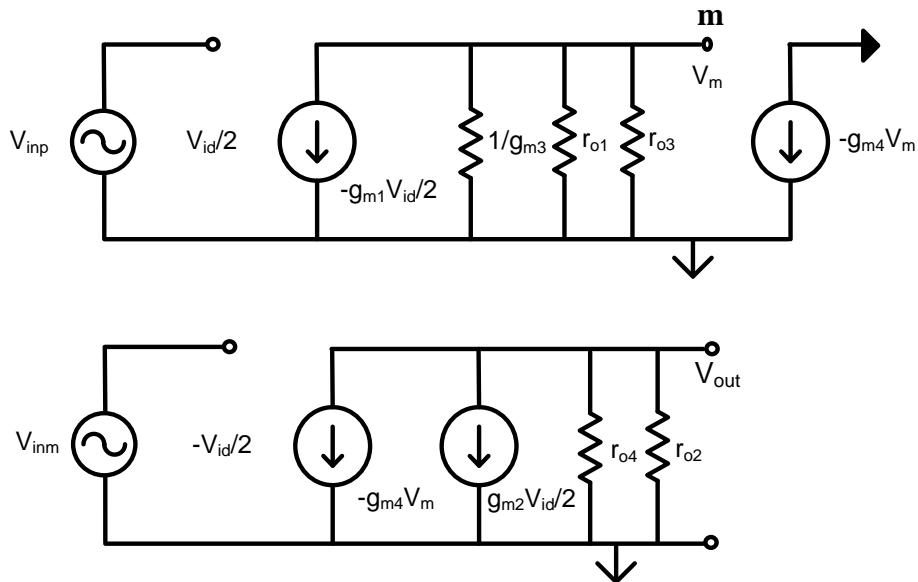

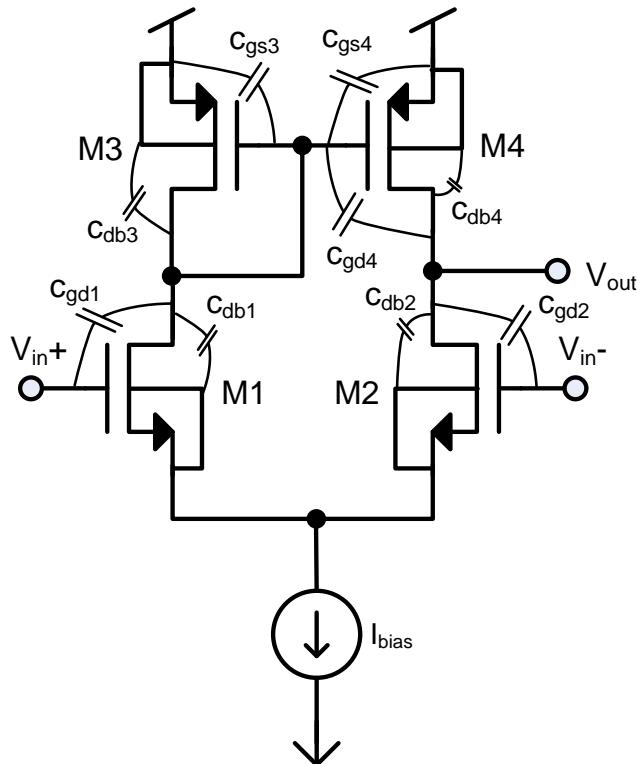

| Figure 6.8 : OTA small signal model                                         | 110 |

| Figure 6.9 : OTA schematic with parasitic capacitance                       | 111 |

| Figure 6.10 : OTA high frequency small signal model                         | 112 |

| Figure 6.11 : Verilog-A code for the OTA                                    | 114 |

| Figure 6.12 : Comparison between behavioural model and transistor model     | 115 |

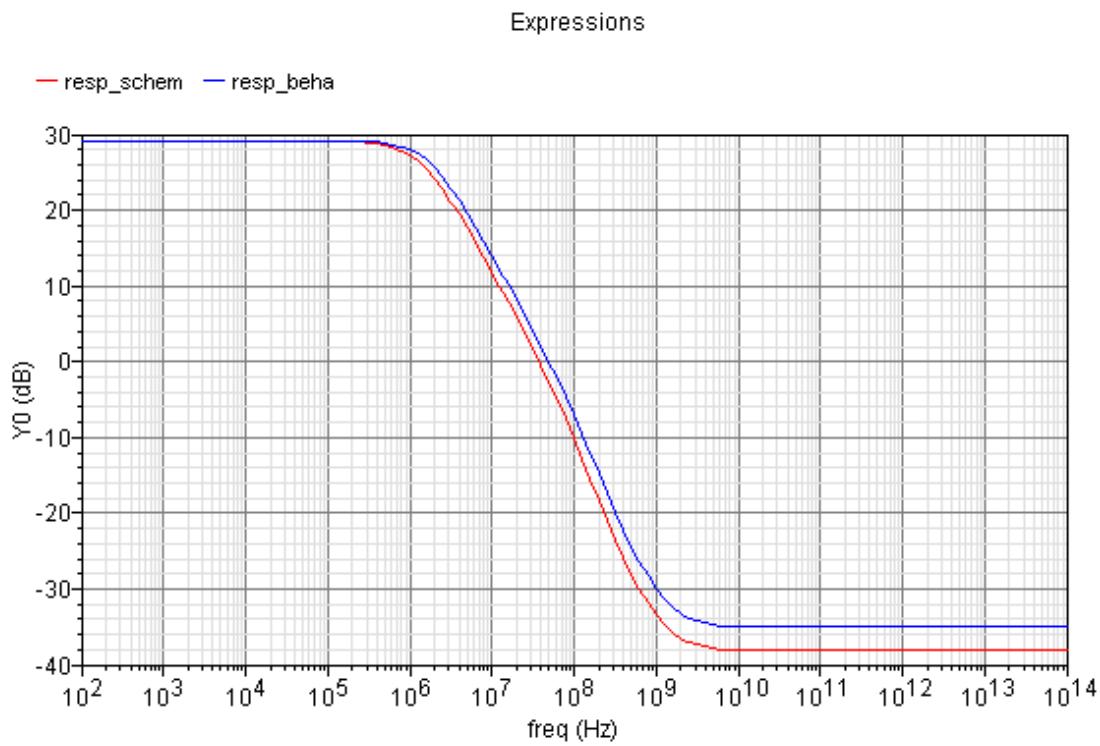

| Figure 6.13 : 7 <sup>th</sup> order low pass elliptic filter                | 116 |

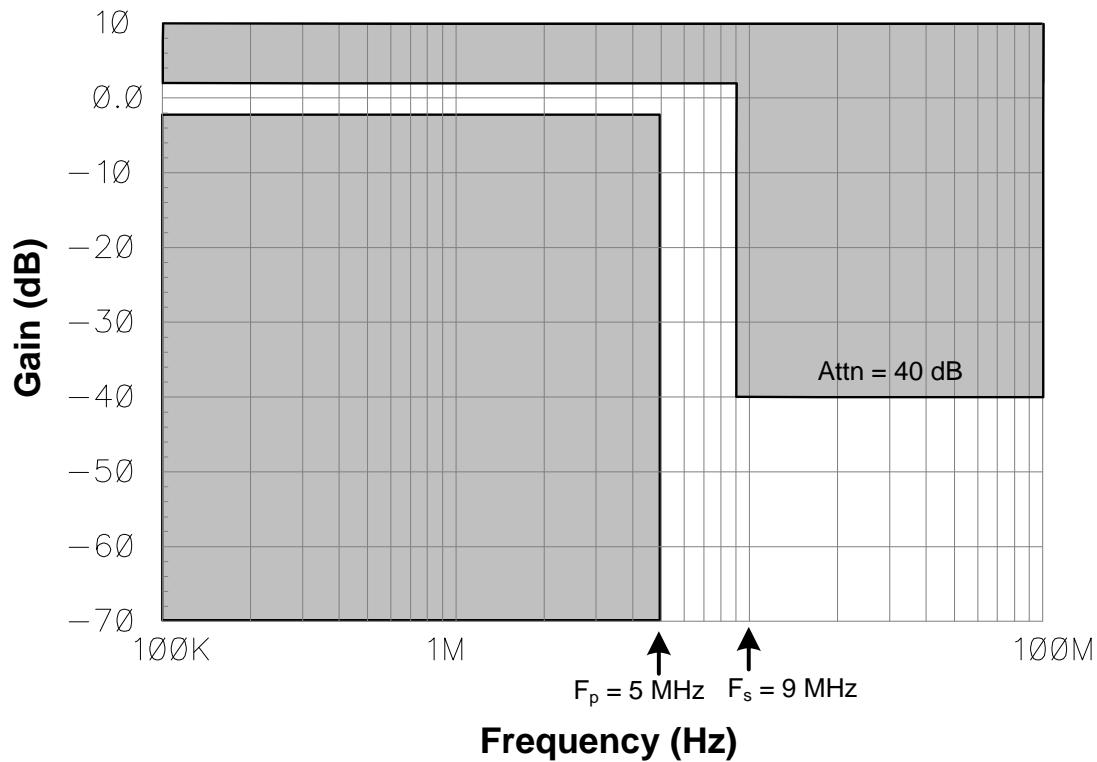

| Figure 6.14 : Filter specification                                          | 116 |

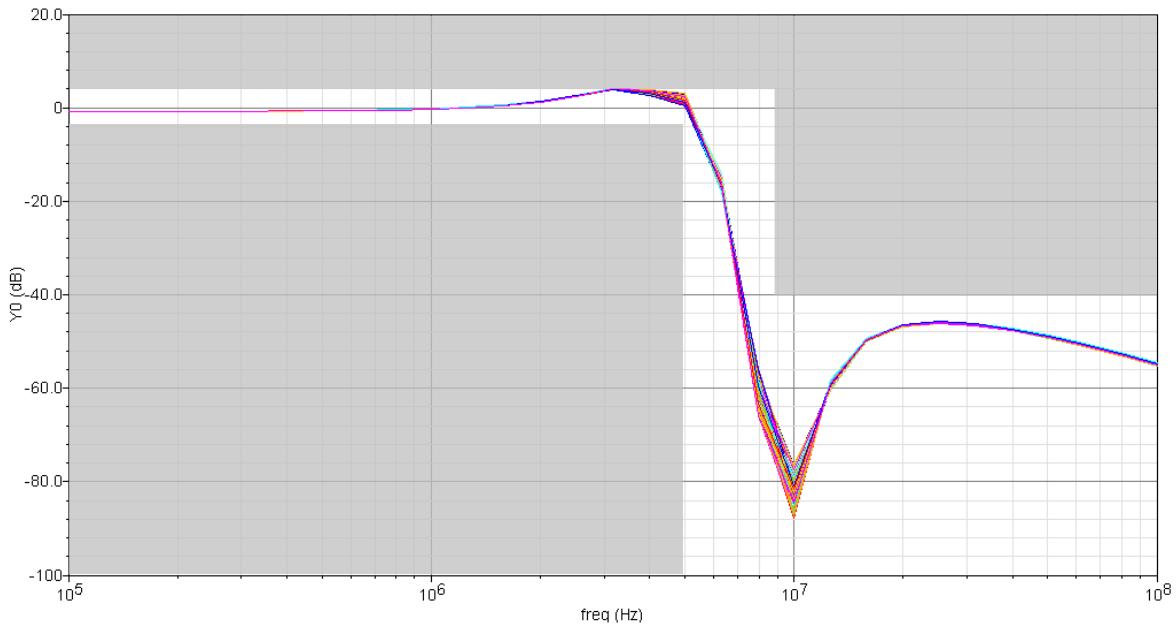

| Figure 6.15 : Monte Carlo plot of filter response                           | 118 |

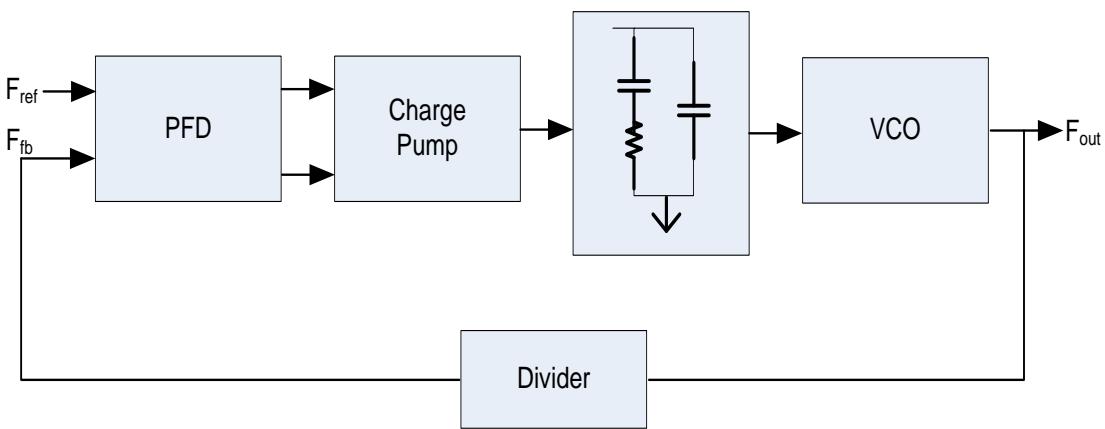

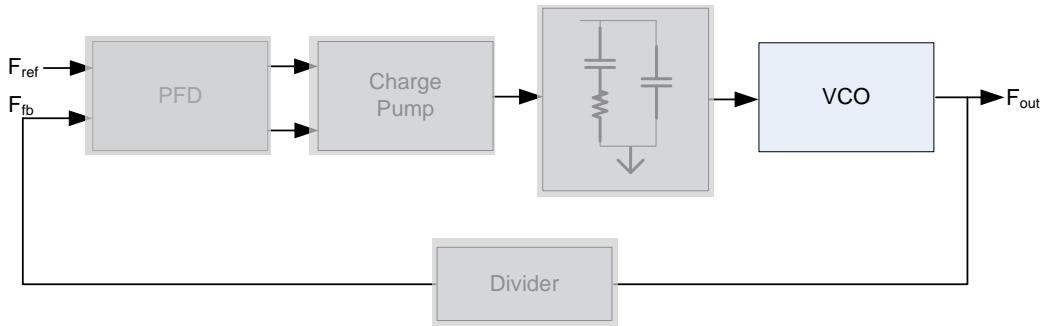

| Figure 7.1 : PLL system block diagram                                       | 121 |

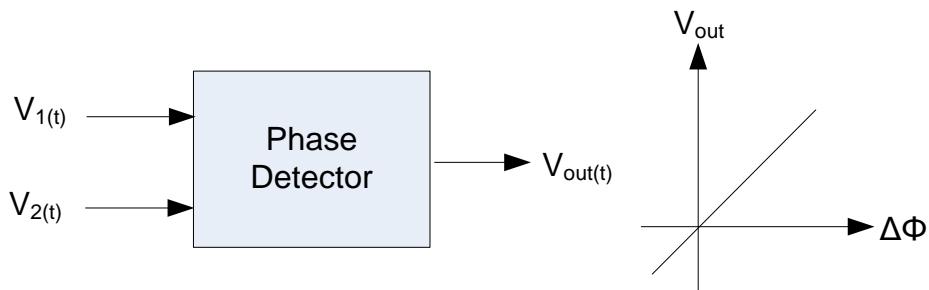

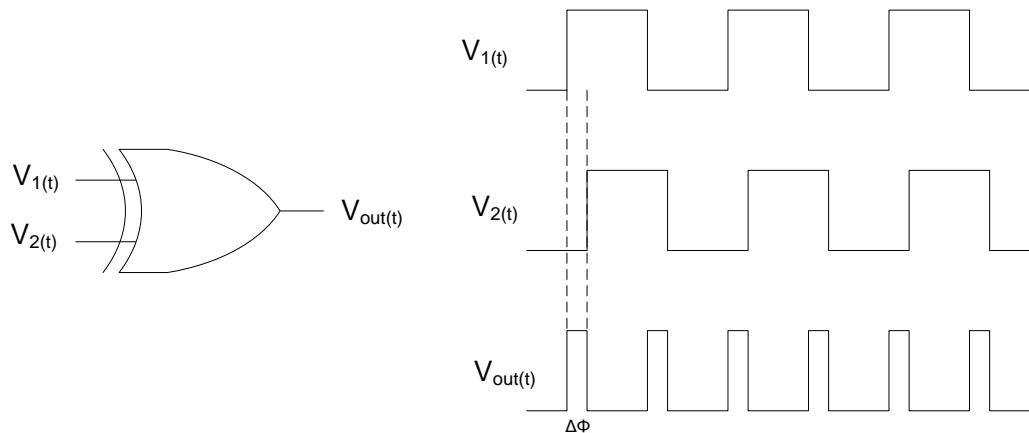

| Figure 7.2 : Phase detector concept                                         | 122 |

| Figure 7.3 : Phase detector plots                                           | 123 |

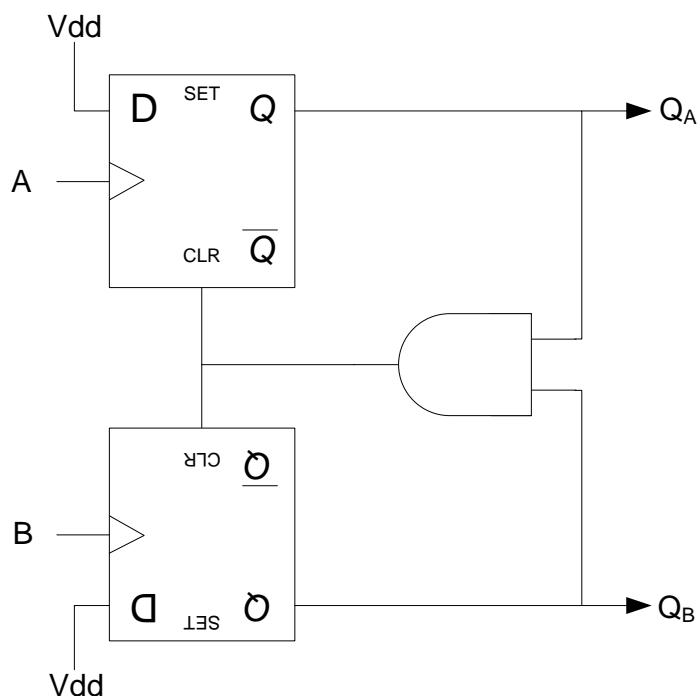

| Figure 7.4 : Phase frequency detector schematic                             | 123 |

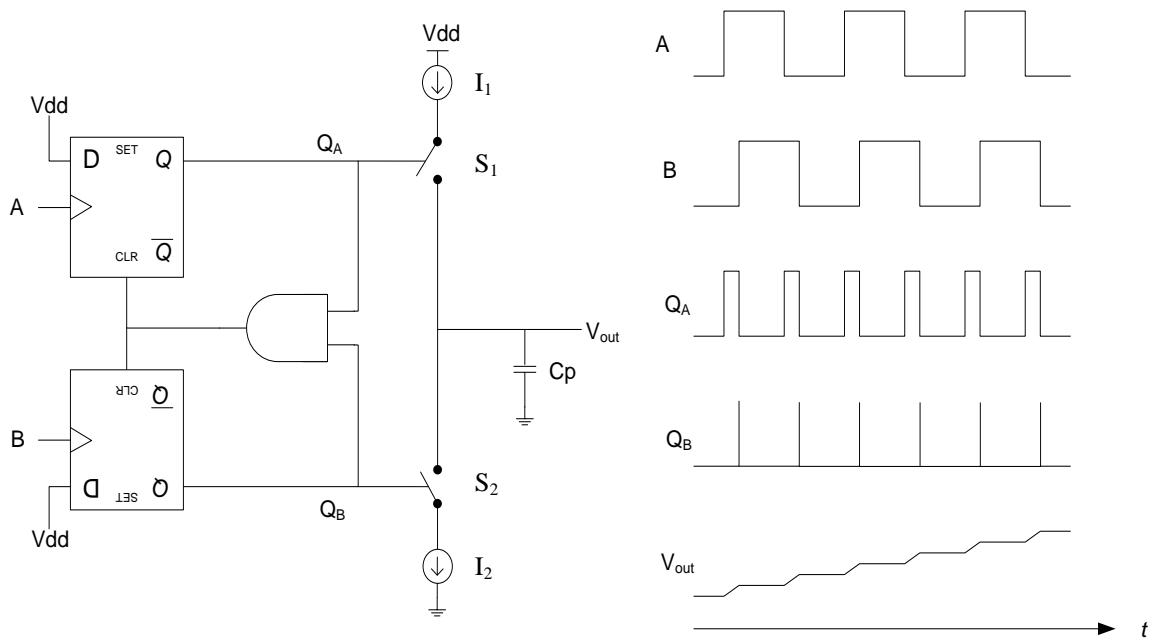

| Figure 7.5 : PFD/CP illustration and its signal plot                        | 124 |

| Figure 7.6 : Loop filter                                                    | 125 |

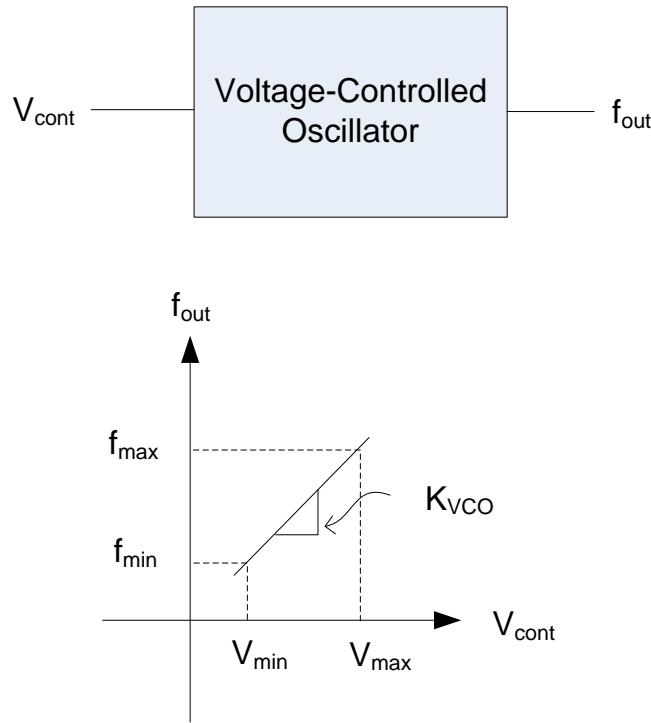

| Figure 7.7 : VCO as a linear function of control voltage                    | 126 |

| Figure 7.8 : A linear PLL model                                             | 127 |

| Figure 7.9 : Bode plot of a 3 <sup>rd</sup> order PLL                       | 129 |

| Figure 7.10 : Noise analysis model for PLL system                           | 130 |

---

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| Figure 7.11 : VCO phase noise illustration                                     | 132 |

| Figure 7.12 : A schematic for PFD/CP and loop filter noise simulation          | 133 |

| Figure 7.13 : Illustration of PFD/CP and loop filter noise                     | 133 |

| Figure 7.14 : VCO behavioural model                                            | 135 |

| Figure 7.15 : PFD/CP behavioural model                                         | 135 |

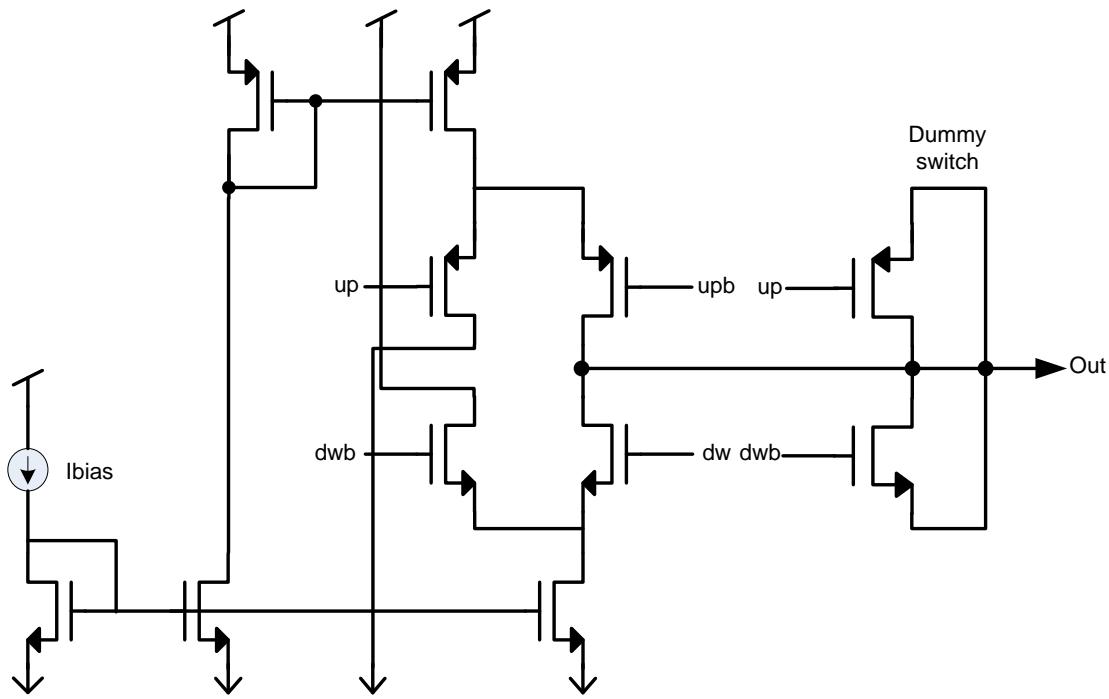

| Figure 7.16 : Charge pump preparation stage                                    | 137 |

| Figure 7.17 : Charge pump (CP) schematic diagram                               | 138 |

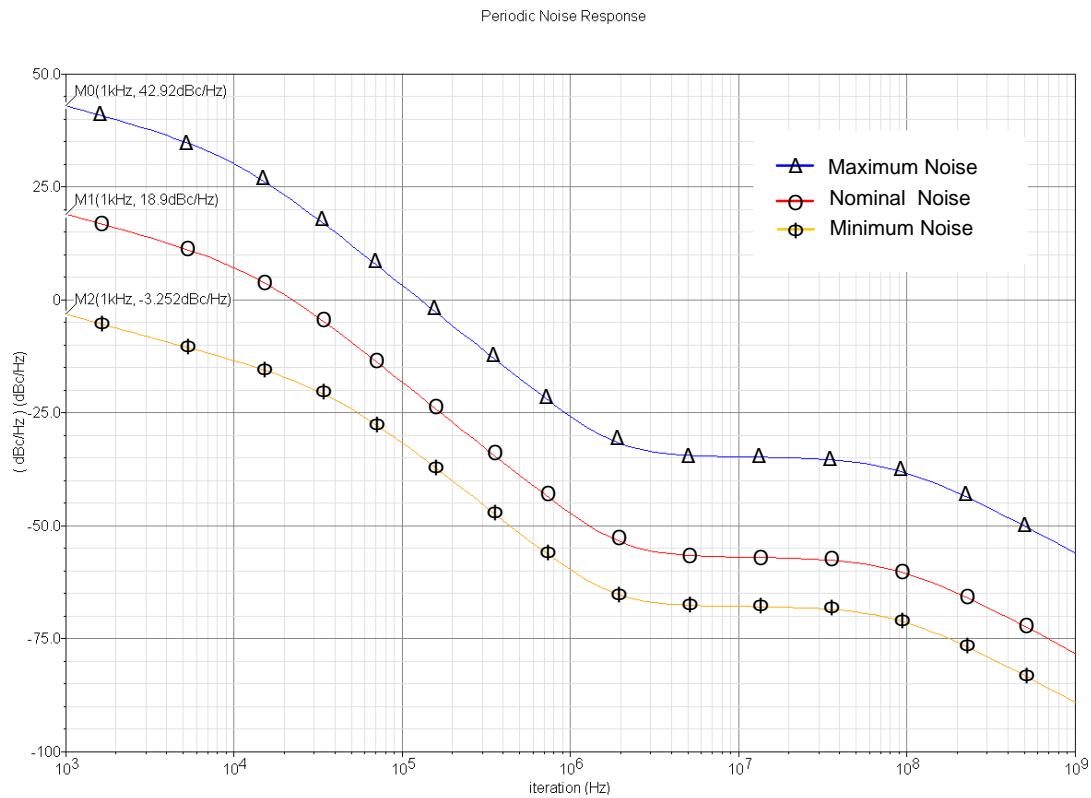

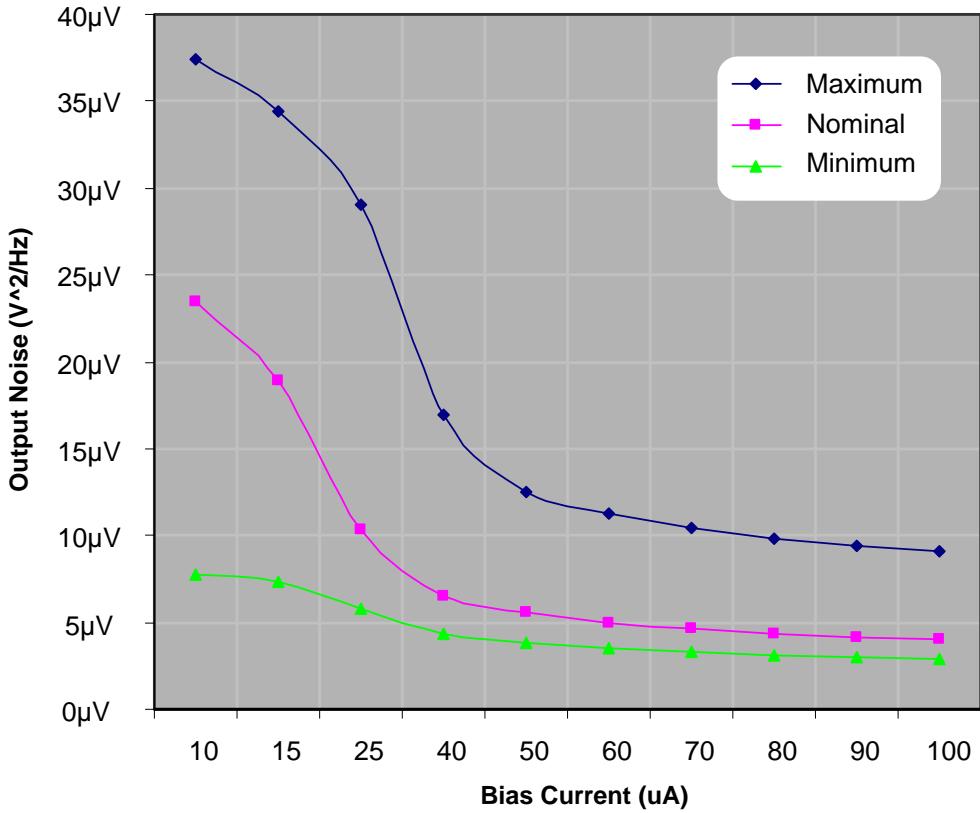

| Figure 7.18 : Nominal, minimum and maximum plot for charge pump noise          | 139 |

| Figure 7.19 : Charge pump Pareto-front with variations                         | 140 |

| Figure 7.20 : PFD/CP table model function for nominal performance              | 141 |

| Figure 7.21 : PFD/CP table model function for minimum performance              | 141 |

| Figure 7.22 : PFD/CP table model function for maximum performance              | 142 |

| Figure 7.23 : VCO preparation stage                                            | 142 |

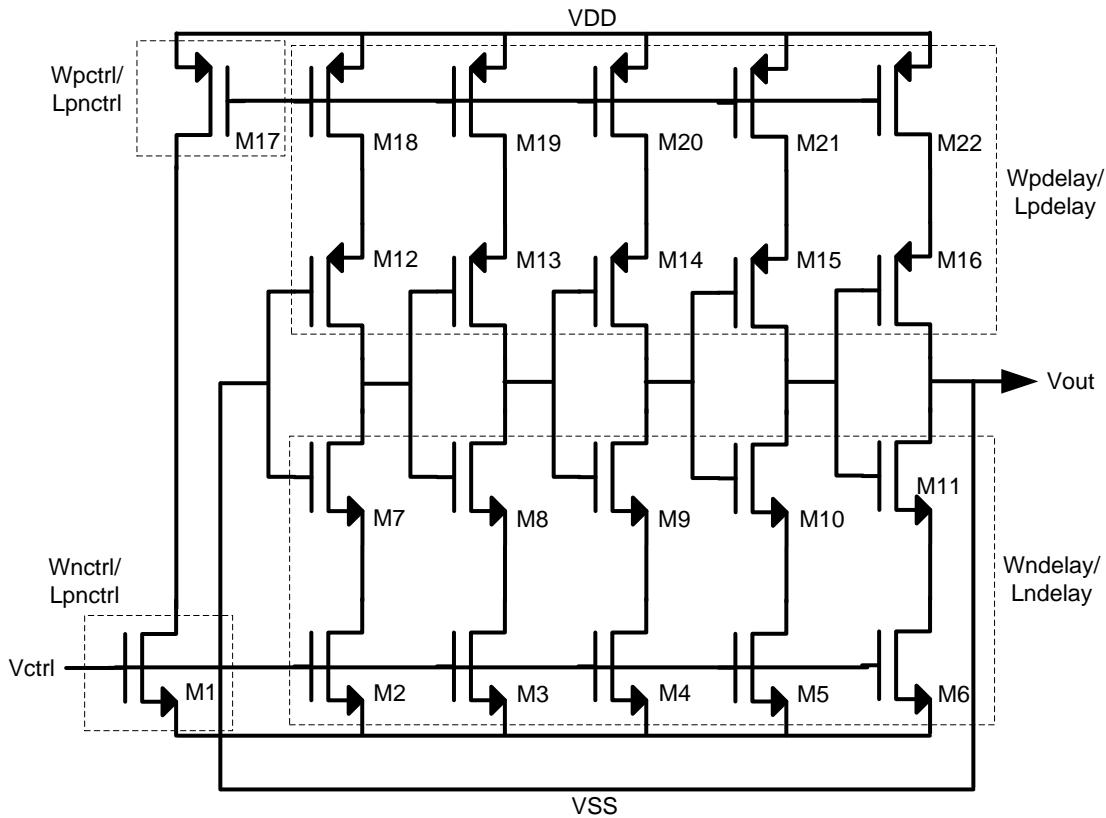

| Figure 7.24 : 5-stage ring VCO schematic                                       | 143 |

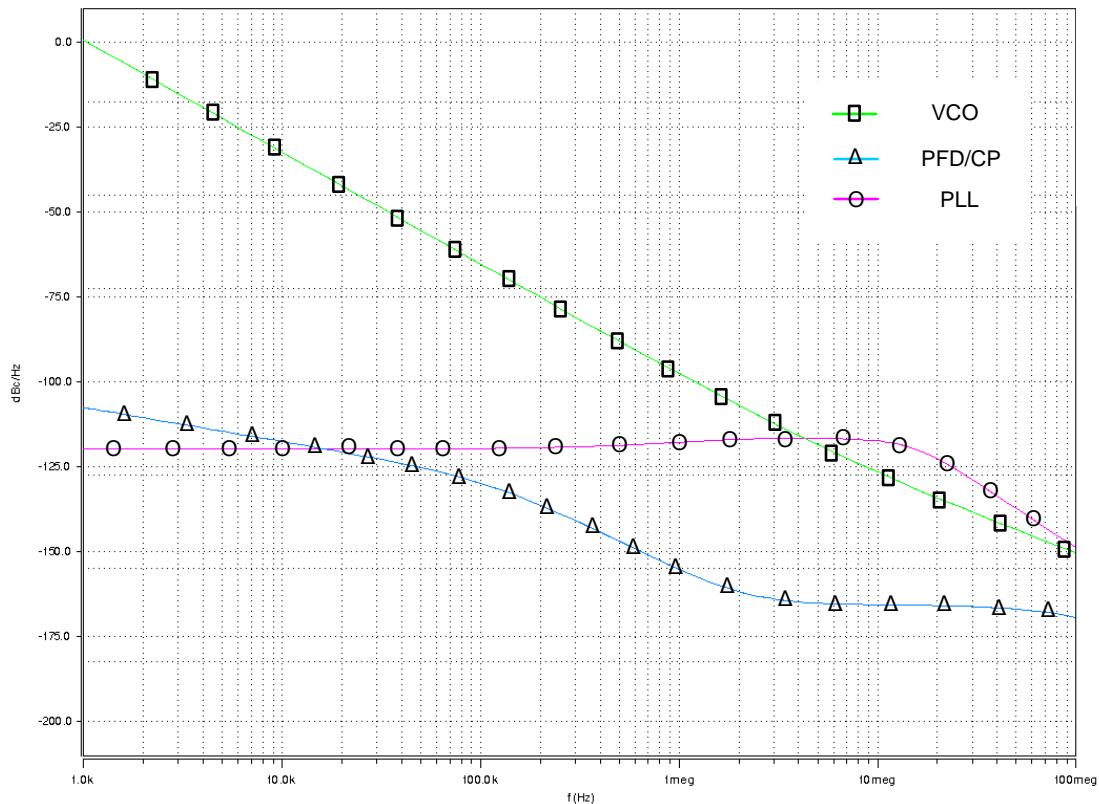

| Figure 7.25 : VCO GA string                                                    | 144 |

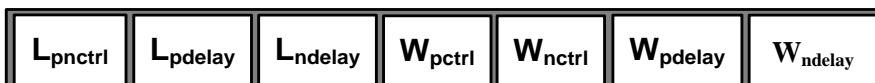

| Figure 7.26 : Nominal, minimum and maximum plot for VCO phase noise            | 146 |

| Figure 7.27 : VCO table model function for nominal performance                 | 147 |

| Figure 7.28 : VCO table model function for minimum performance                 | 148 |

| Figure 7.29 : VCO table model function for maximum performance                 | 149 |

| Figure 7.30 : PLL top level behavioural model                                  | 151 |

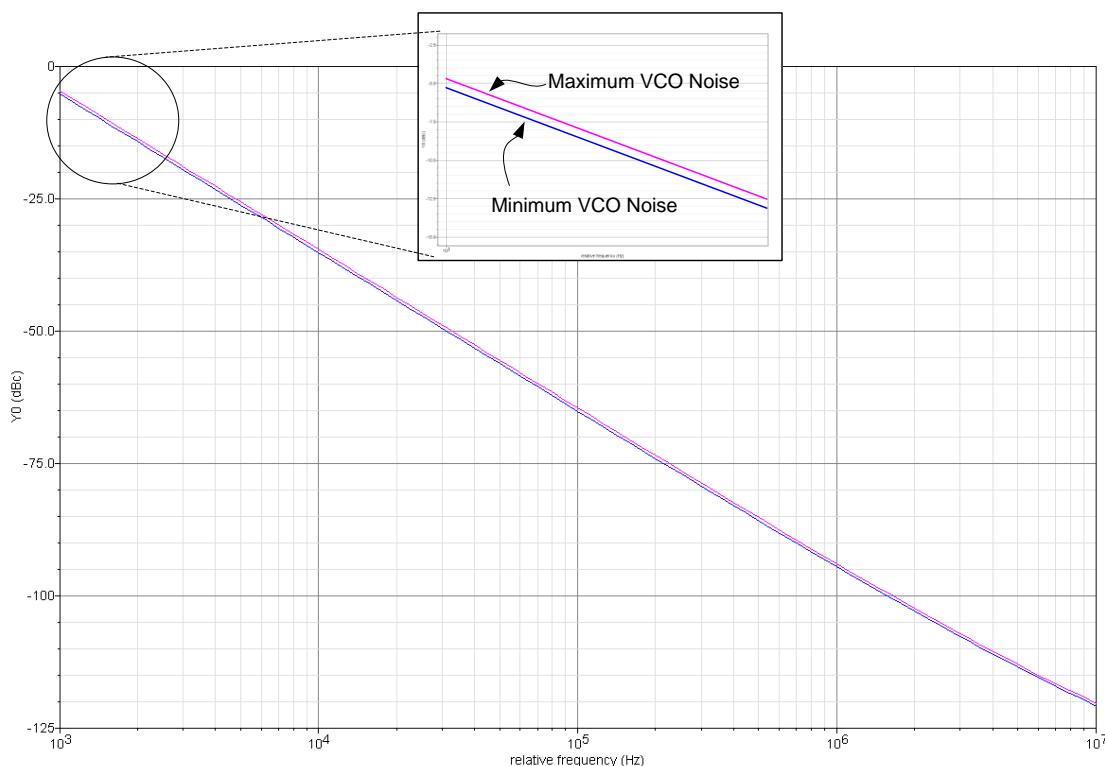

| Figure 7.31 : Noise simulation result of PLL with all the contributing sources | 152 |

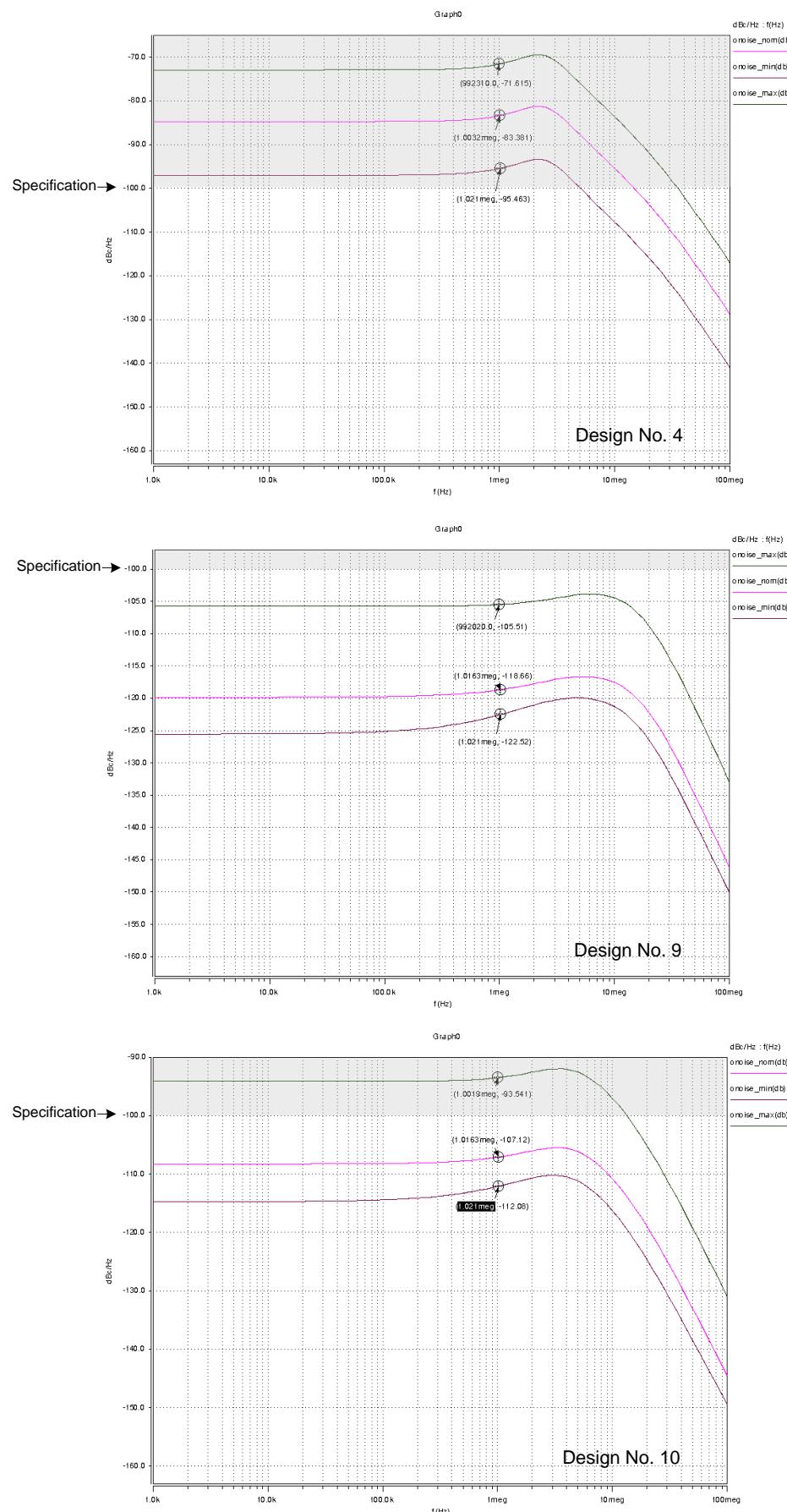

| Figure 7.32 : Phase noise plots for design point no. 4, 9 and 10               | 154 |

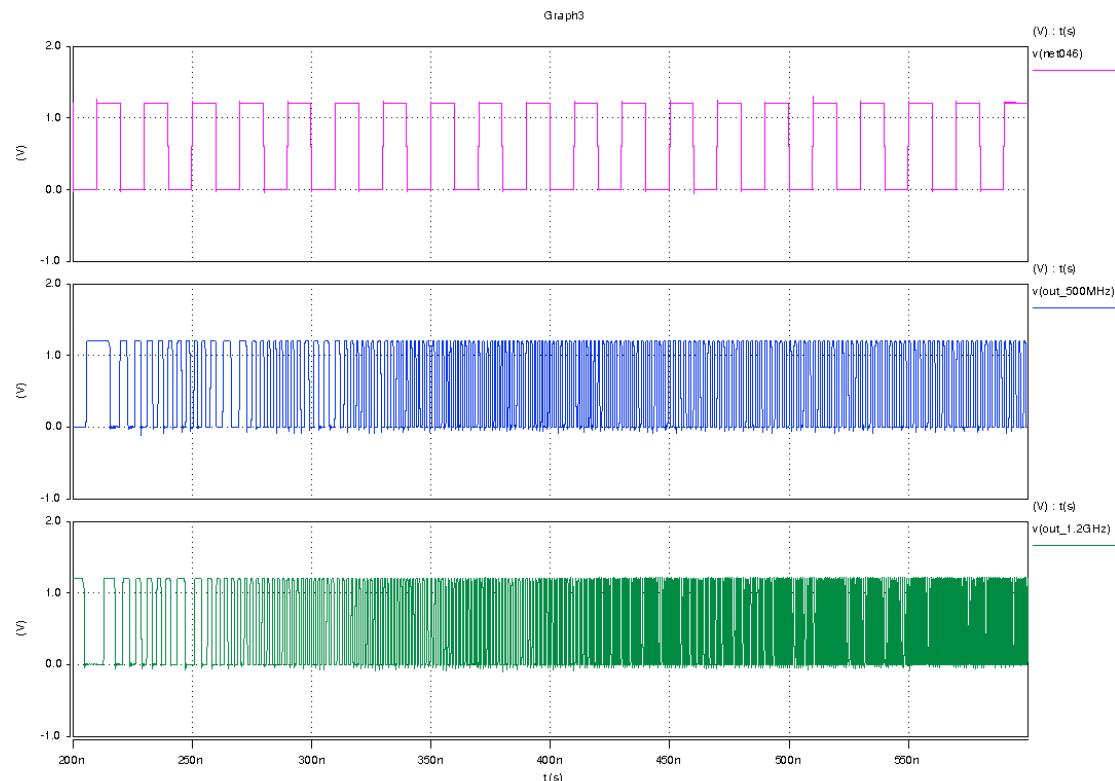

| Figure 7.33 : PLL output frequency range                                       | 157 |

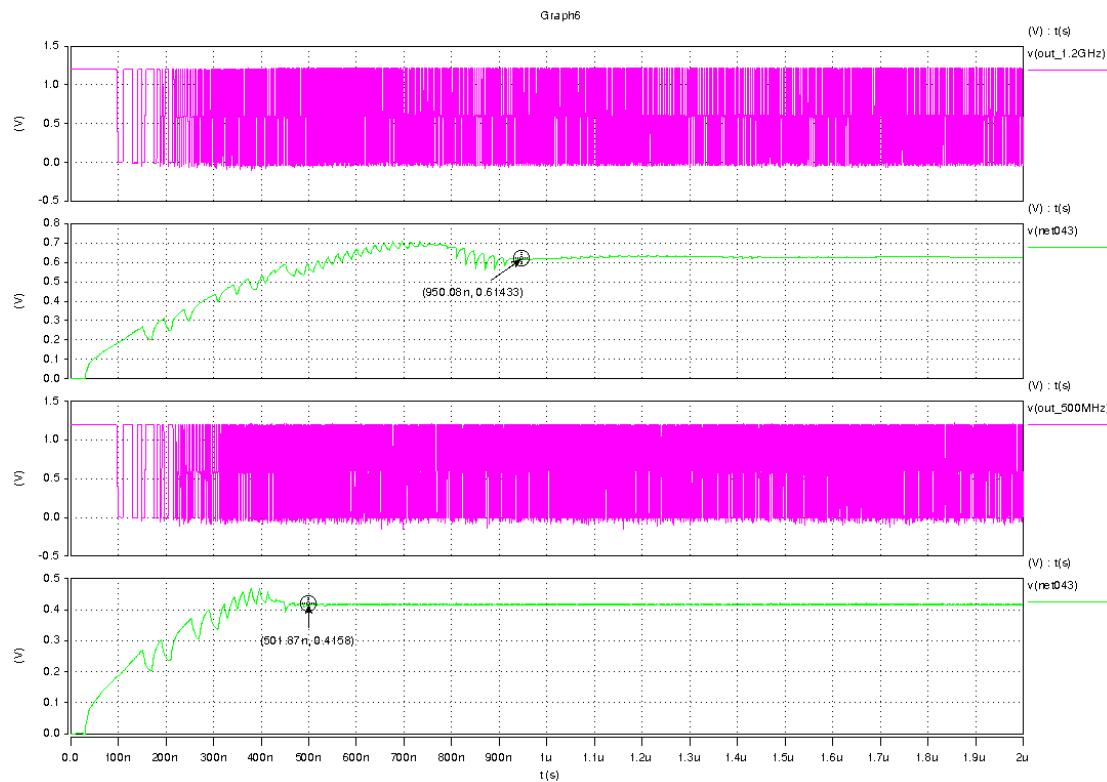

| Figure 7.34 : PLL locking time for minimum and maximum frequency               | 158 |

# List of Tables

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| Table 2.1 : GA control parameters                                      | 32  |

| Table 4.1 : Performance function and specifications                    | 62  |

| Table 4.2 : Design paramters                                           | 63  |

| Table 4.3 : Simulation result and comparison                           | 65  |

| Table 4.4 : Design specifications                                      | 68  |

| Table 4.5 : Design point yield percentage                              | 71  |

| Table 4.6 : Yield optimised design comparison                          | 73  |

| Table 5.1 : Interpolation degree for table_model function              | 82  |

| Table 5.2 : Performance and variation table                            | 85  |

| Table 5.3 : Interpolation example                                      | 89  |

| Table 5.4 : Performance comparison                                     | 89  |

| Table 5.5 : Summary of examples                                        | 92  |

| Table 5.6 : Miller-OTA performance and variation values                | 94  |

| Table 5.7 : 2 <sup>nd</sup> order low pass filter optimisation results | 94  |

| Table 6.1 : Performance and variation samples                          | 109 |

| Table 6.2 : Pareto-front samples for filter optimisation               | 117 |

| Table 7.1 : PLL system level specifications                            | 136 |

| Table 7.2 : VCO Design parameters                                      | 144 |

| Table 7.3 : Pareto-point samples for VCO                               | 145 |

| Table 7.4 : Design parameters for Pareto-point samples                 | 145 |

| Table 7.5 : Sample points from VCO lookup table                        | 147 |

| Table 7.6 : PLL system designable parameters                           | 152 |

| Table 7.7 : PLL system level optimum samples                           | 155 |

| Table 7.8 : PLL design parameters for individual blocks                | 156 |

| Table 7.9 : PLL performance results                                    | 158 |

| Table 7.10 : PLL system design summary                                 | 159 |

# Chapter 1

## Introduction

### 1.1 Integrated Circuits

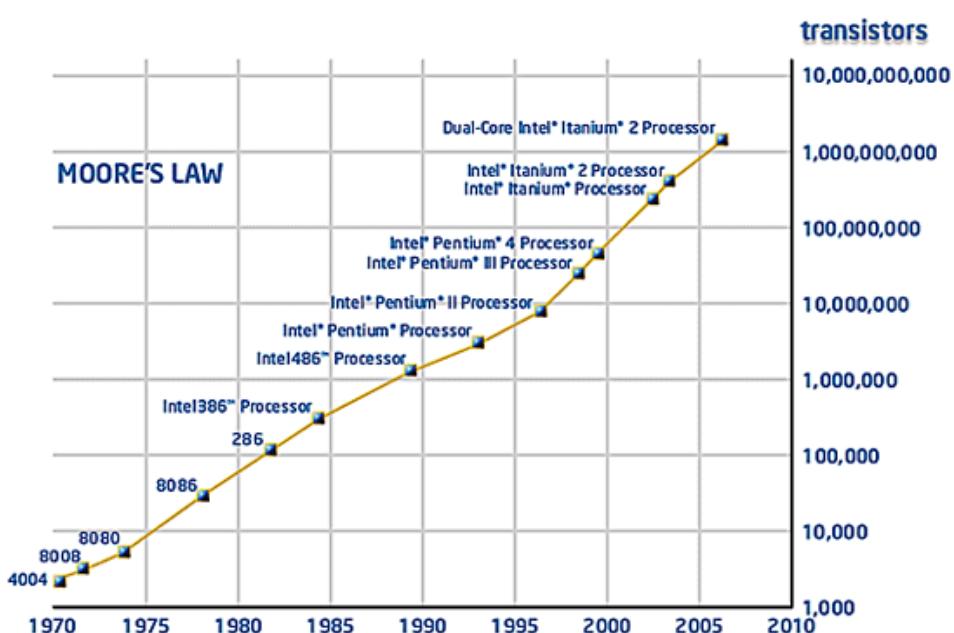

In 1965, Gordon Moore predicted that the number of transistors on a chip will double about every two years [1]. This statement also implies that the density of a single chip will increase due to the higher number of transistors integrated. Since then, the field of electronics had seen a huge development that has revolutionised many aspects of consumer electronics. Moving from a small number of transistors to multi million transistor circuits has provided the functionality that past generations could only dream of. Figure 1-1 shows the trend in transistor complexity for microprocessors that follow the Moore's law prediction.

One of the main reason for this prediction continue to be valid is the continuous development in transistor size reduction. This trend allows the integration of several functional blocks that previously occupied one or more boards onto a single chip, a technique that is termed as System-On-Chip (SoC). Although most of the functional blocks in an integrated system are digital, analogue circuits are still needed to interface to the real world which drives to the integration of analogue and digital circuits in a single system known generally as mixed-signal. This integration is very

attractive due to the significant reduction that can be made to the device size and hence to the overall cost of the system.

One of the most important applications of analogue circuits is to bridge the gap between the 'real' world and the digital domain. The need to go from analogue to digital processing have made the use of analogue-to-digital and digital-to-analogue converters indispensable. Several other important analogue components include filters, amplifiers, integrators and reference circuits for biasing. All these components are found in various applications such as communication systems, signal processors and radio frequency (RF) circuits. It is thus clear that analogue circuit integration is important and necessary in a large range of applications especially when considering SoCs where the link between the analogue and the digital domain will be required in practically every circuit.

With the rising level of integration, the complexity and the challenges of the integrated circuits increases. Such complexity has increased the requirement to use CAD tools for design automation that supports the design on several hierarchy of abstractions. The following section will discuss some of the challenges faced by the analogue circuits. This discussion will lead to the motivation behind the research that is to explore a methodology that can be used for automating and optimising the design flow of analogue circuits.

Figure 1-1: Transistor Complexity's Trend – Moore's Law

## 1.2 Challenges in analogue design

In a complex mixed-signal system, the analogue circuit may occupy a small area compared to the digital circuit but the design time of the analogue circuit is often much longer and can therefore cause a bottleneck in the overall system design [2]. The reasons for this are generally the circuit complexity and the lack of automation tools that can speed up the design process. Unlike digital circuits which can be rapidly synthesized by computer-aided-design tool, most of the analogue circuits are still essentially designed manually.

Another challenge faced by the analogue circuit in a mixed-signal environment is often the requirement to use the same transistor process technology as the digital circuits. For digital circuits, process technology downscaling is desirable due to the capability to reduce power consumption, area and delay. However, this is not necessarily helpful for analogue circuits. For example, a reduction in supply voltage due to the small transistor size, limits the voltage swing of the signals in the circuit and this can increase the signal to noise ratio and total harmonic distortion of the circuit. This has proved to be a significant challenge to analogue circuit designers in term of optimising the design for better performances and meeting the specifications.

Furthermore, as the transistor sizes are scaled down, the resulting variability increases and adversely effect yield. These variations in the process technology have a large influence to the quality and yield of a designed and manufactured circuit. With further shrinking of process technology, the variation is getting worse for each technology node. For technologies larger than 180nm feature sizes, variations are mostly in a range of below 10%. However, shrinking technologies down to 90nm, 65nm and below cause the variations to be more than 50% [3]. With a high correlation of circuit yield to profit, yield maximisation has became a major issue in deep sub-micron integrated circuit design and has been considered as an important factor in the design stages.

This thesis addresses one of the important topics in analogue IC design, which is to optimise the performance and yield of deep submicron integrated circuit design. The method proposed in the thesis starts with performance and variation model

development using a Pareto front approach and is followed by a top-down system design methodology using a hierarchical flow, that provides the designer with the ability to optimise the design for better performance and higher yield at the system level.

### **1.3 Project motivation and goal**

The difficulties in the design of analogue integrated circuit (IC) discussed earlier shows some of the challenges faced by the analogue designer. Increase of design complexity, impact of process variations and demand for design cycle time reduction increase the need to have a new improved methodology for analogue design automation tool. Recent advances in design automation have led to a gradual transition from “hand-calculation” based design to a simulation-based sizing methodology [4]. A Simulation-based approach tests many circuit candidates during the sizing process and evaluates each candidate via detailed circuit simulations. For a large circuit, the searching space for optimization can be very large and this increases the simulation time significantly. One of the solutions to this problem is modelling the performance space of the circuits behaviourally such that the optimisation can be done without the need of repeating extensive circuit simulation, at a transistor level.

In addition, the higher impact of process variation on the design yield has led to the integration of a yield parameter as one of the performance parameters in the design process. Although there is extensive research in this area, most do not model the performance variation together with their performance model and hence has no ability to predict the yield directly. Most of the current methods exist in yield optimised design are based on an approximation model and only focus at circuit level optimisation [5, 6, 7, 8]. The methodology presented in this thesis focuses on performance and variation modelling, and a top-down hierarchical design technique that is suitable for performance and yield optimisation for both at circuit level and system level design. The specific objectives of this project are discussed in the remainder of this chapter.

## **1.4 Project Scope**

### **1.4.1 Introduction**

The scope of this project is to develop the ideas for modelling circuit performance and their variation that can be used efficiently and accurately in the design of analogue integrated circuits.

Specifically, the project involves several activities including:-

- Parameter extraction that relates the circuit performances and their design parameters.

- Yield characterizing that relates the performances and their variations through a minimum and maximum estimation from a Monte Carlo simulation.

- Construction of behavioural model of a circuit example to model the performance and variation.

- Hierarchical-based optimisation design flow for system level design, and

- Methodology verification with practical examples.

When considering a performance and variation model of an analogue circuit, one of the most important factors is the accuracy of the model. Often a trade-off is being made that trades the accuracy for speed of simulation. In this thesis, the accuracy of the model is given a high weighting and the technique chosen for the model development reflects this intention. Several examples have been chosen to demonstrate the model application that includes a complete design flow from design specifications through to silicon implementation.

### **1.4.2 Structure of the Project**

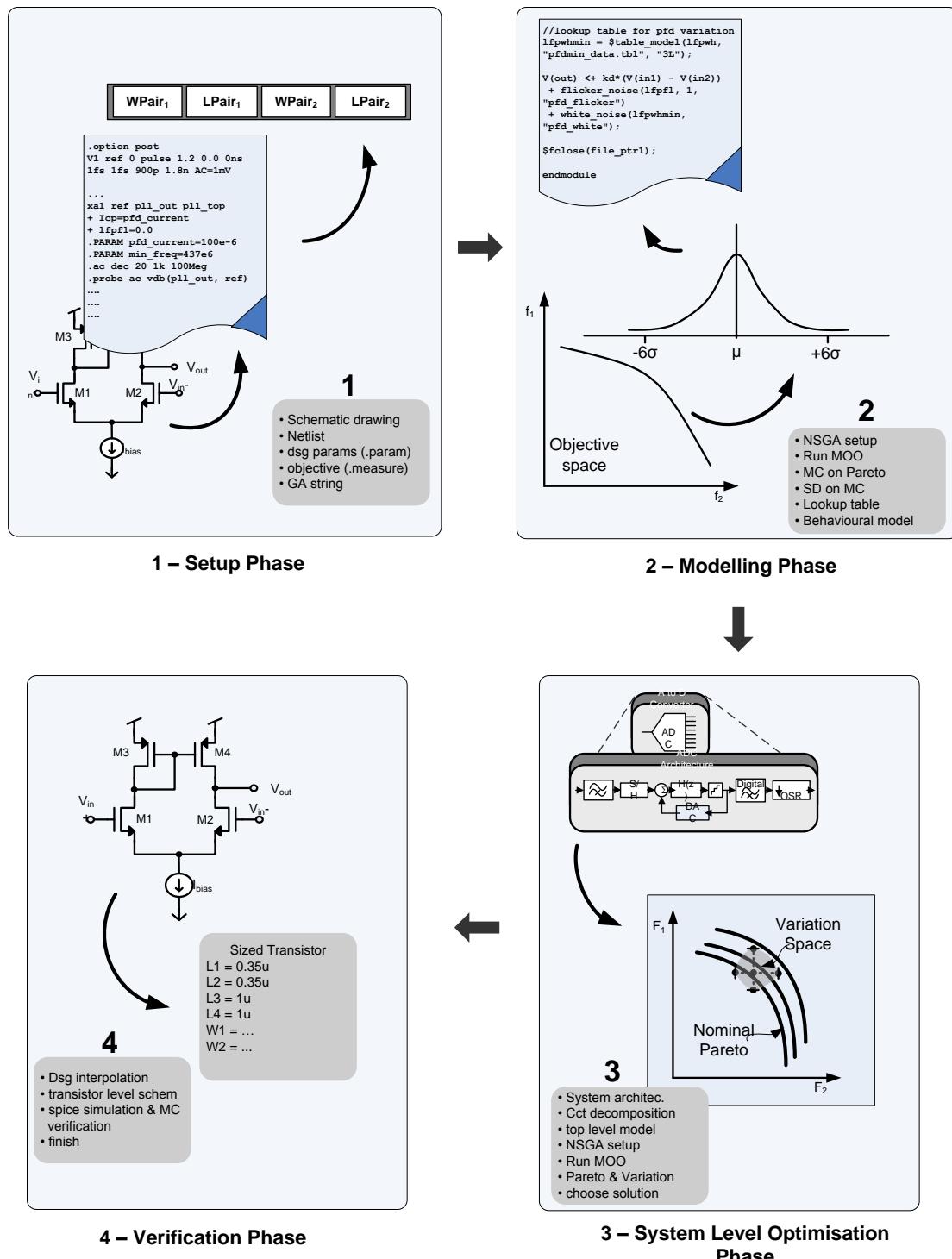

The project was split into three main phases and can be illustrated as shown in figure 1-2 :-

Phase 1: To establish the methods for modelling the performance and variations of a circuit design. This involves extensive review of analogue synthesis techniques and yield optimization methodologies. The transition of design automation and techniques from hand-calculation based to simulation-based was carefully studied in order to choose the suitable and accurate method for the synthesis technique. Comparison was made with other methods especially for yield optimisation technique including design centring methods and the use of commercial optimisation tools.

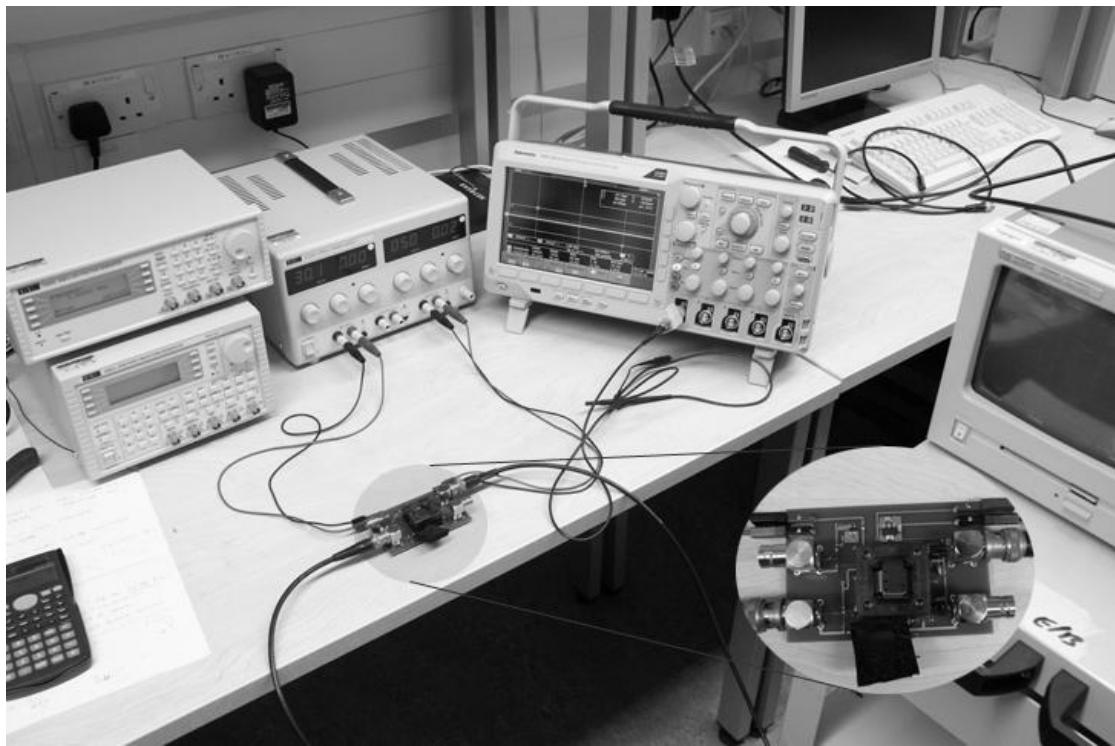

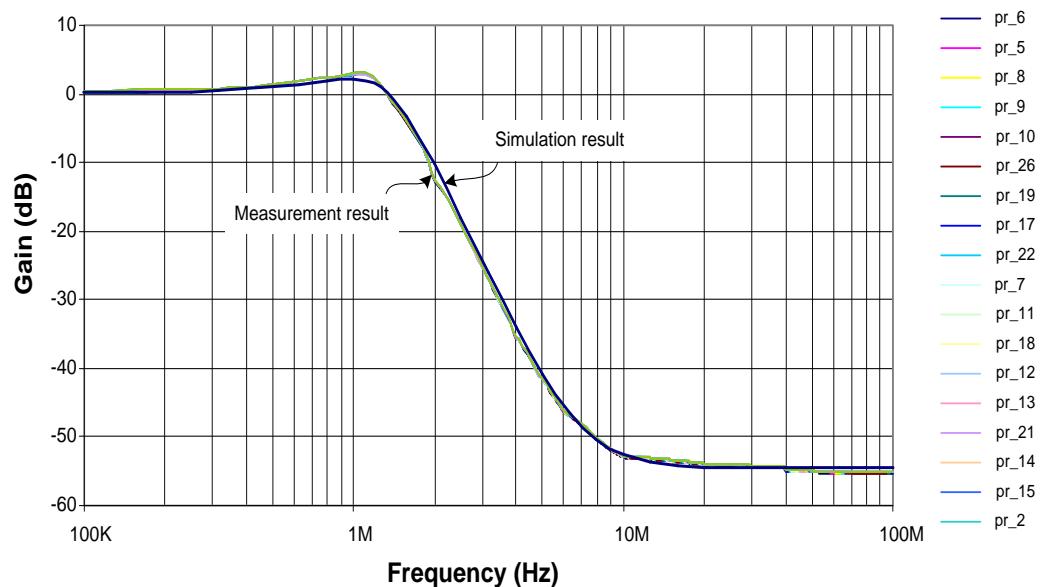

Phase 2: To build the performance and variation model of an example circuit design. This model was built from optimal performance points of the objective space and their minimum and maximum variation estimation based on a 6<sup>th</sup> standard deviation range. Both of the performance and variation model were developed behaviourally making it suitable for fast behavioural level simulation. A silicon prototype of a 2<sup>nd</sup> order filter was developed to demonstrate the practicality of the model and to validate the proposed methodology.

Phase 3: To develop a new hierarchical-based design technique that can be used for system level design. The performance and variation model developed in previous phase was used in the hierarchical design flow to design and optimise a system level block for performance and yield. A mixed-signal charge pump phase locked loop was used to demonstrate the full bottom up and top down design flow of the system for performance and yield optimisation.

Figure 1-2: Project structure

### **1.4.3 Project Hypotheses**

As a basis for the research in this project, several specific hypotheses were made as follows:-

- Existing yield optimised design methodologies have several inadequacies including the ability to predict and optimise the yield at system level design.

- In deep sub-micron technology, where the design complexity and variability has become a significant challenge, the accuracy and the ability to translate the simulated results into a real design is very important.

- Existing approaches for system level design using a hierarchical-based optimisation method do not consider the variations of the sub-block circuits leaving the yield optimisation for the system until the end of the design flow.

- A new hierarchical-based optimisation is needed that can incorporate the performance and variation model of analogue circuits into a top down system level design flow.

- The application of behavioural modelling languages such as Verilog-A allow the ability to model a system that include mixed-signal blocks and offers a huge potential saving in terms of simulation time.

### **1.5 Thesis Structure**

This section explains briefly the main points of each chapter in the thesis. The first part of the thesis, chapters 1-3 contain the background theory and literature review which leads to chapter 4 & 5 describing the implementation of the performance and variation model for analogue circuits. The last part of the thesis investigates a demonstrator application using a proposed hierarchical-based optimisation for mixed-signal system level design. This is covered in chapter 6 and 7. Chapter 8 concludes the project and recommends areas for the future work.

**1.5.1 Chapter 1: Introduction**

The introduction of the thesis describes the motivations and goals to the project. The challenges in analogue circuit design are briefly explained which define the research landscape for the project.

**1.5.2 Chapter 2: Review of Analogue circuit Design and Statistical Design Techniques**

This chapter reviews the techniques and developments in analogue circuit design automation which can be divided into three main categories : Knowledge-based, analytical-based and simulation-based design. The optimisation techniques are reviewed and compared to provide initial understanding that is suitable in this project. Statistical design techniques for analogue circuit are reviewed and their limitations are defined in this chapter.

**1.5.3 Chapter 3: Review of Simulation & Modelling**

The aim of this chapter is to review and explain the modelling principles and techniques used for electronic circuits. Basic concepts of behavioural modelling are introduced here and the advantage given by the behavioural model in a system level design is described.

**1.5.4 Chapter 4: Yield Optimised Design**

This chapter demonstrates how to implement the performance and yield optimization model for analogue circuit design. The method of characterizing the performance and yield space is proposed. The concept of performance trade-offs and Pareto-front that will be used for the remainder of the thesis are introduced in this chapter. The algorithm for the optimization is discussed, with examples, and is compared with existing methodologies to demonstrate the effectiveness of the approach.

### 1.5.5 Chapter 5: Performance and Variation Modelling

This chapter describes how the multi-objective optimisation discussed in the previous chapter is used to model the performance and variation of a circuit design. The concept of performance and variation modelling from the objective space and Pareto-front are introduced in this chapter. A new approach for combining the performance and variation model using a lookup-table implementation in Verilog-A is proposed and the implementation with a behavioural table model function is explained. An example is used to illustrate the development of the performance and variation model and a practical example with a silicon prototype is shown for the practicality aspect of the methodology.

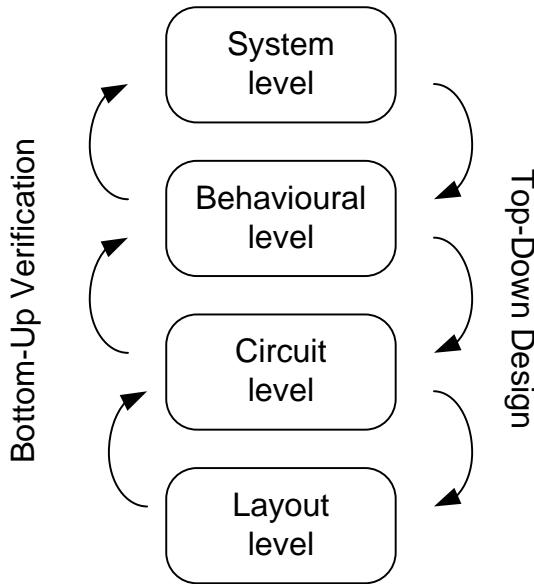

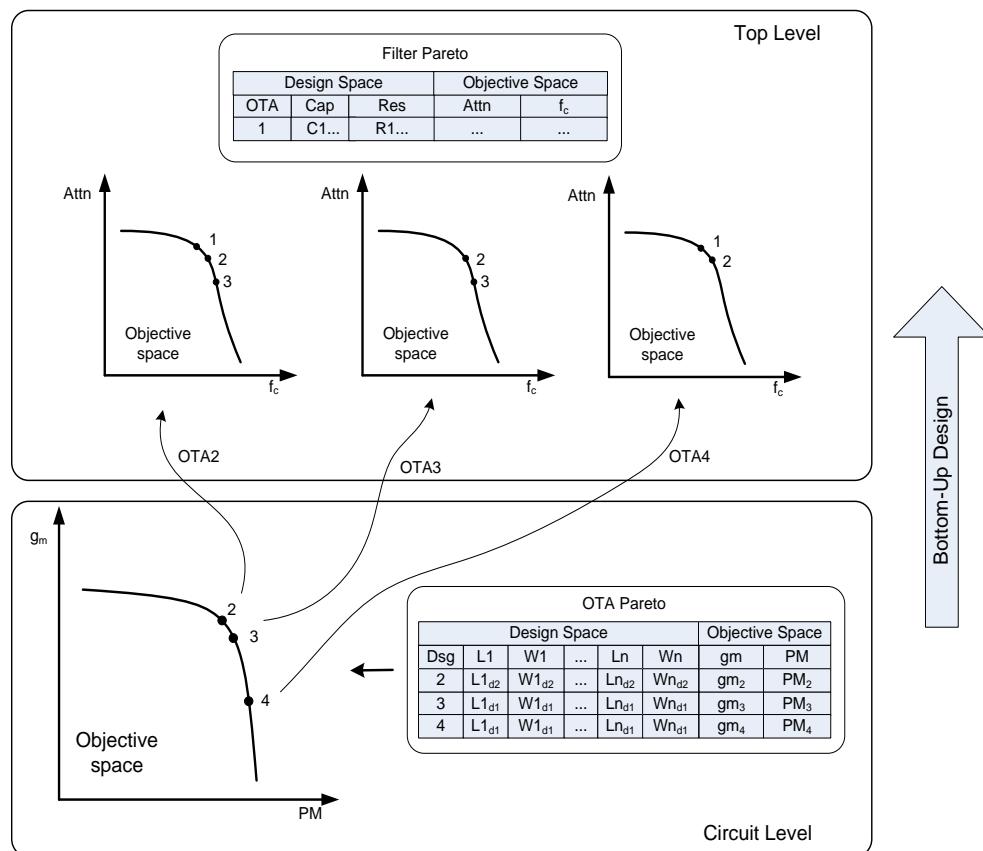

### 1.5.6 Chapter 6: Hierarchical-based Design Optimisation

This chapter describes how the performance and variation model can be used in a system level design using a hierarchical-based optimisation technique. A new modification is done to the hierarchical-based method to include both the multi-objective bottomup modelling and top-down constrained design in the algorithm. A 7th order elliptic filter for video applications is used to demonstrate the methodology.

### 1.5.7 Chapter 7: Mixed Signal System Level Application

In this chapter, A charge pump PLL is used as a mixed-signal system example with higher number of design parameters, objective functions and mixed domain simulations to demonstrate the effectiveness of the proposed methodology to optimise the performance and yield for significant circuit sizes.

### 1.5.8 Chapter 8: Conclusion and Future Work.

In this chapter, the results obtained are discussed. The accuracy of the model especially in a practical example is discussed. Conclusions are drawn from these discussions and a statement about the hypotheses is made. Finally the areas that could provide the basis of future work are highlighted.

# Chapter 2

## Review of Analogue Circuit Design and Optimisation

### 2.1 Introduction

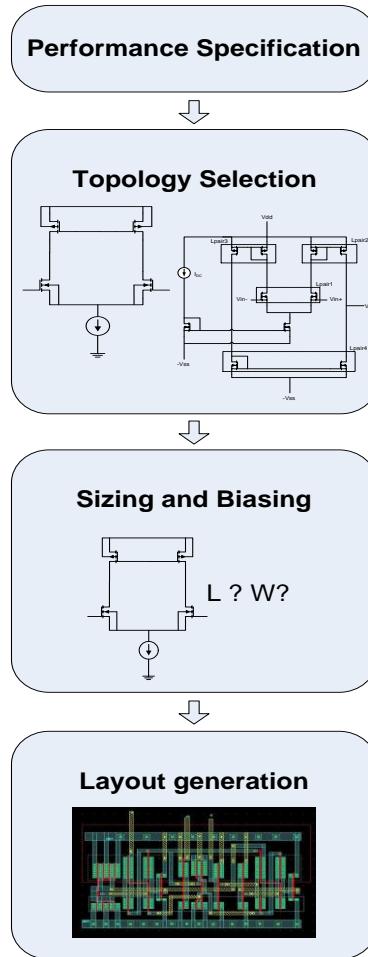

Analogue circuit design can be divided into two main tasks: The selection of an appropriate circuit topology and circuit sizing. The design starts with a circuit specification that defines the performance functions and their upper and lower limits. Based on the specification, a topology will be selected. There is the possibility that several topologies existed, that implements the required functionality. Usually the topology selection is based on design heuristics. The knowledge or experience of the designer is often the main approach used to find the suitable topology that can meet the design requirements. The next step is to determine the size of the devices for the selected topology. This step is called circuit sizing and the parameters to be sized are called design parameters. The sizing process of design parameters will determine the performance of a circuit. This step is a complicated task due to the nonlinear relationship between the design parameters and circuit performance.

Usually the sizes of the design parameters are approximated using simplified hand-calculations. The formulas are based on simple approximations of the transistor characteristics that may differ from the real devices. The approximated circuit sizes will be used as the initial point for the performance evaluation using a circuit simulator such as HSPICE [9] or Spectre [10]. For the purpose of the simulation, a test bench is created where a set of suitable input signals are applied to the circuit in order to extract the performance functions. This will give the initial performance of the circuit and most certainly will not meet the specification. Thus, the device sizes must be adjusted through the optimisation process. Some simulators offer a simple form of optimisation to adjust the device parameters in order to fine-tune the performance functions. If no feasible solution is found during the optimisation and the specifications are not met, a different circuit topology must be selected and the sizing and optimisation processes will need to be repeated. This will eventually increase the design cycle time of the analogue circuits and becomes the bottleneck in the design process. According to [11], the design cycle time reduction can be managed only by the use of computer aided design. Therefore, over the years, the research community has been aggressively working towards the development of computer aided design tools for analogue circuits. A good survey of analogue synthesis techniques is available in [12] and will be reviewed later in this chapter.

Figure 2.1 Typical design flows for analogue IC design

Figure 2.1 shows a typical design flow in analogue IC design. One of the most important aspects in the design flow are the time spent on designing the low-level cells. The time required to design an amplifier for example might be in the order of weeks [13] when all design steps are considered. Decreasing the time spent on the design process through automation techniques for instance will have a large impact on the time-to-market for the whole chip. This automation can be applied at different steps in the design flow, for example, topology selection or circuit sizing. This thesis will focus on circuit sizing automation techniques and the performance and variation models were targeted at the circuit sizing stages. The remainder of this chapter will review the existing approach for analogue circuit sizing.

## 2.2 Automatic Circuit Sizing

The approach in automatic circuit sizing can be classified into two main categories, namely knowledge-based design and optimization-based design. Optimization-based design can be further divided into two approaches, equation-based optimization and simulation-based optimization.

### 2.2.1 Knowledge-Based Design

This is one of the earlier approaches in automated circuit sizing. The basic idea is to have a predefined design plan or design rules on how to size circuit components to meet the performance specifications. The design plan generally consists of a set of design equations for a particular circuit topology. In knowledge-based design, these equations are formulated so that with a given circuit performances, the size of the circuit can be determined.

Once the design plan has been created, the execution time of this approach is short. However, the approach suffers from several disadvantages. First, a design plan must be created for each circuit to be designed. This is a difficult task and requires the knowledge of a skilled designer. It was reported in [14] that the average time to create such a plan was four times longer than manually designed circuit.

In addition to that, the design plan is technology dependent. This means, when the process technology migrates to a new technology, a new design plan must be updated which again requires analogue experts intervention.

Another limitation to the approach is the accuracy which is generally limited. In order to derive the design equations for the design plan, they are bound to be simple. This will result in large deviations in the performance metrics when modern process technologies are used.

This section reviews some of the tools that were developed using this approach.

## **IDAC**

IDAC [15] is one of the first and well-known approaches for knowledge-based design techniques. It was developed in 1980 and support quite large design variety of circuits such as amplifiers, comparators and A/D converters. This tool relies upon a library of circuit design plans. Each design plan contains a set of design equations for particular topologies created by an experienced designer.

From a set of design specifications, a design plan for a particular circuit topology is executed. From this execution, a set of design parameters will be known and a circuit simulator is used to verify the performance of the circuit. If it fails to meet the specifications, the parameters are adjusted and the design plan is executed again.

IDAC contains a predefined library of circuit designs, so the design time is short for circuits already in the library. However, if the designer wants to make changes to the topology for example to improve the performance, a completely new set of design plans must be developed.

While the execution time might be fast for a circuit already in the library, IDAC presents several disadvantages. As mentioned above, the design plan is created by expert designers thus it is highly dependent on the experts whenever a new design or topology needs to be developed. Second, it is not possible to solve equations for high accuracy device models, thus the method is limited to simple models. This yields relatively poor estimation of the circuit performance.

## **OASYS**

OASYS [16] was developed in 1989 at Carnegie Mellon University. This method describes the design problem in a hierarchical style implementation where the circuit is partitioned into several sub-blocks. From the design specification, the tool selects a suitable topology. This topology is then divided into several sub-blocks that correspond to the performance specification. In this way, the problem is decomposed into separate design tasks. There is a possibility that there may be several sub-blocks

with the same functionality. The tool generates a range of possible options, or “styles” and selects the one with the best performance. This is called style selection.

A translation process in the methodology will map the performance specification to the sub-block. In a design, there might be several hierarchical levels and style selection steps and translations. At the bottom level (transistor level), simple device models are used to determine the device sizes based on a knowledge-based approach. Sometimes, there might be a discrepancy in the estimation of the performance of low level blocks. This is overcome by utilizing backtracking strategy to refine the design. This is an iterative process and may be seen as simple form of optimization.

The method forms some sort of reusability since the sub-blocks can be used repeatedly in a large range of circuits. The disadvantages of this method are first, the use of simple device models to determine the device size which yields relatively poor estimation of the performance. Second, the task of creating design plan consume a lot of design time as reported in [16] where the creation of the first design plan required 18 months to be completed.

## BLADES

BLADES (Bell Laboratories Analogue Design Expert system) [17] relies on artificial intelligence to partition and size the circuits. As with OASYS, the strategy is to divide the circuit into several sub-blocks. For example, an operational amplifier might consist of a differential input stage, gain stage and output stage. The rules on how to divide the circuit into sub-blocks are written in “if-then” statements. For the operational amplifier, the tool consists of about 250 different rules.

The bottom level is the transistor level. The transistors are sized in a similar manner to the sub-block composition where a set of rules is used to size the transistor. Here, the decision about the size is decided based on the rules given in the combination of look-up tables where the simulated results for each sub-block are stored.

As with other knowledge-based approaches, the disadvantage of this tool is the requirement to create the design rules for each adjustment and/or addition to the topology of the circuit.

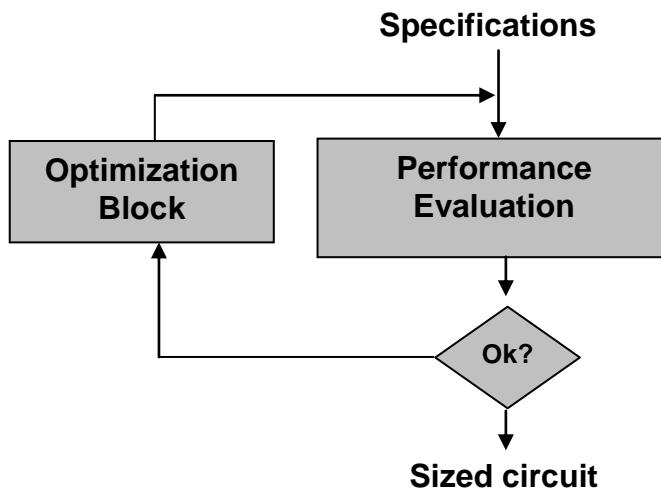

### 2.2.2 Optimization-Based Circuit Sizing

Knowledge-based techniques rely on design plans created for specific topologies. In other words, it is a topology dependent approach. In order to increase the generality of circuit sizing and make it independent of circuit topology, optimization-based design was developed. In this approach, the decision to size the circuit is based on an optimization algorithm rather than design plan. Two important stages of this approach are optimization and evaluation as depicted in figure 2.2.

Figure 2.2 : optimization-based design

There are two types of optimization-based design. The first type is based on a circuit simulator such as SPICE which is used to evaluate the performance of the circuit. A circuit simulator is called at each iteration to determine the performance for a set of design parameters. This approach is called simulation-based optimization.

Another type that is used is equation-based optimization. In this approach, a set of equations that relate the circuit performance and the design parameters is derived. These equations are used to evaluate and determine the performance for a set of

design parameters. This process is continued iteratively until the performance is optimized.

### 2.2.2.1 Equation-based Optimization

Equation-based optimization uses equations to evaluate the circuit performance as oppose to the use of circuit simulator for the simulation-based optimisation. The equations can be derived manually or using symbolic analyzers [18, 19, 20].

The advantage of equation-based optimization is in the execution time since the performance evaluation is performed by evaluating symbolic equations directly [21]. Thus, the equation-based approach offers significantly shorter execution times compared to simulation-based optimization.

The accuracy of the performance predictions is extremely reliant on the design equations. Manually derived equations are usually simplified compared to equations derived by symbolic analyzers. Most of the equations are based on simple device models and are therefore not accurate enough to be used in modern process technologies. Sometimes, if high accuracy device models are used, the equations created are based on approximations in order to reduce the size of expressions for the performance metrics. Small expression sizes will increase the computational efficiency in the expense of accuracy. This is one of the disadvantages in this approach, in that there is clearly a trade-off between accuracy and speed.

Furthermore, using symbolic analyzers to generate the equations automatically will increase the setup time for this approach. With designer instruction, a symbolic analyzer will generate the equation expression for each performance metric. Thus, introducing new types of performance metric into the symbolic analyzer can be time-consuming.

Another disadvantage of this approach is that the generality of the method is limited by the ability to derive the equations for the performance. A symbolic analyzer can be used to derive small-signal performance metrics but for other performance (for example one that uses time-domain analysis such as slew-rate), there is no method to

automatically generate the equations. These type of equations need to be derived manually. For a different device model, new equations must be derived to include the additional parameters of the device model. On top of that, the equations are created by an experienced designer and stored in a library. Thus, the method is often only applicable to a predefined topology in the library.

This section reviews some of the tools that have been developed using this approach.

## **OPASYN**

OPASYN [22] was developed in 1990 at the University of California in Berkeley, USA, and uses simple analytical equations to synthesise and optimize a circuit. It features a design database that contains information on each step in the design flow, including heuristic selection of circuit topology, circuit sizing and optimization and circuit layout.

From a set of performance specifications, a circuit topology is selected from the database. The selection is done using a decision tree where all available topologies are classified according to some key criteria and analytical models is used to size and optimize the circuit. The models consist of manually derived symbolic design equations, netlist descriptions of a particular topology, independent design parameters and upper and lower bounds for the design parameters. The optimization method used is a steepest descent algorithm and to avoid local-minima problem, the optimization is carried out on several starting points.

The disadvantage of the tool is the accuracy of the models. It was reported in [23] that the models have an error of over 200% when compared to SPICE simulations. Although fitting parameters are added to improve the model, the error is still in the order of 20%.

## **Maulik**

Maulik [24] was developed at Carnegie Mellon University in Pittsburg, USA. This tool selects the topology and size the circuit simultaneously. Additional optimization

parameters are used to determine the topology such as the type of the input stage (for example cascade or not). The performance functions are computed from circuit equations and these are used to size the circuit.

Maulik uses a relaxed DC formulation to solve for the correct DC operating point. In this approach, Maulik uses Kirchhoff's law for the DC operating point equation and this is made as a part of the cost function. With a relaxed DC formulation, Maulik avoids the need to re-evaluate the DC operating point at every iteration.

One of the disadvantages of this tool is the requirement to derive the equations manually which leads to the simplified expression thus limiting the accuracy.

## GPCAD

GPCAD [25] is a device sizing tool dedicated to the design of operational amplifiers. It uses geometrical programming (GP) to formulate the sizing task. This is done by writing the design equations (i.e. the cost function and inequality constraints) as posynomial equations. This results in a convex optimization from which a global optimum point can be found in a relatively short time.

Even though the geometric programming formulation simplifies the optimization task and reduces the optimization time, this method suffers from an accuracy problem due to the limitation of using high accuracy models that cannot be formulated as posynomials easily [23]. Furthermore, this tool does not include automatic generation of the equations thus limiting the usage to only predefined circuit structures.

### 2.2.2.2 Simulation-Based Optimization

Simulation-based design uses a standard circuit simulator in the optimization loop to evaluate the circuit performance. In this way, the method can handle a large variety of analogue circuits.

One of the advantages of this approach is that the predicted performance will have the same accuracy as the models used in the circuit simulator, i.e., the same accuracy as

obtained by manual design. Even with the new process technologies, the level of accuracy can be maintained if the process model is used in the simulation.

Another advantage of simulation-based design is short setup time. This is true as long as the circuit performance can be measured using the output of the circuit simulator. The only requirement is to create the test bench in the simulator environment. The test bench describes the simulation environment to measure each performance function for the optimisation.

Furthermore, the generality of simulation-based design is high since the performance can be defined just by extending the test bench. Thus, new circuits can be included easily as long as the circuit simulator can be used to extract the performance metric.

The only disadvantage of this approach is the execution time. In the simulation-based approach, a circuit simulator is called at each of the optimization run. Some of the performance functions such as slew rate which require time domain simulation may consume significant amounts of simulation time. However this factor can be mitigated with the continual advance of computer hardware.

This section reviews some of the tools that have been developed using this approach.

## **DELIGHT.SPICE**

DELIGHT.SPICE [26], was developed in 1980's at the University of California, Berkeley, USA. The tools combined an iterative optimisation based design called DELIGHT with a standard circuit analysis program, SPICE.

The tool also derives the sensitivity of the design parameter variations to the performance functions which enable design centring and yield optimization. The optimization algorithm in DELIGHT.SPICE uses a subset of worst performance and constraint functions to direct the searching process.

The algorithm consists of 3 phases: phase I, the optimisation algorithm tries to decrease the hard constraint violation. Hard constraint is the constraint that must be

satisfied and do not take part in design trade-off. In phase II, the worst normalised values of the objective functions and soft constraint are improved while maintaining the hard constraint satisfaction. In phase III, the worst normalised value of objective functions is improved while both the hard constraint and soft constraint are satisfied.

However, the tool still requires several hours to perform the optimization and in addition to that, a good starting point is needed for the optimization process in order to avoid divergence problem in SPICE [27].

## **FRIDGE**

FRIDGE [28] is a simulation-based optimization approach that performs global searching techniques together with a gradient search for the optimization algorithm. The tool uses modified simulated annealing for the optimization. Instead of slowly cooling scheme of traditional simulated annealing method, this tool uses adaptive cooling where a series of fast cooling and reheating method are used.

The optimization is divided into two stages. The first is to quantize the design parameters according to a grid and the performance of the design parameters that corresponding to one node of the grid is stored. This is used to avoid repeated simulation of the same node. Once the global optimization is completed, a gradient based optimization is used to search in the vicinity of the best grid point.

## **ASTRX/OBLX**

ASTRX/OBLX [4] have been developed in 1996 at the Carnegie Mellon University. The tool relies on asymptotic waveform evaluation (AWE) [29], encapsulated device evaluators, simulated annealing and relaxed DC formulation to size and optimize the circuit.

AWE [29] is used to reduce the long simulation times normally associated with circuit simulators in simulation-based design and low accuracy that is normally achieved in simple models used in equation-based design. AWE uses a reduced complexity model to predict the small signal circuit performance. This approach is efficient to analyse

linear circuits is considerably faster than using a SPICE-like simulator. The rest of the performances (other than small signal) are computed from circuit equations.

Simulated annealing is used to solve the optimization problem. The constrained optimization formulation given in equation 2.1 is solved in an unconstrained fashion. Here,  $x$  is the independent variable – size of semiconductor devices or passive components value that need to be find,  $f(x)$  is a set of objective functions that need to be optimized,  $g(x)$  is a set of constraint functions that specify the specifications and  $w_i$  is the scalar weight to balance the competing objectives.

$$\text{Minimize } \sum w_i f_i(x), \quad g(x) \leq 0 \quad (2.1)$$

The constrained optimization formulation is converted to an unconstrained optimization with the use of additional scalar weights for the constraint parameters. As a results, the goals become a minimization of scalar cost function  $C(x)$ , defined in equation 2.2.

$$C(x) = \sum w_i f_i(x) + \sum w_j g_j(x) \quad (2.2)$$

To solve the DC operating point for each perturbation of design variables, a relaxed DC formulation was used in this tool. Kirchhoff's Law was used to solve the DC operating point and this is included in the constraint function of the optimization formulation similar to Maulik [24] method.

One drawback of this tool is the inability of AWE approach to model nonlinear circuit behaviour. Furthermore, the approximation of the circuit transfer function with a low-order model limits the accuracy of the method.

## ANACONDA and MAELSTROM

Both of these simulation-based techniques were developed at the Carnegie Mellon University in 1999 for MAELSTROM [30] and 2000 for ANACONDA [31]. The difference between these two is in the optimization algorithm. MAELSTROM uses a

combined genetic and annealing algorithm whereas ANACONDA uses a stochastic pattern search.

The tools rely on three key concepts: simulator integration, global search techniques and a parallelism approach to reduce the overall computation time where the searching tasks and circuit evaluations were distributed across a network of cluster workstations.

The optimization formulation was adopted from the OBLX strategy where a constrained optimization formulation that is solved in an unconstrained fashion was used. As with OBLX, this technique introduce scalar weight values to the optimization formulation and the goal becomes minimization of a scalar cost function.

The optimization engine in MAELSTROM is based on a combination of simulated annealing and genetic algorithm. The simulated annealing engine is called Anneal++ that offers a range of annealing cooling schedules, move selection techniques and dynamic update of the cost function weights. The genetic algorithm is used for the purpose of parallel search. The combination of genetic algorithm and annealing in this method is known as the Parallel Recombinative Simulated Annealing (PRSA) as proposed by Goldberg [32].

ANACONDA uses a combination of population search of circuits with pattern search in finding the circuit solution. The pattern search method proposed by Torczon [33] is a direct-search techniques that sample cost function in a deterministic locus around a given solution point and use this sample to construct a deterministic direction and distance to a probable better solution. The combination of population search and pattern search helps the optimization engine to explore a diverse set of samples of the objective (cost) surface.

## 2.4 Optimization Techniques

One of the key components in an optimization-based approach is obviously the optimization block. The function of this block is to optimize the design by searching for the best solution points which are determined by the design parameters. In this context, the purpose of the optimizer is to find the design parameters that will produce the best performance value. The process between the optimizer and the performance evaluator is an iterative one where the performance for a particular design parameters will be evaluated and the design parameters will be changed from run to run in order to improve the performance. The process will be continued until the optimization objective or stopping criteria has been met.

Generally, with the rapid development in optimisation algorithms, the algorithms can be divided into two main categories: population based and single initial solution based. The difference between the two is the type of initial solution. Population based approach starts with a set of solutions called a population while single initial solution starts with one initial solution. Recently, an optimisation approach that uses a heuristic process consisting of many optimisation runs starting from different initial points has been proposed [34]. In this way, the optimisation process becomes a group of individual optimisation runs. The rest of this section will review some of the optimisation techniques that have been used for the circuit optimisation.

### 2.4.1 Direct search Optimisation

This section will discuss several optimisation methods known generally as direct search algorithms. Box *et al* [35] identified three main types of direct search algorithms: tabulation, sequential and linear methods.

#### 2.4.1.1 Tabulation Method

In this method, a user chooses number of points either using a random tabulation or a grid tabulation strategy. The objective function is evaluated at each point and the point with the lowest function value is returned as the optimum solution.

### 2.4.1.2 Sequential Method

In this method, a geometrical figure of the same dimension as the decision space (design variables) are created and the performance function is evaluated at each of the geometrical nodes (vertices) in order to find the minimum point. Decisions are taken on the basis of comparing function values corresponding to the vertices of the geometrical figure. Evolutionary operation [36] was the first sequential method developed. This is followed by an improved algorithms known as simplex method [37]. The geometrical figure used in the simplex method has  $n + 1$  nodes where,  $n$  represents the number of design variables. Thus, the simplex is a triangle for  $n=2$ , tetrahedron for  $n = 3$  and hypertriangle for  $n > 3$ . Once the figure has been determined, the performance is evaluated at each of the nodes and a convergence test is applied. The convergence is said to be met if the standard deviation of the function values at all vertices are less than a user-defined level (to be determine by trial and error).

### 2.4.1.3 Linear Method

This method involves a set of searching sequences along lines in the decision space and can be divided into two main categories : univariate search (and its derivatives) and Powell's method [38] (and its derivatives). In univariate search, the optimisation starts with user specified initial values of the  $n$  design variables. Each of the design variables will be evaluated one at a time to determine the performance function and the design variable will be adjusted until the performance function is minimised. The optimisation is stopped when a user-defined maximum iteration count is exceeded or the performance function at any point falls below a user-defined acceptance level. Even though the univariate search is simple to implement, it has two major limitations. Firstly, the search is carried out sequentially and secondly, the search procedure is completely deterministic which would generally result in a premature convergence to some relatively poor local minima [39]. In addition to that, the convergence rate is relatively slow as the minimum point is approached. The slow convergence rate is enhanced by introducing a pattern move algorithm [40] that involves two procedures: the exploratory move and pattern move. In the exploratory move, a fixed user-defined increment is applied to the initial points. The performance