# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

### UNIVERSITY OF SOUTHAMPTON

### FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Design Methods to Mitigate the Effects of Variation in Analogue and Mixed-Signal Circuits

by

Robert M. Rudolf

Thesis for the degree of Doctor of Philosophy

November 2014

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF PHYSICAL AND APPLIED SCIENCES Electronics and Computer Science

#### Doctor of Philosophy

# DESIGN METHODS TO MITIGATE THE EFFECTS OF VARIATION IN ANALOGUE AND MIXED-SIGNAL CIRCUITS

by Robert M. Rudolf

The continued scaling of CMOS process features enables ever-faster and denser circuits, which comes at the cost of increased device parameter variation. The performance of analogue and mixed-signal circuits in particular degrades in such a high variation environment, which poses an extraordinary challenge in the design and fabrication of such circuits.

This thesis develops a set of tools and methodologies for a post-fabrication calibration system called the Configurable Analogue Transistor (CAT). The principle of the CAT technique is to replace certain transistors in a circuit with calibration devices, which allow adjustment of circuit performance after fabrication to compensate the effects of device parameter variation. Building on initial research on the CAT, this thesis develops a methodology to identify the most suitable calibration devices in their circuit and determine their optimal sizes. Furthermore, the applicability of CAT is extended beyond parameter variation to also include direct compensation of temperature.

A complementary technique to post-fabrication calibration is robust design, where a circuit is designed to be inherently robust against variation in device parameters. In this thesis, a novel closed-loop pick-off circuit for force-balanced MEMS accelerometers is presented. It is comparable in performance to other state-of-the-art techniques, but provides vastly improved robustness against parameter variation and a more intuitive design process.

# Contents

| D | eclar    | ation o  | of Authorship                                                                                       | $\mathbf{v}$ |

|---|----------|----------|-----------------------------------------------------------------------------------------------------|--------------|

| A | ckno     | wledge   | ements                                                                                              | vi           |

| 1 | ion      | 1        |                                                                                                     |              |

|   | 1.1      | CMOS     | S Device Variability                                                                                | 2            |

|   | 1.2      | Analog   | gue Circuits on Nano-Scale CMOS                                                                     | 5            |

|   | 1.3      | Motiva   | ation, Organisation and Contributions                                                               | 7            |

| 2 | Sta      | te of tl | he Art                                                                                              | 10           |

|   | 2.1      | Introd   | ${\it luction} \ \ldots \ $ | 10           |

|   | 2.2      | Calibr   | ration Techniques                                                                                   | 12           |

|   |          | 2.2.1    | Introduction                                                                                        | 12           |

|   |          | 2.2.2    | Trimming                                                                                            | 13           |

|   |          | 2.2.3    | Substrate Biasing                                                                                   | 15           |

|   |          | 2.2.4    | Floating Gates                                                                                      | 17           |

|   |          | 2.2.5    | Calibration Devices                                                                                 | 19           |

|   |          | 2.2.6    | Digitally Adjustable Analogue Circuits                                                              | 20           |

|   | 2.3      |          | tion-Tolerant Design                                                                                | 22           |

|   |          | 2.3.1    | Introduction                                                                                        | 22           |

|   |          | 2.3.2    | Robust Design Techniques                                                                            | 23           |

|   |          | 2.3.3    | Model-Based Robust Design                                                                           | 28           |

|   |          |          | 2.3.3.1 Computer-Aided Design Flow                                                                  | 30           |

|   |          |          | 2.3.3.2 Optimising for Robustness                                                                   | 31           |

|   |          |          | 2.3.3.3 Optimisation Techniques                                                                     | 33           |

|   | 2.4      | _        | n and Calibration Techniques for DACs                                                               | 35           |

|   |          | 2.4.1    | Introduction                                                                                        | 35           |

|   |          | 2.4.2    | General Design Techniques                                                                           | 37           |

|   |          | 2.4.3    | Calibration DACs                                                                                    | 38           |

|   | ~ ~      | 2.4.4    | Switching Sequence Post Adjustment                                                                  | 40           |

|   | 2.5      |          | Configurable Analogue Transistor                                                                    | 42           |

|   |          | 2.5.1    | Introduction                                                                                        | 42           |

|   |          | 2.5.2    | Operating Principle                                                                                 | 42           |

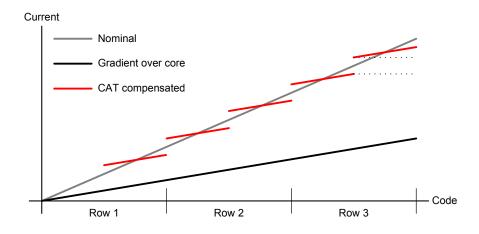

|   |          | 2.5.3    | Improvement of Current Distribution                                                                 | 44           |

|   |          | 2.5.4    | Device Size Optimisation                                                                            | 47           |

|   |          | 2.5.5    | Applicability                                                                                       | 49           |

|   | $^{2.6}$ | Summ     | nary                                                                                                | 50           |

*CONTENTS* iii

| 3 | Des | ign-Time Methodologies for Configurable Analogue Transistors       | <b>5</b> 2 |

|---|-----|--------------------------------------------------------------------|------------|

|   | 3.1 | Introduction                                                       | 52         |

|   | 3.2 | Automated Critical Device Identification                           | 53         |

|   |     | 3.2.1 Introduction                                                 | 53         |

|   |     | 3.2.2 Method                                                       | 53         |

|   |     | 3.2.3 Sensitivity Analysis and CDI                                 | 54         |

|   | 3.3 | Device Size Optimisation                                           | 59         |

|   |     | 3.3.1 Introduction                                                 | 59         |

|   |     | 3.3.2 Method                                                       | 60         |

|   | 3.4 | On-Line Temperature Calibration of Analogue Circuits               | 62         |

|   |     | 3.4.1 Introduction                                                 | 62         |

|   |     | 3.4.2 Method                                                       | 63         |

|   |     | 3.4.3 Design of CAT for Online Temperature Calibration             | 64         |

|   | 3.5 | Case Study 1: Application of CDI and Device Size Optimisation      | 67         |

|   | 3.6 | Case Study 2: Variation-Aware Temperature Compensation Using CAT . | 72         |

|   | 3.7 | Implementation                                                     | 77         |

|   |     | 3.7.1 Simulator Interface                                          | 78         |

|   |     | 3.7.2 Sensitivity Analysis and Critical Device Identification      | 79         |

|   |     | 3.7.3 CAT Device Size Optimisation                                 | 79         |

|   |     | 3.7.4 Final Simulations                                            | 80         |

|   |     | 3.7.5 Parameter Variation                                          | 80         |

|   | 3.8 | Conclusions                                                        | 81         |

| 4 | Apı | olication of Configurable Analogue Transistors to Segmented DACs   | 86         |

| - | 4.1 | Introduction                                                       |            |

|   | 4.2 | Segmented Current-Steering DACs                                    |            |

|   |     | 4.2.1 Segmented DACs                                               |            |

|   |     | 4.2.2 Current-Steering DACs                                        |            |

|   | 4.3 | Application of CAT to a Segmented Current-Steering DAC             |            |

|   | 4.4 | Circuit Design                                                     |            |

|   |     | 4.4.1 Current Cell                                                 |            |

|   |     | 4.4.1.1 Constant Current Sink                                      |            |

|   |     | 4.4.1.2 Switching Transistors                                      |            |

|   |     |                                                                    |            |

|   |     | 4.4.1.4 Cell Select Logic                                          | 94         |

|   |     | 4.4.2 CAT-Enabled Current Cell                                     | 96         |

|   |     | 4.4.3 Thermometer Decoders                                         | 97         |

|   |     | 4.4.4 Biasing Circuit                                              |            |

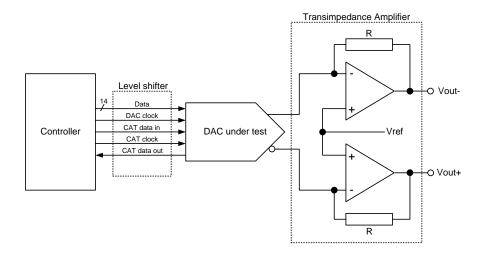

|   | 4.5 | Measurement Methodology                                            |            |

|   |     | 4.5.1 Test Board                                                   |            |

|   |     | 4.5.2 Test Equipment and Procedure                                 |            |

|   |     | 4.5.3 Computer software                                            |            |

|   |     | 4.5.3.1 Application of CAT to a Transfer Function                  |            |

|   |     | 4.5.3.2 Optimisation of CAT Configuration                          |            |

|   | 4.6 | Measurement Results                                                |            |

|   | 1.0 | 4.6.1 Functional Testing                                           |            |

|   |     | 4.6.2 Initial Findings                                             |            |

|   |     |                                                                    |            |

CONTENTS

| 4.6.4 Improving INL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |       | 4.6.3    | CAT Tes       | sting               |                         |        |      | <br> |  |  |  |  | . 111 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|----------|---------------|---------------------|-------------------------|--------|------|------|--|--|--|--|-------|

| 4.6.5 Summary of Results       122         4.7 Discussion       122         4.8 Conclusions       124         5 Variation-Tolerant Design       125         5.1 Introduction       125         5.2 MEMS Accelerometers       128         5.2.1 Electromechanical ΣΔ Modulators       128         5.2.1.1 Oversampling Data Converters       128         5.2.1.2 ΣΔ Converters       131         5.2.1.3 Electromechanical ΣΔ Modulators       133         5.2.2 Frequency- or Phase-based Systems       136         5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       137         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       134         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       145         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       155         6.3 Future Work       155         A Publications       156         C Chip Layout       196                                    |              |       | 4.6.4    |               |                     |                         |        |      |      |  |  |  |  |       |

| 4.7 Discussion   122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |       | 4.6.5    | -             | _                   |                         |        |      |      |  |  |  |  |       |

| 4.8 Conclusions       126         5 Variation-Tolerant Design       127         5.1 Introduction       122         5.2 MEMS Accelerometers       128         5.2.1 Electromechanical ΣΔ Modulators       128         5.2.1.1 Oversampling Data Converters       128         5.2.1.2 ΣΔ Converters       131         5.2.1.3 Electromechanical ΣΔ Modulators       133         5.3 The EM-PLL Technique       133         5.3.1 Electronic Phase-Locked Loops       133         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       136         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       155         A Publications       156         6 Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1                                       |              | 4.7   | Discus   |               | ~                   |                         |        |      |      |  |  |  |  |       |

| 5.1 Introduction       125         5.2 MEMS Accelerometers       128         5.2.1 Electromechanical ΣΔ Modulators       129         5.2.1.2 ΣΔ Converters       129         5.2.1.3 Electromechanical ΣΔ Modulators       131         5.2.1.3 Electromechanical ΣΔ Modulators       132         5.2.2 Frequency- or Phase-based Systems       133         5.3.1 Electronic Phase-Locked Loops       131         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       155         6.3 Future Work       155         A Publications       156         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       190         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings |              | 4.8   |          |               |                     |                         |        |      |      |  |  |  |  |       |

| 5.1 Introduction       125         5.2 MEMS Accelerometers       128         5.2.1 Electromechanical ΣΔ Modulators       129         5.2.1.2 ΣΔ Converters       129         5.2.1.3 Electromechanical ΣΔ Modulators       131         5.2.1.3 Electromechanical ΣΔ Modulators       132         5.2.2 Frequency- or Phase-based Systems       133         5.3.1 Electronic Phase-Locked Loops       131         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       155         6.3 Future Work       155         A Publications       156         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       190         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings | 5            | Vari  | iation-' | Tolerant      | Design              |                         |        |      |      |  |  |  |  | 125   |

| 5.2 MEMS Accelerometers       128         5.2.1 Electromechanical ΣΔ Modulators       125         5.2.1.1 Oversampling Data Converters       129         5.2.1.2 ΣΔ Converters       131         5.2.1.3 Electromechanical ΣΔ Modulators       133         5.2.2 Frequency- or Phase-based Systems       135         5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       133         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       133         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       14         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       155         A Publications       156         6.2 Pinal Conclusions       156         6.3 Future Work       155         A Publication of INL       190         D.1 Calculation of INL       190         D.2 Application of CAT to a Transfer Function          |              |       |          |               | _                   |                         |        |      | <br> |  |  |  |  |       |

| 5.2.1 Electromechanical ΣΔ Modulators       128         5.2.1.1 Oversampling Data Converters       125         5.2.1.2 ΣΔ Converters       131         5.2.1.3 Electromechanical ΣΔ Modulators       132         5.2.2 Frequency- or Phase-based Systems       136         5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       137         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       138         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       146         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       156         6.1 Contributions       156         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol |              | 5.2   |          |               |                     |                         |        |      |      |  |  |  |  |       |

| 5.2.1.1 Oversampling Data Converters       129         5.2.1.2 ΣΔ Converters       131         5.2.1.3 Electromechanical ΣΔ Modulators       132         5.2.2 Frequency- or Phase-based Systems       135         5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       133         5.3.2 Electronic Oscillators       136         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       155         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       199         D.2 Application of CAT to a Transfer Function       190         D.3 Determine Optimal CAT Settings       193         E DAC Interface Protocol       200         F EM-PLL Models and Parame  |              |       |          |               |                     |                         |        |      |      |  |  |  |  |       |

| 5.2.1.2       ΣΔ Converters       131         5.2.1.3       Electromechanical ΣΔ Modulators       132         5.2.2       Frequency- or Phase-based Systems       133         5.3       The EM-PLL Technique       137         5.3.1       Electronic Oscillators       138         5.3.2       Electronic Oscillators       138         5.3.3       EM-PLL Description and Analysis       138         5.4       Simulation Analysis       144         5.4.1       Introduction       144         5.4.2       Output Power Spectrum       144         5.4.3       Input Amplitude Sweep       147         5.4.4       Parameter Variation       145         5.5       Discussion       155         6.1       Conclusions       155         6.2       Final Conclusions       156         6.3       Future Work       157         A       Publications       156         B       Chip Schematics       181         C       Chip Layout       192         D       DAC Calibration Code       196         D.1       Calculation of INL       196         D.2       Application of CAT to a Transfer Function                                                                           |              |       |          |               |                     |                         |        |      |      |  |  |  |  |       |

| 5.2.1.3 Electromechanical ΣΔ Modulators       132         5.2.2 Frequency- or Phase-based Systems       135         5.3 The EM-PLL Technique       13         5.3.1 Electronic Oscillators       136         5.3.2 Electronic Oscillators       136         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       156         6.1 Contributions       156         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application Code       196         D.3 Determine Optimal CAT Settings       193         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201                                             |              |       |          | 5.2.1.2       |                     |                         |        |      |      |  |  |  |  |       |

| 5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       137         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       153         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       155         A Publications       156         B Chip Schematics       181         C Chip Layout       196         D.1 Calculation of INL       196         D.2 Application Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       206         F EM-PLL Models and Parameters       201         F.2 Simulation models       202                                                                                        |              |       |          | 5.2.1.3       |                     |                         |        |      |      |  |  |  |  |       |

| 5.3 The EM-PLL Technique       137         5.3.1 Electronic Phase-Locked Loops       137         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       153         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       155         A Publications       156         B Chip Schematics       181         C Chip Layout       196         D.1 Calculation of INL       196         D.2 Application Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       206         F EM-PLL Models and Parameters       201         F.2 Simulation models       202                                                                                        |              |       | 5.2.2    | Frequenc      |                     |                         |        |      |      |  |  |  |  |       |

| 5.3.1 Electronic Phase-Locked Loops       137         5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       139         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       144         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       206         F EM-PLL Models and Parameters       201         F.2 Simulation models       203                                                                                                                                                                          |              | 5.3   | The El   | =             | -                   |                         |        |      |      |  |  |  |  |       |

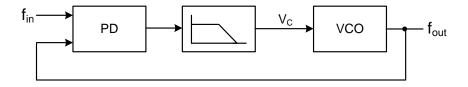

| 5.3.2 Electronic Oscillators       138         5.3.3 EM-PLL Description and Analysis       139         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       156         6.1 Contributions       156         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       199         D.2 Application of CAT to a Transfer Function       199         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       202                                                                                                                                                                                         |              |       |          |               | <del>-</del>        |                         |        |      |      |  |  |  |  |       |

| 5.3.3 EM-PLL Description and Analysis       138         5.4 Simulation Analysis       144         5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                        |              |       | 5.3.2    |               |                     |                         | -      |      |      |  |  |  |  |       |

| 5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       156         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                          |              |       | 5.3.3    |               |                     |                         |        |      |      |  |  |  |  |       |

| 5.4.1 Introduction       144         5.4.2 Output Power Spectrum       145         5.4.3 Input Amplitude Sweep       147         5.4.4 Parameter Variation       148         5.5 Discussion       155         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                          |              | 5.4   | Simula   | tion Anal     | lysis               |                         |        |      | <br> |  |  |  |  | . 144 |

| 5.4.3       Input Amplitude Sweep       147         5.4.4       Parameter Variation       148         5.5       Discussion       153         6       Conclusions       155         6.1       Contributions       155         6.2       Final Conclusions       156         6.3       Future Work       157         A       Publications       158         B       Chip Schematics       181         C       Chip Layout       192         D       DAC Calibration Code       196         D.1       Calculation of INL       196         D.2       Application of CAT to a Transfer Function       196         D.3       Determine Optimal CAT Settings       197         E       DAC Interface Protocol       200         F       EM-PLL Models and Parameters       201         F.1       Model Parameters       201         F.2       Simulation models       203                                                                                                                                                                                                                                                                                                                 |              |       |          |               | -                   |                         |        |      |      |  |  |  |  |       |

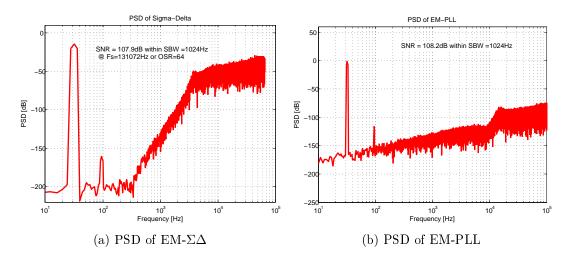

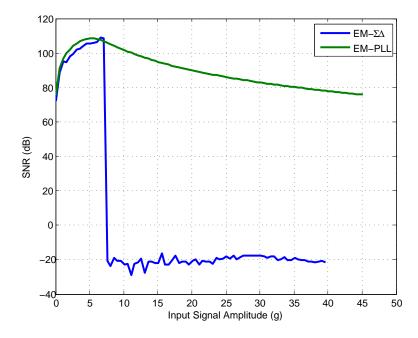

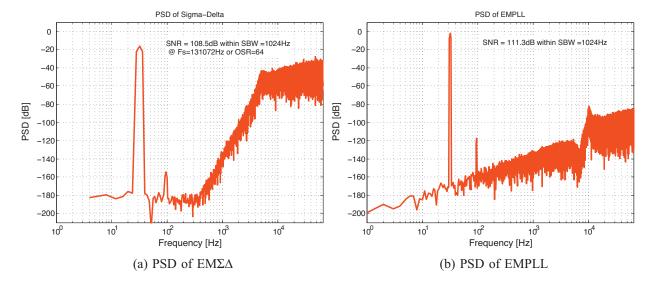

| 5.4.4 Parameter Variation       148         5.5 Discussion       153         6 Conclusions       155         6.1 Contributions       156         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |       | 5.4.2    | Output 1      | Power Sp            | $\operatorname{ectrum}$ |        |      | <br> |  |  |  |  | . 145 |

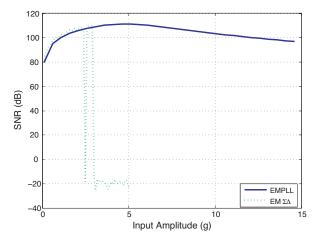

| 5.5 Discussion       153         6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |       | 5.4.3    | Input Ar      | ${ m mplitude}^{-}$ | Sweep                   |        |      | <br> |  |  |  |  | . 147 |

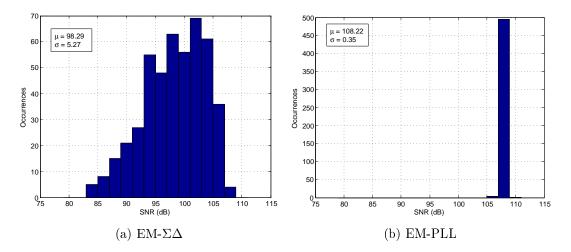

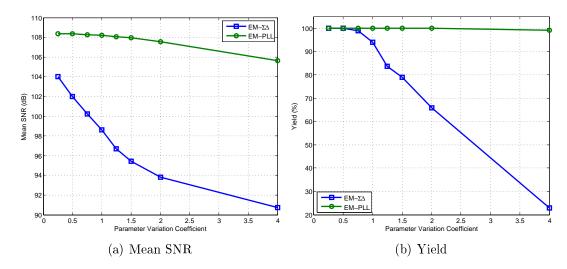

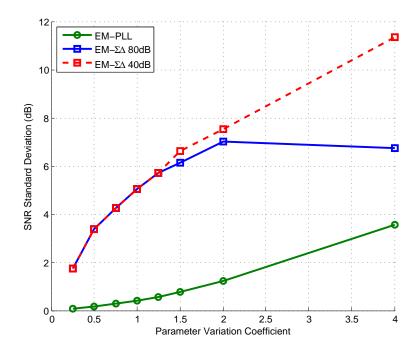

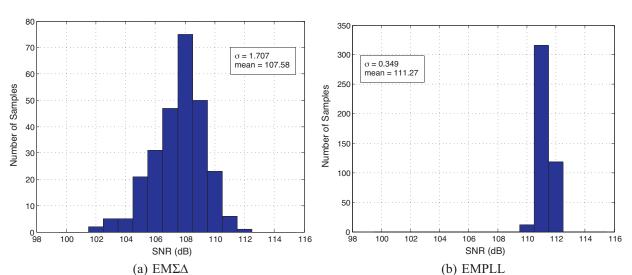

| 6 Conclusions       155         6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       159         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |       | 5.4.4    | Paramet       | er Variati          | ion                     |        |      | <br> |  |  |  |  | . 148 |

| 6.1 Contributions       155         6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 5.5   | Discus   | sion          |                     |                         |        |      | <br> |  |  |  |  | . 153 |

| 6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6            | Con   | clusion  | ıs            |                     |                         |        |      |      |  |  |  |  | 155   |

| 6.2 Final Conclusions       156         6.3 Future Work       157         A Publications       158         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |       |          |               |                     |                         |        |      | <br> |  |  |  |  | . 155 |

| 6.3 Future Work       155         A Publications       156         B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 6.2   |          |               |                     |                         |        |      |      |  |  |  |  |       |

| B Chip Schematics       181         C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | 6.3   |          |               |                     |                         |        |      |      |  |  |  |  |       |

| C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A            | Pub   | licatio  | $\mathbf{ns}$ |                     |                         |        |      |      |  |  |  |  | 159   |

| C Chip Layout       192         D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{R}$ | Chi   | n Scho   | matics        |                     |                         |        |      |      |  |  |  |  | 1 2 1 |

| D DAC Calibration Code       196         D.1 Calculation of INL       196         D.2 Application of CAT to a Transfer Function       196         D.3 Determine Optimal CAT Settings       197         E DAC Interface Protocol       200         F EM-PLL Models and Parameters       201         F.1 Model Parameters       201         F.2 Simulation models       203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ם            | Omj   | p sene.  | matics        |                     |                         |        |      |      |  |  |  |  | 101   |

| D.1 Calculation of INL D.2 Application of CAT to a Transfer Function D.3 Determine Optimal CAT Settings  E DAC Interface Protocol  EM-PLL Models and Parameters F.1 Model Parameters F.2 Simulation models  203  205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{C}$ | Chi   | p Layo   | ut            |                     |                         |        |      |      |  |  |  |  | 192   |

| D.2 Application of CAT to a Transfer Function D.3 Determine Optimal CAT Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D            | DAG   | C Calil  | oration (     | Code                |                         |        |      |      |  |  |  |  | 196   |

| D.3 Determine Optimal CAT Settings 197  E DAC Interface Protocol 200  F EM-PLL Models and Parameters 201  F.1 Model Parameters 201  F.2 Simulation models 203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | D.1   | Calcula  | ation of I    | NL                  |                         |        |      | <br> |  |  |  |  | . 196 |

| E DAC Interface Protocol  F EM-PLL Models and Parameters F.1 Model Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | D.2   | Applic   | ation of C    | CAT to a            | Transfe                 | r Func | tion |      |  |  |  |  | . 196 |

| F EM-PLL Models and Parameters F.1 Model Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | D.3   | Detern   | nine Opti     | mal CAT             | Setting                 | S      |      | <br> |  |  |  |  | . 197 |

| F.1 Model Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{E}$ | DA    | C Inter  | rface Pro     | otocol              |                         |        |      |      |  |  |  |  | 200   |

| F.1 Model Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{F}$ | EM-   | -PLL N   | Models a      | nd Para             | $\mathbf{meters}$       |        |      |      |  |  |  |  | 201   |

| F.2 Simulation models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -            |       |          |               |                     |                         |        |      | <br> |  |  |  |  |       |

| Bibliography 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |       |          |               |                     |                         |        |      |      |  |  |  |  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bi           | bliog | raphv    |               |                     |                         |        |      |      |  |  |  |  | 205   |

# List of Figures

| 1.1  | Hewlett-Packard 200A Audio Oscillator by Colin CC BY-SA [7]              | 2  |

|------|--------------------------------------------------------------------------|----|

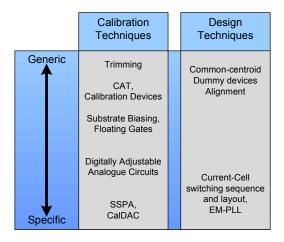

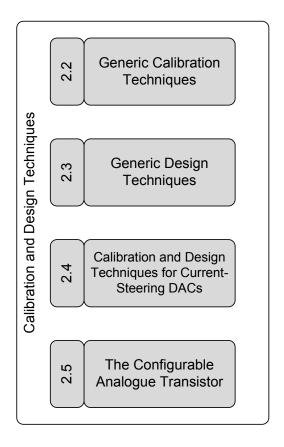

| 2.1  | Categorisation of design and calibration techniques in this chapter      | 11 |

| 2.2  | Structure of this chapter.                                               | 12 |

| 2.3  | Transistor trimming by burning metal links                               | 13 |

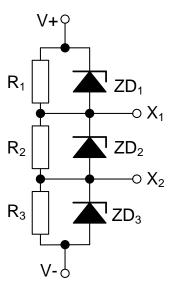

| 2.4  | Principle of "Zener zapping" resistor trimming.                          | 14 |

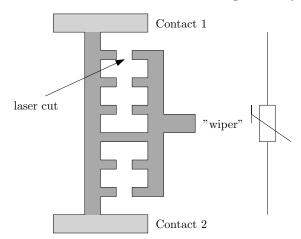

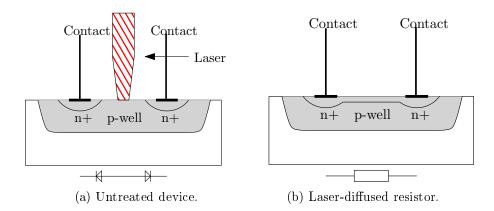

| 2.5  | Laser-trimmed diffusion resistor                                         | 15 |

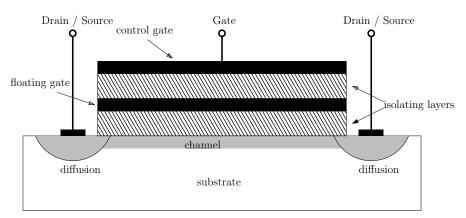

| 2.6  | Schematic diagram of a floating-gate device                              | 17 |

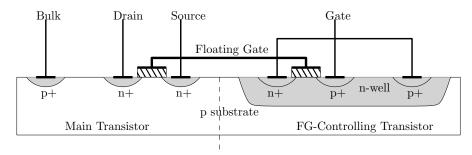

| 2.7  | Schematic diagram of a floating-gate device on a conventional CMOS pro-  |    |

|      | cess without special layers                                              | 18 |

| 2.8  | MOS transistor with programmable length.                                 | 19 |

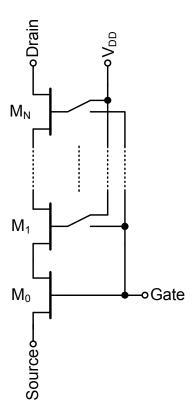

| 2.9  | Principle of a digitally adjustable analogue circuit.                    | 21 |

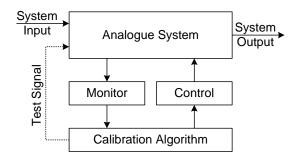

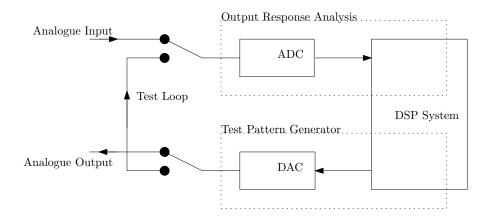

| 2.10 | DSP system with test loop facility.                                      | 22 |

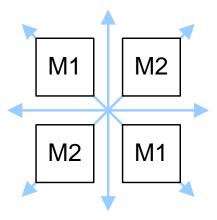

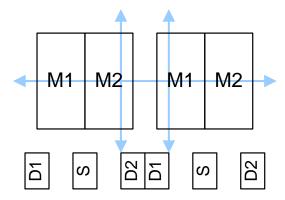

| 2.11 | Concept of common-centroid layout, arrows indicate axes of symmetry      | 24 |

|      | Perfect common-centroid arrangement of source-coupled transistor pair    | 25 |

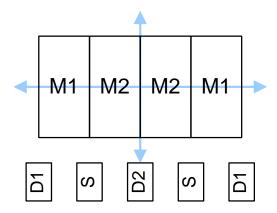

| 2.13 | Imperfect common-centroid arrangement of source-coupled transistor pair. | 25 |

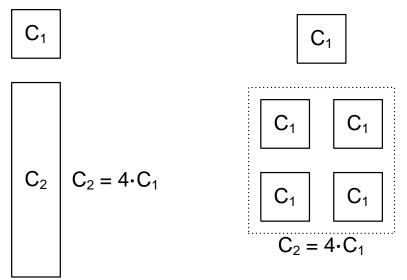

| 2.14 | Application of unit-sized capacitors.                                    | 26 |

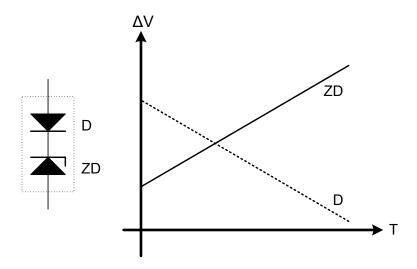

| 2.15 | Temperature-compensated Zener diode.                                     | 27 |

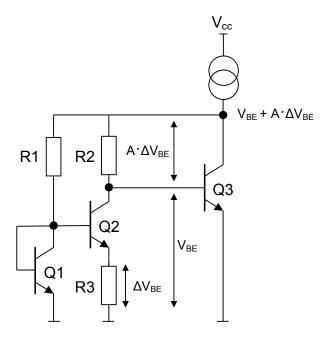

| 2.16 | Concept of early bipolar bandgap reference [55]                          | 28 |

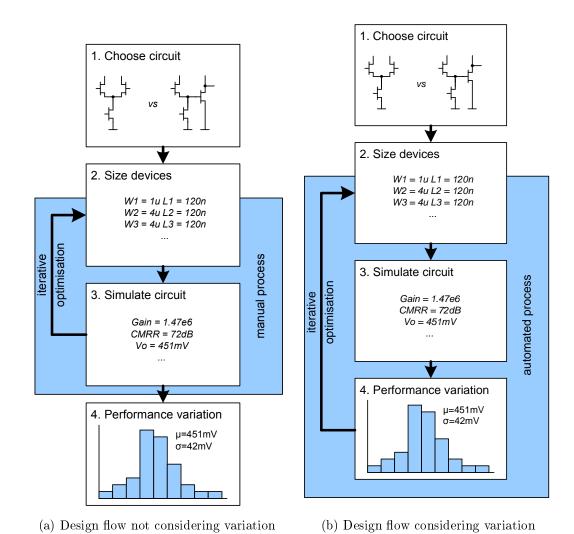

| 2.17 | Design flow with and without concern for variation.                      | 29 |

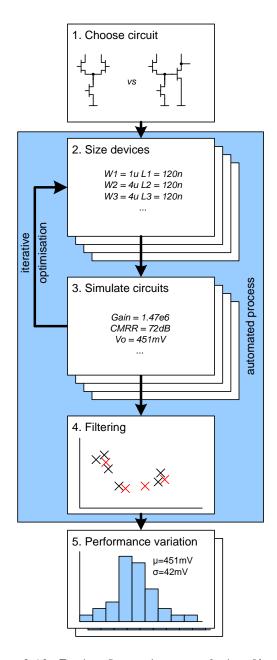

| 2.18 | Design flow using post-design filtering.                                 | 32 |

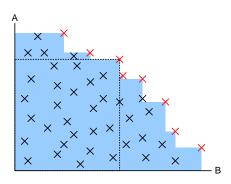

| 2.19 | Illustration of a Pareto Front                                           | 34 |

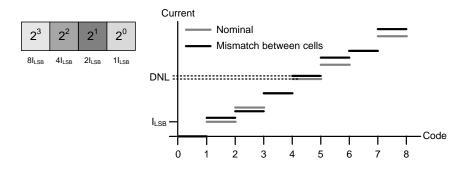

| 2.20 | DNL caused by mismatch in binary current cells                           | 36 |

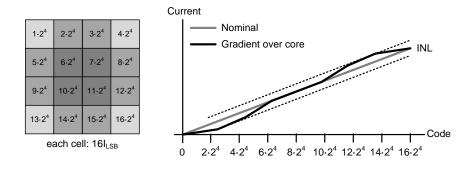

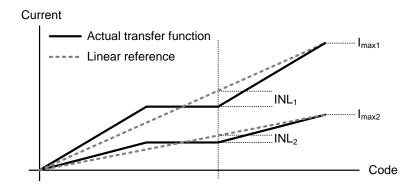

| 2.21 | INL caused by mismatch in unary current cells                            | 36 |

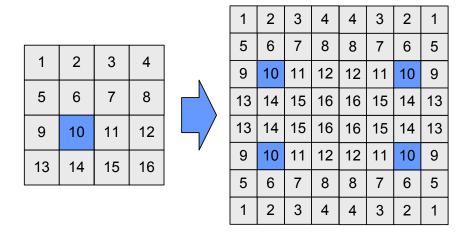

| 2.22 | Distributing current cells across the array.                             | 38 |

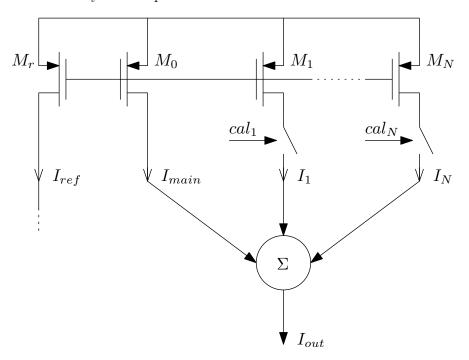

| 2.23 | Schematic diagram of a calibratable current cell                         | 39 |

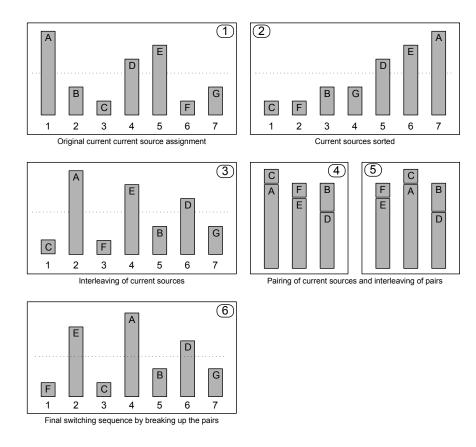

| 2.24 | Operating principle of switching sequence post adjustment                | 41 |

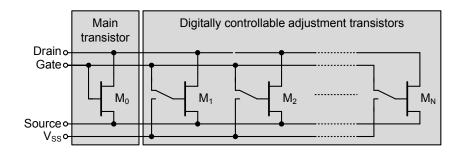

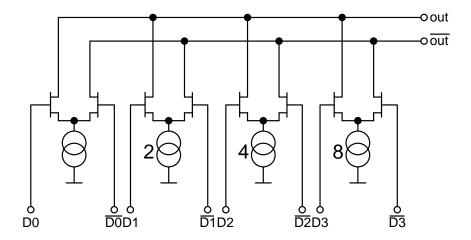

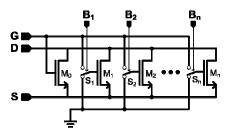

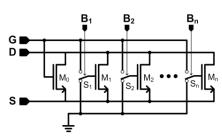

| 2.25 | Schematic of the CAT device                                              | 43 |

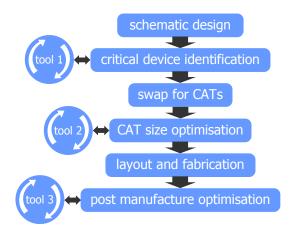

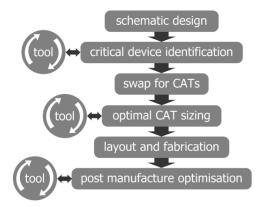

| 2.26 | Design flow when CAT is employed. [81]                                   | 43 |

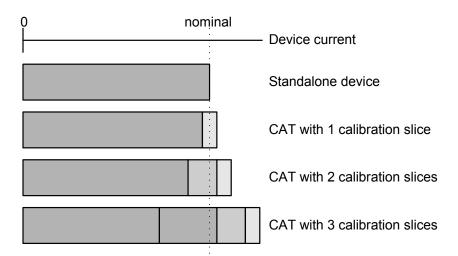

| 2.27 | Illustration of CAT devices with different number of calibration slices  | 44 |

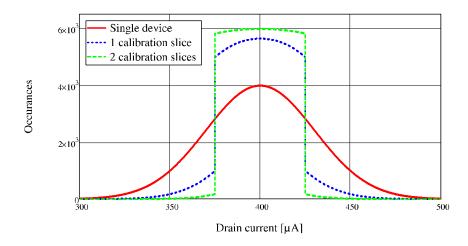

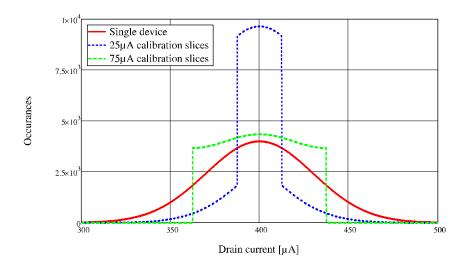

| 2.28 | Effect of adding calibration slices                                      | 45 |

| 2.29 | Effect of different calibration slice sizes.                             | 46 |

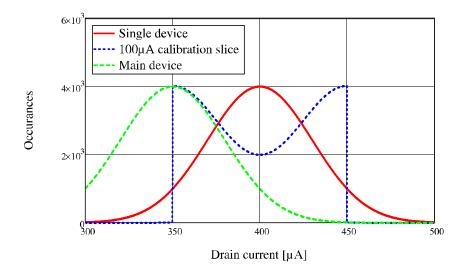

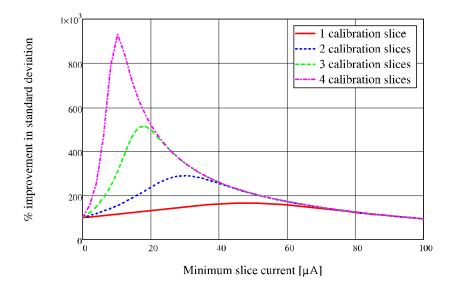

| 2.30 | Effect of a very large calibration slice                                 | 47 |

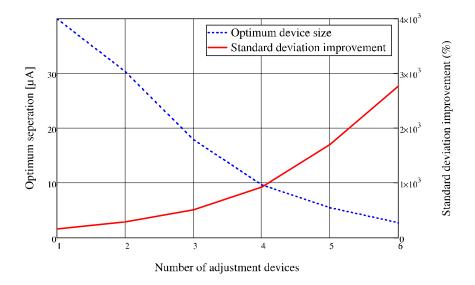

| 2.31 | Improvement in standard deviation                                        | 48 |

| 2.32 | Theoretical maximum improvement and optimised slice size as a function   |    |

|      | of calibration slices.                                                   | 49 |

LIST OF FIGURES v

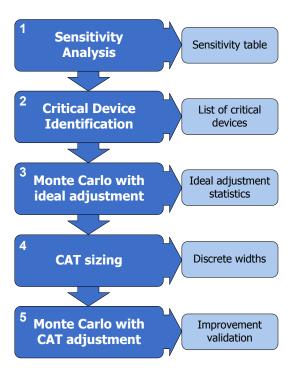

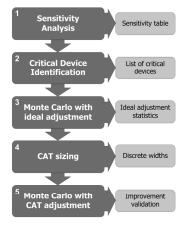

| 3.1  | Process flow of critical device identification and application of configurable | F 4 |

|------|--------------------------------------------------------------------------------|-----|

| 0.0  | analogue transistors.                                                          |     |

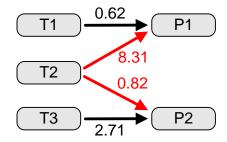

| 3.2  | Different relationships between transistors and performances                   |     |

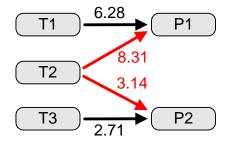

| 3.3  | Illustration of adjustment independence.                                       |     |

| 3.4  | Example sensitivities of a circuit.                                            |     |

| 3.5  | Illustration of the Critical Device Identification process                     | 58  |

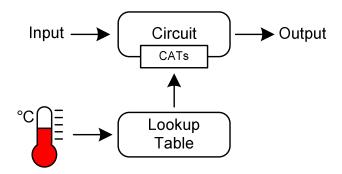

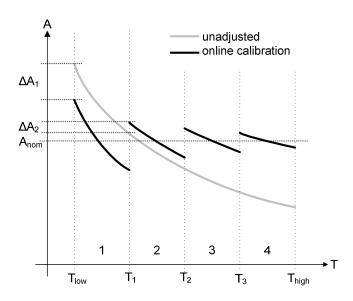

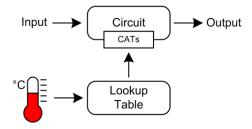

| 3.6  | System structure for online temperature calibration using CATs                 | 63  |

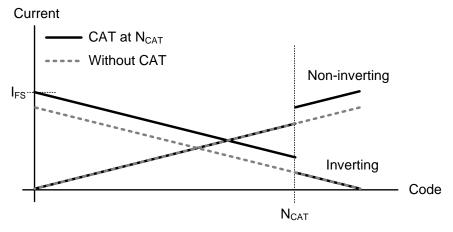

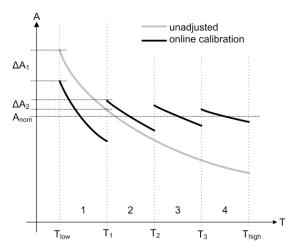

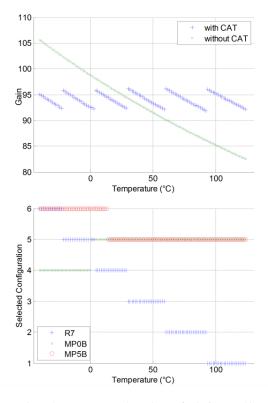

| 3.7  | Principle of temperature compensation using CATs                               | 64  |

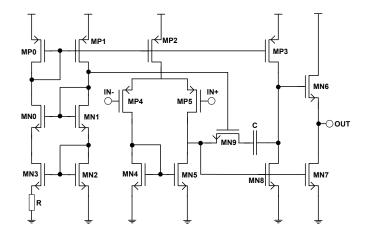

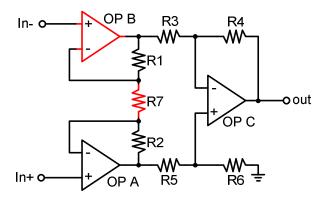

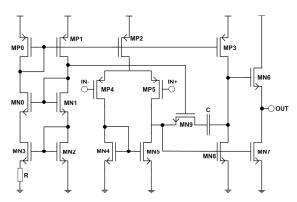

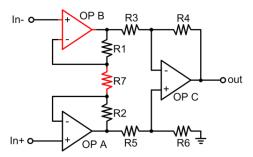

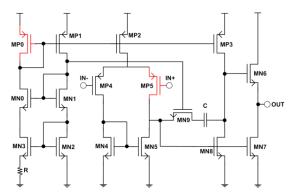

| 3.8  | Circuit diagram of the operational amplifier                                   | 67  |

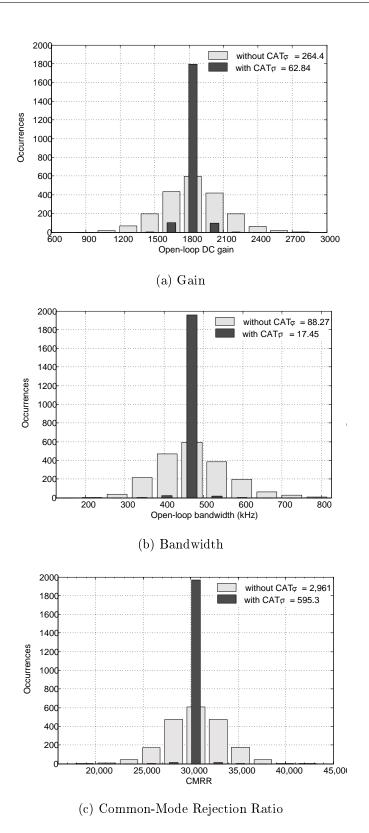

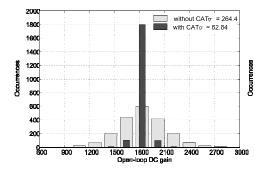

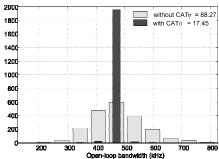

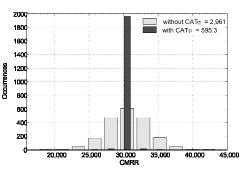

| 3.11 | Histograms of performances before and after CAT adjustment                     | 71  |

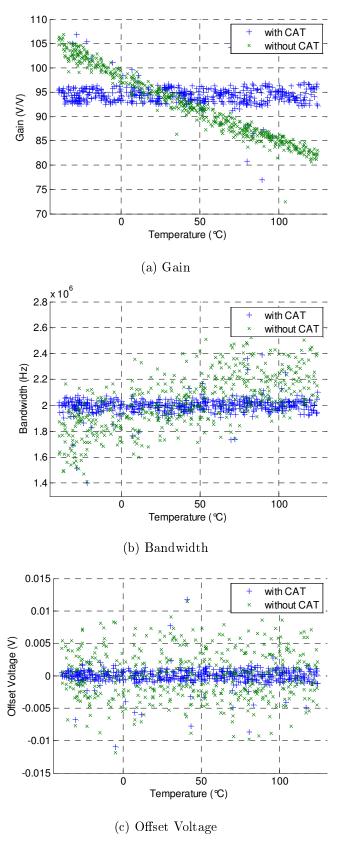

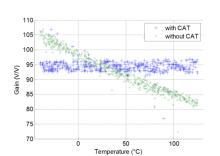

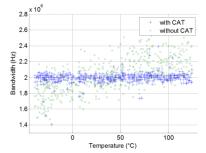

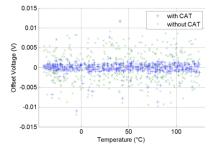

| 3.15 |                                                                                |     |

|      | ation                                                                          | 75  |

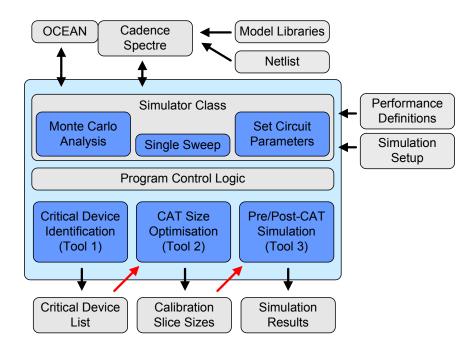

| 3.16 | Block diagram of the simulation environment                                    |     |

| 3.9  | Performance sensitivity to variation in transistors                            |     |

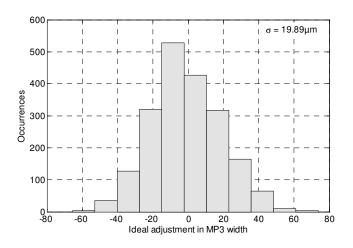

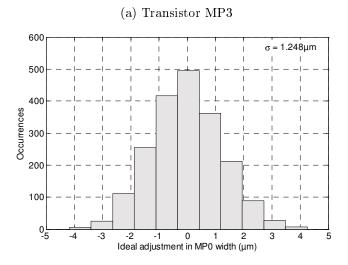

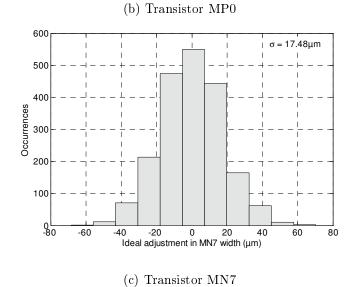

|      | Histograms of ideal relative adjustments                                       |     |

|      | Circuit diagram of the instrumentation amplifier                               |     |

|      | Circuit diagram of the operational amplifier                                   |     |

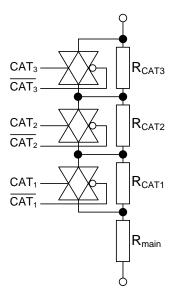

| 3.14 | CAT-like structure with resistors                                              | 85  |

| 4.1  | Example of a segmented DAC.                                                    | 88  |

| 4.1  | Principle of a current-steering DAC.                                           |     |

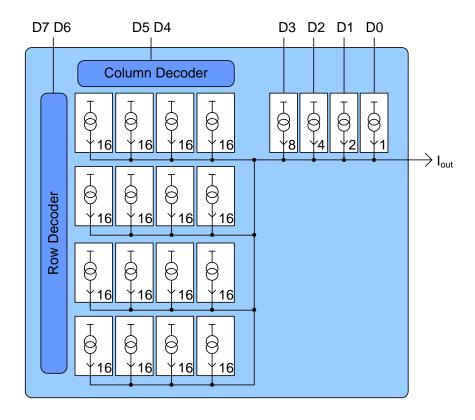

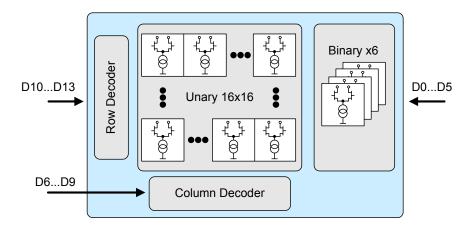

| 4.3  | Block diagram of the 14 bit segmented DAC.                                     |     |

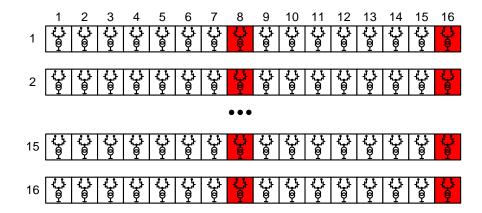

| 4.4  | Unary current cell array and switching sequence                                |     |

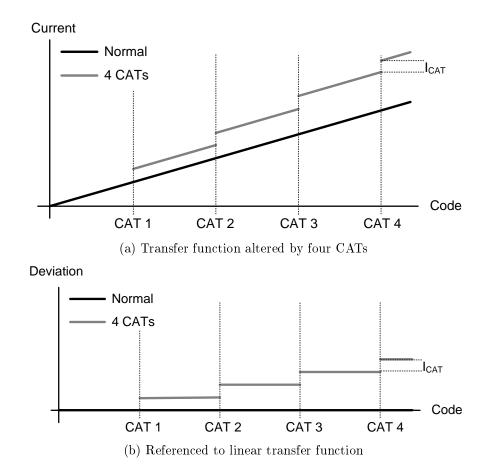

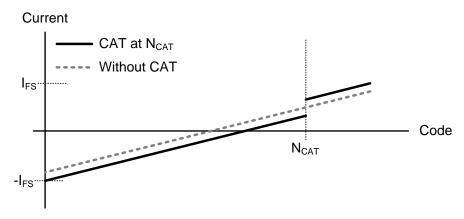

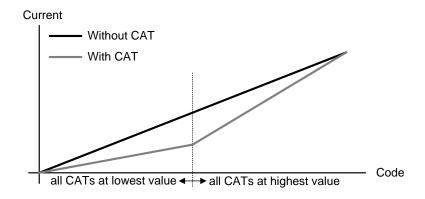

| 4.5  | CAT-compensated output of DAC.                                                 |     |

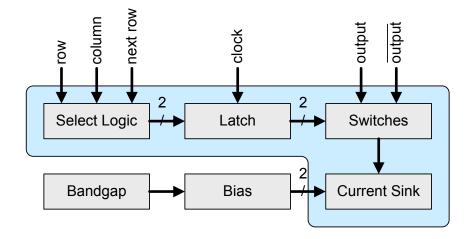

| 4.6  | Block diagram of a current cell with external bias generation.                 |     |

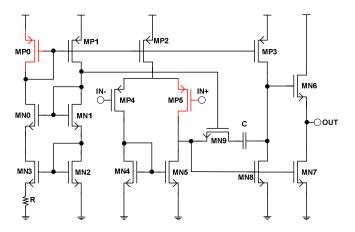

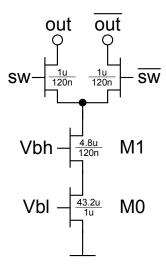

| 4.7  | Schematic diagram of current sink and switching transistors                    |     |

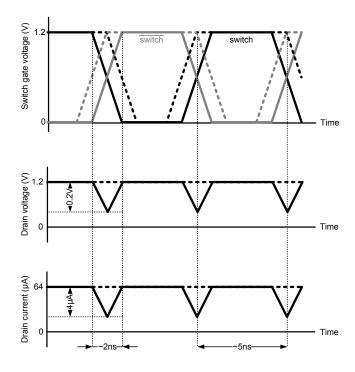

| 4.8  | Switching waveforms and resultant change in current                            |     |

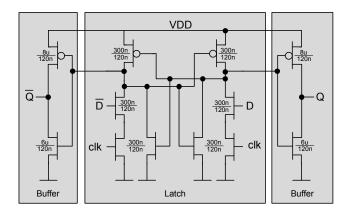

| 4.9  | Schematic diagram of the data latch                                            |     |

|      | Current cell activation from row and column select signals                     |     |

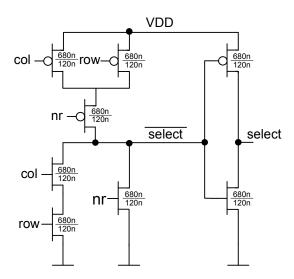

|      | Circuit diagram of the cell select logic                                       |     |

|      | Schematic of a current cell with CAT                                           |     |

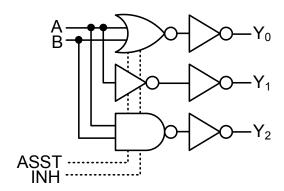

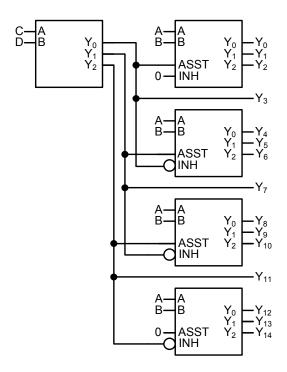

|      | Operation of a 4-to-15 thermometer decoder.                                    |     |

|      | Logic diagram of the 2-to-3 thermometer decoder                                |     |

|      | Block diagram of the 4-to-15 thermometer decoder                               |     |

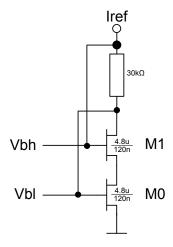

|      | Bias generator for the current cells                                           |     |

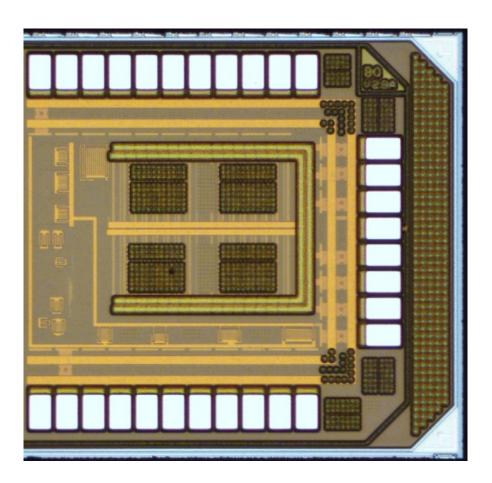

|      | Die photograph of the fabricated chip.                                         |     |

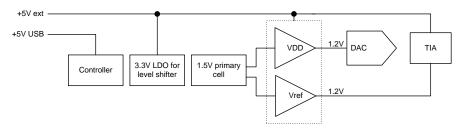

|      | Signal path architecture of the test board.                                    |     |

|      | Supply and reference distribution                                              |     |

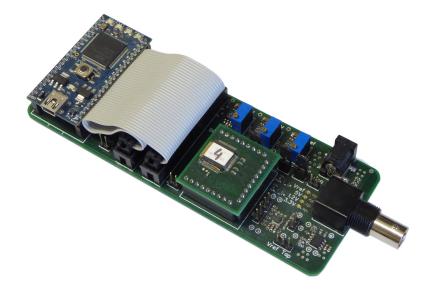

|      | Photograph of the test board                                                   |     |

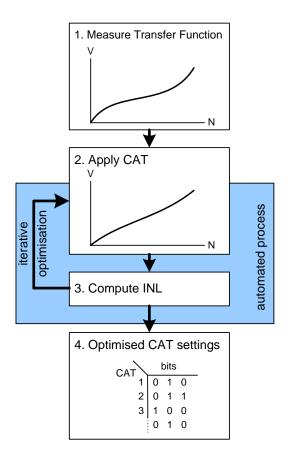

|      | Optimisation of CAT configuration                                              |     |

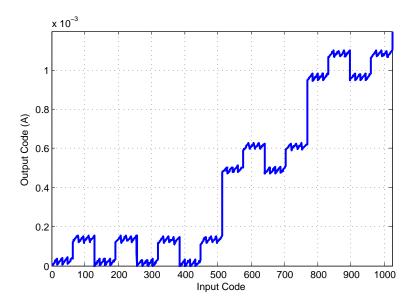

|      | Partial transfer function of a defective chip.                                 |     |

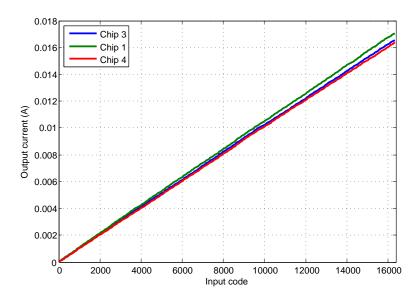

|      | Transfer functions for three chips                                             |     |

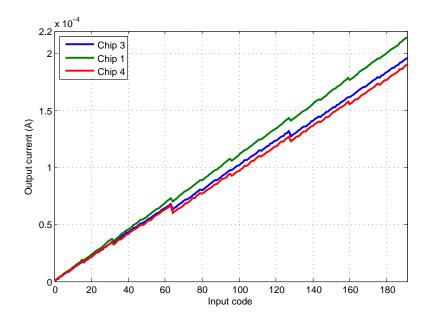

|      | Detail of transfer functions for first 192 codes                               |     |

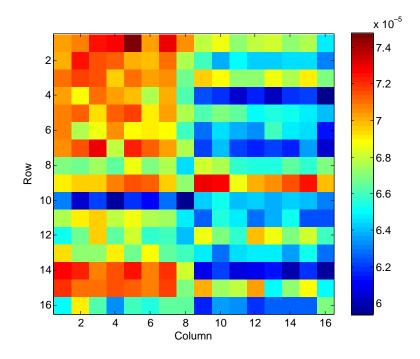

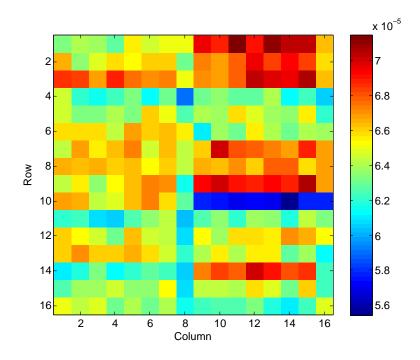

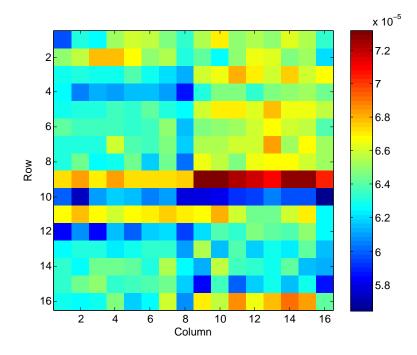

|      | Map of unary current cells of chip 1 (in $A$ )                                 |     |

|      | Map of unary current cells of chip 3 (in $A$ )                                 |     |

|      | Map of unary current cells of chip 4 (in $A$ )                                 |     |

|      | Effects of CAT on the single-ended transfer function.                          |     |

LIST OF FIGURES vii

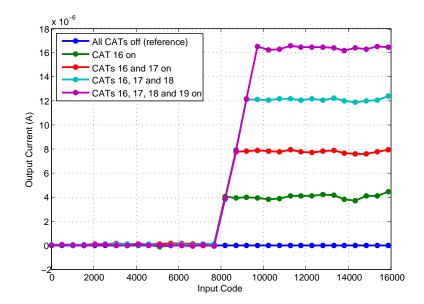

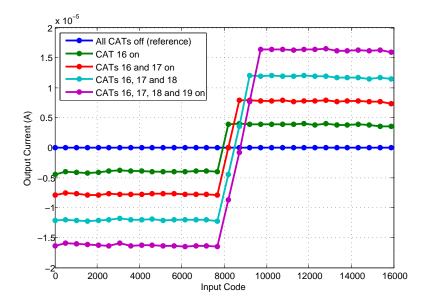

|      | Consecutive CAT's enabled in single-ended DAC.                                            |     |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.30 | Effects of CAT on the differential transfer function                                      | 115 |

| 4.31 | Consecutive CATs enabled in differential DAC                                              | 116 |

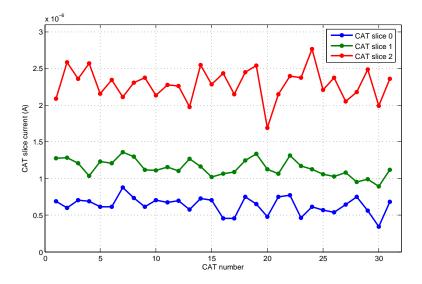

| 4.32 | Size of CAT slices over current cell array.                                               | 117 |

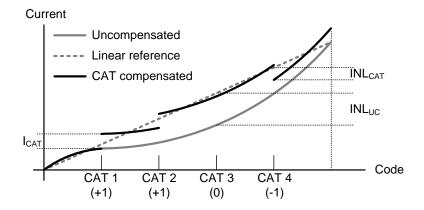

| 4.33 | Illustration of INL compensation with CAT                                                 | 117 |

| 4.34 | Different reference lines for same transfer function with different gain                  | 119 |

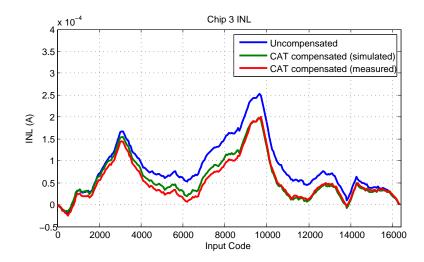

| 4.35 | INL of Chip 3, uncompensated and compensated by CAT                                       | 119 |

| 4.36 | Largest possible adjustment through CAT                                                   | 120 |

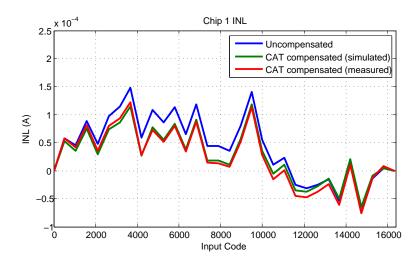

| 4.37 | INL of Chip 1, uncompensated and compensated by CAT                                       | 120 |

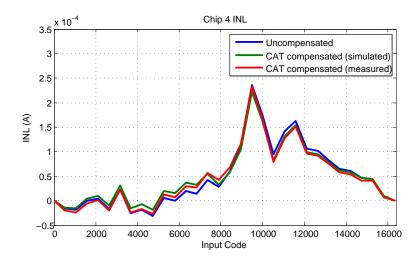

| 4.38 | INL of Chip 4, uncompensated and compensated by CAT                                       | 121 |

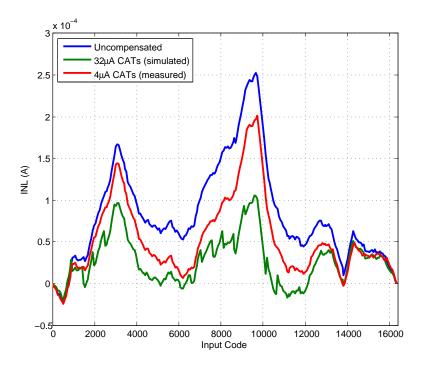

| 4.39 | INL compensated with bigger CATs                                                          | 122 |

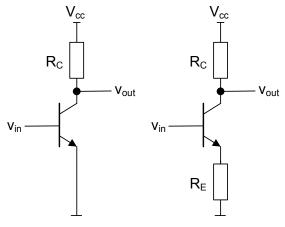

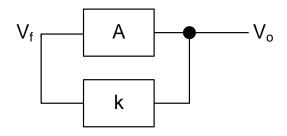

| 5.1  | Bipolar common-emitter amplifiers with and without negative feedback                      | 125 |

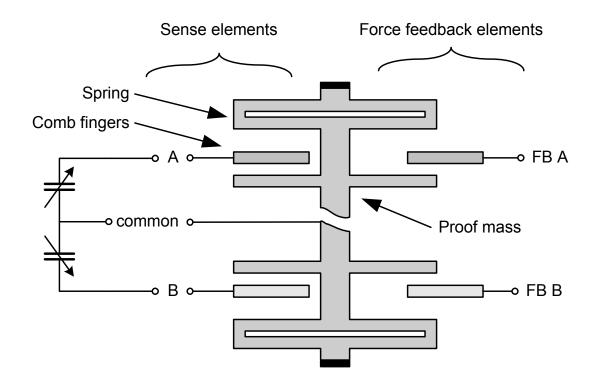

| 5.2  | Structure of a MEMS accelerometer                                                         | 129 |

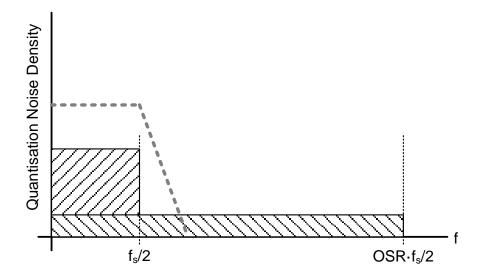

| 5.3  | Quantisation noise spectra for signal at minimum and oversampled sample                   |     |

|      | rates                                                                                     | 130 |

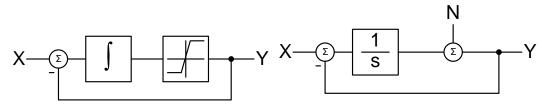

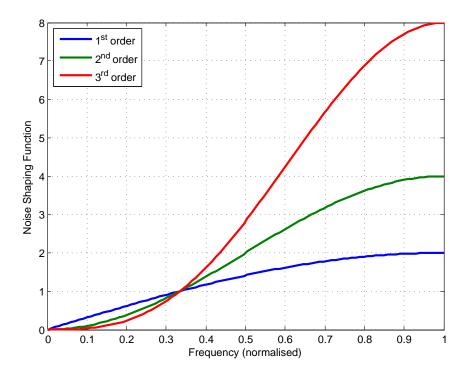

| 5.5  | Noise shaping functions for $\Sigma\Delta$ modulators                                     |     |

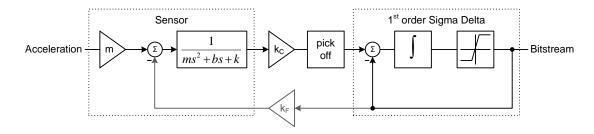

| 5.6  | Block Diagram of an electro-mechanical sigma-delta modulator                              |     |

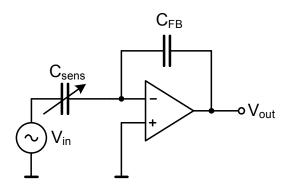

| 5.7  | Basic capacitive sensing circuit.                                                         |     |

| 5.8  | Accelerometer pick-off circuit described in [96].                                         |     |

| 5.9  | Block diagram of a basic PLL                                                              |     |

|      | Block diagram of an oscillator                                                            |     |

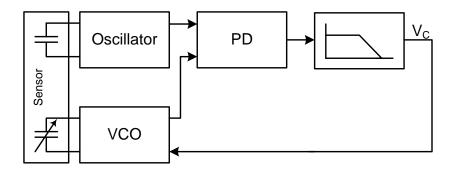

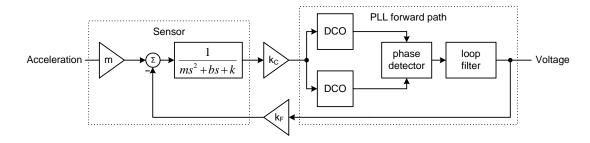

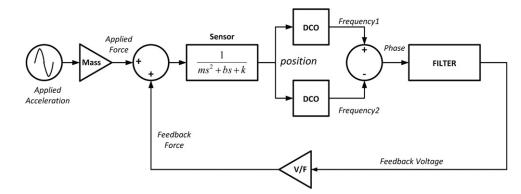

|      | Architecture of the EM-PLL                                                                |     |

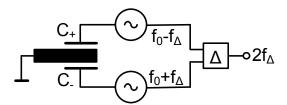

|      | Frequency difference as a measure for acceleration.                                       |     |

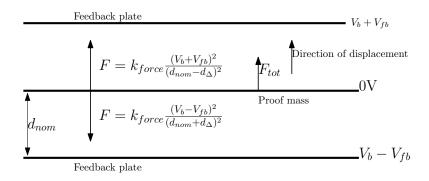

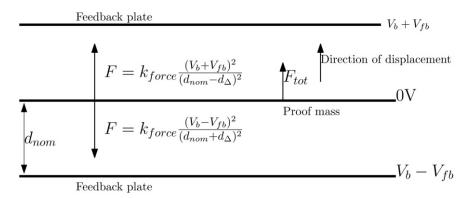

|      | Forces in the force-feedback system.                                                      |     |

|      | Comparison of PSD between EM- $\Sigma\Delta$ and EM-PLL                                   |     |

|      | Input amplitude sweep for EM- $\Sigma\Delta$ and EM-PLL                                   |     |

|      | SNR histograms of EM- $\Sigma\Delta$ and EM-PLL under parameter variation                 |     |

|      | Mean SNR and yield for different levels of parameter variation                            |     |

|      | SNR standard deviation for different levels of parameter variation.                       |     |

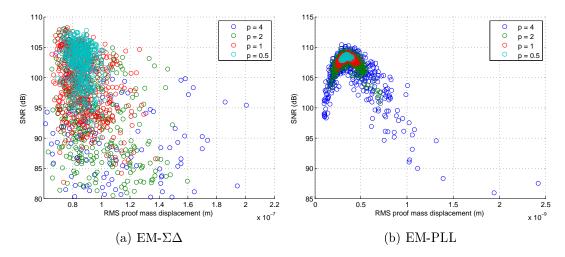

| 5.19 | Scatter plots of SNR and RMS displacement of the Monte Carlo simulation.                  | 152 |

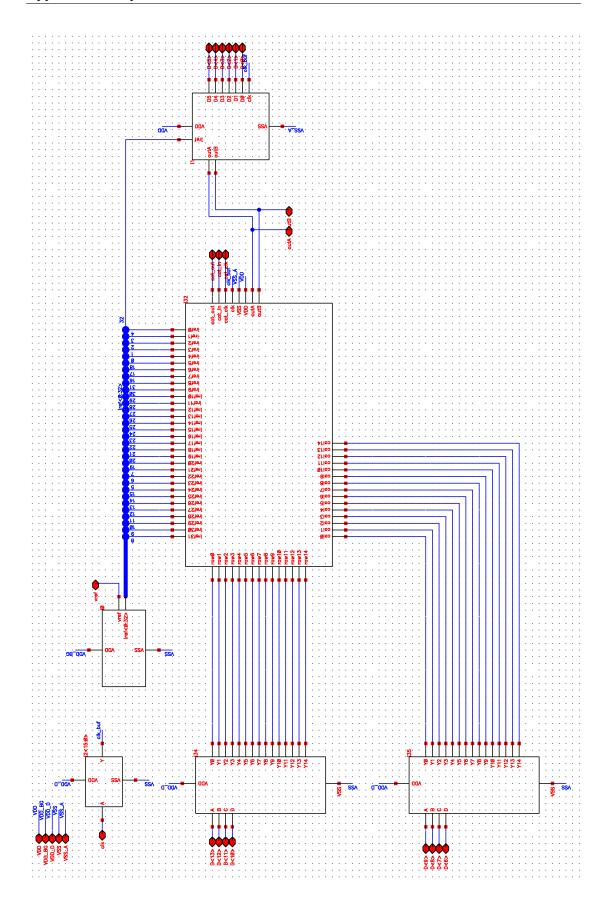

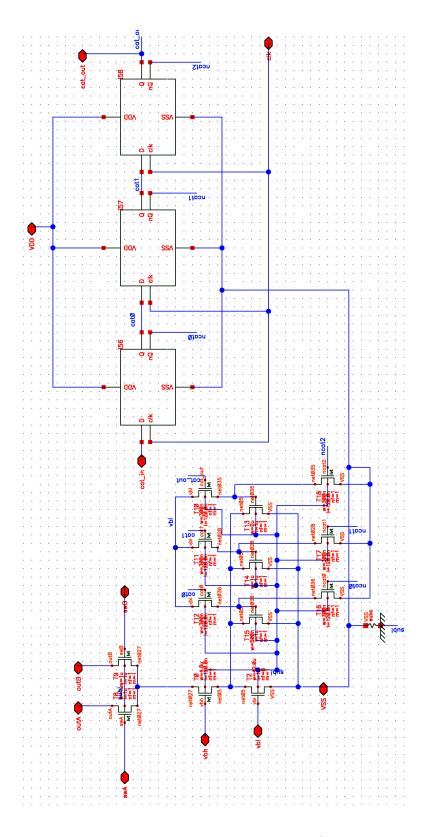

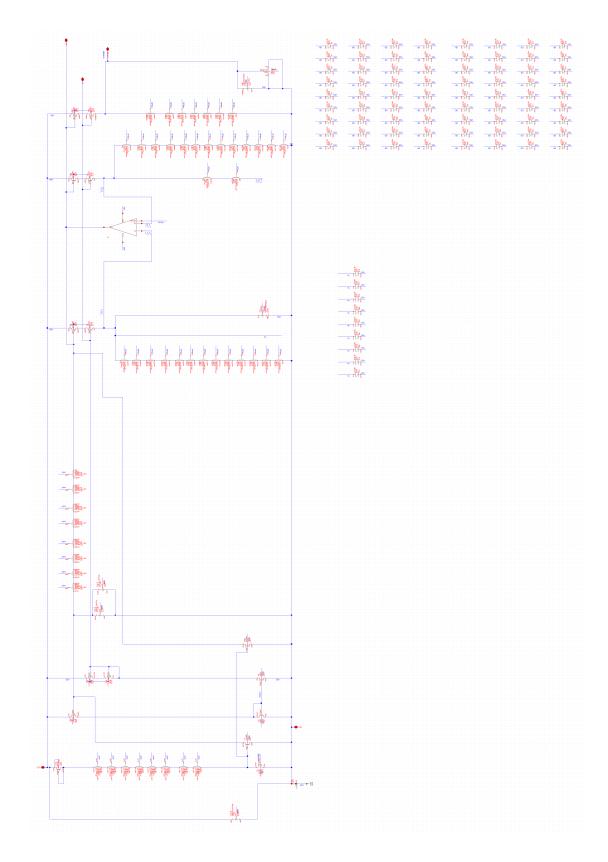

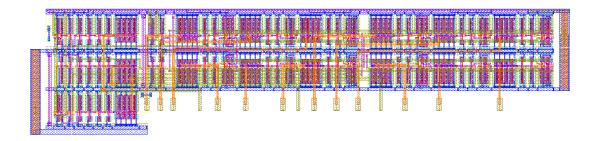

| B.1  | Top-level schematic diagram of the DAC.                                                   |     |

| B.2  | High-level schematic diagram of the 4-to-15 thermometer decoder                           |     |

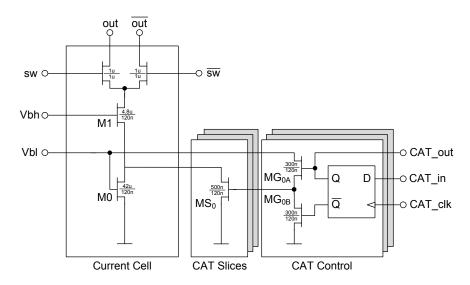

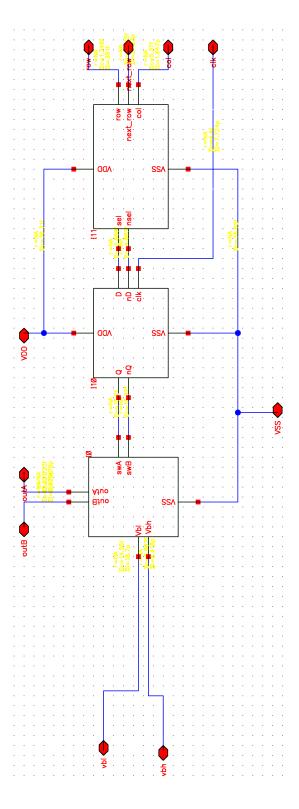

| B.3  | High-level schematic diagram of a current cell in the unary array                         |     |

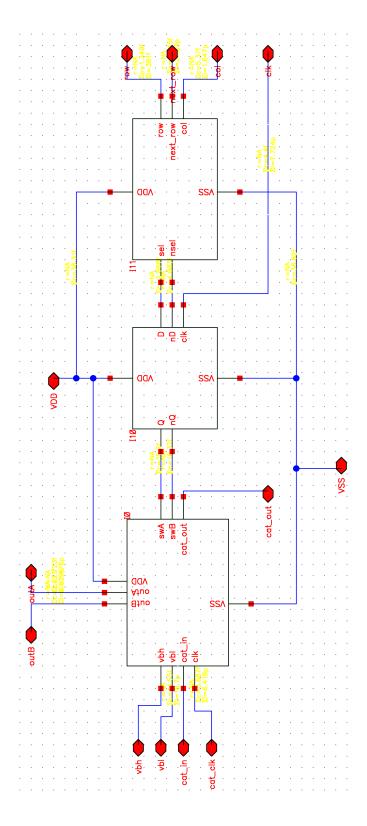

| B.4  | High-level schematic diagram of a current cell in the unary array with CAT.               | 185 |

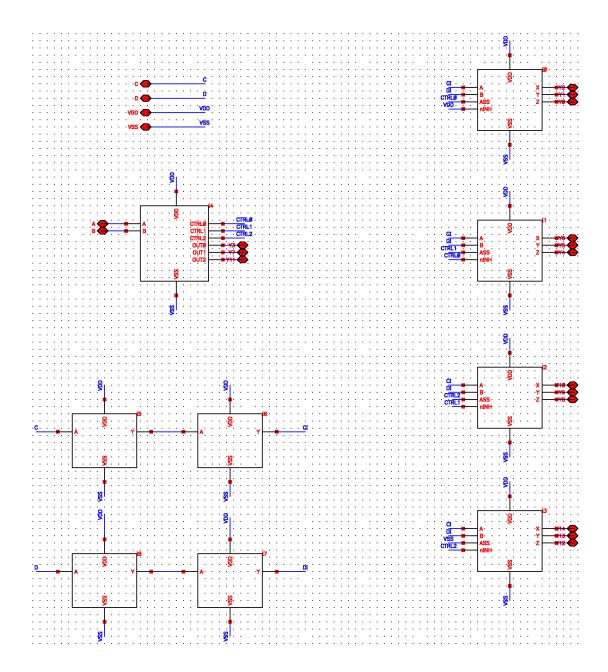

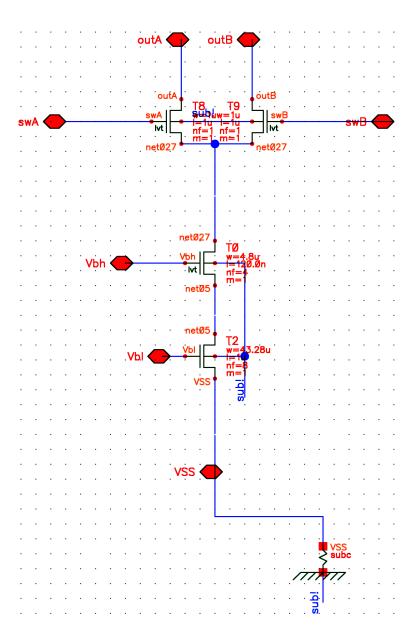

| B.5  | Transistor-level schematic diagram of a $64\mu A$ current sink and switching transistors. | 186 |

| B.6  | Transistor-level schematic diagram of a $64\mu A$ current sink with CAT and               |     |

|      | switching transistors                                                                     |     |

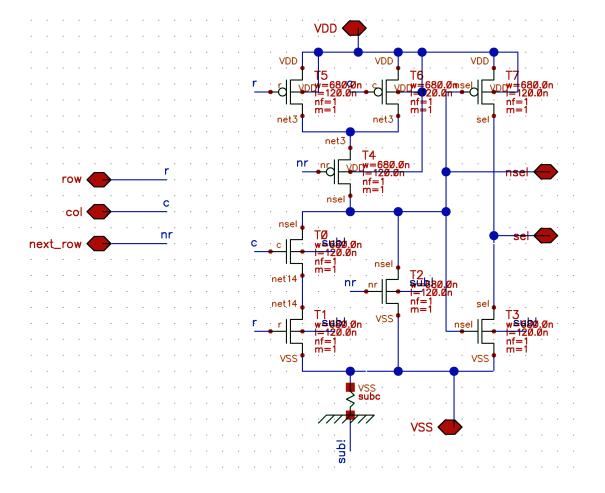

| B.7  | Transistor-level schematic diagram of the cell select logic of a current cell.            |     |

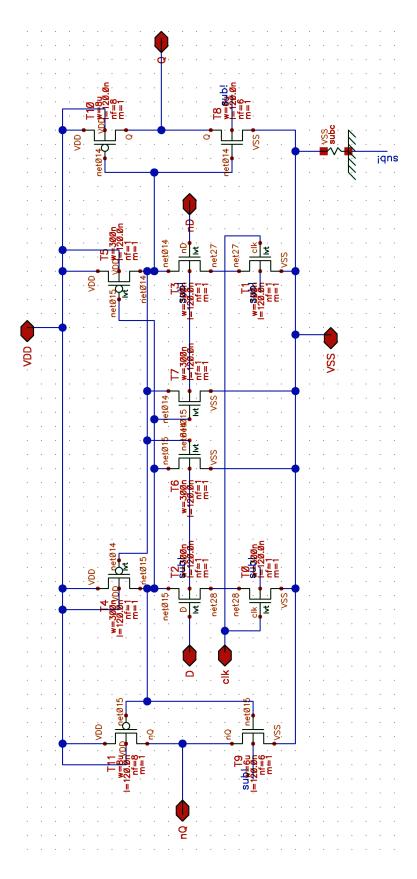

| B.8  | Transistor-level schematic diagram of the data latch of a current cell                    |     |

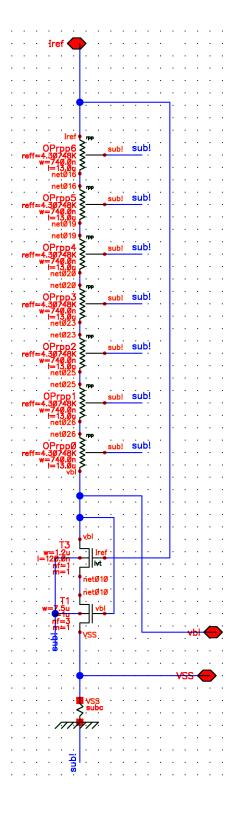

| B.9  | Transistor-level schematic diagram of the bias generator for 8 current cells.             | 190 |

| B.10 | Transistor-level schematic diagram of the bandgap core (designed by Dr                    | 101 |

|      | Li Ke)                                                                                    | 191 |

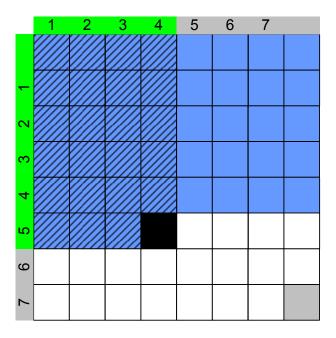

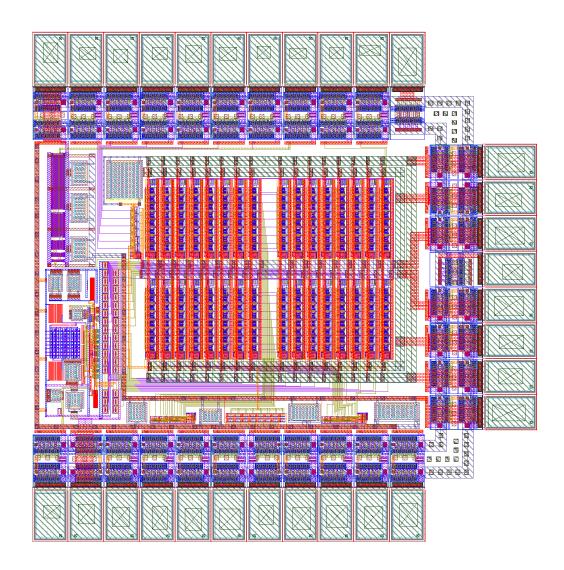

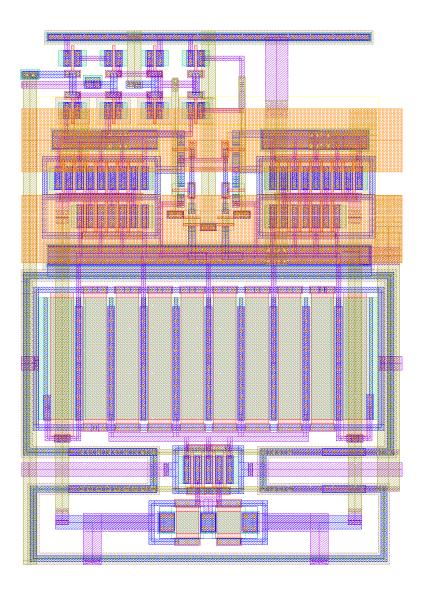

| C.1  | Top-level view of the DAC with pads.                                                      |     |

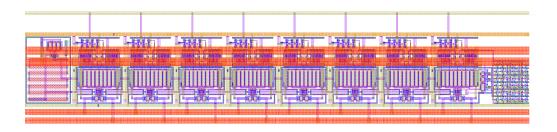

| C.2  | Layout of a half-row block (8 current cells and bias generator)                           | 193 |

LIST OF FIGURES viii

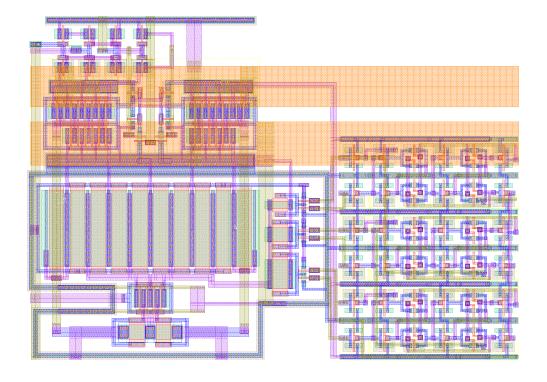

| C.3 | Layout of a regular $64\mu A$ current cell                                | 194 |

|-----|---------------------------------------------------------------------------|-----|

| C.4 | Layout of a $64\mu A$ current cell with CAT (shift register on the right) | 195 |

| C.5 | Layout of the 4-to-15 thermometer decoder                                 | 195 |

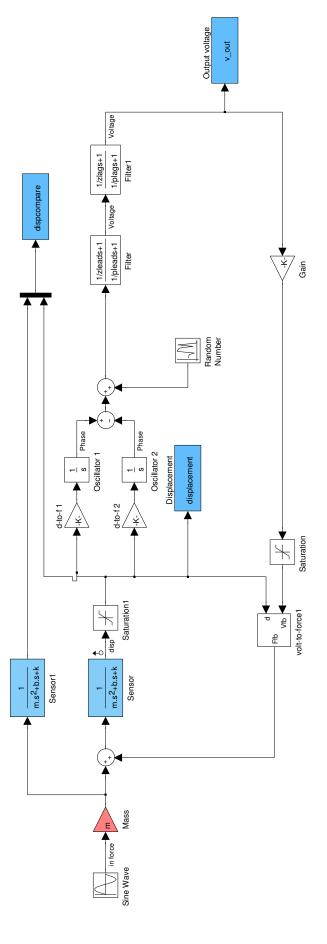

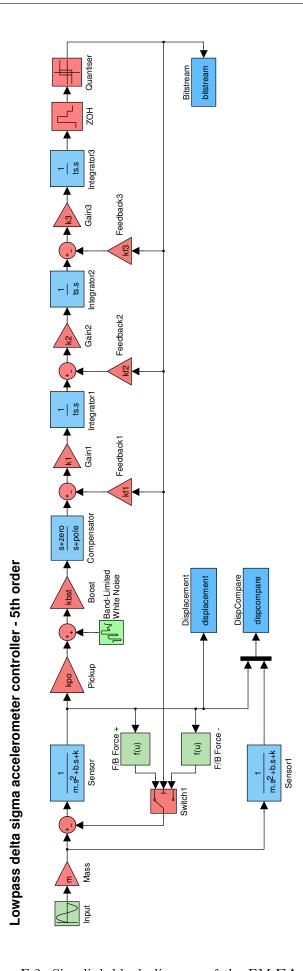

| F.1 | Simulink block diagram of the EM-PLL                                      | 203 |

| F.2 | Simulink block diagram of the EM- $\Sigma\Delta$ [95]                     | 204 |

# List of Tables

| 3.1 | Device sizes and component values                                       |