# Southampton

### University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### **UNIVERSITY OF SOUTHAMPTON**

Faculty of Engineering, Science and Mathematics School of Electronics and Computer Science

# Test and Diagnosis of Resistive Bridges in Multi- $V_{dd}$ Designs

by

Syed Saqib Khursheed

A thesis submitted for the degree of Doctor of Philosophy

February 2010

#### **UNIVERSITY OF SOUTHAMPTON**

ABSTRACT

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE Doctor of Philosophy Test and Diagnosis of Resistive Bridges in Multi-V<sub>dd</sub> Designs

by Syed Saqib Khursheed

A key design constraint of circuits used in hand-held devices is the power consumption, mainly due to battery life limitations. Adaptive power management (APM) techniques aim to increase the battery life by adjusting the supply voltage  $(V_{dd})$  and operating frequency, according to the workload. APM-enabled devices raise a number of challenges for existing manufacturing test and diagnosis techniques, as certain defects exhibit  $V_{dd}$  dependent detectability. This means that to achieve 100% fault coverage, APM-enabled devices should be tested at all operating voltages using repetitive tests. Repetitive tests at several V<sub>dd</sub> settings are undesirable as it increases the cost of manufacturing test. This thesis provides two new and cost-effective Design for Test (DFT) techniques to avoid repetitive tests thereby reducing test cost. The first technique uses test point insertion (TPI) to reduce the number of test  $V_{dd}$  settings. TPI capitalizes on the observation that each resistive bridge defect consists of a large number of logic faults, including detectable and non-detectable logic faults. It targets resistive bridges requiring test at higher V<sub>dd</sub> settings, and converts un-detectable logic faults at the lowest V<sub>dd</sub> setting, into detectable logic faults by using test points. Test points provide additional controllability and observability at the fault site. TPI has shown encouraging results in terms of reducing the number of test  $V_{dd}$ settings, however it does not achieve single V<sub>dd</sub> test for all designs. Taking this issue into account, another gate sizing (GS) based DFT technique is proposed. It targets bridges that require multi-V<sub>dd</sub> test and increases the drive strength of gates driving such bridges. The number of test V<sub>dd</sub> settings are reduced minimizing test cost. Experimental results show that for all designs, the proposed GS technique achieves 100% fault coverage at a single  $V_{dd}$  setting; in addition it has a lower overhead than the TPI in terms of timing, area and power.

The  $V_{dd}$  dependent detectability of resistive bridges demands re-evaluation of existing diagnosis techniques, as all existing techniques use a single voltage setting for fault diagnosis, which may have a negative impact on diagnosis accuracy, affecting subsequent design cycle and yield. This thesis proposes a novel and cost-effective technique to improve diagnosis accuracy of resistive bridges in APM-enabled designs. It evaluates the impact of varying supply voltage on the accuracy of diagnosis accuracy through a novel multi-voltage diagnosis algorithm. The diagnosis cost is reduced by identifying the most useful voltage settings and by eliminating tests at other voltages thereby achieving high diagnosis accuracy at reduced cost. All developed test and diagnosis techniques have been validated using simulations with ISCAS and ITC benchmarks, realistic fault models and actual bridges extracted from physical layouts.

## Contents

| Li | List of Acronyms x |                                                                   |     |  |  |

|----|--------------------|-------------------------------------------------------------------|-----|--|--|

| A  | cknow              | edgements                                                         | xiv |  |  |

| 1  | Intr               | duction                                                           | 1   |  |  |

|    | 1.1                | Low Power Design                                                  | 2   |  |  |

|    | 1.2                | Manufacturing Test                                                | 6   |  |  |

|    | 1.3                | Fault Models                                                      | 9   |  |  |

|    |                    | 1.3.1 Stuck-at fault                                              | 10  |  |  |

|    |                    | 1.3.2 Stuck-open, Stuck-short faults                              | 11  |  |  |

|    |                    | 1.3.3 Bridging fault                                              | 11  |  |  |

|    |                    | 1.3.4 Delay fault                                                 | 12  |  |  |

|    | 1.4                | Test Generation                                                   | 14  |  |  |

|    | 1.5                | Diagnosis                                                         | 16  |  |  |

|    | 1.6                | Design for Testability                                            | 18  |  |  |

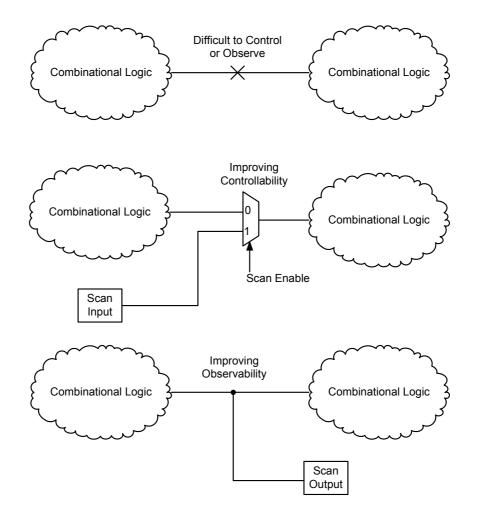

|    |                    | 1.6.1 Test Point Insertion                                        | 18  |  |  |

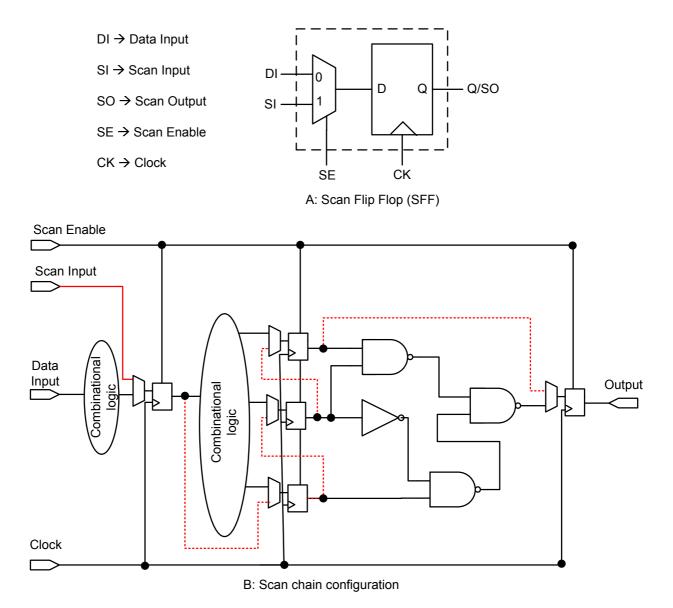

|    |                    | 1.6.2 Scan Chains                                                 | 20  |  |  |

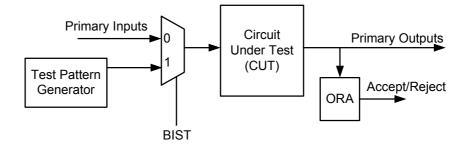

|    |                    | 1.6.3 Built-in Self-Test                                          | 22  |  |  |

|    | 1.7                | Thesis Organization                                               | 23  |  |  |

|    | 1.8                | Contributions                                                     | 24  |  |  |

| 2  | Lite               | ature Survey                                                      | 26  |  |  |

|    | 2.1                | Test for Multi-Voltage Design: Bridge Defect                      | 27  |  |  |

|    |                    | 2.1.1 Resistive Bridge Behavior at Single V <sub>dd</sub> Setting | 27  |  |  |

|    |                    | 2.1.2 Resistive Bridge Behavior at Multi-V <sub>dd</sub> Settings | 33  |  |  |

|    | 2.2                | Test for Multi-Voltage Design: Open Defect                        | 37  |  |  |

|    |                    | 2.2.1 Testing Full Open Defect                                    | 38  |  |  |

|    |                    | 2.2.2 Testing Resistive Open Defect                               | 41  |  |  |

|    | 2.3                | DFT for Low Power Design                                          | 46  |  |  |

|    |                    | 2.3.1 Multi-Voltage Aware Scan                                    | 46  |  |  |

|    |                    | 2.3.2 Power-Managed Scan Using Adaptive Voltage Scaling           | 48  |  |  |

|    | 2.4                | Motivation and Objectives                                         | 50  |  |  |

|   | 2.5  | Relevant Contemporary Research                                     | . 53  |

|---|------|--------------------------------------------------------------------|-------|

|   |      | 2.5.1 Impact of Voltage and Process Variation on Test Quality      | . 54  |

|   |      | 2.5.2 Voltage Scaling for Nanoscale SRAM                           | . 55  |

|   | 2.6  | Concluding Remarks                                                 | . 55  |

| 3 | Test | t Cost Reduction Using Test Points                                 | 57    |

|   | 3.1  | Introduction                                                       | . 57  |

|   | 3.2  | Motivation                                                         |       |

|   | 3.3  | Proposed Test Point Insertion Technique                            |       |

|   |      | 3.3.1 LSC Selection                                                |       |

|   |      | 3.3.2 Preliminary Test Point Insertion at the Defect Site Boundary |       |

|   |      | 3.3.3 Test Points Minimization                                     |       |

|   | 3.4  | Experimental Results                                               |       |

|   |      | 3.4.1 Test V <sub>dd</sub> Reduction Using TPI                     |       |

|   |      | 3.4.2 Impact on Timing, Area and Power                             |       |

|   | 3.5  | Concluding Remarks                                                 |       |

|   |      |                                                                    |       |

| 4 |      | t Cost Reduction Using Gate Sizing                                 | 85    |

|   | 4.1  | Introduction                                                       |       |

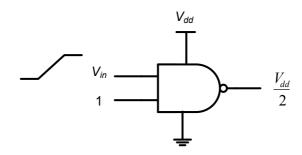

|   | 4.2  | Preliminaries                                                      |       |

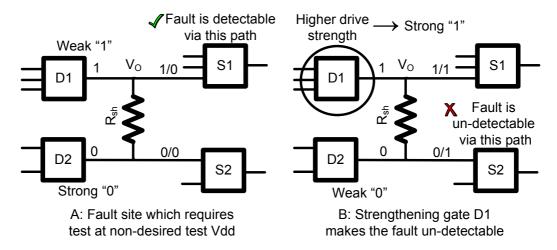

|   | 4.3  | Impact of Gate Sizing on Test V <sub>dd</sub> Reduction            |       |

|   |      | 4.3.1 Modifying Logic Threshold of Driven Gates                    |       |

|   |      | 4.3.2 Modifying Drive Strength of Driving Gates                    |       |

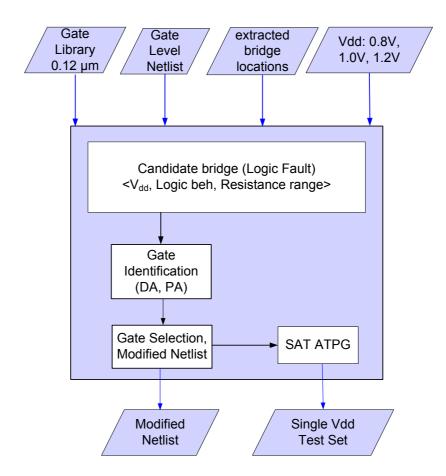

|   | 4.4  | Proposed Technique for Single $V_{dd}$ Test                        |       |

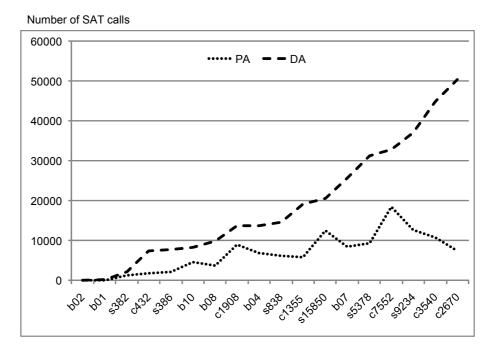

|   |      | 4.4.1 Deterministic Algorithm                                      |       |

|   |      | 4.4.2 Probabilistic Algorithm                                      |       |

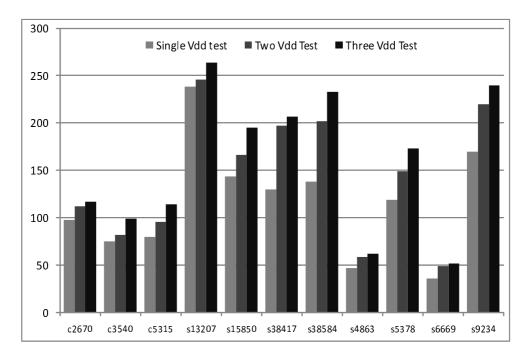

|   | 4.5  | Experimental Results                                               | . 101 |

|   |      | 4.5.1 Test $V_{dd}$ Reduction Using GS                             | . 102 |

|   |      | 4.5.2 Impact on Timing, Area and Power                             | . 110 |

|   | 4.6  | Concluding Remarks                                                 | . 113 |

| 5 | Brid | dge Defect Diagnosis                                               | 114   |

|   | 5.1  | Introduction                                                       | . 114 |

|   | 5.2  | Preliminaries                                                      |       |

|   | 5.3  | Motivations for Multi-V <sub>dd</sub> diagnosis                    |       |

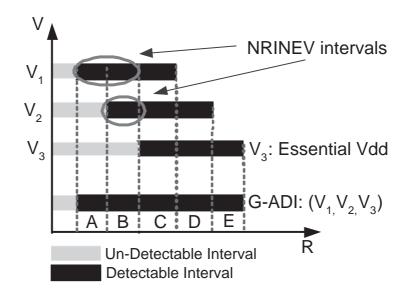

|   |      | 5.3.1 Combining Diagnosis Information                              |       |

|   |      | 5.3.2 Passing Resistance Interval                                  |       |

|   | 5.4  | Multi-V <sub>dd</sub> Diagnosis Algorithm                          |       |

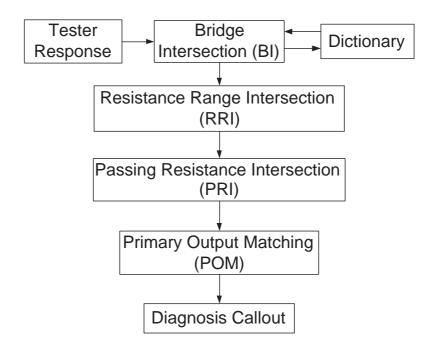

|   |      | 5.4.1 Bridge Intersection (BI)                                     |       |

|   |      | 5.4.2 Resistance Range Intersection (RRI)                          |       |

|   |      | 5.4.3 Passing Resistance Intersection (PRI)                        |       |

|   |      | 5.4.4 Primary Output Matching (POM)                                |       |

|   |      |                                                                    |       |

|   | 5.5  | Experin   | mental Results                                          | 127 |

|---|------|-----------|---------------------------------------------------------|-----|

|   |      | 5.5.1     | Diagnosis Accuracy Using Single-V <sub>dd</sub> Setting | 130 |

|   |      | 5.5.2     | Diagnosis Accuracy Using Multi-V <sub>dd</sub> Settings | 132 |

|   |      | 5.5.3     | Diagnosis Cost Minimization                             | 135 |

|   |      | 5.5.4     | Diagnosis of Hard-Shorts Using Multi- $V_{dd}$ Settings | 137 |

|   |      | 5.5.5     | Impact of High Resolution Test on Diagnosis Accuracy    | 140 |

|   | 5.6  | Conclu    | iding Remarks                                           | 141 |

| 6 | Con  | clusions  | and Future Work                                         | 143 |

|   | 6.1  | Thesis    | Contributions                                           | 143 |

|   | 6.2  | Future    | Work: PV-Aware Test                                     | 148 |

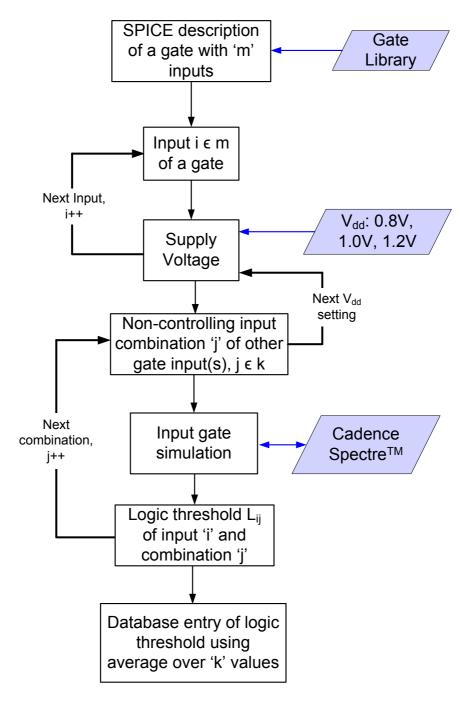

| A | Logi | c Thres   | hold Calculation                                        | 151 |

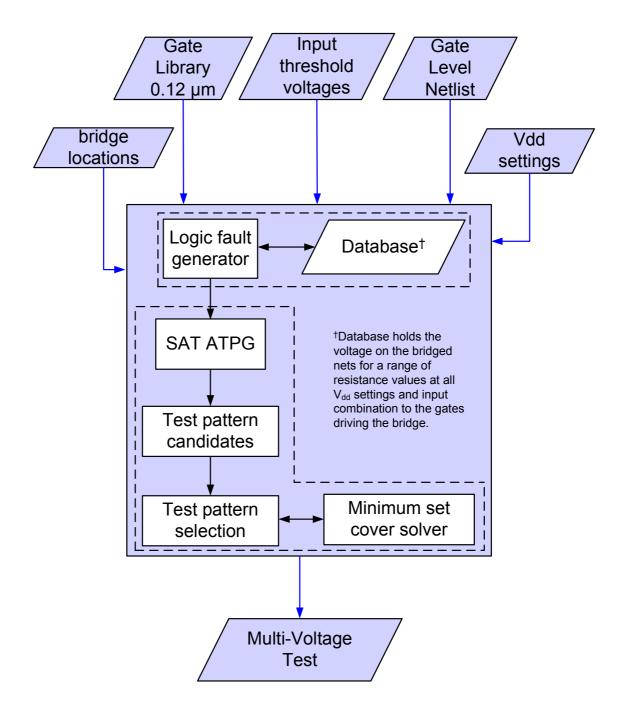

| B | Mult | ti-Voltaș | ge Test Generation                                      | 154 |

| C | ISCA | AS and    | ITC Benchmarks                                          | 157 |

| D | SPIC | CE Mod    | lels                                                    | 160 |

|   |      |           |                                                         |     |

# **List of Figures**

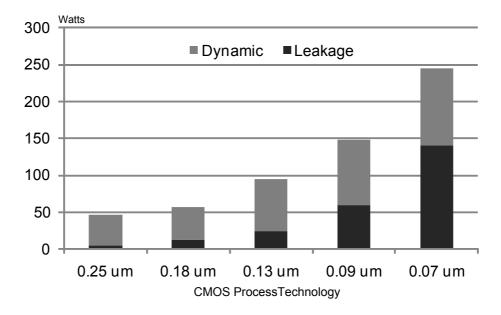

| 1.1  | Static v Dynamic Power Consumption [Smith, 2009]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

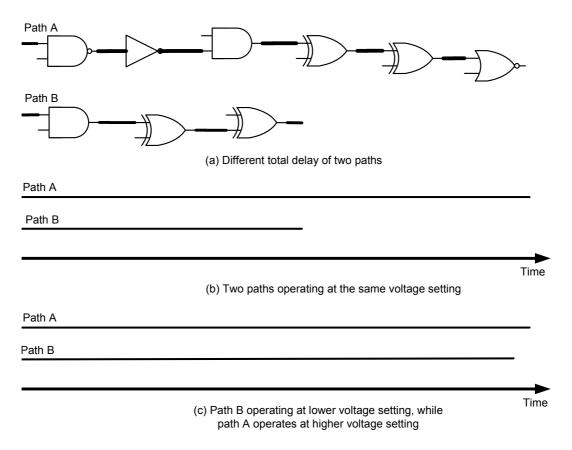

| 1.2  | Multi Voltage design principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

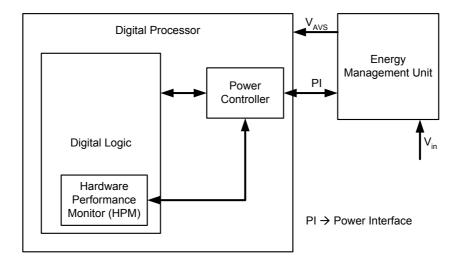

| 1.3  | Adaptive Voltage Scaling [Zarr and Taylor, 2009]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

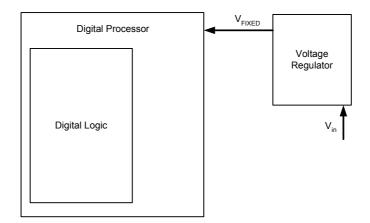

| 1.4  | Fixed Supply Voltage [Zarr and Taylor, 2009]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

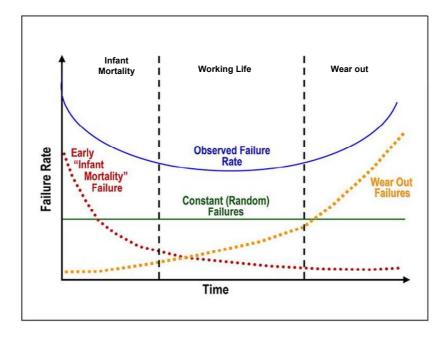

| 1.5  | Bathtub curve [Yan and English, 1997]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

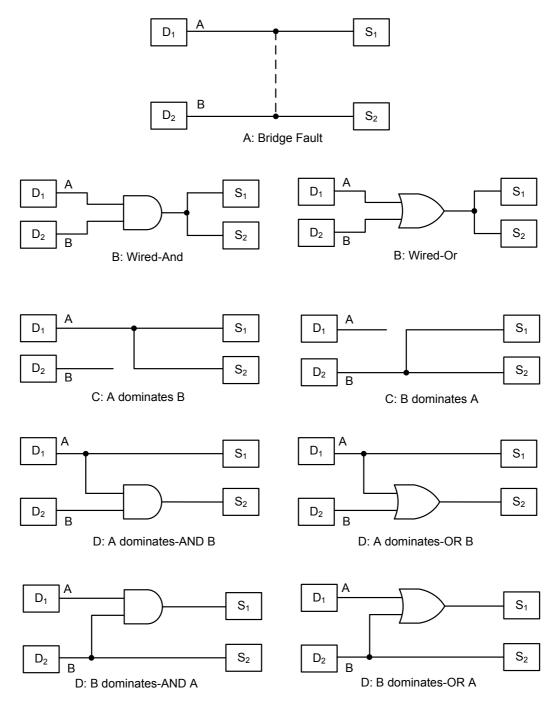

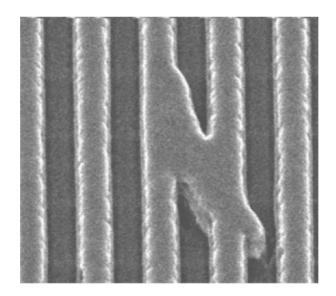

| 1.6  | Evolution of Bridge Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

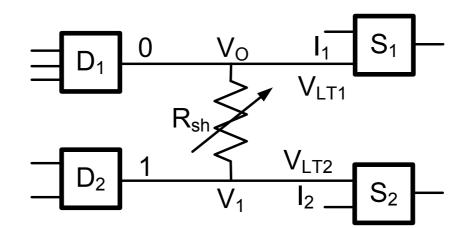

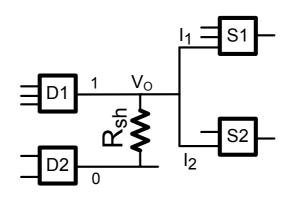

| 1.7  | Parametric bridge fault model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

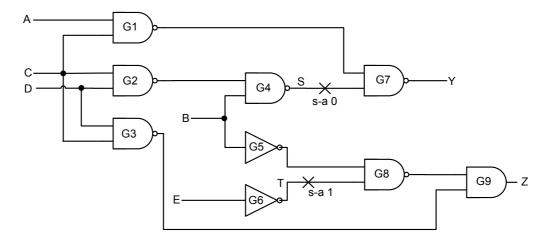

| 1.8  | C17- ISCAS Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.9  | Test Point Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.10 | (A) Scan cell architecture showing a typical scan cell and (B) Scan chain con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | figuration during test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.11 | BIST Architecture [Girard et al., 2009]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

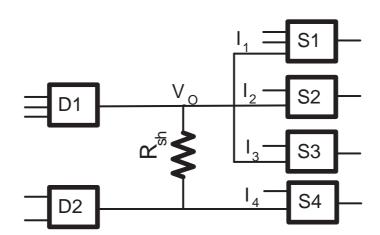

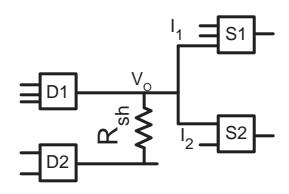

| 2.1  | Resistive Bridge [Kundu et al., 2001]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2  | Example of a Resistive Bridge fault. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

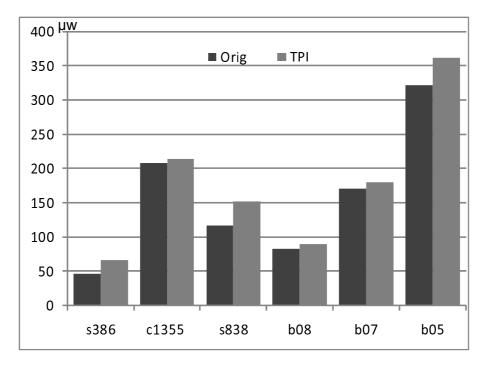

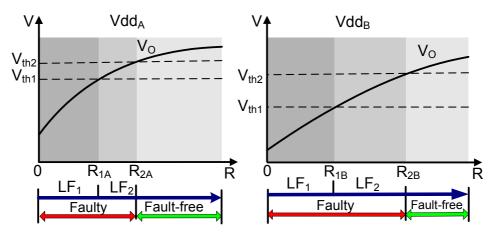

| 2.3  | Behavior of a bridge fault at a single $V_{dd}$ setting in analog and digital domains. 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

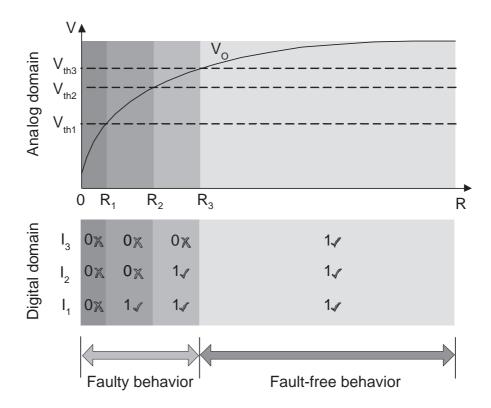

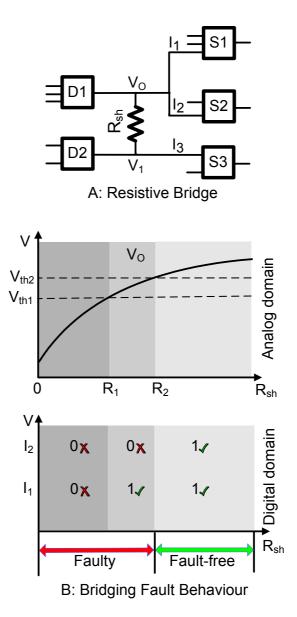

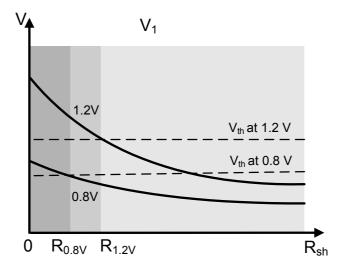

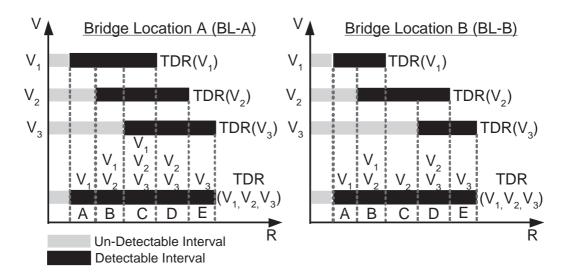

| 2.4  | Resistance values that cannot be detected at the lowest $V_{dd}$ setting [Ingelsson, 2009]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

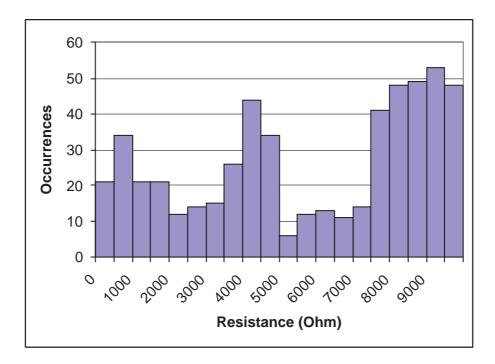

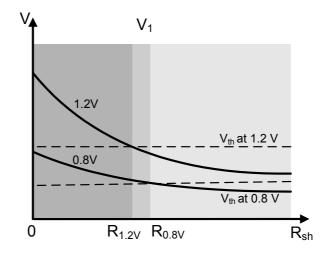

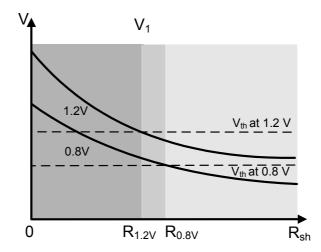

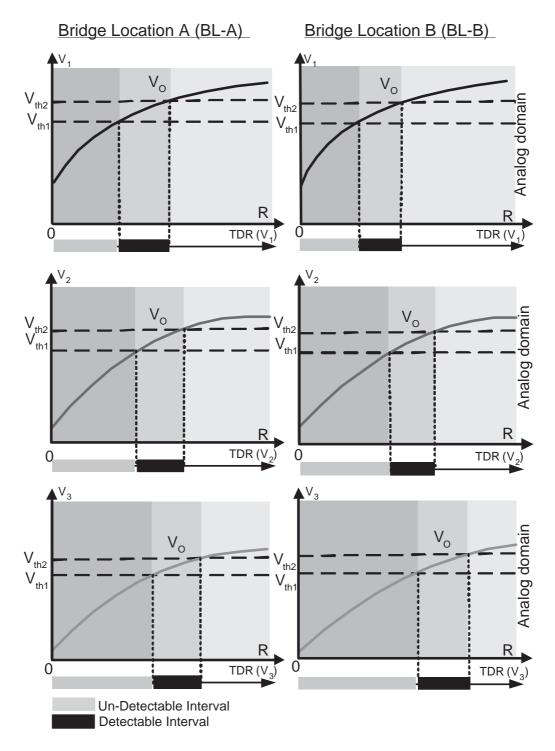

| 2.5  | Effect of supply voltage on bridge fault behavior: Analog domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.6  | Effect of supply voltage on bridge fault behavior: Digital domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

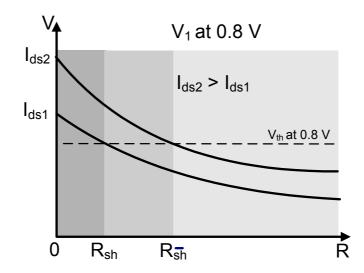

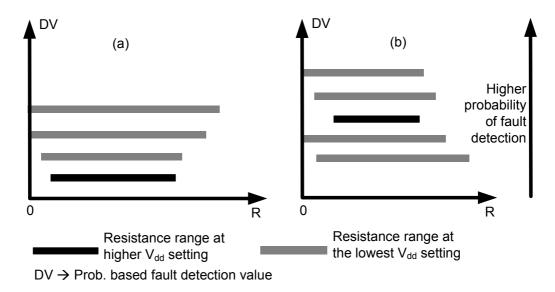

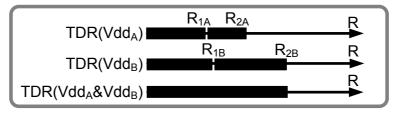

| 2.7  | Effect of supply voltage on bridge fault behavior: Observable bridge resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.0  | ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

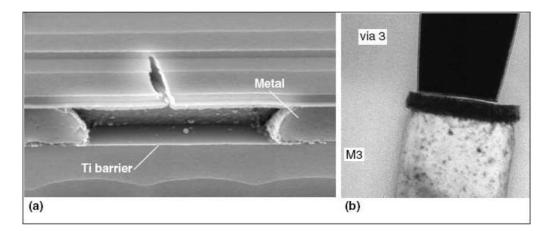

| 2.8  | Resistive or Weak Open Defects: (a) Cross section of metal open line; and (b) a resistive via [Montanes et al., 2002]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

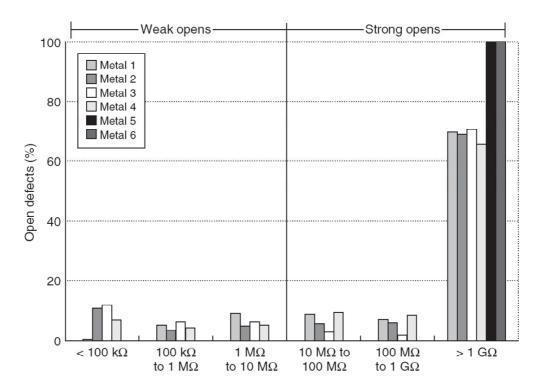

| 2.9  | The second |

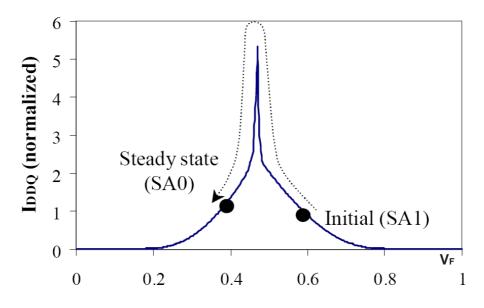

| 2.10 | Change in logic value due to gate tunneling leakage [Arumi et al., 2008a] 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

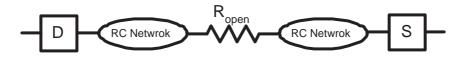

| 2.11 | Circuit Model of Resistive Open Defect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

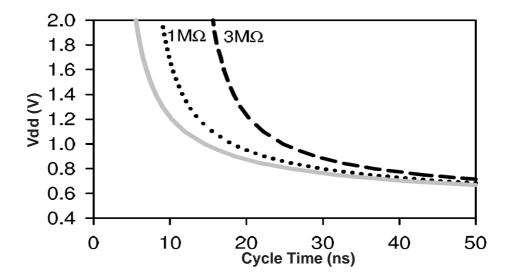

| 2.12 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | different supply voltage settings. Solid gray line shows the fault free design, while dotted and deshed lines show path delays using 1 MO and 3 MO in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | while dotted and dashed lines show path delays using 1 M $\Omega$ and 3 M $\Omega$ in the longest path [K rueman and Heiligers 2006]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | longest path [Kruseman and Heiligers, 2006]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

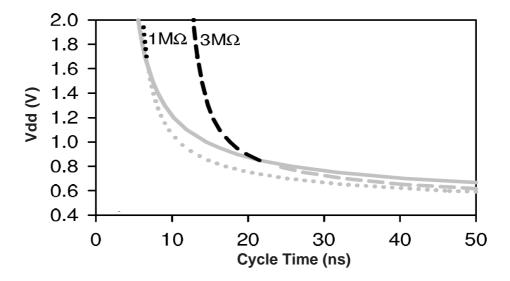

| 2.13 | Comparison of path delays due to resistive open defect in a short path at different supply voltage settings. The longest path is shown by a solid gray line (for the fault free design), while dotted and dashed lines show path delays using 1 M $\Omega$ and 3 M $\Omega$ resistances in a shorter path [Kruseman and Heiligers, 2006] | 44  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

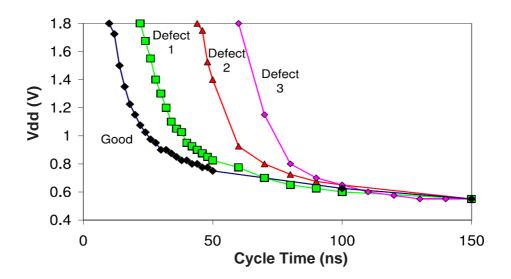

| 2.14 | Delay behavior of fault-free design (marked as "Good") in comparison to delay                                                                                                                                                                                                                                                            | ++  |

| 2.14 | defect behavior due to three different defects [Kruseman and Heiligers, 2006].                                                                                                                                                                                                                                                           | 45  |

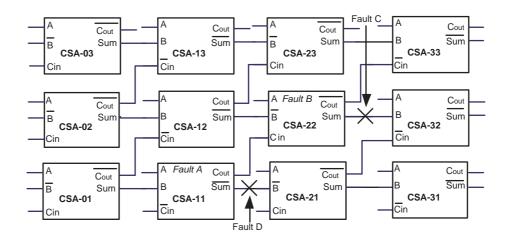

| 2.15 | 4-Level Carry-Save Adder, each adder cell is made of five transmission gates [Zain                                                                                                                                                                                                                                                       | Ali |

|      | and Zwolinski, 2006]                                                                                                                                                                                                                                                                                                                     | 45  |

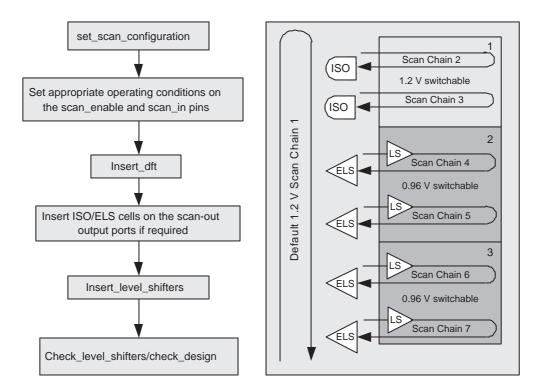

| 2.16 | DFT Synthesis flow for Multi- $V_{dd}$ design using Synopsys Design Compiler [Baby and Sarathi, 2008].                                                                                                                                                                                                                                   | 47  |

| 2.17 | Power-Aware Daisy-chaining scan path [Chickermane et al., 2008]                                                                                                                                                                                                                                                                          | 48  |

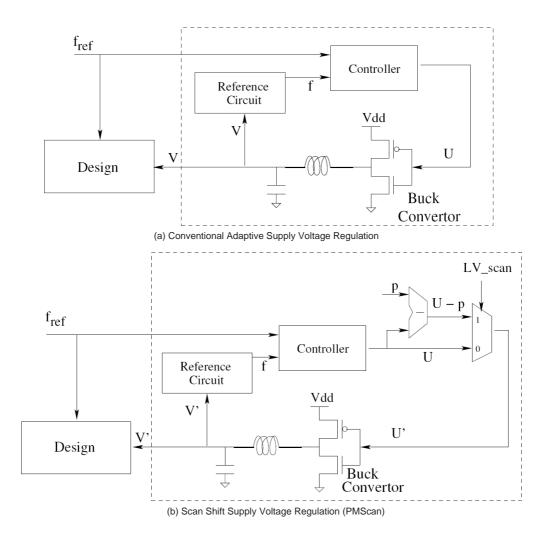

| 2.18 | Block diagram of Adaptive Supply Voltage Regulation in: (a) Conventional de-                                                                                                                                                                                                                                                             |     |

|      | sign, (b) PMScan [Devanathan et al., 2007b].                                                                                                                                                                                                                                                                                             | 50  |

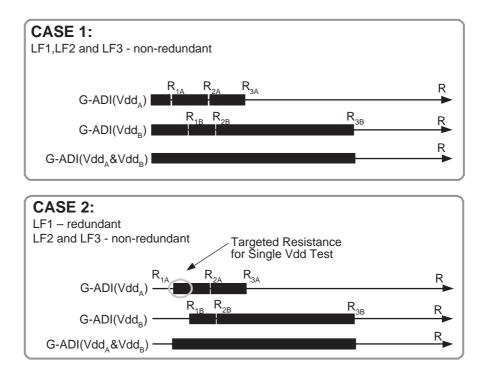

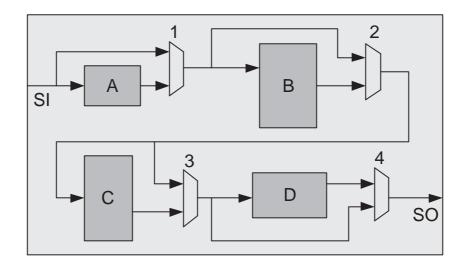

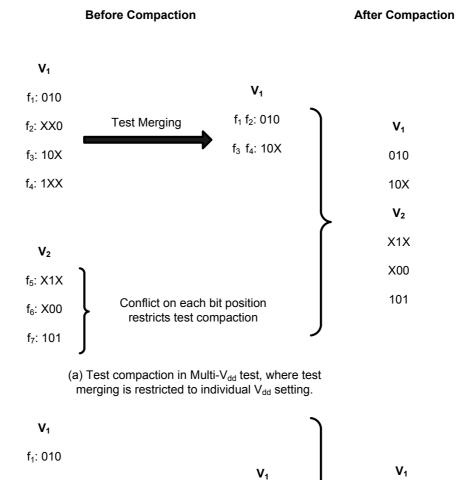

| 3.1  | Test compaction for multi-V <sub>dd</sub> test in comparison with compaction for single                                                                                                                                                                                                                                                  |     |

| 5.1  | $V_{dd}$ test                                                                                                                                                                                                                                                                                                                            | 60  |

| 3.2  | Impact on test compaction.                                                                                                                                                                                                                                                                                                               | 62  |

| 3.3  | Resistive Bridge                                                                                                                                                                                                                                                                                                                         | 63  |

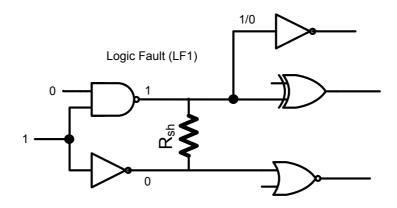

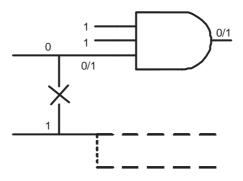

| 3.4  | Reasons for test generation at more than one $V_{dd}$ setting                                                                                                                                                                                                                                                                            | 64  |

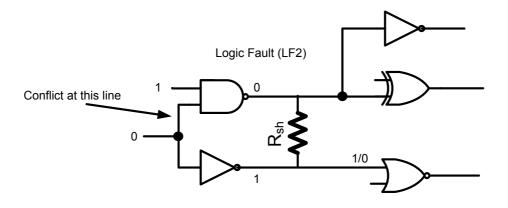

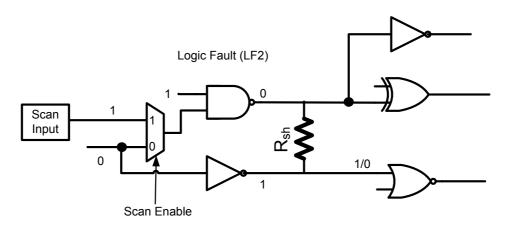

| 3.5  | Use of test points for additional controllability and reduction in test $V_{dd}$ settings                                                                                                                                                                                                                                                | 65  |

| 3.6  | Test Point Insertion                                                                                                                                                                                                                                                                                                                     | 68  |

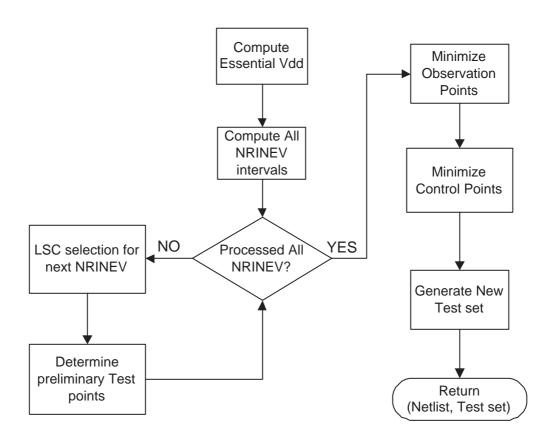

| 3.7  | Algorithmic flow of the proposed TPI technique                                                                                                                                                                                                                                                                                           | 68  |

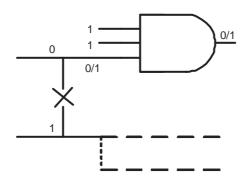

| 3.8  | Observability calculation                                                                                                                                                                                                                                                                                                                | 69  |

| 3.9  | LSC Selection                                                                                                                                                                                                                                                                                                                            | 70  |

| 3.10 |                                                                                                                                                                                                                                                                                                                                          | 72  |

| 3.11 |                                                                                                                                                                                                                                                                                                                                          | 73  |

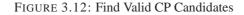

| 3.12 | Find Valid CP Candidates                                                                                                                                                                                                                                                                                                                 | 74  |

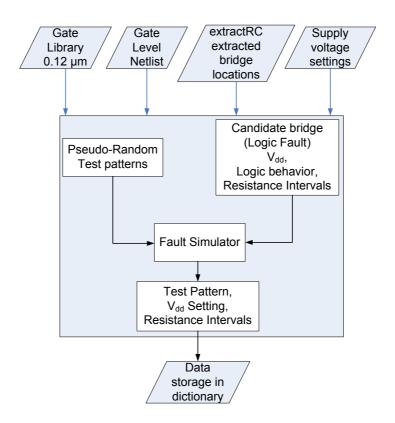

| 3.13 | Tool flow of the proposed TPI technique                                                                                                                                                                                                                                                                                                  | 77  |

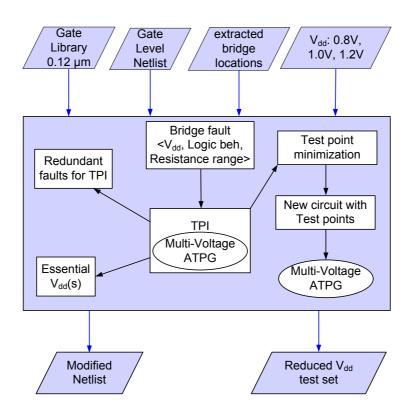

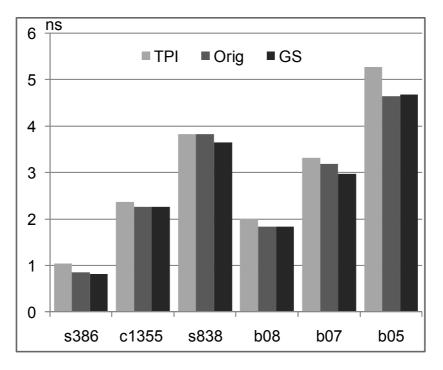

| 3.14 | Impact of TPI on timing in comparison with the original design.                                                                                                                                                                                                                                                                          | 81  |

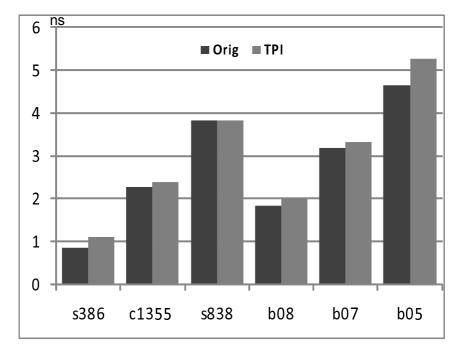

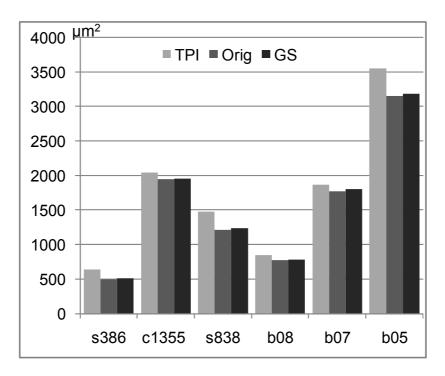

| 3.15 | Impact of TPI on area in comparison with the original design                                                                                                                                                                                                                                                                             | 82  |

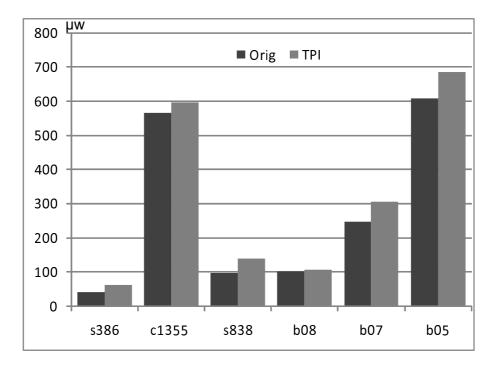

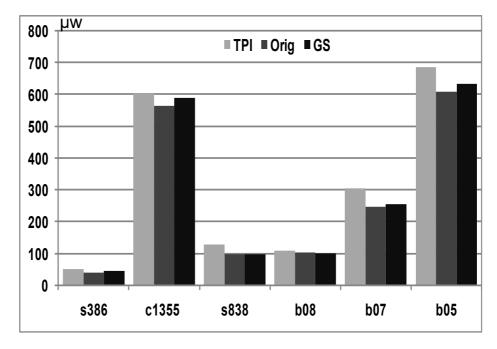

| 3.16 | Impact of TPI on dynamic power in comparison with the original design                                                                                                                                                                                                                                                                    | 82  |

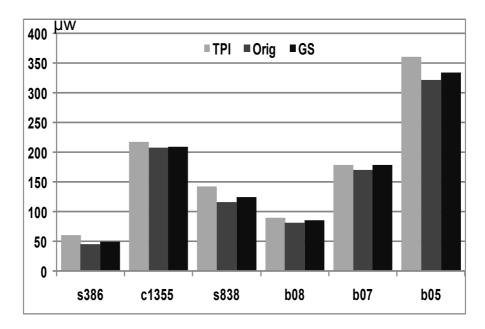

| 3.17 | Impact of TPI on leakage power in comparison with the original design                                                                                                                                                                                                                                                                    | 83  |