# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

# UNIVERSITY OF SOUTHAMPTON FACULTY OF ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Towards the Neurocomputer: An investigation of VHDL Neuron Models

By

Julian A Bailey

A thesis for the degree of Doctor of Philosophy

February 2010

# UNIVERSITY OF SOUTHAMPTON ABSTRACT

# FACULTY OF ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

# TOWARDS THE NEUROCOMPUTER: AN INVESTIGATION OF VHDL NEURON MODELS

By Julian A Bailey

The investigation of neuron structures is an incredibly difficult and complex task that yields relatively low rewards in terms of information from biological forms (either animals or tissue). The structures and connectivity of even the simplest invertebrates are almost impossible to establish with standard laboratory techniques, and even when this is possible it is generally time consuming, complex and expensive. Recent work has shown how a simplified behavioural approach to modelling neurons can allow "virtual" experiments to be carried out that map the behaviour of a simulated structure onto a hypothetical biological one, with correlation of behaviour rather than underlying connectivity. The problems with such approaches are numerous. The first is the difficulty of simulating realistic aggregates efficiently, the second is making sense of the results and finally, it would be helpful to have an implementation that could be synthesised to hardware for acceleration. This work presents a VHDL implementation of a neuron model which is verified through simulations of the Caenorhabditis Elegans (C.Elegans) locomotory system. The C.Elegans system is synthesized into hardware showing a massive improvement in simulation time because the hardware design runs in real-time, meaning a 19 second simulation takes 19 seconds vs. the 1.5 hours taken by the CAD simulation.

Logic cells using the VHDL neuron model are produced and verified through simulation to demonstrate the deterministic side of modelling neuronal circuits. The C.Elegans design is then analysed using these neuron logic cells to produce a simple logic version of C.Elegans which produces the same outputs given the same inputs as the Neuron C.Elegans model.

Finally the hardware neuron concept was extended to the case of a general purpose programmable neuron array designed to have 100 neurons and 200 synapses The configuration of the neurons and synapses is written to the device over a simple SPI bus, with a second SPI bus used to simultaneously write enable data and read the current states of the neuron outputs. The design was demonstrated to work correctly using the reference C.Elegans design.

# **Table of Contents**

| ABSTRACT                                          | .2             |

|---------------------------------------------------|----------------|

| Index of figures                                  | .9             |

| Index of Tables                                   | 13             |

| Declaration of Authorship                         | 14             |

| Acknowledgements                                  | 15             |

| Chapter 1: Introduction                           | 16             |

| Chapter 2: Basic Neuroscience                     | 22             |

| 2.1 Structure of the Nervous System               | 23             |

| 2.2 Neuronal Communication                        | 28             |

| 2.2.1 The Membrane and Resting Membrane Potential | 28             |

| 2.2.2 Changing the membrane Potential             | 29             |

| 2.2.3 Action Potentials                           | 29             |

| 2.3 Sensory Receptors                             | 32             |

| 2.3.1 Nociceptors (Pain Receptors)                | 33             |

| 2.3.2 Chemoreceptors                              | 33             |

| 2.3.3 Mechanoreceptors                            | 33             |

| 2.3.4 Photoreceptors                              | 34             |

| 2.4 Muscle                                        | 35             |

| 2.4.1 Striated Muscle Structure                   | 35             |

| 2.4.2 Sliding Filament Model                      | 36             |

| 2.4.3 From Action Potential to Movement           | 39             |

| 2.5 Summary                                       | <del>1</del> 0 |

| Chapter 3: Modelling & Simulation                 | 11             |

| 3.1 Cla    | asses of Model                     | 41  |

|------------|------------------------------------|-----|

| 3.1.1      | Kinetic Molecular (Markov) Models  | 42  |

| 3.1.2      | Compartmental Models               | 45  |

| 3.1.3      | Cellular Automata Models           | 47  |

| 3.1.4      | Integrate & Fire Models            | 53  |

| 3.1.5      | Binary Models                      | 58  |

| 3.2 Sin    | nulation Techniques                | 59  |

| 3.2.1      | Continuous Time                    | 60  |

| 3.2.2      | Discrete Time                      | 62  |

| 3.2.3      | Conserved Energy or Signal Flow    | 64  |

| 3.3 Su     | mmary                              | 66  |

| Chapter 4: | The VHDL Neuron Model              | 69  |

| 4.1 Int    | roduction to VHDL                  | 70  |

| 4.1.1      | Model Entity                       | 71  |

| 4.1.2      | Model Architecture                 | 72  |

| 4.1.3      | VHDL Example                       | 74  |

| 4.2 Mo     | odel Structure Overview            | 75  |

| 4.3 Ne     | uron Sub Blocks                    | 76  |

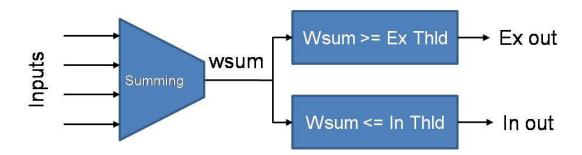

| 4.3.1      | Threshold Block                    | 76  |

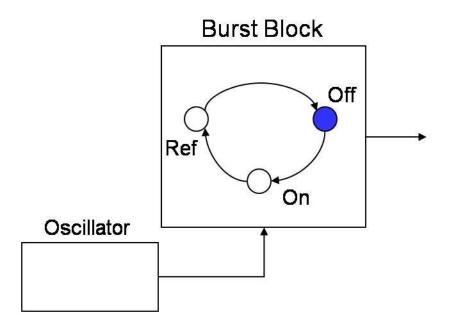

| 4.3.2      | Burst Block                        | 89  |

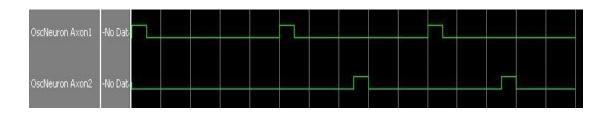

| 4.3.3      | Oscillator Block                   | 97  |

| 4.4 Ne     | uron Model Types                   | 101 |

| 4.4.1      | Neuron 1 (Activated By Synapses)   | 102 |

| 4.4.2      | Neuron 2 (Activated By Oscillator) | 106 |

| 4.5 Syr    | napse Model                        | 109 |

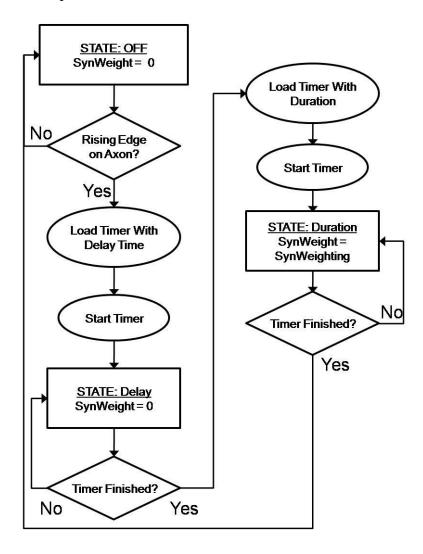

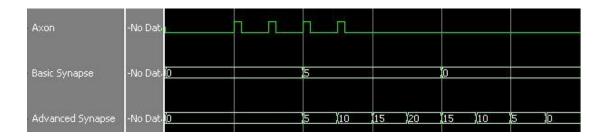

| 4.5.1      | Basic Synapse                      | 110 |

| 4.5.2               | Advanced Synapse                                 | 113 |

|---------------------|--------------------------------------------------|-----|

| 4.5.3               | Synapse Model Discussion                         | 115 |

| 4.6 Th              | e "LibNeuron" VHDL Library                       | 116 |

| 4.7 Su              | mmary                                            | 118 |

| Chapter 5:          | C Elegans Locomotion                             | 120 |

| 5.1 C I             | Elegans                                          | 121 |

| 5.2 The             | e Locomotory System                              | 122 |

| 5.3 The             | e Model                                          | 126 |

| 5.4 Lo              | comotion Unit Implementation                     | 132 |

| 5.4.1               | Design Variations                                | 133 |

| 5.4.2               | The VHDL Entity Definition                       | 134 |

| 5.4.3               | Instantiation Example                            | 135 |

| 5.5 Im <sub>j</sub> | plementation – LibElegans VHDL Library           | 136 |

| 5.6 C.              | Elegans Locomotion Model Entity                  | 138 |

| 5.7 Sin             | nulation                                         | 139 |

| 5.7.1               | Results – Forward/Backward Locomotion            | 140 |

| 5.7.2               | Results – Coiling                                | 142 |

| 5.8 Dis             | scussion of Simulation Results                   | 144 |

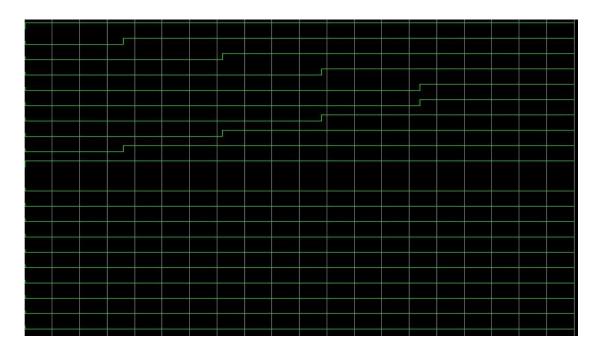

| 5.8.1               | Glitches in Simulation Data                      | 145 |

| 5.8.2               | Threshold Synchronisation                        | 146 |

| 5.8.3               | Simulation Run Time                              | 147 |

| 5.9 Syı             | nthesis of the Design - RoboElegans              | 149 |

| 5.9.1               | RoboElegans Results- Forward/Backward Locomotion | 150 |

| 5.9.2               | RoboElegans Results- Coiling Locomotion          | 151 |

| 5.10                | Synthesis Discussion                             | 153 |

| 5.10.1              | Glitches                                         | 154 |

| 5.10.2       | Performance                                      | 154 |

|--------------|--------------------------------------------------|-----|

| 5.10.3       | Comparison with the MBED Model                   | 155 |

| 5.11 S       | ummary                                           | 157 |

| Chapter 6: 1 | Neuron Logic Cells                               | 159 |

| 6.1 Ider     | ntification of Logic: C Elegans Locomotion model | 159 |

| 6.1.1        | AND Gate                                         | 160 |

| 6.1.2        | OR Gate                                          | 162 |

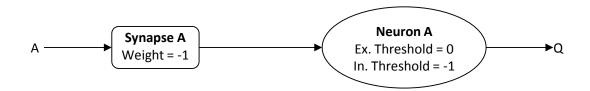

| 6.1.3        | NOT Gate (Inversion)                             | 164 |

| 6.1.4        | Simple Latch                                     | 165 |

| 6.2 Log      | ric C. Elegans                                   | 167 |

| 6.3 Log      | cicElegans Locomotion Model Entity               | 172 |

| 6.4 Sim      | ulation                                          | 173 |

| 6.4.1        | Results – Forward/Backward Locomotion            | 174 |

| 6.4.2        | Results – Coiling                                | 176 |

| 6.5 Syn      | thesis of the Logic Model                        | 177 |

| 6.5.1        | Synthesis Results - Forward/Backward             | 177 |

| 6.5.2        | Synthesis Results - Coiling                      | 179 |

| 6.6 Disc     | cussion                                          | 180 |

| 6.7 Sun      | nmary                                            | 184 |

| Chapter 7: I | Programmable Neuron Array                        | 186 |

| 7.1 Bas      | ic Design                                        | 187 |

| 7.1.1        | Neuron 1                                         | 190 |

| 7.1.2        | Synapses                                         | 191 |

| 7.1.3        | Advanced Synapses                                | 193 |

| 7.2 Stin     | nulus                                            | 194 |

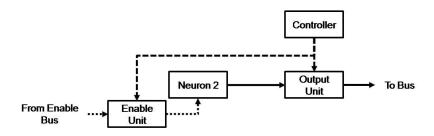

| 721          | Nauron 2                                         | 10/ |

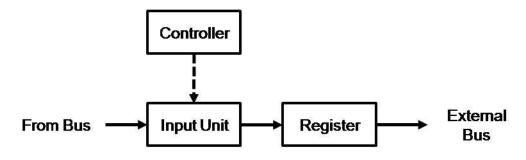

| 7.3 Rec    | cording                                        | 195 |

|------------|------------------------------------------------|-----|

| 7.4 Net    | uron Enable Input                              | 196 |

| 7.5 Coi    | nfiguration                                    | 196 |

| 7.5.1      | Neuron 1                                       | 196 |

| 7.5.2      | Neuron 2                                       | 197 |

| 7.5.3      | Synapse                                        | 198 |

| 7.5.4      | Recording Units                                | 199 |

| 7.5.5      | Address Unit                                   | 199 |

| 7.5.6      | Configuration Structure                        | 200 |

| 7.6 Ext    | ernal Buses                                    | 201 |

| 7.7 Sim    | nulation                                       | 202 |

| 7.8 Sim    | nulation Results                               | 203 |

| 7.8.1      | Configuration                                  | 203 |

| 7.8.2      | External Bus                                   | 204 |

| 7.8.3      | Neuron Operation                               | 205 |

| 7.9 Dis    | cussion                                        | 206 |

| 7.9.1      | Running PNA in hardware                        | 206 |

| 7.9.2      | Comparison with MBED                           | 208 |

| 7.10 S     | Summary                                        | 209 |

| Chapter 8: | Summary, Conclusion & Future Work              | 211 |

| 8.1 Sur    | nmary                                          | 211 |

| 8.2 Coi    | nclusion                                       | 215 |

| 8.3 Fut    | ure Work                                       | 219 |

| 8.3.1      | Synaptic Plasticity                            | 219 |

| 8.3.2      | C.Elegans Touch Circuits and Touch Sensitivity | 220 |

| 833        | Muscle Modelling using VHDL-AMS                | 221 |

| 8.3.    | 4 PNA Internal Bus                          | 222 |

|---------|---------------------------------------------|-----|

| Referen | ces                                         | 224 |

| Append  | ix A: Analysis of Microelectrode Array Data | 229 |

| A.1     | The BioCell System                          | 230 |

| A.2     | Neuron Cultures <sup>1</sup>                | 231 |

| A.3     | Data Collection <sup>1</sup>                | 232 |

| A.4     | Data Analysis                               | 233 |

| A.4     | .1 Spike Detection & Counting               | 235 |

| A.5     | Correlation                                 | 236 |

| A.6     | Results                                     | 237 |

| A.7     | Discussion                                  | 240 |

| A.8     | Conclusion                                  | 241 |

| A.8     | 3.1 Future work in this area                | 242 |

| Append  | ix B: Publications                          | 244 |

# **Index of figures**

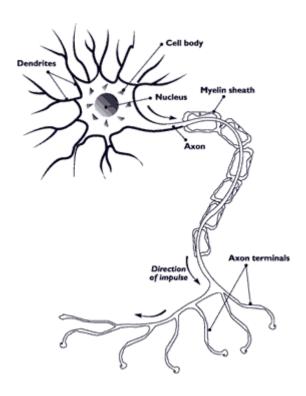

| Figure 2-1: Diagram of a neuron [17]                                     | 24         |

|--------------------------------------------------------------------------|------------|

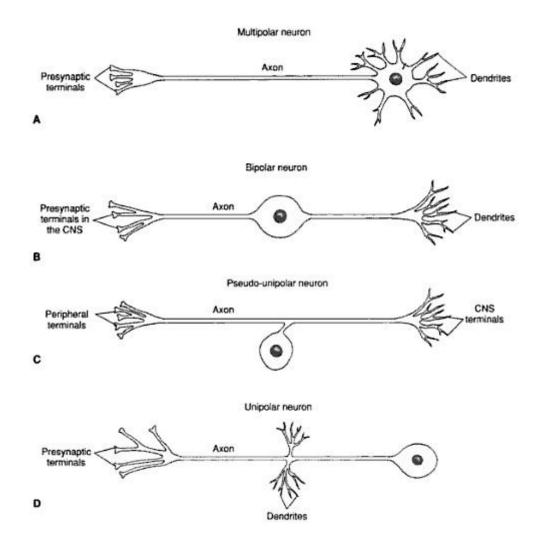

| Figure 2-2: Different Neuron Morphologies (A) Multipolar Neuron (B       | ) Bipolar  |

| Neuron (C) Pseudo-Unipolar Neuron and (D) Unipolar Neuro                 | n [32] .25 |

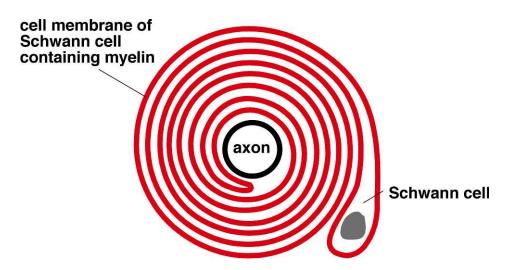

| Figure 2-3: Schwann Cell shown wrapped around an axon [33]               | 26         |

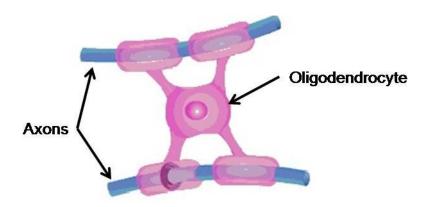

| Figure 2-4: An Oligodendrocyte Cell shown with processes wrapped around  | axons.27   |

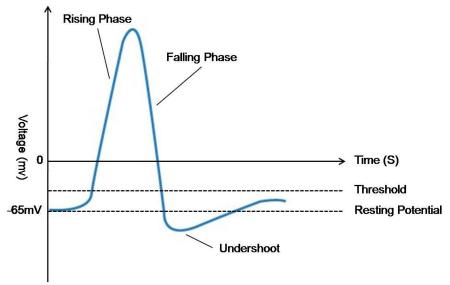

| Figure 2-5: Phases of an Action Potential                                | 30         |

| Figure 2-6: The propagation of an action potential.                      | 31         |

| Figure 2-7: A photograph of striated muscle [36].                        | 35         |

| Figure 2-8: A schematic diagram of a Myofibril.                          | 36         |

| Figure 2-9: The filament lattice structure of the Sarcomere [6]          | 37         |

| Figure 2-10: The Classical Sliding-filament swinging cross-bridge model  | of muscle  |

| contraction [37]                                                         | 38         |

| Figure 3-1: The Scale of Neuron Modelling                                | 42         |

| Figure 3-2: Kinetic Model for Pre-synaptic Neurotransmitter Release      | 43         |

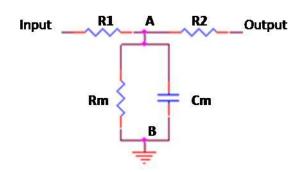

| Figure 3-3 : Compartmental Model Segment                                 | 45         |

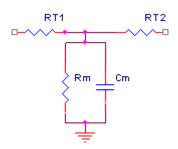

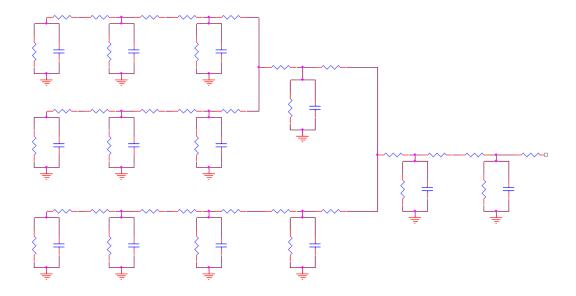

| Figure 3-4 : Compartmental Model for a Dendritic Segment                 | 46         |

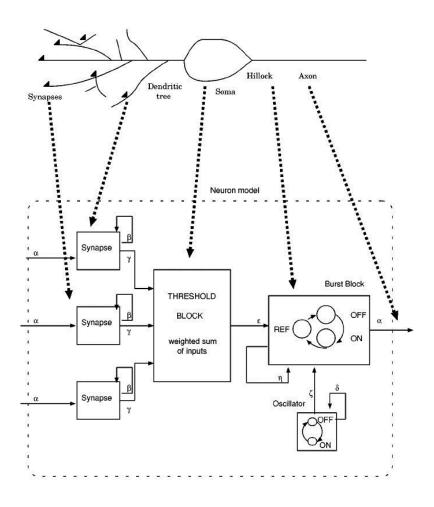

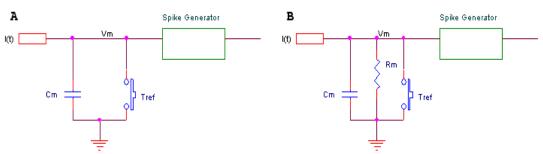

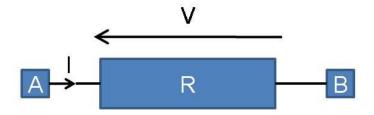

| Figure 3-5: Message-Based Event-Driven Neuron Model[11]                  | 50         |

| Figure 3-6: The Perfect Integrate & Fire Model (A) and the Leaky Integra | ate & Fire |

| Model (B)                                                                | 54         |

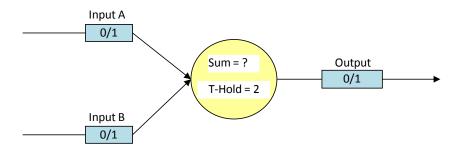

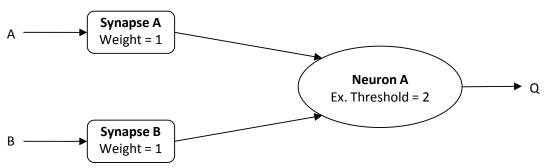

| Figure 3-7: The McCulloch-Pitts Binary Neuron                            | 58         |

| Figure 3-8: Compartmental Model Continuous time example                  | 61         |

| Figure 3-9: Signal Flow Model Example                                    | 64         |

| Figure 3-10: Conserved Energy Model Example                              | 64         |

| Figure 4-1: VHDL Entity Definition Example                               | 71         |

| Figure 4-2: Basic Architecture Structure                                 | 72         |

| Figure 4-3: Declaration of Internal Signals in the Architecture          | 73         |

| Figure 4-4: Simple architecture logic statements                         | 74         |

| Figure 4-5: Example Circuit                                              | 74         |

| Figure 4-6: Simple VHDL Model Example                                    | 75         |

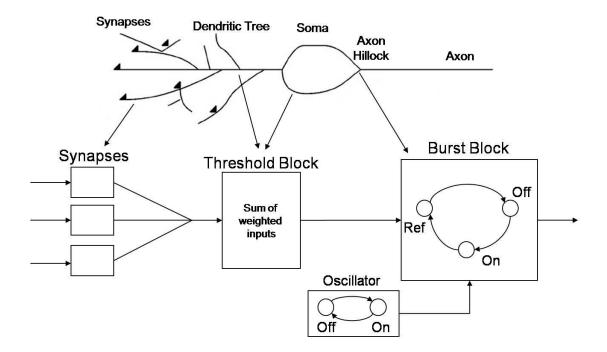

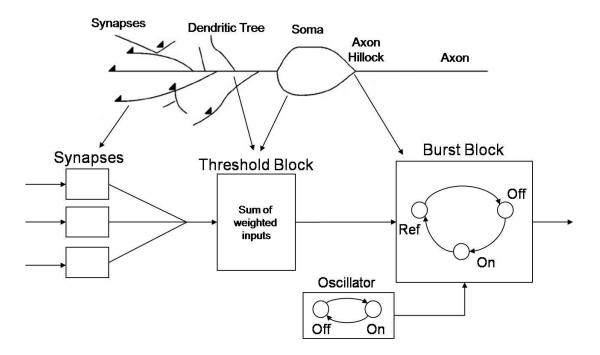

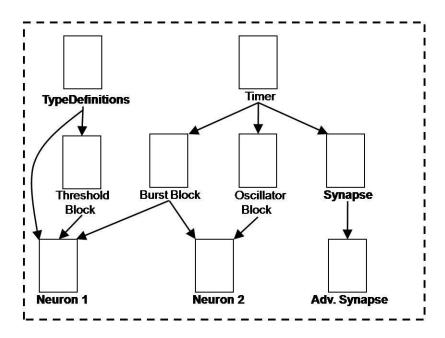

| Figure 4-7: The VHDL neuron model                                        | 76         |

| Figure 4-8: Threshold Block Overview                                     | 77         |

| Figure 4-9: Threshold Block VHDL Entity Definition                 | 78  |

|--------------------------------------------------------------------|-----|

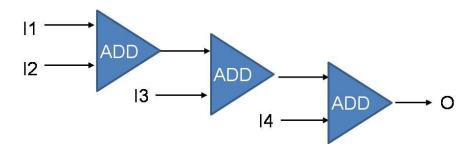

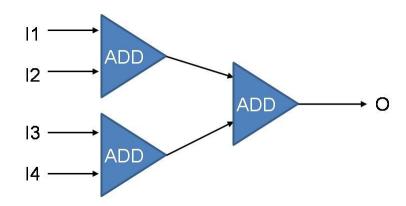

| Figure 4-10: Unbalanced Tree Adder                                 | 79  |

| Figure 4-11: Balanced Tree Adder                                   | 79  |

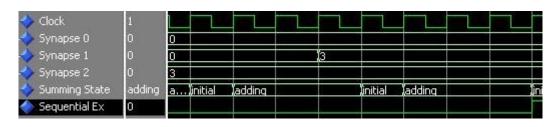

| Figure 4-12: Sequential Threshold Block Flow                       | 81  |

| Figure 4-13: Single Input Threshold Block Simulation               | 82  |

| Figure 4-14: Single input simulation showing the signal lag        | 83  |

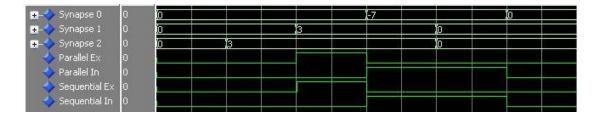

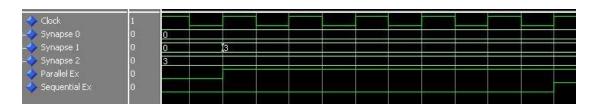

| Figure 4-15: Three Input Threshold Block Simulation                | 84  |

| Figure 4-16: Three Input Threshold Block Showing Lag between the   | Two |

| Configurations                                                     | 85  |

| Figure 4-17: Three Input Threshold Block Explaining Reason for Lag | 85  |

| Figure 4-18: Threshold Synchronisation Example                     | 86  |

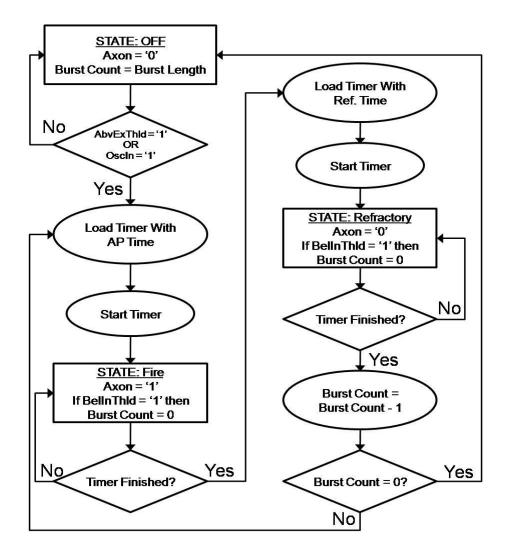

| Figure 4-19: VHDL Entity Definition for the Burst Block            | 89  |

| Figure 4-20: Burst Block State Machine Flow                        | 91  |

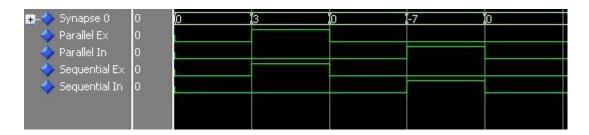

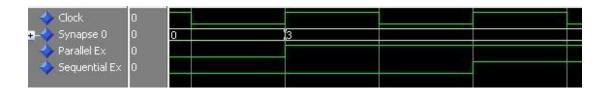

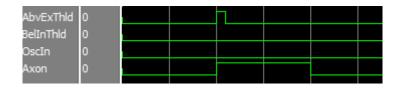

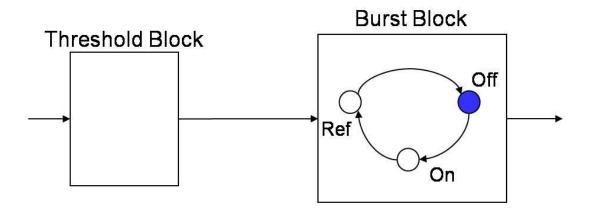

| Figure 4-21: Activation of Burst Block by AbvExThld                | 93  |

| Figure 4-22: Activation of Burst Block by OscIn                    | 93  |

| Figure 4-23: Train of 5 Action Potentials from a single activation | 94  |

| Figure 4-24: Truncation of a Burst of 5 AP's by BelInThld          | 95  |

| Figure 4-25: Oscillator Block Entity Definition                    | 97  |

| Figure 4-26: Oscillator Block Flow                                 | 98  |

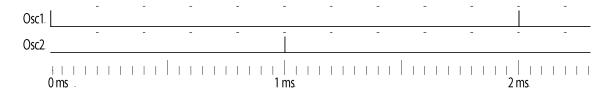

| Figure 4-27: Simulation of Oscillator Block                        | 100 |

| Figure 4-28: Neuron Model Overview                                 | 101 |

| Figure 4-29: Neuron 1 Implementation                               | 102 |

| Figure 4-30: Neuron 1 Entity Definition                            | 103 |

| Figure 4-31: Simulation of Neuron1                                 | 104 |

| Figure 4-32: Simulation of Neuron1 with early termination of burst | 105 |

| Figure 4-33: Implementation of Neuron 2                            | 106 |

| Figure 4-34: Neuron 2 Entity Definition                            | 107 |

| Figure 4-35: Simulation of Neuron 2                                | 108 |

| Figure 4-36: Synapse Entity Definition                             | 110 |

| Figure 4-37: Synapse Flow                                          | 111 |

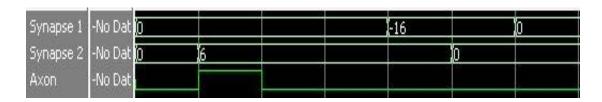

| Figure 4-38: Simulation of the Synapse                             | 112 |

| Figure 4-39: Advanced Synapse Entity                               | 114 |

| Figure 4-40: Advanced Synapse Simulation                           | 114 |

| Figure 4-41: LibNeuron VHDL Library                                             | 117 |

|---------------------------------------------------------------------------------|-----|

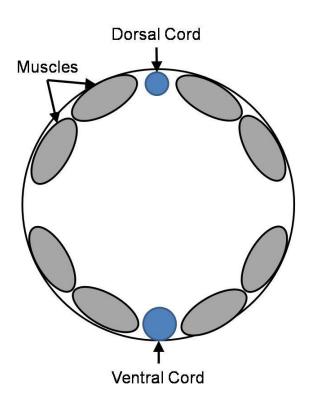

| Figure 5-1: Cross Sectional Structure of the Body Muscles in C. Elegans         | 122 |

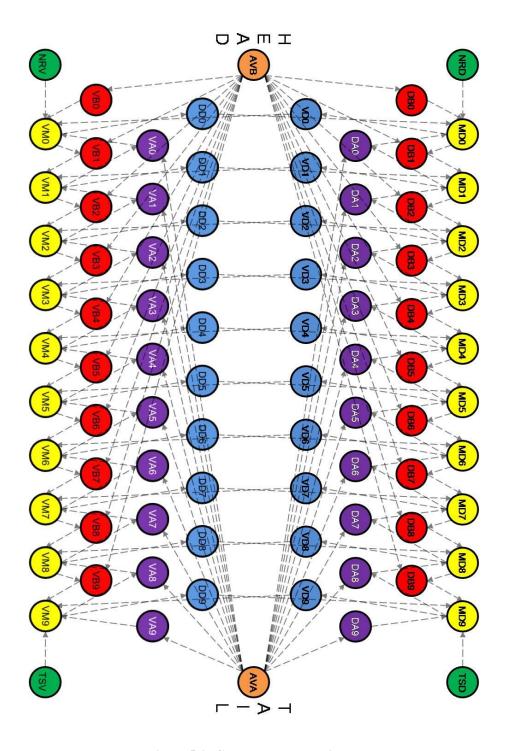

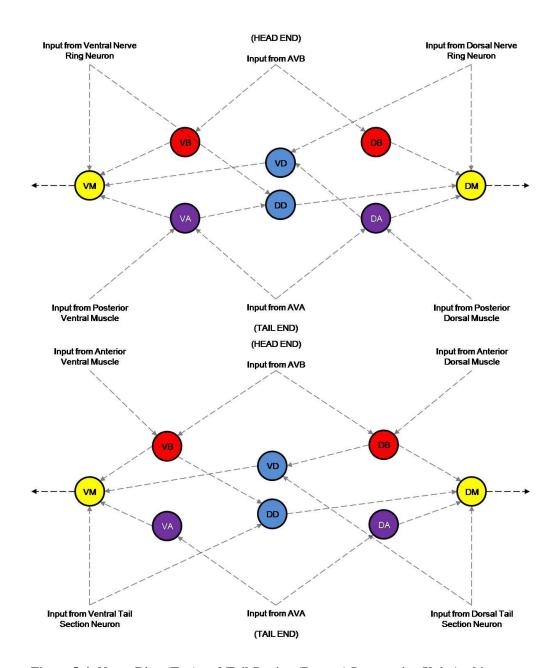

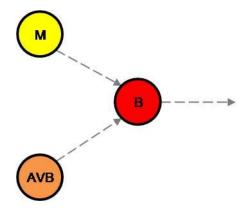

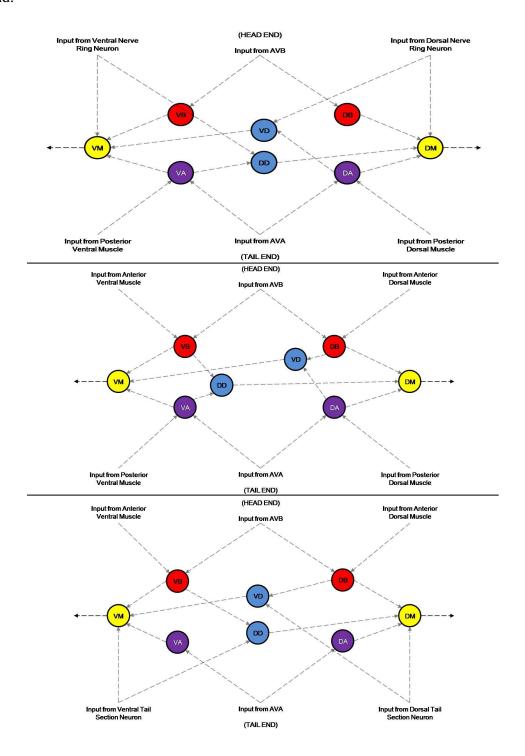

| Figure 5-2: C. Elegans Locomotion Model                                         | 129 |

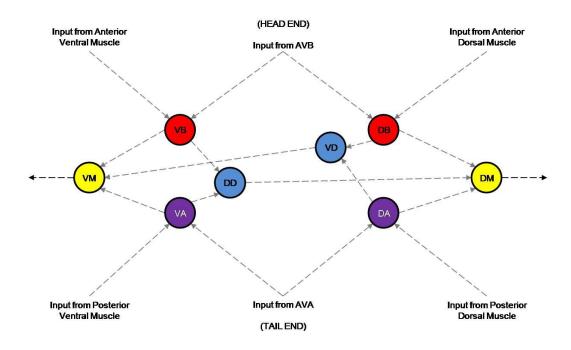

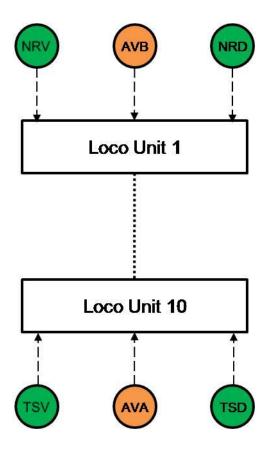

| Figure 5-3: C Elegans Locomotion Unit Structure                                 | 132 |

| Figure 5-4: Nerve Ring (Top) and Tail Section (Bottom) Locomotion               | Uni |

| Architectures                                                                   | 133 |

| Figure 5-5: Locomotion Unit Entity Definition                                   | 134 |

| Figure 5-6: Locomotion Unit Instantiation                                       | 135 |

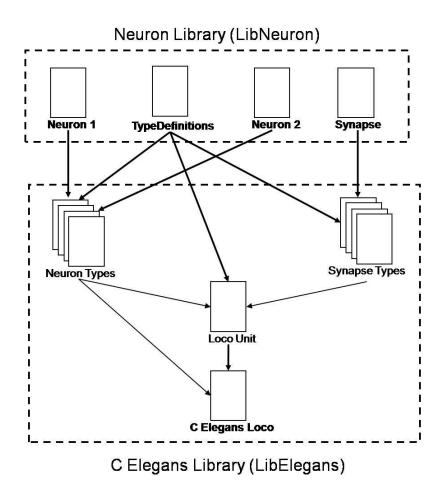

| Figure 5-7: LibElegans VHDL Library Structure                                   | 137 |

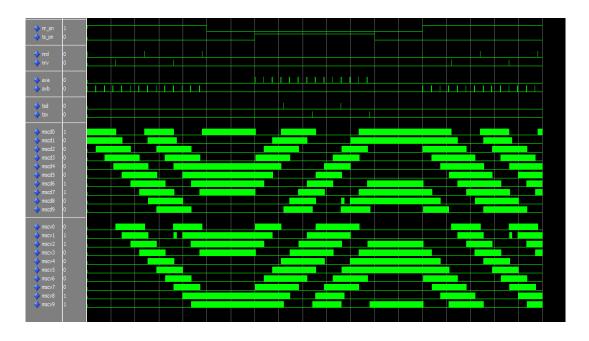

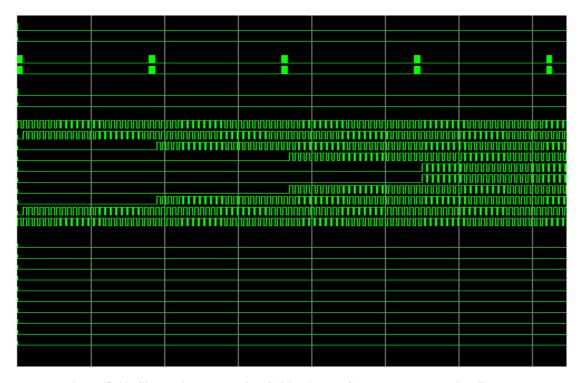

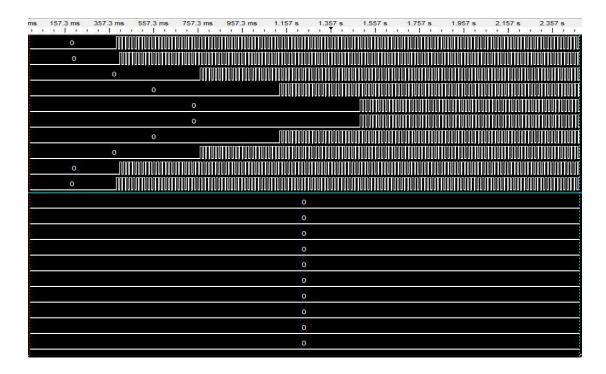

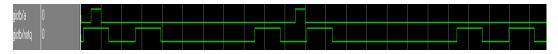

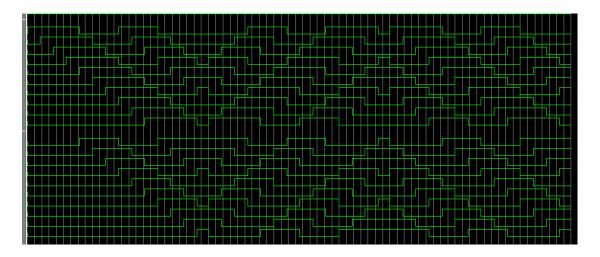

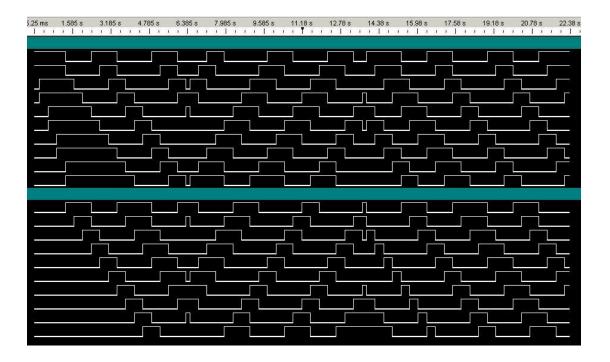

| Figure 5-8: Simulation results from the C Elegans Locomotion system             | 140 |

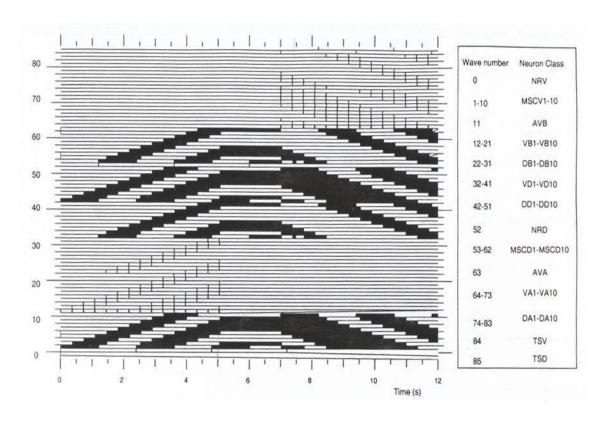

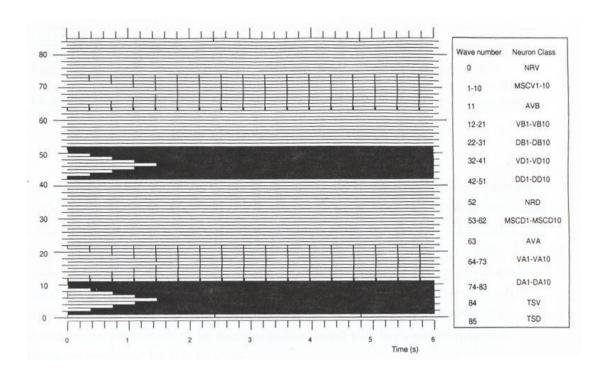

| Figure 5-9: Previous results for the locomotion model obtained by Claverol [11] | 142 |

| Figure 5-10: Simulation results for Coiling in the C Elegans Locomotion System  | 143 |

| Figure 5-11: Previous result for Coiling Locomotion from Claverol [11]          | 144 |

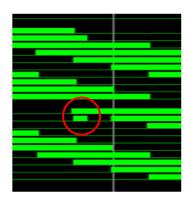

| Figure 5-12: Locomotion model glitch (circled)                                  | 145 |

| Figure 5-13: C Elegans Locomotion Design Running on an FPGA                     | 150 |

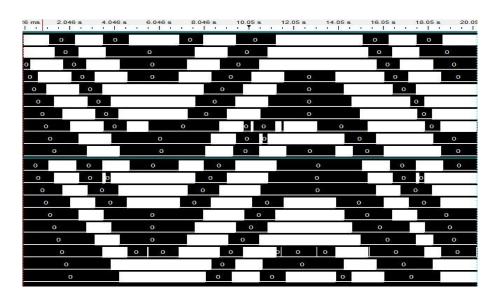

| Figure 5-14: Coiling C Elegans Locomotion Design Running on an FPGA             | 152 |

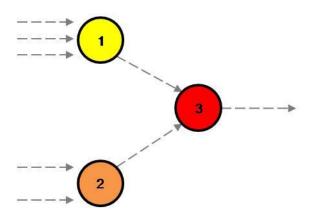

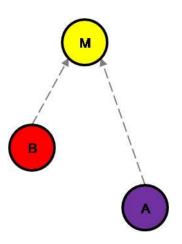

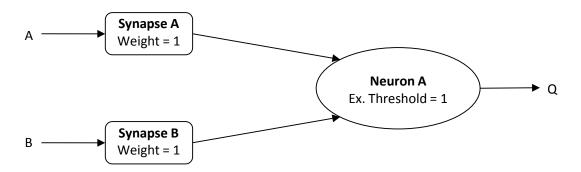

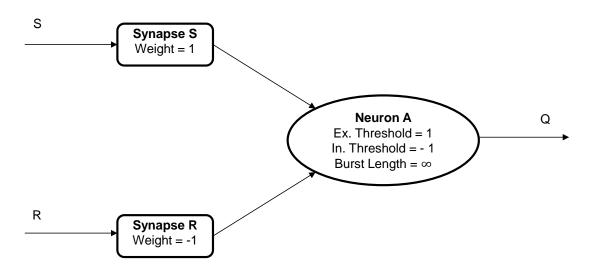

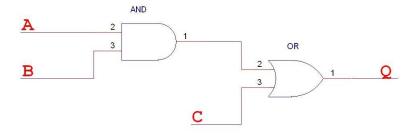

| Figure 6-1: C. Elegans AND Gate Example                                         | 160 |

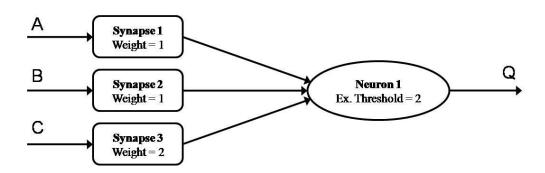

| Figure 6-2: AND Gate Neuron Topology                                            | 161 |

| Figure 6-3: Simulation results for the AND gate design                          | 161 |

| Figure 6-4: C. Elegans OR Gate Example                                          | 162 |

| Figure 6-5: OR Gate Neuron Topology                                             | 163 |

| Figure 6-6: Simulation results for the OR gate design                           | 163 |

| Figure 6-7: NOT Gate Neuron Topology Example                                    | 164 |

| Figure 6-8: C. Elegans Inversion Example                                        | 165 |

| Figure 6-9: Simulation results for NOT Gate Design                              | 165 |

| Figure 6-10: C. Elegans Latch Example                                           | 166 |

| Figure 6-11: SR Latch Topology Example                                          | 166 |

| Figure 6-12: Simulation Result for the SR latch design                          | 167 |

| Figure 6-13: C. Elegans Locomotion Unit Configurations                          | 168 |

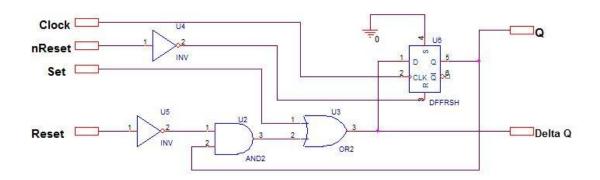

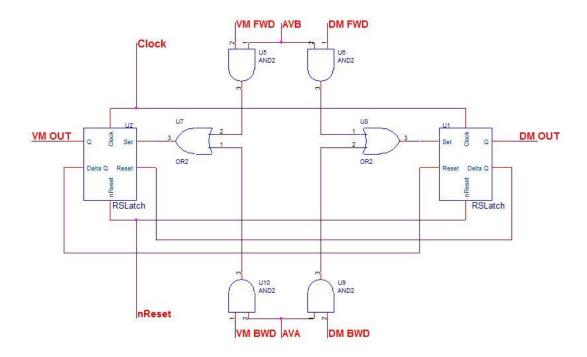

| Figure 6-14: The Synthesized RS Latch                                           | 170 |

| Figure 6-15: Schematic of C Elegans Locomotion Unit                             | 171 |

| Figure 6-16: Logic C Elegans Overview                                           | 172 |

| Figure 6-17 : Simulation Results of Reversing Logic C. Elegans Model            | 175 |

| Figure 6-18: Simulation Results of Coiling Logic C. Elegans Model | 176 |

|-------------------------------------------------------------------|-----|

| Figure 6-19: Logic Elegans Traces                                 | 178 |

| Figure 6-20: Logic Elegans Coiling Run On an FPGA                 | 179 |

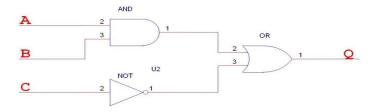

| Figure 6-21: AND + OR gate example                                | 181 |

| Figure 6-22: Composite AND + OR Neuron Logic Gate                 | 181 |

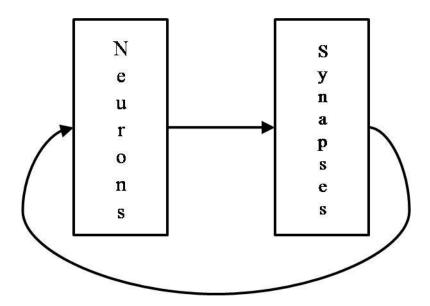

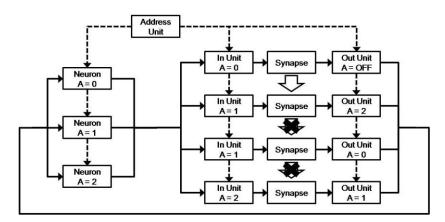

| Figure 7-1: Mapping between Neuron and Synapse Blocks             | 187 |

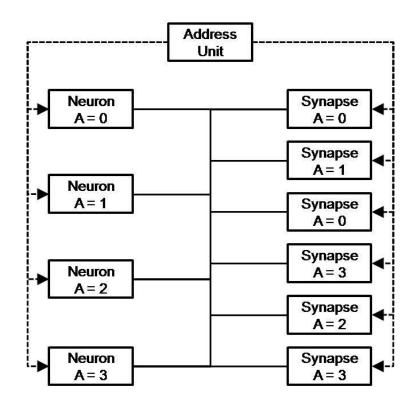

| Figure 7-2: Example of Neuron-Synapse Bus                         | 188 |

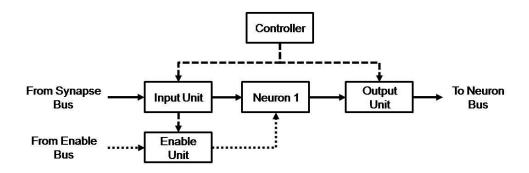

| Figure 7-3: Neuron 1 Structure                                    | 190 |

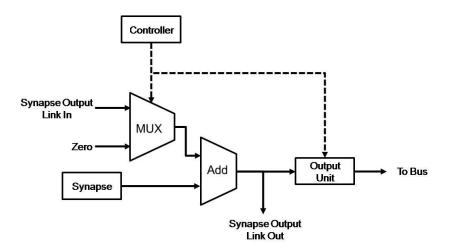

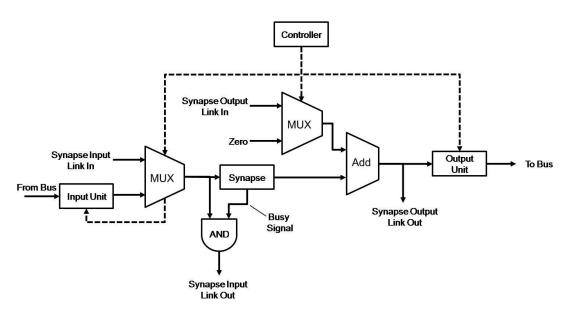

| Figure 7-4: Modified Synapse Output Stage                         | 191 |

| Figure 7-5: Full Connectivity Example                             | 192 |

| Figure 7-6: Complete Array Synapse                                | 193 |

| Figure 7-7: PNA Neuron 2 Structure                                | 195 |

| Figure 7-8: Recording Structure                                   | 195 |

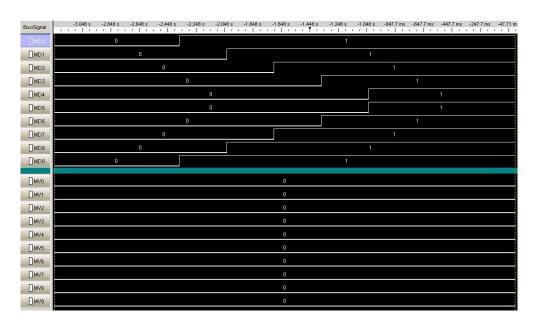

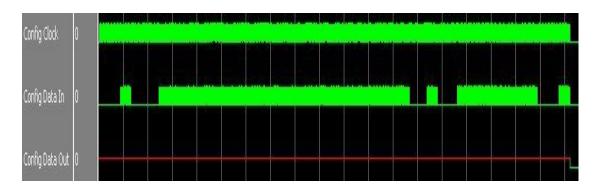

| Figure 7-9: PNA Configuration Phase                               | 203 |

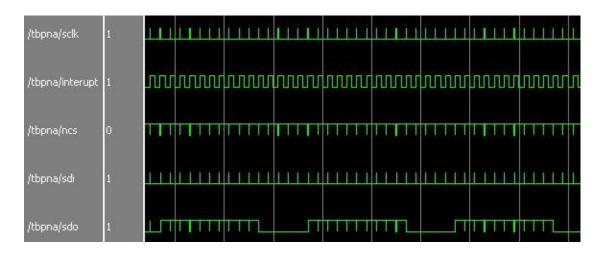

| Figure 7-10: PNA External Bus Cycles                              | 204 |

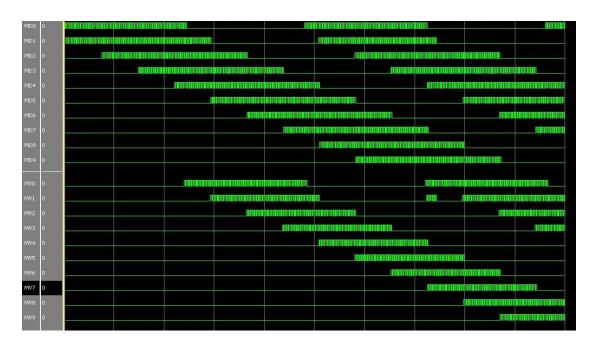

| Figure 7-11: PNA C. Elegans Design                                | 205 |

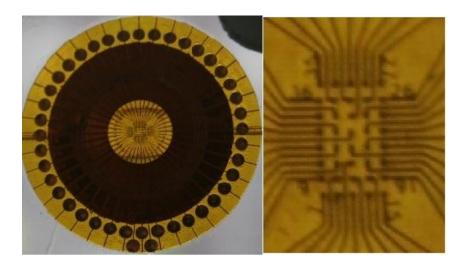

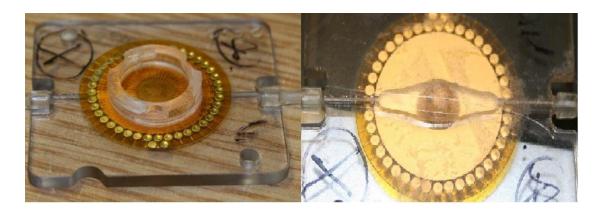

| Figure A-1: Close up of the MEA                                   | 230 |

| Figure A-2: MEA Cartridge                                         | 231 |

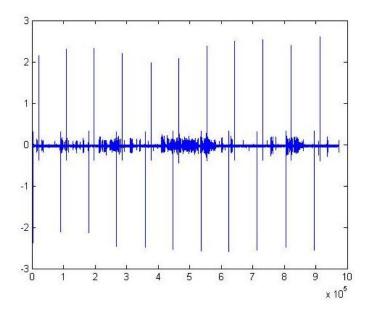

| Figure A-3: Raw MEA Data displaying heater spikes                 | 233 |

| Figure A-4: Removal of Heater Spikes from Data                    | 233 |

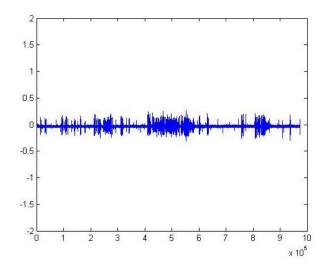

| Figure A-5: Channel Data after Noise Filtering                    | 234 |

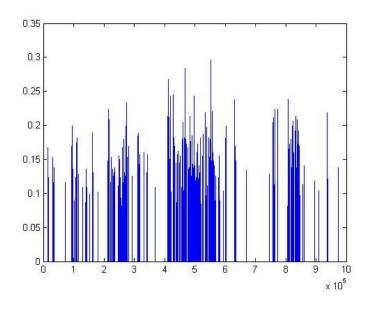

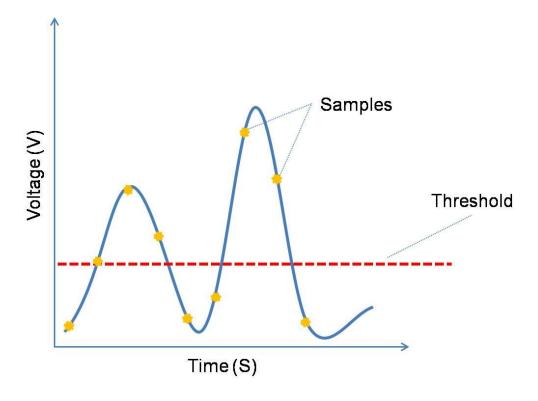

| Figure A-6: Rising Edge Spike Detection                           | 235 |

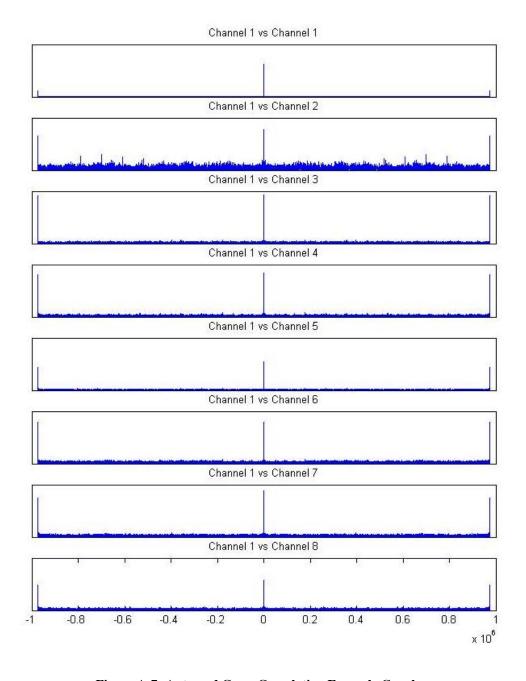

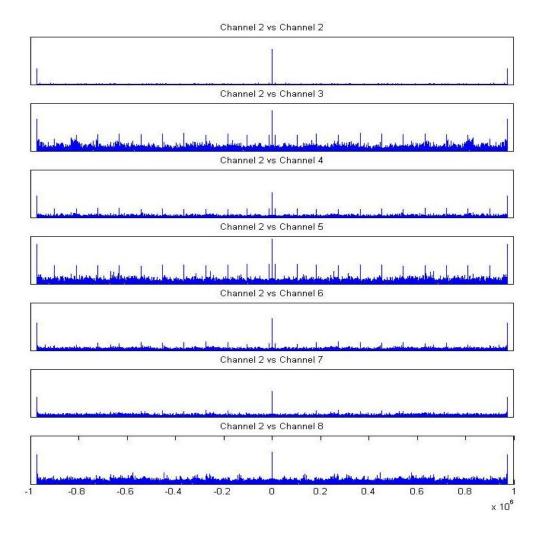

| Figure A-7: Auto and Cross Correlation Example Graphs             | 237 |

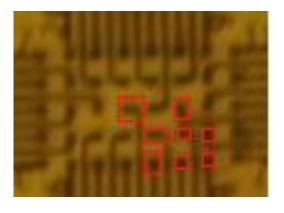

| Figure A-8: Channel 2 Correlations for Dataset A                  | 239 |

| Figure A-9: Electrodes used for Dataset A                         | 239 |

# **Index of Tables**

| Table 2-1: Types of Sensory Receptor                                         | 32       |

|------------------------------------------------------------------------------|----------|

| Table 3-1: MuCulloch-Pitts Binary Neuron Example                             | 58       |

| Table 3-2: Summary of the Five Described Model Types                         | 66       |

| Table 3-3: Types of Model and Types of Simulation for different neuron       | n model  |

| classes                                                                      | 67       |

| Table 4-1: Resource usage for each threshold configuration with a varying nu | ımber of |

| synapses                                                                     | 87       |

| Table 4-2: Comparison between synthesis size of basic and advanced synapses  | s116     |

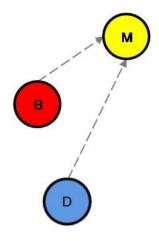

| Table 5-1: Motorneuron Classes Innervating Body Muscles                      | 124      |

| Table 5-2: Results of laser ablation on C. Elegans Neurons                   | 127      |

| Table 5-3: Parameters for Neuron Classes M, B, A and D                       | 130      |

| Table 5-4: Parameters for Driver Neuron Types AVx, NRx and TSx               | 131      |

| Table 5-5: Synaptic Parameters for C Elegans Locomotion System               | 131      |

| Table 5-6: C Elegans Model Operational Modes                                 | 138      |

| Table 5-7: CPU Time required for Simulation                                  | 147      |

| Table 5-8: The size of the C Elegans Locomotion design using different       | synapse  |

| models                                                                       | 153      |

| Table 6-1: A logic table for a two input AND Gate                            | 160      |

| Table 6-2: A logic table for a two input OR Gate                             | 162      |

| Table 6-3: A Logic table for a simple SR Latch                               | 165      |

| Table 6-4: C Elegans Model Operational Modes                                 | 173      |

| Table 7-1: Parameters used by the Neuron 1 Model                             | 196      |

| Table 7-2: Parameters used by the Neuron 2 Model                             | 197      |

| Table 7-3: Parameters used by the Synapse Model                              | 198      |

| Table 7-4: Description of Link Control Parameter                             | 199      |

| Table 7-5: Maximum Clock Frequencies in the PNA                              | 207      |

## **Declaration of Authorship**

- I, Julian Alexander Bailey declare that the thesis entitled "Towards the Neurocomputer: An Investigation of VHDL Neuron Models" and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given.

With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

parts of this work have been published as: [1, 2]

where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

| Signed: | <br> | <br> | <br> | <br> | <br> |

|---------|------|------|------|------|------|

| Date:   |      |      |      |      |      |

## Acknowledgements

I would firstly like to thank my awesome supervisor Peter Wilson for his guidance, support and feedback throughout the course of my PhD. Also I thank John Chad who gave me an introduction to neuroscience and provided guidance in the world of biological sciences.

My gratitude goes out to Joanne Bailey has contributed directly to this work by providing experimental data for the microelectrode array work.

I'd like to thank everyone in the ESD lab. You all provided much needed distraction from my work. I would especially like to thank John Goodwin who sat through many discussions about neurons (amongst other things) and who showed me the "correct way" to write VHDL.

Thank you to my many friends who have had to listen to me complain about my work for the past four years, Cat Allerston, Hamish Hunt, Daniel Friedrich and many others.

Finally, thanks to my parents without whom I would not exist and the rest of my family whose support made this work possible.

## **Chapter 1: Introduction**

Ramón y Cajal, is considered to be one of the "fathers" of modern neuroscience [3]. Using the silver chloride tissue staining technique developed by Camillo Golgi, Cajal stained tissue that had been extracted from the nervous system. His findings lead to the discovery of the Neuron as the basic subunit of the nervous system and won Cajal and Golgi the Nobel prize for medicine in 1906 [4]. The discovery of the basic subunit of the nervous system was a revolution in neuroscience.

The processing and storage of neuronal signals has been and continues to be a central issue of fundamental neuroscience. There is a lack of data describing the properties of neuronal networks which is not aided by the complexity of the neuronal circuitry and the associated neurochemical responses [5, 6]. A common technique used for many years was to take a neuronal network and attach a single measuring electrode (patch clamp) to the neuron and take recordings. This has the disadvantage that an electrical event occurring in the rest of the network is effectively ignored unless it stimulates activity in the observed neuron [5, 6]. The approach of attaching multiple electrodes to the network can cause damage to the delicate neurons due to the electrodes being inserted into the network. This also poses the problem of proper and accurate positioning of the electrodes.

The activity of neurons can also be measured using optical methods [7], by applying voltage sensitive dyes to stain a preparation containing neurons. The dye molecules bind to the excitable membranes of the neurons and act as signal transducers. The neuronal network can then be monitored by measuring the absorption or fluorescence with light monitoring devices. This technique has the advantages that an individual neuron can be effectively injected with a dye allowing only it to be monitored. The technique shows promising results when compared to traditional methods of measurement since it has a sub millisecond time resolution, however:

The signal to noise ratio is poor when compared to intracellular techniques, therefore where possible intracellular techniques should be used in preference.

- The absolute amplitude of the optical signals is not readily calibrated, for example brightness of fluorescence cannot be easily tied to change of voltage.

- Optical Dyes are chemicals and as such they could change the behaviour of the network.

- Spatial Resolution is good in two dimensions but poor in three dimensions.

- The duration of experiments is limited by bleaching and phototoxic effects.

The study of the living organisms requires less invasive approaches. Electron Microscopy is useful for actually looking directly at the neurons although this would not be in feasible on a large live animal.

On the more invasive side, we can use laser ablation to destroy individual or groups of neurons. We can then observe the behaviour of the tissue culture or animal before and after ablation. This allows us to determine the function of the ablated neurons.

Mutant animals follow a similar process by which animals are bred to express or suppress the function of a particular gene whose role concerns the development of the nervous system, for example in C.Elegans, the gene **unc25** codes for an inhibitory neurotransmitter, C. Elegans with the **unc25** knockout cannot make this neurotransmitter which affects normal movement of the animal [8].

The microelectrode array is a non-invasive method for stimulation or recording from electrically excitable cells [9]. The MEA allows the observation of a complex network without causing any damage to the delicate neurons. This is because the neurons rest or adhere to the electrodes and the array surface; therefore the electrodes themselves do not puncture the membrane of the cells. This can be compared to a doctor who places electrodes on the surface of the skin to measure the ECG without having to place long needle electrodes physically in the heart.

The advantage of using the MEA method is that experiments can be performed on an intact fully functioning network that can survive for up to several months [10]

on the array, as long as the correct life support is provided. This would mean that an array can be used several times for the same experiment without worrying if the electrode has been put in exactly the same place each time. The problem here is that neuron cultures tend to be several layers of cells thick and planar microelectrode arrays only have direct access to the surface layer of cells.

Even with these advances it is still difficult to determine parameters from biological networks, such as connectivity and synaptic weighting.

Behavioural modelling can be a powerful ally for studying the nervous system. We can apply our current knowledge and understanding of how a system is wired and how it behaves to derive the parameters for unknown portions of the system. For example by knowing how a system is wired and the behaviour in response to particular inputs the synaptic parameters can be derived by modelling the system and matching the output response to that of the real system.

This is usually an iterative process, requiring the model to be refined slowly until the behaviour matches the actual system. This can be a long process depending on the desired accuracy of the model and this is complicated by the fact that matching behaviour does not mean the connectivity and structure of the networks are the same.

This work uses behavioural modelling and some of the previously mentioned techniques to develop biologically realistic neuron models, which allow for activity dependant reconfiguration for application in basic learning using techniques commonly used for simulation of electronic systems.

The model which forms the basis for this work was originally developed by Enric Claverol [11-15] at the University of Southampton, UK in 2000. Claverol's Message-based event driven (MBED) neuron model applied electronic simulation techniques to develop a computationally efficient model of the neuron, designed to reduce processor time and memory usage whilst enabling very large scale simulations of networks. The model whilst abstract, maintains some biological accuracy including a direct mapping between neuron morphology and the various components of the neuron and synapse models.

So why is there a need to develop yet another neuron model? Are there not enough models out there already?

There has been a drive in recent years towards large scale simulation of neurons, focussing on simulating large sections of the mammalian cortex, the Blue Brain Project [16] being one example. This project relies on vast amounts of computing power to simulate the system, the blue brain project is trying to simulate neocortical columns in the cerebral cortex, and each contains 10,000 neurons connected in a consistent way. For these simulations they use 8192 processor IBM Blue Genie machines which are vast machines requiring vast amounts of power.

If we look to the future where we may wish to have biologically inspired machines with "silicon brains" or repair and replace damage portions of the Central Nervous System it would be impractical to have an expensive, large and power hungry computing system to perform these tasks.

What we are proposing here is a drive towards a more elegant solution, where we can have real-time hardware acceleration of neuron simulations without the need for a large computing system to back it up.

This work aims to develop a VHDL neuron model based on one of the eventdriven MBED software model by Enric Claverol and to show that there are substantial performance advantages of moving towards a hardware based approach.

Once a VHDL version of the model has been developed the next goal is to demonstrate it operates in a similar way to the MBED model, we aim to do this by reproducing a model of the locomotion system of Caenorhabditis Elegans (C. Elegans) and comparing the results against those of Claverol's experiments.

At this point the work divides into two areas:

First we explore if it is possible to build logic gates using neurons, providing simulations of these neuron logic gates. To show that this operation is analogous the nervous system of C. Elegans is analysed swapping groups of neurons and synapses with their logic equivalents, producing a purely electronic logic gate system. • Next a general purpose programmable neuron array is developed so that any nervous system could be downloaded onto it and run in real time.

This work covers a variety of topics from the disciplines of neuroscience and electronics. It is intended that this work be accessible to people from a variety of backgrounds which is why the first three chapters provide a solid foundation of relevant knowledge for the reader. The topics covered are, Basic neuroscience including the structure and operation of Neurons, Synapses, Receptors and Muscles (Chapter 2). Five different types of neuron model are described, compared and contrasted in Chapter 3 as well as different techniques for computer simulation of systems.

The aim of Chapter 4 is to describe the Neuron model developed by Enric Claverol and develop a version of the single cell model in VHDL. The operation of each of the building blocks in the model is described and simulations are provided demonstrating the behaviour of each block. A couple of the blocks have different implementations and these are compared and contrasted with the aid of simulations. Finally this chapter details the structure of a VHDL library called *LibNeuron* which encapsulates all the blocks and functionality into a portable VHDL library.

In Chapter 5, the aim is to demonstrate that the VHDL neuron model developed in Chapter 4 behaves in a similar way as previous work using this neuron model. In order to achieve this, a model of the C. Elegans locomotion system is developed, as was done by Enric Claverol. The system is derived from scratch firstly showing that the original assumptions in the previous work were valid. Next the system is simulated in VHDL in forward, reverse and coiling modes and these results are compared to the previous work showing that both the neuron model and the locomotion model are behaving as expected. This is taken a step further by synthesizing the VHDL model in to hardware and running the system in real time on hardware. The performance of the simulation and real-time hardware are then discussed.

Chapter 6 looks at the deterministic side of neuron modelling, that is how particular structures and configurations of neurons can potentially behave predictably. For this we look at the C. Elegans locomotion model (Chapter 5) and identify

structures that behave like predictably like logic gates, such as AND, OR, NOT gates and latches. Next we see if it is possible to use these newly derived neuron logic cells to substitute groups of neurons in the C. Elegans locomotion model for the gates that have been derived. This results in a purely simple logic based C. Elegans model.

Chapter 7 takes all the previous work further, since it is possible to buy programmable logic arrays is it possible to design a programmable neuron array based on the VHDL neuron model. This chapter serves as a guide through the design decisions and modifications to the VHDL Neuron Model required to make this possible. Again the C. Elegans design is used to test the system and simulations are compared against the work in Chapter 5.

Finally Chapter 8 summarises the achievements and current issues in this work. Directions for future research are proposed, including the addition of Synaptic Plasticity to the neuron model, Touch Sensitivity Circuits in the C. Elegans locomotion system, Muscle modelling in VHDL-AMS and finally improvements to the MEA experiments for characterisation and modelling of random neuronal networks.

Appendix A includes some preliminary work analysing data captured from random networks of neurons grown on microelectrode arrays. This is in order to derive the connectivity so we could try to model them. The current limitations of the system are discussed and a plan to tackle this problem in the future is described.

## **Chapter 2 : Basic Neuroscience**

In the late 1700's physiological investigations of the nervous system by Luis Galvani showed that living nerve cells and muscles produce electricity [17]. Modern electrophysiology developed from work by three German scientists, Emil DuBois-Reymond, Johannes Muller and Hermann von Helmholtz, who showed that electrical activity in one nerve cell, affects the activity in adjacent cells in predictable ways [17].

It is now somewhat difficult to believe that at the beginning of the 20<sup>th</sup> Century it was thought that the nervous system was one continuous nerve cell network or reticulum [18]. The "reticular theory" of nerve cell communication consisted of the belief that all the nerve cells shared a common cytoplasm which allowed them to communicate with each other. This view was championed by many scientists including Camillo Golgi [3]. Golgi was an Italian scientist who invented a silver chloride stain which allowed the visualisation of brain tissue under a microscope. One of the biggest revolutions of modern neuroscience was a discovery made by Santiago Ramon y Cajal. He used Golgi's staining technique but came to a different conclusion, that the nervous system was constructed from independent subunits which he called *Neurons*, separated by small gaps and communicating through specialised structures (later called *Synapses* by Sir Charles Sherrington [3]). In 1906 the Nobel Prize was jointly awarded to Cajal and Golgi for Medicine [4].

In 1902 and 1912, Julius Bernstein showed that action potentials were the result of the change of the permeability of the axonal membrane to ions [19]. This was confirmed by Ken Cole and Howard Curtis who showed that membrane conductance increased during an action potential [20].

Later in 1949, Alan Hodgkin and Bernard Katz refined Bernstein's hypothesis by considering that the axonal membrane may have different permeability's to different types of ion [21]. They demonstrated that the permeability of the membrane towards sodium ions was crucial for the formation of action potentials in the giant squid axon.

With the addition of Andrew Huxley to the team, the trio applied the voltage clamp technique to determine the axon membranes permeability to potassium and sodium ions due to voltage and the passage of time. This resulted in a mathematical model which allowed them to reconstruct the action potential quantitatively [22-26]. Hodgkin and Huxley then went on to correlate their mathematical model with discrete ions channels that could exist in different states, known as "open, "closed" and "inactivated".

This was confirmed by Erwin Neher and Bert Sakmann in the mid-1970's who had developed the patch-clamp technique for examining the conductance of individual ion channels [27].

Today, through the use of atomic-resolution crystal structures [28], fluorescence distance measurements [29] and cryo-electron microscopy [30], researchers are beginning to understand the structural basis for the various conductance states and selectivity of channels for a particular species of ion [31].

The objective of this chapter is to provide the reader with an understanding of the neuroscience principles used as a basis for the remainder of this work. This chapter aims to describe the morphology and operation of various components of the nervous system, including: Neurons, Synapses and how the nervous system interfaces with muscles and receptors which provide input from and output into the real world.

## 2.1 Structure of the Nervous System

The Neuron is the cell responsible for propagating electrical signals throughout the nervous system. A Neuron receives signals from other parts of the nervous system and makes "decisions" based on the activity at its input [3]. Modulating its activity level allows the Neuron to pass information along to other neurons in the Central nervous system (CNS). Neurons have developed a specialised morphology which allows them to perform this function within the CNS.

Figure 2-1: Diagram of a neuron [17]

Neurons are similar to most cells in that they have a Cell Body (or *Soma*) which houses the normal metabolic systems required to maintain a cell, such as, the Nucleus, Mitochondria and other organelles (Figure 2-1). These are then surrounded by a Lipid bi-layer or cell wall and suspended in intracellular fluid, known as cytoplasm.

Specialised processes collectively known as Neurites extend from the cell body and can be divided into two groups, Dendrites and the Axon. The Dendrites can resemble large treelike structures whose role is to receive signals from other neurons through Synapses. The Dendrites are said to be postsynaptic because they occur after the synapse with respect to the flow of information.

The Axon represents a single process extending away from the cell body which transmits information away from the soma to the axon terminals and through synapses to other cells. Since the Axon occurs before the synapse it is said to be presynaptic. It is important to note that entire neurons are described as being situated presynaptically or postsynaptically with respect to a particular synapse.

The Axon terminals have their own specialised structures for passing information across the synapse to other cells in the nervous system. These synaptic connections can be either electrical (also called Gap Junctions) or chemical.

Electrical synapses operate by allowing the action potentials to travel directly from cell to cell. The chemical synapse releases neurotransmitters across the synapse upon arrival of an action potential.

Figure 2-2: Different Neuron Morphologies (A) Multipolar Neuron (B) Bipolar Neuron (C)

Pseudo-Unipolar Neuron and (D) Unipolar Neuron [32]

The four types of neuron are depicted in Figure 2-2, each having a different morphology. The Multipolar neuron is the most common type of neuron in the brain

[32] possessing multiple dendrites and a single axon extending from the cell body. Motor neurons are examples of this type.

Bipolar neurons have two processes extending from an elongated cell body; one process terminates in dendrites whilst the other terminates as an axon. These neurons usually have sensory functions and transmit information received by the dendrites to the CNS.

Pseudo-Unipolar neurons possess a single process arising from the cell body which divides into two branches. One of these branches projects to the periphery and the other projects into the CNS. Both branches have structural and function characteristics of an axon [32]. Information collected by the peripheral branch is transmitted to the CNS via the CNS terminal branch. Examples of this type of cell are sensory cells in the dorsal root ganglion.

Finally we have Unipolar cells which are uncommon in vertebrates [32]. In this type of neuron the dendrites project out of one side of the cell body and the axon then projects out of the site where dendrites are located.

Another feature of the nervous system is Glial cells. These specialised cells do not perform any function in propagating signals within the nervous system but instead perform a support role. Astrocytes, Oligodendrocytes, Microglia and Schwann cells are all glial cells found in the nervous system.

Figure 2-3: Schwann Cell shown wrapped around an axon [33]

The Schwann cells, shown in Figure 2-3, wrap around the axon of the motor neuron and are typical in the peripheral nervous system. These cells form a fatty sheath (Myelin) around the axon which provides electrical insulation of the axon membrane from the extracellular fluid, the areas between the consecutive Schwann cells are the *nodes of ranvier*, which are involved with generation of electrical signals.

Figure 2-4: An Oligodendrocyte Cell shown with processes wrapped around axons

Oligodendrocytes, one of which is shown in Figure 2-4, have processes which extend from the cell body and wrap around axons of nearby nerve cells. The processes that wrap around the axons perform exactly the same function as the Schwann Cells. The difference is that Oligodendrocytes reside in the Central Nervous System (CNS) and the Schwann cells reside in the peripheral nervous system.

Astrocytes are large glial cells with radially symmetrical forms [3]. They surround neurons and come into close contact with the vasculature of the brain. Astrocytes make contact with the blood vessels trough specialised structures called *End Feet* which permit the Astrocyte to transport ions across the vascular wall and create the barrier between the tissues in the central nervous system and the blood. This barrier is known as the blood-brain barrier (BBB). It plays an important role in protecting the CNS from blood-borne chemicals which may affect neuronal activity [3].

Microglia are small irregularly shaped cells which play a role when tissue is damaged [3]. Analysis of damaged tissue shows that the region is invaded by these cells. The Microglia serve a phagocytic role in that they devour and remove damaged cells.

#### 2.2 Neuronal Communication

It is clear from the description of neuron morphology that the neuron's primary function is to transmit information and perform some kind of signal processing on the information during transmission. The neurons transmit information using electrical signalling; therefore it is important to know the process by which these signals are generated. The assumption that the axon can be modelled as a simple electrical wire would be quite incorrect. Neurons are not intrinsically good conductors of electrical currents, which is why the nervous system would not function properly if the currents were passive. The way the neuron compensates for this is to incorporate a system to regenerate the signal as it propagates down the axon. These boosted signals are collectively called *action potentials*.

The process begins when a stimulus, chemical for neurotransmitters and sensations such as sense of smell; or physical stimulus (mechanical stimuli or light in photoreceptors) cause changes in the cell membrane, at the dendrite or cell body. These stimuli cause ionic currents to flow in or out of the cell changing the intracellular concentration of ions in the dendrites and soma. The area where the axon joins the soma is called the axon hillock. This area integrates the different changing currents and generates action potentials. The action potential then travels down the axon to its terminals where some neurotransmitter is released and the process continues in the next neuron.

The neuron membrane is specialised for controlling the flow of ionic currents across the membrane, therefore it makes sense to describe the properties that allow this to happen.

#### 2.2.1 The Membrane and Resting Membrane Potential

The neuron membrane is built from fatty molecules called lipids which effectively separate the intracellular and extracellular spaces. This allows the cell to control the flow of ions, proteins and other molecules across the membrane. The membrane contains proteins which form various transmembrane structures, of which two are of particular interest, ion channels and active transporters or pumps.

Ion channels are formed by transmembrane proteins which create pores through the membrane through which the ions, Potassium (K<sup>+</sup>), Sodium (Na<sup>+</sup>) and

Calcium ( $Ca^{2+}$ ) can flow down concentration gradients. Channels can be ion selective allowing only a single ion type (e.g.  $K^+$ ) or several ions types to pass through the membrane. They may also be passive (non-gated) which are always open or gated which means they can be opened or closed in response to certain electrical, chemical or physical stimuli.

Active transports or Pumps use energy to move ions across the membrane. The most common pump is the (Na<sup>+</sup>/K<sup>+</sup>) ATPase pump [3] which breaks a bond in the energy storing adenosine triphosphate (ATP) molecule and uses the energy to pump potassium ions into the cell and sodium ions out of the cell. This action creates ionic concentration gradients across the membrane which gives rise to the *resting membrane potential* of the neuron. The resting potential of neurons varies but is always a fraction of a volt, typically -40mv to -90mv [18] between the intracellular and extracellular fluid.

#### 2.2.2 Changing the membrane Potential

For the majority of neurons in the CNS the membrane potential will be changed due to the release of neurotransmitters across synapses onto postsynaptic dendrites. Depending on the type of synapse this can raise (Depolarise) or lower (Hyperpolarise) the membrane potential. The neurotransmitters act on ligand gated ion channels which open in response to the application of a particular chemical. These ion channels commonly are ion selective, increasing the permeability of the membrane to a particular ion. The ions flow down the concentration gradients, therefore if a Na<sup>+</sup> selective channel opens then Na<sup>+</sup> will flow into the cell depolarising the membrane where as if a K<sup>+</sup> channel opens then K<sup>+</sup> will flow out of the cell hyperpolarising the membrane.

#### 2.2.3 Action Potentials

Action potentials are generated when the voltage across the membrane of the neuron in the axon hillock reaches the *threshold voltage*. An action potential is shown in Figure 2-5.

Figure 2-5: Phases of an Action Potential

Figure 2-5 shows a sketched graph of an action potential. The x-axis shows time and the y-axis shows membrane voltage.

At T=0 seconds the membrane potential of the axon hillock in this neuron is at the resting potential of -65 mV. Synaptic activity causes ionic currents to flow across the membrane and this causes the membrane potential to rise toward the *threshold voltage*.

When the threshold voltage is reached voltage dependent sodium ion channels open which causes an inrush of sodium ions. This causes the membrane voltage to rise rapidly, inverting the membrane voltage, this is known as the rising phase.

Inactivation of the sodium ions channels causes the membrane voltage to peak meanwhile the activation of potassium ion channels gives rise to the falling phase due to potassium ions leaving the cell. This temporarily re-establishes the resting membrane potential.

Active ion transport in the cell membrane pumps sodium ions out of the cell and potassium ions into the cell; this places the membrane voltage back into its initial resting state.

The falling and undershoot phases form what is known as the *refractory period* where the action potential cannot be generated again because the neuron is rebalancing the ion concentrations to restore the resting membrane potential.

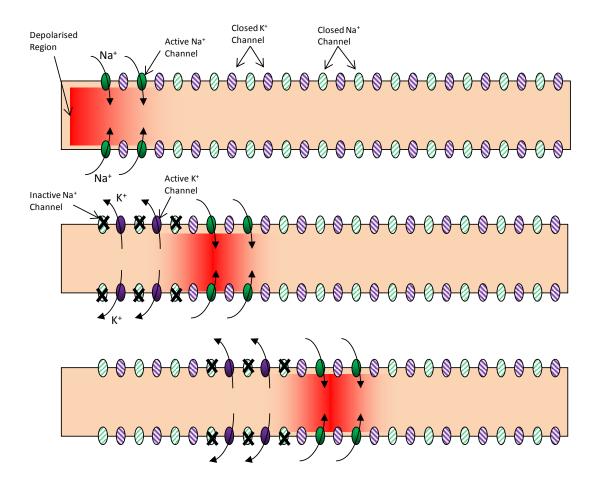

Figure 2-6: The propagation of an action potential.

The diagram in Figure 2-6 shows a section of an axon which is conducting an action potential (shown travelling left to right). In the top picture the depolarised region is shown on the far left of the diagram. The depolarisation causes voltage gated sodium channels to open, this allows sodium ions to enter the cell depolarising the region further. Once a region is depolarised to a certain point, the sodium channels become inactivated and potassium channels open. This allows potassium ions to leave the cell which temporarily repolarises the membrane. This process continues as the wave of depolarisation propagates down the axon.

Myelin modifies the way in which action potentials are conducted in the axon since it provides electrical isolation for the sections of the axon which are covered. This means that when Na<sup>+</sup> currents only leak out of the uncovered portions of the

membrane and so the ionic currents can travel further before being regenerated, which happens at the nodes of Ranvier. The action potential propagates faster since it only needs to be regenerated at each node of Ranvier rather than continuously along the length of the axon. This means the neurons are able to carry more information because they can transmit it faster.

### 2.3 Sensory Receptors

There are many types of receptor are summarised in Table 2-1.

**Table 2-1: Types of Sensory Receptor**

| Receptor Name   | Stimulus                | Example of Receptor                                       |

|-----------------|-------------------------|-----------------------------------------------------------|

| Electroreceptor | Electric Field          | Sharks, the ability to sense weak electrical impulses of  |

|                 |                         | muscle contractions in prey                               |

| Baroreceptors   | Pressure                | Sensors in blood vessels to regulate blood pressure       |

| Chemoreceptors  | Chemical                | Taste buds respond to chemicals in foods                  |

| Mechanoreceptor | Mechanical Stress or    | Hair cells in the cochlea respond to vibration due to     |

|                 | strain                  | sound                                                     |

| Nociceptors     | Damage to tissue, Pain, | Nerve endings in the skin responding to cuts or breaks in |

|                 | Noxious stimuli         | the skins surface                                         |

| Osmoreceptors   | Osmolarity of fluids    | Hypothalamus which controls the amount of water in the    |

|                 |                         | blood ensuring the blood plasma is at the correct         |

|                 |                         | concentration                                             |

| Photoreceptor   | Light                   | Photosensitive cells in the retina of the eye             |

| Proprioceptors  | Sense of Position       | Feedback on the position of parts of the body relative to |

|                 |                         | each other due to musculature tendon and articular        |

|                 |                         | sources.                                                  |

| Thermoreceptors | Temperature             | Receptors in the skin respond to warming or cooling       |

Four of these receptor types are described in greater detail in the next subsections. The four described types are Nociceptors, Chemoreceptors, Mechanoreceptors and Photoreceptors. The reason for describing these four is that they are the major receptor types which interface with the outside world (which is what we are focussing on here) whilst most of the other receptor types are responsible for maintaining Homeostasis.

#### 2.3.1 Nociceptors (Pain Receptors)

Nociceptors are relatively unspecialised nerve endings that initiate the sensation of pain [18], *noci* is derived from the latin for "hurt". They transduce a variety of stimuli into receptor potentials which in turn generate action potentials.

Nociceptors arise from cell bodies in the dorsal root ganglia or the trigeminal ganglion that send one axonal process to the periphery and into the Central Nervous System. They terminate in unspecialised "free endings" which are unmylenated and have complex terminal branches which terminate in the upper dermis and epidermis.

#### 2.3.2 Chemoreceptors

Chemoreceptors respond to chemical stimuli and an example of this are taste buds. In the case of taste buds the receptor itself is a separate cell to the neuron unlike the nociceptor.

The receptor could be triggered through ionic stimuli through ion channels or complex stimuli through receptors on its surface.

In taste buds this causes other ion channels to open in the surface of the cell or through secondary messengers. Depolarisation causes the release of a neurotransmitter (serotonin in a generic taste bud) across a synapse to trigger depolarisation in a post-synaptic neuron.

#### 2.3.3 Mechanoreceptors

Mechanoreceptors are "free-endings" like Nociceptors and show some degree of encapsulation which helps determine the nature of the stimuli which they respond [18]. These receptors respond to deformation or other changes in the surrounding tissue which changes the ionic permeability of the receptor membrane.

The change in permeability of the membrane generates a depolarising current which produces a receptor potential triggering an action potential.

The process by which energy of the stimulus generates an action potential in the sensory neuron is known as sensory transduction.

#### 2.3.4 Photoreceptors

In many sensory systems a stimulus causes the depolarisation of the membrane of the receptor triggering the release of a neurotransmitter onto postsynaptic neurons.

In phototransduction and processing in the retina is mediated by graded potentials, mainly because action potentials are not required to transmit information over such a small distance [18].

In contrast to the other systems shining light on a photoreceptor causes hyperpolarisation, this means the amount of neurotransmitter released onto the postsynaptic neuron decreases as light levels increase. This may appear to be the wrong way around but it is important to remember that it doesn't matter if darkness causes an increase in action potentials in the postsynaptic neurons, only that it is possible to distinguish between changes in luminescence.

If the photoreceptor is in the dark ion channels in the membrane permit sodium and calcium ions to enter the cell which results in depolarisation of the cell. The probability that these channels are open or closed is regulated by the nucleotide cyclic guanosine monophosphate (cGMP).

In light, the level of cGMP within the outer membrane is low which causes means some of the ion channels are closed, leading to hyperpolarisation of the cell whilst in the dark the levels of cGMP within the outer membrane increase causing the ion channels to open and in turn to depolarise the cell. When the cell is depolarised neurotransmitter is released by the receptor across the synapse to the neuron.

This whole process begins when a photon is absorbed by the photopigment in the receptor disks. The photopigment contains a light absorbing chromophore, *retinal*, which is an aldehyde of vitamin A [18]. This is coupled to one of several proteins called *opsins* that can change the wavelength of light which is absorbed. In rods (responsible for vision in low-light) this photopigment is *rhodopsin*.

When a photon is absorbed by *rhodopsin* its configuration changes which causes a series of other alterations in the protein component of the molecule. This causes the activation of an intracellular messenger, *transducin* which activates a

*phosphodiesterase* that hydrolyzes cGMP. This leads to a reduction of cGMP in the membrane of the receptor and closure of the ion channels.

The process for cones is very similar except a different photopigment is present which responds to different wavelengths of light.

#### 2.4 Muscle

This chapter has so far, described the way in which information in the form of electrical signals is transmitted through the nervous system. However, when an animal is observed, we do not generally directly observe the electrical activity of the nervous system. Researchers can watch the reaction of the animal to various situations, such as those in Pavlov's Experiment [34]. The majority of these reactions are due to movement caused by *Muscles*.

This section begins by considering *Striated Muscle*. First, we begin by describing its structure and the *sliding-filament model* and provide relevant evidence for supporting this model. Finally, we shall discuss the mechanisms that take place to turn an action potential into a *contractile event*.

#### 2.4.1 Striated Muscle Structure

Striated muscle is so called because of the obvious transverse stripes that are observed when looking at the tissue through a light microscope [35]. It accounts for the bulk of all muscle found in vertebrates and is mainly voluntary since it can be consciously controlled in the human body and is innervated through motor neurons. This type of muscle is not confined to vertebrates but a large proportion of experimental work has involved vertebrate striated muscle.

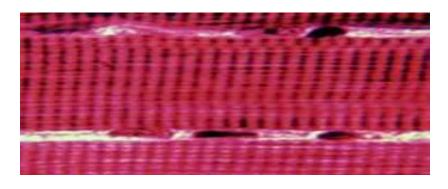

Figure 2-7: A photograph of striated muscle [36].

The photograph in Figure 2-7 shows a section of striated muscle. The striations can be clearly seen running in a transverse direction. An individual striated muscle is made up of bundles of individual muscle fibres (Cells), each of which can be about 100 microns in diameter. In striated muscle it is normal for cells to be multi-nuclei which are distributed near the surface of the fibres. Some muscle fibres can be long, running the entire length of the overall muscle.

Each muscle fibre contains several thousand elements called myofibrils, each about 1 micron in diameter. These units are responsible for the ability for the fibre to change length. The Myofibril can be further divided into repeating sections known as the sarcomere which is broken down into lettered zones. The myofibril is what is responsible for giving the muscle its striated appearance.

# 2.4.2 Sliding Filament Model

The sliding filament model of striated muscle states that the muscle fibres (cells) changes length due to the movement of two different arrays of protein forming distinct filaments in the sarcomere. The filaments can be divided into two types, *thick filaments* containing the protein myosin and *thin filaments* containing the protein actin. The filaments do not change length but merely slide past each other to shorten the overall length of the sarcomere and also the muscle fibre.

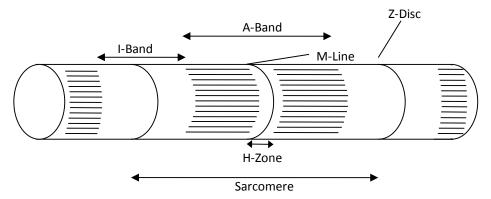

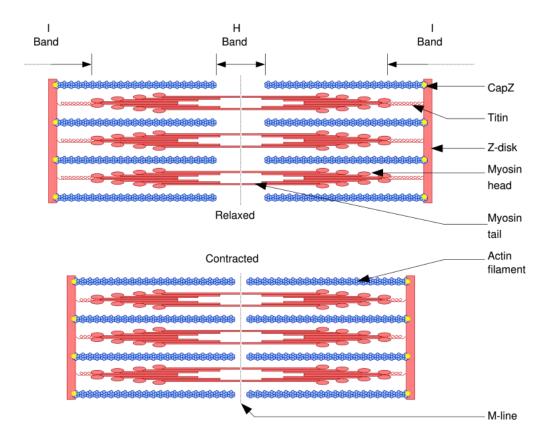

The diagram in Figure 2-8 shows the different bands that make up the myofibrils. Each sarcoma is separated by two dark bands called the Z-lines (Zwischen-Line, from German meaning between).

Figure 2-8: A schematic diagram of a Myofibril.

Z-Lines are separated by two lighter coloured bands called I-bands (Isotropic-Band) and a darker band in the middle called the A-Band (Anisotropic-Band). I-Bands consist of mainly thin actin filaments which are of a smaller diameter so allow the passage of light, whereas the A-Band is mainly myosin filaments. The names Isotropic and Anisotropic refer to the optical properties of living muscle from polarised light microscopy. Within the A-Band are the H-Zone (Helle-Band, from German meaning bright) and the M-Line (Middle Line).

Figure 2-9: The filament lattice structure of the Sarcomere [6]

The filament lattice is the contractile structure which makes up the sarcomere (Figure 2-9). The overlapping thick and thin filaments are able to move past each other to change the length of the sarcomere. In a relaxed state the myosin and actin filaments only partially overlap. In a contracted state the filaments move past each other to overlap more and shorten the length of the sarcomere. The filaments themselves do not change length, this is the sliding filament theory of muscle contraction [35].

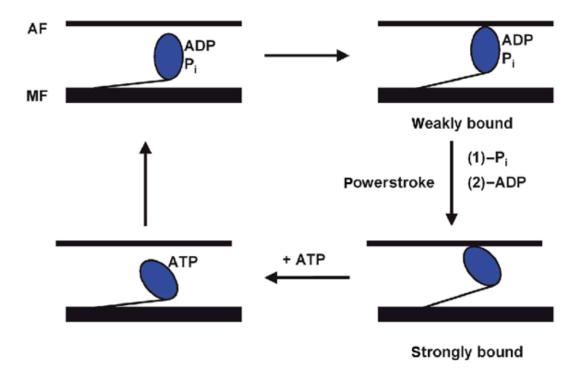

Figure 2-10: The Classical Sliding-filament swinging cross-bridge model of muscle contraction [37]

The swinging cross-bridge theory describes the method by which the Myosin cross-bridge binds to an actin filament and undergoes a swinging motion which "rows" the filament along [35]. The process is shown graphically in Figure 2-10. The thin black line labelled "AF" represents the Actin Filaments and the thick black line labelled MF represents the myosin filament.

In the absence of ATP the myosin cross-bridge binds tightly to the binding site on the actin filament to form a strong complex, Figure 2-10, Bottom Right. When ATP binds to the ATPase site, the myosin cross-bridge rapidly detaches from the actomyosin complex [35], Figure 2-10 Bottom Left. Myosin then hydrolyses ATP and forms a stable Myosin-products complex with ADP and Pi (Adenosine Diphosphate and an inorganic phosphate), Figure 2-10 top left. Actin readily recombines with this complex and forms the original actin-myosin complex [35], Figure 2-10 top right. The structure of the cross-bridge then changes causing the ADP and Pi to be released; this brings about the rowing-like motion of the head, known as the *power-stroke*.

Whilst the structure of the other types of muscle are different to that of striated muscle, the mechanism is very similar with sliding filaments being drawn across each other to shorten the cell.

### 2.4.3 From Action Potential to Movement

We have described how the muscle filaments contract to make the muscle shorter. This section will describe the process by which the action potential in a motor neuron becomes a contractile event which results in the generation of force by the muscle.

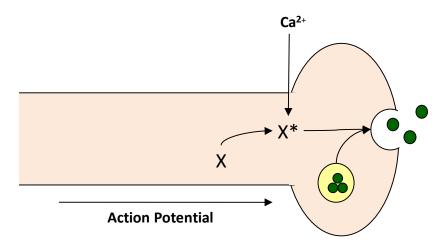

We begin by assuming that there is a motor neuron which is receiving synaptic input from somewhere else in the CNS. This synaptic activity has raised the membrane potential enough to trigger the generation of an action potential down its axon. The action potential now travels down the axon and reaches the axon terminals, where there is a synapse which connects the neuron and the Muscle, known as the *Neuromuscular junction*[17].

The postsynaptic side of this junction is the *end plate*. As the motor neurons axon approaches the muscle fibre it loses its myelin sheath and divides into several smaller branches. The tips of these branches form *synaptic boutons*, from which the neuron releases neurotransmitter across the synapse. The postsynaptic muscle has *junctional folds*, containing neurotransmitter receptors, over which a bouton is positioned. The neurotransmitter released by the motor neurone is called acetylcholine (Ach) [17].

The arrival of the action potential at the axon terminals causes the opening of Ca<sup>2+</sup> ion channels in the presynaptic axon terminal. This in turn causes *vesicles* each containing neurotransmitter to dock with the membrane and release their contents across the synapse. The ACh binds to receptors in the end-plate and causes rapid depolarisation of the membrane, this excitatory postsynaptic potential is called the *end-plate potential*. If the end-plate potential is enough to cause activation of Na<sup>+</sup> channels in the junction folds, then the end-plate potential is converted into an action potential. This action potential then propagates along the muscle fibre causing the release of Ca<sup>2+</sup> from an extensive network of tubules and chambers called the *sarcoplasmic reticulum*. Under low Ca<sup>2+</sup> conditions a troponin-tropomyosin complex

on the actin filament blocks the myosin binding site. This means that the muscle fibre is in a relaxed state where it can be stretched by external forces. The Ca<sup>2+</sup> released from the sarcoplasmic reticulum binds to the troponin-tropomyosin causing a conformational change, which allows the myosin to form cross-bridges. The process that generates the swinging motion of the myosin head takes place until the Ca<sup>2+</sup> is removed from the fibre so that the actin binding site is blocked by the troponin-tropomyosin complex again [17].

# 2.5 Summary

The neuron like many cells has a cell body which houses a nucleus and the metabolic structures required to maintain the cell. There are two sets of processes which extend from the cell body which are collectively referred to as *neurites*. These consist of the dendrites which receive signals and the axon which transmits them.

The electrical signals in the nervous system are called *action potentials*. These signals are due to ions (Sodium and Potassium) flowing through specialised channels to change the voltage across the membrane. Neurons communicate through specialised structures called *synapses*.

Receptors are the structures through which the nervous system can receive stimuli from the outside world. The structure of a receptor is specific to the type of stimuli it is meant to respond to, turning those stimuli into chemical signals which are transmitted across a synapse onto the dendrites of a sensory neuron.

Muscles can be viewed as the mechanism for output from the nervous system to the outside world. They operate in a similar way to neurons, receiving electrical signals and transmitting action potentials down the length of the muscle.

The action potential in the muscle causes a cascade of mechanisms which leads to filaments of actin being drawn past filaments of myosin due to the rowing motion of the *cross-bridges* which connect the two types of filament. This is what causes the shortening of the muscle.

Now that the basic neuroscience has been presented it is now possible to describe different way that neurons can be modelled. This is discussed in the next chapter.

# **Chapter 3 : Modelling & Simulation**

A model is an abstract representation developed by a scientist or engineer to allow them to understand a more complicated real system. It can be said that a good model reduces the complexity of a system whilst still preserving the essential themes and mechanisms of the original system. In the case of Neuroscience there are a wide range of neuron models from those which describe molecular kinetics [38] occurring within a single section of a neuron to those which can describe the behaviour of the entire network as a single entity [39]. It is up to the designer to choose an appropriate model for what he/she expects to see during simulation.

In this chapter we attempt to answer the following two questions:

- What types of models are commonly used for modelling neurons?

- What are the main simulation techniques available for those commonly used models?

To answer the first question we begin by presenting a scale of neuron modelling from those methods which are biophysically accurate to those which are more computationally efficient. Five different types of model that exist on this scale are presented and described in detail.

To answer the second question we look at the two different ways time progresses in *continuous time* models and *discrete time* models. Then we look at two different styles of modelling using *signal flow* or *conserved energy* models.

### 3.1 Classes of Model

There are many different ways for a scientist or engineer to model the nervous system. These range from molecular kinetic models [40] to simplified binary models [41]. The aim here is to give an overview of each type of model and give the advantages and disadvantages of each model.

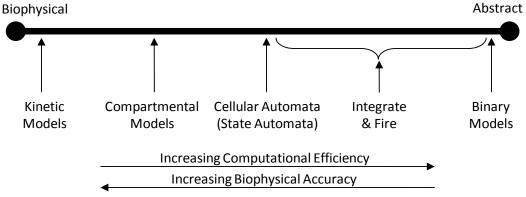

Figure 3-1: The Scale of Neuron Modelling

The diagram in Figure 3-1 represents the scale of modelling. The extremes at each end of the scale are labelled clearly as biophysical and abstract. Biophysical models are based of parameters measured during experiments such as Hodgkin & Huxley [42]. Abstract models take a system and by making assumptions about behaviour and simplify the mechanisms within the system.

The Five classes of model shown in Figure 3-1 will be described in this section. For each class an example of a model will be given to aid the reader in understanding the way in which each model works.

## 3.1.1 Kinetic Molecular (Markov) Models

The overall behaviour of the voltage-dependent ionic currents flowing across the neuron membrane was accurately described by Hodgkin & Huxley in 1952 [42]. Their work with ionic currents in the giant-squid axon can be extended to describe many other types of voltage-dependent currents [38]. Recent work involving newer recording techniques have shown that voltage-dependent currents arise from populations of ion channels undergoing rapid transitions between open (Conducting) and Closed/Inactive (non-conducting) states. This overall behaviour can be captured by kinetic models that describe the transitions between these conformational states. This class of models is more commonly known as "Markov Models".