University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

# Guarded Atomic Actions and Refinement in a System-on-Chip Development Flow: Bridging the Specification Gap with Event-B

by

John Larry Colley

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering, Science and Mathematics

School of Electronics and Computer Science

November 2010

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

by **John Larry Colley**

Modern System-on-chip (SoC) hardware design puts considerable pressure on existing design and verification flows, languages and tools. The Register Transfer Level (RTL) description, which forms the input for synchronous, logic synthesis-driven design is at too low a level of abstraction for efficient architectural exploration and re-use. The existing methods for taking a high-level paper specification and refining this specification to an implementation that meets its performance criteria is largely manual and error-prone and as RTL descriptions get larger, a systematic design method is necessary to address explicitly the timing issues that arise when applying logic synthesis to such large blocks.

*Guarded Atomic Actions* have been shown to offer a convenient notation for describing microarchitectures that is amenable to formal reasoning and high-level synthesis. Event-B is a language and method that supports the development of specifications with automatic proof and refinement, based on guarded atomic actions. Latency-insensitive design ensures that a design composed of functionally correct components will be independent of communication latency. A method has been developed which uses Event-B for latency-insensitive SoC component and sub-system design which can be combined with high-level, component synthesis to enable architectural exploration and re-use at the specification level and to close the specification gap in the SoC hardware flow.

# Contents

|                         |                                                             |          |

|-------------------------|-------------------------------------------------------------|----------|

| <b>Acknowledgements</b> | <b>ix</b>                                                   |          |

| <b>1</b>                | <b>Introduction</b>                                         | <b>1</b> |

| <b>2</b>                | <b>Background</b>                                           | <b>4</b> |

| 2.1                     | Board-level Design and Verification . . . . .               | 4        |

| 2.2                     | Chip-level Design and Verification . . . . .                | 4        |

| 2.3                     | EDA Design and Verification Languages . . . . .             | 5        |

| 2.3.1                   | Modelling Languages . . . . .                               | 5        |

| 2.3.2                   | Test Languages . . . . .                                    | 6        |

| 2.3.3                   | Property Languages . . . . .                                | 6        |

| 2.4                     | EDA Tools . . . . .                                         | 6        |

| 2.4.1                   | Simulation-based Verification . . . . .                     | 6        |

| 2.4.2                   | Disadvantages of Simulation . . . . .                       | 7        |

| 2.4.3                   | Formal Verification . . . . .                               | 7        |

| 2.4.4                   | Disadvantages of Current Model Checking Solutions . . . . . | 8        |

| 2.5                     | Higher-level Modelling Abstractions . . . . .               | 9        |

| 2.5.1                   | Behavioural Modelling . . . . .                             | 9        |

| 2.5.2                   | Transaction-Level Modelling(TLM) . . . . .                  | 10       |

| 2.6                     | SystemC Transaction Level Modelling . . . . .               | 10       |

| 2.6.1                   | TLM level 3 . . . . .                                       | 10       |

| 2.6.2                   | TLM level 2 . . . . .                                       | 11       |

| 2.6.2.1                 | Modelling TLM level 2 Processes . . . . .                   | 11       |

| 2.6.2.2                 | Modelling TLM level 2 Communications . . . . .              | 11       |

| 2.6.3                   | TLM level 1 . . . . .                                       | 12       |

| 2.6.4                   | TLM Architectural Exploration . . . . .                     | 13       |

| 2.7                     | Microprocessor Pipeline Verification . . . . .              | 13       |

| 2.8                     | Modelling Concurrency . . . . .                             | 14       |

| 2.8.1                   | Modelling Concurrency with Partial Orders . . . . .         | 14       |

| 2.8.2                   | Modelling Concurrency with Guarded Atomic Actions . . . . . | 16       |

| 2.8.3                   | Bluespec . . . . .                                          | 16       |

| 2.8.4                   | CAL . . . . .                                               | 16       |

| 2.9                     | Event-B . . . . .                                           | 17       |

| 2.9.1                   | Introduction . . . . .                                      | 17       |

| 2.9.2                   | Refinement . . . . .                                        | 17       |

| 2.9.3                   | Decomposition . . . . .                                     | 18       |

| 2.9.4                   | Variants . . . . .                                          | 18       |

---

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 2.9.5    | Records                                                           | 19        |

| 2.9.6    | Witnesses                                                         | 19        |

| <b>3</b> | <b>Enhancing the SoC Hardware Design Flow with Event-B</b>        | <b>20</b> |

| 3.1      | Background to the Existing Flow                                   | 20        |

| 3.1.1    | Logic Synthesis                                                   | 20        |

| 3.1.2    | Formal RTL Verification                                           | 21        |

| 3.1.3    | RTL Architectural Exploration                                     | 23        |

| 3.1.4    | Closing the Gap: Behavioural Synthesis                            | 24        |

| 3.1.5    | Closing the Gap: High-level Synthesis with Term Rewriting Systems | 25        |

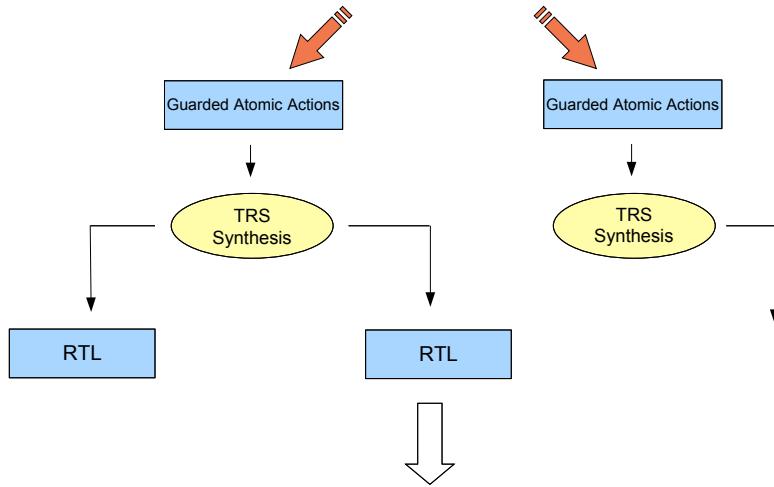

| 3.2      | Closing the Gap: The Event-B method with TRS                      | 29        |

| 3.2.1    | Event-B Specification Refinement in the SoC Flow                  | 30        |

| 3.2.2    | Architectural Exploration at the Specification Level              | 31        |

| <b>4</b> | <b>Developing SoC Components</b>                                  | <b>33</b> |

| 4.1      | Restrictions on SoC Component Size                                | 34        |

| 4.2      | State Machines                                                    | 34        |

| 4.3      | Case Study: Developing an EFSM for Huffman Encoding/Decoding      | 35        |

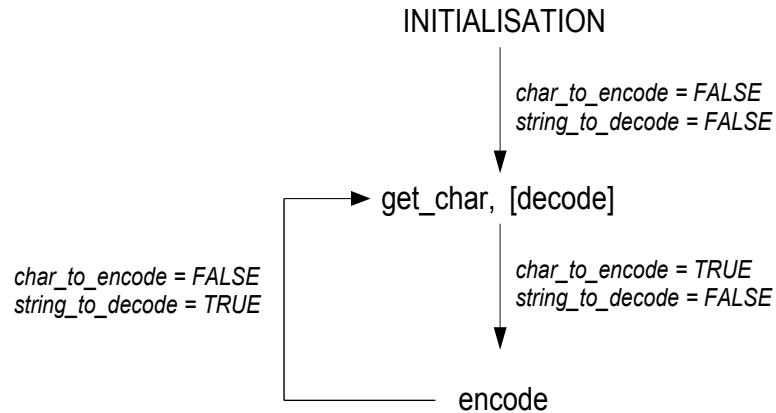

| 4.3.1    | The Abstract Model                                                | 36        |

| 4.3.2    | The First Refinement                                              | 39        |

| 4.3.3    | The Second Refinement                                             | 40        |

| 4.3.4    | The Third Refinement                                              | 41        |

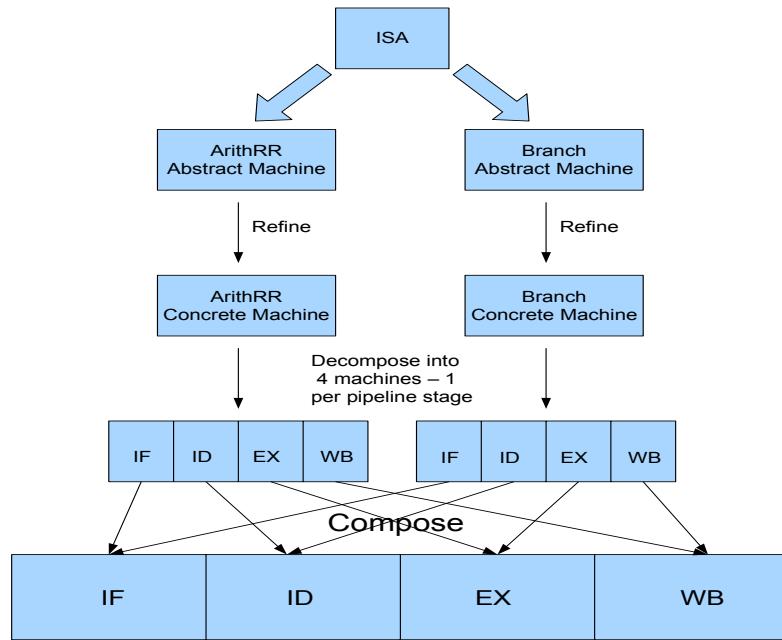

| 4.4      | Pipelines                                                         | 44        |

| 4.4.1    | Modern SoC Microprocessor Pipelines                               | 44        |

| 4.4.2    | Designing and Verifying an SoC Microprocessor Pipeline            | 44        |

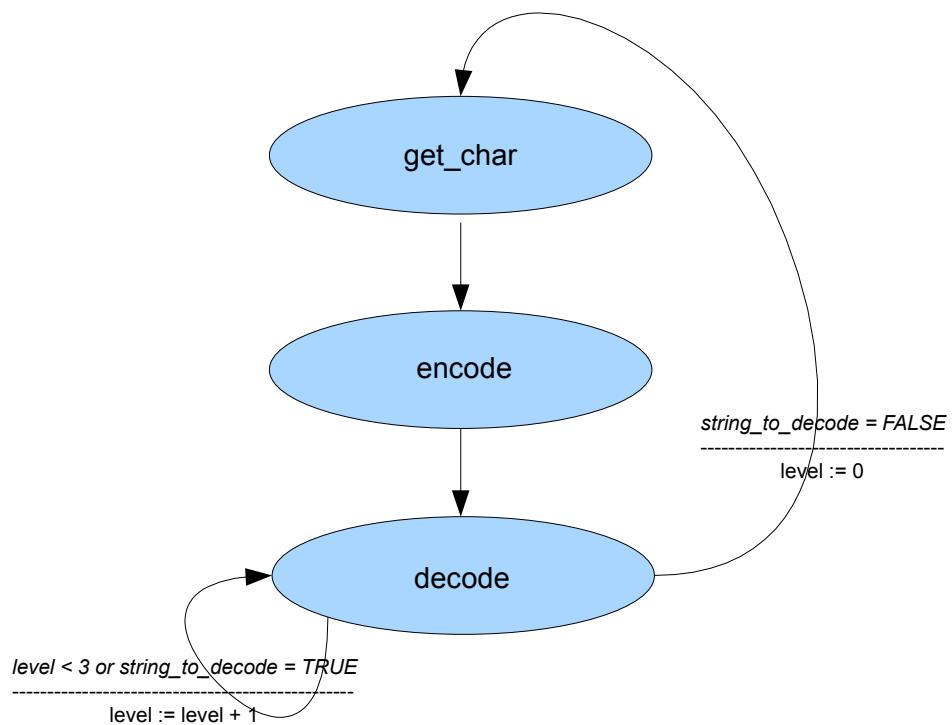

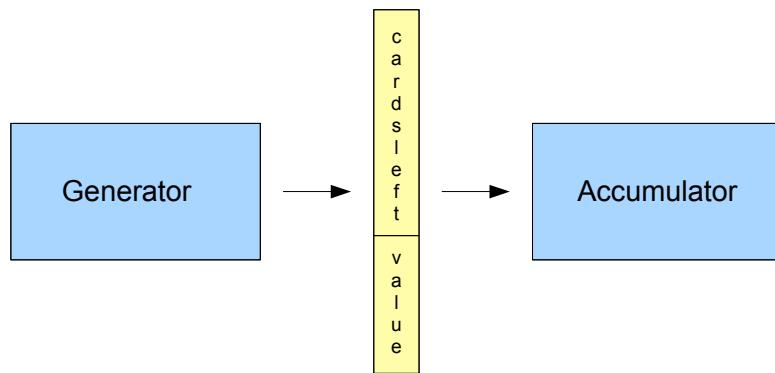

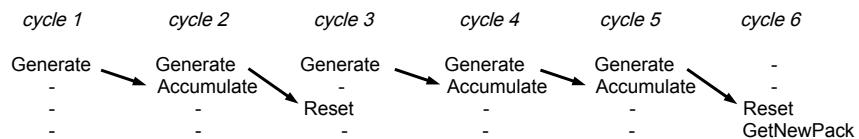

| 4.4.3    | A Pipeline Example: Counting Playing Cards                        | 45        |

| 4.4.4    | Event Simultaneity in Pipelines                                   | 51        |

| 4.4.5    | Measuring Pipeline Complexity at the Specification Level          | 53        |

| 4.4.6    | Pipeline Feedback                                                 | 53        |

| 4.4.7    | An Alternative Compositional Approach to Pipeline Refinement      | 58        |

| 4.4.8    | Pipeline Decomposition                                            | 64        |

| 4.4.9    | Generalising the Approach to Pipeline Verification with Event-B   | 66        |

| <b>5</b> | <b>Developing an SoC Pipelined Microprocessor Model</b>           | <b>68</b> |

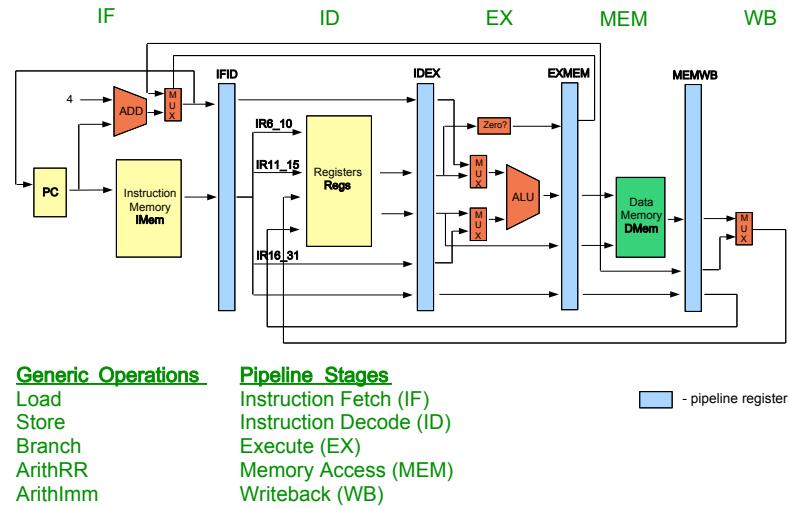

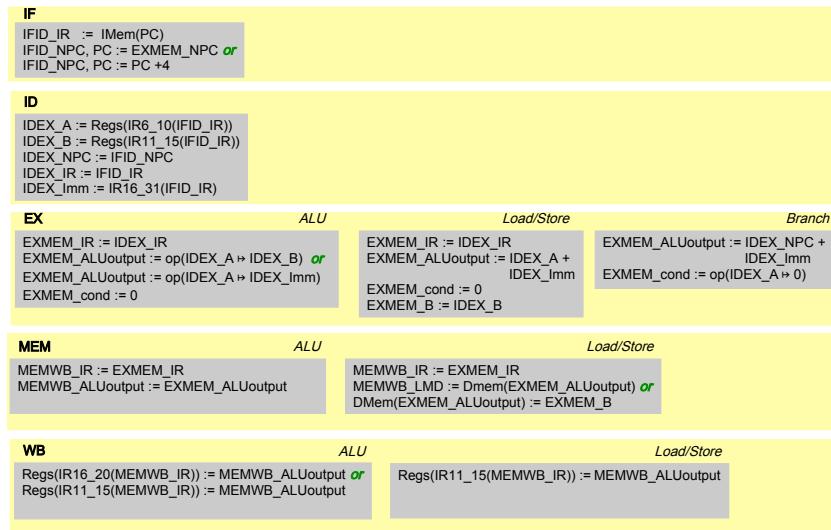

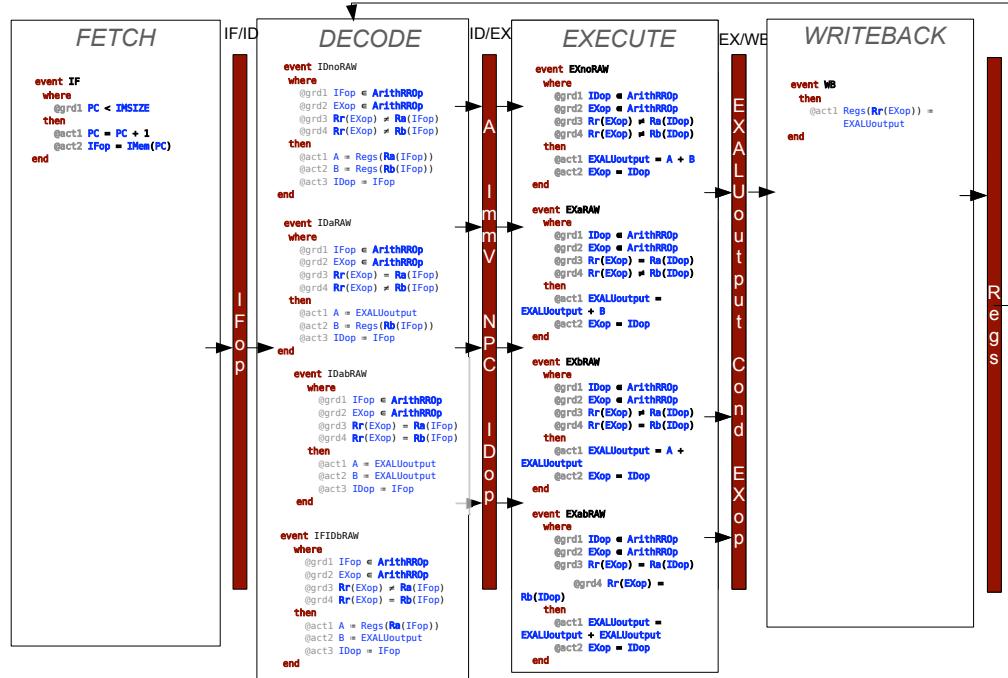

| 5.1      | Modelling DLX with Event-B                                        | 69        |

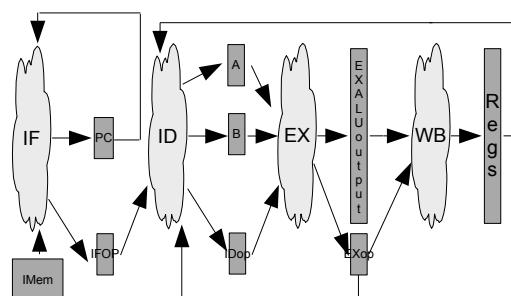

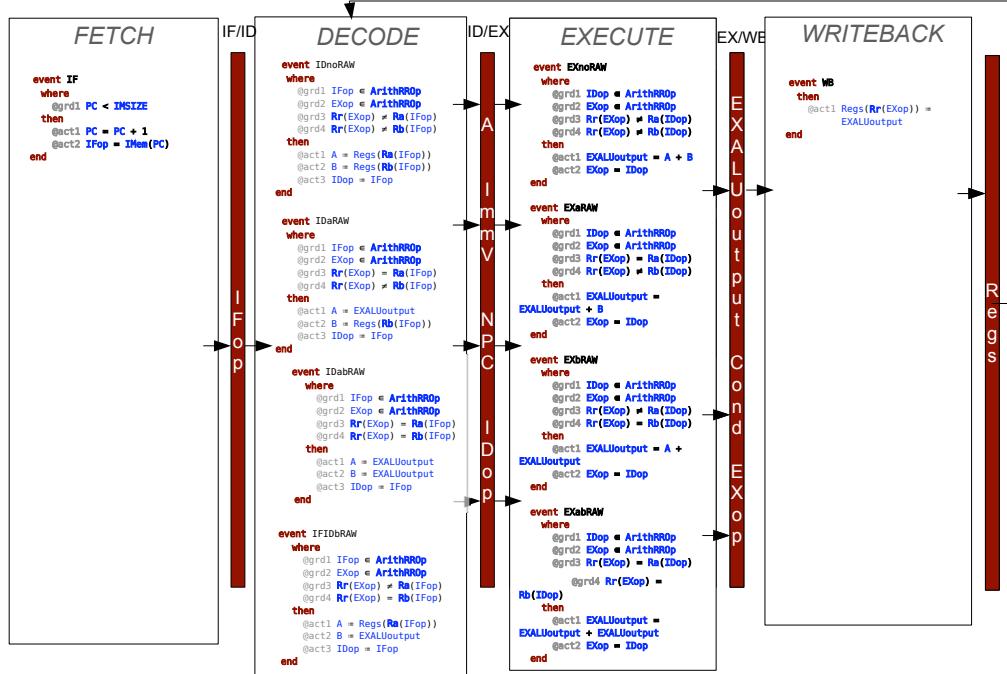

| 5.1.1    | Instruction Fetch (IF)                                            | 69        |

| 5.1.2    | Instruction Decode (ID)                                           | 69        |

| 5.1.3    | Execute (EX)                                                      | 70        |

| 5.1.4    | Memory Access (MEM)                                               | 71        |

| 5.1.5    | Writeback (WB)                                                    | 71        |

| 5.2      | A General Overview of the Method                                  | 73        |

| 5.3      | Abstracting and Refining the Arithmetic Instruction               | 74        |

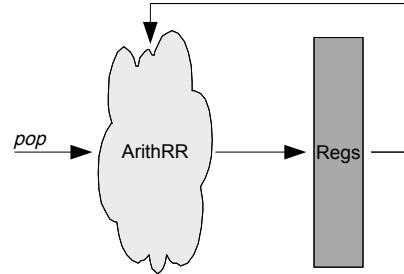

| 5.3.1    | The Abstract ISA Model                                            | 75        |

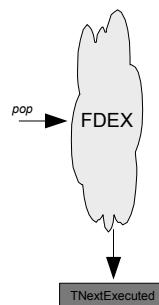

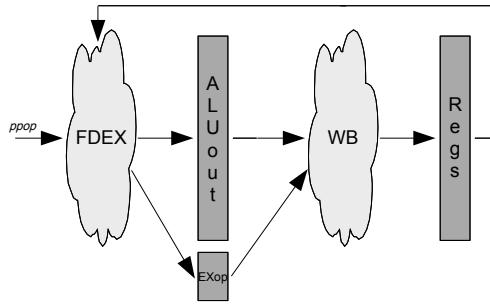

| 5.3.2    | The First Refinement: a 2-stage pipeline                          | 77        |

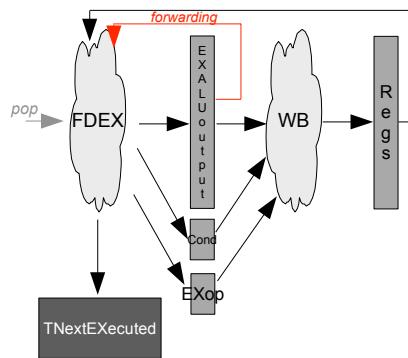

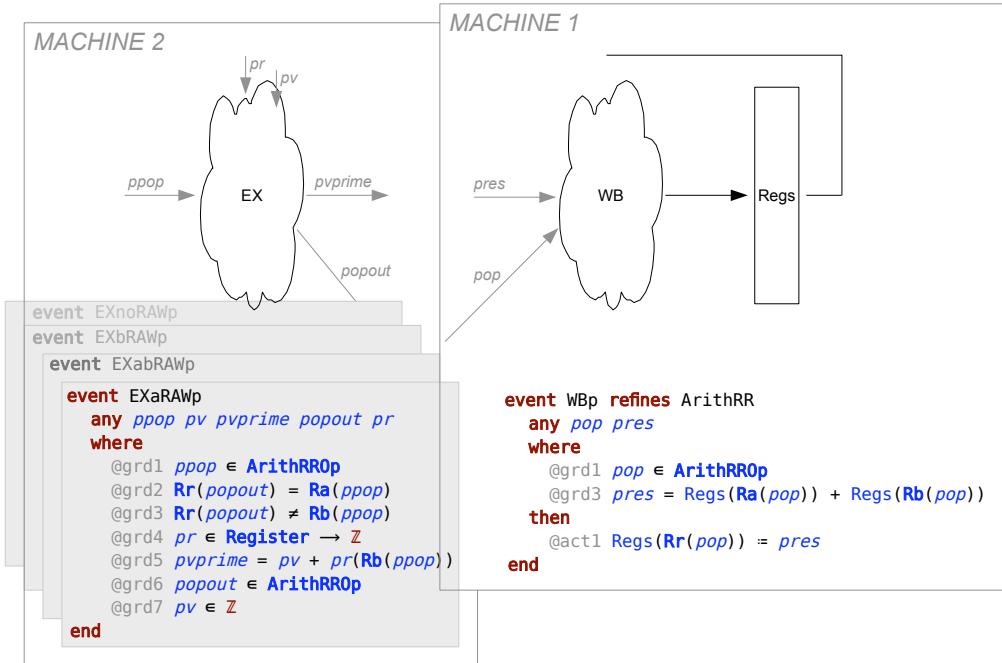

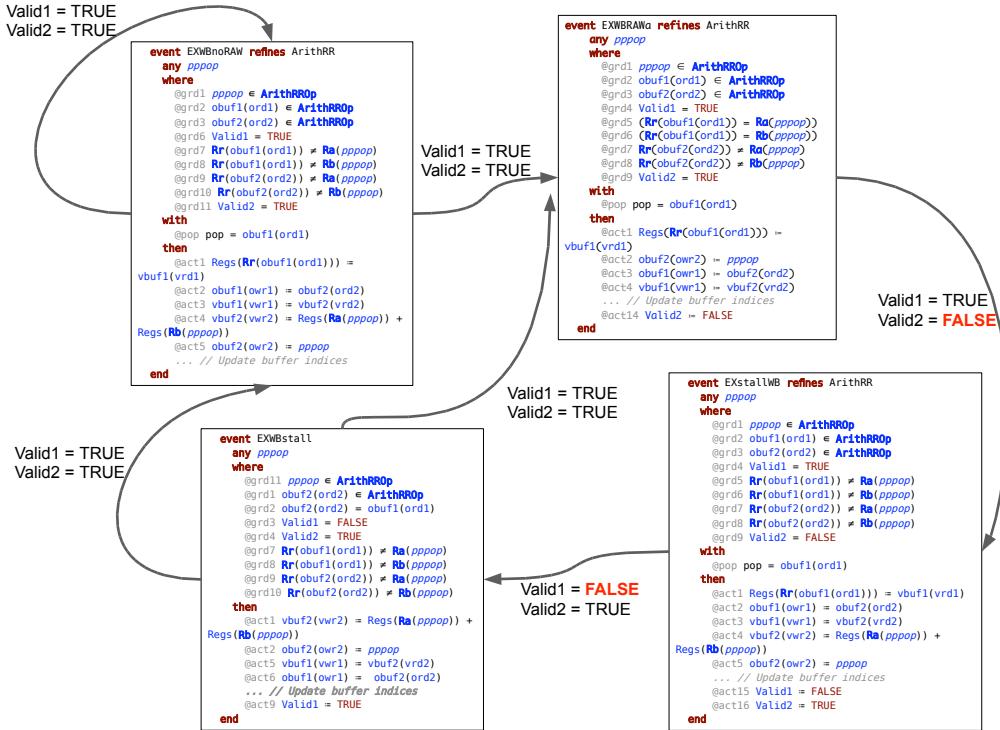

| 5.3.3    | Detecting the RAW Hazard                                          | 79        |

| 5.3.4    | Dealing Correctly with the RAW Hazard                             | 80        |

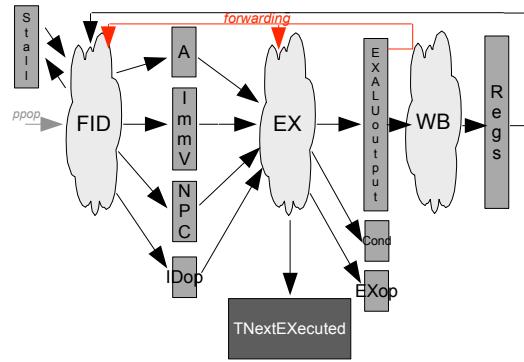

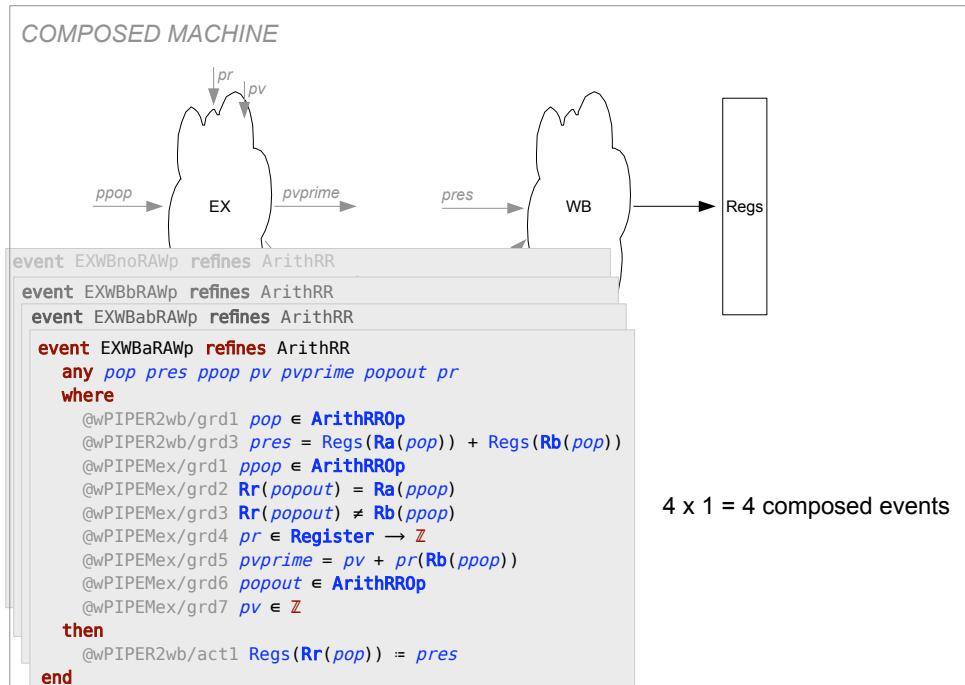

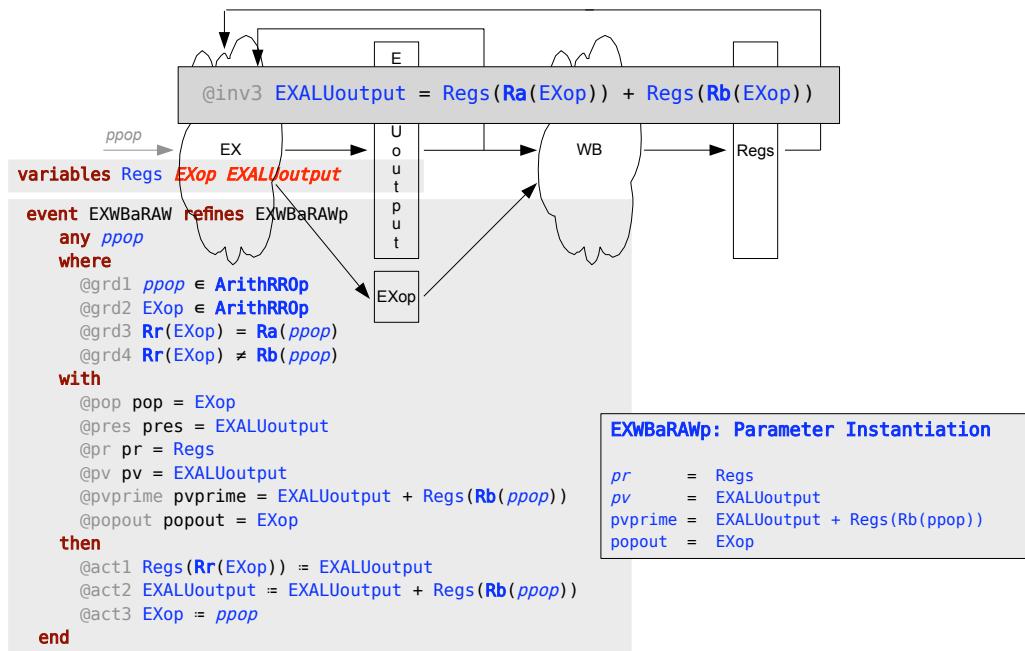

| 5.3.5    | The Second Refinement: a 3-stage pipeline                         | 80        |

---

|          |                                                                                                  |            |

|----------|--------------------------------------------------------------------------------------------------|------------|

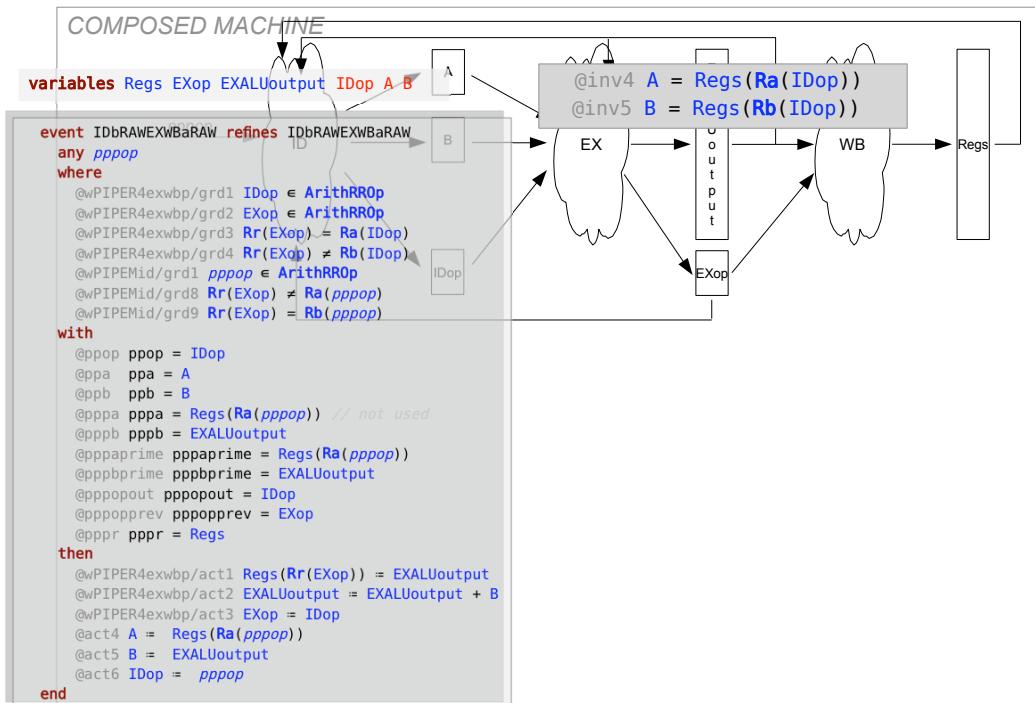

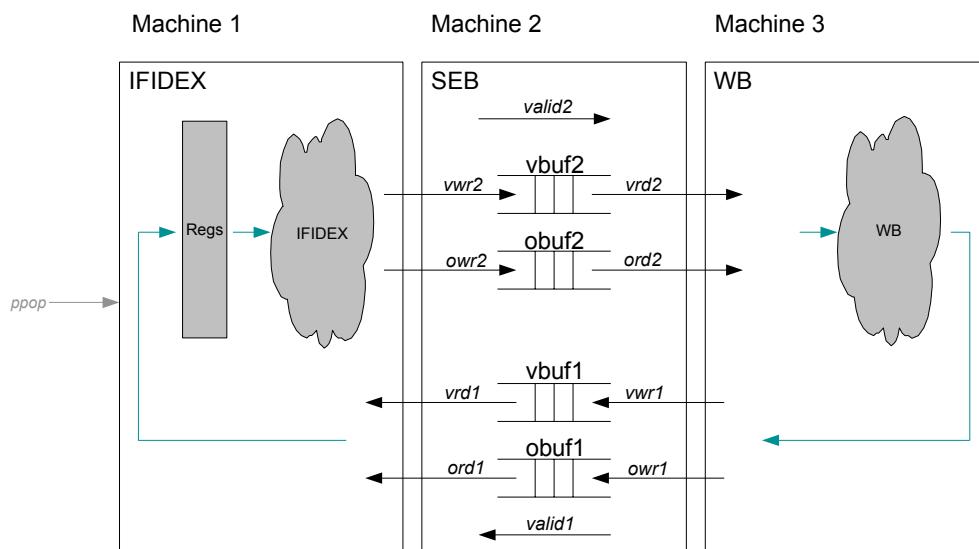

| 5.3.6    | Shared Event Decomposition of the Feedback Loop . . . . .                                        | 85         |

| 5.3.7    | The Third Refinement: a 4-stage pipeline . . . . .                                               | 87         |

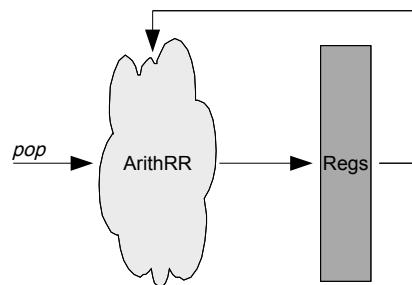

| 5.3.8    | Generalising the ArithRR model . . . . .                                                         | 90         |

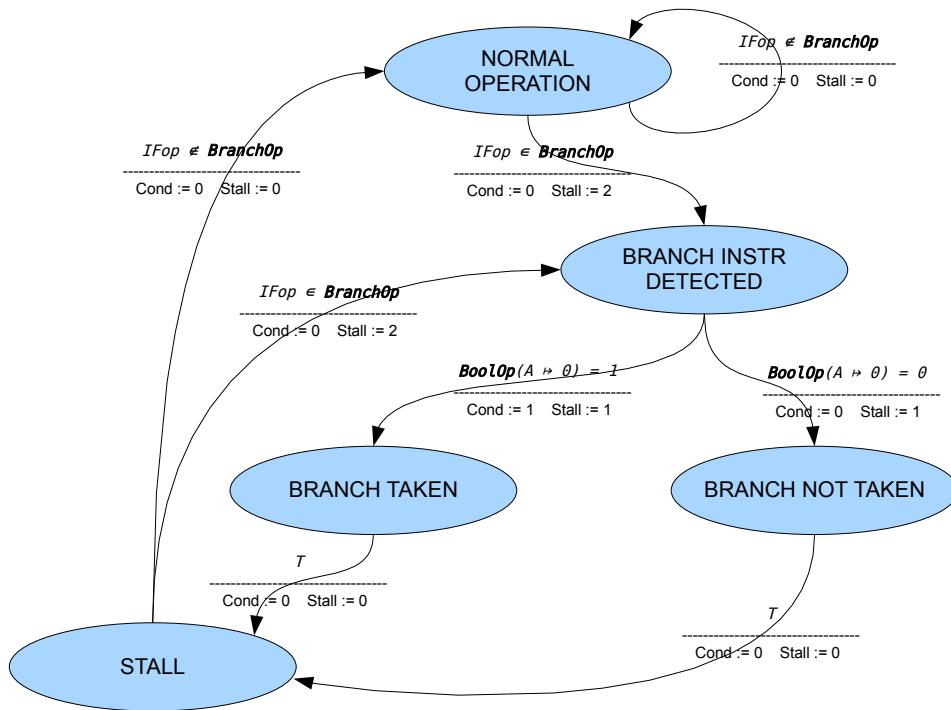

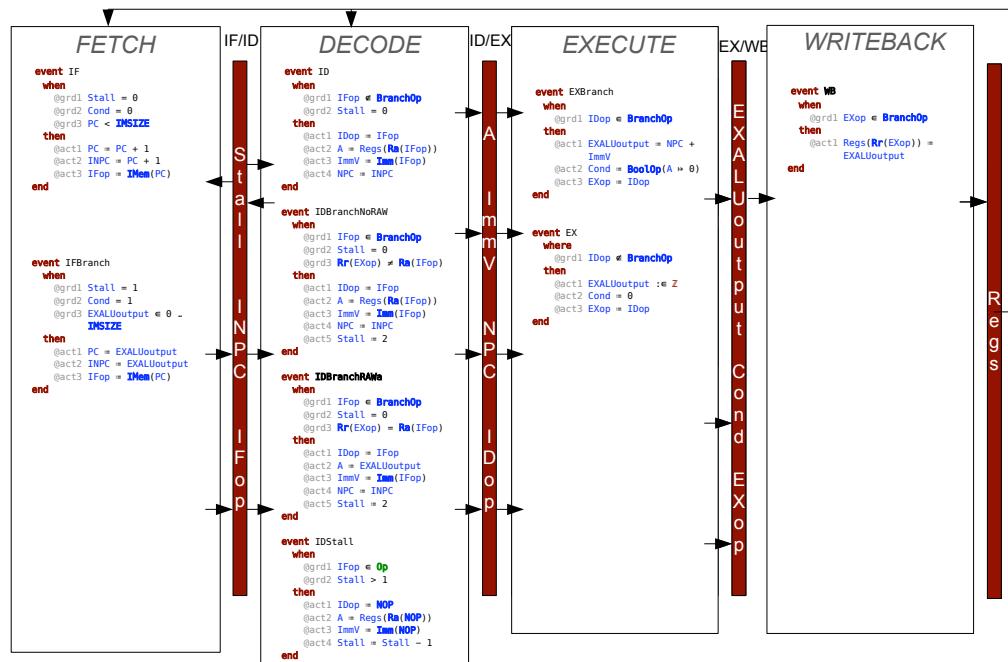

| 5.4      | Abstracting and Refining the Branch Instruction . . . . .                                        | 91         |

| 5.4.1    | The Abstract ISA Model . . . . .                                                                 | 91         |

| 5.4.2    | The First Refinement . . . . .                                                                   | 93         |

| 5.4.3    | The Second Refinement: a 2-stage pipeline . . . . .                                              | 95         |

| 5.4.4    | The Third Refinement: a 3-stage pipeline . . . . .                                               | 98         |

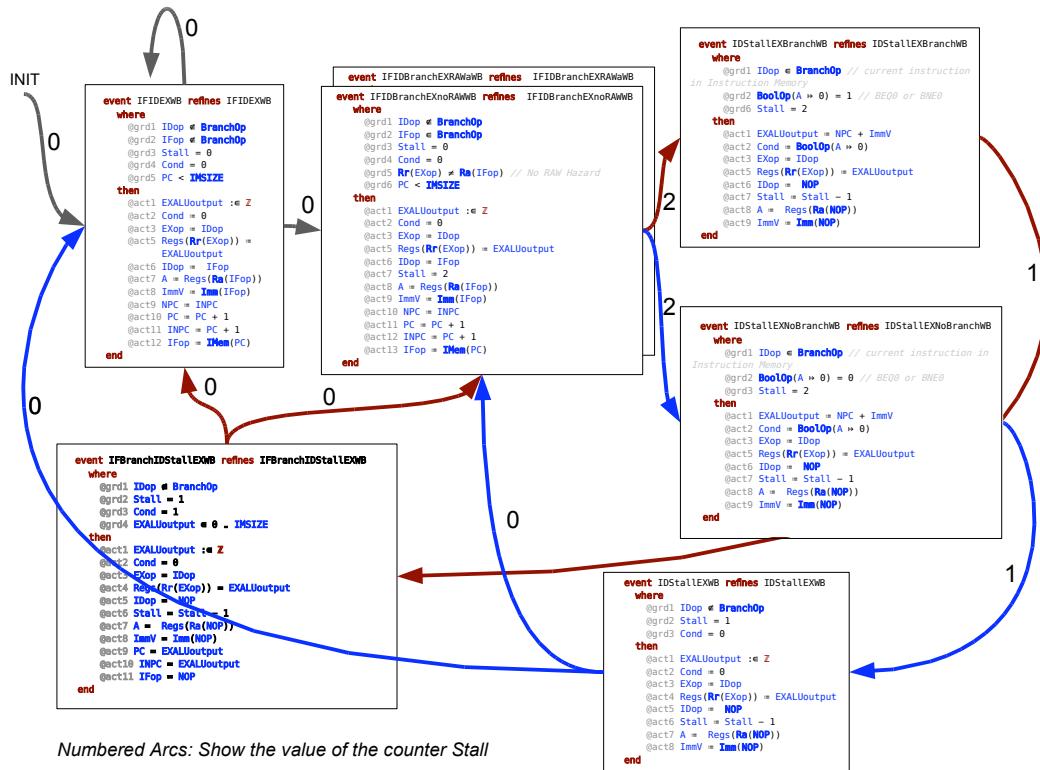

| 5.4.5    | The Fourth Refinement: a 4-stage pipeline . . . . .                                              | 101        |

| 5.4.6    | The Fifth Refinement . . . . .                                                                   | 102        |

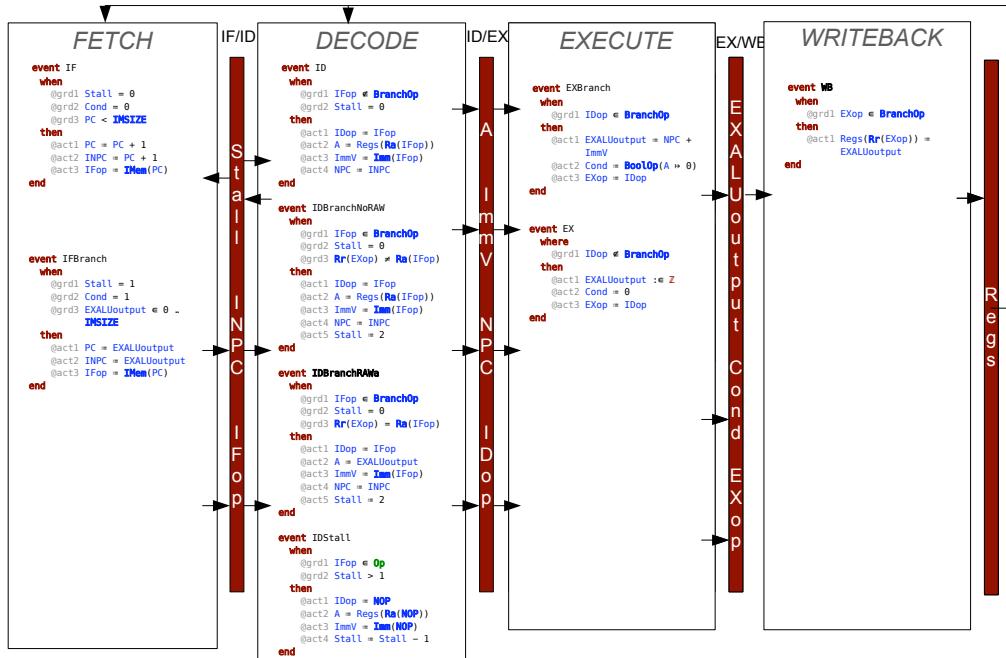

| 5.4.7    | Pipeline Decomposition . . . . .                                                                 | 105        |

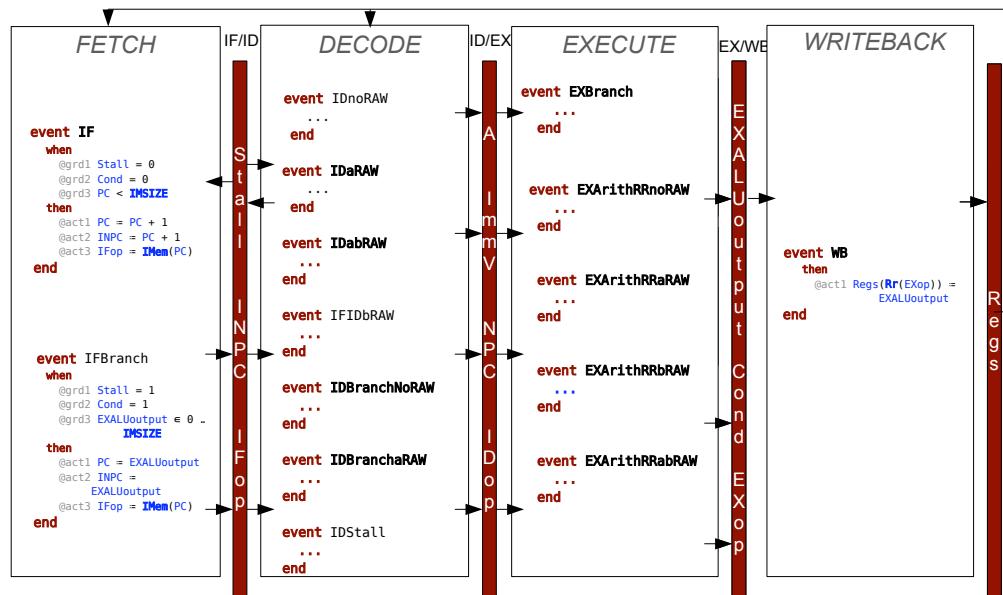

| 5.5      | Pipeline Instruction Composition . . . . .                                                       | 109        |

| 5.6      | Measuring Pipeline Complexity at the Specification Level . . . . .                               | 112        |

| 5.6.1    | Combined State Machine Arc Coverage . . . . .                                                    | 112        |

| 5.6.2    | Combined State Machine Path Coverage . . . . .                                                   | 113        |

| 5.7      | Component Re-use in Pipeline Specifications . . . . .                                            | 116        |

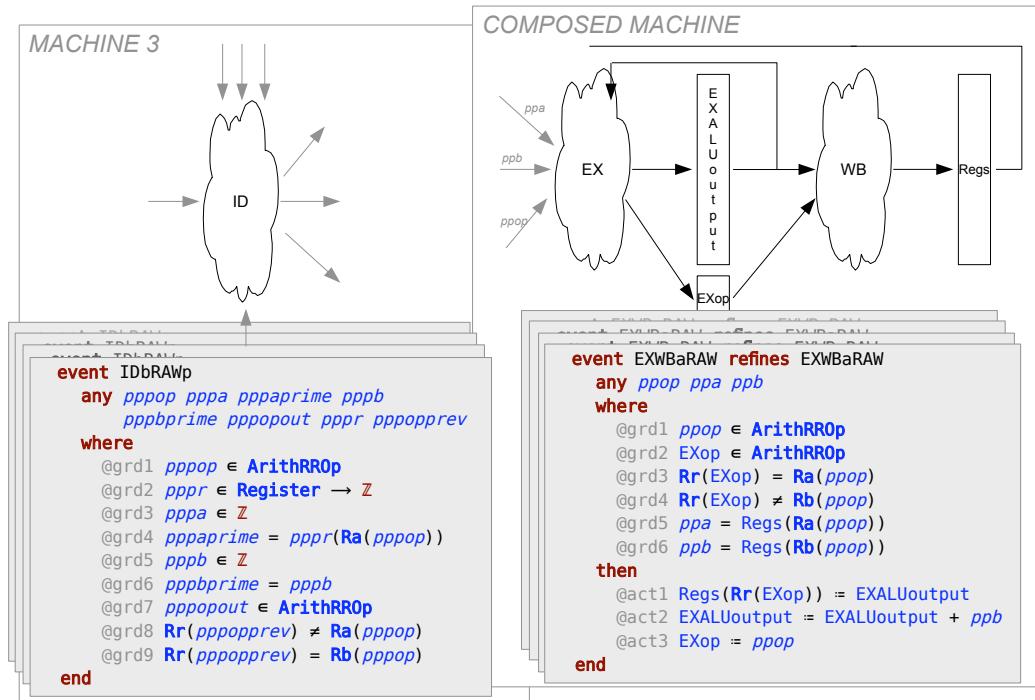

| 5.7.1    | Parameters and Witnesses in Component Re-use . . . . .                                           | 120        |

| 5.8      | A Review of the Pipeline Development Method . . . . .                                            | 120        |

| 5.8.1    | Modelling Data . . . . .                                                                         | 120        |

| 5.8.2    | Modelling Control . . . . .                                                                      | 121        |

| 5.8.3    | Advancing from Modelling to Proving: Problem Decomposition .                                     | 121        |

| 5.8.4    | Automatic Proof . . . . .                                                                        | 121        |

| 5.8.5    | Managing Architectural Complexity . . . . .                                                      | 122        |

| 5.8.6    | Measuring Architectural Complexity . . . . .                                                     | 122        |

| 5.8.7    | Memory Accesses . . . . .                                                                        | 122        |

| <b>6</b> | <b>Memory Accesses: Managing Component Latency</b>                                               | <b>123</b> |

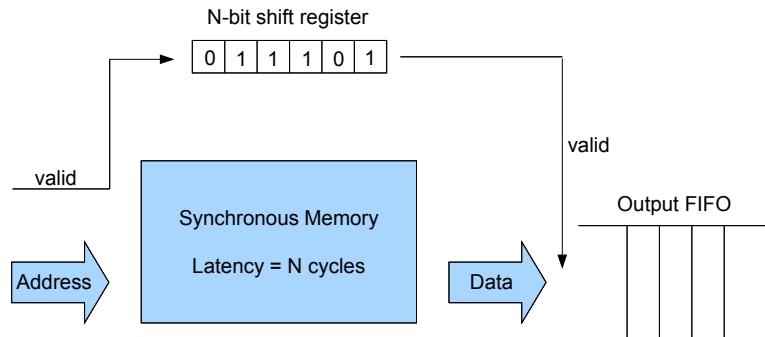

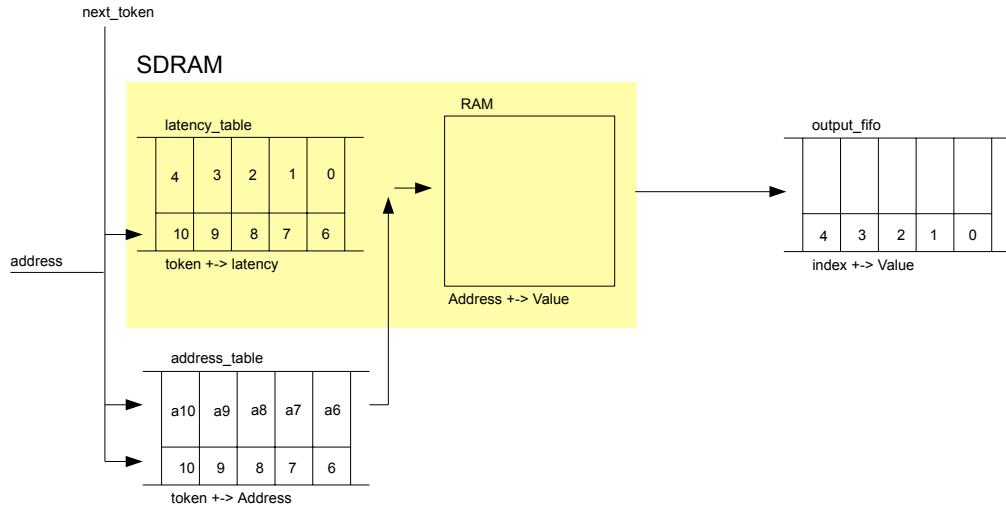

| 6.0.8    | Modelling Synchronous Memory . . . . .                                                           | 123        |

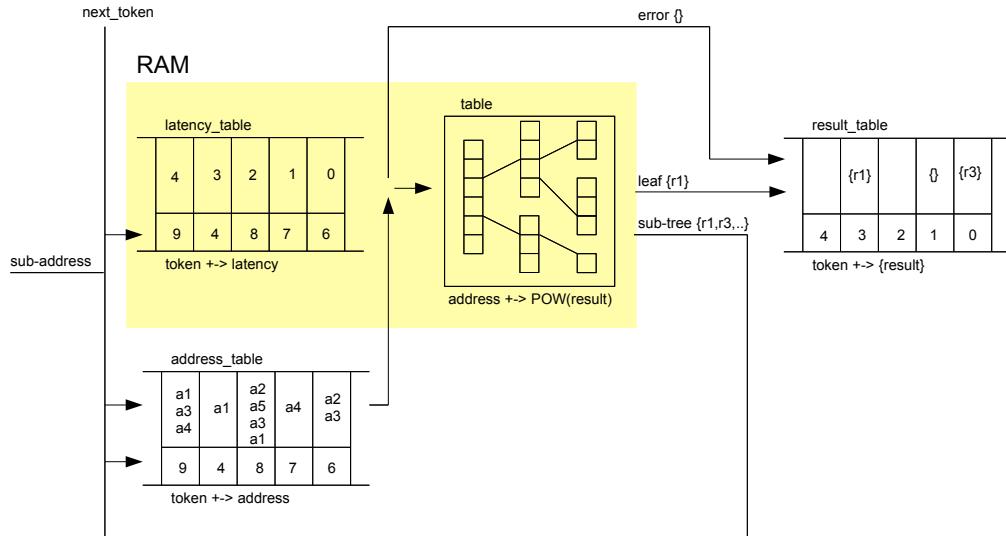

| 6.0.9    | The IP Look-up Circular Pipeline . . . . .                                                       | 126        |

| <b>7</b> | <b>Developing SoC Sub-Systems</b>                                                                | <b>133</b> |

| 7.1      | Managing Design Complexity . . . . .                                                             | 133        |

| 7.2      | Asynchronous Design and Transaction-Level Modelling . . . . .                                    | 134        |

| 7.3      | Unit-Transaction Level Design . . . . .                                                          | 135        |

| 7.4      | Latency-Insensitive Design . . . . .                                                             | 135        |

| 7.5      | Synchronous Elastic Design . . . . .                                                             | 137        |

| 7.6      | Microarchitectural Exploration: Introducing Synchronous Elastic Buffering with Event-B . . . . . | 138        |

| 7.6.1    | The Synchronous Elastic Buffer: An Abstract Specification in Event-B . . . . .                   | 139        |

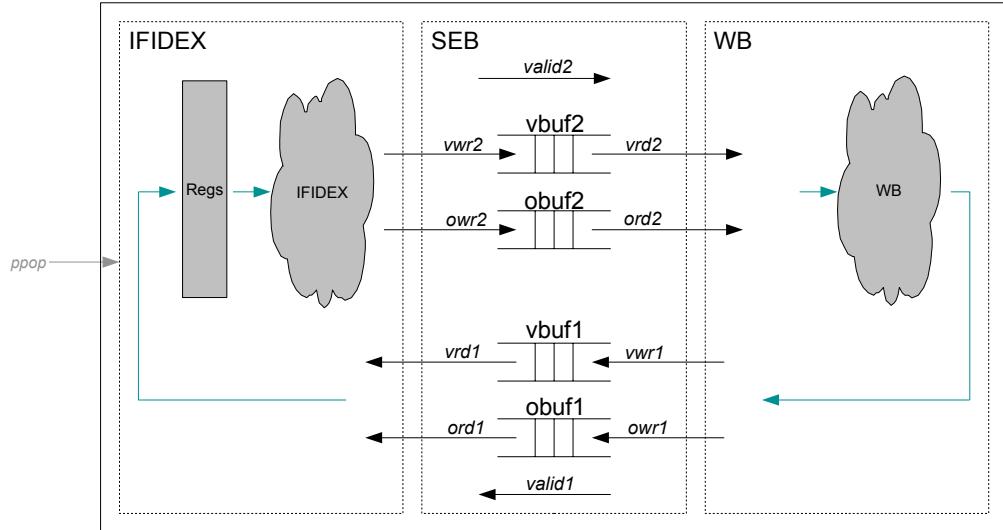

| 7.6.2    | Synchronous Buffering with Forwarding . . . . .                                                  | 141        |

| 7.6.3    | Synchronous Elastic Buffering with Stalling . . . . .                                            | 143        |

| 7.6.4    | Shared Event Pipeline Decomposition . . . . .                                                    | 150        |

| 7.6.5    | A Review of the use of Synchronous Elastic Design with Event-B .                                 | 151        |

| <b>8</b> | <b>Conclusions</b>                                                                               | <b>153</b> |

| <b>A</b> | <b>Published Papers</b>                                                                          | <b>166</b> |

# List of Figures

|      |                                                  |    |

|------|--------------------------------------------------|----|

| 2.1  | Simulation Based Verification . . . . .          | 7  |

| 2.2  | Model Checking . . . . .                         | 8  |

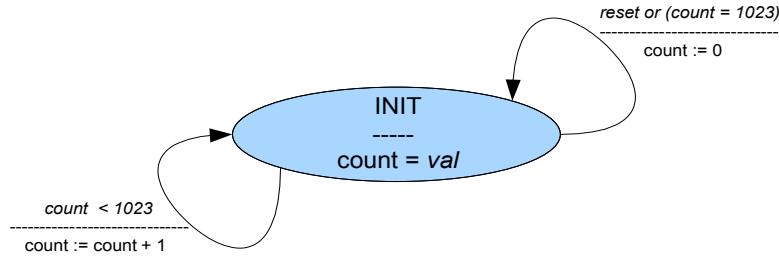

| 2.3  | Counter . . . . .                                | 11 |

| 2.4  | TLM Level 2 Master/Slave Communication . . . . . | 12 |

| 2.5  | channel behaviour . . . . .                      | 15 |

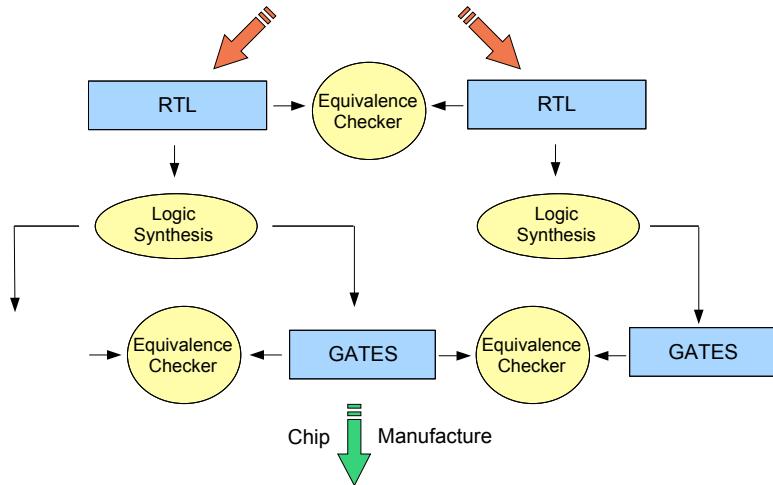

| 3.1  | SoC Flow . . . . .                               | 21 |

| 3.2  | The Role of RTL Synthesis . . . . .              | 22 |

| 3.3  | The Role of Formal RTL Checking . . . . .        | 22 |

| 3.4  | RTL Architectural Exploration . . . . .          | 24 |

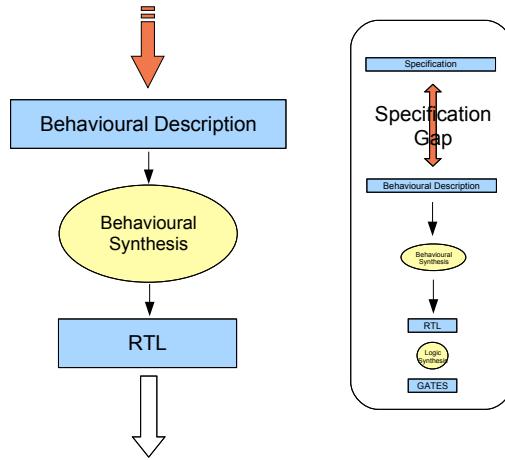

| 3.5  | Behavioural Synthesis Flow . . . . .             | 25 |

| 3.6  | TRS Processor Instruction Rule . . . . .         | 26 |

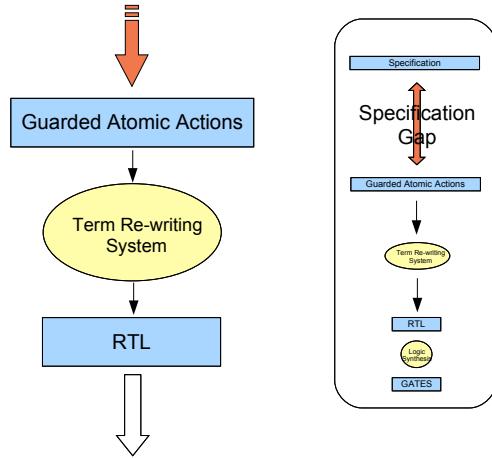

| 3.7  | TRS Synthesis Flow . . . . .                     | 27 |

| 3.8  | TRS Architectural Exploration . . . . .          | 28 |

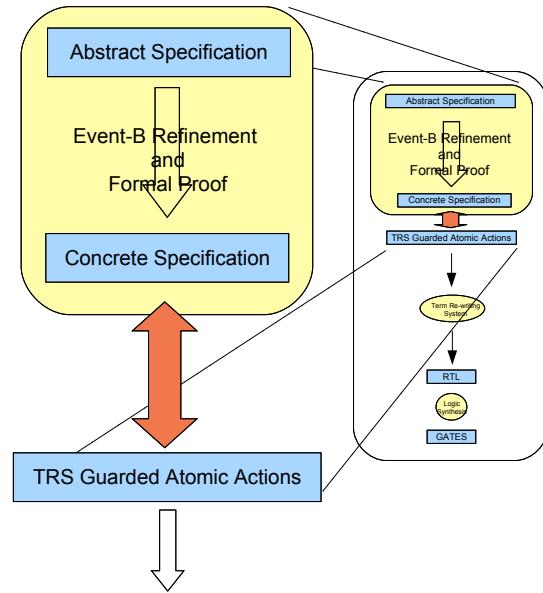

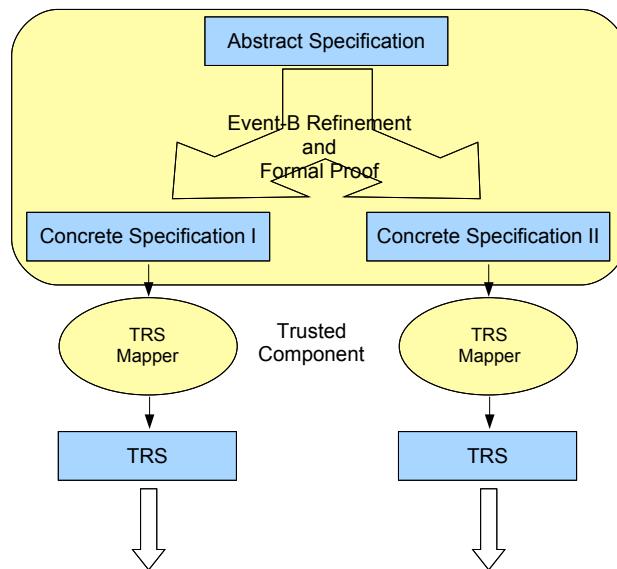

| 3.9  | Event-B and TRS flow . . . . .                   | 30 |

| 3.10 | Event-B Architectural Exploration . . . . .      | 31 |

| 4.1  | Counter . . . . .                                | 35 |

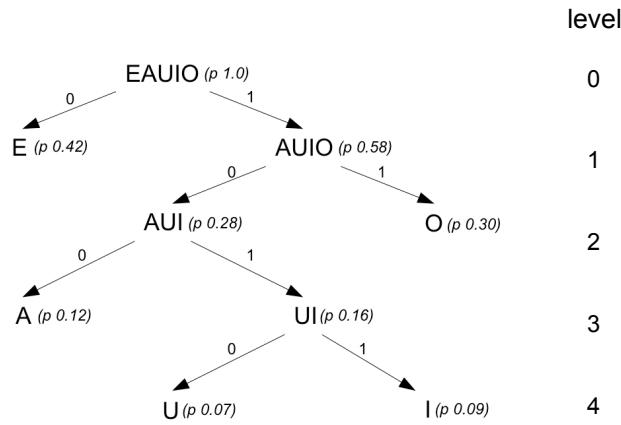

| 4.2  | HUFFMAN Encoding Tree . . . . .                  | 36 |

| 4.3  | HUFFMAN Partial Order . . . . .                  | 37 |

| 4.4  | Huffman EFSM . . . . .                           | 43 |

| 4.5  | The Pipeline . . . . .                           | 48 |

| 4.6  | Pipeline Execution . . . . .                     | 49 |

| 4.7  | Even Number Generator . . . . .                  | 54 |

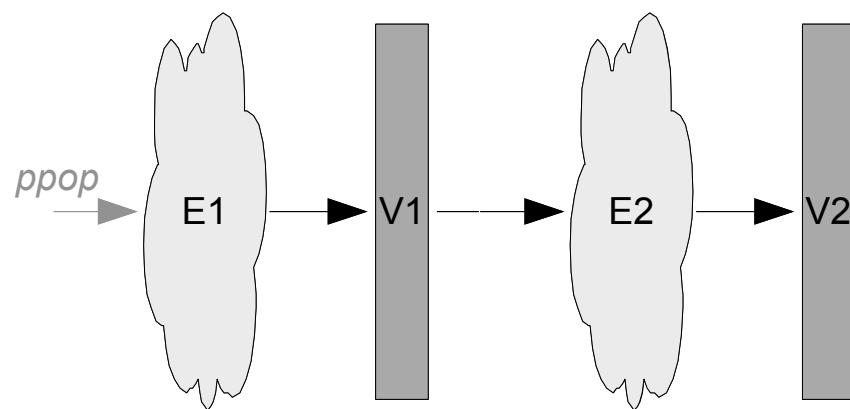

| 4.8  | Pipeline without Feedback . . . . .              | 55 |

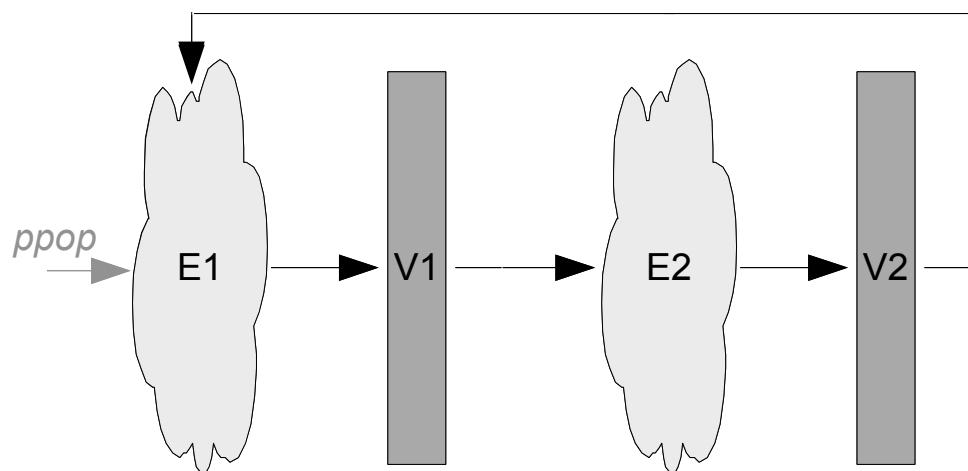

| 4.9  | Pipeline with Feedback . . . . .                 | 55 |

| 4.10 | Abstract Model . . . . .                         | 56 |

| 4.11 | First Refinement . . . . .                       | 57 |

| 4.12 | Abstract Model . . . . .                         | 59 |

| 4.13 | First Refinement . . . . .                       | 60 |

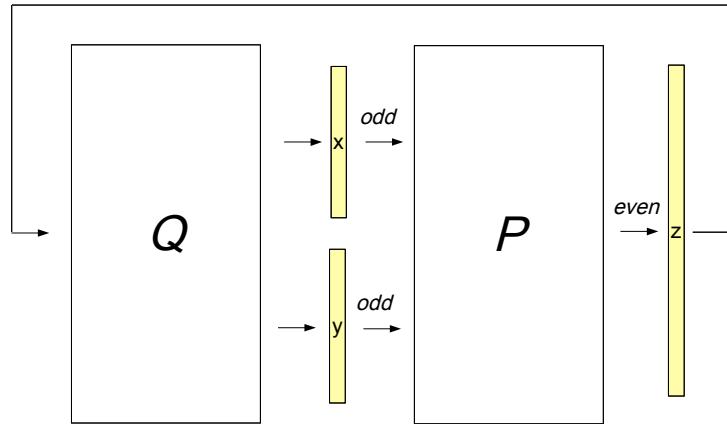

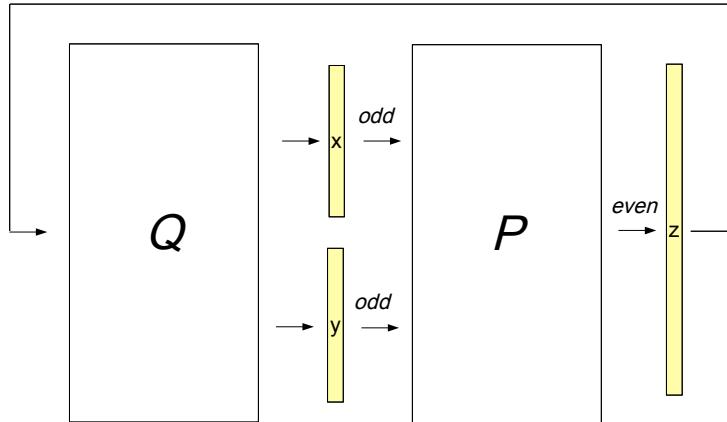

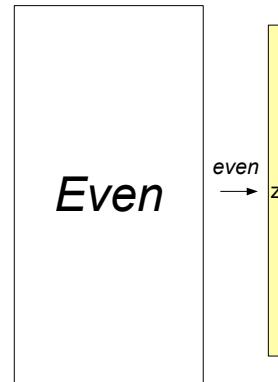

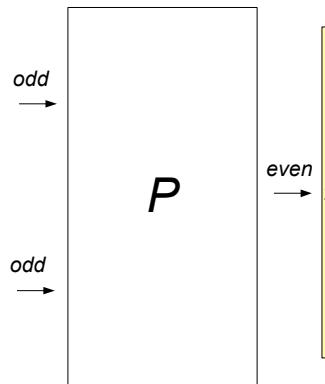

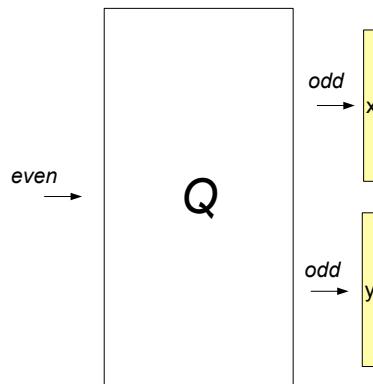

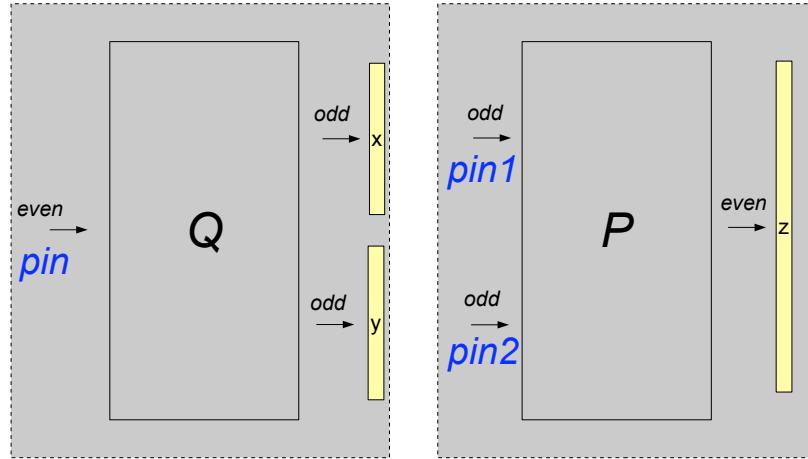

| 4.14 | Component Q and its Environment . . . . .        | 61 |

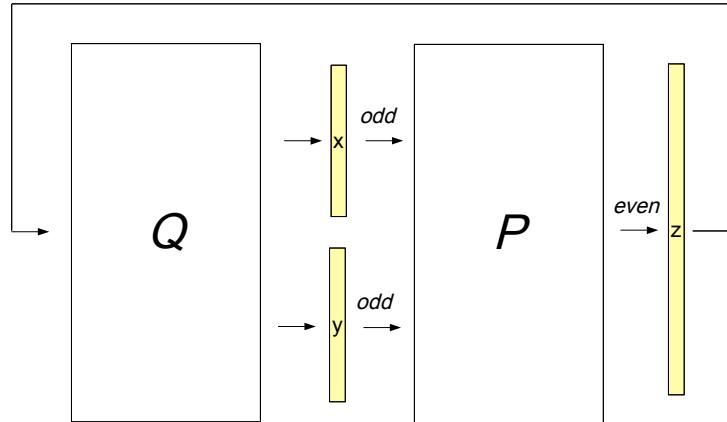

| 4.15 | Initial Component Composition . . . . .          | 63 |

| 4.16 | Pipelined Implementation . . . . .               | 64 |

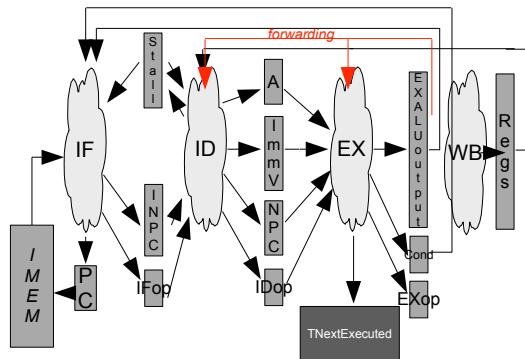

| 5.1  | DLX 5-stage Pipeline . . . . .                   | 69 |

| 5.2  | Event-B DLX Instructions . . . . .               | 71 |

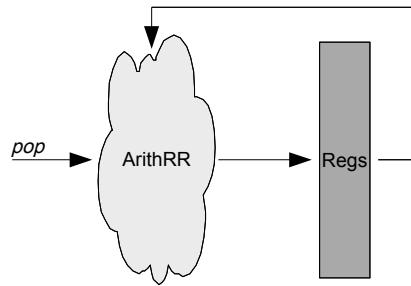

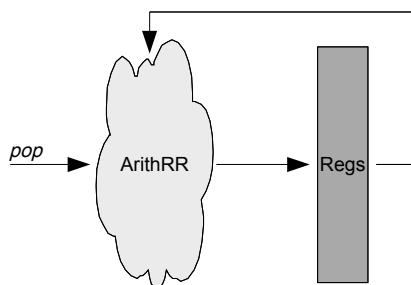

| 5.3  | Abstract Machine: Microarchitecture . . . . .    | 76 |

| 5.4  | Refined Machine: Microarchitecture . . . . .     | 77 |

---

|      |                                                                               |     |

|------|-------------------------------------------------------------------------------|-----|

| 5.5  | Successive Instructions can Interfere . . . . .                               | 79  |

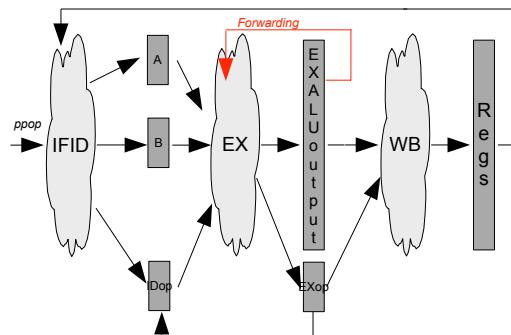

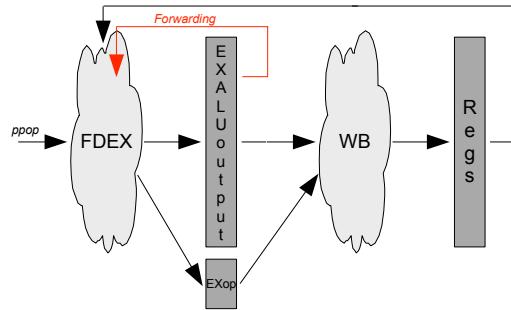

| 5.6  | Refined Machine with Forwarding: Microarchitecture . . . . .                  | 80  |

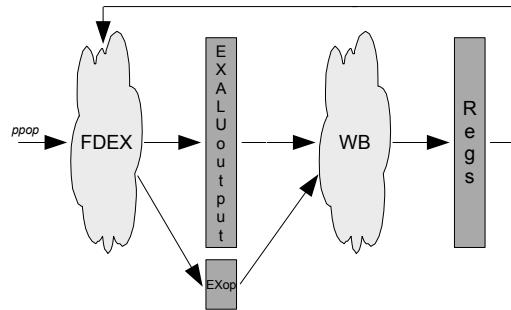

| 5.7  | Second Refinement: Microarchitecture . . . . .                                | 81  |

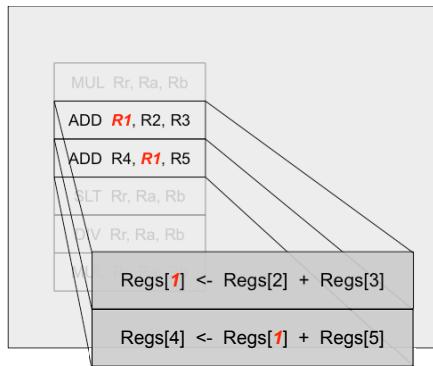

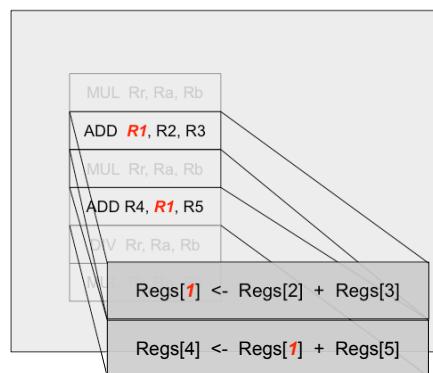

| 5.8  | Instructions one apart can Interfere . . . . .                                | 81  |

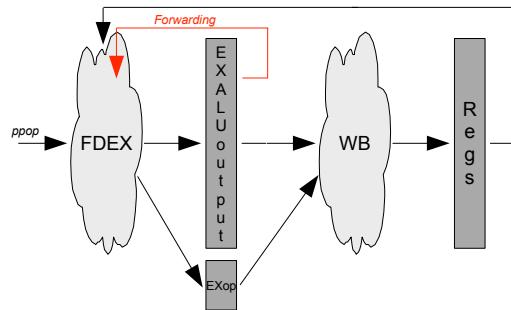

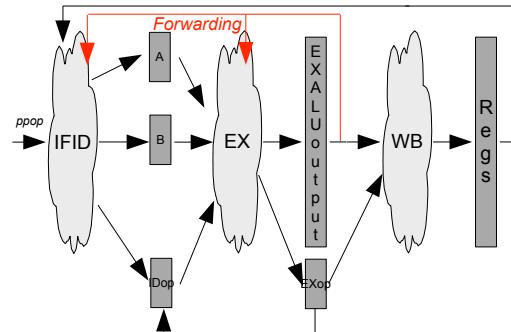

| 5.9  | Second Refinement with Forwarding: Microarchitecture . . . . .                | 85  |

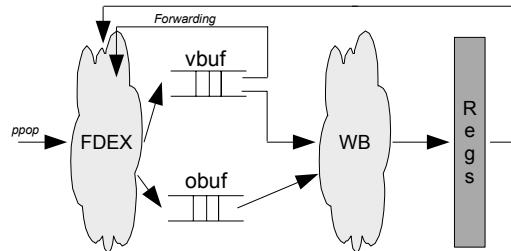

| 5.10 | Third Refinement: Microarchitecture . . . . .                                 | 85  |

| 5.11 | ArithRR 4-stage Pipeline . . . . .                                            | 89  |

| 5.12 | AbstractMachine: Microarchitecture . . . . .                                  | 91  |

| 5.13 | Refined Machine: Microarchitecture . . . . .                                  | 93  |

| 5.14 | Second Refinement . . . . .                                                   | 95  |

| 5.15 | Third Refinement . . . . .                                                    | 98  |

| 5.16 | Fourth Refinement . . . . .                                                   | 102 |

| 5.17 | Fifth Refinement: Combined State Machine . . . . .                            | 103 |

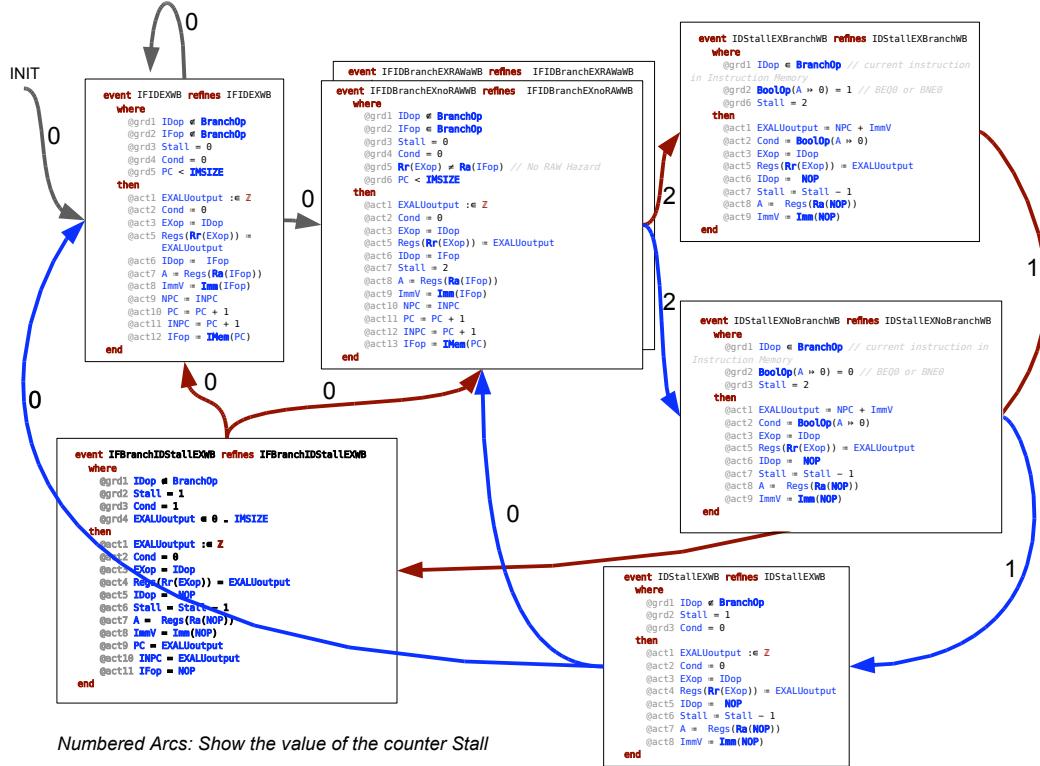

| 5.18 | Fifth Refinement: Events . . . . .                                            | 104 |

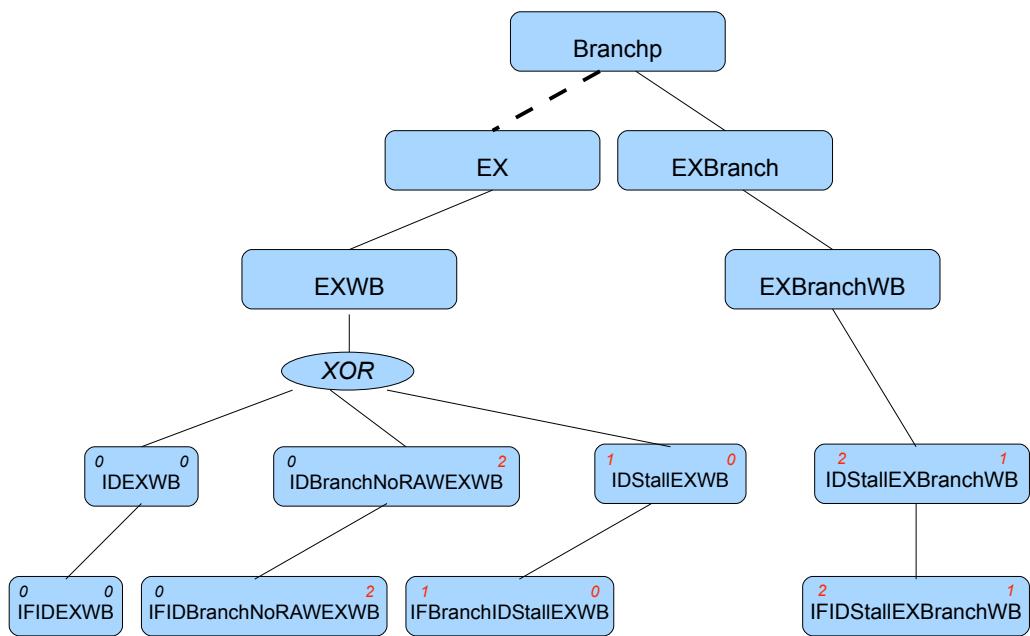

| 5.19 | Branch 4-stage Pipeline . . . . .                                             | 108 |

| 5.20 | The Pipeline Development Flow . . . . .                                       | 109 |

| 5.21 | ArithRR 4-stage Pipeline . . . . .                                            | 110 |

| 5.22 | Branch 4-stage Pipeline . . . . .                                             | 110 |

| 5.23 | Composed 4-stage Pipeline . . . . .                                           | 111 |

| 5.24 | Combined State Machine Arcs . . . . .                                         | 113 |

| 5.25 | Branch Refinement Diagram: 4th Refinement, No RAW . . . . .                   | 114 |

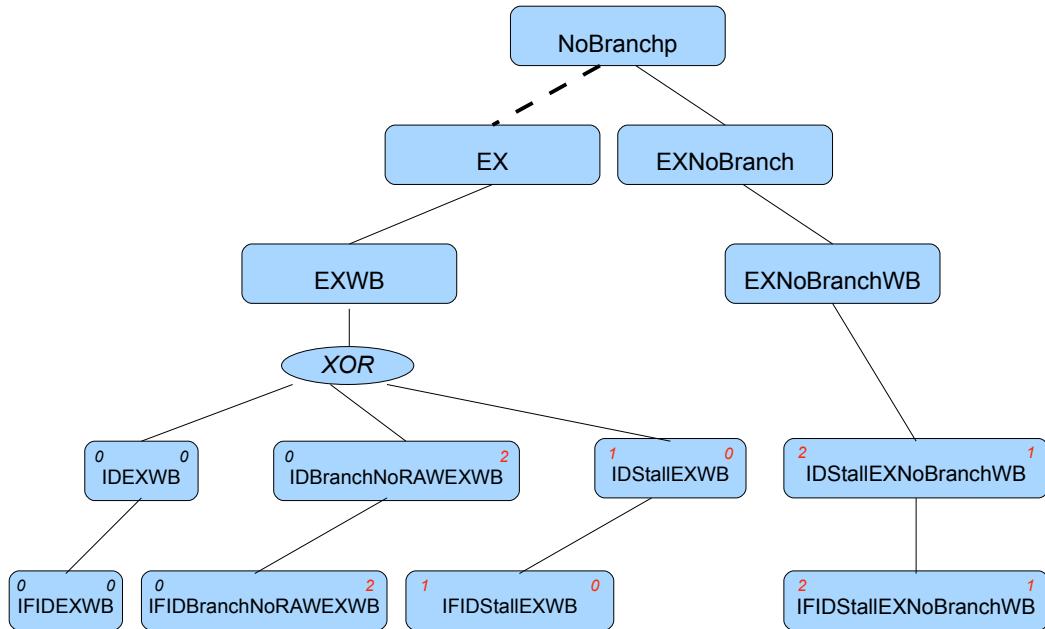

| 5.26 | NoBranch Refinement Diagram: 4th Refinement, No RAW . . . . .                 | 114 |

| 5.27 | Abstract Machine: Microarchitecture . . . . .                                 | 116 |

| 5.28 | First Refinement: Components . . . . .                                        | 117 |

| 5.29 | First Refinement: Component Composition . . . . .                             | 118 |

| 5.30 | Second Refinement: Parameter Instantiation . . . . .                          | 118 |

| 5.31 | Third Refinement: Component Composition . . . . .                             | 119 |

| 5.32 | Third Refinement: Parameter Instantiation . . . . .                           | 119 |

| 6.1  | Managing RAM Latency . . . . .                                                | 124 |

| 6.2  | SDRAM lookup . . . . .                                                        | 125 |

| 6.3  | IP Lookup Circular Pipeline . . . . .                                         | 127 |

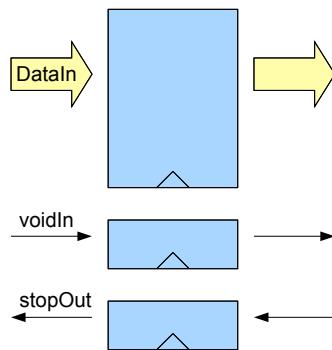

| 7.1  | Latency Insensitive Protocol . . . . .                                        | 136 |

| 7.2  | The SELF Protocol . . . . .                                                   | 137 |

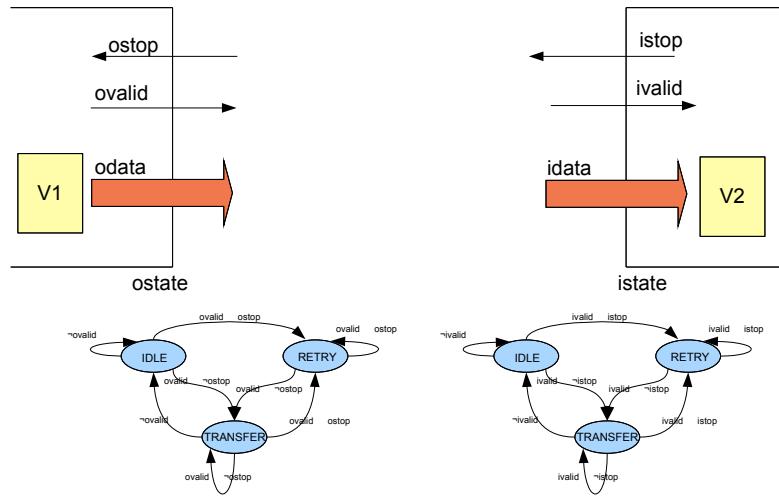

| 7.3  | Connecting 2 Elastic Components . . . . .                                     | 138 |

| 7.4  | Abstract Synchronous Elastic Buffer . . . . .                                 | 139 |

| 7.5  | Abstract Machine: Microarchitecture . . . . .                                 | 140 |

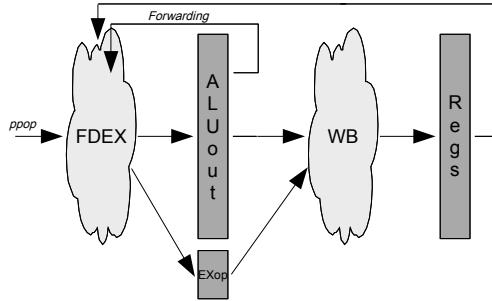

| 7.6  | Refined Machine with forwarding: Microarchitecture . . . . .                  | 141 |

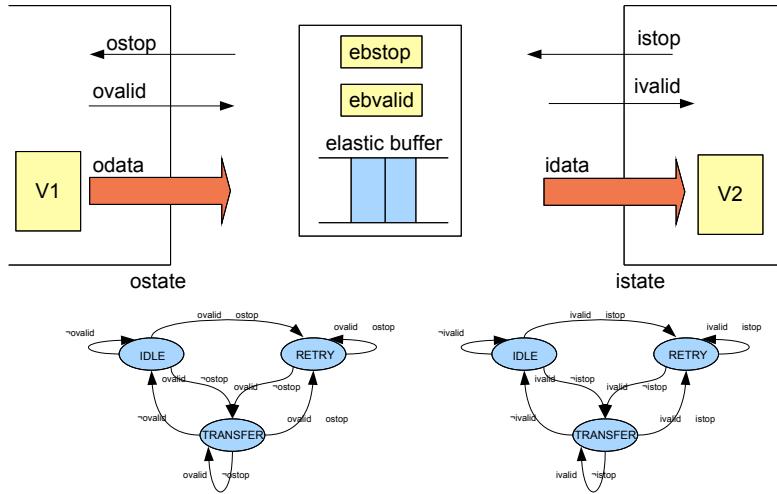

| 7.7  | Refined Machine with buffers and forwarding: Microarchitecture . . . . .      | 141 |

| 7.8  | Refined Machine with synchronous elastic buffers: Microarchitecture . . . . . | 144 |

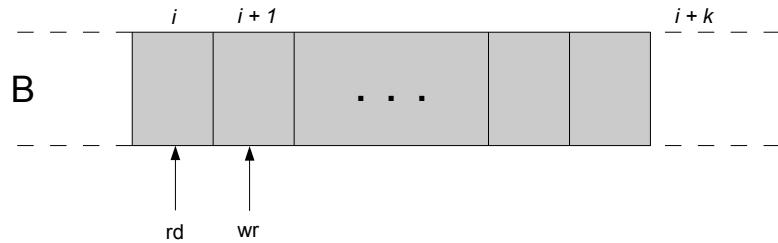

| 7.9  | Synchronous Elastic Buffers: Stalling mechanism . . . . .                     | 149 |

| 7.10 | Synchronous elastic buffer decomposition: Microarchitecture . . . . .         | 150 |

# List of Tables

|     |                                       |     |

|-----|---------------------------------------|-----|

| 4.1 | Huffman Proofs . . . . .              | 42  |

| 4.2 | Abstract Model Events . . . . .       | 47  |

| 4.3 | Refined Model Merged Events . . . . . | 51  |

| 4.4 | Pipeline Proofs . . . . .             | 51  |

| 4.5 | 2-stage 2-event pipeline . . . . .    | 51  |

| 4.6 | 2-stage 4-event pipeline . . . . .    | 52  |

| 4.7 | 2-stage m+n-event pipeline . . . . .  | 52  |

| 4.8 | Verilog RTL Processes . . . . .       | 65  |

| 5.1 | DLX Pipeline Structure . . . . .      | 72  |

| 5.2 | Pipeline Proofs . . . . .             | 84  |

| 5.3 | Pipeline Proofs . . . . .             | 104 |

| 6.1 | IP Lookup State Machine . . . . .     | 131 |

| 6.2 | IP Lookup Proofs . . . . .            | 132 |

| 7.1 | SELF State Machine . . . . .          | 137 |

# Academic Thesis: Declaration Of Authorship

I, John Larry Colley

declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

Guarded Atomic Actions and Refinement in a System-on-Chip Development Flow: Bridging the Specification Gap with Event-B

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Either none of this work has been published before submission, or parts of this work have been published as:

On Proving with Event-B that a Pipelined Processor Model Implements its ISA Specification

Colley, J and Butler, M

Refinement Based Methods for the Construction of Dependable Systems

Dagstuhl, Germany

September 2009

Signed: .....

Date: .....

## **Acknowledgements**

I would like to thank my supervisors Michael Butler and João Marques-Silva for their guidance and Edd Turner, Lis Ball, Renato Silva and Ross Horne for their help during my research.

# Chapter 1

## Introduction

The complexity of modern System-on-Chip (SoC) hardware stretches the existing design and verification flows, languages and tools to the limit of their capabilities [Asanovic et al., 2006], [Sylvester and Keutzer, 2001]. Verification takes a larger and larger proportion of the overall effort and it is often very late in the design process that timing issues, resulting from the very small feature sizes of modern silicon processes, are encountered and can only be corrected by substantial re-design [Carloni and Sangiovanni-Vincentelli, 2002]. The commensurate reduction in the predictability of the verification closure process means that there is a clear need to enhance existing design flows to be better able to manage this increased complexity, without losing the well-established benefits that have driven successful synchronous design.

First, the Register Transfer Level (RTL) description, which forms the input for synchronous, logic synthesis-driven design [Devadas et al., 1994] is at too low a level of abstraction for efficient architectural exploration and re-use [Hoe, 2000] and second, the existing methods for taking a high-level paper specification and refining this specification to an implementation that meets its performance criteria is largely manual and error-prone [Arvind et al., 2004]. Third, as RTL descriptions get larger, a systematic design method is necessary to address explicitly the timing issues that arise when applying logic synthesis to such large blocks [Asanovic, 2007], [Rose et al., 2005].

Term Rewriting Systems (TRS) [Hoe and Arvind, 1999] have been shown to offer a convenient notation, as a set of *guarded atomic actions*, for describing microarchitectures that is amenable to formal reasoning and is used by the industrial tool Bluespec [Nikhil, 2004] for high-level synthesis. Event-B is a language and method [Abrial et al., 2006] that supports the development of specifications with automatic proof and refinement, also based on guarded atomic actions. Latency-insensitive design [Carloni and Sangiovanni-Vincentelli, 2002] is a method for assembling and managing the communication between components in complex synchronous hardware systems which ensures

that a design composed of functionally correct components will be independent of communication latency.

In this work a method has been developed which uses Event-B for latency-insensitive SoC component and sub-system design which can be combined with high-level component synthesis to enable architectural exploration and re-use at the specification level and to close the specification gap in the SoC hardware flow. It will be shown that an abstract specification can be refined systematically to a level where it is possible to represent and reason about the key elements that the hardware designer employs in developing an architecture to meet the required constraints on performance and power. These key elements include pipelining strategies, the size of components, and the communication mechanisms employed between components. The goals of this work are threefold.

First, to show that alternative pipeline architectures within components can be developed from a high-level specification, compared and verified systematically. The challenge here is that all possible combinations of pipeline activity must be identified and explored exhaustively.

Second, that a high-level model for latency-insensitive communication can be developed that can be used at the specification level to verify formally that communicating components obey the latency-insensitive protocol and will not cause deadlock.

Third, that the specification can be refined to a level of abstraction that matches that required for input to high-level or RTL synthesis.

Chapter 2 provides background information, covering the technical and financial motivation for the adoption of verification tools and the need for greater confidence in the quality of a design before sign-off and manufacture. It then looks at current verification technologies and solutions, their strengths and weaknesses, and the recent emergence of new technologies to address these weaknesses. It also covers the new and evolving standard for Transaction-Level Modelling (TLM) in SystemC and how it augments the existing hardware design flow. It goes on to provide a background to methods for modelling concurrency, including the use of guarded atomic actions for modelling and high-level synthesis, and an introduction to the Event-B language and method.

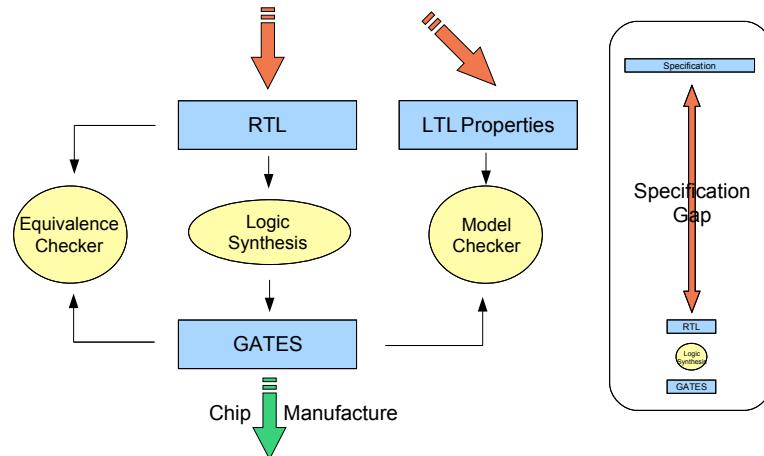

The contribution of Chapter 3 is to show how the existing SoC synchronous hardware design flow can be enhanced by the seamless introduction of a formal specification and verification method that addresses the gap that exists in this flow between the specification and the RTL description used for logic synthesis. It looks at the reasons that behavioural synthesis has not in general helped to close this gap, and how guarded atomic actions can be used to provide efficient high-level synthesis and architectural exploration. It then provides an overview of how the Event-B formal method can be combined with RTL and high-level guarded atomic action synthesis to close the specification gap. This method is then elaborated in detail in the subsequent chapters.

The contribution described in Chapter 4 is an Event-B based method that can be used for developing SoC component specifications that takes into account the restrictions that hardware process technology places on component size. It then shows how the method can be applied to pipelined architectures and explores the implications that such architectures have for how simultaneous pipeline events are managed.

The contribution of Chapter 5 is to show how a SoC microprocessor pipelined implementation can be derived formally from its abstract specification using the Event-B based method described in Chapter 4.

Chapter 6 addresses the issues of latency introduced by memory sub-systems. The contribution of this chapter is to show how latency and out-of-order completion can be modelled formally in an IP Lookup circular pipeline.

Chapter 7 covers the emerging latency-insensitive protocols which can de-couple sub-system design from the complex timing interaction that can occur between components. The contribution is an extension of the method described in Chapter 4 to support latency-insensitive design with formal proof.

# Chapter 2

## Background

### 2.1 Board-level Design and Verification

Before the widespread adoption of complementary metal oxide semiconductor (CMOS) technology [Horowitz and Hill, 1989], the complexity of application-specific hardware designs was limited by transistor size. Transistor Transistor Logic (TTL) [Horowitz and Hill, 1989] packaged 4 NAND gates in a 2cm x 1cm chip so that approximately 500 gates could be placed on a board. Using multiple boards it was possible to build designs with a few thousand gates.

The advantage, however, of using discrete components was that it was very easy to build a working prototype of the design which could be run at full speed on a tester, and in the event of errors in the design it was possible to insert tester probes anywhere on the board to help locate the errors [Williams, 1986]. Errors could be fixed by replacing components or inserting wire patches. Test patterns were developed by hand, and once the prototype passed the tests, track layout could be performed and the boards manufactured [Russell, 1985]. Even if errors were discovered after manufacture, the boards could be patched on-site.

The low cost of failure meant that there was low demand for commercial tools to aid in design verification, and the majority of tools used, for instance to optimise layout, were developed in-house by the electronics companies themselves.

### 2.2 Chip-level Design and Verification

As CMOS technology became more accessible, companies such as Texas Instruments and LSI Logic offered methodology and manufacturing services for application-specific

(ASIC) CMOS design. Coupled with the shrinking transistor sizes enabled by the increasingly sophisticated manufacturing processes developed by the semi-conductor companies, it was now possible for fab-less design companies to develop designs of considerable complexity with very low unit cost. By 2006 it was possible to produce designs with more than 5 million gates on a single chip.

It is, however, far more difficult to verify a design on a single chip than on a board. It is no longer possible to produce a working prototype and, prior to manufacture, a photographic mask of the chip [Ragan et al., 2002], which can cost as much as \$2 million, must be produced. The cost of failure has become extremely high. It is these economic considerations that have driven the development of an Electronic Design Automation (EDA) industry that was, in 2006, valued at \$5.3 billion [Huygen, 2007].

## 2.3 EDA Design and Verification Languages

### 2.3.1 Modelling Languages

Early modelling languages only supported logic gate descriptions and were seldom entered by hand. Schematic capture tools [Russell, 1985] allowed users to enter the design graphically, and the modelling language was used for data interchange between tools [Stanford and Mancuso, 1990], but this technology severely restricted the size of design that could be handled.

In the mid 1980's the modelling languages Verilog [Thomas and Moorby, 2002] and VHDL [Perry, 1994] raised the level of modelling abstraction to the Register Transfer Level (RTL) and enabled a switch from schematic capture to language-driven design.

An RTL description represents the design as a set of communicating processes. Each process can represent a block of combinational logic, a finite state machine or a combination of both. Although the data types are still low level, the significant improvement in control logic abstraction means that much larger designs can be contemplated. Coupled with the availability of Logic Synthesis tools [Devadas et al., 1994], which generate automatically a gate level representation from the RTL, designers had a mechanism for exploiting the increased complexity made available by the new CMOS technology.

At the same time, VHDL and Verilog provided language constructs to support behavioural modelling. VHDL took these constructs, such as procedure calls, from ADA, and Verilog from C. It was hoped that behavioural modelling would supersede RTL modelling, but this has not happened, for reasons that will be discussed later.

### 2.3.2 Test Languages

Because of the very high masking costs, considerable effort has been placed in the EDA industry into designing languages that can be used to ensure that the model of the design has been thoroughly tested before manufacture and, importantly, to provide a measure of how well the tests cover the design. Specman [Kuhn et al., 2001], VERA [Haque and Michelson, 2001] and SystemVerilog [Sutherland et al., 2004] provide object-oriented languages that allow the environment of the design to be modelled at a very high level. Constrained-Random generation of tests means that the number of tests that can be applied to the design can be significantly higher than could be achieved using hand-written directed tests, and there is more chance that unanticipated corner-cases are covered.

The test languages provide a measure of functional coverage which, coupled with traditional code coverage measures, can be used to increase confidence in the signed-off design.

### 2.3.3 Property Languages

While test languages provide a functional view of the properties of the design and its environment, property languages provide a formal view. Based on Linear-time Temporal Logic (LTL) [Huth and Ryan, 2004] the property languages PSL (Property Specification Language) [Foster et al., 2005] and SVA (SystemVerilog Assertions) [Sutherland et al., 2004] augment the test languages by providing a means to specify the temporal behaviour of the design (properties/assertions) and its environment (assumptions). The other major advantage of properties is that they may be embedded in the design itself, so that errors can be flagged locally.

## 2.4 EDA Tools

### 2.4.1 Simulation-based Verification

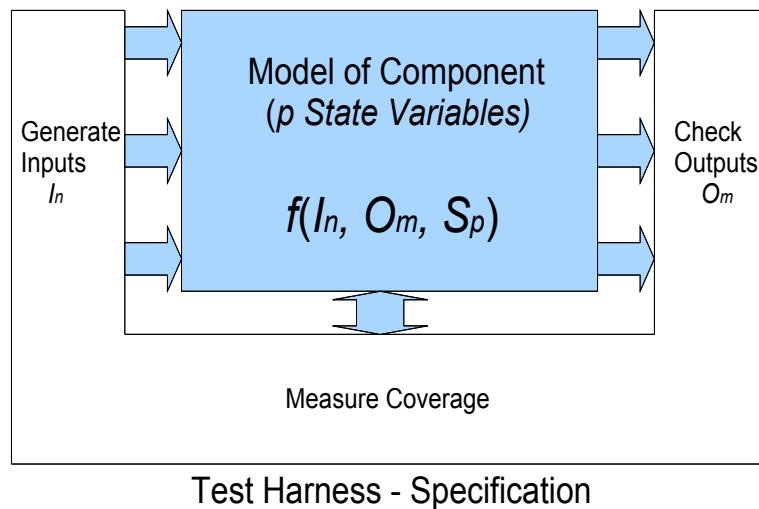

RTL simulation remains the dominant technology for the verification of application-specific hardware designs. Figure 2.1 shows how the model of the design, represented by the function  $f$  of its inputs, outputs and internal state, is placed in a test harness that represents the specification of the design. The test harness may consist of directed-tests, pseudo-random tests and assertions. The design is simulated using the input values generated by each test, and the outputs are checked to ensure correct functionality. At the same time, the code and functional coverage of each test is measured, and these measurements are accumulated to provide an overall value of design coverage. When the accepted coverage threshold is reached, the design is signed-off.

FIGURE 2.1: Simulation Based Verification

#### 2.4.2 Disadvantages of Simulation

Although the use of test languages and functional coverage has provided increased confidence in design sign-off, this has come at a price. The number of tests that can accumulate with a design has increased from hundreds to tens of thousands. Pseudo-random tests can never be as well-targeted as directed tests, and this results in much test duplication. For a 2 million gate design with 20 thousand tests, this can result in simulation times of up to 2 weeks, even if the tests are distributed on simulation farms with hundreds of processors (Infineon, Bristol: Case Studies<sup>1</sup>). The effort required to verify design changes increases greatly as the design progresses.

The real disadvantage of simulation, however, is that the executable specification of the design, the set of tests, is not in any way formal, and therefore any measure of coverage is approximate. For designs that have safety considerations, particularly those in the expanding automotive sector, simulation on its own is not sufficient to give the required confidence for design sign-off.

#### 2.4.3 Formal Verification

Although there was interest in some theorem proving solutions in the 1990's (Larch/VHDL [Baraona and Alexander, 1994], [Alexander and Baraona, 1997] and Lambda [Hadjinicolaou et al., 1994]), their limited capacity and need for expert manual intervention meant that the EDA industry focused on the promise of automatic formal verification

<sup>1</sup>Private Communication

that model checking technology [Clarke and Emerson, 1981], [J.R. Burch et al., 1990] provided.

EDA tool developers and users have put considerable effort into defining the IEEE standard Property Specification Language (PSL), which is based on Linear-time Temporal Logic [Vardi and Wolper, 1984] can be used for both formal and simulation-based verification, and has well-defined formal semantics [Gordon et al., 2003]. The essence of PSL has also been incorporated into SystemVerilog and, as a result, users have access to a mechanism for formal hardware specification in all the major industry tool-sets.

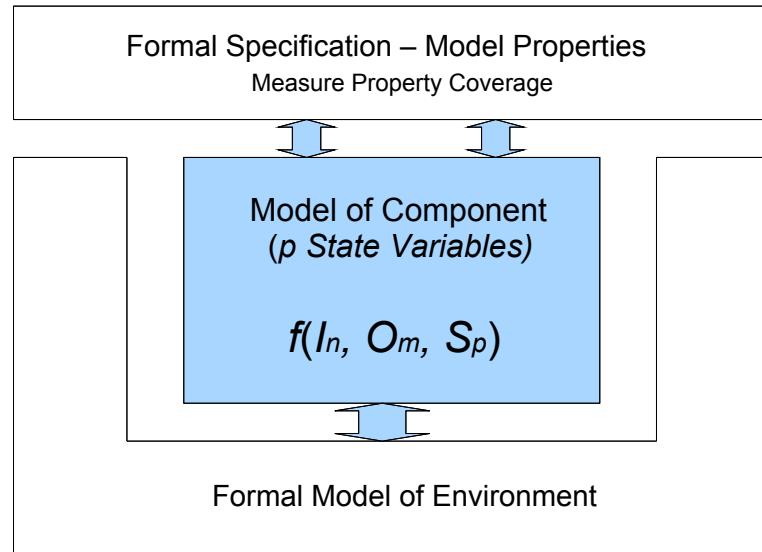

In parallel with the deployment of PSL, considerable advances have been made in model checking technology, particularly with the adoption of SAT-based techniques [Clarke et al., 2001], which means that very large design components can be verified automatically. Model checkers take as input the same RTL model description as used in simulation, and Figure 2.2 shows how the test-bench used for simulation is replaced with a formal description of the design’s environment (the assumptions), and a set of properties (the assertions) that specify the behaviour of the design.

FIGURE 2.2: Model Checking

#### 2.4.4 Disadvantages of Current Model Checking Solutions

Apart from the fact that model checking cannot be used on very large designs, the effort required to write the PSL properties for a design component is large. PSL was designed to be used with the low-level data types used in RTL descriptions, and the properties required to describe RTL behaviour can be long and complex. Although

suitable for parallel interfaces such as ARM AMBA where the state of the bus is defined explicitly by a set of low-level signals [Cohen et al., 2004], for serial interfaces such as PCI Express (TransEDA PCI Express PSL Property Library<sup>2</sup>) where the bus state has to be decoded from the bit stream, the properties become long and unwieldy. In practice, HDL monitors need to be written to present a higher transaction level stream to the PSL checker, but it would be easier if it were possible to raise the level of abstraction and define transaction-level properties in the property language itself.

Property coverage metrics [Chockler et al., 2001] are also immature, so there is no way of measuring that a set of properties adequately covers the functionality of the models. PSL properties are often written as implications and there is no way of telling that an implication has only been vacuously satisfied and that the left hand side of the implication is always false. This situation can occur in simulation-based verification when the test bench is inadequate and the signals comprising the left hand side have not been fully exercised. It can also occur in model checking when the environment is over-constrained.

## 2.5 Higher-level Modelling Abstractions

### 2.5.1 Behavioural Modelling

As described in Section 2.3 on Page 5, modern hardware description languages have inherited the capabilities of the procedural programming languages, ADA and C. Writing procedural descriptions of hardware, excluding all timing and concurrency issues, is termed behavioural modelling. The main advantage of behavioural models is that they can be simulated at speeds orders-of-magnitude faster than their RTL counterparts. The disadvantage is that efficient hardware is not procedural, but highly concurrent, and the translation of a behavioural description to an RTL description that will implement a given hardware architecture is complex and application specific. Much research and development has been undertaken over the last 20 years to automate this translation (behavioural synthesis), but no viable general solution has been found, and it remains largely a manual operation. Without this automatic step in place, any attempts to use behavioural descriptions for formal verification would be of little value.

Currently, behavioural models are usually written in C to provide a behavioural reference specification for the RTL model that can be used in system simulation to improve simulation speed. The C test-bench is re-used to verify the RTL, or the C and RTL models are co-simulated in the design.

---

<sup>2</sup>Private Communication

### 2.5.2 Transaction-Level Modelling(TLM)

Another way of increasing simulation speed is to reduce the number of discrete data communications between processes, and the frequency of those data communications [Donlin, 2004]. Where the interface comprises many bit and bit vector signals, these are bundled into a single packet of data for transfer. In addition, if each communication consists of a sequence of data transfers over time, the data packets can be collected and passed as a single transaction. This abstraction of both simulation data values and events in inter-process communication leads to simpler and faster simulation models.

Although primarily developed to speed up simulation, the event and data abstraction principles on which TLM is founded could provide a major contribution to raising the abstraction level for formal verification.

## 2.6 SystemC Transaction Level Modelling

The Open SystemC Initiative (OSCI), which promotes the SystemC hardware-oriented language based on C++ class libraries, has recognised the importance of TLM [Ghenas-sia, 2006] and produced a draft standard [OSCI-TLMS subgroup, 2007] for TLM modelling in SystemC. The standard focuses on the communication between hardware processes using standardised interfaces [Rose et al., 2005], [Swan, 2006], [Bombieri et al., 2006a].

### 2.6.1 TLM level 3

The highest level, TLM level 3, is a behavioural modelling style but with a well-defined communication mechanism. It is designed for high-performance simulation while supporting a design methodology which establishes an inter-process communication mechanism that can be refined at lower levels. TLM level 3 is **untimed**: there is no notion of time or a clock to control execution of the design and the ordering of events is determined by the order in which the communications (transactions) occur between processes. After an initial evaluation, each process waits until there is a change on one or more of its inputs. The process code is then executed and then suspends again, waiting for further input changes. Each execution of the process code is assumed to take zero time. A Master process is written using sequential C++ code and the Master and Slave communicate via **read** and **write** procedure calls implemented by the slave. High-level types are used to represent the data. The master issues a command to the slave using the write procedure call, the operation is performed by the slave and the return result made available in zero time. The Master may therefore call the read procedure call immediately to get the result. When two independent processes communicate in SystemC, the communication and synchronisation is handled by the scheduler of the simulator kernel [Mueller et al.,

2001]. The request is placed in a priority queue [Brown, 1988], which incurs a context switch in the SystemC simulator. Since Master/Slave communications at TLM Level 3 do not need to use simulator kernel event scheduling, level 3 models simulate quickly, but retain the disadvantages of behavioural modelling described in 2.5.1 on page 9 above.

## 2.6.2 TLM level 2

### 2.6.2.1 Modelling TLM level 2 Processes

At TLM level 2, each process is represented by an Extended Finite State Machine (EFSM) [Gajski et al., 1997], [Bombieri et al., 2006b]. An EFSM provides a more compact representation of the states and transitions of a process than a traditional Finite State Machine (FSM).

In its simplest form, an EFSM has a single state and no variables, and is represented by purely combinational logic; the output values are a function of the input values.

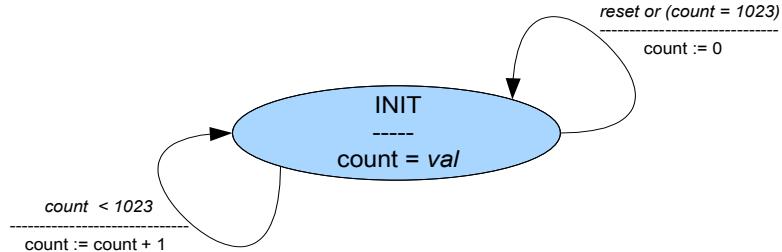

An EFSM with one or more variables may have a single state with one or more transitions representing the allowable value changes of those variables. For instance, a counter has a transition to set or reset the count variable to zero and a transition to increment the count. The input is `reset` and the output is `count`. Each transition has a condition or guard that enables the transition (Figure 2.3).

FIGURE 2.3: Counter

In general, an EFSM has a single state variable, zero or more other variables, a set of states that the state variable may take, and a set of transitions between those states. EFSMs are deterministic; only one transition may be enabled from any given state.

### 2.6.2.2 Modelling TLM level 2 Communications

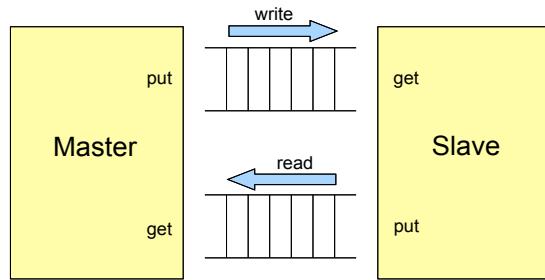

Each process communicates with other processes using uni-directional channels. These channels are based on the standard, bounded SystemC queue and replace the `read` and

`write` calls of the level 3 model. Thus, the Master and Slave at level 2 are modelled as two distinct processes with an output channel to represent the `write` and an input channel to represent the `read` as shown in Figure 2.4. The TLM standard defines `put` and `get` operations for the channels.

FIGURE 2.4: TLM Level 2 Master/Slave Communication

The level 2 processes are also sensitive to input changes: when a process resumes it evaluates the actions associated with its current state and the values of its inputs, and sets the value of the next state. This set of actions is atomic and represents a process `event` which must be scheduled using the simulation kernel. Simulation is therefore slower than at TLM level 3.

TLM level 2 simulation is `event accurate`: the order in which the process events occur is deterministic and an event can represent a transaction that in the hardware implementation will take place over several clock cycles. Simulation is therefore faster than at RTL where every cycle of the transaction must be scheduled through the simulation kernel.

### 2.6.3 TLM level 1

TLM level 1 retains the high-level data types of level 2 but now introduces a clock which synchronises the process behaviour: each process is sensitive to the rising (or falling) edge of the clock and the process executes even if its state not going to change. TLM

level 1 is termed **cycle accurate**. Because of these extra process evaluations and the fact that each cycle of a transaction must be simulated, simulation is slower than at TLM level 2.

This is the final level of abstraction before bit and bit-vector data types are introduced in the RTL.

#### 2.6.4 TLM Architectural Exploration

TLM level 3 is not suitable for architectural exploration because of its untimed, behavioural nature. It is at levels 1 and 2 that designers can begin to explore different possible architectures to meet performance and power consumption constraints. To facilitate such exploration it is desirable to have an automated route to RTL and early feedback of performance and power consumption estimates from tools downstream in the flow.

Forte Design Systems have introduced the TLM synthesis tool Cynthesizer [Cline, 2007a] which promises such an automated route from TLM to RTL and [Cline, 2007b] discusses the early adoption of TLM synthesis by design teams. As TLM synthesis technology matures, designers will be able to focus most of their attention at the electronic system-level (ESL) [Henkel, 2003] rather than RTL and to utilise the performance and power estimation tools currently available at RTL.

It has been a limitation of the TLM standard at level 1 and 2 that standard bus interfaces had to be modelled using standard channels. The June 2007 release of the standard addresses this issue by providing an abstract, black-box bus interface that takes into account the capabilities of industry-standard buses such as AMBA [ARM, 1999], AXI [ARM, 2003] and OCP ([www.ocp.org](http://www.ocp.org)).

This new bus interface facilitates architectural exploration greatly, but is it possible to raise the level at which architectural exploration can be done to the specification level?

## 2.7 Microprocessor Pipeline Verification

Early work in the formal verification of microprocessors was focused on simple, non-pipelined processors described at the Register Transfer Level (RTL). In [Joyce et al., 1986] the RTL is represented in the ML programming language and the HOL proof assistant system [Gordon and Melham, 1993] used to discharge the proofs.

In [Burch and Dill, 1994] and [Jones et al., 1995] the representation of the processor is raised to the Instruction Set Architecture (ISA) level and the techniques described focus on the formal verification of the control logic of first a 3-stage pipelined ALU and then the

full 5-stage DLX processor. ALU operations are represented as uninterpreted functions. In order to show that the pipelined processor will behave in the same way as a notional non-pipelined version, the concept of pipeline *flushing* is introduced. *Stall* instructions are introduced at the pipeline input to ensure that each instruction is completed before the next is initiated. The notion of *refinement maps* are introduced in [Manolios, 2000] and [Manolios and Srinivasan, 2005a] to extend the flushing concepts of Burch and Dill to more complex 3 and 10-stage pipelines, using the ACL2 functional programming language and theorem prover [Kaufmann and Moore, 2004]. [Manolios and Srinivasan, 2005b] takes a pipelined processor model, translates it into a combination of two different formal languages and then shows that this translation meets its specification. None of these methods is incorporated into the top-down design flow, and the formal verification is performed when the RTL has been completed.

[Tahar and Kumar, 1994] focuses its attention on the formalization of the pipeline hazards that can occur when multiple instructions are executed at once in the DLX pipeline. Structural, data and control hazards are represented and checked using the HOL verification system [Gordon and Melham, 1993]. Incremental design techniques with refinement are described in [Borger and Mazzanti, 1997] to show that a notional DLX pipeline with, however, no overlapping instruction execution, can be refined to a pipeline that executes 5 instructions at each clock cycle and manages structural hazards does not encounter a sequence of instructions that would incur data or control hazards. This pipeline is then further refined to model the data and control hazards. Abstract State Machines (ASMs) are used to represent the DLX instructions. In [Kroening and Paul, 2001], a tool that takes a sequential model of the DLX pipeline, which is assumed to be correct, and adds the forwarding logic is described. The tool also provides a proof of correctness for the generated hardware. [Plosila and Sere, 1997] uses Action Systems in a refinement-based approach to processor verification, but does not have the benefit of tool support.

## 2.8 Modelling Concurrency

### 2.8.1 Modelling Concurrency with Partial Orders

A process in a concurrent system may be represented as a set of partially ordered multisets (pomsets) [Pratt, 1986]. Each element of a partial order represents an event, and for two events  $e$  and  $f$ ,  $e < f$  is interpreted as "event  $e$  precedes event  $f$ ". Events are not necessarily atomic and can represent **intervals** as well as **instants**. In this case,  $e < f$  means "the whole of  $e$  must precede the whole of  $f$ ".  $e$  must complete before  $f$  can begin. Actions label events, and an event is an instance (occurrence) of its action.

The motivation for studying partial orders is to investigate an Event-B modelling style where the specification is as loose as possible in the early stages of refinement, decisions

about actual event ordering are deferred for as long as possible and potential concurrency is identified as early as possible. Specifying the behaviour of a component using partial orders means that the specification can be re-used when the component is subsequently re-targeted to a different hardware architecture for power or performance reasons.

### Modelling a Communications Channel as a Partial Order

A channel is a process in which the events **Transmit** (T) data and **Receive** (R) data occur in ordered pairs:-

$$(\text{data}, \text{T}) < (\text{data}, \text{R})$$

For the stream of data 011, the behaviour of the channel is specified in Figure 2.5.

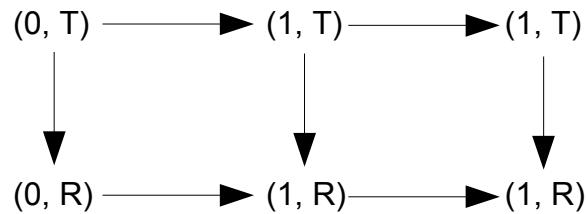

FIGURE 2.5: channel behaviour

The actual order in which **transmits** and **receives** occur in the implementation will depend on the performance characteristics of the processes on each end of the channel.

### Communication Refinement using Partial Orders

[Lieverse et al., 2001] describes a methodology with which multi-task applications can be designed at the abstract level using high-level inter-task communication. The communication can then be refined by transforming the high-level view of the communication primitives into a partially-ordered representation using lower-level primitives. Then, depending on the hardware architecture, the partial order can be refined into the appropriate total order. Factors that govern the most appropriate total order are whether communication is enabled with channels (message passing) or shared memory and how much local memory a processor has to store local results before passing them to the next process.

### 2.8.2 Modelling Concurrency with Guarded Atomic Actions

Any hardware component can be represented as a set of variables that comprise the state of the component, and a set of actions on those variables that updates the state. The actions are atomic, all the variable updates comprising an action occur simultaneously, and are protected by guards, variable predicates, that determine which actions are enabled or disabled for a given state of the component. If more than one action is enabled in a given state, a single action is chosen, non-deterministically, for evaluation. The behaviour of the component is represented by the set of legal sequences of atomic actions.

### 2.8.3 Bluespec

Bluespec is a set of commercial tools, developed from research carried out at MIT [[Rosenband and Arvind, 2004](#)], which allows hardware components to be specified as a set of guarded atomic actions, called rules, simulated and then synthesised automatically to RTL. The toolset enables architectural exploration to be done at the specification level, and then RTL to be generated to meet differing power, size and performance constraints. Links are provided to fit in a SystemC TLM flow and, in particular, a library is provided that converts TLM put and get calls into a sequence of bus-specific operations. AMBA, AXI and OCP busses are supported.

Bluespec synthesis is based on a term-rewriting system [[Hoe and Arvind, 1999](#)], but no formal verification capability is provided for Bluespec models; the tools set is purely simulation based. The semantics of guarded atomic actions are not strictly adhered to, and it is possible for multiple enabled actions to be executed simultaneously. It is also possible for the user to apply priorities to actions using tool pragmas. Bluespec rules are translated to a set of RTL concurrent assignments, which are processes sensitive to changes to variables on the right hand side of the assignment. Simultaneously-firing rules are therefore mapped to concurrent assignments that are evaluated simultaneously in the target HDL; the left hand sides of the assignments are not updated until all the variables on the right hand sides have had their values updated, preventing race conditions.

### 2.8.4 CAL

CAL [[Bhattacharyya et al., 2008](#)] is a language, also based on guarded atomic actions, for hardware/software co-design. It provides routes for both hardware and software synthesis, but no formal verification capability has been developed.

## 2.9 Event-B

### 2.9.1 Introduction

Event-B [Abrial and Mussat, 1998], [Hallerstede, 2007] is a proof-based modelling language and method that enables the development of specifications using refinement. The Rodin platform [Abrial et al., 2006] is the Eclipse-based IDE that provides automated support for Event-B modelling, refinement and mathematical proof.

In Event-B, an abstract model comprises a *machine* that specifies the high-level behaviour and a *context*, made up of sets, constants and their properties, that represents the type environment for the high-level machine. The machine is represented as a set of *state variables*,  $v$  and a set of events, *guarded atomic actions*, which modify the state. If more than one action is enabled, then one is chosen non-deterministically for *execution*, an observable transition on the state variables which must preserve an *invariant* on the variables,  $I(v)$ . A more concrete representation of the machine may then be created which refines the abstract machine, and the abstract context may be extended to support the types required by the refinement. *Gluing invariants* are used to verify that the concrete machine is a correct *refinement*: any behaviour of the concrete machine must satisfy the abstract behaviour. Gluing invariants give rise to proof obligations for pairs of abstract and corresponding concrete events. Events may also have parameters which take, non-deterministically, the values that will make the guards in which they are referenced true.

An event can be represented by the *generalized substitution*,

**any  $x$  where  $P(x, v)$  then  $v := F(x, v)$  end**

where  $x$  represents the event parameters and  $v$  represents the machine state variables. Informally, this event can be fired provided that the guard  $P(x, v)$  can be satisfied for some value  $x$ . The details are explained in [Abrial, 2005].

### 2.9.2 Refinement

Event-B refinement allows a model to be built gradually [Abrial and Hallerstede, 2006], starting with an abstract model and then introducing successive, more concrete refinements. Adding variables achieves *spatial extension* and adding events *temporal extension*. Events in the abstract model may be refined by one or more events in the concrete model. New events, which refine *skip* may also be introduced in the refinement. *Data-refinement* [Abrial, 2005] can also be used to modify the state so that an abstract variable can be replaced with a concrete variable that can be implemented in the target hardware or software.

### 2.9.3 Decomposition

Event-B supports two mechanisms for formal composition and decomposition; *shared event* [Butler, 2009] and *shared variable* [Abrial and Hallerstede, 2006]. Shared event decomposition has tool support in Rodin [Silva et al., 2010].

#### Shared Event Decomposition

[Butler, 2009] describes a parallel composition operator for machines, where the composition of machines  $M$  and  $N$  is written  $M \parallel N$ . Machines  $M$  and  $N$  synchronise over *shared events* which have common names. If  $eM$  and  $eN$  are the shared events in  $M$  and  $N$  respectively and  $m$  and  $n$  are the (disjoint) variables of  $M$  and  $N$  respectively, then  $M \parallel N$  is defined as follows.

if

$eM = \text{any } x \text{ where } P(x, m) \text{ then } v1 := F(x, m) \text{ end}$

$eN = \text{any } y \text{ where } Q(y, n) \text{ then } v2 := G(y, n) \text{ end}$

then

$eM \parallel eN = \text{any } x, y \text{ where } P(x, m) \wedge Q(y, n) \text{ then } v1 := F(x, m) \parallel v2 := G(y, n) \text{ end}$

#### Shared Variable Decomposition

An alternative to shared event decomposition is presented in [Abrial, 2009]. Instead of synchronising over shared events, the machines  $M$  and  $N$  communicate using shared common variables, which must be replicated in  $M$  and  $N$ . When  $M \parallel N$  is decomposed, however, it is necessary to impose the restriction that the shared common variables must not be *data-refined* in any subsequent refinements of  $M$  or  $N$ . Additional events must also be introduced into  $M$  and  $N$ , called *external events*, which *simulate* the way the shared events are managed in the composition  $M \parallel N$ .

### 2.9.4 Variants

A *convergent* event is an event which refines *skip* and has some liveness property associated with it through the definition of a *variant*. A variant is a natural number expression that must be decreased by the convergent event, or a finite set expression that must be made strictly smaller by the convergent event. An *anticipated* event is an event that refines *skip* that is not convergent but will become convergent in a later refinement. [Abrial, 2007]

### 2.9.5 Records

Structuring of data can be achieved in Event-B by using the conventions established in [Evans and Butler, 2006]. For a set representing the data type  $T$ , *projection functions* can be defined which map a field of  $T$  to the field's value. For instance, if  $T$  has two fields  $F1$  and  $F2$  which are natural numbers and one field  $F3$  which is an integer, then the record can be described thus.

`axm1 :  $F1 \in T \rightarrow \mathbb{N}$`

`axm2 :  $F2 \in T \rightarrow \mathbb{N}$`

`axm3 :  $F3 \in T \rightarrow \mathbb{Z}$`

### 2.9.6 Witnesses

When an abstract event with parameter  $p$  is refined then the parameter  $p$  in the concrete event corresponds directly with that in the abstract event. If, however, the parameter  $p$  does not appear in the concrete event, then  $p$  must receive a concrete value, called a *witness* in the refinement. [Abrial, 2007]

# Chapter 3

## Enhancing the SoC Hardware Design Flow with Event-B

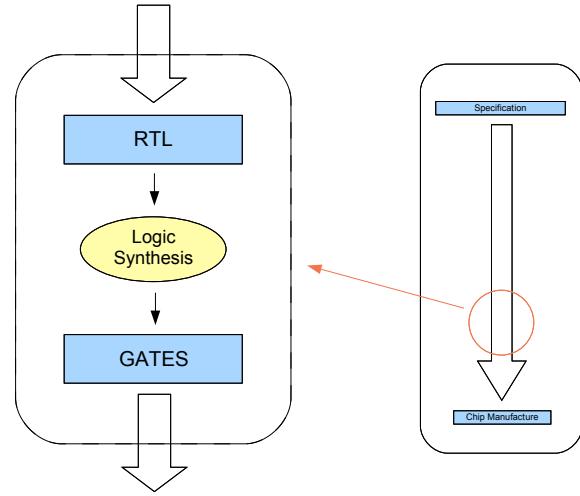

This chapter covers the modern synchronous design flow and the gap that exists in this flow between the specification and the RTL description used for logic synthesis. It looks at the reasons that behavioural synthesis has not in general helped to close this gap, and how the use of guarded atomic actions can provide efficient high-level synthesis and architectural exploration. Although semi-conductor companies express a clear need to raise the design process to the Electronic System Level (ESL) [Asanovic et al., 2006], the approach that the EDA industry has taken to address this need has been fragmentary, no clear standards have emerged, and the tried and proven RTL design methodology still forms the significant bedrock of any modern SoC design flow (Figure 3.1). The hardware description languages are mature and simulators can be second-sourced. It is, however, the increasing maturity of Logic Synthesis [Devadas et al., 1994] that has made the most significant contribution.

The contribution of this chapter is to show how the Event-B formal method can be incorporated into this flow and combined seamlessly with high-level and RTL synthesis to close the specification gap.

### 3.1 Background to the Existing Flow

#### 3.1.1 Logic Synthesis

Logic Synthesis, as shown in Figure 3.2, contributes the first step in bridging the gap between the textual specification and the gate level description from which hardware can be generated automatically. Although RTL descriptions raise the level of abstraction

FIGURE 3.1: SoC Flow

significantly, enable language-driven design and reduce simulation effort, if the translation route to gates were a manual process the RTL would simply represent some useful documentation and would make little contribution to closing the specification gap.

Early users of logic synthesis expended significant simulation effort on verifying that the output from synthesis was correct. Today, very little gate level simulation is performed, not only because logic synthesis is mature but also, more importantly, because formal tools have been introduced to augment the design flow.

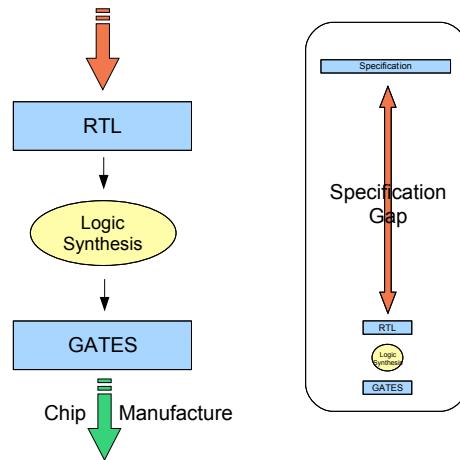

### 3.1.2 Formal RTL Verification

Although modern logic synthesis tools are mature and reliable, they are also very large and complex and present the user with an enormous range of control options. A logic synthesis tool could never represent a *trusted component* [Meyer et al., 2003] in the SoC flow in the sense of representing a provable transformation on the RTL. It would be infeasible to show that the tool, given an RTL description as input produced an *equivalent* gate level description as output. It is possible, however, given the logic synthesis input and output description, to reason about the correctness of the translation using the formal methods *property checking* [J.R. Burch et al., 1990] and *equivalence checking* [Drechsler and Horeth, 2002], as shown in Figure 3.3

FIGURE 3.2: The Role of RTL Synthesis

FIGURE 3.3: The Role of Formal RTL Checking

## Property Checking

A property checking tool takes a set of temporal properties [Cohen et al., 2004], [Sutherland et al., 2004], derived from the specification and checks these properties against the synthesised gate-level description.

Property checking depends on having a comprehensive set of properties to represent the desired behaviour. It is very difficult to establish whether sufficient properties have been written or not, and *property coverage* [Chockler et al., 2001], [Hoskote et al., 1999] is a topic of ongoing research.

Without a measurable outcome, property checking will not become an indispensable component in the SoC flow, but it does provide an independent check on the validity of the design, and is a valuable auxilliary method for flushing out design faults.

### Equivalence Checking

An equivalence checking tool takes the RTL and the synthesised netlist as inputs, converts both into an internal gate-level format and then verifies that they are functionally equivalent. Equivalence checking is a mature technology, requires little user interaction and is now widely used to verify synthesis output.

The combination of logic synthesis with equivalence checking, which provides practical and efficient support for RTL design and a formal link between RTL and gate-level views, represents a significant breakthrough in raising the abstraction level in hardware design. In particular, it raises the level at which architectural exploration and component re-use can be considered.

#### 3.1.3 RTL Architectural Exploration

Before the adoption of RTL synthesis, when design was done using gate-level schematic capture, arriving at an architecture that satisfied performance constraints was laborious and time consuming. Components designed for re-use were only available as gate-level descriptions, which could require significant re-work to be of value in different designs. Once an appropriate architecture had been settled on to target a given hardware technology, represented by a library of cell primitives, even targeting a similar library for a different hardware technology could require significant and time-consuming changes to the gate-level description, including changes to the supposedly re-usable components.

The first clear benefit of RTL synthesis is that it facilitates technology-independent design. The second benefit is that it is possible to explore micro-level architectural alternatives without changing the RTL description. Using the rich set of control options in the synthesis process it is possible to generate differing gate-level implementations to meet differing performance requirements. Re-usable components are now provided as RTL descriptions which can therefore also be manipulated by the synthesis process.

If, however, it is not possible to reach the required targets through synthesis alone, alternative RTL architectures must be developed, and even though RTL/RTL equivalence checking can be used to ensure functional equivalence between different RTL

representations, RTL architectural exploration, shown in Figure 3.4, is still very time consuming.

FIGURE 3.4: RTL Architectural Exploration

### 3.1.4 Closing the Gap: Behavioural Synthesis

As SoC's have become more complex, managing system design, architectural exploration and component re-use at the Register Transfer Level, has become increasingly difficult. Since high-level, behavioural models and system-level specifications are already developed using programming languages such as C and C++, behavioural synthesis from a programming language source is an attractive concept [Edwards, 2005]. If efficient hardware could be generated automatically from a collection of behavioural descriptions, and re-usable components could also be represented in this way, then the gap between specification and implementation would close dramatically. Behavioural Synthesis takes a behavioural description and generates an RTL description that can then be used as an input to logic synthesis. The behavioural synthesis flow is shown in Figure 3.5.

#### Behavioural Synthesis Issues

Although there is a clear relationship between RTL processes and their gate level equivalents, and the transformations between the two levels are well defined, no such relationships and transformations can be easily defined between a behavioural description and an RTL description. Fundamentally, RTL descriptions by their very nature contain architectural information and behavioural descriptions do not. What is needed is a high

FIGURE 3.5: Behavioural Synthesis Flow

level representation that can represent the architecture of the target implementation in an abstract way and is amenable to formal reasoning.

### 3.1.5 Closing the Gap: High-level Synthesis with Term Rewriting Systems

Term Rewriting Systems (TRS) [Baader and Nipkow, 1998] offer a natural way to describe hardware architectures which facilitates architectural exploration at the specification level and allows the designer to explore design trade-offs much earlier in the process [Arvind and Shen, 1999]. TRS can be used to describe both deterministic and non-deterministic behaviour; as an abstract specification is successively refined the non-determinism, which aids greatly in the representation of concise abstract specifications, can systematically be made more concrete. In addition to being amenable to formal analysis, TRS descriptions, in the form of *guarded atomic actions*, have also been demonstrated [Hoe and Arvind, 1999], [Arvind and Hoe, 1999], [Arvind et al., 2004], [Hoe, 2004] to be amenable to high-level synthesis [R. Kumar et al., 1996]. Once a detailed TRS description of a hardware component is available, there is an automatic route to an RTL description [Rosenband and Arvind, 2005] and therefore to hardware using current logic synthesis flows [Devadas et al., 1994]. The commercial, high-level synthesis tool, Bluespec [Nikhil, 2007], is already being used successfully in industrial flows (Figure 3.7).

## Term Rewriting Systems

A Term Rewriting System is a set of *rules* which defines a set of transitions on *state*, represented by TRS *terms*. Each rule is guarded by a predicate on the current state and has an associated *atomic action* which updates the state [Arvind and Shen, 1999]. More formally, a TRS is defined as a  $\text{tuple}(S, R, S_0)$  where  $S$  is a set of terms,  $R$  is a set of re-writing rules and  $S_0$  is a set of initial terms,  $S_0 \subseteq S$ . *States* are represented by TRS *terms* and *transitions* are represented by TRS *rules*. A *rule* is of the form

$$\begin{array}{c} s1 \quad \text{if } p(s1) \\ \rightarrow \quad s2 \end{array}$$

where  $s1$  and  $s2$  are terms and  $p$  is a predicate. The term  $s1$  is rewritten to the term  $s2$ .

Consider a microprocessor *Proc* with an instruction address (program counter) *ia*, a register file *rf* and instruction memory *im*. Any given state of the processor can be represented as  $\text{Proc}(ia, rf, im)$ . The predicate representing the next instruction to be processed in the instruction memory (at the instruction address) can be written as say  $im[ia] = "rd := Op(rs_1, rs_2)"$ . If, for a given state of the processor, this instruction is encountered in the instruction memory, then the rule will fire and the state of the processor will be updated appropriately: the instruction address will be incremented to point to the next instruction location and the value of the target register *rd* in the register file will be updated to reflect the result of the operation on the two source registers *rs<sub>1</sub>* and *rs<sub>2</sub>*. The state of the instruction memory *im* is unchanged. This rule is shown in Figure 3.6.

$$\begin{array}{l} \text{Proc}(ia, rf, im) \quad \text{if } im[ia] = rd := \text{Op}(rs_1, rs_2) \\ \text{Proc}(ia + 4, rf[rd := v], im) \text{ where } v := \text{Op}(rf[rs_1], rf[rs_2]) \end{array}$$

FIGURE 3.6: TRS Processor Instruction Rule

If, for a given state, the predicates of more than one of the rules evaluate to *true*, then one of the enabled rules is chosen non-deterministically for evaluation. [Dave, 2005] describes the use of the commercial high-level synthesis tool Bluespec [Nikhil, 2004], which generates RTL from a TRS description, to design a processor. In practice the TRS synthesis tool allows the use of pragmas to impose event ordering, and if simultaneously enabled events do not conflict (do not attempt to write different values to the same variable) they are scheduled to be evaluated simultaneously. The synthesis tool generates an RTL scheduler to implement these semantics. At present, no formal checker exists to verify that the derived RTL is a correct refinement of the TRS description, but the nature of *guarded atomic actions* means that they are amenable to formal analysis,