University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

University of Southampton

Faculty of Physical and Applied Science

School of Electronics and Computer Science

**Development of a Spring-Less RF MEMS Switch**

by

**Kian Shen KIANG**

Thesis for the degree of Doctor of Philosophy

January 2011

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL AND APPLIED SCIENCE

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

DEVELOPMENT OF A SPRING-LESS RF MEMS SWITCH

by Kian Shen KIANG

This thesis reports on the development of a novel 77GHz low loss MEMS switch with a mechanically unrestrained armature, over a RF transmitting coplanar waveguide. Electrostatic actuation is used during the switching operation. The attractive force from the electrostatic field is generated by a pair of the actuation electrodes on both sides of the armature, depending on the direction of the movement.

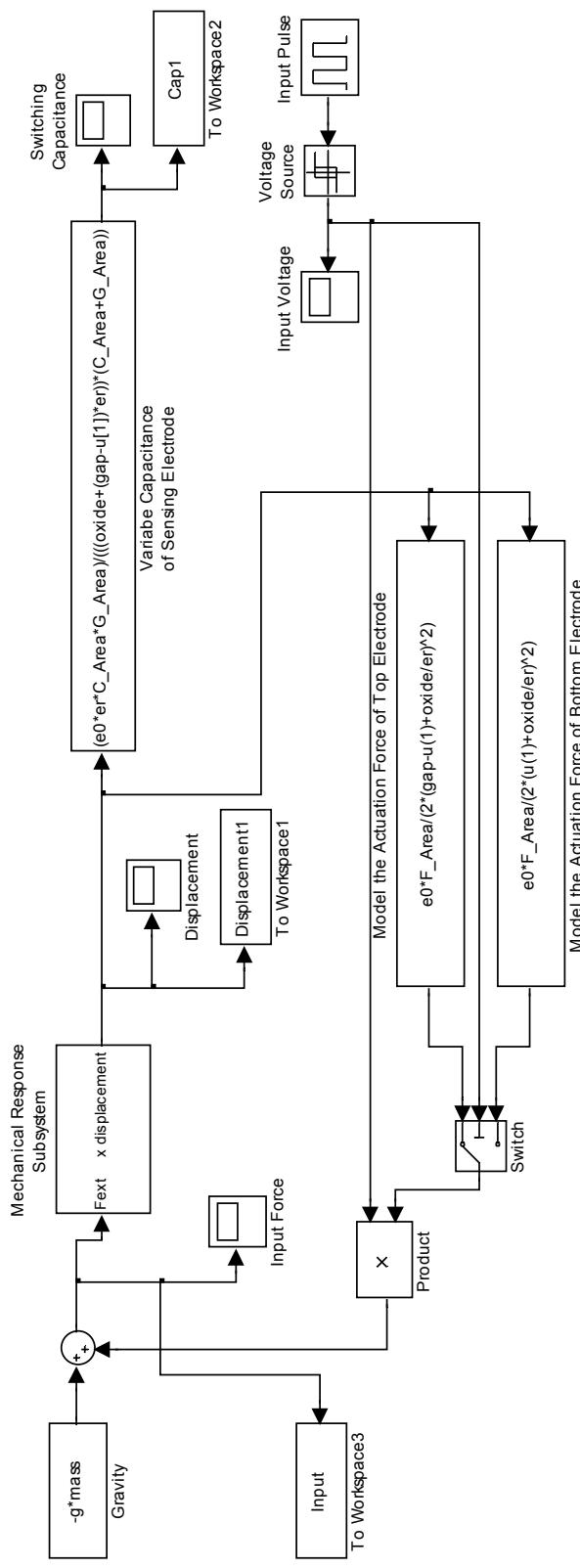

A Simulink model is employed to simulate the mechanical response of the switching armature. Different damping models are deployed into the Simulink model, yielding different actuation time for the switch. This model is also employed to design the dimensions of the MEMS switch in the mechanical domain. The effect of Van der Waal force between the dielectric layer and designed armature is also discussed.

An electrical model of the RF MEMS switch is represented using lumped RLC components and characteristic impedance of the transmission line. The relationship between the electrical model and the scattering parameters is explained with the effects of the individual component on the S-Parameter being studied. Electromagnetic simulations have shown that the designed switch has potential of being employed in automotive collision avoidance system or in Doppler radar application. The proposed design is also capable of operating in lower frequency bands after some tuning, through different armature design.

A clean room fabrication flow is described as part of the development process of this novel switch. This is based on two Pyrex wafers and a SOI wafer utilising a double bonding and DRIE processes. RF characterisation of the coplanar waveguide and the micron-scale prototype at DOWN state is also discussed.

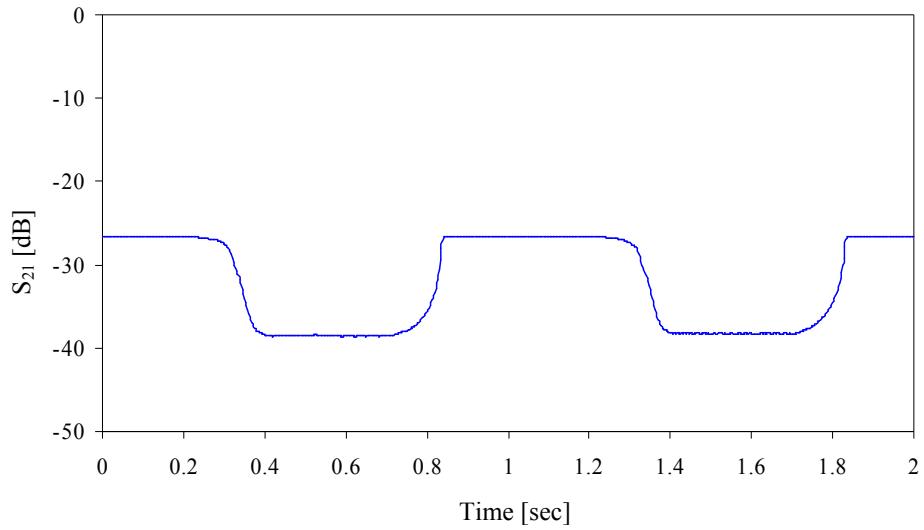

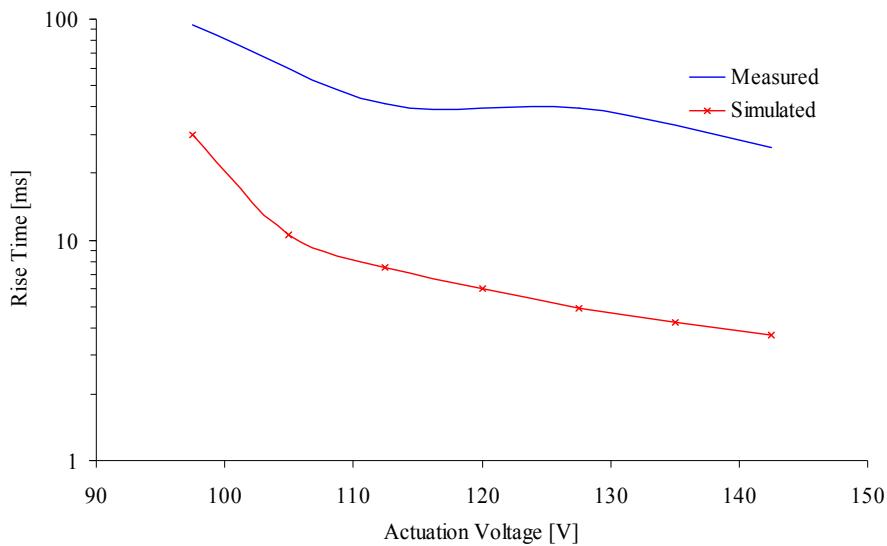

An alternative rapid prototyping technique based on high-frequency PCB and microscopic glass slide has been developed. This process is cheaper and requires shorter turnover time as compared to the clean room prototype. Electromechanical and S-Parameter measurements of the rapid prototype device are reported. These results are verified through simulations. The minimum actuation voltage of the prototype is 93V, with a rise and fall time of 165ms and 180ms. Switching is possible for frequencies from 2.8-5.5GHz and 6.6-10GHz, with the optimum frequency at 3.3GHz and 6.9GHz. The insertion loss and isolation of the prototype are -26.5dB and -38.5dB at 6.9GHz respectively. Although this is far from the state of the art for RF MEMS switches, it nevertheless proves the fundamental concept of a MEMS switch with an unrestrained armature by a prototype realised using a rapid prototype methodology.

# Table of Content

|                                                                                   |              |

|-----------------------------------------------------------------------------------|--------------|

| <b>Table of Content.....</b>                                                      | <b>v</b>     |

| <b>List of Figures .....</b>                                                      | <b>ix</b>    |

| <b>List of Tables .....</b>                                                       | <b>xvii</b>  |

| <b>List of Symbols .....</b>                                                      | <b>xix</b>   |

| <b>List of Abbreviations .....</b>                                                | <b>xxiii</b> |

| <b>Declaration of Authorship.....</b>                                             | <b>xxv</b>   |

| <b>Acknowledgement .....</b>                                                      | <b>xxvii</b> |

| <b>Chapter 1      Introduction.....</b>                                           | <b>1</b>     |

| 1.1 <i>Motivation</i> .....                                                       | 3            |

| 1.2 <i>Thesis Outline</i> .....                                                   | 5            |

| <b>Chapter 2      Background and Literature Review.....</b>                       | <b>9</b>     |

| 2.1 <i>MEMS: A General Overview</i> .....                                         | 9            |

| 2.2 <i>RF MEMS Switches</i> .....                                                 | 10           |

| 2.2.1    RF MEMS Series Contact Switch.....                                       | 11           |

| 2.2.2    RF MEMS Shunt Capacitive Switch .....                                    | 11           |

| 2.3 <i>Comparison of Semiconductor Switch and RF MEMS Switch</i> .....            | 12           |

| 2.4 <i>Literature Review</i> .....                                                | 13           |

| 2.4.1    Development of MEMS Switch with Low Spring System .....                  | 13           |

| 2.4.2    Development of Switch with Armature without Mechanical Spring            | 15           |

| 2.4.3    Development of Switch with Different Electrostatic Actuation Setup ..... | 16           |

| 2.4.4    Development of High-K Dielectric/Dielectric Manipulation Switches .....  | 18           |

| 2.4.5    Development of Non Electrostatic Actuated Switch .....                   | 19           |

| 2.4.6    Development of High Power Application RF MEMS Switch .....               | 22           |

|                  |                                                                                  |           |

|------------------|----------------------------------------------------------------------------------|-----------|

| 2.4.7            | Fabrication Work on MEMS Devices with Mechanically Unrestrained Proof Mass ..... | 23        |

| 2.4.8            | Reliabilities Issues .....                                                       | 27        |

| 2.5              | <i>Summary</i> .....                                                             | 29        |

| <b>Chapter 3</b> | <b>Design Considerations</b> .....                                               | <b>31</b> |

| 3.1              | <i>Principle of Operation</i> .....                                              | 32        |

| 3.1.1            | Electrostatic Actuation .....                                                    | 32        |

| 3.2              | <i>Actuation Voltage</i> .....                                                   | 39        |

| 3.3              | <i>Switching Speed</i> .....                                                     | 41        |

| 3.4              | <i>Effects of Surface Adhesion Force on Actuation Voltage</i> .....              | 44        |

| 3.5              | <i>System Level Modelling</i> .....                                              | 46        |

| 3.5.1            | Squeeze Film Effects .....                                                       | 47        |

| 3.5.2            | Effects of Perforated Holes .....                                                | 52        |

| 3.6              | <i>Summary</i> .....                                                             | 54        |

| <b>Chapter 4</b> | <b>Electromagnetic Modelling</b> .....                                           | <b>57</b> |

| 4.1              | <i>Electrical Model of the Capacitive Shunt MEMS Switch</i> .....                | 57        |

| 4.1.1            | Designing of Coplanar Waveguide .....                                            | 59        |

| 4.1.2            | Switching Capacitance .....                                                      | 66        |

| 4.1.3            | Resistance of the Armature .....                                                 | 68        |

| 4.1.4            | Inductance .....                                                                 | 71        |

| 4.2              | <i>RF Characteristic of the Proposed Switch</i> .....                            | 73        |

| 4.2.1            | Effect of Different Dielectric Material on Isolation Plot .....                  | 80        |

| 4.2.2            | Effect of Different Armature Material on Isolation Plot .....                    | 82        |

| 4.2.3            | Effect of Different Armature Geometries on Isolation Plot .....                  | 83        |

| 4.3              | <i>Summary</i> .....                                                             | 85        |

| <b>Chapter 5</b> | <b>Fabrication</b> .....                                                         | <b>87</b> |

| 5.1              | <i>Fabrication Process of a Micron-Scale Prototype</i> .....                     | 88        |

| 5.1.1            | Pyrex Wafer Fabrication .....                                                    | 88        |

| 5.1.2            | SOI Wafer Fabrication .....                                                      | 90        |

| 5.1.3            | Assembly of Device .....                                                         | 91        |

|                                                                              |                                                                        |            |

|------------------------------------------------------------------------------|------------------------------------------------------------------------|------------|

| 5.1.4                                                                        | Discussion .....                                                       | 93         |

| 5.2                                                                          | <i>Fabrication Plan for a Rapid Prototyping MEMS switch</i> .....      | 106        |

| 5.2.1                                                                        | Glass Slide Fabrication .....                                          | 109        |

| 5.2.2                                                                        | PCB Fabrication .....                                                  | 110        |

| 5.2.3                                                                        | Fabrication of Armature, Spacer and Prototype Assembly.....            | 110        |

| 5.2.4                                                                        | Discussion .....                                                       | 112        |

| 5.3                                                                          | <i>Summary</i> .....                                                   | 113        |

| <b>Chapter 6        Measurement .....</b>                                    |                                                                        | <b>115</b> |

| 6.1                                                                          | <i>RF Characterisation of the Transmission Line</i> .....              | 116        |

| 6.2                                                                          | <i>RF Characterisation of a Shunted Transmission Line</i> .....        | 121        |

| 6.3                                                                          | <i>Measurement of the Rapid Prototype Switch</i> .....                 | 126        |

| 6.3.1                                                                        | RF Measurement of the Rapid Prototype Switch.....                      | 126        |

| 6.3.2                                                                        | Mechanical Response Measurement of the Rapid Prototype Switch<br>..... | 135        |

| 6.4                                                                          | <i>Summary</i> .....                                                   | 140        |

| <b>Chapter 7        Conclusion and Future Works.....</b>                     |                                                                        | <b>143</b> |

| 7.1                                                                          | <i>Future Work</i> .....                                               | 146        |

| 7.1.1                                                                        | Design and Modelling .....                                             | 146        |

| 7.1.2                                                                        | Fabrication.....                                                       | 147        |

| <b>Appendix A: Simulink Model .....</b>                                      |                                                                        | <b>149</b> |

| <b>Appendix B: Fabrication Process Flow for Micron-Scale Prototype .....</b> |                                                                        | <b>151</b> |

| <b>Appendix C: Fabrication Process Flow for Rapid Prototype Device.....</b>  |                                                                        | <b>157</b> |

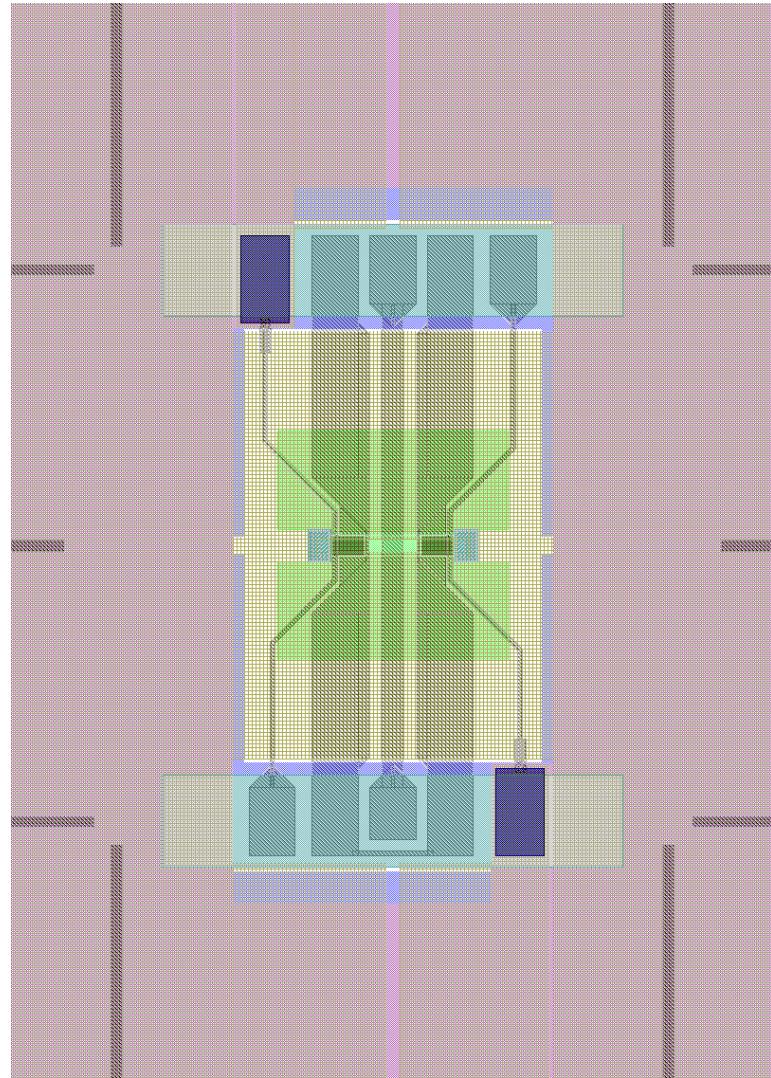

| <b>Appendix D: L-EDIT Layout of the Micron-Scale Prototype .....</b>         |                                                                        | <b>161</b> |

| <b>Reference .....</b>                                                       |                                                                        | <b>163</b> |

# List of Figures

|                                                                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1: Turnover forecast for MEMS market with breakdown into different categories of product from 2007-12 as given in [3].....                                                    | 2  |

| Figure 1.2: Turnover forecast for RF MEMS market with breakdown into different categories of product from 2006-11 as given in [12].....                                                | 2  |

| Figure 1.3: Commercial RF MEMS switch from (a) Radant MEMS [14] (b) Omron 2SMES-01 [15]......                                                                                          | 3  |

| Figure 2.1: A schematic illustration of a series DC contact switch.....                                                                                                                | 11 |

| Figure 2.2: A schematic illustration of a capacitive shunt switch configuration.....                                                                                                   | 12 |

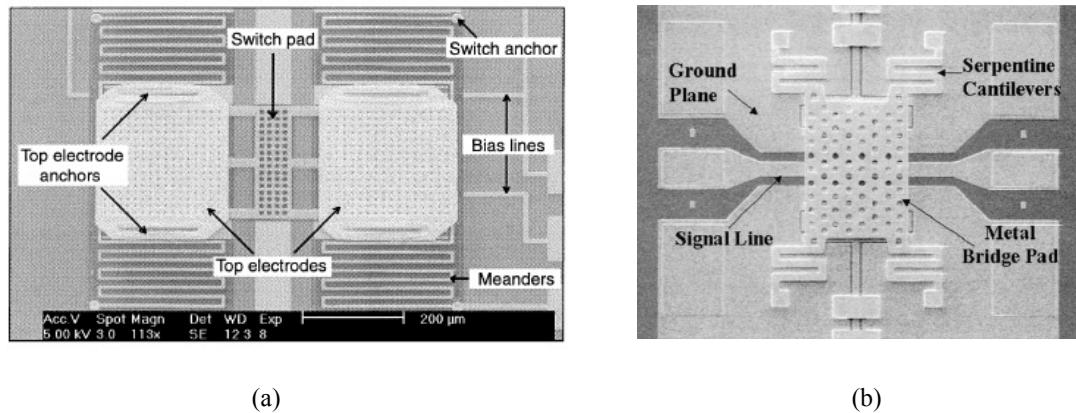

| Figure 2.3: SEM photograph of the (a) capacitive shunt switch mentioned in [19] (b) series contact switch mentioned in [17], employing folded suspension beams.....                    | 14 |

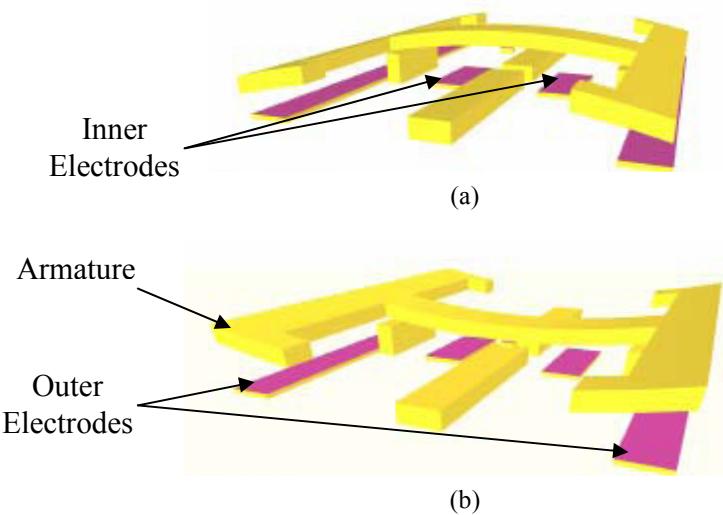

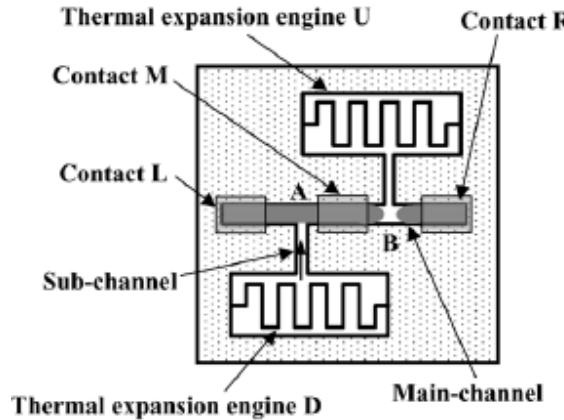

| Figure 2.4: 3-D illustration of the switch proposed in [60] with an actuation voltage of 3.5V during (a) OFF state (b) ON state. ....                                                  | 16 |

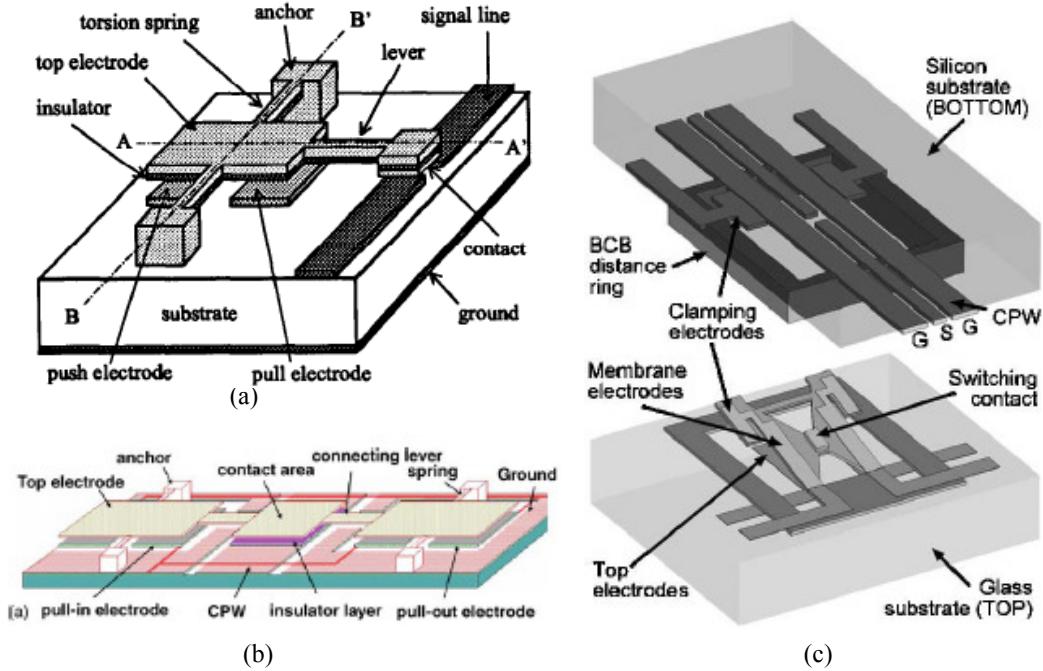

| Figure 2.5: Illustration of (a) the single sided torsion spring designed by [61] (b) symmetric toggle switch design by [62] (c) the S-shaped film contact switch reported in [63]..... | 17 |

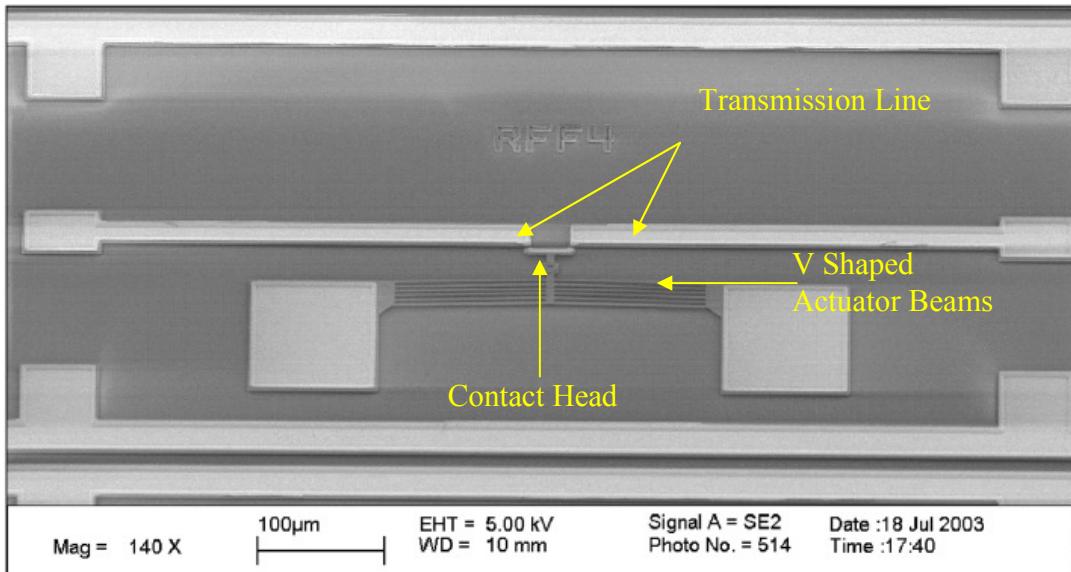

| Figure 2.6: SEM photograph of the electro thermally actuated lateral contact relay reported in [3].....                                                                                | 21 |

| Figure 2.7: The liquid metal micro switch described in [48]. .....                                                                                                                     | 22 |

| Figure 2.8: Process fabrication as described in [71] .....                                                                                                                             | 25 |

| Figure 2.9: Process fabrication as described in [72].....                                                                                                                              | 26 |

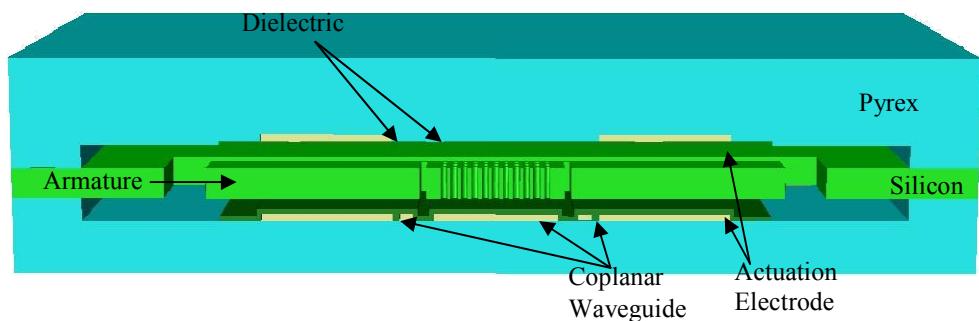

| Figure 3.1: Conceptual illustration of the proposed MEMS switch. ....                                                                                                                  | 31 |

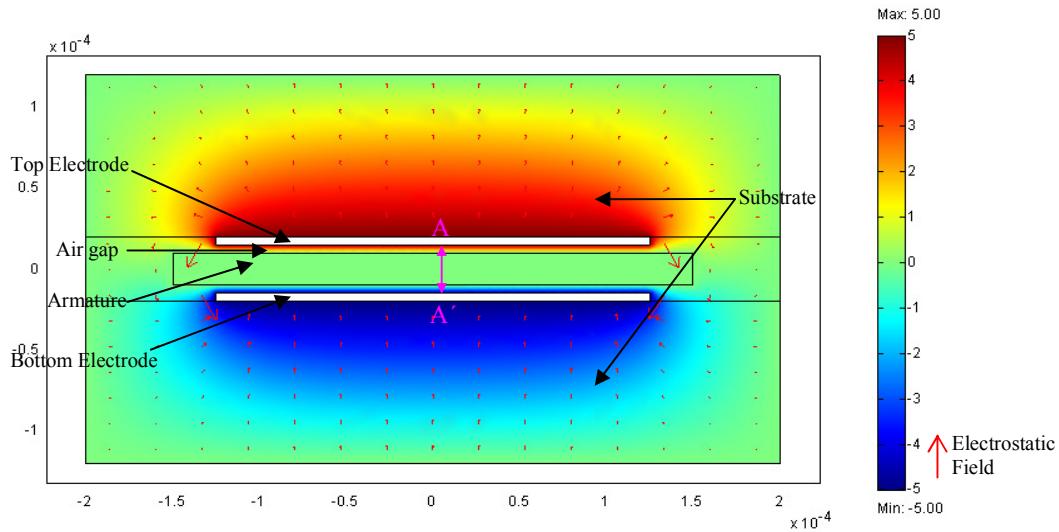

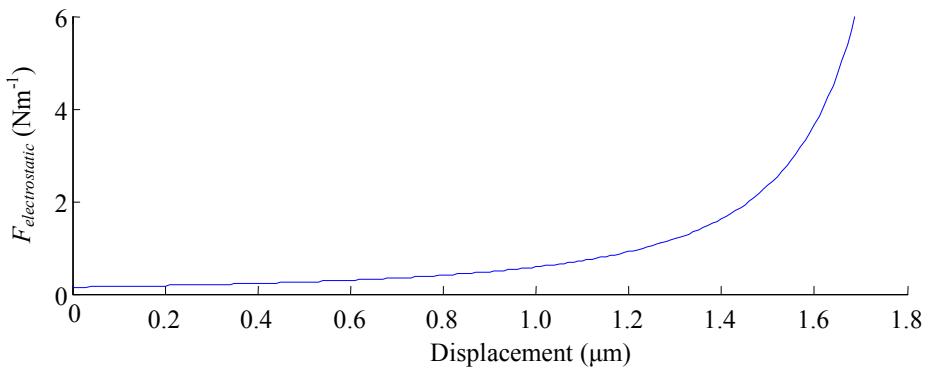

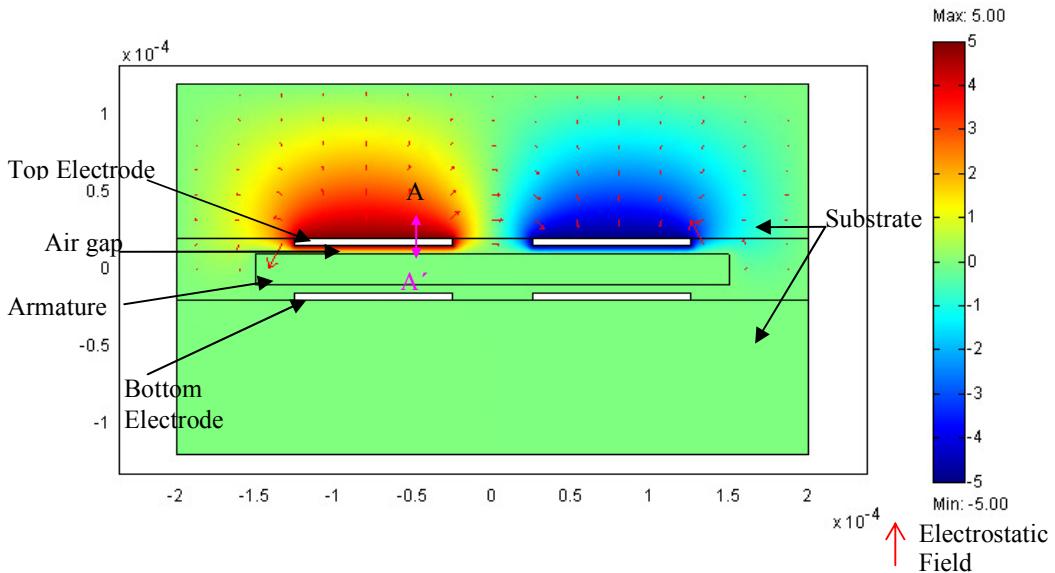

| Figure 3.2: A COMSOL model showing the electrostatic field acting on the armature using $\pm 5V$ for a single top and bottom electrode configuration.....                              | 34 |

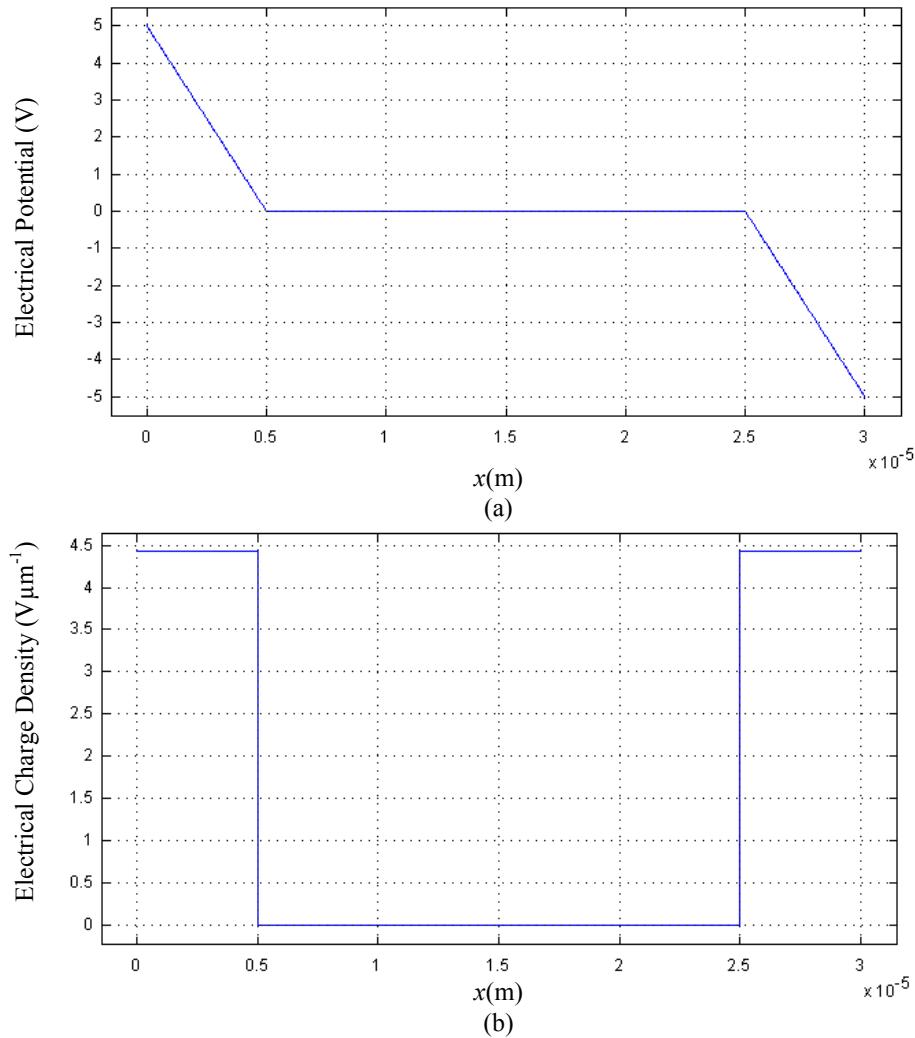

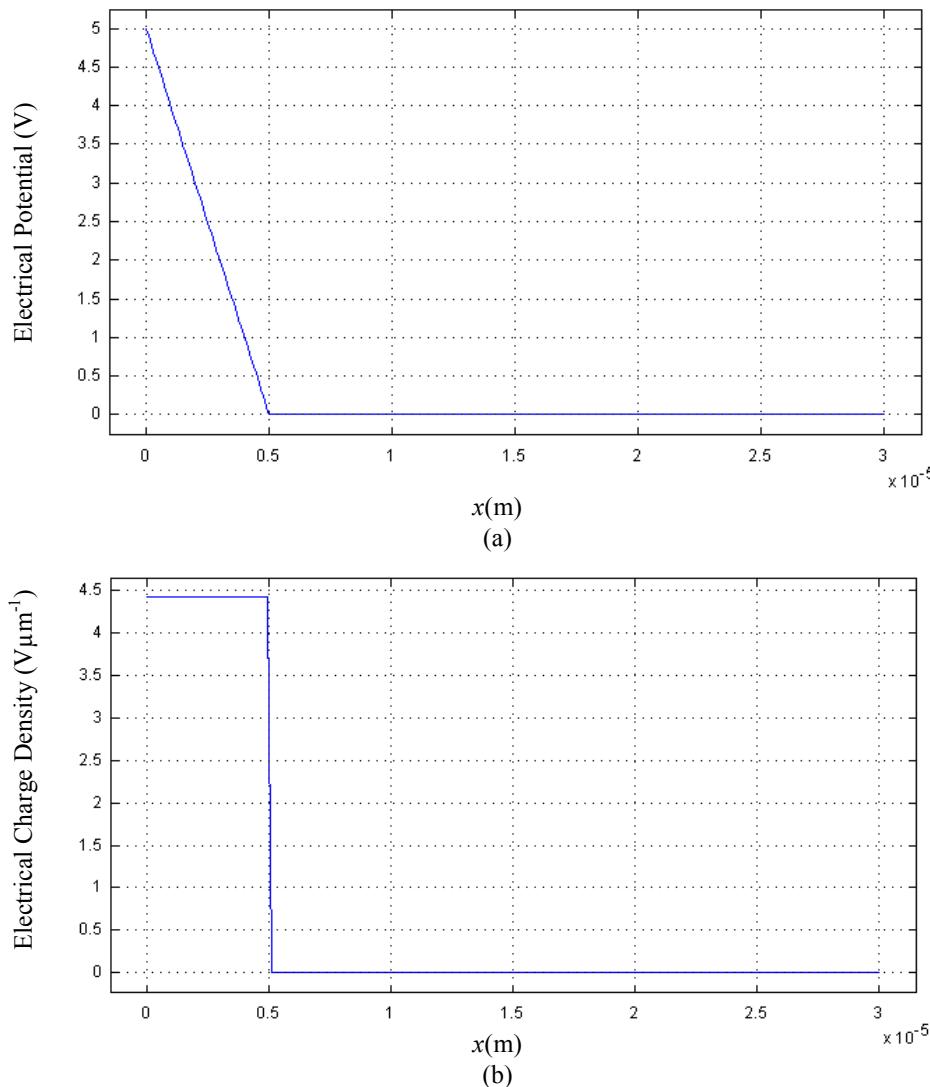

| Figure 3.3: (a) Electrical potential distribution within cavity along A-A' marked out in Figure 3.2 (b) Electrical charge density along A-A' marked out in Figure 3.2.....             | 35 |

|                                                                                                                                                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

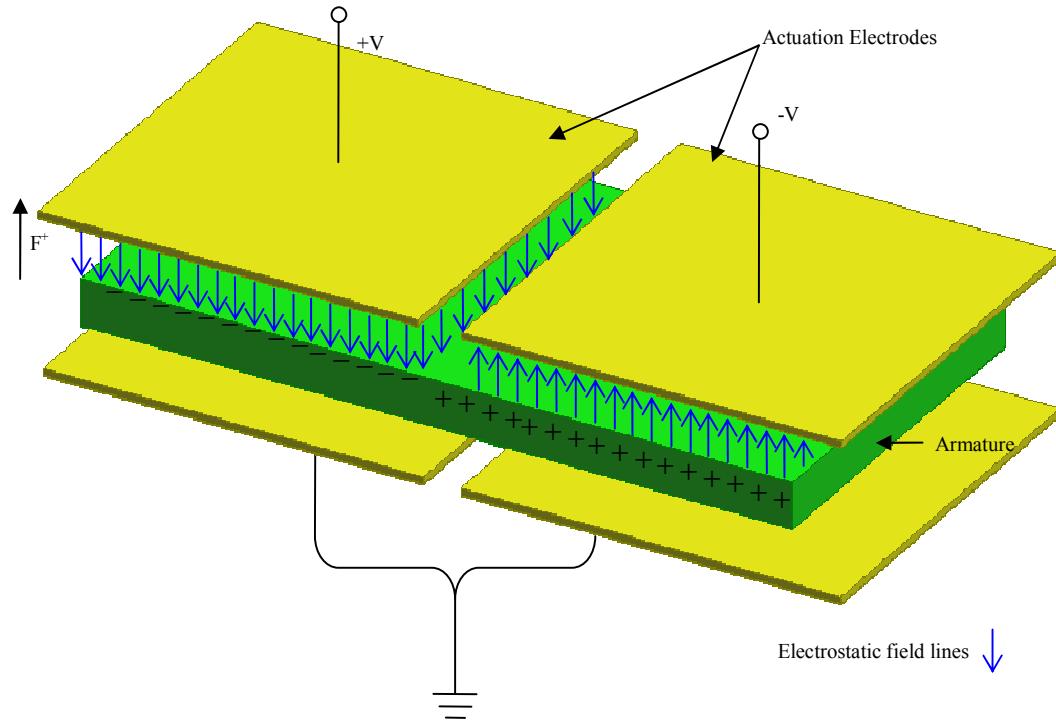

| Figure 3.4: Charge distribution of the armature caused by induction of electrostatic field in attractive force between the armature and the pair of electrodes of different polarities.....                                   | 36 |

| Figure 3.5: The resultant force $F^+$ acting on the armature for the case of a pair of actuation electrodes with different polarities.....                                                                                    | 37 |

| Figure 3.6: A COMSOL model showing the electrostatic field acting on the armature using a pair of actuation electrodes configuration with the two electrodes energised with 5V but of opposite polarities .....               | 37 |

| Figure 3.7: (a) Electrical potential distribution within cavity along A-A' indicated in Figure 3.6. (b) Electrical charge density along A-A' indicated in Figure 3.6.                                                         |    |

|                                                                                                                                                                                                                               | 38 |

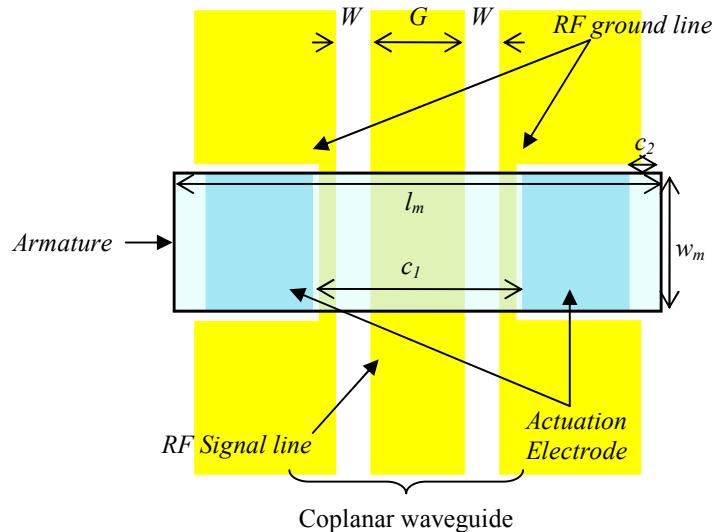

| Figure 3.8: Simplified illustration of a proposed MEMS shunt switch shown in top down view.....                                                                                                                               | 39 |

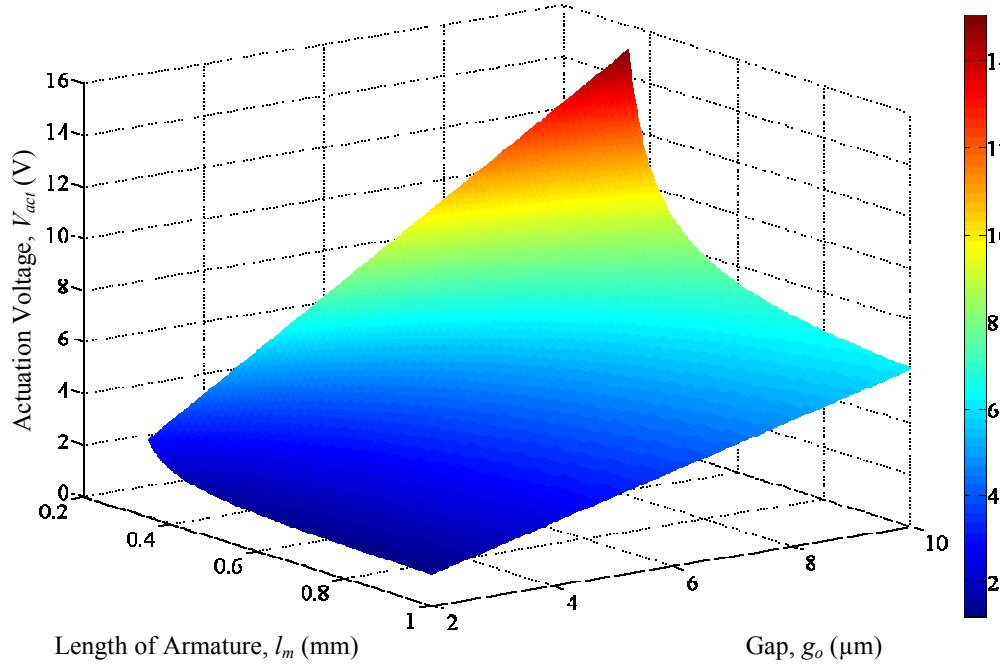

| Figure 3.9: Minimum actuation voltage ( $V_{act(min)}$ ) for different armature length varying from 400 $\mu$ m to 1mm with a variation of initial gap of the device from 2 $\mu$ m to 10 $\mu$ m.....                        | 41 |

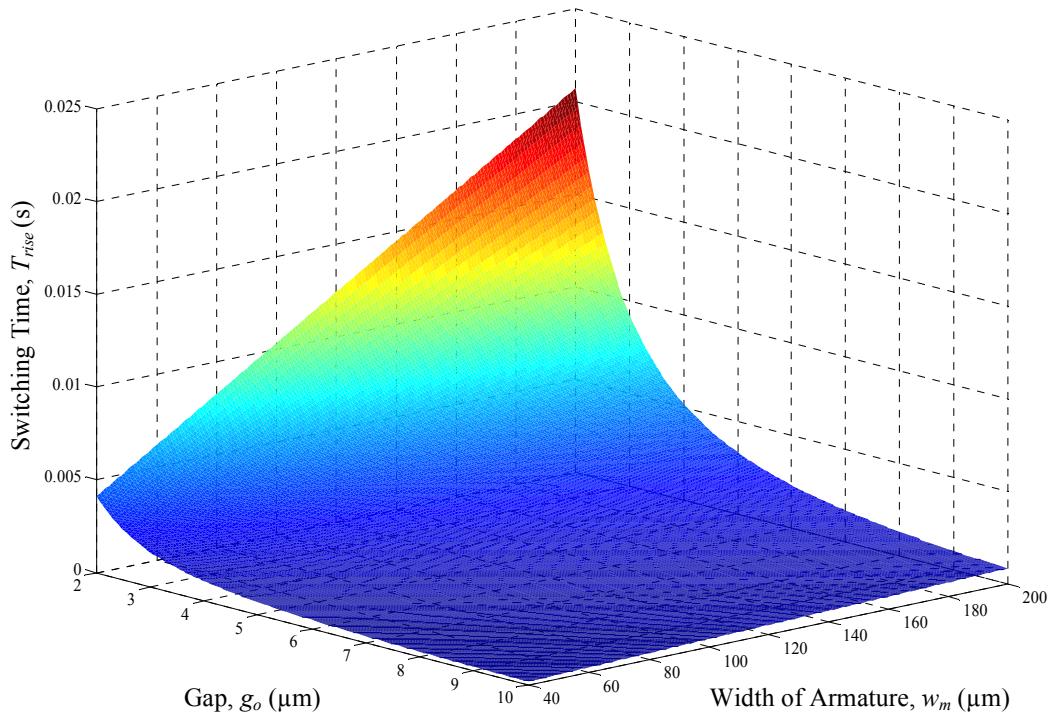

| Figure 3.10: Simulated switching time of the MEMS switch as a function of the width of the armature varying from 40 $\mu$ m to 200 $\mu$ m and air gap from 2 $\mu$ m to 100 $\mu$ m with armature length = 680 $\mu$ m. .... | 42 |

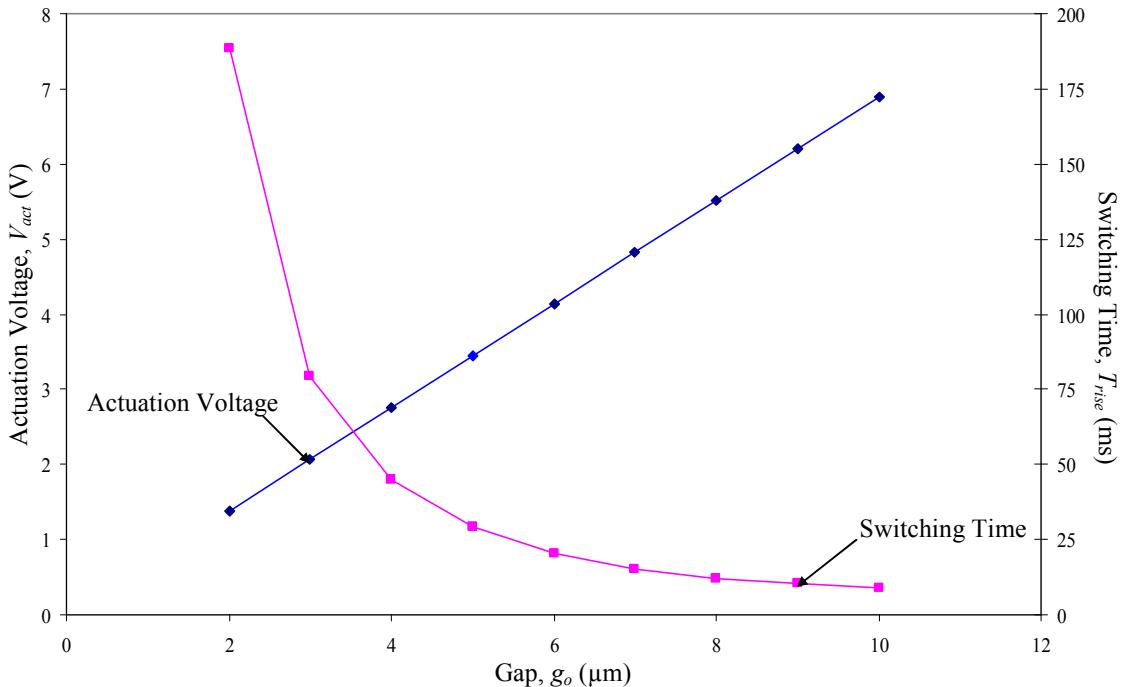

| Figure 3.11: Simulated switching time and minimum actuation voltage of the MEMS switch as a function of the initial capacitive gap of the armature varying from 2 $\mu$ m to 10 $\mu$ m.....                                  | 43 |

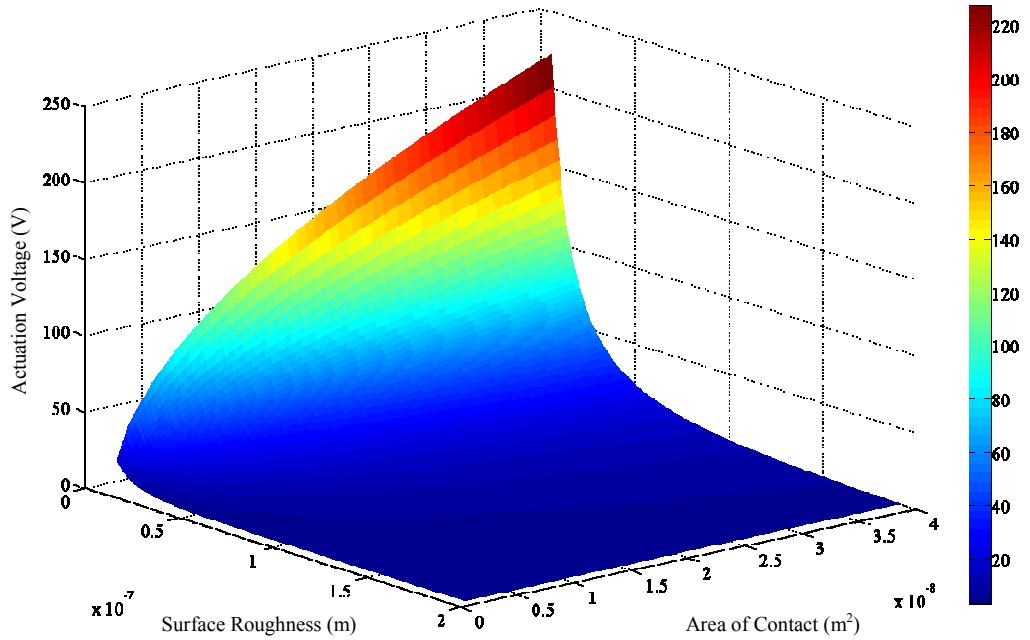

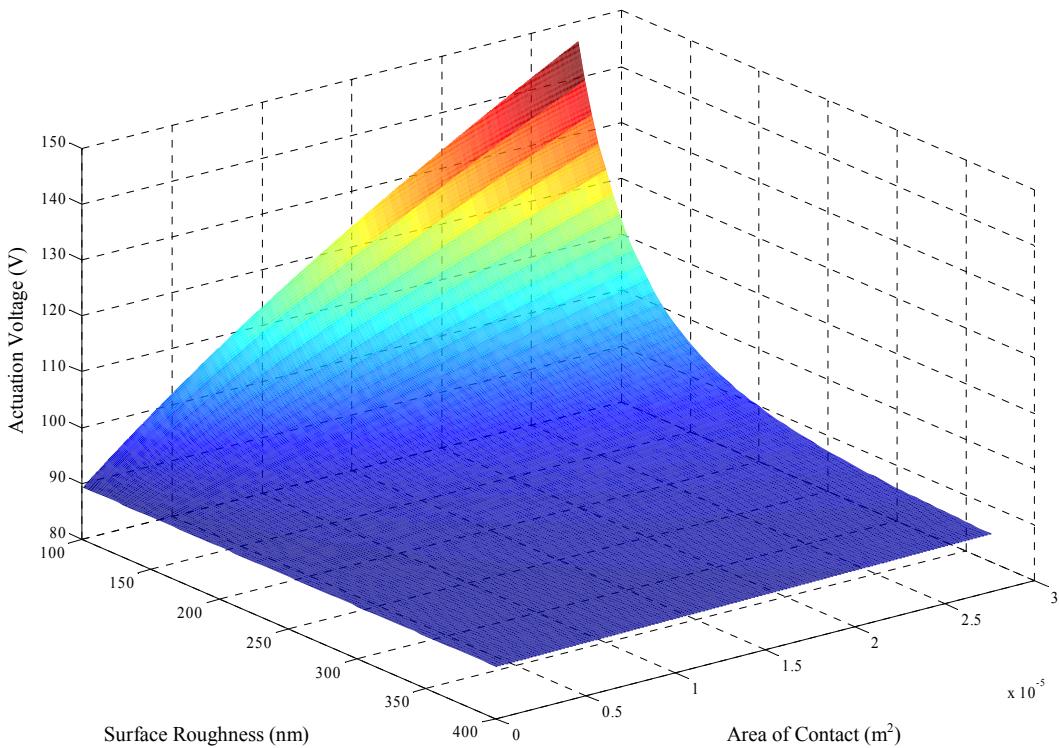

| Figure 3.12: Calculated actuation voltage considering the effects of surface roughness and contact area for a silicon-air-tantalum pentoxide material system. ....                                                            | 46 |

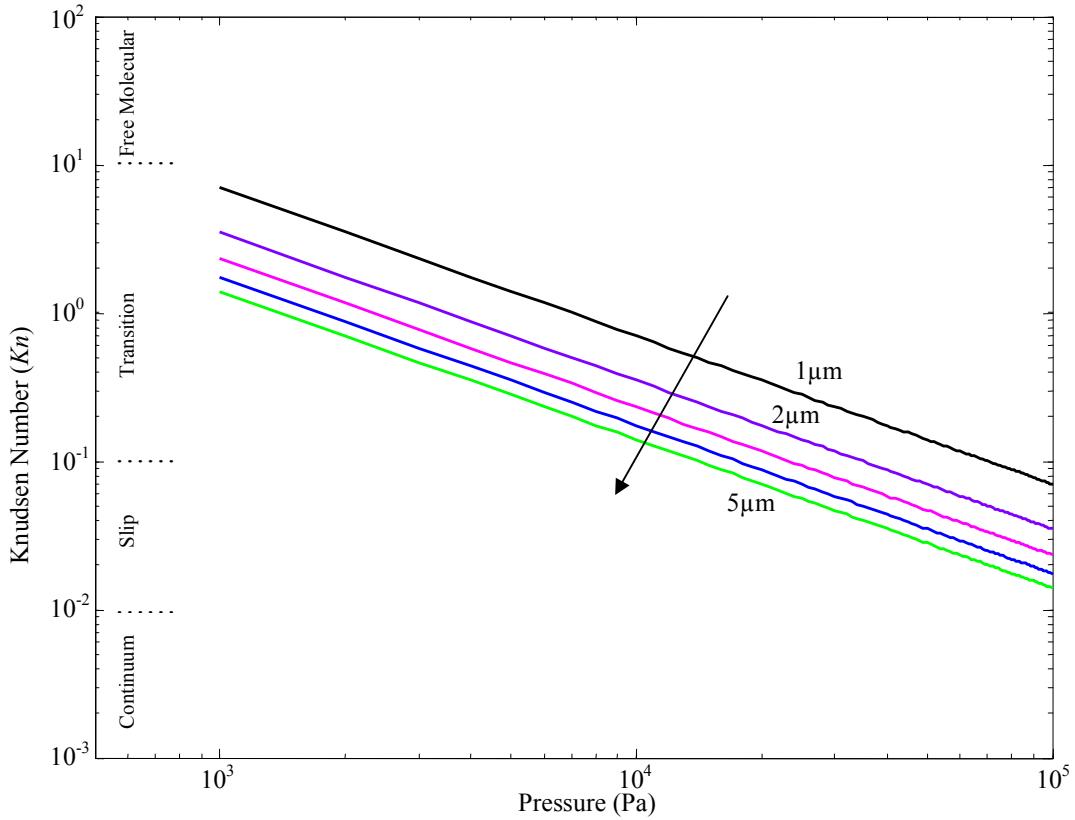

| Figure 3.13: Variation of Knudsen number with pressure for gaps from 1 $\mu$ m to 5 $\mu$ m in 1 $\mu$ m steps.....                                                                                                           | 48 |

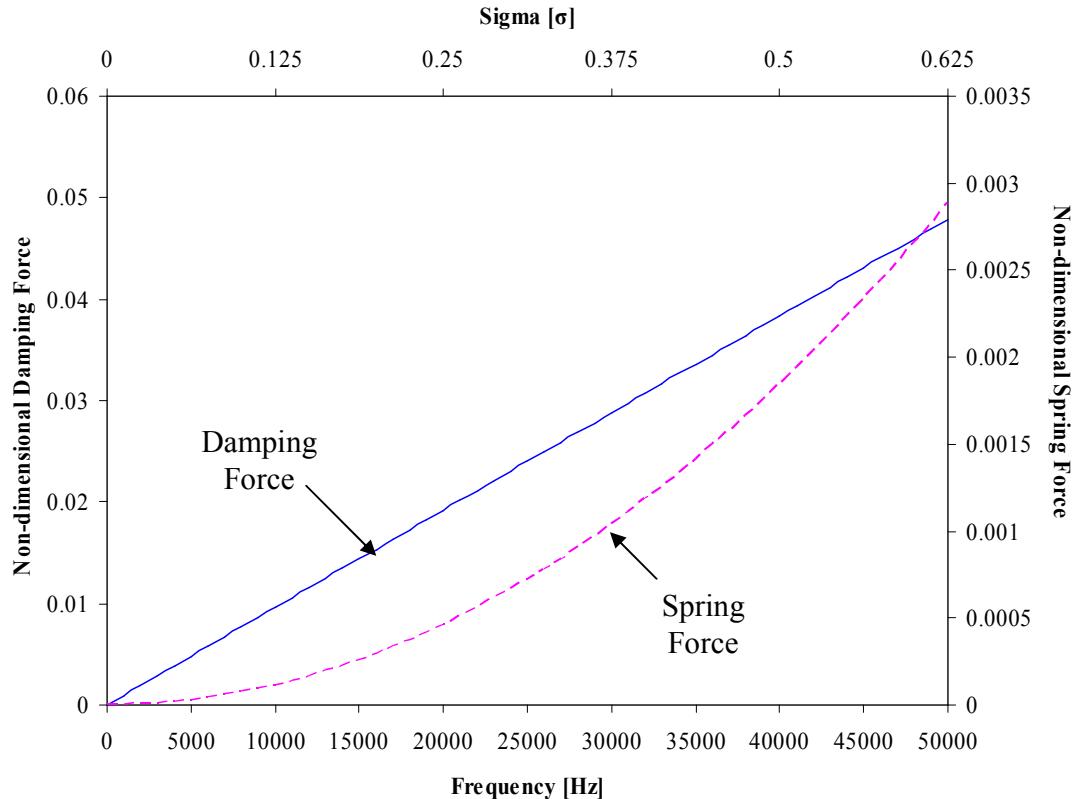

| Figure 3.14: Calculation of damping coefficient and spring constant using linearised Reynolds equation from 0-50KHz. Atmospheric pressure was assumed in these simulations.....                                               | 49 |

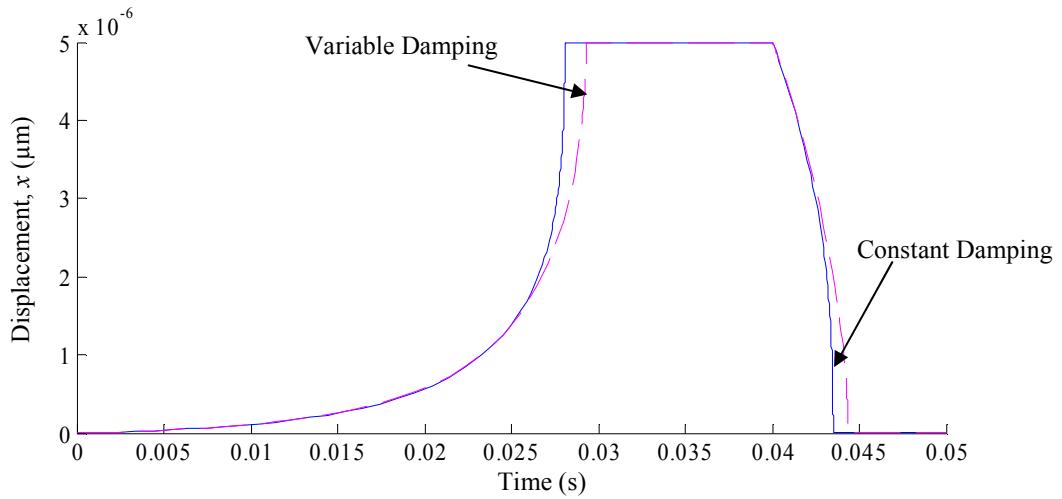

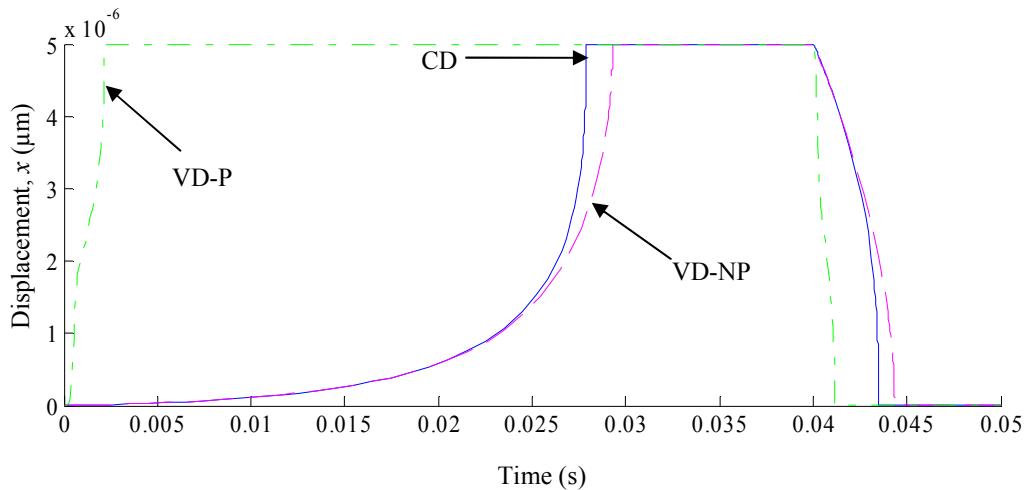

| Figure 3.15: Mechanical response of the armature assuming variable damping (VD) and constant damping (CD) of the MEMS switch. ....                                                                                            | 51 |

|                                                                                                                                                                                                                                                                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

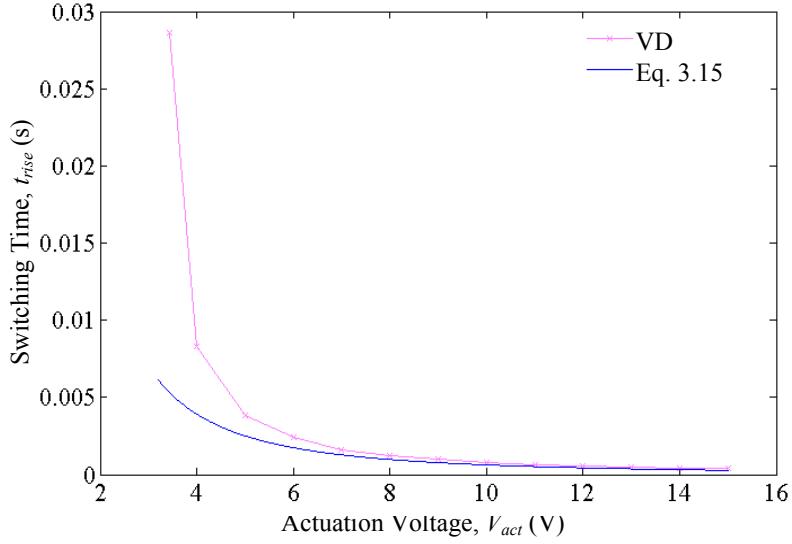

| Figure 3.16: Comparison between the Simulink simulated switching time and equation 3.15 of the MEMS switch as a function of the actuation voltage varying from minimum actuation voltage, $V_{act(min)}$ , to 15V. ....                                                                                                                                                                      | 52 |

| Figure 3.17: Comparison of actuation time and the release time of the MEMS switch, assuming the model using constant damping (CD), variable damping without considering perforated holes (VD-NP) and variable damping with perforated holes (VD-P). ....                                                                                                                                     | 53 |

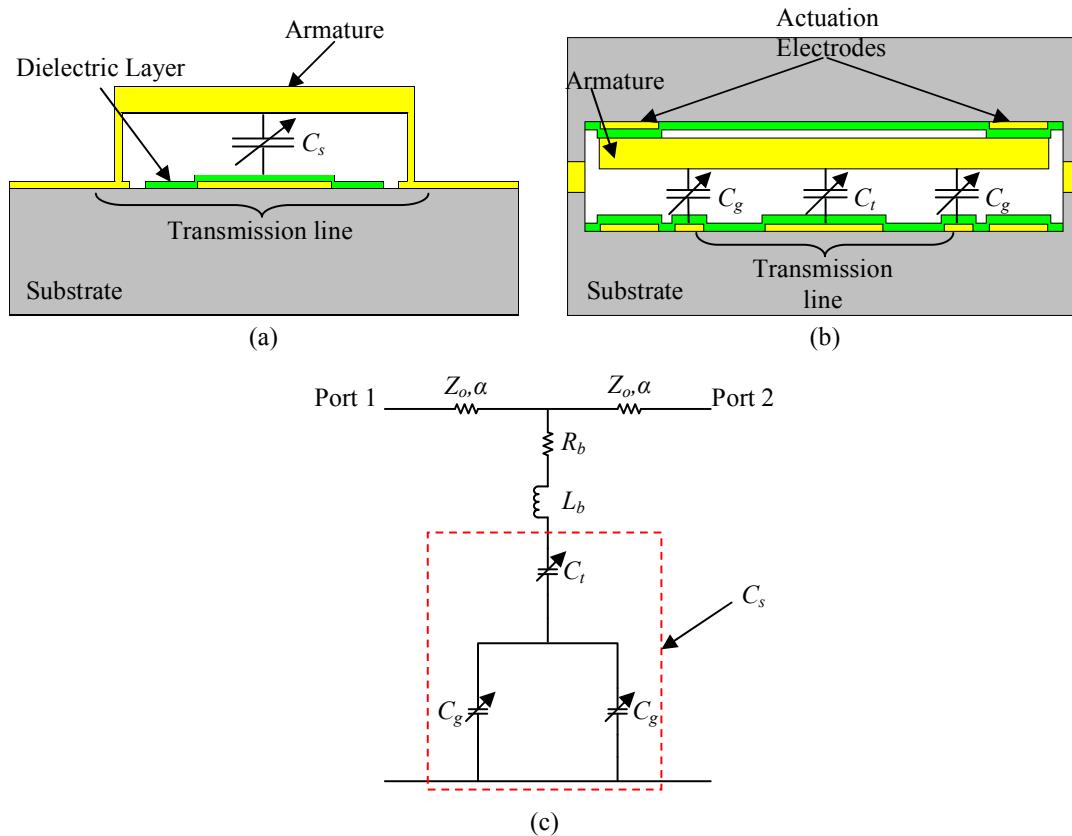

| Figure 4.1: Cross section of (a) a conventional RF MEMS shunt switch (b) Proposed RF MEMS shunt switch. (c) Electrical equivalent circuit of the proposed RF MEMS shunt switch. ....                                                                                                                                                                                                         | 58 |

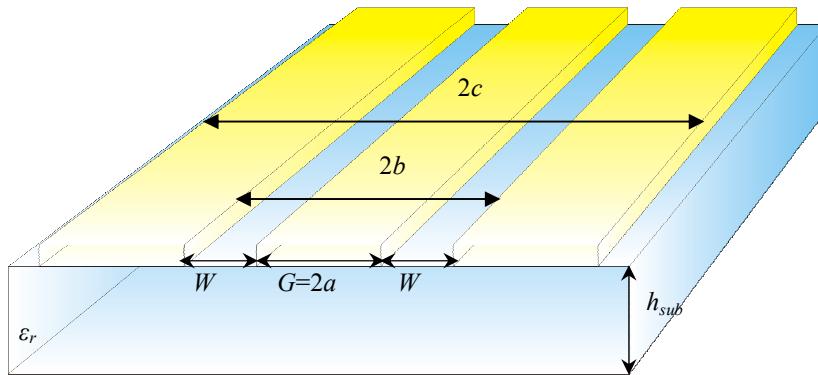

| Figure 4.2: 3-D cross sectional illustration of a finite width coplanar waveguide. ....                                                                                                                                                                                                                                                                                                      | 59 |

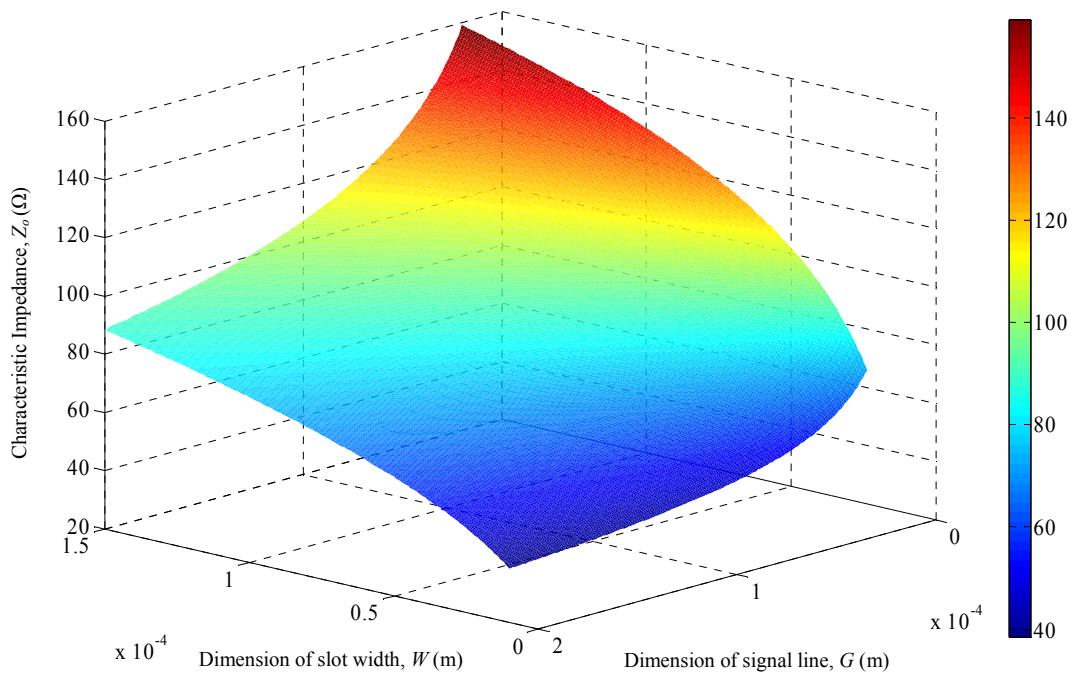

| Figure 4.3: A three dimensional plot showing the characteristic impedance of a finite width conductor backed coplanar waveguide, with respect to the dimension of signal line and slot width using equation 4.12, for width of the ground plane = 250 $\mu$ m and $\varepsilon_r = 4.82$ . ....                                                                                              | 62 |

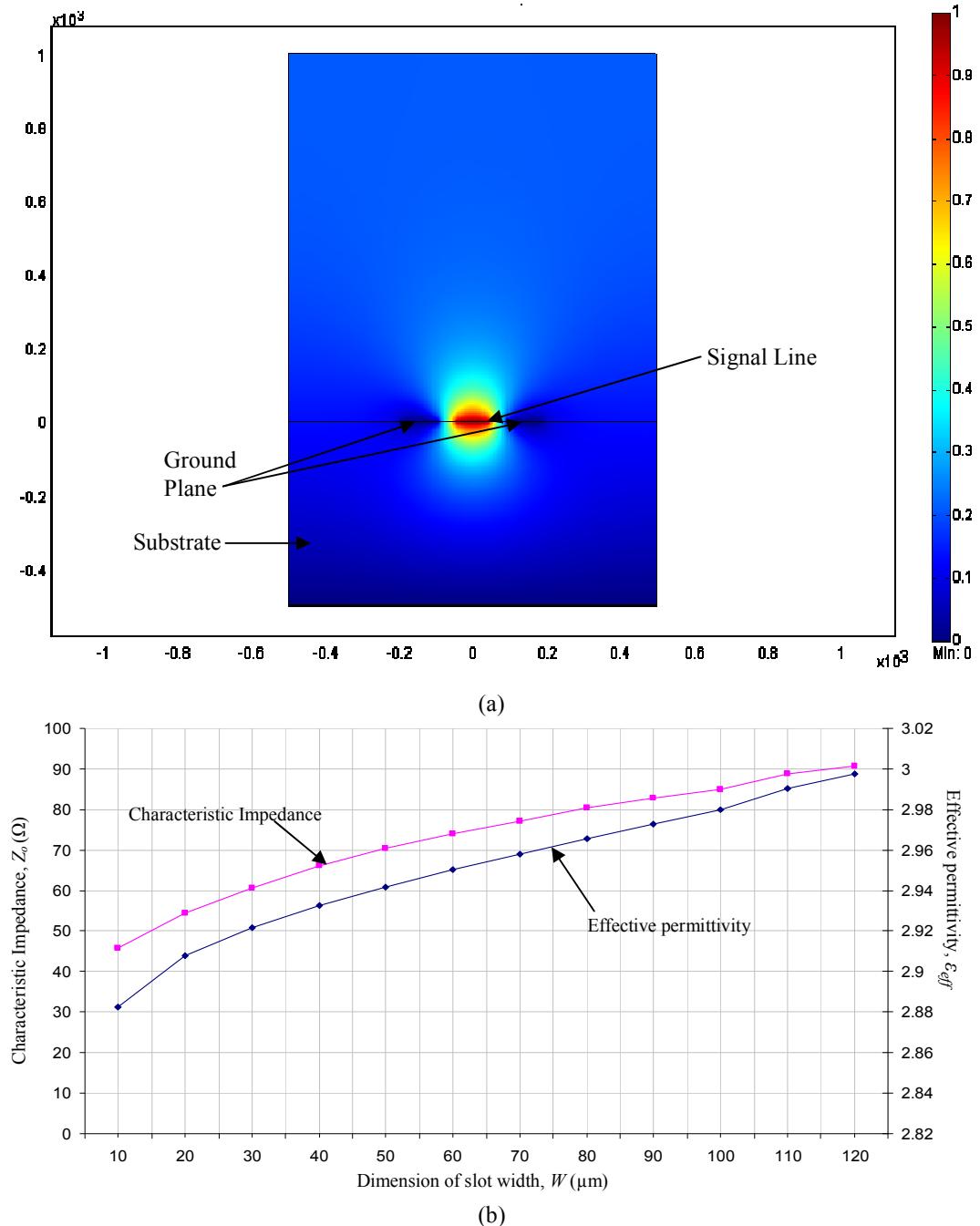

| Figure 4.4 : (a) Electrical potential of a finite width coplanar waveguide using COMSOL when the signal line applied with 1V and the ground plane is set to 0V (b) Simulated characteristic impedance and effective dielectric constant of a finite width coplanar waveguide with $G = 90 \mu\text{m}$ over a range of slot width using COMSOL. ....                                         | 63 |

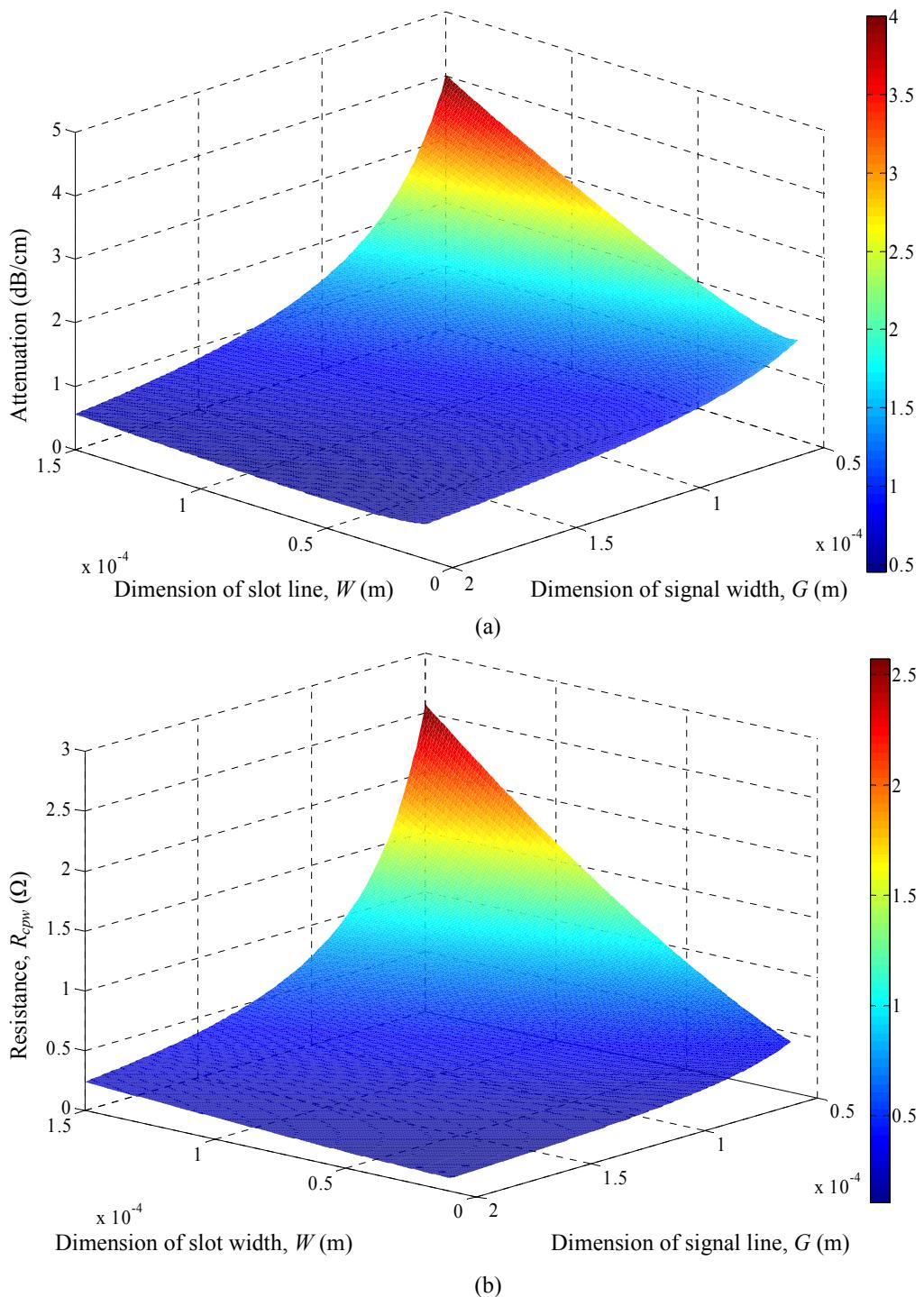

| Figure 4.5: (a) Attenuation of the coplanar waveguide with thickness of conductors of 500nm on Pyrex substrate over a range of signal line width, $G$ , and slot width, $W$ based on equation 4.13. (b) Resistance of the coplanar waveguide conductors, $R_{cpw}$ , based on the length of the transmission line of 2mm over a range of signal line width, $G$ , and slot width, $W$ . .... | 65 |

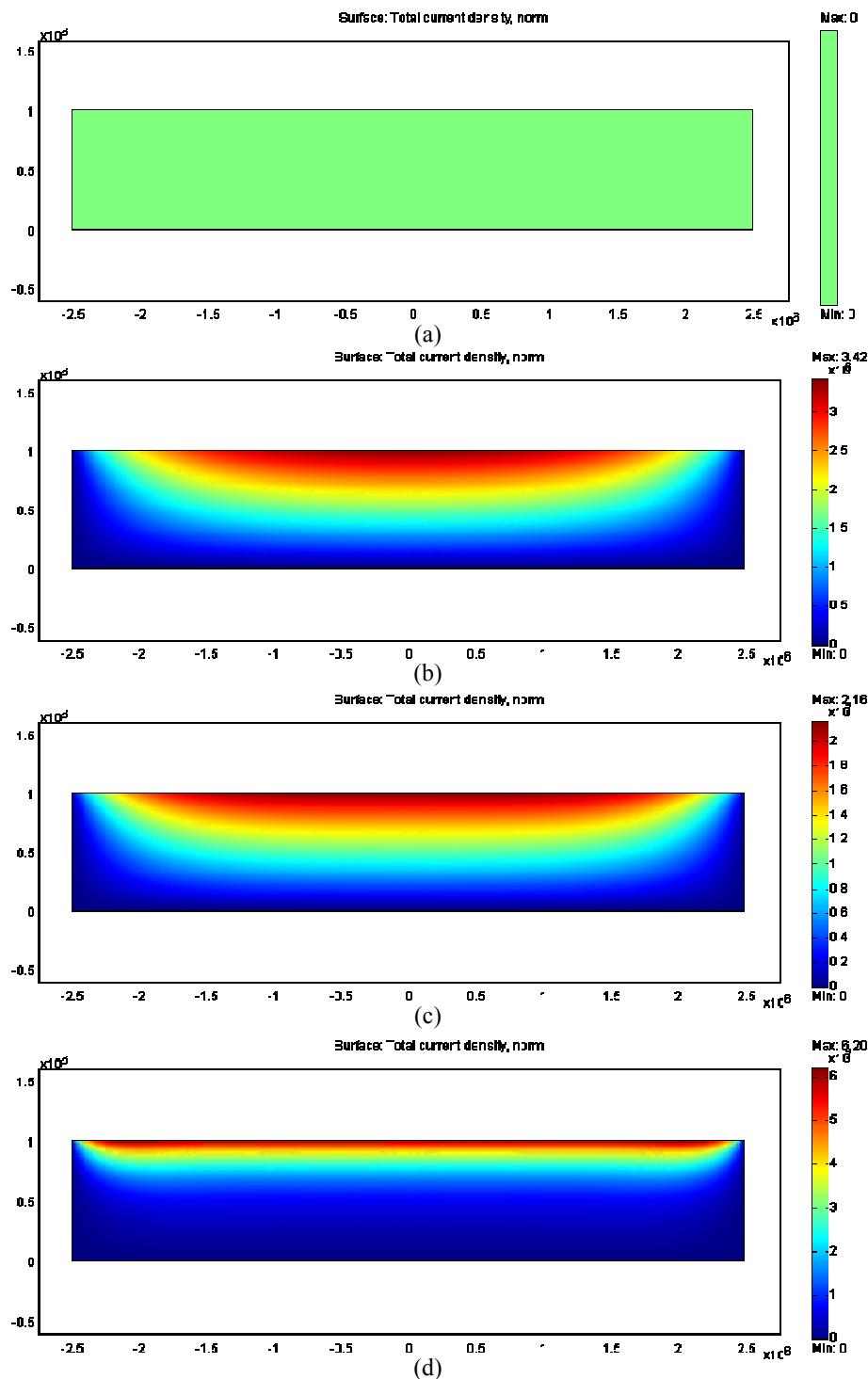

| Figure 4.6: FEMLAB simulation of skin effect of a current transmitting through a 1 $\mu\text{m}$ thick Gold conductor at (a) DC, (b) 1GHz, (c) 10GHz and (d) 100GHz....                                                                                                                                                                                                                      | 70 |

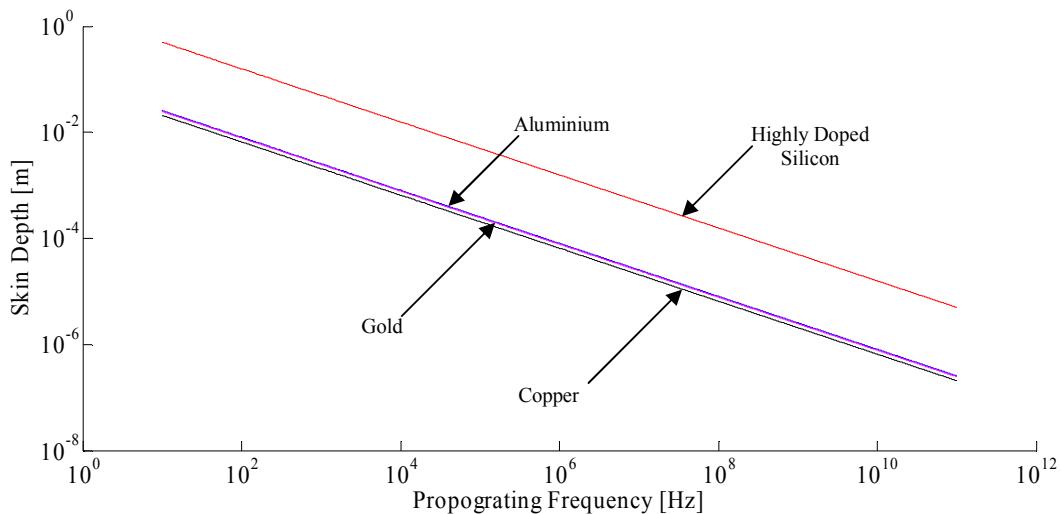

| Figure 4.7: Skin depth of various materials that can be used as armature with respective to propagating frequency from 10Hz to 100GHz based on equation 4.25... 71                                                                                                                                                                                                                           | 71 |

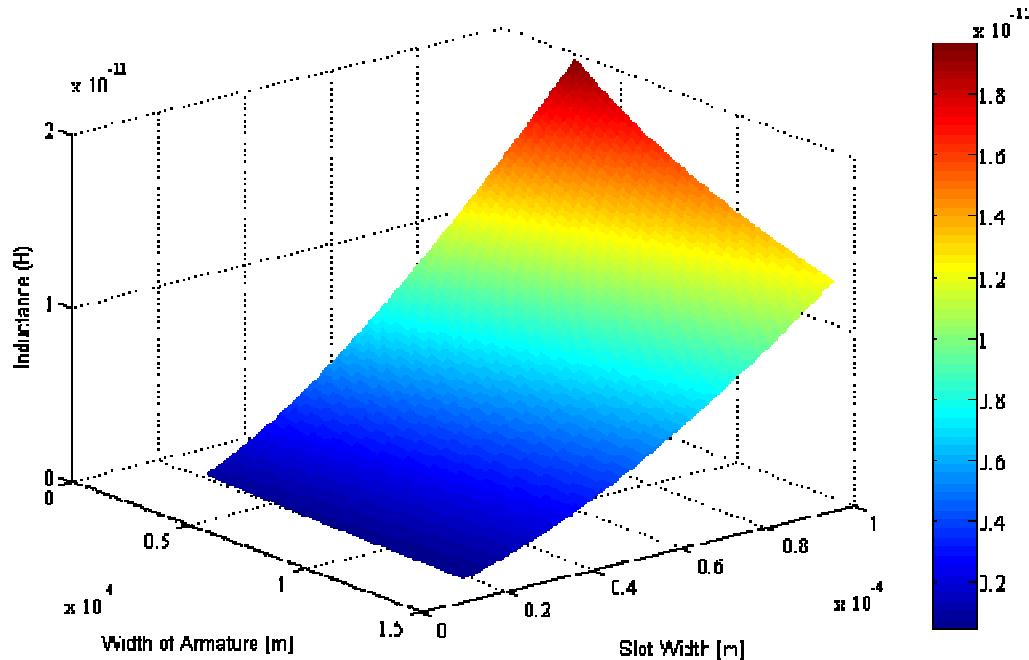

| Figure 4.8: Calculated switch inductance for a 50 $\mu\text{m}$ thick armature over a range of possible slot width and armature width based on equation 4.27.....                                                                                                                                                                                                                            | 72 |

|                                                                                                                                                                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

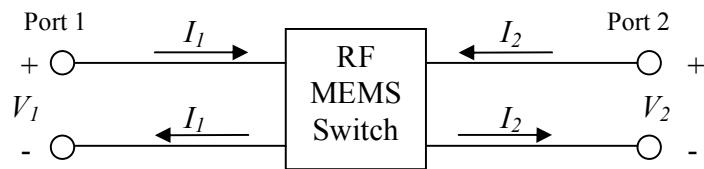

| Figure 4.9: Two-Port network for the RF MEMS Switch.....                                                                                                                                                                                                                                                                                                                    | 73 |

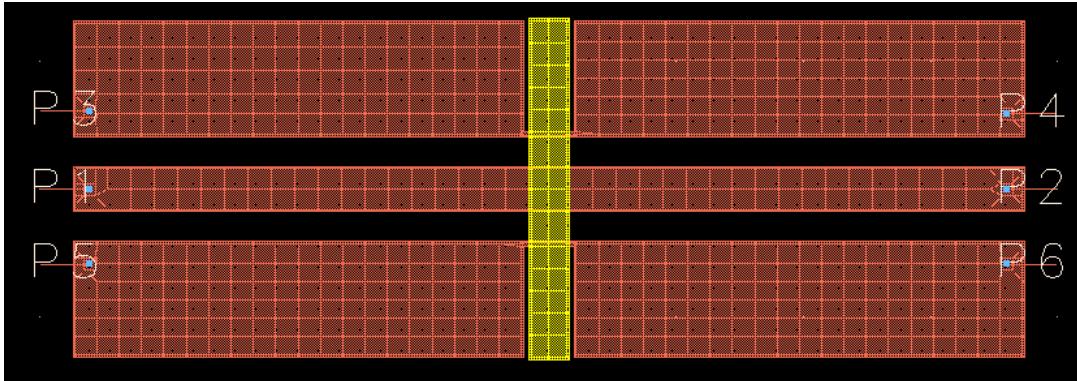

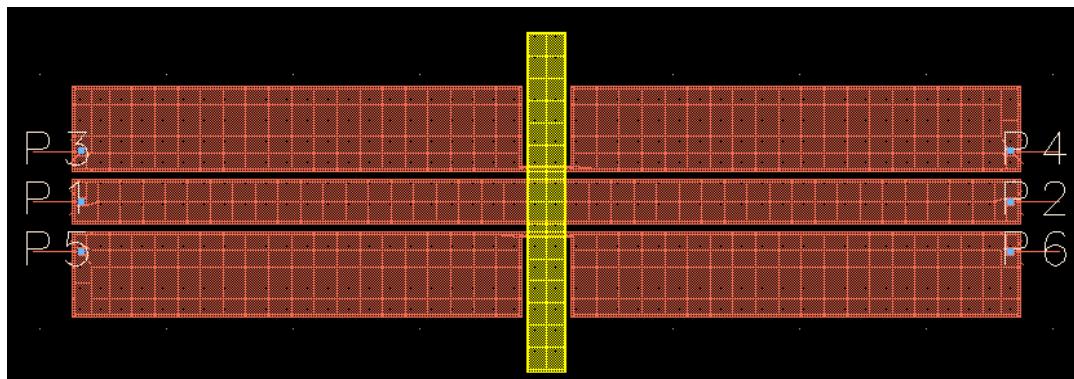

| Figure 4.10: ADS Momentum model of the proposed RF MEMS switch with a $50\Omega$ coplanar waveguide. ....                                                                                                                                                                                                                                                                   | 75 |

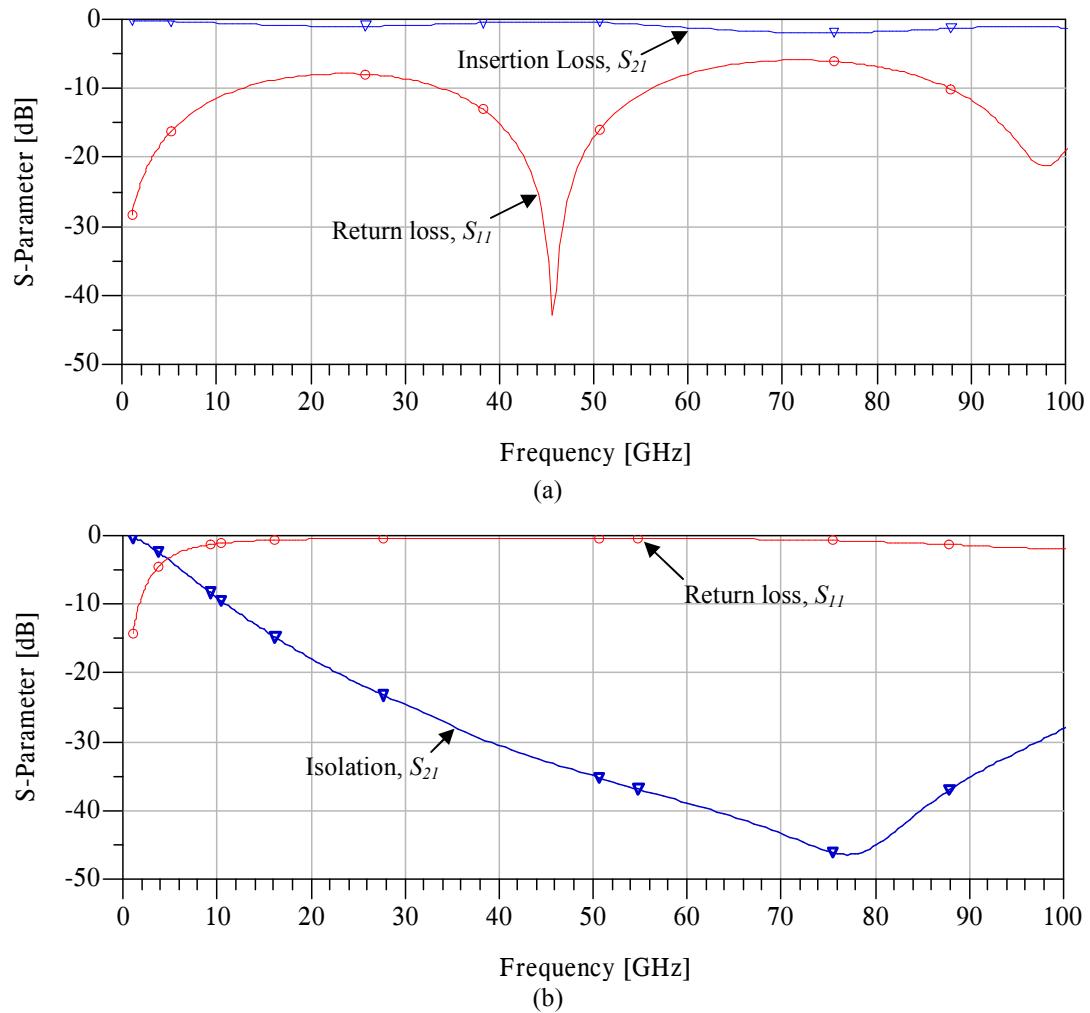

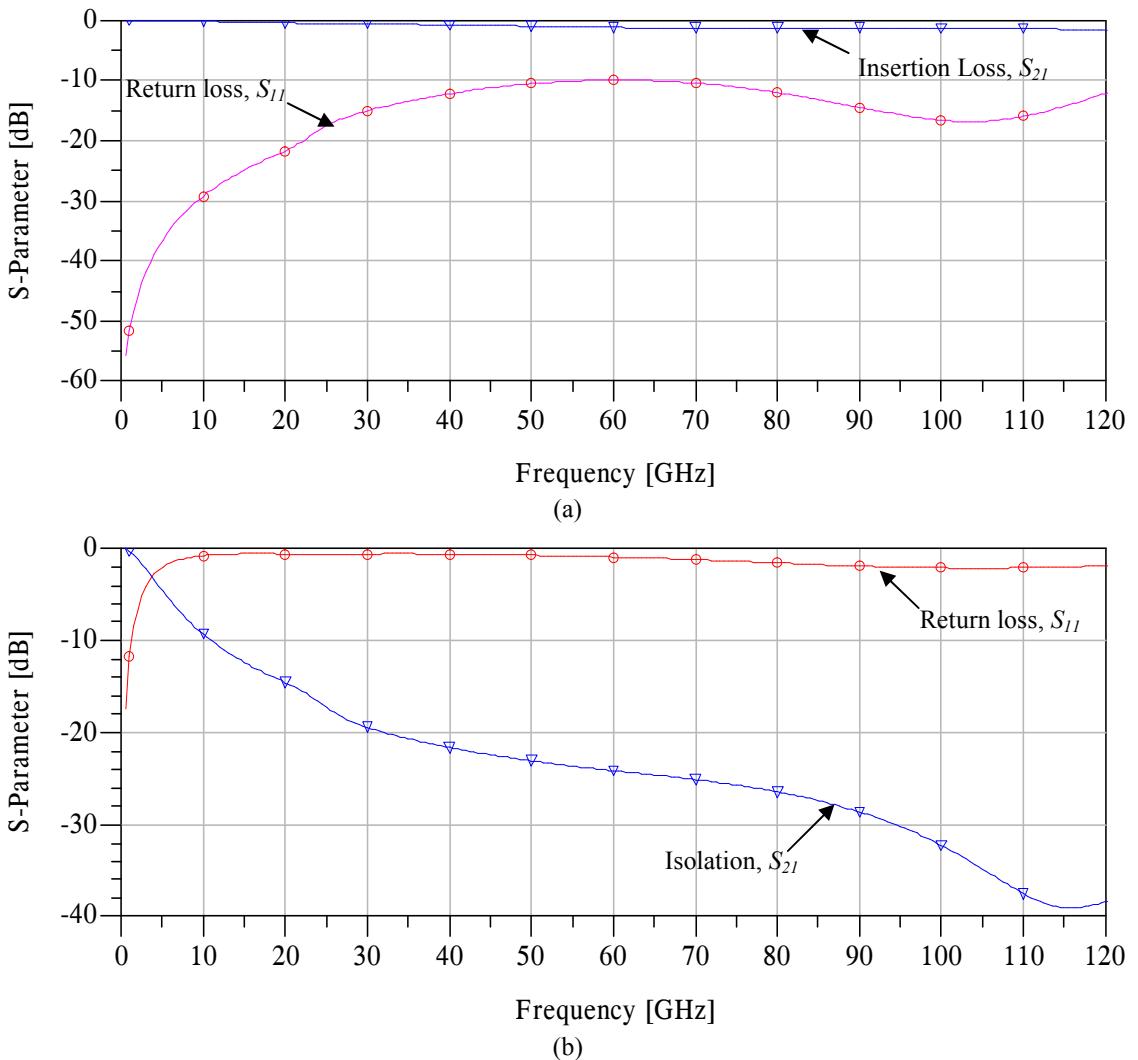

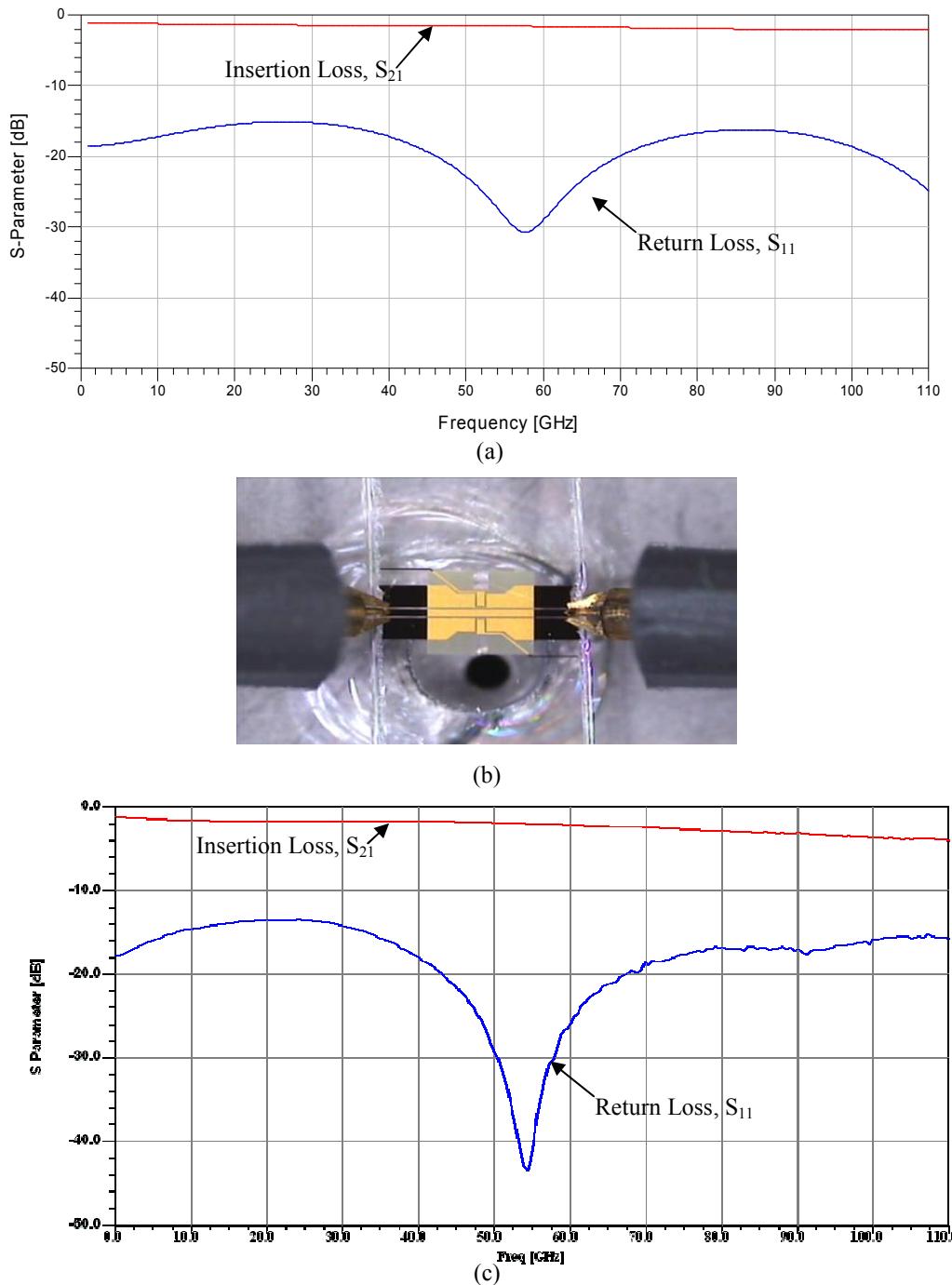

| Figure 4.11: Simulated (a) UP state (b) DOWN state S-Parameter for a $75\Omega$ RF MEMS switch.....                                                                                                                                                                                                                                                                         | 76 |

| Figure 4.12: ADS Momentum model of the proposed RF MEMS switch with a $50\Omega$ coplanar waveguide. ....                                                                                                                                                                                                                                                                   | 76 |

| Figure 4.13: Simulated (a) UP state (b) DOWN state S-Parameter for a $50\Omega$ RF MEMS switch.....                                                                                                                                                                                                                                                                         | 77 |

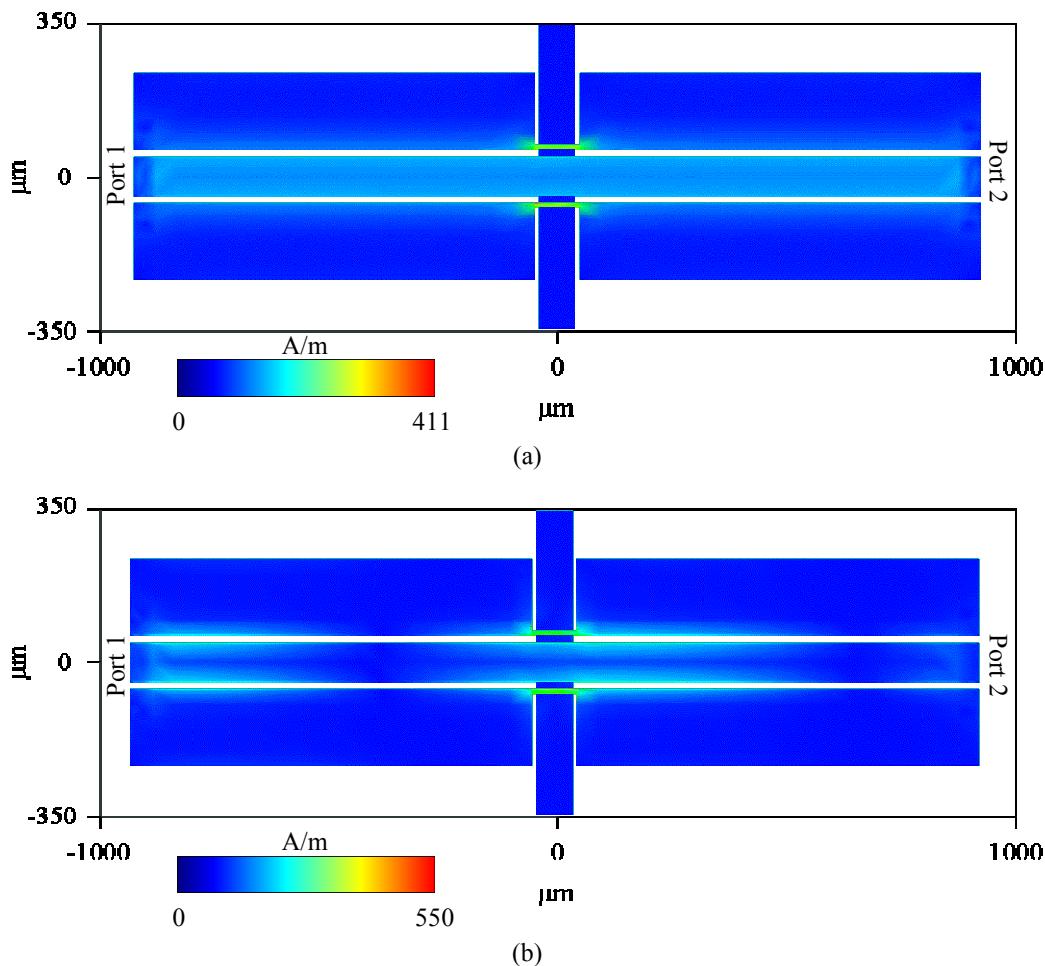

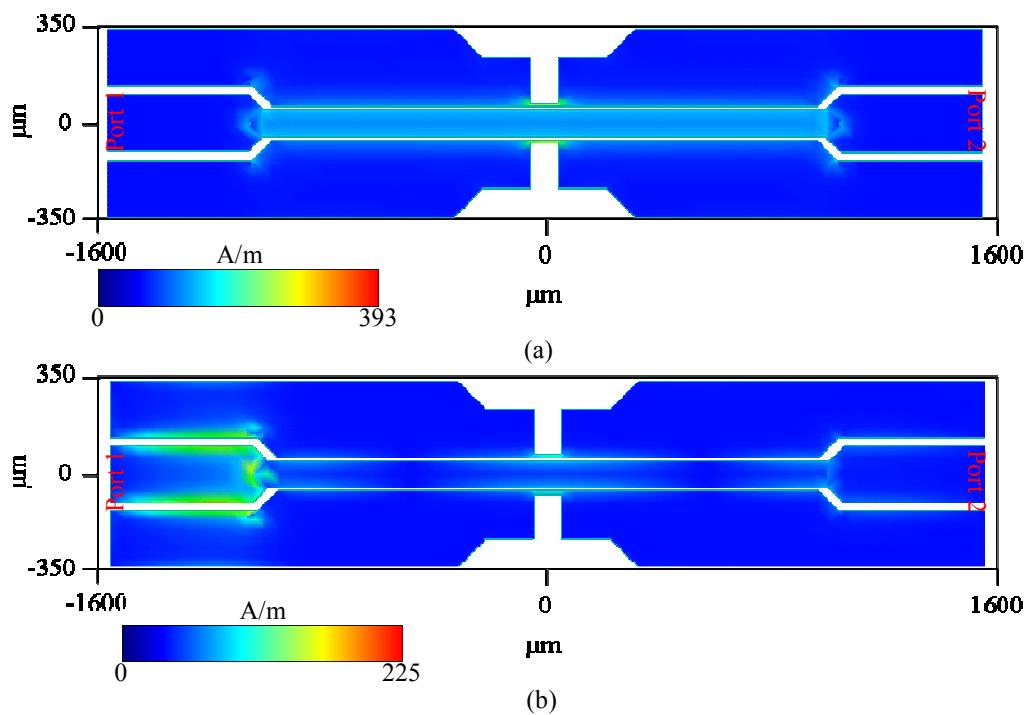

| Figure 4.14: Simulated current flow of the $50\Omega$ RF MEMS switch in the UP state at (a) 1GHz and (b) 75GHz.....                                                                                                                                                                                                                                                         | 78 |

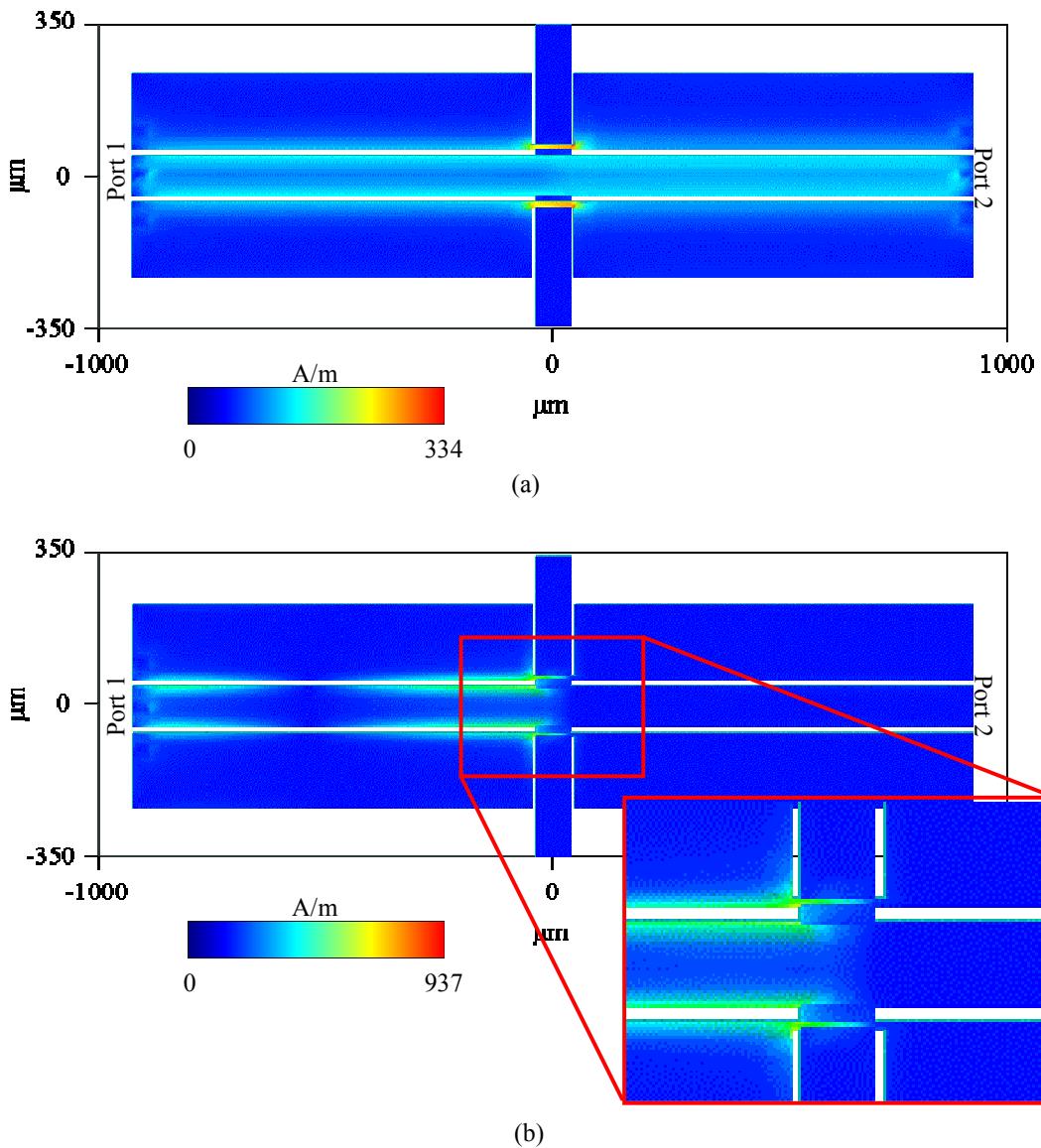

| Figure 4.15: Simulated current density plot of the $50\Omega$ RF MEMS switch in the DOWN state for (a) 1GHz and (b) 75GHz. ....                                                                                                                                                                                                                                             | 79 |

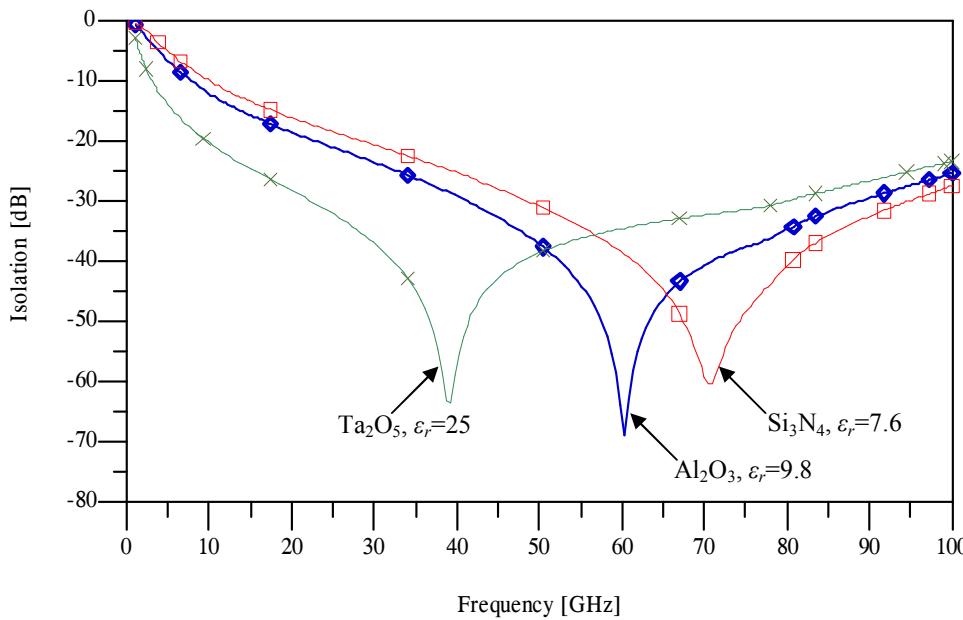

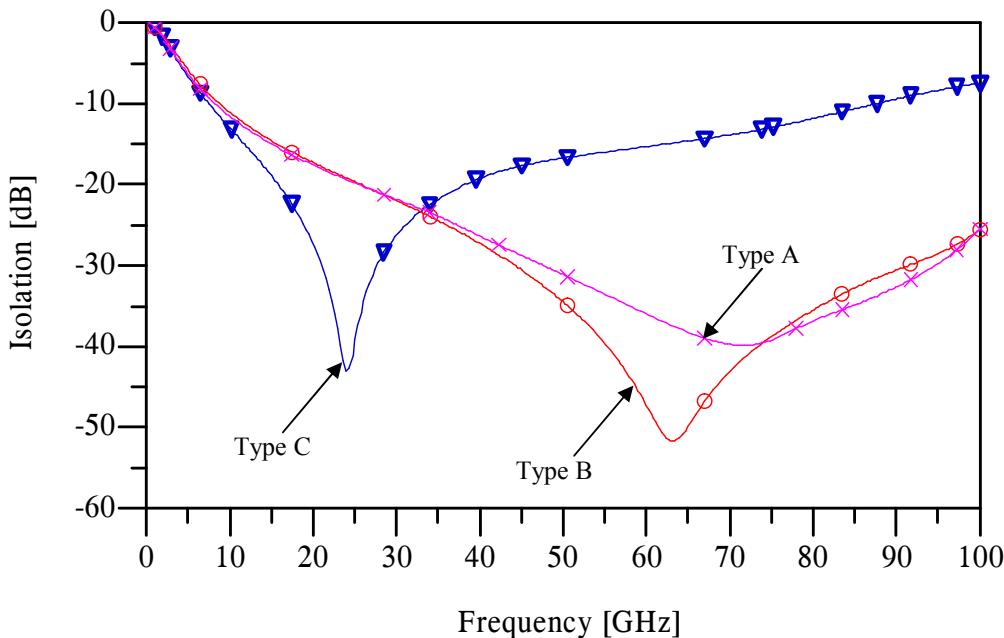

| Figure 4.16: Simulated isolation with based on silicon nitride ( $\text{Si}_3\text{N}_4$ ), aluminium oxide ( $\text{Al}_2\text{O}_3$ ) and tantalum pentoxide ( $\text{Ta}_2\text{O}_5$ ) with a switch design of $l_m=680\mu\text{m}$ , $w_m=80\mu\text{m}$ , $G=90\mu\text{m}$ and $W=60\mu\text{m}$ , $A_r=A_c=7.2\times10^{-9}\text{m}^2$ and $t_d=200\text{nm}$ ..... | 80 |

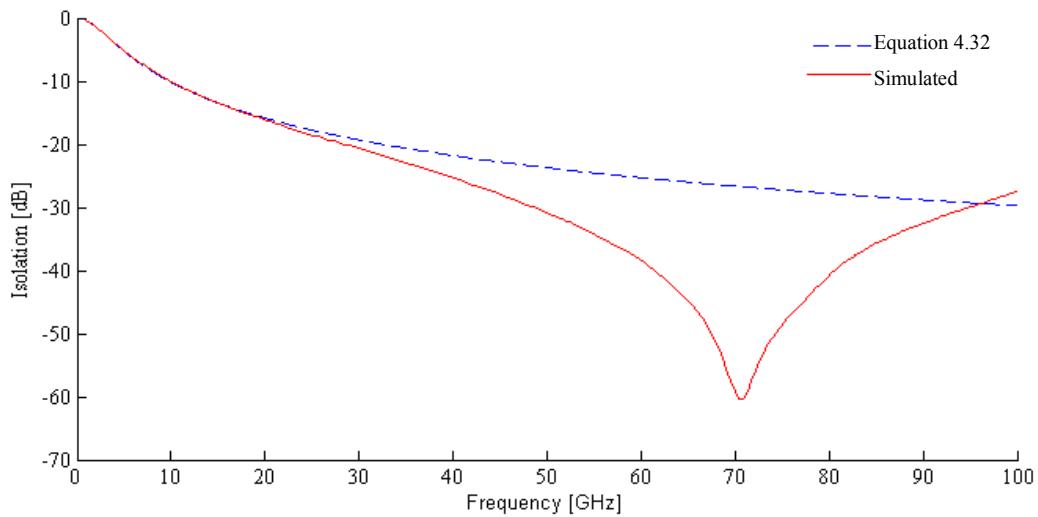

| Figure 4.17: Comparison between simulated isolation and analytical isolation solution using equation 4.32 based on silicon nitride ( $\text{Si}_3\text{N}_4$ ) with a switch design of $l_m=680\mu\text{m}$ , $w_m=80\mu\text{m}$ , $G=90\mu\text{m}$ and $W=60\mu\text{m}$ , $A_r=A_c=3.6\times10^{-9}\text{m}^2$ and $t_d=200\text{nm}$ .....                             | 81 |

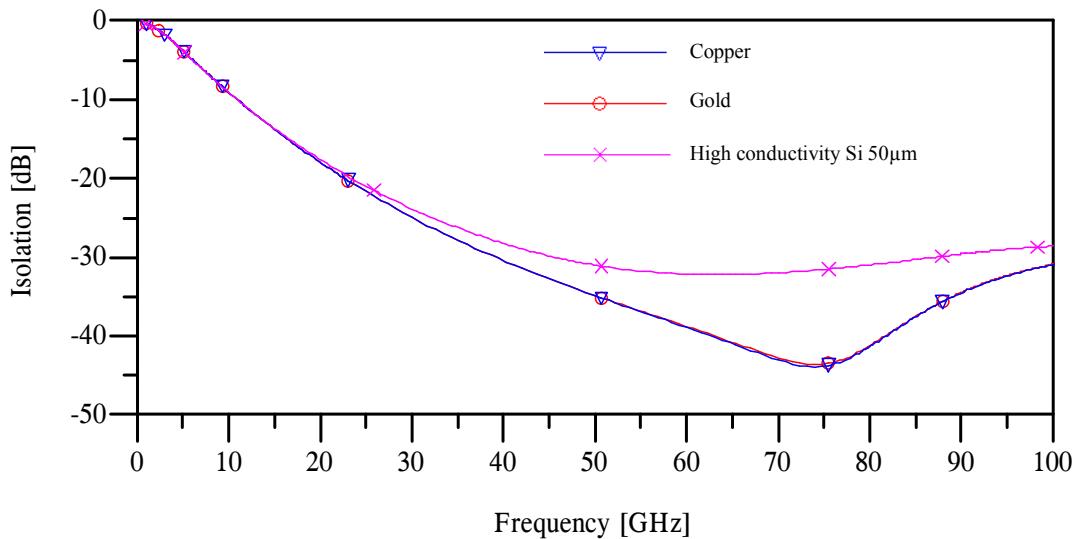

| Figure 4.18: Effect of different armature material on the isolation of the RF MEMS switch with a finite width conductor backed coplanar waveguide $W/G/W=60\mu\text{m}/90\mu\text{m}/60\mu\text{m}$ and on a Pyrex substrate of $\epsilon_r = 4.82$ .....                                                                                                                   | 82 |

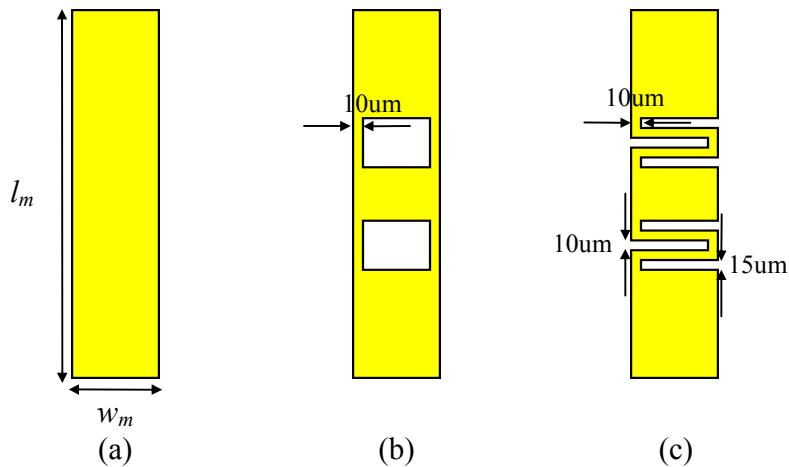

| Figure 4.19: (a) A simple rectangle shape armature, (b) a rectangle armature with rectangle hole over the slot width area and (c) a rectangle armature with a serpentine like design over the slot width area. ....                                                                                                                                                         | 83 |

| Figure 4.20: Isolation of actuated RF MEMS switch with armature geometries from Figure 4.19(a-c) over a finite width conductor backed coplanar waveguide $W/G/W=60\mu\text{m}/90\mu\text{m}/60\mu\text{m}$ and on a Pyrex substrate of $\epsilon_r = 4.82$ , of different inductance value.....                                                                             | 84 |

|                                                                                                                                                                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.1: 3-D view of the (a) with top Pyrex wafer (b) without top Pyrex wafer of proposed MEMS switch (not drawn to scale).....                                                                                                                                                        | 88  |

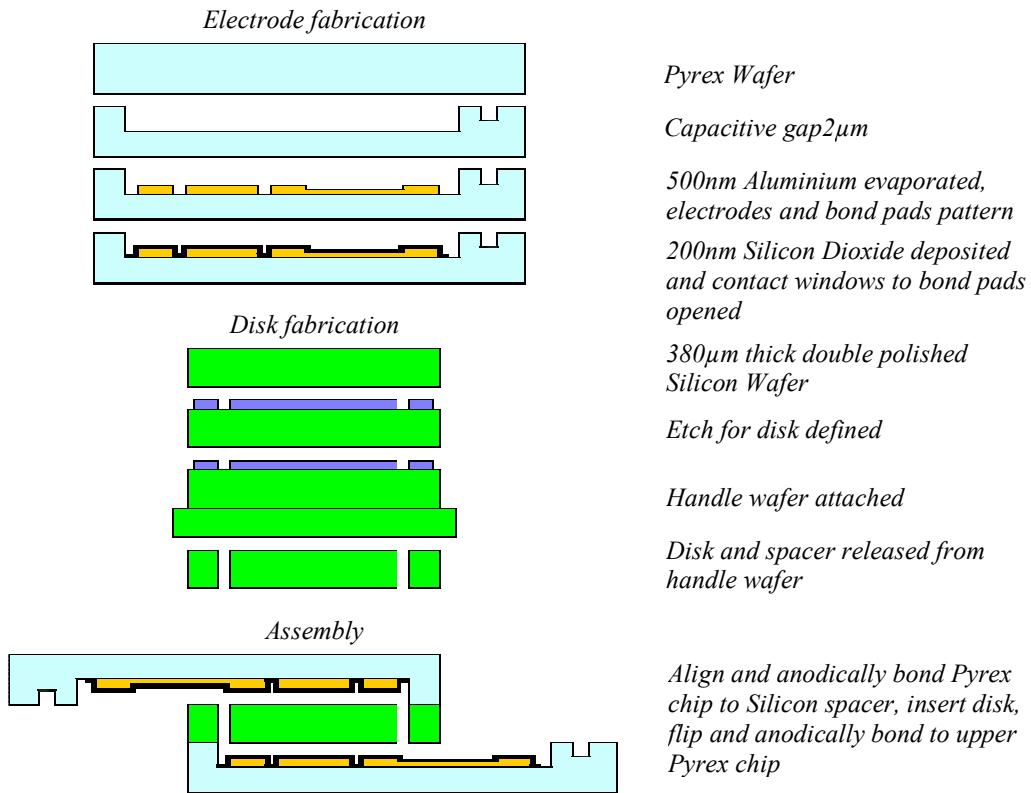

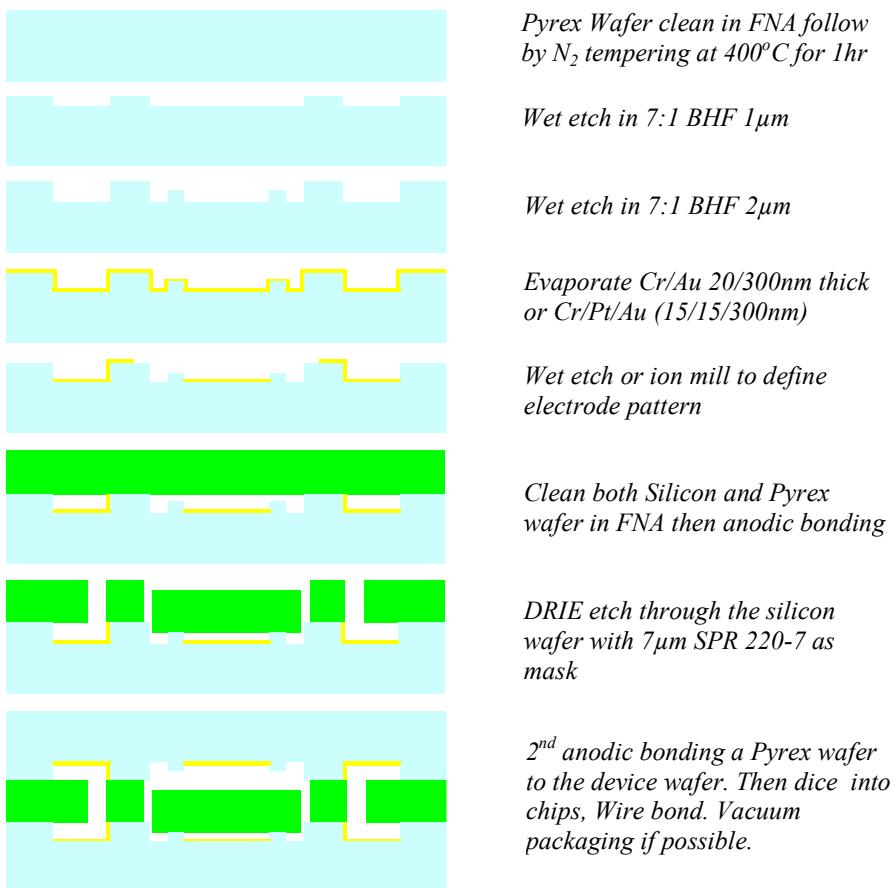

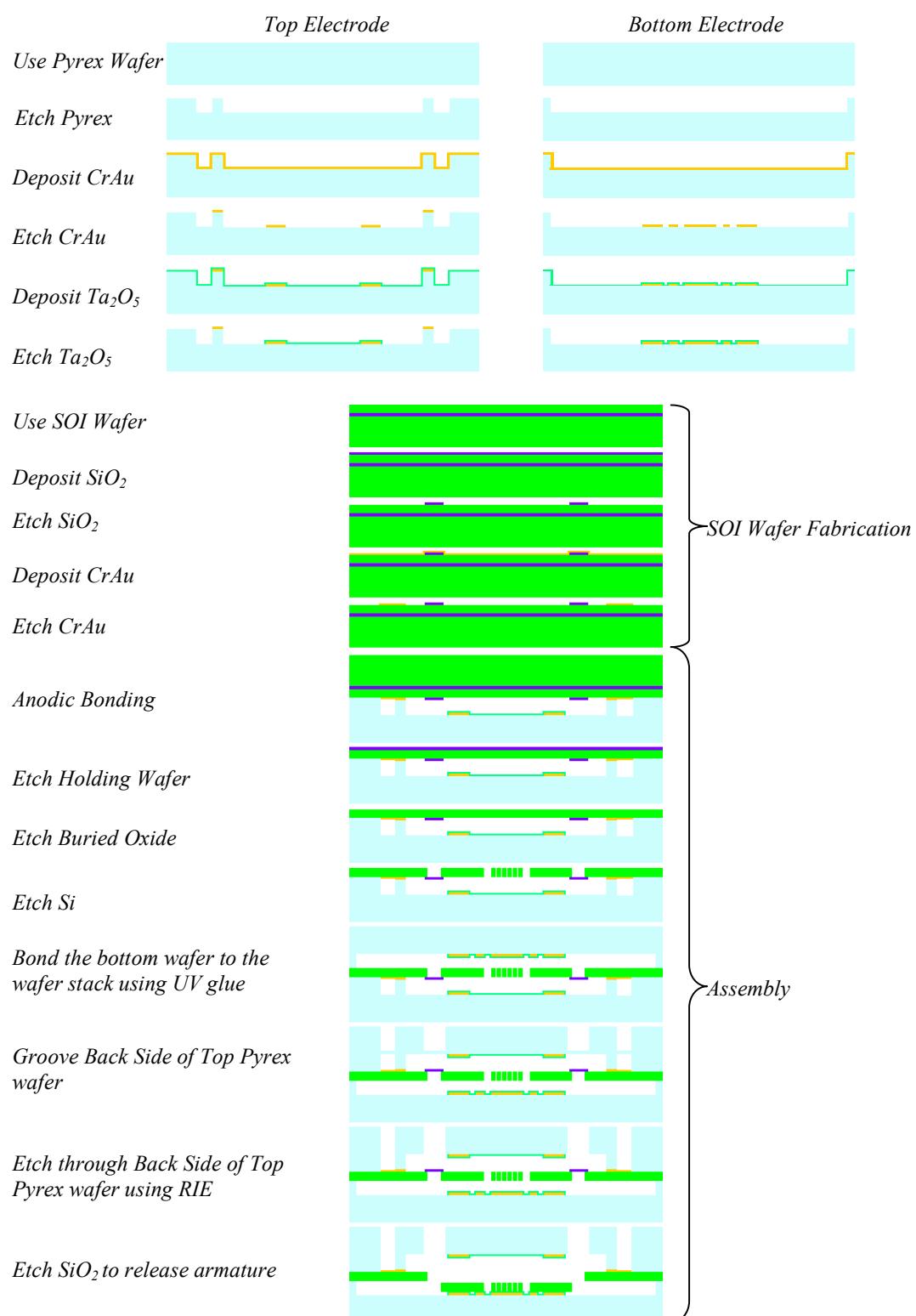

| Figure 5.2: Fabrication flow for 3 wafer stack process for the micron-scale prototype described in section 5.1.....                                                                                                                                                                       | 89  |

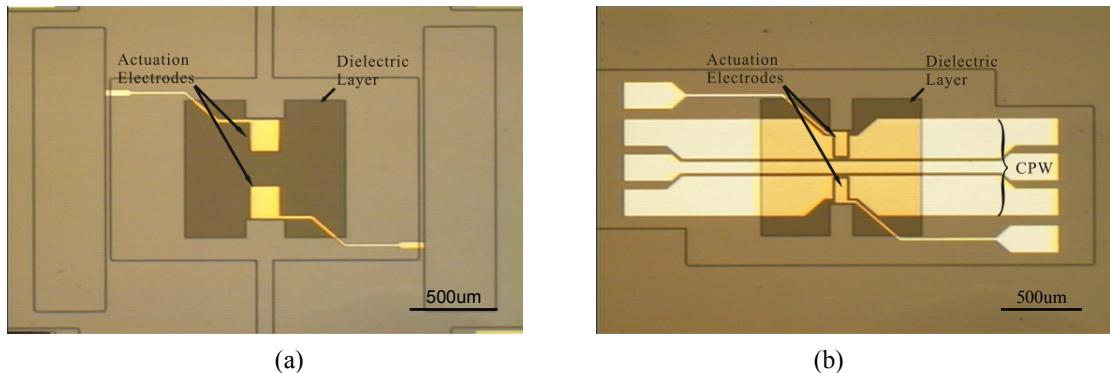

| Figure 5.3: Microscopic picture of structures of a processed (a) top Pyrex wafer (b) bottom Pyrex wafer.....                                                                                                                                                                              | 90  |

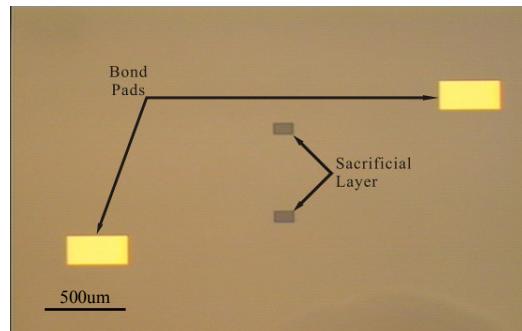

| Figure 5.4: Microscopic picture of structures of a processed SOI wafer.....                                                                                                                                                                                                               | 91  |

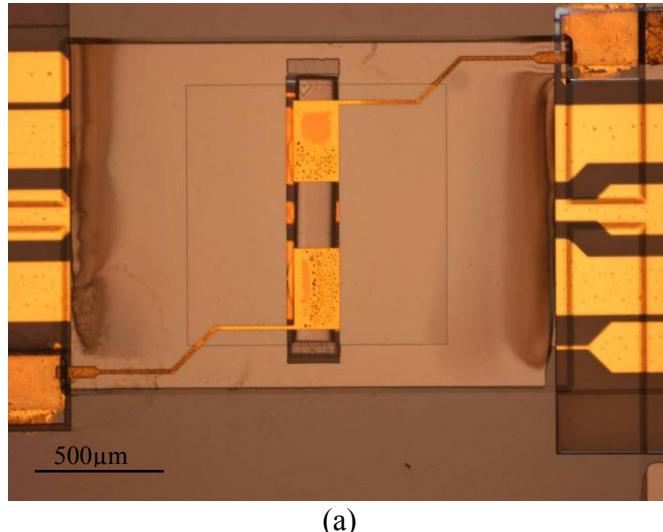

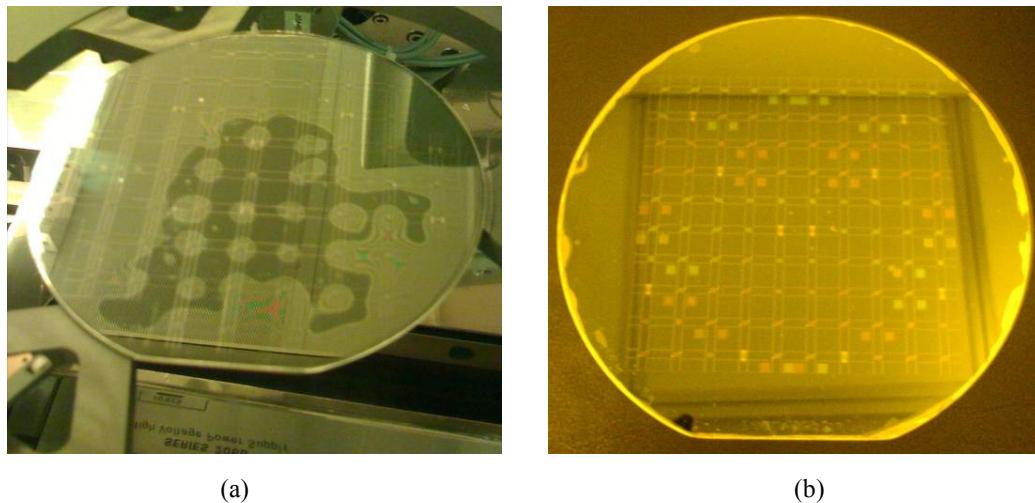

| Figure 5.5: Microscopic picture of a Pyrex-Silicon-Pyrex bonded wafer stack from the (a) top Pyrex wafer of RF MEMS switch design and (b) bottom Pyrex wafer of a RF MEMS switch with a different armature design.....                                                                    | 92  |

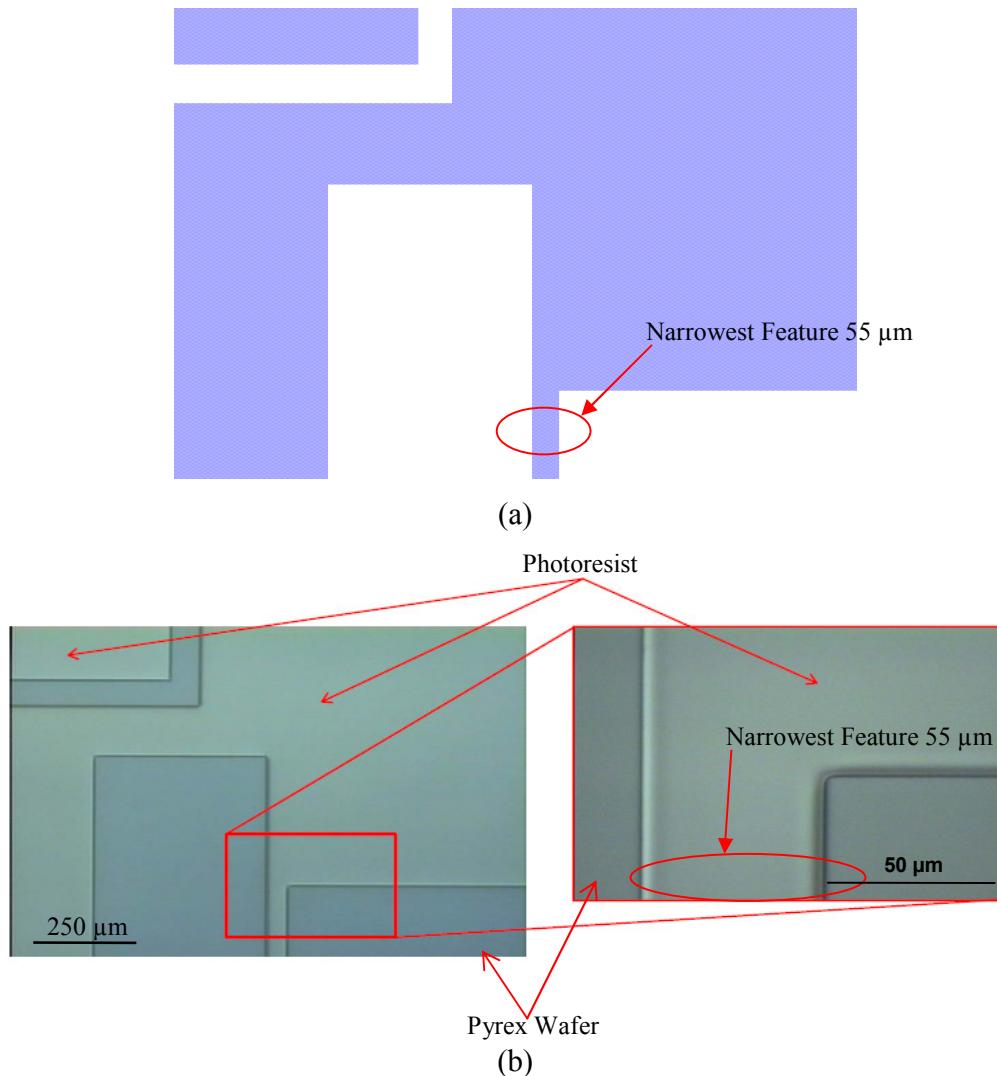

| Figure 5.6: (a) Narrowest device feature to be transferred onto the Pyrex wafer on the dark field mask design (b) Photoresist structure on Pyrex wafer after development.....                                                                                                             | 94  |

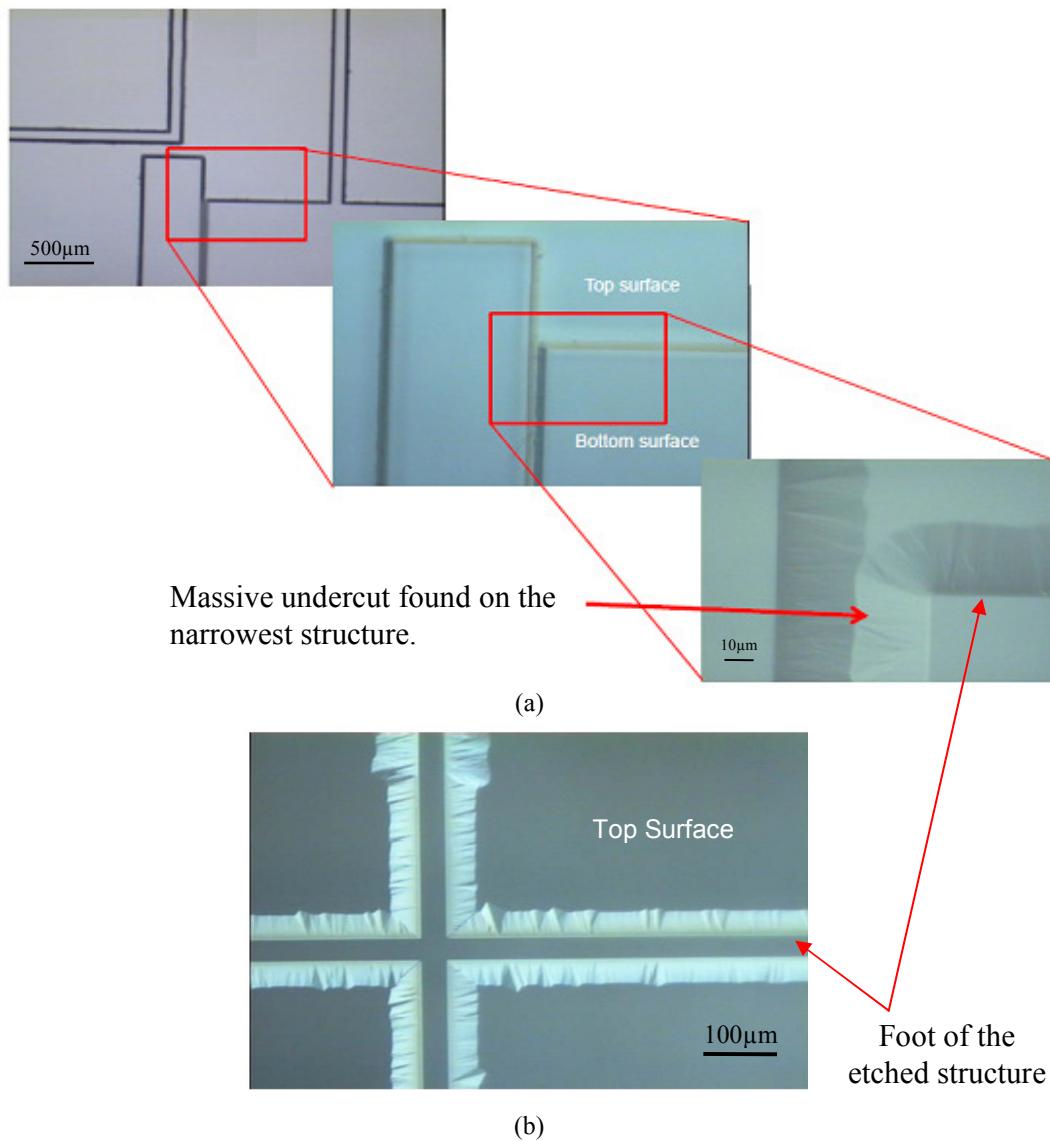

| Figure 5.7: Microscope images of the etch profile on the severity of the undercut at (a) the 55 $\mu$ m wide ridge like structure on the Pyrex wafer using a photoresist mask (b) alignment mark on the Pyrex wafer using a photoresist mask.....                                         | 95  |

| Figure 5.8: (a) 55 $\mu$ m wide ridge-like structure on Pyrex wafer after 1.5 $\mu$ m of etching using a photoresist mask. (b) 55 $\mu$ m wide ridge like structure on Pyrex wafer after 3 $\mu$ m of etching using a metal mask.....                                                     | 96  |

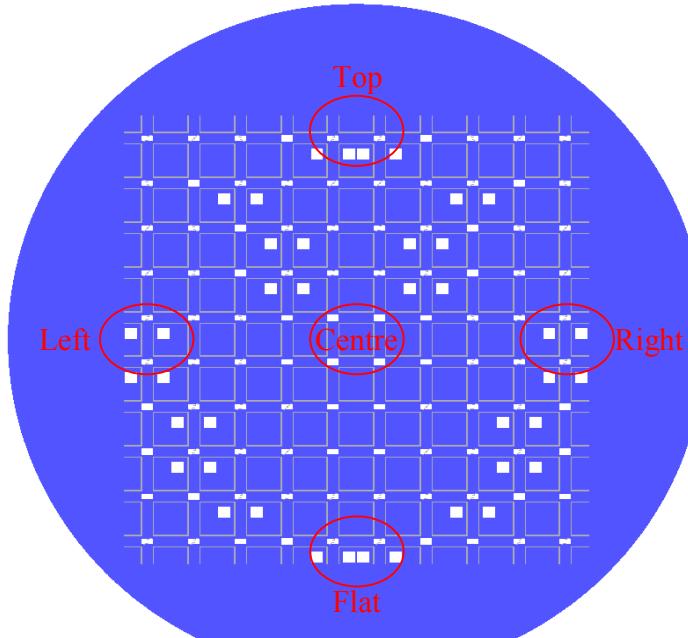

| Figure 5.9: The different sites on the 6 inch Pyrex wafer where the step profiles are measured.....                                                                                                                                                                                       | 98  |

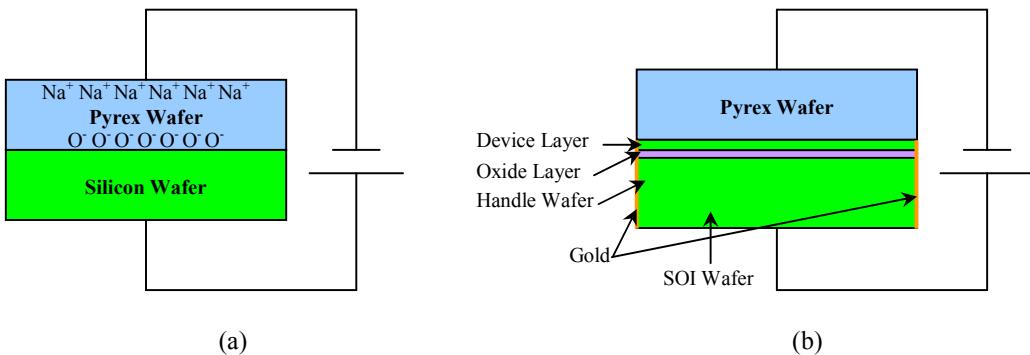

| Figure 5.10: Schematic representation of the layer sequence for (a) Silicon-Pyrex (b) SOI-Pyrex anodic bonding.....                                                                                                                                                                       | 99  |

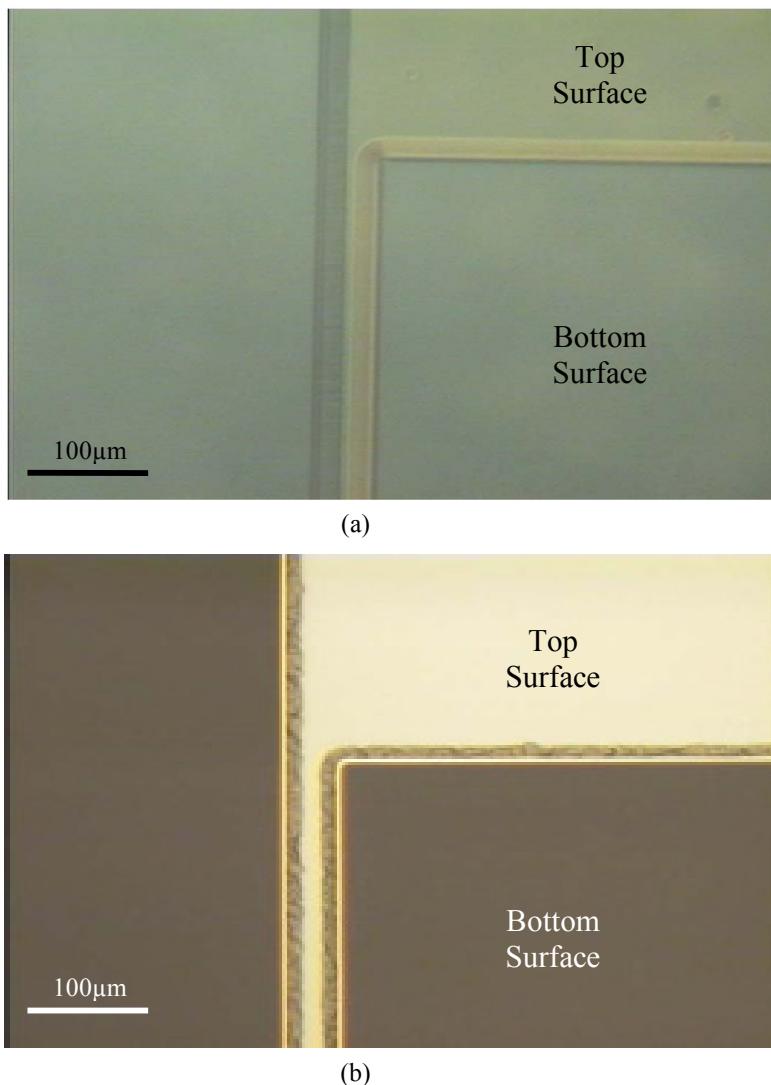

| Figure 5.11: (a) A poorly anodically bonded Pyrex SOI wafer stack using -1200V at 400°C without metal interconnect at the rim of the SOI wafer. (b) A successfully anodically bonded Pyrex SOI wafer stack using -1000V at 385°C with metal interconnect at the rim of the SOI wafer..... | 100 |

| Figure 5.12: Microscopic picture of structures of an anodically bonded Pyrex-Silicon wafer stack using -800V at (a) 375°C (b) 355°C.....                                                                                                                                                  | 101 |

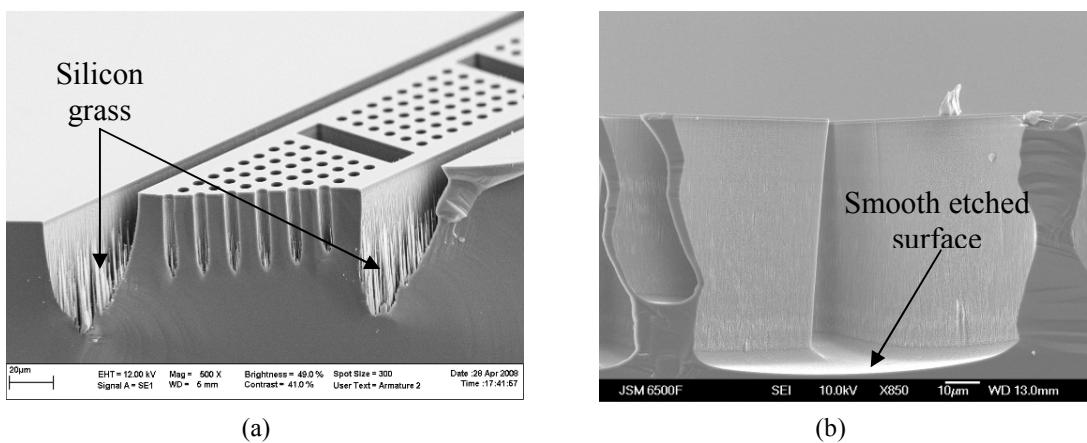

| Figure 5.13: SEM picture of the DRIE trial for grassing issue using platen power at (a) 50W (b) 60W.....                                                                                                                                                                                  | 103 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.14: Micrograph of silicon Pyrex stack after DRIE of (a) a view of the fail etch through the Pyrex wafer with the armature missing (b) a view of the fail etch from the silicon side, showing that the photoresist layer and part of the silicon layer has been etched. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 104 |

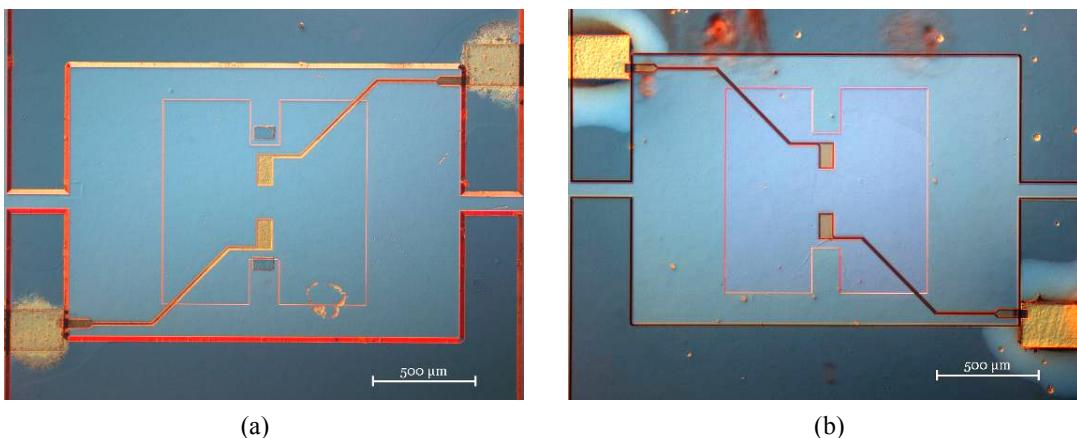

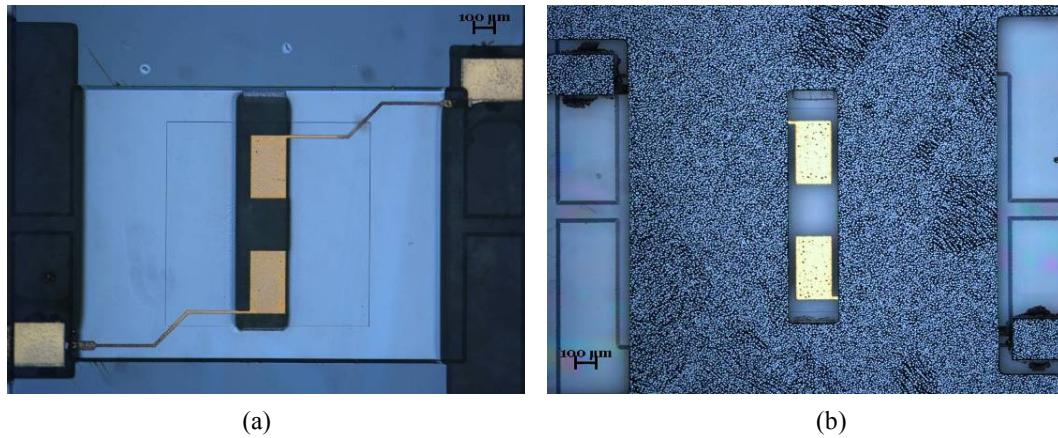

| Figure 5.15: Micrograph of success DRIE etch showing that the silicon layer under the photoresist mask was not etched on the Silicon/Pyrex stack for the (a) RF MEMS switch design (b) a RF MEMS switch with a different armature design. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

| Figure 5.16: Microscopic view of a bonded wafer stack from bottom Pyrex wafer showing the armature is stuck between the bottom Pyrex wafer and silicon wafer. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 106 |

| Figure 5.17: Conceptual drawing of the rapid prototype RF MEMS switch. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107 |

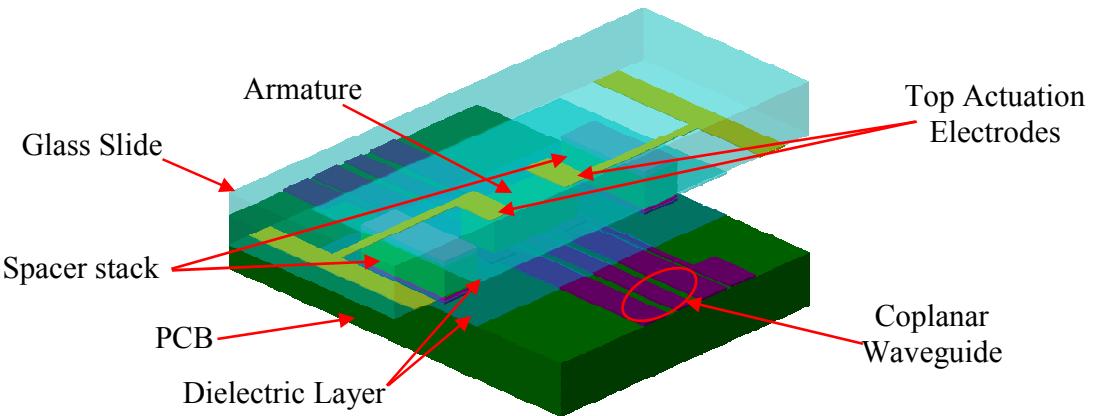

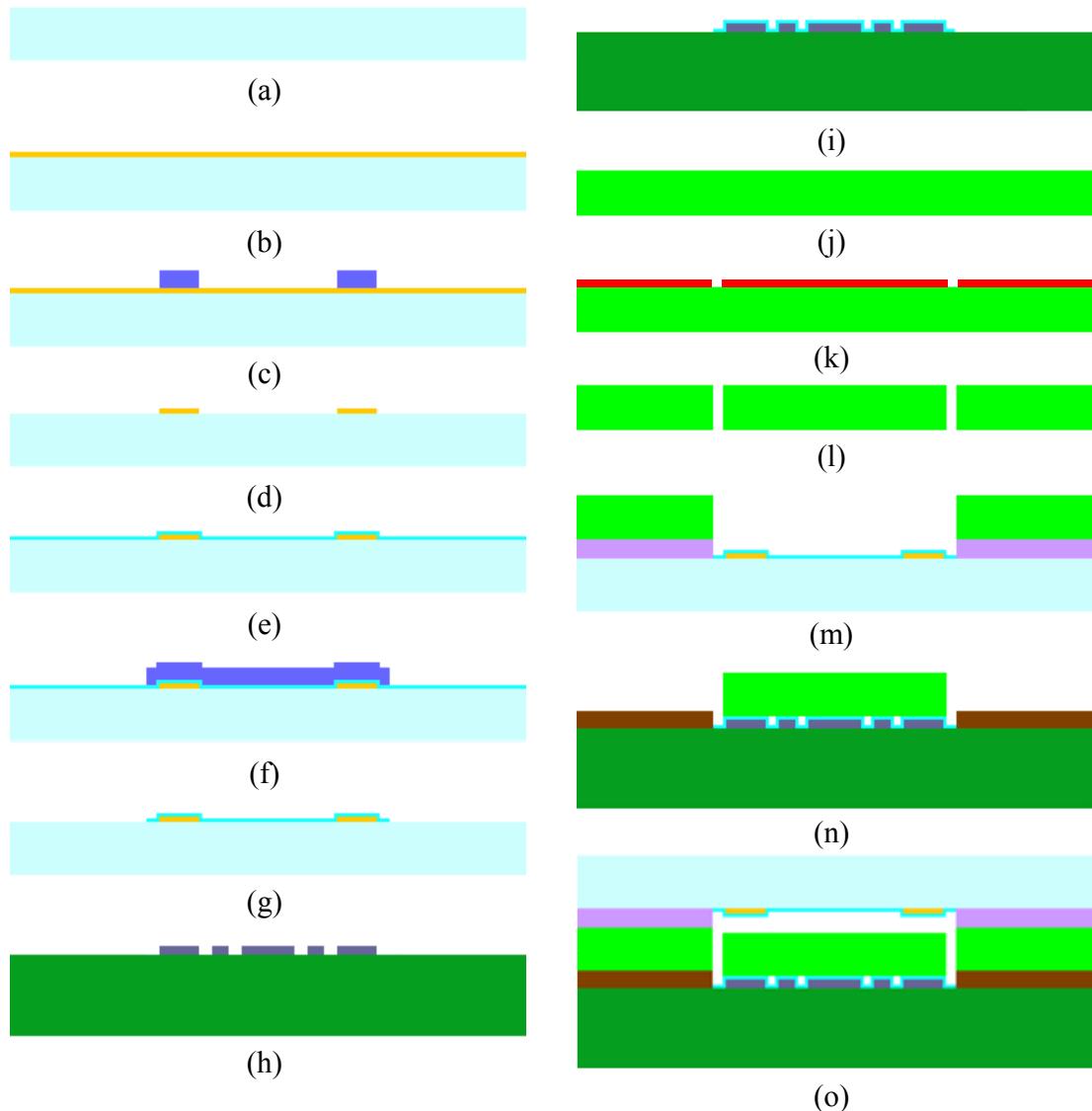

| Figure 5.18: Fabrication flow for an RF MEMS switch based on low cost rapid prototyping process described in section 5.2 (a) Microscope glass slide (b) Deposit chromium-gold layer (c) Laminate, expose and develop a layer of Ordyl AM130 dry film resist (d) Etch chromium-gold layer/Strip dry film resist (e) Deposit $Ta_2O_5$ as dielectric layer (f) Laminate, expose and develop a layer of Ordyl AM130 dry film resist (g) Etch dielectric layer/Strip dry film resist (h) Roger's RO4003 with pre-fabricated CPW (i) Deposit $Ta_2O_5$ on PCB (j) Low resistivity silicon wafer (k) Spin, expose and develop 10 $\mu m$ of AZ9260 photoresist (l) DRIE silicon wafer to form armature and spacer (m) Insert and bond spacer stack (n) Insert Si armature into the bonded stack (o) Apply adhesive to PCB then bond the glass slide and PCB together .. | 108 |

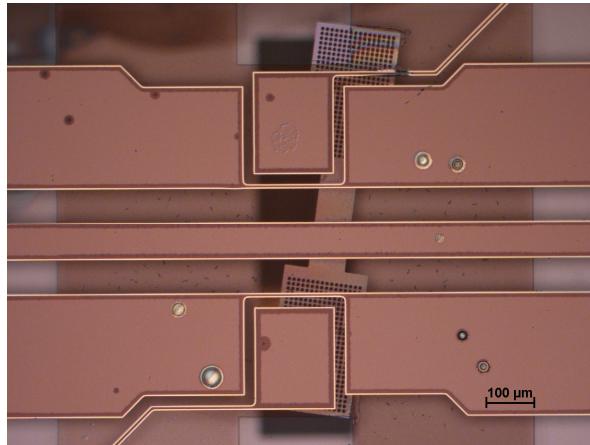

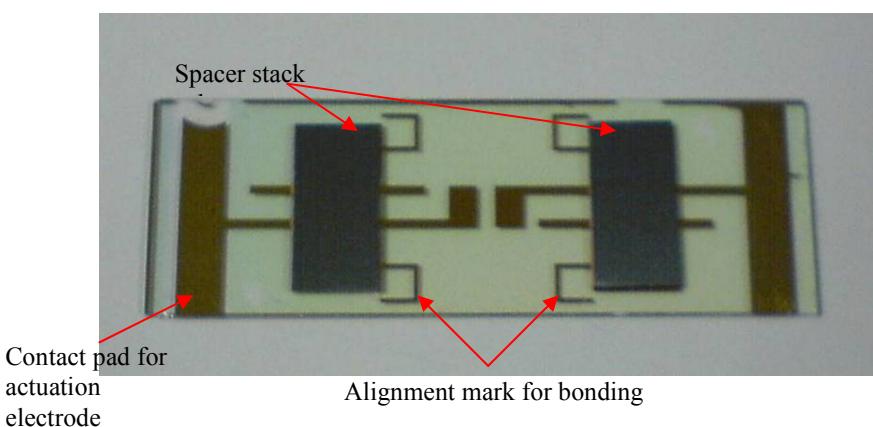

| Figure 5.19: A fully processed glass slide electrode with the bonded spacer stack.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109 |

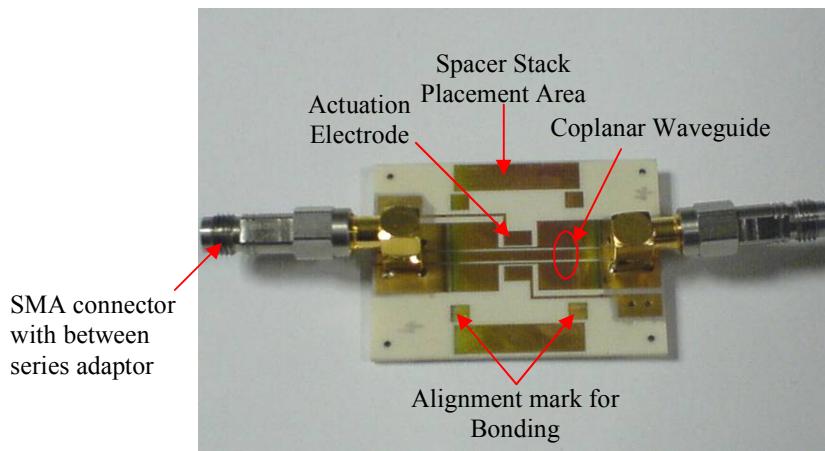

| Figure 5.20: An image of the processed Roger's RO4003 <sup>®</sup> PCB with the SMA connector and between series adaptors mounted to the substrate. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110 |

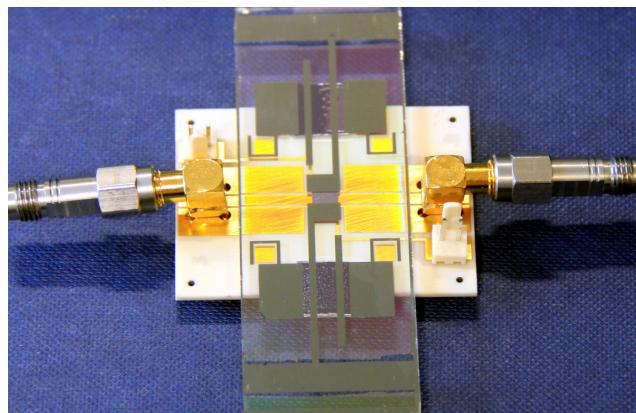

| Figure 5.21: An image of the fully fabricated rapid prototype RF MEMS switch. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 111 |

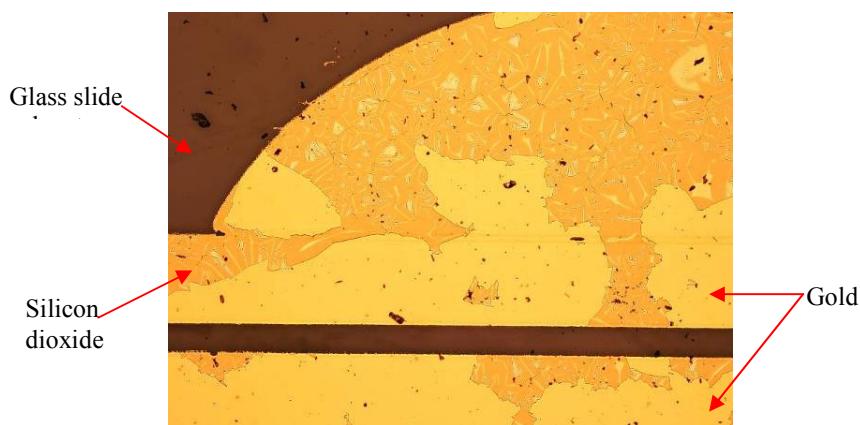

| Figure 5.22: A microscope image of a ion beam deposited silicon dioxide layer poorly adheres to the chrome gold structure on a microscope glass slide. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112 |

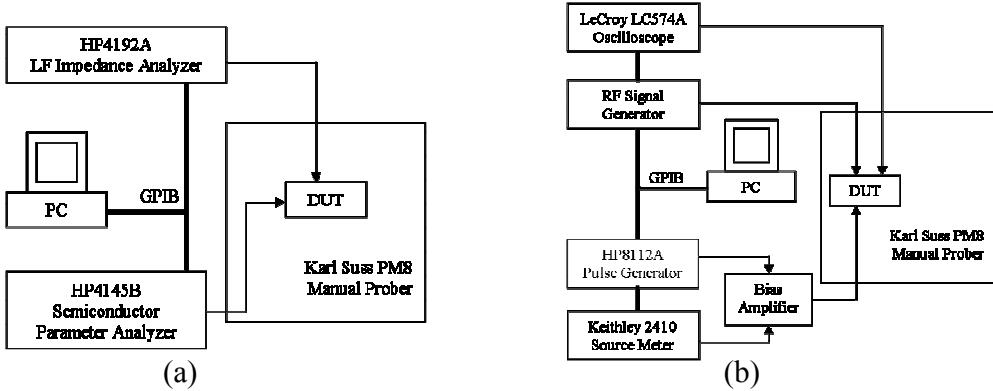

| Figure 6.1: RF MEMS switch testing setup for (a) quasi-static CV measurement (b) life time measurement [158]. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116 |

|                                                                                                                                                                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

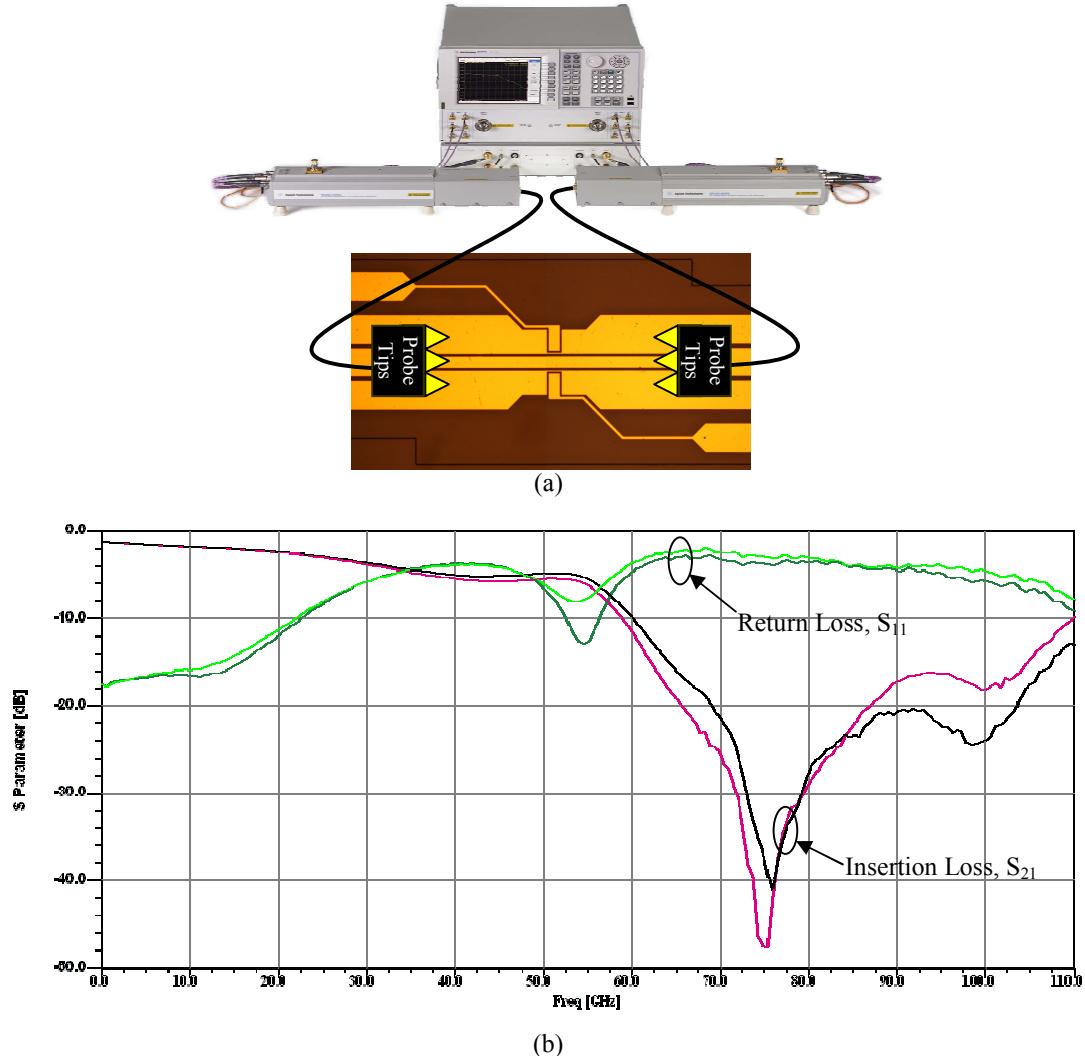

| Figure 6.2: (a) Setup for S-Parameter measurement using Agilent N5250C PNA Millimeter-Wave Network Analyzer with Cascade air coplanar probes on the fabricated CPW. (b) Measured S-Parameter of two $50\Omega$ CPW from 0.1-110GHz .....                                                | 117 |

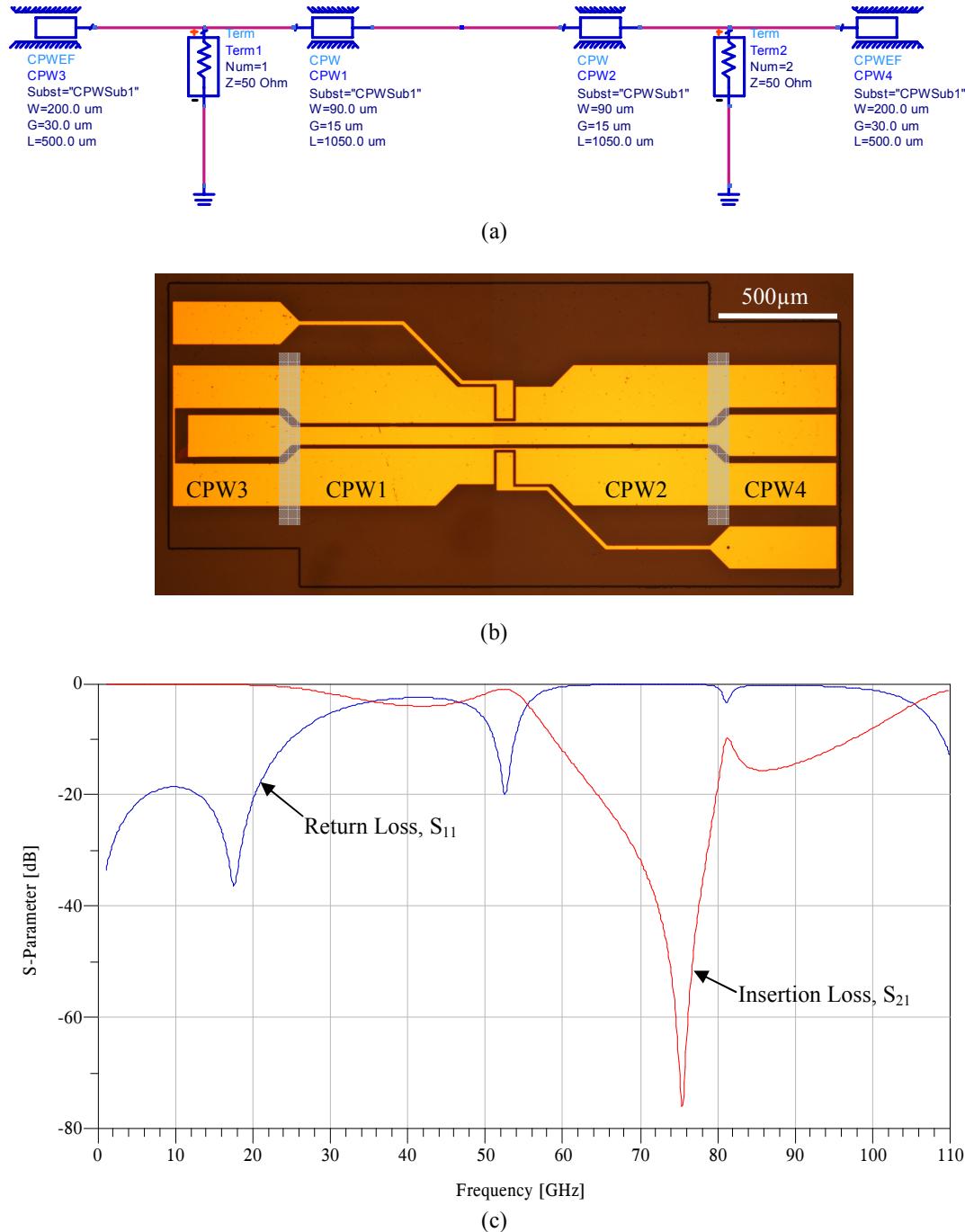

| Figure 6.3: (a) Micrograph of the transmission line under test (b) Lumped model of the transmission line using Agilent ADS (c) Simulation results of the fabricated CPW using Agilent ADS. ....                                                                                         | 118 |

| Figure 6.4: Simulated current density plot of the CPW at (a) 1GHz (b) 79GHZ using Agilent Momentum. ....                                                                                                                                                                                | 119 |

| Figure 6.5 : (a) Simulated S-Parameters of the CPW without probe pads using Agilent ADS. (b) Fabricated transmission line structure with the probe pads being physically removed for the measurement (c) Measured S-Parameters of the transmission line as shown in Figure 6.5(b). .... | 120 |

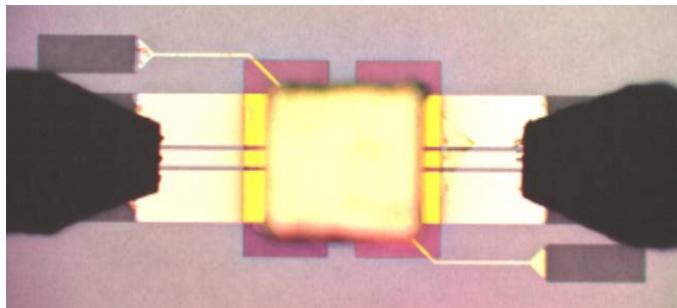

| Figure 6.6: Micrograph of the S-Parameter measurement using Agilent E8361A PNA Millimeter-Wave Network Analyzer with Cascade infinity probes on the fabricated CPW with a $800\mu\text{m}$ by $800\mu\text{m}$ silicon slab acting as armature. ....                                    | 122 |

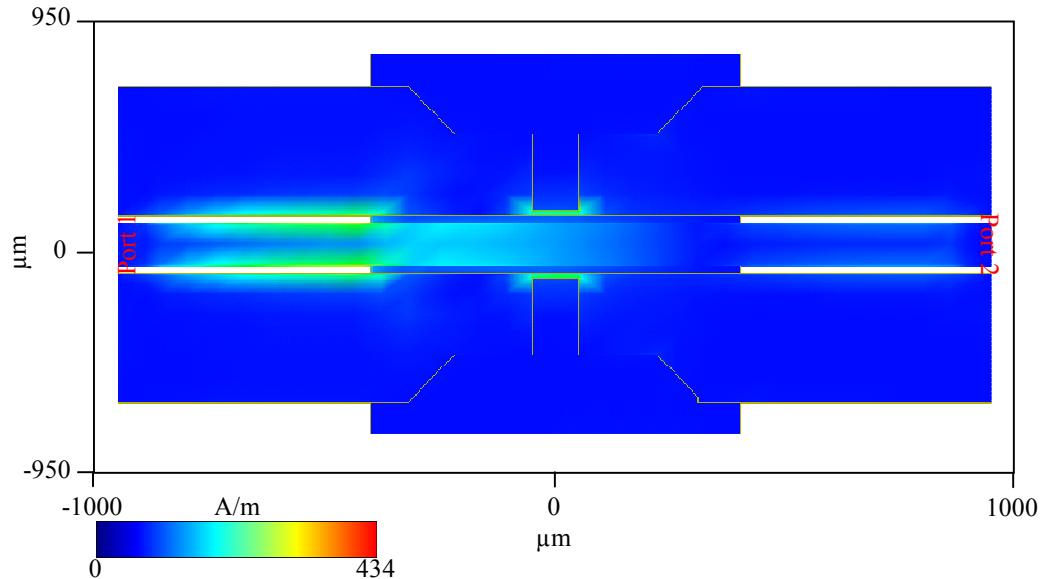

| Figure 6.7 : (a) Measured S-Parameters of the CPW from 0.1-67GHz (b) Simulated current plot of the CPW at 70GHZ using Agilent Momentum. ....                                                                                                                                            | 123 |

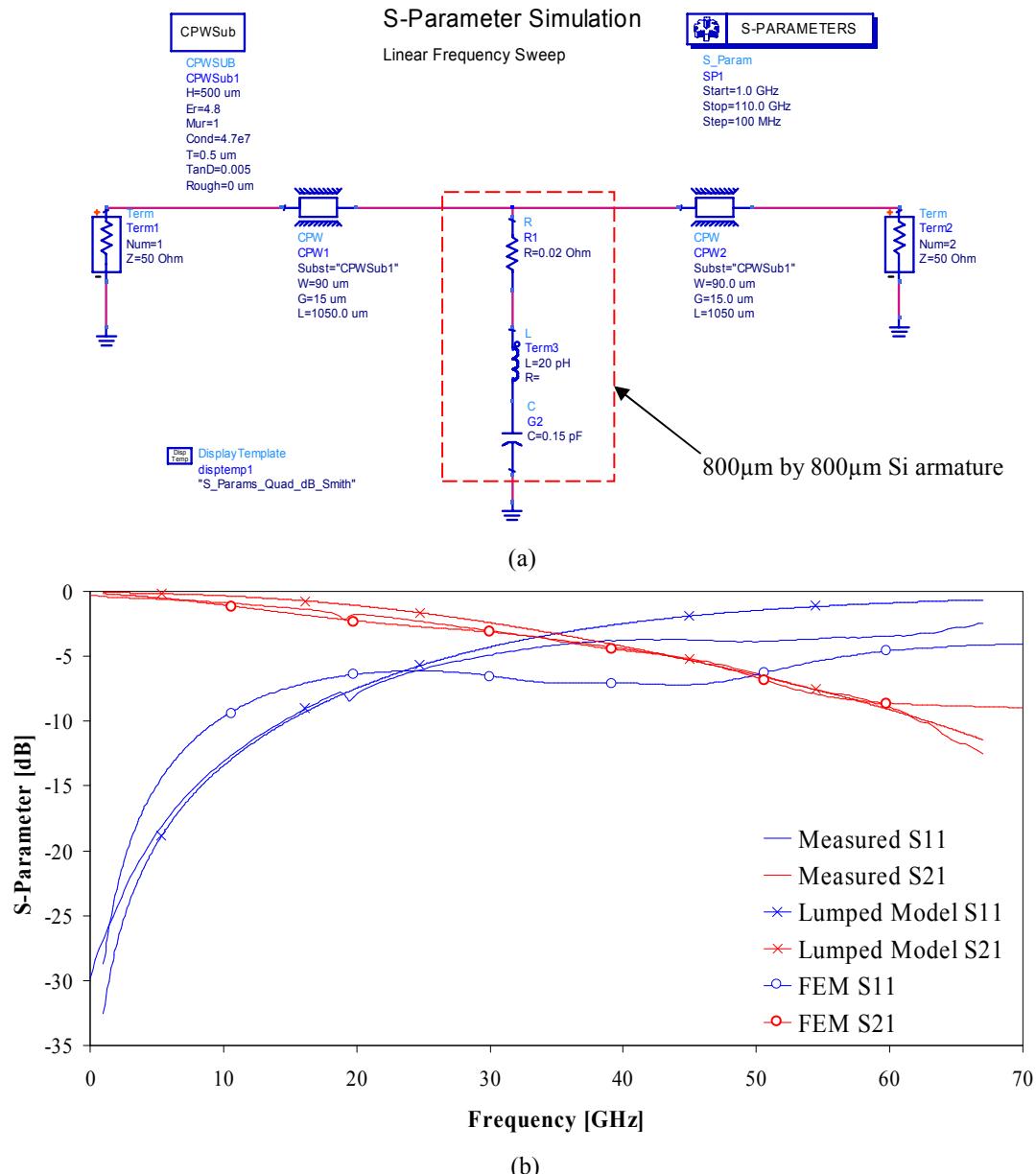

| Figure 6.8 : (a) Agilent ADS lumped model of the RF MEMS switch with a $800\mu\text{m}$ by $800\mu\text{m}$ silicon slab acting as armature. (b) Measured, ADS lumped model simulated and FEM simulated S-Parameters of the RF MEMS switch from 0.1-67GHz. ....                         | 124 |

| Figure 6.9 : Simulated current density plot of the CPW with armature shunting the RF signal at 70GHz using Agilent Momentum. ....                                                                                                                                                       | 125 |

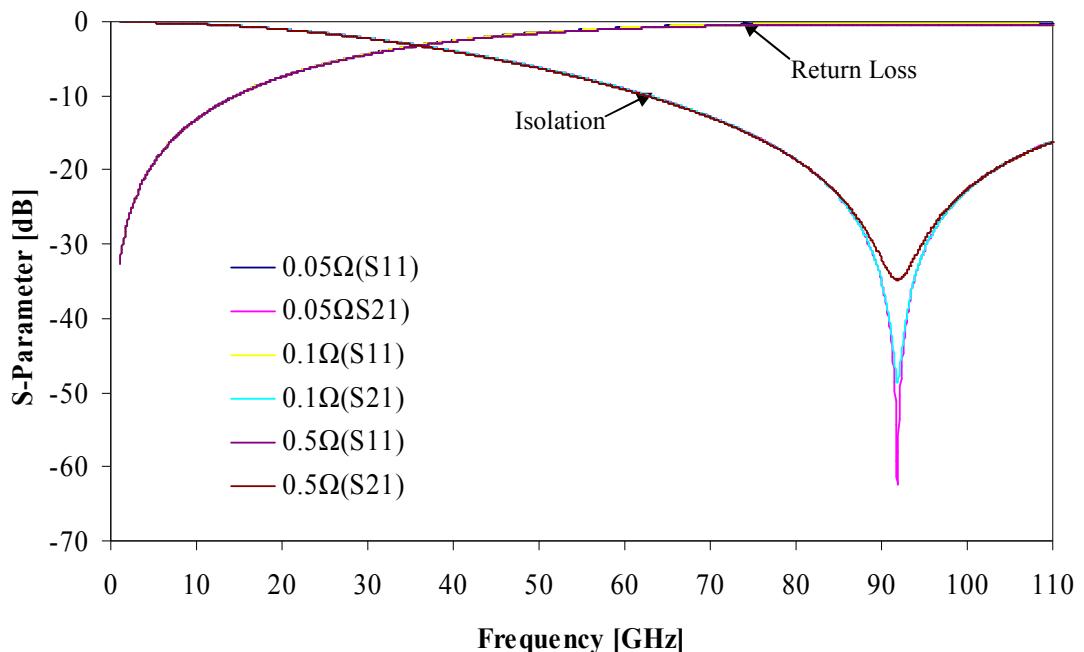

| Figure 6.10 : Simulated Insertion loss and Isolation of proposed RF MEMS switch from 1 – 110GHz for switch resistance value of $0.02\Omega$ , $0.1\Omega$ and $0.5\Omega$ . ....                                                                                                        | 125 |

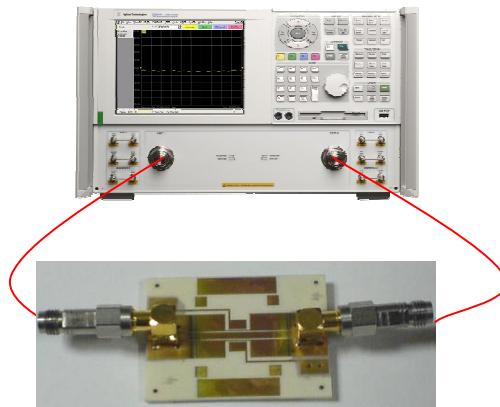

| Figure 6.11: Measurement setup for initial testing of the transmission characteristics of the rapid prototype device using an Agilent E8361A network analyzer. ..                                                                                                                       | 127 |

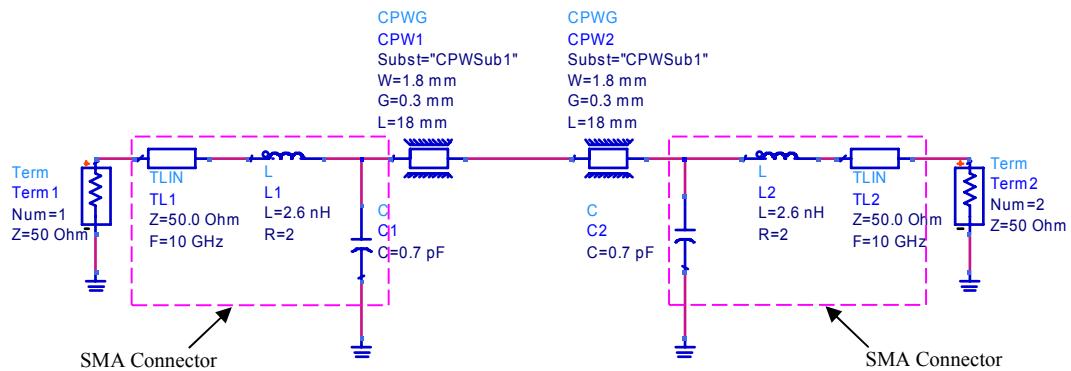

| Figure 6.12: (a) Agilent ADS lumped model of the rapid prototype switch's CPW embeded with SMA connectors. ....                                                                                                                                                                         | 127 |

|                                                                                                                                                                                                                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.13: Measured and simulated (a) $S_{11}$ and (b) $S_{21}$ of the rapid prototype switch's CPW from 0.1-10GHz .....                                                                                                                                                                                                                              | 128 |

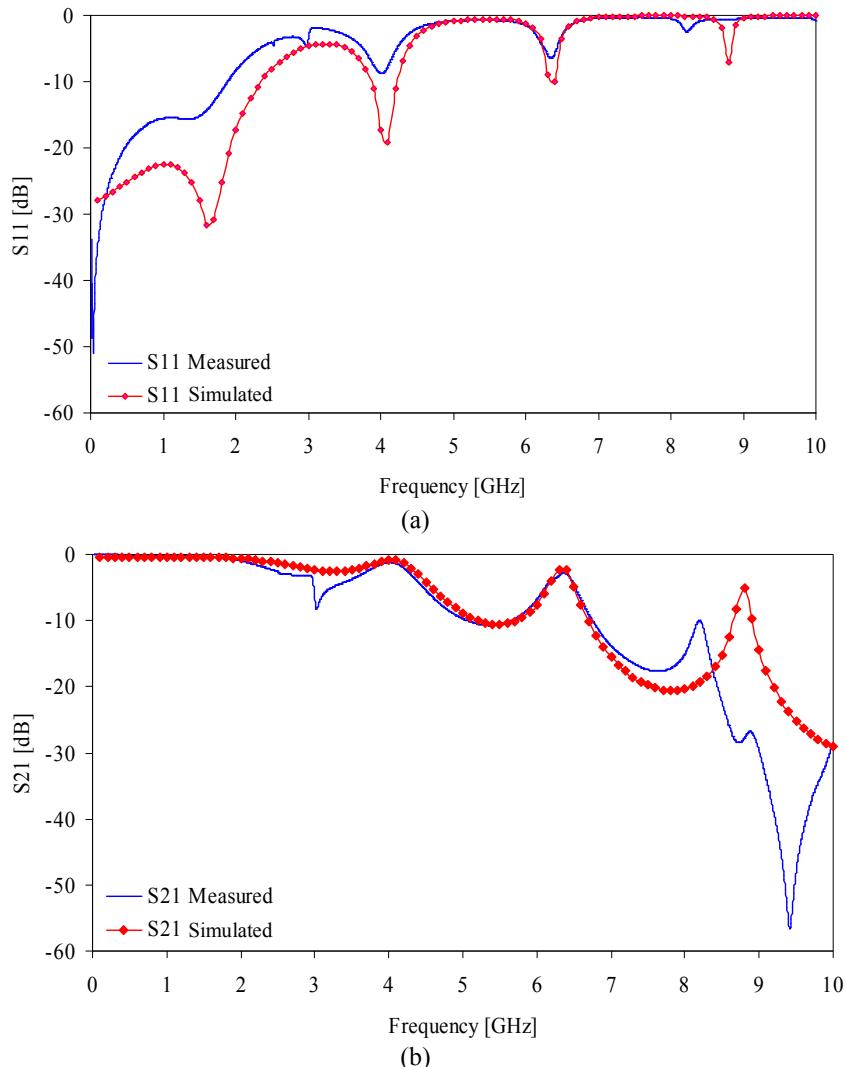

| Figure 6.14: Simulated (a) $S_{11}$ and (b) $S_{21}$ of the CPW from 0.1-10GHz using ADS....                                                                                                                                                                                                                                                            | 130 |

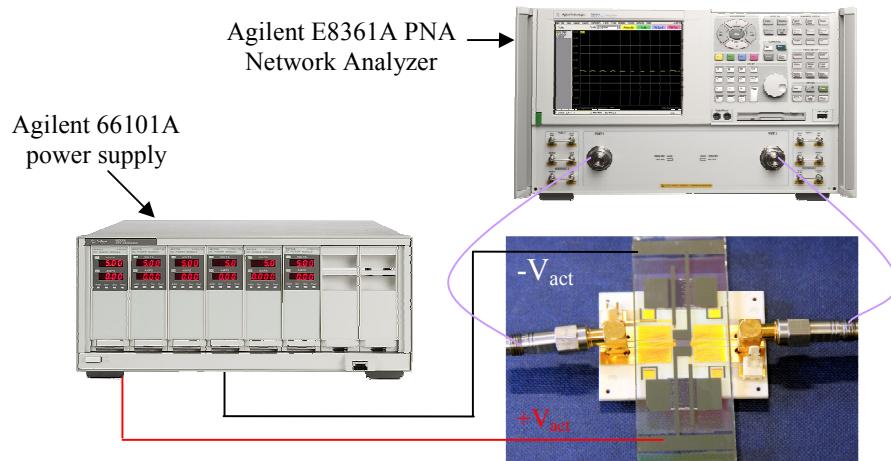

| Figure 6.15: Measurement setup for mechanical response of the rapid prototype device using an Agilent E8361A network analyzer and an Agilent 66101A DC power supply.....                                                                                                                                                                                | 131 |

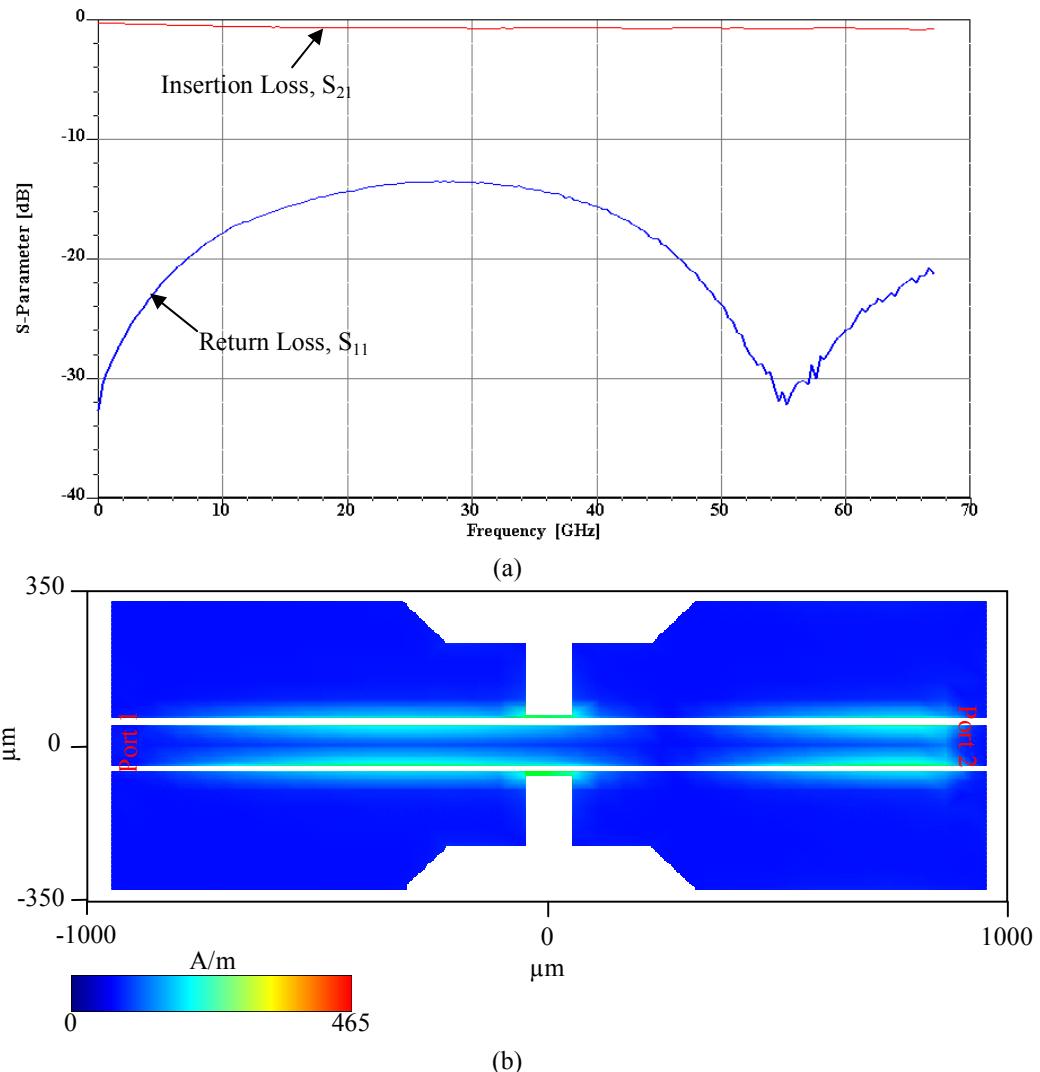

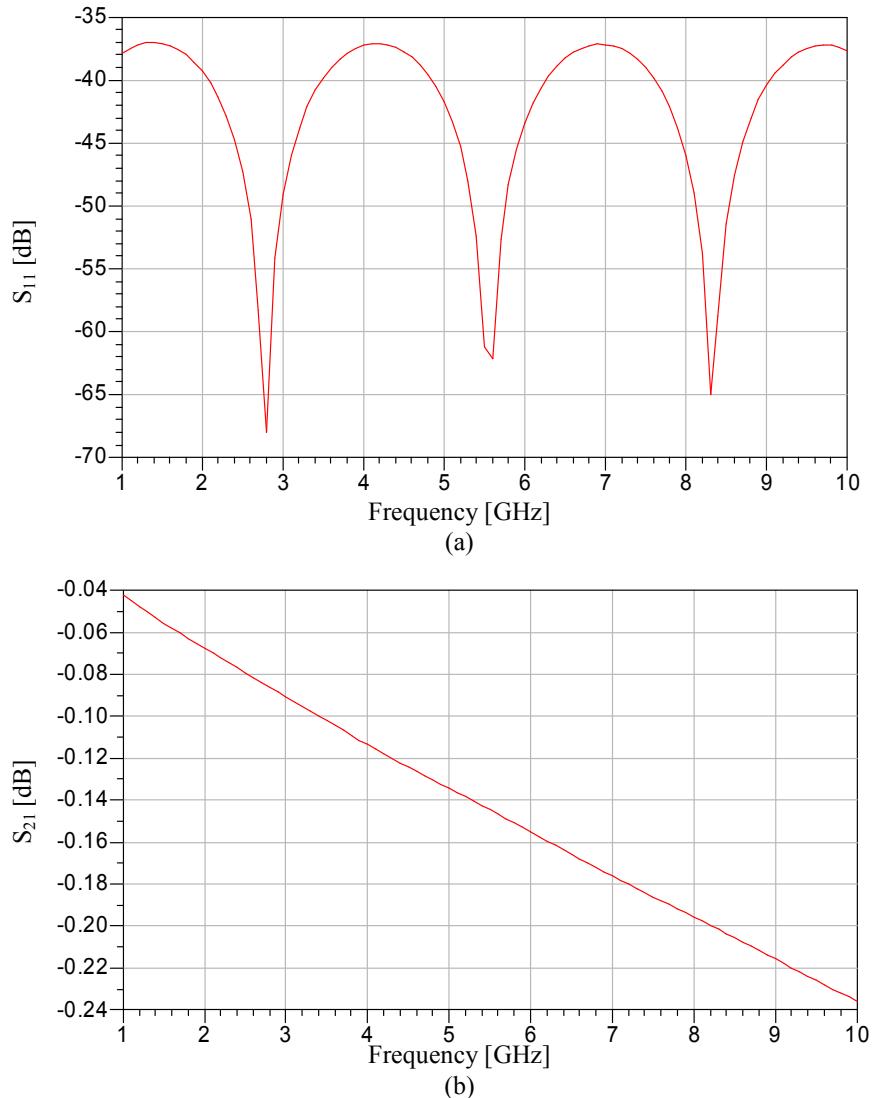

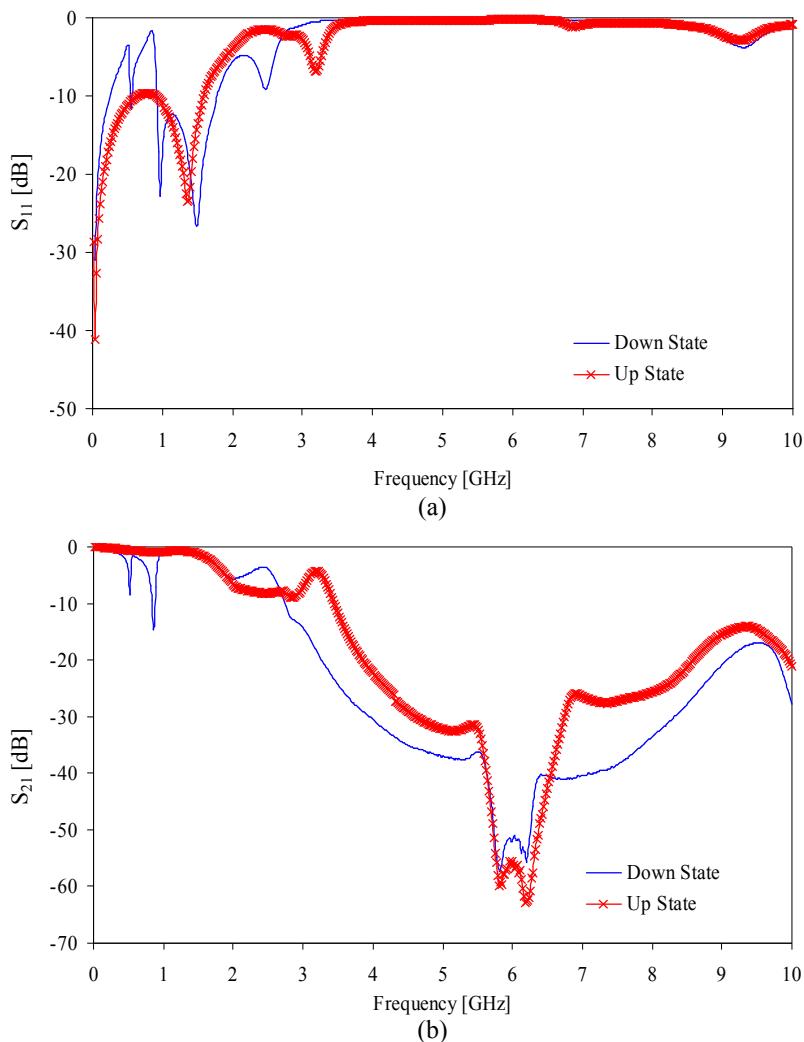

| Figure 6.16: Measured (a) $S_{11}$ (b) $S_{21}$ parameter of the rapid prototype switch when the armature is at the DOWN and UP state from 0.1-10GHz. ....                                                                                                                                                                                              | 132 |

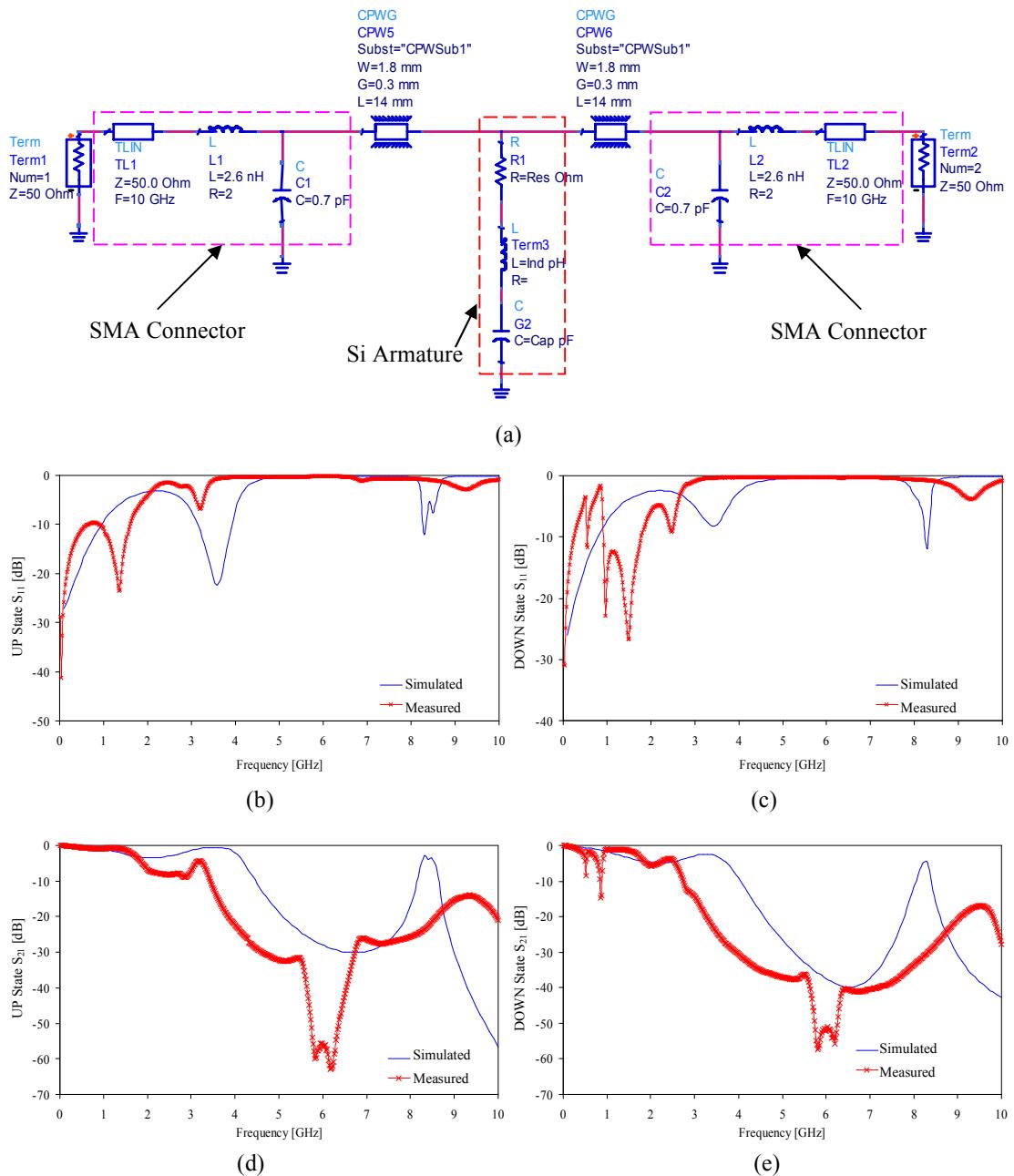

| Figure 6.17: (a) Agilent ADS model for the rapid prototype switch embeded with the SMA connectors. (b) Measured and simulated UP state $S_{11}$ (c) Measured and simulated DOWN state $S_{11}$ (d) Measured and simulated UP state $S_{21}$ (e) Measured and simulated DOWN state $S_{21}$ parameter of the rapid prototype switch from 0.1-10GHz. .... | 133 |

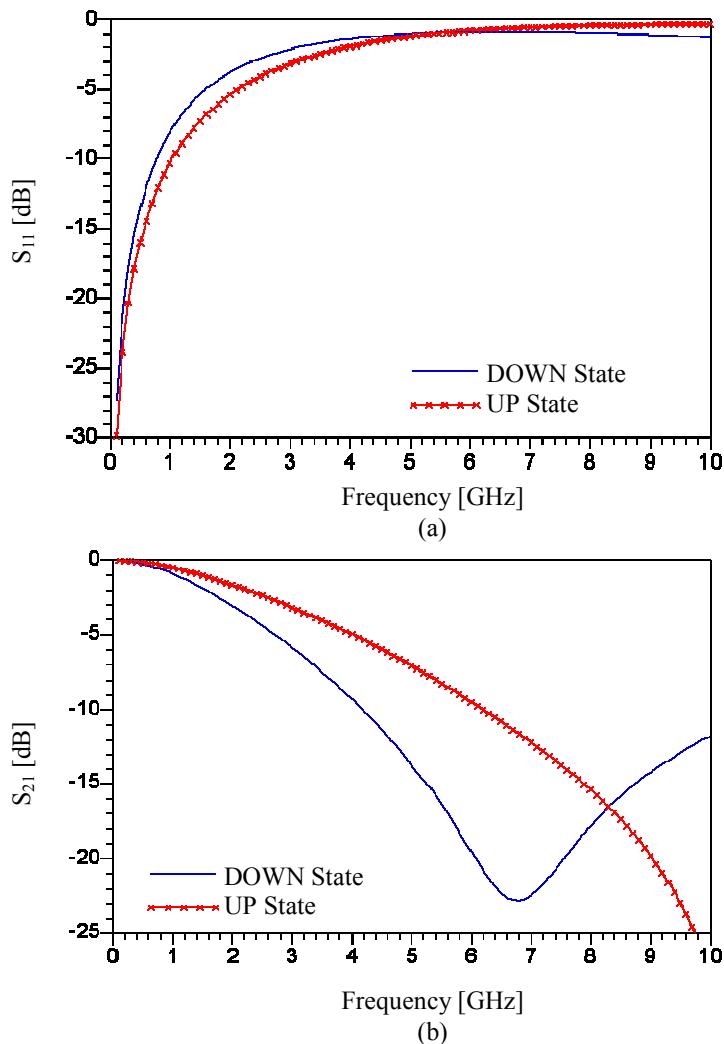

| Figure 6.18: Simulated (a) $S_{11}$ and (b) $S_{21}$ of the rapid prototype switch de-embeded from the SMA connectors using Agilent ADS model from 0.1-10GHz. ....                                                                                                                                                                                      | 135 |

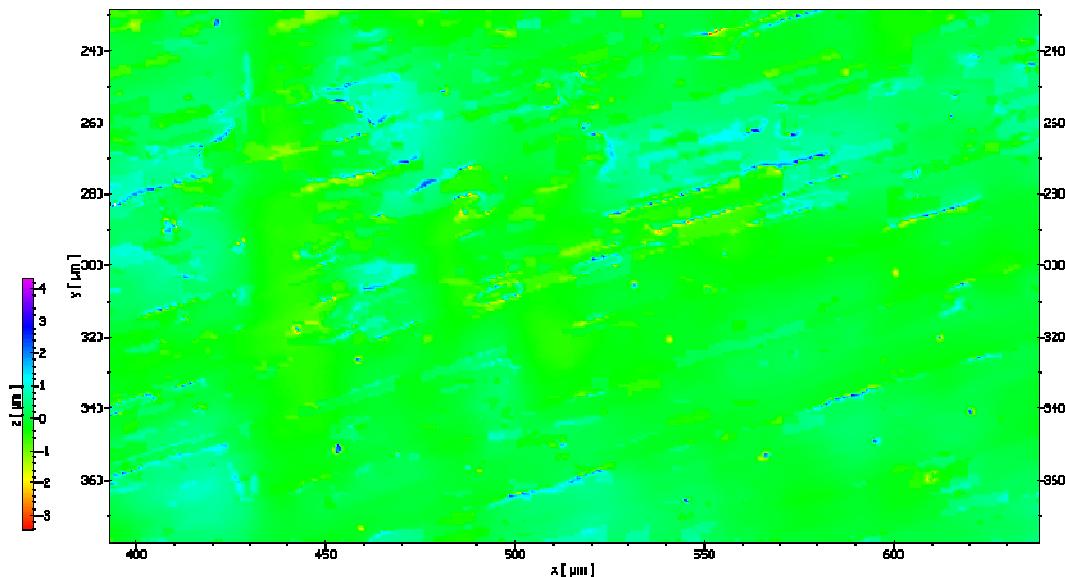

| Figure 6.19: Measured surface roughness over a section of the transmission line where the armature is positioned using a MSA 400 Micro System Analyser.....                                                                                                                                                                                             | 136 |

| Figure 6.20: Calculated minimum actuation voltage considering the effects of surface roughness and contact area for a Tantalum Pentoxide–air–silicon material system for a gap height of 40 $\mu$ m. ....                                                                                                                                               | 137 |

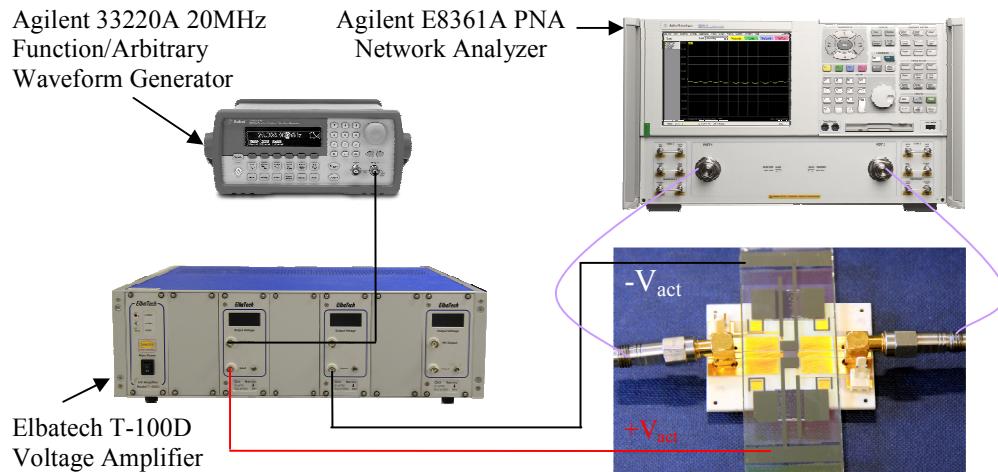

| Figure 6.21: Measurement setup for rapid prototype device using an Agilent E8361A network analyzer, Agilent 33220A 20MHz function/arbitrary waveform generator and Elbatech T-100D voltage amplifier. ....                                                                                                                                              | 138 |

| Figure 6.22: $S_{21}$ signal of the rapid prototype switch using an actuation voltage of $\pm 93V$ at a RF frequency of 7.5GHz. ....                                                                                                                                                                                                                    | 139 |

| Figure 6.23 : Simulated and measured rise time of the rapid prototype device as a function of the actuation voltage. ....                                                                                                                                                                                                                               | 140 |

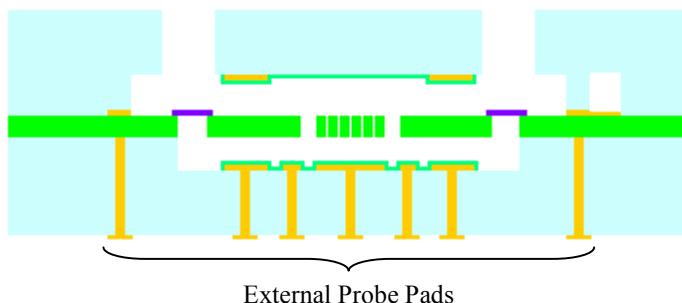

| Figure 7.1: Cross section illustration of the proposed switch with probe pads located on the exterior of the substrate.....                                                                                                                                                                                                                             | 146 |

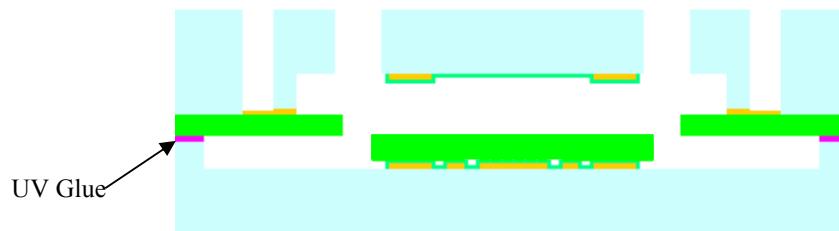

| Figure 7.2: Cross section illustration of the proposed switch with well defined UV glue interface .....                                                                                                                                                                                                                                                 | 148 |

# List of Tables

|           |                                                                                                                                                                                                                                                                                                    |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1:  | A compilation of commercially available RF MEMS switches.....                                                                                                                                                                                                                                      | 7   |

| Table 2:  | shows the difference variation in each category of a MEMS switch.....                                                                                                                                                                                                                              | 10  |

| Table 3:  | Comparison of the performance of FET, PIN Diode and RF MEMS switches [39].....                                                                                                                                                                                                                     | 12  |

| Table 4:  | A compilation of low actuation voltage RF MEMS switches developed by different universities' research group.....                                                                                                                                                                                   | 30  |

| Table 5:  | Proposed dimensions of the MEMS switch optimised based on the actuation voltage, switching speed and fabrication limitation, designed with a $75\Omega$ coplanar waveguide.....                                                                                                                    | 44  |

| Table 6:  | The simulated rise time ( $T_{rise}$ ) and fall time ( $T_{fall}$ ) of the proposed switch with the effect of constant damping, variable damping without perforated holes and variable damping based on the dimension tabulated in Table 5.....                                                    | 53  |

| Table 7:  | Different types of coplanar waveguide design.....                                                                                                                                                                                                                                                  | 59  |

| Table 8:  | Simulated and calculated UP state capacitance for different armature width and gap height with dimensions of armature length, $l_m=680\text{ }\mu\text{m}$ , CPW's signal line width=90 $\mu\text{m}$ , CPW's ground plane width=10 $\mu\text{m}$ $\varepsilon_r=7.6$ and $t_d=200\text{nm}$ ..... | 67  |

| Table 9:  | Etch rate information of a 6 inch Pyrex wafer using BHF7:1 for 110 minutes.....                                                                                                                                                                                                                    | 97  |

| Table 10: | Process parameters for the two anodic bonding trial involving fully processed SOI and Pyrex wafers.....                                                                                                                                                                                            | 100 |

| Table 11: | Dimensions of the RF MEMS prototype switch.....                                                                                                                                                                                                                                                    | 107 |

# List of Symbols

|                                      |                                                                      |

|--------------------------------------|----------------------------------------------------------------------|

| $A$                                  | cross sectional area of the armature                                 |

| $A_{ap}$                             | total area of the actuation pad                                      |

| $A_{arm}$                            | area of the armature                                                 |

| $A_c$                                | contact areas between armature and contacts the signal line          |

| $A_{contact}$                        | total contact area between the armature and dielectric layer         |

| $A_r$                                | contact areas between armature and contacts the ground line          |

| $\alpha$                             | attenuation of the transmission line                                 |

| $\alpha_c$                           | attenuation constant due to conductor loss                           |

| $\alpha_d$                           | attenuation constant due to substrate loss                           |

| $b$                                  | damping coefficient                                                  |

| $c$                                  | speed of light                                                       |

| $C_{air}$                            | capacitance in absence of the substrate per unit length              |

| $C_{cpw}$                            | capacitance of the transmission line per unit length                 |

| $C_d$                                | down state capacitance                                               |

| $C_{down\_rou}$                      | down state capacitance considering the effect of surface roughness   |

| $C_{ratio}$                          | capacitance ratio                                                    |

| $C_s$                                | switching capacitance of the armature                                |

| $C_u$                                | up state capacitance                                                 |

| $\eta$                               | factor for the average damping pressure in a cell caused by air flow |

| $D$                                  | distance between the contact surfaces of the two materials           |

| $\epsilon_1, \epsilon_2, \epsilon_r$ | dielectric constant of the materials                                 |

| $\epsilon_0$                         | permittivity of free space                                           |

| $f$                                  | frequency of the RF signal                                           |

| $F$                                  | electrostatic forces between the bottom electrode and the armature   |

| $F^+$                                | electrostatic forces between the top electrode and the armature      |

| $F_{act}$                            | electrostatic actuation force                                        |

| $F_{contact}$                        | surface adhesion force                                               |

| $F_{damp}$                           | damping force                                                        |

| $F_{electrostatic}$                  | electrostatic actuation force                                        |

| $F_{ext}$                            | external applied inertial force                                      |

| $F_{mg}$                             | gravitation force acting on the armature.                            |

| $F_{mg}$                             | gravitational force acting on the armature                           |

| $f_o$                                | LC series resonating frequency                                       |

|              |                                                             |

|--------------|-------------------------------------------------------------|

| $g$          | earth gravity                                               |

| $G$          | width of the signal line                                    |

| $G_f$        | earth's gravity                                             |

| $g_o$        | initial capacitive gap                                      |

| $h_{sub}$    | substrate thickness                                         |

| $H_{vdW123}$ | hamaker constant                                            |

| $I$          | ionization potential                                        |

| $k$          | spring constant                                             |

| $k$          | spring constant of the MEMS armature.                       |

| $K_n$        | Knudsen number,                                             |

| $k_z$        | mechanical spring constant                                  |

| $l$          | characteristic length                                       |

| $L$          | length of the conducting path                               |

| $l_a$        | actuation electrode length                                  |

| $l_m$        | length of armature                                          |

| $L_b$        | inductance of the armature                                  |

| $\lambda_o$  | free space wavelength                                       |

| $\lambda_o$  | mean free path of the air molecules at atmospheric pressure |

| $m$          | mass of the armature                                        |

| $v_{ph}$     | phase velocity                                              |

| $\mu$        | absolute magnetic permeability                              |

| $\mu$        | mean free path of the air molecules at atmospheric pressure |

| $\mu_{eff}$  | pressure dependent effective viscosity                      |

| $n_1, n_2$   | refractive index of materials                               |

| $p$          | ambient pressure                                            |

| $P_a$        | atmospheric pressure                                        |

| $Q_o$        | nominal small displacement quality factor                   |

| $R_b$        | resistance of the armature                                  |

| $r_c$        | pitch between adjacent holes                                |

| $r_o$        | radius of the perforated hole                               |

| $R_c$        | resistance of the centre signal line                        |

| $R_g$        | resistance of the ground plane                              |

| $\rho$       | density of material                                         |

| $\rho$       | resistivity of the material                                 |

| $S_{11}$     | magnitude of the return loss                                |

| $S_{21}$     | magnitude of the isolation and insertion loss               |

| $\sigma$     | electrical conductivity of the material                     |

|                |                                                                 |

|----------------|-----------------------------------------------------------------|

| $\sigma$       | squeeze number                                                  |

| $T_{actuate}$  | switch-on time                                                  |

| $\tan\delta$   | dielectric tangent loss of the substrate                        |

| $t_d$          | thickness of the dielectric material                            |

| $t_m$          | armature thickness                                              |

| $T_{release}$  | switch-off time                                                 |

| $V_{act}$      | actuation voltage                                               |

| $V_{act(min)}$ | minimum actuation voltage                                       |

| $V_b$          | bottom electrode voltage                                        |

| $V_{Pin}$      | pull-in voltage                                                 |

| $V_t$          | top electrode voltage                                           |

| $W$            | slot width                                                      |

| $w_m$          | width of armature                                               |

| $\omega$       | angular frequency of the RF signal                              |

| $\omega_o$     | resonating frequency of the armature                            |

| $x$            | displacement of the armature                                    |

| $Z_b$          | impedance of the armature                                       |

| $Z_o$          | characteristic impedance of the transmission line               |

| $z_o$          | gap between the armature and the electrodes at nominal position |

# List of Abbreviations

|             |                                                                  |

|-------------|------------------------------------------------------------------|

| AC          | Alternating Current                                              |

| ADS         | Advanced Design System                                           |

| ALD         | Atomic Layer Deposition                                          |

| BAW         | Bulk Acoustic Wave                                               |

| CB-CPW      | Conductor Back Coplanar Waveguide                                |

| CBFW-CPW    | Conductor Back Coplanar Waveguide With Finite Width Ground Plane |

| CD          | Constant Damping                                                 |

| CMOS        | Complementary Metal-Oxide-Semiconductor                          |

| CPD         | Critical Point Drying                                            |

| CPW         | Coplanar Waveguide                                               |

| DC          | Direct Current                                                   |

| DFR         | Dry Film Resist                                                  |

| DRIE        | Deep Reactive Ion Etching                                        |

| DUT         | Device Under Test                                                |

| DUV         | Deep Ultraviolet                                                 |

| FNA         | Fuming Nitric Acid                                               |

| FW-CPW      | Coplanar waveguide with finite width ground plane                |

| GSG         | Ground-Signal-Ground                                             |

| IC          | Integrated Circuits                                              |

| ICP-RIE     | Inductively Coupled Plasma Reactive-Ion Etching                  |

| MEMS        | Micro Electro Mechanical System                                  |

| MIM         | Metal-Insulator-Metal                                            |

| PCB         | Printed Circuit Board                                            |

| PECVD       | Plasma-Enhanced Chemical Vapour Deposition                       |

| Q factor    | Quality Factor                                                   |

| RF          | Radio Frequency                                                  |

| RLC         | Resistor-Inductor-Capacitor                                      |

| SMA         | Sub Miniature version A                                          |

| SOI         | Silicon On Insulator                                             |

| S-Parameter | Scattering Parameter                                             |

| STS         | Symmetric Toggle Switch                                          |

| STS         | Surface Technology Systems                                       |

|       |                                                       |

|-------|-------------------------------------------------------|

| TEM   | Transverse Electromagnetic Mode                       |

| UV    | Ultraviolet                                           |

| VD-NP | Variable Damping without Considering Perforated Holes |

| VD-P  | Variable Damping with Perforated Holes                |

# **Declaration of Authorship**

I, KIAN SHEN KIANG declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

Development of a Spring-Less RF MEMS Switch

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Either none of this work has been published before submission, or parts of this work have been published as: [please list references below]:

## **Journal Publication**

1. Kiang, K.S., Houlihan, R., Gindila, M., Damrongsak, B. and Kraft, M. Design and simulation of a spring-less micro switch. *Electronics World*, Vol. 112, Iss.1844, pp. 30-34, 2006.

## **Conference Publication**

1. Kiang, K.S., Chong, H. M. C. and Kraft, M. A Novel Low Cost Spring-Less RF MEMS Switch Prototype. *Proc. Eurosensors XXIV Conference*, Linz, Austria, Sept. 2010.

2. K. S. Kiang, H. M. H. Chong, C. J. Hwang, L. B. Lok, K. Elgaid And M. Kraft, Development of a low actuation voltage RF MEMS switch. *Proc. Eurosensors XXII Conference*, pp. 1462-1465, Dresden, Germany, Sept. 2008.

3. Kiang, K.S. and Kraft, M. Development of a low voltage MEMS switch for RF applications. Proc. MME 2006 Conference, pp. 105-108, UK, Sept. 2006

Signed:

Date: 21<sup>ST</sup> JANUARY 2011

# Acknowledgement

The completion of this work has taken a long and unexpected journey of life and experience. This would never happen without help and support provided by people from different walks of life.

The first person to thanks is my supervisor, Prof. Michael Kraft. He has provided invaluable guidance and experience throughout my study. Michael's relentless supportive even to some of my wildest ideas, always gave me positive encouragement to my research work. It is my greatest privilege to have him as my supervisor.

Another important person to thanks is Dr Harold Chong. Without his constant advice and help, this work wouldn't have achieved to the standard presented.

I would also like to thanks Dr. Khaled Elgaid, Dr Lai Bun Lok and Dr Chi Jeon Hwang from University of Glasgow for their advice on RF simulation and allowing me to conduct the RF characterisation of the fabricated device in their research laboratory.

Also, I would like to express gratitude to all my colleagues in the Nano group with special thank to Dr. Zakaria Moktadir, Dr. Liudi Jiang, Dr. Ibrahim Sari, Dr. Prasanna Srinivasan, Dr Badin Damrongsakd, Dr. Gareth N. Lewis, Dr. Tristan Temple, Dr. Stuart Boden, Christopher L. Cardwell, Ioannis Karakonstantinos, Sun Kai and Haitao Ding, who has offered help and laughter and made the office an enjoyable place to be in.

I am deeply grateful to the Commonwealth Scholarship Commission for their financial support during my study at the University of Southampton. Special thanks to Ms Irene Costello and Ms Ana Pereira for dealing with administration and deferment of the scholarship

Lastly, but the most important, I must thank to my wife, Hongyan Zhang, my daughter, my parents and siblings for their support and encouragement during my study in Southampton. I will never make it so far without them.

# Chapter 1

## Introduction

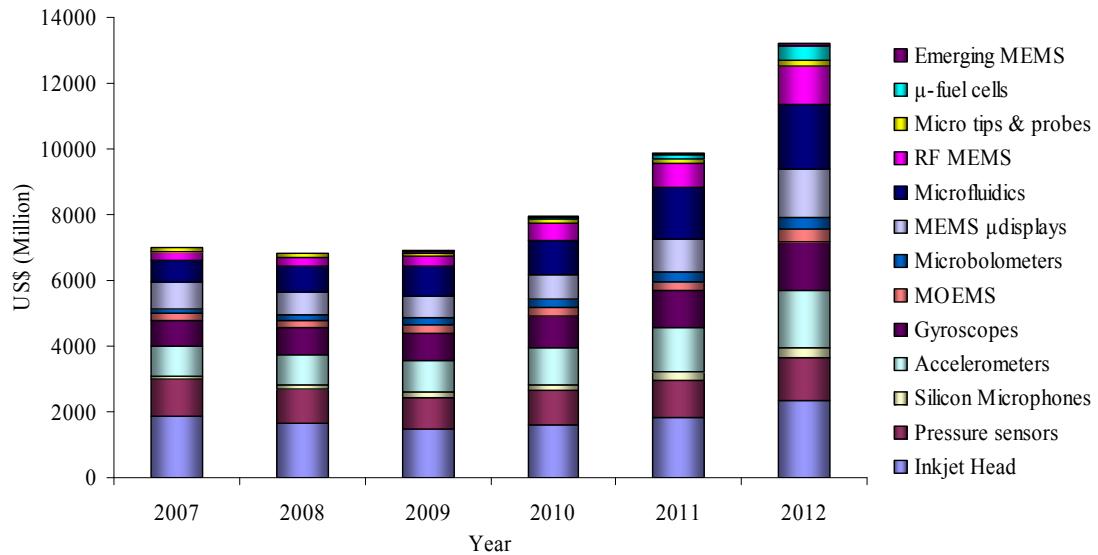

The overall Micro Electro Mechanical System (MEMS) market value was approximately US\$12 billion in 2004 [1] with more than 70% of the market shares belonging to the read/write heads and the inkjet heads. In a market forecast [2] published in 2007, the overall market was predicted to grow from US\$6.8billion in 2006 to approximately US\$11billion in 2011 without the consideration of read/write heads. The forecast [3] was later revised in 2009 with the considerations of the global financial downturn. The size of the market as illustrated in Figure 1.1 remained stable from 2007 to 2009 and the size of the Radio Frequency (RF) MEMS sector is expected to double when the economy recovers.

The majority of the market on RF MEMS are for Bulk Acoustic Wave (BAW) devices [4]. In 2001, a duplexer made commercial debut by Agilent, was costing US\$1,000. Since then, the price has decreased significantly in view of a mass production due to strong demand. At present, a similar duplexer is selling at only US\$2 each, thus becoming an attractive alternative to the ceramic counterparts.

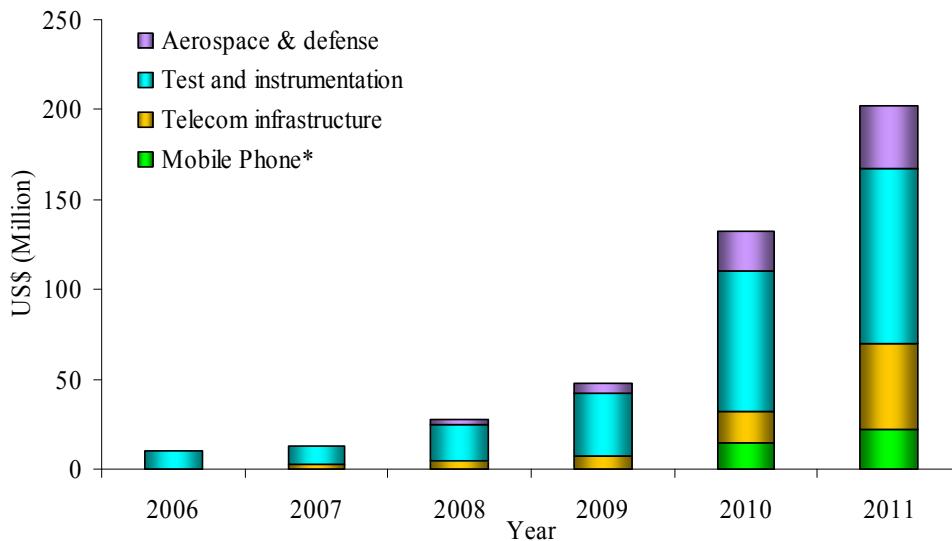

RF MEMS switches can be used in many applications, such as phase array antenna/radar [5-7], portable wireless systems [8], switching networks [9], satellite communication systems [10] and tunable filters [11]. These applications can be grouped into four main categories namely aerospace and defence, test and instrumentation, telecom infrastructure and mobile phones. The market value for RF MEMS switches was US\$6 million in 2006 and is expected to increase to US\$210 million in 2011 [12]. The

forecasted market value for each category can be found in Figure 1.2, with demand in test and instrumentation leading the pack.

Figure 1.1: Turnover forecast for MEMS market with breakdown into different categories of product from 2007-12 as given in [3].

Figure 1.2: Turnover forecast for RF MEMS market with breakdown into different categories of product from 2006-11 as given in [12].

Although there are several commercial manufacturers of RF MEMS switches, they are generally not available for sale as a stand alone product. Advantest is one of such

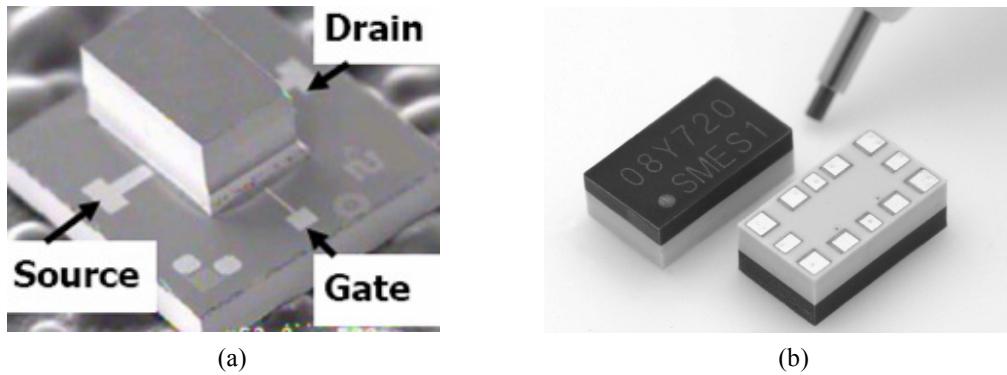

companies who employ the RF MEMS switches into the company's automated test equipment. Omron, Wispry and Radant MEMS are the very few companies which are selling commercial RF MEMS switches as a product, as illustrated in Figure 1.3. The selling price varies from US\$25-US\$100 per unit depending on the specifications and volumes [12]. Therefore, implementation of RF MEMS switches in every mobile phone is still not realisable in the foreseeable future. The main obstacles preventing such implementation are the complex fabrication and packaging processes, control voltages, switching speed and manufacturing costs of the device [13]. A selected list of commercially available RF MEMS switch is tabulated in Table 1.

Figure 1.3: Commercial RF MEMS switch from (a) Radant MEMS [14] (b) Omron 2SMES-01 [15].

### 1.1 Motivation