University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

School of Electronics and Computer Science

**A Prototype Parallel Multi-FPGA

Accelerator for SPICE CMOS Model

Evaluation**

by

**Ahmed Maache**

A thesis submitted for the degree of

Doctor of Philosophy

January 2011

## ABSTRACT

Due to ever increasing complexity of circuits, EDA tools and algorithms are demanding more computational power. This made transistor-level simulation a growing bottleneck in the circuit development process. This thesis serves as a proof of concept to evaluate and quantify the cost of using multi-FPGA systems in SPICE-like simulations in terms of acceleration, throughput, area, and power. To this end, a multi-FPGA architecture is designed to exploit the inherent parallelism in the device model evaluation phase within the SPICE simulator. A code transformation flow which converts the high-level device model code to structural VHDL was also implemented. This flow showed that an automatic compiler system to design, map, and optimise SPICE-like simulations on FPGAs is feasible.

This thesis has two main contributions. The first contribution is the multi-FPGA accelerator of the device model evaluation which demonstrated speedup of 10 times over a conventional processor, while consuming six times less power. Results also showed that it is feasible to describe and optimise FPGA pipelined implementations to exploit other class of applications similar to the SPICE device model evaluation. The constant throughput of the pipelined architecture is one of the main factors for the FPGA accelerator to outperform conventional processors. The second contribution lies in the use of multi-FPGA synthesis to optimise the inter-FPGA connections through altering the process of mapping partitions to FPGA devices. A novel technique is introduced which reduces the inter-FPGA connections by an average of 18%.

The speedup and power efficiency results showed that the proposed multi-FPGA system can be used by the SPICE community to accelerate the transistor-level simulation. The experimental results also showed that it is worthwhile continuing this research further to explore the use of FPGAs to accelerate other EDA tools.

## Declaration of Authorship

I, Ahmed Maache, declare that the thesis entitled: **A Prototype Parallel Multi-FPGA Accelerator for SPICE CMOS Model Evaluation**, and the work presented in it are my own, I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as listed in this thesis.

Signed: \_\_\_\_\_

Date : \_\_\_\_\_

## **Acknowledgements**

First and foremost, I would like to thank both my supervisors, Dr Jeff Reeve and Professor Mark Zwolinski for their valuable help and guidance. Thanks to all members of the Electronics Systems and Devices Group at the University of Southampton for their help and support. Thanks also go to Dr Koushik Maharatna for his fruitful discussions. I would like to thank my family for their unconditional support and love.

# Contents

|                                                           |            |

|-----------------------------------------------------------|------------|

| <b>List of figures</b>                                    | <b>ix</b>  |

| <b>List of tables</b>                                     | <b>xii</b> |

| <b>Listings</b>                                           | <b>xiv</b> |

| <b>List of Acronyms</b>                                   | <b>xv</b>  |

| <b>1 Introduction</b>                                     | <b>1</b>   |

| 1.1 FPGAs and High-Performance Computing . . . . .        | 1          |

| 1.2 Current Technology Limitations . . . . .              | 4          |

| 1.2.1 Efficiency of Parallel Systems . . . . .            | 6          |

| 1.3 Reconfigurable Computing . . . . .                    | 7          |

| 1.3.1 FPGA Architecture . . . . .                         | 7          |

| 1.3.2 Multi-FPGA Synthesis System . . . . .               | 9          |

| 1.3.3 Multi-FPGA Hardware System . . . . .                | 11         |

| 1.4 Research Motivations . . . . .                        | 12         |

| 1.4.1 SPICE Simulation . . . . .                          | 12         |

| 1.4.2 SPICE Simulation Bottleneck . . . . .               | 13         |

| 1.5 Research Scope and Objectives . . . . .               | 14         |

| 1.6 Thesis Structure . . . . .                            | 15         |

| 1.7 Publications . . . . .                                | 17         |

| <b>2 Multi-FPGA Systems Review</b>                        | <b>18</b>  |

| 2.1 High-Level Synthesis . . . . .                        | 18         |

| 2.1.1 Scheduling . . . . .                                | 20         |

| 2.1.2 Allocation . . . . .                                | 21         |

| 2.1.3 Binding . . . . .                                   | 22         |

| 2.2 Multi-FPGA Logic Partitioning . . . . .               | 22         |

| 2.2.1 Partitioning Methodologies . . . . .                | 23         |

| 2.2.1.1 Partitioning Problem Formulation . . . . .        | 23         |

| 2.2.1.2 Kernighan-Lin Algorithm . . . . .                 | 25         |

| 2.2.1.3 Fiduccia-Mattheyses Algorithm . . . . .           | 26         |

| 2.2.1.4 Structural and Behavioural Partitioning . . . . . | 27         |

---

|          |                                                     |           |

|----------|-----------------------------------------------------|-----------|

| 2.2.2    | Existing Multi-FPGA Synthesis Systems . . . . .     | 28        |

| 2.3      | High-Performance Reconfigurable Computing . . . . . | 29        |

| 2.3.1    | HPRC Hardware Platforms . . . . .                   | 30        |

| 2.3.2    | HPRC Programming Environments . . . . .             | 32        |

| 2.3.3    | HPRC Systems Review . . . . .                       | 33        |

| 2.3.4    | Floating-Point Operators and FPGAs . . . . .        | 34        |

| 2.3.5    | Serial Communication and FPGAs . . . . .            | 35        |

| 2.4      | Summary . . . . .                                   | 36        |

| <b>3</b> | <b>Parallel Device Model Evaluation</b>             | <b>38</b> |

| 3.1      | SPICE Simulation Background . . . . .               | 38        |

| 3.1.1    | Newton-Raphson Method . . . . .                     | 41        |

| 3.1.2    | Example Circuit . . . . .                           | 43        |

| 3.2      | SPICE Simulator Parallel Execution . . . . .        | 45        |

| 3.2.1    | Parallelisation Approaches . . . . .                | 45        |

| 3.2.2    | SPICE Simulator Execution Profile . . . . .         | 47        |

| 3.3      | SPICE Simulator Acceleration Related Work . . . . . | 49        |

| 3.3.1    | Multiprocessor Paradigm . . . . .                   | 49        |

| 3.3.2    | Hardware Accelerator Paradigm . . . . .             | 51        |

| 3.3.2.1  | GPU Accelerators . . . . .                          | 51        |

| 3.3.2.2  | FPGA Accelerators . . . . .                         | 52        |

| 3.4      | Parallel Device Model Evaluation . . . . .          | 53        |

| 3.4.1    | Explicit Parallelism Approach . . . . .             | 53        |

| 3.4.2    | Pipelined Approach . . . . .                        | 55        |

| 3.4.3    | Proposed FPGA Accelerator . . . . .                 | 56        |

| 3.5      | Summary . . . . .                                   | 57        |

| <b>4</b> | <b>Multi-FPGA Device Model Accelerator</b>          | <b>60</b> |

| 4.1      | FPGA Design Considerations . . . . .                | 61        |

| 4.1.1    | Pipelined Architecture . . . . .                    | 61        |

| 4.1.2    | SPICE Model Parameters . . . . .                    | 61        |

| 4.1.3    | Data Word Length Considerations . . . . .           | 62        |

| 4.1.4    | Inter-FPGA Serial Communication . . . . .           | 63        |

| 4.2      | CMOS LEVEL 3 Model . . . . .                        | 64        |

| 4.3      | CMOS LEVEL 3 Model FPGA Implementation . . . . .    | 65        |

| 4.3.1    | CMOS LEVEL 3 Parameters . . . . .                   | 65        |

| 4.3.2    | Device Model Code Transformation Flow . . . . .     | 66        |

| 4.3.3    | Software Implementation for Comparison . . . . .    | 71        |

| 4.3.4    | FPGA Acceleration Calculation . . . . .             | 71        |

| 4.4      | Single-FPGA Accelerator System . . . . .            | 72        |

| 4.4.1    | System Architecture . . . . .                       | 72        |

| 4.4.1.1  | With MicroBlaze . . . . .                           | 73        |

| 4.4.1.2  | Without MicroBlaze . . . . .                        | 74        |

---

|          |                                                          |            |

|----------|----------------------------------------------------------|------------|

| 4.4.2    | Experimental Results . . . . .                           | 75         |

| 4.4.2.1  | Software Implementation Runtime . . . . .                | 75         |

| 4.4.2.2  | Single-FPGA Accelerator Runtime . . . . .                | 77         |

| 4.4.3    | Discussion . . . . .                                     | 78         |

| 4.5      | Multi-FPGA Accelerator System . . . . .                  | 80         |

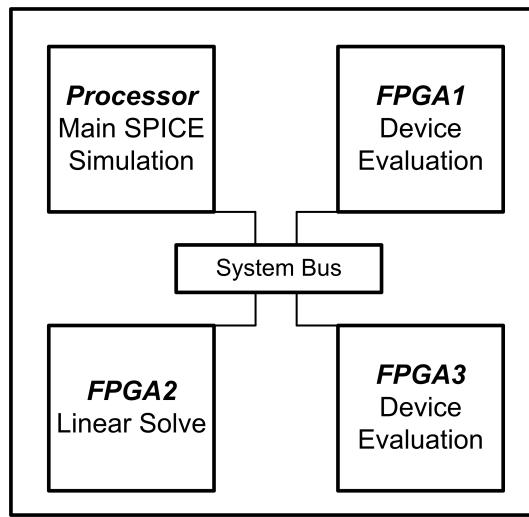

| 4.5.1    | System Architecture . . . . .                            | 80         |

| 4.5.2    | Accelerator Prototype . . . . .                          | 82         |

| 4.5.3    | Theoretical Hardware Execution Time . . . . .            | 82         |

| 4.6      | Experimental Work . . . . .                              | 85         |

| 4.6.1    | Experimental Setup . . . . .                             | 85         |

| 4.6.2    | SPICE Simulation Data . . . . .                          | 85         |

| 4.7      | Summary . . . . .                                        | 87         |

| <b>5</b> | <b>Multi-FPGA Acceleration Results</b>                   | <b>89</b>  |

| 5.1      | Experimental Results . . . . .                           | 89         |

| 5.1.1    | Acceleration Results . . . . .                           | 89         |

| 5.1.2    | Resources Utilisation . . . . .                          | 94         |

| 5.1.2.1  | Slave FPGA . . . . .                                     | 94         |

| 5.1.2.2  | Host FPGA . . . . .                                      | 97         |

| 5.1.3    | Power Consumption Estimation . . . . .                   | 97         |

| 5.1.4    | Results Comparison . . . . .                             | 98         |

| 5.1.4.1  | Resources Usage Comparison . . . . .                     | 99         |

| 5.1.4.2  | Acceleration Comparison . . . . .                        | 101        |

| 5.1.5    | Discussion of Results . . . . .                          | 102        |

| 5.2      | Results Extension . . . . .                              | 103        |

| 5.2.1    | Results Extension to Current SPICE CMOS Models . . . . . | 103        |

| 5.2.1.1  | Resources Estimation Reference Point . . . . .           | 104        |

| 5.2.1.2  | Resources Estimation Results . . . . .                   | 105        |

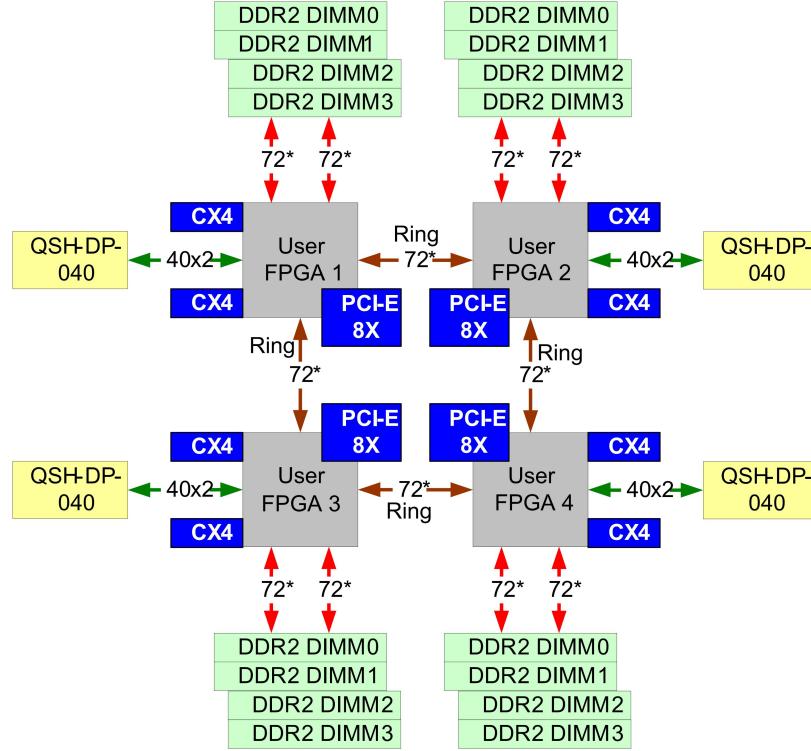

| 5.2.2    | Theoretical Performance Estimation on BEE3 . . . . .     | 106        |

| 5.2.2.1  | Performance Estimation of the XUPV2P System . . . . .    | 107        |

| 5.2.2.2  | Performance Estimation of the BEE3 System . . . . .      | 107        |

| 5.2.3    | Discussion . . . . .                                     | 109        |

| 5.2.4    | Computing Device Model Derivatives . . . . .             | 110        |

| 5.2.4.1  | The Secant Method . . . . .                              | 110        |

| 5.2.4.2  | Accelerating the secant method . . . . .                 | 111        |

| 5.3      | Summary . . . . .                                        | 111        |

| <b>6</b> | <b>Multi-FPGA Partition Mapping</b>                      | <b>113</b> |

| 6.1      | Problem Definition . . . . .                             | 114        |

| 6.2      | Inter-FPGAs Communication Synthesis . . . . .            | 115        |

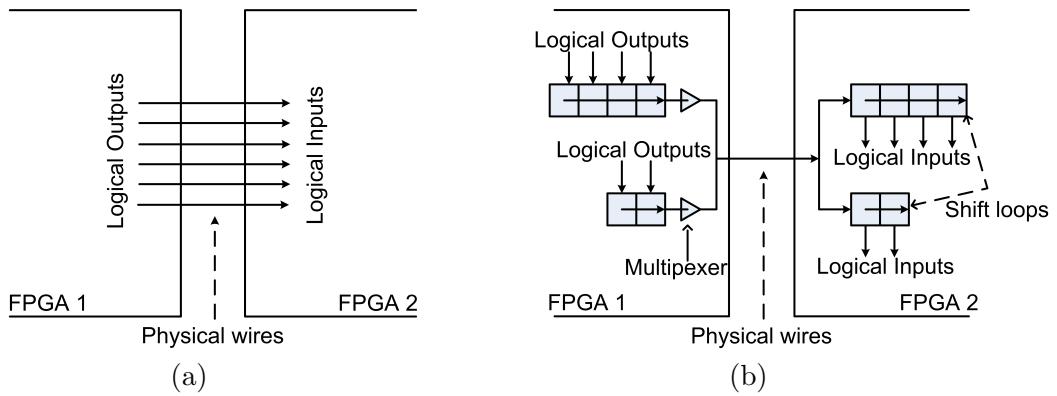

| 6.2.1    | Virtual Wires Approach . . . . .                         | 115        |

| 6.2.2    | FunctionBus Approach . . . . .                           | 116        |

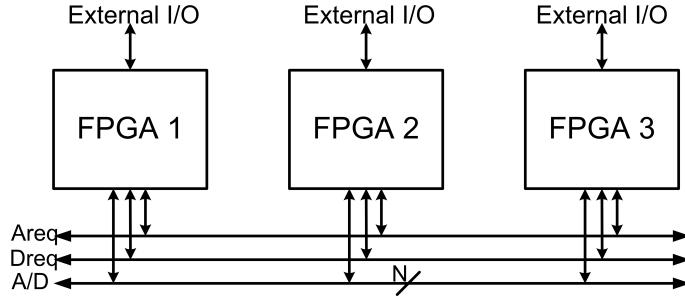

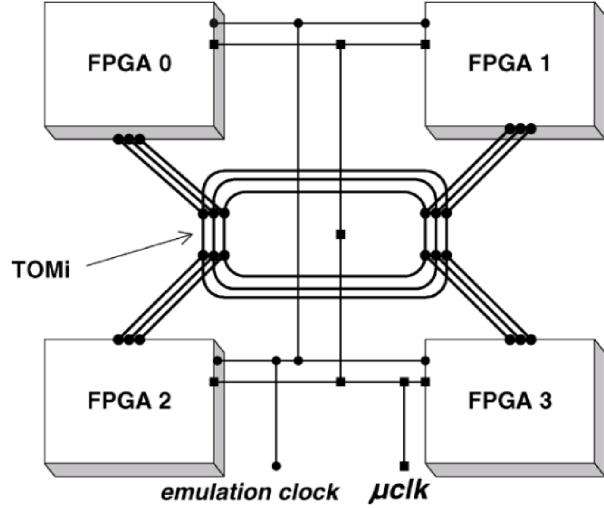

| 6.2.3    | Other Approaches . . . . .                               | 117        |

---

|                   |                                                                    |            |

|-------------------|--------------------------------------------------------------------|------------|

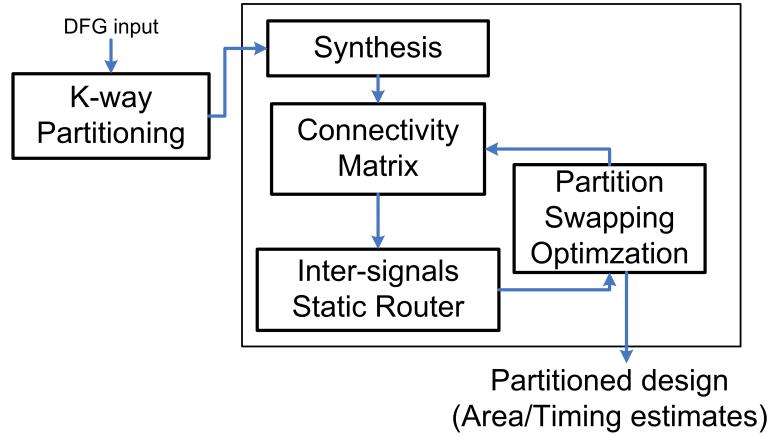

| 6.3               | Multi-FPGA Synthesis System . . . . .                              | 119        |

| 6.3.1             | Input Specification Model . . . . .                                | 119        |

| 6.3.2             | K-way Partitioning . . . . .                                       | 119        |

| 6.3.3             | Synthesis . . . . .                                                | 120        |

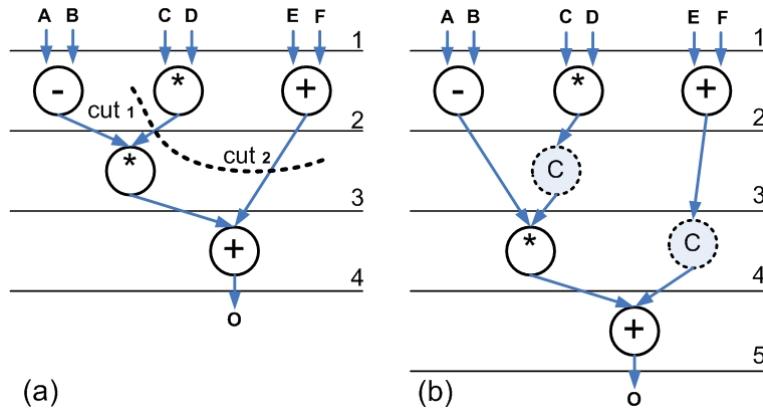

| 6.3.3.1           | Scheduling under Inter-FPGA I/O Constraints . . . . .              | 120        |

| 6.3.4             | Target Architecture Models . . . . .                               | 121        |

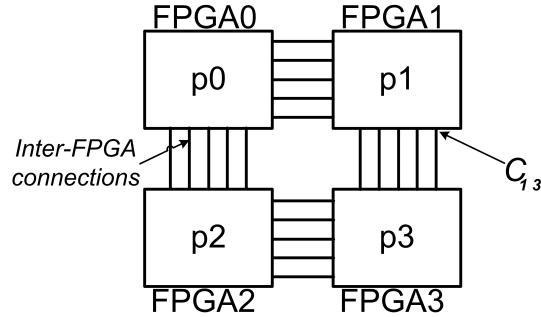

| 6.3.4.1           | Problem Formulation . . . . .                                      | 122        |

| 6.3.4.2           | Connectivity Matrix . . . . .                                      | 123        |

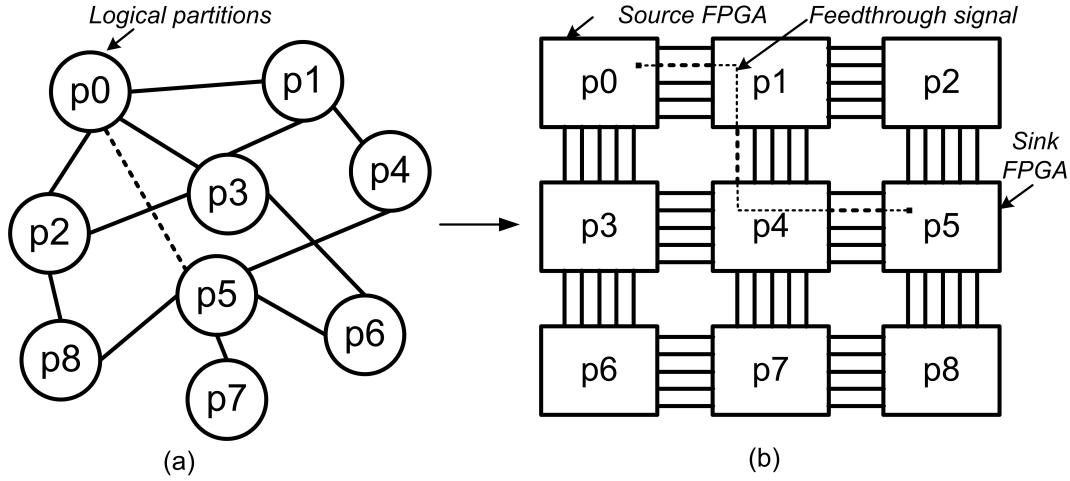

| 6.3.4.3           | The Inter-FPGA I/O Static Router . . . . .                         | 123        |

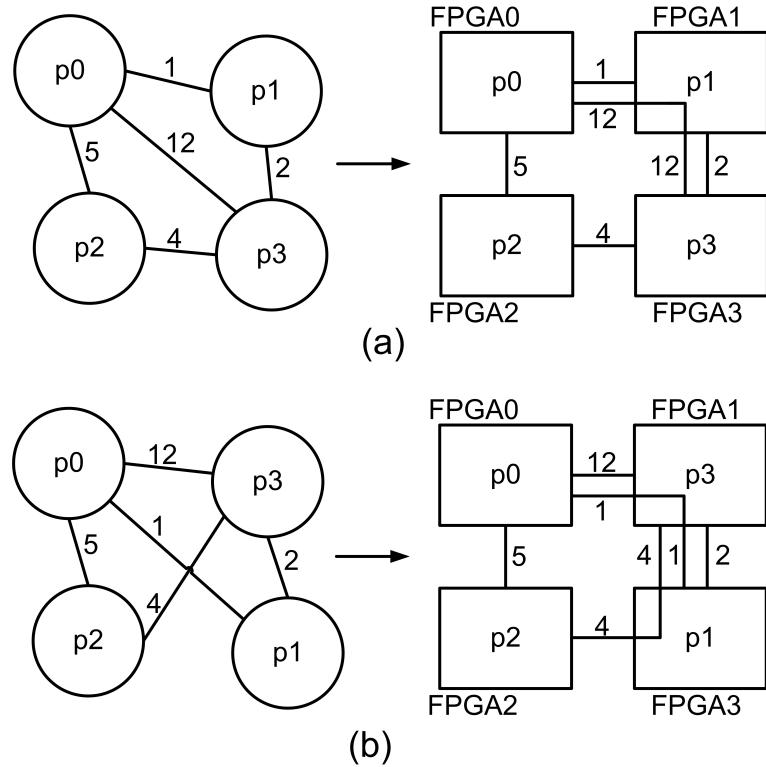

| 6.3.5             | Partition Swapping Optimisation . . . . .                          | 125        |

| 6.3.5.1           | Algorithm Example . . . . .                                        | 126        |

| 6.3.5.2           | Algorithm Pseudo Code . . . . .                                    | 127        |

| 6.4               | Experimental Setup . . . . .                                       | 129        |

| 6.4.1             | Benchmark DFGs . . . . .                                           | 129        |

| 6.4.2             | System Implementation . . . . .                                    | 130        |

| 6.5               | Experimental Results . . . . .                                     | 131        |

| 6.5.1             | Results Comparison . . . . .                                       | 133        |

| 6.5.1.1           | Mesh Model Case . . . . .                                          | 133        |

| 6.5.1.2           | Virtual Model Case . . . . .                                       | 134        |

| 6.6               | Results Analysis . . . . .                                         | 135        |

| 6.7               | Summary . . . . .                                                  | 136        |

| <b>7</b>          | <b>Conclusions and Future Work</b>                                 | <b>138</b> |

| 7.1               | Conclusions . . . . .                                              | 138        |

| 7.2               | Summary of Research Contributions . . . . .                        | 140        |

| 7.3               | Future Work . . . . .                                              | 141        |

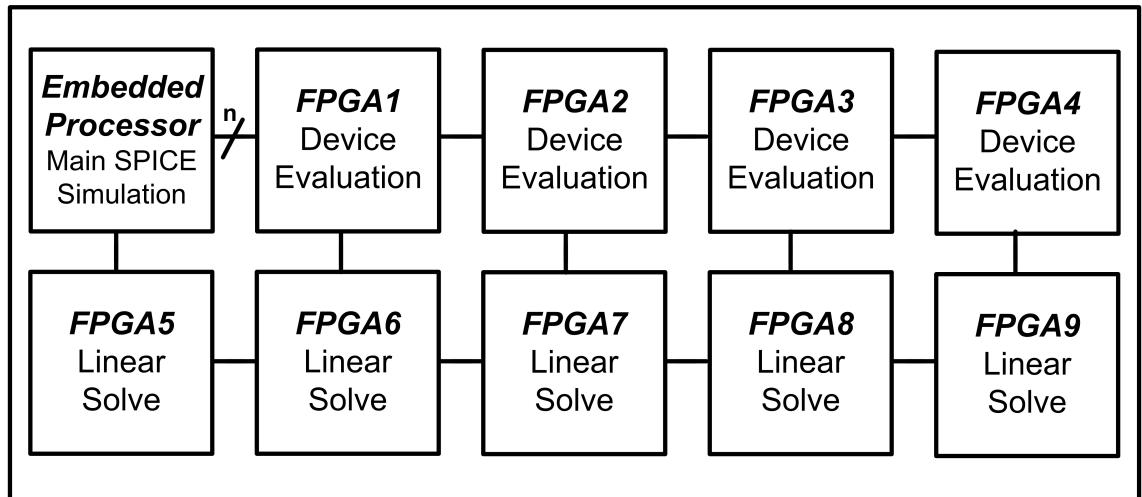

| 7.3.1             | Multi-FPGA SPICE Accelerator . . . . .                             | 141        |

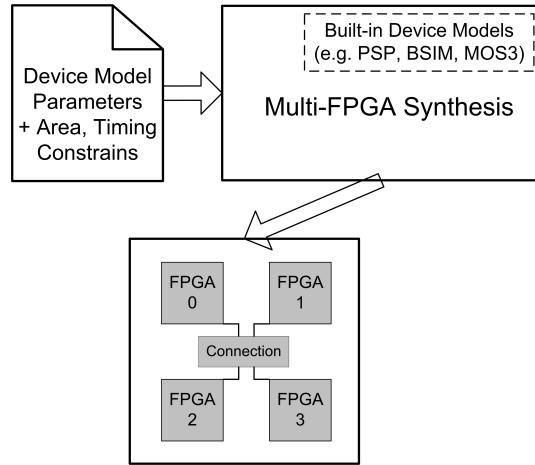

| 7.3.2             | Multi-FPGA Model Evaluation Acceleration . . . . .                 | 142        |

| 7.3.3             | Multi-FPGA Iterative Linear Solve . . . . .                        | 144        |

| <b>References</b> |                                                                    | <b>146</b> |

| <b>A</b>          | <b>CMOS LEVEL 3 VHDL-AMS Model</b>                                 | <b>160</b> |

| A.1               | Simulation Model VHDL-AMS Code . . . . .                           | 160        |

| A.2               | Synthesisable Model VHDL Code . . . . .                            | 165        |

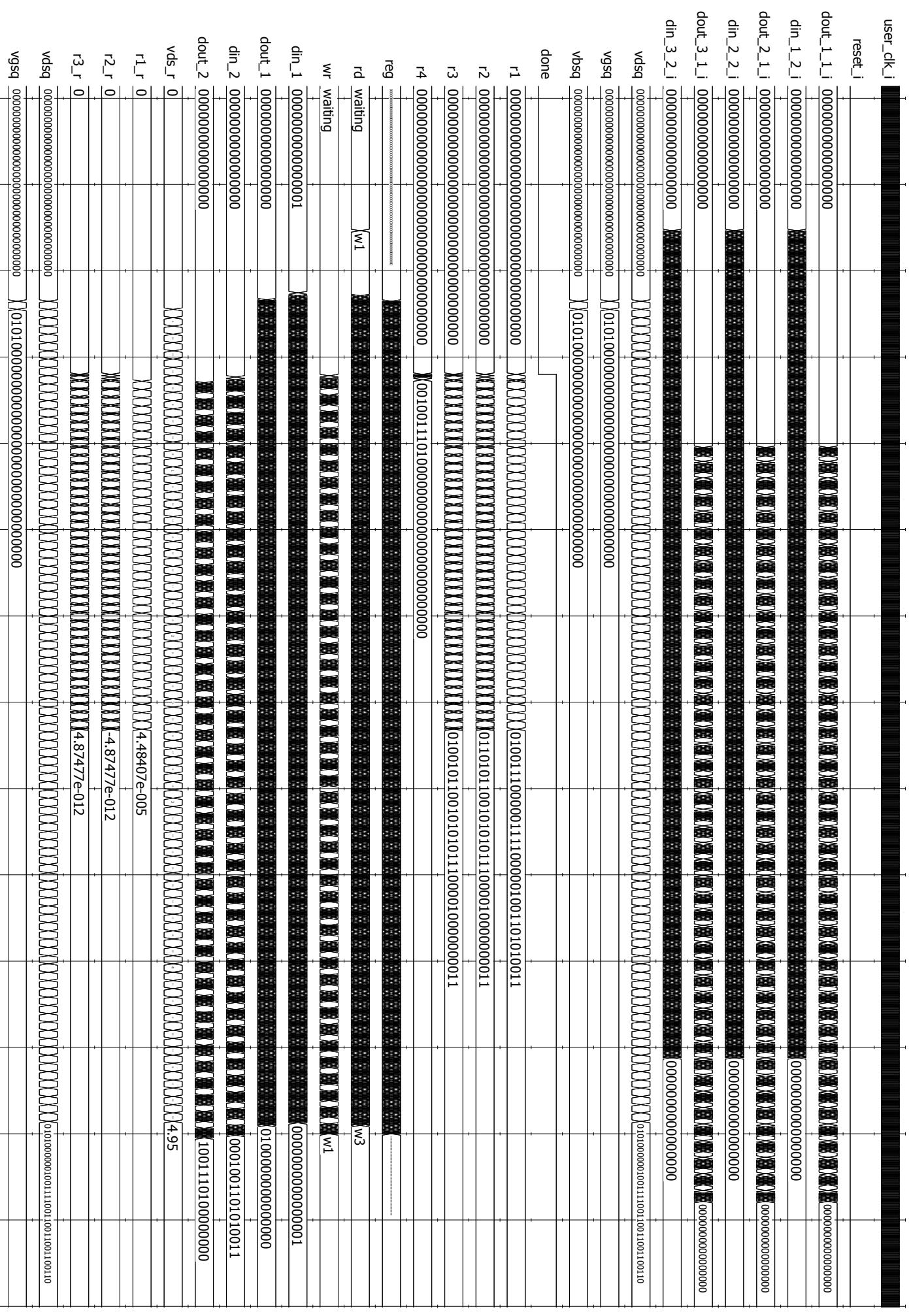

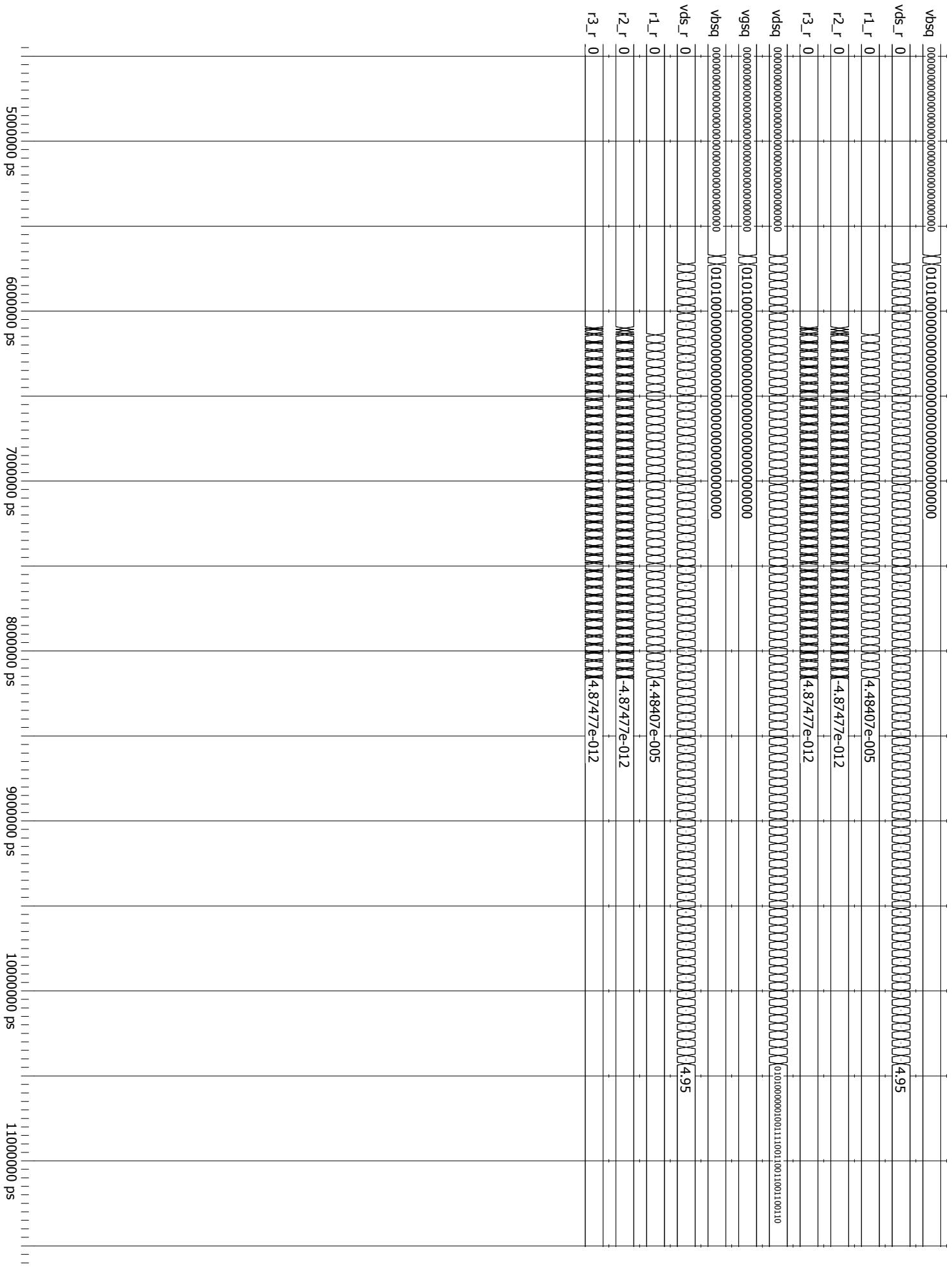

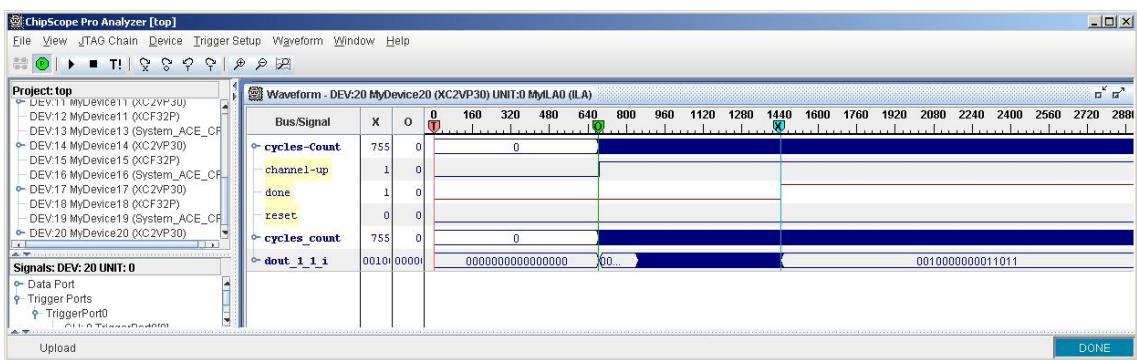

| A.3               | ModelSim Simulation Waveforms for the pipelined CMOS LEVEL 3 model | 171        |

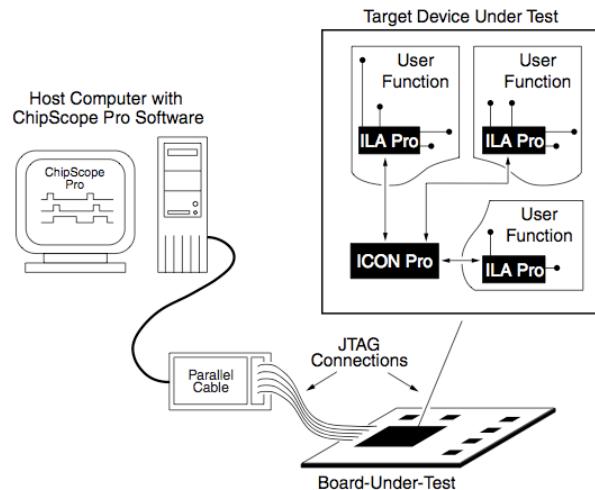

| A.4               | Chipscope Waveforms for the pipelined CMOS LEVEL 3 model . . . . . | 174        |

| <b>B</b>          | <b>Pipelined VHDL Design Synthesis Results</b>                     | <b>176</b> |

| B.1               | Synthesis Reports for both host and slave FPGAs . . . . .          | 176        |

| <b>C</b>          | <b>Xilinx Virtex-II Pro Development Board</b>                      | <b>178</b> |

| <b>D</b>          | <b>JTAG Configuration</b>                                          | <b>180</b> |

|                                                      |            |

|------------------------------------------------------|------------|

| <b>E Measuring Hardware and Software Times</b>       | <b>181</b> |

| E.1 Measuring Hardware Times . . . . .               | 181        |

| E.2 Measuring Software Times . . . . .               | 182        |

| <b>F Floating-Point Operators for FPGAs</b>          | <b>183</b> |

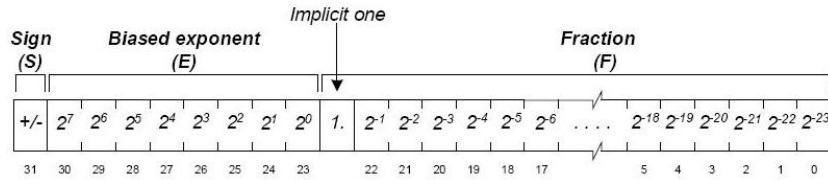

| F.1 Number Representations . . . . .                 | 183        |

| F.1.1 Fixed-Point System . . . . .                   | 183        |

| F.1.2 Binary Floating-Point System . . . . .         | 184        |

| F.1.3 Decimal Floating-Point System . . . . .        | 184        |

| F.1.4 Comparison . . . . .                           | 184        |

| F.2 Floating-Point FPGAs Libraries . . . . .         | 185        |

| F.2.1 New IEEE VHDL Standard Revision . . . . .      | 185        |

| F.2.1.1 Fixed-Point Package ‘fixed_pkg’ . . . . .    | 185        |

| F.2.1.2 Floating-Point Package ‘float_pkg’ . . . . . | 185        |

| F.2.2 OpenCores FPU . . . . .                        | 186        |

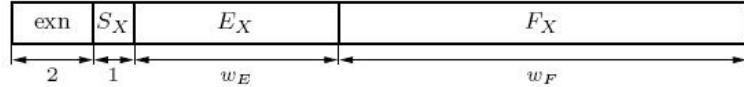

| F.2.3 FPLibrary . . . . .                            | 186        |

| F.2.4 Floating-point Libraries Comparison . . . . .  | 188        |

# List of Figures

|      |                                                                                                          |    |

|------|----------------------------------------------------------------------------------------------------------|----|

| 1.1  | Intel CPU Timeline [19] . . . . .                                                                        | 4  |

| 1.2  | Typical Xilinx FPGA Internal Architecture [5] . . . . .                                                  | 8  |

| 1.3  | Configurable Logic Block (CLB) Basic Architecture [30] . . . . .                                         | 8  |

| 1.4  | FPGA Growth Trend [32] . . . . .                                                                         | 9  |

| 1.5  | A Typical Multi-FPGA Reconfigurable Environment . . . . .                                                | 9  |

| 1.6  | Electronics Design Automation Flow for Typical Reconfigurable Computing Systems [33] . . . . .           | 10 |

| 1.7  | A Typical Reconfigurable Computing Architecture [33] . . . . .                                           | 12 |

| 2.1  | Generic High-Level Synthesis System [52] . . . . .                                                       | 19 |

| 2.2  | Generic structure of the synthesis target circuit . . . . .                                              | 20 |

| 2.3  | Example of ASAP (a) and ALAP (b) schedules . . . . .                                                     | 20 |

| 2.4  | (a) Example circuit, (b) Hypergraph representation . . . . .                                             | 23 |

| 2.5  | Kernighan-Lin Algorithm Pseudo Code . . . . .                                                            | 25 |

| 2.6  | The Gain Bucket Data Structure used in the FM Algorithm . . . . .                                        | 26 |

| 2.7  | Structural (a) and Behavioural (b) logic partitioning [65] . . . . .                                     | 28 |

| 2.8  | TMD Architecture Block Diagram [99] . . . . .                                                            | 31 |

| 2.9  | XD1000 ALTERA-based Coprocessor [105] . . . . .                                                          | 32 |

| 2.10 | Functional diagram of an Aurora-based system . . . . .                                                   | 35 |

| 3.1  | Typical SPICE Simulation Flow . . . . .                                                                  | 39 |

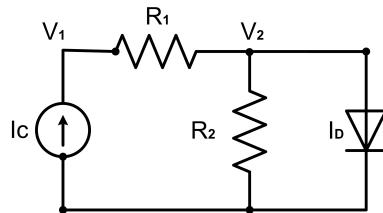

| 3.2  | Example Circuit . . . . .                                                                                | 43 |

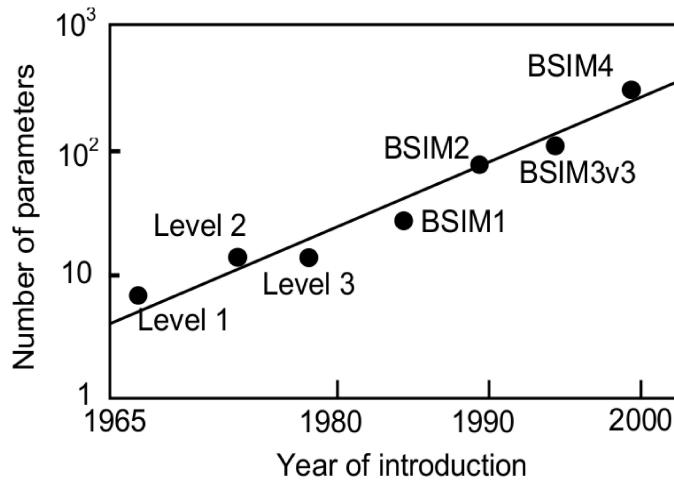

| 3.3  | The Increase of MOSFET Models' Parameters [149] . . . . .                                                | 48 |

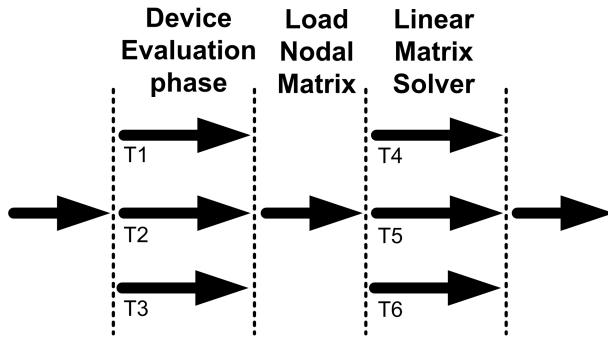

| 3.4  | Parallel Execution of a Newton-Raphson Iteration in the SPICE simulator                                  | 54 |

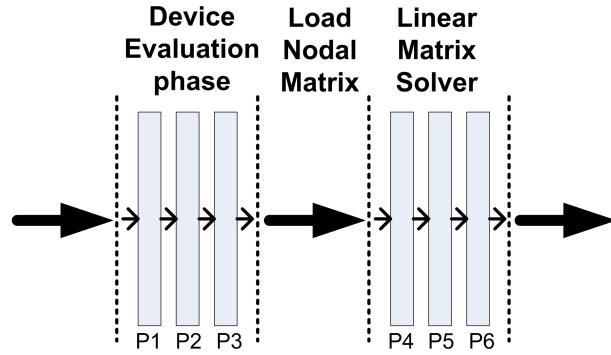

| 3.5  | Pipelined Execution of a Newton-Raphson Iteration in the SPICE simulator                                 | 55 |

| 3.6  | Pipelined Configuration of Multi-FPGA Systems [168] . . . . .                                            | 55 |

| 3.7  | (a) The ASAP schedule (Section 2.1.1) (b) a pipelined implementation of the schedule . . . . .           | 56 |

| 3.8  | The proposed approach to exploit the inherent parallelism in the device model evaluation phase . . . . . | 57 |

| 3.9  | A suggested FPGA coprocessor to accelerate the SPICE simulator . . . . .                                 | 58 |

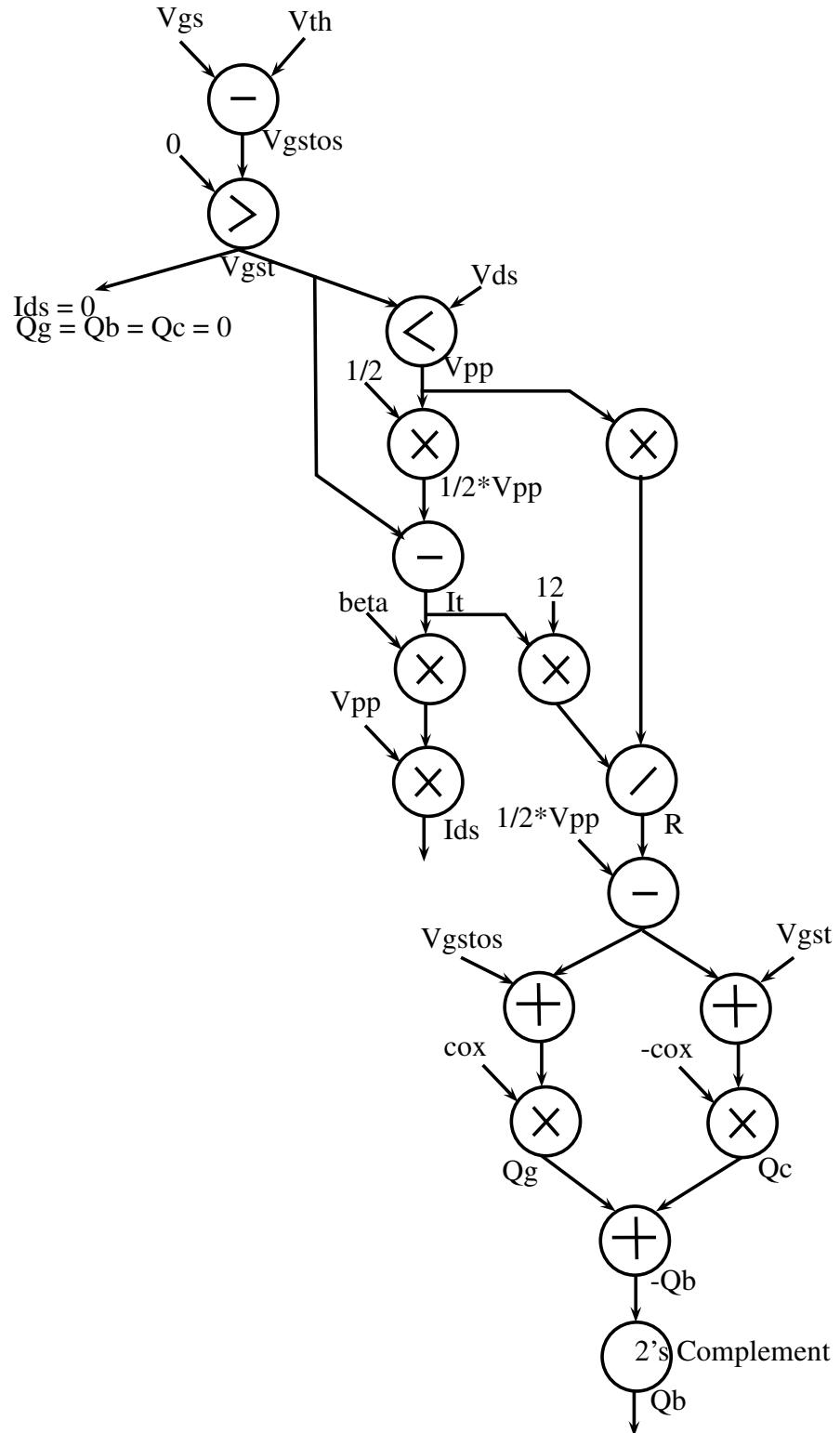

| 4.1  | LEVEL 3 CMOS Model with Parameter Pre-calculation . . . . .                                              | 68 |

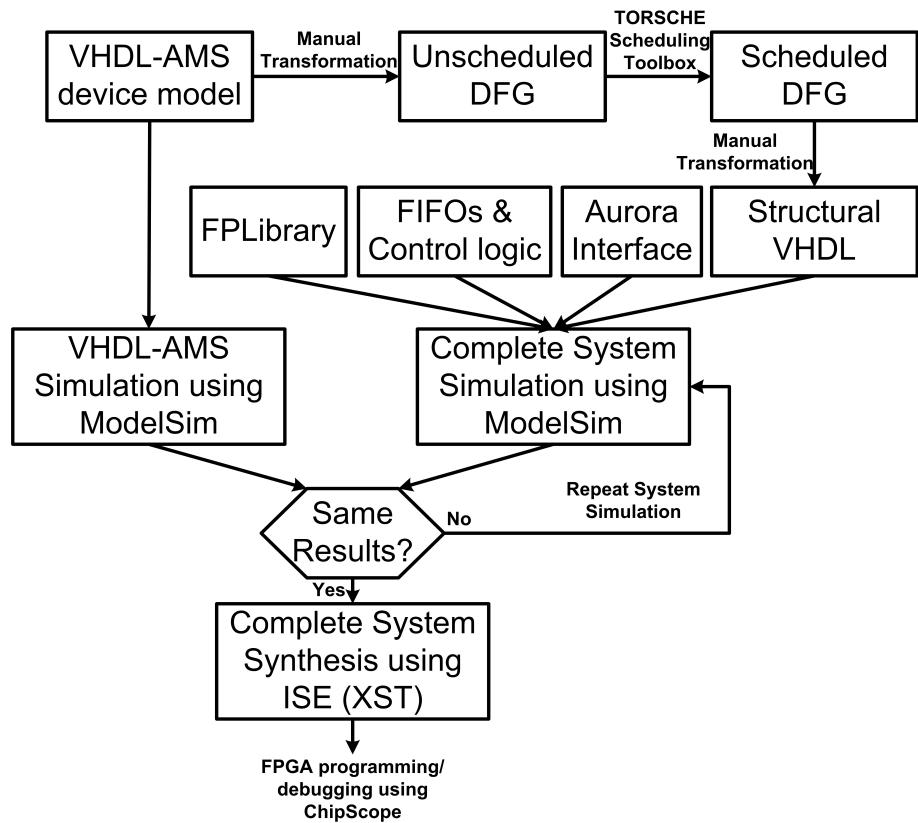

| 4.2  | Transformation Flow of the VHDL-AMS high-level device model code to a Structural VHDL design . . . . .   | 69 |

---

|      |                                                                                                                                     |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3  | The Control-Data Flow Graph of the CMOS LEVEL 3 Model code shown in Figure 4.1                                                      | 70  |

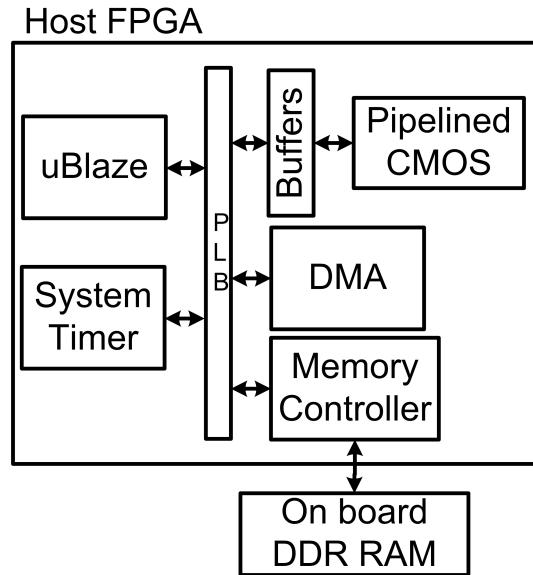

| 4.4  | Block Diagram of the Single FPGA CMOS Accelerator with MicroBlaze                                                                   | 73  |

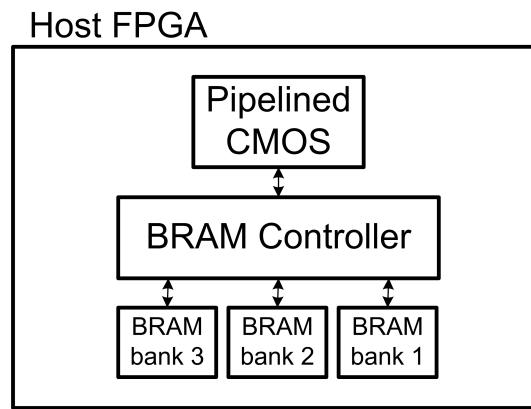

| 4.5  | Block Diagram of the Single FPGA CMOS Accelerator without MicroBlaze                                                                | 74  |

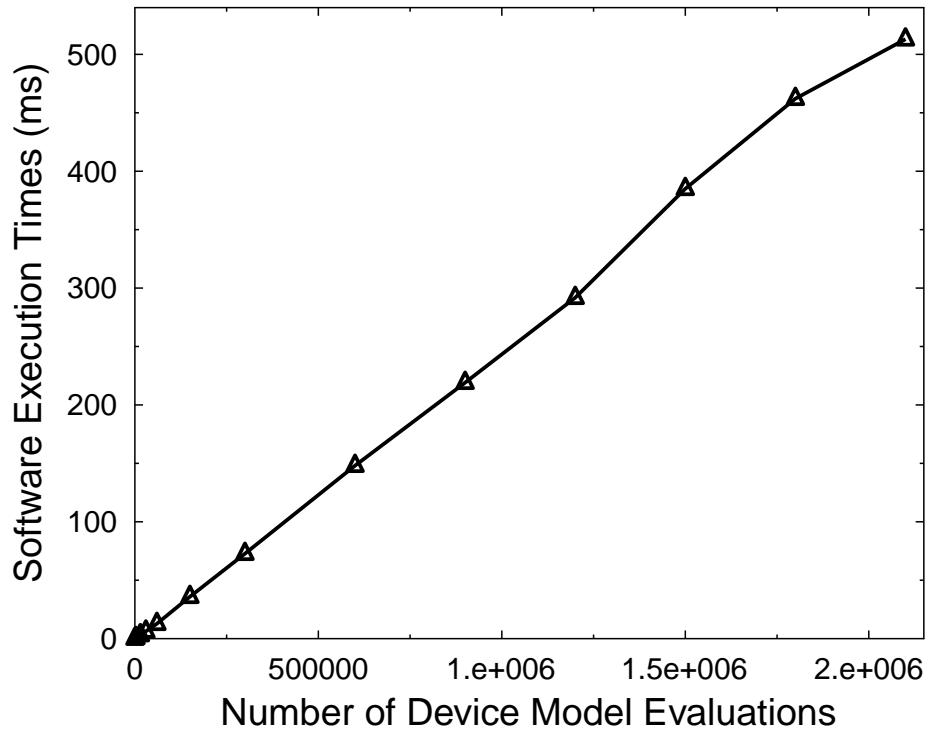

| 4.6  | Change of the software execution times with the number of device evaluations in Table 4.2                                           | 76  |

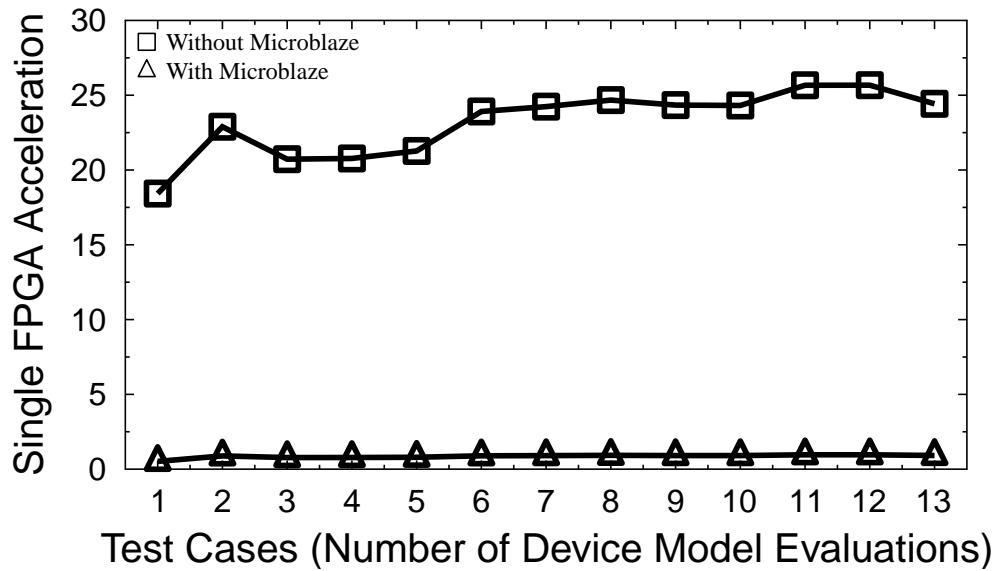

| 4.7  | Single FPGA Acceleration with the number of device model evaluations in Table 4.2                                                   | 77  |

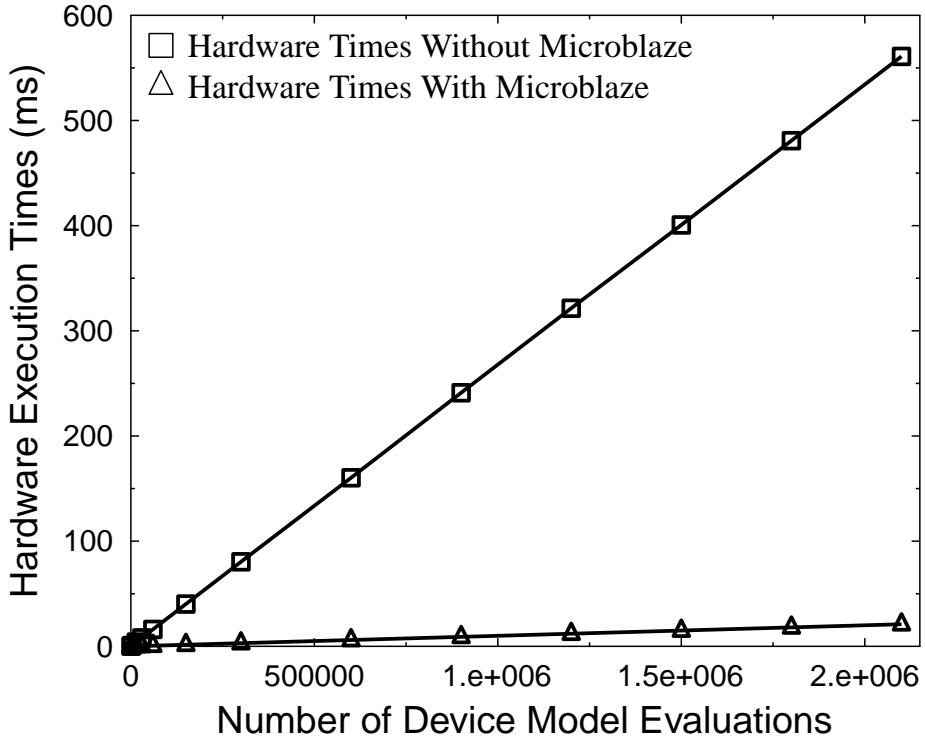

| 4.8  | Change of the hardware execution times with the number of device evaluations in Table 4.2                                           | 79  |

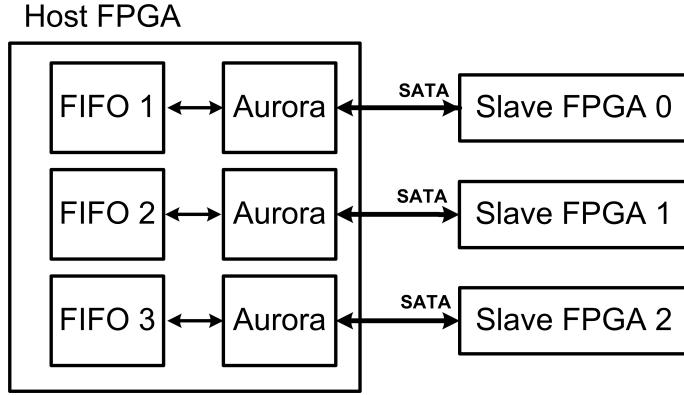

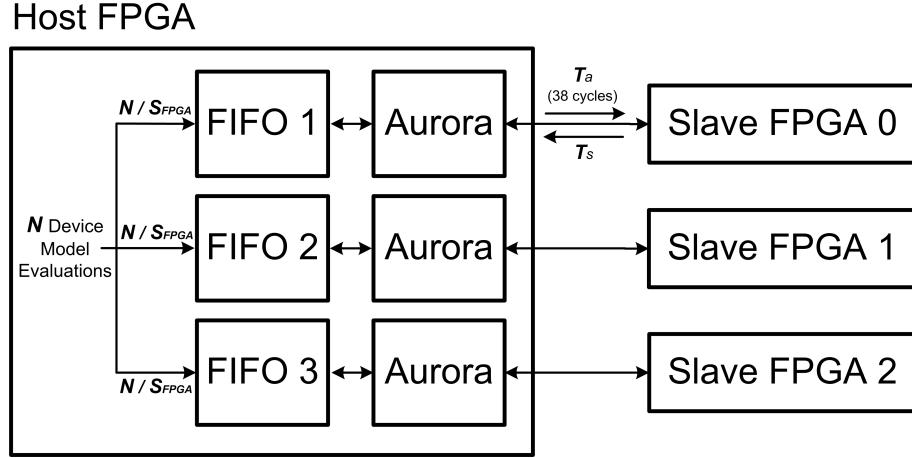

| 4.9  | The Architecture of the multi-FPGA CMOS Accelerator                                                                                 | 81  |

| 4.10 | Hardware execution time estimates annotated on the architecture of the multi-FPGA Accelerator in Figure 4.9                         | 83  |

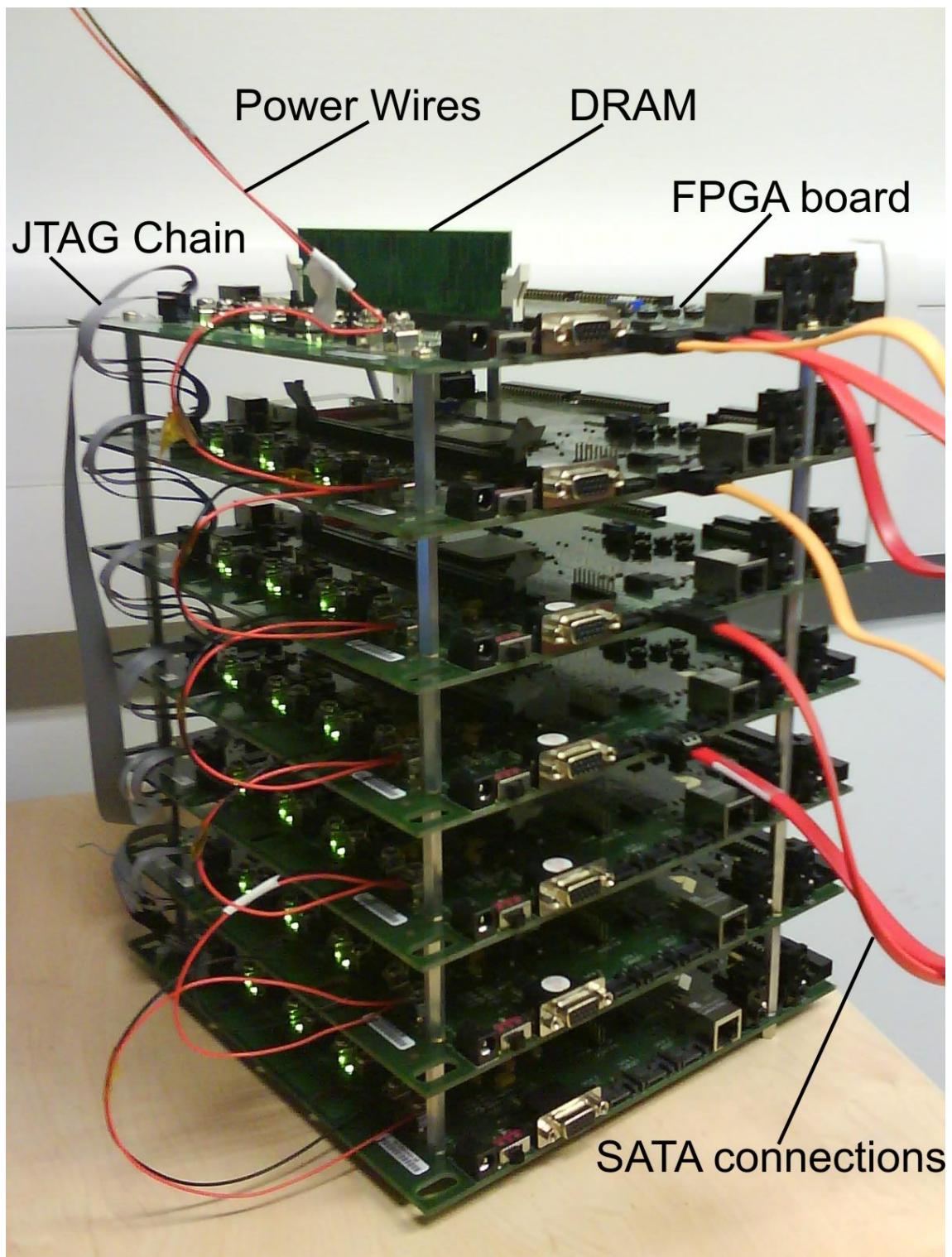

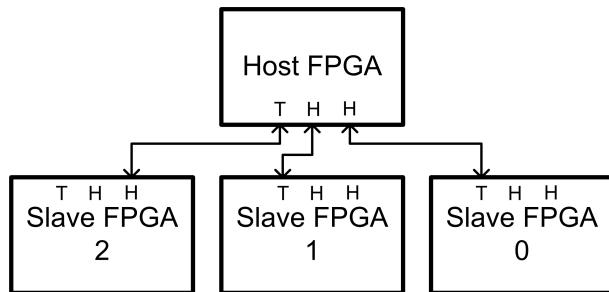

| 4.11 | The Prototype Multi-FPGA System Designed to Accelerate the Device Model Evaluation Phase                                            | 86  |

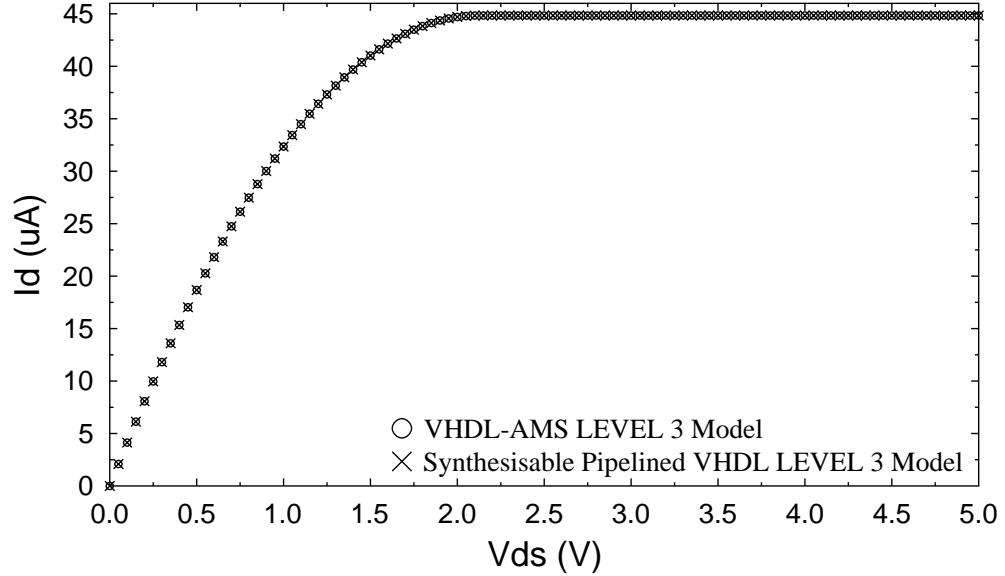

| 5.1  | The drain current $I_d$ vs. the drain-source voltage $V_{ds}$                                                                       | 90  |

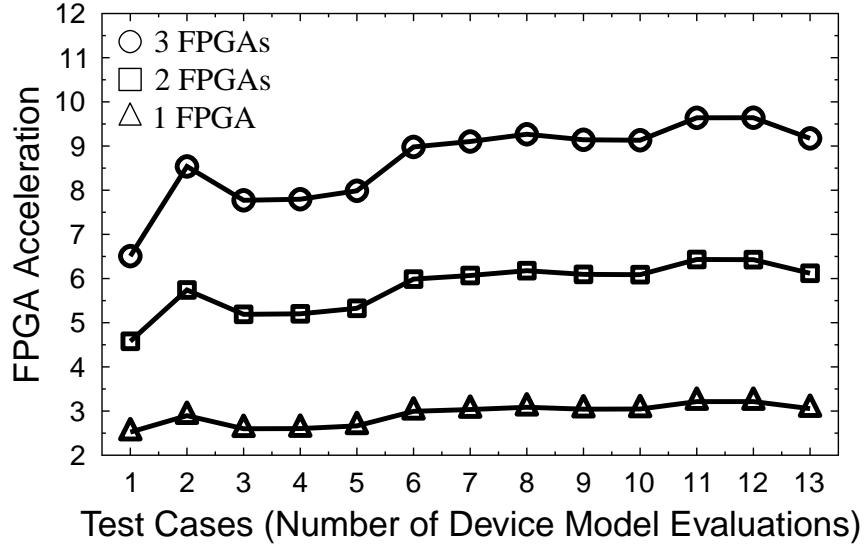

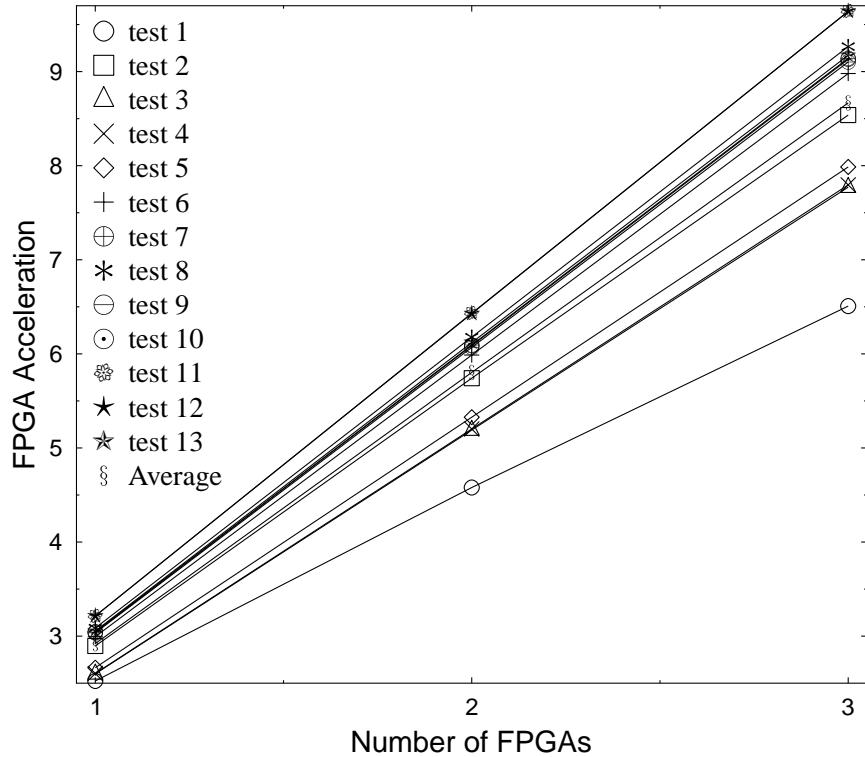

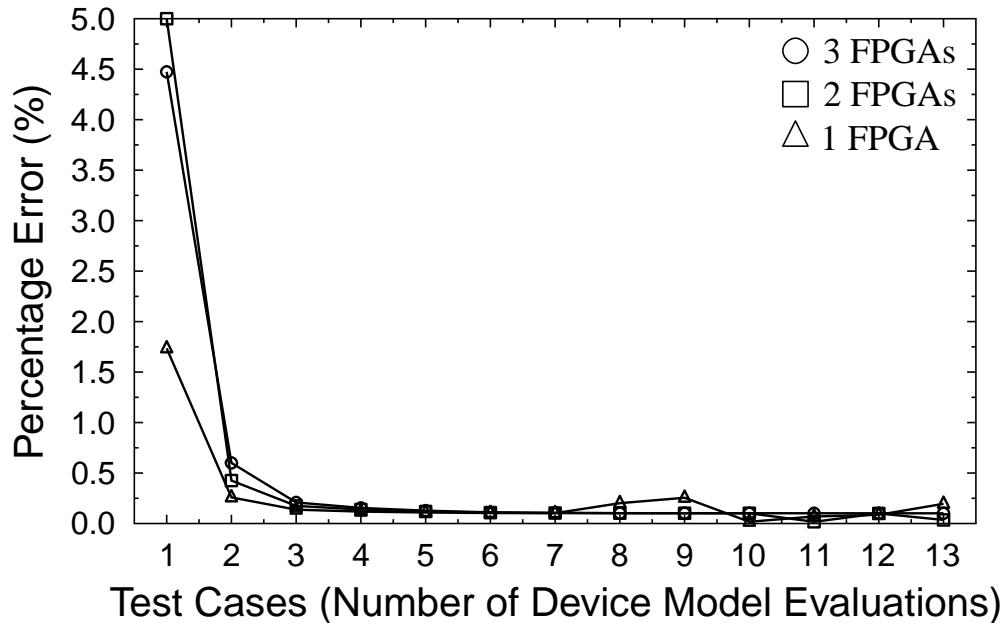

| 5.2  | FPGA Acceleration for the Three Test Configurations in Figure 5.3                                                                   | 91  |

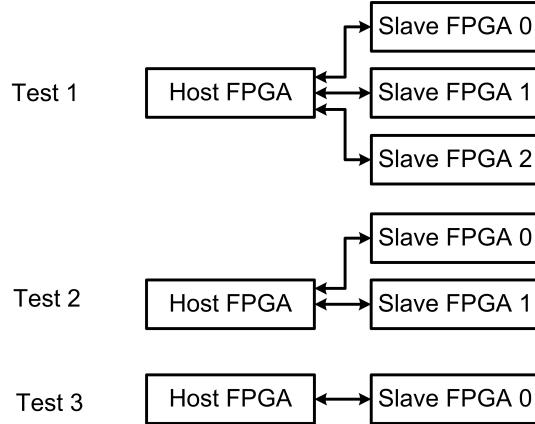

| 5.3  | The Three Test Configurations of the Multi-FPGA System                                                                              | 91  |

| 5.4  | FPGA Acceleration change with the Number of FPGAs                                                                                   | 93  |

| 5.5  | Percentage difference between the theoretical estimation $T_{theory}$ and the practical hardware times $T_{experiment}$             | 94  |

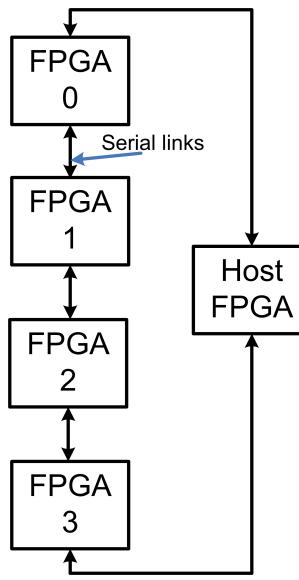

| 5.6  | FPGAs Connected in a Pipelined Ring                                                                                                 | 96  |

| 5.7  | BEE3 Compute Module Block Diagram [179]                                                                                             | 108 |

| 6.1  | Hard wires interconnect (a), Virtual wires interconnect (b)                                                                         | 116 |

| 6.2  | The FunctionBus Architecture                                                                                                        | 117 |

| 6.3  | Block Diagram of the TOMi Architecture [204]                                                                                        | 118 |

| 6.4  | Block Diagram of the Multi-FPGA Synthesis System                                                                                    | 119 |

| 6.5  | Inter-FPGA Communication Nodes Insertion                                                                                            | 121 |

| 6.6  | Typical Mesh Topology                                                                                                               | 122 |

| 6.7  | Static routing of Inter-FPGA signals using Shortest Path Algorithm, (a) Partitioned graph, (b) Partition Mapping and Signal Routing | 124 |

| 6.8  | Partition Swapping Optimisation example: (a) Direct Mapping, (b) Partition Swapping                                                 | 127 |

| 6.9  | The Partition Swapping Optimisation Algorithm                                                                                       | 129 |

| 7.1  | Multi-FPGA system with conventional processors like in XtremeData systems                                                           | 143 |

| 7.2  | A suggested multi-FPGA system to accelerate SPICE                                                                                   | 143 |

| 7.3  | Multi-FPGA framework to synthesise built-in device models                                                                           | 144 |

| A.1  | The Chipscope output waveform similar to the simulation waveforms in Section A.3                                                    | 175 |

|     |                                                                      |     |

|-----|----------------------------------------------------------------------|-----|

| C.1 | The Serial Connections between the FPGAs . . . . .                   | 178 |

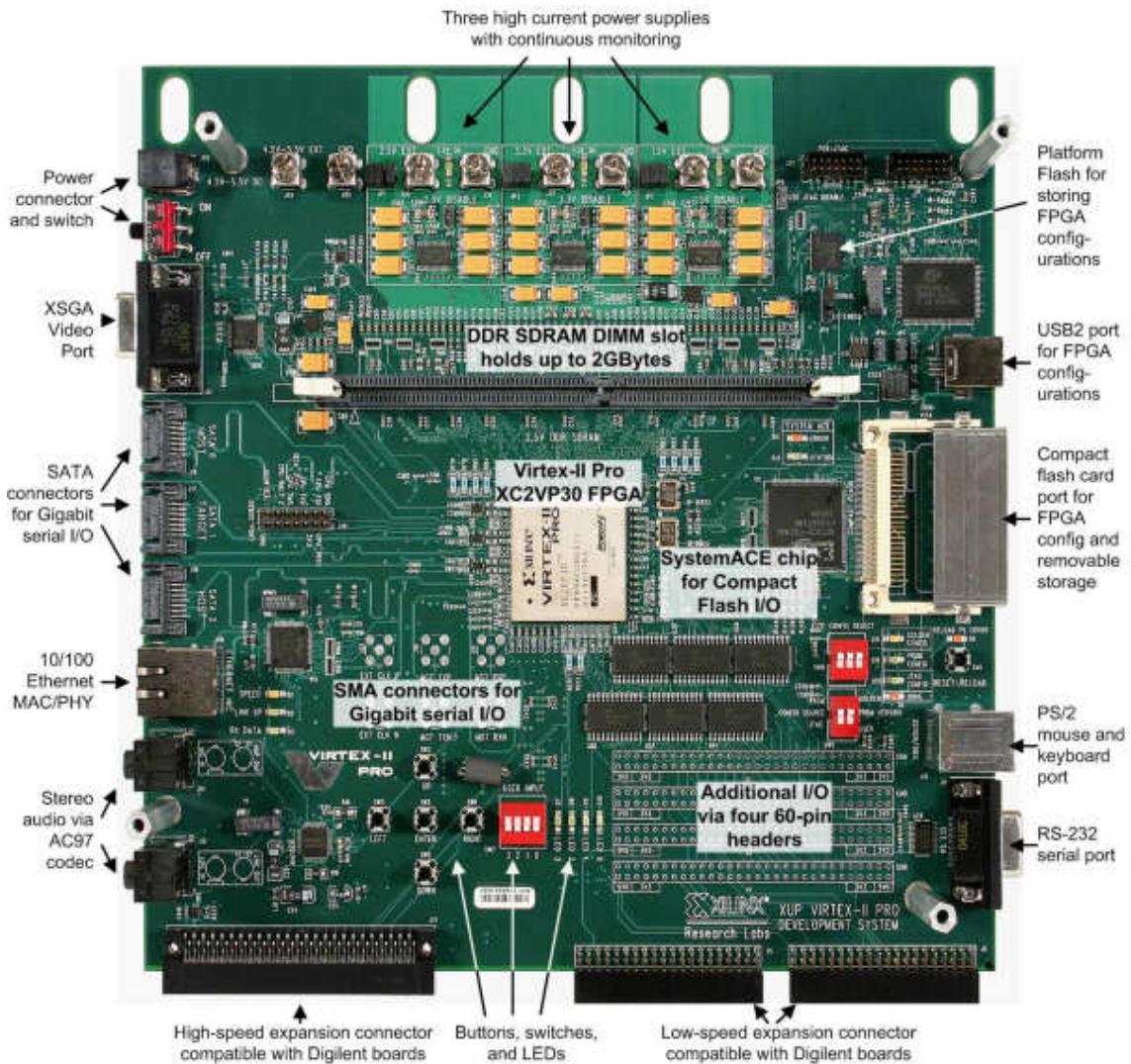

| C.2 | Xilinx University Program Virtex-II Pro Development System . . . . . | 179 |

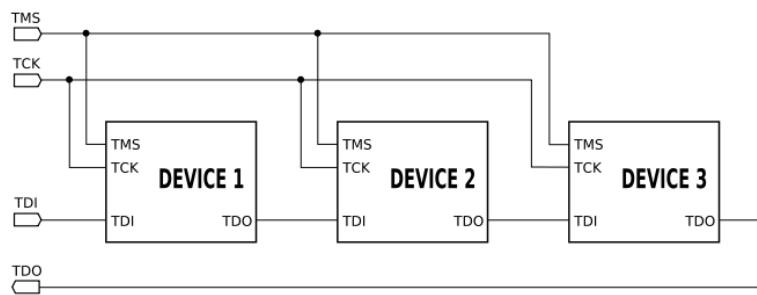

| D.1 | JTAG Chain Arrangement . . . . .                                     | 180 |

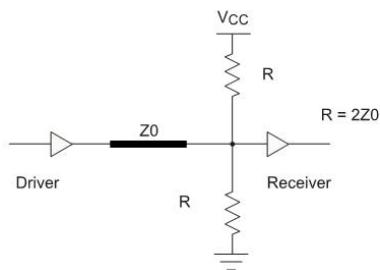

| D.2 | Thevenin Clock Termination . . . . .                                 | 180 |

| E.1 | Chipscope System Block Diagram . . . . .                             | 181 |

| F.1 | IEEE single-precision floating-point format . . . . .                | 184 |

| F.2 | FPLibrary FP number format . . . . .                                 | 187 |

# List of Tables

|      |                                                                                                                    |     |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | Multiprocessor based SPICE simulator acceleration (Previous work) . . . . .                                        | 51  |

| 4.1  | CMOS LEVEL 3 Parameters and default values set at the synthesis level [40] . . . . .                               | 67  |

| 4.2  | The number of device model evaluations $N$ per test case . . . . .                                                 | 76  |

| 5.1  | Average acceleration using the multi-FPGA system . . . . .                                                         | 92  |

| 5.2  | Resources Utilisation of the Full CMOS model Without parameter pre-calculation on the Virtex-II Pro FPGA . . . . . | 95  |

| 5.3  | Resources Utilisation of the CMOS model With parameter pre-calculation on the Virtex-II Pro FPGA . . . . .         | 96  |

| 5.4  | Resources Utilisation of the Slave FPGA Design . . . . .                                                           | 97  |

| 5.5  | Resources Utilisation of the Host FPGA Design . . . . .                                                            | 97  |

| 5.6  | Average power consumption of the multi-FPGA system with different configurations . . . . .                         | 98  |

| 5.7  | Resources Utilisation of the Full CMOS model Without parameter pre-calculation on the V5LX330T FPGA . . . . .      | 100 |

| 5.8  | Resources Utilisation of the CMOS model With parameter pre-calculation on the V5LX330T FPGA . . . . .              | 101 |

| 5.9  | Resources Utilisation of the Slave FPGA Design . . . . .                                                           | 101 |

| 5.10 | Resource Utilisation Estimates for the BSIM4 and the PSP models . . . . .                                          | 105 |

| 6.1  | DFG Benchmarks . . . . .                                                                                           | 130 |

| 6.2  | Wire Count improvement using the Partition Swapping technique for the $4 \times 4$ Mesh Model . . . . .            | 131 |

| 6.3  | Wire Count improvement using the Partition Swapping technique for the $4 \times 4$ Virtual Wires Model . . . . .   | 131 |

| 6.4  | Comparing the wire count improvement with the optimum solution for $3 \times 3$ mesh. . . . .                      | 134 |

| 6.5  | Comparing the wire count improvement with the optimum solution for $3 \times 2$ mesh. . . . .                      | 134 |

| 6.6  | Comparing the wire count improvement with the optimum solution for $3 \times 3$ mesh. . . . .                      | 135 |

| 6.7  | Comparing the wire count improvement with the optimum solution for $3 \times 2$ mesh. . . . .                      | 135 |

|     |                                                            |     |

|-----|------------------------------------------------------------|-----|

| B.1 | Synthesis report of the slave FPGA . . . . .               | 176 |

| B.2 | Synthesis report of the host FPGA . . . . .                | 177 |

| F.1 | Float package synthesis results (Synplify Pro) . . . . .   | 186 |

| F.2 | Number of clock cycles needed for each operation . . . . . | 187 |

| F.3 | Value of X According to Exception Flag . . . . .           | 187 |

| F.4 | Number of clock cycles needed for each operation . . . . . | 188 |

| F.5 | FPLibrary Synthesis Results (Synplify Pro) . . . . .       | 188 |

# Listings

|     |                                                       |     |

|-----|-------------------------------------------------------|-----|

| 4.1 | OpenMP parallelisation of device evaluation . . . . . | 71  |

| A.1 | VHDL-AMS CMOS LEVEL 3 Model . . . . .                 | 160 |

| A.2 | Synthesisable VHDL CMOS LEVEL 3 Model . . . . .       | 165 |

| A.3 | VHDL CMOS LEVEL 3 Model Testbench . . . . .           | 169 |

| E.1 | QueryPerformanceCounter Function usage . . . . .      | 182 |

| F.1 | ‘fixed_pkg’ package usage model . . . . .             | 185 |

| F.2 | ‘float_pkg’ package usage model . . . . .             | 186 |

# List of Acronyms

**ALAP** As Late As Possible

**ANSI** American National Standards Institute

**ASAP** As Soon As Possible

**ASIC** Application Specific Integrated Circuit

**BEE** Berkeley Emulation Engine

**BRAM** Block Random Access Memory

**BSIM** Berkeley Short-channel IGFET Model

**CAD** Computer-Aided Design

**CDFG** Control-Data Flow Graph

**CLB** Configurable Logic Block

**CMOS** Complementary Metal Oxide Semiconductor

**COBRA-ABS** Column Oriented Butted Regular Architecture Algorithmic Behavioural Synthesis

**CPU** Central Processing Unit

**DAG** Directed Acyclic Graphs

**DCT** Discrete Cosine Transform

**DFG** Data Flow Graph

**DMA** Direct Memory Access

**DNA** Deoxyribonucleic Acid

**DSP** Digital Signal Processor

**EDA** Electronic Design Automation

**FCCM** FPGA Custom Computing Machines

**FDS** Force-Directed Scheduling

**FF** Flip Flop

**FIFO** First In First Out

**FLOPS** FLoating-point Operations Per Second

**FM** Fiduccia-Mattheyses

**FP** Floating-Point

**FPGA** Field Programmable Gate Array

**FPU** Floating-Point Unit

**FSL** Fast Simplex Link

**FSM** Finite State Machine

**GA** Genetic Algorithm

**GMRES** Generalized Minimal Residual Method

**GPU** Graphics Processing Unit

**HLS** High-Level Synthesis

**HPC** High-Performance Computing

**HPRC** High-Performance Reconfigurable Computing

**I/O** Input/Output

**ICON** Chipscope Integrated Controller

**ILA** Integrated Logic Analyser

**ILP** Integer Linear Programming

**ILP** Instruction Level Parallelism

**IOB** Input/Output Block

**JTAG** Joint Test Action Group

**KCL** Kirchoff's Current Law

**KL** Kernighan and Lin

**KVL** Kirchoff's Voltage Law

**LU** Lower/Upper Decomposition

**LUT** Lookup Table

**MC** Monte Carlo

**MGT** Multi-Gigabit Transceiver

**MNA** Modified Nodal Analysis

**MOSFET** Metal Oxide Semiconductor Field-Effect Transistor

**MPI** Message Passing Interface

**NoC** Networks-on-Chip

**NP-hard** Non-deterministic Polynomial time

**NR** Newton-Raphson Method

**OpenMP** The OpenMP API specification for parallel programming

**PCB** Printed Circuit Board

**PLB** Processor Local Bus

**PSP** Penn State Philips

**PTHREADS** POSIX -Portable Operating System Interface for Unix- Threads

**RAMP** Research Accelerator for Multiple Processors

**RISC** Reduced Instruction Set Computer

**RTL** Register Transfer Level

**SA** Simulated Annealing

**SATA** Serial Advanced Technology Attachment

**SIMD** Single Instruction Multiple Data

**SoC** System-on-Chip

**SPARCS** Synthesis and Partitioning for Adaptive and Reconfigurable Computer Systems

**SPICE** Simulation Program with Integrated Circuit Emphasis

**SPO** Signal Processing Object

**TMD** Toronto Molecular Dynamics

**VHDL** VHSIC Hardware Description Language

**VHDL-AMS** VHDL Analogue and Mixed-Signal extensions

**VLIW** Very Long Instruction Word

**WR** Waveform Relaxation techniques

# Chapter 1

## Introduction

### 1.1 FPGAs and High-Performance Computing

The term High Performance Computing (HPC) is used to describe systems with large computing capacity (teraFLOPS region), high data throughput, and complex network architecture (e.g Infiniband). HPC uses supercomputers and computer clusters to solve advanced computation problems. The supercomputing term refers to a subset within HPC which uses more powerful computers. According to the TOP500® Supercomputer Sites [1], cluster computing is now the most commonly used architecture in the highest performing systems. Cluster computing has become dominant mainly because of its cost-effectiveness. The architecture relies on standard processors from Intel and AMD, plus standard memory systems and interconnects such as Gigabit Ethernet. Applications are parallelised or partitioned into sections that can run as independent processes on multiple processors.

Regarding the wide spectrum of HPC applications, it is becoming harder for general-purpose CPUs (Central Processing Unit) to keep up with the demands for more computational power [2, 3]. They are running into memory bottlenecks and consuming increasing amounts of power, and dissipating large amounts of heat. Conventional processors also suffer from the increasing latency of using multi-layered caches. The increase in power

consumption and heat dissipation is the result of increasing clock speeds of processors, which subsequently increases the costs of power usage and cooling [4].

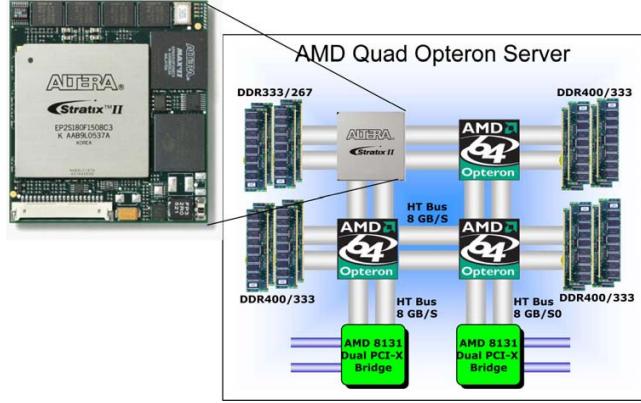

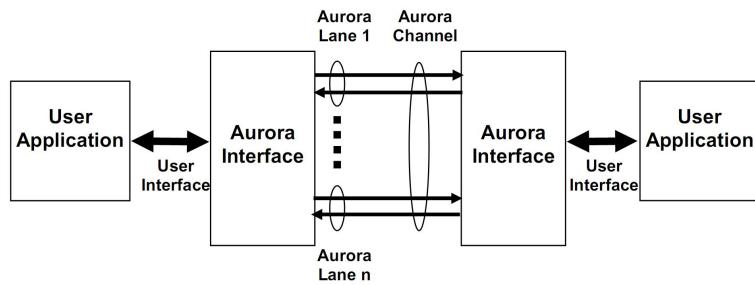

A proposed solution to this new problem is to add Field Programmable Gate Arrays (FPGA) as built-in hardware accelerators to the clusters to boost their computational performance while reducing the power consumption significantly [5, 6, 7, 8, 9]. An FPGA is a semiconductor device that consists of an array of programmable logic elements, interconnects, and I/O (Input/Output) blocks which are user configured to implement complex digital circuits. A number of high-performance system designers have begun exploring the capabilities of FPGAs [10]. This trend highlighted the importance of using multi-FPGA systems in the domain of algorithm acceleration [11]. HPC applications are usually very large algorithms and cannot be fitted on a single FPGA, so these applications are partitioned amongst a number of FPGAs that are connected in a network [12].

FPGAs are reconfigurable hardware devices that can be finely optimised under software control to run applications efficiently. Rather than implementing applications in software, FPGAs allow the execution of applications at near ASIC (Application Specific Integrated Circuit) speeds without the extremely high cost of creating custom silicon. In addition, FPGAs have the ability to exploit the inherent parallelism in the algorithms being implemented [13, 14]. The internal FPGA architecture can be finely tuned to particularly exploit a certain application parallelism unlike conventional processors which are designed to suite broader range of applications. FPGAs also provide higher performance with their high memory bandwidth and hardware parallelism. A processor would need to execute a number of instructions before it can access the data from the memory. However, an FPGA is a hardware circuit that can be connected directly to a system bus, which gives it a direct access to the memory system.

Algorithm parallelism can be addressed at different levels. HPC applications can be structured for multi-thread execution in parallel across a cluster of processors. This level is known as coarse-grain parallelism. Coarse-grained parallelism is usually specified manually using a set of compiler directives at the input source level (e.g. threads,

Message Passing Interface MPI). Another level of parallelism would be to execute a number of instructions simultaneously, which is called fine-grain parallelism. The fine-grained parallelism can be extracted automatically from the behavioural descriptions through the synthesis process. Conventional processors also support this type of parallelism; but FPGAs provide much deeper pipeline than conventional processors and can execute much larger number of instructions simultaneously [14]. Processors usually have to use their own built-in functional units to perform computations, however, FPGA designs can be finely customised and pipelined to a much deeper degree due to their internal reconfigurability features.

Benchmarks in [8] showed that an FPGA operating at a frequency of 200 MHz running the Black Scholes financial simulation [15, 16] can outperform a 3 GHz processor by an order of magnitude or more, while consuming only quarter of the power. In another example, FPGAs have shown 185 to 250 times acceleration in running sequential alignment algorithms for Deoxyribonucleic Acid (DNA) sequences over conventional processors in [17]. An FPGA based accelerator for Monte Carlo (MC) simulation have demonstrated an acceleration of nearly 25 times over the software implementation as reported in [9].

In this work, we target FPGA devices due to their capabilities to provide fine-grain parallelism and reconfigurability. One of the main strengths of FPGAs in high-performance computing lies in the ability to reorganise the internal structure of a machine to feed data-to-data processes at high speed instead of forcing them to make continual memory requests [18]. This can make FPGAs much better at sustaining performance compared to processors, as they do not have to deal with the penalties of cache misses [14].

This made FPGAs an attractive hardware acceleration solution to be used for a wide variety of computing/power-hungry applications. One of the these applications would be to enable the Computer-Aided Design (CAD) community to accelerate Electronic Design Automation (EDA) algorithms and hence reduce the design time. The SPICE (Simulation Program with Integrated Circuit Emphasis) simulator is an example EDA tool which present a growing bottleneck in the development process. This thesis outlines the use of multi-FPGA systems in accelerating the SPICE simulator.

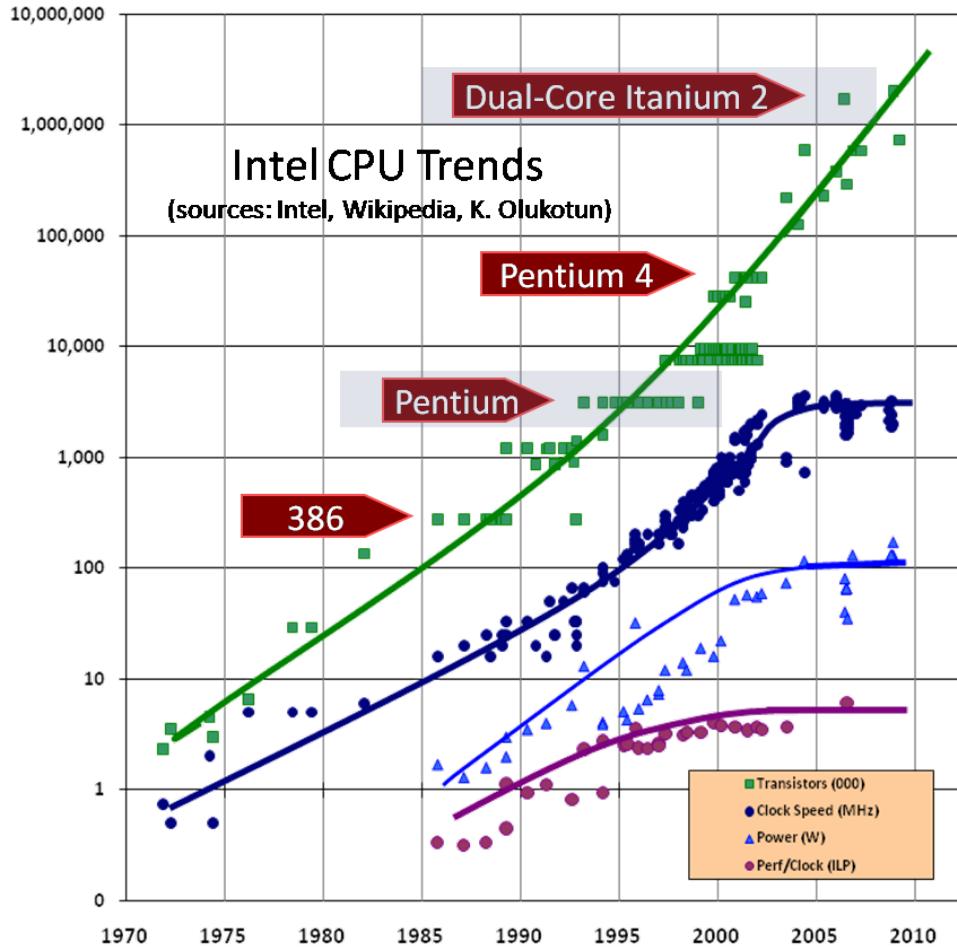

FIGURE 1.1: Intel CPU Timeline [19]

## 1.2 Current Technology Limitations

According to Moore's Law, the number of transistors on a chip doubles every two years. The law also states that improved clock frequency and improved architecture results in doubling of the processor performance every 18 months. This pattern is illustrated in Figure 1.1. The figure shows the Intel processors trend in terms of transistor count, clock speed (MHz), power (W), and performance/clock (ILP) [19], where Instruction-Level Parallelism (ILP) factor is a measure of the number of operations in a computer program that can be performed in parallel.

Current conventional processors largely relied on the gains leveraged by Moore's Law.

However, in recent years, these gains started to shrink as this law is expected to hit physical limitations on feature sizes in the future [20]. The other major limiting factor is the sharp flattening of clock speeds and the performance gain (just after the year 2005 as seen by the second and the third curves from the top in Figure 1.1). Another limiting factor is the wide gap between processor and memory speeds. In other words, as the number of transistors inside chips continues to rise -at least for the time being- clock speeds are flattening because faster processors would consume more power and dissipate larger amounts of heat which will increase system costs.

Current trends indicate that future computing platforms are likely to continue benefiting from the continuation of Moore's Law by relying on massive parallelism [4, 21]. One of the main current trends clearly shows a shift from single-core processors to multi-core processors, which is changing the computing arena [22]. This move is expected to achieve performance gains, given that new parallel computing tools are developed to fully exploit the available hardware parallelism. Processor vendors are already moving to a model where the number of cores available on a single chip will double with each semiconductor process generation [23, 24].

In addition to the current multi-core trend, FPGAs also have been gaining the attention of the HPC community in the last few years [5]. Recent Studies point that the peak FPGA floating-point performance is growing significantly faster than peak floating-point for CPUs. While CPU performance is doubling every 18 months according to Moore's Law, the performance of FPGAs increases by a factor of 4 every two years. For FPGAs with architectural built-in improvements such as built-in multipliers and Digital Signal Processing (DSP) blocks, the performance is estimated to be increasing by a factor of 5 every two years [25]. This rapid advances also includes the doubling in capacity of FPGAs every 18 months [24]. FPGAs now can contain approximately 330,000 logic blocks and around 1,100 I/O pins and an operating frequency of up to 1,600 MHz [26, 27].

Due to the limitation in clock speeds and Moore's Law is coming to its physical limitation, the research community have already suggested a number of ways to continue harvesting the performance gains every year. One of these approaches is to rely on performance delivered using parallelism by adding more cores onto processors and hence moving from single-core to multi-core processors. This can be seen as a fundamental turn toward concurrency in software [19]. Another research direction is to use hardware acceleration engines like FPGAs and GPUs (Graphics Processing Unit) along side conventional processors to continue the performance gain. A vision in the current research is to use heterogeneous computation elements like FPGA, GPUs, CPUs, and ASICs together in one complete system to achieve the maximum achievable speedup.

### 1.2.1 Efficiency of Parallel Systems

Current parallel computer systems provide a large throughput in accelerating computationally intensive tasks. Usually, the cost to develop a parallel system with  $N$  replicated processors is less than designing an  $N$  times faster single-core processor [28]. Hence, it is possible to use lower performance lower cost technology to construct higher performance parallel systems. This can also be applied to FPGAs when used to speedup applications. A number of less performant lower cost FPGAs can be used in parallel to build high performance hardware accelerators.

In order to achieve high efficiency with parallel implementation of an algorithm, one must carefully tune the application to ensure that most processors are busy throughout the execution process, while minimising the parallelisation overhead. Parallel programs are usually composed of sections of one of the following types:

- **Serial Code:** Sections of the code which must be executed on a single processor.

Little or no useful work can be done on other processors.

- **Critical Code:** Sections of the code which can only be executed on a single processor at any given time. Other parallel section can be executed on other processors alongside the protected code.

- Parallel Code: Sections of the code which can be fully executed in parallel.

From Amdahl's Law [29], the ratio between the parallel execution time  $T_{parallel}$  on  $N$  processors and the execution time for a single processor  $T_{single}$  is given by:

$$\frac{T_{parallel}}{T_{single}} = F_{serial} + MAX(F_{critical}, \frac{F_{critical} + F_{parallel}}{N}) \quad (1.1)$$

Where  $F_{serial}$ ,  $F_{critical}$ , and  $F_{parallel}$  are the serial, critical, and parallel fractions of the code respectively. From Equation 1.1,  $F_{serial}$  must be minimised in order not to limit the overall parallel speedup. Each processor runtime usually depends on the data being processed by that processor. If a processor requires more runtime to execute the parallel code on its data, the other processors should wait until the slow process terminates. This granularity problem reduces the gain of parallelisation.

## 1.3 Reconfigurable Computing

### 1.3.1 FPGA Architecture

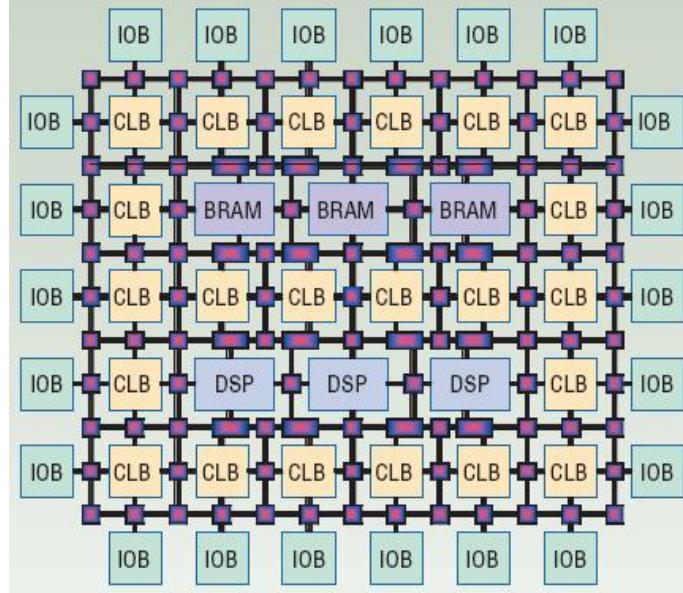

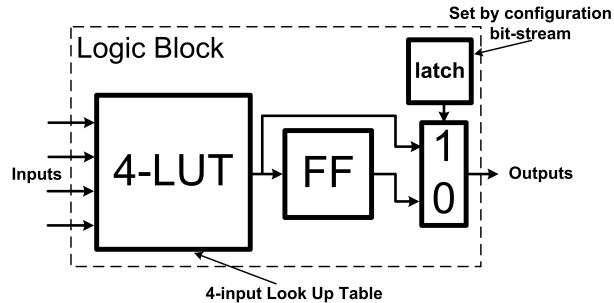

FPGAs are semiconductor devices that consist of arrays of Configurable Logic Blocks (CLB), interconnects, and I/O Blocks (IOB). Xilinx and Altera are the current main FPGA vendors. Figure 1.2 shows the typical Xilinx FPGA architecture, which also contains built-in hardware such as Block Random Access Memory (BRAM) and DSP blocks [5], which are user configured to implement complex digital circuits. The basic architecture of a CLB consists of a Look-Up Table (LUT) with four -or more- inputs and a Flip Flop (FF), as seen in Figure 1.3 [30]. Each IOB provides individually selectable I/O access to one of the external pins.

Usually, ASIC systems are faster than FPGAs, consume less power, and can implement very complex designs. However, FPGAs can be reprogrammed to perform different functionalities [31]. The desired function can be described in any hardware description language and then synthesised to a technology-mapped netlist ready for reprogramming.

FIGURE 1.2: Typical Xilinx FPGA Internal Architecture [5]

FIGURE 1.3: Configurable Logic Block (CLB) Basic Architecture [30]

ASIC chips follow the same design flow, however, netlists are mapped permanently on silicon and cannot be reprogrammed again. Recent advances in FPGA design flow and the increasing device capabilities have made FPGAs increasingly popular. Figure 1.4 shows the FPGA growth trend [32].

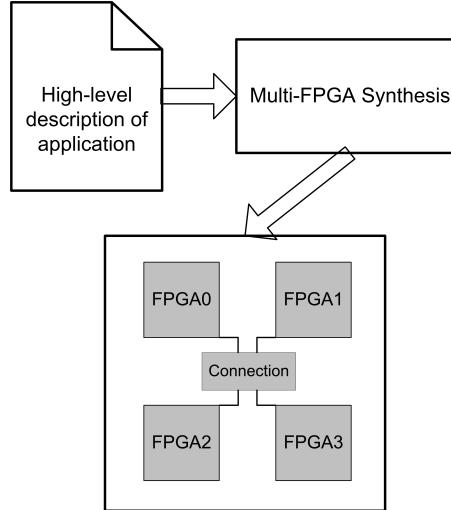

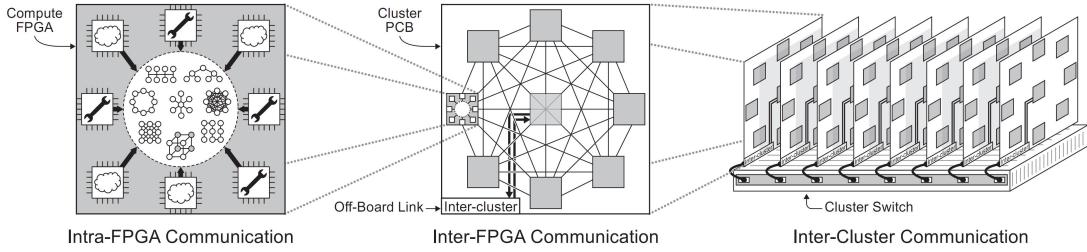

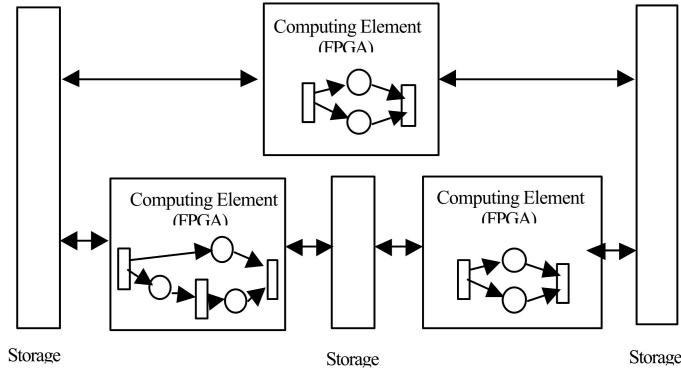

Reconfigurable Computing (RC) is a computer architecture which combines some of the flexibility of software with the high performance of reconfigurable devices like FPGAs. Figure 1.5 demonstrates a typical Multi-FPGA Reconfigurable Environment, which consists of the following two main parts:

- The Synthesis system that maps the high-level description of the application.

FIGURE 1.4: FPGA Growth Trend [32]

- The Multi-FPGA Reconfigurable hardware system to map applications onto.

FIGURE 1.5: A Typical Multi-FPGA Reconfigurable Environment

### 1.3.2 Multi-FPGA Synthesis System

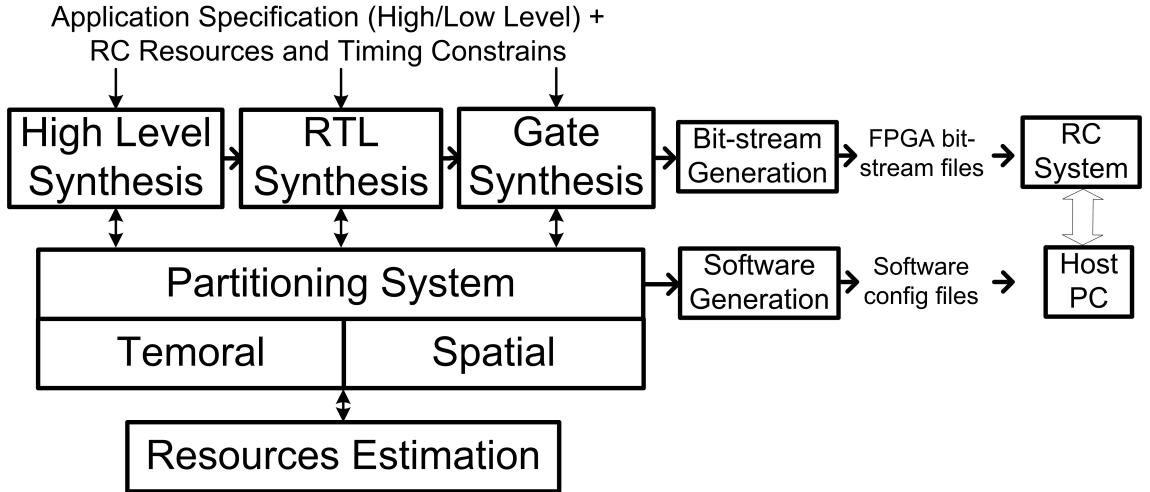

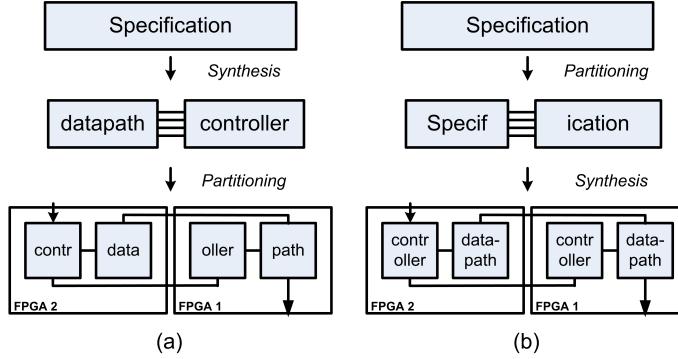

Multi-FPGA Synthesis design flow consists of two main processes: Synthesis and Partitioning as outlined in Figure 1.6 [33]. The input Application Specification can be expressed at three abstraction levels: High-Level (behavioural), Register Transfer Level (RTL), and Gate Level. High-Level designs are specified in the form of algorithmic descriptions; and RTL level designs are structural netlists of components; whereas Gate

level designs are represented as a set of boolean equations. The size of structural details reduces as we move from Gate level up to the High-Level abstraction layer. The design flow also takes as input the RC Resources and Timing Constraints.

FIGURE 1.6: Electronics Design Automation Flow for Typical Reconfigurable Computing Systems [33]

The synthesis step processes the input specification through a number of sub-processes (scheduling, binding, and allocation) to generate a final device netlist. The input specifications are usually converted to graph-based platform independent models, with nodes denoting computations and edges denoting data and control flow. The Partitioning step uses similar model to partition the design specifications into a number of connected sub-graphs (i.e. sub-circuits). If the whole input design cannot be fitted into the RC system, the Temporal Partitioning divides this design description into a sequence of temporal segments. Each temporal segment can use all the RC resources. Dynamic programming approach is used to sequentially program the system with the different temporal portions [34, 35]. The Spatial Partitioning divides the input design into a number of spatial segments to match the number of FPGAs in the system. The system employs a number of resources estimators in order to satisfy the initial RC resources and timing constraints. Finally, the system generates the bit-stream files to configure the hardware system.

The RC Systems design flow shown in Figure 1.6 should determine the appropriate trade-offs between the overall performance of the system, resources utilised, and the inter-FPGAs communication. The synthesis process translates the behavioural/structural description of the system to a generic circuit composed of a datapath and a controller. The main goal of the partitioning process is to achieve the minimum number of signals between the different partitions due to the limited number of I/O pins in FPGAs.

The degree of acceleration that can be achieved depends heavily on the inherent parallelism available in the application itself. Furthermore, the application design flow for RC systems is still not a straightforward task. It can range from designing hardware, which is tedious and error prone, to software that requires hardware knowledge. Therefore, integrating FPGAs in HPC needs programming tools that address the whole parallel architecture.

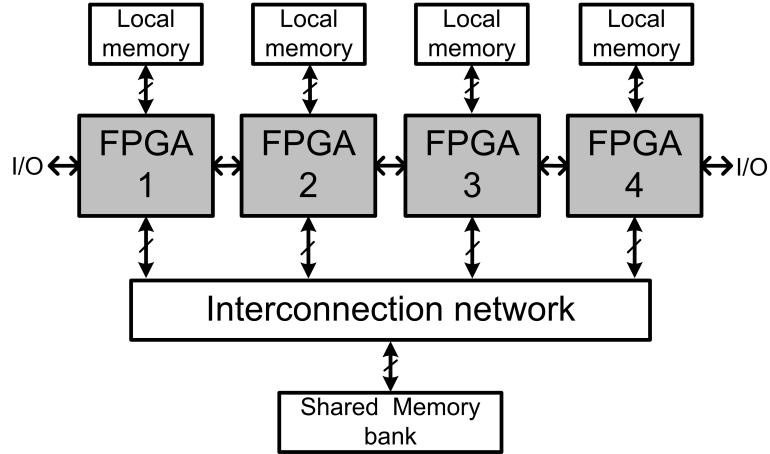

### 1.3.3 Multi-FPGA Hardware System

Typical FPGA-based RC Systems have several FPGAs and memories communicating through a predefined network topology as shown in Figure 1.7. A number of approaches are used for interconnection network like direct connections, programmable interconnects, and buses. The FPGAs are connected to local memory banks or a shared global memory bank depending on the programming model used for each application. Multi-FPGA systems are typically used as co-processors connected to a host PC or as standalone computing systems [33].

RC Systems are generally statically or dynamically programmed. Static programming approach loads the configuration bit-streams onto the FPGA devices once only and the entire application is executed thereafter. Dynamic programming, however, loads partial bit-streams of the application onto the FPGAs and waits for the partial execution to finish; the host PC then re-programs the FPGA devices to perform another portion of the application. Dynamic programming approach provides virtually unlimited hardware resources for the application. However, this approach suffers from long re-programming delays [36].

FIGURE 1.7: A Typical Reconfigurable Computing Architecture [33]

## 1.4 Research Motivations

Given the recent advances in the domain of HPRC systems, a key question to ask is whether we can use multi-FPGA systems to accelerate the SPICE simulator. This thesis explores ways to answer this question.

### 1.4.1 SPICE Simulation

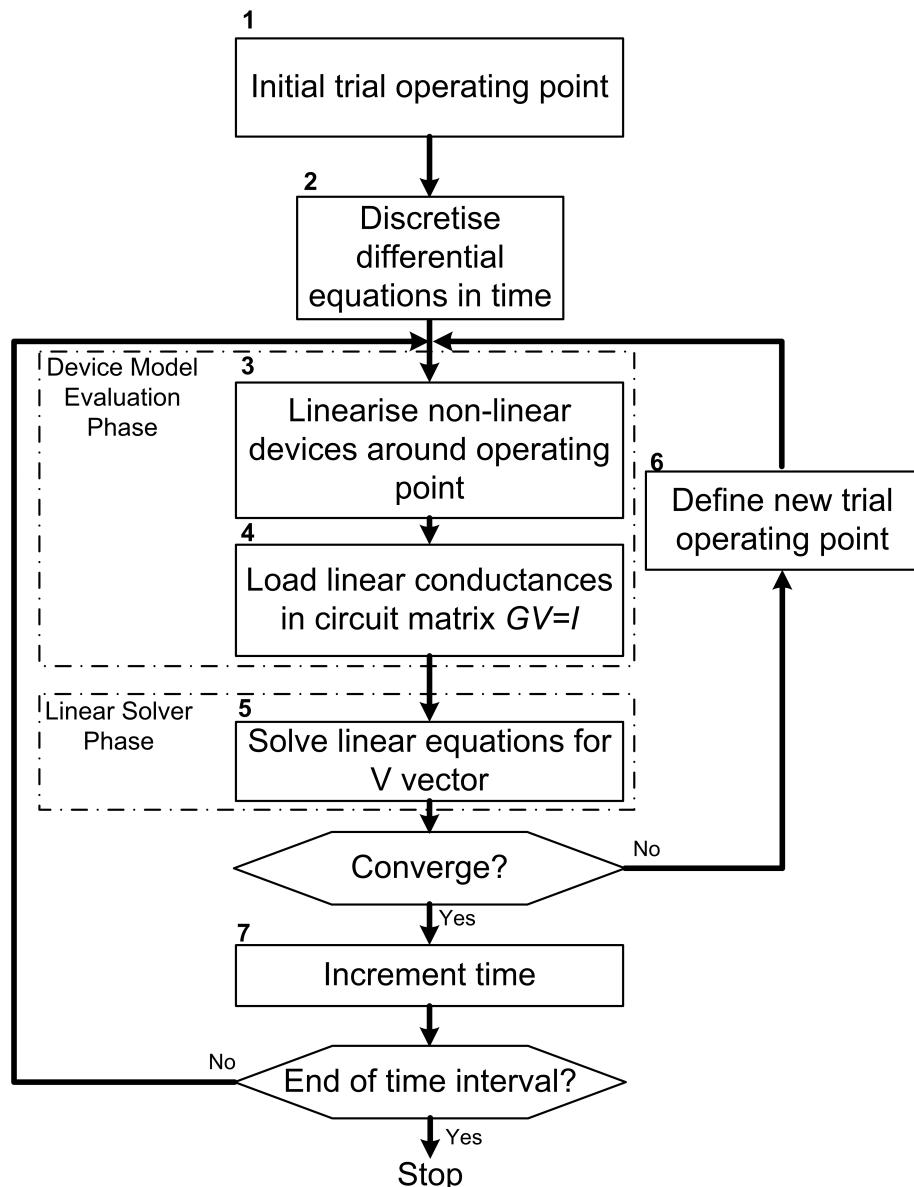

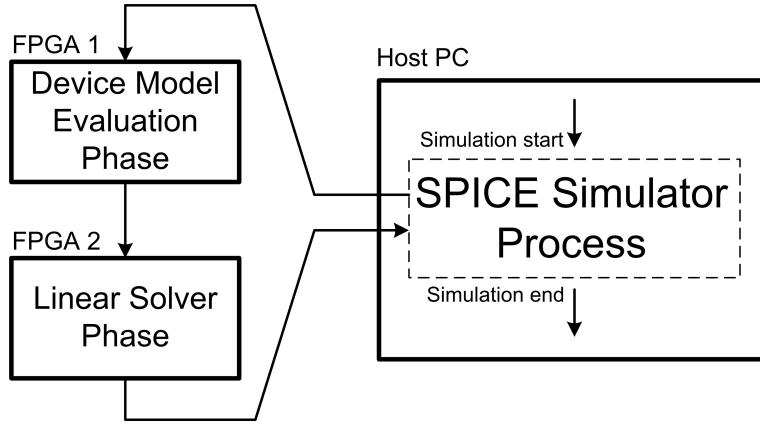

SPICE simulation is an essential step in the design and verification of modern circuits [37, 38, 39]. The SPICE algorithm simulates the behaviour of non-linear circuits. This is done by formulating the circuit equations of the linear devices (e.g. resistors) and non-linear devices (e.g. transistors) using Kirchoff's conservation laws, also known as the Modified Nodal Analysis (MNA) [40] which is explained in Section 3.1. The MNA analysis involves the following steps:

- Formulating the circuit equations of the linear devices (e.g. resistors, capacitors) and non-linear devices (e.g. transistors) using Kirchoff's conservation laws at the different nodes of the circuit.

- Evaluating circuit conductances and current matrices from the device model equations. This phase is called the Device Model Evaluation Phase.

- Solving the circuit models using Newton-Raphson (NR) method.

- Solving the system of the linearised equations representing the circuit using methods like Lower/Upper (LU) decomposition. This phase is called the Linear Solver Phase.

### 1.4.2 SPICE Simulation Bottleneck

Due to the current increase in the complexity of analogue and mixed-signal chips, EDA verification tools are demanding more computational power [41]. This made the transistor-level simulation a growing bottleneck in the overall development process. SPICE simulations of large sub-micron circuits with high accuracy can often take days or weeks of runtime on current processors. SPICE simulation is typically infeasible for circuits larger than 20,000 devices [42]. Also, given the decreasing minimum feature size of devices, their numbers on a single chip has risen significantly over the last few years. The process of down-scaling transistors also impacted the electrical characteristics of devices. As a result, it became very important to run simulations on larger segments of circuits in order to validate their electrical and timing behaviours before fabrication. Hence, there is a very urgent need to accelerate circuit-level simulations without sacrificing accuracy.

The SPICE simulator has a number of components with varying degrees of inherent control and data parallelism. Hence, it is not easily parallelisable on conventional processors due to its irregular structure of computations, limited peak floating-point capacities and constraints due to limited memory bandwidth. The SPICE simulator is used as a benchmark in the SPEC92 collection which represents a set of challenging problems for CPUs [43]. Hence, the SPICE simulator is a challenging application that is worth looking at ways to accelerate through parallelism.

A number of approaches were introduced to reduce the SPICE simulator runtime by parallelisation, which met with mixed success. Attempts either compromised accuracy (which leads to convergence issues) or have employed specialised custom platforms that

has been overtaken by the recent advances in general purpose and multi-core processors [44, 45, 46]. When considering the acceleration of the SPICE simulator through parallelisation, one must consider the two phases of the Newton-Raphson iteration: the Device Model Evaluation and the Linear Solver (Section 1.4.1). A number of studies explored the hardware-based acceleration of both phases, as detailed in Section 3.3.2. FPGAs and GPUs are currently under great interest in order to take advantage of their speedup in boosting the performance of current EDA tools.

## 1.5 Research Scope and Objectives

The area of hardware accelerated SPICE simulator is becoming more important as FPGAs and GPUs are becoming increasingly attractive to continue the performance gain. New acceleration platforms that can be used to accelerate the SPICE simulations should be based on standards in order to facilitate maintainability and portability of such applications [21]. The SPICE simulator bottleneck could be eased by exploiting the inherent hardware parallelism in FPGAs. The FPGA-based accelerators have a great potential in relieving the increasing complexities faced by current EDA tools, and hence shorten the simulation and verification times.

One of the main objectives of this project is to investigate a design methodology for a high performance, low-cost accelerator that exploits the inherent parallelism in the SPICE simulator. This involves identifying the key parts of the algorithm most suitable for FPGA implementation in addition to the design decisions related.

This thesis demonstrates how a Spatial Implementation of Device Model Evaluation phase of the SPICE circuit simulator can be designed and optimised by exploiting the inherent parallelism at different levels. The fully spacial implementation of the SPICE device model would take up the resources of a number of FPGA combined together. This will result in a number of intermediate signals being exchanged between FPGAs which have to be transferred through the I/O resources. However, FPGAs tend to be limited in terms of their available I/O pins. Hence, one of the objectives of this research project

is to look at techniques to optimise the inter-FPGA connections and hence reduce the FPGA pin usage. This thesis addresses the following research questions:

- What are the different degrees of parallelism in the device model evaluation phase that can be exploited using FPGAs.

- How can the device model evaluation phase be mapped efficiently on multi-FPGA systems?

- How much acceleration can be achieved over conventional processors?

- How inter-FPGA connections can be minimised in case large device models have to be mapped on multiple FPGAs?

## 1.6 Thesis Structure

A multi-FPGA system was presented to perform the transistor device model evaluations in parallel. The work showed that FPGAs have a great potential to accelerate the SPICE simulator. Our study also demonstrated a code transformation flow where the device model code can be translated from a high-level description to a structural description ready for FPGA mapping.

This study also highlighted the issue of inter-device in the domain of multi-FPGA synthesis especially if a spatial implementation of large device models is considered. This would require a large number of signals to be exchanged between FPGAs in the multi-FPGA system. This brings to the surface, the optimisation of the pin usage since FPGAs are limited in terms of their resources including I/O pins. A multi-FPGA synthesis system specifically focused on inter-FPGA optimisation was designed. An optimisation approach was introduced to reduce the number of inter-FPGA signals by altering the process of mapping partitions to FPGAs.

The thesis is structured as follows:

Chapter 2 outlines the background information relating to high-level synthesis and partitioning. This Chapter also presents the state of the art advances in the field of High-Performance Reconfigurable Computing (HPRC) in the programming/hardware sides in addition to some applications employing hardware acceleration.

Chapter 3 explains the theoretical background of the SPICE simulator and also outlines the different approaches used to exploit the inherent parallelism in the algorithm. This Chapter outlines our approach to accelerate the SPICE model evaluation using a Spatial FPGA implementation.

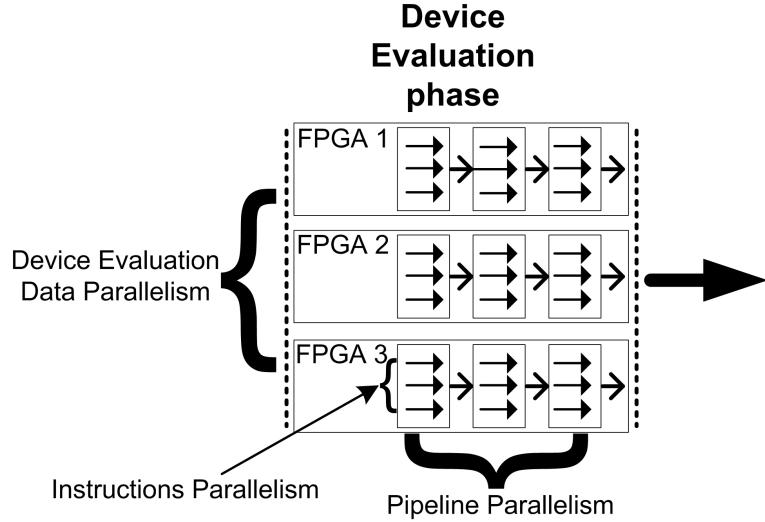

Chapter 4 explains the design and implementation of the prototype multi-FPGA system used to accelerate the device model evaluation as proposed in Chapter 3. A single FPGA implementation is first considered in order to evaluate the acceleration and resources results of the device model. A multi-FPGA system is then prototyped using three off-the-shelf Xilinx Virtex II Pro FPGA boards to demonstrate the amount of acceleration that can be achieved through parallelism.

Chapter 5 presents the synthesis and acceleration results of the experimental work outlined in Chapter 4. The system showed that multi-FPGA systems can effectively be used to accelerate the device model evaluation, and hence SPICE simulations. The results were extended theoretically to include newer SPICE device models and to take advantage of state-of-art multi-FPGA systems.

Chapter 6 presents the design and implementation of a prototype multi-FPGA synthesis system and an optimisation technique used reduce the multi-FPGA pin-usage. This Chapter investigates the use of high-level synthesis and partitioning in the process of pin utilisation optimisation of a mesh-based topology.

Chapter 7 discusses our conclusions, research contributions, and future work. The Chapter showed that our application specific architecture can be used as a high speed co-processor attached to workstations to boost SPICE-like simulations. This Chapter also discusses the use of our device model accelerator for iterative solver based simulation.

## 1.7 Publications

- A. Maache, J. Reeve, and M. Zwolinski. Accelerating CMOS Device Model Evaluation Using Multi-FPGA Systems. In Fifth UK Embedded Forum 2009, Leicester, UK, pages 10–14, September 2009 [47].

- A. Maache, J. Reeve, and M. Zwolinski. Optimising Physical Wires Usage in Mesh-based Multi-FPGA Systems using Partition Swapping. In 21st International Conference on Microelectronics, ICM09, Marrakech, Morocco, pages 246–249, 19–22 December 2009 [48] .

## Chapter 2

# Multi-FPGA Systems Review

This Chapter outlines the background literature in the domain of algorithms acceleration using multi-FPGAs. This domain includes multi-FPGA synthesis which is composed of hardware synthesis and logic partitioning. This Chapter also presents the state of the art advances in the field of High-Performance Reconfigurable Computing. Section 2.1 gives general overview of hardware synthesis. Section 2.2 describes the different circuit partitioning methodologies and a number of existing multi-FPGA synthesis systems. Section 2.3 presents the advances in the architectural/hardware sides and some applications employing hardware acceleration in high performance computers. Section 2.3.2 outlines the current advances from a programming models' perspective. Section 2.4 summarises the design decisions taken to design our multi-FPGA system based on the materials reviewed in this chapter.

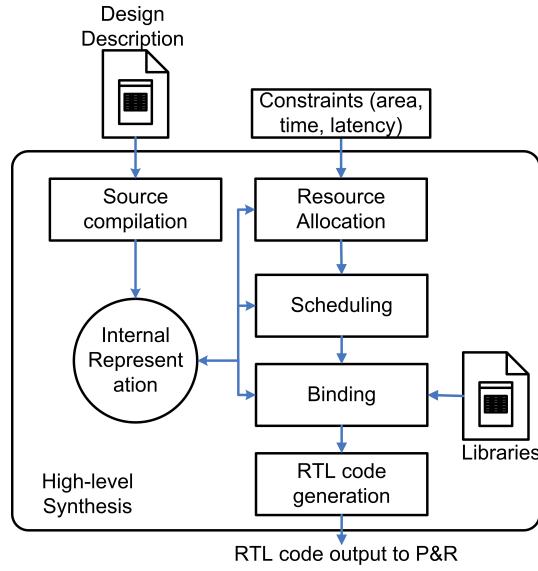

### 2.1 High-Level Synthesis

High-Level Synthesis (HLS) is the process of transforming an abstract specification of the system to a structural description satisfying user constraints on area, delay, and power consumption [49, 50, 51]. Figure 2.1 illustrates a generic HLS system [52]. The HLS system takes as inputs a behavioural description of the design plus user constraints.

The input description is compiled into an internal representation, usually a Control Data Flow Graph (CDFG), which is passed through the three synthesis steps: scheduling, allocation, and binding. Low level module libraries are used to guide the synthesiser through the optimisation process to meet the design objectives. The synthesis output is a mixture of structural and RTL descriptions suitable for the placement and routing tools. Example state-of-art HLS tools includes Symphony HLS from Synopsys [53], and Catapult C from Mentor Graphics [54].

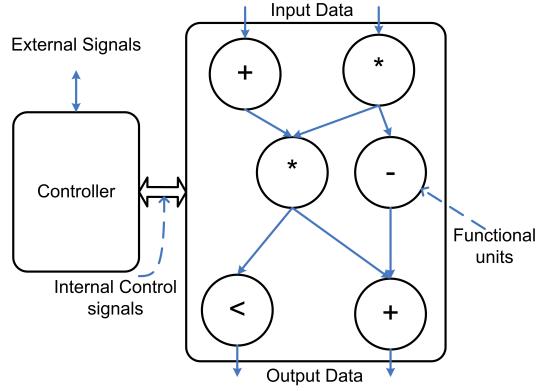

FIGURE 2.1: Generic High-Level Synthesis System [52]

The structural description generated by a typical HLS system consists of a datapath, a controller, and memory elements as seen in Figure 2.2 [55]. The datapath consists of a set of functional units (adders, multipliers, and shifters), storage units (registers, counters, and register files) and interconnections units (wires, multiplexers and buses). The control unit consists of a Finite State Machine (FSM) that controls the functional and storage units by steering the data in the datapath using internal control signals such as register load and multiplexer select signals.

FIGURE 2.2: Generic structure of the synthesis target circuit

### 2.1.1 Scheduling

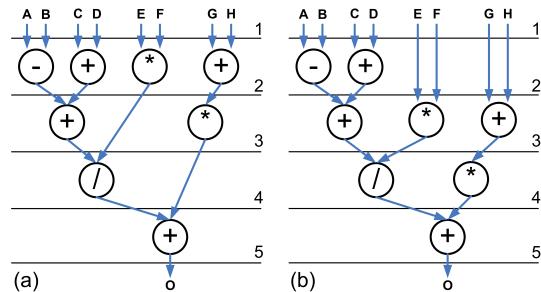

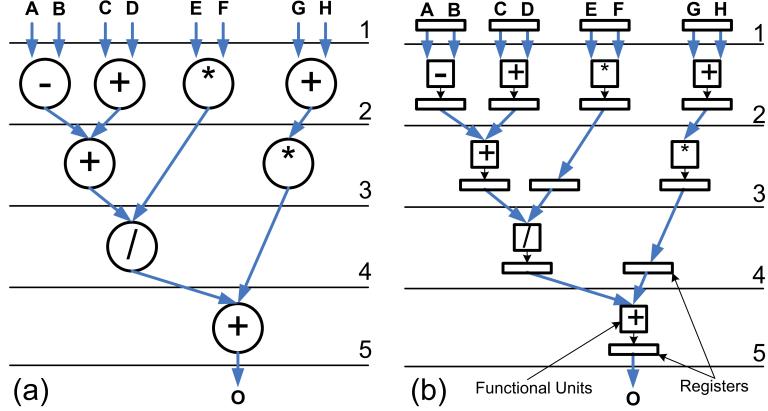

The Scheduling step assigns each operation in the internal representation (CDFG) to a particular time step. Schedules are usually optimised to achieve the user constraints in terms of timing and area. Scheduling algorithms can be generalised into two main categories: *constructive* and *transformational scheduling*. Constructive algorithms are called so because they construct a solution without performing any backtracking. Transformational algorithms, however, work on improving an initial schedule by applying a set of transformations [49, 56]. *As Soon As Possible* (ASAP) and *As Late As Possible* (ALAP) are the simplest constructive schedules. ASAP schedules operations in the earliest possible time step permitted by data dependencies, while ALAP assigns operations to the latest possible time step. Figure 2.3 shows an ASAP and ALAP schedules of the equation:  $O = ((A - B) + (C + D)) / (E * F) + (G + H)^2$ . Operations are treated equally with no priority given to the more critical ones.

FIGURE 2.3: Example of ASAP (a) and ALAP (b) schedules

List Scheduling assigns operations to time steps based on a pre-defined priority function. Operations are scheduled sequentially as long as the required resource is available, otherwise, operations are postponed according to their priority. The Force-Directed Scheduling (FDS) is a constructive algorithm that makes decisions based on a global analysis of operations and control steps [57]. The main issue with the above algorithms is that decisions are made upon local considerations, which might not necessarily produce an optimum schedule.

The transformational approach starts with an initial schedule, generally ASAP or ALAP, and iteratively applies a set of local transformations to improve the schedule towards the user specified constraints. One important advantage of this type of algorithms is that a complete schedule exits after each iteration and hence an accurate estimates of time and area can be obtained. Integer Linear Programming (ILP) is a mathematical method to solve the scheduling problem under resource constraints which provides an exact analytical solution to the scheduling problem. However, ILP formulation and solving processes are computationally expensive and limited by the number of variables used [49, 58].

### 2.1.2 Allocation

Allocation is the process of determining the type and quantity of resources used in the design. It also determines the clocking scheme, pipelining style, and memory hierarchy. The selection process utilises a set of component libraries, which may contain multiple implementations of functional units, each with different properties (size, delay, and power). The main goal of the allocation phase is to perform the optimum trade-off between the design performance and cost. Designs with inherent parallelism can be assigned more hardware resources which results in better performance; but it also increases the area cost. However, allocating less hardware resources reduces the area cost, but results in poorer performance [50].

### 2.1.3 Binding

Binding is the process of assigning the already allocated datapath units from a list of technology-dependent cell/module libraries. The latter may contain one or more implementations of the same functional unit, in which a decision would be made based on the user objectives. Area and time estimates of the library components are also used to guide the scheduling/allocation processes [51]. Binding involves assigning the variables and instructions into one of the following types:

- Functional binding assigns each operation in the schedule to a functional unit such as adders, shifters and multipliers.

- Storage binding assigns variables to storage units such as registers, register files and memory units.

- Interconnect binding assigns an interconnection unit to a multiplexer or a bus, where each interconnect represents a data transfer between functional and storage units.

## 2.2 Multi-FPGA Logic Partitioning

Logic Partitioning for multi-FPGAs systems consists of splitting an internal design representation into a number of balanced partitions. Each partition is programmed to a particular FPGA. A common design representation for partitioning would be a graph based model like Data Flow Graphs [59], Control and Data Flow Graphs [33], or Module Call Graphs [52, 60]. The design representation is partitioned with the aim to satisfy the optimisation criteria and the user constraints in terms of area, speed, power, and I/O pin-usage.

## 2.2.1 Partitioning Methodologies

Partitioning algorithms are categorised into two main categories: *constructive* and *iterative* algorithms [61]. Constructive algorithms finds partitions from a graph representation of the circuit. In other words, partitions are constructed from the original graph in an incremental fashion. The iterative approach, however, works to improve an existing solution. One of the most well-known iterative algorithms is the Kernighan and Lin (KL) algorithm) [62] and its variant, the Fiduccia-Mattheyses (FM) heuristic [63]. The constructive methods include the Simulated Annealing (SA) and Genetic Algorithms (GA) [61, 64].

### 2.2.1.1 Partitioning Problem Formulation

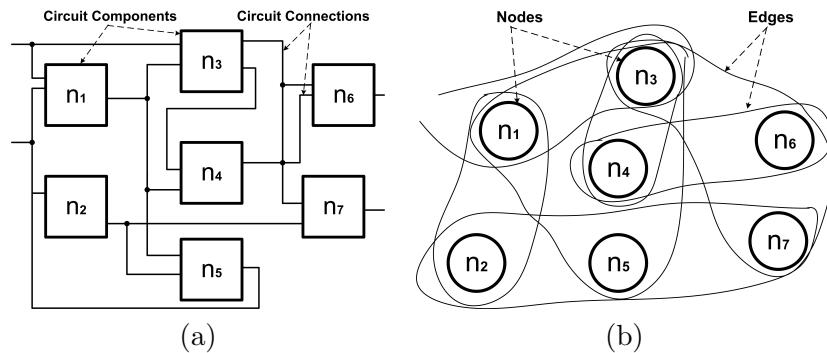

The general graph partitioning consists of dividing a set of components and a netlist of connections between these components into a number of balanced partitions. A graph is a set of nodes (nodes) linked together with a set of edges. Each edge connects exactly two nodes. A *Hypergraph* is a generalisation of a graph, where an edge can connect multiple nodes. A hypergraph is particularly useful for representing typical circuit netlists because connections can be made between multiple components. Figure 2.4 shows an example circuit and its representation using a hypergraph, where the Circuit Components  $\{n_1, n_2, \dots, n_7\}$  are represented as Nodes and the Circuit Connections between these components are modelled as Edges.

FIGURE 2.4: (a) Example circuit, (b) Hypergraph representation

The input design is usually modelled as a hypergraph  $G(V, E)$ , where  $V$  is the set of nodes  $i(n_i)$  corresponding to the components  $\{n_1, n_2, \dots, n_7\}$  as seen in Figure 2.4, and  $E$  represent the signal nets that interconnects the components. A *signal net* is a simple connection between two or more components in the hypergraph, which is represented by the set of groups in Figure 2.4(b). Dividing  $V$  into a set of  $K$  disjoint partitions is called *multi-way partitioning* when  $K > 2$  and *bi-partitioning* when  $K = 2$ . Hence, given the  $K$ -way partition  $\{V\} \rightarrow \{V_1, V_2, \dots, V_K\}$ , the objective of the partitioning algorithm is to minimise:

$$cutsize = \sum_{i,j} k_{ij}, \quad \text{where } i \neq j. \quad (2.1)$$

Where  $k_{ij}$  is a *signal cut net* which represents a signal between the partitions  $V_i$  and  $V_j$ , and *cutsize* is the total number of these inter-partition signals (i.e. the total number of *signal cut nets*).

The cost constraint of each partition  $r$  is specified by:

$$cost(r) = \sum_{n_i \in V_r} c_i \leq C_r, \quad \text{where } 1 \leq r \leq k. \quad (2.2)$$

Where  $c_i$  is the cost associated with the node  $i(n_i)$  and  $C_r$  is the cost constrain on the partition  $r$ .  $C_r$  must be greater or equal to the sum of all the costs associated with the nodes in partition  $r$ . This model aims to minimize the number of signals required between partitions (Equation 2.1) under the cost constraints stated in Equation 2.2. The constraints can denote the area usage of each partition, or may be the power consumed by the individual partitions. Each node in the hypergraph is assigned a weight that corresponds to a particular attribute to be considered like area or power. These weights are used to balance partitions and to calculate overheads.

### 2.2.1.2 Kernighan-Lin Algorithm

The Kernighan-Lin algorithm is an iterative algorithm that starts with two random initial partitions of the input graph  $G(V, E)$ . The algorithm then improves the solution by swapping pairs of nodes to reduce the number of cut nets between partitions (cutsize). The *gain* of moving a node from its current partition to another partition is the difference between the external and the internal nets. Each swap operation is made so that the highest gain value is achieved. After each pair swapping operation, the resulting gain is stored and the swapped nodes are locked and cannot be considered for swapping again. The process continues until all nodes are evaluated and locked. The algorithm terminates when the best gain found in an iteration is less than or equal to zero; in other words, it is no longer possible to achieve any more improvements from pair swapping.

KL pseudo code is shown in Figure 2.5.

```

begin

Step1.  $V$ = set of  $2n$  elements;  $A, B$  is the initial partition where

$|A| = |B|$ ;  $A \cap B = \emptyset$ ; and  $A \cup B = V$ ;

Step2. Compute  $D_v$  for all  $v \in V$ ;  $queue \leftarrow 0$ ; and  $i \leftarrow 1$ ;

$A' = A$ ;  $B' = B$ ;

Step3. Choose  $a_i \in A'$ ,  $b_i \in B'$ , which maximises

$g_i = D_{a_i} + D_{b_i} - 2 c_{a_i b_i}$ ;

Lock  $a_i$  and  $b_i$ , and add the pair  $(a_i, b_i)$  to  $queue$ ;

$A' = A' - \{ a_i \}$ ;  $B' = B' - \{ b_i \}$ ;

Step4. if  $A'$  and  $B'$  are both empty then Goto Step5

else recalculate  $D$  - values for  $A' \cup B'$ ;

$i \leftarrow i + 1$ ; Goto Step3;

end if

Step5. Find  $k$  to maximise the partial sum

$$G_k = \sum_{i=1}^k g_i$$

;

if  $G > 0$  then

Move  $X = \{ a_1, \dots, a_k \}$  to  $B$ ;

Move  $Y = \{ b_1, \dots, b_k \}$  to  $A$ ;

Goto Step2;

else STOP

end if

end

```

FIGURE 2.5: Kernighan-Lin Algorithm Pseudo Code

### 2.2.1.3 Fiduccia-Mattheyses Algorithm

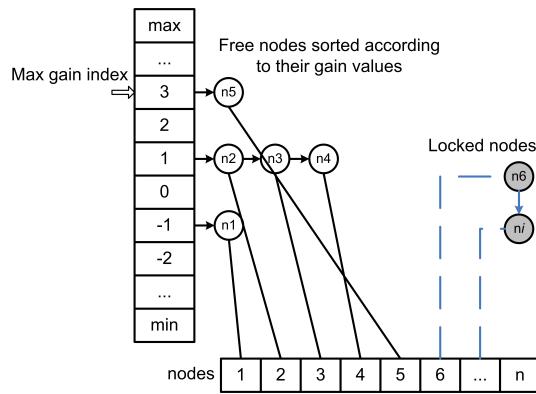

The Fiduccia-Mattheyses algorithm is an extension to the KL algorithm which reduces the time per iteration to a linear time with respect to the size of the netlist [63]. One of the main concepts introduced in the FM algorithm is the *Gain Bucket Data Structure* shown in Figure 2.6, which is a list of the nodes to be moved sorted according to the gain of each move. The list is ordered from maximal to minimal gain, where a positive gain improves the overall solution and a negative gain degrades it. The grey nodes in Figure 2.6 are the ones that have already been moved from their original partition and cannot be selected to be moved again. The free nodes are sorted in the bucket ready for selection. The *Max Gain* index always points to the highest gain value in the bucket data structure.

FIGURE 2.6: The Gain Bucket Data Structure used in the FM Algorithm