# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

### UNIVERSITY OF SOUTHAMPTON

# Resource Constrained Signal Processing Algorithms and Architectures

by

Amit Acharyya

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Engineering and Applied Science Department of Electronics and Computer Science

March 2011

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

### Doctor of Philosophy

### Resource Constrained Signal Processing Algorithms and Architectures

by Amit Acharyya

Emerging applications with limited resources in Wireless sensor networks require sophisticated signal processing algorithms and their efficient hardware implementation. Direct mapping of traditional signal processing algorithms to hardware may not be suitable for such resource constrained applications. It is therefore necessary to investigate low complexity and low power consumption algorithms and their implementation using an algorithm-architecture holistic optimization approach.

Denoising and signal separation are two key signal processing tasks in such applications and often accomplished by Wavelet Transform (WT) and Independent Component Analysis (ICA) algorithms. However these algorithms are computationally intensive in their present form and would consume significant area and power resources when implemented in hardware. This thesis investigates the development of these two important signal processing algorithms and their architectures which facilitates their deployment in emerging resource constrained applications. Firstly a memory reduction methodology based on exploitation of symmetry is proposed leading to a low complexity and low power consumption Discrete WT architecture. Secondly, having identified FastICA as the most efficient algorithm among existing ICA algorithms in terms of convergence speed, the impact of its algorithmic parameters on its corresponding hardware implementation is investigated using an algorithm-architecture holistic optimization approach. Furthermore, a hardware complexity reduction methodology of 2-dimensional FastICA architecture based on eliminating redundant arithmetic operations is proposed. Two new concepts - vector cross product and coordinate rotation are introduced to reduce the implementation complexity of n-dimensional FastICA and their architectures are proposed. It is shown that these concept leads to reduction in complexity and lower power consumption when compared with the traditional implementation. All the proposed methodologies reported in this thesis are substantiated using C and Matlab models as well as VHDL based designs synthesized using  $0.13\mu m$  technology.

## Contents

| A | cknov | wledgements                                                                   | xvi |

|---|-------|-------------------------------------------------------------------------------|-----|

| 1 | Intr  | oduction                                                                      | 1   |

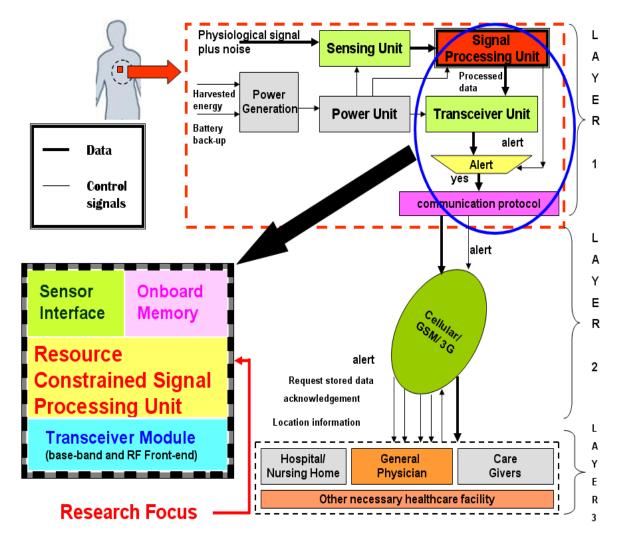

|   | 1.1   | Research Focus                                                                | 2   |

|   | 1.2   | Resource Constrained Signal Processing for Person-Centric Continuous          |     |

|   |       | Remote Health Monitoring                                                      | 2   |

|   |       | 1.2.1 State-of-the Art                                                        | 3   |

|   |       | $1.2.2 \hbox{Envisaged Remote Health Monitoring: Conceptual Architecture}\ .$ | 5   |

|   | 1.3   | Thesis Synopses and Contribution                                              | 7   |

| 2 | Mer   | mory Reduction Methodology for Discrete Wavelet Transform                     | 10  |

|   | 2.1   | Wavelet Transform: A Review                                                   | 11  |

|   | 2.2   | Healthcare: An Important Application Domain of WT                             | 12  |

|   | 2.3   | Preliminaries of DWT and IDWT                                                 | 17  |

|   | 2.4   | DWT Architectures: A Review                                                   | 18  |

|   | 2.5   | Motivational Example: DA Based Approach                                       | 20  |

|   | 2.6   | Proposed Memory Reduction Methodology for DWT/ IDWT                           | 21  |

|   | 2.7   | Architectural Overview                                                        | 23  |

|   |       | 2.7.1 The Memory Unit                                                         | 23  |

|   |       | 2.7.2 Analysis and Synthesis Bank                                             | 25  |

|   | 2.8   | Performance Analysis                                                          | 25  |

|   |       | 2.8.1 Hardware Cost                                                           | 25  |

|   |       | 2.8.2 Functional Validation and Error Analysis                                | 28  |

|   |       | 2.8.3 Comparison with Other Architectures                                     | 29  |

|   |       | 2.8.4 More Results on Architectural Implementation                            | 30  |

|   | 2.9   | Case Study: Fetal ECG Extraction Using WT                                     |     |

|   | 2.10  | Concluding Remarks                                                            | 33  |

| 3 | Low   | Complexity 2-Dimensional FastICA                                              | 34  |

|   | 3.1   | ICA, Its Applications and FastICA                                             | 35  |

|   | 3.2   | Necessity for Algorithm-Architecture Holistic Optimization for ICA            | 36  |

|   | 3.3   | Preliminaries of FastICA                                                      | 37  |

|   |       | 3.3.1 Preprocessing                                                           | 38  |

|   |       | 3.3.2 FastICA Iteration                                                       | 38  |

|   | 3.4   | Identification of FastICA Algorithmic Parameters from Architectural Per-      |     |

|   |       | spective                                                                      | 39  |

|   |       | 3.4.1 Frame-length                                                            | 40  |

|   |       | 3.4.2 Convergence Accuracy                                                    | 40  |

CONTENTS iv

|   |      | 3.4.3 Iteration of Convergence                                                   | 41       |

|---|------|----------------------------------------------------------------------------------|----------|

|   | 3.5  | Basics of Statistical Data Modeling                                              | 41       |

|   |      | 3.5.1 Random Number Generator (RNG)                                              | 41       |

|   |      | 3.5.1.1 Linear Congruential Generator (LCG)                                      | 42       |

|   |      | 3.5.1.2 Linear Feedback Shift Register (LFSR)                                    | 42       |

|   |      | 3.5.1.3 The Mersenne Twister RNG                                                 | 42       |

|   |      | 3.5.2 RNG to be Used for the Generic Signal Modeling                             | 42       |

|   |      | 3.5.3 Monte Carlo Approach and Confidence Interval                               | 43       |

|   | 3.6  | Proposed Generic Signal Model: Stationary and Non-stationary                     | 44       |

|   |      | 3.6.1 Stationary Signal Modeling                                                 | 44       |

|   |      | 3.6.2 Non-Stationary Signal Modeling                                             | 45       |

|   | 3.7  | Impact of Algorithmic Parameters on Architecture Design: Experimental            |          |

|   |      | Results and Discussion                                                           | 47       |

|   |      | 3.7.1 Algorithmic Impact on Architecture                                         | 47       |

|   |      | 3.7.2 Experimental Results                                                       | 51       |

|   | 3.8  | Proposed Algebraic Methodology for Hardware Complexity Reduction of $2D$ FastICA | 53       |

|   | 3.9  |                                                                                  | 55       |

|   | 3.10 | Performance Analysis of the Proposed Methodology - 2D FastICA                    | 57       |

|   |      | 3.10.1 Hardware Reduction                                                        | 59       |

|   |      |                                                                                  | 60       |

|   |      |                                                                                  | 62       |

|   |      | v                                                                                | 64       |

|   | 3.11 |                                                                                  | 65       |

|   |      |                                                                                  |          |

| 4 |      | · · · · · · · · · · · · · · · · · · ·                                            | 66       |

|   | 4.1  |                                                                                  | 68       |

|   | 4.2  | •                                                                                | 69       |

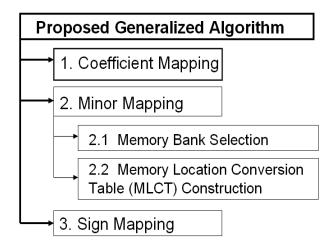

|   |      | 4.2.1 Coefficient Mapping                                                        | 70       |

|   |      | 4.2.2 Minor Mapping                                                              | 72       |

|   |      | 4.2.2.1 Example: Construction of $4D$ to $5D$ MLCT using $3D$                    |          |

|   |      |                                                                                  | 75<br>75 |

|   |      | 4.2.3 Sign Mapping                                                               | 77       |

|   | 4.9  | •                                                                                | 78       |

|   | 4.3  | Architecture of the Proposed Algorithm                                           | 79       |

|   |      | • •                                                                              | 80       |

|   | 4.4  | 4.3.2 Hardware Reduction - Symmetry Based Approach                               | 80       |

|   | 4.4  |                                                                                  | 82       |

|   |      | 4.4.1 Hardware Complexity                                                        | 83       |

|   |      | 4.4.1.1 Proposed Generalized Approach                                            | 84       |

|   |      |                                                                                  | 85       |

|   |      | 4.4.1.3 Comparison of Hardware Complexities                                      | 85       |

|   |      | 4.4.2 Delay Analysis                                                             | 87       |

|   |      | •                                                                                | 87       |

|   |      | · · · · · · · · · · · · · · · · · · ·                                            | 88       |

|   |      | •                                                                                | 89       |

|   |      | 4.4.3 Precision Error Analysis                                                   | 90       |

CONTENTS

|   | 4.5 $4.6$ | _      | imental Results                                               |        |

|---|-----------|--------|---------------------------------------------------------------|--------|

| 5 | Fast      | tICA I | Based on nD Cross Product                                     | 99     |

|   | 5.1       | Motiv  | ation: Proposed Predictive $2D$ FastICA Algorithm             | . 100  |

|   | 5.2       | Propo  | sed Vector Cross Product Based $n{\bf D}$ FastICA Algorithm   | . 104  |

|   | 5.3       | Perfor | mance Analysis                                                | . 110  |

|   |           | 5.3.1  | Important Considerations                                      | . 111  |

|   |           | 5.3.2  | Hardware Complexity: Proposed Predictive $2D$ FastICA         | . 112  |

|   |           | 5.3.3  | Delay Analysis: Proposed Predictive $2D$ FastICA              | . 114  |

|   |           | 5.3.4  | Hardware Complexity: Proposed Cross product based $nD$ FastIC | CA 116 |

|   |           |        | 5.3.4.1 Complexity of $n$ -D Cross product                    | . 116  |

|   |           |        | 5.3.4.2 Complexity of one $n$ -D FastICA Iteration            | . 116  |

|   |           |        | 5.3.4.3 Proof of Low Complexity of the Proposed Algorithm     | . 117  |

|   |           | 5.3.5  | Delay Analysis: Proposed Cross product based $nD$ FastICA     | . 119  |

|   |           |        | 5.3.5.1 Delay of $n$ -D Cross Product                         | . 119  |

|   |           |        | 5.3.5.2 Delay of one $n$ -D FastICA Iteration                 | . 119  |

|   |           |        | 5.3.5.3 Proof of Operational Speed-up                         | . 119  |

|   | 5.4       | Algori | ithm Validation                                               | . 121  |

|   | 5.5       | Concl  | uding Remarks                                                 | . 124  |

| 6 | Fast      | tICA I | Based on Co-ordinate Rotation                                 | 125    |

|   | 6.1       | Prelin | ninaries                                                      | . 127  |

|   |           | 6.1.1  | Conventional FastICA Algorithm                                | . 127  |

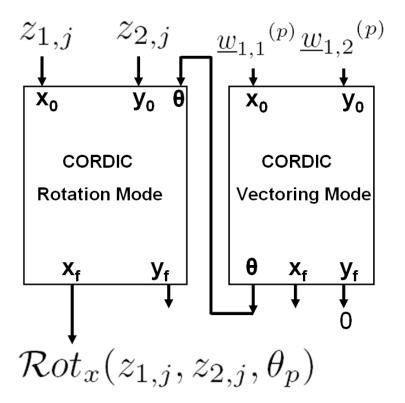

|   |           | 6.1.2  | Coordinate Rotation Digital Computer                          | . 127  |

|   | 6.2       | Propo  | sed CORDIC based 2D FastICA Algorithm                         | . 127  |

|   |           | 6.2.1  | 2D FastICA Iteration Stage                                    |        |

|   |           | 6.2.2  |                                                               |        |

|   |           | 6.2.3  | 2D FastICA Component Estimation Stage                         |        |

|   | 6.3       | Propo  | sed Architecture for CORDIC based 2D FastICA                  |        |

|   |           | 6.3.1  |                                                               |        |

|   |           | 6.3.2  | 2D Normalization Mode: Unfolded Architecture                  |        |

|   |           | 6.3.3  | 2D Estimation Mode: Unfolded Architecture                     |        |

|   |           | 6.3.4  | Multiplexed Architecture: CORDIC Reuse for $2D \dots \dots$   |        |

|   |           | 6.3.5  | Architectural Optimization Possibility                        |        |

|   |           | 6.3.6  | Scope of Dimension Extension                                  |        |

|   | 6.4       |        | osed CORDIC based 3D FastICA Algorithm                        |        |

|   |           | 6.4.1  | 3D FastICA Iteration Stage                                    |        |

|   |           | 6.4.2  | 3D FastICA Normalization Stage                                |        |

|   |           | 6.4.3  | 3D FastICA Component Estimation Stage                         |        |

|   | 6.5       |        | osed Architecture for CORDIC based 3D FastICA                 |        |

|   |           | 6.5.1  | 3D Iteration Mode: Unfolded Architecture                      |        |

|   |           | 6.5.2  | 3D Normalization Mode: Unfolded Architecture                  |        |

|   |           | 6.5.3  | 3D Estimation Mode: Unfolded Architecture                     |        |

|   | 0.5       | 6.5.4  | Multiplexed Architecture: CORDIC Reuse for $3D$               |        |

|   | 6.6       |        | osed CORDIC based 4D FastICA Algorithm                        |        |

|   |           | 6.6.1  | 4D FastICA Iteration Stage                                    | . 144  |

CONTENTS

|     |      | 6.6.2 4D FastICA Normalization Stage                                      | . 146 |

|-----|------|---------------------------------------------------------------------------|-------|

|     |      | 6.6.3 4D FastICA Component Estimation Stage                               | . 149 |

| 6   | 6.7  | Proposed Architecture for CORDIC based 4D FastICA                         | . 150 |

|     |      | 6.7.1 4D Iteration Mode: Unfolded Architecture                            | . 150 |

|     |      | 6.7.2 4D Normalization Mode: Unfolded Architecture                        | . 152 |

|     |      | 6.7.3 4D Estimation Mode: Unfolded Architecture                           | . 153 |

|     |      | 6.7.4 Multiplexed Architecture: CORDIC Reuse for $4D$                     | . 155 |

| 6   | 6.8  | Proposed CORDIC based Generalized $n$ D FastICA Algorithm                 | . 156 |

|     |      | 6.8.1 nD FastICA Iteration Stage                                          | . 156 |

|     |      | 6.8.2 nD FastICA Normalization Stage                                      | . 159 |

|     |      | 6.8.3 nD FastICA Component Estimation Stage                               | . 165 |

| 6   | 6.9  | Generalized Architecture for the Proposed CORDIC based $n{\rm D}$ FastICA | . 166 |

|     |      | 6.9.1 Multiplexer arrays for CORDIC Reuse                                 | . 166 |

|     |      | 6.9.2 CORDIC based Multiplexed $nD$ Architecture                          | . 169 |

| 6   | 6.10 | Doubly Pipelining for the Proposed CORDIC based $n{\rm D}$ FastICA Archi- |       |

|     |      | tecture                                                                   | . 170 |

| (   | 6.11 | Some Necessary Considerations for CORDIC based FastICA Implemen-          |       |

|     |      | tation                                                                    |       |

| (   | 6.12 | Hardware Complexity Analysis                                              |       |

|     |      | 6.12.1 Important Assumptions                                              |       |

|     |      | 6.12.2 Performance Analysis for $2D$                                      |       |

|     |      | 6.12.3 Multiplexer Penalty for $2D$ Architecture                          |       |

|     |      | 6.12.4 Effective Hardware Saving for $2D$                                 |       |

|     |      | 6.12.5 Performance Analysis for $3D$                                      |       |

|     |      | 6.12.6 Multiplexer Penalty for 3D Architecture                            |       |

|     |      | 6.12.7 Effective Hardware Saving for $3D$                                 |       |

|     |      | 6.12.8 Performance Analysis for $4D$                                      |       |

|     |      | 6.12.9 Multiplexer Penalty for 4D Architecture                            |       |

|     |      | 6.12.10 Effective Hardware Saving for $4D$                                |       |

|     |      | 6.12.11 Performance Analysis for $nD$                                     |       |

|     |      | $6.12.12 \mathrm{Multiplexer}$ Penalty for $nD$ Architecture              |       |

|     |      | 6.12.13 Effective Hardware Saving for $nD$                                |       |

|     |      | Algorithm Validation                                                      |       |

| (   | 5.14 | Concluding Remarks                                                        | . 189 |

|     | Con  | nclusions and Future Research                                             | 191   |

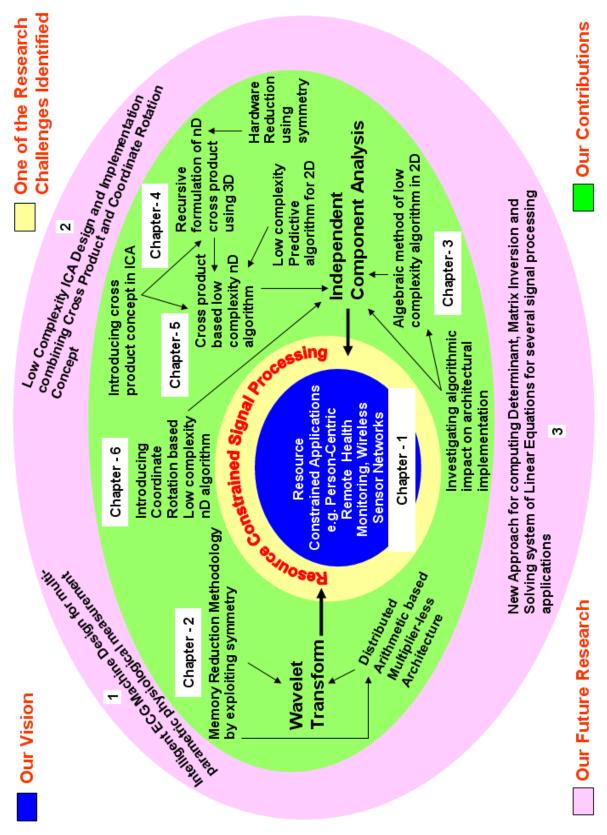

|     | 7.1  | Thesis Contributions                                                      |       |

|     | 7.2  | Future Research                                                           |       |

|     |      | 7.2.1 Intelligent ECG Machine Design for Multi-parametric Physiologi-     | . 101 |

|     |      | cal Measurement                                                           | . 194 |

|     |      | 7.2.2 Low Complexity ICA Design Combining Cross Product and Co-           | . 101 |

|     |      | ordinate Rotation Concept                                                 | . 196 |

|     |      | 7.2.3 New Approach for Computing Determinant, Matrix Inversion and        |       |

|     |      | Solving System of Linear Equations                                        | . 197 |

|     |      |                                                                           |       |

| . ] | Pub  | blications                                                                | 198   |

|     |      |                                                                           |       |

B A Low Complexity Fetal ECG Architecture for Personalized Mobile

CONTENTS vii

|              | Hea        | dthcare                                                             | 200 |

|--------------|------------|---------------------------------------------------------------------|-----|

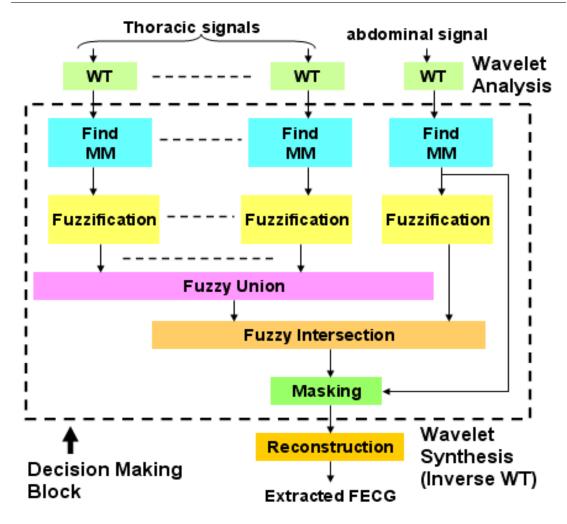

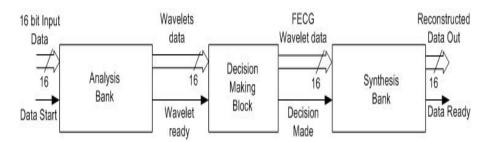

|              | B.1        | Preliminaries                                                       | 202 |

|              |            | B.1.1 FECG Extraction Strategy                                      | 202 |

|              |            | B.1.2 Fuzzy Membership Function                                     | 202 |

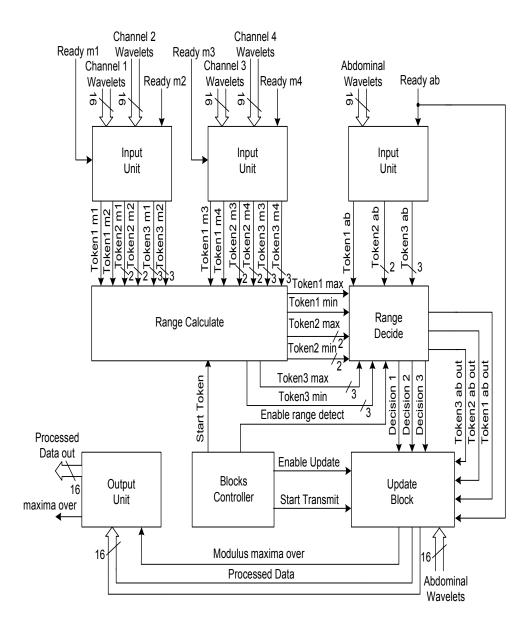

|              | B.2        | Proposed Logic Design for Fuzzy Membership Function: Simplified Ar- |     |

|              |            | chitecture                                                          | 203 |

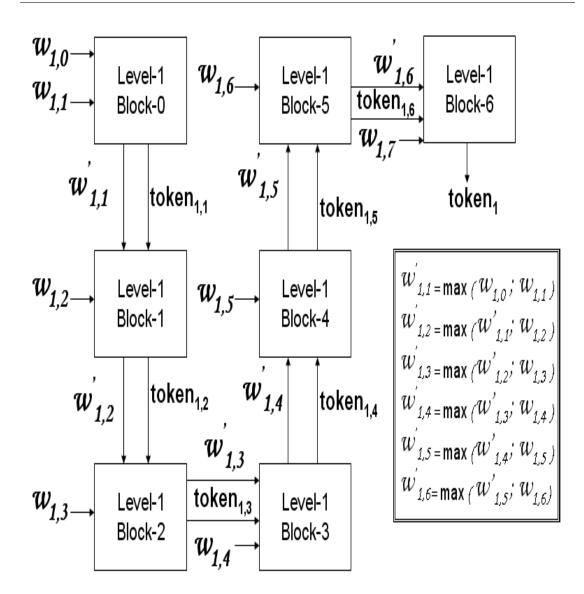

|              |            | B.2.1 Input Unit: Token Assignment                                  | 204 |

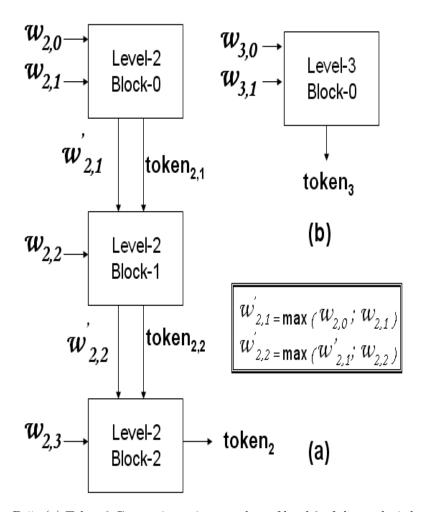

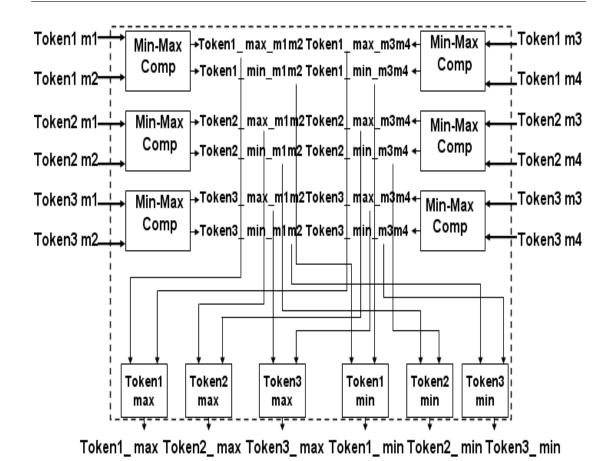

|              |            | B.2.2 Range Calculate Block: Token Min-Max Computation              | 207 |

|              |            | B.2.3 Range Decide Block: Token Comparison                          | 209 |

|              |            | B.2.4 Update Block: MECG Removal                                    | 210 |

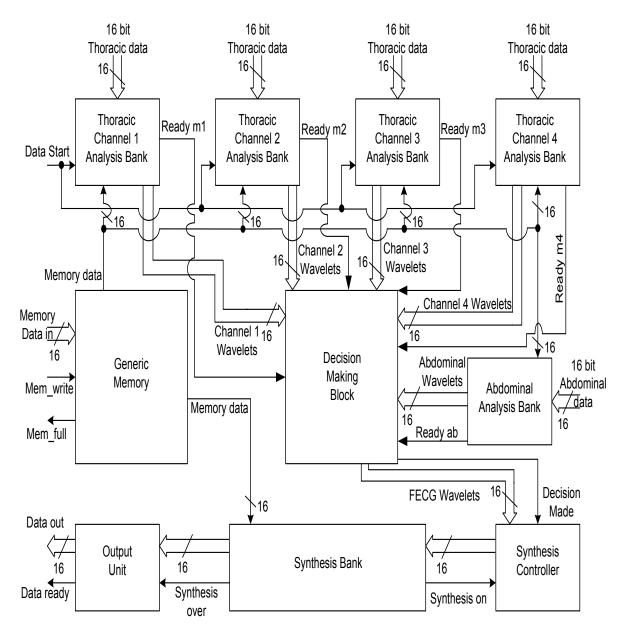

|              | B.3        | Proposed Low Complexity VLSI Architecture for FECG Extraction       | 211 |

|              | B.4        | Discussion and Concluding Remarks                                   | 212 |

|              |            |                                                                     |     |

| $\mathbf{C}$ |            | comated and Robust Channel Identification Scheme: Solving Per-      | 214 |

|              | C.1        |                                                                     |     |

|              | C.1        | Background and Related Work                                         |     |

|              |            | C.1.1 ICA and Permutation Indeterminacy                             |     |

|              | CI O       | C.1.2 Existing Approach                                             |     |

|              |            | Proposed Algorithm                                                  |     |

|              | C.3        | Architecture and Performance Analysis                               |     |

|              |            | C.3.1 Proposed Architecture                                         |     |

|              |            | C.3.2 Hardware Complexity                                           |     |

|              | <b>Q</b> 4 | C.3.3 Delay Analysis                                                |     |

|              | C.4        | Experimental Results                                                |     |

|              | C.5        | Concluding Remarks                                                  | 226 |

| Bi           | bliog      | graphy                                                              | 229 |

# List of Figures

| 1.1  | Conceptual Block diagram of personalized remote health monitoring system, Layer-1: Sensor Layer, Layer-2: Communication Layer, Layer-3: Service Layer.                                                                                                                                                                                                       | 6   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

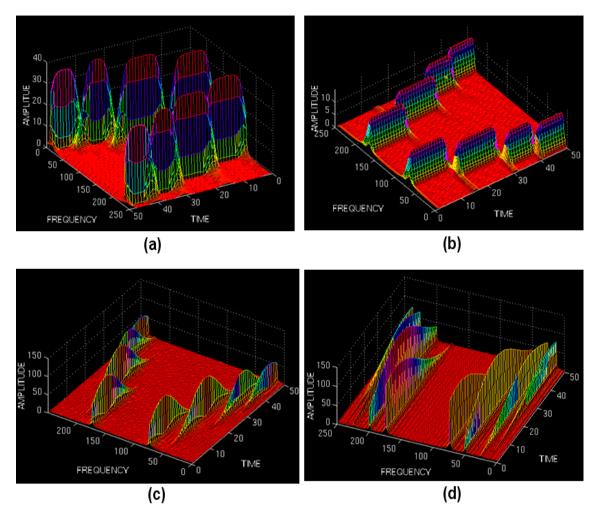

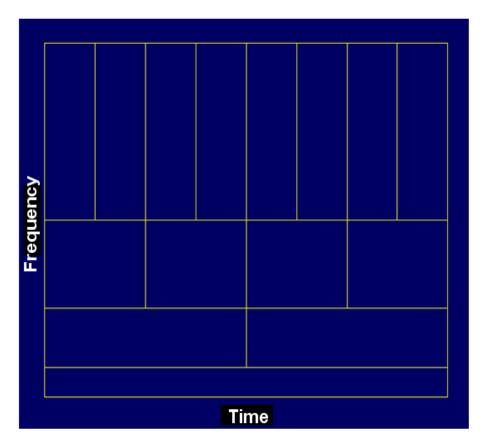

| 2.1  | Short Time Fourier Transform with different window size. (a) and (b) represents same window size but observed from two different angles. Window size decreases from (b) to (d).(Taken from [72])                                                                                                                                                             | 13  |

| 2.2  | Wavelet Transform performed on the same signal chosen for Fig. 2.1. Translation and Scale represent $b$ and $a$ respectively in (2.1).(Taken from [72])                                                                                                                                                                                                      | 15  |

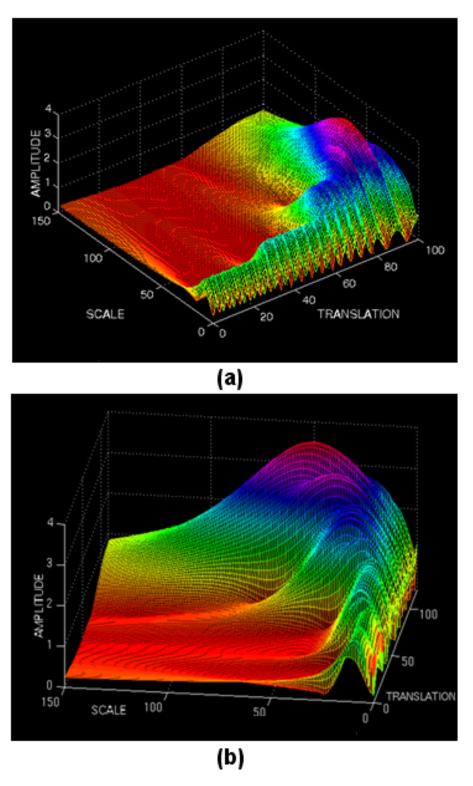

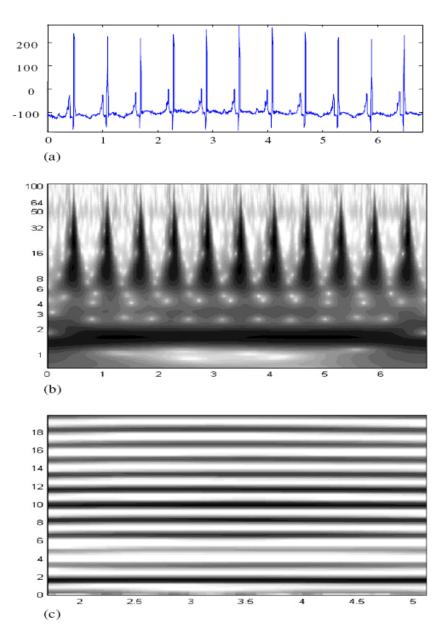

| 2.3  | Wavelet scalogram versus STFT spectrogram for rhythmic signal. (a) original time-domain rhythmic ECG signal (X-axis: time, Y-axis: amplitude). (b) Morlet based scalogram corresponding to (a) (X-axis: time, Y-axis: Scale as defined by $a$ in (2.1)). (c) Spectrogram corresponding to (a) generated using STFT with a 3.4s Hanning window (X-axis: time, | 16  |

| 2.4  | Time-Frequency Localization Property of Wavelet Transform.(Taken from                                                                                                                                                                                                                                                                                        |     |

|      | $[72])  \dots $                                                                                                                                                                                                                                        | 17  |

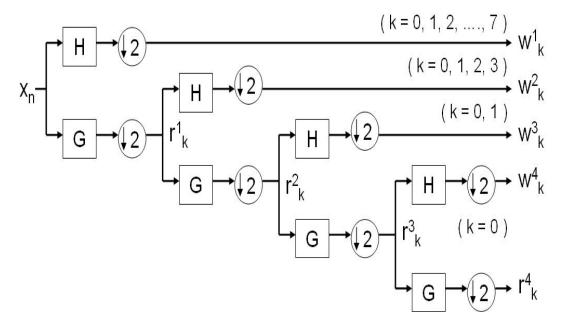

| 2.5  | Four-resolution level Analysis Bank for DWT                                                                                                                                                                                                                                                                                                                  | 18  |

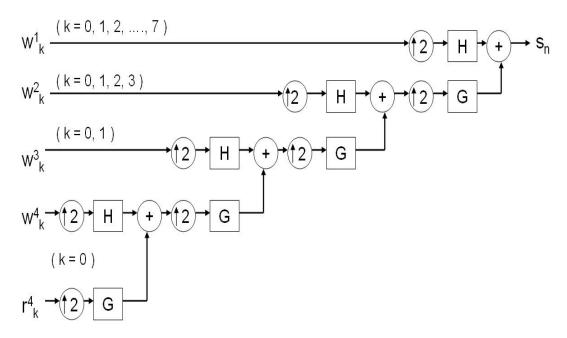

| 2.6  | Four-resolution level Synthesis Bank for IDWT                                                                                                                                                                                                                                                                                                                | 19  |

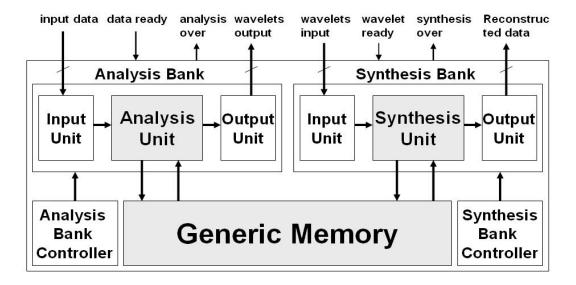

| 2.7  | Proposed VLSI Architecture of DWT and IDWT                                                                                                                                                                                                                                                                                                                   | 23  |

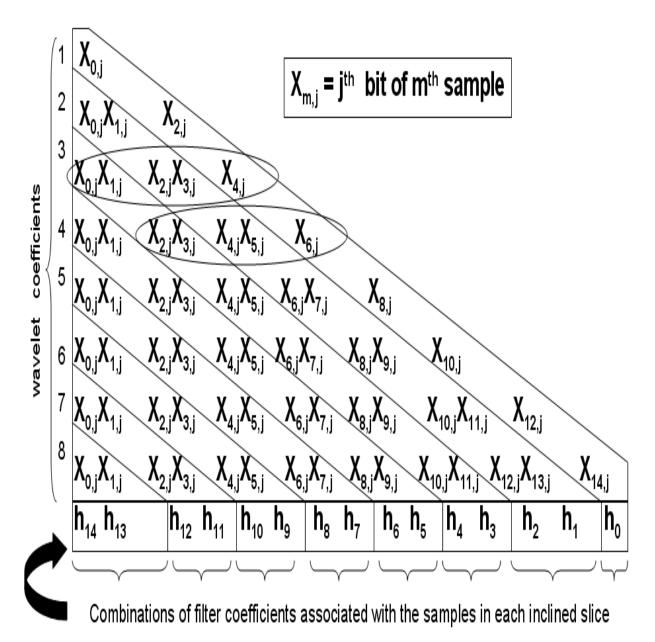

| 2.8  | Example of address generation logic for $1^{st}$ resolution-level wavelet coef-                                                                                                                                                                                                                                                                              |     |

|      | 9                                                                                                                                                                                                                                                                                                                                                            | 24  |

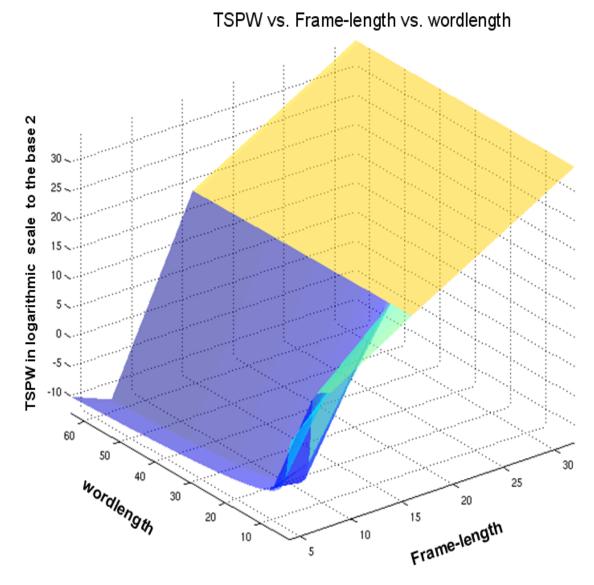

| 2.9  | Variation of TSPW with frame-length and word-length                                                                                                                                                                                                                                                                                                          | 27  |

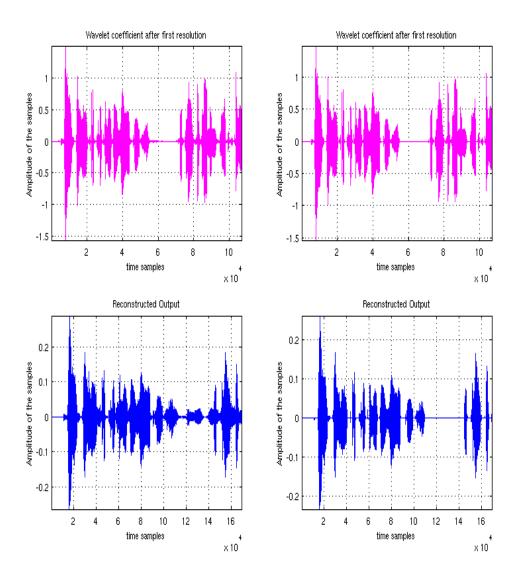

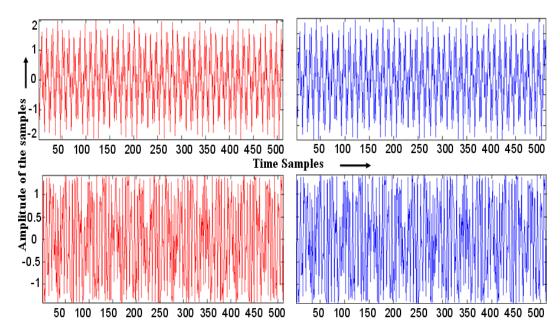

| 2.10 | Comparative study between software and hardware results. Left hand and right-hand columns represent C-model and VHDL-model generated results respectively. The top row represents wavelet coefficients of the first resolution level and bottom row represents the reconstructed output.                                                                     | 29  |

| 2.11 | Probability of Error vs Bit Position in the proposed architecture                                                                                                                                                                                                                                                                                            | 30  |

|      | Latency in Analysis and Synthesis Bank in the designed architecture                                                                                                                                                                                                                                                                                          | 32  |

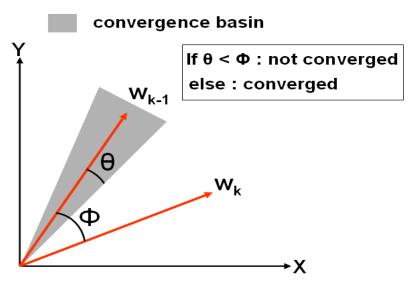

| 3.1  | Concept of Convergence Accuracy in 2-Dimensional (2D) FastICA. $\theta$ denotes the convergence basin. Decreasing value of $\theta$ indicates more accu-                                                                                                                                                                                                     | 4.0 |

| 2.0  | · · ·                                                                                                                                                                                                                                                                                                                                                        | 40  |

| 3.2  | Stationary signal generation flow diagram developed for the experiment.  Non stationary signal generation flow diagram developed for the experiment.                                                                                                                                                                                                         |     |

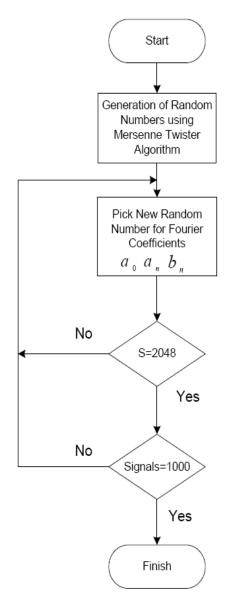

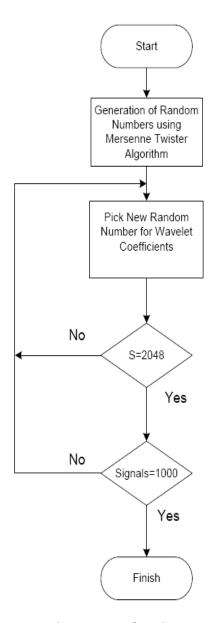

| 3.3  | Non-stationary signal generation flow diagram developed for the experiment. Transistor counts versus the iteration of convergence for (a) data-bus width = 4, (b) data-bus width = 8, (c) data-bus width = 16 and (d)                                                                                                                                        | 40  |

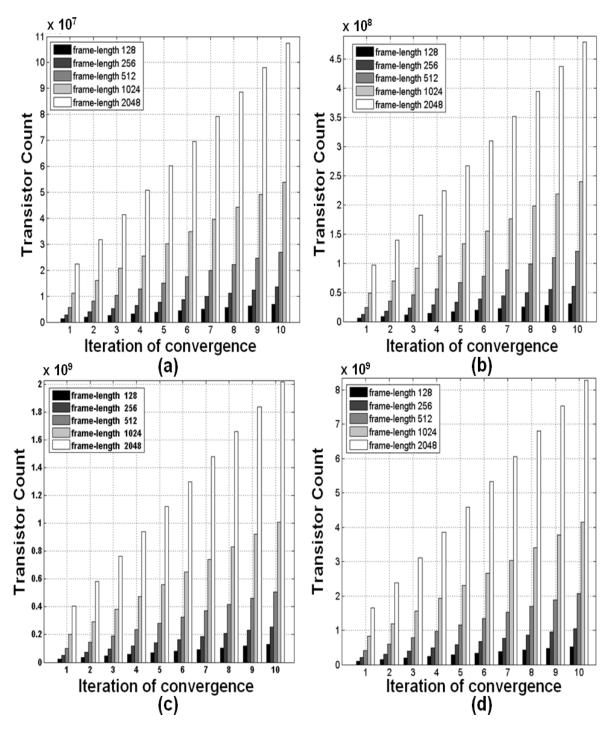

|      | data-bus width = $32$                                                                                                                                                                                                                                                                                                                                        | 48  |

LIST OF FIGURES  $\underline{\hspace{1cm}}$  ix

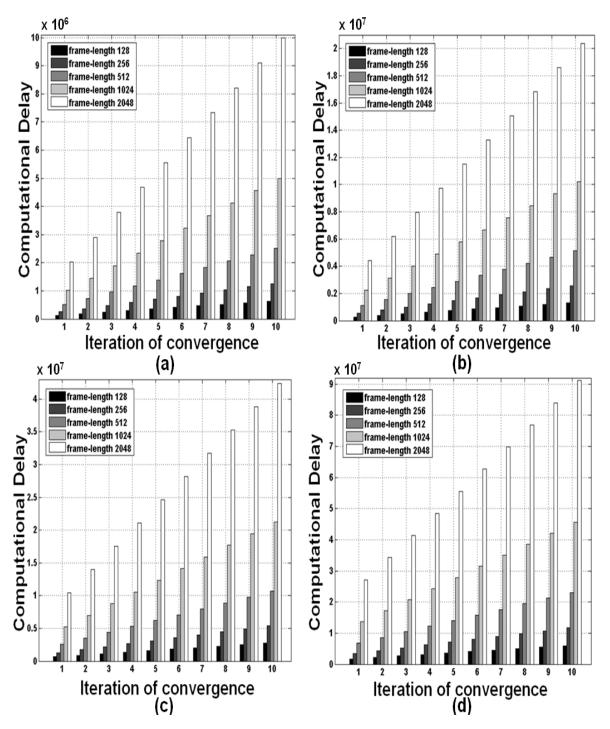

| 3.5        | Computational Delay versus the iteration of convergence for (a) data-bus width = 4, (b) data-bus width = 8, (c) data-bus width = 16 and (d) data-bus width = 32.                                                                                                                                                                                                                                                                                                                                                                                             | 49       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

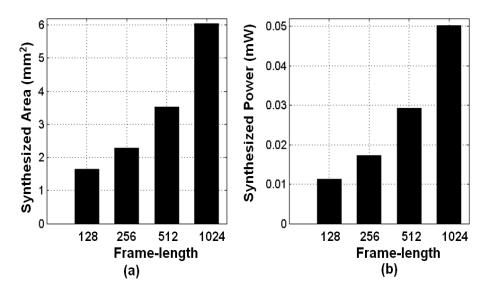

| 3.6        | Synthesized results with different frame-lengths and data-bus width $= 16$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49       |

|            | (a) Core Area in $mm^2$ and (b) Power in $mW$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50       |

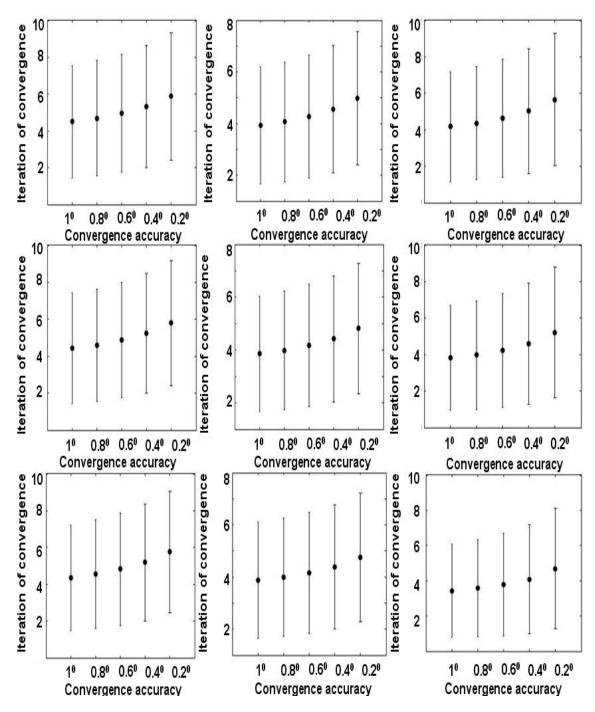

| 3.7        | Iteration of Convergence with Mean and Standard Deviation under the above mentioned categories of the generic signal model with different levels of convergence accuracy. (a) Category - 1 and frame-length = 128, (b) Category - 2 and frame-length = 128, (c) Category - 3 and frame-length = 128, (d) Category - 1 and frame-length = 256, (e) Category - 2 and frame-length = 256, (f) Category - 3 and frame-length = 256, (g) Category - 1 and frame-length = 512, (h) Category - 2 and frame-length = 512 and (i) Category - 3 and frame-length = 512 | 52       |

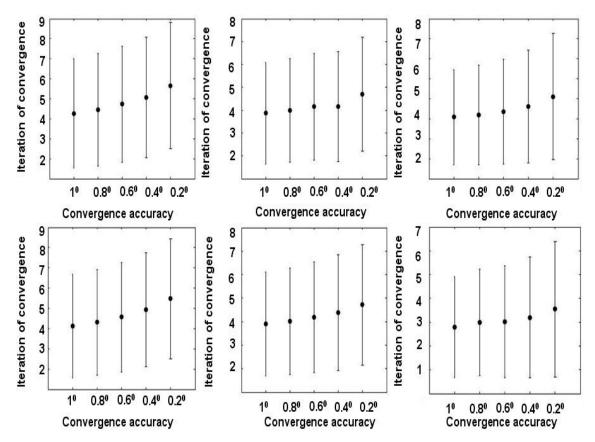

| 3.8        | Iteration of Convergence with Mean and Standard Deviation under the above mentioned categories of the generic signal model with different levels of convergence accuracy. (a) Category - 1 and frame-length = 1024, (b) Category - 2 and frame-length = 1024, (c) Category - 3 and frame-length = 1024, (d) Category - 1 and frame-length = 2048, (e) Category - 2 and frame-length = 2048, (f) Category - 3 and frame-length = 2048                                                                                                                         | 53       |

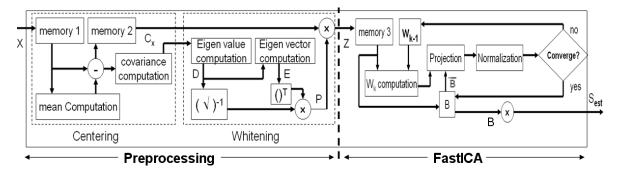

| 3.9        | Overview of 2D FastICA Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55       |

| 3.10       | Proposed divider-less architecture for (a) eigenvalue and (b) eigenvector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|            | computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56       |

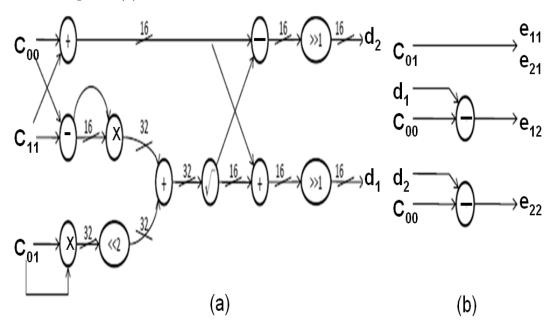

| 3.11       | (a) Proposed architecture of the Whitening block replacing dividers by multipliers, (b) optimized architecture of the segment surrounded by dashed line in (a) exploiting datapath symmetry                                                                                                                                                                                                                                                                                                                                                                  | 57       |

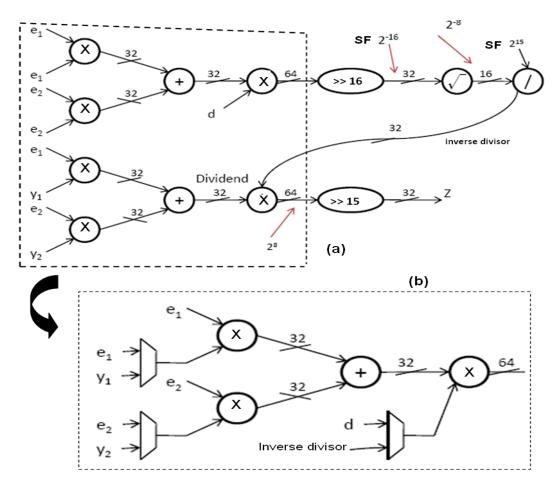

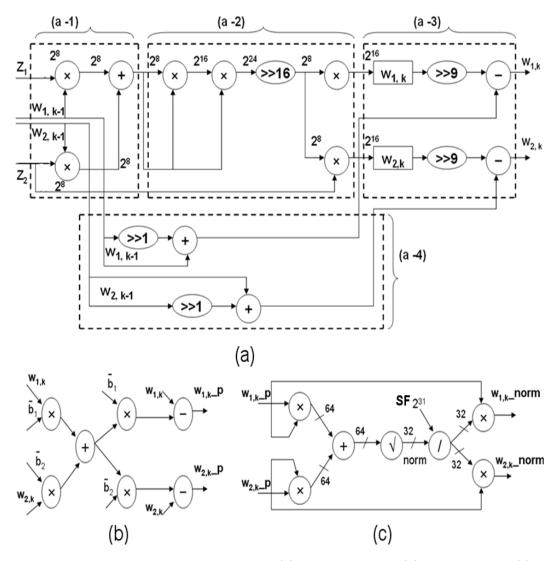

| 3.12       | Fixed-point architecture of (a) $w_k$ computation, (b) Projection and (c) Normalization unit. ' $w_{i,k}$ -P' and ' $w_{i,k}$ -norm' represent "projected" and                                                                                                                                                                                                                                                                                                                                                                                               |          |

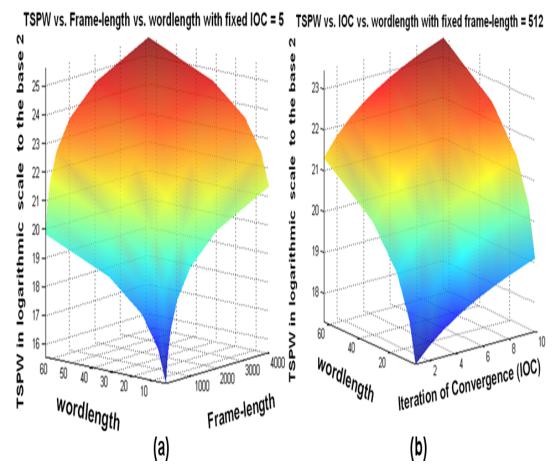

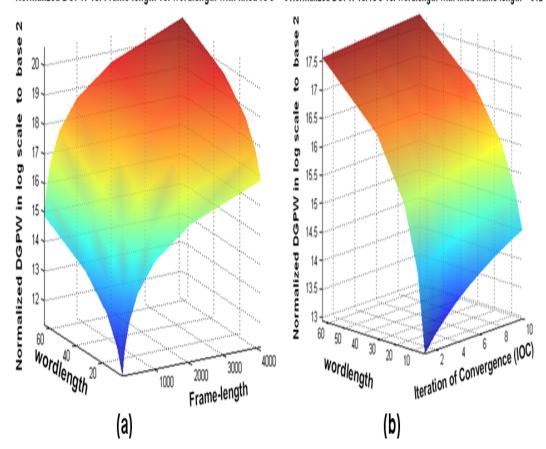

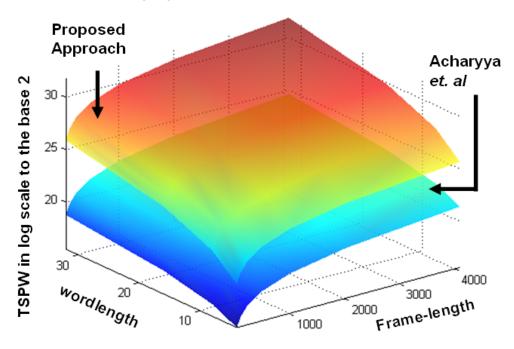

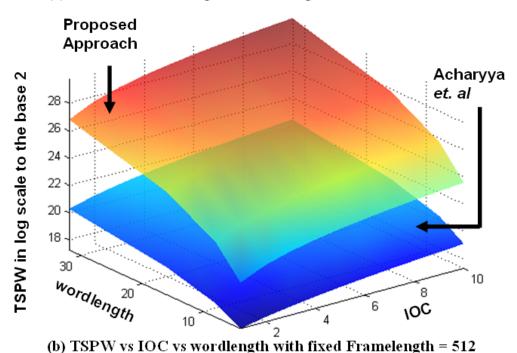

| 3.13       | "normalized" $w_{i,k}$ respectively.  (a) Variation of $TSPW$ with Frame-length and wordlength for fixed IOC = 5, (b) Variation of $TSPW$ with IOC and wordlength for fixed frame-length = 512                                                                                                                                                                                                                                                                                                                                                               | 58<br>60 |

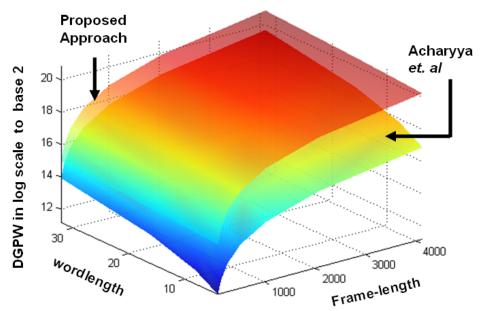

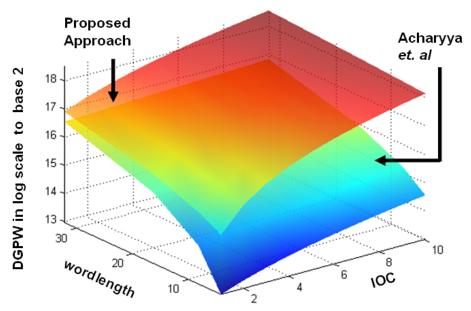

| 3.14       | (a) Variation of Normalized $DGPW$ with Frame-length and wordlength for fixed IOC = 5 , (b) Variation of normalized $DGPW$ with IOC and                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

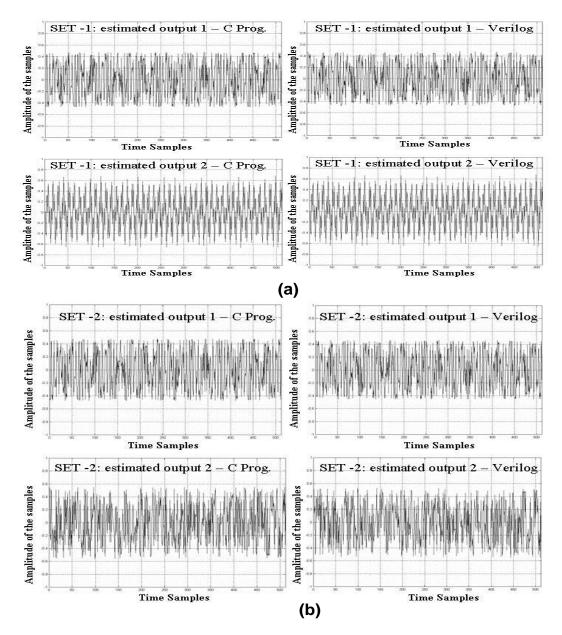

| 3.15       | wordlength for fixed framelength = 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61       |

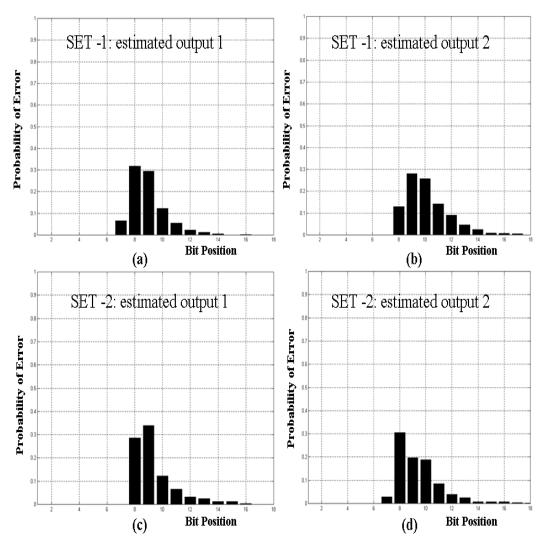

| 3.16       | Probability of error vs. bit position in the proposed architecture. (a) Set-1, estimated source-1, (b) Set-1, estimated source-2, (c) Set-2, estimated source-1, (d) Set-2, estimated source-2                                                                                                                                                                                                                                                                                                                                                               | 64       |

| 4.1        | Flow of the proposed generalized algorithm for $nD$ cross product compu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|            | tation comprising of three mapping schemes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71       |

| 4.2<br>4.3 | 3D to 4D Memory Location Conversion Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74       |

|            | shown in Fig. 4.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75       |

LIST OF FIGURES

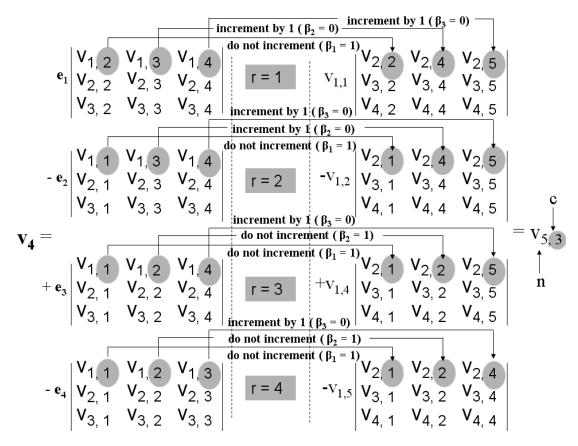

| 4.4  | Structural similarity between $\mathbf{v_4}$ and the third component of $\mathbf{v_5}$ . Left side: expanded form of $\mathbf{v_4}$ , right side: expanded form of $v_{5,3}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76  |

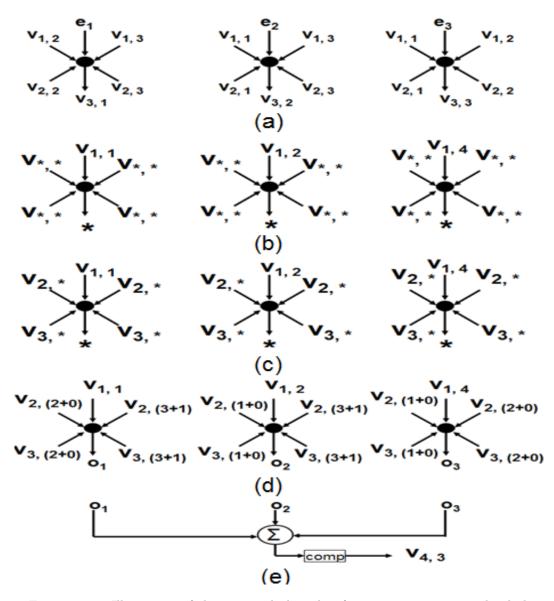

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.5  | Illustration of the proposed algorithm for $v_{4,3}$ computation. The dark node indicates total computation involving the operands pointed by the arrows, "*" means value to be computed and "comp" means complement operation. (a) Data flow graph representation of $3D$ core, (b) step 1 - Coefficient Mapping, (c) step 2 - Memory Bank Selection, (d) step 3 - use of $3D$ to $4D$ <b>MLCT</b> , $o_1$ , $o_2$ and $o_3$ indicates the outputs of this step and                                                                                                                                                                                                                                                                                                                                          |     |

|      | (e) step 4 - Sign Mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78  |

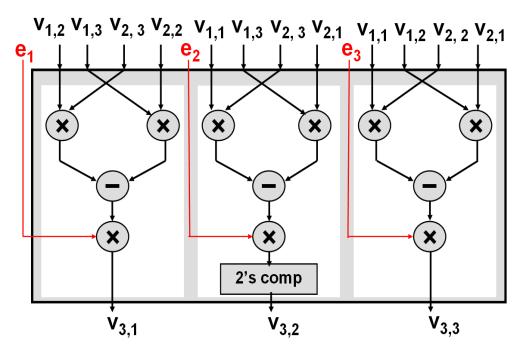

| 4.6  | Architecture of $3D$ Core for the generalized sequential multi-dimensional cross-product computation scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79  |

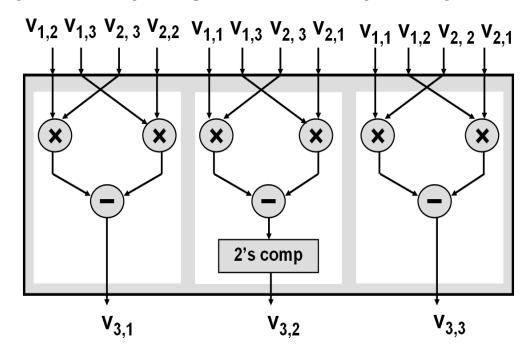

| 4.7  | Architecture of $3D$ cross product computation unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

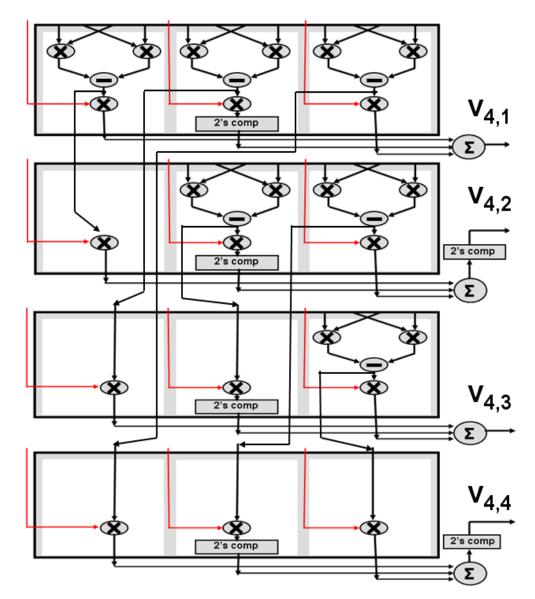

| 4.8  | Architecture of $4D$ cross-product computation unit based on <b>symmetri-</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4.0  | cal approach.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83  |

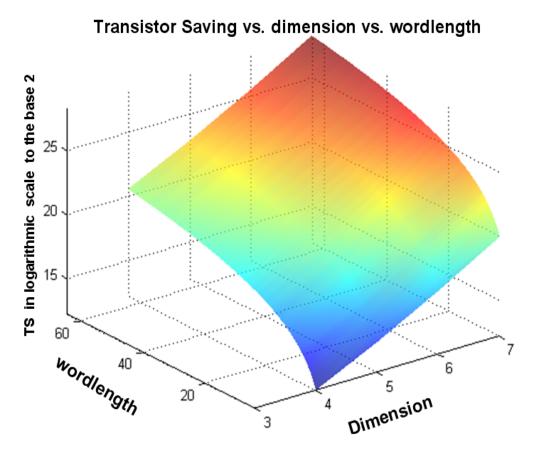

| 4.9  | Variation of Transistor Savings (TS) with dimension and word-length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

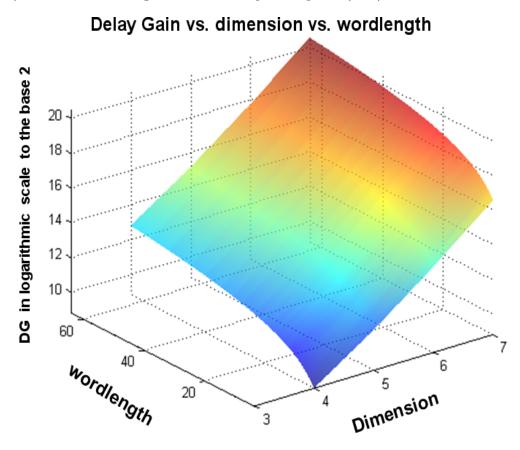

| 4.10 | Variation of Delay Gain (DG) with dimension and word-length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

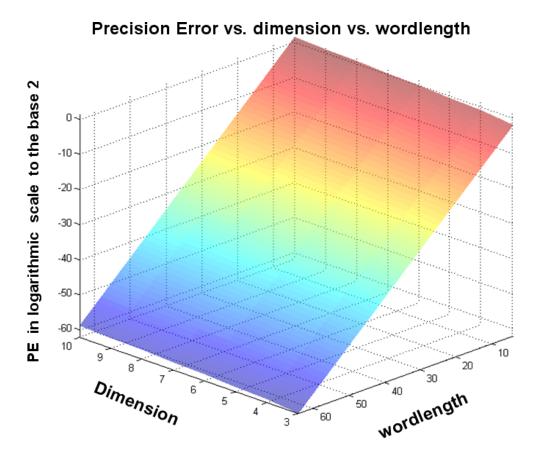

|      | Variation of Precision Error (PE) with dimension and word-length Comparative Post synthesis Power consumption results for different Word-lengths using proposed Generalized Algorithm and Symmetry-based Ap-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92  |

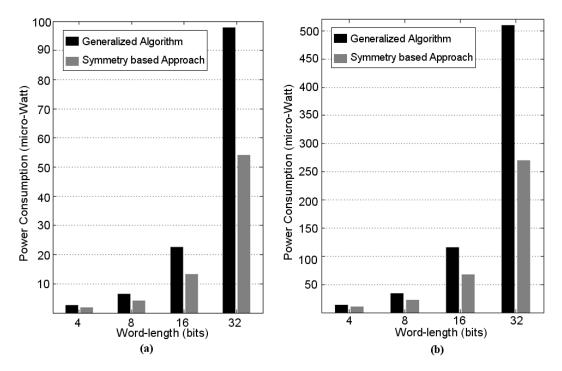

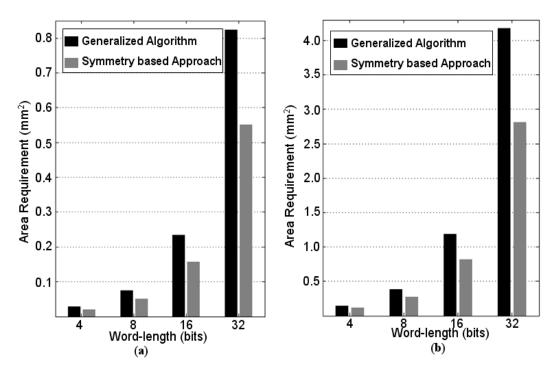

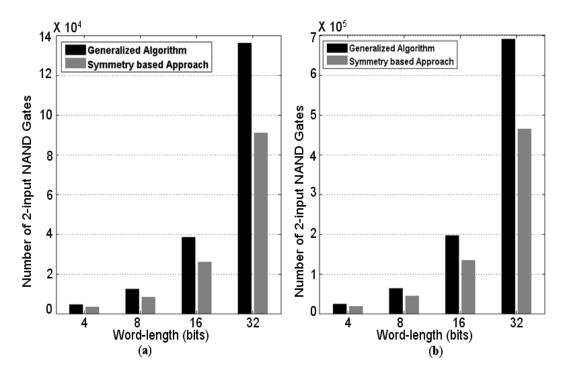

| 4.13 | proach for (a) 4D cross product, (b) 5D cross product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94  |

| 4.14 | lengths using proposed Generalized Algorithm and Symmetry-based Approach for (a) $4D$ cross product, (b) $5D$ cross product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95  |

|      | ent Word-lengths using proposed Generalized Algorithm and Symmetry-based Approach for (a) $4D$ cross product, (b) $5D$ cross product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95  |

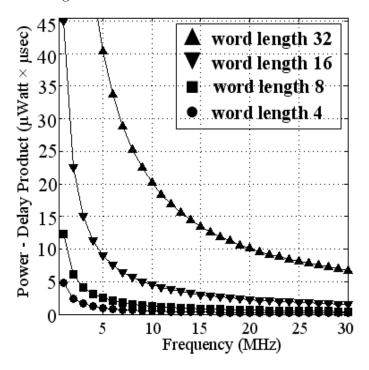

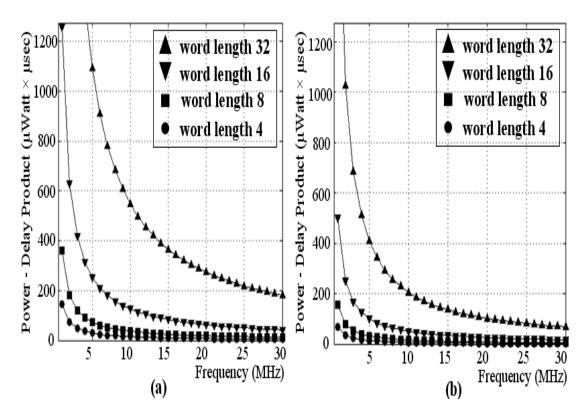

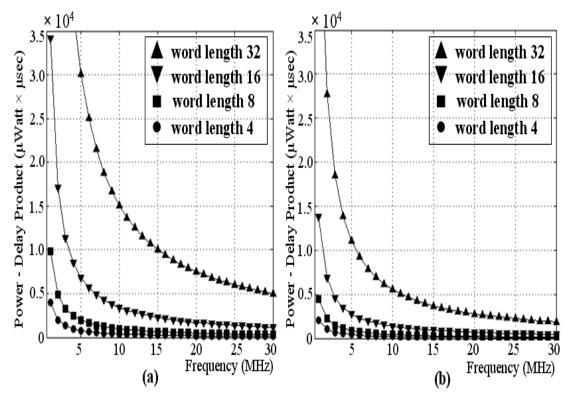

| 4.15 | Variation of Power - Delay Product with frequency and word-length for $3D$ cross product architecture based on the generalized approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96  |

| 4.16 | Variation of Power - Delay Product with frequency and word-length for $4D$ cross product. (a) Generalized Approach, (b) Symmetry based Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97  |

| 4.17 | Variation of Power - Delay Product with frequency and word-length for 5D cross product. (a) Generalized Approach, (b) Symmetry based Ap-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91  |

|      | proach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97  |

| 5.1  | Pseudocode for the proposed Predictive Algorithm based 2-D FastICA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 103 |

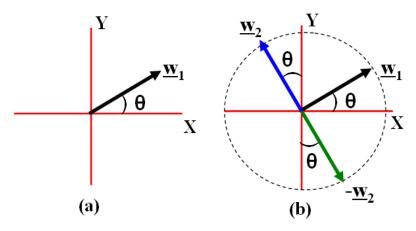

| 5.2  | Geometrical interpretation for the predictive 2-D FastICA. (a) Pre-determin $\underline{\mathbf{w}}_1$ is making an angle $\theta$ with the X-axis in 2-D plane. (b) To maintain the condition of <i>orthonormality</i> , second vector $\underline{\mathbf{w}}_2$ will also make an angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed. |

|      | $\theta$ with the Y-axis in the same plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 104 |

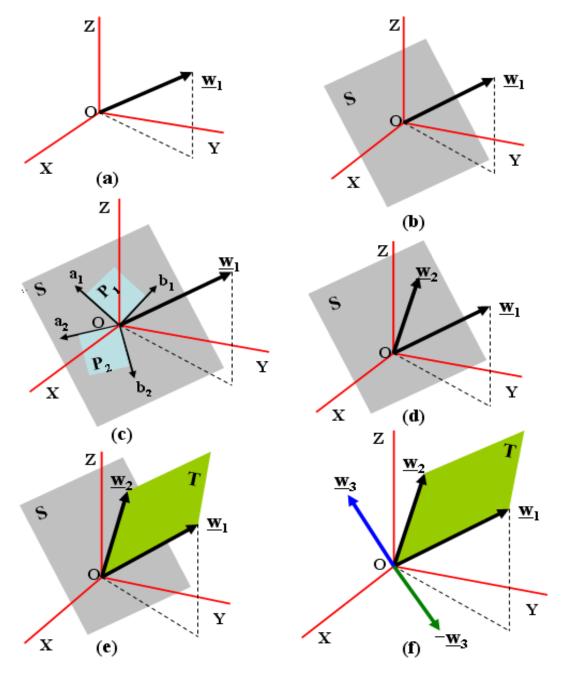

| 5.3  | Geometrical interpretation of the step-by-step development of the $3D$ FastICA based on the concept of vector cross product. (a) $\underline{\mathbf{w}}_1$ is predetermined in 3-D space. (b) $\underline{\mathbf{w}}_1$ can be assumed to be orthonormal to a surface $S$ . (c) Several combinations of a pair of mutually orthonormal vectors in $S$ which are orthonormal to $\underline{\mathbf{w}}_1$ as well. (d) Consider $\underline{\mathbf{w}}_2$ is also known. (e) A 2-D plane $T$ can be considered to be spanned by $\underline{\mathbf{w}}_1$ and $\underline{\mathbf{w}}_2$ . (f) $\underline{\mathbf{w}}_3$ (or $-\underline{\mathbf{w}}_3$ ) can be obtained by taking cross-product between $\underline{\mathbf{w}}_1$ and $\underline{\mathbf{w}}_2$ which is orthonormal to surface $T$ | 105 |

|      | and $\underline{w}_2$ which is difficultinal to surface $1, \ldots, 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TOO |

LIST OF FIGURES xi

| 5.4  | Pseudocode for the Proposed Vector Cross Product based n-D low complexity FastICA Algorithm                                                                                                                                                                                                                                                          | 100   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.5  | Comparative TSPW analysis between [137] and <b>Proposed Approach</b> (i.e. [137] for Preprocessing + proposed algorithm based architecture for FastICA Iteration). (a) Variation of TSPW with Frame-length and                                                                                                                                       | 103   |

|      | word-length for fixed IOC = $5$ , (b) Variation of TSPW with IOC and wordlength for fixed frame-length = $512$                                                                                                                                                                                                                                       | 113   |

| 5.6  | Comparative DGPW analysis between [137] and <b>Proposed Approach</b> . (a) Variation of DGPW with Frame-length and wordlength for fixed IOC = 5, (b) Variation of DGPW with IOC and wordlength for fixed frame-                                                                                                                                      |       |

|      | $length = 512. \dots \dots$                                                                                                                                                                                                                    | 115   |

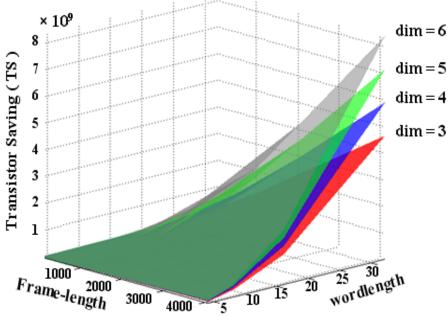

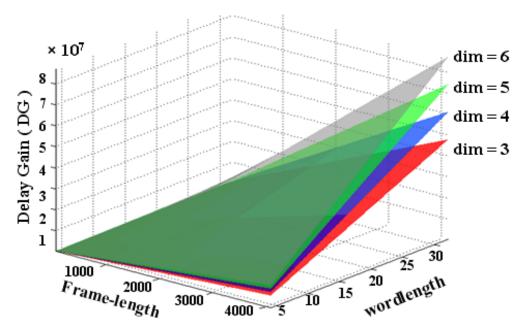

| 5.7  | Comparative Transistor Savings (TS) analysis between the proposed cross-product based FastICA and the conventional FastICA. (a) Variation of TS with Frame-length, Word-length and Dimension (dim = $3, 4, 5, 6$ ) for fixed IOC= $5$ , (b) variation of TS with IOC, Word-length and Dimension (dim = $3, 4, 5, 6$ ) for fixed Frame-length = $512$ | 118   |

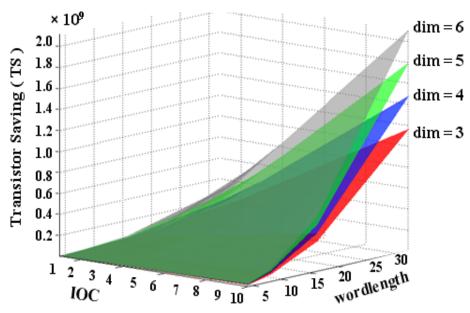

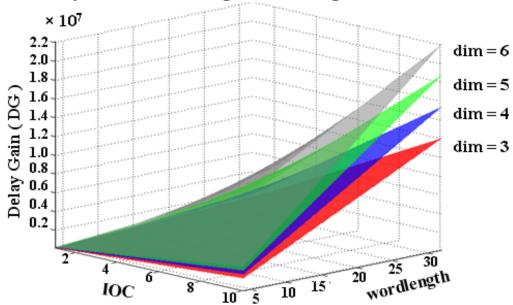

| 5.8  | Comparative Delay Gain (DG) analysis between the proposed cross-product based FastICA and conventional FastICA. (a) Variation of DG with Framelength, Word-length and Dimension (dim = $3,4,5,6$ ) for fixed IOC = $5$ , (b) variation of DG with IOC, Word-length and Dimension (dim =                                                              |       |

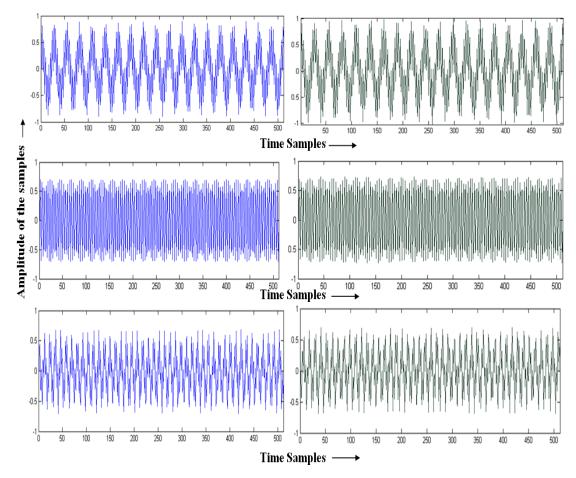

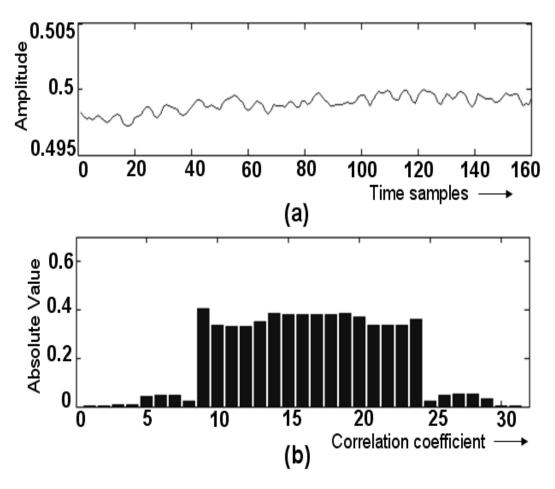

| 5.9  | 3,4,5,6) for fixed Frame-length = 512                                                                                                                                                                                                                                                                                                                | 120   |

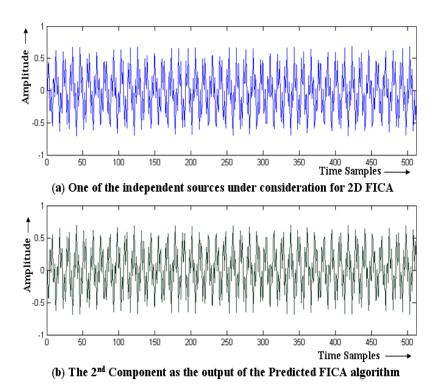

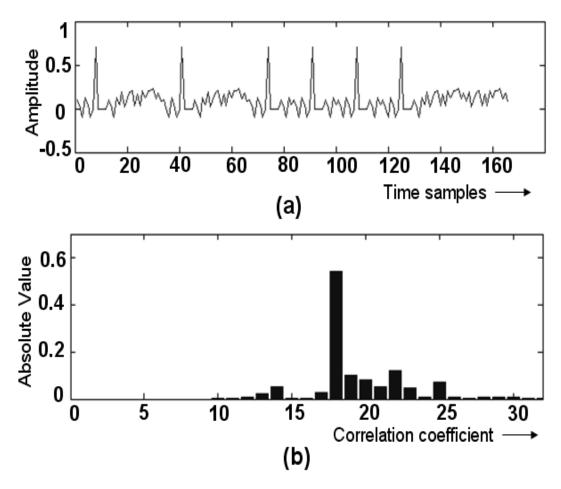

| 5 10 | algorithm given as motivational example in Section 5.1                                                                                                                                                                                                                                                                                               | 121   |

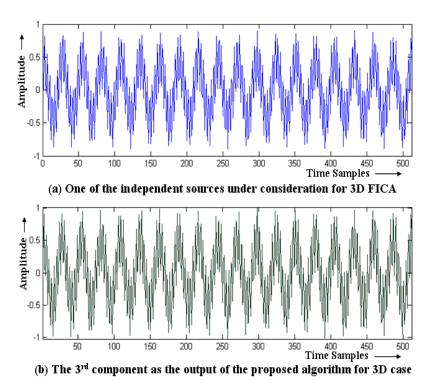

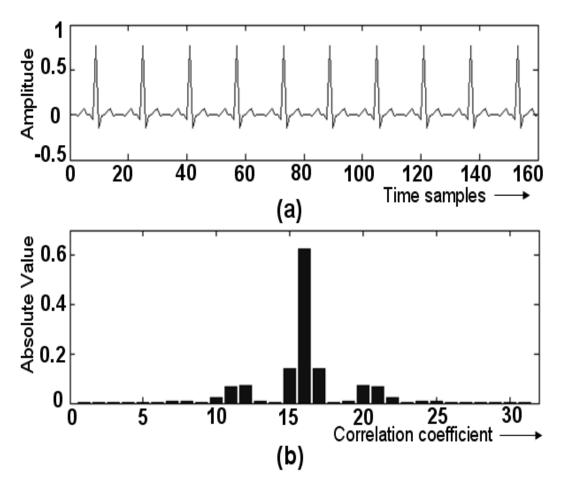

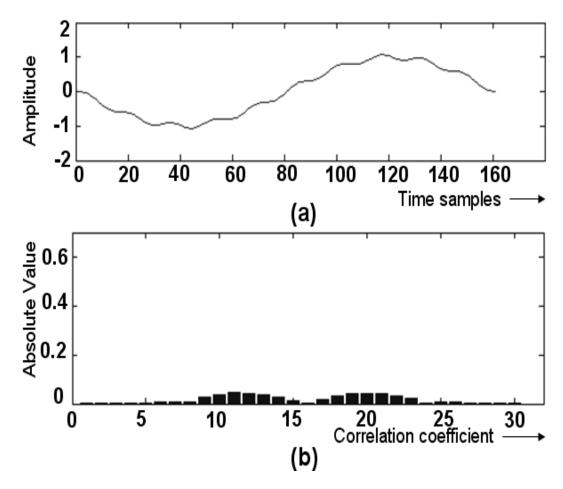

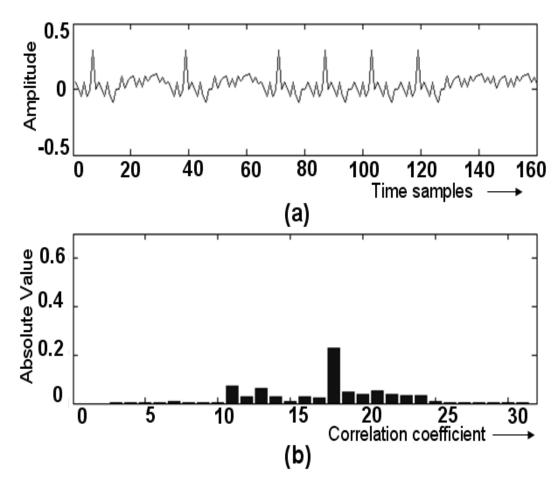

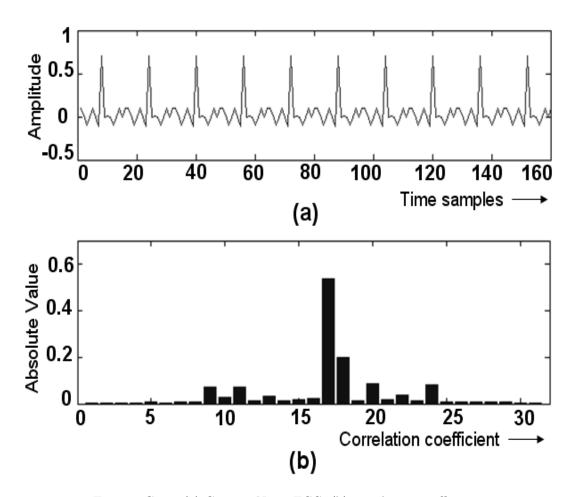

|      | estimated outputs of the 3-D FastICA based on the proposed algorithm                                                                                                                                                                                                                                                                                 | 122   |

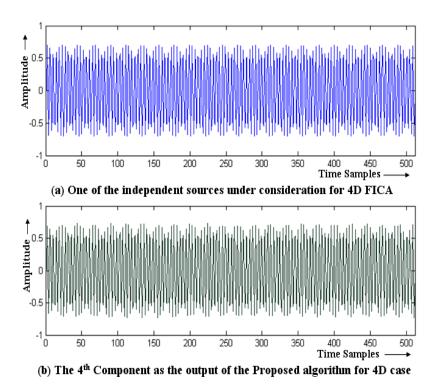

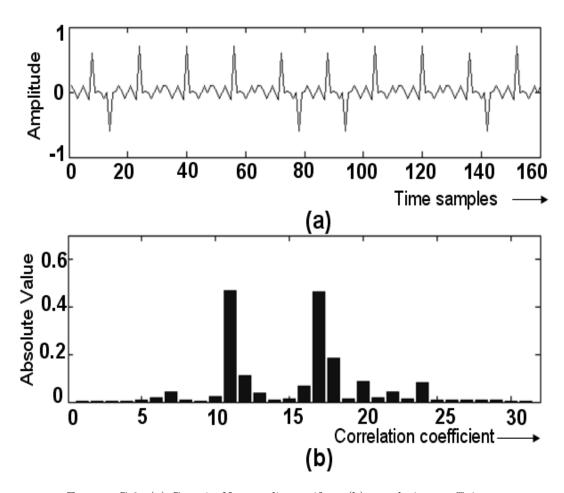

| 5.11 | (a) One of the independent sources for 4-D FastICA, (b) 4 <sup>th</sup> component as one of the estimated outputs of the 4-D FastICA based on the proposed                                                                                                                                                                                           |       |

|      | algorithm                                                                                                                                                                                                                                                                                                                                            | 122   |

| 6.1  | Iteration stage of the proposed CORDIC based 2-D FastICA                                                                                                                                                                                                                                                                                             | 130   |

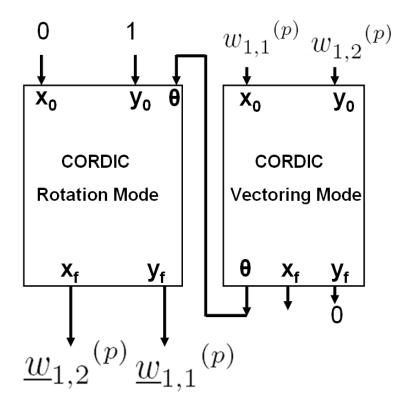

| 6.2  | Normalization stage of the proposed CORDIC based 2-D FastICA                                                                                                                                                                                                                                                                                         | 131   |

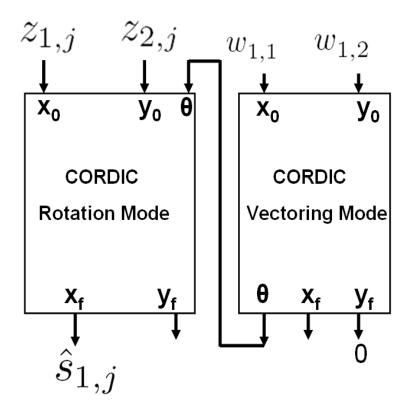

| 6.3  | Estimation stage of the proposed CORDIC based 2-D FastICA                                                                                                                                                                                                                                                                                            | 132   |

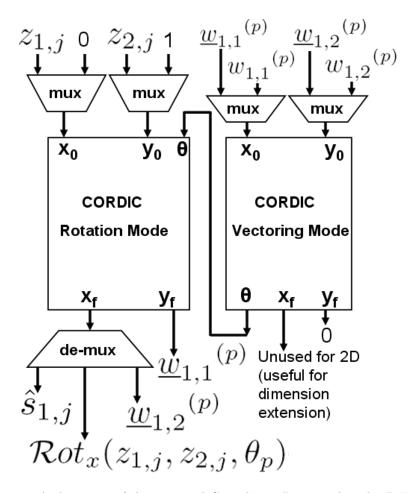

| 6.4  | Architecture of the proposed Co-ordinate Rotation based 2-D FastICA                                                                                                                                                                                                                                                                                  |       |

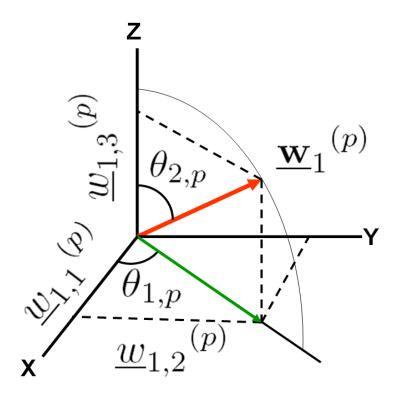

| 6.5  | 3D representation of $\underline{\mathbf{w}}_{1}^{(p)}$ in Spherical Co-ordinate system                                                                                                                                                                                                                                                              |       |

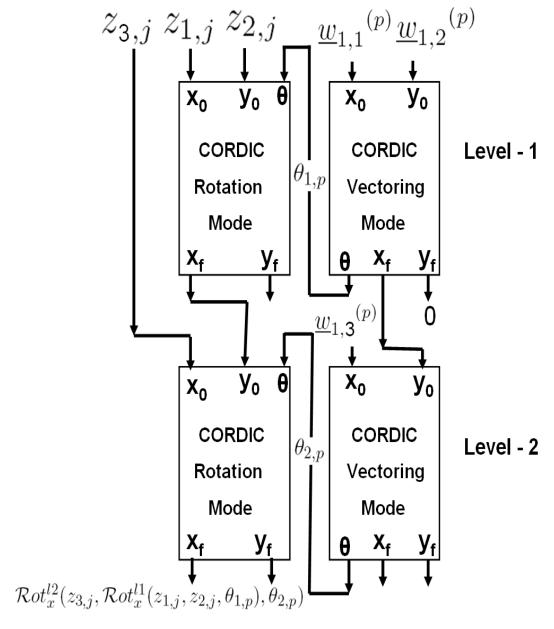

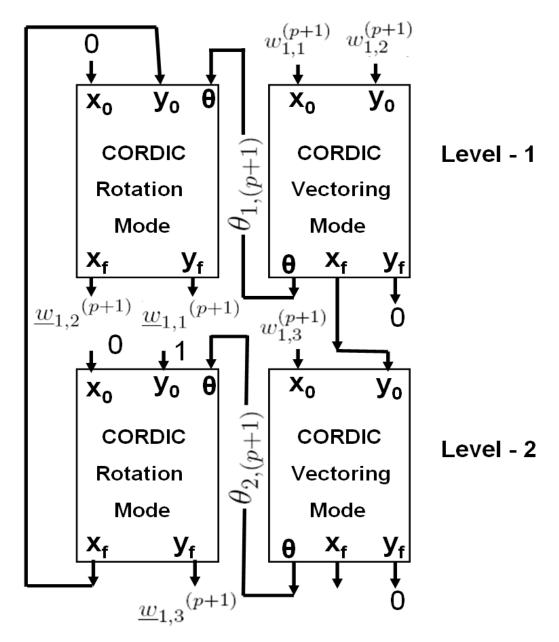

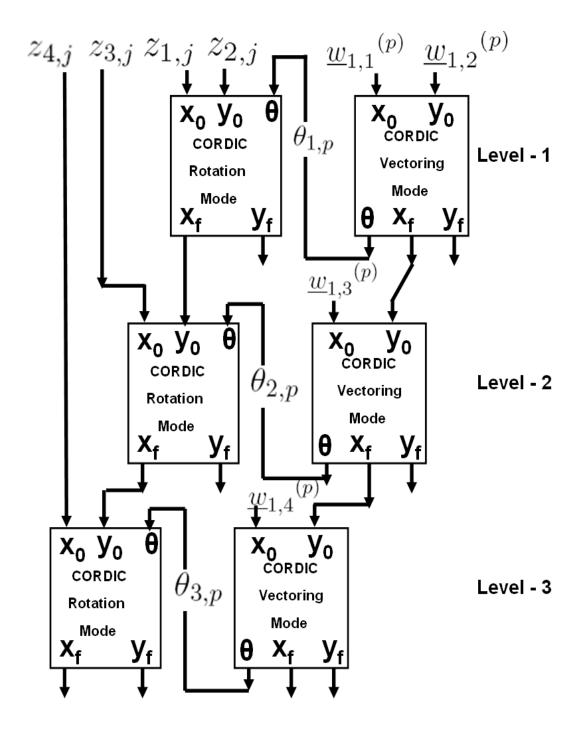

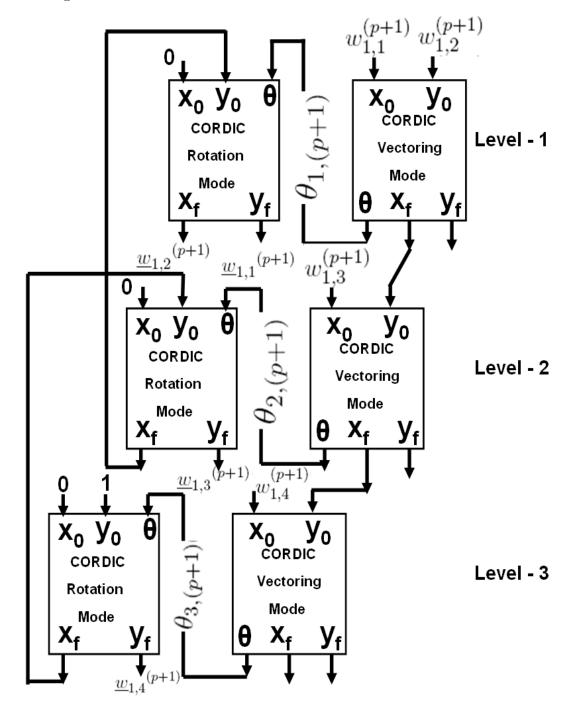

| 6.6  | Iteration stage of the proposed Co-ordinate Rotation based 3-D FastICA.                                                                                                                                                                                                                                                                              | 140   |

| 6.7  | Normalization stage of the proposed Co-ordinate Rotation based 3-D Fas-                                                                                                                                                                                                                                                                              | 1 / 1 |

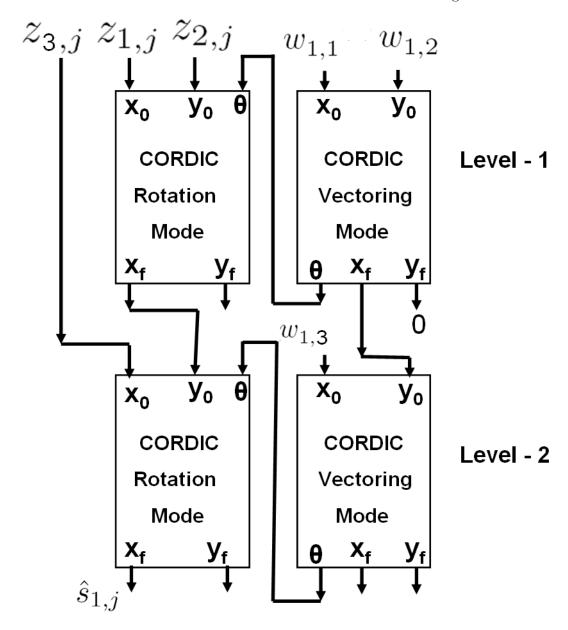

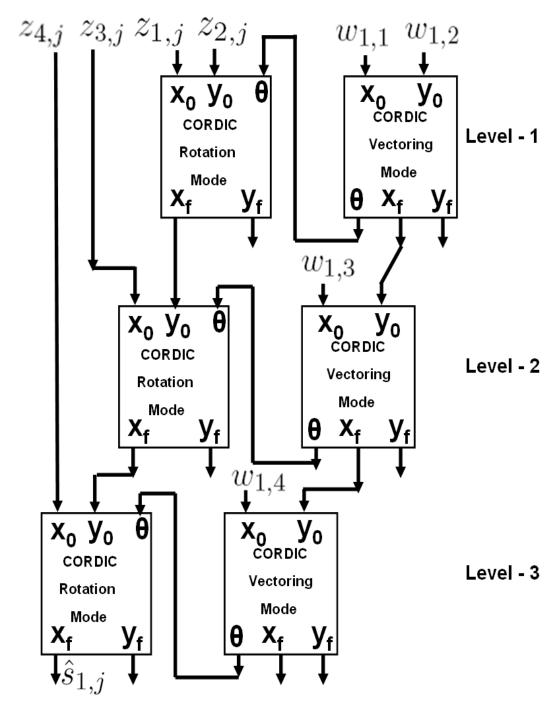

| 6.8  | tICA                                                                                                                                                                                                                                                                                                                                                 |       |

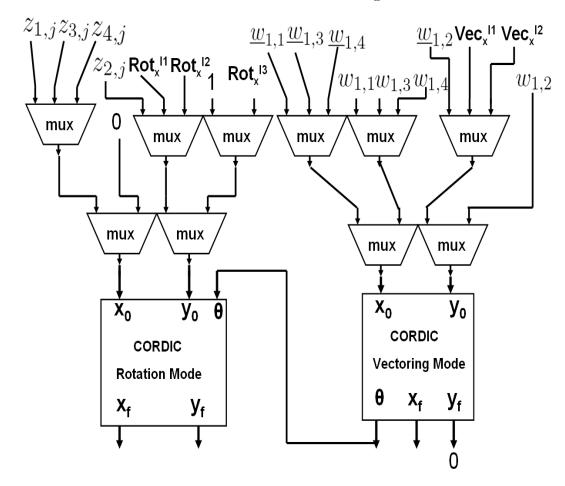

| 6.9  | Architecture of the proposed Co-ordinate Rotation based 3-D FastICA                                                                                                                                                                                                                                                                                  |       |

|      | Iteration stage of the proposed Co-ordinate Rotation based 4-D FastICA.                                                                                                                                                                                                                                                                              |       |

|      | Normalization stage of the proposed Co-ordinate Rotation based 4-D Fas-                                                                                                                                                                                                                                                                              |       |

| e 10 | tICA.                                                                                                                                                                                                                                                                                                                                                | 152   |

| 0.12 | Estimation stage of the proposed Co-ordinate Rotation based 4-D FastICA.                                                                                                                                                                                                                                                                             | 15/   |

| 6.13 | Architecture of the proposed Co-ordinate Rotation based 4-D FastICA                                                                                                                                                                                                                                                                                  |       |

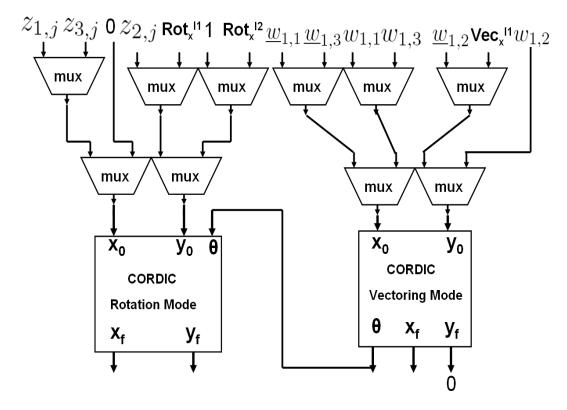

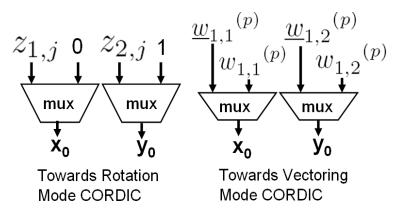

|      | Multiplexer array used in front of the 2-D FastICA                                                                                                                                                                                                                                                                                                   |       |

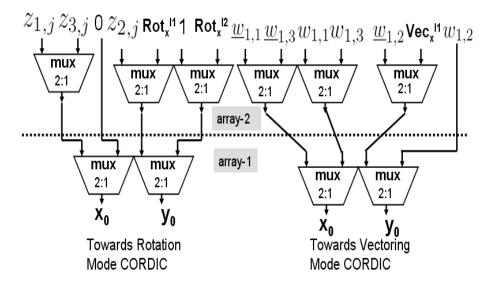

|      | Multiplexer arrays used in front of the 3-D FastICA                                                                                                                                                                                                                                                                                                  |       |

LIST OF FIGURES xii

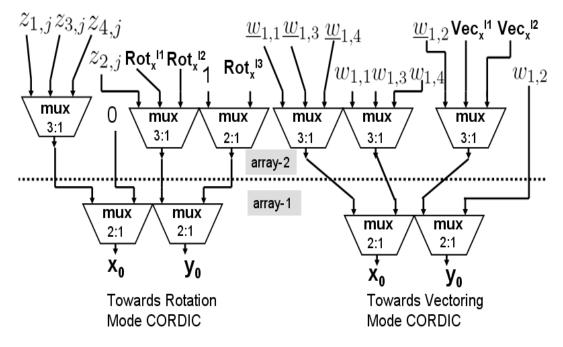

| 6.16 | Multiplexer arrays used in front of the 4-D FastICA                             | . 167 |

|------|---------------------------------------------------------------------------------|-------|

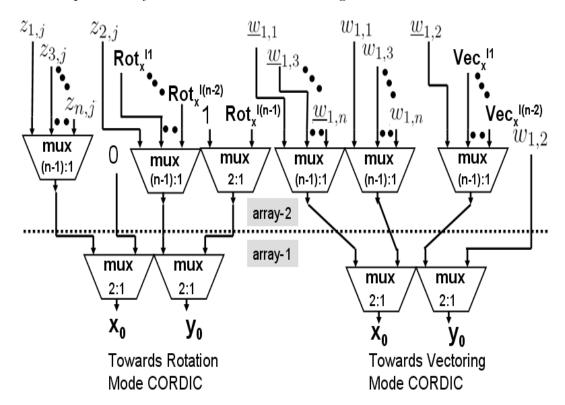

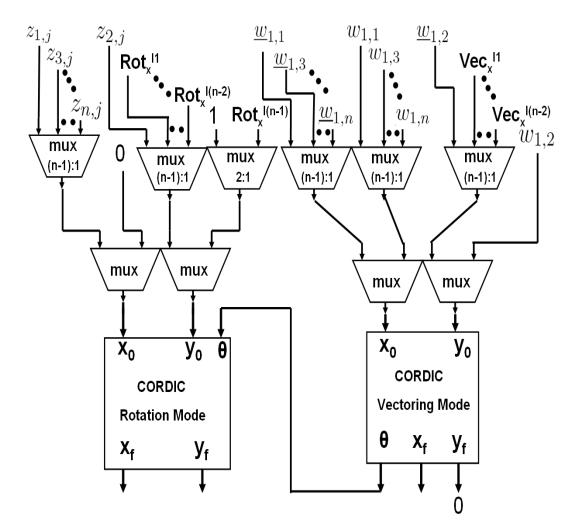

| 6.17 | Multiplexer arrays used in front of the $n$ -D FastICA                          | . 168 |

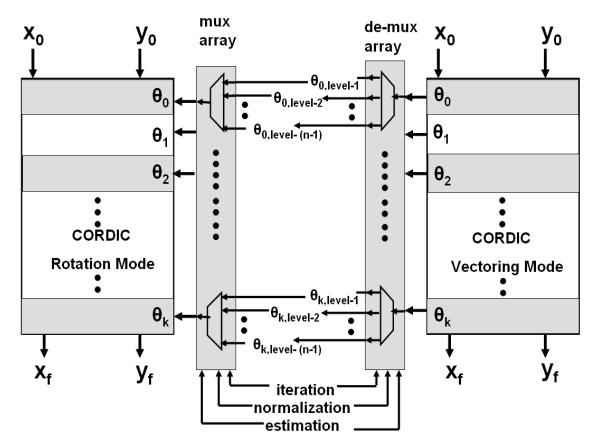

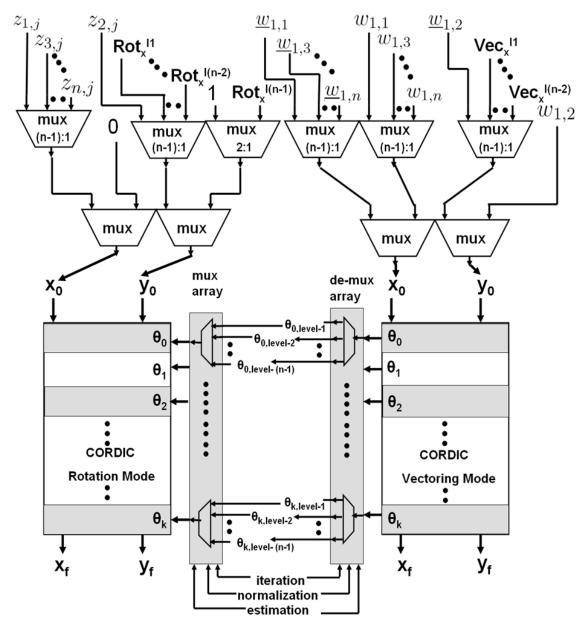

| 6.18 | Architecture of the proposed Co-ordinate Rotation based n-D FastICA.            | . 169 |

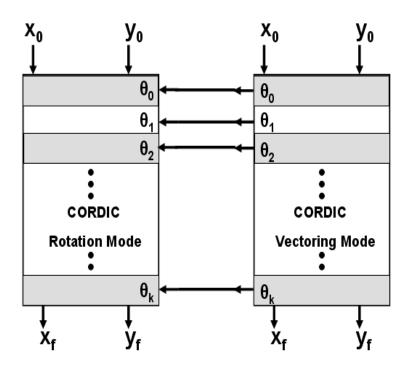

| 6.19 | Doubly Pipelining of the proposed CORDIC based 2-D FastICA archi-               |       |

|      | tecture.                                                                        | . 170 |

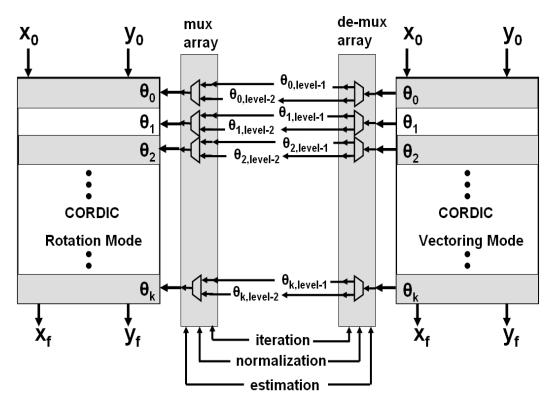

| 6.20 | Doubly Pipelining of the proposed CORDIC based 3-D FastICA archi-               |       |

|      | tecture.                                                                        | . 171 |

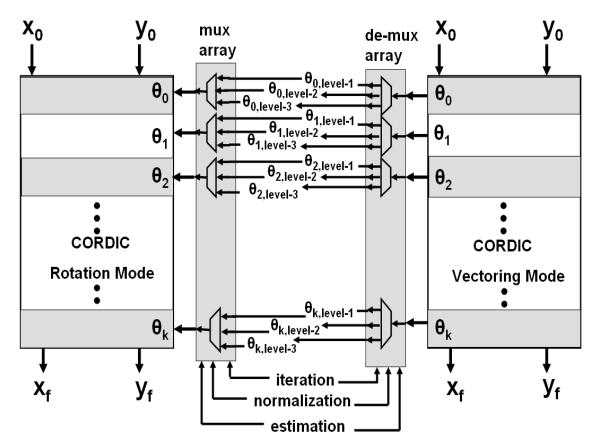

| 6.21 | Doubly Pipelining of the proposed CORDIC based 4-D FastICA archi-               |       |

|      | tecture.                                                                        | . 172 |

| 6.22 | Doubly Pipelining of the proposed CORDIC based n-D FastICA archi-               |       |

|      | tecture.                                                                        | . 173 |

| 6.23 | Overall architecture of the proposed CORDIC based n-D FastICA algo-             |       |

|      | rithm                                                                           | . 174 |

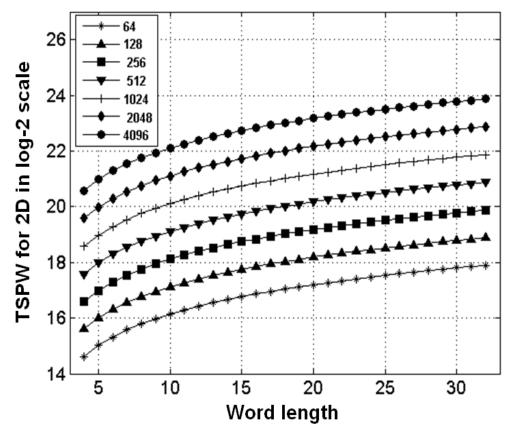

| 6.24 | Variation of Transistor Saving Per Word-length $(TSPW)$ of the proposed         |       |

|      | algorithm for $2D$ with Word-length and frame-length                            | . 180 |

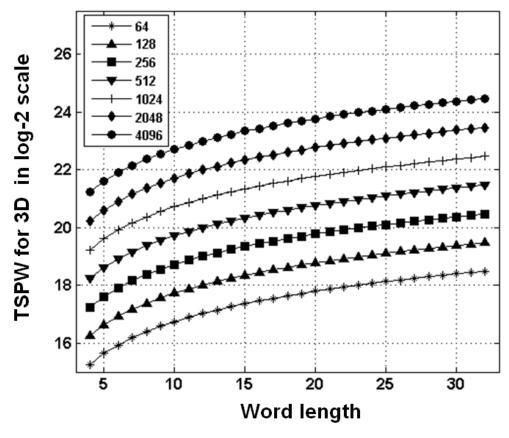

| 6.25 | Variation of Transistor Saving Per Word-length $(TSPW)$ of the proposed         |       |

|      | algorithm for $3D$ with Word-length and frame-length                            | . 182 |

| 6.26 | Variation of Transistor Saving Per Word-length $(TSPW)$ of the proposed         |       |

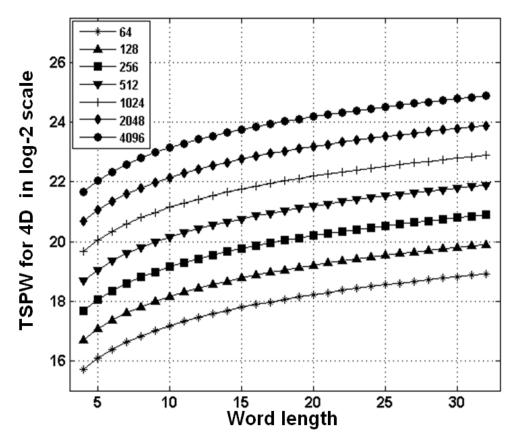

|      | algorithm for $4D$ with Word-length and frame-length                            | . 184 |

| 6.27 | Variation of Transistor Saving Per Word-length $(TSPW)$ of the proposed         |       |

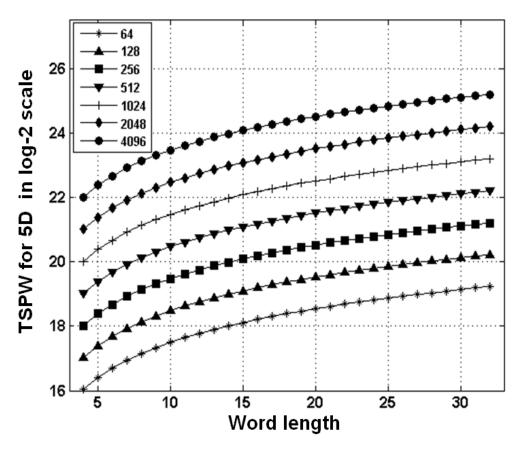

|      | algorithm for $5D$ with Word-length and frame-length                            | . 186 |

| 6.28 | Variation of Transistor Saving Per Word-length $(TSPW)$ of the proposed         |       |

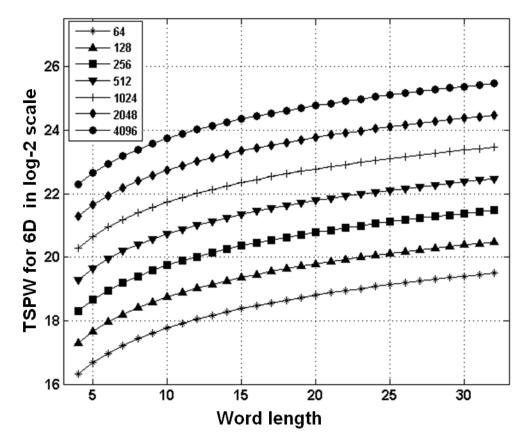

|      | algorithm for $6D$ with Word-length and frame-length                            | . 187 |

| 6.29 | Comparative variation of Transistor Saving Per Word-length $(TSPW)$ of          |       |

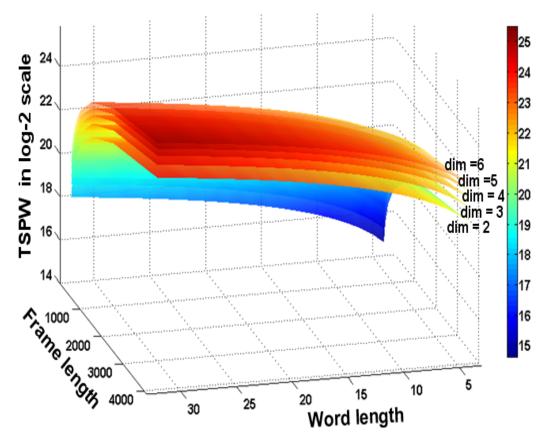

|      | the proposed algorithm with Frame-length and Word-length for $2D$ to $6D$       |       |

|      | (denoted by $\dim = 2$ to $\dim = 6$ )                                          | . 188 |

| 6.30 | Left side - estimated waveforms from conventional $2D$ FastICA, right           |       |

|      | side - estimated waveforms from proposed co-ordinate rotation based $2D$        |       |

|      | FastICA. Source signals were - $0.7\sin(450t)\sin(40t)$ and $0.5\sin[500t +$    |       |

|      | $5\cos(60t)$ ] as obtained from [122]                                           | . 189 |

| 6.31 | Left side - estimated waveforms from conventional $3D$ FastICA, right           |       |

|      | side - estimated waveforms from proposed co-ordinate rotation based $3D$        |       |

|      | FastICA. Source signals were - (i) top: $0.9\sin(800t)\sin(60t)$ , (ii) middle: |       |

|      | $0.7\sin(90t)$ , (iii) bottom: $0.7\sin(450t)\sin(40t)$                         | . 190 |

| 7.1  | Thesis overview: Our vision and research challenges identified in Chapter-      |       |

| 1.1  | 1, Our research contributions as described in Chapter 2 to Chapter 6 and        |       |

|      | the Future Research identified in Chapter 7                                     | 192   |

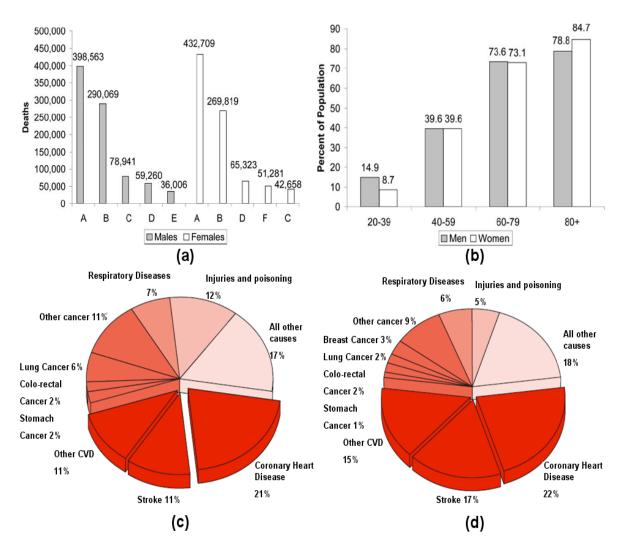

| 7.2  | (a) CVD and other major causes of death for all males and females               | . 102 |

| 1.2  | (United States, 2006). A: CVD plus congenital CVD; B: Cancer; C:                |       |

|      | Accidents; D: Chronic Lower Respiratory Disease (CLRD); E: Diabetes             |       |

|      | and F: Alzheimer's Disease [165], (b) Prevalence of CVD in adults $\geq 20$     |       |

|      | years of age "by age and sex" [165], (c) Deaths by cause, men, year 2008        |       |

|      | in Europe [166], (d) Deaths by cause, women, year 2008 in Europe [166].         | 195   |

LIST OF FIGURES xiii

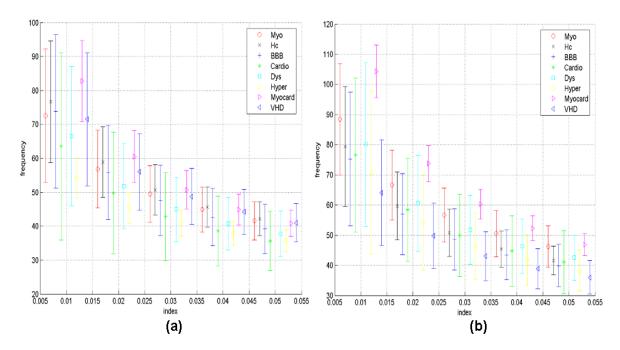

| 7.3  | Mean frequency variation for 8 different cardio vascular diseases for dif-<br>ferent patients at different power spectral density distribution point for |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (a) Lead - i and (b) Lead - ii of standard ECG measurement method.                                                                                       |     |

|      | Error bars indicate the standard deviation across the mean frequency.                                                                                    |     |

|      | Definition of abbreviations used: Myo = Myocardial Infarction, HC =                                                                                      |     |

|      | Healthy Controls, BBB = Bundle Branch Block, Cardio = Cardiomyopa-                                                                                       |     |

|      | thy/ Heart Failure, Dys = Dysrhythmia, Hyper = Myocardial Hypertro-                                                                                      | 106 |

|      | phy, Myocard = Myocarditis, VHD = Valvular Heart Disease                                                                                                 | 190 |

| B.1  | Overview of FECG extraction method [69]. WT and MM indicate Wavelet                                                                                      |     |

|      | Transform and Modulus Maxima respectively                                                                                                                |     |

| B.2  | Block diagram of FECG extraction method                                                                                                                  | 201 |