# Effect of Nanotopography in Direct Wafer Bonding: Modeling and Measurements

K. T. Turner, S. M. Spearing, W. A. Baylies, M. Robinson, and R. Smythe

Abstract—Nanotopography, which refers to surface height variations of tens to hundreds of nanometers that extend across millimeter-scale wavelengths, is a wafer geometry feature that may cause failure in direct wafer bonding processes. In this work, the nanotopography that is acceptable in direct bonding is determined using mechanics-based models that compare the elastic strain energy accumulated in the wafer during bonding to the work of adhesion. The modeling results are presented in the form of design maps that show acceptable magnitudes of height variations as a function of spatial wavelength. The influence of nanotopography in the bonding of prime grade silicon wafers is then assessed through a combination of measurements and analysis. Nanotopography measurements on three 150-mm silicon wafers, which were manufactured using different polishing processes, are reported and analyzed. Several different strategies are used to compare the wafers in terms of bondability and to assess the impact of the measured nanotopography in direct bonding. The measurement and analysis techniques reported here provide a general route for assessing the impact of nanotopography in direct bonding and can be employed when evaluating different processes to manufacture wafers for bonded devices or substrates.

*Index Terms*—Direct bonding, microelectromechanical systems (MEMS), nanotopography, silicon-on-insulator (SOI), wafer bonding.

# I. INTRODUCTION

IRECT wafer bonding is a flexible semiconductor manufacturing process that has become widely used in a range of applications, including the fabrication of silicon-on-insulator (SOI) substrates, microelectromechanical systems (MEMS), and microelectronic devices. While the process offers many benefits, such as high strength and high temperature stable bonds, the process requires that tight flatness and roughness tolerances be maintained on the wafers. Nanotopography [1], which refers to variations of the front surface of the wafer that extend over millimeter-scale wavelengths and typically have a magnitude of tens to hundreds of nanometers, is one of a range of variations that may lead to failure in direct bonding processes. The development of robust bonding processes requires that the impact of nanotopography on direct bonding be

Manuscript received September 30, 2004; revised December 9, 2004. This work was supported by the Cambridge MIT Institute (CMI-059/P-IR(FT)MEMS).

- K. T. Turner is with the Massachusetts Institute of Technology, Cambridge, MA 02139-4307 USA (e-mail: kturner@mit.edu).

- S. M. Spearing was with the Massachusetts Institute of Technology, Cambridge, MA 02139-4307 USA. He is now at the University of Southampton, Southampton SO17 1BJ, U.K. (e-mail: spearing@soton.ac.uk).

- W. A. Baylies is with the BayTech Group, Weston, MA 02493 USA.

- M. Robinson and R. Smythe are with the Zygo Corporation, Middlefield, CT 06455-0448 USA

Digital Object Identifier 10.1109/TSM.2005.845009

understood and that strategies exist to measure and quantify its effect in bonding. The aim of the current work is to present models to assess the effect of nanotopography in direct bonding and to demonstrate how those models may be coupled with measurements of nanotopography to compare and assess the bondability of wafers.

The paper is structured as follows. First, previous work in direct bonding and nanotopography is reviewed to demonstrate the importance of flatness variations in direct bonding and to provide insight into the typical magnitude of, the origins of, and the metrology available to measure nanotopography. Then, an elasticity solution, which allows the strain energy required to bond two sinusoidally varying surfaces to be calculated, is reviewed. The solution is used to develop bonding maps that provide guidance as to the magnitude of nanotopography height variations that are significant in direct bonding. Next, nanotopography measurements of three silicon wafers that were manufactured using different polishing processes are reported. The measurements from the wafers are analyzed and compared to one another and the results are then discussed as to the impact that the measured nanotopography will have in direct bonding.

# II. BACKGROUND

#### A. Direct Bonding

Direct wafer bonding is a two-step process that consists of an initial room temperature bond to join the wafers and a subsequent thermal anneal to strengthen the interface. Achieving complete, void-free bonding in the room temperature step is crucial and requires that the wafers be smooth, flat, and clean. Flatness variations across a range of spatial wavelengths play a role in bonding, but are tolerable if their magnitudes are sufficiently small. Variations with the smallest spatial wavelengths, which are referred to as roughness, can be accommodated in the bonding process by the surface adsorbed species (i.e., water molecules in hydrophilic bonding) [2]. Longer wavelength variations, such as nanotopography (spatial wavelengths of  $\approx$ 0.2–20 mm) and wafer-scale shape variations (i.e., bow and warp), must be accommodated through elastic deformation of the wafers. The effect of flatness variations that are accommodated elastically in the bonding process may be quantified by comparing the strain energy associated with the elastic deformation to the surface energy available to drive the bonding process.

Two wafers that have initially different shapes due to geometric variations will deform during the bonding process and bond completely if the surface energy that is liberated during bonding is greater than the strain energy required for the wafers to deform to a common shape. Models that examine bonding success using this approach have been reported in [3]–[7].

Turner and Spearing [6] proposed a bonding criterion for direct wafer bonding using this energy balance approach

$$\frac{dU}{dA} \le W \tag{1}$$

where dU/dA is the change in strain energy per unit area of bond front advance and W is the work of adhesion. For two dissimilar solids, the work of adhesion is  $W = \gamma_1 + \gamma_2 - \gamma_{12}$ , where  $\gamma_1$ ,  $\gamma_2$  are the surface energies and  $\gamma_{12}$  is the interface energy. The quantity dU/dA is a function of the geometry and elastic properties of the wafers and W is determined by the type and density of bonds on the bonding surfaces. This criterion is convenient as it separates the geometry and elastic properties of the wafers from the work of adhesion, which is a function of the surface chemistry. The term dU/dA may be related to measurements of wafer geometry using analytical or computational mechanics models. Models that connect wafer-scale shape variations to dU/dA are given in [6] and [7], and a relation, based on the solution in [5], that relates nanotopography to the strain energy per unit area required is presented here in Section III.

While several models have been developed to examine bondability in direct wafer bonding processes using energy based approaches, there has been a limited amount of work demonstrating how to connect the models to measurements of wafer geometry. Examples of connecting the models to measurements and experiments has been limited to demonstrations that thicker wafers require better polishing processes in order for bonding to be achieved, as is predicted by basic analytical models, [4]. The primary reason for this lack of coupling between models and measurements has been that the traditional measures of wafer geometry, such as total thickness variation (TTV), bow, and warp, do not provide sufficient information to assess bondability. The principal limitation of these measures is that they provide no information about the spatial wavelength of the variations, which is a critical input in models such as those reported in [4] and [5].

## B. Nanotopography

Nanotopography has emerged as a significant factor in integrated circuit fabrication with the introduction of chemical mechanical polishing (CMP) processes for shallow trench isolation [8]. As a result, the metrology industry has introduced tools to measure it, wafer manufacturers have made efforts to control it, and standards have been developed for reporting it [1].

Numerous studies have been performed to characterize wafer nanotopography, [9]–[14]. From these reports, it is evident that height variations between 10 and 100 nm across spatial wavelengths of 0.2 to 20 mm are typical for standard silicon wafers. Measurements on 200-mm wafers reported in [15] show that peak-to-valley variations over a 20-mm wavelength may be as large as 150 nm. The results reported in [15] also show that nanotopography amplitude and pattern depend to a large extent on the polishing configuration (single side or double side) as well as the details of the polishing process. The effects of different polishing and wafer mounting methods are discussed in [8], [12], [16], and [17]. In general, DSP wafers tend to have less nanotopography than SSP wafers. This is the case because in true DSP processes, where the wafers are free floating and both sides are polished simultaneously, the topography of the back surface

does not get transmitted to and distort the front surface of the wafer during polishing [17].

Measuring nanotopography is challenging due to the large lateral areas that must be imaged while achieving subnanometer vertical resolution. Several specialized systems have been developed for measuring nanotopography, including scanning laser systems as well as interferometric systems that use a white light halogen source [18]. In the nanotopography studies discussed above, 200- and 300-mm wafers have been measured using a commercial laser scanning system (ADE SQM), [19], as well as a commercial white light interferometric system (ADE Phase-Shift Nanomapper), [10], [13]–[15]. A system that uses a Schack-Hartman wavefront sensor has also been reported [20]. While no specific measurement technique is specified in the nanotopography standard [1], interferometric systems, which allow for large area measurements to be acquired rapidly, appear to be the method of choice at the current time for characterizing full wafer nanotopography on 200- and 300-mm silicon wafers.

#### III. MECHANICS MODELING

The critical quantity when assessing the effect of flatness variations that are accommodated through elastic deformation is the strain energy required per unit area of bond front advance, dU/dA. When bonding two surfaces with arbitrary topographies, which may make contact at several points, it is difficult to define a single bond front to calculate dU/dA as has been done in the case of wafer-scale shape variations in [6]. Thus, when examining the effect of nanotopography on bonding, the change in strain energy per change in bond area,  $\Delta U/\Delta A$ , over a reference area is considered rather than dU/dA.

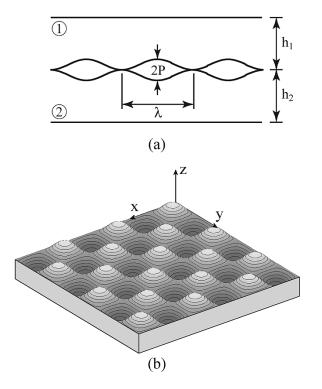

To evaluate  $\Delta U/\Delta A$  for nanotopography, a model that allows the strain energy to be calculated as a function of the surface geometry is required. Yu and Suo [5] presented a model in the context of direct bonding that allows the strain energy required to deform two wafers to close a sinusoidal varying gap at the interface (Fig. 1) to be calculated. The solution given by Yu and Suo is valid across the nanotopography range examined in the current work, assuming that the surface height variations are small compared to the wafer thickness (0.5–1 mm). This assumption is reasonable as the typical nanotopography height variations are on the order of 10–100 nm (Section II-B).

A schematic of the cross section of the model geometry considered in [5] is shown in Fig. 1(a) and a three-dimensional map of the model surface is shown in Fig. 1(b). The gap at the interface that must be closed through elastic deformation during bonding as a function of the spatial coordinates  $\boldsymbol{x}$  and  $\boldsymbol{y}$  can be expressed as

gap =

$$P\left[1 + \cos\left(2\pi\frac{x}{\lambda}\right)\cos\left(2\pi\frac{y}{\lambda}\right)\right]$$

. (2)

The strain energy per unit area required to close this gap is [5]

$$\frac{\Delta U}{\Delta A} = \frac{\pi}{4\sqrt{2}} \frac{P^2}{\lambda} \left( \frac{1}{\bar{E}_1 I\left(\frac{2\pi h_1}{\lambda}\right)} + \frac{1}{\bar{E}_2 I\left(\frac{2\pi h_2}{\lambda}\right)} \right)^{-1} \tag{3}$$

where  $h_1$  and  $h_2$  are the thicknesses of the layers,  $\lambda$  and P are the wavelength and amplitude of the surface topography,  $\bar{E}_1$  and  $\bar{E}_2$  are the plane strain moduli of the wafers  $[\bar{E}_i = E_i/(1-\nu_i^2),$

Fig. 1. Schematic of the model surface. (a) Two-dimensional cross section. (b) Three-dimensional surface plot [5].

$E_i$  is the Young's modulus, and  $\nu$  is the Poisson's ratio], and the function  $I(\alpha)$  is

$$I(\alpha) = \frac{e^{2\sqrt{2}\alpha} + e^{-2\sqrt{2}\alpha} - 2 - 8\alpha^2}{e^{2\sqrt{2}\alpha} - e^{-2\sqrt{2}\alpha} + 4\sqrt{2}\alpha}.$$

(4)

In the case where the wafers have the same elastic properties  $(\bar{E}_1 = \bar{E}_2)$  and equal thickness  $(h_1 = h_2)$ , (3) reduces to

$$\frac{\Delta U}{\Delta A} = \frac{\pi}{8\sqrt{2}} \frac{\bar{E}_1 P^2}{\lambda} I\left(2\pi \frac{h_1}{\lambda}\right). \tag{5}$$

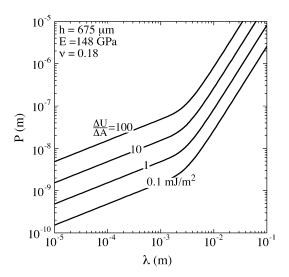

The effect of surface topography on bonding may be more clearly understood by creating maps using (5) that show combinations of amplitude and wavelength that are bondable (assuming no other flatness variations are present) for a given work of adhesion. Figs. 2 and 3 are two examples of such maps. Combinations of wavelength and amplitude that fall below the lines are bondable while those that fall above are not.

Fig. 2 provides guidance on acceptable amplitude and wavelength combinations for various values of work of adhesion when bonding two standard 150-mm silicon wafers ( $h_1 = h_2 = 675~\mu\text{m}$ ,  $E_1 = E_2 = 148~\text{GPa}$ ,  $\nu_1 = \nu_2 = 0.18$ ). Given that typical values of work of adhesion in silicon wafer bonding are on the order of 1 to  $100~\text{mJ/m}^2$  (hydrophobic and hydrophilic bonding, [21]) and that wafer shape variations typically result in a strain energy per unit area of  $1-100~\text{mJ/m}^2$  [6], the  $1~\text{mJ/m}^2$  bound in Fig. 2 is a good reference to determine a lower bound on the range of nanotopography that will play a role in direct bonding. With this consideration, it is seen that at wavelengths of 1 and 10 mm, height variations that are greater than 5 and 90 nm, respectively, would result in nanotopography having an important effect in direct bonding. Given the typical values of

Fig. 2. Bonding map showing  $\Delta U/\Delta A$  as a function of wavelength and amplitude for standard thickness 150-mm-diameter silicon wafers.

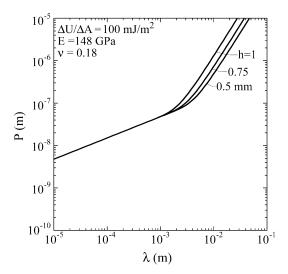

Fig. 3. Bonding map showing the effect of wafer thickness.

nanotopography reported in previous work, it is reasonable to expect that nanotopography may be a contributing factor in direct bonding failures.

The map shown in Fig. 3 demonstrates the importance of wafer thickness when considering nanotopography effects in bonding. At the longer spatial wavelengths (>3 mm) in the nanotopography range, bonding difficulty increases with the cube of thickness, the same scaling observed with wafer-scale shape variation effects in bonding [6]. At spatial wavelengths less than 1 mm, the strain energy required to achieve bonding is independent of wafer thickness. This result suggests that moving to thinner wafers will facilitate bonding if longer wavelength nanotopography variations are present, but will not yield any benefit if shorter wavelength variations are the source of bonding problems.

#### IV. MATERIAL AND MEASUREMENTS

The nanotopography of (100) 150-mm-diameter silicon wafers that were manufactured using three different polishing

TABLE I SUMMARY OF WAFERS MEASURED

| Wafer | Process           | TTV (µm) |  |

|-------|-------------------|----------|--|

| (A)   | single-side       | 1.7      |  |

| (B)   | double-side rough | 2.6      |  |

| (C)   | double-side fine  | 1.8      |  |

processes were measured. The polishing processes are: (A) single side fine polish, (B) double side rough polish, and (C) double side fine polish. The single-side fine polish process used to produce wafer (A) is the same as that used to produce commercially available prime grade 150-mm silicon wafers. The three wafers and their total thickness variations are summarized in Table I.

Nanotopography was measured using a large area Fizeau interferometer that provided comparable resolution to specialized nanotopography metrology tools, but allowed greater flexibility in handling 150-mm wafers. Specifically, a vertically mounted (downward looking) Zygo Verifire AT Fizeau interferometer with a Ring of Fire illumination system [22] was used. The system had a 6-in aperture with an adjustable zoom setting that allowed the size of the imaging area to be set. The camera resolution was fixed at  $776 \times 576$  pixels, thus, the zoom setting determined the size of the measurement area as well as the spatial resolution. A zoom setting which resulted in a spatial resolution of 108.8  $\mu$ m and a measurement area of 84.4 mm  $\times$  62.6 mm was used for all measurements. This setting allowed height variations with spatial wavelengths down to  $\approx$ 0.22 mm (based on a Nyquist consideration) to be measured while also providing a sufficiently large measurement area after filtering to permit statistically significant information on longer wavelength height variations to be obtained. To ensure that the nanotopography measurements obtained would be representative of the surface geometry during direct bonding, the wafers were not mounted to a chuck and were simply rested on a 6-in-diameter reference flat in a horizontal orientation during all measurements.

Long spatial wavelength height variations typically obscure the nanotopography features of interest in raw measurements obtained via interferometric systems. As such, a high-pass filtering routine is required to isolate the spatial wavelengths of interest. Filtering has been used in all nanotopography measurements reported and the selection of filtering techniques has been investigated [23]. The preferred method of filtering reported in [23] and specified in SEMI M43 [1] is a high-pass double Gaussian filter. The double Gaussian filter effectively removes the long wavelength variations without significantly attenuating the height of features in the range of interest.

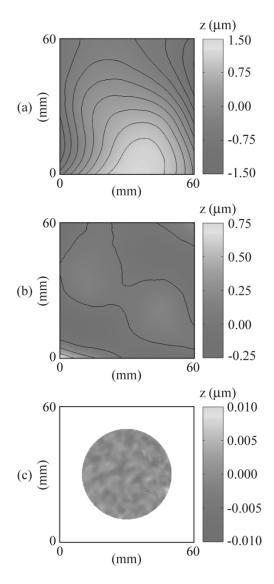

The nanotopography of the surfaces was isolated from the raw measurements through the process shown in Fig. 4. The raw measurement (84.4 mm  $\times$  62.6 mm), which was centered on the wafer, was first cropped to a 60-mm square analysis area [Fig. 4(a)]. A third-order best fit polynomial was then removed from the measurement [Fig. 4(b)] and the resulting surface was filtered using a high-pass double Gaussian filter with a 10-mm cutoff. The filtered data was cropped to a 40-mm circle [Fig. 4(c)] in order to remove nonphysical edge effects that result from the filtering process. This postprocessing was performed externally using a custom MATLAB script.

Fig. 4. Process used to isolate the nanotopography features from the raw measurements [data shown is that for wafer (C)]. (a) Raw measurement. (b) Surface after overall form was removed. (c) Final data after filtering with a 10 mm high-pass double Gaussian filter and cropping to remove edge effects.

#### V. RESULTS AND DISCUSSION

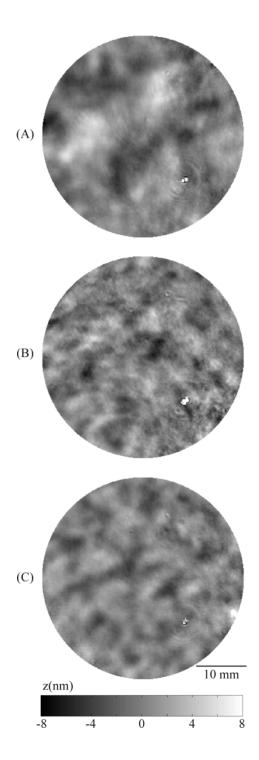

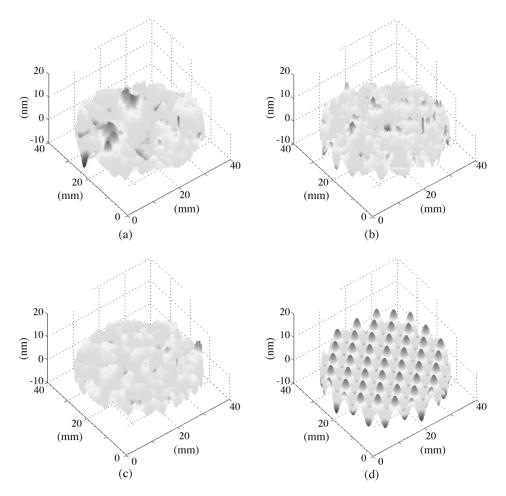

Nanotopography measurements obtained for the three wafers are shown in Fig. 5. The nanotopography height variations observed are in the low end of the range of values reported in the previous studies reviewed in Section II-B. This is likely due to the fact that a double Gaussian filter with a 10-mm cutoff, rather than the more common 20-mm cutoff, was used because of the limited size of the measurement area. The maps shown in Fig. 5 allow clear differences between the three wafers to be identified. The surface height variations of wafer (C) are smaller than those of wafers (A) and (B). The maps also show that the dominant wavelength of the height variations on the DSP wafers, wafers (B) and (C), are less than that on the SSP, wafer (A).

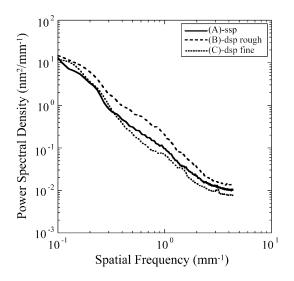

A quantitative comparison between the three wafers may be obtained by examining the power spectral densities (PSDs) of the surfaces. The PSDs are particularly relevant in the current context as they provide information about both the amplitude and wavelength of the height variations on the surfaces. The

Fig. 5. Nanotopography height maps of the three wafers: wafer (A) SSP fine polish, wafer (B) DSP rough polish, and wafer (C) DSP fine polish. Each map is 40 mm in diameter and is centered on the wafer.

PSDs for the three wafers are shown in Fig. 6. The PSDs were obtained by estimating the PSD along line scans in the x and y directions (369 scans in x and y each) and then averaging. The results shown in Fig. 6 show that wafer (B) has the largest PSD and that the magnitudes of the PSDs of wafers (A) and (C) are similar to one another. As the amplitude of the different frequency components of the surface scales with the PSD, it can be concluded from Fig. 6 that wafer (B) would be the most difficult of the three to bond. It is not straightforward though to identify

Fig. 6. Power spectral densities of the nanotopography of three wafers.

Fig. 7. Root mean square of the height variations over a frequency band 0.09 mm<sup>-1</sup> wide versus the mean frequency in the band for each wafer.

whether (A) or (C) has a better nanotopography for bonding as their PSDs cross at a spatial frequency of  $\approx 0.3 \text{ mm}^{-1}$ .

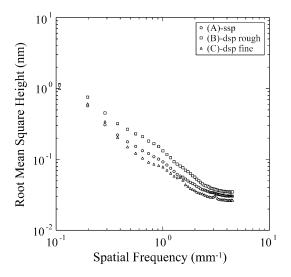

Quantities that are linearly proportional to the amplitude of the height variations provide a more direct route than the PSDs to connect the nanotopography measurements to bondability through the model presented in Section III. Integrating the power spectral density S(f) across a specified frequency band  $(f_l$  to  $f_h$ ), allows the mean square value of the height variations  $\bar{z}^2$  within that frequency band to be estimated [24]

$$\bar{z}^2 = \int_{f_t}^{f_h} S(f)df. \tag{6}$$

Using (6), the root mean square (rms) of the height variations,  $z_{\rm rms} = \sqrt{\bar{z}^2}$ , as a function of spatial wavelength was calculated from the PSDs shown in Fig. 6 over adjacent frequency bands 0.09 mm<sup>-1</sup> wide. The rms values as a function of the mean frequency in each band are plotted in Fig. 7. The plot displays a similar trend to the PSD plot in Fig. 6 and provides a measure

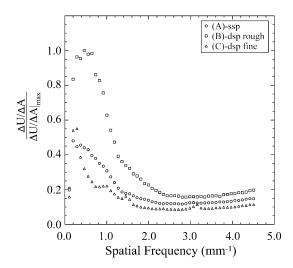

Fig. 8. Normalized  $\Delta U/\Delta A$  resulting from nanotopography for the three wafers.

of the amplitude of the height variations as function of spatial wavelength.

The measurements shown in Fig. 5 clearly reveal that the surface height variations of the wafers are not sinusoidal in nature, which is different from that in the model in Section III. However, to obtain a better understanding of how the three surface topographies relate to bonding, it is assumed that the general scaling with spatial wavelength and amplitude given by the model holds for these surfaces. Using (5) and taking the thickness and elastic properties as  $h_1 = h_2 = 675 \,\mu\text{m}$ ,  $E_1 = E_2 =$ 148 GPa,  $\nu_1 = \nu_2 = 0.18$ , the  $\Delta U/\Delta A$  for each point in Fig. 7 was calculated and normalized by the maximum value of  $\Delta U/\Delta A$  observed across the three wafers. Fig. 8, which shows the relative  $\Delta U/\Delta A$  of the three wafers as a function of spatial frequency, allows the difference in bonding difficulty between the wafers to be quantified. Fig. 8 shows that wafer (C) would be the easiest to bond, wafer (A) would be slightly more difficult, and wafer (B) would be the hardest. This result confirms the conclusion drawn from the PSDs that wafer (B) has the least desirable nanotopography and also allows the difference between (A) and (C) to be discerned.

The importance of the measured nanotopography in direct bonding can be assessed by comparing the  $\Delta U/\Delta A$  of the surfaces to the contributions of other flatness variations and typical values of work of adhesion. Estimating  $\Delta U/\Delta A$  for the wafers is not trivial, as the surfaces have height variations at multiple wavelengths and the model presented in Section III is for a sinusoidally varying surface with a single wavelength. An approach was considered in which the real surfaces could be represented as a summation of sinusoidal components using Fourier decomposition and the  $\Delta U/\Delta A$  could then be calculated by linear superposition of the displacements in the model, as suggested in [5]. While this approach is reasonable, accommodating the phase information of each Fourier component in the superposition scheme is not straightforward and makes implementing this approach difficult. As a result, an alternative approach, in which the strain energy for a reference sinusoidal surface that has an amplitude and wavelength similar to that of the actual surface, was used to estimate  $\Delta U/\Delta A$ .

The goal of the reference surface analysis was to establish an upper bound on  $\Delta U/\Delta A$  for the nanotopography measured in this work. As such, wafer (B), which has the least desirable topography in terms of bonding, was used to determine the geometry of the reference surface. To ensure that the full range of spatial wavelengths was examined, reference surfaces were created from the measurement of wafer (B) processed with filters at three different cutoff wavelengths,  $\lambda_C = 1, 5$ , and 10 mm. The wavelengths for the reference surfaces were estimated by examining the height maps of wafer (B) and measuring the distance between peaks on the surface. It was determined that a conservative estimate (i.e., a shorter wavelength that results in a higher  $\Delta U/\Delta A$ ) of the dominant wavelength on the surface was  $0.75\lambda_C$ . The surface height values have a normal distribution and the mean was set to zero during data reduction, thus the standard deviation  $\sigma$  provides a measure of the amplitude of the height variations on the surface. The peak to valley height P of the reference surface was set to  $7\sigma$ , as 99.96% of the height values are expected to fall within  $+/-3.5\sigma$ . Fig. 9 shows a comparison between the reference surface determined from the data filtered with a 10-mm cutoff and the measurements of the three wafers. The  $\Delta U/\Delta A$  values were calculated for the reference surfaces using (5) and taking  $h_1 = h_2 = 675 \mu \text{m}$ ,  $E_1 = E_2 = 148$  GPa,  $\nu_1 = \nu_2 = 0.18$ . The properties of the reference surfaces and the corresponding  $\Delta U/\Delta A$  values are listed in Table II.

The  $\Delta U/\Delta A$  values for the three reference surfaces are relatively small compared to typical values of work of adhesion in silicon-silicon direct wafer bonding. For a standard hydrophilic bonding process, the work of adhesion is on the order of 100 mJ/m<sup>2</sup>, while in hydrophobic bonding the work of adhesion is typically between 1 and 10 mJ/m<sup>2</sup> [21]. Nanotopography features in the range observed here should clearly not be a concern in hydrophilic bonding processes as the work of adhesion is much larger than the  $\Delta U/\Delta A$ . Even at the low end of the range of work of adhesion values reported for hydrophobic bonding, the  $\Delta U/\Delta A$  that results from the nanotopography observed here is at most a quarter of the work of adhesion. The importance of the nanotopography can further be assessed by comparing its effect to that of other types of flatness variations. Wafer-scale shape variations, such as bow and warp, and etch patterns can lead to dU/dA values of tens of mJ/m<sup>2</sup> [6], which are much larger than the  $\Delta U/\Delta A$  values resulting from the nanotopography measured here. In addition, slight increases in fine scale surface roughness have been shown to reduce the effective work of adhesion in bonding by more than a factor of two [2]. These comparisons suggest that the effect of the nanotopography measured in this work on bonding is small.

The  $\Delta U/\Delta A$  values given in Table II are clearly estimates, though the reference surfaces were chosen conservatively such that the values calculated provide an upper bound on the effect of nanotopography in bonding. The polishing process used to produce wafer (A) is the same as that used to produce commercially available 150-mm prime grade silicon wafers. Given that the nanotopography of wafer (A) is considerably smaller than that of the reference surface used to calculate  $\Delta U/\Delta A$ , nanotopography should clearly not be an important factor in bonding 150-mm prime grade silicon wafers. Furthermore, the fact that none of the polishing processes yielded a nanotopography with a  $\Delta U/\Delta A$  that is large relative to typical values of work of

Fig. 9. Comparison between the measurements of the wafers and the reference surface: (a) wafer (A), (b) wafer (B), (c) wafer (C), and (d) the reference surface.

TABLE II PROPERTIES OF REFERENCE SURFACES AND CORRESPONDING  $\Delta U/\Delta A$

| $\lambda_C$ (mm) | $\sigma$ (nm) | P=7.0σ (nm) | $\lambda_R$ (mm) | $\Delta U/\Delta A~({ m mJ/m^2})$ |

|------------------|---------------|-------------|------------------|-----------------------------------|

| 10               | 1.8           | 12.6        | 7.50             | 0.07                              |

| 5                | 1.0           | 7.0         | 3.75             | 0.22                              |

| 1                | 0.3           | 2.1         | 0.75             | 0.25                              |

adhesion or other flatness variations, suggests that various processes can yield wafers with suitable nanotopography for direct bonding.

## VI. SUMMARY

The effect of wafer nanotopography with spatial wavelengths from  $\approx 0.2$ –10 mm in direct bonding has been investigated. A model that can be used to predict the strain energy required to bond wafers with nanotopography height variations on the surface was reviewed and used to develop bonding maps. It was concluded from the maps that at wavelengths of 1 and 10 mm, height variations of 5 and 90 nm are required for nanotopography to have an influence in direct bonding. The nanotopography of silicon wafers, which were manufactured using three different polishing processes that resulted in different nanotopographies, were measured. The height variations observed were relatively small—less than 20 nm from peak to valley across wavelengths of 10 mm. Spectral analysis was

performed on the surfaces and coupled to an elasticity model which allowed the relative bondability of the three wafers to be assessed. Finally, an upper bound on  $\Delta U/\Delta A$  was estimated based on the measurements of the wafers. The estimate suggests that, in this case, the contribution of nanotopography to the overall strain energy required to bond two wafers is relatively small.

While the nanotopography of the wafers measured in these experiments was determined to have a small effect in silicon–silicon bonding, this may not be true for the nanotopography of wafers manufactured using other polishing processes or in bonding processes where the work of adhesion is significantly lower than that of silicon–silicon bonding. When developing polishing processes for wafers that will be joined using direct bonding processes, it is important to ensure that the nanotopography will not significantly affect the bondability, as was observed here. This work provides an example of how this may be done. The measurement and analysis techniques described are general and provide a route for characterizing nanotopography and relating the measurements to bondability.

### ACKNOWLEDGMENT

The authors appreciate the assistance of Dr. R. Standley at MEMC in obtaining wafers. The authors are also grateful to Prof. D. Boning and Dr. B. Lee, who provided numerous helpful suggestions throughout this work.

## REFERENCES

- SEMI, "SEMI M43-0301: Guide for reporting wafer nanotopography," Semiconductor Equipment and Materials International, 2001.

- [2] N. Miki and S. Spearing, "Effect of nanoscale surface roughness on the bonding energy of direct-bonded silicon wafers," *J. Appl. Phys.*, vol. 94, no. 10, pp. 6800–6806, 2003.

- [3] R. Stengl, K. Mitani, V. Lehmann, and U. Gosele, "Silicon wafer bonding: chemistry, elasto-mechanics, and manufacturing," in *Proc.* 1989 IEEE SOS/SOI Technology Conf., p. 123.

- [4] Q.-Y. Tong and U. Gösele, "Thickness considerations in direct silicon wafer bonding," J. Electrochem. Soc., vol. 142, no. 11, pp. 3975–3979, 1995

- [5] H. Yu and Z. Suo, "A model of wafer bonding by elastic accommodation," J. Mech. Phys. Solids, vol. 46, no. 5, pp. 829–844, 1998.

- [6] K. Turner and S. Spearing, "Modeling of direct wafer bonding: Effect of wafer bow and etch patterns," J. Appl. Phys., vol. 92, no. 12, pp. 7658–7666, 2002.

- [7] K. Turner, M. Thouless, and S. Spearing, "Mechanics of wafer bonding: Effect of wafer bow and etch patterns," *J. Appl. Phys.*, vol. 95, no. 1, pp. 349–355, 2004.

- [8] K. Ravi, "Wafer flatness requirements for future technologies," *Future Fab Int.*, vol. 7, pp. 207–212, 2000.

- [9] D. Boning and B. Lee, "Nanotopography issues in shallow trench isolation CMP," MRS Bull., vol. 27, no. 10, pp. 761–765, 2002.

- [10] B. Lee, D. Boning, W. Baylies, N. Poduje, P. Hester, H. Xia, J. Valley, C. Koliopoulus, D. Hetherington, H. Sun, and M. Lacey, "Wafer nanotopography effects on CMP: experimental validation of modeling methods," in *Proc. Materials Research Society Symp.*, vol. 671, 2001, pp. M4.9.1–M4.9.6.

- [11] B. Lee, T. Gan, D. Boning, P. Hester, N. Poduje, and W. Baylies, "Nanotopography effects on chemical mechanical polishing for shallow trench isolation," in *Proc. IEEE Int. Symp. Semiconductor Manufac-turing Conf.*, 2000, pp. 425–432.

- [12] T. Katoh, J.-G. Park, W.-M. Lee, H. Jeon, U.-G. Paik, and H. Suga, "The nanotopography effect of improved single-side polished wafer on oxide chemical mechanical polishing," *Jpn. J. Appl. Phys. 2, Lett.*, vol. 41, pp. L443–L446, 2002.

- [13] J.-G. Park, T. Katoh, H.-C. Yoo, and J.-H. Park, "Spectral analyses of the impact of nanotopography of silicon wafers on oxide chemical mechanical polishing," *Jpn. J. Appl. Phys. 2, Lett.*, vol. 40, pp. L857–L860, 2001.

- [14] J.-G. Park, T. Katoh, H.-C. Yoo, D.-H. Lee, and U.-G. Paik, "Spectral analyses on pad dependency of nanotopography impact on oxide chemical mechanical polishing," *Jpn. J. Appl. Phys. 2, Lett.*, vol. 41, pp. L17–L19, 2002.

- [15] B. Lee, D. Boning, W. Baylies, N. Poduje, and J. Valley, "Modeling and mapping of nanotopography interactions with CMP," in *Proc. Materials Research Soc. Symp.*, vol. 732E, 2002, pp. I1.1.1–I1.1.12.

- [16] G. Wenski, T. Altmann, W. Winkler, G. Heier, and G. Holker, "Double-side polishing—a technology for 300 mm wafer manufacturing," *Mater. Sci. Semicond. Process.*, vol. 5, pp. 375–380, 2003.

- [17] MEMC, Application Note: AE-008, Aug. 2001.

- [18] J. Valley, C. Koliopoulos, and S. Tang, "Interferometric metrology of wafer nanotopography for advanced CMOS process integration," *Proc.* SPIE-Int. Soc. Opt. Eng., vol. 4449, pp. 160–168, 2001.

- [19] R. Schmolke, R. Deters, P. Thieme, R. Pech, H. Schwenk, and G. Diakourakis, "On the impact of nanotopography of silicon wafers on post-cmp oxide layers," *J. Electrochem. Soc.*, vol. 149, no. 4, pp. G257–G265, 2002.

- [20] T. Raymond, D. Neal, D. Topa, and T. Schmitz, "High-speed noninter-ferometric nanotopographic characterization of Si wafer surfaces," *Proc. SPIE-Int. Soc. Opt. Eng.*, vol. 4809, pp. 208–216, 2002.

- [21] Q.-Y. Tong and U. Gosele, Semiconductor Wafer Bonding: Science and Technology. New York: Wiley, 1999.

- [22] VeriFire AT Interferometer System Operating Manual OMP-0480, Zygo Corp., Middlefield, CT, 2002.

- [23] F. Reidel, H.-A. Gerber, and P. Wagner, "Impact of filtering on nanotopography measurement of 300 mm silicon wafers," *Mater. Sci. Semi*cond. Process., vol. 5, pp. 465–472, 2003.

- [24] "ASTM F1811-97: Standard practice for estimating the power spectral density function and related finish parameters from surface profile data," ASTM Int., 1997.

**K. T. Turner** received the B.S. degree in mechanical engineering from the Johns Hopkins University, Baltimore, MD, in 1999 and the S.M. and Ph.D. degrees in mechanical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 2001 and 2004, respectively.

He is currently a Postdoctoral Associate at MIT and will join the faculty of the Department of Mechanical Engineering at the University of Wisconsin-Madison in August 2005. His research has focused on materials, mechanics, and fabrication processes for MEMS. While at Johns Hopkins, he developed test systems to measure the mechanical properties of polysilicon, a key structural material in MEMS. During his graduate work at MIT, he worked on the development of novel piezoelectric-based microfluidic systems and investigated the fundamentals of wafer-level bonding processes for microsystem manufacturing.

S. M. Spearing became Professor of Engineering Materials at the University of Southampton, Southampton, U.K., in July 2004. Previously, he was Professor of Aeronautics and Astronautics at the Massachusetts Institute of Technology (MIT), Cambridge. His research focuses on developing mechanism-based models and design approaches for advanced engineered materials and processes, with applications including MEMS and other microsystems. From 1995 to 2004, he was the lead for materials and structures issues on several MEMS device projects at MIT, including the Microengine, MicroHydraulic Transducer, MicroRocket, and Micro Chemical Power projects, and he continues to have involvement in these projects in his new role at Southampton. His educational activities focus on integrating the teaching of materials and structures in the undergraduate and graduate curricula.

Dr. Spearing was Deputy Editor of *Acta Materialia* from 1997 to July 2003 and has been an Editor of the IEEE/ASME JOURNAL OF MICROELECTROMECHANICAL SYSTEMS since July 2003. In 2004, he was awarded a Royal Society-Wolfson Research Merit Award.

W. A. Baylies received the B.A. degree in physical sciences from Harvard University, Cambridge, MA.

His career includes over 20 years of management in the electronics industry. The founder of BayTech Group, he is a specialist in international semiconductor, flat panel display, computer disk drive, and general gauging technologies. He has authored numerous technical articles, test methods, international round robin tests, and related research reports.

Mr. Baylies is active in the following high-technology associations: SEMI—a former director and chairman of its Standards Committee, a current member of its International Standards Committee, co-chairman of the N.A. Traceability Committee, chairman of the Wafer Dimensions Subcommittee, working closely with counterpart groups in SEMI's Japan and European organizations. He co-founded SEMI's MEMS Advisory Group in 2002, co-chairs the MEMS Wafer Specification Standards TF, is a member of that TF's Wafer Survey activity, and facilitated at MIT a MEMS-Wafer Bonding Experiment that is expected to lead to a Wafer Bonding Model. A former chairman of ASTM F1 Committee on Electronics, he received the ASTM Award of Merit and was elected an Honorary Fellow of the Society. He is a technical architect on the North American FPD Committee, Technical Editor of the N.A. Traceability Committee, and co-chairs the NA/FPD Substrate Standards Subcommittee.

**M. Robinson** received the B.S. degree in applied physics from California Institute of Technology, Pasadena, in 1993 and the M.S. degree in optical sciences from the University of Arizona, Tucson, in 1995.

She is Metrology Marketing Applications Engineer at Zygo Corporation, Middlefield, CT. Her work at Zygo includes product development, customer education, and precision metrology for internal projects. Her current area of interest is surface profiling of optical and semiconductor surfaces and their application to process development and process control.

**R.** Smythe received the B.S. degree in astro-physics from Michigan State University, East Lansing, in 1975.

He is Vice President, Director of Metrology Marketing at Zygo Corporation, Middlefield, CT. His current area of interest is surface profiling of precision engineered surfaces and their application to advanced material process development.