# Polycrystalline Silicon—Germanium Emitters for Gain Control, With Application to SiGe HBTs

V. Dominik Kunz, C. H. (Kees) de Groot, *Member, IEEE*, Steven Hall, *Member, IEEE*, and Peter Ashburn, *Member, IEEE*

Abstract—This paper investigates germanium incorporation into polysilicon emitters for gain control in SiGe heterojunction bipolar transistors. A theory for the base current of a polySiGe emitter is developed, which combines the effects of the polySiGe grains, the grain boundaries and the interfacial layer at the polySiGe/Si interface into an expression for the effective surface recombination velocity of a polySiGe emitter. Silicon bipolar transistors are fabricated with 0, 10 and 19% Ge in the polySiGe emitter and the variation of base current with Ge content is characterized. The measured base current for a polySiGe emitter increases by a factor of 3.2 for 10% Ge and 4.0 for 19% Ge compared with a control transistor containing no germanium. These values are in good agreement with the theoretical predictions. The competing mechanisms of base current increase by Ge incorporation into the polysilicon and base current decrease due to an interfacial oxide layer are investigated.

*Index Terms*—Bipolar transistors, polysilicon emitters, SiGe, SiGe HBTs, SiGe heterojunction bipolar transistors.

#### I. INTRODUCTION

VER the last few years, the high frequency performance of SiGe HBTs has improved to such an extent that several research groups have reported values of  $f_T$  and/or  $f_{\text{max}}$ over 100 GHz [1]–[5], and the state-of-the-art is approaching 300 GHz [1]. To achieve this performance, it is necessary to minimize parasitic resistance and capacitance and optimize the vertical doping profile so that delay times in all the regions of the transistor are minimized, particularly the base and collector delay. The base delay is minimized by using a narrow basewidth and large Ge gradient across the base to create a built-in electric field [6] that accelerates electrons across the base. The collector/base depletion region delay is minimized by increasing the collector doping to decrease the collector/base depletion width and hence decrease the electron transit time. Unfortunately high collector doping concentrations have the disadvantage of degrading the common emitter breakdown voltage  $BV_{CEO}$  of the transistor.

Manuscript received January 7, 2003; revised April 3, 2002. This work was supported by the European Commission and EPSRC. The review of this paper was arranged by Editor J. N. Burghartz.

V. D. Kunz, C. H. de Groot, and P. Ashburn are with the Department of Electronics and Computer Science, University of Southampton, Southampton SO17 1BJ, U.K. (e-mail: pa@ecs.soton.ac.uk).

S. Hall is with the Department of Electrical Engineering and Electronics, University of Liverpool, Liverpool L69 3GJ, U.K.

Digital Object Identifier 10.1109/TED.2003.813338

The common emitter breakdown voltage  $BV_{CEO}$  of a bipolar transistor is strongly influenced by the common emitter current gain, as can be seen from the following equation [7]:

$$BV_{CEO} = \frac{BV_{CBO}}{\sqrt[n]{\beta}} \tag{1}$$

where  $BV_{CBO}$  is the common base breakdown voltage (i.e., the breakdown voltage of the collector/base junction),  $\beta$  is the common emitter gain and n is an empirical parameter that takes a value between 3 and 6. A gain of around 100 is needed for good circuit operation, but there is little advantage to be obtained from higher gains because of the degradation in  $BV_{CEO}$ . In SiGe HBT's, very high values of gain can be obtained, particularly when a high Ge concentration is used to give a large built-in electric field across the base. For example, Washio  $et\ al.\ [3]$  reported a gain of 1900 in a SiGe HBT with an  $f_{max}$  of 107 GHz and an  $f_T$  of 90 GHz.

In order to optimize  $BV_{CEO}$  for a given  $f_T$ , some method is needed of controlling the gain independently of the base Ge and B profiles. Huizing  $et\ al.$  [8] proposed an epitaxial SiGe layer in the emitter to tune the base current. In this paper we investigate a simpler method, which incorporates Ge into the polySi emitter, creating a polySiGe emitter. A theoretical expression is derived for the base current of a polySiGe emitter, and a comparison made with measured values on silicon bipolar transistors containing different amounts of germanium in the polysilicon. The competing mechanisms in polySiGe emitters of reduced gain from Ge incorporation and increased gain from the interfacial layer [9] are investigated.

#### II. THEORY

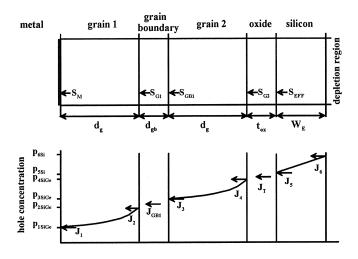

Fig. 1 shows a schematic illustration of the polySiGe emitter. Four regions of the emitter can be identified, namely polySiGe grains, grain boundaries, the interfacial oxide layer and the single-crystal silicon emitter. Hole transport in these regions is modeled using an effective recombination velocity approach, as originally proposed by Yu *et al.* [10] for polySi emitters. An effective recombination velocity is defined at each interface in Fig. 1. For example, the current density at the metal contact can be written as

$$J_1 = qS_M p_{1SiGe} \tag{2}$$

where  $S_M$  is the recombination velocity at the metal contact,  $J_1$  is the hole current density and  $p_{1\mathrm{SiGe}}$  is the hole concentration at the left side of the first polySiGe grain.

Fig. 1. Schematic illustration of a polySiGe emitter showing the effective recombination velocities in the different regions of the emitter and the components of hole current.

The effective surface recombination velocity at the right side of the nth grain,  $S_{Gn}$ , is obtained by deriving, in turn, expressions for the effective recombination velocity at the edge of each grain and grain boundary. The grain interiors are modeled as single-crystal silicon and hence the effective recombination velocity can be calculated by solving the continuity equation for holes. Transport across the grain boundaries is modeled by assuming that the grain boundary has a finite thickness  $d_{gb}$  and a mobility  $\mu_{gb}$  that is different than the mobility in the grain. Recombination in the grain boundaries is modeled at the interfaces between the grain boundaries and the adjacent grains. The effective recombination at the nth grain is then given by

$$S_{Gn} = a_g - \frac{b_g^2}{a_g + a_{gb} - \frac{b_{gb}^2}{a_{gb} + S_{G(n-1)}}}$$

(3)

where  $a_g$ ,  $b_g a_{gb}$ ,  $b_{gb}$ , and  $S_{G(n-1)}$  are given in the Appendix. The effect of the polySiGe layer can be explicitly highlighted

by relating the hole concentration for a polySiGe grain  $p_{SiGe}$  to that for an equivalent polySi grain  $p_{Si}$

$$p_{\text{SiGe}} = \frac{n_{i\text{SiGe}}^2}{n_{i\text{Si}}^2} p_{\text{Si}} = \left(\frac{N_{C\text{SiGe}}N_{V\text{SiGe}}}{N_{C\text{Si}}N_{V\text{Si}}}\right) \exp\left(\frac{\Delta E_G}{kT}\right) p_{\text{Si}}$$

(4)

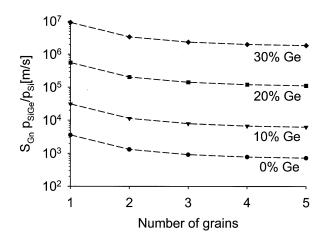

where  $N_{\rm CSiGe}$ ,  $N_{\rm VSiGe}$  are the effective densities of states in the conduction and valence band of SiGe,  $N_{\rm CSi}$ ,  $N_{\rm VSi}$  are the equivalent in Si and  $\Delta E_G$  the band gap difference between Si and SiGe. The effect of the polySiGe layer is illustrated in Fig. 2, which shows a graph of  $S_{\rm Gn}p_{\rm SiGe}/p_{\rm Si}$  as a function of the number of grains for various values of germanium content. In calculating this graph, the parameter values in [10] were used and it was assumed that the density of states in the conduction band, hole diffusion coefficient and hole diffusion length are the same in SiGe as in Si [11]. The density of states in the valence band for SiGe was assumed to be smaller than that for Si and to follow the dependence in [11]. The bandgap difference between Si and SiGe,  $\Delta E_g$ , was taken from [12]. For 0% Ge, the curve is identical to that obtained by Yu et al. [10], as indicated by the circular symbols. For a given number of grains, the effect of the

Fig. 2. Illustration of the effect of the polySiGe emitter by plotting  $S_{Gn}p_{\mathrm{SiGe}}/p_{\mathrm{Si}}$  as a function of the number of polySiGe grains for different Ge concentrations. The parameter values in [10] were used in the calculations.

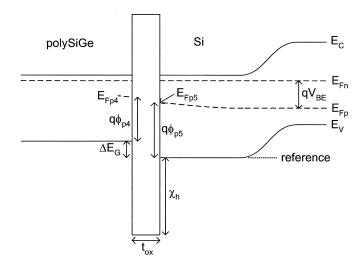

Fig. 3. Band diagram of a polySiGe emitter showing the polySiGe/oxide/Si interface.

germanium is to increase the value of  $S_{Gn}p_{\mathrm{SiGe}}/p_{\mathrm{Si}}$ . This trend can be understood from (A4), which shows that  $p_{\mathrm{SiGe}}$  increases strongly with Ge content. Fig. 2 also shows that the effective recombination velocity changes very little once there are two or more grains in the polySiGe layer. This behavior is predicted by (3) and is identical to the behavior seen in polySi emitters, as extensively discussed in [10].

Fig. 3 shows a band diagram of the polySiGe/oxide/silicon interface. It is assumed that the voltage drop across the interfacial oxide is negligible and that the band bending at the interfacial oxide layer is negligible. The bandgap in the polySiGe at the left side of the interfacial oxide is smaller than that in the single-crystal Si at the right side, and this difference is represented by  $\Delta E_G$ . The hole current tunneling density can be written as

$$J_T = qT_I N_{VSi} \left( \exp\left(\frac{E_{Fp5}}{kT}\right) - \exp\left(\frac{E_{Fp4}}{kT}\right) \right) \quad (5)$$

where  $T_I$  is the tunneling coefficient,  $E_{Fp5}$  is the quasi Fermi level energy for holes on the right side of the oxide interface, and  $E_{Fp4}$  the equivalent on the left side of the interface. Taking

the valence band edge in the single-crystal silicon as the zero energy reference and noting that the energy of holes increases downwards, we can write

$$E_{Fp5} = -q\phi_{p5} \tag{6}$$

$$E_{Fp4} = -q\phi_{p4} - \Delta E_G. \tag{7}$$

The hole concentration can then be related to  $E_{Fp4}$  and  $E_{Fp5}$  using

$$p_{4\text{SiGe}} = N_{V\text{SiGe}} \exp\left(-\frac{q\phi_{p4}}{kT}\right)$$

(8)

$$p_{5\text{Si}} = N_{V\text{Si}} \exp\left(-\frac{q\phi_{p5}}{kT}\right). \tag{9}$$

Combining (5) to (9) gives

$$J_T = qT_I \left( p_{5\text{Si}} - F p_{4\text{SiGe}} \right) \tag{10}$$

where

$$F = \frac{N_{VSi}}{N_{VSiGe}} \exp\left(-\frac{\Delta E_g}{kT}\right). \tag{11}$$

The current density  $J_5$  at the edge of the polySiGe emitter is now given by

$$J_5 = J_T + qS_I p_{5Si} = qS_{EFF} p_{5Si}$$

(12)

where  $S_I$  models recombination at the polysilicon/silicon interface, and is given by an equation analogous to (A8) and  $S_{EFF}$  is the overall effective surface recombination velocity for the polySiGe emitter, which is given by

$$S_{EFF} = S_I + \left(\frac{1}{T_I} + \frac{F}{S_I + S_{Gn}}\right)^{-1}.$$

(13)

It is worth noting that holes tunneling through the oxide become hot as they appear in the polySiGe grain, as they pick up kinetic energy of  $\sim \Delta E_G$ . The holes will quickly thermalize to the valence band edge and continue to diffuse toward the emitter contact. We represent this effect by a break in the hole quasi Fermi level in the SiGe grain, close to the oxide layer.

In modern polysilicon emitters, the emitter/base junction depth is extremely shallow and hence recombination in the single-crystal silicon emitter is very small. In this situation, the following simple equation can be used for the base current [7]

$$I_B = \frac{qAn_{iSi}^2}{\frac{N_{DEFF}W_E}{D_{reSi}} + \frac{N_{DEFF}}{S_{EFF}}} \exp\left(\frac{qV_{BE}}{kT}\right)$$

(14)

where  $N_{DEFF}$  is the effective doping in the single-crystal silicon emitter,  $W_E$  is the junction depth,  $D_{pe}$  is the hole diffusivity in silicon and uniform doping in the emitter has been assumed. This equation will be used together with (13) to interpret the competing transport and recombination mechanisms in polySiGe emitters. It should be noted that (14) models the ideal portion of the base characteristic, whereas in practice nonideal base characteristics are often obtained due to recombination in the emitter/base depletion region. When comparing measured and predicted results, it is important that the ideal portion of

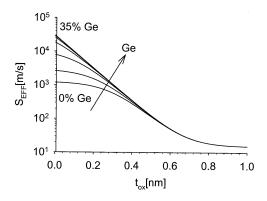

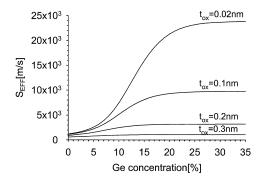

Fig. 4. Calculated values of the effective surface recombination velocity  $S_{EFF}$  of the complete polySiGe emitter as a function of interfacial layer thickness  $t_{ox}$  for different Ge concentrations. The parameter values in Table I were used in the calculations

the measured base characteristic is used in the comparison. This point will be considered in more detail in the discussion.

Fig. 4 illustrates the variation of  $S_{EFF}$  with interfacial layer thickness  $t_{ox}$  for germanium contents of 0 to 35% in 5% steps. In calculating the curves in Fig. 4, the parameters in Table I were used with two grains in the polySiGe layer. Three regions of the characteristic in Fig. 4 can be identified. For an interfacial layer thickness larger than about 0.8 nm,  $S_{EFF}$  saturates at a value of 15 m/s, which corresponds to the value of the effective recombination velocity at the interfacial oxide/silicon interface  $S_I$ . This behavior can be understood from (A13) by noting that  $1/T_I \gg F/(S_I + S_{Gn})$  and  $T_I \ll S_I$  so that  $S_{EFF} \approx S_I$ . For thick interfacial layers, the effective surface recombination velocity and hence the base current is dominated by recombination at the interfacial oxide/silicon interface. The germanium in the polySiGe layer therefore has little effect on the base current. In this region of the characteristic, recombination in the single-crystal emitter would also be expected to have a strong influence on the base current, which is neglected in (14).

For intermediate values of interfacial layer thickness between about 0.4 and 0.8 nm, Fig. 4 shows that  $S_{EFF}$  varies strongly with interfacial oxide thickness. This behavior can be understood from (13) by noting that  $1/T_I\gg F/(S_I+S_{Gn})$  and  $T_I\gg S_I$  so that  $S_{EFF}\approx T_I$ . In this region of the characteristic, the base current is therefore dominated by transport through the interfacial oxide layer. Tunneling is the transport mechanism and hence  $S_{EFF}$  varies strongly with interfacial oxide thickness. The germanium in the polySiGe emitter therefore has little effect on  $S_{EFF}$  in this region of the characteristic.

For values of interfacial layer thickness less than about 0.4 nm,  $S_{EFF}$  varies with both interfacial oxide thickness and germanium content in the polySiGe emitter. For 0% Ge and small interfacial oxide thicknesses,  $S_{EFF}$  saturates at a value of  $1.2 \times 10^3$  m/s, which is equal to the value of  $S_{Gn}$ . This behavior can be understood from (13) by noting that F is equal to unity,  $F/(S_I + S_{Gn}) \gg 1/T_I$  and  $S_{Gn} \gg S_I$  so that  $S_{EFF} \approx S_{Gn}$ . In this region of the characteristic  $S_{EFF}$  is therefore dominated by transport in the polySiGe layer.

For germanium contents of 20% and above,  $S_{EFF}$  appears to vary very little with germanium content but strongly with interfacial layer thickness. This trend is shown more clearly in

$\overline{D_{gb}}$

χh

A

$n_{iSi} \\$

|                 | Emitter and Base Current $I_B$                 |                       |                   |           |

|-----------------|------------------------------------------------|-----------------------|-------------------|-----------|

| Parameter       | Name                                           | Value                 | unit              | Reference |

| $D_{pSiGe}$     | diffusivity of holes in polySiGe grains        | 3.34×10 <sup>-4</sup> | m <sup>2</sup> /s | 11        |

| $L_{pSiGe}$     | hole diffusion length in polySiGe grains       | 2.94×10 <sup>-7</sup> | m                 | 11        |

| $d_g$           | width of a poly grain                          | 1.25×10 <sup>-7</sup> | m                 | measured  |

| $S_M$           | recombination velocity at the metal contact    | 1×10 <sup>4</sup>     | m/s               | 10        |

| $S_{GB}$        | recombination velocity of grain boundary       | 75                    | m/s               | 10        |

| $S_{I}$         | oxide/silicon interface recombination velocity | 15                    | m/s               | 10        |

| d <sub>~b</sub> | grain boundary width                           | 2~10-9                | m                 | 10        |

grain boundary hole diffusivity

intrinsic carrier concentration in silicon

potential barrier

emitter area

TABLE I PARAMETER VALUES USED TO CALCULATE THE THEORETICAL VALUES OF EFFECTIVE RECOMBINATION VELOCITY  $S_{EFF}$  of the Complete polySiGe Emitter and Base Current  $I_B$

Fig. 5. Calculated values of the effective recombination velocity  $S_{EFF}$  of the complete polySiGe emitter as a function of Ge concentration for different interfacial oxide thicknesses  $t_{ox}$ .

Fig. 5, where the value of  $S_{EFF}$  is plotted as a function of Ge content for different values of interfacial layer thickness  $t_{ox}$ . The strong dependence of  $S_{EFF}$  on interfacial oxide thickness indicates that the base current is dominated by tunneling through the interfacial oxide layer under these conditions. This can be understood from (11) by noting that F decreases exponentially with increasing Ge content, so that at high Ge content  $F/(S_I+S_{Gn})\ll 1/T_I$  in (13). Since  $S_I\ll S_{Gn}$  and  $T_I\gg S_I$ , we than have  $S_{EFF}\approx T_I$ . Thus for values of interfacial thickness less than about 0.4 nm and Ge concentrations above about 20%, the value of  $S_{EFF}$  increases only slightly with Ge content because  $S_{EFF}$  is dominated by transport through the interfacial oxide layer. There is therefore little to be gained by using Ge contents in the polySiGe layer higher than about 20%.

### III. EXPERIMENTAL PROCEDURE

Silicon bipolar transistors were fabricated to experimentally determine the effect of germanium incorporation into the polysilicon emitter. The base was fabricated by implanting  $2 \times 10^{13}$  cm $^{-2}$ B at 40 keV through an 80 nm thermal oxide layer. After annealing for 30 min at 950 °C prior to emitter fabrication, the wafers were given an RCA clean, followed by a dip etch in buffered HF to remove any chemical oxide grown during the RCA clean. Immediately following this etch, a 250–290 nm layer of *in-situ* phosphorus doped polycrystalline Si or SiGe was deposited in a Thermo VG Semicon CV200 low pressure chemical vapor deposition (LPCVD) system at a

10

10

10

measured

$m^2/s$

eV

m

m²

5.2×10

1.5

$1.45 \times 10^{16}$

100×10<sup>-12</sup>

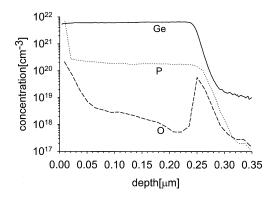

Fig. 6. Measured germanium, phosphorus and oxygen SIMS profiles for bipolar transistors with polySi $_{0.9}$ Ge $_{0.1}$  emitter given an anneal of 30 s at 900 °C.

temperature of 540  $^{\circ}$ C. The SiGe layers were deposited with Ge contents of 10 and 19%. The emitter was completed by annealing for 30 s at 900  $^{\circ}$ C to diffuse the phosphorus from the polycrystalline Si or SiGe into the underlying single-crystal Si. All measurements of the transistor characteristics were performed at a temperature of 25  $^{\circ}$ C.

#### IV. RESULTS

Fig. 6 shows secondary ion mass spectrometry (SIMS) plots through the emitter of the polySiGe transistor with 10% Ge annealed for 30 s at 900 °C. It can be seen that the germanium profile is approximately uniform throughout the 250 nm polySiGe layer. The phosphorus profile in the polySiGe is similarly reasonably uniform with a concentration of  $1.7 \times 10^{20}$  cm<sup>-3</sup>. The oxygen profile in Fig. 5 shows a dose of  $8.8 \times 10^{13}$  cm<sup>-2</sup> at the interface between the polySiGe and the single-crystal silicon. Similar results were obtained for the polySiGe transistor with 19% Ge and the polySi control transistor, as summarized in Table II. The oxygen doses in the three samples lie in the range  $0.7-1.5 \times 10^{14}$  cm<sup>-2</sup>, and there is no discernible trend in the oxygen dose with Ge content. The polySi and polySiGe layer deposition was performed one wafer at a time, and hence the variation in oxygen dose between the wafers is probably due to small differences in the timings of the wafer transfer into the deposition system. Table II also shows values of interfacial layer thickness, calculated assuming a uniform, stoichiometric silicon

| 11.12                                               |    |    |    |  |  |  |

|-----------------------------------------------------|----|----|----|--|--|--|

| SUMMARY OF EXPERIMENTAL DATA OBTAINED FROM THE SIMS |    |    |    |  |  |  |

| MEASUREMENTS                                        |    |    |    |  |  |  |

|                                                     |    |    |    |  |  |  |

| 'a content [0/]                                     | Δ. | 10 | 10 |  |  |  |

TABLE II

| Ge content [%]                            | 0                    | 10                   | 19                   |

|-------------------------------------------|----------------------|----------------------|----------------------|

| Poly layer thickness [nm]                 | 250                  | 250                  | 290                  |

| Poly emitter doping [cm <sup>-3</sup> ]   | 1.5×10 <sup>19</sup> | $1.7 \times 10^{20}$ | 6.0×10 <sup>19</sup> |

| Oxygen interface dose [cm <sup>-2</sup> ] | 1.5×10 <sup>14</sup> | $8.8 \times 10^{13}$ | $7.0 \times 10^{13}$ |

| Interfacial layer thickness [nm]          | 0.031                | 0.018                | 0.015                |

| $W_{E}[nm]$                               | 30                   | 50                   | 40                   |

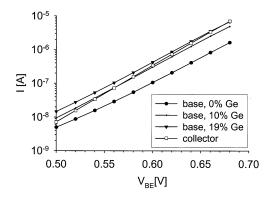

Fig. 7. Measured Gummel plots for transistors with 0%, 10% and 19% Ge in the polySiGe emitter, annealed at  $900\,^{\circ}$ C. The collector currents are identical and only one is shown.

dioxide layer and a silicon atom concentration of  $4.8 \times 10^{22}$  atoms/cm<sup>3</sup> and the thickness of the single-crystal portion of the emitter  $W_E$  extracted from the SIMS profiles.

Cross-sectional transmission electron microscopy (TEM) was used to characterize the structure of the grains in the polySiGe and polySi layers. No discernible difference was found in the structure of the grains in polySiGe and polySi layers. The grains in both materials were of a similar size, with an average diameter of 125 nm. For a polySiGe layer thickness of 250 nm, there are therefore two grains in the polySiGe emitters of the fabricated transistors.

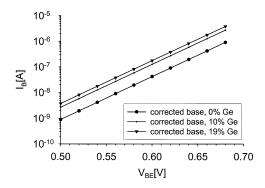

Fig. 7 shows Gummel plots for transistors annealed for 30 s at 900 °C with 10% and 19% polySiGe emitters and for a control transistor with a polySi emitter. The collector characteristics are ideal, with an ideality factor of 1.06 for all three devices. The base characteristics are near ideal, with ideality factors of 1.19, 1.13 and 1.13 at  $V_{BE}=0.6~\rm V$  for Ge contents of 0, 10, and 19%, respectively. The transistors with 10 and 19% Ge show increased base current at  $V_{BE}=0.6~\rm V$  compared with a transistor without Ge by a factor of 3.2 for 10% Ge and 4.0 for 19% Ge.

## V. DISCUSSION

The experimental results in Fig. 7 show that there is a large increase in base current when the germanium content of the polySiGe layer is increased from 0% to 10%, but a much smaller increase when the germanium content is increased from 10% to 19%. This result is in qualitative agreement with the theoretical curves in Fig. 5, which show that the effect of the germanium on the base current saturates for germanium concentrations above about 20%. To quantitatively interpret the experimental results,

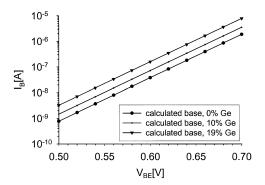

Fig. 8. Calculated base currents  $I_B$  as a function of base/emitter voltage  $V_{BE}$  for 0%, 10%, and 19% Ge concentrations.

TABLE III

COMPARISON OF MEASURED AND CALCULATED VALUES OF BASE CURRENT

| Ge content [%]                                             | 0                    | 10                   | 19                   |

|------------------------------------------------------------|----------------------|----------------------|----------------------|

| Measured I <sub>B</sub> at V <sub>BE</sub> =0.6V [A]       | 1.0×10 <sup>-7</sup> | 3.0×10 <sup>-7</sup> | 4.3×10 <sup>-7</sup> |

| Calculated I <sub>B</sub> at V <sub>BE</sub> =0.6V [A]     | 3.8×10 <sup>-8</sup> | 7.2×10 <sup>-8</sup> | 1.6×10 <sup>-7</sup> |

| Measured I <sub>B</sub> (SiGe)/I <sub>B</sub> (Si) ratio   |                      | 3.0                  | 4.4                  |

| Calculated I <sub>B</sub> (SiGe)/I <sub>B</sub> (Si) ratio |                      | 1.9                  | 4.2                  |

| 1                                                          |                      |                      |                      |

| Corrected [14] I <sub>B</sub> at V <sub>BE</sub> =0.6V [A] | 4.2×10 <sup>-8</sup> | 1.3×10 <sup>-7</sup> | 1.8×10 <sup>-7</sup> |

| Corrected I <sub>B</sub> (SiGe)/I <sub>B</sub> (Si) ratio  |                      | 3.2                  | 4.0                  |

values of base current have been calculated using (14). The measured values of Ge content, interfacial oxide thickness  $t_{ox}$  and emitter depth  $W_E$  in Table II were used in the calculations, together with the values in Table I for the polysilicon parameters [10]. The average doping in the single-crystal silicon emitter was determined from the SIMS profiles and the bandgap narrowing model of del Alamo  ${\it et\,al.}$  [13] used to calculate the effective doping  $N_{DEFF}$ . Calculated base characteristics are shown in Fig. 8.

Table III compares the calculated and measured values of base current and the base current ratios, obtained by taking the ratio of the base current in the appropriate polySiGe transistor to that in the polySi transistor. The measured ratios of 3.2 and 4.0 for 10 and 19% Ge, respectively can be compared with calculated values of 1.9 and 4.2. The agreement between measured and calculated values of base current is excellent for 19% Ge, but less good for 10% Ge. A possible explanation for this discrepancy can be found in Fig. 4. For the interfacial oxide thicknesses used in this work (0.03 nm and below) and a Ge content of 10%, the base current is sensitive to both the Ge content and the interfacial oxide thickness, whereas for a Ge content of 19%, the base current is only sensitive to the interfacial layer thickness. This suggests that the discrepancy in the measured and calculated base current ratio for 10% Ge may be due to an uncertainty in the Ge content in the polySiGe layer.

The agreement in Table III between the absolute values of base current is very poor, with the calculated values being much lower than the measured values in all cases. The explanation for this discrepancy can be found by noting that the measured base characteristics are slightly nonideal (ideality factors of 1.19, 1.13 and 1.13 for 0, 10 and 19% Ge) due to recombination in the emitter/base depletion region, whereas (14) assumes ideal characteristics. One method of addressing this issue is to extract the underlying ideal component of base current using the

Fig. 9. Ideal component of the base current  $I_B$ , determined using the method of Hamel [14], as a function of base/emitter voltage  $V_{BE}$  for 0%, 10%, and 19%  $G_{CB}$

analysis method of Hamel [14]. This method has been applied to the measured base characteristics in Fig. 7 and the ideal component of base current is shown in Fig. 9. In addition, values of the ideal component of base current at  $V_{BE}=0.6~\rm V$  are summarized in Table III for comparison with values calculated using (14). It can be seen that the ideal components of base current agree very well with the calculated values. Agreement is within a factor of 1.1 for 0% Ge, 1.8 for 10% Ge and 1.1 for 19% Ge. This agreement is reasonable considering the uncertainties of the polySiGe parameters in Table I and in the measured SIMS data.

In polysilicon emitters, the interfacial layer has a strong effect on the current gain [9]. It is therefore important to understand how the interfacial oxide thickness influences the base current increase obtained when germanium is introduced into the polysilicon emitter. The opposite trends with germanium content and interfacial layer thickness are shown in Fig. 4 and this indicates that an interfacial layer thickness of less than about 0.3 nm is needed if the germanium is to have a significant effect on the effective recombination velocity  $S_{EFF}$  and the base current. In practice, this could be achieved using an ex-situ HF etch in combination with polySiGe deposition in a cluster tool [15]. Even bigger effects could probably be achieved by breaking up the interfacial layer using an interface anneal prior to polySiGe deposition [9] or by epitaxially regrowing the polySiGe during the emitter anneal.

# VI. CONCLUSION

A theoretical expression has been derived for the effective surface recombination velocity of a polycrystalline SiGe emitter, and predicted values of base current compared with measured values on silicon bipolar transistors with polycrystalline SiGe emitters. The measured results show an increase in base current by a factor of 3.2 for 10% Ge in the polySiGe emitter and by 4.0 for 19% Ge. The theory predicts that, for a given interfacial layer thickness, the base current initially increases with Ge content and then saturates for germanium contents of about 20%, a trend which agrees well with the experimental results. The size of the base current increase with Ge content depends on the thickness of the interfacial layer, with larger increases being obtained for thinner interfacial layers. The introduction of germanium into a polysilicon emitter

therefore allows the base current, and hence the gain, to be controlled by means of the Ge content in the polySiGe emitter. This property is likely to be very useful in advanced SiGe HBT's where high values of gain can be obtained as a result of the high germanium concentration in the SiGe base. Since high values of gain degrade the common emitter breakdown voltage  $BV_{CEO}$ , polySiGe emitters would allow the gain to be controlled independently of the base Ge profile and hence allow the breakdown voltage  $BV_{CEO}$  to be optimized for a given  $f_T$ .

#### **APPENDIX**

The hole current at either side of the first polySiGe grain can be derived by solving the continuity equation for holes

$$J_1 = q(p_{2\text{SiGe}}b_q - p_{1\text{SiGe}}a_q) \tag{A1}$$

$$J_2 = q(p_{2\text{SiGe}}a_q - p_{1\text{SiGe}}b_q). \tag{A2}$$

The parameters  $a_g$  and  $b_g$  depend on the physical properties of the grains and are given by

$$a_g = \frac{D_{p\text{SiGe}}}{L_{p\text{SiGe}}} \coth\left(\frac{d_g}{L_{p\text{SiGe}}}\right)$$

(A3)

$$b_g = \frac{D_{p\text{SiGe}}}{L_{v\text{SiGe}}} \operatorname{csch}\left(\frac{d_g}{L_{v\text{SiGe}}}\right) \tag{A4}$$

where  $d_g$  is the grain width, and  $L_{pSiGe}$  and  $D_{pSiGe}$  are the hole diffusion length and hole diffusivity in the polySiGe grain.

Equating (2) and (A1) gives an equation for  $p_{1SiGe}$  which can then be substituted into (A2) to give the current  $J_2$

$$J_2 = q \left( a_g - \frac{b_g^2}{a_g + S_M} \right) p_{2\text{SiGe}}.$$

(A5)

A comparison with (2) shows that the effective recombination velocity at the right side of the first SiGe grain is

$$S_{G1} = a_g - \frac{b_g^2}{a_g + S_M}. (A6)$$

The current density across the grain boundary is given by

$$J_{GB1} = q \frac{D_{gb}}{d_{gb}} \left( p_{3\text{SiGe}} - p_{2\text{SiGe}} \right) \tag{A7}$$

where  $D_{gb}$  is the hole diffusivity in the grain boundary. Recombination at the grain boundary interfaces is modeled by

$$S_{GB} = \frac{N_{st}}{2} c_p v_{th} \tag{A8}$$

where  $N_{st}$  is the trap density,  $c_p$  the trap capture cross section and  $v_{th}$  the thermal velocity. Using (A5) to (A8), an equation can be derived for the current at the right side of the grain boundary  $J_3$

$$J_3 = qS_{GB1}p_{3SiGe} \tag{A9}$$

where

$$S_{GB1} = a_{gb} - \frac{b_{gb}^2}{a_{gb} + S_{G1}} \tag{A10}$$

$$a_{gb} = \frac{D_{gb}}{d_{ab}} + S_{GB} \tag{A11}$$

$$b_{gb} = \frac{D_{gb}}{d_{qb}}. (A12)$$

The procedure used to derive the current at the right side of the first polySiGe grain can now be repeated to give the current at the right side of the second polySiGe grain  $J_4$

$$J_4 = qS_{G2}p_{4SiGe} \tag{A13}$$

where

$$S_{G2} = a_g - \frac{b_g^2}{a_g + S_{GB1}}. (A14)$$

In general, there may be more than two grains in the polySiGe emitter, in which case, for  $n \ge 2$ , (A14) can be generalized to give (3).

#### REFERENCES

- [1] B. Jagannathan, M. Khater, F. Pagette, J.-S. Rieh, D. Angell, H. Chen, J. Florkey, F. Golan, D. R. Greenberg, R. Groves, S. J. Jeng, J. Johnson, E. Mengistu, K. T. Schonenberg, C. M. Schnabel, P. Smith, A. Stricker, D. Ahlgren, D. Freeman, K. Stein, and S. Subbanna, "Self-aligned SiGe NPN transistor with 285GHz f<sub>MAX</sub> and 207GHz f<sub>T</sub> in a manufacturable technology," *IEEE Electron Device Lett.*, vol. 23, pp. 255–258, May 2002.

- [2] J. Böck, T. F. Meister, H. Knapp, D. Zöschg, H. Schäfer, K. Aufinger, M. Wurzer, S. Boguth, M. Franosch, R. Stengl, R. Schreiter, M. Rest, and L. Treitinger, "SiGe bipolar technology for mixed digital and analogue rf applications," in *IEDM Tech. Dig.*, 2000, pp. 745–748.

- [3] K. Washio, M. Kondo, E. Ohue, K. Oda, R. Hayami, M. Tanabe, H. Shimamoto, and T. Harade, "A  $0.2\mu$  m self-aligned selective epitaxial growth SiGe HBT featuring 107GHz  $f_{\rm max}$  and 6.7ps ECL," *IEEE Trans. Electron Devices*, vol. 48, pp. 1989–1994, Sept. 2001.

- [4] B. Martinet, H. Baudry, O. Kermarrec, Y. Campidelli, M. Laurens, M. Marty, T. Schwartzmann, A. Monroy, D. Bensahel, and A. Chantre, "100GHz SiGe: C HBT's using nonselective epitaxy," in *Proc. Eur. Solid State Device Res. Conf.*, 2001, pp. 97–100.

- [5] T. Hashimoto, F. Sato, T. Aoyama, H. Suzuki, H. Yoshida, H. Fujii, and T. Yamazaki, "A 73GHz f<sub>T</sub> 0.18μm rf SiGe BiCMOS technology considering thermal budget trade-off and with reduced boron spike effect on HBT characteristics," in *IEDM Tech. Dig.*, 2000, pp. 149–152.

- [6] D. L. Harame, J. H. Comfort, J. D. Cressler, E. F. Crabbé, J. Y. C. Sun, B. S. Meyerson, and T. Tice, "Si/SiGe epitaxial base transistors, part I: Materials, physics and circuits," *IEEE Trans. Electron Devices*, vol. 42, pp. 455–467, Mar. 1995.

- [7] P. Ashburn, Design and Realization of Bipolar Transistors. New York: Wiley, 1988, p. 55.

- [8] H. G. A. Huizing, J. H. Klootwijk, E. Aksen, and J. W. Slotboom, "Base current tuning in SiGe HBT's by SiGe in the emitter," in *IEDM Tech. Dig.*, 2001, pp. 899–902.

- [9] I. R. C. Post, P. Ashburn, and G. R. Wolstenholme, "Polysilicon emitters for bipolar transistors: A review and re-evaluation of theory and experiment," *IEEE Trans. Electron Devices*, vol. 39, pp. 1717–1731, July 1992

- [10] Z. Yu, B. Ricco, and R. W. Dutton, "A comprehensive analytical and numerical model of polysilicon emitter contacts in bipolar transistors," *IEEE Trans. Electron Devices*, vol. 31, pp. 773–784, 1984.

- [11] J. Poortmans, "Low-temperature epitaxial growth of Si and strained Si<sub>1-x</sub>Ge<sub>x</sub>-layers and their application in bipolar transistors," Ph.D. dissertation, Katholieke Univ. Leuven, Leuven, Belgium, 1993.

- [12] H.-Y. Jin and L.-C. Zhang, "Bandgap narrowing in strained SiGe base on (001) Si substrate," *Solid State Electron.*, vol. 45, pp. 697–702, 2001.

- [13] J. del Alamo, S. Swirhun, and R. M. Swanson, "Simultaneous measurement of hole lifetime, hole mobility, and bandgap narrowing in heavily doped n-type silicon," in *IEDM Tech. Dig.*, 1985, pp. 290–293.

- [14] J. S. Hamel, D. J. Roulston, and C. R. Selvakumar, "Experimental method for extraction of emitter injection limited gain in bipolar transistors," *Solid-State Electron.*, vol. 35, no. 7, pp. 1021–1022, 1992.

[15] A. I. A. Rahim, C. D. Marsh, P. Ashburn, and G. R. Booker, "Impact of ex-situ and in-situ cleans on the performance of bipolar transistors with low thermal budget in-situ phosphorus doped polysilicon emitter contacts," *IEEE Trans. Electron Devices*, vol. 48, pp. 2506–2513, 2001.

**V. Dominik Kunz** was born in Eberbach, Germany, in 1967. He received the Dipl.Ing. degree in electrical engineering from the Technische Universitaet Berlin, Germany, in 1995 and the Ph.D. degree in CMOS compatible surround gate vertical MOSFETs with reduced parasitics from Southampton University, Southampton, U.K., in 2001.

He then moved to Southampton, U.K., to work for Tandberg Television for five years on the development of digital terrestrial television (DTTV) where he was involved in the first commercially available DTTV ASIC as well as in related hardware and software projects. Since 2001, he has also been a Research Assistant working on SiGe vertical MOSFETs. His research focuses on vertical MOSFETs as well as bipolar transistors.

**C. H.** (Kees) de Groot (M'00) received the M.S. degree in physics from the University of Groningen, the Netherlands, in 1994 and the Ph.D. degree in NdFeB permanent magnets and magnetism in rare-earth intermetallic compounds from the University of Amsterdam, The Netherlands, in 1998.

From 1998 to 2000, he was a Research Fellow at the Francis Bitter Magnet Laboratory, Massachusetts Institute of Technology, Cambridge, where he conducted research on spin tunnel junction and photo-voltaic materials. Since 2000, he has been with the Department of Electronics and Computer Science, University of Southampton, U.K., where he is a Research Lecturer. His current research interest are architecture and materials improvement of field effect transistors, including vertical MOSFETs, high-k dielectrics, and tunnel transistors. He has given presentations at numerous international conferences and symposiums and is author of more than 35 refereed journal articles.

**Steven Hall** (M'93) received the Ph.D. degree in integrated injection logic in the GaAs/AlGaAs materials system from the University of Liverpool, U.K., in 1987

He then joined the lecturing staff, University of Liverpool, where he began work on SOI materials characterization and device physics, subsequently obtaining funding to work in these areas on the SIMOX and oxidized porous Si systems. The work was in collaboration with U.K. university and industrial collaborators. Other areas of activity concerned fabrication and electrical assessment of cobalt disilicide Schottky diodes together with silicon-germanium materials characterization and device physics for both bipolar transistor and MOSFET. The SiGe work currently concerns high performance analog bipolar and new forms of low voltage logic with particular interest in modeling and associated materials characterization. Current SOI work is in the area of low voltage/low power integrated circuits both SiGe HBT and MOS. His other major activity concerns novel design concepts for very deep sub-micron vertical MOSFETs. He is currently Head of the Department of Electrical Engineering and Electronics and serves on a number of U.K. advisory groups.

**Peter Ashburn** (M98) was born in Rotherham, U.K., in 1950. He received the B.Sc. degree in electrical and electronic engineering and the Ph.D. degree in experimental and theoretical study of radiation damage in silicon p-n junctions from the University of Leeds, U.K., in 1971 and 1974, respectively.

In 1974, he joined the Technical Staff of Philips Research Laboratories and worked initially on ion implanted integrated circuit bipolar transistors, and then on electron lithography for sub-micron integrated circuits. In 1978, he joined the Academic Staff of the Department of Electronics and Computer Science, University of Southampton, U.K., as a Lecturer, and currently is the holder of a Personal Chair in microelectronics. Since taking up a post at Southampton University, he has worked on polysilicon emitter bipolar transistors, high-speed bipolar and BiCMOS technologies, gate delay expressions for bipolar circuits, and the effects of fluorine in polysilicon emitters. His current research interests include SiGe heterojunction bipolar transistors, SiGeC and its device applications and vertical MOS transistors for application in sub-100 nm CMOS technology. He has authored and co-authored over 120 papers in the technical literature, given invited papers on polysilicon emitters and SiGe heterojunction bipolar transistors, and has authored a book on bipolar transistors.