# A CMOS-Compatible Rapid Vapor-Phase Doping Process for CMOS Scaling

Takashi Uchino, Member, IEEE, Peter Ashburn, Member, IEEE, Yukihiro Kiyota, and Takeo Shiba, Member, IEEE

Abstract—An advanced CMOS process, which used rapid vapor-phase doping (RVD) for pMOSFETs and solid-phase diffusion (SPD) for nMOSFETs, has been developed. Using the RVD technique, a 40-nm-deep p-type extension with a sheet resistance as low as 400  $\Omega/\mathrm{sq}$  has been realized. These RVD and SPD devices demonstrate excellent short-channel characteristics down to 0.1  $\mu$ m channel length and 40% higher drain current, compared with conventional devices with ion implanted source/drain (S/D) extensions, and high-speed circuit performance. We investigate the effect of the S/D extension structure on the device performance and find that a gate extension overlap of 25 nm enables excellent dc and high-speed circuit performance in 0.1- $\mu$ m devices.

Index Terms—CMOS process, doping, junction, MOSFET.

## I. INTRODUCTION

HE KEY subject in the scaling of nanometer-regime CMOS devices is how to improve device performance without any degradation such as short-channel effects and high power consumption. Achieving high performance, however, is becoming increasingly difficult because of the tradeoff between good short-channel characteristics and high current drivability [1]. Moreover, conventional low-energy ion implantation for the shallow source/drain (S/D) extension formation induces high resistance because it degrades carrier activation efficiency, results in only a low carrier concentration at the surface, and reduces the gate-extension overlap [2]. Furthermore, the transient enhanced diffusion (TED) and the channeling effect create difficulties in the forming of the shallow junction. Thus, techniques to form shallow, abrupt, and low-resistance junctions are required to enable further progress. To overcome these problems, thermal doping technologies such as rapid vapor-phase doping (RVD) [3] or solid-phase diffusion (SPD) from phosphosilicate glass (PSG) [4] have been investigated. These technologies are considered to be appropriate for creating shallow junctions in the regime between 20 and 40 nm [5]. However, there are some primary problems of integrating these processes into a CMOS process, because the diffusion source material for one dopant type must be removed prior to formation of the diffusion source material for the second dopant type.

We have developed an advanced CMOS process that meets these needs and does not require ion implantation to form

Manuscript received April 24, 2003; revised October 7, 2003. The review of this paper was arranged by Editor J. Vasi.

Digital Object Identifier 10.1109/TED.2003.820643

shallow S/D extensions. The fabricated devices use a combination of RVD and SPD, and show a high on-current and excellent threshold voltage rolloff characteristics down to an effective channel length of 0.1  $\mu$ m. The high performance of the devices is due to the shallow and abrupt diffused S/D extensions. The RVD technique was applied to pMOSFET formation, because the requirement of shallow junction formation for pMOSFETs is more serious than that for nMOSFETs. To confirm the effect of the lateral diffusion on the device performance, SPD was applied to nMOSFET formation. In this paper, we present the device design to obtain high drain on-current. To improve the device performance, the S/D extension structure is investigated, and a CMOS-compatible RVD process is presented. Finally, the device structure for 0.1- $\mu$ m CMOS devices is optimized to give the best combination of dc and circuit performance.

## II. FABRICATION PROCESS

## A. Ultrashallow Junction Formation

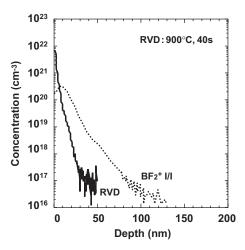

Two key techniques were used to obtain shallow and abrupt junctions with low extension resistance. The first is RVD for pMOSFETs. This is a form of gas-source diffusion using rapid thermal annealing (RTA), and it enables the formation of shallow and heavily doped abrupt junctions. The RVD was done using hydrogen and B<sub>2</sub>H<sub>6</sub> gas around 900 °C for a short time up to 40 s. Hydrogen gas is used to keep the substrate surface clean and reduce boron segregation. Hydrogen gas plays an important role in terminating the dangling bonds and reducing the excessive boron adsorption. These evidences were obtained by using x-ray photoelectron spectroscopy (XPS) and Fourier-transform infrared-attenuated total reflection (FTIR-ATR) [6]. A SIMS profile of an RVD S/D extension is shown in Fig. 1 and compared to a BF<sub>2</sub><sup>+</sup> implanted extension. The RVD extension is less than 30-nm-deep and its abruptness is 3.6 nm/dec. On the contrary, TED and boron channeling were observed in the ion-implanted sample and the tail extends to a depth of 100 nm. The surface doping concentration of the RVD sample is more than 10 times higher than that of the ion-implanted sample. Here, the junction depth was defined as the point at which the doping concentration was equal to  $1 \times 10^{\bar{1}8} \text{ cm}^{-3}$ .

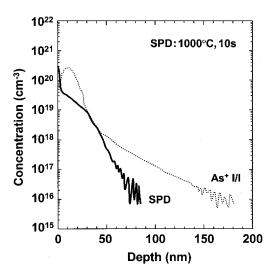

The second technique is SPD from PSG layers for nMOS-FETs. The SPD was done at  $1000\,^{\circ}$ C for  $10\,\text{s}$ . The SIMS profile of the SPD extension shows a shallow junction with only a small tail, and a junction depth of less than  $50\,\text{nm}$  (Fig. 2). Like the RVD sample, the SPD sample has its highest carrier concentration at the surface. Some experiments of the n-type shallow junction formation using PH<sub>3</sub> have been done before [7], [8].

T. Uchino and P. Ashburn are with the Department of Electronics and Computer Science, University of Southampton, Southampton SO 17 1BJ, U.K. (e-mail: tu@ecs.soton.ac.uk).

Y. Kiyota and T. Shiba are with the Central Research Laboratory, Hitachi Ltd., Tokyo 185-8601, Japan.

Fig. 1. SIMS profile of rapid vapor-phase doping (RVD). For comparison, the SIMS profile of BF<sub>2</sub>+ implantation with 10 keV and  $5\times10^{14}$  cm<sup>-2</sup> for conventional devices is shown.

Fig. 2. SIMS profile of solid-phase diffusion (SPD) from phosphosilicate glass. For comparison, The SIMS profile of As+ implantation with 15 keV and  $5\times10^{14}~{\rm cm}^{-2}$  for conventional devices is shown.

We found the upper limit of the n-type doping concentration of RVD is around  $10^{19}\,\mathrm{cm^{-3}}$ . This value is not high enough to form the S/D extension for 0.1- $\mu$ m device. SPD is the only diffusion technique to form an appropriate n-type shallow junction. These rapid thermal diffusion techniques have allowed isotropically diffused S/D extensions to be formed with appropriate gate-extension overlap maintaining shallow junction.

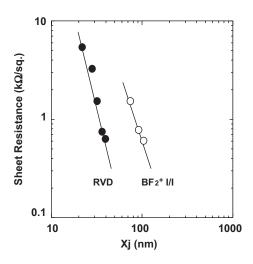

Fig. 3 shows the plot of the p-type sheet resistance versus the junction depth  $X_j$  after RTA at 950 °C for 10 s. High concentration of boron near the surface is electrically activated by the additional annealing. The various junction profiles were obtained by varying  $\rm B_2H_6$  concentration or doping temperature and time. For the RVD sample, a shallow junction depth of 39 nm can be obtained at the same time as a low sheet resistance of 630  $\Omega/\rm sq$ . This difference between RVD and ion-implantation was mainly caused by the difference in surface concentration, TED, and the channeling effect.

Fig. 3. Dependence of the sheet resistance on the junction depth  $(X_j)$  for p-type layers after additional RTA at 950 °C for 10 s. For comparison, data for the conventional junction formation used by  $\mathrm{BF_2}^+$  implantation and RTA are shown.

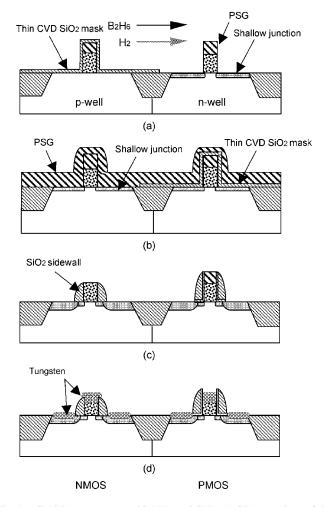

Fig. 4. CMOS process steps with RVD and SPD. (a) S/D extensions of the pMOSFET formed by RVD at 900  $^{\circ}$ C for 40 s. (b) S/D extensions of the nMOSFET formed by SPD from the PSG film at 1000  $^{\circ}$ C for 10 s. (c) Deep S/D formation. (d) Selective tungsten deposition.

## B. A CMOS-Compatible RVD Process

Fig. 4 shows how the vapor- and solid-phase diffusion techniques were applied in a CMOS process. First, a thin 10 nm

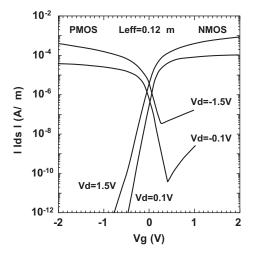

Fig. 5. Subthreshold characteristics of  $0.12-\mu m$  MOSFETs.

chemical vapor deposition (CVD) SiO<sub>2</sub> layer was deposited and patterned in the nMOSFET region. The silicon substrate over the pMOSFET region was exposed by using light wet etching. Then RVD was carried out to obtain shallow pMOSFET junctions [Fig. 4(a)]. The 10 nm CVD SiO<sub>2</sub> layer protects the nMOSFET region from the boron diffusion. Next, a thin CVD SiO<sub>2</sub> layer was deposited again and the silicon substrate was exposed over the nMOSFET region. After that, a PSG layer that contained 8 mol% phosphorus was deposited and SPD from the PSG layer was carried out at 1000 °C for 10 s [Fig. 4(b)]. In the next step, the PSG layer, including the gate cap of the nMOSFETs, was then stripped away [Fig. 4(c)]. The PSG etch rate in hydrofluoric acid solutions is 20 times higher than that of thermal SiO<sub>2</sub>. Thus, the PSG layer is easily removed, which simplifies this otherwise complex CMOS process. After the SiO<sub>2</sub> sidewall formation, deep S/D junctions were formed by using conventional ion implantation combined with RTA at 950 °C for 10 s. Then the PSG gate cap of the pMOSFETs was stripped away. Finally, 50-nm-thick tungsten was selectively deposited on the deep S/D junctions and the gate electrodes to reduce their resistance [Fig. 4(d)]. In this experiment, the gate oxide thickness, estimated from capacitance-voltage (C-V)measurements, was 4.5 nm. Local pocket implantation was done to suppress the short-channel effect. For comparison, conventional devices with ion implanted S/D extensions were also fabricated. The extensions (As<sup>+</sup>3 ×  $10^{14}$  cm<sup>-2</sup> at 15 keV;  $BF_2^{+}5 \times 10^{14} \text{ cm}^{-2}$  at 10 keV) were formed through a 5 nm SiO<sub>2</sub> layer. After the formation of a 70 nm SiO<sub>2</sub> spacer, deep S/D ion implantation (As<sup>+</sup>4  $\times$  10<sup>15</sup> cm<sup>-2</sup> at 40 keV;  $BF_2^{+}3 \times 10^{15}$  cm<sup>-2</sup> at 25 keV) and RTA at 950 °C for 10 s were carried out.

## III. DEVICE CHARACTERISTICS

# A. DC Characteristics

Fig. 5 shows typical subthreshold characteristics for devices with an effective channel length of 0.12  $\mu$ m. The current–voltage (I–V) characteristics for the nMOSFET show no leakage current. On the other hand, leakage current was observed for the pMOSFET. Two types of the leakage current can be considered. One is the junction leakage current due to

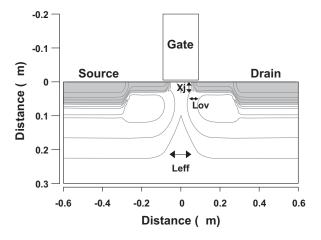

Fig. 6. Schematic cross section of the simulated RVD-pMOSFET. The gate-extension overlap is defined as  $L_{\alpha v}$ .

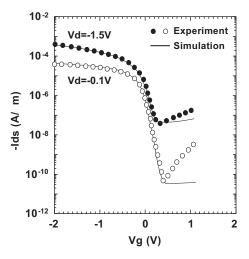

Fig. 7. Measured and simulated subthreshold characteristics of 0.12  $\mu m$  RVD-pMOSFET.

tungsten erosion along the Si/SiO<sub>2</sub> interface into the channel. Excessive dopants at the surface formed by RVD were segregated and they assist metallization into the channel near the gate edge. This local tungsten encroachment was confirmed by cross-sectional scanning electron microscope (SEM). Another one is gate-induced drain leakage (GIDL) current due to heavily doped S/D extension. To confirm this, GIDL current was evaluated by using the two-dimensional process simulator ATHENA and the device simulator ATLAS [9]. Band-band field emission and tunneling [10] were modeled in the simulation. The schematic simulated device structure is shown in Fig. 6. The isotropically diffused extension was formed in the simulated structure by using a thermal diffusion corresponding to the RVD process. Fig. 7 is the calibrated I-V characteristics that were fitted to the measurement results by changing the parameters of GIDL effects. However, the leakage current at  $V_d = -0.1$  V can not be explained by GIDL effects. Thus, it is considered that excessive leakage current at lower  $V_d$ is due to junction leakage. This excessive leakage current can be suppressed by optimizing the selective tungsten deposition. A raised S/D technique using epitaxial growth is alternative solution to avoid the leakage current due to lateral diffusion of metal or silicide.

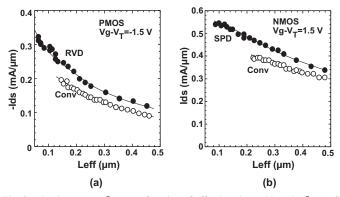

Fig. 8. Drain current  $(I_{ds})$  as a function of effective channel length  $(L_{\rm eff})$  of (a) pMOSFETs and (b) nMOSFETs.

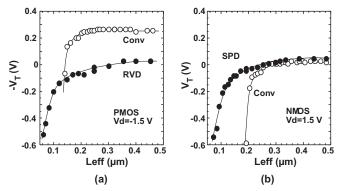

Fig. 9. Threshold voltage  $(V_{\rm T})$  rolloff characteristics of (a) pMOSFETs and (b) nMOSFETs.

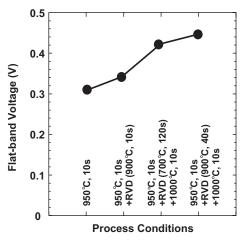

Fig. 8 shows the dependence of the drain current on the effective channel length. The drain current of the RVD and SPD devices was higher than that of the conventional devices. Higher current drivability was obtained through the heavily doped extensions and the lateral diffusion of the extension underneath the gate edge. For the nMOSFETs, the extension sheet resistance of the SPD devices was similar to that of conventional devices, so it can be concluded that lateral diffusion was the main cause of the improved current drivability. Fig. 9 shows the threshold voltage as a function of the effective channel length. Significantly improved threshold voltage rolloff characteristics were observed for the SPD and RVD devices. This improvement was achieved by forming shallow and abrupt S/D extensions. The lower threshold voltage for the RVD devices was due to boron penetration into the channel near the gate edge. The threshold voltage shift in the pMOSFETs was confirmed by C-V measurements. Fig. 10 shows the dependence of the flat-band voltage on the RVD process conditions. The flat-band voltage increased with an increasing thermal budget, and the difference in the flatband voltages between typical RVD devices and the conventional devices was 0.15 V. In the RVD process, boron and hydrogen were supplied from the gate edge because hydrogen was used as a carrier gas. Thus, the boron penetration was enhanced near the gate edge. This boron penetration can be suppressed by forming a thin Si<sub>3</sub>N<sub>4</sub> gate sidewall before the RVD process.

The device parameters are summarized in Table I. The lower S/D extension resistance of  $400 \Omega/\text{sq}$  and the shallow extension junction depth of 40 nm were achieved by using RVD for the pMOSFETs. These values were 80 and 33% lower, respectively,

Fig. 10. Flatband voltage as a function of thermal budget in RVD-pMOSFETs.

TABLE I

DEVICE PARAMETERS OF THE FABRICATED DEVICES

| Device                  |            | NMOS      |      | PMOS      |      |

|-------------------------|------------|-----------|------|-----------|------|

|                         |            | This Work | Conv | This Work | Conv |

| Extension -             | Rs (Ω/sq.) | 510       | 500  | 400       | 1940 |

|                         | Xj (nm)    | 46        | 52   | 40        | 60   |

| Rex (Ω)                 |            | 34        | 64   | 42        | 65   |

| Drain Cap. (fF/ m²)     |            | 1.24      | 1.61 | 1.75      | 1.76 |

| Extension Cap. (fF/ m²) |            | 2.18      | 1.63 | 2.35      | 2.16 |

| Overlap Cap. (fF/ m²)   |            | 0.80      | 0.81 | 1.07      | 0.27 |

than those of conventional devices. The external S/D resistances were reduced by about 40% compared with those of conventional devices because of the large gate-extension overlap. However, the overlap capacitance was about four times larger than that of the conventional devices. To optimize the overall design of the transistor, it is necessary to achieve the best balance between on-current and capacitance. In the next section the optimization of the device structure will be discussed.

## B. Gate-Extension Overlap Effect

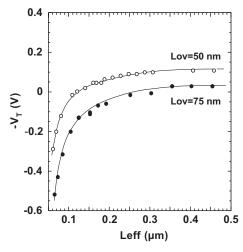

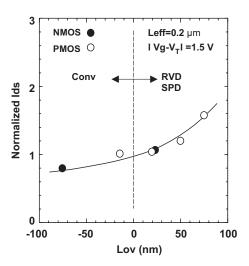

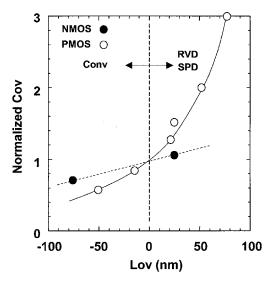

A gate-extension overlap is required to get high on-current. However, excessive gate-extension overlap causes some drawbacks on the device performance. We therefore investigated how the S/D extension structure could be designed to give optimum device performance. The threshold voltage rolloff, drain current  $(I_{ds})$ , and overlap capacitance  $(C_{ov})$  were characterized as a function of the lateral diffusion length  $(L_{ov})$  of S/D extensions. The various  $L_{ov}$  were obtained by changing the doping condition. The dependence of the threshold voltage rolloff on the  $L_{ov}$  for the RVD pMOSFETs is shown in Fig. 11.  $L_{ov}$  was defined as the distance between the drain extension edge and the gate edge (Fig. 6) and it was determined by the channel resistance method [11]. A degradation of threshold voltage rolloff characteristics was observed in the devices with  $L_{ov} = 75 \text{ nm}$ due to increased charge sharing. The short channel effects were improved by a shallower junction and smaller  $L_{ov}$ . The dependence of normalized drain current on  $L_{ov}$  is shown in Fig. 12.

Fig. 11. Comparison of the gate-extension overlap ( $L_{ov}$ ) dependence on  $V_{\rm T}$  rolloff characteristics for RVD-pMOSFETs.

Fig. 12.  $I_{ds}$  versus  $L_{ov}$ .  $I_{ds}$  is normalized by respective  $L_{ov} = 0$  values.

The ion implanted S/D extension devices showed a negative  $L_{ov}$  because of their graded channel profiles due to high counter doping [12]. On the contrary, the RVD and PSD devices had a positive  $L_{ov}$  because of the isotropically and heavily doped S/D extensions. The drain current increased with increasing  $L_{ov}$  because of the reduction of external resistance. The dependence of the overlap capacitance on  $L_{ov}$  is shown in Fig. 13. The overlap capacitance increases with increasing  $L_{ov}$ . The dependence of the overlap capacitance on  $L_{ov}$  is stronger in pMOSFETs than in nMOSFETs due to the interfacial diffusion of boron underneath the gate edge. Similar results have been reported by Young  $et\ al.\ [13]$  who considered that boron is easy to diffuse along the  $Si/SiO_2$  interface into the channel region.

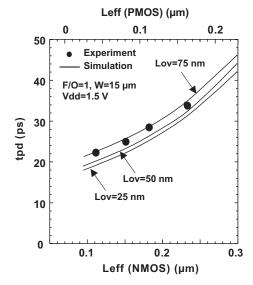

## C. Circuit Performance

To test the circuit performance, unloaded CMOS ring oscillators were used. A CMOS inverter gate delay of 22 ps/gate at a power supply voltage of 1.5 V was obtained. Fig. 14 shows the simulated variation of inverter gate delay with effective channel length for various values of  $L_{ov}$  for the pMOSFETs. The value of  $L_{ov}$  for the nMOSFETs was fixed at 25 nm. The gate delay was decreased with decreasing  $L_{ov}$  due to less overlap capaci-

Fig. 13. Overlap capacitances ( $C_{ov}$ ) versus  $L_{ov}$ .  $C_{ov}$  is normalized by respective  $L_{ov}=0$  values.

Fig. 14. Dependence of CMOS inverter gate delay time (tpd) on Leff.

tance. Thus, we found that pMOSFETs with  $L_{ov}=25$  nm enabled excellent dc and high-speed circuit performance in  $0.1~\mu m$  effective channel length devices. As a result, a shallower junction is required to obtain lower overlap capacitance and higher circuit performance.

## IV. SUMMARY

We have developed an advanced CMOS technology using two techniques in combination: RVD and SPD. The RVD and SPD devices we fabricated have shown excellent threshold voltage rolloff characteristics down to 0.1  $\mu$ m effective channel length, a drain current 40% higher than that of conventional devices, and high-speed circuit performance. This high level of performance was due to the shallow and steep junctions formed by using RVD and SPD. We also investigated the effect of the S/D extension structure on the device performance. We found that a gate-extension overlap of 25-nm enabled excellent dc characteristics and high-speed circuit performance in 0.1- $\mu$ m devices.

#### ACKNOWLEDGMENT

The authors wish to thank the staff of the Process Integration Center, Hitachi Central Research Laboratory, for the device fabrication.

### REFERENCES

- [1] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H.-J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS scaling into the nanometer regime," *Proc. IEEE*, vol. 85, pp. 486–504, 1997.

- [2] S. Thompson, P. Packan, T. Ghani, M. Stettler, M. Alavi, I. Post, S. Tyagi, S. Ahmed, S. Yang, and M. Bohr, "Source/drain extension scaling for 0.1 μm and below channel length MOSFETs," in *Symp. VLSI Tech. Dig.*, 1998, pp. 132–133.

- [3] Y. Kiyota, M. Matsushima, Y. Kaneko, M. Kanemoto, Y. Tamaki, K. Muraki, and T. Inada, "Ultrashallow p-type layer formation by rapid vaporphase doping using a lamp annealing apparatus," *Appl. Phys. Lett.*, vol. 64, pp. 910–911, 1994.

- [4] M. Ono, M. Saito, T. Yoshitomi, C. Fiegna, T. Ohguro, and H. Iwai, "A 40 nm gate length n-MOSFET," *IEEE Trans. Electron Devices*, vol. 42, pp. 1822–1830, Sept. 1995.

- [5] L. A. Larson, "Perspectives on shallow junction technology from the viewpoint of the ITRS," in *Proc. Ext. Abstr. Workshop on Junction Tech*nology, 2000, pp. 7–11.

- [6] Y. Kiyota, F. Yano, S. Suzuki, and T. Inada, "Role of hydrogen during rapid vapor-phase doping analyzed by x-ray photoelectron spectroscopy and Fourier-transform infrared-attenuated total reflection," *J. Vac. Sci. Technol. A*, vol. A16, pp. 1–5, 1998.

- [7] Y. Kiyota, T. Nakamura, K. Muraki, and T. Inada, "Phosphorus direct doping from vapor phase into silicon for shallow junctions," J. Electrochem. Soc., vol. 141, pp. 2241–2244, 1994.

- [8] T. Uchino, A. Miyauchi, and T. Shiba, "MOSFETs with ultrashallow junction and minimum drain area formed by using solid-phase diffusion from SiGe," *IEEE Trans. Electron Devices*, vol. 48, pp. 1406–1411, July 2001.

- [9] ATHENA: 2D Process Simulator, ATLAS: Device Simulator, SILVACO International.

- [10] J. Chen, T. Y. Chan, I. C. Chen, P. K. Ko, and C. Hu, "Subbreakdown drain leakage current in MOSFETs," *IEEE Electron Device Lett.*, vol. EDL-8, pp. 515–517, 1987.

- [11] J. G. J. Chern, P. Chang, R. F. Motta, and N. Godinho, "A new method to determine MOSFET channel length," *IEEE Electron Device Lett.*, vol. ED-1, pp. 170–172, 1980.

- [12] Y. Taur, Y. J. Mii, R. Logan, and H. S. Wong, "On effective channel length in 0.1-μm MOSFETs," *IEEE Electron Device Lett.*, vol. 16, pp. 136–138, Apr. 1995.

- [13] R. Young, L. Su, M. Ieong, and S. Kapur, "A possible mechanism for reconciling large gate-drain overlap capacitance with a small difference between polysilicon gate length and effective channel length in an advanced technology PFET," *IEEE Electron Device Lett.*, vol. 19, pp. 234–236, July 1998.

**Takashi Uchino** (M'98) received the M.S. and Ph.D. degrees in materials science from Tsukuba University, Ibaraki, Japan in 1986, and 1989, respectively.

He joined Central Research Laboratory, Hitachi, Tokyo, Japan, in 1989, where he worked on the development of high-speed silicon bipolar and CMOS technologies. In 2002, he moved to the Department of Electronics and Computer Science, University of Southampton as a Research Fellowship. His current research interests are in the technology and physics of novel device and the development of advanced MOS

devices

Dr. Uchino is a member of the Physical Society of Japan and the Japan Society of Applied Physics.

**Peter Ashburn** (M'98) was born in Rotherham, U.K., in 1950. He received the B.Sc. degree in electrical and electronic engineering and the Ph.D. degree in experimental and theoretical study of radiation damage in silicon p-n junctions from the University of Leeds, U.K., in 1971 and 1974, respectively.

In 1974, he joined the Technical Staff of Philips Research Laboratories and worked initially on ion implanted integrated circuit bipolar transistors, and then on electron lithography for sub-micron

integrated circuits. In 1978, he joined the Academic Staff of the Department of Electronics and Computer Science, University of Southampton, U.K., as a Lecturer, and currently is the holder of a Personal Chair in microelectronics. Since taking up a post at Southampton University, he has worked on polysilicon emitter bipolar transistors, high-speed bipolar and BiCMOS technologies, gate delay expressions for bipolar circuits, and the effects of fluorine in polysilicon emitters. His current research interests include SiGe heterojunction bipolar transistors, SiGeC and its device applications and vertical MOS transistors for application in sub-100 nm CMOS technology. He has authored and co-authored over 120 papers in the technical literature, given invited papers on polysilicon emitters and SiGe heterojunction bipolar transistors, and has authored a book on bipolar transistors.

**Yukihiro Kiyota** was born in Tokyo, Japan, in 1963. He received M.S. and Ph.D. degrees in electronic engineering from Waseda University, Tokyo, in 1988 and 1996.

In 1988, he joined the Central Research Laboratory, Hitachi Ltd., Tokyo, where he engaged in the research and development of high-speed silicon/SiGe bipolar processes and devices. His research topics include vapor-phase doping for shallow pn-junctions and Si/SiGe epitaxial growth. In 2003, he moved to SONY, Kanagawa, Japan, where he engaged in the

development of radio frequency devices, including SiGe BiCMOS.

Dr. Kiyota is a member of the Japan Society of Applied Physics and the Institute of Electronics, Information, and Communication Engineers.

**Takeo Shiba** (M'88) received the B.S. degree in physical engineering and the Ph.D. degree in electronic engineering from the University of Tokyo, Japan, in 1977 and 1996, respectively.

Since 1977, he has been with Hitachi Ltd., Tokyo. From 1977 to 1980, he was involved in the development of high-speed bipolar SRAMs. From 1980 to 1995, he worked in the area of very high-speed Si bipolar/BiCMOS/CMOS device and process technology for mainframe and communication systems in the Central Research Laboratory,

Hitachi Ltd., Tokyo. Since 1998, he has been engaged in the development of low-temperature PolySi thin-film transistors (TFTs) for LCD in the Hitachi Research Laboratory, Hitachi Ltd., Tokyo. His current interests are device and process technologies for high performance and reliability of TFTs.

Dr. Shiba is a member of the Institute of Electronics, Information, and Communication Engineers of Japan.