Analog Integrated Circuits and Signal Processing, 39, 177–190, 2004 © 2004 Kluwer Academic Publishers. Manufactured in The Netherlands.

# Behavioral Fault Modeling and Simulation Using VHDL-AMS to Speed-Up Analog Fault Simulation

## Y. KILIC¹ AND M. ZWOLIŃSKI²

<sup>1</sup>Allegro MicroSystems Europe Ltd., Stuart House, Station Road, Musselburgh, EH21 7PB, UK <sup>2</sup>Department of Electronic and Computer Science, University of Southampton, Highfield, Southampton, SO17 1BJ, UK E-mail: yavuz.kilic@ieee.org; mz@ecs.soton.ac.uk

Received; Revised November 2, 2002; Accepted June 11, 2003

Au: Pls. provide received date.

Abstract. One of the main requirements for generating test patterns for analog and mixed-signal circuits is fast fault simulation. Analog fault simulation is much slower than the digital equivalent. This is due to the fact that digital circuit simulators use less complex algorithms compared with transistor-level simulators. Two of the techniques to speed up analog fault simulation are: fault dropping/collapsing, in which faults that have similar circuit responses compared with the fault-free circuit response and/or with another faulty circuit response are considered equivalent; and behavioral/macro modeling, whereby parts of the circuit are modeled at a more abstract level, therefore reducing the complexity and the simulation time. This paper discusses behavioral fault modeling to speed-up fault simulation for analog circuits.

16 Key Words: behavioral fault modeling, macro modeling, analog fault simulation, VHDL-AMS

## 17 1. Introduction

As transistor sizes shrink, integrated circuits (ICs) have been growing in size and functionality. This growth in IC complexity causes testing to become much more difficult. For digital circuits the problem of testing can be simplified by using standard fault models and fast fault simulation. Faults in digital circuits can be modeled as stuck-at, bridging, delay and open faults. These structural faults can then be used to generate functional test patterns. The objective of a test program for digital circuits translates into determining whether or not a fault exists using the smallest possible number of test patterns [1].

A test pattern is evaluated by looking at its fault coverage. All faults detected with a pattern can be *dropped* from further consideration. Fault simulation is done to assess the fault coverage. There are a number of fault simulation techniques for digital circuits. *Serial fault simulation* is perhaps the simplest method. For each fault, a "faulty" copy of the circuit with that fault inserted is created. Then, all the faulty copies of the circuits along with the fault-free one are simulated with the test pattern. If the output of a faulty circuit differs

from the fault-free output, that fault is considered to be detectable.

Another fault simulation technique for digital circuits is *concurrent fault simulation* [2]. The differences between the faulty and fault-free circuit behaviors might be relatively small. Therefore, in concurrent fault simulation the aim is to avoid redundant element evaluation when the faulty and fault-free behaviors are the same hence reducing the computational effort.

Analog and mixed-signal fault simulation has been limited to the serial technique. Faster digital fault simulation methods are not easily applied to analog circuits and/or mixed-signal circuits, because faults do not affect the behavior of circuit nodes in a binary manner.

One way to speed-up fault simulation for analog and mixed-signal circuits is to use behavioral/macro models, where parts of the circuit are modeled at a more abstract level, reducing the complexity and hence the simulation time. Characterizing behavioral fault models requires low-level simulations and is therefore not applicable in every case. There are three situations in which behavioral fault modeling might be of benefit, however. First, if circuit blocks were reused, low-level fault simulations would not have to be repeated.

67

70

71

72

73

75

**76** 77

78

79

80

81

82

83

85

86 87

88

89

91

92 93

94

95

96

97

98

99

100

101

102

103

104

105 106

107

108

109

110

#### 178 Kiliç and Zwoliński

Second, at the system design stage, information about possible faults and how their effects might be propagated can be used to insert optimal test structures. Third, actual faults can be modeled at a low level (analog or digital), while neighboring circuit blocks can be modeled behaviorally, again reducing the overall simulation time.

In this paper behavioral fault simulation for analog CMOS circuits is investigated. The structure of the rest of the paper is as follows. First, macro modeling for analogue circuits is presented. Then behavioral modeling is discussed with a case study. In Section 4, behavioral modeling using Hardware Description Languages (HDLs) is summarized. In Section 5, a behavioral fault model is developed in VHDL-AMS [3] for an opamp circuit operating in inverting amplifier configuration and the model is simulated using the hAMSter VHDL-AMS simulator [4]. Simulation results are given in Section 6. Finally, in Section 7 some conclusions are drawn.

## **Macromodels for Analogue Circuits**

Simulation at the transistor level for analog circuits is computationally very expensive. One way to reduce this high simulation cost is to partition a large analog circuit into smaller functional blocks such as opamps (operational amplifiers) and to replace each functional block with its macromodel or to describe each block using mathematical equations (a behavioral model). This solution is sometimes called hierarchical fault simula-

The word *macromodel* usually refers to a compact representation of a circuit that captures those features that are useful for a particular purpose while discarding redundant information [6]. Macromodels developed for SPICE-like simulators are basically electrical networks containing devices such as voltage-controlled voltage sources, instead of the full transistor network, and with fewer nodes than the original circuit.

Many circuits are designed in a modular style, in which functional units are connected to achieve design specifications. The behavior of the whole circuit is determined by how the individual units interact with each other, while what happens inside each is unimportant in terms of capturing the input-output relationship for the entire circuit. The accuracy of a macromodel must, therefore, be defined in terms of how closely its inputoutput behavior matches that of the original unit [6].

Since the early 1970s, a number of macromodels 111 have been developed mainly for integrated operational 112 amplifier circuits (opamps) [5, 7]. Boyle et al. presented 113 a macromodel for integrated bipolar opamp circuits [8]. 114 This macromodel was six times less complex (in terms 115) of the node count) than the original opamp circuit, and 116 the simulation time was an order of magnitude faster 117 than the device-level model.

118

128

139

141

144

147

151

The derivation of component values for the Boyle 119 macromodel is not, however, straightforward. Some pa- 120 rameters are modeled using unbalanced input devices 121 and other parameters interact. Therefore, a modular ap- 122 proach was suggested [9], in which a macromodel was 123 derived simply from the published data sheets. Individ- 124 ual parameters were modeled separately and the results 125 combined to provide the output response. Since the pa- 126 rameters were separated they did not interact and only 127 those required were included.

Recent research has focused on how to capture the 129 effect of a fault in an analogue circuit within its macromodel [1, 3, 10]. The fault macromodeling problem 131 was formulated in terms of deriving the macro param- 132 eter set, B, based on the performance parameter set, 133 P (gain, the bandwidth, samples on the frequency or 134 time response curves, etc.) of the transistor-level faulty 135 circuit [5]. The accuracy of the macromodel was evaluated by checking the consistency of the performance 137 parameter set, P, between the transistor-level circuit 138 and the macromodel.

Two steps are needed to obtain the macromodel for 140 a functional block within an analog circuit [5]:

- 1. Perform transistor level fault simulation for each 142 faulty circuit to obtain the value of the performance 143 parameter set P.

- 2. Map each performance parameter set P to the cor- 145 responding macro parameter set, B. This is referred 146 to as parameter mapping.

It was assumed that the transistor-level fault list is given 148 and the macromodel structure and the performance pa- 149 rameter set, P, to be matched are predetermined by the 150 circuit designer.

There are several ways to do parameter mapping. 152 One simple approach is based on analytical design 153 equations that express the macro parameter set, B, as 154 analytical functions of the performance parameter set, 155 P, and the value of B is derived by function evalua- 156 tion. As analog ICs get more complex, this approach 157 is becoming more difficult. Another simple approach 158

162

164

165

166

167

168

169

170

171

172

173

175

176

177

178

180

181

182

183

184

185

186

187

188

189

190

210

217

is to build an empirical mapping function, B = F(P), based on a large number of data pairs (P, B), referred to as the *training set* [5]. Usually the training set is generated by randomly selecting M out of the N performance parameter sets for the faulty circuits obtained by transistor-level simulation and then the value of the macro parameter set B for each selected P is derived. The derivation of each data pair usually requires multiple runs of the macromodel-level simulation [3].

Macromodeling in general and fault macromodeling using SPICE-like languages in particular have, nevertheless, been shown to be very difficult [1, 5-20]. Therefore, another easier and perhaps more efficient way of modeling analog circuits at a higher level is necessary.

#### **Behavioral Modeling** 174 3.

A behavioral model describes a circuit block in terms of mathematical equations modeling the functionality of the block, for example, in terms of the input-output relationship. Behavioral modeling has been used for speeding up analog simulation in general [21] and analog fault simulation in particular [1, 10, 20, 22]. In one approach, analog circuits were modeled behaviorally in the C programming language [21]. Broyden's method [23] was used to formulate and solve the model equations in a custom simulator. The main drawback of this work is that since the technique does not require derivatives it cannot be used for small-signal analysis.

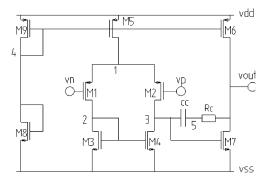

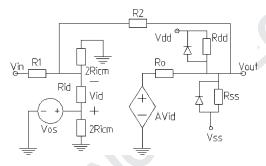

Chang et al. [10] presented a behavioral fault model derived from a macromodel of a CMOS operational amplifier from the IEEE Mixed-Signal Benchmark Suite [24] (Fig. 1). The "faulty" macromodel was de-

Fig. 1. The 2-stage CMOS Miller opamp used in [10] for behavioral fault modeling.

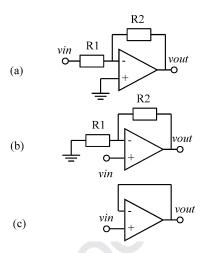

Fig. 2. Three different configurations used in [10] for the benchmark circuit given in [24]: (a) Inverting amplifier, (b) non-inverting amplifier, and (c) unity gain buffer.

veloped using DC-sweep analysis. The DC behavior 191 of the benchmark opamp operating in inverting, non- 192 inverting and unity gain amplifier configurations was 193 first investigated under different fault conditions, as 194 shown in Fig. 2. Single transistor catastrophic faults, 195 bridging/short and nearly open faults, and paramet- 196 ric faults with W (channel width), L (channel length) 197 and  $V_{\rm TH}$  (threshold voltage) varied by  $\pm 10\%$  were 198 used for each transistor. Then an attempt was made 199 to group the different faulty behaviors. By comparing 200 the fault-free offset voltage measured at the inputs of 201 the opamp operating in one of the three configurations 202 with the equivalent faulty circuits, four different equiv- 203 alent fault types were derived [10]: M4 drain-to-gate 204 short (Type I), M5 drain-to-source short (Type II), M7 drain open (Type III), and M5 drain-to-source short 206 (Type IV). The first three fault types were found for the 207 opamp operating in the inverting configuration, where 208 the Type IV fault group was found for the non-inverting 209 configuration.

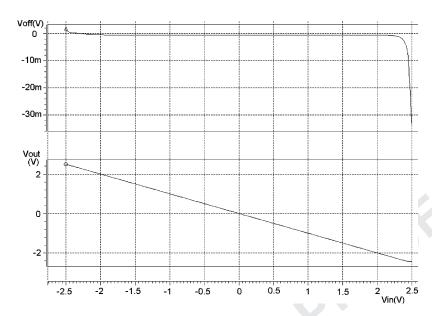

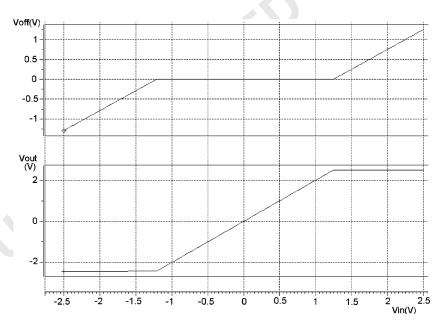

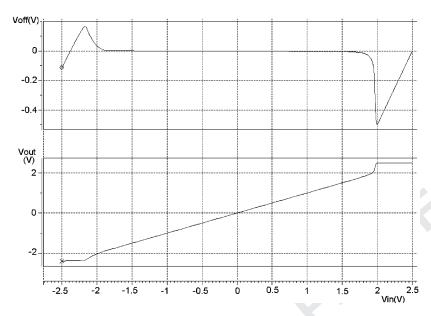

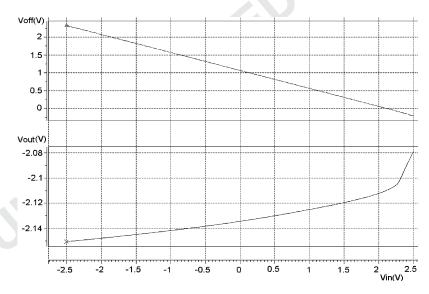

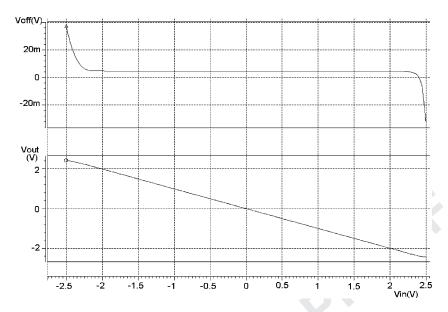

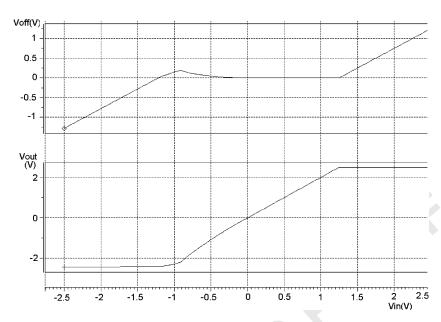

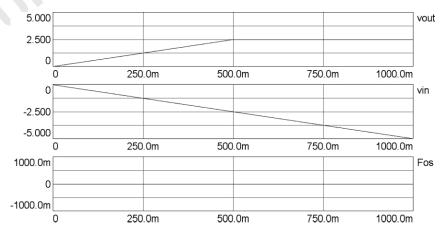

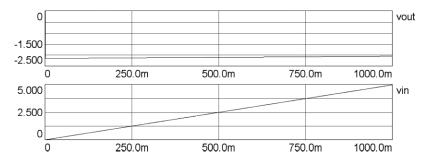

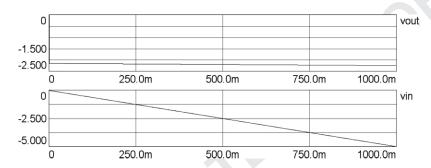

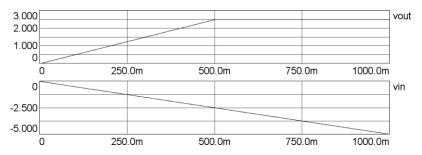

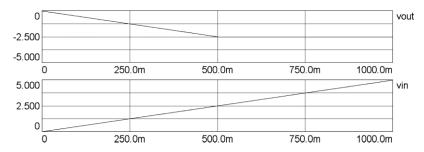

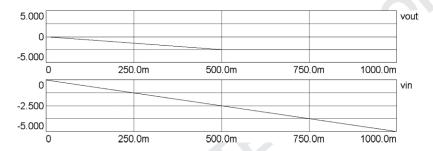

The input offset voltage (measured between the pos- 211 itive and negative inputs of the opamp in the closed- 212 loop configurations) and the output voltage versus the 213 input voltage for the fault-free opamp operating in 214 three configurations were determined by simulation. 215 Our HSPICE simulations of these configurations are 216 shown in Figs. 3–5, respectively.

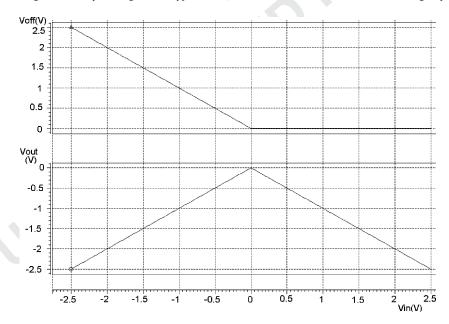

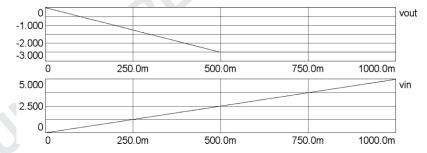

HSPICE simulations of the input offset voltage and 218 the output voltage for each fault group with respect to 219 the input voltage are shown in Figs. 6-9, respectively. 220

## 180 Kiliç and Zwoliński

Fig. 3. Input offset voltage and output voltage versus DC-sweep input voltage for the fault-free inverting amplifier.

Fig. 4. Input offset voltage and output voltage versus DC-sweep input voltage for the fault-free non-inverting amplifier.

As can be seen from Figs. 7 and 9, the output responses of Type II and Type IV faults are quite similar to the fault-free responses given in Figs. 3 and 4. Type II and Type IV input offset voltages are noticeably different from the fault-free responses. The input offset voltage has a small DC level for Type II faults, but has a non-linear characteristic for Type IV faults.

221

222

224225

226

The remaining two faults have very different characteristics to the fault-free equivalents for both input offset voltages and output voltages. It can be concluded from the figures that a Type I fault causes the inverting amplifier output to be "nearly stuck-at" a negative voltage near to the negative supply voltage level. A Type III 233 fault causes the inverting amplifier output to have a 234

Fig. 5. Input offset voltage and output voltage versus DC-sweep input voltage for the fault-free unity gain buffer.

Fig. 6. Input offset voltage and the output voltage for the Type I fault (M4 drain-to-gate short fault for the inverting amplifier configuration).

non-inverting characteristic for the negative values of

the DC input signal, and an inverting characteristic for

the positive values of the DC input signal. As can be

seen from the figures, the input offset voltage at the inputs of the opamp has a linear characteristic for Type I

faults, and a piecewise linear characteristic for Type III

faults.

The macromodel given in Fig. 10 for the inverting opamp can be used to derive the input output relation-

242

243

ship under fault conditions [10]:

244

$$V_{\text{out}} = A_{\text{CL}}[(1+m)V_{\text{in}} + k] \tag{1}$$

where  $A_{\rm CL}$  is the closed-loop gain for the opamp, the parameters m and k are given in [10] as: 246

$$m = \frac{-R2}{D + R2} \tag{2}$$

# 182 Kiliç and Zwoliński

Fig. 7. Input offset voltage and the output voltage for the Type II fault (M5 drain-to-source short fault for the inverting amplifier configuration).

Fig. 8. Input offset voltage and the output voltage for the Type III fault (M6 open drain fault for the inverting amplifier configuration).

247 and

$$k = aVos + bVdd + cVss$$

(3)

$$a = \frac{R2//D}{A_{\text{CL}}(R1//R2//2Ricm//BR2)},$$

$$b = \frac{SF}{A_{\text{CL}}Rdd},$$

$$c = -\frac{SF}{A_{\text{CL}}Rss},$$

$$B = \left(\frac{A}{Ro} - \frac{1}{R2}\right)(Rid//R1//R2//2Ricm),$$

$$A_{\text{CL}} = -\frac{R2}{R1},$$

275

Fig. 9. Input offset voltage and the output voltage for the Type IV fault (M5 drain-to-source short fault for the non-inverting amplifier configuration).

Fig. 10. Macromodel used in [10] to derive the input-output relationship for the closed loop inverting opamp.

$$SF = Rdd//Rss///Ro//(R2//R11)//$$

$$\times \frac{Ro(R11//R2)}{AR11},$$

$$R11 = R1//2Ricm//Rid,$$

and A represents the open-loop gain.

249

250

251 252

253

254

256

The non-ideal effects such as the input offset voltage, Vos, the finite open-loop gain, A, and the finite input and output resistances, Rid (differential mode input resistance), Ricm (common mode input resistance), Ro (output resistance), and the resistances from the output node to the supply rails (Rdd and Rss) to model output stuck-at faults were taken into account when deriving

Eq. (1). Note that for the fault-free case Rid, Ricm, 257 Rdd, Rss, and A would be infinite, Vos, and Ro would 258 be zero, hence  $m \to 0$ , and  $k \to 0$ . When a fault causes 259 the output to be stuck-at some voltage level,  $D \rightarrow 0$ , 260 therefore  $m \to -1$ , and k is the value of the stuck-at 261 output voltage; the closed-loop gain,  $A_{CL}$ , is assumed 262 to be unity. As they are dealt with elsewhere [10], the 263 derivation of the above equations will not be given here. 264

The current limiting effect was also modeled in [10]. 265 This is due to the finite supply voltage at the output of 266 the opamp. It is claimed that the model covers all the 267 parametric faults and 92.5% of the catastrophic faults 268 that were considered. The model could not model the 269 M4 drain-to-gate short, M5 drain-to-source short, M1 270 open-gate faults for the non-inverting amplifier and the 271 M2 drain-to-gate short, M4 drain-to-gate short, M5 272 drain-to-source short, M1 open gate, M3 open source 273 and M5 open gate faults for the unity gain buffer.

## **Behavioral Modeling Using HDLs**

HDLs have been in use for behavioral modeling and 276 simulation of digital circuits as well as analog elec- 277 tronic systems, fluid concentrations in chemical pro- 278 cesses, and even parachute jumps since 1960 [25]. 279 Currently two of the most widely used standards for 280

285

286

287

288 289

290 291

292

293 294

295

296

297

298

299

300

301

317

HSPICE.

#### 184 Kiliç and Zwoliński

modeling digital designs are VHDL [26], and Verilog 282 [27]. For analogue circuits, the choice has been between 283 SPICE and proprietary analog HDLs.

Analog HDLs support the description of systems of differential and algebraic equations (DAEs). The solution of these systems varies continuously with time. Most analog HDLs support both structural composition and conservation semantics, in addition to behavioral descriptions. Examples of such languages are FAS [28], SpectreHDL [29], and Verilog-A [30].

Mixed-signal design has depended on the use of separate HDLs for the analog and digital parts or, again, on proprietary languages. Mixed-signal languages support both event-driven techniques and DAEs in one simulator. Simulators in this category are MAST/Saber [31], VeriasHDL [31], AdvanceMS [28], hAMSter [4].

Both VHDL and Verilog have been extended to analog mixed-signal design: VHDL-AMS [3], and Verilog-AMS [30]. The analog extensions to VHDL and Verilog should alleviate the multiple-language problem [32].

302 Since VHDL-AMS was standardized in 1999 there has been some work done on fault modeling using 303 VHDL-AMS. One reason for the limited progress is, 304 305 perhaps, that there is not yet a robust VHDL-AMS simulator available that has all the VHDL-AMS constructs 307 implemented, such as procedural statements. Perkins 308 et al. attempted to use an analog VHDL for fault modeling and simulation with limited success [1]. The HDL-309 A modeling language with the ELDO simulator from 310 Anacad (now a part of Mentor) was used. Behavioral 311 312 model simulation using HDL-A and ELDO was over 4.6 times slower than the macromodel simulation car-313 ried out using HSPICE [1]. One of the reasons for this is that the semiconductor device models implemented in ELDO were not as efficient as those were in

#### 318 **VHDL-AMS Behavioral Fault Model** 319 for the Inverting Opamp

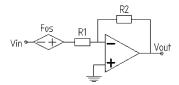

in Eq. (1) has been developed. The values of m and k321 were derived by carrying out transistor level simula-322 323 tions for four fault types and are given in Table 1. 324 Considering only the input-output relationship given

A VHDL-AMS model for the behavioral model given

in Eq. (1), the opamp macromodel given in Fig. 10 can 325 326 now be simplified to that shown in Fig. 11. All the fault effects and non-ideal effects are approximated to Fos = 327

Table 1. The values of m and k for different fault groups.

|             | Parameters                                                                   |                                                                         |  |

|-------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Fault types | m                                                                            | k (V)                                                                   |  |

| Type I      | -1.02                                                                        | 2.15                                                                    |  |

| Type II     | 0                                                                            | 0.011                                                                   |  |

| Type III    | 0  if  vin > 0  V                                                            | 0                                                                       |  |

|             | -2  if  vin < 0                                                              |                                                                         |  |

| Type IV     | $-1$ if vin $> \sim 1.2$ V<br>and vin $< \sim -1.2$ V                        | $V_{dd}/2$ if vin $> \sim 1.V$<br>$V_{ss}/2$ if vin $< \sim -1.2$ V     |  |

|             | $0 \text{ if } \sim -1.2 \text{ V}$<br>< $v \text{in } < \sim 1.2 \text{ V}$ | $0 \text{ if } \sim -1.2 \text{ V}$ $< \text{vin} < \sim 1.2 \text{ V}$ |  |

$mV_{\rm in} + k$ , which is applied to the inverting input of the 328 opamp.

329

A VHDL-AMS implementation of the behavioral 330 model given in Eq. (1) is shown in Figs. 12 and 13 331 [33]. rin represents the input resistance of the opamp 332 in Fig. 12 where it is only used for the third equation 333 in Fig. 13. The third equation is needed as there are 334 three quantities declared in the architecture declaration 335

Fig. 11. Behavioral level DC-offset fault model for the inverting opamp.

```

--behavioral opamp

library disciplines;

library ieee;

use disciplines.electromagnetic_system.all;

use ieee.math real.all;

--entity

entity op behav is

generic ( m : real := 0.0; --fault-free value

k : real := 0.0; --fault-free value

Acl: real:= -1.0; --closed-loop gain

rin : real := 100.0e6);

port (terminal in node, out node : electrical);

end:

```

Fig. 12. The VHDL-AMS entity implementation of the behavioral fault model.

22:29

Behavioral Fault Modeling and Simulation Using VHDL-AMS

```

shown in Fig. 13. Note that this architecture declaration

336

also covers the supply voltage limiting effect at the

337

output of the opamp.

338

In order to simulate the VHDL-AMS model shown

339

in Figs. 12 and 13, one also needs VHDL-AMS models

340

for a resistor, a voltage source and a testbench, which

341

are shown in Figs. 14–16, respectively.

342

```

```

--architecture

library disciplines;

library ieee;

use disciplines.electromagnetic system.all;

use ieee.math_real.all;

architecture behav of op behav is

quantity vout across iout through out node;

quantity vin across iin through in_node;

quantity Fos : real;

-- supply voltage limit

constant v_limit : real := 2.5;

begin

procedural is

variable vout_calc : real;

begin

Fos := m*vin + k:

vout_calc := Acl * (vin + Fos);

iin := (vin - Fos) / rin;

if (vout calc > v limit) then vout := 2.5;

elsif (vout_calc < -v_limit) then vout := -2.5;</pre>

else vout := vout calc;

end if;

end procedural;

end;

```

Fig. 13. The VHDL-AMS architecture implementation of the behavioral fault model.

```

--resistor

library disciplines;

use disciplines.electromagnetic system.all;

entity resistor is

generic (rnom : real := 0.0);

port(terminal p,m : electrical); --interface ports

end resistor:

architecture behav of resistor is

quantity r e across r i through p to m;

begin

r i == r e/rnom;

end behav:

```

Fig. 14. A VHDL-AMS model of a resistor.

```

-- voltage source

library disciplines:

use disciplines.electromagnetic system.all;

--entity declaration.

entity v_source is

generic (dc value : real :=-2.50);

port(terminal p,m: electrical); --interface ports

end v source;

--architecture declaration.

architecture behav of v source is

quantity v_in across i_out through p to m;

v in==dc value*now; -- slow transient

end architecture behav;

Fig. 15. A VHDL-AMS model of a voltage source.

--testbench

library disciplines;

library ieee;

use disciplines.electromagnetic_system.all;

use ieee.math real.all;

entity ex_op_behav is end;

architecture testbench of ex op behav is

terminal in_node, out_node, vsrc : electrical;

op_behav_uut : entity op_behav (behav)

generic map ( m => 0.0, k => 0.0, acl => -1.0)

port map ( in_node => in_node,

out_node => out_node);

vin dc : entity v source (behav)

generic map ( dc_value => 5.0)

port map ( p => vsrc, m => electrical_ground);

rsrc : entity resistor (behav)

generic map (rnom => 100.0)

port map (p => vsrc, m => in node);

```

Fig. 16. A VHDL-AMS testbench used with the hAMSter simulator to simulate the behavioral model shown in Figs. 12 and 13.

end;

Note that input voltage source in the architecture 343 declaration shown in Fig. 15 is realized using a pre- 344 defined VHDL-AMS function, now, which returns the 345 value of the current time at each step as simulation pro- 346 ceeds. This is done in order to simulate the DC-sweep 347 analysis, which is not defined in VHDL-AMS (unlike 348 many SPICE-like simulators). This technique is called 349 slow transient simulation.

350

353

354

355

356

357

358

359

360

361

362

363

364

365

366

186 Kiliç and Zwoliński

#### **Simulation Results** 351 6.

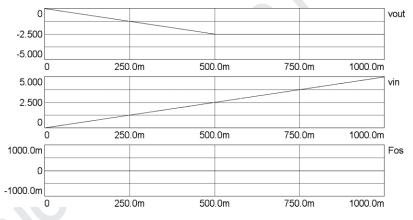

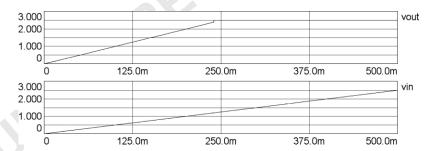

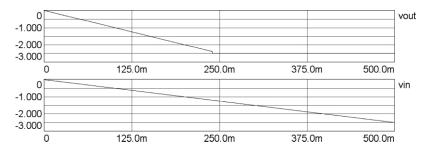

The slow transient simulation results using the hAM-Ster simulator and the behavioral closed-loop VHDL-AMS model of the inverting opamp (the fault free case) with the necessary component and voltage source models and the testbench given in the previous sections are shown in Figs. 17 and 18.

Note that the X-axis in Figs. 17 and 18 represents the time in seconds, where Y-axis represents vout, vin, and Fos in Volts. (Unless otherwise stated, for the rest of the paper it will be assumed that X-axis will represent time in seconds for the simulation results obtained using hAMSter).

Using the values for the parameters m and kfrom Table 1 yields the simulation results shown in Figs. 19-26.

Note that the output response of the opamp, vout, 367 found for the positive values of vin and the negative 368 values of vin for Type I faults (Figs. 19 and 20) are the 369 same ("nearly stuck-at" -2.14 V), as expected.

370

372

374

378

For Type III faults *Fos* is determined using the fol- 371 lowing if-then construct in the VHDL-AMS model.

For Type IV faults Fos is determined using the fol- 373 lowing if-then construct in the VHDL-AMS model.

DC-sweep analysis cannot be performed for VHDL- 375 AMS. Therefore, the transient simulation results for 376 different fault types using the VHDL-AMS behav- 377 ioral models and the hAMSter simulator were compared with the transient simulation results obtained us- 379 ing transistor level models with HSPICE simulator. To 380 do that a sine wave with 2 V peak-to-peak magnitude 381 and 1 KHz frequency was applied to both behavioral 382 and transistor level circuits. The simulators were run

Fig. 17. Slow-transient simulation results using the VHDL-AMS model with hAMSter for the positive values of the input voltage source.

Fig. 18. Slow-transient simulation results using the VHDL-AMS model with hAMSter for the negative values of the input voltage source.

## Behavioral Fault Modeling and Simulation Using VHDL-AMS

187

Fig. 19. Slow-transient simulation using hAMSter for Type I faults for the positive values of vin.

Fig. 20. Slow-transient simulation using hAMSter for Type I faults for the negative values of vin.

Fig. 21. Slow-transient simulation using hAMSter for Type II faults for the positive values of vin.

Fig. 22. Slow-transient simulation using hAMSter for Type II faults for the negative values of vin.

# 188 Kiliç and Zwoliński

Fig. 23. Slow-transient simulation using hAMSter for Type III faults for the positive values of vin.

Fig. 24. Slow-transient simulation using hAMSter for Type III faults for the negative values of vin.

Fig. 25. Slow-transient simulation using hAMSter for Type IV faults for the positive values of vin.

Fig. 26. Slow-transient simulation using hAMSter for Type IV faults for the negative values of vin.

403

418

422page

423 range.

424

425

426

428 429

430

431

432

433

434

435

437

439 440

441

442

443

Table 2. Comparison of CPU times for transistor level transient HSPICE simulations against VHDL-AMS behavioral level hAMSter

|            | The CPU time (s)<br>Simulator |        |

|------------|-------------------------------|--------|

| Fault type | hAMSter                       | HSPICE |

| Fault I    | 90 m                          | 400 m  |

| Fault II   | 90 m                          | 360 m  |

| Fault III  | 100 m                         | 37.37  |

| Fault IV   | 140 m                         | 350 m  |

Au: Pls. cite Fig. 27 in the text.

384

385

386

387

388

389

390

391

392

393

394

396

Fig. 27. if-then construct implemented in the VHDL-AMS model for Type III faults.

Fig. 28. If-then construct implemented in the VHDL-AMS model for Type IV faults.

for 5 ms with 10  $\mu$ s iteration steps. Table 2 shows the CPU time spent for each case with the different approaches.

As can be seen from the table there is an average 4.4 times speed-up for Fault I, Fault II cases. The speed-up for the Type III faults between the behavioral and the transistor level simulations is 373.7 times.

The reason why the behavioral model is so much faster than the transistor level for Type III faults is that Type III faults are open drain faults and HSPICE struggles with an incompletely defined circuit. Finally the speed-up for Type IV faults is around 2.5 times. The behavioral model for Type IV faults is relatively slow compared to other behavioral models due to evaluation of the if-then construct required in the procedural statement (Fig. 28) to model the Type IV faults.

## 7. Conclusions

Capturing circuit behavior under faulty conditions at a 400 higher level using mathematical equations (behavioral 401 modeling) is somewhat simpler than the macromodel 402 approach.

Analog fault simulation is a key factor in 404 analog/mixed-signal test generation. Currently such 405 fault simulation is of limited use due to the speed of 406 analog simulation and the large number of faults to 407 be simulated. Simulation can be speeded up by using 408 number of techniques. Behavioral modelling is one of 409 those techniques. We have shown in this paper how one 410 can increase analog fault simulation speed by using be- 411 havioral models. We have used VHDL-AMS for the 412 behavioral modelling. It is clear that as VHDL-AMS 413 simulators become more powerful it will be easier to 414 model analog/mixed-signal circuits at a higher level so 415 as to speed-up simulation in general and analog fault 416 simulation in particular.

# References

1. A.J. Perkins, M. Zwolinski, C.D. Chalk, and B.R. Wilkins, 419 "Fault modeling and simulation using VHDL-AMS." Analog In- 420 Au: Pls. tegrated Circuits and Signal Processing, vol. 16, pp. 141-155, 421 verify pp. 53-67, 1998.

2. M. Abramovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design, IEEE Press, 1990.

- 3. www.eda.org/analog

- 4. http://www.hamster-ams.com/

- 5. C.-Y. Pan and K.-T. Cheng, "Fault macro modeling for 427 analog/mixed-signal circuits," in IEEE International Test Conference, ITC'97, 1997, pp. 913-922.

- 6. G. Casinovi and A. Sangiovanni-Vincentelli, "A macromodeling algorithm for analog circuits." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 10, no. 2, pp. 150-160, 1991.

- 7. B. Perez et al., "A new nonlinear time-domain op-amp macromodel using threshold functions and digitally controlled network elements." IEEE Journal of Solid-State Circuits, vol. 23, no. 4, 436 pp. 959-971, 1988.

- 8. G.A. Boyle, D.O. Pederson, B.M. Cohn, and J.E. Solomon, 438 "Macromodeling of integrated circuit operational amplifiers." IEEE J. of Solid State Circuits, vol. SC-9, pp. 353–363, 1974.

- 9. M.E. Brinson and D.J. Faulkner, "Modular SPICE macromodel for operational amplifiers." IEE Proc.- Circuits Devices Syst., vol. 141, no. 5, pp. 417-420, 1994.

- 10. Y.-J. Chang et al., "A behavior-level fault model for the closed-444 loop operational amplifier." Journal of Information Science and 445 Engineering, vol. 16, no. 5, pp. 751-766, 2000. 446

455

456

457

458

459

460

464

465

466

467

468

469

470

471

473

474

475

476

477

478

479

480

481

482

483

487

488

489

Au:

Pls.

verify Journal 472

Name

#### 190 Kiliç and Zwoliński

- 447 11. C. Chalk and M. Zwolinski, "Macromodel of CMOS opera-448 tional amplifier including supply current variation." Electronics 449 Letters, vol. 31, pp. 1398-1400, 1995.

- 12. P. Mandal and V. Visvanathan, "Macromodeling of the AC char-450 451 acteristics of CMOS op-amps," in IEEE 1993 Conference on 452 Computer Aided Design, Digest of Technical Papers, 1993, pp. 453 334-339.

- 13. M.E. Brinson and D.J. Faulkner, "A SPICE noise macromodel for operational amplifiers." IEEE Transactions on Circuits and Systems-I: Fundamental Theory and Applications, vol. 42, no. 3, pp. 166-168, 1995.

- 14. G. Krajewska and F.E. Holmes, "Macromodeling of FET/bipolar operational amplifiers." IEEE Journal of Solid-State Circuits, vol. SC-14, no. 6, pp. 1083-1087, 1979.

- 461 15. C. Turchetti and G. Masetti, "A macromodel for integrated all-462 MOS operational amplifiers." IEEE Journal of Solid-State Cir-463 cuits, vol. SC-18, pp. 389-394, 1983.

- 16. M.E. Brinson and D.J. Faulkner, "SPICE macromodel for operational amplifier power supply current sensing." Electronics Letters, vol. 30, no. 23, pp. 166-168, 1994.

- 17. R.V. Peic, "Simple and accurate nonlinear macromodel for operational amplifiers." IEEE Journal of Solid-State Circuits, vol. 26, no. 6, pp. 896-899, 1991.

- 18. B. Al-Hashimi, "Behavioural simulation of filters." IEE Colloquium on Analogue Simulation: The Dream & The Nightmare, pp. 51-55, 1995.

- 19. A.I. Kayssi and K.A. Sakallah, "Macromodel simplification using dimensional analysis," in 1994 Int. Symp. on Circuits and Systems, 1994, pp. 335-338.

- 20. M. Zwolinski, Z.R. Yang, and T.J. Kazmierski, "Using robust adaptive mixing for statistical fault macromodelling." IEE Proceedings: Circuits, Devices and Systems, vol. 147, no. 5, pp. 265-270, 2000.

- 21. G. Casinovi, "Multi-level simulation of large analog systems containing behavioral models." IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 13, no. 11, pp. 1391–1399, 1994.

- 484 22. E. Bruls et al., "Analogue fault simulation in standard VHDL." 485 IEE Proc. Circuits Devices Syst., vol. 143, no. 6, pp. 380-385, 486 1996

- 23. C.G. Broyden et al., "A class of methods for solving nonlinear simultaneous equations," Mathematics of Computation, vol. 19, no. 92, pp. 577-593, 1965.

- 490 24. http://www.ee.washington.edu/mad/benchmarks/benchmarks. 491 html

- 492 25. E. Christen and K. Bakalar, "VHDL-AMS, A hardware descrip-493 tion language for analog applications." IEEE Transactions on 494 Circuits and Systems-II: Analog and Digital Signal Processing, 495 vol. 46. no. 10, pp. 1263-1272, 1999.

- 496 26. VHDL Language Reference Manual, IEEE Standard 1076-497 1993.

- 498 27. Standard Description Language Based on the Verilog<sup>TM</sup> 499 Hardware Description Language, IEEE Standard 1364-**500** 1995.

- 501 28. www.mentor.com

- 502 29. www.cadence.com

- 503 30. www.verilog.com

- 31. www.analogy.com

- 505 32. www.ednmag.com

33. Y. Kilic, "Testing techniques and fault simulation for analogue 506 CMOS integrated circuits." University of Southampton, PhD 507 Thesis, Chapter 6, 2001.

508

Yavuz Kılıç gained his B.Sc. (Hons) (electronics and 509 telecommunications), M.Sc. (microelectronics) from 510 Yıldız Technical University of Istanbul (Turkey), and 511 Ph.D. from the University of Southampton (UK) in 512 1994, 1996, and 2001, respectively. He is currently with 513 Allegro MicroSystems Europe Ltd., Scotland (UK) as 514 a senior design engineer. Prior to this, he has held po- 515 sitions with Cyan Technology, Cambridgeshire (UK) 516 and Philips Semiconductors, Southampton (UK) as a 517 design engineer, and at the University of Southamp- 518 ton (UK) and Yıldız Technical University (Turkey) 519 as a Research Assistant. His current interests include 520 mixed-signal CMOS/BiCMOS integrated circuit de- 521 sign, simulation, test, and power management related 522 IC design. He is a member of the IEEE Circuits and 523 Systems Society.

524

534

Mark Zwolinski received the B.Sc. and Ph.D. 525 degrees in electronics from the University of 526 Southampton, UK, in 1982 and 1986, respectively. He 527 is a Senior Lecturer in the Department of Electron- 528 ics and Computer Science, University of Southampton, 529 UK. His research interests include behavioral synthe- 530 sis, design for test, fault simulation and VHDL. He is 531 chair of the IEEE DATC subcommittee on fault simu- 532 lation. He has co-authored about 100 research papers 533 in technical journals and conferences.