# Analysis of Noise Coupling From a Power Distribution Network to Signal Traces in High-Speed Multilayer Printed Circuit Boards

Jingook Kim, *Student*, *IEEE*, Mihai D. Rotaru, *Member*, *IEEE*, Seungyong Baek, Jongbae Park, Mahadevan K. Iyer, *Senior Member*, *IEEE*, and Joungho Kim, *Member*, *IEEE*

Abstract—As layout density increases in highly integrated multilayer printed circuit boards (PCBs), the noise that exists in the power distribution network (PDN) is increasingly coupled to the signal traces, and precise modeling to describe the coupling phenomenon becomes necessary. This paper presents a model to describe noise coupling between the power/ground planes and signal traces in multilayer systems. An analytical model for the coupling has been successfully derived, and the coupling mechanism was rigorously analyzed and clarified. Wave equations for a signal trace with power/ground noise were solved by imposing boundary conditions. Measurements in both the frequency and time domains have been conducted to confirm the validity of the proposed model.

Index Terms—Analytical modeling, coupling measurement, electromagnetic coupling, power distribution network (PDN), power/ground, scattering, switching noise.

#### I. INTRODUCTION

N today's digital systems, on-chip and off-chip (chip-to-local) clock frequencies are increasing rapidly and are expected to exceed 10 GHz by 2010 [1]. In addition, the supply voltage is scaled down to less than 1 V, and the power dissipation increased to hundreds of watts. These technology trends result in significant simultaneous switching noise (SSN), which is proportional to the switching current magnitude and operating frequency. The noise is primarily generated by high-speed digital processors and is coupled through the power distribution network (PDN), resulting in significant jitter for phase-locked loops (PLL) and phase noise for the RF oscillator, resulting in reduction in the timing margin and the noise margin, and in degradation of the bit error rate (BER) [2].

The noise in a PDN is likely to be increasingly coupled to signal traces as the layout density of the digital circuits increases in highly integrated multilayer structures of packages and printed circuit boards (PCBs). Many signal traces may

Manuscript received March 3, 2005; revised January 2, 2006.

Jingook Kim, S. Baek, and J. Park are with the Terahertz Interconnection and Package Laboratory, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Korea (e-mail: teralab@ee.kaist.ac.kr).

M. D. Rotaru is with the Institute of Microelectronics (IME), Singapore (e-mail: mihai@ime.a-star.edu.sg).

M. K. Iyer is with the Georgia Institute of Technology, Atlanta, GA, 30332 USA (e-mail: mahadevan.iyer@ece.gatech.edu).

Joungho Kim is with the Terahertz Interconnection and Package Laboratory, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Daejon 305-701, Korea. He is also a Visiting Consultant for Automobile EMI/EMC design of Hyundai Motors, Inc., Hwaseong, Kyungki-do, Korea.

Digital Object Identifier 10.1109/TEMC.2006.873865

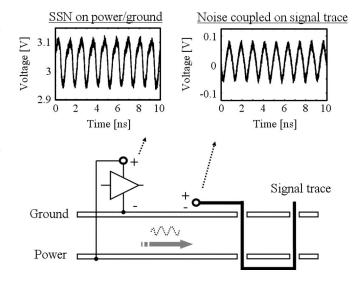

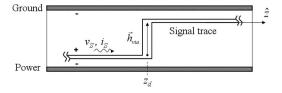

Fig. 1. SSN induced by a digital chip and the noise coupled on a signal trace. SSN can be coupled to nearby signal traces.

be routed, including layer transitions through vias, and some power/ground planes are partitioned into several island planes in highly integrated systems. Simultaneously, the increasing speed of the signal requires tighter noise margins and stricter signal integrity. Therefore, the coupling of the power/ground noise to signal traces causes problems for signal quality and timing and ultimately degrades the high-speed performance. It has been demonstrated, by an experiment shown in Fig. 1, that SSN induced by a digital chip mounted on a multilayer PCB is closely coupled to nearby signal traces and the characteristics of the noise coupling depend on the operating frequency. Therefore, a precise modeling technique to describe the coupling phenomenon is becoming necessary.

There have been related studies to investigate switching noise coupling to signal traces [3]–[9]. A simplified laboratory experiment has been designed to demonstrate noise generated by simultaneously switching circuits on a multireference plane package with vias [3]. Measurements of various switching events have been described and an analytical full-wave solution has been presented and applied to the laboratory experiment. Numerical approaches have also been used to investigate signal via coupling to power/ground planes [4] and power plane noise coupling to signal trace with via transition [5]. Measurements have been made on an experimental board, and numerical modeling has been used to study the electromagnetic interference

resulting from the signal transitions through a dc power bus. In addition, a circuit model has been proposed to describe the effects of switching noise on a signal trace [6]. The combination of circuit models with a current multiplier technique facilitates the simultaneous simulation of coupled signal transmission and power supply switching noise.

To date, in most studies, the whole structure, including both the PDN and signal trace, has been considered to determine how strongly the switching noise is coupled to the signal trace. If factors and mechanisms associated with the coupling are revealed and it is known where and when the dominant coupling occurs, the PDN and signal traces can be analyzed separately and the estimation of coupling strength will be much simpler. In this paper, the authors derive analytical solutions to describe the coupling of switching noise from PDN to the signal traces in multilayer PCBs. A wave equation for the signal trace affected by the electromagnetic field of the switching noise has been derived and solved, with boundary conditions for the case of a signal trace terminated with arbitrary impedance. The closed-form solutions can yield the coupled noise simply and quickly, whereas numerical approaches are time consuming and complex. Measurements in both the frequency and time domains have been conducted to confirm the validity of the proposed model.

## II. MECHANISM OF NOISE COUPLING FROM POWER/GROUND PLANES TO SIGNAL TRACES

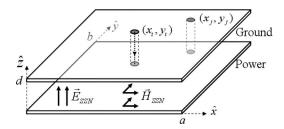

Today's PDNs in multilayer PCBs are typically planar structures that provide planar capacitance for a stable PDN and, simultaneously, an enhanced RF return path for digital signals. Switching currents induce SSN in such a PDN. The SSN propagates as an electromagnetic field, which is confined in the region between planes at frequencies above 10 MHz because the skin depth is thinner than the usual PDN copper planes. The basic equation describing the electromagnetic fields induced by SSN in the planar structure is the two-dimensional (2-D) wave equation (Helmholtz equation) [10], [11]. The field characteristics are independent of the dc potential of the planes and are obtained as a solution of the Helmholtz equation with given boundary conditions. When the spacing between the planes is much smaller than the wavelength and the spacing material is homogeneous and isotropic, the electromagnetic fields are constant along a path normal to the planes. Therefore, the electric field only has a normal component to the planes, whereas the magnetic field only has a tangential component. Fig. 2 shows a pair of rectangular planes of size  $a \times b$  separated by a short distance d. Injection of a current  $I_s$  into a port at  $(x_i, y_i)$  induces an electromagnetic field between the two planes at  $(x_i, y_i)$ , as shown by (1) and (2), assuming that the port sizes are sufficiently small. When there are many switching current sources, the field distribution is obtained by superposing the solutions of the equations from each source:

$$\vec{E}_{SSN} = \hat{z} \cdot \frac{j\omega\mu I_S}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_m^2 \varepsilon_n^2}{k_{mn}^2 - k^2} \cos \frac{m\pi x_i}{a} \times \cos \frac{n\pi y_i}{b} \cos \frac{m\pi x_j}{a} \cos \frac{n\pi y_j}{b}.$$

(1)

Fig. 2. Electromagnetic fields induced by SSN in a pair of rectangular planes.

$$\vec{H}_{SSN} = \hat{x} \cdot \frac{I_S}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_m^2 \varepsilon_n^2}{k_{mn}^2 - k^2} \frac{n\pi}{b} \cos \frac{m\pi x_i}{a}$$

$$\times \sin \frac{n\pi y_i}{b} \cos \frac{m\pi x_j}{a} \cos \frac{n\pi y_j}{b}$$

$$+ \hat{y} \cdot \frac{I_S}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_m^2 \varepsilon_n^2}{k_{mn}^2 - k^2} \frac{-m\pi}{a} \sin \frac{m\pi x_i}{a}$$

$$\times \cos \frac{n\pi y_i}{b} \cos \frac{m\pi x_j}{a} \cos \frac{n\pi y_j}{b}$$

(2)

where  $k=k'-jk'', k'=\omega\sqrt{\mu\varepsilon}$  and  $k''=\omega\sqrt{\mu\varepsilon}(\tan\delta/2+r/2d), k_{mn}^2=(m\pi/a)^2+(n\pi/b)^2$  (m and n are the propagating modes;  $\mu,\varepsilon$ , and  $\tan\delta$  are the permeability, permittivity, and the loss tangent of the dielectric material, respectively;  $r=\sqrt{2/(\omega\mu\sigma)}$ , where  $\sigma$  is the conductivity of the metallization layer), and  $\varepsilon_m,\varepsilon_n=1$  for m,n=0, and  $\sqrt{2}$ , otherwise. The maximum value used for both m and n is 20, as this is adequate to accurately estimate the distribution of the electromagnetic field.

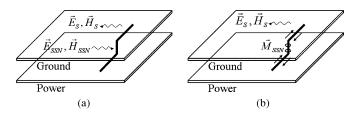

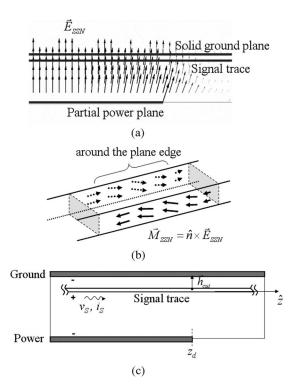

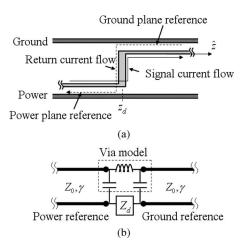

If a signal trace is routed in a multilayer PCB structure, the electromagnetic field induced by the SSN in the planar PDN is scattered by the presence of the signal trace, as shown in Fig. 3(a).  $E_{\rm SSN}$  and  $H_{\rm SSN}$  represent, respectively, the electric and magnetic fields between the planes of the PDN in the absence of the signal trace. From the induction equivalent theorem [12], the scattered field  $(E_S, H_S)$  due to a signal trace can be computed by placing equivalent current densities  $J_{\rm SSN}$  and  $M_{\rm SSN}$  along the boundary of the signal trace such that

$$\mathbf{J}_{SSN} = -\hat{n} \times \mathbf{H}_{SSN}, \mathbf{M}_{SSN} = \hat{n} \times \mathbf{E}_{SSN}$$

(3)

where  $\hat{n}$  is an outward-oriented unit normal vector from the surface of the trace. However, because an electric current element placed near an electric conductor does not radiate, the electric current density  $(J_{\rm SSN})$  is short circuited by the signal trace [12]. As a result, the scattered field is excited only by the equivalent magnetic current density  $(M_{\rm SSN})$  on the boundary of the signal trace, and the equivalent problem reduces to that of Fig. 3(b).

To determine the scattered field in Fig. 3(b), we classified the behavior of the scattered field according to the structure of signal traces. Signal traces consist of microstrip/strip lines as parallel routes to planes of the PDN and vias as vertical routes to the planes. Behavior of the scattered field at a via structure is different from that at a microstrip/strip line, because the pattern of the magnetic current source  $(M_{\rm SSN})$  is different. In addition, the electromagnetic field induced by the SSN creates another

Fig. 3. (a) Original fields  $(E_{\rm SSN}, H_{\rm SSN})$  and the scattered fields  $(E_{\rm S}, H_{\rm S})$  by the presence of a signal trace. (b) Induction equivalent problem of (a).

Fig. 4. (a) Induced equivalent current densities along the surface of a signal trace. (b) Propagation of TEM wave along a signal trace excited by the current densities.

pattern of current density at a strip line when a part of the reference planes is removed. The behavior of the scattered field is rigorously analyzed in Sections II-A and B.

## A. Behavior of Scattered Field at a Strip Line and at a Via Transition

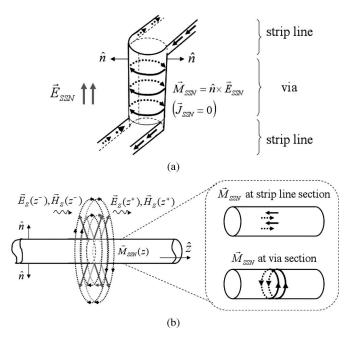

The equivalent magnetic current densities along the surfaces of a via transition and a strip line are obtained from the electric field of the SSN using (3). Fig. 4(a) shows patterns of the magnetic current at the two structures. Current densities exist with opposite directions at both sides of a strip line, but they turn around a via structure. The current densities create scattered fields, which propagate along the trace or radiate outward from the trace.

The dominant mode of a propagating wave along a strip/microstrip line is the transverse electromagnetic (TEM)/quasi-TEM mode, to which the electric field is normal and the magnetic field is concentric with the signal trace. Boundary conditions for the propagating TEM wave are given as (4) and (5) along the trace. The transverse electric field  $\boldsymbol{E}_{S}(z)$  is discontinuous by the magnetic current density  $\boldsymbol{M}_{\mathrm{SSN}}(z)$ , whereas

Fig. 5. Structure of layer transition through a via. A signal trace changes layers at the location of " $z_d$ ."

the transverse magnetic field  $H_S(z)$  is continuous:

$$(\boldsymbol{E}_{S}(z^{+}) - \boldsymbol{E}_{S}(z^{-})) \times \hat{z} = \boldsymbol{M}_{SSN}(z). \tag{4}$$

$$\hat{z} \times (\boldsymbol{H}_S(z^+) - \boldsymbol{H}_S(z^-)) = J_{SSN}(z) = 0.$$

(5)

Fig. 4(b) illustrates the TEM wave propagation along a signal trace and a magnetic current density induced by the SSN. If a current density creates TEM wave mode, a major part of the scattered field is transmitted through the signal trace, as the structure of a signal trace is an excellent waveguide. Considering the direction of the vector on the left with that of the vector on the right in (4), it is found that current densities for a strip line cannot act as sources for the dominant propagating wave mode (TEM), whereas current densities at a via transition do act as the sources. In other words, the field scattered from a via transition propagates well along the trace as a TEM mode, but the field scattered from a strip line cannot propagate along the signal trace and spread out between the planes. In addition, the amount of the spreading scattered field from a strip line is very small, because the opposing current densities at both sides of the strip line cancel each other.

Propagation of the field scattered from a via transition can be understood by constructing boundary conditions. Combining (3) and (4) results in the voltage wave propagating along the signal trace going through an abrupt change equal to the voltage produced at the via by SSN. However, the current wave is continuous, as (5) describes a continuous transverse magnetic field. When a signal trace changes layers through a via transition at location  $z_d$ , as shown in Fig. 5, the boundary conditions for voltage and current at the via location are described by (6) and (7), where  $h_{\rm via}$  represents the vector along the via transition. The electric field of SSN only at the location of the via appears in the equations, and the SSN field at the strip line does not affect and does not create wave propagation along the signal trace:

$$v_S(z_d^-) + \mathbf{E}_{SSN} \cdot \mathbf{h}_{via} = v_S(z_d^+).$$

(6)

$$i_S(z_d^-) = i_S(z_d^+).$$

(7)

As for microstrip lines routed outside of plane pairs, the traces are basically not affected by the electromagnetic field between the planes, because the skin depth is usually thinner than the copper. The boundary conditions at a via transition are given in the same way when a microstrip line penetrates the planes to change layers. Thus, the coupling physics of SSN in the microstrip lines is the same as that in the strip lines. In addition, it is known that the RF return path is discontinuous at a signal

Fig. 6. Stripline structure where a part of power plane is removed. (a) Spatial electric field at 1.5 GHz captured in a full-wave simulator (HFSS). (b) Equivalent magnetic current density on the trace surface around the partial plane edge. (c) Structure used to find the boundary conditions for signal propagation at the plane edge.

transition to an alternating routing plane through a via before and after the via jump. Also, the via transition has both a capacitive and an inductive component. If the return path discontinuity and the capacitive and inductive components are taken into account, the boundary conditions above are modified, as described in Section IV-C.

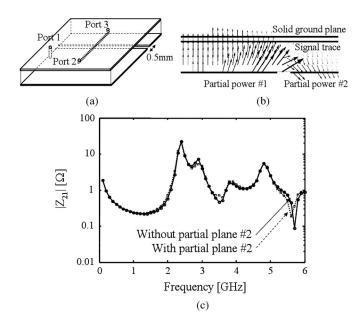

# B. Behavior of Scattered Field at a Strip Line on a Partial Plane Edge

Removal of a part of a power plane is another case in which the electromagnetic field on the PDN can excite a wave propagating along a signal trace. Fig. 6 shows the case where a part of the power plane is removed for some reason. Fig. 6(a) is an illustration of the spatial electric field at 1.5 GHz captured in a full-wave simulator. The simulator describes the direction and strength of the electromagnetic field, using arrows. The length of an arrow represents the field strength at the start point of the arrow. It is found that a fringing field occurs around the plane edge and the field has a longitudinal component to the signal trace. This results in equivalent magnetic current densities, as shown in Fig. 6(b). The current densities around the plane edge induce discontinuities in the electric field  $E_S(z)$  of (4) and excite a wave propagation along the signal trace.

Therefore, similar to the case of a via transition, the voltage wave propagating along the signal trace undergoes a change at the edge of the partial plane. The discontinuity is caused by the reduced electric field of SSN between the signal trace and the

Fig. 7. Boundary conditions for a signal trace under the field of the SSN.  $V_{d1}$ ,  $V_{d2}$ , and  $V_{d3}$  represent all the discontinuities in the voltage wave induced by the electric field of the SSN.

solid plane at the edge, and the boundary conditions at the partial plane edge for signal transmission are given by (8) and (9) for the structure of Fig. 6(c), where  $h_{\rm cut}$  represents the vector from the signal trace to the solid plane:

$$v_S(z_d^-) + \mathbf{E}_{SSN} \cdot \mathbf{h}_{cut} = v_S(z_d^+). \tag{8}$$

$$i_S(z_d^-) = i_S(z_d^+).$$

(9)

The boundary conditions (6)–(9) have the same form, and it is thus implicit that the propagation of the scattered field from a via transition and that from a partial plane edge have the same basic mechanism and that both can be solved using the same method.

## III. ANALYTICAL SOLUTIONS FOR NOISE COUPLING FROM POWER/GROUND PLANES TO SIGNAL TRACES

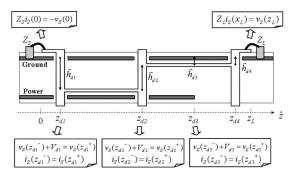

The noise in PDN excites the propagation of the scattered field along a signal trace through the specified structures, and the voltage wave on the signal trace induced by the SSN is the undesired coupled noise voltage. Fig. 7 illustrates an example of a signal trace including three via transitions and a partial power plane. The wave equation for signal transmission along with the boundary conditions of (10) completes the description of propagation of the coupled noise voltage. The symbols  $z_{d1}, z_{d2}, z_{d3}$ , and  $z_{d4}$  represent the locations of the vias and the plane edge.  $V_{d1}, V_{d2}, V_{d3}$ , and  $V_{d4}$  represent all discontinuities in the voltage wave induced by the electric field of the SSN; each value is given in (11). The voltage is simply the multiplication of the electric field and the distance, because the electric field is constant along the path normal to the planes.  $Z_S$  and  $Z_L$  represent the impedance of the source resistor and the load, respectively. Reflection may occur at both terminations of trace if there is impedance mismatching between  $Z_S, Z_L$ , and the trace characteristic impedance. The setup is intended to analyze the propagation of SSN coupling wave along the signal trace, including reflections at the source and at the load end:

$$Z_S i_S(0) = -v_S(0)$$

$$v_S(z_{d1}^-) + V_{d1} = v_S(z_{d1}^+), \quad i_S(z_{d1}^-) = i_S(z_{d1}^+)$$

$$v_S(z_{d2}^-) + V_{d2} = v_S(z_{d2}^+), \quad i_S(z_{d2}^-) = i_S(z_{d2}^+).$$

$$v_{S}(z_{d3}^{-}) + V_{d3} = v_{S}(z_{d3}^{+}), \quad i_{S}(z_{d3}^{-}) = i_{S}(z_{d3}^{+})$$

$$v_{S}(z_{d4}^{-}) + V_{d4} = v_{S}(z_{d4}^{+}), \quad i_{S}(z_{d4}^{-}) = i_{S}(z_{d4}^{+})$$

$$Z_{L}i_{S}(z_{L}) = v_{S}(z_{L}) \qquad (10)$$

$$V_{dn} = \mathbf{E}_{SSN} \cdot \mathbf{h}_{dn}, \quad n = 1, 2, 3, \text{ and } 4. \quad (11)$$

The right side via is outside of the pair of planes by the partial power plane, and there is no electric field of the SSN on the via, so the SSN does not create a discontinuity in signal propagation, and thus boundary conditions at the via are unnecessary. Also, the current wave is proportional to the derivative of the voltage wave from Maxwell equations; therefore, the boundary conditions (10) can be rewritten using only voltage terms as

$$v'_{S}(0) = \gamma Z_{0} Y_{S} v_{S}(0)$$

$$v_{S}(z_{d1}^{-}) + V_{d1} = v_{S}(z_{d1}^{+}), \quad v'_{S}(z_{d1}^{-}) = v'_{S}(z_{d1}^{+})$$

$$v_{S}(z_{d2}^{-}) + V_{d2} = v_{S}(z_{d2}^{+}), \quad v'_{S}(z_{d2}^{-}) = v'_{S}(z_{d2}^{+})$$

$$v_{S}(z_{d3}^{-}) + V_{d3} = v_{S}(z_{d3}^{+}), \quad v'_{S}(z_{d3}^{-}) = v'_{S}(z_{d3}^{+})$$

$$v'_{S}(z_{L}) = -\gamma Z_{0} Y_{L} v_{S}(z_{L}). \tag{12}$$

Here,  $Y_S$  and  $Y_L$  are, respectively, the admittances of the source resistor and the load;  $Z_0$  and  $\gamma$  are the characteristic impedance and the propagation constant for a signal transmission, respectively. The notation  $\prime$  means derivative.

The equations describing the voltage propagation along the signal trace are the solution of the wave equation with the above boundary conditions (12). To simplify the solution, the boundary conditions were separated into three cases, each of which considered only one of the discontinuities. Equation (13) shows boundary conditions for the n th case (n=1,2, and 3); then, the solution with all boundary conditions (12) is equal to the sum of solutions for the three cases, as shown in (14). Equation (14) has the physical implication that the coupled noise voltage on a signal trace is the sum of the coupling components, which are the couplings from via transitions or plane edges:

$$v'_{S,dn}(0) = \gamma Z_0 Y_S v_{S,dn}(0)$$

$$v_{S,dn}(z_{dn}^-) + V_{dn} = v_{S,dn}(z_{dn}^+), \quad v'_{S,dn}(z_{dn}^-) = v'_{S,dn}(z_{dn}^+)$$

$$v'_{S,dn}(z_L) = -\gamma Z_0 Y_L v_{S,dn}(z_L). \tag{13}$$

$$v_S(z) = \sum_{n=1}^{3} v_{S,dn}(z).$$

(14)

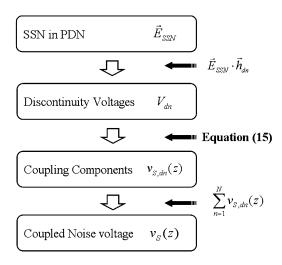

The next step was to obtain the solution for each coupling component with its boundary conditions (13). We have successfully determined the solution in closed forms in (15). Finally, the overall procedure to compute the coupled SSN voltage on a signal trace is summarized in Fig. 8:

$$v_{S,dn}(z) = A \cosh \gamma z + B \sinh \gamma z \quad (0 \le z < z_{dn})$$

$$C \cosh \gamma z + D \sinh \gamma z \quad (z_{dn} \le z < z_L) \tag{15}$$

$$A = \frac{V_{dn} \sinh \gamma (z_{dn} - z_L) - Z_0 Y_L V_{dn} \cosh \gamma (z_{dn} - z_L)}{\Delta}$$

$$B = Z_0 Y_S A$$

Fig. 8. Overall procedure for computing the coupled noise voltage on a signal trace. N is the total number of discontinuities in the signal voltage.

$$C = A + V_{dn} \cosh \gamma z_{dn}$$

$$D = B - V_{dn} \sinh \gamma z_{dn}$$

$$\Delta = Z_0 (Y_S + Y_L) \cosh \gamma z_L + \sinh \gamma z_L$$

$$+ Z_0^2 Y_S Y_L \sinh \gamma z_L.$$

## IV. CORRELATION BETWEEN MODEL AND MEASUREMENT IN THE FREQUENCY DOMAIN

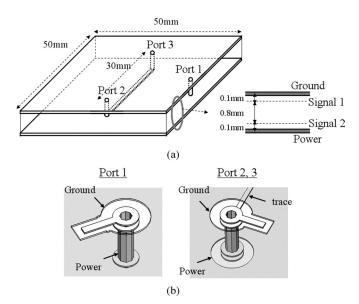

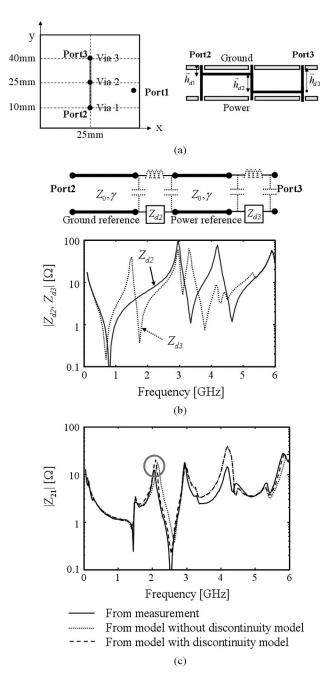

Test vehicles were designed, fabricated, and S-parameter measurements performed in the frequency domain to verify the analytical model presented in the previous section. Fig. 9 illustrates the layout of a test vehicle and the pad structures. The test vehicle consists of four layers with dimensions of  $50 \times 50$  mm. FR4 was used as dielectric material with permittivity of  $\varepsilon_{\rm r}=4.1$ and loss tangent of tan  $\delta = 0.03$ . A signal trace with 0.1-mm width and 18  $\mu$ m thickness exists on inner layers between the power plane and the ground plane. Signal layer 1 is close to the ground plane and layer 2 is close to the power plane, respectively, and the power plane is floated, as the phenomenon of noise coupling is independent of the dc potential. The characteristic impedance of the trace is approximately 50  $\Omega$  in this geometry. Port 1 is connected between the power/ground planes, and port 2 is connected between the signal trace and the ground plane. The measurement is conducted by a G-S-G probe tip in which the space between ground tip and signal tip is 250  $\mu$ m. The S-parameters were measured from 50 MHz to 6 GHz and the impedance parameters extracted.

Using (1) to describe the electric field between planes induced by a switching current at port 1, the noise voltage coupled on the signal trace is computed from the proposed coupling model (Fig. 8). The characteristic impedance  $Z_0$  and the propagation constant  $\gamma$  of the signal trace which are necessary in (15) were extracted from a two-port measurement of the signal trace [13]. We define the z-axis along the signal trace and its origin at the location of port 2; then,  $v_S(0)$  and  $v_S(z_L)$  in (14) are the

Fig. 9. Test vehicle for frequency domain measurements. (a) Layout and cross section. (b) Structures of ports with probing pads.

Fig. 10. Correlation between the model and measurement: (a) Location and cross section of a signal trace with open terminations. (b) Transfer impedances from measurement and the coupling model. The magnitudes of impedance are large at frequencies of plane resonance.

coupled voltage on the signal trace at port 2 and port 3, respectively. Then, we calculate the ratio of the noise voltage coupled on a signal termination  $(V_{\rm port2}, V_{\rm port3})$  to the switching current between planes  $(I_{\rm port1})$ . The ratio is independent of the switching current because the coupled voltage is proportional to the current, and its unit is impedance.

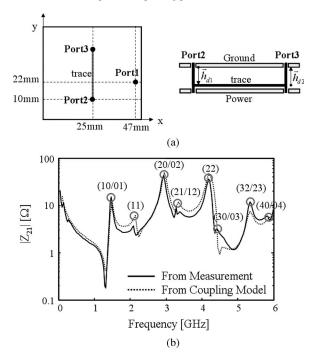

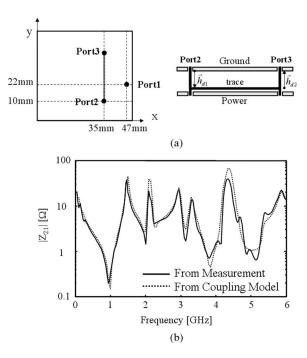

We compare it with the measured transfer impedances  $(Z_{21}, Z_{31})$  between two ports for a test vehicle. A test vehicle sketch is shown in Fig. 10(a), where a signal trace is located at the center of the board and has open terminations. Both these

Fig. 11. Transfer impedances for another location of the signal trace. (a) Location and cross section of a signal trace with open terminations. (b) Transfer impedances from measurement and the coupling model. The coupling characteristics are very dependent on the location of the signal trace.

terminations, however, are not ideally open (infinite resistance), but are given small capacitance by the fringing capacitance at ports. The fringing capacitance comes from the structure of the probe tips and probing pads, and its value was found to be about 200 fF, using a closed-form equation for capacitance between two wide conductors, which are connected together, and a center conductor [14]. Thus, we have considered the openload impedance as a capacitance of 200 fF. The measured and computed transfer impedances for the coupling model are plotted in Fig. 10(b). The impedance values calculated from the coupling model show very good agreement with the experimental values. The magnitude of the impedance is large at the frequencies of plane resonance, which means that a switching current will induce a large voltage that will couple to the signal trace. A switching current creates large noise voltages on the power/ground planes at the resonance frequencies, and the signal trace will suffer from the high-coupled noise voltage. The number of resonant modes is given by the peak values of the transfer impedance in Fig. 10(b).

#### A. Dependence of Noise Coupling on Trace Location and Termination

Fig. 11 shows the transfer impedances for another location of the signal trace with the same open terminations. Comparing Figs. 10 and 11, it can be seen that some of the resonant peaks have increased and others have decreased. The electromagnetic field of SSN on planes of PDN is a function of location and frequency, as shown in (1) and (2). Each resonant mode has its own spatial characteristics and the power/ground noise is strongly dependent on the location of the observation relative

Fig. 12. (a) Signal trace terminated with 56- $\Omega$  resistors. (b) Transfer impedances obtained from measurement and the coupling model.

to the location of the switching current. Therefore, the SSN coupling to a trace is also a function of the location of the signal trace, with dependence on frequency.

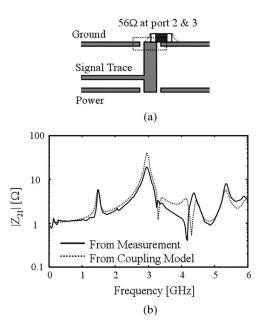

Also, we have investigated the dependence of the SSN coupling on trace terminations. Fig. 12 illustrates the transfer impedance obtained from measurements and the coupling model when the signal trace is located at the center and both ends are terminated with  $56\text{-}\Omega$  resistors. The termination condition of a trace also has a considerable effect on the coupling of the power/ground noise to the trace because the propagation of the SSN coupling wave along the trace depends on this condition. As shown in Fig. 12, the impedance decreases greatly at low frequency and some of the resonant peaks disappear, compared to the impedance measured or computed in the open-termination case (Fig. 10). We note that the proposed coupling model accurately models the effect of signal terminations.

## B. Effects of Via Layer Transitions With Return Current Discontinuity

When a signal trace changes layers with a via transition, the return path of the signal current is broken by a reference change unless both planes are at the same potential and are bonded together. The path of high-frequency return current is completed by displacement current, and the displacement current flows through the impedance between the pair of planes. In Fig. 13, the broken return current path has been simply modeled as impedance  $Z_d$  between the planes at the location of reference change [15], [16]. The impedance  $Z_d$  was computed using (1) and was added to the model of the signal trace. Also, the signal transition to an alternating routing plane through a via has both a capacitive and an inductive component, as shown in Fig. 13(b). However, impedance discontinuity from a broken return path is usually much larger than that from the capacitive and inductive components in a via structure to the range of a few

Fig. 13. (a) Structure of a trace changing its reference plane through a via transition. (b) Equivalent circuit model.

gigahertz [17]; therefore, the capacitive and inductive paths at a via transition are not the dominant factors in analyzing the characteristics of signal propagation along the transition.

If a changing field (the electromagnetic field produced by the SSN between the power/ground planes) is applied across the via transition, a current will start to flow through the power/ground impedance, and a voltage drop will appear between the via terminals. Therefore, the boundary condition at a via transition has to be modified to (16). A new term  $Z_d i_S(z_d^-)$ , representing the voltage drop produced by the via current, appears in the boundary conditions. The solution for the modified boundary conditions is given as a more complex form of.

$$v_{S}(z_{d}^{-}) - Z_{d} \cdot i_{S}(z_{d}^{-}) + \mathbf{E}_{SSN} \cdot \mathbf{h}_{via} = v_{S}(z_{d}^{+})$$

$$i_{S}(z_{d}^{-}) = i_{S}(z_{d}^{+}). \tag{16}$$

$$v_{S,dn}(z) = A \cosh \gamma z + B \sinh \gamma z \quad (0 \le z < z_{dn})$$

$$C \cosh \gamma z + D \sinh \gamma z \quad (z_{dn} \le z < z_{L}) \tag{17}$$

$$A = \frac{V_{dn} Z_{0} \sinh \gamma (z_{dn} - z_{L}) - Z_{0}^{2} Y_{L} V_{dn} \cosh \gamma (z_{dn} - z_{L})}{\Delta_{L} + \Delta}$$

$$B = Z_{0} Y_{S} A$$

$$C = A + \frac{Z_{dn}}{Z_{0}} \cosh \gamma z_{dn} (A \sinh \gamma z_{dn} + B \cosh \gamma z_{dn})$$

$$+ V_{dn} \cosh \gamma z_{dn}$$

$$D = B - \frac{Z_{dn}}{Z_{0}} \sinh \gamma z_{dn} (A \sinh \gamma z_{dn} + B \cosh \gamma z_{dn})$$

$$- V_{dn} \sinh \gamma z_{dn}$$

$$\Delta_{L} = Z_{dn} (\sinh \gamma (z_{L} - z_{dn}) + Z_{0} Y_{L} \cosh \gamma (z_{L} - z_{dn}))$$

$$\times (\sinh \gamma z_{dn} + Z_{0} Y_{S} \cosh \gamma z_{dn})$$

The effect of via transition including a return path discontinuity was investigated in the test vehicle shown in Fig. 14(a), where a signal trace changes layers between inner layer 1 and

$\Delta = Z_0^2 (Y_S + Y_L) \cosh \gamma z_L + Z_0 \sinh \gamma z_L + Z_0^3 Y_S Y_L \sinh \gamma z_L.$

Fig. 14. (a) Test vehicle of signal trace with an additional via transition at the center. (b) Equivalent circuit model including impedance discontinuities at reference path and the impedance plot at both broken return current paths. (c) Transfer impedances with and without considering the impedance of broken return current path.

inner layer 2 with through-hole vias. The reference changes occur at via 2 and via 3, and the power/ground impedances at the locations of the reference changes are added to the model of the trace. Fig. 14(b) shows the equivalent circuit model of the trace including impedance discontinuities at reference path and the impedance plot at each broken return current path. The impedances  $Z_{d2}$  and  $Z_{d3}$  were obtained using (1). The electromagnetic fields produced by the SSN between the power/ground planes are applied across the impedances, and the boundary conditions are given as (16).

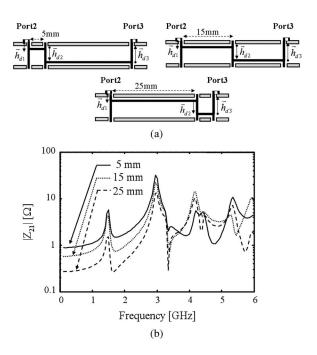

Fig. 15. (a) Cross-sectional view of a signal trace with three different via locations. (b) Calculated transfer impedance at three different locations of via transition. Impedance is smaller over most frequencies when two via transitions with opposite directions are located close to each other.

Fig. 14(c) compares the transfer impedances with and without considering the impedance of the broken return current path. Applying the broken current path impedance, the resonant frequency around 2 GHz shifts lower and is closer to the measured result. The trace length at about 2.3 GHz is half the wavelength, and a standing wave is generated in the trace with both open terminations. Including the impedances of the broken return current paths, the effective length of the signal trace gets longer, because the broken current path impedance is inductive near the resonance frequency. Therefore, the resonance frequency at which a standing wave is generated also shifts lower.

By comparing Fig. 14(c) with Fig. 10(b), it can be seen that the impedance profile changes significantly when using an additional via transition at the center. In the case of Fig. 14, there should be three coupling components at all via transitions and the sum of all coupling components is the total voltage coupled on the signal trace. The coupling component excited from the via transition at the center of planes profoundly interferes with the coupling components excited from both vias at the signal terminations. Therefore, if the location of the via transition shifts from the center to another position, the coupling characteristics also change. Fig. 15 shows the calculated transfer impedances when an additional transition via is at 5, 15, and 25 mm from port 2, and both ends of the signal trace are terminated with 56- $\Omega$  resistors. As two vias with opposite transitions  $(h_{d2}, h_{d3})$ get closer to each other, their coupling components are getting the same magnitudes and opposite polarities. The total coupling is the sum of all coupling components, so the coupling components from the two vias cancel each other in the total SSN coupling. Therefore, the noise voltage coupled on a signal trace is smaller at most frequencies when two via transitions with opposite directions are located close to each other.

Fig. 16. (a) Structure with a partial power plane. (b) Correlation between simulation results using a full-wave simulator and results calculated from the coupling model.

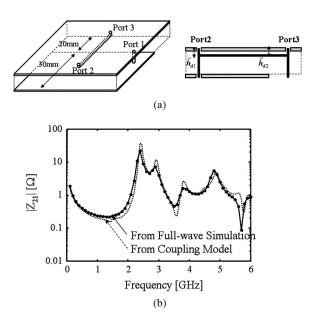

#### C. Effect of a Partial Plane

As described above, the noise signal excitation from a via transition or a partial plane edge have the same basic mechanism. Because of the absence of a fabricated test vehicle, the proposed coupling model for plane discontinuity has been verified by comparison with results obtained by simulation using a full-wave simulator (HFSS). The signal trace with open terminations is routed close to the solid plane to retain almost all the characteristics of the signal transmission in spite of the partial plane. The results obtained from the simulation and the results calculated from the coupling model are in very close agreement, as shown in Fig. 16.

Consider a more common case in which there is a partial plane next to another partial plane. Here, a significant fringing electric field occurs between two partial planes, as shown in Fig. 17. However, the field disappears eventually in the other partial plane, and the field difference between the solid plane and the signal trace still induces a voltage discontinuity in the signal transmission. Therefore, the transfer impedance of the noise coupling changes very little compared to the case without another partial plane, even if the field distribution is quite different. Fig. 17(c) shows the simulated transfer impedances for the two cases.

#### V. CORRELATION BETWEEN MODEL AND MEASUREMENT IN THE TIME DOMAIN

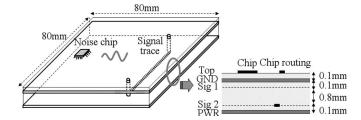

To investigate the correlation between the coupling model and measurements in the time domain another experiment was performed. Test vehicles consist of five-layer board  $80\times80$  mm, as shown in Fig. 18.

A chip that acts as a noise generator and its termination resistors are mounted on the top layer. The ground and power planes are the second and fifth layers, respectively, and the two

Fig. 17. (a) Structure with a partial plane next to another partial plane. (b) Distribution of the electric field. (c) Simulated transfer impedances with and without the second partial plane.

Fig. 18. Test vehicle for time-domain measurement consisting of five  $80 \text{ mm} \times 80 \text{ mm}$  layers. A noise chip and its termination resistors are attached on the top layer. Ground plane is the second layer and power plane is the fifth layer. The two inner layers are used for the routing of signal traces between the pair of planes.

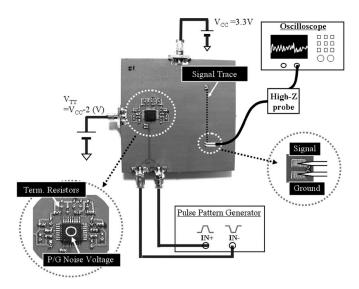

inner layers are used for routing signal traces between the pair of planes. A clock driver (CDCLVP110) is used to generate the power/ground noise. It distributes one differential clock input pair LVPECL/HSTL to ten differential LVPECL clock outputs, with an operating frequency range of dc to 3.5 GHz. The proper termination for a PECL output is 50  $\Omega$  to  $V_{\rm TT}$  ( $V_{\rm CC}$  –2 V). At this termination, both OUT+ and OUT—will typically be  $(V_{\rm CC}-1.3~{\rm V})$ , resulting in a dc flow of approximately 14 mA, and the overall output and internal supply current is approximately 370 mA. The experimental arrangement is shown in Fig. 19. Two dc sources provide the  $V_{\rm CC}$  of 3.3 V and  $V_{\rm TT}$  of 1.3 V, and a pulse pattern generator (Anritsu MP1763B) creates a pair of clock inputs with proper amplitude and dc bias. The oscilloscope (Tektronix TDS8000B) senses the noise voltage by means of a high-impedance probe. The noise voltage generated on the power/ground plane is captured directly under the noise chip, and the noise voltage coupled on the signal trace is detected on a termination pad of the signal trace.

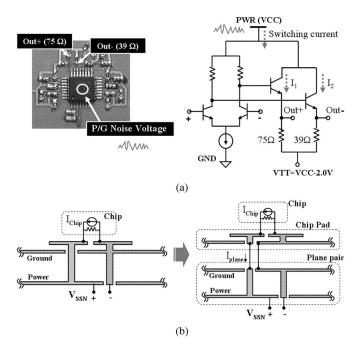

Fig. 20(a) shows a chip mounted on the top layer and the structure of a PECL output stage. Terminations for a differential PECL output were designed with two unbalanced resistors of

Fig. 19. Experimental arrangement for time-domain measurements. Two dc sources provide a  $V_{\rm CC}$  of 3.3 V and a  $V_{\rm TT}$  of 1.3 V, and a pulse pattern generator creates a pair of clock inputs with proper amplitude and dc bias. The oscilloscope senses the noise voltage by means of a high-impedance probe.

Fig. 20. (a) Structure of a PECL output stage with unbalanced terminations of 39 and 75  $\Omega$ . (b) Overall structure including the mounting pad and the plane pair.

39 and 75  $\Omega$  to increase the switching current. The mounting pads for the chip and the terminations have significant effects on the overall impedance of the PDN. Therefore, to compute an accurate overall transfer impedance describing the noise coupling from chip to signal traces, the impedance of the PDN in pads was obtained using a full wave simulator and was merged with the impedance of the plane pair, as shown in Fig. 20(b).

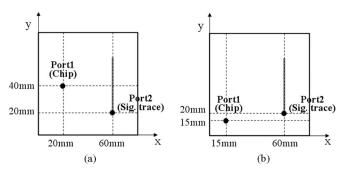

Fig. 21 shows the two different test vehicles used. The noise chip is located at (20 mm, 40 mm) on Case A [Fig. 2(a)], while it is located at (15 mm, 15 mm) on Case B [Fig. 2(b)]. Input

Fig. 21. Two different test vehicles. (a) Case A. The chip as a noise source is located at (20 mm, 40 mm). (b) Case B. The noise chip is located at (15 mm, 15 mm).

Fig. 22. Input impedances at port 1 and transfer impedances between ports 1 and 2. (a) Case A and (b) Case B.

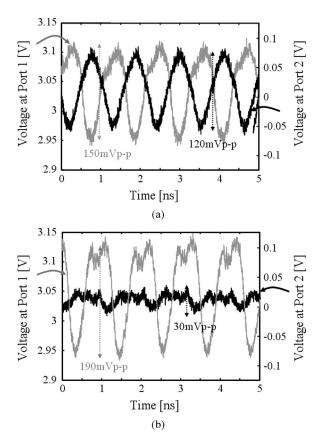

impedances at port 1 and transfer impedances between ports 1 and 2 are plotted together in Fig. 22(a) and (b), when both terminations of the victim trace are high impedance with the capacitance of 200 fF. Input impedances at port 1 were calculated from (1) along with the impedance of the mounting pad. Also, the flow of the switching current into the plane pair was calculated, and then, transfer impedances were calculated from the proposed coupling model. The first resonant peaks appear at 900 MHz in all impedance curves. Fig. 23 shows the voltages measured in the time domain, with the chip operating at a frequency of 900 MHz. We measured the voltage fluctuations at ports 1 and 2 in both the test vehicles. In Case A, shown in Fig. 23(a), the voltage fluctuation on the signal trace was 120 mVp-p, which is comparable with a fluctuation of

Fig. 23. Voltage fluctuations at ports 1 and 2 when the chip operates at 900 MHz. (a) Case A; the voltage fluctuation on the signal trace is comparable with the fluctuation on the power/ground plane. (b) Case B, the voltage fluctuation on signal trace is much smaller than the fluctuation on the power/ground plane.

150 mVp-p on the power/ground plane. However, it can be seen in Fig. 23(b) that the fluctuation on the signal trace is approximately 30 mVp-p, which is much smaller than that on the power/ground plane in Case B, which measured 190 mVp-p. These measured voltage fluctuations agree with the impedance profiles in Fig. 22. The impedance values at 900 MHz are comparable in Case A, whereas the transfer impedance is much smaller than input impedance in Case B. The voltage fluctuations depend mostly on the impedance at 900 MHz, because the impedance values at harmonics of 900 MHz are small enough.

Finally, the voltage fluctuation by coupling of the SSN is superposed on a signal driven by a transmitter. The SSN coupling on a trace may be significant, as shown in the measured waveforms, so it significantly reduces the voltage and the timing margin in the single-ended signaling. However, if the signaling uses the differential scheme, most SSN coupling can be ignored at the receiver (common-mode rejection). The differential signaling scheme is very immune to the SSN coupling.

#### VI. CONCLUSION

The switching noise induced by a digital chip can be closely coupled to nearby signal traces, and the characteristics of the noise coupling depend on the operating frequency. As the layout density increases in highly integrated structures, the noise in the power/ground networks becomes more coupled to the

signal traces, and a precise modeling methodology to describe the coupling phenomenon becomes necessary. In this paper, an analytical model of noise coupling from the power/ground network to signal traces in PCBs has been successfully derived. The physics associated with the noise coupling was investigated and the coupling mechanism was analyzed and clarified using the theorem of induction equivalent. It was found that noise coupling occurs at layer transitions through vias and at partial plane edges, and the sum of the coupling components makes up the total coupled voltage on the signal trace. Wave equations for the signal trace under the power/ground noise were solved by utilizing boundary conditions. The proposed model has been verified up to 6 GHz by comparison with experimental results, and various case studies were successfully completed in the frequency domain. Time-domain measurements have also been performed to confirm the validity of the proposed model.

As shown in this work through the coupling model, the analysis of the power/ground planes and signal layers can be done separately. Once the noise field between the power and the ground is known, the noise coupling to signal trace can be calculated using the analytical coupling model. Using this methodology, the estimation of the coupling noise is simplified, and the estimation time is significantly reduced. It is expected that the switching noise coupling to signal traces can ultimately be reduced by using the differential signaling scheme and by controlling the locations of signal terminations and discontinuities.

#### REFERENCES

- ITRS, "International Technology Roadmap for Semiconductor," 2003 ed. http://public.itrs.net/

- [2] M. Swaminathan, J. Kim, I. Novak, and J. P. Libous, "Power distribution networks for system-on-package: Status and challenges," *IEEE Trans. Adv. Packag.*, vol. 27, no. 2, pp. 286–300, May 2004.

- [3] S. G. Rosser, M. K. Kerr, C. S. Chang, J. Fang, Z. Chen, and Y. Chen, "Measurement and simulation of simultaneous switching noise in the multi-reference plane package," in *Proc. IEEE Electron. Compon. Tech*nol. Conf., May 28–31, 1996, pp. 660–670.

- [4] W. Cui, X. Ye, B. Archambeault, D. White, M. Li, and J. L. Drewniak, "EMI resulting from signal via transitions through the DC power bus," in *Proc. IEEE Int. Symp. EMC*, vol. 2, Aug. 21–25, 2000, pp. 821–826.

- Proc. IEEE Int. Symp. EMC, vol. 2, Aug. 21–25, 2000, pp. 821–826.

[5] J.-N. Hwang and T.-L. Wu, "Coupling of the ground bounce noise to the signal trace with via transition in partitioned power bus of PCB," in Proc. IEEE Int. Symp. EMC, vol. 2, Aug. 19–23, 2002, pp. 733–736.

- [6] Q. Qi, D. Quint, and T. Michalka, "Simulation of a coupled signal and power delivery system in an electronics package," in *Proc. 52nd IEEE Electron. Compon. Technol. Conf.*, May 28–31, 2002, pp. 311–318.

- [7] S. Chun, M. Swaminathan, L. Smith, J. Srinivasan, Z. Jin, and M. K. Iyer, "Modeling of simultaneous switching noise in high speed systems," *IEEE Trans. Adv. Packag.*, vol. 24, no. 2, pp. 132–142, May 2001.

- [8] S. Chun, J. Choi, S. Dalmia, W. Kim, and M. Swaminathan, "Capturing via effects in simultaneous switching noise simulation," in *Proc. IEEE Int. Symp. EMC*, vol. 2, Aug. 13–17, 2001, pp. 1221–1226.

- [9] J. C. Parker, Jr., "Via coupling within rectangular power-ground planes," in Proc. Topical meeting on Electrical Performance of Electronic Packaging, Oct. 2–4, 1995, pp. 61–63.

- [10] T. Okoshi, Planar Circuits for Microwaves and Lightwaves. Munich, Germany: Springer-Verlag, 1984.

- [11] N. Na, J. Choi, S. Chun, M. Swaminathan, and J. Srinivasan, "Modeling and transient simulation of planes in electronic packages," *IEEE Trans.* Adv. Packag., vol. 23, no. 3, pp. 340–352, Aug. 2000.

- [12] C. A. Balanis, Advanced Engineering Electromagnetics. New York: Wiley, 1989, pp. 334–338

- [13] W. R. Eisenstadt and Y. Eo, "S-Parameter-based IC interconnect transmission line characterization," *IEEE Trans. Compon.*, *Hybrids, Manuf. Technol.*, vol. 15, no. 4, pp. 483–490, Aug. 1992.

- [14] K. L. Kaiser, Electromagnetic Compatibility Handbook, vol. 2, Boca Raton, FL: CRC, 2005.

- [15] J. Lee, A. C. W. Lu, W. Fan, L. L. Wai, J. Kim, and J. Kim, "Efficiency of differential signaling on cavity noise suppression in applications with reference plane change," in *Proc. IEEE Int. Symp. EMC*, vol. 1, Aug. 9–13, 2004, pp. 203–208.

- [16] J. Kim, M. D. Rotaru, K. C. Chong, M. K. Iyer, and J. Kim, "Via and reference discontinuity impact on high-speed signal integrity," in *Proc. Int. Symp. EMC*, 2004, pp. 583–587.

- [17] H. W. Johnson and M. Graham, High-Speed Digital Design, Englewood Cliffs, NJ: Prentice-Hall, 1993, Appendix C., pp. 257–259.

- [18] A. A. Smith, Jr., Coupling of External Electromagnetic Fields to Transmission Lines. New York: Wiley, 1977.

- [19] T. Sudo, H. Sasaki, N. Masuda, and J. L. Drewniak, "Electromagnetic interference (EMI) of system-on-package (SOP)," *IEEE Trans. Adv. Packag.*, vol. 27, no. 2, pp. 304–314, May 2004.

- [20] J. Kim, H. Lee, and J. Kim, "Effects on signal integrity and radiated emission by split reference plane on high-speed multilayer printed circuit boards," *IEEE Trans. Adv. Packag.*, vol. 28, no. 4, pp. 724–735, Nov. 2005.

- [21] M. Xu, H. Wang, and T. H. Hubing, "Application of the cavity model to lossy power-return plane structures in printed circuit boards," *IEEE Trans. Adv. Packag.*, vol. 26, no. 1, pp. 73–80, Feb. 2003.

- [22] D. M. Pozar, Microwave Engineering. 2nd ed. New York: Wiley, 1998.

**Jingook Kim** (S'02) received the B.S. and M.S. degrees from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2000 and 2002, respectively, both in electrical engineering. He is currently pursuing the Ph.D. degree at KAIST.

He has been working on power/signal integrity design, package modeling in gigahertz systems, and minimizing EMI radiation. In 2003, he has been with the Institute of Microelectronics, Singapore, as an internship student. His current research interest is the chip/package/board codesign to optimize over-

gigahertz system operation.

Mihai D. Rotaru (M'01) received the B.S. and M.S. degrees from the Technical University of Cluj, Cluj, Romania, and the Ph.D. degree from the University of Southampton, Southampton, U.K., in 1996, 1997, and 2000, respectively, all in electrical engineering.

From 2000 to 2001, he was with the School of Engineering and Mathematical Science, City University London, London, U.K., where he has worked in simulation and modeling of electromagnetic problems for actuators and sensors. Since May 2001, he has been with the Microsystems, Modules, and Compo-

nents Laboratory, Institute of Microelectronics, Singapore, working on design, simulation, and analysis of advanced packaging solution for microelectronics. Presently, he is involved in designing, modeling, and characterization of system-in-package solutions for wireless applications as well as electromagnetic modeling of three-dimensional stack modules. His professional interest includes efficient modeling techniques for complex electromagnetic problems and system-in-package integration solution for RF front ends.

Seungyong Baek received the B.S. degree in radio science and engineering from the Chungnam National University, Daejeon, Korea, in 1999 and the the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, in 2001, where he is currently pursuing the Ph.D. degree.

He has been working with advanced package and connector structures for improved characteristics at gigahertz frequency range and statistical and sensitivity analyses for high-speed channels. His current

research interests include the mode-conversion effect on high-speed serial I/O interfaces.

Jongbae Park received the B.S. degree in avionics from the Hankuk Aviation University, Goyang, Korea, in 2002 and the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2004, where he is currently pursuing the Ph.D. degree.

From 2004 to 2005, he was a Visiting Research Engineer in the Micro-Joining and Substrate Technology Group, Singapore Institute of Manufacturing Technology, Singapore. He has been working on signal/power integrity design of high-speed systems over

gigahertz. His current research interest is the power distribution network design in high-speed mixed-mode systems, using electromagnetic band-gap structures.

**Mahadevan K. Iyer** (M'96–SM'03) received the Ph.D. degree from the Loughborough University of Technology, Loughborough, U.K.

He has more than 20 years of industry and research experience in the design and development of advanced packaging technologies and RF and optoelectronic modules using system-in-package technologies. Until September 2005, he was heading the Microsystems, Modules, and Components Division, Institute of Microelectronics, Singapore. Currently, he is the Director of Research at the Microsystems

Packaging Center, Georgia Institute of Technology, Atlanta. He has more than 150 publications and 12 US patents to his credit. His research interests are in RF and optoelectronic module design, numerical modeling, and high-frequency measurements.

Dr. Iyer has been the Program Chair, Technical Program Chair, and Technical Committee member for many leading International Conferences. He has been the recipient of four Best Paper Awards in leading international conferences.

**Joungho Kim** (A'04–M'04) received the B.S. and M.S. degrees from the Seoul National University, Seoul, Korea, in 1984 and 1986, respectively, and the Ph.D. degree from the University of Michigan, Ann Arbor, in 1993, all in electrical engineering.

In 1993, he joined Picometrix Inc., Ann Arbor, to work as a Research Engineer, where he was responsible for the development of picosecond sampling systems and 70-GHz photo-receivers. In 1994, he joined the Memory Division, Samsung Electronics, Kiheung, Korea, where he was engaged in gigabit-scale

DRAM design. In 1996, he moved to the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently a Professor in the Electrical Engineering and Computer Science Department. From 2001 to 2002, he was on sabbatical leave at Silicon Image Inc., Sunnyvale, CA, as a Staff Engineer and was responsible for low-noise package design of SATA, FC, and Panel Link SerDes devices. He is now a Visiting Consultant for Automobile EMI/EMC design with Hyundai Motors, Inc., Hwaseong, Kyungki-do, Korea. He has more than 180 publications in refereed journals and conferences. His research has centered on modeling, design, and measurement of high-speed interconnection, packages, and PCBs, and research topics include design issues of signal integrity, power/ground noise, and radiated emission in the high-speed SerDes channel, system-on-package (SoP), and multilayer PCBs.

Dr. Kim has been the Chair or the Cochair of the EDAPS Workshop since 2002. Currently, he is an Associate Editor for the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY.