©2007 The Japan Society of Applied Physics

# Integration of Tunnel-Coupled Double Nanocrystalline Silicon Quantum Dots with a Multiple-Gate Single-Electron Transistor

Yoshiyuki KAWATA, Mohammed A. H. KHALAFALLA, Kouichi USAMI, Yoshishige TSUCHIYA, Hiroshi MIZUTA, and Shunri ODA

Quantum Nanoelectronics Research Center and Department of Physical Electronics, Tokyo Institute of Technology, and SORST, Japan Science and Technology Agency, 2-12-1 O-okayama, Meguro-ku, Tokyo 152-8552, Japan

(Received January 22, 2007; accepted April 7, 2007; published online July 4, 2007)

We report on integration of double nanocrystalline silicon quantum dots (nc-Si QDs) of approximately 10 nm in diameter onto the multiple-gate single-electron transistor (SET) used as a highly-sensitive charge polarization detector. The SET with a single charging island is first patterned lithographically on silicon-on-insulator, and the multiple-gate bias dependence of the Coulomb current oscillation is characterized at 4.2 K. The coupling capacitance parameters between the SET charging island and the multiple-gate are estimated and compared with those obtained by using the three-dimensional capacitance simulation. Double nc-Si QDs are then deposited in the immediate vicinity of the charging island of the SET by using the very-high frequency plasma deposition technique. We perform the single-electron circuit simulations and demonstrate that only  $\pm e$  charge polarization of the double QDs can be sensed as a shift of the Coulomb oscillation peaks.

KEYWORDS: double quantum dots, nanocrystalline-silicon quantum dots, qubit, three-dimensional capacitance simulation, single-electron transistor

### 1. Introduction

[DOI: 10.1143/JJAP.46.4386]

The double quantum dots (DQD) structure has recently been studied as a charge qubit to realize the solidstate quantum computer. DQDs have been fabricated in GaAs:AlGaAs heterostructures, where DODs are realized through the depletion of a two-dimensional electron gas using surface gates.<sup>1)</sup> In these devices large numbers of surface gates are used to define the QDs and the barriers, which lead to shallow potentials confinement and cross capacitance problems. DQDs have also been fabricated in the Si-based materials by using the electron beam lithography and the reactive ion etching (RIE) techniques, which results in a "trench-isolated" structure.<sup>2,3)</sup> Charge polarizations in the DQDs are measured using a single-electron transistor (SET). The theoretical limit of charge sensitivity for a SET is about  $1 \times 10^{-6} \, e\text{Hz}^{-1/2}$ . This ultra high charge sensitivity property makes the possibility of detecting the quite small changes in the distribution of charge within a capacitively-coupled structure.

To realize the practical quantum computer, computation steps (= decoherence time/coherent period) must be increased at least by 10<sup>4</sup> times. To meet this computational requirement, increasing the decoherence time and the coherent oscillation frequency is the necessary condition. One of the solutions is using the smaller sized quantum dots which show enhanced quantum effect. In the present work, we succeeded in integrating the lithographically patterned SET and nanocrystalline-Si quantum dots (nc-Si QDs). The nc-Si QDs are fabricated by the pulsed-gas very-highfrequency (VHF) plasma process and approximately 10 nm in size, spherical in shape, and highly pure in nature.<sup>5–7)</sup> These unique properties will help to realize the long decoherence time charge qubits. Integration of nc-Si QDs with patterned substrate has been carried out by atomic force microscope (AFM) or dots solution techniques.<sup>8,9)</sup> But position control for all dots using AFM technique is laborious work. The nc-Si QDs assembly technique has recently been applied for the pre-patterned nanostructures,

but position control of individual nc-Si QDs is not realized yet. In this work we report *in-situ* deposition technique to locate double nc-Si QDs in a nanoscale window patterned in the immediate vicinity of the SET charging island by using high-resolution electron beam lithography. We carried out the differential current measurement to estimate the capacitance coupling parameters and compared them with three-dimensional capacitance simulations. To investigate the effects of the charge polarizations on the SET characteristics, we performed the equivalent circuit simulation.

### 2. SET Fabrication

SETs were fabricated using separation by implantation of oxygen (SIMOX) silicon substrates with initial silicon-oninsulator (SOI) thickness of 100 nm and buried-oxide (BOX) thickness of 200 nm. Negative resist RD-2000N was used for electron-beam (EB) direct writing. Although primarily developed as a deep ultraviolet resist, RD-2000N shows good sensitivity to EB exposure. 10) This resist offers good etching resistance and simple resist handling. The initial SOI layer thickness was reduced to 40 nm by repeated thermal oxidation and wet etching. The fabricated SET is structured with single dot and four side gates. The schematic top-view of the SET is shown in Fig. 1. The top colored regions indicate SOI with phosphorus doping level at 10<sup>19</sup> cm<sup>-3</sup>, the bottom colored region indicates silicon substrate with boron doping of 10<sup>15</sup> cm<sup>-3</sup>, and the white region indicates the BOX layer, where the SOI regions has been etched away using the electron cyclotron resonance RIE (ECR-RIE) technique.

The fabrication process is as follows. At first 60 nm thickness of negative resist RD-2000N was coated on the SOI layer and single dot structured SET (Fig. 1) was patterned using the high-resolution electron beam lithography with a lithographically defined diameter of approximately 90 nm for the island. The adjacent constrictions that act as tunnel barriers connecting the charging island to the source and drain electrodes are of 70 nm in width. The pattern was etched using ECR-RIE technique and was

Fig. 1. (a) Schematic top-view of the lithographically fabricated single dot structured SET with four gates.

thermally oxidized at  $1000\,^{\circ}\text{C}$  to passivate the surface states and reduce the effective thickness of the SOI down to approximately  $30\,\text{nm}$ . This final oxidation leads to resulting overall dot diameter of approximately  $70\,\text{nm}$ .

## 3. Measurements and Three-Dimensional Capacitances Simulation

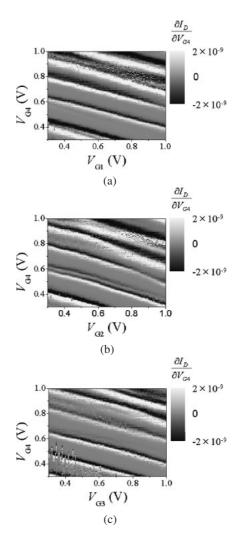

To characterize the fabricated SET, electrical measurements were carried out at the temperature of 4.2 K. The gate voltage dependence of the device was obtained by sweeping the  $V_{\rm G4}$  at the differential values of  $V_{\rm G1}$ ,  $V_{\rm G2}$ , and  $V_{\rm G3}$  as shown in the Figs. 2(a), 2(b), and 2(c) respectively. These plots show the measured differential conductance through the SET  $\partial I_{\rm D}/\partial V_{\rm G4}$ . In these measurements, drain to source bias voltage was kept at 1 mV. The coupling capacitances between G1, G2, G3, and G4, and the SET island extracted from the differential conductance characteristics are  $C_{\rm G1}=0.27\,{\rm aF},\ C_{\rm G2}=0.38\,{\rm aF},\ C_{\rm G3}=0.33\,{\rm aF},\ {\rm and}\ C_{\rm G4}=1.0\,{\rm aF},\ {\rm respectively}.$  The total capacitance of the island is estimated to be  $C_{\rm \Sigma}\approx 16\,{\rm aF}$  from the measured coulomb blockade voltage  $V_{\rm gap}\approx 10\,{\rm mV}.$

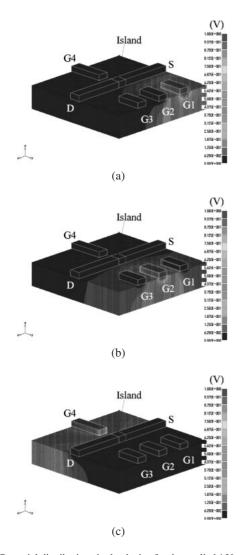

In order to demonstrate the correctness of the extracted gate capacitances values which were obtained from the measurement characteristics, three dimensional capacitance simulations was performed. In the simulation, electric field distribution in the three-dimensional structure is calculated by solving the three-dimensional Poisson's equations for the applied electric potential to the electrodes and electric charge distribution in the device with the specified boundary conditions. From this potential distribution, the capacitance matrix is estimated by computing the electric flux flowing into the SET island. Figure 3 shows the simulated potential distributions in the device for the applied 1 V to the gates G1, G2, and G4 respectively. The simulated capacitance values between the gates and island are found to be  $C_{G1} = 0.30613 \,\text{aF}, \quad C_{G2} = 0.41108 \,\text{aF}, \quad C_{G3} = 0.30613 \,\text{aF},$ and  $C_{\rm G4} = 0.97107 \, \rm aF$ . It is found that these simulated capacitance values agree with the extracted capacitances from the measurements. This capacitance agreement confirms the geometrical defined nature of the fabricated SET.

### 4. Integration of nc-Si QDs with the SET

Fabrication equipment of the nc-Si QD consists of a VHF plasma cell and an ultrahigh-vacuum (UHV) chamber. The nc-Si QD with a diameter of  $\sim \! 10 \, \mathrm{nm}$  is formed in the gas phase of a SiH<sub>4</sub> plasma cell by the decomposition of pulsed

Fig. 2. The gate depended conductance  $\partial I_D/\partial V_{G4}$  for the different values of (a)  $V_{G1}$ , (b)  $V_{G2}$ , and (c)  $V_{G3}$ .

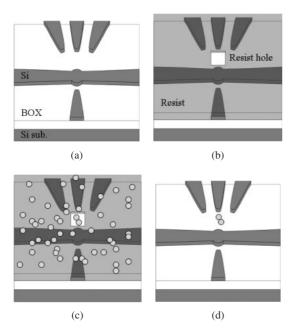

SiH<sub>4</sub> gas supply by VHF plasma and deposited on the substrate randomly. Experimental process and formation of nc-Si QD is discussed in detail in refs. 5–7. Integration of size-controlled nc-Si QDs with the SET was done by depositing nc-Si QDs on fabricated SET in the UHV chamber. After fabricating the SET [Fig. 4(a)], a resist hole was prepared in the narrow region between the SET island and three gate electrodes (G1, G2, and G3) using the electron beam lithography as shown in Fig. 4(b). After that, nc-Si QDs were deposited on the SET patterned substrate [Fig. 4(c)]. In the resist hole area nc-Si QDs contacted directly to the substrate. The unwanted nc-Si QDs on the substrate are removed by lift-off process [Fig. 4(d)].

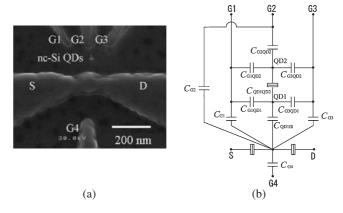

To study the effects of the charge polarizations in the double nc-Si QDs on SET, we carried out three-dimensional capacitance simulation and the equivalent circuit simulation. To estimate the various capacitances in the nc-Si QDs integrated SET [Fig. 5(a)], three-dimensional capacitance simulation was done as explained in measurement and three-dimensional capacitance simulation section for the structure shown in Fig. 3. The simplified equivalent circuit of the SET with nc-Si QDs is shown in Fig. 5(b). QD1 is the nc-Si QD nearer to the SET and QD2 is the nc-Si QD nearer to the triple-gate, and  $C_{\rm OD1OD2}$  is capacitance between QD1

Fig. 3. Potential distributions in the device for the applied 1 V to the gates (a) G1, (b) G2, and (c) G4 respectively.

Fig. 4. Schematic diagrams outlining steps involved in the fabrication process: (a) SET with four side-gate; (b) spin coating the surface with a resist material and a resist hole prepared through electron beam lithography; (c) deposition of nc-Si QDs; (d) removing the unwanted nc-Si QDs on the substrate.

Fig. 5. (a) SEM image of the nc-Si QDs integrated SET. (b) The simplified equivalent circuit of the device shown in (a). QD1 is the nc-Si QD nearer to the SET and QD2 is the nc-Si QD nearer to the triple-gate, and  $C_{\rm QD1QD2}$  is capacitance between QD1 and QD2. On the simulations, capacitance  $C_{\rm G2QD1}$  between G2 and QD1, and capacitance  $C_{\rm QD1GD2}$  between QD2 and the SET island were included, and capacitance  $C_{\rm QD1QD2}$  between the nc-Si QDs was treated as a normal capacitor to estimate the effects of charge polarizations.

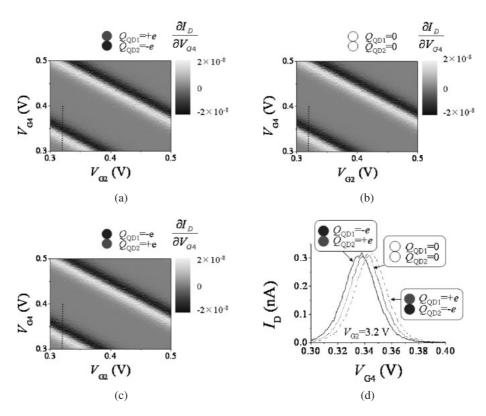

and QD2 in Fig. 5(b). On the simulation, the capacitance between G2 and QD1, and the capacitance between the QD2 and the SET island were included, and  $C_{\rm QD1QD2}$  was treated as a normal capacitor to estimate the effects of charge polarizations. Figure 6 shows differential SET current simulated at 4.2 K and 1 mV drain bias in the condition of: (a) -e in the top nc-Si QD and +e in the bottom nc-Si QD  $(Q_{\rm QD1}=-e,Q_{\rm QD2}=+e)$ ; (b) no charge polarizations in the nc-Si QDs  $(Q_{\rm QD1}=Q_{\rm QD2}=0)$ ; (c) +e in the top nc-Si QD and -e in the bottom nc-Si QD  $(Q_{\rm QD1}=+e,Q_{\rm QD2}=-e)$ .  $I_{\rm D}-V_{\rm G4}$  curves at  $V_{\rm G2}=3.2$  V along with dotted lines in 6(a)-6(c) for the three different charge polarizations are shown in 6(d). These results indicate that charge polarization with the magnitude of as small as a fraction of  $\pm e$  can be sensed as their remarkable shifts.

### 5. Conclusions

The single-electron transistor with multiple side gates has been fabricated in the SOI substrate as a highly-sensitive charge detector. We have extracted the coupling capacitance values from the observed Coulomb oscillation characteristics and have shown good agreement with the theoretical estimates obtained using three-dimensional capacitance simulation. Integration of the tunnel-coupled nc-Si DQDs onto the fabricated SET have been carried out for the first time by using *in-situ* deposition. The equivalent circuit analysis of the nc-Si DQD integrated SET has shown that charge polarization with the magnitude of as small as a fraction of  $\pm e$  in double nc-Si QDs with diameter of  $\sim 10$  nm can be sensed with finite shift of the Coulomb oscillation peaks.

- T. Fujisawa, T. Hayashi, H. D. Cheong, Y. H. Heong, and Y. Hirayama: Physica E 21 (2004) 1046.

- E. G. Emiroglu, David G. Hasko, and D. A. Williams: Appl. Phys. Lett. 83 (2003) 3942.

- J. Gorman, D. G. Hasko, and D. A. Williams: Phys. Rev. Lett. 95 (2005) 090502.

- 4) A. N. Korotkov: Phys. Rev. B 49 (1994) 10381.

- T. Ifuku, M. Otobe, A. Itoh, and S. Oda: Jpn. J. Appl. Phys. 36 (1997) 4031.

Fig. 6. Differential SET current simulated at 4.2 K and 1 mV drain bias in the condition of: (a) -e in the top nc-Si QD and +e in the bottom nc-Si QD  $(Q_{\rm QD1} = -e, Q_{\rm QD2} = +e)$ ; (b) no charge polarizations in the nc-Si QDs  $(Q_{\rm QD1} = Q_{\rm QD2} = 0)$ ; (c) +e in the top nc-Si QD and -e in the bottom nc-Si QD  $(Q_{\rm QD1} = +e, Q_{\rm QD2} = -e)$ .  $I_{\rm D}-V_{\rm G4}$  curves at  $V_{\rm G2} = 3.2$  V along with dotted lines in (a)–(c) for the three different charge polarizations are shown in (d).

- K. Nishiguchi, S. Hara, and S. Oda: Mater. Res. Soc. Symp. Proc. 571 (2000) 43.

- 7) K. Nishiguchi, X. Zhao, and S. Oda: J. Appl. Phys. 92 (2002) 2748.

- 8) S. Oda: Adv. Colloid Interface Sci. **71–72** (1997) 31.

- 9) A. Tanaka, G. Yamahata, Y. Tsuchiya, K. Usami, H. Mizuta, and S. Oda: Curr. Appl. Phys. 6 (2006) 344.

- A. Dutta, S. P. Lee, Y. Hayafune, and S. Oda: J. Vac. Sci. Technol. B 18 (2000) 2857.