# Surface Potential Effect on Gate–Drain Avalanche Breakdown in GaAs MESFET's

HIROSHI MIZUTA, KEN YAMAGUCHI, MEMBER, IEEE, AND SUSUMU TAKAHASHI

Abstract—The surface potential effect on gate-drain avalanche breakdown in GaAs MESFET's is investigated with a two-dimensional device simulator. It is shown that the surface potential effect changes the potential distribution in GaAs MESFET's drastically and therefore plays an important role in determining drain breakdown voltage. In addition, two device structures producing high breakdown voltages, an offset gate structure and a recessed gate structure, are analyzed.

## I. INTRODUCTION

ATE-DRAIN avalanche breakdown is an important Gactor that determines the drain breakdown voltage of GaAs MESFET's. It is necessary to relax the concentration of the electric field and suppress the avalanche multiplication of carriers in order to obtain high drain breakdown voltage. A two-dimensional device simulator is the most powerful tool to investigate the electric field distribution in GaAs MESFET's, and some results have been reported [1], [2]. According to them, a maximum electric field always exists at the gate edge independent of the geometric shape of GaAs MESFET's. These results, however, are inconsistent with various experimental data on avalanche breakdown of GaAs MESFET's. For example, much information on the electric field distribution in GaAs MESFET's has been extracted from the light emission that accompanies avalanche breakdown of GaAs MESFET's [3]-[6]. However, calculated electric field distributions did not agree with these results. Furthermore, two device structures known for their high breakdown voltages, a recessed structure and an offset gate structure, cannot be understood with two-dimensional calculations. These discrepancies come from omitting a certain physical effect in these calculations.

In this paper, we will introduce the surface potential effect of GaAs into a two-dimensional device simulator and will analyze in detail the gate-drain avalanche breakdown in the surface depletion layer. It will be shown that the potential distribution in GaAs MESFET's changes drastically due to the surface potential effect, and that the drain breakdown voltage largely depends on this effect.

#### II. METHOD OF ANALYSIS

In this section, we will show the method of our twodimensional analysis, which includes the surface potential

Manuscript received October 16, 1986; revised February 14, 1987. The authors are with the Central Research Laboratory, Hitachi, Ltd., Tokyo 185, Japan.

IEEE Log Number 8716179.

effect. The motion of carriers in MESFET's will be treated with the classical continuum approximation. When the majority carriers in MESFET's are electrons, fundamental equations are given as follows:

1) Poisson's equation

$$\epsilon \nabla^2 \psi = -q(N_d - N_a - n + p) \tag{1}$$

2) Carrier continuity equation

$$\nabla \cdot J_n = 0 \tag{2}$$

3) Hole density equation

$$p = n_i \exp \left\{ q(\phi_p - \psi)/k_B T \right\} \tag{3}$$

where  $\psi$  is the electrostatic potential, n is the electron density, p is the hole density,  $\phi_p$  is the quasi-Fermi potential for holes,  $\epsilon$  is the dielectric constant, q is a unit charge, and  $J_n$  is the electron current density. These calculations will be performed with the two-dimensional simulator CANNON [7], which can simulate nonplanar GaAs MESFET's. An electron's velocity-electric field relation v(E) is approximated by the following expression [8]:

$$v(E) = \mu E, \quad (E \le v_s/\mu)$$

$$v(E) = v_s, \quad (E > v_s/\mu) \tag{4}$$

where  $v_s$  and  $\mu$  are saturation velocity and low-field mobility of an electron (these values are listed in Table I).

The surface state density of GaAs is very high and carrier electrons near the surface are captured by these states. Thus, there exists a surface depletion layer between the electrodes of GaAs MESFET's; the surface potential is known to be 0.6-0.8 eV [2], [9]-[11]. The origin of the surface states is not well known. Nonperiodic arrangement of atoms on the surface, native oxide of Ga, and defects of As atoms are considered as possible causes. It is necessary to take the surface potential effect into account in order to analyze the gate-drain avalanche breakdown. The surface depletion layer in our calculation is modeled by putting accepter impurities uniformly on the surface between electrodes, giving a surface potential of  $-V_S$  with respect to that of the bulk material beneath. The density of surface accepter impurities  $\sigma_A$  is shown in Table II.

In the present paper, the drain breakdown voltage is determined as follows.

TABLE I

DEVICE PARAMETERS USED FOR TWO-DIMENSIONAL SIMULATION

| Electron concentration in active layer          | 1×10 <sup>17</sup> (cm <sup>-3</sup> ) |  |  |

|-------------------------------------------------|----------------------------------------|--|--|

| Electron concentration in semi-insulating layer | 1×10 <sup>14</sup> (cm <sup>-3</sup> ) |  |  |

| Electron mobility                               | 3500 (cm <sup>2</sup> /V·sec)          |  |  |

| Electron saturation velocity                    | 1×107 (cm/sec)                         |  |  |

| Schottky barrier height                         | 0.8 (V)                                |  |  |

TABLE II SURFACE POTENTIAL  $V_{\mathcal{S}}$  AND DENSITY OF SURFACE ACCEPTOR IMPURITY IN TWO-DIMENSIONAL SIMULATION

| Surface accepter density(×10 <sup>12</sup> cm <sup>-2</sup> ) | 0 | 9.0 | 10.7 | 11.5 | 13.6 |

|---------------------------------------------------------------|---|-----|------|------|------|

| Surface potential(V)                                          | 0 | 0.3 | 0.65 | 0.8  | 1.0  |

- 1) Equations (1)-(3) are solved with drain bias  $V_{DS}$  and the electric field distribution is determined.

- 2) Once the electric field distribution is given, the carrier continuity equation including electron-hole generation can be solved for the one-dimensional case [8]. Therefore, we calculate the ionization integral  $I^*$  [8]

$$I^* \equiv \int \alpha_n \cdot \exp \left[ -\int \left( \alpha_n - \alpha_p \right) dx' \right] dx. \quad (5)$$

along the surface between the gate and drain electrodes with the following ionization rates [12]:

$$\alpha_n(E) = \alpha_p(E) = A \exp \left\{ -(b/E)^2 \right\}$$

$$A = 3.5 \times 10^5 \text{ (cm}^{-1})$$

$$b = 6.85 \times 10^5 \text{ (V/cm)}.$$

(6)

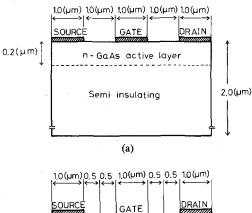

If  $I^* < 1$ , the drain bias is varied to  $V_{DS} = V_{DS} + \Delta V_{DS}$  and 1) and 2) are carried out again. If  $I^* \ge 1$ ,  $V_{DS}$  is considered to be the drain breakdown voltage. Fig. 1 shows cross sections of the planar and recessed GaAs MESFET's, which will be analyzed in the next section; device parameters are shown in Table II.

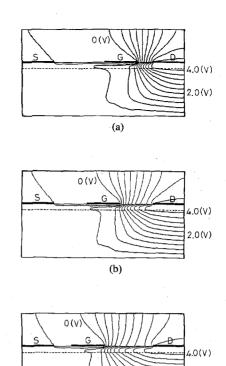

## III. RESULTS OF TWO-DIMENSIONAL SIMULATION

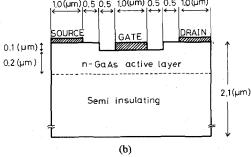

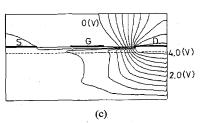

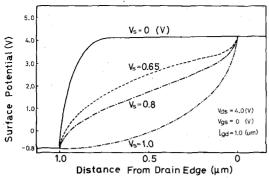

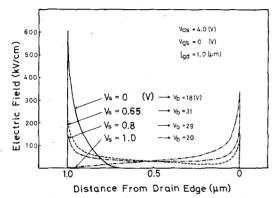

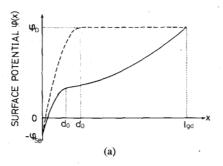

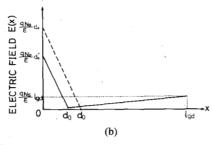

The electric field distribution in GaAs MESFET's changes drastically by introducing the surface potential effect. Fig. 2(a)–(c) shows the potential distributions with various values of the surface potential  $V_S$ . The electric field strength grows weaker with increasing  $V_S$ . Fig. 3 shows the potential distribution on the surface between the gate and drain electrodes. A solid line is the result without the surface potential effect ( $V_S = 0$ ) and there exists only an abrupt potential drop of the Schottky barrier at the gate edge. Increasing  $V_S$ , this potential drop becomes gradual, but the potential drop at the edge of the drain electrode now becomes abrupt. The electric field distribution on the surface with various  $V_S$  is shown in

Fig. 1. Cross sections of analyzed GaAs MESFET's.

Fig. 2. Two-dimensional calculation results. Potential distributions in planar GaAs MESFET with various  $V_S$ : (a) 0 V, (b) 0.65 V, (c) 1.0 V. Bias conditions are  $V_{DS}=4.0$  V and  $V_{GS}=0$  V.

Fig. 4. As shown here, the electric field strength at the gate edge decreases and that at drain edge increases with increasing  $V_S$ . A large value of  $V_S$  represents an increase in the number of electrons captured by the surface states. The charge of these electrons cancels the positive space charge in the depletion layer of the Schottky gate and

Fig. 3. Potential distribution on surface between gate and drain electrodes of planar GaAs MESFET;  $V_{DS}=4.0~{\rm V}$  and  $V_{GS}=0~{\rm V}$ .

Fig. 4. Electric field distribution on surface between gate and drain electrodes of planar GaAs MESFET;  $V_{DS} = 4.0 \text{ V}$  and  $V_{GS} = 0 \text{ V}$ .

therefore weakens the electric field strength at the gate edge. On the other hand, these electrons form a peak of the electric field strength at the drain edge. The drain breakdown voltages  $V_B$  with various  $V_S$  are also indicated in Fig. 4. Values of  $V_B$  correspond to maximum values of the electric field strength, and  $V_B$  is largest when the electric field strength at the gate edge is equal to that at the drain edge. The potential distribution on the surface of GaAs MESFET's was measured by scanning Auger microscopy (SAM) [6]. The results showed that there are potential drops both at the gate edge and the drain edge. This observation corresponds to our analysis with the surface potential effect, and in addition the value of  $V_S$  can now be estimated by comparing the calculated and experimental results quantitatively.

Next, two FET structures having high drain breakdown voltage, that is, an offset gate structure and a recess structure, are investigated. The geometrical effects of these structures can be understood with the surface potential effect.

## A. Offset Gate Structure

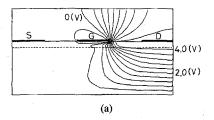

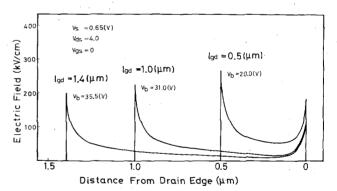

A wider spacing between the gate and drain electrodes  $l_{gd}$  is considered to be effective to obtain a large drain breakdown voltage  $V_B$ . Fig. 5 shows the potential distributions in a GaAs MESFET, and Fig. 6 shows the electric field distribution on the surface between the gate and drain electrodes with  $V_S = 0.65$  eV. The electric field at the

Fig. 5. Potential distributions in planar GaAs MESFET with various gatedrain spacing  $l_{gd}$ : (a) 0.5  $\mu$ m, (b) 1.0  $\mu$ m, (c) 1.4  $\mu$ m;  $V_{DS}=4.0$  V and  $V_{GS}=0$  V.

2.0(V)

Fig. 6. Electric field distribution on surface with  $V_S = 0.65 \text{ V}$ .

gate edge becomes weak and the drain breakdown voltage  $V_B$  grows from 20.0 V ( $l_{gd} = 0.5 \mu m$ ) to 35.5 V ( $l_{gd} = 1.4 \mu m$ ); high drain breakdown voltage can be obtained with the offset gate structure. Increasing  $l_{gd}$ , the number of electrons captured by the surface states between the gate and drain electrodes increases, and the electric field formed by space charges in the depletion layer of the Schottky gate weakens. A more analytic consideration of this effect will be described in Section IV.

### B. Recessed Structure

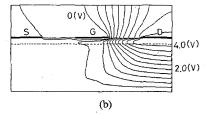

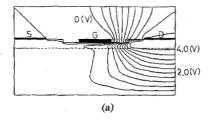

High drain breakdown voltages are obtained with a recessed structure. Thus, the electric field distribution in GaAs MESFET's is considered to change in response to its geometric shape. Fig. 7(a), (b) shows such a geometric

Fig. 7. (a) Potential distribution in recessed GaAs MESFET with  $V_S = 0.65 \text{ V}$ ;  $V_{DS} = 4.0 \text{ V}$  and  $V_{SG} = 0 \text{ V}$ . (b) Electric field distribution on surface of recessed GaAs MESFET.

effect. The horizontal electric field distribution between the gate and drain electrodes of the recessed structure is different from that of the planar structure. Fig. 7(b) shows that a peak of the electric field strength appears at the recess edge and that at the gate edge is weakened. This new peak originates in the potential drop at the recess edge, which is due to the surface potential effect. Thus, the potential difference between the gate and drain,  $V_{di}$ , is divided among the gate edge, the recess edge, and the drain edge. The high drain breakdown voltage of the recessed structure is due to this distribution of the electric field.

As described above, the surface potential effect has a large influence on the breakdown voltage of GaAs MES-FET's. The high drain breakdown voltages obtained with the offset gate structure and the recessed structure are due to this effect. Therefore, GaAs MESFET's with higher drain breakdown voltage can be obtained by control of the surface potential effect.

## IV. DISCUSSION

## A. Comparison with Experimental Data

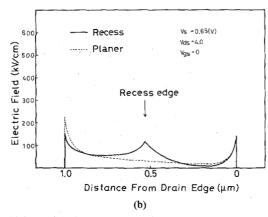

Fig. 8 shows drain breakdown voltages measured in offset gate structured GaAs MESFET's with a carrier concentration  $1.8 \times 10^{17}$  cm<sup>-3</sup> and those calculated with various  $V_S$ . The calculated result without the surface potential effect ( $V_S = 0$  V) is largely different from experimental data. With increasing  $V_S$ , the calculated drain breakdown voltage becomes large, and the theoretical curve fits the experimental data with  $V_S \sim 0.65$  V. This value of  $V_S$  is consistent with reported values measured with photoemission spectroscopy (0.6-0.8 V) [10].

Fig. 8. Drain breakdown voltages versus gate-drain distance measured in offset gate structured GaAs MESFET's. Solid lines are calculated results with various surface potential  $V_{\rm S}$ .

# B. Consideration with a Simple Analytical Model

In this section we investigate potential distribution on the surface between the gate and drain electrodes with a one-dimensional analytical model; physical significance is given to the results in Section III.

We consider the surface between the gate and drain electrodes of GaAs MESFET's and denote charge distribution and potential distribution as  $\rho(x)$  and  $\phi(x)$ , respectively.  $\phi(x)$  is determined by solving the following equation:

$$d^2\phi(x)/dx^2 = -\rho(x)/\epsilon. \tag{7}$$

At first, we consider a case where the surface potential effect is neglected, that is, no electrons are captured by the surface states. In this case, there exists only a space charge in the depletion layer of the Schottky gate (Fig. 9(a)). Boundary conditions are given as follows:

$$\phi(x)\big|_{x=0} = -\phi_{SB}$$

$$\phi'(x)\big|_{x=d_0} = 0$$

$$\phi(x)\big|_{x=d_0} = \phi_D$$

(8)

where  $d_0$  is the width of the depletion layer and  $\phi_{SB}$  and  $\phi_d$  represent the potential of the gate and drain electrodes, respectively. Solving (7) with boundary conditions in (8), we obtain the following:

$$\phi(x) = -\frac{qN_D}{2\epsilon} (x - d_0)^2 + \frac{qN_D}{2\epsilon} d_0^2 - \phi_{SB}, \quad (0 \le x \le d_0)$$

$$\phi(x) = \phi_D, \quad (d_0 < x \le l_{gd})$$

$$d_0 = \left\{ \frac{2\epsilon (\phi_{SB} + \phi_D)}{qN_D} \right\}^{1/2}.$$

(10)

Therefore, the electric field distribution is given by the

(15)

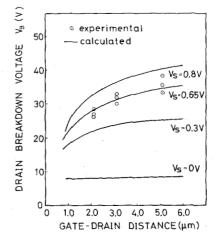

Fig. 9. Model for space-charge distribution on surface between gate and drain. (a) For no surface potential effect. (b) For surface potential effect.

Fig. 10. Potential distribution and electric field distribution on surface between gate and drain electrodes.

following expressions:

$$E(x) = \frac{qN_D}{\epsilon} (x - d_0), \quad (0 \le x \le d_0)$$

$$E(x) = 0, \quad (d_0 < x \le l_{gd}). \tag{11}$$

$\phi(x)$  and |E(x)| are indicated by broken lines in Fig. 10(a) and (b). These correspond to the previous results (solid lines in Figs. 3 and 4). As shown in (11), electric field E(x) is independent of gate-drain distance  $l_{gd}$ . Thus, the effect of the offset gate structure is not obtained in this case.

Next, we consider a model including the surface potential effect. Electrons captured by the surface states are assumed to distribute uniformly on the surface between the gate and drain electrodes (Fig. 9(b)). Boundary condi-

tions are then given as follows:

$$\phi(x)\big|_{x=0} = -\phi_{SB}$$

$$\phi'(x)\big|_{x=d_0-0} = \phi'(x)\big|_{x=d_0+0}$$

$$\phi(x)\big|_{x=d_0-0} = \phi(x)\big|_{x=d_0+0}$$

$$\phi'(x)\big|_{x=l_{gd}} = qN_Sl_{gd}/\epsilon$$

$$\phi(x)\big|_{x=l_{gd}} = \phi_D.$$

(12)

Solving (7) with (12),  $\phi(x)$  and E(x) are obtained as follows:

$$\phi(x) = -\frac{q}{2\epsilon} (N_D - N_S) x^2 + \frac{qN_D}{\epsilon} d_0' x - \phi_{SB},$$

$$(0 \le x \le d_0')$$

$$\phi(x) = \frac{qN_S}{2\epsilon} x^2 - \frac{qN_S}{2\epsilon} l_{gd}^2 + \phi_D,$$

$$(d_0' < x \le l_{gd})$$

$$E(x) = -\frac{qN_D}{\epsilon} d_0' + \frac{q}{\epsilon} (N_D - N_S) x,$$

$$(0 \le x \le d_0')$$

$$E(x) = -\frac{qN_S}{\epsilon} x, \quad (d_0' < x \le l_{gd})$$

$$(14)$$

$\phi(x)$  and |E(x)| are indicated by solid lines in Fig. 10(a) and (b). The electric field at gate edge |E(0)| is obtained as follows:

$d'_{0} = \left\{ \frac{2\epsilon}{aN_{D}} \left( \phi_{SB} + \phi_{D} \right) - \frac{N_{S}}{N_{D}} l_{gd}^{2} \right\}^{1/2}.$

$$\begin{aligned}

\left| E(0) \right| &= \frac{qN_D}{\epsilon} d_0' = \left\{ \frac{2qN_D}{\epsilon} \left( \phi_{SB} + \phi_D \right) \right. \\

&\left. - \frac{N_D}{N_S} \left( \frac{qN_S}{\epsilon} \right)^2 l_{gd}^2 \right\}^{1/2}.

\end{aligned} \tag{16}$$

From this equation, |E(0)| becomes small with increasing  $N_S$ . (This behavior corresponds to the electric field distributions with various  $V_S$  in Fig. 4.) This result is explained with the following mechanism.

At the edge of the gate electrode, positive charge in the gate depletion layer is cancelled by the negative charge of electrons that are captured by the surface states. Thus electric field strength at the gate edge is weakened. Furthermore, the decrease of the electric field strength with increasing  $l_{gd}$  (Fig. 6) can be explained by this mechanism.

#### C. Calculated Results and Light Emission

As mentioned in Section I, light emission due to radiative recombination of carriers is directly observed from GaAs MESFET's [3]-[6]. The source of light emission indicates a strong electric field. Thus, the electric field

distribution obtained in Section III should be compared to experimental results of light emission. Reported experimental results are summarized as follows.

- 1) For a planar structure:

- a) Light emits from the drain edge when gate bias is close to zero  $(V_{gs} \sim 0(V))$ .

- b) Light emits from the gate edge of the drain side when gate bias is close to pinchoff  $(V_{gs} \sim V_p(V))$ .

- 2) For a recessed structure:

- a) Light emits from the recess edge of the drain side  $(V_{gs} \sim 0(V))$ .

- b) Light emits from the gate edge of the drain side  $(V_{gs} \sim V_p(V))$ .

On the other hand, the electric field distribution calculated with the surface potential effect has the following features.

- 1) For a planar structure: Two peaks of the electric field strength exist at the gate edge and the drain edge (Fig. 4).

- 2) For a recessed structure: Three peaks of the electric field strength exist at the gate edge, the recess edge, and the drain edge (Fig. 7(b)).

We can determine much correspondence between locations where light emits and strong electric fields. In particular, light emission from the edge of the drain electrode in planar MESFET's and that from the recess edge in the recessed structure can now be explained by our calculations with the surface potential effect. Thus, our calculations agree with the experimental data of light emission. In order to discuss the dependence of light emission on various gate biases, it is necessary to consider not only the electric field but also the carrier concentration at light emission sources. Formulation of light intensity and quantitative comparison with the experimental data are left for further study.

#### V. Conclusion

We have investigated the surface potential effect on the gate-drain avalanche breakdown in GaAs MESFET's and have obtained the following results.

- 1) The surface potential effect is important to analyze the gate-drain avalanche breakdown in GaAs MESFET's.

- 2) The breakdown voltage  $V_B$  determined by the avalanche breakdown in the surface depletion layer depends on the surface potential  $V_S$ . For instance,  $V_B$  increases from 18 V ( $V_S = 0$  V) to 31 V ( $V_S = 0.65$  V) in GaAs MESFET's with an impurity concentration of  $1.0 \times 10^{17}$  cm<sup>-3</sup> and a gate-drain spacing of  $1.0 \ \mu m$ .

- 3) The effects of the recessed structure and the offset gate structure can be explained by the following mechanisms.

- a) The electric field strength at the gate edge is weakened with increasing gate-drain spacing, so that  $V_B$  increases from 20 V ( $l_{gd} = 0.5 \mu m$ ) to 35.5 V ( $l_{gd} = 1.4 \mu m$ ).

- b) In the recessed structure, peaks of electric field

strength exist at the gate edge, the recess edge, and the drain edge.

- 4) The potential distribution and electric field distribution change drastically by introducing the surface potential effect; consequently, experimental data from light emission and SAM can be well understood.

- 5) Comparing with experimental data for drain breakdown voltage in offset gate structured GaAs MESFET's, the surface potential is estimated to be about 0.65 V. This value is consistent with the experimental value measured with X-ray photoelectron spectroscopy.

#### REFERENCES

- W. R. Frensley et al., "Power-limiting breakdown effects in GaAs MESFET's," IEEE Trans. Electron Devices, vol. ED-28, p. 962, 1981.

- [2] J. P. R. David et al., "Gate-drain avalanche breakdown in GaAs power MESFET's," IEEE Trans. Electron Devices, vol. ED-29, p. 1548, 1982.

- [3] T. Mimura et al., "Visible light emission from GaAs field-effect transistor," Proc. IEEE, vol. 165, p. 1407, 1977.

- [4] D. Yamamoto et al., "Light emission and burnout characteristics of GaAs power MESFET's," IEEE Trans. Electron Devices, vol. ED-25, p. 567, 1980.

- [5] C. Tsironis et al., "Prebreakdown phenomena in GaAs epitaxial layers and FET's," IEEE Trans. Electron Devices, vol. ED-27, p. 277, 1980.

- [6] S. Tiwari et al., "Physical and materials limitations on burnout voltage of GaAs power MESFET's," IEEE Trans. Electron Devices, vol. ED-27, p. 1045, 1980.

- [7] K. Yamaguchi et al., "An extended stream function method for computer analysis of non-planar structures (CANNON)," Solid-State Electron., vol. 29, no. 11, p. 1129, 1986.

- [8] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1981.

- [9] R. Wroblewski et al., "Theoretical analysis of the dc avalanche breakdown in GaAs MESFET's," IEEE Trans. Electron Devices, vol. ED-30, p. 154, 1983.

- [10] W. E. Spicer et al., "New and unified model for Schottky barrier and III-V insulator interface states formation," J. Vac. Sci. Technol., vol. 16, no. 5, n. 1442, 1979

- vol. 16, no. 5, p. 1442, 1979. [11] P. Zaitlin, "Reverse breakdown in GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. ED-33, p. 1635, 1986.

- [12] S. M. Sze et al., "Avalanche breakdown voltages of abrupt and linearly graded p-n junctions in Ge, Si, GaAs and GaP," Appl. Phys. Lett., vol. 8, p. 111, 1966.

Hiroshi Mizuta was born in Kochi, Japan, in 1961. He received the B.S. and M.S. degrees in physics from Osaka University, Osaka, Japan, in 1983 and 1985, respectively.

Since 1985, he has been working for the Central Research Laboratory, Hitachi Ltd., Tokyo, Japan, on GaAs MESFET's. His current research interests are on compound hetero devices and device analysis.

Mr. Mizuta is a member of the Physical Society of Japan and the Japan Society of Applied Physics.

Ken Yamaguchi (M'76) was born in Tokyo, Japan, in 1947. He received the B.Sc. and M.Sc. degrees from Yokohama National University, Yokohama, Japan, in 1970 and 1972, respectively, and the Ph.D. degree from the University of Tokyo, Tokyo, Japan, in 1980, all in electrical engineering.

He joined the Central Research Laboratory, Hitachi Ltd., in 1972, and has been working in the field of semiconductor device design technologies. His current research interests are in device

physics, device modelings, simulation technologies, and CAD systems for

designing semiconductor devices and circuits.

Dr. Yamaguchi is a member of the Physical Society of Japan, the Japan Society of Applied Physics, the Institute of Electronics and Communication Engineers of Japan, and the Electron Devices Society of the IEEE.

Susumu Takahashi was born in Iwate, Japan, in 1944. He received the B.Sc. degree in physics from the University of Hirosaki, Hirosaki, Japan, in 1967 and the Ph.D. degree in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1979.

Since 1967, he has been working for the Central Research Laboratory, Hitachi Ltd., Tokyo, Japan, on low-noise GaAs MESFET's, silicon devices, and GaAs LSI. His current research interests are compound hetero devices and technology.

Dr. Takahashi is a member of the Japan Society of Applied Physics and the Institute of Electronics and Communication Engineers of Japan.