# Fabrication and characterization of nanoscale suspended floating gates for NEMS memory

Nobuyuki Momo<sup>1</sup>, Tasuku Nagami<sup>1</sup>, Shinnosuke Matsuda<sup>1</sup>, Yoshishige Tsuchiya<sup>1,4</sup>, Shinichi Saito<sup>2</sup>, Tadashi Arai<sup>2</sup>, Yoshinobu Kimura<sup>2</sup>, Toshikazu Shimada<sup>2</sup>, Hiroshi Mizuta<sup>3,4,\*</sup>, and Shunri Oda<sup>1,3,4</sup>

<sup>1</sup> Quantum Nanoelectronics Research Center, Tokyo Institute of Technology,

2-12-1, O-okayama, Meguro-ku, Tokyo 152-8552, Japan

<sup>2</sup>Central Research Laboratory, Hitachi Ltd., Tokyo, Japan

<sup>3</sup>Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan

<sup>4</sup>SORST, JST, Tokyo, Japan

\*Phone: +81-3-5734-2542 FAX: +81-3-5734-2542 E-mail: mizuta@pe.titech.ac.jp

## Introduction

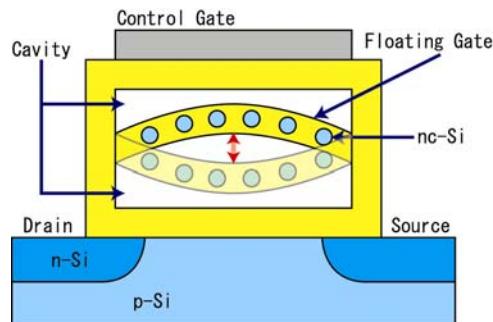

Recent progress of silicon nanofabrication techniques has enabled not only to realize the MOSFETs with sizes of decanometer but also to explore a new field of silicon Nano Electro-Mechanical Systems (NEMS). We proposed a new non-volatile memory device concept based on a mechanically-bistable floating gate (FG) suspended in the cavity, which incorporates nanocrystalline Si (nc-Si) dots (Fig.1)[1]. We have already succeeded in fabricating a 3- $\mu$ m-large suspended SiO<sub>2</sub> beam with mechanical bistability[1]. In this paper we report on fabrication of various suspended FG structures with a top control gate. We also analyze the mechanical stress caused by the buckled FG by using Micro Raman Scattering Spectroscopy.

## Fabrication of the double layered floating gate

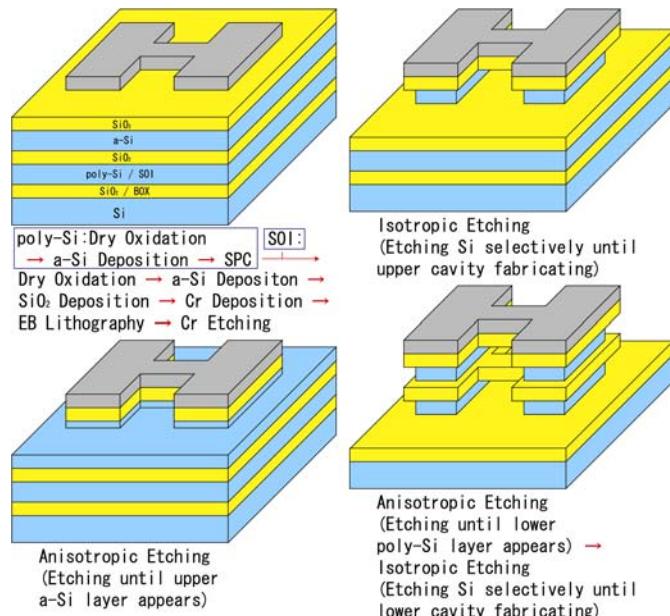

We examined fabricating the double layered structures consisting of the suspended FG (without nc-Si dots) and the control gate by using both bulk-Si and SOI for substrates (see Fig. 2). For the bulk-Si substrate we first oxidized the Si substrate surface and deposited amorphous Si on the SiO<sub>2</sub> and then performed SPC(Solid Phase Crystallization). We oxidized the poly-Si surface again and deposited a-Si, SiO<sub>2</sub> and Cr sequentially to make the Si/SiO<sub>2</sub>/Si/SiO<sub>2</sub>/Si/SiO<sub>2</sub>/Cr stacked structure. For the SOI substrate we took the same processes above except the first oxidation, a-Si deposition and SPC. The same device fabrication processes were used for the both wafers after the stacked structures were prepared. Control gate patterning was performed by using EB lithography and Cr etching. For fabricating the upper and lower cavities, we adopted two different dry etching. The top SiO<sub>2</sub> layer was patterned by anisotropic etching with the control gate as a mask, and then the underneath Si sacrifice layer was etched out by using isotropic etching which have a high Si/SiO<sub>2</sub> etching selectivity. By repeating the same etching process, we fabricated the upper and lower cavities.

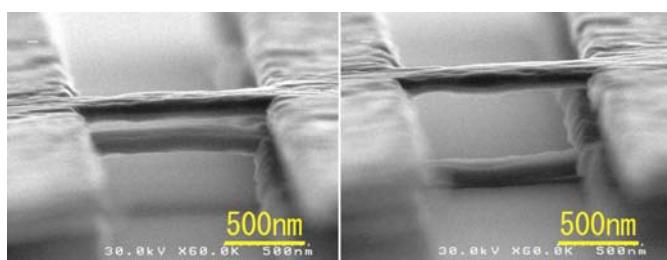

For the both layered structures we succeeded in fabricating the double layered structures and observed both upward and downward bent FGs (Figs. 3 and 4). However, we also observed a remarkable difference in the shape of the bent FGs for the two structures in Figs. 3 and 4. For the SOI based structures (Fig.4), bending was seen only across the beam part. On the other hand, for the poly-Si based structures (Fig. 3), the pad area supporting the beam was also deformed in addition to the beam

bending. We also noticed that about 90% beams showed the upward bending for the SOI based samples while the poly-Si based samples show completely random bending (50% upward and 50% downward). It is likely that the structural difference found here is caused by whether the SiO<sub>2</sub> beam was fabricated by oxidizing bulk-Si(SOI) or poly-Si. From the stand-point of device design, the SOI based beam with good structural control is preferred, and we therefore adopted it in the following experiments.

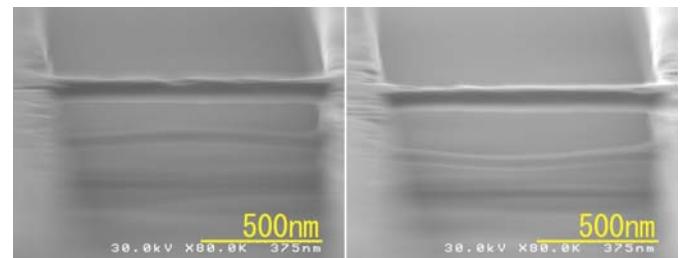

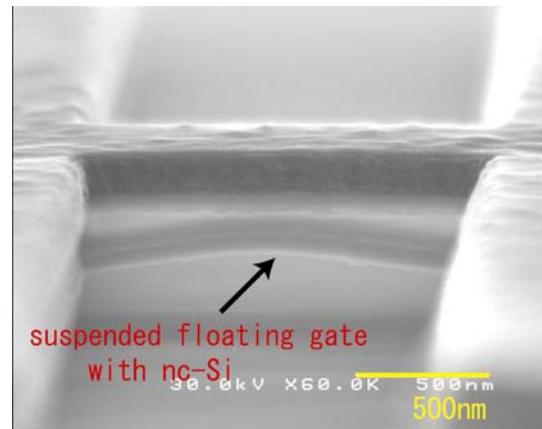

We finally fabricated the double layered structure with the FG which contains the nc-Si dots. The FG layer was made by performing SOI oxidation, nc-Si deposition and SiO<sub>2</sub> deposition. We succeeded in fabricating the nc-Si embedded FG structure as shown in Fig.5. We found that the degree of bending is slightly smaller for the nc-Si embedded FG structure than that for the reference structure without the nc-Si dots. We also found that the nc-Si embedded FGs exhibit only the upward bending. This is presumably caused by the different mechanical properties of the top SiO<sub>2</sub> deposited onto the nc-Si dots. This hypothesis was confirmed by the AFM observation that showed surface roughness of the top SiO<sub>2</sub> due to the embedded nc-Si dots.

## Mechanical stress characterization

Next we characterized the mechanical stress caused by the suspended FG by using Micro Raman Scattering Spectroscopy. When either tensile or compressive stress is applied to Si, Si Raman frequency shifts from its stress-free value. The relation between the shift of Raman frequency and the stress is given as follows [2],

$$\sigma[\text{MPa}] = 434\Delta\omega[\text{cm}^{-1}]$$

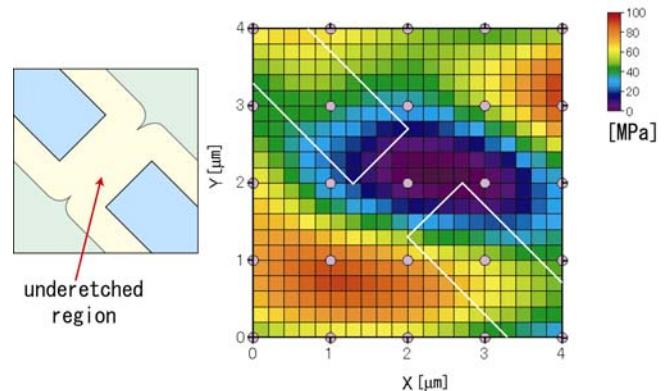

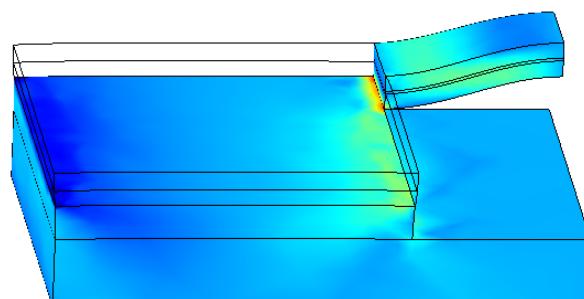

where  $\Delta\omega > 0$  for tensile stress and  $\Delta\omega < 0$  for compressive stress. We scanned a 5 $\mu$ m  $\times$  5 $\mu$ m area on and around the beam part every 1 $\mu$ m step. We prepared three different FG samples: (a) without underetching, (b) half underetched and (c) fully underetched. The sample without underetching did not show any remarkable stress distribution. The half and fully underetched samples, however, showed tensile stress of about 100MPa around both ends of the beams (Fig.6). These results are qualitatively consistent with the stress distribution calculated by using the 3D FEM mechanical simulation (Fig. 7).

## Summary

We succeeded in fabricating the double layered structure

which have the suspended FG and the control gate. We compared the difference in the geometry of the SOI-based and poly-Si-based FGs and found superior structural controllability for the SOI-based structures. Based on these findings we finally succeeded in fabricating the double layered structure with the FG which contains the nc-Si dots. We also characterized the stress distribution around the suspended FG for the first time by using Micro Raman Scattering Spectroscopy.

## References

- [1] Y.Tsuchiya *et al.*, Abstr.of Si Nanoelectronics Workshop, p.101 (2004)

- [2] Ingrid De Wolf, J. Raman Spectrosc. **30**, 877, (1999)

Fig.1: A schematic illustration of a NEMS memory device

Fig.2: Process steps of double layer structure

Fig.3: Double layer structure using poly-Si

Fig.4: Double layer structure using SOI

Fig.5: Double layer structure with nc-Si

Fig.6: Stress distribution of fully underetched sample

Fig.7: Stress distribution calculated by using 3D FEM simulation. Only a quarter of the whole structure is shown.