# Investigation of variable coupling and current percolation paths in nanocrystalline silicon cross transistors

<sup>1</sup>**M. A. H. Khalafalla, <sup>1</sup>H. Mizuta, <sup>1</sup>S. Oda and <sup>2</sup>Z. A. K. Durrani**

1. *Quantum Nanoelectronics Research Centre, Tokyo Institute of Technology, O-Okayama, Meguro-ku, Tokyo 152-8552, Japan. Tel/Fax: +81 3 5734 3591, E.mail: mizuta@pe.titech.ac.jp*

2. *Department of Engineering, University of Cambridge, Trumpington Street, Cambridge CB2 1PZ, U.K.*

Nanocrystalline silicon thin films are promising materials for the development of advanced Large Scale Integration compatible quantum-dot and single-electron charging devices [1]. The films consist of nanometer-scale grains of crystalline silicon, separated by amorphous silicon or silicon dioxide grain boundaries up to a few nanometer thick. These films have been used to fabricate single-electron transistor [1] and memory devices [2], where the grains form single-electron charging islands isolated by tunnel barriers formed by the grain boundaries. The grain boundary tunnel barrier isolating the grains is also of great importance, as this determines the extent of the electrostatic and tunnel coupling between different grains. These effects can lead to the nanocrystalline silicon thin film behaving as a system of coupled quantum dots [3, 4].

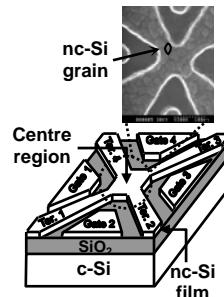

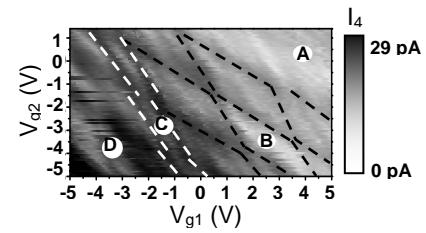

A novel nanocrystalline silicon ‘cross’ transistor (Fig. 1, approximately 70 nm  $\times$  70 nm  $\times$  40 nm), with four side gates and four leads, have been used to study the variation of the electrostatic coupling between the nanocrystalline silicon grains (10 nm to 35 nm in size) as a function of the gate voltages, and to determine the locations of dominant charging grains along the electron current percolation paths. This device allows us to investigate the transition in the conductance mechanism, from conduction through a few grains to conduction through a larger number of grains (Fig. 2). Under an extensive characterization of the currents through the four leads with systematic variation of the biasing conditions and gate voltages, Coulomb oscillation features from different major grains could be identified and from the overall set of measurements the actual locations of these grains on the central cross region of the device could be estimated. It appears from these experiments, that major percolation paths between the different leads and across the central region are established.

## References:

- [1] Y. T. Tan, T. Kamiya, Z. A. K. Durrani, and H. Ahmed, *Appl. Phys. Lett.*, **78**, 1083 (2001).

- [2] K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai, and K. Seki, *IEEE Trans. Electron Devices*, **41**, 1628 (1994).

- [3] M. A. H. Khalafalla, H. Mizuta, and Z. A. K. Durrani, *IEEE Trans. Nanotechnology*, **2**, 271 (2003).

- [4] M. A. H. Khalafalla, Z. A. K. Durrani and H. Mizuta, *Applied Physics Letters*, **85**, 2262 (2004).

**Fig. 1.** Schematic of a nanocrystalline silicon (nc-Si) cross transistor. Inset: SEM of a nc-Si cross transistor.

**Fig. 2.** Current at terminal 4 (Ter.4) versus gate voltages,  $V_{g1}$  and  $V_{g2}$  at  $V_{g3} = V_{g4} = 0$  V and  $T = 4.2$  K. The grains couple differently at regions A, B, C, and D.