## Negative Differential Conductance and Threshold Voltage Distribution in Two-island Single-electron Tunnelling Structures

Gareth J. Evans<sup>1</sup> and Hiroshi Mizuta<sup>2</sup>

<sup>1</sup>*Microelectronics Research Centre, Cavendish Laboratory, Cambridge CB3 OHE, UK*

<sup>2</sup>*Hitachi Cambridge Laboratory, Cavendish Laboratory, Cambridge CB3 OHE, UK*

A huge variety of experimental devices have shown Coulomb Blockade (CB) effects in systems ranging from metal-insulator-metal systems to semiconductor dots produced by electrostatic, geometric or dopant fluctuation confinement. In principle, CB effects allow current flow to be manipulated on a *per electron basis* and has attracted attention as a possible future ULSI technology.

Single-island systems, which are called Single Electron Transistors (SETs), have well-understood simple characteristics. However, the next logical extension, a two-island system, exhibits a huge variety of complex characteristics (for example see [1]).

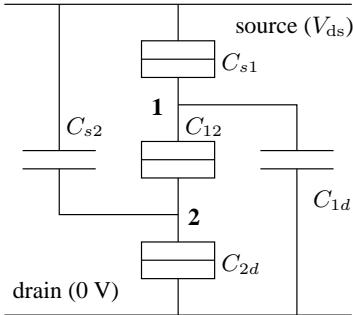

This paper describes the analysis of the two-island system in Figure 1 and relates its behaviour to the development of its two-dimensional phase space ( $\tilde{q}$ ) as the source-drain voltage  $V_{ds}$  changes. We propose a geometrical approximation called *the polytope approximation* to track the changes in phase space. (A *polytope* is a finite volume polyhedron and for the two-island case is a polygon.)

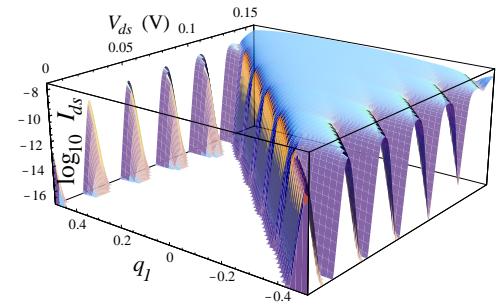

As an example of the variety of behaviour possible for two-island systems, we demonstrate a device that exhibits strong negative differential conductance (NDC) shown in Figures 2 and 3. Interestingly, this NDC is *not* connected to discrete quantum energy levels but due to the charging energy considerations. Previously, Nakashima et al. have shown NDC to exist in linear arrays of seven- and nine-island systems [2,3], while Heij et al. [4] demonstrated a two-island system that exhibited NDC. Shin et al. [5] have also shown that NDC can exist in ring-arrays of junctions. Our two-island system is most similar to Nakashima et al.'s device and the polytope approximation lets us derive the following necessary condition for NDC,

$$\frac{C_{1d}}{C_{s1}} > \frac{C_{2d}}{C_{s2}}$$

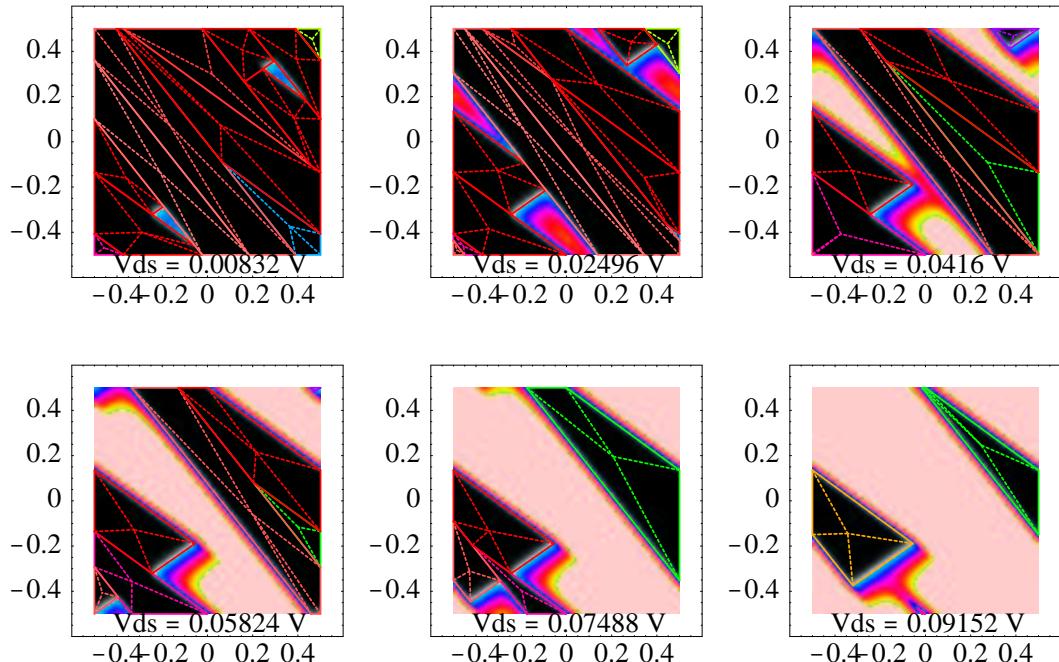

Figure 2 demonstrates that NDC exists only when the offset-charge or gate biases are tuned to the correct part of phase space. The offset-charge problem makes a system's characteristics very unpredictable. Assuming that the offset charge is uniformly distributed in the range  $-0.5e$  to  $+0.5e$  then the threshold voltage distribution for a structure can be calculated from the polytope approximation as shown in Figure 4 and the actual polytopes are shown in Figure 5, where regions less than 1 fA are black.[6,7]

- [1] G. Y. Hu and R. F. O'Connell, *J. Phys.: Condens. Matter* **5** 7259 (1993)

- [2] H. Nakashima and K. Uozumi, *Jpn. J. Appl. Phys.* **34** L1659 (1995)

- [3] H. Nakashima and K. Uozumi, *J. Vac. Sci. Tech. B* **15** (4) 1411 (1997)

- [4] C. P. Heij, D. C. Dixon, P. Hadley and J. E. Mooij, *Appl. Phys. Lett.* **74** (7) 1042 (1999)

- [5] M. Shin, S. Lee, K. Park and El-H. Lee, *J. Appl. Phys.* **84** (5) 2974 (1998)

- [6] G. J. Evans, H. Mizuta and H. Ahmed, *Jpn. J. Appl. Phys.* **40** 5837 (2001)

- [7] G. J. Evans, *Transport in Silicon Nanowires*, PhD Thesis (submitted 2001), University of Cambridge

Figure 1: The two island circuit under analysis. This is the most general two-island *linear* array possible.

Figure 2:  $\log_{10}[I_{ds}]$  as a function of  $V_{ds}$  and the offset charge on island 1. Changing the offset charge on island 2 from  $-0.5$  to  $0$  roughly changes the phase of the oscillations by  $\pi$ .

Figure 3: Part of Fig. 2 in the NDC region at temperatures from  $8.2$  K (top) to  $1.2$  K in  $1$  K steps. Vertical lines are predictions of the valley positions and the solid lines of valley currents.

Figure 4: Threshold voltage distribution for a non-NDC circuit. The line is the polytope approximation's prediction and the dots are from a Monte Carlo simulation of the device.

Figure 5: The current as a function of  $\tilde{q}$  at the  $V_{ds}$  corresponding to the vertical lines in Figure 4. The polytopes are marked with solid lines and their interiors indicated with dashed lines.