# High-Quality Schottky Contacts for Limiting Leakage Currents in Ge-Based Schottky Barrier MOSFETs

Muhammad Khaled Husain, Xiaoli V. Li, Member, IEEE, and Cornelis Hendrik de Groot, Senior Member, IEEE

Abstract—Schottky barrier (SB) Ge channel MOSFETs suffer from high drain-body leakage at the required elevated substrate doping concentrations to suppress source-drain leakage. Here, we show that electrodeposited Ni-Ge and NiGe/Ge Schottky diodes on highly doped Ge show low off current, which might make them suitable for SB p-MOSFETs. The Schottky diodes showed rectification of up to five orders of magnitude. At low forward biases, the overlap of the forward current density curves for the as-deposited Ni/n-Ge and NiGe/n-Ge Schottky diodes indicates Fermi-level pinning in the Ge bandgap. The SB height for electrons remains virtually constant at 0.52 eV (indicating a hole barrier height of 0.14 eV) under various annealing temperatures. The series resistance decreases with increasing annealing temperature in agreement with four-point probe measurements indicating the lower specific resistance of NiGe as compared to Ni, which is crucial for high drive current in SB p-MOSFETs. We show by numerical simulation that by incorporating such high-quality Schottky diodes in the source/drain of a Ge channel PMOS, a highly doped substrate could be used to minimize the sourceto-drain subthreshold leakage current.

Index Terms—Electrodeposition, leakage current, Schottky barrier (SB) MOSFET.

### I. Introduction

OR FUTURE high-speed CMOS technology, Ge channel MOSFETs are considered. MOSFETs are considered as promising devices as they offer high carrier mobilities suitable for large drive current. Schottky barrier (SB) source/drain MOSFETs overcome the problems faced by the conventional transistor scaling caused by the stringent conditions required for doping with low series resistance [1]-[3]. The Ge-based SB p-MOSFETs, however, suffer from increased leakage currents due to their narrow bandgap and low SB height [4]-[6]. We have recently shown that Ni-Si diodes prepared by electrodeposition exhibit superior properties to physical-vapor-deposition-prepared diodes [7], [8]. In this paper, we show that electrodeposited Ni-Ge and NiGe-Ge Schottky diodes on highly doped Ge exhibit nearideal SB behavior with low off current. The experimental data of the diodes are used to calibrate numerical simulations of the Ge SB MOSFET. At short channel lengths, SB MOSFETs

Manuscript received July 16, 2008; revised October 17, 2008. First published February 3, 2009; current version published February 25, 2009. The review of this paper was arranged by Editor C.-Y. Lu.

The authors are with the Nanoscale Systems Integration Group, School of Electronics and Computer Science, University of Southampton, SO17 1BJ Southampton, U.K. (e-mail: mkh05r@ecs.soton.ac.uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2008.2011724

suffer from source-to-drain leakage currents. We show that a highly doped Ge substrate is the key to limiting source-to-drain subthreshold leakage currents. The low off current of the electrodeposited SBs on highly doped substrate might make this possible without increasing the junction leakage current at the drain/body of SB p-MOSFETs.

# II. EXPERIMENTAL TECHNIQUES

For the fabrication of Ni–Ge SBs, Antimony-doped Ge (100) wafers were taken as the starting materials. Square patterns of sizes from 10 to 400  $\mu$ m were transferred to the photoresistcoated substrates by conventional lithography. The back ohmic contacts were defined by Au-Sb evaporation and annealing the samples in an  $H_2/N_2$  inert atmosphere. Subsequently, a 20:1 buffered HF dip for 30 s, followed by DI water dip, was performed to remove any native oxides. For electrodeposition, a Ni sulphate bath and an Autolab AUT72032 potentiostat threeelectrode system with a Pt counter electrode and a saturated calomel reference electrode (SCE) were used. The deposition potential ranged from 1.10 to 1.15 V (against the SCE) for the various Ge substrates. The film thickness was monitored during electrodeposition by observing the charge accumulated at the cathode. Current (I)-voltage (V) and capacitance (C)-voltage (V) characteristic measurements were performed using a Hewlett Packard 4155A semiconductor parameter analyzer and a Hewlett Packard 4280 A, 1 MHz, C Meter/C-V plotter. Germanidation of the Ni films was performed for 20 min in the anneal chamber at temperatures ranging from 300 °C to 500 °C. The various film thicknesses were measured using scanning electron microscopy (SEM) on a cross section of the electrodeposited film.

# III. EXPERIMENTAL RESULTS

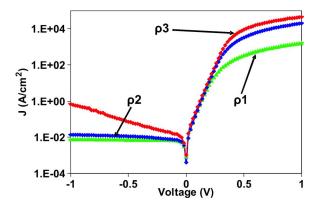

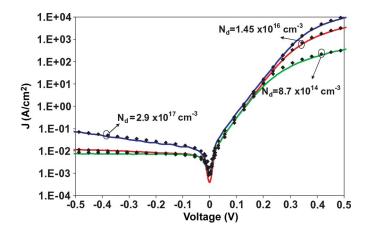

Typical current density (J) versus applied voltage (V) characteristics of electrodeposited Ni–Ge SBs for the three different substrate resistivities ( $\rho 1 = 2-2.4~\Omega \cdot {\rm cm},~\rho 2 = 0.13-0.15~\Omega \cdot {\rm cm},$  and  $\rho 3 = 0.005-0.02~\Omega \cdot {\rm cm})$  and of 10- $\mu {\rm m}^2$  contact area are shown in Fig. 1.

A high-quality rectifying behavior is observed for the SBs. For the highly resistive  $(\rho 1)$  Ge, excellent SBs are achieved with very low reverse bias current, being five orders of magnitude smaller than the forward bias current at 1-V bias. Tunneling effects of this SB are negligible in the reverse bias. SBs on the medium resistive  $(\rho 2)$  Ge showed similar rectifying

Fig. 1. J-V characteristics of the Ni/Ge Schottky diodes (10- $\mu$ m $^2$  contact) as a function of Ge resistivities ( $\rho$ 1 = 2-2.4  $\Omega$  · cm,  $\rho$ 2 = 0.13-0.15  $\Omega$  · cm, and  $\rho$ 3 = 0.005-0.02  $\Omega$  · cm).

TABLE I Extracted  $\phi_n, \eta, R_s$  (From J-V Method) and  $\phi_n, N_d$ , Substrate Resistivity (C-V Method) of the Ni/Ge Schottky Diodes

| Resistivity Label $\Rightarrow$ | $\rho$ 1             | $\rho$ 2              | $\rho$ 3        |

|---------------------------------|----------------------|-----------------------|-----------------|

| η                               | 1.12                 | 1.04                  | 1.09            |

| $R_s(\Omega)$                   | 30.77                | 16.05                 | 11.72           |

| $\phi_n  (\text{eV})$           | 0.52                 | 0.53                  | 0.52            |

| (from J-V)                      |                      |                       |                 |

| $\phi_n  (\text{eV})$           | 0.56                 | 0.53                  | 0.53            |

| (from C-V)                      |                      |                       |                 |

| $N_d$ (cm <sup>-3</sup> )       | $8.7 \times 10^{14}$ | 1.45x10 <sup>16</sup> | $2.9 x 10^{17}$ |

| Resistivity (Ω-cm)              | 2-2.4                | 0.13-0.15             | 0.005-0.02      |

| (nominal)                       |                      |                       |                 |

| Resistivity (Ω-cm)              | 1.84                 | 0.11                  | 0.006           |

| (from C-V)                      |                      |                       |                 |

behavior with a little tunneling current in the reverse direction. On the lowly resistive substrate ( $\rho$ 3), Ni/Ge SB showed increased tunneling effects in the reverse bias. However, even these diodes showed excellent rectifying behavior with the reverse bias current of the diodes at the lowly resistive  $(\rho 3)$ substrate, still being five orders of magnitude smaller than the forward bias current. All currents can be explained by standard thermionic emission (TE) and, additionally, thermionic field emission (TFE) theory for the reverse bias. We will show in the following section by numerical simulation that both forward and reverse bias currents are dominated by electron transport. This is a significant improvement over a similar work done in literature [9], [10] where Schottky diodes grown by evaporation technique exhibited rectification of only 2-3 orders even on highly resistive Ge substrates. Breakdown of the diodes was not observed up to -3-V bias, indicating that edge effects are suppressed as explained in our previous work [11].

From the J-V curves in Fig. 1, the Ni/Ge Schottky electron barrier height  $(\phi_n)$ , ideality factor  $(\eta)$ , and series resistance  $(R_s)$  can be extracted, assuming the TE model in the forward bias [12]. The calculated SB parameters are shown in Table I for all types of substrates. For these calculations, Richardson constant  $(A^*)$  of 50 A  $\cdot$  cm<sup>-2</sup>  $\cdot$  K<sup>-2</sup> [13], [14] was used. It is seen from Table I that the SB heights are virtually constant for the Ge substrates of various resistivities. The low ideality factors indicate TE to be the dominant current conduction mechanism in the forward bias for the SBs on different substrates.

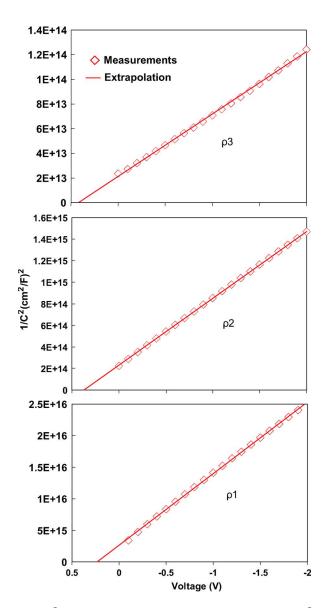

Fig. 2.  $C^{-2}-V$  curve of an electrodeposited Ni–Ge contact (400  $\mu$ m²) for various substrate resistivities ( $\rho 1=2-2.4~\Omega\cdot {\rm cm},~\rho 2=0.13-0.15~\Omega\cdot {\rm cm},$  and  $\rho 3=0.005-0.02~\Omega\cdot {\rm cm}).$

C-V measurements of SBs on Ge were performed for  $A^*$ independent measurement of the SB height. Inverse square capacitance versus voltage characteristics are shown in Fig. 2 for SBs on Ge substrates of various resistivities and having a contact area of 400  $\mu$ m<sup>2</sup>. As expected, a straight line is observed, and from its intercept on the voltage axis, the SB height  $(\phi_n)$  is calculated [15]. Furthermore, from the slope of this characteristic, the Ge doping concentration  $(N_d)$  can be determined. For example, a value of  $2.9 \times 10^{17}$  cm<sup>-3</sup> for  $N_d$  is obtained corresponding to a resistivity of 0.006  $\Omega \cdot \text{cm}$ , which matches the specification of the Ge substrate. Similar C-V measurements were performed on SBs on the medium (0.13–0.15  $\Omega$  · cm) and highly (2–2.4  $\Omega$  · cm) resistive Ge and barrier heights  $(\phi_n)$  of 0.53 and 0.56 eV, respectively, and substrate doping densities of  $1.45 \times 10^{16}$  and  $8.7 \times 10^{14}$  cm<sup>-3</sup> were obtained. The barrier heights obtained are in good agreement with those obtained from the I-V measurements as observed in Table I.

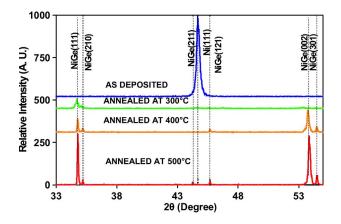

Fig. 3. XRD spectra for the as-deposited and annealed Ni/Ge samples showing transformation from Ni to NiGe.

The electrodeposited Ni films on Ge (0.005–0.02  $\Omega \cdot \text{cm}$ ) were annealed for 20 min at temperatures ranging from 300 °C to 500 °C to investigate their Germanidation mechanism. Phase identification and crystallographic structure determination were carried out using XRD with Cu K $\alpha$  radiation ( $\lambda = 1.5418 \text{ Å}$ ) in a  $\theta$ -2 $\theta$  geometry. Fig. 3 shows the XRD spectra for asdeposited and annealed Ni/Ge samples for initial Ni thicknesses of 70 nm. The initial Ni (111) peak at 44.68° completely disappears after annealing, indicating complete reaction of the Ni film with Ge. Peaks at 34.8°, 35.2°, 44.2°, 45.7°, 53.8°, and 54.4° are observed when the sample was annealed at 500 °C. These peaks are in excellent agreement with the  $\theta$ -2 $\theta$  pattern of the NiGe JCPDS standard. The peaks were identified as NiGe(111), (210), (211), (121), (002), and (301). No peaks corresponding to other Ni-Germanides, e.g., Ni<sub>2</sub>Ge, NiGe<sub>2</sub>, etc., are observed. This clearly shows only polycrystalline Ni-mono-Germanide (NiGe) phase forms at the annealing temperatures. The lattice constants of the formed NiGe are determined to be a = 5.81 Å, b = 5.37 Å, and c = 3.40 Å from the XRD spectra,in agreement with the reported values [16], [17].

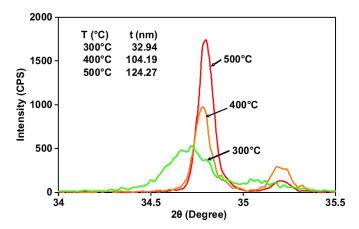

For the 300-°C annealed samples, the NiGe peaks are very weak, while after 400-°C annealing, the peaks become quite strong. The crystallite size (t) of the grown NiGe(111) was investigated by taking further XRD scan within close intervals surrounding the peak. These are shown in Fig. 4 as a function of annealing temperature (T). The crystallite sizes are calculated from the peaks using the Scherrer relation

$$t = \frac{0.9\lambda}{d\cos\theta} \tag{1}$$

where d is the broadening of the peaks due to the crystallite size. It was observed that t increases with increasing T.

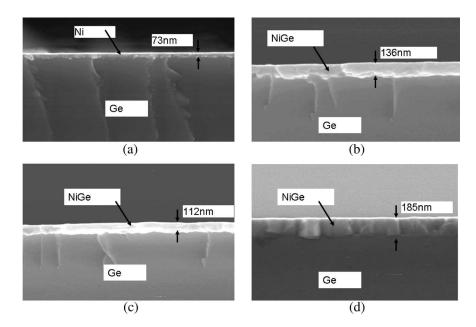

The variation of thickness of the Ni and Ni–Ge films as a function of annealing temperature (T) was determined by SEM as shown in Fig. 5. This thickness is seen to increase with increasing T. Theoretically, the ratio of the atomic volume of NiGe and Ni is 2.44. As shown in Fig. 5, the ratio of the film thickness of NiGe at 500 °C to that of Ni is 2.53. This confirms complete reaction of the 70-nm Ni and formation of NiGe at that temperature.

Fig. 4. XRD spectra showing the NiGe(111) peak of the Ni(70 nm)/Ge samples when annealed at various temperatures. The calculated crystallites are presented in the inset.

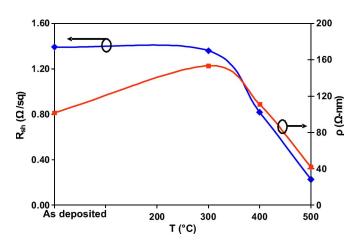

In order to further exploit the Germanidation mechanism, the sheet resistance  $(R_{\rm sh})$  of the grown films was measured using the four-point probe method. The obtained  $R_{\rm sh}$  values were multiplied by the film thicknesses to calculate the film resistivities  $(\rho).$  The results are plotted as a function of annealing temperatures in Fig. 6. It is observed that  $R_{\rm sh}$  decreased with increasing T. The measured  $R_{\rm sh}$  of NiGe is 0.23  $\Omega/{\rm sq}$  when annealed at 500 °C. The low  $R_{\rm sh}$  could be attributed to the increase in crystallite size at 500 °C as shown in Fig. 4. The resistivity of Ni–Ge also decreased when the films were annealed above 300 °C.

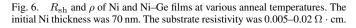

Typical current (I) versus applied potential (V) characteristics of the grown Ni(70 nm)/Ge Schottky diodes under the as-deposited and annealed conditions on lowly resistive  $(0.005-0.02~\Omega \cdot \text{cm})$  Ge are shown in Fig. 7 for a contact pad size of  $20~\mu\text{m}^2$ .

A high-quality rectifying behavior (4–5 orders in magnitude) is observed for all annealing conditions. Again,  $\phi_n$ ,  $\eta$ , and  $R_s$  are calculated, assuming the TE model in the forward bias region, and are presented in Table II. The values of  $\phi_n$  are virtually constant at 0.52 eV. Assuming a Ge bandgap of 0.66 eV, the corresponding hole barrier height  $(\phi_n)$  is 0.14 eV. This value is low enough to guarantee a large on current in SB MOSFET. At low forward bias, there is a considerable overlap of the current curves of the nonannealed Ni-Ge and NiGe-Ge samples as shown in Fig. 7. This indicates both thermal stability and Fermi-level pinning in the Ge bandgap as the barrier height is independent of the metal work function. The reverse current at 1-V bias is 1  $\mu$ A for the various annealed diodes. This is a significant achievement as this value is more than an order of magnitude smaller than the reported value in literature [10] for NiGe/Ge diodes formed by evaporation on highly resistive  $(4-6 \Omega \cdot cm)$  Ge.

The low values of ideality factor for the Schottky diodes presented in Table II indicate TE to be the dominant current conduction mechanism in the forward bias. The series resistance decreases with increasing T (see the inset of Fig. 7), indicating a lower specific resistance of NiGe than Ni. This is consistent with the four-point probe measurement shown in Fig. 6.

Fig. 5. Cross-sectional SEM images of the various Ni/Ge samples: (a) As-deposited, (b) annealed at 300 °C, (c) annealed at 400 °C, and (d) annealed at 500 °C.

Fig. 7. I-V characteristics of the Ni/Ge Schottky diodes, having a contact area of 20  $\mu$ m², as a function of annealing temperatures. Ge resistivity was 0.005–0.02  $\Omega$  · cm. The high forward bias region is magnified in the inset.

# IV. SB MOSFET SIMULATION

The commercial TCAD simulator Sentaurus Device from Synopsys has been used for the simulation work that provided a self-consistent and fully coupled implementation of nonlocal tunnelling models of both electrons and holes. The devices were generated using Sentaurus Structure Editor and its Meshing engine. The simulator was, at first, calibrated by using the SB heights and the various experimental doping densities  $(N_d)$ of the substrates obtained by the C-V methods which were presented in Table I. To account for the substrate series resistances in the experimental results, systematic 3-D simulations of the actual substrate size and thicknesses were performed for a  $10-\mu \text{m}^2$  pad. The corresponding calculated J-V curves for the various substrate doping densities are shown in Fig. 8 along with the experimental curves. Separation of the electron and hole currents in the simulation (not shown) indicates that holes play a negligible role in the reverse and forward bias currents. The concordance of the experimental and simulated

TABLE II EXTRACTED  $\phi_n$ ,  $\eta$ , and  $R_s$  of the Ni/Ge Schottky Diodes With 20- $\mu\mathrm{m}^2$  Contact Area as a Function of Annealing Temperature (T)

| T(°C) | $\phi_n  (\mathrm{eV})$ | η    | $R_s(\Omega)$ |

|-------|-------------------------|------|---------------|

| None  | 0.52                    | 1.1  | 21.32         |

| 300   | 0.52                    | 1.27 | 14.79         |

| 400   | 0.55                    | 1.13 | 11.83         |

| 500   | 0.55                    | 1.08 | 10.85         |

current density curves at the various conditions confirms the full calibration of the simulator tool to both TE and TFE.

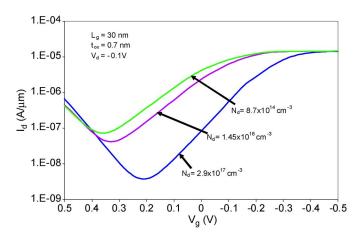

To accurately model the SB MOSFET, a fully coupled 2-D simulation was performed that included physical models, e.g., bandgap narrowing effect and dependence of mobility to normal electric field. The drain current  $(I_d)$  versus gate voltage  $(V_g)$  characteristics for a bulk SB PMOS with channel length  $(L_g)$  of 30 nm and gate oxide thickness  $(t_{\rm ox})$  of 0.7 nm are calculated as a function of various substrate doping densities

Fig. 8. J-V characteristics (dotted lines) for 10- $\mu$ m Ni/Ge contacts for various doping density modeled by Sentaurus Device simulator tool. The corresponding experimental curves (solid lines) are also presented for reference.

Fig. 9. Simulated transfer characteristics of 30-nm Ge channel bulk SB PMOS devices showing the effect of increasing substrate doping density on leakage currents.

$(N_d)$  and are shown in Fig. 9. The source-to-drain subthreshold leakage current can be readily obtained from the curves at  $V_g=0$ . It is found that for a fixed drain bias  $(V_d)$  of -0.1 V, the leakage current is  $4.5\times 10^{-6}$  A/ $\mu$ m when Ge n-type doping density of  $8.7\times 10^{14}$  cm<sup>-3</sup> was used. However, the leakage currents decreased to  $2.1\times 10^{-6}$  and  $8.1\times 10^{-8}$  A/ $\mu$ m when the substrate doping densities were increased to  $1.45\times 10^{16}$  and  $2.9\times 10^{17}$  cm<sup>-3</sup>, respectively. Therefore, we propose that a highly doped Ge substrate could be used for a low-leakage SB MOSFET. At higher positive gate voltages, the leakage current is observed to increase for the various substrate doping densities. This is attributed to the ambipolar behavior typical of an SB MOSFET that results in a gate-induced-drain-leakage (GIDL)-like current. For higher drain voltages, e.g.,  $V_d=-1$  V, this leakage current is very high.

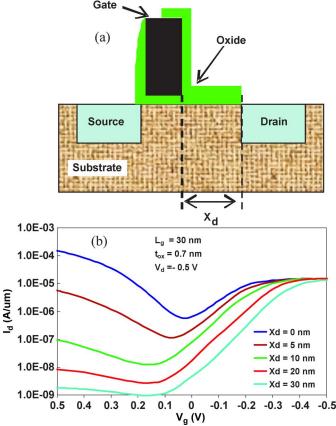

There are several methods available to suppress the GIDL-like leakage in SB MOSFETs. One method uses a field-induced drain extension [18] located between the channel and the Schottky drain. This leakage current could also be alleviated by using a recessed channel and asymmetric source/drain Schottky contacts [19]. As an alternative to these methods, an offset gate structure shown in Fig. 10(a) could be used for a 30-nm gate

Fig. 10. (a) Schematic representation of the SB PMOS structure with gate offset.  $X_d$  is the length of offset region from the drain. (b) Transfer characteristics of 30-nm Ge channel bulk SB PMOS devices for various  $X_d$  showing the effect of gate offset on leakage currents.

length device. Here, the effect of the gate bias responsible for the hole conduction is reduced by increasing the distance  $(X_d)$  between the edges of the gate and the drain.

Here, we perform numerical simulation to investigate the effect of the offset gate structure in the bulk SB PMOS.  $I_d$  versus  $V_g$  characteristics, with  $L_g = 30$  nm,  $t_{ox} = 0.7$  nm, and  $N_d =$  $2.9 \times 10^{17}$  cm<sup>-3</sup>, are calculated for  $V_d = -0.5$  V as a function of various  $X_d$  and are shown in Fig. 10(b). It is observed that for the highly doped substrate, the leakage current is extremely high for a conventional bulk SB PMOS ( $X_d = 0$ ). As the gate offset from the drain is increased, superior p-channel device performance is realized on the Ge SB MOSFET. It can be seen that not only the hole conduction is gradually eliminated but also the OFF-state source-drain subthreshold leakage current is also decreased with increasing  $X_d$ . The parasitic resistance with increasing  $X_d$ , however, has not decreased the on current. This is due to the domination of the source-to-channel tunnel resistance over the resistances in the current conduction path. Therefore, by using the offset-gate structure, the off current of the SB MOSFET could be significantly reduced without affecting the on current of the device.

# V. CONCLUSION

We report that Ni/Ge SBs formed by electrodeposition on highly doped substrate show high rectification with low leakage current in reverse bias. The fabricated Ni/Ge diodes transformed into NiGe/Ge diodes upon annealing at 500 °C. Despite the compositional change, the SB properties were virtually unaltered due to Fermi-level pinning. The series resistances of NiGe decreased with annealing temperature which is important for high drive current in SB MOSFETs. By numerical simulation, we are able to show that the source-to-drain subthreshold leakage current could be minimized by using a highly doped Ge substrate. Therefore, we propose that electrodeposition could be used for source—drain formation of a highly doped Ge-based SB MOSFET to achieve low subthreshold leakage current.

### REFERENCES

- C. Koeneke, S. Sze, R. Levin, and E. Kinsbron, "Schottky MOSFET for VLSI," in IEDM Tech. Dig., 1981, vol. 27, pp. 367–370.

- [2] R. Li, S. Lee, H. Yao, D. Chi, M. Yu, and D.-L. Kwong, "Pt-Germanide Schottky source/drain germanium p-MOSFET with HfO<sub>2</sub> gate dielectric and TaN gate electrode," *IEEE Electron Device Lett.*, vol. 27, no. 6, pp. 476–478, Jun. 2006.

- [3] T. Maeda, K. Ikeda, S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi, "High mobility Ge-on-insulator p-channel MOSFETs using Pt germanide Schottky source/drain," *IEEE Electron Device Lett.*, vol. 26, no. 2, pp. 102–104, Feb. 2005.

- [4] J. Larson and J. Snyder, "Overview and status of metal S/D Schottky-barrier MOSFET technology," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 1048–1058, May 2006.

- [5] R. Li, H. Yao, S. Lee, D. Chi, M. Yu, G. Lo, and D. Kwong, "Metal-germanide Schottky source/drain transistor on germanium substrate for future CMOS technology," *Thin Solid Films*, vol. 504, no. 1/2, pp. 28–31, May 2006.

- [6] S. Zhu, R. Li, S. Lee, M. Li, A. Du, J. Singh, C. Zhu, A. Chin, and D. Kwong, "Germanium pMOSFETs with Schottky-barrier germanide s/d, high-κ gate dielectric and metal gate," *IEEE Electron Device Lett.*, vol. 26, no. 2, pp. 81–83, Feb. 2005.

- [7] M. Kiziroglou, A. Zhukov, M. Abdelsalam, X. Li, P. de Groot, P. Bartlett, and C. de Groot, "Electrodeposition of Ni-Si Schottky barriers," *IEEE Trans. Magn.*, vol. 41, no. 10, pp. 2639–2641, Oct. 2005.

- [8] M. Kiziroglou, A. Zhukov, X. Li, D. Gonzalez, P. de Groot, P. Bartlett, and C. de Groot, "Analysis of thermionic emission from electrodeposited Ni-Si Schottky barriers," *Solid State Commun.*, vol. 140, no. 11/12, pp. 509–513, 2006.

- [9] K. Ikeda, T. Maeda, and S. Takagi, "Characterization of platinum germanide/Ge(100) Schottky barrier height for Ge channel metal source/drain MOSFET," *Thin Solid Films*, vol. 508, no. 1/2, pp. 359–362, Jun. 2006.

- [10] S. Zhu and A. Nakajima, "Annealing temperature dependence on nickel–germanium solid-state reaction," *Jpn. J. Appl. Phys.*, vol. 44, no. 24, pp. L753–L755, 2005.

- [11] M. Kiziroglou, X. Li, A. Zhukov, P. de Groot, and C. de Groot, "Thermionic field emission at electrodeposited Ni–Si Schottky barriers," *Solid State Electron.*, vol. 52, no. 7, pp. 1032–1038, Jul. 2008.

- [12] V. W. L. Chin, J. W. V. Storey, and M. A. Green, "P-type PtSi Schottky-diode barrier height determined from *I-V* measurement," *Solid State Electron.*, vol. 32, no. 6, pp. 475–478, Jun. 1989.

- [13] E. Chan and H. Card, "Optoelectronic properties of metal-Ge Schottky barrier quantum detectors," in *IEDM Tech. Dig.*, 1978, vol. 24, pp. 653–656.

- [14] Y. Hsieh and H. Card, "Germanium photodetectors with induced p-n junctions," *IEEE Trans. Electron Devices*, vol. ED-29, no. 9, pp. 1414– 1420, Sep. 1982.

- [15] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley-Interscience, 1981.

- [16] J. Seger, S.-L. Zhang, D. Mangelinck, and H. H. Radamson, "Increased nucleation temperature of  $NiSi_2$  in the reaction of Ni thin films with  $Si_{1-x}Ge_x$ ," *Appl. Phys. Lett.*, vol. 81, no. 11, pp. 1978–1980, Sep. 2002.

- [17] J. Spann, R. Anderson, T. Thornton, G. Harris, S. Thomas, and C. Tracy, "Characterization of nickel germanide thin films for use as contacts to p-channel germanium MOSFETs," *IEEE Electron Device Lett.*, vol. 26, no. 3, pp. 151–153, Mar. 2005.

- [18] H. Lin, K. Yeh, R. Huang, C. Lin, and T. Huang, "Schottky barrier thin-film transistor (SBTFT) with silicided source/drain and field-induced drain extension," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 179–181, Apr. 2001.

- [19] Y. Zhang, J. Wan, K. Wang, and B.-Y. Nguyen, "Design of 10-nm-scale recessed asymmetric Schottky barrier MOSFETs," *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 419–421, Jul. 2002.

Muhammad Khaled Husain received the M.Eng. degree in electrical engineering from the National University of Singapore, Singapore, in 2003. He is currently working toward the Ph.D. degree in electrical engineering at the School of Electronics and Computer Science, University of Southampton, Southampton, U.K.

His current research interests include Ge-based SB MOSFETs, electrodeposition for SB synthesis, and spintronics.

Xiaoli V. Li (M'07) received the B.Eng. degree in electronics engineering from Xiamen University, Xiamen, China, in 2002. She is currently working toward the Ph.D. degree in nanoelectronics at the School of Electronics and Computer Science, University of Southampton, Southampton, U.K.

Her current research interests include semiconductor fabrication, electrodeposition on semiconductors, and self-assembly technologies applied in spintronics and plasmonics.

Cornelis Hendrik de Groot (SM'06) received the M.S. degree in physics from the University of Groningen, Groningen, The Netherlands, in 1994, and the Ph.D. degree from the University of Amsterdam, Amsterdam, The Netherlands, in 1998, with research carried out at the Philips Research Laboratories, Eindhoven, The Netherlands. His Ph.D. dissertation was on NdFeB permanent magnets and magnetism in rare-earth intermetallic compounds.

From 1998 to 2000, he was a Research Fellow with the Francis Bitter Magnet Laboratory,

Massachusetts Institute of Technology, Cambridge, where he conducted a research on spin tunnel junction. Since 2000, he has been with the Department of Electronics and Computer Science, University of Southampton, Southampton, U.K., where he is currently an Associate Professor. His research interest includes nanoelectronics with emphasis on spintronics and post-CMOS field-effect transistors.