# VHDL-AMS implementation of a numerical ballistic CNT model for logic circuit simulation

Dafeng Zhou, Tom J Kazmierski and Bashir M Al-Hashimi

School of Electronics and Computer Science, University of Southampton, Southampton, SO17 1BJ, UK

dz05r,tjk,bmah@ecs.soton.ac.uk

Abstract—This paper introduces a novel numerical carbon nanotube transistor (CNT) modelling approach which brings in a flexible and efficient cubic spline non-linear approximation of the non-equilibrium mobile charge density. The spline algorithm creates a rapid and accurate solution of the numerical relationship between the charge density and the self-consistent voltage, which leads to the speed-up of deriving the current through the channel without losing much accuracy. This modelling method also allows the flexibility of choosing different cubic spline intervals which may affect the performance of the model, but it is still capable of obtaining an acceleration of more than a 100 times while maintaining the accuracy within less than 1.5% normalised RMS error compared with previous reported theoretical modelling approach. The model has been proved working as transistors in a logic inverter implemented using VHDL-AMS and simulated in SystemVision, which shows the availability of implementing a circuit-level simulators with our proposed model. Additionally, although this model is originally based on the ideal ballistic transport characteristics, it shows good flexibility that the extension with numbers of non-ballistic features are certainly acceptable.

## I. Introduction

Transistors using carbon nanotubes (CNTs) are expected to become the basis of next generation integrated circuits (ICs) [1], [2]. These expectations are motivated by the growing difficulties in overcoming physical limits of silicon-based transistors fabricated using current technologies. A number of theoretical models have been created to describe the interplay between different physical effects within the nanotube channel and their effect on the performance of the device [3], [4], [5], [6], [7], [8]. The standard methodology of modelling CNTs is to derive the channel current from the non-equilibrium mobile charge injected in the channel when voltages are applied on the terminals of the transistor [1]. However, a common problem these models are facing is the complexity of calculating the Fermi-Dirac integral and non-linear algebraic equations which express the relationships between charge densities and the current. Moreover, the channel current between the source and drain is affected not only by the non-equilibrium mobile charge in the nanotube but also by the charges present at terminal capacitances thus adding to the complexity of the current calculation which is a time-consuming iterative approaches. Recently, the standard theoretical methodology has been improved by approaches where the slow Newton-Raphson iterations and the numerical evaluation of the Fermi-Dirac integral are replaced by numerical approximations while still maintaining good performance compared with theories

[6], [9]. These new techniques suggest piece-wise approximation of charge densities, either linear [6] or non-linear [9] to simplify the numerical calculation. However, while both these approaches accelerate current calculations significantly, they are not flexible enough to allow the user to control the trade-offs between the modelling accuracy and implementation speed. In this paper we generalise our earlier piece-wise nonlinear approach [9] and propose a cubic spline piece-wise approximation of the non-equilibrium mobile charge density and develop a very accurate technique where a an accuracy better than 1.5% in terms of average RMS error can be achieved with just a 5-piece spline, which compares favourably with the 5% obtained by the simple non-linear approximation [9]. The spline-based approach still achieves a speed up of around two orders of magnitude compared with a reported theoretical model [10] and allows an easy trade-off between accuracy and speed. The spline approximation is not only capable of describing performance of ideal ballistic CNT models, but also extendable with non-ballistic effects. The model has been implemented and tested in Matlab and VHDL-AMS. As an example, we show how our VHDL-AMS model can be used to simulate a CMOS-like inverter made of two complementary CNTs. This illustrates the feasibility of using this novel model in circuit-level simulators for future logic circuit analysis.

# II. MOBILE CHARGE DENSITY AND SELF-CONSISTENT VOLTAGE

When an electric field is applied between the drain and the source of a CNT, a non-equilibrium mobile charge is generated in the carbon nanotube channel. It can be described as follows[1], [11], [12]:

$$\Delta Q = q(N_S + N_D - N_0) \tag{1}$$

where  $N_S$  is the density positive velocity states filled by the source,  $N_D$  is the density of negative velocity states filled by the drain and  $N_0$  is the equilibrium electron density. These densities are determined by the Fermi-Dirac probability distribution:

$$N_S = \frac{1}{2} \int_{-\infty}^{+\infty} D(E) f(E - U_{SF}) dE \tag{2}$$

$$N_D = \frac{1}{2} \int_{-\infty}^{+\infty} D(E) f(E - U_{DF}) dE \tag{3}$$

$$N_0 = \int_{-\infty}^{+\infty} D(E)f(E - E_F)dE \tag{4}$$

where D(E) is the density of states, f is the Fermi probability distribution, E represents the energy levels per nanotube unit length, and  $U_{SF}$  and  $U_{DF}$  are defined as

$$U_{SF} = E_F - qV_{SC} \tag{5}$$

$$U_{DF} = E_F - qV_{SC} - qV_{DS} \tag{6}$$

where  $E_F$  is the Fermi level, q is the electronic charge and  $V_{SC}$  represents the self-consistent voltage [1] whose presence in these equations illustrates that the CNT energy band is affected by external terminal voltages. The self-consistent voltage  $V_{SC}$  is determined by the device terminal voltages and charges at terminal capacitances by the following non-linear algebraic equation [1], [6]:

$$V_{SC} = -\frac{Q_t + qN_S(V_{SC}) + qN_D(V_{SC}) + qN_0}{C_{\Sigma}}$$

(7)

where  $Q_t$  represents the charge stored in terminal capacitances and is defined as

$$Q_t = V_G C_G + V_D C_D + V_S C_S \tag{8}$$

where  $C_G, C_D, C_S$  are the gate, drain, and source capacitances respectively and the total terminal capacitance  $C_{\Sigma}$  can be derived by

$$C_{\Sigma} = C_G + C_D + C_S \tag{9}$$

## III. NUMERICAL PIECE-WISE APPROXIMATION OF THE CHARGE DENSITY

The standard approach to the solution of equation (7) is to use the Newton-Raphson iterative method and in each iteration evaluate the integrals in equations (3) and (4) to obtain the state densities  $N_D$  and  $N_S$ . This approach has been proved effective in CNT transistor modelling [6], [10], however, the iterative computation and repeated integrations consume immense CPU resources and thus are unsuitable for circuit simulation [9].

Our earlier work [9] proposed a piece-wise non-linear approximation technique that eliminates the need for these complex calculations. It suggested to calculate the charge densities and self-consistent voltage by dividing the continuous density function into a number of linear and non-linear pieces which together compose a fitting approximation of the original charge density curve. Then the  $V_{SC}$  equation 7 is simplified to a group of linear, quadratic and cubic equations, which can be solved easily and fast.

However, although this approach has been shown to be efficient and accurate [9], its weakness is that it requires an optimal fitting process when deciding on the number of approximation pieces and intervals of the ranges, which makes the model inflexible and akward to use. Here we propose to

use a cubic spline piece-wise approximation to overcome these difficulties.

For a set of n+1  $(n \ge 2)$  discrete points  $(x_0, y_0)$ ,  $(x_1, y_1)$ , ...,  $(x_{i+1}, y_{i+1})$  (i = 0, 1, ..., n-1), cubic splines can be constructed as follows [13]:

$$y = Ay_i + By_{i+1} + C\ddot{y}_i + D\ddot{y}_{i+1}$$

(10)

where A,B,C and D are the coefficients for each pieces of the cubic spline. For simple demonstration here, the horizontal interval between every two neighbour points is equal to h, then we have  $x_1-x_0=x_2-x_1=\ldots=x_{i+1}-x_i=h$ . Therefore, the cubic spline coefficients can be expressed as functions of x:

$$A \equiv \frac{x_{i+1} - x}{x_{i+1} - x_i} = \frac{x_{i+1} - x}{h} \tag{11}$$

$$B \equiv 1 - A = \frac{x - x_i}{x_{i+1} - x_i} = \frac{x - x_i}{h}$$

(12)

$$C \equiv \frac{1}{6}(A^3 - A)(x_{i+1} - x_i)^2 \tag{13}$$

$$D \equiv \frac{1}{6}(B^3 - B)(x_{i+1} - x_i)^2 \tag{14}$$

These equations show that A and B are linearly dependent on x, while C and D are cubic functions of x. To derive the y(x) expression, the second-order derivative of y have to be computed via a tridiagonal matrix:

$$\begin{bmatrix} 1 & 4 & 1 \\ 1 & 4 & 1 \\ & \dots & \\ & 1 & 4 & 1 \end{bmatrix} \begin{bmatrix} \ddot{y}_0 \\ \ddot{y}_1 \\ \dots \\ \ddot{y}_n \end{bmatrix} = \frac{6}{h^2} \begin{bmatrix} y_2 - 2y_1 + y_0 \\ y_3 - 2y_2 + y_1 \\ \dots \\ y_n - 2y_{n-1} + y_{n-2} \end{bmatrix}$$

(15)

Now that the cubic spline coefficients and the second derivative have been obtained, the function of each spline can be derived with the coefficients  $a_i$ ,  $b_i$ ,  $c_i$  and  $d_i$  calculated by using equations (11), (12), (13), (14) and (15):

$$y = a_i x^3 + b_i x^2 + c_i x + d_i (16)$$

The two linear regions that extend the cubic splines on both sides can be described as follows:

$$y = y_n, (x > x_n) \tag{17}$$

$$y = a_l x + b_l, (x < x_0)$$

(18)

where  $a_l = \ddot{y}_0 = 3a_0x_0^2 + 2b_0x_0 + c_0$  and  $bl = y_0 - a_lx_0$ . To demonstrate the performance of this approach, we have compared the speed and accuracy of an example model with results of other reported approaches.

## IV. PERFORMANCE OF A MODEL USING NUMERICAL APPROXIMATIONS

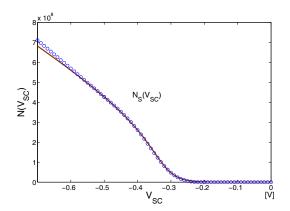

An example model which uses three cubic splines, n=3, and two linear pieces at the ends was compared with the theoretical curves calculated from equations (3) and (4) correspondingly.

Fig. 1. Piece-wise cubic spline approximation with n=3 (circlet line) of mobile charge compared with the theoretical result (solid line).

To solve the resulting 3rd order polynomial equations, Cardano's method [14] is applied to determine the appropriate root which represents the correct value of  $V_{SC}$ .

According to the ballistic CNT transport theory [1], [10] the drain current caused by the transport of the non-equilibrium charge across the nanotube can be calculated using the Fermi-Dirac statistics as follows:

$$I_{DS} = \frac{2qkT}{\pi\hbar} \left[ \mathcal{F}_0(\frac{U_{SF}}{kT}) - \mathcal{F}_0(\frac{U_{DF}}{kT}) \right]$$

(19)

where  $\mathcal{F}_0$  represents the Fermi-Dirac integral of order 0, k is Boltzmann's constant, T is the temperature and  $\hbar$  is reduced Planck's constant.

Since the self-consistent voltage  $V_{SC}$  is directly obtained from the spline model, the evaluation of the drain current poses no numerical difficulty as energy levels  $U_{SF}$ ,  $U_{DF}$  can be found quickly from equations 5,6 and  $I_{DS}$  can be calculated using:

$$I_{DS} = \frac{2qkT}{\pi\hbar} \left[ log(1 + e^{\frac{E_F - qV_{SC}}{kT}}) - log(1 + e^{\frac{E_F - q(V_{SC} - V_{DS})}{kT}}) \right]$$

the effects on the charge densities generated by the substrate voltage. This is especially important for the p-type-like transistor. Figure 3 shows  $I_{DS}$  characteristics of the n-type-like

These calculations are direct and therefore considerably fast, as there are no Newton-Raphson iterations or integrations of the Fermi-Dirac probability distribution. For performance comparison, we have also tried a 4-piece cubic spline approximation (with n=4) which is expected to be more accurate but slower than the first model. Table I shows the average CPU times for both models and those from FETToy [10] and previously reported piece-wise models [9], while Table II compares the accuracy of both numerical model types. It can be seen from Tables I and II that although the spline models sacrifice some speed compared with the

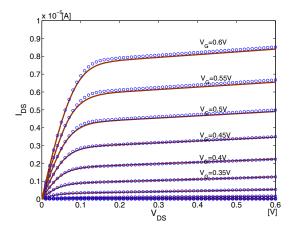

simple piece-wise non-linear models [9], they are still more than two orders of magnitude faster than FETToy. They also achieve a much better accuracy than the simple piece-wise non-linear models. The extent to which the modelling accuracy was compromised by numerical approximation was measured by calculating average RMS errors in the simulations and the results are shown in Table II. As expected, the spline models are more accurate with errors not exceeding 1.0% at T=300K and  $E_F=-0.32eV$  throughout the typical ranges of drain voltages  $V_{DS}$  and gate bias  $V_G$ . Figure 2 shows the  $I_{DS}$  characteristics calculated by FETToy compared with the 3-piece spline model.

Fig. 2. Drain current characteristics at T=300K and  $E_F=-0.32eV$  for FETToy(solid lines) and 3 pieces cubic spline approximation (dashed lines).

The performance of this approach can be affected by the values of  $E_F$ , T, d and terminal voltages. The choice of the number of cubic spline approximation pieces is an obvious trade-off between speed and accuracy as slightly more operations need to be performed with more pieces while the shape of the mobile charge curve is reflected more accurately.

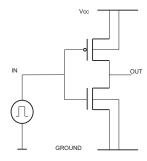

## V. VHDL-AMS IMPLEMENTATION

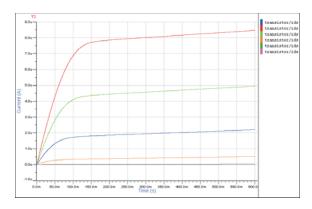

The proposed approach has been used to implement both n-type-like and p-type-like CNT transistor models in VHDL-AMS and to simulate a CMOS-like inverter shown in Figure 4. The bulk voltage was also considered to take into account the effects on the charge densities generated by the substrate voltage. This is especially important for the p-type-like transistor. Figure 3 shows  $I_{DS}$  characteristics of the n-type-like transistor implemented in VHDL-AMS which match closely the MATLAB calculations shown in figure 2.

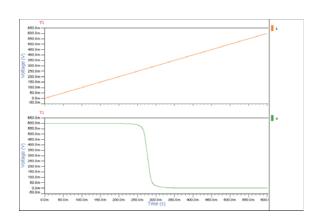

The VHDL-AMS testbench for the inverter invokes the two transistors as well as a ramp voltage source and a constant voltage source. The constant source provides the supply voltage  $V_{CC}$  for the gate, while the ramp source was used to produce the output characteristic of the inverter. The simulation result is shown in figure 5. Considering that the transport characteristics of both transistors are not the same, it is worth noting that the inverter output is not symmetrical wrt n  $V_{CC}/2$  due to the stronger n-type-like transistor.

TABLE I

AVERAGE CPU TIME COMPARISON BETWEEN DIFFERENT MODELS.

| Loops | FETToy     | 3-piece PWNL Model | 4-piece PWNL Model | CS Model 1 n=4   CS Model 2 n=5 |

|-------|------------|--------------------|--------------------|---------------------------------|

| 5     | 64.43Sec   | 0.02Sec            | 0.06Sec            | 0.57Sec 0.95Sec                 |

| 10    | 128.78Sec  | 0.04Sec            | 0.12Sec            | 1.15Sec 1.91Sec                 |

| 50    | 642.44Sec  | 0.19Sec            | 0.56Sec            | 5.82Sec 9.59Sec                 |

| 100   | 1287.45Sec | 0.38Sec            | 1.12Sec            | 11.69Sec 19.33Sec               |

TABLE II Average RMS errors in Piece-wise and cubic spline approximations for 1nm nanotube at  $E_F=-0.32eV$  and T=300K.

| $V_G[V]$ | 3-piece PWNL Model | 4-piece PWNL Model | CS Model n=4 | CS Model n=5 |

|----------|--------------------|--------------------|--------------|--------------|

| 0.1      | 4.4%               | 2.0%               | 1.3%         | 0.9%         |

| 0.2      | 3.6%               | 1.7%               | 1.0%         | 0.8%         |

| 0.3      | 2.7%               | 1.4%               | 0.8%         | 0.6%         |

| 0.4      | 1.9%               | 1.0%               | 0.6%         | 0.5%         |

| 0.5      | 1.6%               | 1.2%               | 0.9%         | 0.7%         |

| 0.6      | 2.2%               | 1.6%               | 1.1%         | 1.0%         |

Fig. 3. Drain current characteristics at T=300K and  $E_F=-0.32eV$  for FETToy(solid lines) and 3 pieces cubic spline approximation using 3-piece (dashed lines).

Fig. 4. Schematics of the simulated inverter.

The VHDL-AMS code of the testbench and transistor models is shown below.

Fig. 5. Inverter simulation result; input ramps from 0V to 0.6V.

```

use IEEE.electrical_systems.all;

entity test_CNTTransistor is

end entity test_CNTTransistor;

architecture test of test_CNTTransistor is

terminal g,i,o: electrical;

alias ground is ELECTRICAL_REF;

begin

vc: entity v_source generic map (1v=>0.6)

port map (po=>g, ne=>ground);

vi: entity v_pulse generic map (pulse=>1.0,tchange=>1sec)

port map(po=>i,ne=>ground);

ntransitor: entity CNTTransistor

generic map (Ef_i=>0.32*1.6E-19)

port map (drain=>o,gate=>i,source=>g,bulk=>g);

ptransistor: entity CNTTransistor

generic map (Ef_i=>-0.32*1.6E-19)

port map (drain=>o,gate=>i,source=>ground,

bulk=>ground);

end architecture test;

-- VHDL-AMS model of CNT Transistor I-V Characteristic

-- using cubic spline approximation of the non-equilibrium

```

-- Testbench

library IEEE;

use IEEE.math\_real.all;

```

-- mobile charge

-- (c) Southampton University 2008

-- Southampton VHDL-AMS Validation Suite

-- Authors:

Dafeng Zhou, Tom J Kazmierski and Bashir M Al-Hashimi

-- School of Electronics and Computer Science,

-- University of Southampton

-- Highfield, Southampton S017 1BJ, United Kingdom

-- Tel. +44 2380 593520

Fax +44 2380 592901

-- e-mail: {dz05r,tjk,bmah}@ecs.soton.ac.uk

-- Created: 1 April 2008

-- Last revised: 11 July 2008 (by Dafeng Zhou)

-- Description

-- This is a fast numerical model of ballistic transport

-- in carbon nanotube transistors. The default value of

-- the Ef_i parameter (Fermi level) produces ntype-like

-- behaviour; a ptype-like transistor can be obtained

-- by modifying the Fermi level.

-- Package cntcurrent provides the spline data and the

-- body of function Fcnt which calculates current Ids

-- from the splines.

library IEEE;

use IEEE.math_real.all;

use IEEE.electrical_systems.all;

library work;

use work.cntcurrent.all;

entity CNTTransistor is

generic ( -- model parameters

T : real := 300.0;

dcnt: real := 1.0E-9;

Ef_i: real := -0.32*1.6E-19

);

port (terminal drain, gate, source,

bulk: electrical

end entity CNTTransistor;

architecture Characteristic of CNTTransistor is

--terminal voltages and drain current

quantity Vdi across drain to bulk;

quantity Vgi across gate to bulk;

quantity Vsi across source to bulk;

quantity Ids through drain to source;

begin

Ids == Fcnt(Vgi, Vsi, Vdi, Ef_i, T, dcnt);

end architecture Characteristic;

```

## VI. CONCLUSION

This paper proposes to use and investigates the numerical performance of cubic splines in numerical calculations of CNT ballistic transport current with the aim to provide a practical and numerically efficient model for implementation in SPICE-like circuit simulators. The cubic spline approximation is more flexible and easier to use than our earlier models [6], [9] and the presented results further reinforce the suggestions that numerical integrations and internal Newton-Raphson iterations can be avoided in the calculation of the self-consistent voltage in the CNT. The cubic spline parameters assure the continuity of the first derivative everywhere and were optimised for fitting accuracy. When compared with FETToy [10], a reference theoretical CNT model, we have demonstrated that the proposed

approximation approach, although marginally slower than our earlier models, still leads to a computational cost saving of more than two orders of magnitude while increasing the modelling accuracy. To verify the feasibility of the proposed model, VHDL-AMS implementations for both n-type-like and p-type-like transistors were derived and used to calculate their  $I_{DS}$  characteristics as well the output characteristic a simple logic inverter using the SystemVision simulator from Mentor Graphics. The results matched closely those from MATLAB simulations. The new VHDL-AMS model is now available on the Southampton VHDL-AMS Validation Suite website [15] for public use.

## VII. ACKNOWLEDGEMENT

This project was funded in part by the EPSRC (UK) grant EP/E035965/1.

## REFERENCES

- Anisur Rahman, Jing Guo, Supriyo Datta, and Mark S. Lundstrom. Theory of ballistic nanotransistors. *Electron Devices*, *IEEE*, 50(9):1853–1864, September 2003.

- [2] Phaedon Avouris, Joerg Appenzeller, Richard Martel, and Shalom J. Wind. Carbon nanotube electronics. *Proceedings of the IEEE*, 91(11):1772–84, November 2003.

- [3] Arash Hazeghi, Tejas Krishnamohan, and H.-S. Philip Wong. Schottky-Barrier Carbon Nanotube Field-Effect Transistor Modeling. In Sixth IEEE Conference on Electron Devices, volume 54, Lausanne, Switzerland. March 2007.

- [4] Thao Dang, Lorena Anghel, and Regis Leveugle. Cntfet basics and simulation. In *IEEE Int. conf. on Design and Test of Integrated Systems* in Nanoscale Technology (DTIS), Tunis, Tunisia, 5-7 September 2006.

- [5] Chris Dwyer, Moky Cheung, and Daniel J. Sorin. Semi-empirical SPICE models for carbon nanotube FET logic. In 4th IEEE Conference on Nanotechnology, Munich, Germany, 16-19 Aug. 2004.

- [6] Hamidreza Hashempour and Fabrizio Lombardi. An efficient and symbolic model for charge densities in ballistic carbon nanotube FETs. *IEEE-NANO*, 1:17–20, June 2006.

- [7] Bipul C. Paul, Shinobu Fujita, Masaki Okajima, and Thomas Lee. Modeling and analysis of circuit performance of ballistic CNFET. In 2006 Design Automation Conference, San Francisco, CA, USA, 24-28 July 2006.

- [8] Arijit Raychowdhury, Saibal Mukhopadhyay, and Kaushik Roy. A circuit-compatible model of ballistic carbon nanotube field-effect transistors. Applied Physics Letters, 23(10):1411–20, October 2004.

- [9] Tom J. Kazmierski, Dafeng Zhou, and Bashir M. Al-Hashimi. Efficient circuit-level modelling of ballistic cnt using piecewise non-linear approximation of mobile charge density. In *IEEE Int. conf. on Design*, Automation and Test in Europe (DATE), Munich, Germany, 10-14 March 2008

- [10] Anisur Rahman, Jing Wang, Jing Guo, Sayed Hasan, Yang Liu, Akira Matsudaira, Shaikh S. Ahmed, Supriyo Datta, and Mark Lundstrom. Fettoy 2.0 - on line tool, 14 February 2006. https://www.nanohub.org/resources/220/.

- [11] Ming-Hsun Yang, Kenneth B. K. Teo, Laurent Gangloff, William I. Milne, David G. Hasko, Yves Robert, and Pierre Legagneux. Advantages of top-gate, high-k dielectric carbon nanotube field-effect transistors. Applied Physics Letters, 88(11):113507–1–3, March 2006.

- [12] Paul L. McEuen, Michael S. Fuhrer, and Hongkun Park. Single-walled carbon nanotube electronics. *Nanotechnology, IEEE Transactions*, 1(1):78–845, March 2002.

- [13] R. Bulirsch and J. Stoer. Introduction to Numerical Analysis, 2nd edition. Springer, April 1996.

- [14] Ulrich K Deiters. Calculation of densities from cubic equations of state. AIChE Journal, 48(4):882–886, April 2002.

- [15] Shaolin Wang and Tom J Kazmierski. Southampton VHDL-AMS validation suite, 18 October 2007. https://www.syssim.ecs.soton.ac.uk/ index.htm.