# Current oscillations observed for sparse Si nanocrystal thin films

Xin Zhou<sup>1</sup>, Ken Uchida<sup>1</sup>, Hiroshi Mizuta<sup>1, 2</sup>, and Shunri Oda<sup>1</sup>

<sup>1</sup>Quantum Nanoelectronics Research Center, Tokyo Institute of Technology and SORST JST (Japan Science and Technology Agency)

2-12-1 Ookayama, Meguro-ku, Tokyo 152-8552, Japan, Phone: +81-3-5734-2542, FAX: +81-3-5734-2542, e-mail: xzhou@neo.pe.titech.ac.jp

<sup>2</sup> School of Electronics and Computer Science, University of Southampton, Southampton Hampshire, UK

## 1. Introduction

Silicon nanocrystals (SiNCs) quantum dots, as one of the functional materials for nano electronics devices, have attracted much attention in recent years because of its novel electronic and optical characteristics [1]. Devices based on SiNCs [2-4], such as memory devices, light emission devices, electron emitters, have been investigated. Understanding carrier transport in SiNC films is essential to develop their device application areas. In most of the previous research work, transport mechanism was investigated for the vertical configurations. However, compared with vertical configurations, the conduction mechanism in the lateral direction could be more unique, due to the sparsity of the SiNCs in the channel.

In this work, we report on unique current oscillations observed for the thin film transistors with sparse SiNC networks. The factors which cause current oscillations will be discussed based on the characteristics of SiNCs.

## 2. Fabrication Process

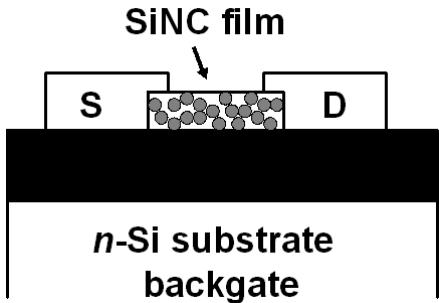

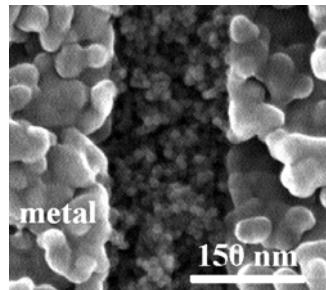

The device structure used for in this experiment is a SiNC thin film transistor (TFT) structure, as demonstrated in Fig.1 (a). First, a 110-nm-thick  $\text{SiO}_2$  was formed as gate dielectric, formed on highly doped n-type Si substrates with resistivity of 0.02  $\Omega\text{cm}$  by thermal oxidation process at temperature of 1100  $^{\circ}\text{C}$ . Second, a size-controlled SiNC thin film, 150 nm in thickness, was deposited on the  $\text{SiO}_2$  layer using the very-high-frequency (VHF)  $\text{SiH}_4$  plasma cell [5]. Third, after deposition, electrodes were fabricated by electron beam (EB) lithography with PMMA as resist. Device fabrication process was finished by depositing a 200-nm-thick Al layer using an e-beam evaporator and lift-off process. The source and drain contacts are Al Schottky contacts. The n-type Si substrates work as a backgate and there is no top-gate in this device structure. The distance between source and drain is about 150 nm, as shown in Fig.1 (b). The density of SiNCs used in this experiment is about  $1.2 \times 10^{18}/\text{cm}^3$ . There are voids existing in this SiNC film caused by SiNCs randomly deposited on substrates. The average size of each SiNC was controlled to be  $6 \pm 1$  nm with the flux of  $\text{SiH}_4$  and Ar of 1.6 sccm and 90 sccm respectively with  $\sim 2\text{W}$  plasma power. Each SiNC is covered by  $\text{SiO}_2$  shell, 1~1.5 nm, formed by a natural oxidation process. Thus, the whole SiNC film can be regarded as a 3D sparse network of Si

cores embedded in  $\text{SiO}_2$ .

## 3. Results and Discussion

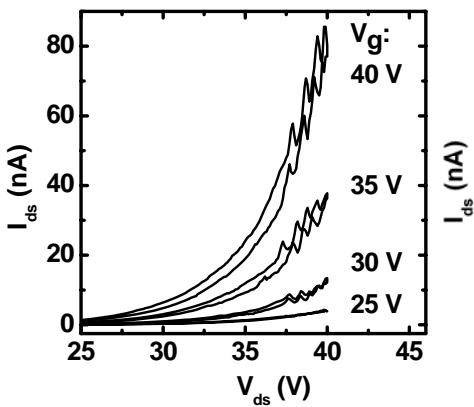

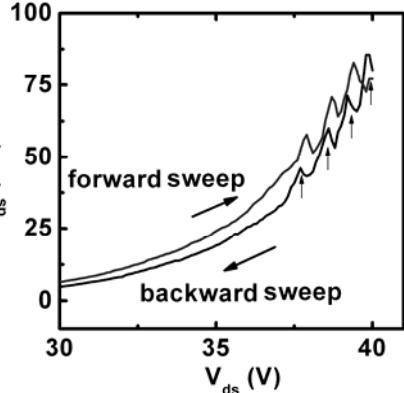

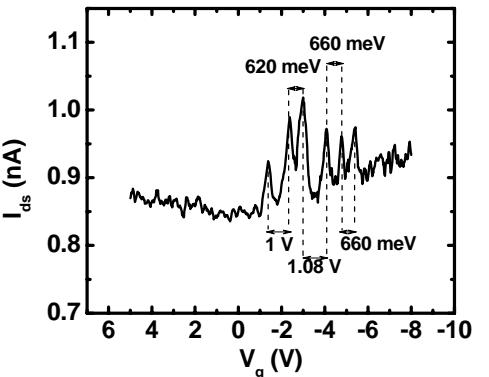

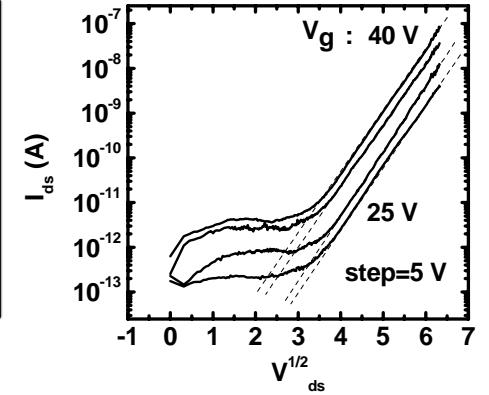

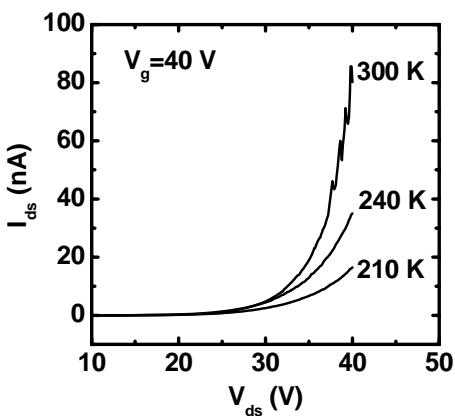

The characteristics of drain current-gate voltage ( $I_{ds}-V_g$ ) at room temperature are shown in Fig.2. With decreasing  $V_g$ , the oscillations of  $I_{ds}$  were clearly observed. The current peak intervals  $\Delta V_g$  are not uniform. The same phenomenon has also been observed by measuring the devices which were fabricated with the Ohmic contact layer by using highly doped SOI layer instead of the directly depositing metal on to the SiNC film. The  $I_{ds}-V_{ds}$  curves also showed current oscillations at high  $V_{ds}$  region for a finite range of  $V_g$ , as shown in Fig.3 (a). In addition, the  $I_{ds}-V_{ds}$  characteristics showed hysteresis, which are attributed to the traps existing in the SiNCs, shown in Fig. 3 (b). Due to the spherical geometry of the SiNCs, there are some voids existing in the film, which result in the number of the current paths much smaller than that in the vertical direction. Thus, the conduction in the lateral direction is quite different from in the vertical direction. During the carriers conducting via SiNCs, the number of the available current paths will be determined by the charging of the SiNCs on the current paths. Current conduction would be blocked once any SiNCs on the path were charged for some reasons. Initially, with increasing  $V_{ds}$ , carriers will be injected into the channel. However, some of those carriers will be trapped in SiNCs. Trapped carriers provide preconditions for the detrapping process. In fig.4,  $I_{ds}$  show  $V_{ds}^{1/2}$  dependence, which indicates field enhance detrapping [6]. Under the modulation of both  $V_g$  and  $V_{ds}$ , trapped carriers escape from the traps, which reopens the blocked the current paths. However, some of the detrapped carriers will be trapped at those SiNCs existing in the current paths again. It decreases the number of current paths. On the hypothesis that the number of available current paths varies depending on the voltage configurations, the current oscillations can be understood. In both forward and backward sweeps of  $I_{ds}$ , current oscillations were observed at the same  $V_{ds}$  region. This fact indicates that the current oscillations were not caused simply by a few SiNCs charged locally. On the other hand, the possibility of Coulomb oscillations has been excluded by the measurement of the  $I-V$  characteristics at the relatively lower temperatures, as shown in Fig.5. The oscillations were not observed when the measurement temperature was reduced. If the number of

current paths is large, the fluctuation of the current path number would not cause such a remarkable change in the conduction current. Thus, a limited number of current paths available in our SiNC films is presumably responsible for the observed current oscillations.

#### 4. Conclusion

We have observed the phenomenon of current oscillations in SiNC thin films, based on thin film transistor structures. The field enhanced detrapping makes the number of the current paths change, which is supposed to be responsible for

Fig.1 (a), schematic of device structures measured in this work

Fig.1 (b), SEM image of electrode pattern formed on SiNC thin films

Fig.3 (a),  $I_{ds}$ - $V_{ds}$  under the modulation of  $V_g$  from 25 V to 40 V

Fig.3 (b),  $I_{ds}$ - $V_{ds}$  under the modulation of  $V_g$  = 40 V at room temperature. The  $I_{ds}$  in Fig.3, under the modulation  $V_g$  = 40 V, show hysteresis characteristics.

Fig.2,  $V_g$  dependence of  $I_{ds}$ , measured at  $V_{ds}$  = 5 V, at room temperature

Fig.4,  $V_{ds}^{1/2}$  dependence of  $I_{ds}$  shown  $V_g$  = 40 V at room temperature. The  $I_{ds}$  in Fig.3, under the modulation  $V_g$  = 40 V, show hysteresis characteristics.

Fig.5,  $I_{ds}$ - $V_{ds}$ , measured at different temperature at  $V_g$  = 40 V. With decreasing temperature, current oscillations cannot be observed.

the current oscillations.

#### References

- [1] S. Oda *et. al.*, Phys. E. **38**, 59, (2007)

- [2] S. Huang *et. al.*, J. Appl. Phys. **93**, 576 (2003)

- [3] W. L. Wilson *et. al.*, Science. **262**, 1242 (1993)

- [4] K. Nishiguchi *et. al.*, J. Appl. Phys. **92**, 2748, (2002)

- [5] T. Ifuku *et. al.*, Jpn. J. Appl. Phys. **36**, 4031, 1997

- [6] X. Zhou *et.al.*, JR08-6138, Submitted to J. Appl. Phys.