## Position-Controllable Ge Nanowires Growth on Patterned Au Catalyst Substrate

Chuanbo Li<sup>1,4\*</sup>, Kouichi Usami<sup>1,4</sup>, Gento Yamahata<sup>1,4</sup>, Yoshishige Tsuchiya<sup>2,4</sup>, Hiroshi Mizuta<sup>2,3,4</sup>, and Shunri Oda<sup>1,4</sup>

Received November 3, 2008; accepted December 6, 2008; published online January 9, 2009

A well position-controllable single Ge nanowire array was grown on patterned Au catalysts substrate by low-pressure chemical vapor deposition. Both transmission electron microscope and X-ray diffraction results indicate that Ge nanowires are single crystalline with diamond structure. By optimizing the electron-beam lithography process, Au patterns with a diameter of 10 nm were prepared by lift-off method. The growth of Ge nanowires can be precisely controlled by adjusting the location of catalysts, which may offer the possibility of *in situ* fabrication of nanowire devices. © 2009 The Japan Society of Applied Physics

**DOI:** 10.1143/APEX.2.015004

ne-dimensional semiconductor nanostructures have attracted much attention because of their potential applications in the design of novel electronic, photonic, and sensing devices. 1) Due to their high mobility of electrons and holes, Ge nanowires are particularly attractive for high-speed field-effect transistors.<sup>2-4)</sup> Moreover, Ge nanowires are potentially useful for building quantum bits because of a long decoherence time due to a predominance of spin-zero nuclei<sup>5,6)</sup> and the advantage of a large excitonic Bohr radius (24.3 nm) which allows the quantum confinement to be observed for relatively large structures<sup>7,8)</sup> and at high temperatures. To realize these applications on a large scale, one of the key challenges is to develop a convenient and parallel method to align bottom-up nanowires into complex patterns or structures.<sup>9)</sup> Recently, a "pick and place" method is most widely used for integrating nanowires. However, these processes lack control in precision and repeatability, and easily induce contamination in the wires. 10) It is expected to selectively grow nanowires directly onto desired areas of the substrate and in situ fabricate the nanowire devices. 11) In the vapor-liquid-solid chemical vapor deposition (CVD) process, gold catalysts initiate and guide the growth of nanowires. 12-15) Hence, precise control the location of nanowires relies on the capability to control the location of Au clusters. 16,17) In this work, we demonstrate the well position-controllable Ge nanowires growth on SiO<sub>2</sub> substrate by combining top-down and bottom-up methods.

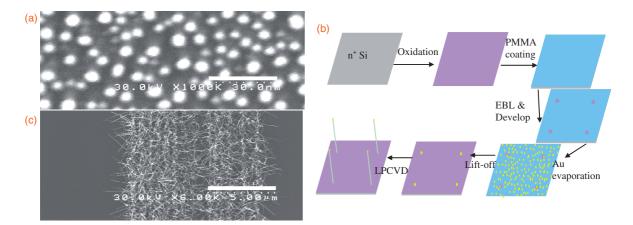

The Ge nanowires were grown by using a low-pressure chemical vapor deposition (LPCVD) method with 10% GeH<sub>4</sub> precursors (in an atmosphere of hydrogen) in a total pressure of 5 Torr at  $300\,^{\circ}\text{C}^{18)}$  on the patterned Au catalysts. All the Au catalysts with a thickness of  $0.5\,\text{nm}$  were evaporated by electron beam evaporation at room temperature on  $\text{SiO}_2$  substrate. Due to the stronger bond between the condensing Au adatoms than to the substrate,  $^{19)}$  Au atoms agglomerate to form high-density islands

E-mail address: cbli@neo.pe.titech.ac.jp

with the diameter of 3–8 nm as shown in Fig. 1(a). Well-ordered Au catalysts were prepared by using a JEOL JBX-5FE electron-beam lithography (EBL) system with a beam voltage of 50 kV and a beam diameter of 8 nm and a lift-off method.

The schematic of the process for patterning Au catalysts and growth of Ge nanowires is shown in Fig. 1(b). After the  $n^+$  Si(111) wafer was oxidized at 1100 °C for 1 h, the positive-type diluted (50%) poly(methyl methacrylate) (PMMA) EB resist with a thickness of 40 nm was coated at 8000 rpm and was prebaked at 170 °C for 30 min. Then, the sample was exposed using EBL under a dose condition of 400  $\mu C/cm^2$  and were developed by xylene for 60 s followed by a rinse with iso-propanol for 30 s. After evaporation of Au particles and lift-off, Au pattern was formed. Finally, Ge nanowires were grown on the Au pattern by LPCVD.

Figure 1(c) shows a scanning electron microscope (SEM) image of high-density Ge nanowire strips grown on patterned Au catalysts. Ge nanowires with a diameter of 5-20 nm and length of 1  $\mu m$  can be grown selectively on the area with Au catalysts. The fluctuation of the diameter of nanowires should originate from the fluctuation of Au catalysts. Maybe due to the nonspecific thermal deposition of Ge atoms on the Ge nanowire surface, the diameters of nanowires are a little bigger than those of Au catalysts. A transmission electron microscope (TEM) of Ge nanowires is shown in Fig. 2(a). Almost all of the nanowires are defect free over the whole length that could be observed. The dark parts on the tips of nanowires in Fig. 2(a) are Au catalysts. High-resolution TEM image in Fig. 2(b) reveal the highquality single-crystalline Ge nanowires grown in (111) direction with a lattice constant of 0.565 nm, which is in excellent agreement with the diamond crystal structure known for Ge. X-ray diffraction (XRD) result [Fig. 2(c)] also indicates that the crystal structure of grown Ge nanowires is cubic diamond structure according to the typical six peaks labeled in the image. And two peaks related to the Au FCC structure were also found.

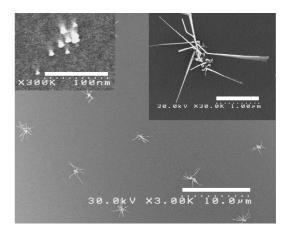

By reducing the size of each Au pattern to contain only a few Au particles (the left inset in Fig. 3), the Ge nanowire array with several nanowires in each area was obtained

<sup>&</sup>lt;sup>1</sup> Quantum Nanoelectronics Research Center, Tokyo Institute of Technology, Tokyo 152-8552, Japan

<sup>&</sup>lt;sup>2</sup> School of Electronics and Computer Science, University of Southampton, Highfield, Southampton, Hampshire, SO17 1BJ, U.K.

<sup>&</sup>lt;sup>3</sup>Department of Physical Electronics, Tokyo Institute of Technology, Tokyo 152-8552, Japan

<sup>&</sup>lt;sup>4</sup> Solution Oriented Research for Science and Technology (SORST), Japan Science and Technology Agency (JST), Kawaguchi, Saitama 332-0012, Japan

<sup>\*</sup>Present address: Atomic Electronics Group, International Center for Materials Nanoarchitectonics, National Institute for Materials Science, 1-1 Namiki, Tsukuba, Ibaraki 305-0044, Japan.

Fig. 1. (a) SEM image of Au catalysts evaporated on SiO<sub>2</sub> substrate. Au dots have a diameter of around 3–8 nm. (b) The schematic of process for patterning Au catalysts and growth of Ge nanowires. (c) SEM image of Ge nanowires strip grown on Au catalysts strip pattern. The wires are selectively grown on the areas with Au catalysts.

Fig. 2. (a) Transmission electron microscope of Ge nanowires grown at  $300\,^{\circ}$ C. The dark part on the tip of nanowire is Au catalyst. (b) High-resolution TEM image of Ge nanowires showing the single-crystal structure. (c) X-ray diffraction image obtained from Ge nanowires grown on a  $SiO_2$  substrate.

(Fig. 3). The right inset of Fig. 3 shows the enlarged image of one of the patterns. Around 10 nanowires were grown in each area.

In order to realize the alignment of single Ge nanowire, the Au catalyst array with only one Au dot in each area is

Fig. 3. SEM images Ge nanowires array with a space distance of  $10\,\mu m$ ; The right inset is the enlarged image of one pattern of Ge nanowires. The scale bar in the inset is  $1\,\mu m$ . And the left inset shows one of the Au patterns containing several Au dots. The scale bar in the inset is  $100\,n m$ .

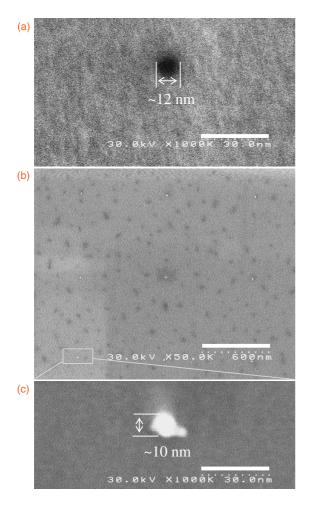

needed. One way to settle this problem is to reduce the size of pattern. In lift-off process, the thickness of the resist plays an important role in controlling the size and shape of the design. The thinner the resist is, the easier it is to control the size of pattern. In the case of Au film with only a thickness of about 0.5 nm, very thin resist can be applied. By reducing the PMMA resist down to 40 nm and optimizing the relationship between the electron dose and develop time in EBL process, a very small hole with the diameter of around 12 nm can be obtained as shown in Fig. 4(a), which is almost same size as the beam spot of EBL. In Fig. 4(a), the black hole area is the SiO<sub>2</sub> substrate and the gray area is PMMA. By choosing a suitable density of the Au particles to make sure that one Au dot could be deposited in this kind of hole, the well-ordered single Au dot array with a space of 700 nm was prepared as shown in Fig. 4(b). According to the enlarged image of one pattern as shown in Fig. 4(c) we can find each Au dot has a diameter of around 10 nm.

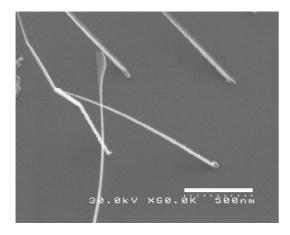

On such well-ordered Au catalyst array, we succeeded in growing the single Ge nanowire array with a space of

Fig. 4. (a) SEM image of one hole formed by EBL. The black hole area with a diameter of  $12\,\mathrm{nm}$  is the  $\mathrm{SiO}_2$  substrate and the gray area is PMMA layer. (b) SEM image of the well-ordered Au dots array with a space of 700 nm. The white dots in the image are Au catalysts. (c) The enlarged image of one of the Au dots in (b).

Fig. 5. SEM image of single Ge nanowire array grown on well-ordered Au pattern.

700 nm. The SEM image in Fig. 5 shows that only one Ge nanowire is grown on each Au dot. Au catalysts initiate and guide the growth of Ge nanowires. And the wires are located precisely where the Au catalysts sit, which may offer the possibility of *in situ* fabrication of large-scale nanowire devices.

In summary, single Ge nanowire array with a space distance of 700 nm was grown by LPCVD method on the patterned Au catalyst substrate. Ge nanowires have a diameter of 5–20 nm. No obvious defect was found by TEM measurement. Six peaks related to the Ge diamond structure are found in the XRD results of Ge nanowires. The wires can be grown selectively on the area with Au catalysts. By controlling the location of Au catalysts, we can precisely control the growth of Ge nanowires.

**Acknowledgment** This work is partially supported by Solution Oriented Research for Science and Technology (SORST), Japan Science and Technology Agency (JST) and Japan Society for the Promotion of Science (JSPS).

- 1) H. J. Fan, P. Werner, and M. Zacharias: Small 2 (2006) 700.

- J. Xiang, W. Lu, Y. J. Hu, Y. Wu, H. Yan, and C. M. Lieber: Nature 441 (2006) 489.

- 3) G. C. Liang, J. Xiang, N. Kharche, G. Klimeck, M. Charles, C. M. Lieber, and M. Lundstrom: Nano Lett. 7 (2007) 642.

- S. M. Sze: Physics of Semiconductor Devices (Wiley, New York, 1981).

- Y. J. Hu, H. O. H. Churchill, D. J. Reilly, J. Xiang, C. M. Lieber, and C. M. Marcus: Nat. Nanotechnol. 2 (2007) 622.

- 6) A. M. Tyryshkin, S. A. Lyon, T. Schenkel, J. Bokor, J. Chu, W. Jantsch, F. Schaffler, J. L. Truitt, S. N. Coppersmith, and M. A. Eriksson: Physica E 35 (2006) 257.

- X. H. Sun, G. Calebotta, B. Yu, G. Selvaduray, and M. Meyyappan: J. Vac. Sci. Technol. B 25 (2007) 415.

- Y. Maeda, N. Tsukamoto, Y. Yazawa, Y. Kanemitsu, and Y. Masumoto: Appl. Phys. Lett. 59 (1991) 3168.

- S. Li, N. Liu, M. B. Chan-Park, Y. Yan, and Q. Zhang: Nanotechnology 18 (2007) 455302.

- J. F. Conley, J. L. Stecker, and Y. Ono: Appl. Phys. Lett. 87 (2005) 223114

- 11) J. Y. Li, C. G. Lu, B. Maynor, S. M. Huang, and J. Liu: Chem. Mater. 16 (2004) 1633.

- 12) J. H. He, J. H. Hsu, C. W. Wang, H. N. Lin, L. J. Chen, L. Zhong, and Z. L. Wang: J. Phys. Chem. B 110 (2006) 50.

- 13) T. I. Kamins, X. Li, R. S. Williams, and X. Liu: Nano Lett. 4 (2004) 503.

- 14) Y. Y. Wu, R. Fan, and P. D. Yang: Nano Lett. 2 (2002) 83.

- 15) S. Kodambaka, J. Tersoff, M. C. Reuter, and F. M. Ross: Science 316 (2007) 729.

- 16) I. Lombardi, A. I. Hochbaum, P. D. Yang, C. Carraro, and R. Maboudian: Chem. Mater. 18 (2006) 988.

- B. Fuhrmann, H. S. Leipner, H. R. Hoche, L. Schubert, P. Werner, and U. Gosele: Nano Lett. 5 (2005) 2524.

- C. B. Li, K. Usami, T. Muraki, H. Mizuta, and S. Oda: Appl. Phys. Lett. 93 (2008) 041917.

- 19) J. A. Venables: J. Vac. Sci. Technol. B 4 (1986) 870.