University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

# Circuit-level Modelling and Simulation of Carbon Nanotube Devices

by

Dafeng Zhou

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering, Science and Mathematics

School of Electronics and Computer Science

July 2010

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

**Circuit-level Modelling and Simulation of Carbon Nanotube Devices**

by **Dafeng Zhou**

The growing academic interest in carbon nanotubes (CNTs) as a promising novel class of electronic materials has led to significant progress in the understanding of CNT physics including ballistic and non-ballistic electron transport characteristics. Together with the increasing amount of theoretical analysis and experimental studies into the properties of CNT transistors, the need for corresponding modelling techniques has also grown rapidly. This research is focused on the electron transport characteristics of CNT transistors, with the aim to develop efficient techniques to model and simulate CNT devices for logic circuit analysis.

The contributions of this research can be summarised as follows. Firstly, to accelerate the evaluation of the equations that model a CNT transistor, while maintaining high modelling accuracy, three efficient numerical techniques based on piece-wise linear, quadratic polynomial and cubic spline approximation have been developed. The numerical approximation simplifies the solution of the CNT transistor's self-consistent voltage such that the calculation of the drain-source current is accelerated by at least two orders of magnitude. The numerical approach eliminates complicated calculations in the modelling process and facilitates the development of fast and efficient CNT transistor models for circuit simulation.

Secondly, non-ballistic CNT transistors have been considered, and extended circuit-level models which can capture both ballistic and non-ballistic electron transport phenomena, including elastic scattering, phonon scattering, strain and tunnelling effects, have been developed. A salient feature of the developed models is their ability to incorporate both ballistic and non-ballistic transport mechanisms without a significant computational cost. The developed models have been extensively validated against reported transport theories of CNT transistors and experimental results.

Thirdly, the proposed carbon nanotube transistor models have been implemented on several platforms. The underlying algorithms have been developed and tested in MATLAB, behavioural-level models in VHDL-AMS, and improved circuit-level models have been implemented in two versions of the SPICE simulator. As the final contribution of this work, parameter variation analysis has been carried out in SPICE3 to study the performance of the proposed circuit-level CNT transistor models in logic circuit analysis. Typical circuits, including inverters and adders, have been analysed to determine the dependence of the circuit's correct operation on CNT parameter variation.

# Contents

|                                                                                                            |           |

|------------------------------------------------------------------------------------------------------------|-----------|

| <b>Acknowledgements</b>                                                                                    | <b>xi</b> |

| <b>1 Introduction</b>                                                                                      | <b>1</b>  |

| 1.1 Overview . . . . .                                                                                     | 1         |

| 1.2 Carbon Nanotube Transistor Modelling . . . . .                                                         | 3         |

| 1.2.1 Research Challenges . . . . .                                                                        | 4         |

| 1.3 Research Aims and Contributions . . . . .                                                              | 5         |

| 1.4 Thesis Organisation . . . . .                                                                          | 8         |

| <b>2 Literature Review</b>                                                                                 | <b>9</b>  |

| 2.1 Semiconductor Device Models . . . . .                                                                  | 9         |

| 2.2 Modelling and Simulation of Semiconductor Devices . . . . .                                            | 11        |

| 2.3 Carbon Nanotube Characteristics . . . . .                                                              | 12        |

| 2.3.1 General Introduction to Carbon Nanotubes . . . . .                                                   | 13        |

| 2.3.2 Electronic Properties of Different Types of Carbon Nanotubes . . . . .                               | 15        |

| 2.3.2.1 Metallic Carbon Nanotubes . . . . .                                                                | 15        |

| 2.3.2.2 Semiconducting Carbon Nanotubes . . . . .                                                          | 16        |

| 2.4 Carbon Nanotube Device Models . . . . .                                                                | 17        |

| 2.4.1 CNT Diodes . . . . .                                                                                 | 18        |

| 2.4.2 Carbon Nanotube Field-Effect Transistors (CNTFETs) . . . . .                                         | 20        |

| 2.5 Existing Carbon Nanotube Transistor Models . . . . .                                                   | 24        |

| 2.6 Theoretical Ballistic CNT Transistor Model . . . . .                                                   | 28        |

| 2.7 CNT Transistor Model Based on Symbolic Approximation of Charge Densities . . . . .                     | 30        |

| 2.8 Logic Circuits Based on CNTs . . . . .                                                                 | 31        |

| 2.9 Variation Analysis for CNT Transistors . . . . .                                                       | 34        |

| 2.10 Concluding Remarks . . . . .                                                                          | 35        |

| <b>3 Ballistic CNT Transistor Model Based on Piece-Wise Approximation</b>                                  | <b>37</b> |

| 3.1 Numerical Analysis of Ballistic Transport Characteristics of CNT Transistors . . . . .                 | 38        |

| 3.1.1 Non-Equilibrium Mobile Charge of CNT Transistors . . . . .                                           | 38        |

| 3.1.2 Self-Consistent Voltage . . . . .                                                                    | 41        |

| 3.2 Numerical Model Based on Piece-Wise Linear Approximation of Mobile Charge Density . . . . .            | 44        |

| 3.2.1 MATLAB Implementation of the CNT Transistor Model Based on Piece-Wise Linear Approximation . . . . . | 44        |

---

|       |                                                                                                             |     |

|-------|-------------------------------------------------------------------------------------------------------------|-----|

| 3.2.2 | Performance of the CNT Transistor Model Based on Piece-Wise Linear Approximation . . . . .                  | 49  |

| 3.3   | CNT Transistor Model Based on Quadratic Polynomial Approximation of Mobile Charge Density . . . . .         | 54  |

| 3.3.1 | MATLAB Implementation of the CNT Transistor Model Based on Quadratic Approximation . . . . .                | 54  |

| 3.3.2 | Performance of the CNT Transistor Model Based on Quadratic Polynomial Approximation . . . . .               | 59  |

| 3.4   | Concluding Remarks . . . . .                                                                                | 65  |

| 4     | <b>Ballistic CNT Transistor Model Based on Cubic Spline Approximation</b>                                   | 67  |

| 4.1   | Cubic Spline Approximation of the Density of States . . . . .                                               | 68  |

| 4.2   | MATLAB Implementation of the CNT Transistor Model Based on Cubic Spline Approximation . . . . .             | 70  |

| 4.3   | Performance of the Cubic Spline Based Model . . . . .                                                       | 73  |

| 4.4   | VHDL-AMS Implementation and Simulation of the Cubic Spline Based Model . . . . .                            | 77  |

| 4.5   | Concluding Remarks . . . . .                                                                                | 84  |

| 5     | <b>Modelling of Non-ballistic Transport Effects of CNT Transistors</b>                                      | 85  |

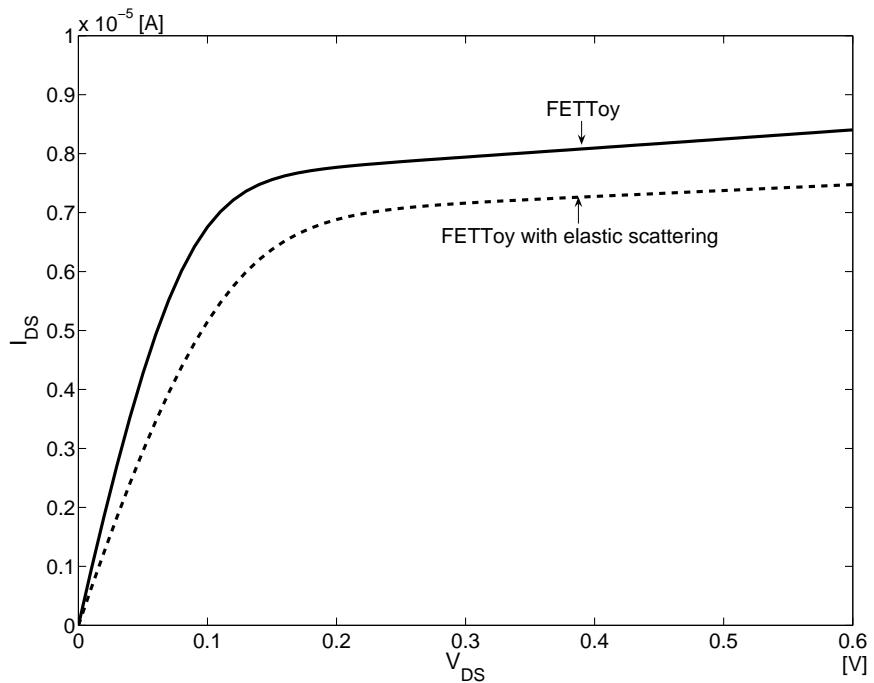

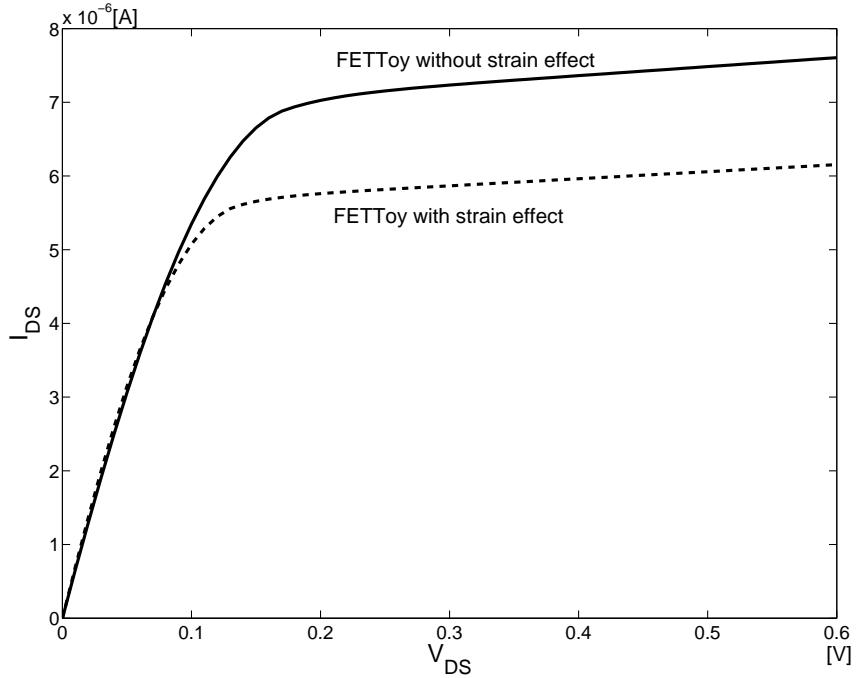

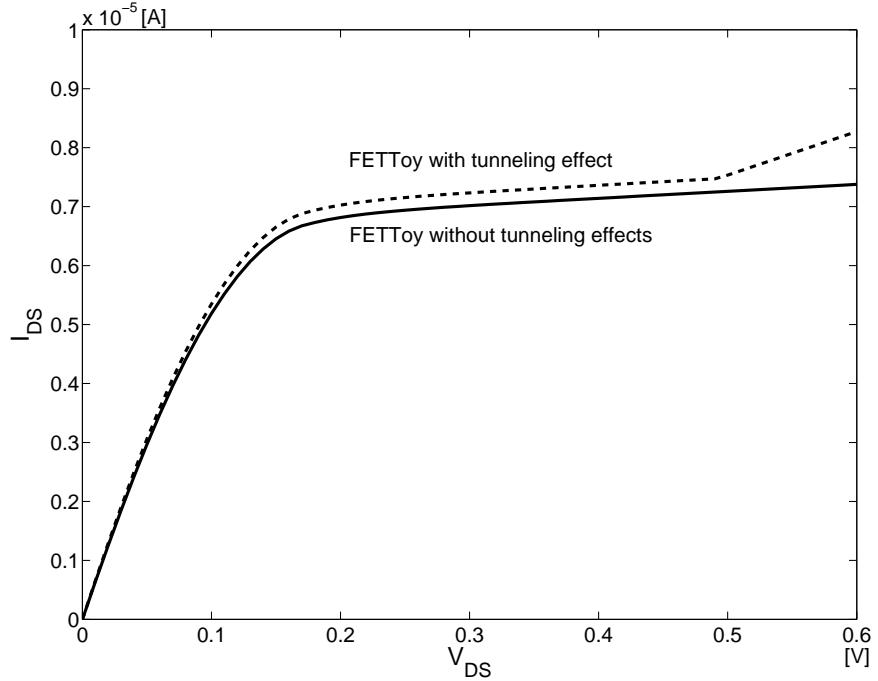

| 5.1   | Non-ballistic Transport of CNT Transistors and FETToy with Non-Ballistic Effects . . . . .                  | 86  |

| 5.1.1 | Elastic Scattering . . . . .                                                                                | 86  |

| 5.1.2 | Band Gap Tuning with Strain . . . . .                                                                       | 88  |

| 5.1.3 | Tunnelling Effect . . . . .                                                                                 | 89  |

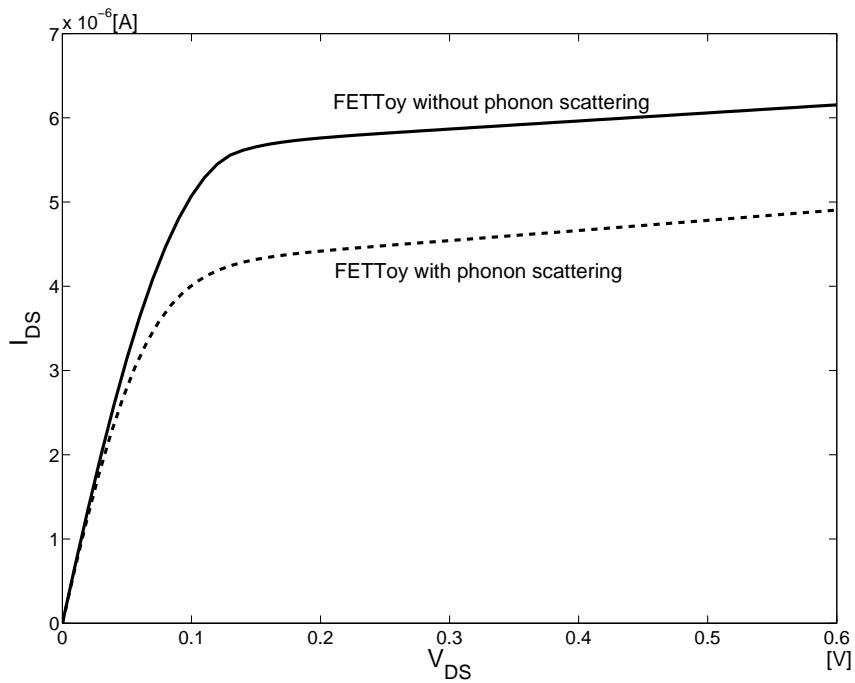

| 5.1.4 | Phonon Scattering . . . . .                                                                                 | 90  |

| 5.1.5 | Implementation of FETToy with Non-Ballistic Transport Effects .                                             | 92  |

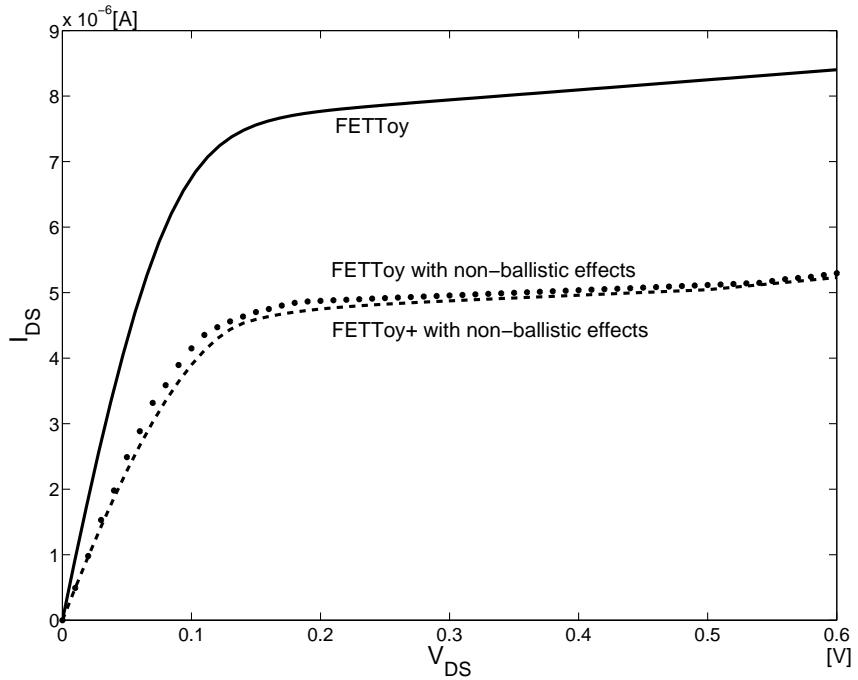

| 5.2   | Non-Ballistic Effects in Cubic Spline Approximation Based CNT Transistor Model ( <i>FETToy+</i> ) . . . . . | 93  |

| 5.2.1 | MATLAB Implementation of <i>FETToy+</i> . . . . .                                                           | 94  |

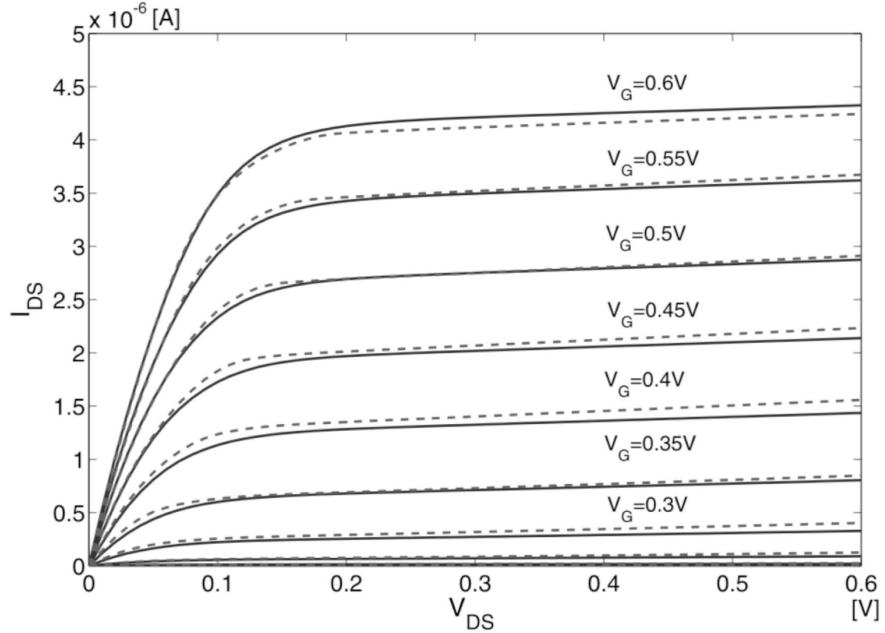

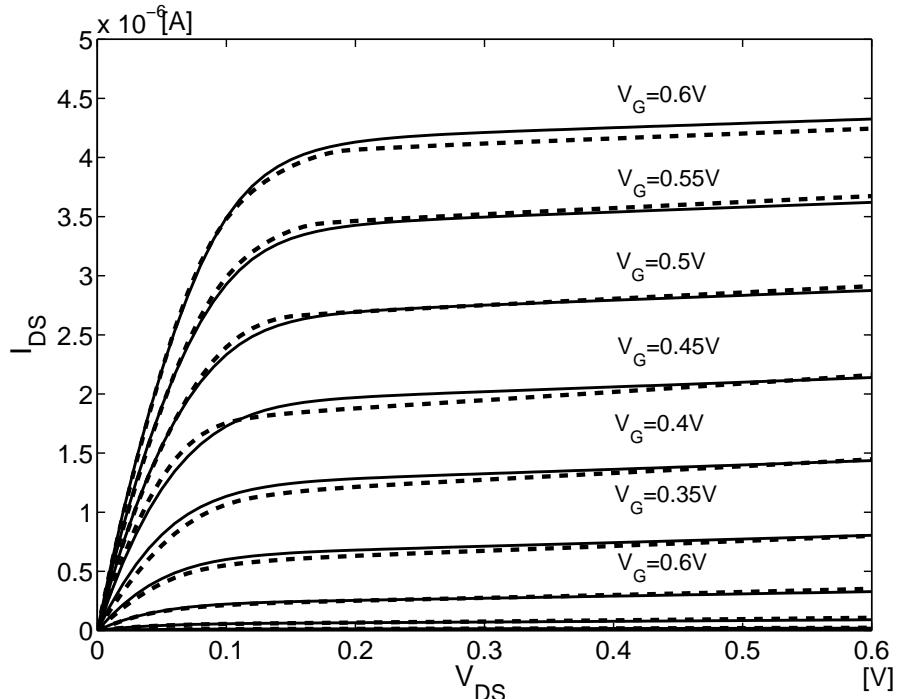

| 5.2.2 | Performance of <i>FETToy+</i> . . . . .                                                                     | 96  |

| 5.3   | Comparison with Experimental Results . . . . .                                                              | 100 |

| 5.4   | Concluding Remarks . . . . .                                                                                | 102 |

| 6     | <b>Implementation of CNT Transistor Models in SPICE</b>                                                     | 103 |

| 6.1   | HSPICE Macromodel of CNT Transistors . . . . .                                                              | 105 |

| 6.1.1 | HSPICE Macromodel Implementation . . . . .                                                                  | 105 |

| 6.1.2 | Performance of the HSPICE Macromodel . . . . .                                                              | 107 |

| 6.2   | SPICE3 Implementation of CNT Transistor Model . . . . .                                                     | 113 |

| 6.2.1 | Berkeley SPICE3 Working Process . . . . .                                                                   | 114 |

| 6.2.2 | Implementation of the SPICE3 Model . . . . .                                                                | 115 |

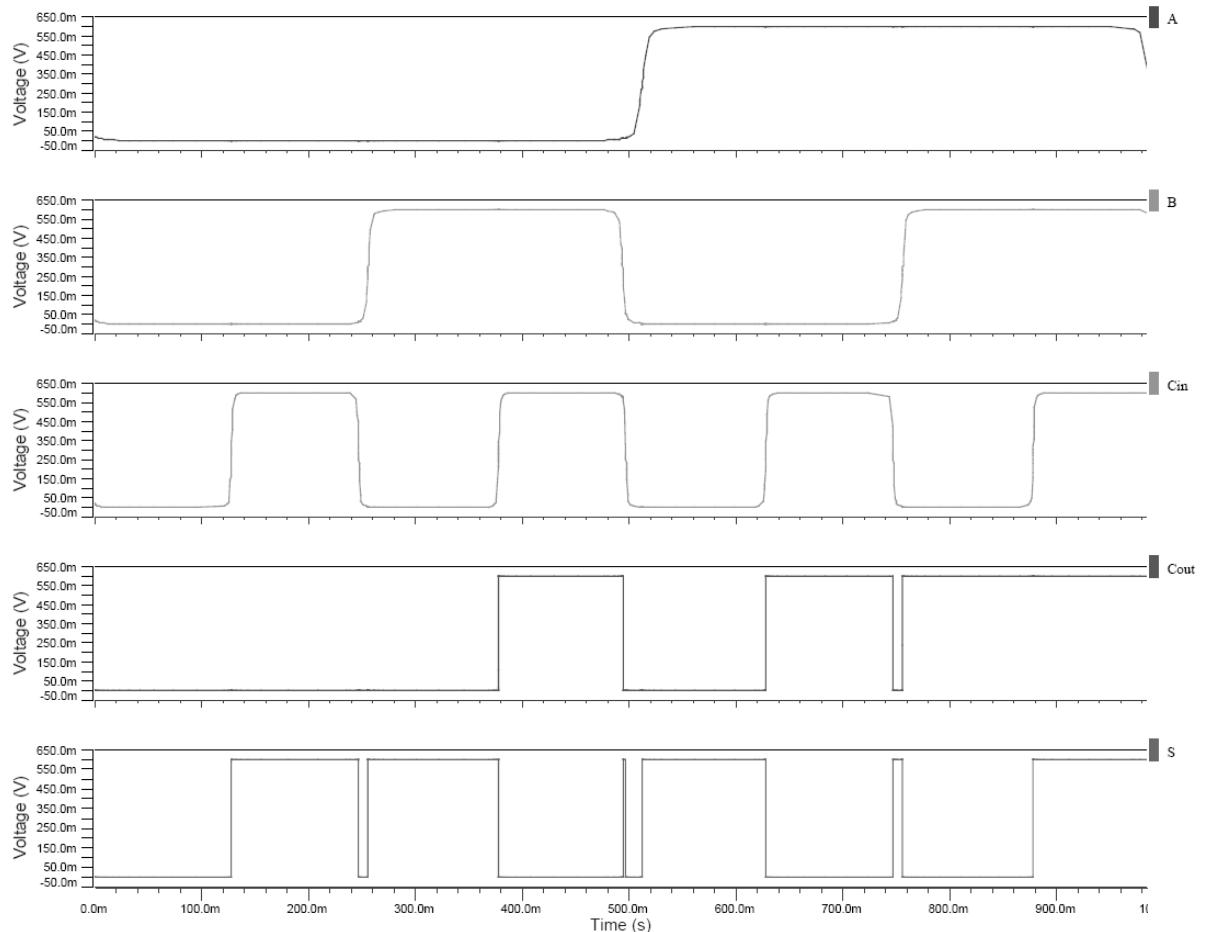

| 6.2.3 | Case Studies of CNT Based Logic Circuits (SRAM and Adder) .                                                 | 119 |

| 6.3   | Variation Analysis . . . . .                                                                                | 126 |

| 6.4   | Concluding Remarks . . . . .                                                                                | 129 |

| 7     | <b>Conclusions and Future Research</b>                                                                      | 131 |

| 7.1   | Thesis Contributions . . . . .                                                                              | 131 |

| 7.2   | Directions for Future Work . . . . .                                                                        | 134 |

|                                                                                                    |            |

|----------------------------------------------------------------------------------------------------|------------|

| <b>A Published Papers</b>                                                                          | <b>136</b> |

| <b>B Implementation of CNT Transistor Models in the Research</b>                                   | <b>138</b> |

| B.1 MATLAB Functions to Implement CNT Transistor Models . . . . .                                  | 138        |

| B.1.1 MATLAB Functions to Implement Ballistic Cubic Spline Based<br>CNT Transistor Model . . . . . | 139        |

| B.1.2 MATLAB Functions to Implement FETToy with Non-Ballistic Ef-<br>fects . . . . .               | 139        |

| B.1.3 MATLAB Functions to Implement <i>FETToy+</i> . . . . .                                       | 139        |

| B.2 VHDL-AMS Functions to Implement Ballistic CNT Transistor Model . .                             | 140        |

| B.3 HSPICE Archives to Implement CNT Transistor Model . . . . .                                    | 141        |

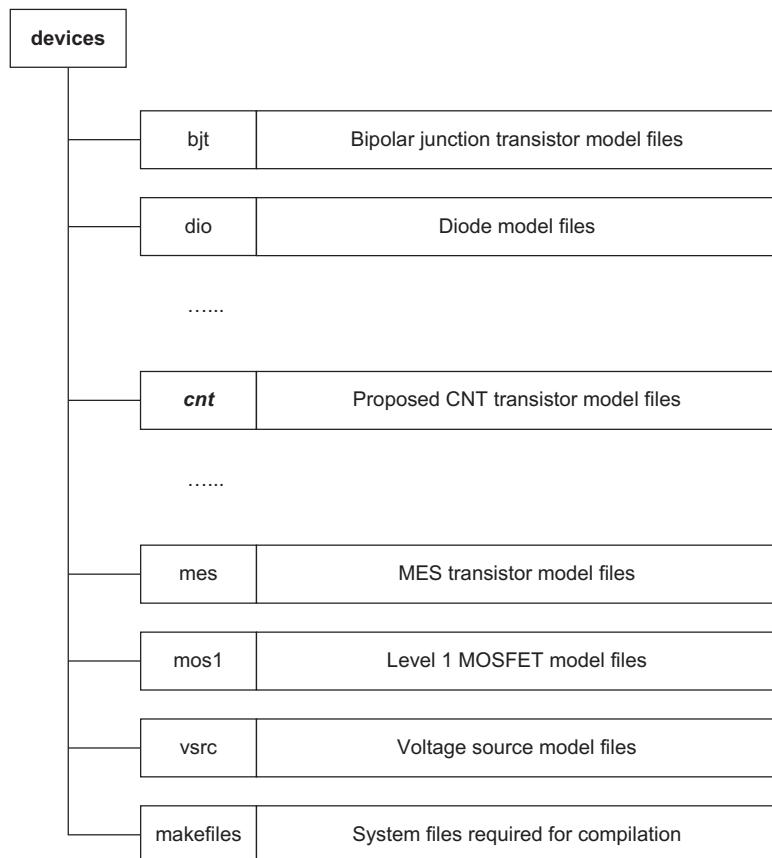

| B.4 Berkeley SPICE3 Library Structure . . . . .                                                    | 142        |

| <b>References</b>                                                                                  | <b>144</b> |

# List of Figures

|      |                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

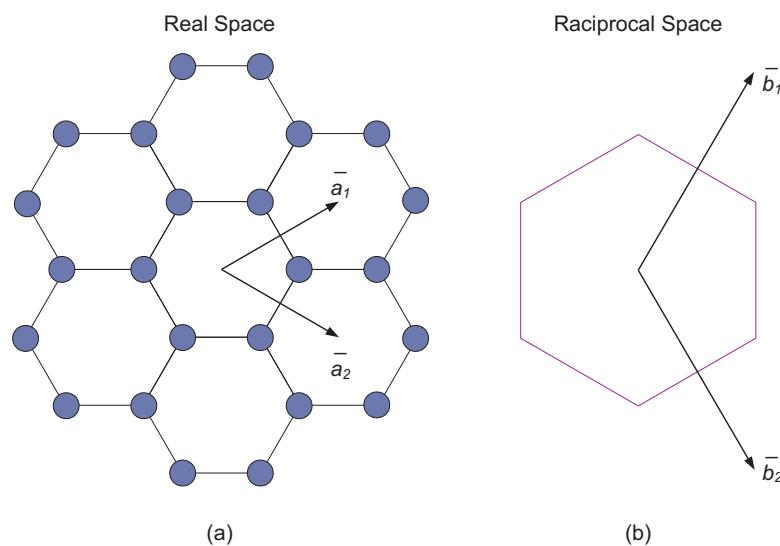

| 2.1  | The graphene lattice in real space and reciprocal space with the basis vectors . . . . .                                                                                                          | 13 |

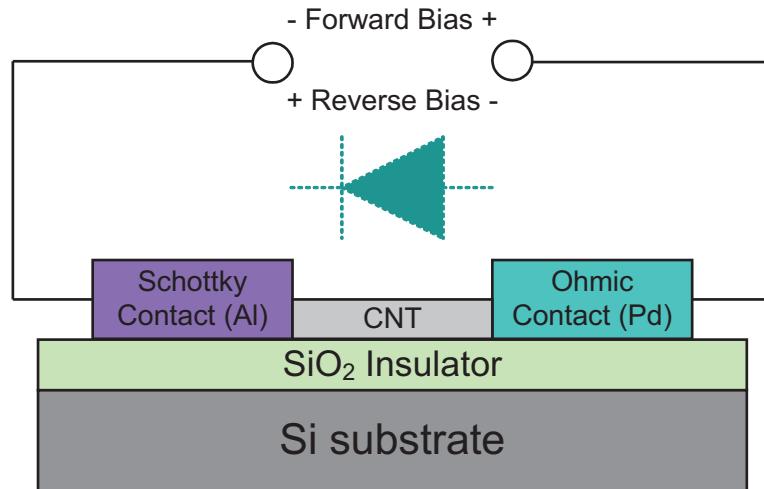

| 2.2  | Carbon nanotube Schottky diode using Al/Pd contacts . . . . .                                                                                                                                     | 19 |

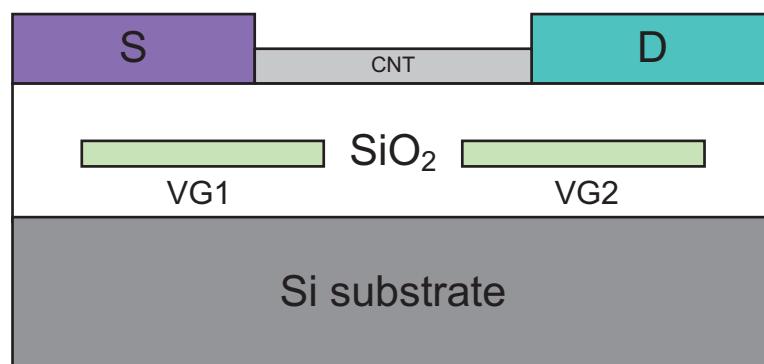

| 2.3  | Schematic cross section of CNT p-n junction diode with split gates . . . . .                                                                                                                      | 19 |

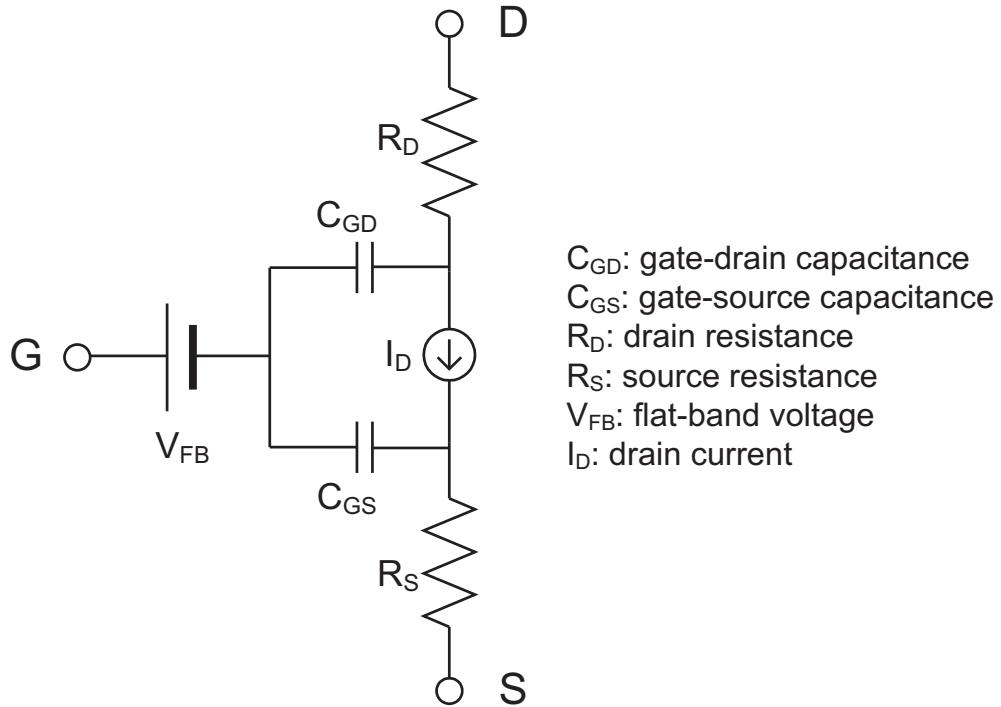

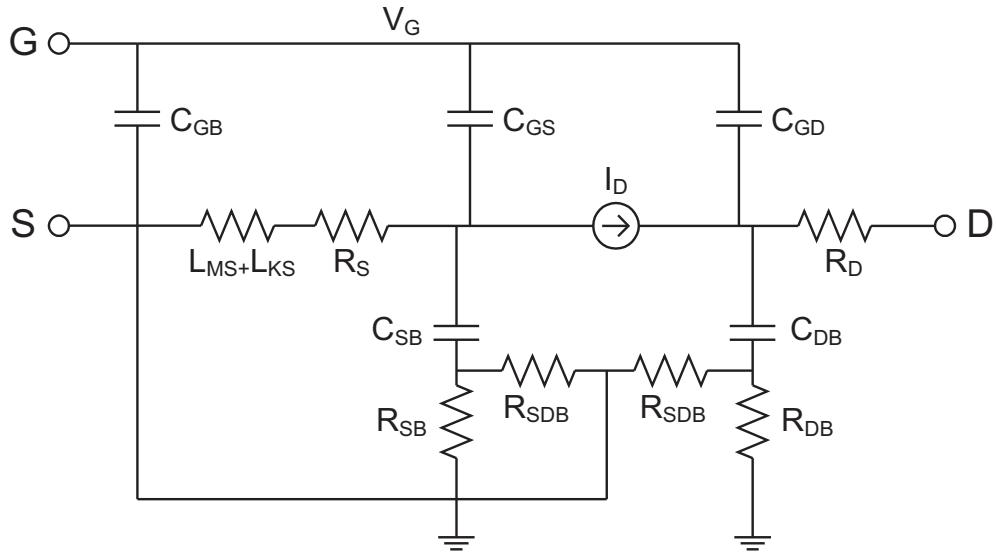

| 2.4  | A MOS-like model of CNT transistor . . . . .                                                                                                                                                      | 25 |

| 2.5  | One circuit compatible model of CNT transistor . . . . .                                                                                                                                          | 25 |

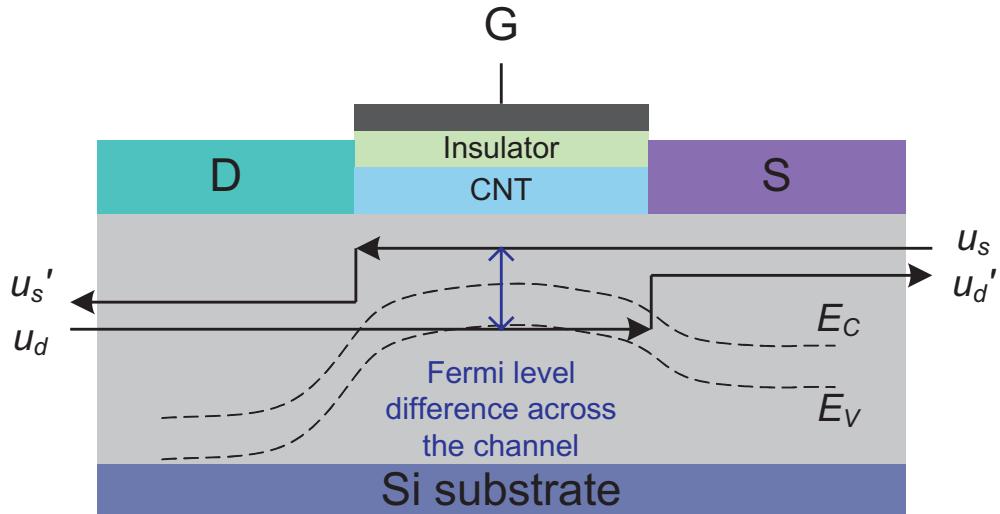

| 2.6  | Ideal CNTFET with ballistic channel . . . . .                                                                                                                                                     | 26 |

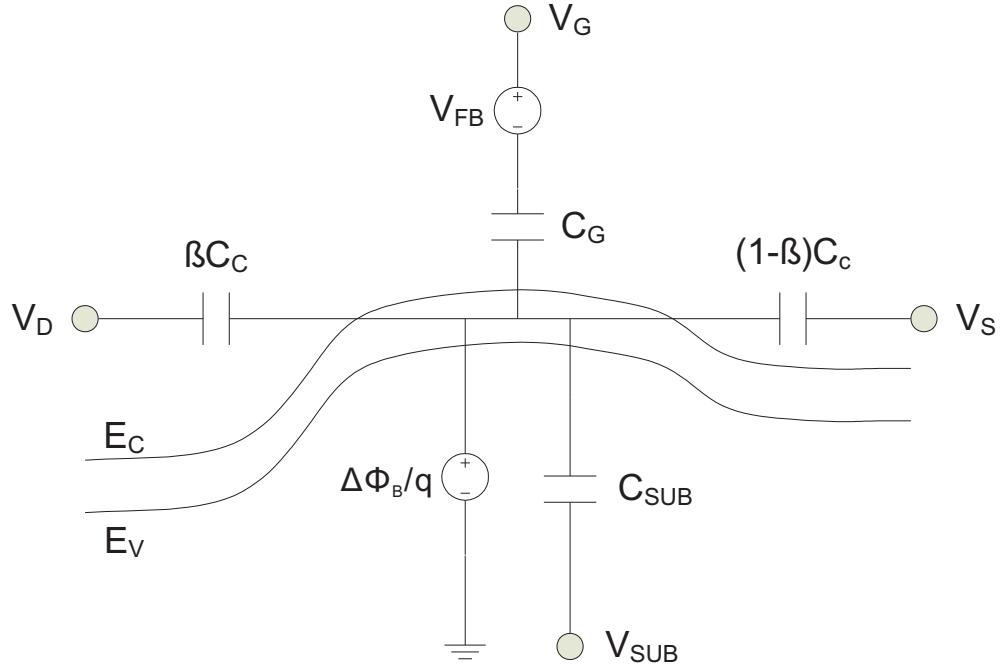

| 2.7  | Electrostatic capacitor model of the channel surface-potential . . . . .                                                                                                                          | 27 |

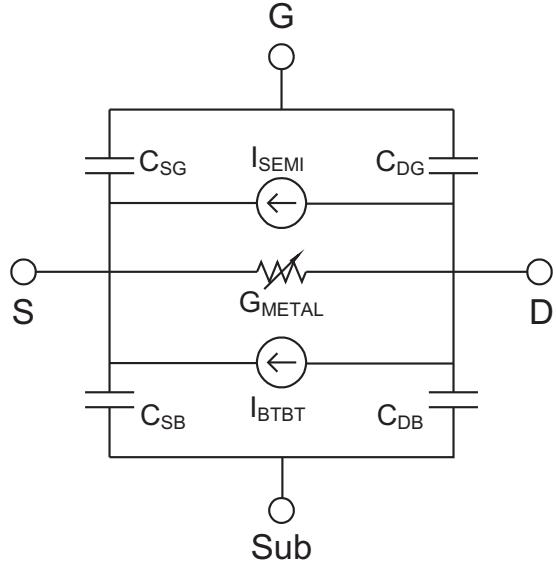

| 2.8  | Equivalent circuit model for the intrinsic channel region of CNTFET . . . . .                                                                                                                     | 27 |

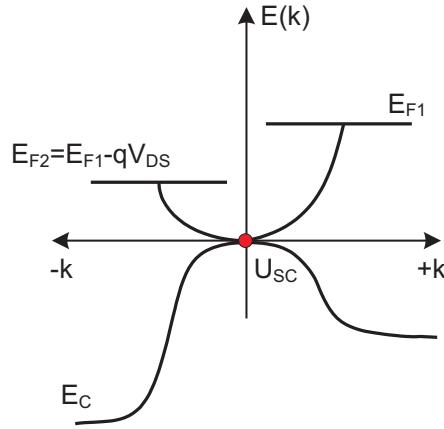

| 2.9  | The $k$ -states at the top of the energy barrier . . . . .                                                                                                                                        | 28 |

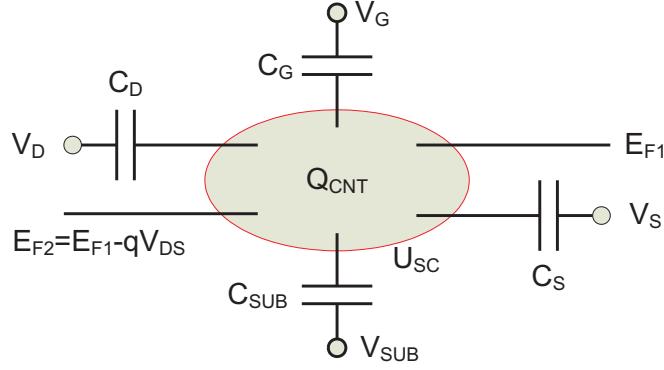

| 2.10 | Two-dimensional model for ballistic CNT transistors . . . . .                                                                                                                                     | 29 |

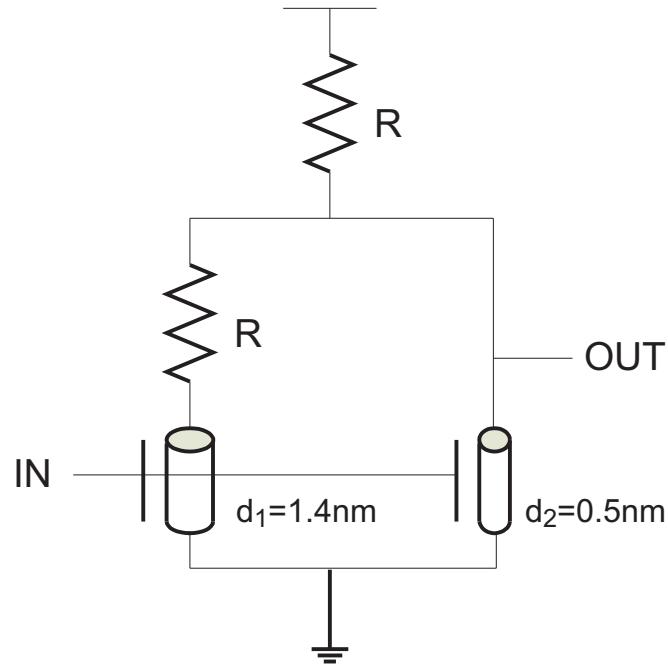

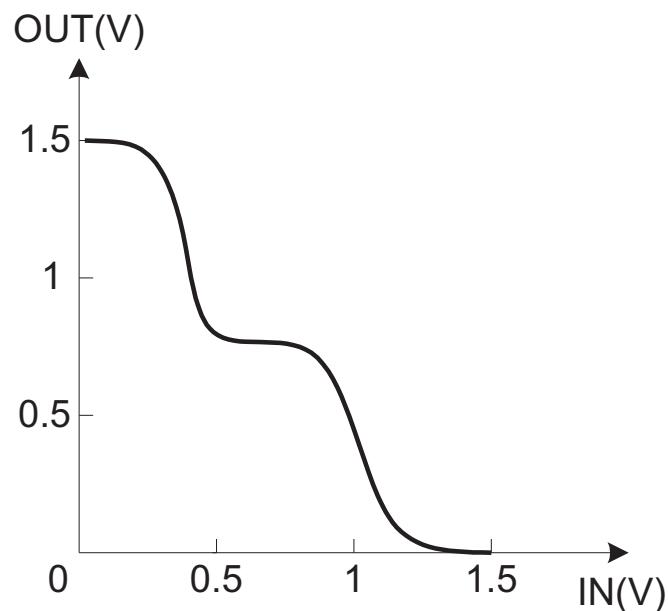

| 2.11 | Schematic of a multi-valued logic gate . . . . .                                                                                                                                                  | 34 |

| 2.12 | Performance of the multi-valued invertor . . . . .                                                                                                                                                | 34 |

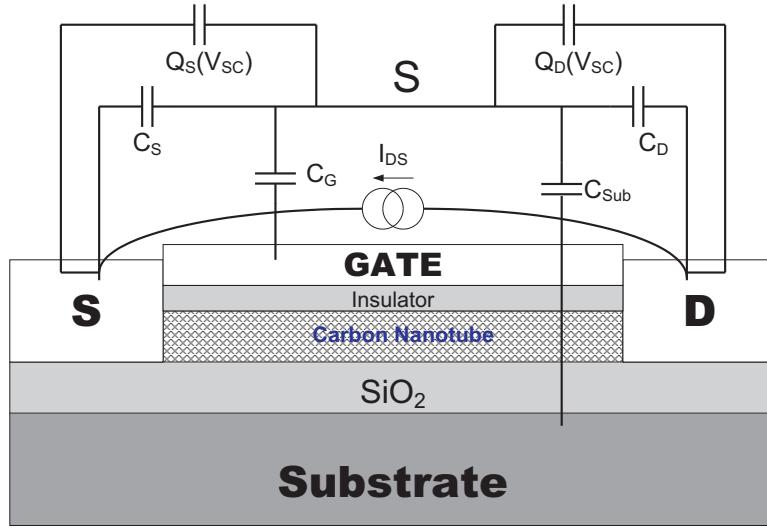

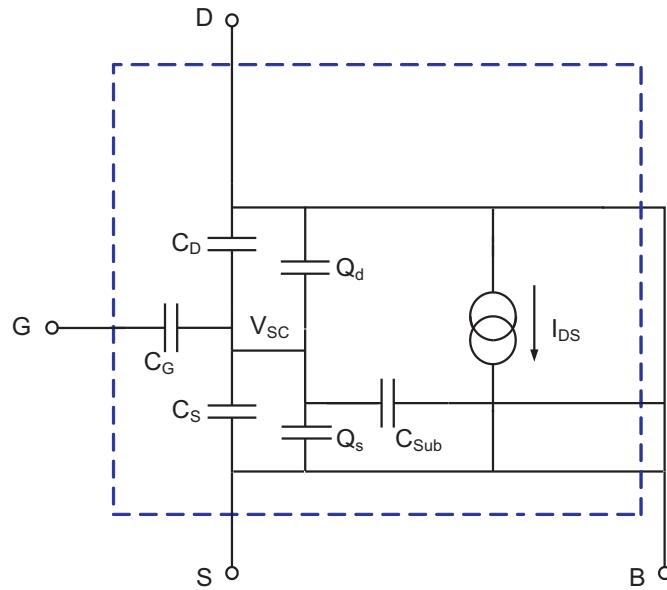

| 3.1  | Schematic of a top-gated CNT transistor . . . . .                                                                                                                                                 | 40 |

| 3.2  | Equivalent circuit of the proposed CNT transistor model . . . . .                                                                                                                                 | 41 |

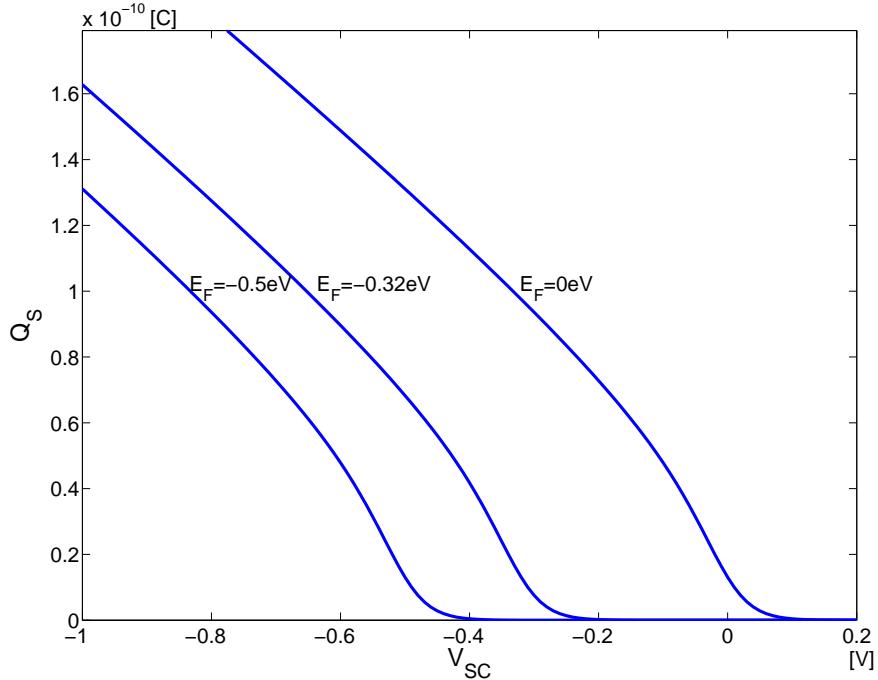

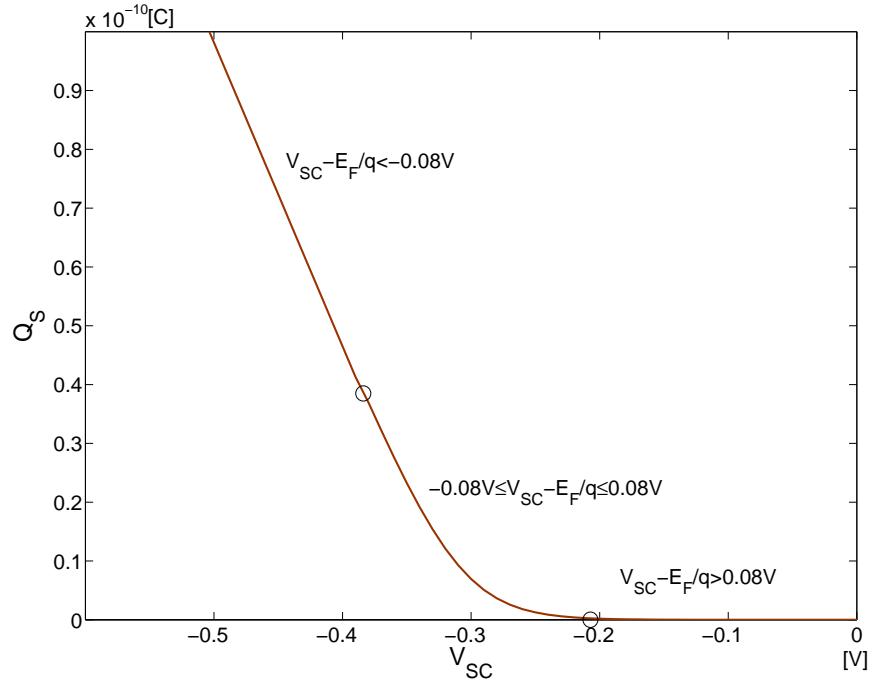

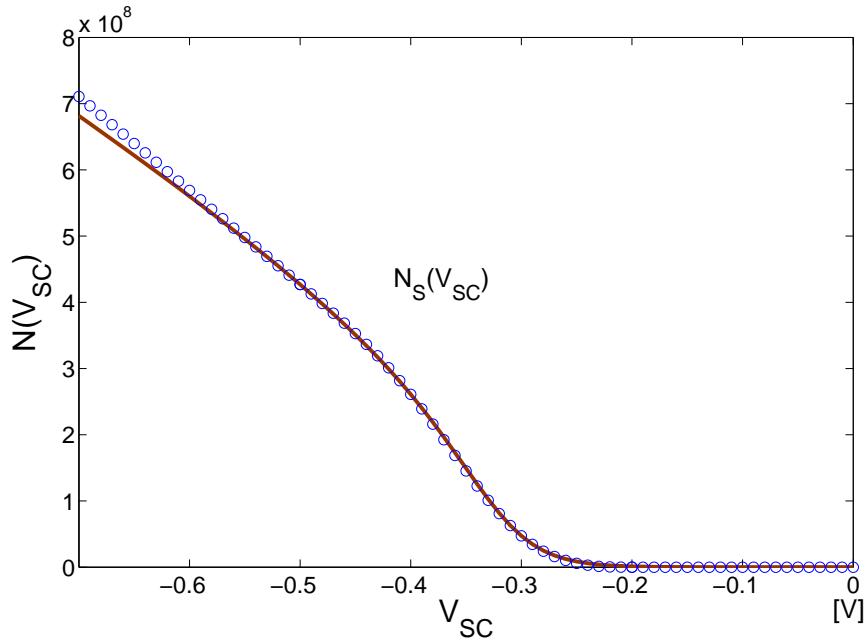

| 3.3  | The theoretical source mobile charge $Q_S$ at different Fermi levels . . . . .                                                                                                                    | 45 |

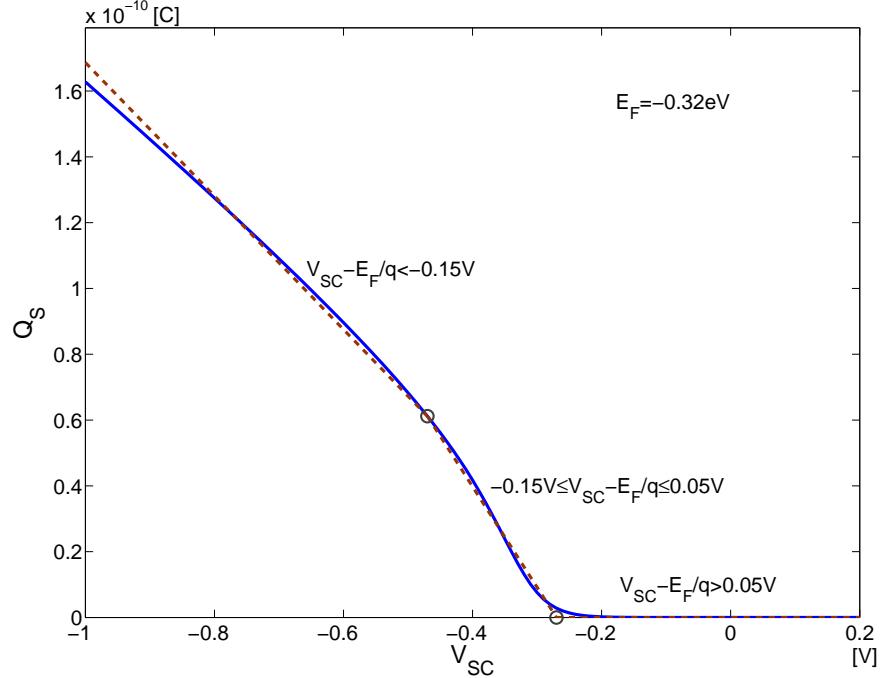

| 3.4  | Example of a 3-piece linear approximation of the source mobile charge $Q_S$ . . . . .                                                                                                             | 48 |

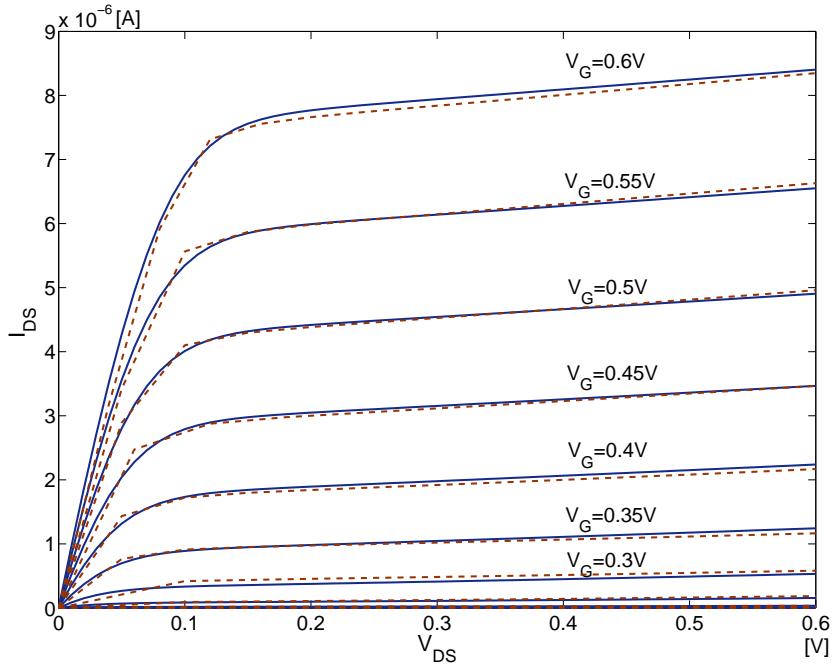

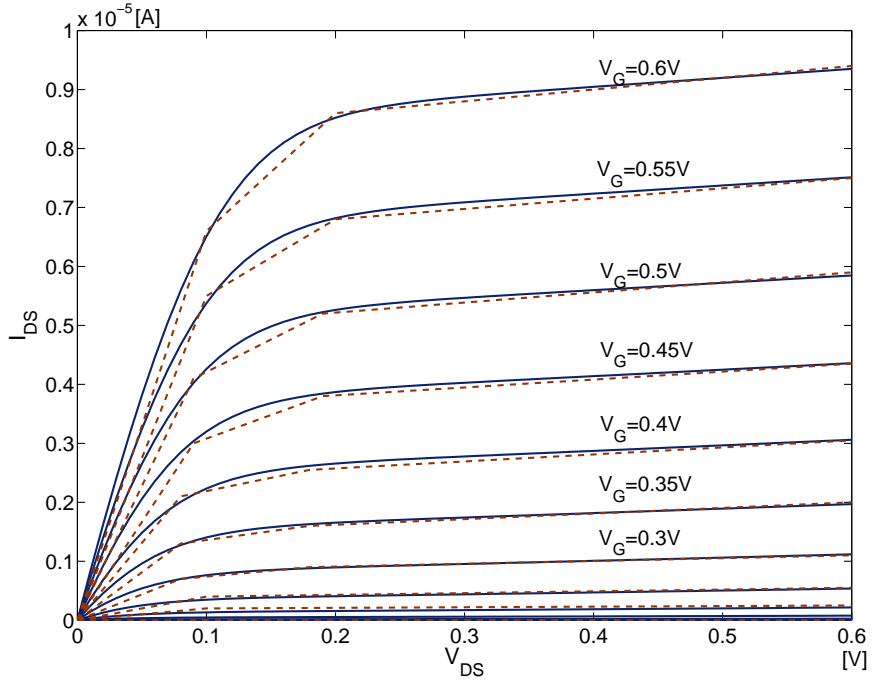

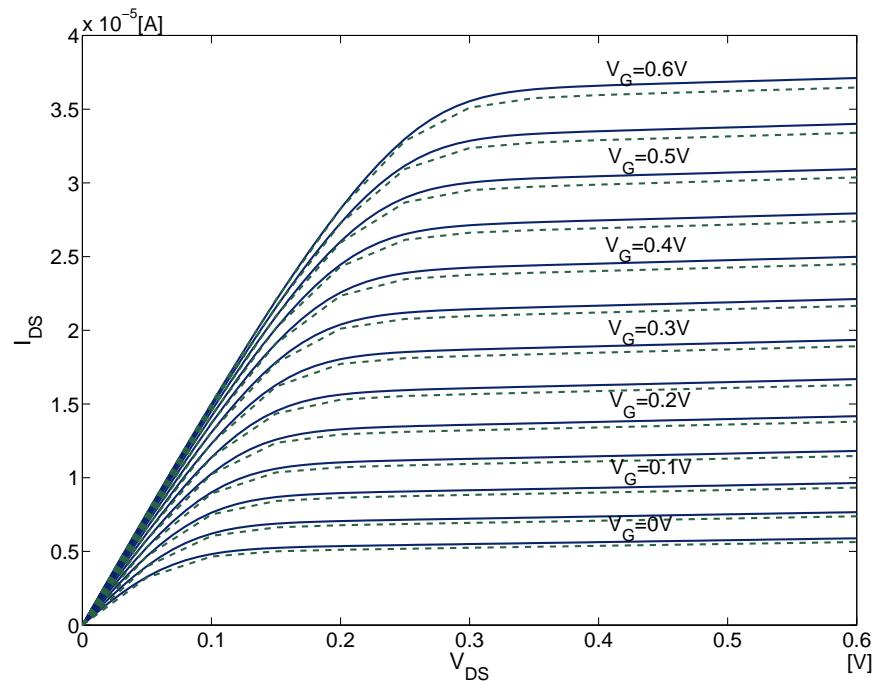

| 3.5  | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece linear approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 300K$ . . . . . | 49 |

| 3.6  | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece linear approximation with $E_F = -0.5eV$ , $d = 1nm$ and $T = 300K$ . . . . .  | 50 |

| 3.7  | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece linear approximation with $E_F = 0eV$ , $d = 1nm$ and $T = 300K$ . . . . .     | 50 |

| 3.8  | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece linear approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 150K$ . . . . . | 51 |

| 3.9  | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece linear approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 450K$ . . . . . | 52 |

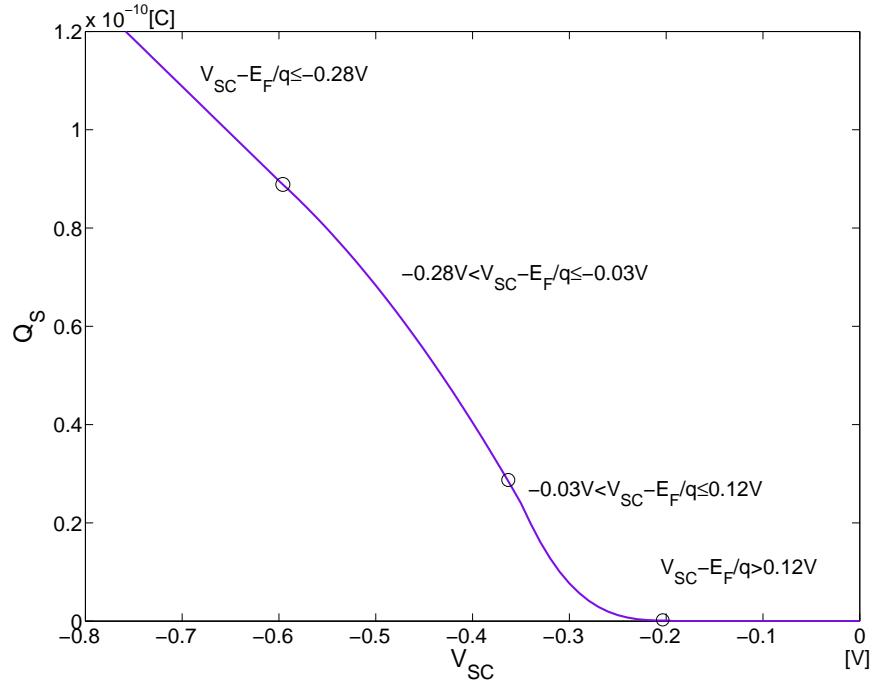

| 3.10 | Three-piece quadratic approximation of source mobile charge of CNT transistor . . . . .                                                                                                           | 57 |

| 3.11 | More accurate four-piece non-linear approximation of source mobile charge of CNT transistor . . . . .                                                                                             | 57 |

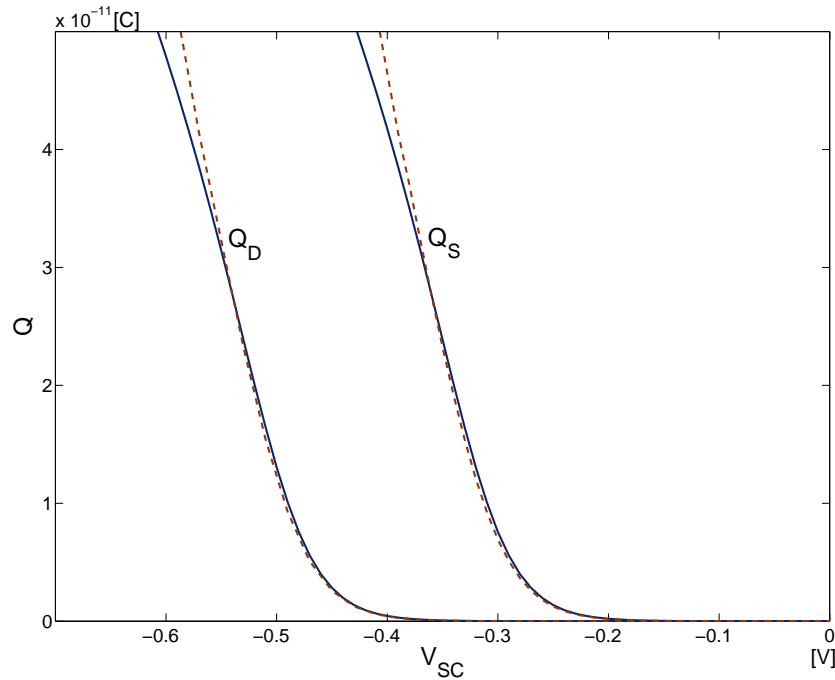

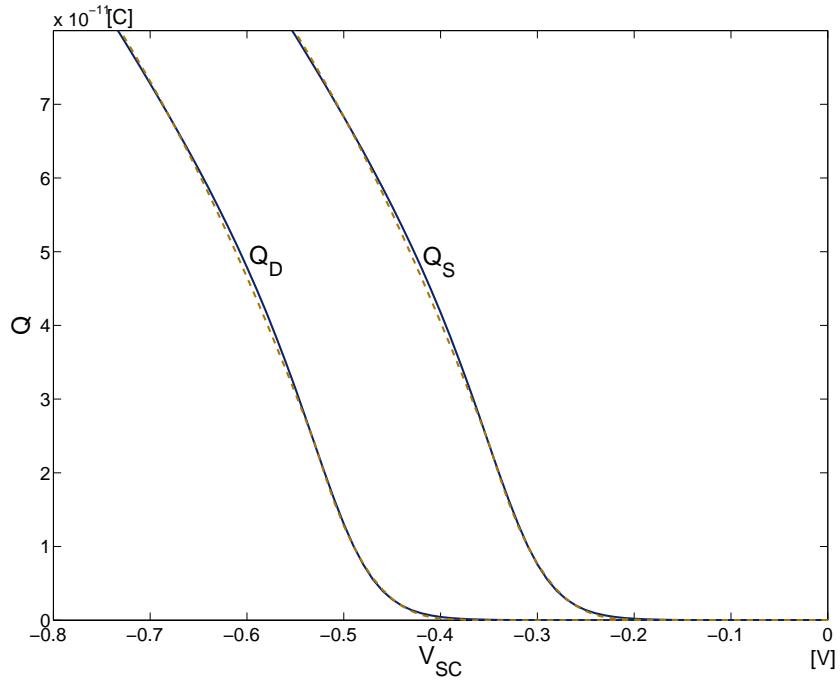

| 3.12 | Mobile charges at drain and source for $T = 300K$ , $d = 1nm$ and $E_F = -0.32eV$ and their piece-wise approximation using Model A . . . . .                                                      | 58 |

|      |                                                                                                                                                                                                      |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Mobile charges at drain and source for $T = 300K$ , $d = 1nm$ and $E_F = -0.32eV$ and their piece-wise approximation using Model B . . . . .                                                         | 59 |

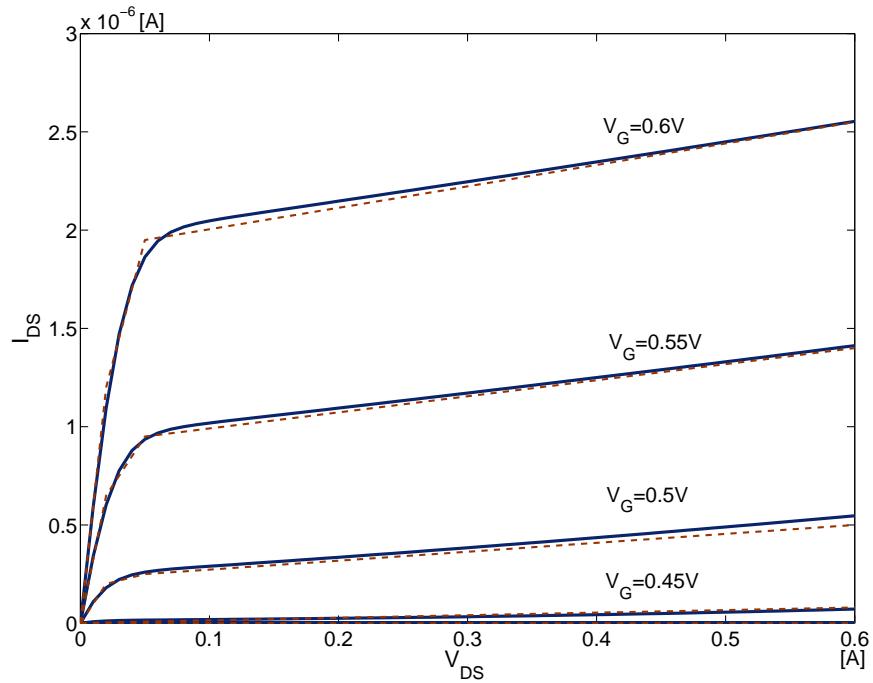

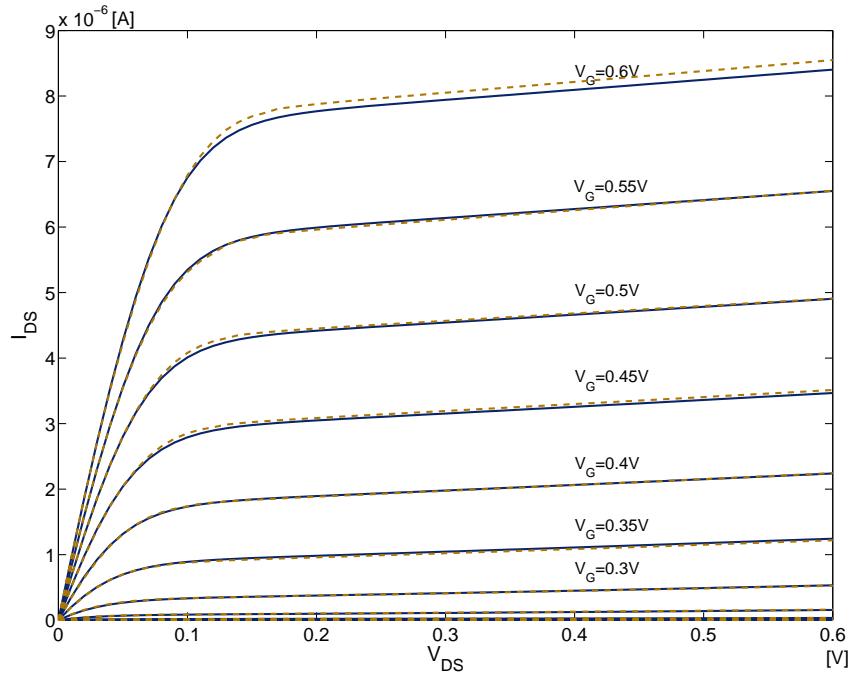

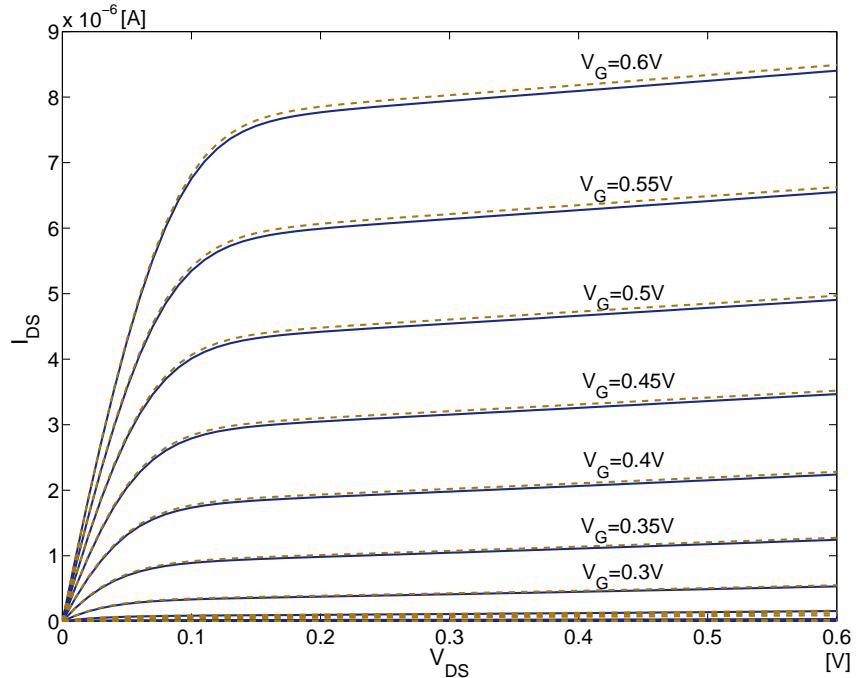

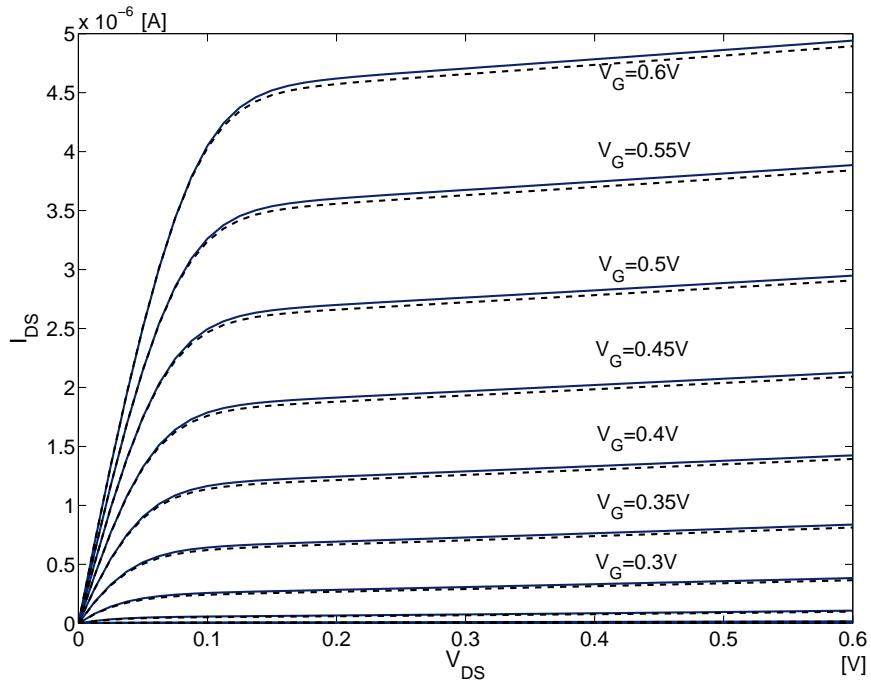

| 3.14 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece quadratic approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 300K$ . . . . . | 60 |

| 3.15 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 4-piece quadratic approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 300K$ . . . . . | 61 |

| 3.16 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece quadratic approximation with $E_F = -0.5eV$ , $d = 1nm$ and $T = 300K$ . . . . .  | 62 |

| 3.17 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece quadratic approximation with $E_F = 0eV$ , $d = 1nm$ and $T = 300K$ . . . . .     | 62 |

| 3.18 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece quadratic approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 150K$ . . . . . | 63 |

| 3.19 | Drain current characteristics of FETToy (solid lines) and the CNT transistor model (dashed lines) based on 3-piece quadratic approximation with $E_F = -0.32eV$ , $d = 1nm$ and $T = 450K$ . . . . . | 64 |

| 3.20 | Drain current characteristics of a CNT transistor with $2nm$ CNT diameter, $T = 300K$ and $E_F = -0.32eV$ using 3-piece quadratic approximation                                                      | 65 |

| 4.1  | Piece-wise cubic spline approximation with $n = 4$ of source mobile charge density of CNT transistor compared with the theoretical result . . . . .                                                  | 71 |

| 4.2  | Drain current characteristics of FETToy and 3-piece cubic spline approximation based model with $T = 300K$ and $E_F = -0.32eV$ . . . . .                                                             | 74 |

| 4.3  | Drain current characteristics of FETToy and 3-piece cubic spline approximation based model with $T = 450K$ and $E_F = -0.32eV$ . . . . .                                                             | 75 |

| 4.4  | Drain current characteristics of FETToy and 3-piece cubic spline approximation based model with $T = 300K$ and $E_F = 0eV$ . . . . .                                                                 | 76 |

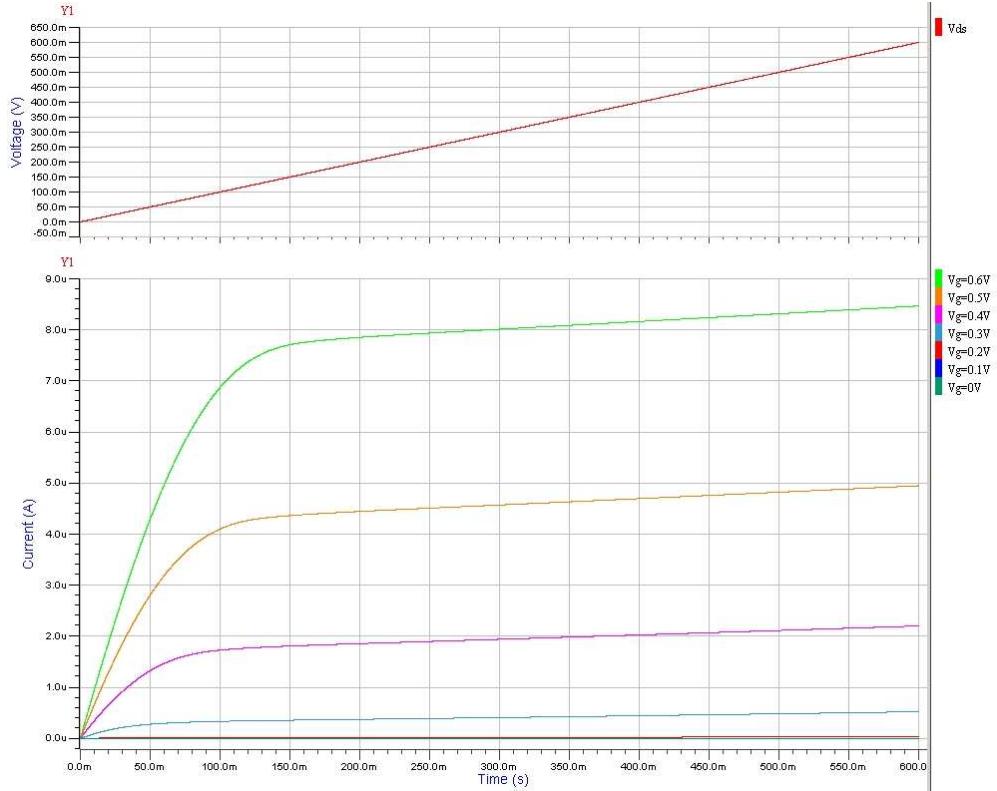

| 4.5  | Simulated drain current of the proposed VHDL-AMS CNT transistor model based on 3-piece cubic spline approximation of charge densities with $T = 300K$ , $d = 1nm$ and $E_F = -0.32eV$ . . . . .      | 80 |

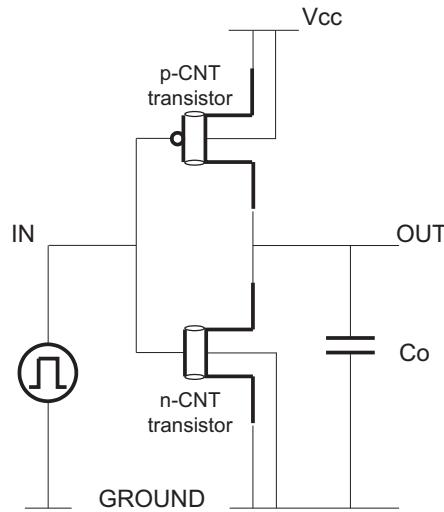

| 4.6  | Schematic of the simulated CNT based inverter in VHDL-AMS . . . . .                                                                                                                                  | 81 |

| 4.7  | Performance of the CNT based inverter in VHDL-AMS . . . . .                                                                                                                                          | 81 |

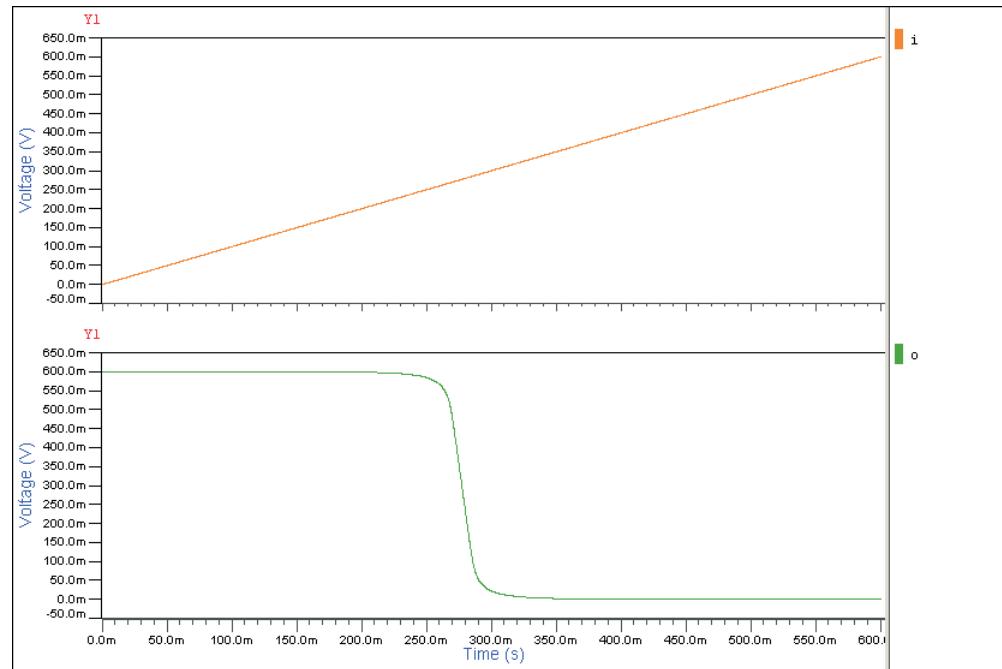

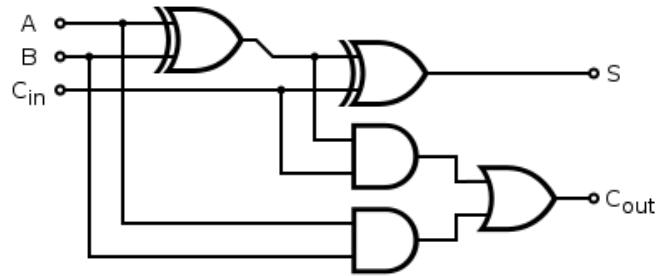

| 4.8  | Schematic of 1-bit full adder . . . . .                                                                                                                                                              | 83 |

| 4.9  | Simulation results of the CNT based 1-bit full adder in VHDL-AMS . . . . .                                                                                                                           | 83 |

| 5.1  | Comparison of the drain current between models with and without the elastic scattering effect . . . . .                                                                                              | 87 |

| 5.2  | Comparison of the drain current between models with and without strain effect . . . . .                                                                                                              | 89 |

| 5.3  | Comparison of the drain current between models with and without tunnelling effect . . . . .                                                                                                          | 90 |

| 5.4  | Comparison of the drain currents between models with and without phonon scattering . . . . .                                                                                                         | 92 |

| 5.5  | Sample comparison of the drain currents between ballistic FETToy, FETToy with non-ballistic effects and <i>FETToy+</i> models . . . . .                                                              | 96 |

|      |                                                                                                                                                                                |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

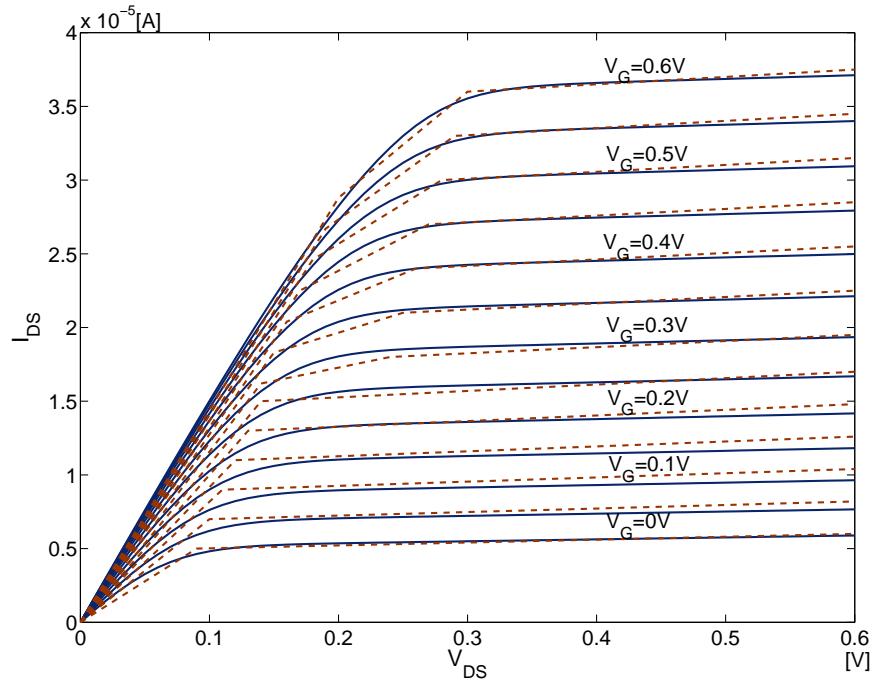

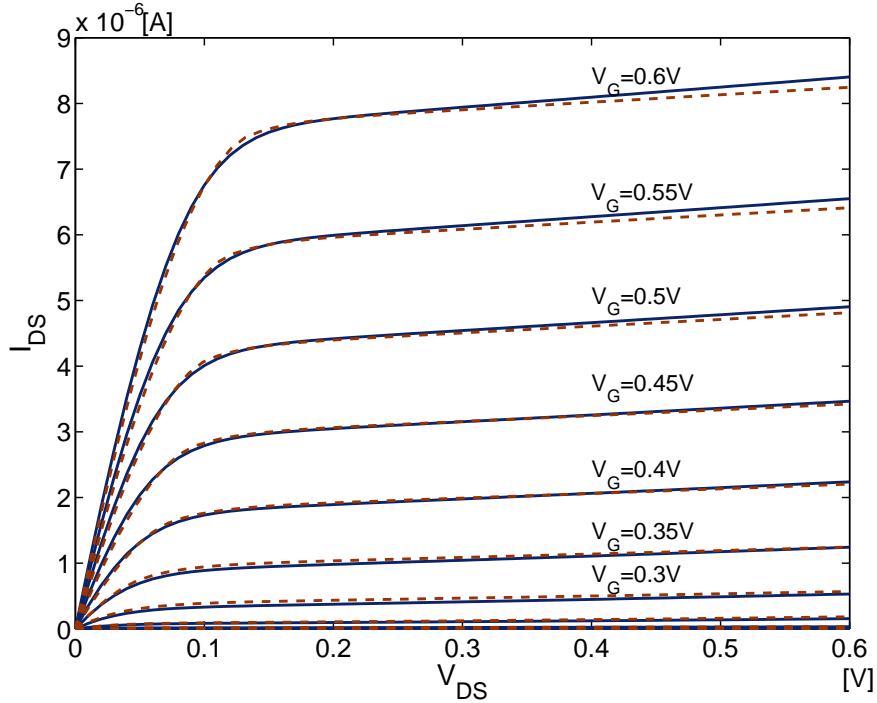

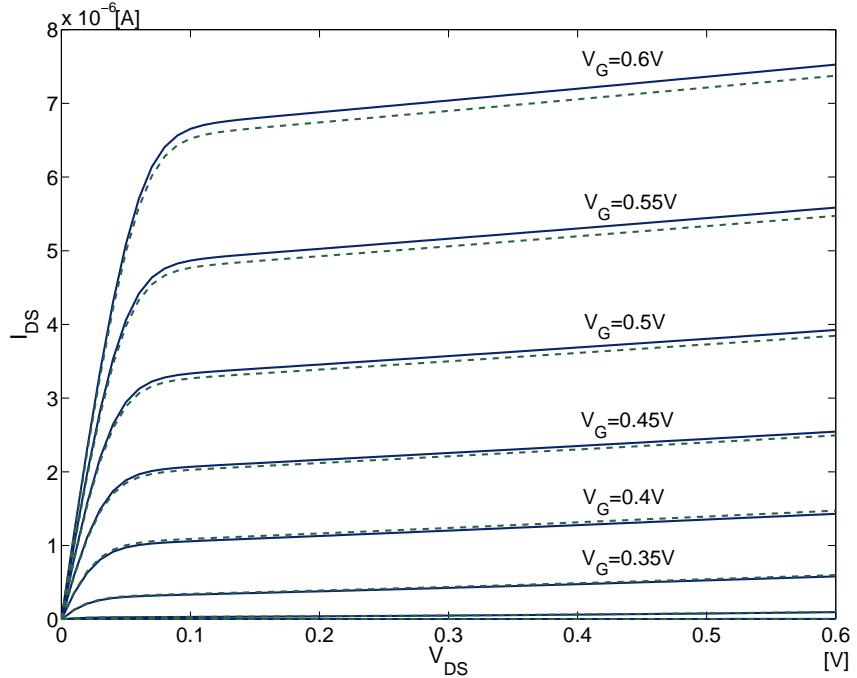

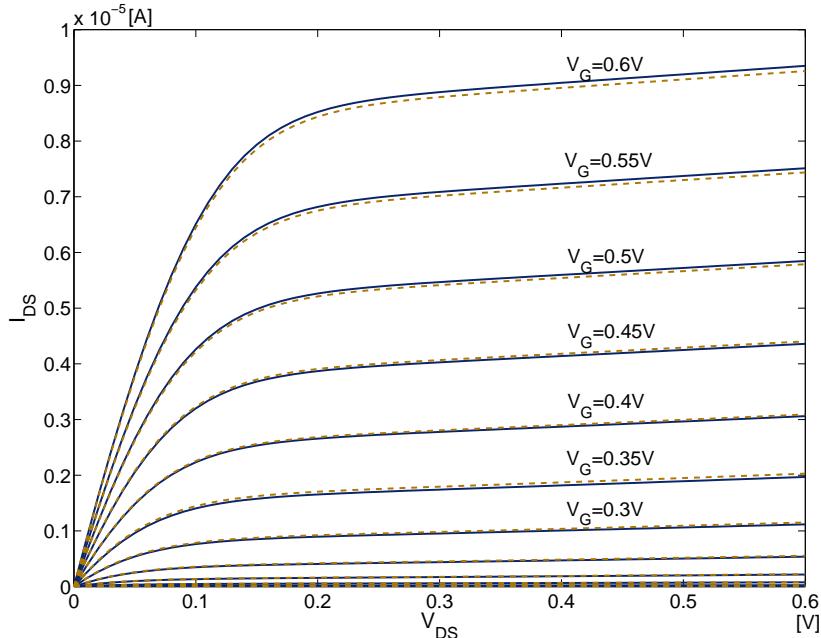

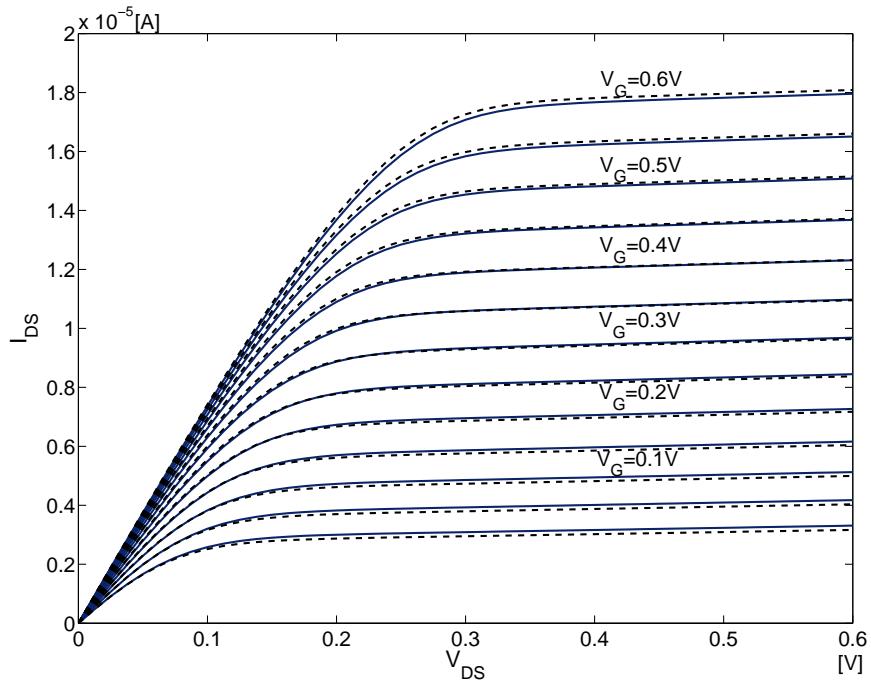

| 5.6  | Drain current characteristics of FETToy with non-ballistic transport and <i>FETToy+</i> Model C with $T = 300K$ , $E_F = -0.32eV$ , $d = 1nm$ and $L = 300nm$ . . . . .        | 97  |

| 5.7  | Drain current characteristics of FETToy with non-ballistic transport and <i>FETToy+</i> Model D with $T = 300K$ , $E_F = -0.32eV$ , $d = 1nm$ and $L = 300nm$ . . . . .        | 97  |

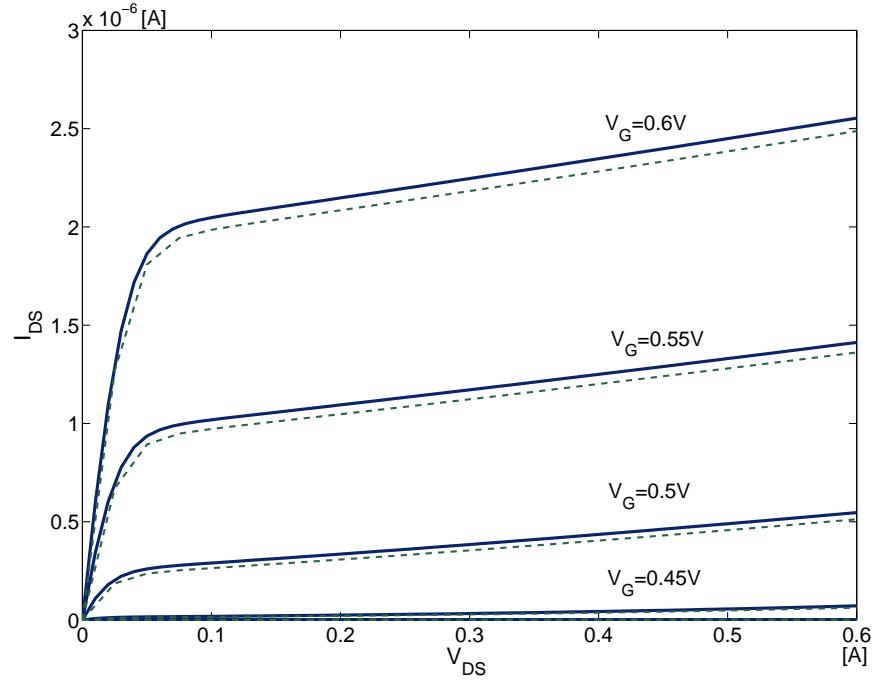

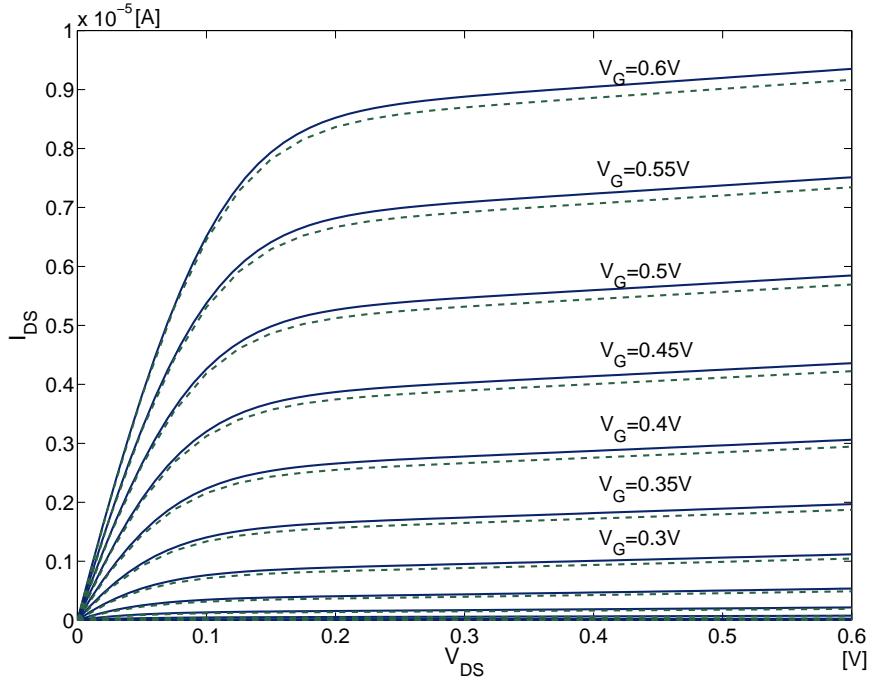

| 5.8  | Drain current characteristics of FETToy with non-ballistic transport and <i>FETToy+</i> Model D with $T = 450K$ , $E_F = -0.32eV$ , $d = 1nm$ and $L = 300nm$ . . . . .        | 98  |

| 5.9  | Drain current characteristics of FETToy with non-ballistic transport and <i>FETToy+</i> Model D with $T = 3000K$ , $E_F = 0eV$ , $d = 1nm$ and $L = 300nm$ . . . . .           | 99  |

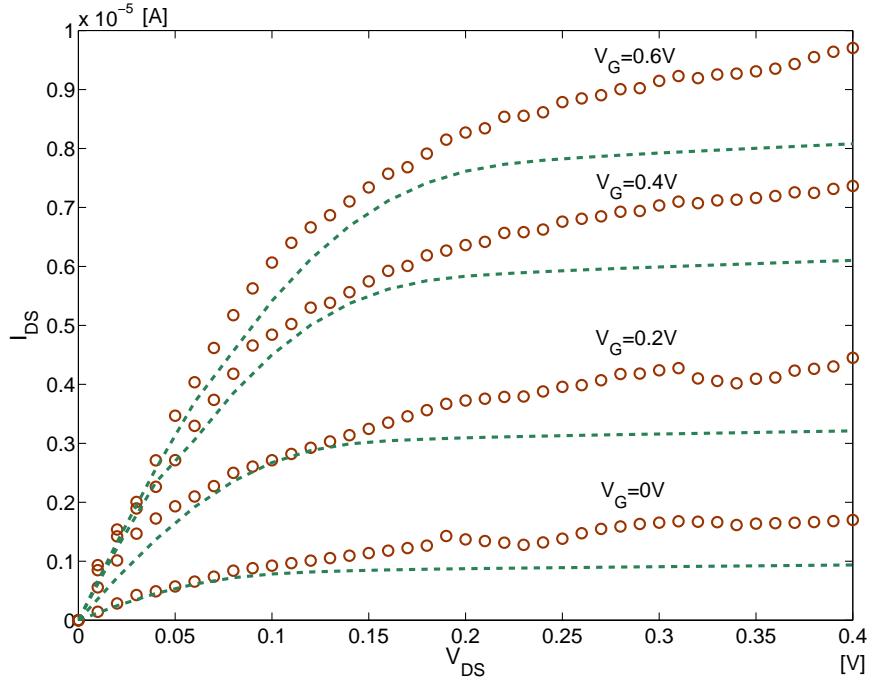

| 5.10 | Drain current comparison between experimental results and the proposed <i>FETToy+</i> model with $n = 5$ . . . . .                                                             | 101 |

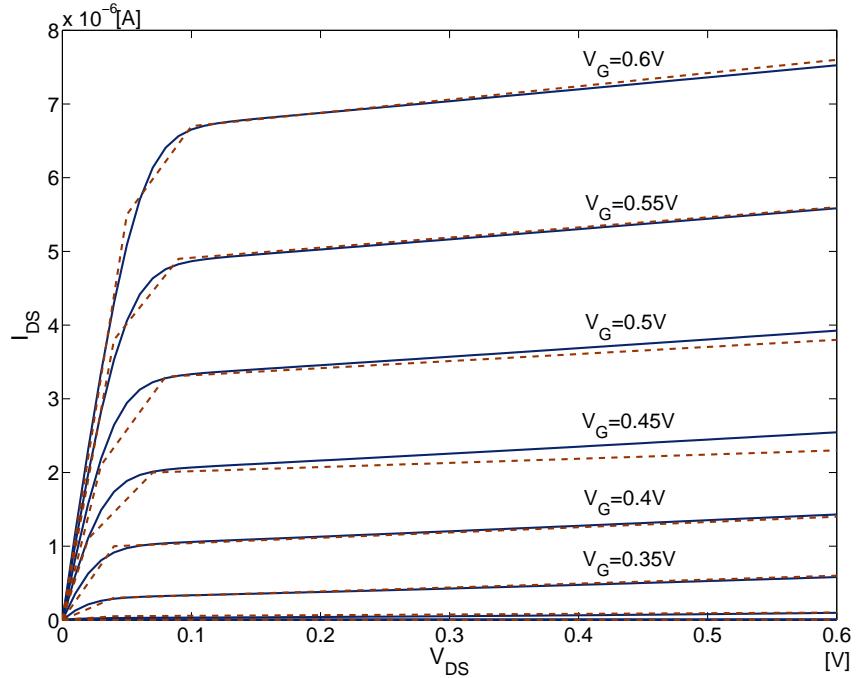

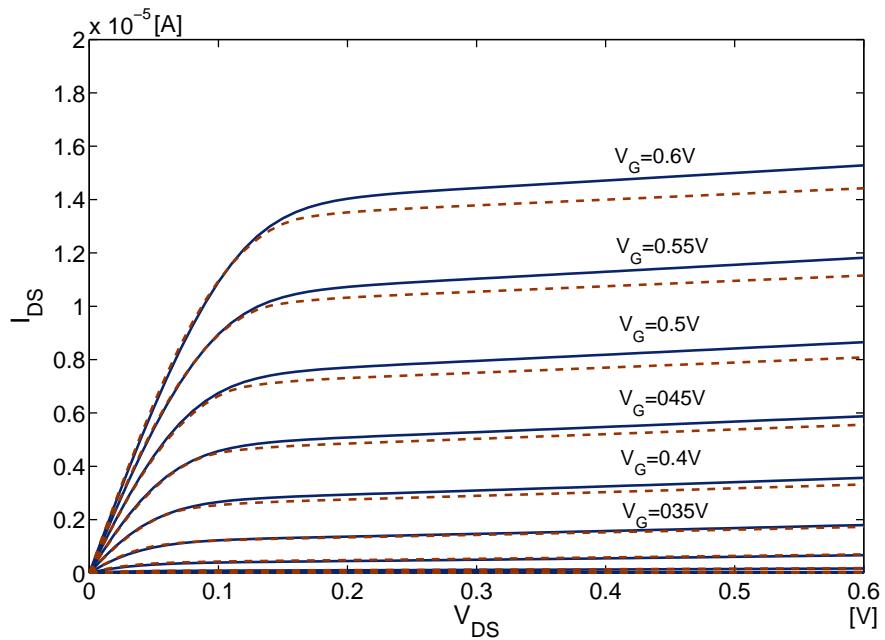

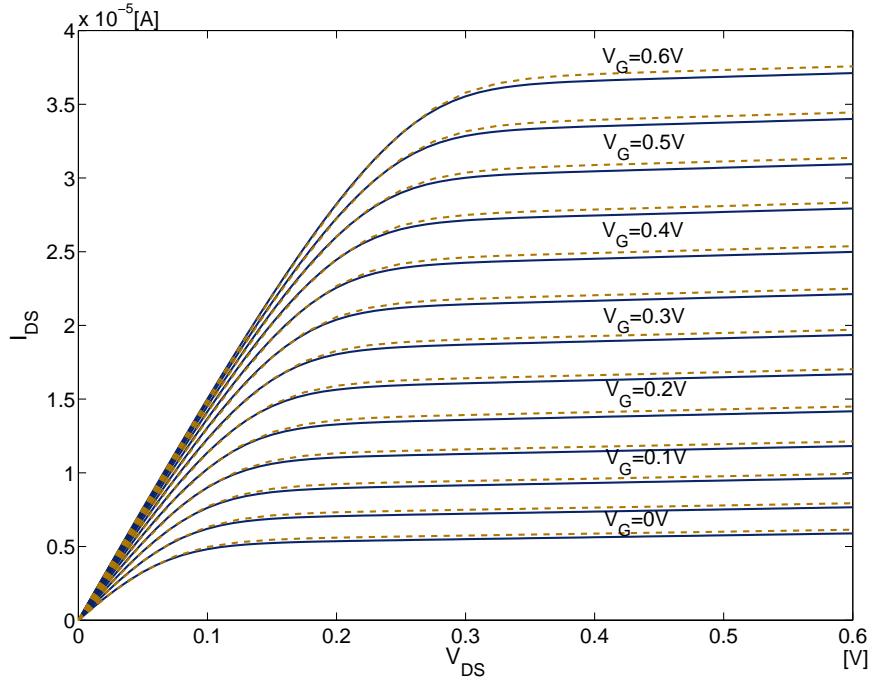

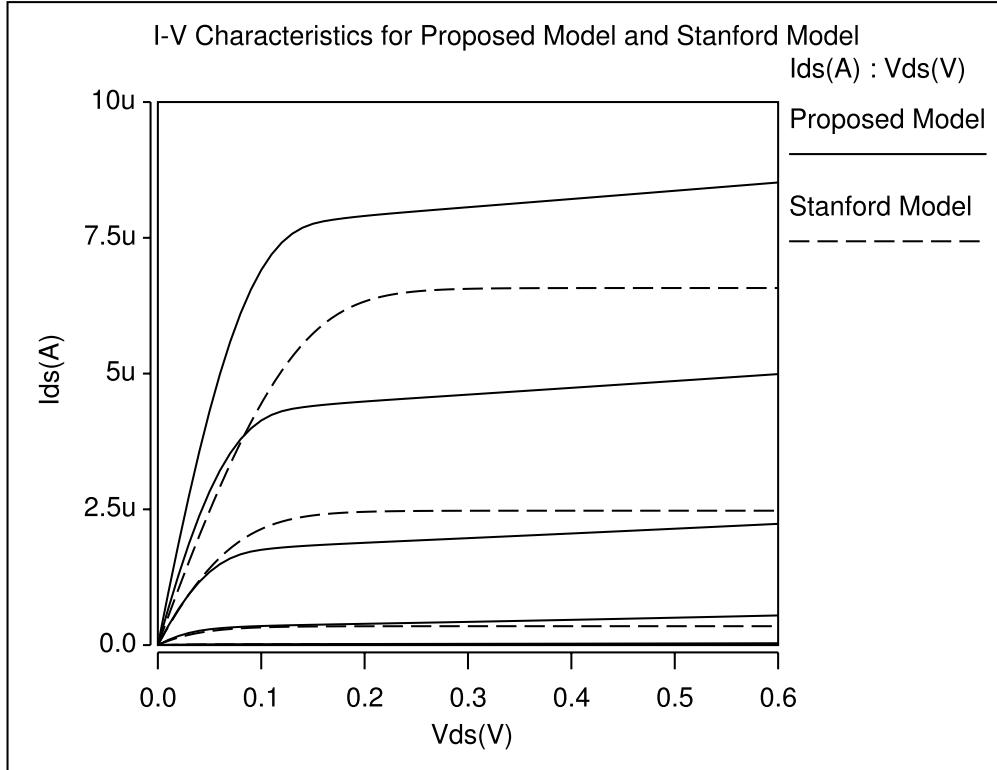

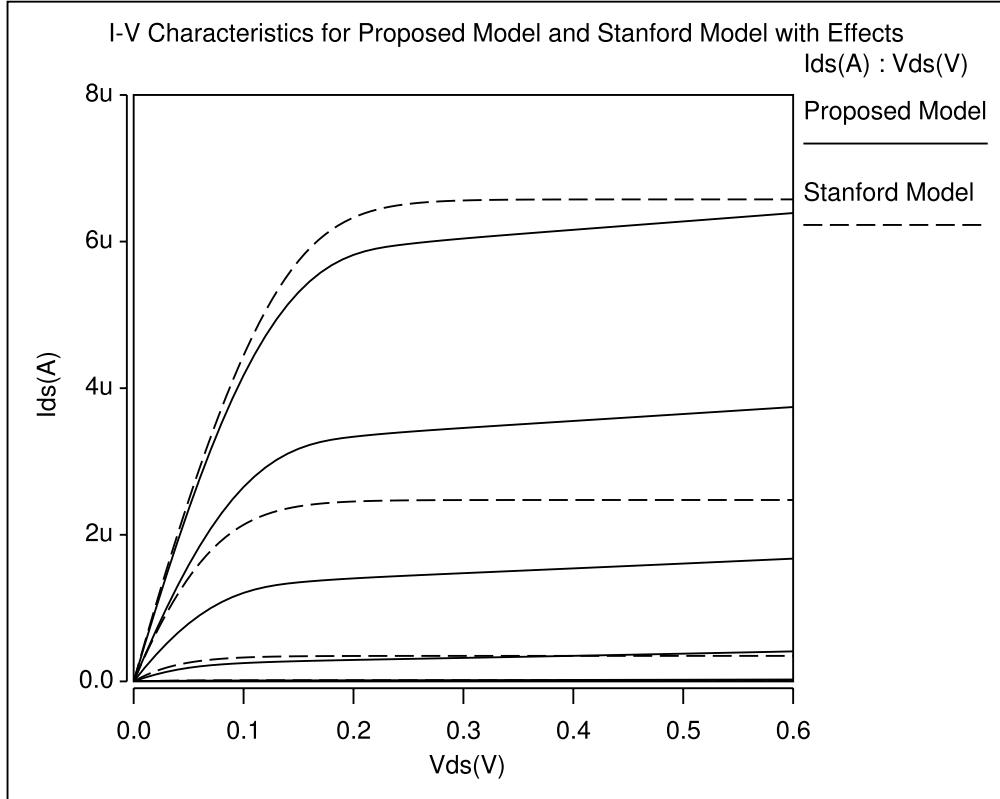

| 6.1  | Sample simulated drain current comparison of ballistic CNT transistors between the HSPICE CNT transistor macromodel and the Stanford circuit-level model . . . . .             | 109 |

| 6.2  | Sample simulated drain current comparison of CNT transistors between the HSPICE macromodel with non-ballistic transport effects and the Stanford circuit-level model . . . . . | 110 |

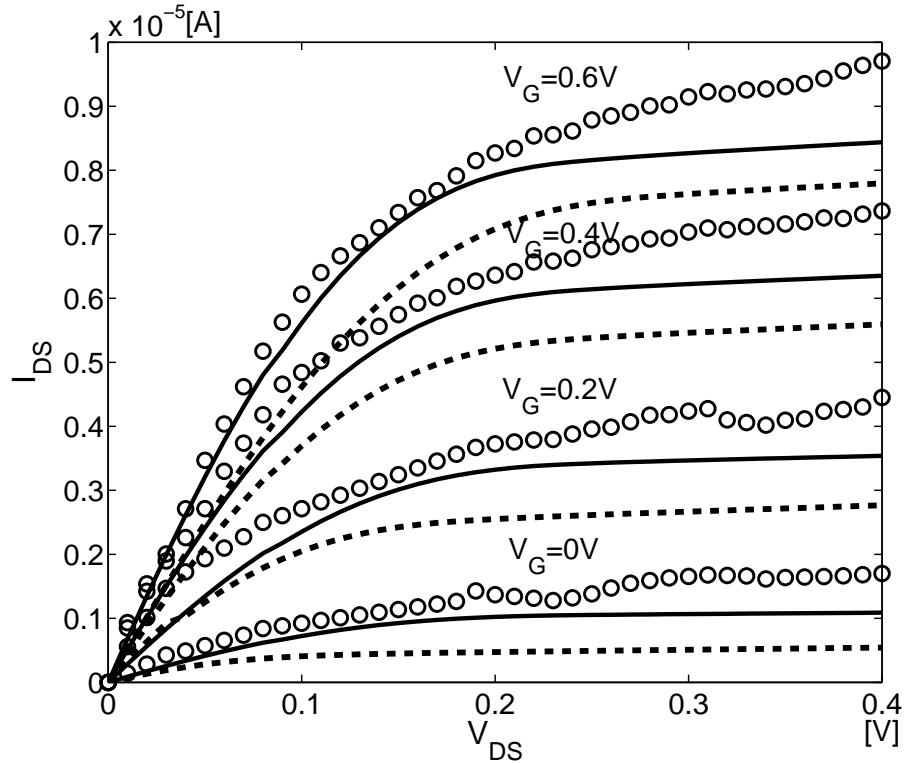

| 6.3  | Drain current comparison between experimental data, the proposed HSPICE macromodel and the Stanford model . . . . .                                                            | 111 |

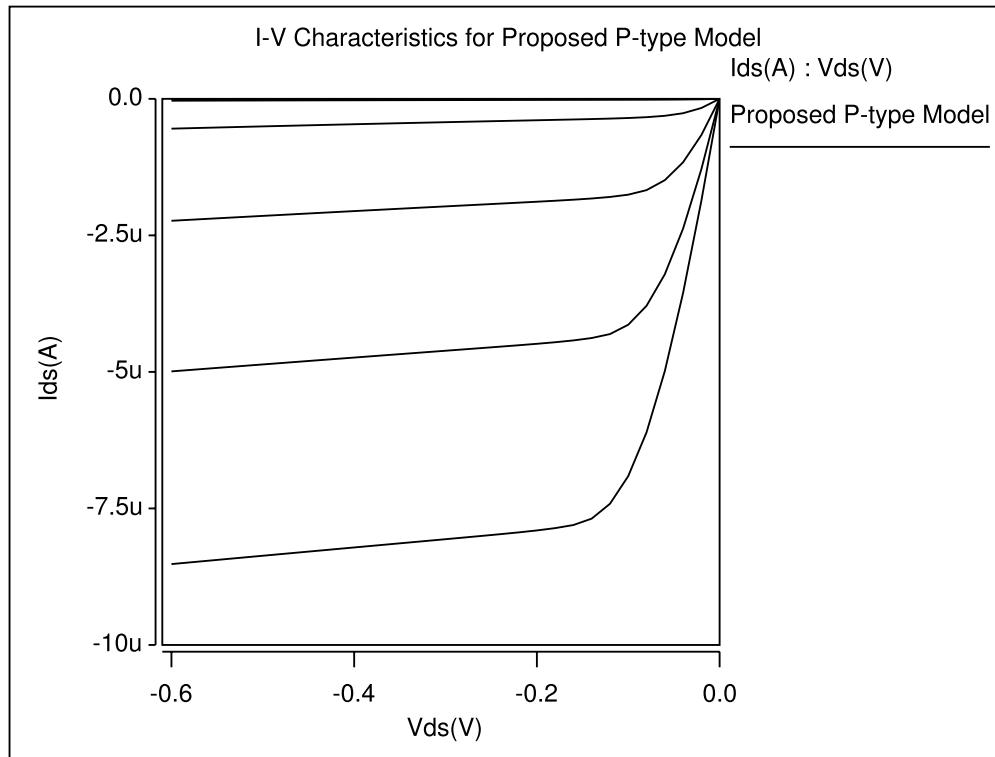

| 6.4  | Simulated drain current characteristics of a p-type CNT transistor macromodel in HSPICE . . . . .                                                                              | 112 |

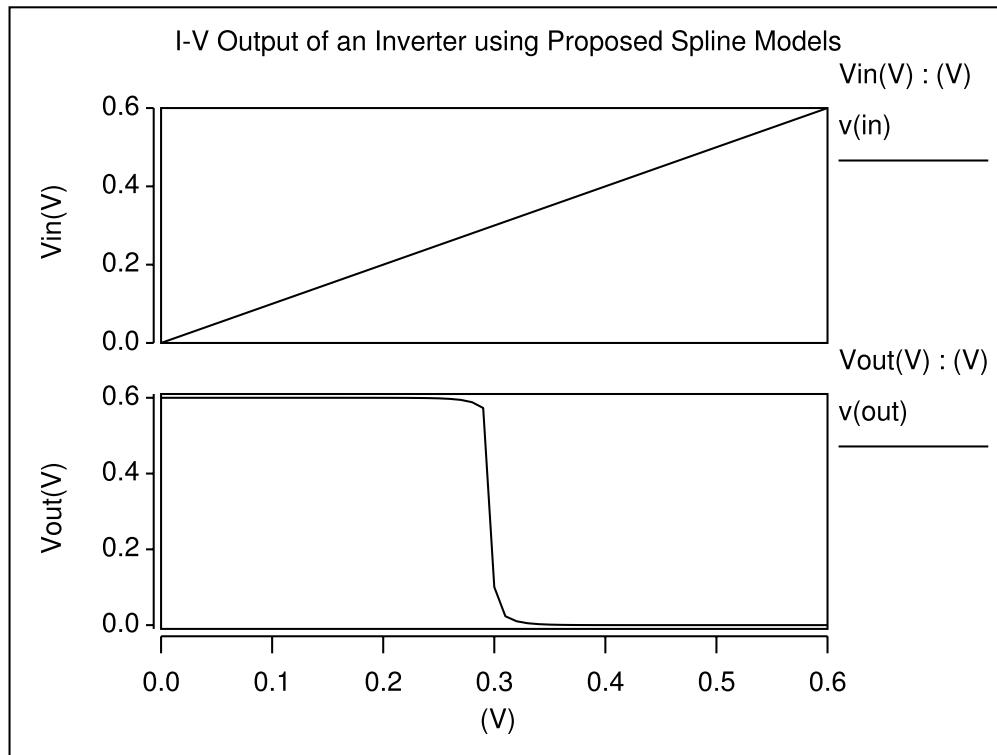

| 6.5  | Performance of a CNT based inverter simulated in HSPICE . . . . .                                                                                                              | 113 |

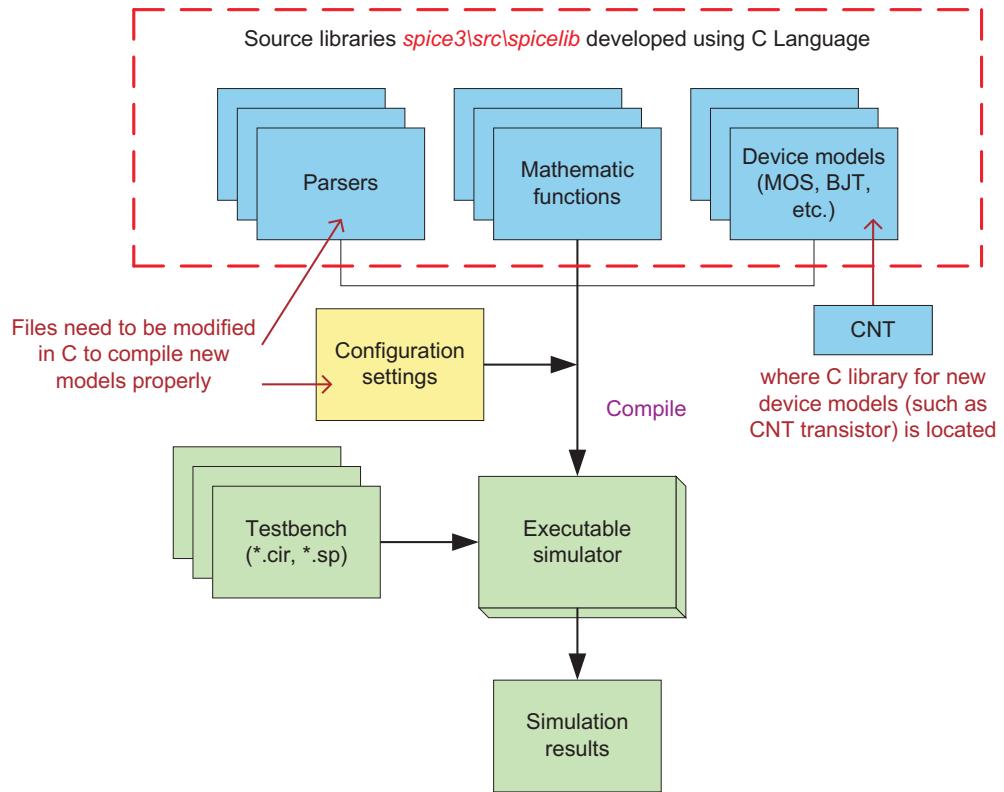

| 6.6  | Proposed work process and steps of composing new models for CNT based circuits in SPICE3 . . . . .                                                                             | 115 |

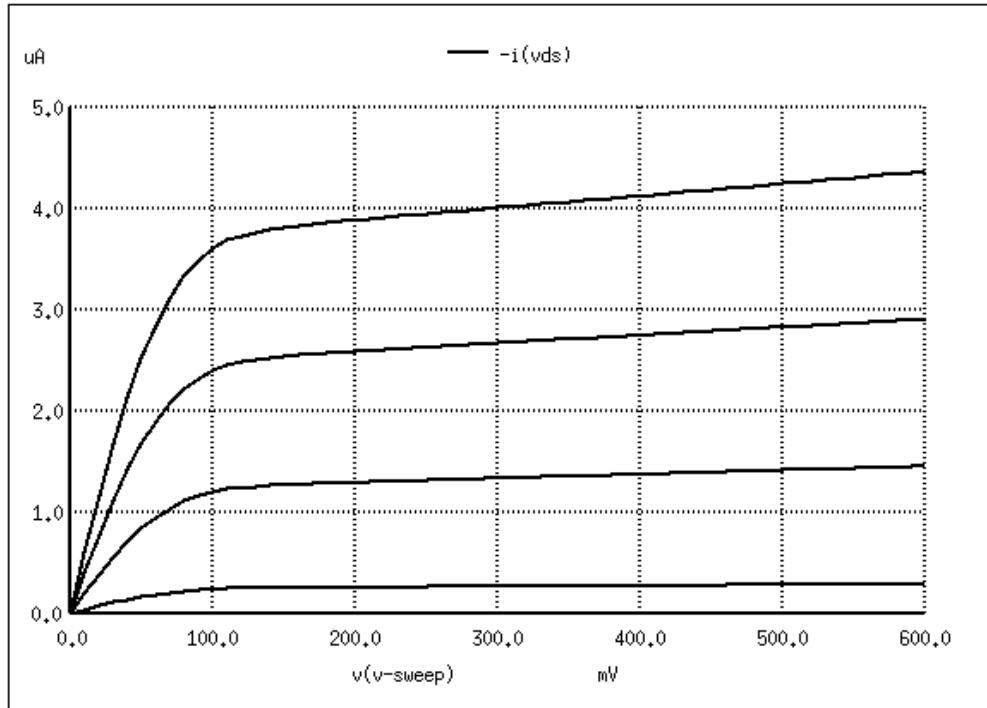

| 6.7  | Drain current characteristics of the proposed n-type SPICE3 CNT transistor model with $T = 300K$ , $L = 300nm$ , $dcnt = 1nm$ and $E_F = -0.32eV$ . . . . .                    | 117 |

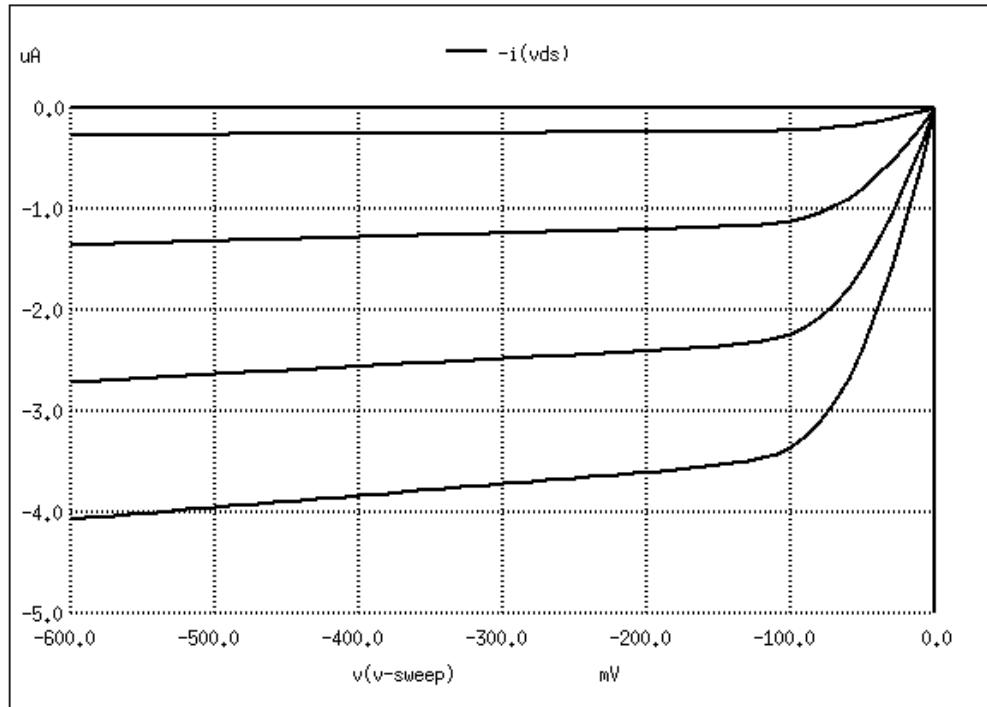

| 6.8  | Drain current characteristics of the proposed p-type SPICE3 CNT transistor model with $T = 300K$ and $E_F = -0.32eV$ . . . . .                                                 | 118 |

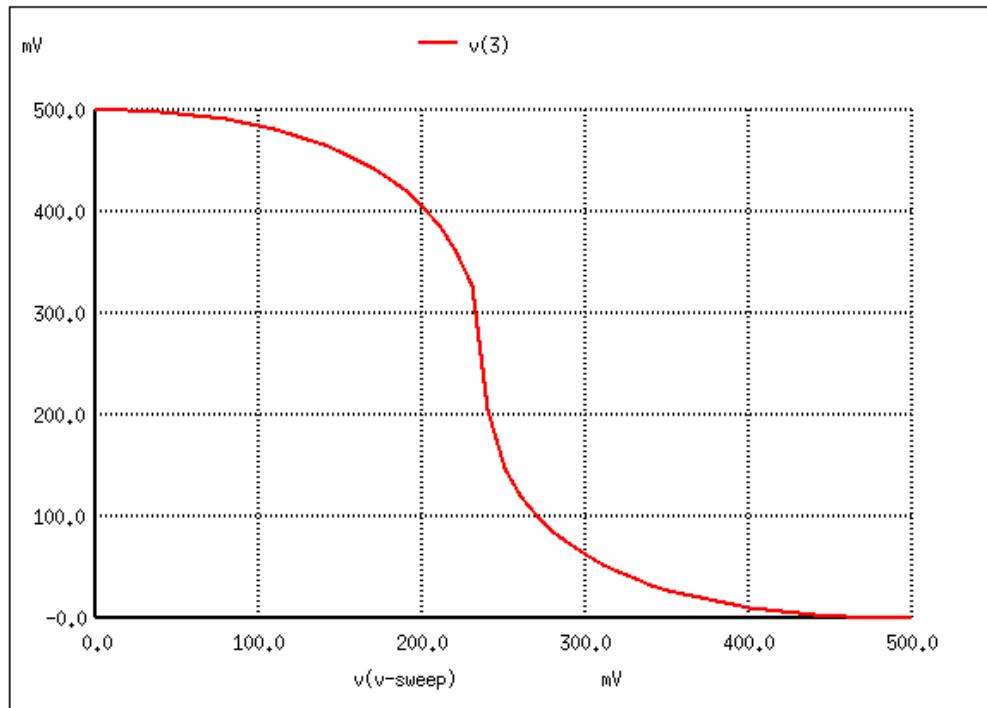

| 6.9  | CNT based inverter simulation result in SPICE3; input ramps from $0V$ to $0.5V$ . . . . .                                                                                      | 118 |

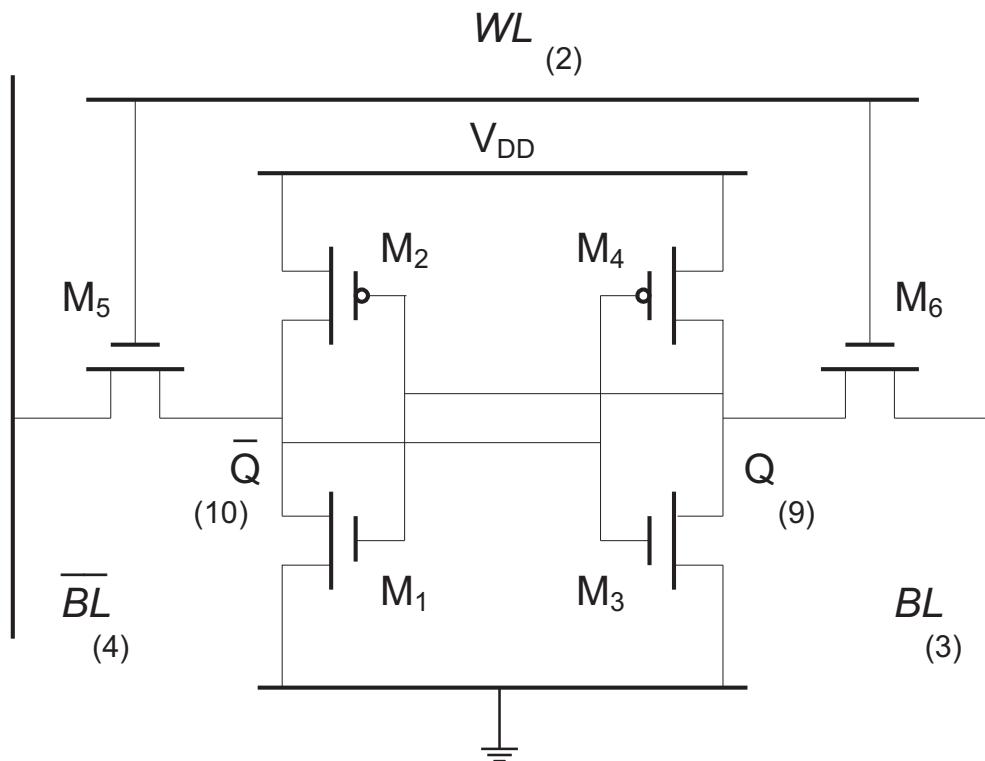

| 6.10 | Schematic of a six-transistor SRAM cell . . . . .                                                                                                                              | 119 |

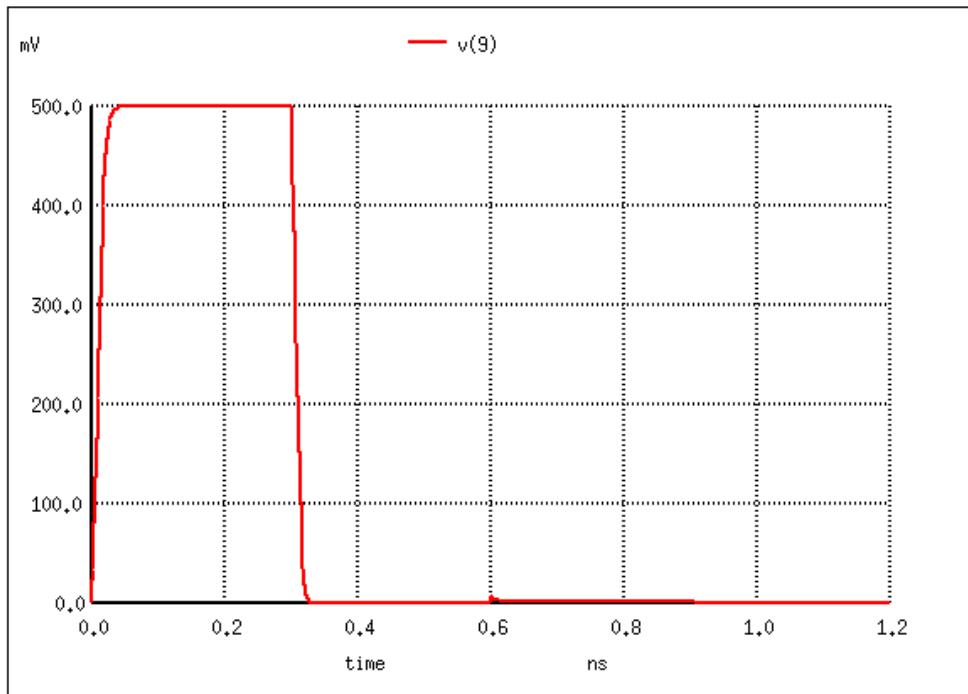

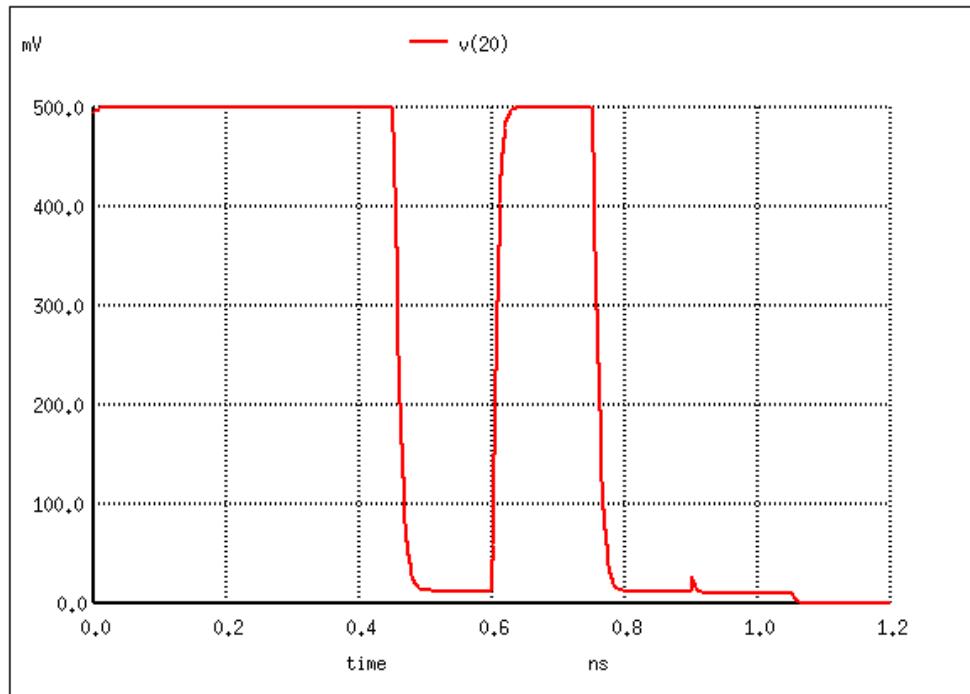

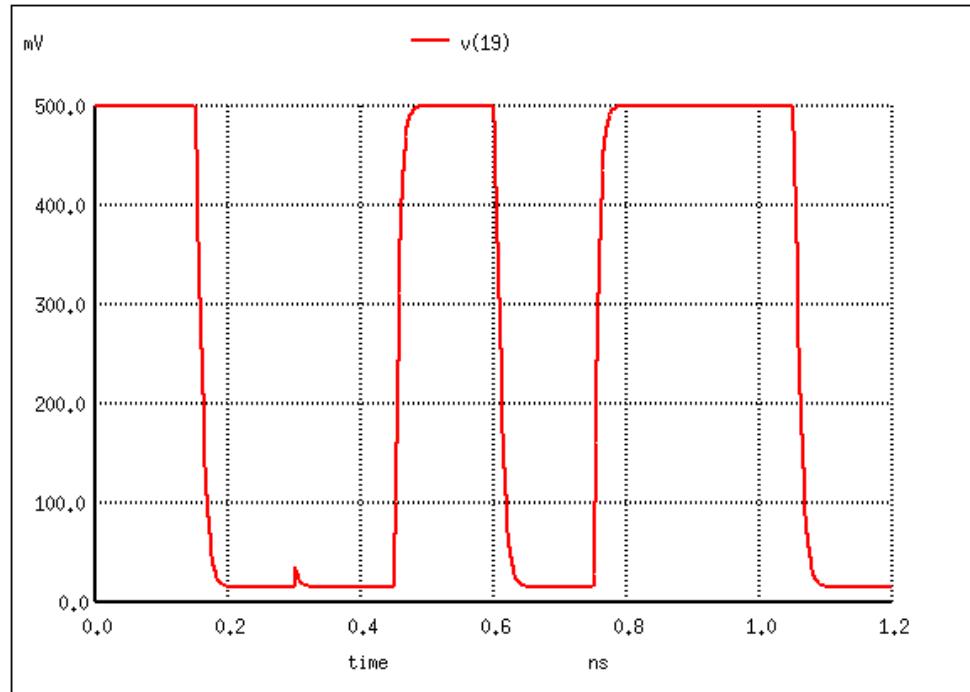

| 6.11 | CNT based SRAM cell output characteristics . . . . .                                                                                                                           | 121 |

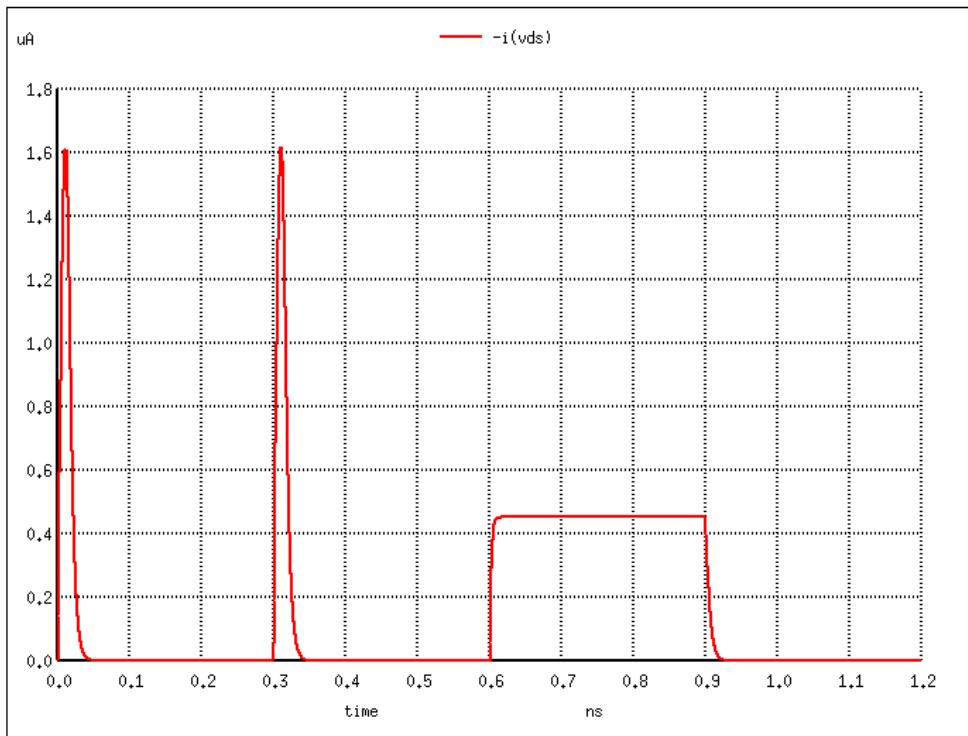

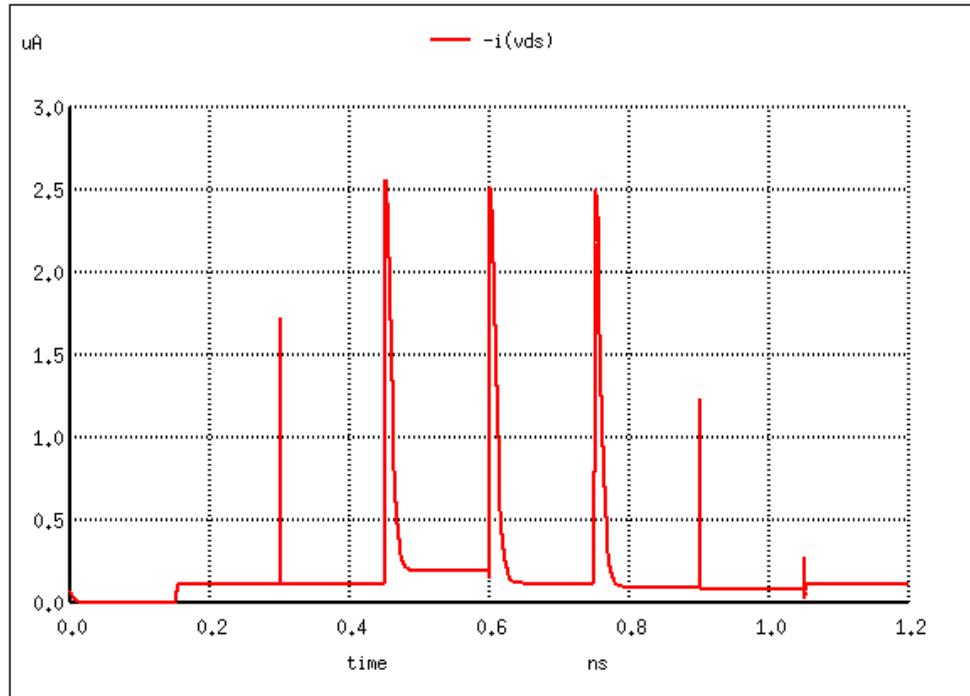

| 6.12 | CNT based SRAM cell current characteristics . . . . .                                                                                                                          | 121 |

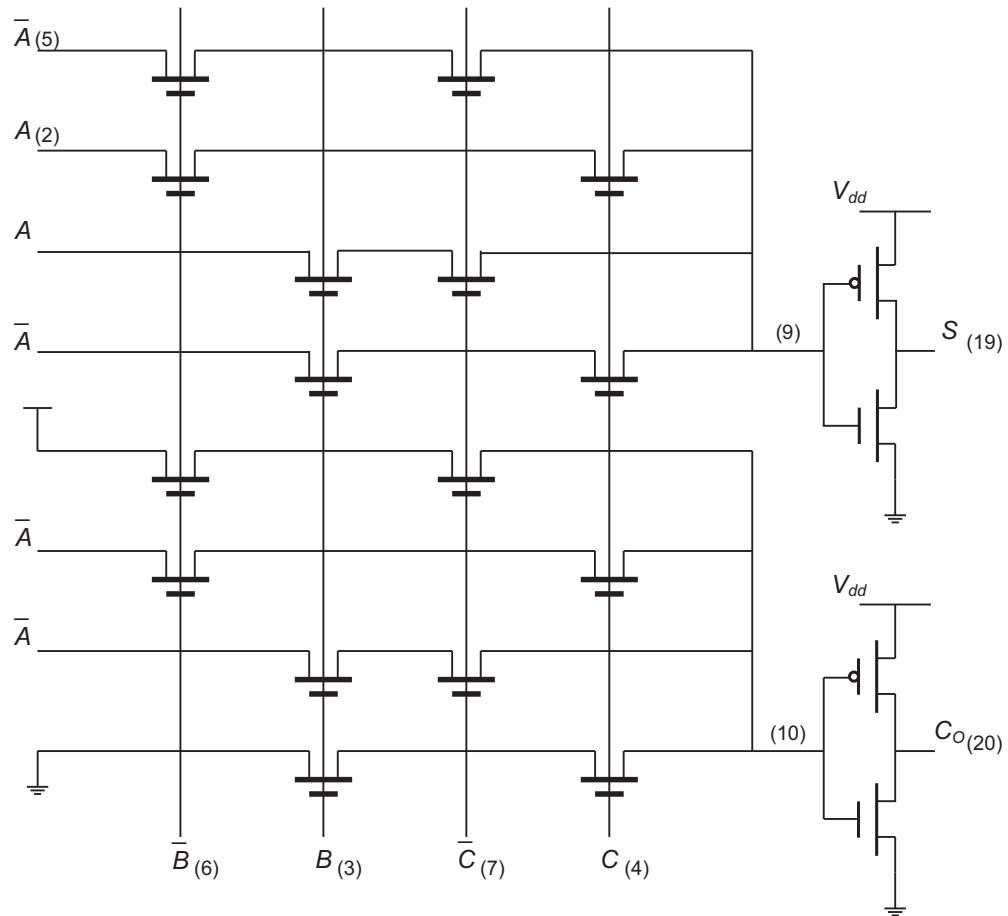

| 6.13 | Schematic of a pass transistor logic 1-bit full adder . . . . .                                                                                                                | 123 |

| 6.14 | Simulated $C_{out}$ performance of the pass transistor logic 1-bit adder based on the proposed SPICE3 CNT transistor model. . . . .                                            | 124 |

| 6.15 | Simulated $S$ performance of the pass transistor full logic 1-bit adder based on the proposed SPICE3 CNT transistor model. . . . .                                             | 124 |

| 6.16 | CNT based PTL full adder current characteristics . . . . .                                                                                                                     | 125 |

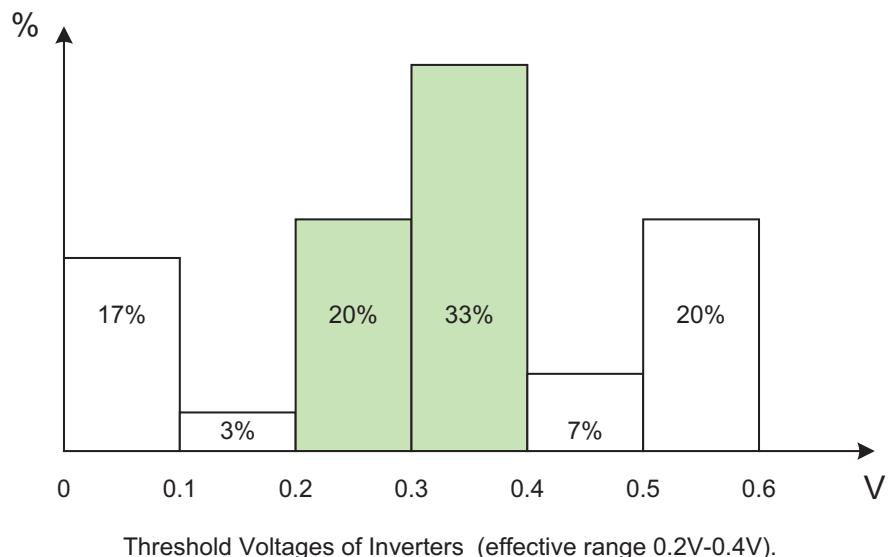

| 6.17 | Distribution of inverter threshold voltages . . . . .                                                                                                                          | 127 |

| B.1  | Schematic of the SPICE3 file structure tree . . . . .                                                                                                                          | 142 |

# List of Tables

|     |                                                                                                                                                                                                                           |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Average CPU Time Comparison between FETToy and the proposed model based on piece-wise linear approximation . . . . .                                                                                                      | 53  |

| 3.2 | Average RMS errors of $I_{DS}$ of the proposed model based on 3-piece linear approximation with $E_F = -0.32eV$ . . . . .                                                                                                 | 53  |

| 3.3 | Average RMS errors of $I_{DS}$ of the proposed model based on 3-piece linear approximation with $E_F = -0.5eV$ . . . . .                                                                                                  | 53  |

| 3.4 | Average RMS errors of $I_{DS}$ of the proposed model based on 3-piece linear approximation with $E_F = 0eV$ . . . . .                                                                                                     | 54  |

| 3.5 | Average RMS errors of $I_{DS}$ of Model A and Model B when $E_F = -0.32eV$ . . . . .                                                                                                                                      | 60  |

| 3.6 | Average CPU time comparison between theoretical and the proposed quadratic based model . . . . .                                                                                                                          | 61  |

| 3.7 | Average RMS errors of $I_{DS}$ of Model A and Model B when $E_F = -0.5eV$ . . . . .                                                                                                                                       | 64  |

| 3.8 | Average RMS errors of $I_{DS}$ of Model A and Model B when $E_F = 0eV$ . . . . .                                                                                                                                          | 64  |

| 4.1 | Average CPU time comparison between FETToy, 3-piece and 4-piece quadratic approximation based models, and spline based models with $n = 4$ and $n = 5$ . . . . .                                                          | 74  |

| 4.2 | Average RMS errors of $I_{DS}$ of proposed models based on quadratic and cubic spline approximation with $E_F = -0.32eV$ and $T = 300K$ . . . . .                                                                         | 75  |

| 4.3 | Average RMS errors of $I_{DS}$ of proposed models based on 3-piece cubic spline approximation with $E_F = -0.32eV$ . . . . .                                                                                              | 76  |

| 4.4 | Average RMS errors of $I_{DS}$ of proposed models based on 3-piece cubic spline approximation with $E_F = -0.5eV$ . . . . .                                                                                               | 77  |

| 4.5 | Average RMS errors of $I_{DS}$ of proposed models based on 3-piece cubic spline approximation with $E_F = 0eV$ . . . . .                                                                                                  | 77  |

| 5.1 | Maximum drain current RMS errors and average CPU time of the proposed <i>FETToy+</i> model compared with FETToy. . . . .                                                                                                  | 98  |

| 5.2 | Average $I_{DS}$ RMS errors of <i>FETToy+</i> Model D with $E_F = -0.32eV$ . . . . .                                                                                                                                      | 99  |

| 5.3 | Average $I_{DS}$ RMS errors of <i>FETToy+</i> Model D with $E_F = -0.5eV$ . . . . .                                                                                                                                       | 100 |

| 5.4 | Average $I_{DS}$ RMS errors of <i>FETToy+</i> Model D with $E_F = 0eV$ . . . . .                                                                                                                                          | 100 |

| 5.5 | Average $I_{DS}$ RMS error comparison to the experimental data between two <i>FETToy+</i> model based on 3-piece and 4-piece spline approximation with $d = 1.6nm, t_{ox} = 50nm, T = 300K$ and $E_F = -0.05eV$ . . . . . | 101 |

| 6.1 | Parameters of the proposed HSPICE CNT transistor macromodel. . . . .                                                                                                                                                      | 107 |

| 6.2 | Average $I_{DS}$ RMS error and CPU time comparison between the Stanford model and the developed HSPICE macromodel with $d = 1.6nm, t_{ox} = 50nm, T = 300K$ and $E_F = -0.05eV$ . . . . .                                 | 111 |

|     |                                                                                                                                                            |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Average CPU Time of the proposed CNT transistor model in SPICE3 compared with HSPICE Stanford model. . . . .                                               | 125 |

| 6.4 | Comparison of power consumption per switch of logic circuits based on the proposed SPICE3 CNT transistor model and conventional MOS based devices. . . . . | 126 |

| 6.5 | Performance of inverters consisting of the proposed SPICE3 CNT transistor model with randomly generated Fermi levels. . . . .                              | 128 |

| B.1 | MATLAB function files for the proposed ballistic CNT transistor model based on cubic spline approximation of mobile charge densities. . . . .              | 139 |

| B.2 | MATLAB function files for the FETToy model with non-ballistic effects. .                                                                                   | 140 |

| B.3 | MATLAB function files for <i>FETToy+</i> . . . . .                                                                                                         | 140 |

| B.4 | VHDL-AMS function files for the proposed cubic spline approximation based model. . . . .                                                                   | 141 |

| B.5 | HSPICE archives to implement the proposed cubic spline based CNT transistor macromodel. . . . .                                                            | 141 |

# List of Listings

|     |                                                                                                                 |     |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Top level module of the proposed cubic spline based CNT transistor model in VHDL-AMS . . . . .                  | 79  |

| 4.2 | Testbench of a logic inverter using the proposed cubic spline based CNT transistor model in VHDL-AMS . . . . .  | 82  |

| 6.1 | Testbench of a n-type CNT transistor model in HSPICE . . . . .                                                  | 108 |

| 6.2 | Testbench of an inverter based on CNT models in HSPICE . . . . .                                                | 112 |

| 6.3 | Testbench of an SRAM cell based on the proposed CNT transistor model in SPICE3 . . . . .                        | 119 |

| 6.4 | Testbench of a 1-bit pass-transistor logic adder based on the proposed CNT transistor model in SPICE3 . . . . . | 122 |

## Acknowledgements

There are many people that I would like to thank who have helped me in completing my research. Firstly, I would like to thank my two supervisors, Professor Bashir M. Al-Hashimi and Dr. Tom J. Kazmierski, an enormous thanks for all that they have done for me. Their supervision and faith in me has provided me with confidence to achieve my goals and fulfill my ambitions. They always made time for me and have given me a solid foundation for the future.

I would like to thank my mother and father for their continued support towards me throughout my studies. Though living in a country far away, they always contact me and stimulate my courage, making me feel like they were by my side all the time. Also, to my fiancée, Xuejiao Zeng, I would like to say a big thank you for providing me with the inspiration in life and study towards achieving my goals and for providing me with occasional words of wisdom at times of high stress.

I would also like to take this opportunity to thank Professor Stephen Hall, Professor Hiroshi Mizuta and Professor Peter Ashburn who provided valuable domain knowledge for the work in this thesis. For the much needed breaks during the course of my PhD, I would like to thank my friends Chuan Bai, Ruiqi Chen, Kai Ying and Chenxu Zhao. I will not forget the good times. During difficult times, I turned to Dr. Neil Ross, who made sure that I could proceed with my work by expelling any frustrations that I had. For this, Neil, I am forever grateful.

Finally, I want to appreciate the EPSRC (Engineering and Physical Sciences Research Council) for providing me with partly financial support via the project.

To everyone mentioned here, I thank you all.

*To my parents.*

# Chapter 1

## Introduction

### 1.1 Overview

Since the discovery of carbon nanotubes (CNTs) by Iijima in 1991[1], this new type of material continues to attract attention for its great potential to be applied as metallic nanowires and active semiconductor devices in next generation integrated circuits (ICs). Significant progress has been achieved in terms of both understanding the fundamental electronic properties and exploring possible engineering applications of CNTs [2]. Nanoelectronic devices have been extensively explored since the demonstration of the first carbon nanotube field-effect transistors (CNTFETs) [3]. CNT based transistors have been demonstrated both theoretically and experimentally. The transport characteristics of CNTs have been considered to be of significant importance for a CNT based transistor and thus have been widely studied. Ideally, for a carbon nanotube with its length much shorter than the mean free path of conduction electrons, a ballistic regime is generally exhibited in the nanotube [4]. However, the transport mechanism of CNT transistors is complicated and the extensive existence of non-idealities may result in non-ballistic transport. The transport type in carbon nanotubes, ballistic or non-ballistic, depends on the energy region, on which the theoretical analysis of CNT transistors should be focused.

The modelling of carbon nanotube devices, especially CNT transistors, has been devel-

oped significantly during the past several years. A number of CNT transistor models have been proposed in both experimental and theoretical studies. Significant progress has been made in understanding the operation mechanisms of CNT transistors. Early research demonstrated that CNT transistors operate like metal-oxide-semiconductor field-effect transistors (MOSFETs) [5, 6] or Schottky-barrier (SB) transistors [7, 8]. Nevertheless, as more electronic characteristics of CNT devices are revealed, both behavioural-level and circuit-level models have recently emerged and been applied into the simulation of CNT logic circuits [9, 10, 11]. Common techniques for modelling CNT transistors depend on the numerical evaluation of integrals or internal Newton-Raphson iterations in the energy domain within the nanotube to find solutions of non-linear dependencies [12], which encounter calculation complexities and are consequently time-consuming. Additionally, early CNT transistor models can only describe ideal ballistic transport properties and are not sufficient for practical use. Recently, new techniques which use symbolic approximation of mobile charge densities [11] and count in subband effects of CNTs [13, 14] have been developed to improve the efficiency and availability of the models. Though great efforts have been made, CNT transistor models are still being developed and novel methodologies remain to be identified.

Similarly to the development of most electronic device models, simulation is needed in order to address scientific and technological questions in the rapidly developing field of modelling CNT transistors [15]. Currently, most CNT transistor models describe the DC transport characteristics within the channel, and simulation can be made to numerically identify the relations between different parameters and the flow of carriers through the carbon nanotube channel, which verify the performance of the proposed models and help to optimise them [9, 10, 11]. A number of theoretical CNT transistor models [12, 16] have been developed, which derive ideal ballistic output results in simulation but consume much CPU resource, and are thus not efficient enough for practical use. Therefore, novel numerical modelling techniques are needed to shorten the simulation periods without losing much accuracy, especially when applied to circuits. Although numerical modelling techniques have recently been proposed [9, 16], the simulation results diverge and there is a lack of comparisons with experiments. In the light of non-idealities (defects, misalignment, etc.) of CNTs, the proposed models are required to be able to

reflect these non-ideal effects on the transport characteristics of CNT transistors in simulation. The performance of the proposed models also needs to be compared with results obtained from both numerical analysis and experiments. Both theoretical analysis of the electronic properties of CNT transistor and improvement of the modelling techniques are needed.

Within this context, this chapter is organised as follows: Section 1.2 gives a broad view on CNT transistor design and illustrates the potential applications of CNT transistors and some main challenges that are tackled as part of this research. Section 1.3 presents the main objectives and contributions of this work. Finally, Section 1.4 outlines the structure of the thesis.

## 1.2 Carbon Nanotube Transistor Modelling

Semiconducting carbon nanotubes have impressive electronic features and as a result are promising new material for the next generation of ICs. CNT transistors have been constructed experimentally and their performance has been demonstrated to exceed conventional silicon FETs [17, 18]. Furthermore, the need for developing models which can describe the characteristics of CNT transistors is increasing. A number of current techniques for CNT transistor modelling employ MATLAB to numerically present the transport mechanism [12, 16, 19]. In numerical models, the electronic parameters of CNT transistors are quantified and the relationships between the inner components are also represented by mathematical equations. However, these models are based on ideal numerical equations and their performance in practice differs from that obtained in simulation since the non-ballistic transport characteristics of CNT transistors are not included in the proposed numerical models. Most recently reported models are based on numerically describing the transport characteristics of CNTs [20, 21, 22], which implies the importance of revealing the electronic mechanism of the nanotube. Although some theories have been suggested, there are still some phenomena that need theoretical explanation. For example, the doping mechanism of CNTs is quite different from silicon and plays a significant role in the mobility of the nanotube. This can explain why

most existing models are focused on the ballistic transport characteristics. Recently symbolic approximation for modelling charge densities in the ballistic region of a CNT transistor has been presented [11, 23]. The approximation technique permits a fast and accurate calculation of the charge densities within the CNT channel, which presents a closed-form solution to the drain-source current in a CNT channel as a function of parameters including temperature, terminal voltages, Fermi level, and CNT diameter of the transistor.

The aim of modelling CNT transistors is to predict the performance of circuits with CNT devices by running simulation before fabrication, expecting that the simulation results can reflect the performance of real devices. At present there is a gap between simulation and experimental results. One reason is that the electronic mechanism of CNTs are yet to be established; another reason is that the fabrication of CNT transistors is difficult to control and no uniform results are obtained from various experiments, which implies that feasible approaches to fabricating CNTs are still under development.

### 1.2.1 Research Challenges

There are a number of challenges in CNT device modelling and this research focuses on the following key challenges:

- A main challenge is the need for efficient and effective modelling techniques to provide fast and accurate simulation of CNT transistors. Some existing models employ numerical methods to present the physical characteristics but at the expense of high simulation time [12, 16]. Recently, symbolic and numerical approximation has been proposed to simplify the calculation complexity of CNT transistor models [11, 23], but more efforts are required in this area. In this research, the trade-off between accuracy and simulation time of models is investigated.

- Current CNT transistor models do not incorporate non-ballistic transport mechanisms including scattering and tunnelling. Also, there is little reported work showing discrepancies between computing simulation and experimental results of

CNT devices. To implement models that can describe both ballistic and non-ballistic characteristics of CNT transistors, theories explaining non-ballistic effects need to be revealed, and numerical equations have to be developed before these effects can be combined in the model. Furthermore, comparison between the simulation results of developed models and those from experiments needs to be carried out to validate the performance of the proposed models.

- Although a number of numerical CNT transistor models have recently been developed, there is a lack of research on SPICE-level implementation of CNT devices. Numerical or behavioural models can describe the general transport characteristics of the CNT transistor. However, some electronic effects that might affect the operation of CNT devices at circuit level, including the bulk effect of the transistor, are not included in the proposed models. SPICE models of CNT transistors which are suitable for practical circuit-level simulation need to be developed.

- Considering the variation of parameters of CNTs ( Fermi level, diameter, band gap, and chirality, etc.) and the existence of defects (metallic nanotube [24] and impurities [25], etc.), variation analysis is necessary for practical CNT transistor models. Some experiments have demonstrated the effects caused by parameter variation [26, 27]. By including such variation in models, users would be able to predict better correlation between simulation and the measured results of practical circuits and obtain the percentage of functionally working devices via simulations.

### 1.3 Research Aims and Contributions

New modelling and simulation techniques are necessary for carbon nanotube devices to establish their potential in logic circuit design. The main aim of this research is to investigate and develop efficient models of CNT transistors based on numerical approximation. It is expected that new modelling techniques for CNT devices can be developed and circuits based on the proposed CNT transistor models can be simulated. This research also involves developing efficient CNT transistor models which can describe both ballistic and non-ballistic transport characteristics and their application for CNT circuit

design. Furthermore, the simulation of proposed models on various platforms (numerical, behavioural and circuit level) is required to analyse the performance of the developed CNT transistor models in logic circuits. This research makes contributions in nanoelectronic circuit design and development of fast and accurate CNT transistor models which allow CNT based circuits with large numbers of such devices to be simulated efficiently and accurately. The contributions of this research are:

- **Numerical approximation techniques for modelling transport characteristics of CNT transistors:** This contribution represents a significant improvement in achieving fast and accurate techniques for modelling CNT transistors. The proposed techniques are based on very efficient numerical approximations (piece-wise linear, piece-wise quadratic and cubic spline) of the non-equilibrium mobile charge density, which considerably accelerate the evaluation of the CNT drain-source current while maintaining high modelling accuracy. Piece-wise approximation can replace complicated calculations in the modelling process and contribute to provide fast and numerically efficient CNT transistor models, while cubic spline algorithm allows an automatic approximation process and operates more accurately. Presented results further reinforce the suggestion that numerical integrations and internal Newton-Raphson iterations can be avoided in the calculation of the self-consistent voltage  $V_{SC}$  of CNT transistors (explained in detail in Section 3.1), and a computational time saving of more than three orders of magnitude can be achieved. Three papers describing this contribution were published at the 2007 Nanoarch conference [28], the 2008 Design, Automation & Test in Europe (DATE) conference [29], and the 2008 Forum on specification & Design Languages (FDL) conference [30].

- **CNT transistor models with non-ballistic transport characteristics:** This contribution demonstrates that effects of elastic scattering, phonon scattering, strain and tunnelling may influence the transport characteristics of CNT transistors. A new model that can reflect these non-ballistic transport characteristics has been developed. A salient feature of the proposed model is its ability to incorporate both ballistic and non-ballistic transport effects without a significant computa-

tional cost. The proposed model has been extensively validated against reported CNT ballistic and non-ballistic transport theories and experimental results. A journal paper introducing the developed model which is capable of analysing both ballistic and non-ballistic performance of CNT transistors has been published in IEEE Transactions on Nanotechnology [31].

- **SPICE-level implementation of CNT transistor models:** Based on the numerical analysis of the self-consistent voltage developed as part of this project, both HSPICE and Berkeley SPICE3 CNT transistor models which combine both ballistic and non-ballistic transport characteristics have been obtained and simulations of both models have been carried out. To validate the performance of the proposed models, some reported experimental characteristics have been compared with the simulation results of the proposed models and the differences are within an acceptable range. This contribution has shown that the proposed SPICE-level models can derive fast and accurate performance with low supply voltages. Additionally, its power efficiency makes the proposed SPICE3 model particularly suitable for implementation in circuit-level simulators where large numbers of such devices may be used to build complex circuits. A paper describing this contribution has been published at the 2009 Forum on specification & Design Languages (FDL) conference [32].

- **Parameter variation analysis of CNT transistor models:** Following the implementation of the SPICE-level models of CNT transistors, variation analysis of the proposed SPICE3 model has been carried out and circuits with non-ballistic CNT transistors have been simulated to verify the feasibility of the model. Parameter variation which can wildly affect the transport characteristics of CNT transistors exists. Simulation of CNT transistors with Fermi level variation has been carried out and estimation of the percentage of working components out of all simulated devices has been made.

## 1.4 Thesis Organisation

This thesis is divided into seven chapters. Chapter 2 provides a literature review which introduces the development of CNT device modelling and presents the potential questions in modelling carbon nanotube transistors. Chapter 3 demonstrates new CNT transistor modelling techniques based on numerical piece-wise approximation (piece-wise linear and quadratic polynomial) of the non-equilibrium mobile charge density within the CNT channel. Ballistic models based on these numerical techniques have been simulated and their efficiency and accuracy have been established. Chapter 4 introduces the cubic spline algorithm for the numerical modelling of CNT transistors, which creates an automatic and accurate solution of the numerical relationship between the mobile charge density and the self-consistent voltage, leading to the speed-up of deriving the current through the channel without losing much accuracy. Behavioural-level implementation of the cubic spline based model has been carried out using VHDL-AMS and simulations of logic circuits based on the proposed CNT transistor model have been made. Chapter 5 presents a new model to incorporate both ballistic transport as well as non-ballistic effects of CNT transistors. The developed model has been developed based on the cubic spline approximation and simulated in MATLAB. The performance of the proposed model has been compared with reported experimental results. Chapter 6 indicates the SPICE-like implementation of CNT transistor models using numerical approximation of non-equilibrium mobile charge densities, and provides simulation results which demonstrate the applications of the proposed models in logic circuits. Detailed simulations of CNT devices using the developed models are presented. Also in Chapter 6, parameter variation analysis of the proposed SPICE3 model is carried out to demonstrate the feasibility of the model in practical circuits. Finally, Chapter 7 concludes the research contributions and discusses potential directions for further research.

# Chapter 2

## Literature Review

Chapter 1 highlighted the importance and challenges of developing modelling techniques for CNT transistors, suggesting novel numerical approximations to simplify the modelling process for both ballistic and non-ballistic transport characteristics of CNTs. Before explaining the specific work in the research, background knowledge of carbon nanotubes is described in this chapter, which covers a brief review of semiconductor device models in Sections 2.1 and 2.2. The electronic characteristics of CNTs are described in Section 2.3, and recent efforts on modelling CNT devices are introduced in Section 2.4. The latest research on circuit-level modelling and simulation of CNT transistors is also presented and serves as an orientation of this research in Sections 2.5 - 2.8. Section 2.9 provides a brief summary of parameter variation and its effect on the performance of CNT transistors. Finally, Section 2.10 concludes this chapter.

### 2.1 Semiconductor Device Models

Silicon has played a fundamental role in the semiconductor industry and most semiconductor device models are based on silicon materials. This section gives a brief introduction of traditional semiconductor devices and the development of these devices during the past decades.

The semiconductor is a type of solid material whose electrical conductivity is in between

a conductor and an insulator. Its special transport characteristics are determined by the small band gaps, which allow a number of environmental factors including temperature and light to control its electrical properties [33].

A p-n junction is a structure formed by combining p-type and n-type semiconductors together in very close contact [34]. The term junction refers to the region where the two regions of semiconductors meet. The p-n junction has been applied widely as a basic structure in modern electronics. One of the most popular applications of the p-n junction is the diode. In a p-n diode, conventional current can flow from the p-type side (the anode) to the n-type side (the cathode), but cannot flow in the opposite direction. Another type of semiconductor diode, the Schottky diode, is formed from the contact between a metal and a semiconductor rather than by a p-n junction [35].

One of the most important semiconductor devices is the bipolar junction transistor (BJT), which was invented at Bell Laboratories in 1947 [36]. In BJTs, both electrons and holes participate in the conduction process. Bipolar transistors have been extensively used in high-speed circuits, analogue circuits, and power applications [37]. The field-effect transistor (FET) is a type of transistor that depends on an electric field to control the conductivity of a channel of one type of charge carrier in a semiconductor material. FETs are sometimes called unipolar transistors to contrast their single-carrier-type transport with the dual-carrier-type operation of BJTs [38]. A traditional metal-oxide-semiconductor (MOS) structure is obtained by depositing a layer of silicon dioxide ( $\text{SiO}_2$ ) and a layer of metal on top of a semiconductor die. As the silicon dioxide is a dielectric material its structure is equivalent to a planar capacitor, with one of the electrodes replaced by a semiconductor [39].

The MOSFET (metal-oxide-semiconductor field-effect transistor) was created by Kahng and Atalla in 1960 [40]. In a MOSFET, the source and drain are connected by a conducting surface channel through which carriers can flow when properly modulated by the gate voltage [41]. The source and drain regions can be either p or n type, but they must both be of the same type, and of opposite type to the body region. Recently, MOSFETs have been scaled down significantly and the Si- $\text{SiO}_2$  interface remains the most important combination [42].

Scaling down the dimensions of MOSFETs is a continuous trend. The difficulties with reducing the size of the MOSFET include the semiconductor device fabrication process, the need for very low voltages, and with poorer electrical performance the necessity of circuit redesign and innovation [43]. It has been stated that smaller transistors switch faster, which is the main motivation for scaling down the dimensions of semiconductor devices [44].

## 2.2 Modelling and Simulation of Semiconductor Devices

In this section, the development of semiconductor modelling techniques is reviewed and a general introduction of simulation is also included.

The physical properties of semiconductor devices are complicated and equivalent models are needed for reliable fabrication in practice. In order to ensure the correct operation of circuits employing semiconductor devices, it is necessary to model the physical phenomena observed in experiments and predict the performance of devices correctly in simulation [45]. The modern transistor has an internal structure that exploits complex electronic mechanisms. Providing information about how the device is formed, process models simulate the manufacturing steps and provide a microscopic description of device geometry to the device simulator [46].

Different from process models, with information about what the device looks like, the device simulator models the physical processes taking place in the device to determine its electrical behaviour in a variety of aspects: DC current-voltage behaviour, transient response, or dependence on device layout, such as long and narrow versus short and wide, or interdigitated versus rectangular, or isolated versus proximate to other devices [47]. Simulations can inform the device designer whether the device process will produce devices with the electrical behaviour needed by the circuit designer, and are used to inform the process designer about any necessary process improvements [48]. Once the process gets close to manufacture, the predicted device characteristics are compared with measurement on test devices to check that the process and device models are working adequately.

In the early years, initial semiconductor devices were modelled in a very simple way, for instance, mainly drift and diffusion current were considered for basic transistor models; but today more effects must be taken into account for a practical model. For example, leakage currents in junctions and insulator, saturation current and non-ballistic transport, quantum mechanical effects and even the combination of multiple materials. Techniques change and the models need updates to adjust for new physical effects, or to provide better performance [49, 50].

As part of the development of modelling techniques, various computer languages for modelling have been developed. VHDL-AMS is a derivative of the hardware description language VHDL [51]. It includes analogue and mixed-signal extensions (AMS) in order to define the behaviour of analogue and mixed-signal systems. The VHDL-AMS standard was created with the intention of enabling the designers of analogue and mixed signal systems and integrated circuits to create and use modules that encapsulate behavioural-level descriptions as well as structural-level descriptions of systems and components. VHDL-AMS has become an industry standard modelling language for mixed signal components and circuits [52].

SPICE (Simulation Program with Integrated Circuit Emphasis) was developed at the University of California, Berkeley, in the early 1970s [53]. It was introduced as a general purpose simulator for analogue electronic circuits which can be used in transistor-level design to check the integrity of circuit designs and to predict circuit behaviour.

Containing analysis and models needed for integrated circuits design, SPICE has become popular and is widely used in industry. SPICE can drive operating point solutions, transient analysis, and various small-signal analysis with components and parameters to simulate circuits with different structures [54].

## 2.3 Carbon Nanotube Characteristics

Carbon nanotubes, as novel materials with unique electronic characteristics, have been anticipated to be exploited to construct electronic devices for their better physical properties than those of conventional silicon, for example, longer mean free path, larger

carrier mobility, and higher transport current density. This section introduces the characteristics of carbon nanotubes and describes some of their potential applications.

### 2.3.1 General Introduction to Carbon Nanotubes

The nanotube can be conceptually viewed as a rolled-up graphene sheet [55]. A common way to describe the one-dimensional energy-lattice vector ( $E - k$ ) relation of the carbon nanotube, which governs its electronic property, is to quantise the two-dimensional  $E - k$  of the graphene sheet along the circumferential direction of the nanotube [22]. Understanding the electronic characteristics of the graphene sheet helps to understand the electronic properties of carbon nanotubes. Graphene is known as a two-dimensional zero-gap semiconductor [56]; for most directions in the graphene sheet, there is a band gap, and electrons are not free to flow along those directions unless extra energy is applied. However, in certain special directions (with zero gap) graphene is metallic, and electrons flow freely along those directions. This feature is not obvious in bulk graphite, since there is always a conducting metallic path which can connect any two points, and hence graphite conducts electricity. However, when rolling up graphene to make a nanotube, a special direction is selected, which is the direction along the axis of the nanotube. Depending on this direction, metallic and semiconducting nanotubes can be obtained [57].

FIGURE 2.1: The graphene lattice in real space and reciprocal space with the basis lattice vectors [55].

The two-dimensional graphene lattice in real space can be created by translating one unit cell by the vectors  $\vec{T} = n\vec{a}_1 + m\vec{a}_2$  with integer combinations (n,m), where  $\vec{a}_1$  and  $\vec{a}_2$  are basis vectors of the real space lattice (as shown in Figure 2.1(a)) and  $\vec{b}_1$  and  $\vec{b}_2$  are basis vectors in the reciprocal space (Figure 2.1(b)). It has been widely proposed that the lattice structure determines the conducting characteristics of the carbon nanotube [22, 55, 58]. If  $(n - m) \bmod 3 = 0$ , the CNT is metallic; if  $(n - m) \bmod 3 \neq 0$ , the CNT is semiconducting [55]. Both metallic and semiconducting nanotubes can be exploited as interconnect and components in circuits. Due to their nanoscale dimensions, electron transport in carbon nanotubes will take place through quantum effects and will only propagate along the axis of the tube. Because of this special transport property, carbon nanotubes are frequently referred to as one-dimensional transport.

In terms of numbers of graphene layers, carbon nanotubes can be cataloged as single-walled carbon nanotubes (SWCNTs) and multi-walled ones (MWCNTs) [2], both of which can be synthesised simultaneously under certain experimental conditions. However, the number of layers and physical features of MWCNTs are difficult to control [59]. Though researchers face a number of problems in generating separate single-walled carbon nanotubes with required characteristics [60], SWCNTs draw much academic interest due to their unique features. The conductivity and resistivity of single walled nanotubes have been measured by placing electrodes at different parts of the CNTs [61]. The resistivity of the single walled nanotubes ropes is of the order of  $10^{-4} \Omega \cdot cm$  at room temperature. This means that single walled nanotube ropes are the most conductive carbon fibers known. The current density that can be achieved is  $10^7 A/cm^2$ , however in theory single walled nanotube ropes should be able to sustain much higher stable current densities, as high as  $10^{13} A/cm^2$ . The prospects of mixed bundle of CNTs as low-power high-speed interconnects for future VLSI applications has been recently investigated [62]. The power dissipation and delay of CNT bundle interconnects have been examined and compared with that of copper (Cu) interconnects at the 32-nm technology. Experimental results showed that a CNT bundle consumes 1.5 to 4-fold less power than Cu for intermediate and global interconnects.

### 2.3.2 Electronic Properties of Different Types of Carbon Nanotubes

In the light of transport conductivity, carbon nanotubes can be catalogued as metallic or semiconducting carbon nanotubes [63], which is decided by the energy band gap between the atoms. The conductive type of the CNTs depends on its chirality [55]. Both metallic and semiconducting CNTs have been studied as potential electronic components and their electronic properties have been established.

#### 2.3.2.1 Metallic Carbon Nanotubes

Devices made from metallic SWCNTs were first measured in 1997 [64], and have been extensively studied since that time. Conductances of two-terminal metallic SWCNTs at room temperature can vary significantly [65]. Most of this discrepancy is due to variation in contact resistance between the electrodes and the tube [66]. As techniques for making improved contacts have been developed, the conductances of CNTs have steadily improved. Additionally, optic and zone-boundary phonons [67] have the necessary momentum to backscatter electrons in nanotubes, and scattering of static disorder is also possible in metallic tubes [68].

A number of experiments have corroborated the statement that metallic CNTs have greater conductivity than conventional metals. Measurement of short tubes was made, in which  $G = 4q^2/h$  was derived [69]. Meanwhile, scanned probe experiments testing the local voltage drop along the length of the nanotube were carried out, which showed that the mean-free path of metallic CNTs corresponding to a room temperature resistivity is about  $10^{-6}m$ , much longer than that of metals. Therefore, the conductivity of metallic nanotubes can be equal to, or even exceed, the conductivity of best metals at room temperature [70].

These long scattering lengths are in contrast to the behaviour observed in traditional metals like copper, where scattering lengths are typically of the order of tens of nanometres at room temperature, due to phonon scattering. The main difference is the significantly reduced phase space for scattering by acoustic phonons in a 1-D system [22]. At room temperature, acoustic phonons have much less momentum than the electrons

at the Fermi energy. In a traditional metal, phonons backscatter electrons through a series of small angle scattering events that eventually reverse the direction of an electron. While the mean-free path is much larger than traditional metals, conductivity is only comparable to slightly better. This is because the effective mobile charge density of states in nanotubes is much lower than in traditional metals [71].

### 2.3.2.2 Semiconducting Carbon Nanotubes

Semiconducting CNTs can be derived by choosing specific chirality for the nanotubes (see Section 2.3.1). The electron transport characteristics for semiconducting, single-walled CNTs with diameters ranging from small to relatively large has been calculated [72]. The Boltzmann transport equation is solved using both an iterative technique and a Monte Carlo method. The basis for the transport characteristics is provided by electronic structure calculations of a tight-binding CNT model.

The electron transport characteristics of semiconducting carbon nanotubes connected to metallic electrons have been investigated [73]. For short nanotubes, the effect of the metallisation of the semiconducting nanotube due to the metallic electrode contact is large. The electrons are transmitted through the semiconducting nanotube even at the Fermi energy due to the contact effect. With an increase in the length of the nanotube, this effect declines and a gap-like structure appears.

It has been demonstrated that the carrier mobility and mean free path of semiconducting CNTs are related to temperature and tube chirality. Both of them drop when the lattice temperature rises. The effect is more significant in CNTs with relatively larger diameters, where non-parabolic effects become dominant [74]. The band structure is approximately independent of chirality in the low-field approximation. The mobility and mean free path both decrease with increasing chiral angle, and are therefore smallest in armchair tubes (with CNT vector (n,n)) and largest in zigzag tubes (with CNT vector (n,0)).

Recently, semiconducting carbon nanotubes have been demonstrated to have potential applications in high-mobility electronic devices [75]. Researchers have found typical mobilities of 1000-10,000 cm<sup>2</sup>/V·s for CVD-grown tubes, with occasional devices hav-

ing mobilities as high as  $20,000 \text{ cm}^2/\text{V}\cdot\text{s}$ , which is significantly higher than the values reported to date in deposited nanotubes [76]. It is also higher than the mobilities in silicon MOSFETs, indicating than SWCNTs are a remarkably high-quality semiconducting material.

Apart from mobilities, the band structure of carbon nanotubes is another significant factor affecting the electronic characteristics. Ming Zang et al. [77] suggested a curvilinear coordinate system in space and in  $k$ -space to study the energy band of single-walled carbon nanotubes wrapped at a helical angle. It is suggested that for tubes with different diameters, there is a distance between their cylindrical Brillouin zones in the radial direction. The Brillouin zone varies with the radius of the tube and the number of cells on the circumference [78]. It is also reported that mobility increases rapidly with tube diameter and increases slowly with temperature [79]. Nonparabolic corrections to the band structure are found to greatly impact transport modelling [80].

Semiconducting CNTs are proposed to be an ideal material for electronic devices. Ambipolar electrical transport has been reported in single-wall carbon nanotube field-effect transistors [81]. The carbide-nanotube junctions are abrupt and robust. In contrast to planar junctions, these contacts present low resistance for the injection of both p- and n-type carriers. The apparent barrier height of the junction is modified by the gate field. The characteristics taken with a small  $V_{DS}$  value as a function of the temperature clearly confirm that the contact barrier is small in both the hole and electron accumulation regimes. Thus semiconducting SWCNTs offer the novel possibility of ambipolar Ohmic contacts.

## 2.4 Carbon Nanotube Device Models

In the previous section the potential of applying semiconducting CNTs as electronic devices was discussed. The electronic characteristics of semiconducting CNTs imply the possibility of constructing semiconductor devices and circuits using this new type of material. As fundamental electronic components, carbon nanotube diodes and transistors have been studied intensively and novel theories of the physical features of the devices

have been proposed as outlined below.

### 2.4.1 CNT Diodes

One of the proposed CNT diode structures is based on the metal-semiconducting CNT junction [82] which performs like a Schottky barrier diode. Ineffective screening of the long-range Coulomb interaction in one-dimensional nanotube systems drastically modifies the charge transfer phenomena compared to conventional semiconductor heterostructures [83]. The length of depletion region varies sensitively over a wide range depending on the doping strength. The Schottky barrier gives rise to an asymmetry of the I-V characteristics of heterojunctions, in agreement with recent experimental results by Yao et al. [84] and Fuhrer et al [85]. Dynamic charge buildup near the junction results in a step-like growth of the current at reverse bias.

The performance of a Schottky barrier diode depends on the metal-semiconductor junction feature, which is related to the work function of metals. Electrical contacts to carbon nanotubes typically exhibit high resistance, posing a serious obstacle to their application in electronic devices. To eliminate this problem, J. Tersoff [86] suggested using a metal with a sufficiently large Fermi wave vector (or perhaps a non-armchair tube with reduced Fermi wave vector), by introducing scattering in the CNT, or by contacting the end of the CNT. In addition, the decay of electron wave functions across the van der Waals spacing between metal and CNT may also be an important factor [87].

Several experimental results confirm the operation of the proposed CNT diode model [88, 89, 90]. SWCNT Schottky diodes with titanium Schottky and platinum Ohmic contacts can be fabricated using angled evaporation of dissimilar metal contacts over a semiconducting SWCNT [90]. M. H. Yang et al. [88] demonstrated the fabrication and operation of a CNT Schottky diode by using a Pd contact (high-work-function metal) and an Al contact (low-work-function metal) at the two ends of a single-wall CNT, which shows the possibility of tuning the rectification I-V characteristics of the CNT through the use of a back gate, as illustrated in Figure 2.2.

FIGURE 2.2: Carbon nanotube Schottky diode using Al/Pd contacts [88].

Apart from Schottky diodes, CNT p-n junction diodes are also proposed. J. U. Lee et al. [91] formed a structure along a single nanotube by electrostatic doping using a pair of split gate electrodes. By biasing the two gates accordingly, the device can function either as a diode or as an ambipolar field-effect transistor [92]. In 2005, General Electric Company (GE) announced the development of a carbon nanotube diode [93] formed by joining a p-type and an n-type semiconducting material using an electrostatic doping technique using two separate gates that couple to two halves of a single carbon nanotube, which operates at the “theoretical limit” [94], as shown in Figure 2.3.