# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Leakage Power Minimisation Techniques for Embedded Processors

by

Jatin Nawnit Mistry

Thesis for the degree of Doctor of Philosophy

February 2013

# UNIVERSITY OF SOUTHAMPTON ABSTRACT

#### FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Doctor of Philosophy

## LEAKAGE POWER MINIMISATION TECHNIQUES FOR EMBEDDED PROCESSORS

by Jatin Nawnit Mistry

Leakage power is a growing concern in modern technology nodes. In some current and emerging applications, speed performance is uncritical but many of these applications rely on untethered power making energy a primary constraint. Leakage power minimisation is therefore key to maximising energy efficiency for these applications. This thesis proposes two new leakage power minimisation techniques to improve the energy efficiency of embedded processors. The first technique, called sub-clock power gating, can be used to reduce leakage power during the active mode. The technique capitalises on the observation that there can be large combinational idle time within the clock period in low performance applications and therefore power gates it. Sub-clock power gating is the first study into the application of power gating within the clock period, and simulation results on post layout netlists using a 90nm technology library show 3.5x, 2x and 1.3x improvement in energy efficiency for three test cases: 16-bit multiplier, ARM Cortex-M0 and Event Processor at a given performance point. To reduce the energy cost associated with moving between the sleep and active mode of operation, a second technique called symmetric virtual rail clamping is proposed. Rather than shutting down completely during sleep mode, the proposed technique uses a pair of NMOS and PMOS transistors at the head and foot of the power gated logic to lower the supply voltage by  $2V_{th}$ . This reduces the energy needed to recharge the supply rails and eliminates signal glitching energy cost during wake-up. Experimental results from a 65nm test chip shows application of symmetric virtual rail clamping in sub-clock power gating improves energy efficiency, extending its applicable clock frequency range by 400x.

The physical layout of power gating requires dedicated techniques and this thesis proposes dRail, a new physical layout technique for power gating. Unlike the traditional voltage area approach, dRail allows both power gated and non-power gated cells to be placed together in the physical layout to reduce area and routing overheads. Results from a post layout netlist of an ARM Cortex-M0 with sub-clock power gating shows standard cell area and signal routing are improved by 3% and 19% respectively. Sub-clock power gating, symmetric virtual rail clamping and dRail are incorporated into power gating design flows and are compatible with commercial EDA tools and gate libraries.

### Contents

| D | eclar | eation of Authorship                              | XV   |

|---|-------|---------------------------------------------------|------|

| A | ckno  | wledgements                                       | xvi  |

| 1 | Inti  | roduction                                         | 1    |

|   | 1.1   | Power in Digital Circuits                         | . 2  |

|   |       | 1.1.1 Dynamic Power                               | . 2  |

|   |       | 1.1.2 Leakage Power                               | . 4  |

|   | 1.2   | Dynamic Power Reduction                           | . 6  |

|   |       | 1.2.1 Clock Gating                                | . 6  |

|   |       | 1.2.2 Glitching, Input Reordering and Gate Sizing | . 7  |

|   |       | 1.2.3 Voltage and Frequency Scaling               | . 8  |

|   | 1.3   | Technology Scaling and Implications on Power      | . 8  |

|   | 1.4   | Leakage Power Reduction                           | . 10 |

|   |       | 1.4.1 Power Gating                                | . 11 |

|   |       | 1.4.1.1 Physical Implementation                   | . 15 |

|   |       | 1.4.2 Minimum Energy Computation                  | . 18 |

|   | 1.5   | Applications                                      | . 22 |

|   | 1.6   | Thesis Organisation                               | . 23 |

|   | 1.7   | Contributions                                     | . 24 |

| 2 | Lite  | erature Survey                                    | 27   |

|   | 2.1   | Design Time: Transistor and Gate Level Techniques | . 28 |

|   | 2.2   | Runtime: Standby Mode Leakage Techniques          |      |

|   |       | 2.2.1 Power Gating                                |      |

|   |       | 2.2.1.1 Header Vs Footer                          |      |

|   |       | 2.2.1.2 Power Gating Alternatives                 |      |

|   |       | 2.2.2 Natural Transistor Stacks                   |      |

|   |       | 2.2.3 Body Biasing                                |      |

|   | 2.3   | Runtime: Active Mode Leakage Techniques           |      |

|   |       | 2.3.1 Power Gating                                |      |

|   |       | 2.3.2 Adaptive Body Biasing                       |      |

|   |       | 2.3.3 Subthreshold                                |      |

|   | 2.4   | Physical Layout                                   |      |

|   | 2.5   | Objectives                                        |      |

|   | 2.6   | Concluding Remarks                                |      |

| 9 | A at  | ive Mode Sub Clock Power Ceting                   | 52   |

vi CONTENTS

|   | 3.1 | Motivation  |                                                          |   | 54   |

|---|-----|-------------|----------------------------------------------------------|---|------|

|   | 3.2 | Proposed S  | Sub-Clock Power Gating Technique                         |   | 57   |

|   |     | 3.2.1 Sub   | -Clock Power Gating Architecture                         |   | 57   |

|   |     | 3.2.2 Des   | ign Flow                                                 |   | 60   |

|   | 3.3 | Simulation  | Results                                                  |   | 60   |

|   |     |             | e Study 1: 16-bit Multiplier                             |   |      |

|   |     |             | e Study 2: ARM Cortex-M0                                 |   |      |

|   |     |             | e Study 3: Event Processor                               |   |      |

|   | 3.4 | Comparati   | ve Analysis with Subthreshold                            |   | 79   |

|   | 3.5 |             | Remarks                                                  |   |      |

| 4 | Syn | nmetric Vi  | rtual Rail Clamping for Sub-Clock Power Gating           |   | 83   |

|   | 4.1 | Wake-Up E   | Energy Cost                                              |   | 84   |

|   |     | 4.1.1 Pow   | ver Gating Techniques                                    |   | 84   |

|   |     | 4.1.2 Pow   | ver Gating Techniques Comparison                         |   | 88   |

|   | 4.2 | Sub-Clock   | Power Gating with Symmetric Virtual Rail Clamping        |   | 89   |

|   | 4.3 | Implement   | ation                                                    |   | 90   |

|   |     | 4.3.1 Silio | con Design Flow                                          |   |      |

|   |     | 4.3.        | 1.1 Design Preparation for Sub-Clock Power Gating        |   | 93   |

|   |     | 4.3.        | 1.2 Layout: Design Planning                              |   | 96   |

|   |     | 4.3.        | 1.3 Verification                                         |   | 98   |

|   |     | 4.3.2 Test  | t Chip Overview                                          |   | 100  |

|   | 4.4 | Experimen   | tal Results                                              |   | 101  |

|   |     | •           | nmetric Virtual Rail Clamping Vs Shut Down Power Gating  |   |      |

|   |     |             | ect of Duty Cycle                                        |   | 107  |

|   |     |             | -Clock Power Gating with Symmetric Virtual Rail Clamping | _ | 108  |

|   |     |             | bund Bounce Analysis                                     |   |      |

|   | 4.5 |             | Remarks                                                  |   |      |

|   |     |             |                                                          |   |      |

| 5 |     | •           | sical Layout Technique for Power Gating                  |   | 115  |

|   |     |             |                                                          |   |      |

|   | 5.2 | •           | Rail Technique                                           |   |      |

|   |     |             | il Layout                                                |   |      |

|   |     |             | il Design Flow                                           |   |      |

|   |     |             | ign Considerations                                       |   |      |

|   | 5.3 | •           | tal Results                                              |   |      |

|   |     |             | e Study 1: ARM Cortex-M0 with SCPG                       |   |      |

|   |     |             | e Study 2: ARM Cortex-A5 Data Engine                     |   |      |

|   |     | 5.3.        | 0                                                        |   |      |

|   | F 4 | 5.3.        |                                                          |   |      |

|   | 5.4 | Concluding  | Remarks                                                  |   | 142  |

| 6 |     |             | d Future Work                                            |   | 145  |

|   | 6.1 |             | tributions                                               |   |      |

|   | 6.2 |             | rk Directions                                            |   |      |

|   |     | 0.2.1 Imp   | proved Sub-Clock Power Gating                            |   | -149 |

CONTENTS vii

|              |        | 6.2.2<br>6.2.3 | Further Applications of Symmetric Virtual Rail Clamping 1<br>Physical Layout for Body Biasing |    |

|--------------|--------|----------------|-----------------------------------------------------------------------------------------------|----|

| A            | Mic    | roproc         | essor Details 1                                                                               | 53 |

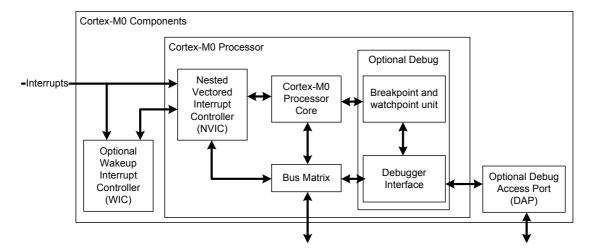

|              | A.1    | ARM            | Cortex-M0                                                                                     | 53 |

| В            | Ben    | chmar          | ks and Simulation 1                                                                           | 57 |

|              | B.1    | Dhryst         | sone Benchmark                                                                                | 57 |

|              | B.2    | Energy         | Harvester Tuning Program                                                                      | 59 |

|              | B.3    |                | e Simulation                                                                                  |    |

|              |        |                | Prerequisites                                                                                 |    |

|              |        |                | Extract RC netlist                                                                            |    |

|              |        |                | Simulation Vectors                                                                            |    |

|              |        |                | Netlist Simulation with HSpice                                                                |    |

| $\mathbf{C}$ | Scri   | $\mathbf{pts}$ | 1                                                                                             | 73 |

|              |        | -              | hip ARM Cortex-M0 UPF                                                                         | 73 |

|              |        |                | LEF Modification Script                                                                       |    |

| Re           | efere: | nces           | 1                                                                                             | 79 |

# List of Figures

| 1.1                                                     | Dynamic power charging and discharging of load capacitance                                                                                                                                                                                                                             | 3                                                  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.2                                                     | Subthreshold, band-to-band tunneling and gate leakage currents in MOS-FETs                                                                                                                                                                                                             | F                                                  |

| 1.3                                                     | Recirculation multiplexer to clock gate (based on [16])                                                                                                                                                                                                                                | 7                                                  |

| 1.4                                                     | ITRS projection for dynamic and leakage power dissipation per device [6]                                                                                                                                                                                                               | 10                                                 |

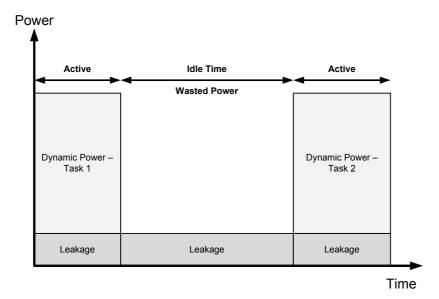

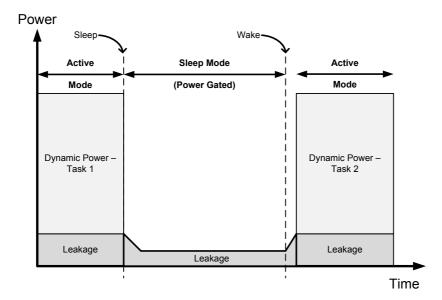

| 1.5                                                     | Digital circuit execution schedule with no power gating                                                                                                                                                                                                                                | 12                                                 |

| 1.6                                                     | Digital circuit execution schedule from Fig. 1.5 using power gating in idle time (based on [3])                                                                                                                                                                                        | 12                                                 |

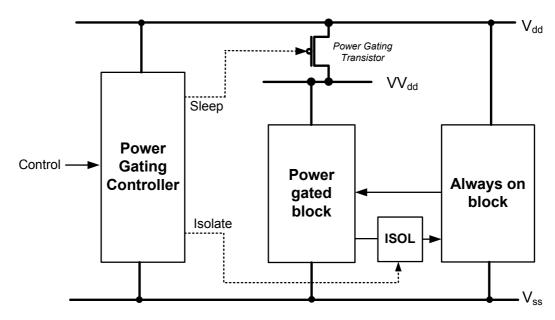

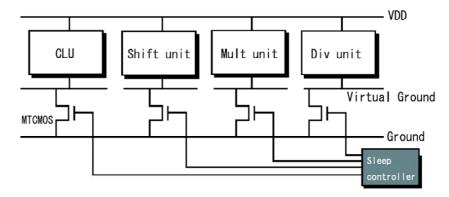

| 1.7                                                     | Example of coarse grain power gating (based on [3])                                                                                                                                                                                                                                    | 13                                                 |

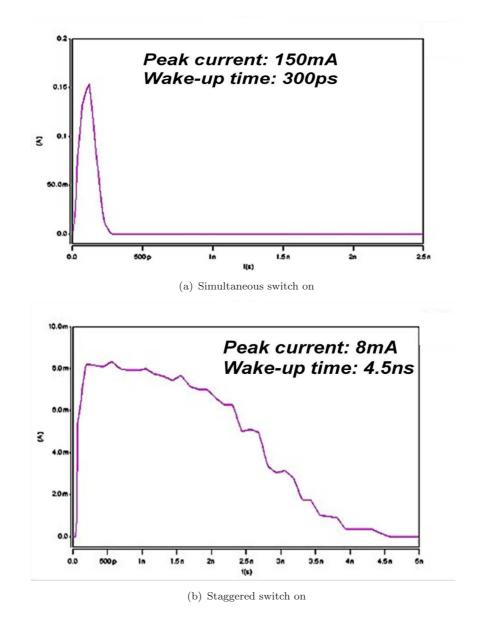

| 1.8                                                     | In-rush current using simultaneous power gate switch on and staggered switch on [45]                                                                                                                                                                                                   | 14                                                 |

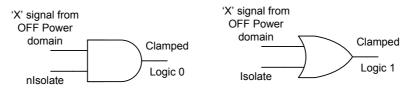

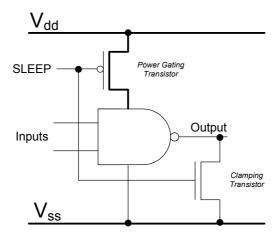

| 1.9                                                     | Typical clamp low and clamp high isolation gates                                                                                                                                                                                                                                       | 15                                                 |

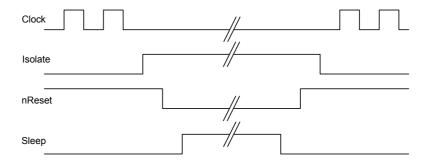

|                                                         | Control of signals during power down and power up                                                                                                                                                                                                                                      | 15                                                 |

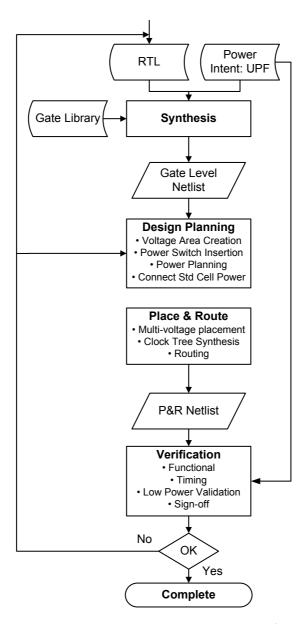

|                                                         | Physical design flow for power gating (based on [3])                                                                                                                                                                                                                                   | 16                                                 |

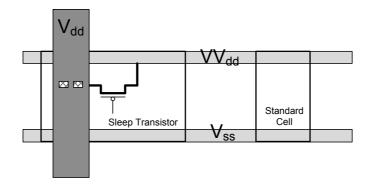

|                                                         | Example of sleep transistor connection in physical layout (based on [3]) .                                                                                                                                                                                                             | 18                                                 |

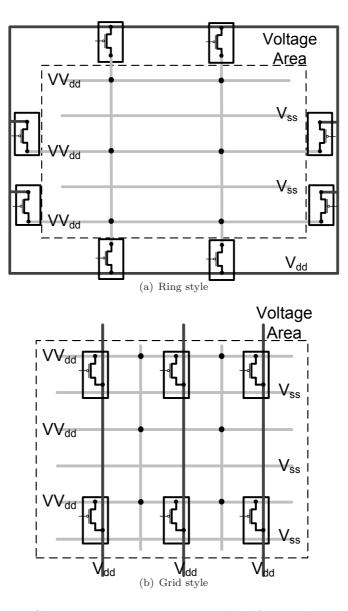

|                                                         | Sleep transistor insertion methods for a voltage area [40]                                                                                                                                                                                                                             | 19                                                 |

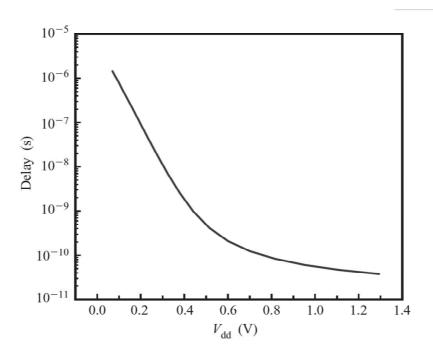

| 1.14                                                    | Delay of an inverter against $V_{dd}$ (130nm Technology) [37]                                                                                                                                                                                                                          | 20                                                 |

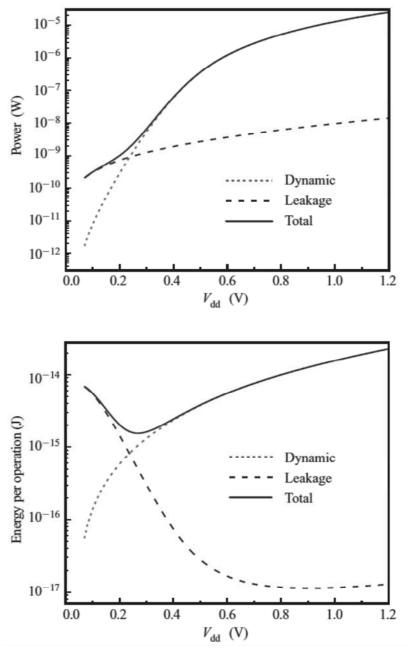

| 1.15                                                    | Simulation of a 50 stage inverter chain (130nm process): Top - Power as a function of $V_{dd}$ , Bottom - Energy per operation as a function of $V_{dd}$ [37]                                                                                                                          | 21                                                 |

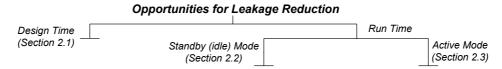

| 2.1                                                     | Opportunities for leakage power reduction                                                                                                                                                                                                                                              | 27                                                 |

| 2.2                                                     | Path balancing during design time (based on [73])                                                                                                                                                                                                                                      | 28                                                 |

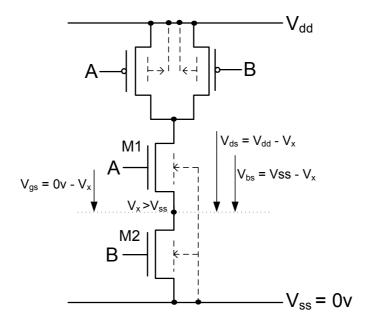

| 2.3                                                     | Stack Effect (based on [88])                                                                                                                                                                                                                                                           | 30                                                 |

| 0.4                                                     |                                                                                                                                                                                                                                                                                        |                                                    |

| 2.4                                                     | Example of zig-zag power gating [95]                                                                                                                                                                                                                                                   | 32                                                 |

| $\frac{2.4}{2.5}$                                       | Example of zig-zag power gating [95]                                                                                                                                                                                                                                                   |                                                    |

|                                                         |                                                                                                                                                                                                                                                                                        | 32                                                 |

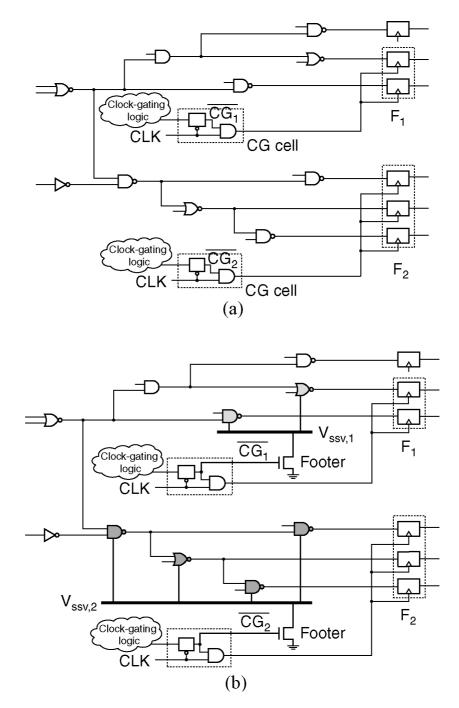

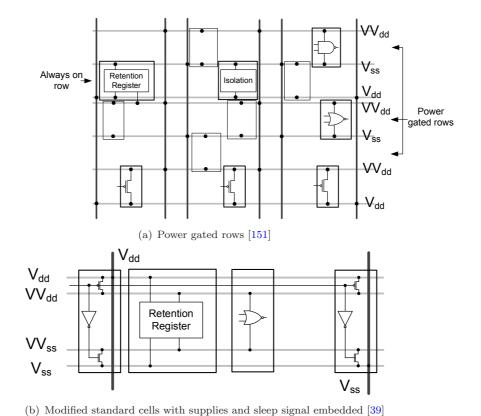

| 2.5                                                     | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3])                                                                                                                                                                                 | 32<br>33<br>35                                     |

| 2.5<br>2.6<br>2.7                                       | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3])                                                                                                                                                                                 | 32<br>33<br>35<br>36                               |

| 2.5<br>2.6<br>2.7<br>2.8                                | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3])                                                                                                                                                                                 | 32<br>33<br>35<br>36<br>37                         |

| 2.5<br>2.6<br>2.7<br>2.8<br>2.9                         | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3])                                                                                                                                                                                 | 32<br>33<br>35<br>36<br>37<br>38                   |

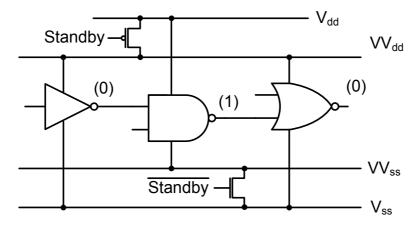

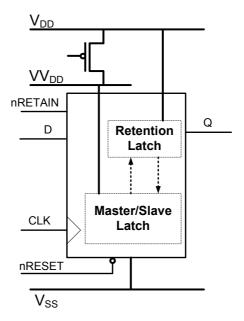

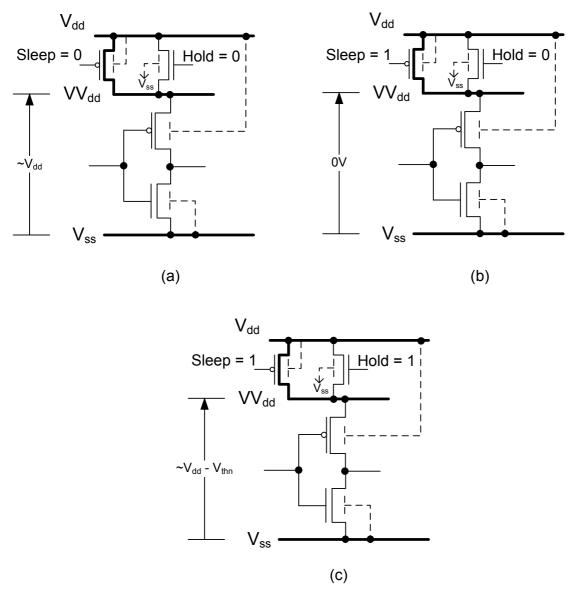

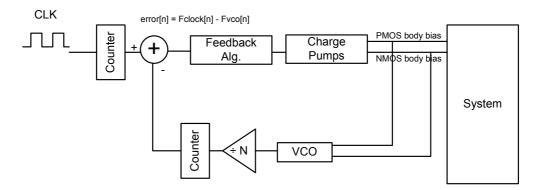

| 2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10                 | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3]) Virtual Rail Clamping using a MOSFET [103] (a) RUN/IDLE mode for normal operation, (b) COLD mode for sleep with full shut down and (c) PARK mode for sleep with state retention | 32<br>33<br>35<br>36<br>37<br>38<br>40             |

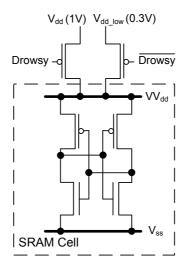

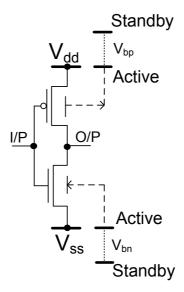

| 2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3]) Virtual Rail Clamping using a MOSFET [103] (a) RUN/IDLE mode for normal operation, (b) COLD mode for sleep with full shut down and (c) PARK mode for sleep with state retention | 32<br>33<br>35<br>36<br>37<br>38                   |

| 2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3]) Virtual Rail Clamping using a MOSFET [103] (a) RUN/IDLE mode for normal operation, (b) COLD mode for sleep with full shut down and (c) PARK mode for sleep with state retention | 32<br>33<br>35<br>36<br>37<br>38<br>40<br>41       |

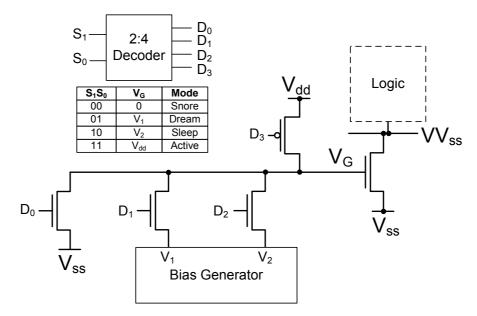

| 2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | Example of fine grain power gating with an NAND gate [40] Example of retention register (based on [3]) Virtual Rail Clamping using a MOSFET [103] (a) RUN/IDLE mode for normal operation, (b) COLD mode for sleep with full shut down and (c) PARK mode for sleep with state retention | 32<br>33<br>35<br>36<br>37<br>38<br>40<br>41<br>43 |

x LIST OF FIGURES

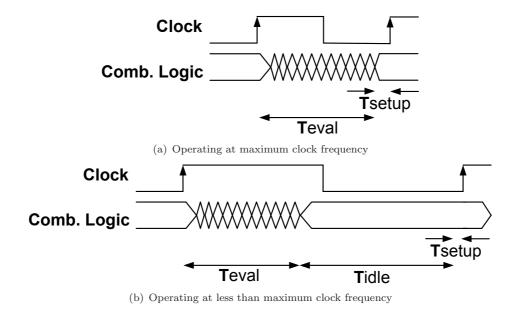

| 3.1  | Idle time within the clock period from reduced clock frequency                                     | 54       |

|------|----------------------------------------------------------------------------------------------------|----------|

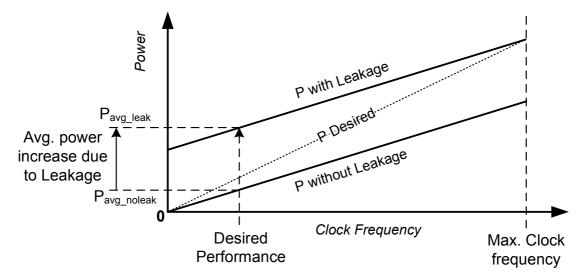

| 3.2  | Increased power consumption at a given low performance target due to                               |          |

|      | leakage power dissipation at fixed $V_{dd}$                                                        | 56       |

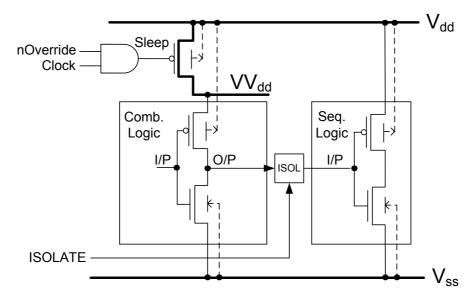

| 3.3  | Sub-clock power gating technique                                                                   | 58       |

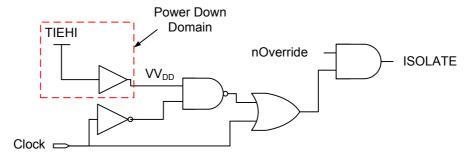

| 3.4  | Isolation control circuit                                                                          | 59       |

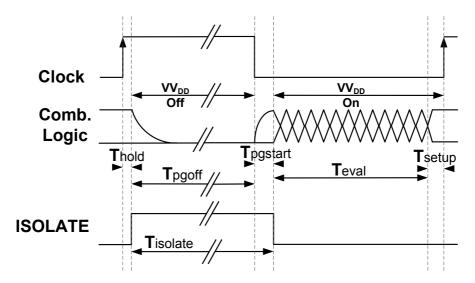

| 3.5  | Sub-clock power gating timing                                                                      | 59       |

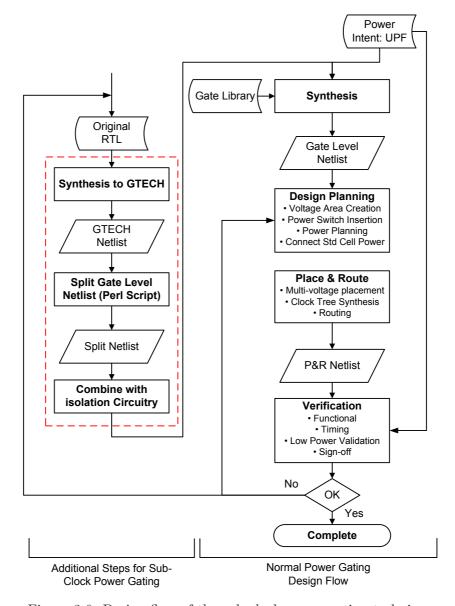

| 3.6  | Design flow of the sub-clock power gating technique                                                | 61       |

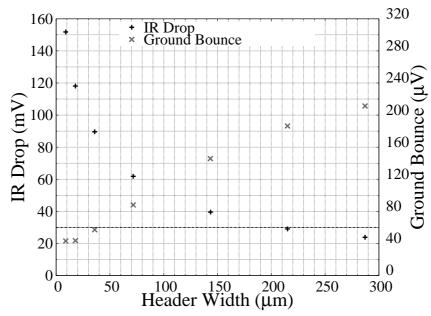

| 3.7  | Experimental flow for generation of sub-clock power gating power results .                         | 62       |

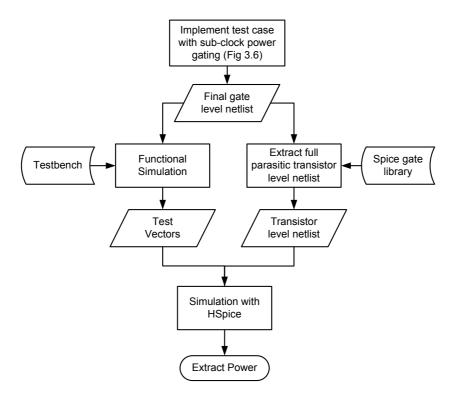

| 3.8  | Effective PMOS power gating transistor width against IR drop and ground                            |          |

|      | bounce in the 16-bit parallel multiplier                                                           | 63       |

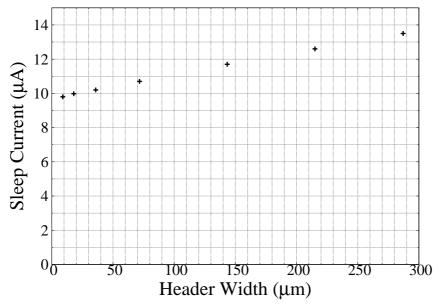

| 3.9  | Effective PMOS power gating transistor width against sleep current in                              | 0.4      |

| 0.10 | the 16-bit parallel multiplier                                                                     | 64       |

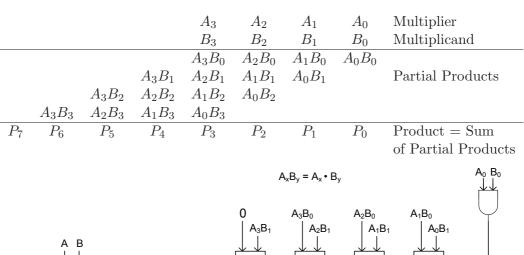

|      | Example of a 4x4 sum of partial products parallel multiplier                                       | 65       |

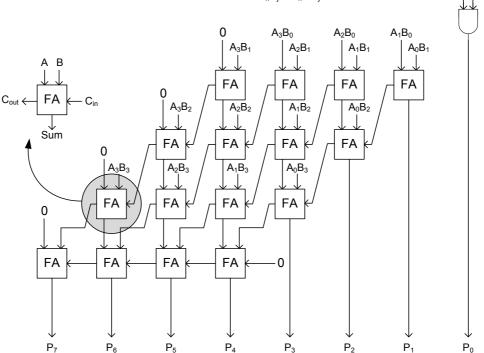

|      | Example of how the multiplier circuit is mapped into the SCPG technique                            | 66       |

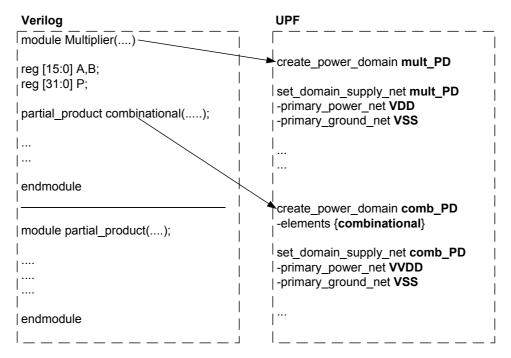

| 3.12 | Example of how modules in Verilog are mapped into the power domain definitions in the UPF          | 67       |

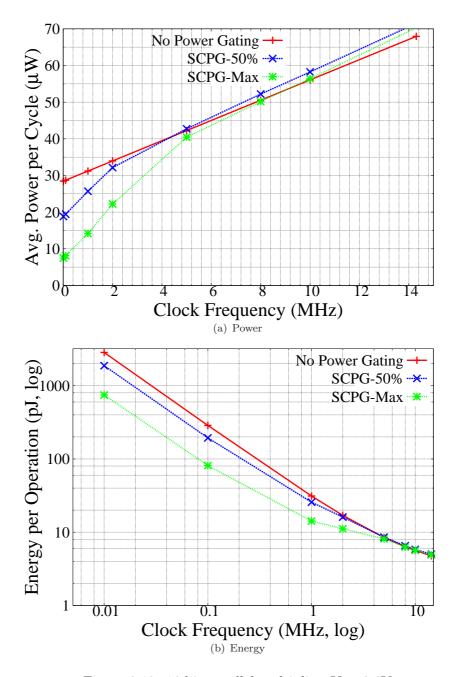

| 9 19 |                                                                                                    | 67<br>69 |

|      | 16-bit parallel multiplier, $V_{dd}$ =0.6V                                                         | 09       |

| 5.14 | lighted                                                                                            | 71       |

| 3 15 | Example of how the Cortex-M0 Core block is mapped into the proposed                                | 11       |

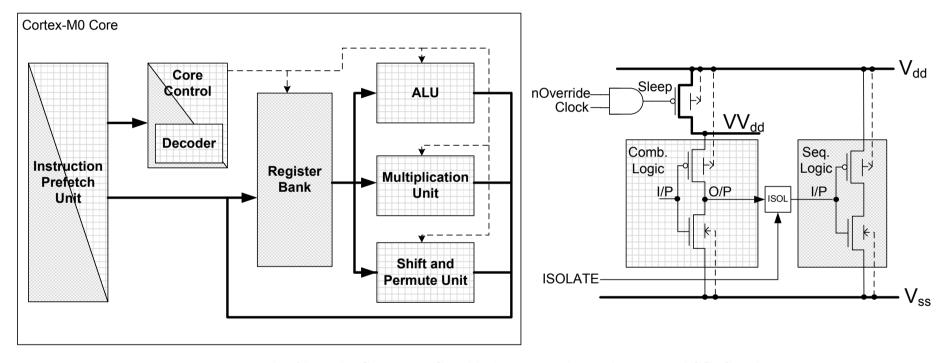

| 0.10 | SCPG technique                                                                                     | 72       |

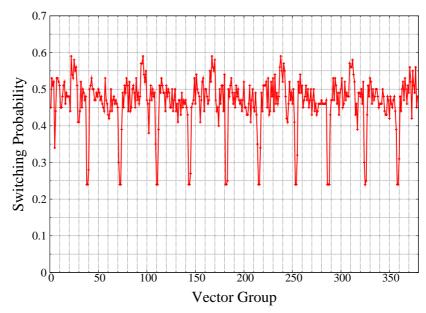

| 3.16 | Switching probability of the Cortex-M0 for each set of 10 vectors from                             | . –      |

| 3,10 | Dhrystone benchmark                                                                                | 73       |

| 3.17 | Cortex-M0, $V_{dd}$ =0.6V                                                                          |          |

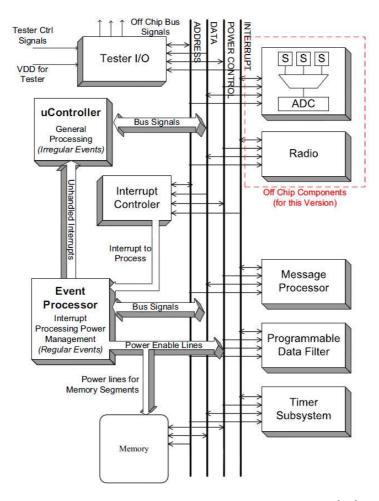

|      | Architecture of the Event Processor [63]                                                           |          |

|      | Event processor state machine, $V_{dd}$ =0.6V                                                      |          |

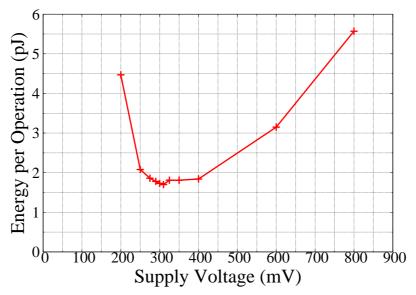

| 3.20 | Supply voltage Vs energy per operation, 16-bit parallel multiplier                                 | 79       |

| 3.21 | Supply voltage Vs energy per operation, Cortex-M0                                                  | 81       |

|      |                                                                                                    |          |

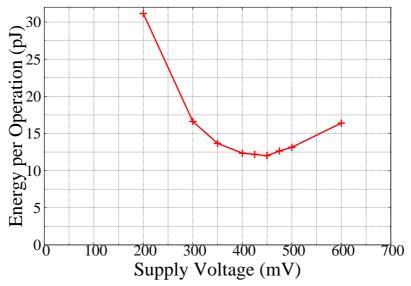

| 4.1  | An inverter with (a) single rail clamping [103] (b) symmetric virtual rail                         | 0.5      |

| 4.0  | clamping                                                                                           |          |

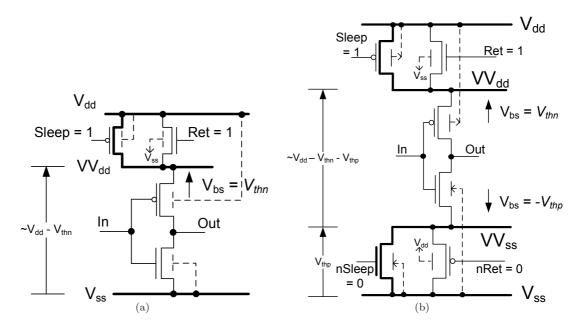

| 4.2  | $V_{dd}$ reduction against time for three power gating techniques                                  | 86       |

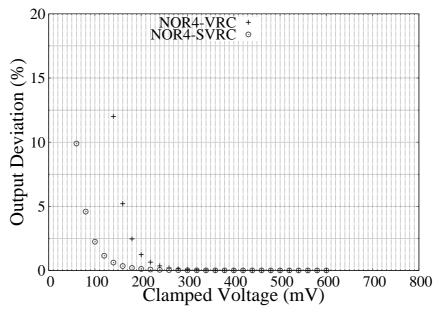

| 4.3  | Output deviation of 4-input NOR gate from Synopsys 90nm library with                               |          |

|      | virtual rail clamping (VRC) and symmetric virtual rail clamping (SVRC) with reduced supply voltage | 87       |

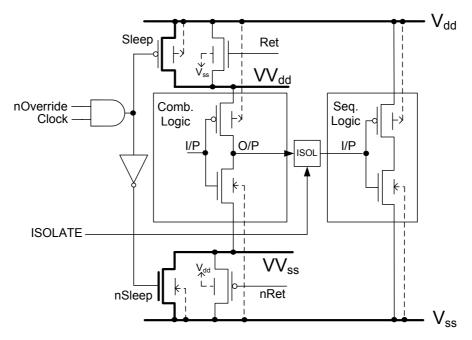

| 4.4  | Sub-clock power gating technique with symmetric virtual rail clamping                              |          |

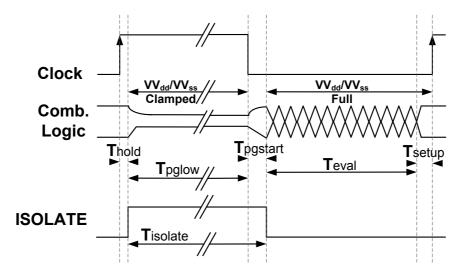

| 4.5  | Combinational logic timing of sub-clock power gating technique with sym-                           | 03       |

| 4.0  | metric virtual rail clamping                                                                       | 90       |

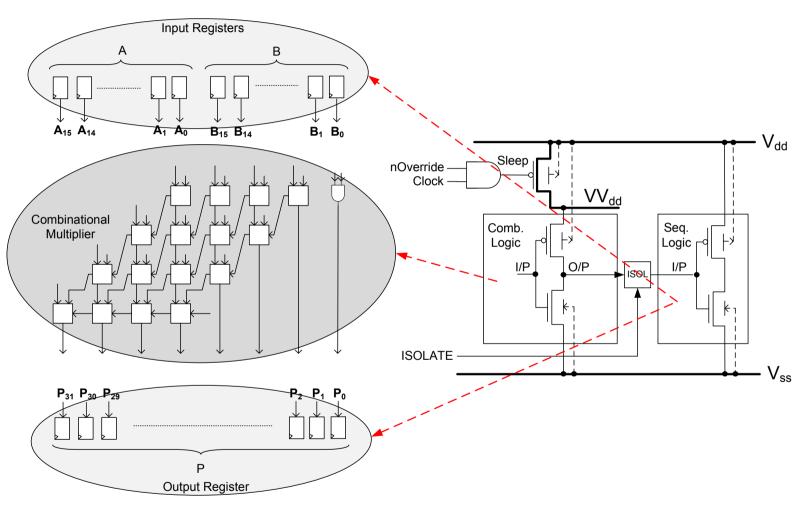

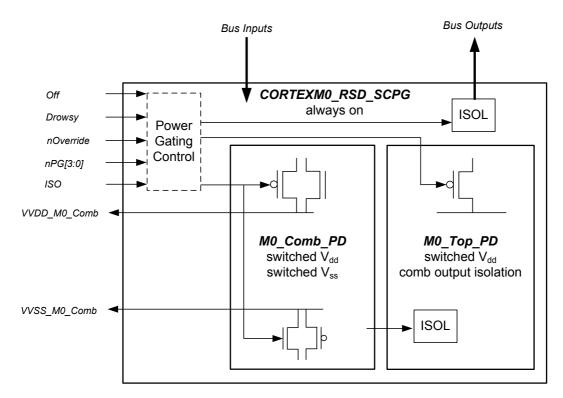

| 4.6  | Power intent of sub-clock Cortex-M0 microprocessor                                                 | 92       |

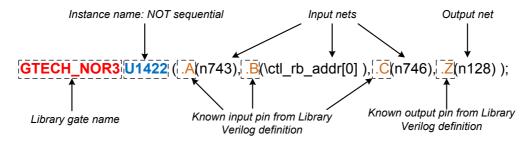

| 4.7  | How the Perl script identifies gates and records their connections                                 | 94       |

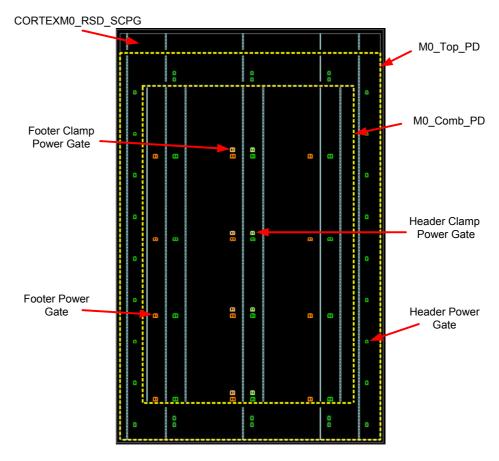

| 4.8  | Voltage area and power gate placement in sub-clock Cortex-M0                                       |          |

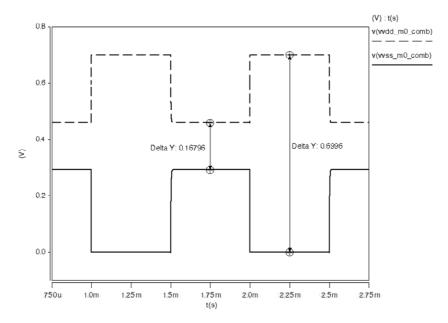

| 4.9  | Simulated $VV_{dd}$ and $VV_{ss}$ in Cortex-M0 with symmetric virtual rail clamp-                  |          |

|      | ing                                                                                                | 98       |

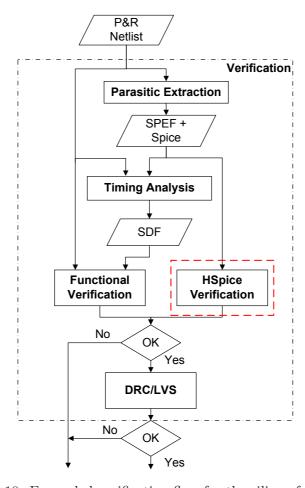

| 4.10 | Expanded verification flow for the silicon fabrication                                             | 99       |

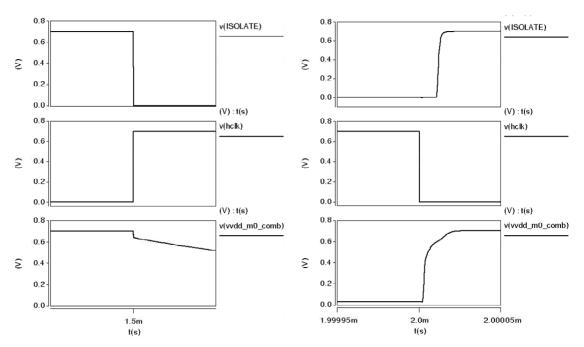

| 4.11 | Simulated transient behaviour of isolation enable signal <i>ISOLATE</i> .                          |          |

|      | Left - entering sleep, Right - exiting sleep                                                       | 99       |

| 4.12 | Final Layout of test chip and sub-clock ARM Cortex-M0                                              | 101      |

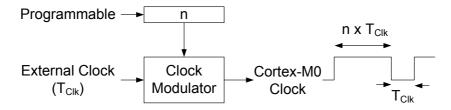

| 4.13 | Clock modulator circuit                                                                            | 101      |

LIST OF FIGURES xi

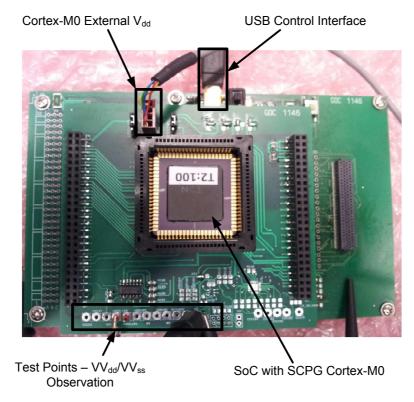

| 4.14                                                          | Testboard for experimental measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 102                             |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

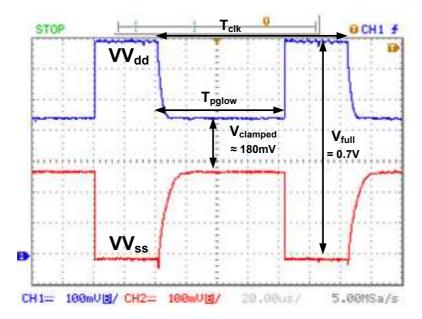

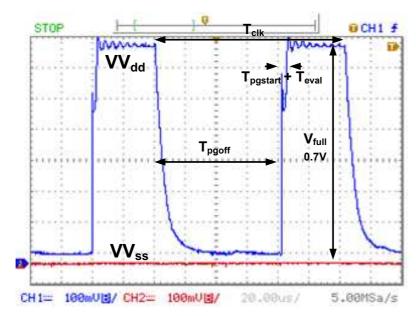

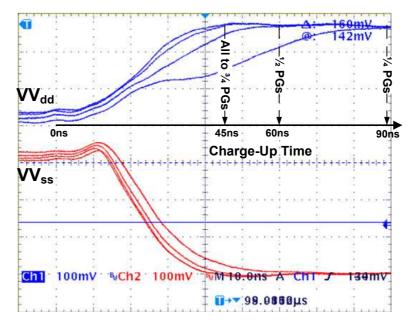

| 4.15                                                          | Measured $VV_{dd}$ and $VV_{ss}$ behaviour in sub-clock power gating using symmetric virtual rail clamping                                                                                                                                                                                                                                                                                                                                                                                        | 103                             |

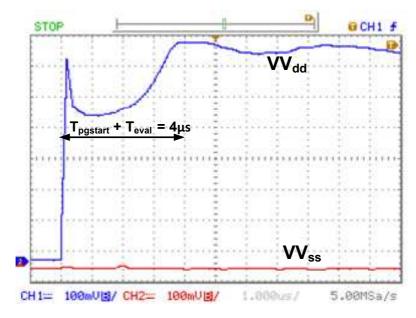

| 4.16                                                          | Measured $VV_{dd}$ and $VV_{ss}$ behaviour in sub-clock power gating using shut down power gating                                                                                                                                                                                                                                                                                                                                                                                                 | 104                             |

| 4.17                                                          | Measured $VV_{dd}$ charge-up and evaluation time in SCPG with shut down power gating                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

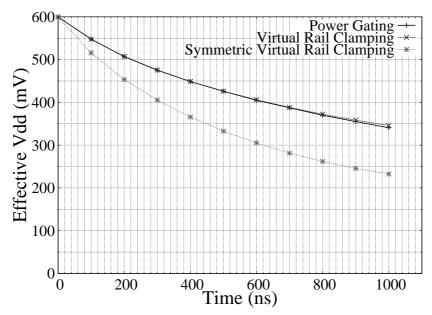

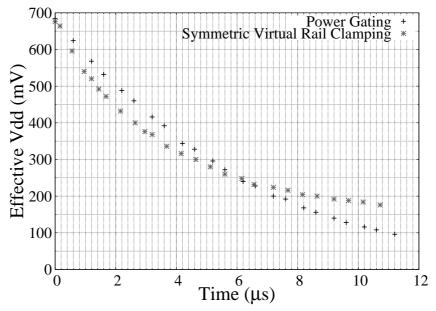

| 4 18                                                          | Measured effective $V_{dd}$ reduction against time                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

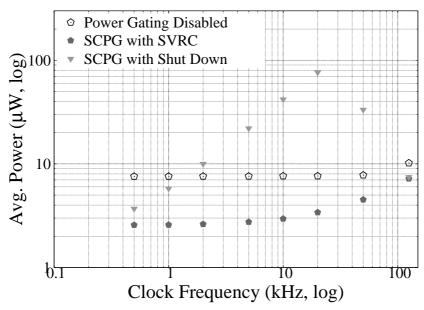

|                                                               | Measured Cortex-M0 power with power gating disabled, proposed SCPG with symmetric virtual rail clamping and SCPG with shut down power gating                                                                                                                                                                                                                                                                                                                                                      |                                 |

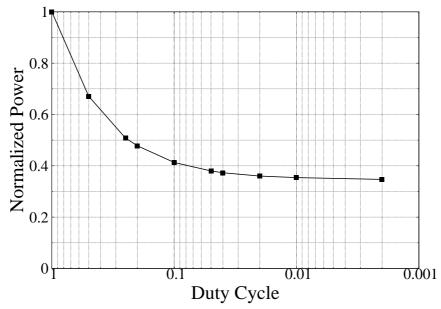

| 4.20                                                          | Normalised measured power of ARM Cortex-M0 microprocessor with $10\text{kHz}$ clock at varying duty cycle in SCPG mode, $V_{dd} = 0.7\text{V}$                                                                                                                                                                                                                                                                                                                                                    | 108                             |

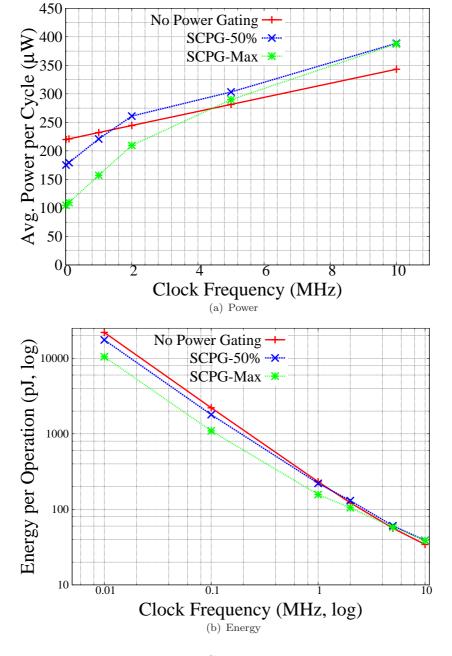

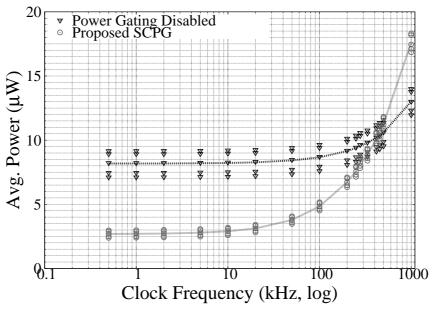

| 4.21                                                          | Dhrystone - Measured power of ARM Cortex-M0 at varying clock frequency, $V_{dd}$ =0.7V                                                                                                                                                                                                                                                                                                                                                                                                            | 109                             |

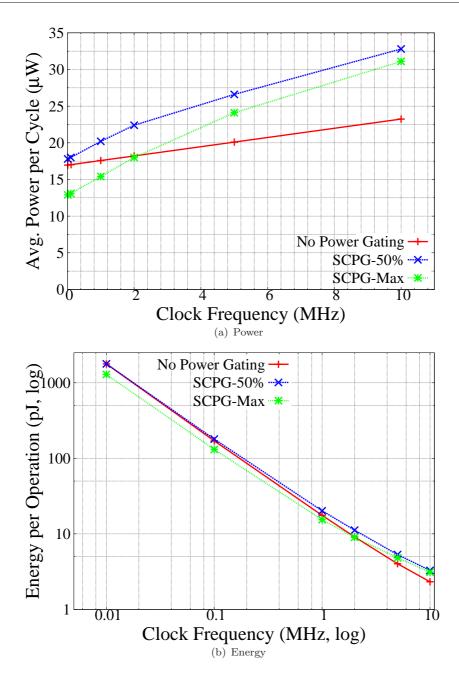

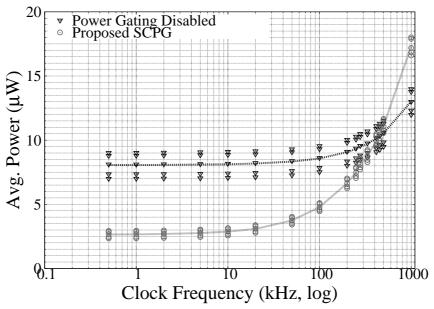

| 4.22                                                          | Tuning Program - Measured power of ARM Cortex-M0 at varying clock frequency, $V_{dd}$ =0.7V                                                                                                                                                                                                                                                                                                                                                                                                       | 111                             |

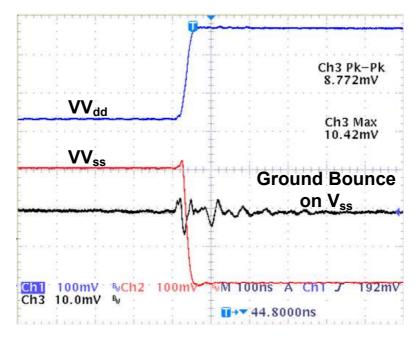

| 4.23                                                          | Measured ground bounce on the always-on $V_{ss}$ supply rail                                                                                                                                                                                                                                                                                                                                                                                                                                      | 112                             |

|                                                               | Measured charge-up time with varied number of active power gates (PGs) in proposed SCPG with symmetric virtual rail clamping                                                                                                                                                                                                                                                                                                                                                                      |                                 |

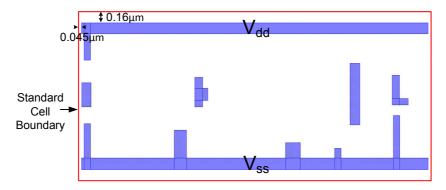

| 5.1                                                           | D-type flip-flop standard cell in TSMC 65nm ARM Artisan $^{\rm TM}$ library [155]                                                                                                                                                                                                                                                                                                                                                                                                                 | ]116                            |

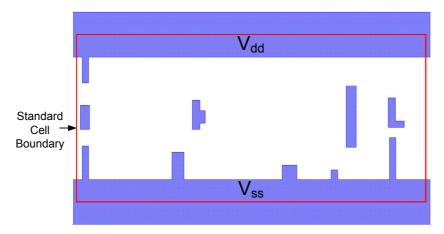

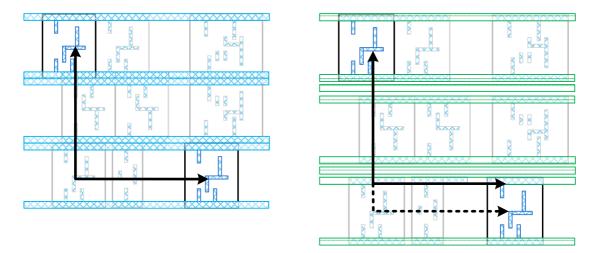

| 5.2                                                           | Conventional standard cell placement and power delivery with no power gating                                                                                                                                                                                                                                                                                                                                                                                                                      | 117                             |

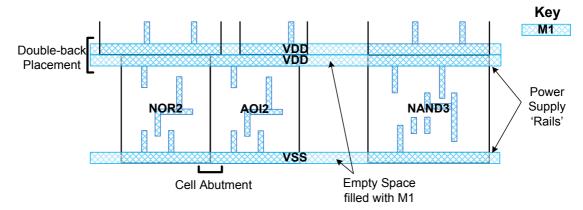

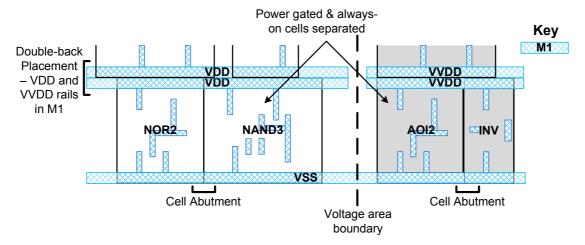

| 5.3                                                           | Example of standard cell separation and power delivery with power gating and voltage area                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

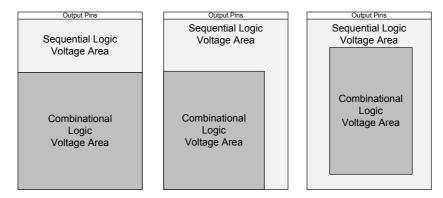

| 5.4                                                           | Different combinational and sequential voltage area locations for Cortex-M0 from Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

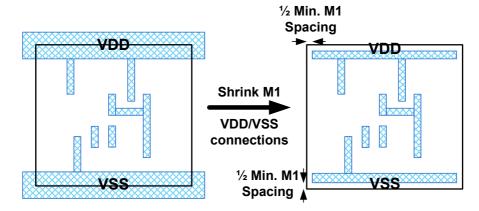

| 5.5                                                           | Shrinking of $V_{dd}$ and $V_{ss}$ pins to stop power and ground sharing                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

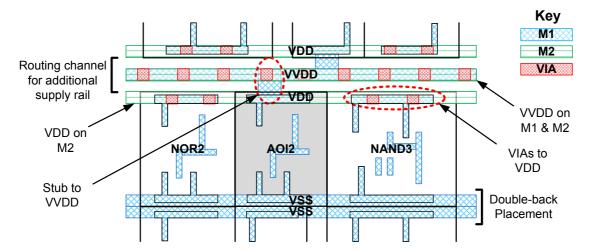

| 5.6                                                           | Power routing and hook-up in the dRail layout for a single $VV_{dd}$                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

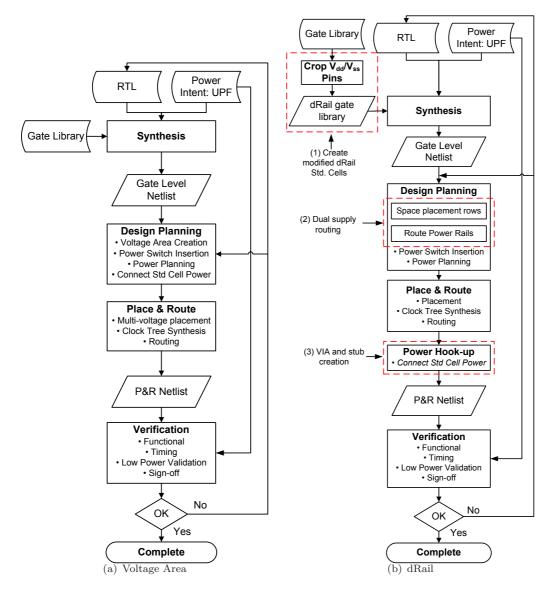

| 5.7                                                           | Power gating physical design flow for (a) traditional voltage area (b) dRai                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 5.8                                                           | Spreading of standard cells due to inclusion of routing channel                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|                                                               | Changes to LEF definition of an inverter logic gate in the TSMC 65nm                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|                                                               | ARM Artisan <sup>TM</sup> Library [155] for dRail technique                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                                                               | D-type flip-flop from Fig. 5.1 modified for dRail                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100                             |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

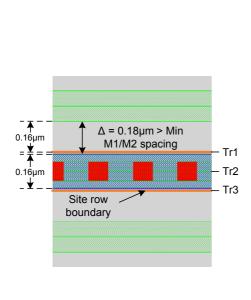

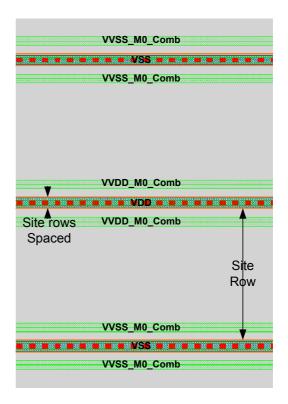

| F 10                                                          | Site row spacing and Metal1 Metal2 rail creation                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 130                             |

|                                                               | Power hook-up in the dRail layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 130                             |

|                                                               | Power hook-up in the dRail layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 130<br>131                      |

| 5.13                                                          | Power hook-up in the dRail layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 130<br>131<br>132               |

| <ul><li>5.13</li><li>5.14</li></ul>                           | Power hook-up in the dRail layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 130<br>131<br>132<br>133        |

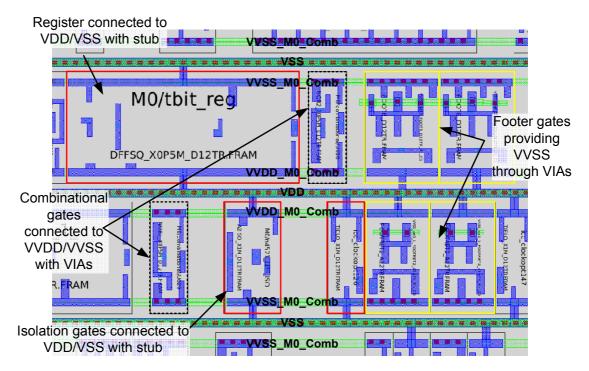

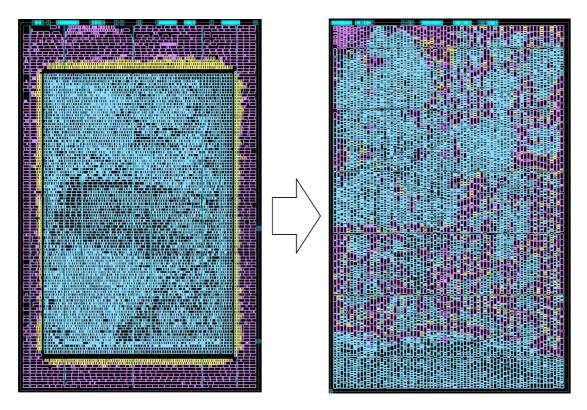

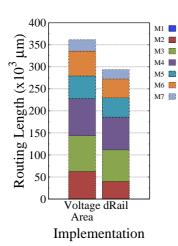

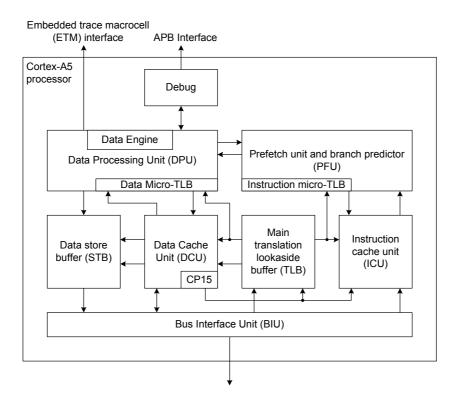

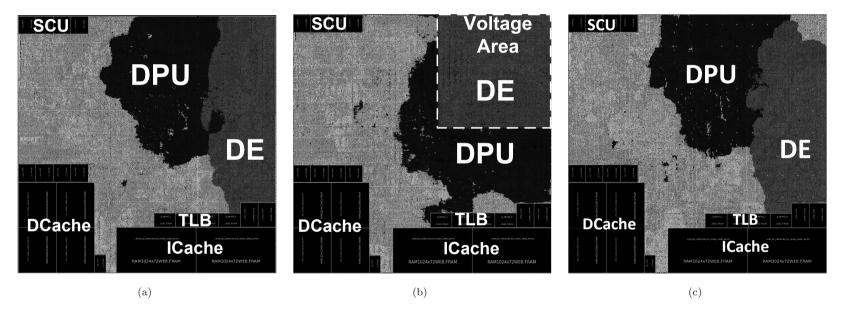

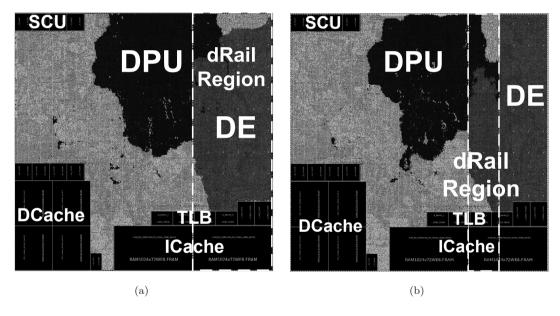

| <ul><li>5.13</li><li>5.14</li><li>5.15</li></ul>              | Power hook-up in the dRail layout  Physical layout of ARM Cortex-M0 with sub-clock power gating using traditional voltage area layout (left) and dRail (right)  Distribution of signal routing in sub-clock power gated Cortex-M0 using voltage area and dRail  Top level block diagram of an ARM Cortex-A5 processor core [165]  Floorplan of A5 with interaction of Data Engine and Data Processing                                                                                             | 130<br>131<br>132<br>133        |

| <ul><li>5.13</li><li>5.14</li><li>5.15</li><li>5.16</li></ul> | Power hook-up in the dRail layout  Physical layout of ARM Cortex-M0 with sub-clock power gating using traditional voltage area layout (left) and dRail (right)  Distribution of signal routing in sub-clock power gated Cortex-M0 using voltage area and dRail  Top level block diagram of an ARM Cortex-A5 processor core [165]  Floorplan of A5 with interaction of Data Engine and Data Processing Unit (a) no power gating (b) DE power gated with voltage area (c) DE power gated with dRail | 130<br>131<br>132<br>133<br>134 |

| <ul><li>5.13</li><li>5.14</li><li>5.15</li><li>5.16</li></ul> | Power hook-up in the dRail layout  Physical layout of ARM Cortex-M0 with sub-clock power gating using traditional voltage area layout (left) and dRail (right)  Distribution of signal routing in sub-clock power gated Cortex-M0 using voltage area and dRail  Top level block diagram of an ARM Cortex-A5 processor core [165]  Floorplan of A5 with interaction of Data Engine and Data Processing Unit (a) no power gating (b) DE power gated with voltage area (c) DE                        | 130<br>131<br>132<br>133<br>134 |

xii LIST OF FIGURES

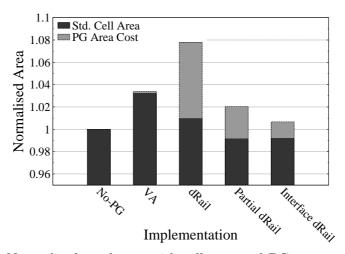

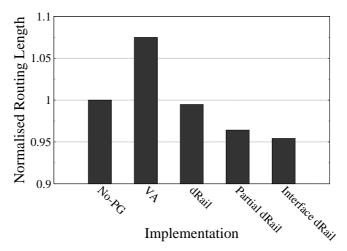

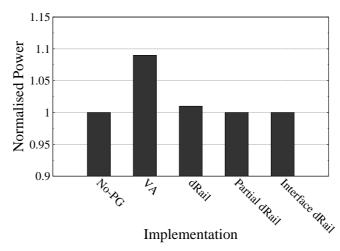

| 5.18 | Normalised total area with cell area and PG area overhead shown 14 |

|------|--------------------------------------------------------------------|

| 5.19 | Normalised total routing length                                    |

| 5.20 | Normalised dynamic and leakage power at 400MHz                     |

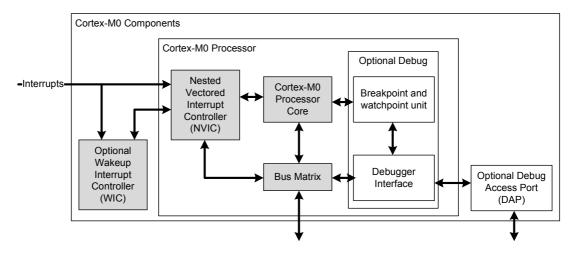

| A.1  | Block diagram of the Cortex-M0 processor                           |

## List of Tables

| 3.1 | Worst case capacitive loaded gate delays                                                                                                   | 55  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Power and energy per operation of sub-clock power gated multiplier, $V_{dd}$ =0.6V                                                         | 68  |

| 3.3 | Power and energy per operation of sub-clock power gated Cortex-M0, $V_{dd}$ =0.6V                                                          |     |

| 3.4 | Power and energy per operation of sub-clock power gated Event Processor,                                                                   |     |

| 3.5 | $V_{dd}$ =0.6V                                                                                                                             | 77  |

|     | performance points, 16bit Multiplier                                                                                                       | 80  |

| 3.6 | Comparison of sub-clock power gating relative to subthreshold operation performance points, Cortex-M0                                      | 81  |

| 4.1 | Ring oscillator wake-up energy, leakage saving and wake-up time                                                                            | 88  |

| 4.2 | Control signals to power gates and corresponding mode of operation                                                                         | 91  |

| 4.3 | Dhrystone - Average measured power and energy in three modes of operation, $V_{dd}$ =0.7V                                                  | 105 |

| 4.4 | Dhrystone - Average measured power and energy over five test chips with power gating disabled (No-PG) & sub-clock power gating (SCPG)      | 109 |

| 4.5 | Tuning Program - Average measured power and energy over five test chips with power gating disabled (No-PG) & sub-clock power gating (SCPG) |     |

| 5.1 | Area comparison of voltage area and dRail layout, Cortex-M0                                                                                | 132 |

| 5.2 | Distribution of signal routing in voltage area and dRail layout, Cortex-M0                                                                 | 133 |

| 5.3 | Sub-clock power gated Cortex-M0 average power of voltage area and dRail layouts, $V_{dd}$ =0.7V                                            | 133 |

| 5.4 | Area, routing and power in no power gating and power gating with voltage                                                                   |     |

|     | area [3], and proposed dRail, Cortex-A5                                                                                                    | 137 |

| 5.5 | Area, routing and power in no power gating and power gating with voltage area [3], partial dRail, and interface dRail, Cortex-A5           | 140 |

| B.1 | Statistics of statements and operands in Dhrystone benchmark                                                                               | 158 |

### Declaration of Authorship

I, Jatin Nawnit Mistry, declare that this thesis entitled *Leakage Power Minimisation Techniques for Embedded Processors* and the work presented in it are both my own, and have been generated by me as the result of my own original research. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- Where I have consulted the published work of others, this is always clearly attributed;

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- Parts of this work have been published as listed in Section 1.7

| Signed: | Date: |

|---------|-------|

| 0       |       |

#### Acknowledgements

I would like to express my sincerest gratitude to Professor Bashir M. Al-Hashimi for his supervision and guidance throughout my Ph.D. I have learnt tremendous amounts from him and without his support and encouragement this work would not have been possible. I would also like to extend my gratitude to my industrial advisory team Professor David Flynn, James Myers and Stephen Hill for their invaluable support and technical discussions throughout my Ph.D. My thanks also go to my second supervisor Iain McNally, internal examiner Dr Geoff Merrett and visiting friend of Professor David Flynn, Dr Harry Oldham for their insightful discussions.

I wish to thank the Engineering and Physical Sciences Research Council (EPSRC) for supporting my work by means of scholarship, the ARM-ECS Research Center in the School of Electronics and Computer Science, University of Southampton for providing state of the art research facilities and ARM Ltd. for allowing me to spend 4 months of my Ph.D working at their offices. My special thanks also go to John Biggs, Anand Savanth, Karthik Sivashankar (ARM) and Matthew Swabey (Purdue University) for their help in fabricating and testing the silicon test chip used in this thesis.

The constructive discussions I shared with my colleagues and friends and invaluable support I have received from them throughout my Ph.D has also contributed to its successful completion. These people include, but is not limited to: Sheng Yang, Shida Zhong, Dr Mustafa Imran-Ali, Dr Saqib Khursheed, Dr Rishad Shafik, Jedrzej Kufel, Luis Maeda-Nunez, Dr Alex Weddell, Dr Richard Lowe, Dan Reid, Dr Harry Rose, Celia Yeung, Ben Waller, Dr Amit Acharyya, Taihai Chen, Alex Wood, Kier Dugan, Tom Redman and Jon Storey. My thanks go to them all.

Finally, I would like to thank my parents, Nawnit Mistry and Narmada Mistry, my brothers Ilesh Mistry and Jayesh Mistry, my sisters-in-law Neeta Mistry and Taejal Mistry, and my sister Bhavika Mistry, in addition to my incredible extended family for their continuous love, support and understanding throughout my Ph.D.

### Chapter 1

### Introduction

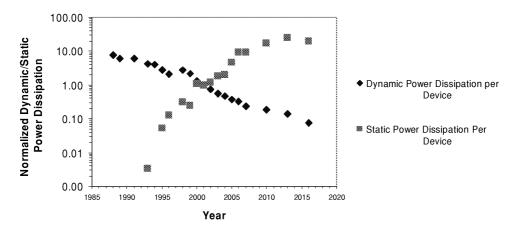

Technology scaling has been the driving force in the microelectronics industry enabling increased integration, cheaper devices, and increased performance with each new generation of CMOS. This is because higher performance and lower cost are two important design goals of many digital integrated circuits [1]. Historically, dynamic power has dominated the power consumption of digital integrated circuits and has been the main focus of power reduction for many years. However, as technology scaling has continued, leakage power has become a cause for concern in power dissipation prompting a variety of leakage reduction techniques to be developed. In some current and emerging applications there is a shift from performance driven design goals to power and energy constraints and as leakage continues to grow in dominance it presents a major obstacle in achieving these targets. This thesis describes new leakage power minimisation techniques, their physical layout and their validations for digital designs in the context of low performance energy constrained applications.

This chapter gives an overview of low power design in digital circuits and provides preliminary information for the subsequent thesis chapters. The major components of power dissipation in digital integrated circuits (IC) are described in Section 1.1. A summary of established dynamic power reduction techniques are outlined in Section 1.2. Section 1.3 discusses the impact of technology scaling on leakage power dissipation and Section 1.4 summarises some effective techniques for improving energy efficiency in digital circuits which are relevant to the work reported in this thesis. Section 1.5 gives examples of energy constrained applications where low performance microprocessors are used. The contribution of each chapter is summarised in Section 1.6 and finally the list of publications generated from the research in this thesis is given in Section 1.7.

#### 1.1 Power in Digital Circuits

In order to design energy-efficient digital circuits it is important to understand the different sources of power dissipation, of which there are mainly two: dynamic power and leakage power [2]. Dynamic power is caused by switching activity and is dissipated whenever the digital circuit is doing useful work whereas leakage power is dissipated whenever the digital circuit is switched on regardless of whether useful work is being performed. This means that when a digital circuit is in the active mode of operation i.e. doing useful work, total power is contributed to by both dynamic and leakage power, however when the digital circuit is in idle mode leakage power is the only contributor of power dissipation. The total power of a digital circuit is therefore given by:

$$P_{total} = P_{dyn} + P_{leak} (1.1)$$

#### 1.1.1 Dynamic Power

The dynamic power in Eqn. 1.1 can be split into two components:

$$P_{dyn} = P_{switching} + P_{sc} \approx P_{switching} \tag{1.2}$$

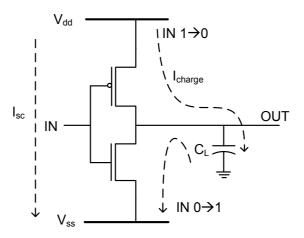

The  $P_{sc}$  term in this equation refers to the short circuit power that is consumed when a logic gate switches due to a direct path from  $V_{dd}$  (power) to  $V_{ss}$  (ground). This can be understood with the example inverter in Fig. 1.1. As the input IN makes a  $0 \to 1$  or  $1 \to 0$  transition, for a short period of time both the NMOS and PMOS transistors may both be conducting and a short circuit current  $I_{sc}$  will flow. The short circuit power dissipation in most circuits can be considered negligible as long as the input signal ramp time is kept short [3]. For this reason dynamic power can be approximated by  $P_{switching}$ .  $P_{switching}$  is due to the charging of load capacitances during switching activity and the inverter in Fig. 1.1 can be used again to understand the energy that is drawn from the power supply.  $C_L$  represents the physical load capacitance at the output node of the inverter. First consider the input IN to be set at 1 such that the PMOS transistor is off, the NMOS transistor is on and  $C_L$  is fully discharged. Now consider a  $1 \to 0$  transition at the input node. The PMOS transistor connects  $C_L$  to  $V_{dd}$  which is charged through the PMOS transistor until the output OUT reaches  $V_{dd}$  at time T resulting in a  $0 \to 1$  transition at the output. The power dissipation of this transition is given by:

$$P_{switching} = V_{dd}.I_{charge} = V_{dd}.C_L \frac{dV_{out}}{dt}$$

(1.3)

Therefore the energy drawn from the power supply in this transition is given by:

Figure 1.1: Dynamic power charging and discharging of load capacitance

$$E_{0\to 1} = \int_{0}^{T} P_{switching} dt = V_{dd}. \int_{0}^{T} I_{charge} dt = V_{dd}. C_{L}. \int_{0}^{V_{dd}} dV_{out} = C_{L} V_{dd}^{2}$$

(1.4)

It should be noted that the energy stored in the capacitor  $C_L$  is  $\frac{1}{2}C_L.V_{dd}^2$ , as half of the energy is dissipated in the PMOS transistor [2]. Furthermore during a  $0 \to 1$  transition at the input, the charge stored in  $C_L$  is discharged through the NMOS transistor resulting in no energy being drawn from the power supply. Although the example given here is for a simple inverter the discussion is true for more complex gates [2, 4]. Therefore, over a number of clock cycles  $N_c$ , the switching energy dissipation of an entire digital circuit can be given by:

$$E_{switching} = N_c \cdot V_{dd}^2 \cdot C_{eff} \tag{1.5}$$

Where  $C_{eff}$  is the lumped average capacitance that is switched in the digital circuit given by the product of switching probability  $\alpha$  and total load capacitance  $C_L$  [2]. Assuming a clock frequency of f, the average switching power of the digital circuit can then be given by:

$$P_{switching} = \frac{E_{switching} \cdot f}{N_c} = f \cdot V_{dd}^2 \cdot C_{eff}$$

(1.6)

It can be seen from the equations of switching energy (Eqn. 1.5) and switching power (Eqn. 1.6) that, assuming a constant  $C_{eff}$  determined by the design of the digital circuit, and fixed number of clock cycles  $N_c$ , then energy is proportional to the square of the supply voltage  $V_{dd}$  whereas power is proportional to the product of f and square of  $V_{dd}$ . Therefore, although reducing the clock frequency can reduce power, the energy required remains the same. It may be thought that a simple fix for improved energy consumption

is reduction in supply voltage, but there is a cost. The propagation delay of a gate can be approximated as [5]

$$T_{prop} \propto \frac{C_L V_{dd}}{(V_{dd} - V_{th})^k} \tag{1.7}$$

where  $V_{th}$  is the threshold voltage of the transistors and k is a technology dependent parameter used to model short channel effects and normally has a value between 1-2. Eqn. 1.7 shows that as  $V_{dd}$  is reduced the propagation delay increases and forces the reduction of the operating frequency.

#### 1.1.2 Leakage Power

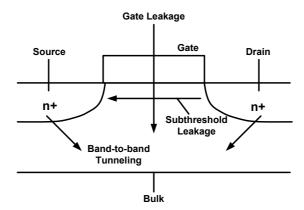

Leakage power unlike dynamic power is present in the digital circuit at all times and is not a function of the useful work done. This means that if a circuit is *idle* - powered but not doing useful work - it still dissipates leakage power. Leakage power is the result of parasitic current flows within the device and is dominated by mainly three sources [6]: subthreshold leakage current, band-to-band tunneling current and gate leakage current

$$P_{leak} = V_{dd}.(I_{sub} + I_{BTBT} + I_{qate}) \tag{1.8}$$

These three sources of current are represented diagrammatically in Fig. 1.2. Gate leakage is current that flows directly between the gate and the substrate due to tunneling of charge carriers through the gate oxide [7]. The current is a result of the electric field that is present across the oxide which increases with reduction in the thickness of the gate oxide,  $T_{ox}$  [6]. Gate leakage current is present at all times in a MOSFET regardless of the state of the device - conducting or not. Band-to-band tunneling (BTBT), also known as PN junction reverse-bias current, is due to the fact that the drain and source to substrate junctions are effectively reverse biased diodes in a MOSFET [2]. PN junction reverse-bias leakage is a function of the junction area and the doping concentration, causing the tunneling current to increase with heavier doping of the N and P regions [6]. Like gate leakage, BTBT is present in the device when the transistor is both conducting or not. Unlike the previous two leakage current sources which are present at all times, subthreshold leakage is the flow of minority carriers from source to drain due to the partial formation of a conduction channel when a MOSFET is cut-off  $(V_{gs} < V_{th})$  and can be approximated by [8]

$$I_{sub} = \mu C_{ox} V_t^2 \frac{W}{L} e^{1.8} e^{\frac{V_{gs} - V_{th}}{nV_t}} [1 - e^{-\frac{V_{ds}}{V_t}}]$$

(1.9)

Figure 1.2: Subthreshold, band-to-band tunneling and gate leakage currents in MOSFETs

Where  $\mu$  is the carrier mobility,  $C_{ox}$  is the oxide capacitance,  $V_t$  is the thermal voltage  $\frac{KT}{g} = 25.9 \text{mV}$  at room temperature, W is the width of the transistor, L is the length of the transistor,  $V_{gs}$  is the gate to source voltage,  $V_{ds}$  is the drain to source voltage,  $V_{th}$  is the threshold voltage and n is a function of the fabrication process. From Eqn. 1.9 it can be seen that lowering  $V_{ds}$ , achieved by lowering the supply voltage, affects the term  $\left[1 - e^{-\frac{V_{ds}}{V_t}}\right]$  and when  $V_{ds} \ll V_t$  this term approaches 1, significantly reducing the subthreshold leakage. Similarly, as can be seen, the subthreshold leakage current is exponentially dependent on  $V_{th}$ . Increasing  $V_{th}$  lowers the subthreshold leakage current and therefore MOSFET gates with higher threshold voltages exhibit less subthreshold leakage current [9]. The threshold voltage can be controlled in mainly two ways, the first is through the manufacturing process, the second is by changing the body-to-source voltage  $(V_{bs})$  of a transistor and is known as the body effect [2]. Traditionally the body of a transistor is at the same potential as its source but can be raised or lowered to affect the threshold voltage [4]. This effect causes a negative  $V_{bs}$  to increase the threshold voltage whereas a positive  $V_{bs}$  lowers the threshold voltage. Both techniques will be discussed further in Chapter 2.

Taking into consideration the leakage power dissipation of a digital circuit the total energy consumed in a digital circuit over a number of cycles  $N_c$  with clock period  $t_p$  can now be expressed as:

$$E_{total} = E_{dyn} + E_{leak} = N_c \cdot V_{dd}^2 \cdot C_{eff} + N_c \cdot V_{dd} \cdot I_{leak} \cdot t_p$$

(1.10)

What is interesting to note with this equation is that the previous discussion with dynamic power (Section 1.1.1), where it was observed that a lower clock frequency equates to lower power but identical energy, now has a new dynamic. A lower clock frequency would lower dynamic power as per Eqn. 1.6, but would increase the clock period  $t_p$ . From Eqn. 1.10 we see that this would result in more energy lost to leakage leading to lower energy efficiency. This observation will be exploited in Chapter 3.

#### 1.2 Dynamic Power Reduction

Dynamic power has dominated the power consumption of digital circuits for many years [2]. Although, power reduction in digital circuits can be achieved through a number of application specific changes including architecture changes and instruction set modification, these improvements are constrained to a particular processor [10]. In this thesis the focus is instead on general purpose techniques i.e. ones that can be applied to any digital circuit. Examining Eqn. 1.6, it can be seen that by reducing the effective load capacitance  $C_{eff}$  by reducing the switching activity  $\alpha$  and load capacitances  $C_L$ , or the operating voltage  $V_{dd}$ , energy consumed to dynamic power can be lowered. Lowering  $V_{dd}$ , however, increases propagation delay, Eqn. 1.7, and therefore techniques to reduce dynamic power ideally attempt to affect these variables without hindering performance. In this section a brief overview of some of the most widely adopted dynamic power reduction techniques is given.

#### 1.2.1 Clock Gating

The dynamic power consumption of a processor is primarily dominated by the clock distribution [11] also known as the clock tree. It has been reported that approximately 32% of the dynamic power dissipation in the Alpha 21264 Microprocessor is due to the global clock network [12]. This large dynamic power comes from the high activity and the sizable capacitive fan-out load of the clock tree. Additionally, although registers may retain the same state over two or more clock cycles, internal switching of the gate from the toggling of the clock adds to the overall dynamic power consumption. This observation of registers not being updated at every clock edge led to clock gating, which was introduced to eliminate the switching of parts of the clock tree where registers did not need to be updated. The result of this is a set of partitioned regions in the clock tree where the clock can be enabled depending on the requirement to update registers within sub-sections of a digital circuit [13]. The simplicity of clock gating enables it to be used in all types of sequential digital logic. R. Gonzalez et al. report a 33% saving in global clock network power dissipation when using clock gating [14] in a microprocessor and S. Huda et al. report over 50% clock power saving when the technique was used in FPGAs [15].

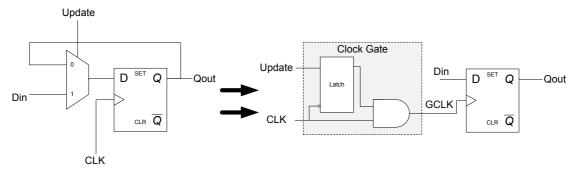

The technique is achieved by adding a logic cell, called a clock gate, into the clock tree allowing a control signal to enable or disable the clock as required. Careful planning of the insertion of clock gating has been proven to even reduce the area of a digital circuit. This is because a digital circuit without clock gating would require recirculation multiplexers to retain the state of registers, and the addition of a single clock gate can remove a number of these multiplexers, demonstrated in Fig. 1.3, leading to greater savings in power. In a case-study by K. C. Pokhrel, it is demonstrated that a circuit

Figure 1.3: Recirculation multiplexer to clock gate (based on [16])

with clock gating is 20% smaller than the same circuit without clock gating [16]. Clock gating is now well supported in industry standard EDA (Electronic Design Automation) tools such as Synopsys Design Compiler making the insertion of clock gating automatic [17].

#### 1.2.2 Glitching, Input Reordering and Gate Sizing

Part of the dynamic power dissipation of CMOS circuits can be accounted to glitching due to imbalanced paths to a gate's inputs [18]. As an example, consider a 2-input NAND gate with inputs '10', if delay causes the second input to change to '1' before the first input changes to '0', the output momentarily takes the value of '0'. This glitch dissipates unnecessary dynamic power due to the recharging of the output load capacitance. By using path balancing, buffers can be added to ensure inputs to gates arrive at the same time to reduce the number of glitches in the circuit by up to 61.5% [19]. The maximum saving is limited by the ability to balance both rising transitions and falling transitions to all inputs which can be difficult.

Since the dynamic power dissipation is also governed by the probability of switching load capacitances,  $C_{eff}$  dynamic power can be minimised by reordering inputs/gates to reduce the probability of switching. By carefully reordering the inputs such that the critical signal is closest to the output, dynamic power dissipation due to spurious intermediate transitions, can be minimised [20]. Probability can also be reduced through an appropriate state encoding strategy to minimise switched capacitance between state transitions [21]. If the probability cannot be reduced then the load capacitance could be reduced by using minimum size gates on non-critical paths [2]. Across a set of test circuits, Y. Huang et al. show that using an effective method of gate sizing, total power can be reduced by an average of 18.5% [22].

#### 1.2.3 Voltage and Frequency Scaling

Dynamic Voltage and Frequency Scaling (DVFS) targets both the supply voltage and the operational clock frequency. The technique capitalises on the times when a system does not need to be operated at its maximum frequency due to workload demands [23]. At these times the voltage can be scaled down to reduce dynamic power and improve energy efficiency, Eqn. 1.5, but results in reduced performance due to the increase in delay, Eqn. 1.7, forcing the reduction of clock frequency too. T.D. Burd et al. report energy efficiency of a processor system being improved by up to 10x when using DVFS [23]. The advantage with DVFS is the ability to switch between high performance, high energy and low performance, low energy states depending on the current workload. Its efficiency at reducing dynamic power dissipation has prompted many DVFS designs and algorithms on a variety of different systems [24–26].

An alternative to DVFS is to statically scale the supply voltage of a system. By using a reduced supply voltage, the dynamic power dissipation is reduced, energy consumption is improved but performance is penalised (Eqn. 1.5 to 1.7). This is effective if a system's performance is not a primary concern as it cannot be increased back to nominal performance as is done with DVFS. This technique can be extended for use in multi-supply/multi-voltage operation [27], where different parts of a system on chip may require different levels of performance enabling a number of different supply voltages to be utilised. By using multiple supplies, voltage islands can be created to partition subsections of the system that are off critical paths, thereby saving dynamic power [3, 28]. Since the sub-section chosen is off a critical path, the path can cope with the increase in delay associated with the reduced supply voltage without affecting overall system performance [3]. This technique is most common in Systems on Chip (SoCs) that require caches to be as fast as possible whereas the CPU and the rest of the SoC can be operated at a reduced voltage whilst still meeting timing constraints [3, 27].

#### 1.3 Technology Scaling and Implications on Power

Over the last 50 years the industry has followed a trend in scaling where geometry dimensions decrease by 30% every two to three years [2, 29]. The main reason behind this scaling trend is to reduce the cost of IC fabrication [1]. With a 30% decrease in process size, area is reduced by 50% (0.7x0.7=0.49) meaning double the number of transistors can fit in the same area on a silicon wafer, significantly reducing manufacturing cost. Additionally, a 30% reduction in device geometry leads to a 30% reduction in gate delay leading to  $\frac{1}{0.7}$  improvement in integrated circuit performance [29]. There are two types of scaling that have taken place in CMOS technology: constant voltage scaling and constant field scaling. In the former case, only the device geometries, length, width and gate oxide thickness are shrunk while the supply voltage remains the same. The advantage

of this is that it provides compatibility with older circuit technologies but suffers an increase in the electric field across the channel of the MOSFET which can lead to velocity saturation, mobility degradation and lower breakdown voltages [2]. Nevertheless, constant voltage scaling was preferred at first and was used down to the  $0.5\mu$ m process [29]. The alternative constant field scaling is based on 'Dennard's Scaling Law' [30] which states the performance of a transistor can be improved if the critical parameters of a device are scaled by a given factor. These parameters include the length, width and gate oxide but also the supply voltage  $V_{dd}$  and transistor threshold voltage  $V_{th}$ . By maintaining a constant electric field across the channel, the problems seen with constant voltage scaling are avoided [2] but also has the secondary advantage of reduced dynamic power consumption. If a 30% reduction in geometry and supply voltage is assumed, dynamic power should reduce by 50% with each new technology node [29]. This can be calculated by substituting the reduced geometry and supply voltage into Eqn. 1.6:

$$P_{dyn} = C_{eff} \cdot f \cdot V_{dd}^2 = 0.7 \times (0.7)^2 \times (1/0.7) \approx 0.5$$

Constant electric field scaling has thus resulted in smaller, faster and lower power devices. However, as each new generation of technology is introduced, the component of subthreshold leakage current has increased and this is because of the necessity to reduce the threshold voltage  $(V_{th})$  as part of the technology scaling [6, 31]. This can be seen from Eqn. 1.9, which shows that as the threshold voltage is reduced, the subthreshold leakage current of the transistor increases exponentially. Maintaining a higher threshold voltage can help to limit the subthreshold leakage power dissipation but results in an increase in gate propagation delay  $(T_{prop})$ , seen in Eqn. 1.7. As  $V_{th}$  is increased in this equation the lower denominator reduces in size resulting in a rise in propagation delay. As explained in Chapter 2, Section 2.1, however, multiple threshold voltage gates are common in digital IC design to help reduce leakage power dissipation.