# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

# UNIVERSITY OF SOUTHAMPTON

# FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

High Resistivity Czochralski-Silicon Using Deep Level Dopant Compensation For RF Passive Devices

by

Ahmed Abuelgasim

Thesis for the degree of Doctor of Philosophy

October 2012

### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF PHYSICAL AND APPLIED SCIENCES

School of Electronics and Computer Science

#### <u>Doctor of Philosophy</u>

# HIGH RESISTIVITY CZOCHRALSKI-SILICON USING DEEP LEVEL DOPANT COMPENSATION FOR RF PASSIVE DEVICES

#### by Ahmed Abuelgasim

Combinations of analytical and experimental results indicate that deep level doping of Czochralski grown silicon wafers is capable of providing very high resistivity wafers suitable for silicon-on-insulator (SOI), integrated passive devices (IPD) and 3D integration configurations.

Deep level doping involves adding trace elements to silicon that compensate for background free carriers introduced by impurities in the silicon and pin the Fermi level near the mid bandgap intrinsic level. Starting from n-type Czochralski-silicon wafers with a nominal resistivity of 50  $\Omega$ cm, gold ion implantation and subsequent annealing were used to increase the resistivity of silicon wafers by up to 3 orders of magnitude, to values as high as 93 k $\Omega$ cm.

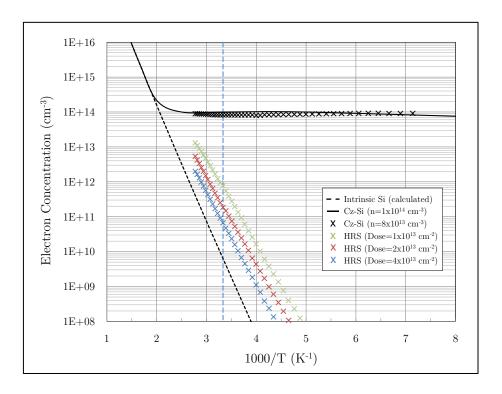

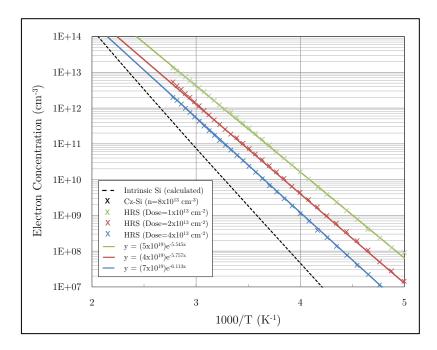

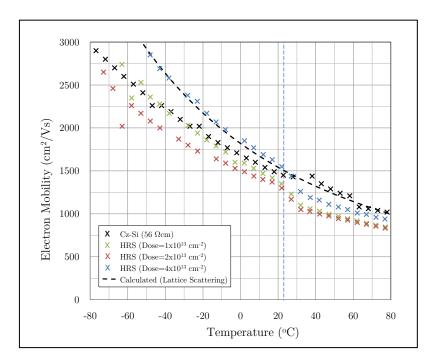

Hall measurements performed over a large temperature range show that the increase in resistivity is solely due to a decrease in carrier concentration and not a decrease in mobility. The carrier concentration is only one order of magnitude larger than that of intrinsic silicon over a temperature range of 200-360 K. Hall results also show that the resistivity of the compensated material remains up to two orders of magnitude larger than that of the uncompensated material at near operating temperatures.

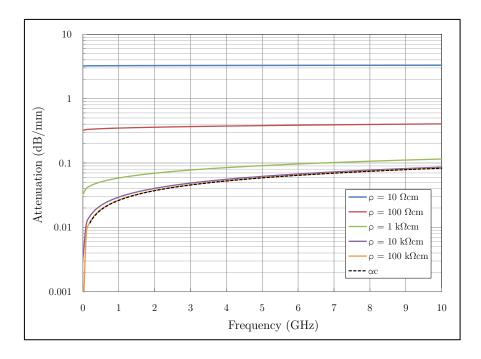

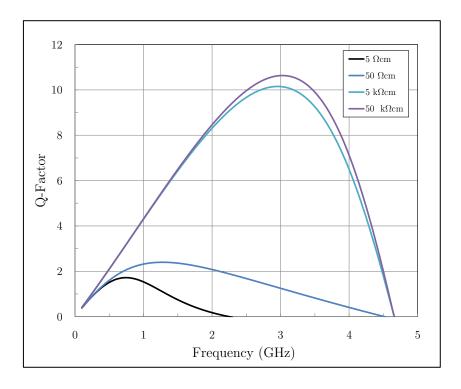

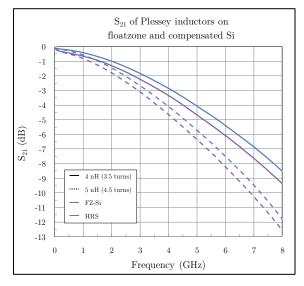

High frequency attenuation measurements in the 1-67 GHz range for coplanar waveguides show attenuation reductions of up to 76% from 0.76 dB/mm to 0.18 dB/mm at 10 GHz for those fabricated on uncompensated and compensated silicon respectively. Spiral inductors fabricated on both compensated and uncompensated silicon show up to a factor of 10 increase in the maximum quality factor from 0.3 to 3.1 for inductors on uncompensated and compensated silicon respectively. A 70% increase in maximum quality factor from 9 to 15.2 is exhibited by inductors commercially fabricated on compensated silicon when compared to those on float-zone silicon.

The coplanar waveguide and spiral inductor results provide clear evidence that deep level dopant compensation is effective in improving the performance of passive devices in the GHz frequency range.

# Contents

| 1          | 1 Introduction                                            |                                                                     |           |  |  |  |

|------------|-----------------------------------------------------------|---------------------------------------------------------------------|-----------|--|--|--|

| 2          | Incr                                                      | easing Silicon Resistivity Using Deep Level Dopant Compensation     | 4         |  |  |  |

|            | 2.1                                                       | Basic Principles of Resistivity                                     | 5         |  |  |  |

|            | 2.2                                                       | Resistivity Measurement Techniques                                  | 7         |  |  |  |

|            | 2.3                                                       | Increasing the Resistivity of Czochralski-Silicon                   | 11        |  |  |  |

|            | 2.4                                                       | Deep Level Dopant Compensation                                      | 16        |  |  |  |

|            | 2.5                                                       | Gold as a Deep Level Dopant                                         | 21        |  |  |  |

|            | 2.6                                                       | Creating High Resistivity Silicon through Gold Doping               | 25        |  |  |  |

|            | 2.7                                                       | Resistivity Measurements of Gold Doped Silicon                      | 28        |  |  |  |

|            | 2.7.1                                                     | Four-point Probe Measurements                                       | 28        |  |  |  |

|            | 2.7.2                                                     | SIMS and SRP Measurements                                           | 32        |  |  |  |

|            | 2.7.3                                                     | Gold Surface Layer                                                  | 35        |  |  |  |

|            | 2.7.4                                                     | Hall Measurements                                                   | 38        |  |  |  |

| 3          | Red                                                       | ucing Coplanar Waveguide Attenuation using Deep Level Doped Silicon | 44        |  |  |  |

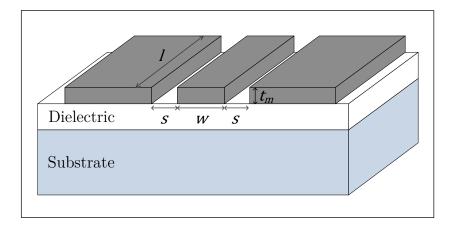

|            | 3.1                                                       | Structure and Attenuation Loses of Coplanar Waveguides              | 44        |  |  |  |

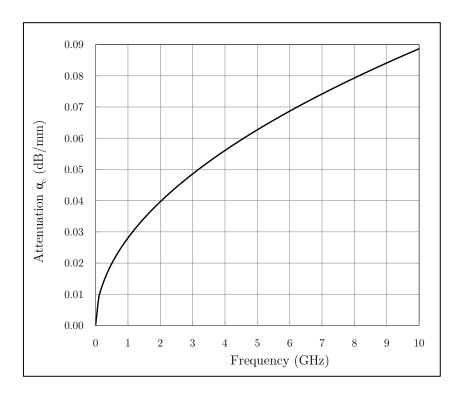

|            | 3.2                                                       | Measuring Coplanar Waveguide Attenuation                            | 49        |  |  |  |

|            | 3.3                                                       | Reducing Coplanar Waveguide Attenuation                             | 51        |  |  |  |

|            | 3.4                                                       | Coplanar Waveguide Design                                           | 55        |  |  |  |

|            | 3.5                                                       | Fabrication of Coplanar Waveguides                                  | 57        |  |  |  |

|            | 3.6                                                       | Coplanar Waveguide Attenuation Measurements                         | 59        |  |  |  |

| 4          | Imp                                                       | roved Efficiency of Spiral Inductors on Deep Level Doped Silicon    | 63        |  |  |  |

|            | 4.1                                                       | Geometry and Inductance of Spiral Inductors                         | 63        |  |  |  |

|            | 4.2                                                       | Quality Factor of Spiral Inductors                                  | 67        |  |  |  |

|            | 4.3                                                       | Spiral Inductor Modelling                                           | 70        |  |  |  |

|            | 4.4                                                       | Maximising Spiral Inductor Quality Factor                           | 77        |  |  |  |

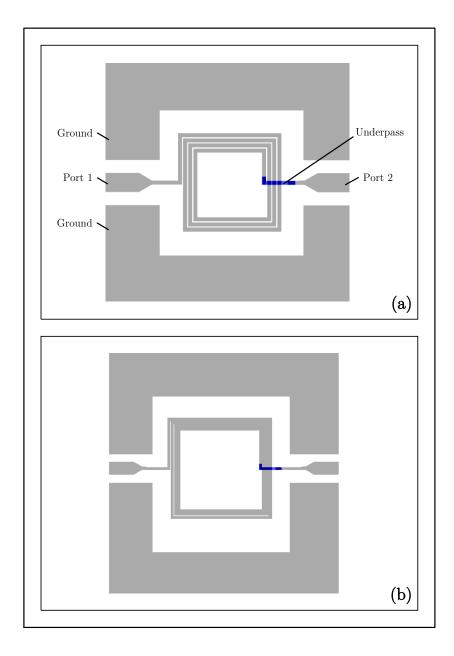

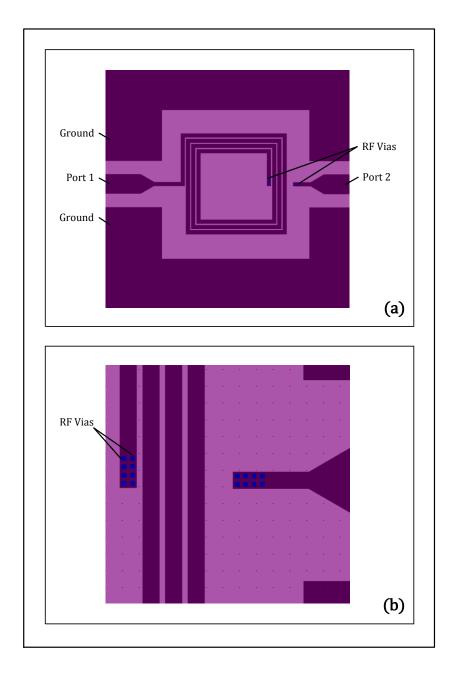

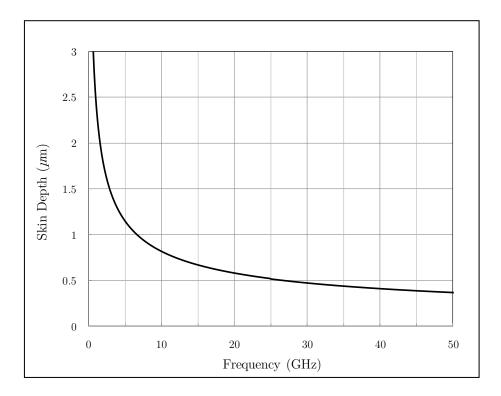

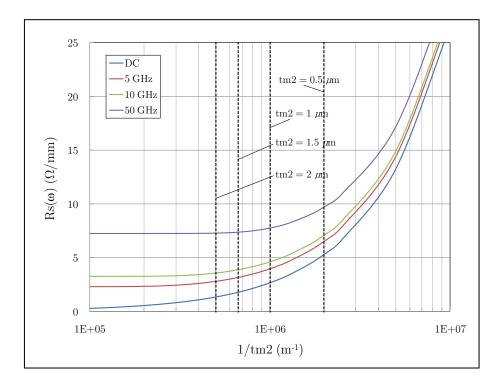

|            | 4.5                                                       | Spiral Inductor Design                                              | 83        |  |  |  |

|            | 4.6                                                       | Spiral Inductor Quality Factor Simulations                          | 90        |  |  |  |

|            | 4.7                                                       | Fabrication of Spiral Inductors                                     | 93        |  |  |  |

|            | 2.6 Creating High Resistivity Silicon through Gold Doping |                                                                     | 100       |  |  |  |

| 5          | Sun                                                       | umary                                                               | 109       |  |  |  |

| 6          | Refe                                                      | erences                                                             | 112       |  |  |  |

| Aı         | pendi                                                     | x A                                                                 | 120       |  |  |  |

| Αı         | pendi                                                     | з B                                                                 | 122       |  |  |  |

|            | -                                                         |                                                                     | 124       |  |  |  |

|            |                                                           |                                                                     |           |  |  |  |

|            | _                                                         |                                                                     | 125 $127$ |  |  |  |

| Appendix E |                                                           |                                                                     |           |  |  |  |

# Declaration of Authorship

I, Ahmed Abuelgasim, declare that the thesis entitled 'High Resistivity Czochralski-Silicon Using Deep Level Dopant Compensation For RF Passive Devices', and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research.

#### I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as shown in the List of Publications that follows.

| Signed: | <br> | <br> |

|---------|------|------|

|         |      |      |

|         |      |      |

|         |      |      |

|         |      |      |

| Date    |      |      |

## List of Publications

- A. Abuelgasim, K. Mallik, K. De Groot, P. Ashburn, D. M. Jordan, and P. R. Wilshaw, "High resistivity Czochralski-silicon using Deep Level Doping Compensation," in 2010 Proceedings of the European Solid-State Device Research Conference (ESSDERC), 2010.

- K. Mallik, A. Abuelgasim, P. Ashburn, and K. De Groot, "Deep level dopant compensated Czochralski silicon substrates for MMICs," in *ARMMS RF & Microwave Society Conference*, 2010.

- A. Abuelgasim, K. Mallik, P. Ashburn, D. M. Jordan, P. R. Wilshaw, R. J. Falster, and C. H. de Groot, "Reduced microwave attenuation in coplanar waveguides using deep level impurity compensated Czochralski-silicon substrates," *Semiconductor Science and Technology*, vol. 26, no. 7, Jul. 2011.

- K. Mallik, A. Abuelgasim, P. Ashburn, C. H. de Groot, and P. R. Wilshaw, "Deep level impurity engineered semi-insulating CZ-silicon as microwave substrates," in *Microwave Integrated European Circuits Conference (EuMIC)*, 2011, pp. 394-397.

- A. Abuelgasim, K. Mallik, C. H. de Groot, and P. Ashburn, "Gold-doped high resistivity Czochralski-silicon for integrated passive devices and 3D integration," in *Proceedings of the European Solid-State Device Research Conference (ESSDERC)*, 2011, pp. 363-366.

- A. Abuelgasim, K. Mallik, P. Ashburn, and C. H. de Groot, "High resistivity Czochralski-silicon using a deep level dopant compensation process," in *International Conference on Micro and Nano Engineering (MNE)*, 2011.

- A. Abuelgasim, K. Mallik, P. R. Wilshaw, P. Ashburn, and C. H. de Groot, "High resistivity Czochralski-silicon using a deep level dopant compensation process," in *Europe's Semiconductor Conference, Innovation in Advanced Manufacturing Processes (S2K)*, 2011.

- A. Abuelgasim, K. Mallik, P. Ashburn, and C. H. De Groot, "Fabrication of low loss coplanar waveguides on gold-doped Czochralski-silicon," in *Society of Photo-Optical Instrumentation Engineers* (SPIE) Conference Series, 2011, vol. 8068, pp. 806811-806811-12.

- A. Abuelgasim, K. Mallik, P. Ashburn, and C. H. de Groot, "High resistivity Czochralski-silicon using deep level dopant compensation," in *International Conference on Nanosciences & Nanotechnologies* (NN12), 2012.

# Acknowledgements

First and foremost above anyone else I must thank **Dr. Kanad Mallik** and **Prof. Cornelis** "Kees" de Groot, to whom I am deeply indebted for all their help, guidance and patience during the last four years.

I must also thank my other supervisors **Prof. Peter Ashburn** and **Prof. William Redman-White** for their advice and support. **Dr. Harold Chong**'s advice on RF inductor design techniques also proved to be extremely beneficial and for that I am very grateful.

Thanks are also in order for my collaborators from the University of Oxford; **Prof. Peter Wilshaw** and **Dr. Doug Jordan**, as well as **Dr. Rob Falster** from MEMC Electronic Materials.

A special thanks to the nicest man in Southampton, **Dr. Stuart Pearce**, for his hours of assistance, training and company during countless hours in the cleanroom.

I also wish to thank the entire Nanogroup especially **Feras AlKhalil** whose anecdotes and complaints helped to break up the monotony of an Excel-filled day. Individual thanks also to **Dr. Ibrahim Sari, Dr. Ioannis Karakonstantinos** and **Rachel Gleeson** specifically for their help with that temperamental wire-bonder.

Thanks also to all the Southampton Nanofabrication Centre staff, particularly Richard Kean, Peter Ayliffe, Dr. Owain Clarke, Dr. Kian Kiang, and Denny Jack. In terms of other facilities and organisations thanks are due for EPSRC, UK, for funding the project, Plessey Semiconductors Ltd for advice and inductor fabrication, Loughborough Surface Science for SIMS, Semiconductor Assessment Services Laboratory for SRP, and the EPSRC ion beam facility at Surrey University for implantation.

Last and most I would like to wholeheartedly thank my loving parents and family because without their support, love and encouragement, none of the following work would have been possible.

Thank you all so much....

Ahmed Abuelgasim

And now the science...

# Chapter 1

# Introduction

The availability of low cost semiconductor technology is a necessity for the demanding modern cellular and wireless markets. The realisation of connectivity systems in a few integrated circuits with low external component count is the subject of a great deal of research academically and in industry. Typical GSM circuits are designed with a single radio frequency integrated circuit (RFIC) that includes most of the necessary sub-systems such as low-noise amplifiers, voltage controlled oscillators, mixers and low power transmit drivers [1]. A major problem associated with these ICs fabricated in silicon (Si) is the undesirable characteristics of the material operated at radio frequency (RF). Passive devices, in particular, fabricated on Si suffer from decreased performance and efficiency due to absorption of microwave power by background free carriers in the substrate, substrate coupling as well as cross-talk and transmission line loss. Passive components are known to greatly outnumber active devices on integrated circuits (ICs) and account for over a third of the cost, particularly in RFICs [2], so it is essential to address any factors affecting their performance on Si, before it can be accepted as a suitable substrate material for RFIC fabrication.

Solutions to these problems have in the past included the use of gallium-arsenide (GaAs) as an alternative to Si, due to its higher electron mobility and hence faster switching speeds. Si however is still preferred to GaAs as it is cheaper and has a native oxide. Other solutions

Chapter 1. Introduction 2

involving Si lie in the manipulation of Si substrates to reduce the background free carrier absorption. One such solution is the creation of high resistivity Si through a method known as deep level dopant compensation, which has been shown to greatly increase the resistivity of Si substrates thereby increasing the efficiency of passive devices fabricated on them.

In this work deep level doping is investigated as a method of increasing the resistivity of Si, and gold (Au) was found to be a great choice of material to achieve this. Deep level doping with Au was used to create high resistivity Si wafers, the properties of which were investigated using four-point probe, spreading resistance profiling and secondary ion mass spectroscopy techniques. Hall effect measurements were used to investigate the effects of deep level doping on the concentration and mobility of background carriers in the Si.

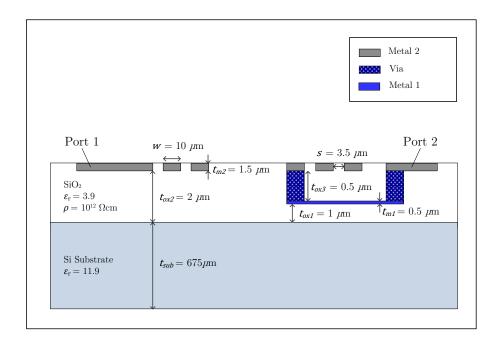

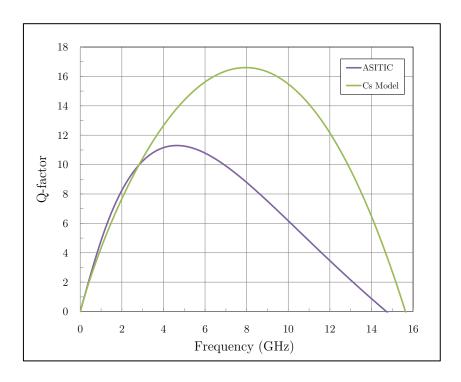

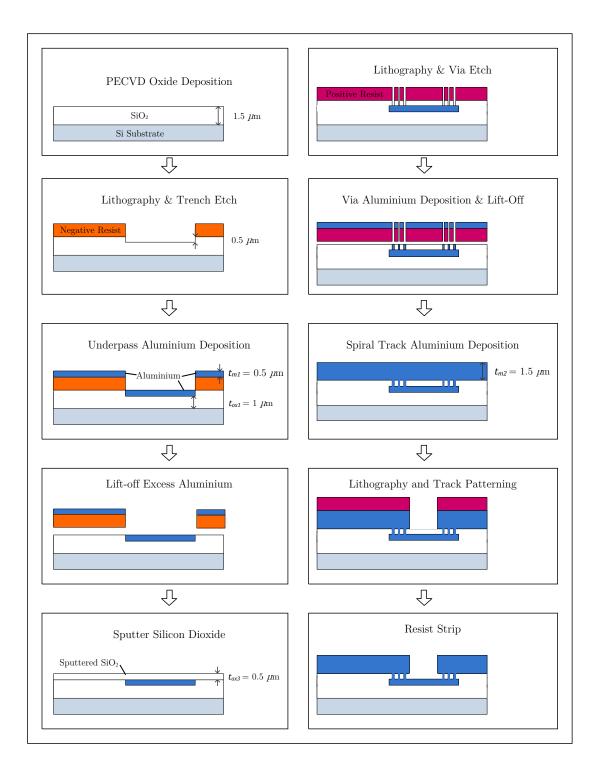

Coplanar waveguides and spiral inductors were chosen as the passive devices to be fabricated on the enhanced wafers in order to investigate any efficiency improvements brought about by the increased Si resistivity. ANSYS HFSS finite element simulations of spiral inductors were performed by Dr. Kanad Mallik, the results of which underpinned some of the decisions made in this work. These simulations, however, have not been included in this thesis. Passives were then fabricated and their RF performance on virgin and high resistivity Si (HRS) substrates were measured and compared. A number of iterations in the design and fabrication of these passives were performed particularly in relation to the development of the spiral inductors which proved to be a lengthy process due to the lack of ideal equipment in the Southampton Nanofabrication Centre where the devices were made. The methods and results of only the devices resulting from the iterations which gave the best results are hence reported.

The first chapter of this thesis covers deep level dopant compensation. Basic resistivity principles and measurement techniques are first explained before a critical review of various techniques that increase Si resistivity, as reported in literature, is given. The concept of deep level dopant compensation is then explained in detail including the use of Au as a deep level dopant. The methods used in this work to create HRS are next described before the results of this process are discussed.

Chapter 1. Introduction 3

The next chapter focuses on coplanar waveguides and their associated substrate related losses. General information about coplanar waveguide structure and attenuation related losses are given before a review of various methods of reducing attenuation as reported in literature. The design process is next explained before the fabrication process is detailed. The measured RF attenuation results are next included and discussed.

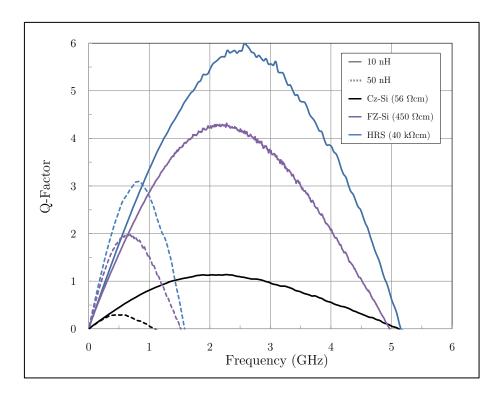

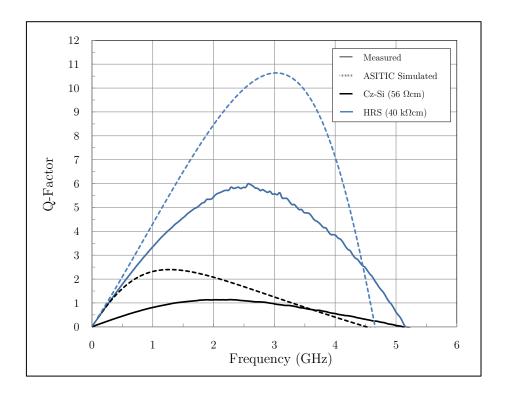

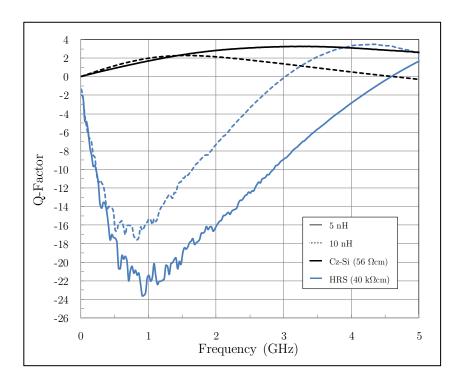

Chapter 4 begins with a basic description of spiral inductor geometry and a description of the major RF loss mechanisms. Inductor quality factor or efficiency is explained and then derived using several spiral inductor models, before different methods of increasing it are compared and critically reviewed. The design considerations of spiral inductors are then discussed after which quality factor frequency sweeps obtained from simulations are given. The fabrication process is finally detailed and RF measurements made are shown and discussed with reference to the simulated results.

# Chapter 2

# Increasing Silicon Resistivity Using Deep Level Dopant Compensation

Silicon grown by the Czochralski method is considered an excellent material for the fabrication of integrated circuits and the point has now been reached where devices based on this technology are capable of operating at frequencies approaching those of many III-V devices. A major remaining obstacle preventing the use of Czochralski-Silicon (Cz-Si) for RF applications lies in the fact that the performance of passive components fabricated on such substrates degrades when operated at RF due to absorption. This absorption is due to background free carriers in the Si and is therefore directly proportional to the conductivity of the substrate [3]; a fact that highlights the dependence of RFIC performance on substrate resistivity.

It is hence clear that high resistivity substrates are required for acceptable operation of passive RF integrated components to ensure device isolation thereby minimising undesirable effects. For these reasons the main aim of this work is the creation of high resistivity Si substrates through deep level dopant compensation. It is therefore important to first establish an understanding of the basic principles of resistivity and how it is measured.

# 2.1 Basic Principles of Resistivity

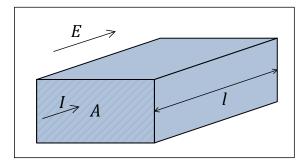

The resistance of a wire increases as the length of the wire increases and decreases as the cross-sectional area decreases, and depends on the material from which the wire is made. This dependence is known as the resistivity of the material and is the reciprocal of conductivity. In the context of a uniformly doped semiconductor bar, such as that shown in Figure 2.1, the resistance will increase if the length increases and decrease if the cross-sectional area increases. The resistance is also dependent upon the resistivity  $\rho$  of the semiconductor and can therefore be expressed as

$$R = \frac{\rho l}{A} \tag{2.1}$$

If an electric field E is applied to the semiconductor bar as shown in Figure 2.1 the electrons begin to move at a velocity known as the electron drift velocity  $v_n$ . This is the average velocity of the electron due to the field and depends on the electron mobility  $\mu_n$  or the ease at which electrons can move through the material, and can hence be expressed as [4]

$$v_n = -\mu_n E \tag{2.2}$$

Similarly, using the hole mobility  $\mu_p$ , the hole drift velocity can be obtained as

$$v_p = \mu_p E \tag{2.3}$$

Figure 2.1 – A uniformly doped semiconductor bar of length l and cross-sectional area A with current I passing through it.

These drift velocities give rise to a drift current through the semiconductor bar. The electron current density of this drift current is the product of the electron drift velocity and the charge -q of each electron and is given by [4]

$$J_n = \frac{I_n}{A} = -qnv_n = qn\mu_n E \tag{2.4}$$

The hole current density can similarly be calculated by

$$J_p = qp\mu_p E \tag{2.5}$$

where n and p are the electron and hole concentrations respectively. The total current density due to the applied force is the sum of the electron and hole current densities giving

$$J = J_n + J_p = q(n\mu_n + p\mu_p)E$$

(2.6)

however it is more commonly expressed using the conductivity of the material  $\sigma$  as [5]

$$J = \sigma E \tag{2.7}$$

The resistivity  $\rho$  of a semiconductor is the reciprocal of the conductivity and using equations (2.6) and (2.7) can be therefore be expressed as

$$\rho = \frac{1}{q(n\mu_n + p\mu_p)} \tag{2.8}$$

In extrinsic semiconductors there is a large difference between the concentrations of electrons and holes and one component dominates equation (2.8). For n-type semiconductors n is significantly larger than p and therefore equation (2.8) can be simplified to

$$\rho = \frac{1}{qn\mu_n} \tag{2.9}$$

and for a p-type semiconductor p >> n, therefore

$$\rho = \frac{1}{qp\mu_p} \tag{2.10}$$

# 2.2 Resistivity Measurement Techniques

A simple and common method of measuring resistivity is the four-point probe technique in which four equally spaced in-line probes are used. A small current is passed through the outer two probes while the voltage between the two inner probes is measured. The current and voltage values are then used to calculate the resistance of the surface of the material, or sheet resistance, which can be multiplied by the sample thickness to obtain the resistivity.

Another method of measuring resistivity is spreading resistance profiling (SRP) [6], where a small voltage is applied across two small probes on the surface of the material and used to measure the resistance and thus determine the resistivity. The probe to material resistance is negligible as there is a good contact between the two. The main benefit of SRP is that it can be used to determine the resistivity depth profile of semiconductor materials by beveling the sample and stepping the probes down the angled face.

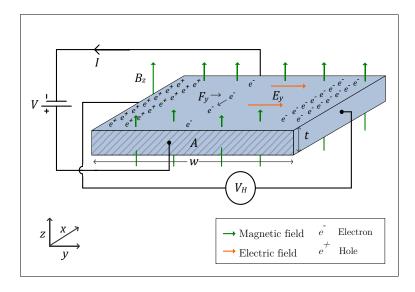

Hall effect measurements can also be used to determine the resistivity of a material. The Hall effect is a consequence of the forces exerted on moving charges by electric and magnetic fields and is used to determine the type of majority carrier in a semiconductor, as well as to determine the majority carrier concentration and mobility. Using these values and equation (2.9) or (2.10) the resistivity can be calculated, depending on the type of majority carrier. The Hall effect relies on the fact that a charged particle moving in a magnetic field will experience a force perpendicular to both the direction of motion and that of the magnetic field.

This force, known as the Lorentz force, is a cross product of the magnetic field B and drift velocity vectors, and is given by [7]

$$F_{\mathbf{y}} = q(v_{\mathbf{x}}B_{\mathbf{z}}) \tag{2.11}$$

The steady state behaviour of an n-type semiconductor sample with a voltage applied across the x-axis and a magnetic field applied across the z-axis is shown in Figure 2.2. The Lorentz force, acting in the y-direction, will cause electrons travelling in the x-direction to move and accumulate at the right hand side of sample. This in turn leads to an electric field  $E_y$  known as the Hall field directed towards the right hand side of the sample, which produces a force on the electrons that eventually balances out the Lorentz force. At this point no net force acts upon the electrons in the y-direction and this relationship, using F = qE [8] and equation (2.11), can be expressed as

$$qE_{y} = q(v_{x}B_{z}) \tag{2.12}$$

Figure 2.2 -–Steady state behaviour of an n-type semiconductor in a magnetic field  $B_z$  with applied voltage V, illustrating the Hall effect.

Using equations (2.4) and (2.12) the Hall field can be expressed as

$$E_{y} = -\frac{J_{n}B_{z}}{qn} \tag{2.13}$$

It is the establishment of the Hall field that is termed the Hall effect and leads to a Hall voltage in the y-direction which, using width w and V = -Ed [9] where d is the distance between the two opposite charges, can be derived as

$$V_H = -E_y w \tag{2.14}$$

In equation (2.13) - 1/qn is termed the Hall coefficient and for p-type semiconductors it is 1/qp. The Hall coefficient is used to determine the type of majority carrier as it is negative and positive for n-type and p-type semiconductors respectively. Using equations (2.13) and (2.14) the majority carrier concentration of n-type semiconductors can also be obtained as

$$n = \frac{J_n B_z w}{q(V_H)} = \frac{(I/A)B_z w}{qV_H} = \frac{IB_z}{qV_H t}$$

(2.15)

in which A and t are the cross-sectional area and sample thickness respectively as previously shown in Figure 2.2. Similarly the carrier concentration of p-type semiconductors can be expressed as

$$p = \frac{IB_z}{qV_H t} \tag{2.16}$$

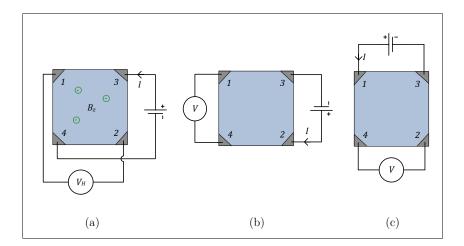

When performing Hall effect measurements on thin samples, I and  $B_z$  are set while  $V_H$  is measured using a technique known as the van der Pauw method [10]. This involves setting up contacts as illustrated in Figure 2.3 (a), where I is fed from contact 3 to contact 4, while  $V_H$  is measured across contacts 1 and 2. When performing van der Pauw measurements the best results are obtained with ohmic contacts, achieved by creating metal contacts atop the semiconductor. The van der Pauw method can also be used to measure the sheet resistance of the semiconductor, which can be used to calculate the resistivity. To achieve this, current is fed through two adjacent contacts such as from contact 2 to contact 3, while the voltage drop

across the other two contacts is measured, as shown in Figure 2.3 (b). The resulting resistance can then be calculated using Ohm's law to give  $R_{41,23} = V_{41}/I_{23}$ . The same is repeated but with the current flowing between contacts 1 and 3, and the voltage measured across contacts 2 and 4, as in Figure 2.3 (c), to give resistance  $R_{24,13}$ . These voltages and currents are then used to calculate the resistivity using [11]

$$\rho = \frac{\pi t (R_{24,13} + R_{41,23}) f}{2 \ln 2} \tag{2.17}$$

where f depends on the ratio  $R_{24,13}/R_{41,23}$ . The mobility of the majority carriers can be obtained using this calculated resistivity and equation (2.9) or (2.10) depending on the type of majority carrier.

Figure 2.3 - The van der Pauw technique as it is used to measure (a) the Hall coefficient and (b) and (c) the resistivity of a small, thin semiconductor sample.

# 2.3 Increasing the Resistivity of Czochralski-Silicon

In III-V semiconductors, such as GaAs, high resistivity substrates can be easily produced because of the wide band-gap which makes it an ideal material for RF passive device operation. Thermal stability of these substrates however is a problem which, coupled with the lack of a native oxide, are reasons why Si is still considered a superior alternative [3].

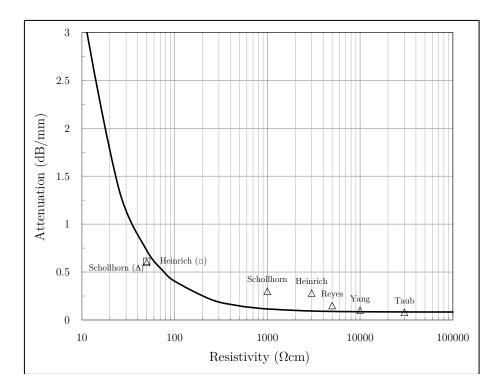

Pure Si with no impurities is known as intrinsic Si and has the highest achievable Si resistivity of 500 k $\Omega$ cm [12]. The most common crystal growth technique is the Czochralski method which involves melting Si in a boron nitride or quartz crucible before specific concentrations of boron (B) or phosphorus (P) are added to dope the Si giving it a desired resistivity. The crucible thus becomes contaminated with B and P, among other impurities, which make it extremely difficult to produce Si with a background, free carrier concentration below  $10^{13}$  cm<sup>-3</sup>. This concentration is equivalent to resistivities of approximately 400  $\Omega$ cm for n-type and 1 k $\Omega$ cm for p-type Si at room temperature and is very low when compared to the intrinsic resistivity of Si. Therefore standard Cz-Si wafers are normally only produced with resistivities less than 100  $\Omega$ cm, with typical values of 10  $\Omega$ cm [13]. For this reason there has been a great deal of research into different methods of producing high resistivity Si substrates.

The development of wafer bonding techniques and the emergence of silicon-on-insulator (SOI) technology provide opportunities to create high resistivity substrates beneath the active Si wafer with an insulation layer, typically Silicon-dioxide (SiO<sub>2</sub>), in between. Examples include the silicon-on-anything (SOA) approach which is capable of producing high resistivity substrates by bonding a thin, active Si wafer to a substrate of any material such as quartz or glass. However, the physical and thermal properties of such materials are responsible for a high thermal resistance leading to self-heating and thermal runaway of devices fabricated on these wafers [14]. Silicon-on-sapphire is one example that can be created at low temperatures, but due to the lattice mismatch crystallographic defects are a major problem. IC processing can also degrade material quality further as the thermal expansion coefficient of sapphire is much greater than that of Si, which makes this solution unsuitable for RFIC fabrication [15].

Due to these disadvantages there is a large interest in increasing the resistivity of Cz-Si substrates to improve the performance of passive devices fabricated on them.

For operation of Cz-Si substrates indistinguishable from GaAs substrates, it has been shown that a resistivity of at least 5 k $\Omega$ cm is required for low absorption loss at frequencies greater than a few hundred MHz [16]. These resistivities can be realised using a high purity alternative to Cz-Si known as float-zone. Float-zone Si (FZ-Si) substrates with resistivities as high as 10 k $\Omega$ cm have been created in the past [17]. HiRes<sup>TM</sup> is another form of high purity Si developed by Topsil Semiconductor Materials that can achieve resistivities of up to 30 k $\Omega$ cm [18]. Nevertheless the main disadvantage of FZ-Si and HiRes substrates is the price as well as the fact that the maximum diameter is limited to 8 inches due to surface tension limitations during growth [18–20]. Hence this process is unsuitable for modern VLSI technology where the standard wafer diameter is 12 inches.

An alternate way of reducing substrate absorption is to remove parts of the substrate itself from under the passives in a process known as micromachining. In one such technique the Si under the passive devices is removed by bonding the wafer, top down, to a glass substrate and removing Si by a wet etch process [21]. Wet etches have also been used to selectively remove Si under the passives, leading to localised reduction of substrate losses [22], [23]. These solutions however lead to increased fabrication complexity as well as an increased cost, and have yet to prove process compatibility and yieldability [13]. For these reason increasing the resistivity of Cz-Si is of greater benefit. A large amount of research has been undertaken in this area and a few examples are mentioned as follows, with details summarised in Table 2.1.

A method for creating a HRS layer was patented by Aoki et al. in which an oxygen or nitrogen ion beam is implanted into amorphous, polycrystalline or single crystal Si [24]. The ions are implanted with an energy of 200 keV and doses of  $3\text{-}7\text{x}10^{17}$  cm<sup>-2</sup> before the substrate is annealed to activate the ions which increase the resistivity of the substrate to between  $10^7$   $\Omega$ cm and  $10^{11}$   $\Omega$ cm. A similar technique was used by Dehan et al. in which high resistivity polycrystalline Si (SIPOS) films were created by the pyrolysis of disilane and nitrous oxide in a

LPCVD chamber [25]. Resistivities of  $10^9$  -  $10^{13}$   $\Omega$ cm can be achieved depending on the oxygen concentration. However, large negative substrate bias voltages produce intense electric fields inside the SIPOS film that induce the emission of free electrons, and in turn increase the conductivity of the material [26]. Similarly a high resistivity silicon-on-defect layer was produced by implanting protons into n-type Cz-Si samples, of initial resistivity 8  $\Omega$ cm, with an energy of 180 keV and a dose of  $2.5 \times 10^{16}$  cm<sup>-2</sup> [27]. The samples were then annealed in a  $N_2$  atmosphere by a rapid thermal anneal (RTA) at 900°C for 10 seconds, followed by furnace annealing at 1180°C for 1 hour. During the first anneal the protons form gas "bubbles" causing structural defects around them thereby forming a buried defect layer in Si that effectively traps free carriers and increases the resistivity up to 1 k $\Omega$ cm.

Proton implantation was used in another instance to achieve a resistivity of 0.1 M $\Omega$ cm [28]. In this case the wafers were implanted with a fixed dose of 10<sup>15</sup> cm<sup>-2</sup> at an energy of 17.4 MeV in six steps by changing the thickness of an aluminium (Al) absorber in order to provide a uniform proton profile throughout the entire depth of the Si substrate. Wu et al. also used proton implantation as well as As<sup>+</sup> ion implantation to increase the resistivity of conventional Si and Si-on-quartz (SOQ) substrates, respectively [29]. The implantation was performed with a dose of  $10^{16}$  cm<sup>-2</sup> and proton implantation energy of 10 MeV was required to give an implantation depth of 698 µm and hence penetrate the entire Si wafer. The resistivity was increased from 10  $\Omega$ cm to values as high as 36 k $\Omega$ cm using As<sup>+</sup> ions and 1.6 M $\Omega$ cm using protons. In another instance HRS was created also using proton implantation on p-type Si wafers, to increase the resistivity to 1 M $\Omega$ cm [30]. The hydrogen ions were implanted with 30 MeV and doses 1x10<sup>16</sup> cm<sup>-2</sup> through 8 stacked 4 inch wafers. In a similar approach Si<sub>28</sub> ions were systematically implanted into conventional low resistivity Si substrates, in a multiimplantation approach, to damage the lattice structure and form an amorphous layer on the surface of Si leading to improved microwave performance [31]. The disadvantage of these implantation techniques lies in the fact that they rely on creating defects in Si which make the material unsuitable for devices that require single crystal Si, rendering the techniques incompatible with modern VLSI technology. Some of the implantation methods also require multi-implantations, wafer stacking arrangements or very high energies to create thick high

resistivity layers; requirements that add to the complexity and cost of VLSI processes. For these reasons there is a need to develop other methods of increasing the resistivity of Si.

An alternative method is to create HRS using a technique known as deep level dopant compensation in which the effects of background free carriers are compensated for by implanted dopant atoms, reducing the carrier concentration thus increasing the resistivity of Cz-Si. This technique was used to implant manganese into Cz-Si with a dose of  $10^{14}$  cm<sup>-2</sup> at 100 keV, followed by a RTA at  $800^{\circ}$ C for 36 seconds, and enhanced the resistivity of Cz-Si from  $600 \Omega$ cm to  $10 k\Omega$ cm [16]. As mentioned this resistivity is high enough to give RF behaviour indistinguishable from that of GaAs. Deep level doping was also used by Wang et al. to create HRS by diffusing Au into Cz-Si [15]. In this example Au was introduced into the Si wafer by diffusion from an evaporated Au layer during an anneal in an inert ambient. A subsequent RTA provided a high temperature step used to activate the Au and increase the resistivity to a value as high as  $100 k\Omega$ cm. The research however does not address the effect of this increased resistivity on RF passive devices. It is clear from this research that deep level dopant compensation is a very promising technique that can be used to increase the resistivity of Cz-Si in a process that is in theory compatible with modern VLSI techniques, and therefore a study of the theory behind deep level dopant compensation follows.

${\bf TABLE~2.1}$  A summary of various techniques for creating high resistivity Si, as reported in literature, highlighting the resulting resistivities.

|                                                                                                                                | 36 1                       | Implanta                             | tion           |                            | Initial                        | Enhanced Resistivity $(\Omega \mathrm{cm})$ |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------|----------------|----------------------------|--------------------------------|---------------------------------------------|--|

| Description                                                                                                                    | Materials<br>used          | Dose<br>(cm <sup>-2</sup> )          | Energy<br>(eV) | Anneal                     | Resistivity $(\Omega { m cm})$ |                                             |  |

| Implantation of<br>oxygen or nitrogen<br>ions before annealing<br>in furnace [24]                                              | $O^+$ or $N^+$             | $3\text{-}7\text{x}10^{17}$          | 200 k          | -                          | -                              | 10 <sup>7</sup> - 10 <sup>11</sup>          |  |

| Pyrolysis of Si <sub>2</sub> H <sub>6</sub> and<br>N <sub>2</sub> O by LPCVD to<br>form doped high<br>resistivity poly-Si [25] | $ m Si_2H_6$ and $ m N_2O$ | -                                    | -              | -                          | -                              | 10 <sup>9</sup> - 10 <sup>13</sup>          |  |

| Proton implantation<br>before rapid thermal<br>and furnace anneals<br>[27]                                                     | H+                         | $2.5 \mathrm{x} 10^{16}$             | 180 k          | 910°C, 10s;<br>1180°C, 1hr | 8                              | $10^3$                                      |  |

| Proton implantation (6 steps) [28]                                                                                             | H+                         | $10^{15}$                            | 17.4 M         | -                          | 10                             | $10^5$                                      |  |

| Proton implantation<br>in Si and As <sup>+</sup>                                                                               | $\mathrm{H}^{+}$           |                                      | 10 M           |                            | 10                             | $10^{6}$                                    |  |

| implantation in Sion-quartz [29]                                                                                               | $\mathrm{As^{+}}$          | $10^{16}$                            | -              | -                          |                                | 36 k                                        |  |

| Proton implantation<br>for local high<br>resistivity region [30]                                                               | $\mathrm{H}^+$             | $10^{16}$                            | 30 M           | -                          | 1                              | $10^6$                                      |  |

| Si <sub>28</sub> ion multi-<br>implantation [31]                                                                               | $\mathrm{Si}_{28}{}^{+}$   | $3 \mathrm{x} 10^9 \mathrm{cm}^{-3}$ | 200 k          | -                          | 5 - 10                         | -                                           |  |

| Deep level doping by Mn implantation before RTA [16]                                                                           | Mn                         | $10^{14}$                            | 100 k          | 800°C, 36s                 | 600                            | $10^4$                                      |  |

| Deep level doping by Au diffusion using two step anneal [15]                                                                   | Au                         | -                                    | -              | 1000°C<br>(RTA)            | -                              | 10 <sup>5</sup> (5k @ 80°C)                 |  |

# 2.4 Deep Level Dopant Compensation

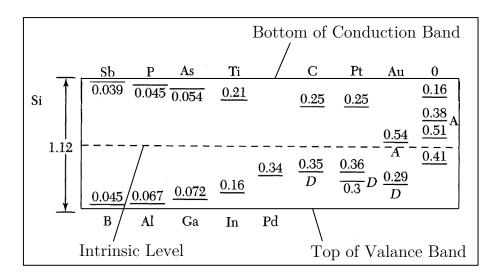

Impurities introduced during the Czochralski crystal growth process often present themselves as dopant atoms which, depending on the impurity, act as donors, acceptors or both. Dopant atoms that introduce electrons are known as donors, those introducing holes are acceptors, while codopants introduce both. Given sufficient energy an electron from an introduced donor atom can break its bond and "jump" into the conduction band to become electrically active or ionised, rendering the material n-type. The same is true for holes jumping into the valence band rendering the intrinsic material p-type. Ionised electrons and holes are free to travel through the lattice thus contributing to the background free carrier concentration and reducing the resistivity. The energy required to ionise electrons or holes of a dopant material is known as the ionisation energy and varies from one dopant to another as can be seen in Figure 2.4. For the purposes of simplicity from this point onwards impurity dopants will be referred to as impurities and the compensating material as dopants.

Figure 2.4 - Ionisation energy levels (in eV) of elements in Si at room temperature. Levels above the intrinsic level are measured from the bottom of the conduction band and are donor levels unless indicated by A. Those below the intrinsic level are measured from the top of the valence band and are acceptor levels unless indicated by D. [32]

The resistivity reducing effects of impurities can be compensated for by deliberately adding donors or acceptors to the Si thus increasing the resistivity to its intrinsic maximum value. This resistivity increasing process is known as dopant compensation.

The resistivity of a Si sample resulting from the introduction of a specific concentration of dopant used to compensate for a known impurity concentration can be determined using the energy levels of the dopants and the methods used by Mallik *et al.* [3]. This technique can be applied to both p-type and n-type Si and involves solving the charge neutrality equation [32]

$$p + \sum_{i} N_{D_{i}}^{+} - n - \sum_{j} N_{A_{j}}^{-} = 0$$

(2.18)

in which  $N_{D_i}^+$  and  $N_{A_j}^-$  are the *i*th and *j*th ionised donor and acceptor concentrations respectively, resulting from all impurities and compensating dopants. These are given by [3]

$$N_{D_i}^+ = N_{D_i} \left( 1 + 2e^{\left( E_F - E_{D_i} \right) / kT} \right)^{-1} \tag{2.19}$$

and

$$N_{A_j}^- = N_{A_j} \left( 1 + 4e^{\left( E_{A_j} - E_F \right)/kT} \right)^{-1} \tag{2.20}$$

where  $E_{D_i}$  and  $E_{A_j}$  are the *i*th and *j*th donor and acceptor ionisation energy levels respectively, k is the Boltzmann constant and T is the temperature in Kelvin.  $E_F$  represents the energy level at which the probability of occupation by an electron is ½ and is known as the Fermi energy level. For intrinsic Si at room temperature almost all the electrons sit in the valence band so the probability of finding an electron is almost unity. This means that the energy level at which the probability of finding an electron is ½ is at the middle of the bandgap, which is known as the intrinsic energy level. Therefore the Fermi level of intrinsic Si is at the mid-bandgap level and its resistivity is the maximum achievable for Si as there are almost no free electrons in the conduction band. Dopant donors make the Si extrinsic by introducing

electrons at the ionisation energy levels of the doping material in Si. This increases the probability of finding an electron near the conduction band and in turn shifts the Fermi level away from the mid-bandgap level and closer to the conduction band. Similarly dopant acceptors shift the Fermi level closer to the valence band.

In equation (2.18) the free electron and hole concentrations are represented by n and p respectively and are given by [32]

$$n = N_C e^{-(E_C - E_F)/kT} (2.21)$$

and

$$p = N_V e^{-(E_F - E_V)/kT} (2.22)$$

where  $E_C$  and  $E_V$  are the energy levels of the conduction and valance bands respectively. The absolute energy level values are not important as the dopant ionisation energy levels are given as values relative to the two bands. Therefore setting  $E_V$  to 0 eV gives  $E_C$  a value equal to the bandgap of Si, which is 1.12 eV at room temperature. The effective density of states of the conduction and valence bands are represented by  $N_C$  and  $N_V$  respectively, which for Si are  $2.8 \times 10^{19}$  cm<sup>-3</sup> and  $1.04 \times 10^{19}$  cm<sup>-3</sup> at room temperature [33]. It is clear from equations (2.19) - (2.22) that  $E_F$  is a factor in all the components in the charge neutrality equation. Therefore in order to solve it,  $E_F$  is iteratively varied until the equation is balanced. Once solved the values for n and p are used to obtain the resistivity  $\rho$  of the compensated Si using equation (2.8).

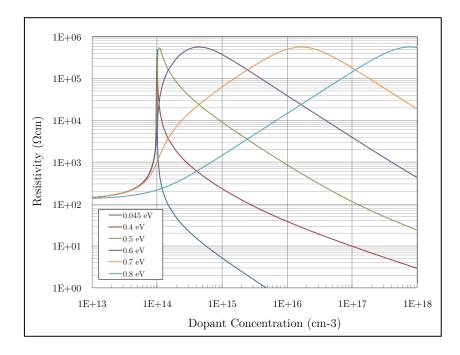

This technique was used to calculate the resistivity at room temperature of B-doped p-type Si as a function of compensating donor concentration, for donors with ionisation energy positions below the conduction band in the range of 0.045 eV - 1 eV. The resulting plot is included in Figure 2.5 shows that the resistivity increases as the dopant concentration increases. Increasing the dopant concentration increases the concentration of ionised donors which begin to compensate for the background B thus increasing the resistivity until a maximum is reached when the ionised donor concentration exactly matches the B concentration. At this point the Fermi level is at the mid-bandgap position and the Si is intrinsic.

Figure 2.5 - Calculated resistivity of p-type Si with a B concentration of  $10^{14}$  cm<sup>-3</sup>, doped with generic donors with different ionisation energy levels, as a function of generic dopant concentration.

Increasing the donor concentration further, however, leads to a reduction in the resistivity due to over-compensation as the excess ionised donors render the material n-type. This is the basic principle of dopant compensation and holds true for n-type samples with dopant acceptors. Dopants with low ionisation energies introduce electrons or holes loosely bound to their host atoms, so at room temperature only a small amount of energy is required to ionise them. These types of dopants are known as shallow level dopants owing to the "depth" of their energy levels in the Si bandgap. The shallower the dopant, the higher the concentration of ionised donors at room temperature.

This explains why the peak resistivity ranges for shallower dopants in Figure 2.5, is much narrower than those for deeper dopants since more donors are ionised and contribute in the compensation process. In theory dopant compensation is possible with shallow level dopants but only with concentrations very close to the impurity concentration. The shallow level dopant concentration must therefore be tightly controlled to an extent that is not practically

possible, which rules out the use of shallow dopants P and B to compensate n-type and p-type Si respectively. Conversely for deep level dopants only a small fraction of donors or acceptors are ionised at room temperature and take part in the compensation. Therefore the increase in ionised donor concentration is gradual with increasing dopant concentration as is the resistivity change, leading to a larger peak resistivity range. Doping Si with deep level dopants to increase resistivity is known as deep level dopant compensation and is a much more practical and achievable option as there is no need to tightly control the dopant concentrations. Doping with deep level acceptors has another vital advantage over shallow level doping in that deep level doped materials are resistant to the effects of thermal donors which are oxygen precipitate related, shallow level impurities in Cz-Si. Thermal donors reduce the resistivity of n-type Cz-Si drastically after short anneals around 500°C [34]. Deep level acceptors can therefore compensate for the effects of P in n-type Si and thermal donors.

A drawback with deep level doping, however, is that relatively large concentrations are required to reach the resistivity peak, which can only be achieved when the solubility of the dopant in Si is high. Also although the effects are much more severe for shallow dopants, over-compensation is a problem still faced by deep dopants. This limits the usefulness of materials that introduce only deep donors or deep acceptors. There exist, however, materials that introduce pairs of donors and acceptors into Si and it has been shown that doping with large concentrations of these materials does not lead to overcompensation [3]. Au has been found to introduce an equal concentration of deep donors and acceptors at energy levels close the intrinsic level [35] as can be seen in Figure 2.4. Au also has a very high solubility in Si and its diffusive and electrical properties in Si are well studied [36–38]. These properties make Au an excellent candidate for deep level doping of Cz-Si, and for these reasons the compensating behaviour of Au in Si is discussed as follows.

## 2.5 Gold as a Deep Level Dopant

Au introduces both a donor and an acceptor level in Si with deep ionisation energies making it a deep level codopant as can be seen in Figure 2.4. For codopants that introduce a single pair of energy levels the ionised donor and acceptor concentrations are given by [3]

$$N_D^+ = N_D \left( 1 + 2e^{(E_F - E_D)/kT} + e^{(2E_F - E_A - E_D)/kT} \right)^{-1}$$

(2.23)

and

$$N_A^- = N_A \left( 1 + 2e^{(E_A - E_F)/kT} + e^{(E_A + E_D - 2E_F)/kT} \right)^{-1}$$

(2.24)

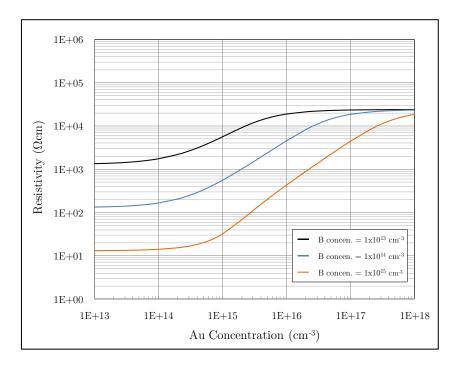

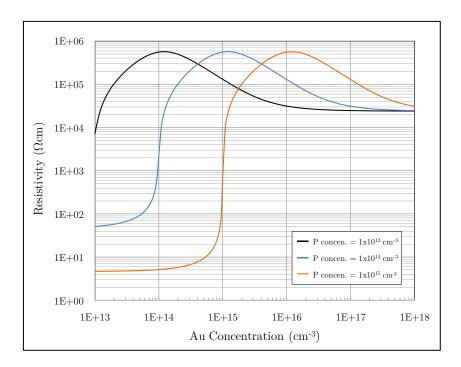

It has been reported that the position of the Fermi level in Si determines the type of active levels, i.e. only the acceptor level is active in n-type material and only the donor level in p-type material [36]. For this reason Au can compensate for both electrons and holes and can therefore be used for p-type and n-type Si which is a major advantage over dopants that only introduce either donors or acceptors. To confirm this, the resistivity at room temperature of p-type and n-type Si doped with Au as a function of Au concentration was calculated and the results are plotted in Figure 2.6 and Figure 2.7 respectively. It is clear from these graphs that not only can Au compensate for both n-type and p-type Si but for both types of Si it is not necessary to tightly control the concentration as it does not lead to overcompensation. It is also evident that for n-type compensation a much smaller Au concentration is required to achieve maximum resistivity.

Au atoms introduced into a Si substrate must take up substitutional sites in the lattice in order to contribute to any resistivity increase. Au diffusion in Si is known to occur by the kick-out mechanism in which each Au atom diffuses rapidly by interstitial diffusion through the lattice interstitials towards the edges of the substrate until it 'kicks out' a Si atom from its lattice site and takes its position as a substitutional atom, leading to a Si self-interstitial [39].

Figure 2.6 - Calculated resistivity of p-type Si with different B concentrations at room temperature as a function of Au concentration.

Figure 2.7 - Calculated resistivity of n-type Si with different P concentrations at room temperature as a function of Au concentration.

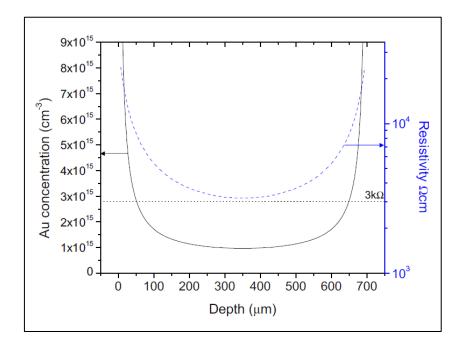

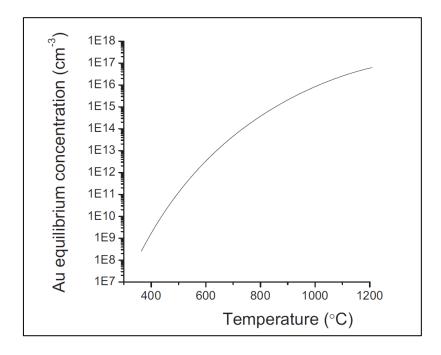

Due to the initial rapid interstitial diffusion the Au surface concentration is much higher than that in the bulk leading to a U-shaped Au concentration depth profile as can be seen in Figure 2.8 [40]. This translates to a U-shaped resistivity profile with maximum resistivity at the edges of the substrate. At higher temperatures the Au atoms have more energy thus the rate of exchange between interstitial and substitutional states of Au atoms increases and the solubility of Au in Si therefore increases with increasing temperature. The solubility of Au in Si has been calculated using thermodynamic data and a Au/Si phase diagram, in [40], and the results are shown in Figure 2.9. This graph was used to calculate the temperature the Si wafer must reach to introduce a required concentration of Au. One problem with using Au in Si is that Au is known as a device killer and would prevent the operation of active devices fabricated in the material. The U-shaped resistivity profile of Au-doped Si allows for implantation of Au into the handle wafer of SOI wafers through the back which would lead to the highest resistivity along the edges of the handle wafer and therefore directly below the active wafer, provided that the buried oxide prevents Au from diffusing into the active wafer.

Figure 2.8 - Calculated Au concentration and resistivity as a function of depth, after a 40 minute anneal at 1050°C of a p-type Cz-Si wafer, illustrating U-shaped Au concentration and resistivity profiles [40].

Figure 2.9 - Solubility of Au in Si as a function of temperature, calculated using thermodynamic data and a Au/Si phase diagram [40].

This ensures that any passives fabricated on the active wafer benefit from a high resistivity substrate underneath. The same principle can be applied with integrated passive device (IPD) and 3D integration technologies. In 3D integration, highly integrated systems can be created by vertically stacking various materials, technologies and functional components and making connection using Si vias. Using these technologies the passive device substrate does not come in direct contact with any active devices and fear of contamination is alleviated. It is hence possible to make use of deep level dopant compensation with Au to improve passive device characteristics and combine this with the advantages of minimizing size and reducing wiring.

For these reason Au was used as the material of choice for increasing the resistivity of Si through deep level dopant compensation in this work. Unlike with previous attempts [15] in this work Au was introduced into wafers by ion implantation as it is more practical than diffusion and allows greater control over concentration. The implanted Cz-Si wafers were then subjected to different temperature anneals that allow Au atoms to take up substitutional sites, leading to a resistivity increase. Coplanar waveguides and spiral inductors were then

fabricated onto these wafers and their microwave performance measured to investigate the effects that an increased resistivity has on passives devices. It was therefore important to develop an understanding of these devices and studies of both follow in the next chapters.

# 2.6 Creating High Resistivity Silicon through Gold Doping

The starting wafers chosen were 6 inch, P-doped, n-type <100> Cz-Si wafers, with an average thickness of 625 µm from MEMC Electronic Materials Inc. An average wafer resistivity of 56  $\Omega$ cm was calculated by measuring the sheet resistance at multiple points on the wafer surface using a Jandel RM3-AR four-point prober and then multiplying the average sheet resistance by the thickness. The wafers were chosen as n-type to investigate if the detrimental effects that thermal donors have on the resistivity of such wafers can be avoided by using deep level As mentioned earlier, thermal donors can cause the resistivity of n-type Cz-Si to decrease at temperatures above 500°C. Since they can be considered n-type shallow donors they should theoretically be compensated for by deep level dopants. After a one hour anneal at 550°C, the resistivity of a sample of the wafers decreased from 56  $\Omega$ cm to 26  $\Omega$ cm, as measured using a four-point probe (FPP) technique, which amounts to a decrease of almost 50%. This is the temperature at which back-end alloy anneals are typically performed so for deep level doping to be compatible with VLSI fabrication techniques, the concentration of deep level dopants introduced into n-type Cz-Si must be sufficient enough to compensate for the background P concentration as well as any thermal donors introduced during back-end processing. In other words the enhanced resistivity of the Cz-Si must at least be higher than 5 kΩcm after the effects of thermal donors for RF performance indistinguishable from that of GaAs substrates [16].

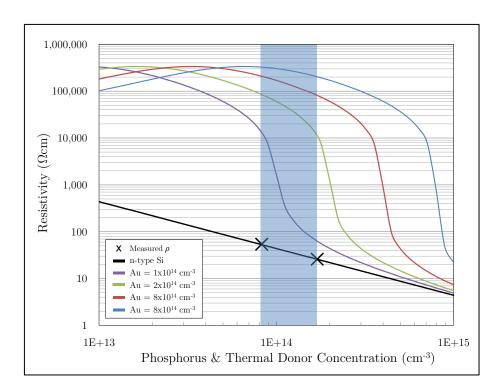

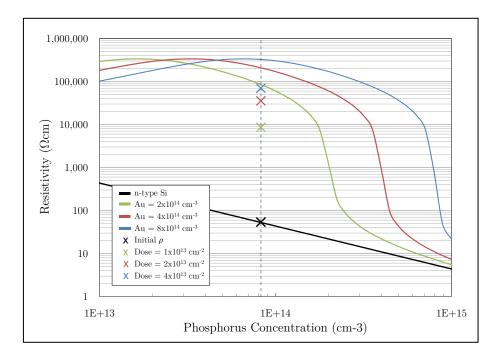

To investigate this requirement the resistivity of n-type Si at room temperature was calculated as a function of P and thermal donor concentrations for Au doping concentrations of  $1x10^{14}$  cm<sup>-3</sup>,  $2x10^{14}$  cm<sup>-3</sup>,  $4x10^{14}$  cm<sup>-3</sup> and  $8x10^{14}$  cm<sup>-3</sup>, using the methods described in the work of Mallik *et al.* [3]. Figure 2.10 shows the results of these calculations including the measured

resistivity of the Si sample before and after the thermal donor anneal. The blue band represents the effects the thermal donors have on the resistivity of a Cz-Si wafer with an initial resistivity of 54  $\Omega$ cm, as mentioned earlier. For deep level compensation to be resistant to thermal donor effects the enhanced Si resistivity must remain higher than 5 k $\Omega$ cm even after the increase in n-type dopants caused by thermal donor activation, i.e. the resistivity must not decrease below this value within the blue band. It is therefore clear from this graph that for Au concentrations above  $2 \times 10^{14}$  cm<sup>-3</sup> the resistivity should be relatively stable at values greater than  $10 \text{ k}\Omega$ cm, even after the degrading effects of the thermal donors.

Figure 2.10 - Si resistivity as a function of phosphorous and thermal donor concentration, with different Au concentrations. Measured resistivities of a Si sample before and after a  $550^{\circ}$ C anneal are also displayed (crosses). The blue band represents the drop in resistivity caused by thermal donors.

Ion implantation was chosen as the preferred method for introducing Au into the Si wafers as greater control over the dopant concentration is achievable in comparison to diffusion methods such as those used in [15] and [40]. Using the results in Figure 2.10, Au concentrations of  $2x10^{14}$  cm<sup>-3</sup>,  $4x10^{14}$  cm<sup>-3</sup> and  $8x10^{14}$  cm<sup>-3</sup> were chosen for implantation into the wafers, which correspond to implantation doses of approximately  $1x10^{13}$  cm<sup>-2</sup>,  $2x10^{13}$  cm<sup>-2</sup> and  $4x10^{13}$  cm<sup>-2</sup> respectively. As mentioned earlier for the implanted Au atoms to take part in the compensation they must take up substitutional sites through the kick-out mechanism and the Si must be annealed to achieve this. Using the Au solubility graph in Figure 2.9 in section 2.5, it is clear that in order to introduce Au with concentrations in the  $10^{14}$  cm<sup>-3</sup> range an anneal temperature of at least  $800^{\circ}$ C is required. For this reason temperatures of  $900^{\circ}$ C,  $950^{\circ}$ C and  $1000^{\circ}$ C were chosen for these activation anneals.

To begin with the wafers were cleaned for 15 minutes in fuming nitric acid (FNA) before a 20 nm thermal oxide was grown by dry oxidation in a Tempress furnace at 950°C for 28 minutes. This oxide was used as a sacrificial layer to protect the wafer from implantation damage and as a layer to prevent out diffusion of Au during subsequent anneals. The wafers were then divided into batches to be implanted with an energy of 100 keV and an implantation dose of  $1 \times 10^{13}$  cm<sup>-2</sup>,  $2 \times 10^{13}$  cm<sup>-2</sup> or  $4 \times 10^{13}$  cm<sup>-2</sup> at the EPSRC ion implantation facility at Surrey University. The wafers were implanted through the front (polished) and back (unpolished) sides. The wafers were then divided into further batches to be annealed in another Tempress furnace at 900°C, 950°C or 1000°C in argon for 1 hour. The sacrificial oxide was then stripped by a wet-etch in buffered hydrofluoric (HF) acid solution (20:1) until hydrophobic.

## 2.7 Resistivity Measurements of Gold Doped Silicon

The Au-doped, HRS wafers were examined using a variety of techniques that include sheet resistance measurements using the four-point probe (FPP) technique; resistivity measurements through spreading resistance profiling (SRP) and Hall measurements; and Au concentration measurements using secondary ion mass spectroscopy (SIMS). All measurements with the exception of the Hall measurements were performed on both the front (polished) and back (unpolished) sides of the wafers or samples, for different implantation doses and activation anneal temperatures.

#### 2.7.1 Four-point Probe Measurements

A Jandel RM3-AR four-point prober was used to measure the sheet resistance of the front and back sides of the wafers before and after Au implantation, as well as after anneals at 900°C, 950°C or 1000°C. The RM3-AR is essentially a combined constant current source and a digital voltmeter designed to make sheet resistance measurements that can be converted into resistivity by multiplying by the thickness of the wafer.

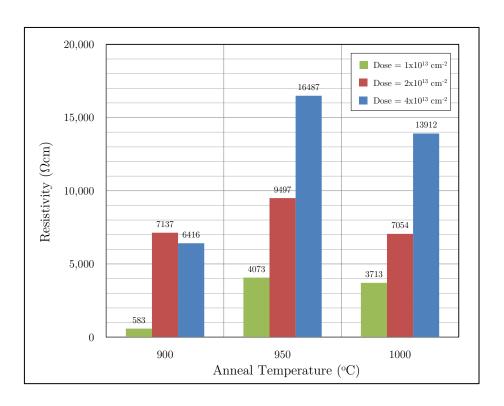

The sacrificial oxide was removed immediately before the measurements to ensure a good contact between the probe and the Si. Sheet resistance measurements were performed on full wafers at five points on either side with forward and reverse biased current and then averaged to give a mean sheet resistance for each side of the wafer. This was performed for wafers implanted with all three doses and annealed at all three temperatures. The measured sheet resistances were converted to resistivities by multiplying by the average thickness of the wafers of  $675 \, \mu \text{m}$ . The as-implanted and post-anneal resistivities are displayed in Table 2.2, for the front and back sides as well as the average of the two. Figure 2.11 shows a plot of the averaged post-anneal resistivities from Table 2.2.

${\bf TABLE~2.2} \\ {\bf As-implanted~and~post-anneal~resistivities~of~Au-doped~wafers}, \\ {\bf measured~using~a~four-point~probe~technique}.$

|                        | Front Side $[\Omega cm]$ |      |      | Back Side $[\Omega cm]$ |      |     | Averaged $[\Omega cm]$ |      |      |      |

|------------------------|--------------------------|------|------|-------------------------|------|-----|------------------------|------|------|------|

| Au<br>Dose             | Anneal Temp. [°C]        |      |      | Anneal Temp. [°C]       |      |     | Anneal Temp. [°C]      |      |      |      |

| $[\mathrm{cm}^{-2}]$   | -                        | 900  | 950  | 1000                    | 900  | 950 | 1000                   | 900  | 950  | 1000 |

| $1 \mathrm{x} 10^{13}$ | 49.8                     | 637  | 4.2k | 3.7k                    | 529  | 4k  | 3.7k                   | 583  | 4.1k | 3.7k |

| $2 \mathrm{x} 10^{13}$ | 51.4                     | 7.3k | 9.1k | 7k                      | 7k   | 10k | 7k                     | 7.1k | 9.5k | 7k   |

| $4 \mathrm{x} 10^{13}$ | 51.3                     | 6k   | 15k  | 12k                     | 6.8k | 18k | 15k                    | 6.4k | 16k  | 14k  |

Figure 2.11 – The averaged resistivities of Au-doped Si wafers implanted with different Au doses and annealed at different temperatures, measured using a four-point probe technique.

These results show a large increase in resistivity of Cz-Si after Au implantation and subsequent annealing proving the effectiveness of deep level dopant compensation. The results also confirm that the resistivities of the front and back sides are very similar suggesting a U-shaped Au concentration profile. It is also clear that the resistivity increases with dose and hence concentration of the implanted Au for all anneals, with the highest values measured for the largest dose, with the exception of the 900°C anneal. The as-implanted resistivity values match those before the implant as an insignificant amount of Au is active and hence confirm the necessity of annealing, with all three temperatures leading to an increase in resistivity. It is interesting to note that for all three doses, the highest resistivity values were obtained after an activation anneal at 950°C, but this is not as expected since theoretically an activation anneal at 1000°C should result in a higher resistivity due to the higher solubility.

The average measured resistivity values of the wafers annealed at 950°C were plotted with the theoretical resistivity profiles for different Au concentrations in Figure 2.10, as shown in Figure 2.12. It is clear from this that although the measured resistivity values agree qualitatively with the theoretical profiles, the actual values fall short by just over one order of magnitude. To investigate these discrepancies SIMS and SRP measurements were performed, the results of which are reported in the following section.

The resistivity of the wafer implanted through the back side was also measured and found to be in close comparison to those implanted with the same dose through the front side. Both wafers received an implantation dose of  $4 \times 10^{13}$  cm<sup>-2</sup> and were subsequently annealed at 950°C, and their measured resistivities are shown in Table 2.3. These results suggest that there is not much of a difference between the two implantation methods, both producing very similar resistivities, indicating that either can be used to successfully create HRS, allowing for the implantation of Au through the back of SOI wafers to increase the resistivity of the handle wafer directly beneath the active wafer. It is also clearly noticeable from Table 2.2 and Table 2.3 that the back sides of the wafers generally have a slightly higher resistivity than the front sides. This could be due to the different surface conditions as the polished nature of the front sides may provide less resistive contacts for the FPP probes.

Figure 2.12 – Si resistivity as a function of P concentration, with different Au concentrations and measured averaged resistivity values of wafers annealed at 950°C along with the initial resistivity of 54  $\Omega$ cm. Crosses and curves are measured and calculated values respectively.

$\label{thm:thm:thm:constraint} {\bf TABLE~2.3}$  Measured resistivities of front and back implanted wafers, with doses of  $4x10^{13}~{\rm cm}^{-2}$  and annealed at 950°C.

|            | Resistivity [k $\Omega$ cm] |              |  |  |  |  |

|------------|-----------------------------|--------------|--|--|--|--|

|            | Front Implant               | Back Implant |  |  |  |  |

| Front Side | 15                          | 13           |  |  |  |  |

| Back Side  | 18                          | 18           |  |  |  |  |

#### 2.7.2 SIMS and SRP Measurements

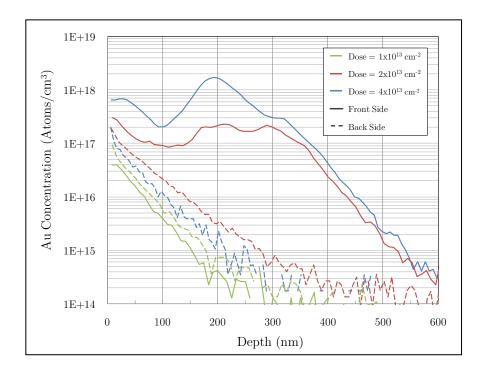

SIMS measurements were performed at Loughborough Surface Science Ltd on 1 cm<sup>2</sup> samples of wafers annealed at all temperatures, for all three Au doses. The integrated dose of the asimplanted samples agreed with the nominal dose to within 1% providing evidence of the good calibration of the SIMS measurements. It must be noted that the resolution limit of the SIMS measurement is approximately  $1 \times 10^{14}$  cm<sup>-3</sup> and therefore the lower limit of the graphs have been set to this value.

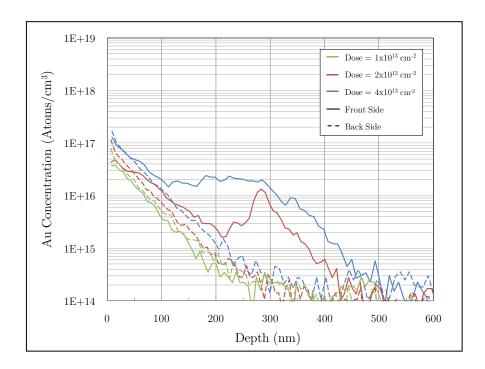

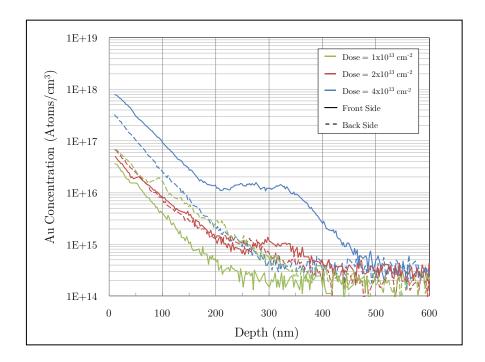

The results for samples annealed at 900°C, 950°C and 1000°C are given in Figure 2.13, Figure 2.14 and Figure 2.15, and show that the post-anneal Au concentration is generally highest at the edges of the wafer decreasing with depth. These results also point to a U-shaped Au concentration profile, although SIMS measurements only detect a small section of it.

Figure 2.13 – SIMS profiles of Au-doped Si with different implantation doses after a 900°C annual. Solid and dashed lines represent the profiles of the front side and back side of the wafers respectively.

Figure 2.14 – SIMS profiles of Au-doped Si with different implantation doses after a 950°C anneal. Solid and dashed lines represent the profiles of the front side and back side of the wafers respectively.

Figure 2.15 – SIMS profiles of Au-doped Si with different implantation doses after a  $1000^{\circ}$ C annual. Solid and dashed lines represent the profiles of the front side and back side of the wafers respectively.

For the higher two doses the SIMS profiles of the front sides of the samples show a large amount of Au around a depth of 300 nm that is not present in the back side of the wafer. It is also clear that this Au concentration decreases with anneal temperature suggesting that a substantial amount of implanted Au is trapped at the front side of the wafer. This Au is believed to be electrically inactive because of the lower than expected resistivities measured and the fact that Au must be electrically active, or in substitutional lattice sites, to contribute to the compensation process. The trapped Au may be due to many factors of which agglomeration, or clustering, is the most likely.

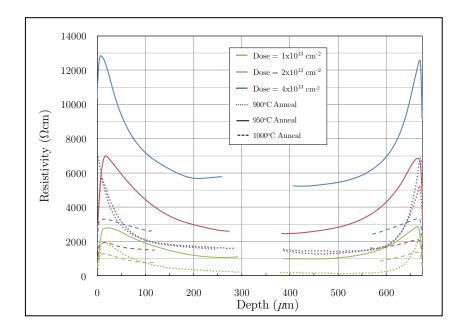

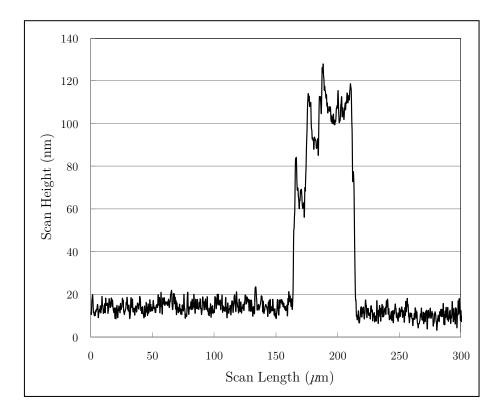

SRP measurements were performed on the front and back sides of small samples of the wafers with areas of 1 cm<sup>2</sup>, for all implantation doses and anneal temperatures, at the Semiconductor Assessment Services Laboratory. The resistivity depth profiles obtained from these measurements are given in Figure 2.16 and clearly confirm that Au-doped Si has a U-shaped, steeply varying, graded resistivity profile and that the front and back sides of the wafers are very symmetric for all cases. These results coupled with the SIMS profiles link the presence of Au atoms to the high resistivity values measured.

The absolute levels of resistivity were found to be within a factor of 1.5 of the FPP results, but in view of the complicated scaling methods applied to obtain SRP resistivities from measured resistances the discrepancy is not serious [41]. It is however clear that the resistivity at the edges is much lower than the peak value even though the SIMS profiles show that the maximum Au concentration is at the edges. This indicates that most of the Au at the surface is electrically inactive and does not contribute to the resistivity increase, since SIMS results do not distinguish between the different possible states of the Au atoms. These results therefore suggest the existence of a thin inactive Au layer on the wafer surfaces most likely formed by Au atoms pushed out of the substrate during the rapid interstitial diffusion phase. This Au layer would reduce the surface sheet resistance measured by the FPP and does not contribute to the compensation and could be the reason for the lower than expected resistivity values.

Figure 2.16 – Spreading resistance profiling results of Au-doped Si samples with different implantation dose. Dotted, solid and dashed lines represent anneal temperatures of 900°C, 950°C and 1000°C respectively.

#### 2.7.3 Gold Surface Layer

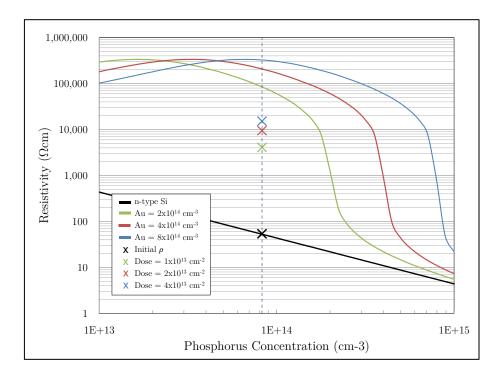

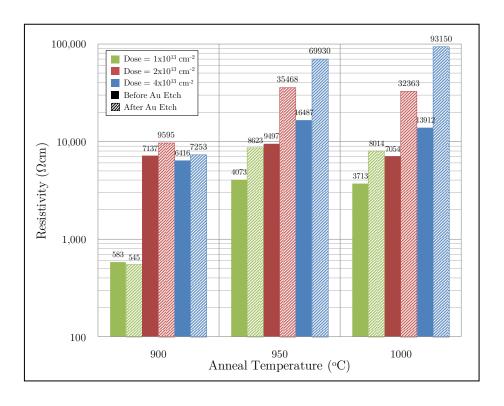

To determine if a Au surface layer exists the wafers were given a 1 minute dip in an iodine-based Au etchant before being re-measured using the four-point prober. The resistivities after the Au etch are shown in Table 2.4 and in Figure 2.17 along with the pre-etch resistivities. It is clear from these results that the Au etch leads to an increased resistivity indicating the removal of a surface Au layer. The 950°C anneals however still produce the highest resistivities, with the exception of the highest dose. Since the surface Au layer is most likely formed by Au atoms being pushed out of the bulk towards the surfaces during annealing, a larger amount of Au would theoretically be pushed to the surface at higher anneals and could explain why 1000°C anneals result in lower resistivities.

TABLE 2.4

Four-point probe measured, average resistivities of Au-doped wafers annealed at different temperatures, before and after Au etching.

| Au Dose<br>[cm <sup>-2</sup> ] | Pre-Au Etch  Average $ ho$ [ $\Omega$ cm]  Anneal Temp. [ $^{\circ}$ C] |      |      | Post-Au Etch Average $ ho$ [ $\Omega$ cm]  Anneal Temp. [ $^{\circ}$ C] |        |        |

|--------------------------------|-------------------------------------------------------------------------|------|------|-------------------------------------------------------------------------|--------|--------|

|                                | 900                                                                     | 950  | 1000 | 900                                                                     | 950    | 1000   |

| $1 \mathrm{x} 10^{13}$         | 583                                                                     | 4.1k | 3.7k | 545                                                                     | 8.6 k  | 8 k    |

| $2 \mathrm{x} 10^{13}$         | 7.1k                                                                    | 9.5k | 7k   | 9.6 k                                                                   | 35.5 k | 32.4 k |

| $4 \mathrm{x} 10^{13}$         | 6.4k                                                                    | 16k  | 14k  | 7.3 k                                                                   | 70 k   | 93.2 k |

Figure 2.17 – Four-point probe measured resistivities of Au-doped wafers implanted with different Au doses and annealed at different temperatures, before and after a Au etch.

The average resistivity values for wafers annealed at 950°C that received the Au etch are plotted in Figure 2.18 and it can be seen that although there is still a significant difference between these and the theoretical values, this difference falls to within one order of magnitude. The inactive Au atoms forming the surface Au layer do not compensate for free carriers in the Si which explains why the resistivity is lower than expected since the actual active Au concentration is lower than that implanted.

Another possible reason for the lower than expected resistivities may be the agglomeration of Au atoms leading to cluster formation inside the bulk [37], and since these atoms do not take up substitutional sites they do not contribute to the compensation process. It is also suspected that oxygen precipitates or clusters resulting from oxygen introduced into the wafers during the crystal pulling process, may prevent Au atoms from taking up substitutional sites [42].

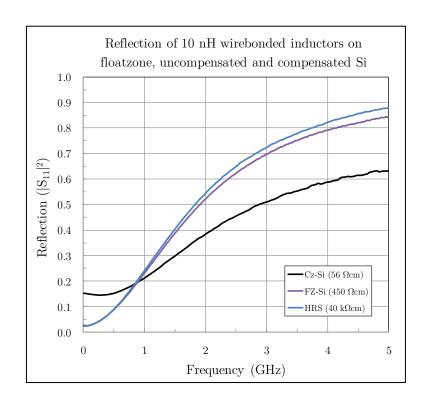

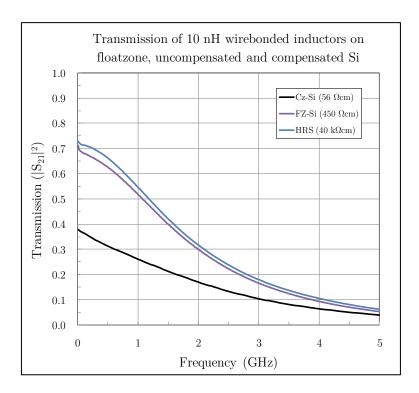

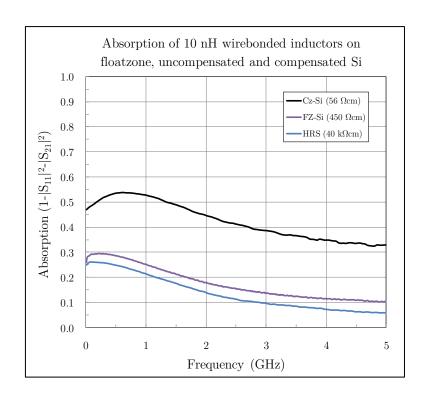

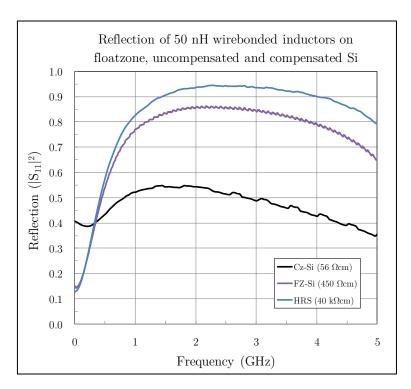

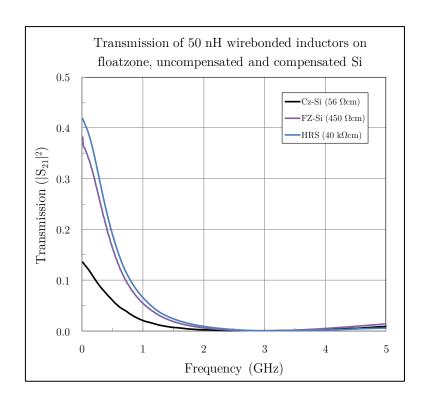

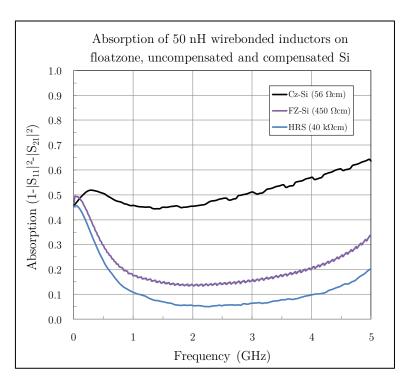

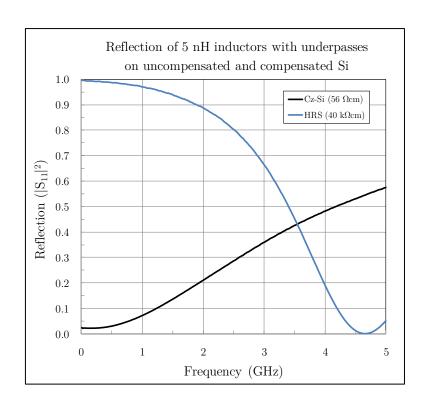

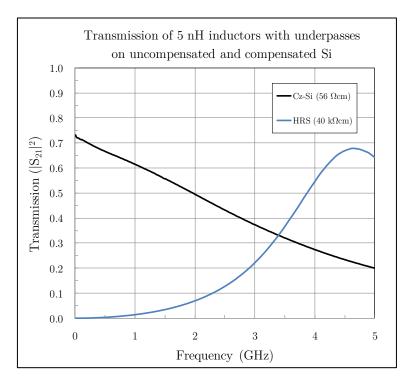

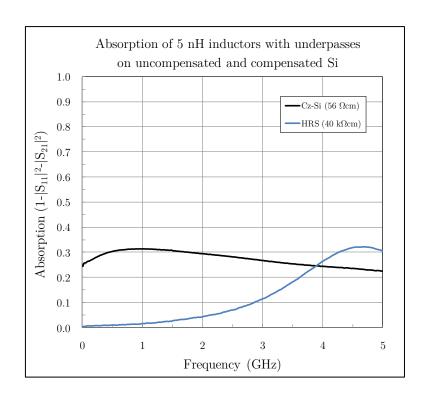

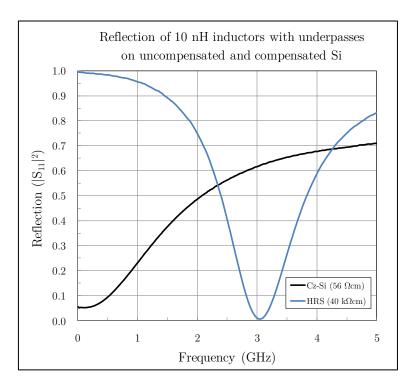

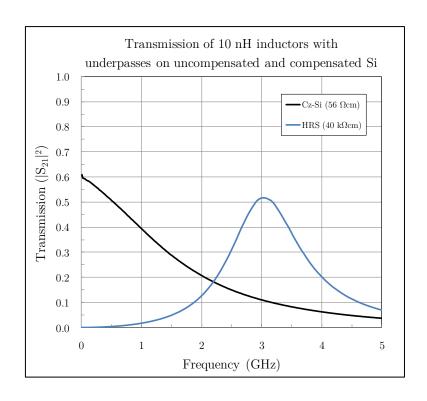

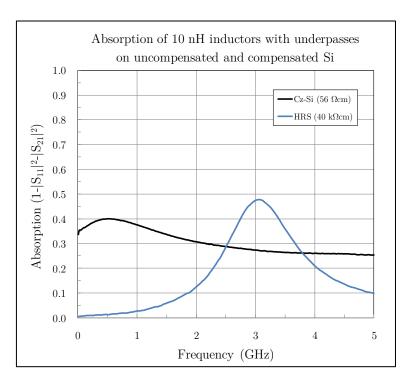

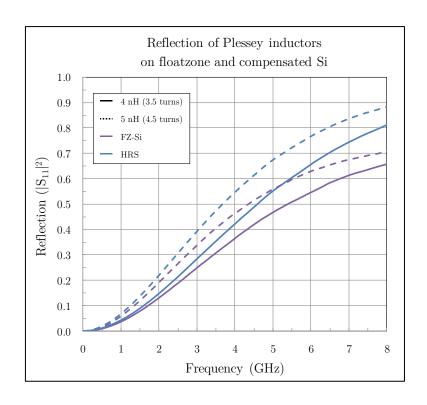

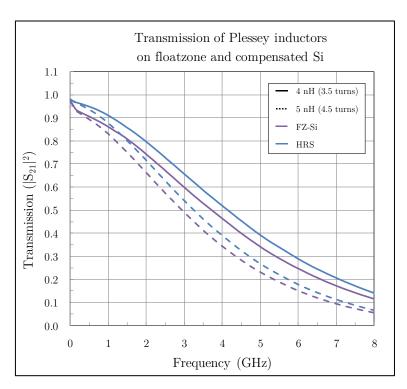

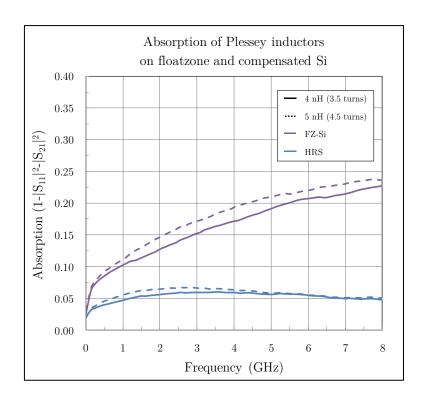

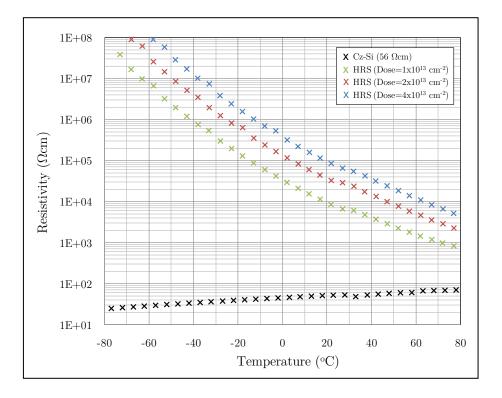

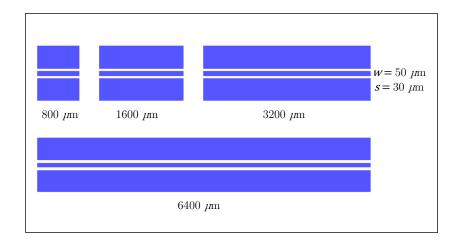

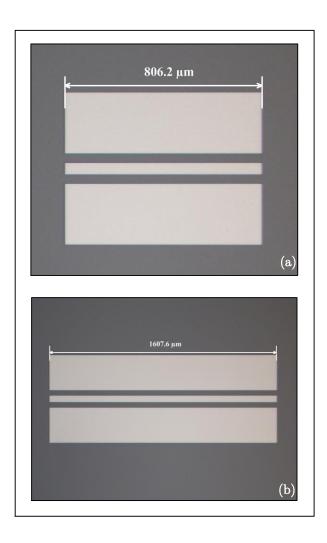

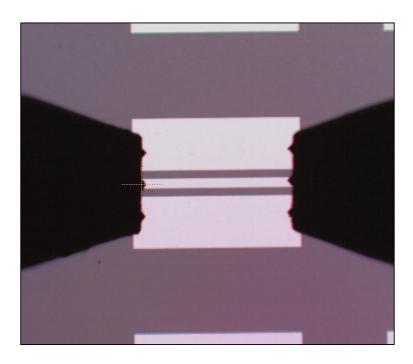

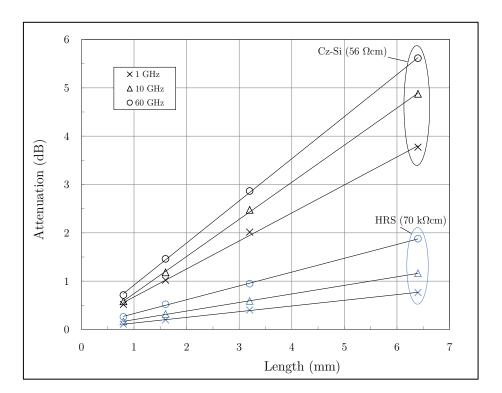

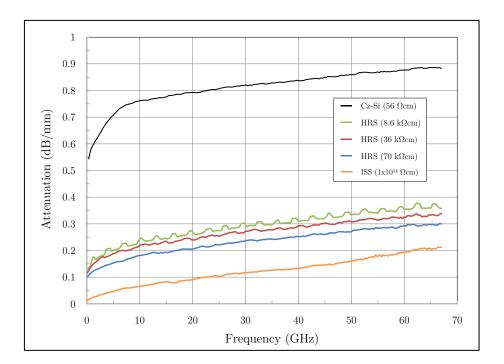

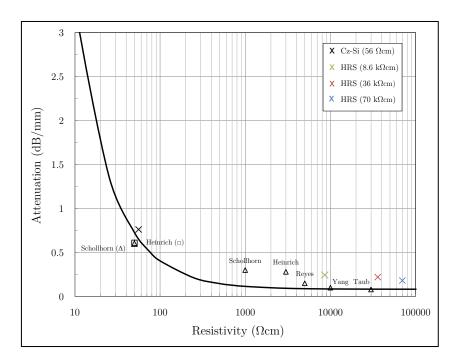

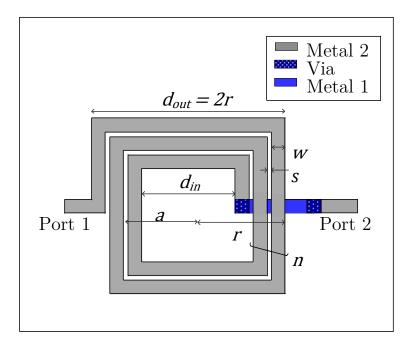

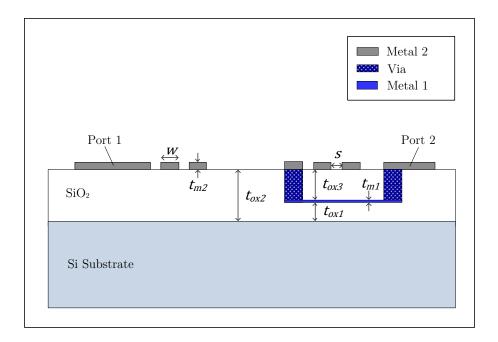

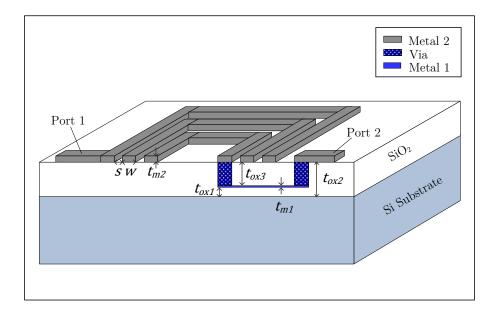

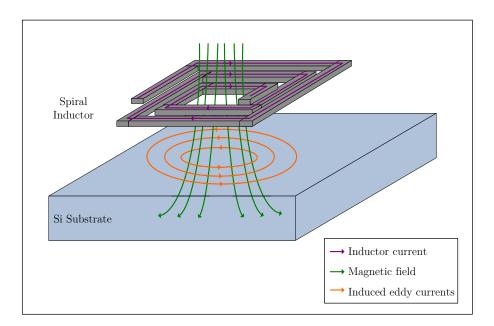

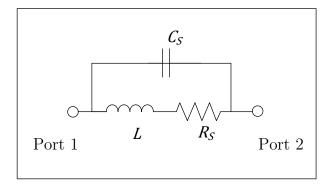

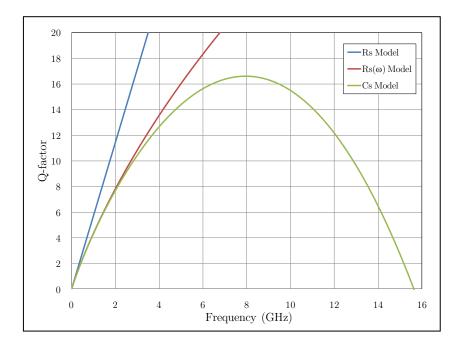

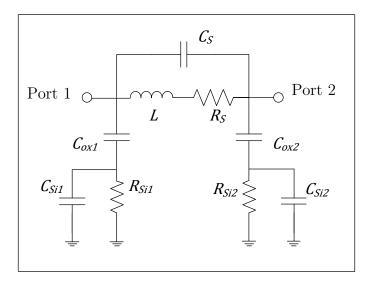

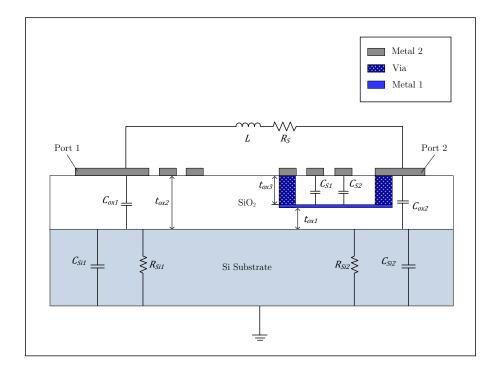

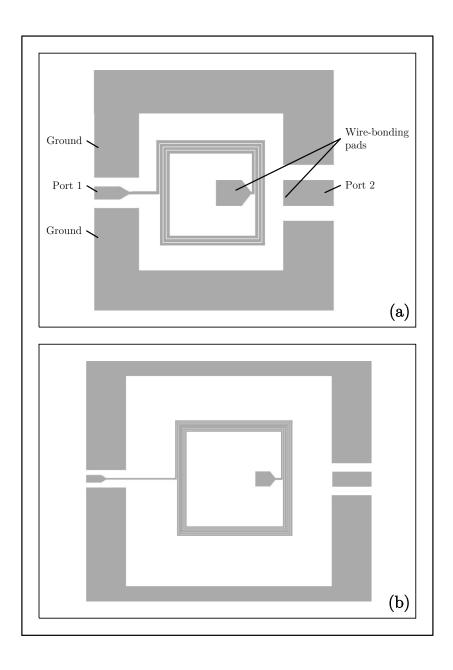

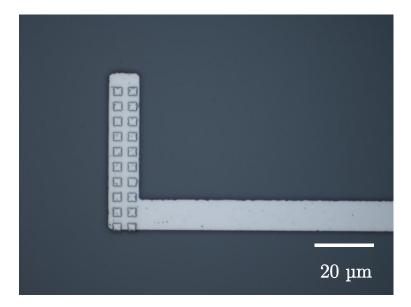

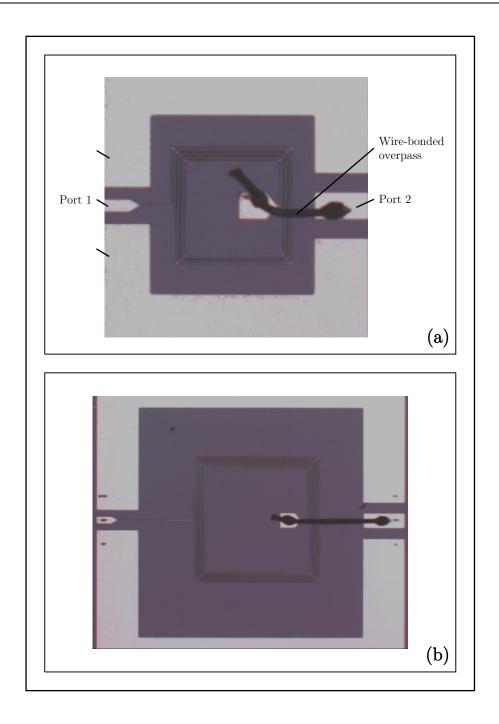

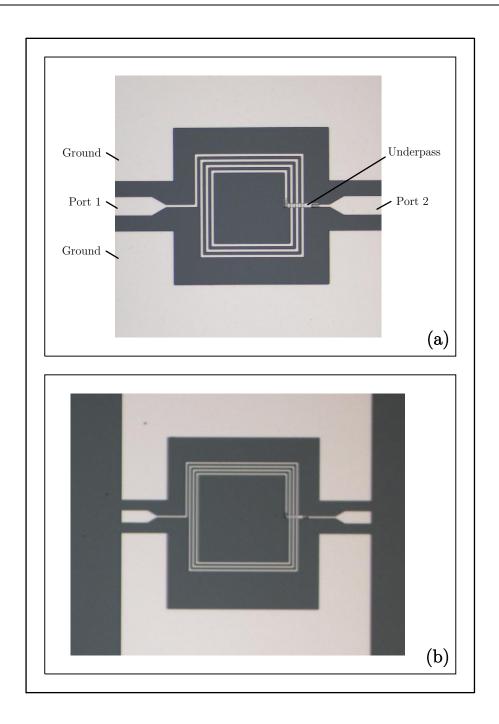

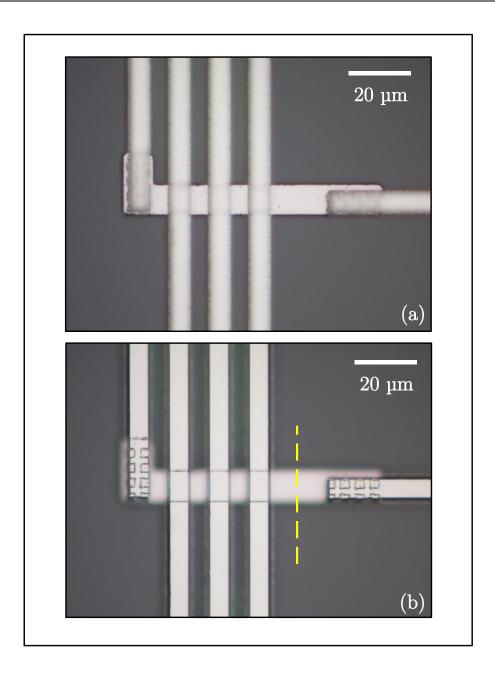

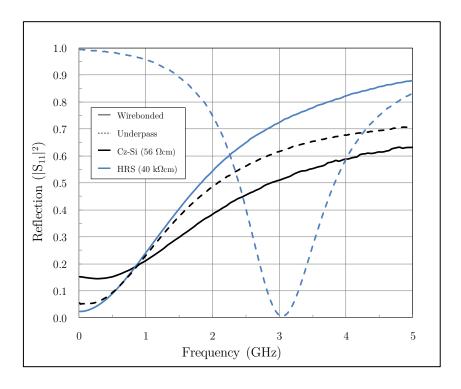

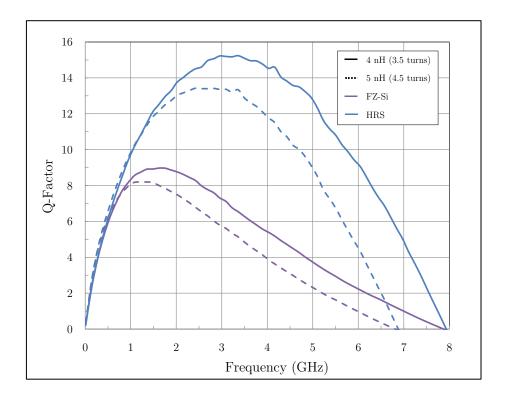

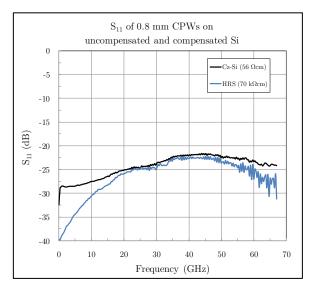

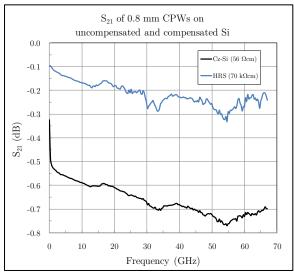

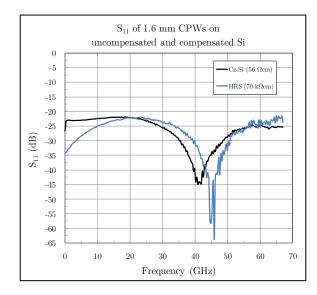

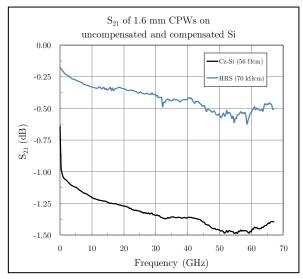

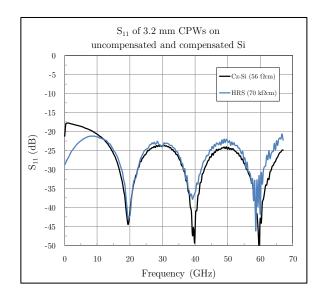

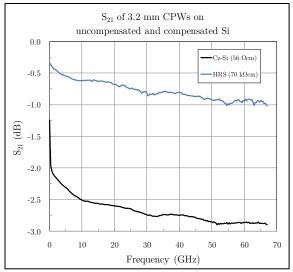

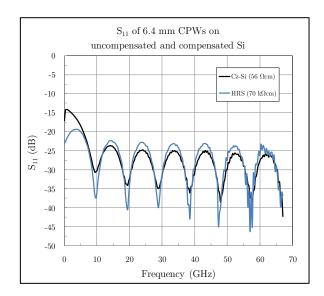

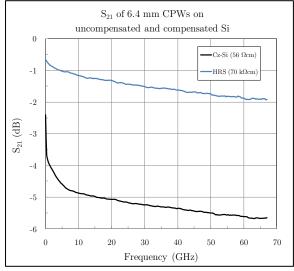

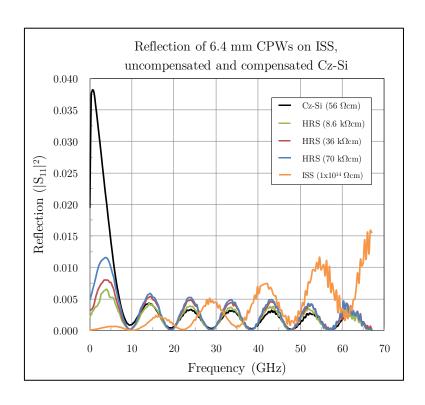

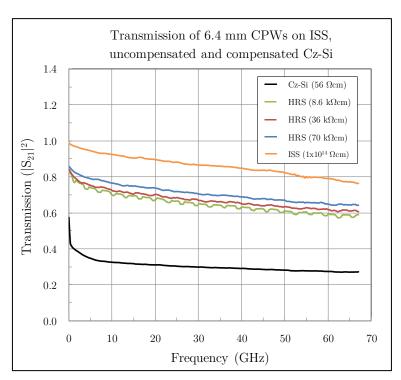

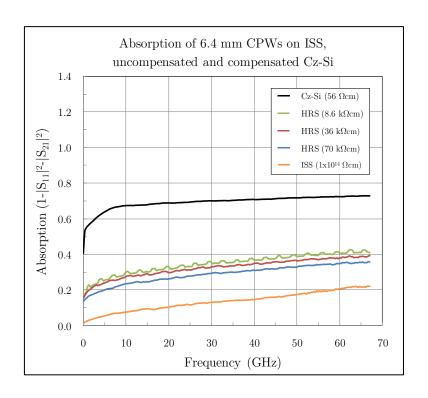

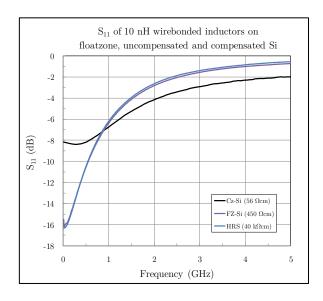

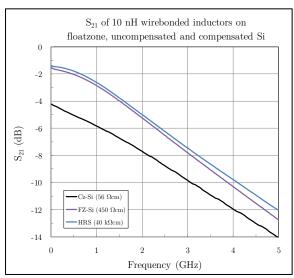

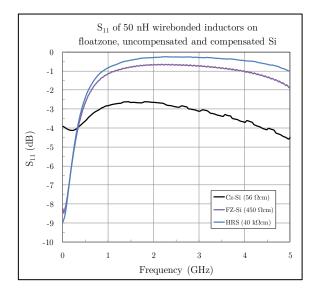

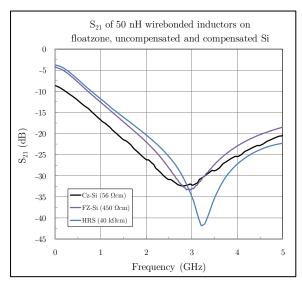

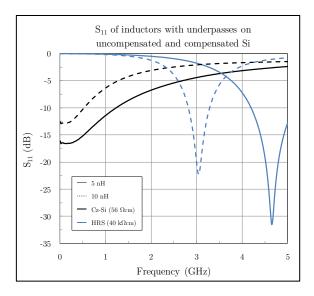

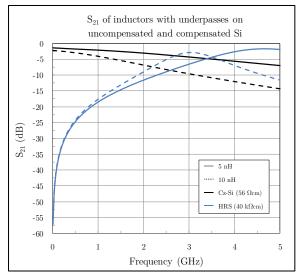

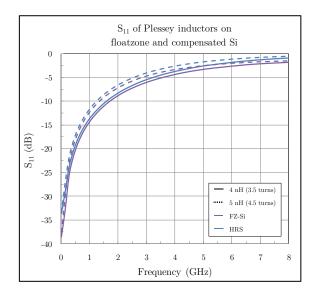

Figure 2.18 –Si resistivity as a function of P concentration, with different Au concentrations and measured average resistivity values of wafers annealed at 950°C that received a Au etch. Crosses and curves are measured and calculated values respectively.