University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND THE ENVIRONMENT

**ANALYSIS AND REDUCTION OF DC-LINK CAPACITOR VOLTAGE/CURRENT

STRESS IN THREE-LEVEL PWM CONVERTERS**

by

**Georgios I. Orfanoudakis**

Thesis for the degree of Doctor of Philosophy

December 2012

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND THE ENVIRONMENT

SCHOOL OF ENGINEERING SCIENCES

Doctor of Philosophy

ANALYSIS AND REDUCTION OF DC-LINK CAPACITOR VOLTAGE/CURRENT

STRESS IN THREE-LEVEL PWM CONVERTERS

by Georgios I. Orfanoudakis

Power electronic converters are in the heart of modern renewable energy and motor drive systems. This Thesis focuses on the converter dc-link capacitor (bank), which is a costly component and a common source of failures. The Thesis is divided into two parts.

The first part examines the voltage and current stress induced on dc-link capacitors by the three most common converter topologies: The conventional two-level converter, the Neutral-Point-Clamped (NPC) three-level converter, and the Cascaded H-Bridge (CHB) three-level converter. The expressions derived for the rms capacitor current and its harmonics can be used as a tool for capacitor sizing.

The harmonic analysis is then extended to systems that incorporate multiple converters connected to a common dc-link capacitor. The effect of introducing a phase shift to the converter carrier waveforms is examined, showing that reductions in the order of 30 to 50% in the common capacitor rms current can be achieved using appropriate phase shifts.

The second part tackles the dc-link capacitor balancing problem, also known as Neutral Point (NP) balancing problem of the three-level NPC converter. Initially, a circuit that halves the voltage stress caused by the NP voltage oscillations (ripple) on the switching devices the NPC converter is proposed. The circuit consists of low voltage rated components which offer the advantages of lower losses, volume and cost, as compared to other balancing circuits.

Subsequently, the study focuses on modulation strategies for the NPC converter. Starting with Nearest-Vector (NV) strategies, it proves that the criterion of the direction of dc-link capacitor imbalance, which is commonly adopted by NV strategies for performing the task of capacitor balancing, poses a barrier in achieving minimum NP voltage ripple. A new criterion is proposed instead, together with an algorithm that incorporates it into existing NV strategies. For the interesting case of NPC converters operating as motor drives, the resulting reduction in the amplitude of NP voltage ripple ranges from 30 to 50%.

The study finishes with an extension of the previous concept to create hybrid (combinations of NV and non NV) strategies for the NPC converter. Hybrid strategies are proposed that can eliminate NP voltage ripple, introducing lower switching losses and output voltage distortion as compared to other methods used for the same purpose. The proposed strategies perform equally well when the converter operates with non linear or imbalanced loads. All results are verified by extensive simulations using MATLAB-Simulink.

## ***Declaration of authorship***

---

I, Georgios I. Orfanoudakis, declare that the thesis entitled “Analysis and reduction of dc-link capacitor voltage/current stress in three-level PWM converters” and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published in peer-reviewed conferences and journals (please see list of publications in the following page).

**Signed:** .....

**Date:** .....

## ***List of publications***

---

1. G. I. Orfanoudakis, S. M. Sharkh, M. A. Yuratich and M. A. Abu – Sara, “Loss comparison of two- and three-level inverter topologies”, *5th IET International Conference on Power Electronics, Machines and Drives (PEMD 2010)*, 19 – 21 Apr. 2010.

2. G. I. Orfanoudakis, S. M. Sharkh and M. A. Yuratich, “Analysis of DC-link capacitor losses in three-level neutral-point-clamped and cascaded H-bridge voltage source inverters”, *IEEE International Symposium on Industrial Electronics (ISIE 2010)*, 4 – 7 July 2010.

3. G. I. Orfanoudakis, S. M. Sharkh and M. A. Yuratich, “Circuit for reducing devices voltage stress due to DC-link capacitor voltage ripple in a Neutral-Point-Clamped inverter”, *14th European Conference on Power Electronics and Applications (EPE 2011)*, 30 Aug. – 1 Sept. 2011.

4. G. I. Orfanoudakis, S. M. Sharkh and M. A. Yuratich, “Capacitor size reduction for multiple inverter systems”, *IET Conference on Renewable Power Generation (RPG 2011)*, 6 – 8 Sept. 2011.

5. G. I. Orfanoudakis, M. A. Yuratich and S. M. Sharkh, “Nearest-Vector Modulation Strategies with Minimum Amplitude of Low-Frequency Neutral-Point Voltage Oscillations for the Neutral-Point-Clamped Converter”, *IEEE Transactions on Power Electronics*, 2012 (to be published, available on IEEE Xplore).

6. G. I. Orfanoudakis, M. A. Yuratich and S. M. Sharkh, “Hybrid Modulation Strategies for Eliminating the Low-Frequency Neutral-Point Voltage Oscillations in the Neutral-Point-Clamped Converter”, *IEEE Transactions on Power Electronics*, 2012 (to be published, available on IEEE Xplore).

7. G. I. Orfanoudakis, M. A. Yuratich and S. M. Sharkh, “Analysis of DC-link Capacitor Current in Three-Level Neutral-Point-Clamped and Cascaded H-Bridge Inverters”, *IET Power Electronics*, 2012 (to be published).

## *Acknowledgements*

---

*Πᾶσα δόσις ἀγαθὴ καὶ πᾶν δώρημα τέλειον*

*ἄνωθέν ἐστι, καταβαῖνον ἐκ σοῦ*

*τοῦ Πατρὸς τῶν φώτων*

*Every pure donation and every perfect gift*

*comes from above, descending from you*

*the Father of lights*

(from the Orthodox liturgy and the Epistle of James)

I feel full of gratitude towards God for the gifts He gave me during these years of my PhD. I can clearly see that the patience to acquire knowledge, the ideas for contributing to research, and the obstacles and strength to overcome them were all gifts, laid pedagogically in my way to help me become a better man. He also made me a series of other great gifts, the people I was brought close to, who I would like to thank below.

Dr. Suleiman Sharkh, my supervisor, is a man with great understanding and patience, who was ready to support me with anything I needed during my PhD. His advice and thorough feedback on my research were essential for producing, developing and properly presenting the results of this Thesis. Moreover, the balance he kept between freedom and guidance as a supervisor helped me take the responsibility of my work and slowly grow up as a researcher, which will be a valuable skill for the future. I would like to thank him for the above, as well as for always keeping our relationship very human, being sensitive with the difficulties and worries I had at different stages of the PhD.

Dr. Michael Yuratich, my PhD advisor and Managing Director of my sponsoring company, also helped me from his position in many ways. Apart from the financial support, he provided me with ideas and feedback on my work, relating it to practical aspects but with great respect for the research nature of the PhD. In addition, he gave me the opportunity to

work in the industrial environment of TSL Technology Ltd., very often devoting time for informing and instructing me. I would like to thank him because his approachable attitude, wide knowledge, and love for scientific thinking have been inspiring for me, setting an example which made me enjoy my work in the company.

I would also like to thank Mr. Andy Jewell and Dr. Ashraf Abdulrahman whom I worked with in TSL Technology, learning from their knowledge and experience. Furthermore, I would like to thank and wish the best to my fellow PhD students in the Electro-mechanical Research Group of the University of Southampton, particularly to Shayan Motamed Fakhr and Ali Qazalbash, for our useful discussions and nice company in our office.

During these years in the University I also met other students and made friendships that offered me a valuable support. I will not forget our coffee breaks with Hani Tabbara and our company with Polyvios Polyviou during the first three years of my PhD. Nor will I forget the way Thomas and Peristera, Antonis and Eutychia, Spiros and Antigoni, Ioanna and Iliana stood by me during the fourth year, participating in my effort to finish in time. The same is true for my friends from Greece, Tasos, Kostis, Nikolas, Petros, Dimosthenis, Dimitris, Kyriakos, Menelaos, Babis, Myron and others, who had been close to me although far away.

Regarding my family in Greece, my father Ioannis, my mother Mary, and my brother Nikos with his fiancée Maria, I don't know how to express my love and gratitude for what they have done for me before and during these years. They encouraged me to start this PhD and helped me finish it by caring and supporting me at any time. The same did my grandparents and close relatives, especially my grandmother Chryssoula with her letters and prayers, my uncle Stelios, and my godmother Rena. I would like to send my warmest wishes to all of them, as well as to Fr. Christos, Fr. Prodromos, Fr. Arsenios and others who had been like fathers to me at any difficult moment.

Finally, I would like to sincerely thank the two people that were closest to me during these years in Southampton, Fr. Vasileios Mavroudis and Alexandros Nikolaou, for their love and care, and for their key role in meeting and marrying my wife Agathi. Agathi and her entire family, Ioannis and Julia, Christos, Egli and Tasos, offered me unconditional support and understanding without which I wouldn't have been able to reach the end of this journey. I thank her from the bottom of my heart and hope to do the same for her in our future, common journey.

To my beloved wife Agathi,

to our families,

and to the memory of

Nikolaos Papadakis,

Eirini Orfanoudaki,

Nikolaos Liapakis,

Anastasia Liapaki,

Adamantia Voulgaraki,

Aikaterini Voulgaraki,

who left during these years

## Table of Contents

---

|          |                                                                                             |                                                                                                                         |           |

|----------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Chapter 1</b>                                                                            | <b>Introduction.....</b>                                                                                                | <b>1</b>  |

| 1.1      | Multilevel power converters.....                                                            | 2                                                                                                                       |           |

| 1.2      | DC-link capacitors – Challenges in three-level converters.....                              | 5                                                                                                                       |           |

| 1.2.1    | The dc-link of the NPC converter.....                                                       | 6                                                                                                                       |           |

| 1.2.2    | The dc-link of the CHB converter .....                                                      | 8                                                                                                                       |           |

| 1.3      | Aim, structure, and contribution of the Thesis .....                                        | 8                                                                                                                       |           |

| <b>2</b> | <b>Chapter 2</b>                                                                            | <b>Converter topologies – Structure, modulation and modelling.....</b>                                                  | <b>13</b> |

| 2.1      | Converter Topologies.....                                                                   | 14                                                                                                                      |           |

| 2.1.1    | The two-level converter.....                                                                | 14                                                                                                                      |           |

| 2.1.2    | The NPC converter .....                                                                     | 15                                                                                                                      |           |

| 2.1.3    | The CHB converter.....                                                                      | 17                                                                                                                      |           |

| 2.2      | Pulse Width Modulation strategies .....                                                     | 19                                                                                                                      |           |

| 2.2.1    | Carrier-based strategies .....                                                              | 19                                                                                                                      |           |

| 2.2.2    | SVM strategies .....                                                                        | 24                                                                                                                      |           |

| 2.3      | Modelling.....                                                                              | 28                                                                                                                      |           |

| <b>3</b> | <b>Chapter 3</b>                                                                            | <b>Analysis of dc-link capacitor current in three-level Neutral-Point-Clamped and Cascaded H-Bridge inverters .....</b> | <b>33</b> |

| 3.1      | Introduction.....                                                                           | 34                                                                                                                      |           |

| 3.2      | Inverter dc-link capacitor sizing.....                                                      | 35                                                                                                                      |           |

| 3.3      | Analytical derivation of dc-link capacitor current rms expressions .....                    | 37                                                                                                                      |           |

| 3.3.1    | Two-level inverter .....                                                                    | 38                                                                                                                      |           |

| 3.3.2    | NPC inverter .....                                                                          | 40                                                                                                                      |           |

| 3.3.3    | CHB inverter.....                                                                           | 43                                                                                                                      |           |

| 3.4      | Analytical derivation of dc-link capacitor current harmonics .....                          | 45                                                                                                                      |           |

| 3.4.1    | Two-level inverter .....                                                                    | 46                                                                                                                      |           |

| 3.4.2    | NPC inverter .....                                                                          | 47                                                                                                                      |           |

| 3.4.3    | CHB inverter.....                                                                           | 49                                                                                                                      |           |

| 3.5      | Numerical derivation of dc-link capacitor current rms value and amplitude of voltage ripple | 51                                                                                                                      |           |

| 3.6      | Simulation results.....                                                                     | 54                                                                                                                      |           |

| 3.7      | Discussion.....                                                                             | 56                                                                                                                      |           |

|            |                                                                                                                                                                                |           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.7.1      | Comparison of capacitor size for the NPC and CHB inverters .....                                                                                                               | 56        |

| 3.7.2      | Comparison of methods for analysing dc-link capacitor current .....                                                                                                            | 58        |

| 3.7.3      | Extension to higher-level inverters.....                                                                                                                                       | 59        |

| 3.7.4      | DC-link capacitor current harmonics due to the inverter Front-End.....                                                                                                         | 60        |

| 3.7.5      | Using the analysis to select dc-link capacitors .....                                                                                                                          | 60        |

| <b>3.8</b> | <b>Conclusion .....</b>                                                                                                                                                        | <b>62</b> |

| <b>4</b>   | <b>Chapter 4 Capacitor size reduction for multiple inverter systems .....</b>                                                                                                  | <b>65</b> |

| 4.1        | Introduction.....                                                                                                                                                              | 66        |

| 4.2        | Common dc-link capacitor current harmonics.....                                                                                                                                | 67        |

| 4.3        | System cases - Results.....                                                                                                                                                    | 68        |

| 4.3.1      | Single-phase (CHB) inverter systems .....                                                                                                                                      | 69        |

| 4.3.2      | Three-phase (two-level) inverter systems .....                                                                                                                                 | 72        |

| 4.4        | Discussion .....                                                                                                                                                               | 73        |

| 4.5        | Conclusions.....                                                                                                                                                               | 74        |

| <b>5</b>   | <b>Chapter 5 Circuit for reducing devices voltage stress due to dc-link capacitor voltage ripple in an NPC inverter .....</b>                                                  | <b>77</b> |

| 5.1        | Introduction.....                                                                                                                                                              | 78        |

| 5.2        | Proposed circuit .....                                                                                                                                                         | 79        |

| 5.2.1      | Structure .....                                                                                                                                                                | 79        |

| 5.2.2      | Operation.....                                                                                                                                                                 | 80        |

| 5.2.3      | Rating .....                                                                                                                                                                   | 83        |

| 5.3        | Comparison with other solutions.....                                                                                                                                           | 84        |

| 5.3.1      | Increment of capacitor size.....                                                                                                                                               | 85        |

| 5.3.2      | Increment of switching frequency .....                                                                                                                                         | 86        |

| 5.3.3      | Balancing circuits .....                                                                                                                                                       | 86        |

| 5.4        | Conclusion .....                                                                                                                                                               | 87        |

| <b>6</b>   | <b>Chapter 6 Nearest-Vector modulation strategies with minimum amplitude of low-frequency Neutral-Point voltage oscillations for the Neutral-Point-Clamped converter .....</b> | <b>89</b> |

| 6.1        | Introduction.....                                                                                                                                                              | 90        |

| 6.2        | NPC converter modulation strategies .....                                                                                                                                      | 90        |

| 6.3        | Minimum NP ripple achievable by NV strategies.....                                                                                                                             | 93        |

| 6.3.1      | Locally averaged NP current.....                                                                                                                                               | 94        |

| 6.3.2      | Effect of switching constraints .....                                                                                                                                          | 96        |

|                   |                                                                                                                                                             |            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.3.3             | Zero-ripple region.....                                                                                                                                     | 98         |

| 6.3.4             | A lower boundary for the NP voltage ripple.....                                                                                                             | 98         |

| <b>6.4</b>        | <b>Proposed Band-NV strategies .....</b>                                                                                                                    | <b>101</b> |

| 6.4.1             | Criterion used by conventional NV strategies .....                                                                                                          | 101        |

| 6.4.2             | Proposed criterion.....                                                                                                                                     | 102        |

| 6.4.3             | Regions of operation.....                                                                                                                                   | 103        |

| 6.4.4             | Algorithm.....                                                                                                                                              | 106        |

| 6.4.5             | Switching sequences – Conversion to Band-NV .....                                                                                                           | 109        |

| <b>6.5</b>        | <b>Performance of Band-NV strategies.....</b>                                                                                                               | <b>109</b> |

| 6.5.1             | NP voltage ripple .....                                                                                                                                     | 109        |

| 6.5.2             | Effective switching frequency – Output voltage harmonic distortion .....                                                                                    | 112        |

| <b>6.6</b>        | <b>Simulation results.....</b>                                                                                                                              | <b>113</b> |

| <b>6.7</b>        | <b>Discussion.....</b>                                                                                                                                      | <b>117</b> |

| <b>6.8</b>        | <b>Conclusion .....</b>                                                                                                                                     | <b>119</b> |

| <b>7</b>          | <b>Chapter 7 Hybrid modulation strategies for eliminating low-frequency Neutral-Point voltage oscillations in the Neutral-Point-Clamped converter .....</b> | <b>121</b> |

| 7.1               | Introduction.....                                                                                                                                           | 122        |

| 7.2               | Proposed Hybrid strategies .....                                                                                                                            | 123        |

| 7.3               | Simulation results.....                                                                                                                                     | 124        |

| 7.4               | Discussion.....                                                                                                                                             | 128        |

| 7.5               | Conclusion .....                                                                                                                                            | 129        |

| <b>8</b>          | <b>Chapter 8 Conclusions.....</b>                                                                                                                           | <b>131</b> |

| <b>8.1</b>        | <b>Thesis conclusions and contribution .....</b>                                                                                                            | <b>132</b> |

| <b>8.2</b>        | <b>Future work.....</b>                                                                                                                                     | <b>134</b> |

| 8.2.1             | Experimental results .....                                                                                                                                  | 134        |

| 8.2.2             | Extension of work on Band-NV strategies .....                                                                                                               | 135        |

| 8.2.3             | Extension of work on Hybrid strategies .....                                                                                                                | 139        |

| <b>Appendix A</b> | <b>SVM for the NPC converter – MATLAB-Simulink models .....</b>                                                                                             | <b>141</b> |

| <b>A.1</b>        | <b>Calculation of duty cycles for nearest Space Vectors .....</b>                                                                                           | <b>141</b> |

| <b>A.2</b>        | <b>NP current rms value.....</b>                                                                                                                            | <b>143</b> |

| <b>A.3</b>        | <b>Symmetric modulation strategy.....</b>                                                                                                                   | <b>144</b> |

| <b>A.4</b>        | <b>MATLAB-Simulink models .....</b>                                                                                                                         | <b>145</b> |

| <b>Appendix B</b> | <b>Converter IGBT-diode losses.....</b>                                                                                                                     | <b>157</b> |

| <b>B.1</b>        | <b>Switching losses .....</b>                                                                                                                               | <b>157</b> |

|                   |                                                                       |            |

|-------------------|-----------------------------------------------------------------------|------------|

| B.1.1             | Switching losses in the two-level inverter.....                       | 160        |

| B.1.2             | Switching losses in the NPC inverter .....                            | 161        |

| B.1.3             | Switching losses in the CHB inverter.....                             | 162        |

| <b>B.2</b>        | <b>Conduction losses.....</b>                                         | <b>163</b> |

| B.2.1             | Conduction losses in the two-level inverter .....                     | 165        |

| B.2.2             | Conduction losses in the NPC inverter.....                            | 166        |

| B.2.3             | Conduction losses in the CHB inverter .....                           | 168        |

| <b>B.3</b>        | <b>Converter loss calculator .....</b>                                | <b>170</b> |

| <b>Appendix C</b> | <b>Single-phase transformerless PV inverter (Patent pending).....</b> | <b>175</b> |

| <b>C.1</b>        | <b>Motivation .....</b>                                               | <b>175</b> |

| <b>C.2</b>        | <b>Solution – Existing topologies .....</b>                           | <b>176</b> |

| C.2.1             | Topologies based on the NPC inverter.....                             | 176        |

| C.2.2             | Topologies based on the H-Bridge inverter.....                        | 177        |

| <b>C.3</b>        | <b>Proposed topology.....</b>                                         | <b>182</b> |

| C.3.1             | Concept – Structure .....                                             | 182        |

| C.3.2             | Switching states and common-mode voltage .....                        | 182        |

| C.3.3             | Simulation results.....                                               | 184        |

| <b>9</b>          | <b>References.....</b>                                                | <b>187</b> |

## List of Figures

---

|                                                                                                                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

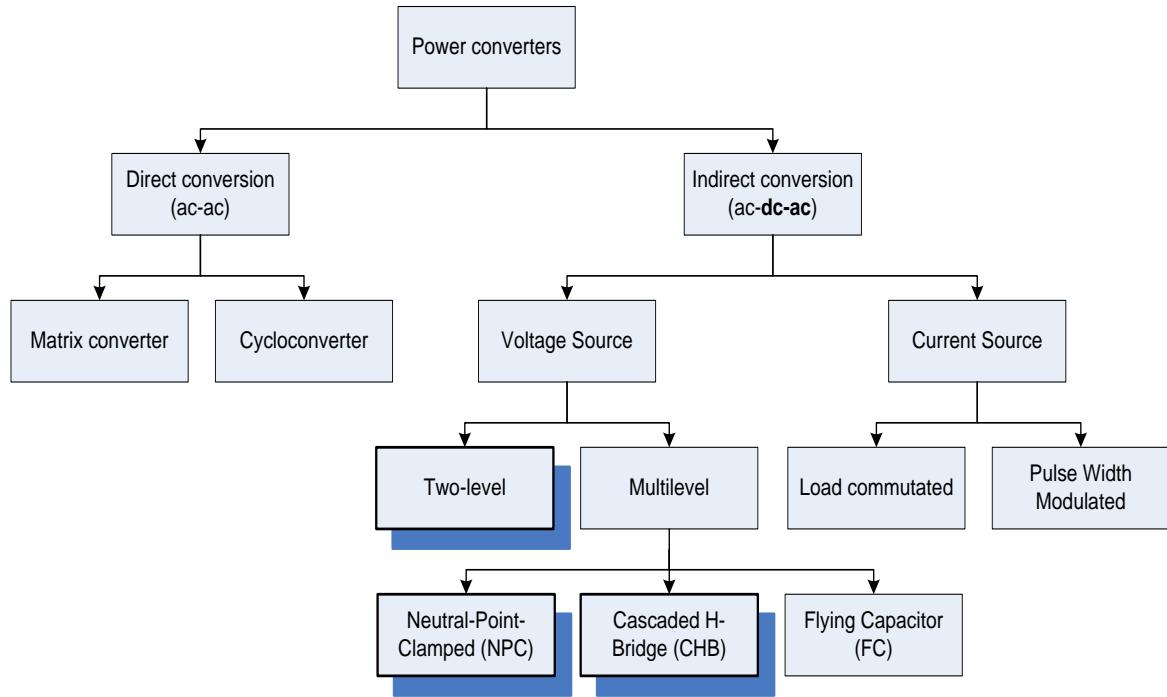

| Figure 1.1. Multilevel converter classification [4, 5].....                                                                                                                                                                                                | 3  |

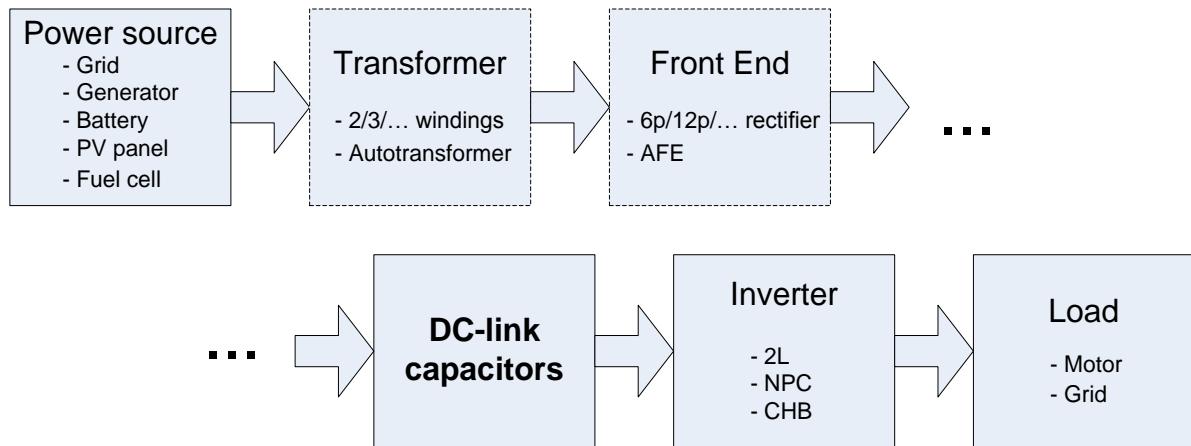

| Figure 1.2. General block diagram of a power conversion system. Dashed-line boxes denote components that may not be present in certain systems.....                                                                                                        | 5  |

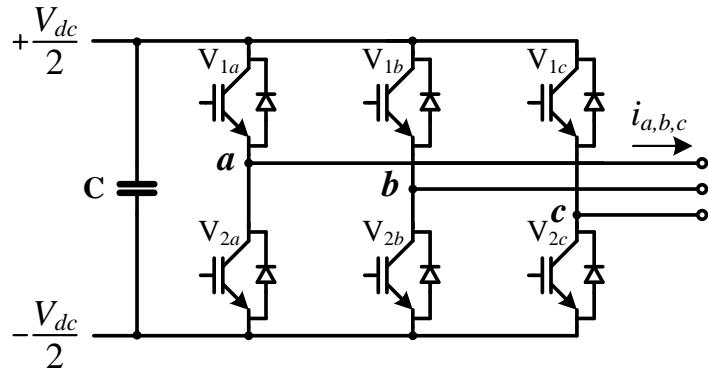

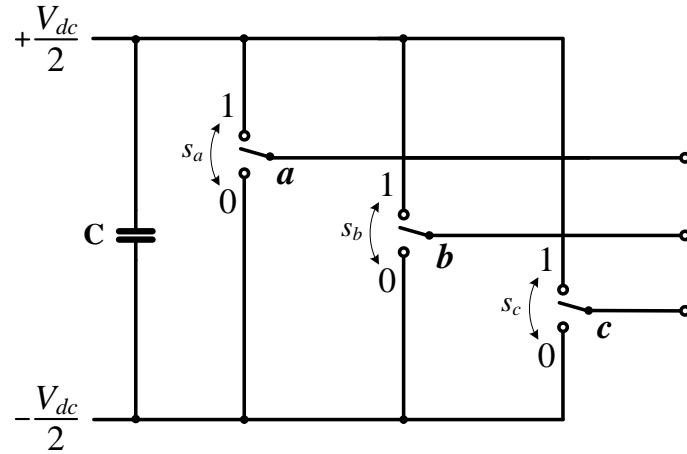

| Figure 2.1. Two-level converter topology.....                                                                                                                                                                                                              | 14 |

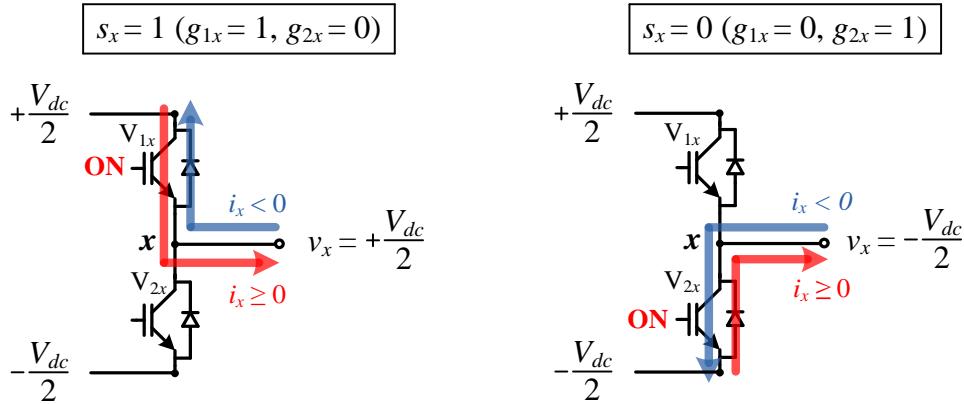

| Figure 2.2. Switching states and conduction paths for a leg of the two-level converter.....                                                                                                                                                                | 15 |

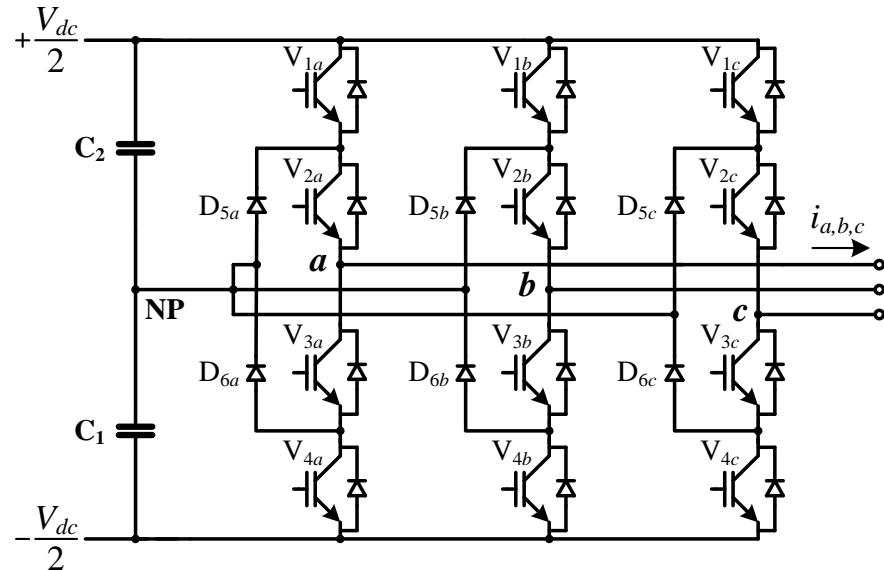

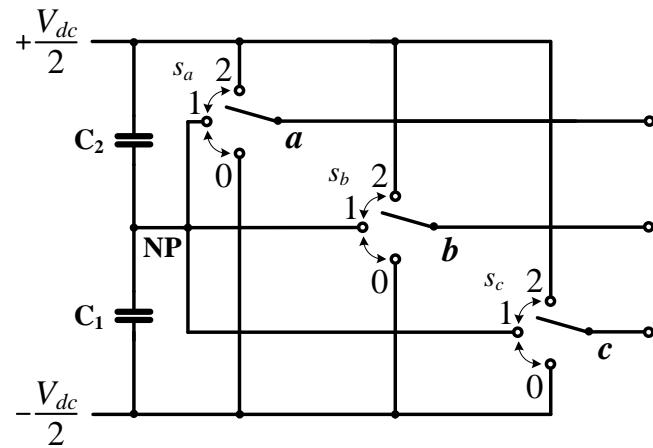

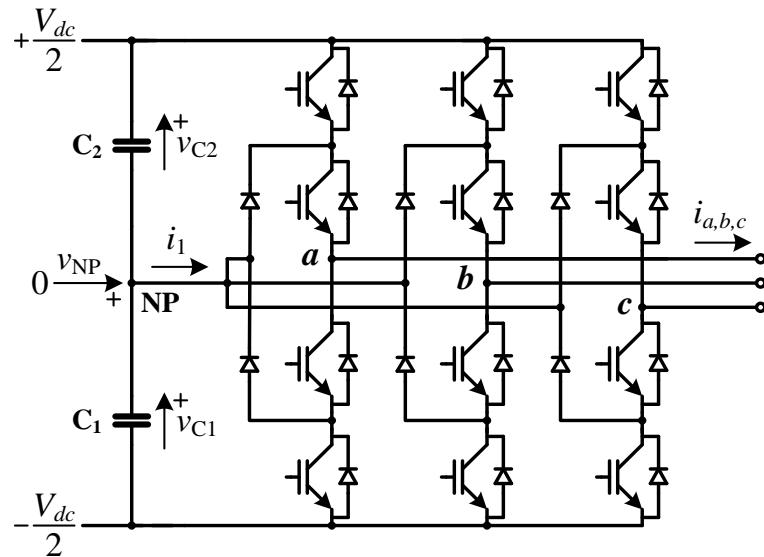

| Figure 2.3. NPC converter topology. ....                                                                                                                                                                                                                   | 15 |

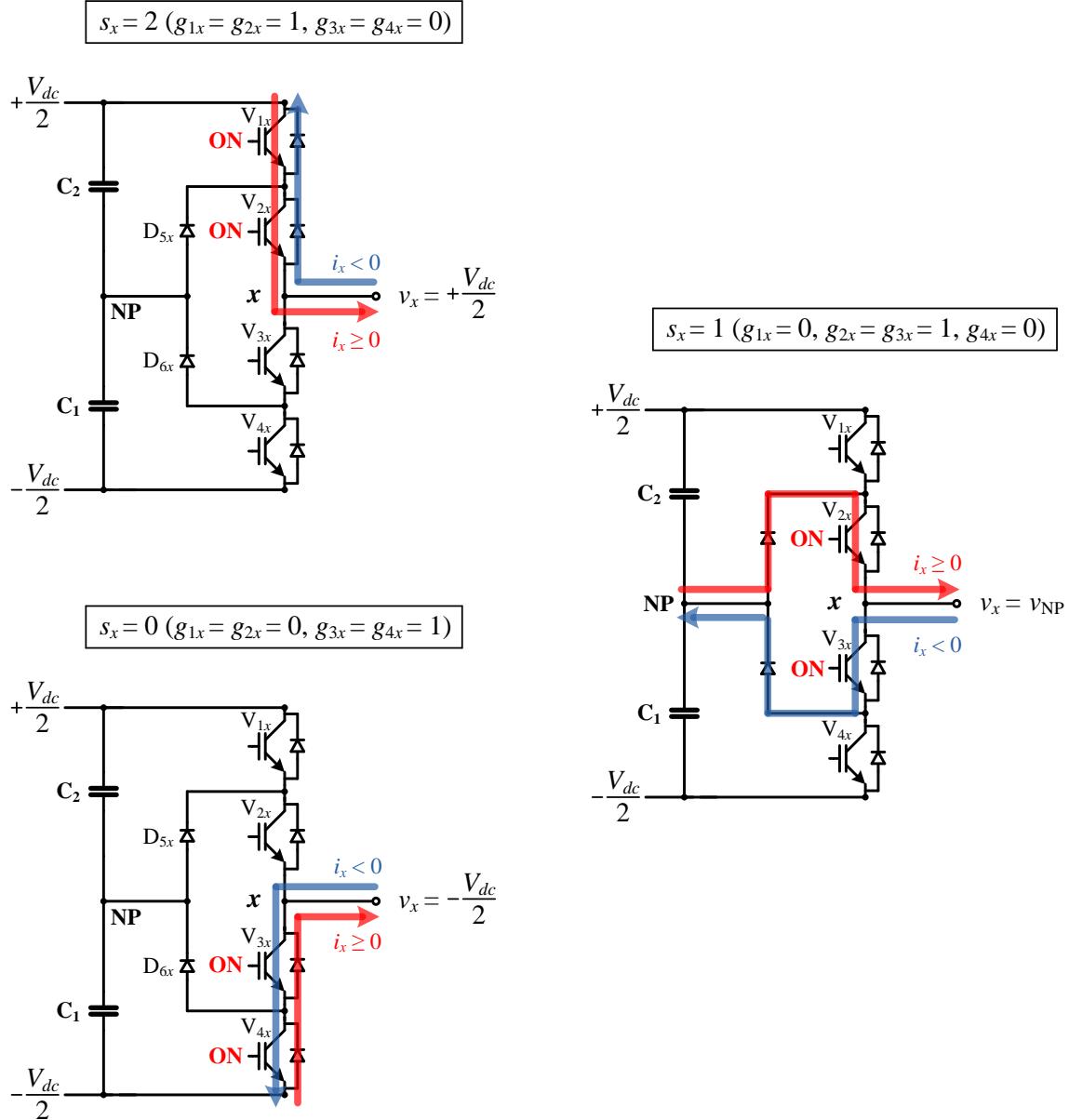

| Figure 2.4. Switching states and conduction paths for a leg of the NPC converter.....                                                                                                                                                                      | 16 |

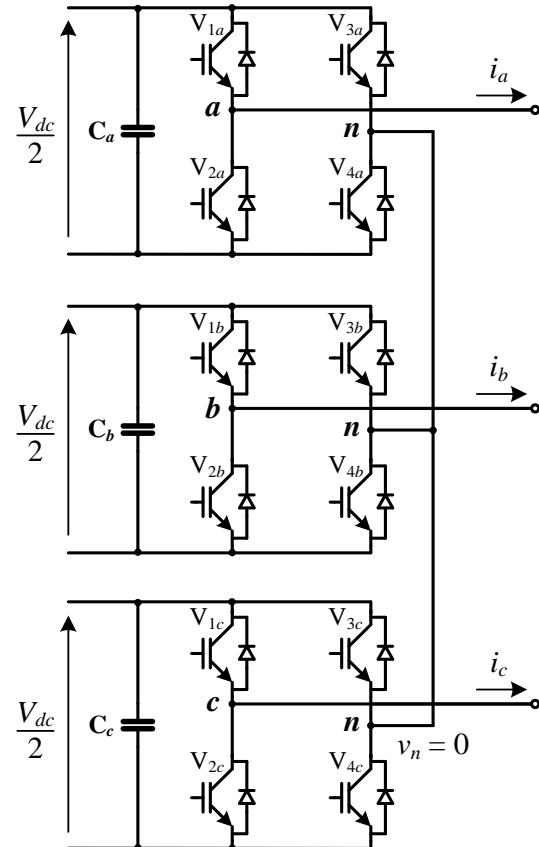

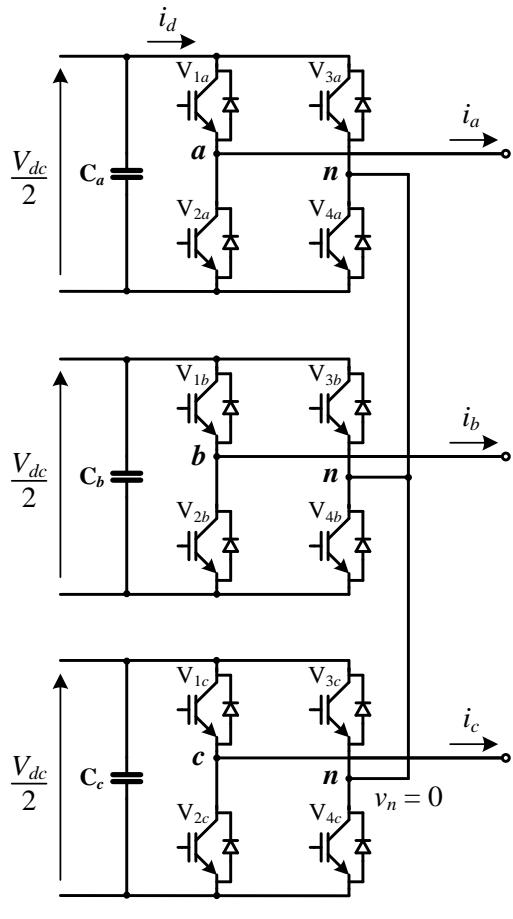

| Figure 2.5. CHB converter topology.....                                                                                                                                                                                                                    | 17 |

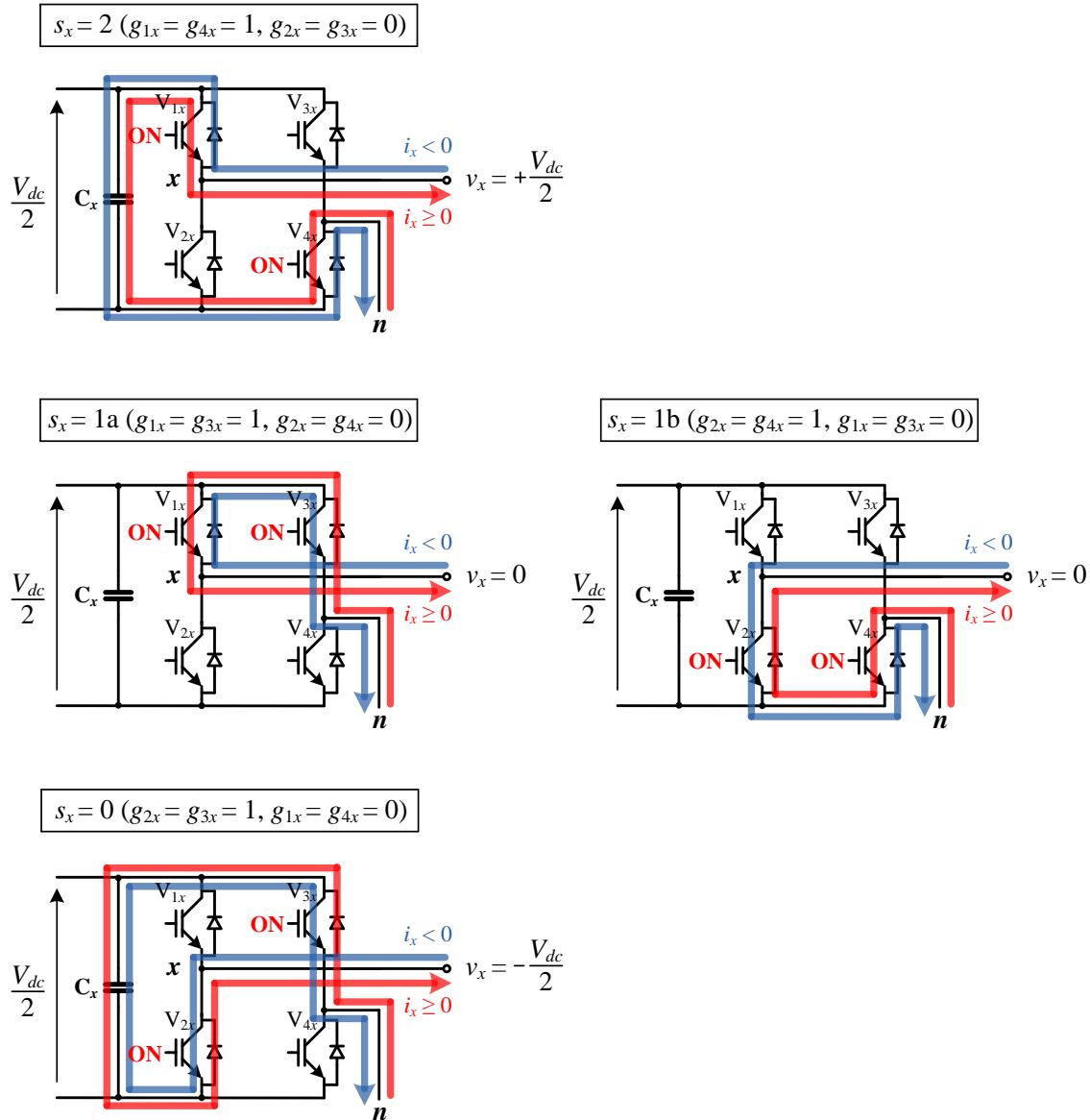

| Figure 2.6. Switching states and conduction paths for a leg (H-Bridge) of the CHB converter. ....                                                                                                                                                          | 18 |

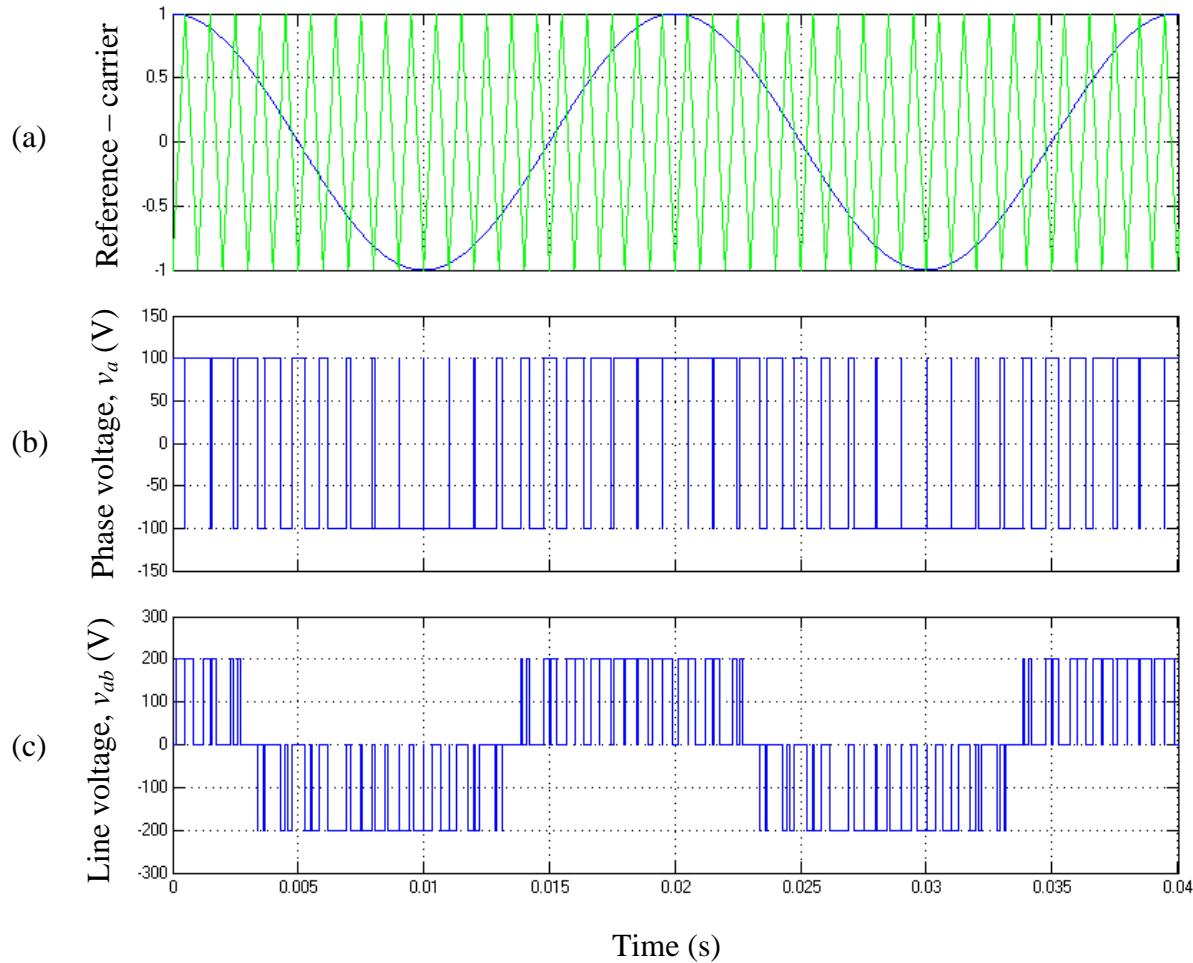

| Figure 2.7. (a) Reference – carrier waveforms for phase $a$ , (b) Phase voltage $v_a$ , and (c) Line voltage $v_{ab}$ for a two-level converter, assuming $V_{dc} = 200$ V, $f = 50$ Hz, and $f_s = 1$ kHz. ....                                           | 20 |

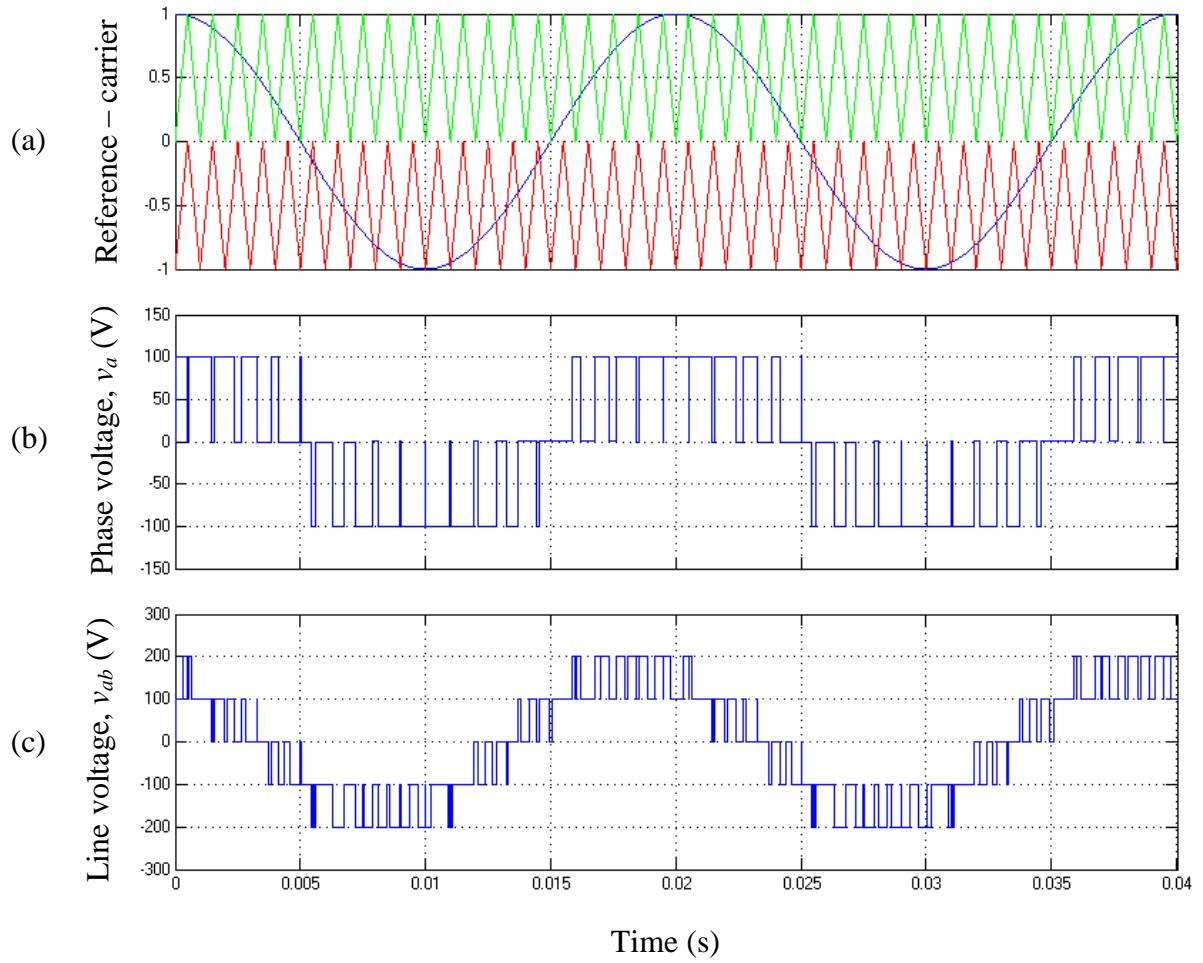

| Figure 2.8. (a) Reference – carrier waveforms for phase $a$ , (b) Phase voltage $v_a$ , and (c) Line voltage $v_{ab}$ for a three-level converter, assuming $V_{dc} = 200$ V, $f = 50$ Hz, and $f_s = 1$ kHz. ....                                         | 21 |

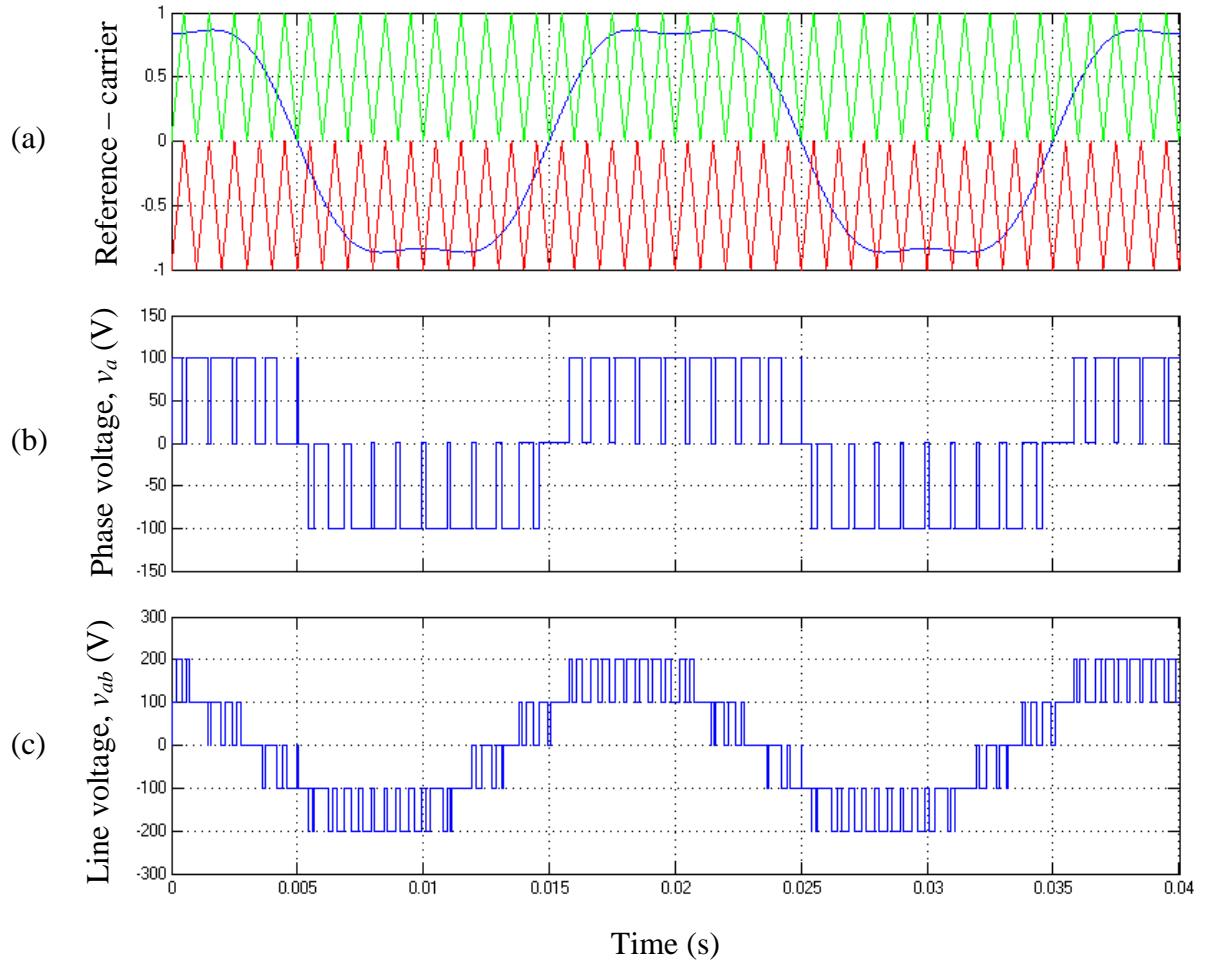

| Figure 2.9. (a) Reference – carrier waveforms for phase $a$ , (b) Phase voltage $v_a$ , and (c) Line voltage $v_{ab}$ for a three-level converter modulated by SPWM+3 <sup>rd</sup> harm., assuming $V_{dc} = 200$ V, $f = 50$ Hz, and $f_s = 1$ kHz. .... | 23 |

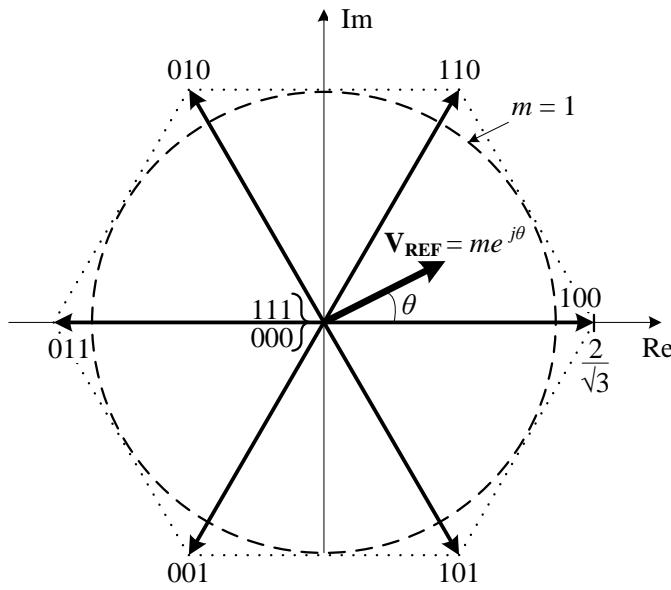

| Figure 2.10. Functional diagram of the two-level converter.....                                                                                                                                                                                            | 25 |

| Figure 2.11. Space Vector diagram for the two-level converter. ....                                                                                                                                                                                        | 26 |

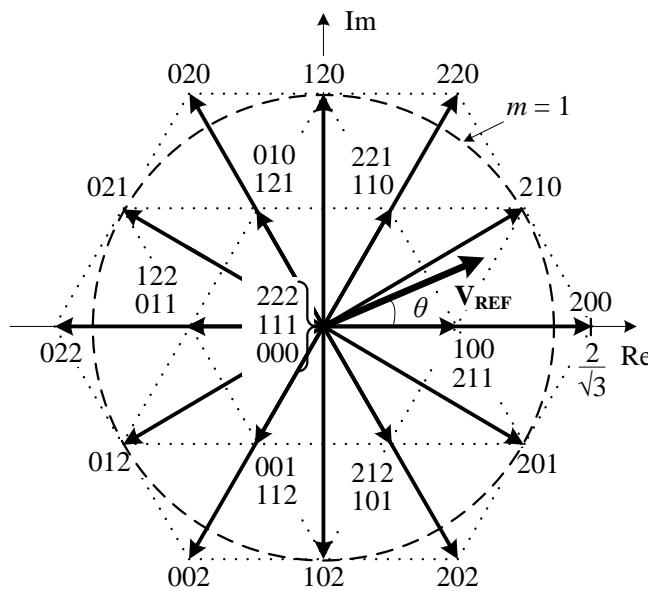

| Figure 2.12. Functional diagram of the NPC converter. ....                                                                                                                                                                                                 | 27 |

| Figure 2.13. Space Vector diagram for three-level converters. ....                                                                                                                                                                                         | 28 |

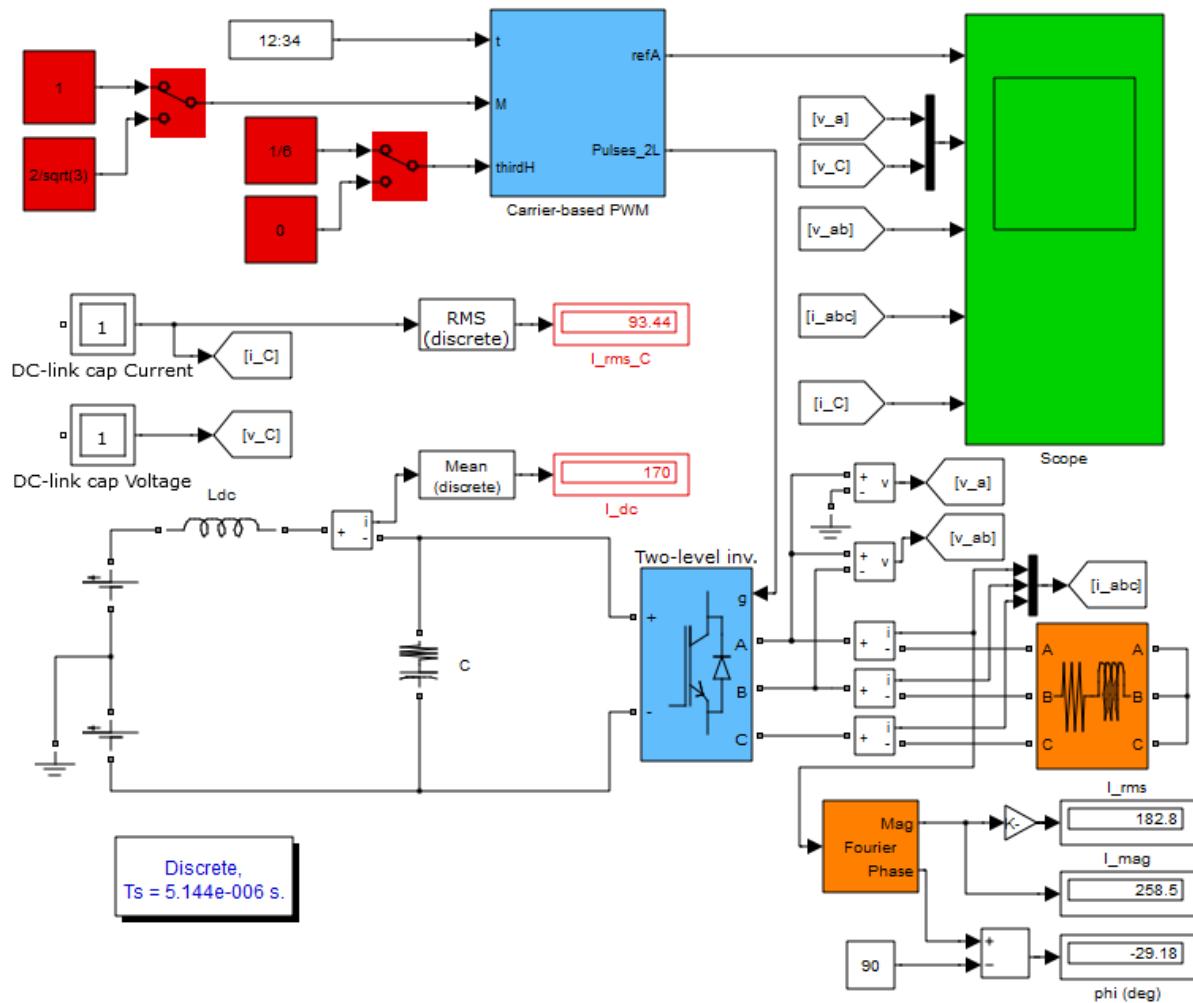

| Figure 2.14. Simulink model for the two-level converter.....                                                                                                                                                                                               | 29 |

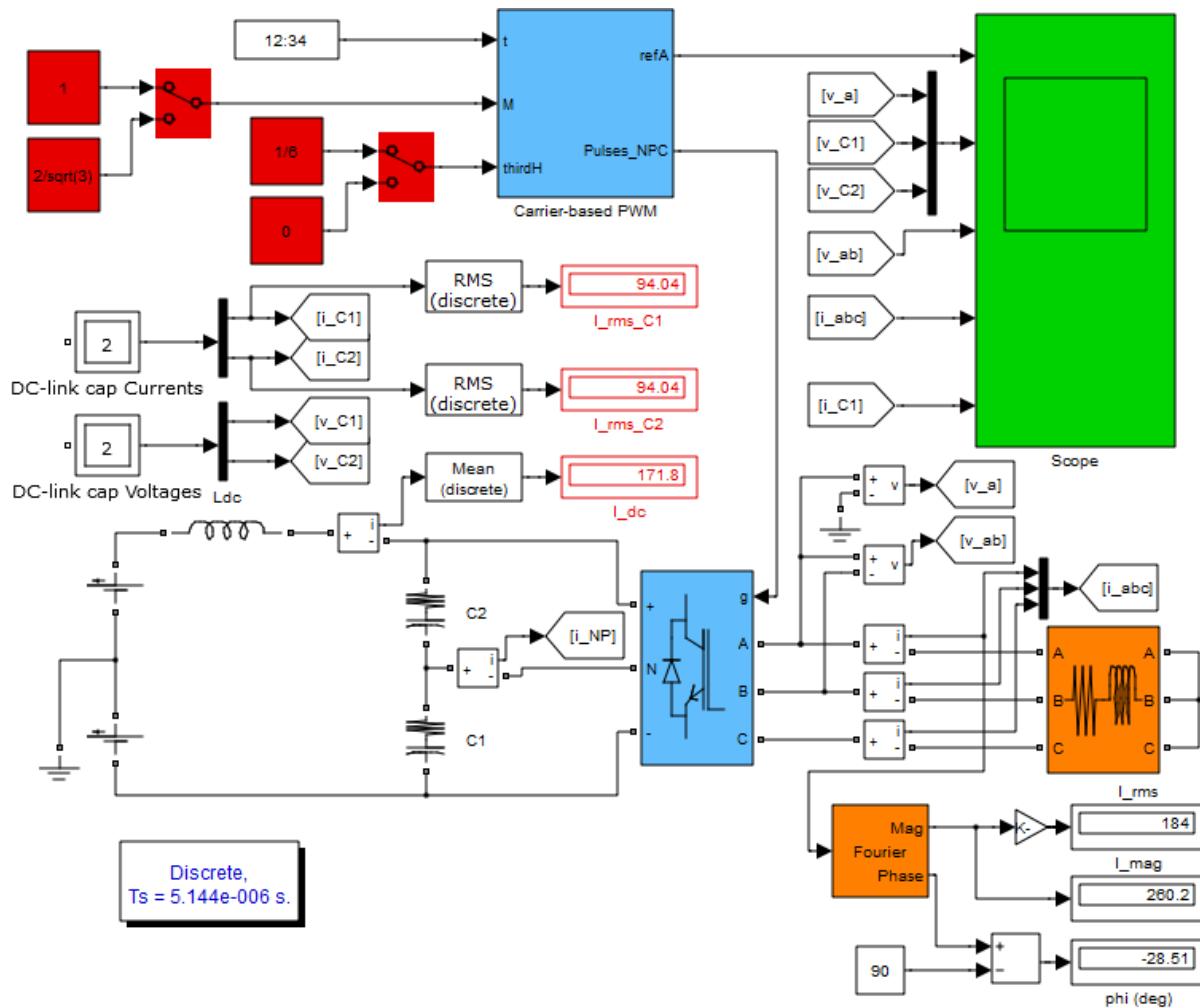

| Figure 2.15. Simulink model for the NPC converter. ....                                                                                                                                                                                                    | 30 |

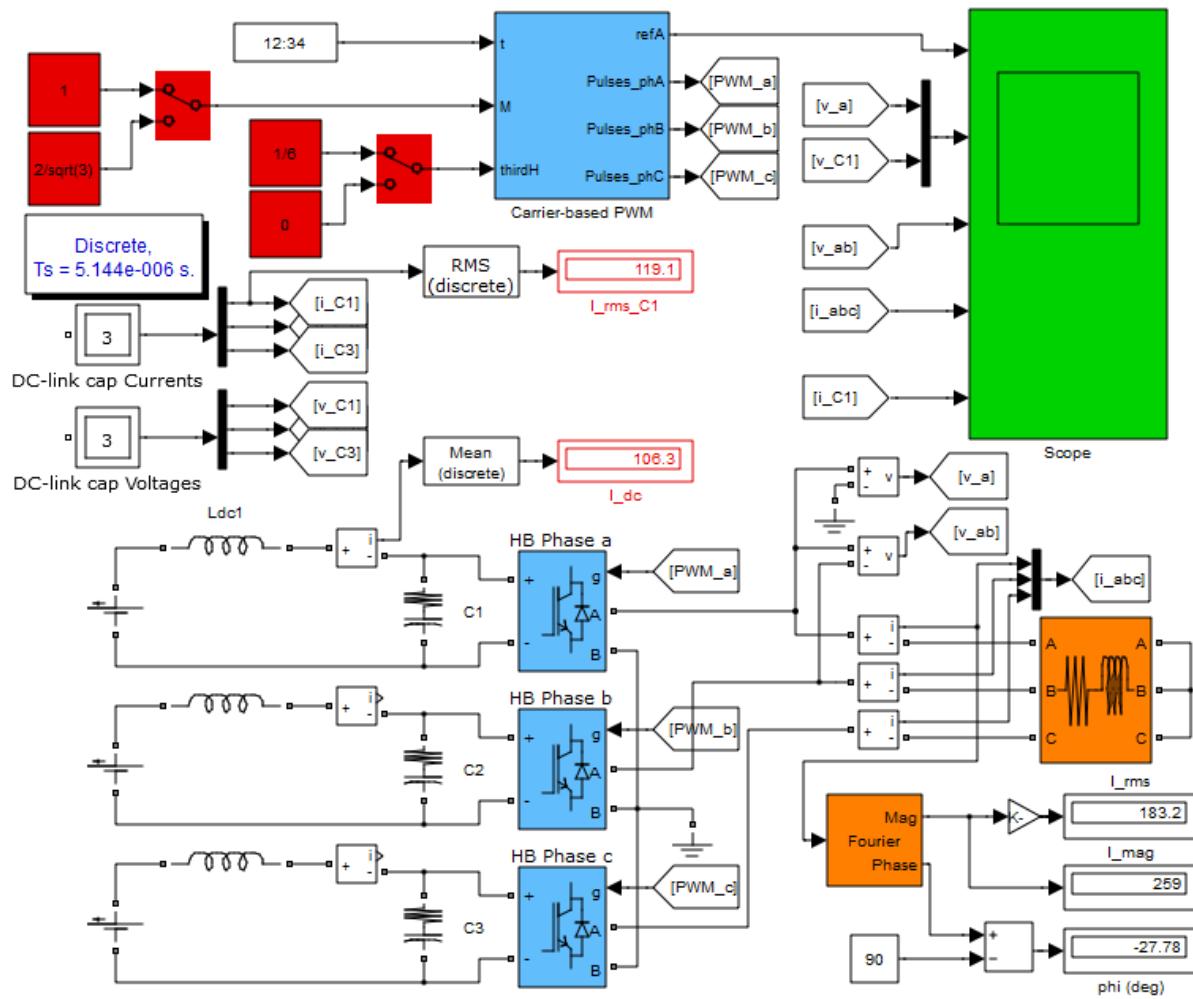

| Figure 2.16. Simulink model for the CHB converter.....                                                                                                                                                                                                     | 31 |

|                                                                                                                                                                                                                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

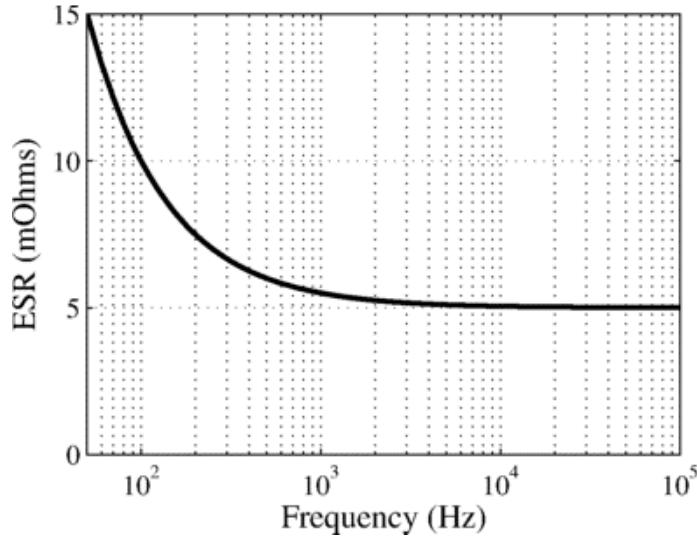

| Figure 3.1. ESR – frequency characteristic of a 4.7 mF / 450 V capacitor (reproduced from [42]). .....                                                                                                                                                                                                              | 36 |

| Figure 3.2. Two-level inverter topology, illustrating upper module currents and current $i_d$ ... .....                                                                                                                                                                                                             | 38 |

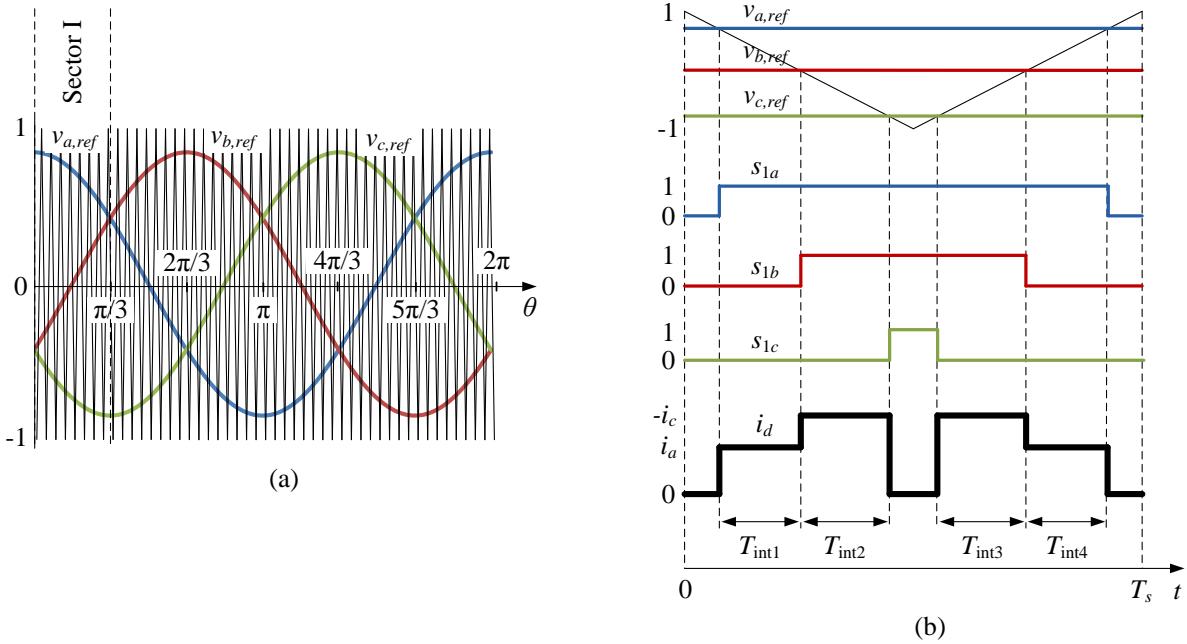

| Figure 3.3. (a) Reference and carrier waveforms for the two-level inverter, and (b) analysis of a switching cycle for Sector I of the two-level inverter..... .....                                                                                                                                                 | 39 |

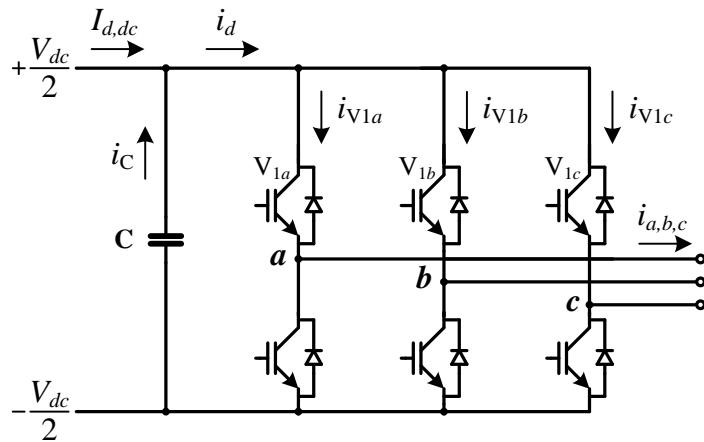

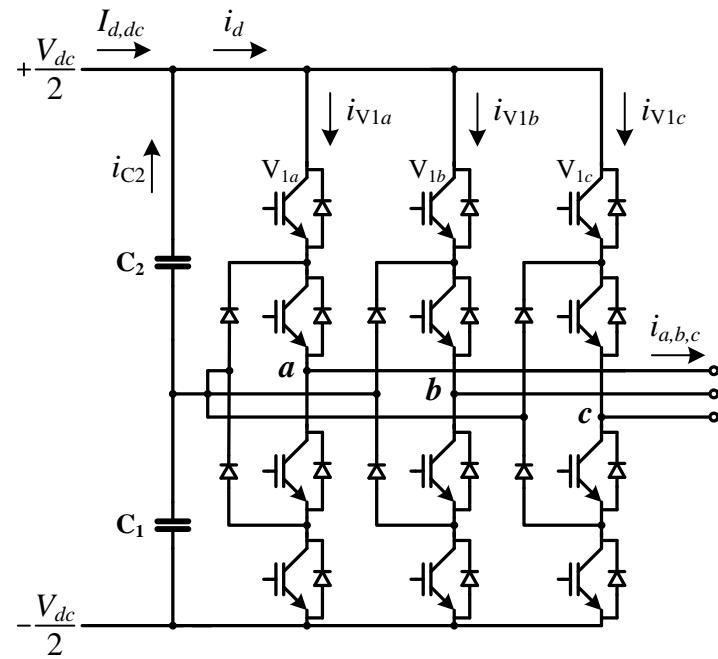

| Figure 3.4. Three-phase NPC inverter, illustrating upper module currents and current $i_d$ ..... .....                                                                                                                                                                                                              | 41 |

| Figure 3.5. Reference and upper carrier waveforms for the NPC inverter..... .....                                                                                                                                                                                                                                   | 41 |

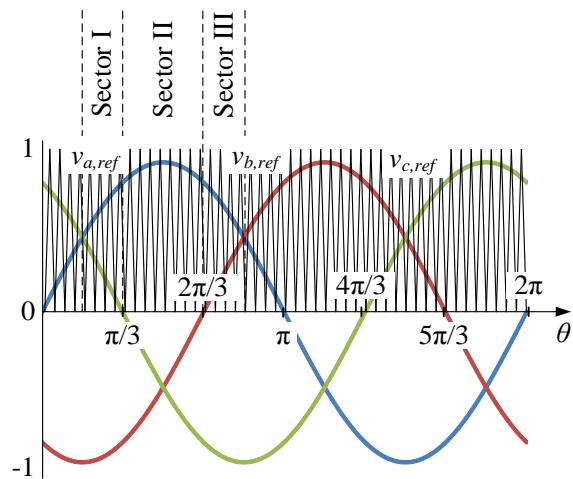

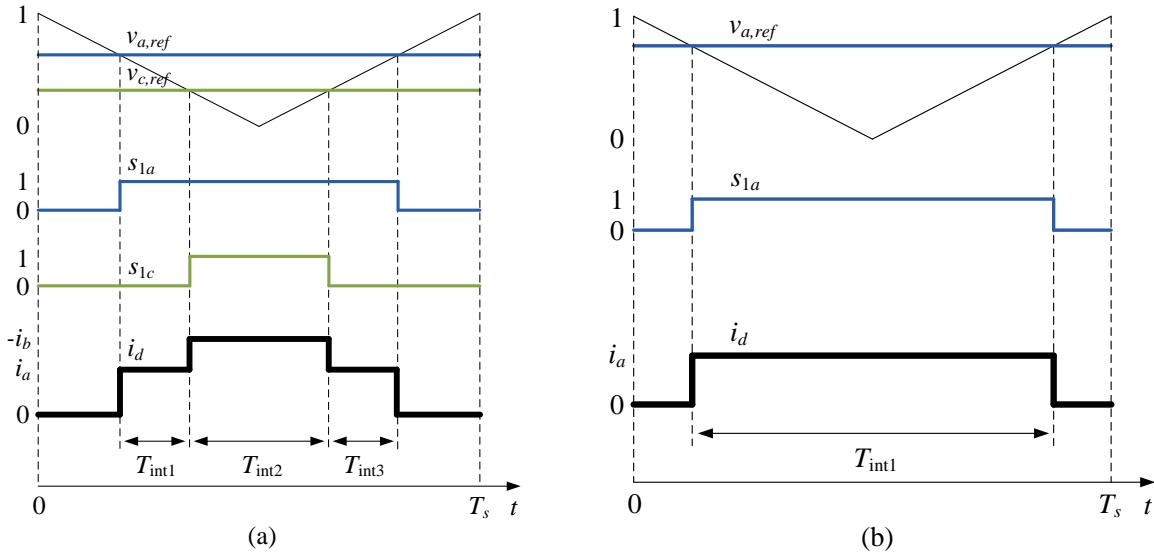

| Figure 3.6. Analysis of a switching cycle for (a) Sector I, and (b) Sector II, of the NPC inverter .....                                                                                                                                                                                                            | 42 |

| Figure 3.7. Three-phase CHB inverter, illustrating current $i_d$ .....                                                                                                                                                                                                                                              | 44 |

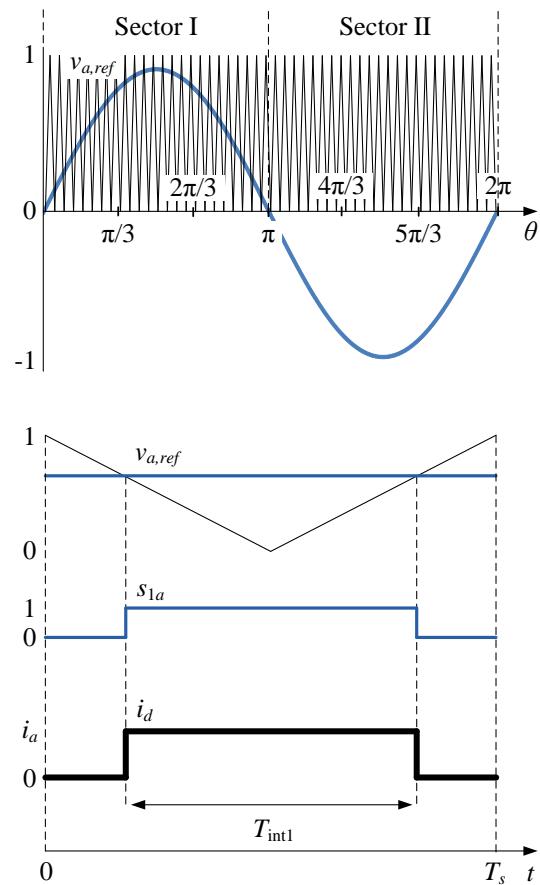

| Figure 3.8. Analysis of a switching cycle for Sector I of the CHB inverter..... .....                                                                                                                                                                                                                               | 44 |

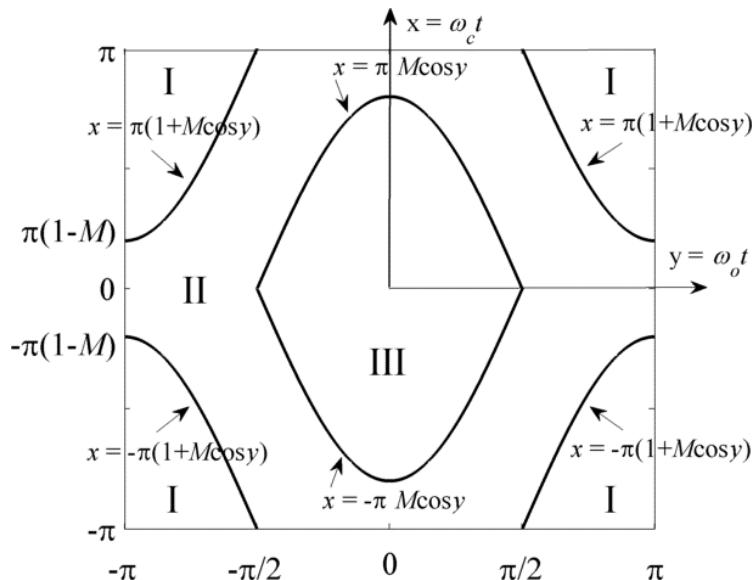

| Figure 3.9. Unit cell for the three-level PD PWM modulation strategy [13]. .....                                                                                                                                                                                                                                    | 47 |

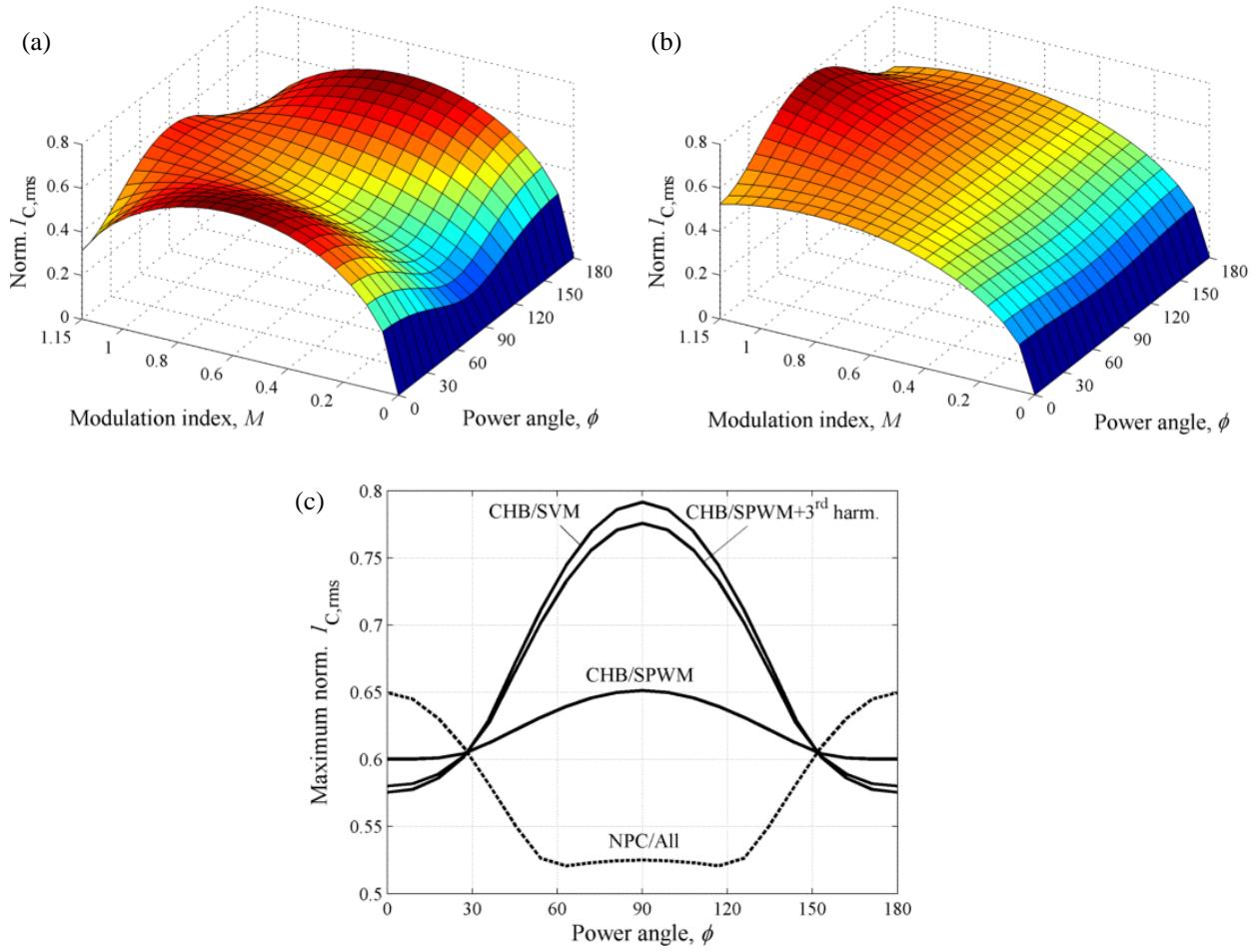

| Figure 3.10. (a) Normalized rms capacitor current for the NPC inverter (same for all modulation strategies), (b) Normalized rms capacitor current for the CHB inverter modulated by the SVM strategy, and (c) Maximum normalized rms capacitor current for the NPC and CHB inverters, as a function of $\phi$ ..... | 52 |

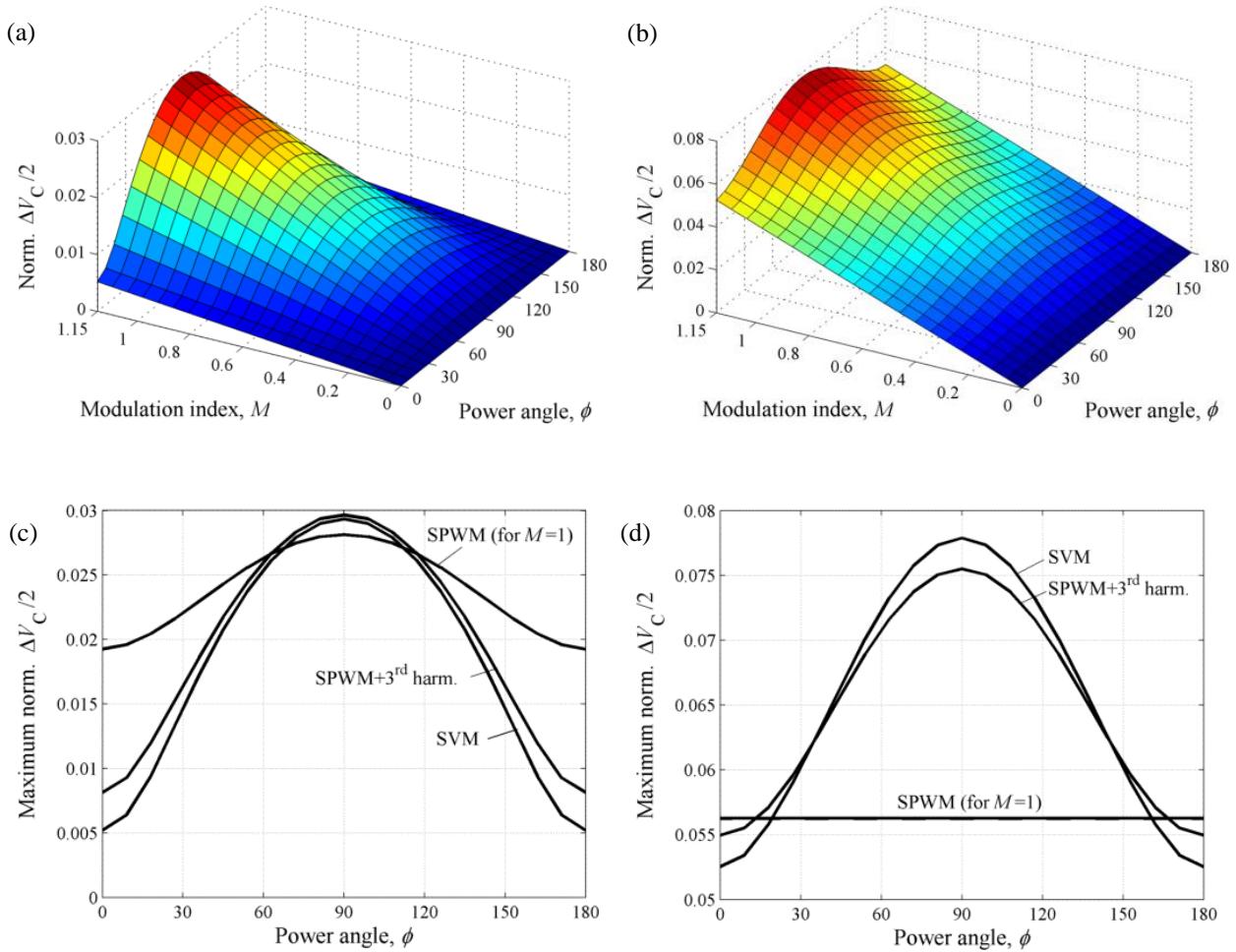

| Figure 3.11. Normalized amplitude of capacitor voltage ripple for (a) the NPC, and (b) the CHB inverter, modulated by the SVM strategy, and maximum normalized amplitude of capacitor voltage ripple for (c) the NPC, and (d) the CHB inverter, as a function of $\phi$ ..... .....                                 | 53 |

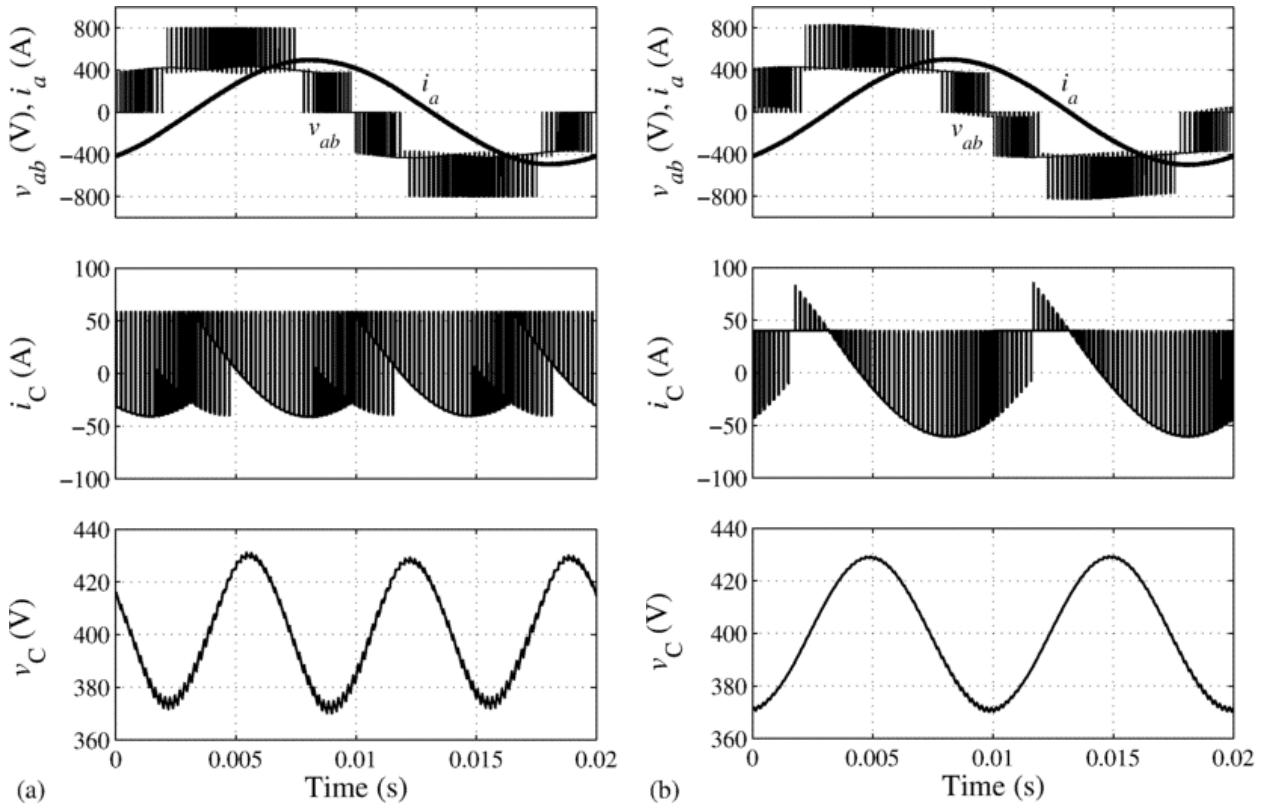

| Figure 3.12. Simulation results for (a) the NPC ( $C = 1$ mF) inverter, and (b) the CHB inverter ( $C = 2.5$ mF)..... .....                                                                                                                                                                                         | 55 |

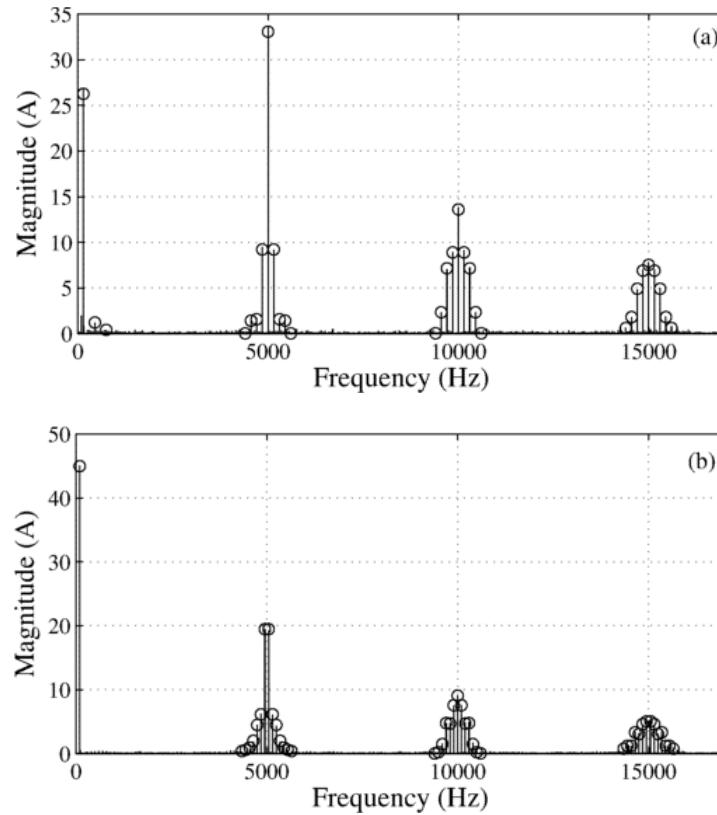

| Figure 3.13. Spectrum of dc-link capacitor current for (a) the NPC and (b) the CHB inverter. Lines and circles represent the simulated and analytically derived magnitudes of the current harmonics, respectively. .....                                                                                            | 56 |

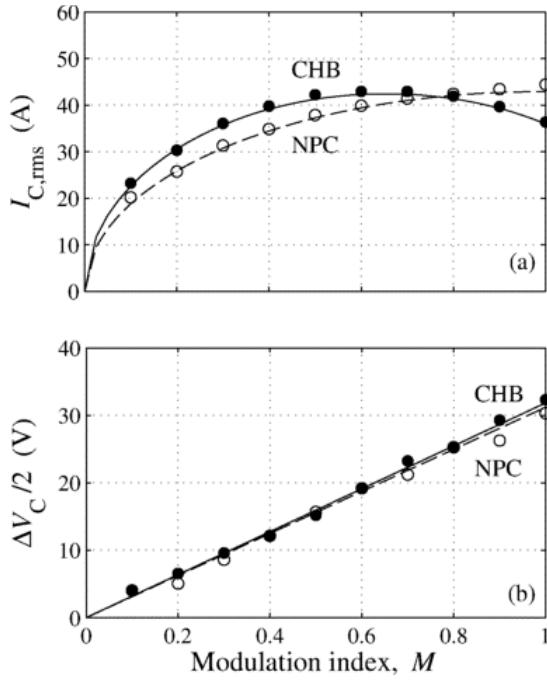

| Figure 3.14. (a) DC-link capacitor rms current, and (b) amplitude of voltage ripple for the NPC ( $C = 1$ mF) and CHB ( $C = 2.5$ mF) topologies as a function of $M$ , for the parameters shown in Table 3.6. .....                                                                                                | 57 |

|                                                                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

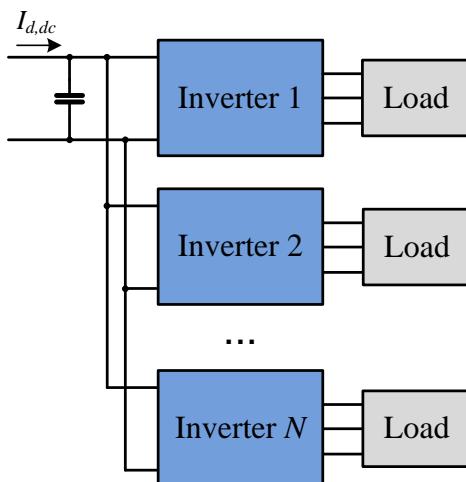

| Figure 4.1. Block diagram of system with $N$ three-phase inverters sharing a common dc-link capacitor.....                                                                                                                                                                                | 66 |

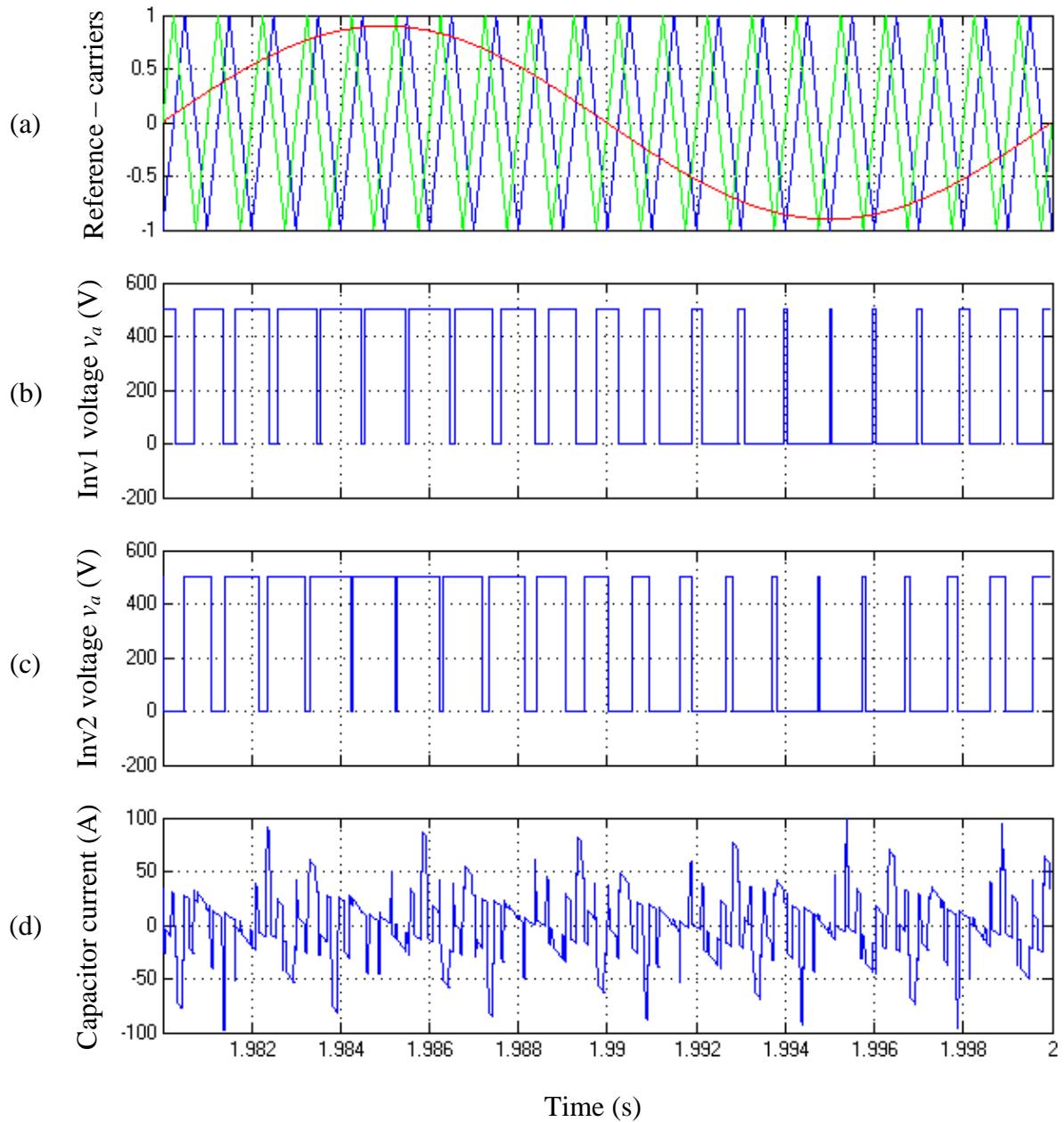

| Figure 4.2. (a) Phase $a$ reference – carrier waveforms for Inv1 and Inv2, (b) Phase voltage $v_a$ for Inv1, (c) Phase voltage $v_a$ for Inv2, and (d) Common capacitor current. The inverters are modulated with SPWM, assuming $V_{dc} = 500$ V, $f = 50$ Hz, and $f_s = 1$ kHz.....    | 69 |

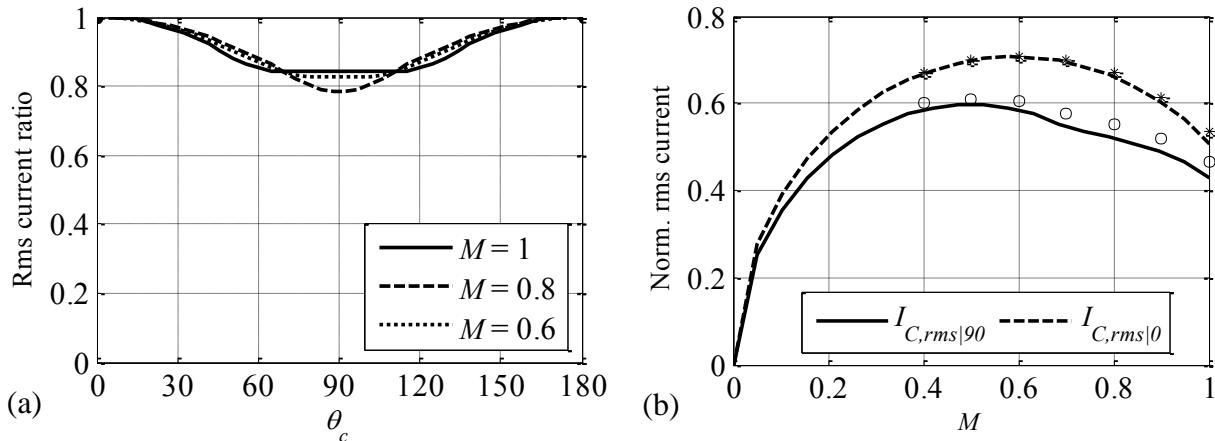

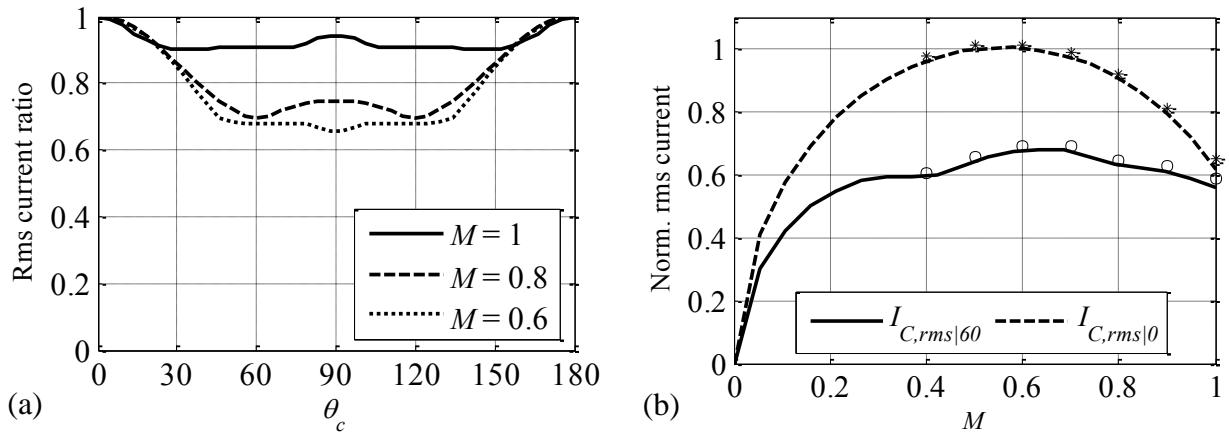

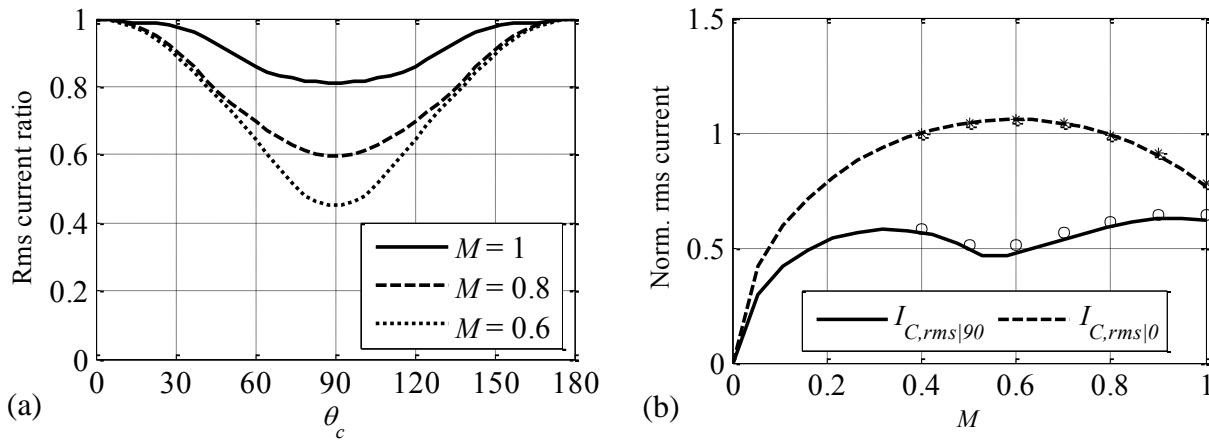

| Figure 4.3. Capacitor rms current versus $\theta_c$ and $M$ for a single-phase inverter system with $N = 2$ , $\theta_o = 90$ degrees.....                                                                                                                                                | 70 |

| Figure 4.4. Capacitor rms current versus $\theta_c$ and $M$ for single-phase inverter system with $N = 3$ , $\theta_o = 60/120$ degrees.....                                                                                                                                              | 71 |

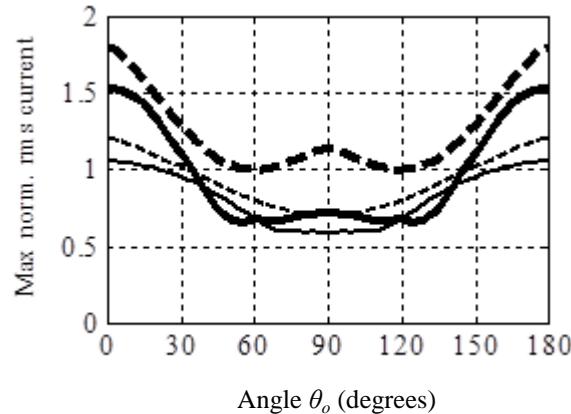

| Figure 4.5. Maximum capacitor rms current $I_{C,rms \theta_c,opt}$ (continuous line) and $I_{C,rms/0}$ (dashed line) versus $\theta_o$ , for single-phase inverter systems: Thin lines for $N = 2$ and bold for $N = 3$ .....                                                             | 71 |

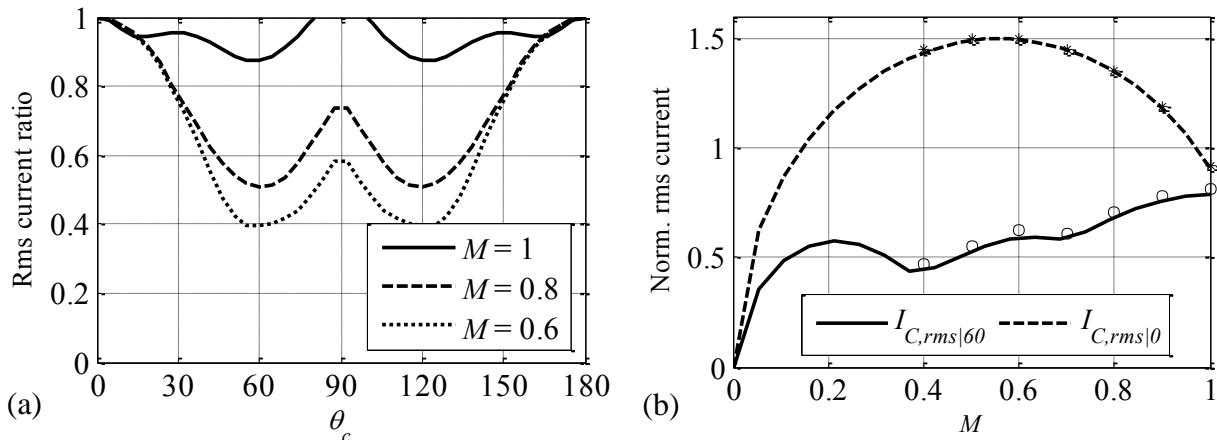

| Figure 4.6. Capacitor rms current versus $\theta_c$ and $M$ for three-phase inverter system with $N = 2$ , $\theta_o = 30/90$ degrees.....                                                                                                                                                | 72 |

| Figure 4.7. Capacitor rms current versus $\theta_c$ and $M$ for three-phase inverter system with $N = 3$ , $\theta_o = 30/90$ degrees.....                                                                                                                                                | 72 |

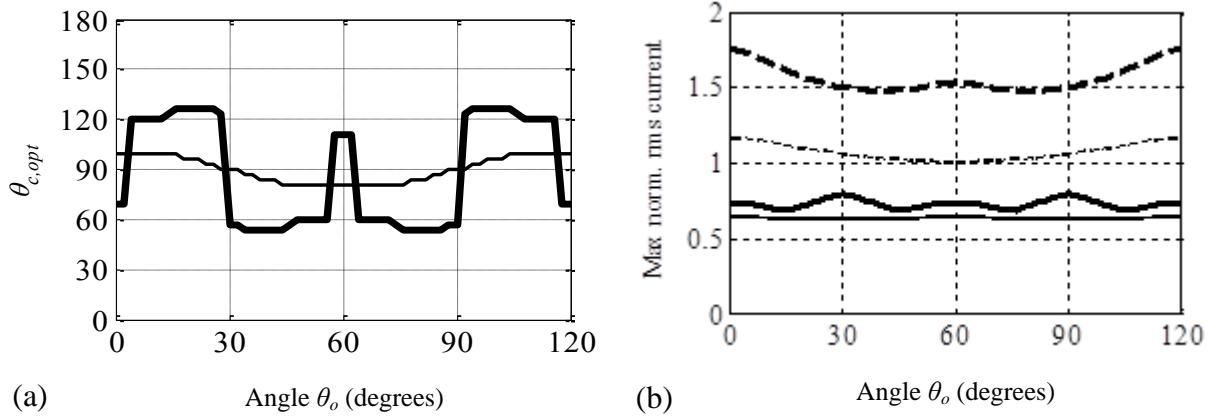

| Figure 4.8. (a) Optimal carrier phase shift and (b) maximum capacitor rms current $I_{C,rms \theta_c,opt}$ (continuous line) and $I_{C,rms/0}$ (dashed line) versus $\theta_o$ , for three-phase inverter systems: Thin lines for $N = 2$ and bold for $N = 3$ .....                      | 73 |

| Figure 5.1. Three-level NPC converter, illustrating NP voltage and current.....                                                                                                                                                                                                           | 78 |

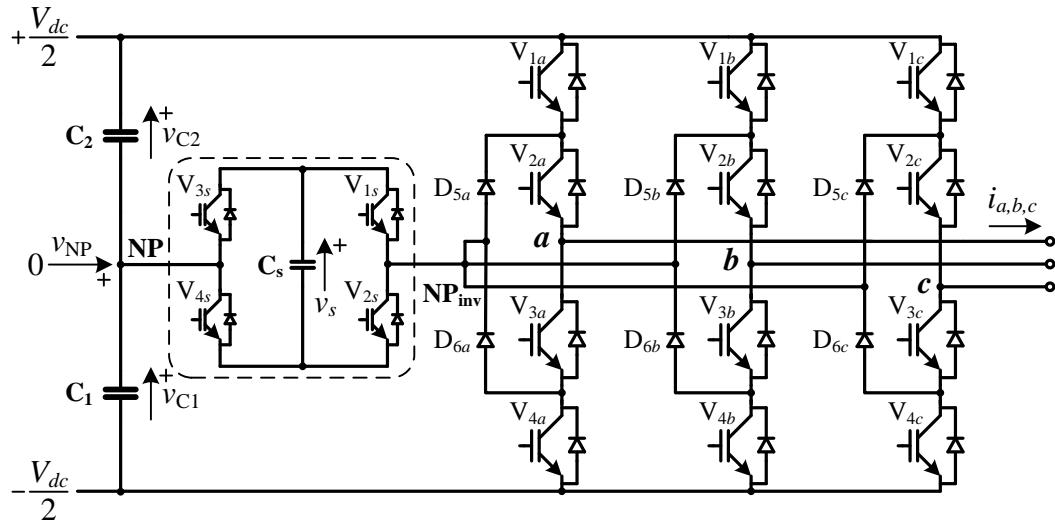

| Figure 5.2. Three-level Neutral-Point-Clamped inverter with NPS circuit (encircled with dashed line).....                                                                                                                                                                                 | 80 |

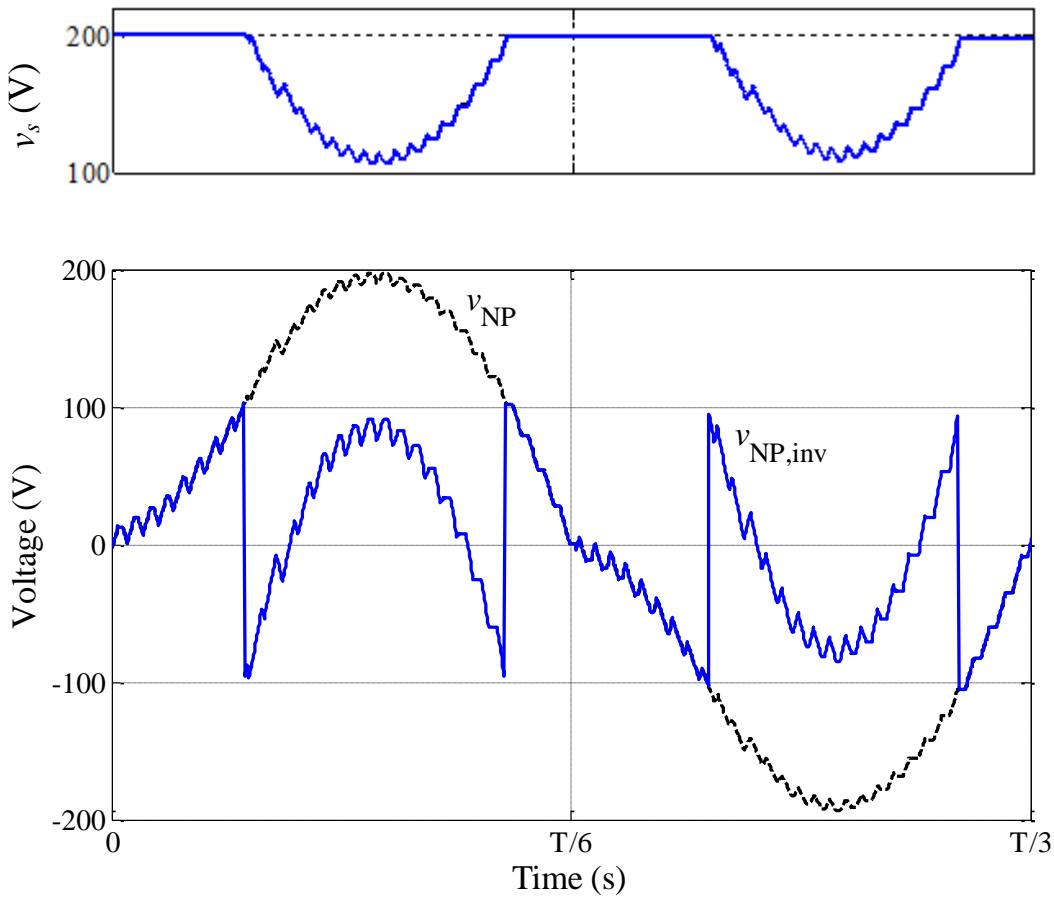

| Figure 5.3. Simulation result illustrating voltages $v_s$ , $v_{NP}$ and $v_{NP,inv}$ , during a period of NP voltage oscillations, for an NPC inverter using the NPS circuit (Appendix A.4). The amplitude of NP voltage ripple seen by the inverter is decreased from 200 to 100 V..... | 82 |

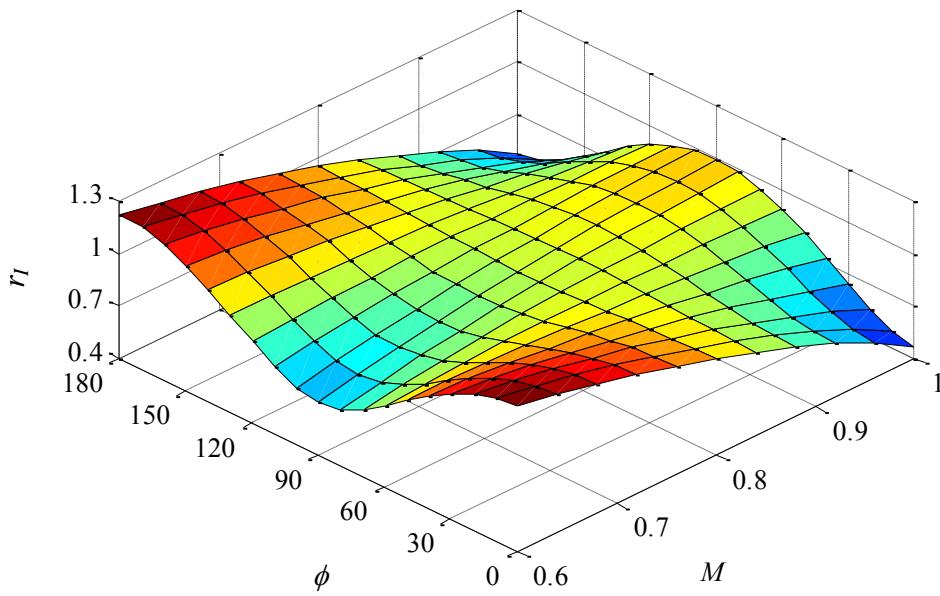

| Figure 5.4. Ratio $r_I$ of NP ( $I_{NP,rms}$ ) over output ( $I_o$ ) rms current for the range of $M$ and $\phi$ where NP voltage ripple can be generated.....                                                                                                                            | 84 |

|                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

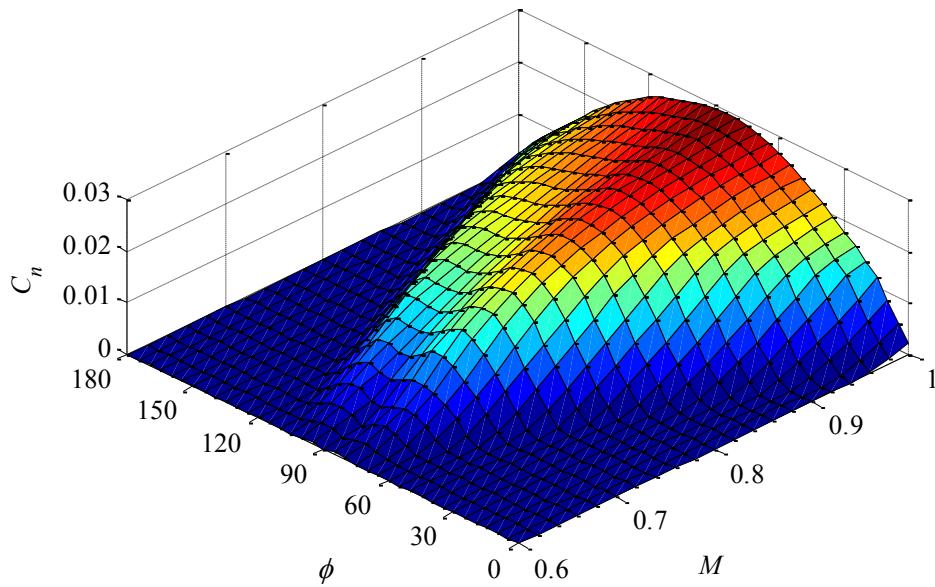

| Figure 5.5. Normalized capacitance ( $C_n$ ) required for the dc-link capacitors of an NPC inverter modulated with the NTV strategy [51]. .....                                                                                                                                                                                                                                                               | 86  |

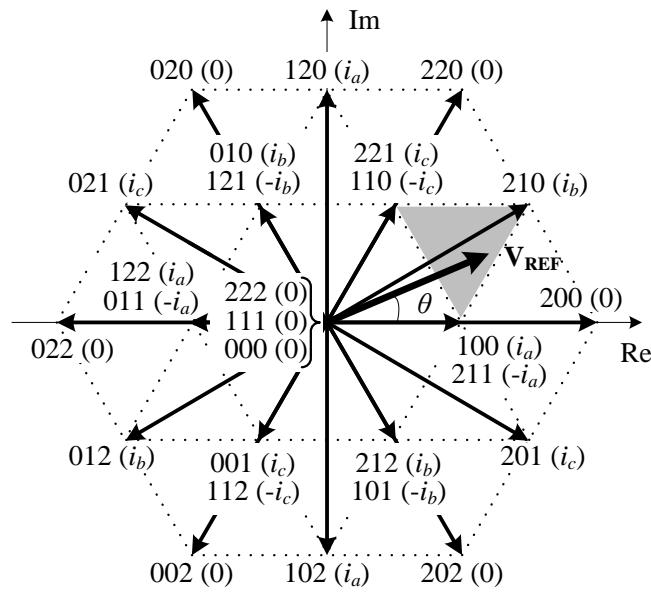

| Figure 6.1. Space Vector diagram for a three-level NPC converter. NV strategies can only use the nearest vectors of $V_{REF}$ , located at the edges of the respective small triangle (here: 100, 211, 210, 221, and 110). The NP current corresponding to each vector is shown in parentheses.....                                                                                                           | 91  |

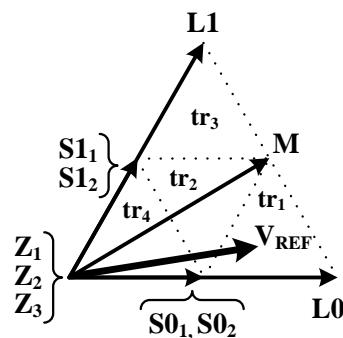

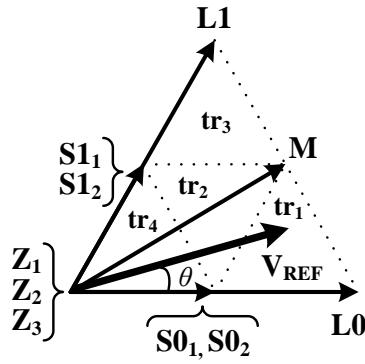

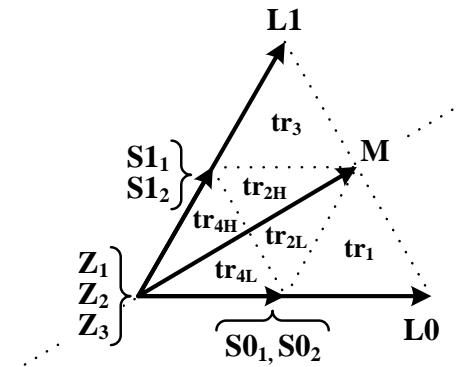

| Figure 6.2. Space Vectors and triangles $tr_1 - tr_4$ , in one sextant of a three-level converter. By convention, $S0_1$ and $S1_1$ will stand for positive (i.e. corresponding to $i_a$ , $i_b$ or $i_c$ ), whereas $S0_2$ and $S1_2$ for negative small vectors.....                                                                                                                                        | 93  |

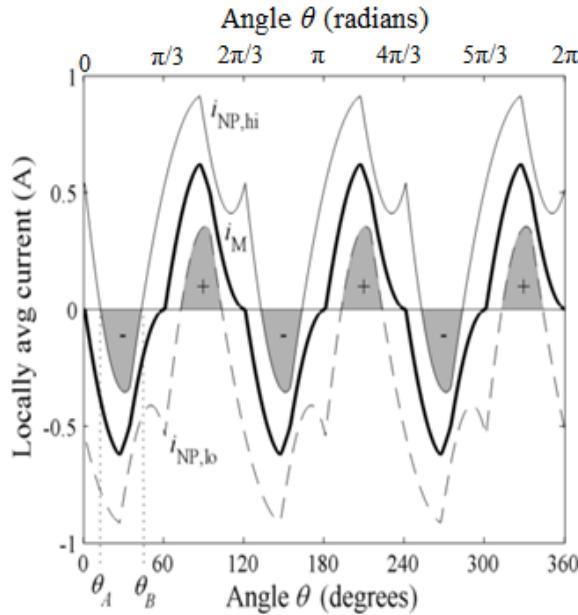

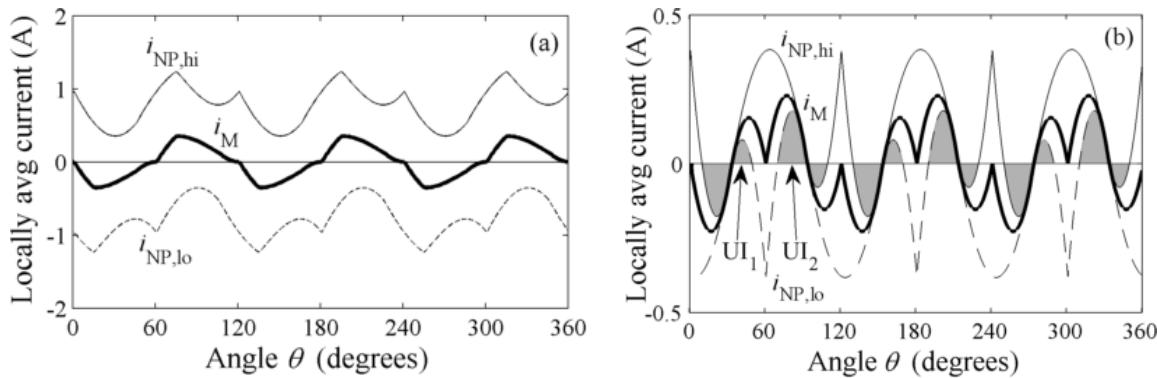

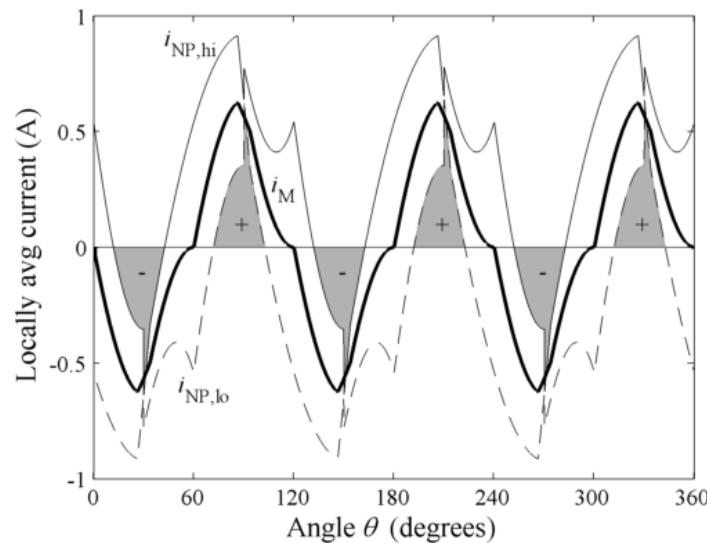

| Figure 6.3. $i_{NP,lo}$ , $i_{NP,hi}$ and $i_M$ during a fundamental cycle, for $\phi = -30$ degrees and $m = 0.9$ ( $I_o = 1$ A).....                                                                                                                                                                                                                                                                        | 99  |

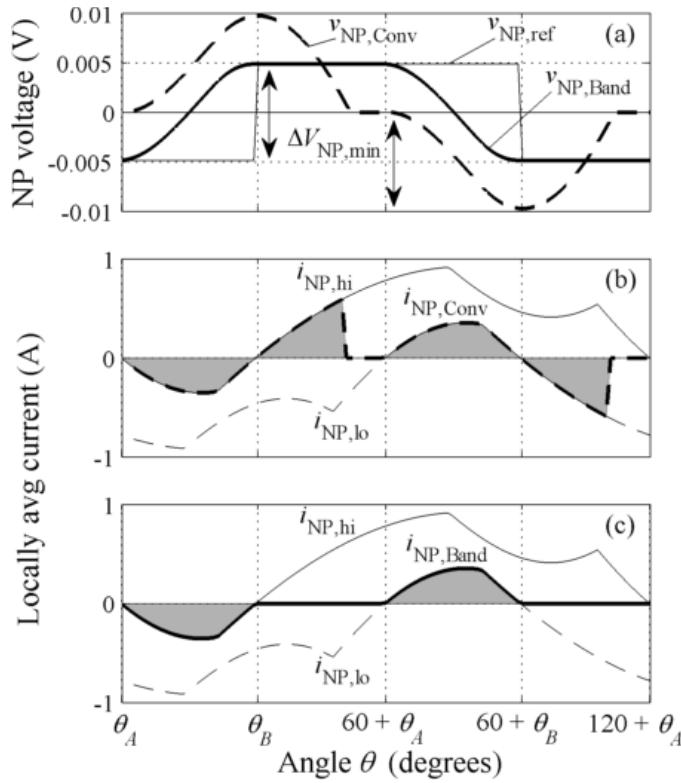

| Figure 6.4. (a) $v_{NP,Conv}$ , $v_{NP,Band}$ and $v_{NP,ref}$ , (b) $i_{NP,Conv}$ , $i_{NP,lo}$ and $i_{NP,hi}$ , and (c) $i_{NP,Band}$ , $i_{NP,lo}$ and $i_{NP,hi}$ during a third of a fundamental cycle, for $\phi = -30$ degrees and $m = 0.9$ ( $I_o = 1$ A, $f = 1$ Hz, $C = 1$ F). .....                                                                                                             | 102 |

| Figure 6.5. $i_{NP,lo}$ , $i_{NP,hi}$ and $i_M$ during a fundamental cycle, for (a) $\phi = -30$ degrees, $m = 0.7$ (Region 0), and (b) $\phi = -3$ degrees, $m = 1$ (Region 2). .....                                                                                                                                                                                                                        | 104 |

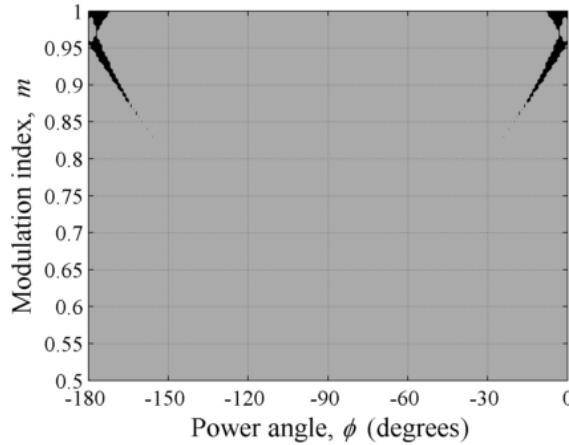

| Figure 6.6. Regions of NPC converter operation: (White) Region 0, (Grey) Region 1, (Black) Region 2. .....                                                                                                                                                                                                                                                                                                    | 104 |

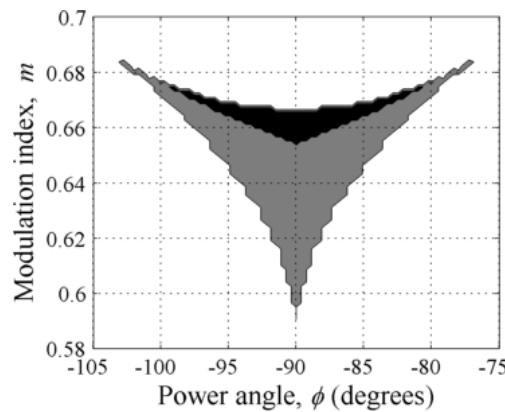

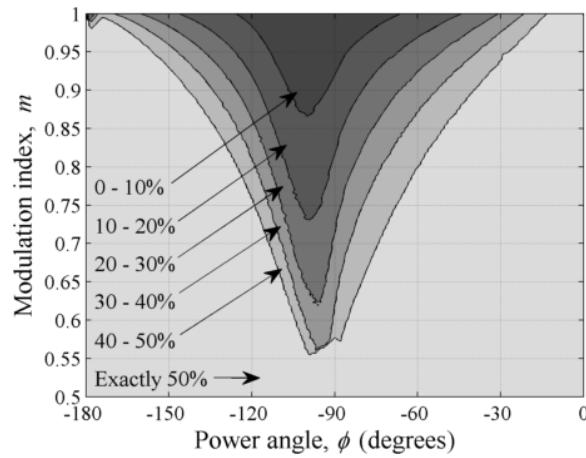

| Figure 6.7. (White) Region 1, (Grey) Part of Region 2 where $\Delta V_{NP,min}$ can be achieved, (Black) Part of Region 2 where $\Delta V_{NP,min}$ cannot be achieved. .....                                                                                                                                                                                                                                 | 105 |

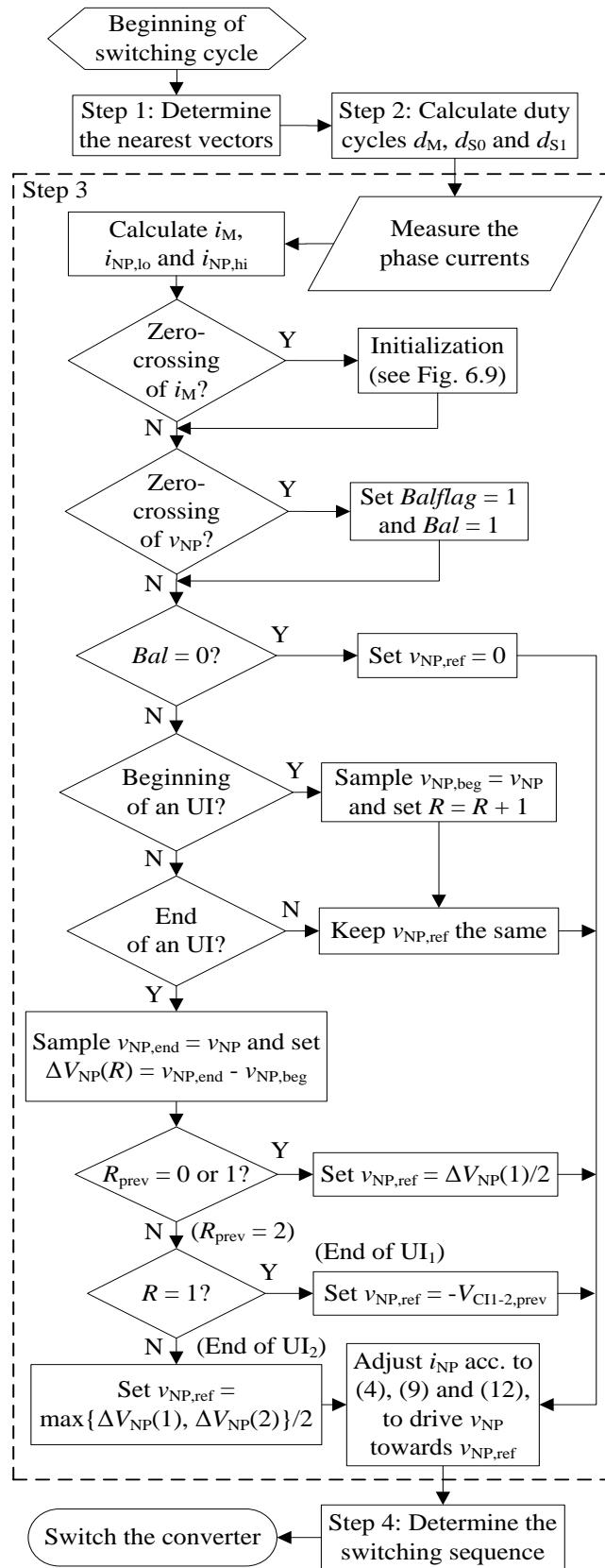

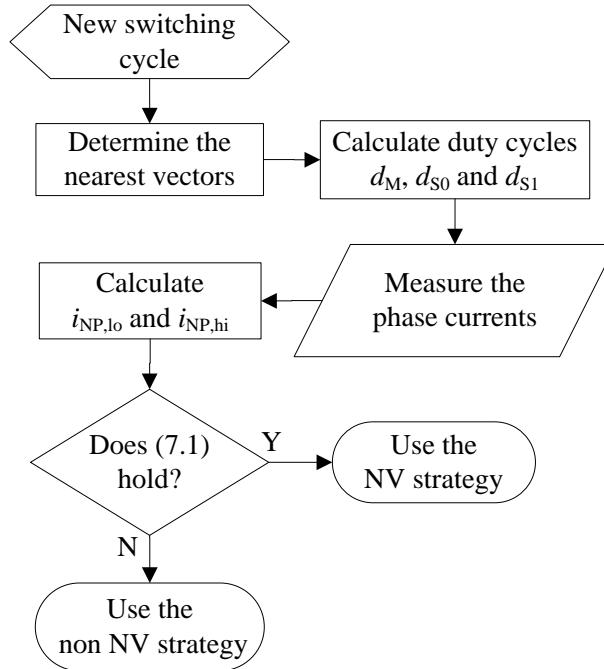

| Figure 6.8. Flowchart of the proposed algorithm for the operation of Band-NV strategies..                                                                                                                                                                                                                                                                                                                     | 107 |

| Figure 6.9. Pseudocode for the algorithm's initialization block.....                                                                                                                                                                                                                                                                                                                                          | 108 |

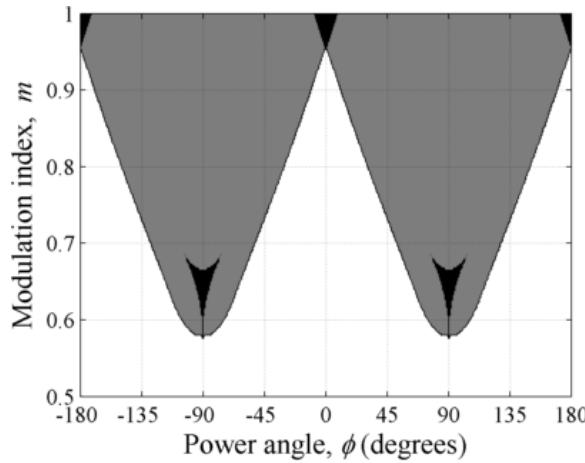

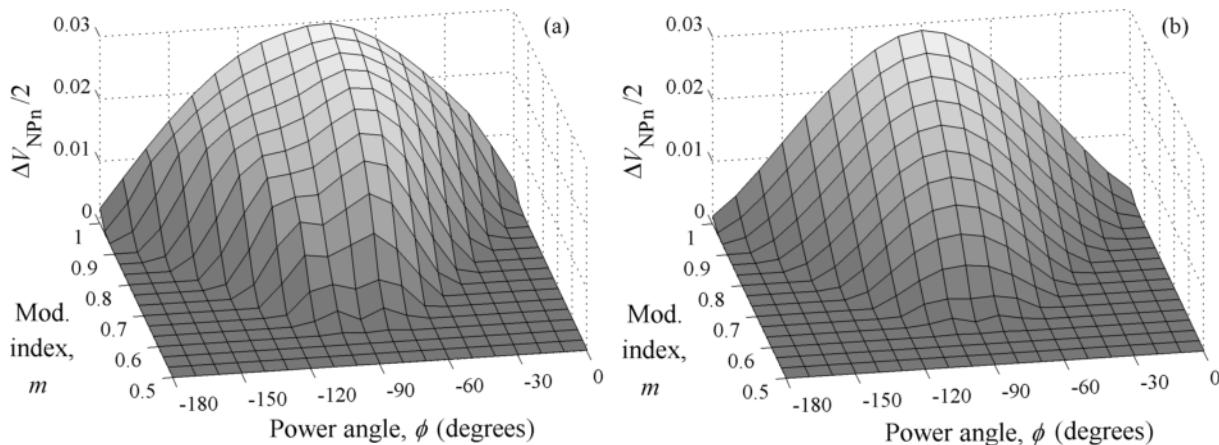

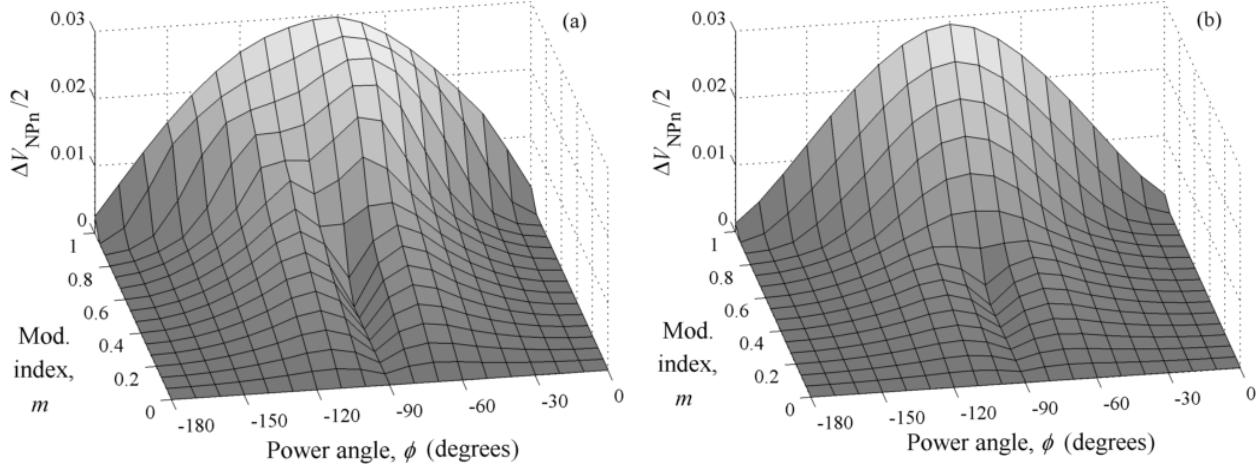

| Figure 6.10. Minimum normalized amplitude of NP voltage ripple ( $\Delta V_{NPn}/2$ ) for (a) Conventional NV, and (b) Band-NV strategies.....                                                                                                                                                                                                                                                                | 110 |

| Figure 6.11. Value of $decr$ as a function of $\phi$ and $m$ . .....                                                                                                                                                                                                                                                                                                                                          | 110 |

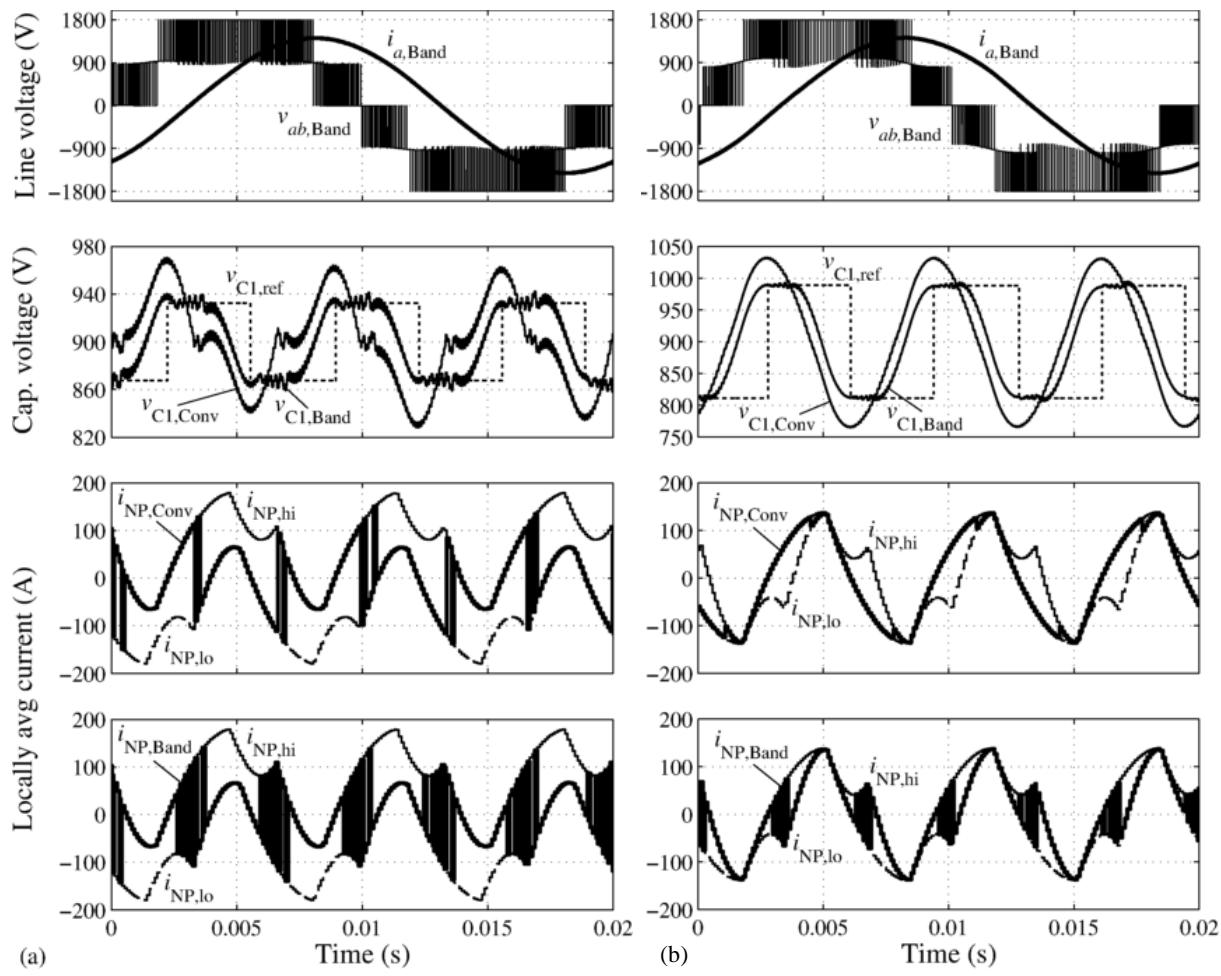

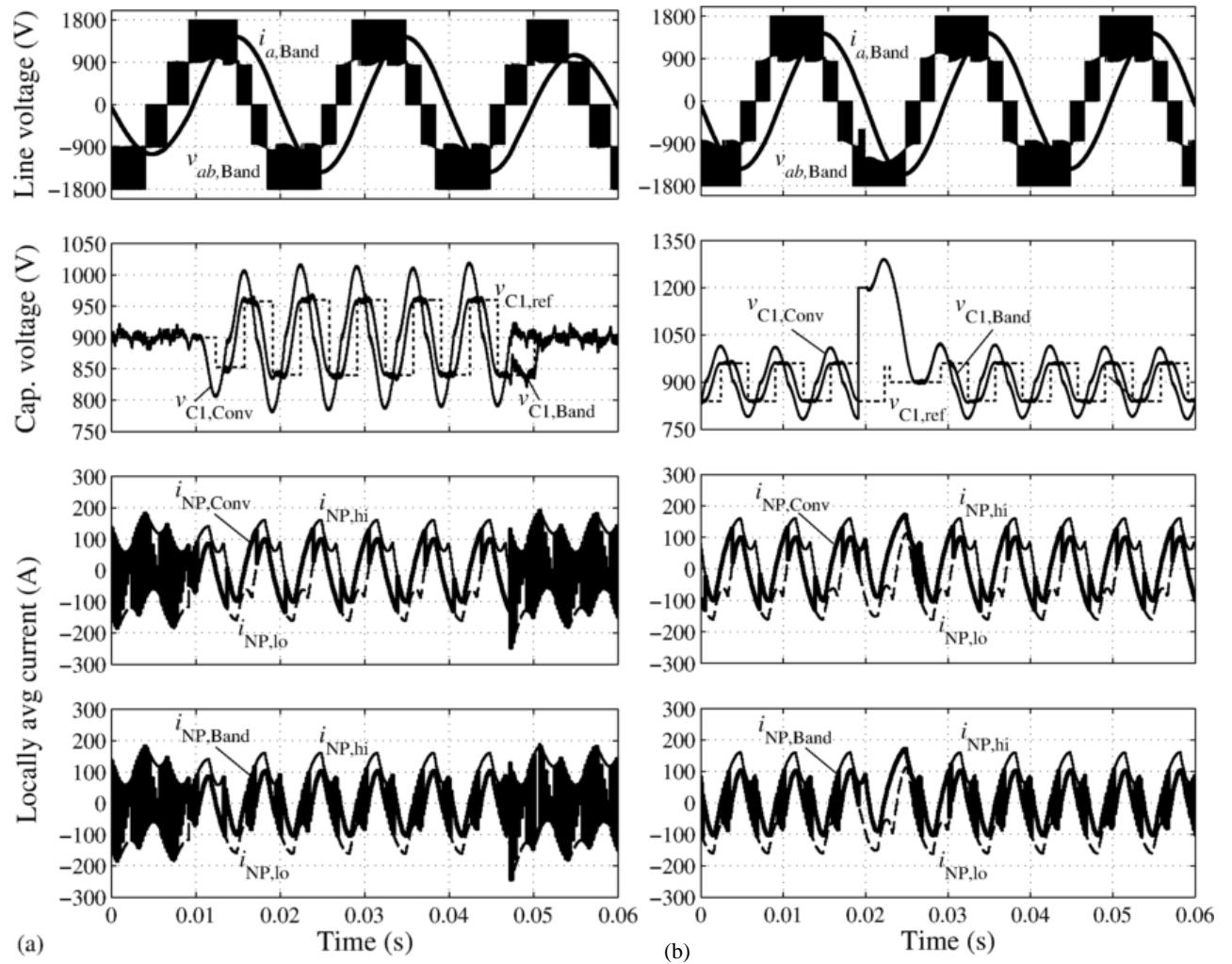

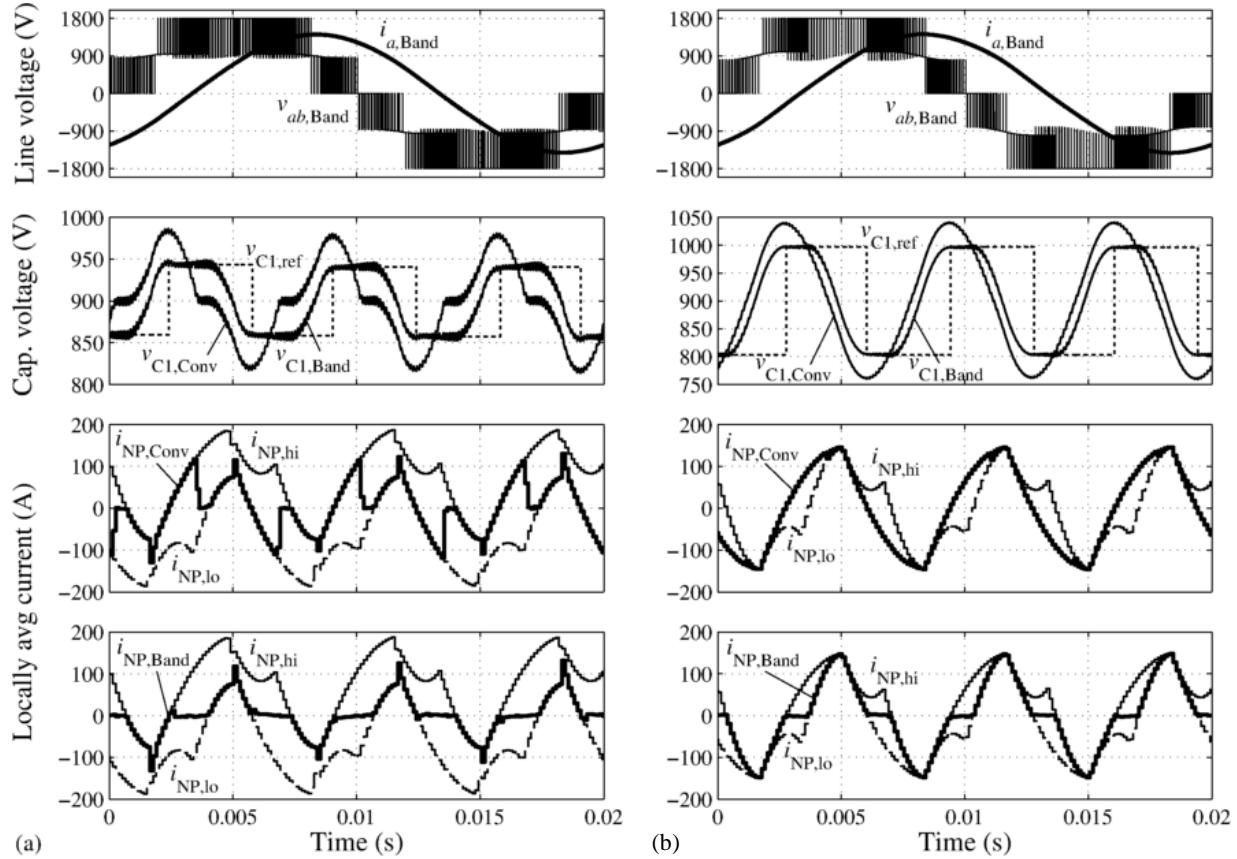

| Figure 6.12. Simulation comparing the Band-NTV to the conventional NTV strategy during a fundamental cycle, for $\phi = -30$ degrees and (a) $m = 0.9$ , (b) $m = 1$ . i) (top) Line voltage $v_{ab}$ and current $5 \times i_a$ , ii) $v_{C1,Conv}$ , $v_{C1,Band}$ and $v_{C1,ref}$ , iii) $i_{NP,Conv}$ , $i_{NP,lo}$ and $i_{NP,hi}$ , and iv) (bottom) $i_{NP,Band}$ , $i_{NP,lo}$ and $i_{NP,hi}$ ..... | 114 |

Figure 6.13. Simulation comparing the Band-NTV to the conventional NTV strategy, for transient responses, (a) Change of  $m$  from 0.7 to 0.95 and back to 0.7, for  $\phi = -30$  degrees, and (b) Balancing after a transient imbalance, while the inverter operates at  $\phi = -30$  degrees and  $m = 0.95$ . *i*) (top) Line voltage  $v_{ab}$  and current  $5 \times i_a$ , *ii*)  $v_{C1,Conv}$ ,  $v_{C1,Band}$  and  $v_{C1,ref}$ , *iii*)  $i_{NP,Conv}$ ,  $i_{NP,lo}$  and  $i_{NP,hi}$ , and *iv*) (bottom)  $i_{NP,Band}$ ,  $i_{NP,lo}$  and  $i_{NP,hi}$  ..... 115

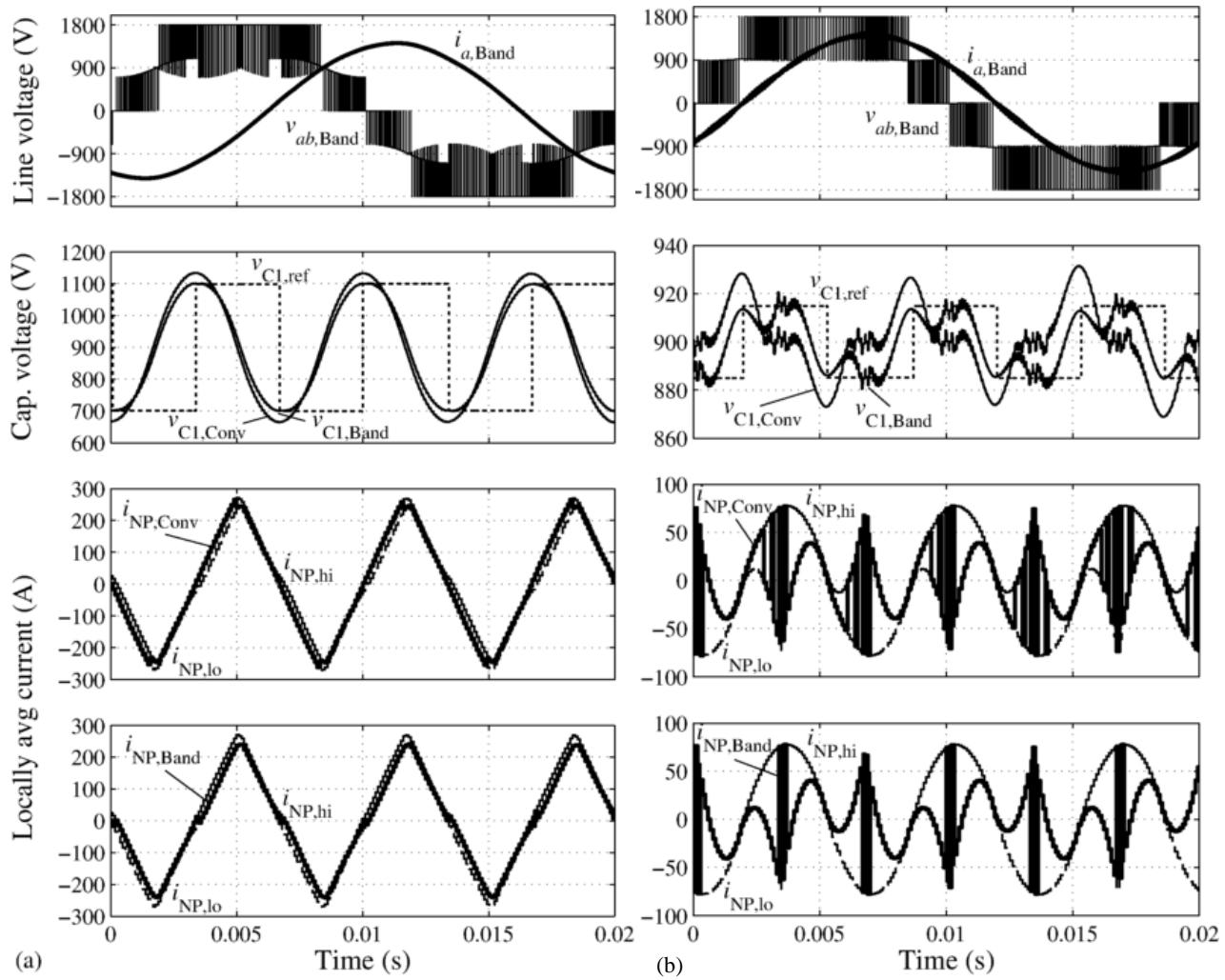

Figure 6.14. Simulation comparing the Band-NTV to the conventional NTV strategy during a fundamental cycle, for (a)  $\phi = -83$  degrees,  $m = 0.95$  (Region 1), and (b)  $\phi = -6$  degrees,  $m = 1$  (Region 2). *i*) (top) Line voltage  $v_{ab}$  and current  $5 \times i_a$ , *ii*)  $v_{C1,Conv}$ ,  $v_{C1,Band}$  and  $v_{C1,ref}$ , *iii*)  $i_{NP,Conv}$ ,  $i_{NP,lo}$  and  $i_{NP,hi}$ , and *iv*) (bottom)  $i_{NP,Band}$ ,  $i_{NP,lo}$  and  $i_{NP,hi}$  ..... 116

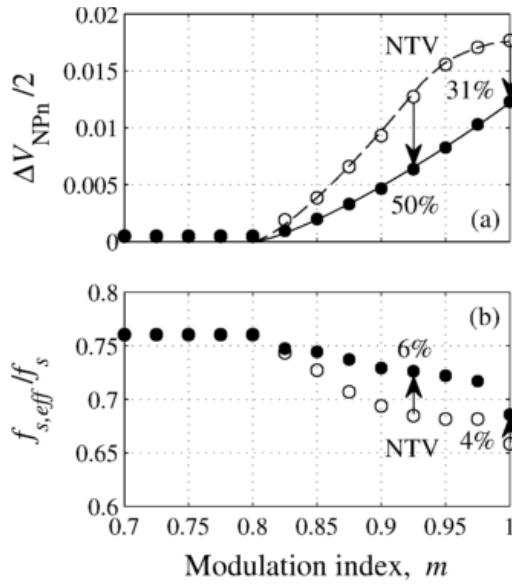

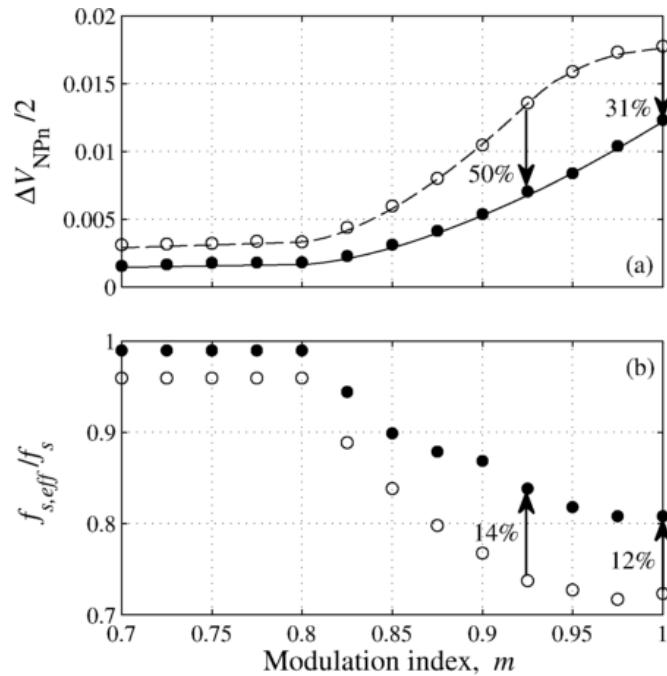

Figure 6.15. For  $\phi = -30$  degrees and  $m \geq 0.7$ , (a) Normalized amplitude of NP voltage ripple: (continuous line)  $\Delta V_{NPn,Band}/2$ , (dashed line)  $\Delta V_{NPn,Conv}/2$ , (filled circles) Simulation for Band-NTV strategy, (empty circles) Simulation for NTV strategy, and (b) Ratio of  $f_{s,eff}$  over  $f_s$  ..... 118

Figure 7.1. Flowchart for the proposed hybrid strategies. ..... 124

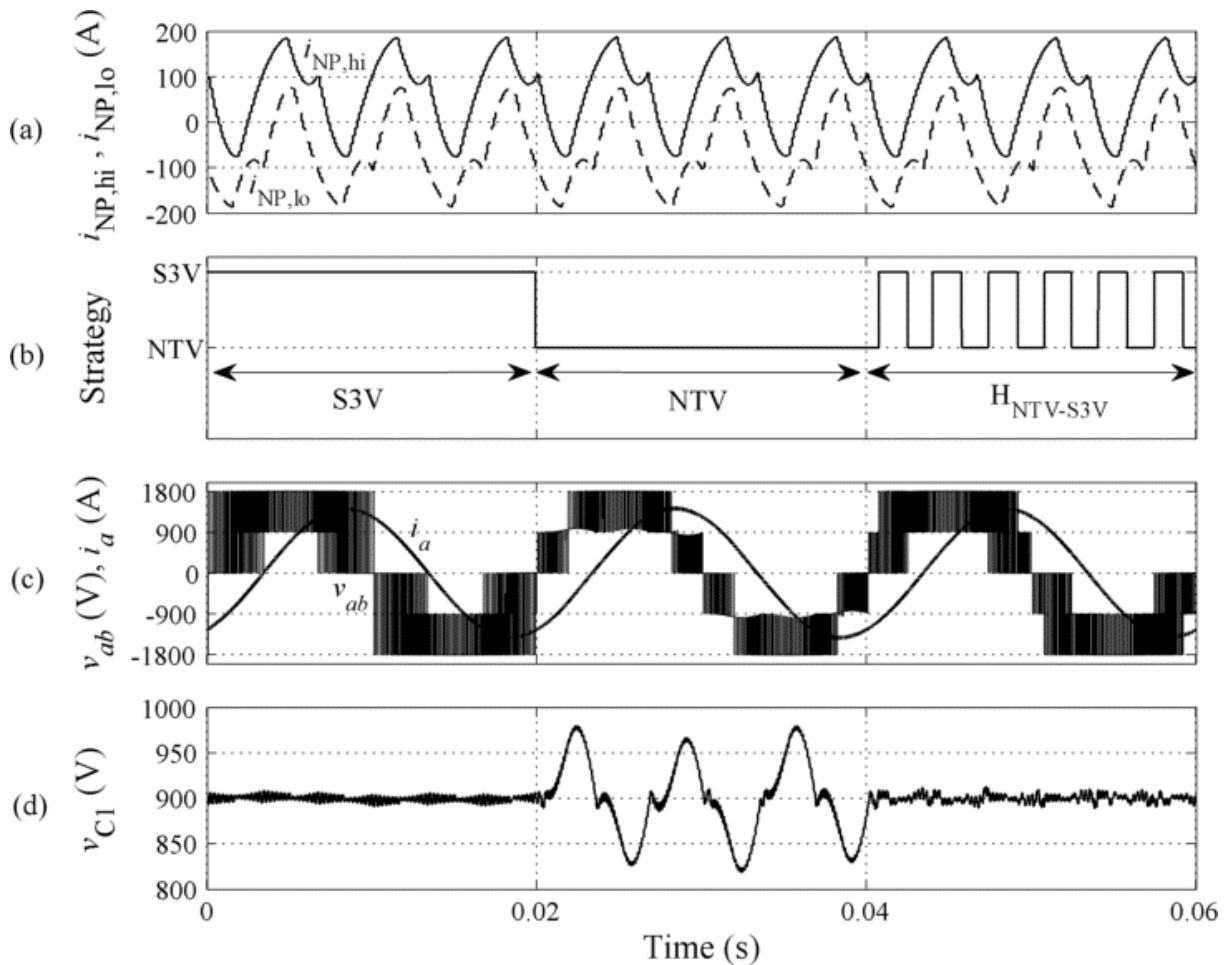

Figure 7.2. Simulation of NPC inverter modulated successively by the S3V, NTV and  $H_{NTV-S3V}$  strategies: (a) Locally averaged currents  $i_{NP,lo}$  and  $i_{NP,hi}$ , (b) Applied modulation strategy, (c) Line voltage  $v_{ab}$  and current  $5 \times i_a$ , and (d) Capacitor voltage  $v_{C1}$  ..... 125

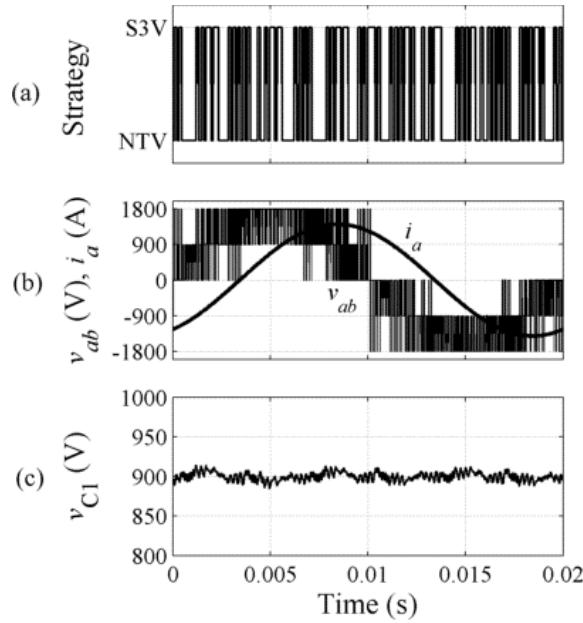

Figure 7.3. Simulation of NPC inverter modulated by a hybrid strategy combining the NTV and S3V according to [52] ( $v_{NP,max} = 5$  V): (a) Applied modulation strategy, (b) Line voltage  $v_{ab}$  and current  $5 \times i_a$ , and (c) Capacitor voltage  $v_{C1}$  ..... 126

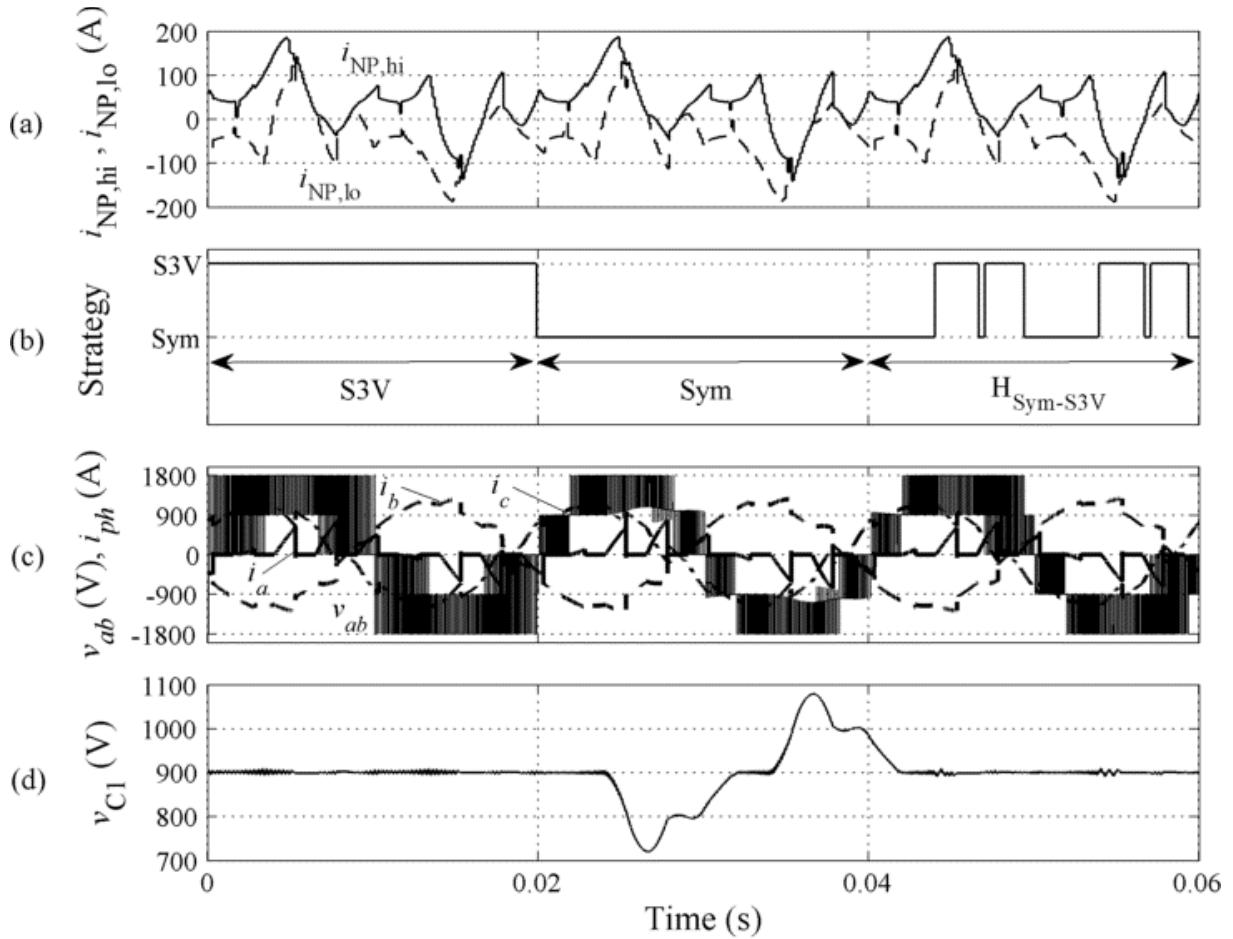

Figure 7.4. Simulation of NPC inverter modulated successively by the S3V, Symmetric (Sym) and  $H_{Sym-S3V}$  strategies, supplying a non linear and imbalanced load: (a) Locally averaged currents  $i_{NP,lo}$  and  $i_{NP,hi}$ , (b) Applied modulation strategy, (c) Line voltage  $v_{ab}$  and three-phase currents  $5 \times i_a$ ,  $5 \times i_b$ , and  $5 \times i_c$ , and (d) Capacitor voltage  $v_{C1}$  ..... 127

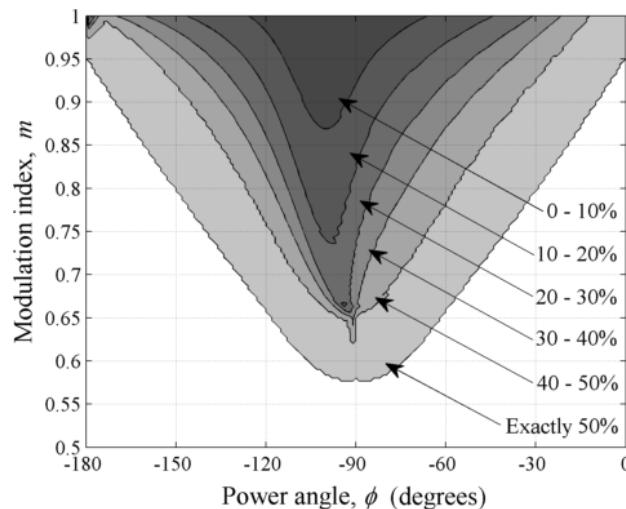

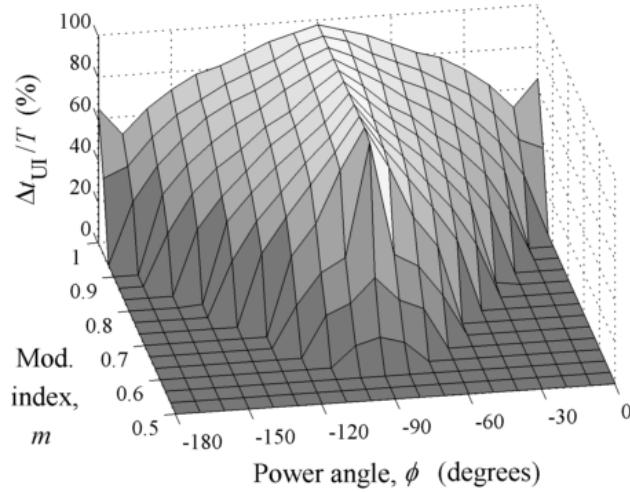

Figure 7.5. Percentage duration of uncontrollable intervals as a function of  $\phi$  and  $m$  according to (6.4) and (6.9) – (6.12), for sinusoidal and balanced phase currents. ..... 128

|                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.1. Waveforms of $i_{NP,hi SC}$ and $i_{NP,lo SC}$ for the Symmetric strategy, for $\phi = -30$ degrees and $m = 0.9$ .....                                                                                                                                                                                                                                                                   | 135 |

| Figure 8.2. Normalized amplitude of NP voltage ripple ( $\Delta V_{NPn SC}/2$ ) for the (a) Symmetric, and (b) Band-Sym strategy. .....                                                                                                                                                                                                                                                               | 136 |

| Figure 8.3. Value of <i>decr</i> as a function of $\phi$ and $m$ , for the Symmetric and Band-Sym strategies. .....                                                                                                                                                                                                                                                                                   | 136 |

| Figure 8.4. Regions of converter operation for the Symmetric strategy: (Grey) Region 1, (Black) Region 2.....                                                                                                                                                                                                                                                                                         | 137 |

| Figure 8.5. Simulation comparing the Band-Sym to the Symmetric strategy during a fundamental cycle, for $\phi = -30$ degrees and (a) $m = 0.9$ , (b) $m = 1$ . i) (top) Line voltage $v_{ab}$ and current $5 \times i_a$ , ii) $v_{C1,Conv}$ , $v_{C1,Band}$ and $v_{C1,ref}$ , iii) $i_{NP,Conv}$ , $i_{NP,lo}$ and $i_{NP,hi}$ , and iv) (bottom) $i_{NP,Band}$ , $i_{NP,lo}$ and $i_{NP,hi}$ ..... | 137 |

| Figure 8.6. For $\phi = -30$ degrees and $m \geq 0.7$ , (a) Normalized amplitude of NP voltage ripple: (continuous line) $\Delta V_{Band-Sym}/2$ , (dashed line) $\Delta V_{Sym}/2$ , (filled circles) Simulation for Band-Sym strategy, (empty circles) Simulation for Symmetric strategy, and (b) Ratio of $f_{s,eff}$ over $f_s$ .....                                                             | 138 |

| Figure A.1. Space Vectors and triangles $tr_1 - tr_4$ , in one sextant of a three-level converter.                                                                                                                                                                                                                                                                                                    | 142 |

| Figure A.2. Space Vectors and small triangles for the Symmetric strategy. ....                                                                                                                                                                                                                                                                                                                        | 144 |

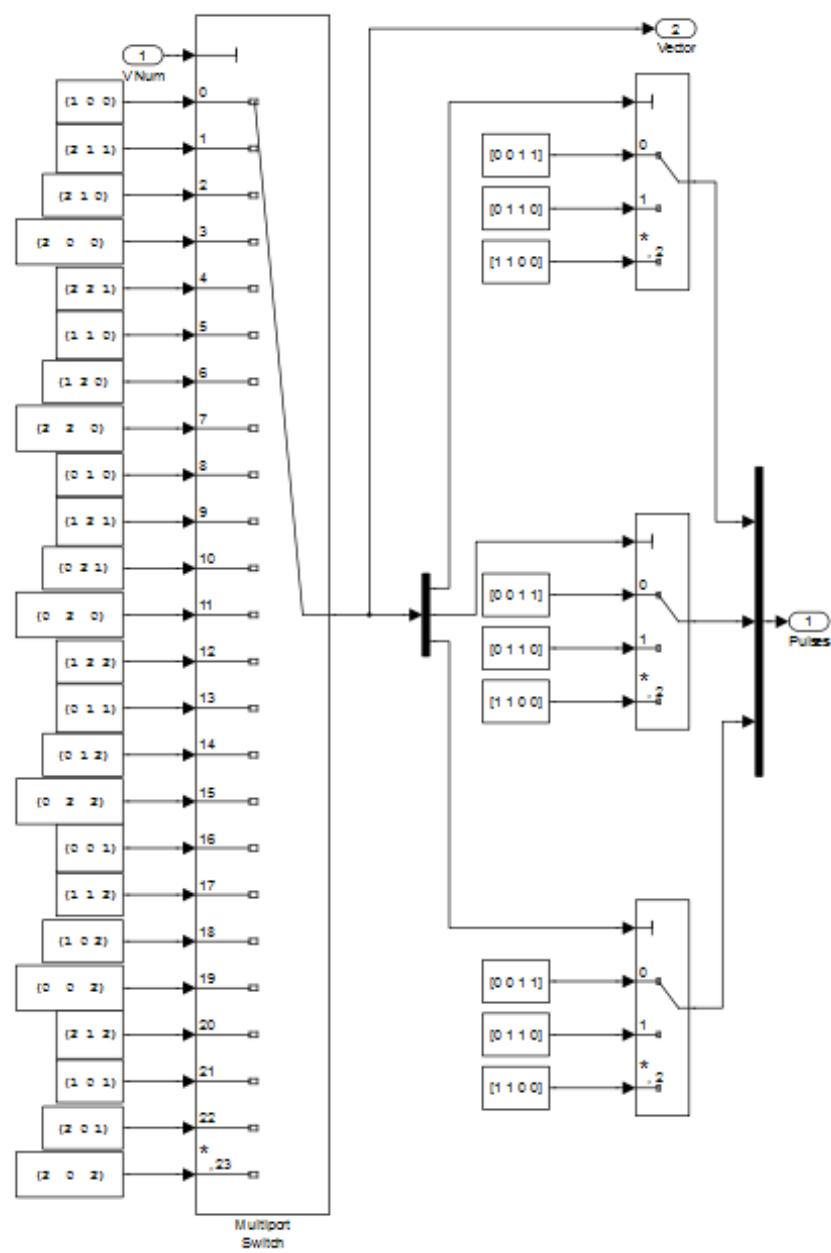

| Figure A.3. Vector selection block. ....                                                                                                                                                                                                                                                                                                                                                              | 148 |

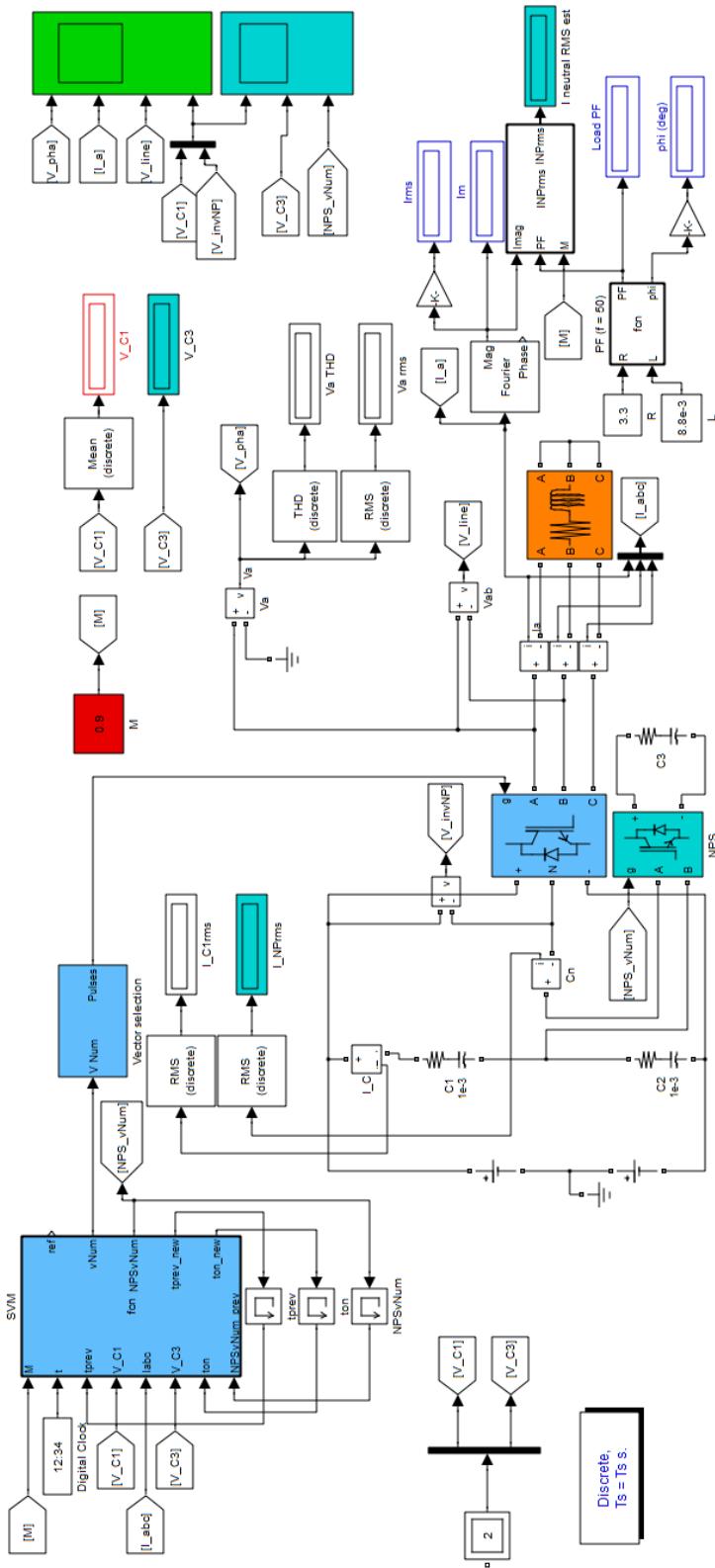

| Figure A.4. Simulink model of NPC converter with NPS circuit. ....                                                                                                                                                                                                                                                                                                                                    | 149 |

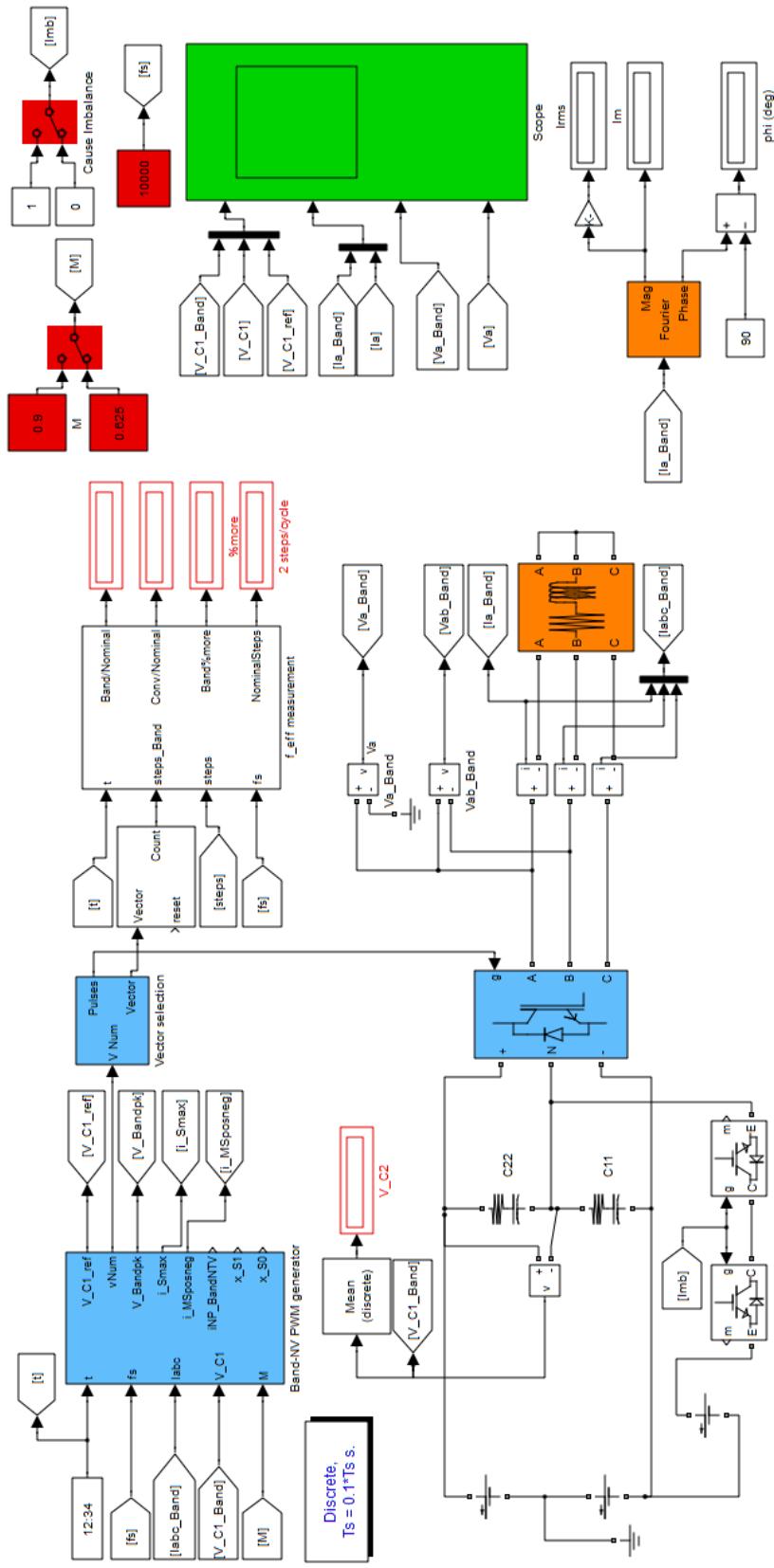

| Figure A.5. Simulink model of NPC converter modulated with the Band-NTV strategy....                                                                                                                                                                                                                                                                                                                  | 150 |

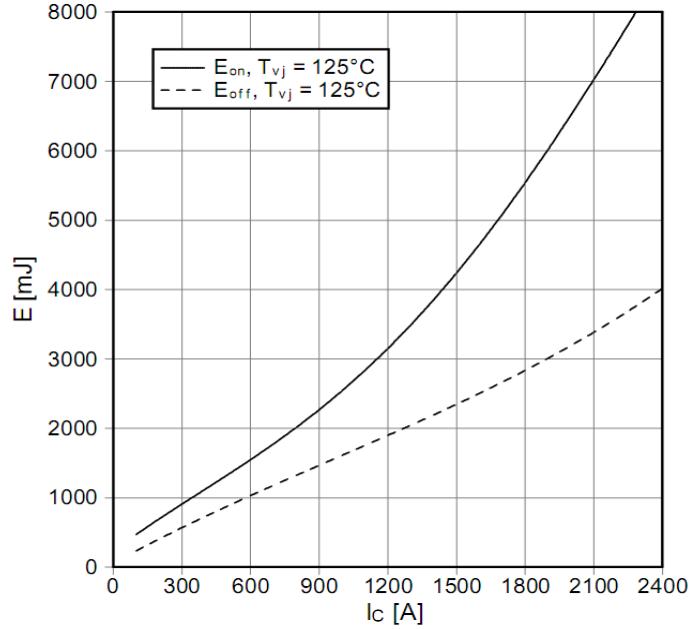

| Figure B.1. IGBT turn-on and turn-off energy losses [76].....                                                                                                                                                                                                                                                                                                                                         | 159 |

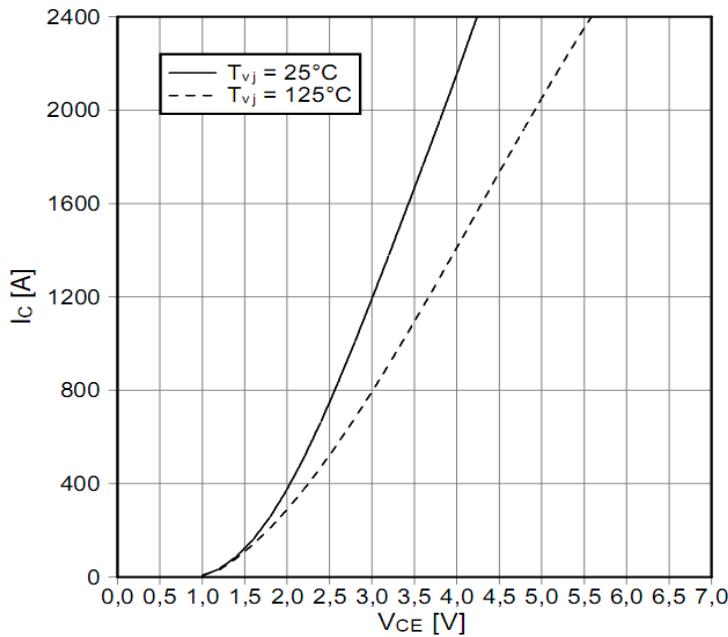

| Figure B.2. IGBT <i>I-V</i> characteristic [76].....                                                                                                                                                                                                                                                                                                                                                  | 164 |

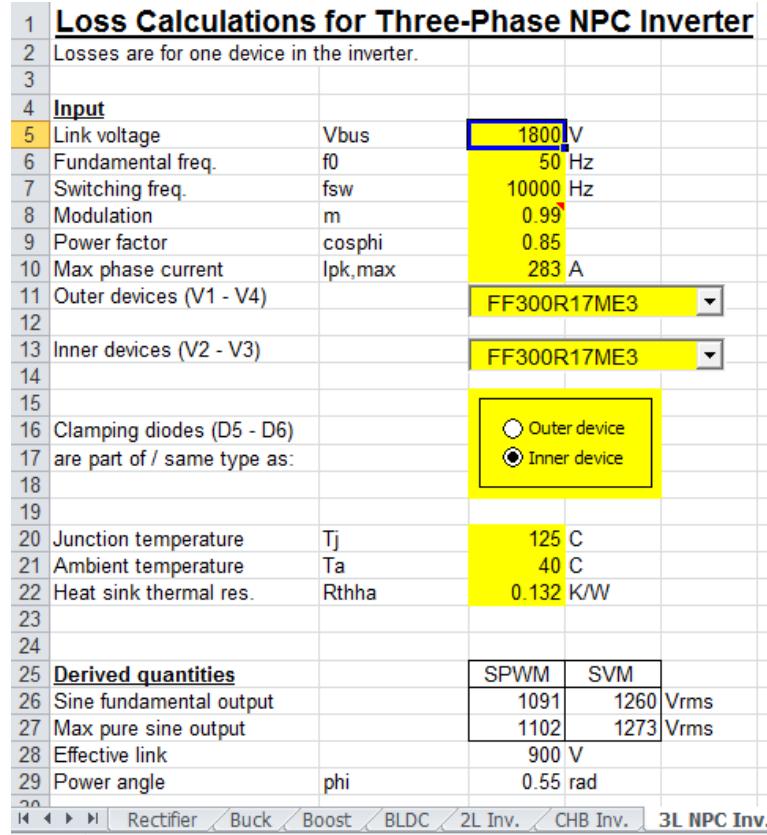

| Figure B.3. Converter selection and input parameters for the NPC inverter sheet of the CLC. ....                                                                                                                                                                                                                                                                                                      | 171 |

| Figure B.4. Datasheet values and derived loss coefficients for the selected IGBT-diode module. ....                                                                                                                                                                                                                                                                                                   | 171 |

|                                                                                                                                                                                                                                                                                                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

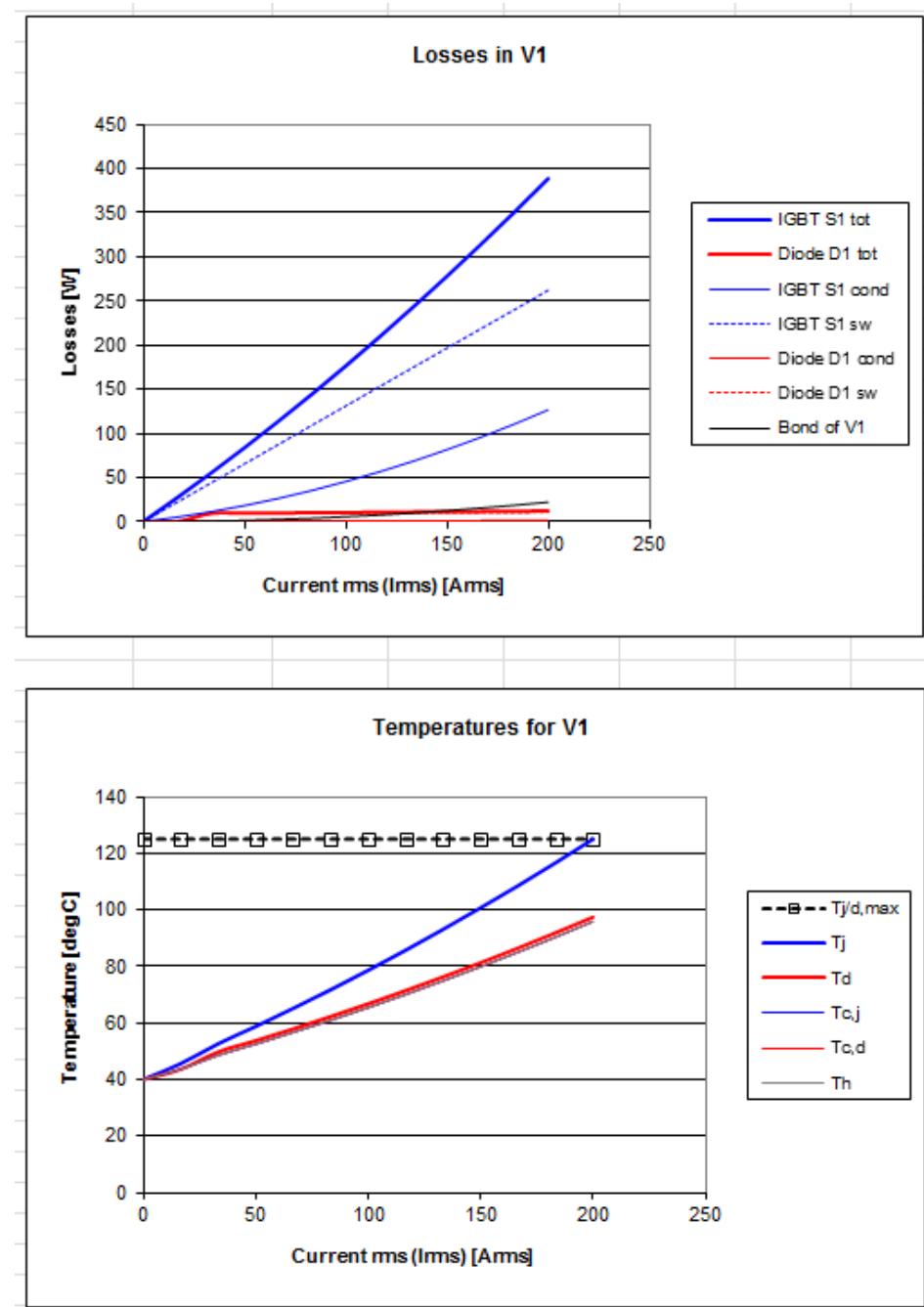

| Figure B.5. Losses and temperatures for each semiconductor, as a function of the output current.....                                                                                                                                                                                                 | 172 |

| Figure B.6. Losses and temperatures for module $V_{1x}$ , in a graphical form.....                                                                                                                                                                                                                   | 173 |

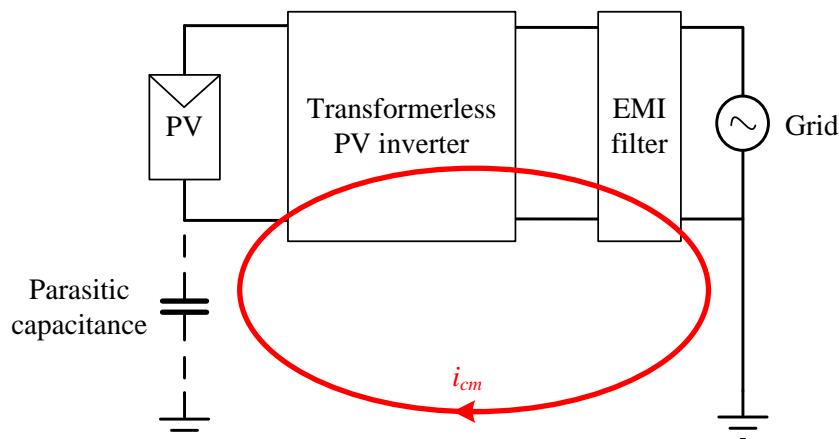

| Figure C.1. Common-mode current ( $i_{cm}$ ) circulation path, through the PV array's parasitic capacitance [83].....                                                                                                                                                                                | 175 |

| Figure C.2. NPC inverter topology [49].....                                                                                                                                                                                                                                                          | 177 |

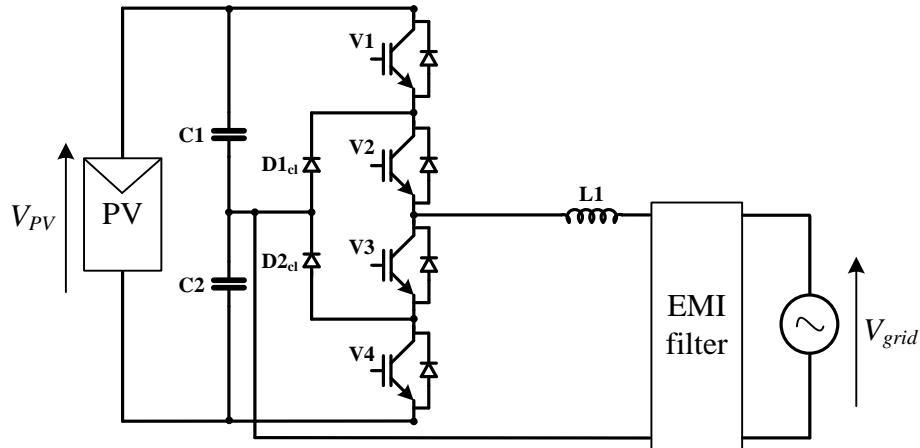

| Figure C.3. Conergy inverter topology [84].....                                                                                                                                                                                                                                                      | 177 |

| Figure C.4. Conventional H-Bridge inverter topology. ....                                                                                                                                                                                                                                            | 178 |

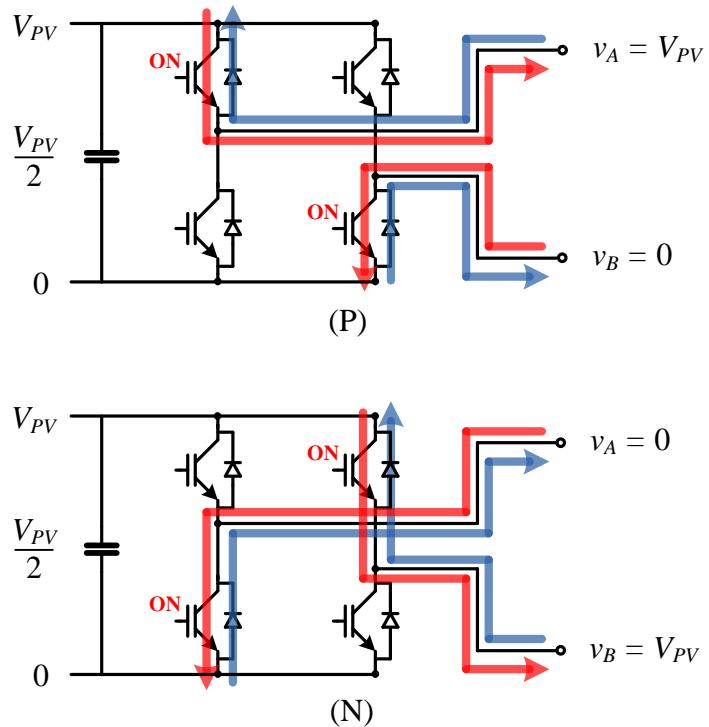

| Figure C.5. Switching states and conduction paths for the H-Bridge inverter under bipolar modulation: (P) $v_{AB} = V_{PV}$ , and (N) $v_{AB} = -V_{PV}$ . Voltages $v_A$ and $v_B$ are shown w.r.t the negative PV rail. Arrows illustrate the conduction paths for both directions of current..... | 178 |

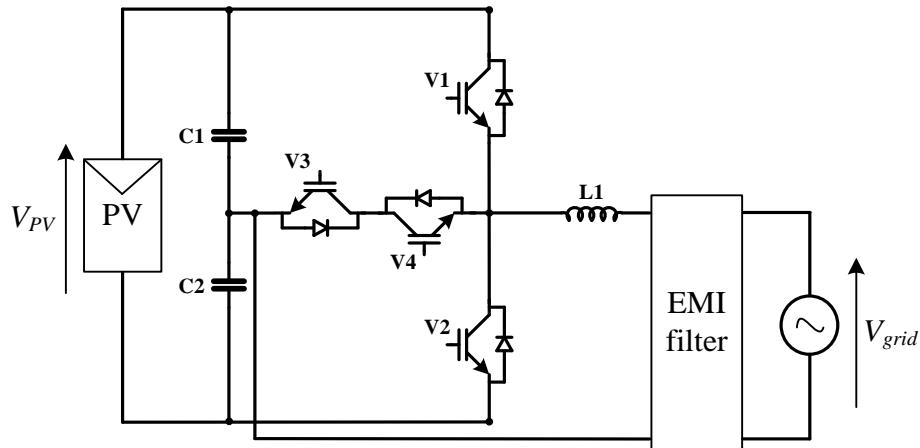

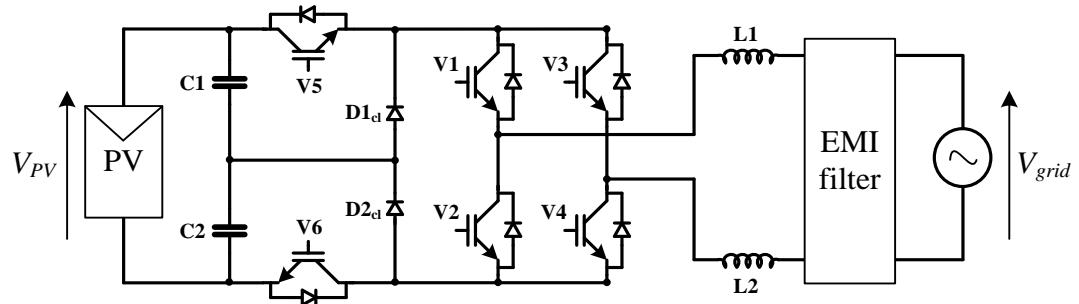

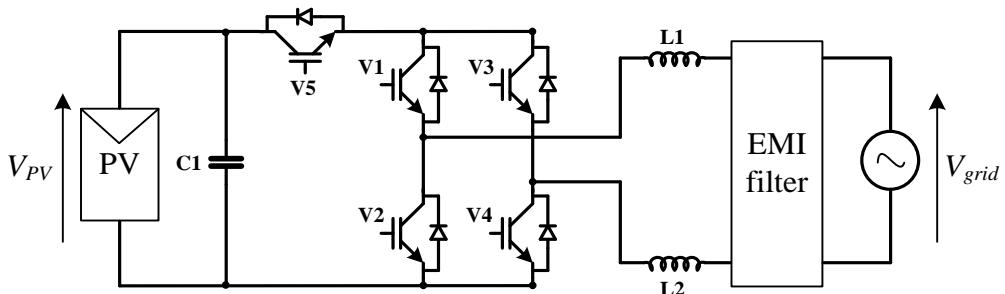

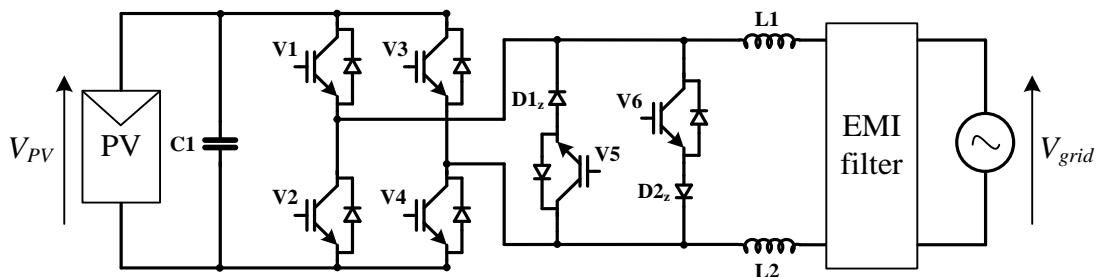

| Figure C.6. iH5 PV inverter topology [87]. .....                                                                                                                                                                                                                                                     | 181 |

| Figure C.7. H6 PV inverter topology [88, 89]. .....                                                                                                                                                                                                                                                  | 181 |

| Figure C.8. H5 PV inverter topology [90]. .....                                                                                                                                                                                                                                                      | 181 |

| Figure C.9. HERIC PV inverter topology [91]. .....                                                                                                                                                                                                                                                   | 181 |

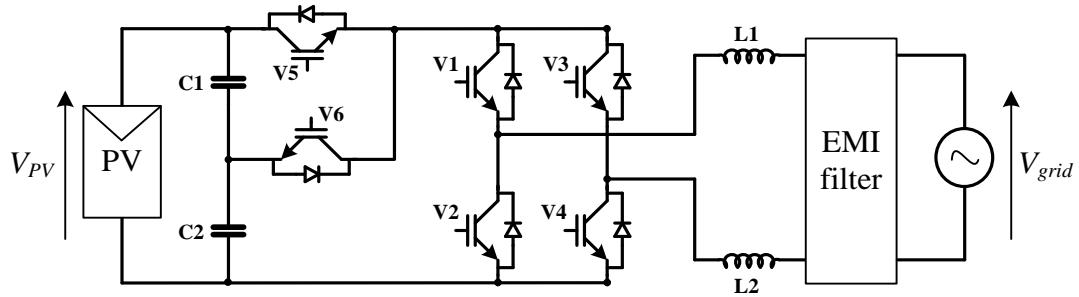

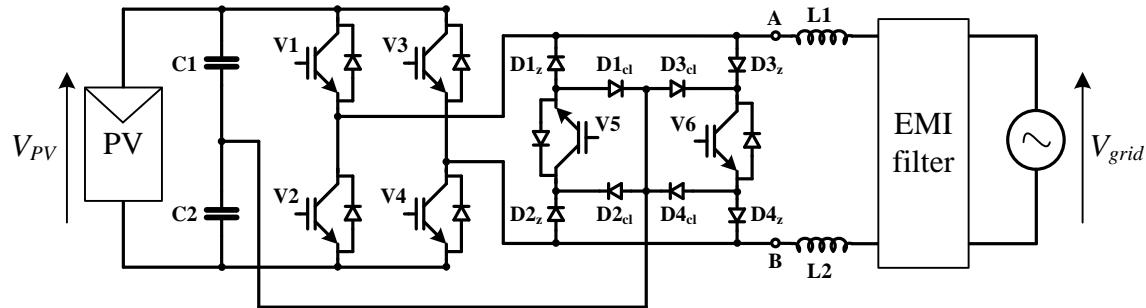

| Figure C.10. Proposed transformerless PV inverter topology. ....                                                                                                                                                                                                                                     | 182 |

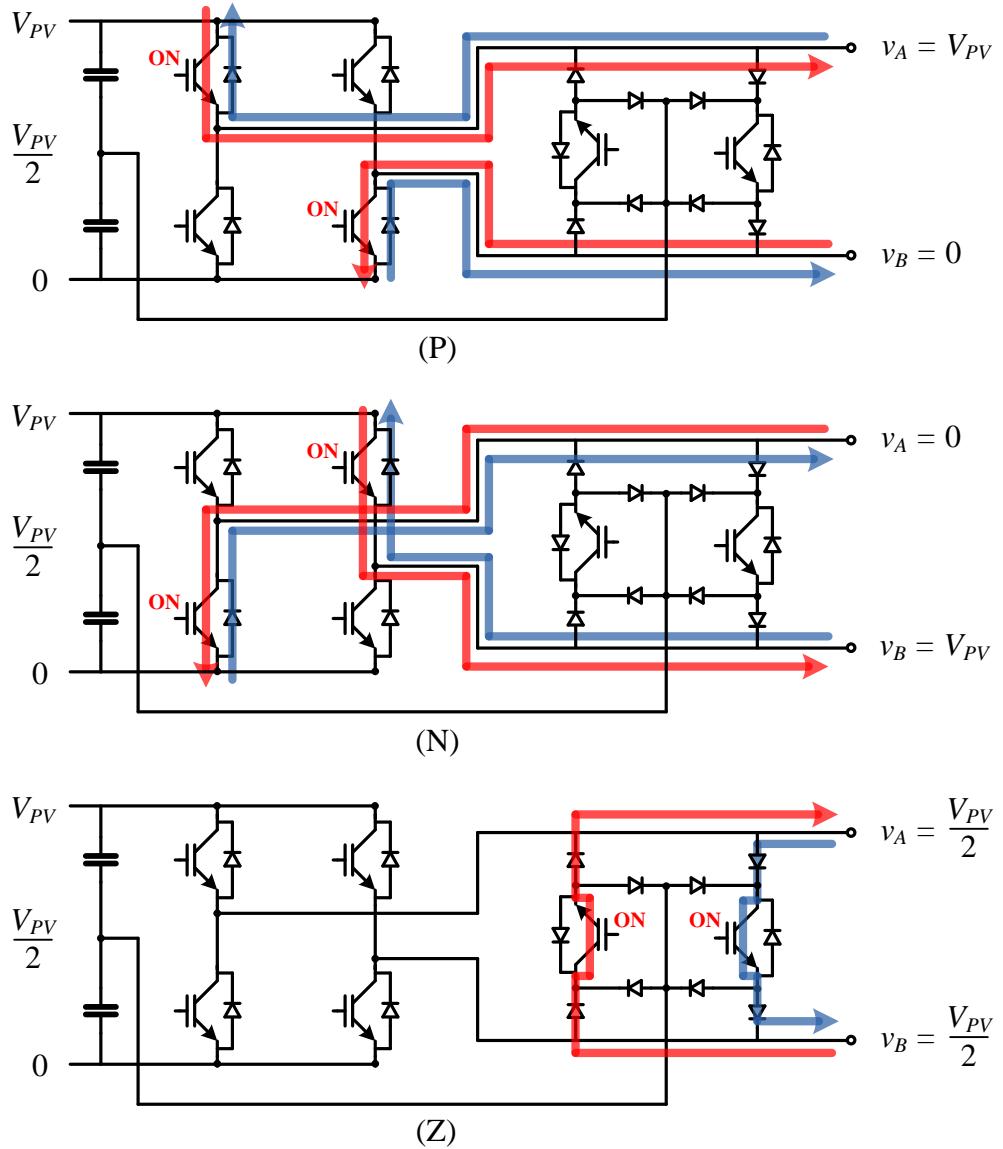

| Figure C.11. Switching states and conduction paths for the proposed PV inverter: (P) $v_{AB} = V_{PV}$ , (N) $v_{AB} = -V_{PV}$ , and (Z) $v_{AB} = 0$ . Voltages $v_A$ and $v_B$ are shown w.r.t the negative PV rail.....                                                                          | 183 |

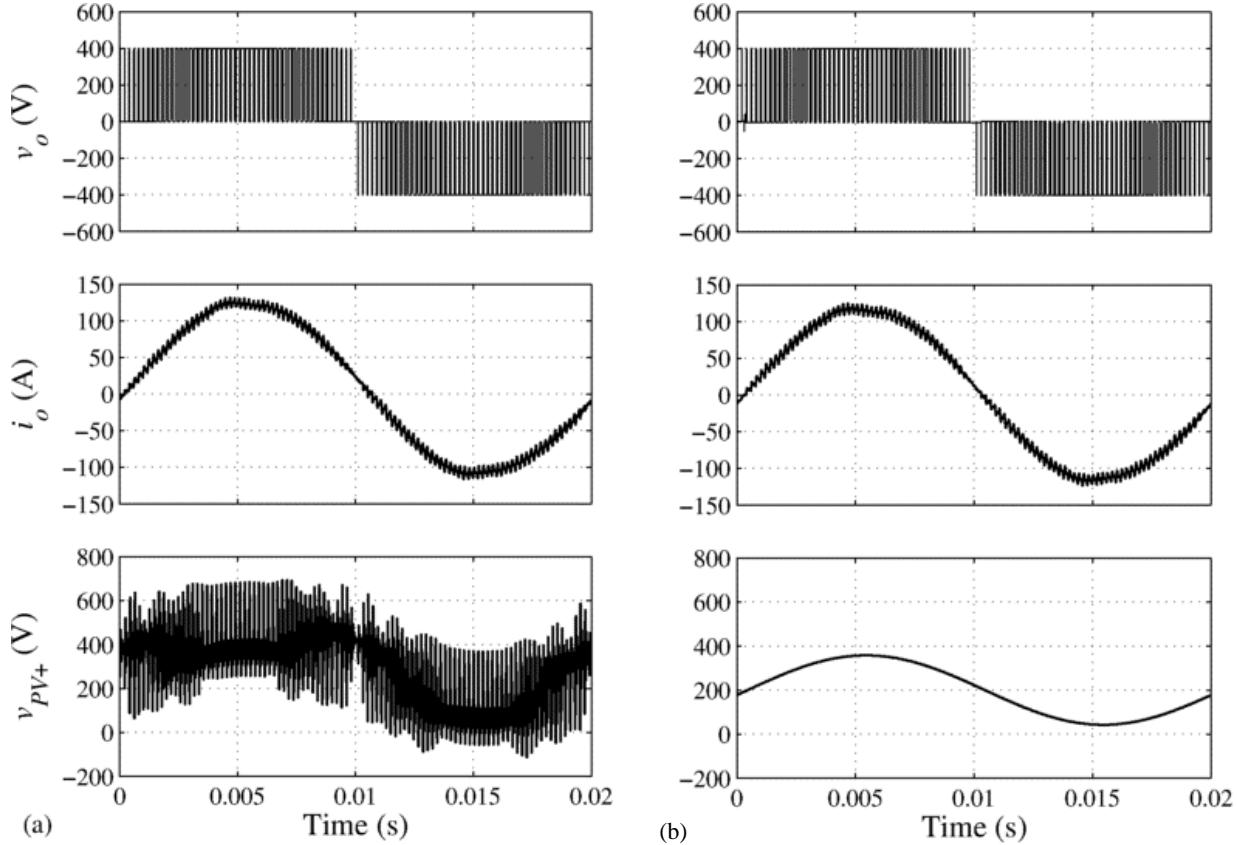

| Figure C.12. Simulated results of the proposed PV inverter operating with the parameters of                                                                                                                                                                                                          |     |

## List of Tables

---

|                                                                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1. Space Vectors and line voltages for the two-level converter states. ....                                   | 25  |

| Table 3.1. Switching intervals for Sector I ( $0 - \pi/3$ ) of the two-level inverter. ....                           | 39  |

| Table 3.2. Switching intervals for Sector I of the NPC inverter. ....                                                 | 42  |

| Table 3.3. Switching intervals for Sector II of the NPC inverter. ....                                                | 42  |

| Table 3.4. Expressions for $i_{d,dc}(\theta)$ and $i_{d,rms}(\theta)$ for the three sectors of the NPC inverter. .... | 42  |

| Table 3.5. Switching intervals for Sector I of the CHB inverter. ....                                                 | 44  |

| Table 3.6. Simulation parameters. ....                                                                                | 54  |

| Table 4.1. Summary of results for the examined single-phase inverter systems. ....                                    | 71  |

| Table 4.2. Summary of results for the examined three-phase inverter systems. ....                                     | 73  |

| Table 5.1. NPS switching states. ....                                                                                 | 80  |

| Table 5.2. Example operating parameters for the NPC inverter. ....                                                    | 84  |

| Table 6.1. Duty cycle distribution factors and switching sequences for the NTV strategy [51]. ....                    | 96  |

| Table A.1. Duty cycle distribution factors and switching sequences for the Symmetric strategy [51]. ....              | 145 |

| Table B.1. Conduction intervals for the NPC inverter. ....                                                            | 167 |

| Table B.2. Conduction duty cycles for three-level inverters. ....                                                     | 167 |

| Table B.3. Conduction intervals for the CHB inverter. ....                                                            | 169 |

| Table C.1. Switching states for the H-Bridge inverter under bipolar modulation. ....                                  | 179 |

| Table C.2. Zero (forbidden) switching states $Z_P$ and $Z_N$ for the H-Bridge transformerless PV inverter. ....       | 179 |

| Table C.3. Zero states for transformerless topologies based on the H-Bridge inverter. ....                            | 180 |

| Table C.4. Switching states for the proposed PV inverter. ....                                                        | 183 |

| Table C.5. Simulation parameters. ....                                                                                | 184 |

## List of Abbreviations and Acronyms

---

|          |                                                                 |

|----------|-----------------------------------------------------------------|

| 2L       | two-level                                                       |

| 3L       | three-level                                                     |

| ac       | alternating current                                             |

| AFE      | active front end                                                |

| Band-NTV | Band implementation of nearest-three-vector modulation strategy |

| Band-NV  | Band nearest vector                                             |

| Band-Sym | Band implementation of Symmetric modulation strategy            |

| BLDC     | brushless dc                                                    |

| CHB      | cascaded H-bridge                                               |

| CI       | controllable interval                                           |

| CLC      | converter loss calculator                                       |

| dc       | direct current                                                  |

| EMI      | electro-magnetic interference                                   |

| ESR      | capacitor equivalent series resistance                          |

| FE       | front end                                                       |

| GTO      | gate turn-off thyristor                                         |

| HF       | high frequency                                                  |

| IGBT     | insulated gate bipolar transistor                               |

| IGCT     | integrated gate commutated thyristor                            |

| LF       | low frequency                                                   |

| ML       | multilevel                                                      |

| MOSFET   | metal oxide semiconductor field effect transistor               |

| NP       | neutral point                                                   |

| NPC      | neutral point clamped                                           |

|                         |                                                                     |

|-------------------------|---------------------------------------------------------------------|

| NPS                     | neutral point shifter                                               |

| NTV                     | nearest-three-vector modulation strategy                            |

| NV                      | nearest vector                                                      |

| PD                      | phase disposition                                                   |

| PV                      | photovoltaic                                                        |

| PWM                     | pulse width modulation                                              |

| rms                     | root mean square                                                    |

| SHE                     | selective harmonic elimination                                      |

| SPWM                    | sinusoidal pulse width modulation                                   |

| SPWM+3 <sup>rd</sup> h. | sinusoidal pulse width modulation with 1/6 third harmonic injection |

| SV                      | space vector                                                        |

| SVM                     | space vector modulation                                             |

| Sym                     | Symmetric modulation strategy                                       |

| THD                     | total harmonic distortion                                           |

| UI                      | uncontrollable interval                                             |

| VSC                     | voltage source converter                                            |

| WTHD                    | weighted total harmonic distortion                                  |

## List of Symbols

---

|                      |                                                                |

|----------------------|----------------------------------------------------------------|

| <b>C</b>             | capacitor                                                      |

| $C$                  | capacitance                                                    |

| <b>D</b>             | diode                                                          |

| $d_V$                | duty cycle of Space Vector $\mathbf{V}$                        |

| $D_{1x}$             | anti-parallel diode of module $V_{1x}$                         |

| $decr$               | decrement of NP voltage ripple decrement by Band-NV strategies |

| $F$                  | function for the geometric wall model                          |

| $f$                  | fundamental frequency                                          |

| $f_s$                | switching frequency                                            |

| $f_{s,eff}$          | effective switching frequency                                  |

| $i_{NP}$             | locally averaged NP current                                    |

| $I_{NP}(\mathbf{V})$ | NP current resulting from Space Vector $\mathbf{V}$            |