University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

**Error Resilient Techniques for Storage Elements of Low Power Design**

by

**Sheng Yang**

Thesis for the degree of Doctor of Philosophy

July 2013

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Doctor of Philosophy

ERROR RESILIENT TECHNIQUES FOR STORAGE ELEMENTS OF LOW

POWER DESIGN

by **Sheng Yang**

Over two decades of research has led to numerous low-power design techniques being reported. Two popular techniques are supply voltage scaling and power gating. This thesis studies the impact of these two design techniques on the reliability of embedded processor registers and memory systems in the presence of transient faults; and with the aim to develop and validate efficient mitigation techniques to improve reliability with small cost of energy consumption, performance and area overhead.

This thesis presents three original contributions. The first contribution presents a technique for improving the reliability of embedded processors. A key feature of the technique is low cost, which is achieved through reuse of the scan chain for state monitoring, and it is effective because it can correct single and multiple bit errors through hardware and software respectively. To validate the technique, ARM<sup>®</sup> Cortex<sup>™</sup>-M0 embedded microprocessor is implemented in FPGA and further synthesised using 65-nm technology to quantify the cost in terms of area, latency and energy. It is shown that the presented technique has a small area overhead (8.6%) with less than 4% worst-case increase in critical path. The second contribution demonstrates that state integrity of flip-flops is sensitive to process, voltage and temperature (PVT) variation through measurements from 82 test chips. A PVT-aware state protection technique is presented to ensure state integrity of flip-flops while achieving maximum leakage savings. The technique consists of characterisation algorithm and employs horizontal and vertical parity for error detection and correction. Silicon results show that flip-flops state integrity is preserved while achieving up to 17.6% reduction in retention voltage across 82-dies. Embedded processors memory systems are susceptible to transient errors and blanket protection of every part of memory system through ECC is not cost effective. The final contribution addresses the reliability of embedded processor memory systems and describes an architectural simulation-based framework for joint optimisation of reliability, energy consumption and performance. Accurate estimation of memory reliability with targeted protection is proposed to identify and protect the most vulnerable part of the memory system to minimise protection cost. Furthermore, L1-cache resizing together with voltage and frequency scaling is proposed for further energy savings while maintaining performance and reliability. The contributions presented are supported by detailed analyses using state-of-the-art design automation tools, in-house software tools and validated using FPGA and silicon implementation of commercial low power embedded processors.

# Contents

|                                                               |             |

|---------------------------------------------------------------|-------------|

| <b>Declaration of Authorship</b>                              | <b>xv</b>   |

| <b>Acknowledgements</b>                                       | <b>xvii</b> |

| <b>1 Introduction</b>                                         | <b>1</b>    |

| 1.1 Impacts of Technology Scaling . . . . .                   | 2           |

| 1.2 Power Reduction Techniques . . . . .                      | 3           |

| 1.2.1 Dynamic Power Reduction . . . . .                       | 3           |

| 1.2.2 Leakage Power Reduction . . . . .                       | 4           |

| 1.3 Reliability of Digital Designs . . . . .                  | 7           |

| 1.3.1 Permanent Faults . . . . .                              | 8           |

| 1.3.2 Transient Errors . . . . .                              | 9           |

| 1.4 Error Control Coding . . . . .                            | 11          |

| 1.4.1 Hamming Code . . . . .                                  | 11          |

| 1.4.2 CRC Code . . . . .                                      | 12          |

| 1.5 Low Power Reliable Design Challenges . . . . .            | 13          |

| 1.6 Thesis Organisation . . . . .                             | 14          |

| 1.7 Publications . . . . .                                    | 15          |

| 1.7.1 Journal Publications . . . . .                          | 15          |

| 1.7.2 Conference Publication . . . . .                        | 15          |

| <b>2 Literature Review</b>                                    | <b>17</b>   |

| 2.1 Reliability of Power-gated Designs . . . . .              | 17          |

| 2.2 Reliability of Voltage Scaled Designs . . . . .           | 20          |

| 2.3 Impacts of Process Variation on Reliability . . . . .     | 21          |

| 2.4 Impacts of Soft Errors on Reliability . . . . .           | 24          |

| 2.5 Embedded Processor Reliability . . . . .                  | 26          |

| 2.6 Research Objectives . . . . .                             | 27          |

| <b>3 Improving The Reliability of State Retention Designs</b> | <b>29</b>   |

| 3.1 Proposed Method . . . . .                                 | 30          |

| 3.1.1 Step 1: Architecture . . . . .                          | 30          |

| 3.1.2 Step 2: Controller . . . . .                            | 32          |

| 3.1.3 Step 3: Synthesis Flow . . . . .                        | 36          |

| 3.2 Case Study 1: FIFO . . . . .                              | 36          |

| 3.2.1 Error Generation and Injection . . . . .                | 38          |

| 3.2.2 Experimental Results . . . . .                          | 41          |

| 3.2.3 Trade-off Analysis . . . . .                            | 42          |

---

|          |                                                                                                |            |

|----------|------------------------------------------------------------------------------------------------|------------|

| 3.3      | Case Study 2: ARM Cortex-M0 . . . . .                                                          | 47         |

| 3.3.1    | Processor System Components . . . . .                                                          | 52         |

| 3.3.2    | Error Generation and Injection . . . . .                                                       | 55         |

| 3.3.3    | Experimental Results . . . . .                                                                 | 59         |

| 3.3.4    | Trade-off Analysis . . . . .                                                                   | 63         |

| 3.4      | Concluding Remarks . . . . .                                                                   | 68         |

| <b>4</b> | <b>Improving the State Integrity of Flip-flops under PVT Variation</b>                         | <b>71</b>  |

| 4.1      | State Integrity Challenges under PVT Variation . . . . .                                       | 72         |

| 4.1.1    | Measuring Inter-die Process Variation Impact on State Retention .                              | 75         |

| 4.1.2    | Effect of within Die Process and Voltage Variation . . . . .                                   | 78         |

| 4.1.3    | Effect of Temperature Variation . . . . .                                                      | 80         |

| 4.2      | PVT Aware State Protection Technique . . . . .                                                 | 83         |

| 4.2.1    | MRV Characterisation Algorithm . . . . .                                                       | 84         |

| 4.2.2    | MRV Control Flow . . . . .                                                                     | 86         |

| 4.2.3    | Two-dimensional Parity for Improving Flip-flops State Integrity .                              | 86         |

| 4.3      | Test Chip . . . . .                                                                            | 88         |

| 4.4      | Experimental Results . . . . .                                                                 | 98         |

| 4.4.1    | Improved State Integrity . . . . .                                                             | 98         |

| 4.4.2    | Aggressive Voltage Scaling . . . . .                                                           | 99         |

| 4.5      | Concluding Remarks . . . . .                                                                   | 100        |

| <b>5</b> | <b>Modelling Framework to Optimise Memory System Reliability</b>                               | <b>101</b> |

| 5.1      | Motivation . . . . .                                                                           | 102        |

| 5.2      | Framework for Memory System Reliability Analysis . . . . .                                     | 103        |

| 5.2.1    | Hardware Configuration Method . . . . .                                                        | 104        |

| 5.2.2    | Benchmark Applications . . . . .                                                               | 107        |

| 5.2.3    | Reliability, Performance and Energy Profiling . . . . .                                        | 108        |

| 5.2.4    | Modelling voltage and frequency scaling . . . . .                                              | 114        |

| 5.3      | Reliability, Performance and Power Analysis . . . . .                                          | 116        |

| 5.3.1    | Impact of VFS on reliability, performance and energy . . . . .                                 | 117        |

| 5.4      | Cost Effective Reliable Design Methodology . . . . .                                           | 122        |

| 5.4.1    | Improve L1-cache Reliability through Resizing . . . . .                                        | 123        |

| 5.4.2    | Energy Minimization through Dynamic ECC Protection and Cache Resizing . . . . .                | 127        |

| 5.5      | Concluding Remarks . . . . .                                                                   | 133        |

| <b>6</b> | <b>Conclusion and Future Work</b>                                                              | <b>135</b> |

| 6.1      | Thesis Contributions . . . . .                                                                 | 135        |

| 6.2      | Future Work Directions . . . . .                                                               | 138        |

| 6.2.1    | Improving Reliability of Power Management Hardware . . . . .                                   | 139        |

| 6.2.2    | Reliability Enhancement of Multi-core Processors through Hardware-Software Co-design . . . . . | 139        |

| <b>A</b> | <b>Low Power Embedded Processors</b>                                                           | <b>141</b> |

| <b>B</b> | <b>Embedded Processor Power Domain Description</b>                                             | <b>143</b> |

|                                                |            |

|------------------------------------------------|------------|

| <b>C Firmware For Software Recovery</b>        | <b>147</b> |

| <b>D HSPICE Monte-Carlo Simulation</b>         | <b>153</b> |

| <b>E Example Script for Joint Optimisation</b> | <b>157</b> |

| <b>References</b>                              | <b>159</b> |

# List of Figures

|      |                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Clock gating architecture [22]. . . . .                                                                                                                                                           | 4  |

| 1.2  | Power gating design architecture . . . . .                                                                                                                                                        | 6  |

| 1.3  | State Retention Flip-Flop . . . . .                                                                                                                                                               | 6  |

| 1.4  | Scaled voltage leakage reduction . . . . .                                                                                                                                                        | 7  |

| 1.5  | Relation between leakage power and supply voltage when ARM926 processor is in idle mode for 65nm technology . . . . .                                                                             | 8  |

| 1.6  | Available leakage reduction techniques and their trade-offs . . . . .                                                                                                                             | 8  |

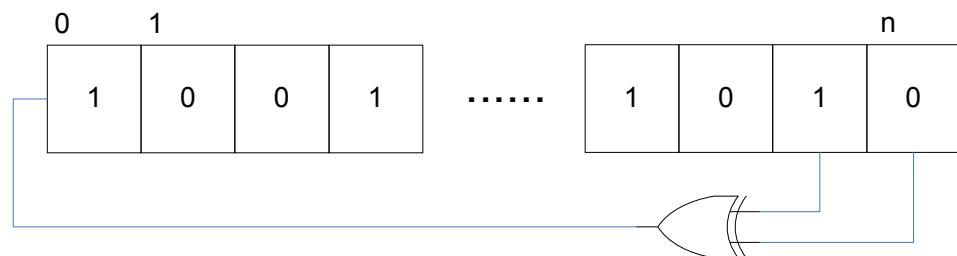

| 1.7  | CRC generation using Linear Feedback Shift Register (LFSR) [64]. . . . .                                                                                                                          | 13 |

| 1.8  | Technology scaling and its effects on performance, power and reliability . . . . .                                                                                                                | 14 |

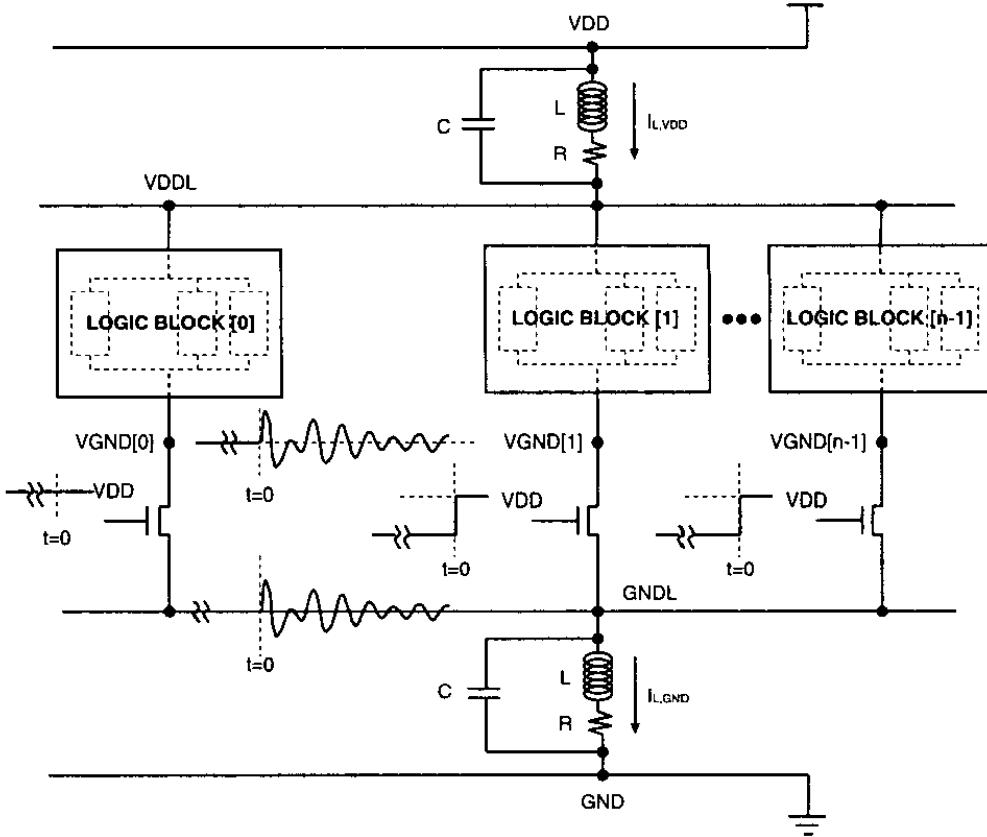

| 2.1  | Ground bounce in power-gated design [65]. . . . .                                                                                                                                                 | 18 |

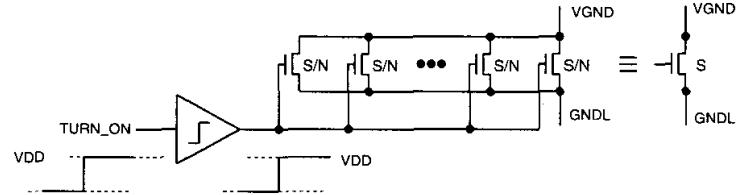

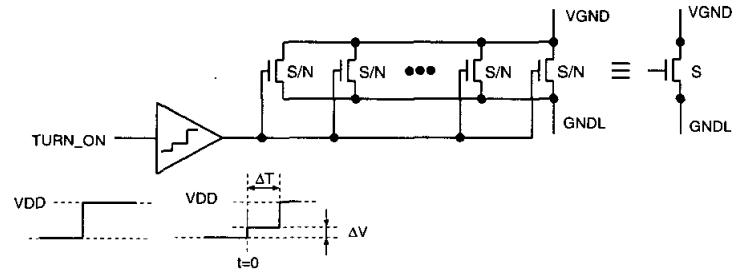

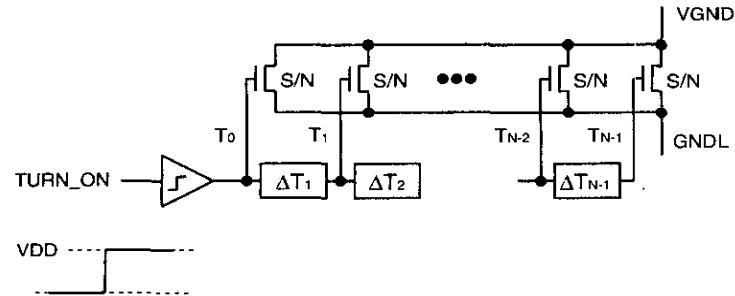

| 2.2  | Change power switches arrangement for ground bounce reduction [65]. . . . .                                                                                                                       | 19 |

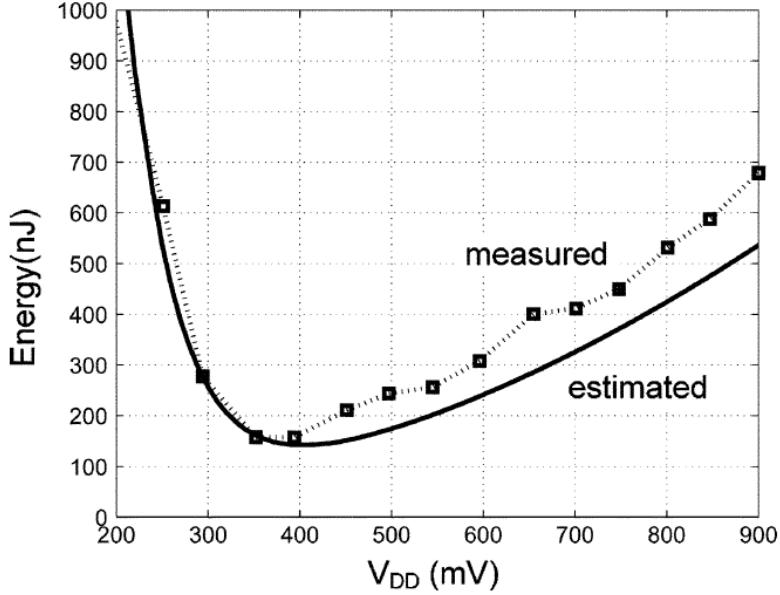

| 2.3  | Energy dissipation under different supply voltage [74]. . . . .                                                                                                                                   | 20 |

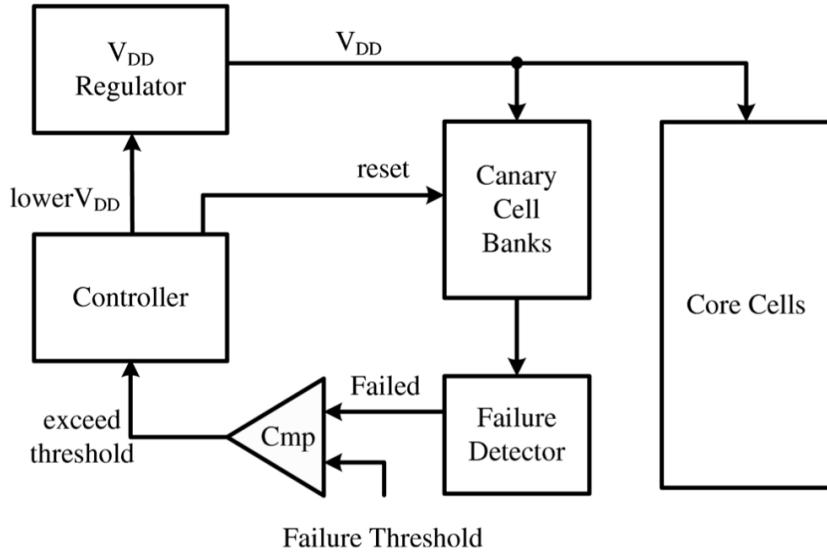

| 2.4  | Architecture of the Canary-based feedback loop for SRAM standby $V_{DD}$ scaling [79]. . . . .                                                                                                    | 21 |

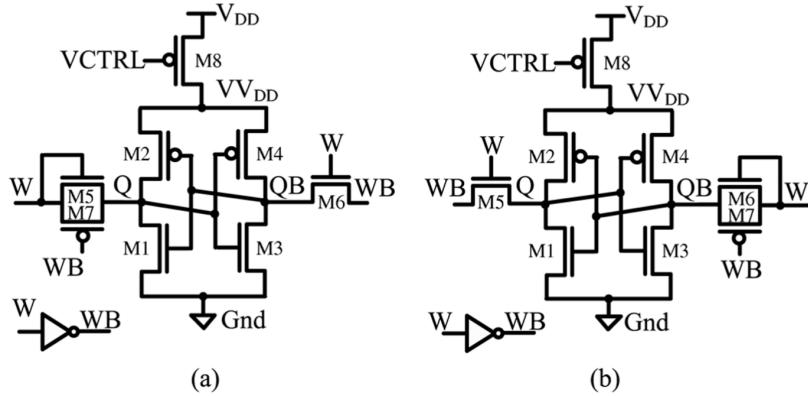

| 2.5  | Schematic of Canary cell (a) for storing '1' and (b) for storing '0' [79]. . . . .                                                                                                                | 22 |

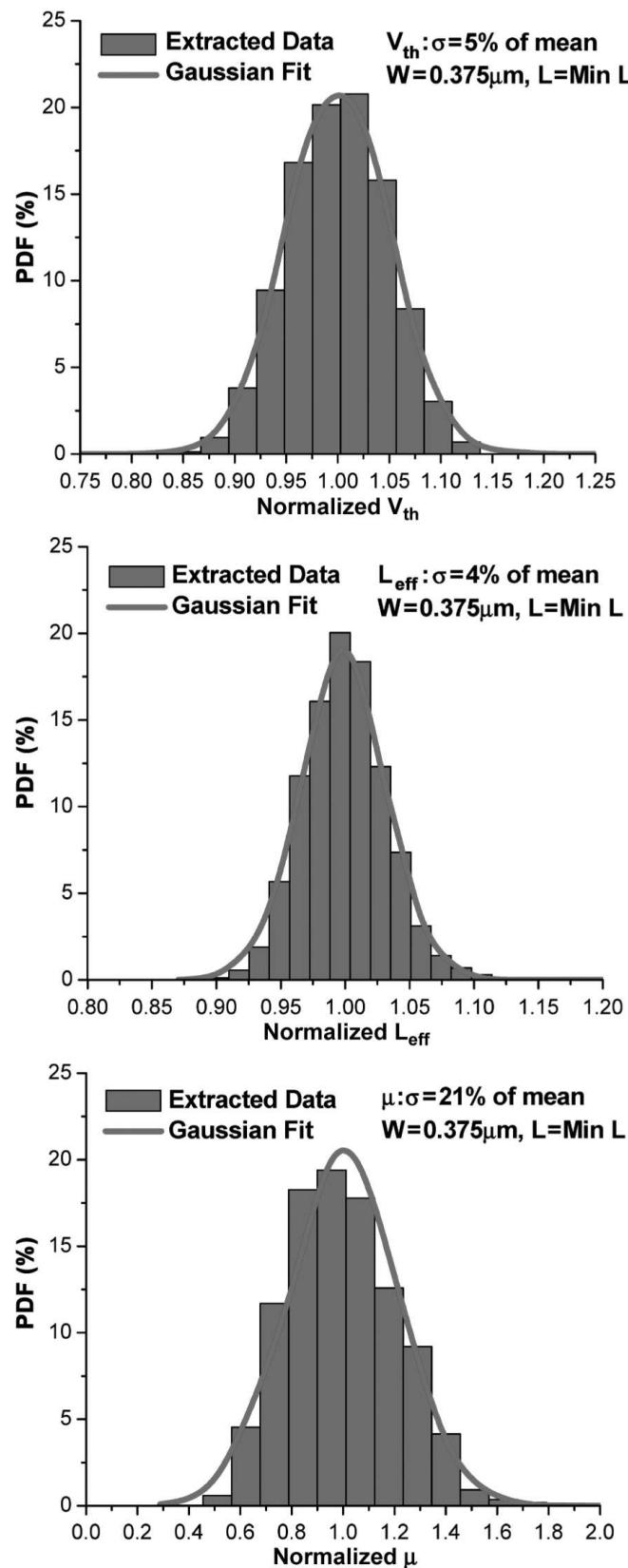

| 2.6  | Variations of threshold voltage, effective channel length and carrier mobility for 65nm CMOS [90]. . . . .                                                                                        | 23 |

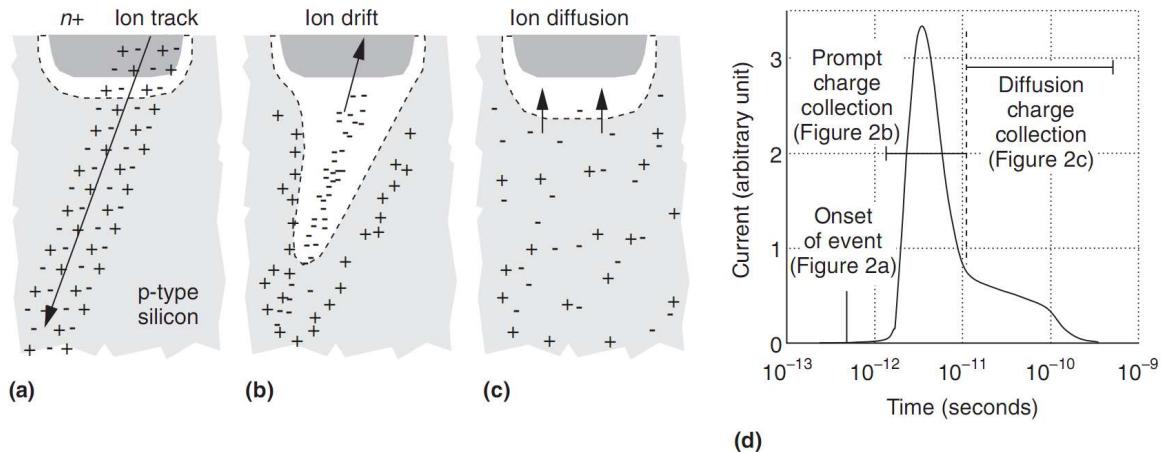

| 2.7  | Charge collection in a silicon junction (a) after an ion strike, (b) during drift collection, (c) during diffusion collection, and (d) junction current induced as function of time [13]. . . . . | 24 |

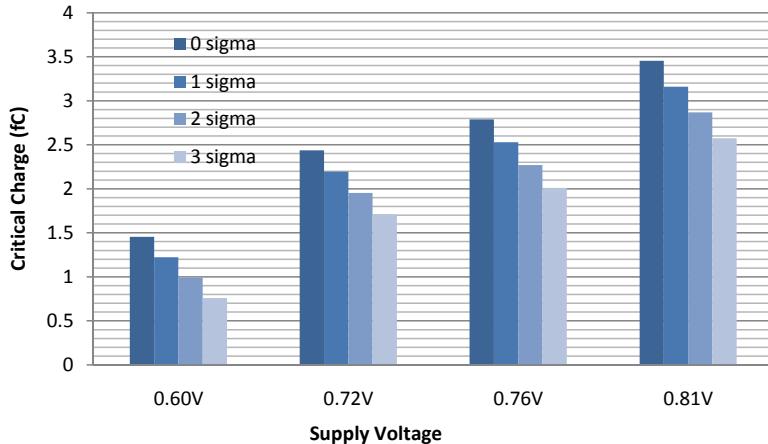

| 2.8  | Critical charge and supply voltage in the presence of process variation. . . . .                                                                                                                  | 26 |

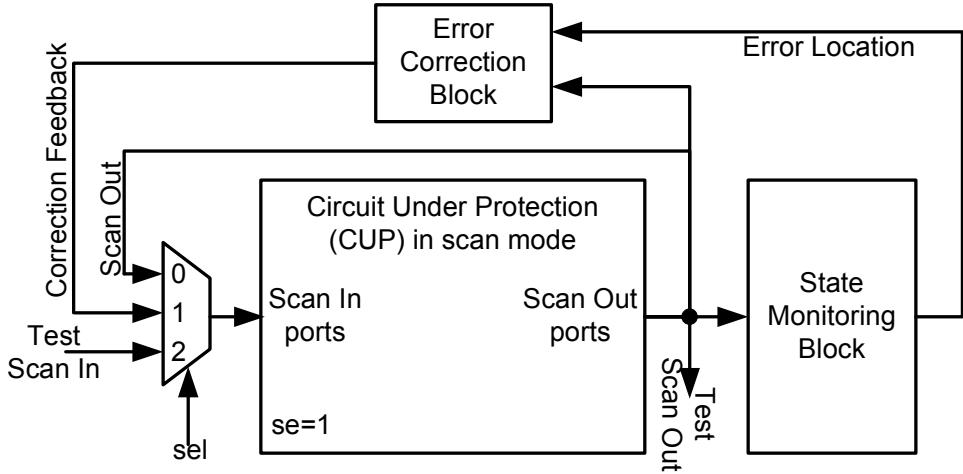

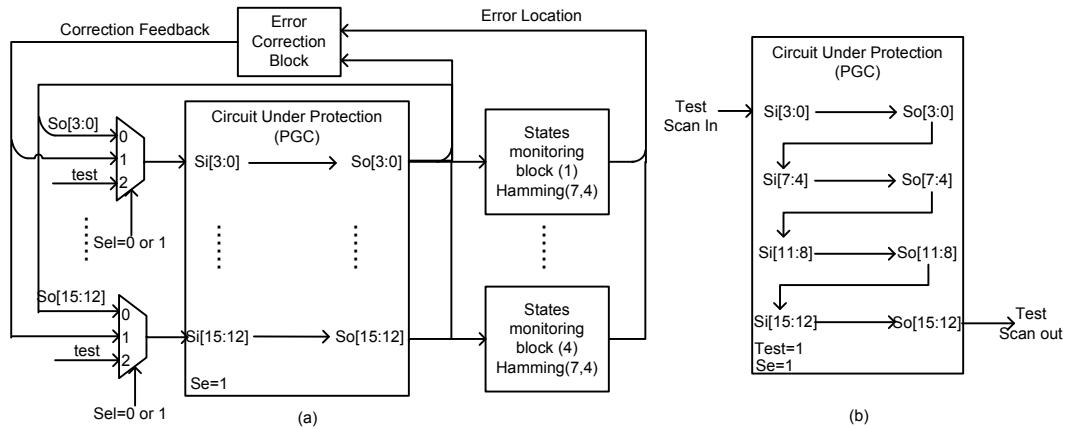

| 3.1  | Architecture of State Monitoring and Recovery Block (SMRB). . . . .                                                                                                                               | 31 |

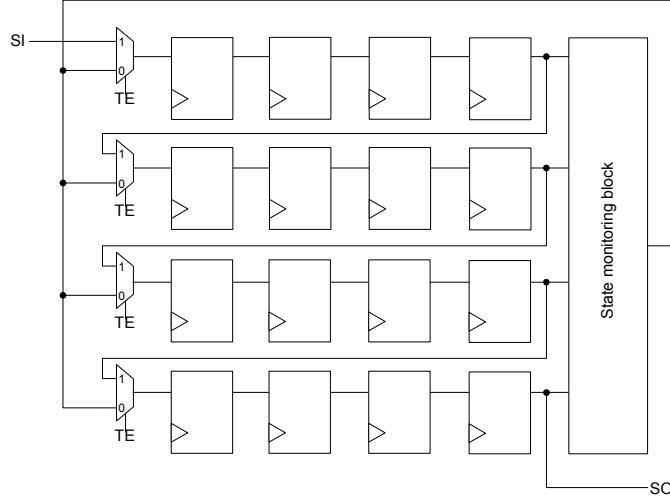

| 3.2  | Reuse and partition manufacturing test scan chain for state monitoring. . . . .                                                                                                                   | 33 |

| 3.3  | Scan chain configurations (a) state monitoring (b) manufacturing test. . . . .                                                                                                                    | 33 |

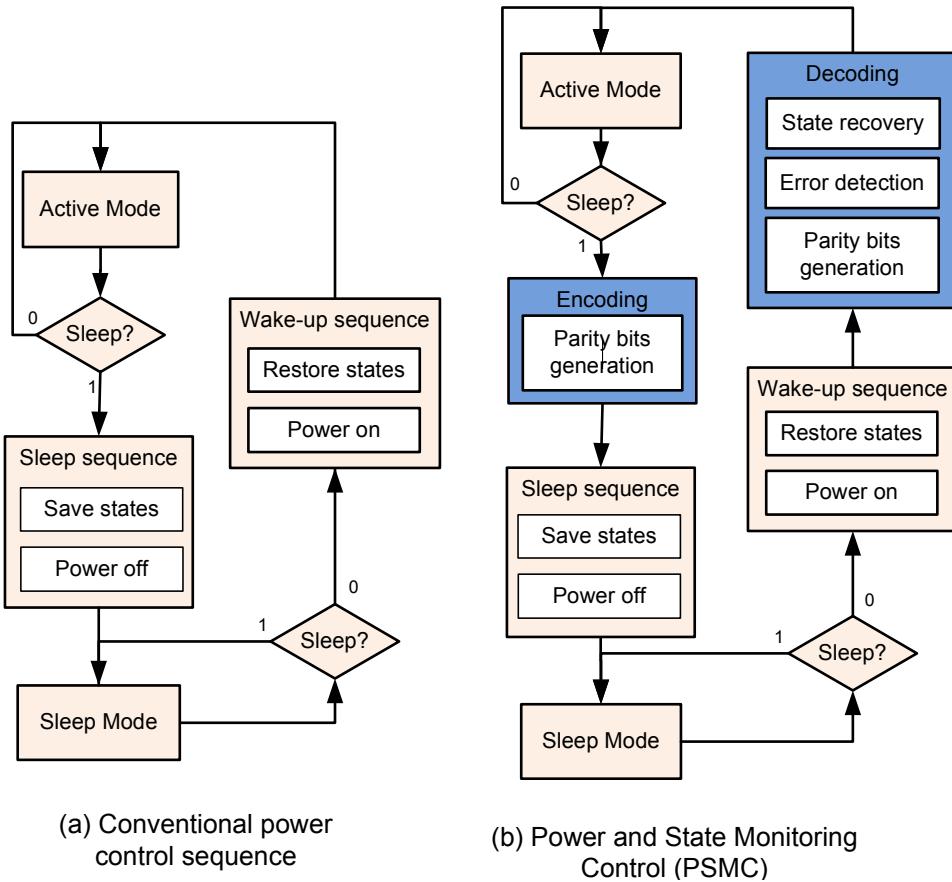

| 3.4  | Control sequence (a) conventional (b) proposed Power and State Monitoring Controller (PSMC) . . . . .                                                                                             | 34 |

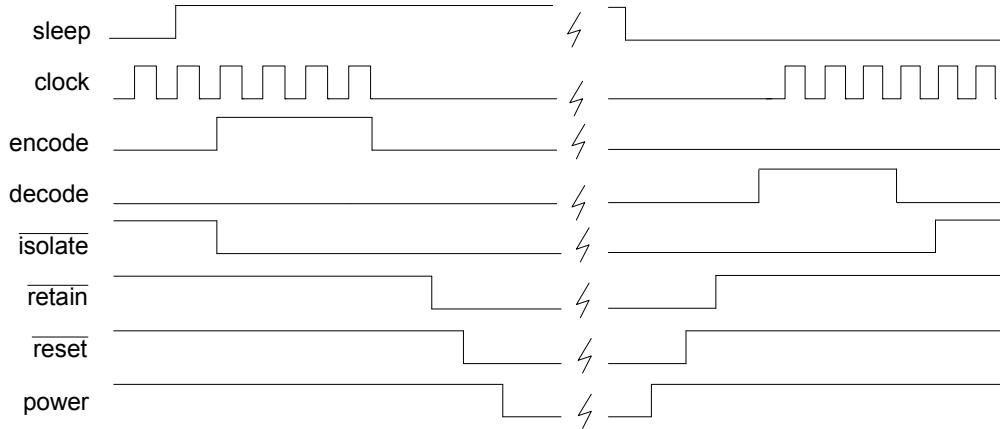

| 3.5  | Power and State Monitoring Control timing diagram . . . . .                                                                                                                                       | 35 |

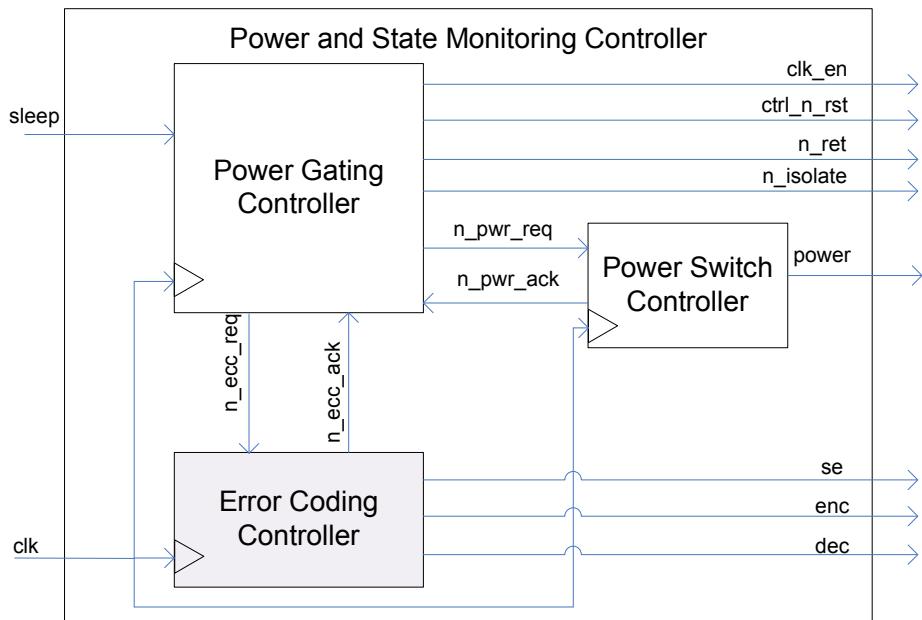

| 3.6  | Power and State Monitoring Controller block diagram . . . . .                                                                                                                                     | 35 |

| 3.7  | Example code snippet for (a) power gating control and (b) scan based ECC control . . . . .                                                                                                        | 37 |

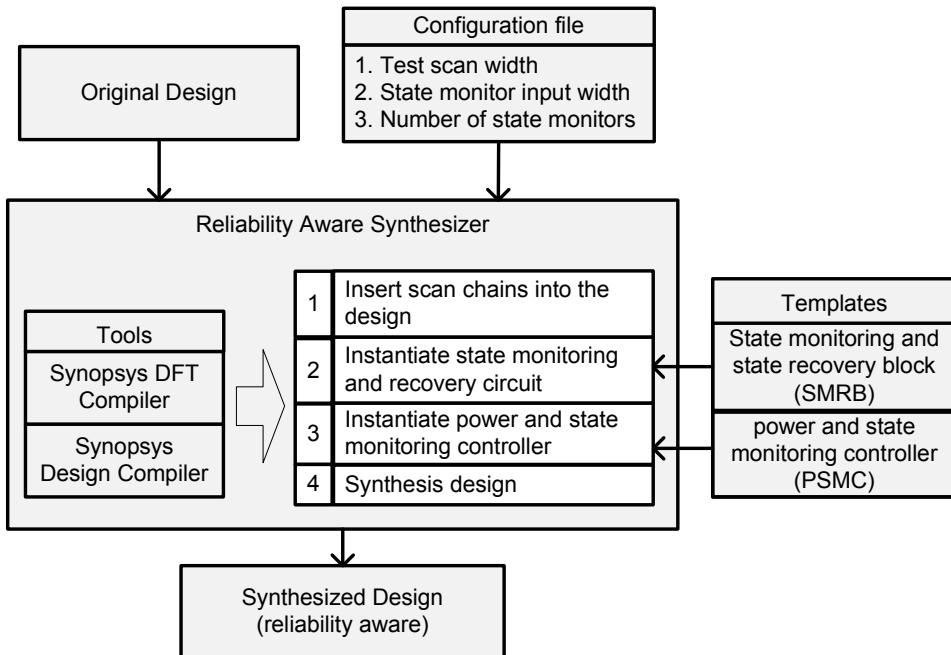

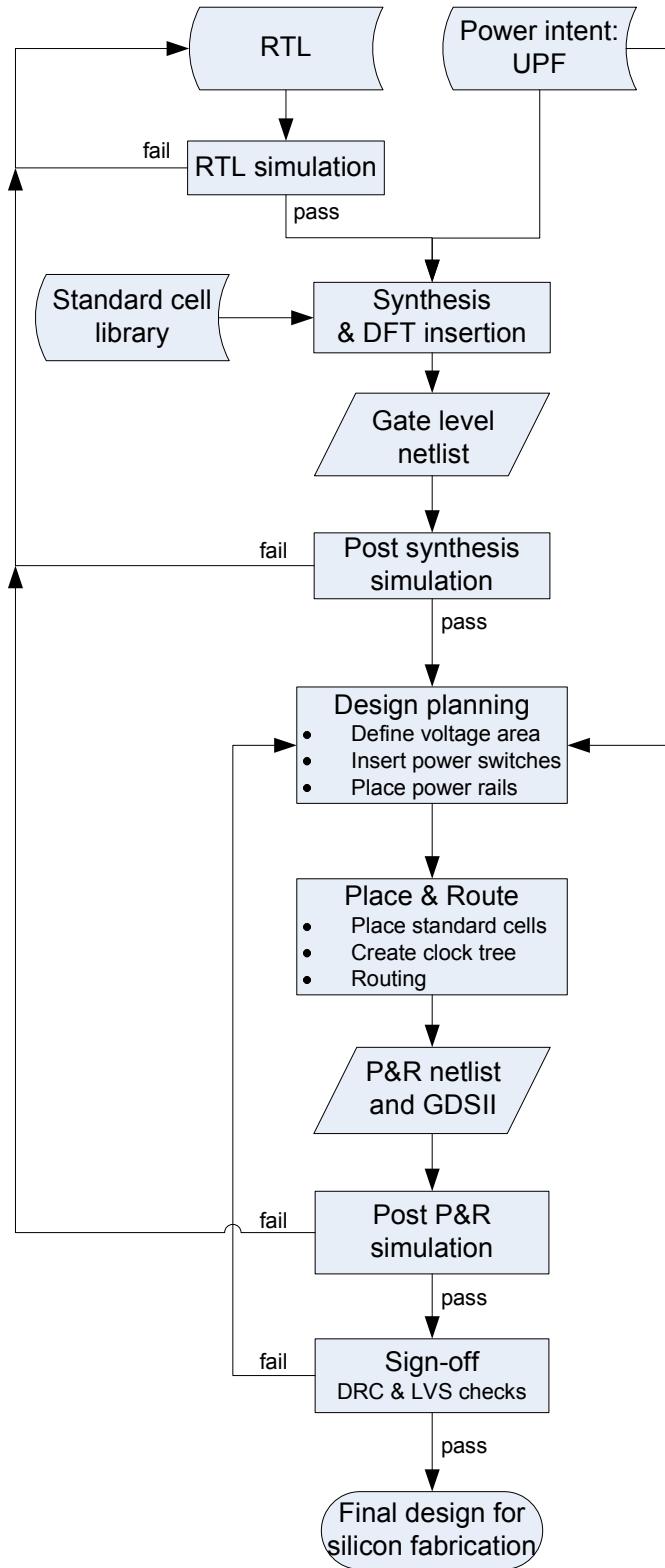

| 3.8  | Proposed design flow for reliable state retention power gating design . . . . .                                                                                                                   | 38 |

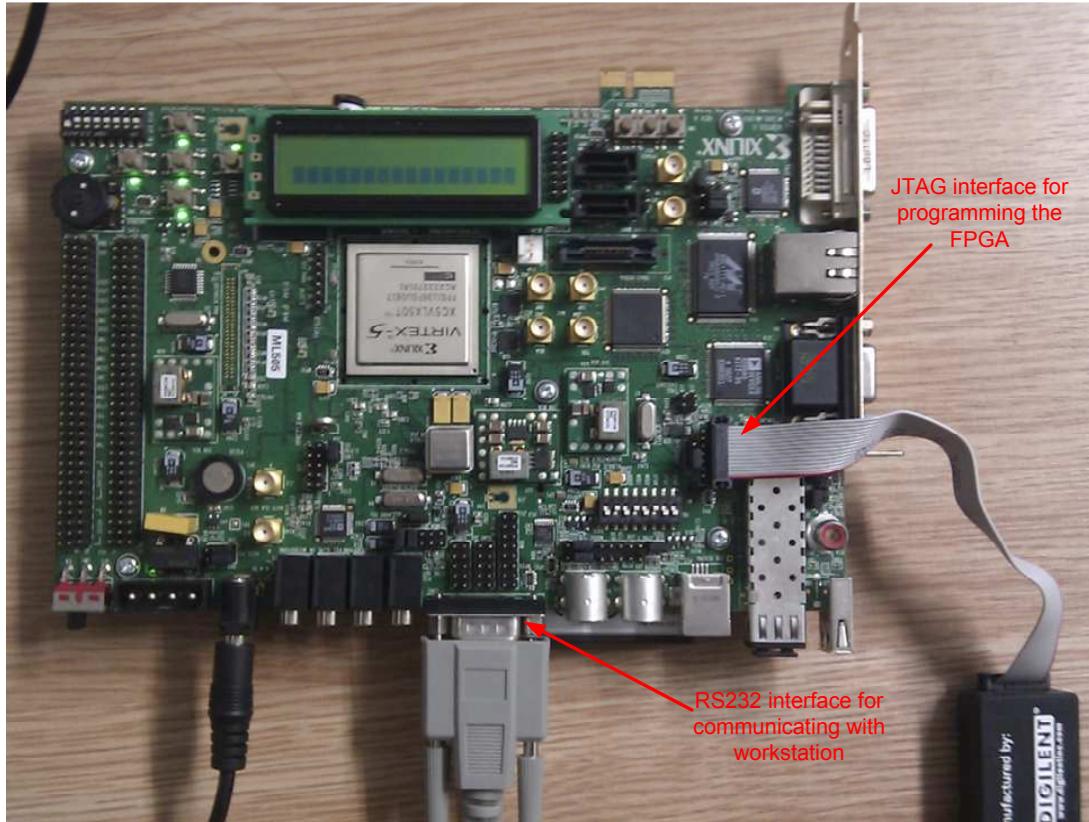

| 3.9  | Xilinx ML505 FPGA evaluation board for functional verification of the method . . . . .                                                                                                            | 39 |

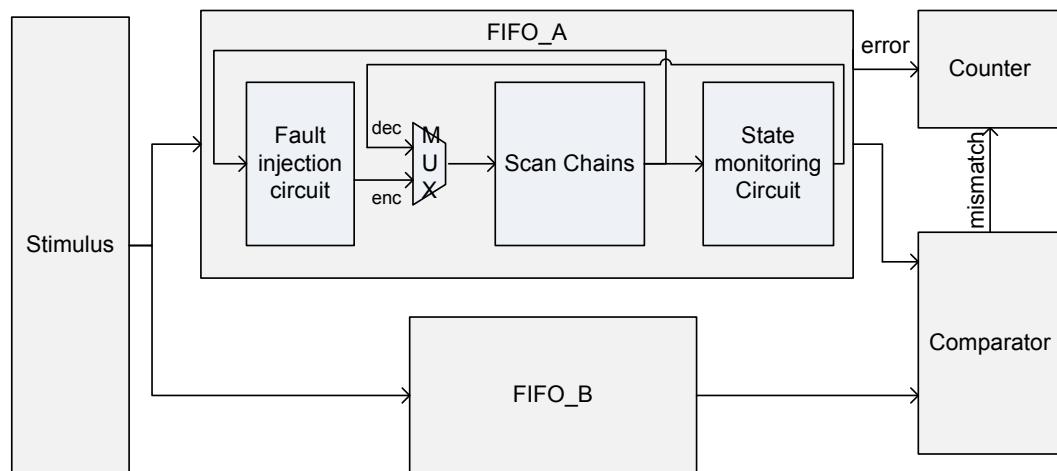

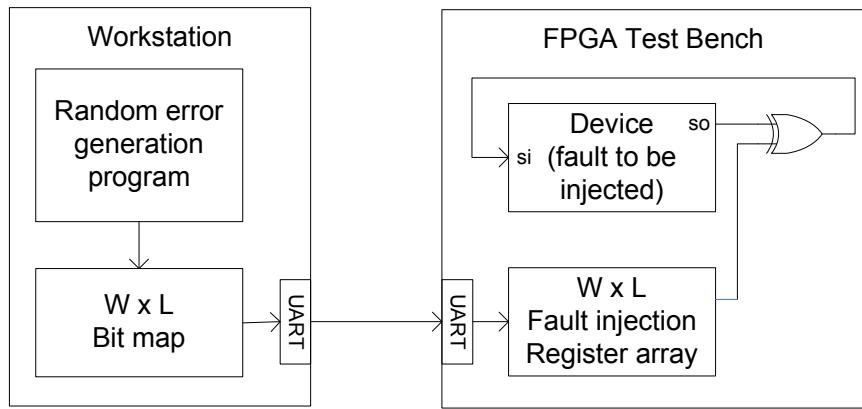

| 3.10 | FPGA test bench for functional verification of the method . . . . .                                                                                                                               | 39 |

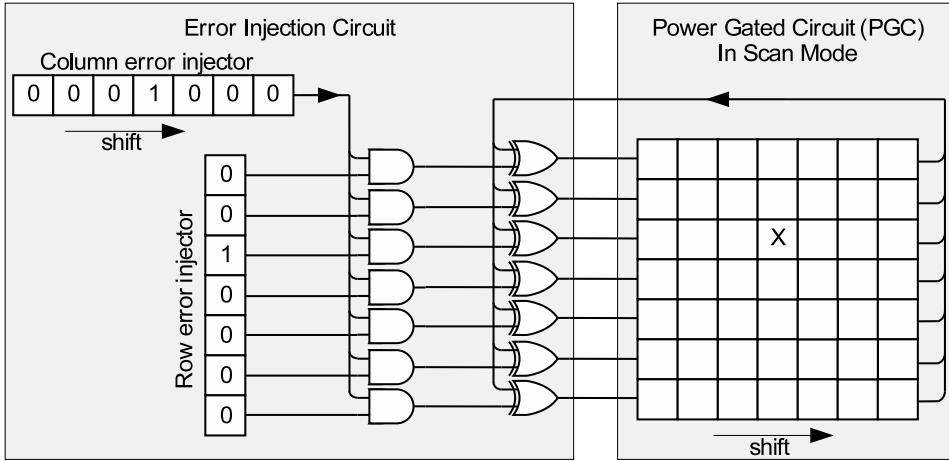

| 3.11 | Error injection architecture. . . . .                                                                                                                                                             | 40 |

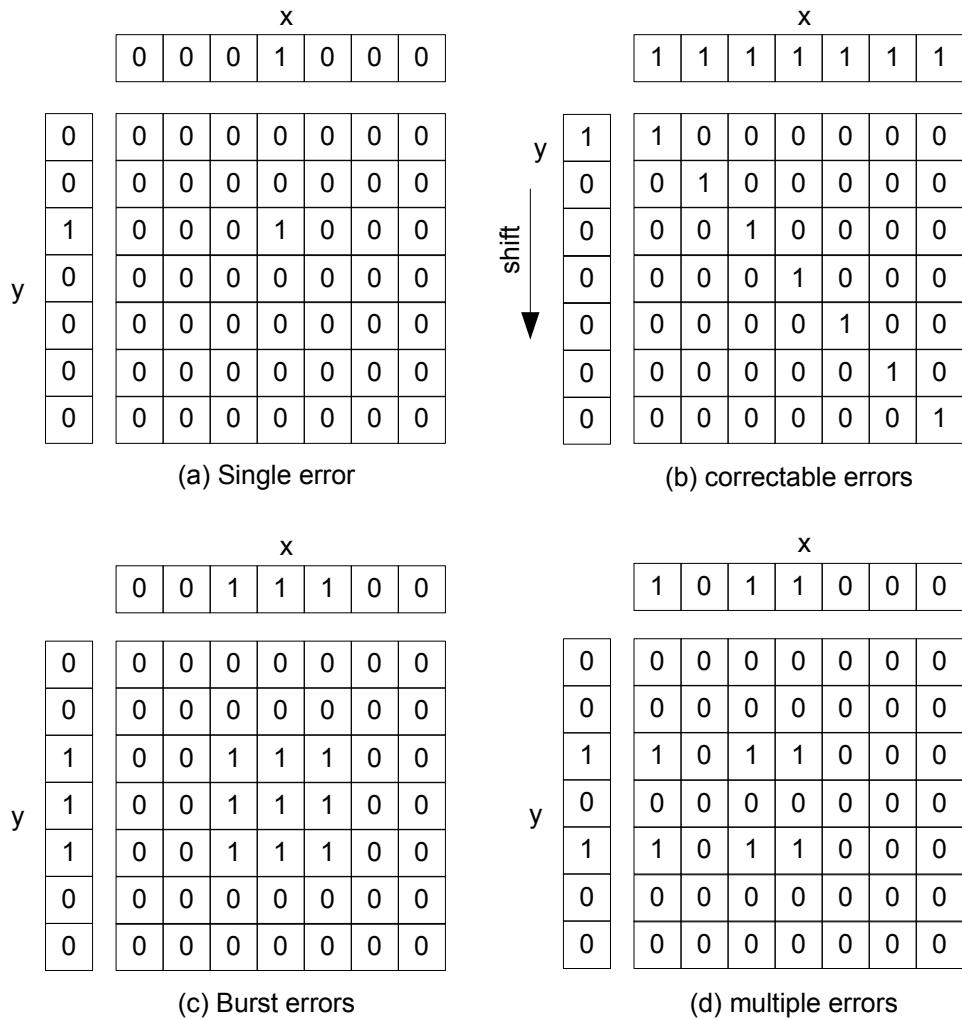

| 3.12 | Error injection patterns. . . . .                                                                                                                                                                 | 41 |

| 3.13 | Linear Feedback Shift Registers . . . . .                                                                                                                                                         | 41 |

---

|                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

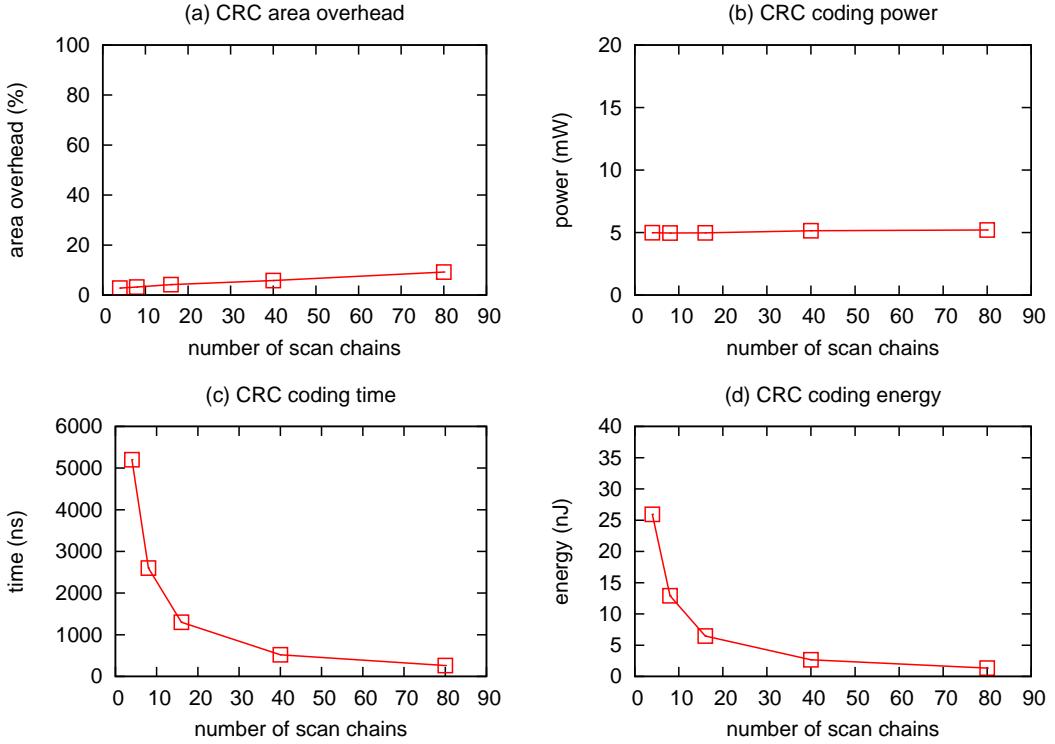

| 3.14 FIFO case study: CRC code implementation trades offs . . . . .                                                                                                                                                         | 44 |

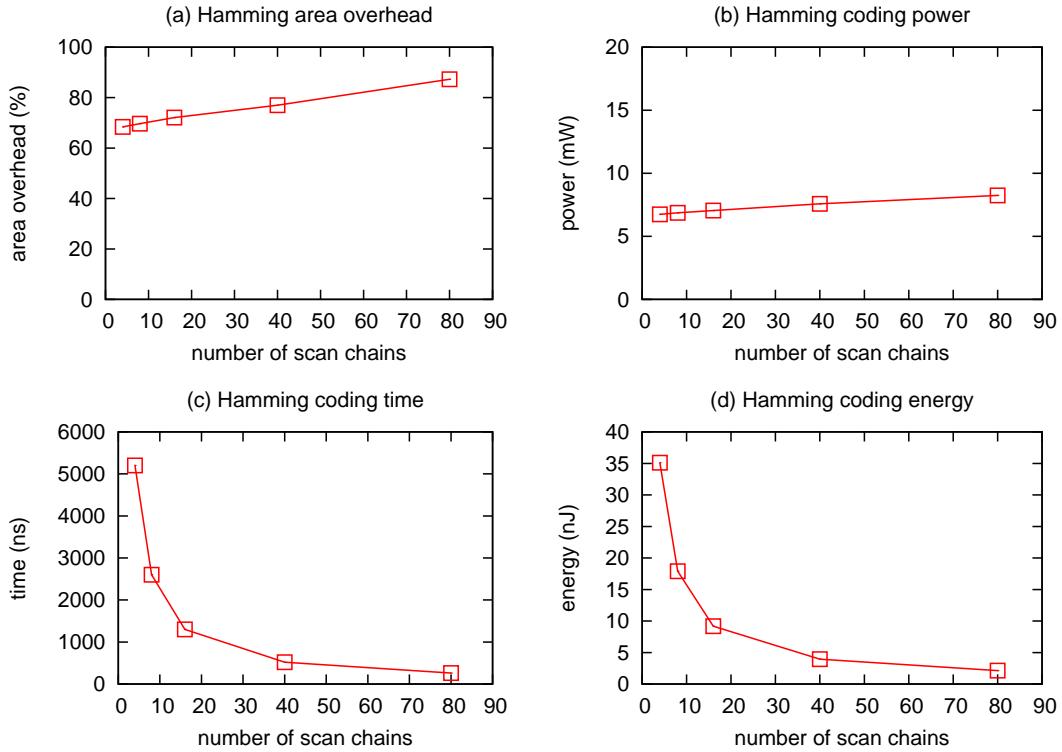

| 3.15 FIFO case study: Hamming code implementation trades offs . . . . .                                                                                                                                                     | 45 |

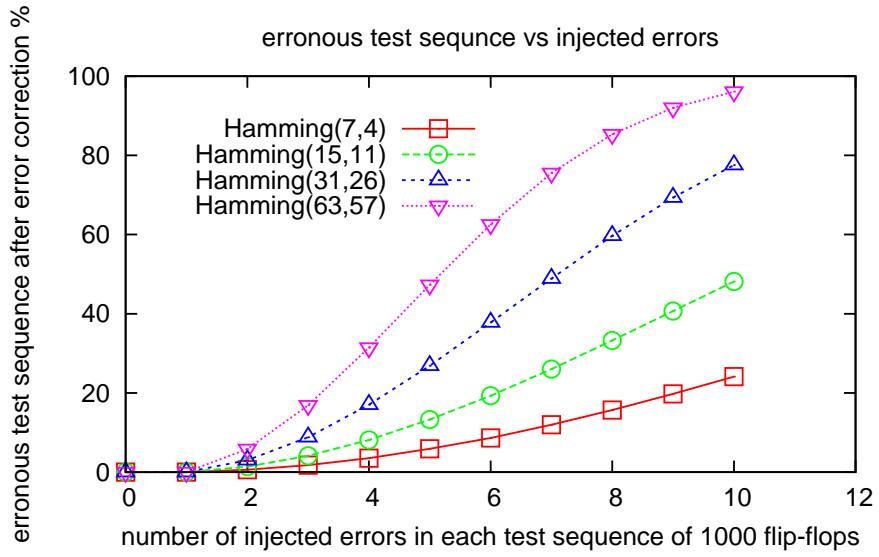

| 3.16 The probability of erroneous test sequence after error correction when multiple errors injected in each test sequence of 1000 flip-flops . . . . .                                                                     | 46 |

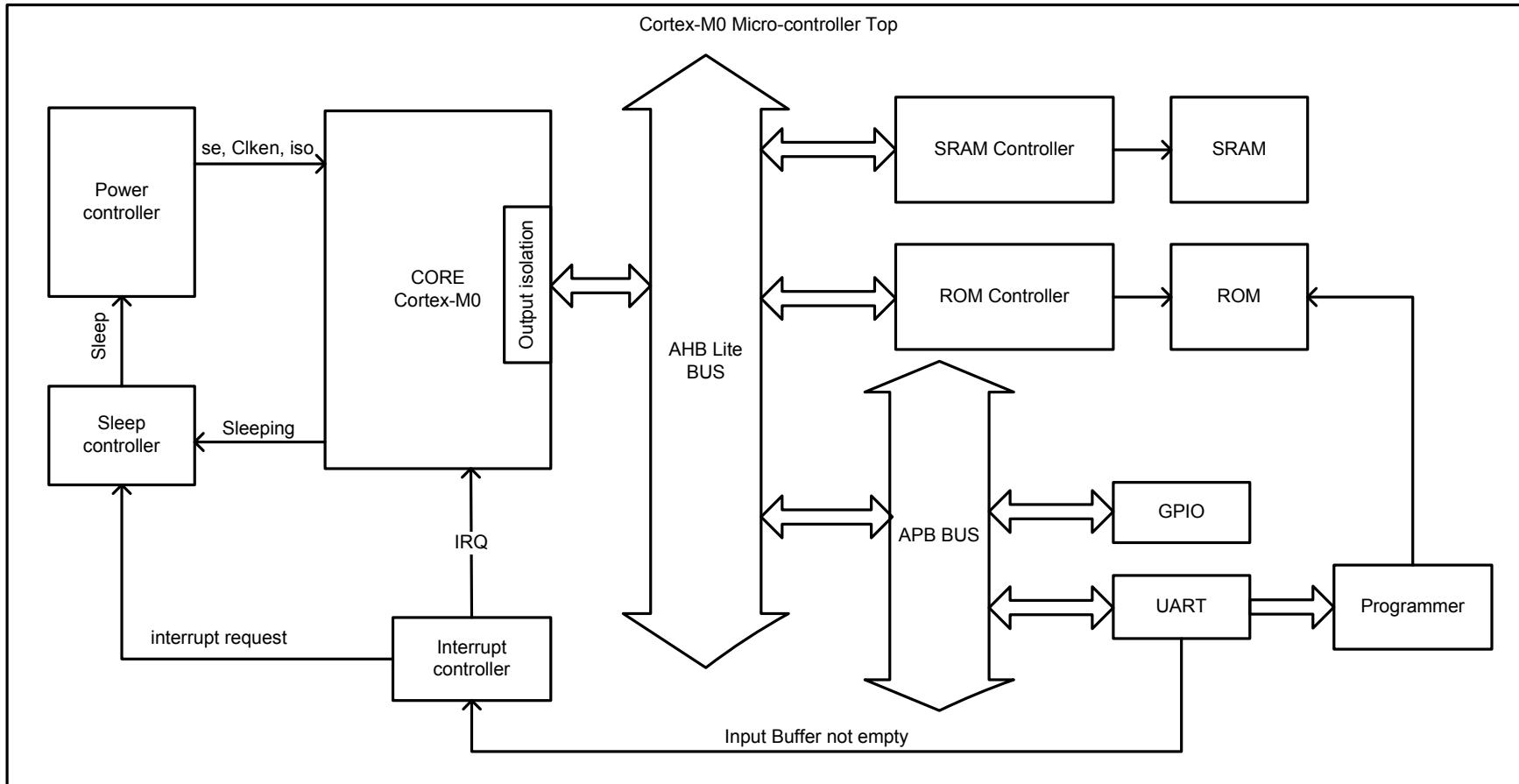

| 3.17 ARM Cortex-M0 processor platform block diagram . . . . .                                                                                                                                                               | 48 |

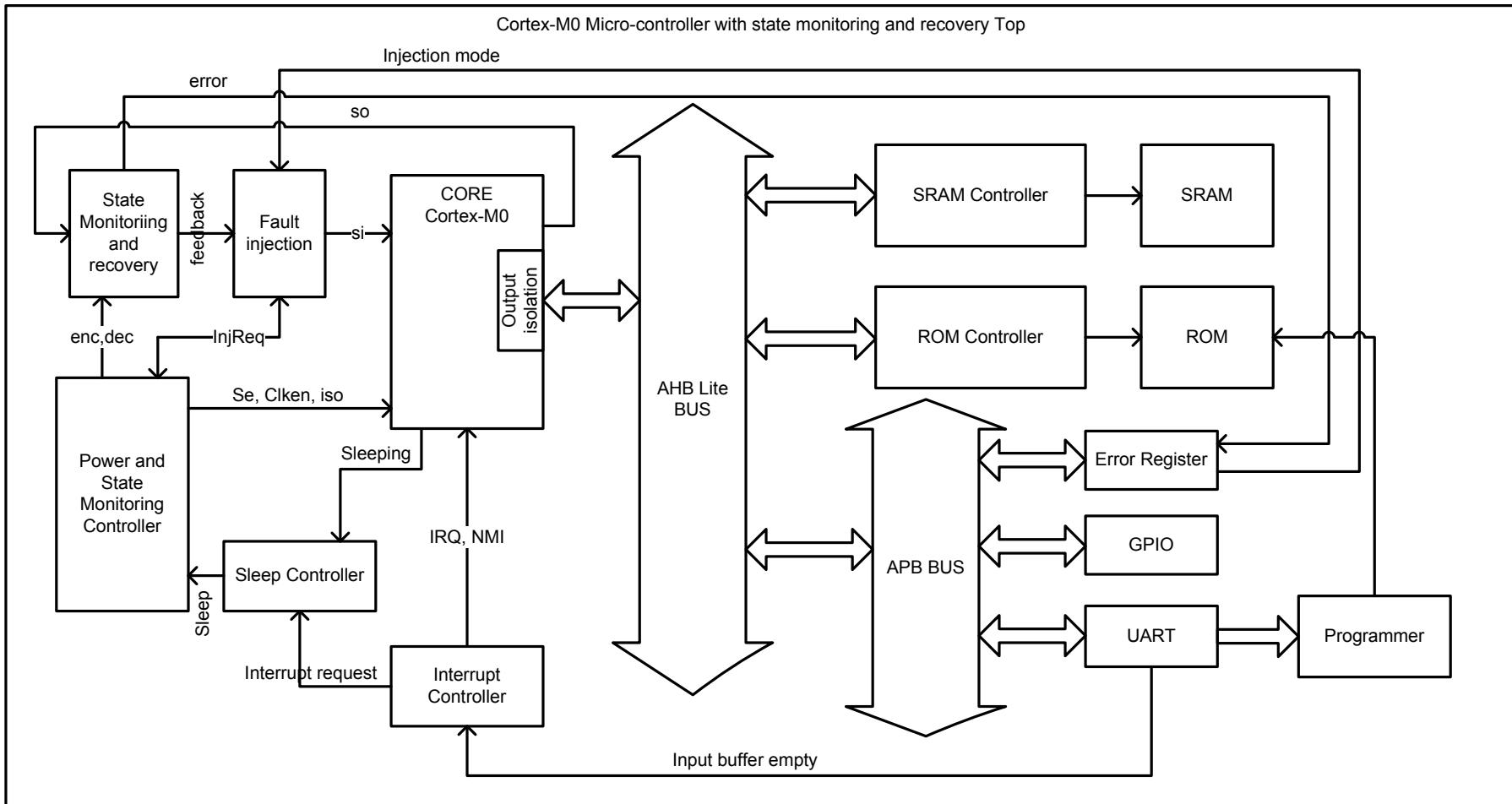

| 3.18 ARM Cortex-M0 processor platform with state monitoring and recovery block diagram . . . . .                                                                                                                            | 49 |

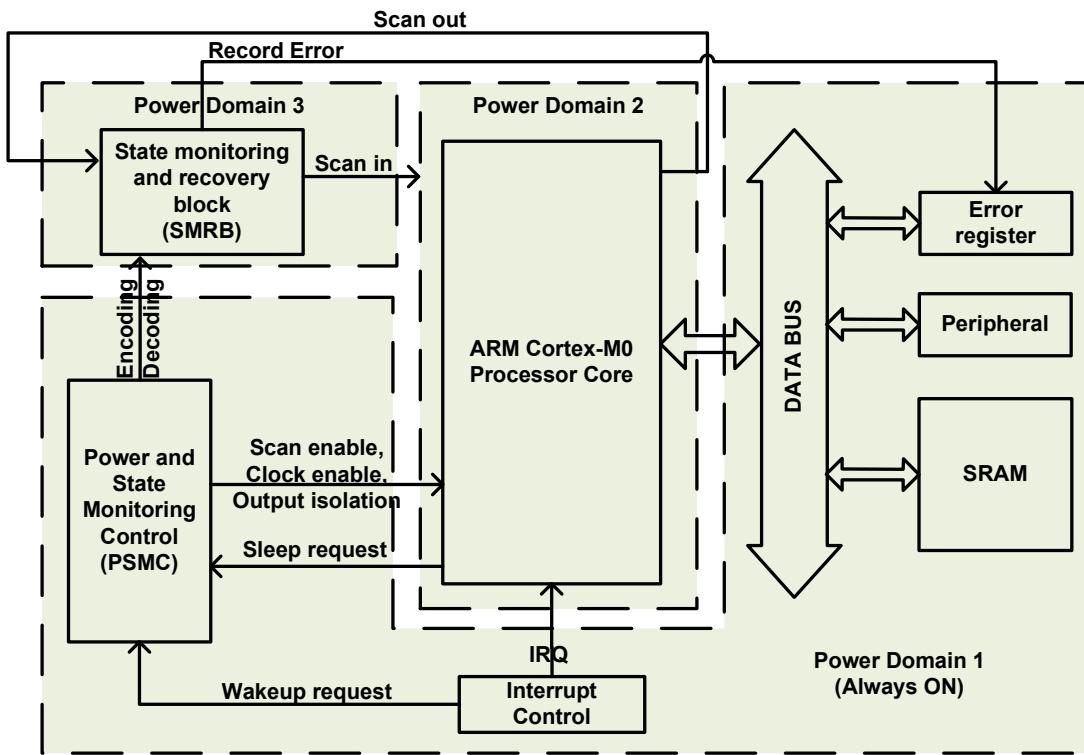

| 3.19 Block diagram of the proposed state monitoring and recovery technique using ARM Cortex-M0 as a case study. . . . .                                                                                                     | 50 |

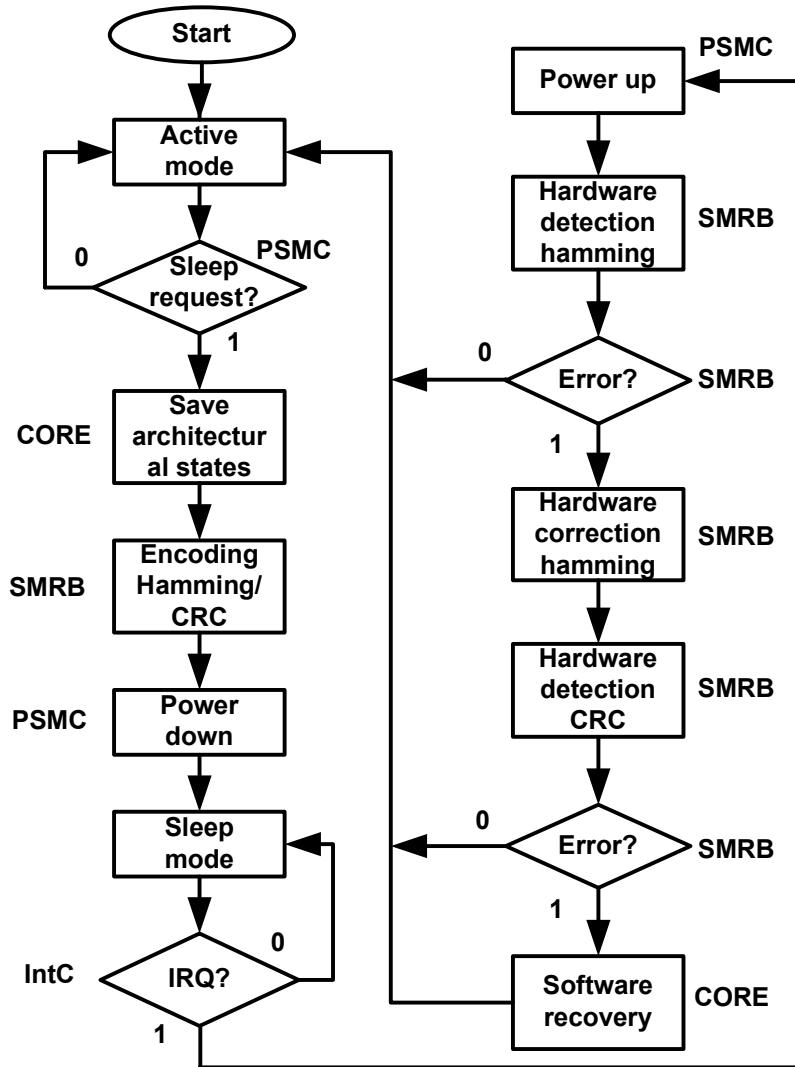

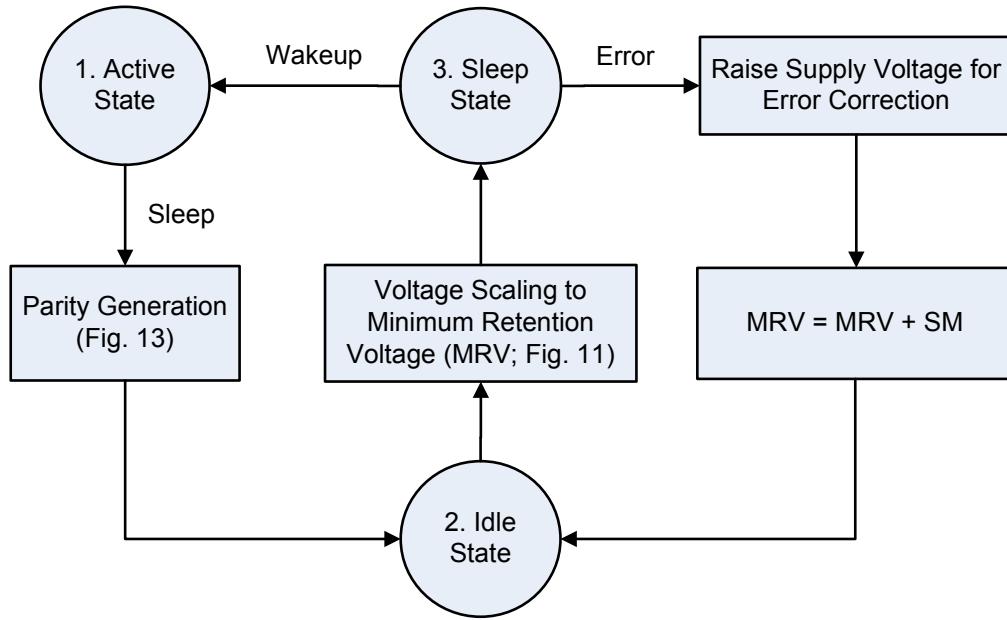

| 3.20 Control flow of error detection and state recovery mechanism. . . . .                                                                                                                                                  | 51 |

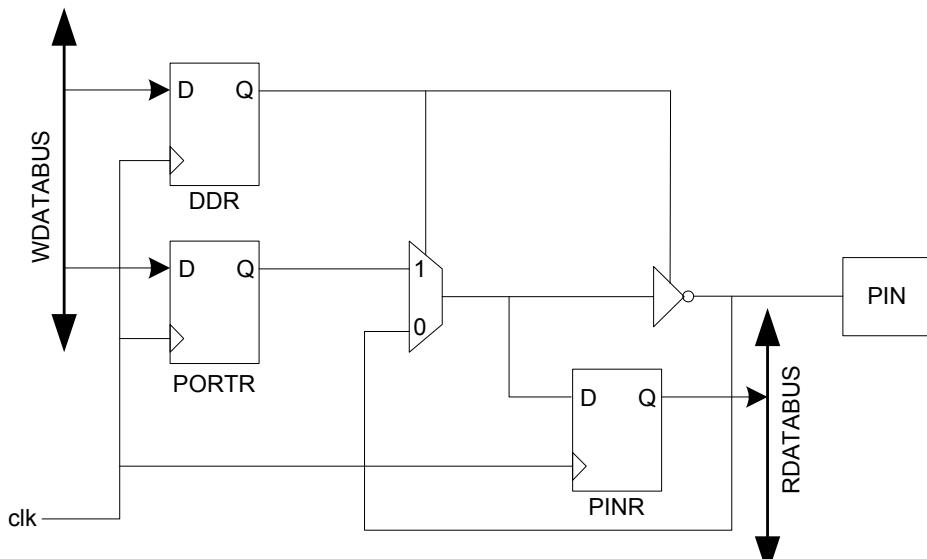

| 3.21 General purpose input and output port schematic . . . . .                                                                                                                                                              | 52 |

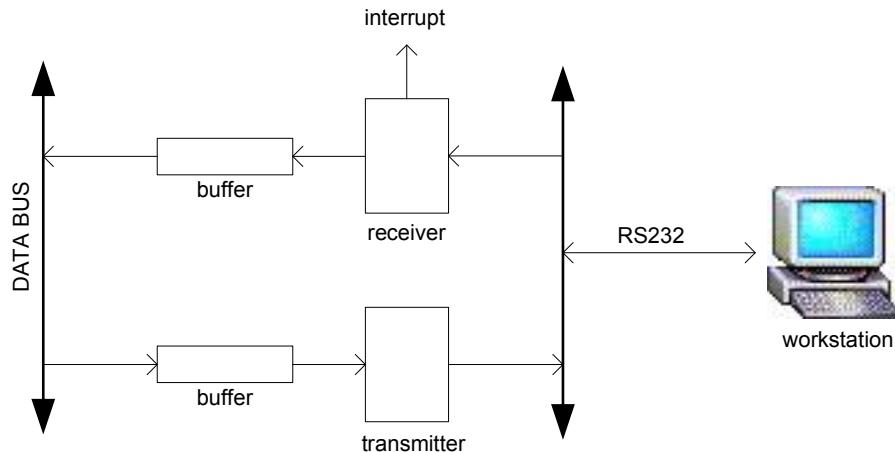

| 3.22 Universal asynchronous receiver and transmitter schematic . . . . .                                                                                                                                                    | 53 |

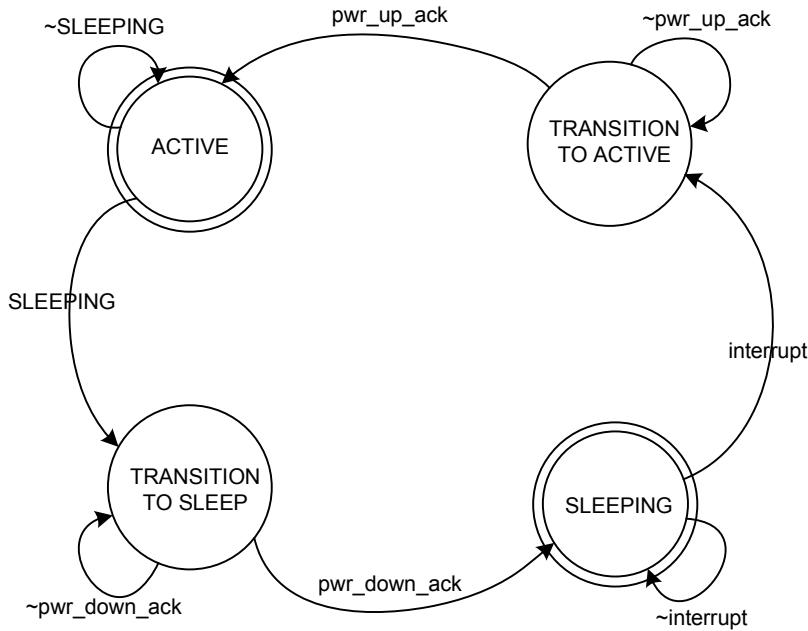

| 3.23 Sleep controller state machine . . . . .                                                                                                                                                                               | 54 |

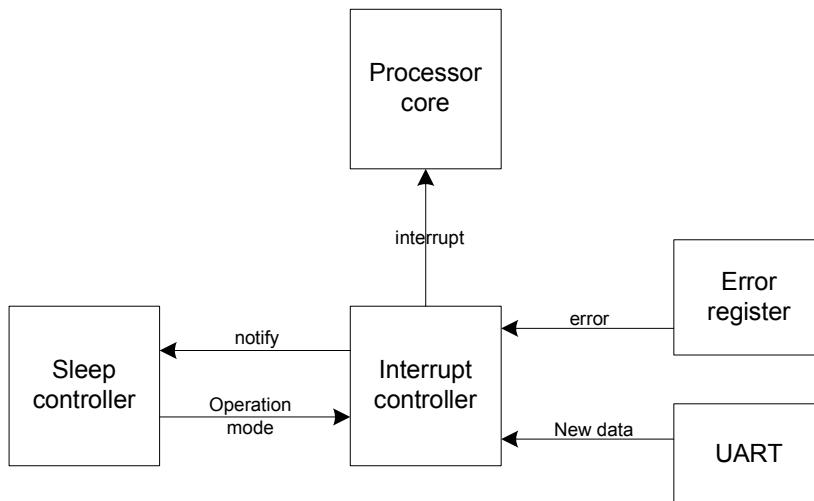

| 3.24 Interrupt controller . . . . .                                                                                                                                                                                         | 54 |

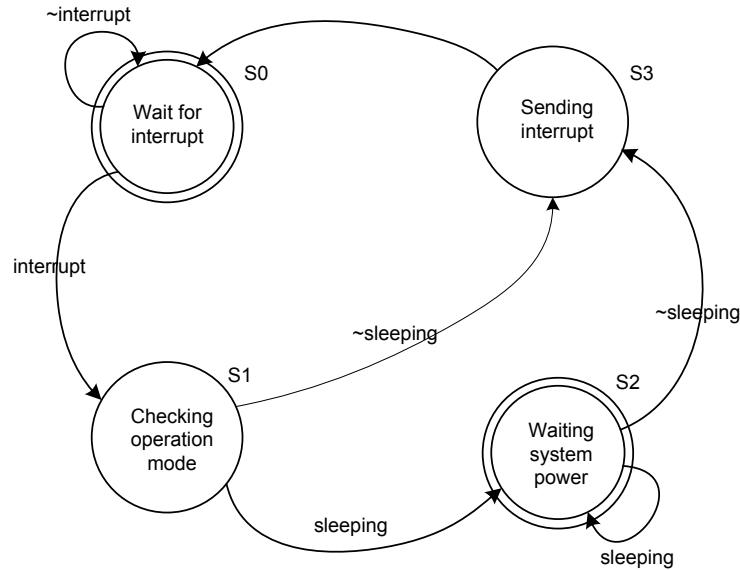

| 3.25 Interrupt controller state machine . . . . .                                                                                                                                                                           | 55 |

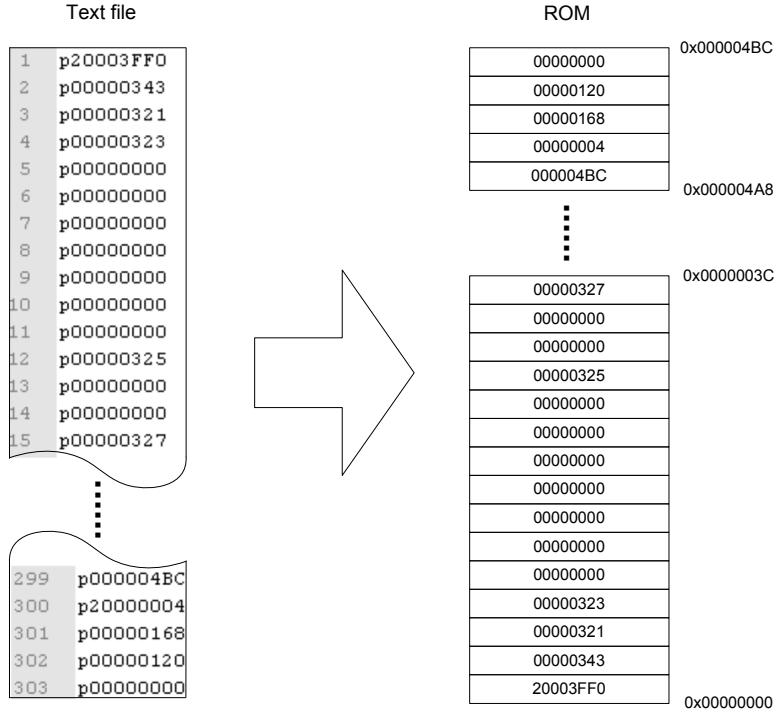

| 3.26 Programmer converts text file to data in ROM . . . . .                                                                                                                                                                 | 56 |

| 3.27 Processor Memory Map . . . . .                                                                                                                                                                                         | 57 |

| 3.28 Cluster error injection implementation . . . . .                                                                                                                                                                       | 58 |

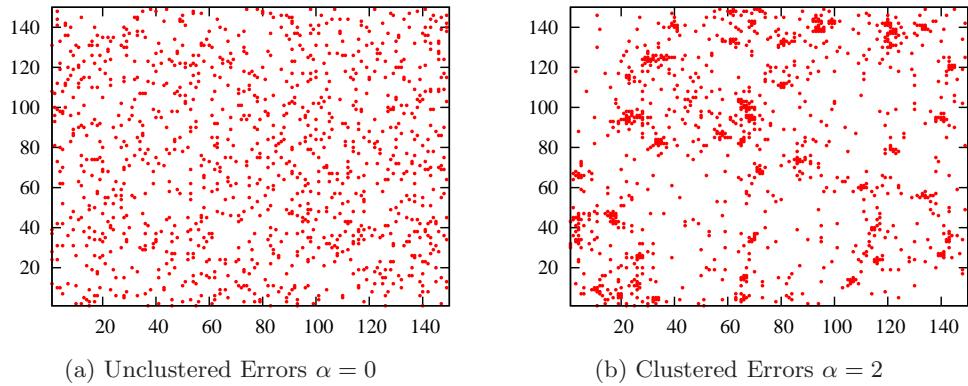

| 3.29 Error distribution using error injection method shown in Algorithm 1 . .                                                                                                                                               | 59 |

| 3.30 Hardware error injection architecture . . . . .                                                                                                                                                                        | 59 |

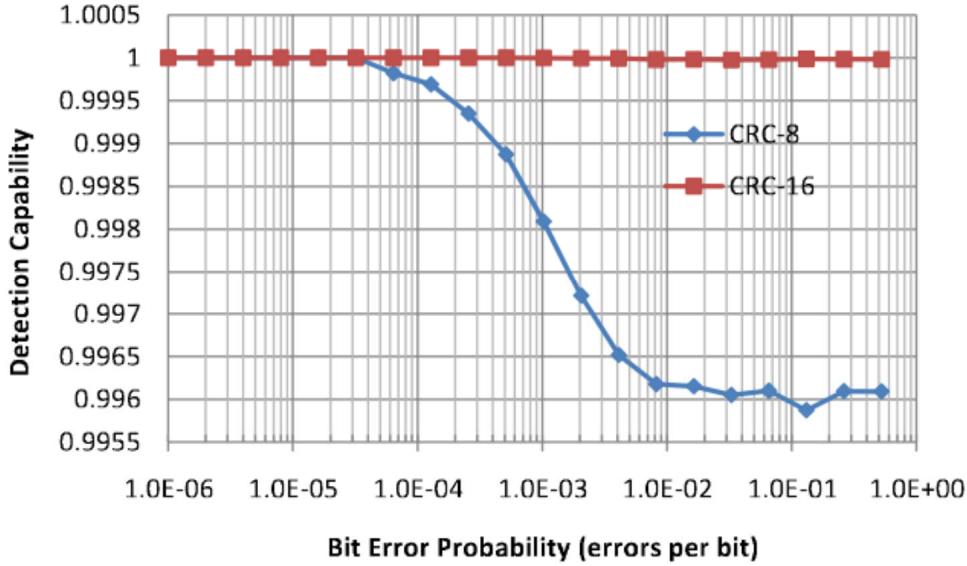

| 3.31 Detection Capability of CRC-8 and CRC-16 on Cortex-M0 as a case study                                                                                                                                                  | 60 |

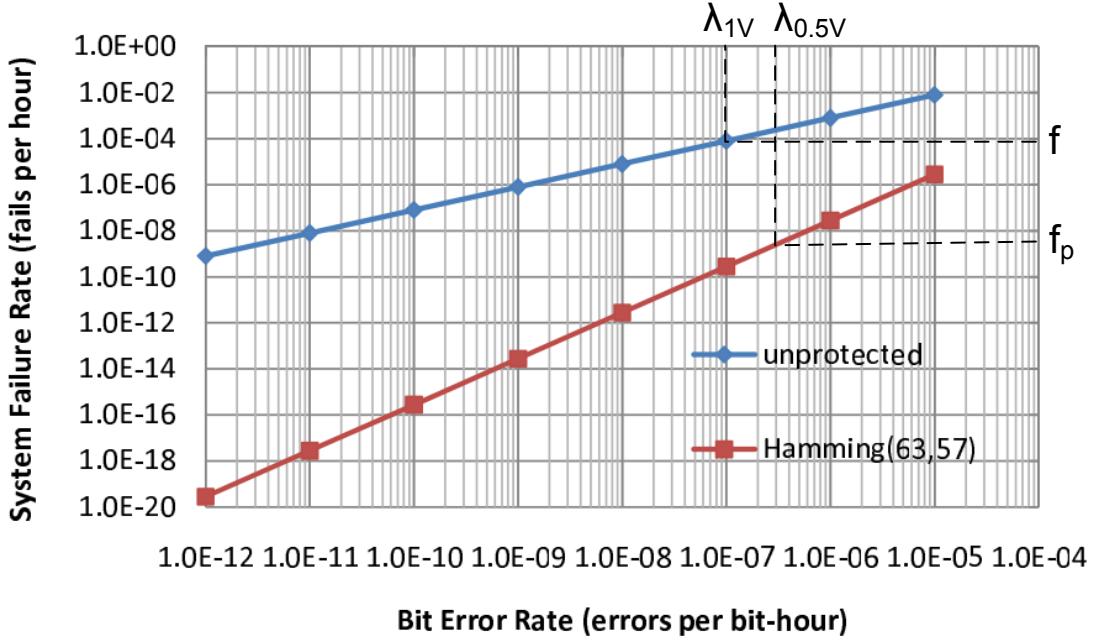

| 3.32 The system failure rate with and without hardware error recovery on Cortex-M0 as a case study . . . . .                                                                                                                | 62 |

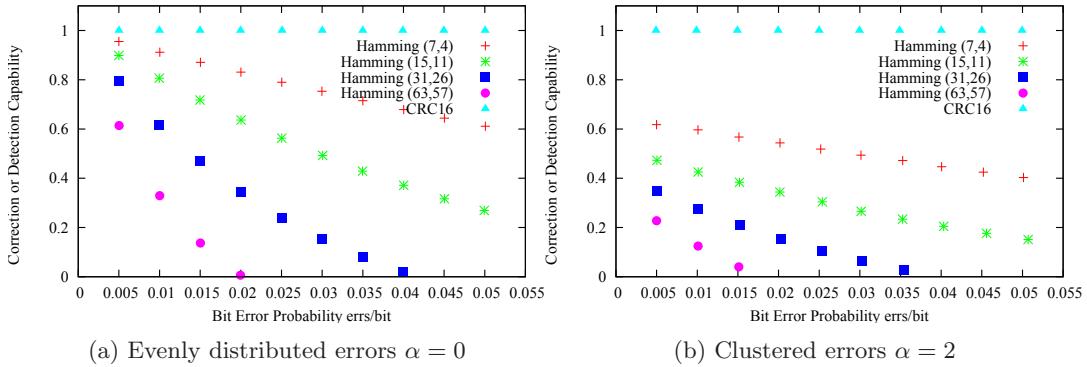

| 3.33 Error correction capability of Hamming codes and error detection capability of CRC-16 at bit error probability of 0.005 to 0.05 errors/bit. . . . .                                                                    | 62 |

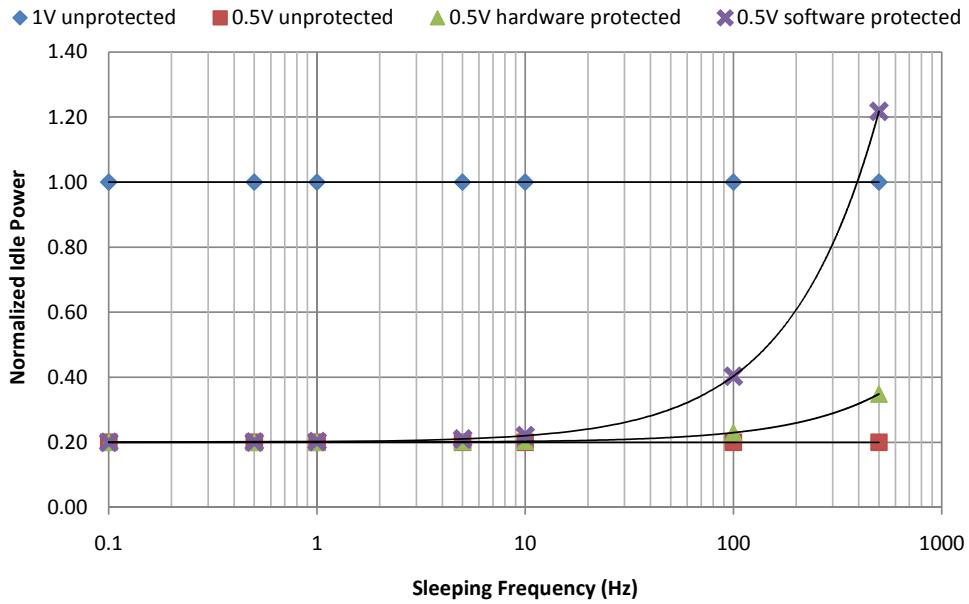

| 3.34 Trade-off analysis between leakage power saving and sleep frequency of the processor core at 0.5-V supply voltage . . . . .                                                                                            | 68 |

| <br>                                                                                                                                                                                                                        |    |

| 4.1 Test silicon fabricated and packaged for evaluation. . . . .                                                                                                                                                            | 73 |

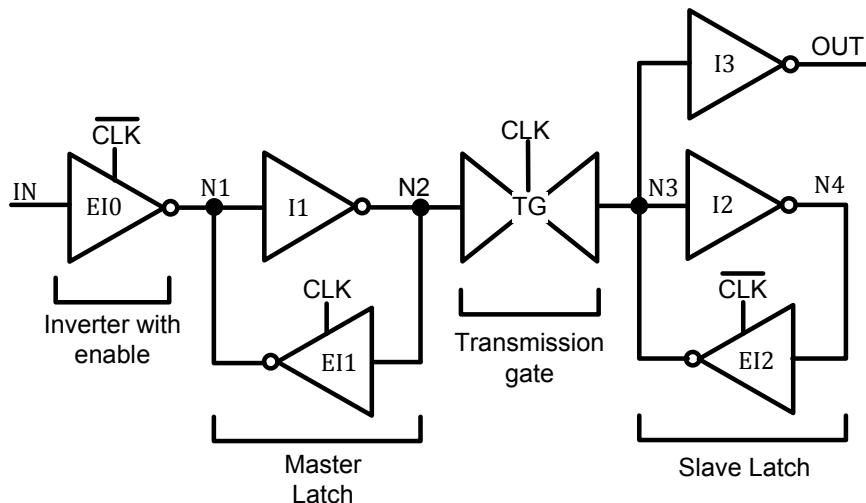

| 4.2 Schematic of master-slave flip-flop. . . . .                                                                                                                                                                            | 73 |

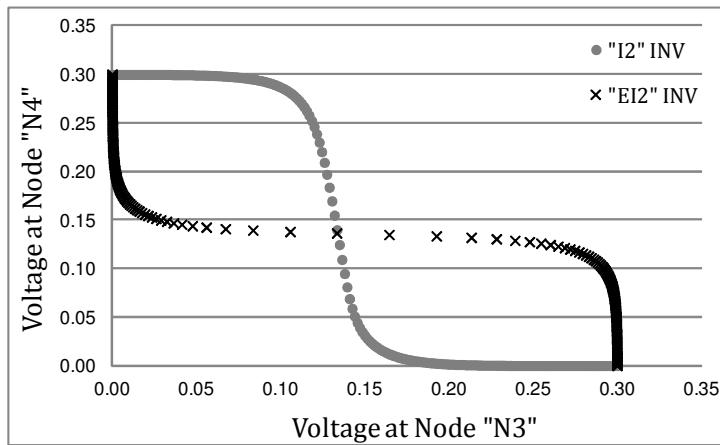

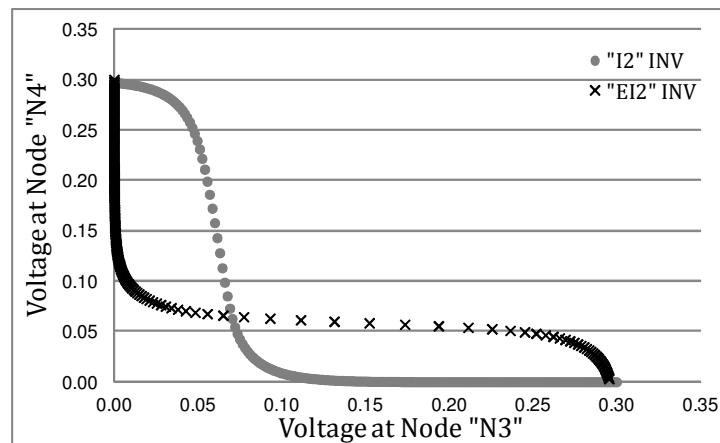

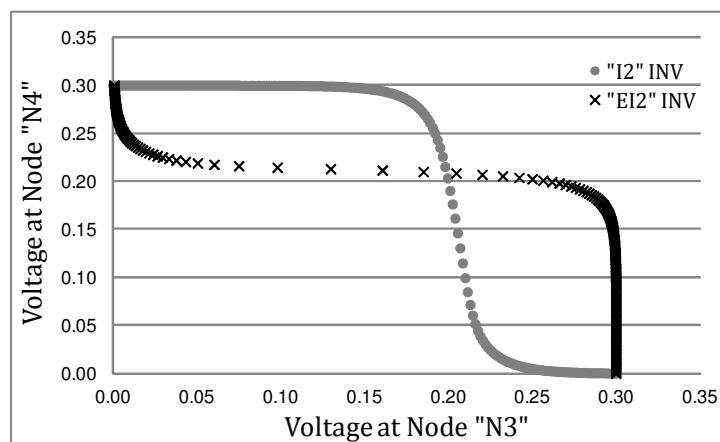

| 4.3 Simulated results showing noise margins of a typical flip-flop for state retention (Figure 4.2) when operating at 0.3-V, and reduced noise margins due to process variation at fast-slow and slow-fast corners. . . . . | 74 |

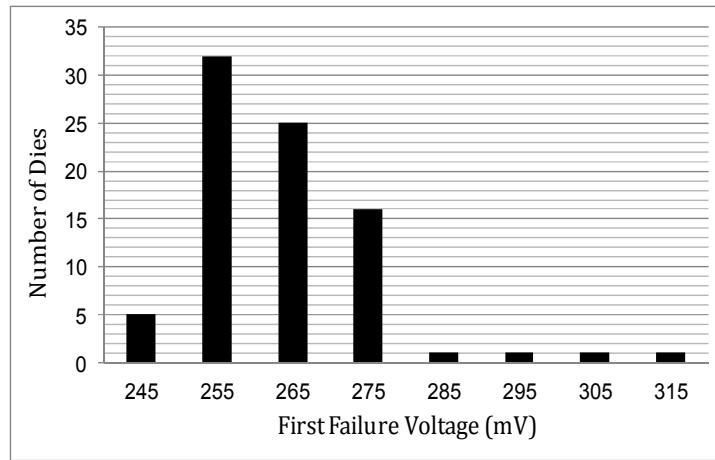

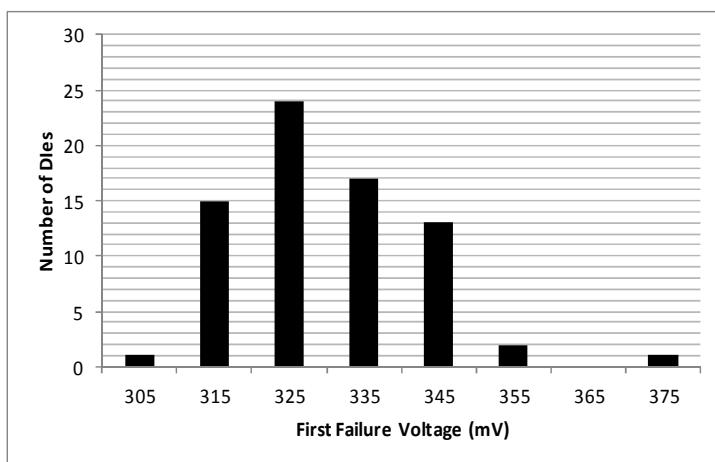

| 4.4 Results from 82 dies and Monte-Carlo simulations showing the spread of first failure voltage point of voltage-scaled flip-flop for state retention in room temperature (25°C). . . . .                                  | 76 |

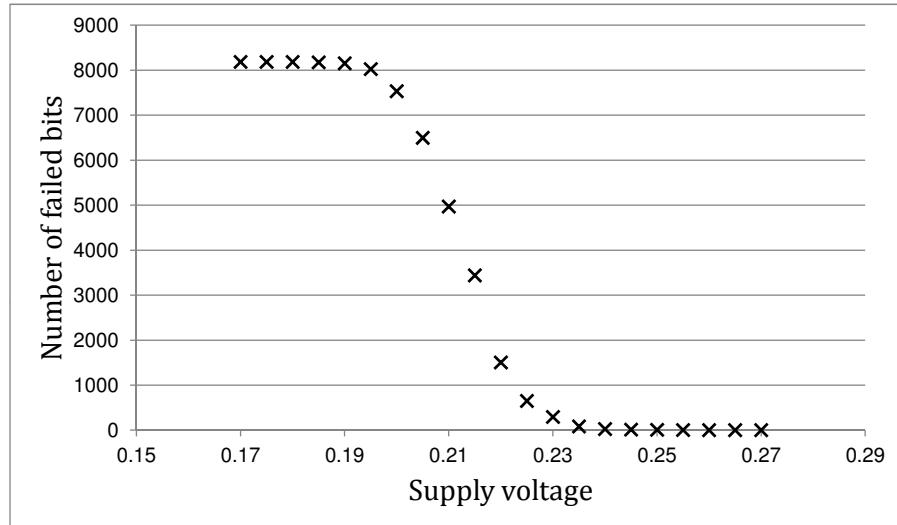

| 4.5 Measured results showing failure bit locations mapped on the circuit physical layout in the retention register block of the test chip. . . . .                                                                          | 77 |

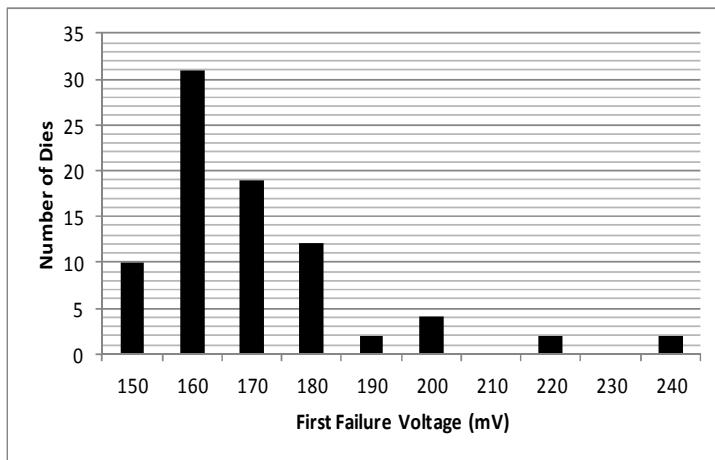

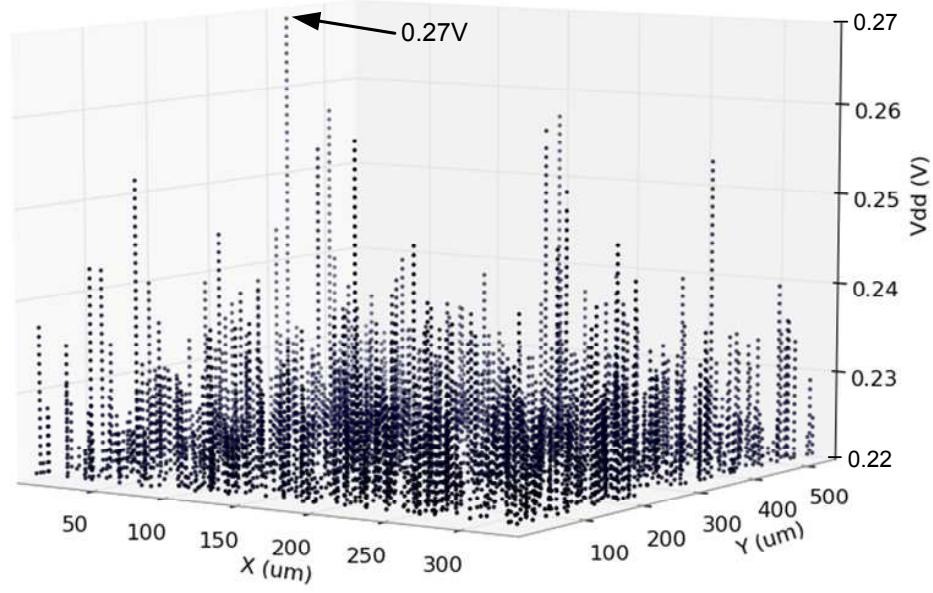

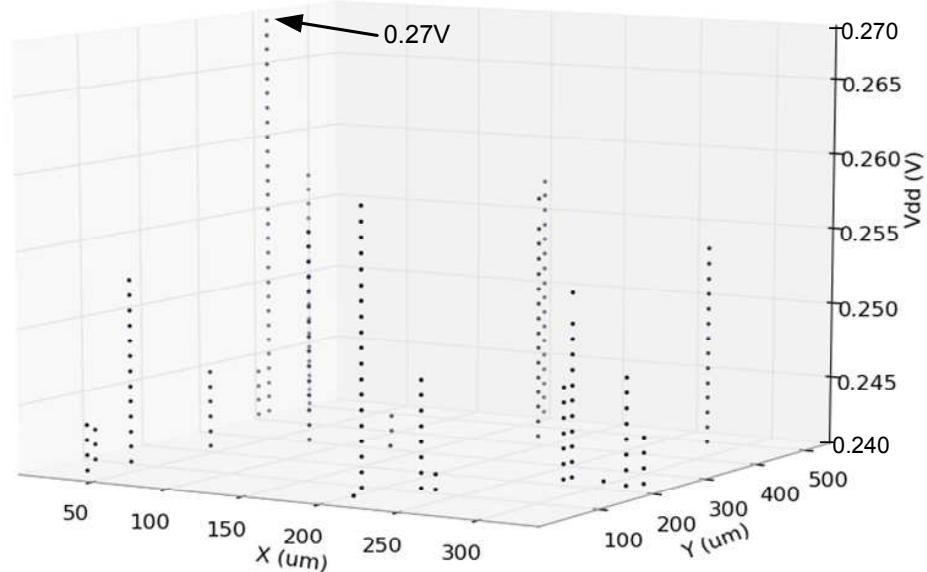

| 4.6 Measured results showing the distribution of failing voltage point of flip-flops at reduced supply voltage. . . . .                                                                                                     | 79 |

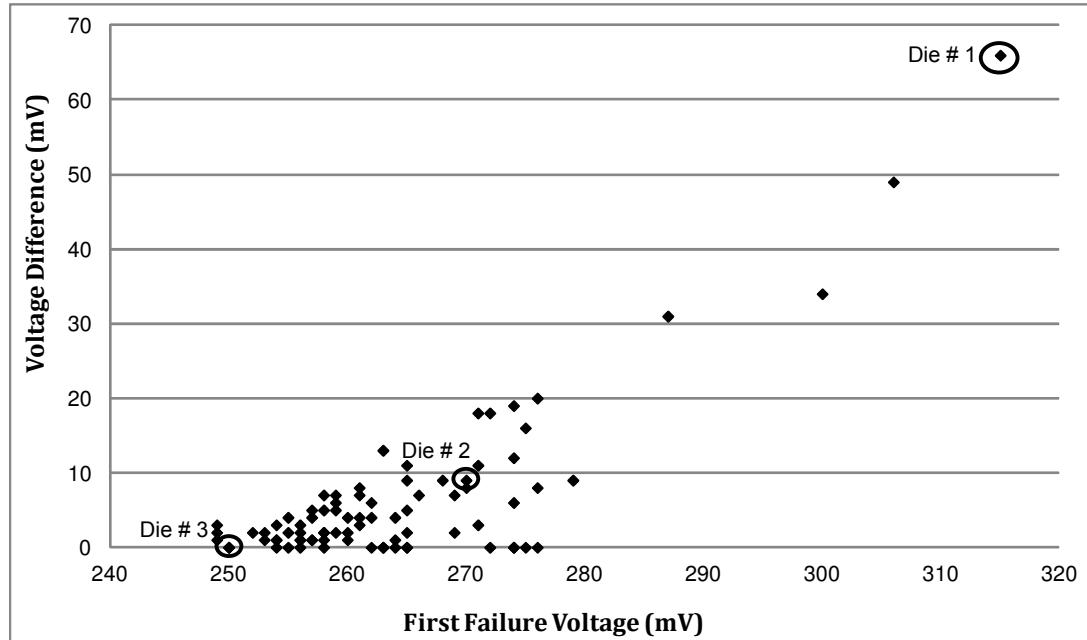

| 4.7 Measured results from 82 dies showing voltage difference between flip-flop's first failure voltage and subsequent failure voltages, three dies were selected from the population and re-numbered 1-2-3. . . . .         | 80 |

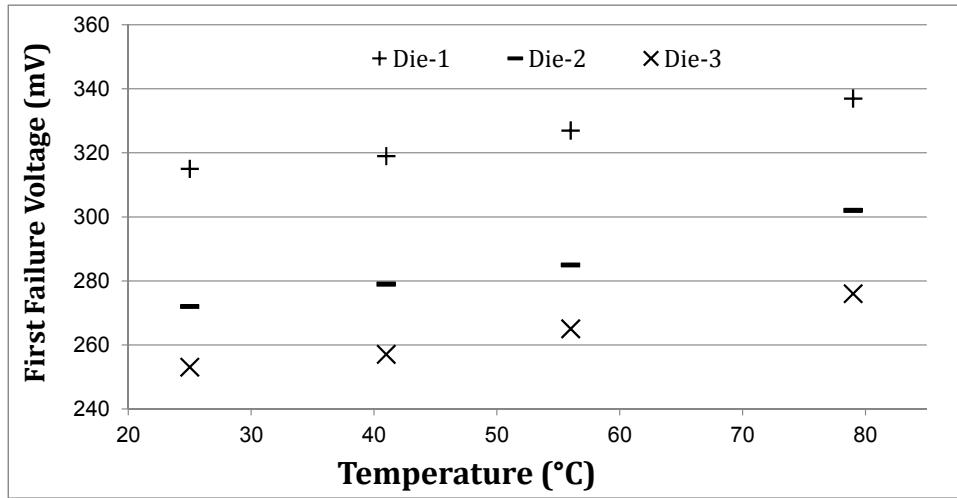

| 4.8 Measured results showing the first failing voltage point of flip-flops due to within-die temperature variation. . . . .                                                                                                 | 81 |

---

|      |                                                                                                                                                                                                                                                                         |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

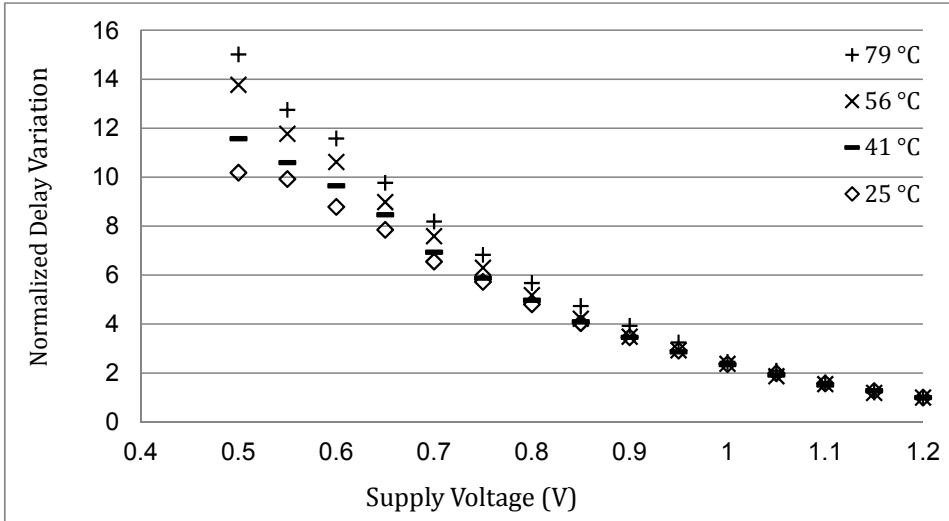

| 4.9  | Measured results of Intra-Die PVT Variation on delay of the test chip. These results demonstrate that due to change in temperature the effect of within die process variation gets worse as shown by within die higher normalised delay variation. . . . .              | 82  |

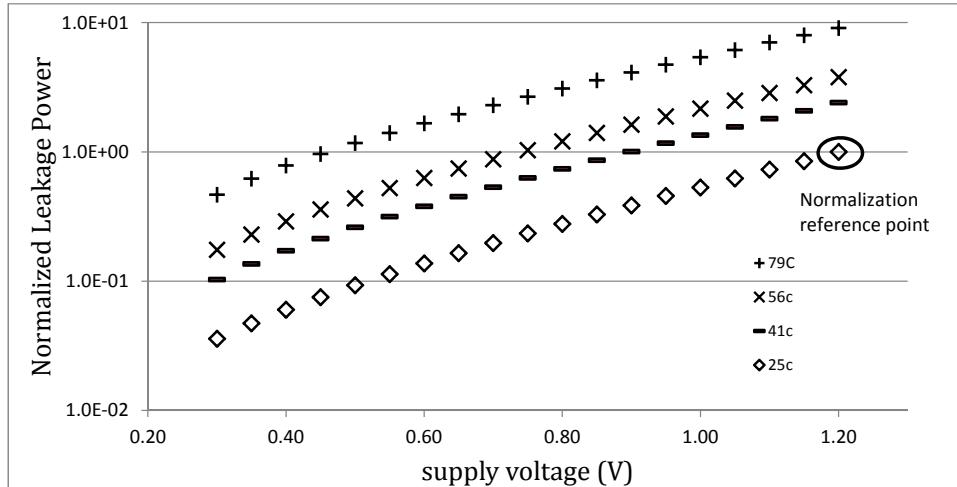

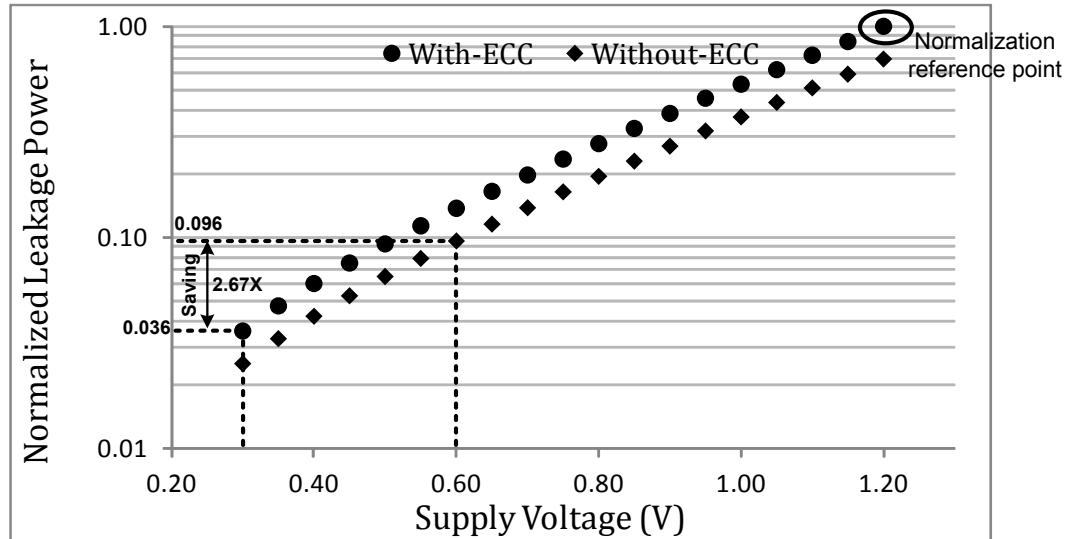

| 4.10 | Measured test chip leakage power normalised to 1.2V nominal supply voltage at 25°C. . . . .                                                                                                                                                                             | 83  |

| 4.11 | Process and Temperature Variation Aware Minimum Retention Voltage (MRV) Characterisation Algorithm at 25°C. . . . .                                                                                                                                                     | 84  |

| 4.12 | Control Flow for State Monitoring and Protection of Flip-Flops for Voltage-Scaled State Retention. . . . .                                                                                                                                                              | 85  |

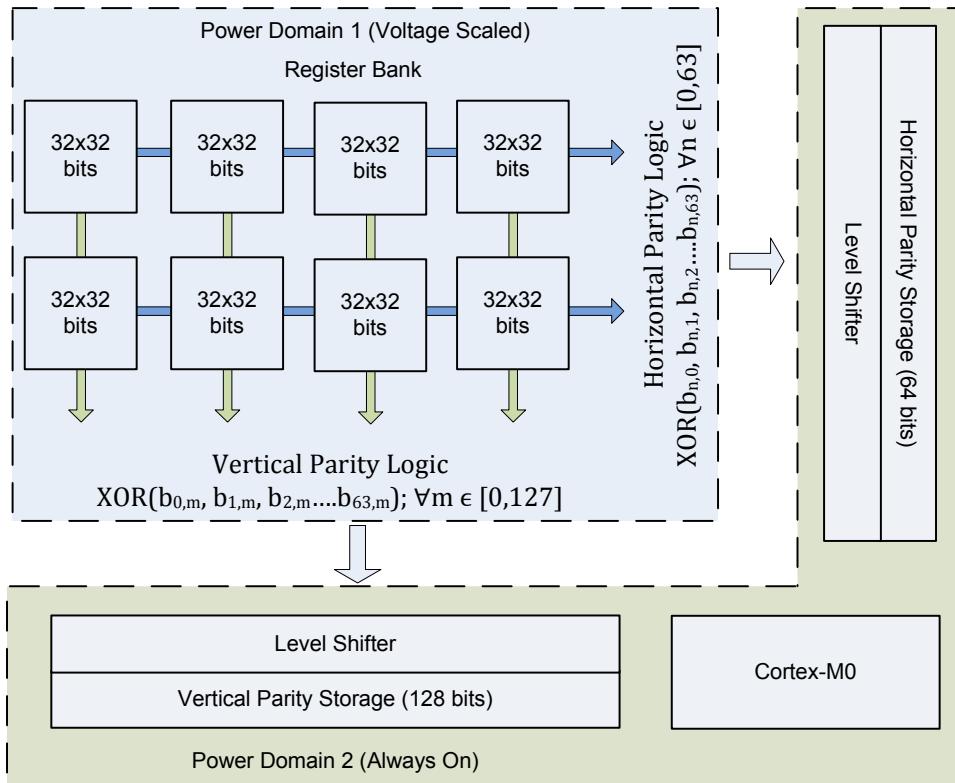

| 4.13 | Vertical and horizontal parity protected retention register block. . . . .                                                                                                                                                                                              | 87  |

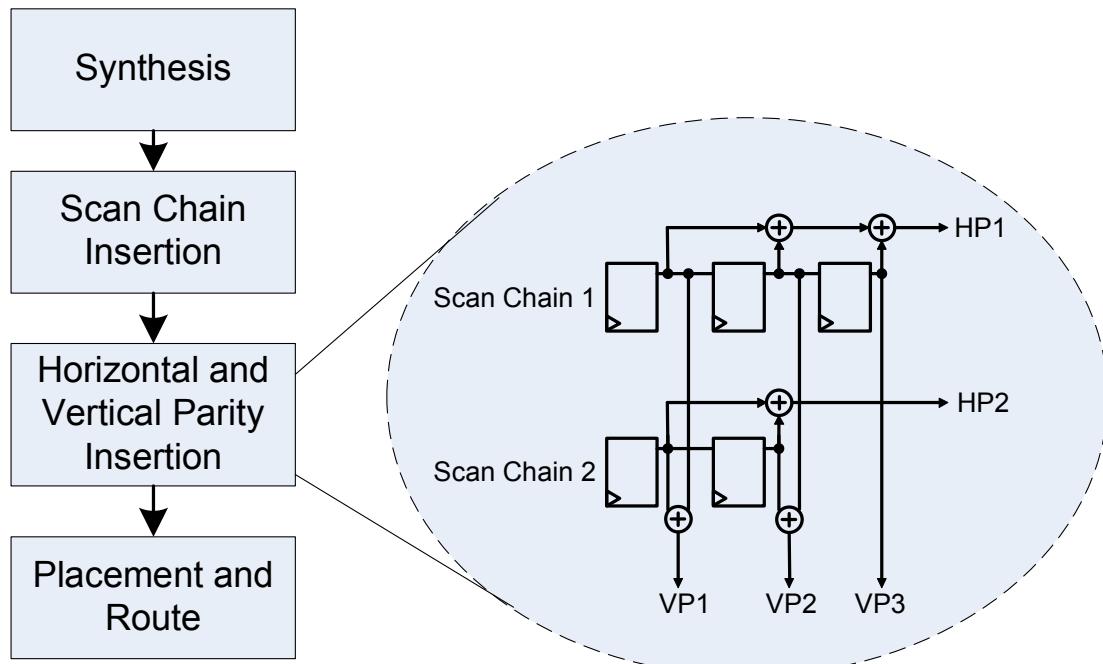

| 4.14 | Vertical and horizontal parity insertion synthesis flow. . . . .                                                                                                                                                                                                        | 88  |

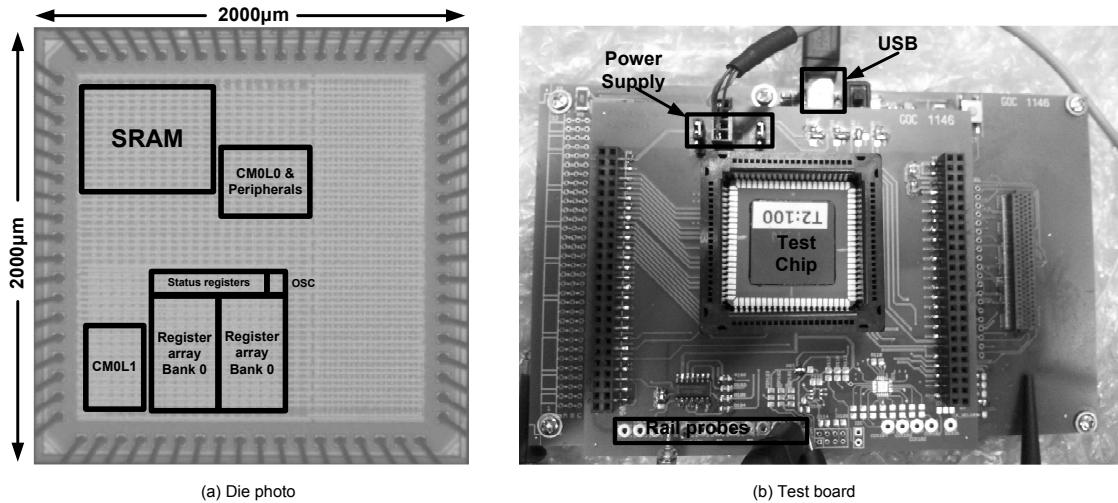

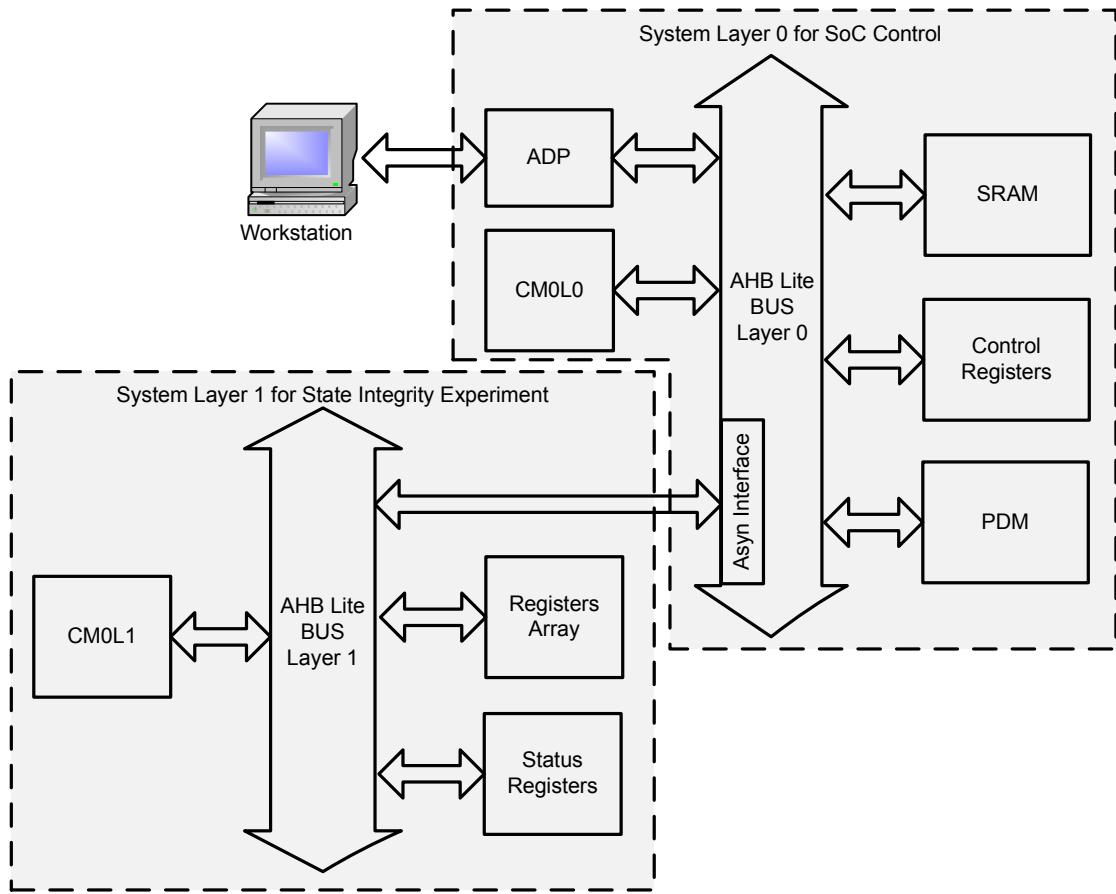

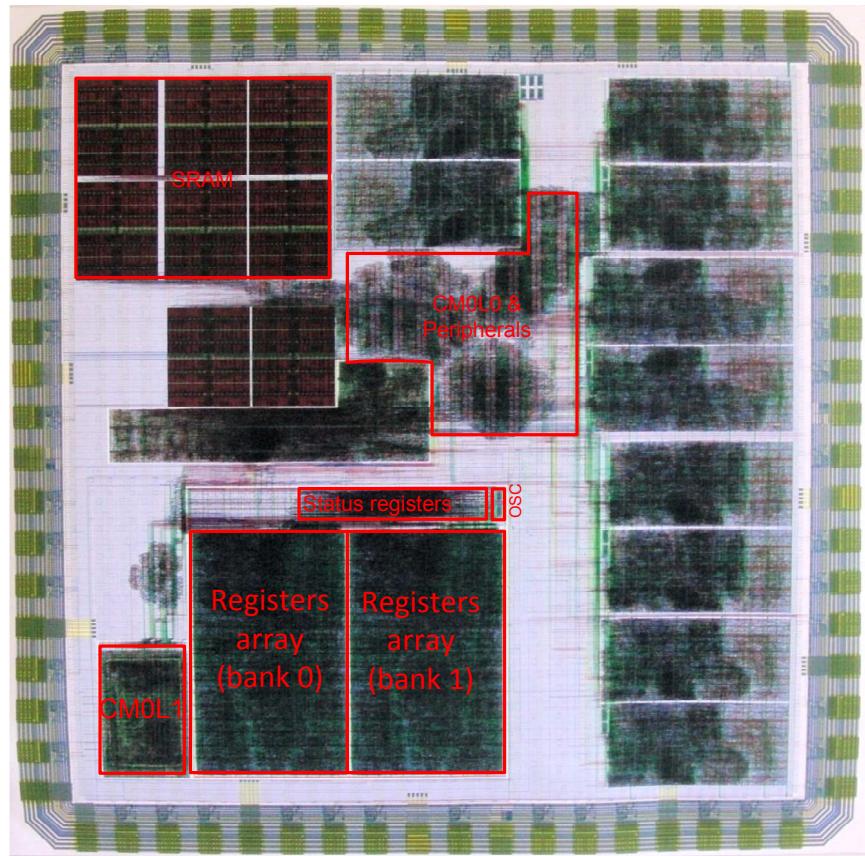

| 4.15 | Test chip architecture. . . . .                                                                                                                                                                                                                                         | 89  |

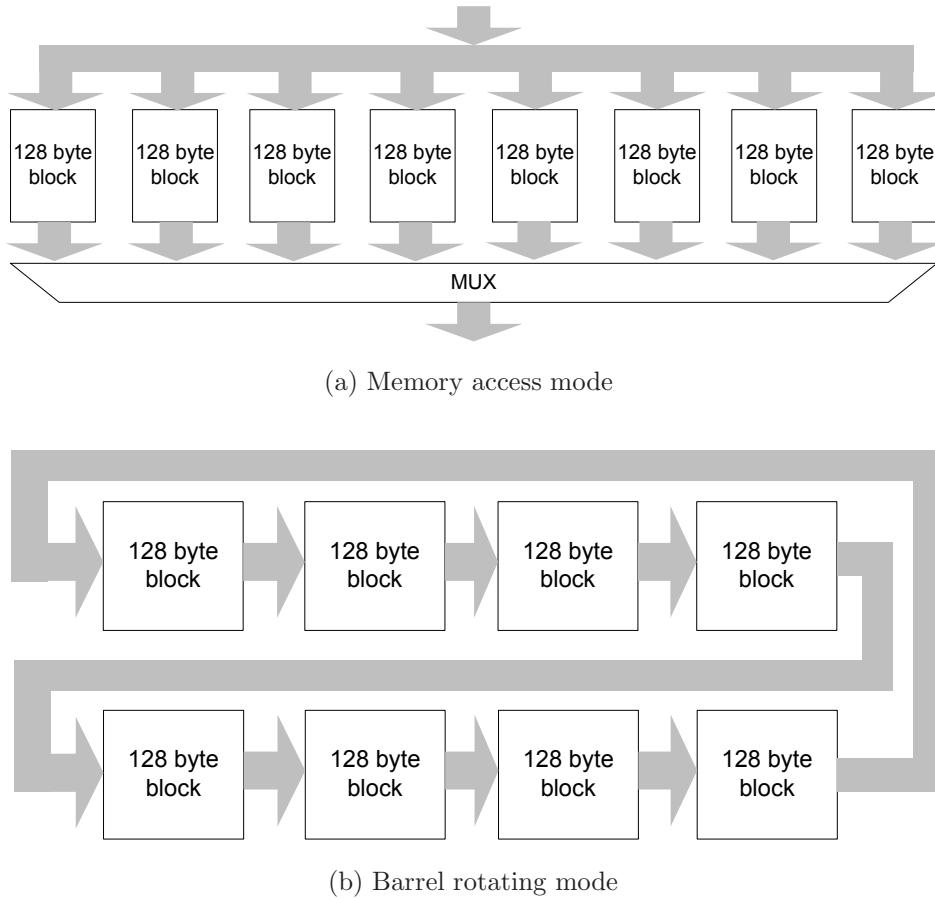

| 4.16 | 8192 flip-flops divided into 8 blocks register array each with 128 flip-flops, there are two mode of operations . . . . .                                                                                                                                               | 90  |

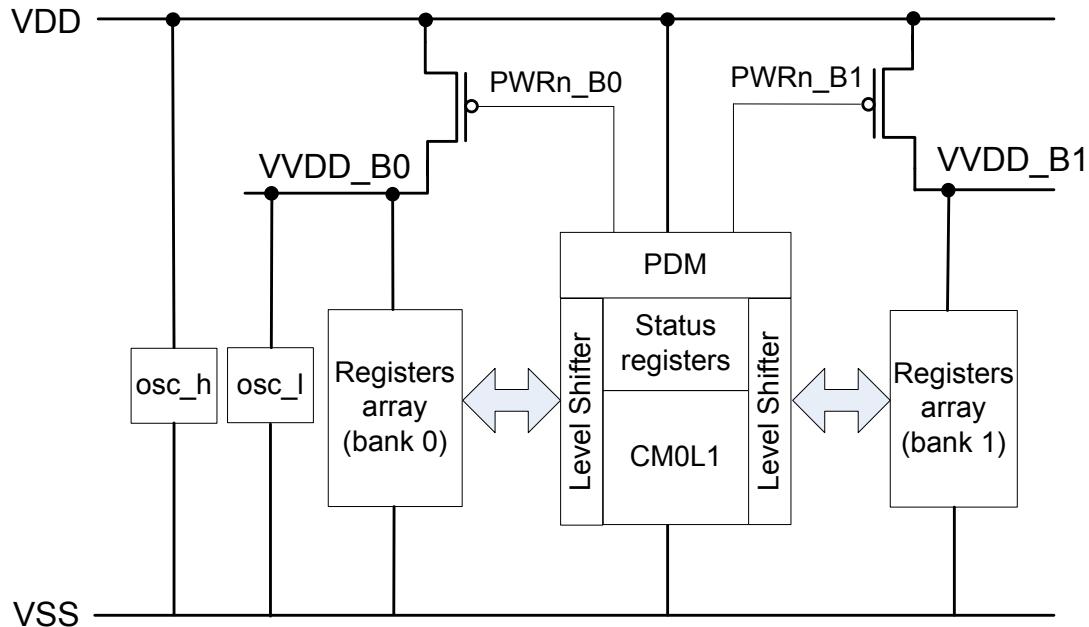

| 4.17 | Power configuration of flip-flop state integrity experiment. . . . .                                                                                                                                                                                                    | 91  |

| 4.18 | Memory map of components used for flip-flop state integrity experiments. .                                                                                                                                                                                              | 91  |

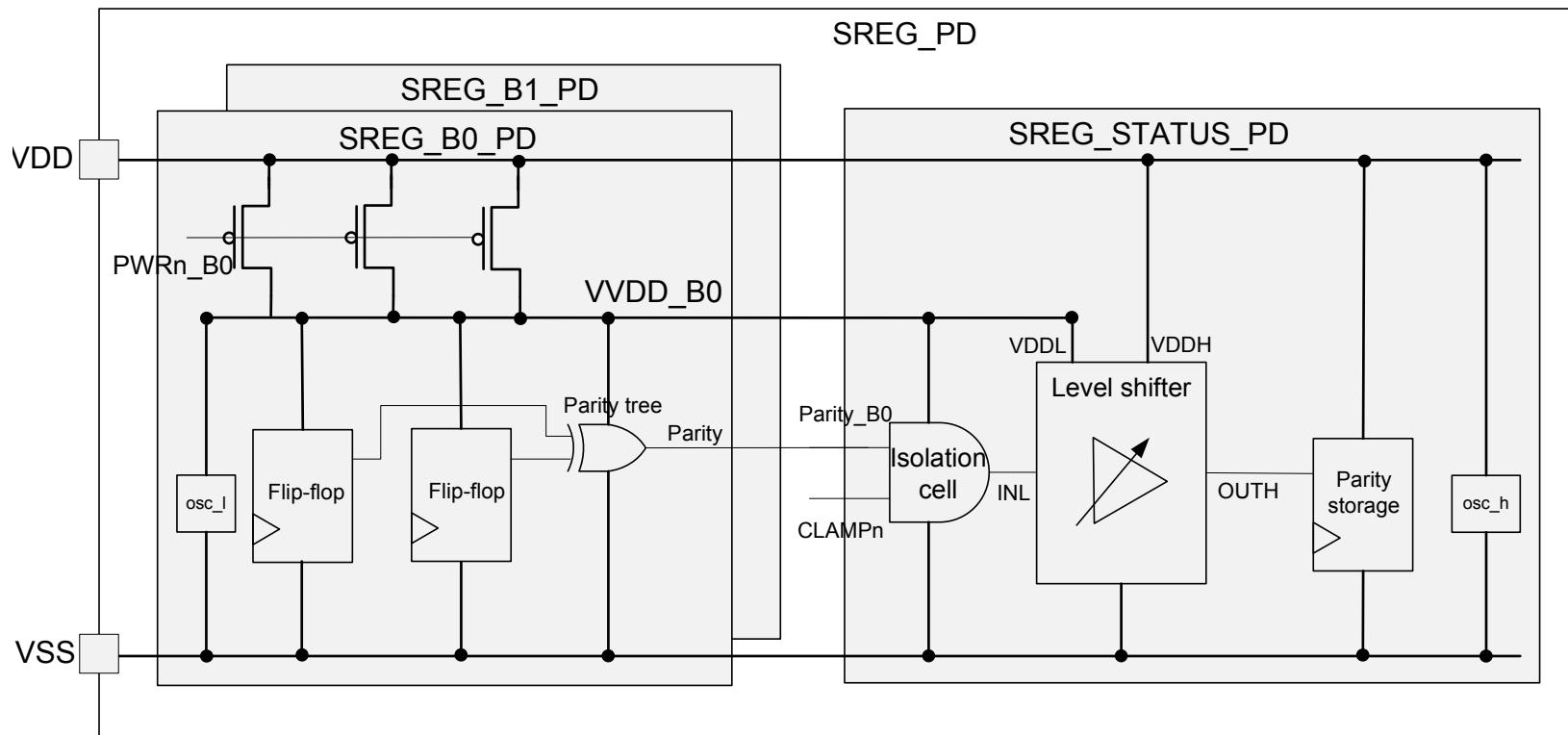

| 4.19 | Power intent of flip-flop state integrity experiment. . . . .                                                                                                                                                                                                           | 93  |

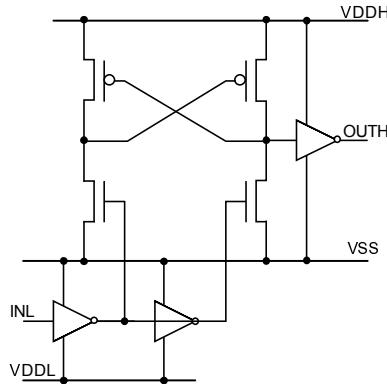

| 4.20 | Level shifter schematic [38]. . . . .                                                                                                                                                                                                                                   | 94  |

| 4.21 | Synthesis and physical implementation flow. . . . .                                                                                                                                                                                                                     | 96  |

| 4.22 | Final layout of test chip. . . . .                                                                                                                                                                                                                                      | 97  |

| 4.23 | Measured Leakage Power at room temperature normalised to 1.2 V supply voltage: With ECC vs. Without ECC. . . . .                                                                                                                                                        | 99  |

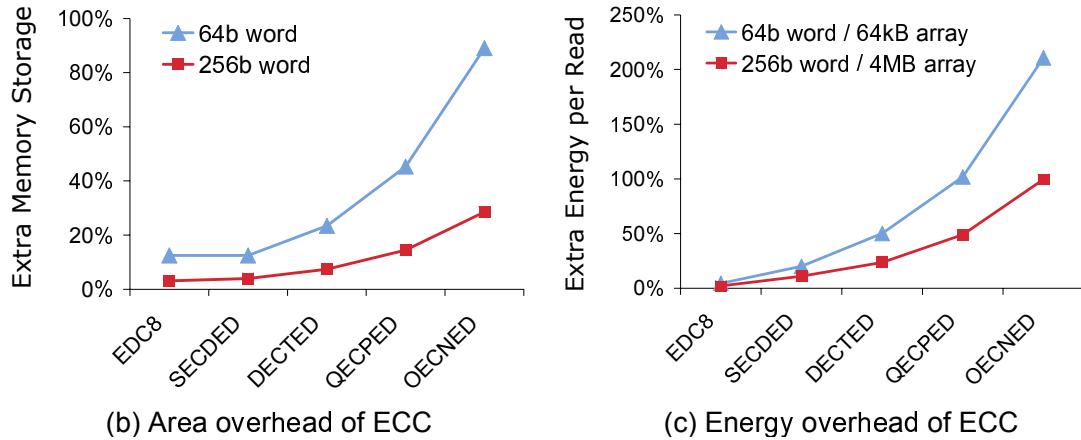

| 5.1  | ECC overhead in terms of (a) area (b) energy [169]. . . . .                                                                                                                                                                                                             | 102 |

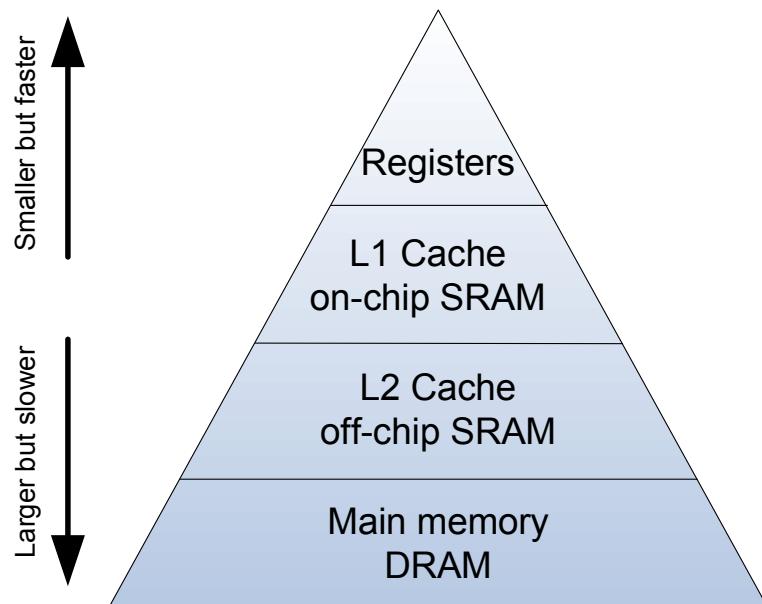

| 5.2  | Low-medium performance microprocessor memory hierarchy . . . . .                                                                                                                                                                                                        | 103 |

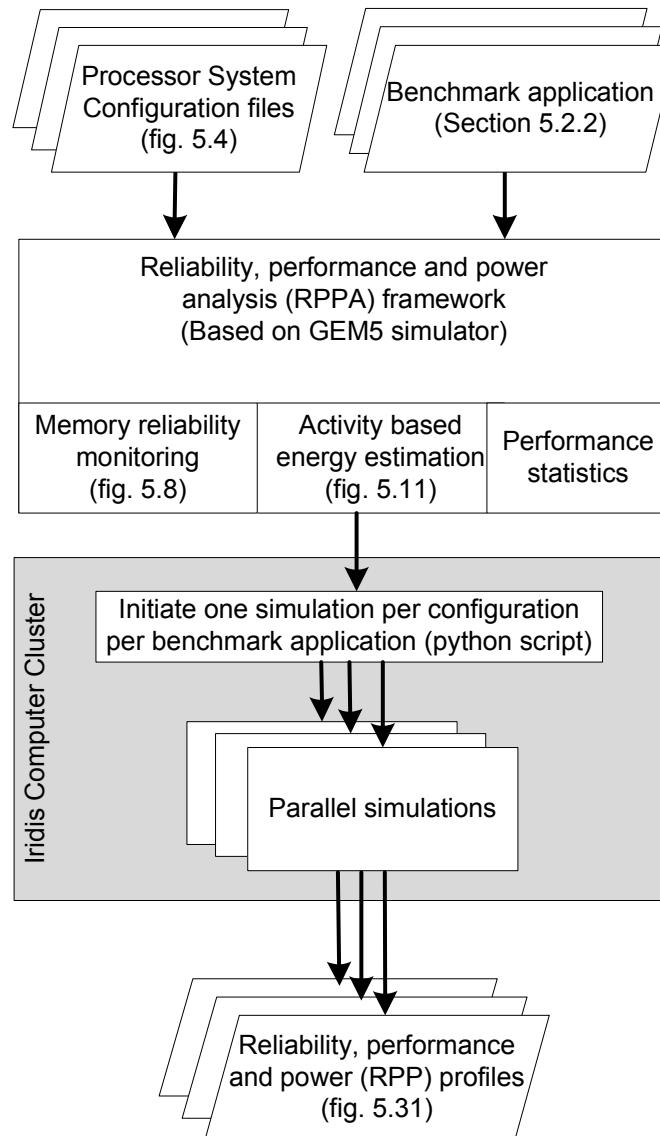

| 5.3  | Proposed framework to analyse reliability, performance and energy consumption . . . . .                                                                                                                                                                                 | 105 |

| 5.4  | Example Python script for GEM5 used to configure (a) processor core (b) cache memory . . . . .                                                                                                                                                                          | 106 |

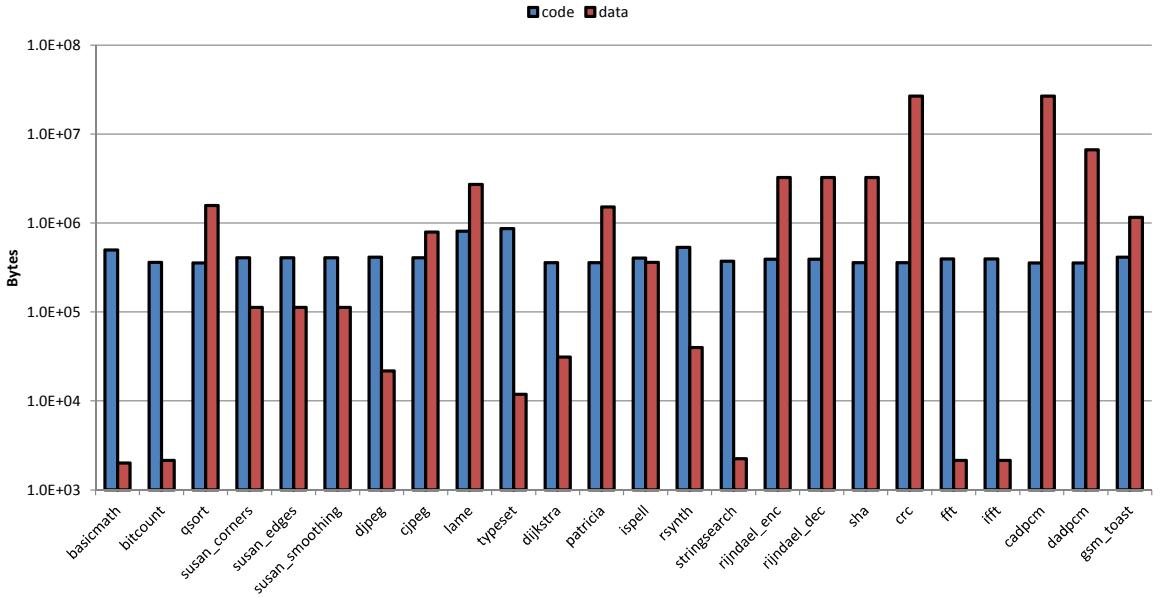

| 5.5  | Code and data size of MiBench benchmark applications (Memory footprints)                                                                                                                                                                                                | 109 |

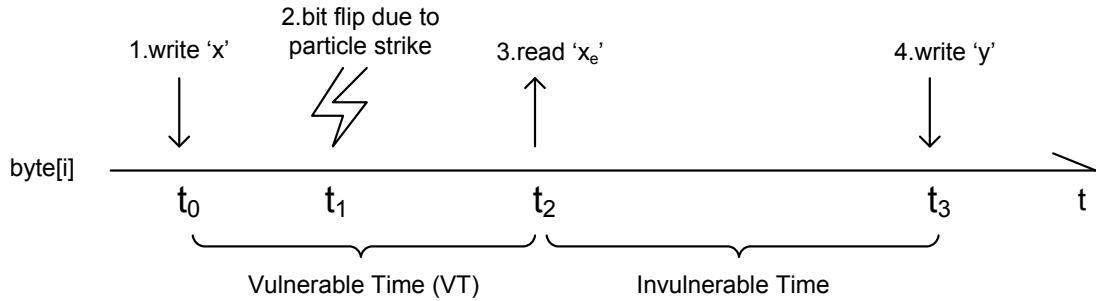

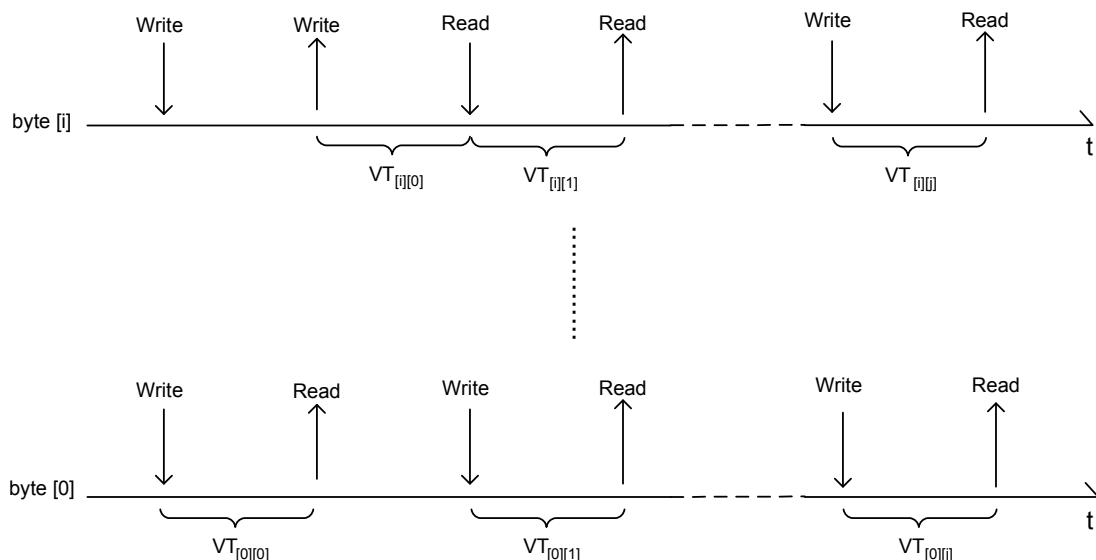

| 5.6  | Storage cells data lifetime . . . . .                                                                                                                                                                                                                                   | 110 |

| 5.7  | Collection of vulnerable time slices. . . . .                                                                                                                                                                                                                           | 110 |

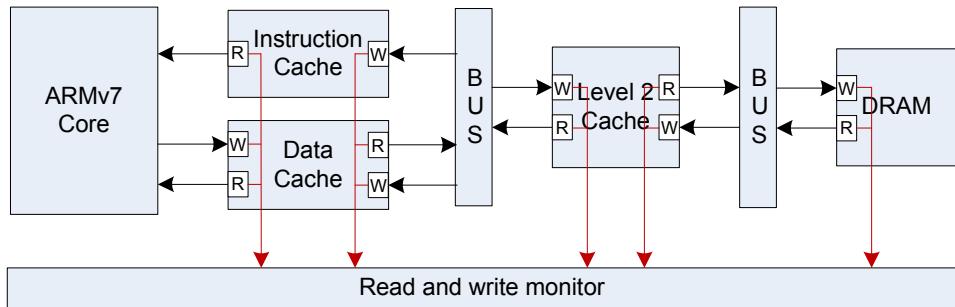

| 5.8  | Memory system architecture and read/write access monitor . . . . .                                                                                                                                                                                                      | 111 |

| 5.9  | Example code for main memory (DRAM) read and write monitoring . .                                                                                                                                                                                                       | 112 |

| 5.10 | Example code for cache (L1 and L2) read and write monitoring . . . .                                                                                                                                                                                                    | 113 |

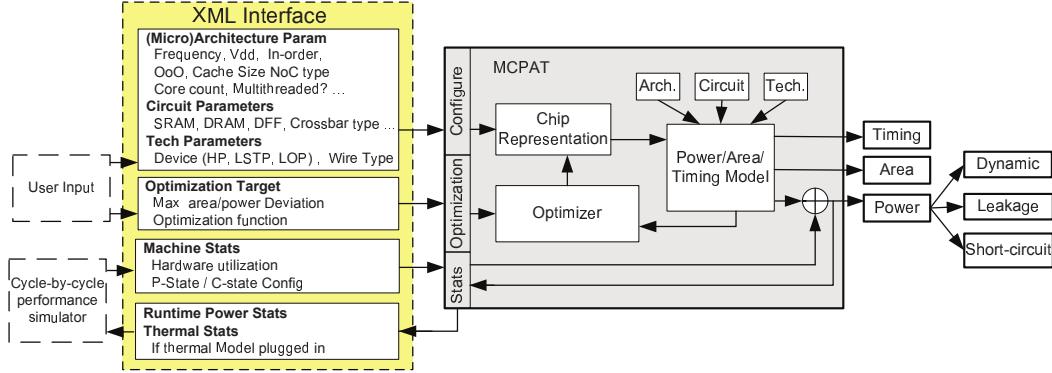

| 5.11 | Block diagram of McPAT [178] . . . . .                                                                                                                                                                                                                                  | 114 |

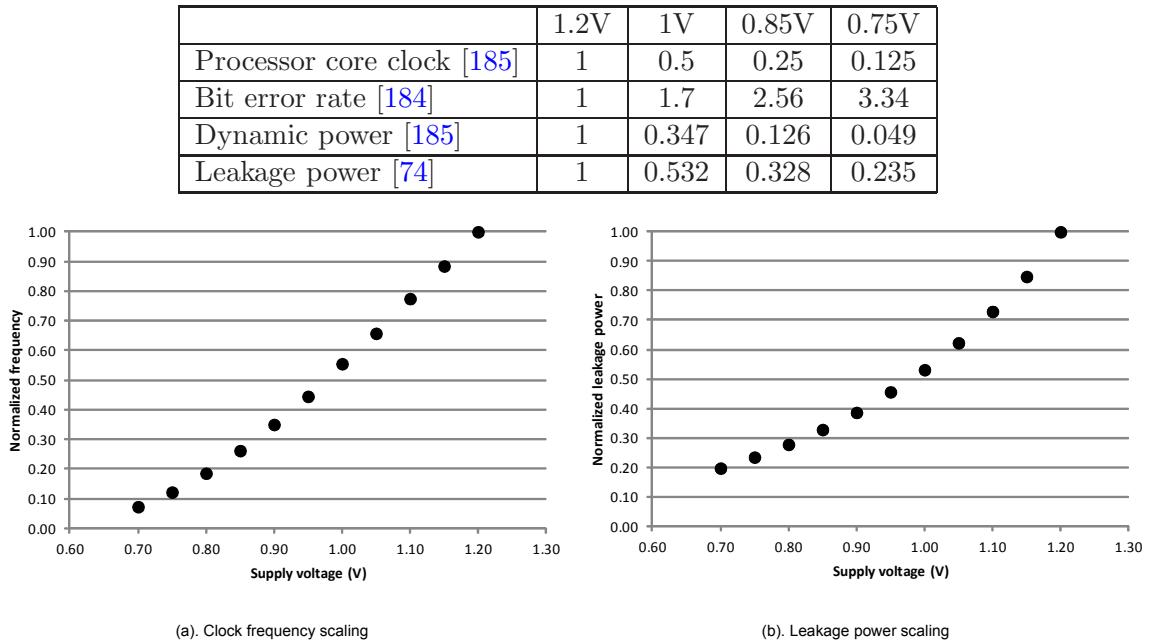

| 5.12 | (a) Measured clock frequency under supply voltage scaling for 65nm low-power technology library, (b) Measured leakage power under supply voltage scaling for 65nm low-power technology library at room temperature. .                                                   | 115 |

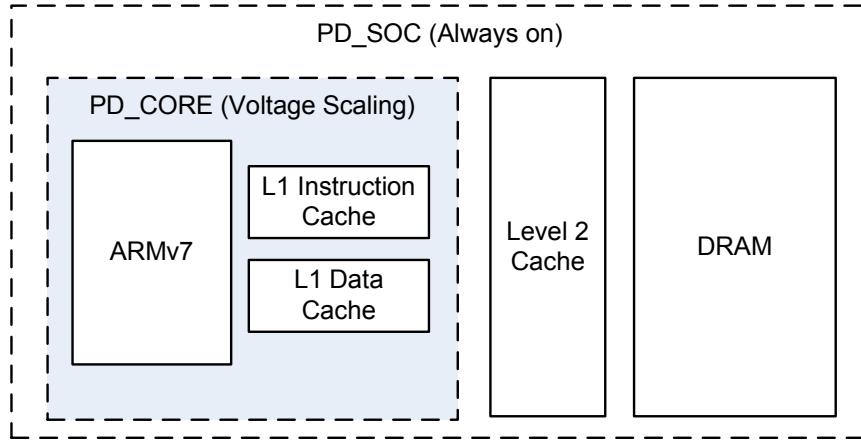

| 5.13 | Power domains . . . . .                                                                                                                                                                                                                                                 | 116 |

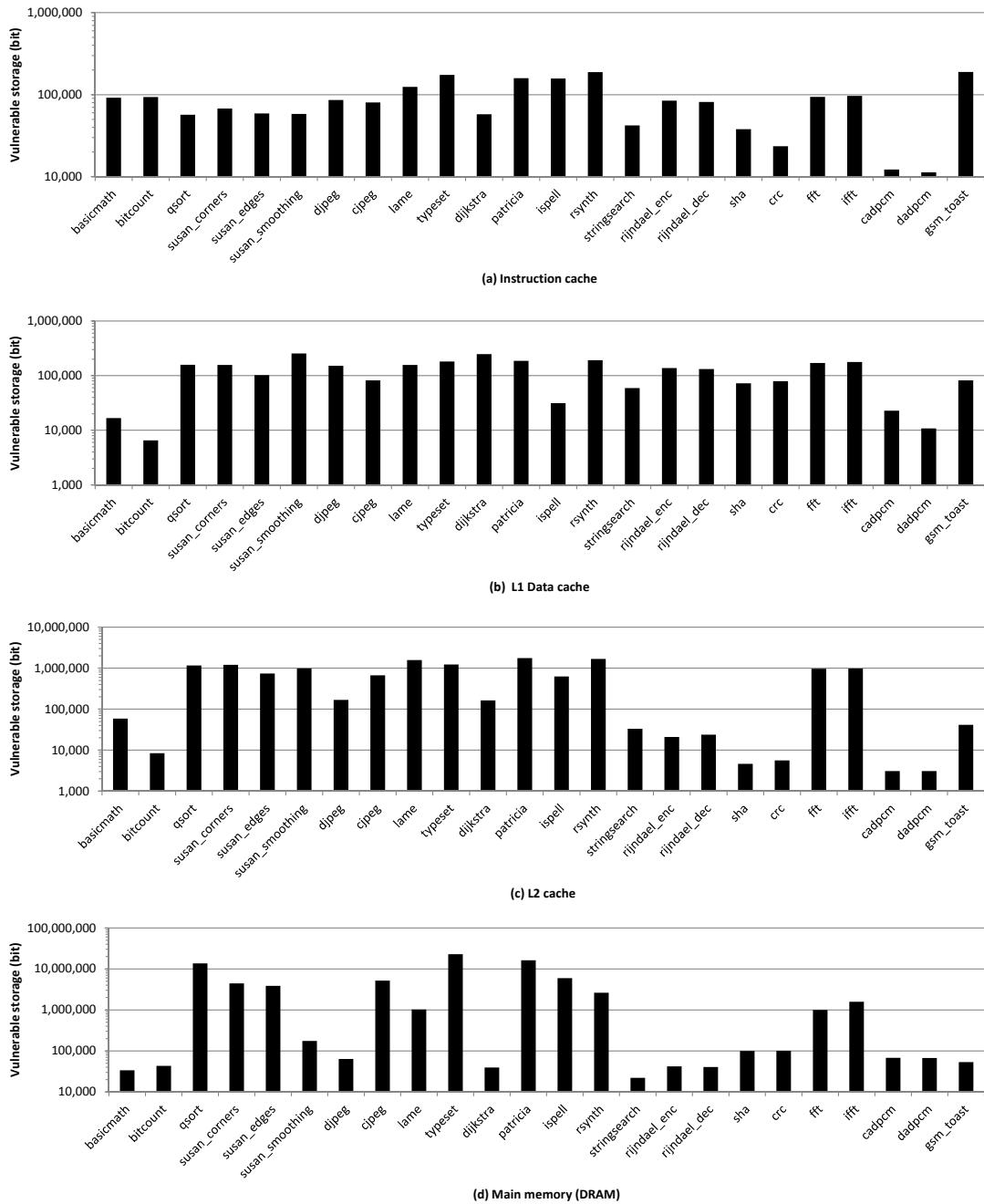

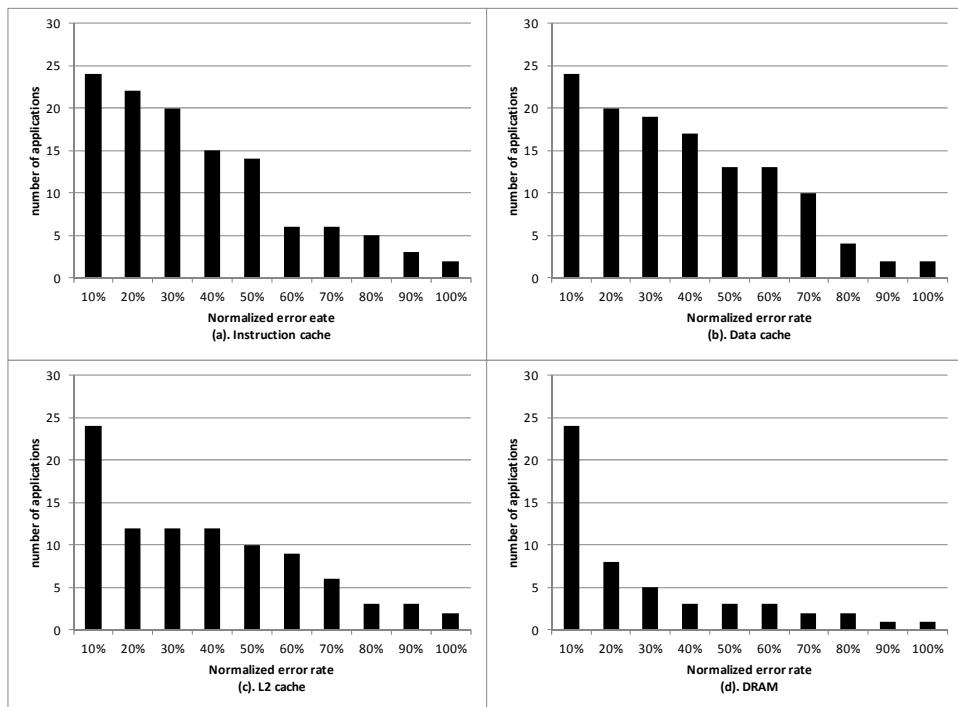

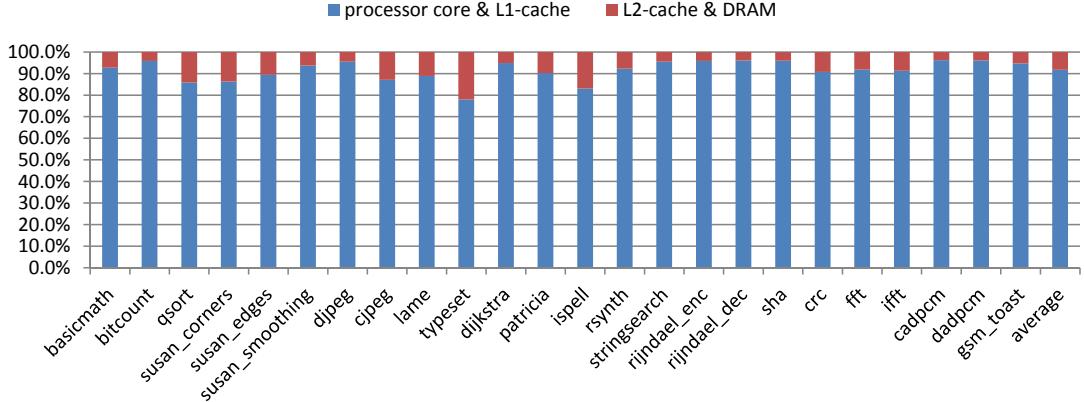

| 5.14 | Memory components vulnerable storage . . . . .                                                                                                                                                                                                                          | 118 |

| 5.15 | Average, minimum and maximum vulnerable storage of memory components across applications. . . . .                                                                                                                                                                       | 119 |

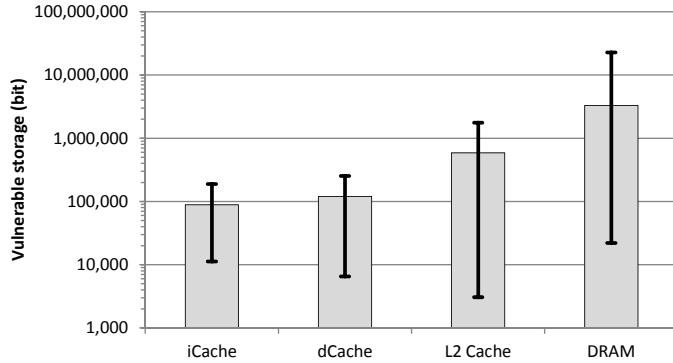

| 5.16 | Distribution of memory component error rate for MiBench benchmark applications: (a) L1 Instruction Cache (I-Cache), (b) L1 Data Cache (D-Cache), (c) L2 cache and (d) DRAM. The error rate is normalised to the worst case error rate of each memory component. . . . . | 119 |

|                                                                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.17 Processor system power distribution at nominal supply voltage of 1.2V . . . . .                                                         | 120 |

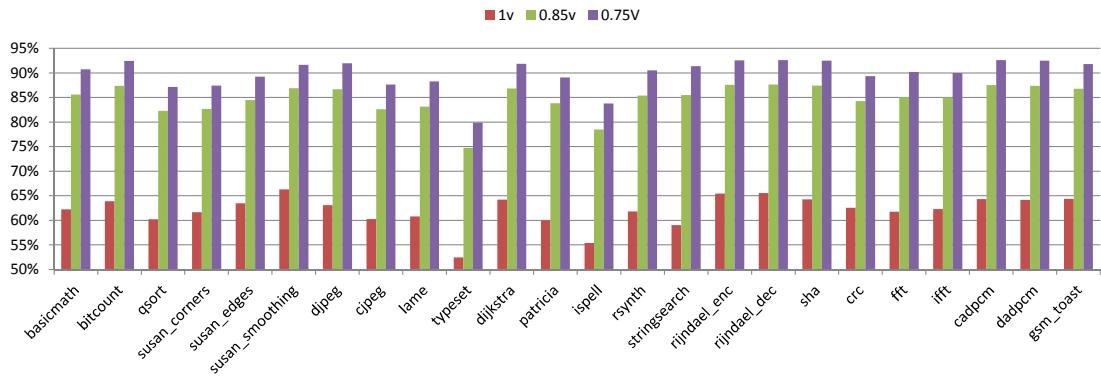

| 5.18 The power reduction through VFS when compared with nominal supply voltage of 1.2V. . . . .                                              | 120 |

| 5.19 The processor core and L1-cache power consumption as a percentage of system power. . . . .                                              | 120 |

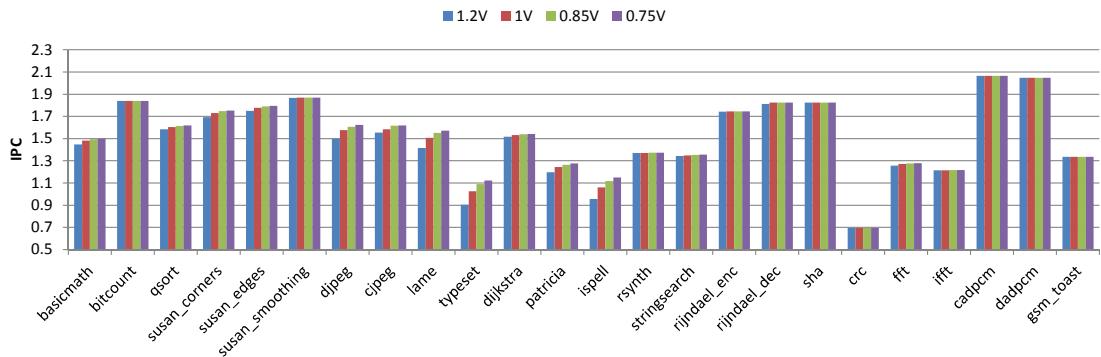

| 5.20 The impact of VFS on performance measured with Instruction Per Cycle (IPC). . . . .                                                     | 121 |

| 5.21 The L1-cache miss latency expressed as percentage of runtime under VFS. . . . .                                                         | 121 |

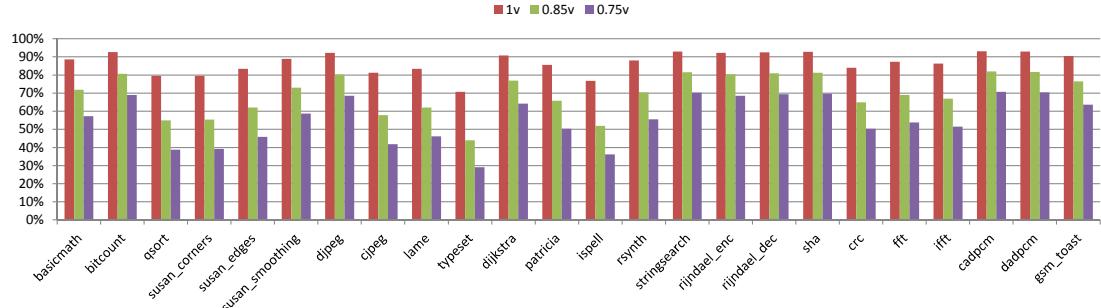

| 5.22 Energy reduction through VFS when compared with nominal supply voltage of 1.2V. . . . .                                                 | 122 |

| 5.23 The impact of voltage and frequency scaling on L1-cache reliability. . . . .                                                            | 122 |

| 5.24 Cost effective and reliable processor system design flow. . . . .                                                                       | 124 |

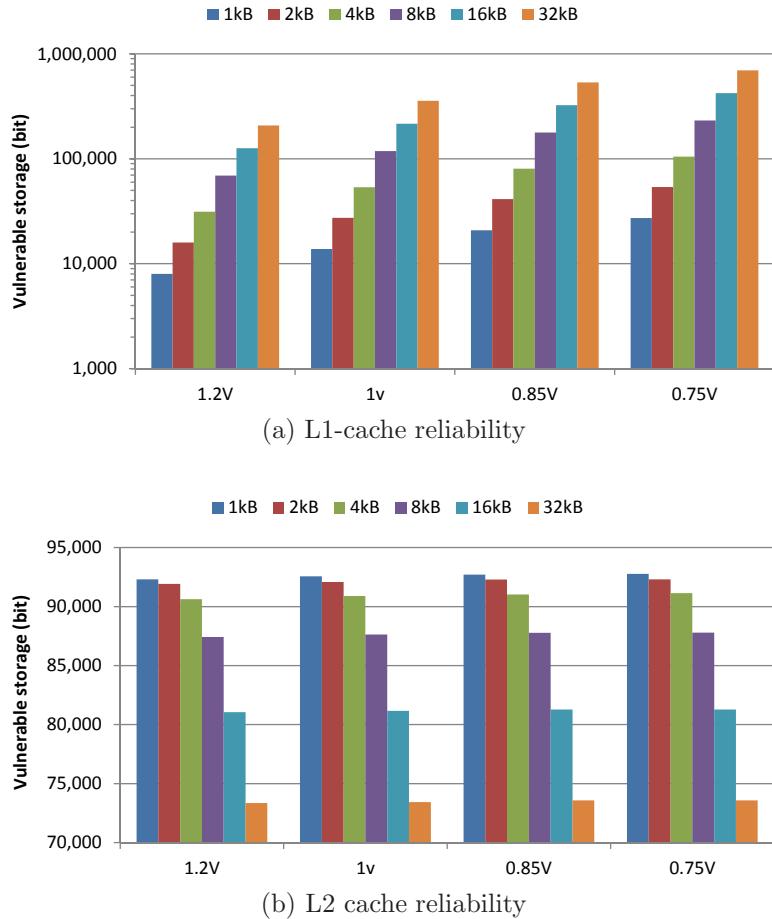

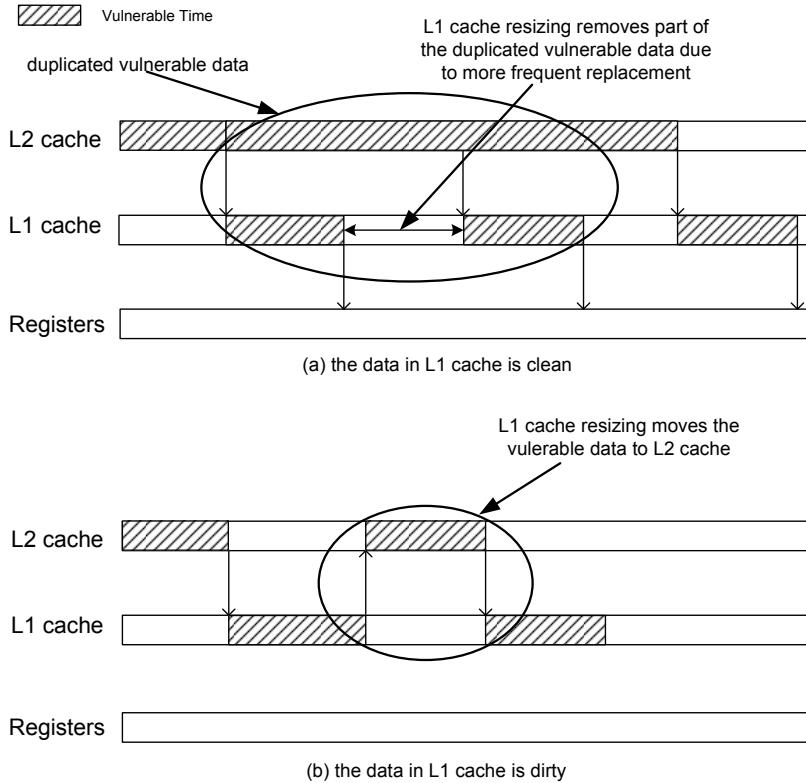

| 5.25 L1-cache resizing impact on (a) L1-cache reliability and (b) L2 cache reliability. . . . .                                              | 125 |

| 5.26 The impact of L1-cache resizing on vulnerable time. . . . .                                                                             | 126 |

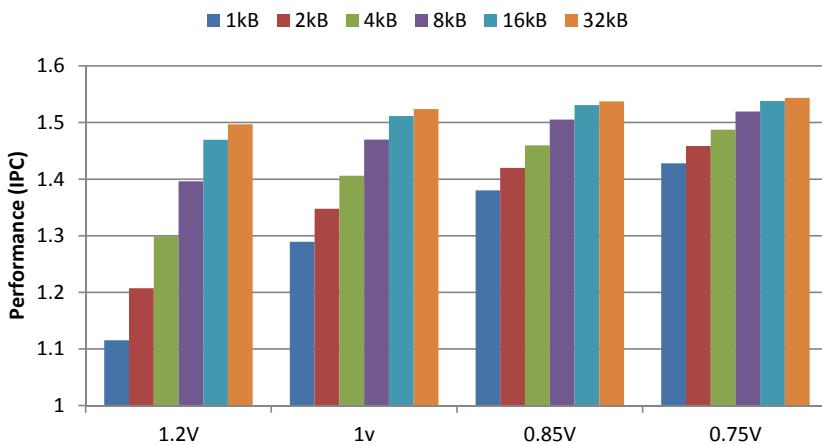

| 5.27 The impact of L1-cache resizing on performance. . . . .                                                                                 | 126 |

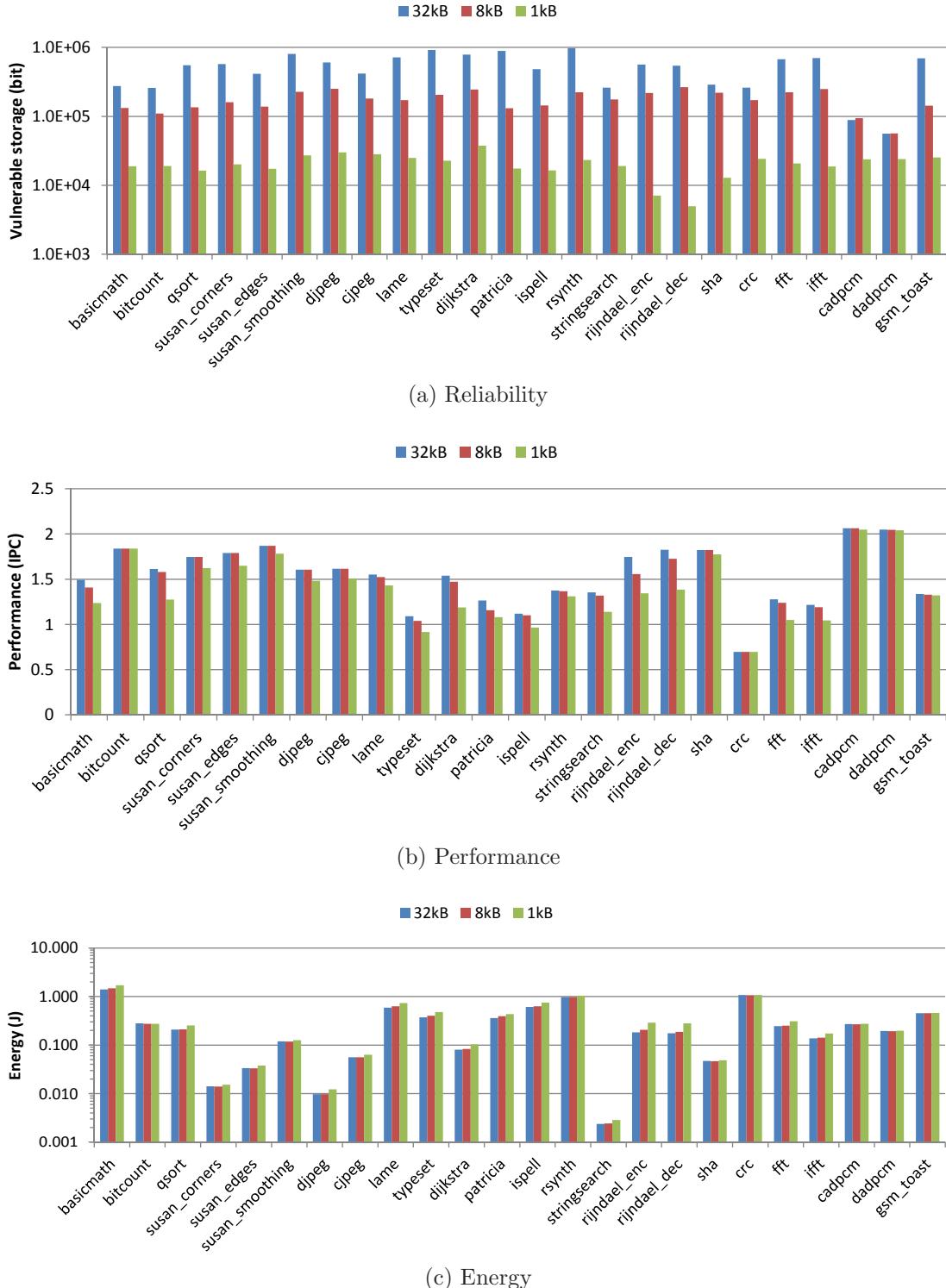

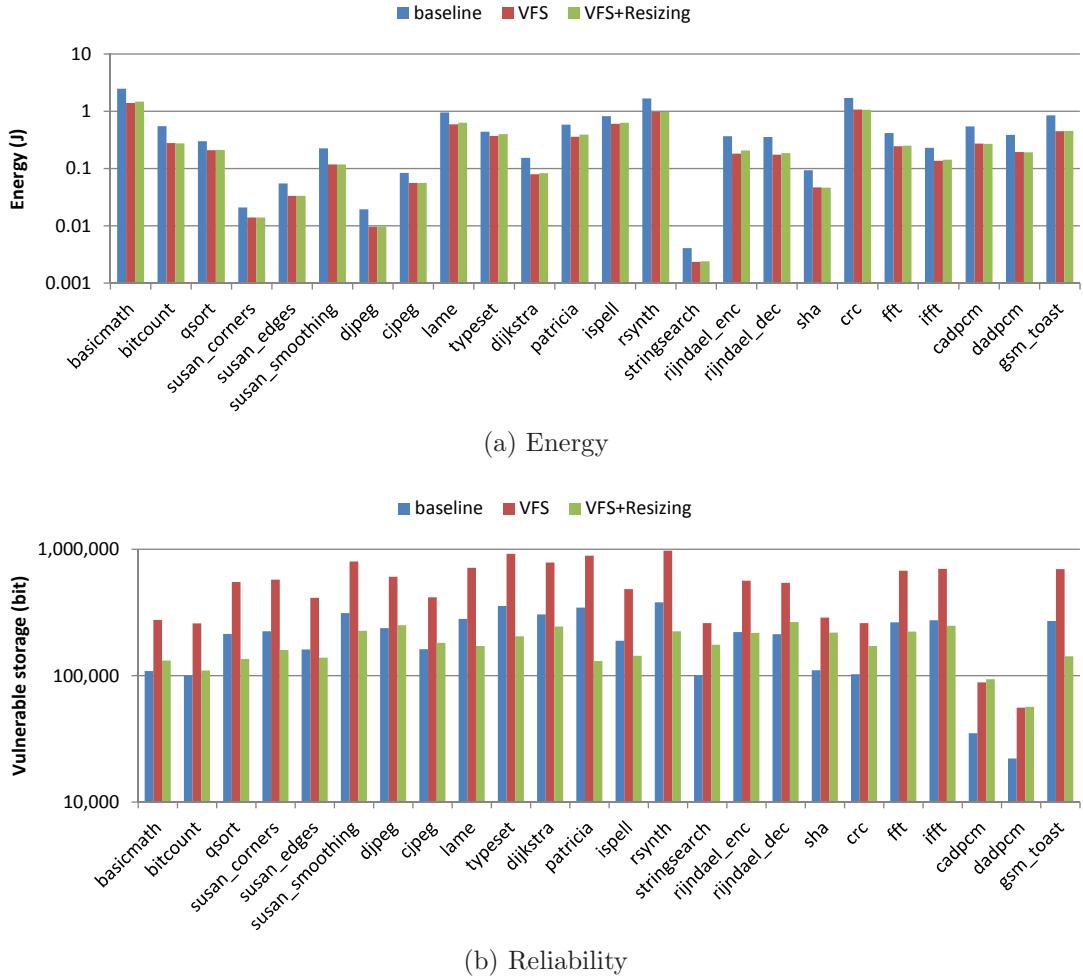

| 5.28 The impact of L1-cache resizing on (a) reliability, (b) performance, (c) energy under 0.85V supply voltage across applications. . . . . | 128 |

| 5.29 Combined effects of VFS and L1-cache resizing on (a) energy (b) reliability. . . . .                                                    | 129 |

| 5.30 Reliability and performance constrained energy optimisation algorithm. . . . .                                                          | 130 |

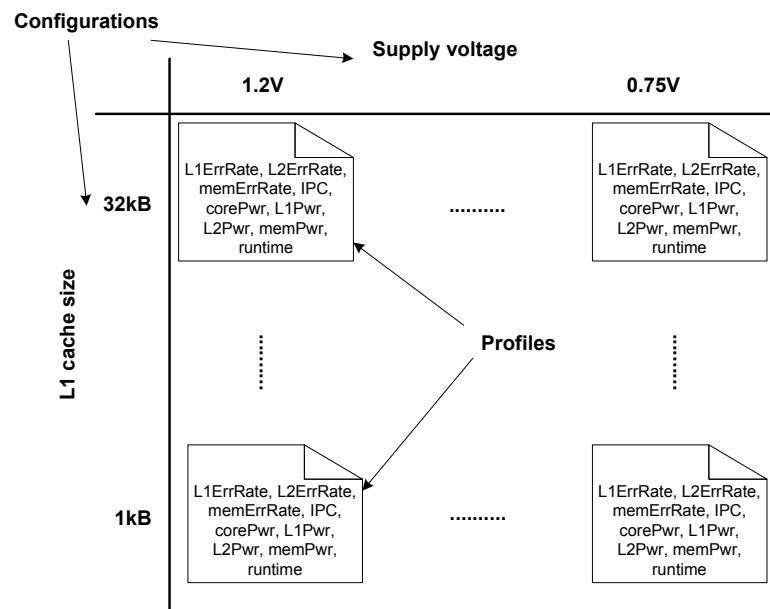

| 5.31 Example of Reliability, Power and Performance Profiles (RPPP). . . . .                                                                  | 131 |

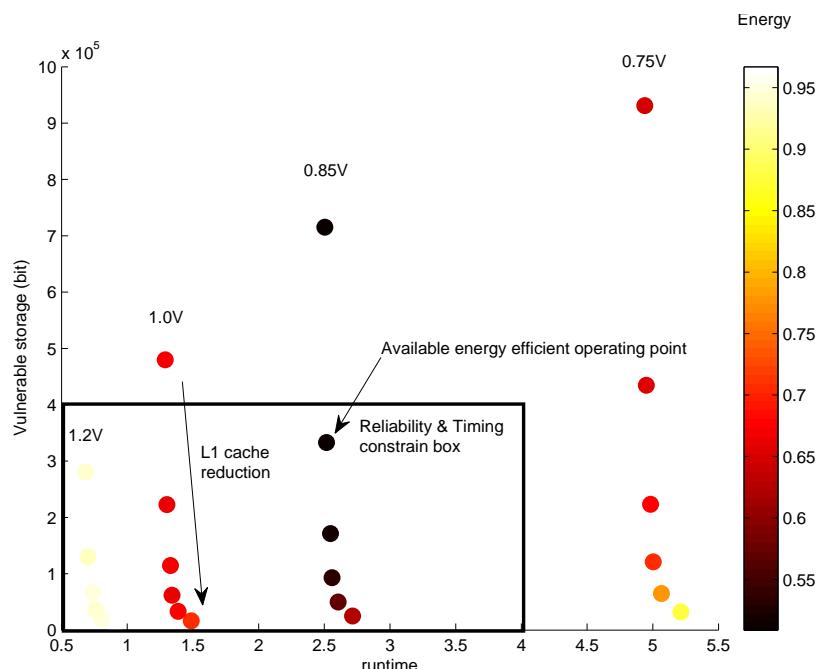

| 5.32 Example of reliability and performance constrained energy optimisation for application “lame”. . . . .                                  | 131 |

| 6.1 Various Aging Effects . . . . .                                                                                                          | 140 |

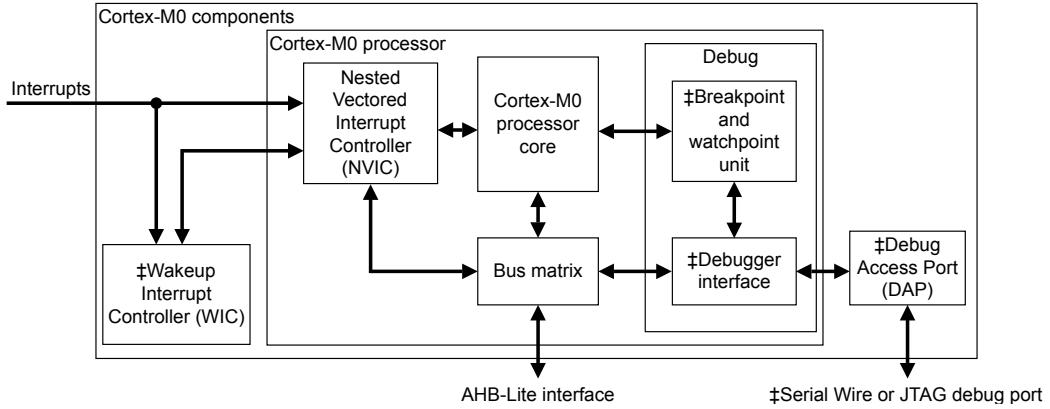

| A.1 ARM Cortex-M0 processor block diagram [187]. . . . .                                                                                     | 142 |

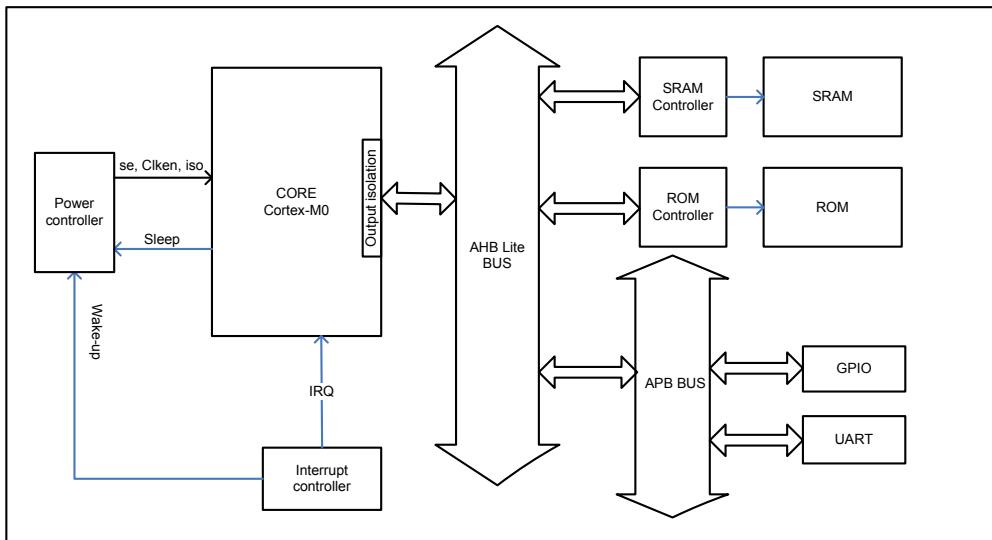

| A.2 ARM Cortex-M0 based embedded processor system block diagram. . . . .                                                                     | 142 |

# List of Tables

|     |                                                                                                                                                                                                                            |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | FPGA fault injection, error detection and correction result . . . . .                                                                                                                                                      | 43  |

| 3.2 | Encoding and decoding circuit area overhead, power, latency and energy consumption for CRC-16 code with different scan chain configurations . . . . .                                                                      | 43  |

| 3.3 | Encoding and decoding circuit area overhead, power, latency and energy consumption for Hamming (7,4) code with different scan chain configurations . . . . .                                                               | 44  |

| 3.4 | Encoding and decoding circuit area overhead, power, latency and correction capability of code to protect state for different Hamming codes . . . . .                                                                       | 46  |

| 3.5 | Parameters for calculating area, latency, power and energy consumption for hardware corrections . . . . .                                                                                                                  | 65  |

| 3.6 | Error detection (CRC-16) overhead on timing, area, latency, power and energy consumption using different scan chain configurations . . . . .                                                                               | 65  |

| 3.7 | Error correction (Hamming) overhead on timing, area and energy consumption using different scan chains configuration . . . . .                                                                                             | 67  |

| 4.1 | Measured results for three selected dies shown in Figure 4.7 at 79°C in “Sleep State” . . . . .                                                                                                                            | 99  |

| 5.1 | System configuration used in analysis . . . . .                                                                                                                                                                            | 106 |

| 5.2 | MiBench benchmarks [177] . . . . .                                                                                                                                                                                         | 108 |

| 5.3 | Benchmarks size . . . . .                                                                                                                                                                                                  | 108 |

| 5.4 | Normalised voltage and frequency scaling table . . . . .                                                                                                                                                                   | 115 |

| 5.5 | Energy saving by combining VFS, L1-cache resizing and dynamic protection under memory components reliability constraint of $2.5 \times 10^5 \lambda_{bit}$ , the constraint is chosen for demonstration purposes . . . . . | 132 |

## Declaration of Authorship

I, **Sheng Yang**, declare that the thesis entitled *Error Resilient Techniques for Storage Elements of Low Power Design* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as listed in Chapter 1 Section 1.7

Signed:.....

Date:.....

## Acknowledgements

I am indebted to my supervisor professor Bashir M. Al-Hashimi for his supervision and continuous guidance throughout my PhD. I have learnt tremendous amounts from him, and especially, I am inspired by his research vision and devotion to work. This PhD project would not have been possible without his supports and encouragement. I would also like to extend my deepest gratitude to my industrial advisor professor David Flynn for his excellent technical advice and support, and invaluable discussions on research ideas. My thanks also go to Dr. Saqib Khursheed and Dr. Harry Oldham for their insightful discussions and reviewing of this work.

I would like to thank the Engineering and Physical Sciences Research Council (EPSRC) for supporting my work by means of scholarship, the ARM-ECS Research Center in the School of Electronics and Computer Science, University of Southampton for providing state of the art research facilities. I want to thank ARM Ltd. for allowing me to spend 4 months working at their offices for my Ph.D. My special thanks goes to James Myers, John Biggs, Anand Savanth and Karthik Sivashankar from ARM, and Matthew Swabey from Purdue University, for their technical support in successfully fabricating and testing the silicon chip used in this thesis. I also benefited from the technical discussions with Dr. Shidhartha Das, David Bull, Sachin Idgunji, Dave Howard and Dr. Paul Whatmough during my time in ARM.

I would like to take this opportunity to acknowledge my colleagues for their invaluable support and useful discussions throughout my Ph.D. These people include, but are not limited to: Dr. Rishad Shafik, Dr Geoff Merrett, Dr. Amit Acharyya, Dr. Saqib Khursheed, Dr. Mustafa Imran-Ali, Dr. Zhou Dafeng, Dr. Aissa Melouki, Hamed Shahidipour, Dr. Jatin Mistry, Dr. Zhong Shida, Jedrzej Kufel and Luis Maeda-Nunez.

And finally, I like to offer warmest thanks to my father Shuijin Yang, my mother Ping Zhang, and my girl friend Yunxu Zhang for their love and support, without which it would not have been possible for me to do my research.

# Chapter 1

## Introduction

Since the invention of integrated circuits in 1958, and driven by the demand for cost reduction and increasing functionality, CMOS transistor technology scaling (including transistor size scaling and supply voltage scaling) has enabled the IC industry to integrate more transistors within the same silicon area. Borkar, et al. [1] showed that each transition to a new generation, reduces transistor size and supply voltage by 30%, doubles the chip density, reduces gate delay by 30%, reduces overall power by 50% and increases leakage power by around 5x. The side effect of technology scaling is the reduction of system reliability. This is because smaller transistors lead to lower critical charge and higher integration level increases system complexity. The other side effect of technology scaling is the increase in power density due to the increase in transistor density. Historically dynamic power has dominated the power consumption of digital integrated circuits and has been the main focus of power reduction. As technology scaling continues, leakage power consumption continues to grow in dominance and leakage power reduction also becomes an important part of modern digital circuits. Both leakage and dynamic power reduction techniques exacerbate reliability problems. This thesis describes new methods to improve the reliability of modern low power digital circuits. These methods have been implemented using standard EDA tools and validated on commercial low power processors.

This chapter gives an overview of reliability and low power design of digital integrated circuits and provides preliminary information for the subsequent thesis chapters. Technology scaling and its major impacts are discussed in Section 1.1. Digital circuit power reduction techniques are discussed in Section 1.2, which includes dynamic power reduction and leakage power reduction techniques. Digital circuit reliability problems are discussed in Section 1.3. Error control coding is an effective technique for ensuring data integrity which can be applied to improve system reliability, which is discussed in Section 1.4. The challenges facing low power reliable design are discussed in Section 1.5. The contribution of each chapter is summarised in Section 1.6 and finally the list of publications generated from the research in this thesis is given in Section 1.7

## 1.1 Impacts of Technology Scaling

Cost reduction of IC fabrication is the main reason behind technology scaling. For the past 50 years semiconductor technology scaling has reduced transistor size by 30% and doubled the performance every two to three years. Transistor performance is inversely proportional to propagation delay which can be approximated as Equation 1.1 [2]:

$$T_d \propto \frac{C_L \cdot V_{dd}}{V_{dd} - V_{th}} \quad (1.1)$$

where  $C_L$  is load capacitance,  $V_{dd}$  is supply voltage and  $V_{th}$  is threshold voltage. Transistor size scaling reduces load capacitance and leads to shorter propagation delay. However supply voltage scaling increases propagation delay, so to maintain or further reduce propagation delay the threshold voltage has to be scaled down. Transistor dynamic power consumption is described using Equation 1.2 [3]:

$$p_{dynamic} = \alpha \cdot V_{dd}^2 \cdot C_L \quad (1.2)$$

where  $\alpha$  is activity factor,  $C_L$  is load capacitance and  $V_{dd}$  is supply voltage. Dynamic power is proportional to load capacitance and the square of supply voltage. Both load capacitance and supply voltage reduce with technology scaling, and dynamic power reduces with technology scaling. There are two main components of leakage power: gate leakage and sub-threshold leakage. Gate leakage current increases exponentially with reduction in gate oxide thickness [4]; however high-k metal gate reduces the leakage by 2-3 order of magnitude [5, 6]. The most significant contributor to leakage power consumption of current technology generation is sub-threshold leakage current which is calculated by Equation 1.3 [3]:

$$I_{ds} \propto e^{\frac{V_{gs} - V_{th}}{n \cdot V_T}} \cdot (1 - e^{-\frac{V_{ds}}{V_T}}) \quad (1.3)$$

where  $V_{gs}$  is gate to source voltage,  $V_{th}$  is transistor threshold voltage,  $V_{ds}$  is drain to source voltage and  $V_T$  is thermal voltage  $\frac{KT}{q}$ . For  $V_{ds} \gg V_T$   $1 - e^{-V_{ds}/V_T} \approx 1$ , which means that if  $V_{ds}$  is larger than 100-mV then sub-threshold leakage is almost independent of  $V_{ds}$ . Sub-threshold leakage can be approximated as:

$$I_{ds} \propto e^{\frac{V_{gs} - V_{th}}{n \cdot V_T}} \quad (1.4)$$

Sub-threshold leakage current increases exponentially with the reduction of threshold voltage  $V_{th}$ . Threshold voltage is reduced in order to maintain the performance of

the transistor (Equation 1.1). As the result, sub-threshold leakage current increases exponentially with technology scaling.

Technology scaling also has a number of impacts on system reliability. This is because small transistor size and high integration density increases system soft error rate [7]. As transistor size continues to shrink, process variation in transistor channel length, width, oxide thickness and dopant concentration increases. These variations cause the difference in transistor threshold voltage [8, 9] that leads to the uncertainty in circuit delay of timing paths and performance of fabricated chips. Process variation also exacerbates the reliability problem by reducing the critical charge and noise margin of the storage units. The degradation of reliability and the increases in leakage power are becoming major obstacles for further transistor scaling [10–13].

## 1.2 Power Reduction Techniques

There are two power consumption components in an digital circuit: dynamic power and leakage power. Various power reduction techniques are described in this section, which is divided into dynamic power reduction and leakage power reduction techniques.

### 1.2.1 Dynamic Power Reduction

Dynamic power has been the dominant part of digital circuit power consumption for many years. It can be seen from Equation 1.2 that switching activity, load capacitance and supply voltage are three contributing factors of dynamic power. Load capacitance is reduced with transistor size scaling inherently. Dynamic power reduction techniques involve reducing switching activity, reducing supply voltage or both.

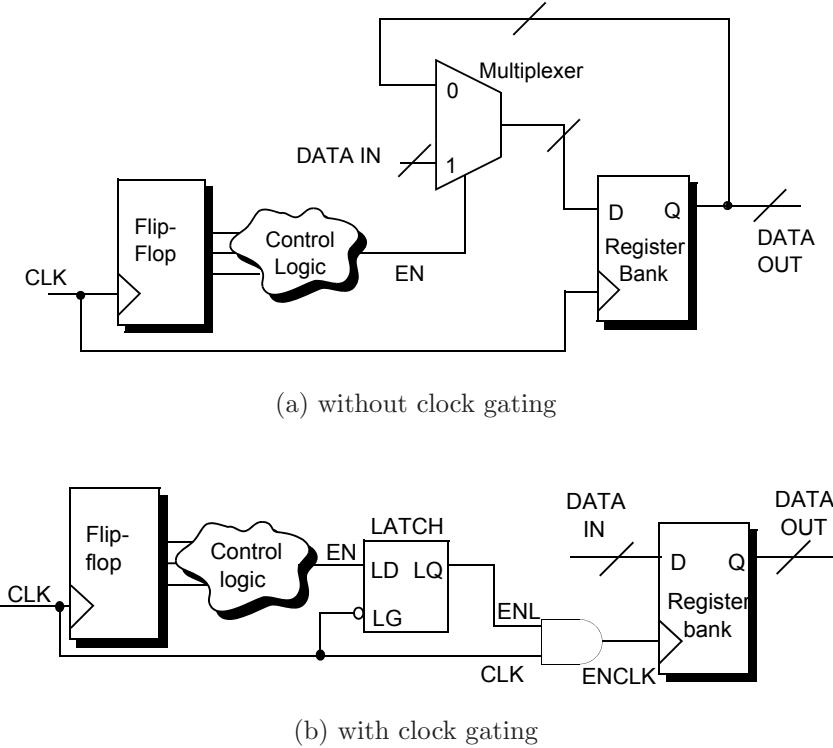

In synchronous digital circuits, the clock tree dominates dynamic power consumption due to the constant switching of clock signals and the large fan-out of clock tree. Clock gating can reduce clock tree power consumption [14–18]. Registers are used to store data and states information, whose update is controlled by clock signals. Not all registers require update in every clock cycle; hence clock gating was introduced to stop the switching of parts of clock tree where registers do not need updating. This is achieved by inserting a clock gating cell between clock tree buffers and registers, which allows the clock control signal to enable or disable the register's clock input. Figure 1.1 shows the difference between designs with and without clock gating. Figure 1.1.(a) shows a circuit without clock gating. To enable or disable the updates of an register, a multiplexer is inserted which selects the input between updating new data or recirculating old data stored in the register. Figure 1.1.(b) shows a circuit with clock gating, where a clock gating cell including a latch and an AND gate is used to stop the toggling of the clock signal. When multiple registers are controlled by one enable signal, clock gating can

Figure 1.1: Clock gating architecture [22].

even reduce the chip area. This is because, without clock gating, each register requires one multiplexer, whereas with clock gating, a group of registers can share a single clock gating cell. Various automatic clock gating insertion algorithms [19–21] were developed to improve the effectiveness of clock gating designs, which are well supported by standard EDA (Electronic Design Automation) tools such as the Synopsys Power Compiler.

As the dynamic power is proportional to the square of the supply voltage (Equation 1.2), the most effective way to reduce dynamic power is through supply voltage scaling. When supply voltage is reduced circuit delay is increased (Equation 1.1); however digital circuits do not always operate at their maximum frequency due to workload demands [23]. Dynamic Voltage and Frequency Scaling (DVFS) reduces the supply voltage and operating frequency of circuits under light workload to improve energy efficiency. Various DVFS algorithms [17, 24–29] were developed to maximise energy reduction.

### 1.2.2 Leakage Power Reduction

Leakage power becomes an increasingly significant part of overall chip power consumption with CMOS technology scaling [30]. There are three types of leakage current in a MOSFET transistor: gate leakage, sub-threshold leakage and junction tunnelling leakage. Gate leakage current increases exponentially with reduction in the gate oxide thickness [4]. With silicon dioxide gate thickness approaching scaling limits there is a

rapid increase in gate leakage current [31, 32]. When the transistor size is scaled below 40nm, with  $SiO_2$  as the gate dielectric, the gate leakage current density would exceed the current density limit [30]. The threshold voltage of MOSFET transistors is reduced to increase the performance, but the sub-threshold leakage current increases exponentially with the reduction of threshold voltage (equation 1.4). Junction tunnelling leakage is an order of magnitude less than gate leakage and sub-threshold leakage for the recent technology generation [33], therefore it will not be discussed in detail in this work.

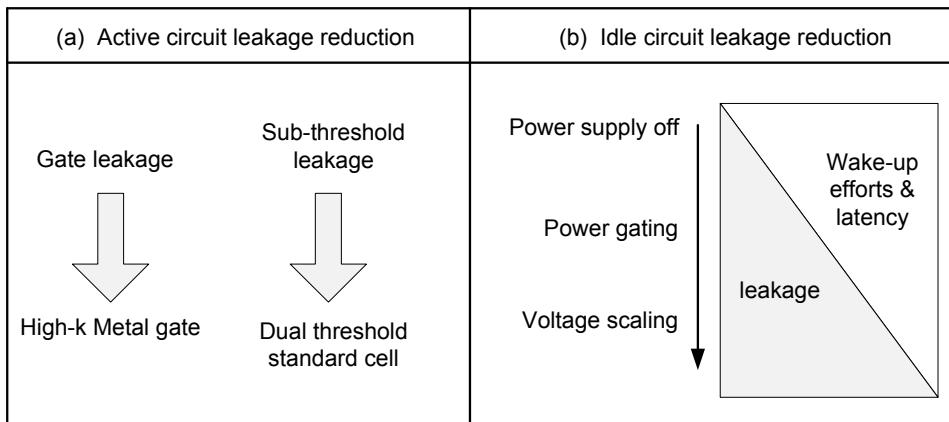

A circuit has two states: an active state where it is doing useful work and an idle state where it is not doing any work. Numerous approaches have been proposed to minimise the leakage power, which can be categorised into active circuit leakage power reduction and idle circuit leakage power reduction. The active circuit leakage reduction technique includes high-k metal gate [34], dual-threshold standard cells [35]. The high-K metal gate was proposed [34] to reduce the gate leakage, which has been implemented in technology nodes of 45nm and below [36]. To reduce the sub-threshold leakage while maintaining the performance, dual threshold standard cell synthesis was proposed [35] to reduce the sub-threshold leakage of the gates in the non-critical path by replacing low-V<sub>t</sub> high performance transistors with the high-V<sub>t</sub> less leaky transistors. These slower high-V<sub>t</sub> transistors are not in the critical path so they will not affect the performance of the circuit.

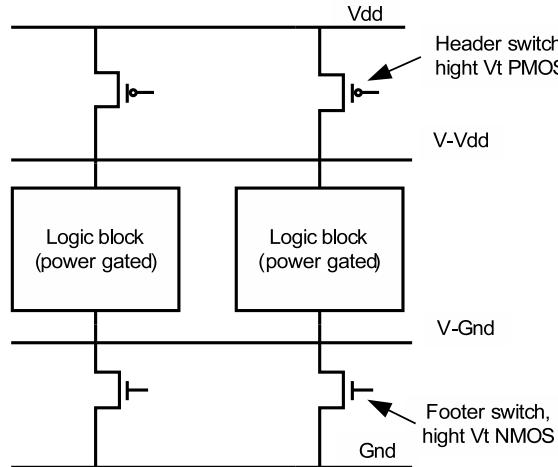

A circuit's leakage power can be further reduced by cutting off or scaling its power supply when the circuit is in an idle state. There are three leakage reduction techniques involved powering off/down a idle circuit. If a chip is idle for a long time and there is no constraint on the wake-up delay, then its external power supply can be turned off completely during sleep mode; in this way the maximum leakage reduction can be achieved. However, the switching of the external power supply takes relatively long time, and some energy and time are wasted in initializing the circuit when it wakes up. If a device has a relatively short idle time and requires fast wake-up, cutting off the chip power supply will reduce its reaction speed. Therefore power gating [37] was proposed to reduce the leakage power of a circuit in sleep mode but maintain a fairly short wake-up latency. In a power-gated circuit, the logic blocks are connected to power supply through high-V<sub>t</sub> power transistors shown in Figure 1.2. When the circuit is idle the power transistors are turned off and the leakage power of the logic blocks is limited by those power transistors, it was reported that power gating achieves 95% of leakage power reduction for ARM926EJ<sup>TM</sup> [38].

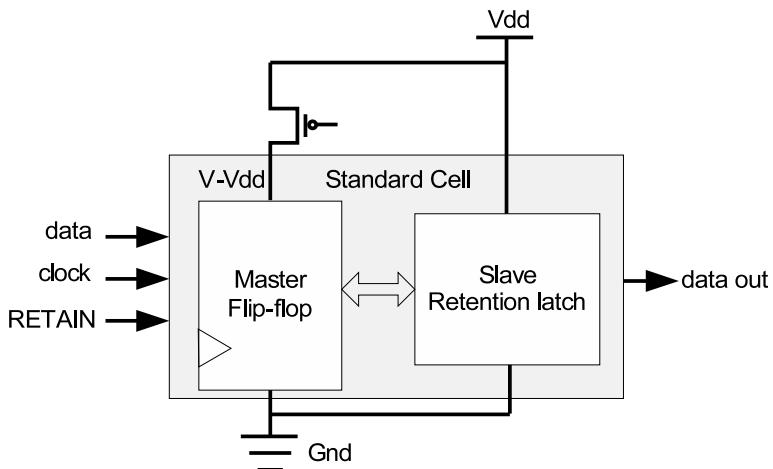

Power gating turns off logic and registers, so the states of registers are lost. For energy efficiency the state of registers can be preserved while logic is powered down so-called State Retention Power Gating (SRPG). To support this, a state retention latch [39] can be added which is kept powered during power gating of the rest of the circuit. Figure 1.3 shows a specially designed flip-flop incorporating state retention latch. The master flip-flop is connected to Vdd through a power transistor and the slave retention latch is kept

Figure 1.2: Power gating design architecture

Figure 1.3: State Retention Flip-Flop

always-on. The master flip-flop consists of low-Vt transistors for fast switching during active mode. The slave retention latch consists of high-Vt transistors for low leakage during sleep mode. In addition to the data and clock input the state retention flip-flop has a control signal, RETAIN. When the power-gated circuit is switched to sleep mode, RETAIN is set to '1' to transfer data from the master flip-flop to the slave retention latch, and before the power-gated circuit is switched to active mode, RETAIN is set to '0' to restore data back to the master flip-flop.

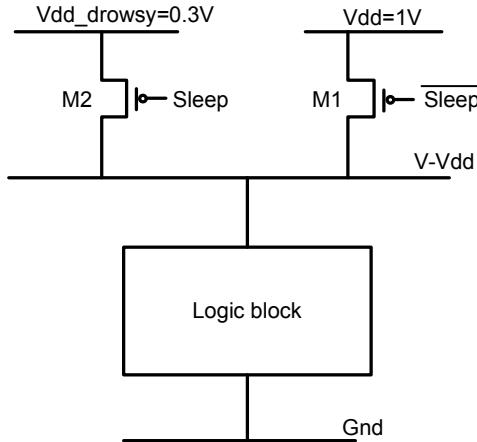

The other idle circuit leakage power reduction technique is voltage scaling. The supply voltage of idle circuit can be scaled down aggressively to the point where the storage cells still retain their data [40–42]. The architecture of scaled voltage state retention is shown in Figure 1.4. In active mode signal 'Sleep' is 0, sleep transistor M1 is on and M2 is off, and the logic block is connected to nominal Vdd and clocked with full speed. In sleep mode signal 'Sleep' is 1, sleep transistor M1 is off and M2 is on, and the logic block is connected to scaled Vdd to achieve leakage saving. This technique does not require

Figure 1.4: Scaled voltage leakage reduction

additional state retention latches and has a smaller wake-up delay; however, the leakage power saving is less than power gating.

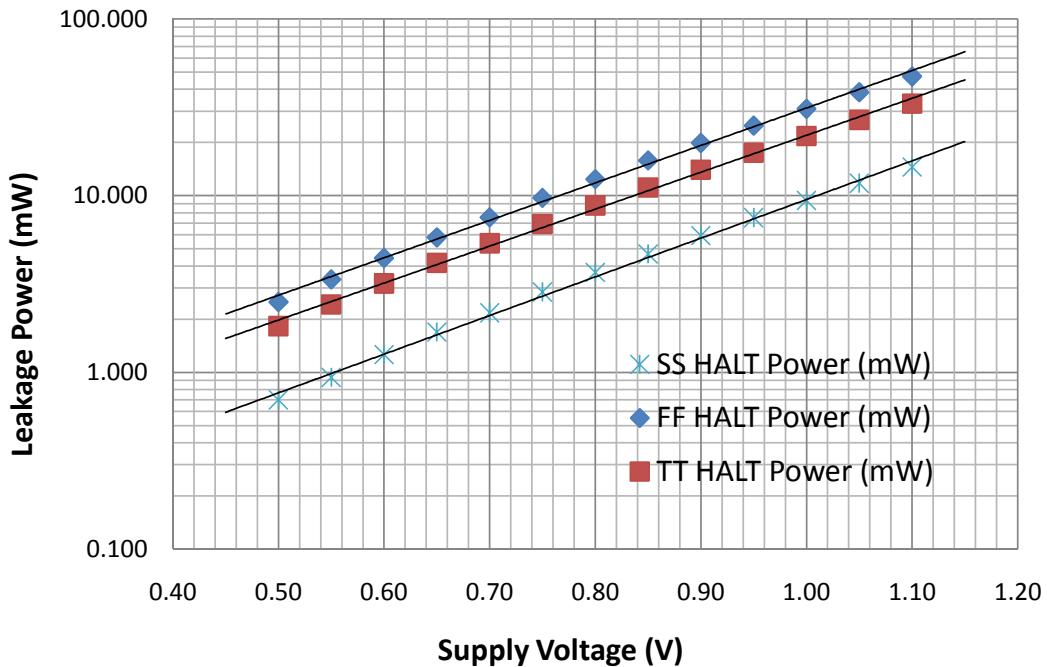

Figure 1.5 demonstrates the effect of supply voltage scaling on leakage power, where the x-axis represents the supply voltage and the y-axis represents the leakage power in log-scale. The result covers 3 process corners: the slow(NMOS)-slow(PMOS) corner is represented using cross markers, the fast-fast corner is represented using diamond markers and the typical-typical corner is represented using square markers. The power is measured during idle mode where no switching activities are present, and is measured for a range of supply voltages ranging from 0.5V to 1.1V. It can be seen that the leakage power reduces exponentially with the reduction in supply voltage, and 15% reduction of supply voltage results in 50% reduction in leakage power.

Leakage power reduction techniques are summarised in Figure 1.6. The left column shows active circuit leakage reduction techniques, where gate leakage can be reduced by using high-k metal gate transistors, and sub-threshold leakage can be addressed by using dual threshold standard cell design. The right column shows the idle circuit leakage reduction techniques: turning off the power supply, power gating and voltage scaling. Turning off the power supply has the lowest leakage but longer wake-up latency, while voltage scaling has the highest leakage and shortest wake-up latency.

### 1.3 Reliability of Digital Designs

There are different types of faults affecting the reliability of integrated circuits that can be classified into two categories: permanent faults which have lasting effects on the system reliability and transient errors which just affect the system reliability temporarily.

Figure 1.5: Relation between leakage power and supply voltage when ARM926 processor is in idle mode for 65nm technology

Figure 1.6: Available leakage reduction techniques and their trade-offs

### 1.3.1 Permanent Faults

All permanent faults can be either related to a manufacturing defect where the devices are damaged during the manufacturing process, or related to ageing effects where the devices degrade gradually during their lifetime. The fabrication of integrated circuit is very complex. Imperfect process manufacturing such as foreign particles or impurities in the silicon wafer may cause bridged connections or missing features [43, 44]. In modern ICs, the most common defects are bridges “shorts” where unintended connections form between circuit nodes, and “opens” where intended connections between circuit nodes are missing. For resistive bridge and open defects, the unintended connections are

not fully short-circuit, and for resistive-opens the broken connection is not fully open-circuit. Fault models have been developed to emulate how defects affect the operation of a circuit: the popular fault models are gate level “stuck-at” fault model [45], transistor level “stuck-at” fault model [46], bridging fault models [47] and delay fault models [48]. Automatic test pattern generation (ATPG) [44, 46] algorithms are used to generate the test patterns, and the fault coverage statistics are collected by using fault simulation. Scan chains can be used to shift the test pattern into the registers of a digital circuit. Internal scan design is the most popular design-for-test (DFT) technique which can achieve high fault coverage by isolating the combinational logic block for a complex sequential design [46].

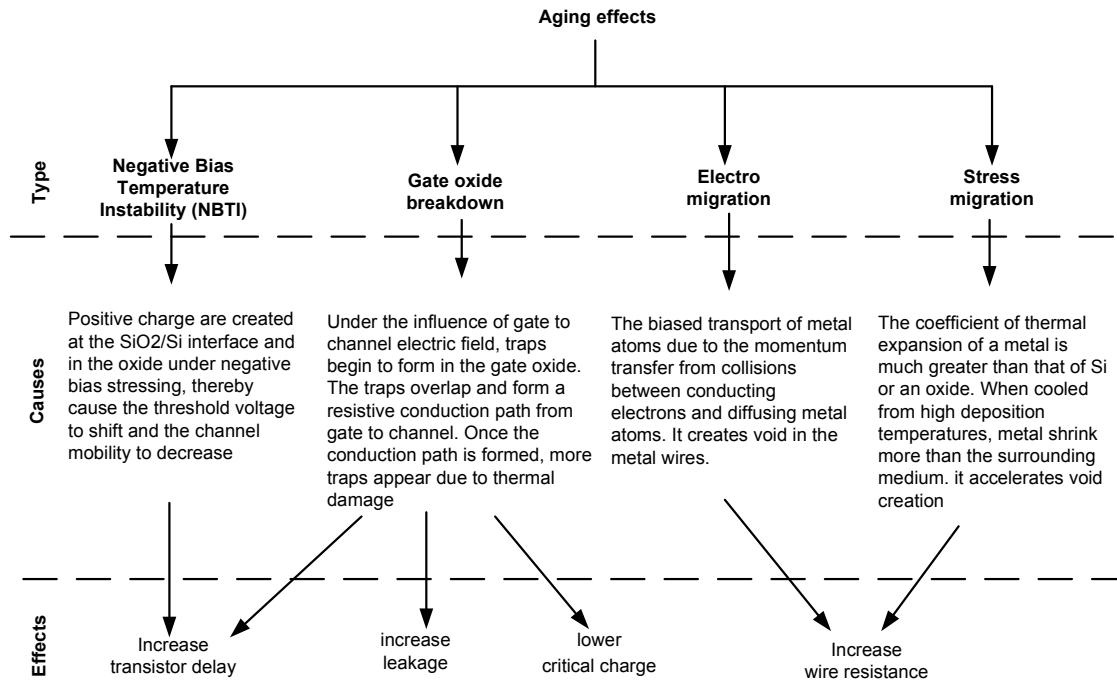

An IC degrades gradually during its lifetime due to the various stresses it experiences in normal operations. Technology scaling reduces the feature sizes but increases the power densities and accelerates the wear-out based failures [10]. Various wear-out effects have been reported: Negative bias temperature instability (NBTI) is due to the positive charge created at the  $\text{SiO}_2/\text{Si}$  interface and in the oxide under negative bias stressing, thereby causing the threshold voltage to shift and decrease the channel mobility which leads to an increase in transistor delay [49]. Gate oxide breakdown is caused by the traps formed in the gate oxide under the influence of gate-to-channel electric field. The traps accumulates and forms a resistive conduction path from gate to channel and the phenomenon is soft oxide breakdown (SBD). Once the conductive path is formed, more traps appear at an increasing pace and finally lead to hard oxide breakdown (HBD), which will increase gate leakage, delay and energy, and lower critical charge [12, 50]. Electro-migration is caused by the momentum transfer from collisions between conducting electrons and diffusing metal atoms leading to biased transport of metal atoms, which creates voids in the metal wires. It results in increased resistance which creates resistive shorts or opens in wires [51, 52]. Stress migration is due to the difference in thermal expansion coefficient between metal, silicon and oxide. When cooled from high temperatures, metal shrinks more than the surrounding medium. Therefore metal is left in a state of very high tensile stress. Coupled with electro-migration, it accelerates void creation [53]. Thermal cycling is the name given to the cyclic thermal strains due to power cycling, which can lead to the thermal fatigue failure in packaging such as short-circuit in the bonding and solder joints [54, 55].

### 1.3.2 Transient Errors

Transient errors are caused by electrical noise or external radiation rather than design or manufacturing defects [56]. The effects of transient errors are temporary. Inductive effects have long been known to cause problems at various levels of the system such as chip package and board level. In modern IC technology generation the inductive noise becomes an increasing concern due to the faster switching speed and higher levels of

integration [57]. Inductive noise is generated from the switching current in neighbouring circuits, it starts to cause problems in the  $0.25\mu\text{m}$  technology node [58], and the problem has increased for more advanced technology nodes [59, 60]. Inductive noise also occurs in the power supply lines due to simultaneous switching noise generated by core logic and input/output circuitry, that can also impact the performance and data integrity of the electronic circuit [61].

The other source of transient errors is “soft errors” or Single Event Upset (SEU) induced by particles strikes. Most modern digital systems use synchronised designs consisting of sequential logics and combinational logics. Sequential logics are used to store the current state of the system while combinational logics are used to evaluate the next state of the system in each clock cycle. Due to the fundamental difference in their functionality the radiation event will have different effects on them.

When an ionised particle strikes a combinational logic node it generates a current pulse. The current pulse may propagate through the combinational logic tree and finally be captured by the sequential logic, which leads to state corruption. However the current pulse may not always be captured by sequential logic. There are three types of masking effects [56]: firstly, if the current pulse is small it will be attenuated by the logic tree and the pulse seen in the output will be too small to be captured by sequential logic; this is called electrical masking. Secondly, when a particle strikes a combinational logic in the early phase of the clock cycle, by the time sequential logic is clocked and the next state recorded at the output of the combinational logic tree, the current pulse generated may already faded away; this is called latching window masking. Lastly some logic gates can also mask the current pulse at one of its inputs because the output is determined by its other input values; for example if one input of an NAND gate is connected to logic ‘0’ then the output of the gate will still be logic ‘1’ despite the particle strike affecting the other input. In this case the particle strike has no effect on the output; this is called logic masking.

The sequential logic consists of many storage nodes; each storage node is comprised of a feedback circuit for holding the last state. When a storage node is struck by an ionised particle a current pulse is generated. If this current pulse overcomes the feedback current and exceeds the stored charge of the node, the state of this storage node is flipped so the data is corrupted. The sensitivity of a transistor to radiation-induced soft errors is dependant on its node capacitance and the supply voltage [13], both of which decrease with technology scaling. The reduction of supply voltage reduces the noise margin; the noise in the power supply rails may also impact device reliability. The failure rate of a system is the accumulation of each component’s failure rate, and the increasing scale of system integration exacerbates the system reliability problem [11]. In addition, power reduction techniques such as dynamic voltage frequency scaling and power gating [37] also tend to impact the system reliability.

In this work the state integrity of digital circuit storage elements such as flip-flops or memory cells is studied. State integrity is referred as the capability of retaining the storage elements' original logic value.

## 1.4 Error Control Coding

Error Control Coding (ECC) is concerned with methods for delivering information from a source to a destination with minimum errors [62]. ECC provides forms of protection by introducing redundancy, in theory error rate can be reduced to a desired level with enough redundancy. ECC is also widely used for the protection of data storage elements in processors. High performance coding schemes have been developed to protect noisy communication channels; these coding schemes may need complex encoding and decoding which is not suitable for protecting an embedded processor. Hamming code and CRC code are used in this work (Chapter 3) due to the simplicity of their encoder and decoder which means smaller area, power and latency overheads. Hamming code and CRC code are both systematic codes where the original message is part of the codeword. In this section, all addition, subtraction, multiplication and division operations are GF(2) arithmetic or modulo 2 arithmetic. In GF(2) arithmetic, addition and subtraction are identical which can be implemented using an XOR gate. The implementation of multiplication uses an AND gate.

### 1.4.1 Hamming Code

Hamming code is a single error correcting and double error detecting code which is capable of correcting one error and detecting two errors in a codeword. For any positive integer  $m \geq 3$  there exists a Hamming code with the following parameters [63]:

- Code length:  $n = 2^m - 1$

- Information bits:  $k = 2^m - m - 1$

- Check bits:  $n - k = m$

Hamming code is commonly expressed as Hamming  $(n, k)$ . The encoding and decoding can be represented by generator matrix and parity check matrix. The parity check matrix  $H$  is arranged as:

$$H = [I_m \ Q] \quad (1.5)$$

where  $I_m$  is an identity matrix of size  $m$ .  $Q$  consist of  $k$  columns; each column is size  $m$  with Hamming weight 2 or more. For example, the parity check matrix for Hamming(7,4) is:

$$H = \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 0 & 1 & 1 & 1 & 0 \\ 0 & 0 & 1 & 0 & 1 & 1 & 1 \end{bmatrix} \quad (1.6)$$

The columns of  $Q$  can be arranged in any order without affecting the property of the code. The parity generation matrix  $G$  is arranged as:

$$G = [Q^T I_k] \quad (1.7)$$

where  $Q^T$  is the transpose of  $Q$  and  $I_k$  is an identity matrix of size  $k$ . The process of encoding can be represented by:

$$v = u \cdot G \quad (1.8)$$

where  $u$  is the information vector,  $v$  is the generated codeword vector, and  $G$  is the generation matrix. The process of decoding can be represented by:

$$s = (v + e) \cdot H^T \quad (1.9)$$

where  $s$  is the syndrome vector which indicates the error location,  $e$  is the error added to the original codeword  $v$ , and  $H$  is the parity check matrix. If there is no error, the syndrome vector  $s$  will be all zeros.

### 1.4.2 CRC Code

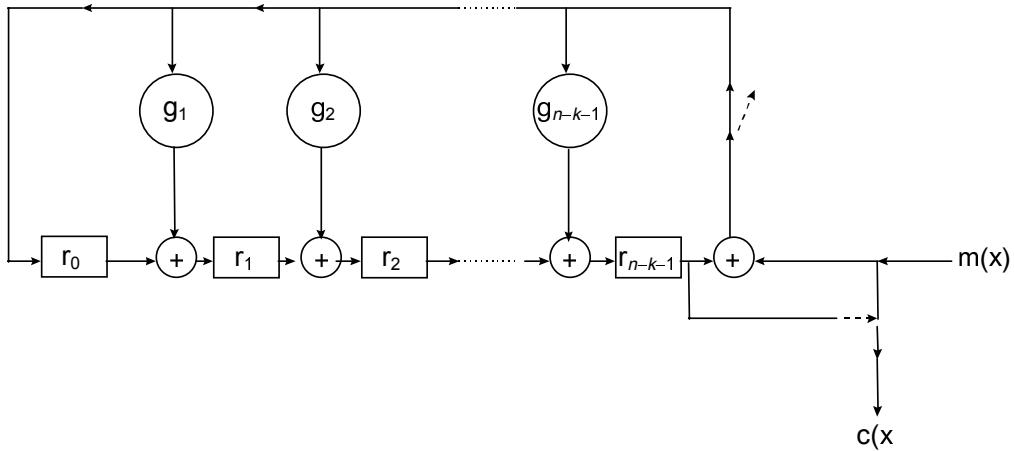

Cyclic Redundancy Code (CRC) is a linear block code with high error detection capability and low redundancy. If the information vector is interpreted as polynomial  $m(x)$ , the encoding can be explained as:

$$r(x) = m(x) \bmod g(x) \quad (1.10)$$

where  $g(x)$  is the generator polynomial, and  $r(x)$  is the CRC check bits which is the remainder of  $m(x)$  divided by  $g(x)$ . The decoding is the same as encoding where another set of CRC check bits  $r'(x)$  is generated. Both sets of CRC check bits are compared;

Figure 1.7: CRC generation using Linear Feedback Shift Register (LFSR) [64].

if  $r(x) \neq r'(x)$ , then an error is detected. The implementation can be done using an Linear Feedback Shift Register LFSR as shown in Figure 1.7. At every clock cycle, the input data is shifted into the registers; when all input bits have been processed the data remain in the registers are the CRC check bits.

## 1.5 Low Power Reliable Design Challenges

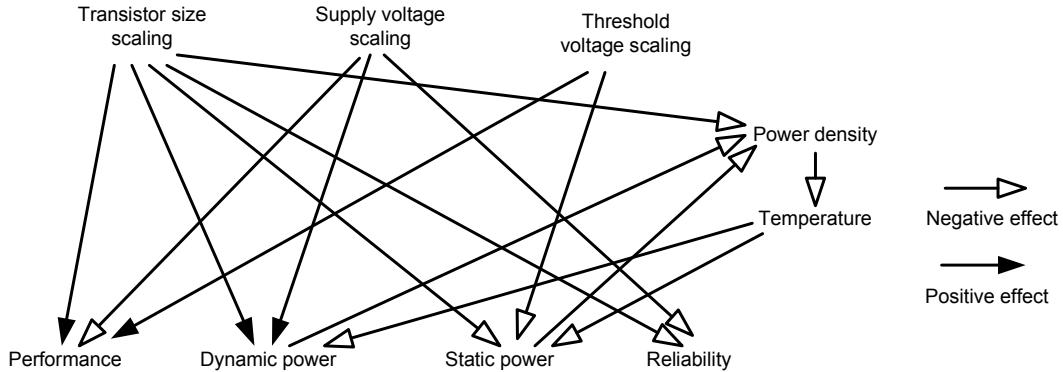

Figure 1.8 shows how CMOS technology scaling affects the performance, power and reliability of integrated circuits. The solid arrows represent the positive influences and the hollow arrows represent the negative influences. As can be seen, three factors are scaled with each technology generation: transistor size, supply voltage and threshold voltage. Transistor size scaling increases the performance and reduces dynamic power; at the same time it increases the static power consumption and power density and reduces the reliability. Supply voltage scaling is used to further reduce the dynamic power; however it decreases the performance and reliability. Threshold voltage reduction is used to improve the device performance but increases the static power at the same time. The power density of the chip increases with the reduction of transistor size, and it also increases with device dynamic and static power. The increase of the power density leads to higher temperature, which will further increase the power consumption [38]. To summarise, the transistor performance and dynamic power consumption benefit from technology scaling while static power consumption and system reliability are affected negatively. These technology scaling associated problems such as increase in leakage power, worsened process variation, and resulting in degradation in reliability and increasing levels of complexity need to be addressed. Power reduction techniques have been extensively used to address the increasing power density problem; however they have detrimental effects on reliability. Therefore maintaining reliability while reducing power consumption with minimum cost is the aim of this research.

Figure 1.8: Technology scaling and its effects on performance, power and reliability

## 1.6 Thesis Organisation

This thesis presents three complimentary but orthogonal contributions. Chapter 3 presents the first contribution that deals with improving reliability of states stored in state retention registers, which are affected by fluctuations in the supply rail due to rush current in the power supply network when power gating logic is turned on from sleep mode. It is shown that this problem is further exacerbated because the critical charge of a storage node is affected by the combined effect of process variation and supply voltage scaling. To improve state protection, a combination of hardware and software based error monitoring and recovery method is proposed for single and multi-bit error recovery. Through two case studies, including implementation of a commercial embedded processor (ARM Cortex<sup>TM</sup>-M0), it is shown that it is possible to achieve more than 2 orders of magnitude improvement in system reliability compared to a design without error protection, when considering maximum soft error rate observed at normal operating conditions. Area overhead is minimised through reuse of the scan chains for state encoding using ECC codes.

Chapter 4 presents the second contribution that uses measured results from 82 test chips to characterise state integrity challenges of voltage scaled flip-flops in the presence of process, voltage and temperature (PVT) variations. Measured results show that the minimum retention voltage of a design varies across dies and therefore a single retention voltage for all dies lead to overall higher leakage power consumption during sleep mode. A novel solution is presented to address this state integrity challenge, while minimizing leakage power of flip-flops during sleep mode. The proposed solution uses a characterisation algorithm to minimise data retention voltage for each die thereby reducing leakage power and uses a control flow for error detection and single bit error recovery. Silicon results show that at characterised data retention voltage, state integrity is preserved, while achieving up to 17.6% reduction in retention voltage across the 82 dies, thereby saving leakage power.

Chapter 5 presents the last contribution that deals with the reliability of the complete memory system and describes an architectural simulation-based framework for joint optimisation of reliability, energy consumption and performance. Memory systems are highly susceptible to soft errors and blanket protection of every part of memory system through ECC is not cost effective. Therefore, an accurate estimation of memory reliability with targeted protection is proposed. The proposed solution identifies and protects the most vulnerable part of the memory system to minimise protection cost. Furthermore, local level-1, L1 resizing together with voltage and frequency scaling is proposed for further energy savings while maintaining performance and reliability of an embedded processor system. Detailed evaluation shows that energy reduction is possible for most applications in a reliability constrained design.

These three contributions presented in this thesis are supported by detailed analysis using state-of-the-art design automation tools, and in-house software tools and, where necessary, are validated through FPGA implementation of commercial low power embedded processors and measured results from fabricated designs.

## 1.7 Publications

The contributions of the research presented in this thesis have been published as follows:

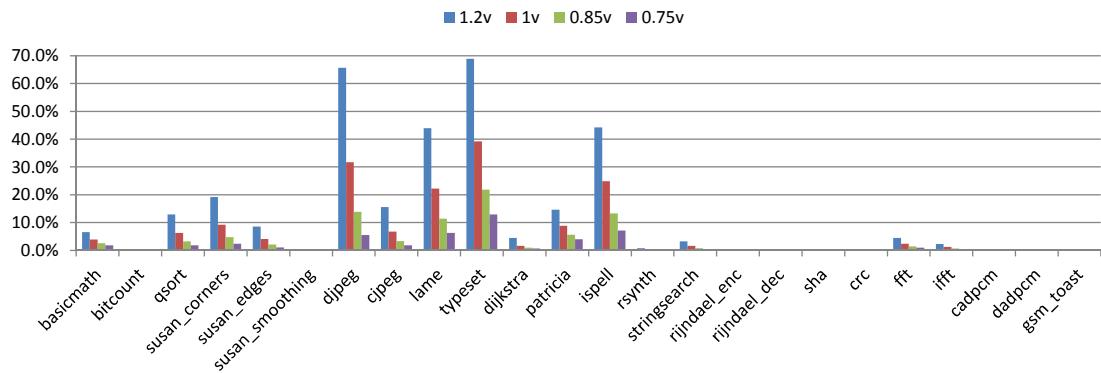

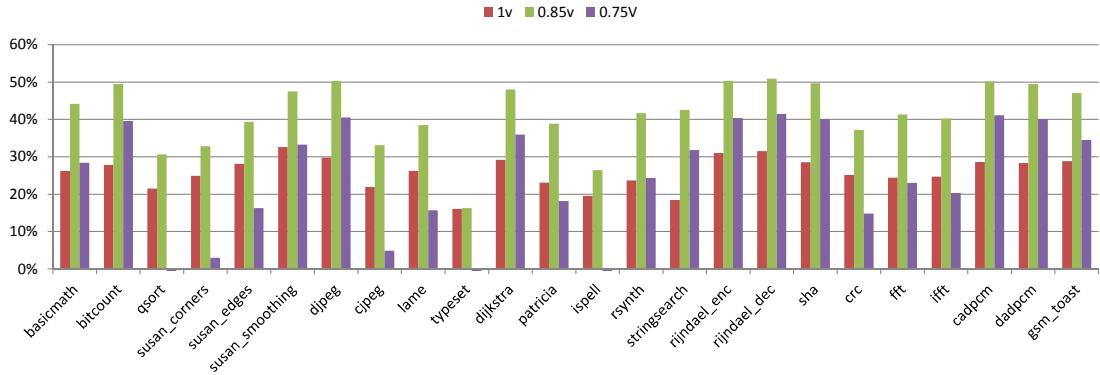

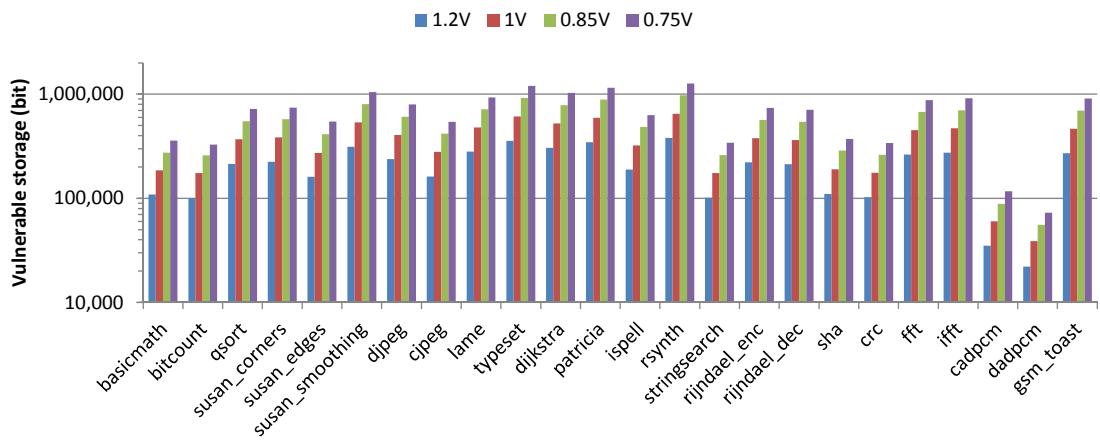

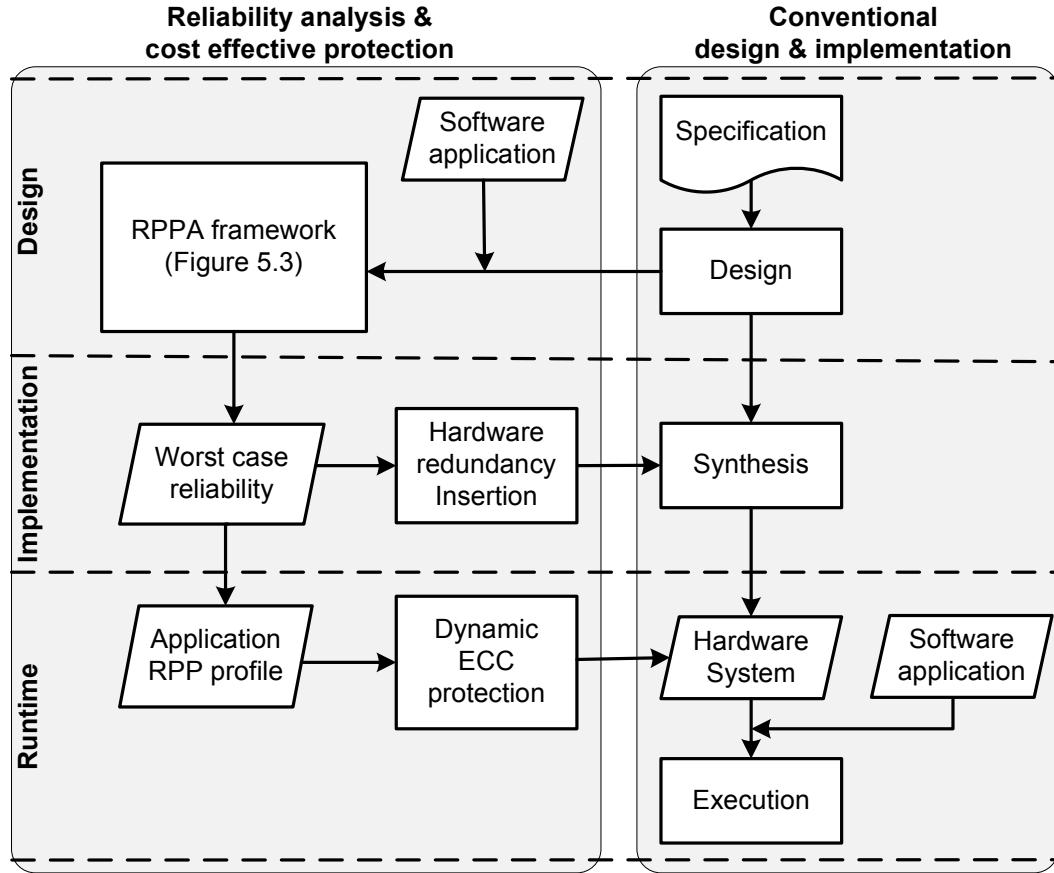

### 1.7.1 Journal Publications