## **University of Southampton**

Faculty of Physical Sciences and Engineering

School of Electronics and Computer Science

# Development of Novel Fabrication Technology for SOI Single Electron Transfer Devices

By: Feras M. Alkhalil

Thesis for the degree of Doctor of Philosophy

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

#### **Doctor of Philosophy**

# DEVELOPMENT OF NOVEL FABRICATION TECHNOLOGY FOR SOI SINGLE ELECTRON TRANSFER DEVICES

By: Feras M. Alkhalil

This report presents the design, simulation and fabrication of a spin qubit platform on ultrathin SOI (Silicon-on-Insulator) using Al FinSET (Single electron transistor) gates and Si side gates. A new design layout is proposed for the double spin qubits co-integrated with a single electron electrometer, a waveguide and a nanomagnet. This platform aims to demonstrate the full operation of double spin qubits by integrating the following three key techniques in one compact footprint: a precisely controlled single electron transfer technology, a high speed charge detection technique and a single spin detection technology based on spin to charge conversion. A single electron transfer device (SETD) integrated with an electrometer is introduced here as the main building block of the spin qubit platform. The single electron transfer device consists of three nanowire MOSETs connected in series, and is capacitively coupled to an SET electrometer. A unique layout design for the SETD and a novel single electron transfer voltage pulse sequence are introduced. Simulation and dynamic analysis of this device operation are preformed using a finite element capacitance based simulation method and a Monte Carlo based single electron circuit simulation. The simulations demonstrated the ability of this platform to transfer single electrons and these characteristics are analyzed to optimize the layout. A novel fabrication process to realize high density silicon quantum dots (QDs) with Al FinSET gates and close proximity Si gates on ultrathin SOI, for single electron transfer and detection, is successfully established with a number of different device layouts realized. In these devices, Al FinSET gates surround an SOI nanowire channel forming electrically tunable potential barriers and defining QDs among them; Si plunger side gates are included to enable precise control of the QDs potential. Five SETD and electrometer device generations have been realized, tested and analyzed to improve the device yield; this extensive process development work is concluded with a novel fabrication approach to demonstrate successful FinSET Al gate technology for SOI nanowires. This QDs platform is fabricated using a multi-layer electron beam lithography process that is fully compatible with metal oxide semiconductor technology. The fabrication process is fully developed with a yield of 92% and a great flexibility to enable the realization of more complex structures and even for devices beyond the scope of this project as shown in the appendices of this report.

# **Contents**

| 1 Introduction                                                             | 1  |

|----------------------------------------------------------------------------|----|

| 1.1 Quantum Information Processing                                         | 1  |

| 1.2 Report Structure                                                       | 2  |

|                                                                            |    |

| 2 Single electron devices                                                  | 4  |

| 2.1 Single electron devices                                                | 4  |

| 2.1.1 Single electron devices operating principle                          | 4  |

| 2.1.2 The single electron transistor                                       | 6  |

| 2.1.3 Theory of carrier transport in single electron devices               | 10 |

| 2.1.4 Single electron turnstile devices                                    | 14 |

| 2.1.5 The single electron transistor as an electrometer                    | 15 |

| 2.2 Spintronics and spin based quantum computing                           | 16 |

| 2.3 Summary                                                                | 16 |

|                                                                            |    |

| 3 Physical realizations of quantum computing                               | 17 |

| 3.1 Introduction                                                           | 17 |

| 3.2 Quantum computing and the DiVincenzo criteria                          | 17 |

| 3.3 Quantum computing physical realizations                                | 18 |

| 3.3.1 Nuclear spin of phosphorous donor atoms in silicon                   | 19 |

| 3.3.2 Quantum dot quantum computing (The Loss-DiVincenzo quantum computer) | 22 |

| 3.3.3 Electron spin in GaAs gate defined double quantum dots               | 23 |

| 3.3.4 Electron charge in double quantum dots                               | 24 |

|   | 3.3.5 Quantum computing with electron spin in silicon                           | 25 |

|---|---------------------------------------------------------------------------------|----|

|   | 3.4 Summary                                                                     | 33 |

| 1 | Ciliaan bagad Integrated Single Sain Oventum Information Technology (SISSOIT)   | 26 |

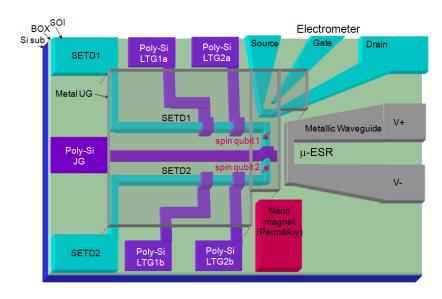

|   | Silicon-based Integrated Single-Spin Quantum Information Technology (SISSQIT)   | 36 |

|   | 4.1 Introduction                                                                | 36 |

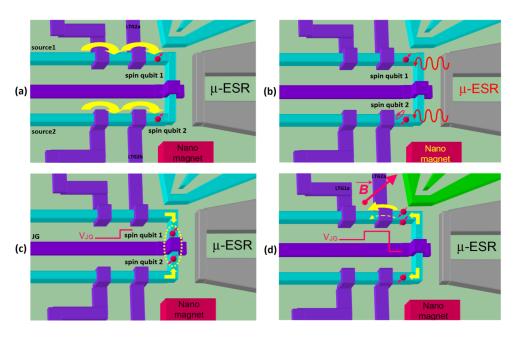

|   | 4.2 Overview of the SISSQIT Platform                                            | 37 |

|   | 4.3 SISSQIT Operating Principles                                                | 38 |

|   | 4.3.1 Single electron turnstile technology                                      | 38 |

|   | 4.3.2 High speed charge detection                                               | 40 |

|   | 4.3.3 Spin to charge conversion                                                 | 43 |

|   | 4.3.4 Controlled interaction of two electron spins                              | 45 |

|   | 4.4 SISSQIT Operation                                                           | 46 |

|   | 4.5 Project Methodology                                                         | 47 |

|   | 4.6 Summary                                                                     | 48 |

|   |                                                                                 |    |

| 5 | The Single Electron Transfer Device (SETD)                                      | 49 |

|   | 5.1 Introduction                                                                | 49 |

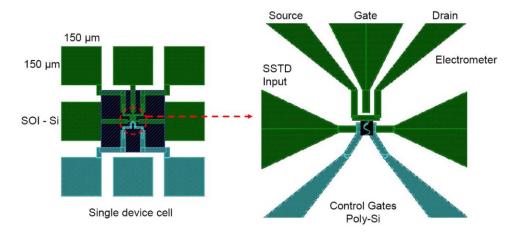

|   | 5.2 Layout of the SETD with an electrometer                                     | 49 |

|   | 5.3 3D FEM capacitance simulations                                              | 51 |

|   | 5.4 Monte Carlo single electron circuit simulation                              | 53 |

|   | 5.5 Fabrication process of the single electron transfer device and electrometer | 57 |

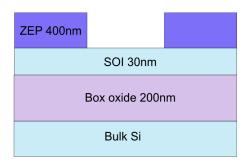

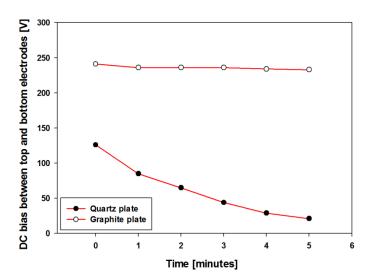

|   | 5.5.1 Thermal oxidation and SOI thinning                                        | 59 |

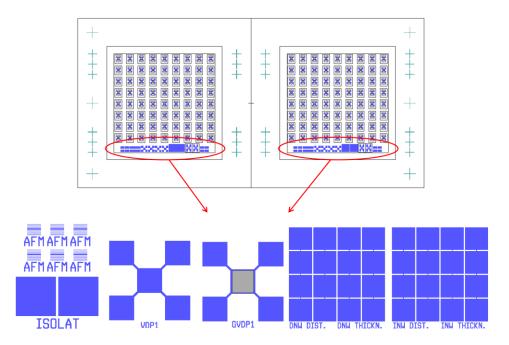

|   | 5.5.2 Sample layout                                                             | 62 |

|   | 5.5.3 Electron beam lithography                                                 | 63 |

|     | 5.5.4 Alignment marks definition using ZEP520A e-beam lithography                       | 64  |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | 5.5.5 Alignment marks pattern transfer using relative ion etching                       | 65  |

|     | 5.5.6 Spin on dopant and oxide doping mask definition using UVN30 e-beam lithography    | 69  |

|     | 5.5.7 Doping mask pattern transfer using reactive ion etching                           | 72  |

|     | 5.5.8 Phosphorus spin on dopant process                                                 | 72  |

|     | 5.5.9 Si device layer definition using HSQ e-beam lithography                           | 75  |

|     | 5.5.10 HSQ device layer pattern transfer using reactive ion etching                     | 78  |

|     | 5.5.11 Phosphorus dopant redistributing during thermal oxidation                        | 79  |

|     | 5.5.12 Al control gates layer definition using PMMA e-beam lithography                  | 81  |

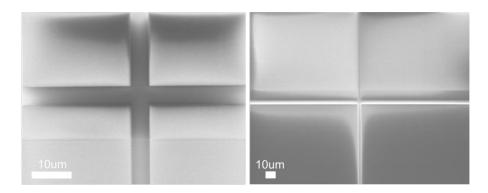

|     | 5.5.13 Al control gates continuity over SOI NW channels                                 | 86  |

|     | 5.5.14 Top gate oxide and contact via layer formation using bi-layer e-beam lithography | 87  |

|     | 5.5.15 Al top gate and contacts layer definition using bi-layer e-beam lithography      | 88  |

| 5   | .6 FinSET device layouts                                                                | 89  |

| 5   | .7 Summary                                                                              | 91  |

|     |                                                                                         |     |

| 6 C | characterization and Evolution of the Single Electron Transfer Device                   | 92  |

| 6   | .1 First device generation with Al FinSET barrier gates                                 | 92  |

|     | 6.1.1 Double quantum dots SET                                                           | 93  |

|     | 6.1.2 Single quantum dot SET with a charge sensor                                       | 95  |

| 6   | .2 Second device generation with Al side gates                                          | 106 |

| 6   | .3 Third device generation with Au FinSET barrier gates                                 | 110 |

| 6   | .4 Fourth device generation with Al FinSET barrier gates and SiO2 spacers               | 111 |

| 6   | .5 Fifth device generation with Al FinSET gates on atomically defined NW side walls     | 117 |

|     | 6.5.1 TMAH mock definition                                                              | 110 |

| 6.5.2 Nanowires mask design                       | 119 |

|---------------------------------------------------|-----|

| 6.5.3 Nanowires fabrication                       | 120 |

| 6.5.4 Shared Al barriers and metal coverage tests | 123 |

| 6.6 Summary                                       | 124 |

|                                                   |     |

| 7 Conclusions                                     | 126 |

| 7.1 Project Summary                               | 126 |

| 7.2 Future Work                                   | 127 |

|                                                   |     |

| Appendix A                                        | 128 |

| Appendix B                                        | 132 |

| Appendix C                                        | 136 |

| Appendix D                                        | 141 |

| Appendix E                                        | 143 |

| References                                        | 146 |

# **Declaration of Authorship**

I, Feras Alkhalil, declare that the thesis entitled 'Development of Novel Fabrication Technology for SOI Single Electron Transfer Devices', and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research.

#### I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has been previously submitted for a degree or any other qualification at this University of any other institution, this has been clearly stated;

- Where I have consulted published work of others, this is always clearly attributed;

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledges all main sources of help;

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- Parts of this work have been published as shown in the list of publications that follows.

| Signed: | <br> | <br> | <br> |

|---------|------|------|------|

| C       |      |      |      |

|         |      |      |      |

| Date:   |      |      |      |

# **List of Publications**

## **Journal publications**

- Alkhalil, F.M., Perez-Barraza, J.I., Husain, M.K., Lin, Y.P., Lambert, N., Chong, H.M.H, Tsuchiya, Y., Williams, D.A., Ferguson, A.J., Saito, S. and Mizuta, H. Realization of Al tri-gate single electron turnstile co-integrated with a close proximity electrometer SET (2013). Microelectronics Engineering, 111, 64-67. doi: 10.1016/j.mee.2013.02.007.

- Lin, Y. P., Husain, M. K. and Alkhalil, F. M. et al. (2013) VLSI compatible parallel fabrication of scalable few electron Silicon Quantum Dots. IEEE TNANO, doi:10.1109/TNANO.2013.2263964.

- Boden S A, Moktadir Z, Alkhalil F M, Mizuta H, Rutt H N and Bagnall D M (2012)

Nanofabrication with the helium ion microscope Proc. MRS Journal Proceedings, 1412, mrsf11-1412-ff08-08 doi:10.1557/opl.2012.978.

- Lin, Y. P., Husain, M. K. and Alkhalil, F. M. et al. (2012) Design and fabrication of densely integrated silicon quantum dots using a VLSI compatible hydrogen silsesquioxane electron beam lithography process (2012). Microelectronics Engineering, 98, 386-390. doi:10.1016/j.mee.2012.07.011.

## **Conference publications**

- Alkhalil, F.M., Perez-Barraza, J.I., Husain, M.K., Lin, Y.P., Lambert, N., Chong, H.M.H., Tsuchiya, Y., Williams, D.A., Ferguson, A.J. and Mizuta, H. (2012) Realization of fully tunable FinFET double quantum dots with close proximity plunger gates. In, 12th International Conference on Nanotechnology (IEEE NANO 2012), Birmingham, GB, 20 23 Aug 2012. 2pp.(doi:10.1109/NANO.2012.6321993).

- Alkhalil, F., Perez-Barraza, J., Husain, M., Lin, Y., Lambert, N., Chong, H., Tsuchiya, Y, Williams, D., Ferguson, A. and Mizuta, H. (2012) Al FinFET single electron devices with close proximity Si plunger gates. At Silicon Quantum Information Processing Meeting, Warwick, GB, 14 Sep 2012. 1pp.

- Alkhalil, F., Perez-Barraza, J., Husain, M., Lin, Y., Lambert, N., Chong, H., Tsuchiya, Y., Williams, D., Ferguson, A. and Mizuta, H. (2012) Realization of Al FinFET single electron turnstile co-integrated with a close proximity electrometer SET. In, 38th International Conference on Micro and Nano Engineering (MNE 2012), Toulouse, FR, 16 20 Sep 2012.

- Lin, Y.P., Perez-Barraza, J.I., Husain, M.K., Alkhalil, F.M., Lambert, N., Chong, H.M.H., Ferguson, A.J., Williams, D.A. and Mizuta, H. (2013) Fabrication and characterisation of down-scaled multi-configuration Silicon quantum dot devices. At the 2013 Silicon Nanoelctronics Workshop (SNW), Kyoto, Japan.

- Husain, M., Lin, Y., Alkhalil, F., Perez-Barraza, J.I., Lambert, N., Williams, D., Ferguson, A., Chong, H. and Mizuta, H. (2012) Improved silicon quantum dots single electron transfer operation with hydrogen silsesquioxane resist technology. At 38th International Conference on Micro and Nano Engineering (MNE 2012), Toulouse FR, 16 20 Sep 2012. 1pp.

- Lin, Y.P., Perez-Barraza, J.I., Husain, M.K., Alkhalil, F.M., Lambert, N., Chong, H.M.H., Ferguson, A.J., Williams, D.A. and Mizuta, H. (2012) VLSI Compatible parallel fabrication of scalable few electron silicon quantum dots. In, 12th International Conference on Nanotechnology (IEEE NANO 2012), Birmingham, GB, 20 23 Aug 2012. 2pp.

- Alkhalil, F. M., Husain, M. K., Lin, Y. P., Chong, H. M. H., Ferguson, A. J., Tsuchiya, Y. and Mizuta, H. (2011) Realization of an integrated double spin qubit device on ultra-thin Silicon-on-insulator. At Quantum information processing and communication international conference at ETH Zurich, Zurich, 05 09 Sep 2011. (Submitted).

- Husain, M., Lin, Y., Alkhalil, F., Chong, H., Tsuchiya, Y., Lambert, N., Ferguson,

A. and Mizuta, H. (2011) Fabrication of Silicon-based single spin quantum devices using

Hydrogen silsesquioxane electron beam resist. At The 37th International Conference on

Micro and Nano Engineering, Berlin, Germany, 19 23 Sep 2011.

- Lin, Y. P., Husain, M. K., Alkhalil, F. M., Chong, H. M. H., Ferguson, A. J. and Mizuta, H. (2011) Design and fabrication of single electron spin qubits in lithographically defined silicon quantum dots. At Quantum information processing and communication international conference at eth Zurich, Zurich, 05 09 Sep 2011. Quantum information processing and communication international conference at eth Zurich, 112-112.

- Mizuta, H., Husain, M., Alkhalil, F., Lin, Y., Moktadir, Z., Boden, S., Tsuchiya, Y., Lambert, N., Ferguson, A. and Chong, H. (2011) Silicon nanofabrication for QIP in Southampton (Invited Talk). At UK Silicon QIP Meeting, Cambridge,

- Alkhalil, F. M., Chong, H. M. H., Ferguson, A. J., Tsuchiya, Y. and Mizuta, H. (2010) Design and Analysis of Double Spin Qubits Integrated on Ultra-thin Silicon-oninsulator. At ESSDERC, Seville, Spain,

- Alkhalil, F., Chong, H., Tsuchiya, Y., Ferguson, A. and Mizuta, H. (2010) Silicon-based integrated single spin quantum information technology [SISSQIT]. At International Symposium on Atom-scale Silicon Hybrid Nanotechnologies for 'More-than-Moore' and 'Beyond CMOS' Era, Southampton, GB, 01 02 Mar 2010.

# Acknowledgments

First and foremost, I would like to express my sincere gratitude and appreciation to my supervisors Prof. Hiroshi Mizuta and Dr. Yoshishige Tsuchiya Without their constant guidance and support; this work would not have been possible.

For much help and advice, I owe a debt of gratitude to Dr. Harold Chong, Prof. Shinichi Saito, Dr. Zakaria Moktadir and special thanks are in order for Dr. Muhammad Husain and Yun Lin.

I would also like to extend my thanks and gratitude to our collaborators from the University of Cambridge, Dr. Andrew Ferguson, Julia Perez-Barraza and Dr. Nick Lambert as well as Dr. David Williams from the Hitachi Cambridge laboratory.

Thanks to all the Southampton Nanofabrication Centre staff, Dr. Iain Anteney, Peter Ayliffe, Dr. Owain Clarke, Richard Kean, James Farmer, Dr. Kian Kiang, and Denny Jack.

In terms of organisations many thanks are due for the school of electronics and computer science and the Hitachi Cambridge laboratory for financially supporting my studies, and the Engineering and physical research council for funding this project.

I would like to express my appreciation to all my colleagues in the Nano research group. Special thanks are reserved for Rachel Gleeson, her support and encouragement has made this journey much easier and made this one of the most enjoyable experiences I will ever have.

Finally, I would like to dedicate this work to my late father, whose inspiration and guidance still drives me forward everyday. I want to thank my loving mother and sister for their unconditional support, love and encouragement throughout this journey and always.

# **Chapter 1**

# Introduction

## 1.1 Quantum information processing

The remarkable growth of the electronics industry is reflected by the increasing number of transistors on a single chip and the spectacular size reduction of these transistors. However, as the electronics industry approaches the nanometre scale, the laws of quantum mechanics starts to control the behaviour of electrons in semiconductors. This has led to serious research and investigation into alternative directions for the electronics industry: one of these new directions is the use of the electron spin degree of freedom, in what is known as spintronics.

The purpose of spin based devices (Spintronics) is to control the quantum mechanical properties of the electron spin. Therefore, it is possible to employ spin based devices to perform quantum information processing tasks, like single electron spin initialization, manipulation and readout [1]. The term quantum information processing describes devices and systems in which information is handled and processed under the laws of quantum mechanics [2].

Quantum computing and quantum information processing have been proposed as a possible solution to maintain the growth of the transistor density on a chip, as predicated by Moore's law. The field of quantum computing started in the early 1980s, and it describes systems in which all the components are in the nanometer scale, since quantum mechanics control the behavior of devices in the nanoscale, these nanoscale systems will exhibit quantum behavior, hence the term quantum computers [1].

The spin state of localized electrons is naturally a two level system; this makes it an ideal candidate to realize a quantum bit (qubit is the elementary unit of quantum information processing) [1]. Electron spins can be localized by confining them to lithographically defined quantum dots, where the quantum dot (QD) is a fabricated structure that provides confinement in all three spatial dimensions [3]. The ability to realize a system where a single bit of information can be represented by a single electron would possibly be one of the most revolutionary achievements in the field of information processing and computing, because devices like this would be ultra fast and would consume very little power [4]. Such systems would have components that are able to transfer, manipulate and detect single electrons.

Quantum systems are extremely complex systems, and simulation of their dynamics is a very demanding task for classical computers, because the resources required for simulating a quantum system increase exponentially with the system size. The state of a quantum system is represented by a Hilbert space element, and the computational space dimensions required to simulate the state of n qubits is  $2^n$ , i.e. to simulate an n qubit quantum system, an exponential number of  $2^n$  classical bits are required [1]. Therefore, Richard Feynman concluded in the 1980s that some quantum mechanical effects cannot be properly simulated using classical computers, and he proposed that quantum systems should be simulated by a device of the same nature; a quantum device [1], [5].

The field of quantum computing didn't really take off until 1994, when Peter Shor introduced a Polynomial time quantum algorithm for large-scale prime factorization of integers. Factoring an N digit number using a classical algorithm would require an exponentially growing time (logN), while Shor's algorithm requires a time growth that is bound by a polynomial [1]. This discovery showed a clear advantage of this quantum factoring algorithm over classical factoring algorithms, especially in the field of cryptography, where the RSA public key algorithm currently used for cryptography is based around the fact the large scale prime factorization of over than 100 digits using classical computers is unfeasible. In 2001, a remarkable breakthrough was made when researchers at IBM demonstrated Shor's algorithm to factor the number 15 using a liquid state NMR quantum computer [5]. Another milestone in quantum computing was the introduction of error correcting codes. Error correcting codes compensate the effect of noise and the interactions with the environment [1]. The appearance of various quantum algorithms and the development of error correction codes have simulated a great deal of interest in different quantum computing proposals; some of these proposals will be discussed in detail in chapter 3 of this report.

This work presents a novel silicon based double spin qubits system integrated with an electrometer, and the aim of this platform is to demonstrate spin initialization, manipulation and readout operations. However, this report mainly focuses on the design, simulation, nanofabrication techniques and process developments necessary to realize this platform.

## 1.2 Report Structure

This report is divided into five main chapters.

Chapter two gives an overview of single electron devices operating principles, carrier transport theory, Coulomb blockade, Coulomb blockade oscillation, Coulomb diamond analysis and single electron tunnelling. It covers: the single electron box, the single electron transistor, double dot single

electron transistor and the single electron turnstile device. This chapter also gives an overview of spintronics and spin based quantum computation.

Chapter three examines various theoretical concepts and experimental efforts made towards the realization of solid quantum information processing. This chapter discusses the DiVincenzo criteria for quantum computing, and describes in detail many quantum computing proposals especially those based on electron charge, electron spin and impurity spins in semiconductor quantum dots.

Chapter four is dedicated to the Silicon-based Integrated Single-Spin Quantum Information Technology (SISSQIT) project. This chapter describes in great detail the components of the SISSQIT platform, the SISSQIT operation, techniques that will be employed for this system and the project methodology.

Chapter Five introduces the main building block of the SISSQIT platform, the single electron/spin transfer device (SETD) with an electrometer. This chapter discusses the significance behind this device for the experimental characterization of single electron transfer and single electron detection. Also in this chapter, layout of the SETD device with the electrometer, 3D FEM capacitance simulation, a unique single electron transfer scheme, and a full comprehensive description of the fabrication process is included.

Chapter six discusses the electrical characteristics, at room temperature and 4 K, of the first device batch in detail. It describes the process challenges and the proposed solutions and modifications required. A total of five device generations are discussed in this chapter, highlighting the process evolution of the metal FinSET quantum dot devices from a low yield first device batch to the first successful fabrication technology, to the best of my knowledge, for realizing FinSET-like metal gates for SOI nanowire structures.

Appendix A, B, C, D and E of this report include, respectively, a detailed step by step guide to the fabrication process, an overview of the different device layouts realized, the realization of a phosphorus doped charge qubits platform consisting of two quantum dots electrostatically coupled to a double quantum dot electrometer using lithographically defined constrictions, the development of extremely thin SOI (ETSOI) samples (approximately 7 nm thick) and He Ion lithography experiments on ETSOI, and finally the realization of an Extraordinary Magnetoresistance (EMR) platform for low temperature magnetic field experiments.

# Chapter 2

# Single electron devices

## 2.1 Single electron devices

Single electron devices (SEDs), as the name implies, have the ability to control, manipulate and transfer electrons on an elementary charge level. This property is based on the Coulomb blockade (CB) principle, which is a product of electrostatic forces generated by the confinement of electrons in small conductive structures [6].

Both metals and group III-V compound semiconductors SEDs have been implemented. However, Silicon SEDs are of special interest because of their ability to be integrated with other conventional complementary metal-oxide semiconductor (CMOS) circuits. Using Silicon based SEDs also means that the advanced CMOS large scale integrated circuits fabrication technologies can be utilized for the fabrication of the single electron devices extremely small structures [6].

Since SEDs have the potential of manipulating a single electron; they offer substantial savings in power consumption, their operating principle is relatively simple, and the performance of SEDs improves as they are scaled down. These factors make SEDs an attractive alternative for CMOS in future large scale integrated circuits [6].

## 2.1.1 Single electron devices operating principle

Single electron devices operation is based on two phenomena: Coulomb blockade and single electron tunnelling. The simplest example of a single electron device is the single electron box (SEB), the SEB will be used to give an overview of the operating principle of single electron devices.

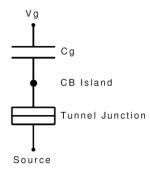

The SEB consists of a small conducting island (also referred to as a quantum dot) and a specially fabricated junction, referred to as a tunnel junction, which permits quantum mechanical tunnelling of electrons. The SEB also has two electrodes, one connected to the island via the tunnel junction and the second electrode is capacitively coupled (through a gate capacitance  $C_g$ ) to the island, the gate capacitance  $C_g$  does not permit quantum electron tunnelling which leaves the tunnel junction as the only way for an electron to transfer to or from the island [6],[7].

Fig. 2.1: Single electron box (SEB) equivalent circuit.

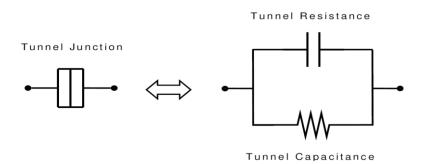

From a physical point of view, the tunnel junction is a thin insulating region that may be formed by a pattern dependant oxidation process (PADOX); this insulating region creates an energy barrier (tunnel junction) where electrons can tunnel through to reach the island [6]. PADOX oxidation for SOI (Silicon-on-Insulator) nanostructures is governed by two phenomena; the suppression of oxidation by mechanical stress (induced by mechanical expansion of the newly grown oxide) and oxidation from below the nanostructure (oxygen atoms diffusing through the buried oxide layer), this local oxidation process is strongly dependant on the size and shape of the nanostructure [8].

Fig 2.2: Equivalent circuit of a tunnel junction.

For a single electron device in thermal equilibrium at a temperature T, its steady state operation should satisfy the following relationship [9]:

$$\frac{\Gamma_{+}}{\Gamma_{-}} = \frac{1}{\exp(-eV/k_{B}T)}$$

(2.1)

Where  $\Gamma_+$  is the electron tunnelling rate in the forward direction,  $\Gamma_-$  is the electron tunnelling rate in a reverse direction, e is the elementary electron charge,  $k_B$  is Boltzmann constant, V is the voltage applied across the terminals of the tunnel barrier and eV is the amount of energy dissipated by forward electron tunnelling and is equivalent to the work done by the voltage source [9].

The net transfer of electrons in the forward direction ( $\Gamma_{net}$ ) can be expressed by [9]:

$$\Gamma_{\text{net}} = \Gamma_{\perp} - \Gamma_{\perp} = \Gamma_{\perp} [1 - \exp(-eV / k_{\text{R}}T)]$$

(2.2)

And the current in the forward direction can be given by [9]:

$$I(V) = e\Gamma_{\text{net}}$$

(2.3)

From equations (2.2) and (2.3), the electron tunnelling rate in the forward direction can be expressed by [10]:

$$\Gamma_{+} = \frac{I(V)}{e} \times \frac{1}{1 - \exp(-eV / k_{B}T)}$$

(2.4)

Therefore, the tunnelling of electrons through a tunnel barrier is dependent on the voltage applied across the terminals of the tunnel barrier. Looking back at the single electron box of fig. 2.1, to add a single electron to the CB (Coulomb blockade) island a voltage must be applied across the tunnel barrier, and the energy required to add a single electron to the island is known as the charging energy (E<sub>c</sub>), E<sub>c</sub> can be expressed by [11]:

$$E_c = e^2 / 2C_{\Sigma}$$

(2.5)

Where e is the electron charge and  $C_{\Sigma}$  is the total capacitance of the island.

When an electron transfers to the island, an electric field is created that resists the addition of further electrons to the island. Provided that the island size is small enough (nanoscale), the electric field created is inversely proportional to the square of the island size. This phenomenon is known as Coulomb blockade [11], [7].

The charging energy represents the Coulomb blockade energy (the electrochemical potential required to overcome the blockade), it increases as the CB island becomes smaller in size. For large values of  $E_c$ , no additional electron can transfer across the tunnel junction to the CB island unless the island potential is reduced [6].

#### 2.1.2 The single electron transistor

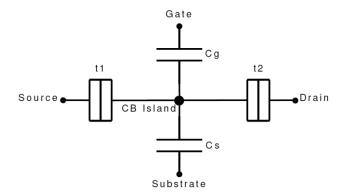

A three terminal example of a single electron device is the single electron transistor (SET), the SET has a single island (quantum dot), two tunnel junctions and a voltage source to control the number of electrons in the island [6].

Fig. 2.3: Single electron transistor (SET) equivalent circuit.

The total capacitance  $C_{\Sigma}$  of the SET (Fig. 2.3) CB island is given by:

$$C_{\Sigma} = C_{t1} + C_{t2} + C_{g} + C_{s} \tag{2.6}$$

Where  $C_g$  is the SET gate capacitance,  $C_s$  is the substrate capacitance;  $C_{t1}$  and  $C_{t2}$  are the capacitances of the two tunnel junctions.

There are two criteria that must be met to ensure successful operation of a single electron transistor, or any single electron device in general:

ullet To ensure that each electron in the system is localized to a particular conducting island at any time, the resistance of the tunnel junction ( $t_1$  and  $t_2$ ) must be larger than the quantum resistance  $R_q$

[11], [6]:

$$R_t >> R_q$$

(2.7)

Where the quantum resistance is given by [6]:

$$R_{q} = h / e^{2} \cong 25.8k\Omega \tag{2.8}$$

Relation (2.7) means that a tunnel junction with low electron transparency limits the quantum mechanical uncertainty of an electron location, which makes controllable manipulation of a single electron possible [11].

• To ensure that thermally heated electrons are not able to transfer across the tunnel barriers and consequently prevent the formation of a CB region, the charging energy must be sufficiently larger than the thermal energy. From (2.5) this condition can be expressed by [6]:

$$E_c = \frac{e^2}{2C_{\Sigma}} >> k_B T \tag{2.9}$$

Assuming that the CB island has a spherical shape with a diameter d, and is immersed in a dielectric medium with a dielectric constant of  $\varepsilon$ , the island capacitance  $C_{\Sigma}$  can then be expressed by [6]:

$$C_{\Sigma} = 2\pi d\varepsilon_{o} \varepsilon \tag{2.10}$$

Equations (2.9) and (2.10) suggest that a smaller island size increases the charging energy, and consequently allows operation at a higher temperature. However, this introduces a greater challenge of fabricating such extremely small structure to achieve SEDs room temperature operation.

If the total capacitance of the single electron transistor (SET) island is close to  $10^{-15}$  F, then the charging energy of adding a single electron to the SET island is larger than the thermal energy  $k_BT$  only at cryogenic temperatures, and conduction across this single electron transistor is accomplished by applying a source-drain potential higher than the island charging energy. On the other hand, room temperature SET operation requires the island total capacitance to be in aF range, this translates to an SET island of 10nm or less in size [12].

The single electron transistor has a very important property, where at constant source drain voltage; the source-drain current of an SET in Coulomb blockade is a periodic function of the gate voltage  $(V_g)$  with the period  $\Delta V_g$  given by [11]:

$$\Delta V_{g} = \frac{e}{C_{g}}$$

(2.11)

The amplitude of these periodic oscillations is given by [11]:

$$e/C_{\Sigma}$$

(2.12)

If  $V_g$  changes by  $\Delta V_g$ , the charge in the CB island changes by e. The change in the island charge is then compensated for by an electron tunnelling into or from the island.

This phenomenon is known as Coulomb blockade oscillation (shown in Fig. 2.4 (b)), where the gate voltage effect is similar to injecting the island with a charge equal to  $V_gC_g$ , by allowing the island potential to periodically overcome the island charging potential producing an Ids oscillation with a period equal to (2.11). This change in the island charge effects the charge balance at the tunnel junction capacitances  $C_{t1}$  and  $C_{t2}$  [11].

The electron transport mechanism through a single electron transistor relies on the electrochemical potential of its charging island (CB island), the charging island is a small conductive island holding a charge Q, the island is separated from the external bias electrodes by two tunnel junctions and the gate and substrate capacitances. The electrostatic energy of the SET before any electron transfer events can be given by [13]:

$$E_{1} = \frac{Q^{2}}{2C_{y}}$$

(2.13)

Q here is the background charge of the island and can be expressed as:

$$Q = N \times e$$

(2.14)

Where N is the number of electrons in the CB island.

Assuming a single electron tunnels from the source across the tunnel barrier t1, the electrostatic energy of the system can then be expressed by [13]:

$$E_{2} = \frac{(Q - e)^{2}}{2C_{5}}$$

(2.15)

An electron can transfer to the charging island only if it decreases the total energy of the system, this can be verified with the following [13]:

$$E_1 - E_2 = \frac{e(Q - e/2)}{C_{\Sigma}} > 0 \tag{2.16}$$

Q can also be described with the following [13]:

$$Q = C_{\Sigma} |V|$$

(2.17)

Where |V| is the potential drop across a tunnel junction, from (2.16) and (2.17); electron transfer across a tunnel junction is only possible if the potential across that tunnel junction satisfies the following [13]:

$$\left|V\right| \ge \frac{e}{2C_{x}} \tag{2.18}$$

|V| in equation 2.18 represents the Coulomb blockade threshold voltage, and if the potential difference across a tunnel junction is less than |V|; then there is no electron transfer as the device is in Coulomb blockade.

With this conclusion in mind, the potential conditions required for SET operation can be easily described. For the SET shown in fig. 2.3, the gate and drain electrodes are connected to external bias sources  $V_g$  and  $V_d$  respectively, while the source and substrate electrode are chosen to be grounded. The potential of the charging CB ( $V_{island}$ ) before any electron transfer can be given by [13]:

$$V_{island} = \frac{C_g}{C_v} V_g + \frac{C_{t2}}{C_v} V_d$$

(2.19)

$C_{t2}$  is the capacitance of the tunnel junction t2.

From (2.18), electron transfer across the tunnel junction t1 is only possible if [13]:

$$\left|V_{island}\right| > \frac{e}{2C_{\Sigma}}$$

(2.20)

And electron transfer across the tunnel junction t2 is only possible when [13]:

$$\left| V_{d} - V_{island} \right| > \frac{e}{2C_{x}} \tag{2.21}$$

Considering all the information mentioned above and to ensure electron transfer across both tunnel junctions of the SET, the following scheme can be adopted [13]:

The source and substrate are kept grounded; the drain voltage is kept at  $e/2C_{\Sigma}$  and only the gate voltage is varied (from zero to any higher positive value). This setup ensures that the island potential will have a voltage range from  $eC_{\tau 2}/2C_{\Sigma}^2$  to higher positive values linearly with any increase of the gate voltage [13]. These conditions satisfy both (2.20) and (2.21) allowing electron transport across the SET.

#### 2.1.3 Theory of carrier transport in single electron devices

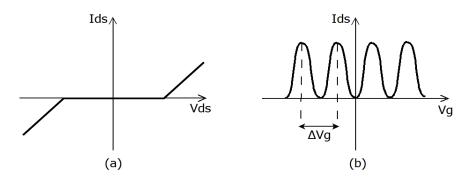

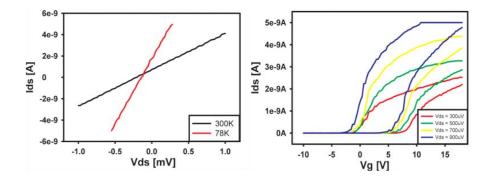

Analysis of single electron transport characteristics through quantum dots is very important; it provides means of verifying quantum dots formation and assists in evaluating their capacitance characteristics. A typical single electron transistor, like the one shown in Fig. 2.3, will be used in this section to explore the single electron transport via a single quantum dot. Fig. 2.4 (a) shows the SET Coulomb blockade characteristics, the CB region reflects the suppression in the number of electrons due to the quantum dot electrostatic energy. Addition of an electron to the charging island requires that the charging island electrochemical potential be lower than that of the source and the drain, otherwise no electron can tunnel to the charging island. To overcome the Coulomb blockade; a large potential bias (larger than the charging energy) must be applied. In addition, the electron thermal energy can also overcome Coulomb blockade. Therefore, low bias voltages and low temperature measurements are necessary to observe the Coulomb blockade characteristics [14].

The Ids-Vds characteristics as shown in Fig. 2.4(a) are linear outside the Coulomb blockade gap for similar SET tunnel resistances, if the two SET tunnel resistance are very different then the Ids-Vds characterises are stepped and these characteristics are referred to as Coulomb staircases [12].

Fig. 2.4: Schematics showing (a) Coulomb blockade characteristics and (b) Coulomb blockade oscillation characteristics [14].

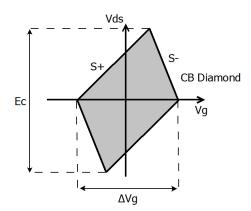

For a single electron transistor, the current can be plotted as a function of the gate voltage and the source drain voltage to give the schematic shown in Fig. 2.5. This schematic is known as the Coulomb diamond, the shadowed region represents the region where single electron transfer is suppressed (Coulomb blockade region).

Fig. 2.5: Coulomb Blockade diamond, the shadowed region represents zero conduction current [14].

The SET shown in Fig. 2.3 has two control gates, the first one is the gate electrode that is coupled to the charging island through the gate capacitance  $C_g$ , and the second electrode is the substrate electrode which is capacitively coupled to the island through the substrate capacitance  $C_s$ . In this case two Coulomb blockade diamonds have to be considered: one for the current as a function of gate voltage and source drain voltage, and the other for the current as a function of the substrate voltage and the source drain voltage. From these two Coulomb diamonds, all the capacitance characteristics between the quantum dot and the other electrodes of the single electron transistor can be concluded [14].

The first diamond (current as a function of gate voltage and source drain voltage) gives the following capacitance information [14]:

$$\Delta V_{g} = \frac{e}{C_{g}}$$

(2.22)

$$S_{+} = \frac{C_{g}}{C_{g} + C_{t2} + C_{s}}$$

(2.23)

$$S_{-} = -\frac{C_{g}}{C_{t1}}$$

(2.24)

The second diamond (current as a function of the substrate voltage and the source drain voltage) gives the following capacitance information [14]:

$$\Delta V_{g} = \frac{e}{C_{s}} \tag{2.25}$$

$$S_{+} = \frac{C_{s}}{C_{s} + C_{t2} + C_{g}}$$

(2.26)

$$S_{-} = -\frac{C_{s}}{C_{t1}} \tag{2.27}$$

S<sub>+</sub> and S<sub>-</sub> are the positive and negative slopes of the Coulomb diamond.

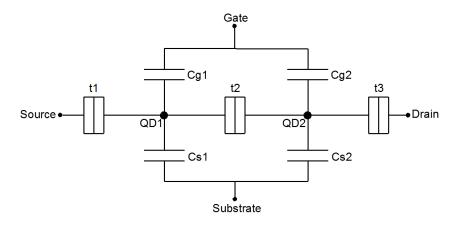

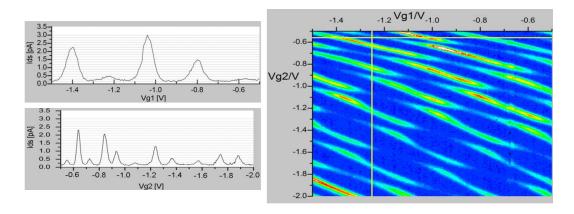

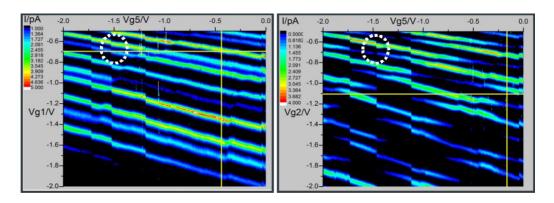

To further extend on the Coulomb blockade diamond analysis, a double quantum dot (DQD) single electron transistor will be discussed here. A double dot SET is a series connected double quantum dots with two control gates (same as the normal SET) are coupled to each quantum dot, a schematic diagram of this device is shown in Fig. 2.6. Single electron transport through the DQD structure requires Coulomb blockade tuning of both the quantum dots, and the Coulomb oscillation characteristics of the DQD are no longer single periodic oscillations as it is the case for a single dot SET [14].

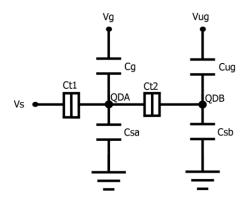

Fig. 2.6: Equivalent circuit of a double quantum dot (DQD) SET.

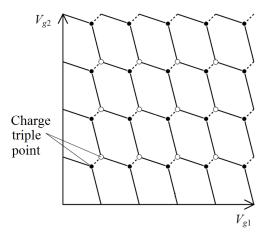

Sweeping both control gates of the DQD SET in Fig. 2.6 (the gate and the substrate) alters the electrochemical potential of each QD, plotting the current resulting from this sweep produces a contour plot known as the stability diagram. On the stability diagram the point of maximum current conduction is known as a triple point; this point represents the point at which the electrochemical potential (energy bands) of the two quantum dots are aligned together. The region enclosed by the triple points constitutes a region of stable electron numbers; it also has a honeycomb shape and is usually referred to as the honeycomb region [14]. A schematic of the stability diagram for a DQD SET is shown in Fig. 2.7 below. The electron transport via the DQD at zero temperature occurs only at the triple points. While at higher temperatures (for example 4.2 K) the electrons are transferred around the triple points, this effectively defines the boundaries of the honeycomb stable region [14].

Fig. 2.7: Stability diagram of an intermediately coupled DQD SET [14].

The shape of the honeycomb pattern is specific to the electrical characteristics of the structure and is mainly defined by the coupling between the two QDs. The honeycomb pattern shown in Fig. 2.7 shows an anti-crossed charging lines pattern; this is a signature pattern of intermediately coupled quantum dots [14].

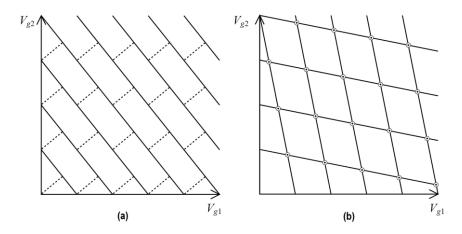

For strongly coupled QDs (Fig. 2.8 (a)), single parallel charging lines are observed in the stability diagram. The strongly coupled QDs in this case effectively behave as a single dot, and therefore this pattern is usually observed in single dot SETs [14]. On the other hand, weak coupling between the two QDs (Fig. 2.8 (b)) produces a stability diagram where each charging line crosses one triple point. The characteristics observed for very weakly coupled QDs are the same as the characteristics observed for series connected SETs [14].

Fig. 2.8: Stability diagrams of (a) strongly coupled DQDs (equivalent to a single QD) and (b) weakly coupled DQDs [14].

Another important observation is that the stability diagram of a multiple QD structure, like the one in Fig. 2.7, shows charging lines with more than three different slopes. While, only a single uniform slope can be observed in the stability diagram of a single QD structure (Fig. 2.8 (a)) [14]. Stability diagrams analysis of multiple QD systems can be used to extract all the capacitance characteristics of

the systems, it also indicates the number of QDs formed their sizes and positions. Such analysis of electron transport characteristics is discussed in great detail by Wiel et. al. in [15].

#### 2.1.4 Single electron turnstile devices

A single electron transistor is capable of transferring electrons one by one. However, the stochastic nature of tunnelling makes the time period of each tunnelling event uncontrollable in a SET. Therefore, it is harder for a single electron transistor to transfer one electron while stopping a second electron from transferring [4].

This lead to the development of a group of devices capable of transferring single electrons with high accuracy, known as the single charge transfer devices, this group includes single electron turnstiles, single electron pumps and single electron charged coupled devices [4].

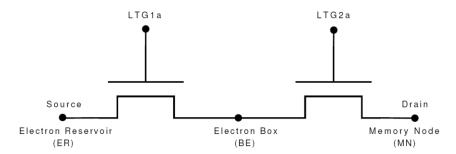

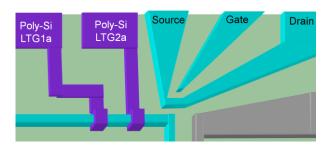

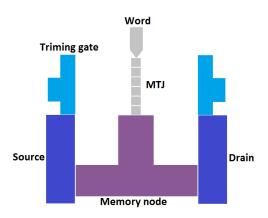

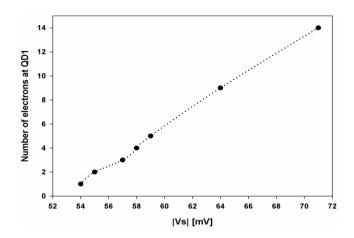

Fig. 2.9 shows the equivalent circuit of a turnstile device. Formed by two series connected MOSFETs, control gates of the two MOSFETs (LTG1a and LTG2a) act as single electron barriers and are used to transfer single electrons from the electron reservoir (turnstile source) to the memory node (MN) (turnstile drain). By applying periodic pulse voltages ( $V_{g1}$  and  $V_{g2}$ ) to the two gates, the potential barriers under theses gates change and the channel under each gate can be turned ON and OFF [4], [16].

Fig. 2.9: Turnstile device equivalent circuit, the FET gates here are acting as single electron barriers.

With the gate voltages ( $V_{g1}$  and  $V_{g2}$ ) cycled periodically, a single electron can be transferred from the source to the drain of the turnstile each cycle.

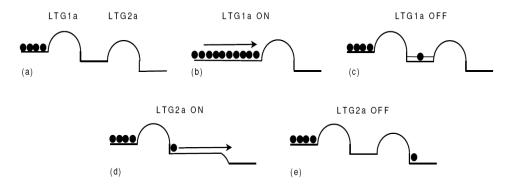

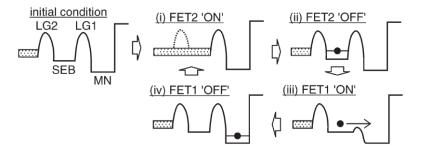

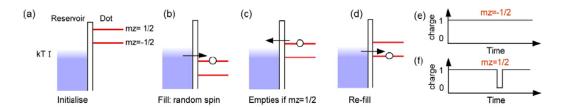

One cycle of the turnstile operation has the following steps [4], [16]:

- In the initial step (fig. 2.10 (a)), the island is isolated with both gates turned OFF.

- In the second step (fig. 2.10 (b)), LTG1a turns ON and the island between the two gates is connected to the source.

- In the third step (fig. 2.10 (c)), the potential barrier under gate LTG1a is raised and the gate turns OFF. A CB island is formed between the two gates, the island is electrically isolated from the source and a single electron remains in the island.

- In the next step (fig. 2.10 (d)), the gate LTG2a turns ON and the electron in the island is transferred to the drain because the island energy potential is higher than the energy potential of the drain.

- In the final step (fig. 2.10 (e)), LTG2a turns OFF and the electron is stored in the drain.

The operation sequence of the proposed turnstile device is shown below [4], [16]:

Fig. 2.10: Single electron transfer sequence of a turnstile device.

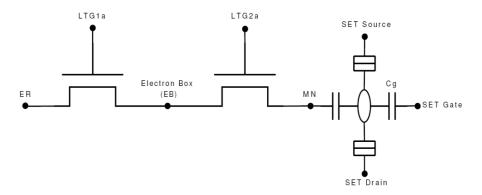

#### 2.1.5 The single electron transistor as an electrometer

By biasing a single electron transistor slightly higher than the Coulomb blockade threshold voltage, the SET can be used as an electrometer. Where any change in the SET island potential causes a variation in the  $I_{ds}$ - $V_g$  (Coulomb oscillation) characteristics of the single electron transistor [4]. By capacitively coupling the memory node of the turnstile device to the island of a single electron transistor, it is possible to detect the number of electrons at MN by observing the changes in the SET current oscillation. The figure below shows an equivalent circuit of the proposed configuration [4], [16], [17]:

Fig. 2.11: Equivalent circuit of a turnstile device and a SET electrometer.

## 2.2 Spintronics and spin based quantum computing

Spin is one of the natural fundamental properties of all elementary particles. In classical physics, spin is defined as a small magnetic moment. However, measurement of a spin state in the presence of an external magnetic field, results in one of two discrete spin states: parallel or anti-parallel to the magnetic field. This behaviour, of having only two possible outcomes for the spin state, is the basis of the quantum mechanical nature of the spin [18].

Applications like magnetic resonance imaging and magneto electric devices have employed ensembles of many spins. On the other hand, the quantum mechanical nature of individual spins (the electron spin is a two state system, spin up and spin down), have made them suitable candidates for non-volatile memory applications, and to carry quantum information by using an individual spin to represent a quantum bit (qubit), where the single spin can potentially provide the ultimate bound for information storage [1], [3], [18]. The purpose of spin based devices (Spintronics) is to control the quantum mechanical properties of the electron spin. Therefore, it is possible to employ spin based devices to perform quantum information processing tasks, like single electron spin initialization, manipulation and readout [1].

Semiconductor structures, like quantum dots can be used to confine electrons, this provides a good degree of control and isolation of the electron spin state from its environment [1]. In addition, a technique like single electron turnstile (together with the application of a magnetic field) is capable of preparing the initial state of a single spin, and the spin state of a single electron can be detected using a spin to charge conversion method which utilizes spin dependant single electron tunnelling [19].

# 2.3 Summary

In this chapter, an overview of single electron devices and their operating principle was given. Single electron devices have proven to provide various advantages, including savings in power consumption, simple operation and high performance when scaled down. Single electron devices like the single electron transistor and the single electron turnstile will be utilized in this project for single electron detection and single electron transfer.

Spintronics and spin based quantum computing have also been covered in this chapter. This chapter provides a background overview for the project presented in this report. The SISSQIT project, presented in this report, proposes an integrated single electron double spin qubits system on a silicon on insulator platform, silicon has a low nuclear spin density, therefore increasing the spin decoherence time of our qubit.

# **Chapter 3**

# Physical realizations of quantum computing

### 3.1 Introduction

In version 2 (2004) of the quantum information science and technology roadmap, the relevant technology experts panel concluded that solid state quantum computing proposals (especially those related to localized spin or charge qubits) offer the best chances of progress towards the realization of a quantum computer [20]. In this chapter, we will describe various theoretical and experimental approaches for the realization of a semiconductor-based solid state quantum computing system, and we start by describing the DiVincenzo criteria, this criteria discusses the requirements for implementing a functional quantum computer.

## 3.2 Quantum computing and the DiVincenzo criteria

A quantum computer by definition is a machine that employs the full complexity of a many-particle quantum wavefunction to solve a computational challenge [21]. In quantum computing, the computational space available increases exponentially with the number of bits used. Therefore, quantum computing provides exponential parallelism; this in principle can lead to exponentially faster quantum algorithms than any other classical alternatives [22].

To understand the principle of quantum computing we can look at the basic principle of classical computing: we have a principle information unit known as the bit; this bit can have only one of two states 0 or 1. These classical 0 and 1 states can be represented by the ON/OFF state of a transistor, the presence/absence of charge in a memory cell or the magnetization direction of a magnetic body in a hard disk. Similar to a classical computer, a quantum computer uses a quantum bit (qubit) as its principle information unit expressed with two states of 0 and 1 to represent quantum information. The main difference here, is that quantum computing has a special state knows as superposition, in this state a qubit can take on the characteristics of both 0 and 1 states simultaneously at any moment in time. Therefore, a two qubit system in a superposition state can have any of the following states: 00,

01, 10 and 11 all at any one time. By employing superposition states expressed with N qubits, a quantum computer can perform simultaneous parallel processing of 2<sup>N</sup> values; this property allows quantum computers to perform high speed processing faster than any processing speed available with classical computers [23].

There are a number of requirements that defines the implementation of a true quantum computer, these requirements are known as the DiVincenzo criteria and include [2]:

1. A scalable physical system with well characterized qubits.

A well characterized qubit can be implemented by using a two level quantum system. For example, an electron, a spin ½ nucleus, or two orthogonal polarization states of a single photon.

2. The ability to initialize the state of the qubits to a simple fiducial state.

Assuming a two level qubit, initialization would be achieved by polarizing the qubit to one of the two quantum levels.

3. Long decoherence times, much longer than the gate operation time.

Decoherence is caused by the interaction of quantum states with the environment and leads to the degradation of most quantum states. Decoherence time doesn't necessarily have to be large, as long as the ratio of decoherence time to gate operation time satisfies this criteria at all times.

4. A universal set of quantum gates.

Sufficient quantum computation operations can be carried out by having a gate for single qubit rotations and a two qubit gate to control the interactions between two qubits.

5. A qubit-specific measurement capability.

A measurement capability provides readout of the qubit computation (interaction) outcome.

## 3.3 Quantum computing physical realizations

Various quantum computing proposals have been introduced in the past few years, based on a wide range of quantum phenomena, below is a list of some of these candidates [1]:

- Solid and liquid state NMR [24] and [25].

- Trapped ions [26].

- Cavity quantum electrodynamics [27] and [28].

- Neutral atoms in optical lattice.

- Linear optics [29].

- Solid state spin based and charge based systems.

- Charge, flux and phase Josephson junctions [30] and [31]

- Electrons on liquid helium surface [32].

Some of the early quantum computing proposals were cavity quantum electrodynamics (QED) [28], trapped ions and nuclear magnetic resonance. These proposals offer relatively high decoherence times, but they mostly fail to meet the scalability condition of the DiVincenzo criteria.

In this chapter, we will mostly discuss solid state quantum computing proposals with emphasis on electron spin and electron charge proposals.

#### 3.3.1 Nuclear spin of phosphorous donor atoms in silicon

The first Si based qubit proposal was by B. E. Kane in 1998 [33], he proposed to use the nuclear spins of an array of <sup>31</sup>P donor atoms in a spin free <sup>28</sup>Si substrate, therefore this proposal offered very long decoherence times of nuclear spins in Si. Kane described this system at low <sup>31</sup>P concentrations and at a temperature of 1.5K, with an electron relaxation time of up to thousand of seconds and a <sup>31</sup>P nuclear relaxation time of about 10 hours, indicating that if this system is implemented it would provide the longest relaxation times for quantum computation [33].

The Phosphorous nuclear spins and the electron spins are coupled by a hyperfine interaction, where spin polarization can be conveyed between the electrons and the nuclear spins systems. This means that nuclear spins can be manipulated and detected electronically by integrating them with electronic devices. Larger hyperfine interaction between the two spin systems results in a system with better sensitivity. Electrons are sensitive to external electric fields, therefore, the hyperfine interaction and consequently the nuclear spin dynamics can be controlled by applying external voltages to metallic electrodes in silicon based devices [34].

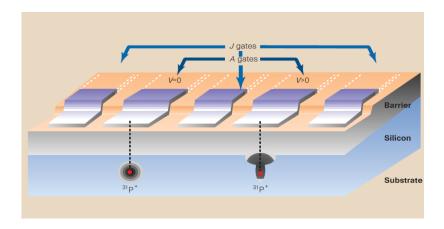

Figure 3.1: Quantum computing with nuclear spin of P donors in Silicon [35].

The nuclear spin states are detected by converting their polarization to electrons, these interactions are mediated through the use of a 2DEG layer, and then the electrons spin state is determined from the electron orbital wavefunctions by special capacitance measurements. Finally, operations must be carried out at low temperature (around 1.5K), to ensure that electrons only occupy non-degenerate low energy states in order to prevent reverse interactions between electrons and nuclear spins [34].

Kane's proposal satisfies all the theoretical requirements for quantum computing (the DiVincenzo criteria). However, this proposal requires very challenging bottom-up nanotechnologies, to control the number and position of the phosphorous atoms in the silicon substrate and there is little control over the exact position of the <sup>31</sup>P donor atoms in silicon. The donor atoms used in this proposal must be organised in a one or two dimensional array placed at only hundreds of angstroms beneath the surface of Si and under the barrier layer, conventional techniques like ion implantation and lithography are not useful. Another difficult element is the growth of subsequent Si layer on top of the donor array. The control gates needed must have dimensions and spacing in the range of 100 angstroms (10 nm). Even with the advanced nanofabrication techniques currently available, pattering such dimensions is considered very challenging [34].

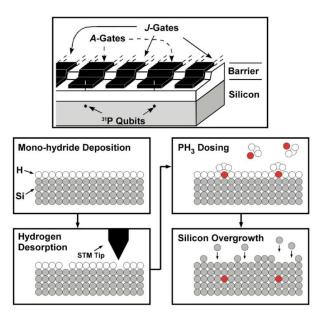

There have been attempts to realize the Kane proposal by using Scanning tunnelling microscopy (STM) lithography and Hydrogen resist technology in what is known as STM induced hydrogen desorption technology. However, the use of STM lithography for atomic level arrangement in semiconductors is a challenging process because of the strong covalent bonds present in semiconductors [36], a schematic process flow is shown in fig. 3.2 below. That being said, the STM and hydrogen-resist lithography approach has progressed significantly from its early start and has demonstrated not only individual manipulation of atoms and molecules but also recently achieved deterministic placement of a single phosphors donor atom within an epitaxial silicon structure forming the first ever single atom transistor [37]

Figure 3.2: Process flow to realize the Kane architecture [36].

More developments in this field have been demonstrated by Morello et. al. also from the University of New South Wales. By using phosphorus implanted donors in Si coupled to a 2DEG single electron transistor, they successfully demonstrated a single shot readout of a single electron spin bound to a phosphorus implanted donor in Si. Their experiment showed an electron spin life time of about 6 seconds at a magnetic field of 1.5 Tesla and a spin readout fidelity of 90% [38]. Previous electron spin readout experiments in GaAs/AlGaAs employed charge sensors that are electrostatically coupled to the electron location, and the spin detection technique used was based on spin dependant tunnelling (this method will be described in detail in the next chapter) to a nearby electron reservoir. In the structure used by Morello et. al., the charge sensor used was electrostatically and tunnel coupled to the electron site where the electrometer island is used as the electron reservoir for the donor electron to directly tunnel to the electrometer island during the read out stage, this strong coupling between the electron site and the electrometer provides a charge transfer signal an order magnitude higher than signals obtained with electrostatically coupled charge sensors and it is the reason they managed to show such high fidelity rates in their single shot spin dependant tunnelling measurements.

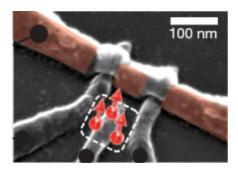

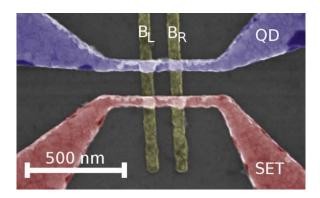

Figure 3.3: SEM image of the device used by Morello et. al., the dashed region shows the P donors location, the red region shows the 2DEG channel induced by the Al gates [38].

An SEM image of the device used in this experiment is shown in fig. 3.3 above, the electrometer is defined electrostatically in the underlying SiO2 layer using metal gates, the phosphorus donors are implanted in a small 90 nm x 90 nm region close to the electrometer QD, a top electrometer gate and a plunger gate over the donors location are also used to provide complete electrostatic control. The tunnelling between the charge site and the electrometer quantum dot is spin dependant when a large external magnetic field is applied (Zeeman splitting effect), under the influence of the magnetic field (B) the spin up state has a higher energy level than the spin down state by a quantity equal to the Zeeman splitting energy  $(E_z)$  [38], [39]:

$$E_z = g u_B B \tag{3.1}$$

Where g is the spin gyromagnetic ratio, and u<sub>B</sub> is the Bohr magnetron. Spin to charge conversion is then accomplished by tuning the electrometer island potential so that only the spin up state energy is higher than the electrochemical potential of the electrometer island [38], [39].

More recently, with the addition of a microwave strip line to the structure shown in Fig. 3.3, the same researche demonstrated coherent manipulation of an individual electron spin bound to a phosphorus donor atom. Electron spin resonance and Han echo pulse sequence were used to trigger a Rabi oscillation with and measure a spin coherence time of approximately 200 us [40].

# **3.3.2** Quantum dot quantum computing (The Loss-DiVincenzo quantum computer)

A different approach to the donor atoms array for quantum computing is the confinement of single electron spins in nanofabricated structures known as quantum dots (QDs). In 1998, Daniel Loss and David DiVincenzo described a detailed set-up of a coupled quantum dot computing system, the qubit was realised using the spin states of a confined electron in the QD. Loss and DiVincenzo proposed initializing the qubits by applying an external magnetic field at low temperature. Single qubits

operations (like spin rotation) can be accomplished by applying a large gradient magnetic field to alter the effective Zeeman splitting of individual qubits, and two qubits gated operation is achieved by modifying the electrostatic potential barrier between the two coupled QDs [41].

Loss and DiVincenzo predicted that decoherence times of electron spin in QDs to be longer than decoherence times of charge degrees of freedom in QDs, because the common decoherence caused by electric potential fluctuations has only a small effect on the spin degree of freedom [41].

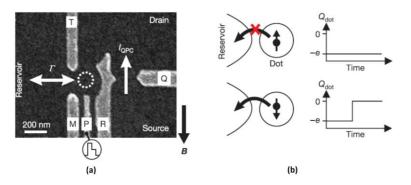

#### 3.3.3 Electron spin in GaAs gate defined double quantum dots

This proposal was originally introduced by researchers at Harvard University, and is based on confining single electron spins in quantum dots. To define the quantum dots, they used electrostatic gates on top of AlGaAs/GaAs heterostructure grown by molecular beam epitaxy with a two dimensional electron gas below the surface [42].

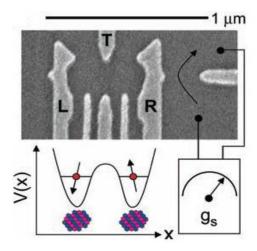

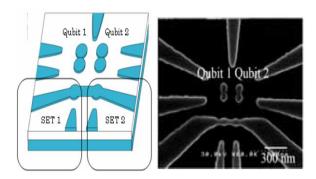

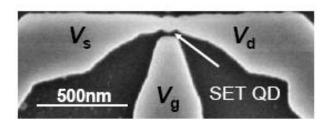

Figure 3.4: SEM image of the device proposed by Petta et al. [42].

Gate voltages  $V_L$  and  $V_R$  (Fig. 3.4) control the transfer of electrons from the reservoirs to the right and left dots, and gate voltage  $V_T$  is used to control the tunnel coupling between the two quantum dots. The readout technique is based on using a quantum point contact (QPC), sensitive to the number of electrons in the right QD, and employs spin to charge conversion technique to detect the electron spin state [42]. This quantum computing proposal showed coherent control over the electron spin state using fast electrical control of the exchange interaction of two neighbouring electron spins, and demonstrated most of the initialization and measurement operations with integrated electrostatic gates. This work also provided measurement of spin dephasing (decoherence) time in the range of 10 nanoseconds [42]. However, gallium arsenide itself is a nuclear spin rich environment, and the hyperfine interaction of the electron spin with the gallium arsenide host nuclei leads to rapid loss of the electron spin coherence. Petta et al. have since used a spin echo pulse sequence to overcome the

hyperfine dephasing problem, and they were able to demonstrate a two electron spin state coherence time of more than 1 microsecond [42]. Nevertheless, without using quantum control techniques like spin echo pulse sequence, the electron spin coherence times in gallium arsenide remain very short for quantum information processing purposes.

#### 3.3.4 Electron charge in double quantum dots

Electron charge has also been utilized for quantum computing applications. Relatively long decoherence times has been achieved by confining electrons in isolated quantum dot structures with control gates capacitively coupled to the qubit. One clear advantage of using charge qubits is the inherently simple measurement of the charge qubit, charge readout can be achieved by using a capacitively coupled quantum point contact (QPC) or a single electron transistor (SET). A major source of decoherence for charge qubits would be fluctuations of the gates voltages that are used to control the qubits electrically. Therefore, most charge qubit proposals tend to have isolated qubits, where the control gates effect the charge qubits electrostatically.

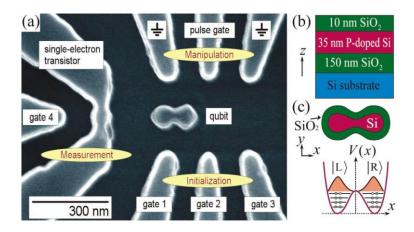

Gorman et al. demonstrated complete operation of isolated charge qubits by using dedicated capacitively coupled gates for initialization and manipulation of the charge qubit, a single electron transistor was also used to readout the charge qubit [43].

Fig. 3.5: (a) SEM image of the device introduced by Gorman et al. (b) material profile of the QD and c) Oxidized double quantum dot and localized electron charge configurations  $|L\rangle$  and  $|R\rangle$  [43].

The structure was fabricated using high resolution electron beam lithography and reactive ion etching. The platform of this device uses an SOI wafer with an active region doped with phosphorous, this layered insulator structure provides confinement in the vertical direction. Electrons are strongly isolated and confined to the double well potential formed by the QDs, the two QDs are connected together by a 20 nm wide constriction (tunnel barrier like structure) to form the qubit, and the potential of the QDs can be controlled by externally applied electric fields [43]. Gorman et al.

observed qubit coherence time of 200 ns, they attribute this to the presence of decoherence sources like: the back-action of the stochastic tunnelling events through the SET electrometer on the isolated double quantum dots, and the coupling of electromagnetic noise from the coplanar waveguide. They also suggested the use of an RF-SET to improve the charge qubit coherence times [43].

A similar isolated silicon double quantum dots device was also introduced by researchers from Hitachi Cambridge Laboratory. They used phosphorous doped (doping level of  $3x10^{19}$  cm<sup>-3</sup>) SOI isolated QDs coupled electrostatically to an SET electrometer and in-plane side gates, to demonstrate single charge transitions in the isolated quantum dots and they successfully controlled the charge occupancy of the QDs using in-plane side gates. They also observed clear variations in the electrometer current and shifts in the gate voltage Coulomb peaks of the electrometer as a result of inter dot single electron transfers in the isolated double QDs [44], [45].

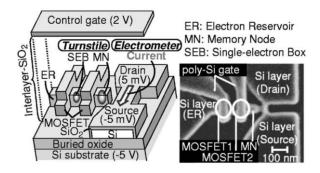

Another charge qubit proposal was introduced by Kawata et al., their project featured two charge qubits integrated with a double dot single electron transistor (DSET) readout, where the DSET is used to measure the charge polarization of two charge qubits [46].

Fig. 3.6: Schematic and SEM image of the system proposed by Kawata et al [46].

The system was also fabricated on phosphorous doped silicon on insulator substrate, the double quantum dots were fabricated using electron beam lithography and reactive ion etching, and finally thermal oxidation was used to reduce the overall dimensions and to passivate the surface states. Kawata et al. demonstrated the possibility of having multiple SETs connected in series, instead of having dedicated SETs for individual qubits (which can take up a considerably large substrate area) and therefore demonstrating a scalable readout method [46].

#### 3.3.5 Quantum computing with electron spin in silicon

Silicon is a fundamental element in the electronics industry, silicon processing and fabrication technology is well established and mature compared to other semiconductors. Natural silicon has the advantage of having only 4.7% (<sup>29</sup>Si) nuclear spin carrying isotopes, where the other 95.3% (<sup>28</sup>Si and

<sup>30</sup>Si) are spin free; this effectively reduces the effect of the hyperfine interaction. In addition, spin orbit interactions in silicon are weak [47]. Therefore, Silicon is a very strong candidate for quantum computing applications.

Friesen et al proposed one of the early Si-based systems for quantum dot qubits in silicon-germanium heterostructures, where electron spins are used as qubits in this scalable system [48].

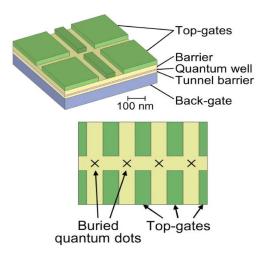

Fig. 3.7: SiGe two (top) and four dot (bottom) quantum computer proposed by Friesen et al [48].

The proposed structure (fig. 3.7) has a quantum well that provides confinement in the vertical direction, while the surface top gates provide electron confinement in the lateral direction. The presence of the top gates and the tunnel coupled back gate, allows lateral and vertical electron tunnelling to the quantum dots [48]. Similar to the Loss DiVincenzo proposal, an electrostatic control gate is employed here to control the wavefunctions overlap between two neighbouring electron, and consequently control the two qubit operations. They have also developed a spin to charge transduction technique to provide spin readout and initialization for this system [15].

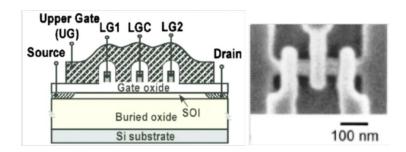

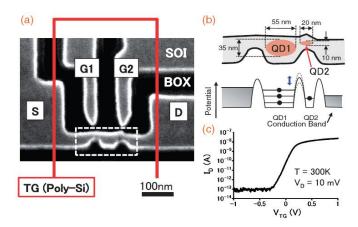

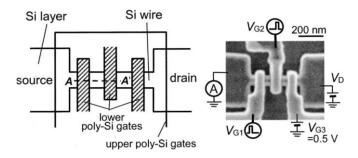

Liu et. al. proposed a Si double quantum dot MOS structure with a 15 nm SOI thick layer as a platform for spin based quantum computing. They managed to tune the tunnel coupling between two dots to demonstrate an excitation spectrum for weakly coupled dots and energy level anticrossing for strongly coupled ones at 30 mK. For weakly coupled dots they describe a resonant tunneling through the quantized energy levels reflecting the electrostatic interdot coupling between the two dots. As for the strongly coupled dots, they observe a clear energy level anticrossing caused by quantum interdot tunneling [50]. The structure used by Liu et. al. can be seen in fig. 3.8 below. A positive potential is applied to the top gate to form an electron inversion layer in SOI, and negative potentials are applied to the lower poly-si gates to deplete electrons in the underlying SOI layer and create tunnel barriers the at define the Si quantum dots. This structure presented a fully tunable Si QDs with both charge and energy quantization. However, this structure may suffer from parasitic dots formation due to the oxidation process, the roughness at the Si/SiO2 interface or in the Poly-Si gates themselves [50].

Figure 3.8: Schematic of the SOI MOS-like double QDs structure introduced by Liu et. al. [50].

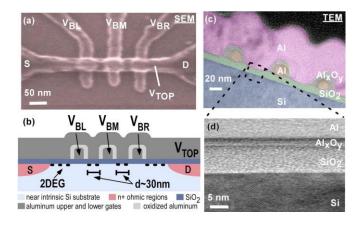

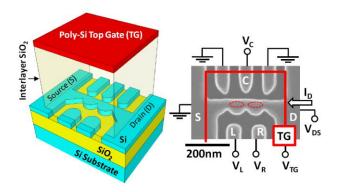

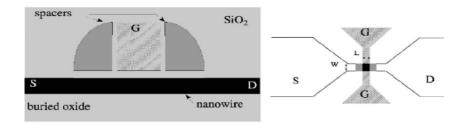

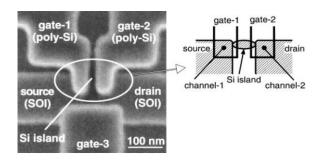

A Si 2DEG proposal was introduced by Lim et. al. from the University of New South Wales. They developed a tunable gated double quantum dots in intrinsic Si, Al gates were used to define two series connected QDs in the intrinsic underlying Si layer. The middle Al barrier gate offered a wide electrical tuning range of the interdot coupling between the QDs from the weakly coupled to the strongly coupled regime, demonstrating resonant single electron tunneling through the double QDs ground and excited states [51]. The device was fabricated by defining metal barrier gates and a metal top gate on top of an 8 nm oxide layer that covers the intrinsic Si device layer, the two Al gates layers are separated by 5 nm Al2O3 produced by oxidizing the first Al barrier gates layer in oxygen plasma. The device is show in fig. 3.9 below, the top gate and the three barrier gates form a 2DEG layer in the intrinsic Si and the barrier gates locally deplete the 2DEG to form three tunnel barrier forming two adjacent QDs in the intrinsic Si, the quantum dots size is defined by the Al gates dimension and spacing to be 30 nm x 50 nm [51].

Fig. 3.9: (a) SEM image of the Si 2DEG MOS device introduced by Lim. et. al., (b) and (c) schematic and TEM cross sections of the same device, (d) TEM cross section image of the Si substrate, 8 nm SiO2, 5 nm Al2O3 and the Al top gate [51].

They reported a charging energy of 5 and 2.5 meV for the two QDs at 50 mK, and they estimated 20 electrons dot occupancy. To enable device operation in the few electron regime, the authors propose integrating a charge detector into their structure and to introduce more plunger gates to control each QD independently [51].

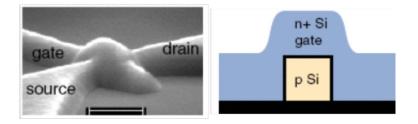

As a follow up to the Si 2DEG efforts at the University of New South Wales, Podd et. al. introduced a similar structure that includes a charge sensor which can be used to confirm QD single electron occupancy and to provide single shot measurement of the electron spin state. This structure consisted of two single electron transistors (SET) electrostatically formed in bulk Si using Al surface gates, the two SETs are facing each other, one used as a quantum dot and the second as an electrometer. They demonstrated that the addition of one electron to the quantum dot induced a charge equal to 0.2e on the SET electrometer at 100mK [52]. An SEM image of the device is shown below. The shared Al barrier gates approach was adopted for ease of fabrication, however because they are used to define both the QD and the electrometer operating regime, this approach has limited the device operation. Due to this the minimum QD electron occupancy number was 25 at the lowest possible barrier gate potential (lowest possible for the electrometer to also be operational) and the authors concluded with the need to replace the shared barrier gates with independent control gates to allow access to the few electron regime and provide a more tunable device [52].

Fig. 3.10: SEM image of the Si 2DEG device introduced by Podd et. al. [52].

The Si MOS double QDs device shown in fig. 3.9 included barrier control gates to define the tunnel barriers and a top gate to control the quantum dot and the accumulation layer electron density at the source-drain simultaneously. As a result the source-drain become depleted and switched off as the number of electrons in the QD is reduced, this makes it difficult to reach single electron dot occupancy with such structures. Therefore, a more advanced silicon metal oxide semiconductor quantum dot was once more reported by Lim et. al. in 2009, the device they developed this time included electrostatic gates that control the quantum dot and the source-drain electron densities independently, enabling this device to operated in the single electron regime where the QD occupancy can be reduced to a single electron while maintaining a large electron density in the source and the drain. This optimized structure is shown in fig. 3.11 below [53].

Fig. 3.11: SEM image and schematic cross section of the Si MOS three control gates layers structure developed by Lim et. al. [53].

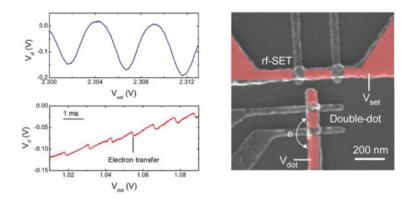

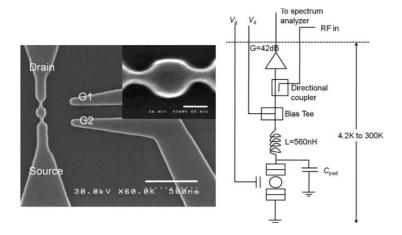

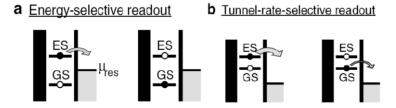

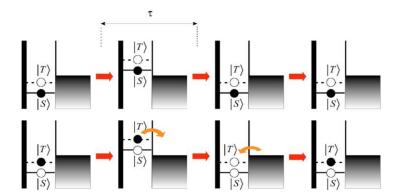

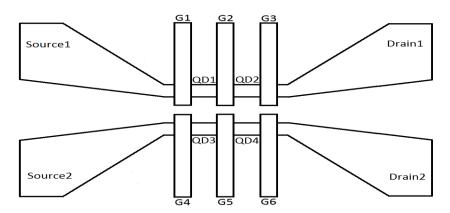

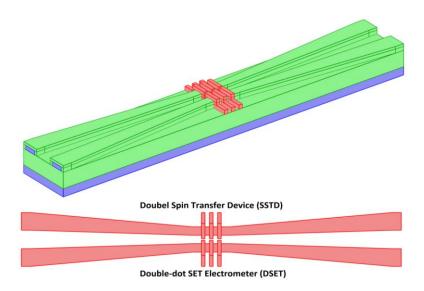

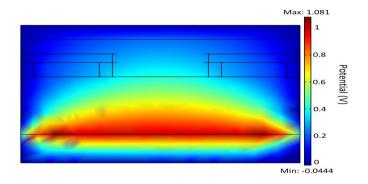

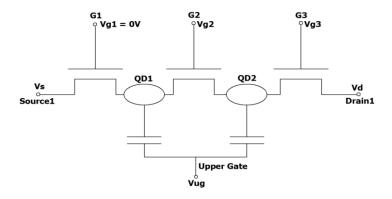

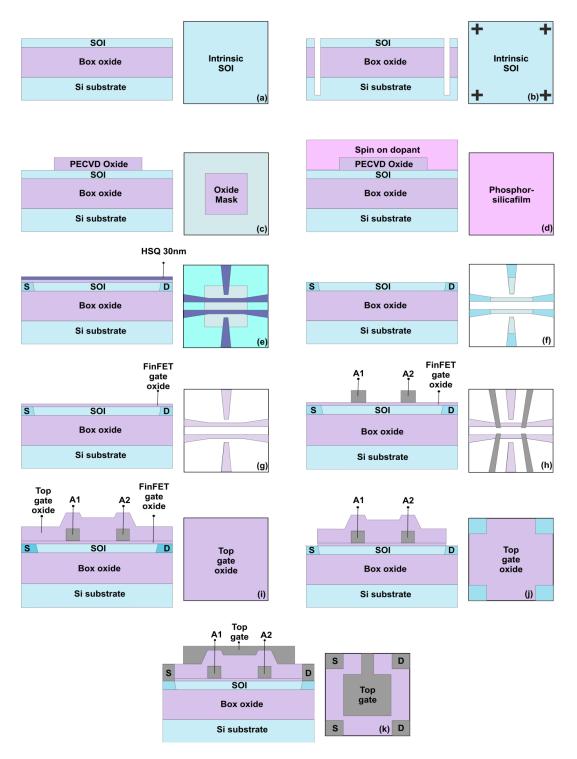

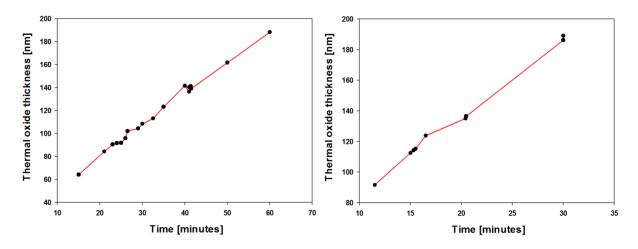

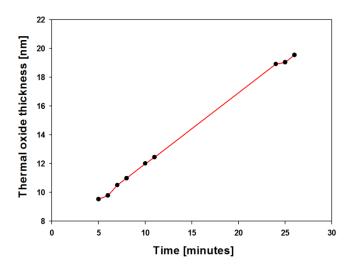

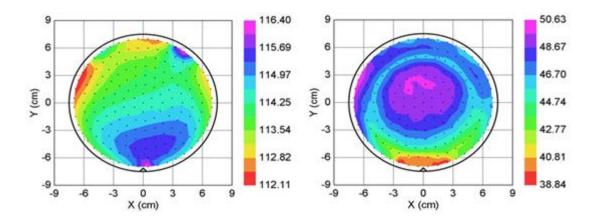

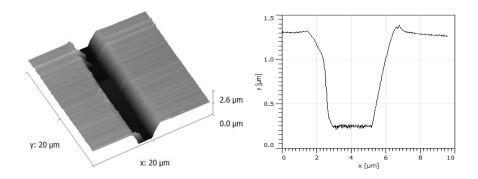

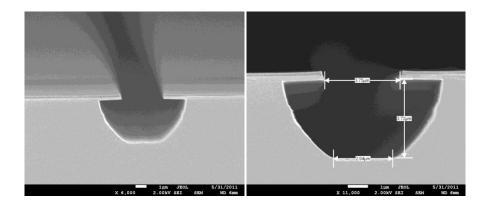

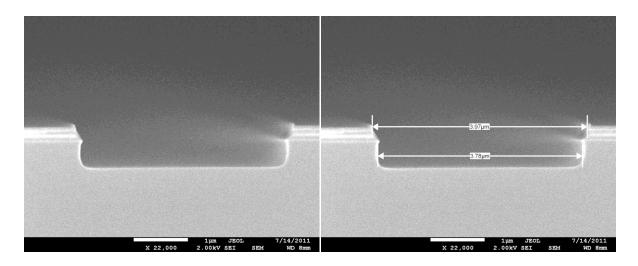

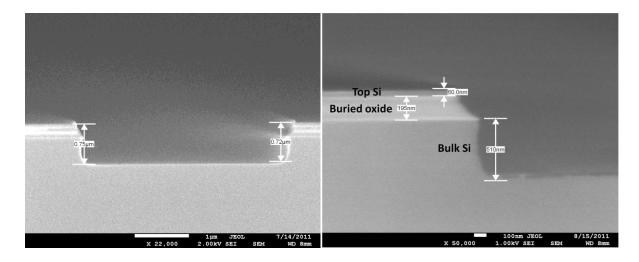

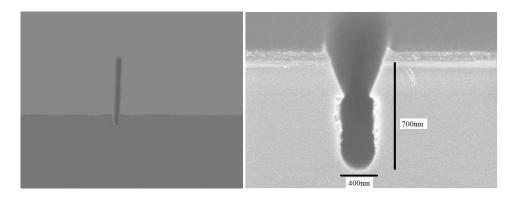

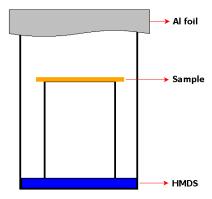

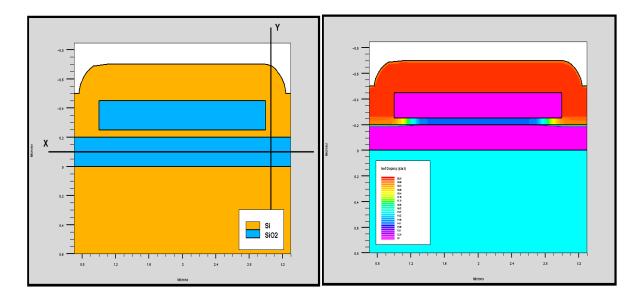

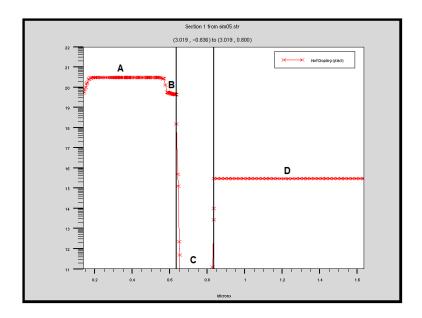

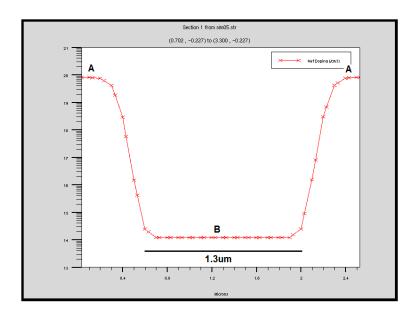

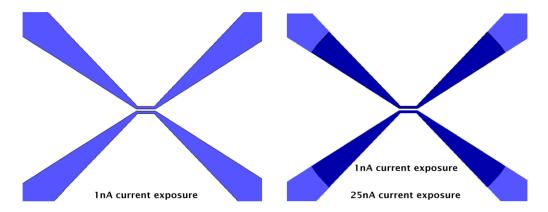

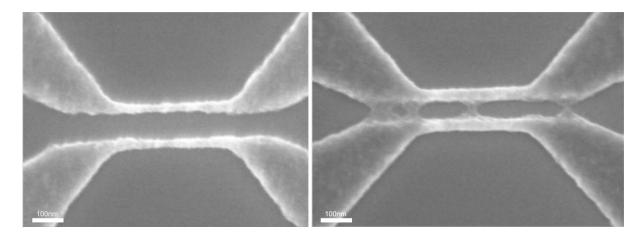

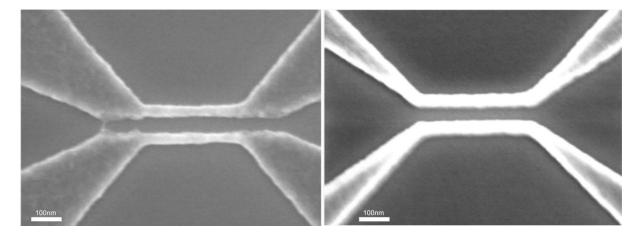

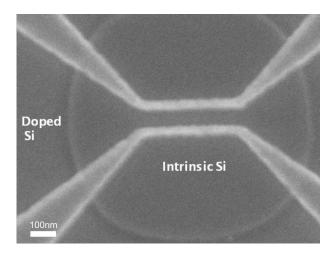

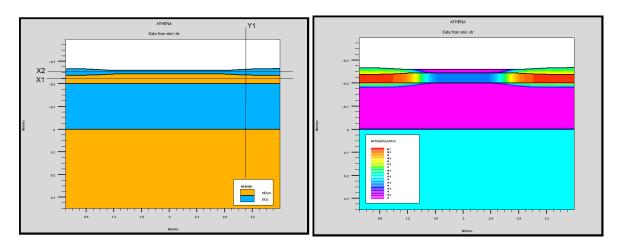

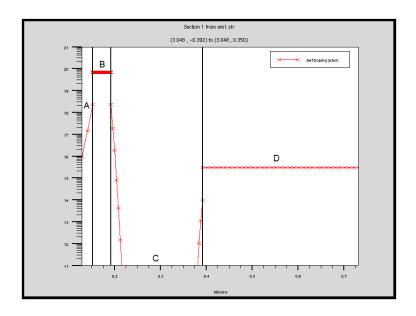

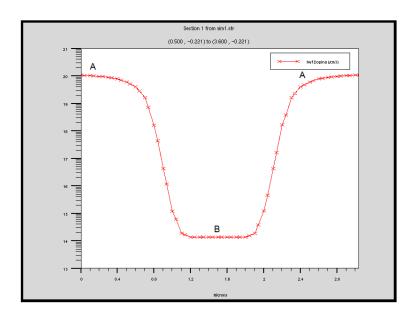

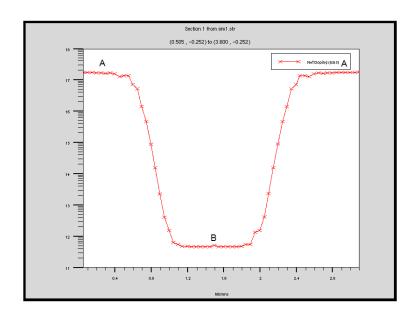

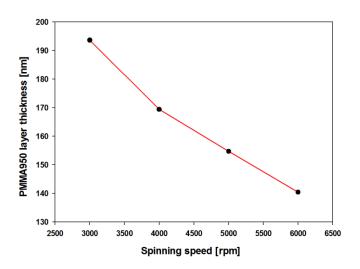

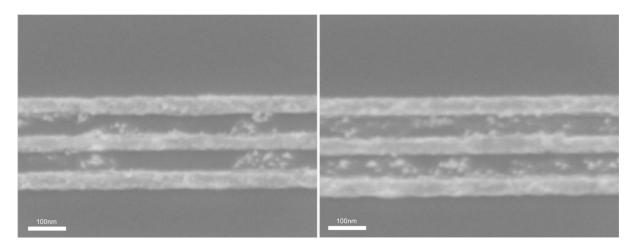

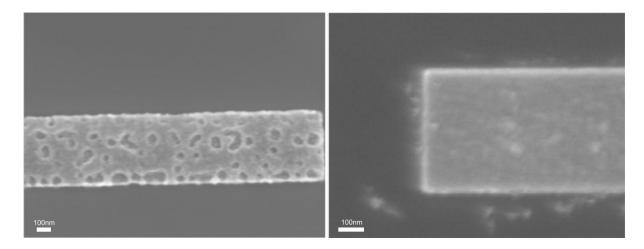

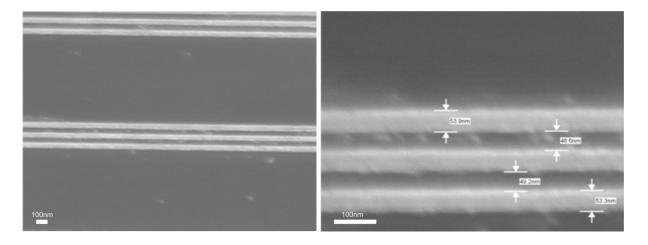

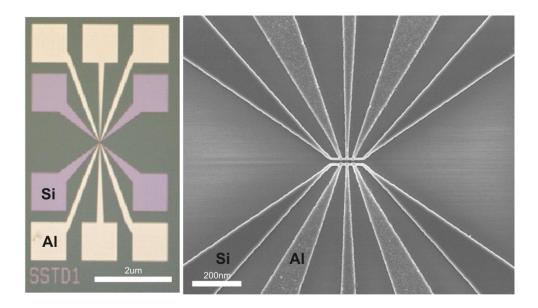

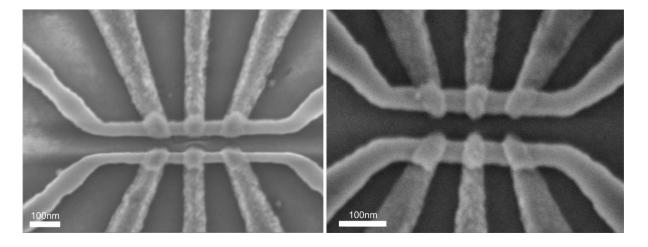

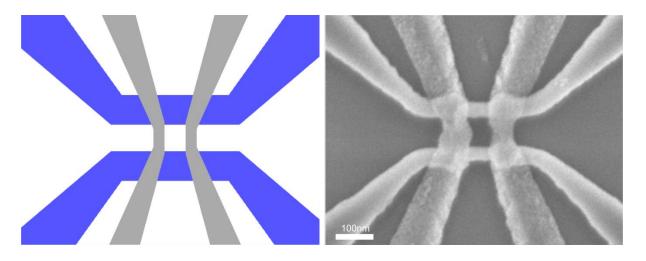

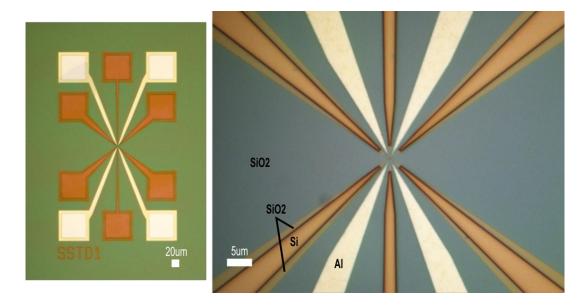

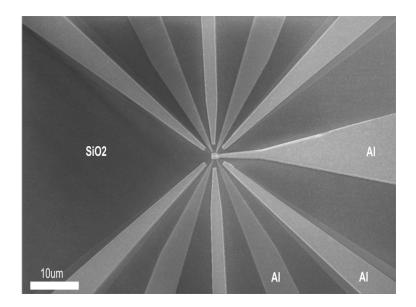

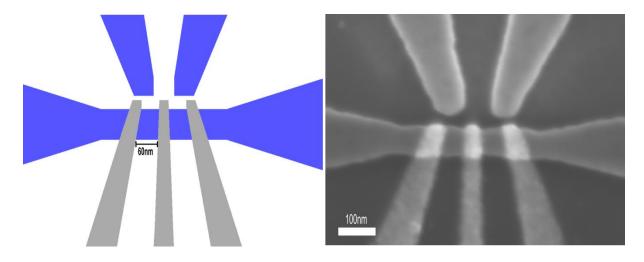

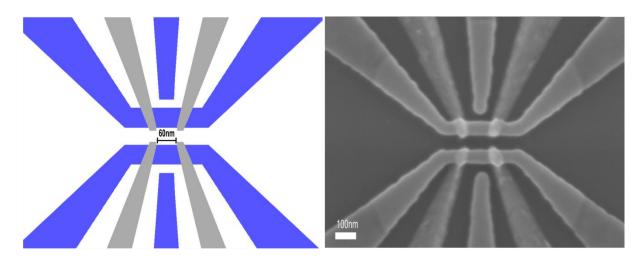

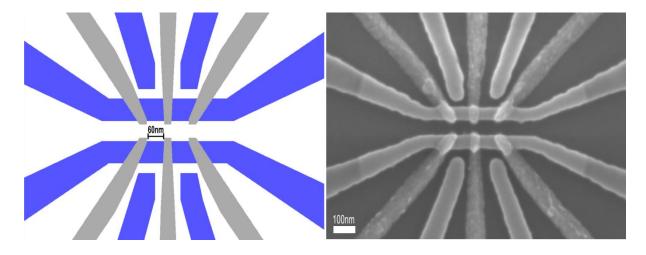

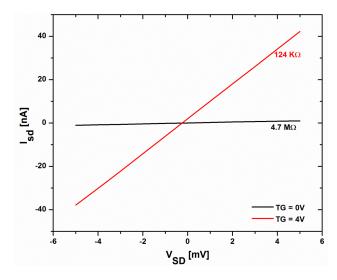

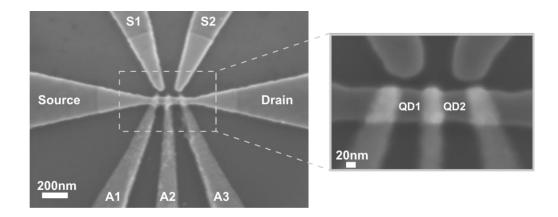

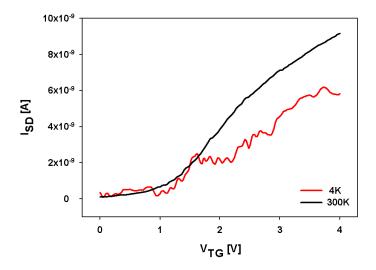

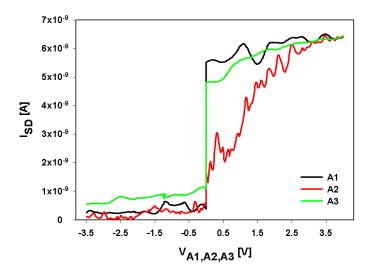

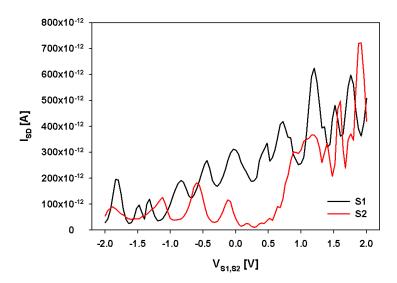

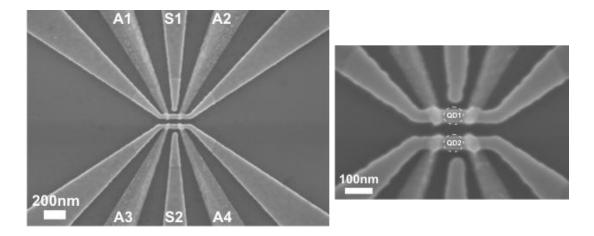

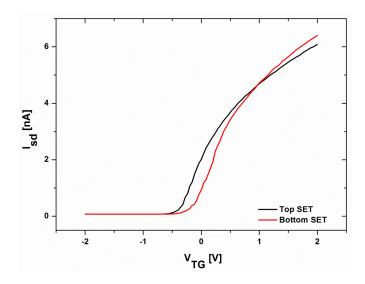

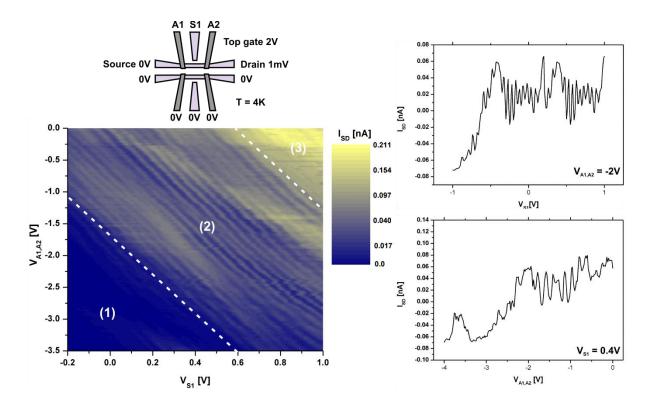

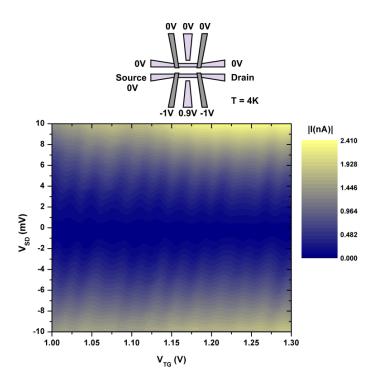

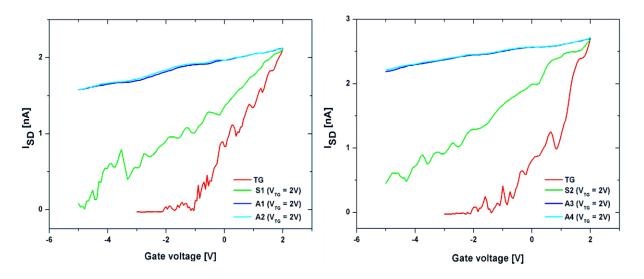

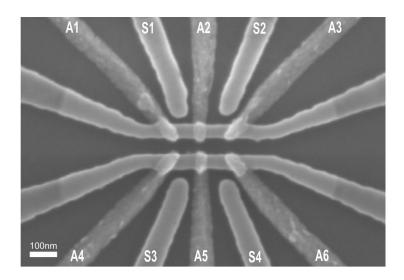

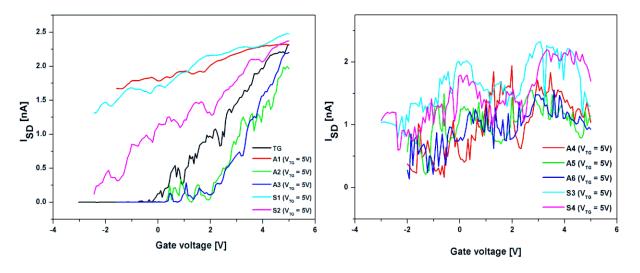

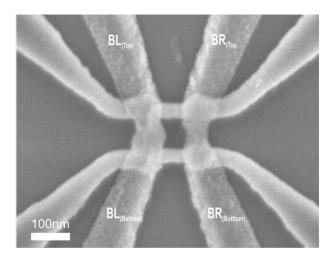

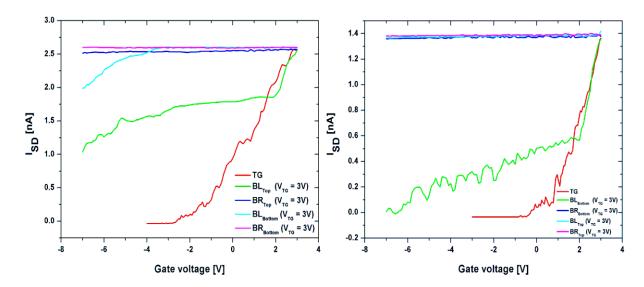

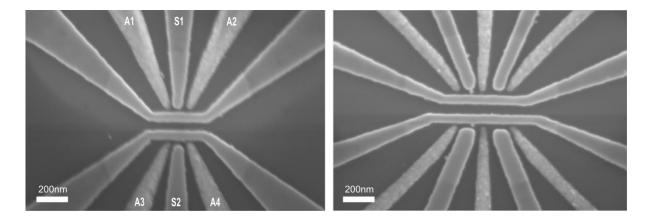

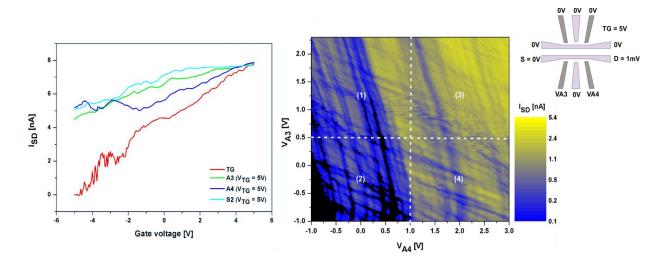

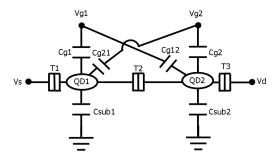

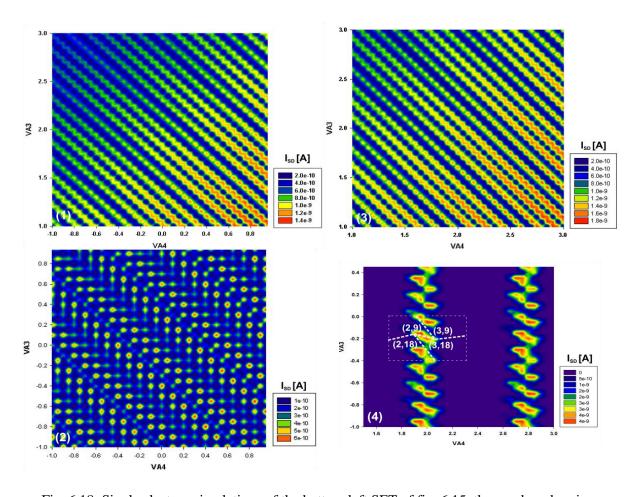

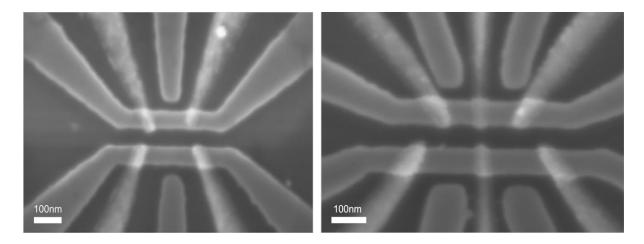

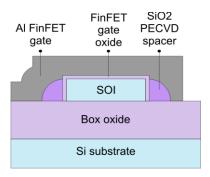

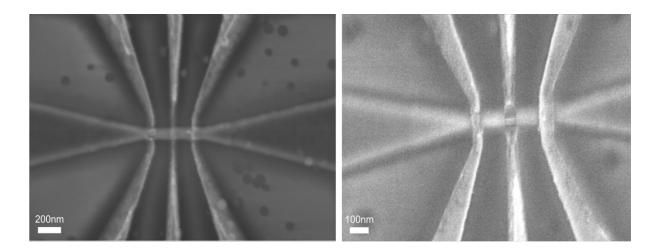

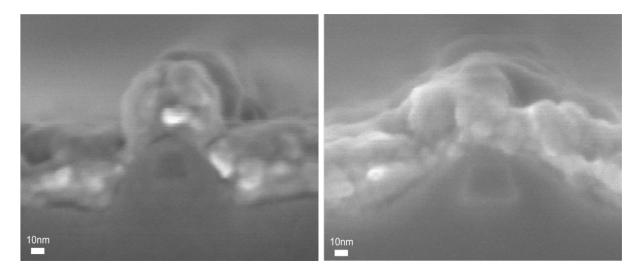

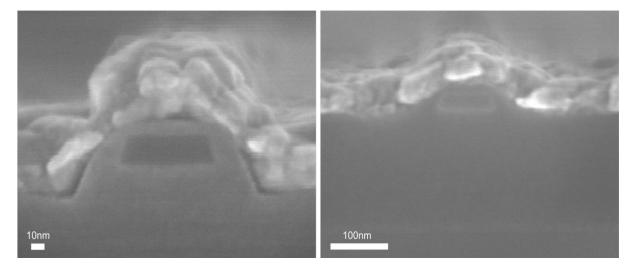

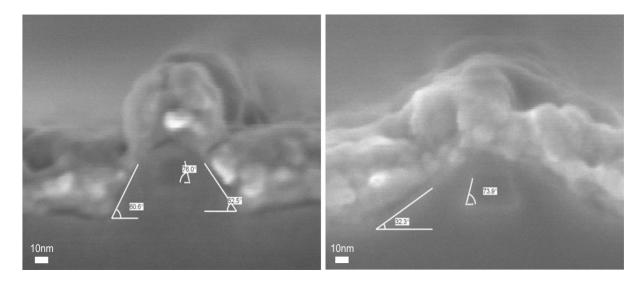

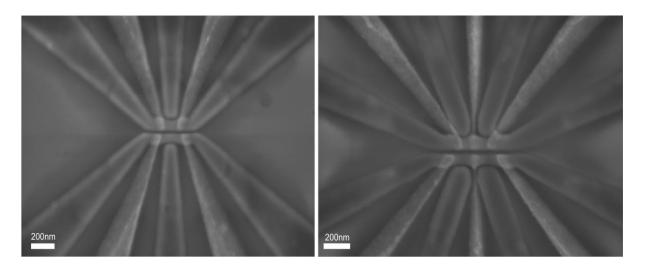

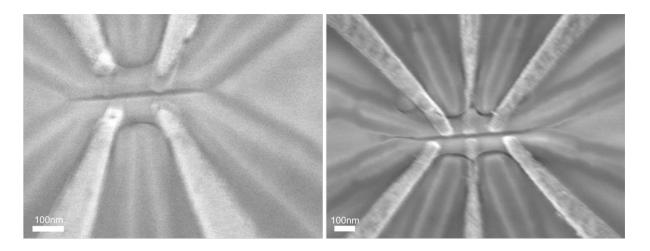

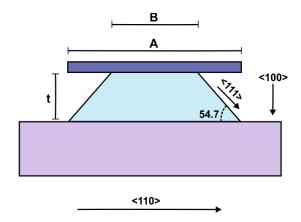

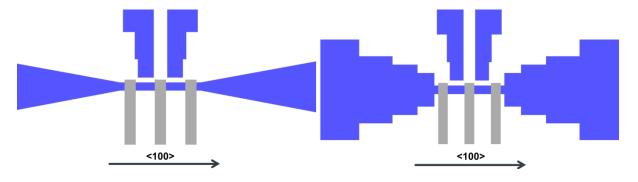

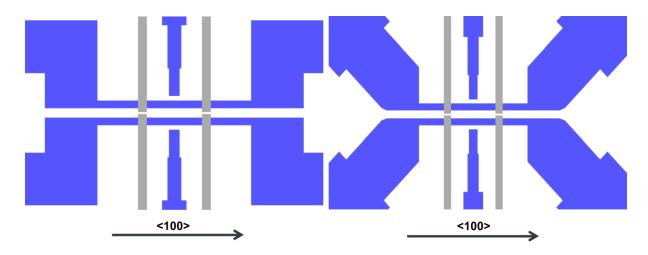

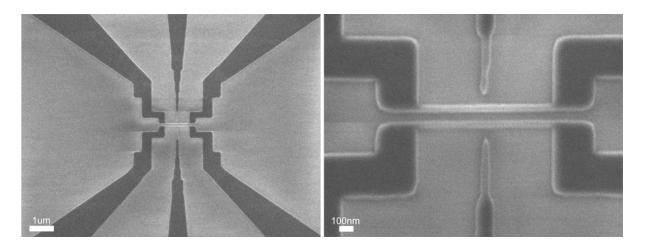

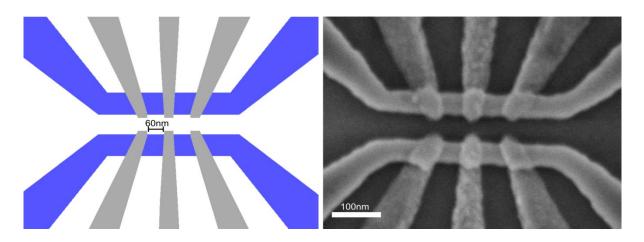

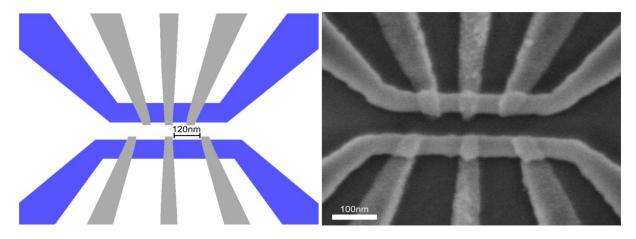

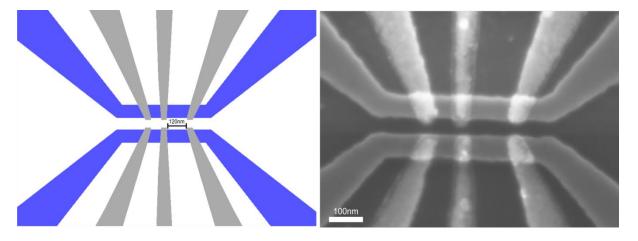

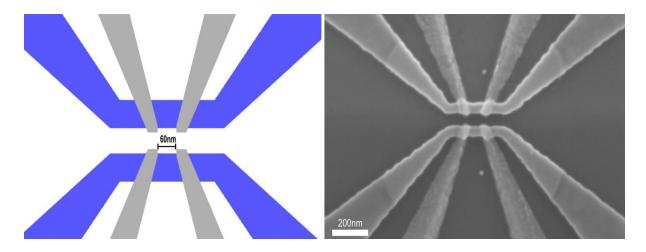

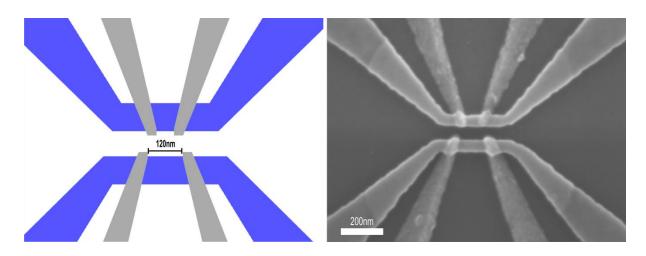

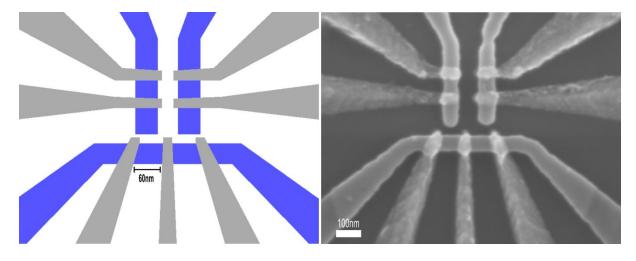

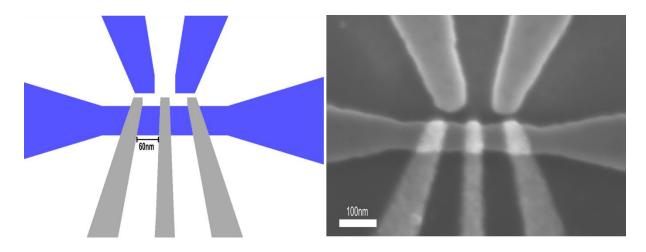

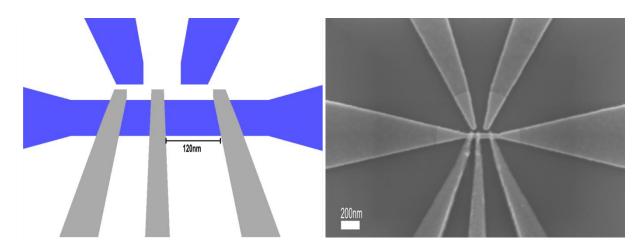

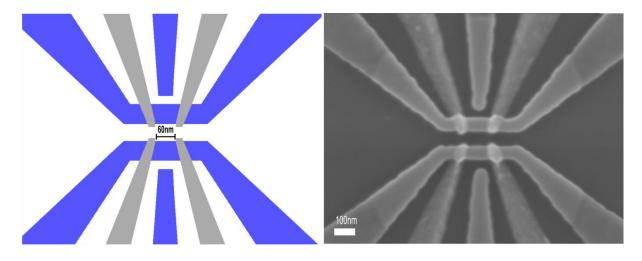

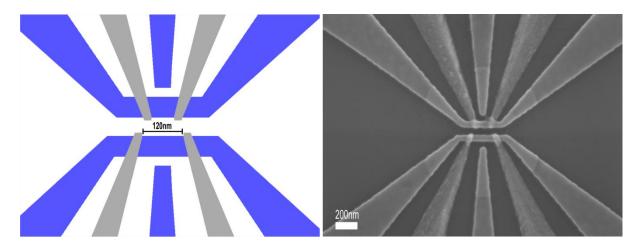

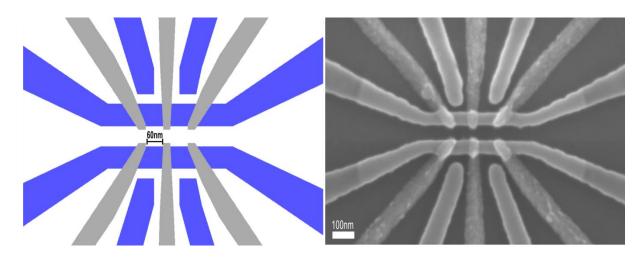

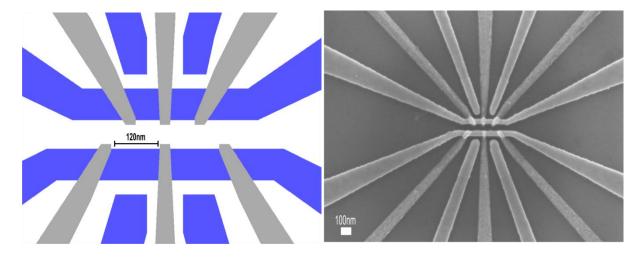

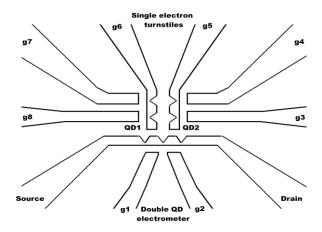

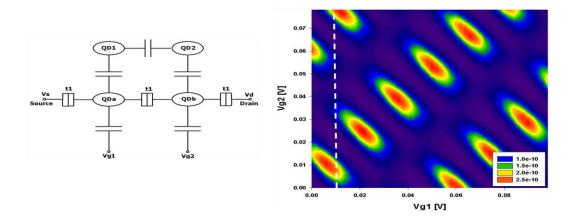

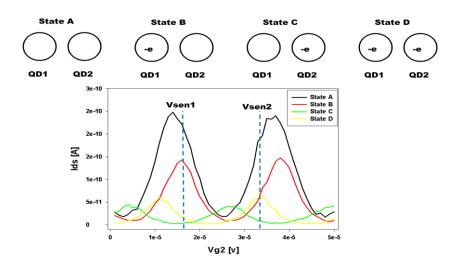

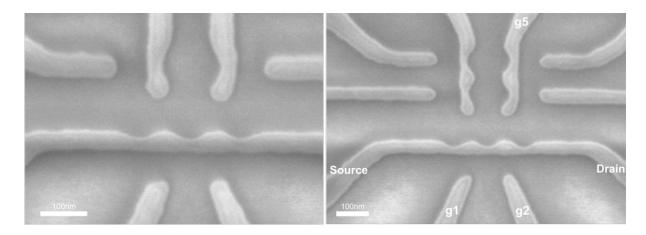

The QD formed by this structure has a size of 30 nm X 50 nm and 50 mK measurements showed that the QD has a charging energy of 6meV. With this high tunability QD structure the authors observed single electron occupancy in the Si QD [53]. In 2011, the same research group from the University of New South Wales integrated the device shown in fig. 3.11 with another identical structure to be used as a charge detector. The spacing between the QD and the island of the SET charge sensor was 120 nm, and they successfully identified single electron QD occupancy using the electrometer [54].