University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

**CMOS COMPATIBLE VERTICAL

SURROUND GATE MOSFETS WITH

REDUCED PARASITICS**

by

Veit Dominik Kunz

A thesis submitted for the degree of

Doctor of Philosophy

FACULTY OF ENGINEERING AND APPLIED SCIENCES

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

April 2003

This thesis is dedicated to my father,

Veit Martin Kunz

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCES

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

CMOS COMPATIBLE VERTICAL SURROUND GATE MOSFETS WITH

REDUCED PARASITICS

by Veit Dominik Kunz

The international technology roadmap for semiconductors predicts that downscaling of the dimensions of electronic devices will continue according to Moore's law for the next 10 to 15 years. However, device scaling is getting more and more complicated due to physical limitations. Novel device architectures are needed to overcome these problems. Vertical transistors could be one potential solution since the channel length is independent from the device layout.

In this thesis, novel concepts to reduce parasitic behaviour in vertical single and surround gate MOSFETs are presented. This includes a novel fillet local oxidation (FILOX) process, optimisations of the pillar, a pillar top insulator and the incorporation of polySiGe into the source of a vertical MOS transistor.

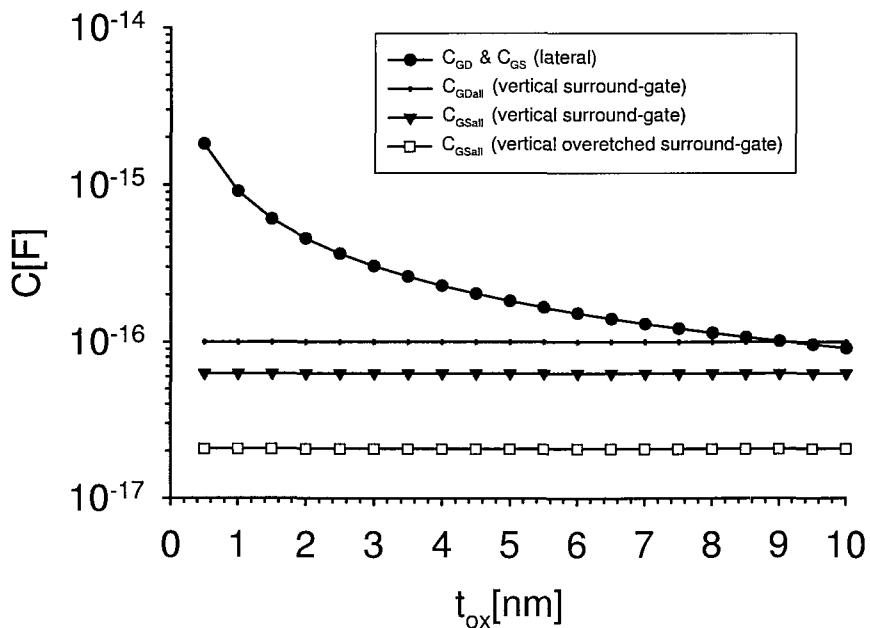

Calculations based on industry layout rules at the 100nm technology node for vertical and lateral devices are presented. For the optimised minimum geometry single gate vertical MOSFET incorporating FILOX with optimised pillar structure, the gate/drain capacitance is 40% and the gate/source overlap capacitance 60% of that of a minimum dimension lateral MOS device. For optimised surround gate transistors the overlap capacitance is 20% and 5% of that of a lateral transistor. These calculations demonstrate the potential of optimised vertical MOS transistors.

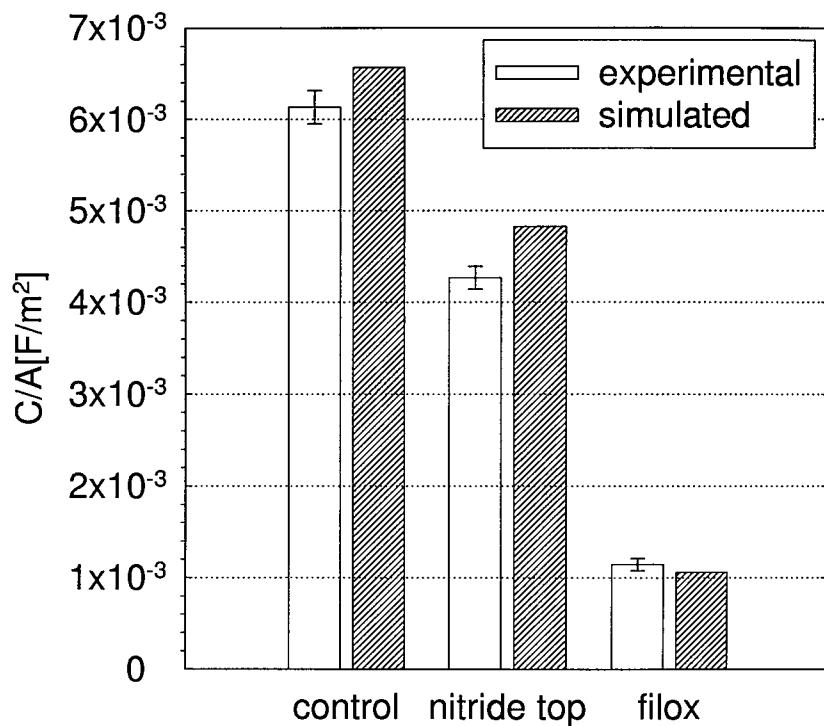

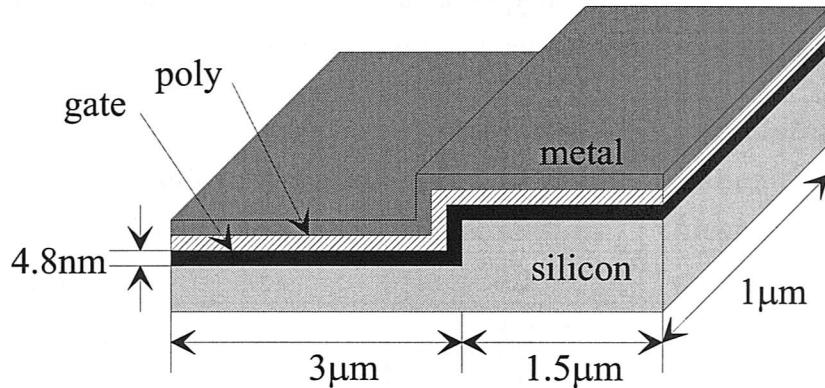

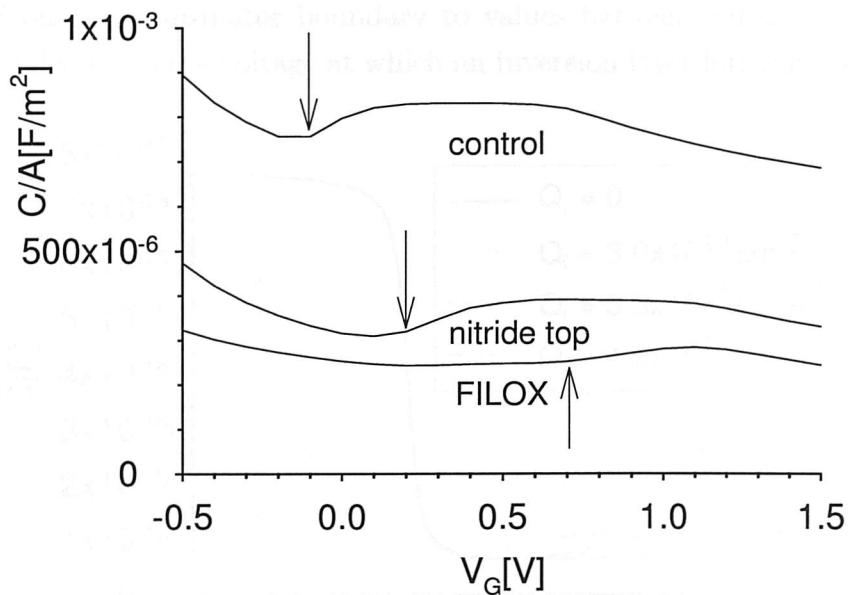

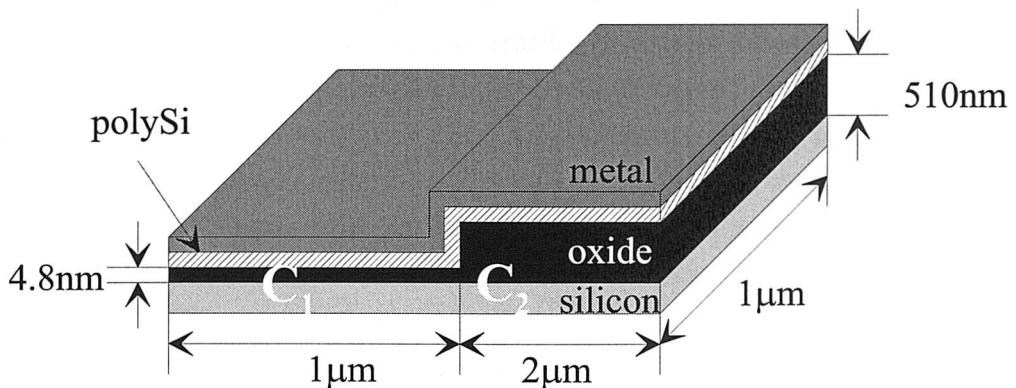

Pillar capacitors incorporating the FILOX process have been fabricated and a reduction in the measured capacitance is obtained by a factor of 1.4 and 5.6 for structures with nitride top and nitride top and FILOX, respectively. Device simulations confirm the measured reduction in capacitance. The extracted oxide thickness on the pillar sidewall is 9.3nm for the fabricated structures, which agrees within a factor of 1.18 with the simulated oxide thickness on the sidewall. Kinks in CV measurements have been investigated and explained by the formation of an inversion layer underneath the field oxide.

A low overlap capacitance, surround gate, vertical MOSFET technology is presented, which uses FILOX to reduce the overlap capacitance between the gate and the drain on the bottom of the pillar. Fabricated n-channel devices show subthreshold slopes of 111 and 123mV/decade for 3nm gate oxide thickness and a channel length of about 105nm for single and surround gate devices, respectively. The devices show good symmetry between the source on top and source on bottom configuration.

To reduce parasitic transistor action in vertical MOS transistors a theory for the base current of a polySiGe emitter (source) is developed, which combines the effects of the polySiGe grains, the grain boundaries and the interfacial layer at the

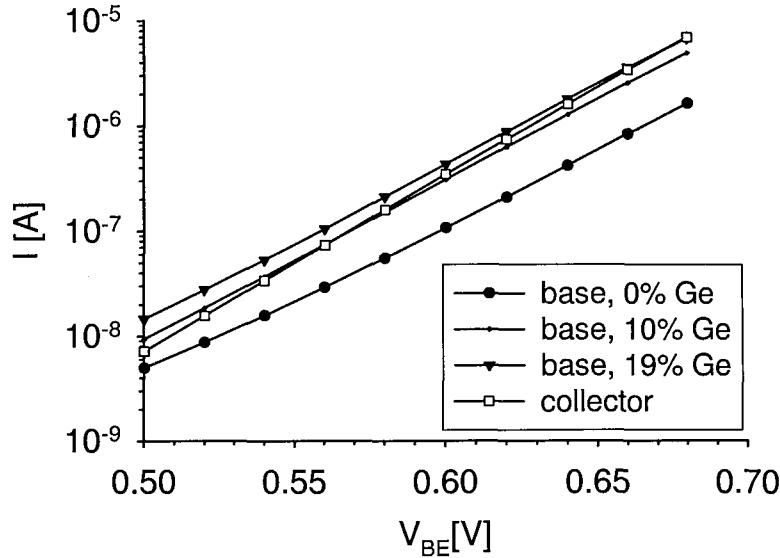

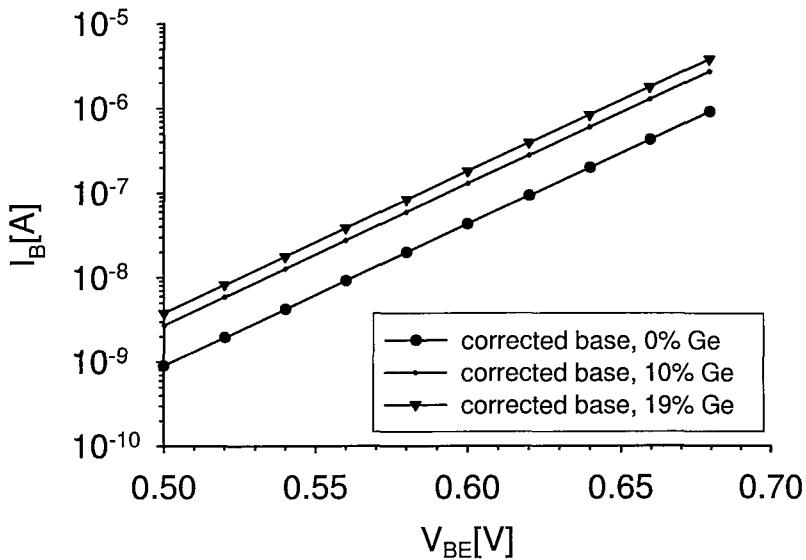

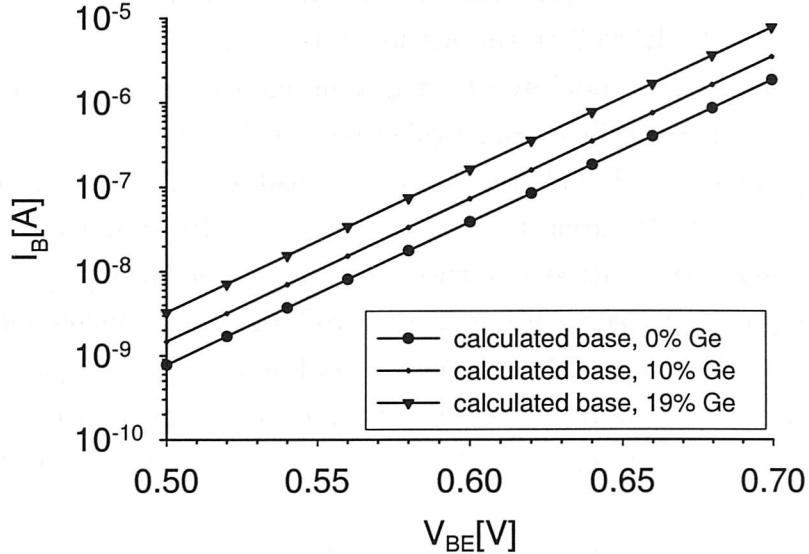

polySiGe/Si interface into an expression for the effective surface recombination velocity of a polySiGe emitter (source). Silicon bipolar transistors have been fabricated with 0, 10 and 19% Ge in the polySiGe emitter and the variation of base current with Ge content is characterised. The measured base current for a polySiGe emitter increases by a factor of 3.2 for 10% Ge and 4.0 for 19% Ge compared with a control transistor containing no germanium. These values are in good agreement with the theoretical predictions. The competing mechanisms of base current increase by Ge incorporation into the polysilicon and base current decrease due to an interfacial oxide layer are investigated.

# Contents

|                                                                                                         |            |

|---------------------------------------------------------------------------------------------------------|------------|

| <b>Abstract</b>                                                                                         | <b>i</b>   |

| <b>Contents</b>                                                                                         | <b>iii</b> |

| <b>List of figures</b>                                                                                  | <b>vi</b>  |

| <b>List of tables</b>                                                                                   | <b>ix</b>  |

| <b>List of symbols</b>                                                                                  | <b>xi</b>  |

| <b>Acknowledgements</b>                                                                                 | <b>xv</b>  |

| <b>1 Introduction</b>                                                                                   | <b>1</b>   |

| <b>2 Theory of MOSFETs</b>                                                                              | <b>6</b>   |

| 2.1 Two-terminal MOS structure . . . . .                                                                | 6          |

| 2.1.1 Work Function Difference . . . . .                                                                | 10         |

| 2.1.2 Oxide Interface Traps . . . . .                                                                   | 11         |

| 2.1.3 Small-signal capacitance . . . . .                                                                | 12         |

| 2.2 Four-terminal MOS structure . . . . .                                                               | 13         |

| 2.2.1 Linear operation . . . . .                                                                        | 13         |

| 2.2.2 Saturation operation . . . . .                                                                    | 15         |

| 2.2.3 Body bias effect . . . . .                                                                        | 16         |

| 2.2.4 Detailed MOSFET analysis . . . . .                                                                | 17         |

| 2.2.5 Subthreshold region . . . . .                                                                     | 18         |

| 2.2.6 Short channel and narrow-width effects . . . . .                                                  | 19         |

| 2.2.7 Parasitic bipolar effects . . . . .                                                               | 24         |

| <b>3 Parasitic capacitances in vertical MOSFETs</b>                                                     | <b>26</b>  |

| 3.1 Introduction . . . . .                                                                              | 26         |

| 3.2 Assumptions . . . . .                                                                               | 26         |

| 3.2.1 Technological considerations . . . . .                                                            | 26         |

| 3.2.2 Layout considerations . . . . .                                                                   | 28         |

| 3.3 Overlap capacitances of lateral and single gate vertical MOSFETs . . . . .                          | 31         |

| 3.3.1 Calculation of overlap capacitances for lateral- and basic single gate vertical devices . . . . . | 33         |

| 3.3.2 Optimisation of pillar fabrication . . . . .                                                      | 34         |

| 3.3.3 Optimisation of $C_{GS}$ : pillar top insulator . . . . .                                         | 34         |

| 3.3.4 Optimisation of $C_{GD}$ : FILOX . . . . .                                                        | 35         |

|       |                                                                                |     |

|-------|--------------------------------------------------------------------------------|-----|

| 3.3.5 | Calculation of overlap capacitances for optimised single gate vertical devices | 37  |

| 3.4   | Overlap capacitances of optimised surround gate vertical MOSFETs               | 38  |

| 3.4.1 | Overetching the surround gate                                                  | 41  |

| 3.4.2 | Alternative gate process sequence                                              | 42  |

| 3.5   | Junction capacitance in lateral and vertical MOSFETs                           | 45  |

| 3.6   | Dielectric pocket vertical MOSFET                                              | 48  |

| 3.6.1 | Overlap capacitance of dielectric pocket vertical MOSFET                       | 48  |

| 3.6.2 | Junction capacitance of dielectric pocket vertical MOSFET                      | 49  |

| 3.7   | Summary                                                                        | 49  |

| 4     | <b>Simulation of the fillet local oxidation (FILOX) process</b>                | 52  |

| 4.1   | Introduction                                                                   | 52  |

| 4.2   | Fabrication of the calibration structure                                       | 52  |

| 4.3   | Simulation models                                                              | 54  |

| 4.4   | Calibration of the simulator                                                   | 55  |

| 4.5   | FILOX simulation results                                                       | 59  |

| 4.6   | FILOX with nitride top insulator                                               | 65  |

| 4.7   | Summary                                                                        | 69  |

| 5     | <b>CV-characteristics of FILOX vertical capacitors</b>                         | 70  |

| 5.1   | Introduction                                                                   | 70  |

| 5.2   | Experimental procedure                                                         | 70  |

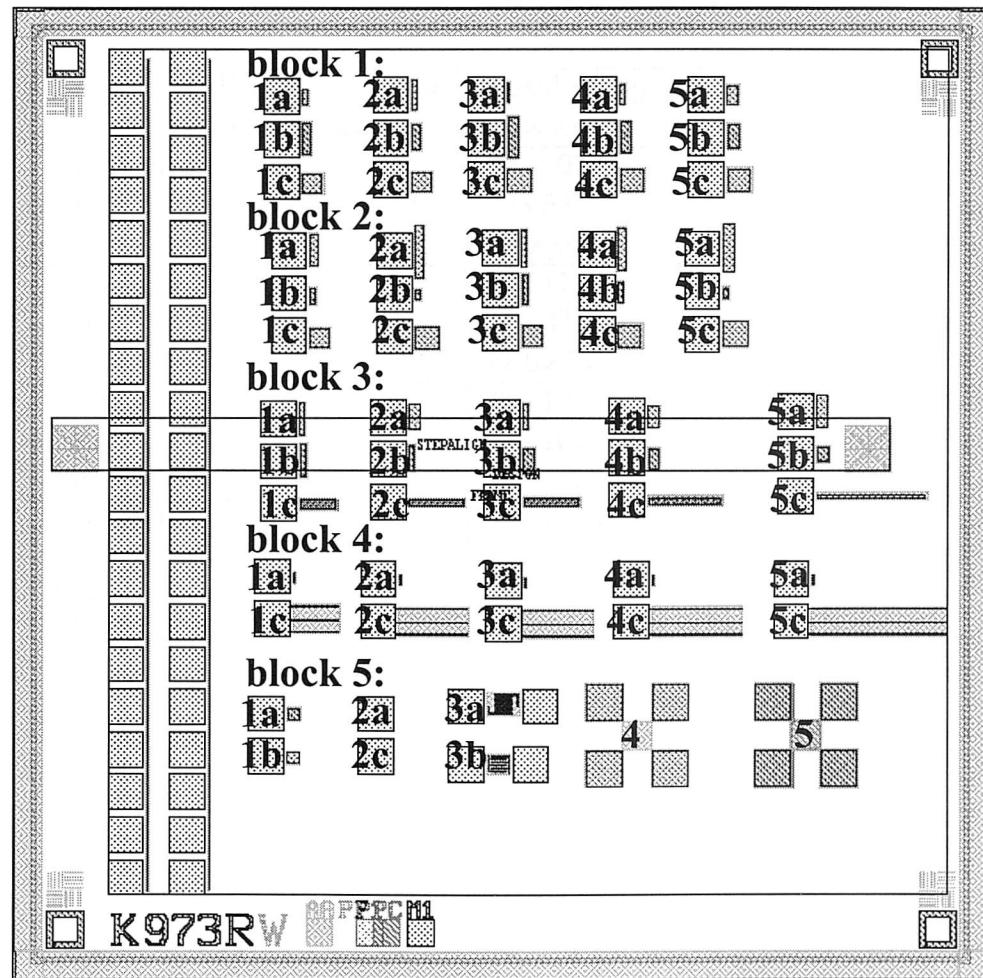

| 5.2.1 | Mask layout                                                                    | 73  |

| 5.2.2 | Electrical characterisation                                                    | 75  |

| 5.2.3 | Calibration of the simulator                                                   | 75  |

| 5.3   | Measured CV characteristics                                                    | 75  |

| 5.4   | Simulated CV characteristics                                                   | 76  |

| 5.5   | Discussion                                                                     | 79  |

| 5.5.1 | Extraction of oxide thickness on the pillar sidewall                           | 79  |

| 5.5.2 | Behaviour in inversion                                                         | 80  |

| 5.6   | Summary                                                                        | 86  |

| 6     | <b>DC-characteristics of FILOX vertical MOSFETs</b>                            | 88  |

| 6.1   | Introduction                                                                   | 88  |

| 6.2   | Concept                                                                        | 88  |

| 6.3   | Experimental procedure                                                         | 89  |

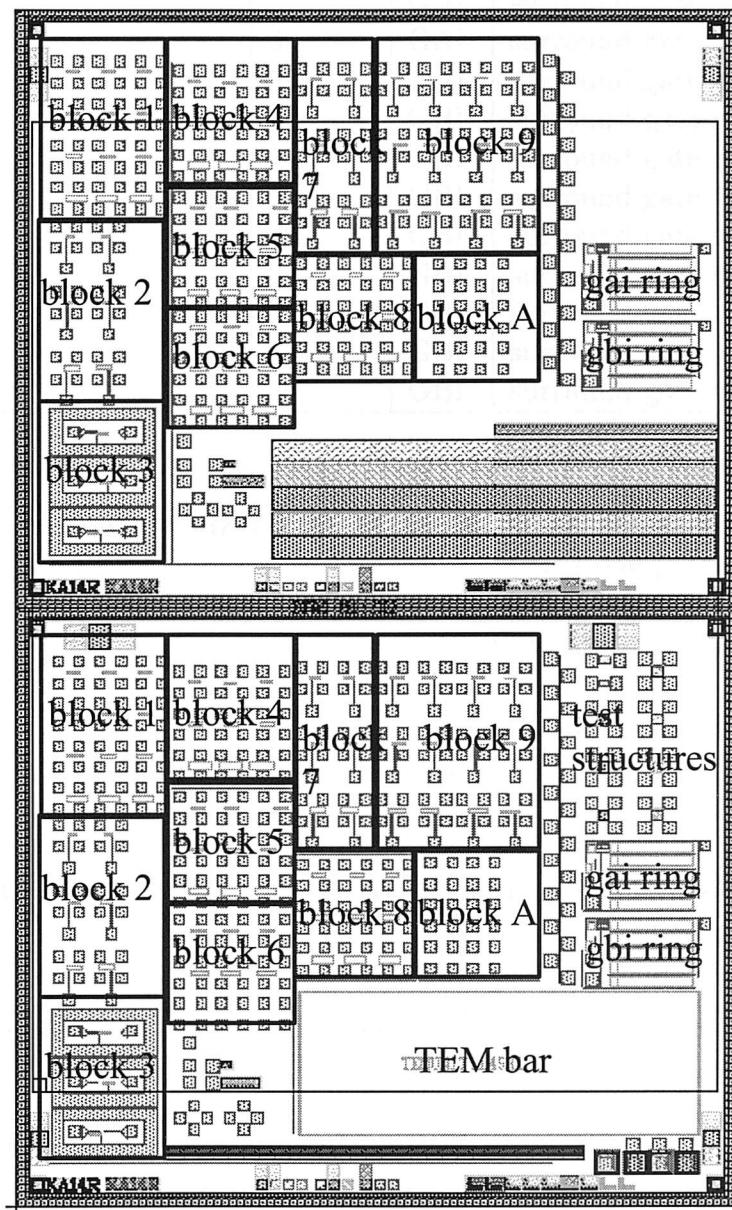

| 6.4   | Mask layout                                                                    | 92  |

| 6.5   | Results on GAI devices                                                         | 94  |

| 6.5.1 | SEM cross-sections                                                             | 94  |

| 6.5.2 | Single gate transistors                                                        | 99  |

| 6.5.3 | Surround gate transistors                                                      | 100 |

| 6.5.4 | Reproducibility of single and surround gate MOS transistors                    | 101 |

| 6.5.5 | Process/device simulations of a single gate transistors                        | 101 |

| 6.6   | Results on GBI devices                                                         | 104 |

| 6.7   | Logic gates                                                                    | 107 |

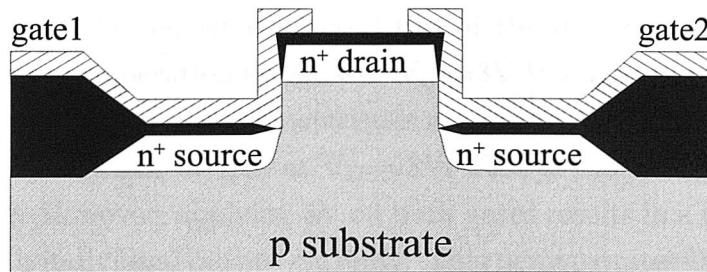

| 6.7.1 | Concept of a vertical NOR gate                                                 | 107 |

| 6.7.2 | Results                                                                        | 108 |

---

|                   |                                                                         |            |

|-------------------|-------------------------------------------------------------------------|------------|

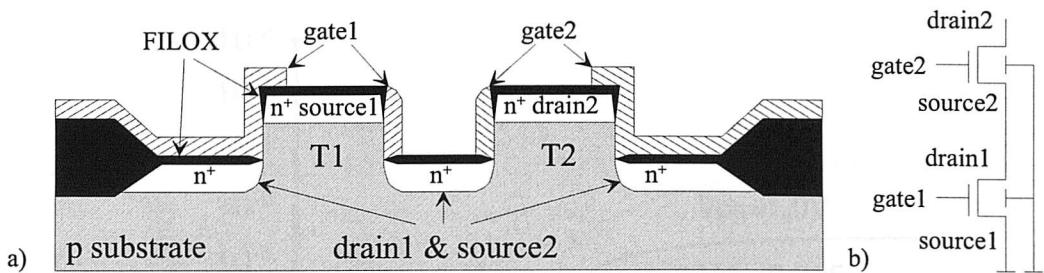

| 6.7.3             | Concept of a NAND gate based on two pillars . . . . .                   | 110        |

| 6.7.4             | Results . . . . .                                                       | 111        |

| 6.8               | Summary . . . . .                                                       | 112        |

| <b>7</b>          | <b>Reducing parasitic bipolar transistor action in vertical MOSFETs</b> | <b>114</b> |

| 7.1               | Introduction . . . . .                                                  | 114        |

| 7.2               | Theory . . . . .                                                        | 115        |

| 7.3               | Experimental Procedure . . . . .                                        | 122        |

| 7.4               | Results . . . . .                                                       | 123        |

| 7.5               | Discussion . . . . .                                                    | 125        |

| 7.6               | Vertical MOSFET with polySiGe source . . . . .                          | 128        |

| 7.7               | PolySiGe emitter for gain control in SiGe HBTs . . . . .                | 129        |

| 7.8               | Summary . . . . .                                                       | 130        |

| <b>8</b>          | <b>Conclusions</b>                                                      | <b>131</b> |

| <b>9</b>          | <b>Suggestions for future work</b>                                      | <b>133</b> |

| <b>A</b>          | <b>Simulation script files</b>                                          | <b>135</b> |

| A.1               | FILOX device simulations . . . . .                                      | 135        |

| A.1.1             | Extraction of stress . . . . .                                          | 141        |

| A.2               | FILOX device simulations with top insulator . . . . .                   | 142        |

| A.3               | CV device/process simulations - calibration . . . . .                   | 149        |

| A.4               | CV device/process simulations - control . . . . .                       | 151        |

| A.5               | CV device/process simulations - nitride top . . . . .                   | 153        |

| A.6               | CV device/process simulations - FILOX . . . . .                         | 155        |

| A.7               | Nitride and pad oxide etch for bird's beak extraction . . . . .         | 158        |

| A.8               | Vertical MOSFET device/process simulations . . . . .                    | 159        |

| <b>B</b>          | <b>Mask description</b>                                                 | <b>164</b> |

| B.1               | Vertical capacitors . . . . .                                           | 164        |

| B.2               | Vertical MOSFETs . . . . .                                              | 167        |

| <b>C</b>          | <b>Batch listings</b>                                                   | <b>171</b> |

| C.1               | Batch listing for FILOX test batch . . . . .                            | 171        |

| C.2               | Batch listing for vertical capacitors . . . . .                         | 173        |

| C.3               | Batch listing for vertical MOSFETs . . . . .                            | 175        |

| <b>D</b>          | <b>Publications</b>                                                     | <b>179</b> |

| D.1               | Conference papers . . . . .                                             | 179        |

| D.2               | Journal papers . . . . .                                                | 180        |

| <b>References</b> |                                                                         | <b>181</b> |

# List of Figures

|      |                                                                         |    |

|------|-------------------------------------------------------------------------|----|

| 1.1  | Vertical MOSFET based on epitaxy . . . . .                              | 2  |

| 1.2  | Vertical MOSFET based on selective epitaxy . . . . .                    | 3  |

| 1.3  | Vertical replacement-gate MOSFET . . . . .                              | 3  |

| 1.4  | Vertical MOSFET based on ion implantation . . . . .                     | 4  |

| 2.1  | Band diagram of a two-terminal MOS structure . . . . .                  | 6  |

| 2.2  | One-dimensional MOS structure . . . . .                                 | 8  |

| 2.3  | Energy band diagram showing the onset of strong inversion . . . . .     | 8  |

| 2.4  | Energy band diagram showing flat band condition and zero bias . . . . . | 10 |

| 2.5  | Oxide traps in the gate oxide . . . . .                                 | 11 |

| 2.6  | Capacitance of a two-terminal MOS structure . . . . .                   | 13 |

| 2.7  | Four terminal MOSFET structure . . . . .                                | 14 |

| 2.8  | Idealised output characteristic . . . . .                               | 16 |

| 2.9  | Idealised subthreshold characteristic . . . . .                         | 19 |

| 2.10 | Schematic diagram of a charge sharing model . . . . .                   | 20 |

| 2.11 | Channel under pinch-off condition . . . . .                             | 22 |

| 2.12 | Output characteristic of a MOSFET with channel length modulation        | 22 |

| 2.13 | Narrow width effect of lateral MOSFETs . . . . .                        | 23 |

| 2.14 | Parasitic bipolar transistor action . . . . .                           | 24 |

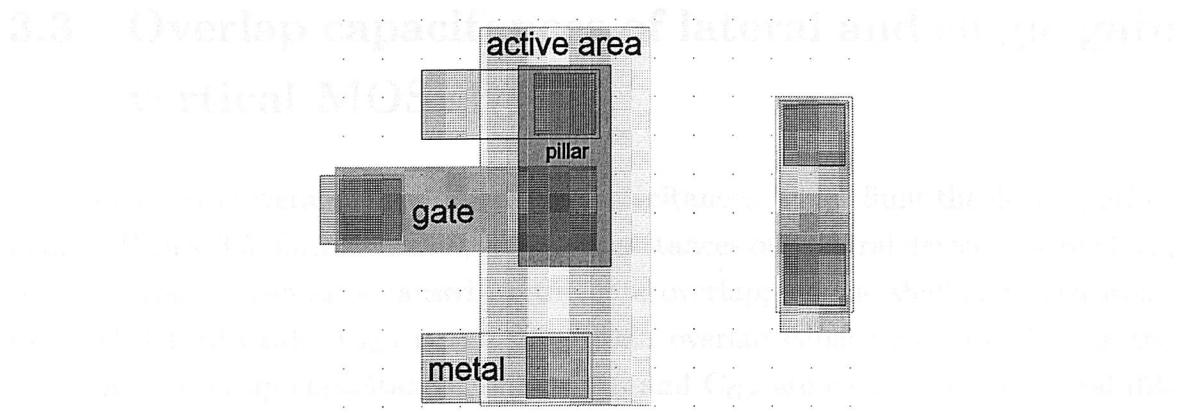

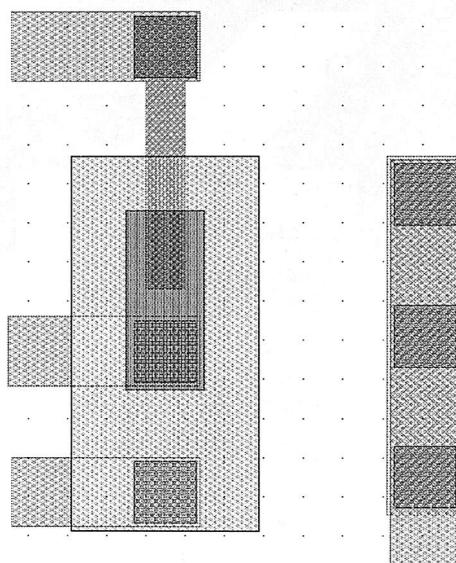

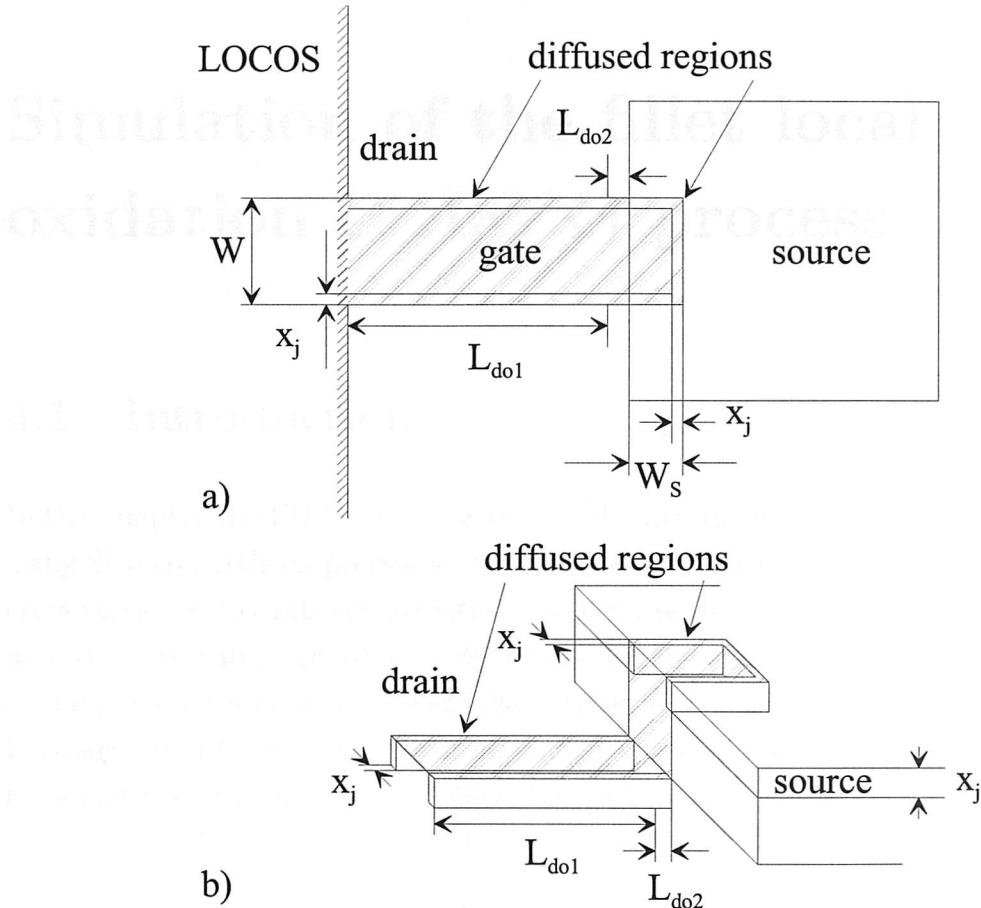

| 3.1  | Lateral MOSFET layout ( $W=220\text{nm}$ ) . . . . .                    | 29 |

| 3.2  | Lateral MOSFET layout ( $W=1.32\mu\text{m}$ ) . . . . .                 | 29 |

| 3.3  | Vertical MOSFET layout ( $W=220\text{nm}$ ) . . . . .                   | 30 |

| 3.4  | Vertical MOSFET layout ( $W=1.32\mu\text{m}$ ) . . . . .                | 30 |

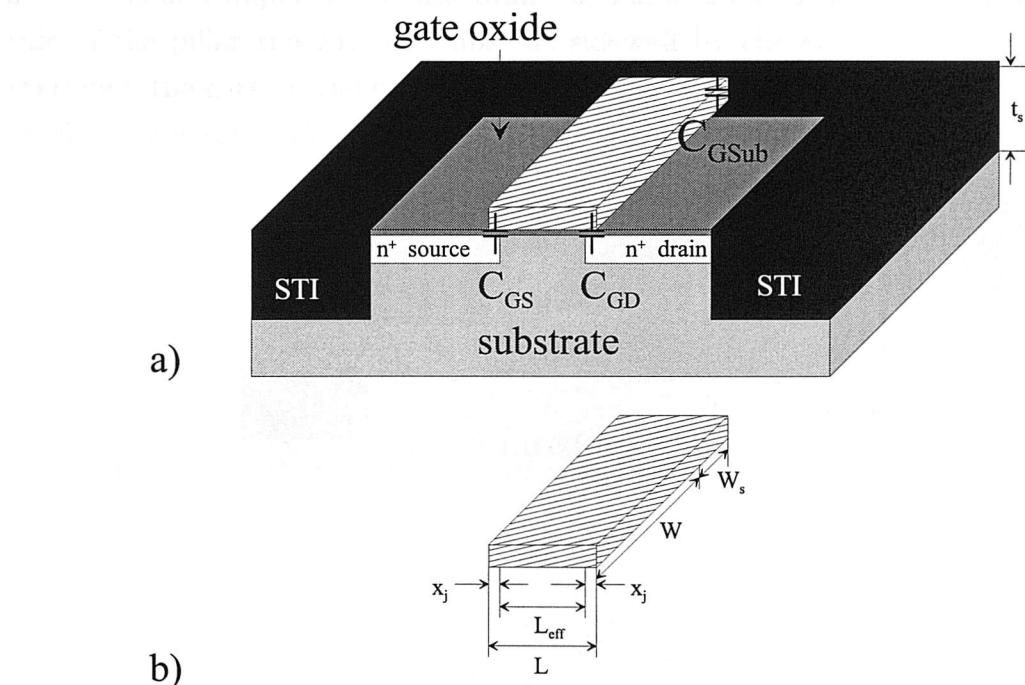

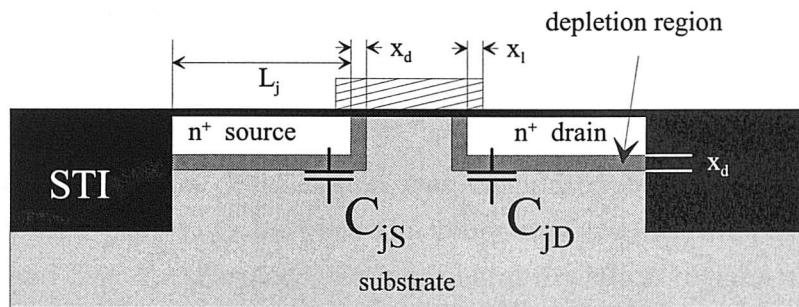

| 3.5  | Parasitic capacitances of a lateral MOSFET . . . . .                    | 31 |

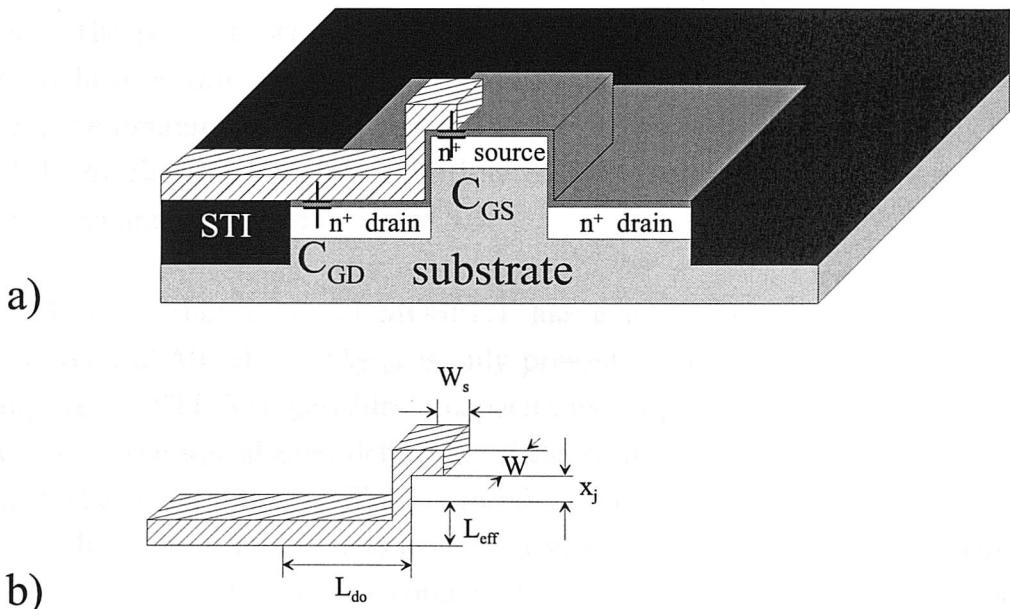

| 3.6  | Parasitic capacitances of a basic vertical MOSFET . . . . .             | 32 |

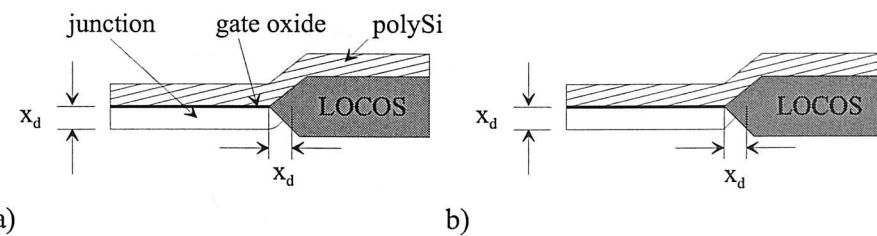

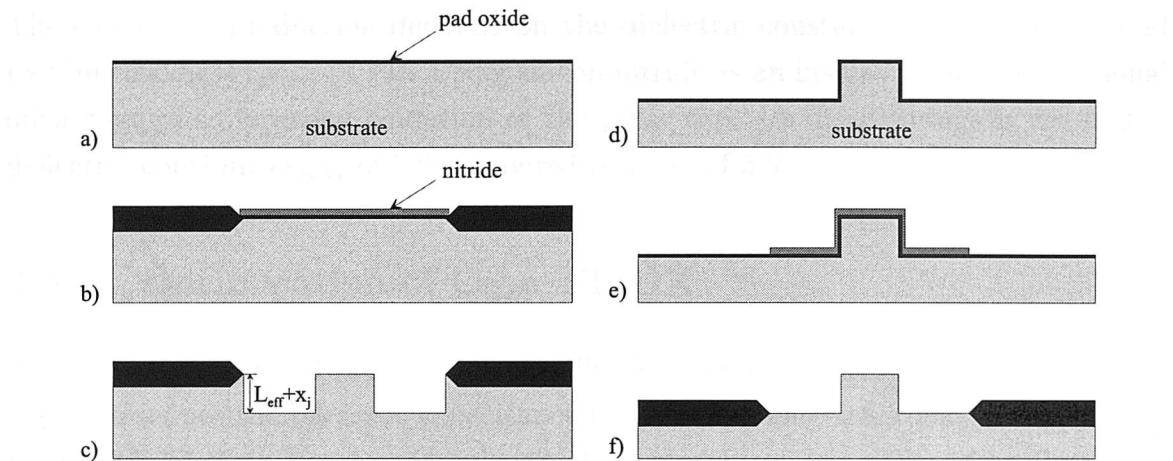

| 3.7  | Process sequences of two ways to define the pillar structure . . . . .  | 34 |

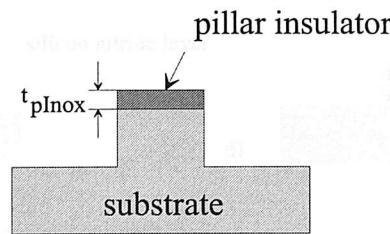

| 3.8  | Insulator on top of the pillar . . . . .                                | 35 |

| 3.9  | FILOX process flow . . . . .                                            | 36 |

| 3.10 | Bird's beak dimensions caused by FILOX process . . . . .                | 36 |

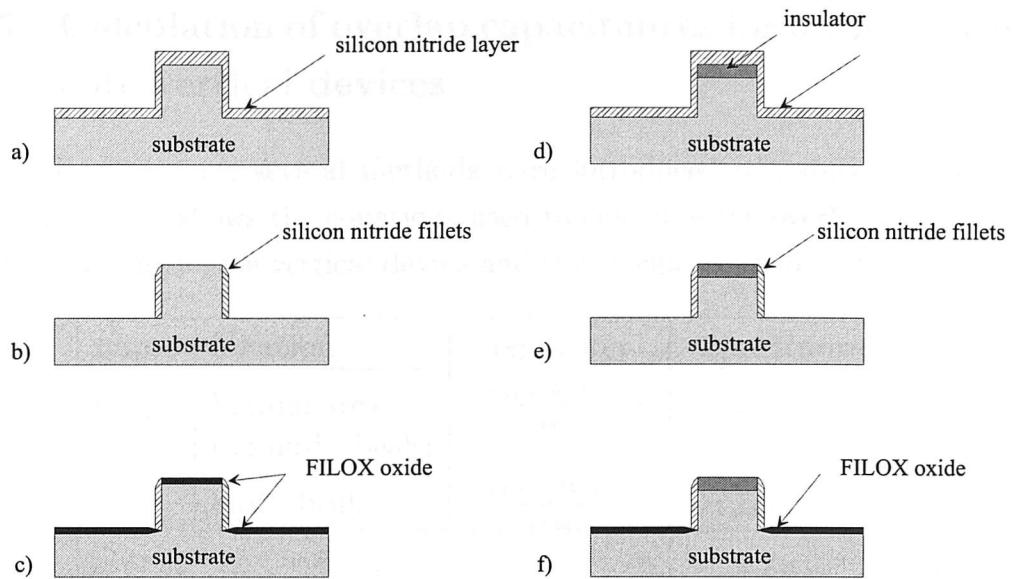

| 3.11 | Cross-section showing polysilicon fillets . . . . .                     | 39 |

| 3.12 | Top-view of a vertical MOSFET . . . . .                                 | 39 |

| 3.13 | Cross-section showing overetched polysilicon fillets . . . . .          | 41 |

| 3.14 | Gate/source and gate/drain overlap capacitances . . . . .               | 42 |

| 3.15 | GBI MOSFET . . . . .                                                    | 43 |

| 3.16 | Lateral MOSFET with junction and depletion regions . . . . .            | 45 |

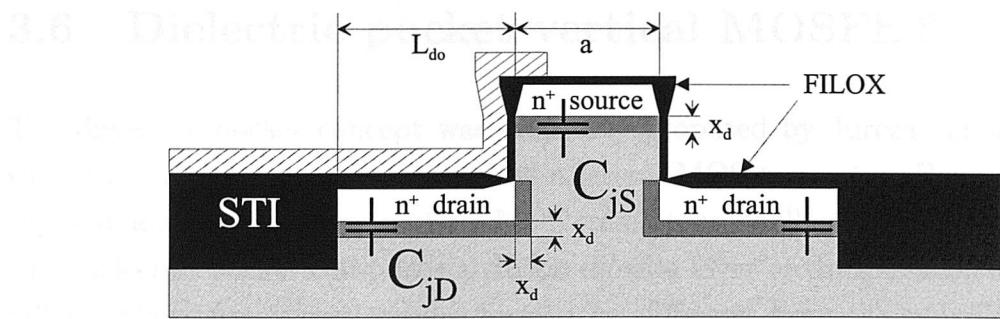

| 3.17 | Optimised vertical single gate MOSFET . . . . .                         | 47 |

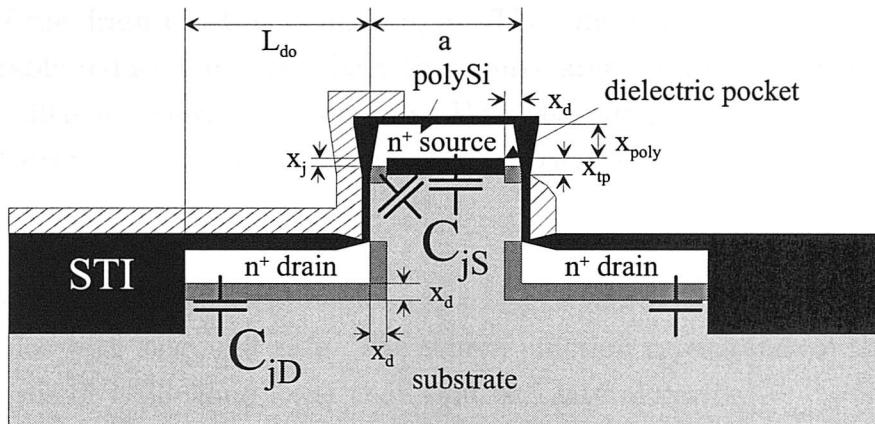

| 3.18 | Dielectric pocket vertical MOSFET . . . . .                             | 48 |

|      |                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

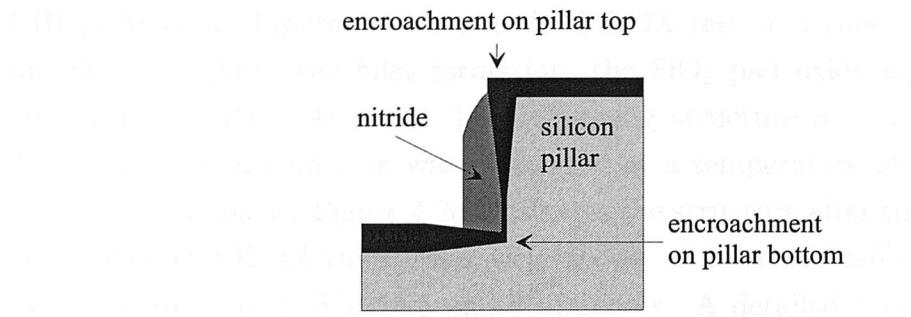

| 4.1  | Nitride encroachment due to FILOX oxidation . . . . .                                                                 | 53 |

| 4.2  | Process flow of the FILOX test structures . . . . .                                                                   | 54 |

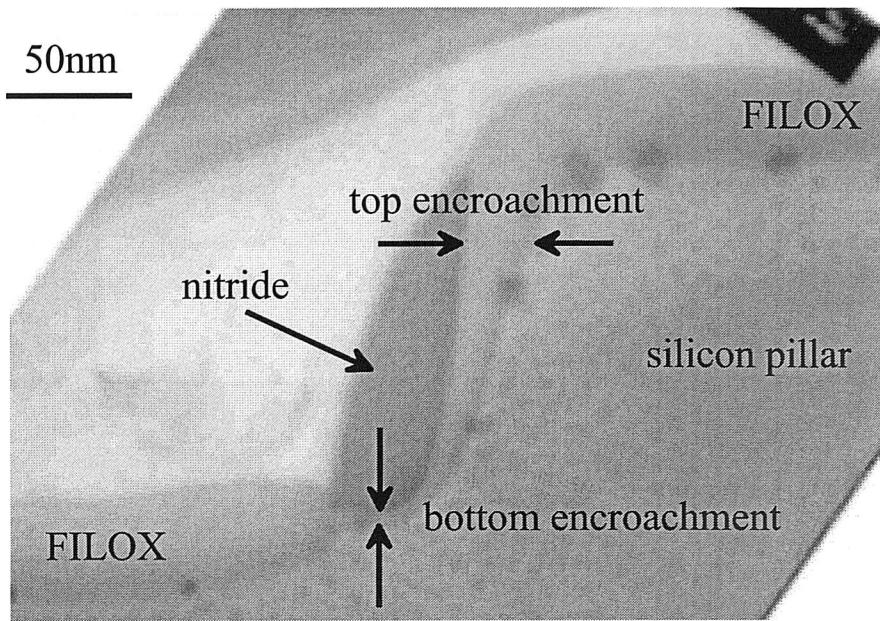

| 4.3  | TEM cross-section of a FILOX test-structure . . . . .                                                                 | 56 |

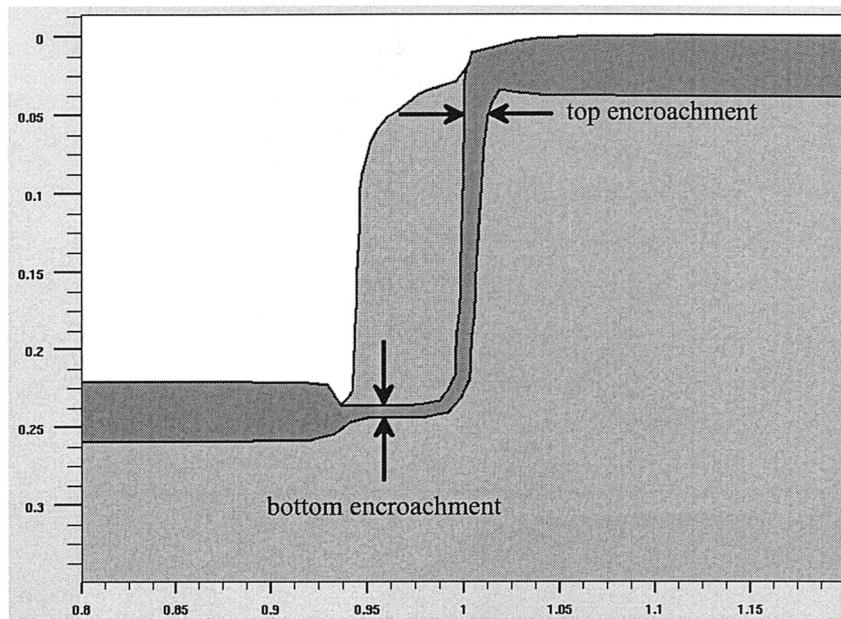

| 4.4  | FILOX simulation using the default parameter . . . . .                                                                | 57 |

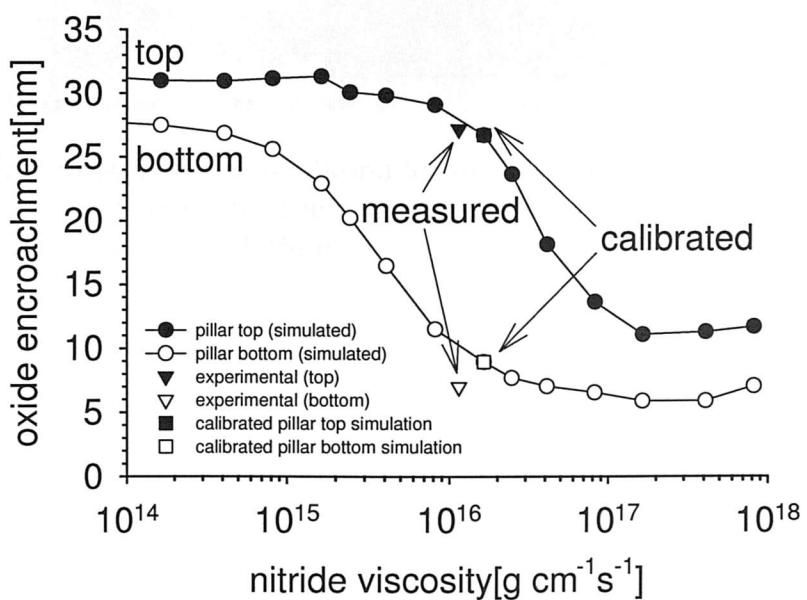

| 4.5  | Encroachment on the pillar top and pillar bottom . . . . .                                                            | 57 |

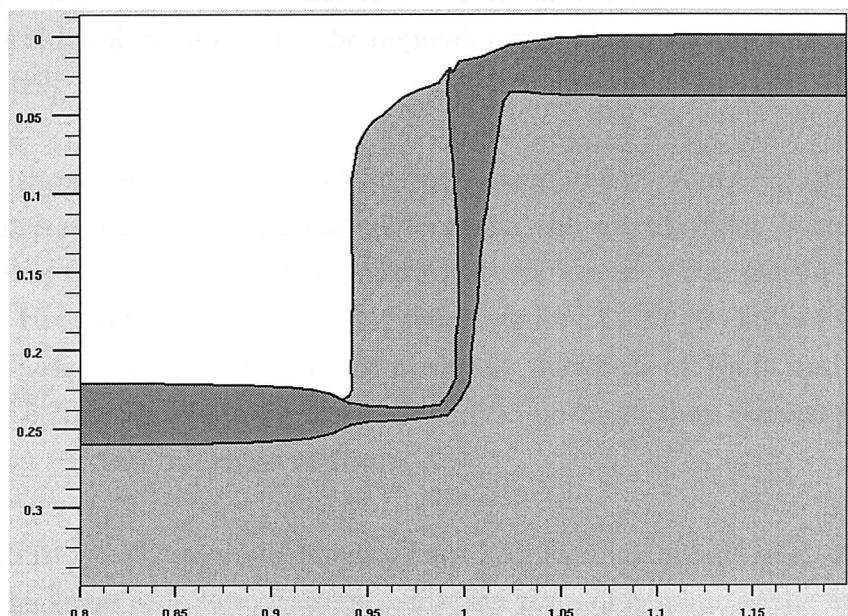

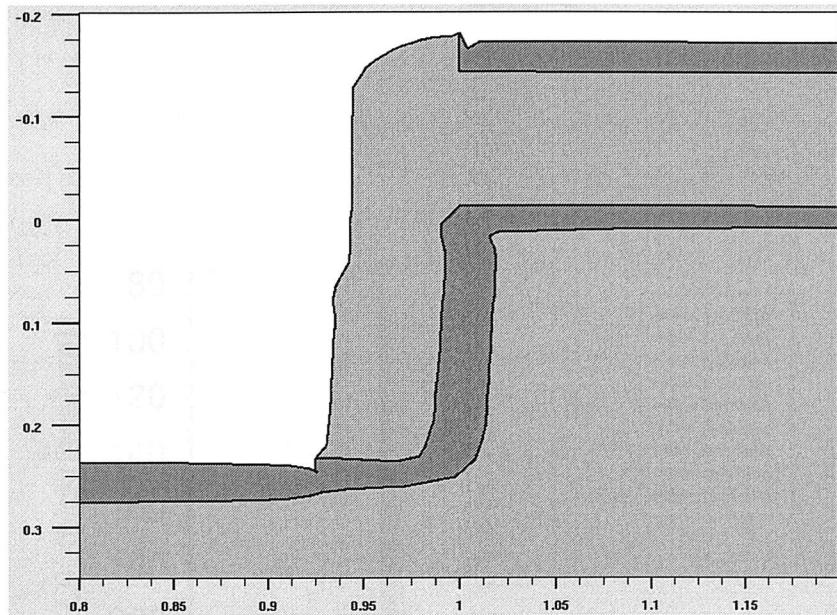

| 4.6  | Calibrated FILOX simulation . . . . .                                                                                 | 58 |

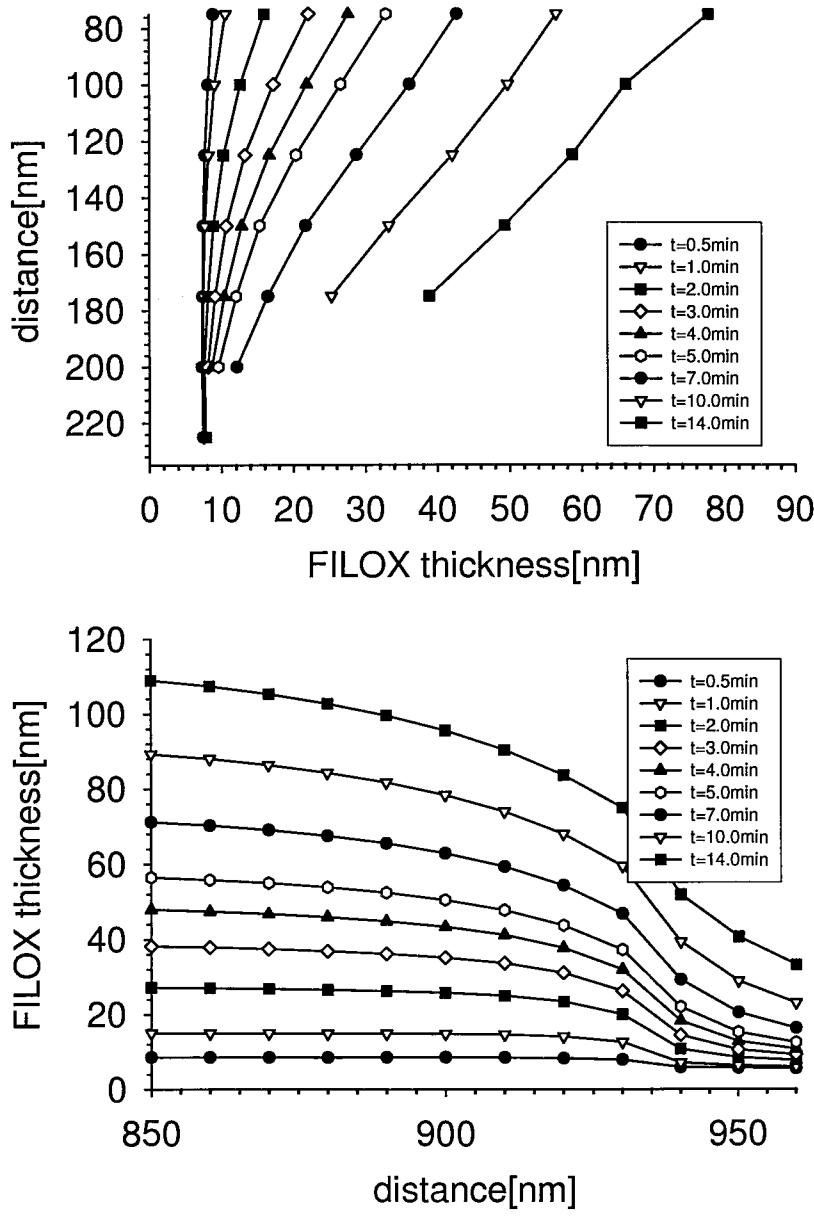

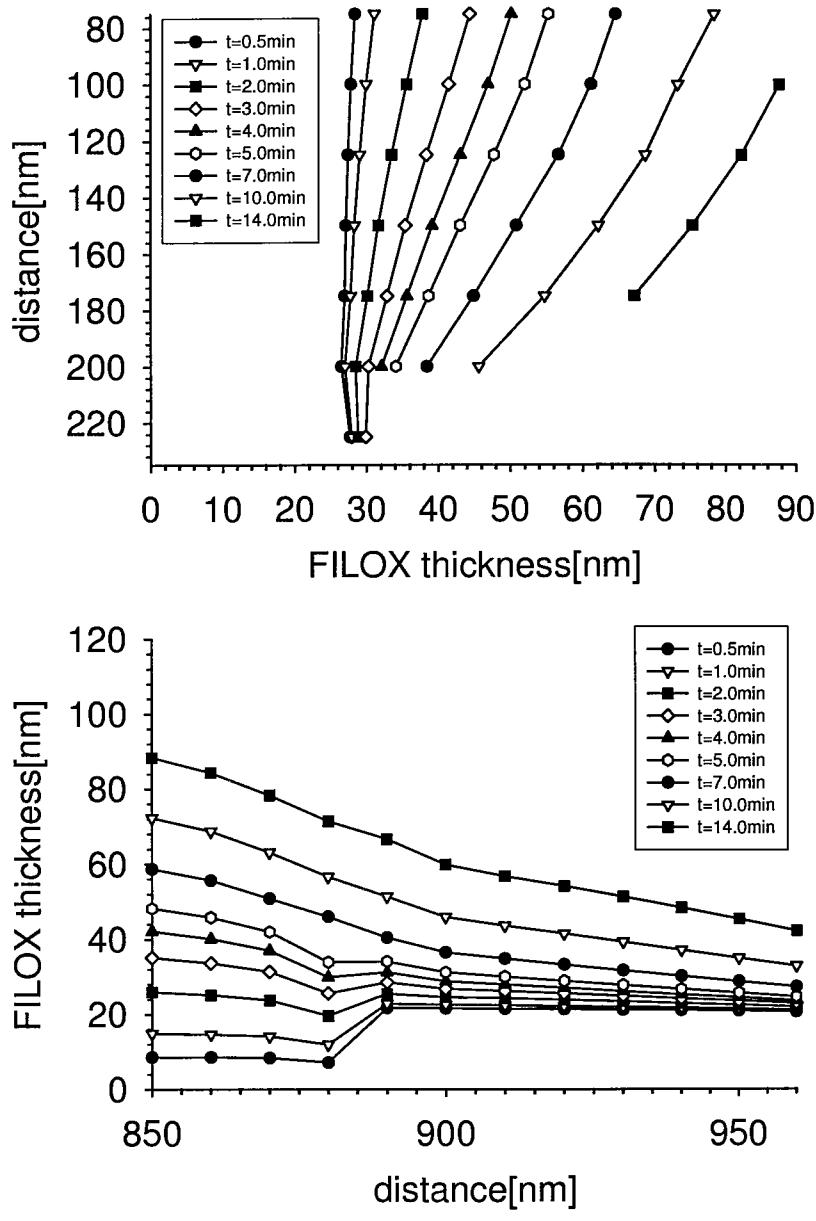

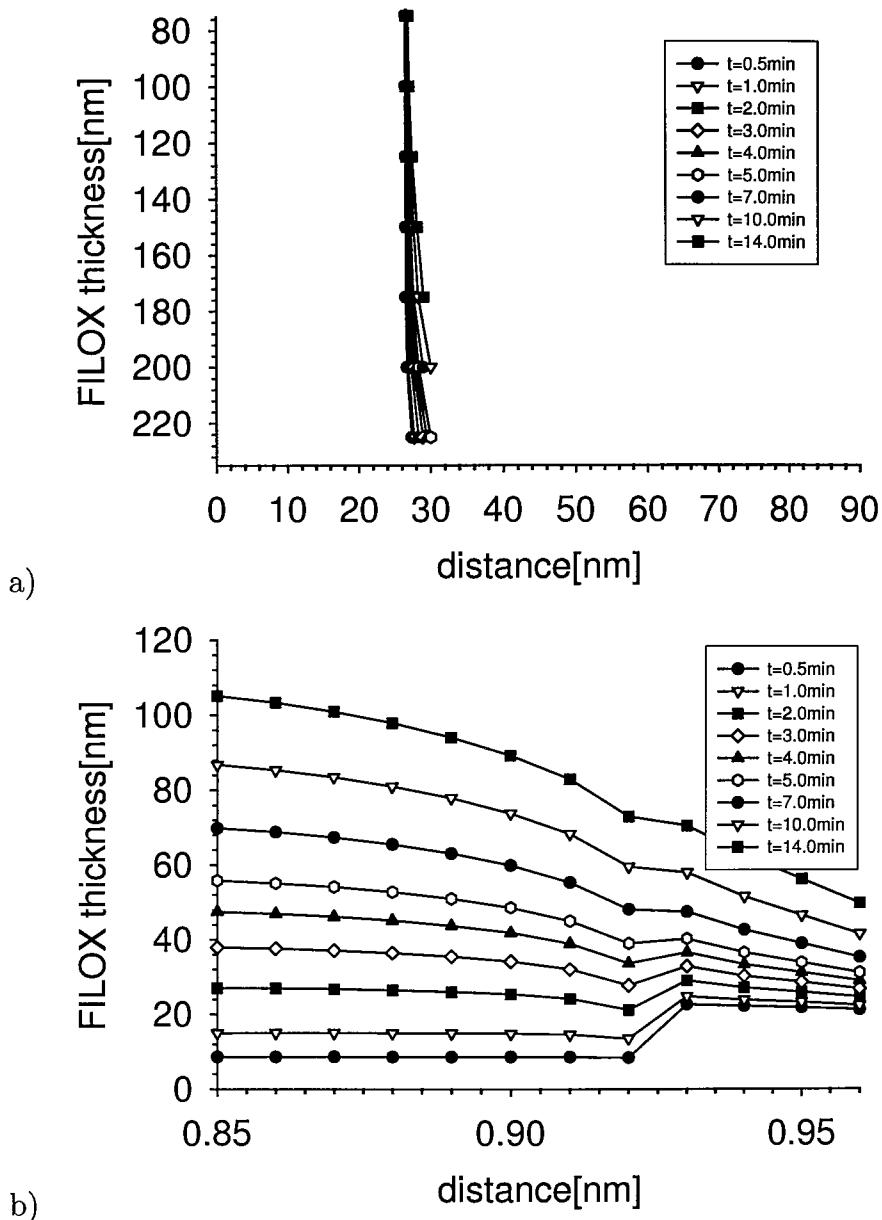

| 4.7  | FILOX thickness as a function of distance for a 5.3nm pad oxide and 70nm nitride thickness . . . . .                  | 60 |

| 4.8  | FILOX thickness as a function of distance for a 5.3nm pad oxide and 130nm nitride thickness . . . . .                 | 61 |

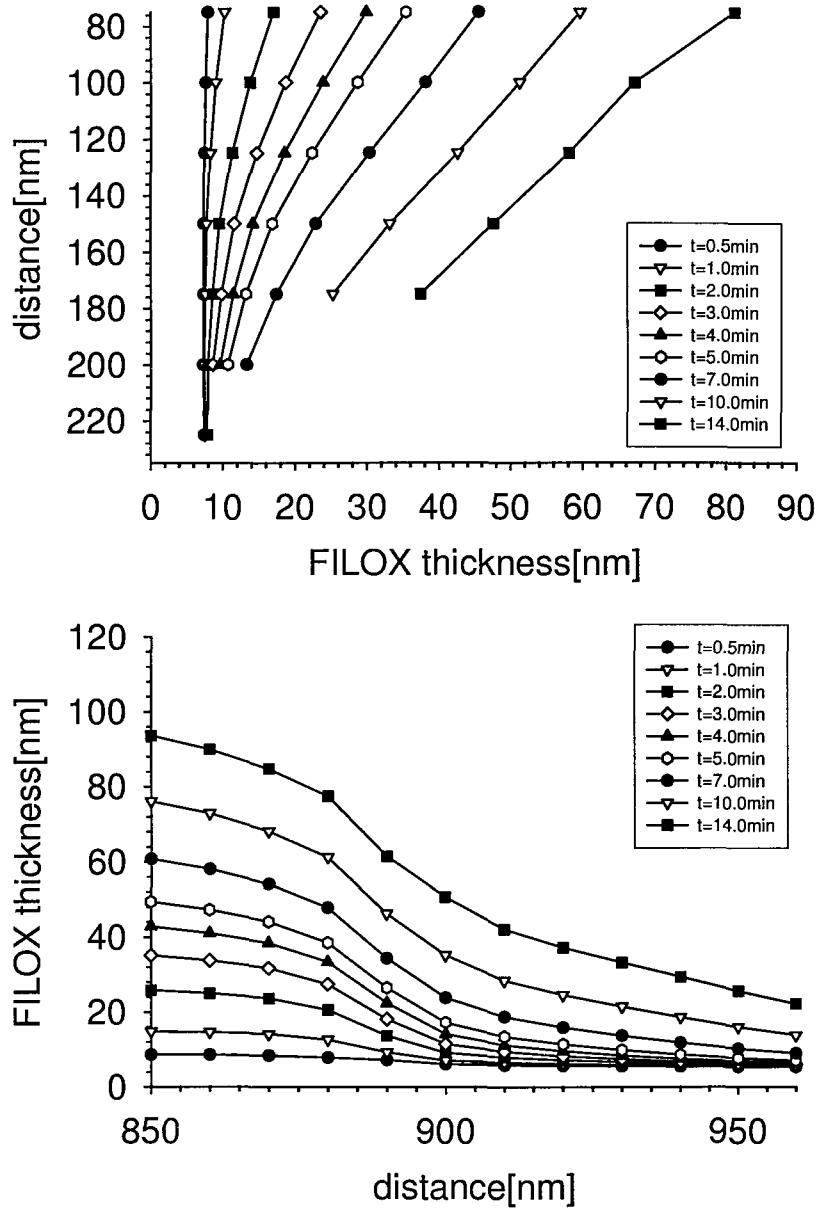

| 4.9  | FILOX thickness as a function of distance for a 20.4nm pad oxide and 130nm nitride thickness . . . . .                | 62 |

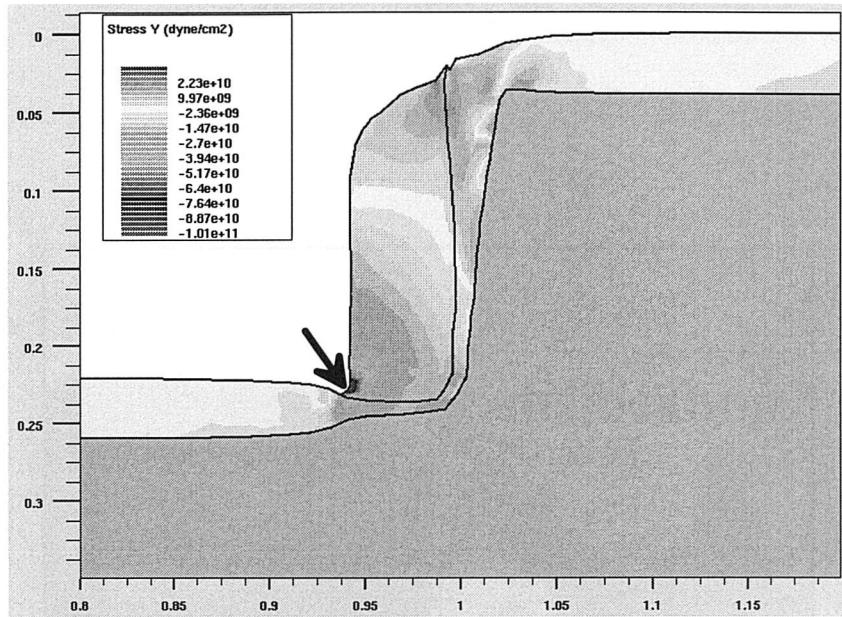

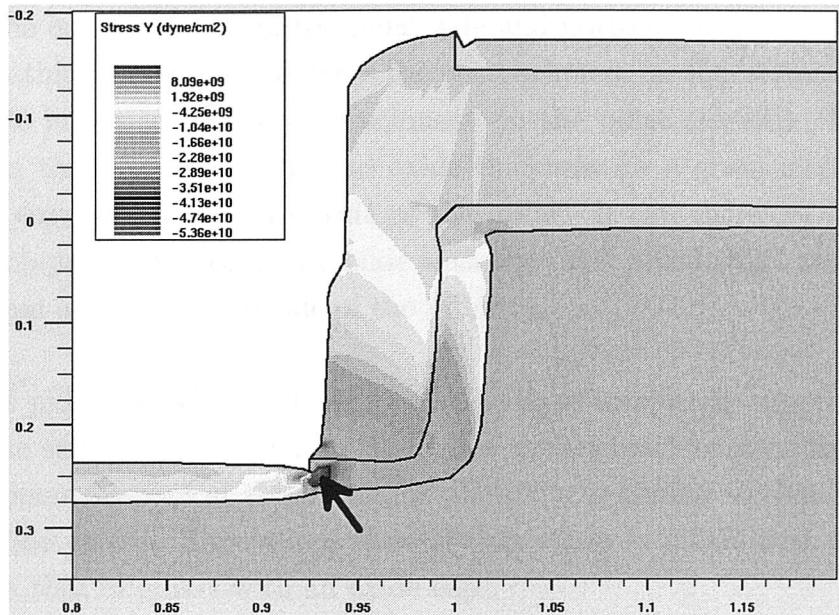

| 4.10 | Regions of normal stress in nitride . . . . .                                                                         | 63 |

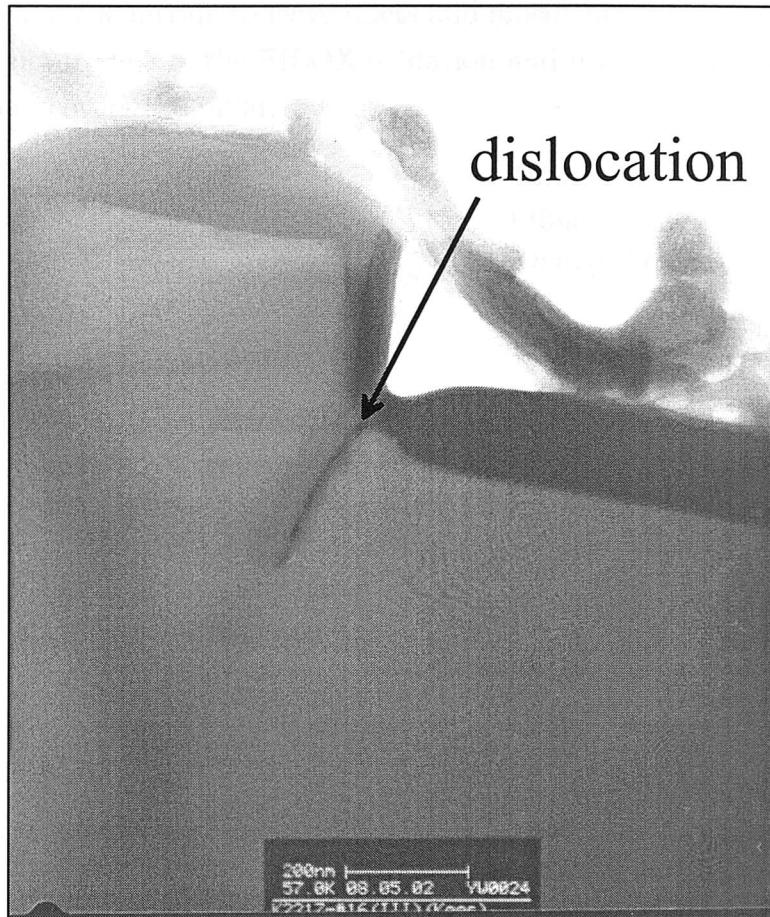

| 4.11 | TEM cross-section showing dislocations . . . . .                                                                      | 64 |

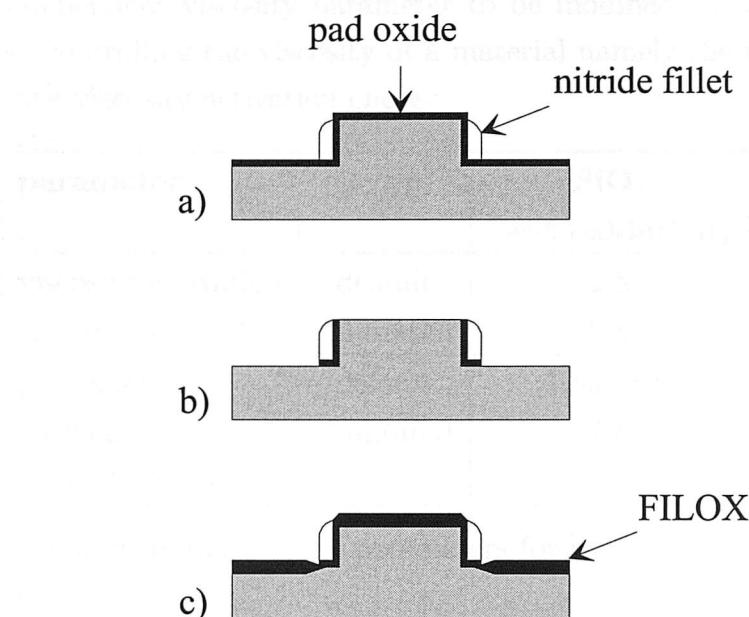

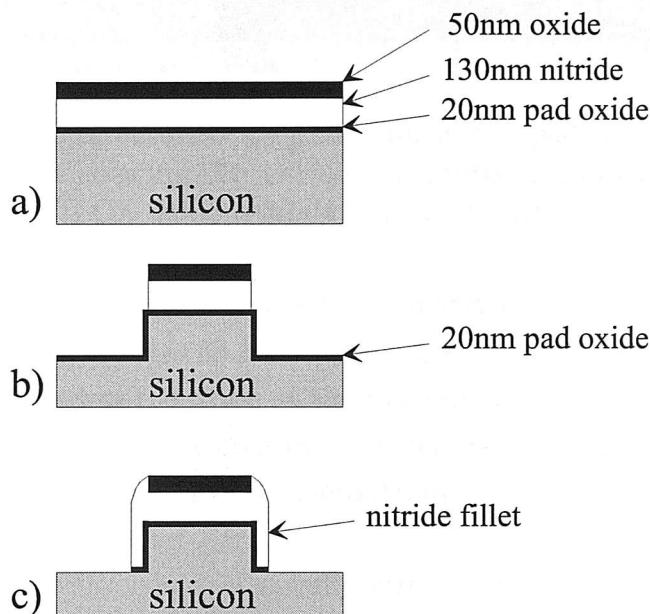

| 4.12 | Process flow of a structure with nitride as a top insulator . . . . .                                                 | 65 |

| 4.13 | Simulated structure with a 20.4nm initial pad oxide grown at 1000°C and 70nm nitride fillet . . . . .                 | 66 |

| 4.14 | FILOX thickness as a function of distance for a 20.4nm pad oxide and 70nm nitride thickness . . . . .                 | 67 |

| 4.15 | Regions of normal stress $\sigma_{yy}$ in nitride for a 20.4nm initial pad oxide and 70nm nitride thickness . . . . . | 68 |

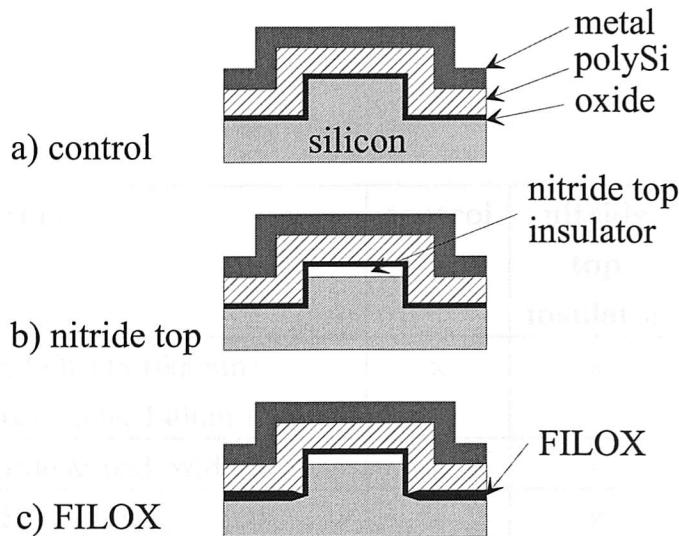

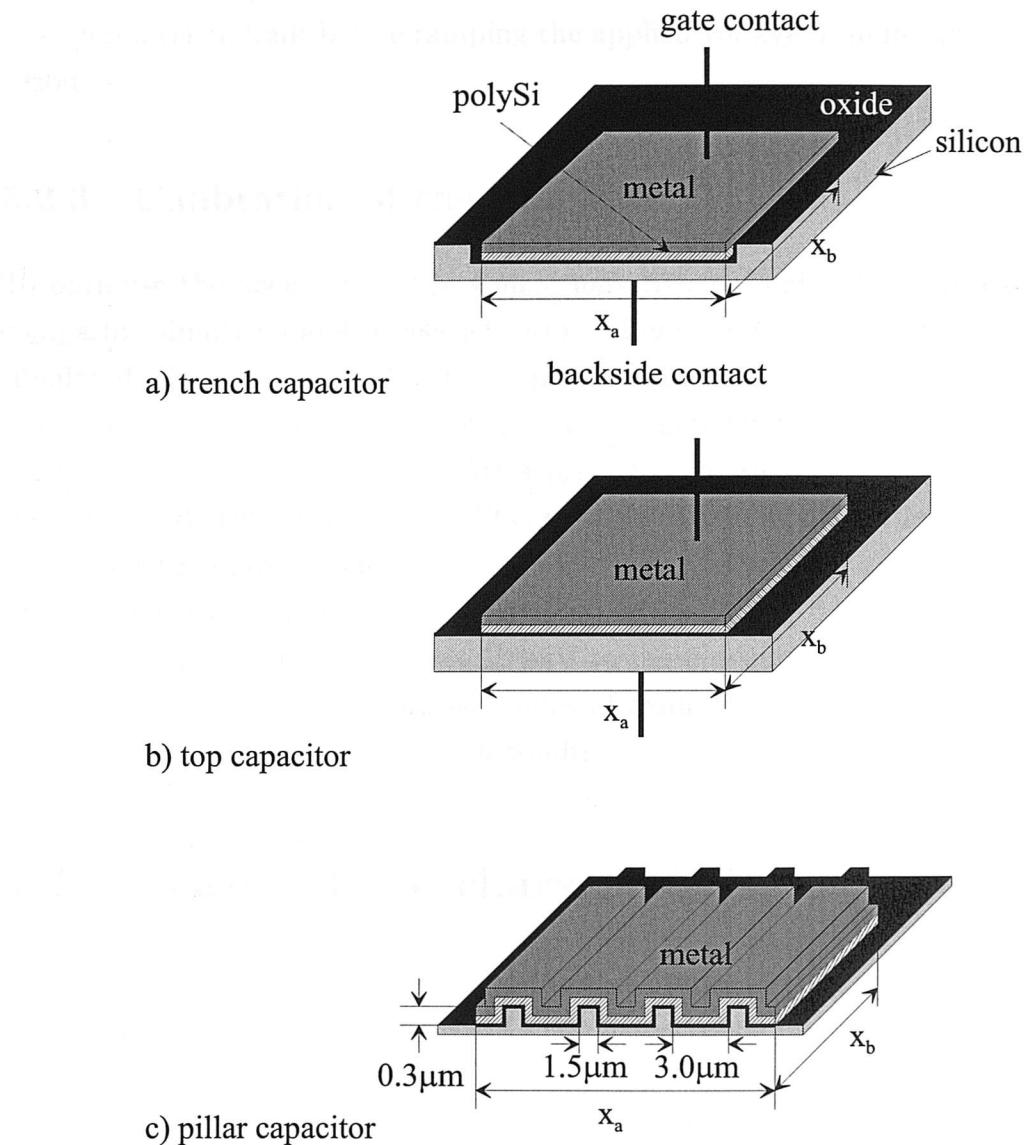

| 5.1  | Cross-sections of fabricated capacitors . . . . .                                                                     | 71 |

| 5.2  | Fabricated capacitors . . . . .                                                                                       | 74 |

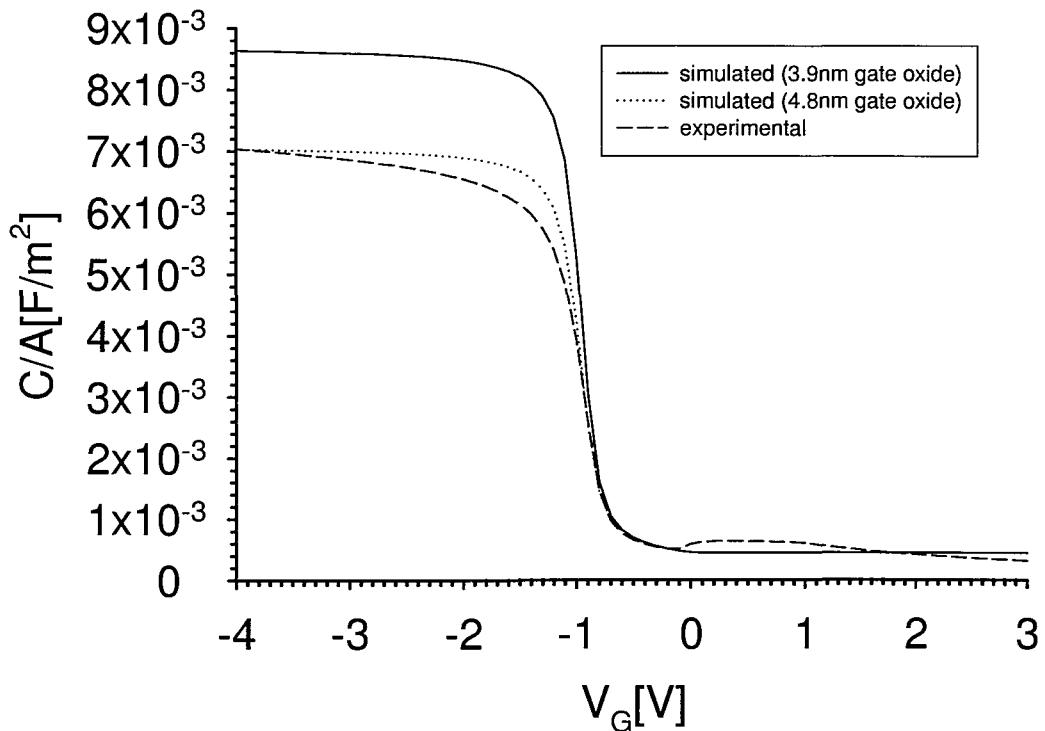

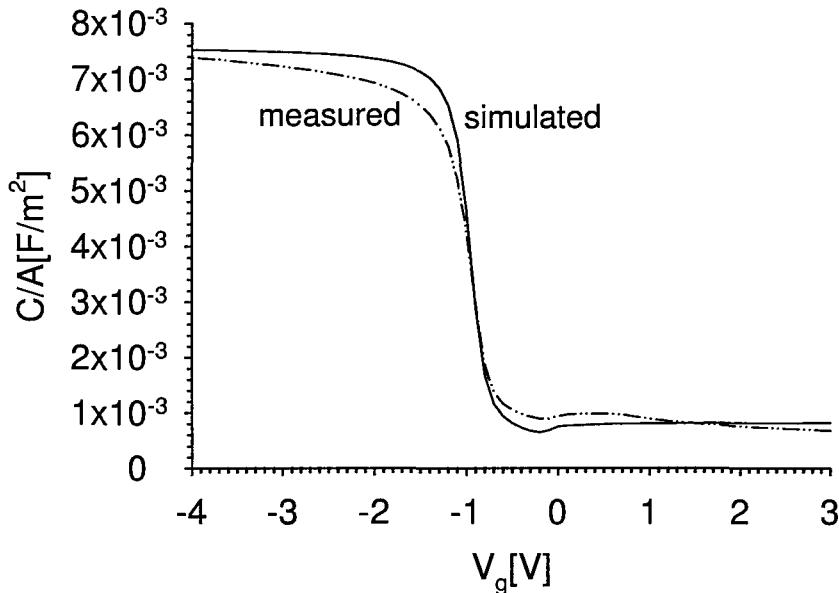

| 5.3  | Comparison of simulated default, calibrated and measured capacitances                                                 | 76 |

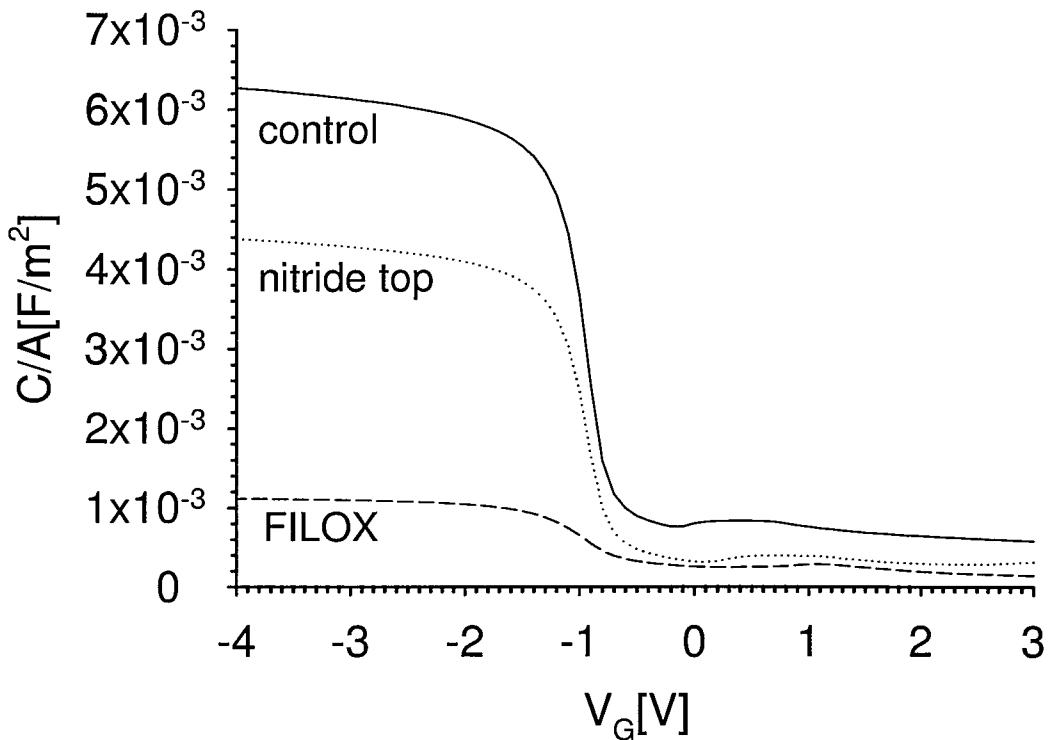

| 5.4  | Comparison of measured CV graphs of a control, nitride top insulator and FILOX capacitor . . . . .                    | 77 |

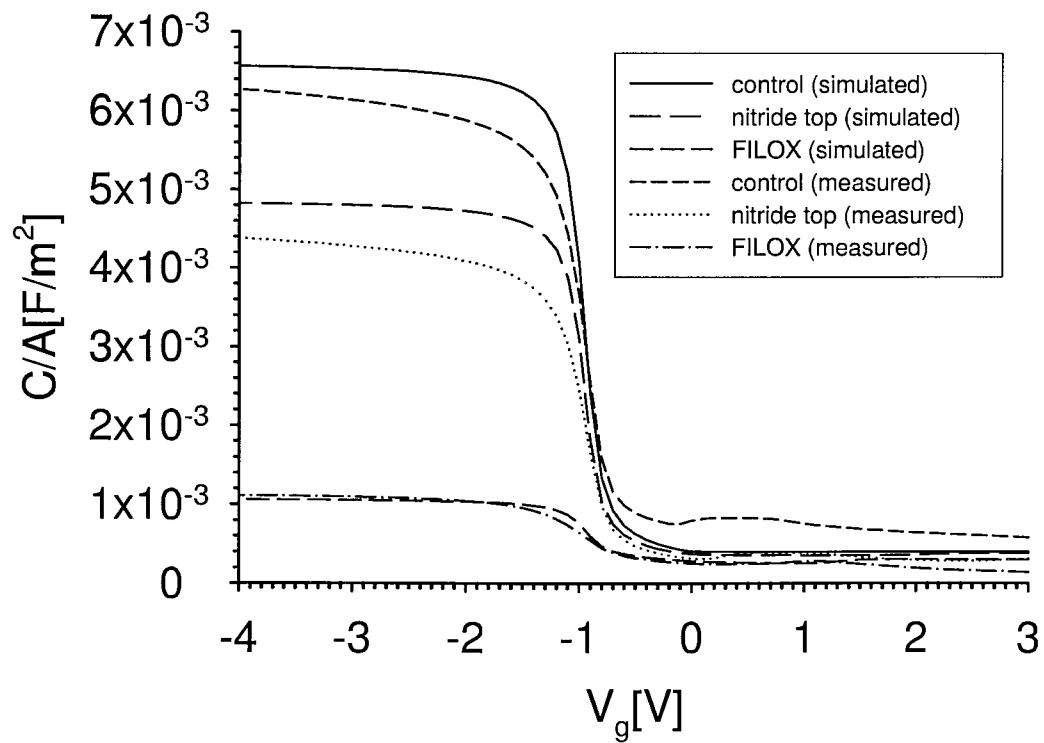

| 5.5  | Comparison of calibrated simulated and measured CV graphs of control, nitride top and FILOX capacitors . . . . .      | 77 |

| 5.6  | Comparison of calibrated simulated and measured capacitances . . . . .                                                | 78 |

| 5.7  | Cross-section of a control capacitor cell . . . . .                                                                   | 79 |

| 5.8  | Measured CV graphs of a control, nitride top insulator and FILOX capacitor in inversion . . . . .                     | 81 |

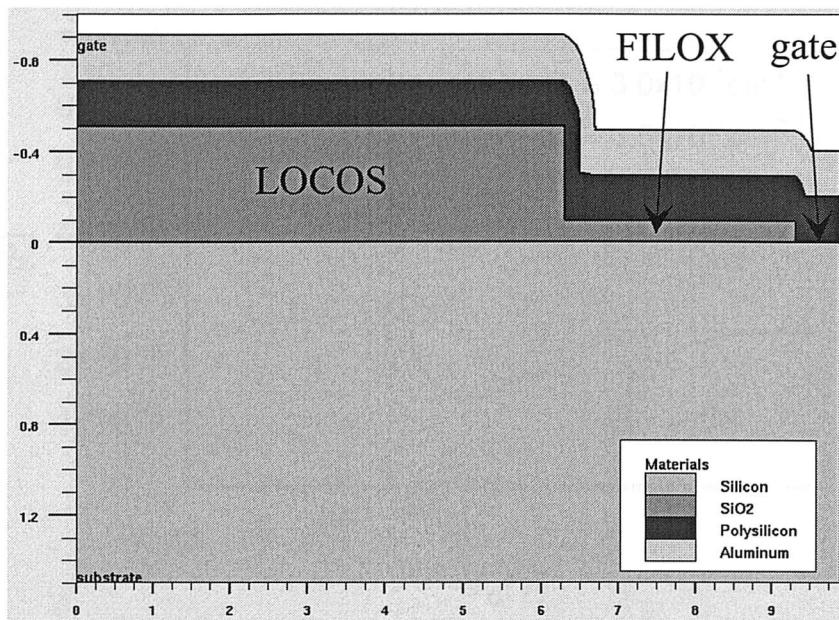

| 5.9  | Simulated structure with two different oxide thicknesses . . . . .                                                    | 81 |

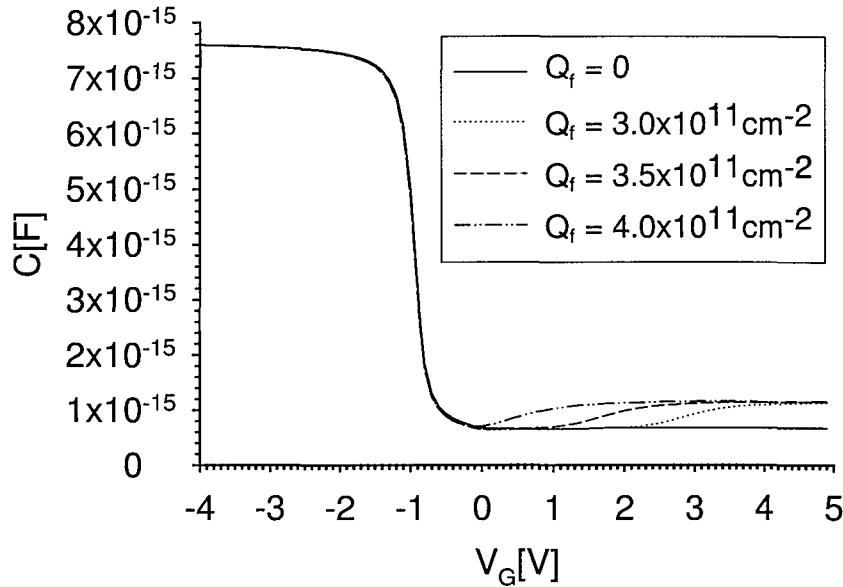

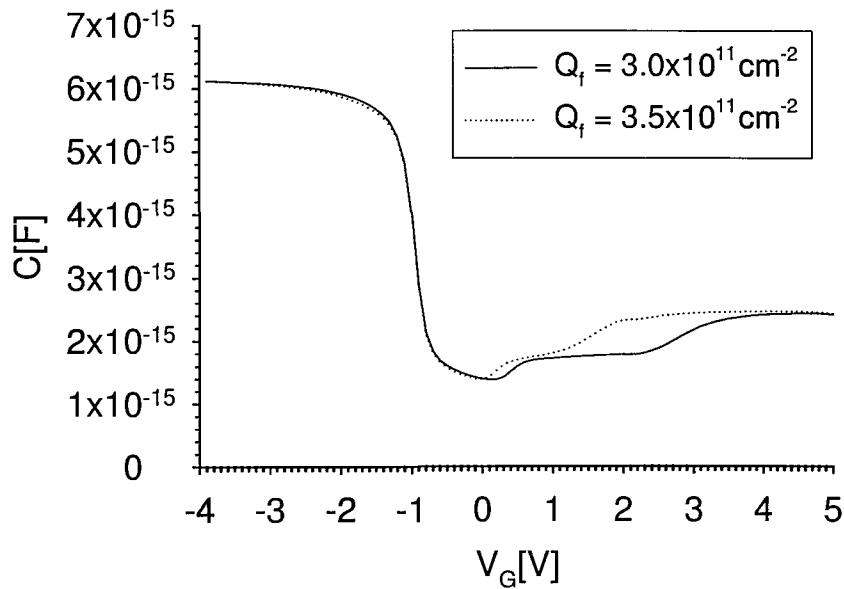

| 5.10 | Simulated CV graphs for various interface charges . . . . .                                                           | 82 |

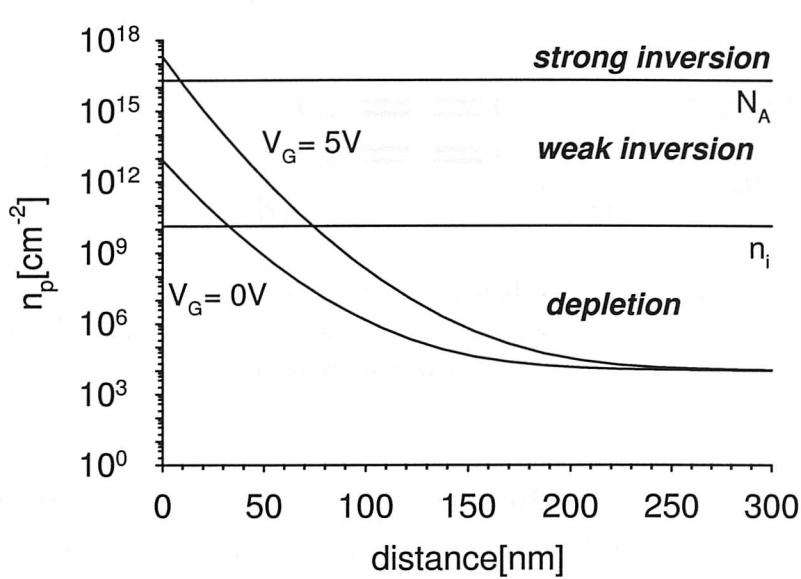

| 5.11 | Simulated electron concentration in the substrate . . . . .                                                           | 83 |

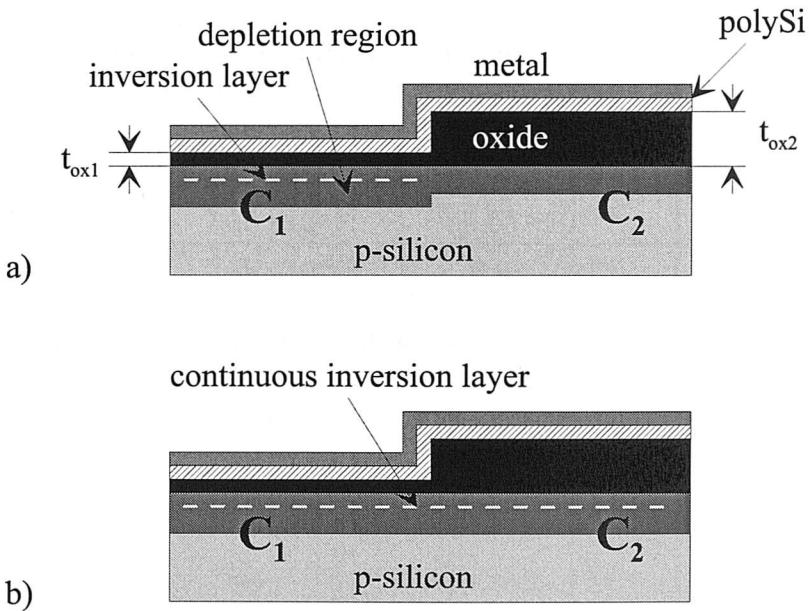

| 5.12 | Cross-section of a capacitor with two different oxide thicknesses . . . . .                                           | 83 |

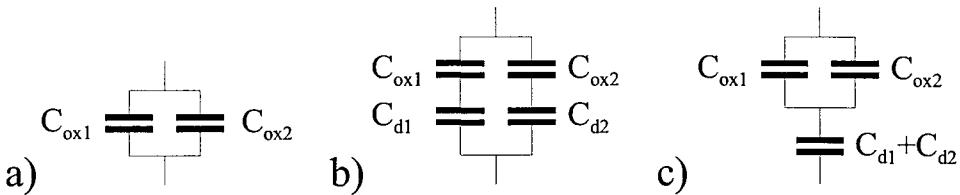

| 5.13 | Equivalent circuits for three modes of operation . . . . .                                                            | 84 |

| 5.14 | Simulated and measured results of a control device and probe pad . . . . .                                            | 85 |

| 5.15 | Simulated structure with three different oxide thicknesses . . . . .                                                  | 86 |

| 5.16 | Simulated CV graphs for two interface charges . . . . .                                                               | 87 |

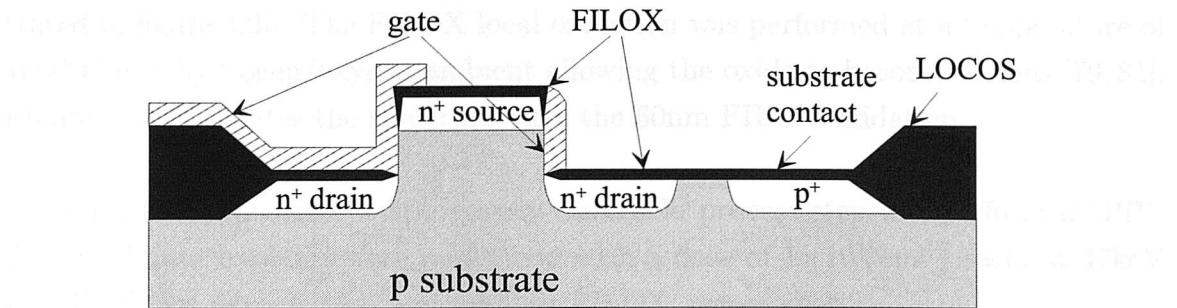

| 6.1  | Cross-section of a surround gate vertical MOSFET with FILOX . . . . .                                                 | 89 |

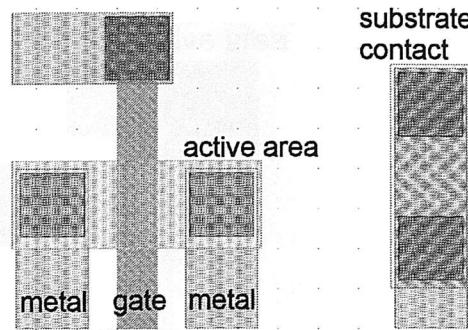

| 6.2  | Top-view of a vertical MOSFET structure . . . . .                                                                     | 89 |

| 6.3  | Source/drain implant steps . . . . .                                                                                  | 90 |

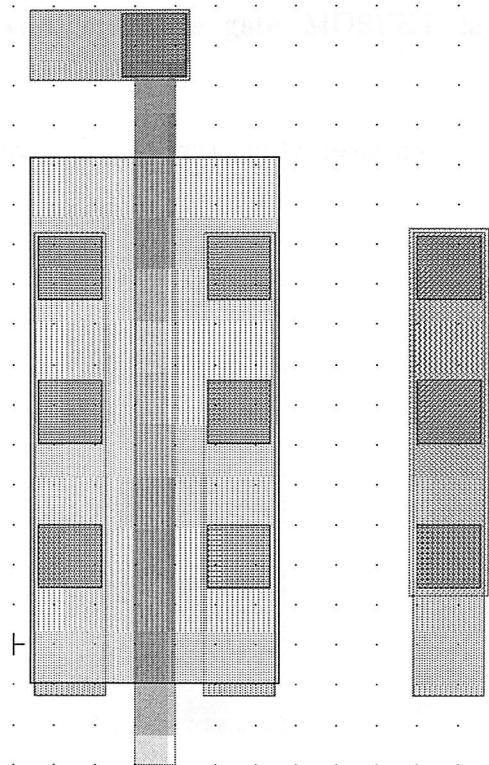

| 6.4  | Vertical surround gate MOSFET layout . . . . .                                                                        | 93 |

| 6.5  | Mask alignment sequence . . . . .                                                                                     | 93 |

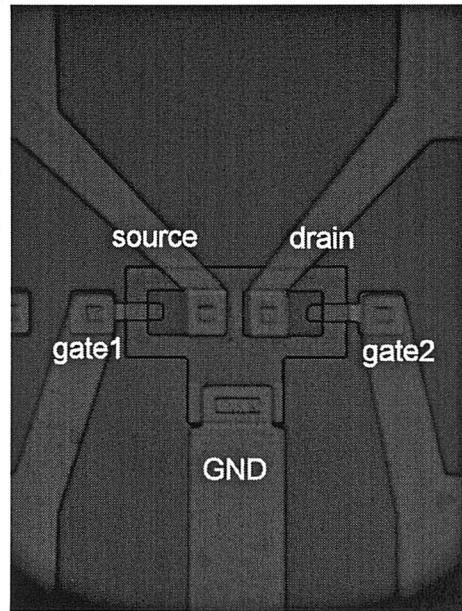

| 6.6  | Top-view of a fabricated MOSFET with surround gate . . . . .                                                          | 94 |

|      |                                                                                 |     |

|------|---------------------------------------------------------------------------------|-----|

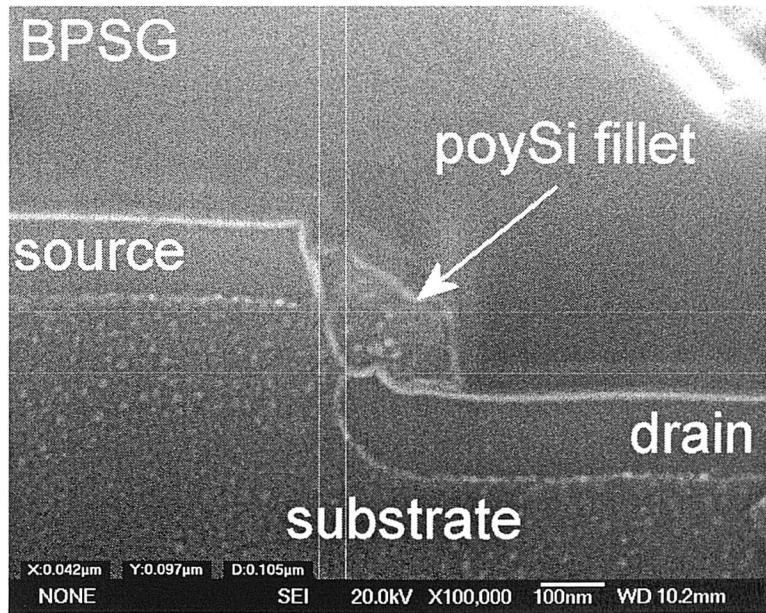

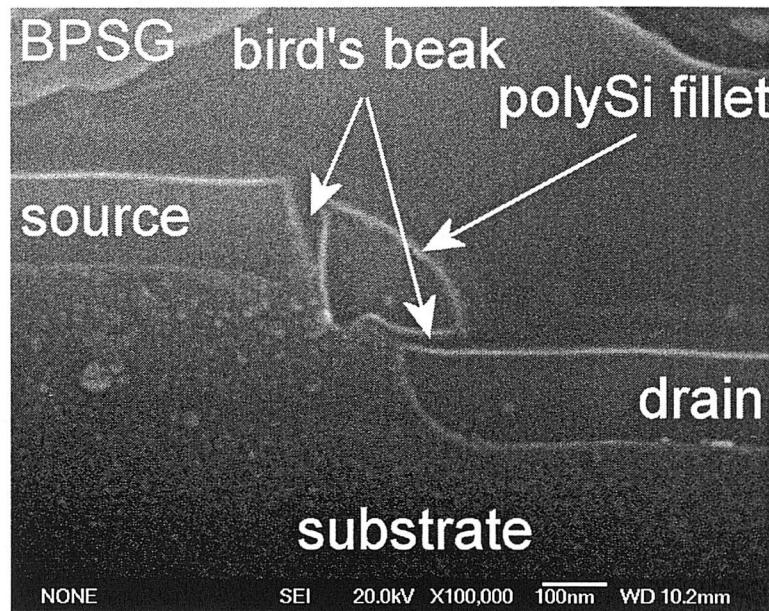

| 6.7  | FESEM cross-section of a GAI vertical n-MOSFET (1) . . . . .                    | 95  |

| 6.8  | FESEM cross-section of a GAI vertical n-MOSFET (2) . . . . .                    | 96  |

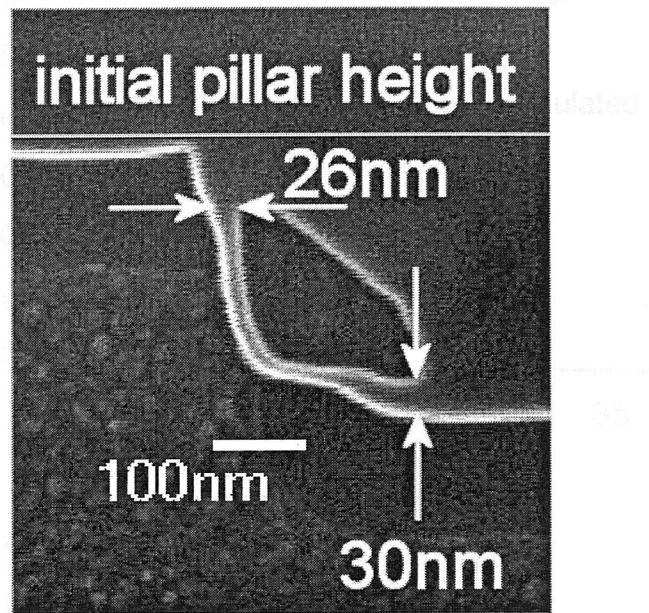

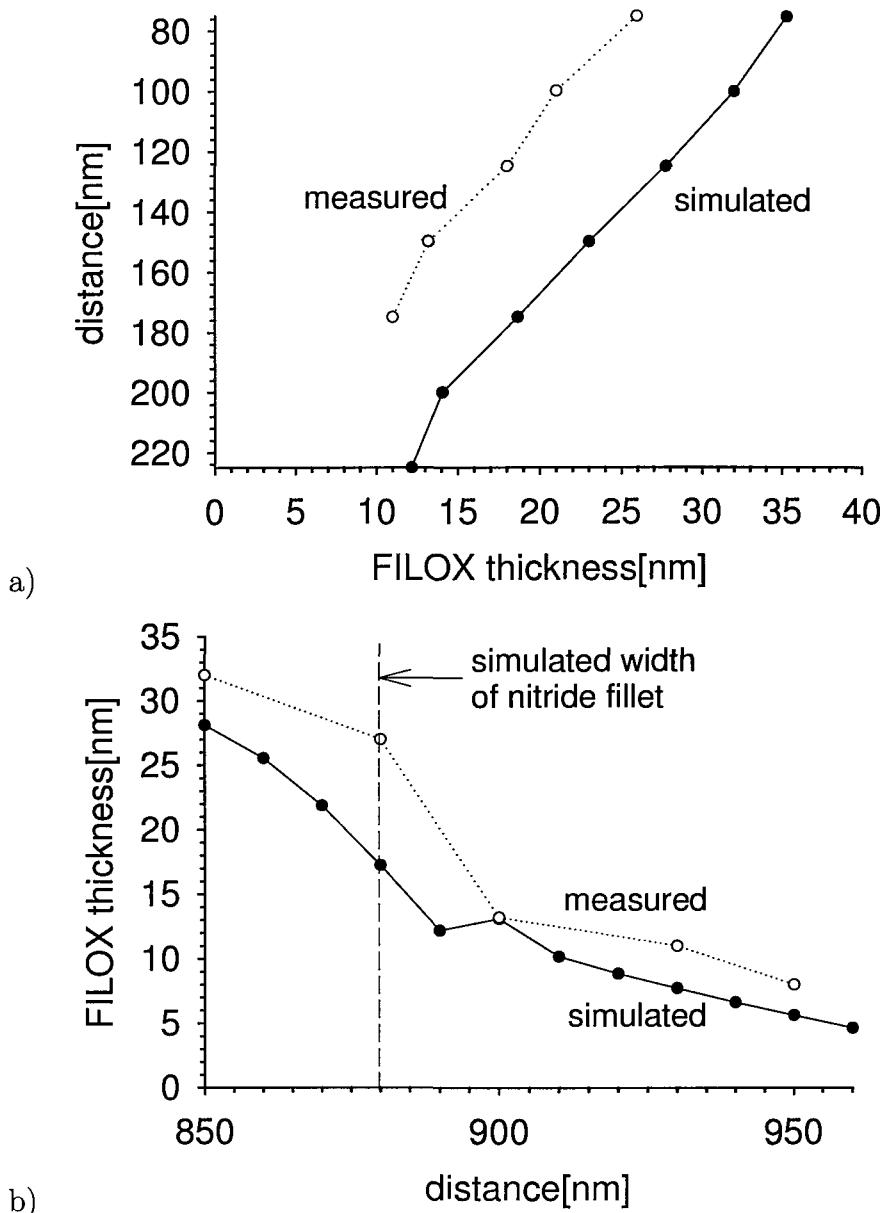

| 6.9  | Measured and simulated FILOX thickness . . . . .                                | 97  |

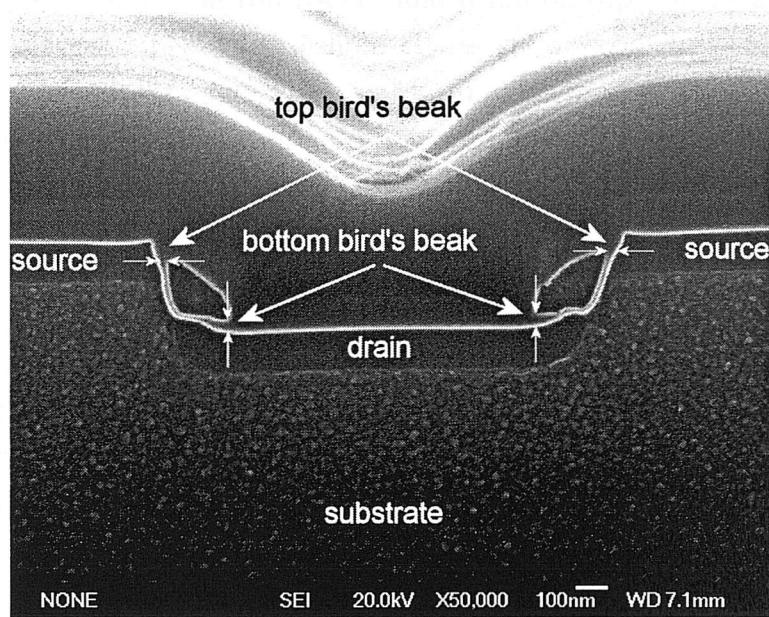

| 6.10 | FESEM cross-section of two GAI vertical n-MOSFET structures . . . . .           | 98  |

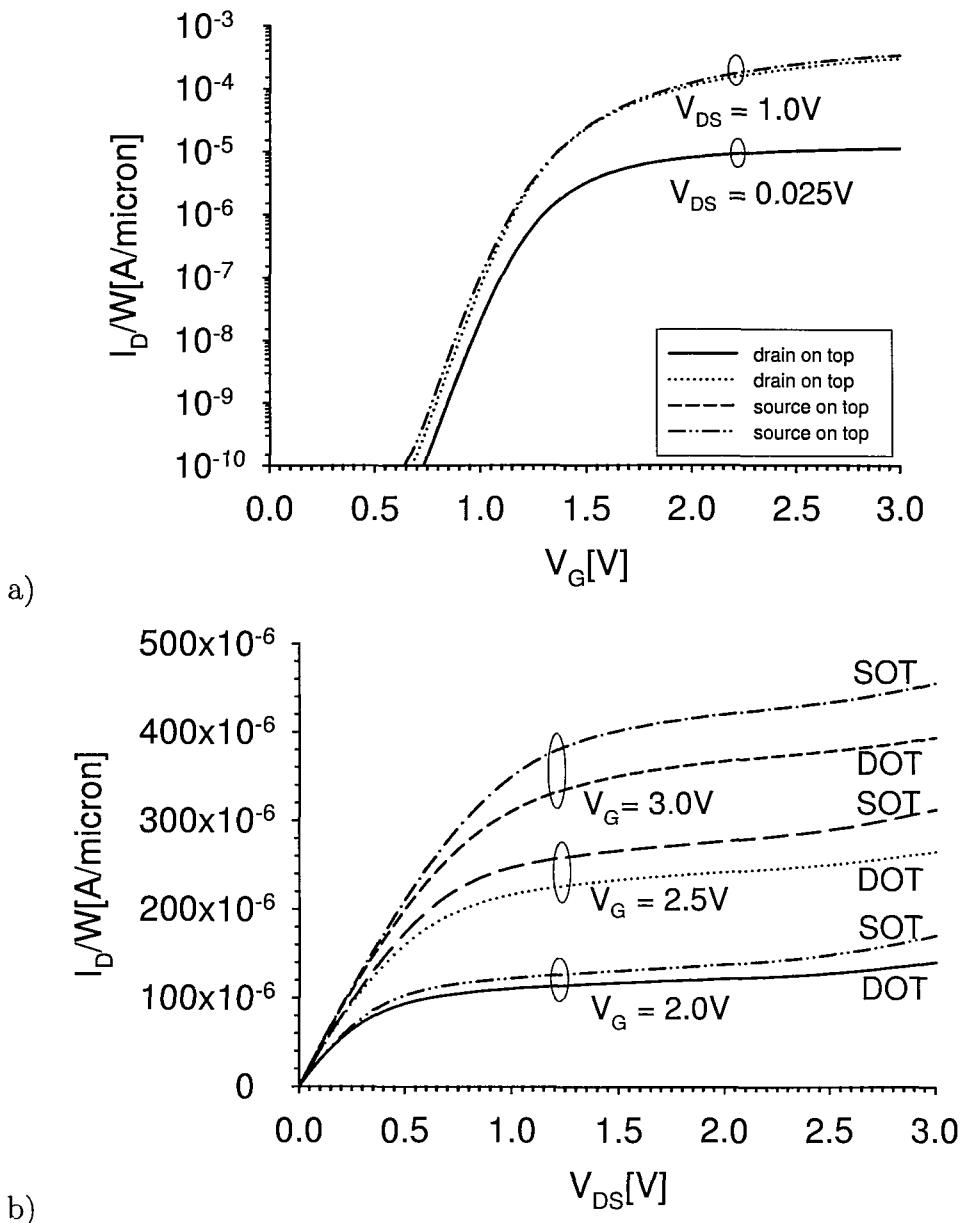

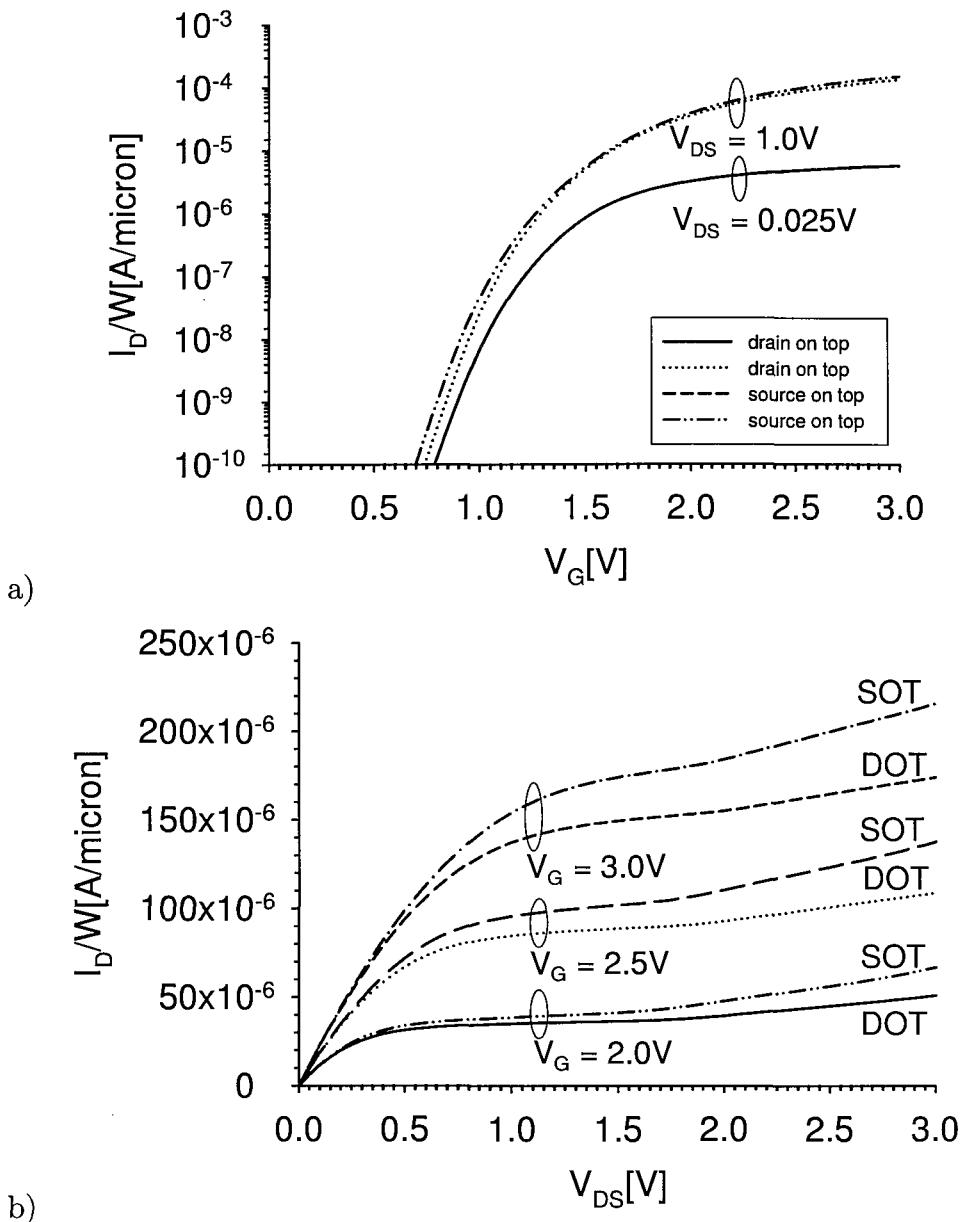

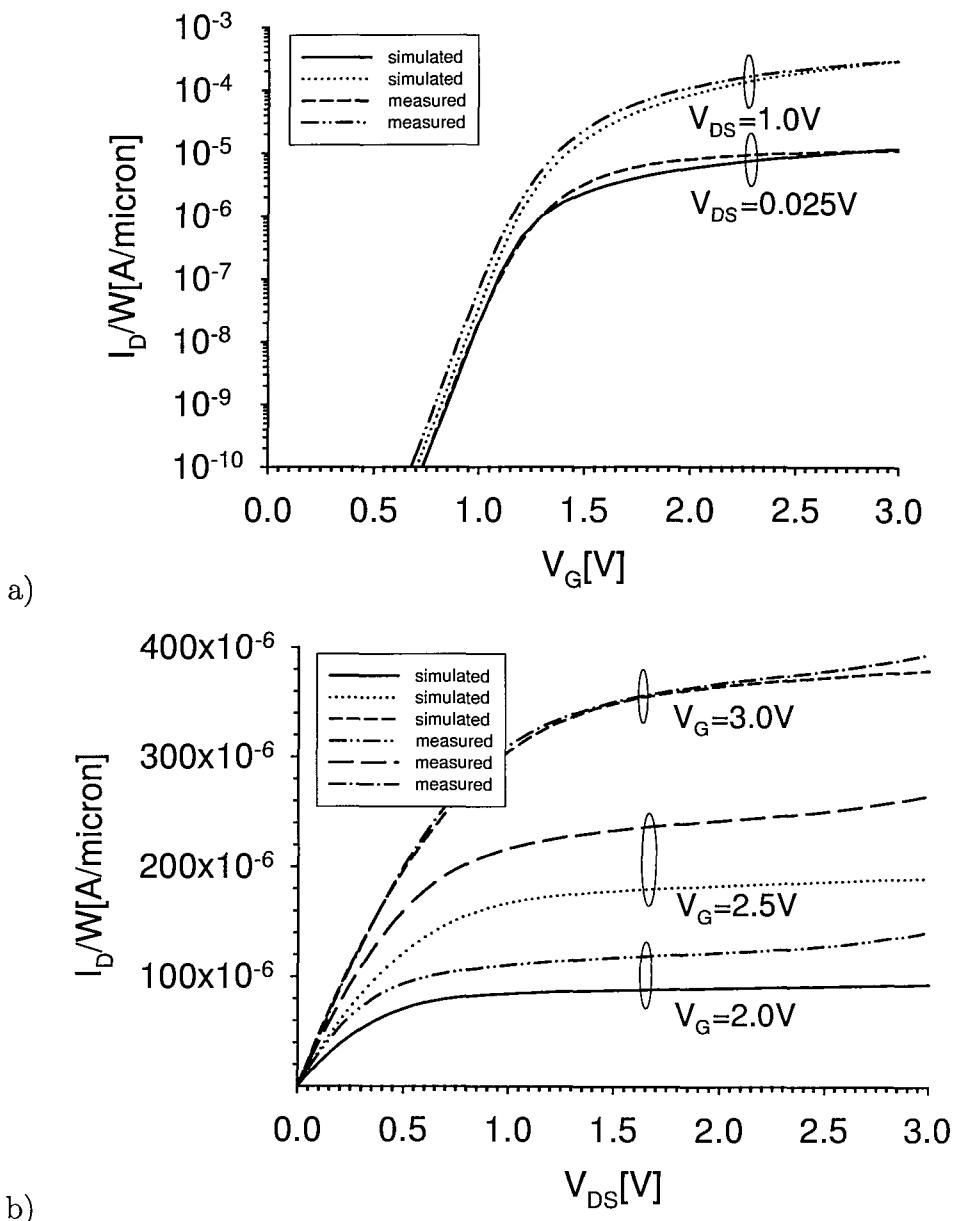

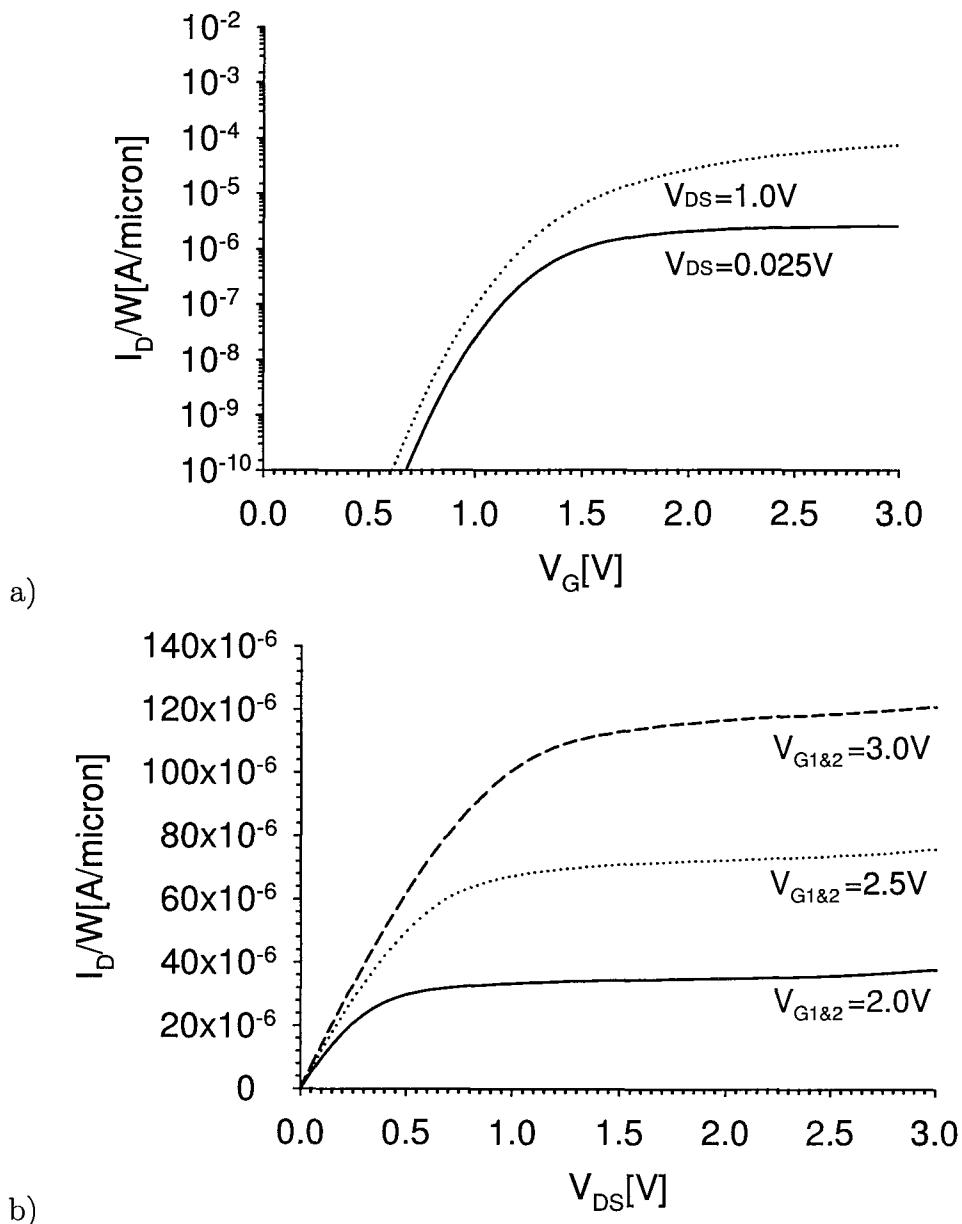

| 6.11 | Typical elect. char. of a single gate GAI vertical n-MOSFET . . . . .           | 100 |

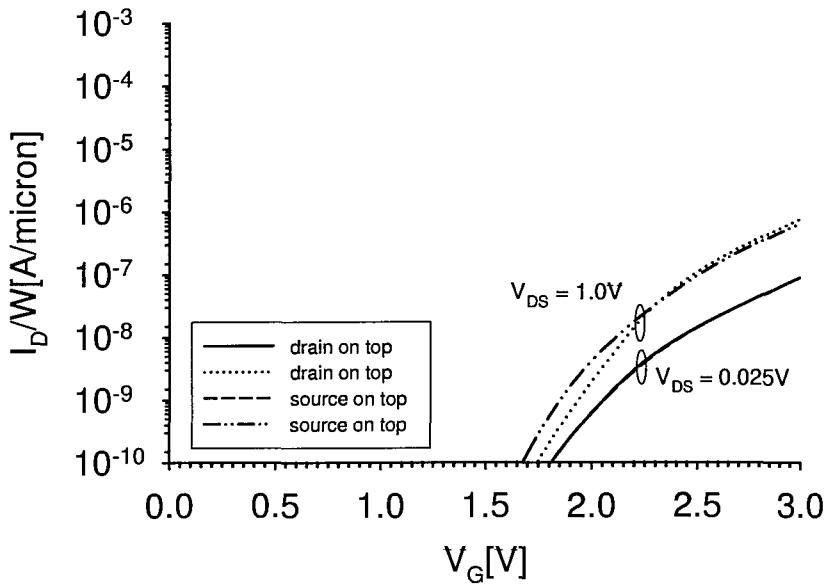

| 6.12 | Typical elect. char. of a surround gate GAI vertical n-MOSFET . . . . .         | 102 |

| 6.13 | Variation of subthreshold characteristics . . . . .                             | 103 |

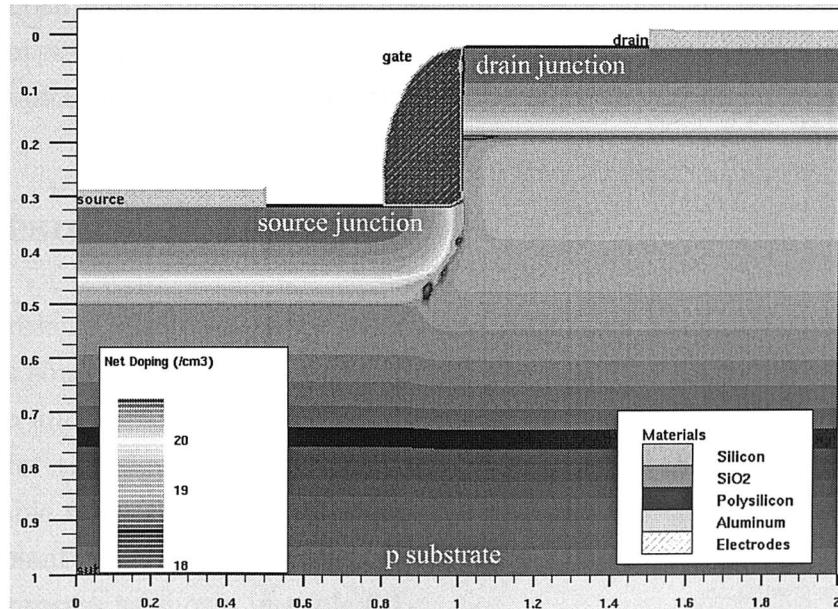

| 6.14 | Simulated structure of a single gate GAI vertical n-MOSFET . . . . .            | 103 |

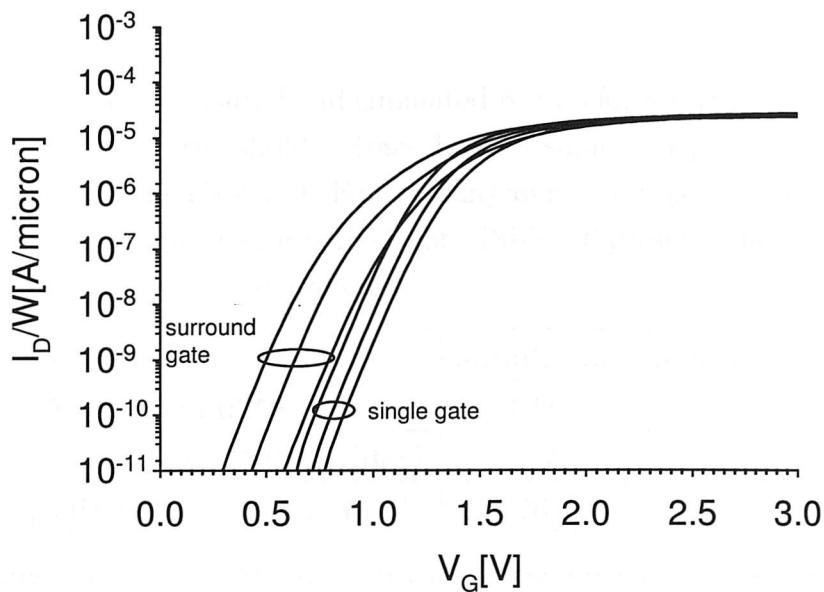

| 6.15 | Simulated and measured electrical characteristics . . . . .                     | 105 |

| 6.16 | FESEM cross-section of a GBI vertical n-MOSFET . . . . .                        | 106 |

| 6.17 | Subthreshold characteristics of a surround gate GBI vertical n-MOSFET           | 107 |

| 6.18 | Cross-section of a vertical NOR gate. . . . .                                   | 108 |

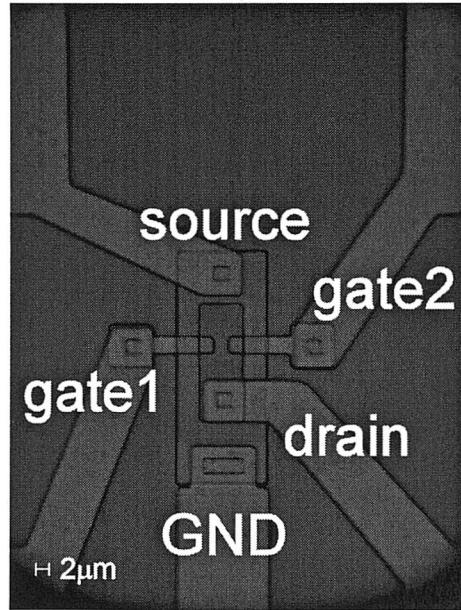

| 6.19 | Top-view of a fabricated vertical NOR gate . . . . .                            | 108 |

| 6.20 | Simulated and measured electrical characteristics of a vertical NOR gate        | 109 |

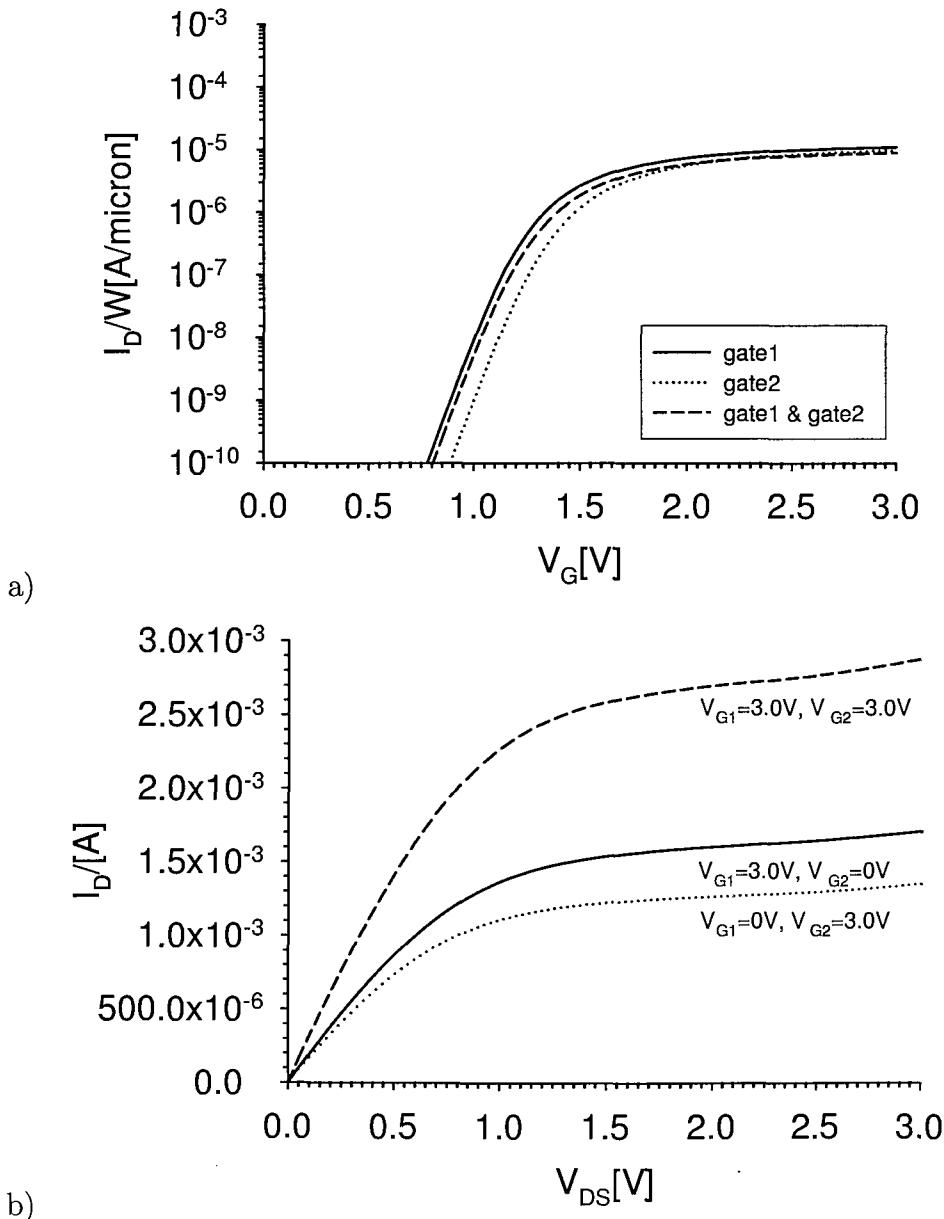

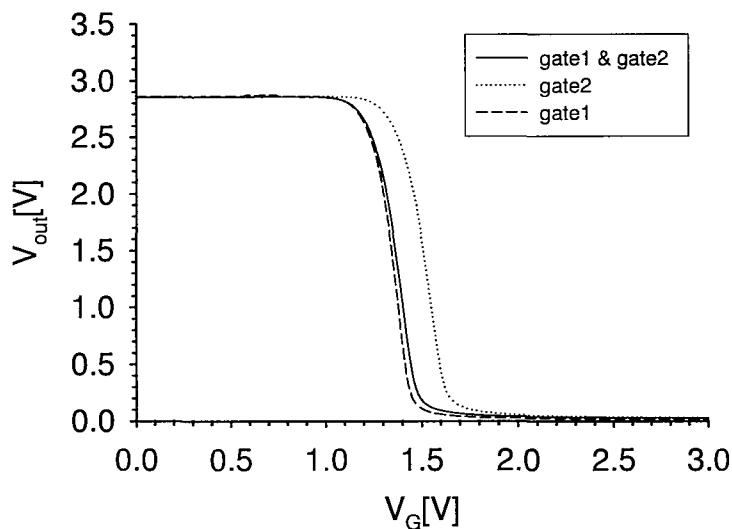

| 6.21 | Transfer characteristics of a typical vertical NOR gate . . . . .               | 110 |

| 6.22 | Cross-section of a vertical NAND gate . . . . .                                 | 111 |

| 6.23 | Top-view of a fabricated vertical NAND gate . . . . .                           | 111 |

| 6.24 | Typical electrical characteristics of a vertical NAND gate . . . . .            | 112 |

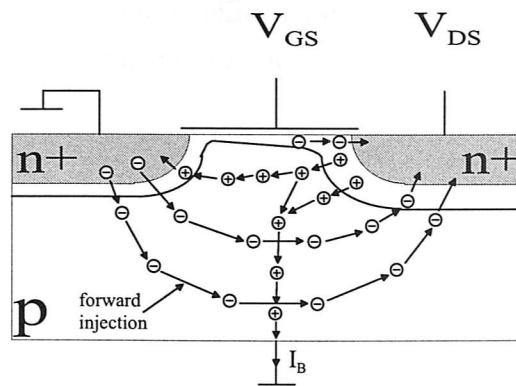

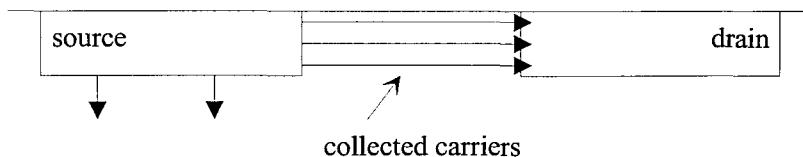

| 7.1  | Schematic illustration of carrier collection in a lateral MOSFET . . . . .      | 114 |

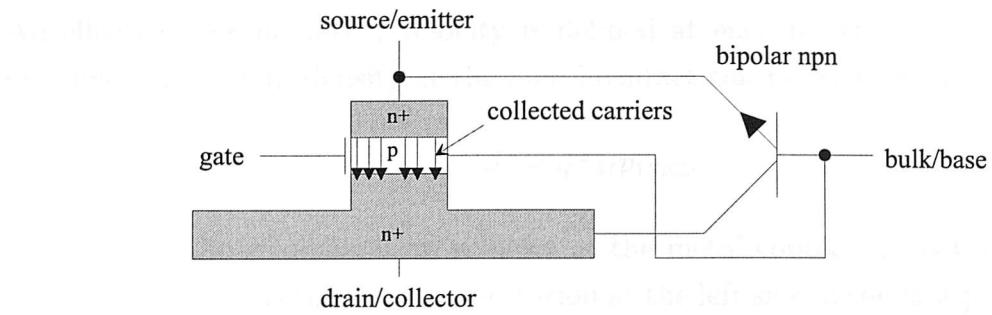

| 7.2  | Parasitic transistor action in vertical n-MOSFET . . . . .                      | 115 |

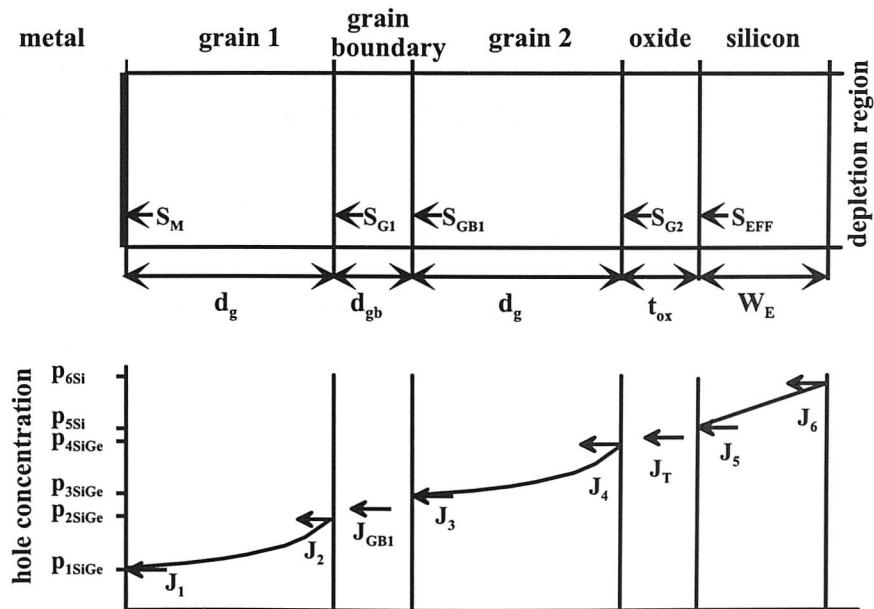

| 7.3  | Schematic illustration of a polySiGe emitter . . . . .                          | 115 |

| 7.4  | Illustration of the effect of the polySiGe emitter . . . . .                    | 118 |

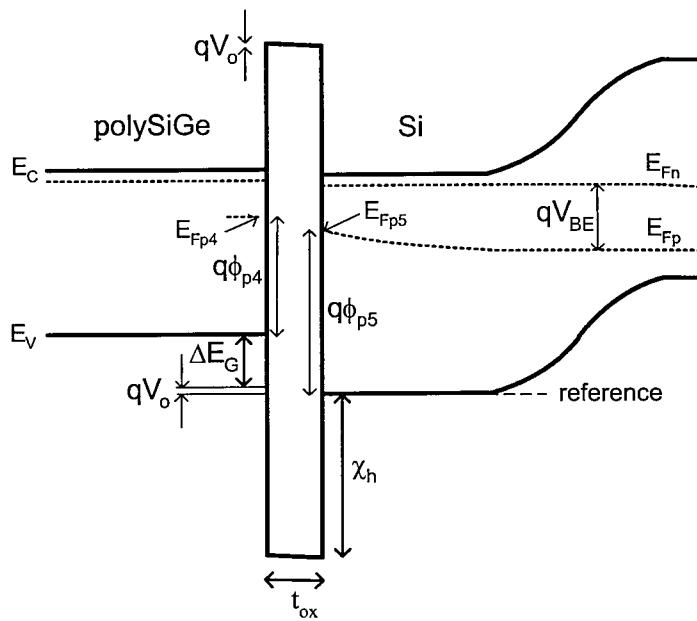

| 7.5  | Band diagram of a polySiGe emitter . . . . .                                    | 119 |

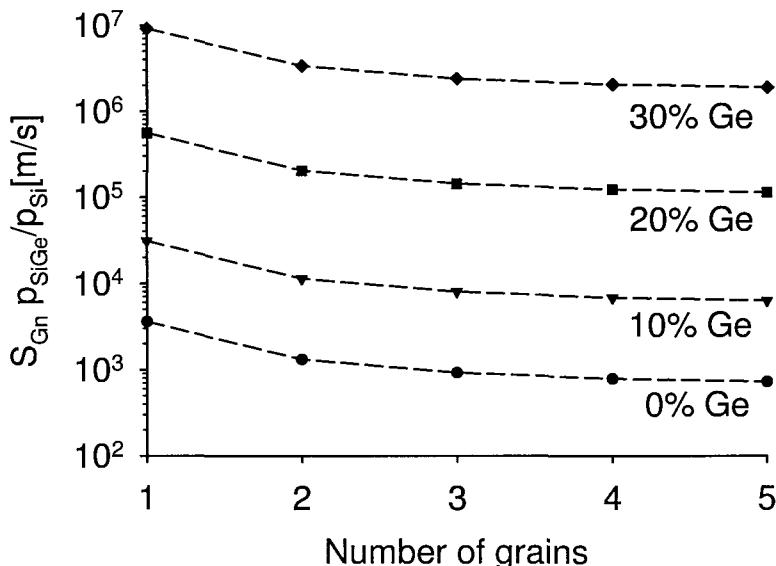

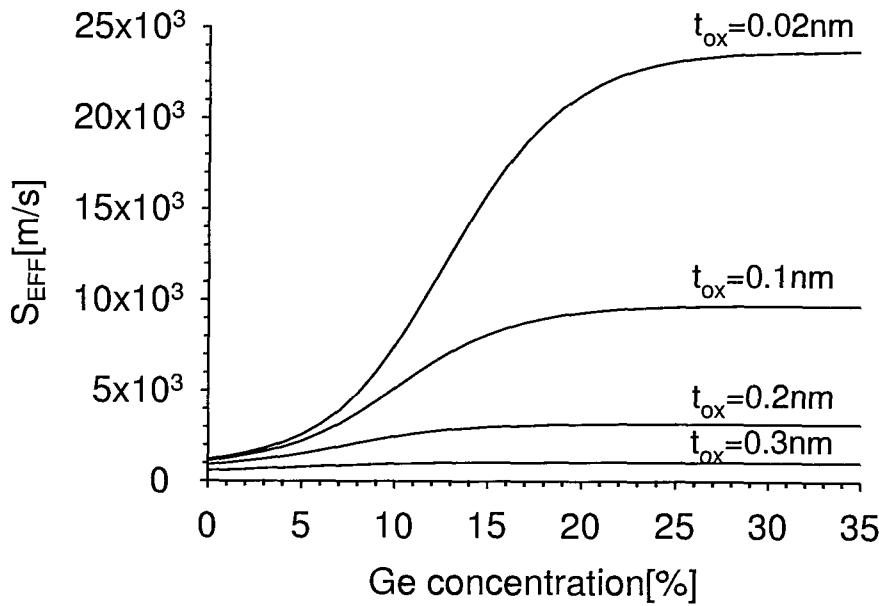

| 7.6  | Calculated values of the effective surface recombination velocity . . . . .     | 120 |

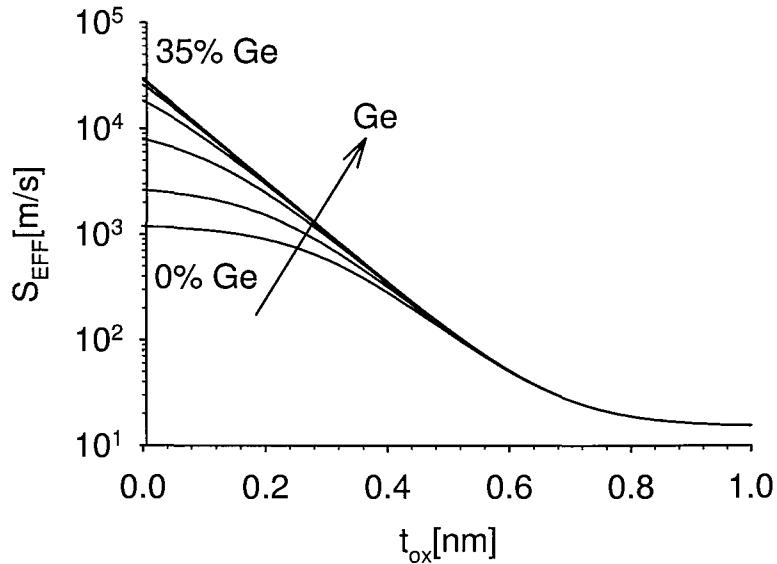

| 7.7  | Calculated values of the effective recombination velocity $S_{EFF}$ . . . . .   | 122 |

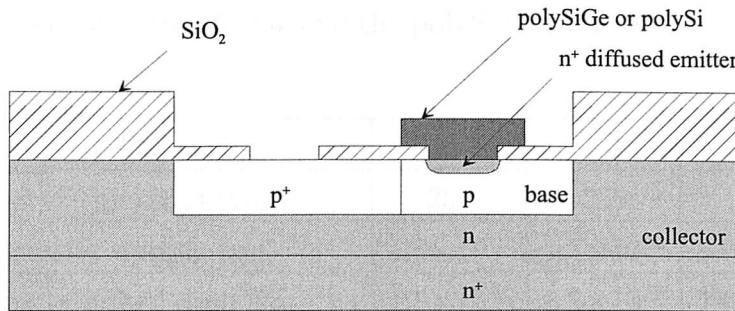

| 7.8  | Cross-section of the manufactured bipolar transistor . . . . .                  | 123 |

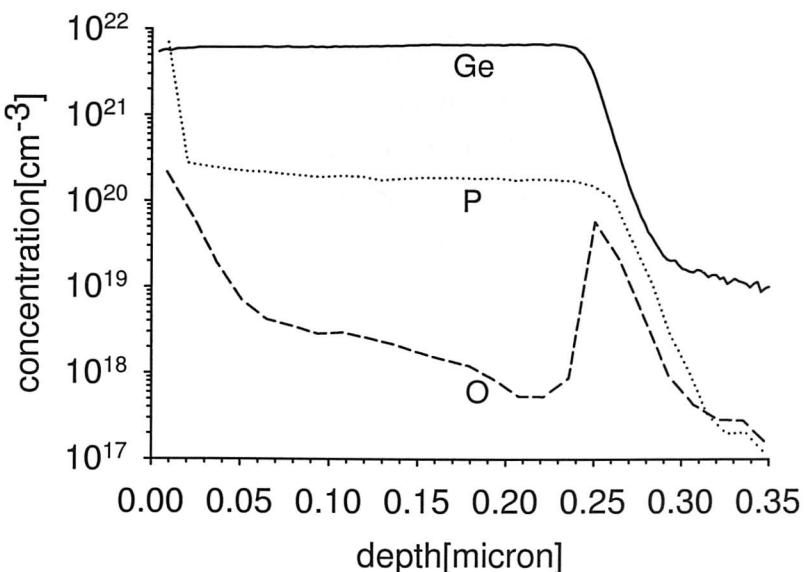

| 7.9  | Measured germanium, phosphorus and oxygen SIMS profiles . . . . .               | 123 |

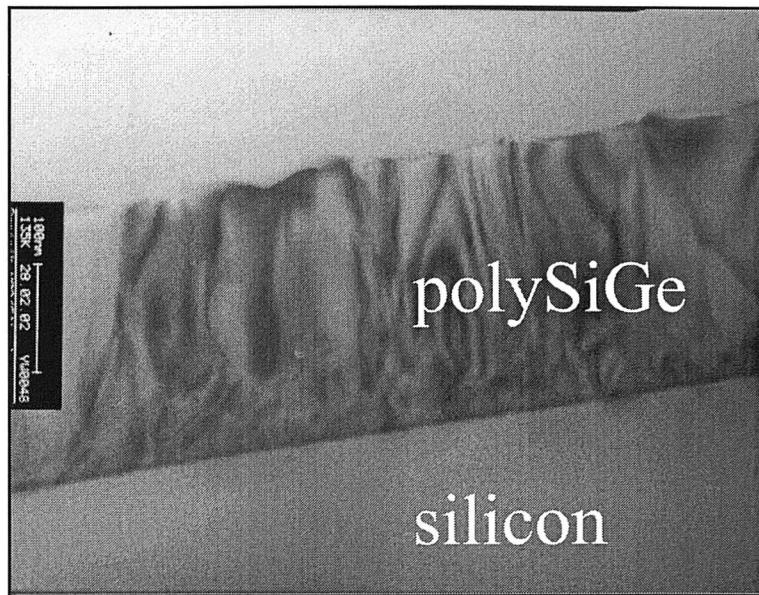

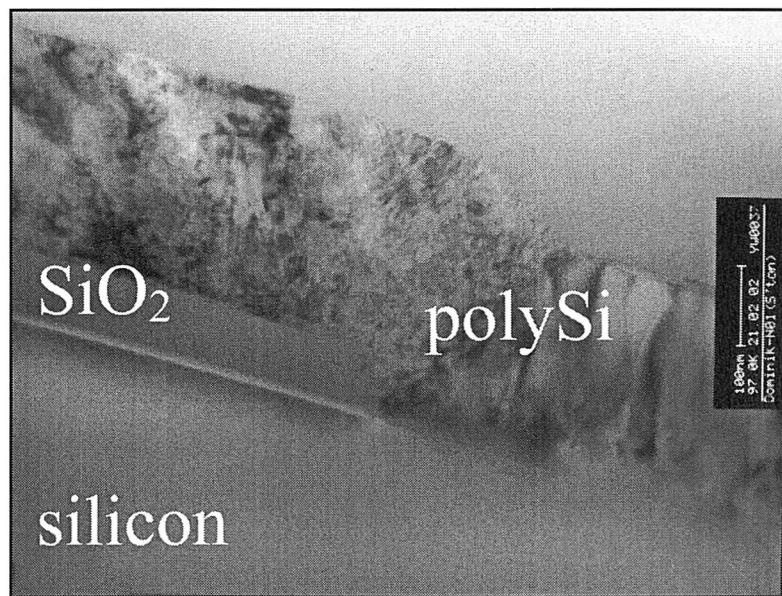

| 7.10 | TEM cross-section of a $\text{polySi}_{0.90}\text{Ge}_{0.10}$ emitter . . . . . | 125 |

| 7.11 | TEM cross-section of a polySi emitter . . . . .                                 | 125 |

| 7.12 | Measured Gummel plots . . . . .                                                 | 126 |

| 7.13 | Corrected base currents . . . . .                                               | 127 |

| 7.14 | Calculated base currents . . . . .                                              | 128 |

| 7.15 | Polycrystalline SiGe source . . . . .                                           | 128 |

| B.1  | Layout of one cell of the fabricated vertical capacitors . . . . .              | 164 |

| B.2  | Layout of two cells of the fabricated vertical MOS devices . . . . .            | 167 |

| C.1  | Listing for FILOX test structures . . . . .                                     | 172 |

| C.2  | Listing for vertical capacitors . . . . .                                       | 174 |

| C.3  | Listing for vertical MOS transistors . . . . .                                  | 178 |

# List of Tables

|      |                                                                                                                                                                                            |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Form factors for modelling the narrow width effect . . . . .                                                                                                                               | 24 |

| 3.1  | Parasitic overlap capacitances of a lateral device . . . . .                                                                                                                               | 32 |

| 3.2  | Parasitic overlap capacitances of a basic vertical device . . . . .                                                                                                                        | 33 |

| 3.3  | Calculated overlap capacitances for a lateral and a basic single gate vertical device ( $W=220\text{nm}$ ) . . . . .                                                                       | 33 |

| 3.4  | Parasitic overlap capacitances of an optimised single gate vertical device                                                                                                                 | 37 |

| 3.5  | Calculated overlap capacitances for a lateral and an optimised single gate vertical device ( $W=220\text{nm}$ ) . . . . .                                                                  | 38 |

| 3.6  | Calculated overlap capacitances caused by fillets ( $W=1.32\mu\text{m}$ ) . . . . .                                                                                                        | 40 |

| 3.7  | Calculated overlap capacitances for a lateral device and an optimised surround gate vertical device . . . . .                                                                              | 40 |

| 3.8  | Calculated overlap capacitances for a lateral device and an optimised surround gate vertical device with overetched fillets ( $W=1.32\mu\text{m}$ ) . . . . .                              | 42 |

| 3.9  | Parasitic overlap capacitances of an optimised single gate vertical device based on the GBI process sequence . . . . .                                                                     | 44 |

| 3.10 | Calculated overlap capacitances for a lateral device and optimised vertical surround gate GBI and GAI devices ( $W=1.32\mu\text{m}$ ) . . . . .                                            | 45 |

| 3.11 | Parasitic junction capacitances for a single gate device and a surround gate vertical device (GAI) . . . . .                                                                               | 46 |

| 3.12 | Calculated zero bias junction capacitances for a lateral device and a vertical single gate device (GAI) with $W=220\text{nm}$ . . . . .                                                    | 47 |

| 3.13 | Calculated zero bias junction capacitances for a lateral device and a vertical surround gate device (GAI) with $W=1.32\mu\text{m}$ . . . . .                                               | 47 |

| 3.14 | Calculated overlap capacitances for a lateral device and a dielectric pocket surround gate devices with overetched surround gate fillets ( $W=1.32\mu\text{m}$ ) . . . . .                 | 49 |

| 3.15 | Calculated junction capacitances for a lateral device and an optimised vertical dielectric pocket surround gate device based on the GAI process sequence ( $W=1.32\mu\text{m}$ ) . . . . . | 49 |

| 3.16 | Summery of parasitic overlap capacitances for GAI based vertical devices                                                                                                                   | 50 |

| 3.17 | Summery of parasitic junction capacitances for GAI based vertical devices . . . . .                                                                                                        | 51 |

| 4.1  | Process list for FILOX test structures . . . . .                                                                                                                                           | 53 |

| 4.2  | Default and calibrated parameters for stress dependent viscous oxidation simulations. . . . .                                                                                              | 55 |

| 4.3  | Extracted amounts of stress and their location in the nitride fillet and oxide for the structure shown in figure 4.10. . . . .                                                             | 63 |

|     |                                                                                                                                   |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4 | Extracted amounts of stress and their location in the nitride fillet and oxide for the structure shown in figure 4.15. . . . .    | 68  |

| 5.1 | Process list and batch splits for vertical capacitors . . . . .                                                                   | 72  |

| 5.2 | Measured material thicknesses for control, nitride top and FILOX capacitors . . . . .                                             | 73  |

| 5.3 | Extracted capacitance values for control, nitride top and FILOX capacitors . . . . .                                              | 80  |

| 5.4 | Extracted and simulated oxide thickness on the pillar sidewalls for control, nitride top insulator and FILOX capacitors . . . . . | 80  |

| 5.5 | Calculated and simulated capacitances . . . . .                                                                                   | 84  |

| 6.1 | Process list and batch splits for FILOX vertical MOSFETs . . . . .                                                                | 91  |

| 6.2 | Sheet resistances, implant dose and doping concentrations of the fabricated vertical GAI MOSFETs . . . . .                        | 95  |

| 6.3 | Top and bottom encroachment of two MOS structures . . . . .                                                                       | 98  |

| 6.4 | Measured and extracted electrical parameter for a GAI single gate vertical MOSFET . . . . .                                       | 99  |

| 6.5 | Measured and extracted electrical parameter for a GAI surround gate vertical MOSFET . . . . .                                     | 101 |

| 6.6 | Simulated and measured electrical parameters for a GAI single gate vertical MOSFET . . . . .                                      | 104 |

| 6.7 | Sheet resistances, implant dose and doping concentrations of the fabricated vertical GBI MOSFETs . . . . .                        | 105 |

| 6.8 | Measured electrical parameters for a GBI surround gate vertical MOSFET . . . . .                                                  | 107 |

| 7.1 | Parameter values used to calculate the theoretical values . . . . .                                                               | 121 |

| 7.2 | Summary of experimental data obtained from the SIMS measurements                                                                  | 124 |

| 7.3 | Comparison of measured and calculated values of base current . . . . .                                                            | 127 |

| B.1 | Layout description of fabricated vertical capacitors . . . . .                                                                    | 166 |

| B.2 | Layout description of fabricated vertical MOSFETs . . . . .                                                                       | 170 |

# List of Symbols

|              |   |                                                                            |

|--------------|---|----------------------------------------------------------------------------|

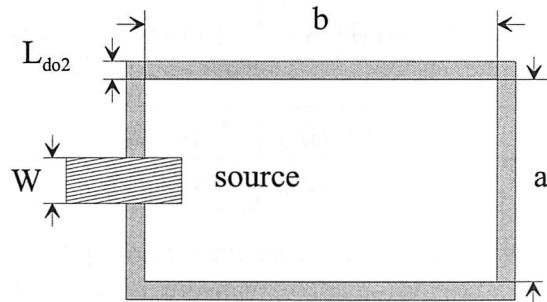

| $a$          | - | pillar length [m]                                                          |

| $a_{AA}$     | - | width of active area [m]                                                   |

| $A_c$        | - | cross-section area of the channel [ $\text{m}^2$ ]                         |

| $A_{ox}$     | - | oxide area [ $\text{m}^2$ ]                                                |

| $A_{sub}$    | - | cross-section area of current flow [ $\text{m}^2$ ]                        |

| <br>         |   |                                                                            |

| $b$          | - | pillar width [m]                                                           |

| $b_{AA}$     | - | length of active area [m]                                                  |

| $BV_{CBO}$   | - | common base breakdown voltage [V]                                          |

| $BV_{CEO}$   | - | common emitter breakdown voltage [V]                                       |

| $\beta$      | - | common emitter gain / process transconductance parameter                   |

| <br>         |   |                                                                            |

| $C_d$        | - | depletion capacitance [F]                                                  |

| $C_{GD}$     | - | gate/drain overlap capacitance [F]                                         |

| $C_{GDall}$  | - | overall gate/drain overlap capacitance [F]                                 |

| $C_{GDfill}$ | - | gate/drain overlap capacitance caused by fillets [F]                       |

| $C_{GS}$     | - | gate/source overlap capacitance [F]                                        |

| $C_{GSall}$  | - | overall gate/source overlap capacitance [F]                                |

| $C_{GSfill}$ | - | gate/source overlap capacitance caused by fillets [F]                      |

| $C_{GSsub}$  | - | gate/substrate overlap capacitance [F]                                     |

| $C_{jD}$     | - | drain junction capacitance [F]                                             |

| $C_{jDall}$  | - | overall drain junction capacitance [F]                                     |

| $C_{jS}$     | - | source junction capacitance [F]                                            |

| $C_{jSall}$  | - | overall source junction capacitance [F]                                    |

| $C_{ox}$     | - | oxide capacitance [ $\text{F m}^{-2}$ ]                                    |

| $c_p$        | - | trap capture cross section [ $\text{m}^{-2}$ ]                             |

| <br>         |   |                                                                            |

| $d_g$        | - | polySiGe grain width [m]                                                   |

| $d_{gb}$     | - | grain boundary thickness [m]                                               |

| $D_{gb}$     | - | hole diffusion coefficient in grain boundary [ $\text{m}^2\text{s}^{-1}$ ] |

| $D_n$        | - | electron diffusion coefficient [ $\text{m}^2\text{s}^{-1}$ ]               |

| $D_{nb}$     | - | electron diffusion coefficient in base [ $\text{m}^2\text{s}^{-1}$ ]       |

| $D_{pe}$     | - | hole diffusion coefficient in emitter [ $\text{m}^2\text{s}^{-1}$ ]        |

| $D_{pSiGe}$  | - | hole diffusion coefficient in polySiGe grain [ $\text{m}^2\text{s}^{-1}$ ] |

| <br>         |   |                                                                            |

| $E$          | - | electric field [ $\text{V m}^{-1}$ ]                                       |

| $E_c$        | - | energy level of the conduction band [eV]                                   |

| $E_f$        | - | Fermi energy level [eV]                                                    |

|                    |   |                                                                  |

|--------------------|---|------------------------------------------------------------------|

| $E_{Fp}$           | - | quasi Fermi level [eV]                                           |

| $E_g$              | - | semiconductor band gap [eV]                                      |

| $E_i$              | - | intrinsic energy level [eV]                                      |

| $E_s$              | - | electric field at the silicon surface [V/m]                      |

| $E_v$              | - | energy level of the valence band [eV]                            |

| $\epsilon_0$       | - | vacuum permittivity [F/m]                                        |

| $\epsilon_{Si}$    | - | relative dielectric constant of silicon                          |

| $\epsilon_{SiO_2}$ | - | relative dielectric constant of silicon dioxide                  |

| $\eta$             | - | viscosity [ $\text{kg m}^{-1}\text{s}^{-1}$ ]                    |

| $f_{max}$          | - | maximum oscillation frequency [Hz]                               |

| $f_T$              | - | cutoff frequency / transit frequency [Hz]                        |

| $\phi_f$           | - | Fermi potential [V]                                              |

| $\phi_m$           | - | metal work function [V]                                          |

| $\phi_{poly}$      | - | Fermi potential of polySi [V]                                    |

| $\phi_s$           | - | silicon work function [V]                                        |

| $\phi_{ms}$        | - | metal/silicon work function difference [V]                       |

| $\phi_{ss}$        | - | surface potential at the source [V]                              |

| $\psi_{bi}$        | - | built-in voltage of the pn-junction [V]                          |

| $\psi_s$           | - | surface potential [V]                                            |

| $I_B$              | - | base current [A]                                                 |

| $I_C$              | - | collector current [A]                                            |

| $I_D$              | - | drain current [A]                                                |

| $I_{Dsub}$         | - | subthreshold drain current [A]                                   |

| $I_{on}$           | - | on-current [A]                                                   |

| $J$                | - | hole current density [ $\text{A m}^{-2}$ ]                       |

| $k$                | - | Boltzmann constant [ $\text{J K}^{-1}$ ]                         |

| $K$                | - | form factor for narrow-width effect                              |

| $L$                | - | channel length [m]                                               |

| $L_{do}$           | - | pillar to active area spacing [m]                                |

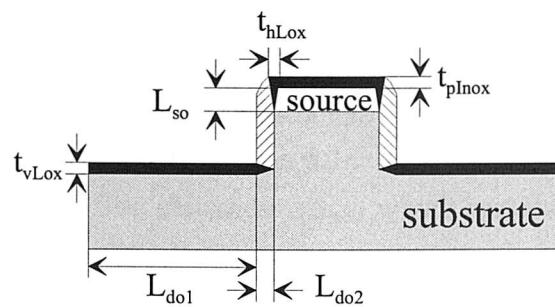

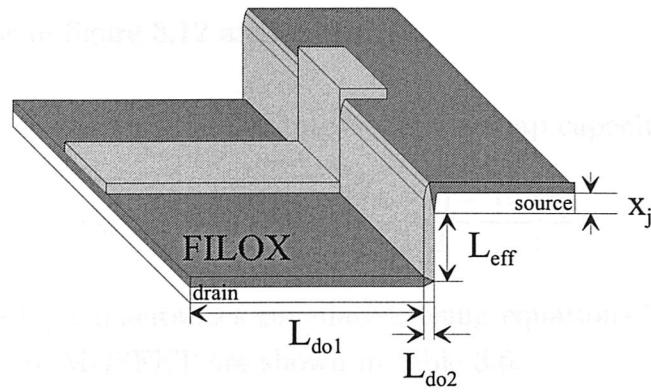

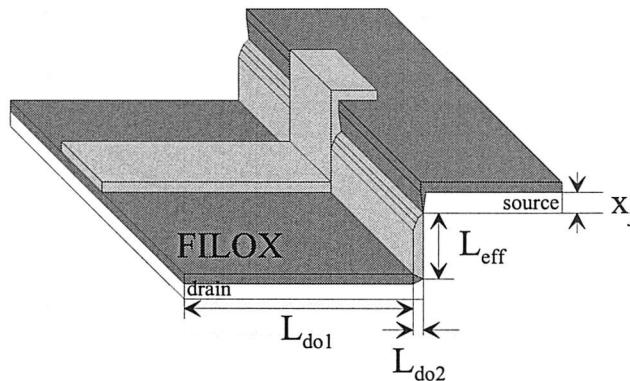

| $L_{do1}$          | - | FILOX length at the bottom of the pillar [m]                     |

| $L_{do2}$          | - | bird's beak length at the bottom of the pillar [m]               |

| $L_{eff}$          | - | effective channel length [m]                                     |

| $L_j$              | - | implanted length [m]                                             |

| $L_P$              | - | pinch-off length [m]                                             |

| $L_{pSi}$          | - | hole diffusion length in Si [m]                                  |

| $L_{pSiGe}$        | - | hole diffusion length in SiGe [m]                                |

| $L_{so}$           | - | bird's beak length at the top of the pillar [m]                  |

| $\mu_n$            | - | channel mobility [ $\text{m}^2 \text{V}^{-1} \text{s}^{-1}$ ]    |

| $n$                | - | electron concentration [ $\text{m}^{-3}$ ]                       |

| $N_A$              | - | acceptor doping concentration [ $\text{m}^{-3}$ ]                |

| $N_{Abeff}$        | - | effective acceptor concentration in the base [ $\text{m}^{-3}$ ] |

|               |   |                                                                        |

|---------------|---|------------------------------------------------------------------------|

| $N_{CSi}$     | - | effective densities of states in the Si conduction band [ $m^{-3}$ ]   |

| $N_{CSiGe}$   | - | effective densities of states in the SiGe conduction band [ $m^{-3}$ ] |

| $N_D$         | - | donor doping concentration [ $m^{-3}$ ]                                |

| $N_{Deeff}$   | - | effective donor concentration in the emitter [ $m^{-3}$ ]              |

| $n_i$         | - | intrinsic carrier concentration in silicon [ $m^{-3}$ ]                |

| $n_{iSiGe}$   | - | intrinsic carrier concentration in SiGe [ $m^{-3}$ ]                   |

| $n_p$         | - | electron concentration in substrate [ $m^{-3}$ ]                       |

| $N_{st}$      | - | trap density [ $m^{-3}$ ]                                              |

| $N_{VSi}$     | - | effective densities of states in the Si valence band [ $m^{-3}$ ]      |

| $N_{VSiGe}$   | - | effective densities of states in the SiGe valence band [ $m^{-3}$ ]    |

| $v_{th}$      | - | thermal velocity [ $m s^{-1}$ ]                                        |

| $p_{Si}$      | - | hole concentration in silicon [ $m^{-3}$ ]                             |

| $p_{SiGe}$    | - | hole concentration in SiGe [ $m^{-3}$ ]                                |

| $q$           | - | elementary charge [ $A s$ ]                                            |

| $Q_B$         | - | depletion charge density [ $C cm^{-2}$ ]                               |

| $Q_f$         | - | fixed-oxide charge [ $cm^{-2}$ ]                                       |

| $Q_{it}$      | - | interface-trapped charge [ $cm^{-2}$ ]                                 |

| $Q_m$         | - | mobile ionic charge [ $cm^{-2}$ ]                                      |

| $Q_{ot}$      | - | oxide-trapped charge [ $cm^{-2}$ ]                                     |

| $\rho$        | - | charge density [ $Cm^{-3}$ ]                                           |

| $S$           | - | subthreshold swing [V/decade]                                          |

| $S_{EFF}$     | - | effective surface recombination velocity [ $m s^{-1}$ ]                |

| $S_G$         | - | surface recombination velocity at the grain boundary [ $m s^{-1}$ ]    |

| $S_{GB}$      | - | recombination velocity at grain boundary contact [ $m s^{-1}$ ]        |

| $S_I$         | - | recombination at the polySi/silicon interface [ $m s^{-1}$ ]           |

| $S_M$         | - | recombination velocity at metal contact [ $m s^{-1}$ ]                 |

| $\sigma_{xx}$ | - | normal stress in x-direction [dyne $m^{-2}$ ]                          |

| $\sigma_{yy}$ | - | normal stress in y-direction [dyne $m^{-2}$ ]                          |

| $T$           | - | temperature [K]                                                        |

| $T_I$         | - | tunnelling coefficient [ $m s^{-1}$ ]                                  |

| $t_{hLox}$    | - | bird's beak thickness at the top of the pillar [m]                     |

| $t_{ox}$      | - | oxide thickness [m]                                                    |

| $t_{pInox}$   | - | insulator thickness on top of the pillar [m]                           |

| $t_s$         | - | shallow trench isolation oxide thickness [m]                           |

| $V_B$         | - | substrate bias voltage [V]                                             |

| $V_{be}$      | - | base emitter voltage [V]                                               |

| $V_c$         | - | channel voltage [V]                                                    |

| $V_{DS}$      | - | drain/source voltage [V]                                               |

| $V_{DS,sat}$  | - | source/drain voltage at saturation [V]                                 |

| $V_{FB}$      | - | flat band voltage [V]                                                  |

| $V_G$         | - | gate voltage [V]                                                       |

| $V_j$         | - | reverse bias voltage across the junction [V]                           |

---

|             |   |                                               |

|-------------|---|-----------------------------------------------|

| $V_T$       | - | threshold voltage [V]                         |

| $V_{Tbias}$ | - | threshold voltage with substrate bias [V]     |

| $V_{TSCE}$  | - | short-channel threshold voltage [V]           |

| $V_{TNWE}$  | - | narrow-width threshold voltage [V]            |

| $V_{ox}$    | - | voltage at the oxide [V]                      |

| $V_0$       | - | voltage drop across the interfacial oxide [V] |

| $W$         | - | channel width [m]                             |

| $W_{all}$   | - | overall channel width [m]                     |

| $W_B$       | - | base width [m]                                |

| $W_E$       | - | emitter depth [m]                             |

| $W_s$       | - | gate over STI overlap [m]                     |

| $x_a$       | - | length of capacitor [m]                       |

| $x_b$       | - | width of capacitor [m]                        |

| $x_c$       | - | channel thickness [m]                         |

| $x_{ceff}$  | - | effective channel thickness [m]               |

| $x_d$       | - | depletion region width [m]                    |

| $x_{poly}$  | - | polysilicon layer thickness [m]               |

| $\chi_e$    | - | electron affinity [V]                         |

| $\chi_h$    | - | hole affinity [V]                             |

# Acknowledgements

I would like to thank my supervisor Prof. P. Ashburn, for his guidance and support during my PhD project. Throughout this project a number of people joined the VMOS team at Southampton University who also contributed to the success of this project: Dr C.H. de Groot, Dr T. Uchino and E. Gili. Many thanks are also due to Prof. S. Hall from Liverpool University for his cooperation and suggestions.

My project involved a lot of fabrication work. I would therefore like to thank the cleanroom team for their support. Furthermore, thanks to Dr I. M. Anteney and Dr A. I. Abdul-Rahim for fabricating the SiGe HBTs and Dr Y. Wang from the University of Surrey for extracting the TEM pictures from my samples. Thanks also to Dr S. Wang from the University of Southampton for the FESEM introduction.

Right from the start of my project I enjoyed the friendly atmosphere in the Microelectronics group. So, many thanks to all of you!

Above all, I would like to thank my parents Veit Martin and Sibylle as well as my two sisters Nanna and Nina for their support over all these years.

# Chapter 1

## Introduction

According to the semiconductor roadmap the gate length of MOS transistors will be decreased to 40nm in production by 2011 [1]. To achieve device scaling down to 40nm and below double gate devices are currently considered the most promising option because the double gate gives better control of the channel and hence better short-channel effects [2]. In general, three possible architectures can be classified by the orientation of the channel:

- planar SOI

- SOI fin (horizontal current flow)

- vertical (vertical current flow)

Planar SOI double gate transistors are an extension of the conventional SOI-MOSFET. A back gate for better control of the channel is added by etching a cavity into the buried oxide layer underneath the active silicon region [3]. The fabrication process of planar double gate devices is complicated and can involve several critical steps like epitaxy and chemical mechanical polishing (CMP) [4]. The authors in [5] suggest a bonding techniques to achieve the oxide/gate/oxide structure.

An early approach to SOI fins, called the DELTA transistor, was presented in [6, 7]. These devices were fabricated by oxidising the silicon underneath the active channel area to obtain a SOI structure. However, very good control of the oxidation is needed to accurately control the thickness of the silicon fin which is protected by nitride fillets at the sidewalls. A similar device called the FinFET [8–23] has recently gained attention by the industry and channel lengths of less than 20nm have been reported in [10, 17]. To increase the current drive, the width of the device is increased by the parallel connection of several fins. However, Chang et al. [17] reported increased source and drain resistances for very thin fins.

All of the above concepts require stepper lithography to define the channel region. Lithography tools for sub 100nm channel lengths are extremely expensive and CMOS mask sets cost over \$1 million per set. Recently there has therefore been considerable interest in vertical MOS transistors to overcome these lithography limitations. By arranging the channel vertically the channel length becomes independent of the lithography capability. Several approaches have been investigated for the design and fabrication of vertical MOSFETs. These approaches can be partitioned into four broad categories, namely epitaxy, replacement gate, ion implantation and vertical devices incorporating SiGe.

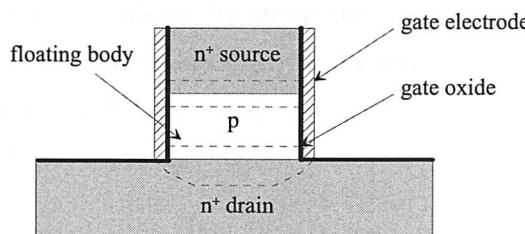

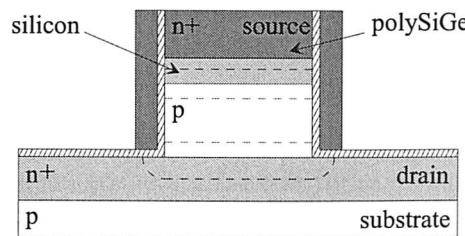

The epitaxy approach is illustrated in figure 1.1 [24–34]. A MOS transistor is created by growing epitaxial layers for the  $n^+$  drain, p-channel and  $n^+$  source. The channel length can be very small because of the good control of layer thickness that can be achieved using molecular beam epitaxy (MBE) or low pressure chemical vapor deposition (LPCVD). Following epitaxy, a pillar is etched, a gate oxide is grown and a polysilicon gate deposited to create the vertical MOS transistor. Transistors with channel lengths in the range 100–30nm have been produced in this way [32]. There are three main disadvantages of this approach. The first is overlap capacitance where the polysilicon gate passes over the drain at the bottom of the pillar and over the source at the top of the pillar. The second is the very high parasitic bipolar transistor gain that is obtained because both the source and drain extend across the full width of the pillar. The third is the integration of epitaxial layers into a standard CMOS process.

Figure 1.1: Vertical MOSFET based on epitaxy

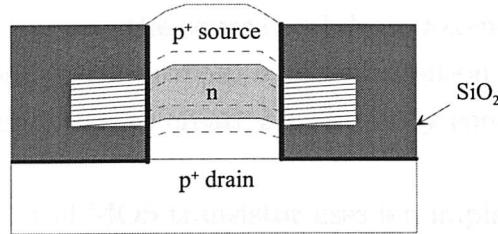

A variant of the epitaxy approach has been developed, which uses selective epitaxy [35–39], as illustrated in figure 1.2. In this approach, an oxide/polysilicon/oxide stack is created before the epitaxy. A gate oxide layer is then formed on the side of the polysilicon gate and the  $n^+$  drain, p-channel and  $n^+$  source are grown using selective epitaxy. This approach has the advantage that the overlap capacitance is eliminated, but the high parasitic bipolar gain remains as a problem. Furthermore, additional problems are introduced, in particular the growth of a high quality gate oxide on polysilicon and the problem of controlling facets during selective epitaxy.

Figure 1.2: Vertical MOSFET based on selective epitaxy with reduced overlap capacitance

In a final variant of the epitaxy approach [32–34], a surround gate or double gate structure is created by extending the polysilicon gate over the entire width of the pillar. If the pillar width is dramatically reduced, a fully depleted device can be produced analogous to those produced using SOI technology. A double gate, fully depleted vertical MOS transistor would be very attractive for deep sub  $0.1\mu\text{m}$  CMOS because of improved short channel effects. However, such a device would potentially have the same disadvantages as the transistor in figure 1.1, namely high overlap capacitance and high parasitic bipolar gain.

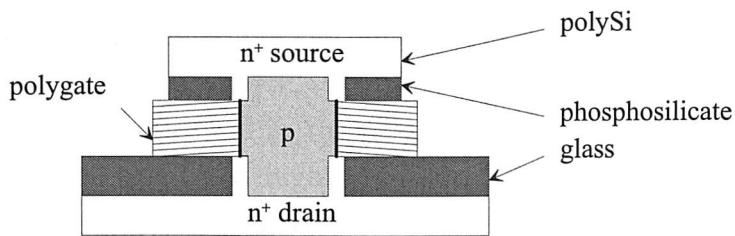

The second category of vertical MOS transistor [40–42] uses layer deposition to create a channel length that is defined by the layer thicknesses, as illustrated in figure 1.3. The source and drain regions are created by diffusion from PSG. This means that the channel length is defined by the thickness of the gate layer and by the amount of out-diffusion from the PSG layers. The p-channel region is grown by selective epitaxy, and the faceting problem is avoided by growing the layer thicker than needed and polishing back. A gate replacement technique is used to create the gate which means that the gate oxide can be grown on single crystal silicon rather than on polysilicon as in the device in figure 1.2.

Figure 1.3: Vertical replacement-gate MOSFET

Contact to the drain is made through a buried  $n^+$  layer and to the source through a  $n^+$  polysilicon source pad. In this device, overlap capacitances are lower than in the device in figure 1.1 because it is determined by the thickness of the insulators between the PSG layers and the gate layer. However, parasitic bipolar transistor

action is still a problem because the source and drain extend across the entire width of the pillar. The authors in [42] propose a partial solution to this problem by using a shallow polysilicon source pad to create a leaky body contact.

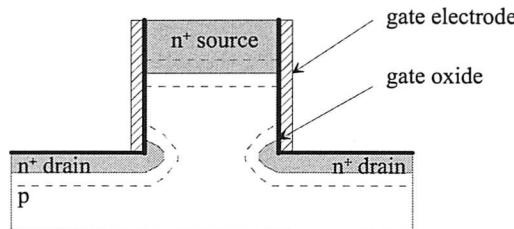

The third category of vertical MOS transistor uses ion implantation [43–53] to create the source and drain regions, as illustrated in figure 1.4. In this device, the channel length is defined by the pillar height and the implant energy. The drain region behaves like an elevated source/drain. Ion implanted devices with threshold voltage adjustment using phosphorous silicate glass (PSG) as a dopant source have been proposed by Mori et al. [52, 53]. The parasitic bipolar gain is lower than that in the device shown in figure 1.1, because the drain does not penetrate across the width of the pillar. However, overlap capacitances are still a problem.

Figure 1.4: Vertical MOSFET based on ion implantation

The fourth category of vertical MOS transistor is appropriate for p-channel transistors and uses SiGe in the source. The insertion of SiGe into the source has the advantage of introducing a potential energy barrier that decreases drain induced barrier lowering and hence improves short channel effects [54–59]. Devices down to a channel length of 25nm have been fabricated [59]. Unfortunately, this technique can only be used in p-channel transistors because a potential energy barrier is not obtained in n-type SiGe. This device again has the disadvantage of a high overlap capacitance, though the SiGe layer has the benefit of reducing the parasitic bipolar gain.

Strained SiGe has also been used in the channels of vertical MOSFETs as reported in [55, 60–63]. The SiGe gives a higher surface mobility and as a result increased current drives of up to 100% and 50% over silicon control devices for PMOS and NMOS devices, respectively. To overcome the problem of oxidising SiGe the authors in [58, 64] deposited a silicon epitaxial layer (Si-cap) which is oxidised during gate oxidation.

The above literature review demonstrates that overlap capacitance and parasitic bipolar gain are two fundamental problems with vertical MOS transistors. This work addresses the reduction of overlap capacitance by using a fillet local oxidation

(FILOX) scheme to reduce the overlap capacitance between the polysilicon gate track and the source and drain. It is shown that the FILOX process is capable of reducing the overlap capacitance by a factor of 3.9 in vertical capacitors. Electrical characterisation of 105nm channel length NMOS transistors incorporating the FILOX process are presented and show a subthreshold slope of 111mV/decade. Parasitic bipolar gain is investigated through the use of a polycrystalline SiGe layer in the source. It is shown that the polySiGe source reduces the parasitic bipolar gain by up to a factor of 4.0. A dielectric pocket in combination with a retrograde channel is proposed to confine the source regions to the corners of the pillar and reduce short-channel effects.

QUESTION

$$V_{FB} = \phi_m - \phi_s + q\chi_e + q\phi_m = \left( \phi_m + \frac{q\chi_e}{2} \right) + q\phi_m - q\phi_s$$

where  $V_{FB}$  is the flat band voltage,  $\phi$  is the potential,  $\chi$  is the charge density,  $q$  is the elementary charge,  $\phi_m$  is the metal work function,  $\phi_s$  is the silicon work function,  $\chi_e$  is the surface potential and  $t_{ox}$  is the oxide thickness.

## Chapter 2

# Theory of MOSFETs

In this chapter the fundamental theory of MOS devices will be discussed. The following considerations are made for a uniformly doped p-type semiconductor substrate.

### 2.1 Two-terminal MOS structure

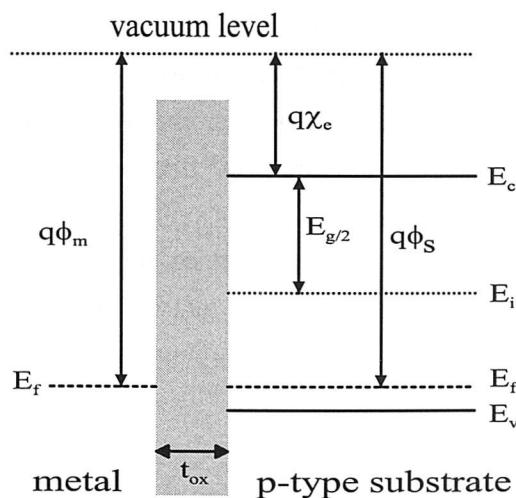

A two-terminal metal oxide semiconductor (MOS) structure, also known as a MOS capacitor, consists of three layers namely a semiconductor layer, an embedded insulator layer and a conducting layer. Figure 2.1 illustrates the energy band diagram of an ideal two-terminal MOS structure.

Figure 2.1: Band diagram of an idealised two-terminal MOS structure in flat band condition

In an idealised MOS structure the flat band voltage  $V_{FB}$  defined as the energy band difference between the metal work function  $\phi_m$  and the silicon work function  $\phi_s$  is

zero so that

$$qV_{FB} = q\phi_{ms} = q\phi_m - q\phi_s = q\phi_m - \left( q\chi_e + \frac{E_g}{2} + q\phi_f \right) = 0 \quad (2.1)$$

where  $\phi_{ms}$  is the work function difference,  $q$  is the elementary charge,  $\chi_e$  is the electron affinity,  $E_g$  the band gap between the conduction and valence band,  $E_v$  the energy level of the valence band,  $E_c$  the energy level of the conduction band,  $\phi_f$  is named the Fermi potential and is the difference between the Fermi level  $E_f$  and the intrinsic energy level  $E_i$  divided by the electron charge  $q$ .

The Fermi potential of a p-type substrate can be calculated using the substrate doping concentration  $N_A$  and the intrinsic carrier concentration  $n_i$  as

$$\phi_f = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \quad (2.2)$$

where  $k$  is the Boltzmann constant and  $T$  the temperature in Kelvin.

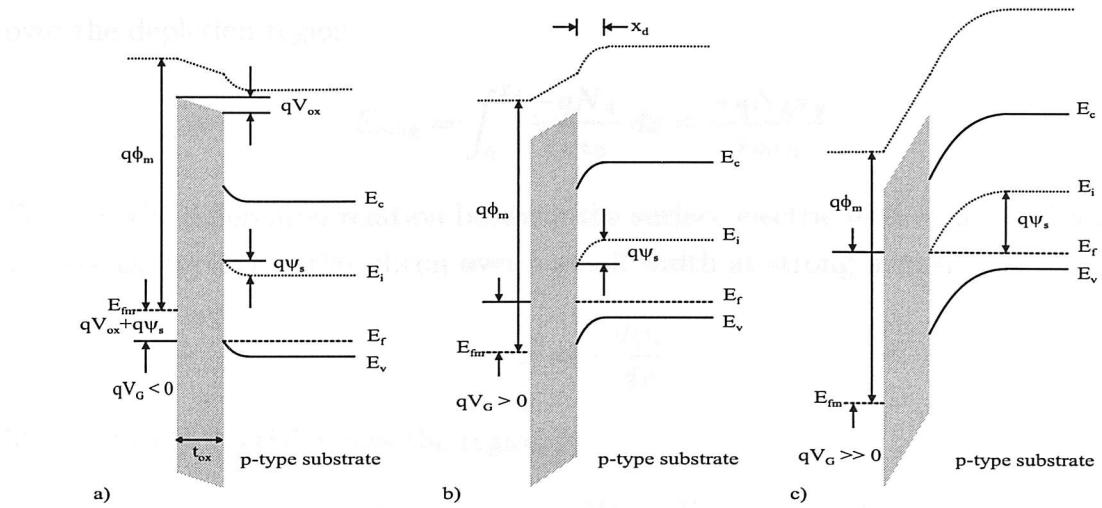

Applying a voltage to the semiconductor changes the charge in the substrate. Three modes of operation can be differentiated between namely accumulation, depletion and inversion, as shown in figure 2.2. In the case of a p-type substrate and a voltage  $V_G < 0V$  applied to the gate contact, whilst the substrate is connected to ground, free charge carriers (holes) are accumulated under the insulation layer (oxide). Since free holes are moving towards the silicon surface layer, the surface charge is of the same type as in the substrate, but of higher concentration. This layer is called accumulation layer (figure 2.2a). The applied voltage causes a voltage drop over the oxide as well as bending the energy bands in the substrate. At the oxide/semiconductor interface the surface potential  $\psi_s$  can be found.

If  $V_G > 0V$ , free positive charge carriers are pushed away from the surface layer and thereby a depletion region of the width  $x_d$  is formed. This process is termed depletion (figure 2.2b).

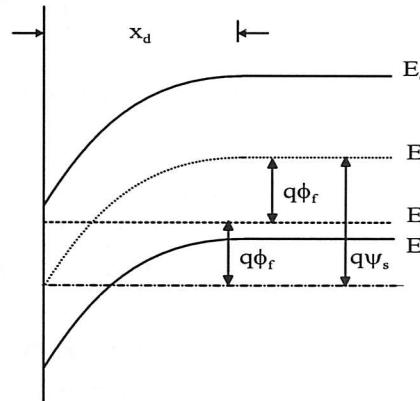

In figure 2.2c a large voltage is applied to the gate. The surface layer inverts from p-type to n-type as nearly all free holes are pushed away from the surface layer and at the same time free electrons accumulate underneath the oxide. As soon as the intrinsic level  $E_i$  increases beyond the Fermi level  $E_f$  to obtain a negative charged surface layer, the surface is in weak inversion mode ( $\psi_s \geq \phi_f$ ). At the onset of strong inversion the surface potential barrier  $\psi_s$  is defined by  $\psi_s = 2|\phi_f|$  as shown in figure 2.3.

Figure 2.2: One-dimensional MOS structure a) accumulation ( $\psi_s < 0$ ) b) depletion ( $0 < \psi_s < \phi_f$ ) c) onset of weak inversion ( $\psi_s = \phi_f$ )

Figure 2.3: Energy band diagram showing the onset of strong inversion ( $\psi_s = 2\phi_f$ )

The gate voltage to bring the surface layer into strong inversion is termed the threshold voltage  $V_T$ . In order to calculate the threshold voltage, first the depletion width  $x_d$  of a doped semiconductor needs to be calculated. This can be achieved by solving the one-dimensional Poisson's equation which relates the electric field  $E(x)$  to the charge density  $\rho(x)$  as follows

$$\frac{dE(x)}{dx} = \frac{\rho(x)}{\epsilon_{Si}\epsilon_0} \quad \text{for } 0 < x < x_d \quad (2.3)$$

where  $\epsilon_0$  is the dielectric constant in vacuum and  $\epsilon_{Si}$  is the dielectric constant of silicon [65].

The charge density equals the number of acceptors in the substrate  $\rho(x) = -qN_A$  for an abrupt junction. The maximum field can now be calculated by integrating

over the depletion region

$$E_{max} = \int_0^{x_d} \frac{-qN_A}{\epsilon_{Si}\epsilon_0} dx = \frac{-qN_Ax_d}{\epsilon_{Si}\epsilon_0} \quad (2.4)$$

Further, the differential relation between the surface electric field  $E$  at  $x = 0$  and the voltage  $\psi_s$  applied to the silicon over a small width at strong inversion is

$$E = -\frac{d\psi_s}{dx} \quad (2.5)$$

The surface potential across the region is

$$\psi_s = - \int_0^{x_d} E dx = - \int_0^{x_d} \frac{-qN_Ax_d}{\epsilon_{Si}\epsilon_0} dx = \frac{qN_Ax_d^2}{2\epsilon_{Si}\epsilon_0} \quad (2.6)$$

The depletion layer width for a p-type semiconductor can hence be calculated as

$$x_d = \sqrt{\frac{2\epsilon_{Si}\epsilon_0|\psi_s|}{qN_A}} \quad (2.7)$$

The substrate depletion charge  $Q_B$  density at the onset of strong inversion ( $\psi_s = 2|\phi_f|$ ) can be written as

$$Q_B = -qN_Ax_d = -qN_A \sqrt{\frac{2\epsilon_{Si}\epsilon_0 2|\phi_f| qN_A}{q^2 N_A^2}} = -\sqrt{4qN_A\epsilon_{Si}\epsilon_0|\phi_f|} \quad (2.8)$$

The applied gate-substrate voltage drops over the oxide as well as over the depletion region. The threshold voltage  $V_T$  is therefore

$$\begin{aligned} V_T &= V_{ox} + |\psi_s| = -\frac{Q_B}{C_{ox}} + 2|\phi_f| \\ &= \frac{\sqrt{4qN_A\epsilon_{Si}\epsilon_0|\phi_f|}}{C_{ox}} + 2|\phi_f| \end{aligned} \quad (2.9)$$

where  $V_{ox}$  is the oxide voltage.

Equation 2.9 shows that varying the substrate doping concentration changes the threshold voltage. This knowledge can be used to explicitly influence the threshold voltage in order to change the on/off voltage of the transistor. The desired threshold voltage is typically  $\pm 0.3V$  for n- and p-channel MOSFETs, respectively.

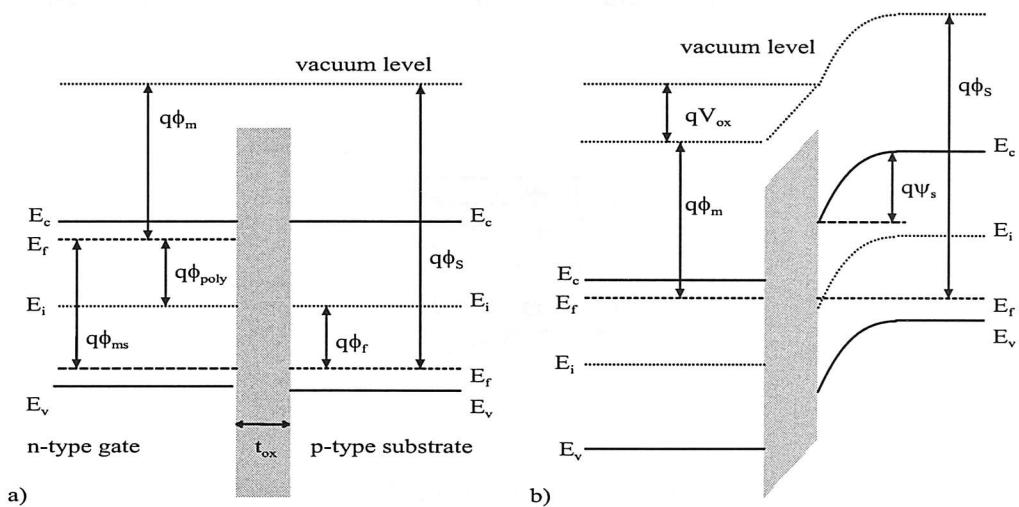

### 2.1.1 Work Function Difference

In practice, the work function in the silicon is different than the work function in the gate. This is certainly true for polysilicon, which is commonly used as a gate material in CMOS, as shown in figure 2.4. In this case the Fermi potential  $\phi_{poly}$ , assuming non-degeneration, of the n-type poly silicon can be written as

$$\phi_{poly} = \frac{kT}{q} \ln \left( \frac{n_i}{N_D} \right) \quad (2.10)$$

where  $N_D$  is the doping concentration of the poly silicon gate.

However, if the doping concentration of the polysilicon gate is higher than  $10^{18}$ - $10^{19}$  cm $^{-3}$  the Fermi level is equal to the energy level of the conduction band, so that  $E_f \simeq E_c$  [66].

Figure 2.4: Energy band diagram of a MOS structure with degenerated polysilicon a) flat band condition b) zero bias

Figure 2.4a illustrates the semiconductor/oxide semiconductor stack in flat band. The work function difference in this case is

$$q\phi_{ms} = -(q\phi_{poly} + q\phi_f) \quad (2.11)$$

If the gate and the substrate are under zero bias condition the semiconductor is depleted as shown in figure 2.4b. Here, the Fermi energy levels  $E_f$  of the gate and the substrate are aligned and the MOS structure is in weak inversion.

The threshold voltage can now be written as

$$V_T = \frac{\sqrt{4qN_A\epsilon_{Si}\epsilon_0|\phi_f|}}{C_{ox}} + 2|\phi_f| + V_{FB} \quad (2.12)$$

### 2.1.2 Oxide Interface Traps

The oxide charge  $Q_{ox}$  is the inherent charge embedded between the gate and semiconductor and is strongly affected by the gate oxidation conditions as well as the crystal orientation. In the previous section the voltage to achieve flat band  $V_{FB}$  was only dependent on the work function difference  $\phi_{ms}$  so that  $V_{FB} = \phi_{ms}$ .

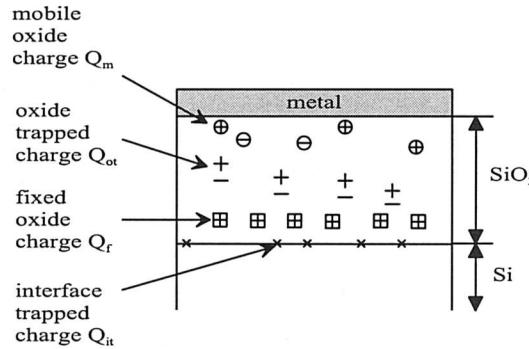

The flat band voltage needs to be modified to take care of charges in the silicon/gate oxide interface. These charges are namely interface-trapped charges, fixed-oxide charges, oxide-trapped charges and mobile ionic charge carriers as shown in figure 2.5.

Figure 2.5: Oxide traps in the gate oxide

Interface-trapped charges  $Q_{it}$ , with energy states in the silicon forbidden band gap are located at the Si-SiO<sub>2</sub> interface. The interface trap density is orientation dependent. A variation in the order of one magnitude can be found in <100> orientation compared with silicon in <111> orientation. Sze [67] reports values of  $Q_{it}$  in the region of  $10^{10} cm^{-2}$ .

Fixed-oxide charges  $Q_f$  are also depending on the oxidation and annealing conditions. Typical densities for a <100> surface are  $10^{10} cm^{-2}$  and for a <111> surface  $5 \times 10^{10} cm^{-2}$ .

Oxide-trapped charges  $Q_{ot}$  are caused by defects in the  $SiO_2$  layer due to X-ray radiation or high energy electrons.

Contamination during the oxidation process can leave alkali ions as mobile carriers in the silicon oxide causing mobile ionic charges  $Q_m$ . Assuming that all charges are very close to the oxide/silicon interface, the flat band voltage including the above discussed oxide charges can be written as

$$V_{FB} = \phi_{ms} - \frac{Q_{it} + Q_f + Q_m + Q_{ot}}{C_{ox}} \quad (2.13)$$

### 2.1.3 Small-signal capacitance

So far the two terminal MOS structure has been evaluated under static conditions. In this section the ac signal behaviour will be investigated. The capacitance  $C_{ox}$  between two plates of a parallel plate capacitor is given by

$$C_{ox} = \frac{\epsilon_{ox} \epsilon_0 A_{ox}}{t_{ox}} \quad (2.14)$$

where  $t_{ox}$  is the thickness of the oxide and  $A_{ox}$  the area.

Equation 2.14 is valid to calculate the capacitance in accumulation as shown in figure 2.6. If the two-terminal MOS structure is in depletion condition, the oxide capacitance and the capacitance of the depletion region are in series. The overall capacitance under this condition is

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_d} = \frac{C_{ox} + C_d}{C_{ox}C_d} \quad (2.15)$$

where  $C_d$  is the depletion capacitance.

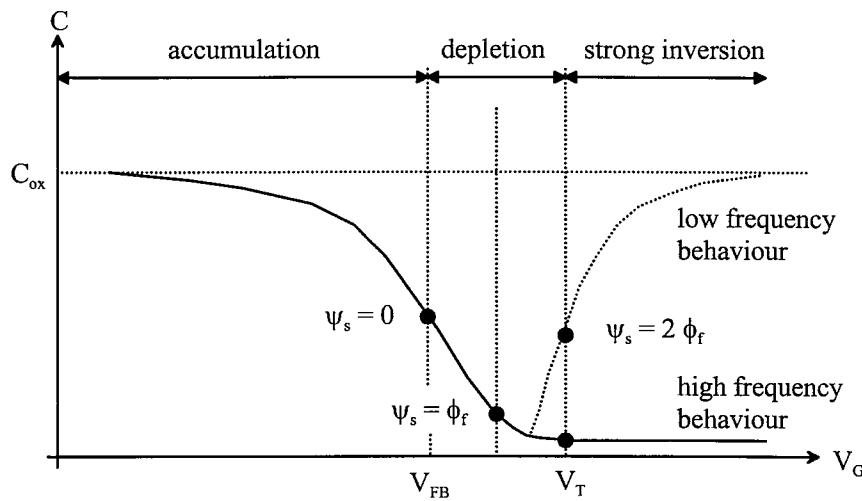

At high measurement frequencies, as the gate voltage is increased the capacitance drops to its minimum value so that the capacitance is given by equation 2.15. This is because the inversion layer charge (minority charge carriers) cannot keep up with the fast changing voltage applied to the device and only the depletion charge can respond to the applied ac-signal. The inversion layer charge can only be changed by the mechanism of thermal generation and recombination which is a relatively slow processes.

At low measurement frequencies a different behaviour is observed because the inversion layer charge can follow the variation of the applied signal. In this case the depletion charge is constant. All of the applied voltage drops across the oxide so that  $C=C_{ox}$  as in accumulation. Thus, if the capacitance is plotted as a function of  $V_G$ , a graph similar to figure 2.6 is obtained.

Figure 2.6: Capacitance of a two-terminal MOS structure as function of gate voltage. dotted line: deviation found at low frequencies

## 2.2 Four-terminal MOS structure

The four-terminal MOS structure or MOSFET is similar to a two-terminal MOS structure with the addition of source and drain regions. Two types of MOS transistors can be distinguished, namely enhancement mode and depletion mode devices. In this section the enhancement mode MOSFET will be discussed. For the following description of the device, it is assumed that the source is tied to ground.

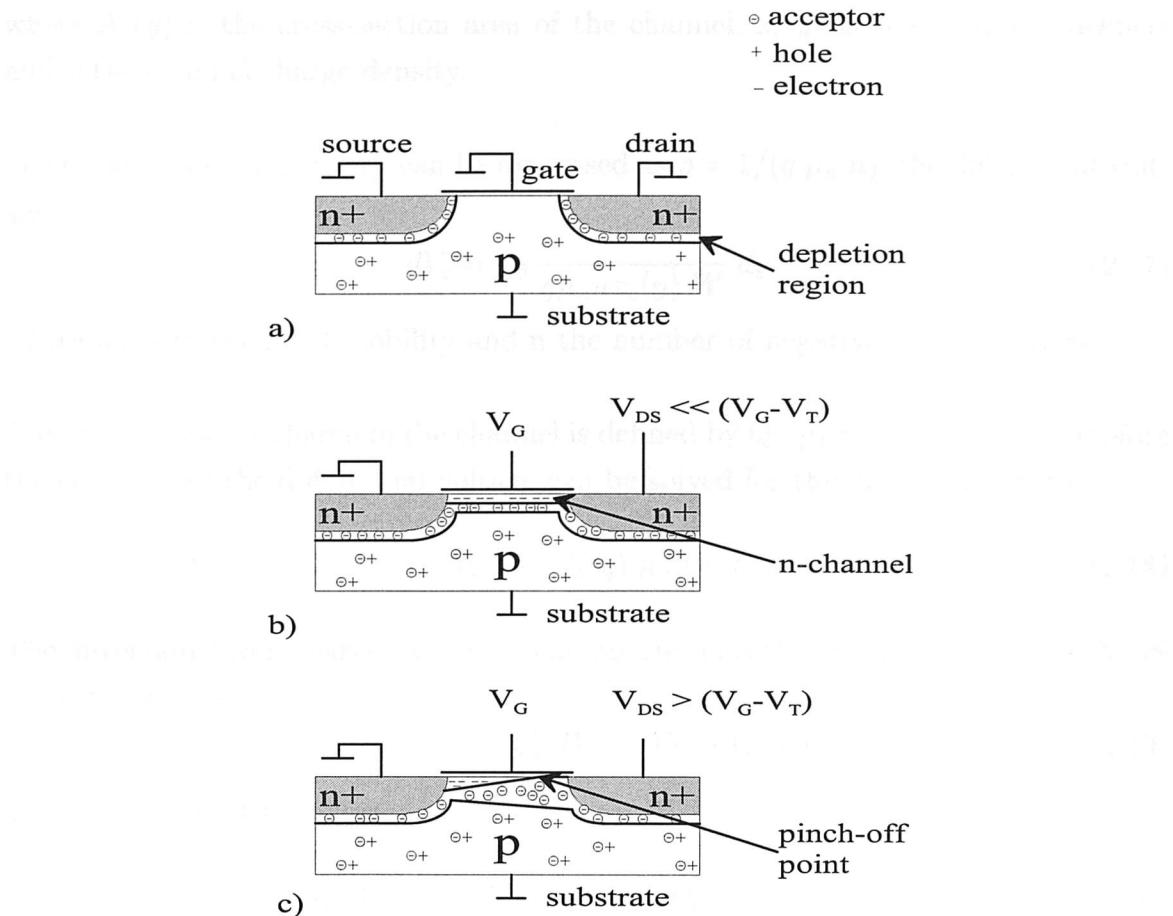

Figure 2.7a shows a zero biased gate, source, drain and substrate. Around the  $n^+ - p$  junctions, there is a small depletion region. The resistance between source and drain is very high, as the two pn-junctions are of opposite polarity.

Applying a gate voltage  $V_G$  of  $V_{FB} < V_G < V_T$  depletes the p-type semiconductor underneath the gate oxide. The space charge region around source and drain now extends under the gate. Increasing the gate voltage so that  $V_G > V_T$  adds to the already existing depletion region an inversion layer connecting the source and drain regions. However, since there is no voltage difference between the source and drain, no current can flow and  $I_D = 0$ .

### 2.2.1 Linear operation

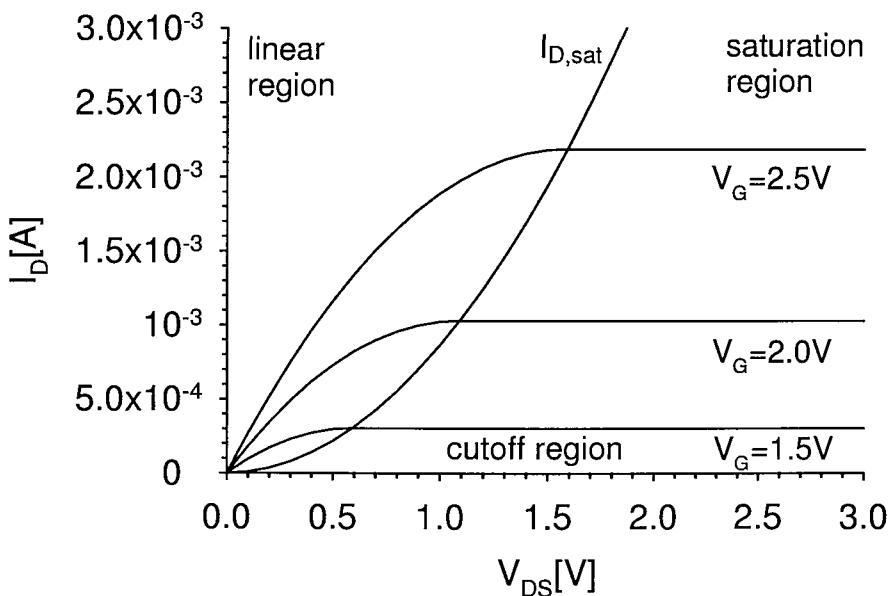

A positive gate voltage  $V_G$  of  $V_{FB} < V_G < V_T$  as well as a positive voltage connected to the drain ( $V_{DS} > 0$ ) forms a depletion layer underneath the gate oxide. Since the

Figure 2.7: Four terminal MOSFET structure a) with zero biased gate b) in cutoff mode c) in saturation

gate voltage is not sufficient to create an inversion layer, no channel exists to connect the source and drain regions. Without taking leakage currents into account it can be said that  $I_D=0$ . This mode of operation is called the cutoff mode. For the condition of  $V_G > V_T$  and  $V_{DS} < (V_G - V_T)$ , a channel is formed, connecting source and drain as shown in figure 2.7b. The MOSFET is said to be nonsaturated. Due to the inversion layer, free electrons lower the drain/source resistance, which is now much less than in depletion mode and, furthermore, can be controlled by the positive gate voltage. This mode of operation is called linear mode. The maximum channel voltage ( $V_{c,max}(y = L) = V_{DS}$ ) can be found at the drain and drops to  $V_{c,min}(y=0)=0V$  at the source.

It is assumed that the channel is of constant length  $L$ , and of constant width  $W$  and its thickness changes between source and drain. In the following, the drain current for the linear region will be derived. The differential voltage drop in the inversion channel, parallel to the surface is defined as

$$dV_c = I_D dR = I_D \frac{\rho}{A_c(y)} dy = I_D \frac{\rho}{x_c(y) W} dy \quad (2.16)$$

where  $A_c(y)$  is the cross-section area of the channel,  $x_c(y)$  is the channel thickness and  $\rho$  the channel charge density.

Since the channel resistivity can be expressed as  $\rho = 1/(q \mu_n n)$ , the differential voltage is

$$dV_c = I_D \frac{1}{q\mu_n n x_c(y) W} dy \quad (2.17)$$

where  $\mu_n$  is the channel mobility and  $n$  the number of negative charge carriers.

The inversion layer charge in the channel is defined by  $Q_I(y) = -q n x_c(y)$ . Therefore the equation of the differential voltage can be solved for the drain current, to

$$I_D dy = -Q_I(y) \mu_n W dV_c \quad (2.18)$$

The inversion layer charge is dependent on the effective voltage across the MOS capacitor so that

$$Q_I(y) = -C_{ox}(V_G - V_T - V_c(y)) \quad (2.19)$$

The drain current becomes

$$I_D dy = C_{ox}(V_G - V_T - V_c(y)) \mu_n W dV_c \quad (2.20)$$

Integrating the left term of the equation over the given channel length  $L$ , whilst integrating the right term of equation 2.20 over the voltage drop across the channel gives

$$\begin{aligned} I_D \int_0^L dy &= C_{ox} \mu_n W \int_0^{V_{DS}} (V_G - V_T - V_c(y)) dV_c \\ I_D L &= C_{ox} \mu_n W \left( (V_G - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right) \end{aligned} \quad (2.21)$$

With

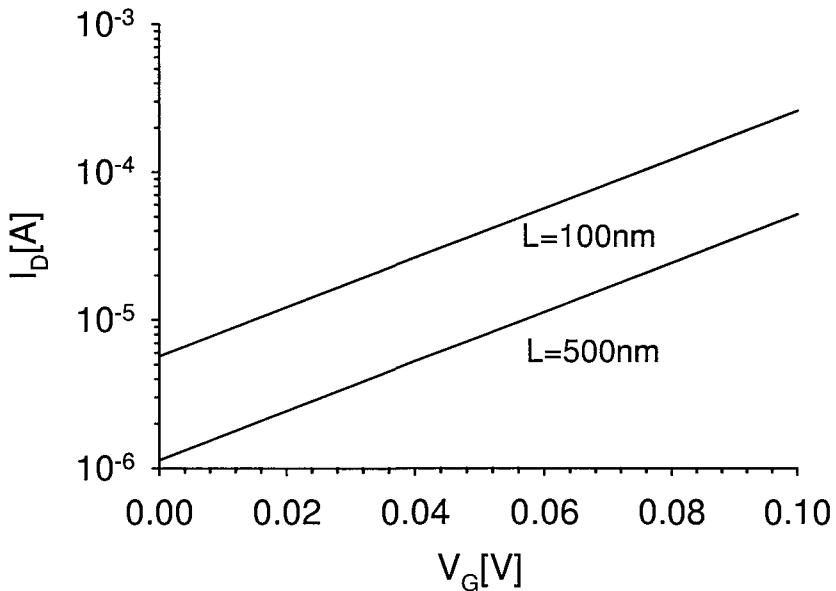

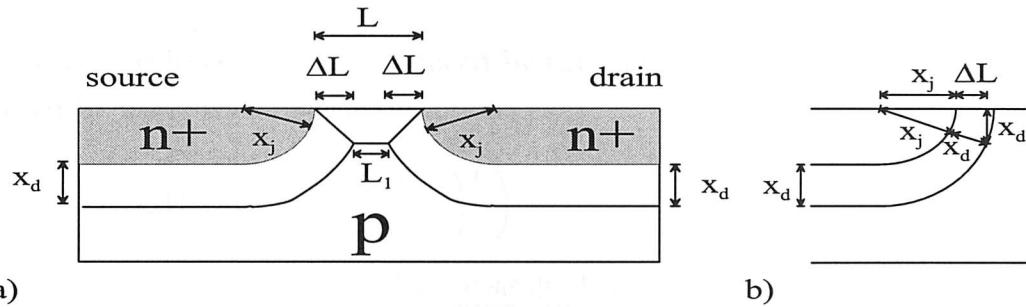

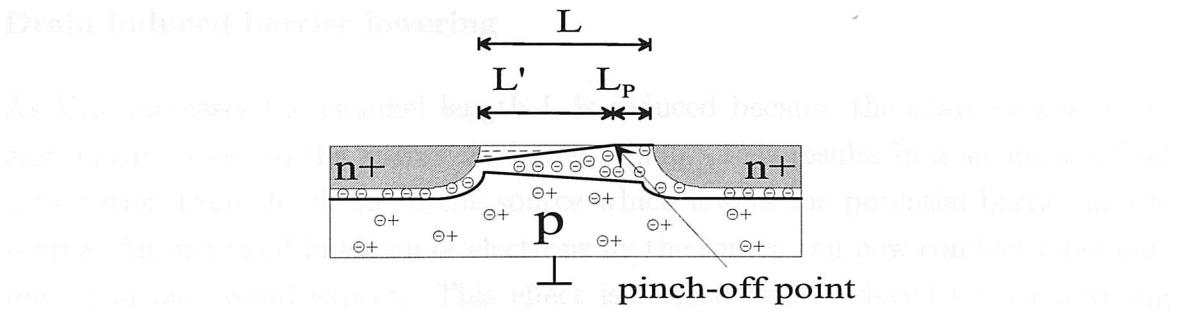

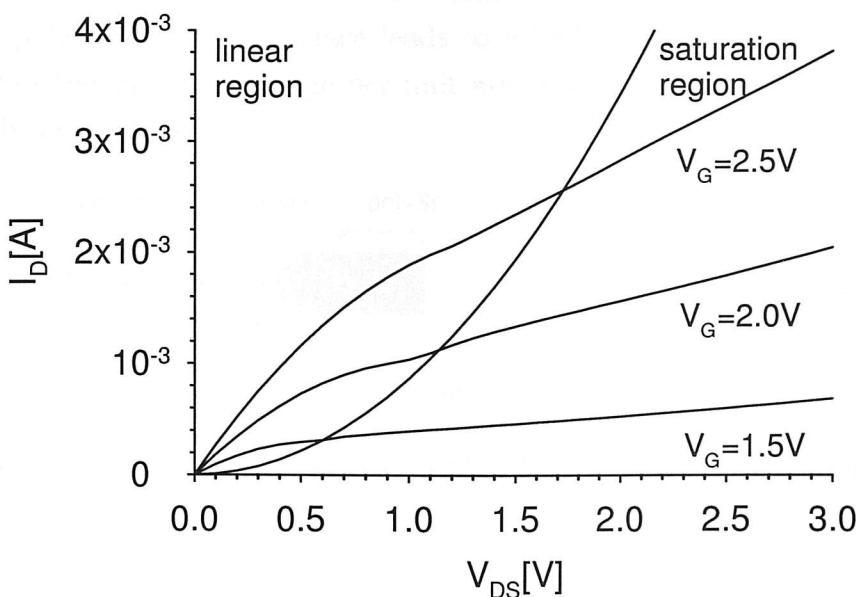

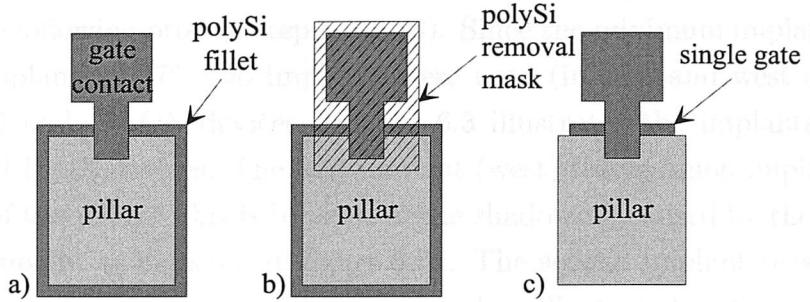

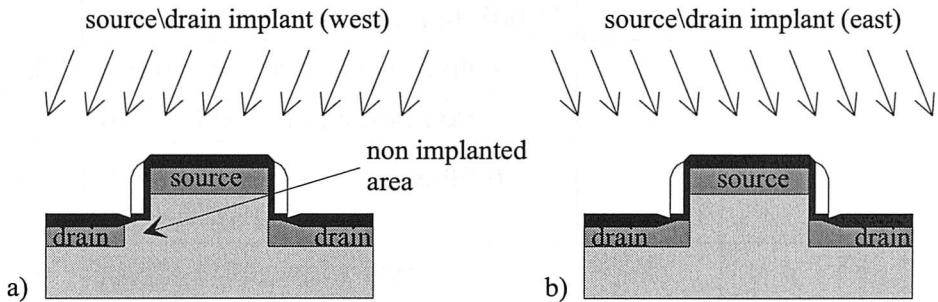

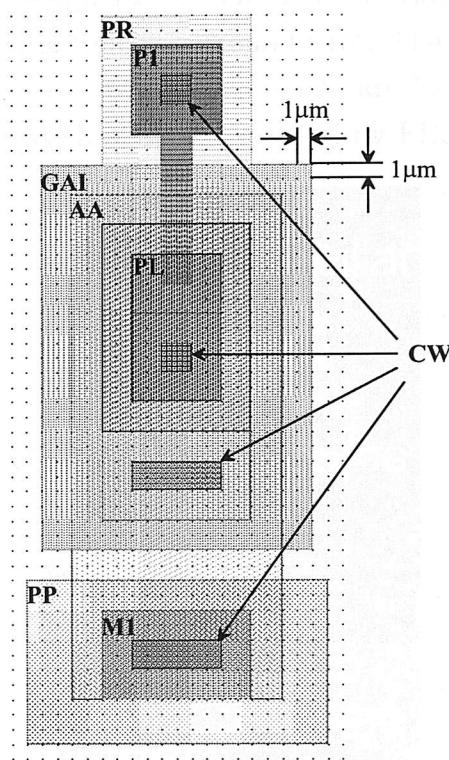

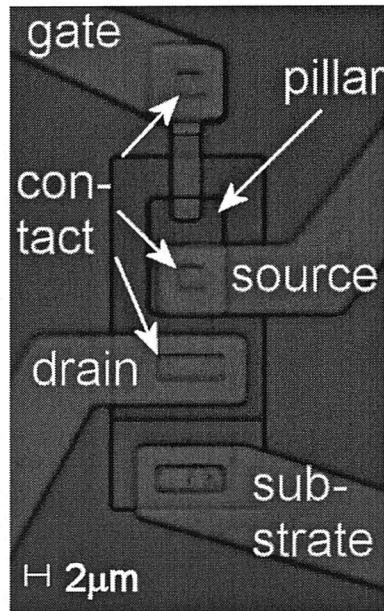

$$\beta = C_{ox} \mu_n \frac{W}{L} \quad (2.22)$$