# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL AND APPLIED SCIENCE

School of Electronics and Computer Science

# A STUDY ON THE EFFECTS OF VARIABILITY ON PERFORMANCE OF CNFET BASED DIGITAL CIRCUITS

By

Hamed Shahidipour

A thesis submitted for the degree of Doctor of Philosophy

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

#### FACULTY OF PHYSICAL AND APPLIED SCIENCE

#### SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### **Doctor of Philosophy**

#### A STUDY ON THE EFFECTS OF VARIABILITY ON PERFORMANCE OF CNFET BASED DIGITAL CIRCUITS

#### By Hamed Shahidipour

With the continuous trend of reducing feature sizes, and employing continuously smaller components on integrated circuits, new challenges arise on the way of silicon CMOS circuits and devices. Emerging "nanodevices" promise the possibility of increased integration density and reduced power consumption. The emerging and new devices, partially due to their extremely small dimensions, show large variations in their behaviour. The variation shown by these devices affects their reliability and the performance of circuits made from them. The Carbon Nano-Tube (CNT) is one such device which is also the device of choice in this work. This work is concerned with building reliable systems out of these unreliable components. The work was done in HSPICE with the help of the Stanford CNFET model. Logic gates are implemented using CNT Field Effect Transistors (CNFETs) which are in turn made from CNTs with different physical attributes. Given a CNT manufacturing process, there exists a mean and standard deviation (STD) for the diameter distribution of the manufactured CNTs which depend on the accuracy of the manufacturing process

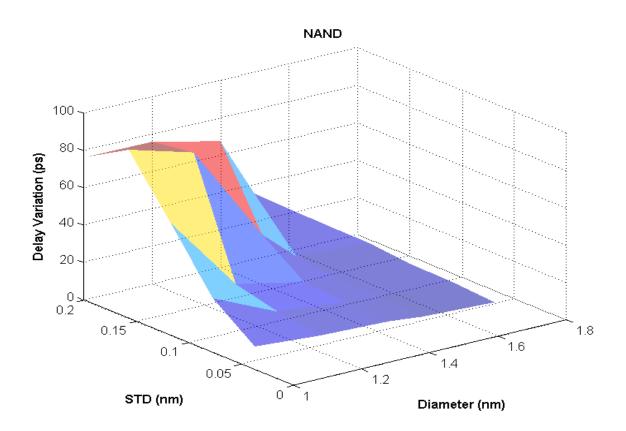

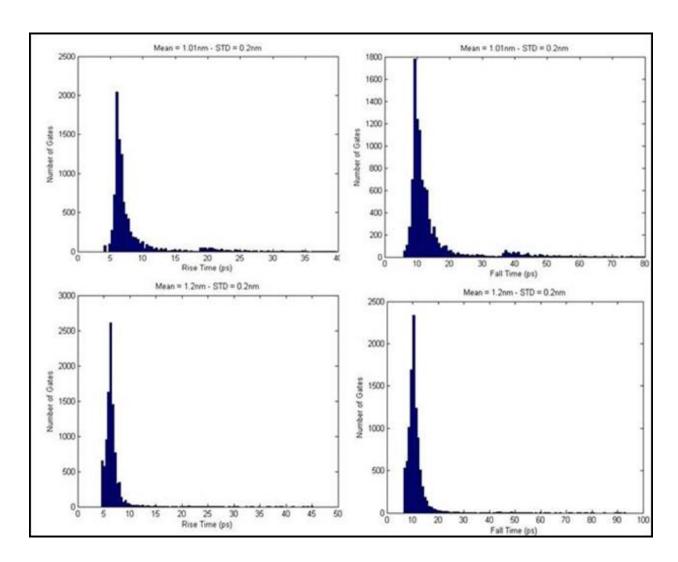

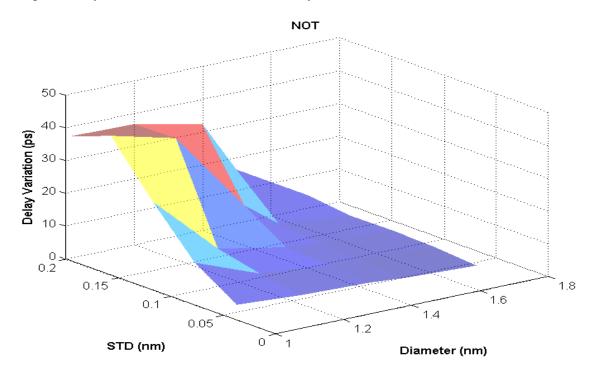

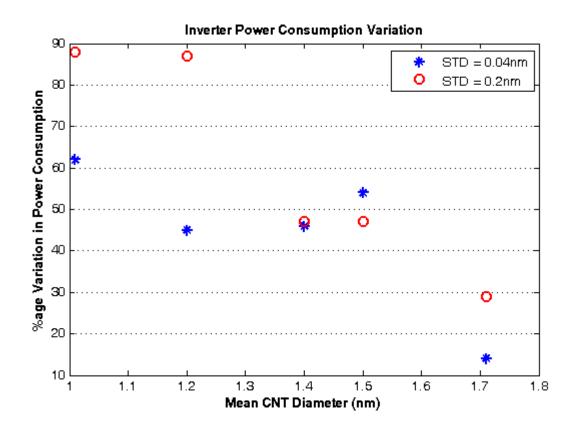

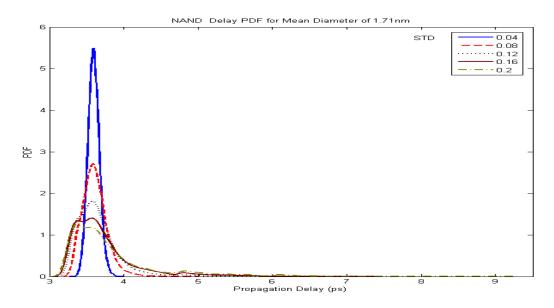

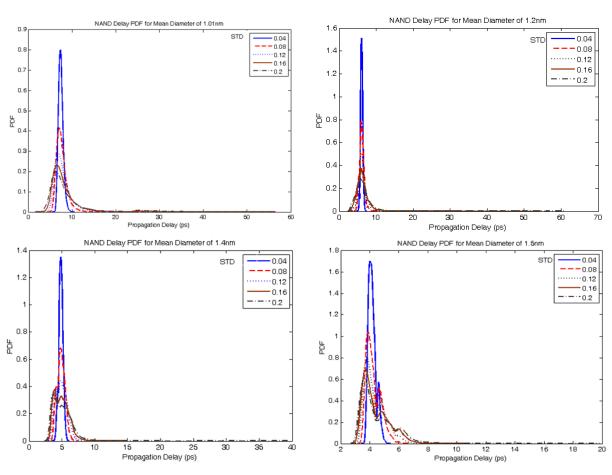

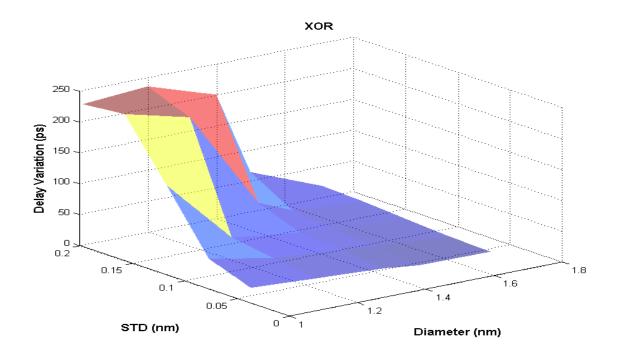

In the first part of this work, CNTs with different mean diameters and standard deviations (STD) in their diameter distribution are considered. Simulation results show that logic gates made from CNTs with larger mean and smaller STDs in their diameter distribution show less variation in their timing behaviour (propagation delay, rise and fall times) and a promise of more reliable operation.

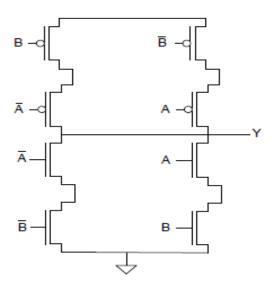

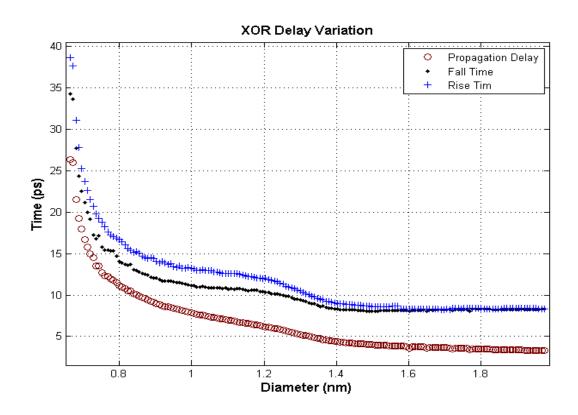

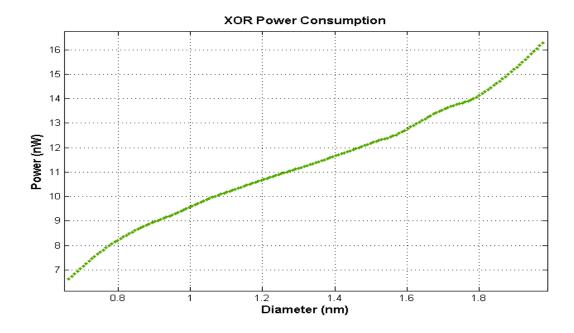

Alternative structures were then explored in the form of multiplexers and XOR gates. It is shown that these structures have the advantage over the gates studied previously in that they exhibit similar rise and fall transition times and hence are better suited to CNFET-based circuit design.

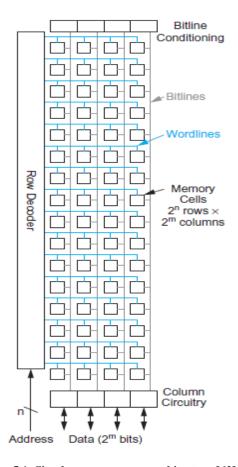

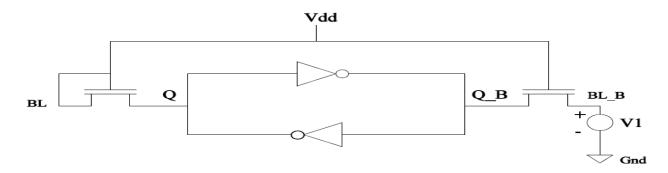

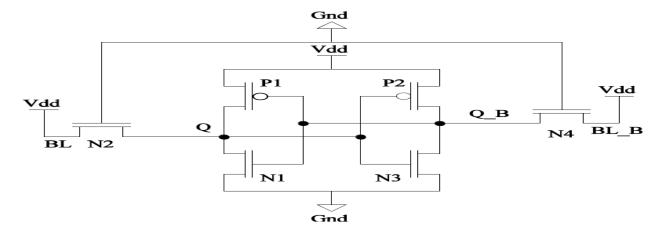

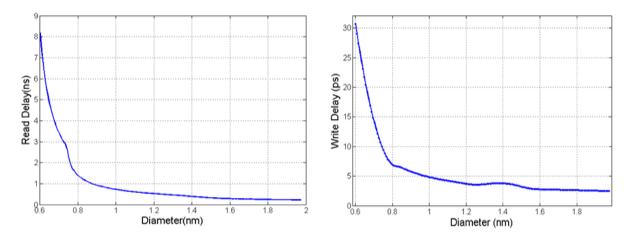

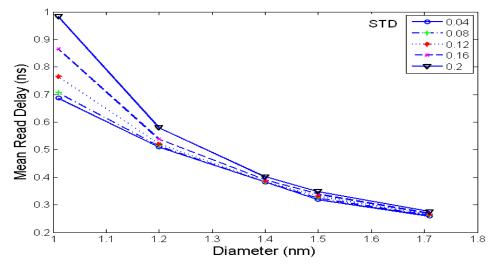

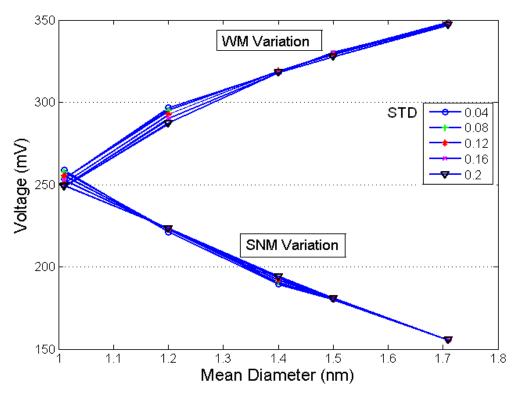

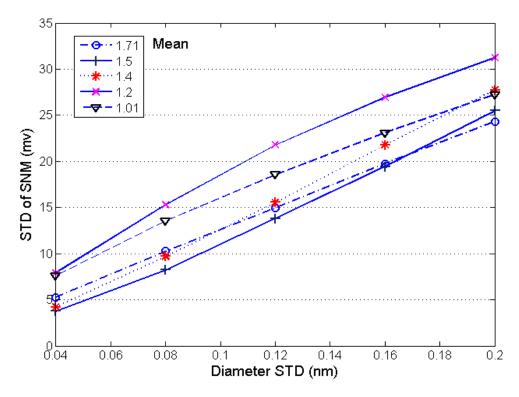

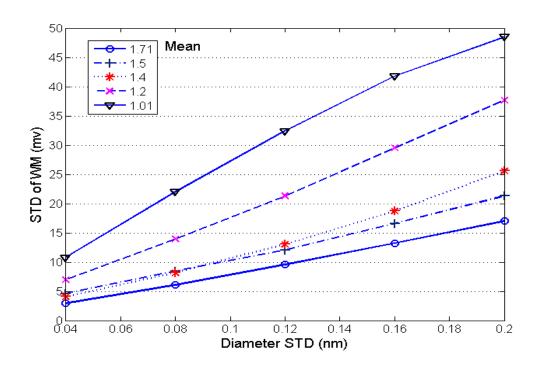

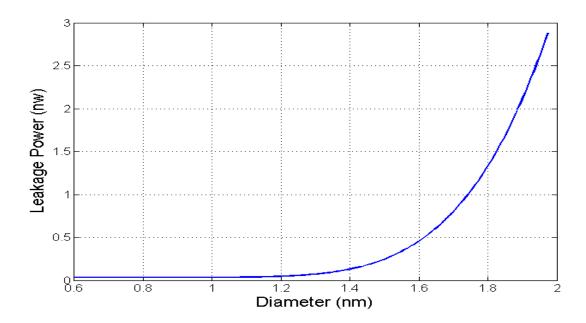

The next stage of this work involves implementation and simulation of a memory structure (SRAM). Parameters such as Static Noise Margin (SNM), leakage power and read/write delays were studied and the effects of CNT diameter variation on them examined.

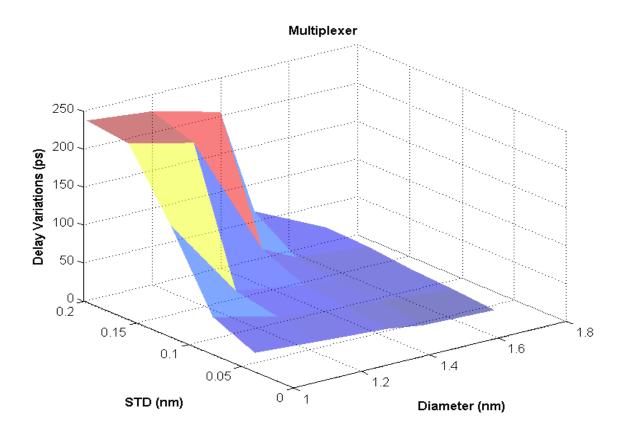

The next contributions of this work are empirical models developed for a library of CNFET-based logic gates/circuit structures. The models can predict both the mean and standard deviation (STD) in various circuit performance parameters of a given CNFET-based logic gate/SRAM given the mean and STD of the diameter of CNTs used in their manufacture. The aim is, given a target reliability specification (timing requirements, power, speed, etc.), for various logic gates, and larger circuit components, to come up with a design strategy to suggest what physical properties the nano-device of choice should have to meet the target specification or vice versa. Best-case CNT diameter mean and STD selection scenarios are proposed to minimise circuit parameter variations.

In the last part of this work, the effects of doping fluctuations in the source/drain regions of the CNFETs on the performance of logic gates made from them are studied. The work concludes that if doping concentration is kept above 1%, variation in doping concentration has a minimal effect on performance parameters.

### **Contents**

| CHAPTER 1 INTRODUCTION                                                    | 3  |

|---------------------------------------------------------------------------|----|

| 1.1 Motivation                                                            | 3  |

| 1.2 THE CARBON NANOTUBE                                                   |    |

| 1.2.1 SWCNT                                                               | 8  |

| 1.2.2 MWCNT                                                               | 9  |

| 1.3 APPLICATIONS OF CARBON NANOTUBES                                      | 10 |

| 1.4 Thesis Outline                                                        | 10 |

| CHAPTER 2 LITERATURE REVIEW                                               | 13 |

| 2.1 Background                                                            | 13 |

| 2.2 CNT FIELD EFFECT TRANSISTORS (CNFETS)                                 | 14 |

| 2.3 Existing CNFET Models                                                 | 19 |

| 2.4 CNFET-BASED LOGIC STRUCTURES                                          | 21 |

| 2.5 CHARGE TRANSPORT IN CNFETS                                            | 23 |

| 2.6 CNFET-BASED DESIGN CHALLENGES                                         | 25 |

| 2.6.1 Sources of Variation                                                | 25 |

| CHAPTER 3 CNT BASED LOGIC GATES IN THE PRESENCE OF CNT DIAMETER VARIATION | 28 |

| 3.1 SIMULATION METHODOLOGY                                                | 29 |

| 3.1.1 CNFET Structure Used                                                | 29 |

| 3.1.2 Statistical Simulation Strategy                                     | 31 |

| 3.1.3 Parametric Analysis                                                 | 33 |

| 3.2 SIMULATION RESULTS                                                    | 34 |

| 3.2.1 NAND Gate                                                           | 34 |

| 3.2.2 NOR Gate                                                            | 51 |

| 3.2.3 NOT Gate                                                            | 59 |

| 3.4 MODELLING OF DELAY                                                    | 67 |

| 3.4.1 Response Surface Methodology                                        | 67 |

| 3.4.2 Model Verification                                                  | 68 |

| 3.4.3 Model of Mean Propagation Delay of Logic Gates                      | 69 |

| 3.4.4 Model of STD in Propagation Delay of Logic Gates                    | 70 |

| 3.5 DISCUSSION                                                            | 70 |

| 3.6 CONCLUSION                                                            | 72 |

| CHAPTER 4 COMPLEX LOGIC STRUCTURES                                        | 73 |

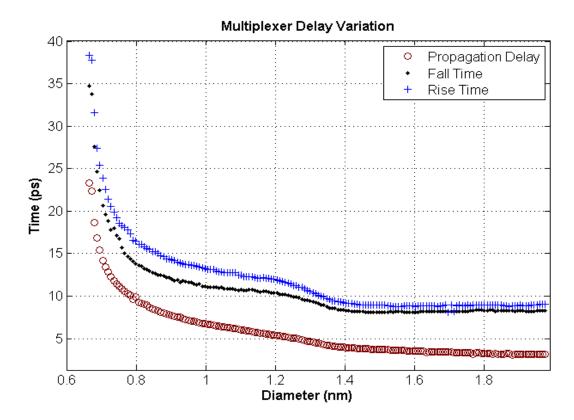

| 4.1. Multiplexer                                                          | 74 |

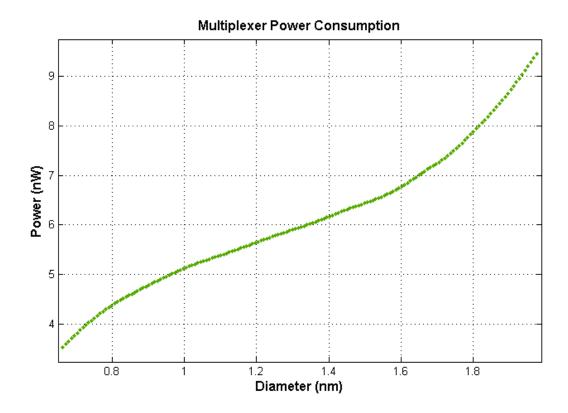

| 4.1.1 Power-Delay Product                                                 | 83 |

| 4.2. XOR GATE                                                             | 84 |

| 4.3 MODELLING OF DELAY                                                    | 90 |

| 4.3.1 Mean Propagation Delay Model                                        | 91 |

| 4.3.2 Propagation Delay STD Model                                         | 91 |

| 4.2 Congregation                                                          | 02 |

| CHAPTER 5 CNT BASED STATIC RANDOM ACCESS MEMORY IN THE PRESI<br>DIAMETER VARIATIONS |     |

|-------------------------------------------------------------------------------------|-----|

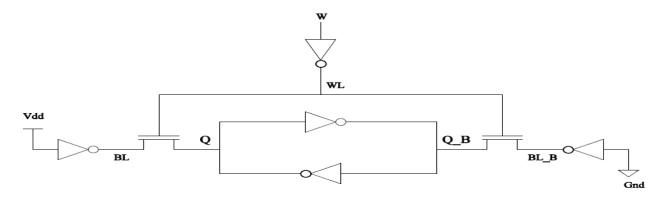

| 5.1 SRAM                                                                            | 94  |

| 5.2 SIMULATION METHODOLOGY & PERFORMANCE MEASUREMENT                                | 96  |

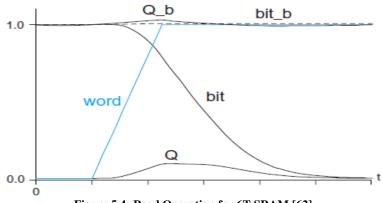

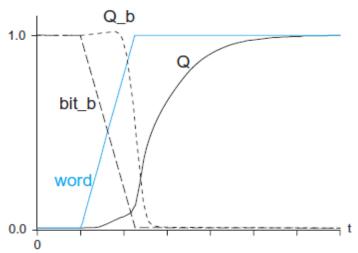

| 5.2.1 Read Operation                                                                | 97  |

| 5.2.2 Read operation measurements                                                   |     |

| 5.2.3 Write Operation                                                               | 98  |

| 5.2.4 Write operation measurements                                                  | 99  |

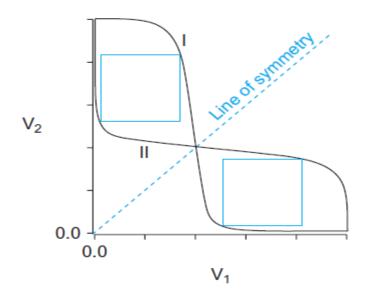

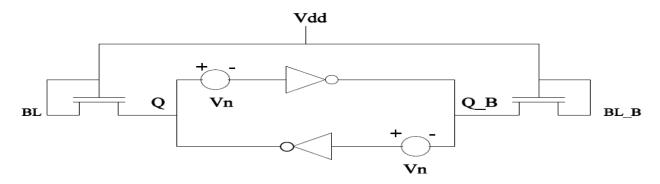

| 5.2.5 SNM measurement                                                               | 99  |

| 5.2.6 Write Margin Measurement                                                      | 101 |

| 5.2.7 Standby Leakage Power Measurement                                             | 101 |

| 5.3 SIMULATION RESULTS                                                              | 102 |

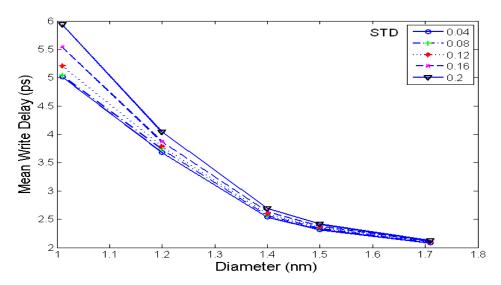

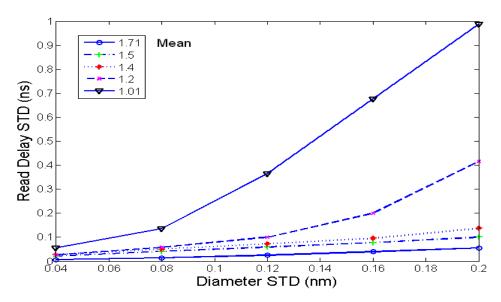

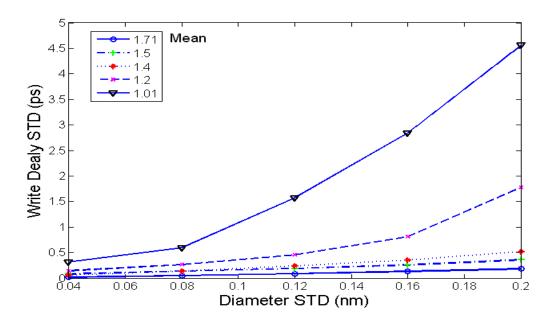

| 5.3.1 Read/Write Delay                                                              | 102 |

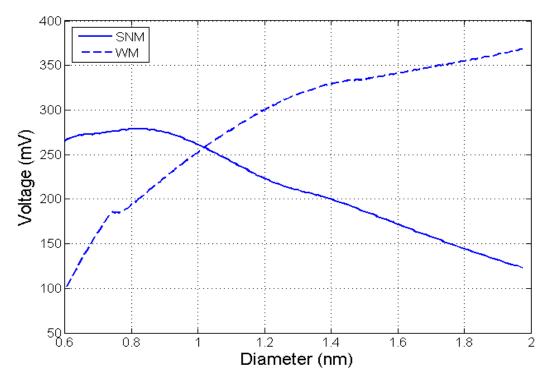

| 5.3.2 Static Noise Margin                                                           | 106 |

| 5.3.3 Write Margin                                                                  | 108 |

| 5.3.4 Standby Leakage Power                                                         | 109 |

| 5.4 MODELLING OF SRAM PERFORMANCE PARAMETERS                                        | 111 |

| 5.5 CONCLUSION                                                                      | 113 |

| CHAPTER 6 CONCLUSIONS                                                               | 115 |

| 6.1 CONCLUSIONS AND CONTRIBUTIONS                                                   | 115 |

| 6.2 Future work                                                                     | 119 |

| REFERENCES                                                                          | 121 |

| APPENDIX A: PUBLICATIONS                                                            | 130 |

| APPENDIX B: SAMPLE HSPICE CODES                                                     | 132 |

## **Chapter 1 Introduction**

#### 1.1 Motivation

Silicon device scaling in future faces limitations. As the silicon industry moves into the 45nm node and beyond, increasing technology challenges will be imposed by silicon CMOS device scaling. Among the most important obstacles against further device scaling is the performance variation introduced by increased process variations as feature sizes shrink and the standby power dissipation [1]. Increased device density and device parametric variation, rising sub-threshold leakage current and gate tunnelling current and higher device temperatures all contribute to the power problem. As CMOS approaches the 25nm node, stochastic threshold variation caused by dopant implant position in ultra-small inversion regions [2] will give rise to more than 100mV of threshold variation. The timing behaviour of devices is also greatly affected by spatial and temporal process parameter tolerance and voltage and temperature variation. Continued channel length reduction is prevented by the limitation to reduce gate insulator thickness. This leads to a lack of control over static leakage, short channel effects and drain voltage induced barrier lowering.

Short channel effects occur in devices where the channel length is of the same order of magnitude as the source/drain region depths. This can have a number of consequences including velocity saturation, drain-induced barrier lowering (DIBL) and charge sharing. Velocity saturation occurs when the carriers in a short channel device become velocity saturated due to the high electric field in the channel region. As the applied electric field is increased beyond the point of velocity saturation, carrier velocity no longer increases as carrier energy is lost through increased lattice collisions. DIBL is also an issue; as the source and drain get closer, they become electrostatically coupled, so that the drain bias can affect the potential barrier to carrier flow at the source junction. This leads to an increase in both off-current and sub-threshold slope. As a result, threshold voltage is reduced.

In a short channel device, a large proportion of the electric field lines associated with the depletion region is terminated on the source and drain junctions. This 2 dimensional sharing of the depleted substrate charge between the source, drain and gate terminals dramatically affects device

behaviour. As channel length shrinks, increased charge sharing from source/drain degrades the controllability of gate voltage over channel current. The reduced control of the gate over the channel depletion region in turn reduces the threshold voltage. The threshold voltage is the minimum value of gate to source voltage which is required to allow current to flow (refer to section 2.2).

Floating body effects are observed in silicon on insulator devices. Holes generated by impact ionisation in an n-type device accumulate in the body. The collection of these carriers increases the body potential and lowers the threshold voltage of the device. This phenomenon can however arise in any MOS device with the body floating.

Three primary approaches for addressing these challenges are put forward [1, 3]:

- Extending silicon scaling through innovations in materials and device structure;

- Expanding the level of integration through 3-dimensional structures comprised of silicon through-via holes and chip stacking in order to enhance functionality and parallelism;

- Exploring post-silicon CMOS innovation with new nano-devices based on distinctly different principles of physics, new materials, and new processes, such as spin-dependent electronics (spintronics) [4], carbon nanotubes, nanowires [5], or molecular systems which utilise the molecular electrostatic potentials and vibrational states of molecules to perform logical operations and transmit signals [6].

The issue of power consumption could be addressed by reducing the operating voltage albeit increasing delay [7]. Supply voltage reduction mitigates active as well as static power, but low voltage operation requires adding complexity in supply distribution and modulation [1]. If however, the issue of power consumption can be managed, it is variability that becomes the ultimate challenge in the way of scaling [1]. What the optimal device/technology of the future will be, depends to a great extent on how critically its performance varies with process variations.

Emerging and future devices exhibit dimensions in the order of the de-Broglie wavelength of electrons [8]. These include single electron transistors [8], electrons confined to sufficiently small dimensions and allowed to tunnel to metallic leads; silicon nanowires [5] which are extremely thin silicon wires that form a transistor's channel; graphene sheet transistors [9] which utilise the very fast carrier transport of monolayer graphene; and carbon nanotubes (CNTs) [10]. The extremely

small scales mean that the behaviour of these devices is no longer governed by the classical laws of physics; rather it is dictated by quantum physics [10]. As quantum physics is probabilistic in nature, these new devices in most cases are likely to be very unpredictable and unreliable. Any electronic system based on these devices will in turn be prone to noise and disturbances such Single Event Upsets (SEUs). At the nanoscale SEUs can be caused by thermal noise as well as radiated particles. A foreign particle can cause a register on a digital integrated circuit to accidentally change its state. Thermal noise at room temperature could prevent the output of a combinational block to be sampled correctly by the subsequent register, at the rising or falling edge of the clock.

Some key advantages of employing CNTs over silicon for building transistors include:

- High carrier mobility

- High current density

- High gate capacitance

- Compatibility with high-k gate dielectrics

Disadvantages include issues with reliability and mass production. It is difficult to produce significant amounts of semi-conducting CNTs without the presence of unwanted metallic CNTs.

Appropriate circuit design methods and process development strategies have to be devised in order to tackle the abovementioned issues on power dissipation and variability. This work concentrates on the CNT as one of the most promising of emerging nanodevices. Though holding a great promise for future electronics, CNTs are extremely prone to various sources of variations. As the electrical characteristics of CNTs are directly related to their physical structure, atomic structural changes can translate into significant variation in their electronic behaviour. This work aims to facilitate CNT-based design in the presence of CNT diameter and doping variations. To achieve this, an exhaustive study is carried out to examine the effects of CNT physical characteristics variations on circuit performance variables. The effect of CNT diameter variations on performance parameters (delay, power consumption, etc.) of various logic and memory structures is studied in depth. Through various simulation strategies, an optimum CNT mean diameter for use in CNT-based logic design is put forward for the first time. Further, novel mathematical models for the prediction of delay behaviour of CNT-based circuits in the presence of diameter variations are developed.

#### 1.2 The Carbon Nanotube

A CNT is a hollow cylinder constructed by rolling up a sheet of graphene. Graphene is a single atomic layer of graphite which in turn is a crystalline form of carbon. Its conducting properties are determined by the nature of the electronic states near the Fermi energy  $(E_{\rm F})$  which is the energy of the highest occupied electronic state at absolute zero. All bonds in a CNT are satisfied and the surface is atomically smooth, hence, there is no scattering of carriers by surface states and the roughness that plagues conventional FETs at high voltages is also absent [11]. With their ultralong mean-free paths (~ µm) for elastic scattering, CNTs are good candidates for use in electronics [12-15]. The quasi-ballistic nature of carrier movement in a CNT [12] means that electrons are confined in the radial and circumferential directions and are only free to move along the direction of the tube axis [16], hence only forward and backward scattering due to electron-phonon interactions are possible for carriers. This gives CNTs unique electrical properties. CNTs' electrical conductivity can be varied by doping them with impurity atoms. In this way both p-type and n-type CNTs can be obtained which then enables the creation of complementary logic structures such as those adopted in conventional CMOS design. In graphite (and hence in CNTs) the atoms of carbon are very closely packed in the basal planes, the distance between their centres (nearest neighbour distance) being only 1.42 Å, which is even closer than in diamond. One consequence of this small nearest-neighbour distance is that impurity species are unlikely to enter the covalently bonded in-plane lattice sites substitutionally [17] but rather occupy some interstitial position between the graphene layer planes which are bonded by a weak van der Waals force. The only impurity atom that can easily do this is boron, hence, CNTs are usually doped using boron atoms; however, alkali metals and halogens such as bromine and iodine are also used. CNTs can exhibit either semiconducting or metallic behaviour depending on their chiral angle. The conductivity and robustness of metallic nano-tubes make them suitable for future interconnects. As for the semiconducting CNTs, they exhibit the desired properties for making field effect transistors. The restricting issue here is to selectively separate metallic and semiconducting CNTs. A number of methods have been proposed for the separation of metallic and semiconducting CNTs including [18, 19]. In [20] a new method for separation of metallic and semiconducting CNTs proposes selective suspension in aqueous sodium dodecyl sulphate according to electronic

structure. A recent work by IBM [21] utilises this separation technique and achieves a high-density integration of CNTs allowing wafer-scale integration using highly purified CNTs.

Continuous films of Single Walled Carbon Nanotubes (SWCNTs) can be produced by dielectrophoretic deposition onto interdigitated electrode arrays. SWNCTs produced this way possess a significantly different degree of alignment with respect to the electric field. The dependence of SWCNT alignment on the electric field allows the separation of metallic and semiconducting SWCNTs using electrode-less dielectrophoresis through nanopores.

Another technological challenge is the capability to precisely place CNTs on wafer. The inability to absolutely control the alignment of CNTs under the metal gate affects the functionality of CNT-based cells. Current technology cannot eliminate all misaligned CNTs at the physical level; hence, this problem is normally addressed at the design level. This means that the layout of these standard cells must incorporate fault tolerant techniques and be designed robust enough to overcome probable misalignments at the physical level.

Electrophoresis has been employed for separating CNTs according mainly to their electrical properties (metallic or semiconducting) together with length and diameter. Charged macromolecules are commonly separated by electrophoresis using gel in an electric field. To be able to process the CNTs in the gel, they would have to be individually dispersed with the aid of a surfactant such as sodium dodecylsulfonate. The metallic/semiconducting separation using this technique utilises different polarisable characters between them under an electric field. Dielectrophoresis was first used for the alignment and purification of CNT bundles in isopropyl alcohol [22, 23]. It was extended to separation of individually dispersed CNTs.

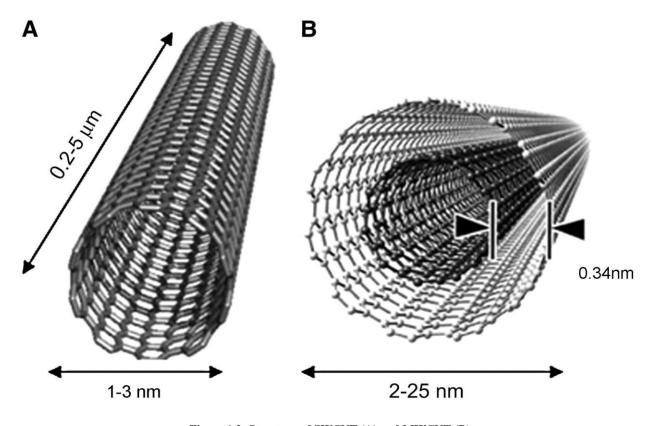

CNTs, due to their advantages over other new devices, amongst which are their very high performance and integration capabilities are emerging as the dominant future nano-electronic device. Actual CNT samples are usually found in one of two forms: Multi-Wall Carbon Nanotubes (MWCNTs) or Single Wall Carbon Nanotubes (SWCNTs).

#### 1.2.1 SWCNT

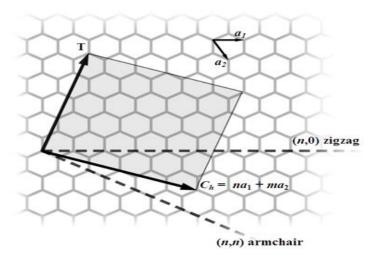

SWCNTs are carbon nano-tubes made of a single layer of graphene. SWCNTs can be produced by laser vaporisation method or the carbon arc method in the presence of metal catalysts such as the transition metals Fe, Co, or Ni [17]. Typical SWCNT diameters range from 1 to 3 nanometres (nm) [17] and the chiral angle ranges from 0 to 30 degrees. Two of the most important physical properties of CNTs are their diameter and the chiral angle. The vectors  $a_1$  and  $a_2$  shown in fig. 1.1 are unit vectors and n and m are integers.  $C_h$  is the axis along which the graphene sheet is rolled up to form the CNT and is called the chiral vector. The chiral angle of a nanotube is defined as the angle between the vector  $C_h$  and the vector  $a_1$ . Although graphene is a zero band-gap semiconductor, SWCNTs can be metals or semiconductors with different size energy gaps, depending on the diameter and chirality of the tubes, i.e. on the indices (n,m). Generally (n,n) tubes are metals, also known as armchair CNTs; (n, m) tubes with n-m=3j, where j is a nonzero integer, are very tiny band-gap semiconductors and all others are large band-gap semiconductors. (n, 0)tubes are zigzag and (n,m) tubes are chiral. Zigzag and chiral CNTs are metallic when (n-m)/3 is an integer and semiconducting otherwise. Energy band gap is important as it determines the ease with which charge carriers can move from one energy band to the other and hence determines the conductivity of the material. A smaller band gap means that a transistor made of CNTs with larger diameters can exhibit higher on-currents

Figure 1.1: The honeycomb lattice of a CNT [19]

#### 1.2.2 MWCNT

A MWCNT consists of a nested coaxial array of SWCNTs separated from one another by approximately 0.34nm, the interlayer distance of graphite. Unlike SWCNTs which require a catalyst for their growth MWCNT production requires no catalyst [17]. In [24] it has been shown that interlayer coupling has little effect on the electronic properties of individual SWCNTs. Thus, two coaxial zigzag CNTs that would be metallic as SWCNTs yield a metallic double-wall tube. Semiconducting tubes behave similarly. They also showed that coaxial metallic-semiconducting and semiconducting-metallic tubes retained their respective characters when interlayer interactions were introduced suggesting that double walled CNTs could be used as insulated nanowires. Subsequent works [25, 26] considering a double-wall CNT consisting of two metallic SWCNTs looked at the effect of changing the relative position of one tube with respect to the other found that in certain configurations the interlayer interactions can cause both SWCNTs to become semiconducting. These experiments underline the fact that further work needs to be done to determine the electronic properties of multi-wall zigzag and chiral CNTs.

Figure 1.2: Structure of SWCNT (A) and MWCNT (B)

#### 1.3 Applications of Carbon Nanotubes

The potential of CNTs for developing high-speed and power-efficient logic applications is vast [21]. Ensembles of nano-tubes have been used for field emission based flat-panel displays [17], composite materials with improved mechanical properties and electromechanical actuators [17]. Bulk quantities of CNTs have been suggested to be useful as high capacity hydrogen storage media [17]. Nanotubes have also been used for field emission sources, tips for scanning probe microscopy and nano-tweezers [17]. Nano-tubes have significant potential as the central elements of nanoelectronic devices such as field effect transistors [17]. These CNT based transistors have been utilised recently to implement various electronic structures such as logic gates and memory structures. Intercalated CNTs could also be used in super high capacity batteries.

CNTs have been shown to have potential benefits in medicine too. SWCNTs with a diameter of 1.4nm have shown potential for targeted delivery of radionuclides to cancer cells in the field of nuclear medicine [27].

Since CNT electronic properties are strong functions of atomic structure, mechanical deformations or chemical doping can induce strong changes in conductance. Such changes can be easily detected by electron current signals making CNTs suitable for VLSI application as extremely small sensors sensitive to their chemical and mechanical environments [28].

#### 1.4 Thesis Outline

This work is motivated by the need for nano-electronic circuitry, such as logic and memory structures, based on CNTs to operate in spite of the inherent variations which exist due to the nature and size of these nanodevices. As variations in structural properties of CNTs can cause significant variation in the electrical properties of these devices, it is envisaged that any electronic component based on these nano-devices would be prone to variations in circuit speed and power consumption. Therefore there is a need for the circuit designer to be able to predict the performance of a design based on the CNT structural properties and their variations.

Chapter 2 gives an overview of the various techniques for the fabrication of CNTs together with their advantages and disadvantages. The doping of CNTs is also discussed together with the types and properties of field-effect transistors (FETs) that can be made using CNTs. Various existing models for CNFETs are then discussed together with their strengths and shortcomings. Construction of logic structures from CNFETs is then discussed and the design challenges are identified.

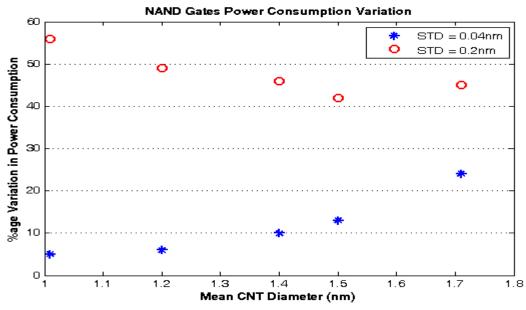

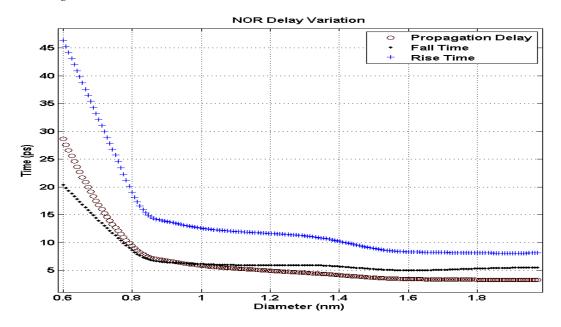

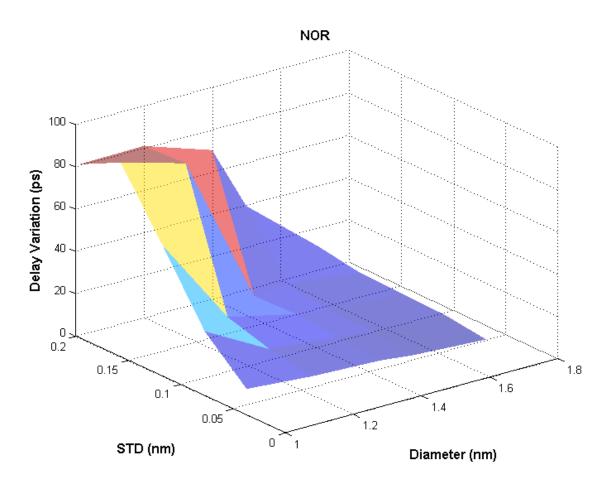

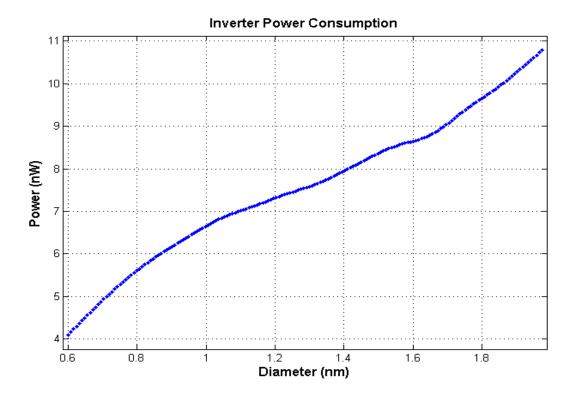

In Chapter 3, the electrical behaviour of basic CNT-based logic gates is studied through Monte Carlo and parametric simulations. It is shown that time delay and power consumption of NOT, NAND and NOR gates are direct functions of variation in CNT diameter. As the first contribution of this work, a CNT diameter threshold is suggested in order to keep delay variation to a minimum. This threshold diameter is valid for all the logic gates studied in this chapter. The second contribution of this chapter is in the form of mathematical models developed for the prediction of mean and STD in propagation delay based on given CNT diameter mean and STD for the various logic gates.

In Chapter 4 more complex logic structures i.e. multiplexers and XOR gates are studied under the presence of CNT diameter variations. It is suggested that the use of the specific structures for multiplexers and XOR gates detailed in this chapter would be advantageous for CNT-based design as the structures discussed exhibit similar rise and fall times. Propagation delay, fall/rise time and power consumption of these structures are examined. It's found that time delay rises sharply below a CNT diameter of 0.85nm, a threshold consistent with that observed in Chapter 3. The chapter further examines power consumption, delay and energy variations in the presence of CNT diameter mean and STD variation. Finally mathematical models based on Response Surface Methodology technique have been developed to model and predict the mean propagation delay and STD in propagation delay of the multiplexers and the XOR gates based on CNT diameter mean and STD.

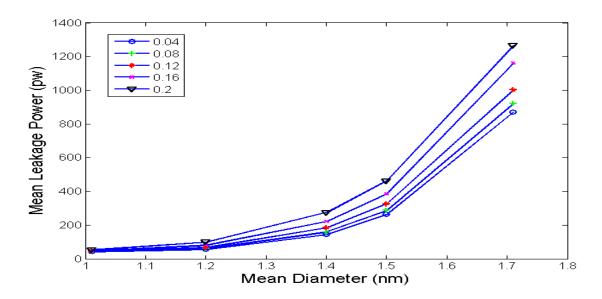

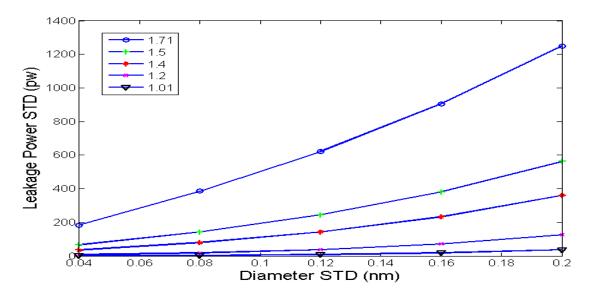

Chapter 5 is concerned with the performance of a CNT-based SRAM cell. SRAM performance parameters such as delay, Static Noise Margin (SNM), Write Margin (WM) and standby leakage power are studied in the presence of CNT diameter variations. It is observed that read and write delay are reduced with larger CNT diameters and that delay values show a sharp rise below a CNT diameter of 0.85nm. It is further revealed that as SNM depends on threshold voltage, and threshold voltage is determined by CNT diameter, diameter variations cause significant variation in SRAM SNM. As far as leakage is concerned, standby leakage power rises sharply above a CNT diameter of 1.5nm, but below this value it is relatively constant. Predictive statistical models are developed

for the various performance parameters of the SRAM discussed in this chapter and shown to be reliable and accurate through the adjusted  $R^2$  measure.

Predictive models for mean propagation delay and Standard Deviation (STD) in propagation delay are developed in this work. These models will work as guidelines for the logic designer to forecast the performance of a design based on the mean and STD in distribution of fabricated CNT diameters given by a certain technology.

#### Contributions of this work are:

- The Stanford CNFET model has been modified to allow for easier and fault-free simulations of semi-conducting CNT diameter variations.

- A comprehensive study on the effects of CNT diameter variations on various circuit performance parameters such as delay characteristics and power consumption is carried out.

- A relation is proposed by which a minimum mean CNT diameter can be chosen to ensure minimum delay variation for various CNT-based logic gates.

- A CNT-based SRAM is designed and simulated. The effects of CNT diameter variations

on the delay characteristics, stability metrics and power consumption of the SRAM cell

have been studied.

- Predictive models have been developed to relate the various CNT-based circuit performance metrics to CNT diameter and variations in CNT diameter.

- Effects of doping fluctuations on CNT-based logic gates have been studied.

## **Chapter 2 Literature Review**

#### 2.1 Background

Carbon filaments having diameters of less than 10nm were first prepared in the 1970s through the synthesis of vapour grown carbon fibres by the decomposition of hydrocarbons at high temperatures in presence of transition metal catalyst particles of less than 10nm in diameter [29, 30]. However, it was the publication of Ijima's work in 1991 [31] that launched the field of Carbon Nanotubes.

Three principal techniques for synthesis of SWCNTs exist

- Laser ablation [32]

- Electric arc discharge [33, 34]

- Chemical Vapour Deposition (CVD) [35, 36]

Laser ablation and arc-discharge techniques involve the condensation of hot gaseous carbon atoms generated from the evaporation of solid carbon. The downside of these two techniques is the large amount of energy consumption and the sophisticated equipment required [35, 36]. Also both these techniques are limited in the volume of sample they can produce in comparison with the size of the carbon source. Furthermore, more impurities accompany the CNTs generated in the form of amorphous carbon and catalyst particles because of the high temperature nature of the heat source. Laser ablation and arc discharge produce mainly MWCNTs which are poorly aligned as a result of limited control over the synthesis techniques.

The prominent industrial approach for CNT synthesis is CVD. The technique is the irreversible deposition of a solid form of a gas or mixture of gases through a heterogeneous chemical reaction. The growth process can be controlled either by diffusion or by surface kinetics. CVD is the preferred technique for fabrication of thin layers of metals, insulators and semiconductors on various substrates [37-39]. CVD has the highest yield out of the other synthesis techniques and produces the lowest impurity CNTs at moderate temperatures. Also because of the equilibrium nature of the chemical reactions involved, CVD provides better growth control. Finally, CVD has

the capability to control the size, shape and alignment of the CNTs through patterning of the catalysts on the substrate's surface [40].

Both SWCNTs and MWCNTs can be doped by either electron donors or electron acceptors [40]. Performance improvement especially in the on state of CNFETs by chemically doping the CNT to n-type has been demonstrated experimentally [41]. As-grown p-type CNT devices have been converted to n-type devices by controlled doping [42, 43]. Doped CNTs exhibit high on currents [42, 43]. To obtain MOSFET-like contacts in a 50 nm CNT, a doping concentration value of (5×10<sup>-3</sup>) or higher dopants per atom is required [44].

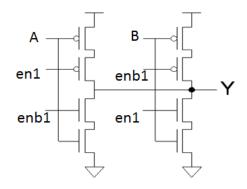

CNTs can exhibit ambipolar behaviour. Ambipolar conduction is characterized by a superposition of electron and hole currents. Ambipolar behaviour has been reported in carbon nanotube field effect transistors (CNFETs) [10]. As opposed to unipolar silicon CMOS devices whose p-type or n-type behaviour is determined during fabrication, the polarity of ambipolar devices can be switched from n-type to p-type by changing the gate bias [45]. The electrostatic field applied at the back gate of the CNT-to-metal contacts is responsible for controlling the device polarity. Because CNT ambipolarity can be controlled in-field, this property of CNT devices can be utilized for building libraries of complex logic gates that efficiently embed XOR functions [46]. However ambipolar behaviour is unsuitable for CMOS as the switching activity of ambipolar devices cannot be controlled in the same way as the switching of unipolar devices can.

#### 2.2 CNT Field Effect Transistors (CNFETs)

CNTs have been used to build Carbon Nanotube Field Effect Transistors (CNFETs). As described earlier, a CNT has an atomic and electronic structure that gives it unique advantages as a FET channel. These include low scattering of carriers and long mean free paths [14]. Its small diameter enhances the gate's ability to control the potential of the channel [11].

The first CNFETs were fabricated in 1998 [47, 48]. These were based on individual CNTs. Since then CNFETs have been shown to be suitable for the fabrication of circuits, sensors and NanoElectroMechanical Systems (NEMS) [48-50]. A primary advantage of CNFETs over silicon MOSFETs is their much lower capacitance value (roughly 0.05 aF/nm) which alleviates the power dissipation problem that limits the scaling of MOSFETs [11]. CNFETs can be used in conjunction with high-k gate dielectric material; also, in MOSFET-like CNFETs, the gate and source/drain can

be separated by the length of the source/drain extension region which greatly reduces the parasitic capacitance. Dynamic switching of a device takes energy of  $\frac{1}{2}$   $CV^2$  where C represents capacitance and V is the voltage.

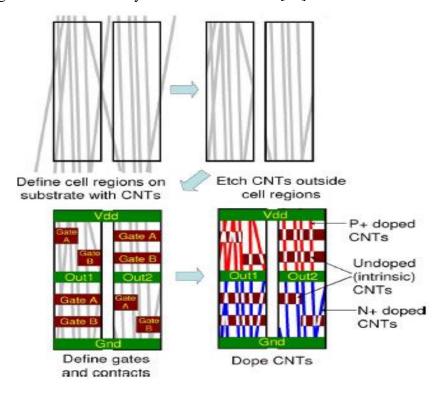

During the fabrication of a CNFET, parallel CNTs are grown on or transferred to a silicon oxide substrate [52]. The regions of the CNTs under the gate are undoped. The conductivity of these undoped regions is controlled by the gate. The source and drain regions of the CNTs are heavily doped. The gate, source and drain contacts and interconnects are defined by conventional lithography. In this way, a large proportion of the existing design and manufacturing structure for FET-based large-scale electronics systems can be utilized [53].

Figure 2.1: CNFET circuit fabrication process [53]

The process of manufacturing CNFET circuits involves growth or transfer of semiconducting CNTs on a substrate. The regions of logic cells are defined using lithography, and CNTs outside these cell regions are etched away. The gate and contact regions are subsequently defined using lithography and CNTs outside these regions are etched away. The next step involves p-type doping of CNT regions which correspond to PFET transistors, while lithographically masking the NFET regions. Then CNT regions corresponding to NFET transistors are doped n-type, while masking

the PFET regions. The CNT regions under the gates remain undoped as they are masked during the doping steps in this self-aligned process. Interconnects are defined using lithography at the final stage of the process.

Figure 2.2: CNFET cross section [54]

The fundamental operation of the CNFET is similar to conventional silicon devices. They are normally 3 terminal devices which employ semiconducting CNTs acting as the conducting channel between the source and drain contacts. The metal gate is used to electrostatically turn the device on or off (fig. 2.4).

Two alternative device configurations are prominent:

- Schottky Barrier (SB) FET [55]

- MOSFET-like FETs [56, 57].

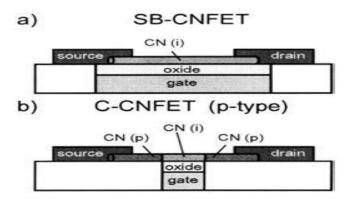

In SB-CNFETs, metal source/drain contacts are directly connected to the gate controlled CNT channel [58] and hence a Schottky barrier is formed at the junction of CNT and Source/Drain contact (fig. 2.3). Compact models for SB-CNFETs have been reported [59]. SB-CNFETs show ambipolar behaviour [60] which is undesirable as far as complementary logic design goes because it contributes to higher leakage [60] as a parasitic current due to holes can flow easily. The SB contact reduces the ON current by reducing the effective voltage across the channel, thus lowering the I<sub>on</sub>/I<sub>off</sub> ratio [61].

In MOSFET-like CNFETs, the ungated portions of the structure are doped and thus the structure behaves similarly to CMOS transistors (fig. 2.3). MOSFET-like CNFETs show unipolar behaviour and as far as fabrication is concerned they are easier to make (fig. 2.3).

Figure 2.3: (a) gating occurs over entire nano-tube channel. (b) p/i/p doping profile exists along the tube in a MOSFET-like CNFET. Only the intrinsic portion of the nano-tube is gated [58]

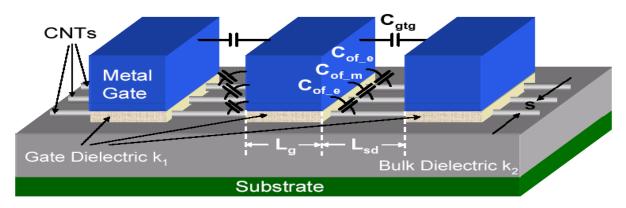

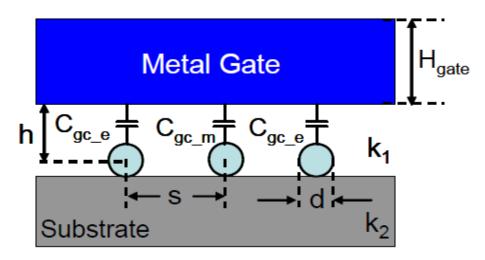

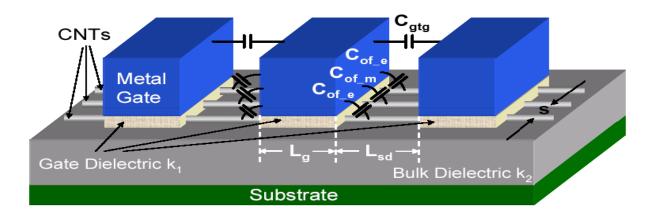

Fig. 2.4 shows the cross section of the channel region in a CNFET. In this figure, 'd' denotes the diameter of a CNT and 'h' is the distance between the metal gate and the centre of a CNT. 's' is inter-CNT separation. ' $C_{gc}$ ' is gate to channel capacitance.  $C_{gc\_m}$  and  $C_{gc\_e}$  denote the gate capacitance to middle and edge CNT channels respectively.

Figure 2.4: Cross section of a CNFET

The intrinsic CNTs act as the undoped channel region of the CNFET. The other regions are heavily doped and act as the source/drain extension regions and/or interconnect between two adjacent devices. In the limit of near-ballistic transport, the drive current highly depends on  $C_{gc}$ . As a MOSFET-like CNFET, the structure shown in fig. 2.4 operates on the basis of barrier height modulation by application of a gate potential. The current of a CNFET depends on the number, position and the spacing of CNTs under the gate.

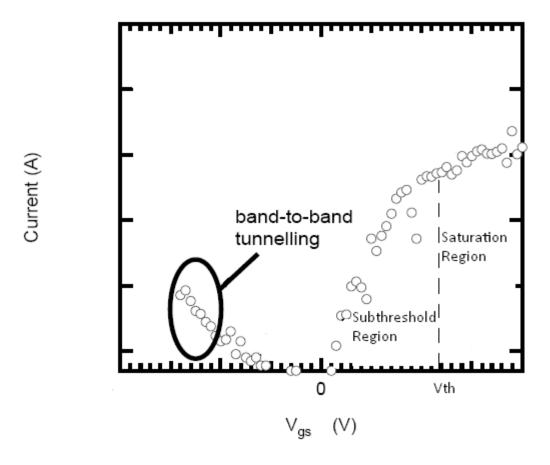

Figure 2.5: Transistor sub-threshold plot showing drain current against voltage [45]

Plot of fig. 2.5 shows a plot of drain current versus gate to source voltage for a CNFET. The transition from the ON state to the OFF state is gradual. Current rises exponentially before threshold voltage ( $V_{th}$ ) is reached. This current is essentially the channel-source PN junction current. An important consideration from this observation is that a low threshold voltage is desired for high ON current; however, as it can be observed from the plot, to keep OFF current to a minimum, a high  $V_{th}$  is required. The slope of the plot in the sub-threshold region is called the sub-threshold slope. A steep sub-threshold slope indicates faster switching for the device.

#### 2.3 Existing CNFET Models

Many of the developed CNFET models are numerical, involving self-consistent equations which circuit solvers like SPICE are not able to handle. As these models show the essential physics of an individual CNFET, they are not suitable from a circuit designer's point of view and for logic level simulations. To evaluate the potential of CNFET-based structures to replace silicon CMOS technologies in digital circuits, a semi-empirical SPICE model for CNTFET logic is proposed in [63]. Another circuit-compatible model of ballistic CNTFETs is proposed in [56]. Both of these models are used for single-walled semiconducting CNTs. Compact models are circuit models which are sufficiently simple to be incorporated in circuit simulators and at the same time are accurate enough to give circuit designers useful simulation outcomes.

Other models aiming to evaluate semiconducting CNFET potential performance at device level for digital logic applications have also been developed [10, 11]. These models exhibit promising dc performance over silicon CMOS. The issue with all the CNFET models discussed so far is that they use one or more lumped static gate capacitances. In this way the model assumes that the temperature difference inside the "lump" is negligible thereby simplifying the complex differential heat equations needed to be solved by the model. This simplification reduces the accuracy and reliability of these models. Further, the carrier transport model used in these compact models, assumes ideal ballistic transport. These simplifications render the evaluation of the transient response and device dynamic performance questionable. Models of [10,11] are difficult to implement in circuit simulators such as HSPICE as a result of the intensive calculation effort required to solve the integral function used in these models. The model implemented in [8] employs a polynomial fitting approach, thereby improving the run time over [64, 65] but as far as a comprehensive evaluation of the CNFET performance goes, especially for considering variability with different device parameters, the same approach renders the model inconvenient. The typical CNFET gate structure consists of gate oxide on top of silicon dioxide insulating bulk. However the models in [63-65] all use a coaxial or planar gate structure.

In [66] a non-iterative physics based CNT transistor compact model is presented. This model is scalable to key process and design parameters including diameter and chirality. However this model is directed mainly towards CNTs as interconnects and Schottky-barrier transitors.

FETToy is another compact model developed for calculating the I-V characteristics of CNFETs [67]. This is a set of MATLAB scripts which assumes a cylindrical gate geometry for the CNFETs. Further, only the lowest energy sub-band is considered which hinders the accuracy of the model by ignoring the effects of other sub-bands (specifically considering the second sub-band could increase accuracy significantly). FETToy assumes ballistic transport which renders the model too optimistic meaning the results can be too optimistic.

A numerically efficient CNFET model for HSPICE has been developed by the University of Southampton [68]. This model is accurate and efficient in comparison with existing models such as FETToy, however its accuracy is hindered by failing to consider sub-band effects which have an effect on current. This model still needs to be further matured to represent a realistic CNFET with all the non-idealities present including the channel length dependence of current drive, contacts resistance, geometry dependence of the gate to channel capacitance and the interconnect wiring capacitance.

None of the models discussed here account for having multiple CNTs under one gate and the effect that this would have on the effective gate capacitance due to charge screening effect which is how charge carriers in adjacent CNTs compete for the electric field of the metal gate. These models do not incorporate the non-idealities that are common place in CNFET-based devices.

The Stanford CNFET model which is used in this work is presented in [54, 69]. It is a MOSFET-like CNFET compact model. The Stanford CNFET model is a universal circuit compatible model implemented in HSPICE and accounts for various non-idealities such as scattering in the channel region, the screening effect by the parallel CNTs for CNFETs with multiple CNTs, hence more than one CNT under the gate of each device can be modelled.

The model describes unipolar MOSFETs with semiconducting SWCNTs as channels and is based on a quasi-ballistic transport model. It includes an accurate description of the capacitor network in a CNFET.

Other non-idealities including the parasitic capacitance between the gate and the source/drain formed by multiple 1D nanotubes, the gate-to-gate and gate-to-contact-plug capacitances, the access resistance of the source/drain extension regions, the Schottky-barrier resistance at the metal-CNT contact interfaces and the band-to-band leakage current are all accounted for by the model.

By incorporating a full transcapacitance network, the Stanford model produces better predictions of the dynamic performance and transient response. The model's accuracy and ability to be implemented in HSPICE have contributed to its selection for use in this work.

This model has been modified in this work to allow for a study of CNT diameter variation and its effects on circuit performance. The HSPICE code for this is given Appendix B. The model only accepts semiconducting CNTs, a reasonable assumption given recent works in [18-20].

#### 2.4 CNFET-based Logic Structures

Two scenarios have been suggested under which logic circuits can be constructed using CNTFETs [70]:

- 1) Transposing existing CMOS-based logic functions directly to CNFET technology. Non-volatile memories [71] and logic gates [72] have been constructed this way.

- 2) Properties explicit to CNFETs are exploited allowing the implementation of completely new logic functions, inaccessible to MOSFET-based circuits. As an example, the band gap and hence the threshold voltage is inversely proportional to the CNT diameter. This allows for circuit branches with different switching levels to be constructed.

So far, simple circuits such as inverters [57, 73] and ring oscillators [73, 74] have been successfully fabricated. Oscillators are composed of an odd number of pairs of inverters made by appropriate doping of the CNTs.

Several works have been published on the performance comparison of various CNFET-based structures against that of conventional MOSFET-based designs. In [75], designs for different logic gates (NOT, NAND and NOR) are simulated under the same minimum gate length and different operational conditions. This work reports that the power-delay product and the leakage power for the CNFET based gates are lower than the MOSFET based logic gates by 100 to 150 times, respectively.

In [76, 77] designs for ternary logic inverters using CNFETs have been put forward. These works exploit the dependency of the threshold voltage on CNT diameter in a CNFET to design ternary logic inverters. Multiple-valued logic circuits are of interest due to their capability to increase information content per unit area.

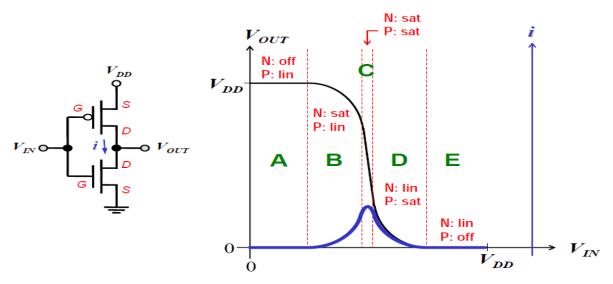

Figure 2.6: Inverter Transfer Characteristics

Fig. 2.6 depicts the transfer characteristics of an inverter and current flow during the switching process. The figure shows the different operational regions of the inverter for when the transistors are linear, saturated or cut-off. In region A, the nFET is off so the pFET pulls the output to  $V_{DD}$ . In region B, the nFET is starting to turn on as  $V_{IN}$  exceeds the threshold voltage,  $V_{th}$ . As electron and hole mobility is assumed equal,  $V_{th}$  for both nFET and pFET is also assumed to be equal here. Both transistors are saturated in region C. for the nFET  $V_{th}$  is smaller than  $V_{IN}$  and for the pFET  $V_{IN}$  is smaller than  $V_{th} + V_{DD}$  If transistors were ideal, region C would only last as long as  $V_{IN} = V_{DD}/2$  and the slope of the transfer curve would be  $-\infty$  corresponding to an infinite gain. As transistors in reality are not ideal, there exists a finite output resistance and hence a finite slope and a wider C region. In region D, the pFET is partially ON (saturated). In region D, the pFET is OFF, hence the linear nFET can pull the output down to ground. As  $V_{IN}$  passes through voltages 0 and  $V_{DD}$  both transistors are momentarily ON which results in a current being drawn from the power supply.

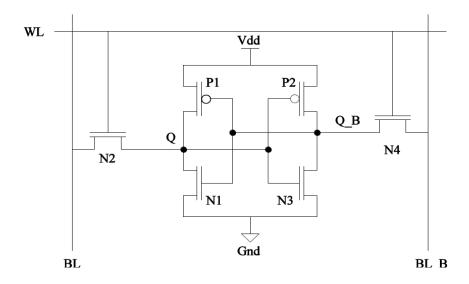

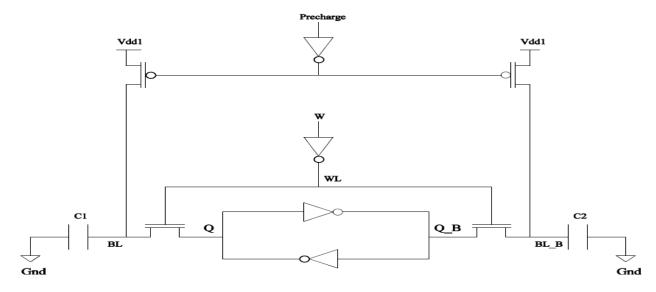

The use of SWCNFETs in SRAM design has been investigated in [78-80]. As the threshold voltage of the CNFET can be easily controlled by changing the chiral vector of the CNTs, a dual-diameter CNFET SRAM cell configuration with different threshold voltages is designed in [78], which is made possible by using different diameters for the P-type and N-type CNTs in the cell. The work of [79] explores the performance of a CNFET-based 6T SRAM cell and compares it with that of the conventional CMOS cell at a deep submicron 32nm technology node. The work reports that

due to inherent characteristics of CNFET, such as good gate controllability, drive current and immunity to short channel effect, the CNFET cell outperforms in leakage power, write margin, speed and read Static Noise Margin (SNM) as compared with the CMOS cell. It is also reported that the CNFET- based SRAM cell has more stable SNM against temperature variations.

#### 2.5 Charge Transport in CNFETs

Charge carriers in CNTs are confined within the atomic plane of graphene. The quasi-1D structure of CNTs means that carrier motion in CNTs is strictly restricted. The only direction in which carriers can move is along the tube axis. This results in the prohibition of all wide angle scatterings. Only forward scattering and backscattering due to electron phonon interactions are possible for carriers in CNTs.

Various works have reported that CNTs exhibit ultra-long elastic scattering mean-free path (MFP) of ~1µm [12, 13]. This long MFP suggests near-ballistic transport in CNTs. This near-ballistic transport can be achieved under low voltage bias in CNTs [12, 13].

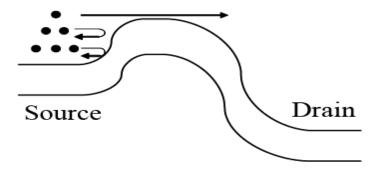

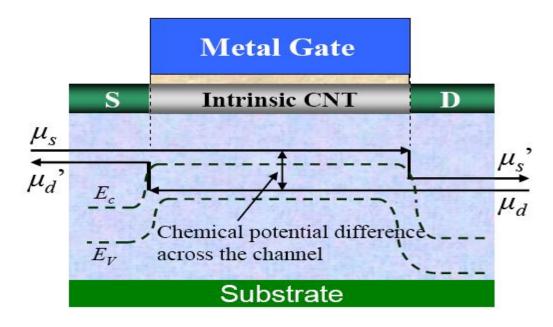

SB-CNFETs exhibit ambipolar behaviour. MOSFET-like CNFETs on the other hand exhibit unipolar behaviour by suppressing either electron or hole transport with heavily doped source/drain. The gate source bias modulates the non-tunnelling potential barrier at the channel region and thereby controls the conductivity of the device. Figs. 2.7 and 2.8 depict the energy band diagram for a MOSFET-like CNFET. Four different Fermi levels are shown in fig. 2.8. These are both input and output Fermi levels for the source and the drain.

Figure 2.7: Energy-band diagram for a MOSFET-like CNFET

As 1-D devices, the drive current of CNFETs in the limit of near-ballistic transport highly depends on the gate to channel capacitance. In the case of having multiple CNTs under the gate of a CNFET, the parallel CNTs have a screening/imaging effect on the actual potential profile in the gate region, thereby affecting the capacitance.

Figure 2.8: Fermi level profiles for ballistic transport [54]

In fig. 2.8, the chemical potential represents the Fermi level in the device. The potential can be either electrostatic potential or chemical potential (Fermi level). In the case of 1D devices, the Fermi level potential does not necessarily follow the electrostatic potential around the contacts especially for devices that are connected serially without an intermediate electron reservoir provided by a metal contact, hence, the chemical potential needs to be considered for describing the behaviour of these devices.  $\mu_{s}$  and  $\mu_{d}$  are the source Fermi level and the drain Fermi level respectively, while  $E_{c}$  and  $E_{v}$  are the conduction and valence bands.

For the high doping level of CNFETs considered in this work (1%), the first two sub-bands of the doped source/drain region are assumed to be degenerated while only the first sub-bands of the intrinsic channel region is degenerated at on-state. Sub-bands are degenerate if the Fermi level is above the first conduction band of the CNT and the sub-bands are populated in by charge carriers. The high doping level here also has the effect of suppressing the SB resistance and making the metal/CNT contact essentially ohmic through tunnelling.

#### 2.6 CNFET-based Design Challenges

Controlled doping in nanoscale devices is difficult, and fluctuations in the number and position of the dopants can have a profound effect on device performance. CNFETs, along with other post-silicon device candidates suffer from extreme amounts of statistical variation in device behaviour, leading to a lack of robustness. Innovations in design, test and verification methodologies must accompany advances in manufacturing technology to address the reliability issue [81].

#### 2.6.1 Sources of Variation

Various sources of variation exist when dealing with CNT-based circuits:

- Variations in CNT diameter,

- Chirality variation (leading to metallic or semiconducting CNTs),

- Doping variations,

- Variation in CNT alignment under the gate,

- Mispositioned CNTs

Diameter and doping variations in CNTs cause drain current variations whilst metallic and mispositioned CNTs affect the functionality of the gates. This work is concerned with CNT diameter variations and source/drain doping fluctuations which cause drain current variations.

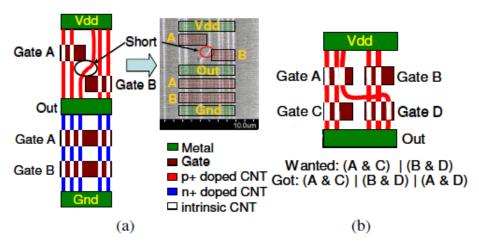

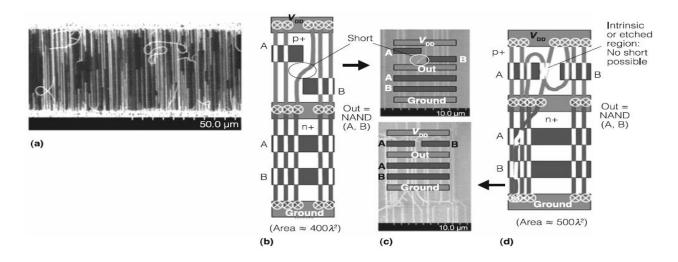

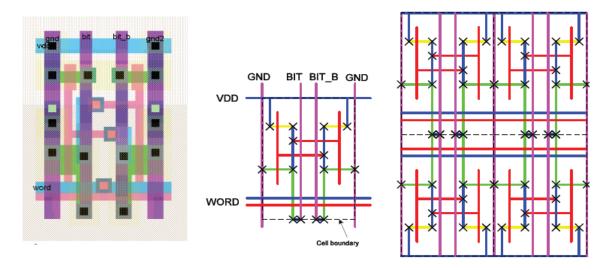

A CNFET NAND cell layout overlaid on an SEM image of CNTs is shown in Figure 2.8a. The misaligned CNT in Fig. 2.8a causes Vdd to output short in this NAND cell because the portion of this CNT between Vdd and output is entirely p-doped. A misaligned CNT may also cause an incorrect logic function implementation as illustrated in Fig. 2.9b.

Figure 2.9: (a) Short inside NAND gate caused by misaligned CNT. (b) Incorrect logic function due to misaligned CNT [81]

CNTs can exhibit either semiconducting or metallic behaviour depending on their diameter and chiral angle (chirality) [17]. The diameter of nanotubes can be controlled to some extent but there is no control over the chiral angle of CNTs. The band gap energy of CNTs is inversely proportional to their diameter. As the energy band gap affects current through a CNT, the diameter and chiral angle are determining factors with regards to its current-voltage characteristics. Chirality is difficult to control during manufacturing, this results in conducting (metallic) nanotubes and defective CNTFETs similar to stuck-on (SON or source-drain short) faults, as encountered in classical MOS devices [82].

Figure 2.10: CNT issues: largely aligned CNTs with misaligned CNTs (a), layout of misaligned-CNT-vulnerable NAND gate (b), SEM image of CNTFET overlaid with gates (c), misaligned-CNT-immune CNTFET-based NAND gate (d) [80]

Misaligned CNTs and metallic CNTs in CNFETs are two of the main challenges in the way of progress in nano-scale technologies. As figures 2.10(b) and 2.10(c) show, misaligned CNTs cause shorts and incorrect logic functions [49]. Design techniques to build CNFET-based circuits while ensuring functional immunity to misaligned CNTs have been put forward in [53, 81, 83]. Also, semiconducting CNTs are required for CNTFETs; metallic CNTs create source-drain shorts resulting in excessive leakage and severely degraded noise margins [80]. No known CNT growth technique guarantees the total absence of metallic CNTs. Therefore, metallic CNT removal techniques are necessary [52]. Unfortunately, such removal techniques alone are imperfect and insufficient; hence, co-optimization of processing techniques for metallic CNT removal together with CNFET-based circuit design is necessary. The impact of the presence of metallic CNTs in logic circuits has been studied [84-86]. Design and processing guidelines that enable design of CNFET-based digital circuits in presence of metallic CNTs are introduced in [87].

The challenges mentioned in this section along with the lack of control of the current technology on CNT physical characteristics, highlight the importance of low cost variation tolerant design techniques which, when applied to designs impose minimal changes on design methodologies Although various CNFET models and logic structures do exist, there is no systematic study on the performance of CNT-based logic structures in the presence of the specific variation sources mentioned in this section.

In standard cell design techniques, cells are pre-designed. For the purpose of timing analysis of circuits made from these pre-designed cells, the designer needs to know how much delay each cell would introduce into the circuit. Since delay is a variable of technology, a predictive model for the prediction of delay is required. The same is true for the case of power consumption as energy usage of electronic components is an increasingly important aspect of design as sizes get smaller. This work represents a proposal for a guideline for effective CNT-based electronic design.

Lithography could also be an issue. Line-edge roughness (LER) is a random fluctuation in the width of a resist feature. The amplitude of LER can be a significant fraction of the overall resist feature width at small feature dimensions. LER is a key factor hindering the advancement of lithography to nanoscale dimensions; however this is mainly a challenge for CMOS.

# Chapter 3 CNT Based Logic Gates in the Presence of CNT Diameter Variation<sup>1</sup>

The electronic properties of carbon nanotubes (CNTs) are directly related to CNT physical characteristics. The main structural properties of a CNT affecting its electrical behaviour are diameter and chirality. As the energy band gap of a CNT is inversely proportional to its diameter, changes in CNT diameter translate into changes in electrical current through the CNT. As manufacture of CNTs with exact unified diameters is not achievable with current technology, CNFET-based electronics design and circuitry is prone to electric current variation. The variation in current through different CNFETs causes an avalanche of other variations such as variation in propagation delay and power consumption.

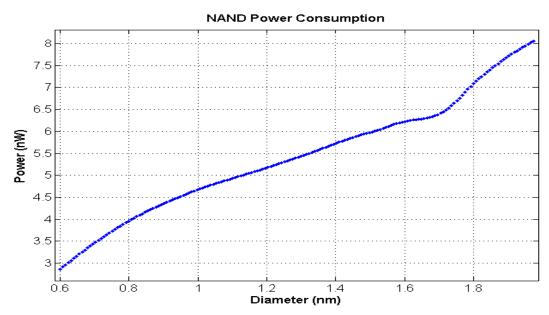

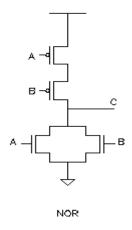

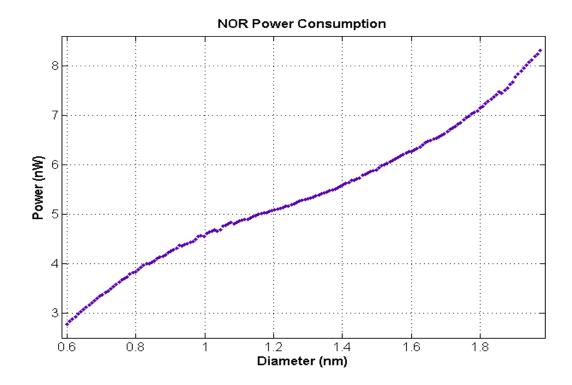

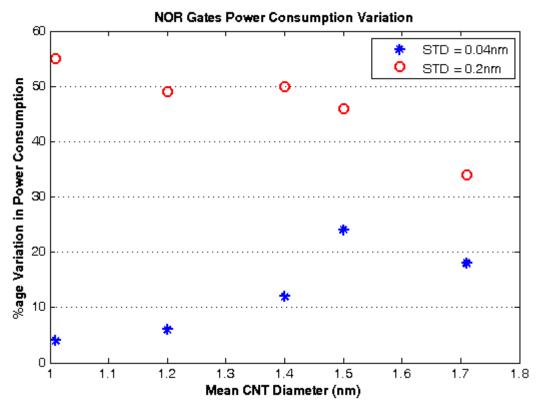

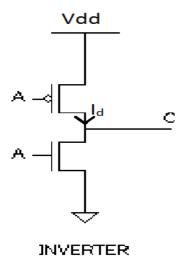

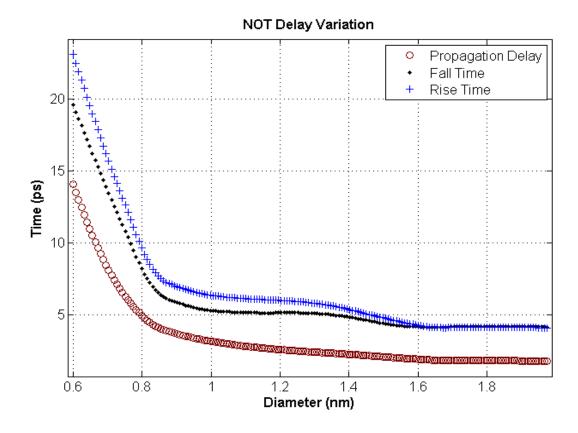

The ability to cope with these variations adds further weight to the proposition for CNFET as replacement for current silicon CMOS technology. In this chapter the performance of various logic gates in the presence of CNT diameter variations is studied. For the purpose of simulating the CNFET-based logic gates, the Stanford CNFET model is used [54, 68]. Logic gates (NOT, NAND and NOR) are studied and parameters (propagation delay, rise time, fall time and power consumption) are examined in the presence of CNT diameter variations. The CNT-based logic gates are designed and implemented in HSPICE. Parametric and Monte Carlo simulations are then carried out to obtain timing and power consumption characteristics.

Predictive models for the prediction of mean worst case propagation delay and also Standard Deviation (STD) in propagation delay based on given CNT mean diameter and STD have been developed in this chapter. Also two models for the prediction of mean power consumption and STD in power consumption of the logic gates given CNT diameter mean and STD have been developed.

<sup>&</sup>lt;sup>1</sup> Most of the contents of this chapter are taken from the paper "Effect of Variability in SWCNT-Based Logic Gates", by Hamed Shahidipour et. al. Refer to appendix A.

#### 3.1 Simulation Methodology

#### 3.1.1 CNFET Structure Used

For this work a MOSFET-like CNFET structure is used as this type of device behaves in a similar fashion to CMOS FETs, exhibits unipolar behaviour and is easier to fabricate [56, 57]. The CNFET model developed by Stanford University [54] is utilised. The model implements a circuitcompatible compact model for CMOS-like single-walled (SW)-CNFETs and is implemented in HSPICE. The model is superior to previous compact models as it accounts for scattering in the channel region, the resistive source/drain, the Schottky barrier resistance and the parasitic gate capacitances. Also by addition of a full trans-capacitance network it produces better predictions of the dynamic performance and transient response. Previous models used one or more lumped static gate capacitances and an ideal ballistic transport model in which it is assumed that no scattering occurs in the channel region and all carriers emitted from the source reach the drain [56, 63-65]. The model has been calibrated against experimental CNFET data to within 90% accuracy [88]. The CNFET structure used in this work is shown in figure 3.1. The section of the SWCNT under the gate is intrinsic. For doped source/drain extension regions doping level is taken as 1% of the total number of carbon atoms which is above the first conduction band of the SWCNT. Carrier mobility in CNTs is  $10^4$  cm<sup>2</sup>/V·s. The model assumes equal electron and hole mobility in CNTs. The mean free path (MFP) in the intrinsic section of the CNTs under the gate is 200nm. MFP in the doped CNT regions is 15nm throughout the work.

Figure 3.1: CNFET with multiple CNTs [54]

As mentioned earlier on, work in this chapter concentrates on the CNFET circuit performance benchmarked with the standard digital library cells such as the NOT, NAND and NOR gates. CNFET circuit performance analysis is extended to more complicated circuit structures such as multiplexers and memory modules.

Three SWCNTs per CNFET have been used in the simulations. Having more than one SWCNT per transistor has the potential advantage of improving current drive, however extra CNTs occupy extra space and impose an area cost on the transistor. Having 3 CNTs at a typical diameter of 1.5nm, with an in inter-CNT spacing of 20nm, requires a gate width of 48nm. Adding any extra CNTs would add an extra area cost in terms of the spacing required between the CNTs and the diameter of the CNT itself.

The effect of chirality variation at low-voltage operation (as is the case in most digital applications) is negligible on device electrostatics [90]; hence, in this work CNT diameter variations are considered for analysing the performance of CNFET-based logic gates and other circuit structures under process parameter variations.

As long as CNT diameter is less than 3 nanometres (nm) (which is typical for CNT devices) and the transistor is taken to be a short-channel device (less than 100nm) only the first conduction/valence bands have a significant effect on the current with a power supply of less than 1V [54, 91]. A physical channel length of 32nm is assumed together with an oxide thickness of 4 nm. This channel length is short enough for the device to be assumed short channel and long enough for the model to be able to correctly simulate the device. The model cannot simulate CNFETs with channel lengths under 10nm correctly. The physical metal gate width is assumed to be 48nm. This physical width affects the parasitic capacitance but the on-current depends on the actual *effective* gate width which is determined by the number of CNTs under the gate and the spacing between them. A power supply voltage of 0.9V is used in accordance with the ITRS roadmap for 32nm technology [3]. 10,000 samples were taken and Monte Carlo iterations were run for each mean CNT diameter ( $D_{\mu}$ ) and CNT diameter standard deviation ( $D_{\delta}$ ) considered. All simulations are run for the 32nm technology node. The performance parameters considered are propagation delay, rise time, fall time and power consumption. The following definitions of delays are used [62]:

*Propagation delay*: maximum time from the input crossing 50% to the output crossing 50%. This has been taken as the high to low output transition for NAND gates and low to high output transition for NOT and NOR gates.

Rise time: time for a waveform to rise from 10% to 90% of its steady-state value

Fall time: time for a waveform to fall from 90% to 10% of its steady-state value

Propagation delay and hence the device speed strongly depend on the parasitic gate capacitance, including the outer fringe gate capacitance ( $C_{\rm of}$ ) and the gate to gate (source/drain) coupling capacitance ( $C_{\rm gtg}$ ) (Fig. 3.1). The parallel conducting channels have screening/imaging effect on the actual potential profile in the gate region, and therefore affect the capacitance. For devices at 32nm node, as is the case in this work,  $C_{\rm gtg}$  is around 11 aF. The gate to channel capacitance ( $C_{\rm gc}$ ) strongly depends on the device geometry and both  $C_{\rm gc}$  and  $C_{\rm of}$  are affected by screening of neighbouring CNTs especially if CNTs are closely spaced thereby providing large current drive per unit device width.

#### 3.1.2 Statistical Simulation Strategy

The most commonly used statistical CNT diameter models adopt a Gaussian distribution [91]. If the rate of carbon feeding is fixed at any given growth condition there is an optimal diameter of nano-particles that nucleate nanotubes [92]. Any smaller diameter nano-particle cannot nucleate as it is "overfed" with carbon feedstock and any nano-catalysts with larger diameters are inactive as they're "under-fed". Assuming that the process of defining the catalyst particle size can be optimized to give a narrow allocation around a specified mean diameter, for large numbers of fabricated CNTs it can expected that the spread in diameter to follow a normal (Gaussian) distribution. A Gaussian distribution is also reported by other groups [92-95]. A positive distribution is considered as the diameter of a CNT always has a positive value.

As there is an inherent uncertainty in the diameter of CNTs produced during fabrication, a Monte Carlo (MC) approach is used with a normal distribution of CNT diameters for the simulations. MC simulations were performed to analyse how mean CNT diameter ( $D_{\mu}$ ) and diameter STD ( $D_{\delta}$ ) variation affect the mean and STD of the various performance parameters. 10,000 different

samples (logic gates) were assumed and for each run the diameter distribution properties were varied in the range 1.01 nm to 1.71 nm for mean diameter and 0.04 to 0.2 nm for standard deviation. Only semi-conducting CNTs are considered. Five different samples for mean diameter were taken into account. For each mean diameter sample, 5 categories of standard deviation in the range 0.04nm to 0.2nm were considered (as shown in table 3.1).

To be consistent with the work of [96], different values for mean diameters in the range 1.01 nm to 1.71 nm were taken into account. Considering the inaccuracy of fabrication techniques, a standard deviation from the mean in the range of 0.04nm to 0.2nm [96] was introduced for each mean diameter value.

HSPICE scripts are used to measure the average power consumption of the various logic gates simulated. This is done by measuring the average power drawn from the voltage source  $V_{DD}$  throughout the operation of the circuit when input voltage waveforms are applied. This period also covers any switching of the circuits and thereby the dynamic power used by the circuit. The procedure for measuring the average power consumption of the circuits is shown in sample HSPICE scripts in appendix B.

Figure 3.2: Inverter showing current and capacitance during switching [62]

Sources of power dissipation are dynamic power dissipation and static power dissipation. In CNFET-based circuitry, dynamic power dissipation is due to charging and discharging load capacitances as the gate switches and also the short circuit power due to short circuit current while

both pFET and nFET stacks are partially ON [62]. Static power dissipation arises from sub-threshold leakage through OFF transistors and gate leakage through gate dielectric [62].

The top part of fig. 3.2 shows an inverter with a connected load. The capacitance C in the figure represents the load capacitance due to the fan out. When the circuit is actively switching, the power consumed to charge and discharge the capacitor C is the dynamic power. When the gate is not switching, a current, I<sub>static</sub> is leaked through between power and ground due to the OFF transistor. This leakage gives rise to leakage power. In these simulations, the instantaneous and average power delivered by the voltage source is measured as the power consumption of the circuit. Power consumption measured in the simulations includes both the dynamic (switching + short circuit power) and the static (sub-threshold leakage + gate leakage) components.

#### 3.1.3 Parametric Analysis

Parametric simulations were performed to study how diameter variation affects the performance parameters of the various logic gates considered such as delay characteristics and power consumption.

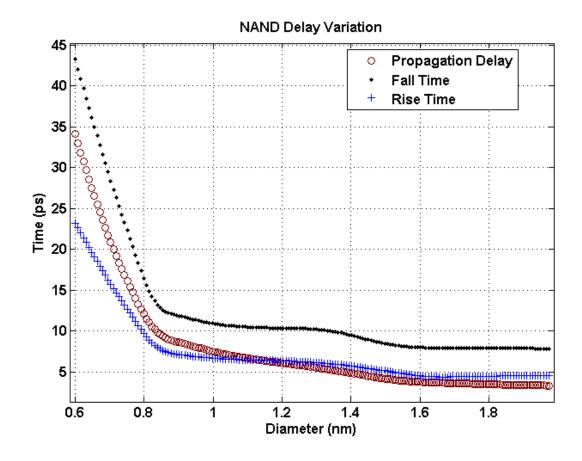

Parametric simulations were run for the various logic gates considered in this study. In the parametric analysis, the diameter of the CNTs used in the fabrication of each logic gate were swept linearly from a minimum CNT diameter of 0.6nm (the smallest physically achievable diameter) to a maximum diameter of 2nm in a transient analysis using HSPICE. Performance parameters such as propagation delay, rise time, fall time and the power consumed for each diameter case were then recorded.

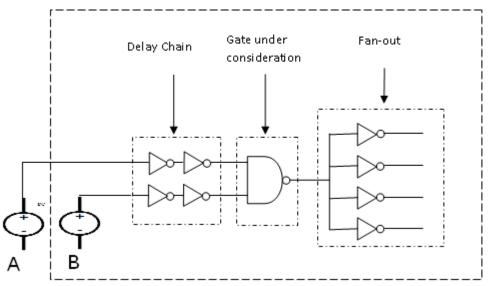

The complete circuit consists of a 2-input logic gate together with 2 CNFET-based inverters in series which introduce a skew in the ideal input signal at each input thereby providing non-ideal conditions for the simulations, and 4 CNFET-based inverters in parallel as the fan-out of the NAND gate as is the case in standard practice (fig. 3.3). The fanout-of-4 (FO4) inverter delay is the delay of an inverter driving a load capacitance that has four times the inverter's input capacitance [97]. The FO4 metric is not substantially changed by process technology or operating conditions. The test circuit structure of fig. 3.3 is used in all the logic gates simulations in this work.

Figure 3.3 Test Circuit

### 3.2 Simulation RESULTS

#### 3.2.1 NAND Gate

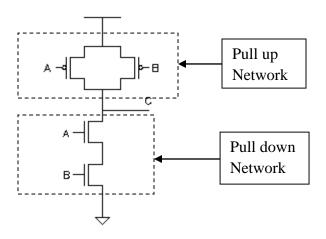

Figure 3.4: Schematic of the simulated NAND gate

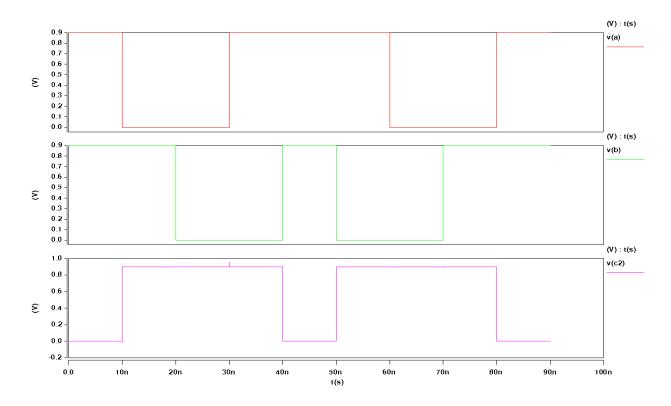

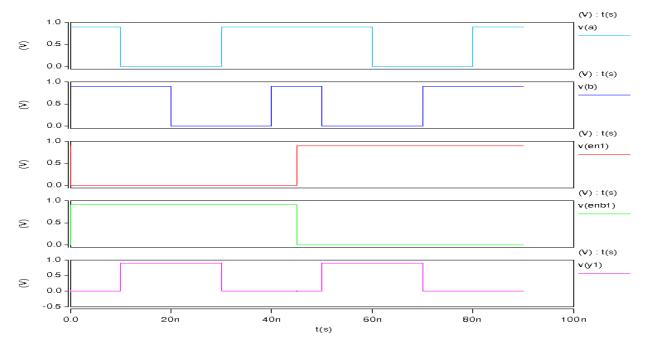

The performance of a CNFET based NAND gate is analysed. The circuit consists of a 2-input NAND gate (composed of two P-type CNFETs and two N-type CNFETs) together with fan-in and fan-out as described in section 3.1.3. The input waveforms shown in Fig. 3.4 were given as the inputs to the NAND gate. The output waveform is v(c2) in the bottom of fig. 3.5:

Figure 3.5: Gate Input/Output waveforms

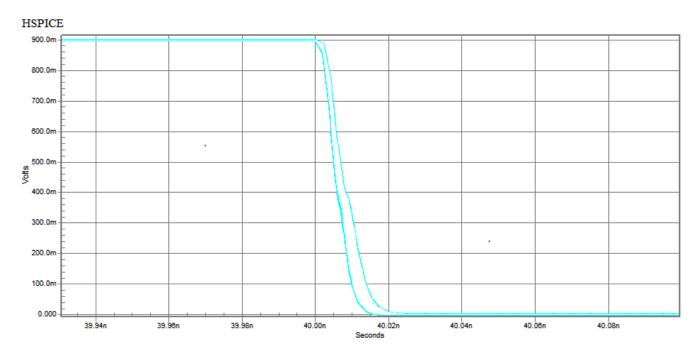

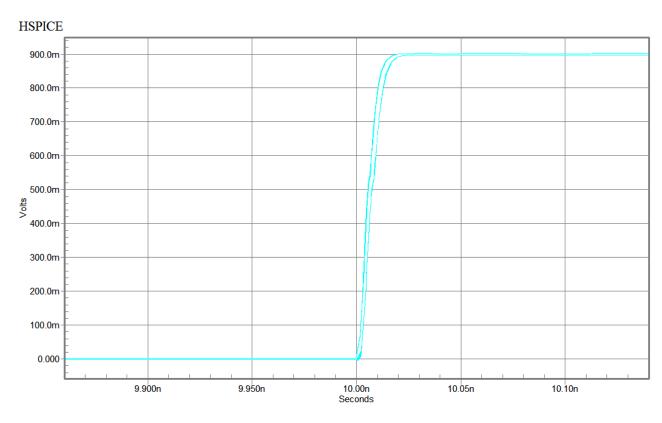

Fig. 3.6 shows a falling edge of the output waveform of the NAND gate (v(c2) in fig. 3.5) in more detail in a smaller time frame.

Figure 3.6: NAND waveform showing part of the output waveform falling edge

During each low to high output transition the load is charged through the PMOS transistors drawing a certain amount of energy from the power supply. It is discharged during the high to low output transition and the stored energy is dissipated through the NMOS transistors.

The input waveforms and the time duration are chosen so that the analysis covers the different behavioural regimes of the gates. The two signals cover the cases where both inputs to the gate A and B are high (at Vdd = 0.9V); where A is low (at 0 Volts) and B is high, also when input A is high and input B is low and finally when both inputs A and B are low; this covers the full logic input combination for the 2-input NAND gates. The input signals are almost ideal so that rise and fall times are  $\sim$ 0, however the fan-in inverters in the test circuit are there to introduce the necessary skew in the rise/fall times of the input signals.

The two P-type CNFETs (PCNFETs) are connected to the supply voltage Vdd. As P-type transistors close when their gate signal is low, the two parallel PCNFETs imply that if either or both inputs *A* and *B* are low, then the gate output is high (at Vdd). NCNFETs behave in the opposite way as they close when the signal on their gate is high, hence, the two series NCNFETs provide a connection to ground only when both *A* and *B* are high.

### 3.2.1.1 Timing Behaviour

When both A and B are high, the two PCNFETs are off and the two NCNFETs are both on, providing a connection to ground, hence output is zero (low). The two series NCNFETs here offer greater resistance in the path of current and fall time is expected to take longer than when current would be passing through one transistor only. When both A and B are low, the two PCNFETs are on and the two NCNFETs are off. Gate output here would be high. The path offered to current through the parallel pull-up network of the PCNFETs has half the resistance of a single transistor and rise time is expected to be faster than the fall time for the NAND gates.

The case for worst case delay happens when one input (*A* in Fig. 3.5) is high and the other input (*B* in Fig. 3.5) changes from low to high. While *B* is still low, the PCNFET connected to *A* is off and the other PCNFET connected to *B* is on. The NCNFET connected to *A* is on and the NCNFET connected to *B* is off. Under this condition the output terminal is charged through the PCNFET connected to *B* to approximately Vdd. In this case the drain regions of the on-NCNFET are also

charged to Vdd. When *B* changes from low to high, the on PCNFET turns off and the off NCNFET turns on. Now the two series NCNFETs are on and the output terminal of the NAND gate discharges to ground, but the charge previously stored at the drain region of the NCNFET connected to *A* must also be discharged at the same time. This discharge takes place through the NCNFET connected to the *B* input and hence the discharge of the NAND gate's output terminal must wait until this is done.

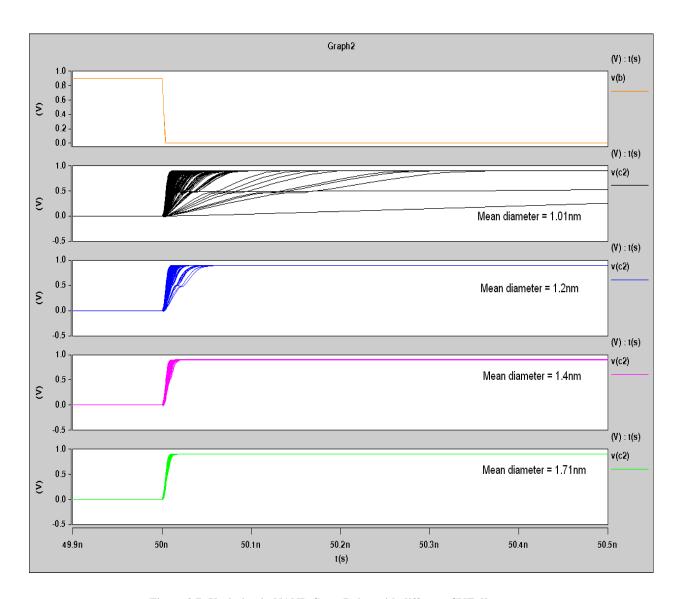

Figure 3.7: Variation in NAND Gates Delay with different CNT diameters

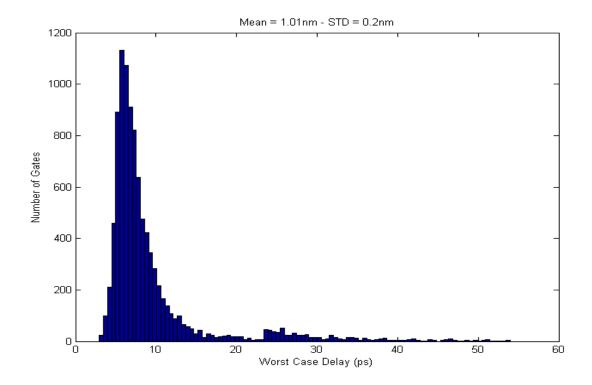

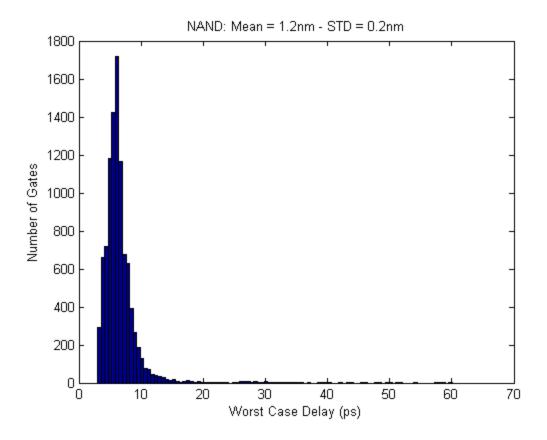

Fig. 3.7 shows output voltages obtained from 10000 Monte Carlo simulation iterations of NAND gates with various CNT mean diameters for a given input voltage. It can be seen from the plots that for NAND gates employing larger diameter CNTs, variation in output voltage becomes smaller.

As the band gap of a carbon nanotube is inversely proportional to its diameter [97-104], CNTs with larger diameters have smaller band gaps. A smaller band gap means that a transistor made of CNTs with larger diameters can exhibit higher on-currents. CNTs with smaller diameters have higher source/drain resistance which can be explained by the fact that at small diameters only the first sub-band is degenerate (zero bandgap, i.e. the subbands are populated by charge carriers) [69].

From figure 3.6 it can be observed that at smaller diameters, the effects of diameter variations as a process parameter are more profound. By varying the diameter the band gap of the CNT is modified. Assume two sets of CNTs. One set has a mean diameter of 1.01nm and the other set has a mean diameter of 1.71nm. Assume also a STD of 0.2 nm. The 3 sigma point of the distribution is taken (according to the empirical rule this covers over 99.7% of the values drawn from the normal distribution) into account, so that this STD roughly translates into an 11.7% deviation from mean diameter in the case of 1.71nm mean, but the same STD implies almost a 20% deviation for the 1.01nm CNTs. Hence, a diameter change of 0.2nm causes greater band gap variation for CNTs with small mean diameters compared with those with larger mean diameters.

Table 3.1: NAND Gates delay behaviour

| Mean         | Diameter | Mean Delay          | Min. Delay | Max. Delay | $\Delta T_d$ |

|--------------|----------|---------------------|------------|------------|--------------|

| Diameter(nm) | STD (nm) | T <sub>d</sub> (ps) | (ps)       | (ps)       | (ps)         |

|              |          |                     |            |            |              |

|              | 0.04     | 7.44                | 5.75       | 10.31      | 4.56         |

|              | 0.08     | 7.62                | 4.56       | 26.69      | 22.13        |

| 1.01         | 0.12     | 8.15                | 3.43       | 49         | 45.57        |

|              | 0.16     | 8.97                | 3.03       | 55.41      | 52.38        |

|              | 0.2      | 9.63                | 2.81       | 54.82      | 52.01        |

|              | 0.04     | 6.09                | 4.79       | 7.33       | 2.54         |

|              | 0.08     | 6.11                | 3.62       | 9.72       | 6.1          |

| 1.2          | 0.12     | 6.18                | 3.21       | 19.49      | 16.28        |

|              | 0.16     | 6.35                | 2.99       | 53.81      | 50.82        |

|              | 0.2      | 6.71                | 3          | 60.11      | 57.11        |

|              | 0.04     | 4.85                | 3.71       | 5.93       | 2.22         |

|              | 0.08     | 4.85                | 3.33       | 7.07       | 3.74         |

| 1.4          | 0.12     | 4.88                | 3.12       | 9          | 5.89         |

|              | 0.16     | 4.95                | 3.1        | 13.9       | 10.8         |