University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

**Variation and Reliability in Digital CMOS Circuit Design**

by

**Massoud Mokhtarpour Ghahroodi**

Thesis for the degree of Doctor of Philosophy

April 2014

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Doctor of Philosophy

VARIATION AND RELIABILITY IN DIGITAL CMOS CIRCUIT DESIGN

by **Massoud Mokhtarpour Ghahroodi**

The silicon chip industry continues to provide devices with feature sizes at Ultra-Deep-Sub-Micron (UDSM) dimensions. This results in higher device density and lower power and cost per function. While this trend is positive, there are a number of negative side effects, including the increased device parameter variation, increased sensitivity to soft errors, and lower device yields. The lifetime of next-generation devices is also decreasing due to lower reliability margins and shorter product lifetimes.

This thesis presents an investigation into the challenges of UDSM CMOS circuit design, with a review of the research conducted in this field. This investigation has led to the development of a methodology to determine the timing vulnerability factors of UDSM CMOS that leads to a more realistic definition of the Window of Vulnerability (WOV) for Soft-Error-Rate (SER) computation.

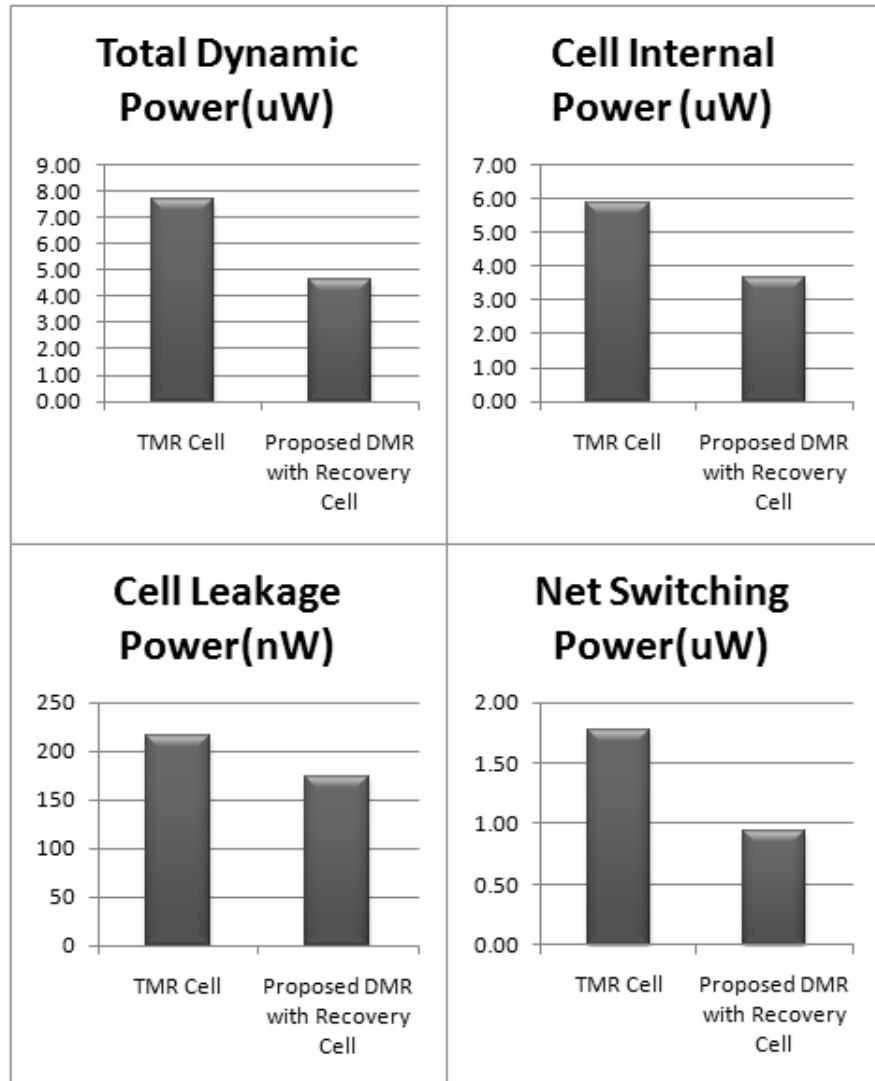

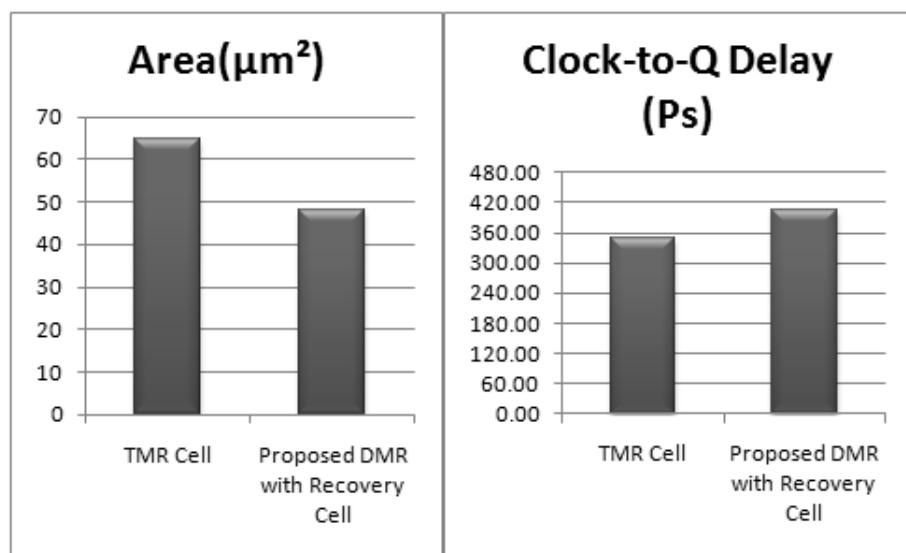

We present an implementation of a Radiation-Hardened 32-bit Pipe-lined Processor as well as two novel radiation-hardening techniques at Gate-level. We present a Single-Event-Upset (SEU) tolerant Flip-Flop design with 38% less power overhead and 25% less area overhead at 65nm technology, compared to the conventional Triple Modular Redundancy (TMR) technique for Flip-Flop design. We also propose an approach for in-field repair (IFR) by trading area for reliability. In the case of permanent faults, spare logic blocks will replace the faulty blocks on the fly. The simulation results show that by tolerating approximately 70% area overhead and less than 18% power overhead, the reliability is increased by a factor of x10 to x100 for various component failure rates.

# Contents

|                                                                                                 |             |

|-------------------------------------------------------------------------------------------------|-------------|

| <b>Nomenclature</b>                                                                             | <b>xv</b>   |

| <b>Declaration of Authorship</b>                                                                | <b>xvii</b> |

| <b>Acknowledgements</b>                                                                         | <b>xix</b>  |

| <b>1 Introduction</b>                                                                           | <b>1</b>    |

| 1.1 Motivations For Research . . . . .                                                          | 1           |

| 1.2 Power-Performance-Yield-Reliability . . . . .                                               | 2           |

| 1.2.1 Power . . . . .                                                                           | 2           |

| 1.2.2 Performance . . . . .                                                                     | 2           |

| 1.2.3 Yield . . . . .                                                                           | 3           |

| 1.2.4 Reliability . . . . .                                                                     | 3           |

| 1.3 Objectives . . . . .                                                                        | 4           |

| 1.4 Contributions . . . . .                                                                     | 4           |

| 1.5 Thesis Structure . . . . .                                                                  | 5           |

| <b>2 Literature Review</b>                                                                      | <b>7</b>    |

| 2.1 Process Variation . . . . .                                                                 | 7           |

| 2.1.1 Performance . . . . .                                                                     | 10          |

| 2.1.2 Power Consumption . . . . .                                                               | 11          |

| 2.2 Radiation and Soft Errors . . . . .                                                         | 14          |

| 2.2.1 Single Event Effects Definition . . . . .                                                 | 15          |

| 2.2.2 Major Soft Error Problems . . . . .                                                       | 16          |

| 2.3 The Reliability Issues . . . . .                                                            | 20          |

| 2.3.1 Major Reliability Issues in Ultra Deep-Sub-Micron CMOS .                                  | 21          |

| 2.3.2 Negative Bias Temperature Instabilities (NBTI) & Hot-Carrier<br>Injection (HCI) . . . . . | 21          |

| 2.3.3 Time-Dependent Dielectric Breakdown (TDDB) or "Wear-<br>Out" . . . . .                    | 24          |

| 2.4 Solutions and state-of-the-art . . . . .                                                    | 27          |

| 2.4.1 Tackling Variations At Design-Time . . . . .                                              | 27          |

| 2.4.1.1 Analysis Techniques . . . . .                                                           | 27          |

| 2.4.1.2 Implementation Techniques . . . . .                                                     | 29          |

| 2.4.2 Tackling Variations At Run-time . . . . .                                                 | 30          |

|          |                                                                                  |           |

|----------|----------------------------------------------------------------------------------|-----------|

| 2.4.2.1  | Dynamic Voltage and Frequency Scaling (DVFS) . . . . .                           | 32        |

| 2.4.2.2  | Considerations . . . . .                                                         | 38        |

| 2.4.3    | Soft Error Mitigation Techniques: Radiation Hardening By Design (RHBD) . . . . . | 39        |

| 2.4.3.1  | RHBD at device/Layout Level . . . . .                                            | 40        |

| 2.4.3.2  | RHBD at Transistor Level . . . . .                                               | 41        |

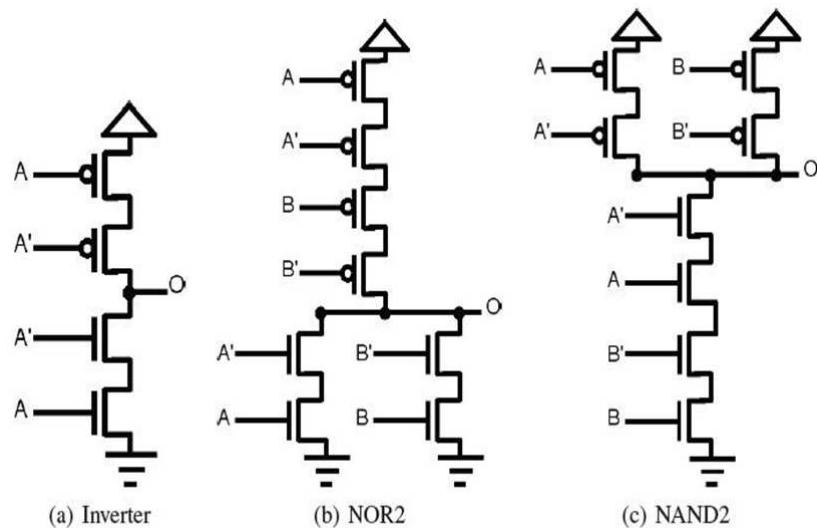

| 2.4.3.3  | RHBD at Gate Level . . . . .                                                     | 44        |

| 2.4.3.4  | RHBD at Register Transfer Level . . . . .                                        | 44        |

| 2.4.3.5  | RHBD at Software Level . . . . .                                                 | 45        |

| 2.4.4    | Dealing with the Reliability issues . . . . .                                    | 46        |

| 2.5      | Concluding Remarks . . . . .                                                     | 54        |

| <b>3</b> | <b>Soft Errors and Timing Vulnerability</b>                                      | <b>55</b> |

| 3.1      | Introduction . . . . .                                                           | 55        |

| 3.2      | Window of Vulnerability . . . . .                                                | 56        |

| 3.3      | Methodology . . . . .                                                            | 59        |

| 3.4      | Results . . . . .                                                                | 59        |

| 3.5      | SET, WOV and Mitigation Factors . . . . .                                        | 61        |

| 3.6      | Variation and the WOV . . . . .                                                  | 63        |

| 3.7      | WOV and Soft Error Rate . . . . .                                                | 64        |

| 3.8      | Discussion . . . . .                                                             | 69        |

| 3.9      | Concluding Remarks . . . . .                                                     | 70        |

| <b>4</b> | <b>Soft Errors and Radiation Hardening By Design</b>                             | <b>71</b> |

| 4.1      | Introduction . . . . .                                                           | 71        |

| 4.2      | Radiation Hardening of a 32 bit real-time processor at gate-level . . . . .      | 74        |

| 4.3      | Discussion . . . . .                                                             | 82        |

| 4.4      | SEU-Tolerant Flip-Flop Design . . . . .                                          | 88        |

| 4.5      | Radiation-Hardening and Clock-Gating Design . . . . .                            | 92        |

| 4.6      | Concluding Remarks . . . . .                                                     | 97        |

| <b>5</b> | <b>Reliability and In-field Logic Repair</b>                                     | <b>99</b> |

| 5.1      | Introduction . . . . .                                                           | 99        |

| 5.2      | In-Field Repair in CMOS Circuit Design . . . . .                                 | 101       |

| 5.2.1    | Motivation . . . . .                                                             | 101       |

| 5.2.2    | In-Field Logic Repair . . . . .                                                  | 102       |

| 5.2.3    | Sphere of Replication and Levels of Granularity . . . . .                        | 103       |

| 5.2.4    | In-Field Logic Repair at Pipeline Level . . . . .                                | 108       |

| 5.2.4.1  | Switch Boxes . . . . .                                                           | 110       |

| 5.2.4.2  | Error Detection Mechanism . . . . .                                              | 111       |

| 5.2.4.3  | Self-Checking Controller . . . . .                                               | 111       |

| 5.2.5    | Results . . . . .                                                                | 115       |

| 5.2.5.1  | Overhead Comparisons . . . . .                                                   | 115       |

| 5.2.5.2  | Reliability Comparisons . . . . .                                                | 117       |

| 5.3      | Challenges in Static Timing Analysis of our proposed schemes . . . . .           | 118       |

|                                                     |            |

|-----------------------------------------------------|------------|

| 5.4 Variation-and-Ageing Resilient Design . . . . . | 120        |

| 5.5 Concluding Remarks . . . . .                    | 124        |

| <b>6 Conclusions</b>                                | <b>127</b> |

| 6.1 Conclusions . . . . .                           | 127        |

| 6.2 Future work . . . . .                           | 129        |

| <b>A 45nm DFF Schematic</b>                         | <b>131</b> |

| <b>References</b>                                   | <b>133</b> |

# List of Figures

|      |                                                                                                                                                                                                                                               |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

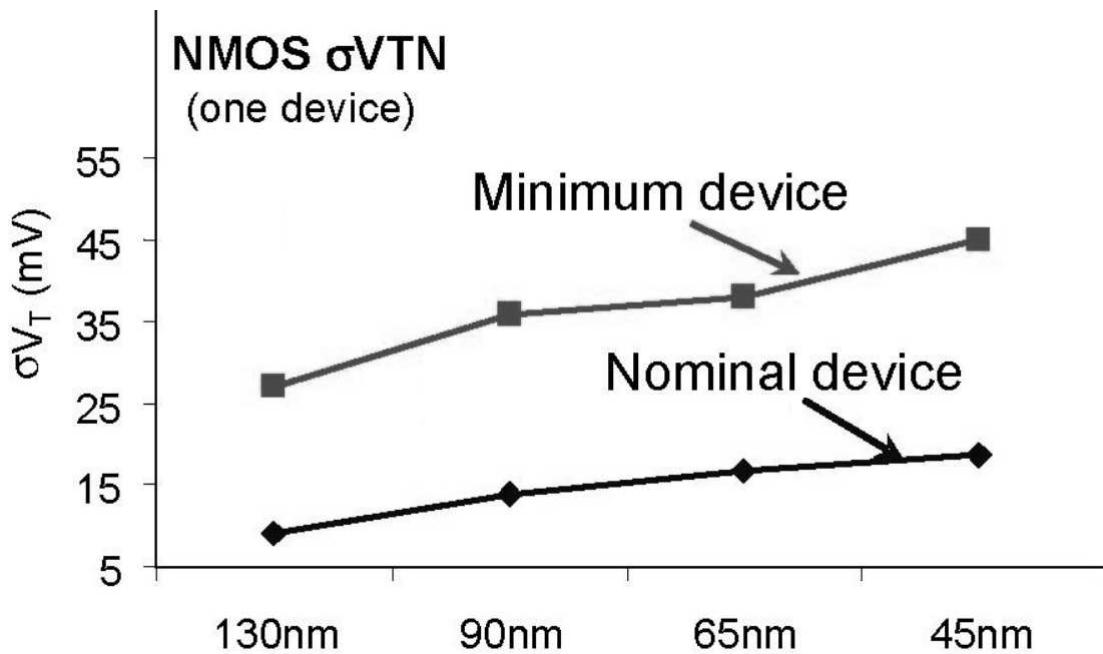

| 2.1  | Variation in threshold voltage of devices [1] . . . . .                                                                                                                                                                                       | 8  |

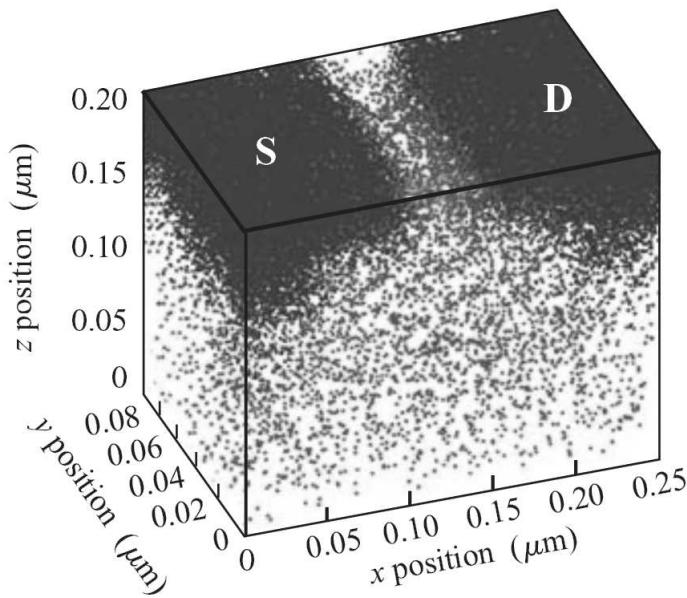

| 2.2  | Random placement of dopant atoms a 50-nm channel-length MOS-FET [2] . . . . .                                                                                                                                                                 | 9  |

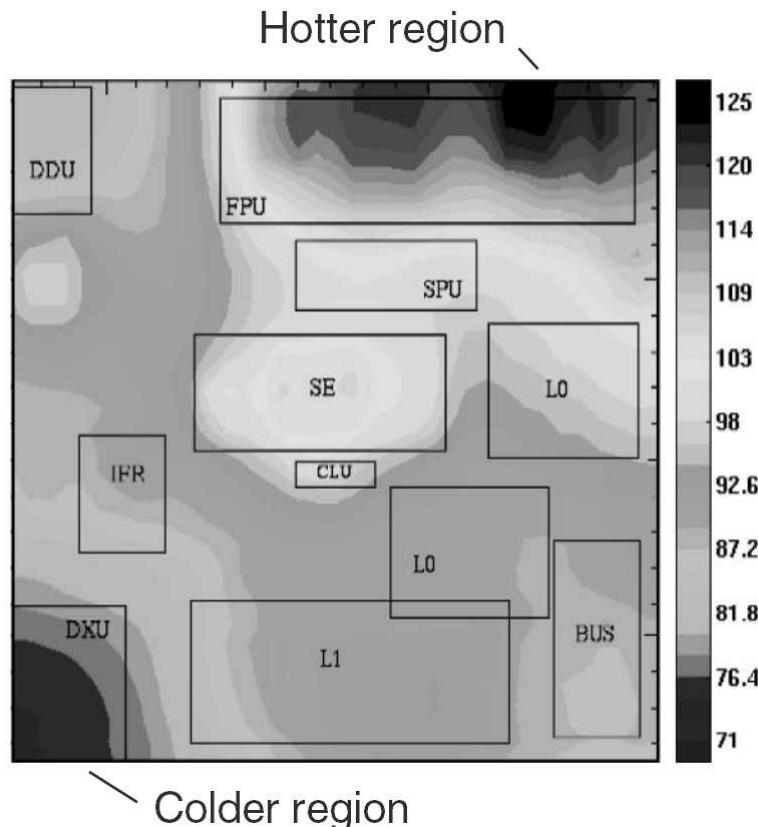

| 2.3  | Temperature differences on a die: 40C to 50C temperature difference leads to 20% performance variation [3] . . . . .                                                                                                                          | 11 |

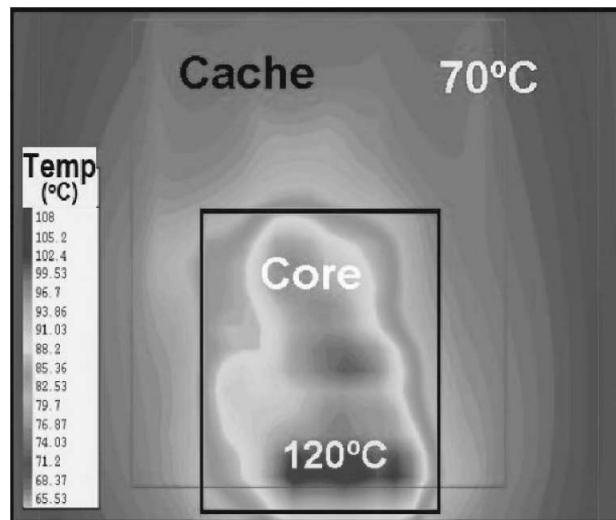

| 2.4  | A Temperature Distribution Map of a Typical Chip with a Core and Cache [3] . . . . .                                                                                                                                                          | 12 |

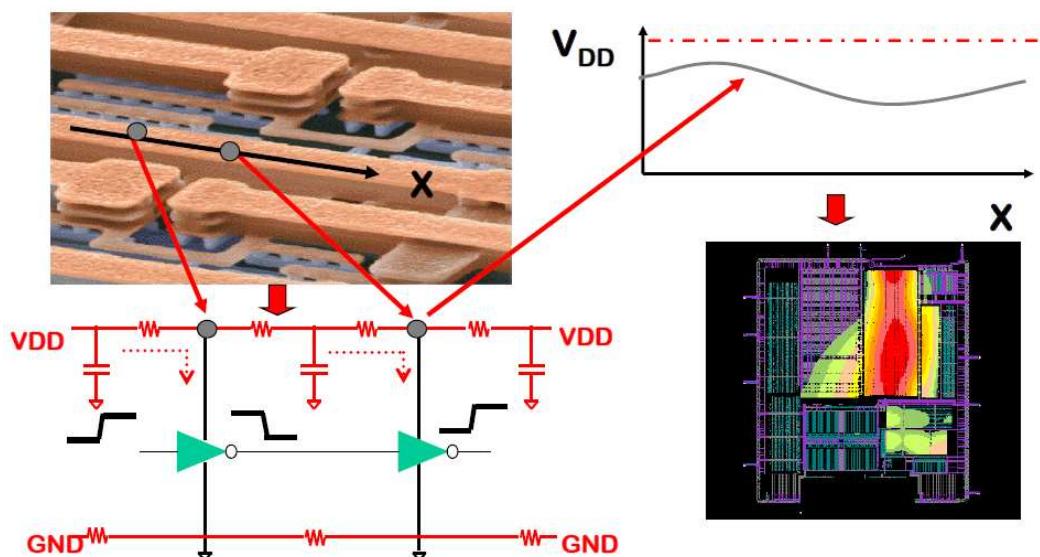

| 2.5  | IR Drop in Power Distribution Network due to non-ideal components [4] [5] . . . . .                                                                                                                                                           | 13 |

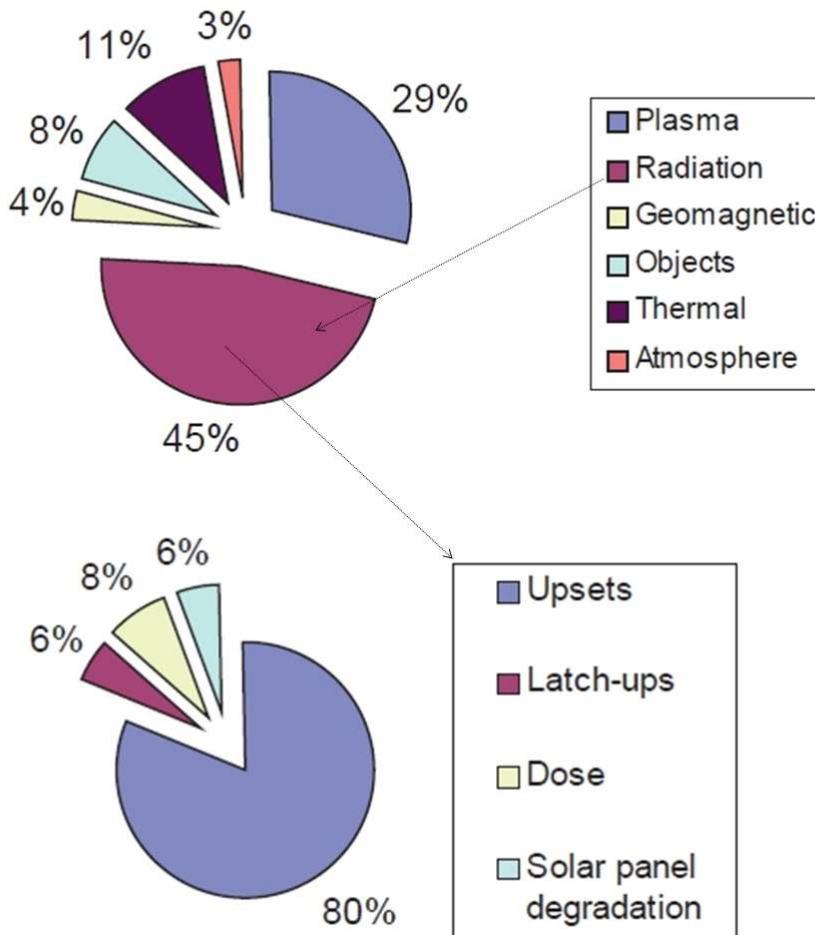

| 2.6  | Spacecraft anomalies due to the space environment [6] . . . . .                                                                                                                                                                               | 14 |

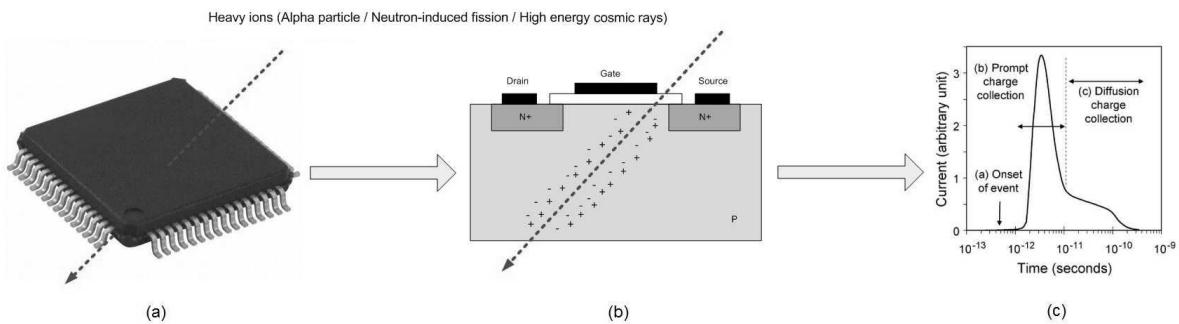

| 2.7  | Illustration of single event transient pulse generation. Funnelling in an n+/p silicon junction following the ion strike and the resulting electrical transient current caused by the passage of a high-energy ion [7] [8]. . . . .           | 16 |

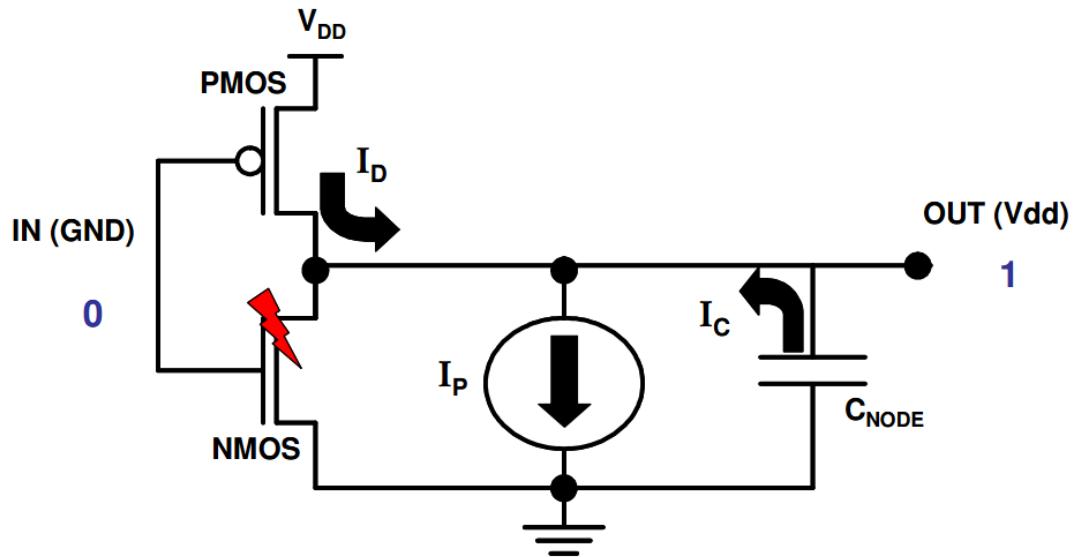

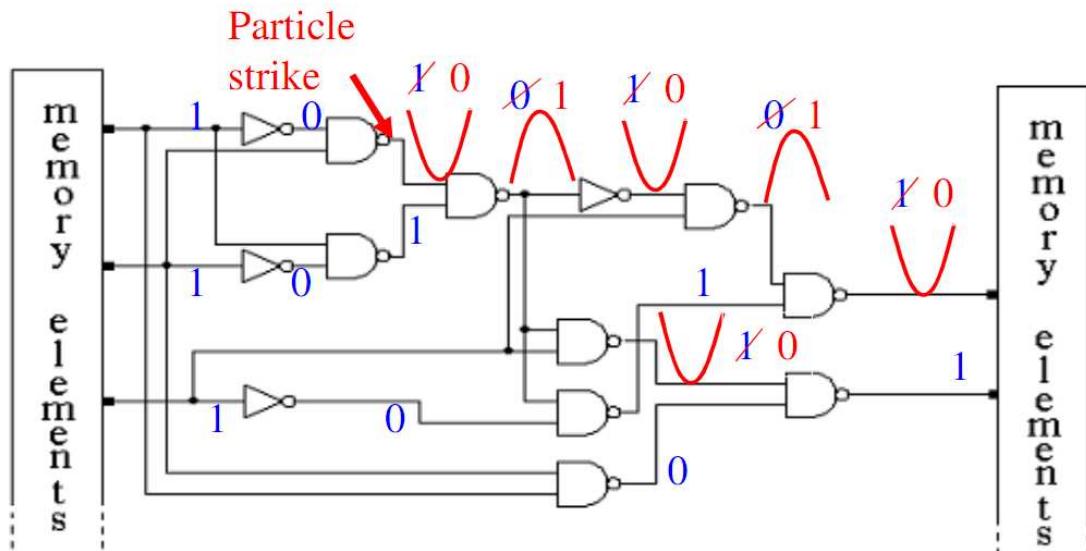

| 2.8  | Particle strike on a sensitive node . . . . .                                                                                                                                                                                                 | 17 |

| 2.9  | SET in Combinational Logic . . . . .                                                                                                                                                                                                          | 17 |

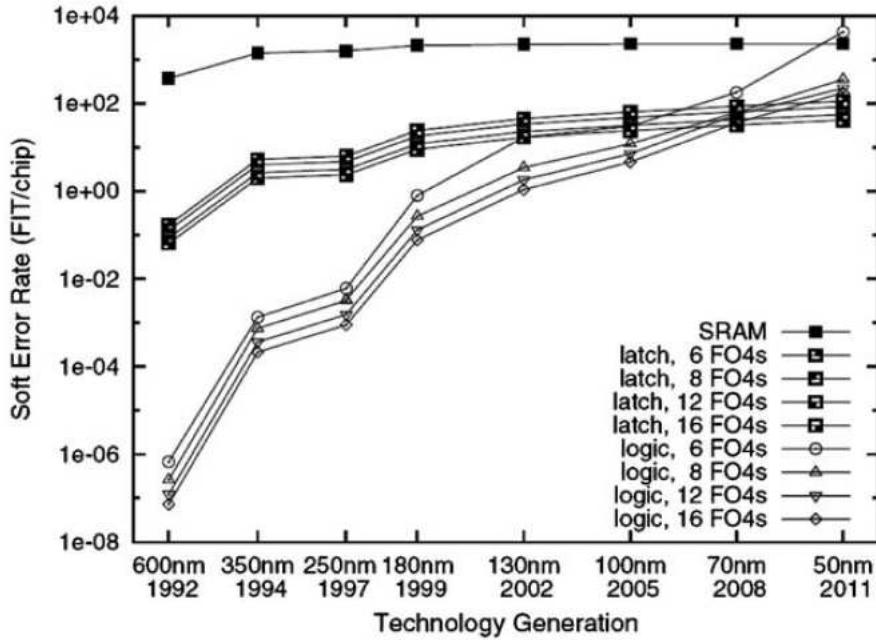

| 2.10 | SER of an alpha processor for different technology nodes [9] . . . . .                                                                                                                                                                        | 20 |

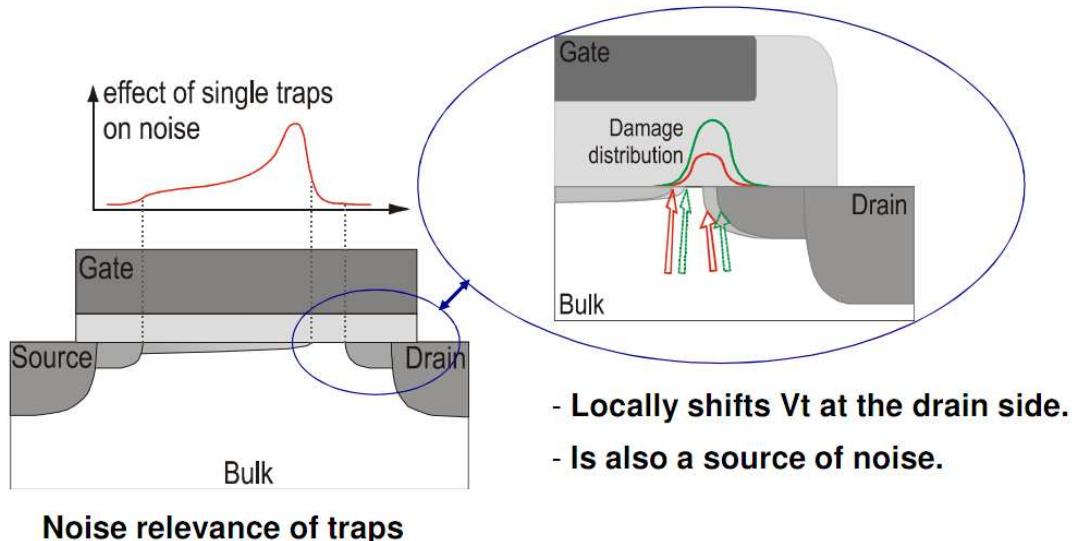

| 2.11 | Hot carrier stress generates additional trap states near to the drain . . . . .                                                                                                                                                               | 21 |

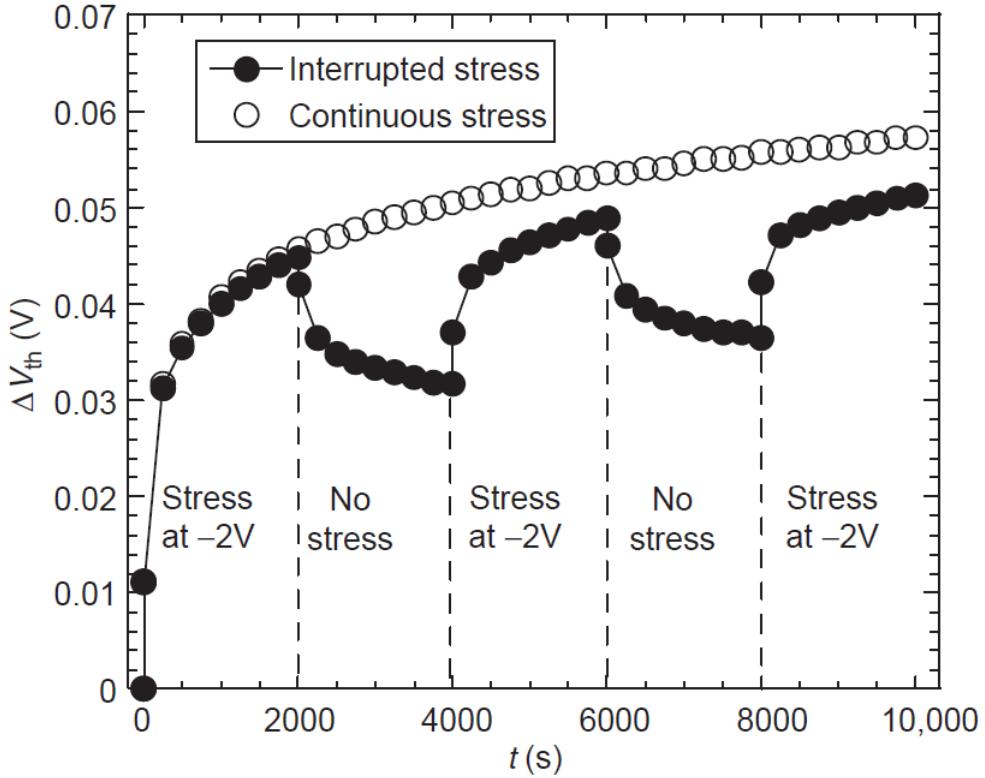

| 2.12 | V <sub>th</sub> differences as a function of stress time, showing the threshold voltage degradation during the stress and the partial-recovery when the gate bias is switched to 0V. From [10]. . . . .                                       | 22 |

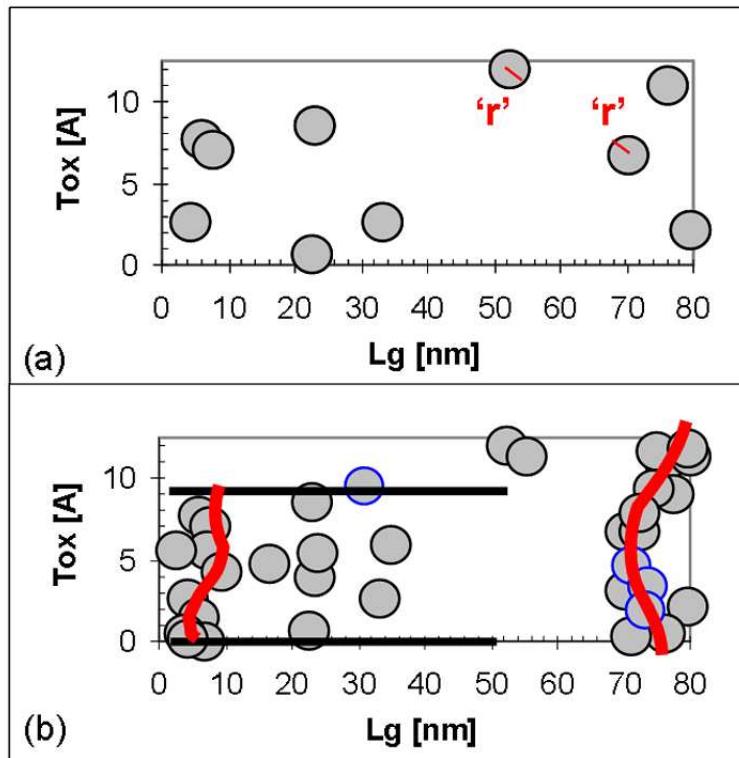

| 2.13 | Percolation Theory describes traps as spheres of radius "r. When several of them form a complete chain from anode to cathode, breakdown (BD) occurs. The thinner the dielectric, the fewer the traps needed to cause Break down [11]. . . . . | 26 |

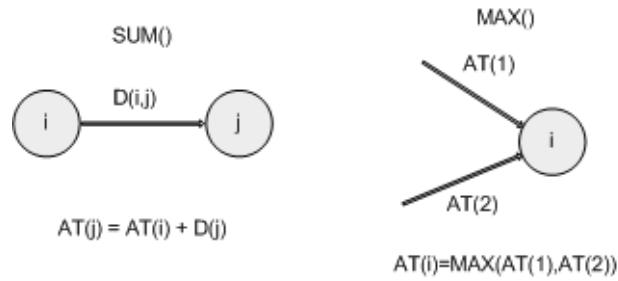

| 2.14 | SUM and MAX Operations . . . . .                                                                                                                                                                                                              | 29 |

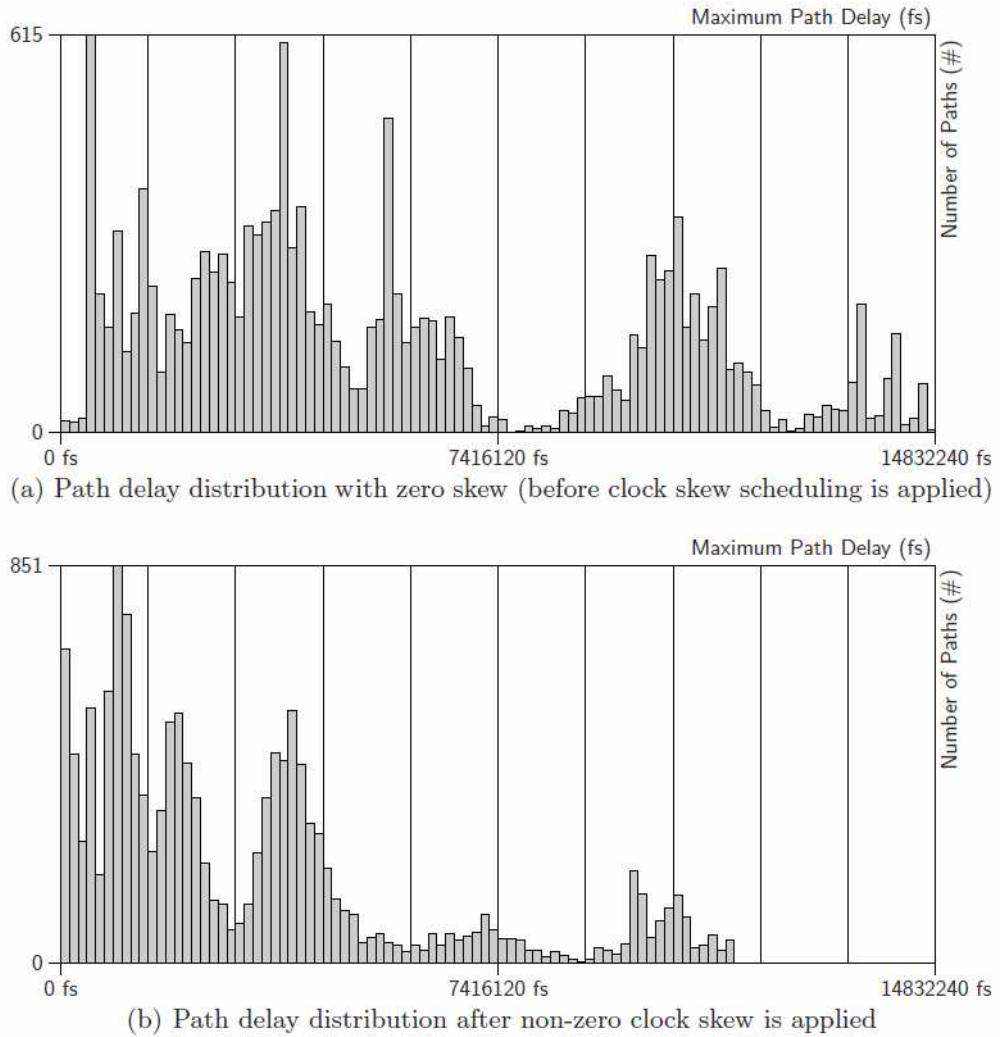

| 2.15 | The application of clock skew scheduling to a commercial integrated circuit with 6,890 registers (note that the time scale is in femtoseconds) [12] . . . . .                                                                                 | 31 |

| 2.16 | Dynamic and sub-threshold leakage power components for a fixed operating frequency in 140nm. As $V_{DD}$ increases, $V_{body}$ is adjusted to maintain the operating speed [13]. . . . .                                                      | 33 |

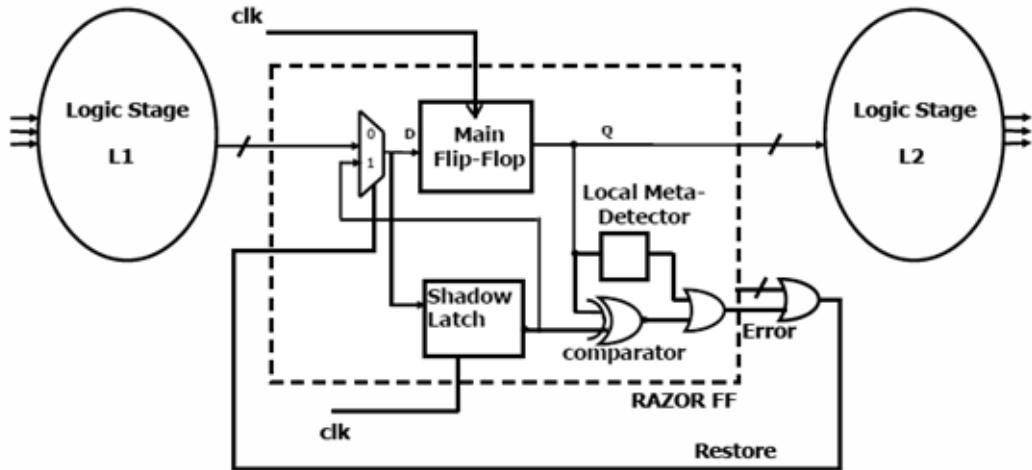

| 2.17 | Razor Architecture [14] . . . . .                                                                                                                                                                                                             | 36 |

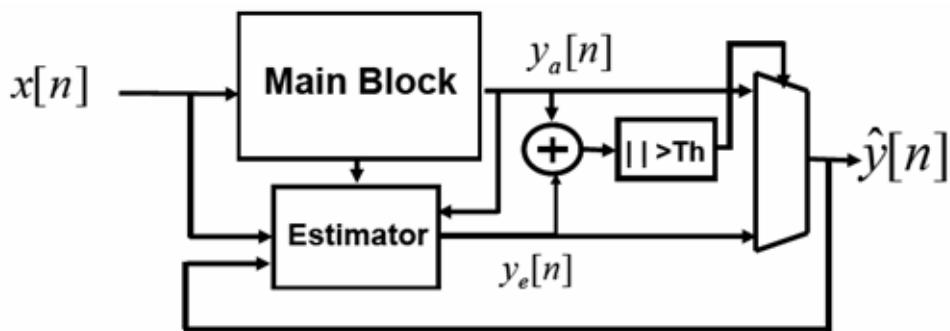

| 2.18 | ANT Architecture [15] . . . . .                                                                                                                                                                                                               | 36 |

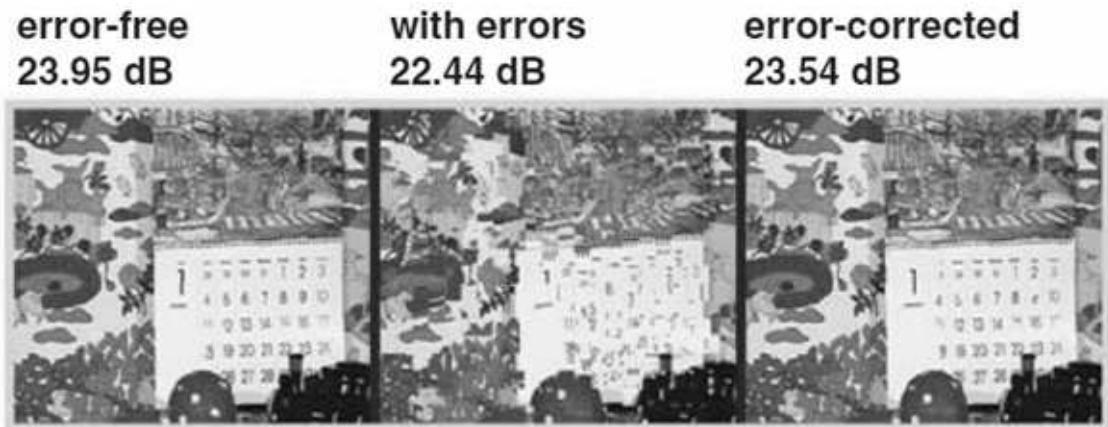

| 2.19 | An example result of Motion Estimation with ANT error correction [15] . . . . .                                                                                                                                                               | 37 |

|                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

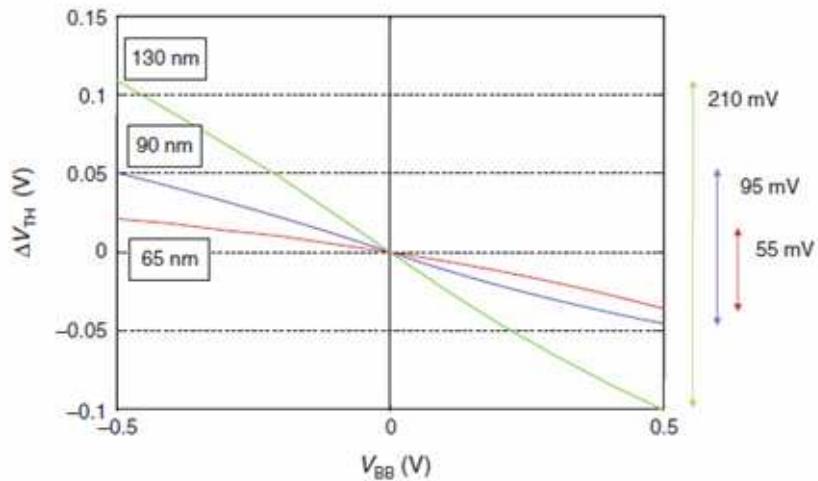

| 2.20 Comparison of body bias effectiveness in three technologies [15] . . . . .                                                                                                                                             | 38 |

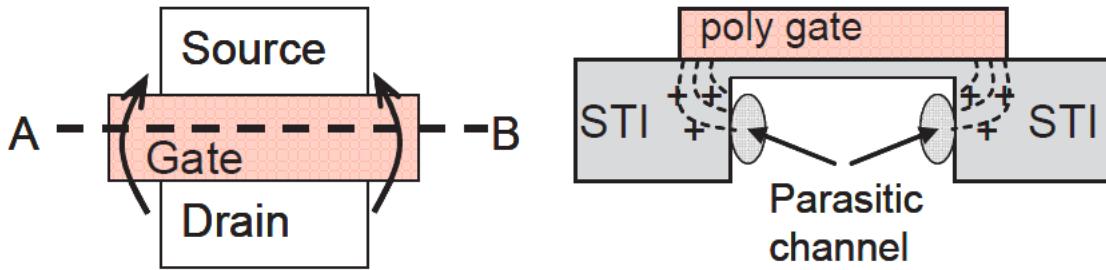

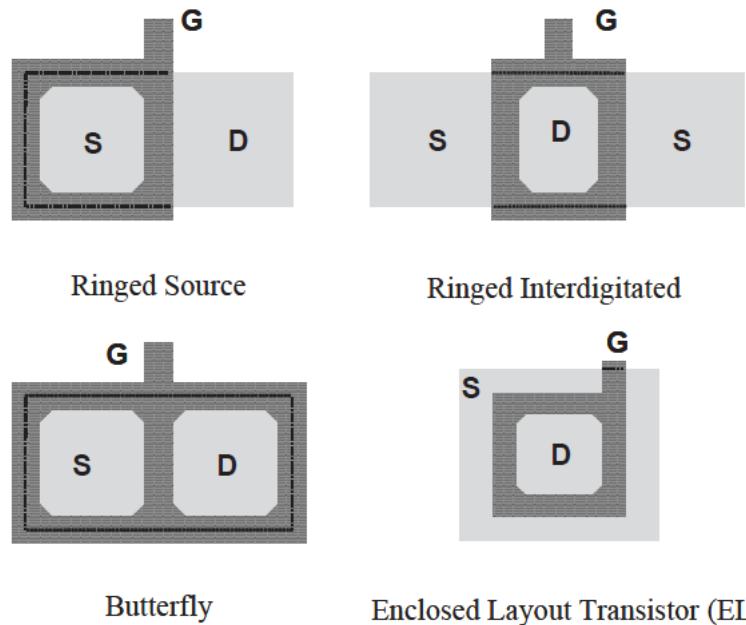

| 2.21 Top view of an open-layout NMOS transistor (left), and along its A-B line (right, view from the source or the drain electrode to the transistor channel) [16] [17] . . . . .                                           | 40 |

| 2.22 Transistor layout view for some of the possible NMOS designs eliminating the radiation-induced leakage current between source and drain [16] [17] . . . . .                                                            | 41 |

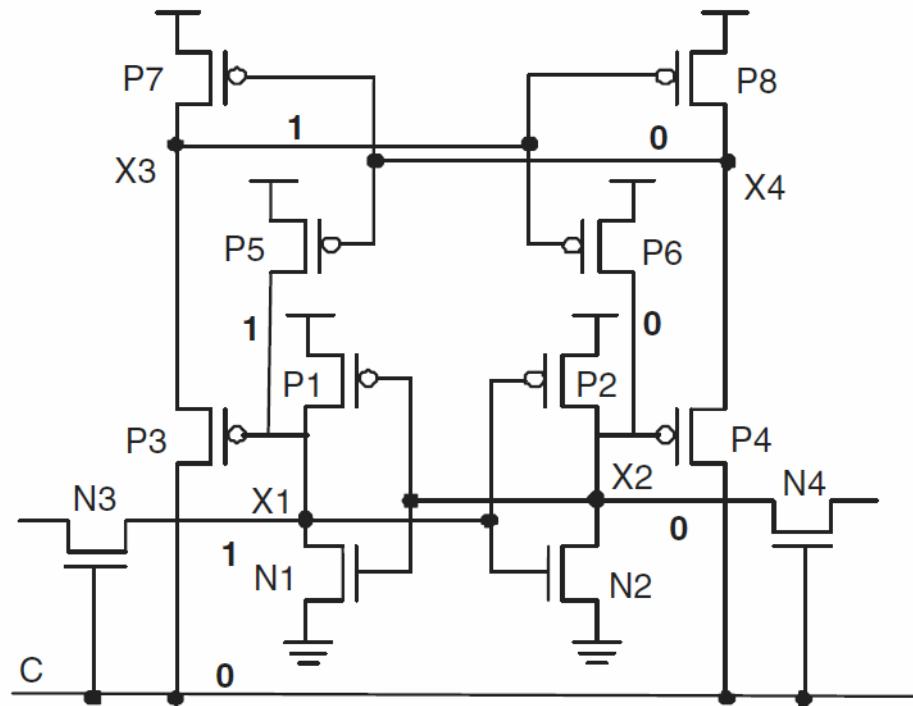

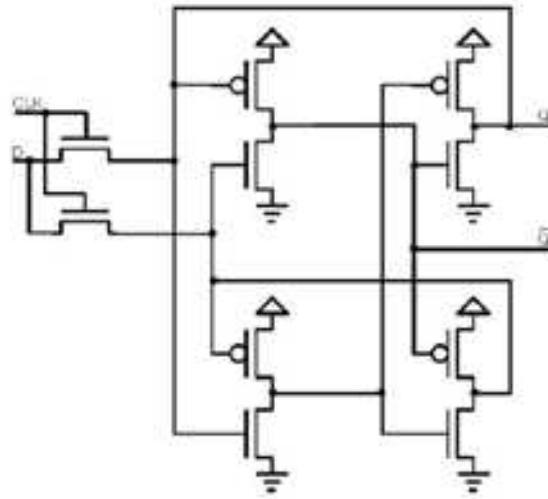

| 2.23 A hardened store holding cell - DICE [18] . . . . .                                                                                                                                                                    | 43 |

| 2.24 Code Word State Preserving (CWSP) . . . . .                                                                                                                                                                            | 43 |

| 2.25 Dual Interlock Cell (DICE) . . . . .                                                                                                                                                                                   | 44 |

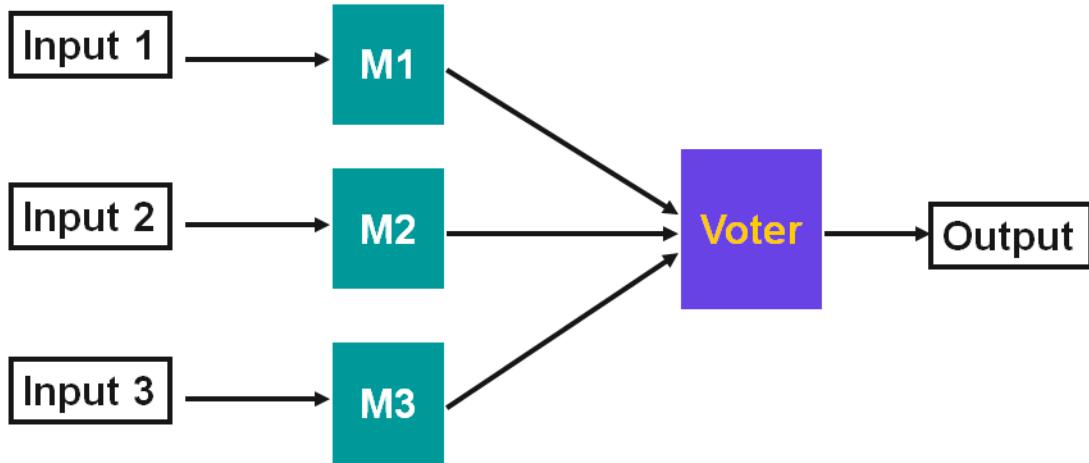

| 2.26 Triple modular redundancy . . . . .                                                                                                                                                                                    | 45 |

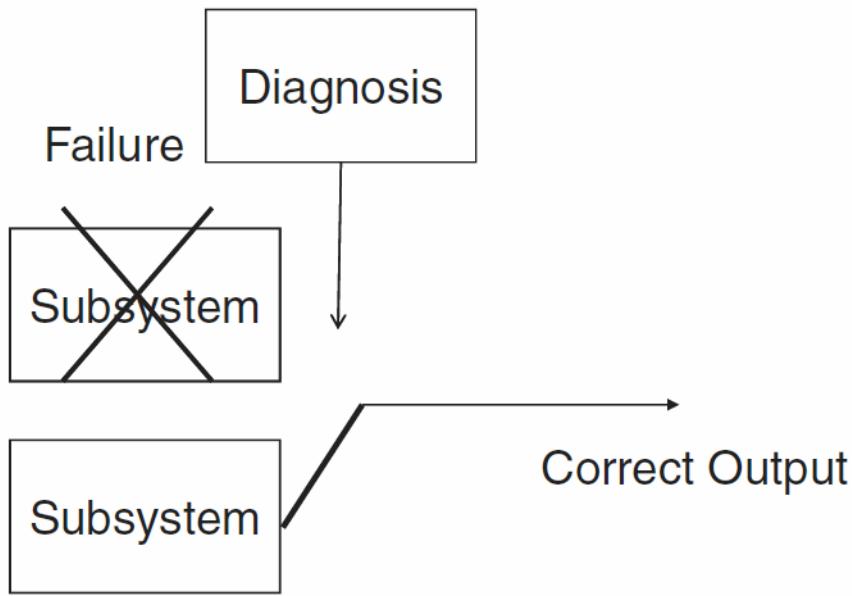

| 2.27 Stand-by redundancy . . . . .                                                                                                                                                                                          | 46 |

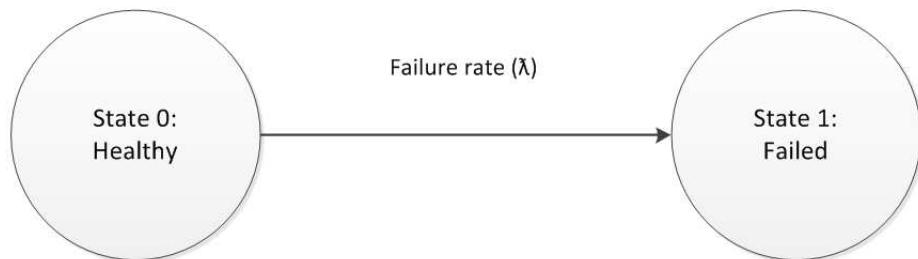

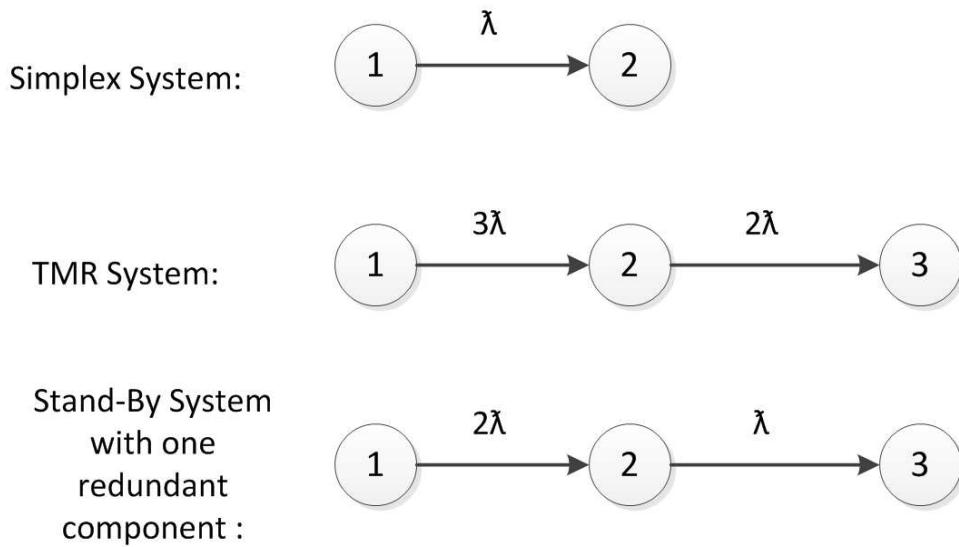

| 2.28 Markov model of a simple system . . . . .                                                                                                                                                                              | 49 |

| 2.29 Markov models . . . . .                                                                                                                                                                                                | 50 |

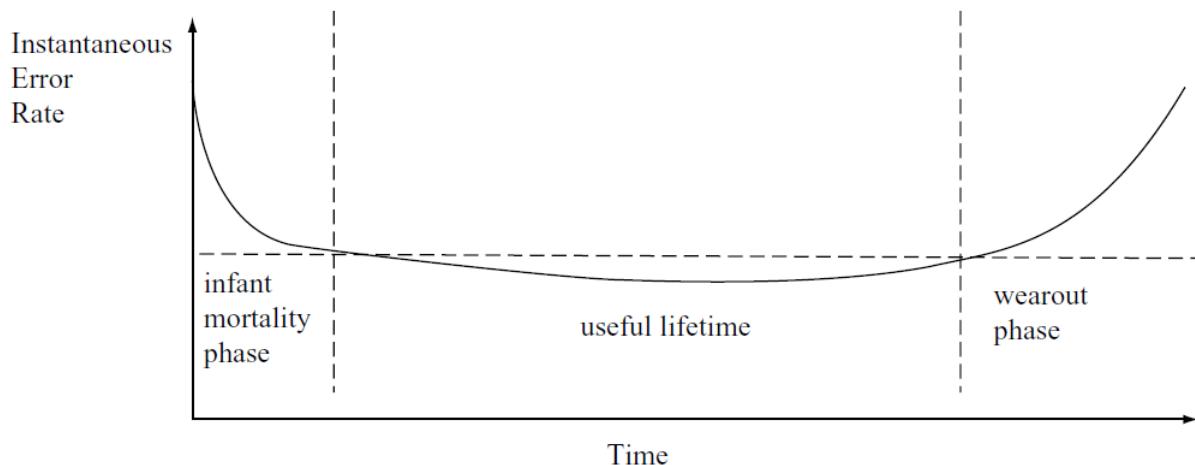

| 2.30 Bathtub curve showing the relationship between failure rate, infant mortality, useful lifetime, and wearout phase [19]. . . . .                                                                                        | 50 |

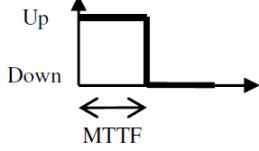

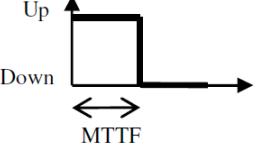

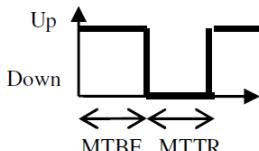

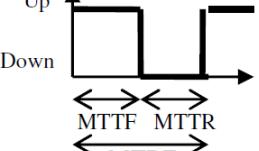

| 2.31 Definitions for MTBF [20] [21] . . . . .                                                                                                                                                                               | 52 |

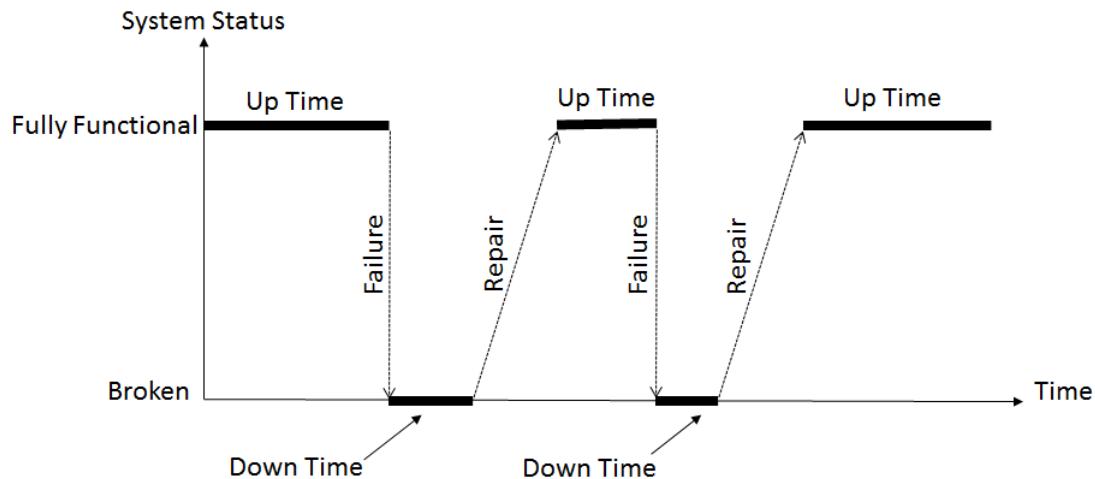

| 2.32 Different phases of a repairable system . . . . .                                                                                                                                                                      | 52 |

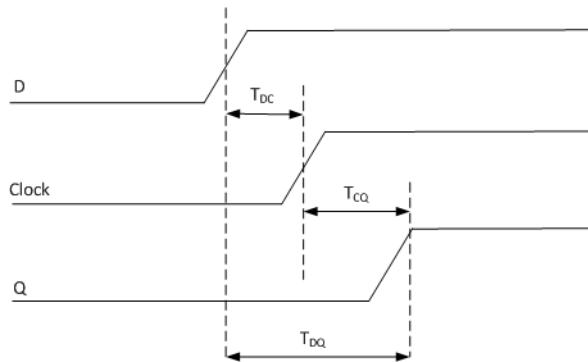

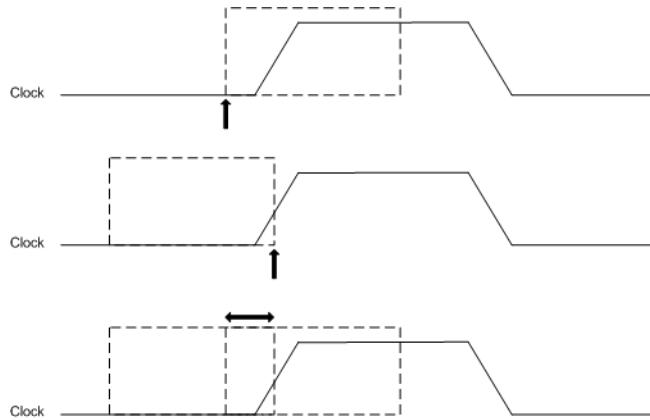

| 3.1 Flip-Flop Timing . . . . .                                                                                                                                                                                              | 56 |

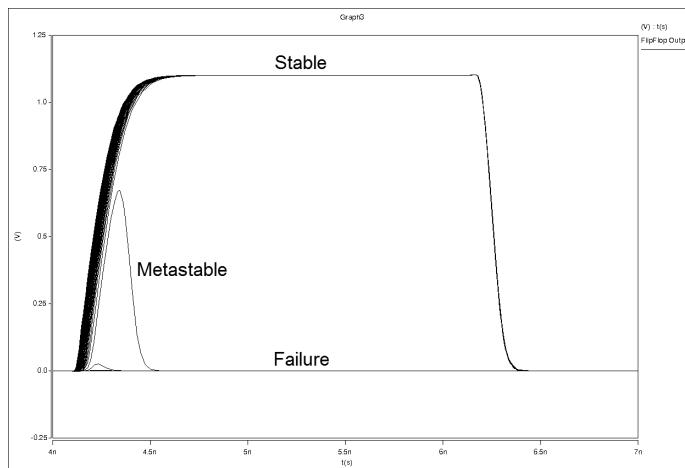

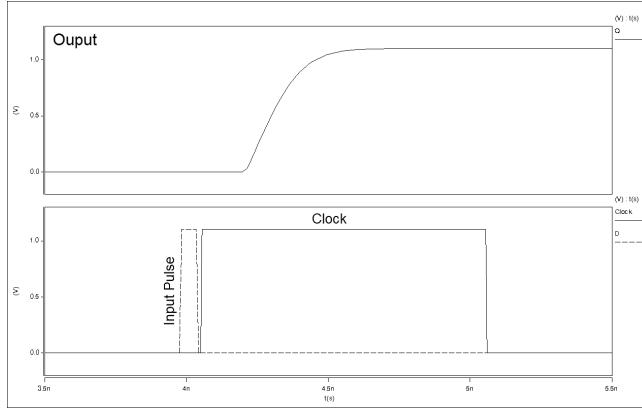

| 3.2 45nm Technology - SPICE simulation of Flip-Flop output using Nangate 45nm SPICE models: When the input pulse is '1' for one clock cycle with varying input pulse width: Stable, Metastable and Failure regions. . . . . | 57 |

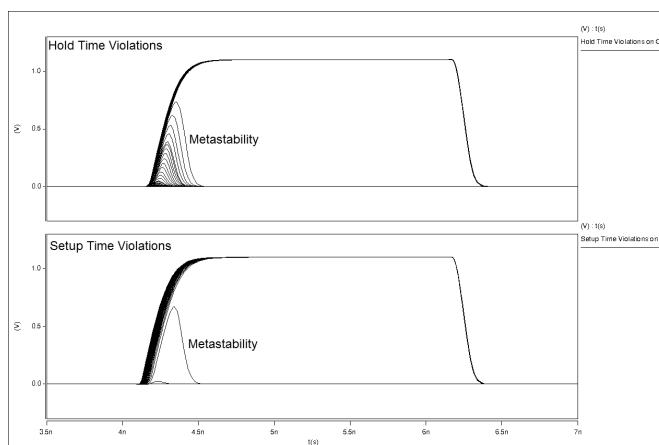

| 3.3 45nm Technology - SPICE simulation of Flip-Flop output using Nangate 45nm SPICE models: Chances of metastability due to Hold time violations and Setup time violations. . . . .                                         | 57 |

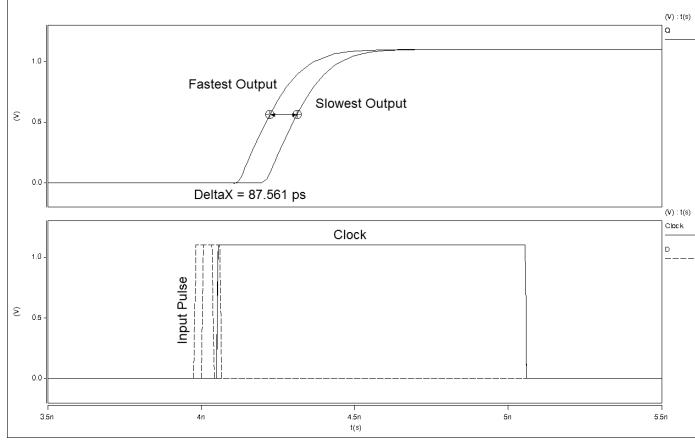

| 3.4 Fastest output vs Slowest output depending on the input pulse width and the pulse arrival time - 45nm technology . . . . .                                                                                              | 58 |

| 3.5 Defining the Window of Vulnerability . . . . .                                                                                                                                                                          | 60 |

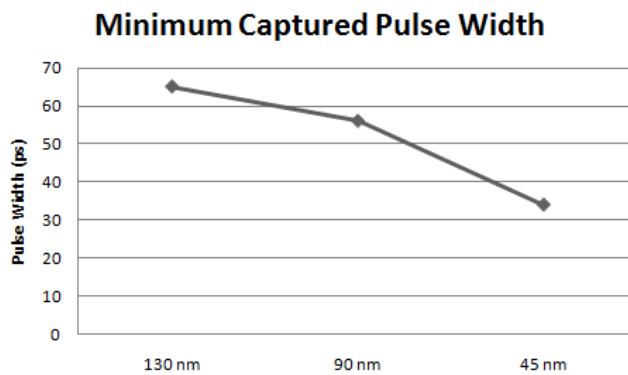

| 3.6 Minimum Captured Pulse Width by the Flip-Flops at three different technology nodes. . . . .                                                                                                                             | 61 |

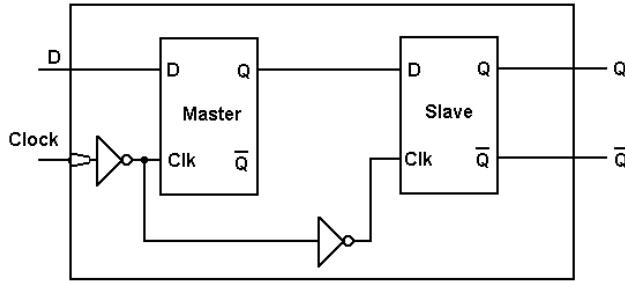

| 3.7 Master-Slave Flip-Flop . . . . .                                                                                                                                                                                        | 62 |

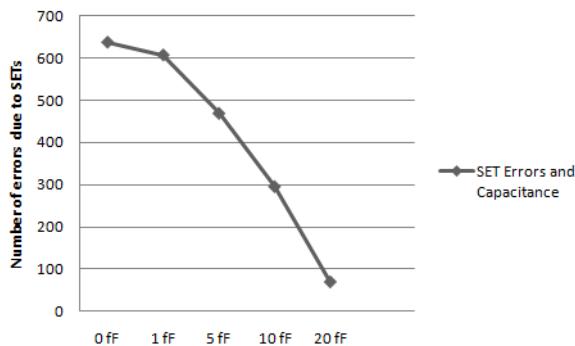

| 3.8 Capacitance at the struck node and SER . . . . .                                                                                                                                                                        | 63 |

| 3.9 Narrow pulse properly captured right before the clock edge - 45nm technology . . . . .                                                                                                                                  | 64 |

| 3.10 45nm technology . . . . .                                                                                                                                                                                              | 65 |

| 3.11 45nm technology . . . . .                                                                                                                                                                                              | 65 |

| 4.1 Razor I Flip-Flop [14] . . . . .                                                                                                                                                                                        | 72 |

| 4.2 Razor II Flip-Flop [14] . . . . .                                                                                                                                                                                       | 73 |

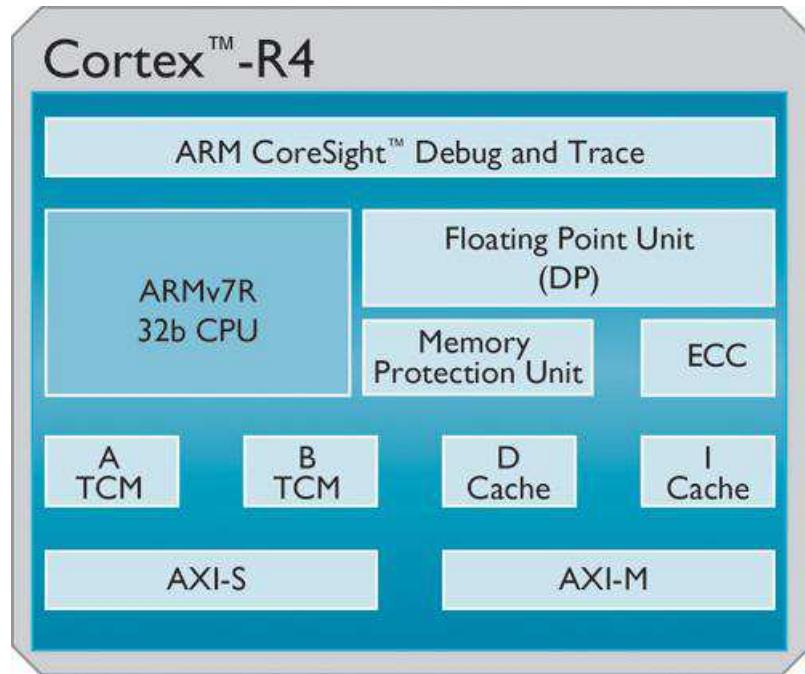

| 4.3 ARM Cortex-R4 [22] . . . . .                                                                                                                                                                                            | 75 |

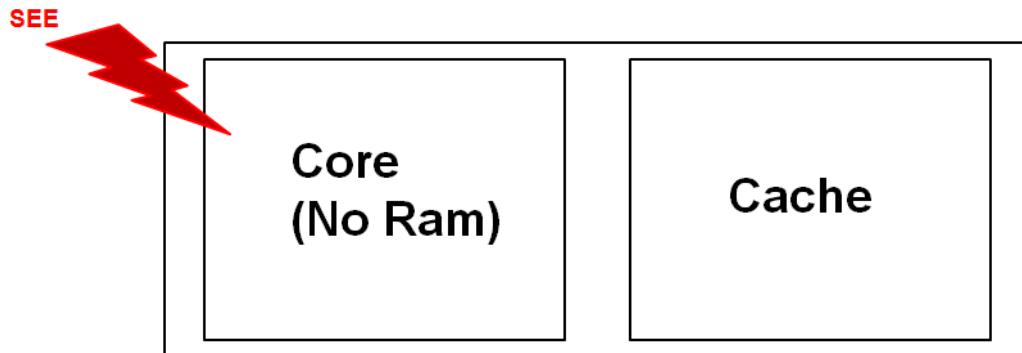

| 4.4 Processor Core . . . . .                                                                                                                                                                                                | 77 |

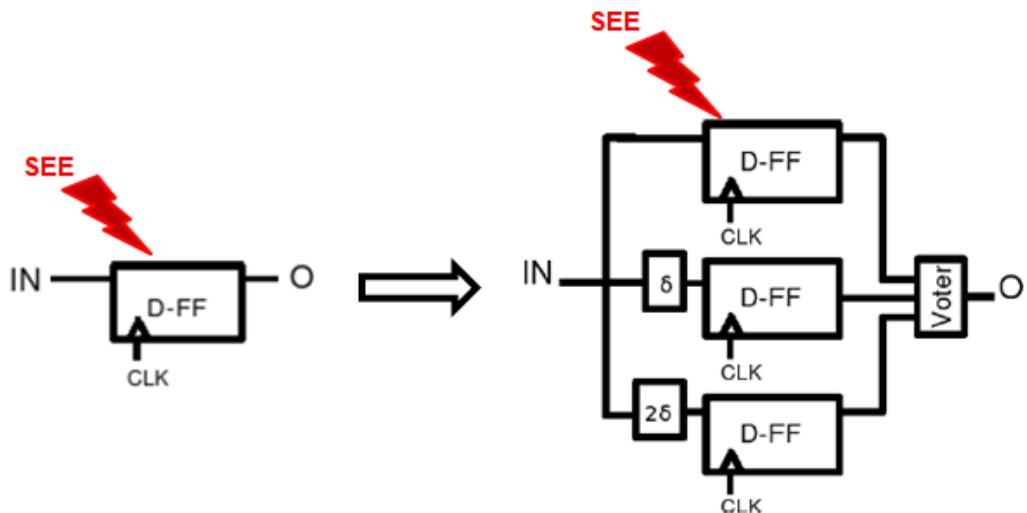

| 4.5 SEE Tolerant TMR Flip-Flop . . . . .                                                                                                                                                                                    | 77 |

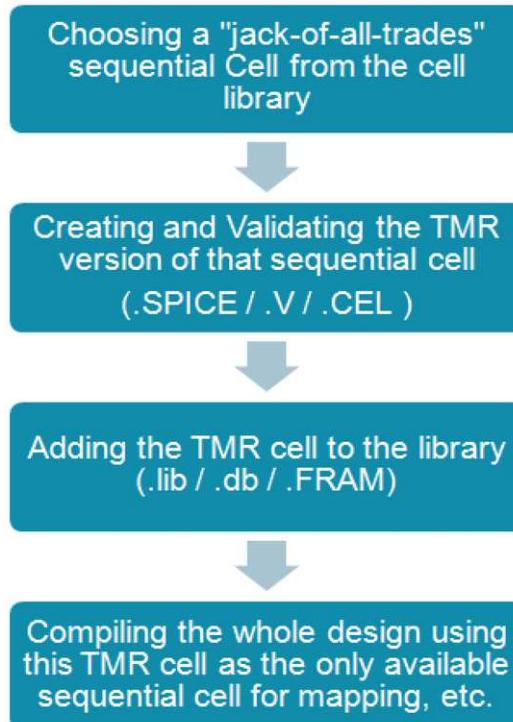

| 4.6 The proposed flow and the major steps in implementing a Rad-Hard core . . . . .                                                                                                                                         | 78 |

---

|      |                                                                                                                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

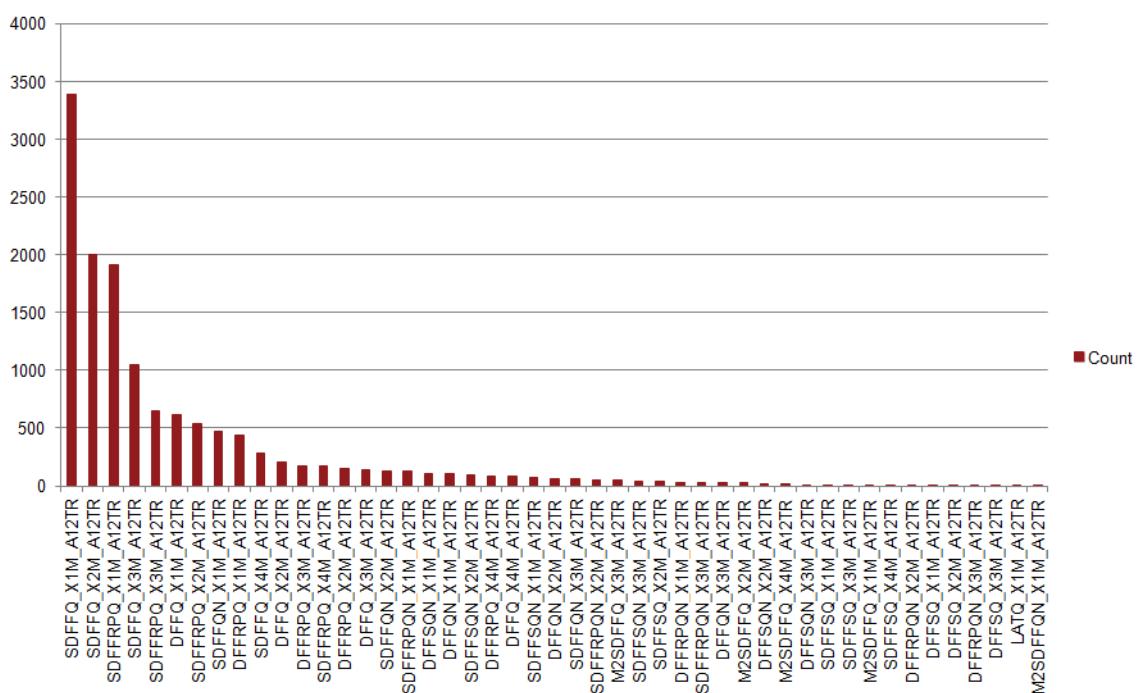

| 4.7  | Default Sequential Cell usage by the core . . . . .                                                                                                                                                                                                   | 78 |

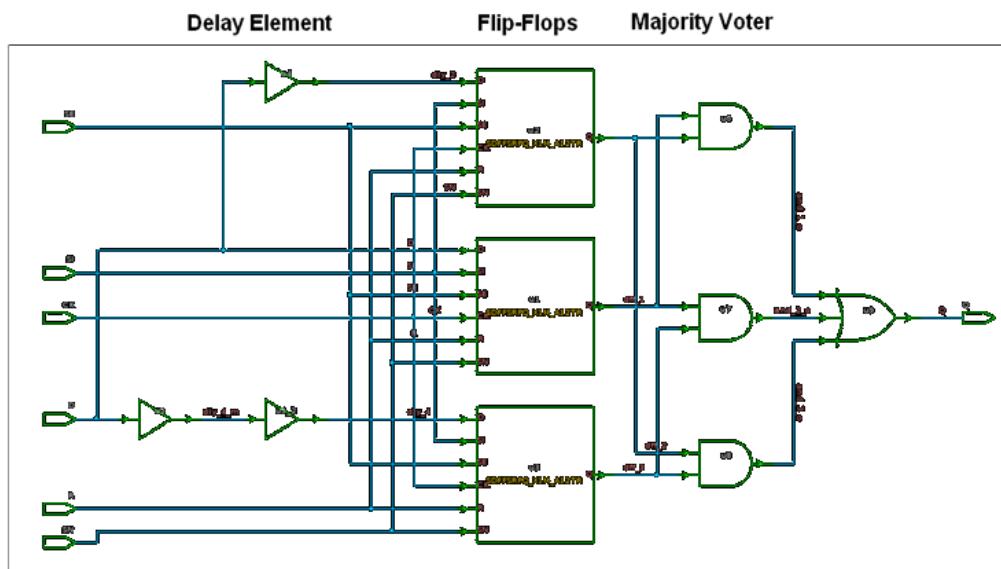

| 4.8  | TMR cell schematic . . . . .                                                                                                                                                                                                                          | 79 |

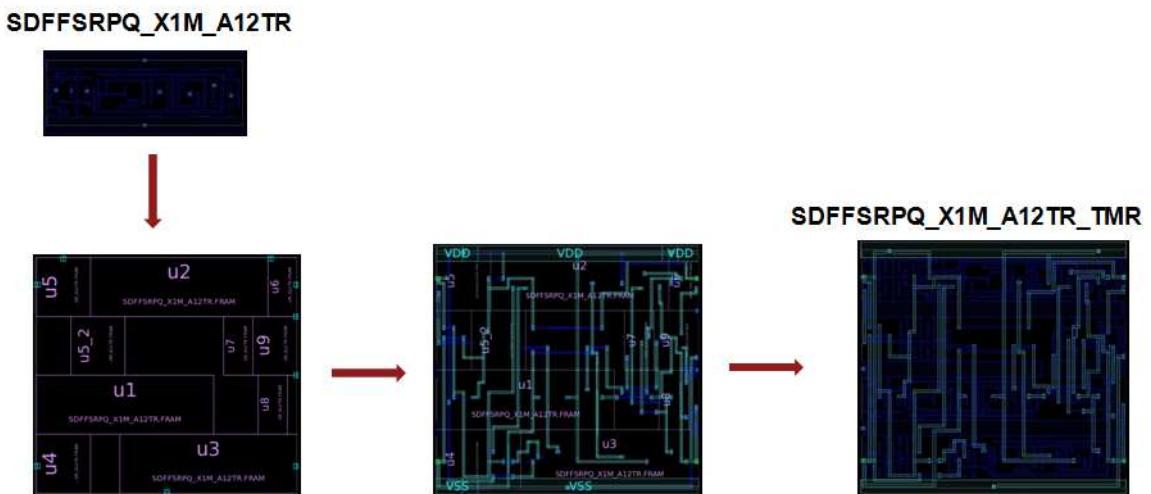

| 4.9  | TMR cell layout . . . . .                                                                                                                                                                                                                             | 79 |

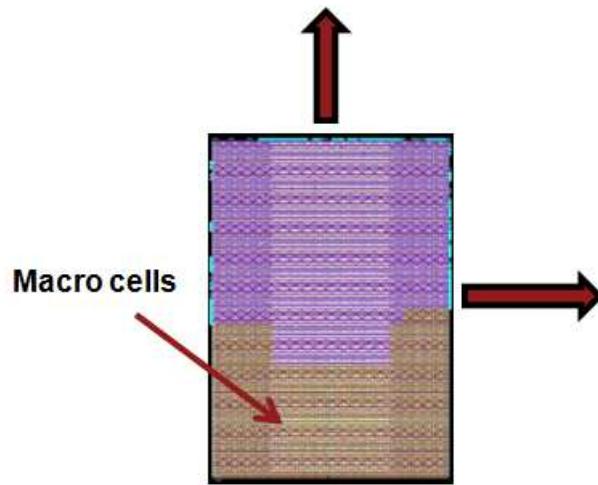

| 4.10 | Extending Floor Plan . . . . .                                                                                                                                                                                                                        | 80 |

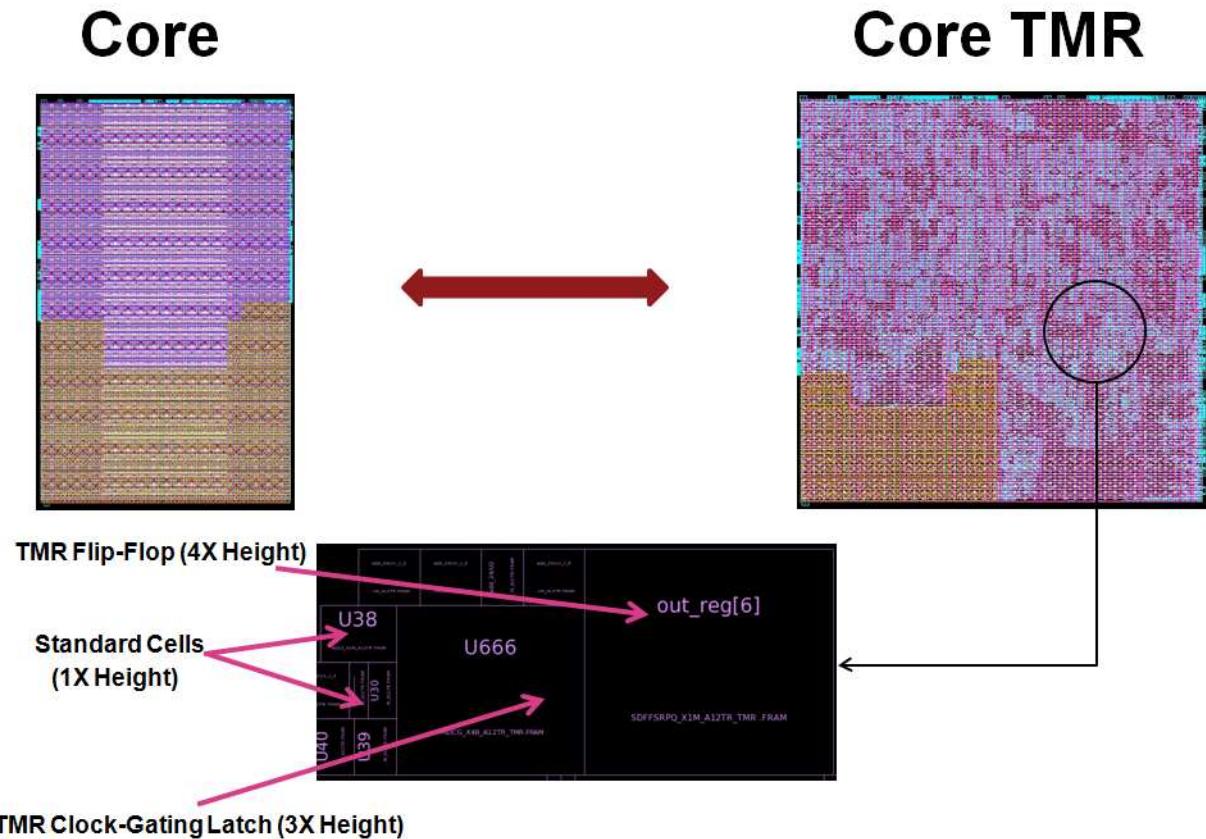

| 4.11 | Core vs Core TMR . . . . .                                                                                                                                                                                                                            | 81 |

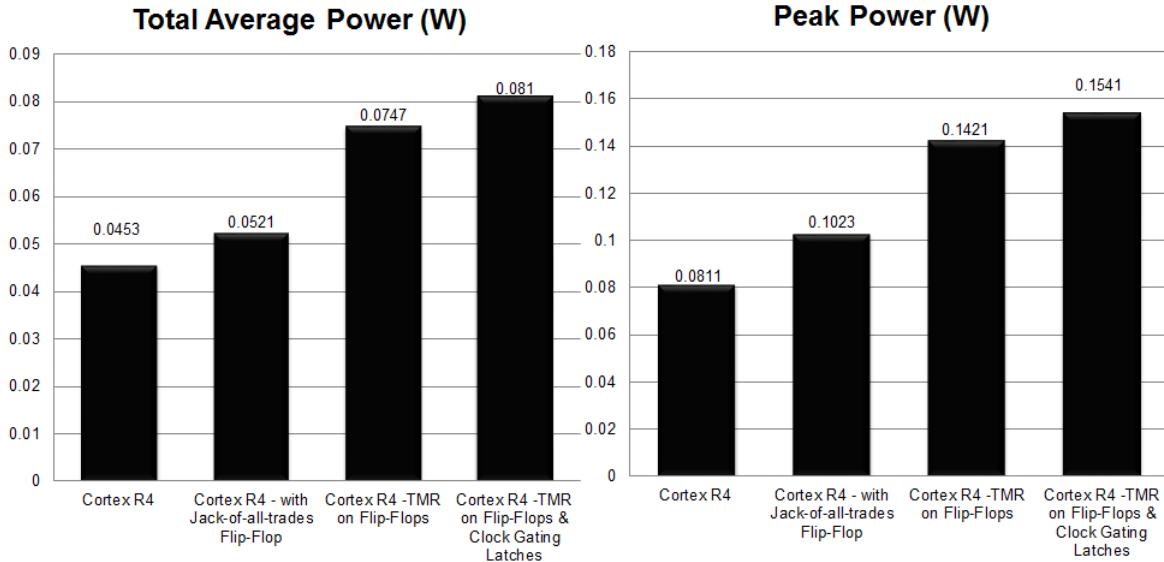

| 4.12 | Total Average Power and Peak Power Consumptions - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . .        | 82 |

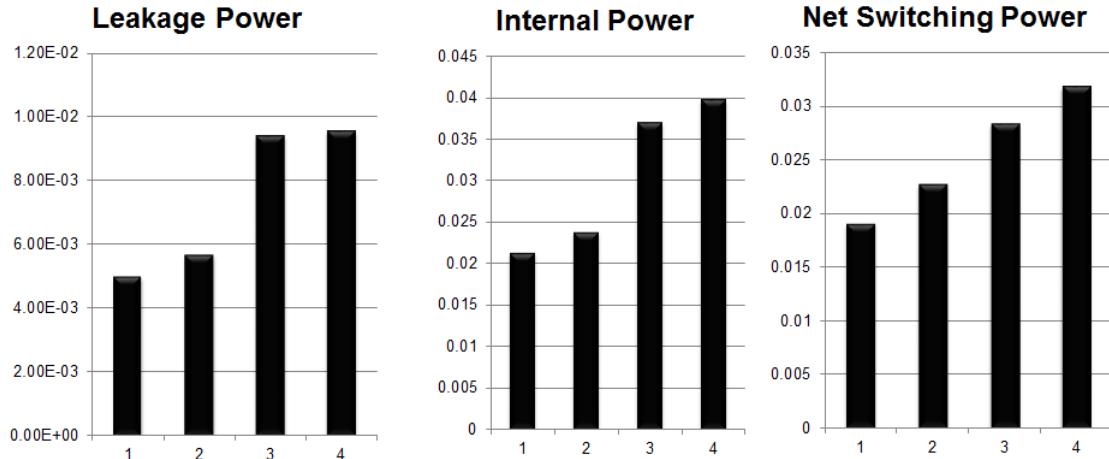

| 4.13 | Leakage, Internal and Net Switching Power Consumptions - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . . | 82 |

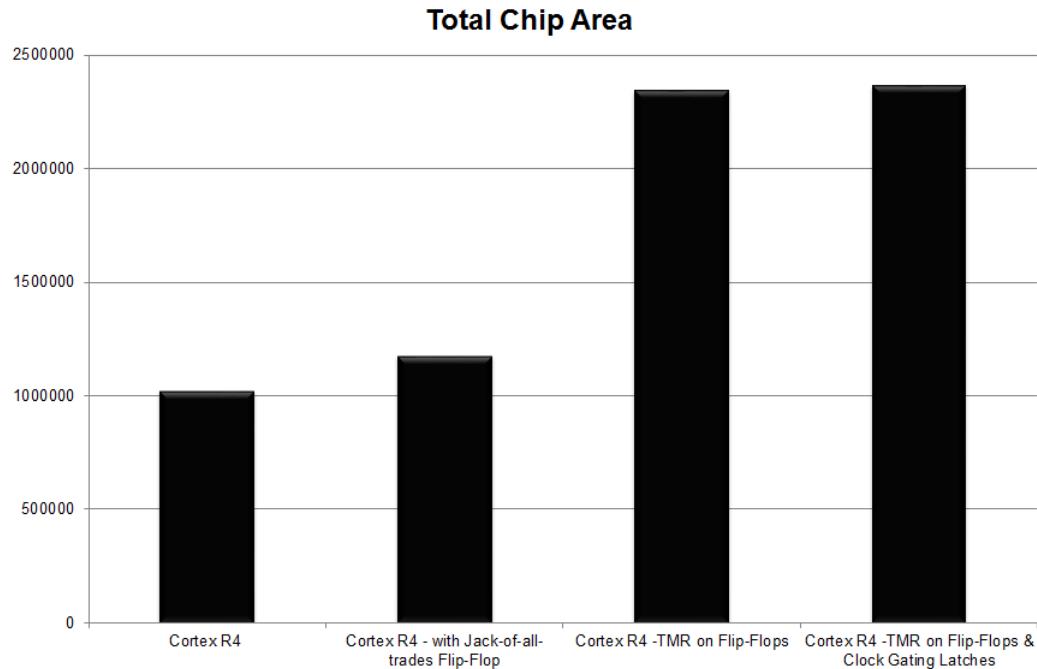

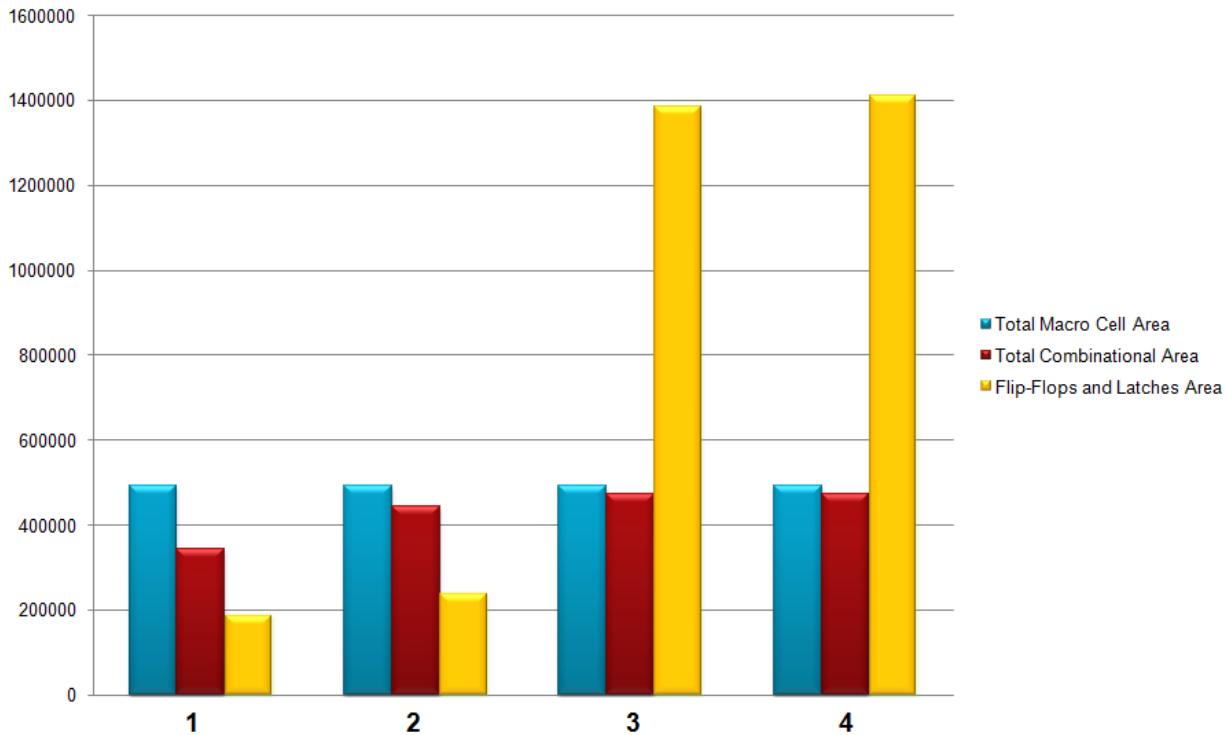

| 4.14 | Area Comparisons in Total - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . .                              | 83 |

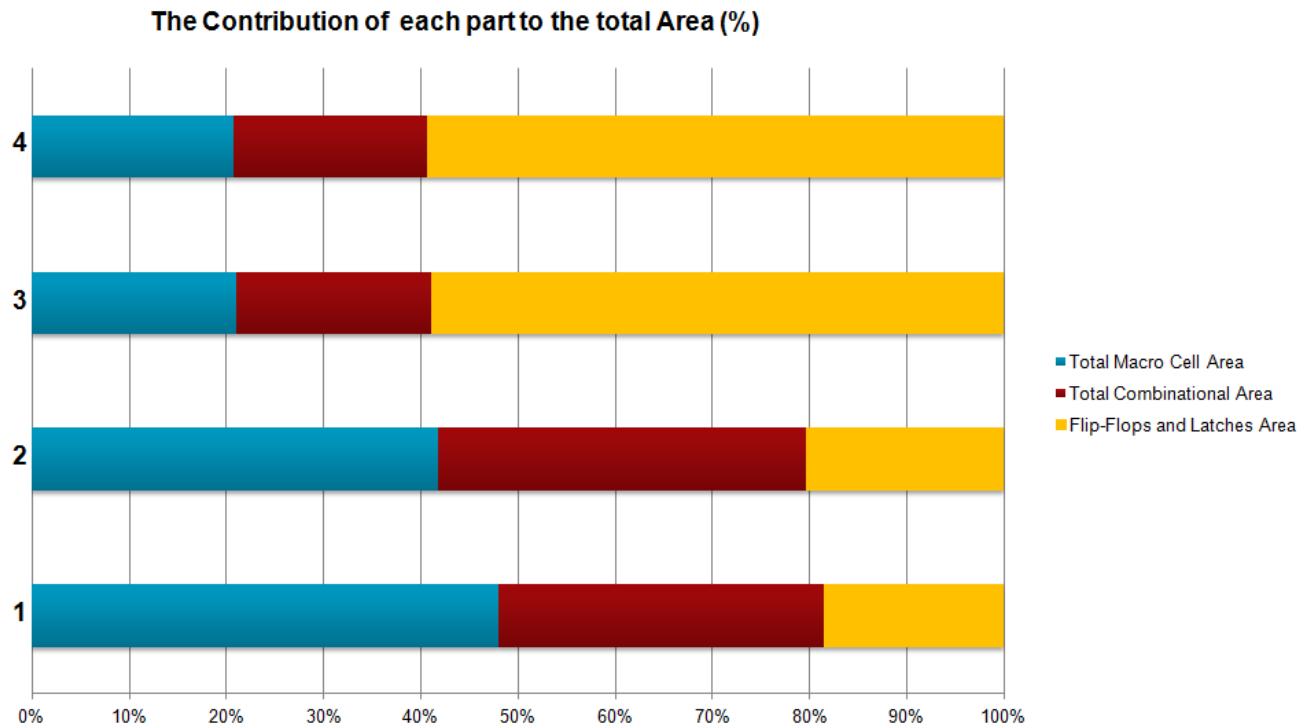

| 4.15 | Area Comparisons in more Details I - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . .                     | 84 |

| 4.16 | Area Comparisons in more Details II - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . .                    | 85 |

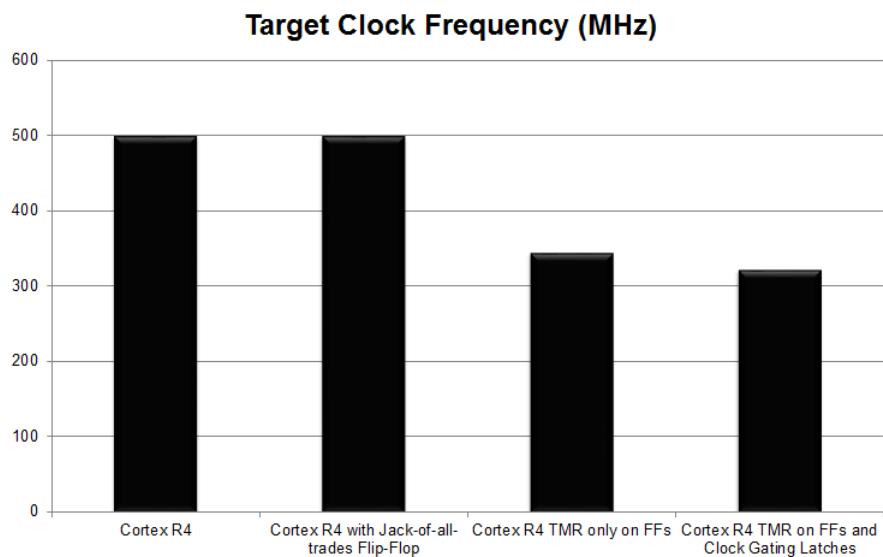

| 4.17 | Performance Comparisons - 1) The default core, 2) The core with the jack- of-all-trades Flip-Flop, 3) The core with the TMR Flip-Flop, 4) The core with TMR scheme on Flip-Flops and the Clock gating latches. . . . .                                | 85 |

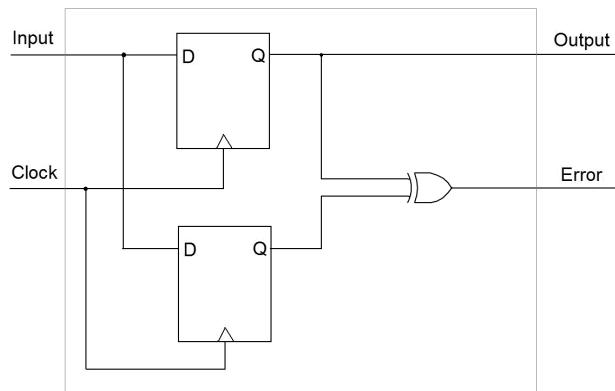

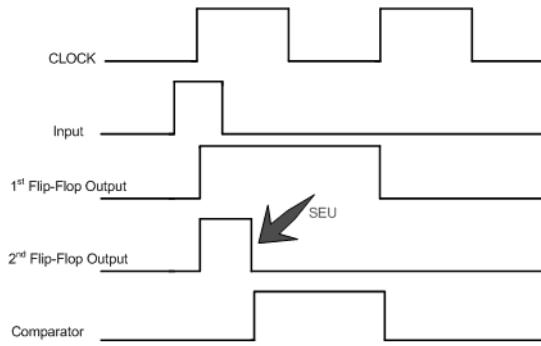

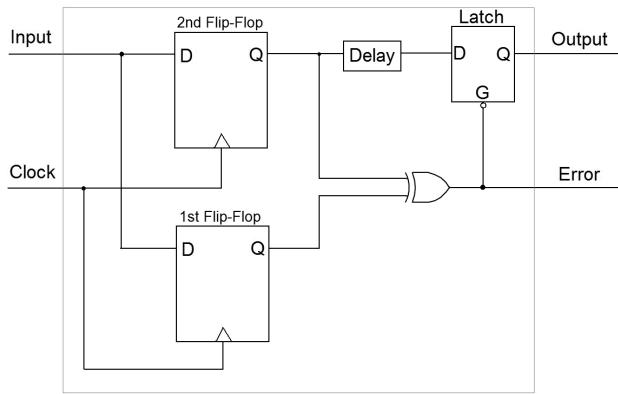

| 4.18 | Dual-Module-Redundancy (DMR) . . . . .                                                                                                                                                                                                                | 88 |

| 4.19 | DMR Timing Diagram . . . . .                                                                                                                                                                                                                          | 89 |

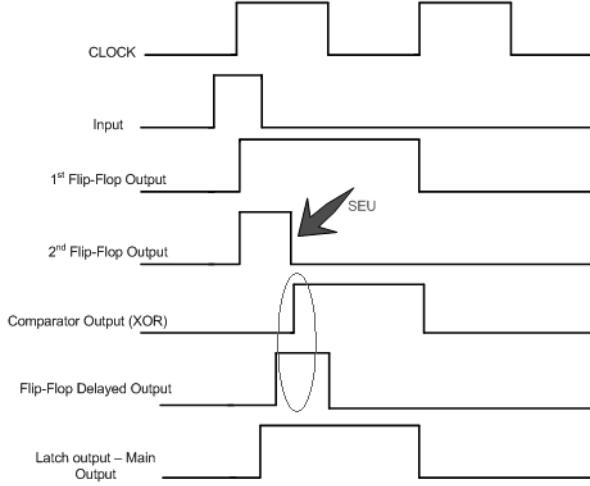

| 4.20 | Proposed SEU-Tolerant Scheme - DMR with Error Recovery. . . . .                                                                                                                                                                                       | 89 |

| 4.21 | DMR with Error Recovery Timing Diagram - In the occurrence of an SEU, the latch closes on the correct value (the region under the oval), thus the main output is always correct. . . . .                                                              | 90 |

| 4.22 | Power, area & delay comparisons between two radiation-hardened sequential cells: a TMR cell <i>vs.</i> the proposed DMR with Recovery cell . . . . .                                                                                                  | 91 |

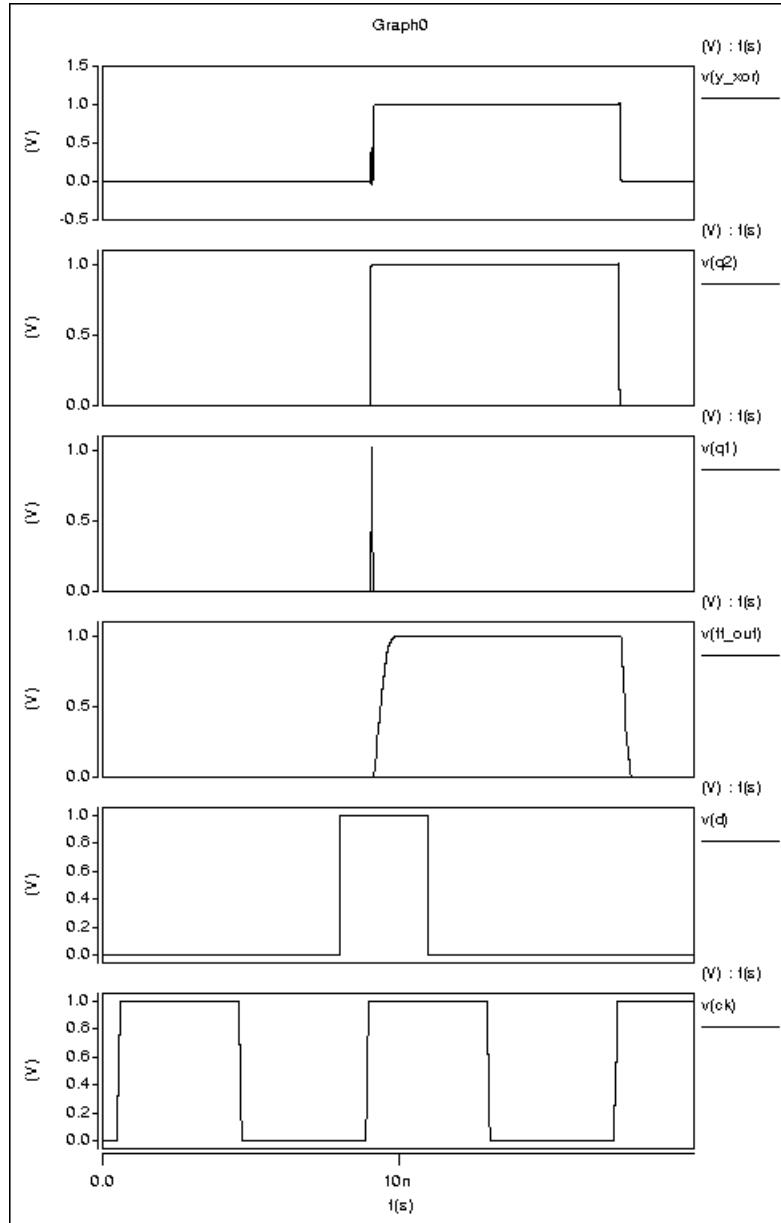

| 4.23 | SPICE-level simulation. Despite one of the flip-flop outputs <i>q1</i> being almost destroyed due to an SEU, the main output <i>ff-out</i> is still correct. . . . .                                                                                  | 93 |

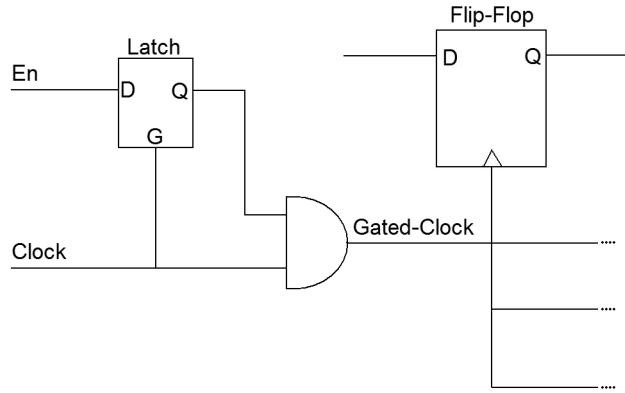

| 4.24 | Conventional clock-gating scheme. . . . .                                                                                                                                                                                                             | 94 |

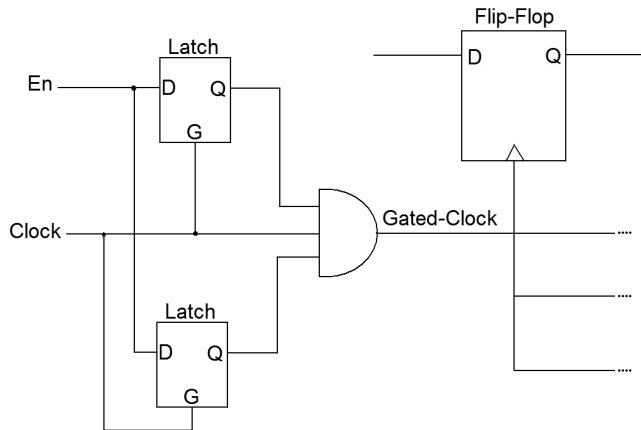

| 4.25 | Proposed SEU-tolerant clock-gating scheme . . . . .                                                                                                                                                                                                   | 94 |

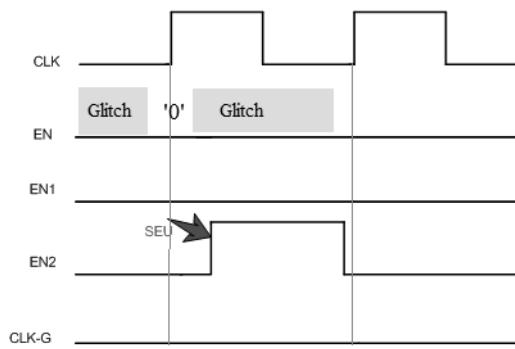

| 4.26 | Timing Diagram for the proposed SEU-tolerant clock-gating scheme                                                                                                                                                                                      | 95 |

|                                                                                                                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

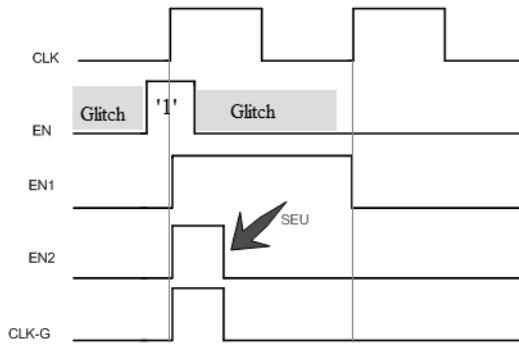

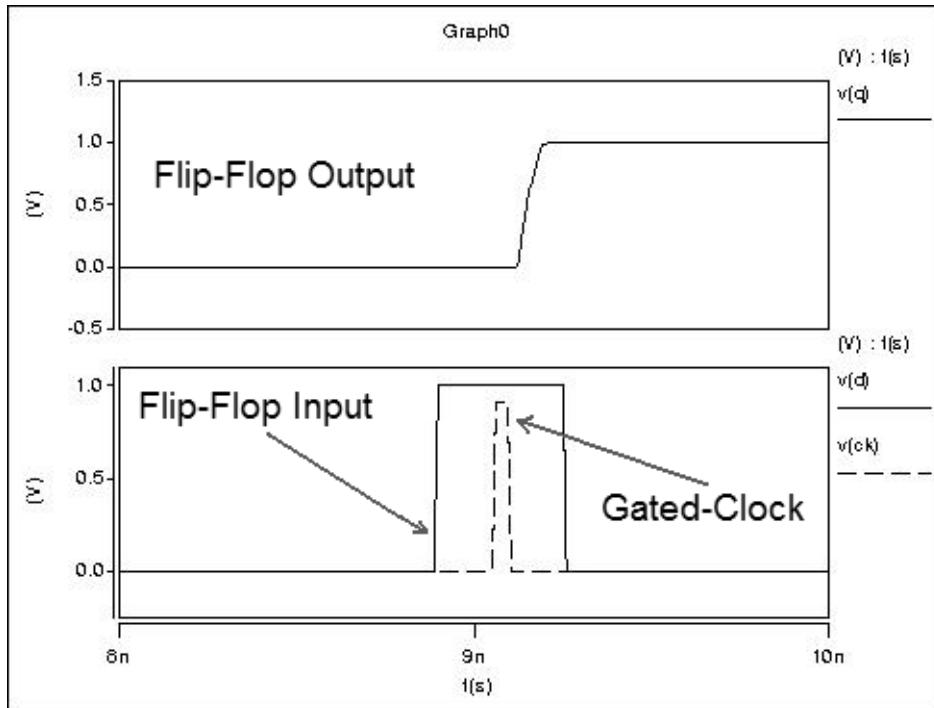

| 4.27 SEU-tolerant clock-gating scheme: A worst case scenario - The clock signal is almost destroyed by the SEU, but the flip-flop still gets updated properly but with a bit longer clock-to-q delay. . . . .                              | 96  |

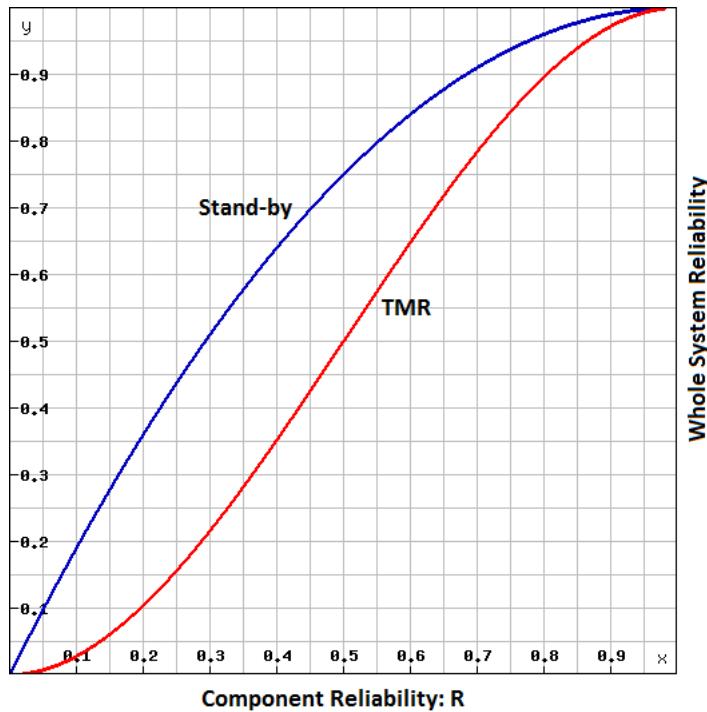

| 5.1 Reliability Comparisons . . . . .                                                                                                                                                                                                      | 101 |

| 5.2 General idea of logic in-field repair: Spare logic blocks can be exact replicas of relevant logic blocks or functionally equivalent structures, or even a simplified version of the logic blocks with reduced functionalities. . . . . | 103 |

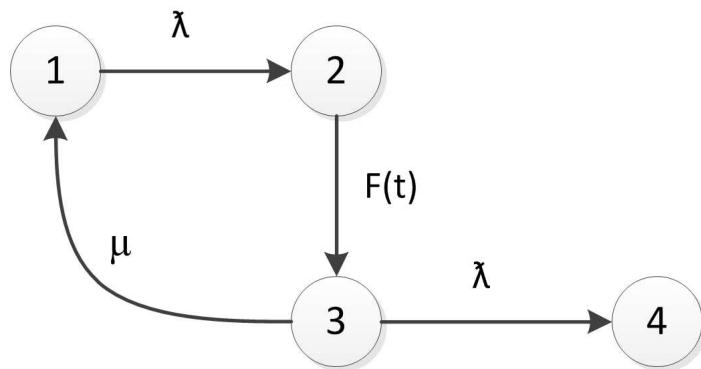

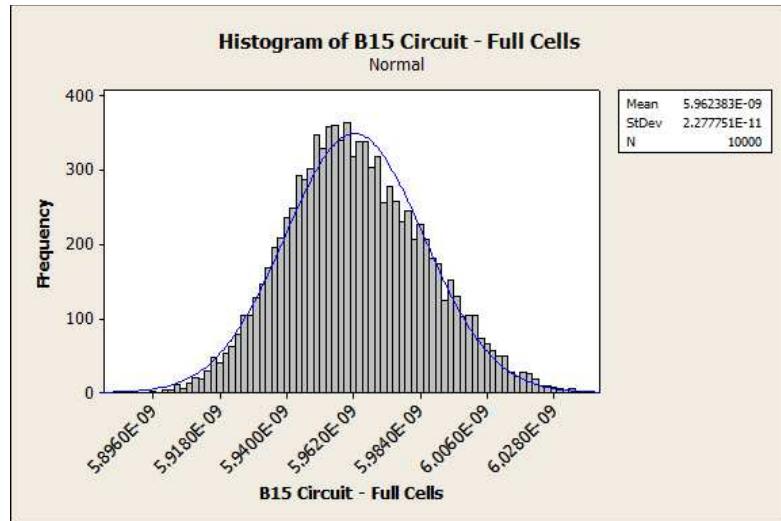

| 5.3 Markov model of In-Field Repair system . . . . .                                                                                                                                                                                       | 106 |

| 5.4 NASA SURE plot for TMR systems - Mission time: 1000 hours . .                                                                                                                                                                          | 107 |

| 5.5 NASA SURE plot for the proposed general In-Field Repair system - Mission time: 1000 hours . . . . .                                                                                                                                    | 108 |

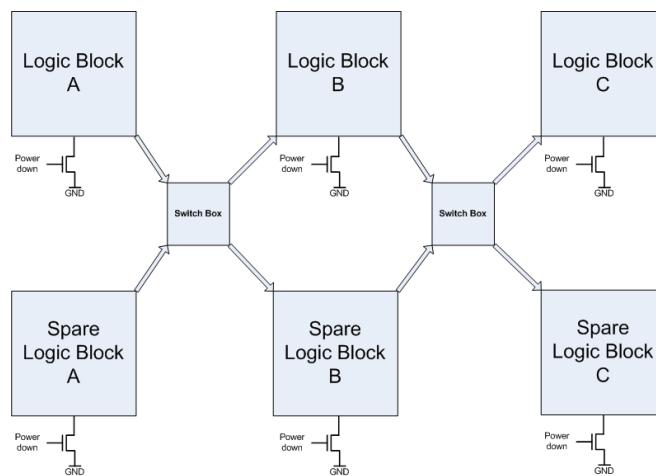

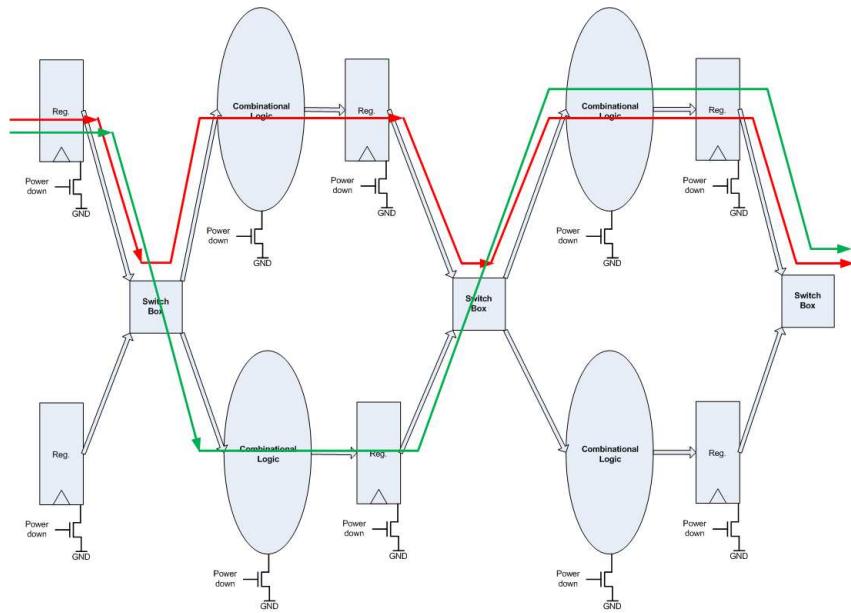

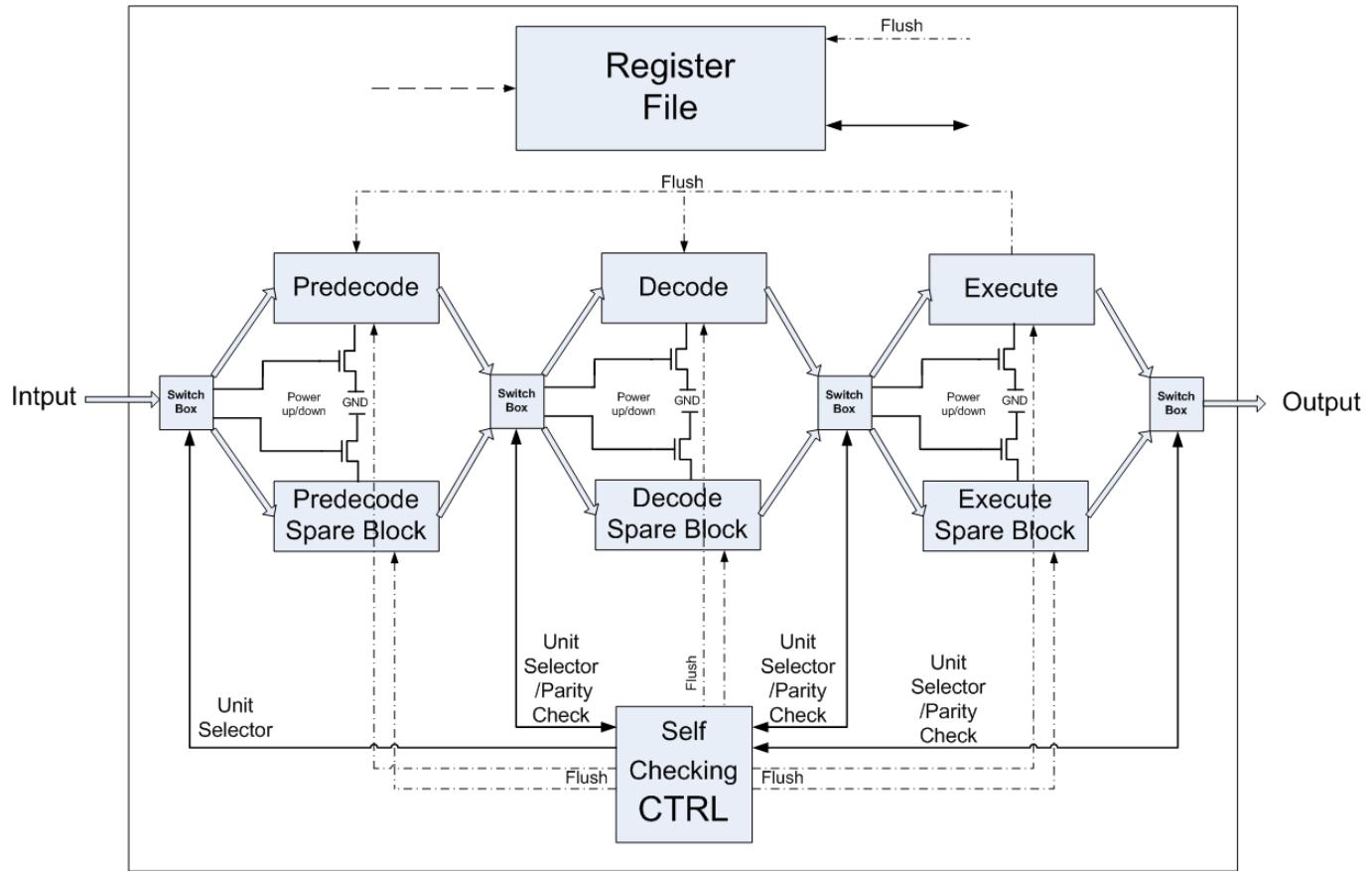

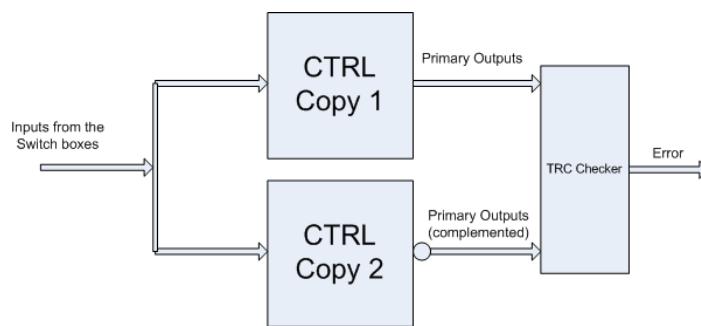

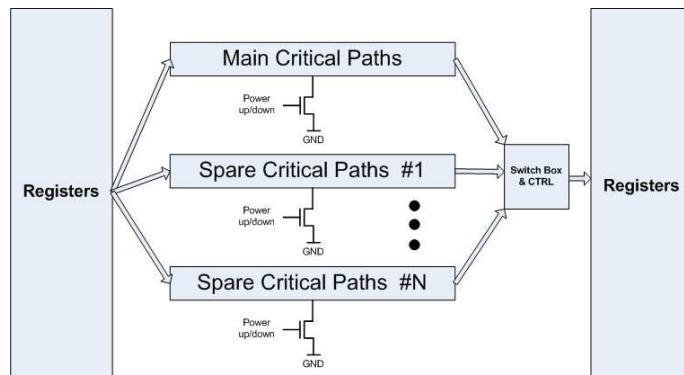

| 5.6 Proposed architecture . . . . .                                                                                                                                                                                                        | 109 |

| 5.7 In-field repair architecture: Main pipeline blocks, spare-Blocks, the switch boxes and the controller. . . . .                                                                                                                         | 110 |

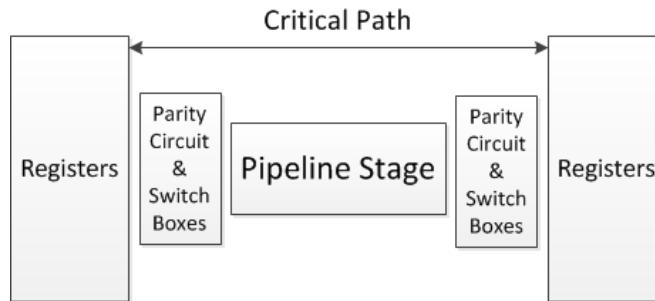

| 5.8 critical path . . . . .                                                                                                                                                                                                                | 110 |

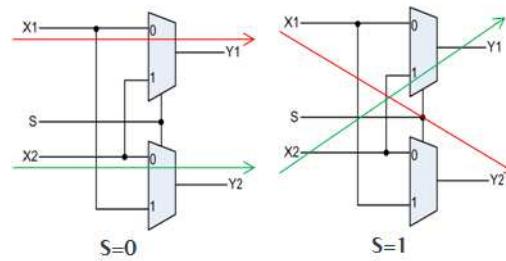

| 5.9 A 2-way switch for a single bit (costs: 20 transistors using 45nm cell library, almost equal to a D-flip-flop in size). . . . .                                                                                                        | 111 |

| 5.10 Self-checking controller . . . . .                                                                                                                                                                                                    | 111 |

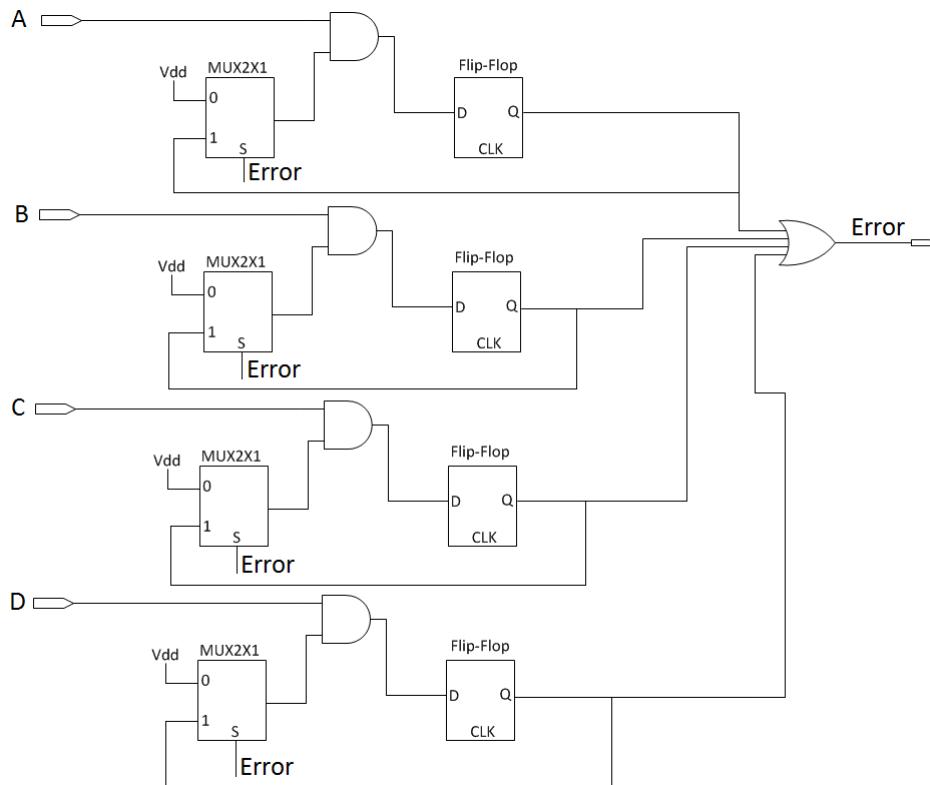

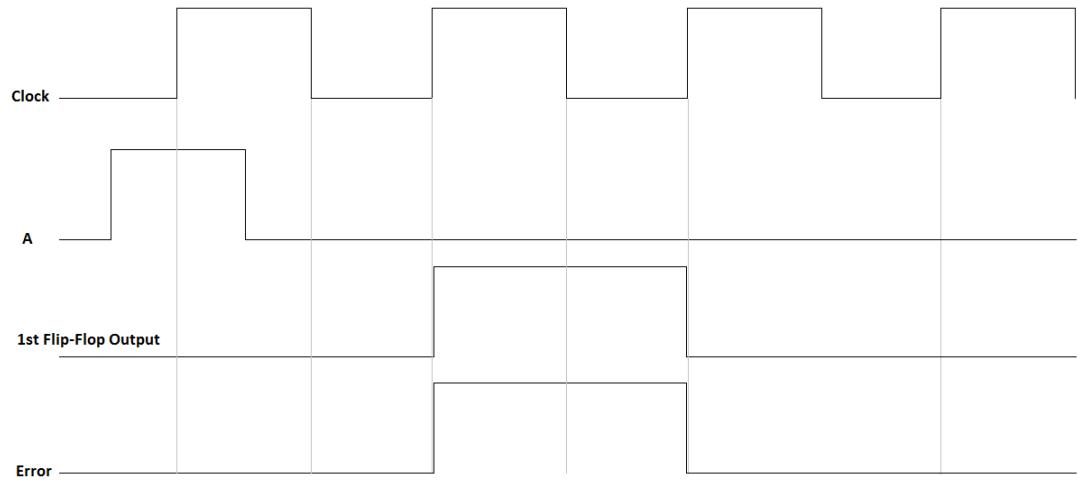

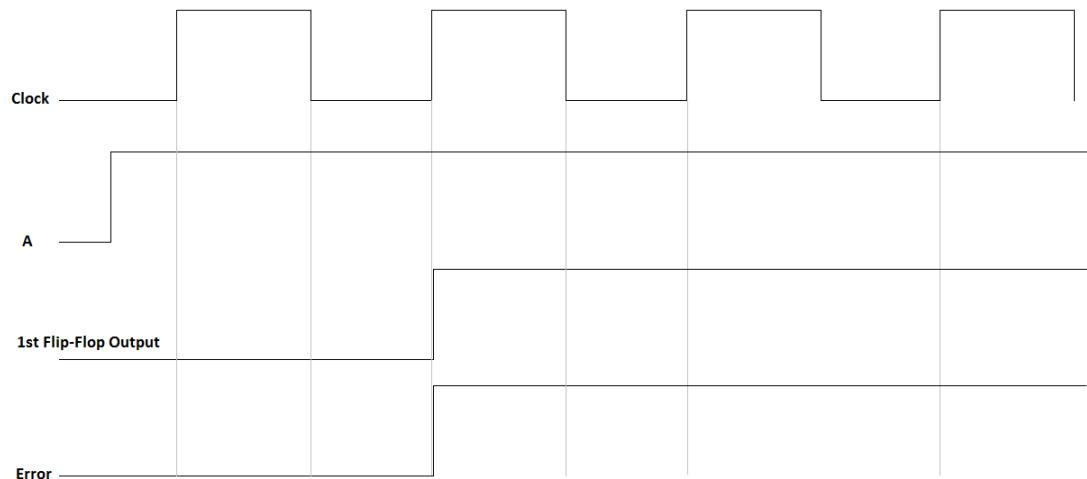

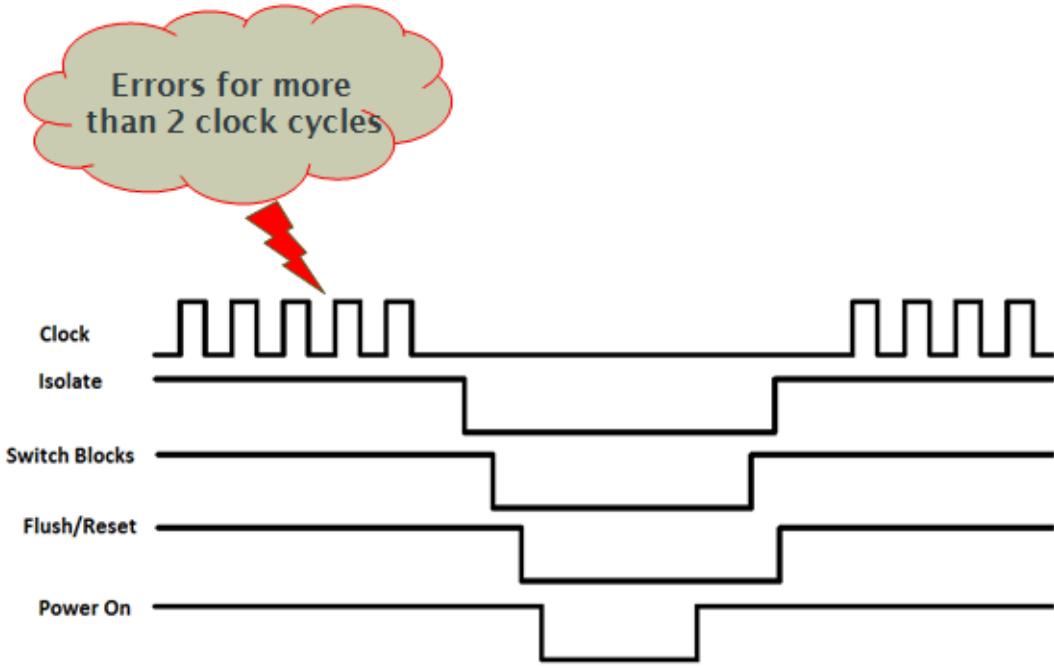

| 5.11 Differentiating permanent faults from transient faults . . . . .                                                                                                                                                                      | 112 |

| 5.12 Transient fault . . . . .                                                                                                                                                                                                             | 113 |

| 5.13 Permanent fault . . . . .                                                                                                                                                                                                             | 113 |

| 5.14 An example of the sequence of timings of power management unit based on the methodology in [23] . . . . .                                                                                                                             | 114 |

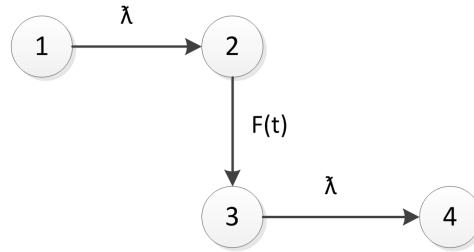

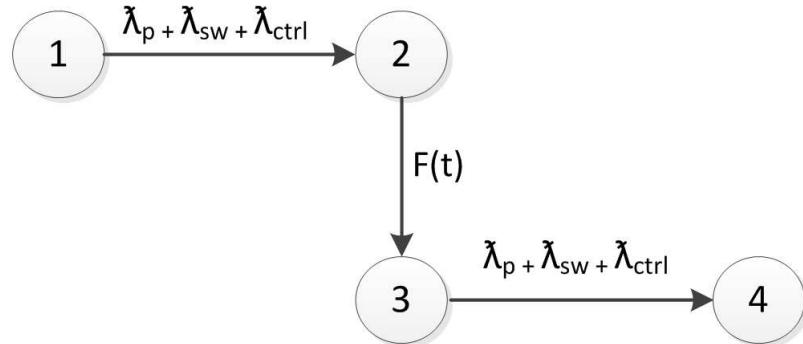

| 5.15 Markov model of IFR at pipeline level . . . . .                                                                                                                                                                                       | 115 |

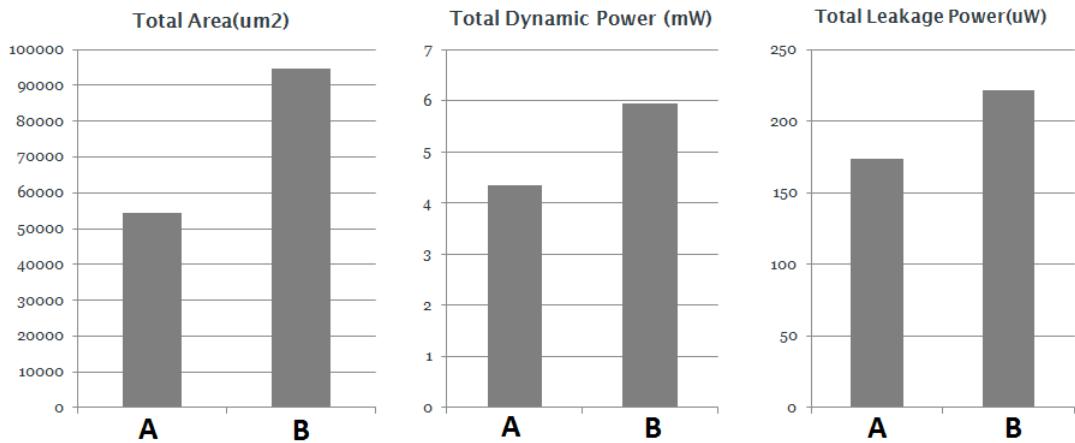

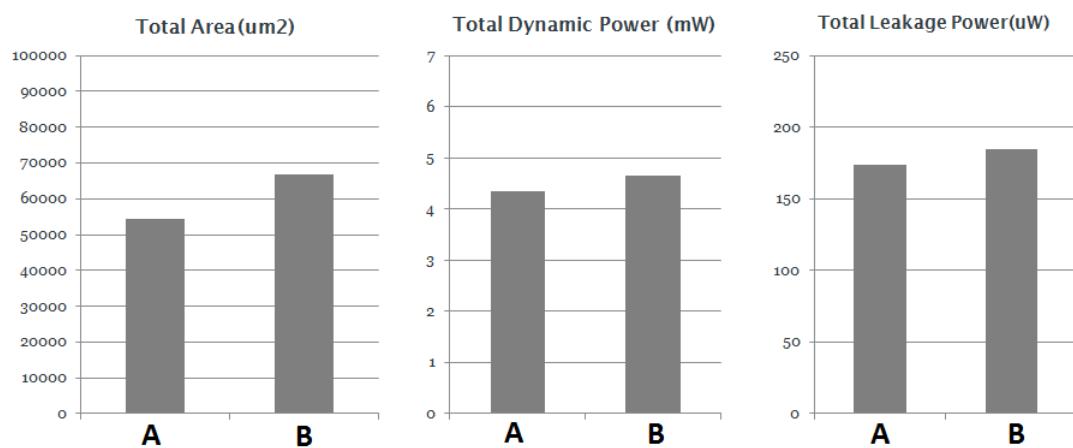

| 5.16 Area, power and performance comparisons: A)Simple core B)In-field repair core . . . . .                                                                                                                                               | 116 |

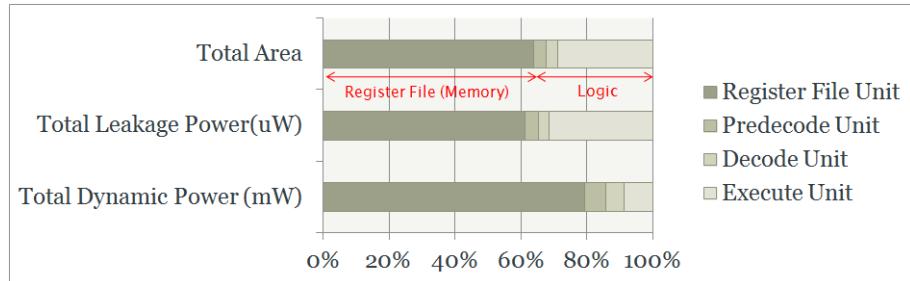

| 5.17 Contribution of each processor pipeline stage to the total area and power consumptions. . . . .                                                                                                                                       | 117 |

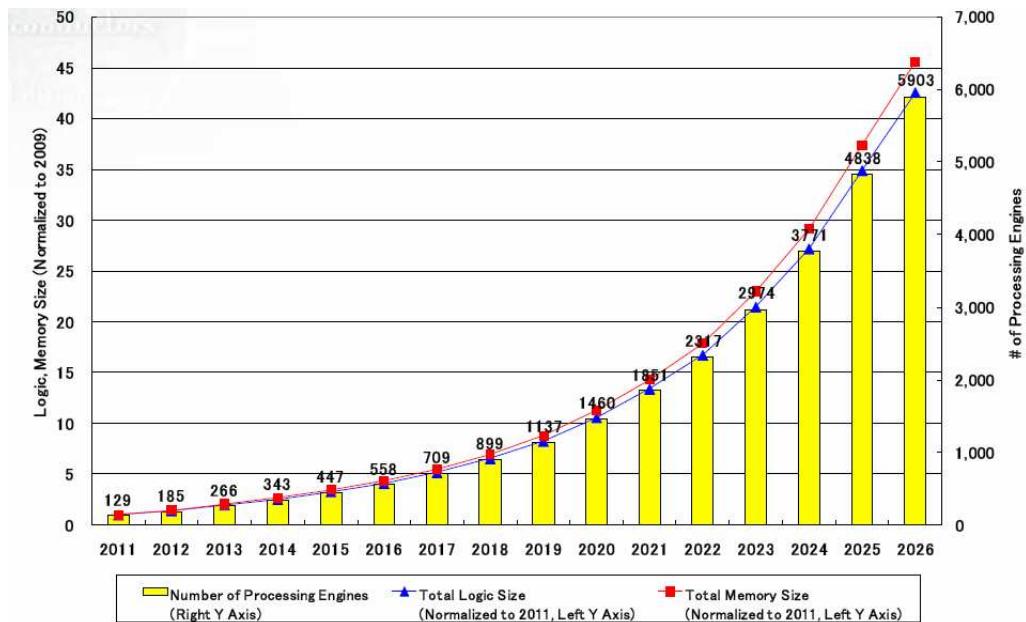

| 5.18 ITRS - Logic vs memory roadmap [24] . . . . .                                                                                                                                                                                         | 117 |

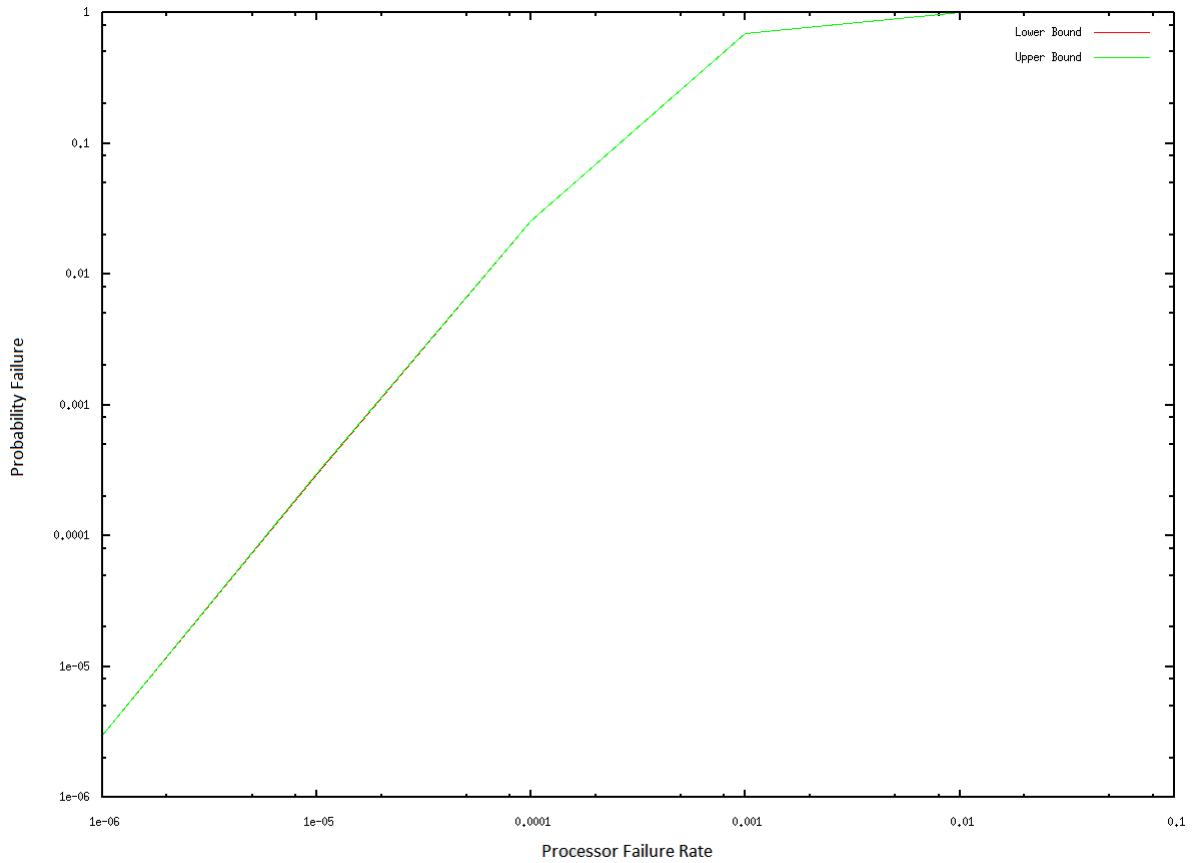

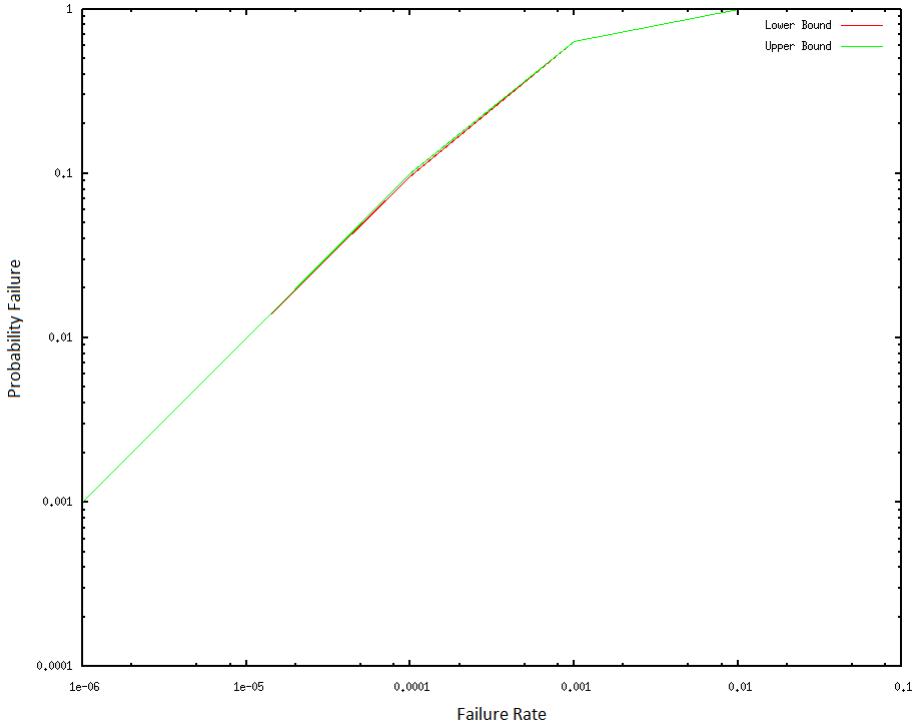

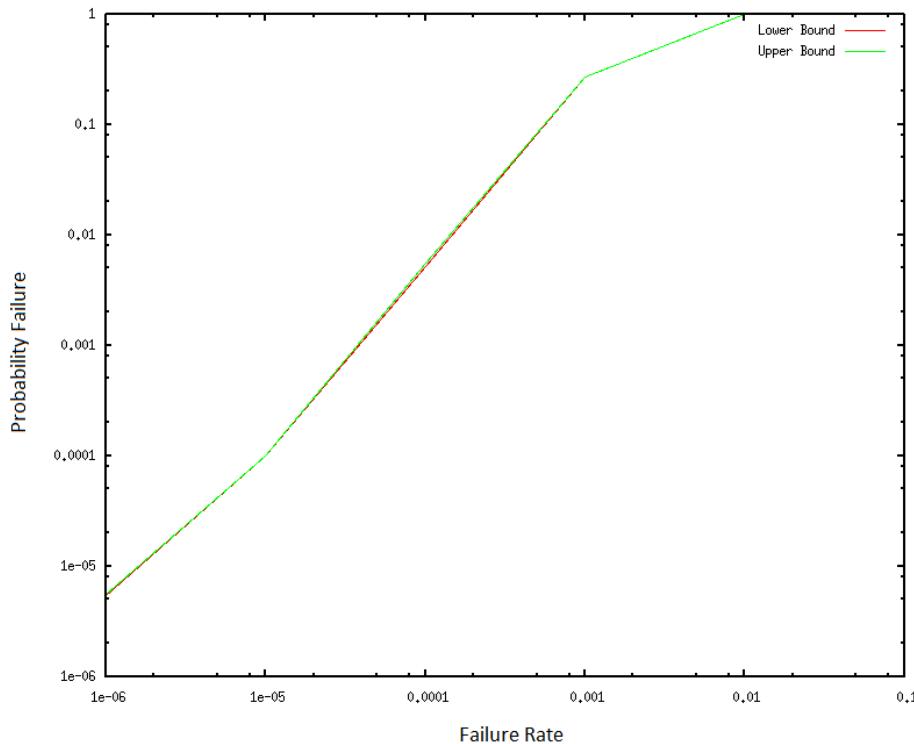

| 5.19 NASA SURE plot for probability failure of the simple core . . . .                                                                                                                                                                     | 118 |

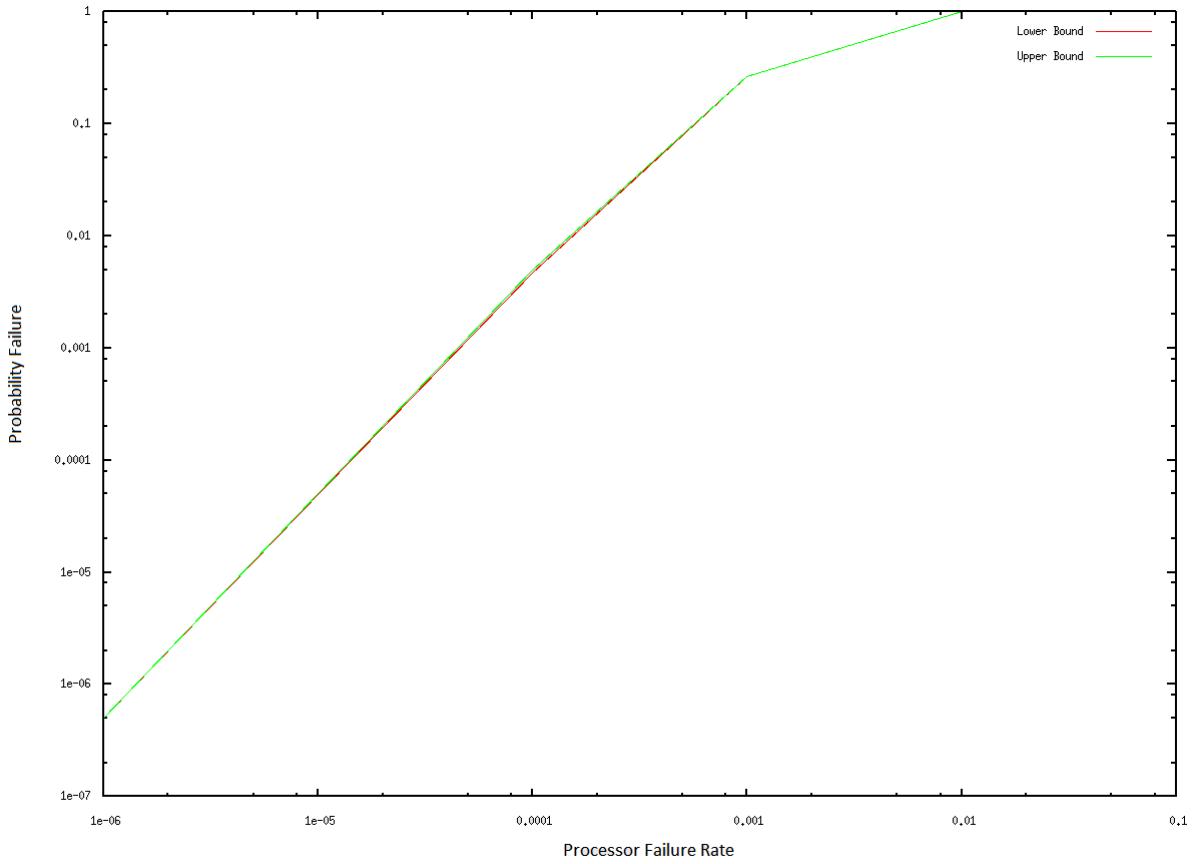

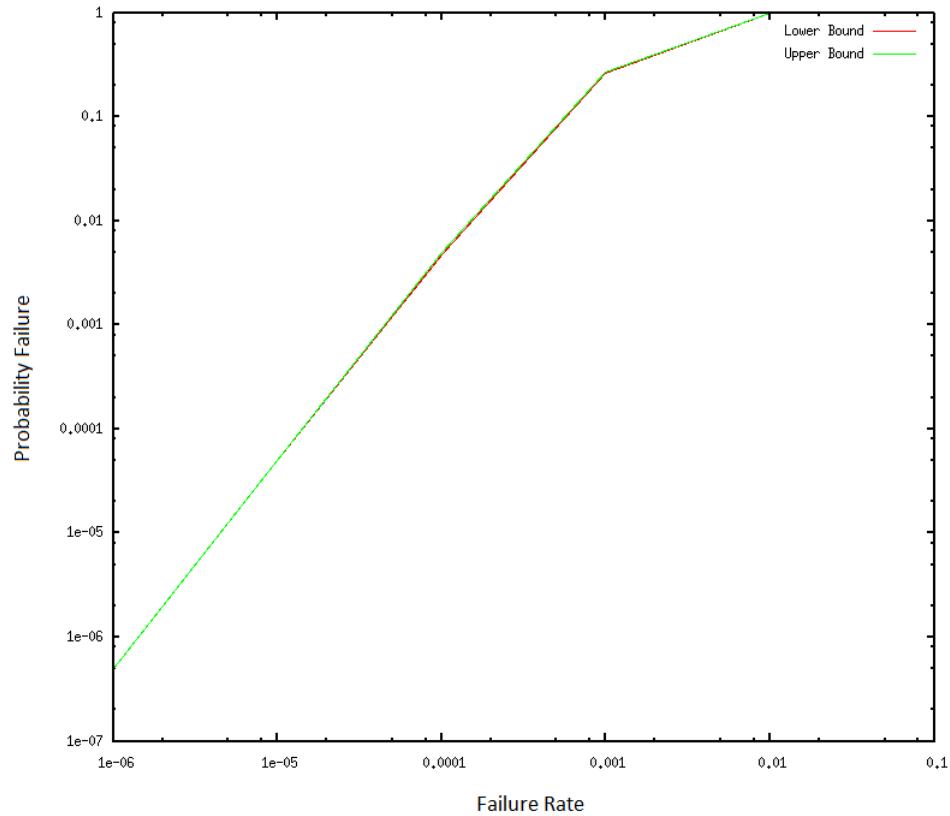

| 5.20 NASA SURE plot for probability failure of the IFR core . . . .                                                                                                                                                                        | 119 |

| 5.21 Variation-and-ageing resilient design . . . . .                                                                                                                                                                                       | 120 |

| 5.22 Markov model of Variation-and-Ageing Resilient Design . . . .                                                                                                                                                                         | 121 |

| 5.23 NASA SURE plot for probability failure of variation-and-ageing resilient design . . . . .                                                                                                                                             | 122 |

| 5.24 Area, power and performance comparisons: A)Simple core B)Variation-and-ageing resilient design core . . . . .                                                                                                                         | 122 |

| 5.25 Optional caption for list of figures . . . . .                                                                                                                                                                                        | 125 |

| 5.26 Optional caption for list of figures . . . . .                                                                                                                                                                                        | 126 |

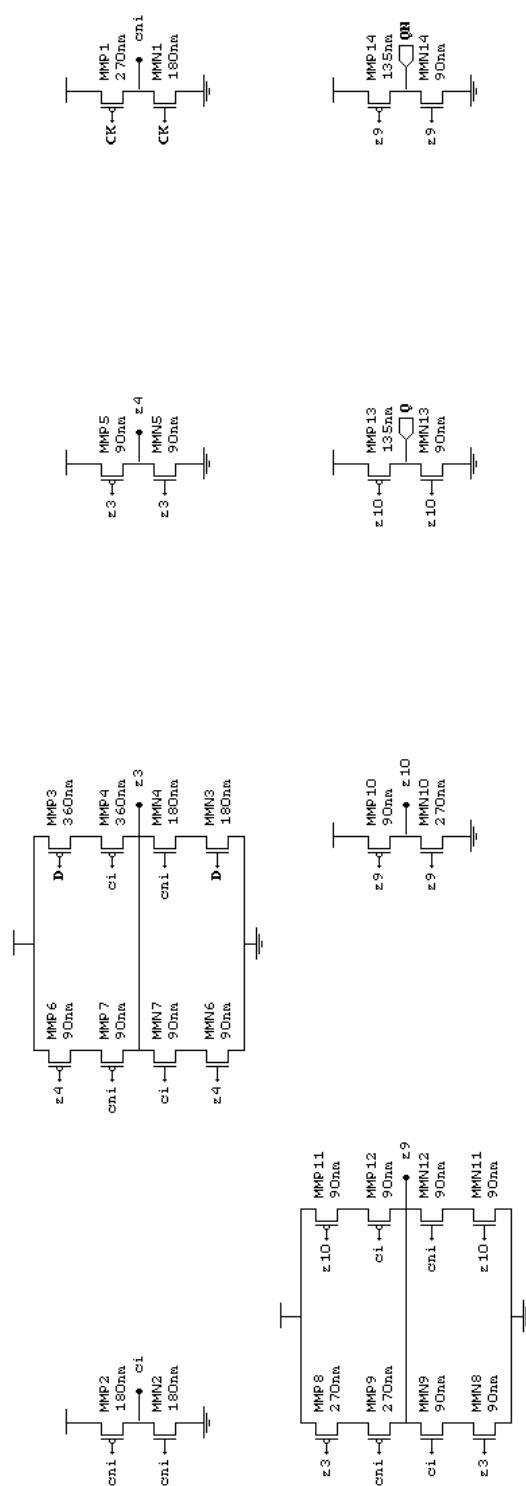

| A.1 45nm DFF - Transistor Level . . . . .                                                                                                                                                                                                  | 132 |

# List of Tables

|     |                                                                                                                                                                                                       |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | An example of determining the minimum capturable pulse width - SPICE simulations using Nangate 45m technology library . . . . .                                                                       | 60  |

| 3.2 | Decreasing SET susceptibility using internal buffering re-sizing at 45 nm technology. Note that non-default values are non-physical as this is an experiment to look at operating boundaries. . . . . | 63  |

| 3.3 | Average of SET-induced SER of different technology nodes - SER = FIT : Number of failures in $10^9$ hours of operation . . . . .                                                                      | 67  |

| 3.4 | FIT-SET Char Table : INVX1 - Input = 0 - DFFX1 . . . . .                                                                                                                                              | 68  |

| 4.1 | Availability and Applications of Conventional Radiation Hardening Schemes . . . . .                                                                                                                   | 84  |

| 4.2 | Rad-Hard CPUs and their performance overheads . . . . .                                                                                                                                               | 86  |

| 4.3 | Applications . . . . .                                                                                                                                                                                | 96  |

| 5.1 | . . . . .                                                                                                                                                                                             | 105 |

| 5.2 | . . . . .                                                                                                                                                                                             | 105 |

| 5.3 | IFR Core Fault Test . . . . .                                                                                                                                                                         | 116 |

| 5.4 | STA Scenarios of the in-field repair scheme in functional modes with n=3 leading to 8 functional modes . . . . .                                                                                      | 120 |

# Nomenclature

|             |                                                     |

|-------------|-----------------------------------------------------|

| <i>ABB</i>  | Adaptive Body Biasing                               |

| <i>ASET</i> | Analogue Single Event Transient                     |

| <i>AVS</i>  | Adaptive Voltage Scaling                            |

| <i>BTI</i>  | Bias Temperature Instability                        |

| <i>CDF</i>  | Cumulative Distribution Function                    |

| <i>CMP</i>  | Chemical Mechanical Polishing                       |

| <i>CWSP</i> | Code Word State Preserving                          |

| <i>DCLS</i> | Dual Core Lock Step                                 |

| <i>DMR</i>  | Dual Modular Redundancy                             |

| <i>DVFS</i> | Dynamic Voltage and Frequency Scaling               |

| <i>ECC</i>  | Error Correcting Code                               |

| <i>EDA</i>  | Electronic Design Automation                        |

| <i>ELT</i>  | Enclosed Layout Transistors                         |

| <i>FIT</i>  | Failure In Time                                     |

| <i>H</i>    | Wire Height                                         |

| <i>HBD</i>  | Hard Break Down                                     |

| <i>HCI</i>  | Hot-Carrier Injection                               |

| <i>HMR</i>  | Hybrid Modular Redundancy                           |

| <i>ITRS</i> | International Technology Roadmap for Semiconductors |

| <i>L</i>    | Length                                              |

| <i>LET</i>  | Linear Energy transfer                              |

| <i>MBU</i>  | Multi-Bit Upset                                     |

| <i>MCU</i>  | Multi-Cell Upset                                    |

| <i>MPU</i>  | Memory Protection Unit                              |

| <i>MTBF</i> | Mean Time Between Failures                          |

| <i>MTTF</i> | Mean Time To Failures                               |

| <i>NBTI</i> | Negative Bias Temperature Instability               |

| <i>NMR</i>  | N Modular Redundancy                                |

| <i>PCA</i>  | Principal Component Analysis                        |

|             |                                     |

|-------------|-------------------------------------|

| <i>PDF</i>  | Probability Density Function        |

| <i>PLL</i>  | Phase-locked Loop                   |

| <i>RSM</i>  | Response Surface Methodology        |

| <i>RTL</i>  | Register Transfer Language          |

| <i>SBD</i>  | Soft Break Down                     |

| <i>SEB</i>  | Single Event Burnout                |

| <i>SEE</i>  | Single Event Effect                 |

| <i>SEFI</i> | Single Event Functional Interrupt   |

| <i>SEL</i>  | Single Event Latch-up               |

| <i>SER</i>  | Soft Error Rate                     |

| <i>SET</i>  | Single Event Transient              |

| <i>SEU</i>  | Single Event Upsets                 |

| <i>SILC</i> | Stress Induced Leakage Current      |

| <i>SNR</i>  | Signal-to-Noise Ratio               |

| <i>SOI</i>  | Silicon-on-Insulator                |

| <i>STA</i>  | Static Timing Analysis              |

| <i>TDDB</i> | Time-Dependent Dielectric Breakdown |

| <i>TCM</i>  | Tightly Coupled Memories            |

| <i>TMR</i>  | Triple Modular Redundancy           |

| <i>Tox</i>  | Oxide Thickness                     |

| <i>TRC</i>  | Two-Rail Checkers                   |

| <i>TSC</i>  | Totally Self Checking               |

| <i>UV</i>   | Ultraviolet                         |

| <i>VHDL</i> | VHSIC Hardware Description Language |

| <i>VRM</i>  | Voltage Regulator Module            |

| <i>Vth</i>  | Threshold Voltage                   |

| <i>WM</i>   | Wire Width                          |

| <i>WOV</i>  | Window of Vulnerability             |

| <i>UDSM</i> | Ultra Deep Sub Micron               |

## Declaration of Authorship

I, **Massoud Mokhtarpour Ghahroodi**, declare that the thesis entitled *Variation and Reliability in Digital CMOS Circuit Design* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as papers in peer-reviewed international conferences;

Signed:.....

Date:.....

## **Acknowledgements**

I owe my deepest gratitude to my supervisor Professor Mark Zwolinski for his continuous help and support in this work. It has been an honour to be his Ph.D. student. I appreciate all his contributions of time, ideas, and funding to make my Ph.D. experience productive and stimulating.

I would like to extend my appreciation to Cisco Systems Inc., ARM Ltd. and HiPEAC (European Network of Excellence on High Performance and Embedded Architecture and Compilation) for their support for the development of the work in this thesis.

*To my dad.*

# Chapter 1

## Introduction

### 1.1 Motivations For Research

This work is motivated by the challenges faced in designing reliable circuits in modern technology nodes. As the feature size of CMOS devices shrink to Ultra-Deep-Sub-Micron (UDSM) dimensions, intrinsic parameter fluctuations of atomic scale transistors drastically impact the power, performance and yield of manufactured chips and limit the scaling and integration of them. In other words, due to intrinsic variations, unavoidable in modern fabrication processes, the taped-out chips can vary radically as every single UDSM transistor out of the billions of transistors on a die have different characteristics.

Moreover the incredible growth and complexity of semiconductor fabrication facilities has resulted in the isolation of process/device engineers from circuit design engineers, leading to some lack of understanding of the impact of circuit designs upon manufacturability and testability due to the fundamental limitations of technology and device physics. Most of today's technologies are subject to very high defect density. Increasing defect density decreases yield and with such a high defect densities in UDSM chips, the manufacturing costs can be prohibitively high, making chip yield a critical metric for manufacturers. From a performance point of view, the circuit must meet its speed requirements over a range of voltages and temperatures that reflect the environment in which the circuit will operate; while the performance requirements must be met at a set of worst-case conditions for speed, the power requirements must be simultaneously met at another set of worst case conditions.

Moreover, from a reliability perspective, the incidence of transient errors increases at UDSM dimensions, and consequently, the dependability of the systems decreases. Reliability is therefore another required metric for every UDSM-based system in general and safety-critical systems in particular.

Therefore any design methodology must consider the Power, Performance, Yield and Reliability figures of merit in the design and manufacturing flow. At present, there are neither methodologies nor EDA tools that can capture the full complexity of these problems and be used successfully to predict both the characteristics and scale of the intrinsic fluctuations in UDSM transistors and interconnects, and their subsequent impacts on the power-performance-yield and reliability of circuits and systems.

## 1.2 Power-Performance-Yield-Reliability

### 1.2.1 Power

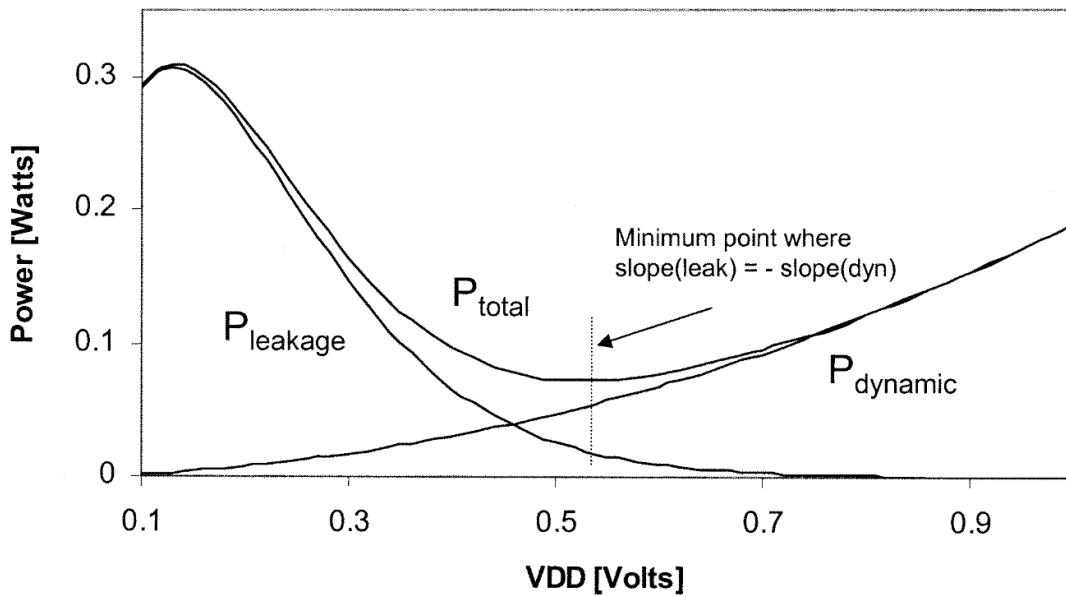

Power consumption which is the rate of energy dissipation in a system is always an important issue; but due to the technology scaling to UDSM dimensions with more and more transistors on a chip, power consumption, thermal and cooling issues are some of the major problems in chip design especially for battery operated devices. Although the dominant factor of power consumption is the dynamic power dissipation which is related to the operating voltage, frequency, capacitance and the required performance specifications, at UDSM, leakage power dissipation is not ignorable anymore, in such a way that as reported in the literature, leakage power will represent up to 40 percent of total power consumption in near-future devices [25].

### 1.2.2 Performance

As the name suggests, higher performance or faster computation is always desired. However applying today's design methodologies and traditional deterministic worst-case timing analysis at UDSM is too pessimistic [12]. Moreover, due to the unavoidable variations in global buffer loads and interconnect wire length, the global clock signal arrives at different components at different times. This phenomenon which is known as the clock skew makes the traditional globally

synchronous design methodology impractical; because the clock signal cannot be distributed to all of the millions of flip-flops and registers on the chip at the same time significantly degrading the achievable clock speed.

### 1.2.3 Yield

Generally, the key metric in determining the success of a technology in chip design (especially from the market perspective) is the number of devices on the die which are fully functional and applicable. This generally necessitates that every single transistor out of billions of transistors on a chip work properly. This issue is known as yield. Any malfunction in a single device can potentially lead to yield loss. This yield loss can be either catastrophic or parametric; catastrophic yield loss is caused by physical defects (such as stuck-at, opens, bridging faults) which typically manifest themselves as functional failures on the chip, leading to defective chips which must be thrown away. In parametric yield loss, manufactured devices do not perform according to the design specification i.e. chip functionality is correct but they may work slower or consume more power than expected in the design process.

For a long time the parametric yield was not considered serious and catastrophic yield loss was the main yield issue and various solutions such as adding redundancy and fault-defect tolerant methodologies were used to surmount this type of yield loss. But at UDSM dimensions, not only catastrophic yield loss is important but due to the variations, the parametric yield loss is rapidly increasing as well [26].

### 1.2.4 Reliability

Semiconductor manufacturing continues to provide smaller feature sizes resulting in lower power, higher density, and lower cost per function. While this trend is positive, there are a number of negative side effects, including increased semiconductor parameter variability, increased sensitivity to soft errors, and lower device yields. These issues become more and more important for the semiconductor industry and modelling is increasingly required to provide design tools not only to achieve better device performance but also more robust reliability margins. Dependability, or the ability of a system to function correctly under given operating conditions during a given period of time can be quantified using measures of Reliability or Failure In Time (FIT). The lifetime of next-generation devices is decreasing due

to lower reliability margins and shorter product lifetimes putting the reliability and dependability of such systems at stake [10].

Another major emerging reliability problem that cannot be furthermore ignored in UDSM technologies is the susceptibility to Soft Errors. As clearly stated in The International Technology Roadmap For Semiconductors(ITRS) 2009-2011 [24]:”The impact of Soft Error Rate (SER) over the years is almost constant or even increasing in spite of the reduced sensitivity for the single units due to device scaling and the use of countermeasures (e.g., SOI, redundancy, error detection and correction). This is because of the corresponding increase of the number of units in a system. Viable models and simulators are still lacking to extrapolate the SER from the cell up to the system level from accelerated tests, which are able to keep track of the error propagation and to provide enough statistical accuracy.”

## 1.3 Objectives

The main objectives of this research are:

- To investigate the impacts of variation and reliability issues on UDSM CMOS circuits from a design perspective.

- To investigate timing vulnerability of UDSM combinational circuits and present a more realistic methodology to determine the vulnerability.

- To investigate timing vulnerability of UDSM sequential circuits and state-holding elements and propose a possible hardening-by-design solution.

- To investigate ageing and the reliability issues of UDSM circuits and processors and propose a repair mechanism to avoid fatal shut-downs.

## 1.4 Contributions

This thesis provides a survey of various UDSM impacts on circuits and devices, reviewing current research and providing a summary of the state-of-the-art techniques to mitigate the UDSM impacts. Moreover, techniques are introduced to deal with UDSM impacts in terms of performance and reliability. These include a novel radiation-hardened flip-flop design and an in-field logic repair mechanism for UDSM reliable circuit design.

## 1.5 Thesis Structure

In this chapter, the main problems, obstacles and motivations for this research have been briefly presented. The second chapter provides a survey of various UDSM impacts on circuits and devices in the literature and the existing techniques to tackle them. First, the pre-silicon or design-time techniques are discussed and then post-silicon or run-time solutions are provided, followed by a brief survey of the reliability issues. Chapter 3 addresses timing vulnerabilities mainly due to soft errors in combinational logic. Chapter 4 discusses timing vulnerability of sequential circuits and state-holding elements. Chapter 5 provides a discussion of other reliability issues such as ageing and possible in-field repairable architectures. The last chapter summarises the conclusions of the thesis.

# Chapter 2

## Literature Review

In this chapter, we take a brief survey of the major impacts of UDSM scaling on design. First we discuss process and intrinsic parameter variations, and their impacts on Performance and Power consumption. Then we take a brief survey of the effects of radiation and soft errors on UDSM CMOS circuits. Afterwards, the major reliability issues will be discussed and finally, state-of-the-art and the proposed solutions in the literature to tackle process variation and to mitigate soft errors and the reliability issues will be discussed.

### 2.1 Process Variation

One of the major impacts of UDSM on logic are increased levels of fabrication process variation and additional random uncertainties caused by the random placement of dopant atoms in the channel of each transistor at UDSM dimensions. This intrinsic randomness of the placement of atoms, along with the extrinsic limitations in controlling the manufacturing process and its precision, have impacted various parameters such as oxide thickness ( $T_{ox}$ ), threshold voltage ( $V_{th}$ ) and transistor channel length (L) directly. The impacts of process variation are not limited to the transistors. Interconnect parameter variation on wire height (H) and wire width (WM) are also increasing dramatically. Such phenomena will result in huge variation in gate delays and interconnect delays. Moreover due to nanometre scale geometries of devices with very thin (angstrom scale) gate oxide layers, the reliability issues of such UDSM designs have been increasing at very high rates [27] [28] [29].

This is mainly due to the inability of semiconductor manufacturing industries to improve tolerance levels in the fabrication-lithography stage and keep up with the technology scaling. For instance, the light source (with a wavelength of 193 nm) used in lithography in older technologies (above 130 nm) is still used in newer technologies [30]. Lithography tolerances are limited by the granularity of the resist materials. for UDSM process, various immersion and multiple exposures lithography techniques are used which will result more expensive manufacturing processes.

The doping density of the transistor channel is the major determinant of threshold voltage in bulk and polysilicon gate MOSFETs. To achieve the desired doping density and consequently the desired threshold voltage, certain number of dopant atoms are required. Due to the fact that the implantation of dopant atoms in devices is random, the eventual exact number of dopant atoms in the transistor channel is also random. Because of technology scaling, such number of atoms in the channel region is becoming smaller, as the channel volume decreases, and thus the relative effect of a single change in dopant number is increasing [30] [31]. There is a similar situation for interconnects, however the main factors which are responsible for variation in interconnects are the limitations in process control over the manufacturing process.

Figure 2.1: Variation in threshold voltage of devices [1]

Fig. 2.1, shows how the variance of the threshold voltage of an NMOS transistor has almost doubled between the 45nm and the130nm technology nodes. It can also be seen that the absolute value of the threshold voltage in 130nm technology is about 0.35V which is higher than 45nm technology (0.28V approx.). Hence the prediction of the device behaviors and eventually estimating the circuit performance metrics in the presence of device and interconnect variation is a major challenge for the chip industry.

From manufacturing perspective, one can classify the sources of variation in the transistor threshold voltage into two main categories: Global and Local. Global variation is caused by manufacturing process variations and local intrinsic variation is caused by local parameter fluctuations. For short channel transistors (channel length = 20nm in 45nm technology), the threshold voltage variation is caused by transistors geometries, and specifically the  $L_{eff}$  parameter which can be classified as being local. In the case of long channel (channel length = 40nm in 45nm technology) transistors, the variation on  $V_{th}$  is mainly due to dopant diffusions, gate dielectric thickness, ion implantation and so forth that can be considered as being global [32]. For long channel transistors it is the average dopant diffusion that is more important. As shown in Fig. 2.2, the source and drain doping is very dense, but the channel doping is very vulnerable to variation.

Figure 2.2: Random placement of dopant atoms a 50-nm channel-length MOSFET [2]

From another perspective, we can categorize variation as being either random or systematic [30] [33] [34]. Random physical effects such as poly-silicon gate line-edge roughness, random fluctuations of the number and the location of dopant atoms in the MOSFET channel and so forth [35] [33] [30]. Systematic variations are usually due to spatial dependencies of the manufacturing mechanisms for device processing, such as variation in chemical mechanical polishing (CMP) which produces predictable variation trends across the die [36], or predictable variations such as those caused by optical proximity effects [37].

It is also noteworthy to mention that when comparing the delay contribution of device variation to interconnect variation, delay variations due to interconnect are still less significant and device variations still hold the biggest share of the total delay variability in UDSM technologies [30]. The contribution of fluctuations in device parameters is about 90% of the total delay variation of a design in the real world [33].

### 2.1.1 Performance

Typically, the performance of a circuit is determined by the speed of the circuit which is rated by the operating clock frequency. Delays are generally the boundaries that determine this operating frequency. The rate at which information can propagate through the circuit depends on the longest path delay, and from a synchronous design perspective, the maximum clock frequency of a circuit is limited by the path with the maximum delay. Variation in process parameters will cause distributed small delay variations along any given path and when summed up, the path can become timing critical and even fail to meet the timing constraints, hence the chip can fail as a result. Random variations can cause a significant mismatch in the electrical performance of two identical devices placed next to each other. On the other hand, performance and timing verification in the presence of process variation is difficult because the critical path is no longer unique. This means different paths can become timing critical depending on the process-voltage corners that the manufactured chip is coming from. Therefore Critical Path selection and analysis cannot be deterministic anymore [38].

### 2.1.2 Power Consumption

Power consumption and thermal issues have always been important, but due to the high device density and integration of logic with UDSM dimensions, the problem has become even more serious. While dynamic power dissipation is the dominant component in the total power consumption, in UDSM, leakage power in forms of gate leakage or sub-threshold leakage is increasingly becoming a severe problem [39].

Thermal issues and generated heat in to days and future high performance and highly integrated devices is another significant factor. Dynamic power consumption activity can produce local hot spots on the die. These local hot spots can be several tens of degrees hotter than the rest of the die, even after application of the best cooling techniques to the package itself. As depicted in Fig. 2.3, a temperature difference of 40C to 50C corresponds to a 20 percent performance variation [3].

Figure 2.3: Temperature differences on a die: 40C to 50C temperature difference leads to 20% performance variation [3]

As it can be seen in Fig. 2.3, there are huge temperature differences between the cache area and the core area, with the core area being much hotter and the cache region is much colder also depicted in Fig. 2.4. This non-uniformity in thermal gradients is very prevalent in micro processors and it can be observed by doing local calculation (or local sensing) on the power densities at different locations on a chip. From a dynamic power dissipation point of view, slower devices are the result of higher temperatures. However according to the power consumption formula (i.e.  $C \times V^2 \times f$ ), the total consumed power will remain the same. Nevertheless, the main issue will be because of the leakage power that grows exponentially that can potentially cause major IR drop issues [26]. In other words, dynamic power grows linearly with chip frequency (and since chip frequency used to be proportional to scaling, power draw would scale linearly with device shrink) but leakage power is increasing exponentially with device shrink.

Figure 2.4: A Temperature Distribution Map of a Typical Chip with a Core and Cache [3]

IR drop is supply voltage drop across the chip. According to Ohms Law  $V=I \times R$ , where  $R$  is the equivalent path DC resistance between the source location and the cell/macro location and  $I$  is the average current the chip draws from the supply down the paths. The power grid or the power mesh is comprised of multi-level metal structures. This includes planes, vias and tracks that feed the all of the standard cells and the memories and the macros across the chip. The supply voltage is produced by a voltage regulator module (VRM), which is usually a DC-DC converter that is connected to the power grid and distributes power across the chip.

Wire resistance can lead to excessive current draw from the power mesh that can cause significant performance degradations and signal integrity issues (an illustrated 2.5) . Due to smaller interconnect geometries the power mesh at UDSM scales, the level of vulnerability to power supply non-uniformity and IR drop is significant. The manifestation of such issues will be more sensitivity to noise and increased delay variation and eventually delay faults and timing errors. These impacts are aggravated when there are gates with different supply voltage levels that are connected across the chip communicating through level-shifters [4].

Figure 2.5: IR Drop in Power Distribution Network due to non-ideal components [4] [5]

The effective amount of resistance through the path between the voltage regulator module and the design blocks on the chip is the metric to estimate the IR drop. It should be mentioned that the topic of IR drop is not limited to the design of blocks on the chip. There are three main categories to be considered: On-chip IR drop, Package IR drop, and Board-level IR drop. Because of UDSM dimensions, accurate analysis of IR drop on the chip is critical as this is the most significant factor in determining if the chip is going to fail because of IR drop issues. However recently package IR drop and board level IR drop have become more important and their contribution to the over-all IR drop budget cannot be ignored [40]. This is mainly because of decreased supply voltage and increase vulnerability to noise issues that can have fatal impacts on the operation of high speed circuits. The increase in temperature and the creation of hot-spot across the chip will also add up to the IR drop that can potentially lead the chip towards failure [41].

## 2.2 Radiation and Soft Errors

The Earth and its surroundings are protected by the atmosphere, which acts as a filter, to let throughout visible light and heat, while stopping a significant amount of radiation and Ultraviolet (UV) light. Because of this natural protection , human beings and electronic devices are able to cope with solar flares, solar winds and cosmic rays. As reported in NASA reference publications [42] and also in [6], the two major sources of environment related spacecraft anomalies are, statistically, plasma and radiation effects, i.e. effects related to the charged particles from the space environment.

Figure 2.6: Spacecraft anomalies due to the space environment [6]

With technology scaling, radiation particle strikes are becoming increasingly problematic for both combinational circuits and memory elements even at sea level. The first report of serious industrial problem due to soft errors goes back to 1978 on the 2107-series 16-KB DRAMs by Intel. It was reported that the errors were

caused by the traces of radioactivity due to  $\alpha$  particles in the package materials which led to radiation-induced Single-Event-Upsets (SEU) at sea level, referred to as “soft errors” [43]. From that era until now, radiation-induced problems have been some of the most challenging reliability issues in circuits and systems, not only in safety-critical applications and avionics, but also for Commercial, off-the-shelf (COTS) products. Therefore, the circuits used in these application must be tolerant to radiation particle strikes. In this section, we take a brief survey of radiation-induced errors on circuits and systems.

### 2.2.1 Single Event Effects Definition

Soft errors are a subset of non-destructive Single-Event Effects (SEEs) [44]. The interaction of nuclear particles with electronic components can create a series of SEEs. Such effects can be categorized as hard effects and soft effects. Hard effects or hard errors are permanent and non-recoverable. Soft errors are temporary and might be recoverable by applying power shut down, reset or rewriting the corrupted data. In CMOS-based circuits, the main hard error issues are Single Event Burnout (SEB) that can occur in power MOS devices, SEGR or die-electric breakdown caused by single event effects and micro-dose-induced threshold voltage variations due to SEEs in CMOS transistors. The PNPN parasitic structures can also be vulnerable. A Single Event Latch-up (SEL) can cause a strong current which can lead to overheating of the device, that if it is not stopped by a power cycle, it can have destructing impacts on the transistor. These hard errors are not discussed in this thesis, but they represent the most significant hard issues in the topic of SEEs.

Multi-Cell Upset (MCU) will occur when one high energy particle hits many state holding elements in a given clock cycle. On the other hand, Multi-Bit Upset (MBU) occurs when more than one bit of a word is struck by a single particle. There is another phenomenon known as Single Event Functional Interrupt (SEFI), that can happen in more sophisticated circuits and systems. SEFIs can cause loss of functionality because of perturbation of clocks or control registers that can lead to long periods of malfunctions in the system. Recovery might be obtained by switching off and back on, or rewriting configuration registers, or by applying a reset [45].

## 2.2.2 Major Soft Error Problems

Silicon devices have become more susceptible to radiation and energetic particle strikes. The energetic particle strikes can create localized ionization events in the silicon devices and if this happens in the sensitive region on the CMOS device, the resulting electron-hole pair can cause a transient current pulse that may alter the logic state of the struck node as depicted in Fig. 2.7 and Fig. 2.8. This is known as a single event upset (SEU) on a memory element since it can upset the storage elements; if the particles strike any combinational node they can cause a transient current pulse that eventually becomes a voltage pulse at the output of the struck node. It is known as a single event transient (SET) on a combinational element [46] [47] [48] [49]. The transient pulse caused by a particle strike can be captured by the sequential elements depending on the existence of an active path from the struck node to the storage element, the arrival time and the width of the transient pulse at the storage element input as shown in Fig. 2.9 [50] [51]. The errors caused by SEUs or SETs are known as major soft error issues.

Figure 2.7: Illustration of single event transient pulse generation. Funneling in an n+/p silicon junction following the ion strike and the resulting electrical transient current caused by the passage of a high-energy ion [7] [8].

As mentioned earlier, the transient pulse can be captured by a flip-flop and cause an error, provided that it is not masked by any of the following three derating factors or masking phenomena:

- Logic Masking happens when the particle strikes either a non-controlling input of a combinational logic gate, or the transient pulse is filtered out by other controlling nodes on the path to a sequential element.

- Electrical Masking occurs for transient pulses which will be attenuated due to characteristics of CMOS gates, such as size and load capacitance.

Figure 2.8: Particle strike on a sensitive node

Figure 2.9: SET in Combinational Logic

- Temporal Masking occurs when the transient pulse is either narrower than the flip-flop window of vulnerability or the transient pulse is wide enough but reaches the memory element outside of the clock transition region and hence it is not sensed and captured.

The main sources of Soft Errors are reported to be [52] [47] :

- Alpha particles (caused solely by silicon packaging and radioactive impurities)

- Neutron-induced fission (interaction of neutrons from cosmic rays and boron in the silicon packaging)

- High-energy cosmic rays

The physical effects of radiation-induced charges on devices and circuits can be classified as: Direct and Indirect ionization. In direct ionization, as a high energy particle passes through a semiconductor material, it generates electron-hole pairs. As the radiation particle passes through the silicon, it loses its energy and after expending all its energy, the particle will come to rest. To define the transferred energy from the particle, the linear energy transfer (LET) value is used. LET is defined as the transferred energy that the radiation particle induced to generate the electronhole pair per unit length, normalized by the density of the target material (for VLSI designs, this is the density of Silicon) [31].

Indirect ionization consists of a light radiation particle with high energy that passes through the semiconductor material. Such particle can have a collision with the nucleus that can lead to a nuclear reaction. Protons and neutron particles are good examples indirect ionization. Such phenomenon can also create secondary particles such as heavy ions or alpha particles. Such secondary particle can then go through a direct ionization process and if the charge gets placed in different locations across the chip, multiple soft-errors can arise [31] [53].

Advances in packaging and fabrication have gradually reduced the effect of the alpha-particle induced soft errors and the neutron-induced soft errors dominate in most UDSM circuits [52]. Experimental results with heavy ions and alpha particles indicate that SET pulse widths can range from about 100 ps to over 1 ns for the 90-nm process. Such pulse widths are comparable to valid logic signals in 130nm and 90nm processes and indicate that as technology is scaled to lower operating voltages and higher operating frequencies, SETs may become a significant reliability problem [54] [55] [56].

The soft-error rate (SER) is measured in FIT units (failures in time), where 1 FIT denotes one failure per billion device hours (i.e., one failure per 114,077 years). For electronic systems, usually the SER values range between a few hundreds and around 100,000 FIT. This is about one soft error per year. The failure rate induced by soft errors can be relatively high in electronic devices, compared to other reliability issues that will be discussed later. The experimental results show that the failure rate for hard errors (for example latch-ups) is approximately equal to or lesser than 10 FIT. However, the soft-error rate is much higher. For instance,

the SER for an SRAM block with the size of 1 Mbit is usually of the order of 1,000 FIT in UDSM process technologies, which makes the memory blocks some of the most vulnerable parts of the chip [57]. The situation becomes even worse for systems with multiple memory blocks (which is the case for most of modern chips) in a way that it exceeds the cumulative failure rates because of other reliability issues. However, it should be noted the consequences of soft errors are totally different from hard errors. In the case of soft errors, the fault usually disappears when the system is reset or new data replaces the corrupted data, hence the damage is not permanent.

As depicted in Fig. 2.10, in previous technologies, memory elements such as SRAMs, flip-flops and latches contributed more to the overall SER of the chip and the contributions of of combinatorial logic to the overall SER was much lower. Therefore, memories (SRAMs, DRAMs, and latches) were mainly under consideration as they were more vulnerable to radiation particle hits. However, as the feature size of CMOS devices go below UDSM, the contribution of combinatorial logic gates to the overall SER has take a much bigger share, while the contribution of memory elements such as SRAMs to the overall SER has relatively remained constant. The is due to the fact that by using deeply pipe-lined circuits, the lengths of the combinatorial logic paths have been reduced dramatically which can result in the reduction of the masking or derating factors. In other words, because fewer number of SETs will get filtered out, the particle hits on combinatorial circuits can cause more faults and aggravate the overall SER of the chip.

As the clock frequency increases, the probability that transient pulses will be captured as valid data in combinational logic increases linearly. Particularly in the case of deeply pipe-lined processors, with an increase in circuit speeds, the chances of a given transient pulse propagating through the combinatorial circuit and getting latched increases, because the combination paths will become shorter and there will be pipeline registers at every pipeline stage latching the data, hence increasing the probability of an SET getting latched. However, we can also speculate that the duration of transient pulses decreases. Nevertheless due to both their higher chances to propagate in high-speed circuits and their higher probability of getting captured by the next stage state holding elements, such as flip-flops and latches, SETs have been predicted to become a very critical issue in deep Ultra-Deep Sub-Micron circuits [57].

Figure 2.10: SER of an alpha processor for different technology nodes [9]

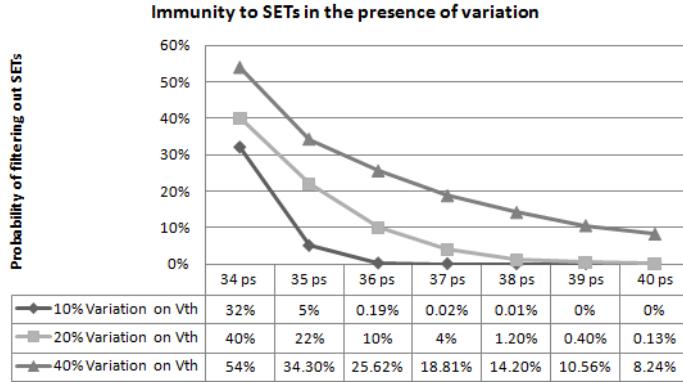

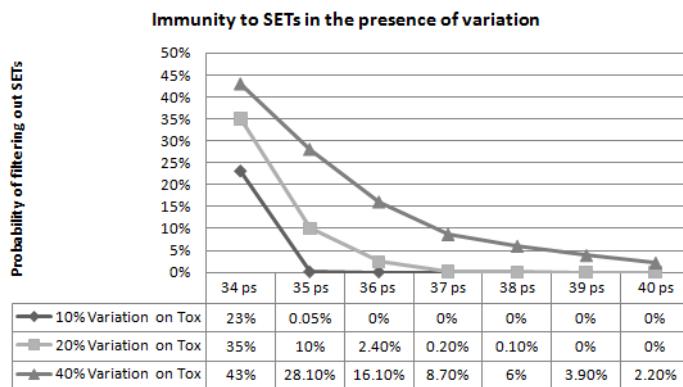

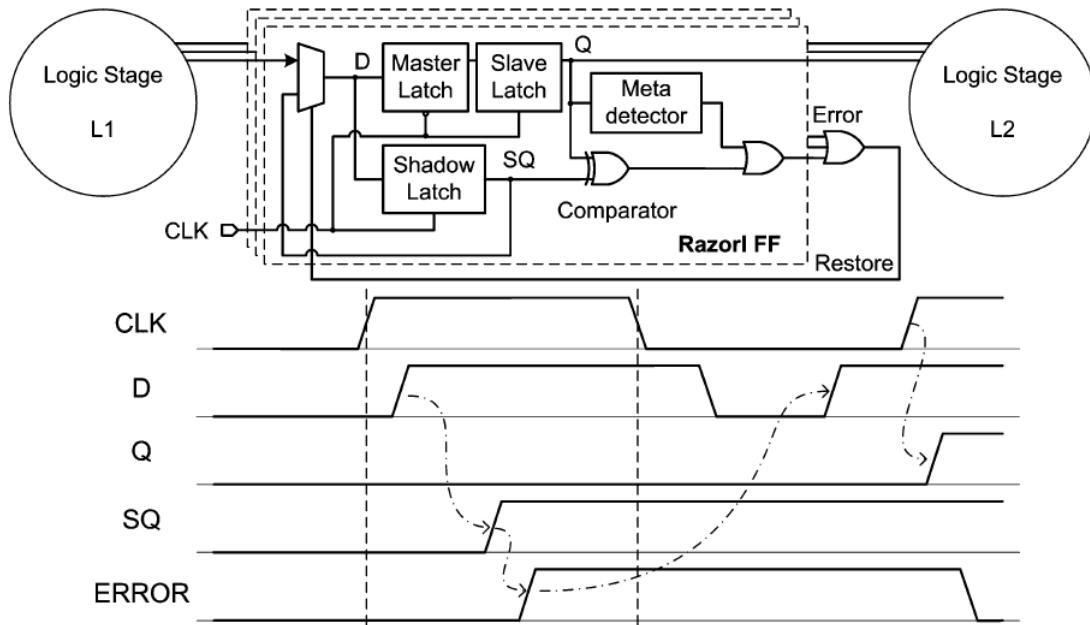

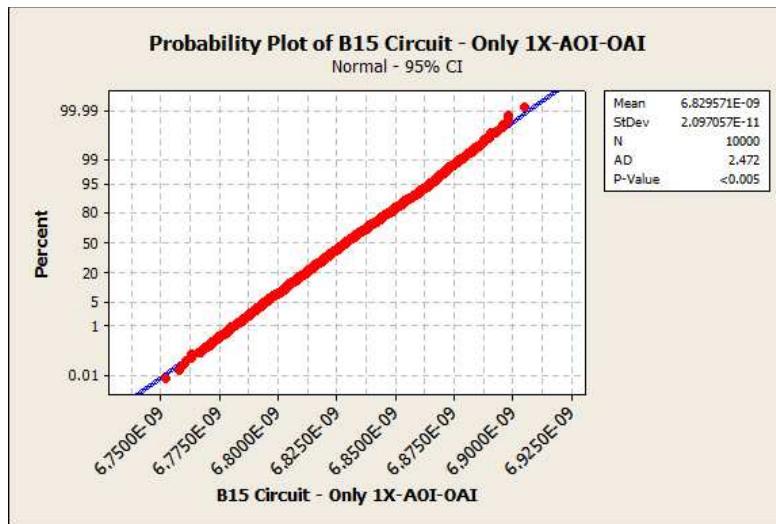

## 2.3 The Reliability Issues