# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

# UNIVERSITY OF SOUTHAMPTON

### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

# Efficiency Improvement in MEMS Thermoelectric Generators Employing Solar Concentration

by

Maria Theresa G. de Leon

Thesis for the degree of Doctor of Philosophy

$\mathrm{May}\ 2014$

#### UNIVERSITY OF SOUTHAMPTON

# **ABSTRACT**

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

#### Electronics and Computer Science

Thesis for the degree of Doctor of Philosophy

# EFFICIENCY IMPROVEMENT IN MEMS THERMOELECTRIC GENERATORS EMPLOYING SOLAR CONCENTRATION

Maria Theresa G. de Leon

Thermoelectric generators (TEGs) are devices that convert heat into electricity. The efficiency of thermoelectric generators depends on the temperature difference across the device, the average temperature of operation, and on the thermoelectric properties of the material. Most work on improving the TEG efficiency deals with improving the thermoelectric properties of the material. In this work, a method of improving the efficiency of the TEG by increasing the temperature difference is proposed. To accomplish this, a lens is used to concentrate solar radiation on the membrane of the TEG. By focusing solar radiation, the input heat flux increases; the temperature difference also increases; and the efficiency of the TEG improves as well.

Two implementations of the TEG are explored. The first one involves a simple TEG implementation using a glass substrate with p-type polysilicon and aluminum as the thermoelectric materials. Although a significant amount of heat is lost through the substrate, test results still demonstrate that a significant improvement in the device efficiency as the input heat flux is increased. The second implementation involves fabricating the TEG on a SOI substrate where the buried oxide layer is not etched and a thin portion of the handle layer is retained to provide additional structural stability. The thermoelectric materials for this TEG implementation are p-type silicon and aluminum. Although this implementation performs poorly than when both handle and buried oxide layers of the SOI under the membrane and thermoelements are etched, a SOI wafer with a thinner device layer is used to compensate for the losses.

The fabricated TEGs are characterized using a laser test set-up where the input power is varied up to 1 W and the spot size diameter is fixed at 1 mm. Measurement results on fabricated TEGs with 1 W input power exhibited a temperature difference of up to 226 °C, open-circuit voltage of 3 V, output power of 25  $\mu$ W, and about 10 times improvement in conversion efficiency. The fabricated TEGs are also tested using a solar simulator and three lenses of different diameters to emulate conditions where the device would be deployed as a solar TEG. Using a 50.8 mm diameter lens, the largest temperature difference measured is 18 °C, which gives an open-circuit voltage and output power of 803 mV and 431 nW, respectively.

# **Table of Contents**

| ABST   | TRACT      |                                                                |       |

|--------|------------|----------------------------------------------------------------|-------|

| List o | of tables  |                                                                | v     |

| List o | of figures | · · · · · · · · · · · · · · · · · · ·                          | ix    |

| DECI   | LARATI     | ON OF AUTHORSHIP                                               | xvi   |

| Ackn   | owledge    | ments                                                          | . xix |

| Defin  | itions ar  | nd Abbreviations                                               | .xx   |

| Chap   | ter 1:     | Introduction                                                   | 1     |

| 1.1    | Motiva     | tion                                                           | 1     |

| 1.2    | Objecti    | ves                                                            | 5     |

| 1.3    | Contrib    | outions                                                        | 4     |

| 1.4    | Thesis     | Organization                                                   | 4     |

| Chap   | ter 2:     | Thermoelectric Generators                                      | 7     |

| 2.1    | Thermo     | pelectricity                                                   | 7     |

|        | 2.1.1      | Seebeck Effect                                                 | 7     |

|        | 2.1.2      | Peltier Effect                                                 | 9     |

|        | 2.1.3      | Thomson Effect                                                 | 9     |

|        | 2.1.4      | Kelvin Relationships                                           | 10    |

|        | 2.1.5      | TEG Performance Metrics                                        | 10    |

| 2.2    | Types      | of Micro-TEGs                                                  | 13    |

| 2.3    | Lateral    | /lateral TEG Implementations                                   | 17    |

|        | 2.3.1      | Metal-based TEGs                                               | 17    |

|        | 2.3.2      | Silicon-based TEGs                                             | 19    |

|        | 2.3.3      | Polysilicon-based TEGs                                         | 20    |

|        | 2.3.4      | Bismuth Telluride-based TEGs                                   | 24    |

|        | 2.3.5      | Other semiconductor-based TEGs                                 | 26    |

|        | 2.3.6      | Summary and Analysis of Published Lateral/lateral TEGs $\dots$ | 27    |

| 2.4    | Summa      | ry                                                             | 33    |

| Chap   | ter 3:     | Solar Thermoelectric Generators                                | 35    |

| 3.1    | STEG       | Concept                                                        | 35    |

| 3.2  | STEG    | Implementations                                       | 36   |

|------|---------|-------------------------------------------------------|------|

|      | 3.2.1   | STEGs with Thermal Collectors                         | 37   |

|      | 3.2.2   | STEGs with Solar Concentrators                        | 39   |

|      | 3.2.3   | STEGs with both Solar and Thermal Concentration       | 44   |

| 3.3  | PV-TE   | E Hybrid Devices                                      | 47   |

| 3.4  | Summa   | ary                                                   | 50   |

| Chap | ter 4:  | STEG Simulation and Modelling                         | 51   |

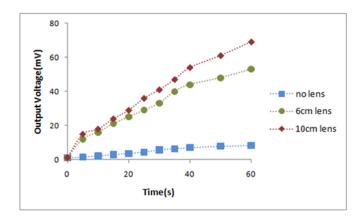

| 4.1  | Proof-o | of-Concept Experiments                                | 51   |

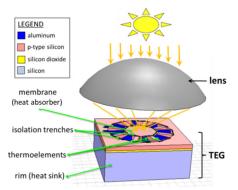

| 4.2  | Concep  | ptual Design of Solar TEG                             | 52   |

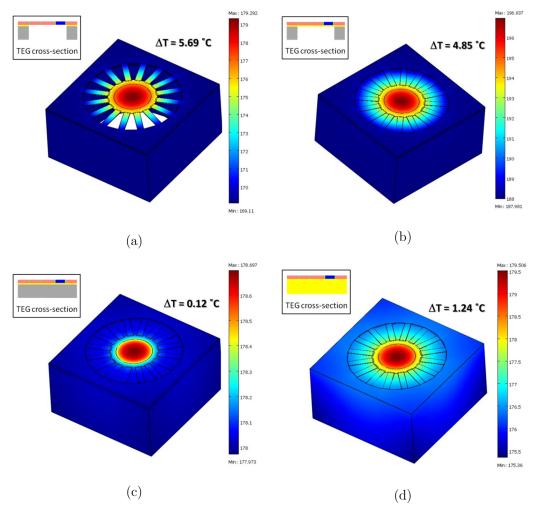

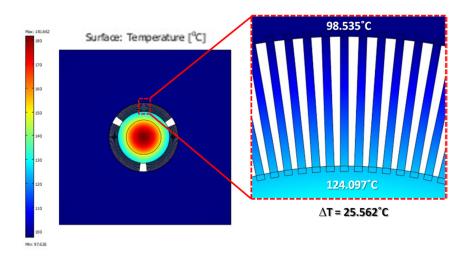

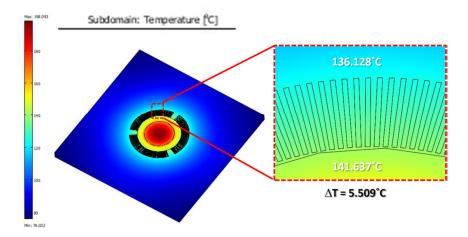

| 4.3  | Heat T  | Transfer Simulations                                  | 54   |

| 4.4  | STEG    | Thermal Model                                         | 58   |

| 4.5  | Simula  | tions vs. Thermal Model                               | 64   |

| 4.6  | Conclu  | isions                                                | 68   |

| Chap | ter 5:  | TEG Design and Proposed Fabrication                   | 69   |

| 5.1  | TEG I   | Design                                                | 69   |

| 5.2  | TEG I   | Layout Implementation                                 | 76   |

|      | 5.2.1   | TEG Layout                                            | 76   |

|      | 5.2.2   | Auxiliary Layouts                                     | 80   |

| 5.3  | Propos  | sed TEG Fabrication Process                           | 82   |

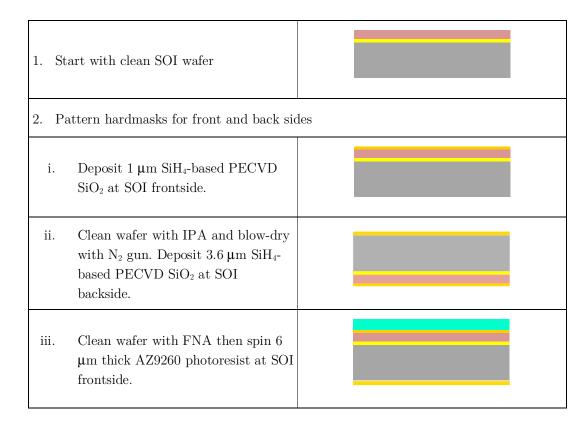

|      | 5.3.1   | Hardmask Patterning of Front and Back Sides           | 85   |

|      | 5.3.2   | Frontside RIE                                         | 88   |

|      | 5.3.3   | Refilling of Isolation Trenches                       | 88   |

|      | 5.3.4   | Aluminum Deposition and Lift-off                      | 97   |

|      | 5.3.5   | Backside DRIE                                         | 98   |

|      | 5.3.6   | HF Vapor Phase Etching                                | 99   |

|      | 5.3.7   | Problems Encountered                                  | 99   |

| 5.4  | Conclu  | nsions                                                | 101  |

| Chap | ter 6:  | TEG Implementation on a Glass Substrate               | 103  |

| 6.1  | Design  | and Modelling of TEGs Implemented on a Glass Substrat | e103 |

| 6.2  | TEG I   | Fabrication Process on a Glass Substrate              | 109  |

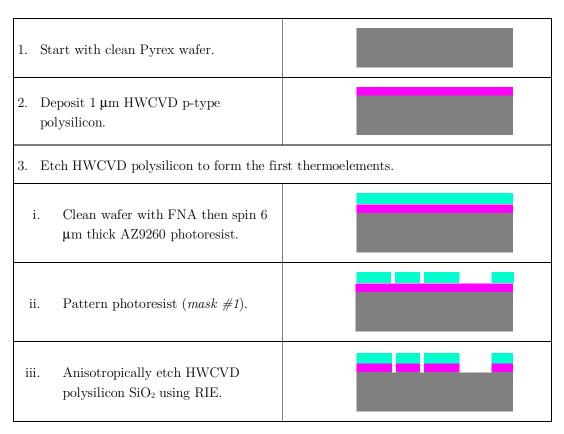

|      | 6.2.1   | HWCVD Polysilicon Deposition and Etching              | 110  |

|      | 6.2.2   | Aluminum Deposition and Lift-off                      | 113  |

|      | 6.2.3     | Wafer Dicing and Chip Wirebonding                    | . 113 |

|------|-----------|------------------------------------------------------|-------|

| 6.3  | HWCV      | D Polysilicon Characterization                       | . 115 |

|      | 6.3.1     | Electrical Resistivity                               | . 115 |

|      | 6.3.2     | Seebeck Coefficient                                  | . 116 |

|      | 6.3.3     | Thermal Conductivity                                 | . 118 |

|      | 6.3.4     | Contact Resistance                                   | . 119 |

| 6.4  | Measur    | ement Results                                        | . 120 |

|      | 6.4.1     | Laser Testing                                        | . 120 |

|      | 6.4.2     | Solar Simulator Testing                              | . 129 |

| 6.5  | Conclus   | sions                                                | . 135 |

| Chap | ter 7:    | TEG Implementation on a SOI Substrate                | 137   |

| 7.1  | Design    | and Modelling of TEGs Implemented on a SOI Substrate | . 137 |

| 7.2  | TEG F     | abrication Process on a SOI Substrate                | . 144 |

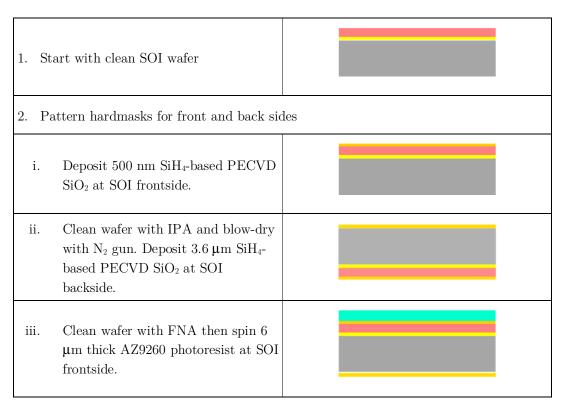

|      | 7.2.1     | Hardmask Patterning of Front and Back Sides          | . 145 |

|      | 7.2.2     | Frontside RIE                                        | . 146 |

|      | 7.2.3     | Aluminum Deposition and Lift-off                     | . 147 |

|      | 7.2.4     | Wafer-level Backside DRIE                            | . 147 |

|      | 7.2.5     | Wafer Dicing                                         | . 147 |

|      | 7.2.6     | Chip-level Backside DRIE and Wirebonding             | . 148 |

| 7.3  | SOI De    | vice Layer Characterization                          | . 149 |

|      | 7.3.1     | Electrical Resistivity                               | . 149 |

|      | 7.3.2     | Seebeck Coefficient                                  | . 149 |

|      | 7.3.3     | Thermal Conductivity                                 | . 150 |

|      | 7.3.4     | Contact Resistance                                   | . 150 |

| 7.4  | Measur    | ement Results                                        | . 151 |

|      | 7.4.1     | Laser Testing                                        | . 151 |

|      | 7.4.2     | Solar Simulator Testing                              | . 157 |

| 7.5  | TEG or    | n Glass vs. TEG on SOI                               | . 160 |

| 7.6  | Conclus   | sions                                                | . 163 |

| Chap | ter 8:    | Conclusions and Recommendations                      | 165   |

| Арр  | pendix A: | TEG Thermal Models in MATLAB                         | . 175 |

| Арр  | pendix B: | TEG Performance Parameters                           | . 189 |

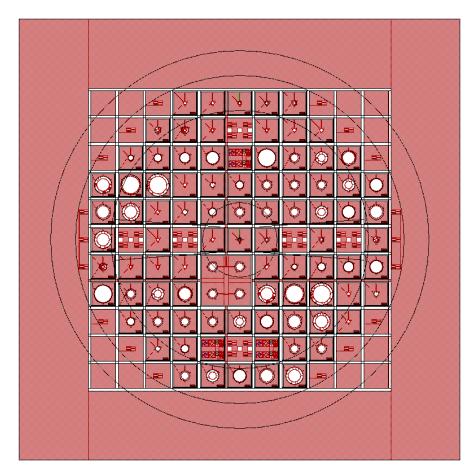

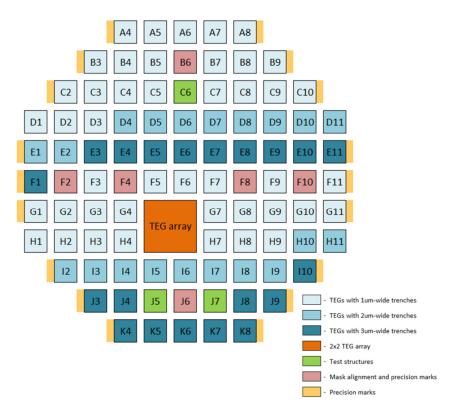

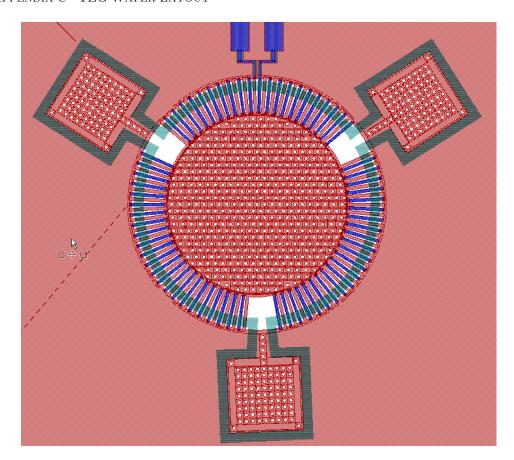

|    | Appendix C: TEG Wafer Layout                            | 195  |

|----|---------------------------------------------------------|------|

|    | Appendix D: Proposed TEG Fabrication Process            | 201  |

|    | Appendix E: TEG Fabrication on a Glass Substrate        | 205  |

|    | Appendix F: TEG Fabrication on a SOI Substrate          | 207  |

|    | Appendix G: Laser Measurements (TEG on Glass)           | 211  |

|    | Appendix H: Laser Measurements (TEG on SOI)             | 221  |

|    | Appendix I: Solar Simulator Measurements (TEG on Glass) | 227  |

|    | Appendix J: Solar Simulator Measurements (TEG on SOI)   | 229  |

| Bi | bliography                                              | .231 |

|    |                                                         |      |

# List of tables

| Table 2-1: Comparison of published lateral/lateral TEGs.    29                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4-1: Temperature difference and Carnot efficiency of $10\times10~\text{mm}^2$ TEG with length = $500~\mu\text{m}$ , width = $30~\mu\text{m}$ , membrane diameter = $3~\text{mm}$ , and $81$ thermocouples, lens transmittance of $90\%$ , membrane absorptance of $50\%$ , and varying concentration factors, with a 1 mm diameter solar radiation spot size. |

| Table 4-2: Electrical and thermal properties of p-type Si and Al.    58                                                                                                                                                                                                                                                                                             |

| <b>Table 4-3</b> : Performance parameters derived using the thermal model for various geometries. In all cases, $\gamma = 900$ , $\tau_{ens} = 90\%$ , $\alpha_{mem} = 50\%$ , $h_{conv} = 25 \text{ W/m}^2\text{K}$ , $\epsilon = 0.6$ , and solar radiation is concentrated on the TEG membrane with $d_{spot} = 1 \text{mm}$                                     |

| Table 5-1: Dimensions of TEGs proposed for fabrication grouped according to width of isolation trenches.       75                                                                                                                                                                                                                                                   |

| Table 5-2: Standard and modified recipes for TEOS-based SiO <sub>2</sub> deposition                                                                                                                                                                                                                                                                                 |

| <b>Table 5-3</b> : Comparison between deposition and etch parameters for stoichiometric $Si_3N_4$ and silicon-rich SiN films. $N_2$ gas flow rate is 500 sccm, table temperature is 350 °C, and chamber pressure is 750 mTorr.                                                                                                                                      |

| Table 5-4: Backside DRIE settings                                                                                                                                                                                                                                                                                                                                   |

| <b>Table 6-1</b> : Boron-doped HWCVD polysilicon experiments. In all cases, filament temperature is 2100 °C, substrate temperature is 440 °C, and chamber pressure is at 0.024 mB. Resistivity is calculated as the product of the film thickness and the sheet resistance measured with a four-point probe system.                                                 |

| Table 6-2: Results of measurements made on HWCVD polysilicon Van der Pauw         structure fabricated on a Pyrex substrate.       116                                                                                                                                                                                                                              |

| Table 6-3: Results of measurements made on polysilicon planar structure fabricated on a Pyrex substrate.       117                                                                                                                                                                                                                                                  |

| Table 6-4: Results of measurements made on polysilicon cantilever structure fabricated         on a Pyrex substrate.       119                                                                                                                                                                                                                                      |

| Table 6-5: Parameters used in thermal model of TEG on glass substrate to emulate         conditions in laser test set-up.       126                                                                                                                                                                                                                                 |

| Table 6-6: Efficiency factor of TEGs fabricated on a glass substrate. The TEG with the best efficiency factor is highlighted in <b>bold</b>                                                                                                                                                                                                                         |

| <b>Table 6-7</b> : Parameters of plano-convex lenses used in the test set-up. <i>CA</i> refers to the clear aperture as dictated by the lens mount used                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 6-8</b> : Minimum and actual spot sizes for each of the three lenses used. The distance $d_{lens}$ refers to the distance of the actual spot to the flat side of the lens131                                                                                                                                                                  |

| Table 6-9: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying thermoelement lengths ( $w = 15 \mu \text{m}$ and $d_{mem} = 3 \text{ mm}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements  |

| Table 6-10: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying thermoelement widths ( $l = 500 \mu\text{m}$ and $d_{mem} = 3 \text{mm}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements   |

| Table 6-11: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying membrane diameters ( $l=500~\mu\mathrm{m}$ and $w=15~\mu\mathrm{m}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements        |

| Table 7-1: Settings for chip-level backside DRIE.    148                                                                                                                                                                                                                                                                                               |

| Table 7-2: Results of measurements made on silicon Van der Pauw structure fabricated         on a SOI substrate.       149                                                                                                                                                                                                                             |

| Table 7-3: Results of measurements made on a silicon planar structure fabricated on a         SOI substrate.       150                                                                                                                                                                                                                                 |

| Table 7-4: Results of measurements made on a silicon cantilever structure fabricated on a SOI substrate.       150                                                                                                                                                                                                                                     |

| Table 7-5: List of TEGs successfully fabricated on a SOI substrate.         151                                                                                                                                                                                                                                                                        |

| Table 7-6: Parameters used in thermal model of TEG on a SOI substrate to emulate         conditions in laser test set-up.       153                                                                                                                                                                                                                    |

| Table 7-7: Efficiency factor of TEGs fabricated on a SOI substrate. The TEG with the         best efficiency factor is highlighted in bold.       157                                                                                                                                                                                                  |

| Table 7-8: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying thermoelement lengths ( $w = 15  \mu \text{m}$ and $d_{mem} = 3  \text{mm}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements |

| Table 7-9: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying thermoelement widths ( $l = 500  \mu \text{m}$ and $d_{mem} = 3  \text{mm}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 7-10: Open-circuit voltage, series resistance, temperature difference, and matched output power of TEGs implemented on a glass substrate with varying membrane diameters ( $l=500~\mu \mathrm{m}$ and $w=15~\mu \mathrm{m}$ ). For each of the three types of plano-convex lenses used, data is taken from the average of five measurements      |

| Table 7-11: Comparison between the electrical and thermoelectric properties of polysilicon and silicon materials used in the TEG on glass and TEG on SOI implementations, respectively                                                                                                                                                                 |

| <b>Table 7-12:</b> Comparison between efficiency factors of TEGs fabricated on glass and TEGs fabricated on SOI. The TEG with the best efficiency factor is highlighted in bold.162                                                                                                                                                                    |

| Table 7-13: Comparison between solar simulator measurements of both TEG on glass and TEG on SOI with $l=1000~\mu\text{m},~w=15~\mu\text{m},~d_{mem}=3~\text{mm},$ and $N=114~\text{using a}$ LA1050 ( $D=50.8~\text{mm}$ ) plano-convex lens.                                                                                                          |

| <b>Table 8-1</b> : Comparison between parameters of both TEG on glass and TEG on SOI with $l=500~\mu\text{m},~w=15~\mu\text{m},~d_{mem}=1~\text{mm},$ and $N=31$ for an input power of 1 W168                                                                                                                                                          |

| Table 8-2: TEGs with the highest output voltage based on solar simulator measurements for both TEG on glass and TEG on SOI implementations using a LA1050 ( $D=50.8~\mathrm{mm}$ ) plano-convex lens.                                                                                                                                                  |

| Table 8-3: Comparison of TEGs examined in this work with selected published         lateral/lateral TEGs.       170                                                                                                                                                                                                                                    |

# List of figures

| Figure 2-1: Diagram of a basic thermocouple                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

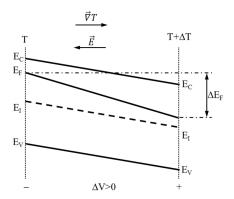

| Figure 2-2: Energy band diagram showing the change in Fermi energy of an n-type semiconductor when a temperature difference is applied across it                                                               |

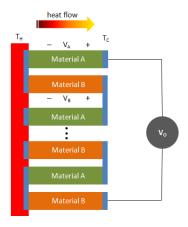

| Figure 2-3: A basic thermoelectric generator                                                                                                                                                                   |

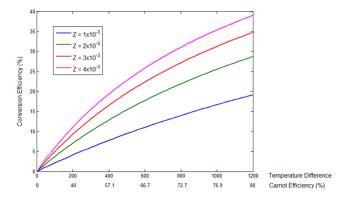

| Figure 2-4: Conversion efficiency as a function of temperature and thermocouple material figure of merit $Z$ . Cold junction temperature is $300K$                                                             |

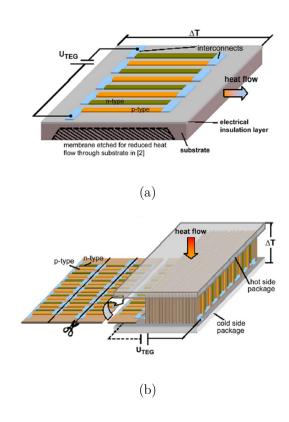

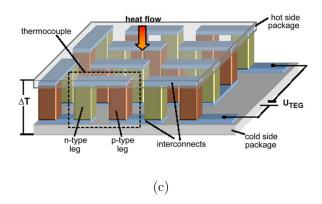

| Figure 2-5: Three types of micro-TEGs. (a) Lateral/Lateral TEG, (b) Vertical/Lateral TEG, and (c) Vertical/Vertical TEG. (Glatz et al. 2009)                                                                   |

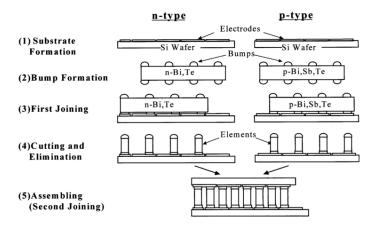

| Figure 2-6: Fabrication process of vertical/vertical TEG formed using two substrates.  (Kishi et al. 1999)                                                                                                     |

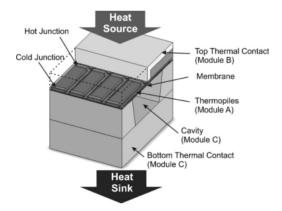

| Figure 2-7: Illustration of TEG consisting of three modules to optimize the heat flow path. (Huesgen, Woias, and Kockmann 2008)                                                                                |

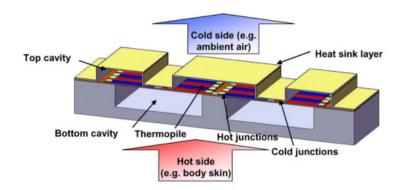

| Figure 2-8: Diagram of TEG with top and bottom vacuum cavities to optimize heat flux path. (Xie et al., 2010)                                                                                                  |

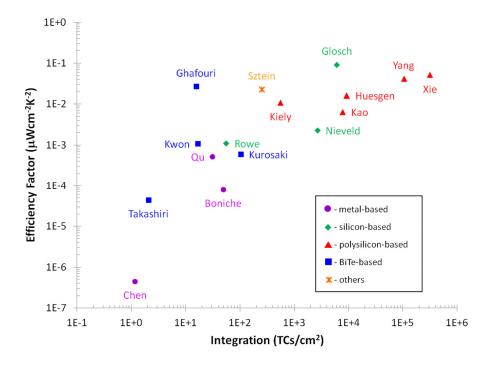

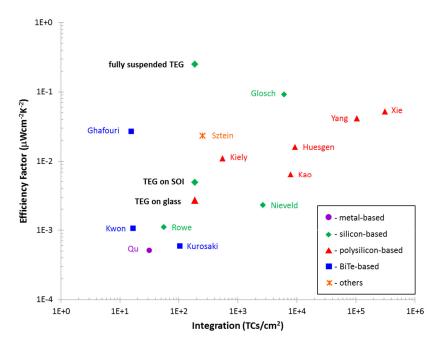

| Figure 2-9: Comparison of efficiency factor vs. level of integration of published lateral/lateral μTEGs grouped according to thermoelectric material used                                                      |

| Figure 2-10: A lateral/lateral TEG using a SOI wafer. (Egbert, Harvey, and Otis 2007)33                                                                                                                        |

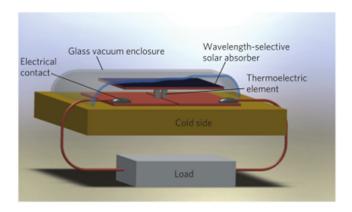

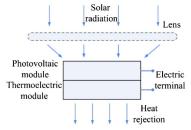

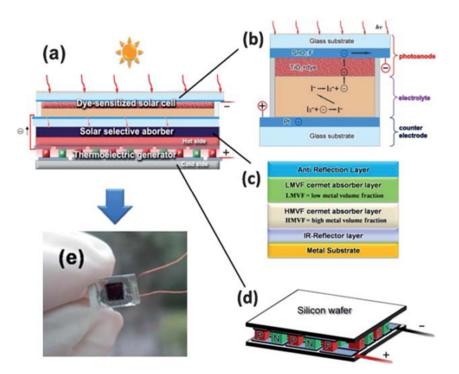

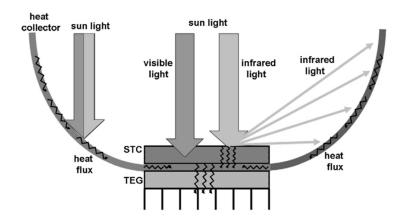

| Figure 3-1: (a) STEG implemented with a TEG and thermal collector. (b) STEG implemented with a TEG and a solar concentrator. (c) STEG implemented with a TEG and both solar concentrator and thermal collector |

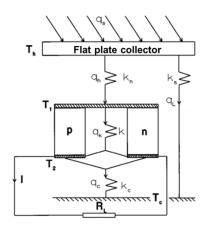

| Figure 3-2: Schematic diagram used to develop a thermodynamic model of a solar thermoelectric generator implemented with a TEG and a flat plate thermal collector.  (Chen 1996)                                |

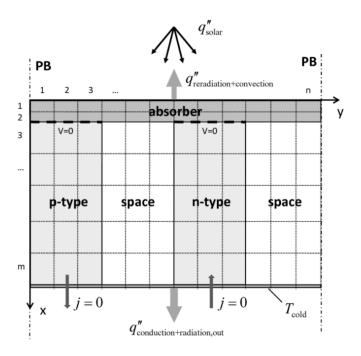

| Figure 3-3: Cross section of heat transfer model divided into m × n cells, with indicated boundary conditions. (Suter et al. 2010)                                                                             |

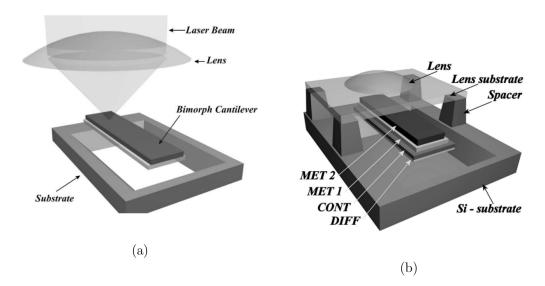

| Figure 3-4: (a) Proposed structure of the photo-thermo-mechanical microactuator. (b) Illustration showing the use of spacers to mount lens above the microactuator. (Baglio et al. 2002b)                      |

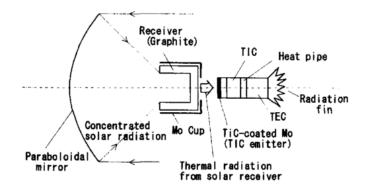

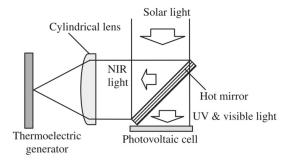

| Figure 3-5: Schematic diagram of solar-powered conversion system developed in Tohuku University, Japan, (Naito et al. 1996)                                                                                    |

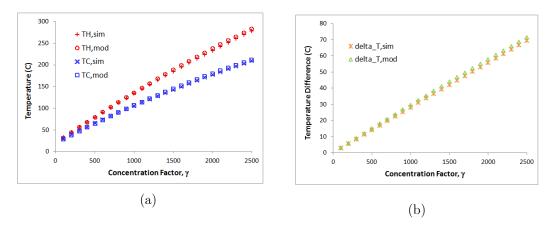

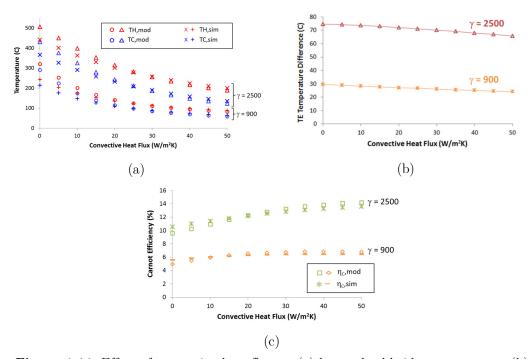

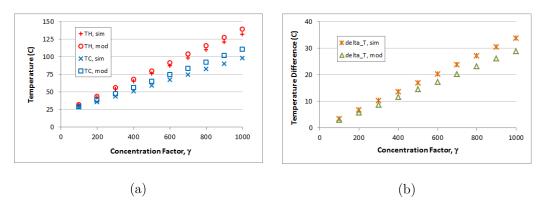

| varying solar concentration ratio for (a) hot $(T_H)$ and cold $(T_C)$ side temperatures and (b) temperature difference $T$ . TEG has the following parameters: $l = 500 \ \mu\text{m}$ , $w = 30 \ \mu\text{m}$ , $d_{mem} = 3 \ \text{mm}$ , $N = 81$ , $\varepsilon = 0.6$ , $h_{conv} = 25 \ \text{W/m}^2\text{K}$ , $\tau_{lens} = 0.9$ , $\alpha_{mem} = 0.5$ , and $d_{spot} = 1 \ \text{mm}$ .  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

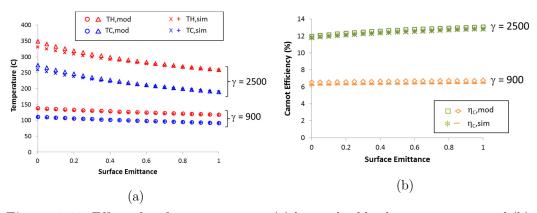

| Figure 4-10: Effect of surface emittance on (a) hot and cold side temperatures, and (b) Carnot efficiency at different concentration ratios. TEG parameters: $l = 500 \ \mu \text{m}$ , $w = 30 \ \mu \text{m}$ , $d_{mem} = 3 \ \text{mm}$ , $N = 81$ , $h_{conv} = 25 \ \text{W/m}^2 \text{K}$ , $\tau_{lens} = 0.9$ , $\alpha_{mem} = 0.5$ , and $d_{spot} = 1 \ \text{mm}$ . 65                     |

| Figure 4-11: Effect of convective heat flux on (a) hot and cold side temperatures, (b) temperature difference, and (c) Carnot efficiency at different concentration ratios. TEG parameters: $l = 500 \ \mu\text{m}$ , $w = 30 \ \mu\text{m}$ , $d_{mem} = 3 \ \text{mm}$ , $N = 81$ , $\varepsilon = 0.6$ , $\tau_{lens} = 0.9$ , $\alpha_{mem} = 0.5$ , and $d_{spot} = 1 \ \text{mm}$                 |

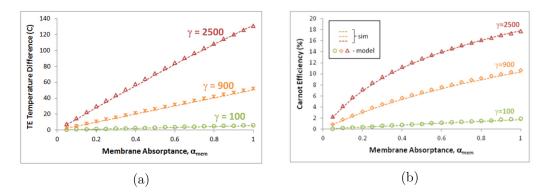

| <b>Figure 4-12</b> : Effect of membrane absorptance on (a) TEG temperature difference and (b) Carnot efficiency and for different concentration ratios. TEG parameters: $l = 500 \ \mu \text{m}$ , $w = 30 \ \mu \text{m}$ , $d_{mem} = 3 \ \text{mm}$ , $N = 81$ , $h_{conv} = 25 \ \text{W/m}^2 \text{K}$ , $\boldsymbol{\varepsilon} = 0.6$ , $\tau_{lens} = 0.9$ , and $d_{spot} = 1 \ \text{mm}$ . |

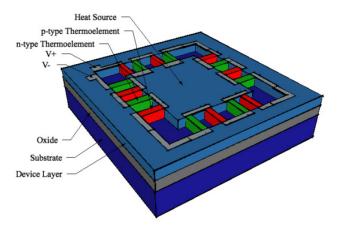

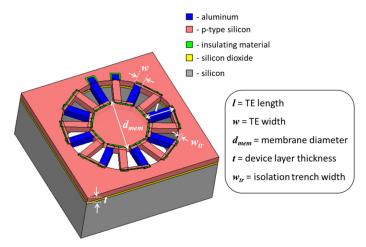

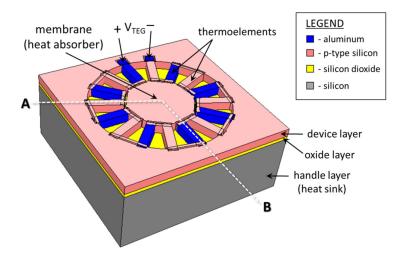

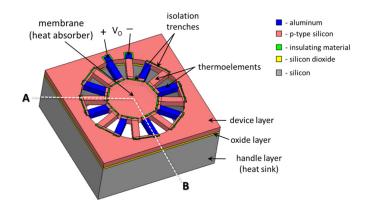

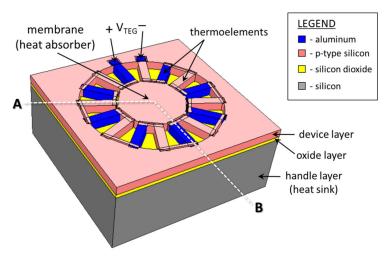

| Figure 5-1: TEG design with the SOI device layer as one of the thermoelements. Design parameters based on the geometry of the device are also indicated                                                                                                                                                                                                                                                 |

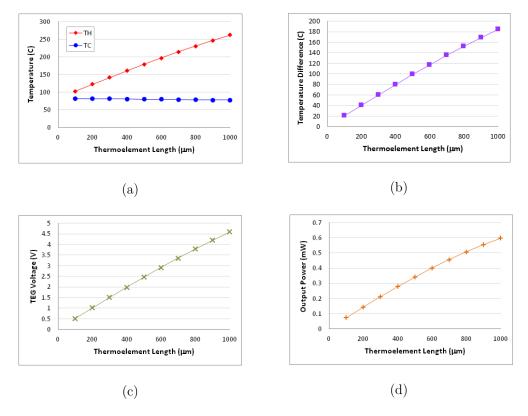

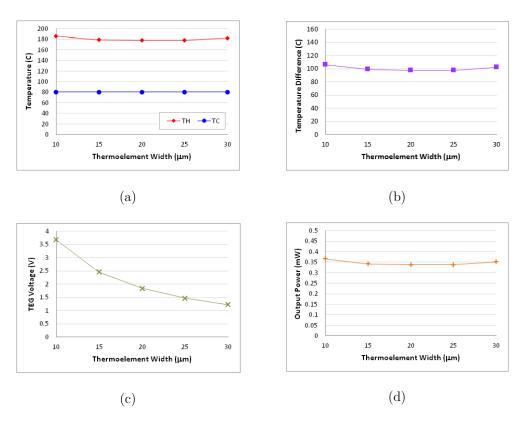

| Figure 5-2: (a) Hot and cold side temperatures, (b) Temperature difference, (c) open circuit TEG voltage, and (d) output power to a matched load for different thermoelement lengths ( $w=15~\mu m,~d_{mem}=1~mm,$ and $N=66$ ). Parameters derived from the thermal model with $\gamma=1000,~h_{conv}=50~\mathrm{W/m^2K},~\alpha_{mem}=0.5,$ and $\tau_{lens}=171$                                     |

| Figure 5-3: (a) Hot and cold side temperatures, (b) Temperature difference, (c) open circuit TEG voltage, and (d) output power to a matched load for different thermoelement lengths ( $l = 500 \ \mu m$ and $d_{mem} = 1 \ mm$ ). Parameters derived from the thermal model with $\gamma = 1000$ , $h_{conv} = 50 \ W/m^2 K$ , $\alpha_{mem} = 0.5$ , and $\tau_{lens} = 1$ 72                         |

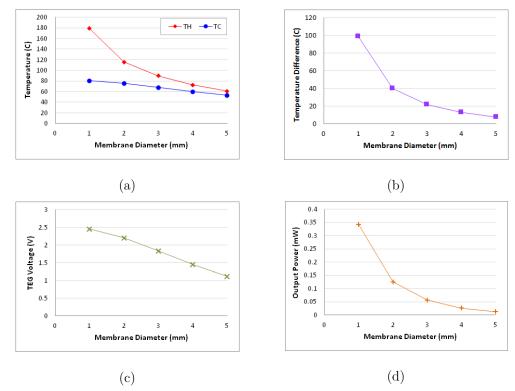

| <b>Figure 5-4</b> : (a) Hot and cold side temperatures, (b) Temperature difference, (c) open circuit TEG voltage, and (d) output power to a matched load for different thermoelement lengths ( $l=500~\mu \text{m}$ and $w=15~\mu \text{m}$ ). Parameters derived from the thermal model with $\gamma=1000,~h_{conv}=50~\text{W/m}^2\text{K},~\alpha_{mem}=0.5,~\text{and}~\tau_{lens}=173$             |

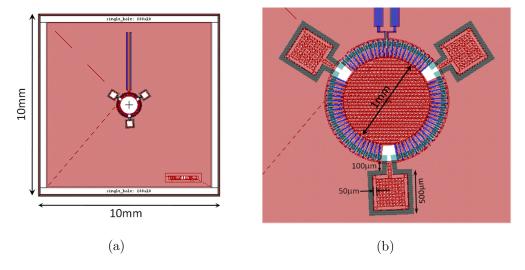

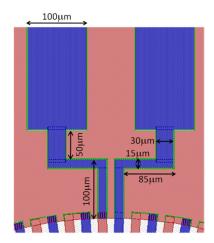

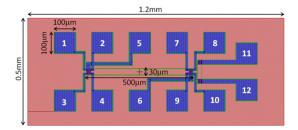

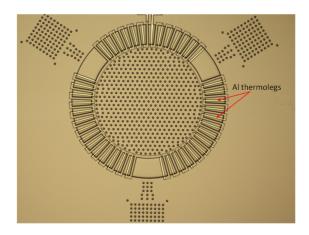

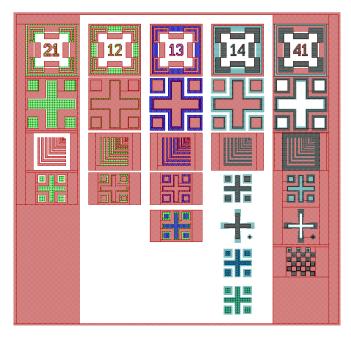

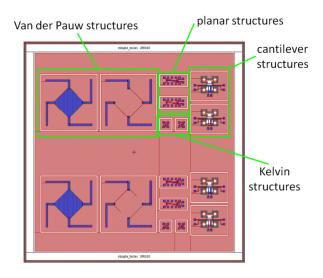

| <b>Figure 5-5</b> : (a) whole TEG layout and (b) zoomed-in layout of TEG with $l=200~\mu\text{m},~w=15~\mu\text{m},$ and $d_{mem}=1~\text{mm}.$                                                                                                                                                                                                                                                         |

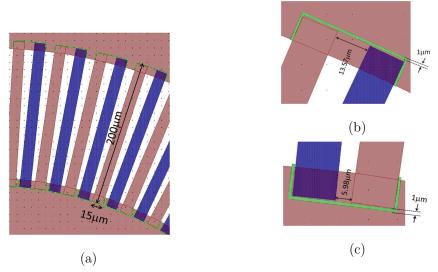

| Figure 5-6: (a) TEG legs, (b) outer trench, and (c) inner trench                                                                                                                                                                                                                                                                                                                                        |

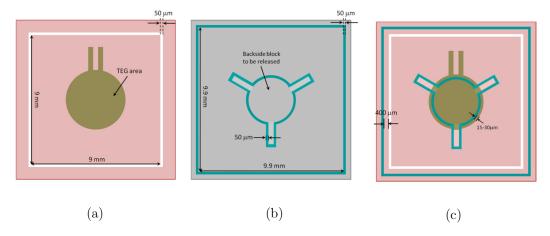

| Figure 5-7: (a) Frontside showing TEG device area and 50 $\mu$ m wide front trenches, (b) Backside showing block to be released and 50 $\mu$ m wide back trenches, and (c) Front and back trenches 400 $\mu$ m apart                                                                                                                                                                                    |

| Figure 5-8: Close-up view of pads and wires. Trench surrounding pads and wires are 1 $\mu$ m wide.                                                                                                      |

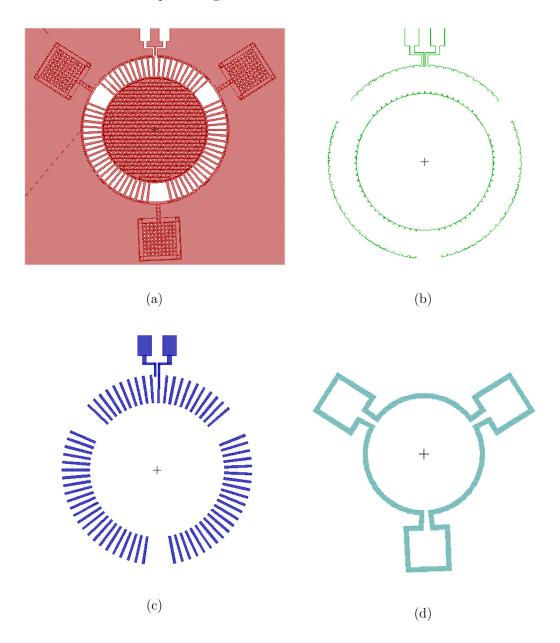

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-9: (a) Mask 1 for frontside patterning of membrane and silicon thermoelements, (b) Mask 2 for isolation trenches, (c) Mask 3 for aluminum thermoelements, and (d) Mask 4 for backside trenches |

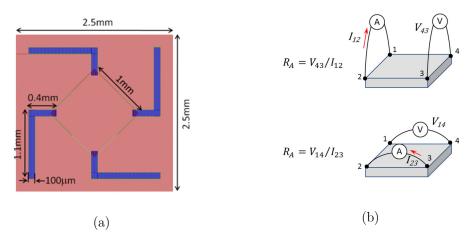

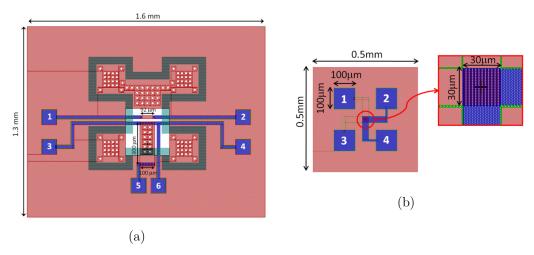

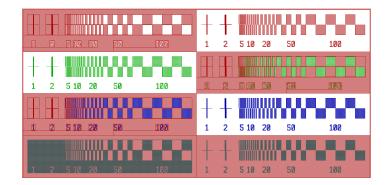

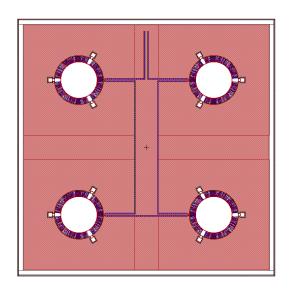

| Figure 5-10: (a) Van der Pauw structure to measure electrical resistivity and (b) Van der Pauw schematic                                                                                                |

| Figure 5-11: Planar structure to measure Seebeck coefficient                                                                                                                                            |

| Figure 5-12: (a) Cantilever structure to measure thermal conductivity and (b) Kelvin structure to measure contact resistance                                                                            |

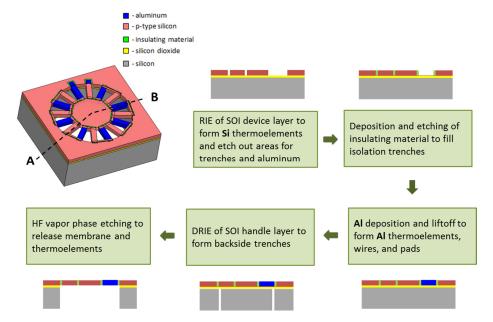

| Figure 5-13: Proposed TEG fabrication process using a SOI wafer with a doped device layer. Cross-sectional view is along AB                                                                             |

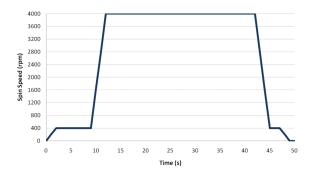

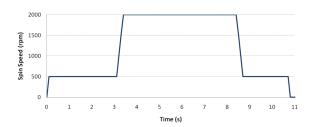

| Figure 5-14: Spin settings for a target 6 $\mu m$ thick AZ9260 photoresist86                                                                                                                            |

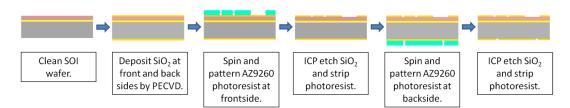

| Figure 5-15: Process of patterning hardmasks for both front and back sides of the SOI wafer.                                                                                                            |

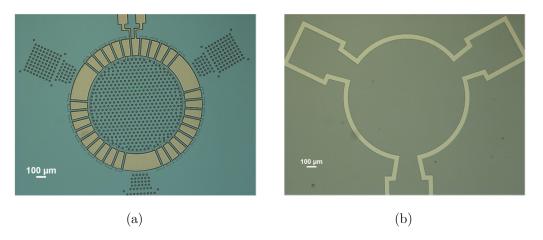

| Figure 5-16: Optical micrographs of (a) frontside and (b) backside hardmasks87                                                                                                                          |

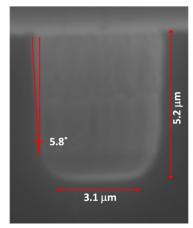

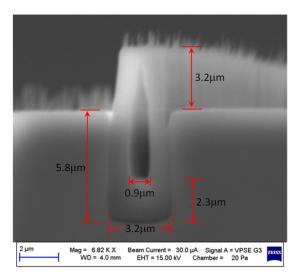

| Figure 5-17: SEM image of a 3 $\mu$ m wide isolation trench after 1100 seconds of frontside RIE.                                                                                                        |

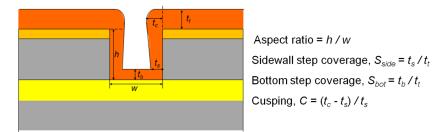

| Figure 5-18: Parameters that characterize step coverage and conformality of deposited film.                                                                                                             |

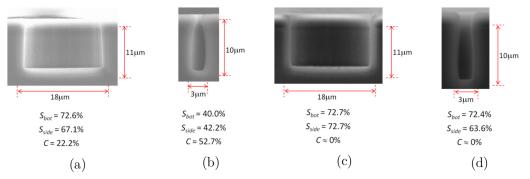

| <b>Figure 5-19</b> : Step coverage of SiH <sub>4</sub> -based SiO <sub>2</sub> for (a) wide and (b) narrow trenches; and TEOS-based SiO <sub>2</sub> for (c) wide and (d) narrow trenches               |

| Figure 5-20: Cracks in 3 $\mu$ m thick TEOS-based deposited SiO <sub>2</sub> film using standard PECVD recipe90                                                                                         |

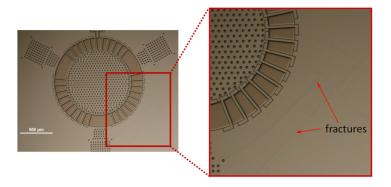

| Figure 5-21: Fractures in 4 $\mu m$ thick TEOS-based SiO <sub>2</sub> deposited using modified recipe.91                                                                                                |

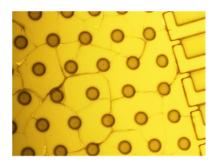

| Figure 5-22: Trench filled with TEOS-based SiO <sub>2</sub> using dual-frequency deposition and then anisotropically etched using an ICP etcher                                                         |

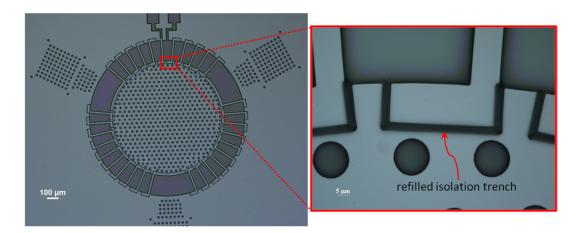

| <b>Figure 5-23</b> : Optical micrograph of TEG on SOI wafer after refilling isolation trenches with TEOS-based SiO <sub>2</sub> capped with silicon-rich silicon nitride                                |

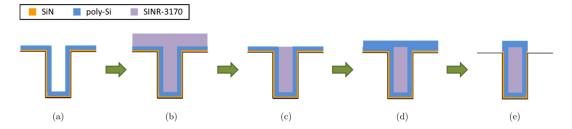

| Figure 5-24: Second method of refilling isolation trenches: (a) Line trench with HWCVD silicon nitride and intrinsic polysilicon. (b) Spin coat with SINR-3570. (c) Dry                                 |

| etch SINR-3570. (d) Cap trench with HWCVD intrinsic polysilicon. (e) Dry etch intrinsic polysilicon and silicon nitride that are not part of isolation trenches95                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

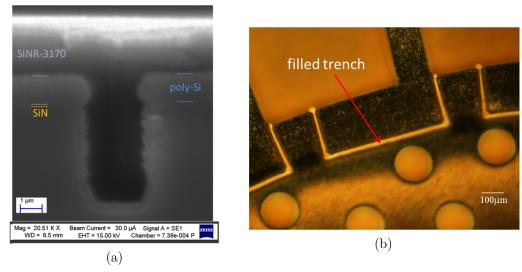

| Figure 5-25: (a) SEM image of 3 $\mu$ m wide trench after etching 4 m of the SINR-3570 film. (b) Optical micrograph of trench filled with SINR-3570 after planarization96                                                                                                                                                                                                                                                                                                                        |

| Figure 5-26: Spin settings for a target 14 $\mu m$ thick AZnlof2070 photoresist97                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 5-27: Optical micrograph of TEG after aluminum deposition and lift-off98                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 5-28: SEM image of trench after 70 minutes of backside DRIE99                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 5-29: Images illustrating problems encountered after HFVPE: (a) broken thermoelements, (b) membrane separating from thermoelements, and (c) membrane and thermoelements separates from device rim                                                                                                                                                                                                                                                                                         |

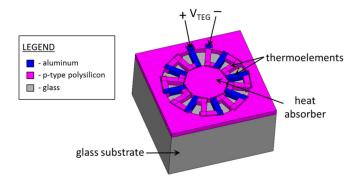

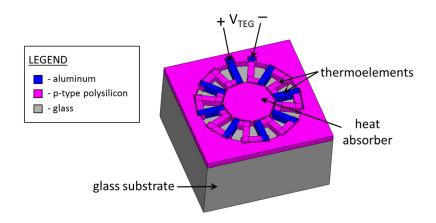

| Figure 6-1: TEG implementation on a glass substrate with p-type polysilicon and aluminum as thermoelement materials                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 6-2: Thermal equivalent model of TEG implemented on a glass substrate. $T_{SUB}$ is the temperature at the bottom of the substrate, $K_{SUB}$ is the thermal conductance of the portion of the substrate directly below the heated area of the device, and $Q_{CONV,SUB}$ represents heat lost due to convection at the bottom of the substrate                                                                                                                                           |

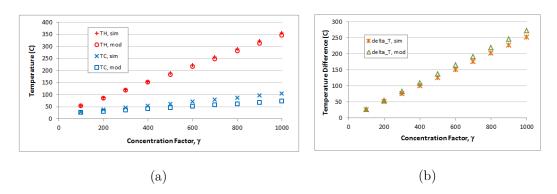

| Figure 6-3: (a) Hot $(T_H)$ and cold $(T_C)$ side temperatures and (b) temperature difference $T$ between simulations $(sim)$ and thermal model $(mod)$ of TEG on a glass substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ . |

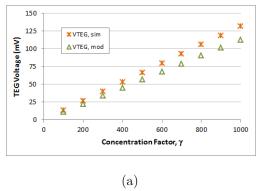

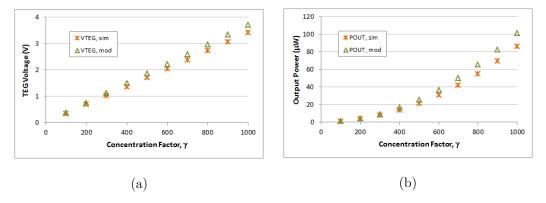

| Figure 6-4: (a) Open-circuit TEG voltage and (b) matched output power between simulations ( $sim$ ) and thermal model ( $mod$ ) of TEG on a glass substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ .108                      |

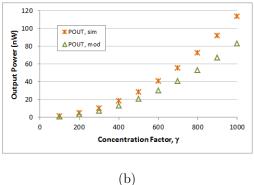

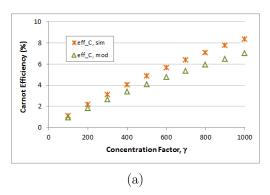

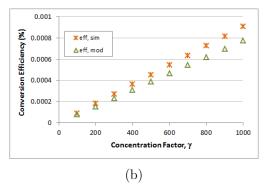

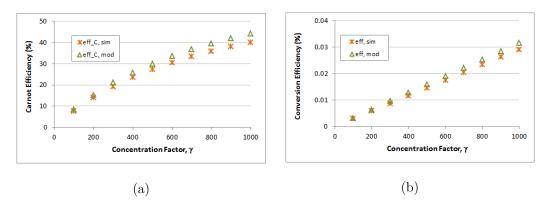

| Figure 6-5: (a) Carnot efficiency and (b) conversion efficiency between simulations (sim) and thermal model (mod) of TEG on a glass substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ 109                                     |

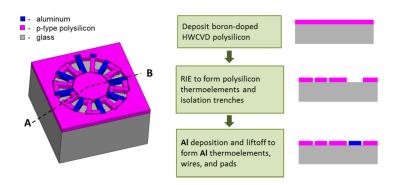

| <b>Figure 6-6</b> : TEG fabrication process using a Pyrex wafer with HWCVD p-type polysilicon and aluminum as thermoelement materials. Cross-sectional view is along AB.110                                                                                                                                                                                                                                                                                                                      |

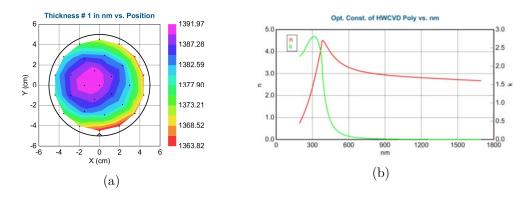

| Figure 6-7: (a) Thickness representation and (b) optical constants based on ellipsometry results of p -type HWCVD polysilicon deposited on a Pyrex substrate for 2.5 hours 112                                                                                                                                                                                                                                                                                                                   |

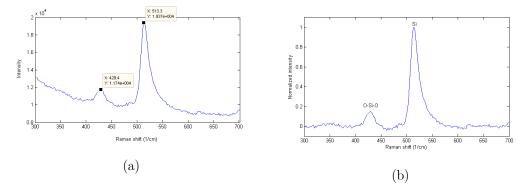

| Figure 6-8: (a) Raw and (b) baseline-corrected Raman spectra of boron-doped HWCVD polysilicon deposited on a Pyrex substrate                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

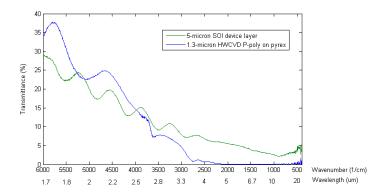

| Figure 6-9: FTIR spectra of SOI device layer and HWCVD p-type polysilicon113                                                                                                                                                                                                                                                                                                                  |

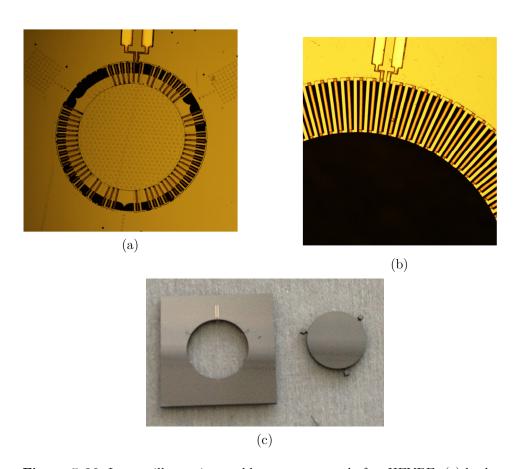

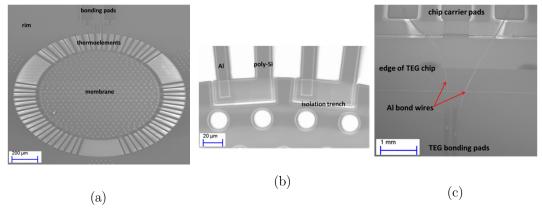

| Figure 6-10: (a) TEG with thermolength of 200 $\mu$ m, thermowidth of 15 $\mu$ m and membrane diameter of 1 mm with 31 thermocouples. (b) Closer view of connection between thermoelements. (c) Bonding wires connecting the TEG to the chip carrier114                                                                                                                                       |

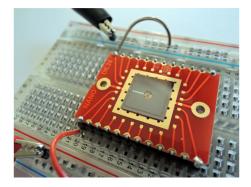

| Figure 6-11: TEG with thermolength of 500 $\mu$ m, thermowidth of 15 $\mu$ m, membrane diameter of 1 mm, and 34 thermocouples on a prototyping board                                                                                                                                                                                                                                          |

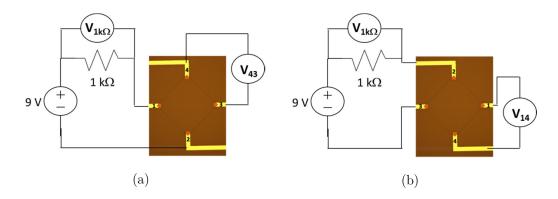

| Figure 6-12: Two circuits used to derive the two characteristic resistances $R_A$ and $R_B$ of a Van der Pauw structure                                                                                                                                                                                                                                                                       |

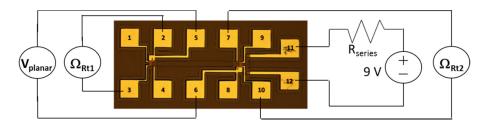

| Figure 6-13: Circuit for determining Seebeck coefficient of HWCVD polysilicon utilizing planar structure                                                                                                                                                                                                                                                                                      |

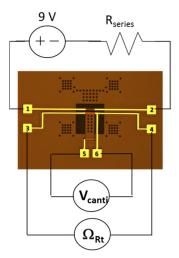

| Figure 6-14: Circuit for determining thermal conductivity of HWCVD polysilicon utilizing cantilever structure                                                                                                                                                                                                                                                                                 |

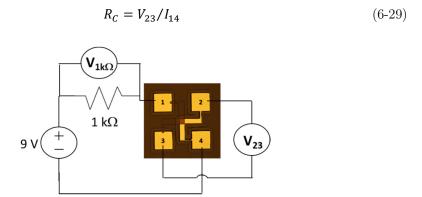

| Figure 6-15: Circuit for determining contact resistance utilizing Kelvin structure 119                                                                                                                                                                                                                                                                                                        |

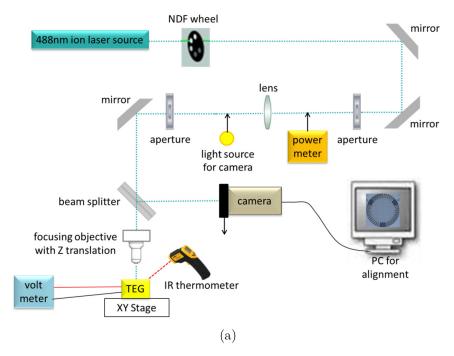

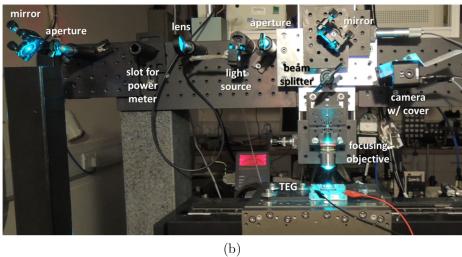

| Figure 6-16: (a) Illustration and (b) partial photograph of laser testing set-up with a 488 nm ion laser. Input power is varied using the NDF wheel. Alignment is done by inserting the power meter and light source as indicated, and removing the camera cover. The power meter is inserted to the set-up each time that the NDF wheel is adjusted to record the change in input power.     |

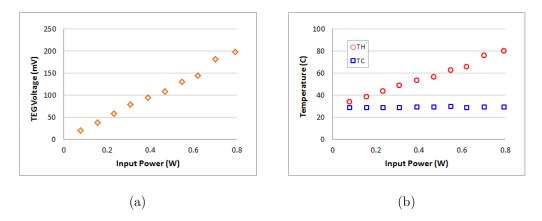

| <b>Figure 6-17</b> : Measured (a) open-circuit TEG voltage and (b) hot and cold side temperatures versus laser input power of a TEG implemented on a glass substrate with these dimensions: $l = 500 \ \mu\text{m}$ , $w = 15 \ \mu\text{m}$ , $d_{mem} = 1 \ \text{mm}$ , and $N = 34$                                                                                                       |

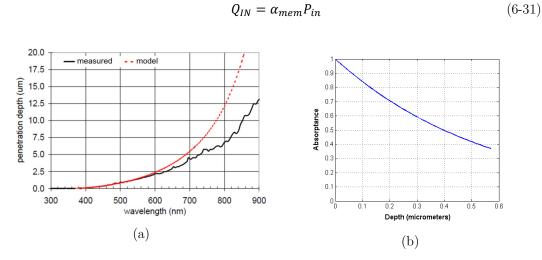

| Figure 6-18: (a) Optical penetration depth of silicon (Lange 2000). (b) Absorptance of light with a wavelength of 488 nm on silicon.                                                                                                                                                                                                                                                          |

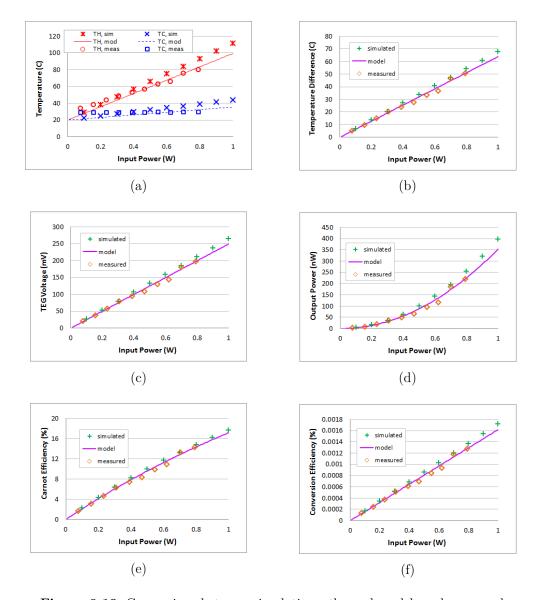

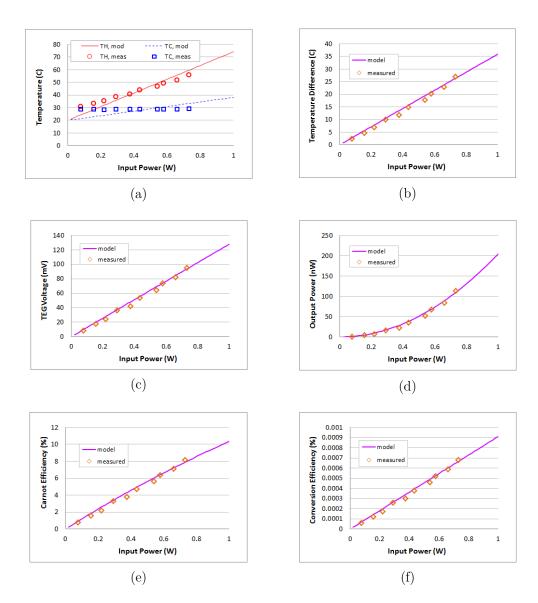

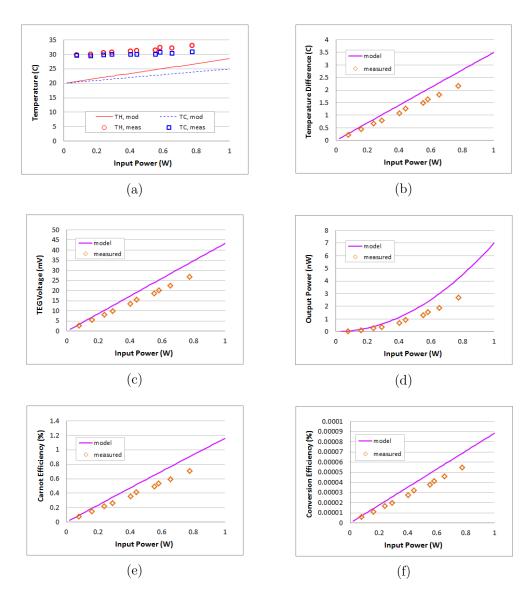

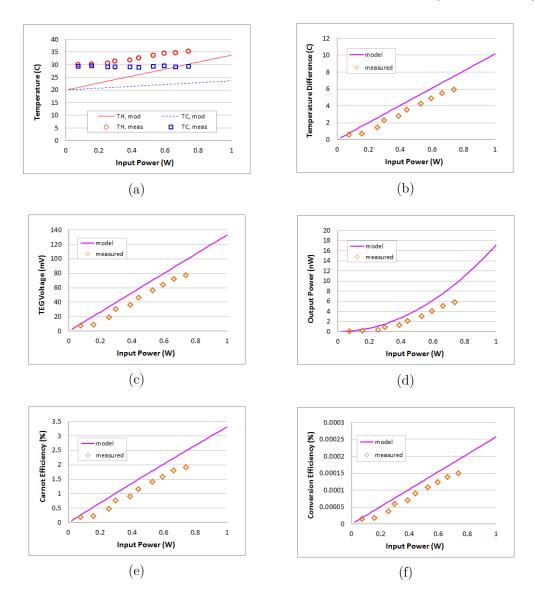

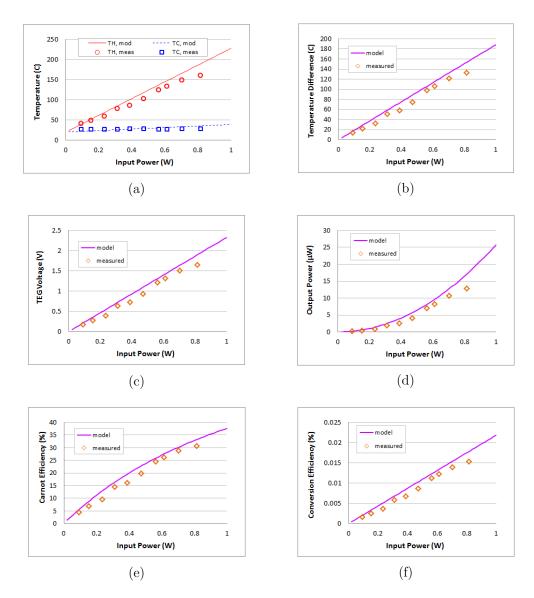

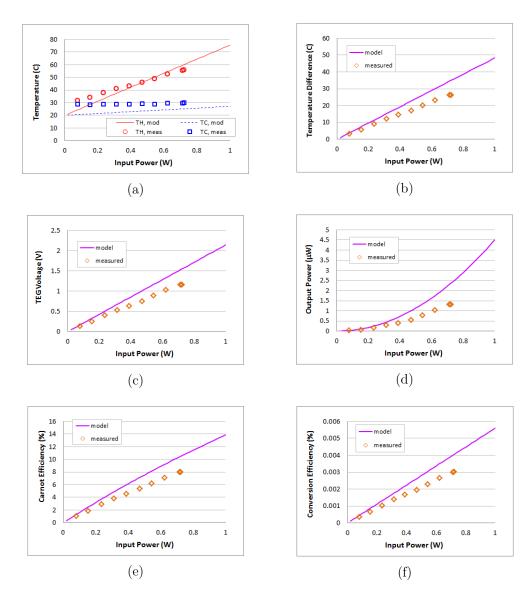

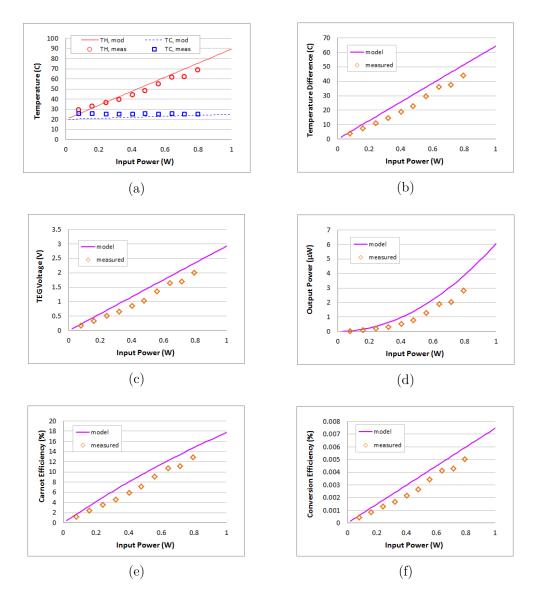

| Figure 6-19: Comparison between simulations, thermal model, and measured parameters: (a) hot and cold side temperature, (b) temperature difference, (c) open-circuit TEG voltage, (d) matched output power, (e) Carnot efficiency, and (f) conversion efficiency for a TEG implemented on a glass substrate with $l=500~\mu\text{m},~w=15~\mu\text{m},~d_{mem}=1~\text{mm},~\text{and}~N=34.$ |

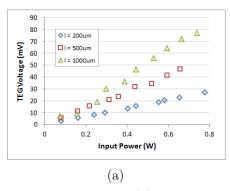

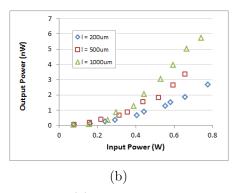

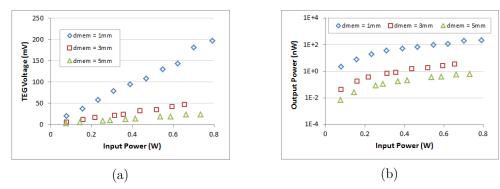

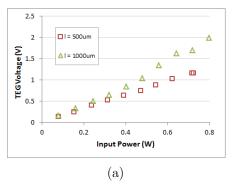

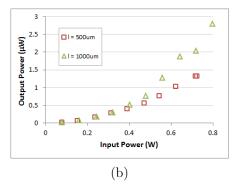

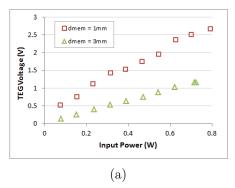

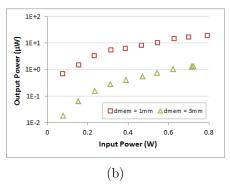

| <b>Figure 6-20</b> : Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a glass substrate with varying thermoelement lengths ( $w = 15 \mu m$ and $d_{mem} = 3 \text{ mm}$ )                                                                                                                                                                           |

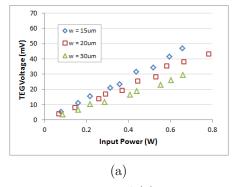

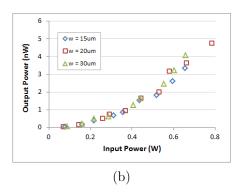

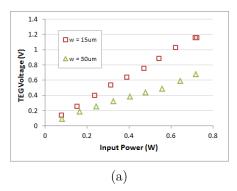

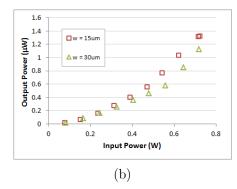

| Figure 6-21: Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a glass substrate with varying thermoelement widths ( $l = 500  \mu \text{m}$ and $d_{mem} = 3  \text{mm}$ )                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-22: Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a glass substrate with varying membrane diameters ( $l=500~\mu m$ and $w=15~\mu m$ )                                                                                                                                                                                                                                                                                                    |

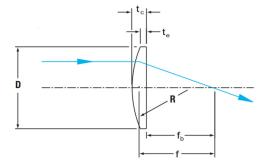

| Figure 6-23: Diagram of plano-convex lens indicating the lens diameter $(D)$ , center thickness $(t_c)$ , edge thickness $(t_e)$ , radius of curvature $(R)$ , back focal length $(f_b)$ , and focal length $(f)$ .                                                                                                                                                                                                                                                                            |

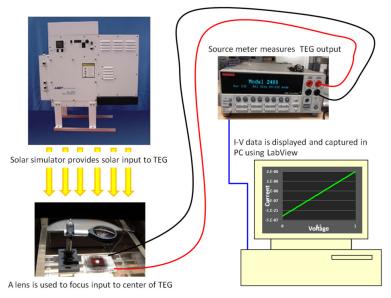

| <b>Figure 6-24</b> : Measurement set-up with a solar simulator providing solar input and a Keithley Model 2400 source meter sensing the TEG's output                                                                                                                                                                                                                                                                                                                                           |

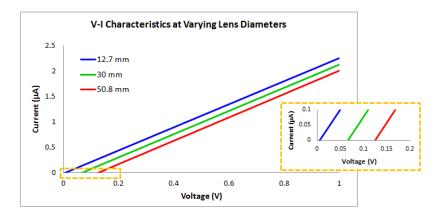

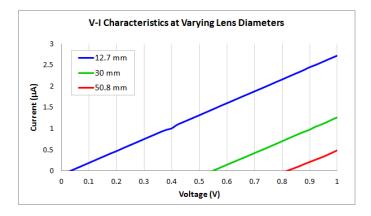

| Figure 6-25: V-I characteristics of TEG implemented on a glass substrate with $l=1000$ $\mu$ m, $w=15$ $\mu$ m, $d_{mem}=5$ mm, and $N=191$ using three different lens diameters. Inset shows a zoomed-in plot of the intersection of the V-I characteristics with the x-axis which denotes the open-circuit voltages.                                                                                                                                                                         |

| Figure 7-1: Modified TEG design on a SOI substrate with buried oxide layer and thin part of handle layer retained for added structural stability                                                                                                                                                                                                                                                                                                                                               |

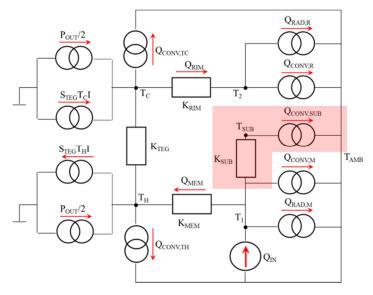

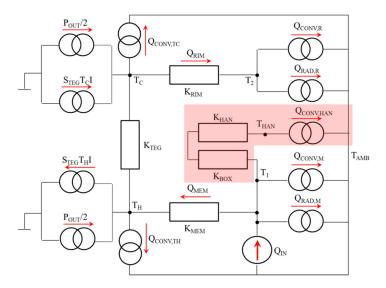

| Figure 7-2: Thermal equivalent model of TEG implemented on a SOI substrate with buried oxide layer retained. $T_{HAN}$ is the temperature at the bottom of the thinned area of the handle layer, $K_{BOX}$ and $K_{HAN}$ are the thermal conductances directly below the heated area of the device of the buried oxide and handle layers, respectively, and $Q_{CONV,HAN}$ represents heat lost due to convection at the bottom of the thinned handle layer139                                 |

| Figure 7-3: (a) Hot $(T_H)$ and cold $(T_C)$ side temperatures and (b) temperature difference $T$ between simulations $(sim)$ and thermal model $(mod)$ of TEG on a SOI substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ . |

| Figure 7-4: (a) Open-circuit TEG voltage and (b) matched output power between simulations (sim) and thermal model (mod) of TEG on a SOI substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ .143                              |

| Figure 7-5: (a) Carnot efficiency and (b) conversion efficiency between simulations (sim) and thermal model (mod) of TEG on a SOI substrate with varying solar concentration ratio. TEG has the following parameters: $l = 500  \mu \text{m}$ , $w = 15  \mu \text{m}$ , $d_{mem} = 1  \text{mm}$ , $N = 34$ , $\varepsilon = 0.6$ , $h_{conv} = 50  \text{W/m}^2 \text{K}$ , $\alpha_{mem} = 0.5$ , $\tau_{lens} = 1$ , and $d_{spot} = 1  \text{mm}$ 143                                     |

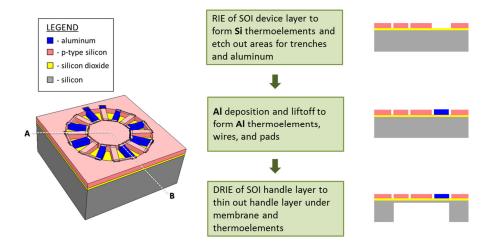

| Figure 7-6: Overview of TEG fabrication process using a SOI wafer with p-type silicon and aluminum as thermoelement materials. Cross-sectional view is along AB                                                                                                                                                                                                                                                                                                                                |

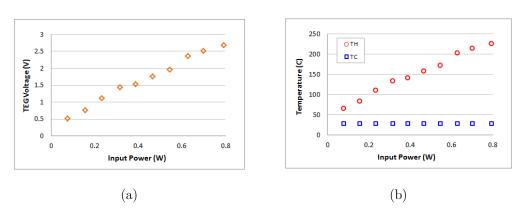

| Figure 7-7: Measured (a) open-circuit TEG voltage and (b) hot and cold side temperatures versus laser input power of a TEG implemented on a SOI substrate with these dimensions: $l=500~\mu\text{m},~w=15~\mu\text{m},~d_{mem}=1~\text{mm},~\text{and}~N=34.$                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

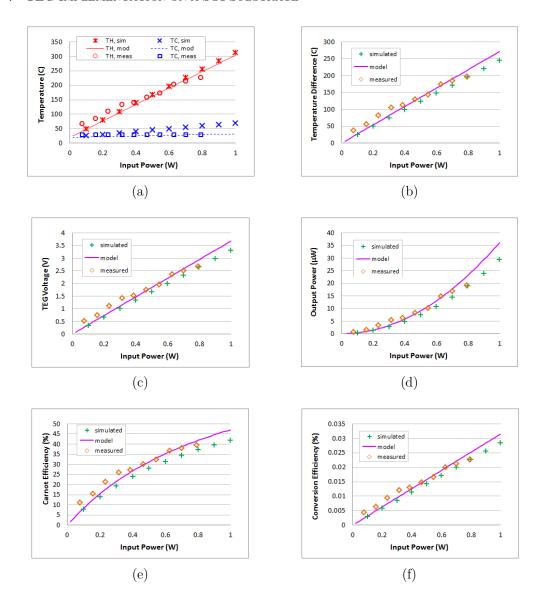

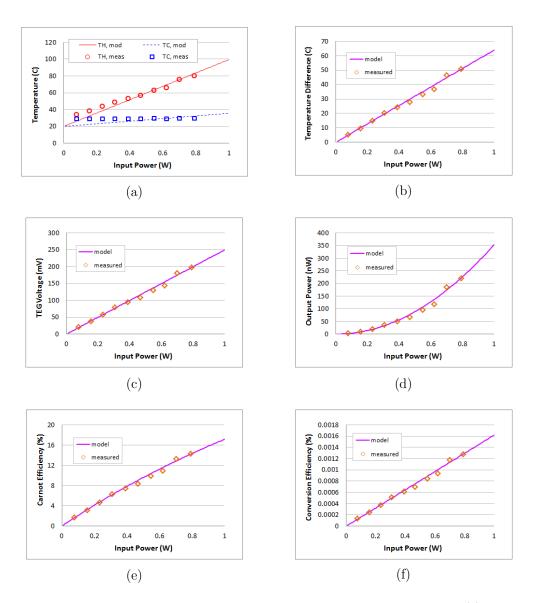

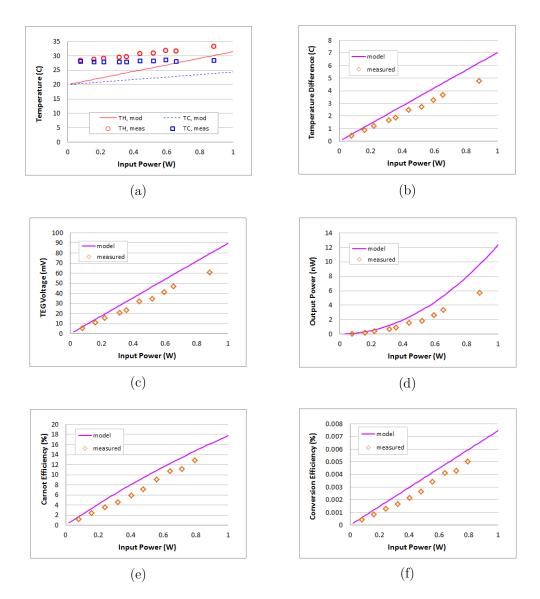

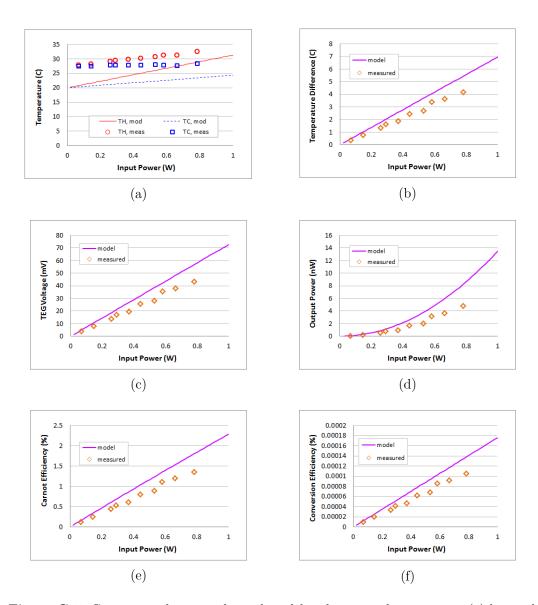

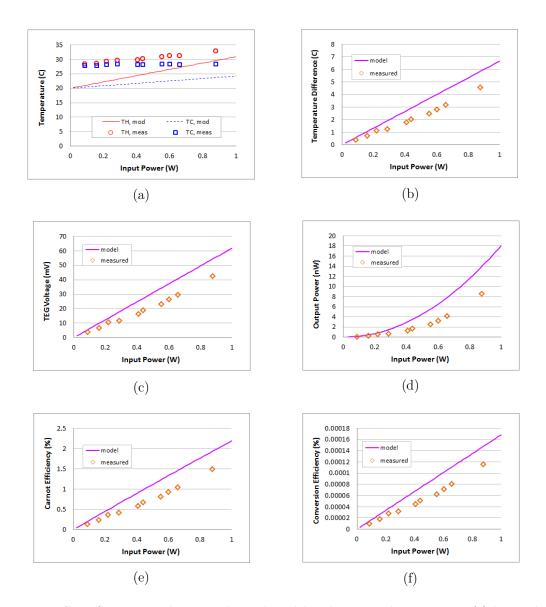

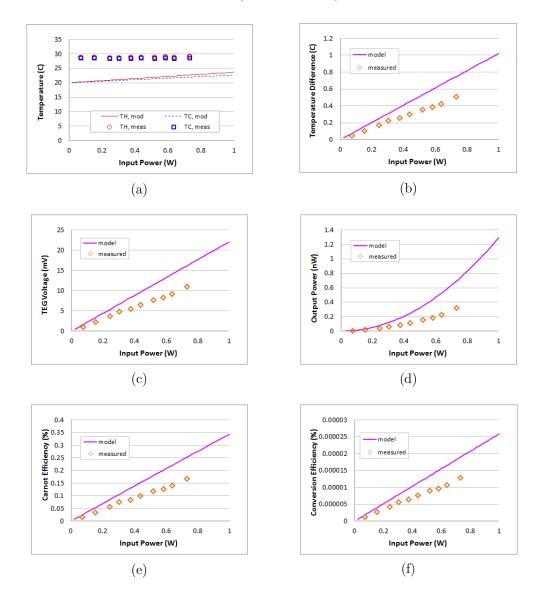

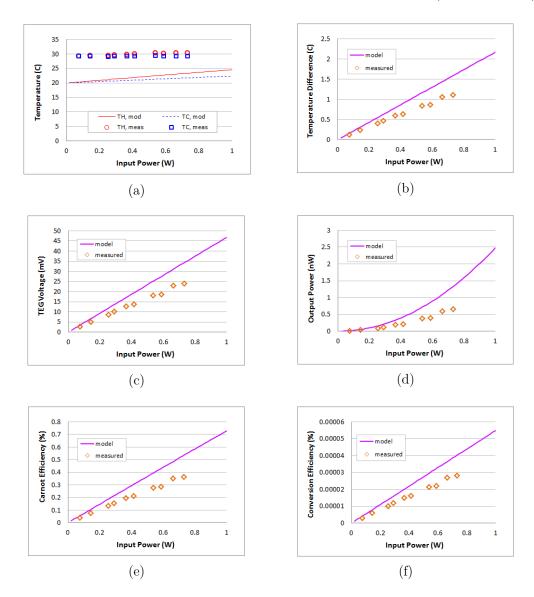

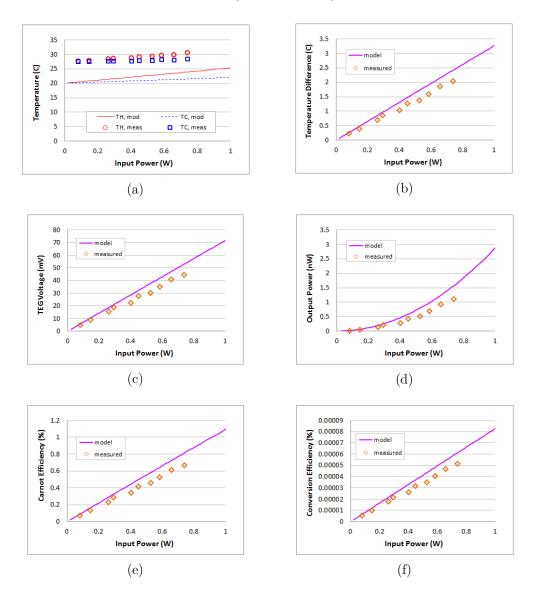

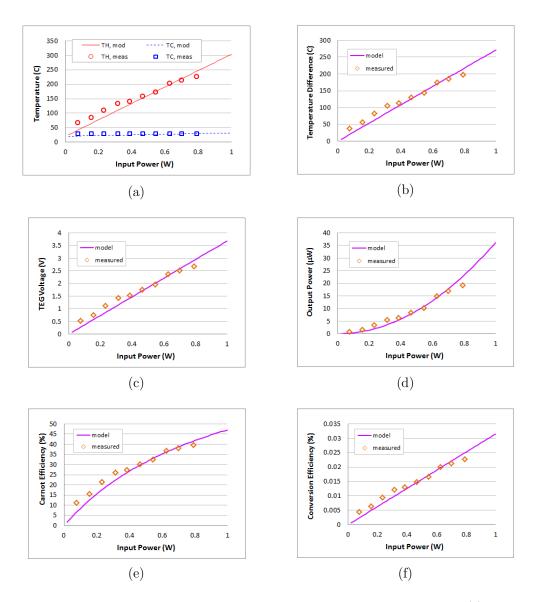

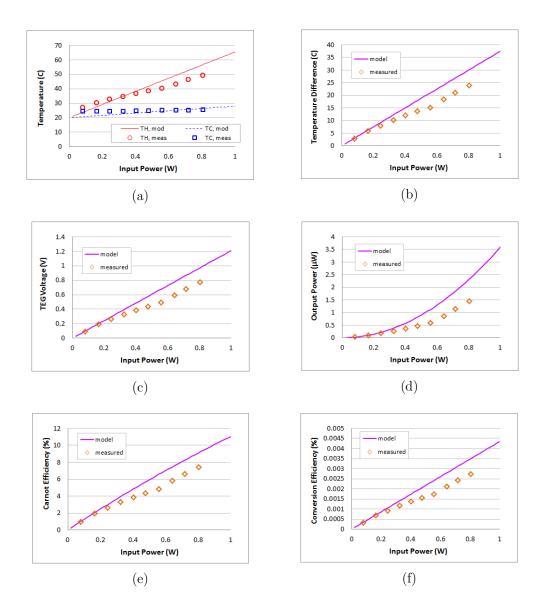

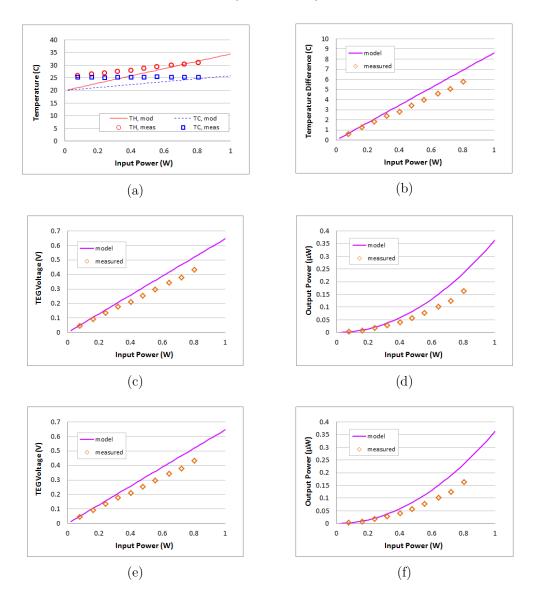

| Figure 7-8: Comparison between simulations, thermal model, and measured parameters: (a) hot and cold side temperature, (b) temperature difference, (c) open-circuit TEG voltage, (d) matched output power, (e) Carnot efficiency, and (f) conversion efficiency for a TEG implemented on a SOI substrate with $l=500~\mu\text{m},~w=15~\mu\text{m},~d_{mem}=1~\text{mm},$ and $N=34$ . |

| Figure 7-9: Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a SOI substrate with varying thermoelement lengths ( $w = 15 \mu m$ and $d_{mem} = 3 \text{ mm}$ )                                                                                                                                                                               |

| Figure 7-10: Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a SOI substrate with varying thermoelement widths ( $l = 500  \mu \text{m}$ and $d_{mem} = 3  \text{mm}$ )                                                                                                                                                                      |

| Figure 7-11: Measured (a) open-circuit TEG voltage and (b) matched output power of TEGs implemented on a SOI substrate with varying membrane diameters ( $l=500~\mu m$ and $w=15~\mu m$ )                                                                                                                                                                                              |

| Figure 7-12: V-I characteristics of TEG implemented on a SOI substrate with $l=1000$ $\mu$ m, $w=15$ $\mu$ m, $d_{mem}=3$ mm, and $N=114$ using three different lens diameters158                                                                                                                                                                                                      |

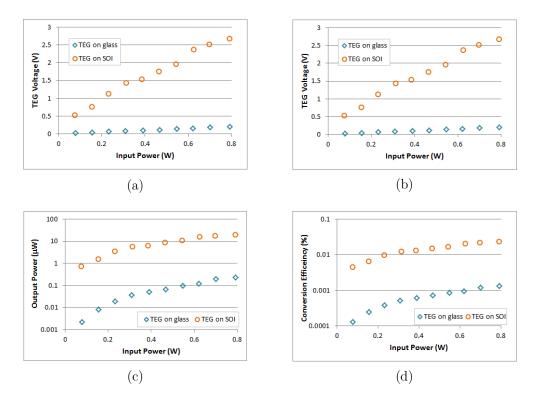

| Figure 7-13: Comparison between measured (a) temperature difference, (b) open-circuit TEG voltage, (c) matched output power, and (d) conversion efficiency of both TEG on glass and TEG on SOI with $l=500~\mu\text{m},~w=15~\mu\text{m},~d_{\textit{mem}}=1~\text{mm},$ and $N=34162$                                                                                                 |

| Figure 8-1: Comparison of efficiency factor vs. level of integration of TEGs investigated in this study and published lateral/lateral TEGs grouped according to thermoelectric material used.                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                        |

## DECLARATION OF AUTHORSHIP

I, Maria Theresa G. de Leon, declare that this thesis entitled

"Efficiency Improvement in MEMS Thermoelectric Generators Employing Solar Concentration "

and the work presented in it are my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as:

- de Leon, Taatizadeh, and Kraft. 2010. Improving the Efficiency of Thermoelectric Generators by Using Solar Heat Concentrators. Proceedings of the 21<sup>st</sup> Micromechanics and Microsystems Europe Workshop (Enschede, The Netherlands).

- de Leon, Chong, and Kraft. 2012. Design and Modelling of SOI-Based Solar Thermoelectric Generators. Procedia Engineering, vol. 47, pages 76-79.

| Signed: |  |

|---------|--|

|         |  |

|         |  |

|         |  |

|         |  |

| Date:   |  |

# Acknowledgements

First and foremost, I would like to thank Michael Kraft for giving me the opportunity to come to the University of Southampton for my PhD studies. I am extremely grateful for his support and supervision. I would also like to thank the following academics: Harold Chong for his guidance and encouraging words, Roland Schmechel and Steve Beeby for the important insights they shared during the final viva, Harvey Rutt for the enlightening discussions, Darren Bagnall for his constructive comments during my ninemonth and transfer vivas, and Sakellaris Mailis for giving me a chance to do my laser measurements in his lab. I would also like to extend my sincerest gratitude to Antulio Tarazona for his invaluable help with the HWCVD tool and the opportunity to work on interesting projects.

I would like to thank all the research and technical staffs (Kian, Owain, Mike, Denny, Jim, Richard K., Richard B., Peter, Ibrahim, Ioannis, Sun Kai, Stuart P., Stuart B., Katie, Sally) of the Southampton Nanofabrication Center for their helpfulness and endless patience. Thanks also to Glenys Howe for being the most dependable group secretary. I would also like to thank my fellow PhD students (Hwanjit, Nima, Feras, Rachel, Rares, David, Taha, Suhana, Ali, Graham, Lee, Chirenjeevi, Rob, Ahmed, Mario, Mehdi, Amirjan, Wazz, and others) with whom I have shared my cleanroom and research experiences with. You have all made life in the cleanroom more enjoyable, even at the most frustrating of times. Many thanks also to Gregorio Martinez for helping me set up the laser experiments.

I would like to thank the Engineering Research and Development for Technology program of the Department of Science and Technology, Philippines for providing my scholarship. Thank you to Rowena Guevara and Joel Marciano, Jr. of the University of the Philippines Electrical and Electronics Engineering Institute for their support in my quest to pursue postgraduate studies.

Finally, I would like to thank my family and friends for their unwavering love and support. To my husband, Franz, thank you for sharing this journey with me. I am looking forward to our next adventures together. I am dedicating this work to our first child who inspires me a lot as she grows inside me.

Maraming, maraming salamat po!

# **Definitions and Abbreviations**

$T_H$ Hot side temperature  $T_C$ Cold side temperature  $\Delta T$ Temperature difference  $V_{O}$ Open-circuit voltage Seebeck coefficient of thermocouple with materials A and B $\alpha_{AB}$ Ι Current through conductor Heating rate qPeltier coefficient of thermocouple with materials A and B $\pi_{AB}$ β Thomson coefficient N Number of thermocouples Seebeck coefficient of material A $\alpha_A$ Seebeck coefficient of material B $\alpha_B$  $R_L$ Load resistance  $P_{O,max}$ Maximum power delivered to the load  $R_{TEG}$ Electrical resistance of TEG TEG efficiency  $\eta_{\mathit{TEG}}$ Carnot efficiency  $\eta_C$  $\bar{T}$ Average absolute temperature ZThermoelectric figure-of-merit Seebeck coefficient  $\alpha$ λ Thermal conductivity  $\rho$ Electrical resistivity TEG efficiency factor TEG chip area  $A_G$ Total efficiency  $\eta_{tot}$ Solar concentrator efficiency  $\eta_s$ Thermal collector efficiency  $\eta_{\it th}$ Heat power density of incoming heat flux  $q_h$ Solar concentration factor Lens transmittance  $au_{lens}$ Membrane absorptance  $\alpha_{mem}$

Solar irradiation density

$q_s$

$d_{lens,eff}$  Effective lens diameter

$d_{spot}$  Spot size diameter

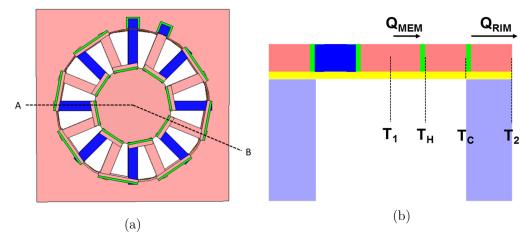

$Q_{MEM}$  Heat flow rate from heat absorber to TEG

$Q_{RIM}$  Heat flow rate from TEG to rim

$T_1$  Membrane temperature

$T_2$  Rim temperature

$\alpha_{Al}$  Seebeck coefficient of aluminum

$\alpha_{p\text{-}Si}$  Seebeck coefficient of p-type silicon

$\rho_{Al}$  Electrical resistivity of aluminum

$\rho_{p-Si}$  Electrical resistivity of p-type silicon

$\lambda_{Al}$  Thermal conductivity of aluminum

$\lambda_{p-Si}$  Thermal conductivity of p-type silicon

l Thermoelement length

w Thermoelement width

t Thermoelement thickness

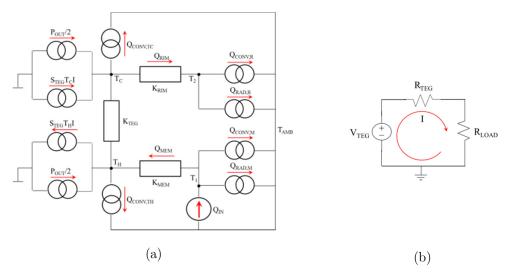

$S_{TEG}$  Total Seebeck coefficient of TEG

$K_{TEG}$  Total thermal conductance of TEG

$V_{TEG}$  Open-circuit TEG voltage

$P_{OUT}$  TEG output power under matched load conditions

$A_h$  Surface area of heated part of TEG membrane

$Q_{IN}$  TEG input power

$K_{MEM}$  Thermal conductance between thermocouples and heat

absorber

$K_{RIM}$  Thermal conductance between thermocouples and rim

$Q_{CONV,M}$  Heat loss due to convection at membrane

$Q_{CONV,R}$  Heat loss due to convection at rim

$Q_{RAD,M}$  Heat loss due to radiation at membrane

$Q_{RAD,R}$  Heat loss due to radiation at rim

$A_{MEM}$  Surface area of membrane

$A_{RIM}$  Surface area of rim

$A_{TEG}$  Surface area of thermoelements

$\varepsilon$  Surface emissivity

$\sigma$  Stefan-Boltzmann constant

$h_{conv}$  Convective heat transfer coefficient

$d_{mem}$  Membrane diameter

$w_{tr}$  Isolation trench width

$R_A$ ,  $R_B$  Van der Pauw structure's characteristic resistances

$R_S$  Sheet resistance

U Thermovoltage between two ends of a planar structure

$R_C$  Contact resistance

$S_{side}$  Sidewall step coverage  $S_{bot}$  Bottom step coverage

C Cusping

$T_{SUB}$  Temperature at bottom of glass substrate

$K_{SUB}$  Thermal conductance of substrate directly below heated area

of membrane

QCONV,SUB Heat loss due to convection through substrate

$A_{SUB}$  Surface area of substrate

$TCR_{Al}$  Temperature coefficient of resistance of aluminum

$R_{series}$  Series resistance

$R_{t\theta}$  Initial resistance of temperature monitor

$R_t$  Resistance of temperature monitor

$V_{planar}$  Voltage across planar structure

$V_{canti}$  Voltage across cantilever structure

$\alpha_{poly}$  Seebeck coefficient of HWCVD polysilicon

$ho_{poly}$  Electrical resistivity of HWCVD polysilicon

$\lambda_{poly}$  Thermal conductivity of HWCVD polysilicon

$P_{in}$  Actual laser input power to the TEG

$T_{amb}$  Ambient temperature

$\lambda_{glass}$  Thermal conductivity of glass substrate

$d_{spot,min}$  Minimum spot size

D Lens diameter

f Lens focal length

n Lens refractive index

k Lens shape factor

$t_c$  Lens center thickness

$t_e$  Lens edge thickness

R Lens radius of curvature

$f_b$  Lens back focal length

$d_{lens-to-spot}$  Distance between the flat side of the plano-convex lens to

the actual spot size

$K_{BOX}$  Thermal conductance of buried oxide layer directly below

heated area of membrane

$K_{HAN}$  Thermal conductance of thinned handle layer directly below

heated area of membrane

$T_{HAN}$  Temperature at the bottom of the thinned handle layer  $Q_{CONV,HAN}$  Heat loss due to convection through thinned handle layer

Thermal conductivity of buried oxide layer

$\alpha_{Si}$  Seebeck coefficient of SOI device layer  $\rho_{Si}$  Electrical resistivity of SOI device layer  $\lambda_{Si}$  Thermal conductivity of SOI device layer

CA Clear Aperture

$\lambda_{SiO2}$

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical Mechanical Polishing

CPC Compound Parabolic Collector

DI Deionized

DRIE Deep Reactive Ion Etching

DSSC Dye-Sensitized Solar Cell

EEG Electroencephalogram

ETC Evacuated Tube Collector

FNA Fuming Nitric Acid

FPC Flat Plate Collector

FTIR Fourier Transform Infrared Spectroscopy

HF Hydrofluoric Acid

HFVPE HF Vapor Phase Etching

HWCVD Hot Wire Chemical Vapor Deposition

ICP Inductively Coupled Plasma

IPA Isopropyl Alcohol

IR Infrared

KOH Potassium Hydroxide

LF Low Frequency

LPCVD Low Pressure Chemical Vapor Deposition

MEMS Microelectromechanical Systems

MIF Metal Ion Free

MOCVD Metal Organic Chemical Vapor Deposition

NDF Neutral Density Filter

NIR Near Infrared

NMP N-Methyl-2-Pyrrolidone

OIPT Oxford Instruments Plasma Technology

ORC Optoelectronics Research Center

PCB Printed Circuit Board

PECVD Plasma Enhanced Chemical Vapor Deposition

PV Photovoltaic

RF Radio Frequency

RIE Reactive Ion Etching

SEM Scanning Electron Micrograph

SOI Silicon-on-Insulator

SSA Solar Selective Absorber

STC Silicon Thin-Film Cell

STEG Solar Thermoelectric Generator

TC Thermocouple

TE Thermoelectric

TEC Thermoelectric Cooler

TEG Thermoelectric Generator

TEOS Tetraethyl Orthosilicate

TIC Thermoionic Converter

TSG Tantalum-Antimony-Germanium

USG Undoped Silicate Glass

UV Ultraviolet

# Chapter 1: Introduction

The global energy crisis has paved the way for researchers to explore alternative means of generating power. One approach to providing electrical energy is by direct conversion of heat to electricity with the use of thermoelectric generators (TEGs). It is attractive to use TEGs because they have no mechanical parts; hence resulting in an alternative power system that is silent, stable, reliable, environment-friendly, and possess virtually unlimited lifetime (Deng & Liu 2009)(Strasser et al. 2004).

A major challenge in the design of TEGs is its limited efficiency. A typical thermoelectric device exhibits only 5-10% conversion efficiency depending on the materials used and the temperature difference involved (Matsubara and Matsuura 2006). Meanwhile, the best solar cell at present is 3-5 times more efficient than thermoelectric devices (Savage 2011). One way to increase the conversion efficiency of a TEG is by increasing the temperature difference across the thermoelements (Rowe 2006a)(Chen & Ren 2010). An increase in temperature difference can be realized by using a high input heat flux such as that coming from the sun (Chen et al. 2011). In this regard, the use of a solar concentrator to improve the efficiency of TEGs by focusing solar radiation onto the hot junction of the TEG is proposed. By doing so, the temperature difference across the device can be increased; subsequently improving the TEG's efficiency.

### 1.1 Motivation

Several implementations of TEGs focus on improving its efficiency by exploring advanced thermoelectric materials such as skutterudites (Wang et al. 2001)(Chen et al. 2011), clathrates (Kleinke 2010), Zn-Sb alloys (Caillat & Fleurial 1996), Pb-Te alloys (Gelbstein, Dashevsky, and Dariel 2008)(Heremans et al. 2008)(Mu 2010)(Pei et al. 2011), InGaN alloys (Pantha et al. 2009), and ZnO alloys (Schaeuble et al. 2008)(Ong, Singh, and Wu 2011). Higher efficiency TEGs have also been designed by using segmented thermoelectric legs to exploit the operating temperatures of several materials;

#### 1 Introduction

thereby optimizing heat flow across the thermoelements (Fleurial et al. 1996)(Caillat et al. 2001)(Maciá 2004)(Snyder 2004). Meanwhile, other researchers emphasized nanostructuring of bulk materials to improve the material's thermoelectric figure merit (Majumdar 2004)(Qiu 2008)(Singh & Terasaki 2008)(Lan et al. 2010). In nanostructuring, the material's figure of merit is increased by creating materials composed of nanosized grains. By doing so, the thermal conductivity of the material is decreased while maintaining its electrical conductivity. The technique of nanostructuring has been applied to silicon (Bunimovich 2007) (Hochbaum et al. 2008)(Lee et al. 2008)(Bux et al. 2009)(Ramayya and Knezevic 2009)(Boukai 2010)(Cerofolini et al. 2010)(Hao et al. 2010), silicon germanium (Ghamaty 2006)(Wang et al. 2008), bismuth telluride alloys (Venkatasubramanian et al. 2001)(Wang et al. 2005)(Koukharenko et al. 2008)(Lan et al. 2009)(Minnich et al. 2009), and complex cobalt oxides (Robert et al. 2005).

The above-mentioned techniques focus on improving the thermoelectric properties of the materials to improve the efficiency of the TEG. While results obtained by these techniques are promising, synthesizing novel compounds, fabricating segmented thermoelements, and creating nanostructured materials are quite complex.

Another aspect that can be explored to improve the efficiency of a TEG is by increasing the temperature difference across the thermoelements. This can be accomplished by increasing the amount of input heat flux at the hot junction of the generator. In this regard, a solar concentrator can be used to concentrate solar radiation onto the hot side of the TEG. Several researches have demonstrated the functionality of such systems on a large scale by using commercially-available solar concentrators and TEG modules.

At chip scale, the use of a lens to concentrate light onto a TEG that serves as power supply to a microactuator have already been proposed (Baglio et al. 2002a). Recently, an improvement in TEG efficiency has been achieved by employing both solar and thermal concentration on a flat-panel solar thermoelectric generator composed of a pair of n- and p-type thermoelectric materials based on nanostructured Bi<sub>2</sub>Te<sub>3</sub> alloys (Kraemer et al. 2011). Despite having the best thermoelectric figure of merit, the use of Bi<sub>2</sub>Te<sub>3</sub> alloys in

MEMS systems is hindered by challenges in technological compatibility (Roncaglia & Ferri 2011). It is therefore more practical to use materials like silicon or polysilicon as thermoelectric materials as they have better compatibility with standard CMOS and MEMS processes. Thus, it is worthwhile to investigate the feasibility of implementing solar thermoelectric generator (STEG) systems utilizing conventional materials in MEMS and CMOS processing and characterize its improvement in efficiency as this gives way to future advancements in solar energy harvesting.

Preliminary heat transfer simulations on a proposed STEG design have shown promising results in terms of increasing the temperature difference across the device. Hence, a prototype of this system is to be developed using simple fabrication processes that are compatible with existing CMOS and MEMS technologies. It is important to choose materials and processes that will enable easy integration of the solar-driven TEG with on-chip electronics as this microscale system is envisioned to have promising applications in on-board power sources, sensor networks, and autonomous microsystems.

## 1.2 Objectives

The main objective of this study is to demonstrate the effectiveness of using solar concentrators in improving the efficiency of thermoelectric generators. To do this, several TEGs with different geometries must be designed and fabricated so the effects of the physical parameters of the device on its performance can be investigated. The fabricated TEGs must then be tested and properly characterized to establish the improvement in efficiency. Note that it is envisioned to have TEGs with a temperature difference of more than 300 °C. This would govern decisions made during the study concerning the dimensions of the devices to be fabricated, as well as the materials to be used in fabrication.

The secondary objective of this work is to develop an analytical model that predicts the performance of the TEG depending on its geometry, material properties, and input conditions. By having an analytical model that can closely estimate the actual performance of the device; it can be demonstrated how much improvement in efficiency is

#### 1 Introduction

can be achieved by using solar concentrators along with TEGs that have better thermoelectric materials.

### 1.3 Contributions