University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

**Towards a Systematic Process for Modelling Complex Systems in

Event-B**

by

**Eman Alkhammash**

Thesis for the degree of Doctor of Philosophy

May 2014

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

Doctor of Philosophy

TOWARDS A SYSTEMATIC PROCESS FOR MODELLING COMPLEX SYSTEMS

IN EVENT-B

by **Eman Alkhammash**

Formal methods are mathematical techniques used for developing large systems. The complexity of growing systems pose an increasing challenge in the task of formal development and requires a significant improvement of formal techniques and tool support.

Event-B is a formal method used for modelling and reasoning about systems. The Rodin platform is an open tool that supports Event-B specification and verification. This research aims to address some challenges in modelling complex systems. The main challenges addressed in this thesis cover three aspects: The first aspect focuses on providing a way to manage the complexity of large systems. The second aspect focuses on bridging the gap between the requirements and the formal models. The third aspect focuses on supporting the reuse of models and their proofs.

To address the first challenge, we have attempted to simplify the task of formal development of large systems using a compositional technique. The compositional technique aims at dividing the system into smaller parts starting from requirements, followed on by a construction of the specification of each part in isolation, and then finally composing these parts together to model the overall behaviour of the system. We classified the requirements into two categories: The first category consists of a different set of requirements, each of which describes a particular component of the system. The second category describes the composition requirements that show how components interact with each other. The first category is used to construct Event-B specification of each component separately from other components. The second category is used to show the interaction of the separated models using the composition technique.

To address the second and the third challenges, we proposed two techniques in this thesis. The first technique supports construction of a formal model from informal requirements with the aim of retaining traceability to requirements in models. This approach makes use of the UML-B and atomicity decomposition (AD) approaches. UML-B provides the UML graphical notation that enables the development of an Event-B formal model, while the AD approach provides a graphical notation to illustrate the refinement structures and assists in the organisation of refinement levels. The second technique supports the reusability of Event-B formal models and their respective proof obligations. This approach adopts generic instantiation and composition approaches to form a new methodology for reusing existing Event-B models into the development process of other models. Generic instantiation technique is used to create an instance of a pattern that consists of refinement chain in a way that preserves proofs while composition is used to enable the integration of several sub-models into a large model. FreeRTOS (real-time operating system) was selected as a case study to identify and address the above mentioned general problems in the formal development of complex systems.

# List of Figures

|      |                                                                                               |    |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.1  | An example of B specification. . . . .                                                        | 6  |

| 1.2  | The outline of an event . . . . .                                                             | 7  |

| 1.3  | An example of Event-B specification. . . . .                                                  | 8  |

| 1.4  | The structure of VDM-SL module. . . . .                                                       | 10 |

| 1.5  | An example of VDM-SL specifications . . . . .                                                 | 11 |

| 2.1  | Shared event composition style. . . . .                                                       | 19 |

| 2.2  | Generic instantiation. . . . .                                                                | 21 |

| 2.3  | The structure of inference rule definitions. . . . .                                          | 22 |

| 2.4  | Definition of sequence operator. . . . .                                                      | 22 |

| 2.5  | Atomicity decomposition diagram [33]. . . . .                                                 | 23 |

| 2.6  | Atomicity decomposition diagram for the most abstract level. . . . .                          | 24 |

| 3.1  | The RTOS structure. . . . .                                                                   | 28 |

| 3.2  | The architecture of the reuse approach. . . . .                                               | 38 |

| 4.1  | Steps for constructing a traceable formal models. . . . .                                     | 45 |

| 4.2  | The class diagram for REQ1. . . . .                                                           | 52 |

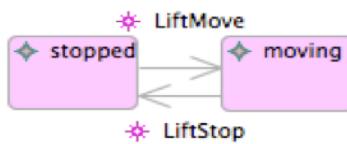

| 4.3  | The state machine diagram for REQ2. . . . .                                                   | 52 |

| 4.4  | The state machine diagram for REQ3. . . . .                                                   | 52 |

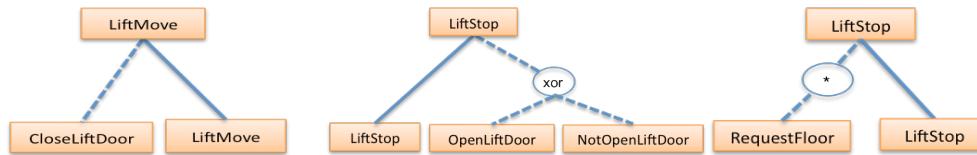

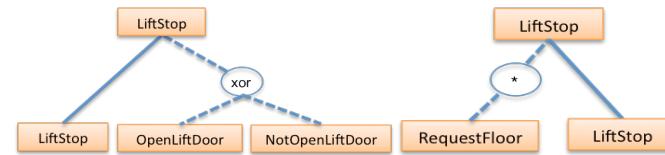

| 4.5  | The ADD for REQ6. . . . .                                                                     | 53 |

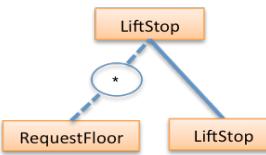

| 4.6  | The ADD for REQ7. . . . .                                                                     | 53 |

| 4.7  | The ADD for REQ8. . . . .                                                                     | 53 |

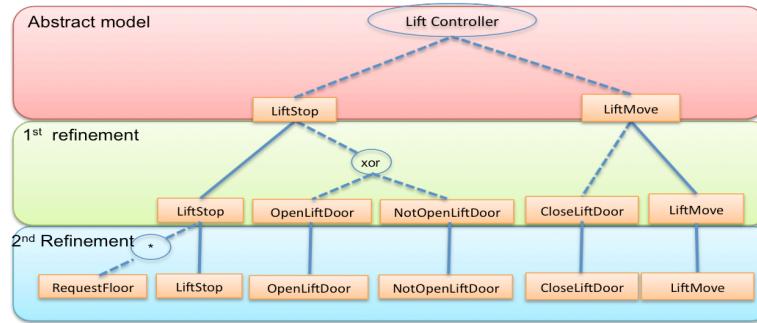

| 4.8  | The combined AD diagrams for the lift controller. . . . .                                     | 54 |

| 4.9  | Sets, constants and axioms generated from the class and state machine diagrams. . . . .       | 55 |

| 4.10 | Variables, invariants and events generated from the class and state machine diagrams. . . . . | 56 |

| 4.11 | The Event-B specification of the structured English for the requirement <i>REQ5</i> . . . . . | 57 |

| 4.12 | The Event-B specification generated from the AD diagram (loop pattern). . . . .               | 57 |

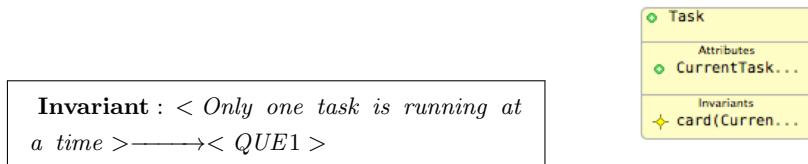

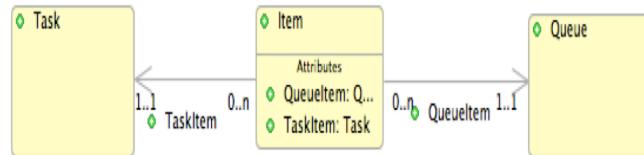

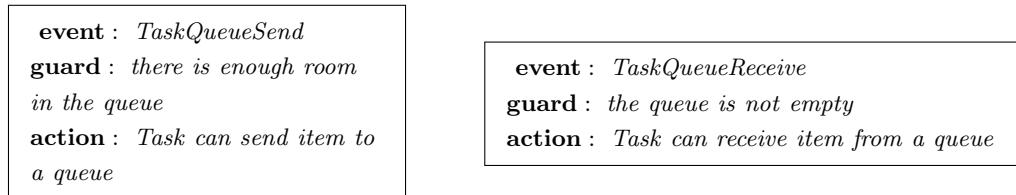

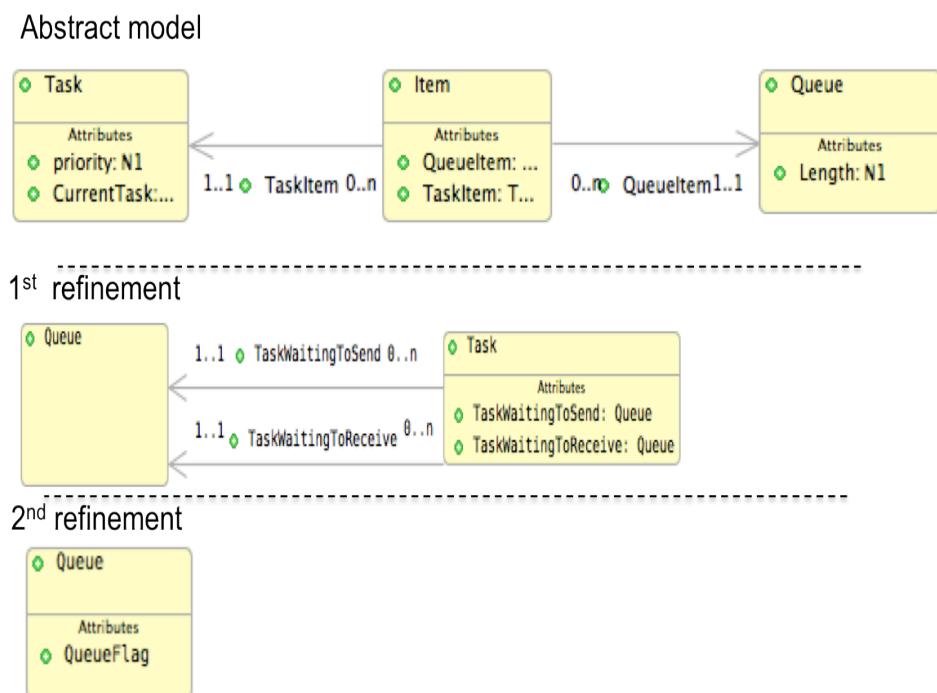

| 5.1  | The class diagram for QUE1. . . . .                                                           | 70 |

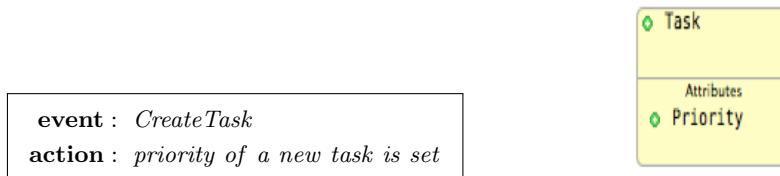

| 5.2  | The class diagram for TSK3. . . . .                                                           | 70 |

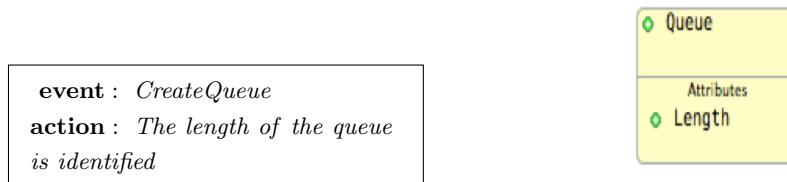

| 5.3  | The class diagram for QUE2. . . . .                                                           | 71 |

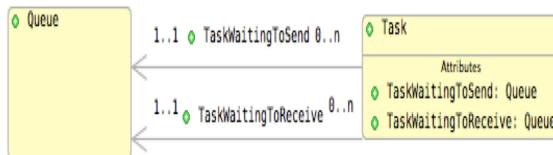

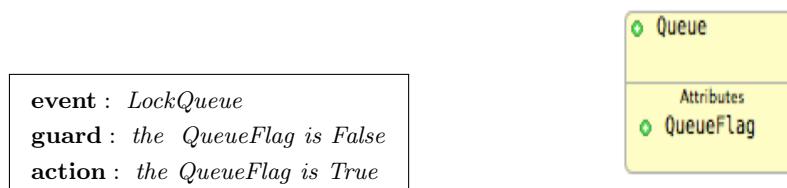

| 5.4  | The class diagrams for QUE3. . . . .                                                          | 71 |

| 5.5  | The class diagrams for QUE5. . . . .                                                          | 72 |

| 5.6  | The class diagram for QUE10. . . . .                                                          | 74 |

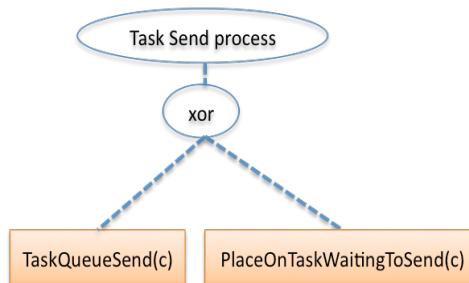

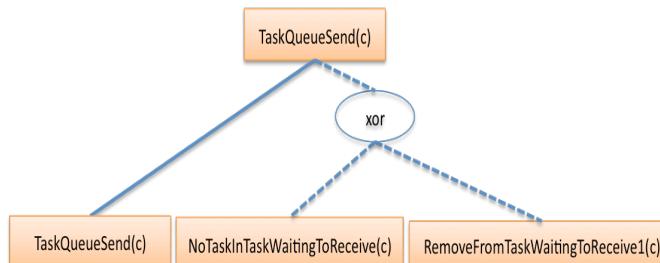

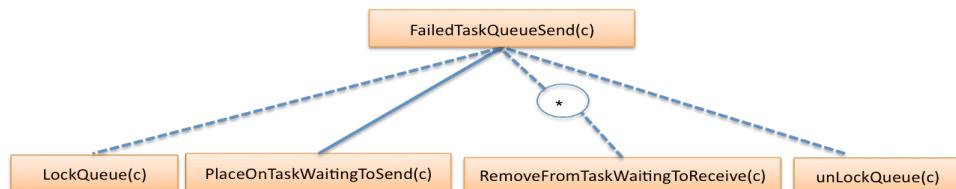

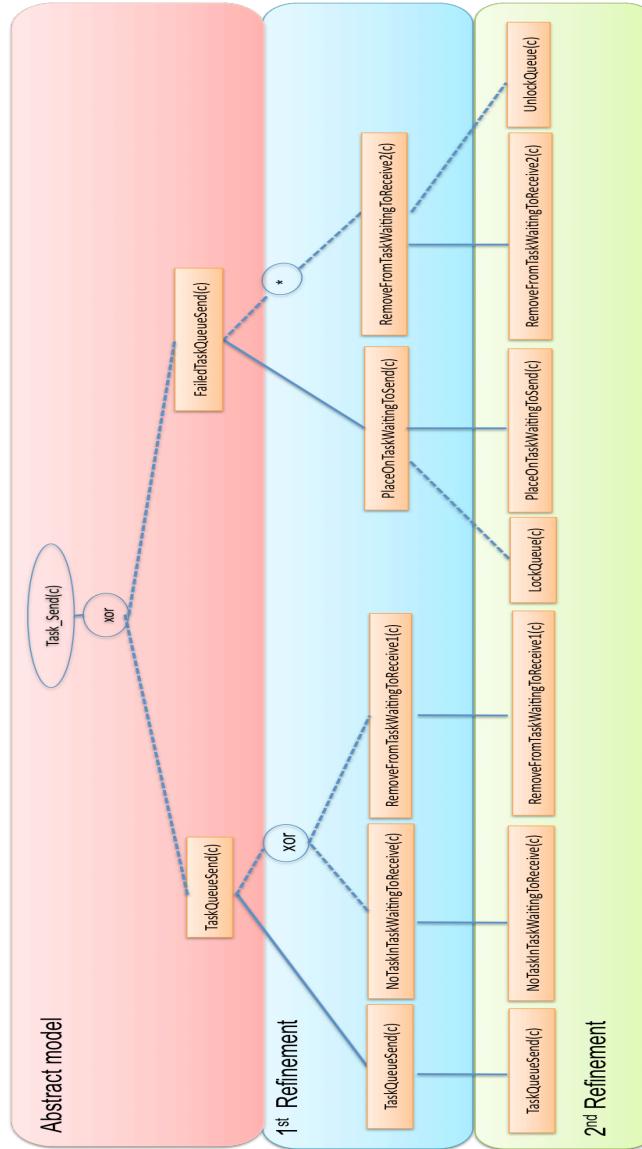

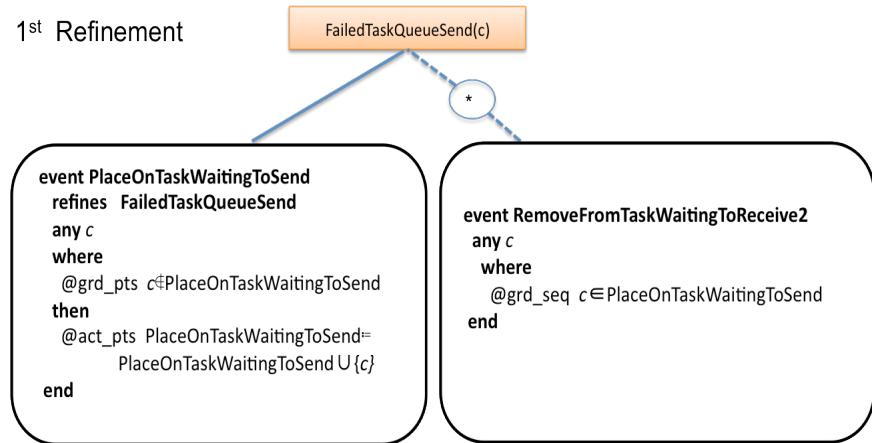

| 5.7  | ADD for Flow1. . . . .                                                                        | 76 |

---

|      |                                                                                                                                    |     |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8  | ADD for Flow2 . . . . .                                                                                                            | 76  |

| 5.9  | ADD for Flow3 . . . . .                                                                                                            | 77  |

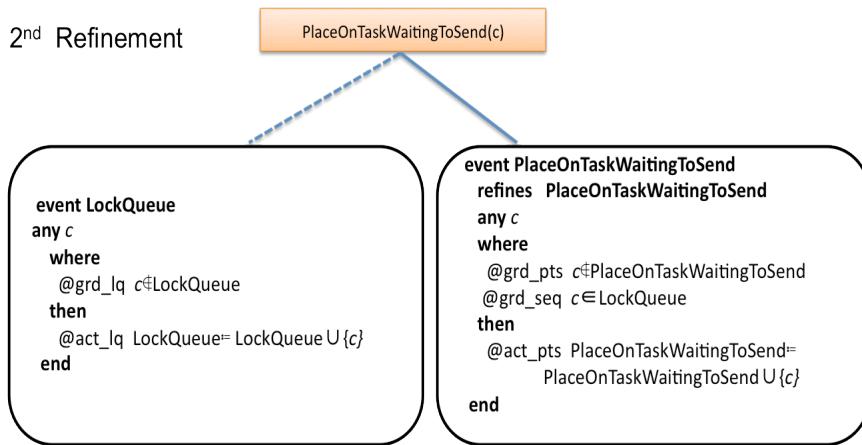

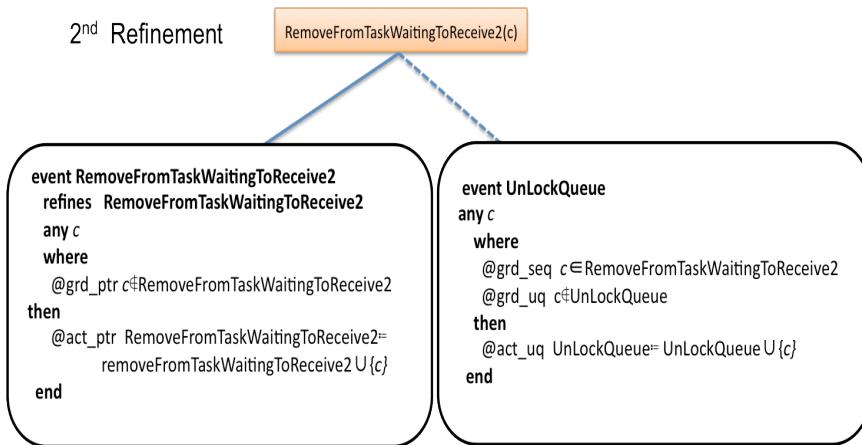

| 5.10 | The combined ADD for task-send . . . . .                                                                                           | 79  |

| 5.11 | Queue management class diagrams . . . . .                                                                                          | 80  |

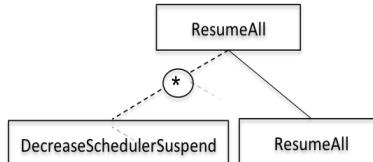

| 6.1  | Refinement diagram of event <i>ResumeAll</i> . . . . .                                                                             | 91  |

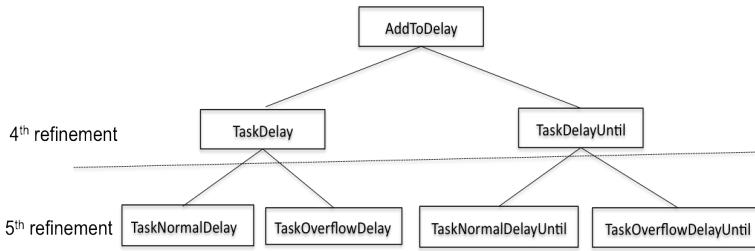

| 6.2  | The structure of delay events in the fourth/fifth refinement levels . . . . .                                                      | 92  |

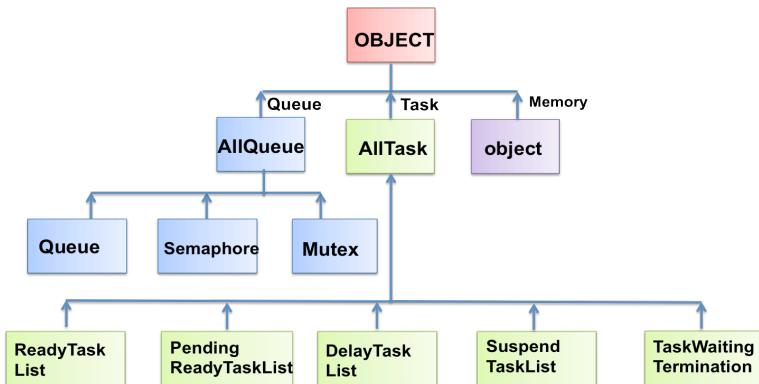

| 6.3  | Shared entity “Object” between Task, Queue, and Memory models . . . . .                                                            | 94  |

| 6.4  | Context <i>C</i> of <i>model1</i> and <i>model2</i> . . . . .                                                                      | 98  |

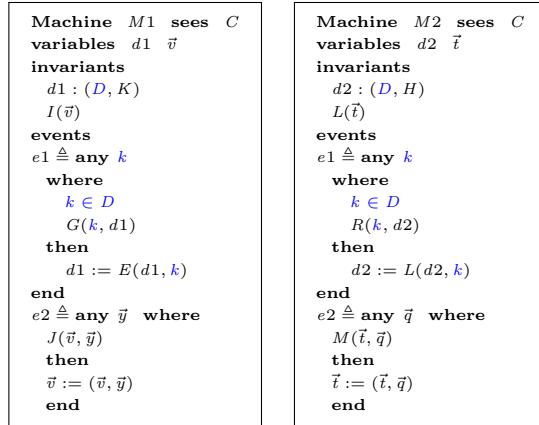

| 6.5  | Generic machine <i>M1</i> of <i>model1</i> and <i>M2</i> of <i>model2</i> . . . . .                                                | 98  |

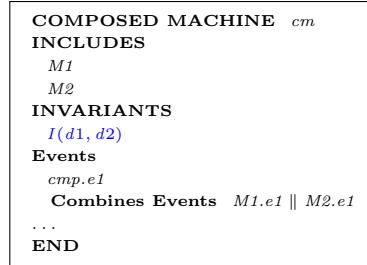

| 6.6  | The composed machine <i>cm</i> . . . . .                                                                                           | 99  |

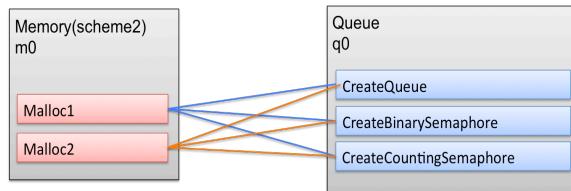

| 6.7  | <i>CreateQueue</i> event, <i>CreateBinarySemaphore</i> event and <i>CreateCountingSemaphore</i> event in the queue model . . . . . | 100 |

| 6.8  | <i>Malloc1</i> event and <i>Malloc2</i> event of memory model . . . . .                                                            | 100 |

| 6.9  | The composition diagram of sub-models with shared entities . . . . .                                                               | 101 |

| 6.10 | The composed machine <i>cm</i> of sub-models with shared entities . . . . .                                                        | 102 |

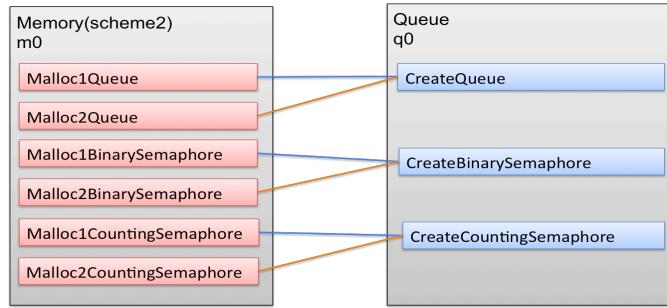

| 6.11 | <i>Malloc1Queue</i> event and <i>Malloc2Queue</i> event of the modified machine <i>m0</i> of memory model . . . . .                | 103 |

| 6.12 | The composition diagram of sub-models with shared variables . . . . .                                                              | 103 |

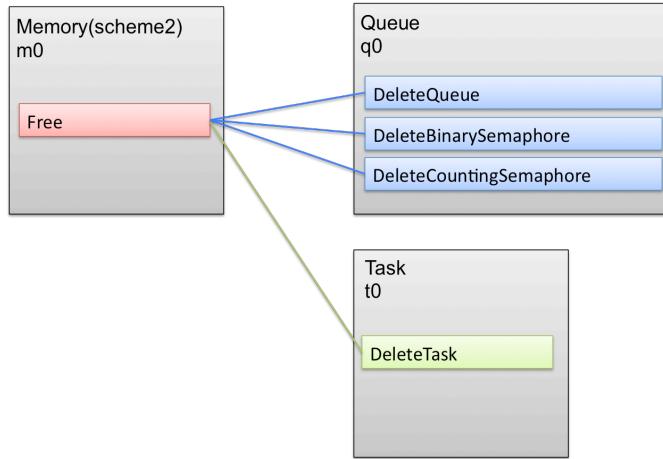

| 6.13 | The composed machine <i>cm</i> of sub-models with shared entities . . . . .                                                        | 104 |

| 6.14 | The abstract <i>CreateAllQueue</i> event of the modified machine <i>q0</i> in the queue model . . . . .                            | 105 |

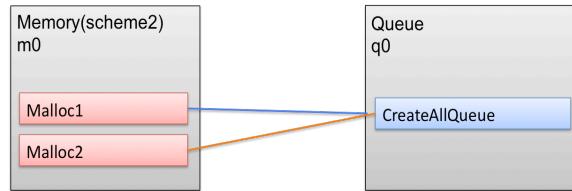

| 6.15 | The composition diagram after the abstraction of <i>q0</i> of the queue model . . . . .                                            | 106 |

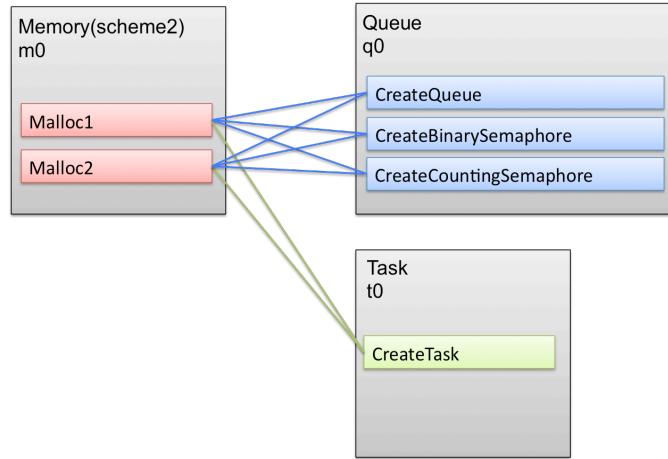

| 6.16 | The composition diagram of the requirement COMP1-EVT . . . . .                                                                     | 107 |

| 6.17 | The composition diagram of the requirement COMP2-EVT . . . . .                                                                     | 108 |

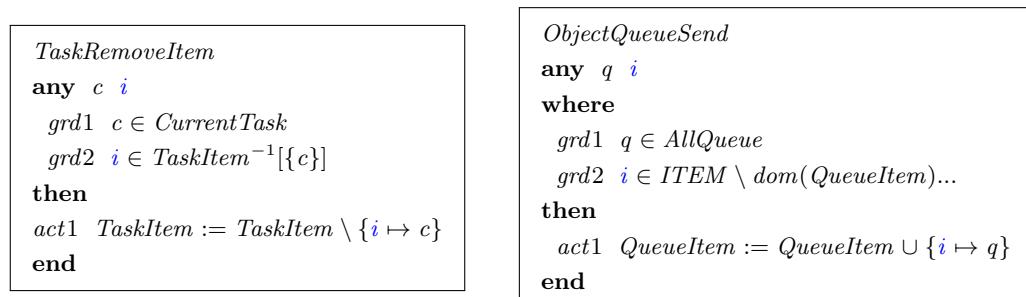

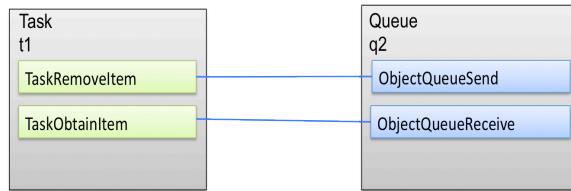

| 6.18 | <i>TaskRemoveItem</i> event of task model and <i>ObjectQueueSend</i> event of queue model . . . . .                                | 108 |

| 6.19 | The composition diagram of the requirement COMP3-EVT . . . . .                                                                     | 109 |

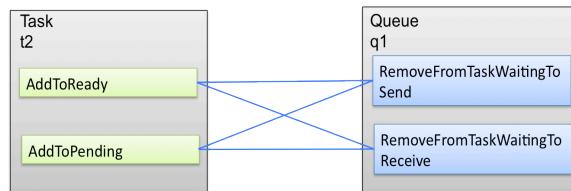

| 6.20 | <i>AddToReady</i> event of task model and <i>RemoveFromTaskWaitingToSend</i> event of queue model . . . . .                        | 110 |

| 6.21 | The composition diagram of the requirement COMP4-EVT . . . . .                                                                     | 110 |

| 6.22 | The composition diagram of the requirement COMP5-EVT . . . . .                                                                     | 111 |

| 6.23 | The composition diagram of the requirement COMP6-EVT . . . . .                                                                     | 111 |

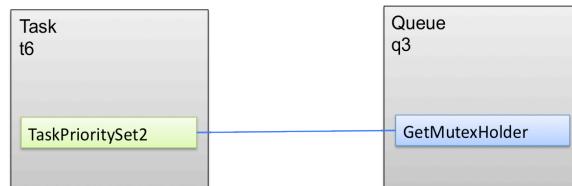

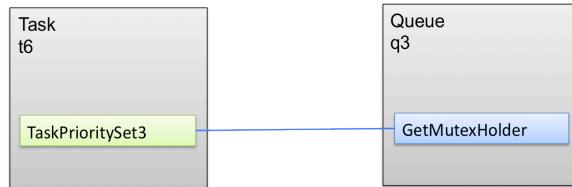

| 6.24 | <i>PrioritySet2</i> event of task model and <i>GetMutexHolder</i> event of the queue model .                                       | 112 |

| 6.25 | The composition diagram of the requirement COMP7-EVT . . . . .                                                                     | 112 |

| 6.26 | The composition diagram of the requirement COMP8-EVT . . . . .                                                                     | 113 |

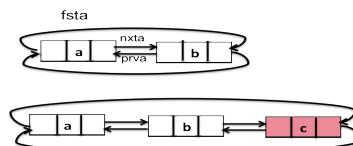

| 7.1  | Circular doubly linked list structure . . . . .                                                                                    | 122 |

| 7.2  | inserting an element at the end of the circular doubly linked list . . . . .                                                       | 122 |

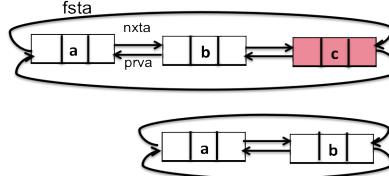

| 7.3  | delete the last element from the circular doubly linked list . . . . .                                                             | 124 |

| 7.4  | Circular doubly linked list structure . . . . .                                                                                    | 126 |

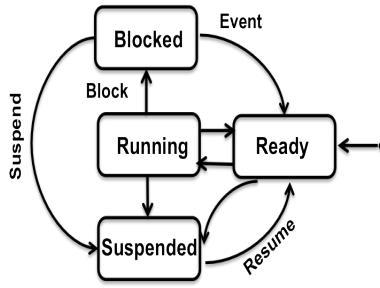

| 8.1  | Process states . . . . .                                                                                                           | 138 |

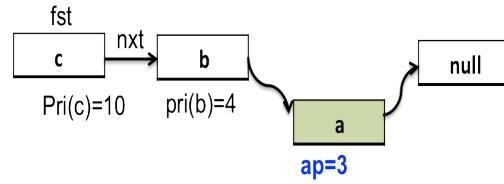

| 8.2  | inserting a node based on its priority to descendingly ordered singly linked list . . . . .                                        | 157 |

# List of Tables

|     |                                                                                     |     |

|-----|-------------------------------------------------------------------------------------|-----|

| 2.1 | Description of the AD patterns.                                                     | 24  |

| 3.1 | Proof statistics of the FreeRTOS models.                                            | 33  |

| 4.1 | Description of flow requirements.                                                   | 50  |

| 5.1 | Data-oriented, Event-oriented, and Constraint-oriented Requirements classification. | 67  |

| 5.2 | Flow Oriented Requirements Classification.                                          | 68  |

| 8.1 | General RTOS Concepts: FreeRTOS, UCOS, eCos, and VxWorks                            | 135 |

# Contents

|                                                                                        |             |

|----------------------------------------------------------------------------------------|-------------|

| <b>Declaration of Authorship</b>                                                       | <b>xiii</b> |

| <b>Acknowledgements</b>                                                                | <b>xv</b>   |

| <b>1 Introduction</b>                                                                  | <b>1</b>    |

| 1.1 Thesis Motivation and Contribution . . . . .                                       | 1           |

| 1.1.1 Summary of Contributions . . . . .                                               | 3           |

| 1.2 What is a Formal Method? . . . . .                                                 | 4           |

| 1.3 B Method . . . . .                                                                 | 5           |

| 1.4 Event-B . . . . .                                                                  | 6           |

| 1.5 Z Specification Language . . . . .                                                 | 8           |

| 1.6 Vienna Development Method (VDM) . . . . .                                          | 10          |

| 1.7 Refinement . . . . .                                                               | 12          |

| 1.8 Comparison of B, Event-B, Z and VDM . . . . .                                      | 13          |

| 1.9 The Motivation Behind Selecting Event-B For Modelling FreeRTOS . . . . .           | 14          |

| <b>2 Techniques in Event-B</b>                                                         | <b>17</b>   |

| 2.1 Introduction . . . . .                                                             | 17          |

| 2.2 Proof Obligations . . . . .                                                        | 18          |

| 2.3 Composition and Decomposition . . . . .                                            | 19          |

| 2.4 Generic Instantiation . . . . .                                                    | 20          |

| 2.5 The Theory Extension . . . . .                                                     | 21          |

| 2.6 Atomicity Decomposition Approach . . . . .                                         | 22          |

| 2.7 UML-B . . . . .                                                                    | 24          |

| <b>3 Experiences, Challenges and Contribution</b>                                      | <b>27</b>   |

| 3.1 Introduction . . . . .                                                             | 27          |

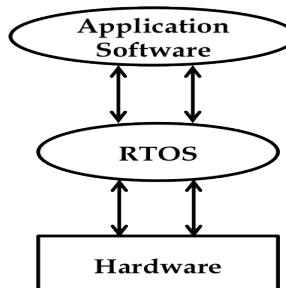

| 3.2 An Overview of RTOS . . . . .                                                      | 28          |

| 3.2.1 FreeRTOS . . . . .                                                               | 29          |

| 3.3 FreeRTOS Models . . . . .                                                          | 30          |

| 3.4 Experiences and Challenges . . . . .                                               | 33          |

| 3.5 Two Approaches Supporting Formal Developments in Event-B . . . . .                 | 37          |

| 3.5.1 An Approach for Reusing Event-B Models . . . . .                                 | 38          |

| 3.5.2 An Approach for Building Traceable Event-B Model from the Requirements . . . . . | 39          |

| 3.6 Related work . . . . .                                                             | 39          |

| <b>4 Staged Approach for Constructing Models from the Requirements</b>                 | <b>43</b>   |

---

|          |                                                                                                                |           |

|----------|----------------------------------------------------------------------------------------------------------------|-----------|

| 4.1      | Introduction . . . . .                                                                                         | 43        |

| 4.2      | Requirements Classification . . . . .                                                                          | 46        |

| 4.3      | Steps for Constructing Traceable Event-B Models . . . . .                                                      | 49        |

| 4.3.1    | Step 1: Classify Requirements . . . . .                                                                        | 49        |

| 4.3.2    | Step 2: Construct Semi-formal Artifacts and Develop Refinement Strategy . . . . .                              | 51        |

| 4.3.2.1  | Stage 1: Use Semi-Formal Artifacts (UML-B, AD, and Structured English) . . . . .                               | 51        |

| 4.3.2.2  | Stage 2: Merging Structured English of a Single Event . . . . .                                                | 53        |

| 4.3.2.3  | Stage 3: Develop Refinement Strategy . . . . .                                                                 | 53        |

| 4.3.3    | Step3: Construct Formal Models . . . . .                                                                       | 55        |

| 4.4      | Related Work . . . . .                                                                                         | 59        |

| 4.5      | Conclusions . . . . .                                                                                          | 62        |

| <b>5</b> | <b>The Application of the Staged Approach for Constructing Queue Management Model</b>                          | <b>65</b> |

| 5.1      | Introduction . . . . .                                                                                         | 65        |

| 5.2      | The Application of the Staged Approach to Construct Queue Management Event-B Model from Requirements . . . . . | 66        |

| 5.2.1    | Step1: Classify Requirements . . . . .                                                                         | 66        |

| 5.2.2    | Step2: Construct Semi-Formal Artifacts and Develop Refinement Strategy . . . . .                               | 69        |

| 5.2.2.1  | Stage1: Use Semi-Formal Artifacts (UML-B, AD, and Structured English) . . . . .                                | 69        |

| 5.2.2.2  | Stage3: Develop Refinement Strategy . . . . .                                                                  | 78        |

| 5.2.3    | Step3: Construct Formal Models . . . . .                                                                       | 80        |

| 5.3      | Conclusions . . . . .                                                                                          | 83        |

| <b>6</b> | <b>Linking Composite Requirements with Composed Model</b>                                                      | <b>85</b> |

| 6.1      | Introduction . . . . .                                                                                         | 86        |

| 6.2      | Task and Memory Event-B Models . . . . .                                                                       | 86        |

| 6.2.1    | Task Management . . . . .                                                                                      | 86        |

| 6.2.1.1  | An Abstract Specification-Some Basic Functionality of Task Management and the Kernel . . . . .                 | 87        |

| 6.2.1.2  | First Refinement- Scheduler States . . . . .                                                                   | 88        |

| 6.2.1.3  | Second Refinement- Task States . . . . .                                                                       | 89        |

| 6.2.1.4  | Third Refinement- Hardware Clock and Timing Properties                                                         | 89        |

| 6.2.1.5  | Fourth Refinement- Delay Operations . . . . .                                                                  | 90        |

| 6.2.1.6  | Fifth Refinement- Clock Overflow . . . . .                                                                     | 91        |

| 6.2.1.7  | Sixth Refinement- Priority . . . . .                                                                           | 93        |

| 6.2.1.8  | Seventh Refinement- Contexts . . . . .                                                                         | 93        |

| 6.2.2    | Memory Management . . . . .                                                                                    | 93        |

| 6.2.3    | Scheme1 . . . . .                                                                                              | 94        |

| 6.2.3.1  | An Abstract Specification- Memory Blocks and Addresses                                                         | 95        |

| 6.2.4    | Scheme2 . . . . .                                                                                              | 96        |

| 6.3      | Description of the Approach . . . . .                                                                          | 97        |

| 6.3.1    | An Example of Shared Event Composition with Shared Entities .                                                  | 99        |

---

|          |                                                                                           |            |

|----------|-------------------------------------------------------------------------------------------|------------|

| 6.3.2    | An Example of Shared Event Composition with Shared Variables Sub-models . . . . .         | 102        |

| 6.3.3    | Simplifying the Connection Between Sub-models with Abstraction . . . . .                  | 105        |

| 6.4      | The Composition of FreeRTOS Specifications . . . . .                                      | 106        |

| 6.4.1    | Requirement COMP1 . . . . .                                                               | 106        |

| 6.4.2    | Requirement COMP2 . . . . .                                                               | 107        |

| 6.4.3    | Requirement COMP3 . . . . .                                                               | 108        |

| 6.4.4    | Requirement COMP4 . . . . .                                                               | 109        |

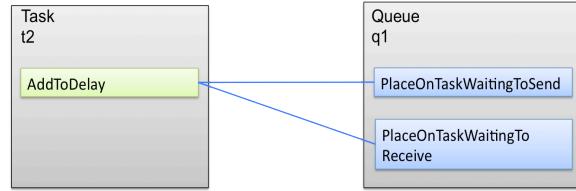

| 6.4.5    | Requirement COMP5 . . . . .                                                               | 110        |

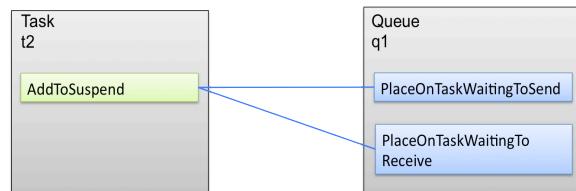

| 6.4.6    | Requirement COMP6 . . . . .                                                               | 111        |

| 6.4.7    | Requirement COMP7 . . . . .                                                               | 111        |

| 6.4.8    | Requirement COMP8 . . . . .                                                               | 112        |

| 6.5      | Conclusions . . . . .                                                                     | 113        |

| <b>7</b> | <b>Reusing Data Refinement Patterns through Generic Instantiation and Composition</b>     | <b>115</b> |

| 7.1      | Introduction . . . . .                                                                    | 115        |

| 7.2      | Description of the Approach . . . . .                                                     | 116        |

| 7.2.1    | Example of a Pattern and Its Instantiation into a Problem Refinement . . . . .            | 119        |

| 7.3      | Theory of Circular Doubly Linked List . . . . .                                           | 122        |

| 7.3.1    | Operators for Inserting an Item to the End of a Circular Doubly Linked List . . . . .     | 122        |

| 7.3.2    | Operators for Removing an Item from a Circular Doubly Linked List . . . . .               | 124        |

| 7.3.2.1  | Inference Rules . . . . .                                                                 | 125        |

| 7.4      | Circular Doubly Linked List Pattern . . . . .                                             | 125        |

| 7.5      | Applying the Proposed Approach to Resume the Development of FreeRTOS Case Study . . . . . | 127        |

| 7.6      | Related Work . . . . .                                                                    | 129        |

| 7.7      | Conclusions . . . . .                                                                     | 130        |

| <b>8</b> | <b>Guidelines for Modelling and Theory Development based on FreeRTOS Experiences</b>      | <b>133</b> |

| 8.1      | Introduction . . . . .                                                                    | 133        |

| 8.2      | Task Management . . . . .                                                                 | 136        |

| 8.2.1    | Process . . . . .                                                                         | 136        |

| 8.2.2    | Process Table . . . . .                                                                   | 136        |

| 8.2.3    | Process Priority . . . . .                                                                | 137        |

| 8.2.4    | Process States . . . . .                                                                  | 138        |

| 8.2.5    | Null Process . . . . .                                                                    | 139        |

| 8.2.6    | Timing Behaviour . . . . .                                                                | 139        |

| 8.3      | Scheduler States . . . . .                                                                | 141        |

| 8.4      | Scheduling and Context Switching . . . . .                                                | 142        |

| 8.4.1    | Context Switch . . . . .                                                                  | 142        |

| 8.5      | Interrupts and Interrupt Service Routines . . . . .                                       | 144        |

| 8.6      | Queue Management . . . . .                                                                | 147        |

| 8.6.1    | Waiting Messages . . . . .                                                                | 149        |

|                   |                                                                                          |            |

|-------------------|------------------------------------------------------------------------------------------|------------|

| 8.7               | Memory Management . . . . .                                                              | 150        |

| 8.8               | Comparison . . . . .                                                                     | 152        |

| 8.9               | Some Tips on Developing Theories in Event-B . . . . .                                    | 154        |

| 8.9.1             | Defining Polymorphic Constants . . . . .                                                 | 155        |

| 8.9.2             | Conditional Expressions . . . . .                                                        | 156        |

| 8.9.3             | Composition of Operators . . . . .                                                       | 156        |

| 8.9.4             | Decomposition of Operators . . . . .                                                     | 156        |

| 8.9.5             | How to Check the Validity of the Operators . . . . .                                     | 158        |

| <b>9</b>          | <b>Conclusions and Future Work</b>                                                       | <b>159</b> |

| 9.1               | Summary of Contributions . . . . .                                                       | 160        |

| 9.1.1             | Building Traceable Event-B Model from Requirements . . . . .                             | 160        |

| 9.1.2             | Linking Composite Requirements with Composed Model . . . . .                             | 160        |

| 9.1.3             | Reusing Data Refinement Patterns through Generic Instantiation and Composition . . . . . | 161        |

| 9.2               | Future Work . . . . .                                                                    | 162        |

| 9.2.1             | Reverse Engineering of Structured Languages to Event-B . . . . .                         | 162        |

| 9.2.2             | Verifying Linear Temporal Properties . . . . .                                           | 162        |

| 9.2.3             | Evaluate the General Guidelines for Modelling RTOS Kernels . . . . .                     | 163        |

| <b>A</b>          | <b>FreeRTOS Requirements</b>                                                             | <b>165</b> |

| A.1               | Task management requirements . . . . .                                                   | 165        |

| A.2               | Queue management requirements . . . . .                                                  | 169        |

| A.3               | Memory management requirements . . . . .                                                 | 170        |

| A.4               | Composition requirements . . . . .                                                       | 170        |

| <b>B</b>          | <b>Queue Event-B Model</b>                                                               | <b>173</b> |

| <b>References</b> |                                                                                          | <b>183</b> |

## Declaration of Authorship

I, **Eman Alkhammash**, declare that the thesis entitled *Towards a Systematic Process for Modelling Complex Systems in Event-B* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: [8]

Signed:.....

Date:.....

## **Acknowledgements**

First praise is to ALLAH, the Almighty, on whom ultimately we depend for sustenance and guidance.

I am heartily thankful to my supervisors, Dr Corina Cîrstea and Prof Michael Butler whose encouragement, guidance, support and patience made this thesis come true.

I would also like to thank my thesis reviewer, Dr Thai Son Hoang from ETH Zurich, for his time and efforts while reviewing the thesis and providing with his invaluable comments to improve this work.

This PhD would not have been possible without the support of my beloved parents, and my dear husband, my sisters and brothers, and my friends. To all these people, I cannot thank you enough for your support over the course of my PhD.

# Chapter 1

## Introduction

Formal methods have been used for constructing the models of complex systems. There are a number of different formal method languages such as B [2], Event-B [4], Z [79], and VDM [22]. The research work focuses on methods that assist in the formal development of the systems and cover issues such as the requirements and reusability. The quality of requirements has a major influence on the construction and validation of formal models, whereas the reuse of the formal models has the potential to reduce the time and effort for developing systems. This chapter introduces the contribution of this thesis and presents relevant background on formal methods. Section 1.1 outlines the thesis motivation and contribution. Section 1.2 is an introduction on formal methods. Sections 1.3, 1.4, 1.5, and 1.6 give an overview of several formal methods including B, Event-B, Z, and VDM. Section 1.7 describes refinement. Section 1.8 shows comparison of B, Event-B, Z, and VDM. Finally, Section 1.9 describes the motivation behind selecting Event-B for modelling FreeRTOS.

### 1.1 Thesis Motivation and Contribution

One of the activities that addresses the Grand Challenges pilot projects, concerns with the development of approaches supported by tools that cover all the aspects of verified software construction [41, 85].

This thesis attempts to address some challenges in modelling complex systems. The challenges cover three main issues: managing the complexity of large systems, bridging the gap between the requirements and the formal models, and supporting reusability of the models and their respective proof obligations. This thesis presents general techniques for addressing the challenges that have emerged from the FreeRTOS case study.

**FreeRTOS** [11, 10] is a mini real time kernel for small embedded real time systems. The development is realised with Event-B and the Rodin tool [6, 5, 3, 17]. **Event-B** is a

formal method used for specifying and reasoning about systems. The **Rodin platform** is an open tool that supports the Event-B specification and verification.

Different modelling techniques are investigated throughout the modelling process which are generic instantiation [72], the theory feature [18], UML-B [77], atomicity decomposition approach [15, 33], and composition [73]. The **generic instantiation** technique facilitates the reuse of Event-B models; it provides means of instantiating generic models in a way that ensures the proofs associated to a generic model remain valid in the instantiated one. The **theory feature** is another technique which provides facility to extend the Event-B language and the proving infrastructure. It allows the development of operators, new data types, rewrite and inference rules, and polymorphic theorems. **UML-B** is a graphical modelling environment that allows the development of an Event-B formal model through the use of UML graphical notation. The **atomicity decomposition** approach provides a graphical notation to structure refinement and control flow between the events. Finally, the **shared event composition** approach allows sub-components to interact via synchronisation over shared events.

The first step towards achieving the research goal is to choose the appropriate development strategy to manage the complexity of FreeRTOS development. We address complexity by choosing a compositional strategy to build specification of FreeRTOS case study. This involves the decomposition of the FreeRTOS development into components that are easy to manage and then composing these components to show the overall behaviour of the system. Hence, FreeRTOS requirements are analysed into three main set of requirements, each of which corresponds to a particular FreeRTOS components: task, queue, and memory. The division of the requirements based on the system components assist in managing the complexity of the system and allows to focus on modelling a particular component separately without considering its interaction with the other components. This in effect simplifies the development of the system and helps in producing loosely coupled modelling components that can easily be reused in the development of different systems. The interaction between the separated components then became an explicit development task. Hence, another set of requirements called the composition requirements were introduced to show how the different FreeRTOS components are linked together.

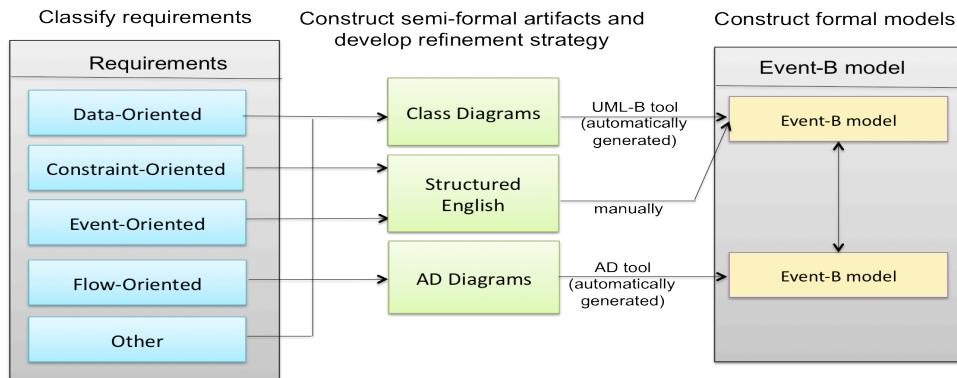

Our focus after that was directed to find a way to bridge the gap between the requirements and the Event-B formal models and retain traceability to requirements in Event-B. In order to achieve this purpose, we investigated an approach that consists of three main steps: The first step focuses on categorizing the requirements based on Event-B structure. The second step focuses on using semi-formal artifacts described in UML-B and AD diagrams to represent the requirements. Representing requirements using semi-formal artifacts is reasonably simple, and at the same time the movement from the semi-formal artifacts to Event-B is straightforward. The third step is to use the UML-B

tool and the AD tool to generate the Event-B models. This approach was successfully used to build traceable Event-B model for some features of the queue component.

Moreover, three separate specifications: task, queue, and memory were constructed in Event-B and some general guidelines for modelling the FreeRTOS kernel were drawn from our experiment.

The composition task was carried out based on shared-event composition technique; composition requirements assist in selecting which events to be composed to show the overall behaviour of the system. Since, shared event composition is proved to be monotonic [74], we were able to data refine the models individually.

The basic data structures of FreeRTOS are linked lists. This forces us to think of a systematic approach to reuse the modelling patterns of the linked lists. Therefore, we dedicated some time to study the possibility of building reusable modelling patterns for linked lists that can be used to resume the specification of abstract structure of FreeRTOS models “set” to the concrete data structures of linked lists. As there is little support for modelling the linked lists, we dedicated time to the development of theories that aid the modelling of linked lists using the theory feature. The developed linked list theories have been used to build reusable modelling patterns for linked lists in Event-B. We then focussed on the task of the incorporation of the developed modelling patterns to resume the specification of FreeRTOS models. Therefore, we investigated an approach based on generic instantiation and shared event composition approach to perform the incorporation task. Generic instantiation technique is used to instantiate the modelling pattern. The composition technique is applied to integrate the instantiated pattern into the problem. The approach has been used successfully to refine the abstract “set” of FreeRTOS models to linked list structures. It allows us to incorporate several instances of a modelling pattern into a development with the advantage that all the refinement steps required for the development of the pattern can be incorporated into the development in a single step. This is because generic instantiation allows us to instantiate the pattern several times and the composition technique allows us to incorporate different refinement levels of one or more patterns into the development.

### 1.1.1 Summary of Contributions

The following points summarise the main contributions of our work:

- Adopted compositional strategy to manage the complexity of systems development. This involves the process of classifying requirements into a set of requirements for each individual component, and a set of requirements for the compositional purposes. The individual components then are modelled separately in Event-B, and then are composed based on the composite requirements using the composition technique.

- Investigated an approach for constructing traceable Event-B models based on UML-B and AD approaches. The investigated approach bridges the gap between requirements and the Event-B models and enables the validation of the models against their corresponding requirements.

- Proposed an approach for reusing the modelling *patterns* in Event-B based on composition and generic instantiation techniques. The approach has been used to carry out the data refinement of the abstract “set” of FreeRTOS specifications to concrete linked lists structures.

We also have other sub-contributions as follows:

- Constructed Event-B models for FreeRTOS using compositional strategy. Three Event-B models have been developed that correspond to the main components of FreeRTOS: task, queue, and memory. The constructed models can contribute to the Verified Software Repository [41, 85].

- Devised general modelling guidelines for RTOS kernels in Event-B. The guidelines introduce Event-B modelling concepts for the basic features of an RTOS such as scheduling, memory allocation, and interrupt handling.

- Developed theories with a set of reusable operators and rules of inference for linked lists using the theory feature. The linked list theories can be used to supply a library of Event-B theories in the future.

## 1.2 What is a Formal Method?

Formal methods are techniques used in the specification, development and verification of complex systems based on mathematics and formal logics [4].

There are a wide range of formal methods, frequently supported by tools, each of which is suited to a different domain and the emphasize on different aspects of the systems based upon the adoption of different maths and formal logics. Formal specification languages and formal verification are two types of formal methods. Formal specifications are formal description of what systems should do, whereas the formal verification is a mathematical proof of the systems correctness. Formal specifications are normally based on set theory and first order predicate calculus. Event-B, Z and VDM are some dominating formal specification languages. Formal verification, on the other hand, such as model checking [20] are based on temporal logics. Various projects have been successfully developed using formal methods including those pertaining to air traffic control, railway signalling, and smart cards applications [87, 9, 12].

The adoption of the formal method approach for systems development has many advantages; one such advantage is that one is allowed to think more carefully and critically about the system being specified before becoming too much involved in the coding. This leads to a deeper understanding of the system and forces a detailed analysis of the requirements, thus enabling the production of software that meets the requirements. Formal methods provide precise and unambiguous system specifications. Many proofs have to be performed in order to ensure that the final system is “correct by construction”. Another important benefit is the ability to detect defects earlier in the software life-cycle, which enables the production of a reliable system. Formal methods can be applied to different aspects of systems and throughout the various phases of the software cycle. It encourages the identification of certain properties and analysis of the system before any code is written, and this is an advantageous feature of formal methods which is not replicated in other software approaches.

This chapter highlights four formal methods: B [2], Event-B [4], Z [79], and VDM [22] with emphasis to Event B as it is the language employed to the model of the FreeRTOS case study.

### 1.3 B Method

The B-method [2] (classical B) is a state-based method developed by Abrial in the mid 1980s. It is used for the formal development of software systems. The B method uses the set theoretic constructs such as sets, relations and functions to define variables and invariants (constraints of variables). There are a number of safety-critical system applications which have been developed successfully in classical B such as *Paris Metro Line 14* [12].

AtelierB [21] is a set of tools that provide support for writing B specification including static checkers, automatic and interactive provers, and code generation.

B does not include facility to support user-defined extension of the mathematical language and theory of B. Nevertheless, Event-B (an extension of the B formalism) includes facility of extending the Event-B language and proving infrastructure, and allows users to define new operators and data types.

```

MACHINE M

SETS NAME

VARIABLES name, id

INVARIANTS

name ⊆ NAME

id ∈ name → ID

INITIALISATION

name :=  $\emptyset$

id :=  $\emptyset$

OPERATIONS

Add_Student(s,i)=

PRE

s ∈ NAME \ name

i ∈ ID \ ran(id)

THEN

id := id ∪ {s ↦ i}

name := name ∪ {s}

END

Delete_Student(i)=

PRE

i ∈ ran(id)

THEN

id := id ▷ {i}

name := name \ {id-1(i)}

END

```

Figure 1.1: An example of B specification.

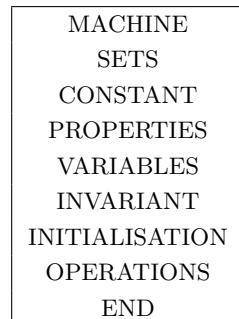

The structure of B method abstract machine is given above. The **MACHINE** clause specifies the name of the machine, The **SETS** clause specifies all the sets which are used in the machine. The **CONSTANT** clause specifies all the constants which are used in the machine. The **PROPERTIES** clause specifies the constraints on the constants and the sets. The **VARIABLES** clause specifies all the variables which are used in the machine. The **INVARIANT** clause specifies the properties of the variables that must always remain true such as the type of the variables. The **INITIALISATION** clause specifies the initial state of the machine. The **OPERATIONS** clause specifies operations that can cause the variables to change their values.

Figure 1.1 shows a simple example of a B model that describes a student database with two operations *Add\_Student* which adds a student to the student data base and *Delete\_Student* operation that deletes a student from the student database.

There are two variables in this model: *name* that is defined as a set and *id* that is defined as a function that maps names to their ids. There are two operations in this machine *M*: *Add\_Student* operation and *Delete\_Student* operation. The **PRE** clause identifies the preconditions which required to hold in order to execute the actions within a **THEN-END** block.

## 1.4 Event-B

Event-B [4] is a successor language of B developed by Jean-Raymond Abrial. Event-B uses set theory and first order logic to provide a formal notation for the creation of models of discrete systems and the undertaking of several refinement steps. An abstract Event-B specification can be refined by adding more detail and bringing it

- (a) when  $S(c, v)$  then  $R(v, c, v')$  end

- (b) any  $t$  where  $S(t, c, v)$  then  $R(v, t, c, v')$  end

- (c) begin  $R(c, v')$  end

Figure 1.2: The outline of an event

closer to an implementation. A refined model in Event-B is verified through a set of proof obligations expressing that it is a correct refinement of its abstraction. Event-B may be used for parallel, reactive or distributed systems development, and has shown success in the development of different complex real-life systems [16, 9]. The Event-B notation contains two constructs: a context and a machine. The context is the static part in which we can define the data of the model: sets, constants, axioms that are used to specify assumptions about sets and constants, and theorems that are used to describe properties derivable from the axioms. The dynamic and functional behaviour of a model is represented in the machine part, which includes variables to describe the states of the system, invariants to constrain variables, theorems to describe properties that follow from the invariants, and events to trigger the behaviour of the machine. The outline of an event takes one of the three forms described in Figure 1.2. In (a), the body of the event is fired only when the commanded guard is true.  $R(v, c, v')$  describes the relationship between the values of the variables before and after the event is executed. The second form (b) takes a local variable,  $t$ , that satisfies the guard  $S(t, c, v)$ , and then executes the body  $R(v, t, c, v')$ . The third form (c) is free of a guard and can be used for initialisation.

Rodin [6, 5, 3, 17] is a platform used in the development of Event B models. Rodin exhibits many features and can be extended further with supportive plug-ins; for example, ProB [55] is an example of a Rodin plug-in which provides an automatic animation and model checking of Event B models. The theory plug-in [18] allows users to define reusable polymorphic operators, data types, rewrite rules, inference rules and polymorphic theorems. Shared event composition plug-in [73] allows the interaction between the sub-models through the composition of events. The model decomposition plug-in [75] allows to decompose a model into several sub-models. The generic instantiation plug-in [72] allows reusability of existing models by instantiating the model and ensuring that the proofs associated to an existing model remain valid in an instantiated development. The atomicity decomposition plug-in [33] controls the order between the events (flows) and demonstrates the relationship between refinement levels.

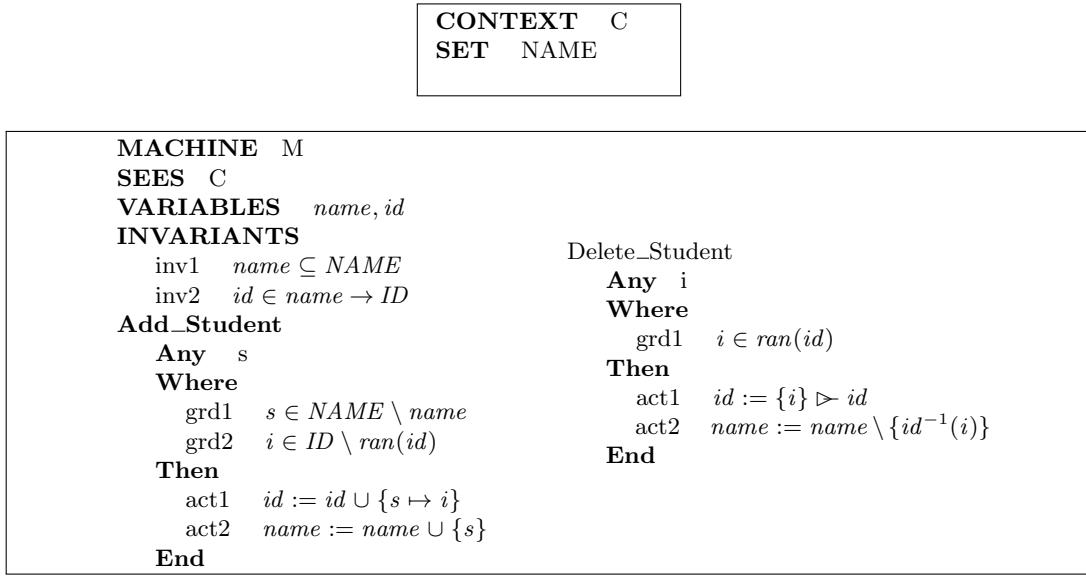

We use the student database example here to describe the two events: *Add\_Student* and *Delete\_Student* event in Event-B.

There are two variables in this machine  $M$ :  $name$  that is defined as a subset of the carrier set  $NAME$ , the carrier set  $NAME$  is defined in the context  $C$ . The machine  $M$  explicitly sees the context  $C$ , so it can access the context  $C$  components (Here  $NAME$  set).

Figure 1.3: An example of Event-B specification.

There are two events: *Add\_Student* and *Delete\_Student*. The guards are the necessary conditions for the event; they must hold in order for the actions to be performed.

## 1.5 Z Specification Language

Z [79] is a formal specification language based on first order predicate logic and Zermelo-Fraenkel (ZF) set theory. The language was first developed at the Oxford University in the 1980s. Z combines two sub-languages: mathematical language and schema language. States, properties and operations of the system are described by mathematical language, whereas the schema language is used for structuring the specification. A Z specification is constructed as a series of schemas. Schema declarations contain state schemas and operation schemas. State schemas describe states, the relationship between them, as well as the restriction (constraining predicates) on them.

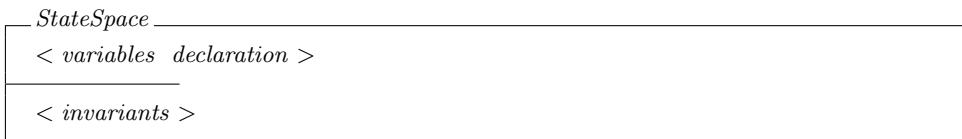

The structure of state schemas contains two parts: the part above the central line represents the variables declaration part and the variables local to the schema; and the part below the line represents the predicate part of the schema that specifies the invariants or the relationships that remain true in every state of the system. Operation schemas, on the other hand, describe the changes in these states before and after executing the operations. The Schema Calculus offers operators such as conjunction, disjunction, composition, etc that are used to construct a large Z specification from some existing

schemes. Schema can also be extended easily by adding new components, additional invariants and operations.

Z contains a mathematical tool-kit [79] of useful definitions built on top of the basic language. This tool-kit includes a collection of types and operators for sets, products, relations, functions, and sequences. The following schema illustrates the student database example as a Z specification focusing on the addition and deletion of student's information.

```

StudentDB _____

name :  $\mathbb{P}$  NAME

studentId : NAME  $\rightarrow$  ID

_____

name = dom studentId

```

This schema describes the state space of the system; it contains the variable declarations and invariants. We have two variables: *name* of type *NAME* and *studentId* which is a function that maps a student's name to its id. We have one invariant to indicate that the set *name* is the same as the domain of the function *studentId*, and it should be maintained by every operation on it. This invariant allows the value of the variable *name* to be derived from the value of *studentId*.

```

AddStudent _____

$\Delta$ StudentDB

name? : NAME

id? : ID

_____

id?  $\notin$  ran(studentId)

studentId' = studentId  $\cup$  {name?  $\mapsto$  id?}

name' = name  $\cup$  {name?}

```

```

DeleteStudent _____

$\Delta$ StudentDB

id? : ID

_____

studentId' = studentId  $\triangleright$  {id?}

name' = name  $\setminus$  name{ id? }

```

These two schemas are operation schemas; the first adds new entry where *name?* and *id?* are input parameters. The second, *DeleteStudent* operation, removes the entry associated with a particular id (*id?*).

The  $\Delta$  convention indicates that states do change; the variables  $name'$  and  $id'$  are the states after the change, whereas the variables  $name$  and  $id$  are the states before the change.

## 1.6 Vienna Development Method (VDM)

VDM [22, 71] is a popular formal method that was developed in the 1970s by Cliff Jones and Dines Bjørner at IBM labs in Vienna. The method is used to model systems at different levels of abstraction, hence it combines a specification language and an approach to refine the specifications into code. VDM has been successfully used in many projects, such as the development of compilers and in disciplines of programming language semantic such as CHILL, Modula-2, and Ada [48].

There are three dialects of VDM: VDM-SL [36], VDM-RT [81, 82] and VDM++ [35]. VDM-SL is a specification language standardised by the International Standards Institute (ISO) in the 1990s. VDM-RT is a version used to model real time embedded and distributed systems and VDM++ is an object-oriented extension based on VDM-SL that is used for the specification of object-oriented models. VDM is supported by strength tools called VDMTools [1] that were developed by IFAD in the 1990s, and are now owned by CSK Systems.

The VDMTools provide a type checker, theorem prover, and a facility for testing specifications. The tools can be used for producing an executable code of a subset of VDM through the automated code generation feature, or the simulation of model feature.

VDM uses modules for system specifications. The structure of a module is shown as follows:

```

module Module_Name

...

definition types

...

state

....

functions

...

operations

...

end Module_Name

```

Figure 1.4: The structure of VDM-SL module.

```

types

Name=String;

String=seq of char;

ID= nat;

StudentID= map Name to ID;

functions

AddStudent: Name*ID*StudentID -> StudentID

AddStudent(name, id, studentID) ==

studentID munion {name | -> id}

pre id not in set ran studentId;

DeleteStudent: ID*StudentID -> StudentID

DeleteStudent(id, studentID) ==

studentID ▷ { id}

pre id in set ran studentId;

```

Figure 1.5: An example of VDM-SL specifications

The **type** clause is used to specify the various types to be used in the specification. The **state** clause specifies the state definition of the global variables which can be referenced inside the operations. The **operation** clause specifies the behaviour of a system. The **functions** clause defines the functionality of the system used to specify a rule for obtaining a result from zero or more arguments. The difference between operations and functions is that, operations can manipulate both global and local variables but functions can not access global variables or define local variables.

Figure 1.5 shows the simple student database example in VDM-SL that focuses on two operations: *AddStudent*, which adds a new entry to the system, and *DeleteStudent*, which deletes a student's entry from the system.

The specification above has two parts: data definition part and the function definition part. In the data definition part, *Name* is defined as a string, *ID* is defined using a basic data type *nat* which stands for natural numbers, *StudentID* is defined from other types by “mapping type” constructor that consists of two parts domain data type *Name* and range data type *ID*.

The function part consists of two functions, *AddStudent* to add a student to student database. *DeleteStudent* to delete a student from the student database.

The definition of a function in function block of a VDM-SL specification, may include a signature, an explicit function definition, and pre/post conditions. The signature part shows the inputs and outputs data types. For example, the input parameter data types of *AddStudent* function are *Name*, *ID*, and *StudentID* and the output data type is *StudentID*. “munion” is used to add student to *ID* mapping whereas  $\triangleright$  is used to delete a student from *ID* mapping.

## 1.7 Refinement

Refinement [29, 7] refers to the process of transforming the abstract specification to a more concrete specification through a series of refinement steps. Refinement assists in managing the complexity of a system being developed. The core functions of a system can be focused on in an abstract model whereas other aspects of the system can be focused on through different refinement levels. The posit-and-prove and transformational are two main refinement styles [14, 53]. In the first style, a refined model is verified through a set of proof obligations to prove that it is a correct refinement of its abstraction. This is done using theorem provers or model checkers (i.e.  $S \sqsubseteq S'$  if and only if  $S'$  satisfies all desired properties that  $S$  satisfies). The latter style, however, is performed by transforming the abstract model into a concrete one by applying transformation rules in the abstract model to automatically extract a concrete model satisfying its abstraction.

There are also two aspects of refinement to make a model closer to implementation: horizontal refinement and vertical refinement [4]. Horizontal refinement or superposition is also known as a feature augmentation refinement, and centres on enriching the model gradually by integrating the system's details through different refinement steps [4]. In the horizontal refinement stage, the specifier follows the system requirements document and extracts the variables and events, formalising them through several steps of refinement. It is possible to add new variables and guards, or strengthen guards in a refined model. It is also possible to add new actions to an event or even extra events. This kind of refinement is usually finalised when the specifier reaches the point where there is no further requirement element left to be formalised.

Vertical refinement or data refinement is a type of refinement in Event-B which centres on the replacement of the abstract model with more design details in each refinement step down to an implementation [4]. Data refining finite set variables to array structure is a typical example of the vertical refinement [4]. In this kind of refinement, we can eliminate unnecessary variables of the prior models and identify gluing invariant(s) that relate the new concrete variables and the abstract ones [4].

The concrete level of the model must reflect the behaviour of the abstract level to ensure the correctness of the system. This can be achieved through the validation of the refinement level via specific proofs, called the refinement proofs.

The refinement in classical B is one to one; each abstract operation is refined by only one concrete operation and it is not allowed to introduce new operations. In Event-B, several different refined events may refine the same abstract event. It is also possible in Event-B to introduce new events during the stepwise refinement steps. Z employs some rules for the operation and data refinement. The validity of the refinement is ensured by simulations. A simulation is a representation of one state by another. It combines some rules to validate a refinement. There are two ways of simulations: downward simulation

(ensures the correctness of refinement from an abstract state to a concrete one) and upward simulation (ensures the correctness of refinement from a concrete state to an abstract one) [86]. The refinement mechanism in VDM is done through data reification and operation decomposition; data reification maps the abstract data types to more concrete ones, while operation decomposition is performed later and is used to map operations and functions to algorithmic representations [22].

## 1.8 Comparison of B, Event-B, Z and VDM

B, Event-B, Z, and VDM are model based languages that view a system as a state machine with a set of states and a collection of operations over these states. Event-B, Z and VDM are different but they all describe a system precisely as a mathematical entity and use set theory and first-order predicate logic. This section gives a comparison of Event-B, Z and VDM in terms of syntactic changes, data types, tool support and mathematical extension and refinement.

**Syntactic Changes:** As mentioned previously, the syntaxes differ between B, Event-B, Z, and VDM. In what follows, we will mention two examples of the most obvious syntax changes between the three languages. The first example is of state changing specification, Z uses prime variables to distinguish the states of the model after change. B and Event-B do not use specific symbols to denote the initial value of the variable before and after change. VDM, however, uses hooked variable for the before state and unhooked variable for after state.

The second example is of inputs and outputs specification, B and Event-B do not have any explicit way of distinguishing inputs from outputs. Input variable names in Z, however end up in “?” whereas output variable names end with “!”. In VDM *rd* “read only” is used for states that are not allowed to be changed and *wr* “write” keyword is used for states that can change.

**Data types:** The basic data types in B, Event B and Z are sets and relations. VDM does not have the notion of relation data type and consequently it does not support relational image which Z and Event-B do support.

VDM and Z include record types and B does not; however, in Event B, it is possible to specify record types following the Evans and Butler approach [32].

VDM has different data types such as character type that are not found in Z, B and Event-B.

**Tool Support:** Z has some proof tools such as Proofpower-Z [54] and Z/EVES [66] theorem prover. AtelierB is a set of tools for B formalism that provides syntax checker, automatic and interactive provers, and code generation. RODIN is a platform used

for developing Event-B models that provides support for refinement and mathematical proof. It has different supportive plug-ins such as proof obligation generator, automated and interactive provers, theory plug-in that provides capabilities of mathematical extension in Event-B language and the proving infrastructure, and moreover RODIN offers code generation plug-in that aids in translating Event-B into a C or Ada code. VDM-Tools support VDM and include set of tools support software development and provides a bunch of features such as a type checker, document generator, theorem prover, and code generation to C++ or Java.

**Mathematical Extension:** B lacks the ability to extend the B mathematical language; Event-B, on the other hand, adopts theory plug-in, which is a recent feature providing support for extending Event-B language and proving infrastructure. It allows the development of new data types, set of operators, inference and rewrite rules, and theorems.

Z has an extensible mathematical tool-kit that provides a library of standard mathematical notions of operators and data types useful for building a system specification.

VDM, on the other hand, is a rich language of operators and data constructors such as union, sequences and record types from which user-defined data types can be built. It also has a large expression and statement language such as if-then-else and while-do.

**Refinement:** With respect to the refinement, operations in B, VDM and Z are “refined” on a one-to-one basis, therefore, one abstract operation is refined by only one concrete operation. In Event-B, however, an abstract event can be refined by one or more concrete events. It is also possible in Event-B to introduce new events (stuttering steps) in the refinement step.

## 1.9 The Motivation Behind Selecting Event-B For Modelling FreeRTOS

Event-B is a natural candidate for the FreeRTOS case study. We chose Event-B to develop FreeRTOS because Event-B is a stepwise formal method which has a platform supported with various plugins. The stepwise methodology allows the complexity to be managed through several refinement steps. Rodin, the platform for Event-B, is supported by useful plugins. As FreeRTOS uses complex data structures (circular linked lists), we make use of several plug-ins that facilitate building and reusing complex formal models involving complex data structures such as linked lists. We use the theory plug-in to develop reusable data structures including operators, polymorphic theorems, and inference rules. Generic instantiation is used to create an instance of a generic model while preserving the proofs associated with the generic model. A composition technique is used to compose the separated modelling components into a single model. We also

make use of the atomicity decomposition technique to manage flows between events and organise refinement steps. We also combine several techniques in Event-B to propose new approaches that facilitate building traceable formal models and support the reuse of Event-B modelling patterns. Chapter 4 and chapter 7, outline respectively an approach for building traceable Event-B models and an approach for reusing Event-B modelling patterns.

# Chapter 2

## Techniques in Event-B

This chapter describes some of the techniques in Event-B used in this thesis. The techniques cover: proof obligations, shared event (de)composition, generic instantiation, the theory definition, the atomicity decomposition and UML-B.

### 2.1 Introduction

This chapter presents relevant technical background of some techniques in Event-B which are adopted in the research. During the development of FreeRTOS, we adopted a number of techniques in Event-B such as: (de)composition, generic instantiation, the theory feature, the atomicity decomposition and UML-B. Applying the decomposition technique results in obtaining simpler models and enables the developer to focus on certain aspects of an Event-B model. For the purpose of developing reusable modelling component “patterns”, generic instantiation technique provides us with a mechanism for instantiating Event-B models in a way that ensures the validity of the instantiated model proofs. On the other hand, the theory technique provides us with the facility of defining a set of reusable operators, polymorphic theorems, rewrite and inference rules. The atomicity decomposition approach provides a graphical notation to illustrate the refinement structures and assists in the organisation of the refinement levels. The UML-B provides UML graphical notation that enables the development of an Event-B formal model. Finally, the shared event composition allows sub-components to interact via synchronisation over shared events to show the overall behaviour of the FreeRTOS. Chapter 4 and Chapter 7 present new approaches for bridging the gap between the requirements and the formal models and support reusability in Event-B using some existing Event-B techniques.

Section 2.2 to section 2.7 describe the proof obligations, the composition and decomposition techniques, the generic instantiation technique, the theory feature, the atomicity decomposition, and the UML-B.

## 2.2 Proof Obligations

A proof obligation is a mathematical formula that requires to be proven, in order to ensure the correctness of an Event-B model. Proofs in Event-B are constructed using a number of sequents. A sequent is of the form  $(H \vdash G)$ , where  $H$  is a hypothesis that contains a finite set of predicates and  $G$  is the goal. The proofs of the sequent are carried out using inference rules that prove that the goal is a consequence of the hypotheses. The POs can be classified into consistency and refinement POs. In order to check the consistency of an Event-B machine, three main proof obligations should be proven true for each event: the well-definedness PO (WD), the event feasibility PO (FIS) and the invariant preservation PO (IP). The well-definedness PO ensures that invariants, guards, events, axioms, and variants (used to prove that a convergent event do not take over the execution) are well defined, for instance, in order to prove the well-defineness of the cardinality of a set  $s$ :  $card(s)$ , the set  $s$  must be a finite set. The event feasibility states that it should be possible to execute an event from any state when both the machine invariant and the event guard hold. The invariant preservation states that the invariant should always be maintained. On the other hand, there are several proof obligations generated for refinement. Here we mention three important POs for refinement: the guard strengthening PO (GRD), the action simulation PO (SIM) and the variant decreasing PO (VAR). The guard strengthening PO ensures that the concrete guard in the refined event is stronger than the abstract one. The action simulation PO ensures that the concrete event action simulates the abstract event actions. Finally, the variant decreasing PO ensures that the new convergent event reduces the variants to ensure that the convergent event do not take over the execution. The variants are defined as an integer number or a finite set and has to become smaller each time the convergent event is executed to prove that the convergent events do not execute forever.

The POs are generated by the proof generator and can be discharged either automatically or interactively. The automatic theorem prover discharges many proofs automatically, however, it is possible that some POs are not discharged automatically, in which case they can be discharged by the user using the interactive prover.

Assuring consistency of requirements is important. The properties of the system driven by requirements are encoded as invariants in Event-B model. The invariants must not contradict each other. Proving that an invariant is always true for a given Event-B model through initialisation and event consistency POs ensures consistency (i.e. Absence of contradiction from the invariants). However, adding more invariants to an Event-B model may add inconsistency, but, the standard POs will detect that and it can be fixed.

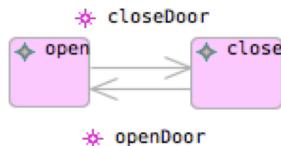

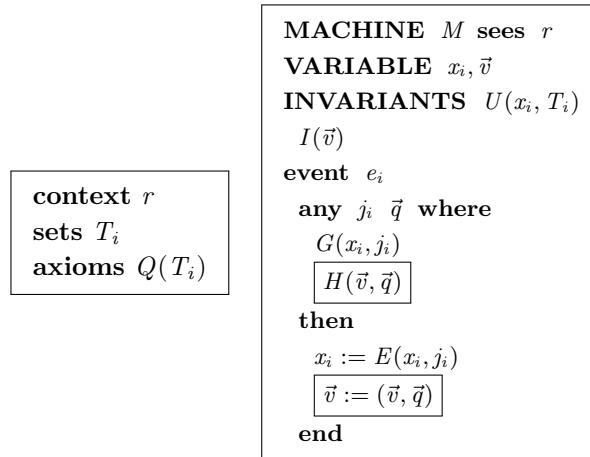

## 2.3 Composition and Decomposition

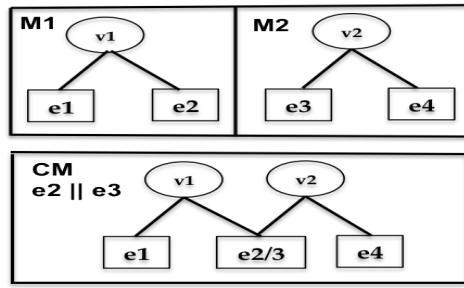

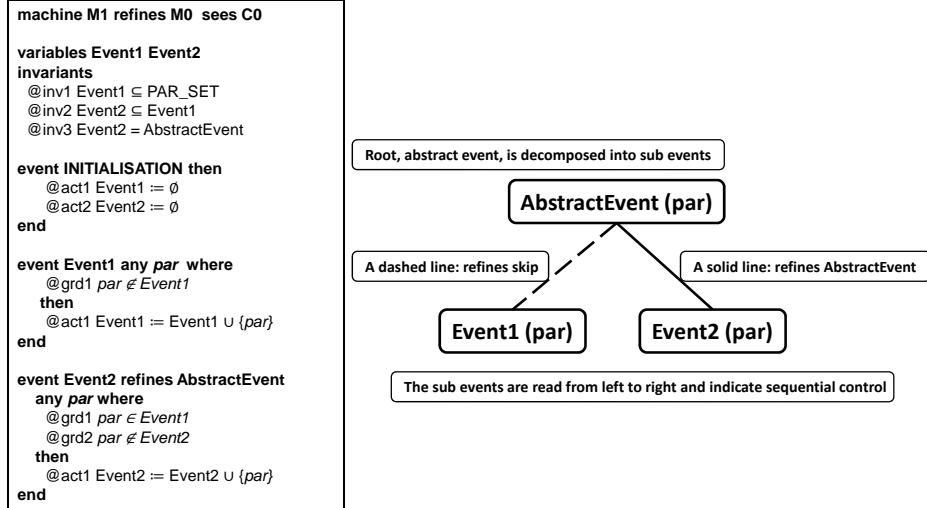

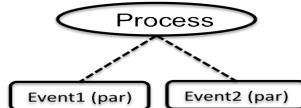

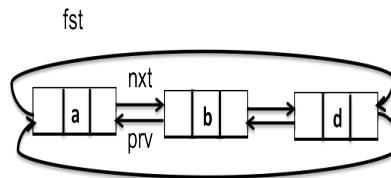

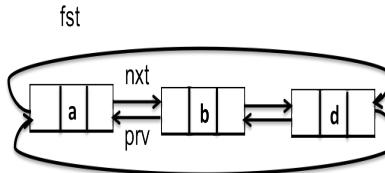

Composition [73] is the process of composing several sub-models in a variety of styles. Composition has the potential of model reusability where it provides a way of constructing specifications as a combination of other different specifications. We focus on shared event composition style [73]. In this style, sub-models interact through synchronised events. Several events can be composed in a single event. The composed event includes the conjunction of guards of sub-model events and combines the actions of sub-model events. The approach has a restriction that prevents the sub-models to include any shared variables. A tool has been developed to support this style of composition in Rodin [73].

Figure 2.1: Shared event composition style.

Figure 2.1 illustrates this style; suppose we have a model  $M1$  that has events  $e1, e2$  with variable  $v1$ . Model  $M2$  has events  $e3, e4$  with variable  $v2$ . Events  $e2$  and  $e3$  can be synchronised since  $e2$  updates  $v1$  and  $e3$  updates  $v2$  and  $v1$  and  $v2$  are independent variables.

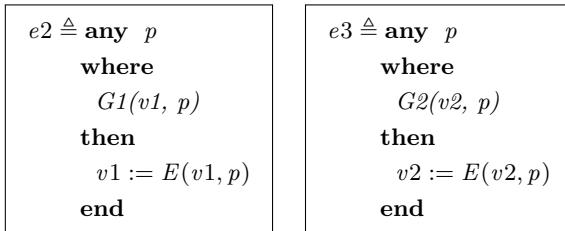

Event  $e2$  in  $M1$  and event  $e3$  in  $M2$  have the following form:

Therefore,  $e2$  from model  $M1$  and  $e3$  from model  $M2$  are composed. The resulted composed model  $cm$ , therefore, share the two independent variables:  $v1$  and  $v2$ .

The resulted composed event has the following form:

```

$e2 \parallel e3 \triangleq \text{any } p$

where

$G1(v1, p)$

$G2(v2, p)$

then

$v1 := E(v1, p)$

$v2 := E(v2, p)$

end

```

Composition may also be applied in reverse in a top-down way by factorising a model into a composition of smaller models. We refer to this as decomposition. The decomposition approach is used to divide a model into sub-models that can be refined separately than the whole. Large system models involve a large number of features (state variables and machine events) which are extended throughout the refinement steps. As the model becomes larger, some state variables and machine events are considered in the next level. Thus, decomposition [7] is used as a means of dividing the system into small and manageable parts that ease dealing with the whole system.

Event-based decomposition is a style of decomposition proposed by Butler [74]. In this style, the machine events are split into sub-models and variables can not be shared between the sub-models. Figure 2.1 can be used to illustrate this style. The modeler can start with the model  $cm$ , and then decomposes it into two sub-models  $M1$  and  $M2$ . Where variables  $v1$  and  $v2$  of model  $cm$  are partitioned between  $M1$  and  $M2$  and event  $e2/3$  is split into two events  $e2$  and  $e3$ . Event  $e2$  updates variable  $v1$  and therefore is located in  $M1$  whereas event  $e3$  updates variable  $v2$  and is located in  $M2$ .

A decomposition plug-in [75] has been developed for the Rodin tool which can be used to support event based decomposition.

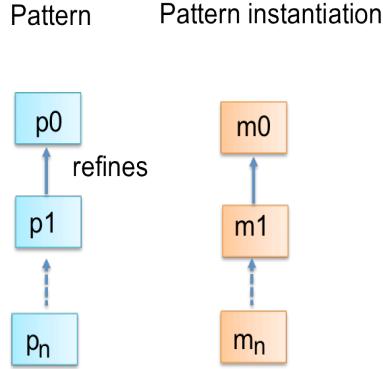

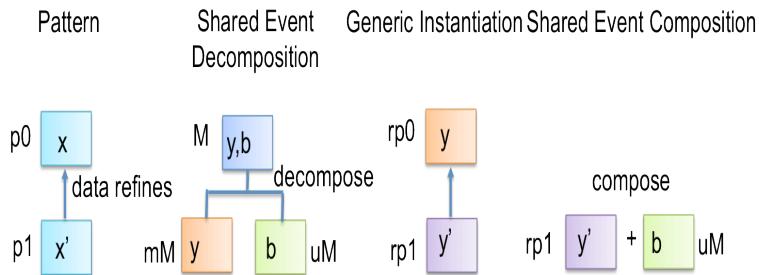

## 2.4 Generic Instantiation

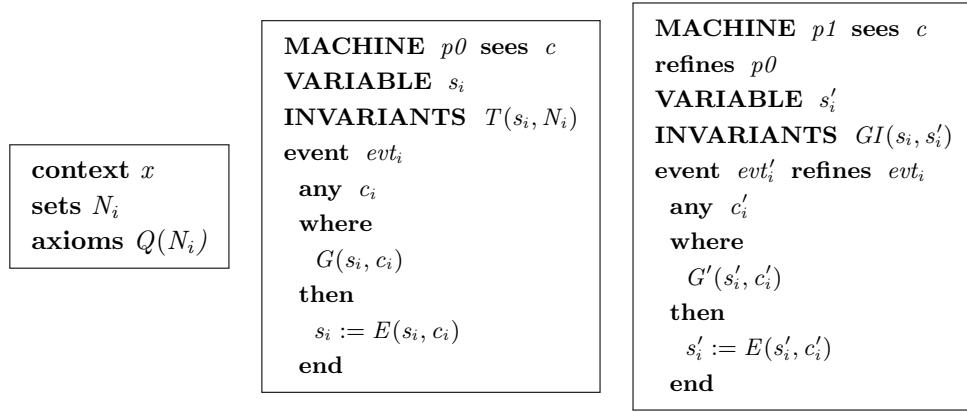

Instantiation means the reuse of a pattern (chain of machines and contexts) where variables, events, constants and carrier sets can be renamed in an instance and reused in another development [72]. It ensures that the proofs associated with a generic development (pattern) remain valid in the instantiated development. This requires the creation of a new context (called “*parameterisation* context”) containing the carrier sets and constants that will be used by the instance machine (or chain of machines). After the creation of an instance from the pattern, the pattern axioms are converted into theorems in the instantiated machine to ensure the correctness of the instantiation [72].

To illustrate this approach, suppose we have a generic pattern  $P$  with machines  $p_0$  to  $p_n$ . Suppose that in some points in another development  $M$ , we find that its useful to reuse development  $P$  with some slight modification to resume development  $M$ . This

can be achieved by instantiating the various variables, events of  $P$ . The pattern axioms of development  $P$  should become theorems in development  $M$  in order to show the correctness of the instantiation by satisfying the pattern assumptions. This approach is also supported by a tool [72].

Figure 2.2: Generic instantiation.