University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

# Graphene FET Circuit-level Device Modelling

by

Ime J. Umoh

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering and Applied Science

School of Electronics and Computer Science

June 2014

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCE

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

**Graphene FET Circuit-level Device Modelling**

by **Ime J. Umoh**

This thesis presents models for a graphene based field effect transistor (GFET). The graphene material has been widely studied since its synthesis in 2004 and the material holds promise for the next generation electronic applications. Therefore, there is a need to model its device characteristics.

In this respect the contributions presented here are, firstly, a SPICE-compatible model for both dual gate and single gate graphene transistors. The derivation of the carrier transport of both hole and electron conduction results in a set of analytical equations. These derivations cover the three identified regions of operation as well as the boundary voltage conditions that define the regions. The Jacobian entries are shown to be continuous across the region boundaries.

Secondly, circuit levels model of a single-layer GFET and multi layer GFET suitable for a direct implementation in SPICE. In this contribution, a more accurate threshold voltage compared to other models is derived. This contribution also shows how models can be extended to as many layers the graphene channelled transistor has.

Finally, the introduction of a thermionic resistance, which is modelled in parallel with the resistance due to gate induced charges, provides a model for the temperature dependent channel resistance. The contribution goes further to derive equations between the off current and the vertical electric fields. Thus, giving a good estimation of the tunable bandgap opening in graphene.

The models in this contributions are validated against experimentally measured transistor characteristics which have been carried out by other research groups and the models show a good agreement in all cases validated. The thesis equally presents the use of a floating gate to optimize the transistors characteristics. To illustrate these contributions, algorithms of the models have been implemented on the following CAD tools, HSPICE, VHDL-AMS and Berkeley SPICE. During the course of this work one journal and five conference papers have been published.

# Contents

|                                                                  |              |

|------------------------------------------------------------------|--------------|

| <b>Nomenclature</b>                                              | <b>xvi</b>   |

| <b>Acknowledgements</b>                                          | <b>xviii</b> |

| <b>1 Introduction</b>                                            | <b>1</b>     |

| 1.1 Carbon nanotubes . . . . .                                   | 1            |

| 1.2 Graphene . . . . .                                           | 1            |

| 1.2.1 Graphene Transistor Modelling . . . . .                    | 2            |

| 1.3 Research Challenges . . . . .                                | 2            |

| 1.4 Research Aims and Contributions . . . . .                    | 3            |

| 1.5 Thesis Organisation . . . . .                                | 5            |

| <b>2 Literature Review</b>                                       | <b>7</b>     |

| 2.0.1 Single-Layer Tight Binding . . . . .                       | 8            |

| 2.0.1.1 Brillouin Zone . . . . .                                 | 9            |

| 2.0.1.2 Energy Dispersion . . . . .                              | 10           |

| 2.0.2 Bilayer Tight Binding . . . . .                            | 11           |

| 2.0.2.1 Bernal Stacking . . . . .                                | 11           |

| 2.0.2.2 Energy Dispersion . . . . .                              | 12           |

| 2.0.3 Energy Dispersion Close to the K-points . . . . .          | 12           |

| 2.0.4 Electron Confinement Using a Potential Barrier . . . . .   | 12           |

| 2.1 Graphene Transistor Modelling . . . . .                      | 14           |

| 2.1.1 Carrier Scattering . . . . .                               | 14           |

| 2.1.2 Metal Contact . . . . .                                    | 15           |

| 2.1.3 Parasitic Capacitance and Series Resistance . . . . .      | 17           |

| 2.1.4 Channel Conductance . . . . .                              | 19           |

| 2.1.4.1 Conductance Against Changes in Gate Voltage . . . . .    | 20           |

| 2.1.4.2 Drain Current Against Changes in Drain Voltage . . . . . | 22           |

| 2.1.5 Quantum Capacitance . . . . .                              | 23           |

| 2.1.6 Thermal Transport . . . . .                                | 24           |

| 2.2 Improving the Transistor . . . . .                           | 25           |

| 2.3 Graphene Bandgap Engineering . . . . .                       | 25           |

| 2.3.1 Methods That Destroy the Honeycomb . . . . .               | 25           |

| 2.3.1.1 Graphene Nanoribbons . . . . .                           | 26           |

| 2.3.1.2 Graphene Nanomeshes . . . . .                            | 27           |

| 2.3.1.3 Chemical Functionalization . . . . .                     | 28           |

| 2.3.2 Methods That Preserve the Honeycomb . . . . .              | 28           |

---

|          |                                                               |           |

|----------|---------------------------------------------------------------|-----------|

| 2.3.2.1  | Graphene Substrate Interaction                                | 29        |

| 2.3.2.2  | Strain Application                                            | 29        |

| 2.3.2.3  | Electric Field Application                                    | 30        |

| 2.4      | Existing Graphene Device Circuit Models                       | 32        |

| 2.4.1    | Modelling Assumptions                                         | 33        |

| 2.4.2    | Equivalent Circuit                                            | 33        |

| 2.4.3    | Popular CAD Tools Used for Graphene Modelling                 | 34        |

| 2.4.4    | Tunneling Through Gate Oxides                                 | 35        |

| 2.4.4.1  | Mechanisms of Tunnelling                                      | 35        |

| 2.4.4.2  | Electric Field Responsible For Tunneling                      | 36        |

| 2.4.4.3  | Band Offset of Various Dielectrics                            | 37        |

| 2.4.4.4  | Work Function of Graphene                                     | 37        |

| 2.5      | Graphene and World Economics                                  | 38        |

| 2.6      | Graphene Based Applications                                   | 39        |

| 2.6.1    | Ring Oscillator                                               | 40        |

| 2.6.2    | Frequency Mixer and Multipliers                               | 40        |

| 2.6.3    | Digital Applications                                          | 41        |

| <b>3</b> | <b>Graphene FET drift-current perspective</b>                 | <b>44</b> |

| 3.1      | The Graphene Transistor                                       | 44        |

| 3.2      | Hole Conduction                                               | 47        |

| 3.2.1    | The Triode Region                                             | 48        |

| 3.2.2    | The Unipolar Saturation Region                                | 49        |

| 3.2.3    | Ambipolar Saturation Region                                   | 50        |

| 3.3      | Electron Conduction                                           | 51        |

| 3.3.1    | The Triode Region                                             | 52        |

| 3.3.2    | The Unipolar Saturation Region                                | 53        |

| 3.3.3    | The Ambipolar Saturation Region                               | 53        |

| 3.4      | SPICE Jacobian Entries                                        | 54        |

| 3.5      | Summary                                                       | 54        |

| <b>4</b> | <b>Single-Layer graphene FET model for circuit simulation</b> | <b>55</b> |

| 4.1      | Dual-gate Single-Layer                                        | 55        |

| 4.1.1    | Electrostatics                                                | 55        |

| 4.1.2    | Surface Potential                                             | 58        |

| 4.1.2.1  | Analytical model                                              | 58        |

| 4.1.2.2  | Numerical model                                               | 60        |

| 4.1.2.3  | Comparison of both models                                     | 60        |

| 4.1.3    | Threshold Voltage                                             | 61        |

| 4.1.4    | Effective Gate Capacitance                                    | 61        |

| 4.2      | Off-current Hole/Electron Activation Energy                   | 62        |

| 4.2.1    | Electric Field Dependent Energy                               | 62        |

| 4.2.2    | Temperature Dependence of the off-current                     | 64        |

| 4.3      | Single-gate Single-Layer                                      | 65        |

| 4.3.1    | Graphene Device Fabrication                                   | 65        |

| 4.3.2    | Capacitance Model                                             | 66        |

| 4.3.2.1  | Using a simplified analytical method                          | 66        |

---

|          |                                                                 |            |

|----------|-----------------------------------------------------------------|------------|

| 4.3.2.2  | Using the Drude model . . . . .                                 | 67         |

| 4.3.2.3  | Comparison between both methods . . . . .                       | 67         |

| 4.3.3    | Singe-gate Activation Energy of the off-current . . . . .       | 69         |

| 4.4      | Experimental Validation . . . . .                               | 70         |

| 4.4.1    | Single-gate Case . . . . .                                      | 70         |

| 4.4.2    | Dual-gate FET . . . . .                                         | 71         |

| 4.4.3    | Single-layer Model Applied To Bilayer Graphene . . . . .        | 77         |

| 4.4.4    | Single-layer Model Applied To a Four Layer Graphene Channel . . | 81         |

| 4.5      | Summary . . . . .                                               | 83         |

| <b>5</b> | <b>Dual-gate multi-layer graphene FET model</b>                 | <b>85</b>  |

| 5.1      | Bilayer Capacitance Model . . . . .                             | 86         |

| 5.1.1    | Surface Potential . . . . .                                     | 87         |

| 5.1.2    | Effective Gate Capacitance . . . . .                            | 89         |

| 5.1.3    | Threshold Voltage . . . . .                                     | 89         |

| 5.2      | Four-layer Capacitance Model . . . . .                          | 90         |

| 5.2.1    | Surface Potential . . . . .                                     | 90         |

| 5.2.2    | Effective Gate Capacitance . . . . .                            | 92         |

| 5.2.3    | Threshold Voltage . . . . .                                     | 92         |

| 5.2.4    | Bilayer Electric Field Gap . . . . .                            | 93         |

| 5.2.5    | Four-layer Electric Field Gap . . . . .                         | 95         |

| 5.2.6    | Temperature Dependence . . . . .                                | 96         |

| 5.3      | Experimental Validation . . . . .                               | 97         |

| 5.3.1    | Test Case A . . . . .                                           | 97         |

| 5.3.2    | Test Case B . . . . .                                           | 100        |

| 5.3.3    | Test Case C . . . . .                                           | 105        |

| 5.3.4    | Test Case D . . . . .                                           | 111        |

| 5.3.5    | Test Case E . . . . .                                           | 114        |

| 5.4      | Summary . . . . .                                               | 118        |

| <b>6</b> | <b>CAD Tool Design and Transistor Optimization</b>              | <b>119</b> |

| 6.1      | CAD Tool Development . . . . .                                  | 119        |

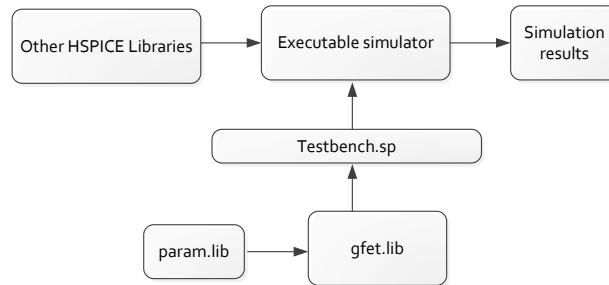

| 6.2      | HSPICE Project Library Development . . . . .                    | 120        |

| 6.2.1    | Structure of the graphene FET library . . . . .                 | 120        |

| 6.2.2    | Simulating with the HSPICE graphene library . . . . .           | 121        |

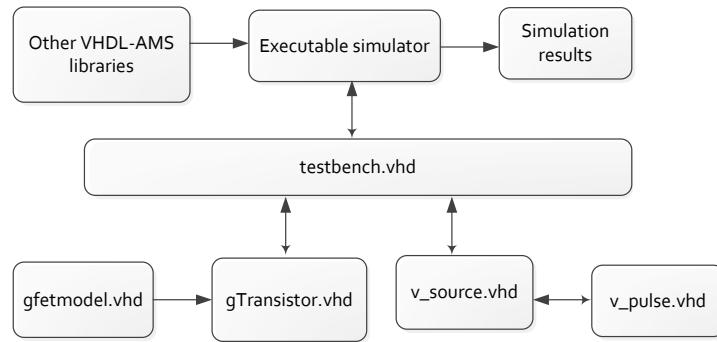

| 6.3      | VHDL-AMS Project Library Development . . . . .                  | 123        |

| 6.3.1    | Structure of the VHDL-AMS Project Library . . . . .             | 123        |

| 6.3.2    | Simulating with the VHDL-AMS graphene library . . . . .         | 124        |

| 6.4      | Berkeley SPICE Project Library Development . . . . .            | 126        |

| 6.4.1    | Important Files to be updated . . . . .                         | 126        |

| 6.4.2    | Installing the simulator . . . . .                              | 128        |

| 6.4.3    | Running the SPICE simulator . . . . .                           | 128        |

| 6.4.4    | Simulating with the graphene FET library . . . . .              | 129        |

| 6.4.5    | Example circuits . . . . .                                      | 133        |

| 6.4.5.1  | Voltage Amplifier . . . . .                                     | 133        |

| 6.4.5.2  | Frequency multiplier . . . . .                                  | 136        |

| 6.5      | Transistor Optimization using a floating-gate . . . . .         | 138        |

|          |                                                                            |            |

|----------|----------------------------------------------------------------------------|------------|

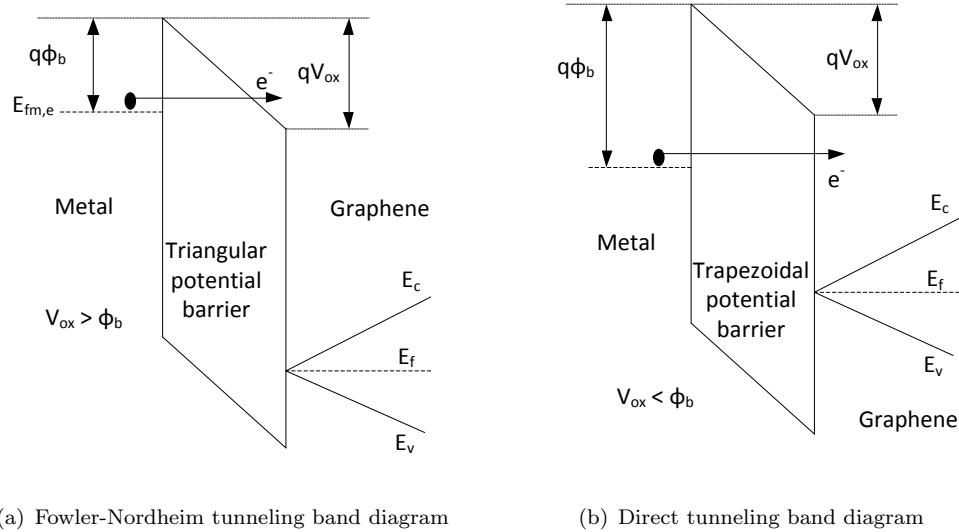

| 6.6      | Carrier Tunnelling . . . . .                                               | 138        |

| 6.7      | Electronic Transport and Channel Resistance . . . . .                      | 140        |

| 6.8      | Simulations of Transistor characteristics . . . . .                        | 141        |

| 6.9      | Complementary Inverter with Symmetrical Transfer Characteristics . . . . . | 143        |

| 6.10     | Summary . . . . .                                                          | 145        |

| <b>7</b> | <b>Conclusion</b>                                                          | <b>147</b> |

| 7.1      | Chapter: Further Research . . . . .                                        | 148        |

| <b>A</b> | <b>Published papers</b>                                                    | <b>149</b> |

| <b>B</b> | <b>CAD Tools</b>                                                           | <b>150</b> |

| B.1      | Behavioural model code for HSPICE . . . . .                                | 150        |

| B.2      | Behavioural model code for VHDL-AMS . . . . .                              | 151        |

|          | <b>Bibliography</b>                                                        | <b>155</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

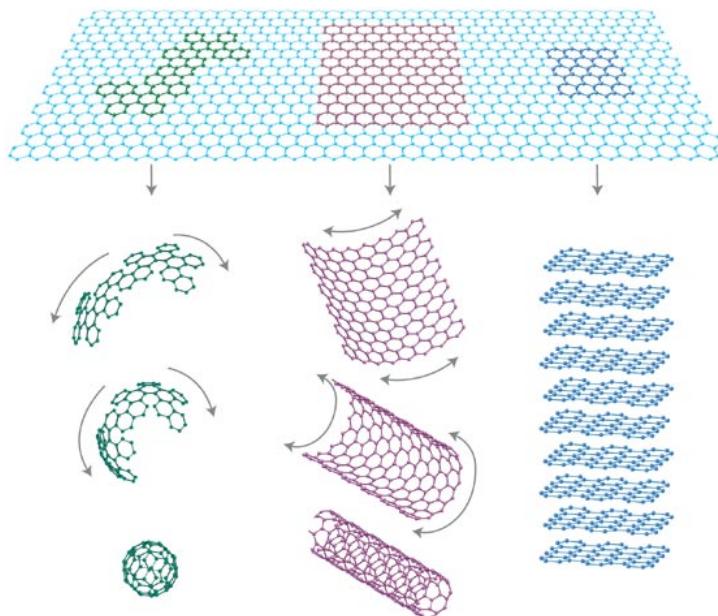

| 2.1  | A two-dimension graphene rolled into a zero-dimension fullerene (left), one-dimension carbon nanotube (middle) and stacked into three-dimension graphite (right). Reprinted with permission from [16]. Copyright 2007, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                                                                                                                                             | 7  |

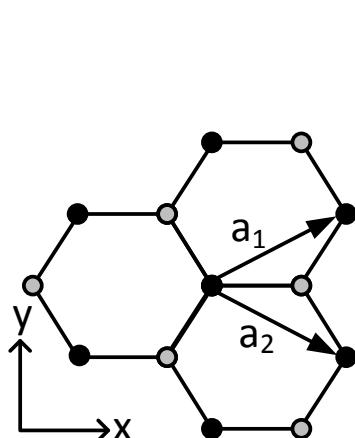

| 2.2  | The lattice structure of an atomic layer of graphene . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

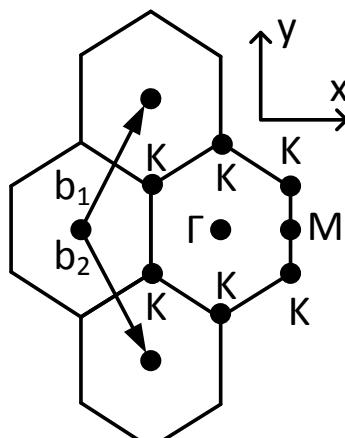

| 2.3  | The energy band spectrum for graphene in the Brillouin zone . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

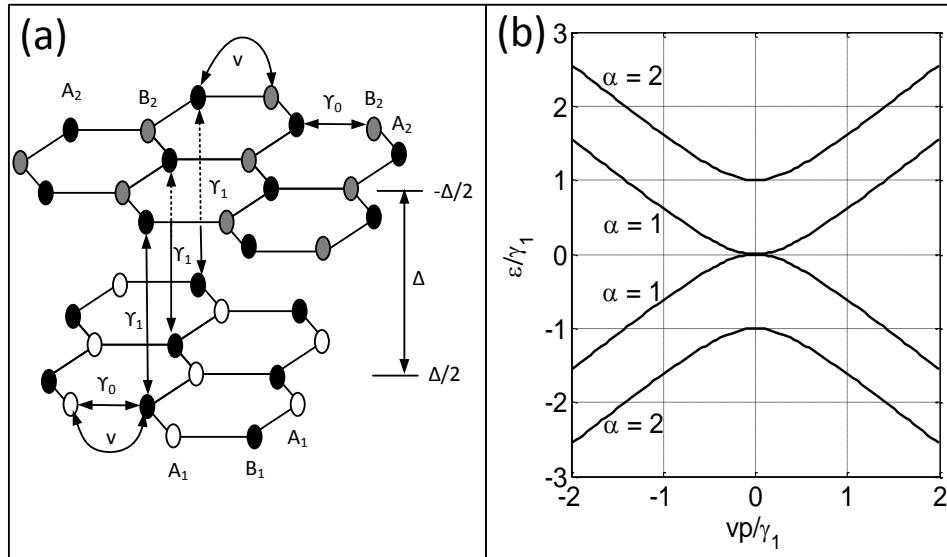

| 2.4  | (a) bilayer lattice in Bernal stacking. (b) low energy bands near the K-points . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

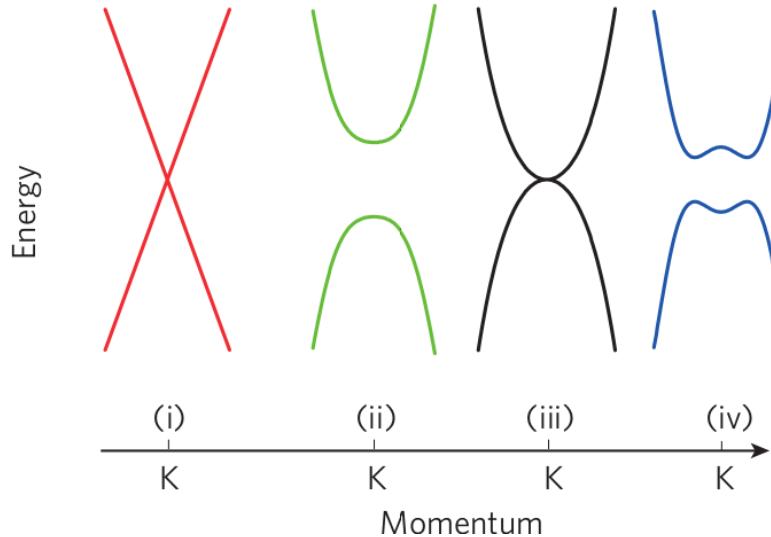

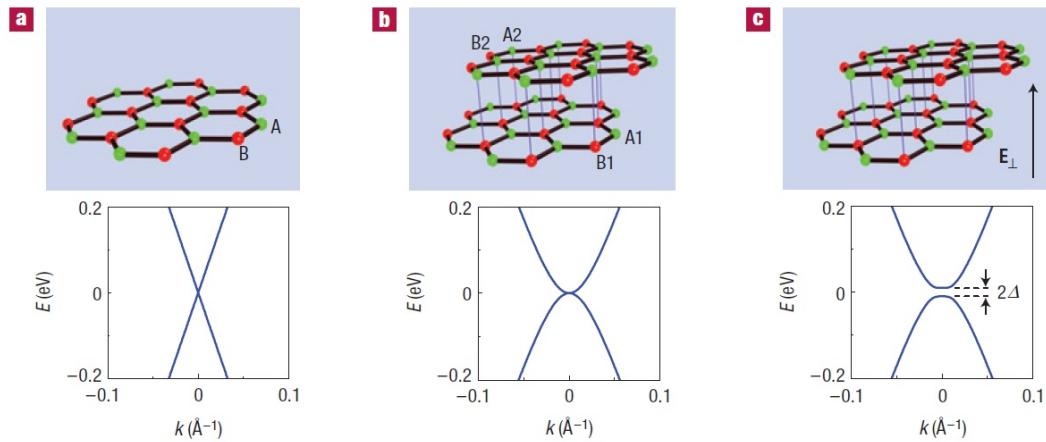

| 2.5  | The energy dispersion close to the K-points for i) single-layer ii) nanoribbons iii) bilayer with zero electric field and iv) bilayer in the presence of an electric field. Reprinted with permission from [53]. Copyright 2010, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                                                                                                                                   | 13 |

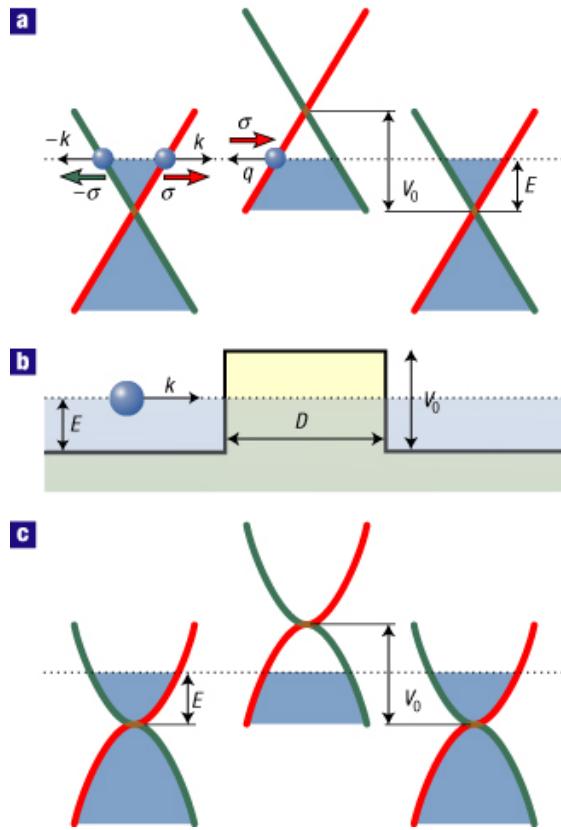

| 2.6  | (a) Single-layer energy dispersion. (b) Rectangular potential barrier and (c) Bilayer energy dispersion. Reprinted with permission from [56]. Copyright 2006, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                                                                                                                                                                                                      | 14 |

| 2.7  | Characteristic of a metal on a thin semiconductor . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

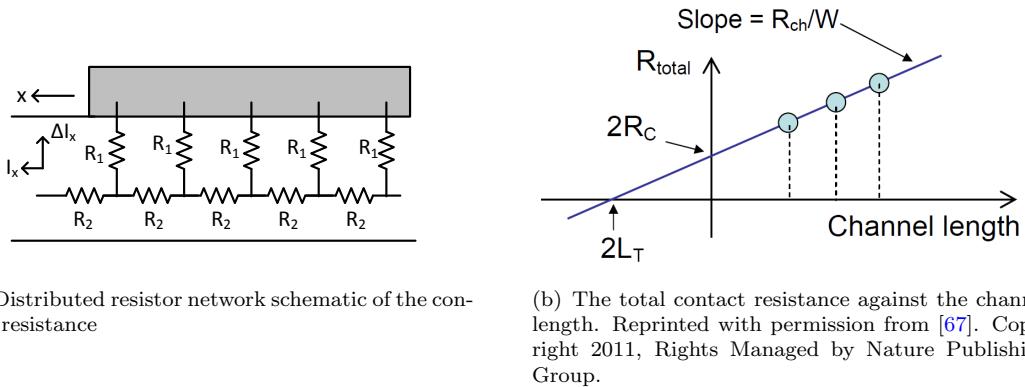

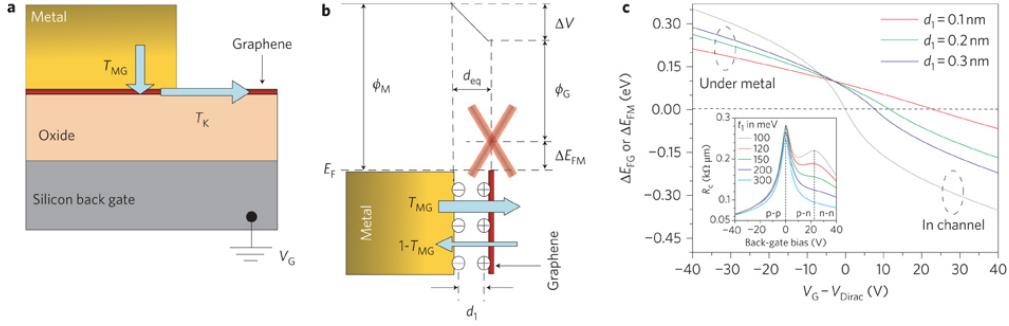

| 2.8  | (a) Layout of the transistor under the metal contact (b) Charge distribution between the graphene and metal contact. (c) Energy level for a sweep in the gate voltage. Reprinted with permission from [67]. Copyright 2011, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                                                                                                                                        | 16 |

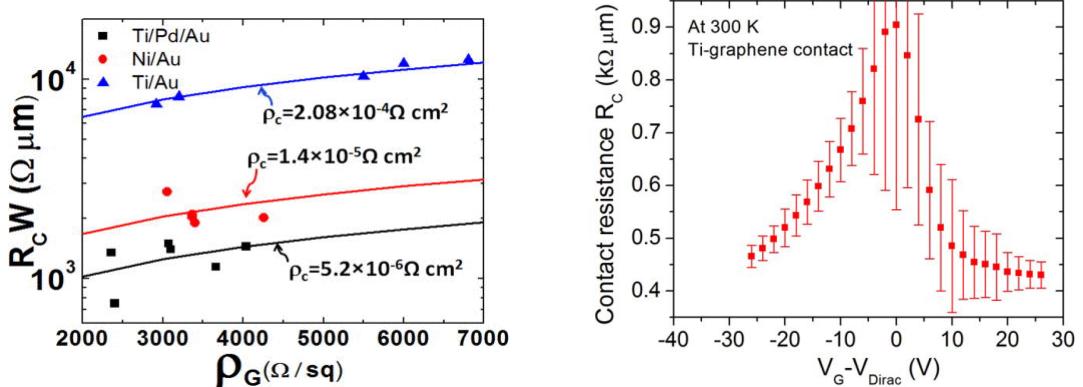

| 2.9  | Comparison of various contact resistance and the gate modulation of Ti contact resistance on graphene . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 |

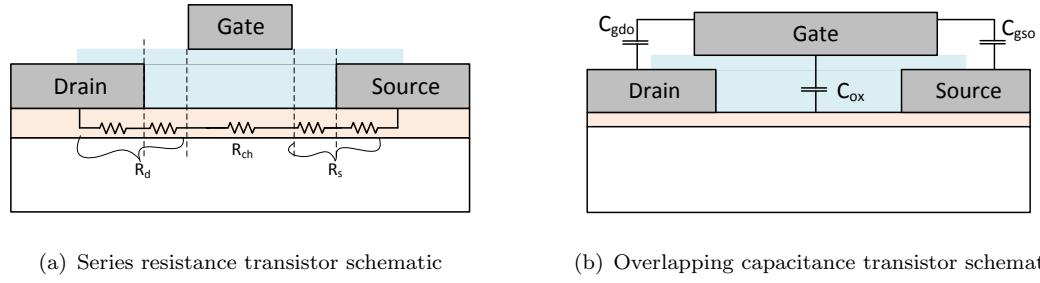

| 2.10 | Field effect transistor layout . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 |

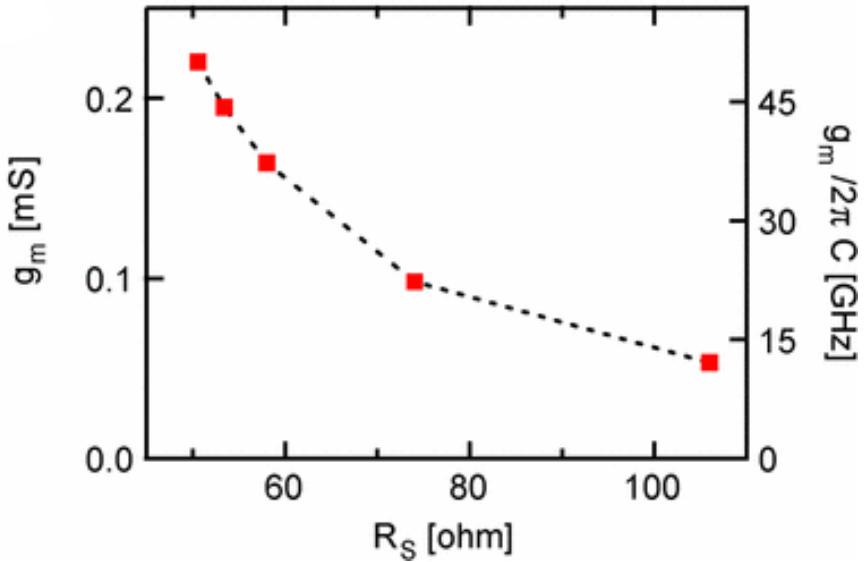

| 2.11 | The transconductance and cut-off frequency versus the series resistance. Reprinted with permission from [26]. Copyright 2010, Rights Managed by IEEE. . . . .                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

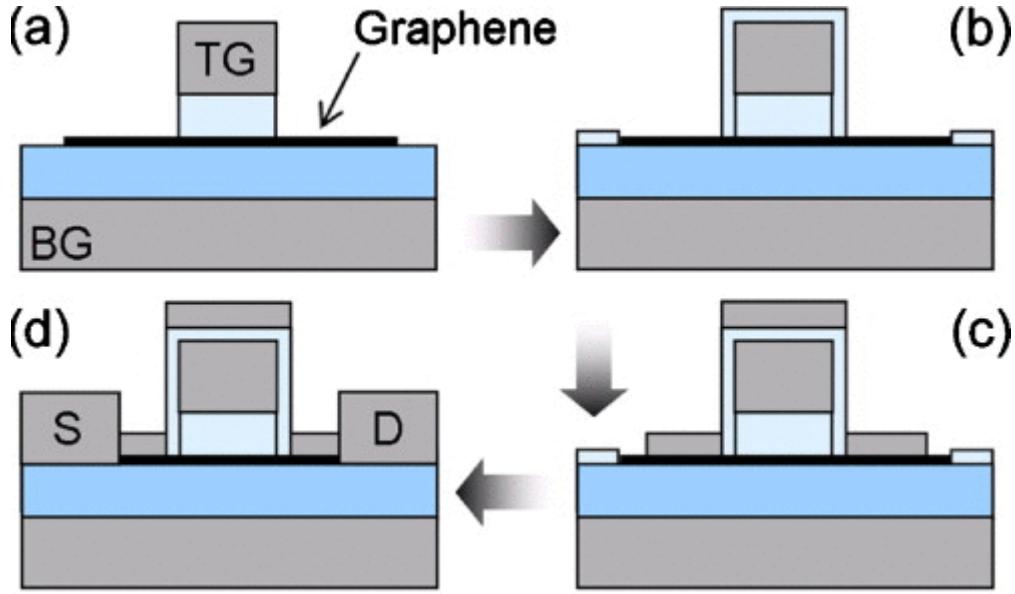

| 2.12 | The fabrication process for a self-align graphene FET. Reprinted with permission from [70]. Copyright 2010, Rights managed by AIP Publishing LLC. . . . .                                                                                                                                                                                                                                                                                                                                                                                             | 18 |

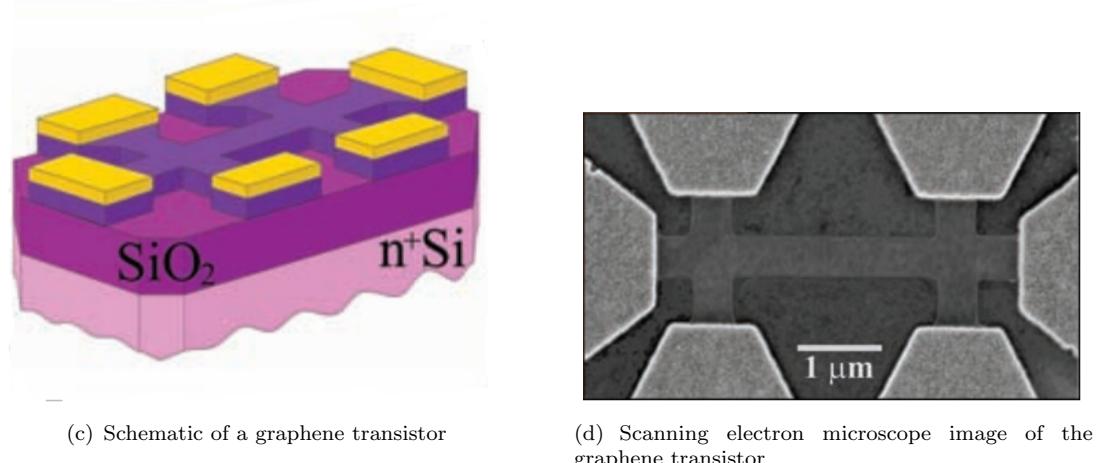

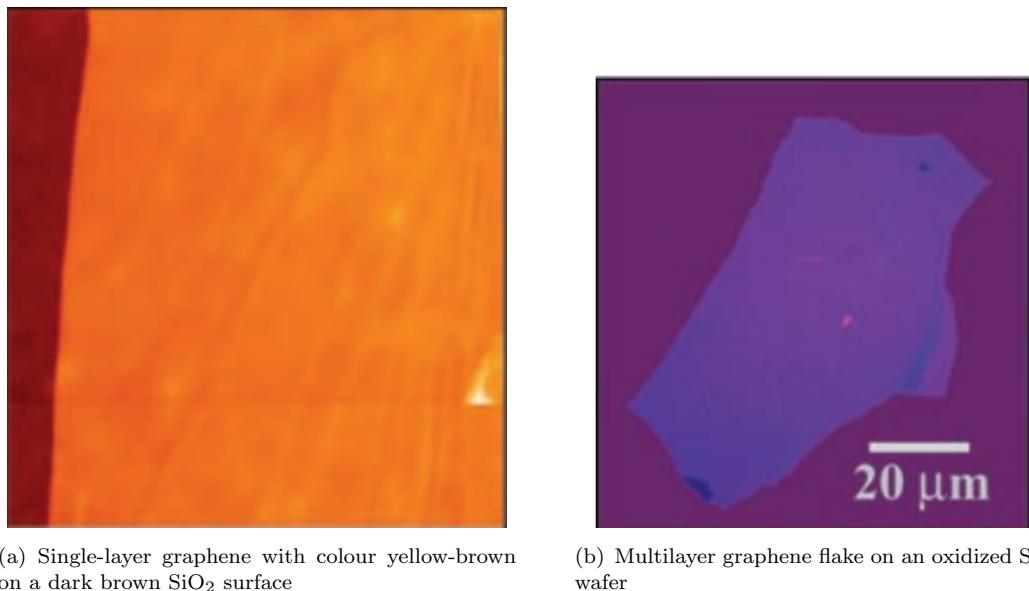

| 2.13 | Device feature of the graphene transistor. Reprinted with permission from [14]. Copyright 2004, Rights Managed by American Association for the Advancement of Science. . . . .                                                                                                                                                                                                                                                                                                                                                                        | 19 |

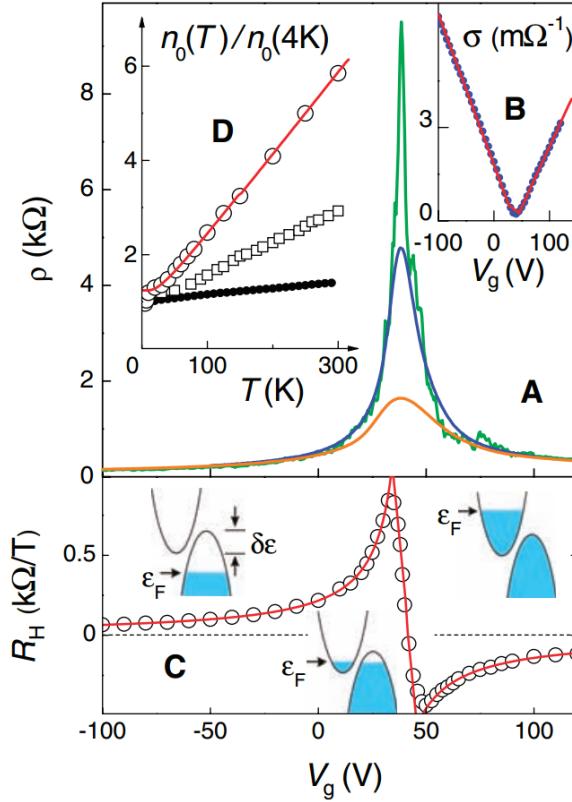

| 2.14 | Transport characteristic of the field effect graphene (A) dependence of the resistivity on the gate voltage (B) A plot of the conductivity against the gate voltage (C) The Hall coefficient $R_H$ versus the top-gate (D) The dependence of the carrier concentration on the temperature. $\varepsilon_F$ is the Fermi energy and $\partial\varepsilon$ is the overlap between the conduction and valence bands. Reprinted with permission from [14]. Copyright 2004, Rights Managed by American Association for the Advancement of Science. . . . . | 20 |

---

|      |                                                                                                                                                                                                                                                                                                                                            |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

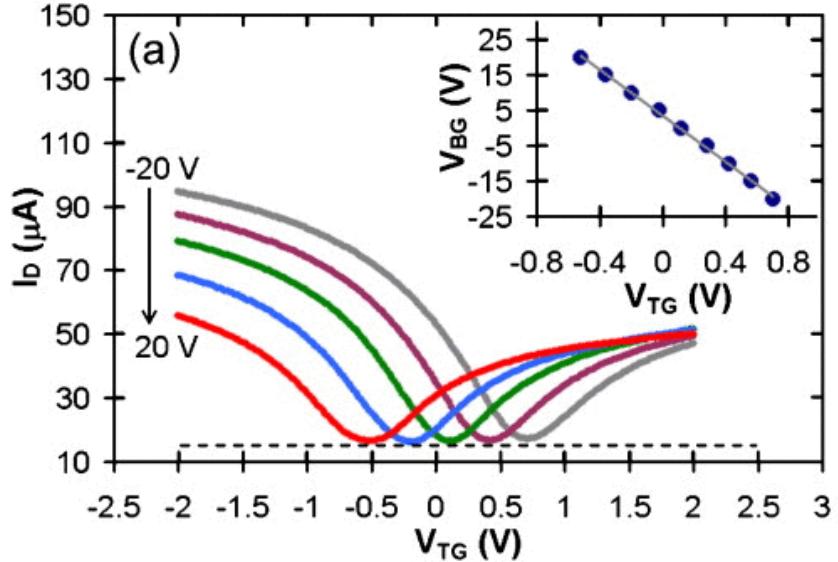

| 2.15 | Electronic transport in single-layer graphene FET. Reprinted with permission from [70]. The transport characteristics of the top-gate voltage $V_{TG}$ against the drain current $I_D$ . Inset is the is relationship between $V_{TG}$ and the back-gate voltage, $V_{BG}$ . Copyright 2010, Rights managed by AIP Publishing LLC. . . . . | 21 |

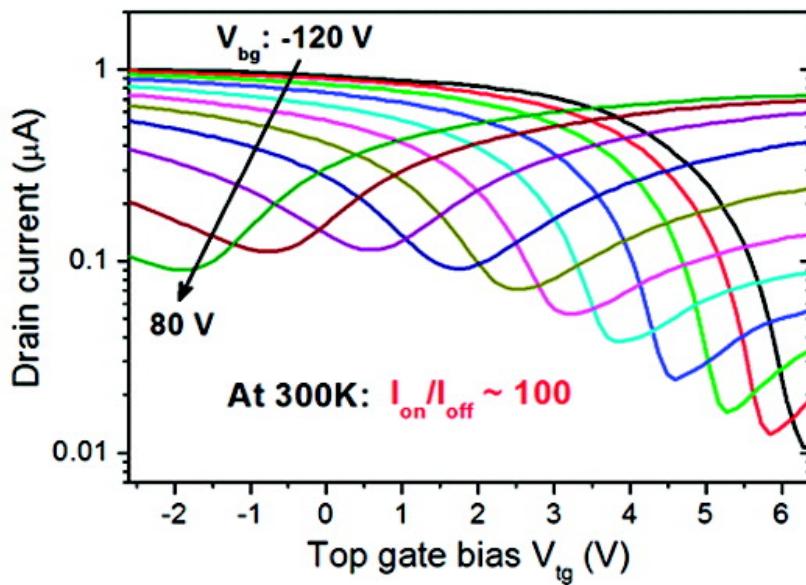

| 2.16 | Electronic transport in bilayer graphene FET. Reprinted with permission from [77]. The transport characteristics of the top-gate voltage $V_{tg}$ against the drain current for a sweep of the back-gate voltage $V_{bg}$ . Copyright 2010, Rights Managed by American Chemical Society. . . . .                                           | 22 |

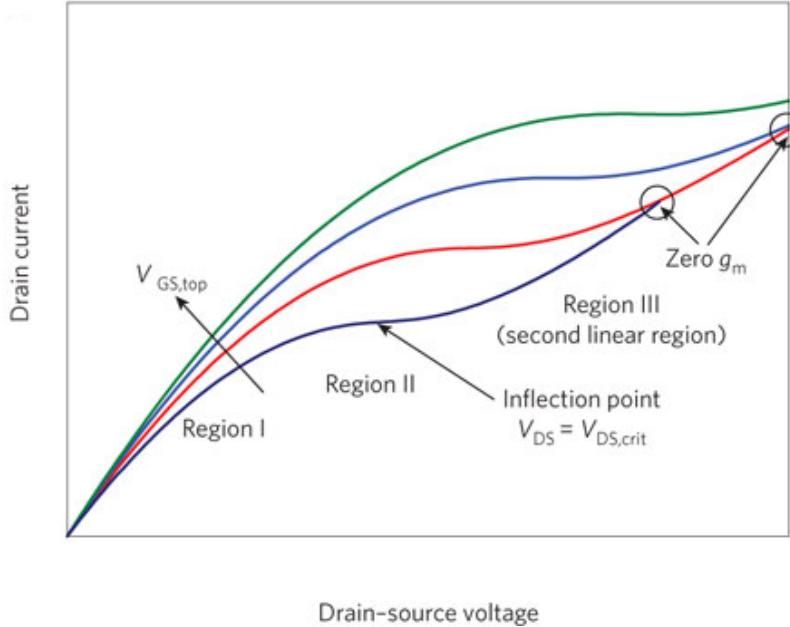

| 2.17 | The regions of operation of a graphene transistor for variations in the drain voltage. Reprinted with permission from [53]. Copyright 2010, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                             | 23 |

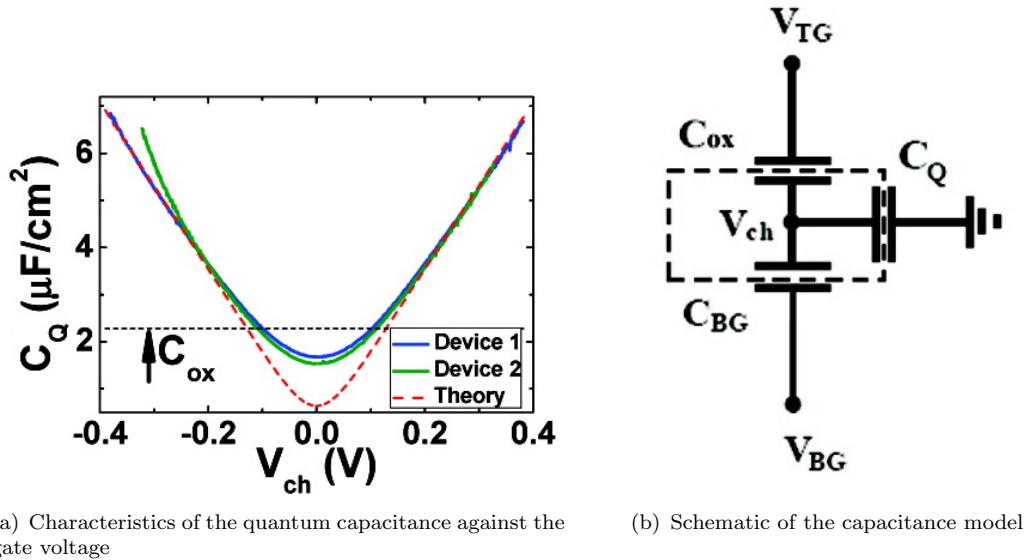

| 2.18 | Interaction of the quantum capacitance in the graphene channel. Reprinted with permission from [85]. Copyright 2011, Rights Managed by American Chemical Society. . . . .                                                                                                                                                                  | 24 |

| 2.19 | Thermal transport in bilayer graphene. Reprinted with permission from [89]. Copyright 2008, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                                                             | 24 |

| 2.20 | Schematic of graphene nanoribbon FET. . . . .                                                                                                                                                                                                                                                                                              | 26 |

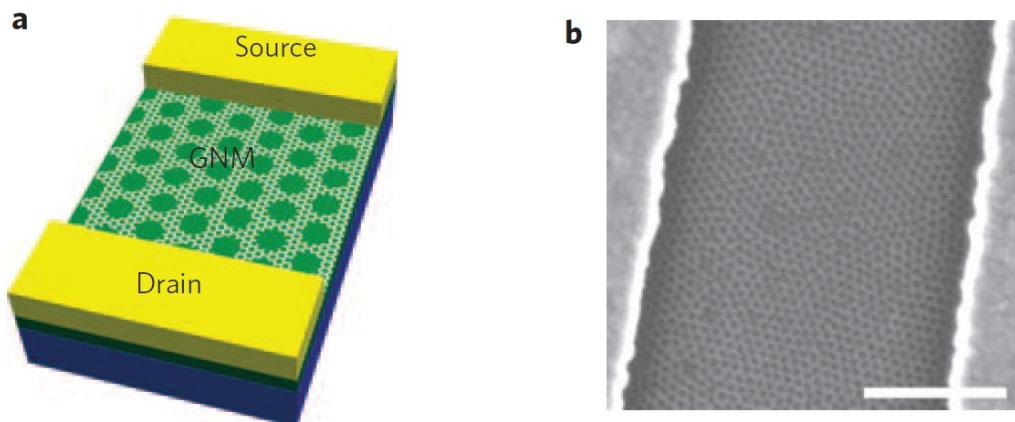

| 2.21 | a) Transistor layout with graphene nanomesh b) SEM image of a GNM device. Reprinted with permission from [107]. Copyright 2010, Rights Managed by Nature Publishing Group. . . . .                                                                                                                                                         | 27 |

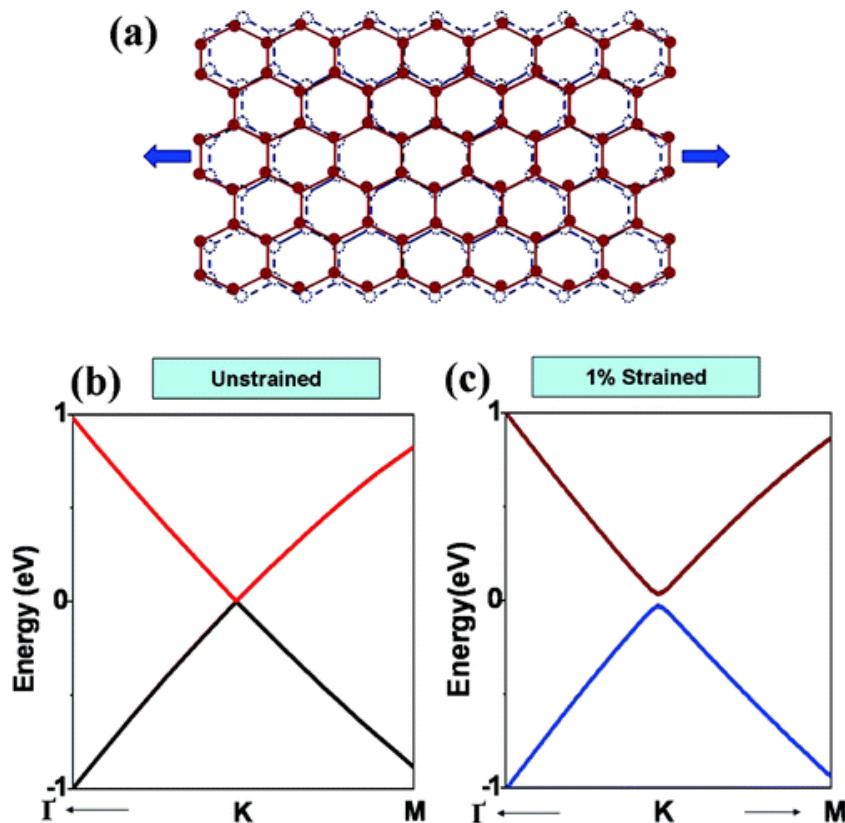

| 2.22 | a) Uniaxial strain on multi layer graphene. Energy dispersion for b) unstrained and c) strained graphene. Reprinted with permission from [120]. Copyright 2008, Rights Managed by American Chemical Society. . . . .                                                                                                                       | 30 |

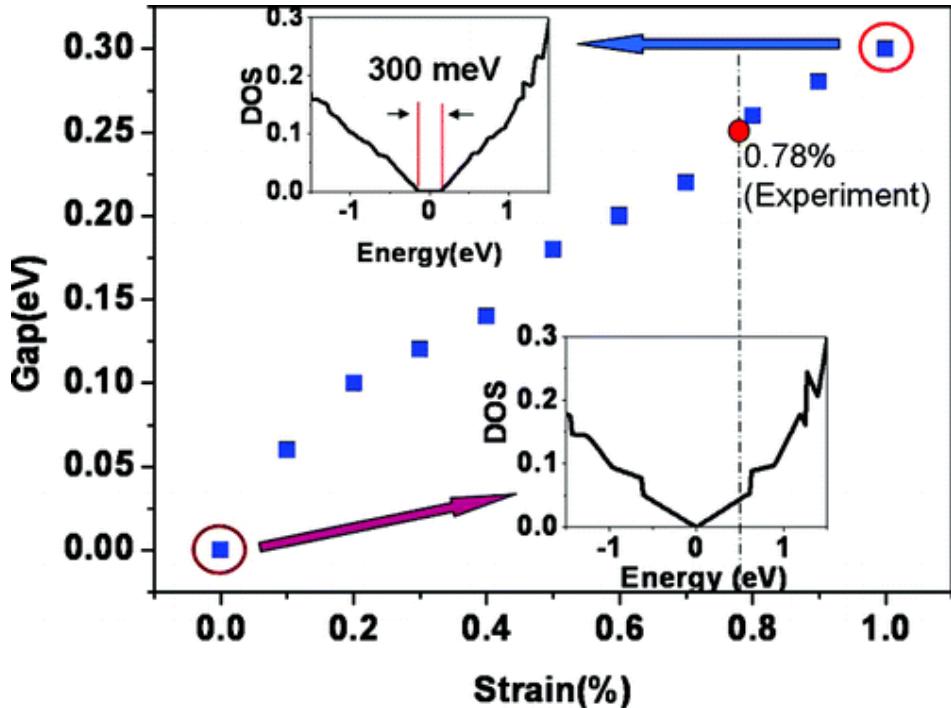

| 2.23 | The predicted bandgap against the amount of uniaxial strain. Reprinted with permission from [120]. Copyright 2008, Rights Managed by American Chemical Society. . . . .                                                                                                                                                                    | 31 |

| 2.24 | Energy dispersion and the sublattice structure for a) single-layer, b) bilayer graphene without electric field and c) bilayer graphene with vertical electric field applied. Reprinted with permission from [89]. Copyright 2008, Rights Managed by Nature Publishing Group. . . . .                                                       | 31 |

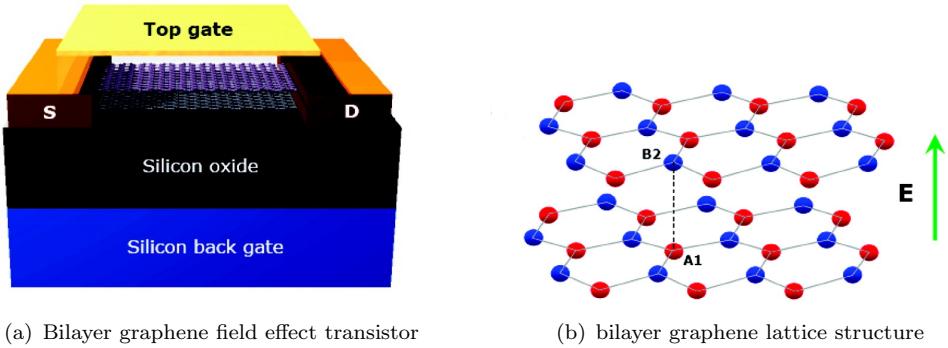

| 2.25 | Fabricated bilayer transistor and corresponding sublattice interaction. Reprinted with permission from [77]. Copyright 2010, Rights Managed by American Chemical Society. . . . .                                                                                                                                                          | 32 |

| 2.26 | Schematic of the graphene transistor . . . . .                                                                                                                                                                                                                                                                                             | 32 |

| 2.27 | Graphene FET small signal model . . . . .                                                                                                                                                                                                                                                                                                  | 34 |

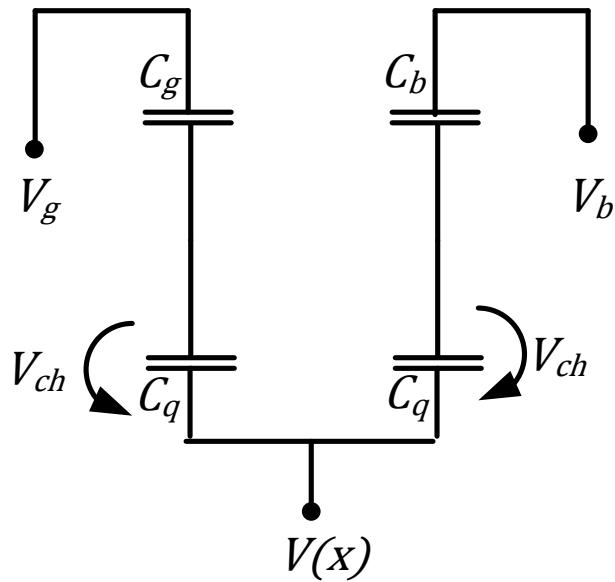

| 2.28 | The capacitance model for a graphene FET. Reproduced with permission from [32]. Copyright 2010, Rights managed by AIP Publishing LLC. . . . .                                                                                                                                                                                              | 34 |

| 2.29 | Mechanisms for tunneling through the gate oxide . . . . .                                                                                                                                                                                                                                                                                  | 36 |

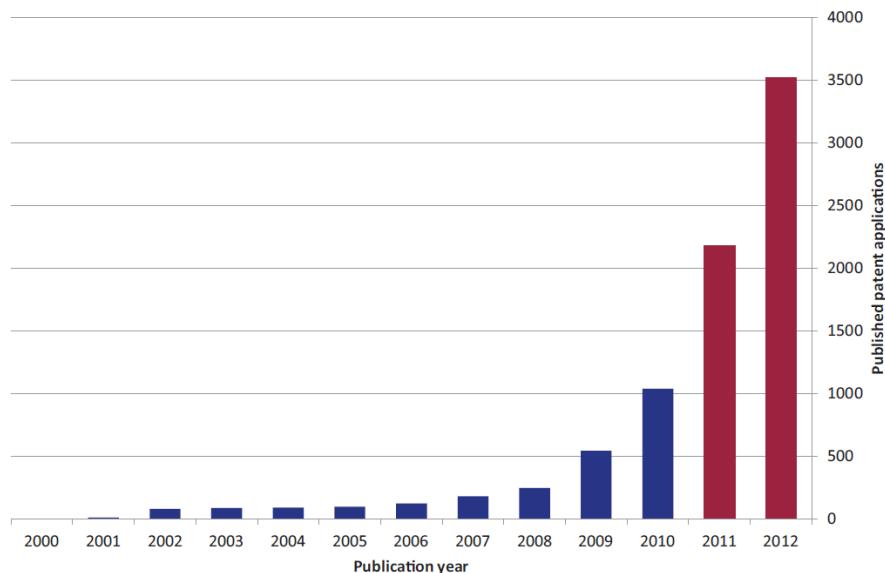

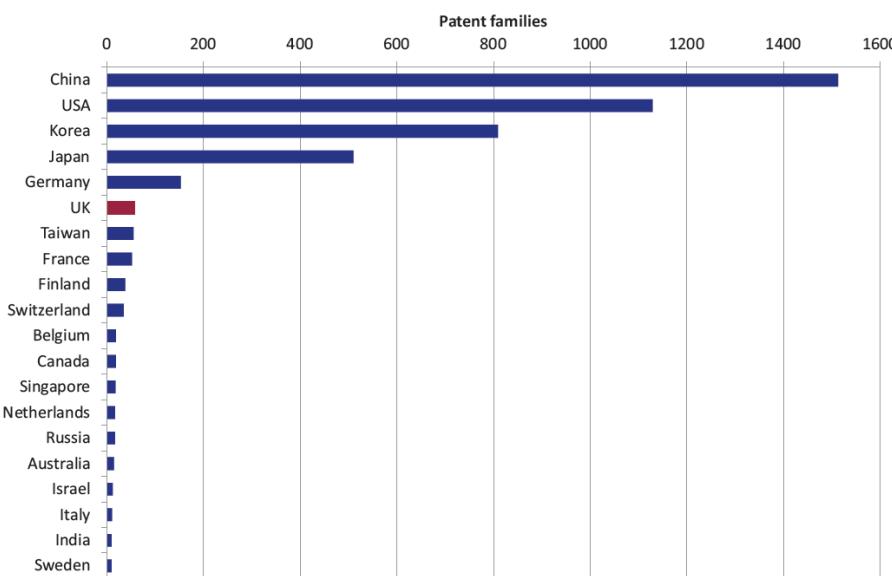

| 2.30 | Worldwide published patents and year of application. Reprinted with permission from [170]. Copyright 2013, Rights managed by Intellectual Property Office. . . . .                                                                                                                                                                         | 38 |

| 2.31 | Worldwide published patents and year of application. Reprinted with permission from [170]. Copyright 2013, Rights managed by Intellectual Property Office. . . . .                                                                                                                                                                         | 39 |

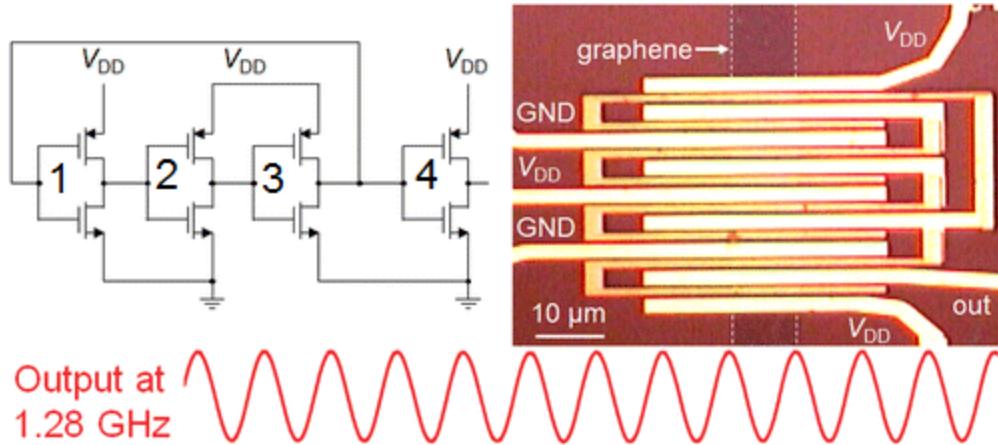

| 2.32 | Schematic of a graphene ring oscillator. Reprinted with permission from [29]. Copyright 2013, Rights Managed by American Chemical Society. . . . .                                                                                                                                                                                         | 40 |

---

|      |                                                                                                                                                                                                             |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

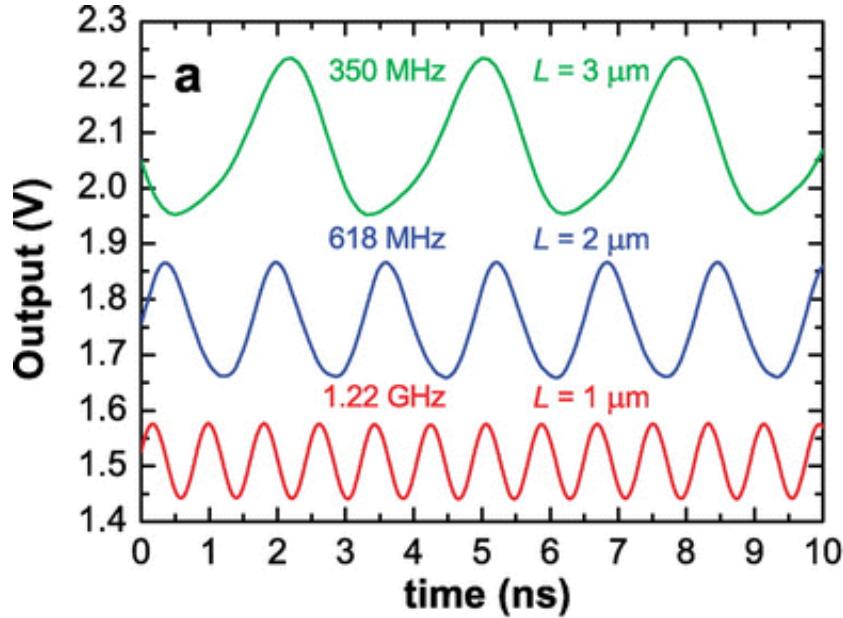

| 2.33 | Operating frequency and output voltage for varying length. Reprinted with permission from [29]. Copyright 2013, Rights Managed by American Chemical Society. . . . .                                        | 41 |

| 2.34 | Operating frequency and output voltage for varying length. Reprinted with permission from [173]. Copyright 2010, Rights Managed by IEEE. . . . .                                                            | 41 |

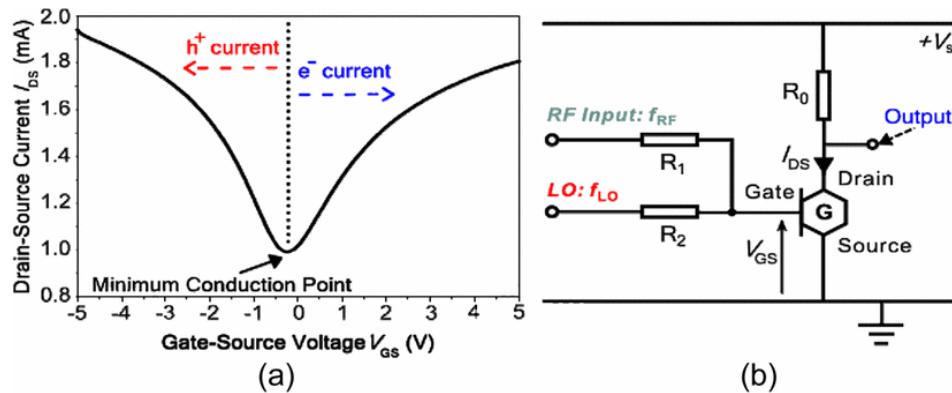

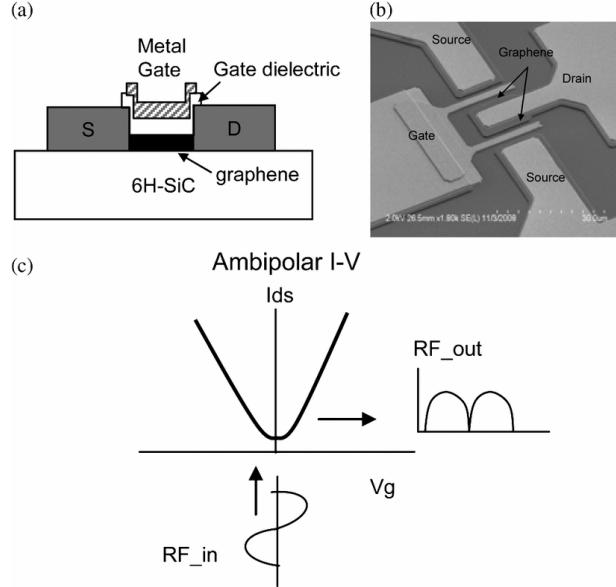

| 2.35 | Mode of operation of graphene frequency multiplier. Reprinted with permission from [174]. Copyright 2011, Rights Managed by IEEE. . . . .                                                                   | 42 |

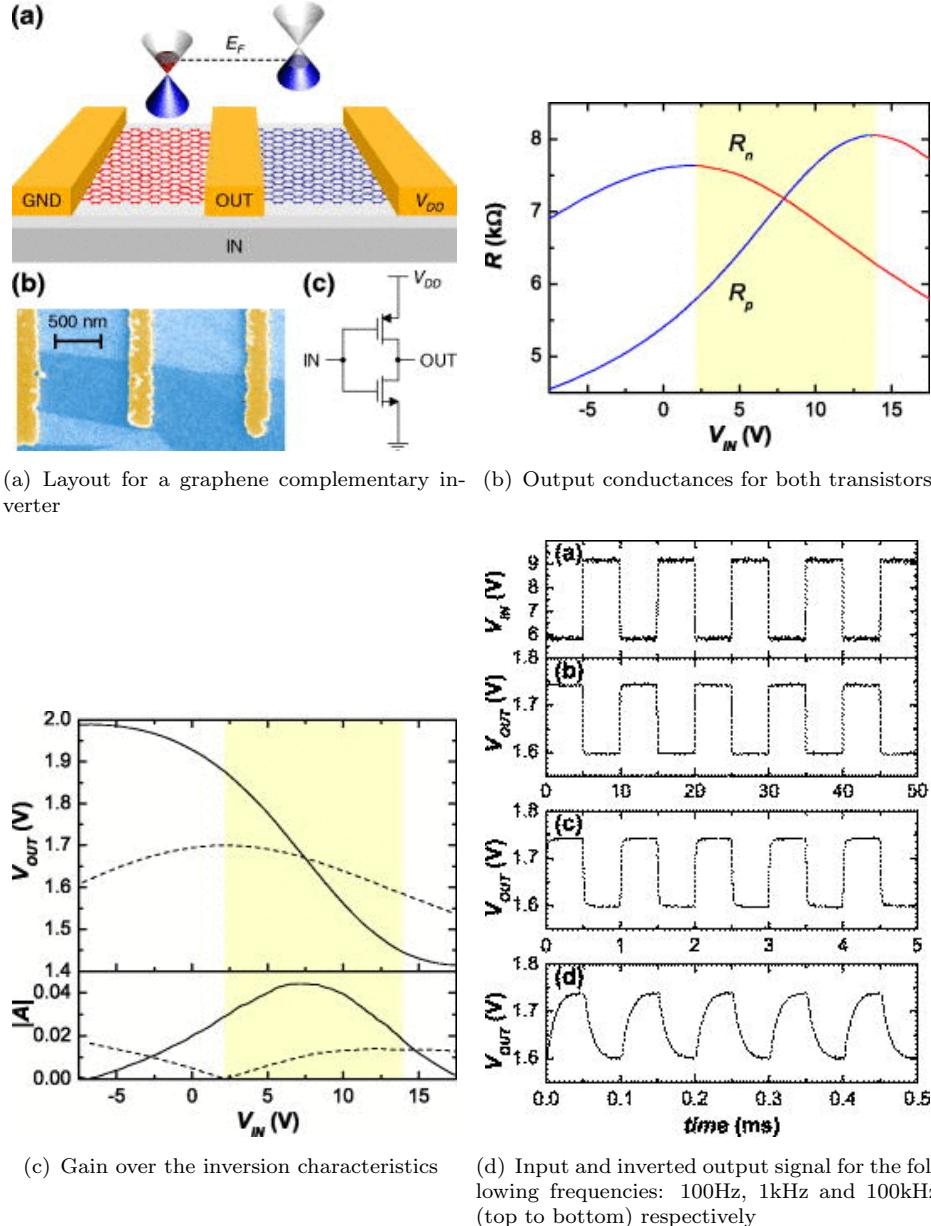

| 2.36 | Properties of a graphene complementary inverter. Reprinted with permission from [178]. Copyright 2009, Rights managed by AIP Publishing LLC. . . . .                                                        | 43 |

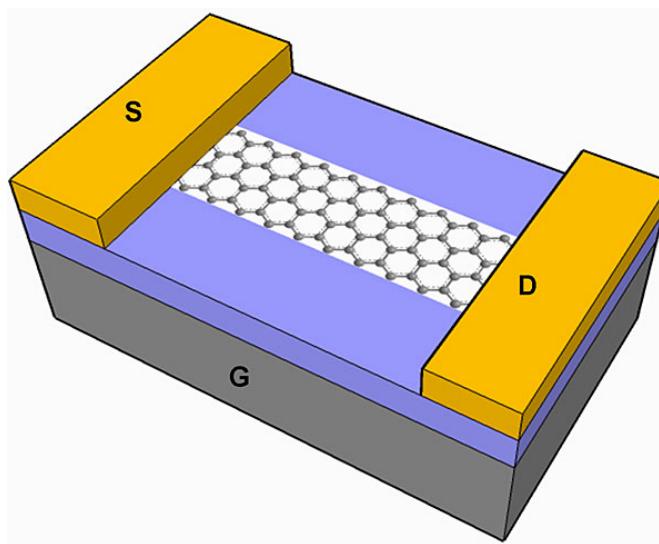

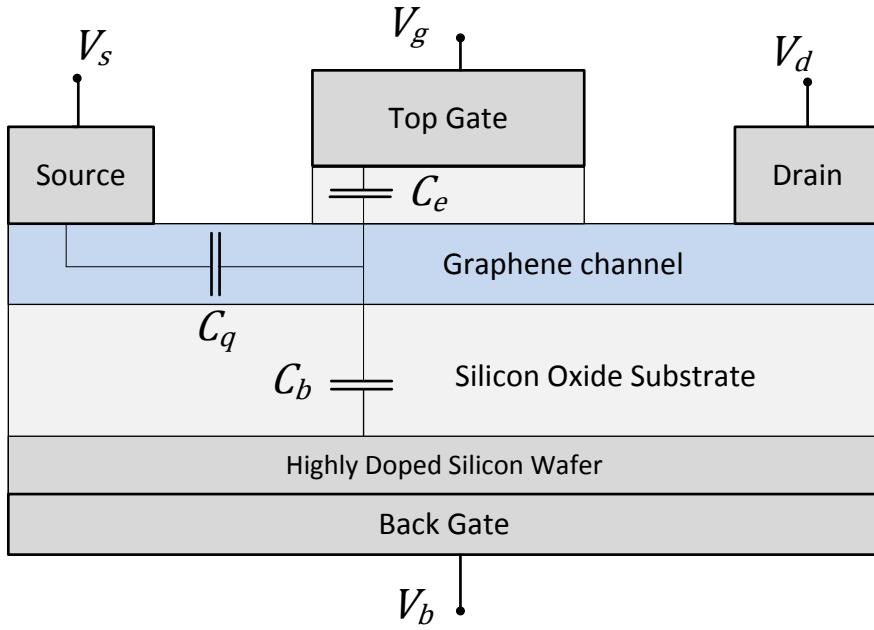

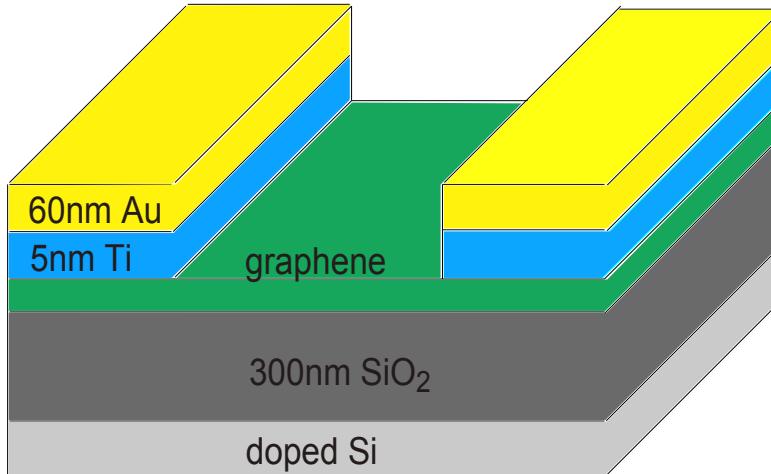

| 3.1  | Schematic layout of the graphene field effect transistor . . . . .                                                                                                                                          | 45 |

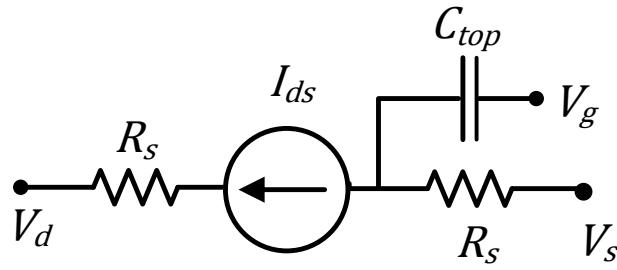

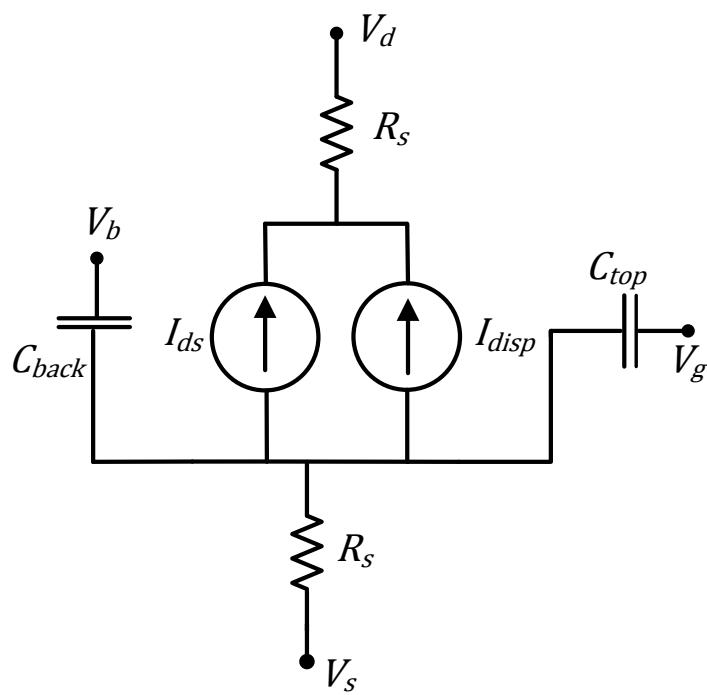

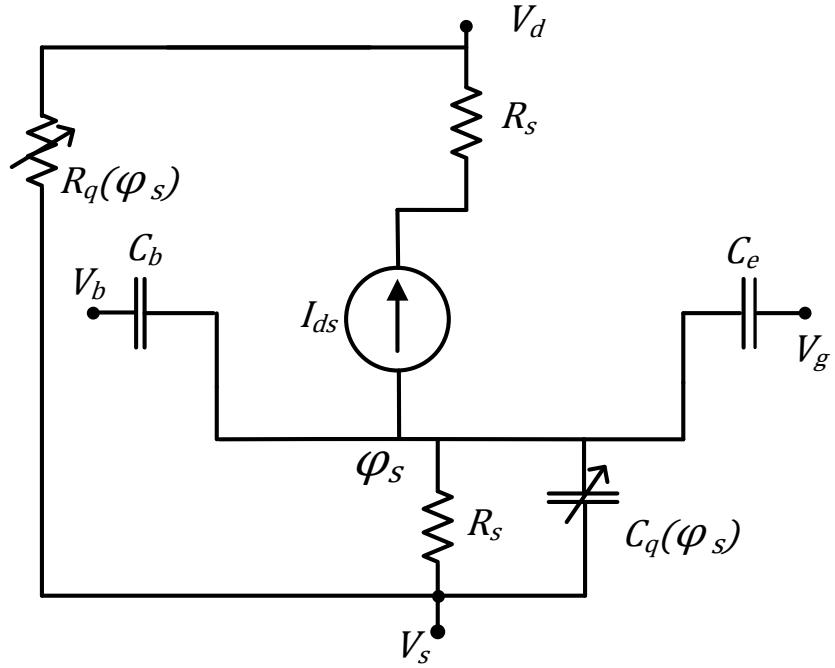

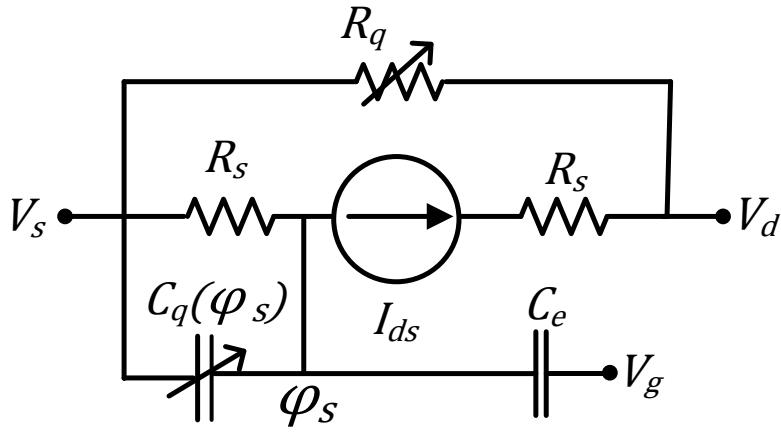

| 3.2  | Proposed general circuit model schematic for the dual-gate graphene field effect transistor . . . . .                                                                                                       | 45 |

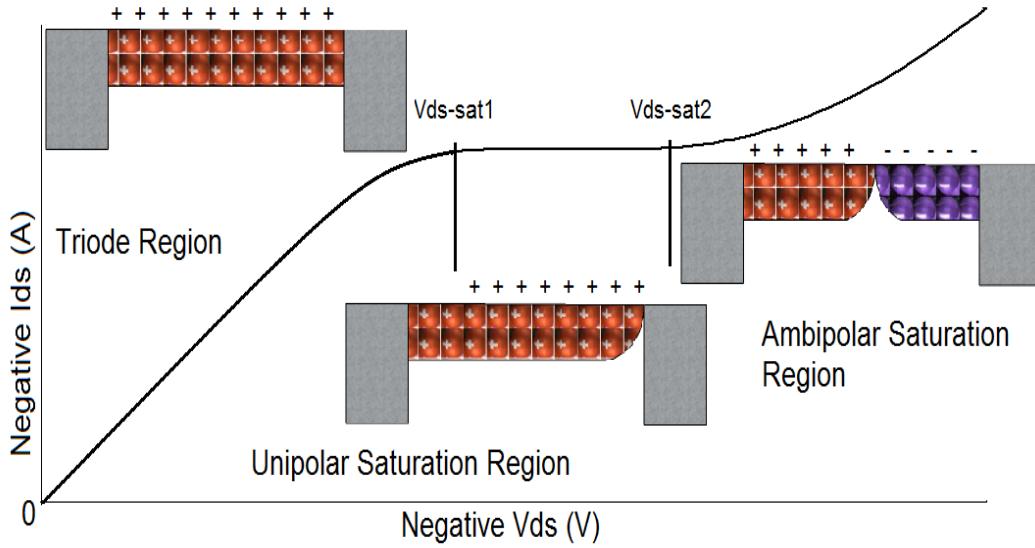

| 3.3  | I-V characteristics showing the three regions identified as the triode region, the unipolar saturation region and the ambipolar saturation region along with the charge interaction in the channel. . . . . | 46 |

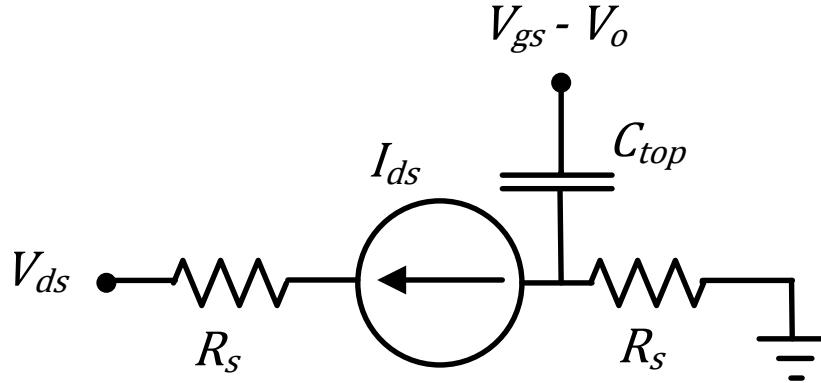

| 3.4  | A proposed general graphene model for both single-gate and dual-gate field effect transistor. $V_{bs}$ and $C_{back}$ are represented by an offset voltage, $V_o$ . . . . .                                 | 46 |

| 3.5  | Transfer characteristic of a graphene channel field effect transistor . . . . .                                                                                                                             | 47 |

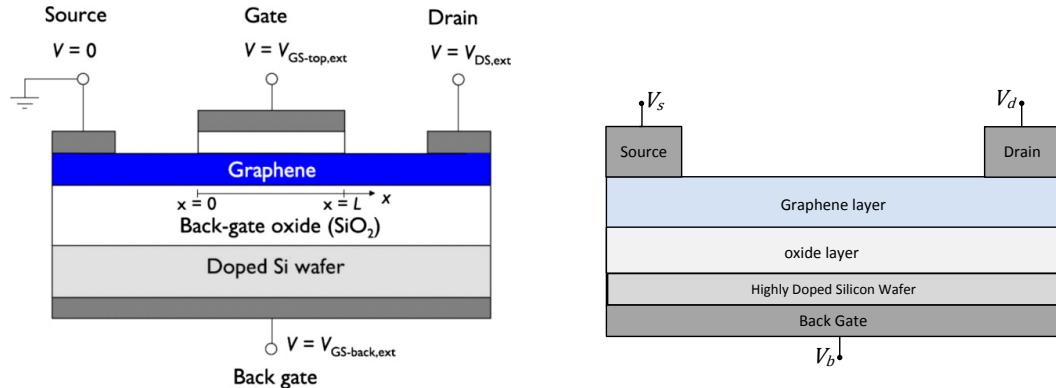

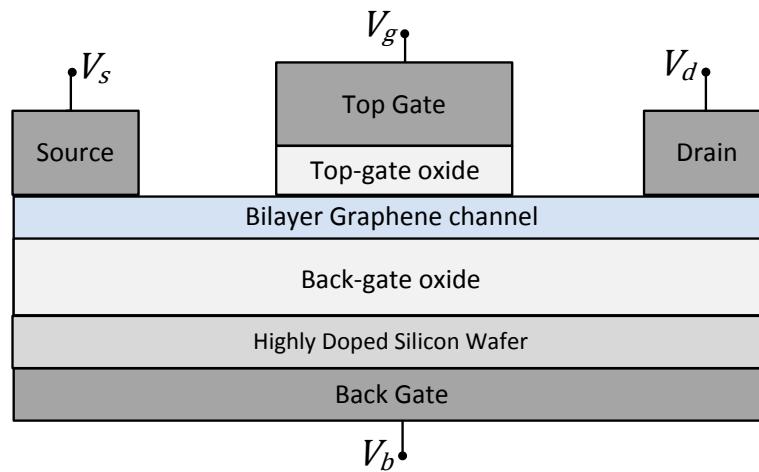

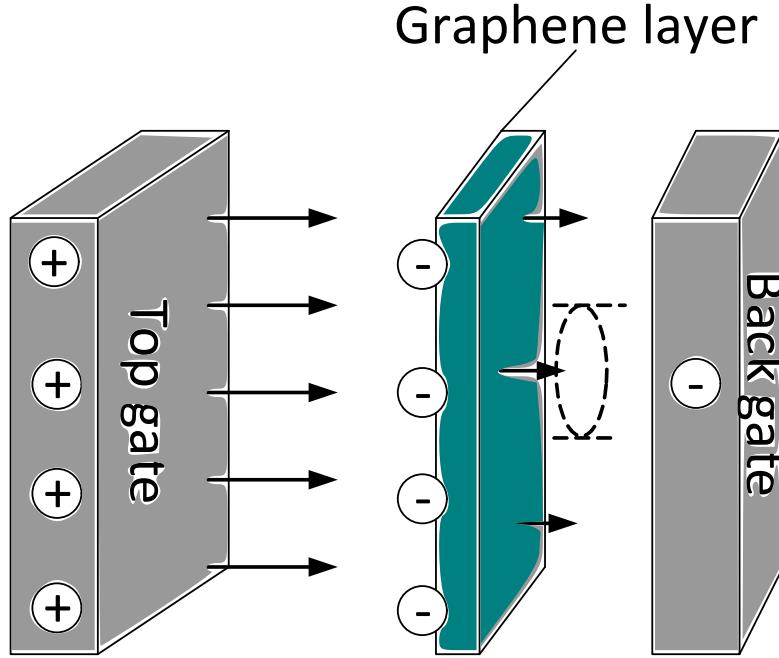

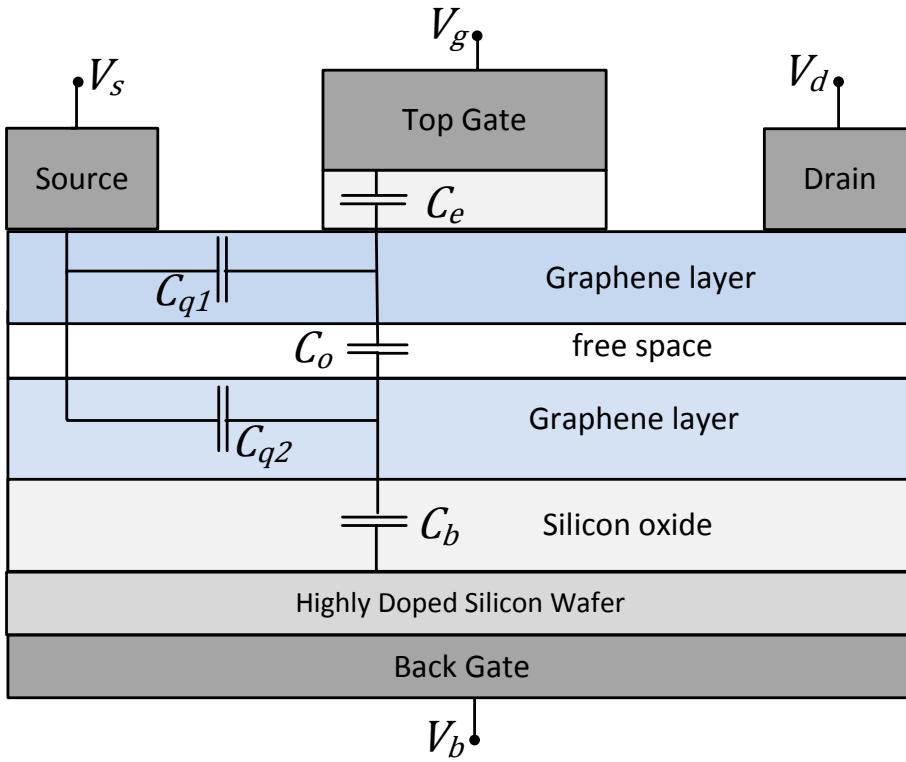

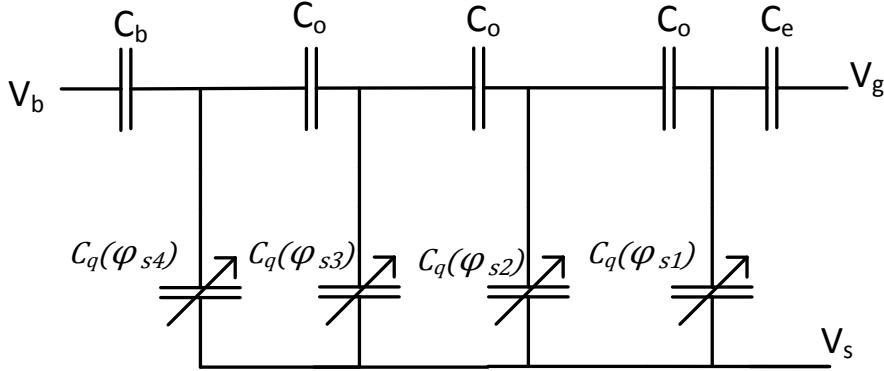

| 4.1  | Structure of a dual-gate single-layer graphene transistor with geometric capacitances. . . . .                                                                                                              | 56 |

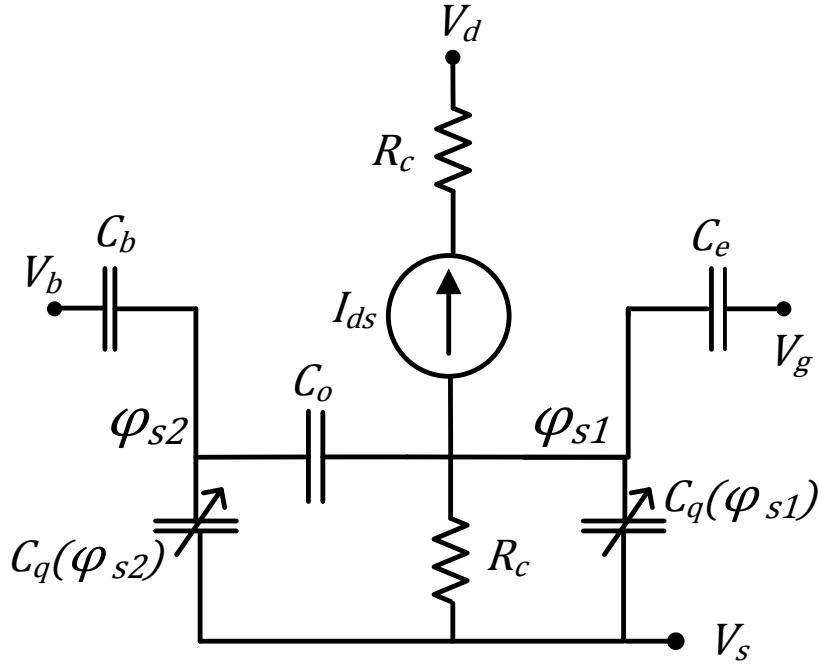

| 4.2  | Equivalent circuit model for a single layer graphene transistor . . . . .                                                                                                                                   | 57 |

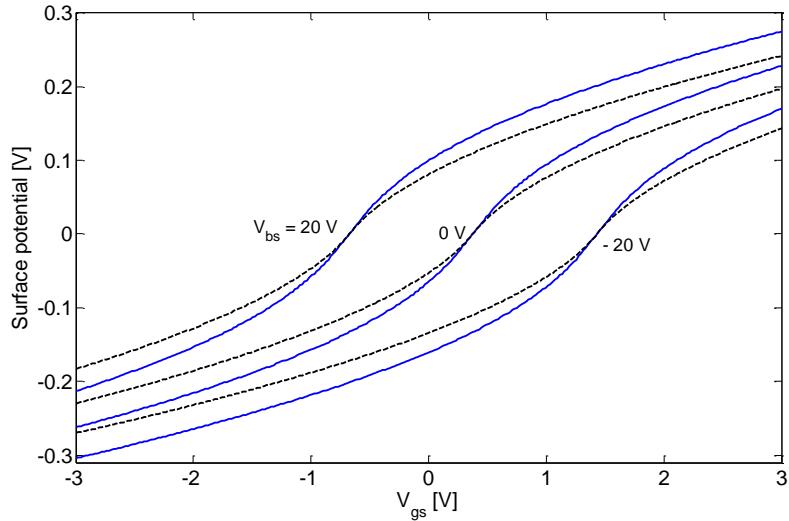

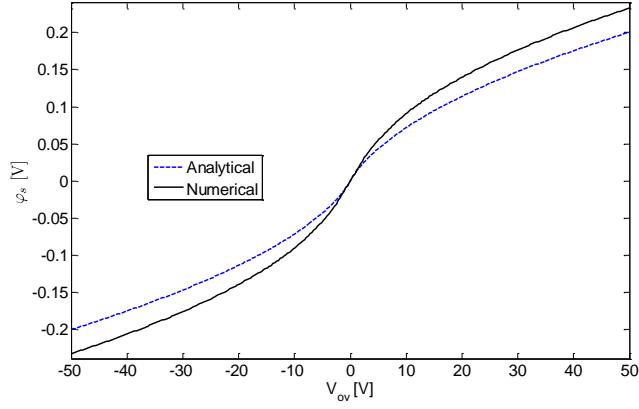

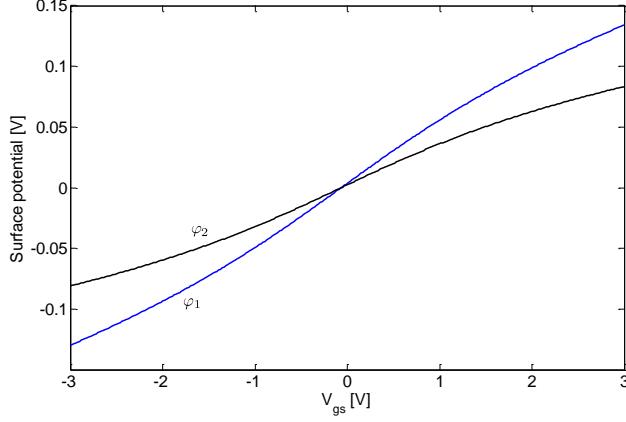

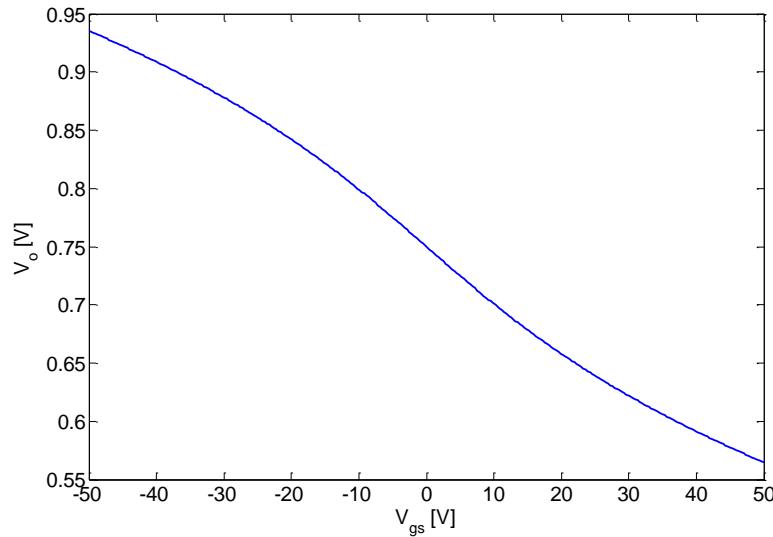

| 4.3  | The surface potential, $\varphi_s$ , as a function of $V_{gs}$ for $V_{bs}$ of 20V, 0V and -20V for both the analytical (dash) and numerical model (solid) . . . . .                                        | 60 |

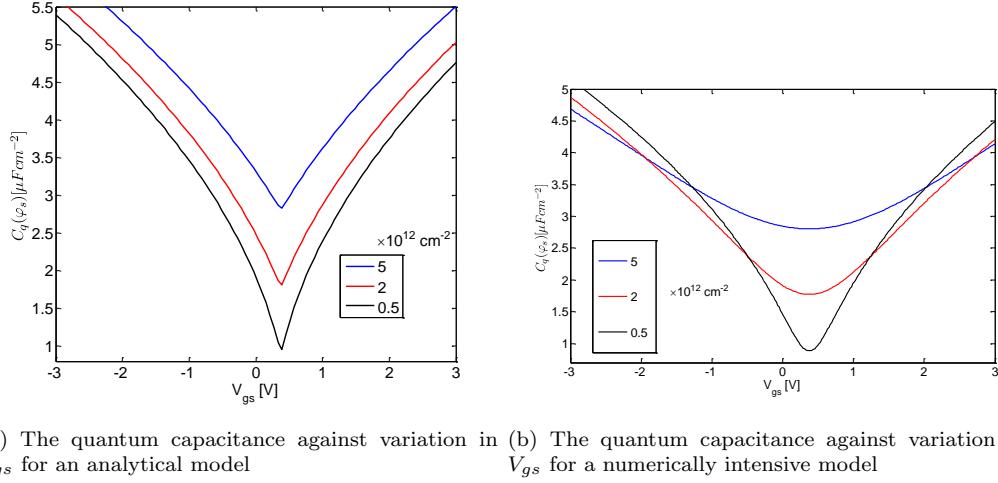

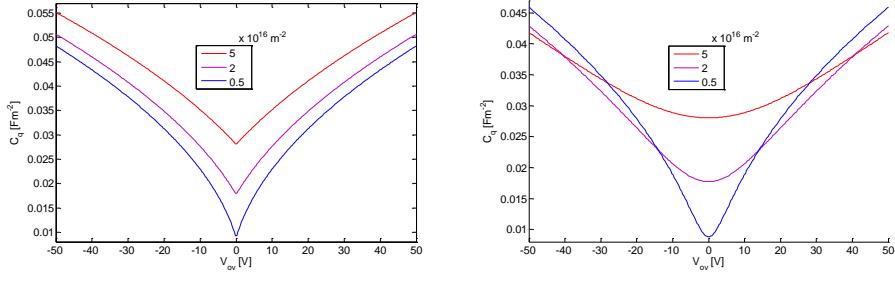

| 4.4  | The quantum capacitance against variation in $V_{gs}$ for a minimum charge density of 0.5, 2 and $5 \times 10^{12} \text{ cm}^{-2}$ respectively . . . . .                                                  | 61 |

| 4.5  | Schematic of a single-layer graphene with metallic gate terminal showing the electric field. The dash lines show the Gaussian surface which is induced by the electric field between the layers . . . . .   | 62 |

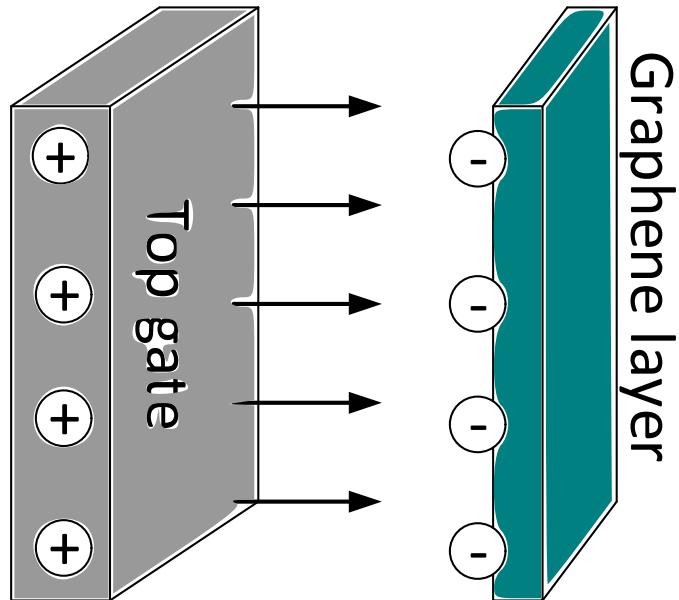

| 4.6  | Schematic diagram of a single-layer graphene FET . . . . .                                                                                                                                                  | 65 |

| 4.7  | Equivalent circuit-level diagram for a single-gate graphene field effect transistor . . . . .                                                                                                               | 66 |

| 4.8  | Surface potential for both an analytical model and the Drude based numerical model. . . . .                                                                                                                 | 68 |

| 4.9  | Quantum capacitance for a single-gate single-layer transistor . . . . .                                                                                                                                     | 68 |

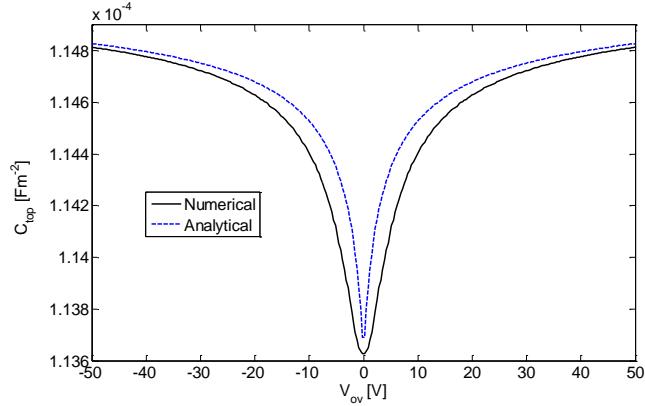

| 4.10 | Effective gate capacitance against variations in the gate voltage . . . . .                                                                                                                                 | 69 |

| 4.11 | Schematic of a single-layer graphene with a single metallic gate terminal showing the electric field and the excess charge. . . . .                                                                         | 69 |

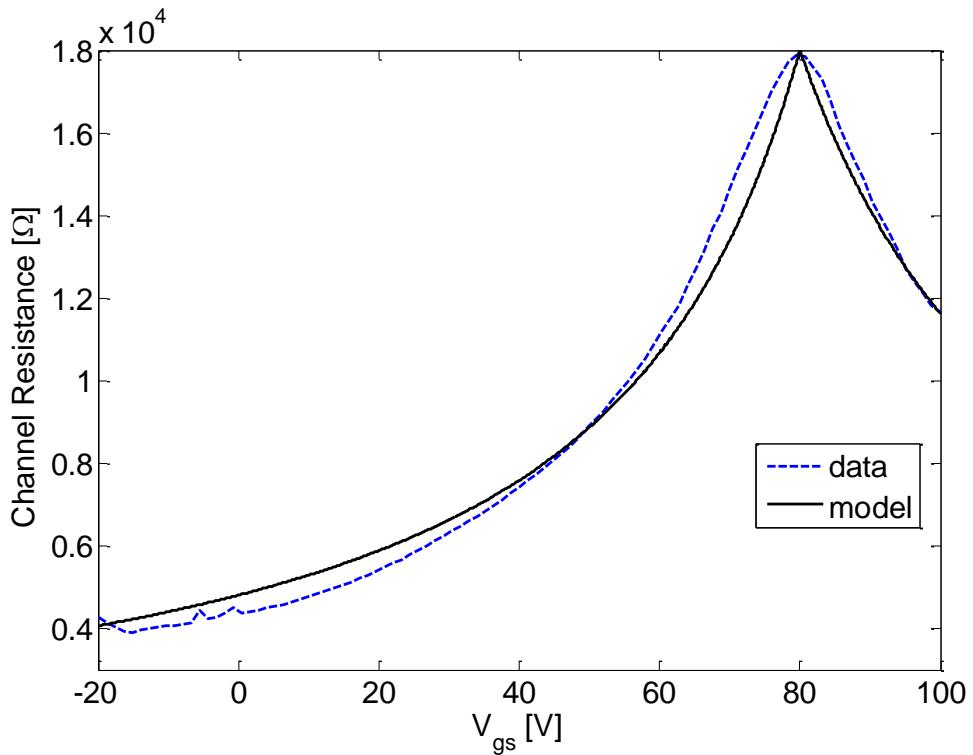

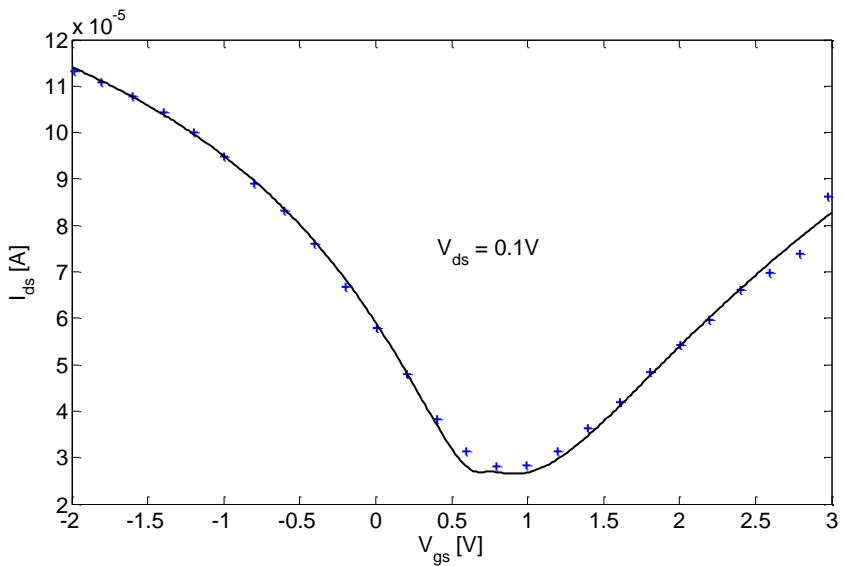

| 4.12 | Transfer characteristics of a single-gate monolayer transistor at room temperature [76]. . . . .                                                                                                            | 71 |

| 4.13 | Experimental data (circles) [89] and the proposed model (solid line) of the threshold voltages of a single-layer graphene FET . . . . .                                                                     | 72 |

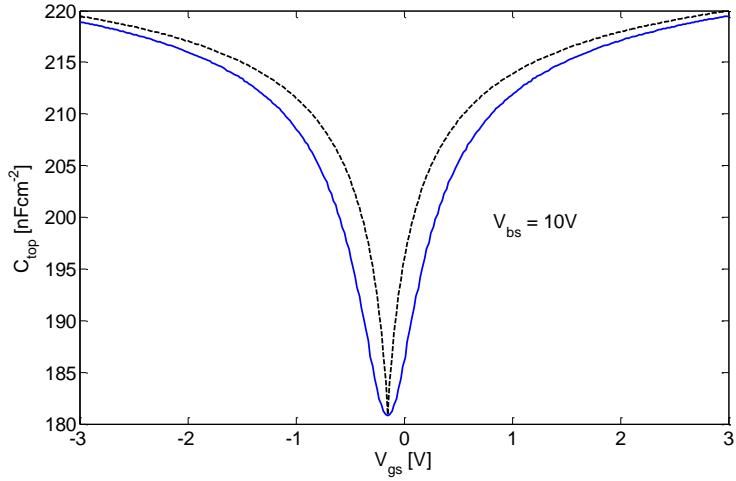

| 4.14 | The effective top-gate capacitance, $C_{top}$ against a sweep of $V_{gs}$ for both the analytical (dash) and Drude numerical (solid) models from -3V to 3V for $V_{bs} = 10V$ . . . . .                     | 73 |

|                                                                                                                                                                                                                                                                                                                                          |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

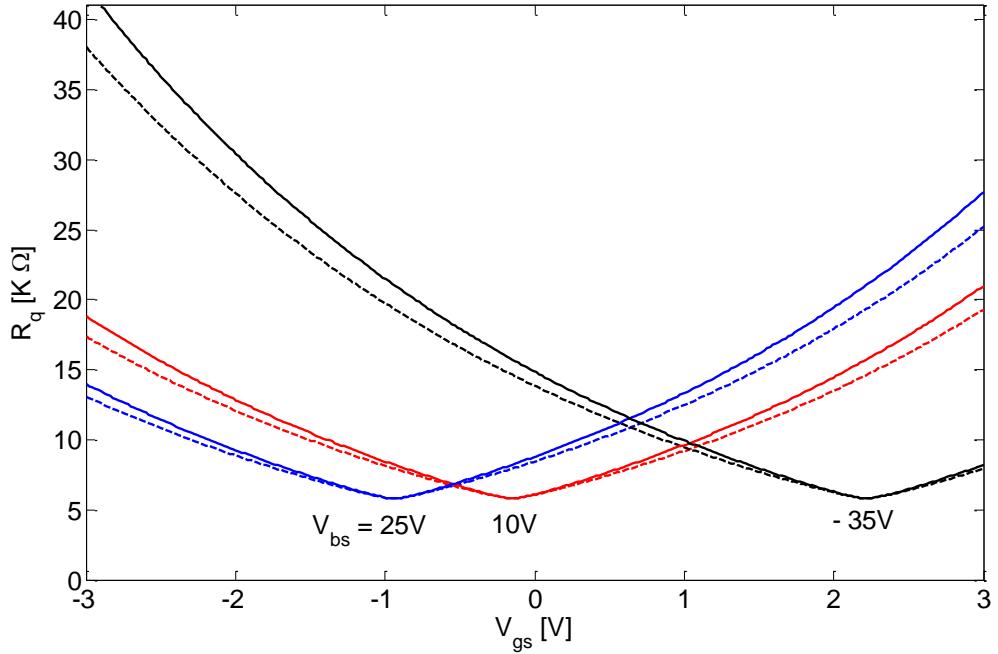

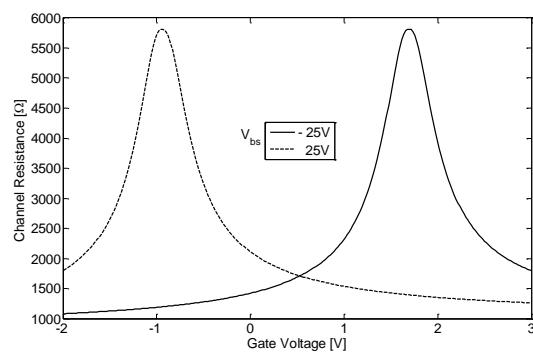

| 4.15 Characteristics of $R_q$ against $V_{gs}$ for $V_{bs}$ of 25V, 10V, 0V and -35V respectively. Plots of the characteristics for an analytical (dash) and a Drude numerical (solid) model. . . . .                                                                                                                                    | 73 |

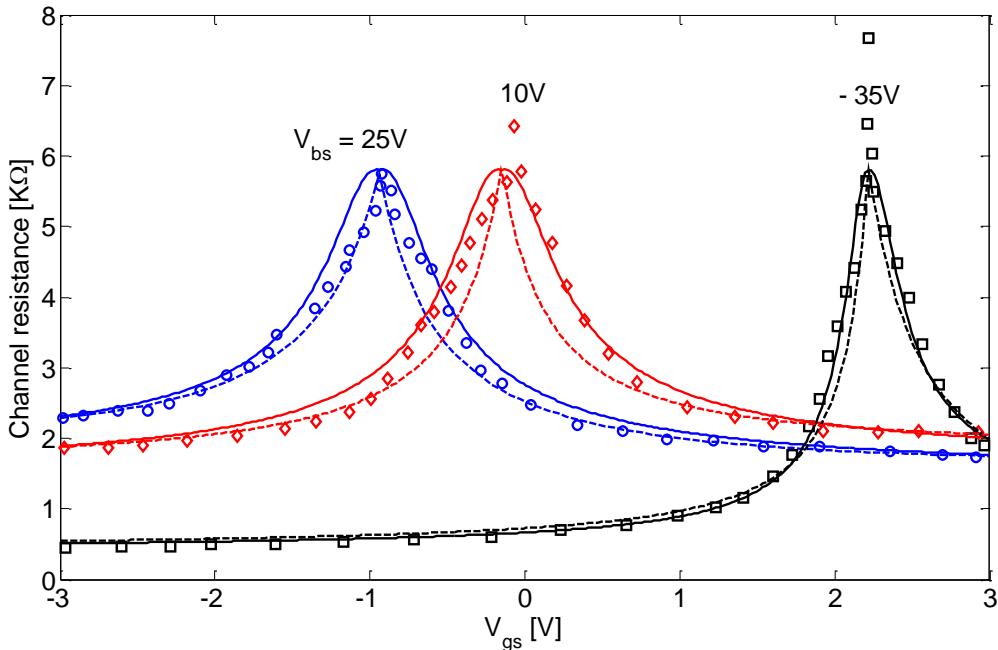

| 4.16 Experimental data ( $\circ$ $\diamond$ $\square$ ) [89], the analytical model (dash) and the Drude numerical model (solid) for the channel resistance against $V_{gs}$ at a temperature of 4.7K, $V_{bs}$ of 25V, 10V and -35V respectively and $V_{ds} = 0.01V$ . . . . .                                                          | 74 |

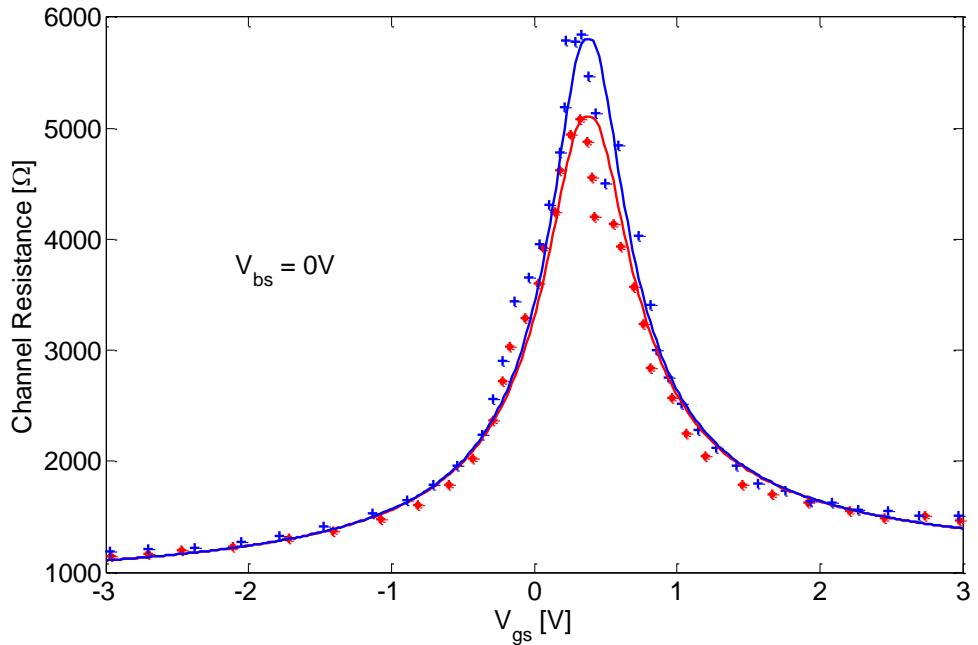

| 4.17 Experimental data (cross and star) [89] and the Drude based model (solid and dash lines) of the channel resistance against $V_{gs}$ for temperatures of 4.7K and 52K respectively, at $V_{bs}$ of 0V . . . . .                                                                                                                      | 75 |

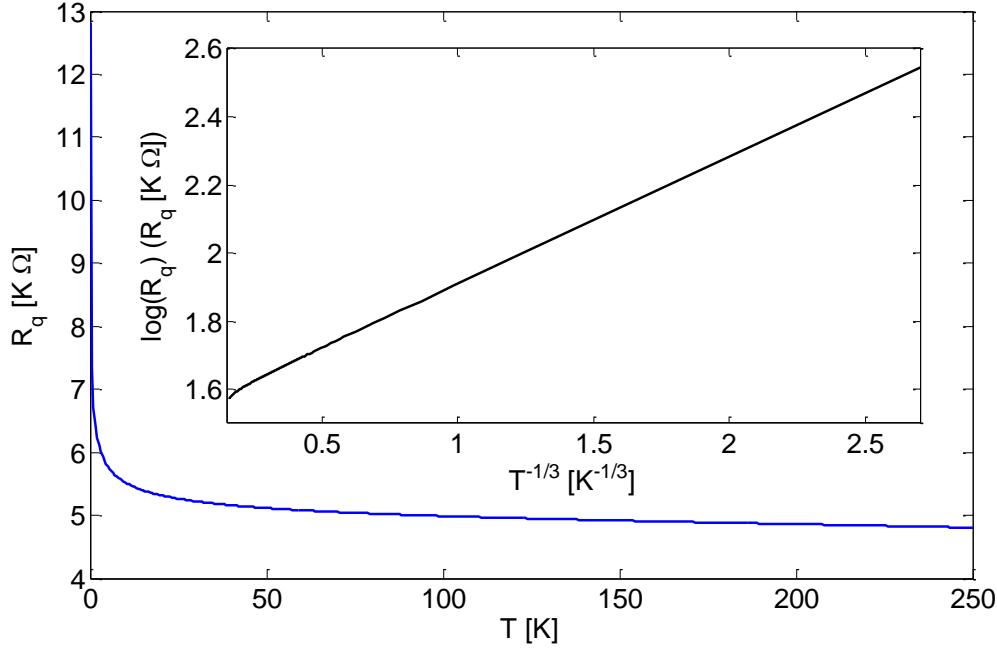

| 4.18 Interpolation of the dependence of the maximum channel resistance with respect to changes in temperature for a temperature sweep from 0.05K to 250K . . . . .                                                                                                                                                                       | 76 |

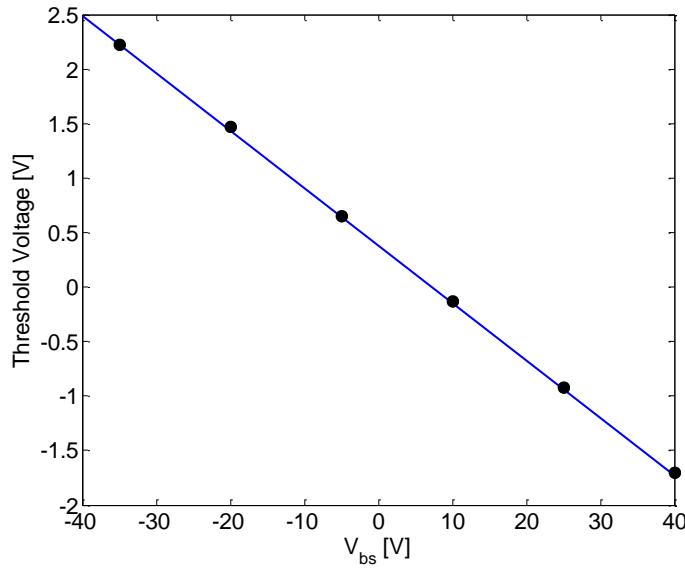

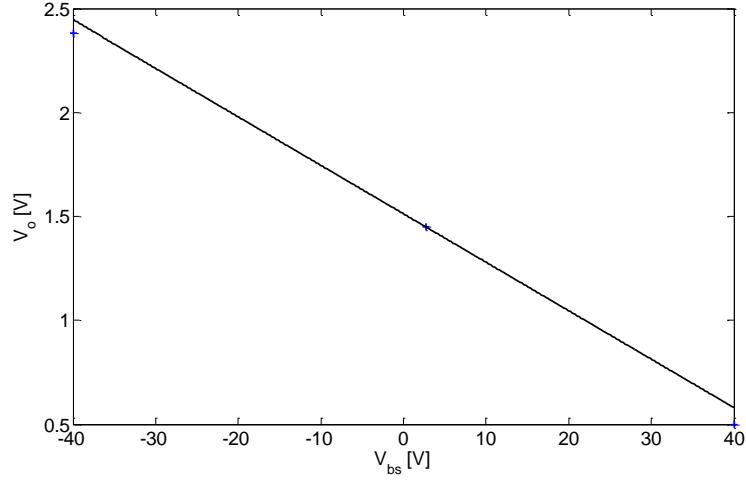

| 4.19 Threshold voltage against $V_{bs}$ (Experimental data(+) [33], proposed model(-)) . . . . .                                                                                                                                                                                                                                         | 78 |

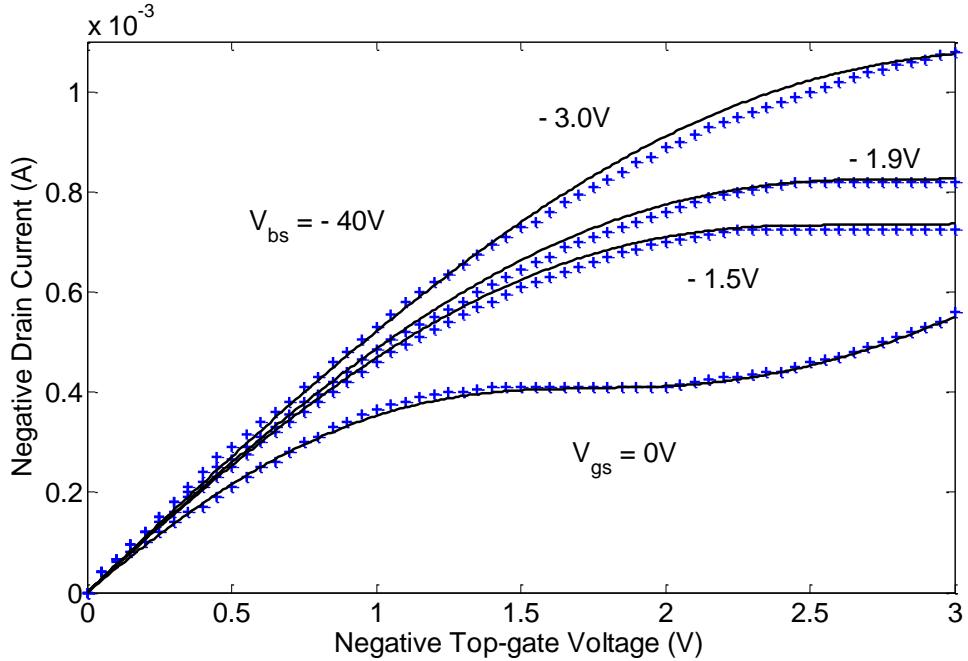

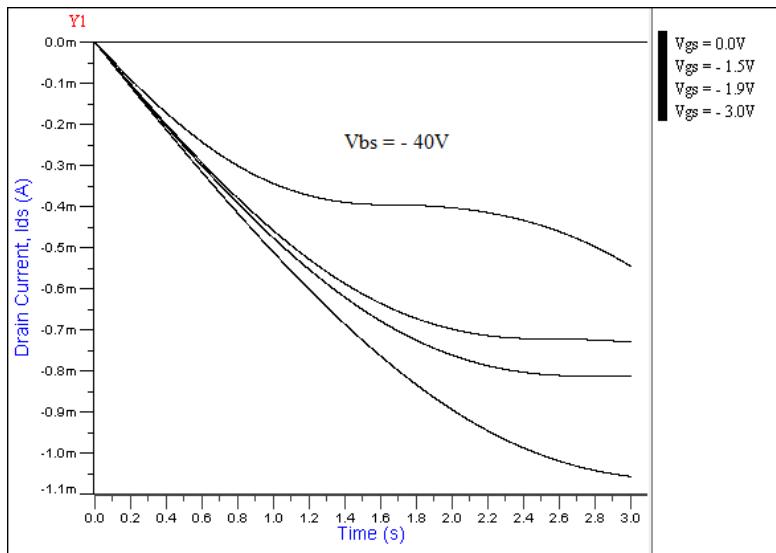

| 4.20 Experimental data (+) [33] and the proposed model (-) at an operating temperature of 1.7K for negative $I_{ds}$ vs negative $V_{ds}$ characteristics at $V_{bs} = -40V$ . $V_{ds}$ is varied from 0 to -3V for top-gate voltages of 0V, -1.5V, -1.9V and -3.0V (from bottom to top) . . . . .                                       | 78 |

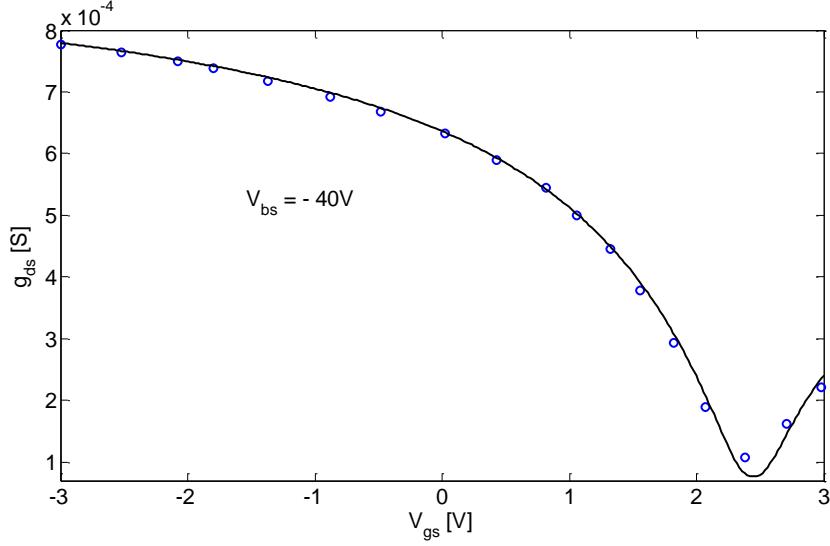

| 4.21 Characteristics of the channel output conductance against the top-gate voltage for $V_{bs} = -40V$ (Experimental data(o) [33], proposed model(-)) . . . . .                                                                                                                                                                         | 79 |

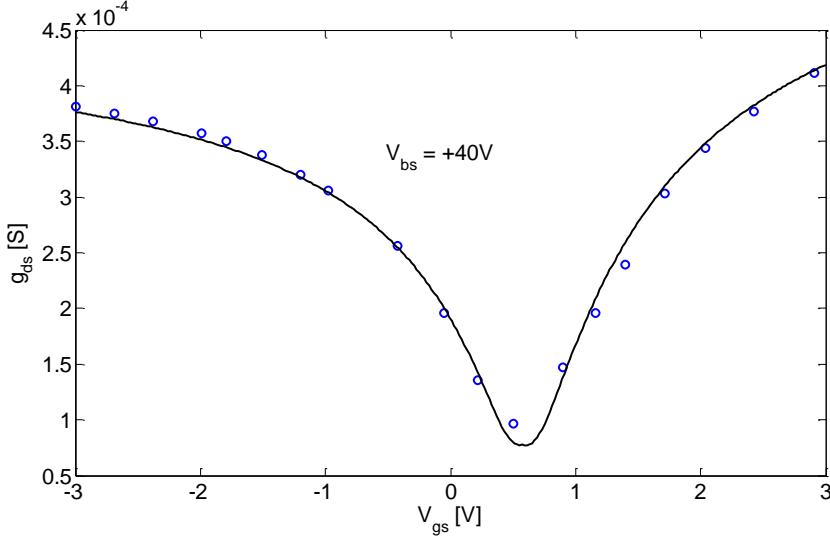

| 4.22 Characteristics of the channel output conductance against the top-gate voltage for $V_{bs} = 40V$ (Experimental data(o) [33], proposed model(-)) . . . . .                                                                                                                                                                          | 79 |

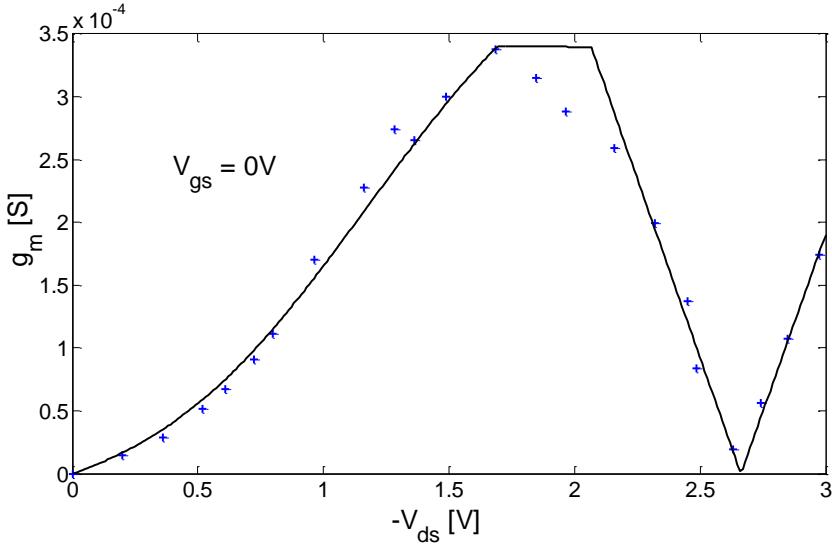

| 4.23 Characteristics of the channel transconductance against the top-gate voltage for $V_{bs} = -40V$ (Experimental data(+) [33], proposed model(-)) . . . . .                                                                                                                                                                           | 80 |

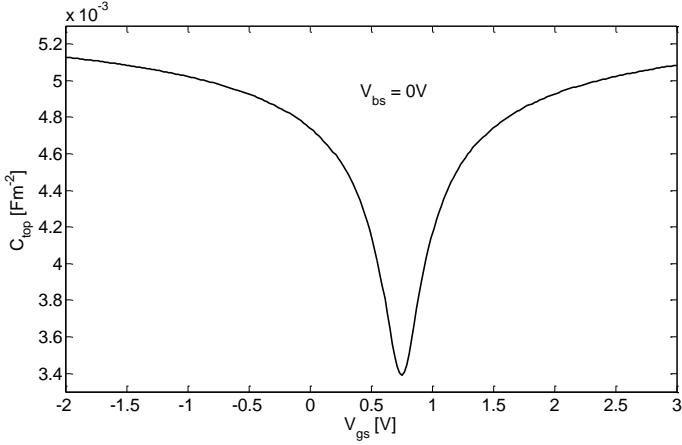

| 4.24 The effective top-gate capacitance, $C_{top}$ against a sweep of $V_{gs}$ from -3V to 3V for test case two . . . . .                                                                                                                                                                                                                | 82 |

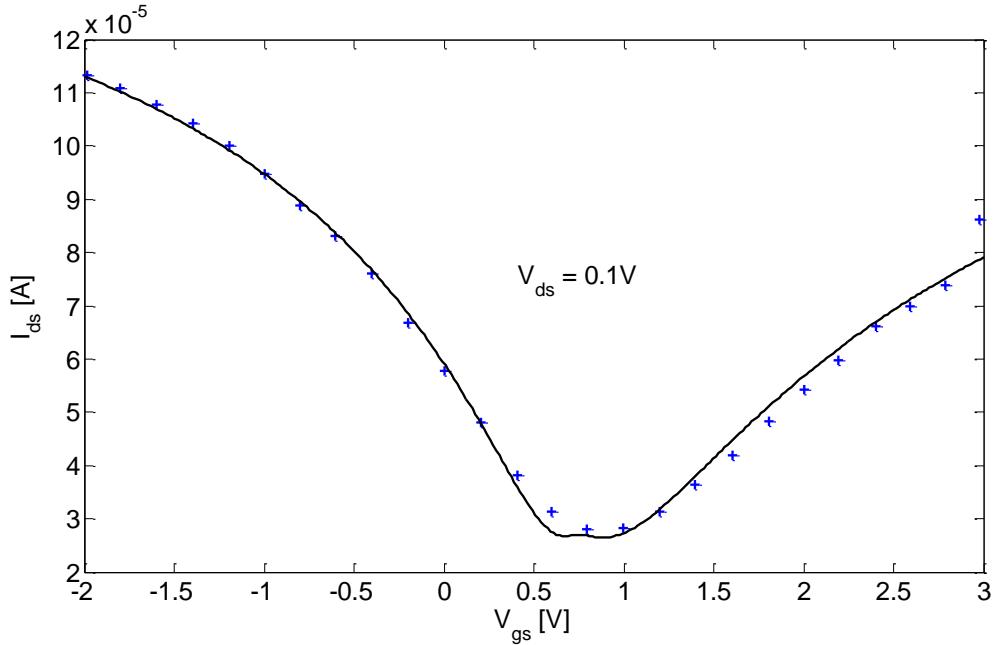

| 4.25 Characteristics of the channel Drain current against the top-gate voltage for $V_{ds} = 0.1V$ at room temperature (Experimental data(+) [127], proposed model(-)) . . . . .                                                                                                                                                         | 82 |

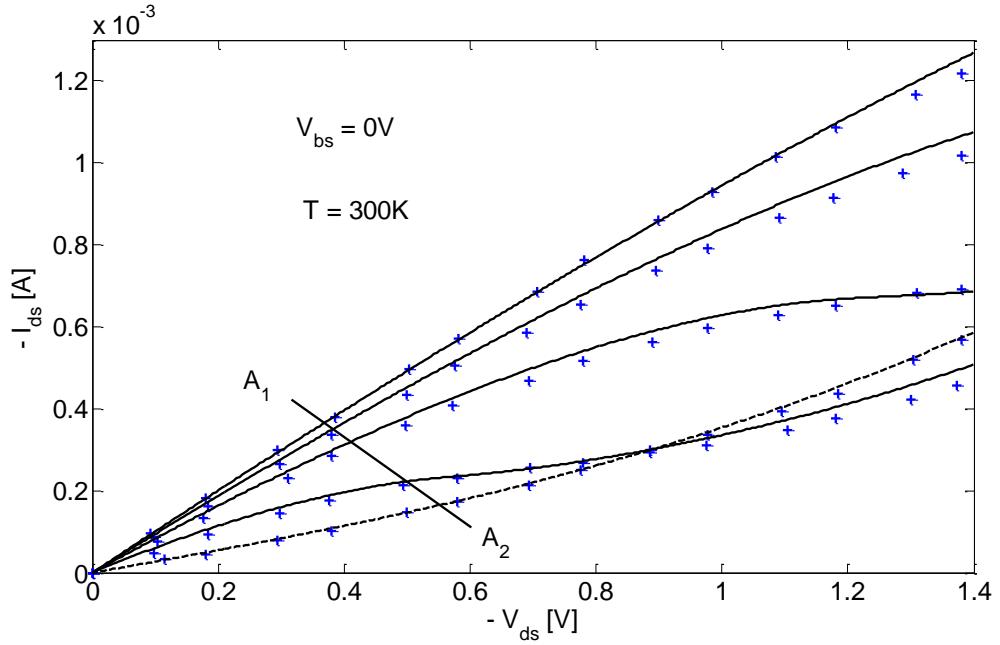

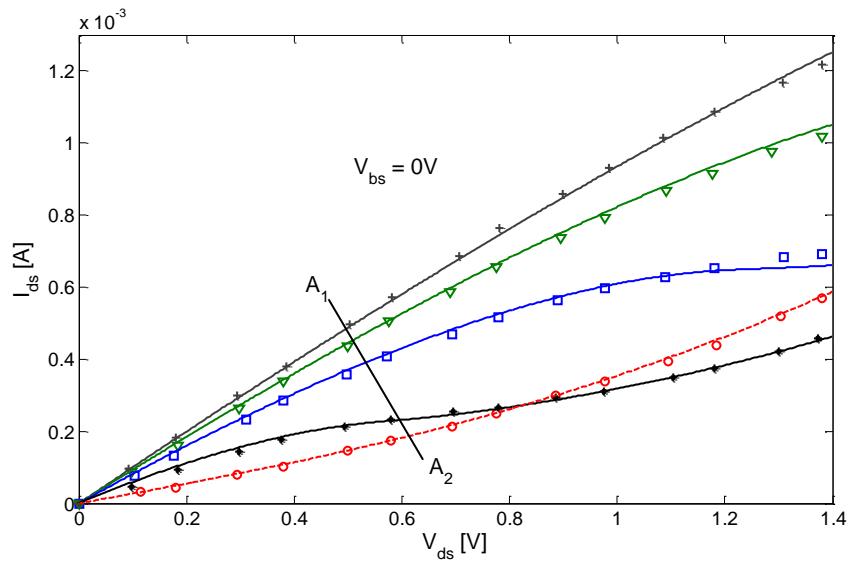

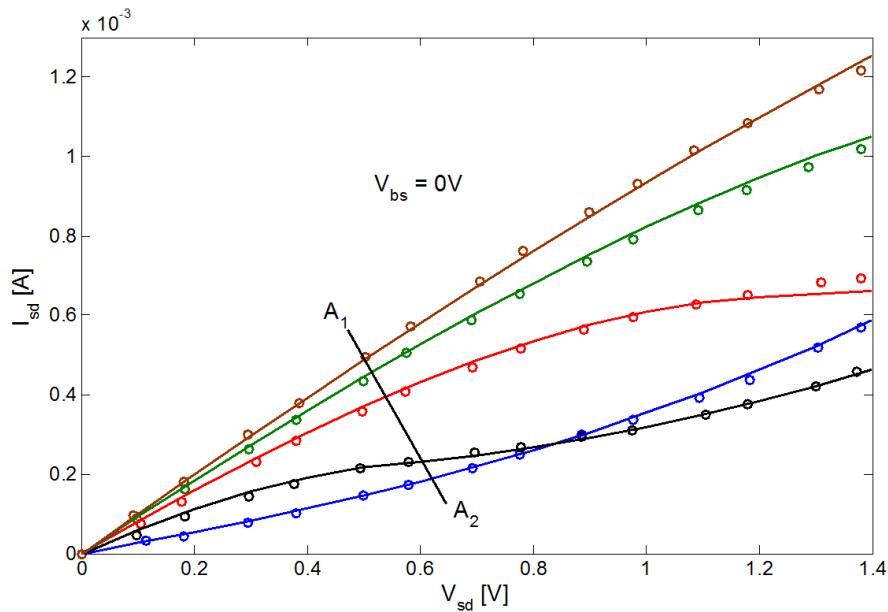

| 4.26 Experimental data (+) [127] and the proposed model (-) for negative $I_{ds}$ vs negative $V_{ds}$ characteristics at room temperature for $V_{bs} = 0V$ . $V_{ds}$ is varied from 0 to -1.4V for top-gate voltages of -1.25V, -0.75V, -0.25V, 0.25V and 0.75V (from top to bottom between cross-section $A_1$ and $A_2$ ) . . . . . | 83 |

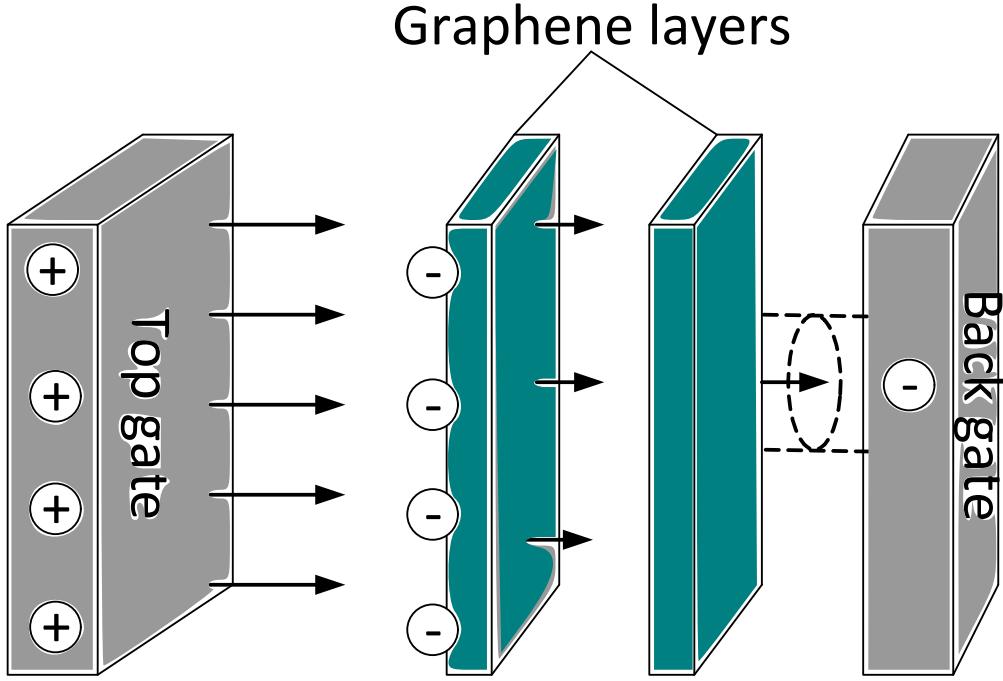

| 5.1 Bilayer graphene transistor layout . . . . .                                                                                                                                                                                                                                                                                         | 86 |

| 5.2 Proposed equivalent circuit for a bilayer graphene transistor . . . . .                                                                                                                                                                                                                                                              | 87 |

| 5.3 The surface potential $\varphi_{s1}$ and $\varphi_{s2}$ of the layers as a function of $V_{gs}$ at $V_{bs} = 50V$ . . . . .                                                                                                                                                                                                          | 88 |

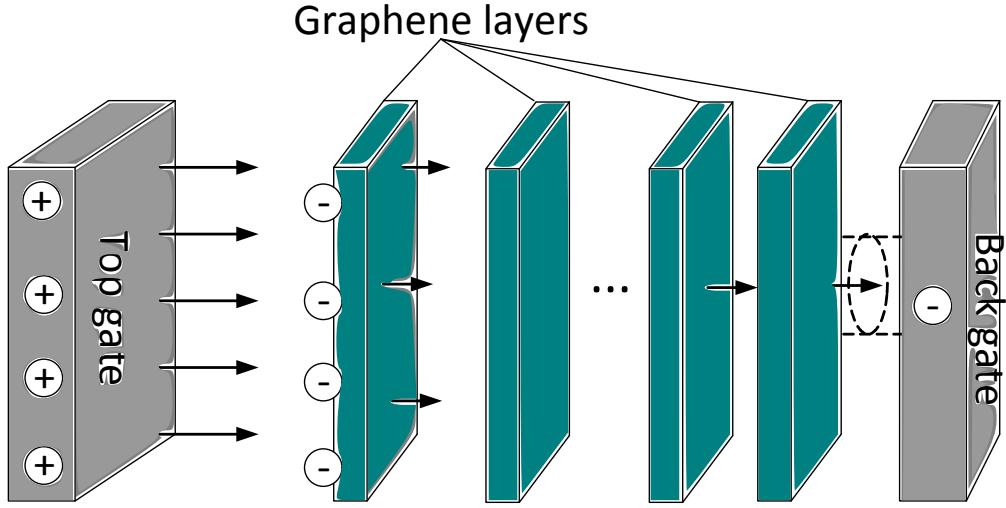

| 5.4 schematic four-layer graphene transistor capacitance model . . . . .                                                                                                                                                                                                                                                                 | 90 |

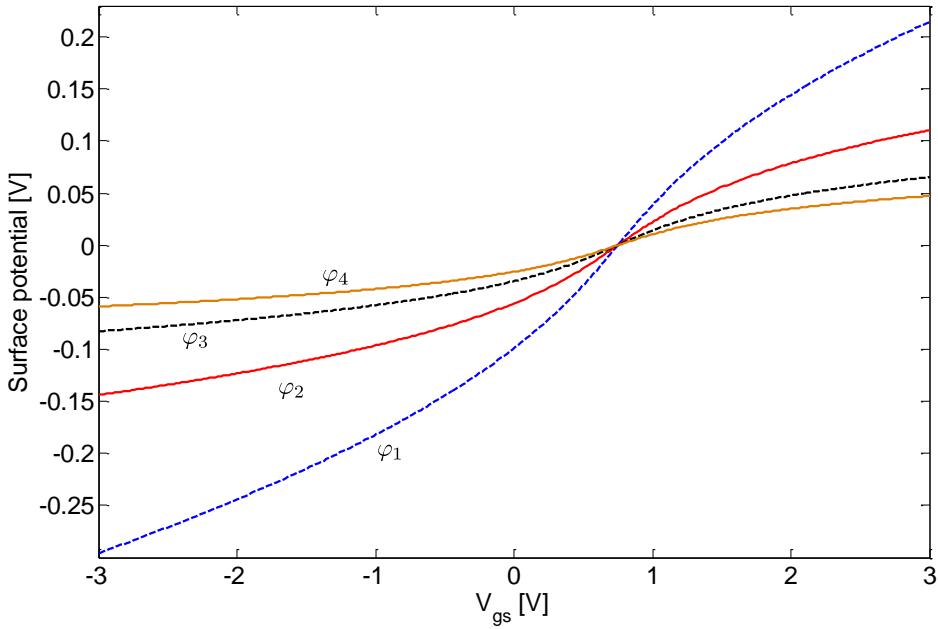

| 5.5 The surface potential for each of the four layers as a function of $V_{gs}$ at $V_{bs} = 0V$ . . . . .                                                                                                                                                                                                                               | 92 |

| 5.6 Schematic of a bilayer graphene with metallic gate terminal showing the electric field. The dash lines show the Gaussian surface which is induced by the electric field between the layers . . . . .                                                                                                                                 | 94 |

| 5.7 Schematic of a multi-layer graphene with metallic gate terminal showing the electric field. Where $m$ is the number of graphene layers. The dash lines show the Gaussian surface which is induced by the electric field between the layers . . . . .                                                                                 | 96 |

|      |                                                                                                                                                                                                                                                                                                                                                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

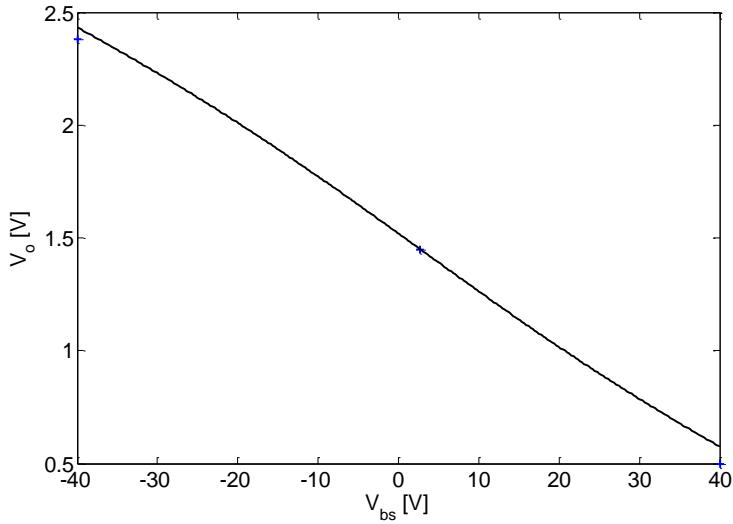

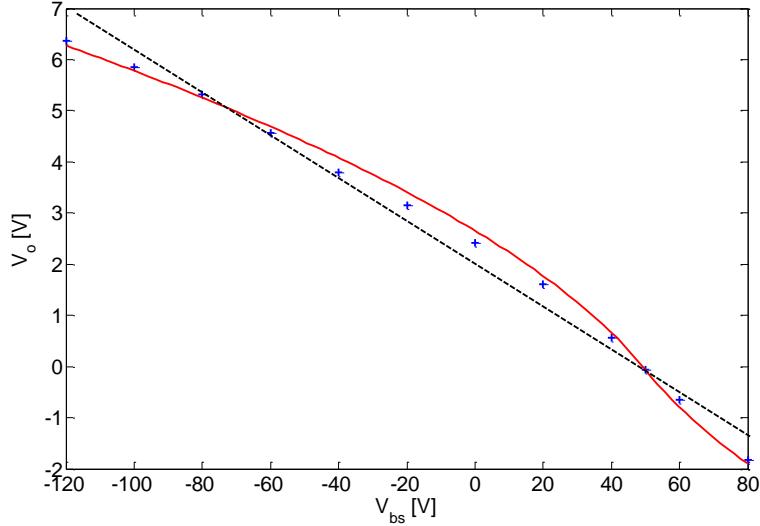

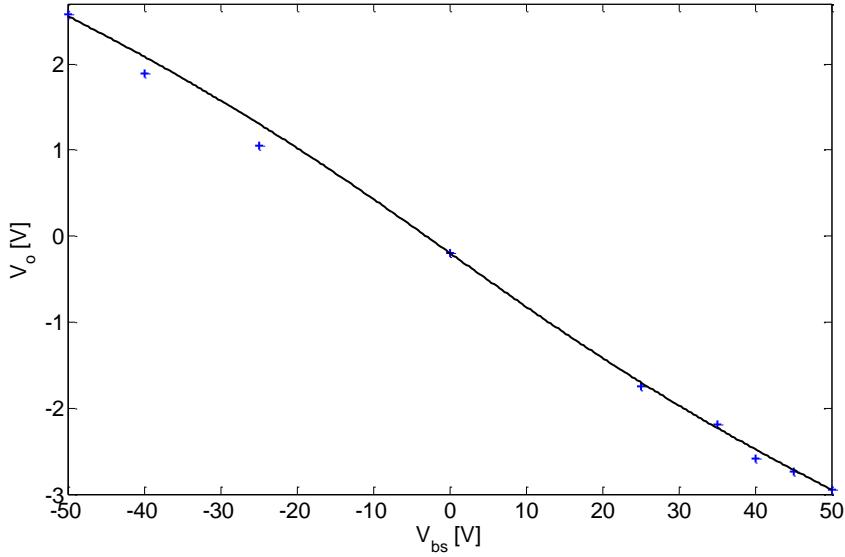

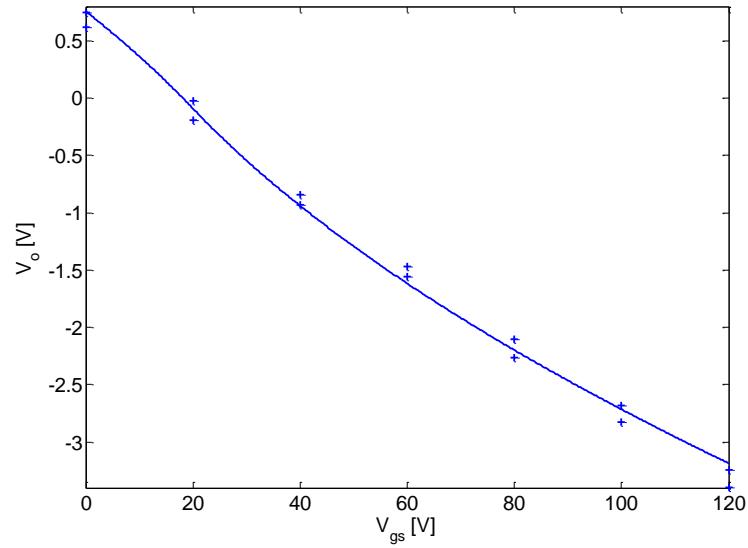

| 5.8  | The threshold voltage, $V_o$ , against $V_{bs}$ for the Experimental data (+) [33], the proposed model (solid line) . . . . .                                                                                                                                                                                                                                              | 98  |

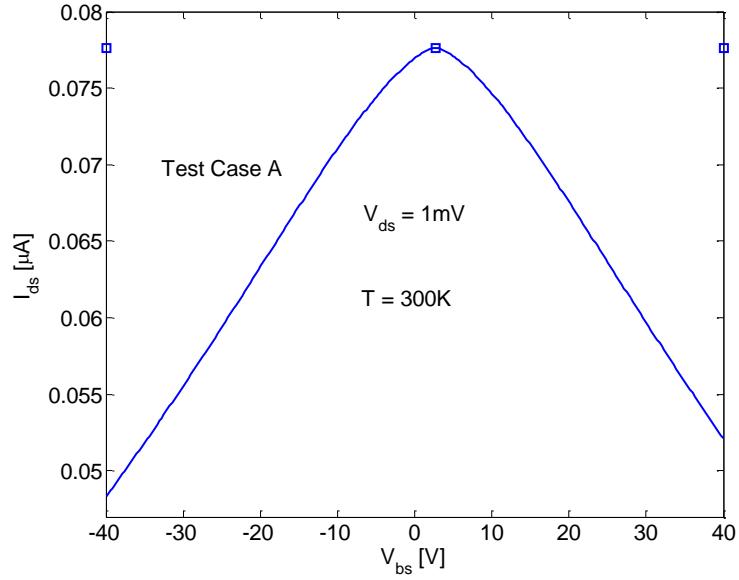

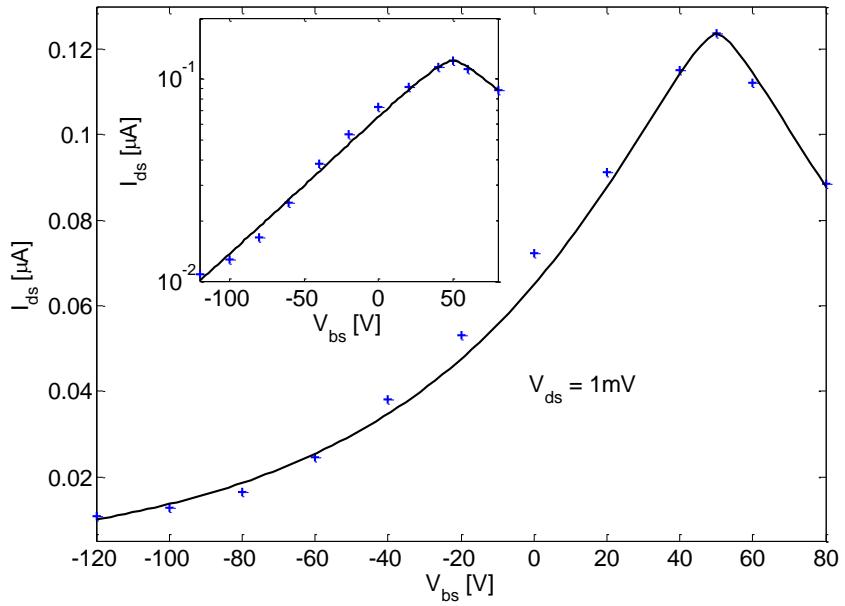

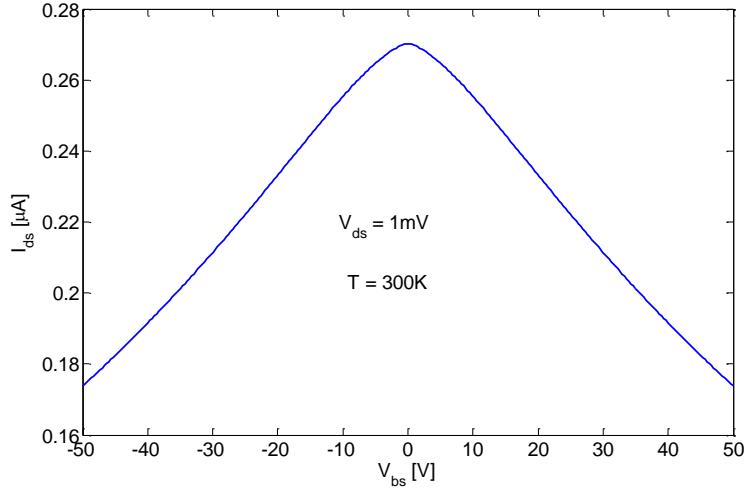

| 5.9  | A plot of the device off-current against $V_{bs}$ for $V_{ds} = 1mV$ shows the proposed model against experimental data for case A (experimental data (□) [33]) at room temperature . . . . .                                                                                                                                                                              | 99  |

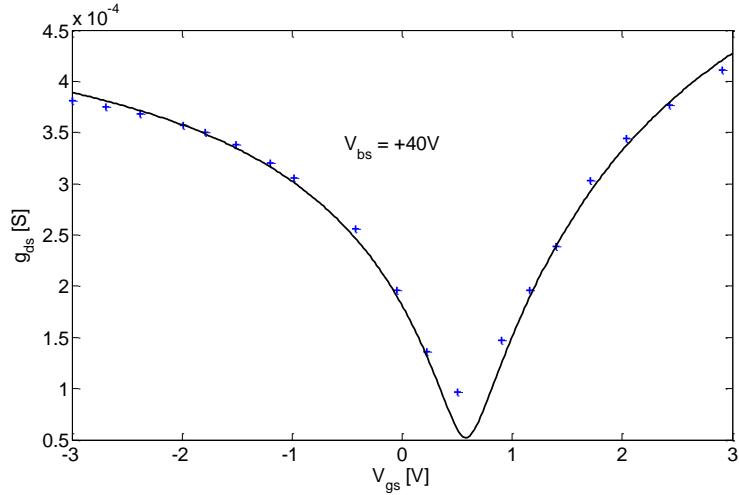

| 5.10 | Transfer Characteristics of the channel output conductance at room temperature against the top-gate voltage for $V_{bs} = 40V$ for published experimental data(+) [33] and the proposed model(–) . . . . .                                                                                                                                                                 | 99  |

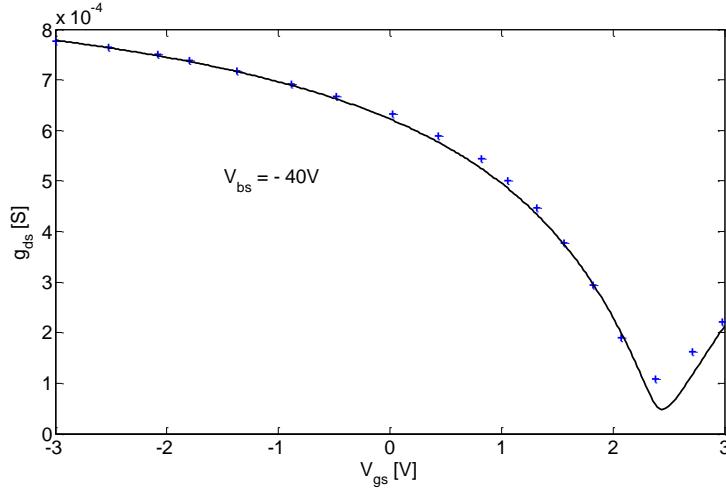

| 5.11 | Transfer characteristics of the channel output conductance at room temperature against the top-gate voltage for $V_{bs} = -40V$ for published experimental data(+) [33] and the proposed model(–) . . . . .                                                                                                                                                                | 100 |

| 5.12 | Threshold voltage, $V_o$ , against $V_{bs}$ for published experimental data (+) [77], the proposed model (solid line) and the best fit of a straight line (dash lines) . . . . .                                                                                                                                                                                           | 101 |

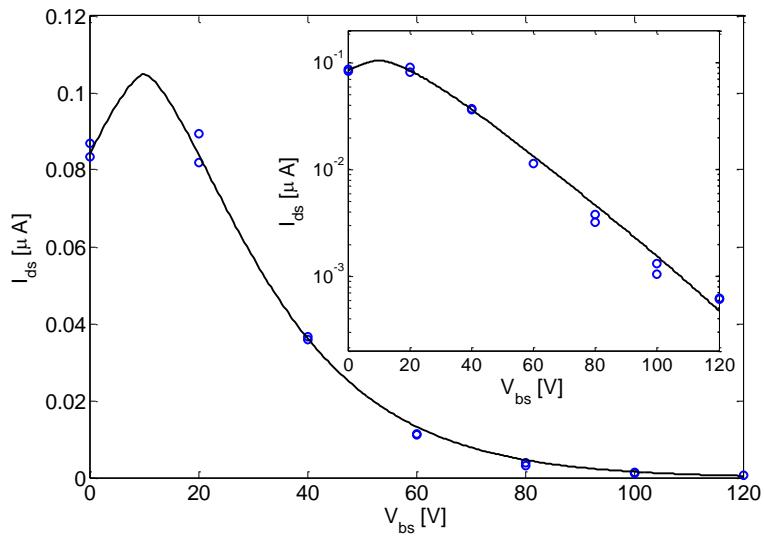

| 5.13 | Validation of the transistor off-current against various back-gate voltages for published experimental data (+) [77] and the proposed model (–) at room temperature. Analysis is carried out at a constant drain voltage, $V_{ds} = 1mV$ . Inset: A logarithm plot of the off-current against $V_{bs}$ . . . . .                                                           | 102 |

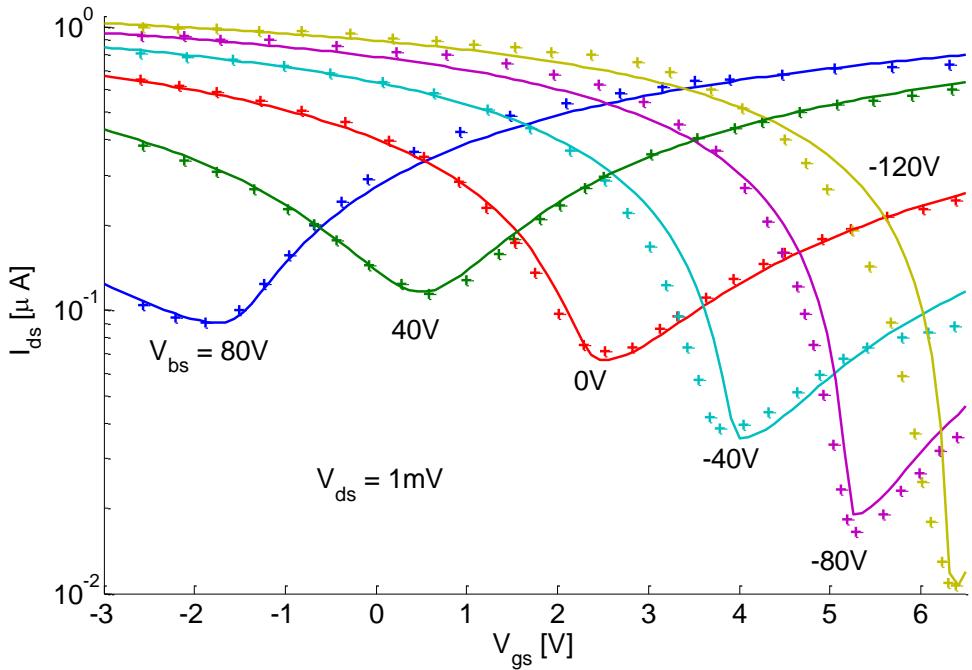

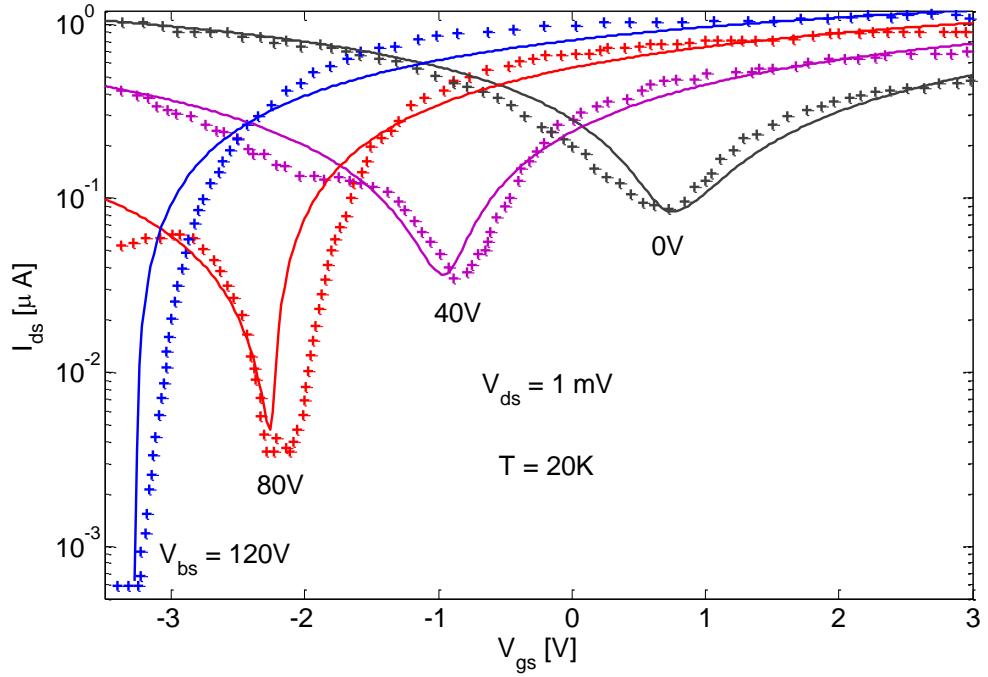

| 5.14 | Transfer characteristics of the transistor drain current against variations in $V_{gs}$ at room temperature. Validation between published experimental data (+) [77] and the proposed model (–). $V_{bs}$ is varied from 80V to -120V in steps of 40V at a constant drain voltage, $V_{ds} = 1mV$ . . . . .                                                                | 102 |

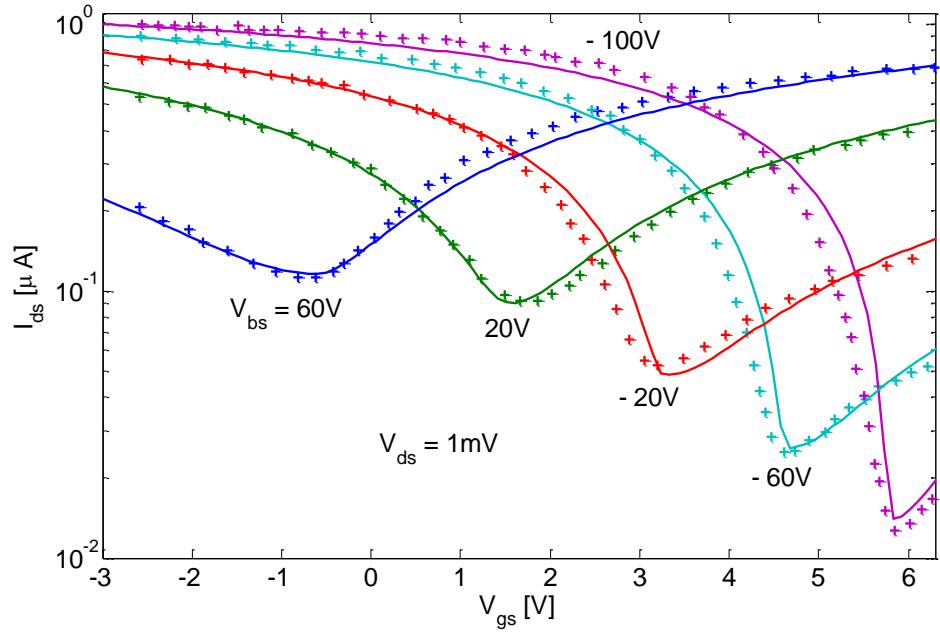

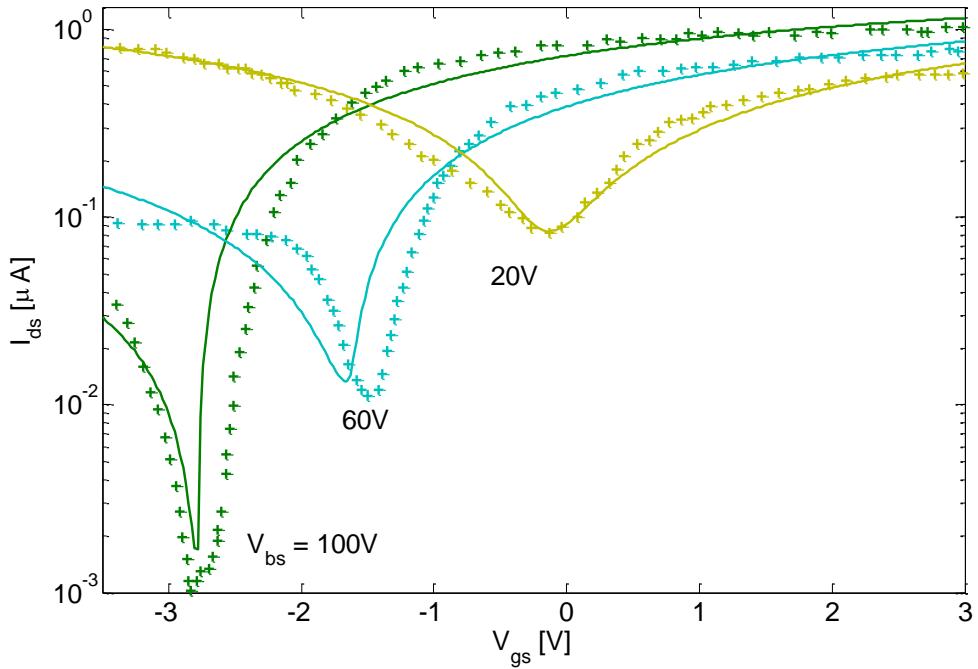

| 5.15 | Transfer characteristics of the transistor drain current against variations in $V_{gs}$ at room temperature. Validation between published experimental data (+) [77] and the proposed model (–). $V_{bs}$ is varied from 60V to -100V in steps of 40V at a constant drain voltage, $V_{ds} = 1mV$ . . . . .                                                                | 103 |

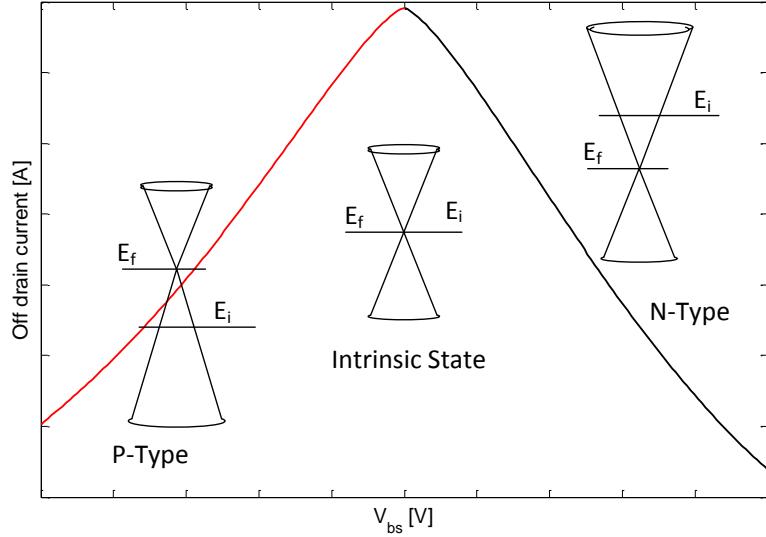

| 5.16 | Representation of the energy levels and the conduction and valence bands symmetry for the characteristics of the off-current against variations in $V_{bs}$ . $E_i$ and $E_f$ are the intrinsic and Fermi energy levels. . . . .                                                                                                                                           | 105 |

| 5.17 | The threshold voltage, $V_o$ , against $V_{bs}$ for published experimental data (+) [89] and the proposed model (solid line) . . . . .                                                                                                                                                                                                                                     | 106 |

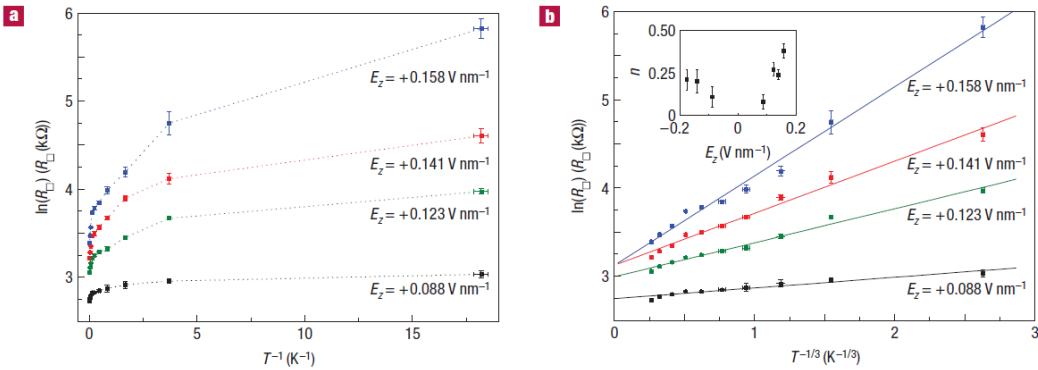

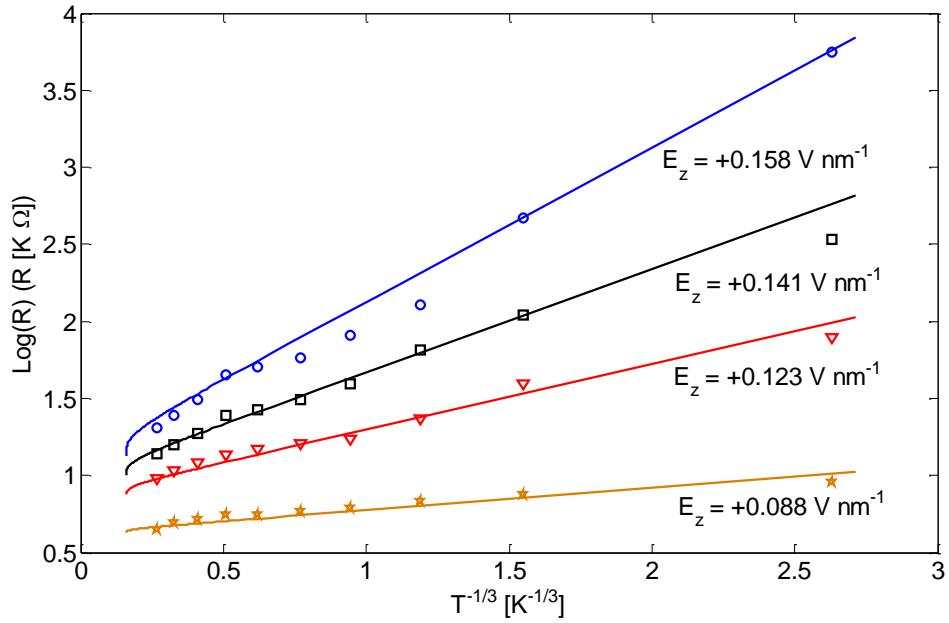

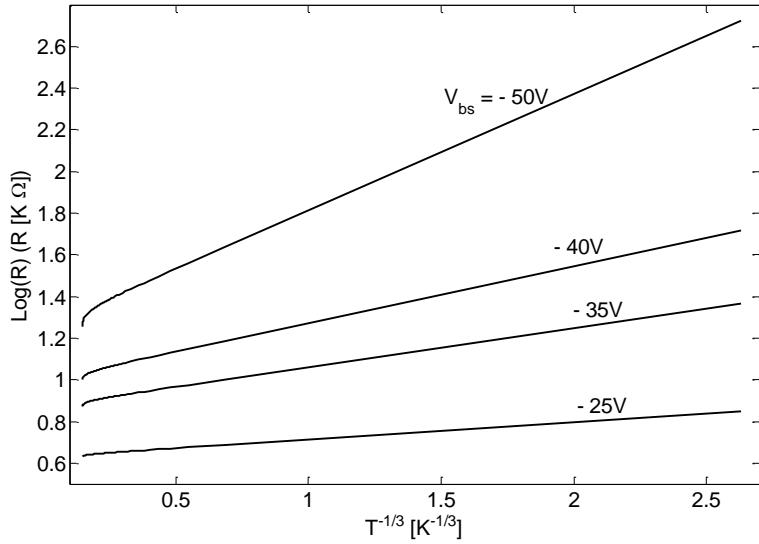

| 5.18 | A logarithm of the peak channel resistance against inverse cube root of the temperature for a range of perpendicular electric fields $((V_{bs} - V_o)/(t_{ox} + H_{sub}))$ where $t_{ox}$ and $H_{sub}$ are the thickness of the top-gate and back-gate dielectric). Published experimental data [89] is shown in crosses and the model is shown in a solid line . . . . . | 107 |

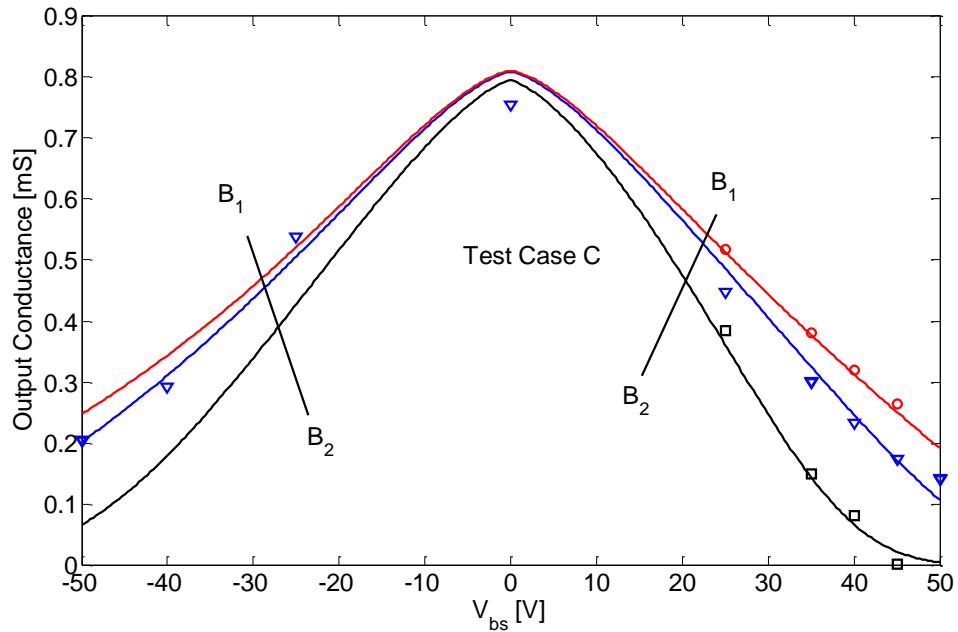

| 5.19 | A plot of the device charge neutrality conductance against $V_{bs}$ for test case C. cross-section $B_1$ to $B_2$ (top to bottom) shows the proposed model against experimental data [89] at a temperature of 53K (○), 4.2K (▽) and 0.055K (□) . . . . .                                                                                                                   | 107 |

| 5.20 | A logarithm of the maximum channel resistance against inverse cube root of the temperature for various back-gate voltages. Back gate voltages are -50V, -40V, -35V and -25V respectively . . . . .                                                                                                                                                                         | 108 |

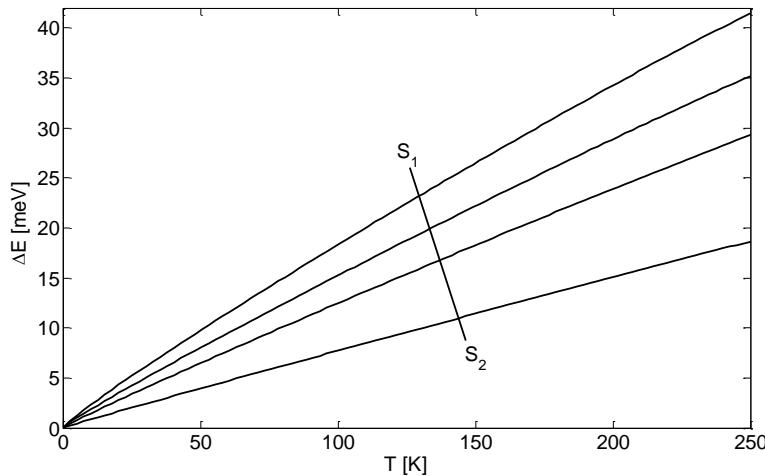

| 5.21 | Estimated energy bandgap created by varying the operating temperature from 0K to 250K at various vertical electric fields. The electric fields are $0.158Vnm^{-2}$ , $0.141Vnm^{-2}$ , $0.123Vnm^{-2}$ and $0.088Vnm^{-2}$ respectively from top to bottom of cross section $S_1$ to $S_2$ . . . . .                                                                       | 109 |

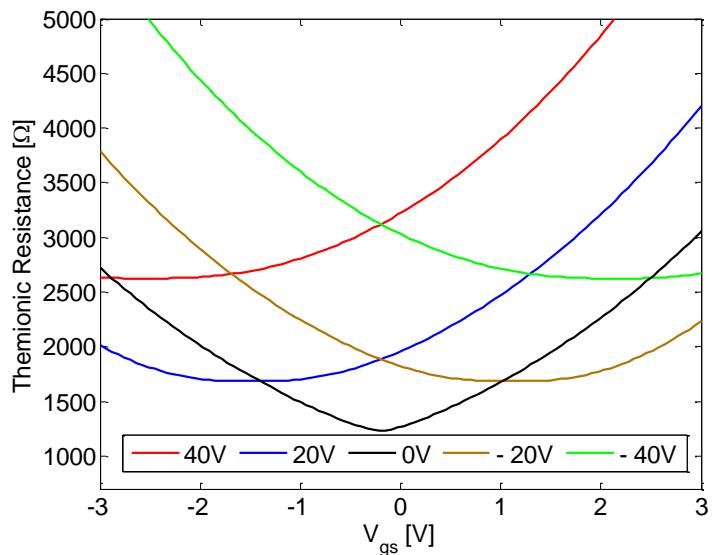

| 5.22 | Transfer characteristic of $R_q$ against $V_{gs}$ at room temperature for $V_{bs}$ from 40V to -40V in steps of 20V . . . . .                                                                                                                                                                                                                                              | 109 |

|                                                                                                                                                                                                                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

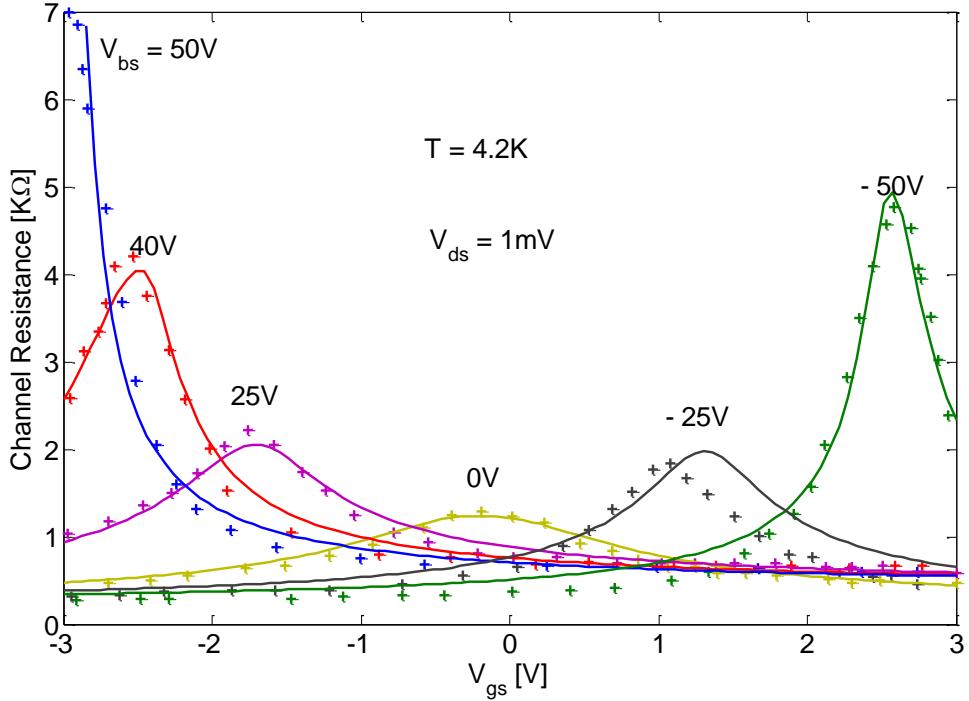

| 5.23 Transfer characteristics of the transistor output resistance at a temperature of 4.2K against $V_{gs}$ . Validation between published experimental data (+) [89] and the proposed model (–) for $V_{bs}$ of 50V, 40V, 25V, 0V, -25V and -50V respectively and a constant $V_{ds} = 1mV$ . . . . .                                  | 110 |

| 5.24 The threshold voltage, $V_o$ , against $V_{bs}$ for published experimental data (+) [77] and the proposed model (solid line) . . . . .                                                                                                                                                                                             | 112 |

| 5.25 Transfer characteristics of the minimum drain current at the charge neutrality point against the respective $V_{bs}$ at an operating temperature of 20K. Published experimental data [77] is shown in crosses and the model is shown in solid line. Inset: A logarithmic plot of the minimum drain current with $V_{bs}$ . . . . . | 112 |

| 5.26 Transfer characteristics of the transistor drain current against variations in $V_{gs}$ at 20K. Validation between published experimental data (+) [77] and the proposed model (–). $V_{bs}$ is varied by 120V, 80V, 40V and 0V respectively at a constant drain voltage, $V_{ds} = 1mV$ . . . . .                                 | 113 |

| 5.27 Transfer characteristics of the transistor drain current against variations in $V_{gs}$ at 20K. Validation between published experimental data (+) [77] and the proposed model (–). $V_{bs}$ is varied by 100V, 60V and 20V respectively at a constant drain voltage, $V_{ds} = 1mV$ . . . . .                                     | 114 |

| 5.28 The threshold voltage, $V_o$ , against $V_{bs}$ . . . . .                                                                                                                                                                                                                                                                          | 115 |

| 5.29 Transfer characteristics of the minimum drain current at the charge neutrality point against the respective $V_{bs}$ at an room temperature. . . . .                                                                                                                                                                               | 116 |

| 5.30 Experimental data (+) [127] and the proposed model (–) for negative $I_{ds}$ vs negative $V_{ds}$ characteristics at $V_{bs} = 0V$ . $V_{ds}$ is varied from 0 to -1.4V for top-gate voltages of -1.25V, -0.75V, -0.25V, 0.25V and 0.75V (from top to bottom between cross-section $A_1$ and $A_2$ ) . . . . .                     | 117 |

| 5.31 Characteristics of the channel Drain current against the top-gate voltage for $V_{ds} = 0.1V$ (Experimental data(+) [127], proposed model(–)) . . . . .                                                                                                                                                                            | 117 |

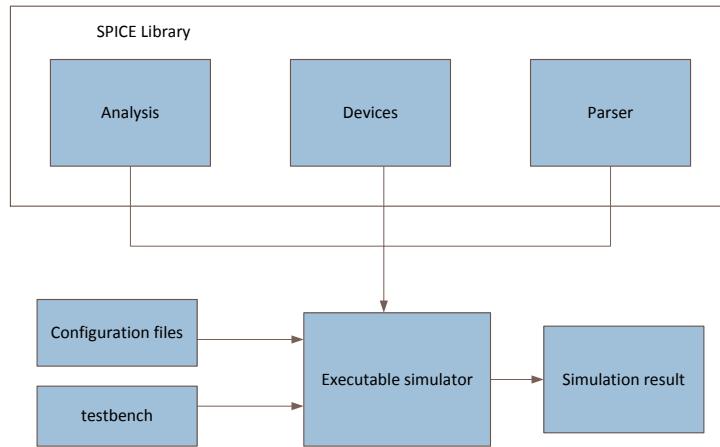

| 6.1 Interaction between the behavioural model and the simulator . . . . .                                                                                                                                                                                                                                                               | 120 |

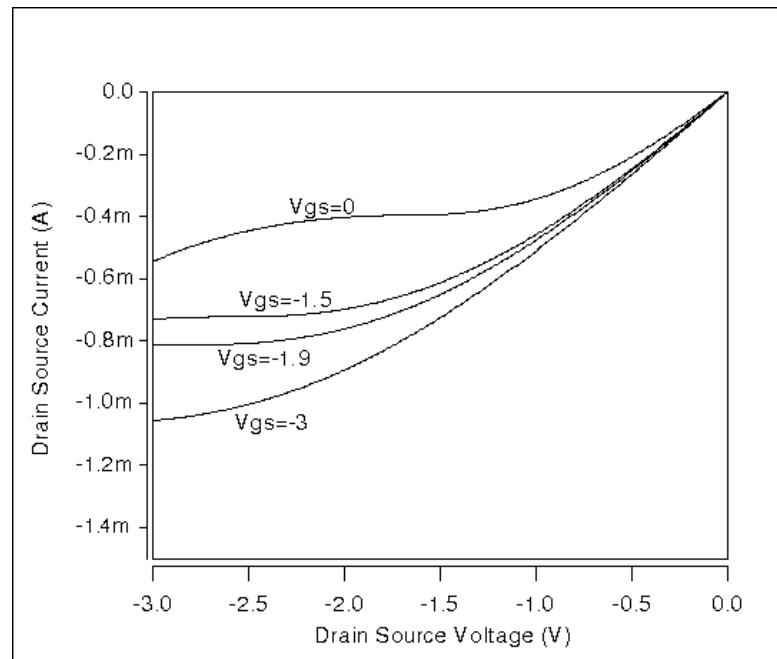

| 6.2 An HSPICE plot of the drain current $I_{ds}$ as a function of the drain voltage $V_{ds}$ for a back-gate voltge $V_{bs} = -40V$ for the top-gate voltages 0V, -1.5V, -1.9V and -3V respectively . . . . .                                                                                                                           | 121 |

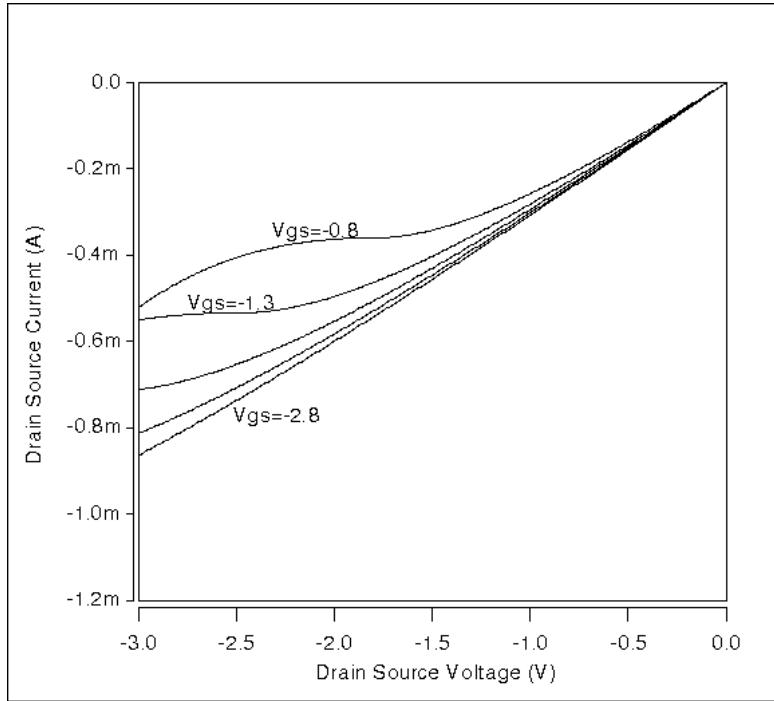

| 6.3 An HSPICE plot of the drain current $I_{ds}$ as a function of the drain voltage $V_{ds}$ for a back-gate voltge $V_{bs} = +40V$ for the top-gate voltages -0.8V, -1.3V, -1.8V, -2.3V and -2.8V respectively . . . . .                                                                                                               | 122 |

| 6.4 Layout of the interactions of the VHDL-AMS files used in the behavioural model . . . . .                                                                                                                                                                                                                                            | 124 |

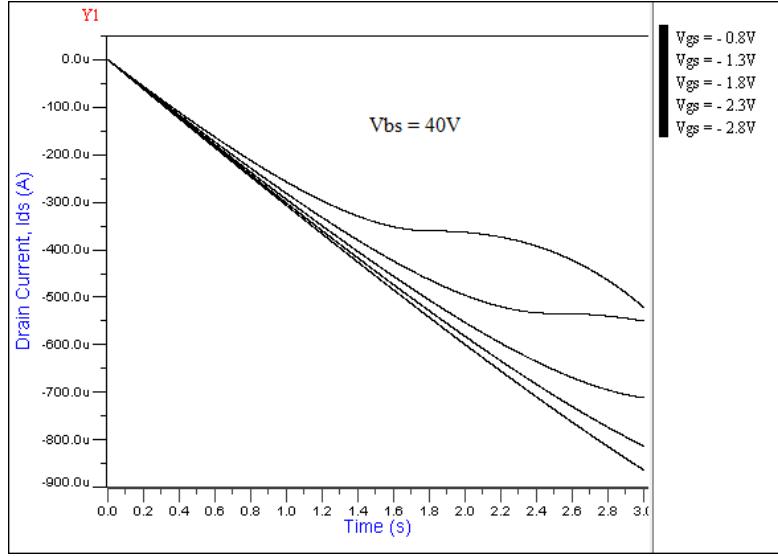

| 6.5 A VHDL-AMS plot of the drain current $I_{ds}$ as a function of the time for a back-gate voltge $V_{bs} = -40V$ for the top-gate voltages 0V, -1.5V, -1.9V and -3V respectively (from top to bottom). . . . .                                                                                                                        | 124 |

| 6.6 A VHDL-AMS plot of the drain current $I_{ds}$ as a function of the drain voltage $V_{ds}$ for a back-gate voltge $V_{bs} = +40V$ for the top-gate voltages -0.8V, -1.3V, -1.8V, -2.3V and -2.8V respectively (from top to bottom). . . . .                                                                                          | 125 |

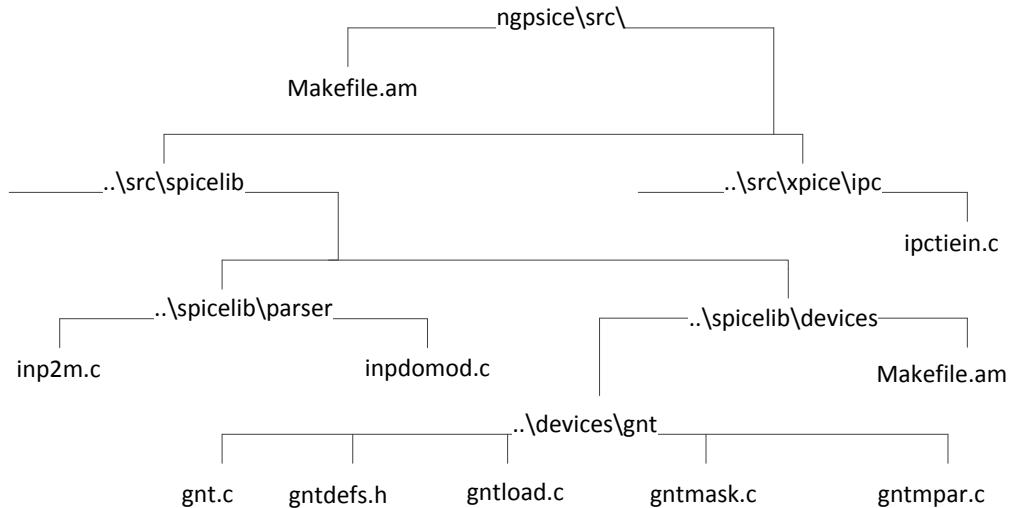

| 6.7 Layout of the interactions of the Berkeley SPICE files used in the model . . . . .                                                                                                                                                                                                                                                  | 127 |

| 6.8 A tree of the Berkeley SPICE files updated in the project . . . . .                                                                                                                                                                                                                                                                 | 127 |

---

|      |                                                                                                                                                                                                                                                                                                                                          |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.9  | Experimental data (o) [127] and the Berkeley SPICE simulator model (–) for $I_{sd}$ vs $V_{sd}$ characteristics at $V_{bs}=0V$ . $V_{ds}$ is varied from 0 to -1.4V for top-gate voltages of -1.25V, -0.75V, -0.25V , 0.25V and 0.75V (from top to bottom between cross-section $A_1$ and $A_2$ ) . . . . .                              | 130 |

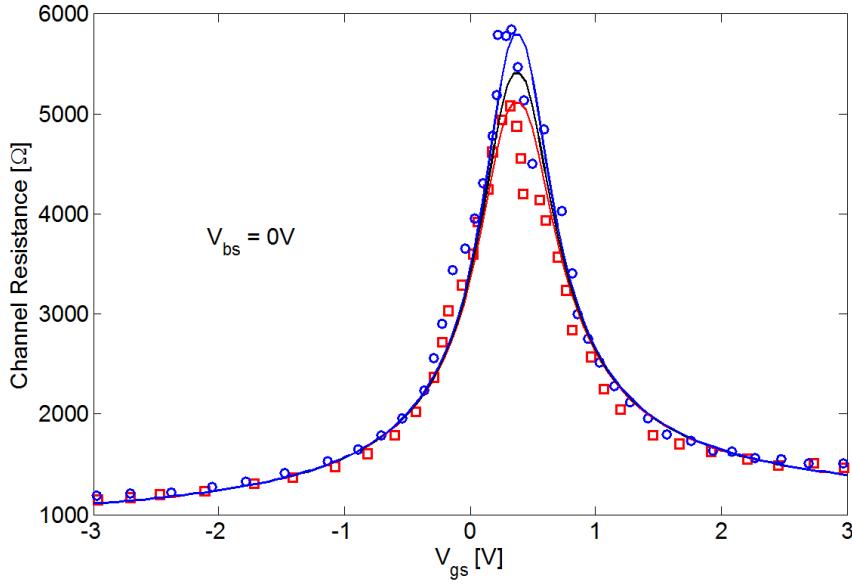

| 6.10 | Characteristics of the channel Drain current against the top-gate voltage for $V_{ds} = 0.1V$ (Experimental data(o) [127], Berkeley SPICE simulator model(–)) . . . . .                                                                                                                                                                  | 132 |

| 6.11 | Characteristics of the channel resistance against $V_{gs}$ at $V_{bs} = 0V$ for various operating temperatures. Result from the SPICE simulator is shown in solid line for temperatures 4.7K (blue), 14.4K (black) and 53K (red) (top to bottom). The experimental measurement [89] is shown in $\square$ (53K) and $o$ (4.7K) . . . . . | 132 |

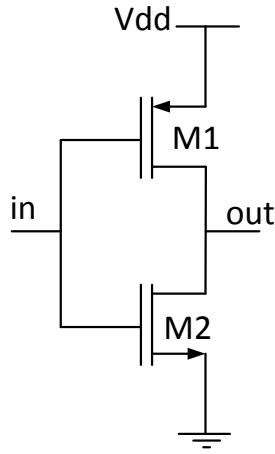

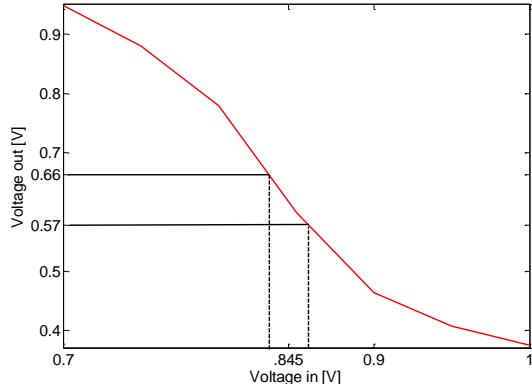

| 6.12 | Circuit design and characteristics of the voltage amplifier . . . . .                                                                                                                                                                                                                                                                    | 134 |

| 6.13 | Normalized single-layer graphene FET characteristics of a small signal voltage amplifier . . . . .                                                                                                                                                                                                                                       | 135 |

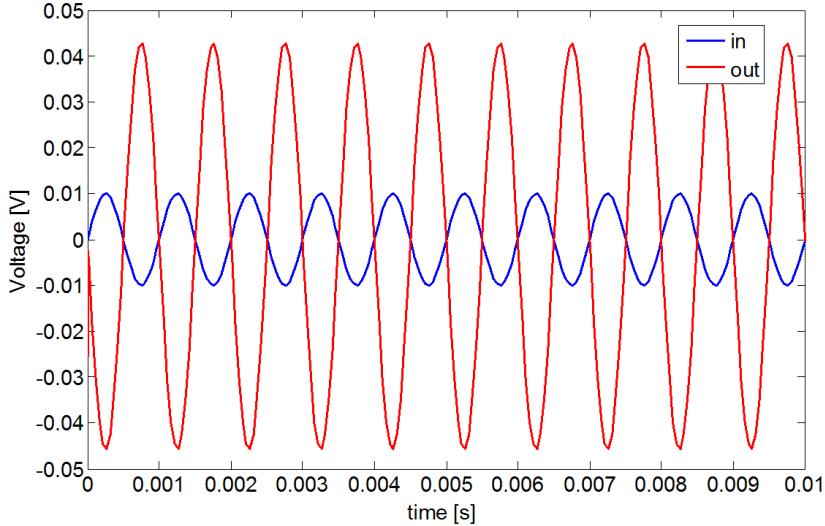

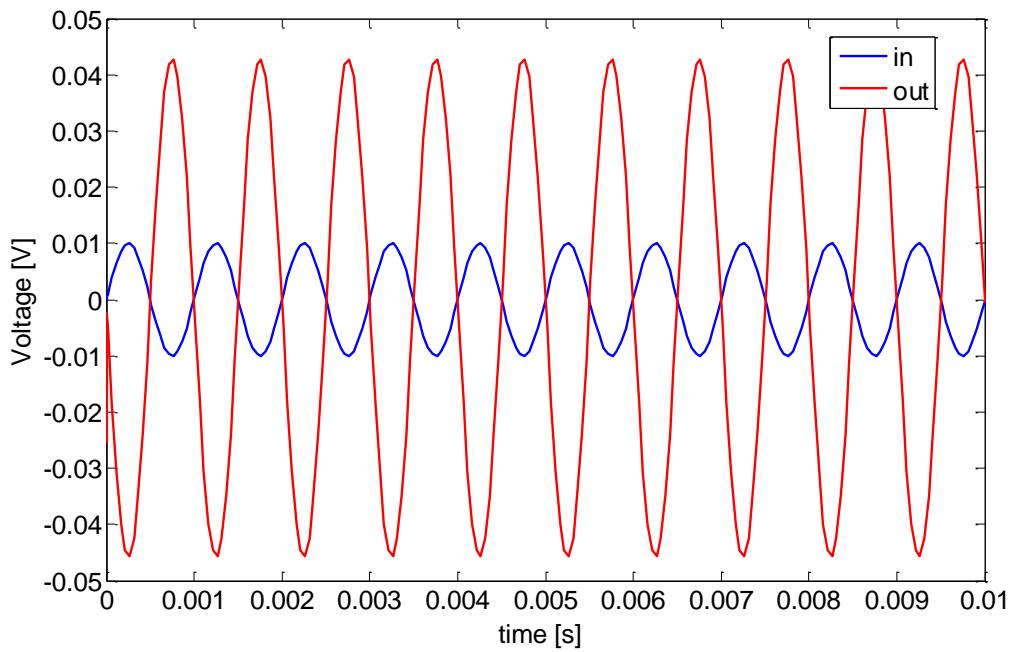

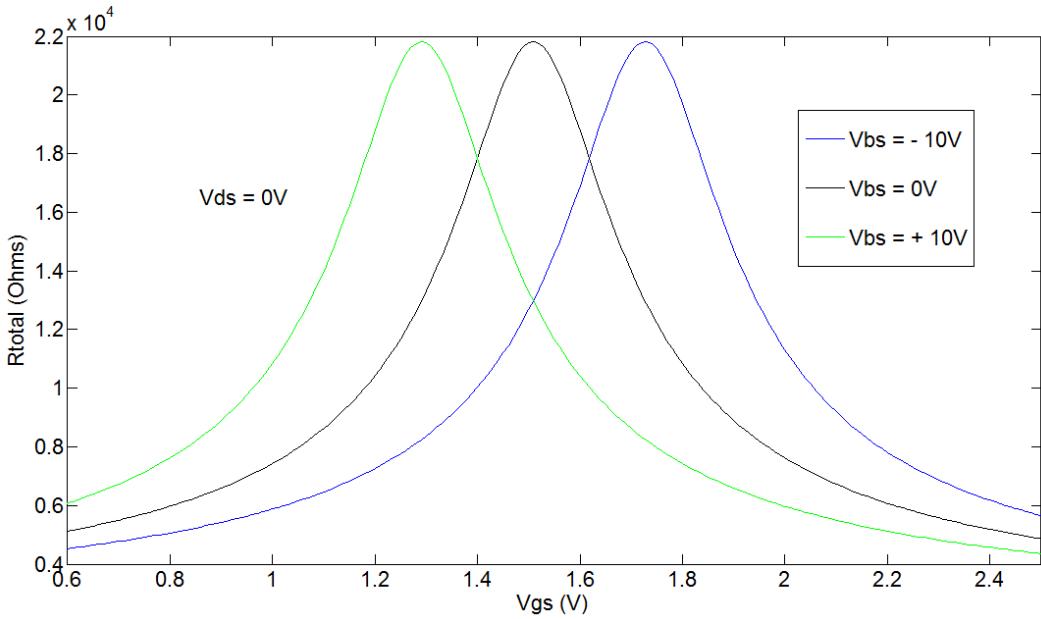

| 6.14 | Circuit design for a graphene FET frequency doubler . . . . .                                                                                                                                                                                                                                                                            | 136 |

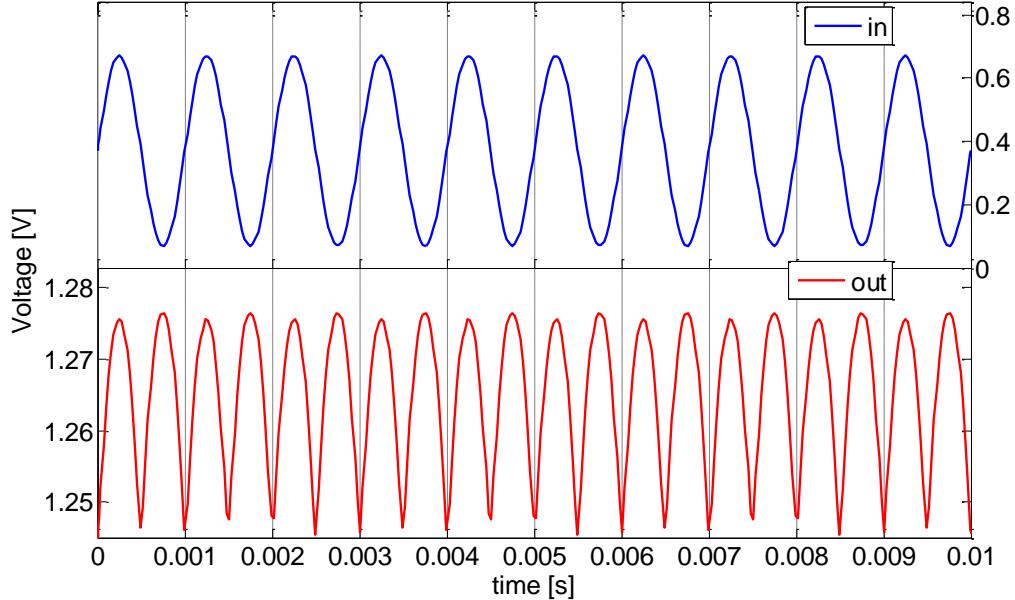

| 6.15 | Single-layer graphene FET characteristics of a frequency doubler . . . . .                                                                                                                                                                                                                                                               | 136 |

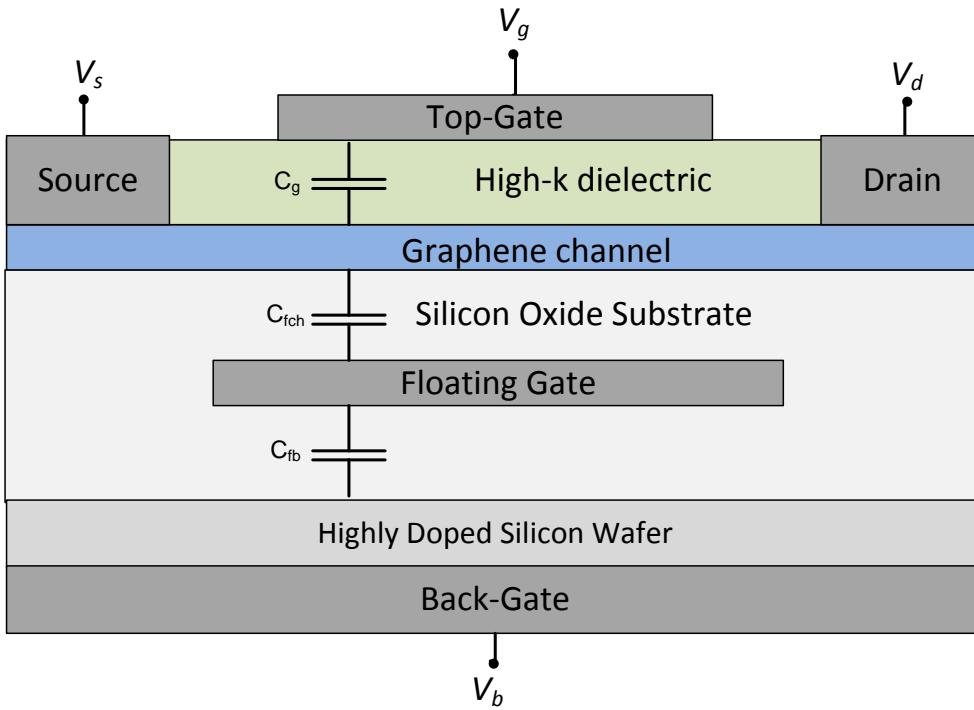

| 6.16 | Transistor layout. . . . .                                                                                                                                                                                                                                                                                                               | 138 |

| 6.17 | The capacitor and transistor equivalent of the floating-gate transistor . . . . .                                                                                                                                                                                                                                                        | 139 |

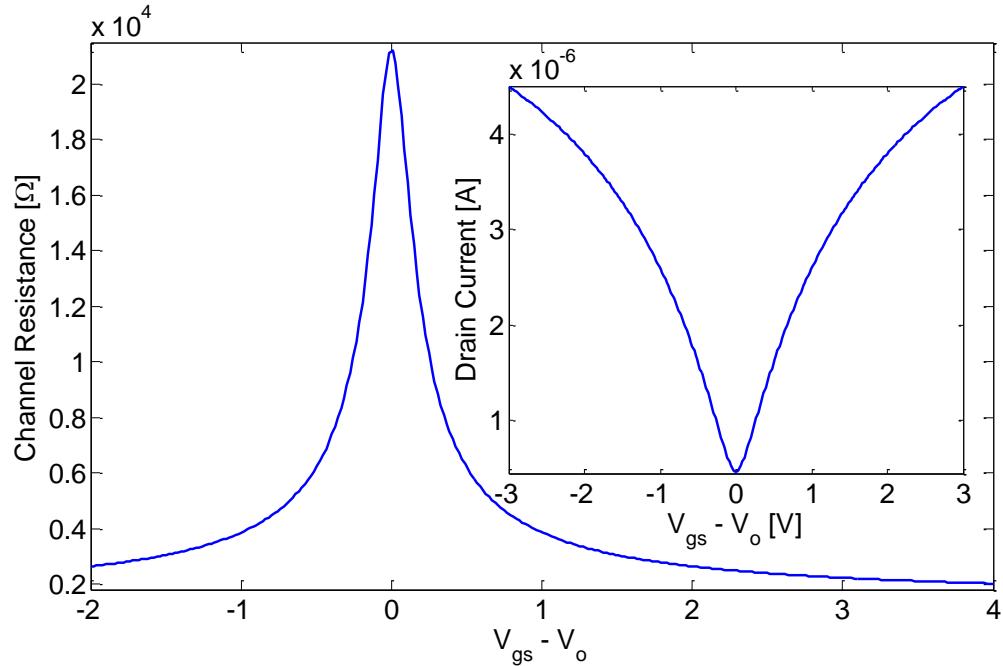

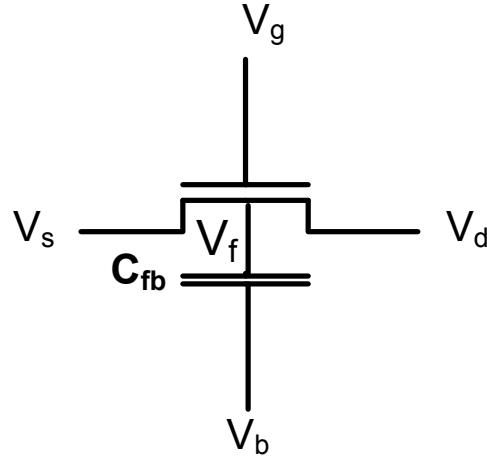

| 6.18 | Channel resistance characteristics for graphene bilayer FET without a floating-gate . . . . .                                                                                                                                                                                                                                            | 142 |

| 6.19 | Electrons injected into the floating-gate . . . . .                                                                                                                                                                                                                                                                                      | 142 |

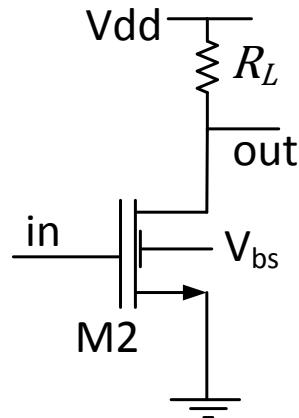

| 6.20 | Channel resistance vs the top-gate voltage for a graphene transistor with and without a floating-gate . . . . .                                                                                                                                                                                                                          | 144 |

| 6.21 | Complementary inverter layout using a floating-gate . . . . .                                                                                                                                                                                                                                                                            | 144 |

| 6.22 | floating-gate complementary inverter characteristics for transistors induced with 27.3fC and 8.4fC respectively. . . . .                                                                                                                                                                                                                 | 145 |

# List of Tables

|      |                                                                  |     |

|------|------------------------------------------------------------------|-----|

| 2.1  | Allotropes of graphene [45]                                      | 8   |

| 2.2  | World Bank Gross Domestic Product 2012 [171]                     | 39  |

| 4.1  | Model parameters for single-gate monolayer graphene FET          | 71  |

| 4.2  | Model parameters for monolayer graphene FET                      | 72  |

| 4.3  | Experimental data fitting parameters using analytical model      | 75  |

| 4.4  | Experimental data fitting parameters using Drude model           | 75  |

| 4.5  | Experimental data fitting parameters using the Drude based model | 76  |

| 4.6  | Model parameters for bilayer graphene FET                        | 77  |

| 4.7  | Experimental data fitting parameters for output conductance      | 80  |

| 4.8  | Model parameters for a four-layer GFET                           | 81  |

| 5.1  | Model parameters for bilayer graphene FET in test case A         | 98  |

| 5.2  | Model parameters for bilayer graphene FET                        | 100 |

| 5.3  | Experimental data fitting parameters for Fig. 5.14               | 103 |

| 5.4  | Experimental data fitting parameters for Fig. 5.15               | 104 |

| 5.5  | Model parameters for bilayer graphene FET                        | 105 |

| 5.6  | Experimental data fitting parameters for Fig. 5.23               | 111 |

| 5.7  | Model parameters for bilayer graphene FET                        | 111 |

| 5.8  | Experimental data fitting parameters for Fig. 5.26               | 113 |

| 5.9  | Experimental data fitting parameters for Fig. 5.27               | 113 |

| 5.10 | Model parameters for four-layer graphene FET for Fig. 5.30       | 115 |

| 6.1  | HSPICE Model parameters for bilayer graphene FET                 | 121 |

| 6.2  | Command Line option for ngspice [145]                            | 129 |

| 6.3  | Ngspice Model parameters for the graphene FET library            | 130 |

| 6.4  | Simulation Model Parameters                                      | 141 |

# Listings

|     |                                                                                                           |     |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 6.1 | Testbench of the HSPICE graphene library in file gfetmodel.sp                                             | 122 |

| 6.2 | Testbench of the VHDL-AMS test circuit                                                                    | 125 |

| 6.3 | Netlist for a four-layer graphene FET $I_{ds}$ Vs $V_{ds}$ characteristics shown in Fig. 6.9              | 131 |

| 6.4 | Netlist for a four-layer graphene FET $I_{ds}$ Vs $V_{gs}$ characteristics shown in Fig. 6.10             | 131 |

| 6.5 | Netlist for a Single layer graphene FET channel resistance Vs $V_{gs}$ characteristics shown in Fig. 6.10 | 133 |

| 6.6 | Netlist for a single-layer graphene FET Voltage Amplifier shown in Fig. 6.13                              | 134 |

| 6.7 | Netlist for a Single layer graphene FET frequency doubler circuit                                         | 136 |

| B.1 | The HSPICE param.lib file                                                                                 | 150 |

| B.2 | Graphene FET HSPICE library file gfet.lib                                                                 | 150 |

| B.3 | Time dependent voltage sweep in v_pulse.vhd                                                               | 151 |

| B.4 | Voltage sources in v_source.vhd                                                                           | 152 |

| B.5 | The graphene FET model package in gfetmodel.vhd                                                           | 152 |

| B.6 | Top level of the graphene FET model in gTransistor.vhd                                                    | 153 |

# Nomenclature

|                            |                                                 |

|----------------------------|-------------------------------------------------|

| $x, y$                     | Axis direction                                  |

| $a_1, a_2$                 | Primitive vectors                               |

| $b_1, b_2$                 | Reciprocal vectors                              |

| $k_1, k_2$                 | wave function                                   |

| $v$                        | plane velocity                                  |

| $A_1, A_2, B_1, B_2$       | lattice sites                                   |

| $\hbar$                    | Reduced Plank's constant                        |

| $\Delta, E_g$              | Band gap energy                                 |

| $\gamma$                   | Nearest neighbour hopping energy                |

| $M, K, K', \Gamma$         | Points in the first brillouin zone              |

| $E(k)$                     | Dispersion energy                               |

| $p$                        | momentum                                        |

| $v_F$                      | Fermi velocity                                  |

| $\mu$                      | mobility                                        |

| $\epsilon$                 | Permittivity of free space                      |

| $\epsilon_1, \epsilon_2$   | Relative permittivity                           |

| $q$                        | Electronic charge                               |

| $K_B$                      | Boltzmann's constant                            |

| $T$                        | Absolute temperature                            |

| $V_g, V_b, V_d, V_s$       | Potential of top-gate, back-gate, drain, source |

| $\varphi, V_{ch}$          | Surface potential                               |

| $V_{bs}^0$                 | Back-gate voltage offset                        |

| $V_{gs}^0$                 | Top-gate voltage offset                         |

| $V_{ds-sat1}, V_{ds-sat2}$ | Saturation voltage for unipolar, ambipolar      |

| $C_{ox}, C_e, C_{TG}$      | Top-gate capacitance                            |

| $C_b, C_{BG}$              | Back-gate capacitance                           |

| $C_q$                      | Quantum capacitance                             |

| $\alpha, \beta, \eta, n$   | Characteristic constant                         |

| $E_c$                      | Critical electric field                         |

| $E_{ox}, E$                | Electric field                                  |

| $V_{ox}$                   | Potential drop across oxide                     |

| $v_{sat}$                  | Velocity saturation                             |

---

|                  |                                 |

|------------------|---------------------------------|

| $V_E$            | Drift velocity                  |

| $C_{top}$        | effective top-gate capacitance  |

| $C_{back}$       | effective back-gate capacitance |

| $V_o$            | Threshold velocity              |

| $W$              | Width                           |

| $L$              | Length                          |

| $t_{ox}, t$      | Top-gate dielectric thickness   |

| $H_{sub}$        | Back-gate dielectric thickness  |

| $R_s$            | Series resistance               |

| $I_{ds}$         | Drain current                   |

| $I_{ds-sat}$     | Unipolar saturation current     |

| $I_{disp}$       | Saturation displacement current |

| $I_{off}$        | Drain off-current               |

| $g_m$            | Transconductance                |

| $g_{ds}$         | Output conductance              |

| $U$              | Potential energy per unit area  |

| $\phi_b, \phi_g$ | Potential barrier               |

| $V_T$            | Voltage constant                |

| $T_\alpha$       | Temperature constant            |

| $T_{ref}$        | Reference temperature           |

| $T_o$            | Temperature parameter           |

| $n_0$            | Minimum charge density          |

| $R_s^0$          | Intrinsic resistance            |

| $R_q$            | off-current resistance          |

| $C_o$            | Interlayer capacitance          |

## Acknowledgements

First and foremost, I offer my sincerest gratitude to my supervisor, Dr Tom J. Kazmierski, who has supported me throughout my thesis with his patience and knowledge whilst allowing me the room to work in my own way.

Besides my supervisor, I would like to thank Prof. Bashir M. Al-Hashimi and Dr. Zakaria for their insightful comments and contributions on which I am able to write this thesis. Also, I am grateful to Prof. Stephen Hall and Dr. Yoshi Tsuchiya for the time and effort you put into reading my thesis to make sure it is a source of knowledge.

I must express my gratitude to my fiancée, Sheris Leo, who continually encouraged me during the ebbs and flows of my research. In a similar light, I would like to thank all my friends: Sr. Catherine Cruz, Aurore Bunga, Isabelle Kirby, Joseph Matiko, Abiodun Komolafe, Alex Wood, Tom Redman, Matthew Gussin, Raphael Briand and James Rogers for taking the time to proof read my thesis. Also, I am grateful to all my friends in the Zepler Level 4 laboratory. You all made a positive impact on me.

I would also like to thank my friends who we play football and basketball together. You have been an important source of helping me spend my leisure hours. I especially like to thank the members of the Catholic Society for the social and spiritual events and also thank my good friends Arinze Ekwosimba, Nathaniel Ugbomah, Didi Oguejiofor and Henry Adu who have been great to be with.

I would like to appreciate the Petroleum Technology Development Fund (PTDF) for providing me with partial funding for this project.

Finally, I thank my parents, my sister and her family, and my brothers and their family for supporting me throughout all my studies by way of phone calls to know how I am doing, financial support and prayers. Also, I wish to use this medium to thank God for His forgiveness, graces and blessings.

*To My Parents*

# Chapter 1

## Introduction

Bare graphene is a two dimensional structure of tightly bound carbon atoms with a honey combed lattice. This structure can be wrapped up into a zero-dimension buckminsterfullerene, a one-dimension carbon nanotube and a three-dimensional stacked graphene commonly called graphite. In the last two decades there has been a lot of research into the behaviour and possible application of both carbon nanotubes and graphene.

### 1.1 Carbon nanotubes

The carbon nanotube (CNT) was first synthesised in the early 1990s [1, 2, 3] with many potential applications in the fields of nanoelectronics, optics and material science. The nanotube is categorized into two groups, single-walled and multi-walled. A single-walled nanotube is formed by rolling just one atomically thin graphene sheet while a multi-walled nanotube refers to the rolling of two or more stacks of graphene sheets. Experiments and theory have shown that both of the nanotube categories can be either metallic [4, 5] or semiconducting [6]. Either of the forms of CNTs has potential application in future generation integrated circuits (ICs). As such there have been a number of compact models developed [7, 8, 9, 10, 11]. With one of the models [11] using cubic spline approximations to ensure shorter circuit simulation time. Since CNT is analysed as a rolled up two-dimensional graphene, therefore its remarkable electrical properties originates from the electronic structure of graphene [12, 13]

### 1.2 Graphene

The isolation of graphene from graphite came much later than the CNT in 2004 [14], by mechanical exfoliation. Like the CNT, two dimensional graphene holds a lot of prospects as a possible candidate to complement silicon in the next generation ICs

because of its high carrier mobility and high current density. Graphene being flat makes it easy to be integrated into the current CMOS lithographic process [15]. Similar to the categorization in CNTs, graphene has single-layers, bilayers, trilayer and so forth. For eleven and greater stacked layers of graphene sheets, the structure is considered to be three-dimensional graphite [16, 17] and between three to ten layers, the structure is referred to as few layer graphene [16].

Particular interest will be given to devices with single-layer to a few layers. Other than mechanical exfoliation, few layered graphene has been grown epitaxially by chemical vapour deposition on metal substrates [18, 19, 20, 21] as well as by thermal deposition on silicon carbide (SiC) [22]. Chemical vapour deposition in making transistors is more commercially viable than mechanical exfoliation and also a more viable route to electronic applications. One of the most remarkable features of graphene is its high carrier mobility at room temperature [23]. To put this in perspective, suspended graphene has a recorded mobility in excess of  $200,000\text{cm}^2/\text{Vs}$  [24] at room temperature compared to  $1,400\text{cm}^2/\text{Vs}$  for silicon and  $8,500\text{cm}^2/\text{Vs}$  for gallium arsenide [25]. In terms of cut-off frequency and high speed electronics, graphene currently out-performs other semiconductors with a cut-off frequency of up to 300GHz [26, 27, 28]. Both graphene and CNT transistor were used to implement a ring oscillator. The graphene based ring oscillator had a frequency as high as 1.28GHz while the CNT based ring oscillator was limited to 52MHz [29].

### 1.2.1 Graphene Transistor Modelling

Despite its remarkable carrier mobility among other physical properties, graphene does not have a bandgap. It is referred to as a semi-metal because both its conduction and valence bands touch at the Fermi level. The gapless nature of graphene is the reason it is modelled as an ambipolar device [14, 30, 31] whereby carriers can be tuned from being hole-like to electron-like. The main aim of modelling graphene transistors is to be able to predict its performance in circuit designs. As the fabrication of graphene becomes more controlled, the current models will be greatly improved to predict the behaviour of a transistor prior to fabrication.

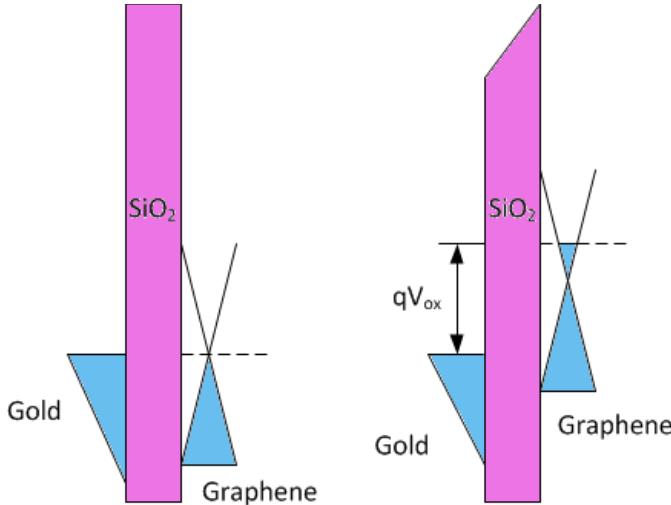

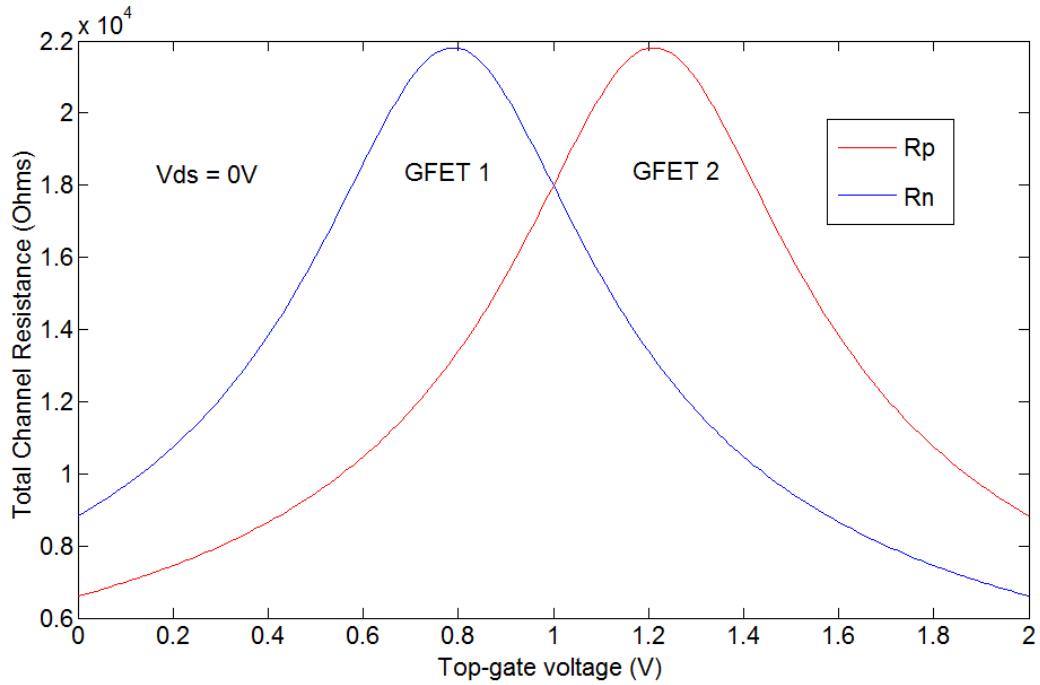

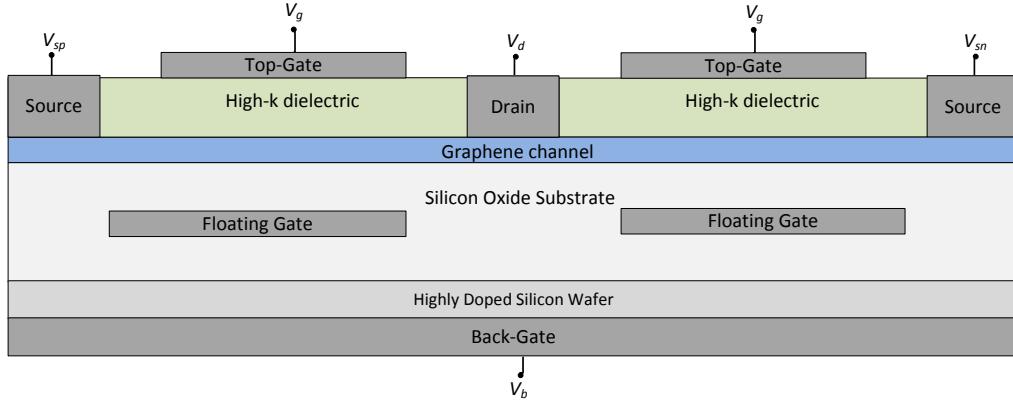

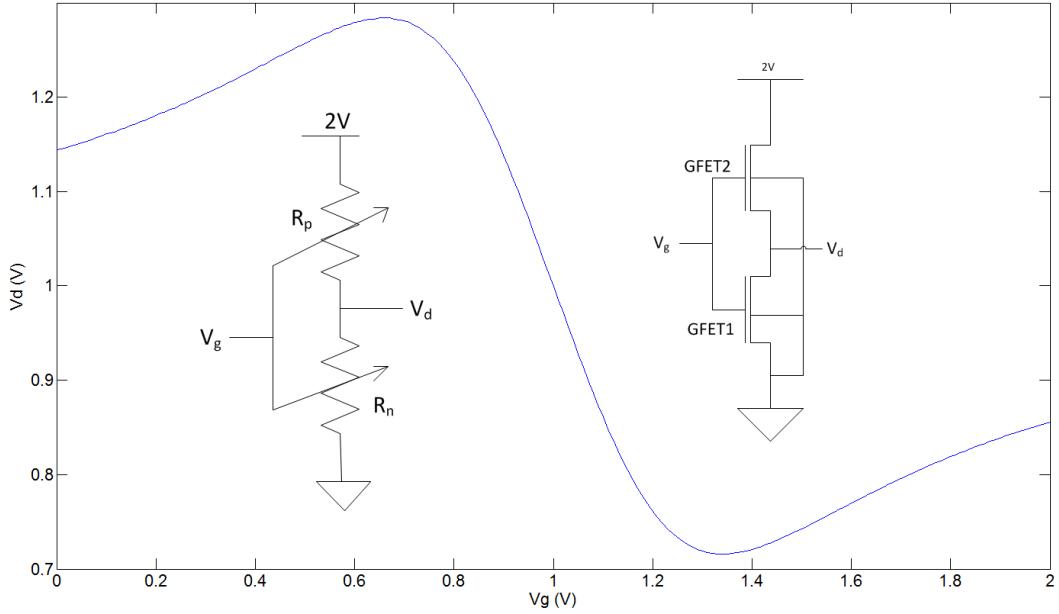

## 1.3 Research Challenges