University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

---

**UNIVERSITY OF SOUTHAMPTON**

**FACULTY OF PHYSICAL SCIENCES AND ENGINEERING**

**Electronics and Computer Science**

Investigation into Yield and Reliability

Enhancement of TSV-based Three-dimensional Integration Circuits

by Yi Zhao

Thesis for the degree of Doctor of Philosophy

Oct 2014

---

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

Doctor of Philosophy

**Investigation into Yield and Reliability**

**Enhancement of TSV-based Three-dimensional Integration Circuits**

by Yi Zhao

Three dimensional integrated circuits (3D ICs) have been acknowledged as a promising technology to overcome the interconnect delay bottleneck brought by continuous CMOS scaling. Recent research shows that through-silicon-vias (TSVs), which act as vertical links between layers, pose yield and reliability challenges for 3D design. This thesis presents three original contributions.

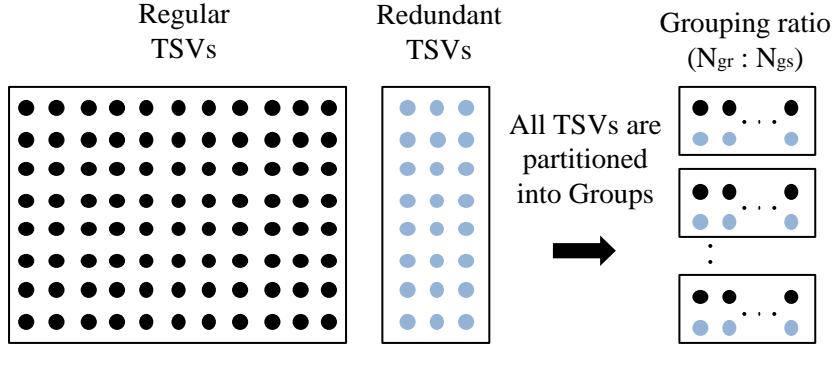

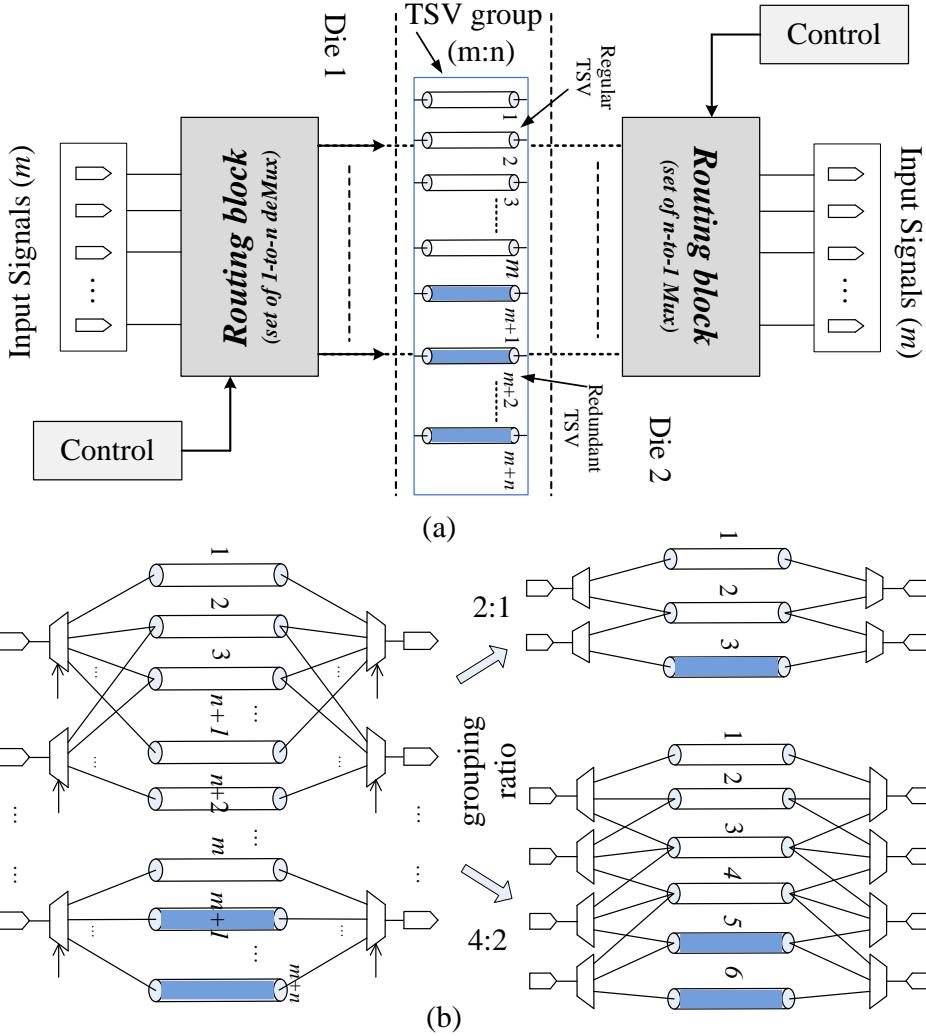

The first contribution presents a grouping-based technique to improve the yield of 3D ICs under manufacturing TSV defects, where regular and redundant TSVs are partitioned into groups. In each group, signals can select good TSVs using rerouting multiplexers avoiding defective TSVs. Grouping ratio (regular to redundant TSVs in one group) has an impact on yield and hardware overhead. Mathematical probabilistic models are presented for yield analysis under the influence of independent and clustering defect distributions. Simulation results using MATLAB show that for a given number of TSVs and TSV failure rate, careful selection of grouping ratio results in achieving 100% yield at minimal hardware cost (number of multiplexers and redundant TSVs) in comparison to a design that does not exploit TSV grouping ratios. The second contribution presents an efficient online fault tolerance technique based on redundant TSVs, to detect TSV manufacturing defects and address thermal-induced reliability issue. The proposed technique accounts for both fault detection and recovery in the presence of three TSV defects: voids, delamination between TSV and landing pad, and TSV short-to-substrate. Simulations using HSPICE and ModelSim are carried out to validate fault detection and recovery. Results show that regular and redundant TSVs can be divided into groups to minimise area overhead without affecting the fault tolerance capability of the technique. Synthesis results using 130-nm design library show that 100% repair capability can be achieved with low area overhead (4% for the best case). The last contribution proposes a technique with joint consideration of temperature mitigation and fault tolerance without introducing additional redundant TSVs. This is achieved by reusing spare TSVs that are frequently deployed for improving yield and reliability in 3D ICs. The proposed technique consists of two steps: TSV determination step, which is for achieving optimal partition between regular and spare TSVs into groups; The second step is TSV placement, where temperature mitigation is targeted while optimizing total wirelength and routing difference. Simulation results show that using the proposed technique, 100% repair capability is achieved across all (five) benchmarks with an average temperature reduction of 75.2°C (34.1%) (best case is 99.8°C (58.5%)), while increasing wirelength by a small amount.

---

# Content

|                                                                             |      |

|-----------------------------------------------------------------------------|------|

| Declaration of Authorship.....                                              | viii |

| Acknowledgements.....                                                       | x    |

| <u>1.</u> Introduction.....                                                 | 1    |

| 1.1 Introduction to 3D-IC Structure and Fabrication Process.....            | 3    |

| 1.1.1 Packaging-based 3D Integration Technology .....                       | 3    |

| 1.1.2 Overview of TSV-based 3D Integration .....                            | 3    |

| 1.1.3 Various Implementation Technologies of TSV-based 3D Integration...    | 5    |

| 1.2 Benefits of 3D-ICs .....                                                | 13   |

| 1.2.1 Wirelength Reduction and Performance Enhancement .....                | 13   |

| 1.2.2 Power Reduction of 3D-ICs.....                                        | 14   |

| 1.2.3 Footprint and Device Density of 3D-ICs .....                          | 15   |

| 1.2.4 Heterogeneous System Integration .....                                | 16   |

| 1.3 Design and Test Challenges in 3D-ICs .....                              | 16   |

| 1.3.1 Thermal Management in 3D-ICs .....                                    | 16   |

| 1.3.2 Design Exploration of 3D Architecture .....                           | 18   |

| 1.3.3 Yield Challenges in 3D-ICs .....                                      | 19   |

| 1.3.4 Reliability challenges of 3D-ICs.....                                 | 21   |

| 1.3.5 Testing and Fault Tolerance for 3D-ICs.....                           | 24   |

| 1.4 Motivation and Thesis Outline.....                                      | 26   |

| 1.5 Publications.....                                                       | 28   |

| <u>2.</u> Literature Review.....                                            | 29   |

| 2.1 TSV Modeling.....                                                       | 30   |

| 2.2 TSV Defects Characterization and Modeling .....                         | 31   |

| 2.3 TSV Defect Testing.....                                                 | 35   |

| 2.4 Prior Work on Improving Yield of 3D-ICs .....                           | 38   |

| 2.4.1 Yield Improvement from Design Perspective .....                       | 38   |

| 2.4.2 Yield Improvement from Test Perspective.....                          | 39   |

| 2.5 Prior Work on Improving Reliability of 3D-ICs .....                     | 41   |

| 2.5.1 Microchannel Cooling and Thermal-aware Floorplanning.....             | 41   |

| 2.5.2 TSV Repair for In-field Reliability Improvement .....                 | 42   |

| 2.6 Concluding Remarks and Research Objectives .....                        | 45   |

| <u>3.</u> Grouping-based TSV Repairing for Yield Improvement of 3D-ICs..... | 47   |

| 3.1 Introduction.....                                                       | 48   |

|                                                                                                 |     |

|-------------------------------------------------------------------------------------------------|-----|

| 3.2 Motivation and Problem Formulation.....                                                     | 49  |

| 3.2.1 Motivation.....                                                                           | 49  |

| 3.2.2 Problem Formulation .....                                                                 | 53  |

| 3.3 TSV Redundancy Modeling and Yield Analysis .....                                            | 54  |

| 3.3.1 TSV Redundancy Modeling and Yield Analysis for Independent Defect Distribution.....       | 54  |

| 3.3.2 TSV Redundancy Modeling and Yield Analysis for Clustering Defect Distribution .....       | 55  |

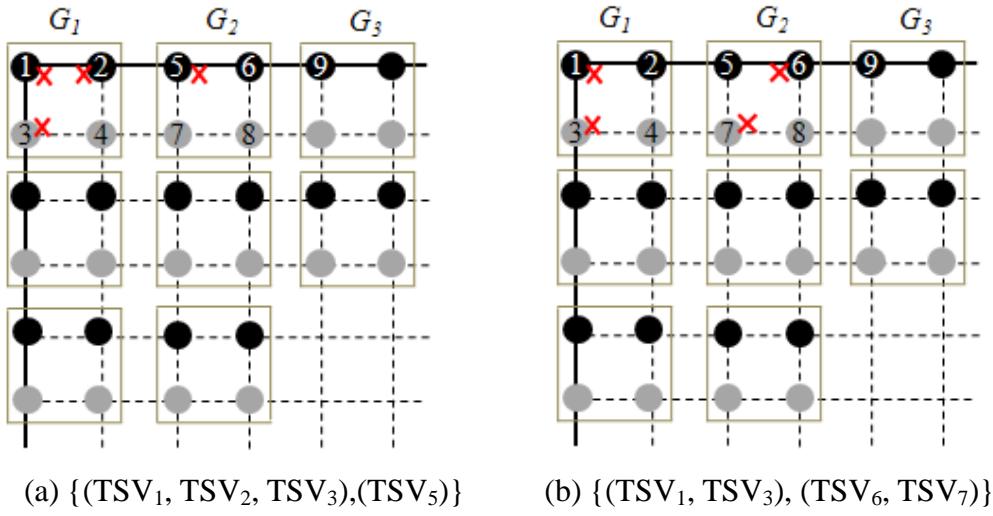

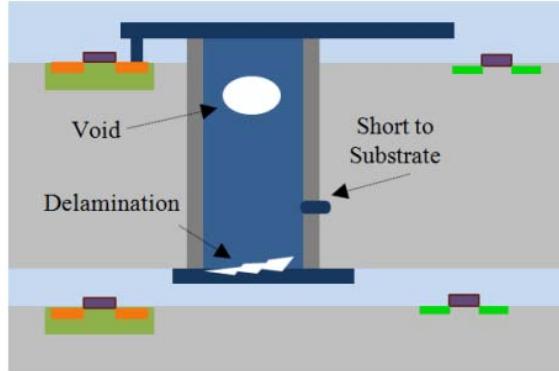

| 3.3.3 Exhaustive search for best grouping ratio.....                                            | 59  |

| 3.4 Simulation Results .....                                                                    | 60  |

| 3.4.1 Simulation Flow.....                                                                      | 60  |

| 3.4.2 Evaluation of Proposed Grouping-based TSV Repairing Technique .                           | 61  |

| 3.5 Concluding Remarks.....                                                                     | 67  |

| <br><u>4. Online Fault Detection and Recovery for TSV-based 3D-ICs.....</u>                     | 68  |

| 4.1 Introduction.....                                                                           | 69  |

| 4.2 Preliminaries .....                                                                         | 70  |

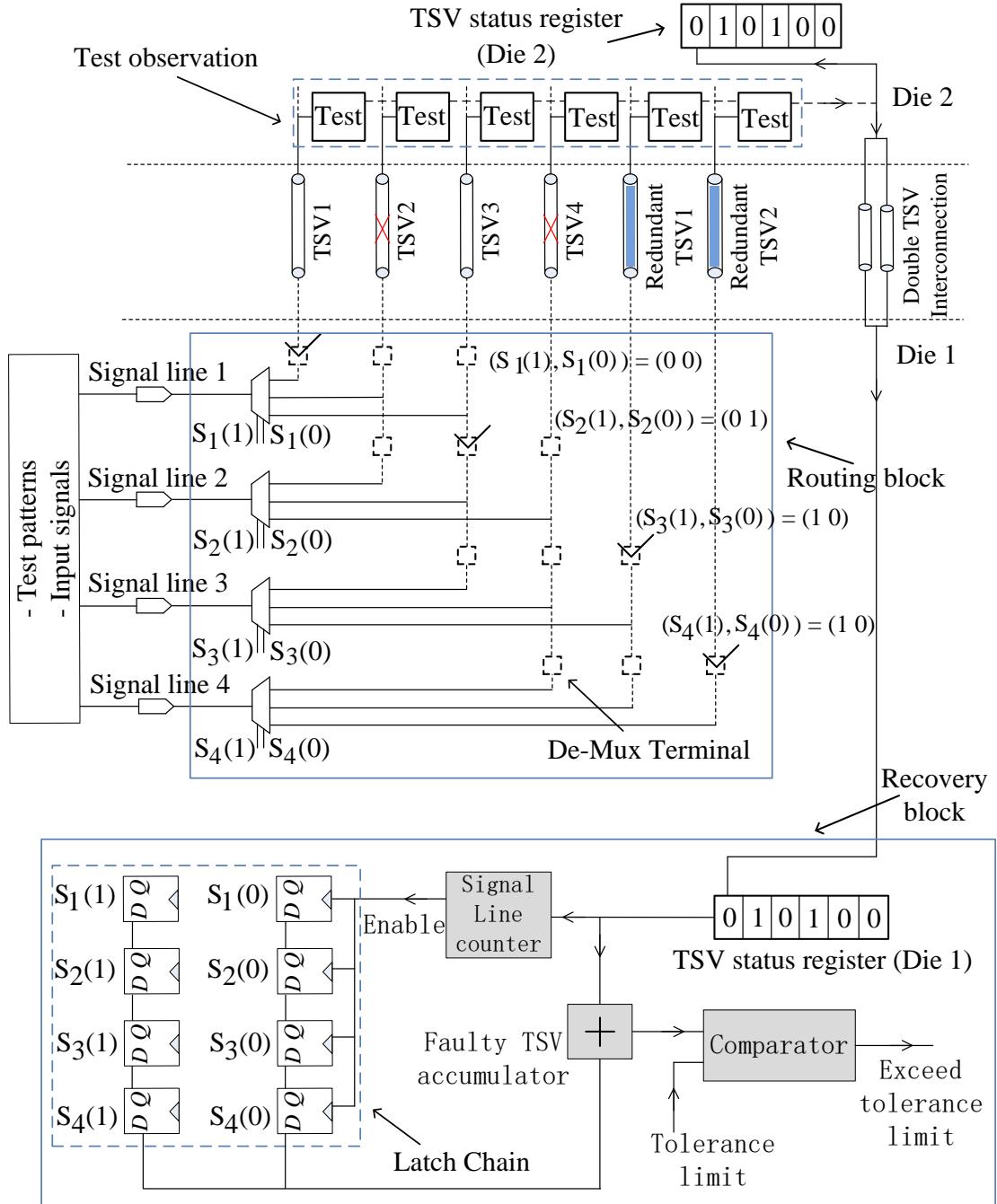

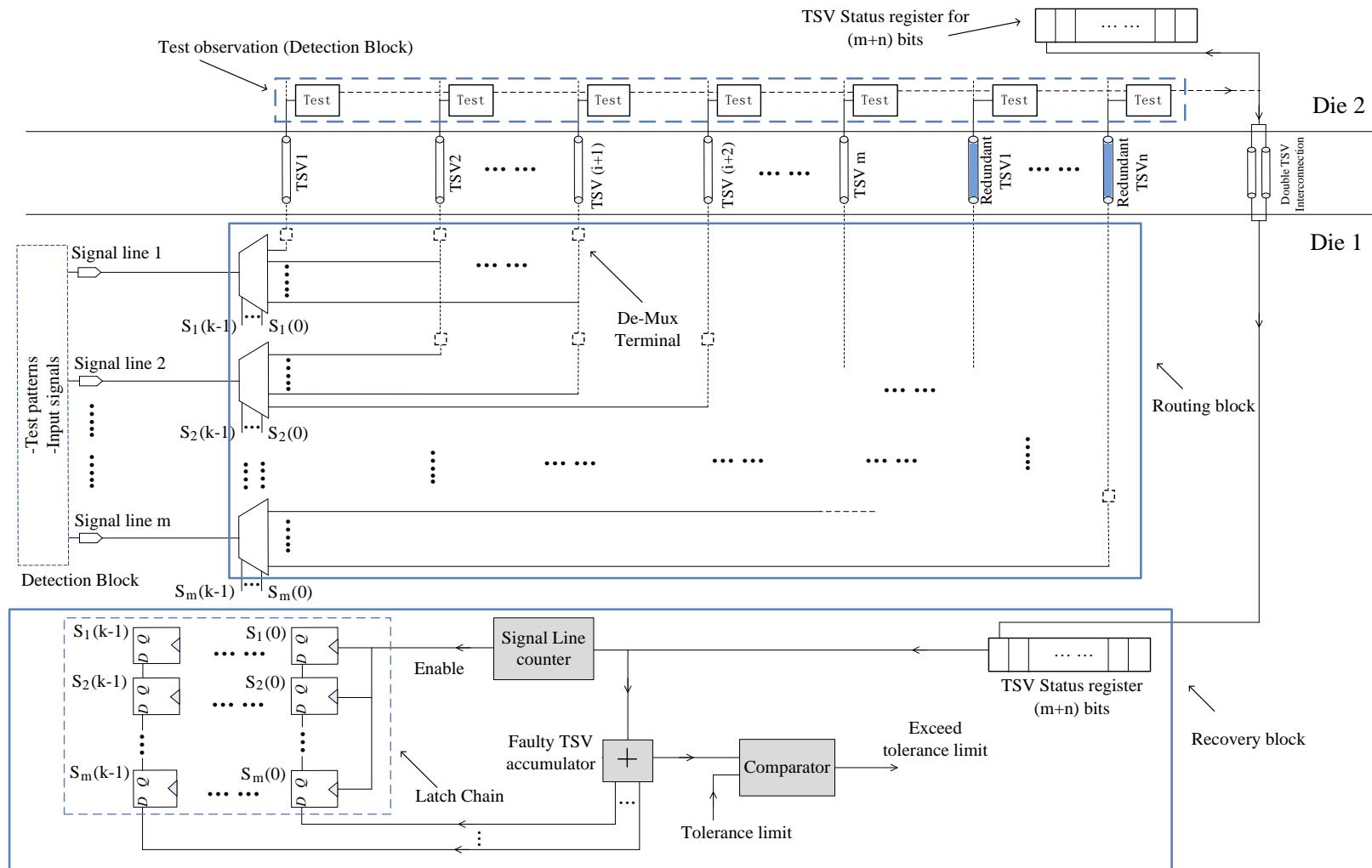

| 4.3 TSV Fault Tolerance Technique.....                                                          | 73  |

| 4.3.1 Detection Block .....                                                                     | 75  |

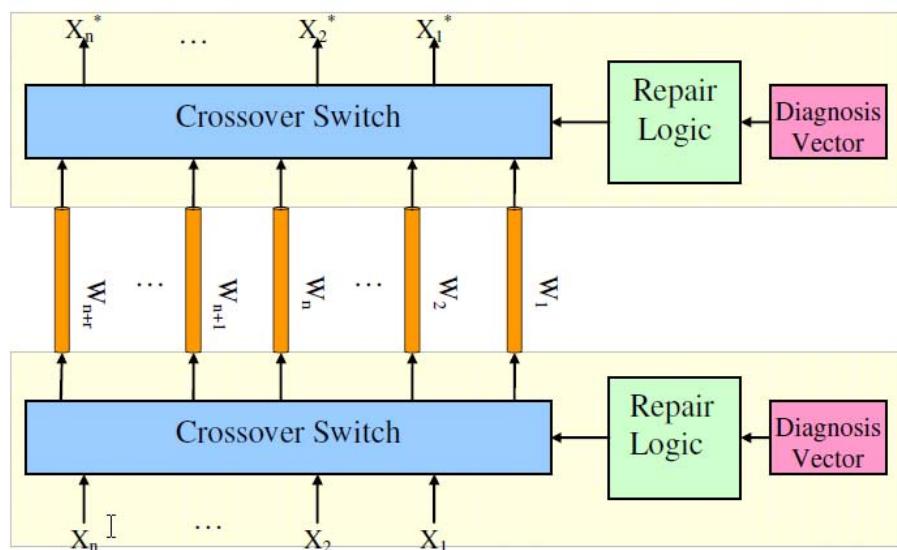

| 4.3.2 Recovery Block.....                                                                       | 79  |

| 4.4 Simulation Results .....                                                                    | 85  |

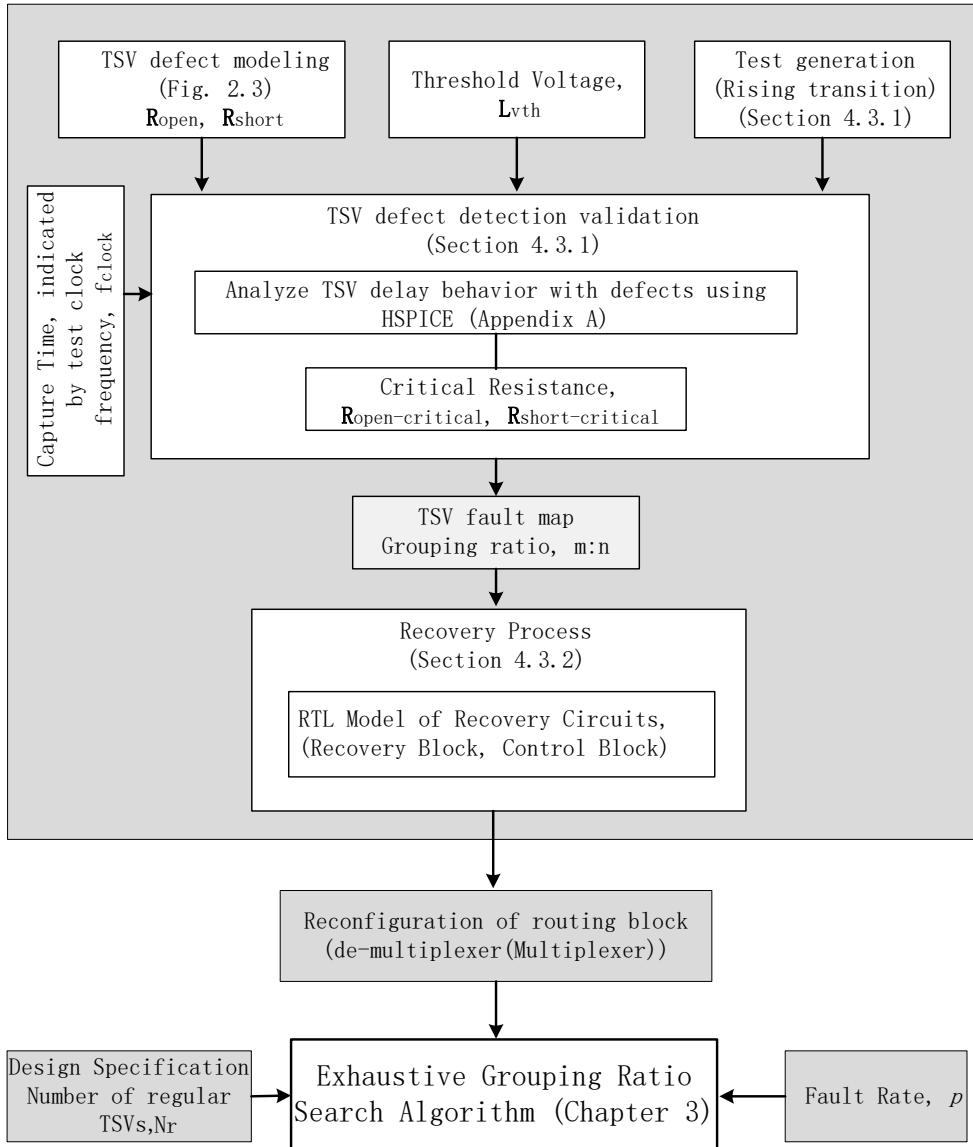

| 4.4.1 Proposed Fault Tolerance Technique Simulation Flow .....                                  | 85  |

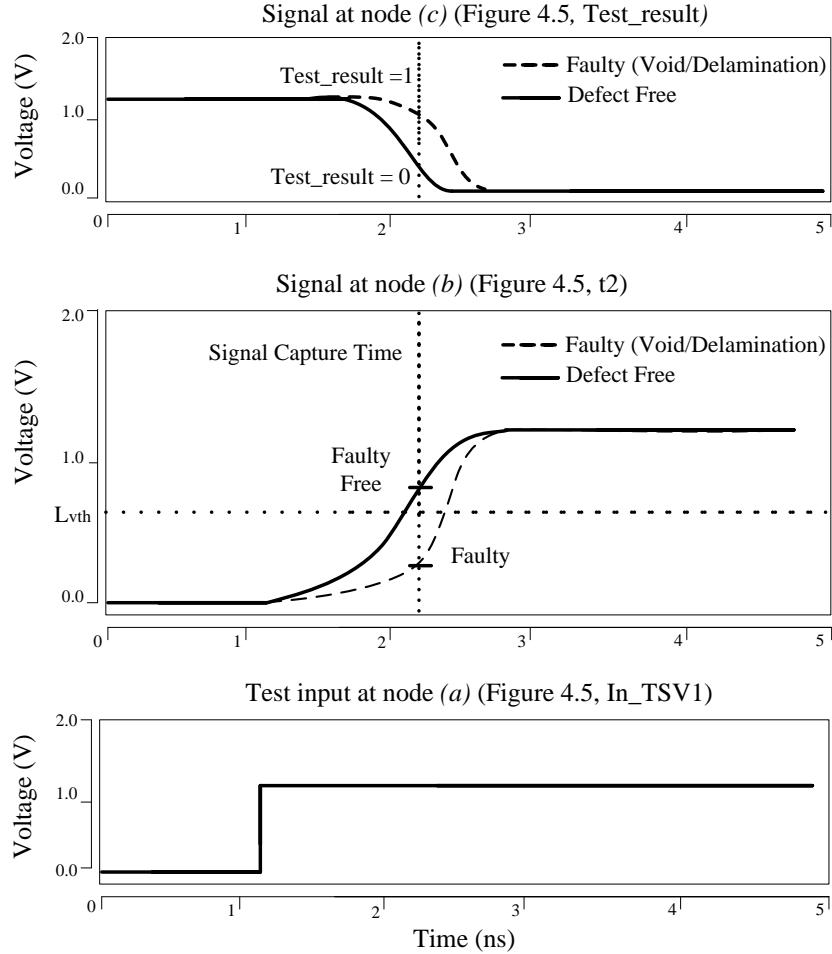

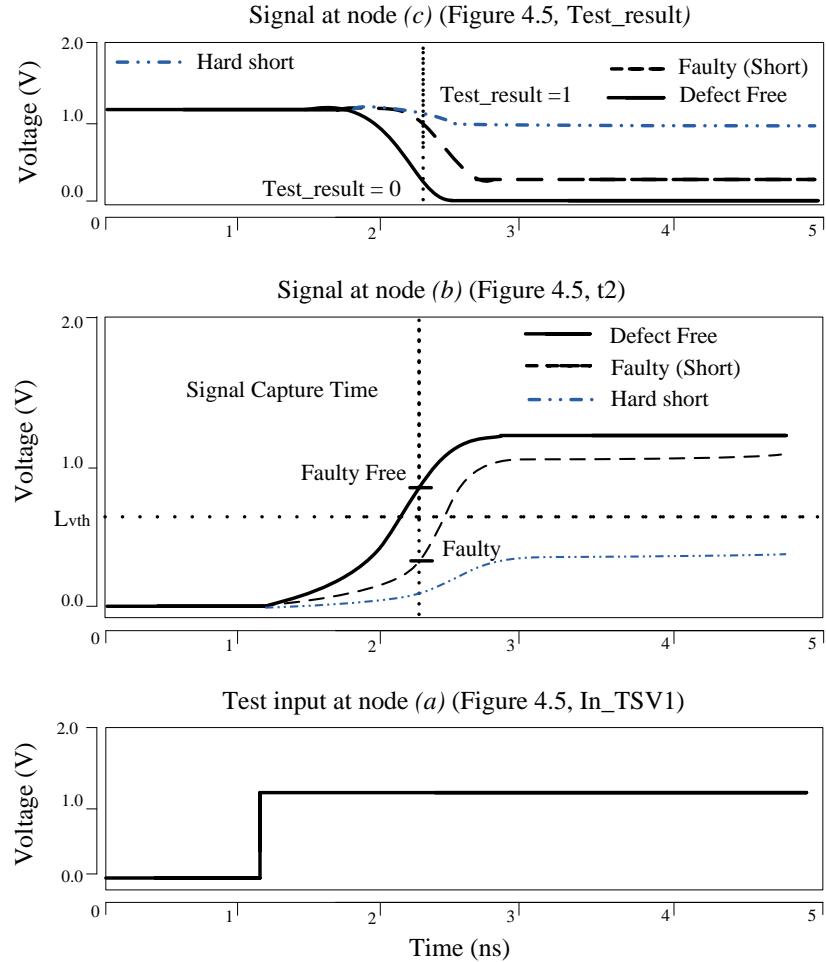

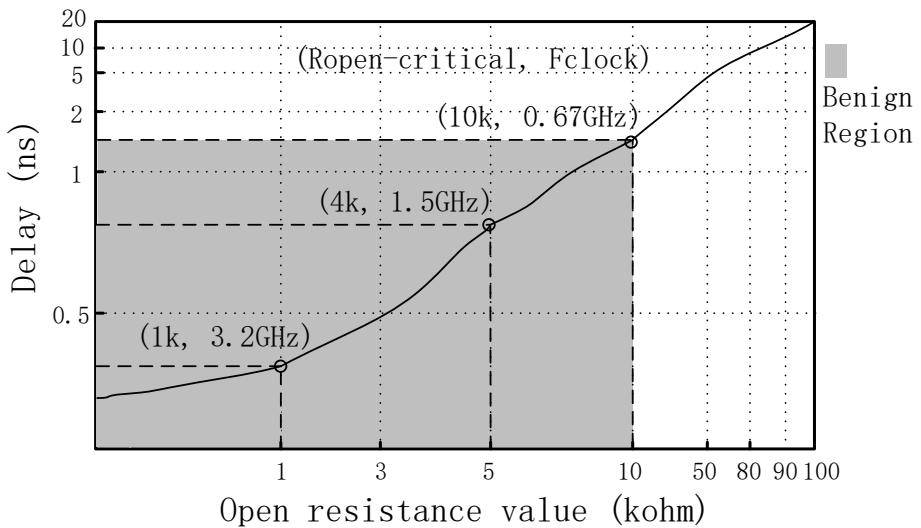

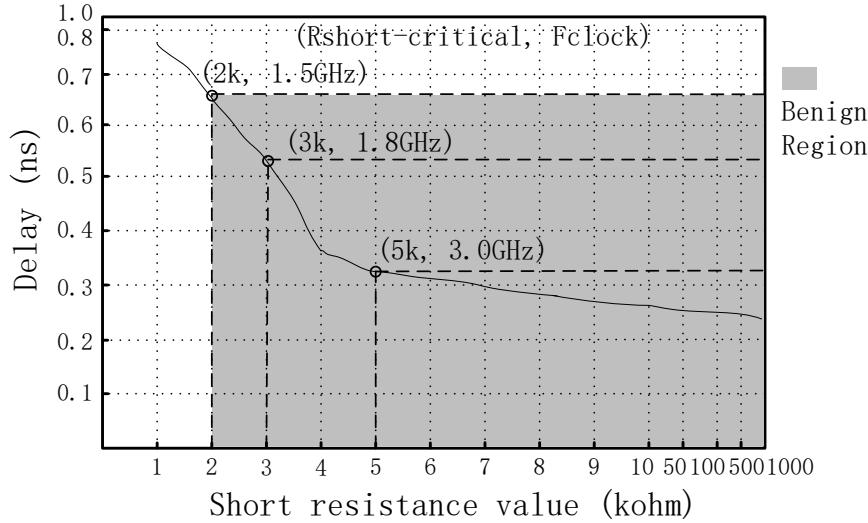

| 4.4.2 Detection Block Validation .....                                                          | 86  |

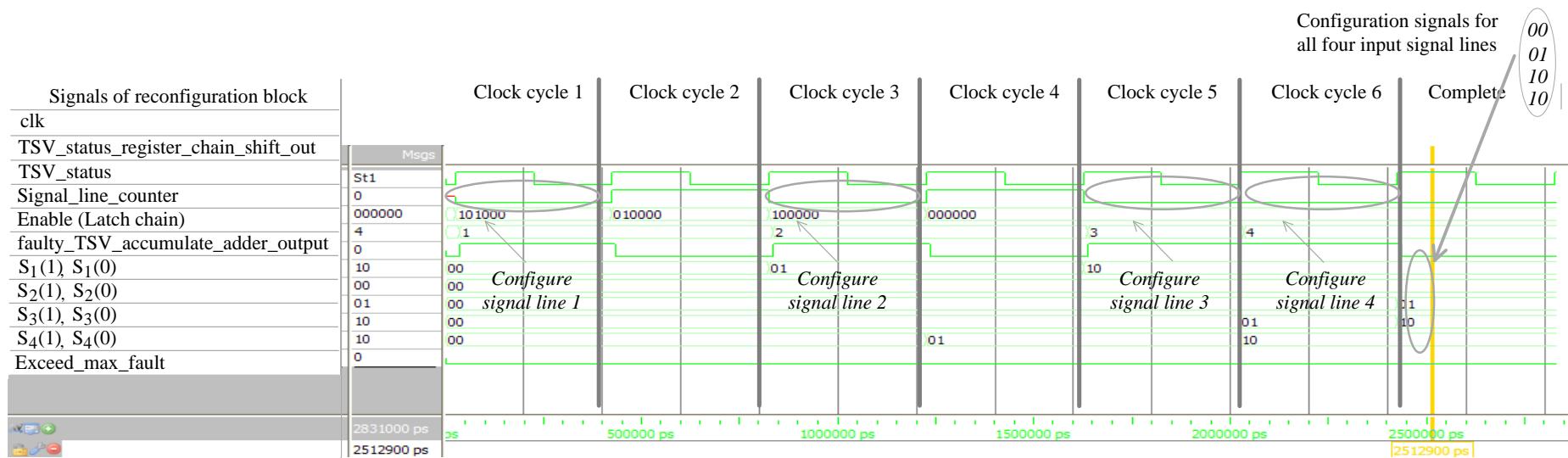

| 4.4.3 Recovery Block Validation .....                                                           | 89  |

| 4.4.4 Repair Capability and Area Overhead .....                                                 | 92  |

| 4.5 Concluding Remarks.....                                                                     | 96  |

| <br><u>5. Joint Consideration of Fault Tolerance and Temperature Mitigation for 3D-ICs ....</u> | 97  |

| 5.1 Introduction.....                                                                           | 98  |

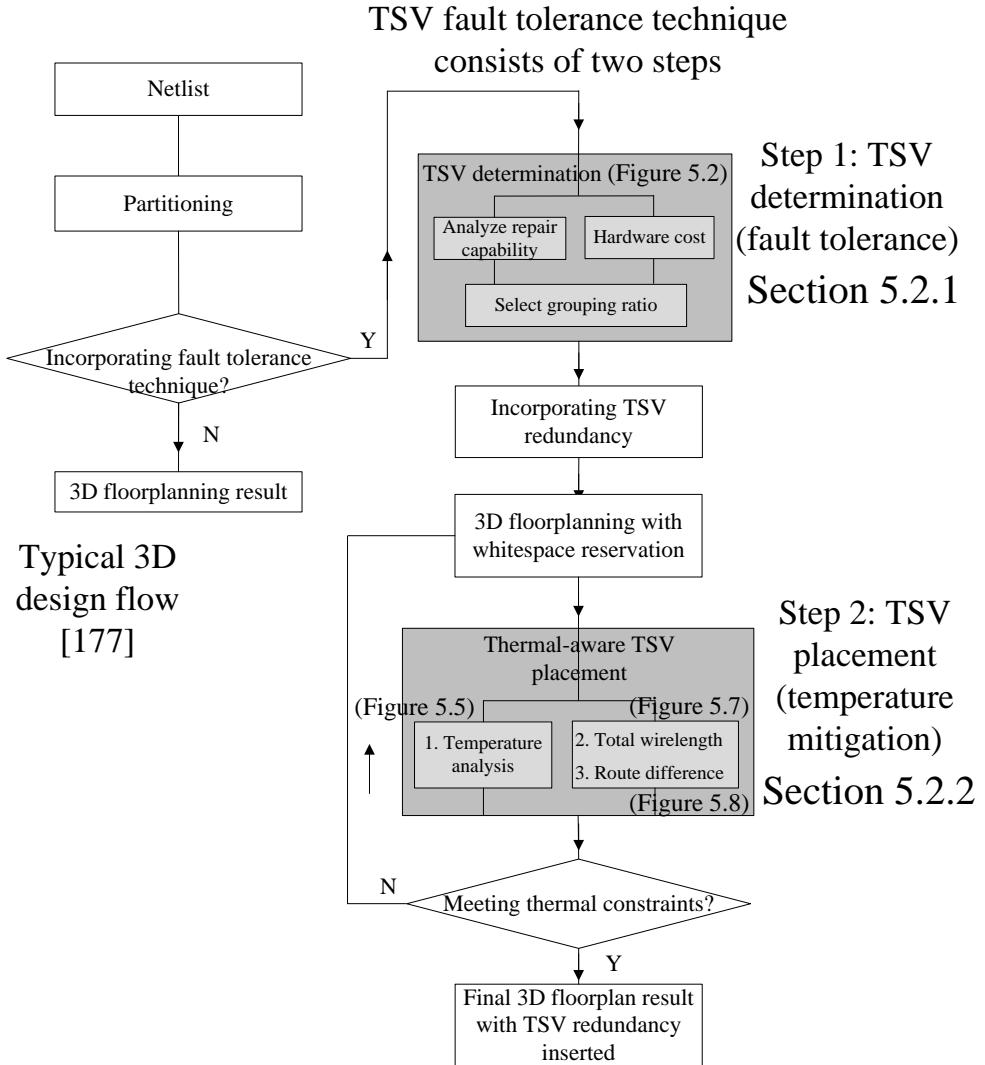

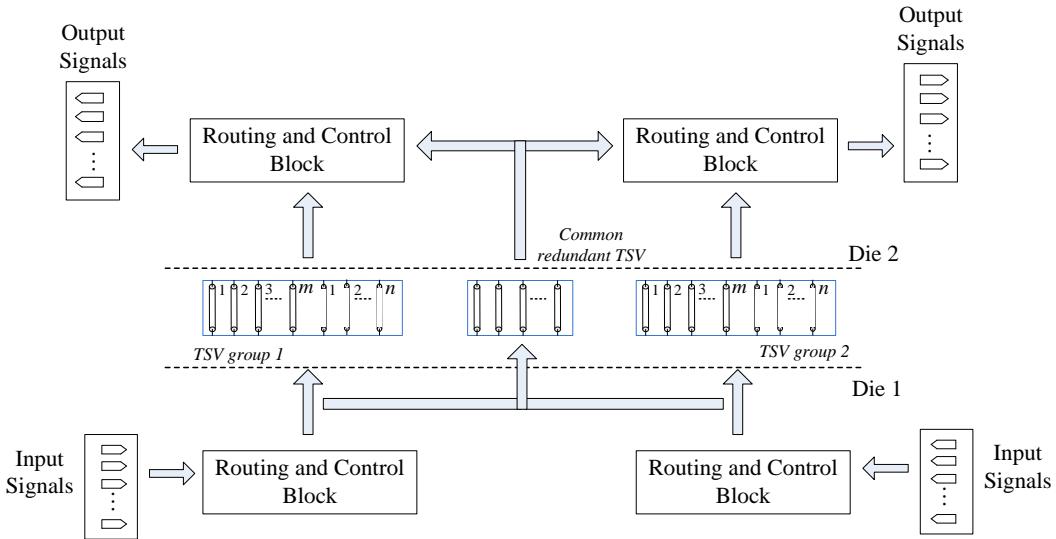

| 5.2 Proposed TSV Fault Tolerance Technique .....                                                | 99  |

| 5.2.1 TSV Determination Step.....                                                               | 100 |

| 5.2.2 TSV Placement Step .....                                                                  | 103 |

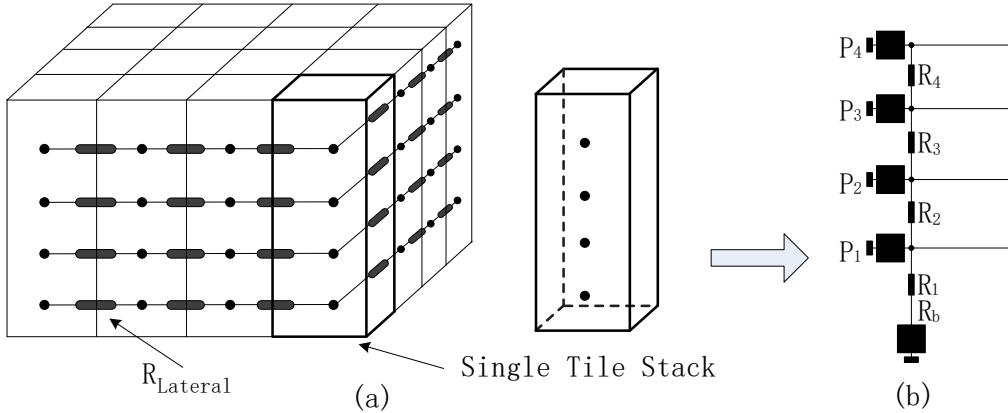

| 5.2.2.1 Temperature Analysis.....                                                               | 104 |

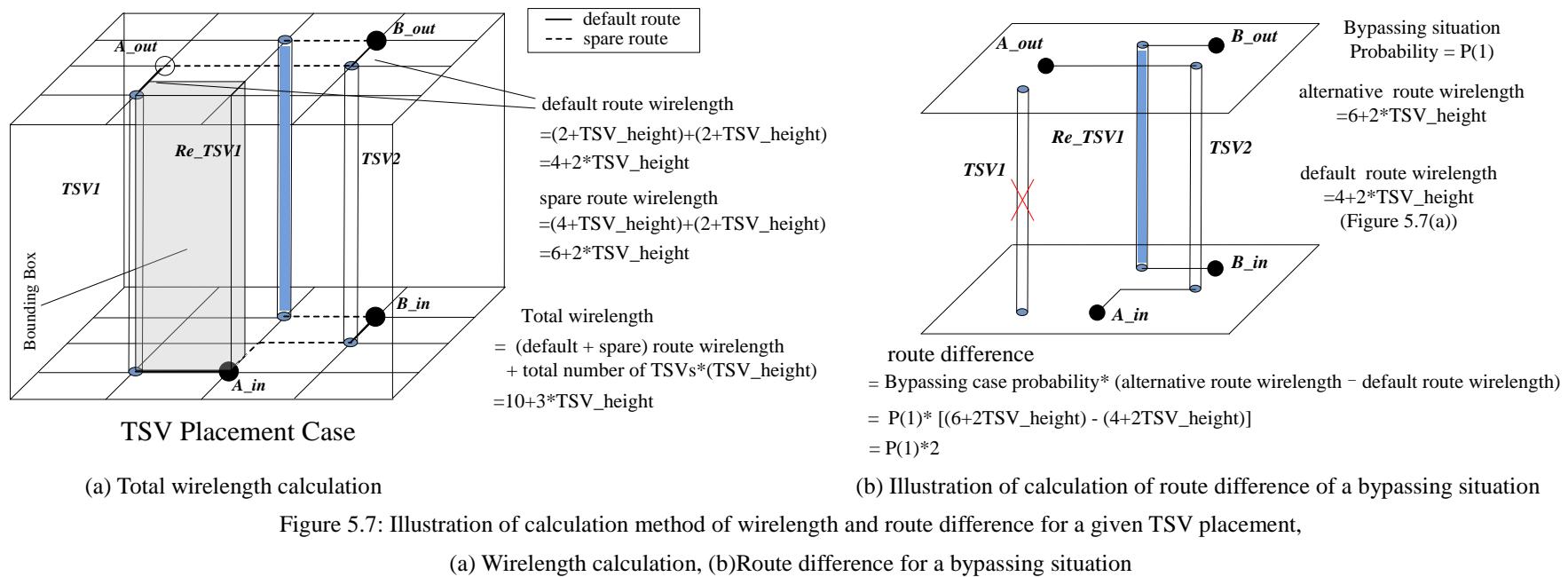

| 5.2.2.2 Wirelength Calculation .....                                                            | 105 |

| 5.2.2.3 Route Difference Calculation .....                                                      | 108 |

| 5.3 Simulation Results .....                                                                    | 108 |

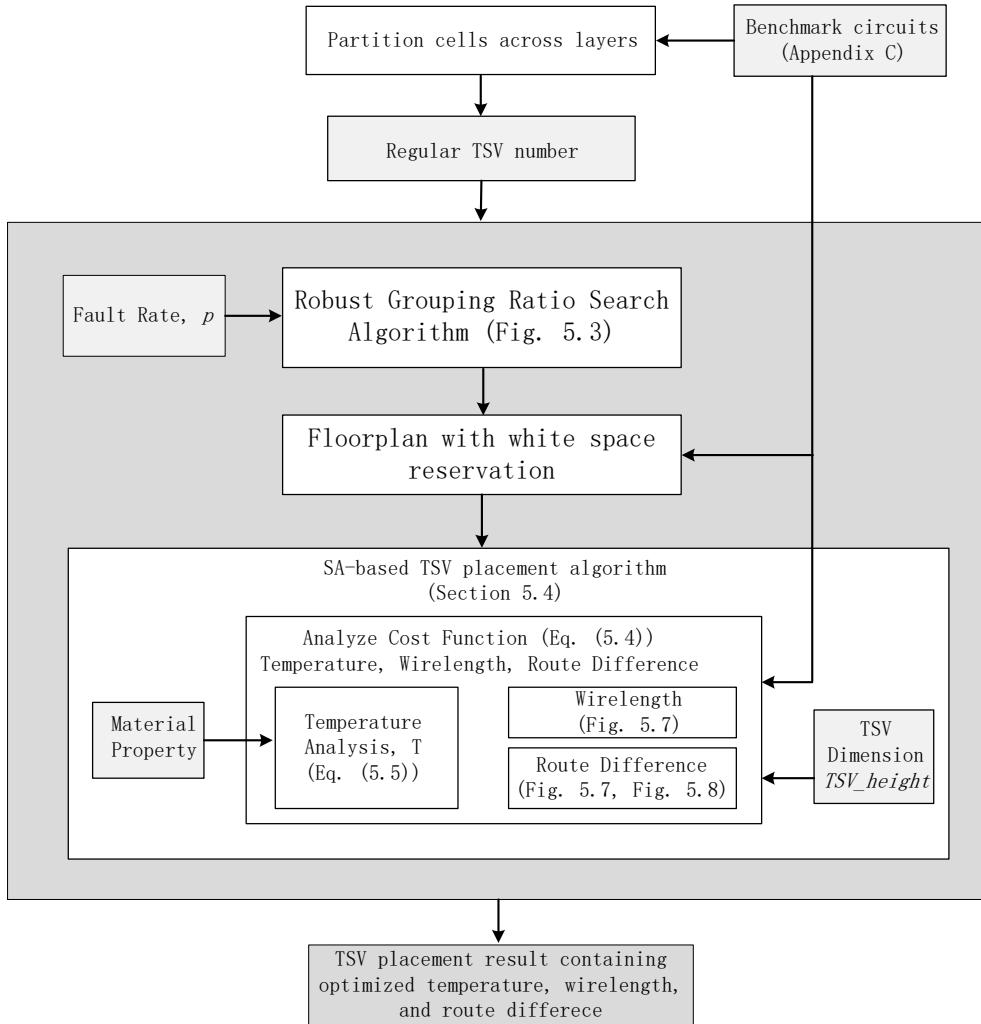

| 5.3.1 Proposed Simulation Flow.....                                                             | 109 |

| 5.3.2 Cost-effective TSV Determination Algorithm .....                                          | 110 |

| 5.3.3 Performance Evaluation of TSV Placement Algorithm .....                                   | 111 |

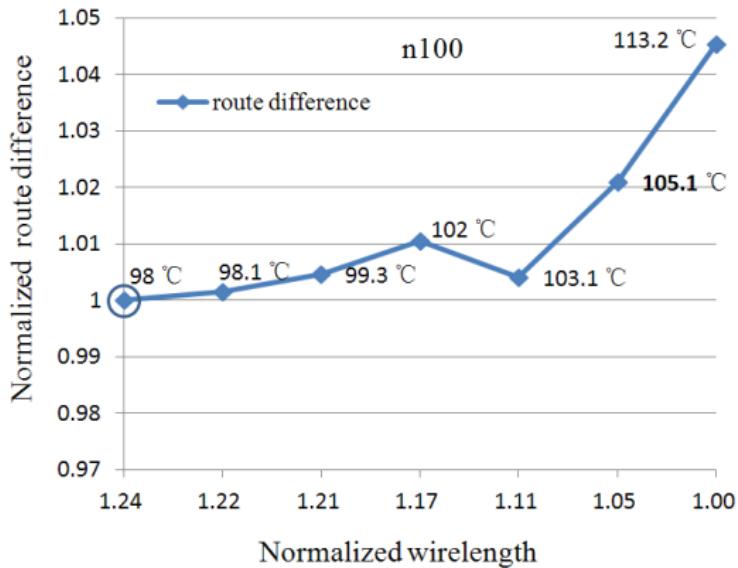

| 5.3.4 Effect on Wirelength and Route Difference.....                                            | 112 |

| 5.4 Concluding Remarks.....                                                                     | 113 |

|                                                    |     |

|----------------------------------------------------|-----|

| <u>6.</u> Conclusions and Future Work.....         | 115 |

| 6.1 Thesis Contributions .....                     | 115 |

| 6.2 Future work.....                               | 118 |

| References.....                                    | 120 |

| Appendix A HSPICE Simulation.....                  | 137 |

| Appendix B RTL Description of Recovery Block ..... | 140 |

| Appendix C MCNC/GSRC Benchmark circuits.....       | 143 |

---

# Declaration of Authorship

I, **Yi Zhao**, declare that this thesis entitled *Investigation into Yield and Reliability Enhancement of TSV-based Three-dimensional Integration Circuits* and the work presented in it are both my own, and have been generated by me as the result of my own original research. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- Where I have consulted the published work of others, this is always clearly attributed;

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- Parts of this work have been published as listed in Chapter 1 Section 1.5

Signed:

Date:

---

## Acknowledgements

First of all, I would like to thank my supervisor Prof. Bashir Al-Hashimi for his great support and guidance in this project. Also, I sincerely thank my colleague Dr. Saqib Khursheed for his patient support and help. Working with him has encouraged me a great deal in completing this project. I am grateful for the funding and research facilities provided by the School of Electronics and Computer Science at the University of Southampton. I would also want to thank Dr. Sheng Yang and Dr. Shida Zhong for their valuable inputs. My thanks also go to Dr. Saqib Khursheed for his insightful discussions and reviewing of this work.

This work has directly and indirectly benefited from discussions, advice and feedback from colleagues and friends to whom I would like to greatly acknowledge. I am thankful to Dr. Rishad A. Shafik, Dr. Mustafa Imran Ali, Dr. Amit Acharyya, Dr. Ke Li, Dr. Sheng Yang, Dr. Shida Zhong, Dr. Jatin Mistry, Dr. Evangelos Mazomenos, Fan Lu, Hamed Shahidipour, Jędrzej Kufel, Erik Marinissen (IMEC Belgium) and Luis A Maeda-Nunez for their helpful discussions and feedback.

Finally, I would like to thank my parents (Jianjun Zhao and Aihua Xu) for their love, patience, support and understanding, without which it would not have been possible for me to complete my PhD over the past four years.

# Chapter 1

## Introduction

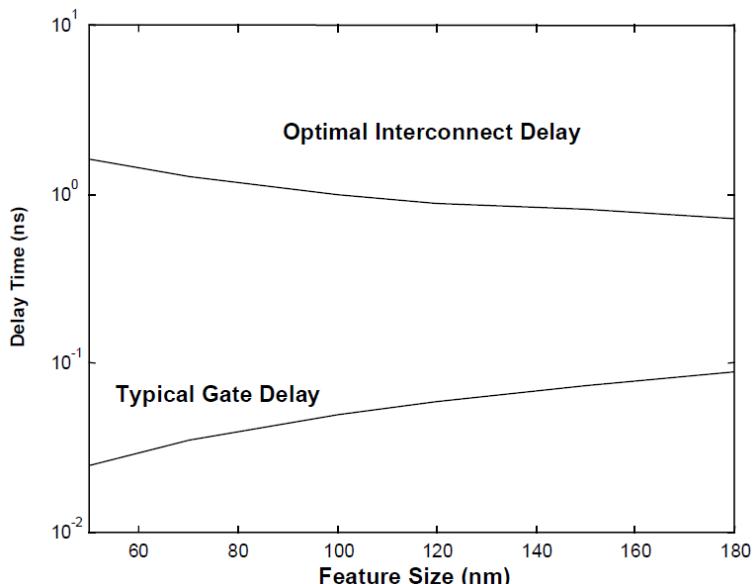

Over the past few decades, great efforts have been made to miniaturize microelectronic circuits. Microelectronic circuits are required to have higher performance, increasing functionality, and low power consumption. The International Technology Roadmap for Semiconductors (ITRS) predicts that the performance enhancement due to CMOS transistor scaling will be significantly reduced unless a new design methodology shift from current IC paradigm takes place. Continuous shrinking of CMOS transistor feature size enables performance enhancement of gates, however, interconnects delay rapidly increase as well which lead to system performance bottleneck [1]. As illustrated in Figure 1.1, gate delay drops with shrinking technology nodes whereas the interconnect delay increases [2].

Figure 1.1: Interconnect Delay and Gate Delay for different CMOS feature sizes [2].

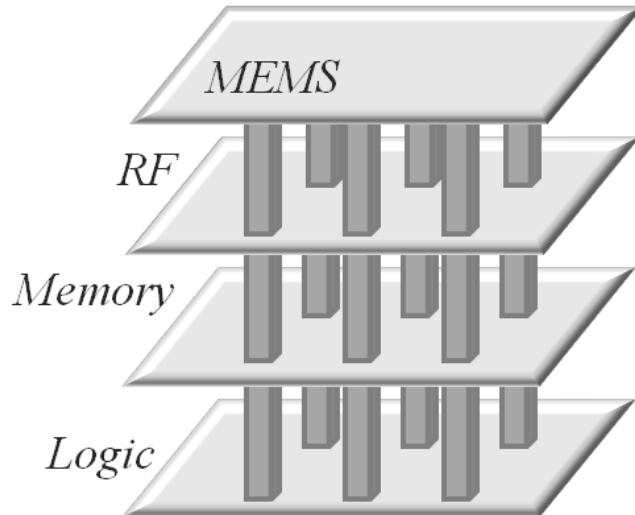

Although, repeaters and flip-flops can be inserted to make long global interconnection delay tractable to prevent system performance degradation, the additional power consumption of these components is very large, and can be a major fraction of system power consumption [3, 4]. Three-dimensional Integrated circuits (3D-ICs) has been acknowledged as a promising technology to overcome this performance bottleneck. A three-dimensional integrated circuit is any circuit in which devices are not restricted to be placed on a single plane. Such a circuit can be regarded as a stack of individual conventional two-dimensional (2D) integrated circuits (ICs), each of which is called a “device layer”, “tier”, or simply a “silicon die” [1], where through silicon vias (TSVs) are used for communication between different device layers, as shown in Figure 1.2.

3D integration technology intuitively enables a larger device density under a given footprint area when compared to conventional planar ICs. Moreover, by using vertical inter-layer connection instead of the long horizontal wires [5, 6, 7], aggressive reduction in interconnects length can significantly improve the system performance (wire delay) and reduce the power consumption. Integration of heterogeneous technology, such as logic and memory, analog device, RF circuits, and MEMS, can also be realized using 3D integration (Figure 1.2). Heterogeneous integration also means incorporating different technology nodes such as 180nm and 90nm in the same device. TSVs are critical components which guarantee that all stacked device layers work as expected. However, recent research has highlighted that TSVs failures are either due to manufacturing defects or thermal-induced aging defects resulting in yield and reliability issues in 3D circuits. This thesis focuses on investigating and developing cost-effective solutions targeting yield and reliability issue brought by TSVs to ensure that communication between dies using TSVs interconnects is not affected.

Figure 1.2: Schematic diagram of a 3D-IC with heterogeneous technology integration.

This chapter provides preliminary information for the subsequent chapters in this thesis. An overview of the state-of-the-art 3D-ICs fabrication process is discussed in Section 1.1. Section 1.2 elaborates on the reported benefits brought by moving from 2D to 3D integration. Section 1.3 outlines the challenges of adapting 3D-ICs and explains the challenges that are targeted in this thesis. The motivation for this research in the subsequent chapters is discussed in Section 1.4 while Section 1.5 provides the outline of this thesis. Finally, the list of publications generated from the research in this thesis is given in Section 1.6. Note that a journal paper with the title of ‘Thermal-aware fault tolerance scheme of TSV-based 3D-ICs with global sharing of redundant TSV’ is under prepared based on the research in this thesis.

## 1.1 Introduction to 3D-IC Structure and Fabrication Process

Enabling 3D integration in microelectronic design has recently become an active research area, motivated by the need to achieve higher performance in a smaller system. Current 3D integration technologies can be classified into two categories: 1) Packaging-based technology [8, 9], and 2) TSV-based 3D integration technology [10].

### 1.1.1 Packaging-based 3D Integration Technology

Figure 1.3: System-in-Package (Die stacking using wire-bonding) [11].

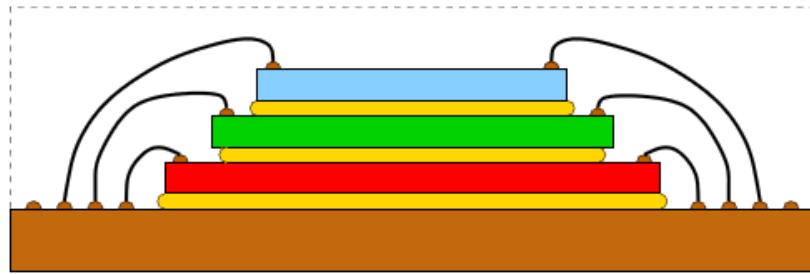

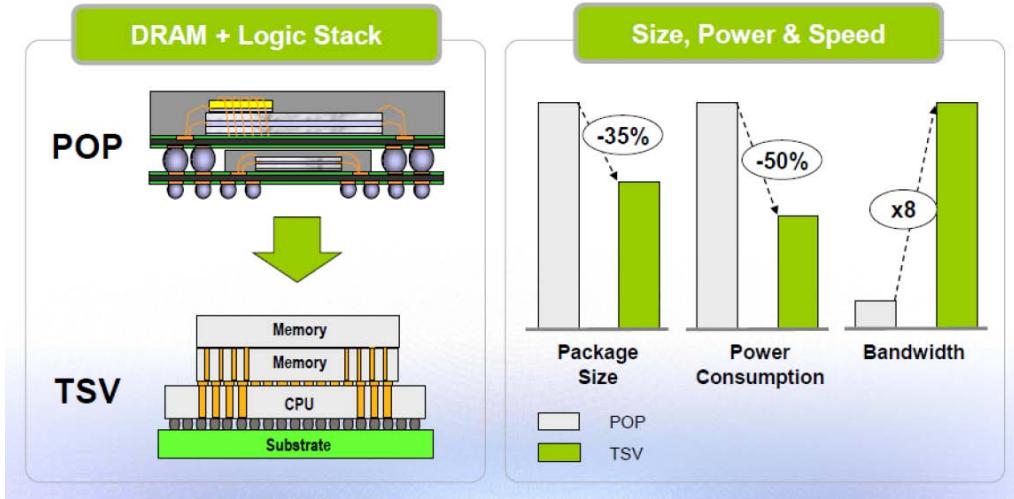

This type of technology achieves three-dimensional integration at package level which stacks fabricated 2D chips through wire-bonding and flip-chip bonding methods [1, 12], including System-in-Package (SiP) and Package-on-Package (PoP) structures. Multi-chip-module (MCM) is a popular method to form SiP by stacking of chips using wire-bonding, as shown in Figure 1.3. This type of technique is widely used in the telecommunication industry for smaller portable products (e.g., stack of 16 NAND flash dies in a signal multichip package for a 16GB memory by Samsung Electronics [13]). PoP technology allows for the stacking of multiple chip packages by connecting them with solder-bumps, which offers higher interconnect density than the MCM-based SiP Chip. Note that each single chip of a PoP stack can be a wire-bonding based MCM as well (Figure 1.3). Package-based 3D integration does not introduce new manufacturing process and can use the existing assembly process enabling short time-to-market. However, its interconnect density is limited to package level which prohibits performance enhancement achieved by this type of 3D integration technology. Thus, a new promising 3D integration technology which is TSV-based 3D-ICs is favoured by the industry. In comparison to package-level stacking technology, the TSV-based 3D chip provides higher bandwidth and lower power consumption with a smaller chip footprint, as shown in Figure 1.4. The benefits brought by TSV-based 3D integration technology are discussed in detail in Section 1.2.

### 1.1.2 Overview of TSV-based 3D Integration

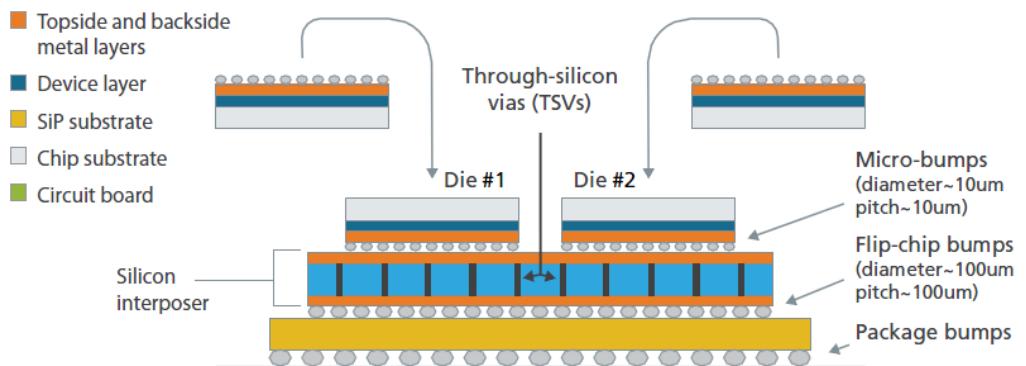

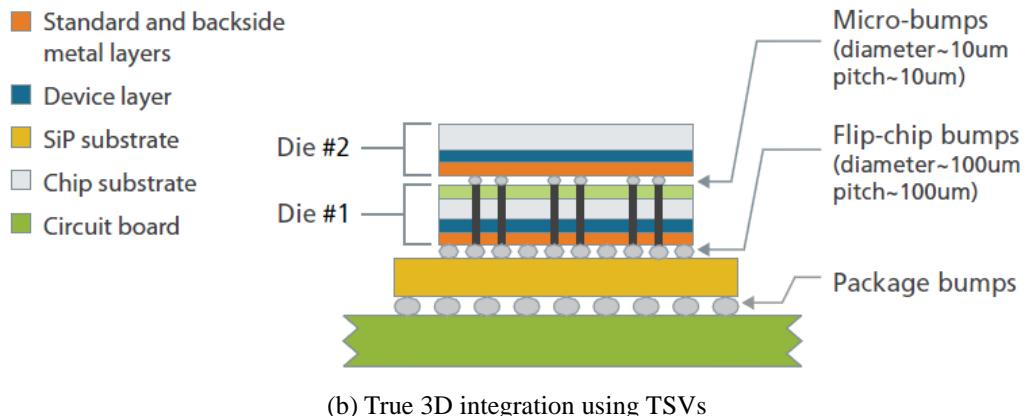

There are two main technologies that employ TSVs for 3D integration, as illustrated in Figure 1.5. The first is the interposer-based 3D integration, where multiple chip slices are integrated

side-by-side on a passive silicon interposer (Figure 1.5(a)). The passive interposer contains high density interconnections (TSVs) and no active device in the silicon substrate [14]. The key innovation is to augment the standard I/Os with thousands of die-to-die connections

Figure 1.4: Comparison between PoP-based and TSV-based 3D integration technologies.

through passive traces fabricated on the silicon interposer. This approach provides high connectivity (more than 10,000 connections between two dice) and low latency ( $\sim 1\text{nS}$ ) without incurring the power penalty of traditional I/O structures. Sometimes this technology is referred to as 2.5D integration [15]. However, a true 3D integration can integrate chips with TSVs directly and no interposer layer is needed (Figure 1.5(b)). The true 3D integration allows even higher interconnects density and the TSV diameter can range from 1 to 30 microns [15]. In this research, there is no distinguish between the interposer-based 2.5 integration and the true 3D integration, since they both employ TSV interconnects for communication between dies. Furthermore, the research work proposed in this thesis is to address the yield, reliability and thermal issue for both types of TSV-based 3D circuits.

(a) Interposer-based 3D integration

Figure 1.5: TSV-based 3D integration technologies [15].

### 1.1.3 Various Implementation Technologies of TSV-based 3D Integration

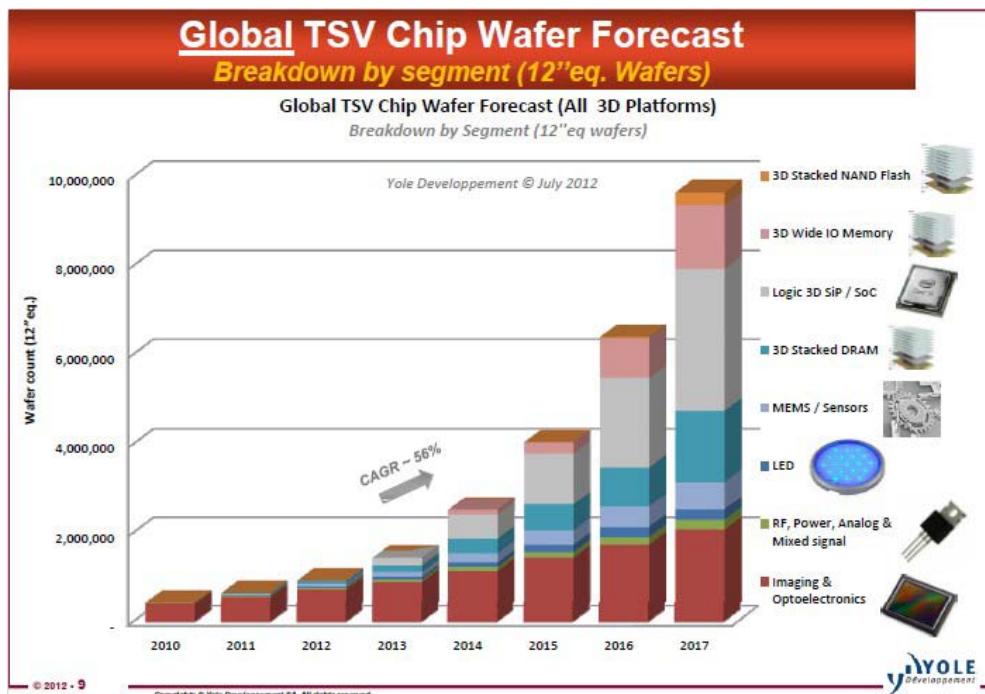

Figure 1.6: Forecast of TSV-based 3D products [16].

Nowadays, TSV-based 3D integration has drawn extensive attention from the industry, as predicted by [16], the digital produce market can be boosted by TSV-based 3D chips (Figure 1.6). Nowadays, research organizations across academic and industry have reported a number of TSV-based 3D technologies with a plethora of alternative implementation process flows in terms of substrate types, stacking methods, via process flows, and bonding approaches [10]. Wafers can have silicon-on-insulator (SOI) substrate or thicker bulk substrate. Due to the removal of entire substrate in the upper layers (Figure 1.8) of the SOI-based design, finer size

and shorter TSVs can be realized when compared to the bulk Si substrate 3D integrated circuits. However, its fabrication process is more costly and requires extremely aggressive alignment accuracy [10]. Existing TSV-based 3D integration technologies differ from each other in terms of stacking methods, bonding orientation and via formation procedure, and bonding methodologies.

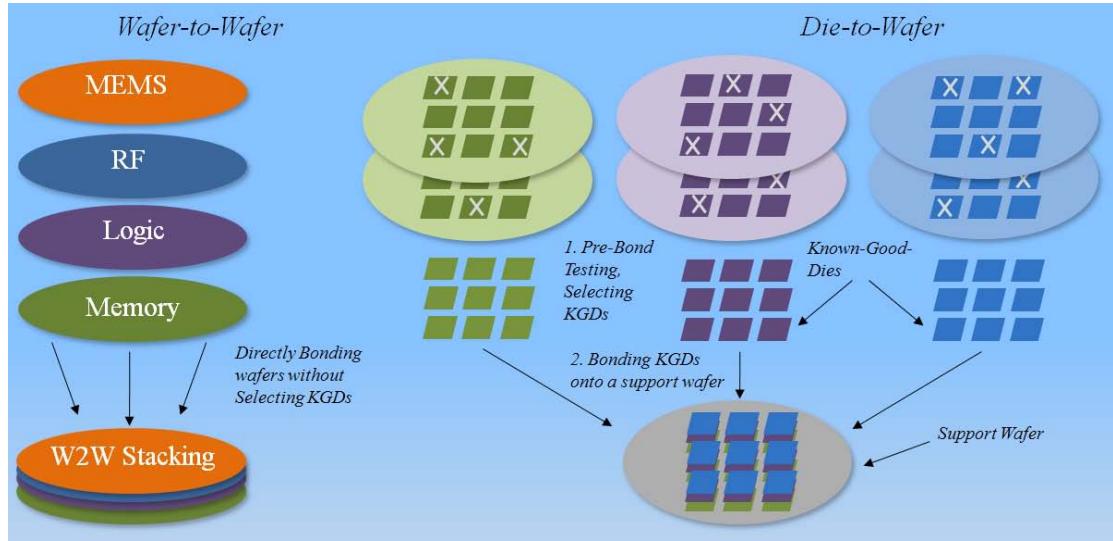

Figure 1.7: Demonstration of D2D (D2W) and W2W bonding approaches. W2W bonding directly stacks multiple wafers while D2D (D2W) introduces the KGD test prior to the bonding process.

## Stacking Method

Depending on the individual units to be stacked, 3D-ICs stacking methods can be categorized into: wafer-to-wafer (W2W), die-to-die (D2D) and die-to-wafer (D2W). In W2W stacking, entire wafers are directly bonded together, and then cut into dies [17]. Due to the elimination of the die selecting procedure prior to bonding, W2W offers the highest throughput. However, it involves yield issue as prior to bonding, it is not ensured that all dies are good, bad dies may be stacked with good dies and one bad die may fail the whole design. The D2W(D2D) stacking method allows the diced dies to be tested individually, such that only Known-Good-Dies (KGDs) are used in the 3D integration (Figure 1.7), which improves the overall chip yield. Moreover, D2W(D2D) has a higher flexibility in die size. However, the testing and pre-selection of KGDs decreases throughput thus increasing the manufacturing time and cost [17].

## Die stacking orientation and Via formation process

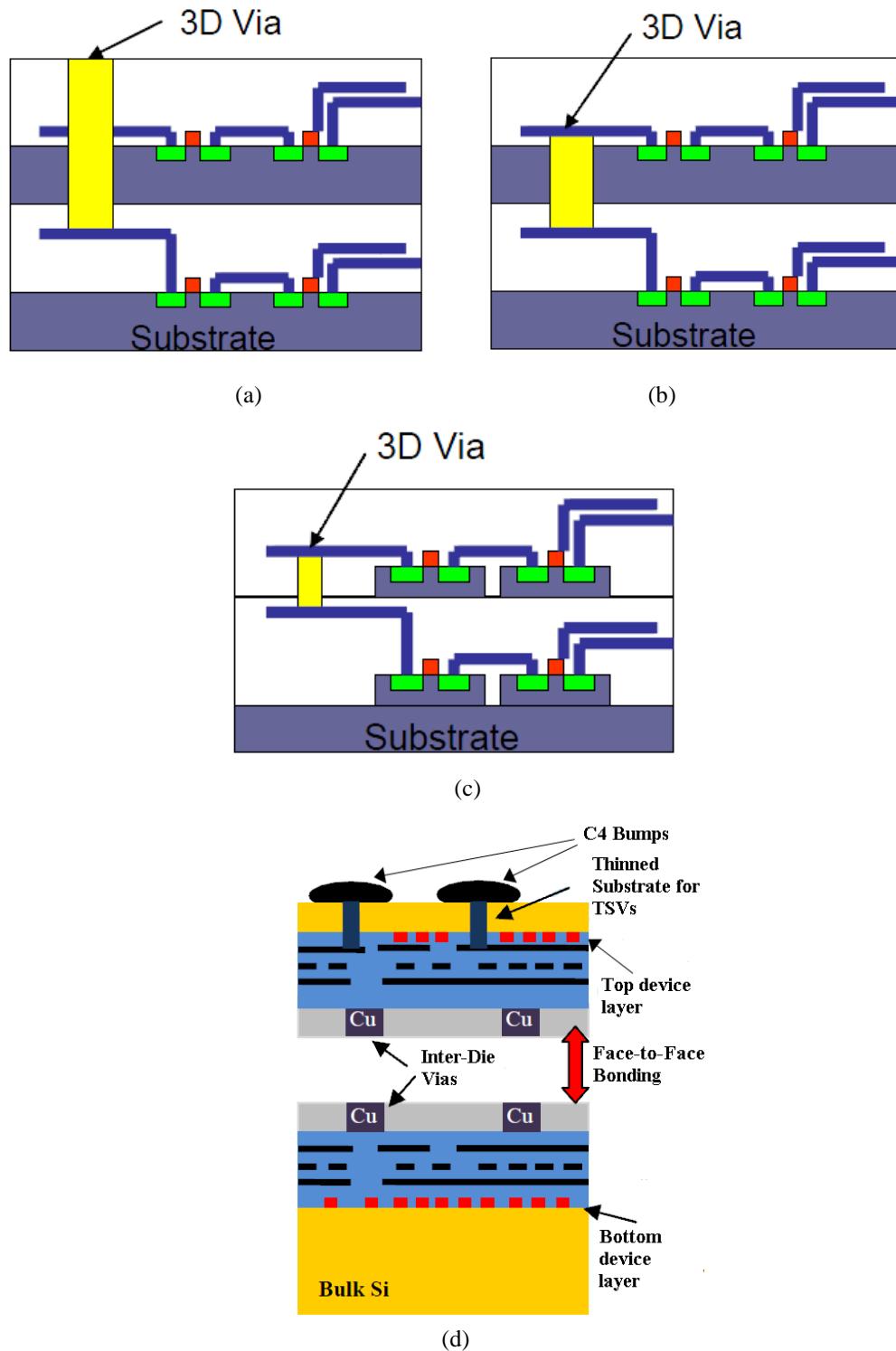

There are two types of stacking manners with respect to stacking orientation of two dies during bonding: Face-to-Back (F2B) and Face-to-Face (F2F) processing. Structures in Figure 1.8(a)-(c) are implemented in F2B fashion, where the bottom die places its face (device layer) up and is connected to the upper (second) die with its back side (metal layer) down. F2B bonding is easier to scale to a stack containing more than two dies, while F2F bonding orientation is limited to the stacking of two dies (Figure 1.8(d)). Additionally, the F2F process has finer inter-die interconnects (i.e., higher density of inter-layer interconnects), nevertheless

Figure 1.8: Schematic diagrams for (a) F2B, Via-last bulk Si 3D-ICs [18], (b) F2B, Via-first bulk Si 3D-ICs [18], (c) F2B, Via-last SOI-based 3D-ICs [168] and (d) F2F bulk Si 3D-ICs [19]. Note that Via-first and via-last terminologies are usually for F2B stacking orientation technologies.

it requires deep and large area-consuming vias for power and I/Os of package (Figure 1.8(d)). In terms of the through-silicon-via fabrication process, recent research proposed two main TSV manufacturing processes: Via-first and Via-last TSV formation flow, where the main difference is the order of TSV processing. In the via-first TSV process, as shown in Figure 1.8(b), 3D vias are etched and deposited before the front-end-of-line (FEOL, i.e., building device layer) process and the back-end-of-line (BEOL) metal layer formation process. However, in via-last TSV process TSVs are formed after FEOL and BEOL process, as shown in Figure 1.8(b). Via-first process has little impact on the device layer and metal layer formation, and is effective for creating higher 3D via density when compared to the via-last process, however, it requires more complex process resulting in higher cost [20]. Via-middle process flow also appeared in recently published result [21], where TSV formation is after FEOL process but prior to BEOL process. Note that Figure 1.8(c) illustrates the SOI based 3D structure proposed by IBM [22] which uses via-last process as well, however, it has the smallest via size and shortest distance between layers, due to the removal of the entire silicon substrate. [10].

The filling of TSVs uses various materials, such as Cu [23, 24, 25], W [26], and poly-Si [27, 28]. Poly-Si, as a doping material, is a stable material which can avoid metal atom contamination and affect device features less than other material [27, 28]. However, Cu filling can enable even lower interconnection resistance and finer via size. Additionally, via diameter size varies with different 3D-IC schemes from 0.4um to 140um [22, 29].

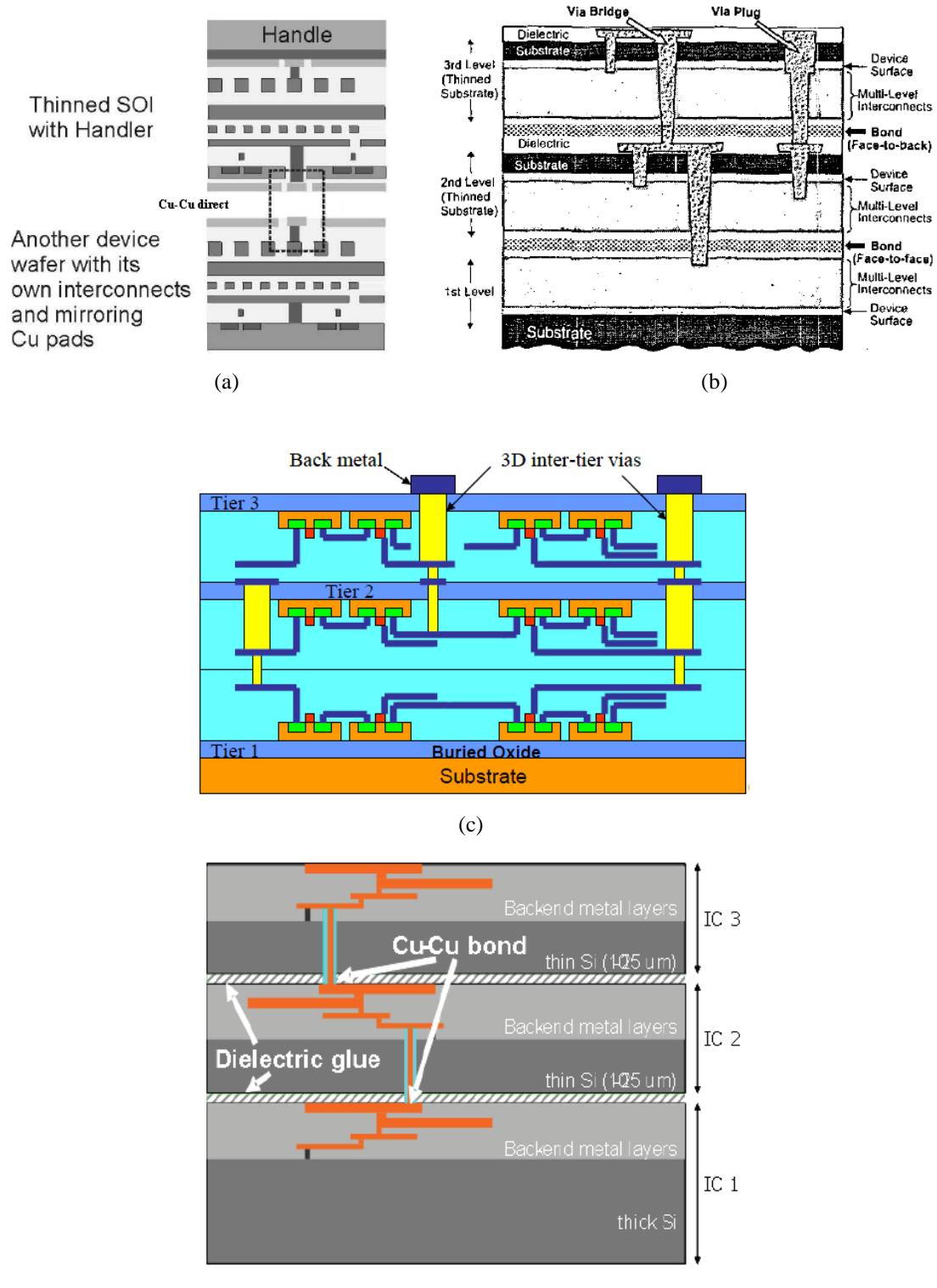

### **3D-ICs Bonding approach**

There are primarily three types of bonding approaches, referred to as, thermal-compression Cu-Cu bonding, dielectric adhesive bonding, and oxide-oxide (oxide-fusion) bonding. Thermal compression Cu-Cu [24] bonds layers with inter-die vias with Cu pads, as shown in Figure 1.9(a), where a F2B stacking fashion is used. Two layers are bonded at 400 °C to achieve mechanically reliable Cu-Cu bonding interface and to minimize metal oxidation at the interface. Mechanical properties of Cu-Cu bonding and possible bonding conditions and procedures are investigated in reference [30]. Cu-Cu bonding is preferred by industries, as it introduces low contact resistance at the bonding interface. Adhesive bonding uses an additional glue layer, such as Benzocyclobutene (BCB) to bond the adjacent layers, as shown in Figure 1.9(b) [31, 32]. It can achieve good bonding interface strength, however, the bonding accuracy using adhesive glue may be degraded, as adhesive may become viscous which can cause unexpected alignment patterns shift. Direct oxide-oxide bonding approach bonds two adjacent layers immediately without introducing any extra bonding material [33], as illustrated in Figure 1.9(c). A study [22] implemented oxide-oxide bonding by oxide fusion at room temperature, which is better than the temperature required in Cu-Cu bonding, thus the status of the bonding interface remains solid and stable during bonding, unlike it is in the adhesive bonding. There is also a hybrid bonding approach (Figure 1.9(d)) which combines Cu-Cu bonding and adhesive bonding methods which employs the advantages of both

Figure 1.9: Four main bonding approaches: (a) Cu-Cu bonding [24], (b) adhesive bonding [32], (c) direct oxide-oxide bonding [18], and (d) Hybrid bonding which combines adhesive and Cu-Cu bonding method [34].

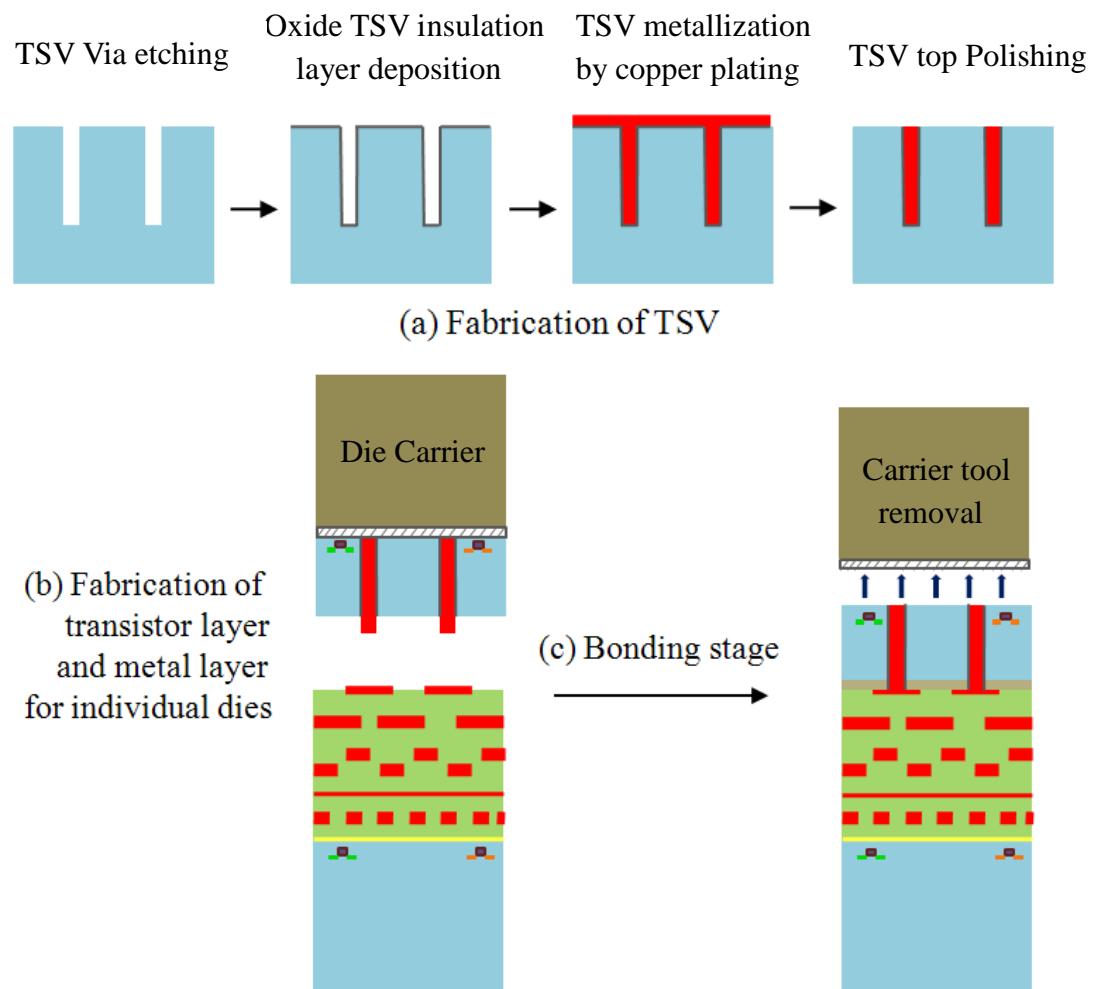

methods [34, 35]. A typical 3D integration process that uses the hybrid bonding method is illustrated in Figure 1.10. As shown, TSVs are formed using via-first TSV formation process flow. Then, device and metal layers are created, followed by the bonding stage where dies are stacked together using both Cu-Cu bonding and an adhesive glue layer. Because the top die needs to be thinned for exposing TSV tips, a handle wafer is required to provide the necessary mechanical support for the thinned die as it is very fragile [36]. This thesis focuses on the hybrid bonding-based 3D integration process, as it offers high TSV density with via-first process and good bonding quality resulting from a combined bonding fashion. The Cu-filled TSVs have good thermal conductivity, thus benefiting the thermal management of 3D design. Moreover, it is well studied regarding its electrical property [37], therefore facilitating further defect and fault modeling research [38].

Current 3D integration includes various implementation processes. To under different fabrication processed, reported methodologies from both academic and industry are summarized in Table 1.1. Besides the organizations listed in Table 1.1, extensive exploration in 3D architecture has also been done, such as quality research on 3D microprocessor design (Pennsylvania State University [3, 36, 39], Intel [25, 40]), 3D signal processing circuits (North Carolina University [41]), 3D Processor-Memory architecture exploration (NEC Electronics [28]), EDA tools (3D layout tools provided by Massachusetts Institute of Technology [6, 7], 3D floorplanning/placement tool provided by Georgia Institute of Technology [42], thermal-aware floorplanning program presented by University of California, Los Angeles [43, 44]). The first 3D products would be extremely high density memory stacks (e.g., flash memory from Samsung Electronics [45]).

Table 1.1: 3D integration technologies summary (extracted from organizations across academic and industry)

| Company /University      | TSV size (um) | TSV process   |                  | Bonding Orientation | Bonding Method | Stacking Method | Status                          |

|--------------------------|---------------|---------------|------------------|---------------------|----------------|-----------------|---------------------------------|

|                          |               | Via formation | Filling material |                     |                |                 |                                 |

| Tezzaron [47]            | ~1.2          | Via-first     | W/Cu             | F2F/F2B             | Cu-Cu          | W2W             | Processor-Memory Stack          |

| MIT Lincoln Lab [26]     | 1.5           | Via-last      | W                | F2F/F2B             | Oxide-fusion   | W2W             | 3D CMOS Image Sensor [48]       |

| IMEC [49]                | 5             | Via-first     | Cu               | F2B                 | Cu-Cu /Hybrid  | D2D /D2W        | Prototype test chip             |

| Tohoku [31]              | 2             | Via-last      | W                | F2F/F2B             | Metal-Metal    | D2D /D2W        | 3D shared Memory test chip [50] |

| Fraunhofer IZM [17]      | 1-3           | Via-last      | Cu/W             | F2B                 | Metal-Metal    | D2W /W2W        | Prototype test chip             |

| IBM [10]                 | <1            | Via-last      | Cu               | F2B                 | Oxide fusion   | W2W             | 3D Prototype test vehicle       |

| STM [18] & CEA-LETI [27] | 0.75-3        | Via-last      | Cu               | F2F                 | Oxide fusion   | D2W /W2W        | Prototype test chip             |

| Honda [51]               | -             | Via first     | W                | F2F                 | Adhesive       | D2W /W2W        | Processor-Memory Stack [52]     |

| RPI [35]                 | -             | Via first     | Cu               | F2F/F2B             | Hybrid         | W2W             | Prototype test chip             |

Figure 1.10: Flow chart of a hybrid bonding based 3D-ICs fabrication process [46].

## 1.2 Benefits of 3D-ICs

The industry paradigm shifting from conventional planar ICs to 3D-ICs is stimulated by its potential benefits. This section explains these benefits from four key aspects wirelength and interconnect RC delay, power consumption, chip footprint, and heterogeneous technologies integration, along with recently published results showing the progress.

### 1.2.1 Wirelength Reduction and Performance Enhancement

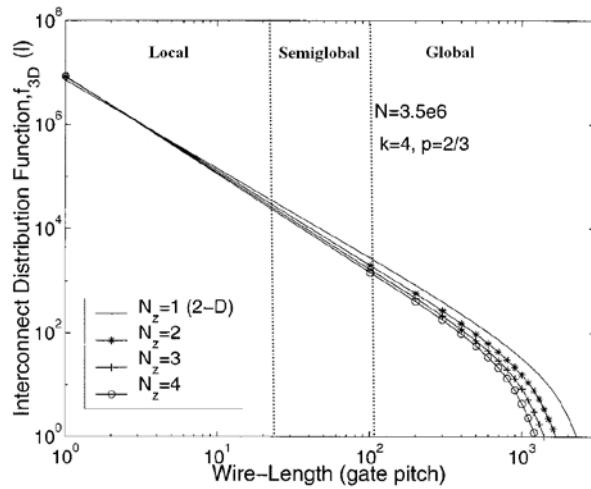

Figure 1.11: The wire-length distribution of 3D-IC for a varying number of integrated layers [53].

The intuitive benefit of 3D integration is the reduction in wirelength due to adoption of 3D stacking to shorten the long horizontal interconnects. It is investigated in a study [54] that the 3D stacking mechanism enables the wirelength to drop by a factor of square root of device layers  $\sqrt{N_z}$  in the best case scenario. However, to gain a deeper observation on how 3D structure affects interconnects length. Another study [53] provided an analysis on the interconnect distribution which show how local, semi-global, and global interconnects vary across different number of device layers. An estimation of interconnect distribution of a 3D design of 3.5 million gates implemented in up to four layers is shown in Figure 1.11, where  $N_z=1$  indicates the circuit in 2D implementation while  $N_z= (2, 3, 4)$  indicates the number of layers in respective 3D designs. Wirelength is divided into three regions which represent local, semi-global, and global interconnects respectively, as depicted in Figure 1.11. Wirelength is measured in gate pitches where gate pitch is the distance between adjacent logic gate which is equal to  $\sqrt{A_c/N_{gates}}$ , where  $A_c$  is the chip area,  $N_{gates}$  is the total number of gates within the design. As shown in Figure 1.11, 3D design gains little reduction in local interconnects amounts, whereas significant reduction has been achieved in number of semi-global and global interconnects. However, wire length distribution depends on the actual circuit implementation and layout methodology. By applying a placement tool [6], PR3D, proposed by Das *et al.*, on ISPD placement benchmark circuits [55], 28% to 51% reduction in total

wirelength is achieved by using two to five device-layer 3D implementation in comparison to the 2D case. During placement, a typical criterion is interconnect delay performance. Through analyzing the circuit performance of a 32-bit Fast-Fourier-Transform (FFT) datapath, an implementation of the DES cryptographic algorithm, and a 64-bit multiplier-accumulator (MAC) chip, Reference [1] reported up to 54% reduction in wire-delay performance. From layout perspective, the performance improvement of interconnect delay is also demonstrated in another study [7] for a 8-bit encryption processor mapped into 3D layout using 3D Magic [7] which is an extension of the existing layout tool Magic [56]. Similarly, 31%-58% and 28%-51% reduction in longest wire length and total wire length respectively, are demonstrated in two studies [5, 6] that employ 3D Magic layout tool.

Since 3D technology enables memories to be stacked on logic circuits, high performance microprocessor architecture can be generated by taking advantage of bandwidth increment based on processor-memory stack system [57]. The access time between cache and processors is critical to the design performance. Using 3D Cacti, a cache performance analysis tool [36], the evaluation of how to partition caches across dies in a 3D processor for maximizing the performance (delay) can be achieved. Kiran *et al.*, showed that [58] a 3D implementation of a 256-entry physical register file composed of two layers achieved a 24% reduction in latency. Moreover, the clock frequency in a 3D processor can also be increased due to the higher bandwidth of 3D integration.

### 1.2.2 Power Reduction of 3D-ICs

The benefit of wire-length reduction not only translates into shorter wire-delay and higher bandwidth, but also into power savings, as interconnects contribute a large portion to system power consumption. The total interconnect power consumption of a chip ( $P_{interconnect}$ ) is calculated as [59]:

$$P_{interconnect} = \frac{\alpha}{2} C_{int} (L_{total} P_{gate}) V_{DD}^2 f_{clock} \quad (1.1)$$

where  $\alpha$  is the switching activity factor,  $C_{int}$  is the capacitance per unit interconnect length,  $L_{total}$  is the total interconnect length in gate pitches and gate pitch  $P_{gate}$ ,  $f_{clock}$  is the chip clock frequency, and  $V_{DD}$  is the power supply voltage. In this expression,  $L_{total}$ , and  $P_{gate}$  refer to the interconnect dominated parameters, which will be simultaneously reduced when interconnects length drops, hence decreasing power consumption.

Meanwhile, due to smaller wirelength, the requirement of repeater associated with long global interconnects in 2D circuits can also be decreased as well. This leads to a significant reduction in total power dissipation of a design. Nevertheless, 3D integration with reduced interconnects length results in smaller wire capacitance, therefore transistor feature size and its driving current will be scaled down to achieve more overall power saving. The

interconnect power reduction is roughly determined by a factor of square root of device layers in a 3D circuit (i.e., 3D design implemented with four layers can reduce the total interconnect power by 50%) [59]. However, this is a rough estimation from system-level modeling analysis the actual result will vary according to different types of design. For instance, a register file designed for a 3D microprocessor implemented in a two-die stack and four-die stack shows 58.5% and 58.2% power reduction respectively [58]. Intel reported a iA32 microprocessor using 3D integration of two dies with simultaneous 15% power savings and 15% performance enhancement [40].

### 1.2.3 Footprint and Device Density of 3D-ICs

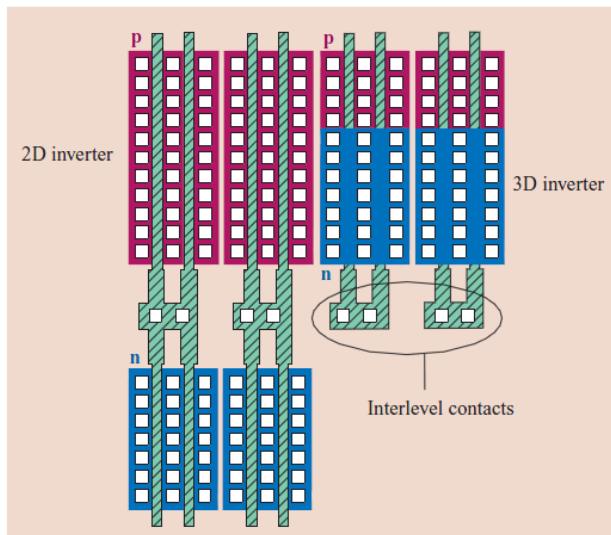

A planar IC can be partitioned and allocated on multiple dies, resulting in smaller footprint and greater device density. The ideal footprint area of a 3D design can be derived according to a shrinking factor related to the number of device layers to be stacked which can be expressed as  $A_{3D} = A_{2D}/N_{layer}$ , where  $A_{3D}$  and  $A_{2D}$  are the areas of the 3D and 2D chips respectively, and  $N_{layer}$  is the number of dies. However, in practice, the scaling speed of footprint area shrinking with increasing number of layers will depend on the actual layout and may not be as high as expected. Figure 1.12 shows the layouts of a 2D inverter and a 3D inverter, of which n-FET is placed over a p-FET for the 3D inverter layout. It is shown that the total area including device area and the metal routing area of the 3D inverter is 30% less than the 2D one. This also predicts that for a given footprint, significant device density increase can be achieved due to the ability of stacking circuit components. It should be noticed that chip area consists of two parts: the device area and the interconnect area. Wirelength reduction due to 3D integration also contributes to reduction in chip area. However, as device layer increases, the chip area becomes more device-limited, which means that design routing plays an important role in reducing chip area [53].

Figure 1.12: Layout of 2D and 3D inverters showing 30% areal reduction in 3D case [10].

### 1.2.4 Heterogeneous System Integration

With the demand for higher functionality in a single microelectronic design, heterogeneous technologies including logic and memory, analog RF, opto-electronic, and MEMS can be integrated in a single 3D integration design. These technologies may involve different processes, hence to fabricate them on a single die is difficult and may result in malfunction during operation. However, using 3D integration, each die contains unique functional circuit which is fabricated separately, and then stacked together to form a complete system. This allows, for instance, the noise isolation between the communication of a digital circuit and a noise-sensitive RF circuit, as they are placed onto different dies with separate substrates [60]. Additionally, due to the shorter interconnects and its consequent lower load capacitance in 3D integrated circuits, the noise due to simultaneously switching events and noise-coupling between signal interconnects will be reduced, providing better signal integrity for same die or inter-die communication.

## 1.3 Design and Test Challenges in 3D-ICs

Even though great improvements have emerged with 3D-ICs, there are still some challenges which need to be addressed with respect to both design and testing issues. This section firstly discusses the thermal management issue in 3D integration (Section 1.3.1) and system level design exploration with respect to how to partition circuits across different layers in a 3D design (Section 1.3.2). Then 3D yield and reliability problem are explained in Section 1.3.3 and Section 1.3.4 respectively. Finally, this section discusses the testing and fault tolerance challenges of 3D-ICs.

### 1.3.1 Thermal Management in 3D-ICs

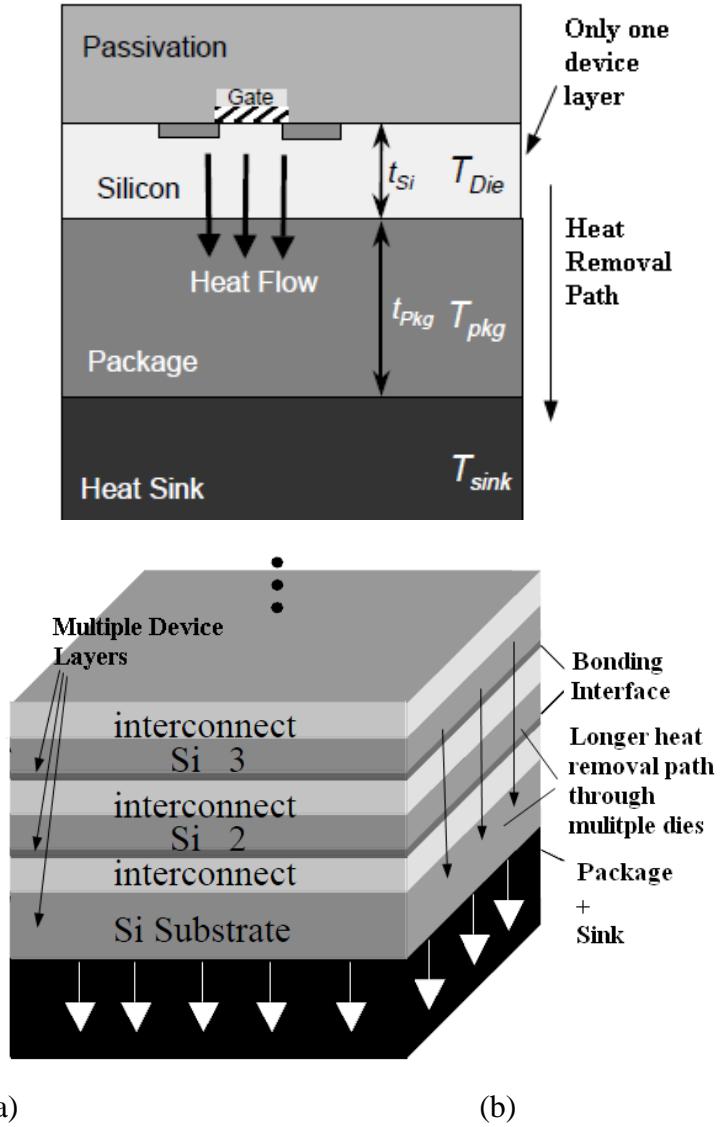

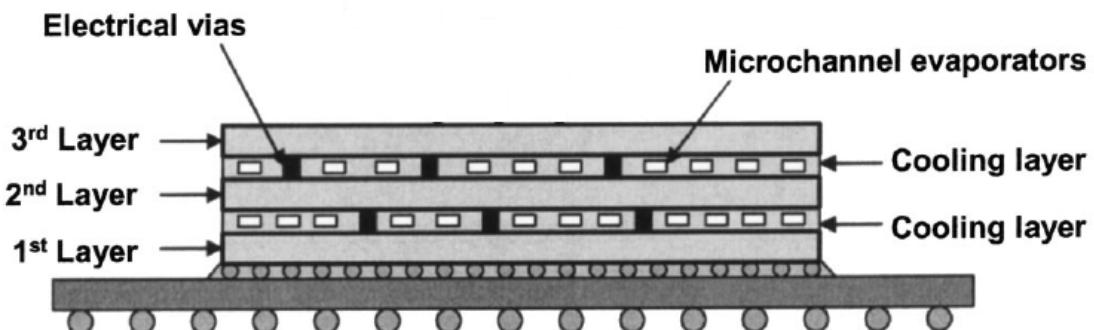

Similar to conventional planar IC, thermal dissipation has been addressed as a critical issue which significantly affects the system performance and reliability. However, this is more serious in 3D integration, as the power density of a 3D chip is much higher when compared to the 2D integration. Furthermore, the temperature removal path in a 3D chip is much longer than it is in a 2D one because of the stacking of multiple dies, as shown in Figure 1.13.

Figure 1.13: (a) Schematic diagram of heat removal path of a planar chip [61], and (b) longer heat dissipation path of a 3D design with multiple device layers [62].

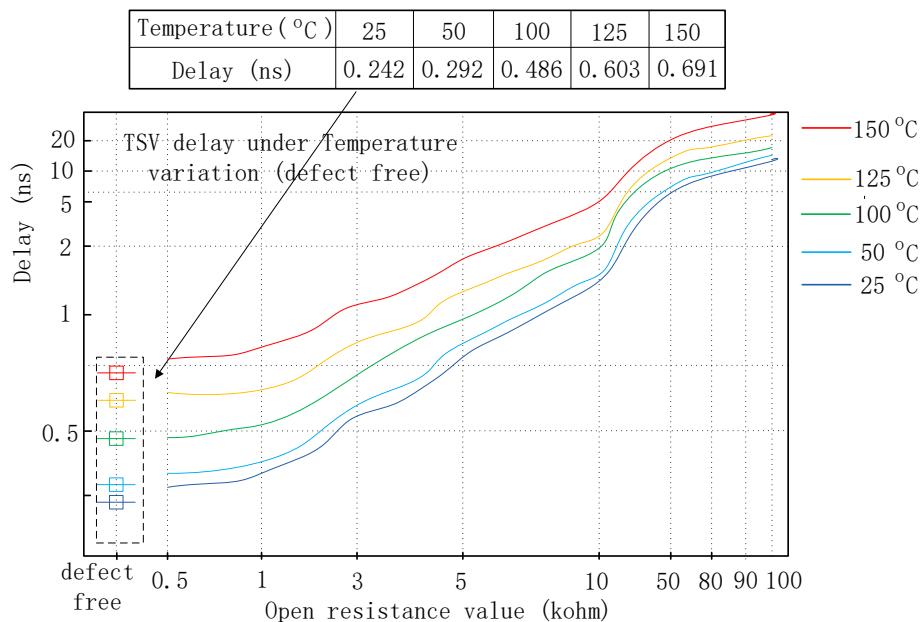

Lower thermal dissipating efficiency in 3D-ICs affects the system in three ways: Firstly, in the case of interconnect performance, the resistance of interconnects increases with higher temperature leading to a higher wire delay. This is more severe in 3D-ICs, as TSVs have bigger resistance and capacitance, thus the effect of varying temperature scales faster than it is in normal 2D designs. Secondly, the chip reliability affect system performance, particularly due to interconnects reliability. Interconnects may fail during the design lifetime due to thermal-induced reliability issue. TSV, as a new component in 3D-ICs, can have latent defects due to thermal load (e.g., crack in TSV, delamination between TSV, and its landing pad). TSV related reliability problems are discussed in Chapter 2. Thirdly, high temperature impacts chip clock performance [63]. As stated in a study [10], 15% increase in temperature decrease the clock buffer performance by 1.2% and 1.32% for SOI and bulk silicon based devices respectively. Also, high thermal gradient, namely, variation in temperature across dies affects the clock-tree performance (i.e., in the case of a 60 °C gradient over a 1000 um clock tree,

the clock skew will have 5% clock-driver-to-load-delay degradation, which is a considerable amount compared with nominal skew [64]. Therefore, good thermal management in 3D-ICs is critical. Early thermal optimization work for 3D NOC design has been proposed in [65, 66] for improve on-chip design reliability and computational performance for 3D NOC circuit. Recent work has been done on thermal-aware floorplanning strategies and embedded microfluid cooling channel in 3D chip, which are discussed in Chapter 2.

### 1.3.2 Design Exploration of 3D Architecture

3D IC design flow is different from 2D ICs because it introduces more complex task when determining components to be placed on separate device layers as it involves various partitioning granularity. Generally, there are four partitioning granularity levels: core-stacking level, core-splitting level, functional block splitting level, and logic gate splitting level. For core stacking level 3D design, entire cores are placed on different dies, therefore, most of the existing 2D design methodologies can be leveraged. Core-splitting level, where cores are split across layers while entire functional blocks are still on the same layer, this finer partitioning granularity level introduces more vertical interconnects, providing more space in wirelength reduction. In functional block splitting based 3D circuit, each functional block is divided onto different layers. At this granularity, even the functional block itself contains incomplete function prior to bonding which provide a greater challenge to validate the block function before bonding. As testing, even access to the incomplete functional circuit block is difficult. At the gate splitting level, which is the finest level of 3D circuit partitioning, design validation at this partitioning level is no longer a trivial thing. Even gate logic function is not complete prior to bonding. There is no integral logic gate on a single layer, each gate is implemented with the P-MOS transistor on one layer, while the N-MOS transistor is implemented on another layer.

The determination of partitioning strategy can be considered in line with the floorplanning and placement step to meet the various objectives and constraints, such as hardware cost (i.e., total wirelength, chip area, TSV usage, etc.), and thermal-awareness. As mentioned earlier (Section 1.2.3), placement and routing significantly affects the design wirelength and final chip area. TSVs consume more area than other devices, so the usage of TSVs should be reduced to save design cost. However, this brings a trade-off in the floorplanning/placement stage whereby more TSVs will reduce the total wirelength which is also a dominant cost factor. In a recent study [6], the wirelength reduction can be deemed from 51% to 17% if the aim of TSVs volume minimization has been taken into consideration. The floorplanning/placement strategies will become even more complicated if temperature is taken into consideration as better thermal profile of a 3D chip may require more hardware cost. Lack of EDA tools is another barrier when adopting 3D integration.

### 1.3.3 Yield Challenges in 3D-ICs

Yield modeling is a relatively mature topic in traditional integrated circuit design. A commonly used yield model for integrated circuits is the Poisson model [67]. It assumes defects to be point-like, and randomly distributed across the wafer. Following this, early work in yield modeling of integrated circuits assumes defects has the same distribution property. Let  $\lambda$  be the average number of defects on a chip, where the chip is partitioned into  $n$  small areas. The probability of having  $k$  defects on a chip  $P(X=k)$  ( $X$  denotes the number of defects) follows binomial distribution [68]:

$$P(X=k) = C_n^k \left(\frac{\lambda}{n}\right)^k \left(1 - \frac{\lambda}{n}\right)^{n-k} \quad (1.2)$$

If the partitioned area is small enough to let  $n \rightarrow \infty$ , the probability of having  $X=k$  defects becomes the Poisson distribution which is commonly used to model chip yield that can be expressed as:

$$P(X=k) = \frac{e^{-\lambda} \lambda^k}{k!} \quad (1.3)$$

Hence, the chip yield when  $k=0$  equals to:

$$Y_{\text{chip}} = P(X=0) = e^{-\lambda} \quad (1.4)$$

To clearly show the relationship between chip yield and chip area, we convert  $\lambda$  into  $A_c D_0$ , where  $A_c$  and  $D_0$  denote the chip area and average defect rate, respectively. Thus, the chip yield can be modeled as a function of defect rate and chip area:

$$Y_{\text{chip}} = P(X=0) = e^{-A_c D_0} \quad (1.5)$$

However, Murphy claimed that the value of  $D_0$  varies from chip to chip (area to area) [69], such that the overall yield of a chip is:

$$Y_{\text{2D-IC}} = \int_0^{\infty} e^{-D A_{\text{2D-IC}}} f(D) dD \quad (1.6)$$

where  $f(D)$  is the normalized defect rate distribution and  $A_{\text{2D-IC}}$  is the overall chip area. It is found that the Poisson model is not accurate and gives a pessimistic estimation of yield, since defects tend to cluster to some extent rather than randomly distributed [70, 71]. In reference [71], the clustering effect in defect distribution is accounted for, thus the probability of having  $k$  defects is:

$$P(X=k) = \frac{\Gamma(k+\alpha)}{k!\Gamma(\alpha)} \frac{(A_{2D-IC}\beta)^k}{(A_{2D-IC}\beta+1)^{k+\alpha}} \quad (1.7)$$

Eq. (1.7) is known as the negative binomial yield formula, where  $\Gamma(\alpha)$  is the Gamma function, and  $\alpha$  and  $\beta$  are two distribution parameters, such that the yield of integrated circuits is:

$$Y_{2D-IC} = P(X=0) = \frac{1}{(A\beta+1)^\alpha} = (1 + \frac{A_{2D-IC}D_0}{\alpha})^{-\alpha} \quad (1.8)$$

where, average defect density  $D_0 = \alpha\beta$ ,  $\alpha$  can be regarded as the parameter to model the clustering extent in defect distribution.

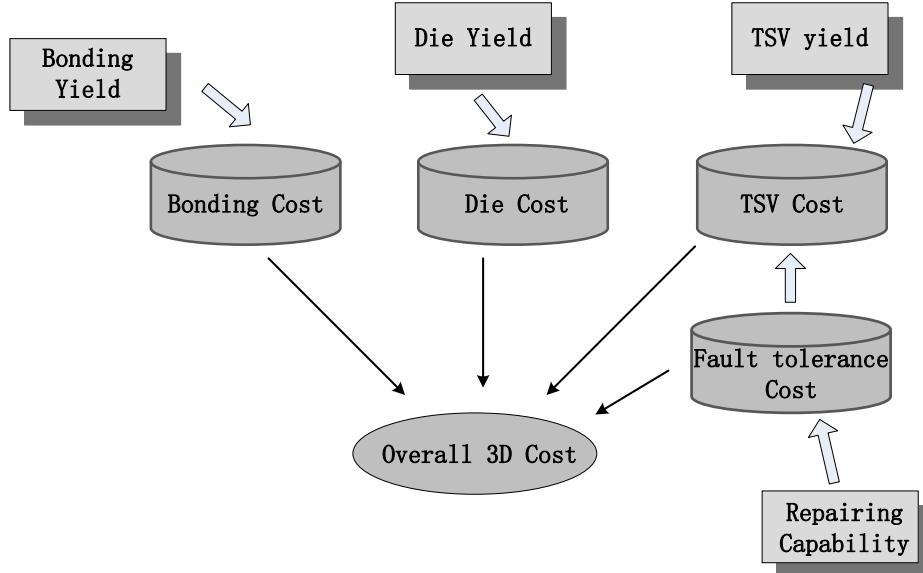

To obtain the yield of 3D-ICs,  $Y_{3D-ICs}$ , the following aspects should be taken into consideration: 1) Individual dies to be stacked: each die can be regarded as a planar 2D chip, of which the yield can be obtained using Eq. (1.8). 2) The bonding process, for stacking  $n$  dies together,  $n-1$  bonding procedures will take place, and each time the bonding process is implemented, this can cause yield loss to the final 3D design. 3) TSVs which undertake the vertical communication between dies, a defective TSV in any layer will damage the overall 3D chip yield.

Thus, the final yield of 3D-ICs,  $Y_{3D-ICs}$ , can be derived based on the cumulative yield property [72] as follows:

$$Y_{3D-ICs} = Y_{2D-stack} \cdot Y_{overall-bonding} \cdot Y_{TSVs} \\ = \prod_{i=1}^N Y_{2D-IC_i} \cdot \prod_{i=1}^{N-1} Y_{bond_i} \cdot \prod_{i=1}^{N-1} Y_{TSV_i} \quad (1.9)$$

where  $N$  is the number of device layers in a 3D chip,  $Y_{2D-stack}$  is overall yield of  $N$  dies to be stacked,  $Y_{overall-bonding}$  is the cumulative yield of  $N-1$  bonding procedures while  $Y_{bond(i)}$  denotes the yield of the  $i$ -th bonding process, and  $Y_{TSVs}$  is the yield of all TSVs while  $Y_{TSV(i)}$  denotes the yield of the TSVs on  $i$ -th layer. Note that the bottom layer does not include any TSVs.

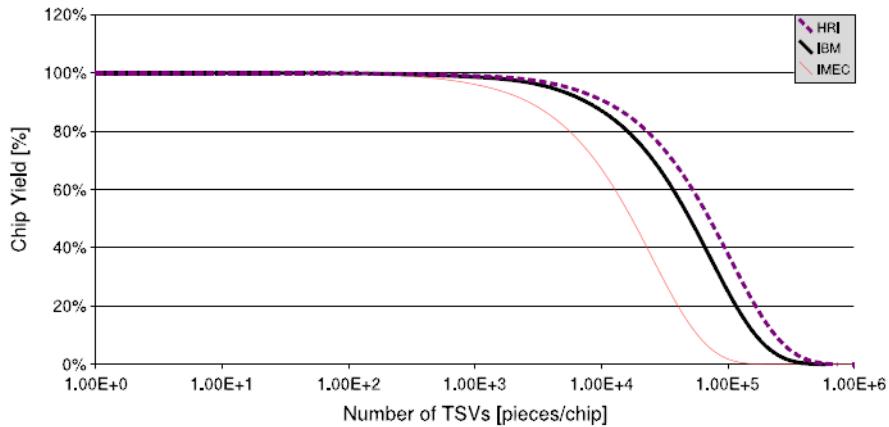

In this thesis, we focus on improving the yield of 3D-ICs in terms of overall TSVs yield, as the other two parts in Eq. (1.9) can be improved by either a better fabrication process or the existing 2D defect tolerance technique. However, TSVs, which are new components in 3D-ICs, involve new defect types, testing challenges, and reliability issues that are elaborated in the following sections. The cost for yield improvement pays off as yield directly impacts the overall cost [73, 74], as shown in Figure 1.14. It can be seen that by introducing fault tolerance structure, the yield of TSVs can be improved thus reducing the overall cost, however, the hardware cost of a fault tolerance scheme should be accounted for as well.

Figure 1.14: Cost factors in 3D-ICs.

### 1.3.4 Reliability challenges of 3D-ICs

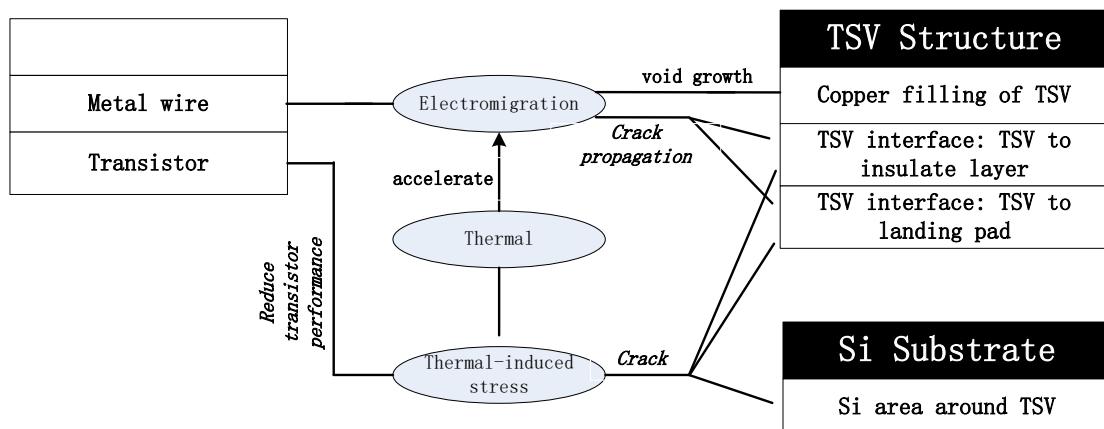

Reliability has been acknowledged as a major concern when moving from traditional IC design to 3D-ICs. This is mainly due to two reasons: 1) Firstly, devices (transistors) and interconnects on individual dies to be stacked suffer critical reliability issue due to higher thermal density and lack of efficient thermal dissipation path, particularly for the devices and wires placed on the top die. 2) The TSV interconnect itself introduces new defect mechanisms due to imperfect fabrication process or thermal load during operation. Since 3D integration is composed of traditional components (transistors and horizontal wires) and newly introduced TSVs, the reliability issues related to each part in 3D chip are shown in Figure 1.15. As can be seen that Electromigration (EM) and thermal-induced stress are two main driving force under thermal stimulation that cause reliability problems.

Figure 1.15: Different positions in a 3D structure that suffers from reliability issue.

*Horizontal wire interconnects (2D)* (Figure 1.15) involve the EM problem as in 2D integrated circuits. Electromigration is the gradual displacement of metal atoms in a semiconductor. It occurs when the current density is high enough to cause the drift of metal ions in the direction of the electron flow, and is characterized by the ion flux density. There are two failure mechanisms caused by EM [75]: 1) void in metal wires, due to the outgoing ion flux exceeds the incoming ion flux, resulting in an open interconnect defect, and 2) hillock (short circuit) that creates short between interconnects because the incoming ion flux exceeds the outgoing ion flux. The EM phenomenon is mainly affected by current density and temperature. Black *et al.* [75] claimed that the meantime to failure (MTTF) of a metal interconnect subjected to EM effect can be expressed as:

$$MTTF = \frac{A}{J^N} \exp^{\frac{E_a}{kT}} \quad (1.10)$$

where the parameters of the equation are defined as:

|       |                                        |

|-------|----------------------------------------|

| A     | Cross-section area-dependent constant  |

| J     | Current density                        |

| N     | Scaling factor, usually set to 2       |

| $E_a$ | Activation energy for electromigration |

| k     | Boltzmann constant                     |

| T     | Temperature                            |

A study [76] has shown, however, that Black's equation can be improved to take stress gradient induced migration and atomic migration due to atomic concentration gradient into consideration.

*Performance of transistors* (Figure 1.15) placed near TSVs is affected by TSV-induced thermal mechanical stress [77, 78, 79]. Such stress is induced due to the mismatch between coefficients of thermal expansion (CTEs) of copper-filled TSV and silicon substrate around TSVs, as the CTE of copper is  $17 \times 10^{-6} \text{ K}^{-1}$  at  $20^\circ\text{C}$  and the CTE of Si is  $3 \times 10^{-6} \text{ K}^{-1}$  at  $20^\circ\text{C}$ . An analytical model of TSV stress-induced mobility variation in [78] indicated that the tensile stress on silicon can change mobility of carriers, where the hole mobility of PMOS transistors can vary from -22% to +10% while the electron mobility of NMOS transistors can increase up to +24%, causing more than 20% variation for single cell delay. Moreover, if cells on a critical path are placed near TSVs, the path delay will be affected as well. However, carrier mobility change not only depends on TSV-induced stress but also on the orientation between the stress and the channel position in PMOS/NMOS transistor. By taking this into consideration, recent work in [78] proposed a layout algorithm that can improve the cell delay and critical path delay by 14% and 6.5% respectively, where results are obtained from the presented analytical model. It should also be noted that during cell placement, it is suggested that cells are placed at a minimum distance from the TSVs which is implied by the

Keep-out-Zone (KOZ) [80]. A larger KOZ can reduce the impact of TSV stress on surrounding cells, however, it costs higher area overhead. This trade-off is analyzed in [80] when guiding the overall 3D placement strategy. Moreover, when considering the TSV-induced stress, the work presented in [78] and [80] do not consider the isolation layer between TSV and the silicon substrate which is formed by silicon oxide ( $\text{SiO}_2$ ), of which the CTE is  $0.5*10^{-6} \text{ K}^{-1}$  at  $20 \text{ }^{\circ}\text{C}$  and lower than that of both TSV and Si substrate. By taking this into account the timing variation of cells can be as much as  $\pm 15\%$  [79].

*TSV structure*, as a new component in 3D integration, can introduce new reliability challenges in four aspects (Figure 1.15): Firstly, the imperfect TSV formation process can introduce a void inside the TSV, and void growth can be driven by EM effect [81], moreover, this EM effect will be accelerated by temperature load during operation. Secondly, due to the mismatch of CTE between TSV and silicon, the thermal-induced stress can drive crack growth between isolation dielectric layer and silicon substrate [79, 82]. This interface crack is analyzed in a study [83] by taking the impacts of TSV pitch, KOZ size, TSV dimension, dielectric layer thickness, and TSV placement. It is known that such a TSV isolation layer crack should be considered from the full-chip scale, incorporating multiple TSV structure influence instead of a single TSV. Thirdly, cracks can happen at the TSV interface between TSVs and its landing pad leading to delamination defect due to the thermal-induced stress during fabrication or normal operation [84, 85, 86]. For a TSV interface that employs microbumps, studies [87, 88, 89] show that its reliability is also at risk due to both TSV-induced stress and EM effect, and cracks can occur in the joints [90, 91]. Lastly, due to the large size discrepancy between TSVs and the connected metal wires (Figure 1.16), the current density in the metal interconnects is much larger than it is in TSVs, leading to a serious EM issue [92, 93]. Meanwhile it is shown by reference [93] that thermal-induced stress is the dominant contribution factor to EM performance rather than current density. Electromigration is modeled at the joint between wires and TSVs (landing pad) in reference [94] for investigating the impact of size of a TSV and its landing pad.

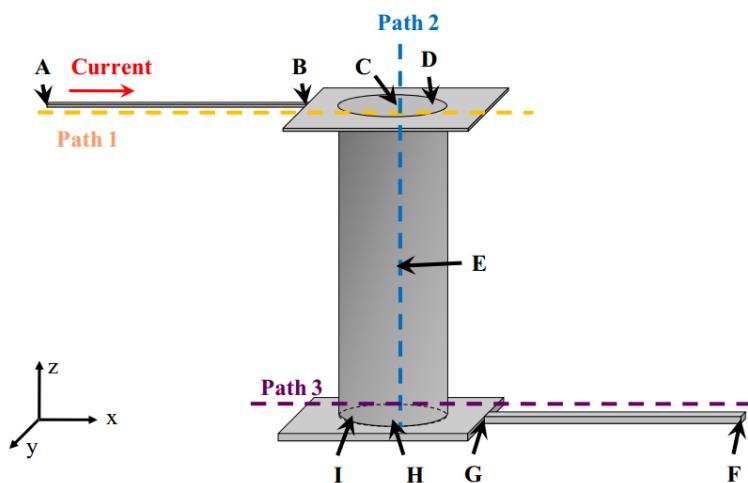

Figure 1.16: Illustrative diagram of metal layers connected to a TSV structure containing TSV and its landing pad.

### 1.3.5 Testing and Fault Tolerance for 3D-ICs

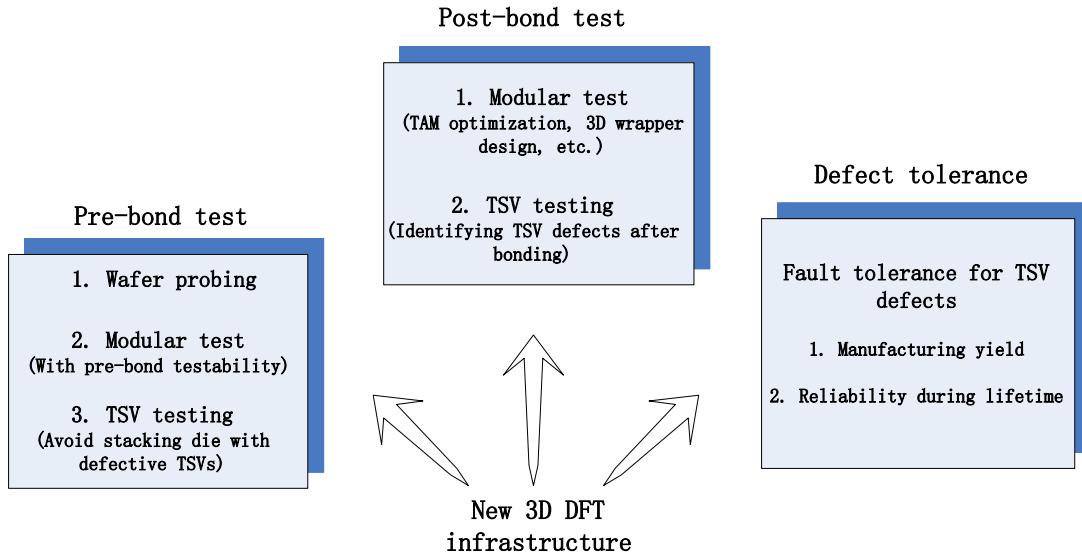

Figure 1.17: Testing and fault tolerance issues of 3D-ICs.

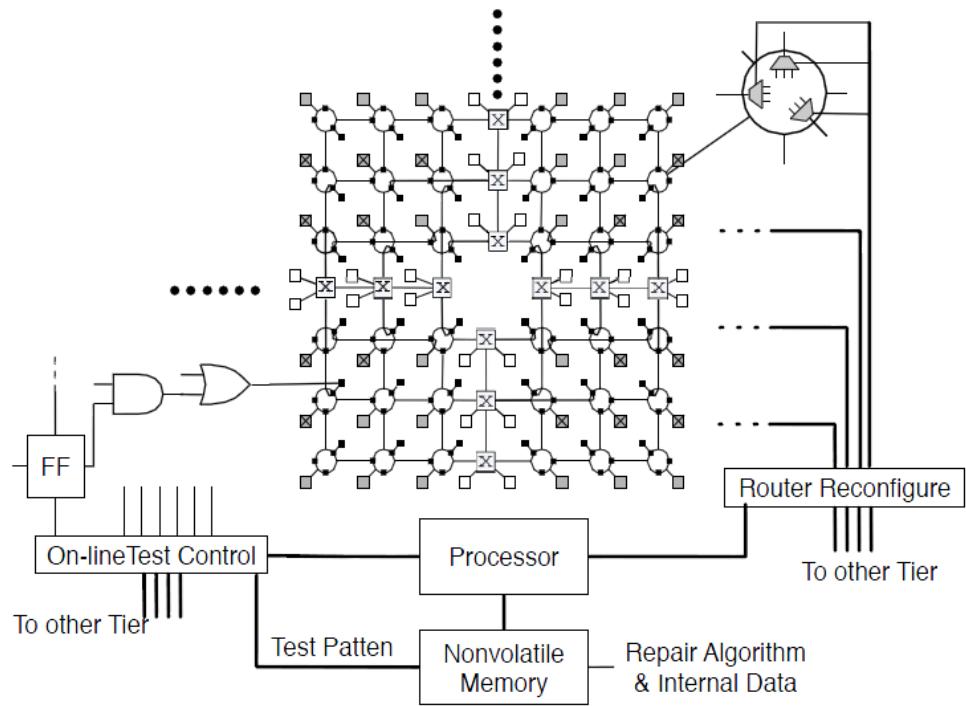

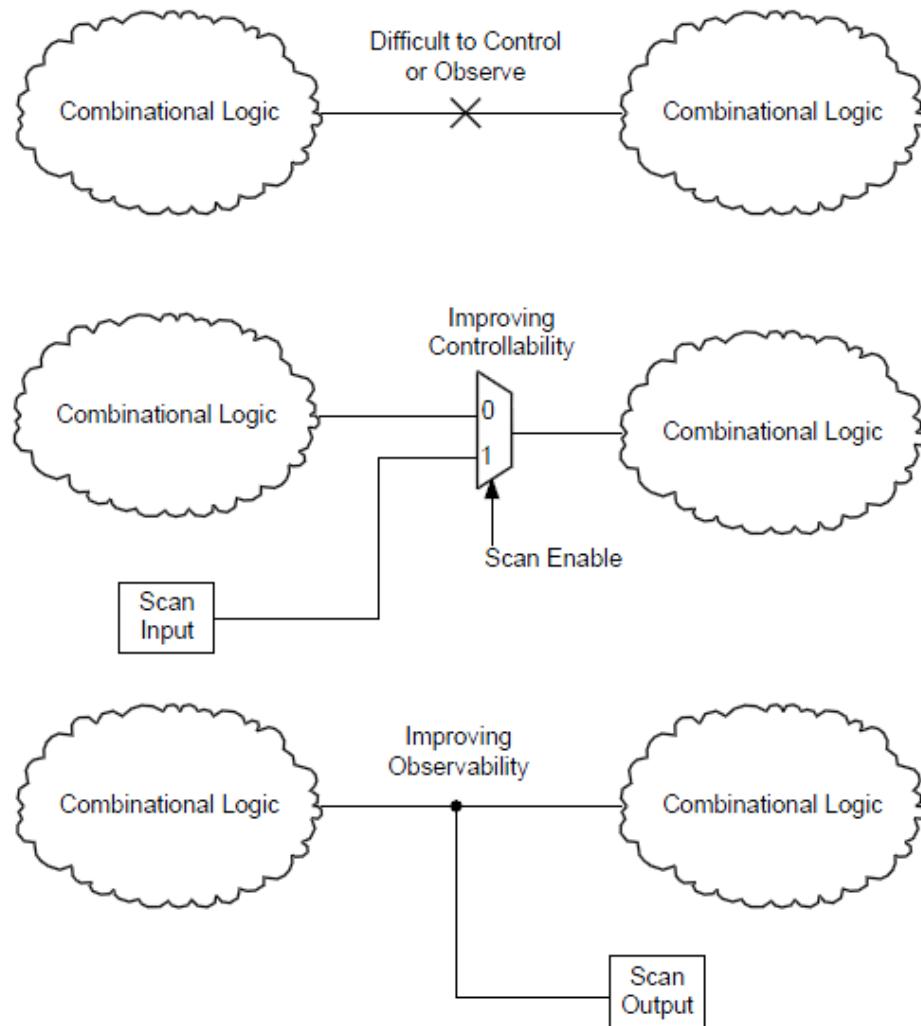

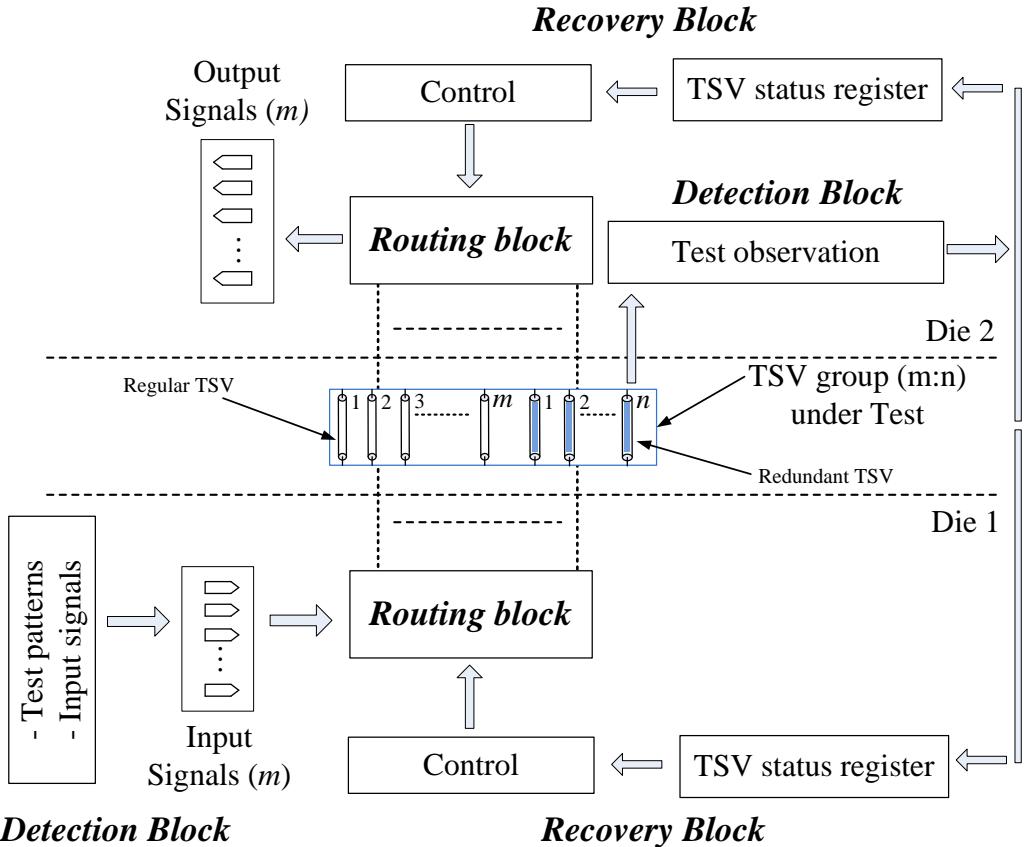

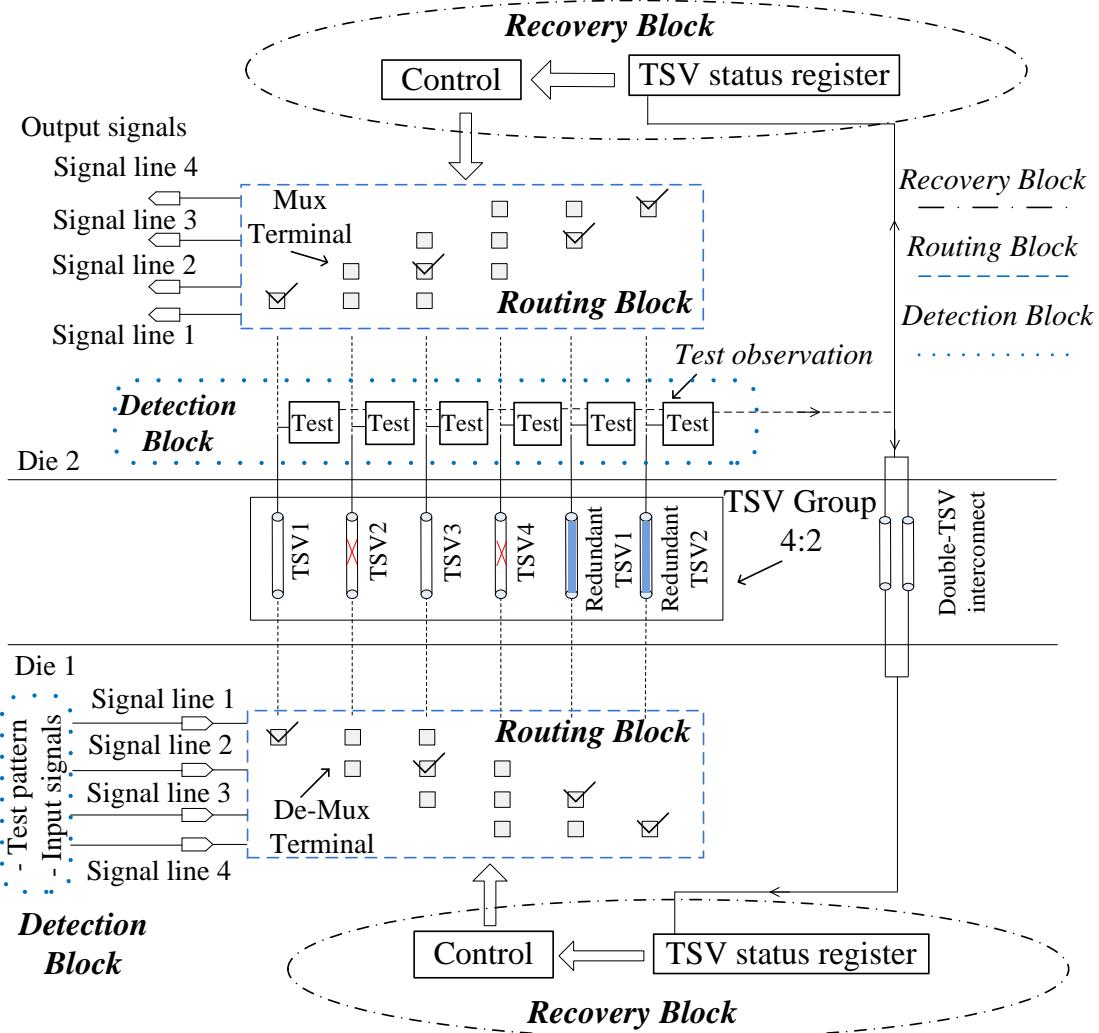

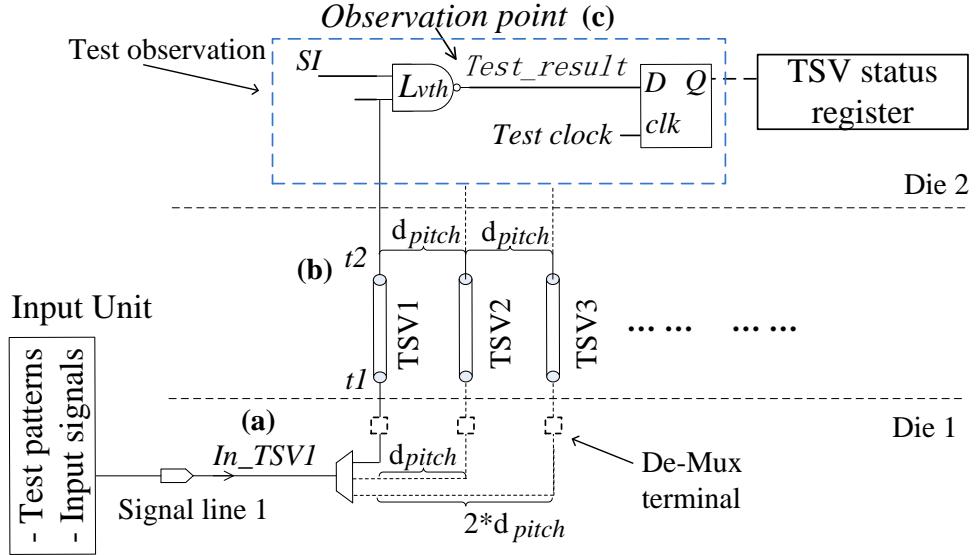

As can be seen in Figure 1.17, 3D-ICs involve various yield and reliability issues. Thus, fault detection and tolerance mechanisms are essential for 3D-ICs. Providing testability for 3D-ICs comprises three stages: pre-bond test, post-bond test and fault tolerance (Figure 1.17). Pre-bond testing undertakes defect detection for individual dies to be stacked before they are bonded together, which ensures that dies to be stacked are known-good dies (KGDs), while post-bond testing is used to ensure that all partitioned circuits across dies work properly. Additionally, post-bond test also targets testing of vertical interconnects defects (i.e. TSVs defects) as defects can be introduced during bonding stage. However, it is not trivial to implement pre-bond and post-bond tests, as a great deal of work needs to be investigated regarding new die probing equipment, new test infrastructure design, new test access optimization scheme, and etc. Moreover, as TSVs are critical to the 3D system, providing fault tolerance scheme for TSVs will significantly increase the yield of 3D-ICs and extend the design lifetime.

**Pre-bond testing** – Firstly, for pre-bond testing, the wafer probing poses many challenges. It is extremely different to probe TSVs directly due to their tiny size and access ability. Current probing technology requires a minimum pitch of 35um, however, a TSV has a diameter size of 5um and pitch size of 10um [21]. Also, the probe force is too large for thinned wafers to be probed, low contact force is necessary as the thinned wafer is fragile [95]. A possible solution is to introduce contactless probing based on capacitive or inductive coupling [96, 97]. Secondly, because 3D design has different partitioning granularities which split and place partitioned cores or functional blocks on different dies (as discussed in Section 1.3.2), such that it is difficult to implement pre-bond testing on these partial circuits without complete functionality. A scan-island based test method has been developed in recent study [98], to

achieve the pre-bond testability for split cores (i.e., functional blocks spread across multiple dies) by employing a dedicated controller and scan chains on each die. For circuits partitioned at a finer level, such as split adder or register file, Dean *et al.* [99] proposed a test methodology using a partitioned eight bit Kogge-Stone adder and a port-split register file, to investigate the pre-bond testability at functional block splitting level. Finally, testing of TSVs prior to bonding has to be investigated. Since prior to bonding a TSV only has one end, it is difficult to detect defects of this single end component. Moreover, the test circuits which are dedicated to pre-bond testing of TSVs may become useless after the bonding stage and manufacturing stage of a 3D chip [19]. Some recent published work on pre-bond testing of TSVs is reviewed in Section 2.3.

*Post-bond testing* – Post-bond testing should be incorporated to ensure the function of both blocks placed across dies and the TSVs between dies. Firstly, new test infrastructure and optimization methods (with new objectives, e.g., TSV usage) are required for post-bond testing when employing modular test in 3D design, such as TAM optimization and wrapper design for a 3D system [100, 101]. Xie *et al.* [102] developed an integer-linear-program (ICP) based algorithm to minimize the test time under a constraint of TAM width and TSV usage. Besides TAM optimization, a IEEE.Std.P1500 wrapper design methodology is proposed in reference [103] to minimize the length of wrapper chain under a constraint of TSVs number. Secondly, post-bond TSV testing is inevitable, since pre-bond TSV testing does not scale well when TSVs suffer from defects during bonding process or thermal-induced latent defects in use. Prior work on both pre-bond and post-bond TSV testing is studied in Section 2.3. Note that post-bond testing should be implemented for  $n-1$  times for a design with  $n$  stacked dies [21].

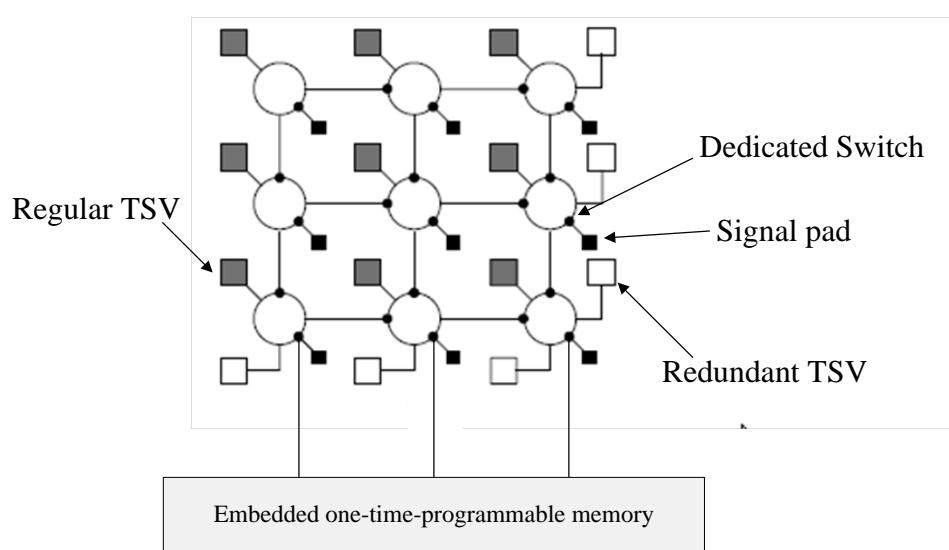

*Fault tolerance* – Even though pre-bond and post-bond TSV testing can avoid the case of bad dies being stacked on good dies. Without fault tolerance schemes, the cost due to dumping bad dies with defective TSVs can still be high, particularly for 3D design with high TSV density and high defect rate. There are two main fault tolerance methods for implementing fault tolerance for TSV-based 3D-ICs: 1) Fault tolerance technique that is implemented without using redundant TSVs, such as signal recovery for faulty TSVs. In a recent study [104], each TSV is connected to a built-in-self-test/repair block, targeting detection of a short TSV defect causing signal degradation. Once a defective TSV is found, the output signal of that defective TSV is recovered through using of a dedicated level converter circuit embedded in the self-repair circuit. This method eliminates the usage of redundant TSVs, however, the tuning of the level converter circuit will affect the signal recovery quality. Moreover, fault tolerance method presented in reference [104] has a limitation that if the defect size in a TSV exceeds the tolerant range, such defective TSV cannot be repaired. 2) TSV repair with TSV redundancy [105, 106, 107, 134], where redundant TSVs are employed to replace the defective ones. It is acknowledged that TSV repair can be realized at two stages: One is for improving the TSV yield by repairing defective TSVs after manufacturing test that provides a defective TSV map. This stage is relatively simple for implementation because it does not

have to consider the repair task for latent defect tolerance during the lifetime of the design. The other stage is for in-field reliability to extend design lifetime, which can tolerate the TSVs aging defects. Existing fault tolerance work in terms of TSV repair for improving yield and in-field reliability are discussed in Section 2.4.2 and Section 2.5.2 respectively.

## 1.4 Motivation and Thesis Outline

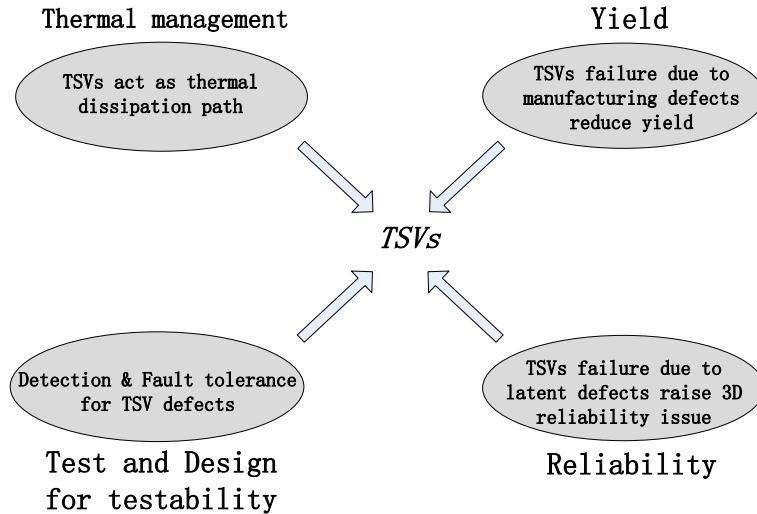

Figure 1.18: Illustration of critical issues in 3D-ICs that are related to TSVs.

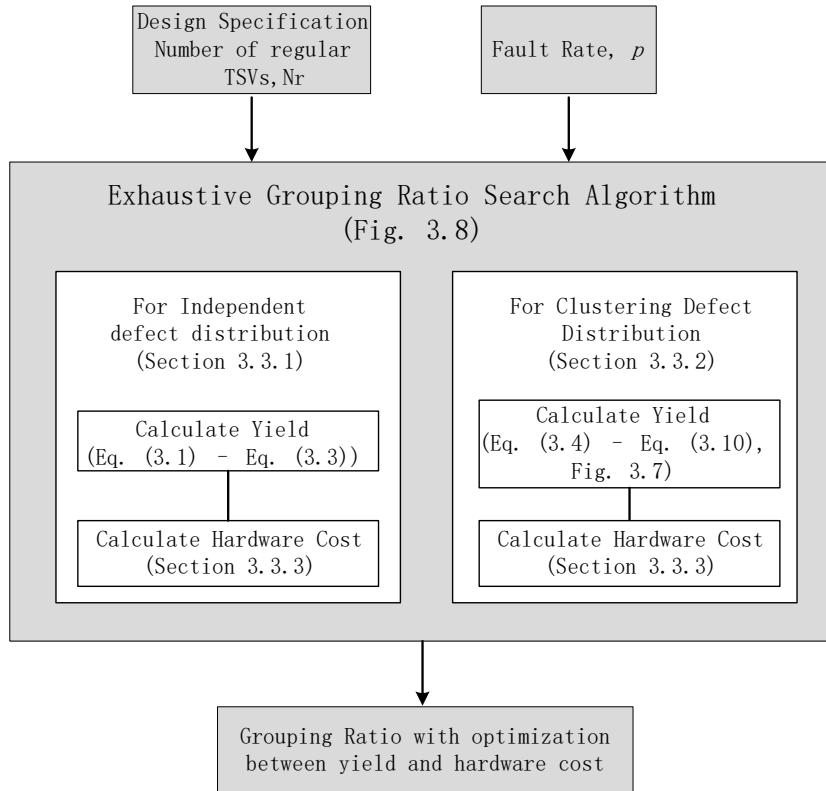

As a concluding remark after the discussion about critical issues in 3D-ICs, it is easy to establish that TSVs play a critical role related to thermal management, yield and reliability, and testing challenges of 3D-ICs, as illustrated in Figure 1.18. Existing work revealed that voids inside the TSV [109] and TSV short to substrate defect [110] are two main TSV manufacturing defect types [38, 104, 111, 112], which cause significant yield loss thus increasing the manufacturing cost. Although, in conventional planar design, open and bridge defect of interconnects are well studied, testing of TSV voids and short to substrate defects raise new challenges to be explored. Meanwhile, as TSV is a major cost of 3D integration, when employing TSV redundancy for TSV repairing, we have to examine the trade-off between TSV usage and the yield improvement brought by redundant TSVs. Furthermore, 3D chip involves a critical thermal issue, and latent defects such as void growth and delamination between TSV and its landing pad can happen during its lifetime resulting in 3D reliability challenges. All these problems motivate this thesis to develop high quality and cost-effective solution for improving yield and reliability of 3D-ICs.

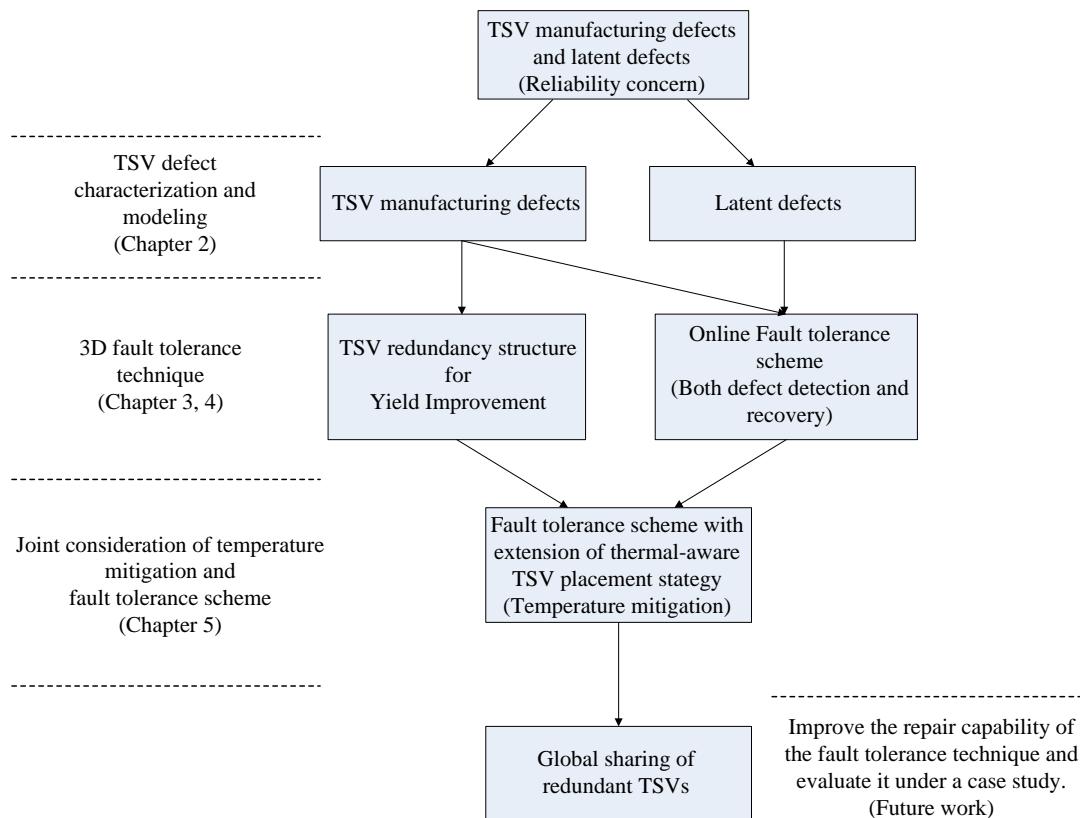

The rest of the thesis is organized as follows:

Chapter 2 presents a literature review on TSV defects modeling, existing testing methodology for TSV defects, and existing work on improving yield and reliability from design and test

points of view respectively. This chapter also outlines a number of important research problems that are addressed in this thesis to develop a cost-effective fault tolerance scheme for TSV-based 3D-ICs.

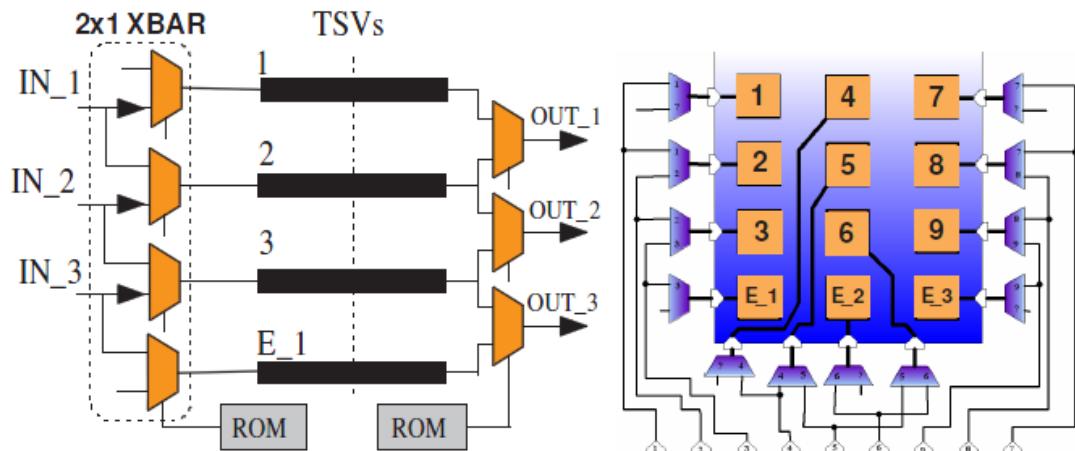

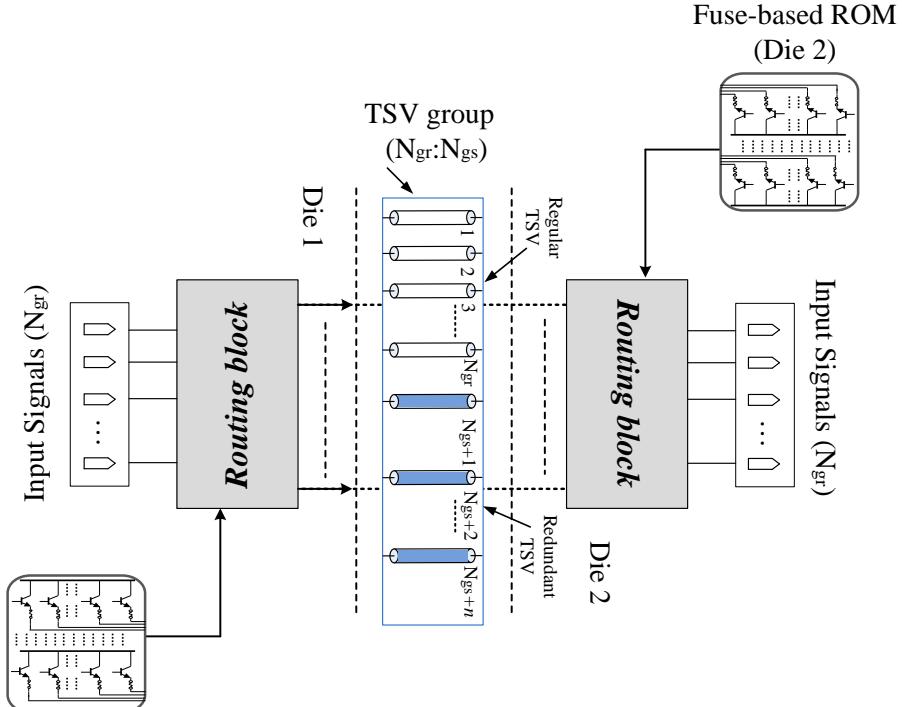

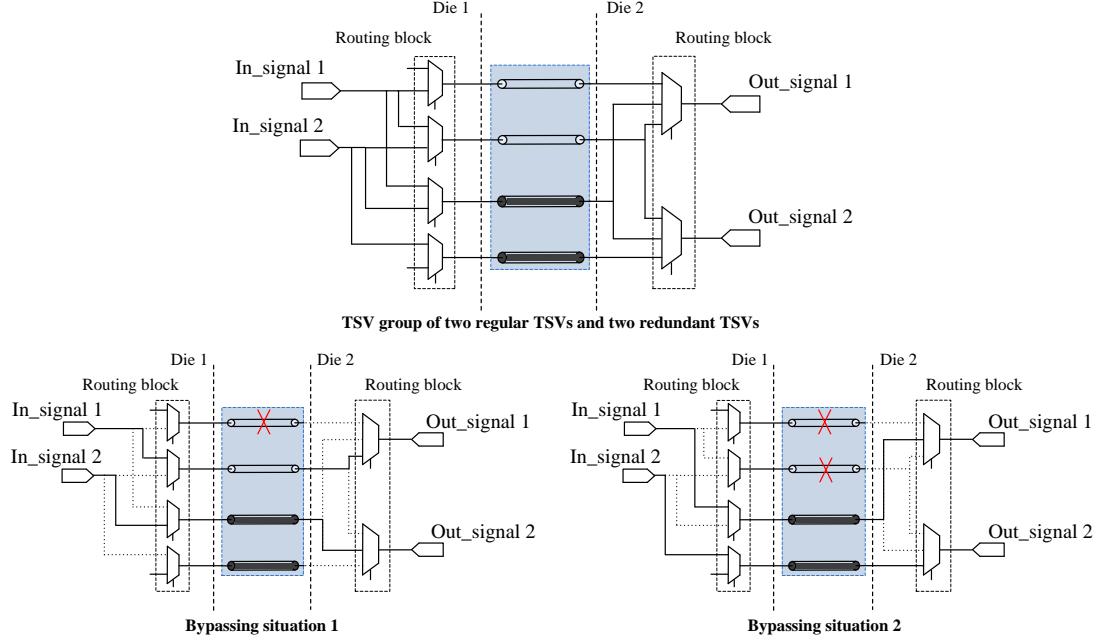

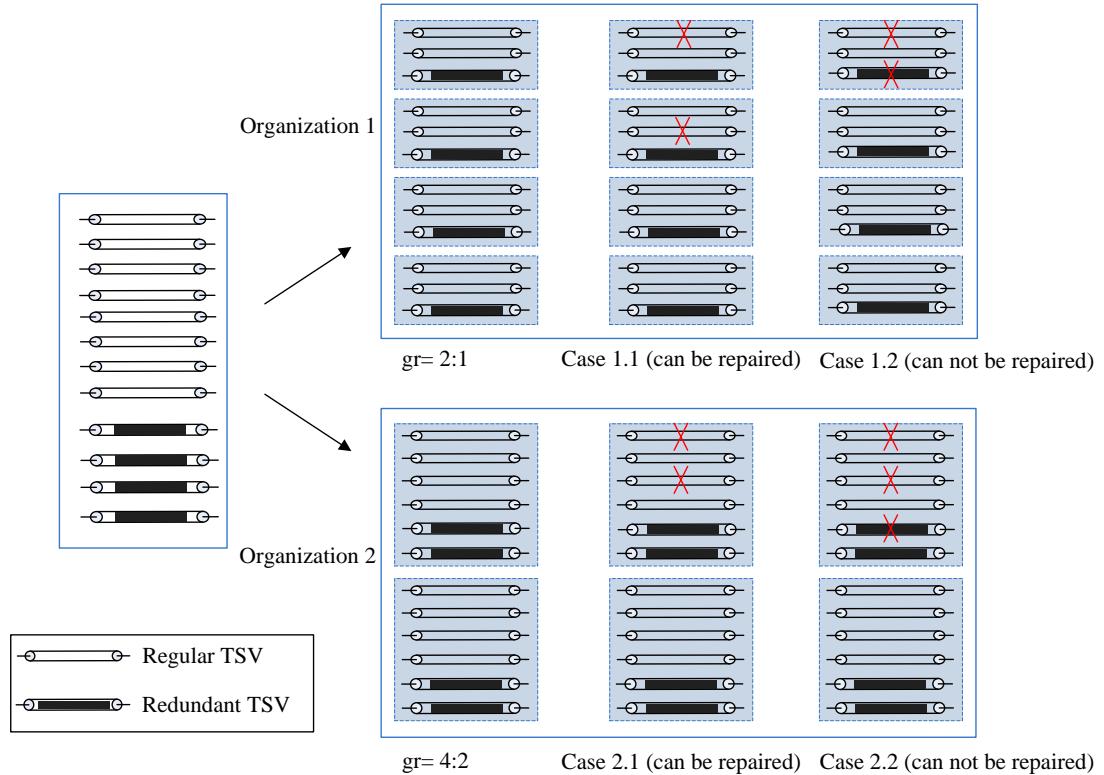

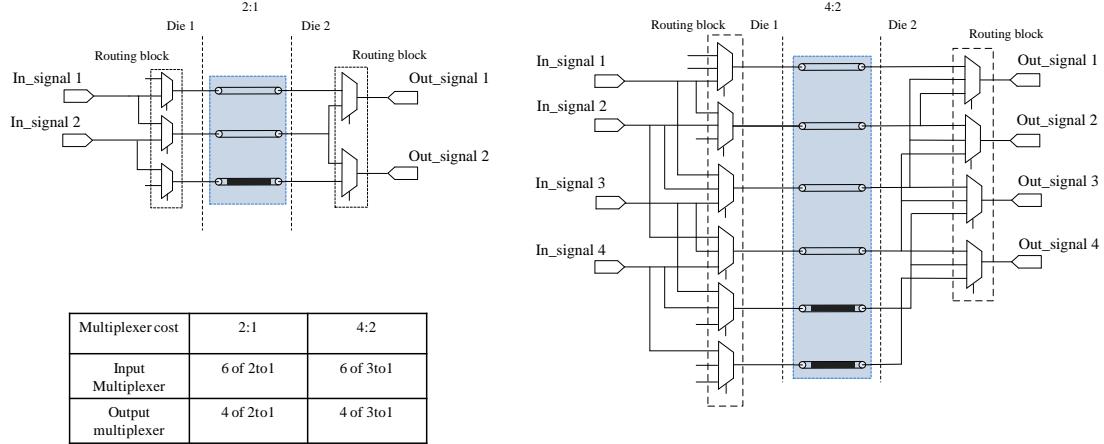

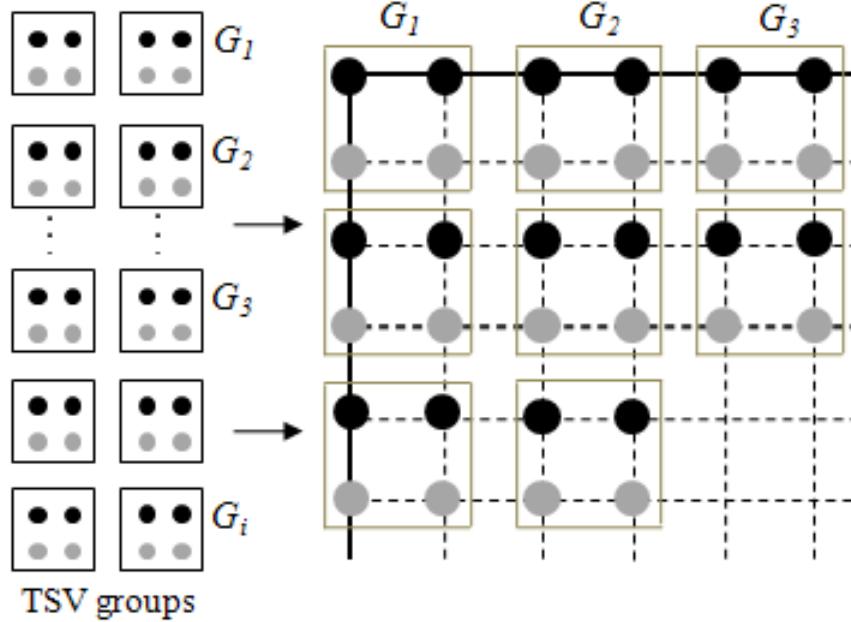

Chapter 3 presents a redundant TSVs grouping technique, which partitions regular and redundant TSVs into groups. For each group, a set of multiplexers is used to select good signal paths while avoiding defective TSVs. Probabilistic models for yield analysis under the influence of independent and clustering defect distributions are proposed to investigate the impact of grouping ratio (regular-to-redundant TSVs in one group) on trade-off between yield and hardware overhead. Simulation results show that for a given number of TSVs and TSV failure rate, careful selection of grouping ratios lead to achieving 100% yield at minimal hardware cost, in comparison to a design that does not exploit TSV grouping ratios.

Chapter 4 presents the design, validation and evaluation of an efficient online fault tolerance technique for fault detection and recovery in the presence of three TSV defects: voids, delamination between TSV and landing pad, and TSV short-to-substrate. Unlike the work presented in Chapter 3, where the TSV repair is only for yield improvement, the proposed fault tolerance technique also copes with in-field reliability concern. The proposed efficient technique requires a small (2 x number of TSVs per group) number of clock cycles for fault detection and recovery. Simulations using HSPICE and ModelSim are carried out to validate fault detection and recovery. Results show that regular and redundant TSVs can be divided into groups to minimize area overhead without affecting fault tolerance capability of the proposed technique. Synthesis results using 130-nm design library show that 100% repair capability can be achieved with low area overhead (4% for the best case).

Chapter 5 presents a scheme with joint consideration of temperature mitigation and fault tolerance for TSV based 3D ICs, as TSV failures due to manufacturing defects and thermal-induced latent defects result in yield and reliability issues in 3D-ICs. This is achieved by reusing spare TSVs that are frequently deployed for improving yield and reliability in 3D ICs. The spare TSVs are placed in such a way that temperature is reduced without affecting fault tolerance capability, since TSVs are effective in reducing temperature by providing thermal conductivity. The proposed scheme consists of two steps: The first step is TSV determination step, which provides optimised allocation between regular and spare TSVs into groups to achieve expected repair capability. The second step is TSV placement, where temperature mitigation is targeted while optimizing total wirelength and route difference, where route difference takes into account the additional routing overhead due to transferring signals from regular to spare TSV as in the case of bypassing a defective TSV. Results show that, using the proposed technique, 100% repair capability is achieved across all (five) benchmarks with an average temperature reduction of 34.1% (75.2°C) (best case is 58.5% (99.8°C)), while increasing wirelength and route difference by a small amount.

Chapter 6 summarizes the contributions presented in this thesis along with the description of how the objectives of this research have been achieved. This chapter also outlines research issues that merit further investigation to develop efficient and cost-effective solutions for improving yield and reliability of future 3D integrated circuits.

## 1.5 Publications

Contributions of the research work presented in this thesis have been published as follows:

1. Y. Zhao, S. Khursheed, B. Al-Hashimi, “Cost-Effective TSV Grouping for Yield Improvement of 3D-ICs”, *Asian Test Symposium*, 2011

2. Y. Zhao, S. Khursheed, B. Al-Hashimi, “Online Fault Tolerance Technique for TSV-based 3D-IC”, *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, 2013.

3. Y. Zhao, S. Khursheed, B. Al-Hashimi, “Joint Consideration of Fault Tolerance and Temperature Mitigation for TSV-based 3D-ICs”, *DATE*, 2015 (Under review)

# Chapter 2

## Literature Review

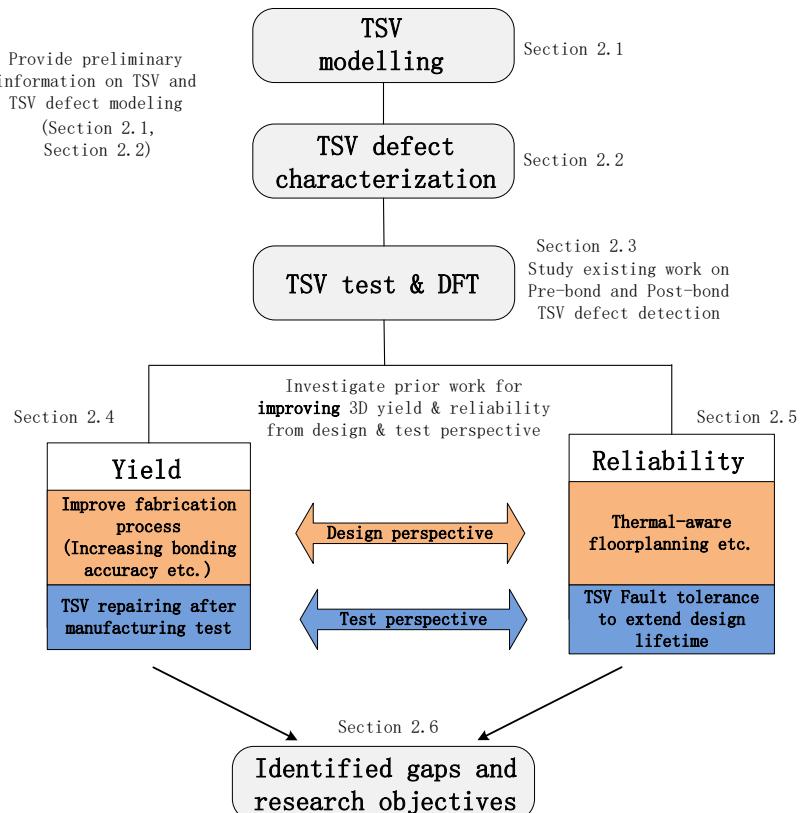

This chapter presents a detailed literature review of the state-of-the-art research that is related to this thesis and that has been carried out in recent years. Figure 2.1 shows the structure and main topics covered in this chapter. As can be seen, before looking into the yield and reliability issues of 3D-ICs, the fundamental work of TSVs characterization and modeling is firstly studied in Section 2.1. This is followed by a description of the electrical models of major TSV defect types: such as voids, delamination between TSV and its landing pad, and TSV short to substrate. Section 2.3 summarizes the available testing techniques targeting these types of TSV defects. As discussed earlier (Section 1.3.5), 3D testing strategies can be applied at pre-bond and post-bond stage. In Section 2.3 TSV testing under both testing strategies are investigated. Published work on techniques for improving yield and reliability of 3D-ICs is reviewed from both design and test perspective in Section 2.4 and Section 2.5 respectively. Finally, Section 2.6 identifies the gaps in recent research and outlines the research objectives of this thesis in light of reviewed research. Note that, to complement this literature review, each of Chapter 3, 4, and 5 has its own brief literature review along with the contributions described in these chapters.

Figure 2.1: Summary of reviewed problems in Chapter 2.

## 2.1 TSV Modeling

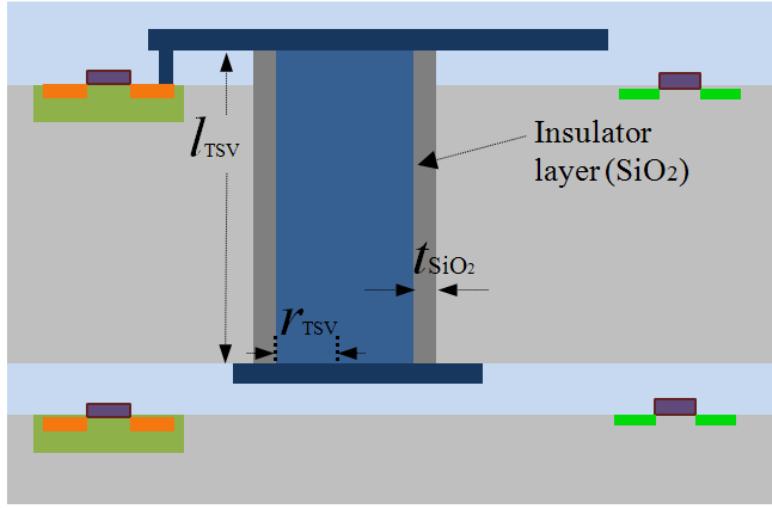

Figure 2.2: A general schematic diagram of TSV architecture.

A number of studies have shown that TSV can be modeled using its physical dimensions and material characteristics. Resistance ( $R_{tsv}$ ) and Capacitance ( $C_{tsv}$ ) should be derived to observe the equivalent circuit of TSV using a lumped RC model. The analytical expression of the resistance of TSV ( $R_{tsv}$ ) and capacitance of TSV ( $C_{tsv}$ ) are given by [37]:

$$R_{tsv} = \frac{\rho l_{tsv}}{A_{tsv}} = \frac{\rho l_{tsv}}{\pi r_{tsv}^2} \quad (2.1)$$

$$C_{tsv} = \frac{2 \pi \epsilon_{SiO_2} l_{tsv}}{\ln \frac{(t_{SiO_2} + r_{tsv})}{r_{tsv}}} \quad (2.2)$$

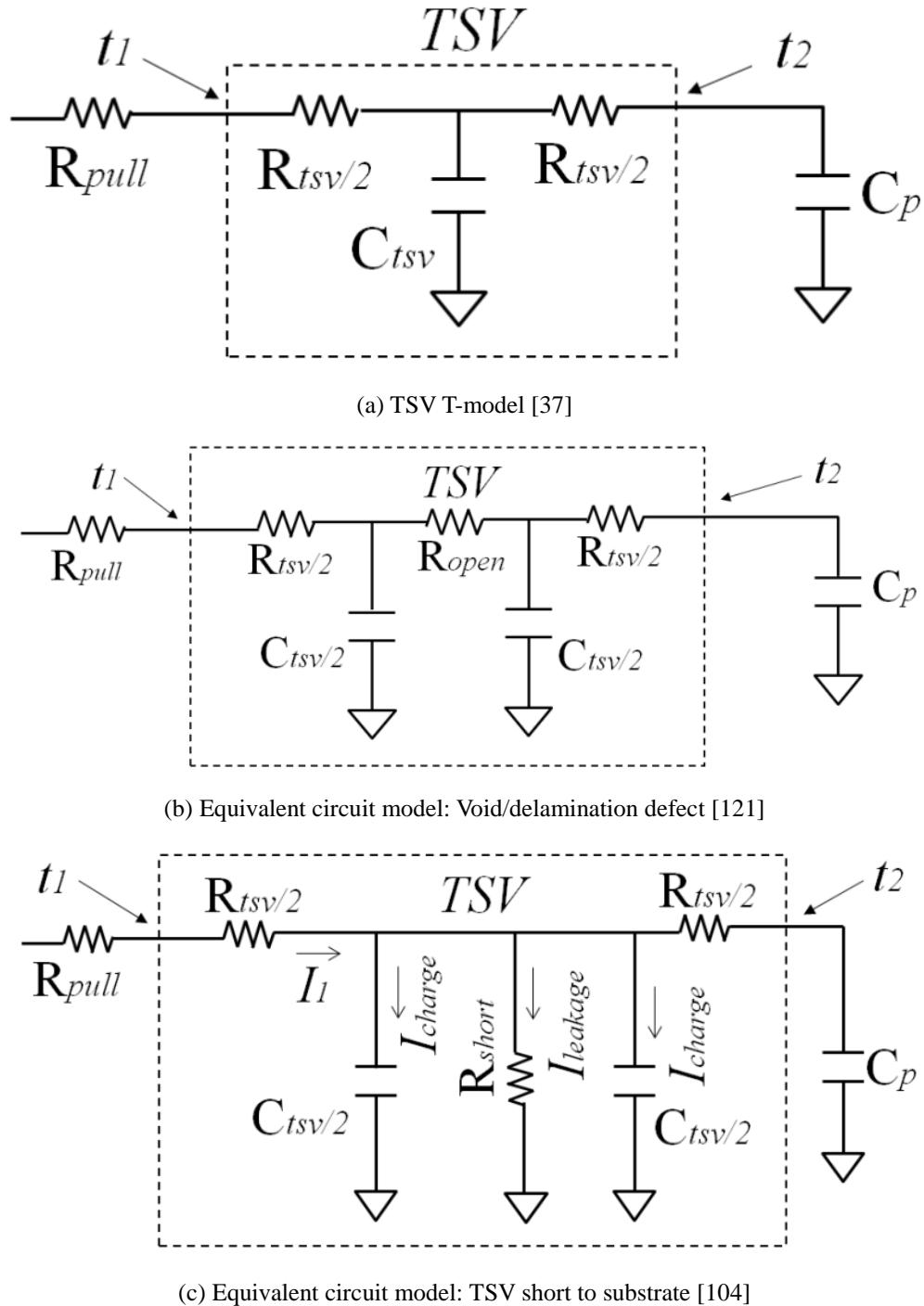

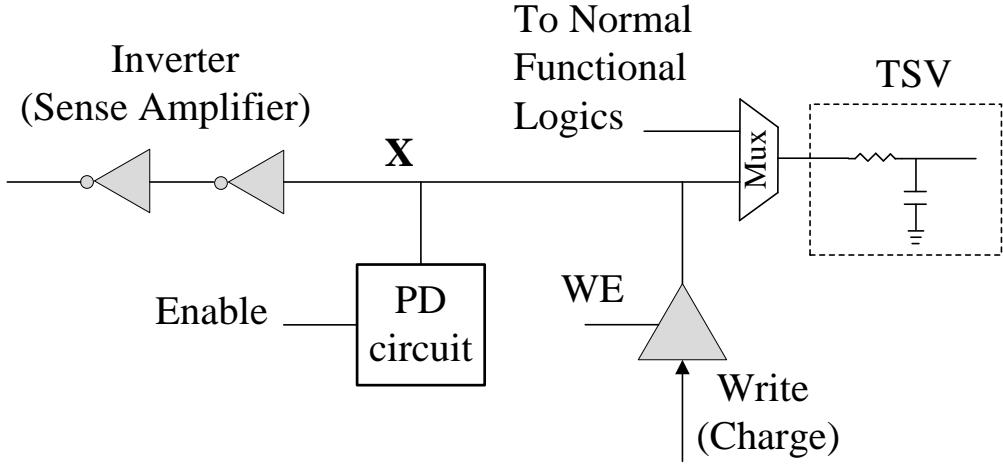

where  $\rho$  is the resistivity of the TSV conducting material, in this work, copper is used as commonly used in practice [113],  $A_{tsv}$  represents the area of the TSV bottom side,  $r_{tsv}$  and  $l_{tsv}$  are the radius and length of TSV respectively (Figure 2.2),  $\epsilon_{SiO_2}$  is the dielectric constant of the  $SiO_2$  isolation layer between TSV and Si substrate, and  $t_{SiO_2}$  is the thickness of the dielectric isolation layer. Eq. (2.1) implies that any defects that lead to change in  $r_{tsv}$  and  $l_{tsv}$  can be a resistive defect. The capacitance equation (Eq. (2.2)) shows that  $C_{tsv}$  is directly proportional to the length of TSV and inversely proportional to the TSV dielectric layer thickness, which implies that the defect in the dielectric layer can cause conductor defect resulting in change of  $C_{tsv}$ . With the modelling of TSV resistance and capacitance, the equivalent circuit of TSV can be achieved based on T-model [37] which is widely used in modelling the interconnect in 2D circuit, as illustrated in Figure 2.3(a), where  $R_{pull}$  denotes the pull-up resistance of the driving gate.

## 2.2 TSV Defects Characterization and Modeling

In a recent study [114], various types of TSV defects are investigated, some are due to the imperfect fabrication process, while others can happen during the lifetime of 3D design. By applying manufacturing test, some invisible small defects that may escape the detection process can be identified. Nevertheless, these invisible defects may become large enough to cause system malfunction due to thermal and mechanical stress as discussed in Section 1.3.4. Table 2.1 shows four important TSV defect types. For those manufacturing defects that may become latent defects, the stimulus turning them into latent defects are also shown.

Table 2.1: Four TSV defect types summary.

| <b>Defect</b>      | <b>Reason (during fabrication)</b>                              | <b>Conversion to latent defect</b> |                                                                                                            | <b>Characterization</b>                       |

|--------------------|-----------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                    |                                                                 | Possibility                        | Reason (in use)                                                                                            |                                               |

| Void               | Insufficient plating/filling [109]                              | Yes                                | void growth due to electromigration (EM)                                                                   | TSV resistance increase                       |

| Short to substrate | Non-conformal sidewall deposition [115, 116]                    | Yes                                | crack induced by thermal-stress due to mismatch in coefficient of thermal expansion (CTE) of TSV structure | Leakage from TSV to Si substrate (short path) |

| Delamination       | Thermal-stress due to mismatch in CTE of TSV structure [84, 86] | Yes                                | crack growth due to EM/thermal-stress                                                                      | TSV resistance increase                       |

| Misalignment       | Weak bonding accuracy [117]                                     | -                                  | -                                                                                                          | TSV interface contact resistance increase     |

\* Note that this table can be linked with Figure 1.13 which shows 3D reliability issues, nevertheless, this table provide details of the defects that occurred in TSV structure (Figure 1.13) from both manufacturing defect and latent defect points of view.

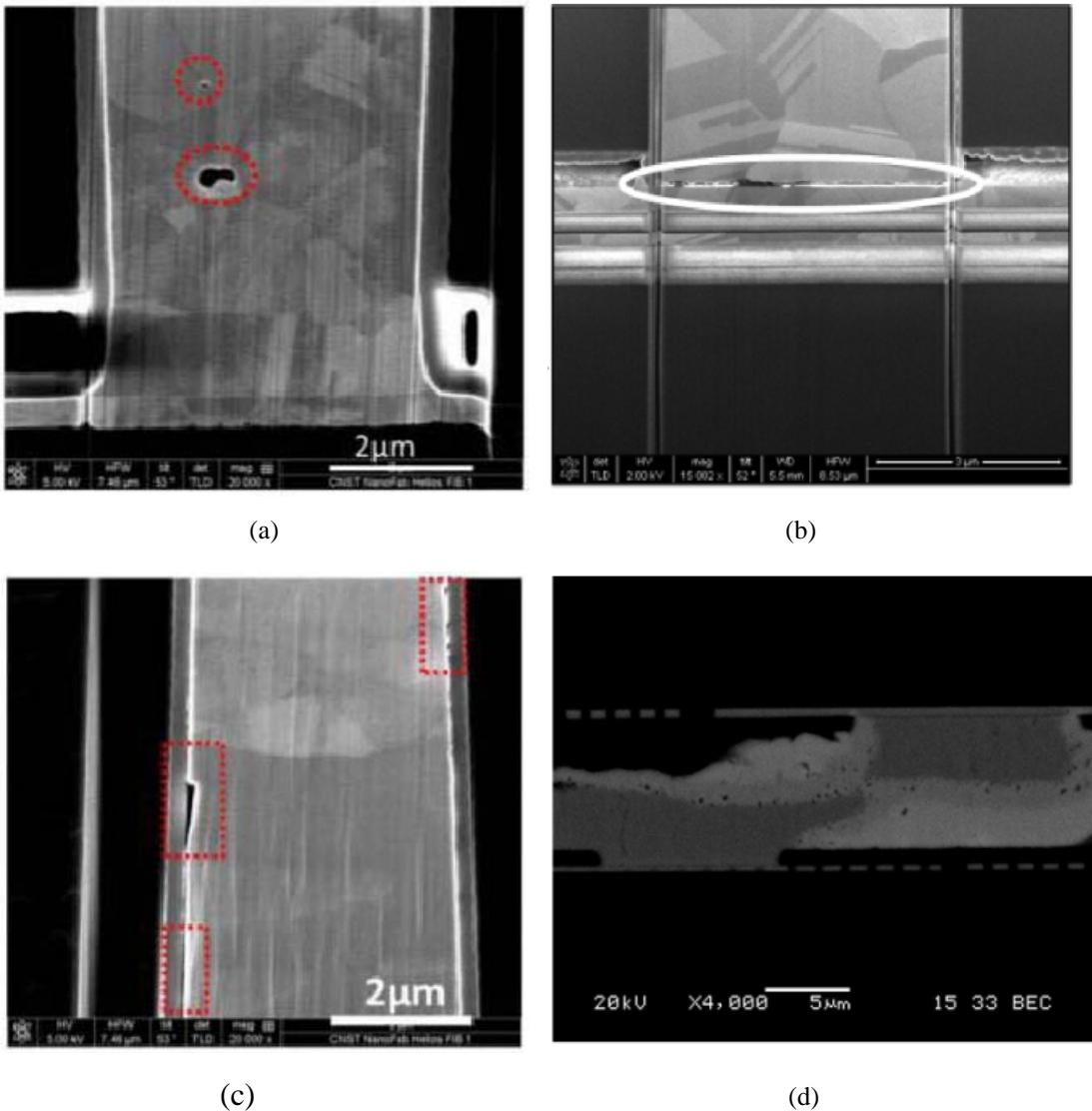

Figure 2.4: Examples of TSV defects: (a) Void inside TSVs [118], (b) Delamination at bottom of TSV [119], (c) TSV short to substrate defect (Crack in sidewall of TSV) [118], and (d) Misalignment at TSV bonding interface [120].

Void inside TSVs (Type I) can result from an imperfect TSV fabrication process such as insufficient via copper doping [109]. Void growth driven by electromigration can happen during operation converting small voids inside TSVs into a bigger void. A detailed TSV failure analysis [118] revealed that after 2000 thermal cycles, a void with  $\sim 0.5\mu\text{m}$  width is found inside the TSV structure (Figure 2.4(a)). Note that a thermal cycle is defined as driving the sample circuit from  $30\text{ }^{\circ}\text{C}$  to  $150\text{ }^{\circ}\text{C}$  and this then cooled back to  $30\text{ }^{\circ}\text{C}$  in five minutes [118]. This type of defect increases the TSV resistance [121] and causes a delay fault.

The second type of defect is delamination at the TSV interface, as shown in Figure 2.4(b), which usually occurs between TSV and its landing pad. This type of defect is either due to voids existing at the bottom of the TSV (Figure 2.4(b)) or cracks caused by thermal-induced stress during operation. Delamination also causes TSV resistance to increase, such that

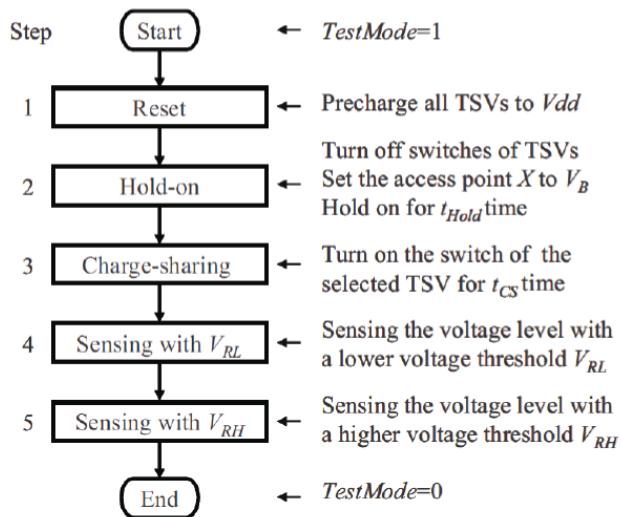

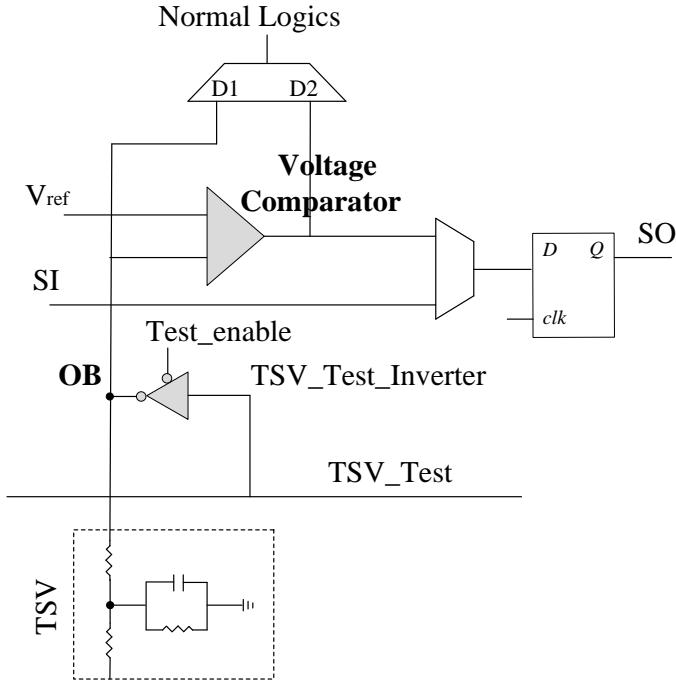

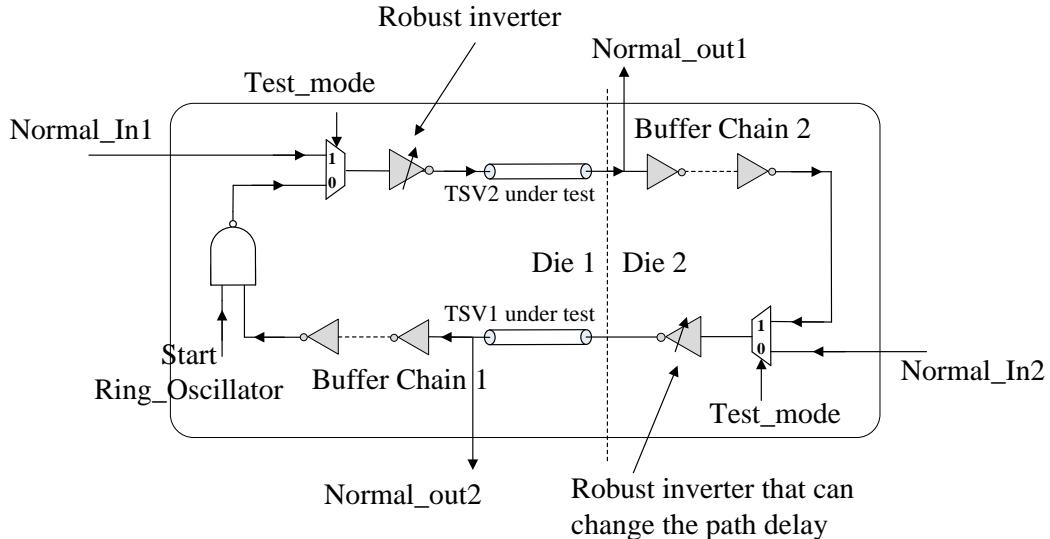

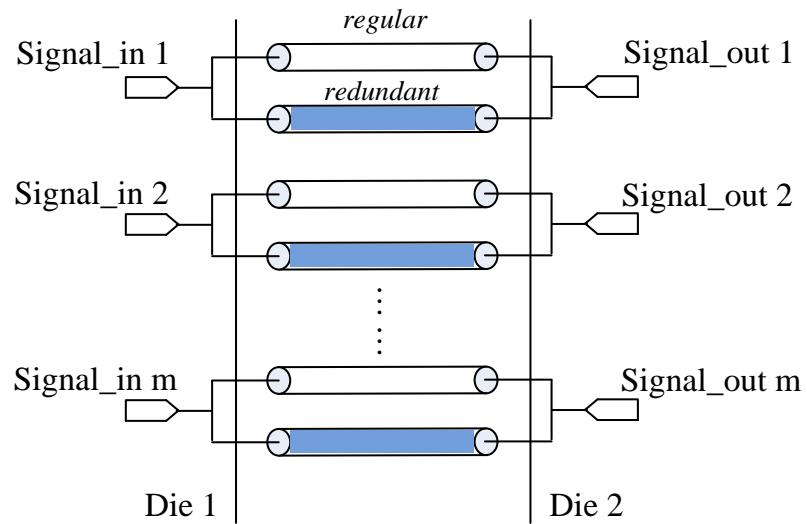

delamination between TSV and its landing pad and void inside TSV are modelled as the same type of open resistive defect. The equivalent electrical model of void/delamination TSV defect is shown in Figure 2.3(b). It can be seen that a resistor ( $R_{open}$ ) is added to the TSV model (Figure 2.3(a)). HSPICE description of void/delamination TSV defect is in Appendix A. Note that  $C_p$  denotes the parasitic capacitance of the circuit and it is assumed that signal is transmitted from TSV terminal in die 1 (referred as terminal  $t1$ ) by a driving gate to the TSV terminal in die 2 (referred as terminal  $t2$ ).