University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND APPLIED SCIENCE

School of Electronics and Computer Science

---

Development of High Yield Fabrication Technology

for Graphene Quantum Dots for Single Electron

Transistor applications

by

Nima Kalhor

Thesis for the degree of Doctor of Philosophy

August 2014

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCE

School of Electronics and Computer Science

Doctor of Philosophy

DEVELOPMENT OF HIGH YIELD FABRICATION TECHNOLOGY FOR GRAPHENE

QUANTUM DOTS FOR SINGLE ELECTRON TRANSISTOR APPLICATIONS

by Nima Kalhor

Since the seminal work by Loss and DiVincenzo, quantum dots (QDs) have been extensively studied as building blocks for quantum information processing (QIP). Presently, the most advanced implementations of QD qubits are realised in III/V heterostructures (GaAs/AlGaAs). However, the strong spin-orbit and hyperfine interactions in these compounds pose fundamental limits to the spin coherence time, and so stimulating the search for alternative host materials.

Graphene, a two-dimensional single atomic layer of carbon atoms, was successfully produced for the first time in 2004. Despite its short history, its unique material properties have ensured a rapid growth of interest in several areas of science and technology. Spin-orbit coupling and hyperfine interaction with carbon nuclei are both small in graphene, and a very long spin relaxation length has been demonstrated, which make graphene a promising candidate for quantum information technology and spin qubit embodiment.

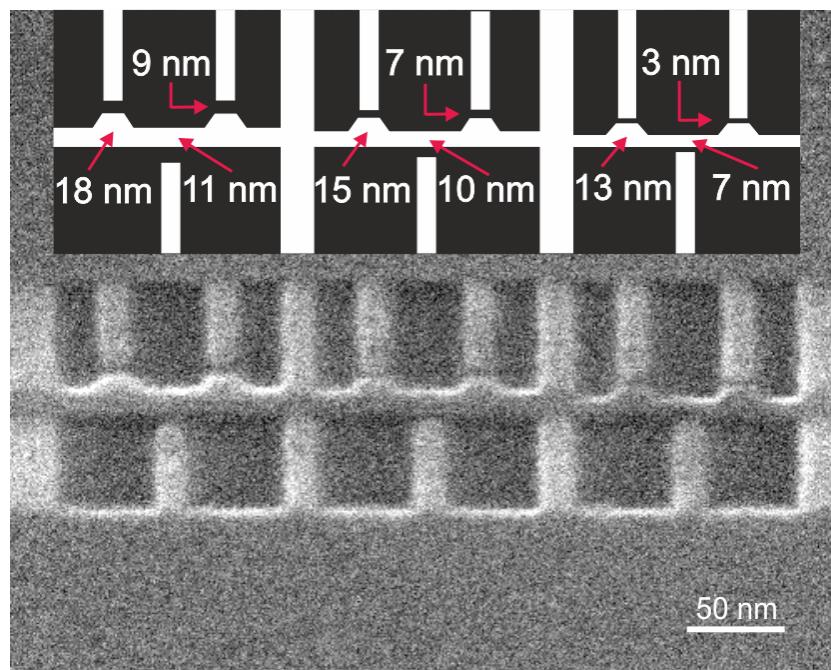

Superior transport properties of graphene encourage the downscaling of graphene devices to the regime where coherent nature of electronic and spin states can be fully exploited. This requires the development of ultrafine patterning technologies which enables accurate nanoscale fabrication beyond the present electron-beam lithography technique. Therefore, inspired by the on-going trend towards device miniaturization, we present a novel hybrid fabrication method for graphene nano devices (e.g. graphene QDs devices) with minimum feature sizes of  $\sim 3$  nm (i.e. the gap between the graphene side-gates and channel). Here, for the first time we combine

conventional e-beam lithography and direct milling with the sub-nm focused helium ion beam generated by a helium ion microscope to fabricate high resolution graphene QDs devices, reliably and reproducibly. The highly controllable, fine scale fabrication capabilities offered by this approach could lead to a more detailed understanding of the electrical characteristics of graphene quantum devices and pave the way towards room-temperature operable graphene quantum dot devices.

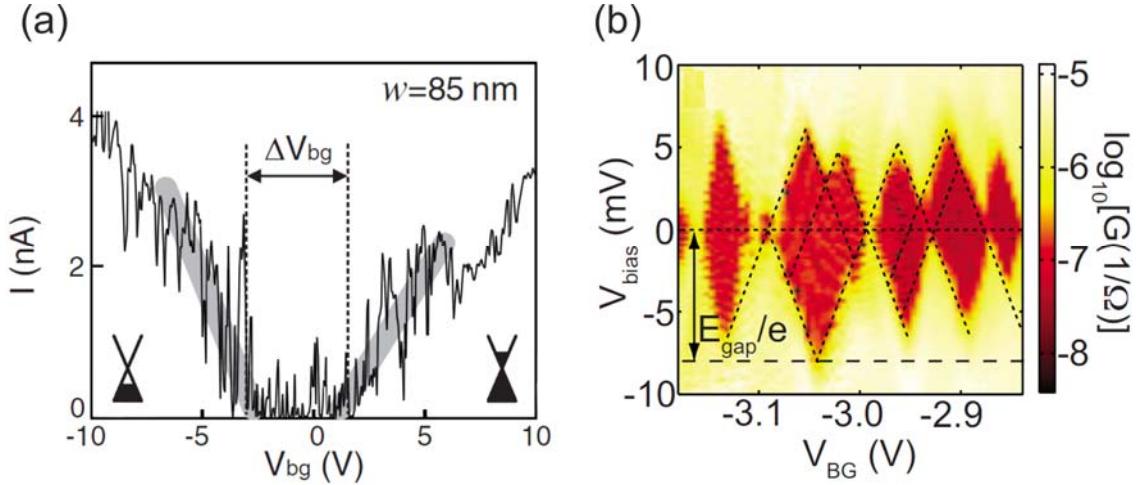

Furthermore, we demonstrate successful fabrication of graphene QDs devices by means of e-beam lithography and RIE etch for the first time at Southampton Nanofabrication Centre. The electrical characterisations of the final fabricated devices at room temperature and cryogenic temperatures confirmed successful fabrication of graphene QDs devices, and so resulted in observation of Coulomb diamonds at ~6 Kelvin. The accurate optimisation of our fabrication process resulted in ~80% fabrication yield (from 57 fabricated devices) for graphene samples produced by mechanical exfoliation and ~58% fabrication yield (from 160 fabricated devices) for CVD graphene samples. These values represent the percentage of fabricated QDs devices which had to exhibit ambipolar behaviour, no observable current leakage from the channel, no observable current leakage between in-plane graphene side-gates, and no observable back gate leakage through the  $\text{SiO}_2/\text{Si}$  substrate.

# Contents

|       |                                                                     |    |

|-------|---------------------------------------------------------------------|----|

| 1     | Introduction                                                        | 1  |

| 1.1   | Quantum information technology.....                                 | 1  |

| 1.2   | Graphene .....                                                      | 2  |

| 1.3   | Helium ion microscopy .....                                         | 4  |

| 1.4   | Research motivations and contributions .....                        | 5  |

| 1.5   | Thesis overview .....                                               | 6  |

| 2     | Graphene                                                            | 10 |

| 2.1   | Introduction.....                                                   | 10 |

| 2.2   | Atomic structure and carrier transport properties of graphene ..... | 11 |

| 2.3   | Graphene production methods .....                                   | 15 |

| 2.3.1 | Mechanical exfoliation                                              | 16 |

| 2.3.2 | Epitaxial growth on SiC single crystal                              | 16 |

| 2.3.3 | Chemical vapour deposition (CVD)                                    | 16 |

| 2.4   | Identifying graphene flakes.....                                    | 17 |

| 2.4.1 | Optical microscopy                                                  | 17 |

| 2.4.2 | Atomic force microscopy                                             | 18 |

| 2.4.3 | Raman spectroscopy                                                  | 18 |

| 3     | Single Electron Transistors with Quantum Dot                        | 21 |

| 3.1   | Single Electron Transistors (SETs) .....                            | 21 |

| 3.2   | Single electron transistors with quantum dot .....                  | 23 |

| 3.2.1 | Coulomb blockade (CB)                                               | 24 |

| 3.2.2 | Carrier transport in single electron transistors                    | 26 |

| 3.2.3 | Single electron transistors with double quantum dot (DQD)           | 29 |

|       |                                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 3.3   | An experimental review on graphene nano devices.....                        | 37  |

| 3.3.1 | Graphene nanoribbons                                                        | 37  |

| 3.3.2 | Graphene quantum dots devices                                               | 41  |

| 4     | Fabrication of extremely downscaled graphene QDs by helium-ion beam milling | 50  |

| 4.1   | Introduction.....                                                           | 51  |

| 4.2   | Helium-ion microscopy .....                                                 | 55  |

| 4.3   | An experimental review on nanofabrication by HIM milling.....               | 59  |

| 4.3.1 | Plasmonic nano devices                                                      | 59  |

| 4.3.2 | Graphene nano devices                                                       | 60  |

| 4.3.3 | Other applications                                                          | 65  |

| 4.4   | Fabrication of GDQD by HIM milling.....                                     | 66  |

| 4.4.1 | Sample preparation                                                          | 66  |

| 4.4.2 | Setting-up a He-ion beam                                                    | 67  |

| 4.4.3 | HIM milling on pristine graphene samples                                    | 68  |

| 4.4.4 | HIM milling on e-beam processed graphene samples                            | 74  |

| 4.5   | Challenges and issues associated with He-ion milling .....                  | 80  |

| 4.6   | Electrical characterisations and analysis.....                              | 83  |

| 4.7   | Conclusions.....                                                            | 91  |

| 5     | Fabrication of GQDs devices by electron-beam lithography and RIE etch       | 93  |

| 5.1   | Introduction.....                                                           | 93  |

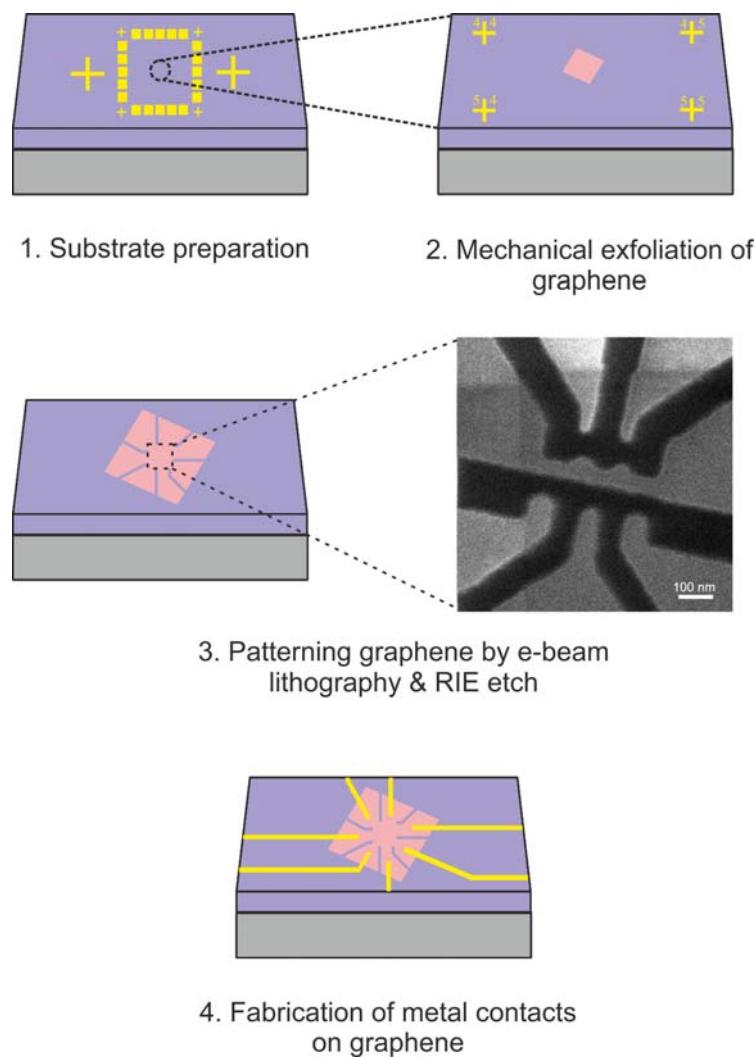

| 5.2   | Substrate preparation.....                                                  | 95  |

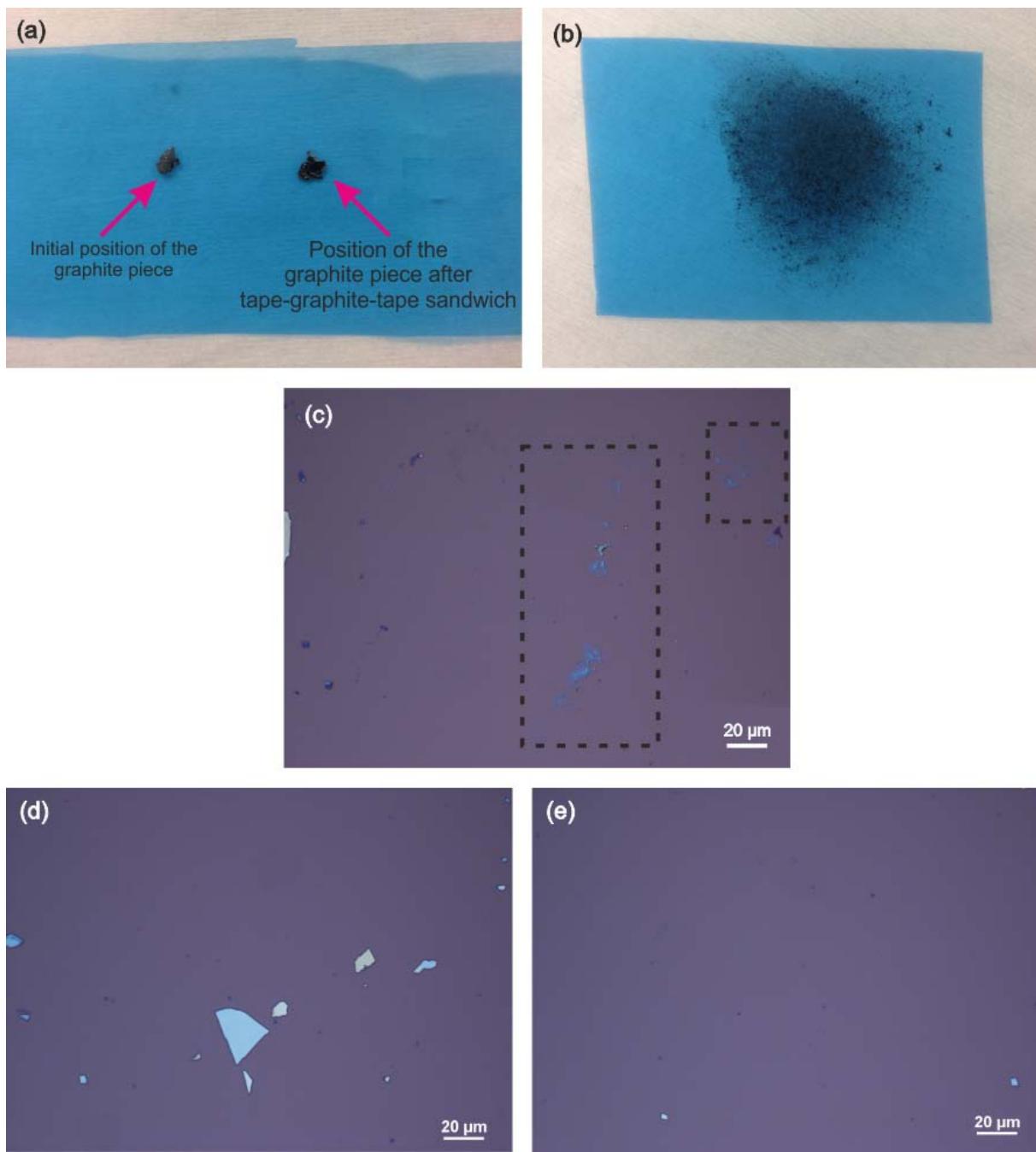

| 5.3   | Mechanical exfoliation of graphene .....                                    | 98  |

| 5.4   | Patterning of graphene by e-beam lithography and RIE etch .....             | 103 |

|            |                                                                                       |     |

|------------|---------------------------------------------------------------------------------------|-----|

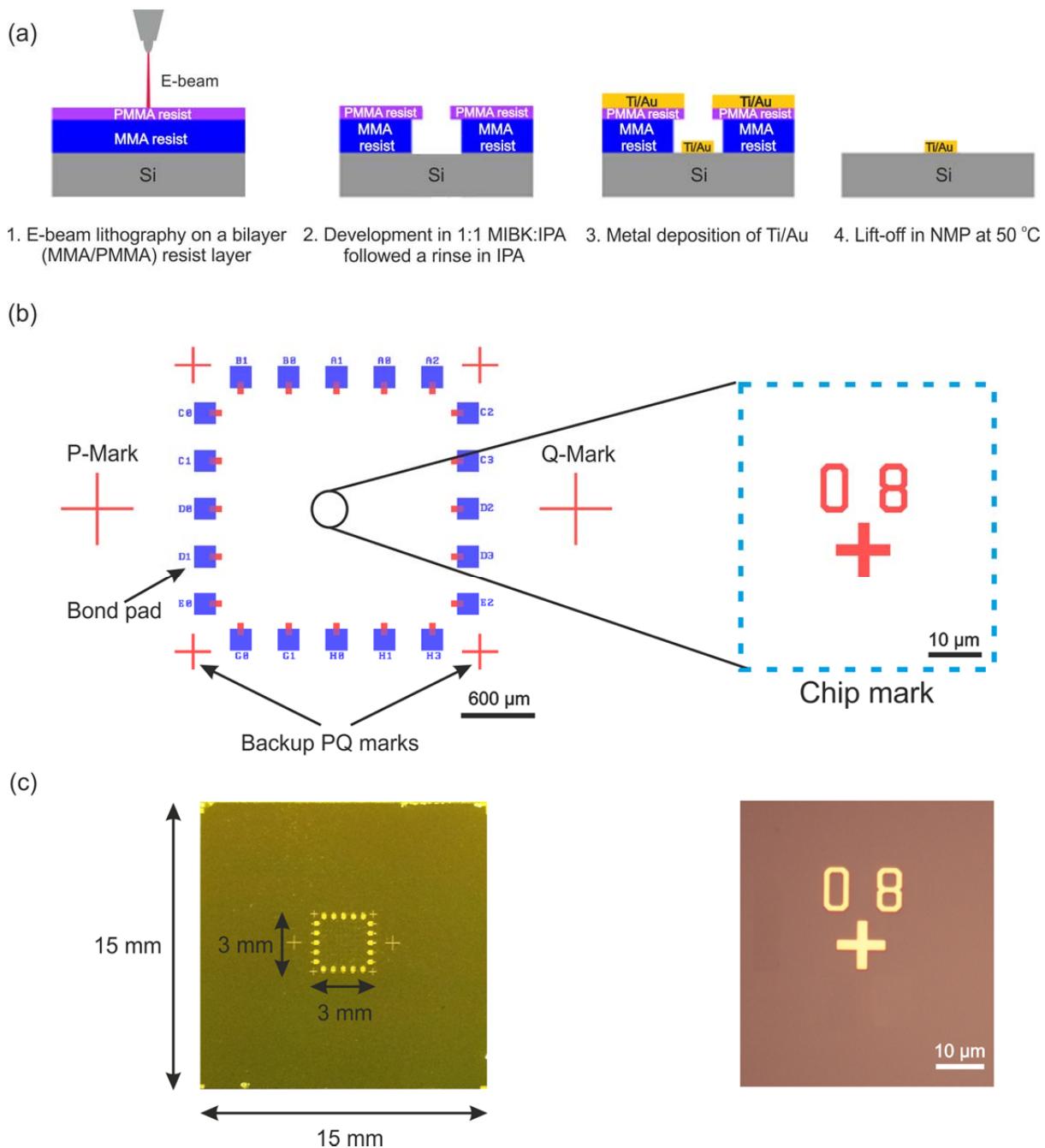

| 5.5        | Fabrication of metal contacts onto graphene samples .....                             | 112 |

| 5.6        | Issues associated with the EBL and RIE process.....                                   | 117 |

| 5.6.1      | Impact of the bulk graphite pieces                                                    | 117 |

| 5.6.2      | Impact of metal contacts in the EBL process                                           | 118 |

| 5.7        | Conclusions.....                                                                      | 119 |

| 6          | Electrical characterisations and analysis of EBL/RIE fabricated GQDs devices          | 120 |

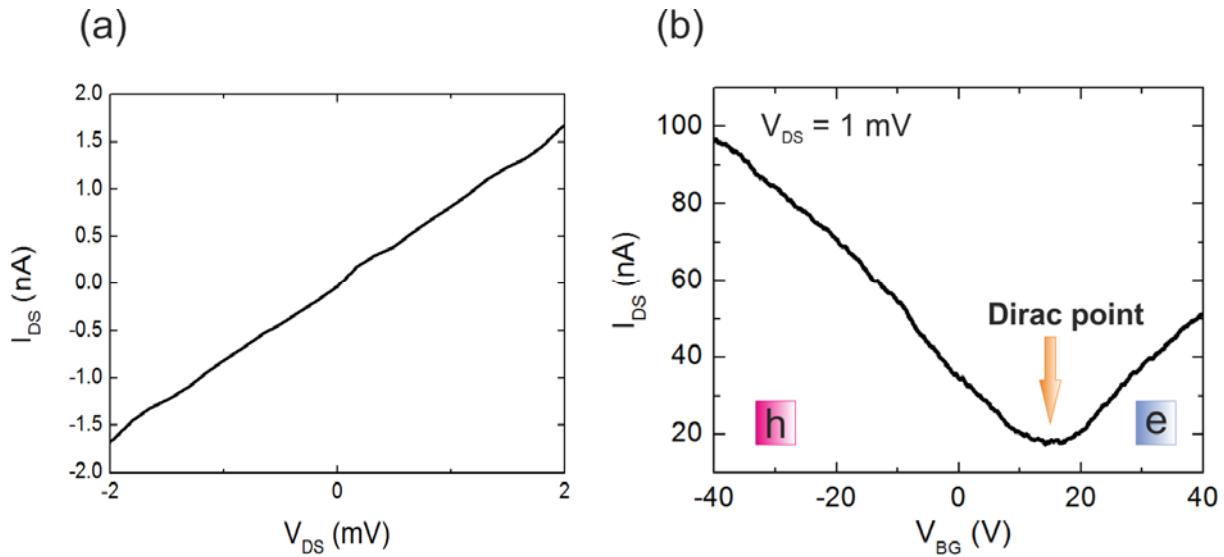

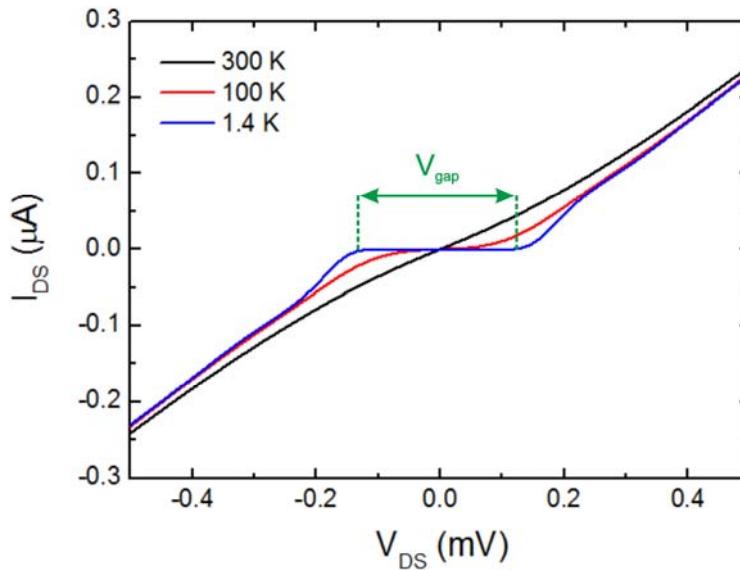

| 6.1        | Room temperature characterisation .....                                               | 121 |

| 6.2        | Cryogenic temperature characterisation.....                                           | 125 |

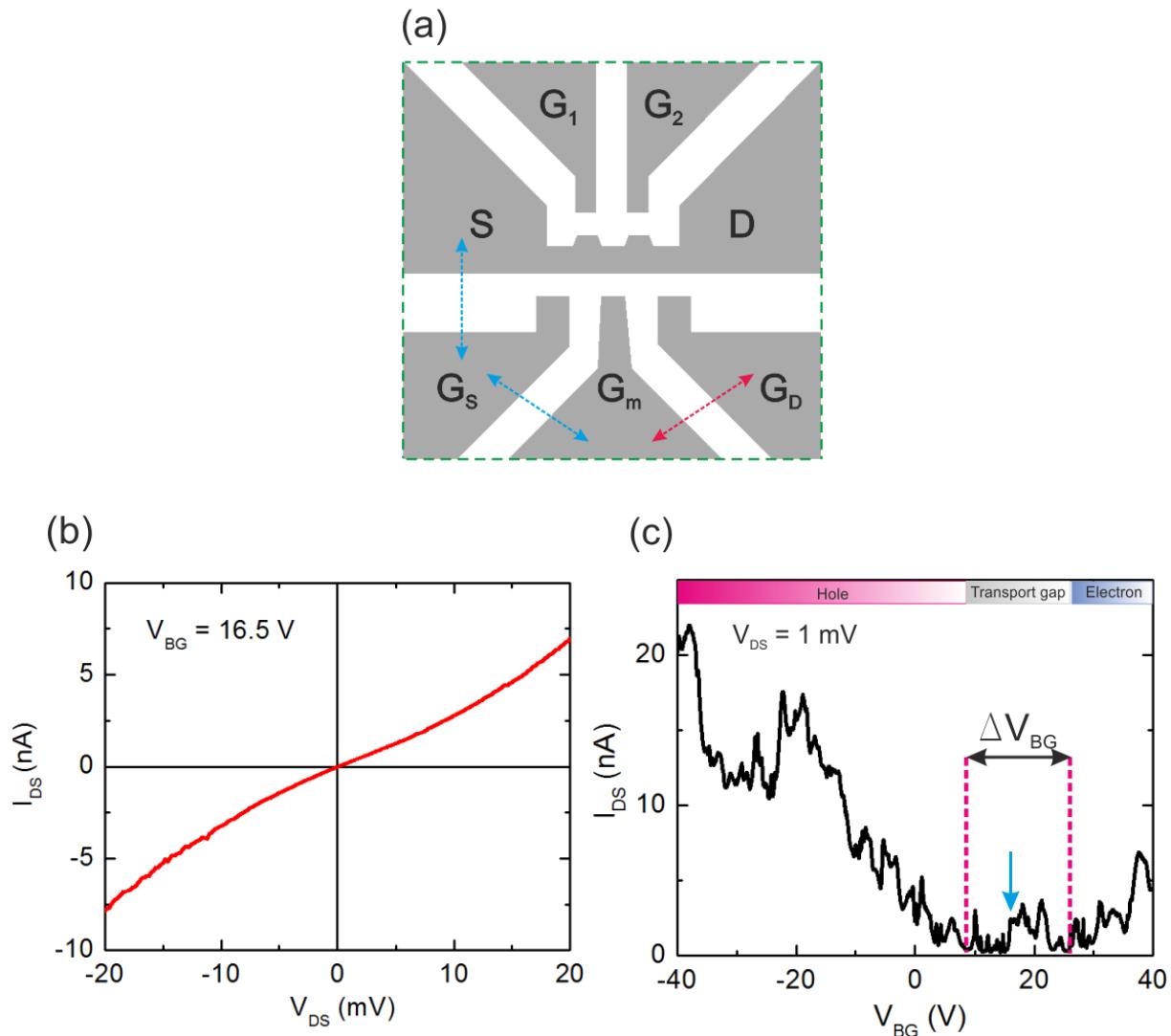

| 6.2.1      | DQD devices fabricated in CVD grown graphene samples                                  | 127 |

| 6.2.2      | QD devices fabricated in mechanically exfoliated graphene samples                     | 140 |

| 6.3        | Design and dynamic simulation of the fabricated GDQD devices by the EBL/RIE process.. | 147 |

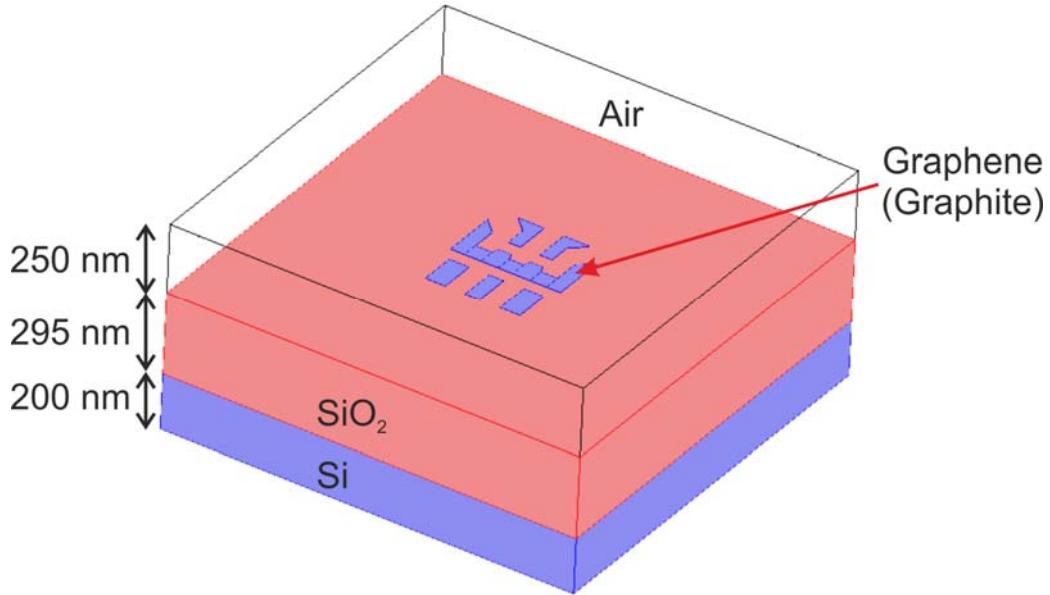

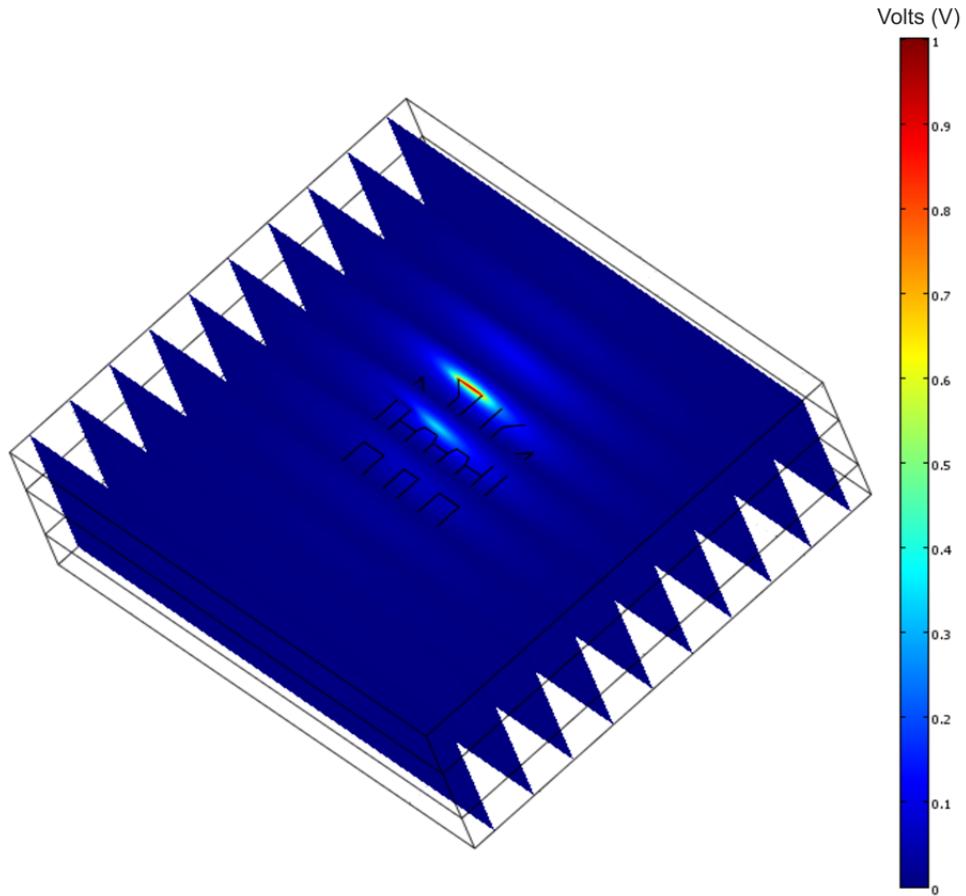

| 6.3.1      | Device design and capacitance simulation methodology                                  | 147 |

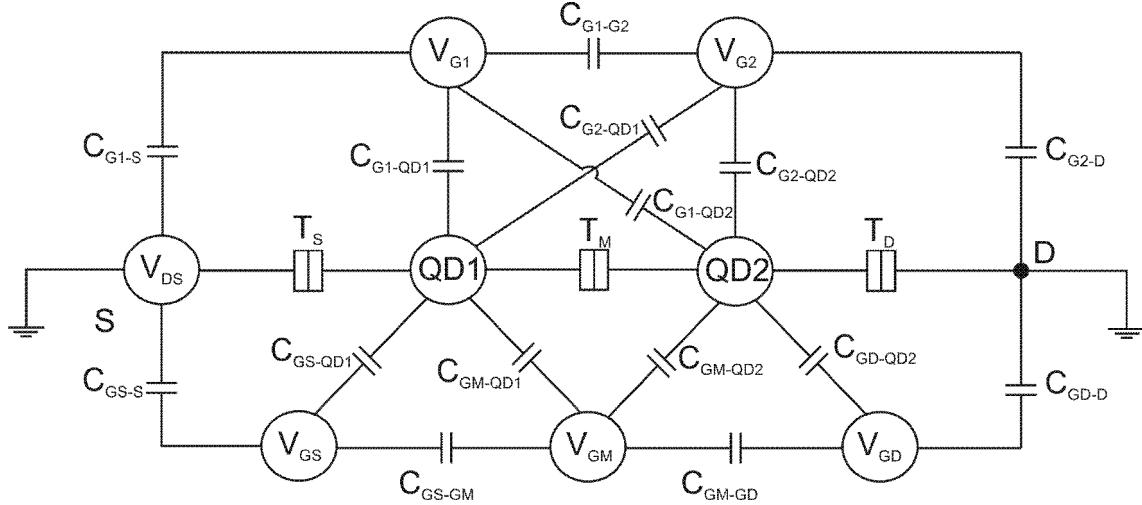

| 6.3.2      | Equivalent circuit and device simulation methodology                                  | 151 |

| 6.4        | Conclusions.....                                                                      | 158 |

| 7          | Conclusions and future work                                                           | 160 |

| 7.1        | Conclusions.....                                                                      | 160 |

| 7.2        | Future works .....                                                                    | 163 |

| 7.2.1      | EBL/RIE fabrication method                                                            | 163 |

| 7.2.2      | HIM milling fabrication method                                                        | 164 |

| Appendix A |                                                                                       | 167 |

| Appendix B |                                                                                       | 170 |

| Appendix C |                                                                                       | 173 |

| References |                                                                                       | 181 |

## Declaration of Authorship

I, Author, declare that the thesis entitled 'Thesis Title', and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research.

I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as shown in the List of Publications that follows.

**Signed:**.....

**Date:**.....

## List of Publications

### Journal publications

[1] N. Kalhor, S. A. Boden, H. Mizuta, “Sub-10 nm patterning by focused He-ion beam milling for fabrication of downscaled graphene nano devices”. *Microelectronic Engineering* **114**, 70.

[2] H. Mizuta, N. Kalhor, S. Hang, S. Boden, Z. Moktadir, H. Rutt, D. Bagnall. “Ultrafine graphene nanodevice fabrication”. SPIE proceedings (Newsroom). DOI: 10.1117/2.1201302.004739

### Conference oral presentations

[1] H. Mizuta, Z. Moktadir, S. A. Boden, N. Kalhor, S. Hang, M. E. Schmidt, N. T. Cuong, D. H. Chi, N. Otsuka, M. Manoharan, Y. Tsuchiya, H. Chong, H. N. Rutt, D. M. Bagnall. “Fabrication and ab initio study of downscaled graphene nanoelectronic devices”, August 2012, at SPIE conference.

[2] H. Mizuta, T. Iwasaki, N. Kalhor, J. Sun, M. Manoharan. “Downscaled graphene nanodevices: Helium ion beam based nanofabrication, Graphene single-carrier transistors (GSCTs) and Nano-electro-mechanical (GNEM) switches, October 2014, at ICSICT conference.

### Conference poster presentations

[1] N. Kalhor, S. A. Boden, H. Mizuta. “Fabrication of Graphene Double Quantum Dot Devices by He-ion Beam Milling” at IMAGINENANO (Graphene), April 2013, Bilbao, Spain.

[2] N. Kalhor, S. Hang, T. Iwasaki, Z. Moktadir, S. Boden, M. Manoharan, H. Mizuta. “Sharp edged sub-20 nm graphene single-electron devices by Helium ion beam milling technique”, at JSAP-MRS Join Symposia, Symposium C: Advanced Nano Carbon Devices and Materials, September 2013, Kyoto, Japan.

[3] S. Hang, Z. Moktadir, N. Kalhor, H. Mizuta, “Direct helium ion milling technology: towards the fabrication of extremely down-scaled graphene nanodevices”, at Silicon Nanoelectronics Workshop (SNW), 2013, Kyoto, Japan.

## Acknowledgements

*‘God is with those who are patient [Holy Quran 2:249]; and whosoever puts his trust in God, then he will suffice him [Holy Quran 57:4]’.*

I would like to express my gratitude to people who helped me during my PhD. First and foremost, I would like to express my sincerest gratitude to my parents and my sister for their unconditional love, invaluable advice, support and encouragement throughout my life.

A very special acknowledgement goes to my lovely girlfriend Hwanjit Rattanasonti, for all her love and support particularly during the final tough months of my PhD.

I would like to especially thank Prof. Hiroshi Mizuta for giving me the unique opportunity to study on such interesting topics and for his continuous guidance, support and encouragement throughout my PhD research. Additionally, I am very grateful for all the life advice, intellectual freedom and trust which he afforded me.

I would like to express my sincerest gratitude to Dr. Stuart A. Boden, Dr. Muhammad Khaled Husain and Dr. Hossein Nili, whom I cannot thank enough for their invaluable help, advice and support.

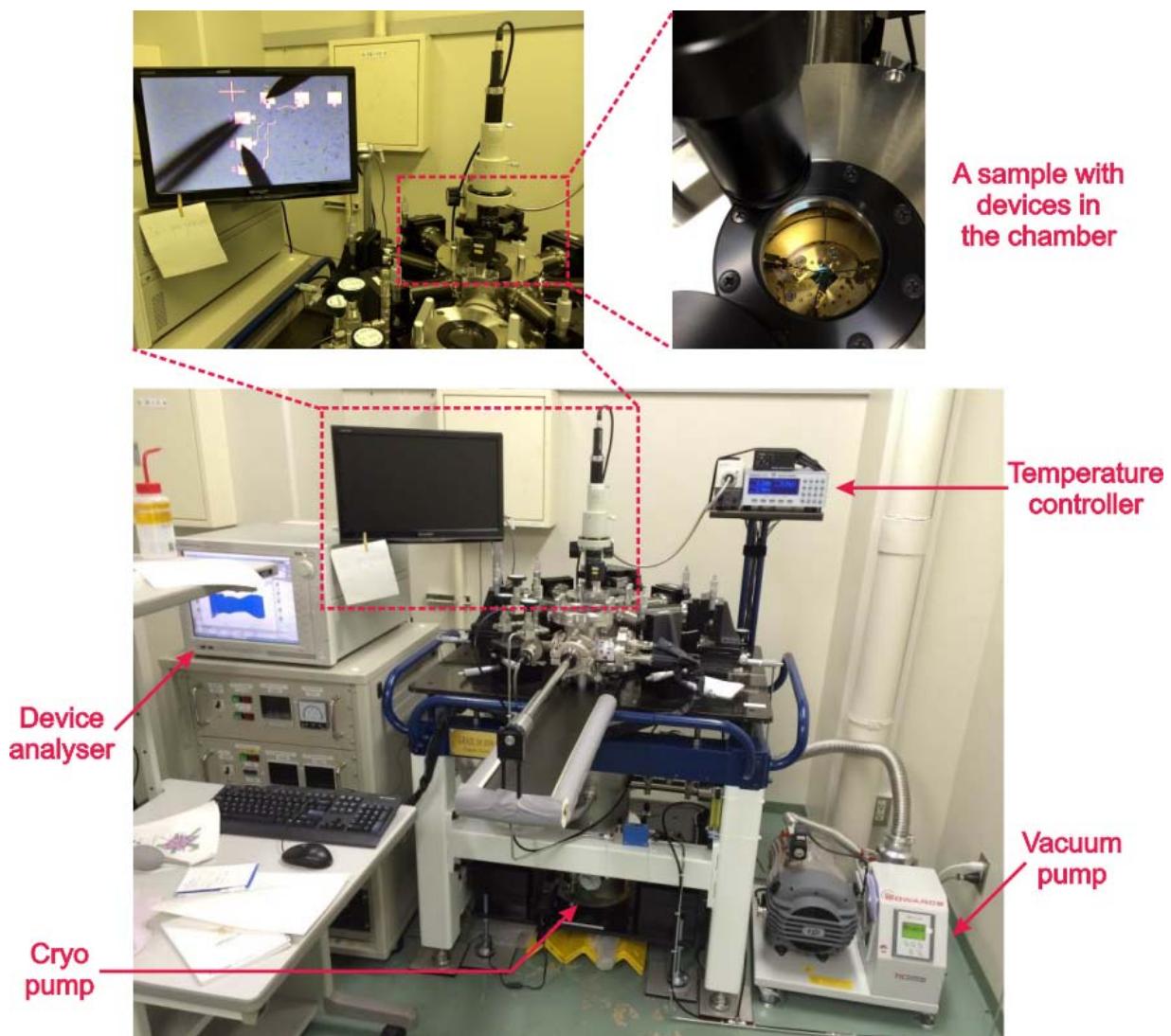

I am very grateful for the help of all the technicians at Southampton Nanofabrication Centre. In particular, I would like to thank Mr. Peter Ayliffe, Dr. Owain D. Clark, Mr. Michael G. Perry and Mr. Richard S. Kean for all their help and support in the cleanroom. In addition, I would like to express my gratitude to our collaborating researchers from the Japan Advanced Institute of Science and Technology (JAIST); Prof. Muruganathan Manoharan and Mr. Takuya Iwasaki for their invaluable help and effort in performing the low temperature measurements and useful discussions.

I am very grateful to Prof. Shinichi Saito for his suggestions and insightful discussions on fabrication. I would like to thank every member of the Nano Research Group and colleagues for their help and kindness over the past years. I would especially like to thank my friends and colleagues Dr. Stuart Pearce, Dr. Sara Aghdaei, Mr. Sam J. Fishlock, Dr. Asa Asadollahbaik, Dr. Yudong Wang, Mr. Shuojin Hang, Dr. Anna Regoutz and Mr. Jamie D. Reynolds for all their help, support and useful discussions.

*I dedicate this work to my parents Mr. Yadollah Kalhor (MSc.) and Dr. Mehri Najafi Sani for their invaluable love and continuous support throughout my life. Also, to my aunt Pauline Jennifer Najafi Sani (who passed away during my PhD after long battle with cancer) for all her tremendous help, support and advice in my life and my career.*

# Chapter 1

## Introduction

### 1.1 Quantum information technology

Since 1948, when the transistor was invented by J. Bardeen, W. Brattain and W. Shockley [1], many studies and experiments have focused to miniaturize these devices. The motivations for device miniaturization can be expressed as:

- I) The miniaturized devices have lower capacitances and shorter interconnects and yield to faster systems;

- II) Reducing the volume of transistors allows for lower power dissipation;

- III) The costs drop by more devices on chip sizes.

The quest for device miniaturization is governed by Moore's Law. This law states that the number of transistors that can be placed on integrated circuits doubles every two years [2].

Although owing to new fabrication technologies, presently, MOSFETs with 10 nm gate length can be fabricated [3], [4] but factors such as source to drain tunnelling and dopant fluctuations are setting the limits for device miniaturization [2]. Therefore, there is an intense on-going search for new device principles that not only allow for the scaling limits to be pushed even further but also make use of the quantized nature of the charge carriers evident in small device structures (i.e. 'Beyond CMOS' domain).

Single-Electron Transistors as one of the new device principles in ‘Beyond CMOS’ domain was first proposed in 1985. Averin and Likharev, at the University of Moscow, proposed the idea of a new type of transistor with three terminals called a Single-Electron tunnelling Transistor (SET). The potentials of the single electron concept are rather breath-taking and have made these devices a very hot topic in electronics. In contrast with field-effect transistors, single-electron devices are operating based on an intrinsically quantum phenomenon called the tunnel effect. The most fascinating property of single electron transistors is the possibility to switch the device by adding one electron to the gate electrode, whereas a common MOSFET needs about 1000-10,000 electrons. Downscaling of the island region of a SET (and so artificial confinement of electrons) results in a zero-dimensional electron system, commonly known as a Quantum Dot (QD).

Since the seminal work by Loss and DiVincenzo [5], quantum dots have been extensively studied as building blocks for quantum information processing (QIP). Because electron spin is a two level system (spin  $|\uparrow\rangle$  or  $|\downarrow\rangle$ ), it has become a popular candidate for realization of a qubit (a quantum bit) in quantum dots devices. Presently, the most advanced implementations of QD qubits are realised in III/V heterostructures (GaAs/AlGaAs) [6]–[8]. However, the strong spin-orbit and hyperfine interactions in these compounds pose fundamental limits to the spin coherence time, and so stimulating the search for alternative host materials.

## 1.2 Graphene

Recent discoveries of two-dimensional materials, such as graphene, have made a great impact in present science and technology.

Graphene, a two-dimensional single atomic layer of carbon atoms, was successfully produced for the first time in 2004. Despite the short history of graphene, its unique material properties have ensured a rapid growth of interest in several areas of science and technology. Its impact was recently highlighted by the 2010 Nobel prize for Kostya Novoselov and Andrea Geim for their ground breaking studies on graphene. Furthermore, huge investments by different

governments (e.g. British government) and particularly the US department of defence, signify the importance of graphene in the future of science and technology.

Although the future of graphene is still far behind the horizon which we cannot assess but, as the Si-based technology is reaching fundamental limits, graphene could be a promising material to take over. Experimental results have shown that graphene has a remarkably high electron mobility at room temperature (and in excess of  $200,000 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  at low temperatures [9]) which could pave the way for fabrication of room-temperature ballistic transistors. Unfortunately, the absence of a band gap and  $4e^2/h$  minimum conductivity even at nominally zero carrier densities [10] prevent a graphene FET device to fully “gate” and limit the on-off ratio.

As mentioned, spin-orbit and hyperfine interactions in materials are two main mechanisms that pose fundamental limits in spin coherence time. This stimulates the search for host materials with smaller spin-orbit and hyperfine interactions for QIP. Graphene is considered as an exotic material for fabrication of quantum dots devices and spin qubit embodiment [10], [11] and a very long spin relaxation length has been demonstrated [12], [13]. That is due to (i) the absence of hyperfine interaction as carbon materials consist predominantly of the nuclear spin free  $^{12}\text{C}$  isotope (99%) and, (ii) extremely weak spin-orbit coupling as the carbon nuclei is light [10], [12], [13]. In spin-orbit coupling (a relativistic effect), the electric field experienced by an electron is equivalent to  $+Z|e|$  where  $Z$  is the atomic number of the host material [14], [15]. Therefore, spin-orbit coupling is weak for light materials [16]. The strength of intrinsic spin-orbit interaction in graphene, induced by the intra-atomic Coulomb potential, is estimated to be a very small energy of  $\lesssim 24 \text{ }\mu\text{eV}$  due to the small atomic number  $Z = 6$  of carbon [17], [18]. However, in GaAs (the host material of the most advanced implementations of QD qubits so far [6]–[8]), the spin-orbit interaction (i.e. the Dresselhaus spin-orbit coupling) is significantly stronger (0.341 meV [19]) and dominates spin relaxation [20], [21]. These values provide a suitable comparison between these two host materials, and so suggesting graphene as an excellent material for realisation of spin qubits [10].

An interesting novel proposal for a graphene device with spin function is spin-based logic circuits which are expected to offer high-speed operation at low power dissipation [22]. Recently, graphene drums (i.e. graphene mechanical resonators) have been suggested to have

great potential as quantum memory chips in future quantum computers [23], [24]. It has been also demonstrated that under extremely powerful magnetic fields and at low temperatures graphene can effectively filter electrons according to the direction of their spin, resulting in an unusual conduction along the edge (virtually a one-dimensional wire) which can be used as a building block for realising novel quantum circuits [25], [26].

These superior transport properties encourage the downscaling of graphene devices further to the regime where the coherent nature of electronic and spin states can be fully exploited. However, this requires the development of ultrafine patterning technologies which enables accurate nanoscale fabrication beyond the present electron-beam lithography technique.

For research and prototyping, electron beam lithography (EBL) is the most established lithography method for fabrication of nano devices. Despite all the developments (e.g. 100 keV acceleration voltage), which have made EBL with sub-10 nm resolution in resist possible, the electron-resist interactions along with the resist development are limiting the resolution of this technique [27]. This stimulates the search for alternative high resolution patterning techniques.

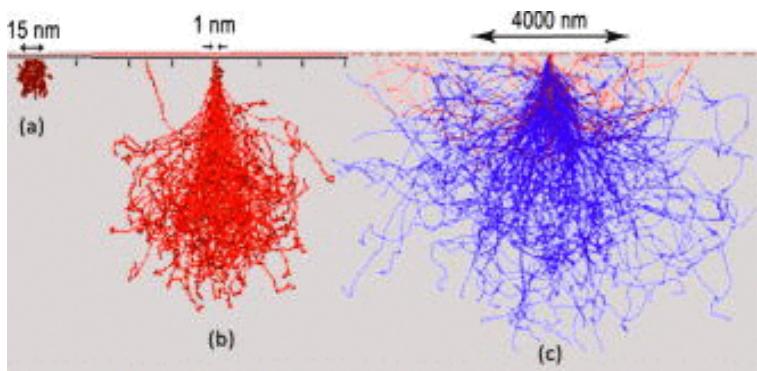

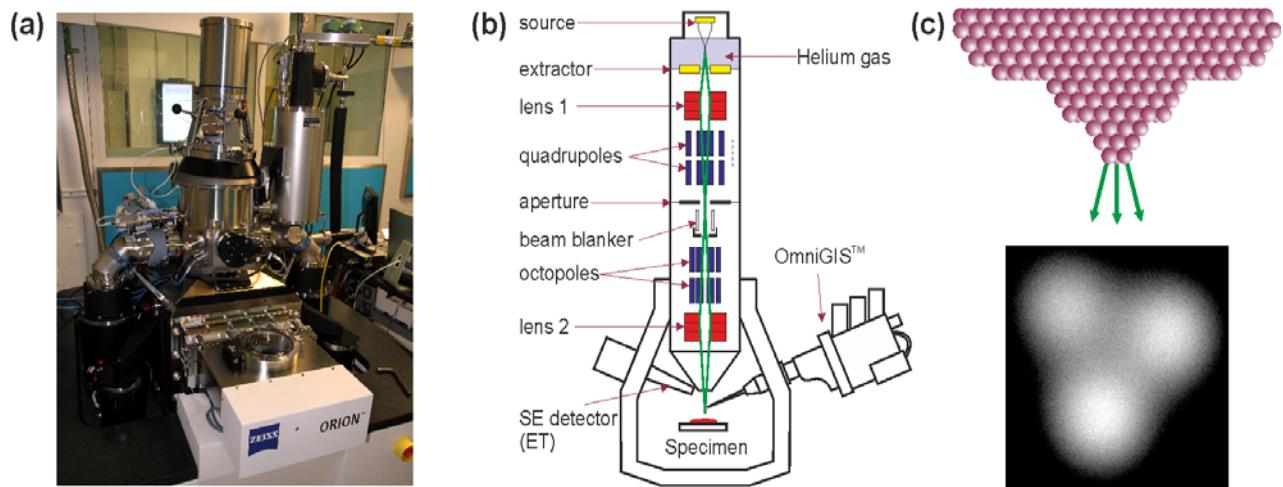

### 1.3 Helium ion microscopy

In 2007, Carl Zeiss SMT introduced Helium-Ion Microscopy (HIM) as a new surface imaging technique [28]–[32]. It involves scanning a focused beam of helium ions across a surface to generate an image from the resulting secondary electron (SE) emission. An atomically sharp and extremely bright source, combined with the larger momentum (and so smaller de Broglie wavelength) of helium ions compared to electrons, enables a sub-nanometre probe size at the sample surface. Additionally, He ions produce far fewer collision cascades (and so low amount of beam divergence) in the first  $\sim$ 100 nm of entering the substrate. This results in a small interaction volume and so high resolution imaging routinely below 1 nm (edge resolution) and, with the latest versions of the tool, below 0.35 nm [33]–[35].

Helium ion microscopy was primarily developed and introduced as an ultra-high resolution imaging technology, with unique contrast mechanisms and imaging abilities. However, as it

produces an intense focused beam of He-ions, it is also capable of patterning (milling and lithography) and sputtering that are more commonly associated with a conventional Ga-ion beam. Therefore, shortly after its introduction, it was recognised as potential patterning tool for fabrication of state-of-the-art nano devices which, it has already made an exhilarating impact on fabrication of plasmonic nano devices [36]–[38].

However, it is worth mentioning that graphene samples are very susceptible to beam irradiations [39]–[44]. For instance, He-ion beam irradiation results in creation of defects (i.e. modification of the atomic lattice) and degradation of the electronic properties of graphene samples [39]. Hence, extra care is required to avoid/minimise beam irradiation damage on graphene samples during imaging.

## 1.4 Research motivations and contributions

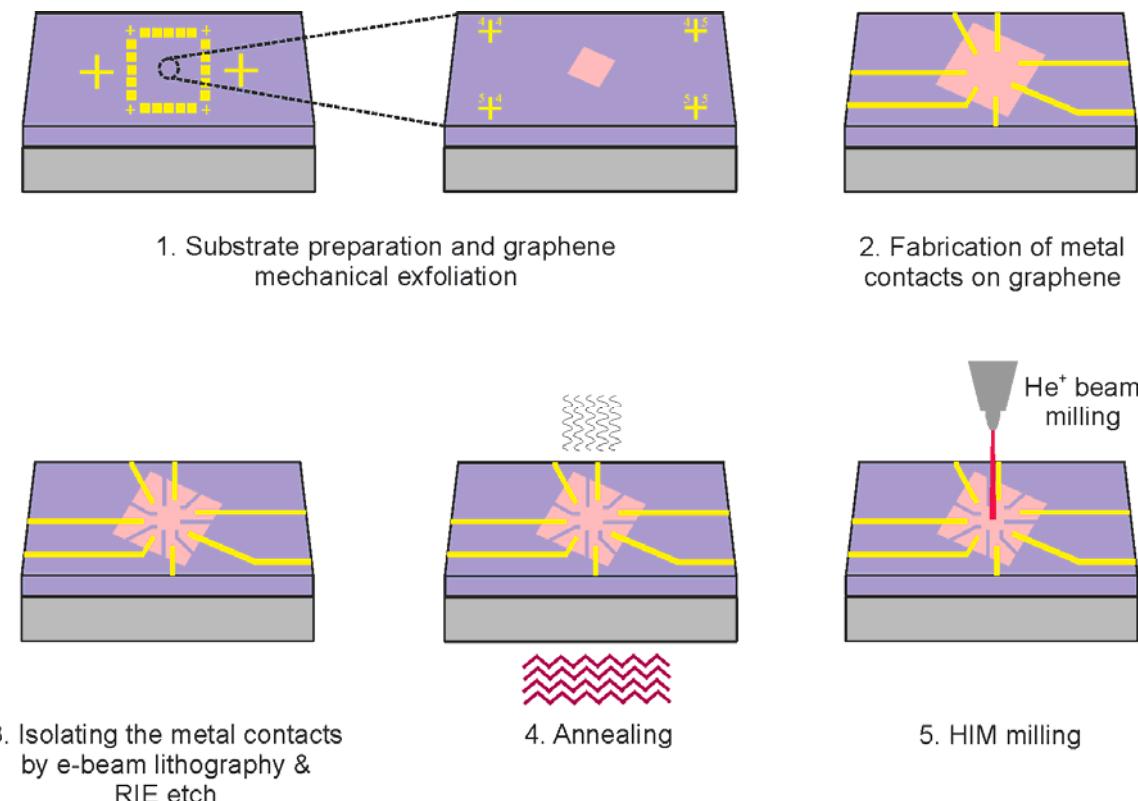

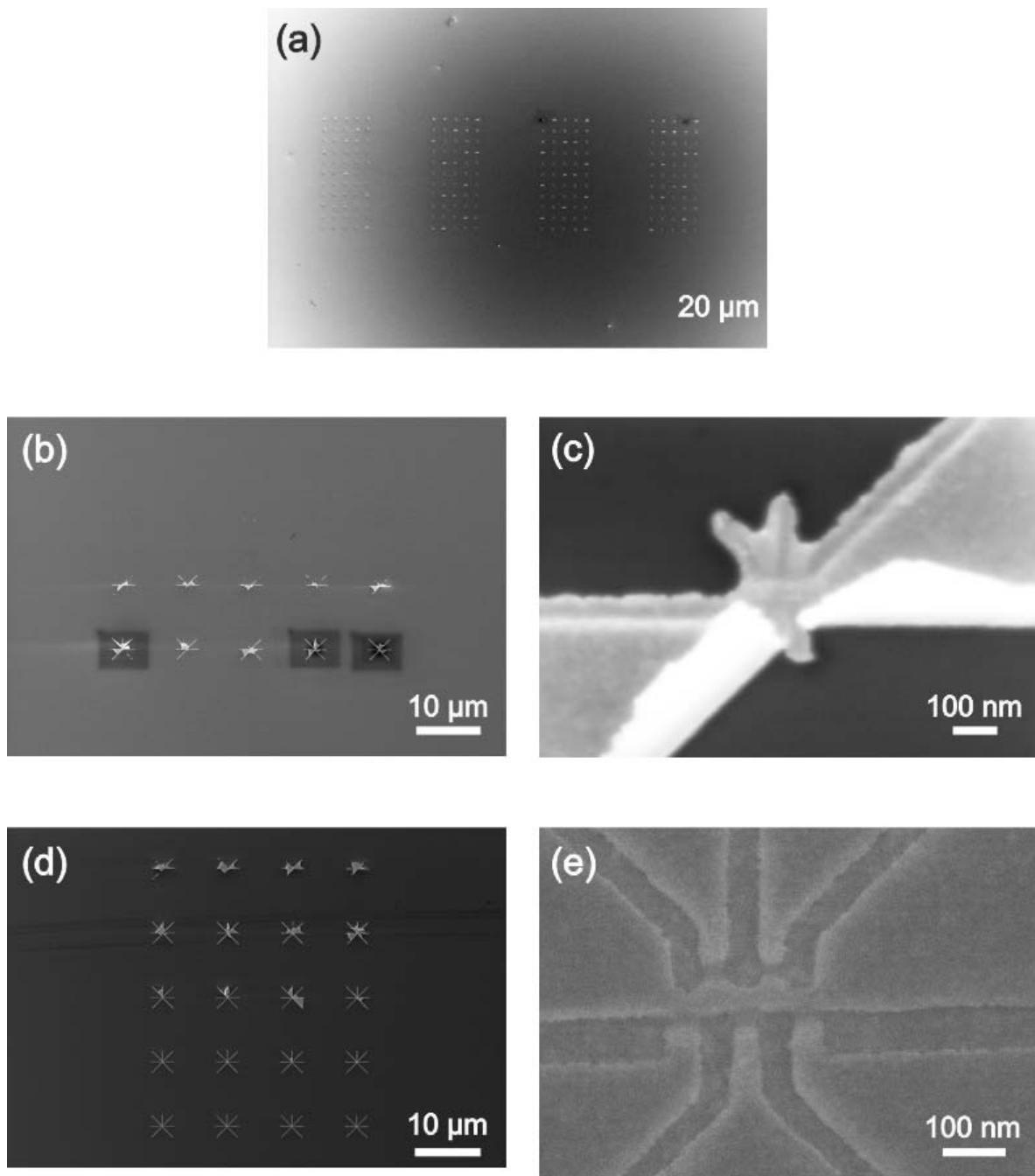

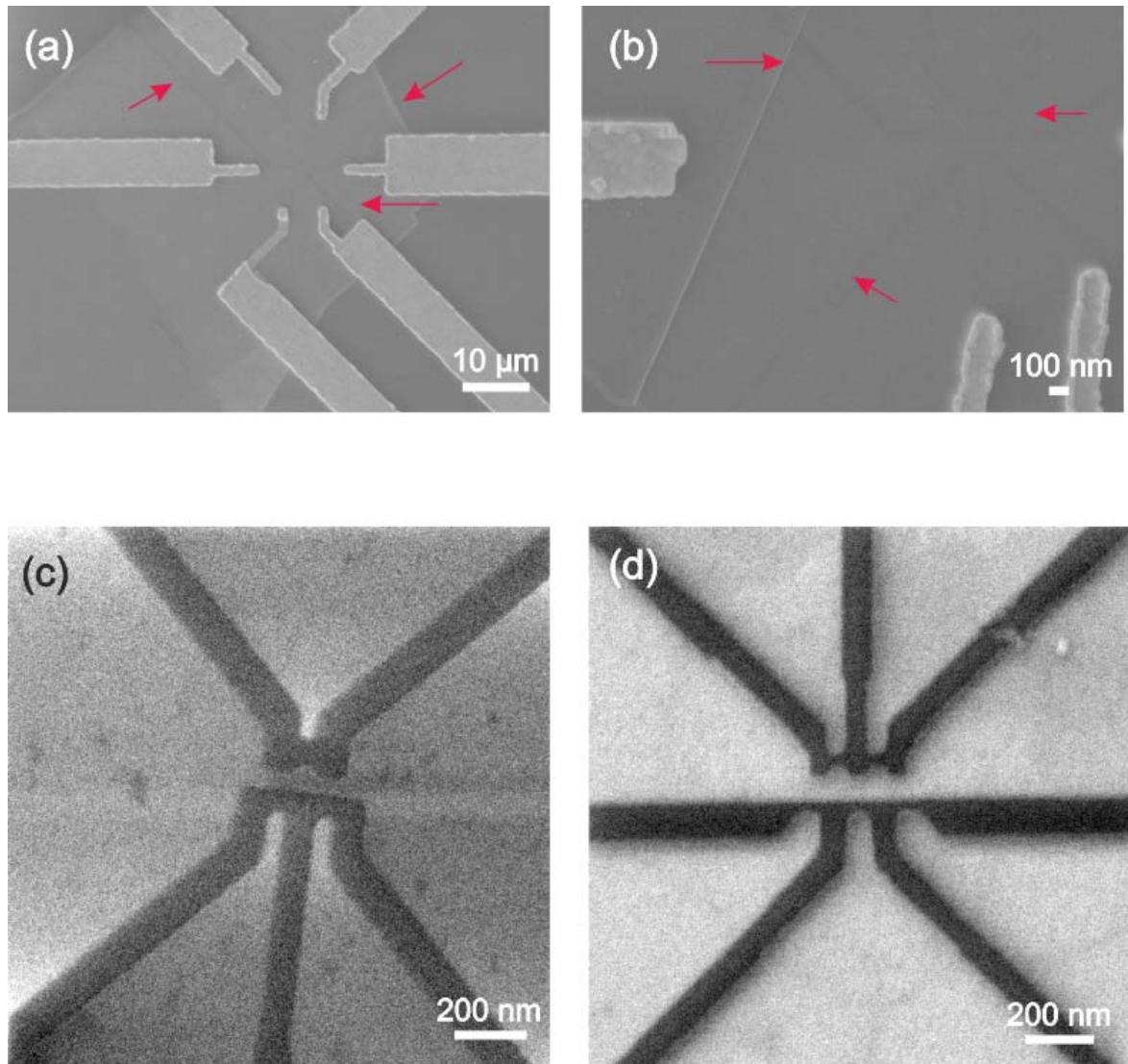

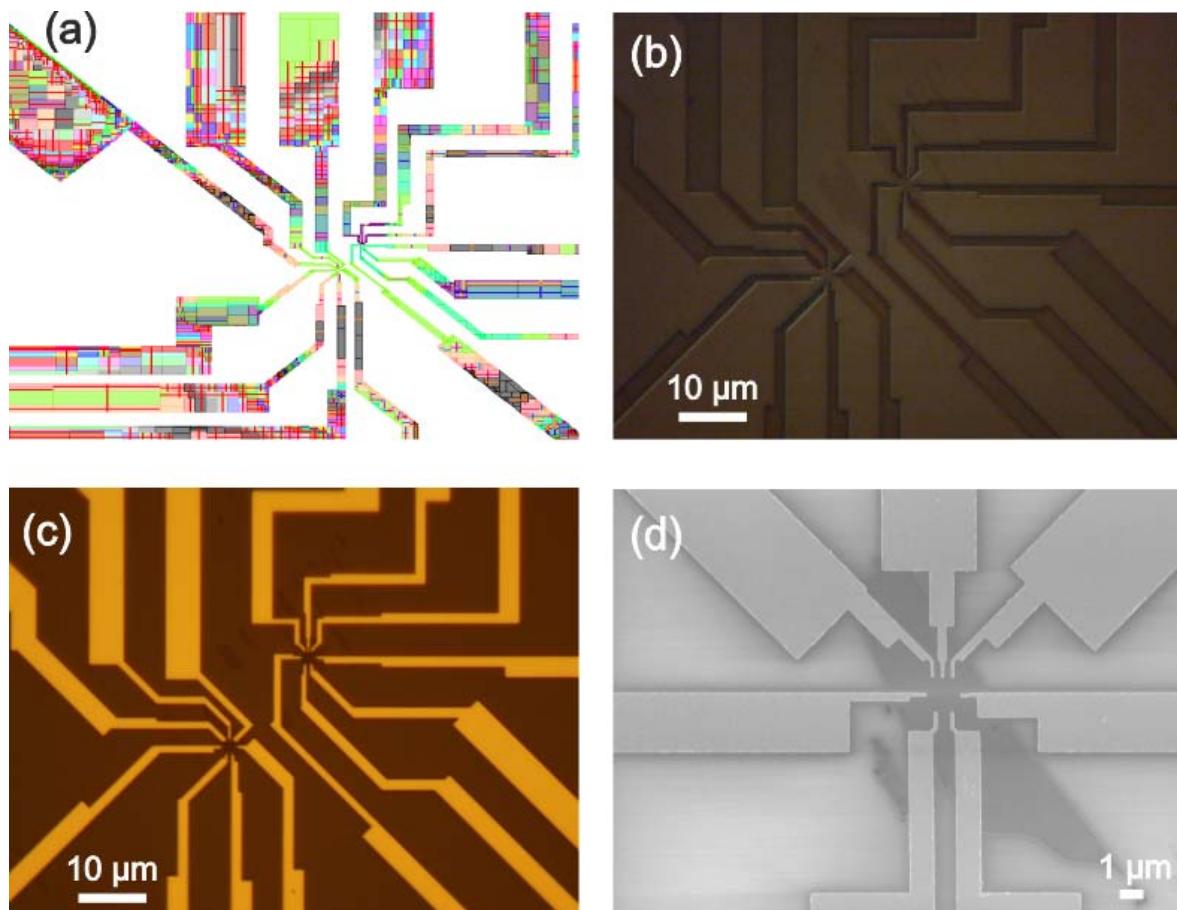

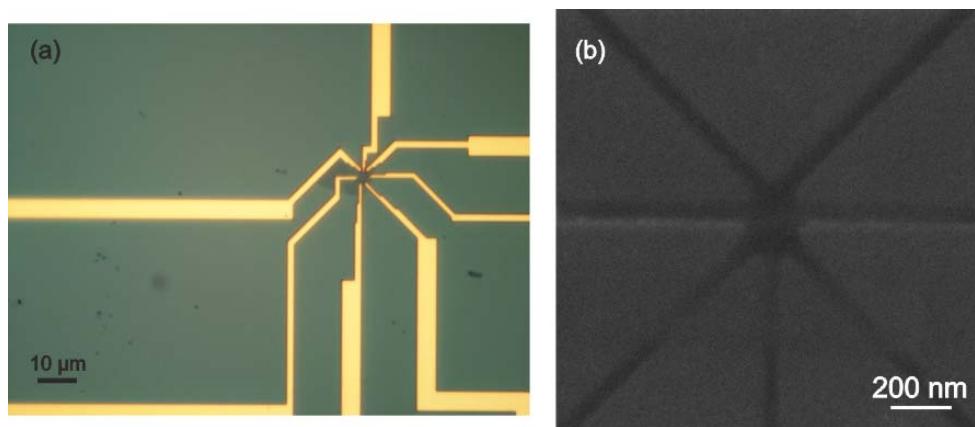

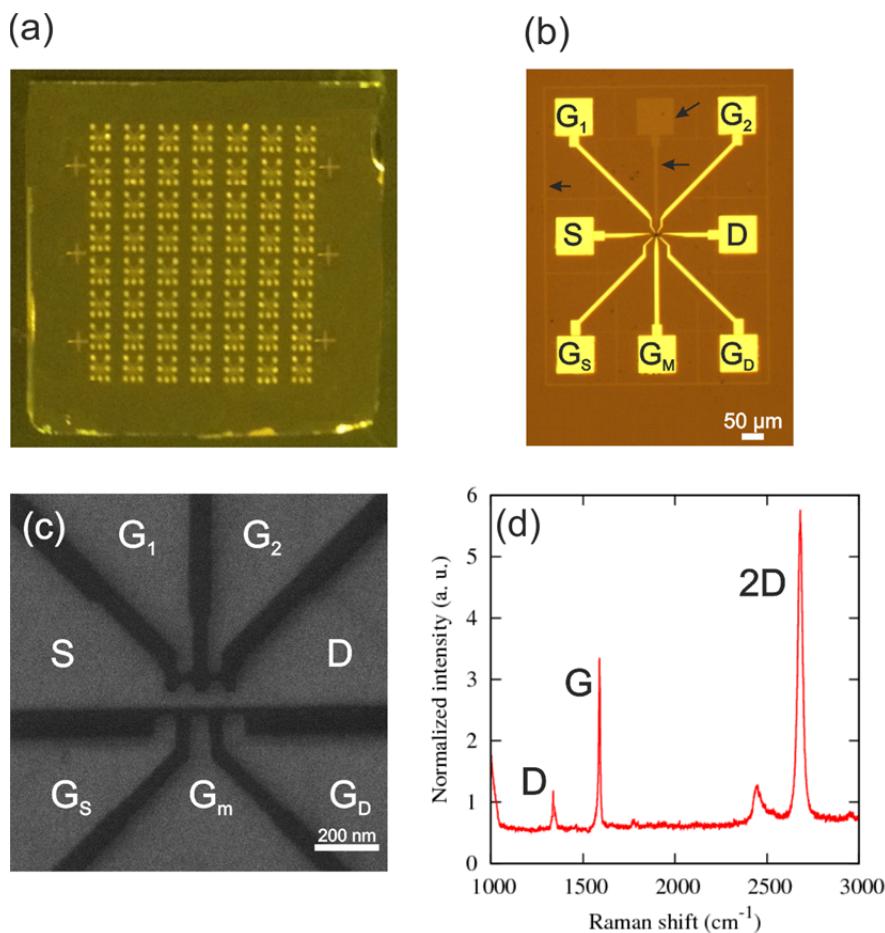

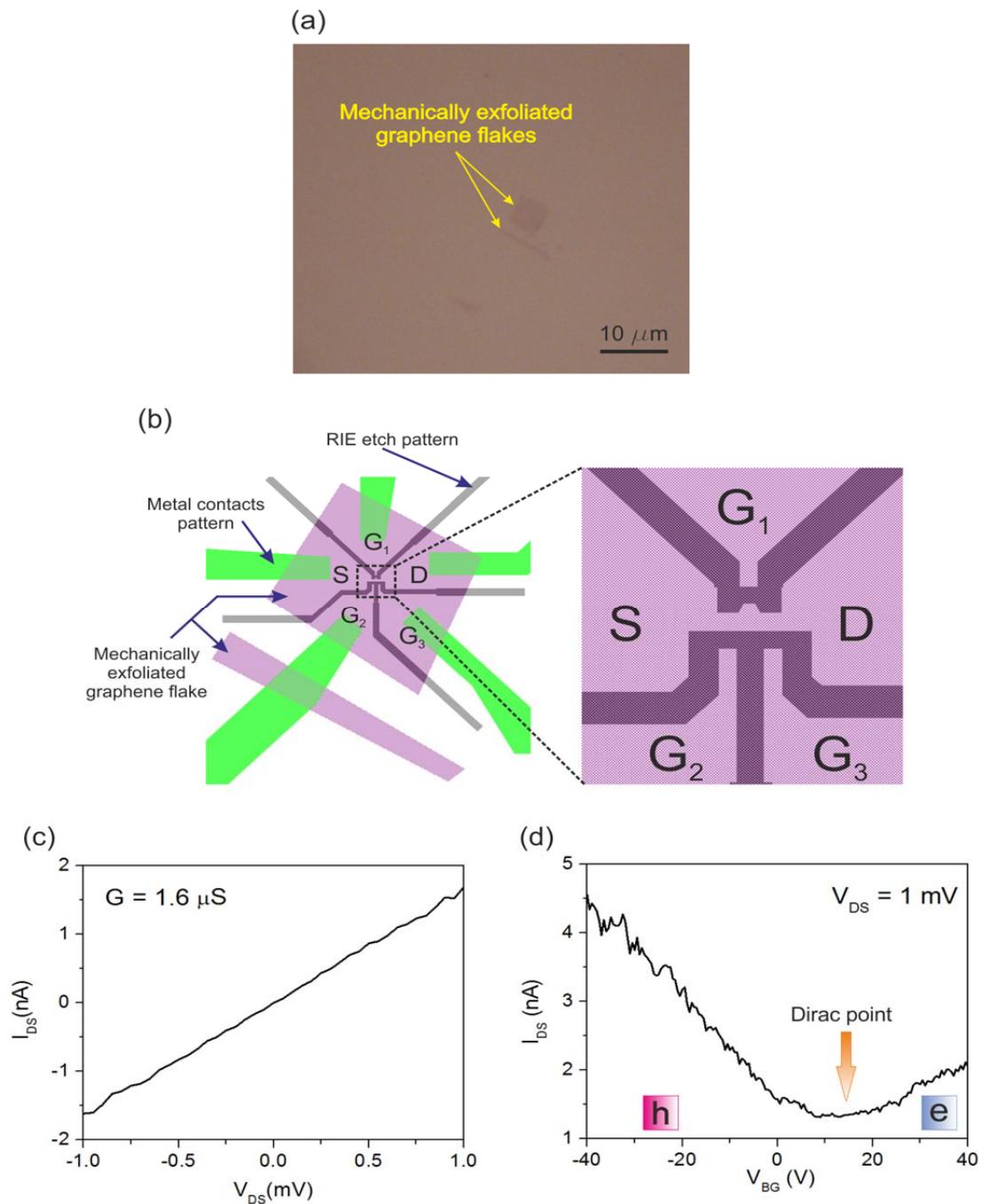

In this work we aim to develop and demonstrate successful fabrication of graphene nano devices for the first time at Southampton Nanofabrication Centre (SNC). This is demonstrated by means of e-beam lithography followed by reactive-ion-etch (RIE) which is employed to fabricate single electron transistors with quantum dots devices with a better pattern resolution than that of demonstrated in majority of other reported works. The capability and high yield of our process is highlighted by successful fabrication of arrays of quantum dots devices on CVD graphene samples.

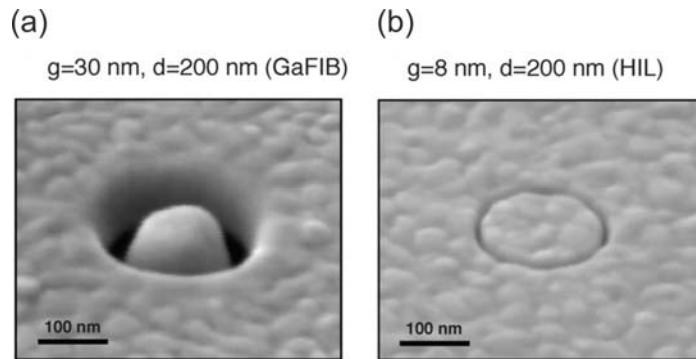

Although currently EBL/RIE method is the most established method for fabricating graphene devices but, we argue that the parameters such as e-beam spot size, proximity effect and undercutting of the resist layer during etching can limit the resolution of this technique. Furthermore, uneven thickness of the resist layer, which may be caused by the presence of graphite pieces and metallic alignment marks, can also limit resolution and affect the symmetry of the patterns fabricated by this method.

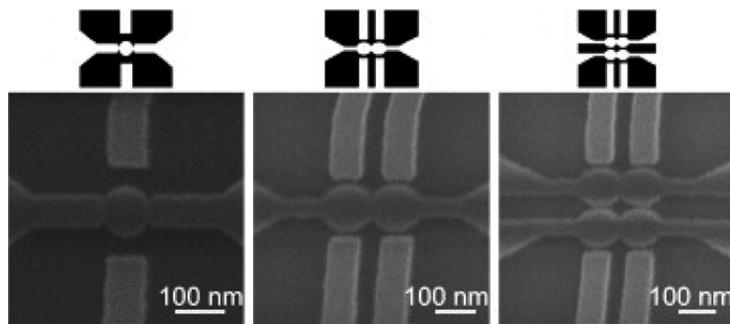

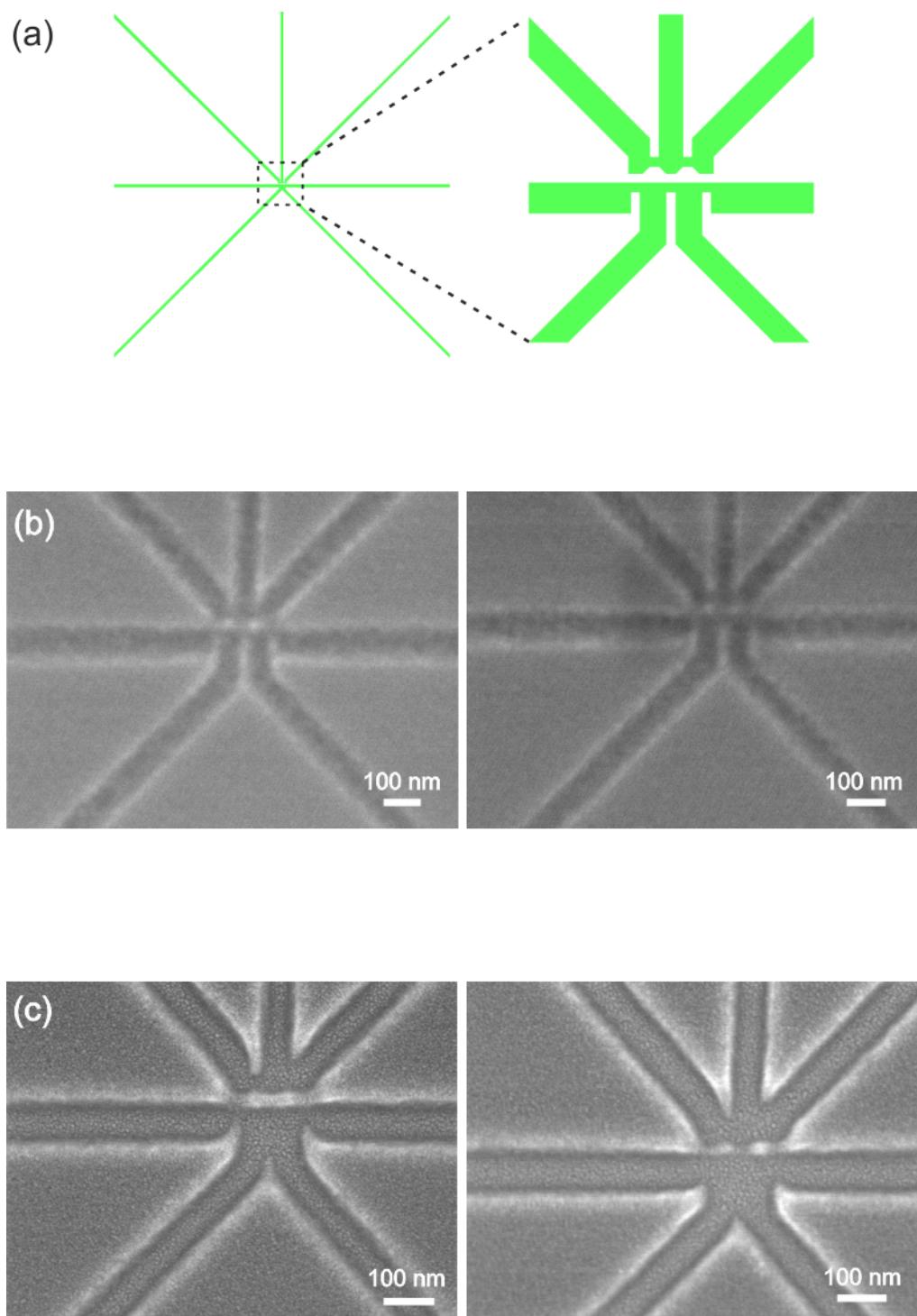

Therefore, inspired by the on-going trend towards device miniaturization, we present a novel hybrid fabrication method for graphene nano devices (e.g. graphene QDs devices) with

minimum feature sizes of  $\sim 3$  nm (i.e. the gap between the side-gates and channel) and high yield. Here, for the first time, we combine conventional e-beam lithography and direct milling with the sub-nm focused helium ion beam generated by a helium ion microscope to fabricate high resolution graphene QDs devices, reliably and reproducibly. The highly controllable, fine scale fabrication capabilities offered by this approach could lead to a more detailed understanding of the electrical characteristics of graphene quantum devices and pave the way towards room-temperature operable graphene quantum dot devices.

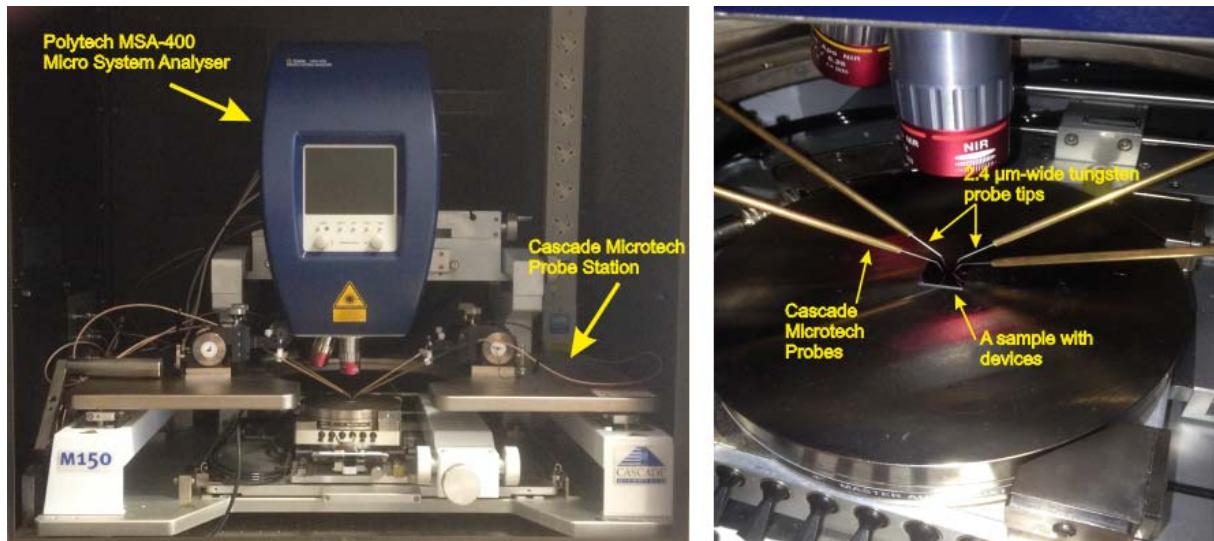

The final fabricated devices by both fabrication methods are then electrically characterised at room temperature and cryogenic temperatures (only for EBL/RIE devices) to confirm successful fabrication of the desired devices. The cryogenic temperature measurements were conducted to verify the ability to control single electron tunnelling in the fabricated devices, and so observing Coulomb diamonds.

## 1.5 Thesis overview

This thesis consists of 7 chapters.

Chapter 2 introduces graphene and presents a brief review on some of its remarkable properties related to this work. This includes a discussion of graphene's atomic structure, electronic properties, production and identification methods.

Chapter 3 provides an extensive study on the operation of single electron transistors (SETs) with quantum dots (QDs) devices as building blocks for quantum information technology. The electron transport via Coulomb Blockade (CB), observation of Coulomb diamond and stability diagram are explained in detail. Furthermore, an experimental review on the behaviour of graphene quantum dots devices through a literature review, which highlights the most important experimental methods relevant to our work, is given.

Chapter 4 begins by highlighting the limitations of the EBL/RIE fabrication process and introducing helium ion microscopy (HIM) as an ultra-high resolution imaging tool. In addition, we discuss the capability of HIM milling for nanofabrication through a literature review which highlights the most interesting recent experimental works. We then propose our novel hybrid

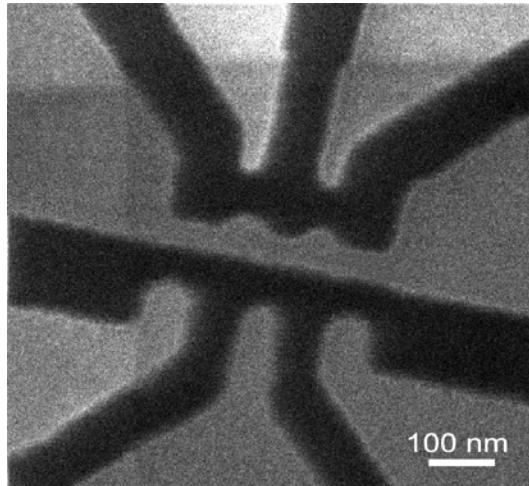

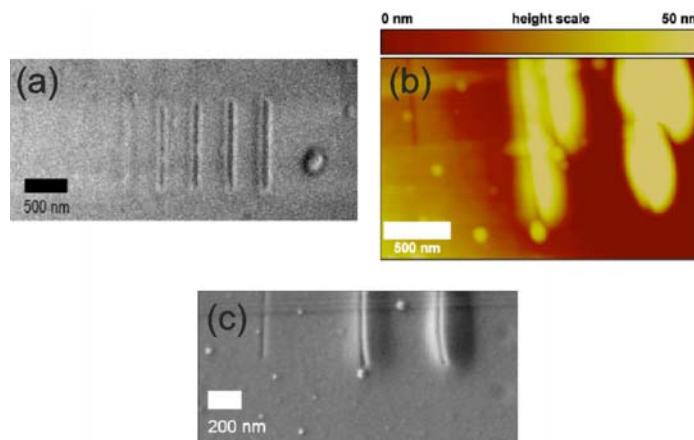

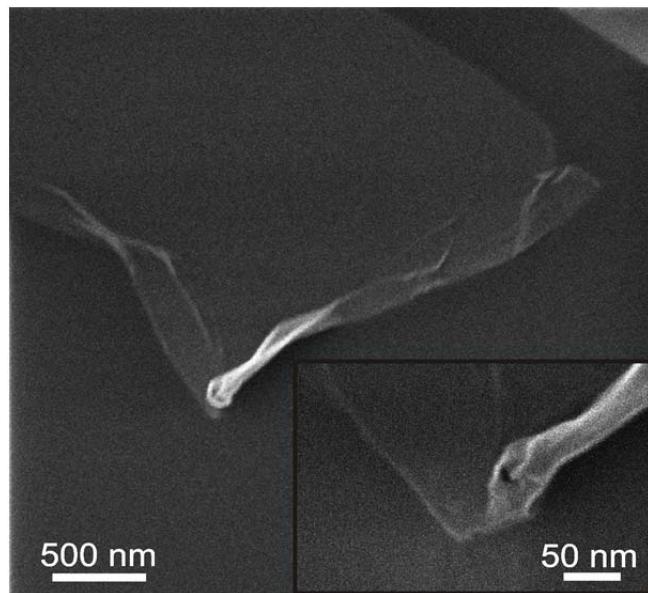

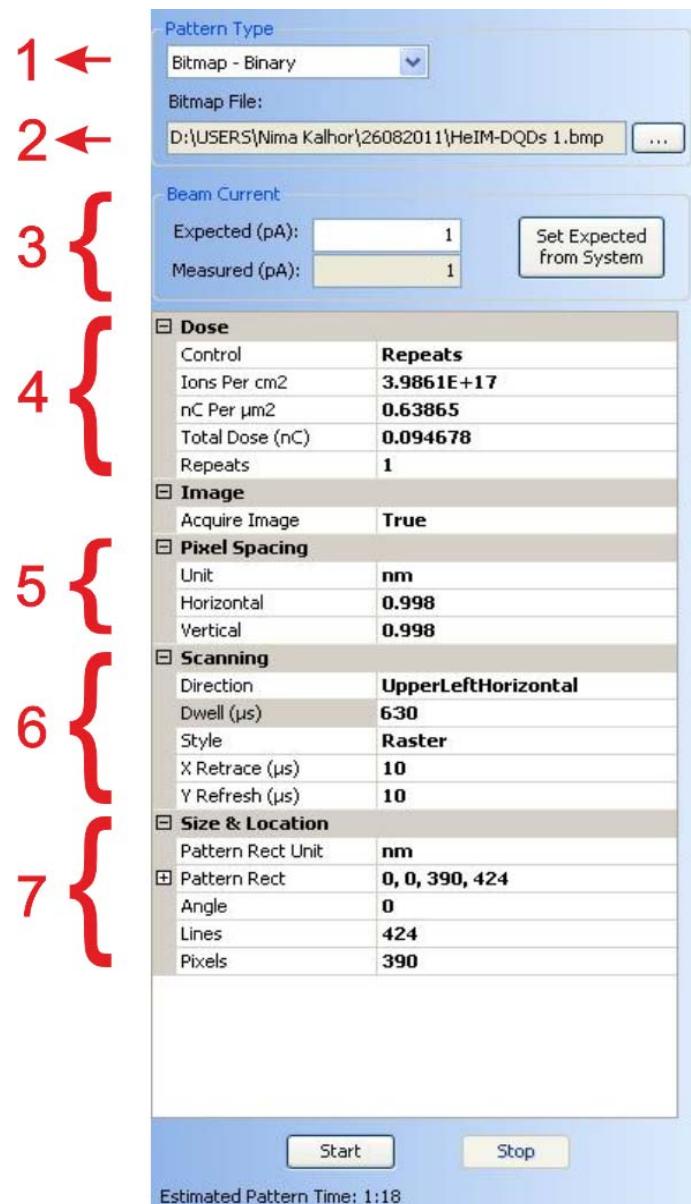

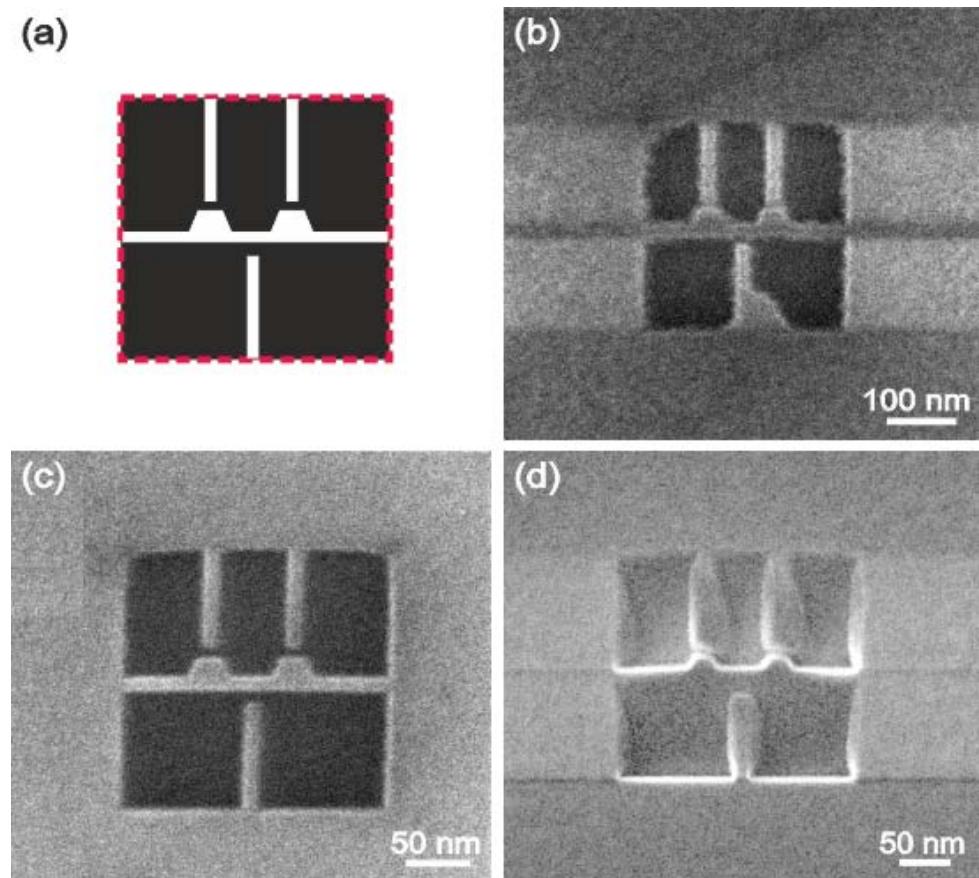

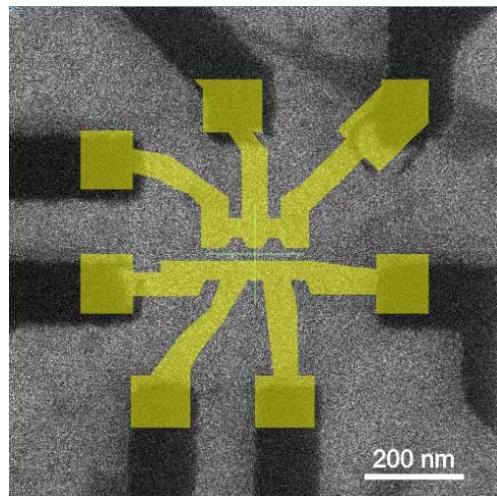

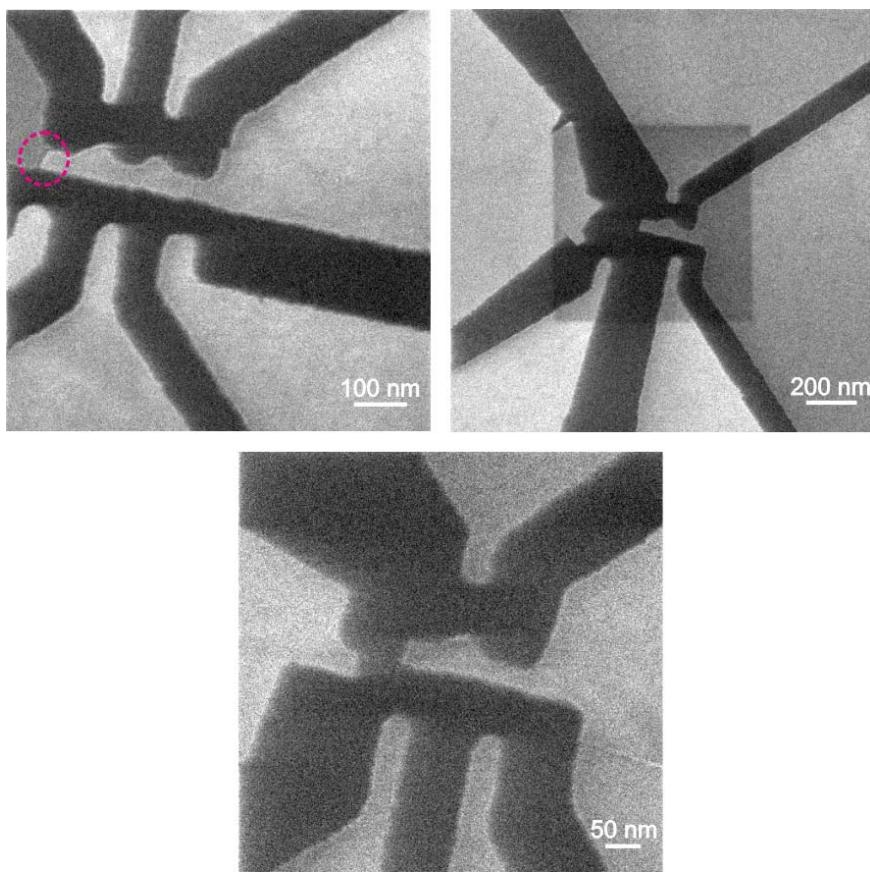

fabrication method for extremely downscaled graphene quantum dots devices by combining conventional e-beam lithography and direct milling with a sub-nm focused helium ion beam for the first time. The helium ion milling is used to pattern graphene flakes with intricate QD devices, with sub-10 nm resolution and high fidelity. We established this novel fabrication approach for the first time and extensive effort was employed to overcome number of challenges, such as the He-ion beam drift during milling which can jeopardise pattern fidelity for long exposure times. To obtain the desired high resolution HIM milling, we suggest an annealing process in  $H_2/N_2$  gas flow to remove the contamination produced during the e-beam lithography steps on the surface of the graphene samples. Furthermore, we highlight the limitations associated with this fabrication method. The chapter is then finalised by discussing the electrical measurements collected from the final fabricated devices. The electrical characterisation of the final device demonstrates the successful fabrication of the first electrically characterised He-ion beam patterned graphene device, which we published as a journal paper. Our novel approach could pave the way to a better understanding and more detail study of graphene quantum devices.

Chapter 5 explains our fabrication process for graphene QD devices by means of conventional e-beam lithography followed by RIE etch (i.e. EBL/RIE process). Our fabrication process, which can be also employed to fabricate variety of graphene nano devices, was developed and established for the first time at Southampton Nanofabrication Centre. All the steps involved in the fabrication process are explained systematically in great detail in order to pave the way for future graphene projects in Southampton Nano Group. To minimise e-beam induced damage on our graphene samples during e-beam lithography, we employ a single layer of *Methyl Methacrylate* (MMA) resist for the first time as a radical method for fabrication of metal contacts onto graphene devices. The high electron beam sensitivity of MMA resist allows the use of a dramatically lower e-beam dose to that of required for a bilayer resist layer (and so less beam induced damage onto the graphene samples) which, using our optimised process, also ensures consistent and successful lift-off outcome with minimum feature size of  $\sim 150$  nm. This was achieved by simultaneous tuning of the resist thickness (i.e. MMA), e-beam lithography process, metal deposition conditions (i.e. metal deposition at a rate of  $0.5$  Å/second), thickness of the deposited metal layer (i.e. Ti/Au 5 nm/ 60 nm), and performing the lift-off process in

warm *N*-Methyl-2-Pyrrolidone (NMP). Furthermore, we conclude this chapter by highlighting issues and limitations associated with the EBL/RIE fabrication process.

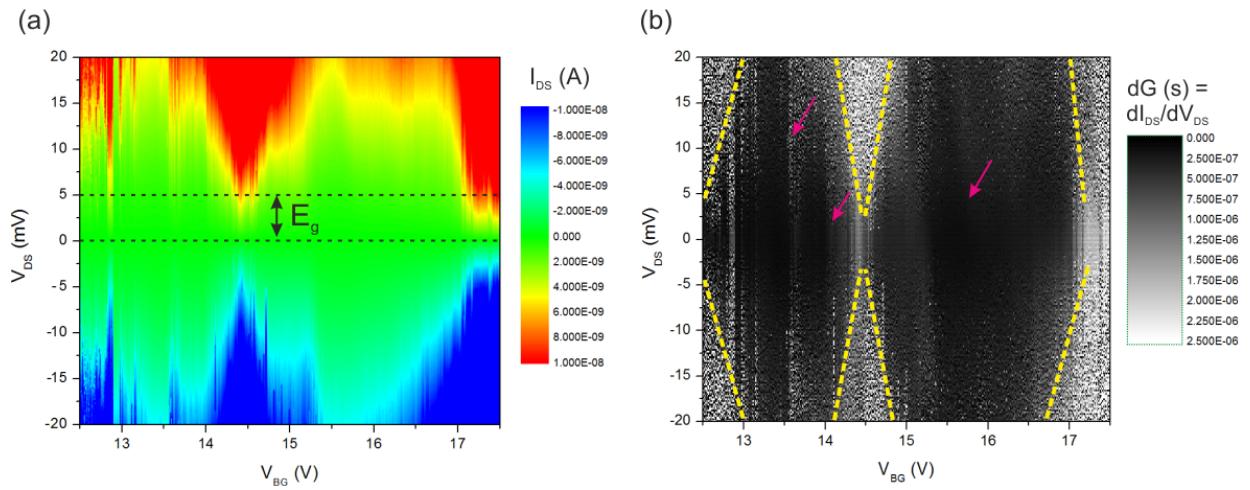

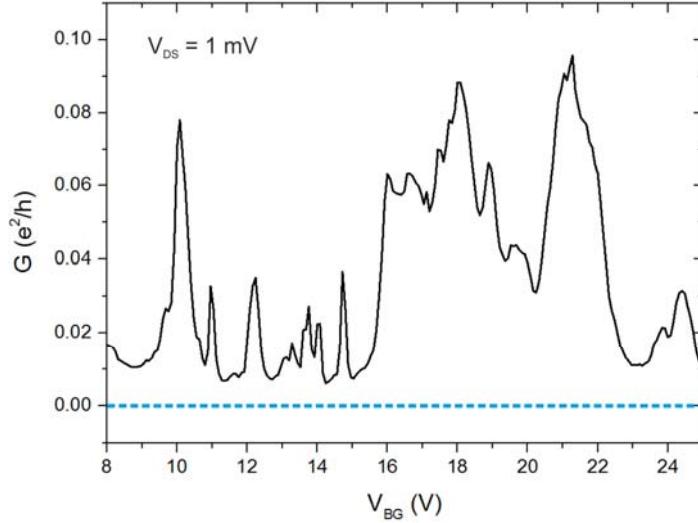

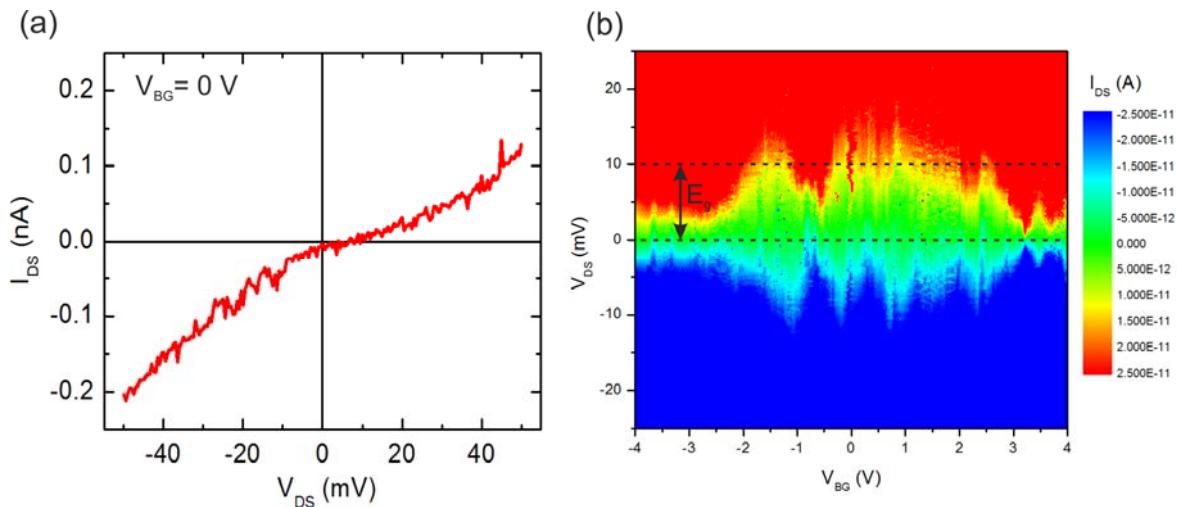

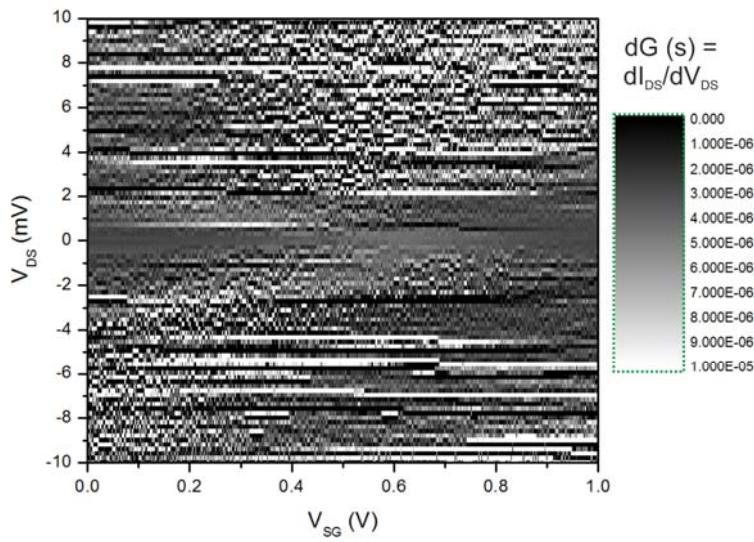

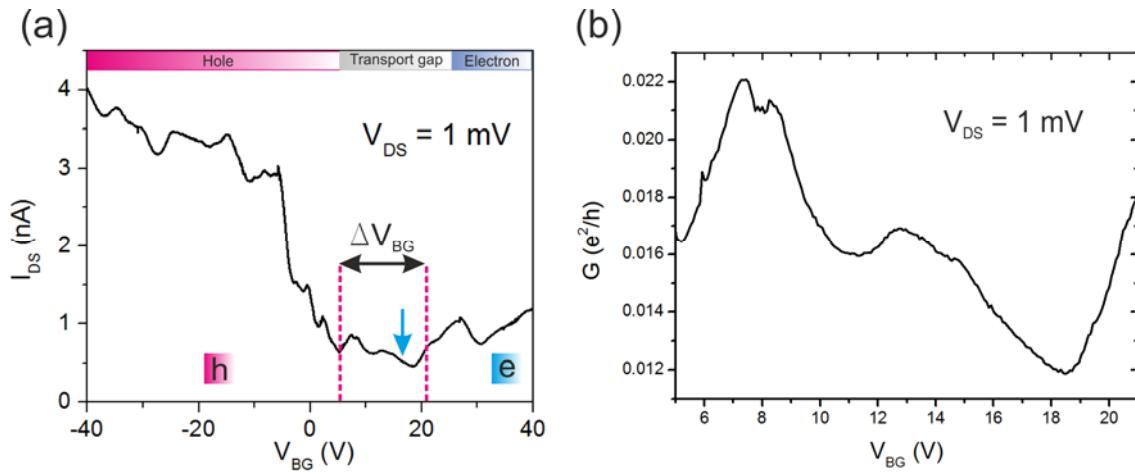

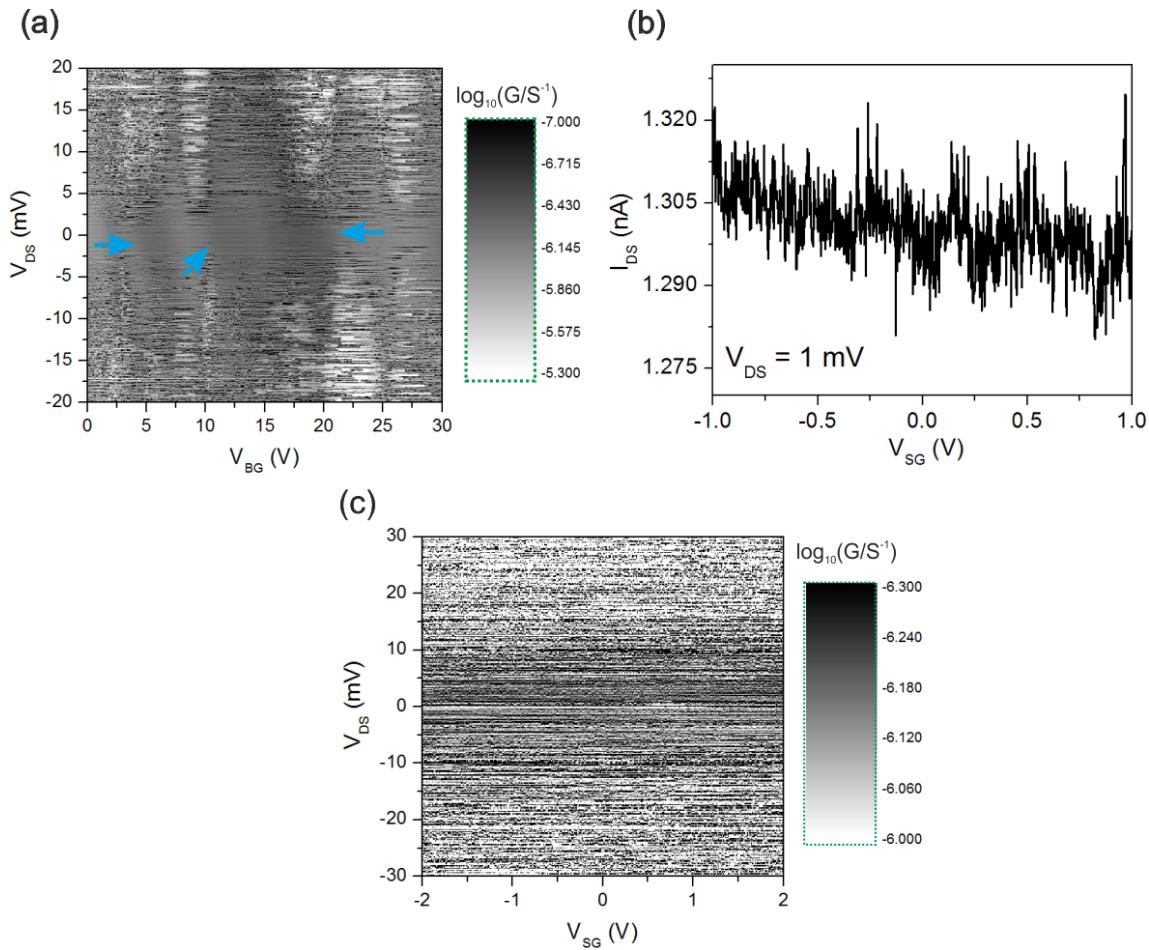

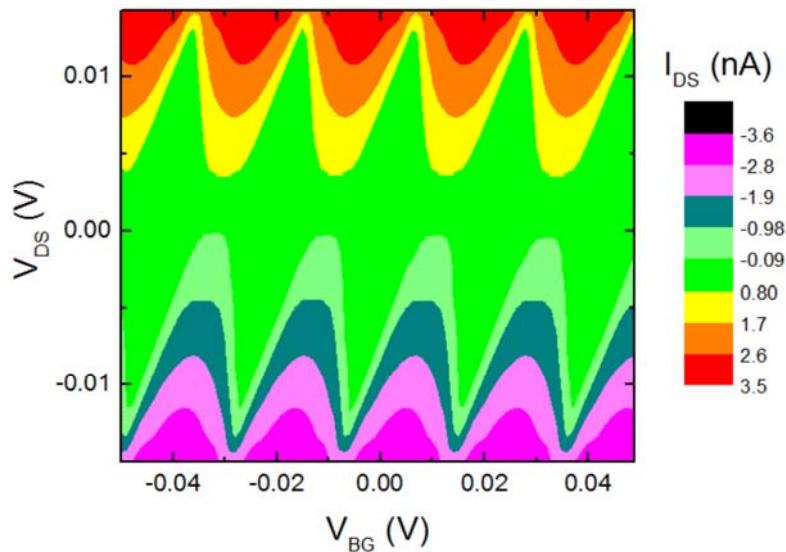

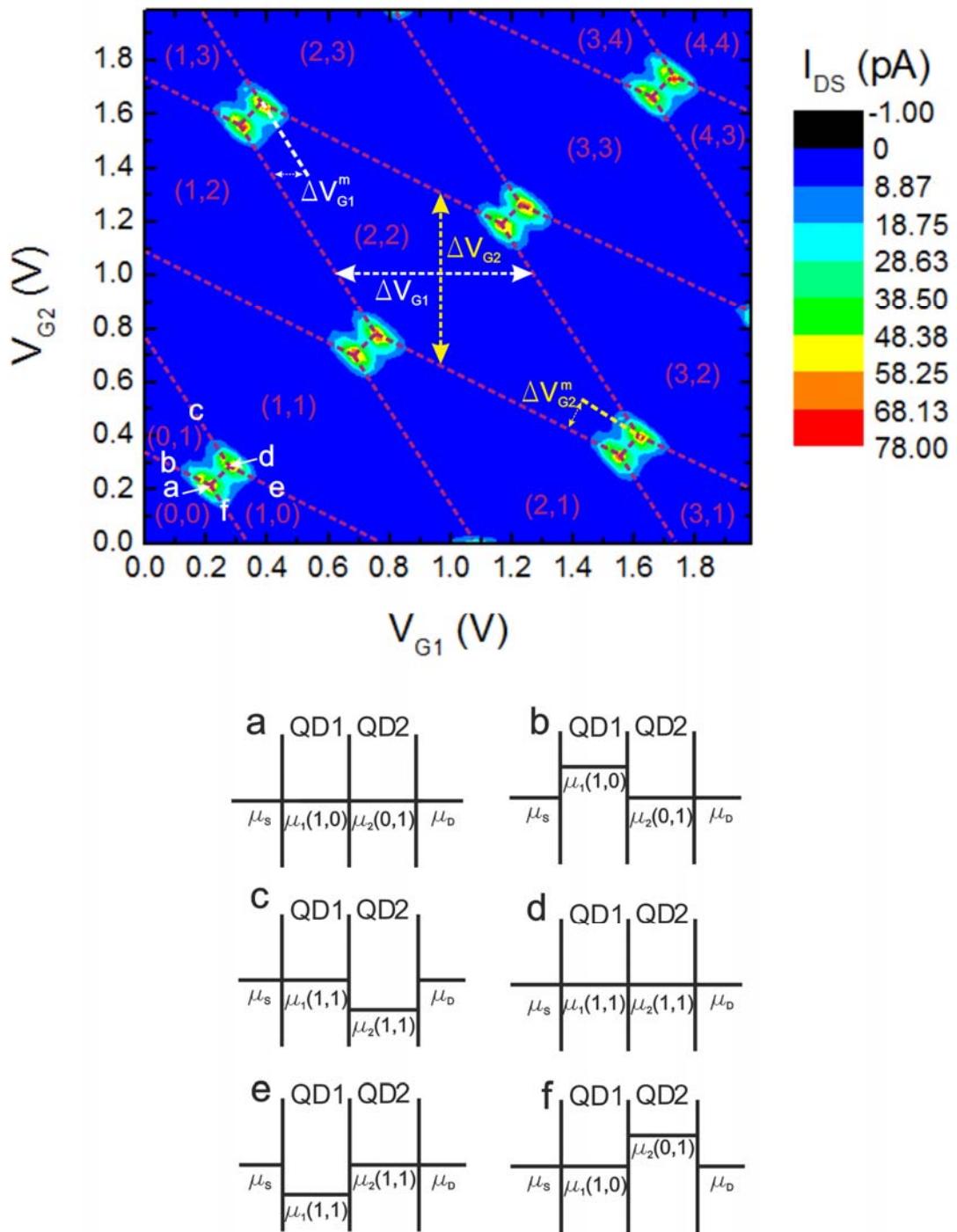

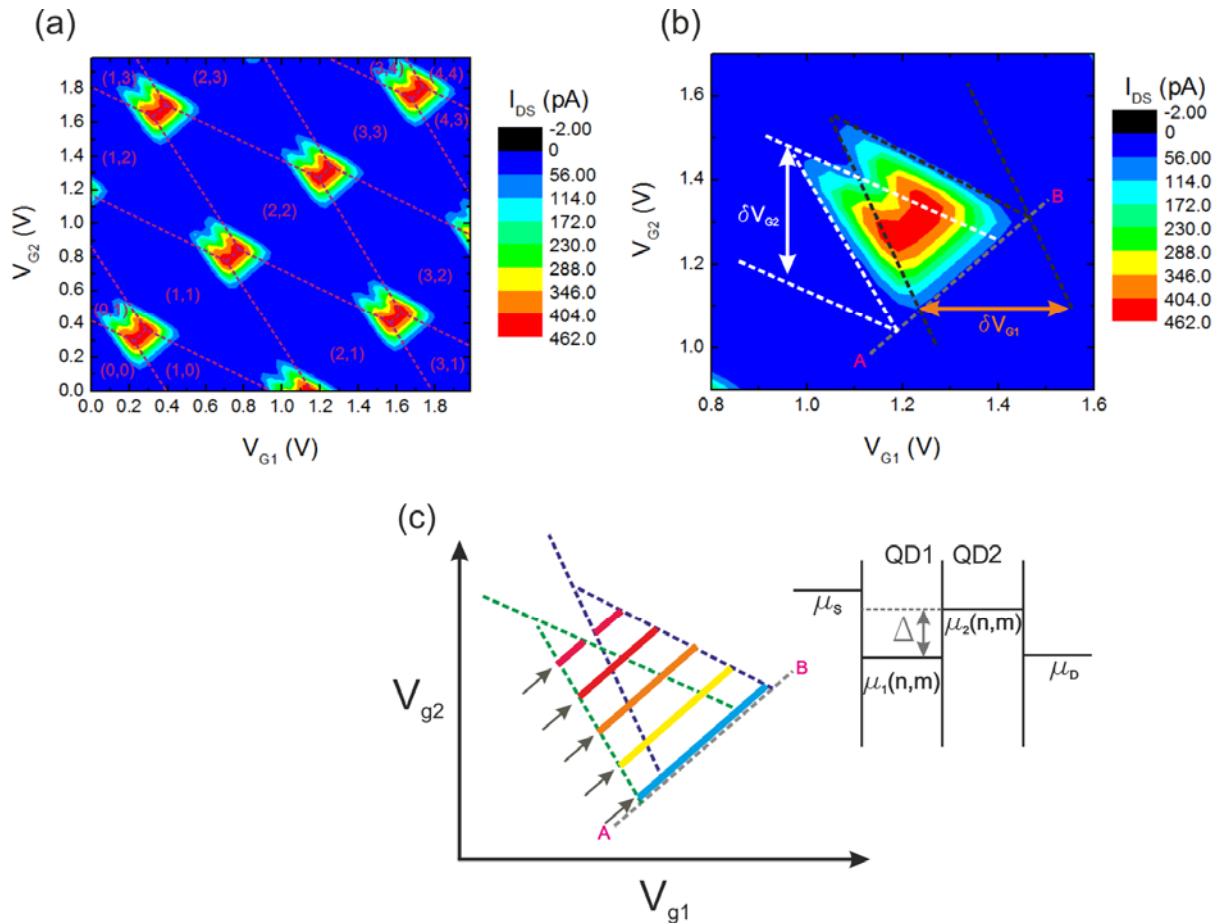

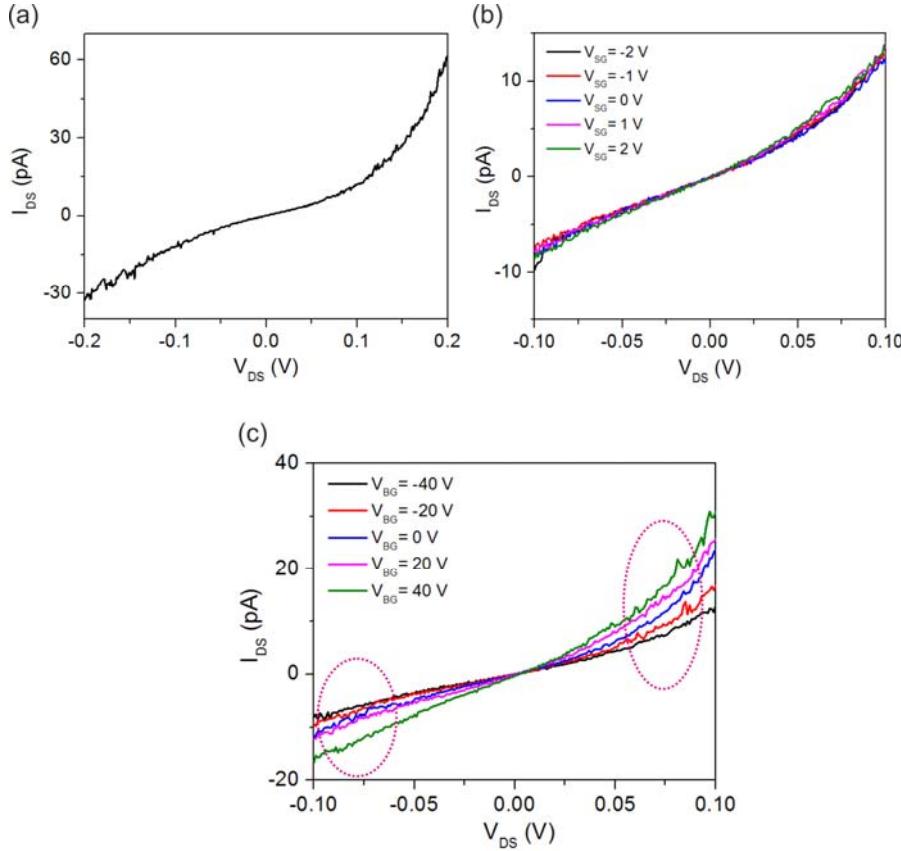

Chapter 6 concentrates on the electrical characterisations of the fabricated graphene quantum dot devices by our EBL/RIE process. Two different types of devices are discussed in this chapter. These are graphene double quantum dot (DQD) devices fabricated on CVD grown monolayer graphene samples and a GQD device fabricated on a mechanically exfoliated monolayer graphene sample. To our best of knowledge, this is the first attempt and demonstration ever of high-density arrays of graphene QD devices on CVD graphene. Also, our successful demonstration of fabrication of high-density arrays of QD devices on CVD graphene with high reproducibility highlights the versatility of our fabrication process with its well-optimised steps. The electrical characteristics of the devices are discussed at room temperature as well as cryogenic temperature (i.e.  $\sim$ 6 K). Room temperature measurements are used to justify the successful development of our EBL/RIE process and to calculate the statistical yield of our process. We estimated an  $\sim$ 80% statistical yield from 57 fabricated devices on graphene samples produced by mechanical exfoliation and  $\sim$ 58% from 160 fabricated devices on CVD graphene samples. These values represent the percentage of fabricated QDs devices which had to exhibit ambipolar behaviour, no observable current leakage from the channel, no observable current leakage between in-plane graphene side-gates, and no observable back gate leakage through the  $\text{SiO}_2/\text{Si}$  substrate. We attributed the lower fabrication yield on CVD graphene samples to the quality and consistency of the flakes. Cryogenic temperature measurements resulted in observation of complex and dense Coulomb diamond arrangements in the collected  $V_{DS} - V_{BG} - I_{DS}$  plots, particularly for the devices fabricated on CVD graphene samples. We discuss these observations in detail and attribute them to formation of unintentional QDs along the etched patterns in graphene during RIE process and existence of grain boundaries in CVD graphene. Furthermore, to determine the feasibility of our DQD device design for single electron tunnelling behaviour (i.e. Coulomb blockade), we present a simulation study by means of COMSOL Multiphysics and Monte Carlo single electron circuit simulations (SETSPICE) to discuss the electrical behaviour of these devices in more detail.

Chapter 7 concludes this thesis by presenting a summary of our findings, including our extensive work in successful development of two fabrication methods for graphene nano devices. In addition, we introduce number of interesting future directions for this work.

# Chapter 2

## Graphene

Carbon-based materials play a major role in present science and technology. Graphene, a two-dimensional (2D) single atomic layer of graphite, had been initially predicted theoretically more than 60 years ago [45]. However, it was only about a decade ago that, using a scotch tape, scientists managed to discover a monolayer graphene sheet experimentally [46]. Despite its short history, its unique material features have ensured a rapid growth of interest in several areas of science and technology. In this chapter, we present a literature review on number of remarkable properties of graphene.

### 2.1 Introduction

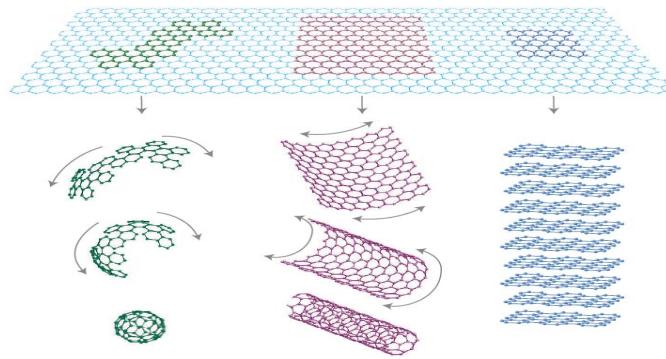

Graphene was discovered by Andre Geim and Konstantin Novoselov in 2004 [46]. Graphene is an  $sp^2$  bonded network of carbon atoms arranged in a shape of honeycomb lattice. It was initially produced by repeatedly peeling away graphite layers with a scotch tape to isolate a single atomic layer of carbon atoms [46]. It can be wrapped up into a zero dimensional fullerenes, rolled into one dimensional nanotubes or stacked into three dimensional graphite (Figure 2.1) [10]. Furthermore, charge carriers can travel thousands of interatomic distances without scattering.

Figure 2.1 – Graphene is a two-dimensional single atomic layer of graphite but yet, it can be shaped into a zero, one and three-dimensional structure. Figure from ref. [10].

## 2.2 Atomic structure and carrier transport properties of graphene

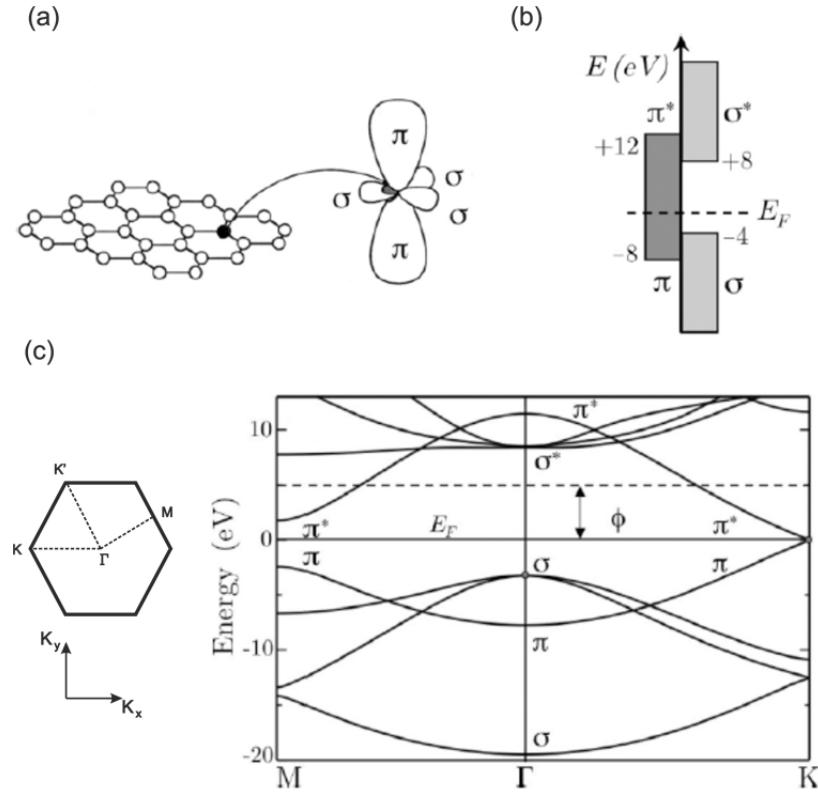

A monolayer graphene flake consists of  $sp^2$  carbon hexagonal networks and is characterized by two types of C-C bonds ( $\sigma$ ,  $\pi$ ). The carbon-carbon bond distance  $a_{C-C}$  in graphene is 1.42 Å. The strong three  $\sigma$  bonds connect a C atom to its three neighbouring atoms, resulting in optical-phonon frequencies much higher than observed in diamond [47]. The electronic characteristics of graphene is determined by the bonding  $\pi$  and antibonding  $\pi^*$  orbitals that construct wide electric valence and conduction bands. The schematic illustration of the carbon valence orbitals in graphene is shown in Figure 2.2(a). The bonding and the antibonding  $\sigma$  bands are separated by a large energy gap of  $\sim 12$  eV, whereas the bonding and antibonding  $\pi$  bands lay in the vicinity of the Fermi level ( $E_F$ ) (Figure 2.2(b)). Hence, to predict the electronic properties of graphene around the Fermi energy the  $\sigma$  bands are usually neglected. Theoretical calculations demonstrated that in graphite, the  $\pi$  band overlap fades away as the layers are further separated over their equilibrium distance, resulting in decoupled graphene layers. Because of this, graphene can be described as a zero-gap semiconductor [47], [48].

Figure 2.2 – (a) The schematic illustration of the carbon honeycomb network and the valence orbitals in a graphene sheet that is constructed from four valence orbitals, i.e. three in-plane  $\sigma$  orbitals and an  $\pi$  orbital perpendicular to the sheet. (b) The energy diagram of  $\sigma$  and  $\pi$  bonds. The  $\sigma$  and  $\sigma^*$  bonds have a large energy gap but  $\pi$  and  $\pi^*$  lie in the vicinity of Fermi level. (c) The dispersion relation of the electronic band structure at three high symmetry points within the first Brillouin zone of a monolayer graphene sheet.  $K_x$  and  $K_y$  correspond to the reciprocal space coordinate axes.  $\Gamma$  point is at the zone centre.  $M$  point is in the middle of the hexagonal side.  $K$  and  $K'$  points are at the corners of the hexagon cell. Note that  $\phi$  is the work function. Figure from ref. [47].

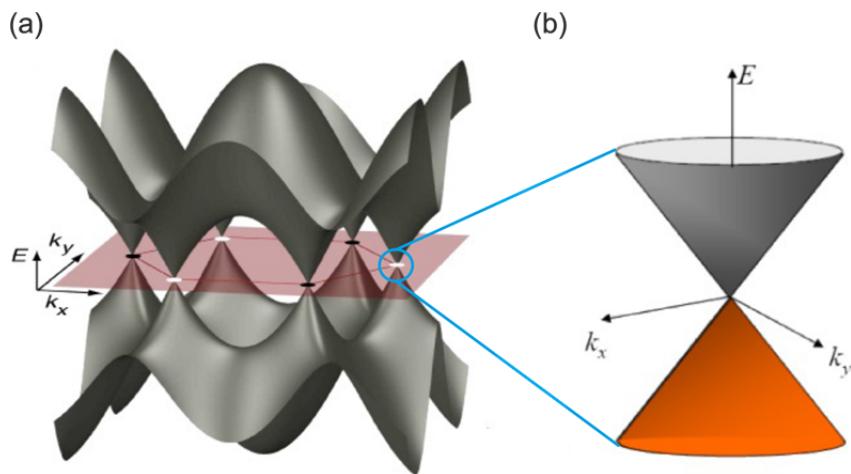

The dispersion relation of the electronic band structure at three high symmetry points within the first Brillouin zone of a monolayer graphene sheet is shown in Figure 2.2(c). The dispersion relation reveals a large energy gap that separates the bonding  $\sigma$  and the antibonding  $\sigma^*$  bands. At the  $K$  and  $K'$  points, the bonding  $\pi$  (highest valence band) and the antibonding  $\pi^*$  (lowest conduction band) bands touch. In a typical band-gap diagram of neutral graphene, the filled valence band and the empty conduction band are drawn as two cones that meet at their apex at a point known as Dirac crossing (Figure 2.3) [10]. This is due to the linear slope of the  $\pi$

band electronic dispersion curve near the corners of the Brillouin zone (e.g. K point) that can be observed in Figure 2.2(c). Hence, at low energies  $E$  near the Dirac crossing points, charge carriers mimic relativistic particles (known as massless Dirac fermions) that allows them to travel at an effective speed of light ( $v \sim 10^6$  m/s) [10], [49].

Figure 2.3 – (a) The Dirac crossing points at the corners of the first Brillouin zone (e.g. K point) in a graphene sheet. (b) A magnified area of the linear energy band at a Dirac crossing point, i.e. a Dirac cone. A modified figure from ref. [50].

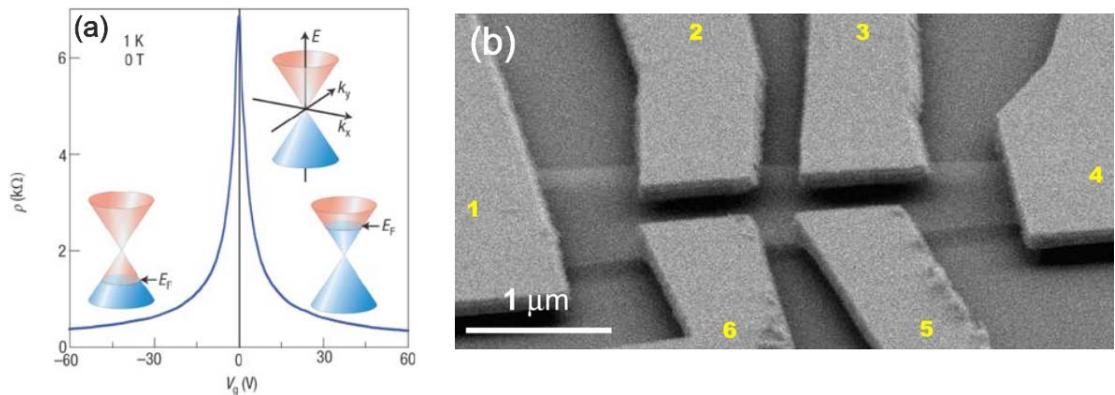

One of many interesting electrical properties of graphene is its ambipolar electric field effect, shown in Figure 2.4(a). That is, charge carriers can be tuned continuously between electrons and holes under a varying gate voltage in concentrations ( $n = \alpha V_g$ , where  $\alpha = 7.2 \times 10^{10} \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  for graphene FET devices fabricated on a 300 nm-thick layer of  $\text{SiO}_2$ ) as high as  $10^{13} \text{ cm}^{-2}$ , with their mobilities weakly dependent on temperature and can exceed  $15,000 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  even under ambient conditions [10].

Weak carrier scattering is one of the most notable properties of graphene. Since graphene is a nearly perfect crystal and free of structural defects, it is suggested that scattering of charge carriers in graphene is mainly due to extrinsic sources [9], [10].

Carrier scattering mechanisms in graphene can be divided into two categories:

I) Intrinsic scattering mechanisms that arise from structural imperfections in graphene lattice, e.g. defect sites in the lattice, edge scattering, grain boundaries and phonon scattering [51]. Structural imperfections (i.e. intrinsic scattering) result in either a change in the local electronic structure or an injection of charges to the lattice, which in fact depends highly on graphene synthesis methods. That is, in exfoliated graphene samples, due to their high crystalline order, intrinsic defect density was found to be less than  $10^{10} \text{ cm}^{-2}$  [9]. However, for graphene samples produced by chemical vapour deposition (CVD) or by epitaxial growth on SiC, graphene exhibits multiple nucleation sites which in turn increase defect density [52], [53]. Furthermore, carrier scattering at the edges of a graphene ribbon (known as edge scattering) results in a size-dependent thermal conductivity [54] and degradation in carrier mobility [55], [56]. That is, carriers in graphene ribbons experience diffusive scattering (i.e. carriers scatter at rough edges with a loss in momentum) at the edges rather than specular scattering (i.e. carriers scatter at smooth edges without any loss in momentum in their direction of propagation). In fact, the effect of edge scattering in graphene ribbons can intensify after patterning/etching of graphene flakes due to increase in edge roughness. Edge roughness results in mixing of edge states which elevates semiconducting states and suppresses metallic states [57]. Therefore, improving current patterning methods to fabricate graphene devices with smoother edges, and so minimising the impact of edge roughness, is essential [58].

II) Extrinsic scattering mechanisms that arise from neighbouring materials, e.g. charged impurities on/under graphene and residues/contaminations produced by processing graphene [59], [60], defects in the underlying substrate and surface charge traps on substrates surface [9], [61]–[63], substrate stabilized ripples [64]–[66], interfacial phonons [9], [61]. It is worth mentioning that annealing graphene samples at elevated temperatures has been proposed as an effective method to remove surface contaminants resided/absorbed on graphene surface [64]. By suspending a graphene flake over a  $\text{SiO}_2/\text{Si}$  substrate (so minimising the substrate effects), as shown in Figure 2.4(b), and a current annealing at  $\sim 130^\circ\text{C}$  in vacuum (so removing residues/contaminants on the suspended graphene flake) prior to the electrical characterisations, Bolotin *et al.* [9] recorded a mobility of  $\sim 230,000 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  at electron densities of  $\sim 2 \times 10^{11} \text{ cm}^{-2}$  at  $\sim 5 \text{ K}$ .

Figure 2.4 – (a) Ambipolar electric field effect in monolayer graphene, i.e. varying  $V_g$  tunes electrons and holes concentration in the flake. In addition, the figure shows the changes in the position of the  $E_F$  with changing of  $V_g$ . Figure from ref. [10]. (b) SEM image of a suspended graphene device with six probes, taken at 15° angle. Figure from ref. [9].

Another interesting electronic behaviour of graphene is its theoretical minimum conductivity of  $\sigma_{min} = 4e^2/h\pi$  [10]. This means that it is impossible to fully “gate” a graphene FET device and the device will always exhibit a non-zero current flow even when tuned at the Dirac point (i.e. where concentration of charge carriers approaches zero). Furthermore, unlike all other materials in which such a low  $\sigma$  eventually results in metal-insulator transition at low temperatures, no sign of such transition has been seen for graphene. However, the experimental obtained values of  $\sigma_{min}$  are  $\pi$  times smaller than the theoretical value, i.e.  $\sigma_{min} = 4e^2/h$ , which different explanations have been reported regarding this discrepancy, e.g. charged-impurity scattering [67], electron-hole puddles around the charge neutrality point [10], [68], aspect ratio of the samples [69].

## 2.3 Graphene production methods

Large-scale (wafer-scale) production of high quality graphene sheets remains a challenge in the commercial-level manufacturability of graphene-based devices. In this section, we address the three most established production methods for graphene samples.

### 2.3.1 Mechanical exfoliation

This simple method, also known as scotch-tape technique, was discovered to produce monolayer graphene flakes for the first time [46]. As we will discuss in detail in section 5.3 of this report, this is also the method that we employed to produce our graphene samples. The method includes peeling away graphite layers with an adhesive tape. A piece of graphite consists of many graphene layers that are stacked and kept together by Van Der Waals force. Due to an inter-layer Van der Waals interaction energy of  $\sim 2$  eV/nm<sup>2</sup>, the magnitude of the force needed to exfoliate graphite is about 300 nN/ $\mu$ m<sup>2</sup>. This very weak force can be easily applied to a piece of graphite with an adhesive tape. Despite the simplicity of the method, so far, the produced graphene samples have shown the highest electrical and structural quality compared to any other method. However, the produced flakes are limited in size (typically, a few micrometres) and not suitable for large-scale production.

### 2.3.2 Epitaxial growth on SiC single crystal

In this approach, graphene is produced from a silicon carbide (SiC) substrate. That is, silicon atoms are thermally desorbed from the surface layers at temperatures between 1250-1450 °C in an ultra-high vacuum chamber [70], [71]. A very recent work by Baringhaus *et al.* [72] reported epitaxial grown graphene nanoribbons with sheet resistances below 1 Ω/square, and so surpassing theoretical predictions for perfect graphene.

However, the major disadvantages of this method are (i) the high processing temperatures and (ii) the high cost of SiC wafers.

### 2.3.3 Chemical vapour deposition (CVD)

In this method, carbon atoms are grown onto a metal film (e.g. nickel, ruthenium, iridium, or copper) in an argon/methane/hydrogen gas mixture at different temperatures. The deposited graphene films are then transferred onto a desired substrate after etching the metal film layer. The process is fast but, CVD graphene is poly-crystalline and is not as pristine as mechanically

exfoliated flakes [73]. Furthermore, the transfer process may cause wrinkles in a grown graphene flake and leave organic residues/contaminants on the sample.

However, very recently, Samsung Co. reported uniform wafer-scale growth of single-crystal monolayer graphene sheets on germanium [74].

## 2.4 Identifying graphene flakes

The growing interest in remarkable properties of graphene asks for a reliable and appealing method to identify and characterise produced graphene samples. That is, the characterisation method must be quick, non-destructive and with high resolution. In this section, we address three main methods of identifying graphene flakes.

### 2.4.1 Optical microscopy

This was the method that helped scientists to discover monolayer graphene flakes for the first time [46], [75]. However, monolayer graphene flakes cannot be observed under an optical microscope, equipped with a white-light illumination, on most substrates. They only become visible when transferred onto a Si substrate with an accurately tuned thickness of an oxide layer, i.e. 90 or 300 nm  $\text{SiO}_2$ . That is, at those oxide thicknesses, even a monolayer flake adds to the optical path of the reflected light, and so producing a feeble interference-like contrast compared to an empty substrate [10], [76], [77]. The thickness of the  $\text{SiO}_2$  layer is a crucial factor to identify thin graphene flakes with this method successfully. For instance, even a 5% difference in the  $\text{SiO}_2$  thickness can make a monolayer graphene completely invisible [10]. However, the major drawback of this method is the fact that the obtained images do not offer any useful information regarding the structural properties of graphene.

It is worth mentioning that graphene flakes were recently observed on other oxide layers too, i.e.  $\text{Al}_2\text{O}_3$  [78] and  $\text{HfO}_2$  [79].

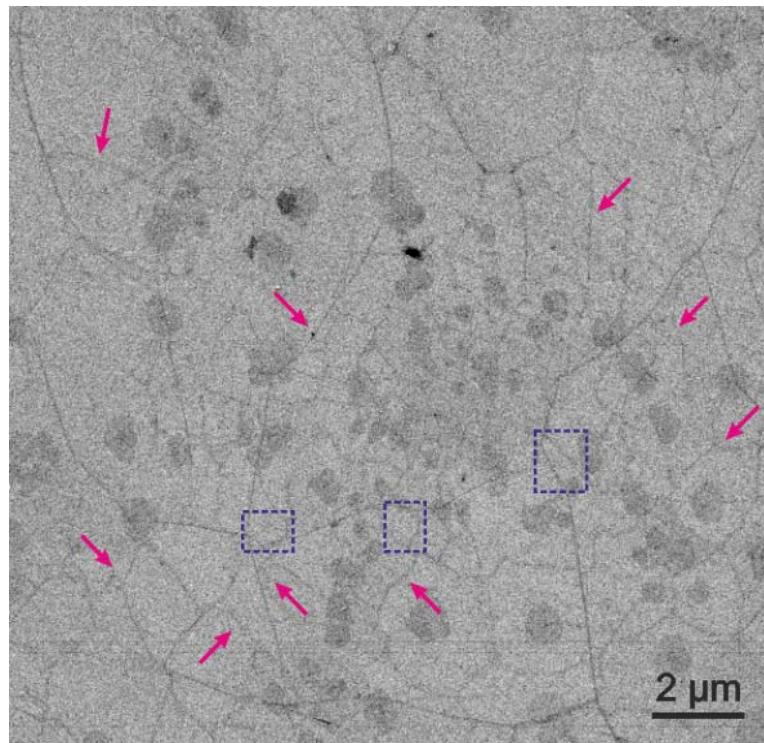

### 2.4.2 Atomic force microscopy

Atomic force microscopy (AFM) is another technique that is employed to identify single and few layers graphene flakes [46], [75]. Because of its high imaging resolution, it can also be used as an imaging tool for etched patterns into graphene flakes [80]–[83]. However, its throughput is low and it can be destructive to the samples. Moreover, if graphene flakes contain folds or wrinkles, the accuracy of this technique limits only to distinguish between monolayer and bilayer flakes [76].

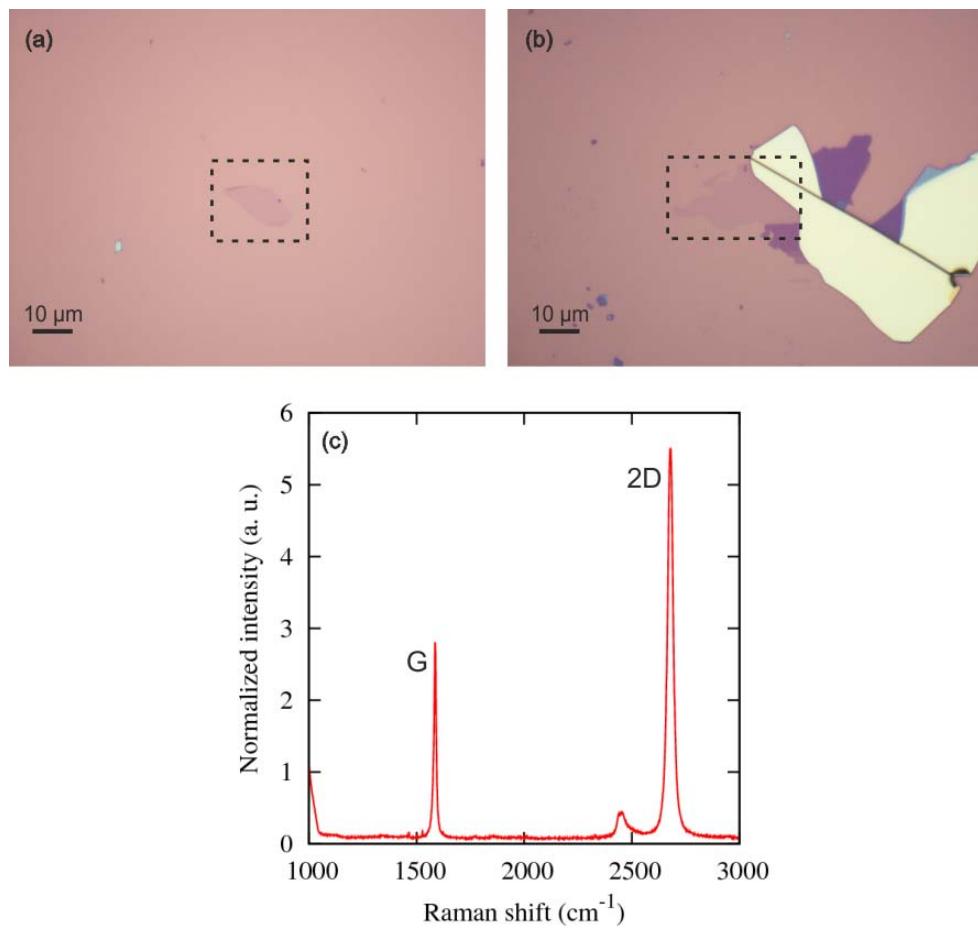

### 2.4.3 Raman spectroscopy

This technique is considered as the best way to characterise structural properties of produced graphene flakes with high accuracy that also offers high-throughput and is non-destructive to the samples [76].

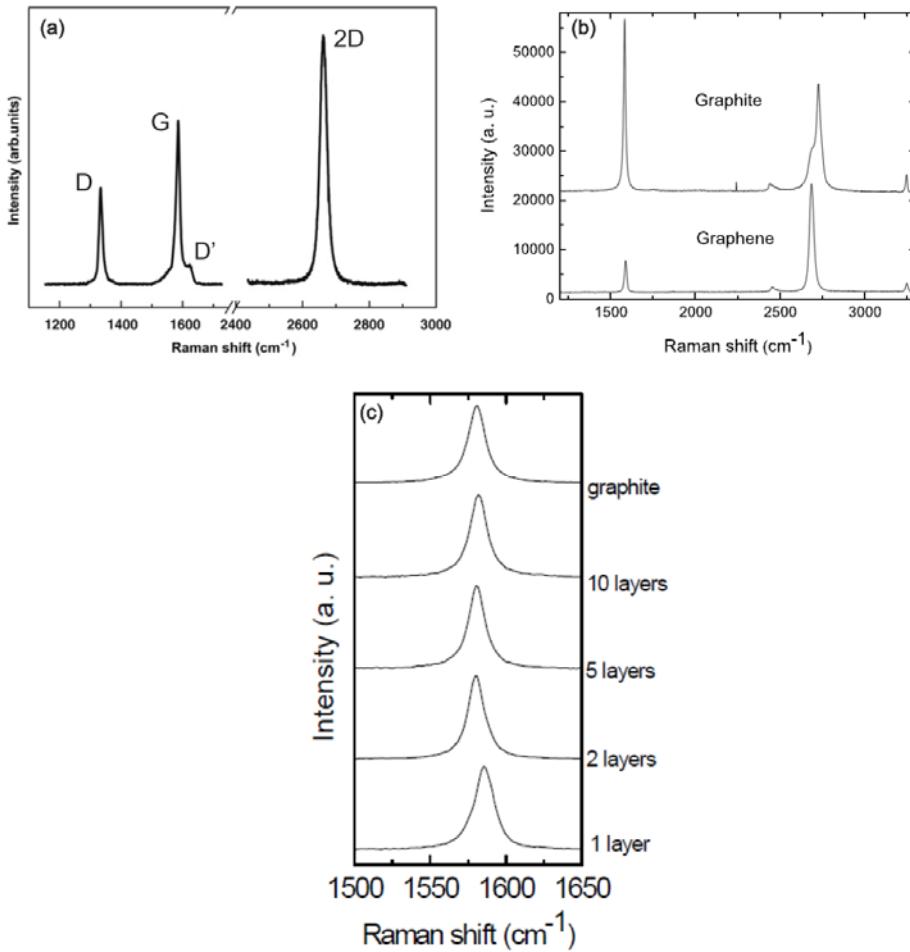

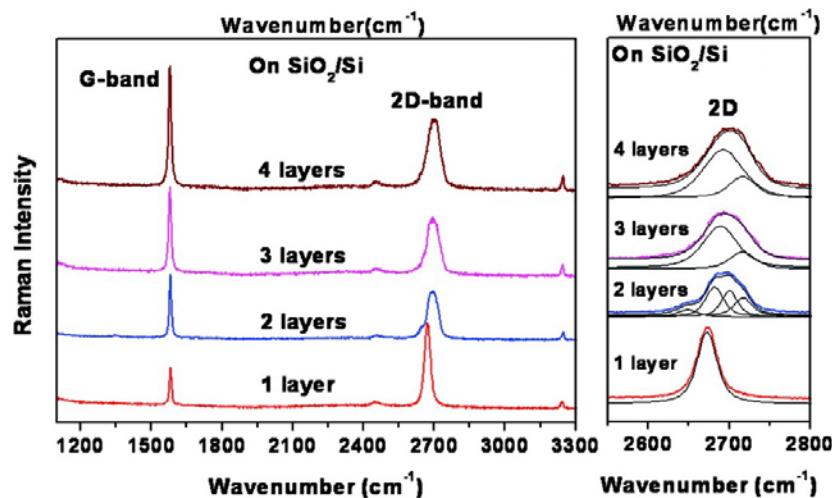

The predominant mode of light scattering when it encounters atoms or molecules is elastic scattering, known as Rayleigh scattering. In this case, the scattered photons have the same energy (frequency) and wavelength as the incident photons. However, it is possible that a small fraction of the incident photons to interact with atoms in a fashion that energy is gained or lost. Consequently, the scattered photons are shifted in frequency and usually have lower frequencies than the incident photons. This inelastic scattering is called Raman scattering [84], [85]. The Raman spectra of all carbon materials show common features in the 1000-3000  $\text{cm}^{-1}$  region. Figure 2.5(a) illustrates the main features (peaks) of Raman spectrum of a graphene flake.

Figure 2.5 – (a) The main features (peaks) in Raman spectrum of graphene, with  $E_{\text{laser}} = 2.41$  eV. Modified figure from ref. [86]. (b) Comparison of Raman spectra for bulk graphite and graphene at a 532 nm wavelength laser. Figures from ref. [76]. (c) Slight upshift in the position of the G peak by  $\sim 5$  cm<sup>-1</sup> with the number of graphene layers. Figure from ref. [87].

The G peak (at  $\sim 1580$  cm<sup>-1</sup> [88]) and the 2D (at  $\sim 2676$  cm<sup>-1</sup> [88]) peak are the most important features in Raman spectrum of graphene. In the first-order Raman spectrum, the G-band corresponds to the in-plane optical phonons mode of two neighbouring carbon atoms on a graphene layer. Interestingly, the G-band frequency ( $\omega_G$ ) slightly upshifts with increasing the number of layers ( $\beta$ ) and follows  $1/\beta$  dependence [76], [89]. The slight upshift in  $\omega_G$ , i.e.  $\sim 5$  cm<sup>-1</sup>, with the number of graphene layers can be seen in Figure 2.5(c). Unlike bulk graphite, the intensity of the 2D peak ( $I(2D)$ ) is much larger than that of the G peak in graphene

(Figure 2.5(b)), i.e.  $I(2D)/I(G) = 4$  in graphene [86]. Furthermore, the G peak intensity increases almost linearly with the number of graphene layers (observable in Figure 2.6).

The D-band and 2D-band originate from a second order process. That is, the  $\omega_D$  and  $\omega_{2D}$  vary as a function of the energy of the incident laser ( $E_{laser}$ ). Such behaviour is understood to originate from a double resonance Raman process [86]. The 2D peak appears as a single peak in monolayer graphene but, according to Figure 2.6, it broadens as the number of layers is increased. In fact, the symmetric and sharp 2D-band ( $\sim 30 \text{ cm}^{-1}$ ) is considered the best indicator of monolayer graphene flakes [88]. It is worth mentioning that, unlike the G peak and the 2D peak, the D peak (at  $\sim 1350 \text{ cm}^{-1}$  [86]) intensity depends on the amount of disorder in a graphene sheet.

Note that the D' peak (see Figure 2.5(a)) is another weak disorder-induced feature in the Raman spectrum of graphene which appears at  $\sim 1620 \text{ cm}^{-1}$  [86].

Figure 2.6 – The evolution in Raman spectrum of graphene as the number of layers is increased. Figure from ref. [88].

# Chapter 3

## Single Electron Transistors with Quantum Dot

This chapter provides an extensive study on the operation of single electron transistors (SETs) with quantum dot (QD) devices as building blocks for quantum information technology. The electron transport via Coulomb Blockade (CB) in such devices is discussed extensively. Furthermore, an experimental review on the behaviour of graphene quantum dots devices through a literature review, which highlights the most important experimental methods relevant to our work, is given.

### 3.1 Single Electron Transistors (SETs)

As explained in section 1.1, for years, the semiconductor industry has been trying to continue the downscaling trend (i.e. Moore's law) to improve the packaging density, circuit speed, power dissipation and cost. However, we discussed that the traditional scaling techniques are reaching their limits. Therefore, to find alternative methods to overcome the associated challenges is essential.

In 1985, Likharev and co-workers predicted the behaviour of a single nanometre-size tunnel junction in detail and proposed the idea of a single electron tunnelling Transistor (SET) [90]–[92]. Though, it must be mentioned that C. J. Görter initiated the study of single electron

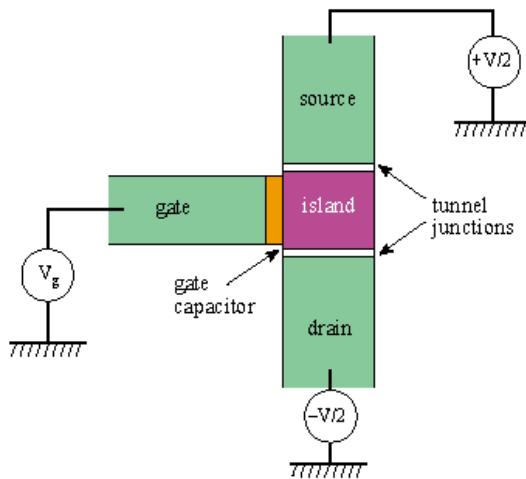

effects by proposing the Coulomb blockade phenomena (see the discussion in section 3.2.1) as early as 1950s [92], [93]. However, it was in 1987 when the first SET device was fabricated by Fulton and Dolan at Bell labs in the US [92], [94]. Schematic illustration of a SET is shown in Figure 3.1. In a SET, there are two tunnel junctions which share one common electrode with a low self-capacitance, called the island. In addition, there are two tunnel junctions to prevent electrons entering or exiting the island unintentionally. The gate is connected to the island capacitively. Hence, by accurate tuning of the bias voltage ( $V_{SD}$ ) and the gate voltage ( $V_g$ ), electrons can propagate from source to drain via the island.

Figure 3.1 – A schematic illustration of a single electron transistor.

Figure from ref. [95].

The island consists of number of energy levels that are evenly spaced. The energy difference between the levels is equal to  $\Delta E$ .  $\Delta E$  is the energy needed to each subsequent electron to tunnel onto the island that acts as a self-capacitance  $C$ . Note that  $\Delta E$  is inversely proportional to  $C$ , i.e.  $\Delta E \propto \frac{1}{C}$ . When there is no voltage at the gate electrode, no accessible energy level is within tunnelling range of the electrons on the source contact and all energy levels on the island with lower energies are occupied. By applying a positive voltage to the gate electrode

the energy levels of the island can be lowered. In this case, an electron can then tunnel into the island and occupy a previously vacant energy level.

Single electron transistors are considered as a promising candidate to replace standard MOSFETs. The most fascinating feature of SETs is the possibility to switch the device by adding one electron to the gate electrode. In contrast, a common MOSFET needs about 1000-10,000 electrons [96]. Indeed, the reduction in the number of electrons in a switching transition significantly lowers the circuit power dissipation, raising the possibility of even higher levels of circuit integration [97]. In addition, SETs have the potential to be much faster than conventional MOSEFETs. That is, the switching time in SETs is determined by RC-time constants of the constrictions (i.e. tunnel junctions) that, thanks to improvements in nanofabrication and lithography tools, can be fabricated in very small dimensions [96].

### 3.2 Single electron transistors with quantum dot

The artificial confinement of electrons in a semiconductor structure leads to two-, one- or zero-dimensional electron systems. Quantum-mechanical effects become pronounced when extension of a structure in one dimension becomes of the order of the Fermi wavelength (i.e. de Broglie-wavelength at the Fermi level)  $\lambda_F$ . In this case, the electronic density of states is distributed on discrete subbands with energy of  $E_i$ . The electrons occupy only the lowest subbands with energy of  $E_0$  at sufficiently low temperatures. The system with such characteristics is called a two-dimensional electron system (2DES). A 2DES can be confined in one further dimension to become a one-dimensional electron system (1DES). Consequently, reducing the last free dimension leads to a 0DES, commonly known as a Quantum Dot (QD) [96], [98].

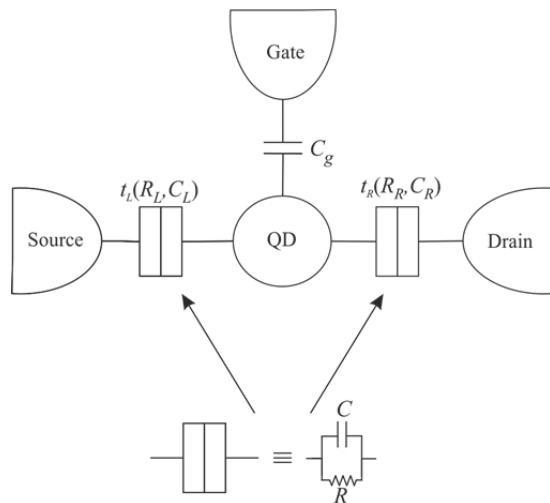

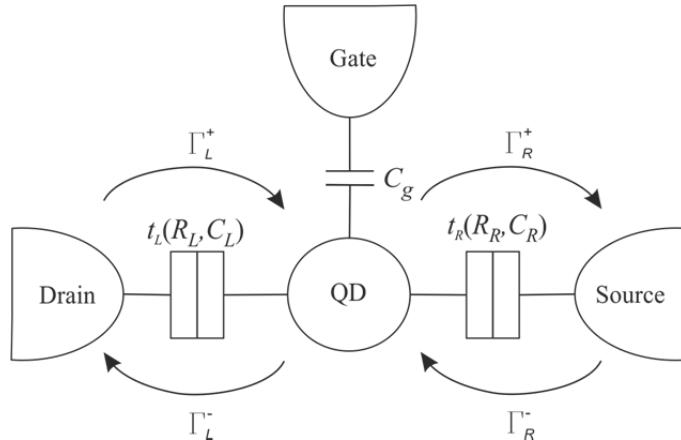

A QD device is modelled as a network of tunnel resistors and tunnel capacitors. A schematic circuit diagram of a SET with a single QD is shown in Figure 3.2. The electronic transport in a quantum dot device is influenced strongly by quantum mechanics at low temperatures that lead to formation of a discrete energy spectrum. An important phenomenon, which influences the electronic behaviour of quantum dot devices, is Coulomb Blockade (CB).

Figure 3.2 – A schematic circuit diagram of a SET with a single QD. The QD is connected to the source (drain) terminal via tunnel barrier  $t_L(t_R)$ . Tunnel barriers are represented by a tunnel resistance ( $R$ ) and a tunnel capacitor ( $C$ ) connected in parallel. Also, the QD is capacitively coupled to the gate terminal.

### 3.2.1 Coulomb blockade (CB)

Increase in resistance at small bias voltages of an electronic device with at least one low capacitance tunnel barrier is called Coulomb Blockade (CB). Because of this, the device resistance increases to infinity for a zero bias voltage and is also not constant at low bias voltages. Hence, the current flow through a tunnel barrier is a series of events which, only one electron tunnels through the tunnel barrier at a time. When an electron tunnels into a QD, part of the supplied energy by the voltage source (e.g.  $V_{DS}$ ) is not immediately dissipated. A certain amount is used to charge the tunnel barrier capacitor (e.g.  $C_L$ ) with an elementary charge. The build-up voltage in the capacitor will be large enough to prevent a new electron from tunnelling and is equal to  $V_b = \frac{e}{C_{L(R)}}$ , where  $e$  is the elementary charge. Therefore, at low bias voltages, the current flow is suppressed and the device resistance is not constant anymore. To tunnel an additional electron into the dot requires compensation of the repulsing electric field. The energy required to achieve this is called the charging energy of the dot ( $E_c$ ) and is expressed by:

$$E_c = \frac{e^2}{2C_\Sigma}, \quad (3.1)$$

with

$$C_\Sigma = C_L + C_g + C_R. \quad (3.2)$$

To observe coulomb blockade effects and so ensuring a successful single electron tunnelling, there are two important criteria that must to be satisfied [98], [99]:

I) To ensure constant number of electrons in a QD (i.e. each electron in the system is localised), the tunnel barriers' resistance  $R_T$  (i.e.  $R_{L(R)}$ ) must be larger than the quantum resistance:

$$R_T \gg R_Q, \quad (3.3)$$

where  $R_Q$  is the quantum resistance and is equal to  $R_Q = h/e^2$ . Based on Heisenberg time-energy uncertainty principle, we then have:

$$E_C \Delta t > \frac{h}{4\pi}, \quad (3.4)$$

where  $h$  is Planck's constant. Moreover,

$$\Delta t \cong R_T C_T, \quad (3.5)$$

where  $\Delta t$  is the time required by an electron to tunnel into or out of a QD with a charging energy of  $E_c$ . By combining Eqs. (3.1), (3.4), (3.5), the value of  $R_T$  can be calculated as:

$$R_T > \frac{h}{2\pi e^2} = 25813 \Omega \cong 26 \text{ k}\Omega \quad (3.6)$$

II) To prevent the electrons entering or exiting the QD freely, the thermal energy must be much lower than the charging energy  $E_c$ . In other words, the charging energy must be large enough to suppress the thermal fluctuations which can be expressed as:

$$k_B T \ll E_c, \quad (3.7)$$

where  $k_B$  is Boltzmann constant and  $T$  is temperature in Kelvin.

### 3.2.2 Carrier transport in single electron transistors

The total energy of a QD system depends on polarisation, background charge ( $Q_0$ ) and the number of electrons ( $N$ ) that have tunneled through the source and the drain tunnel barriers in direction of positive  $V_{DS}$ . Furthermore, the rate of single electron tunnelling per unit time through a potential barrier ( $i$ ) can be expressed as [99]:

$$\Gamma_i^\pm = \frac{1}{e^2 R_i} \frac{\frac{\Delta E_i^\pm}{e}}{1 - \exp\left(\frac{-\Delta E_i^\pm}{k_B T}\right)}, \quad (3.8)$$

where  $\Gamma_i$  corresponds to single electron tunnelling rate through source ( $\Gamma_L$ ) or drain ( $\Gamma_R$ ) tunnel barriers in positive direction (“+”) or negative direction (“-“) of a positive  $V_{DS}$ .  $R_i$  is the source ( $R_L$ ) or the drain ( $R_R$ ) tunnel barrier resistance. The four possible tunnelling transitions in a QD device are shown in Figure 3.3.

Figure 3.3 – The four possible tunnelling transitions in a SET with a single QD. The arrows show the direction of the electron tunnelling. That is, “+” (“-“) sign shows if the tunnelling is in positive (negative) direction with respect to polarity of the  $V_{DS}$ .

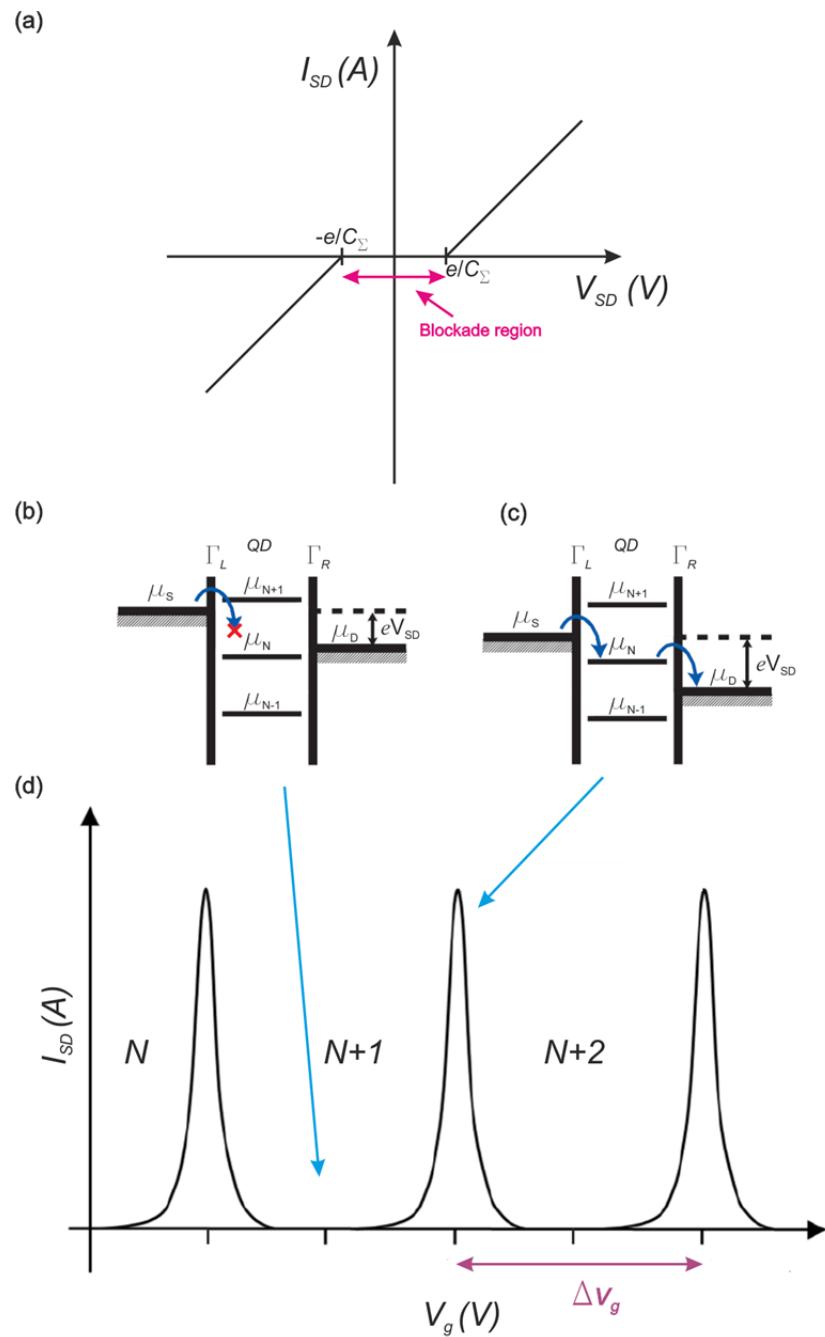

The expected  $I - V$  characteristics of a QD device at a temperature of 4.2 K are shown in Figure 3.4. The blockade region in the  $I_{SD} - V_{SD}$  characteristic, shown in Figure 3.4(a), reflects CB effect. That is, the conduction only occurs when  $V_{SD}$  is large enough such that the

electrons' energy at the contacts, e.g. source, exceeds the charging energy ( $E_c$ ) of the QD. The energy required to add an additional electron into a QD with  $N$  electrons, e.g.  $\mu_{QD}(N + 1) - \mu_{QD}(N)$ , equals to  $E_c$ . Note that  $\mu_{QD}$  is the electrochemical potential of the dot. However, as we previously mentioned, the strong confinement in a QD leads to formation of a discrete energy spectrum. Therefore, the condition required to ensure successful single electron tunnelling via the tunnel barriers can be expressed as:

$$eV_{SD} > E_{add}, \quad (3.9)$$

where  $E_{add} = \Delta E + E_c$  and  $\Delta E$  is the energy spacing between two discrete quantum energy levels in a QD (Figure 3.4(b)). By varying the gate voltage ( $V_g$ ), the electrochemical potential of the dot ( $\mu_{QD}$ ) can be tuned relative to that of the source and drain terminals. That is, for  $V_g = 0$ , there is no accessible energy level in the bias window, formed by  $eV_{SD} = \mu_S - \mu_D$ , for an electron to occupy (Figure 3.4(b)). However, for  $V_g \neq 0$ , a vacant energy level can be tuned in the bias window so that an electron can tunnel into the QD (Figure 3.4(c)). The electron can then tunnel into the drain via the  $t_R$  tunnel barrier. In the  $I_{SD} - V_g$  output plot, single electron tunnelling events appear as pronounced peaks (known as CB peaks) that are evenly spaced by  $\Delta V_g \approx \frac{e}{C_g}$  (shown in Figure 3.4(d)).

It is worth mentioning that such single electron transition in a QD device is considered as linear transport regime. That is, only the ground states (represented as black lines in the quantum dot region in Figure 3.4(b) and Figure 3.4(c)) contribute to the carrier transport and electrons tunnel elastically through the device.

Figure 3.4 –  $I - V$  characteristics of a QD device at a temperature of 4.2 K. (a) The  $I_{SD} - V_{SD}$  output plot. For  $|V_{SD}| < \frac{e}{C_{\Sigma}}$ , the current flow is suppressed due to the  $E_c$  of the QD. (b) The energy level diagram of a QD device in its Coulomb blockade state. (c) The energy level diagram of a QD device in its single electron tunnelling state. (d)  $I_{SD} - V_g$  output plot of the device where each single electron tunnelling event appears as a pronounced CB peak.

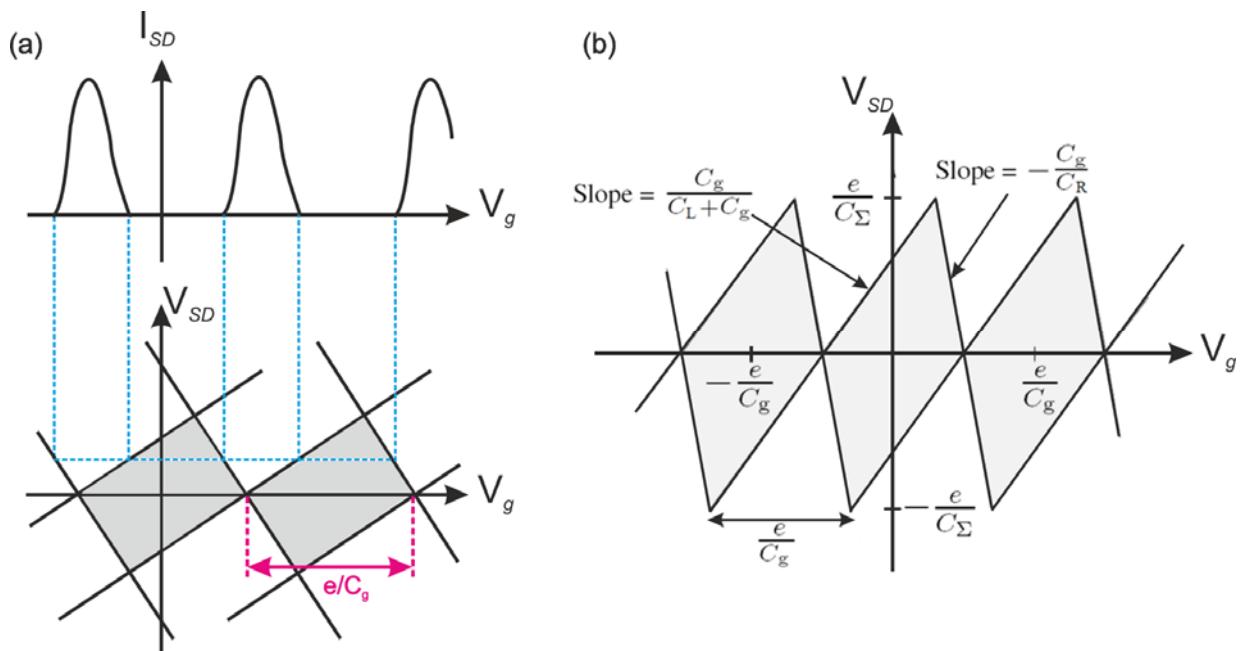

A stability diagram of a QD device is defined as the  $V_{SD} - V_g$  output plot and is shown in Figure 3.5. The blockade regions (shaded regions in Figure 3.5) are called Coulomb diamonds. Note that we have not considered a background charge ( $Q_0$ ) effect in Figure 3.5, i.e.  $Q_0 = 0$ . However, since  $Q_0$  is a constant, it only shifts the diagram by  $-\frac{Q_0}{C_g}$  in the negative direction of the  $V_g$  axis.

Figure 3.5 – (a) The appearance of Coulomb diamonds with respect to the Coulomb oscillation peaks, with a period of  $\frac{e}{C_g}$ . (b) Stability diagram of a QD device with  $Q_0 = 0$ . Note that the blockade regions are shaded. Also, the axes are arbitrary units.

### 3.2.3 Single electron transistors with double quantum dot (DQD)

Lateral double quantum dots (DQD) coupled in series is an interesting and popular SET device structure. DQD devices are considered as promising candidates for basic information storage elements in quantum computer architecture [100]. In this section, we concentrate on the electron transport in such devices.

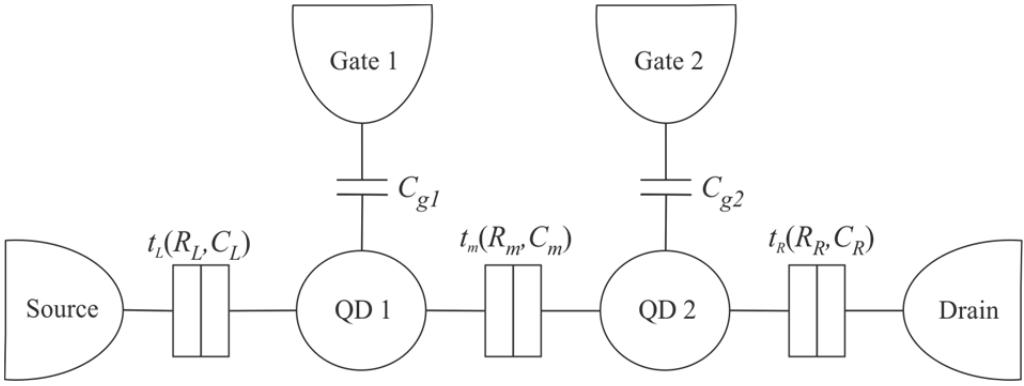

A simplified schematic circuit diagram of a SET with DQD is shown in Figure 3.6.

Figure 3.6 – A simplified schematic circuit diagram of a SET with double quantum dots (DQD).  $t_m$  ( $R_m, C_m$ ) is the coupling tunnel barrier (coupling resistance, coupling capacitance) between the two dots.

The schematic circuit diagram of a DQD device is similar to that of a QD device. Source (drain) terminal is connected via  $t_L$  ( $t_R$ ) to the *QD 1* (*QD 2*). The electrochemical potential of *QD 1* (*QD 2*) is controlled capacitively via  $C_{g1}$  ( $C_{g2}$ ) by a gate electrode  $V_{g1}$  ( $V_{g2}$ ). In addition, the two quantum dots are coupled to each other by a tunnel barrier (i.e.  $t_m$ ), known as interdot coupling tunnel barrier. Note that in Figure 3.6, we consider a simplified schematic circuit diagram of a DQD device. That is, in practice, there is a finite cross capacitance from each gate to the other which is known as gate cross capacitance. Moreover, the schematic does not take into account a back gate or a top gate.

The following discussion follows the approach from van der Wiel *et al.* [101]. We consider the following assumptions for a linear electron transport regime:

- I) The number of electrons in each QD is considered to be  $N_1$  and  $N_2$ , respectively.

- II) The electric charges of QDs are  $Q_{QD1} = -N_1|e|$  and  $Q_{QD2} = -N_2|e|$ , respectively.

- III) Drain electrode is grounded and the bias voltage applied to the source electrode is zero, i.e.  $V_L = V_R = 0$ .

- IV) The gate cross capacitances are negligible.

Based on these assumptions, the total charge on each QD is written as:

$$Q_{QD1} = C_L(V_{QD1} - V_L) + C_{g1}(V_{QD1} - V_{g1}) + C_m(V_{QD1} - V_{QD2}), \quad (3.10)$$

$$Q_{QD2} = C_R(V_{QD2} - V_R) + C_{g2}(V_{QD2} - V_{g2}) + C_m(V_{QD2} - V_{QD1}). \quad (3.11)$$

where  $V_{QD1}$  and  $V_{QD2}$  are the voltages of the two QDs.

Based on Eqs. (3.10), (3.11), the electrostatic energy of the double dots circuit can be written as:

$$U(N_1, N_2) = \frac{1}{2}N_1^2 E_{C1} + \frac{1}{2}N_2^2 E_{C2} + N_1 N_2 E_{Cm} + f(V_{g1}, V_{g2}), \quad (3.12)$$

and

$$f(V_{g1}, V_{g2}) = \frac{1}{-|e|} \{ C_{g1} V_{g1} (N_1 E_{C1} + N_2 E_{Cm}) + C_{g2} V_{g2} (N_1 E_{Cm} + N_2 E_{C2}) \} + \frac{1}{e^2} \left\{ \frac{1}{2} C_{g1}^2 V_{g1}^2 E_{C1} + \frac{1}{2} C_{g2}^2 V_{g2}^2 E_{C2} + C_{g1} V_{g1} C_{g2} V_{g2} E_{Cm} \right\}, \quad (3.13)$$

with

$$E_{C1} = e^2 \frac{C_2}{C_1 C_2 - C_m^2}, \quad (3.14)$$

$$E_{C2} = e^2 \frac{C_1}{C_1 C_2 - C_m^2}, \quad (3.15)$$

$$E_{Cm} = e^2 \frac{C_m}{C_1 C_2 - C_m^2}. \quad (3.16)$$

$E_{C1}$  ( $E_{C2}$ ) is the charging energy of QD 1 (QD 2). The energy change of one dot when an electron is added to the other dot is denoted by  $E_{Cm}$  and is known as the electrostatic coupling energy. Note that the total capacitance applied to each dot is written as:

$$C_{1(2)} = C_{L(R)} + C_{g1(g2)} + C_m. \quad (3.17)$$

Based on Eqs. (3.1), (3.17), the charging energy of each QD and the coupling energy can be rewritten simply as:

$$E_{C1} = \frac{e^2}{C_1} \left( 1 - \frac{C_m^2}{C_1 C_2} \right)^{-1}, \quad (3.18)$$

$$E_{C2} = \frac{e^2}{C_2} \left( 1 - \frac{C_m^2}{C_1 C_2} \right)^{-1}, \quad (3.19)$$

$$E_{Cm} = \frac{e^2}{C_m} \left( \frac{C_1 C_2}{C_m^2} - 1 \right)^{-1}. \quad (3.20)$$

In a DQD system, the electrochemical potential of the *QD 1(2)* is denoted as  $\mu_{1(2)}(N_1, N_2)$  and is the energy required to add the  $N_{1(2)}$ <sup>th</sup> electron to *1(2)*, whilst having  $N_{2(1)}$  electrons on the *QD<sub>2(1)</sub>*. The electrochemical potential of each dot (based on the electrostatic energy of the double dot system presented in Eq. (3.12)) can be written as:

$$\begin{aligned}\mu_1(N_1, N_2) &\equiv U(N_1, N_2) - U(N_1 - 1, N_2) \\ &= \left(N_1 - \frac{1}{2}\right)E_{C1} + N_2E_{Cm} - \frac{1}{|e|}(C_{g1}V_{g1}E_{C1} + C_{g2}V_{g2}E_{Cm}),\end{aligned}\quad (3.21)$$

$$\begin{aligned}\mu_2(N_1, N_2) &\equiv U(N_1, N_2) - U(N_1, N_2 - 1) \\ &= \left(N_2 - \frac{1}{2}\right)E_{C2} + N_1E_{Cm} - \frac{1}{|e|}(C_{g1}V_{g1}E_{C1} + C_{g2}V_{g2}E_{C2}).\end{aligned}\quad (3.22)$$

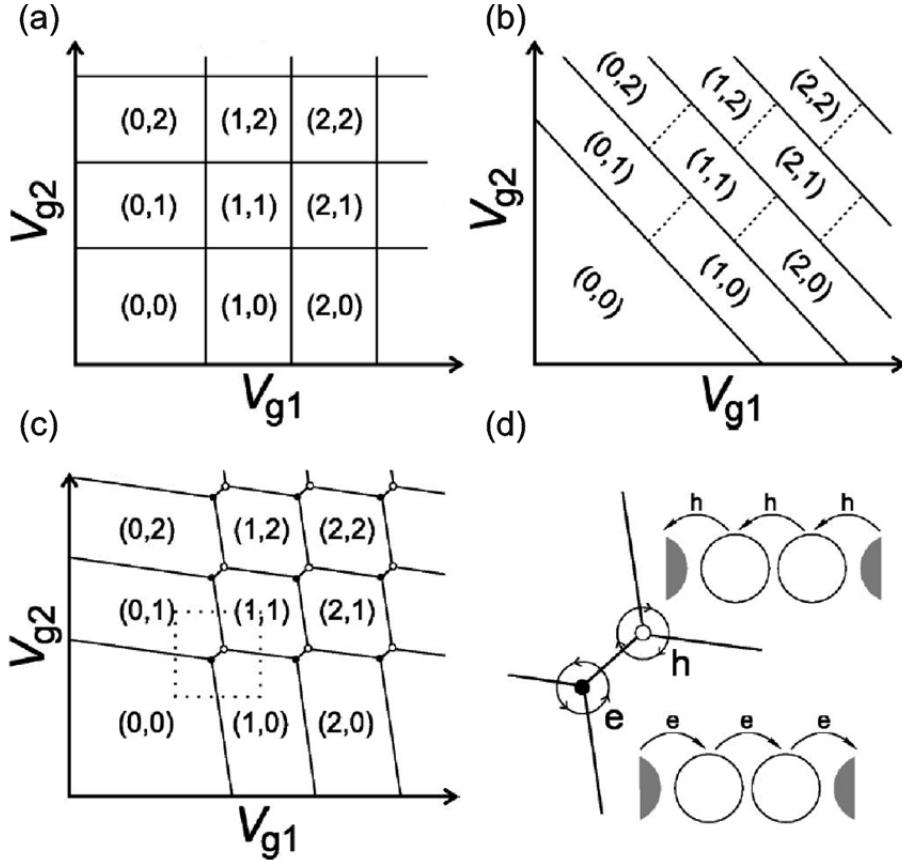

The stability diagram of a DQD system can be discussed based on the value of the coupling capacitance ( $C_m$ ). Since no bias voltage is applied, we have  $\mu_S = \mu_D = 0$ . Therefore, the double dots' equilibrium charges are the largest integers  $N_1$  and  $N_2$  for which both  $\mu_1(N_1, N_2)$  and  $\mu_2(N_1, N_2)$  are less than zero. That is, electrons can escape to the left or right terminals if either  $\mu_1(N_1, N_2)$  or  $\mu_2(N_1, N_2)$  is larger than zero. Due to this, the stability diagram of the system is constructed in a hexagonal shape. The stability diagram is categorised into following three categories:

I) The double dots behave as two independent dots if  $C_m = 0$ . That is,  $E_{Cm} = 0$ . The stability diagram of such a DQD system as a function of number of electrons in each dot ( $N_1, N_2$ ) and applied gate voltages ( $V_{g1}, V_{g2}$ ) is shown in Figure 3.7(a). Here, sweeping each gate voltage only affects the charge of its corresponding QD. Therefore, for a completely decoupled double dots system, the electrostatic energy in Eq. (3.12) can be written as a sum of the energies of the two dots. That is,

$$U(N_1, N_2) = \frac{(-N_1|e| + C_{g1}V_{g1})^2}{2C_1} + \frac{(-N_2|e| + C_{g2}V_{g2})^2}{2C_2}. \quad (3.23)$$

II) If  $C_m$  becomes the dominant capacitance in the system, i.e.  $C_m > C_{1(2)}$ , the double dots behave as one big dot (Figure 3.7(b)). Therefore, Eq. (3.17) is simply:

$$\mathbb{C}_{1(2)} = C_{1(2)} - C_m. \quad (3.24)$$

In this case, the electrostatic energy of the single big dot with charge  $N_1, N_2$  can be written as:

$$U(N_1, N_2) = \frac{[-(N_1 + N_2)|e| + C_{g1}V_{g1} + C_{g2}V_{g2}]^2}{2(\mathbb{C}_1 + \mathbb{C}_2)}. \quad (3.25)$$

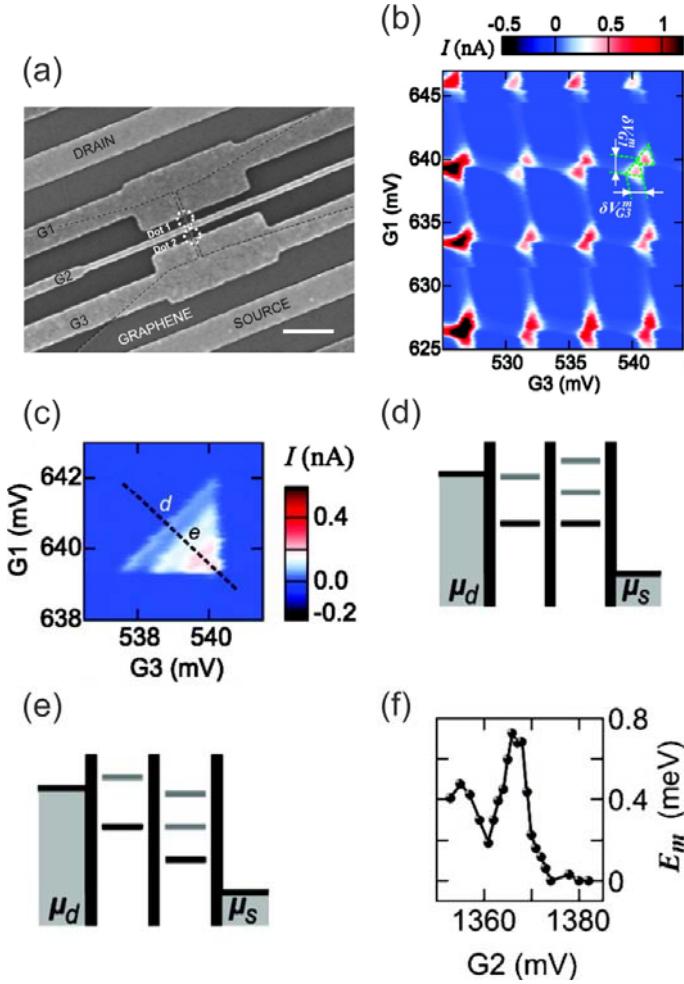

III) If  $0 < C_m < 1$ , the stability diagram forms an interesting arrangement of hexagons which is known as “honeycomb” pattern (Figure 3.7(c)). As Figure 3.7(c) illustrates, each hexagon is constructed by a number of small points (i.e.  $\bullet/\circ$ ) that are known as “triple points”. The name comes from the fact that a conductance resonance occurs when an electron tunnels through both dots. This condition is satisfied at times that three charge states become degenerated. The black points ( $\bullet$ ) and the white points ( $\circ$ ) represent different type of tunnelling. As shown in Figure 3.7(d), a  $\bullet$  triple point represents an electron tunnelling event from the source to drain electrode. Therefore, the sequence of charge states can be written as:

$$U(N_1, N_2) \rightarrow (N_1 + 1, N_2) \rightarrow (N_1, N_2 + 1) \rightarrow (N_1, N_2). \quad (3.26)$$

However, a  $\circ$  triple point represents a ‘hole’ tunnelling event. Note that here ‘hole’ means reverse tunnelling of electrons from the drain to source electrode across both dots. Therefore, the sequence of charge states can be written as:

$$(N_1 + 1, N_2 + 1) \rightarrow (N_1 + 1, N_2) \rightarrow (N_1, N_2 + 1) \rightarrow (N_1 + 1, N_2 + 1). \quad (3.27)$$

Figure 3.7 – Schematic of the stability diagram of a DQD system for, (a) completely decoupled double dots system (i.e.  $C_m = 0$ ), (b) strong coupling capacitance (i.e.  $\frac{C_m}{C_{1(2)}} \rightarrow 1$  ), (c) intermediate coupling capacitance (i.e.  $0 < C_m < 1$  ). (d) The sequence of charge states at the  $\bullet/\circ$  triple points. The axes are arbitrary units. Figures from ref. [101].

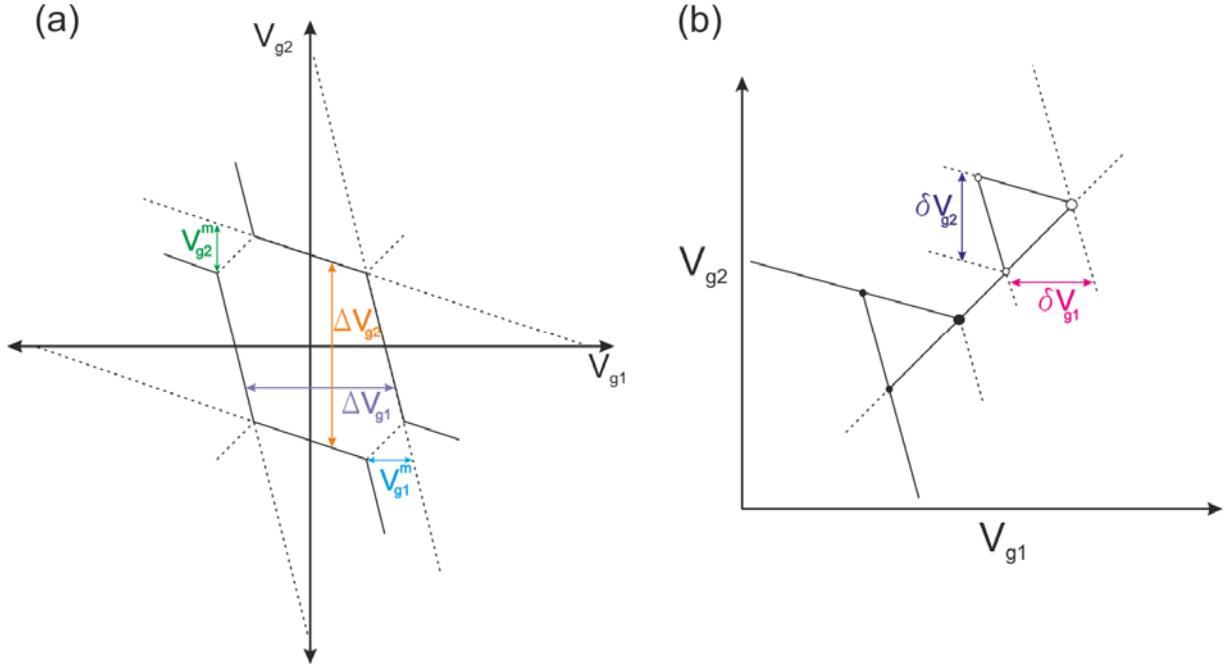

It is worth mentioning that the sequential tunnelling events through double quantum dots coupled in series are only permitted at charge triple points. Because it is only at those points that  $\mu_{QD1}$ ,  $\mu_{QD2}$ ,  $\mu_S$  and  $\mu_D$  are aligned [101], [102]. Furthermore, geometry of a honeycomb cell in a stability diagram is shown in Figure 3.8(a). Geometry of the honeycomb cell can be expressed as [101]:

$$\Delta V_{g1} = \frac{|e|}{C_{g1}}, \quad (3.28)$$

$$\Delta V_{g2} = \frac{|e|}{C_{g2}}, \quad (3.29)$$

$$\Delta V_{g1}^m = \frac{|e|C_m}{C_{g1}C_2} = \Delta V_{g1} \frac{C_m}{C_2}, \quad (3.30)$$

$$\Delta V_{g2}^m = \frac{|e|C_m}{C_{g2}C_1} = \Delta V_{g2} \frac{C_m}{C_1}. \quad (3.31)$$

Figure 3.8 – (a) Geometry of a honeycomb cell of the stability diagram of a DQD device with an intermediate coupling capacitance. (b) Geometry of the bias triangles formed at the triple points at a finite bias voltage. The axes are arbitrary units.

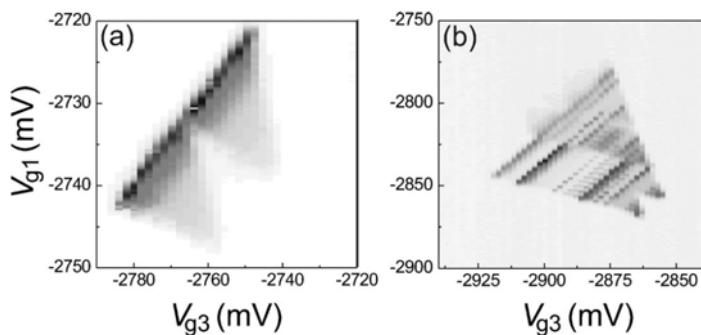

At a finite  $V_{SD}$  (i.e. nonlinear transport regime), the conductance regions of the stability diagram, i.e. the triple points, change to triangular-shaped regions (shown in Figure 3.8(b) and Figure 3.9(a)). These regions are called bias windows or bias triangles. The weak-grey-colour regions of the bias triangles in Figure 3.9(a) are attributed to off-resonance current. The off-resonance conductance in the bias triangles is as a result of inelastic tunnelling (due to phonon or photon absorption or emission) [103], [104] and co-tunnelling [101]. Note that an inelastic tunnelling occurs when there is an energy mismatch between the energy levels of the two dots but, the energy levels still lie between  $\mu_S - \mu_D$  (i.e. bias window).

The bias triangles correspond to the region in which, determining the detuning of the DQD potentials is in the range of the bias window. If we assume [101],

$$\text{I}) -|e|V_{SD} = \mu_s \geq \mu_1,$$

$$\text{II}) \mu_1 \geq \mu_2,$$

$$\text{III}) \mu_2 \geq \mu_D = 0,$$

then the dimensions of the bias triangles can be expressed as [101]:

$$\gamma_1 \delta V_{g1} = \frac{c_{g1}}{c_1} |e| \delta V_{g1} = |eV_{SD}|, \quad (3.32)$$

$$\gamma_2 \delta V_{g2} = \frac{c_{g2}}{c_2} |e| \delta V_{g2} = |eV_{SD}|. \quad (3.33)$$

$\gamma_1$  and  $\gamma_2$  are the conversion factors between the gate voltage and energy.

The triangle regions grow in size with increasing the bias voltage. In addition, for a sufficiently large bias voltage, a number of discrete energy levels can appear between the ground states of the dots, known as excited states. These excited states can also contribute to the conductance. Hence, successive alignment of ground states and excited states leads to resonances within the bias triangles. These resonances are observed as lines with different colours (due to change in the current through the device) in the bias triangle. This is shown in Figure 3.9(b).

Figure 3.9 – (a) A pair of bias triangle with  $V_{SD} = -200 \mu V$ . The dark line is the elastic tunnelling via alignment of ground states in the two dots. The grey-colour region is the off-resonance current. (b) Observation of current resonance in the bias triangles due to the excited states.  $V_{SD} = -1 mV$ . Figures from ref. [101].

### 3.3 An experimental review on graphene nano devices

As discussed in section 1.2, spin-orbit coupling and hyperfine interactions with carbon nuclei are both small in graphene, and a very long spin relaxation length has been demonstrated [12], [13], which make graphene a promising candidate for Quantum Information Technologies (QIT) [11]. However, so far, to our best of knowledge, there are very few groups who are actively investigating graphene QDs (GQDs) devices. This is probably due to graphene's short history and its huge impact in several areas of science and technology. In this section, we present a brief literature review which highlights some of the conducted experiments on graphene nano devices relevant to our work.

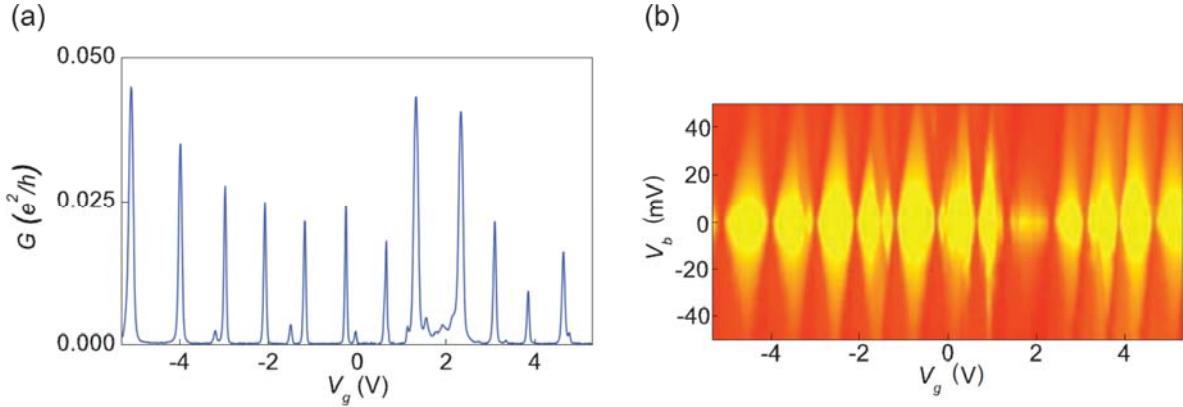

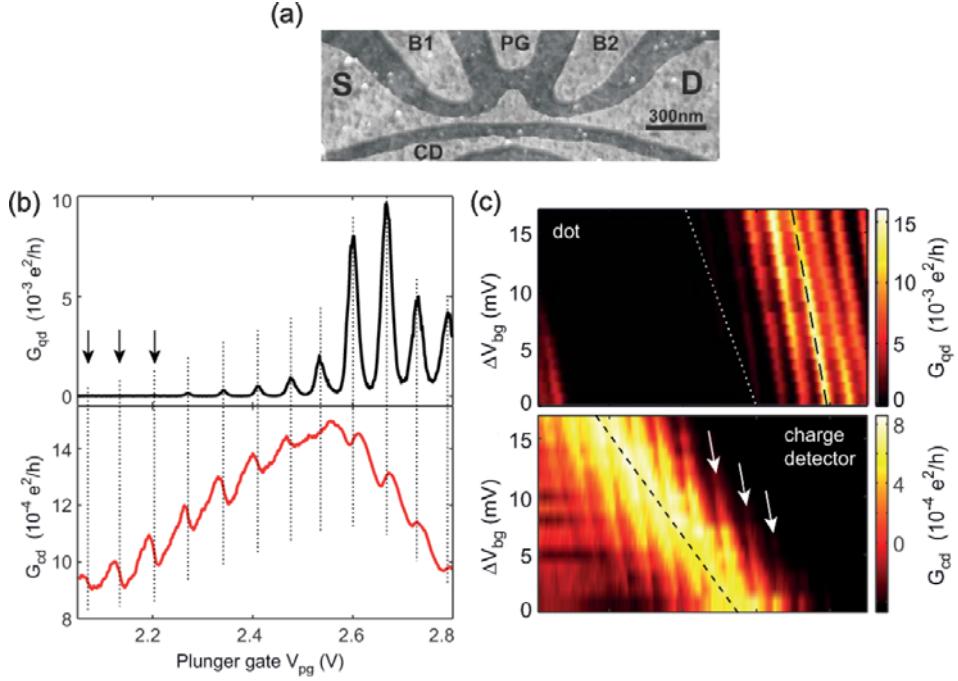

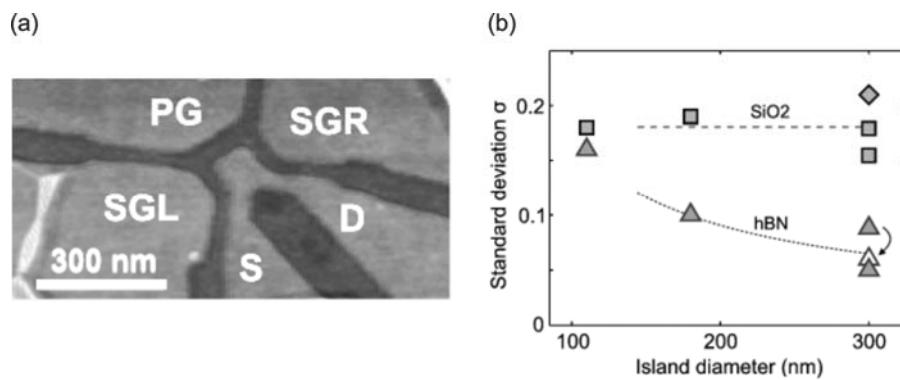

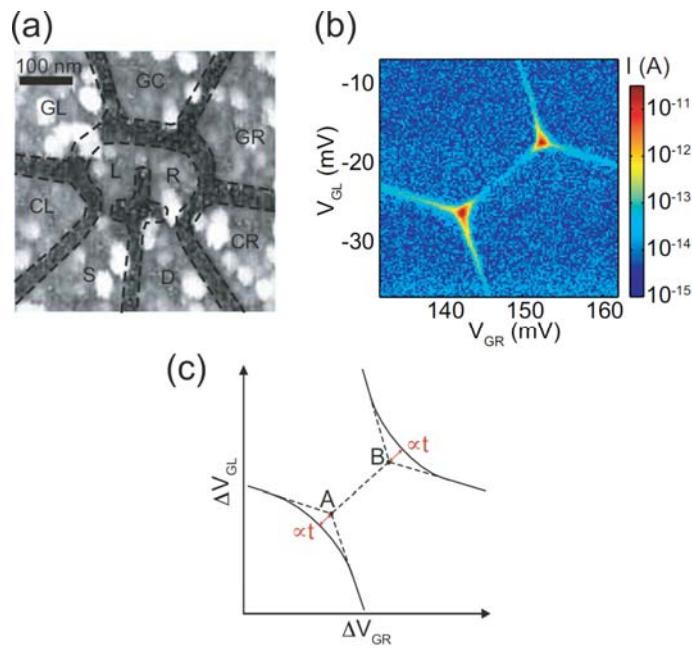

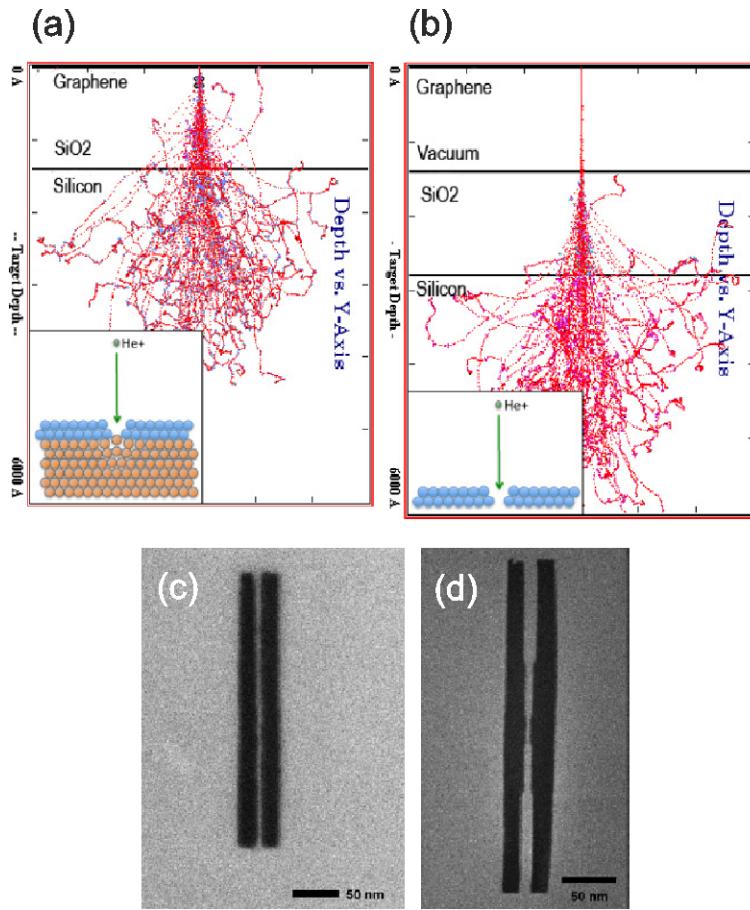

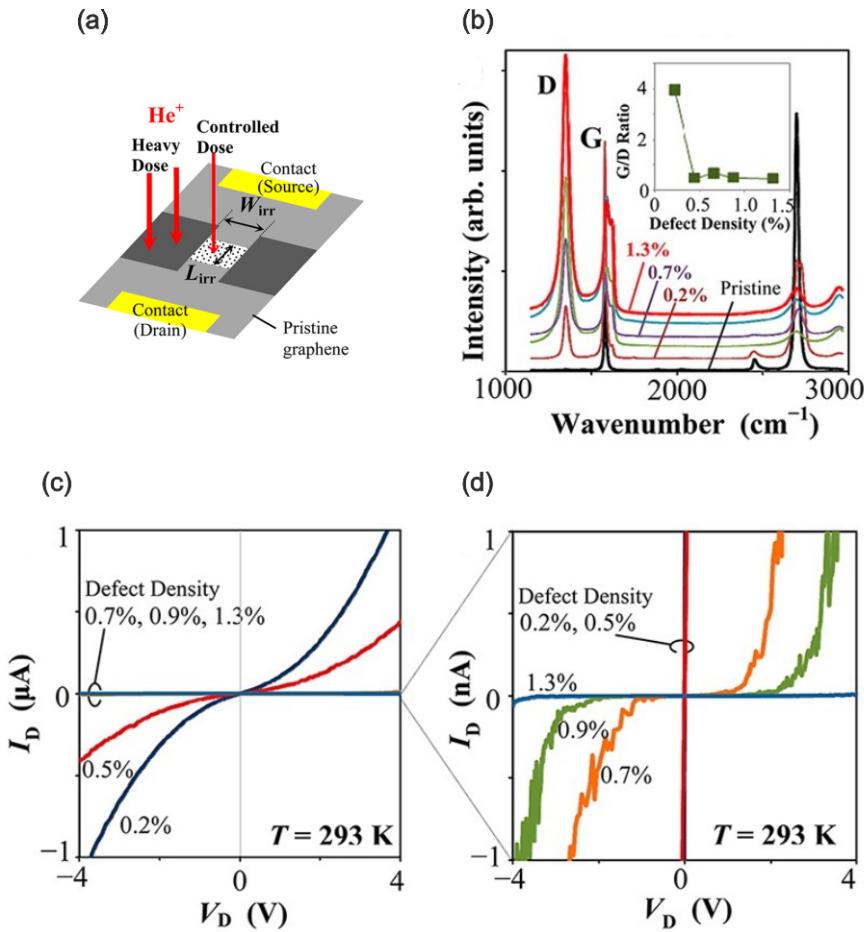

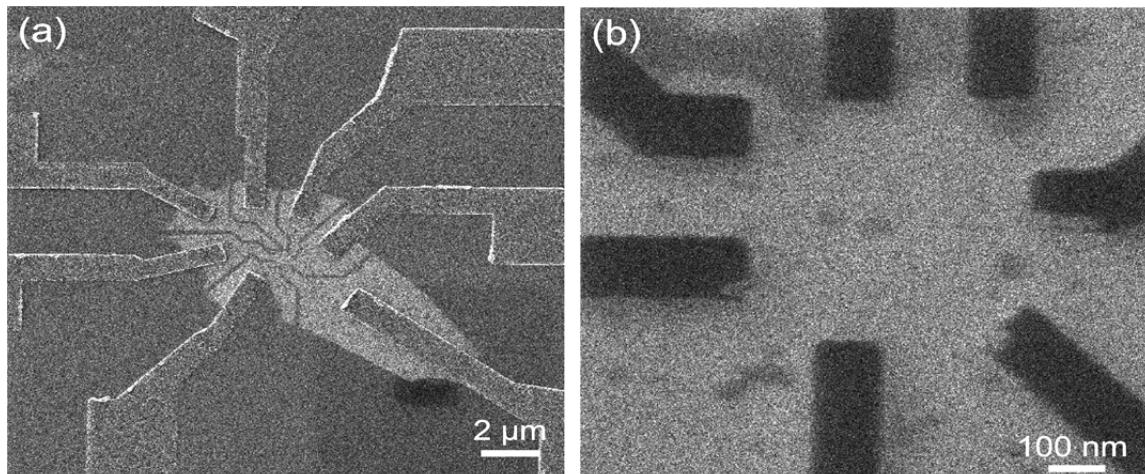

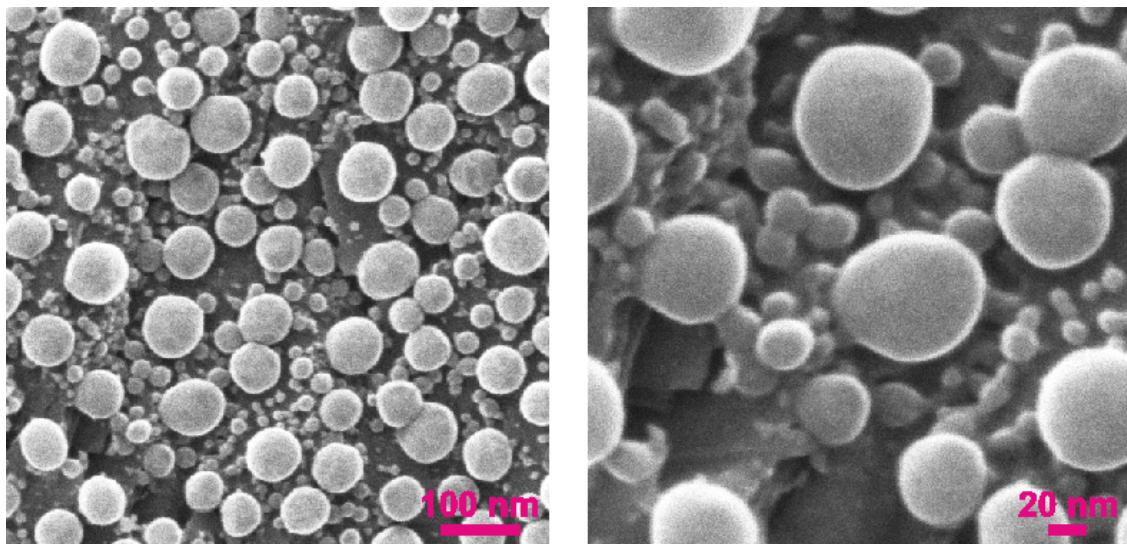

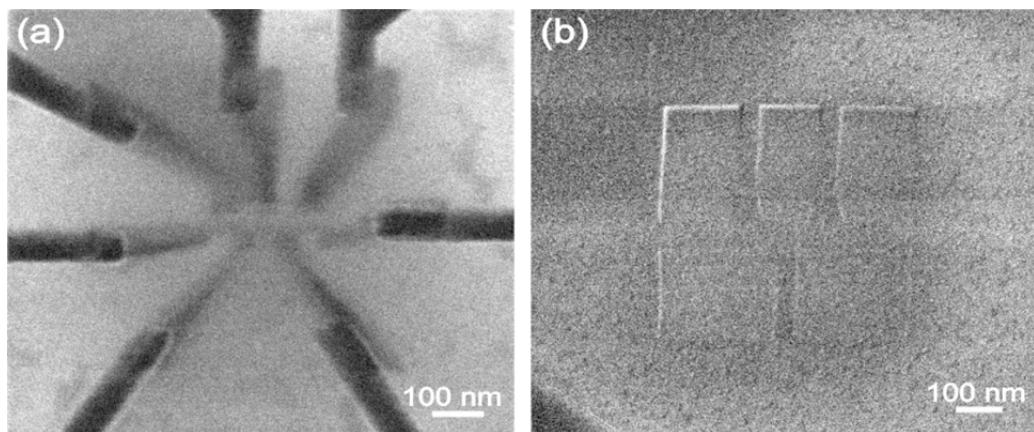

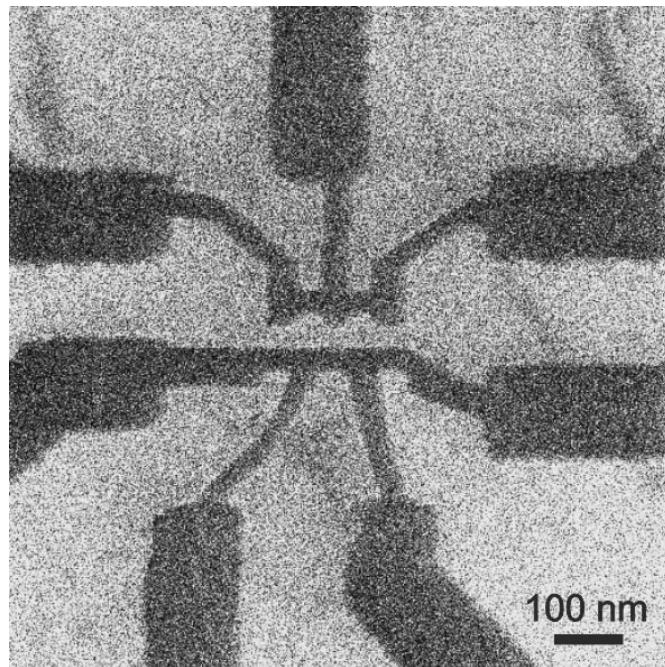

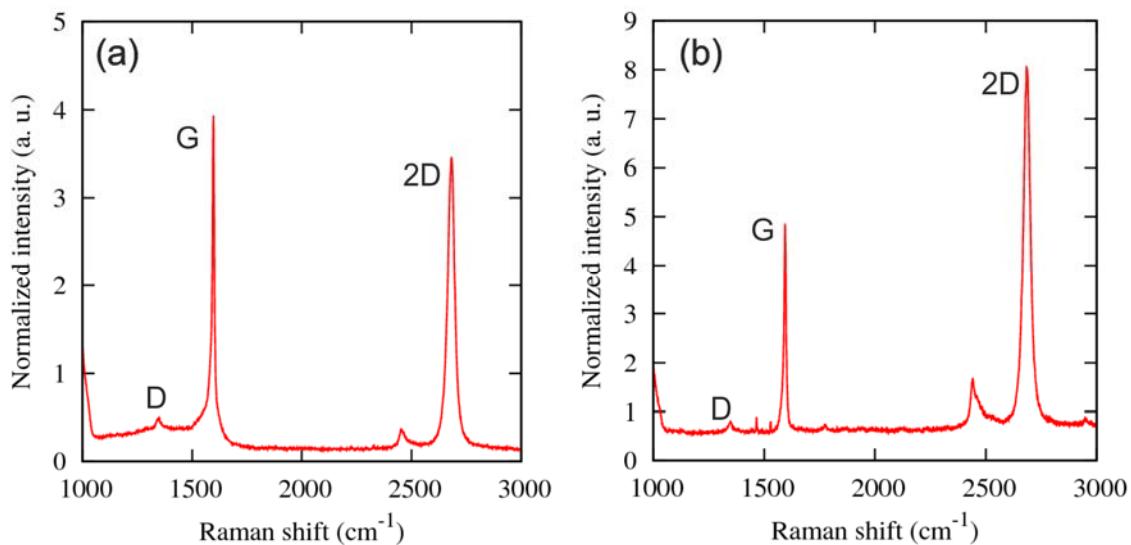

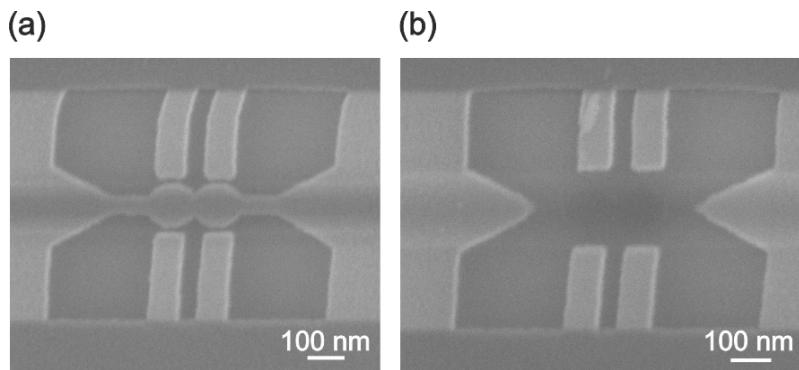

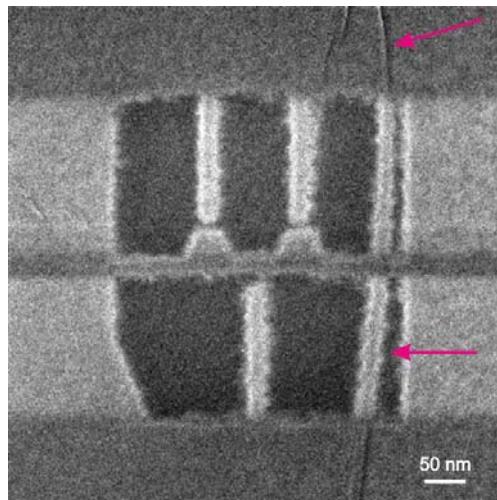

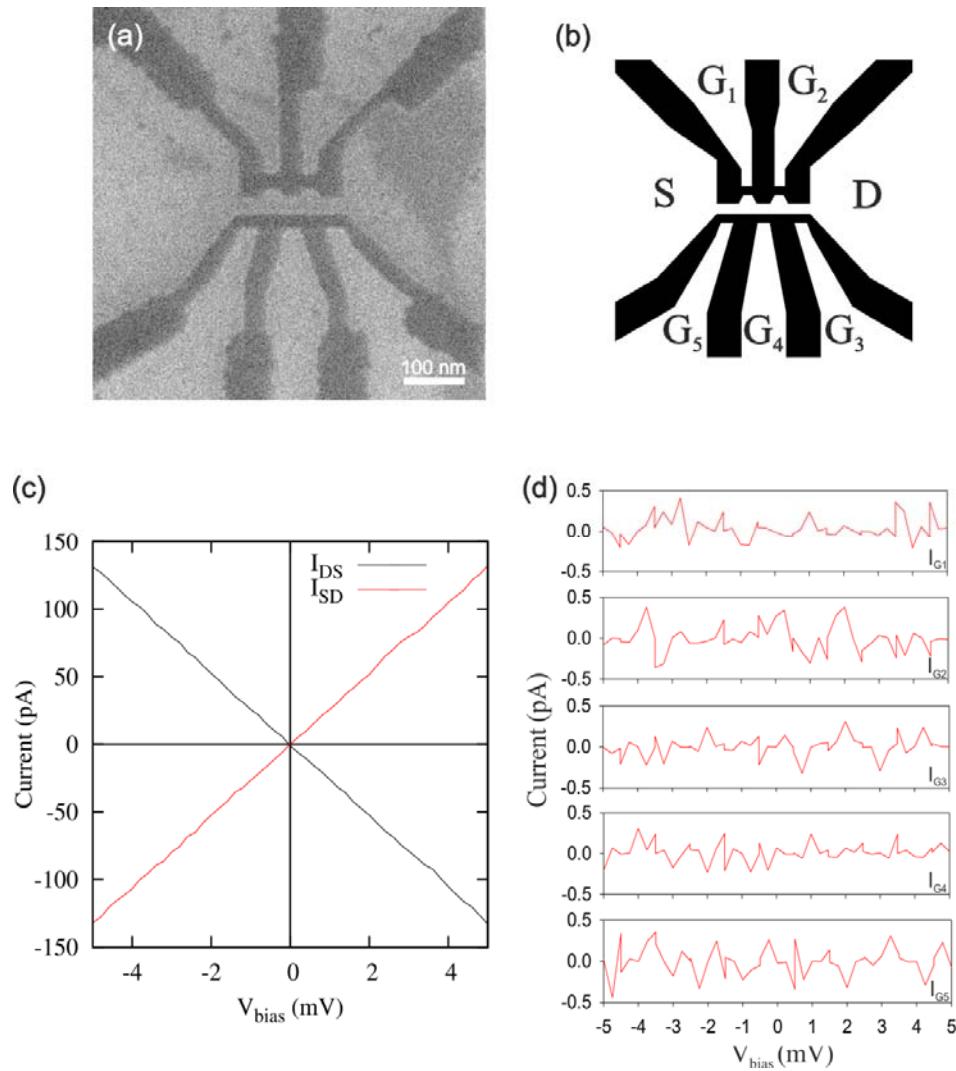

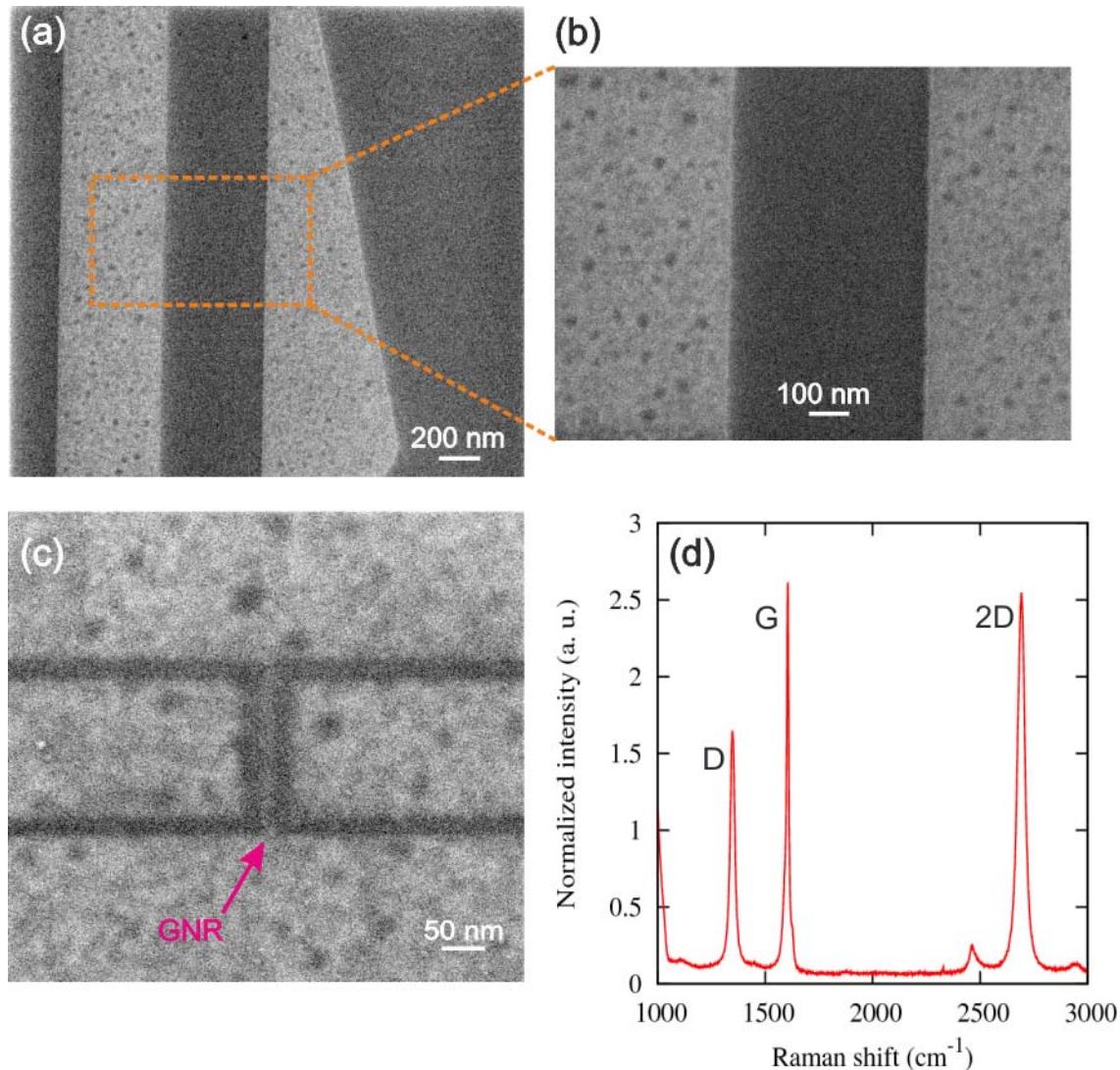

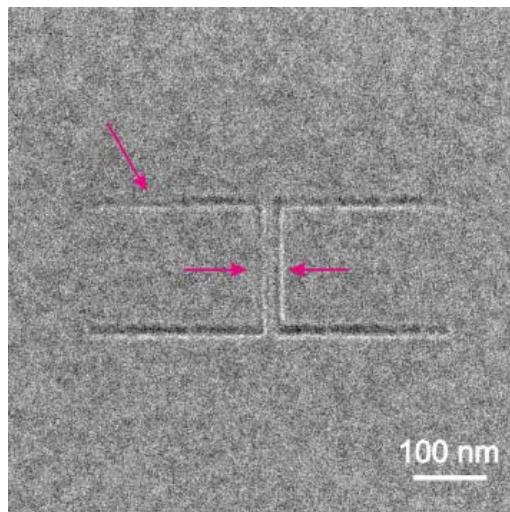

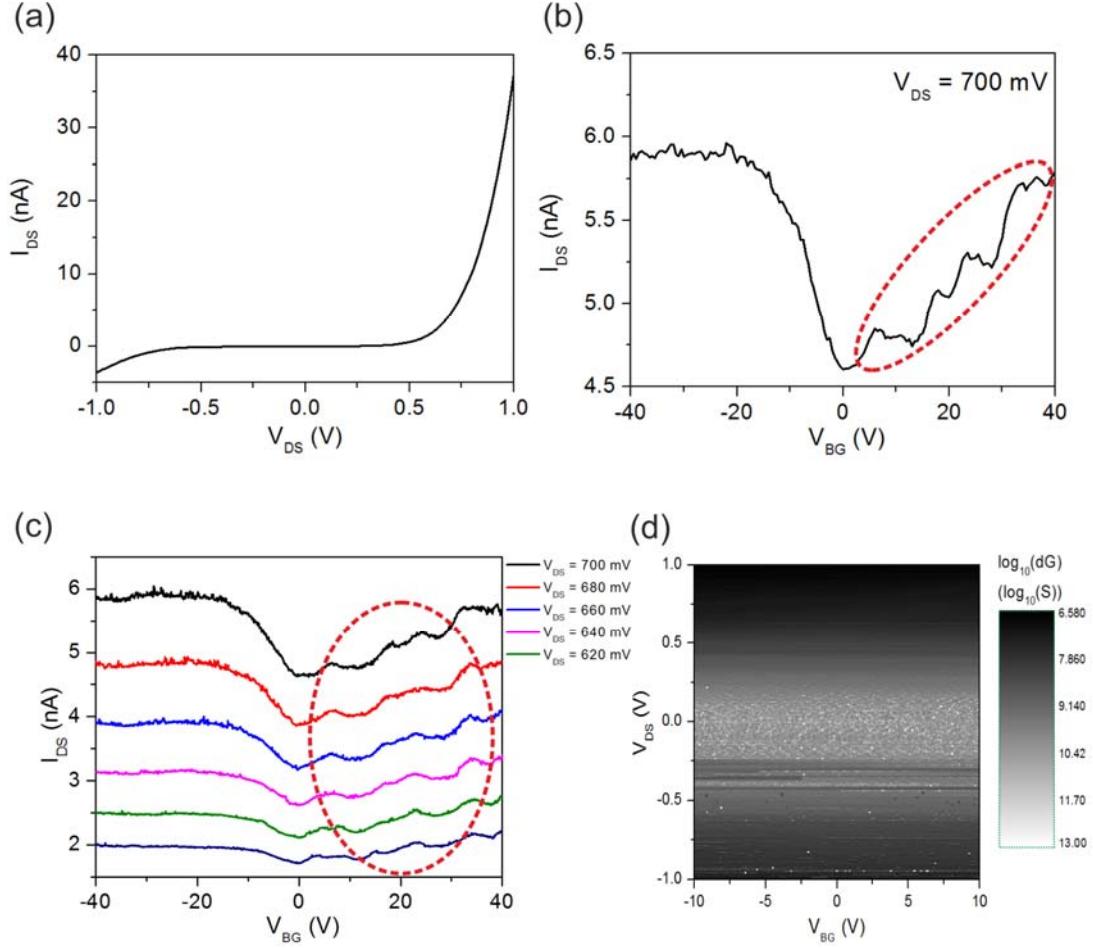

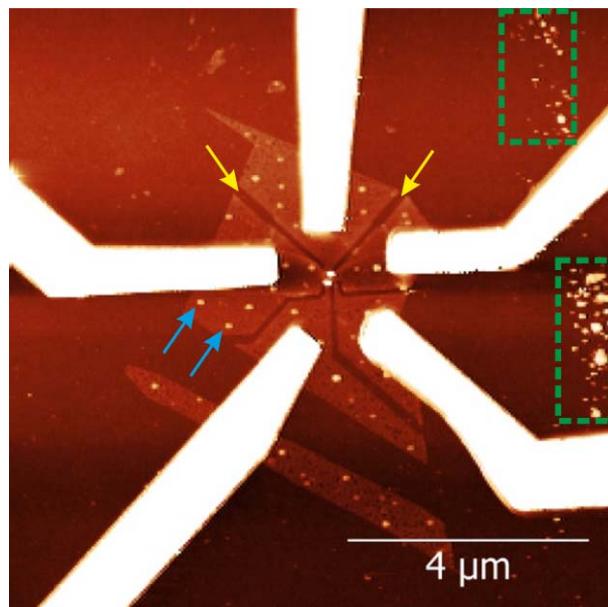

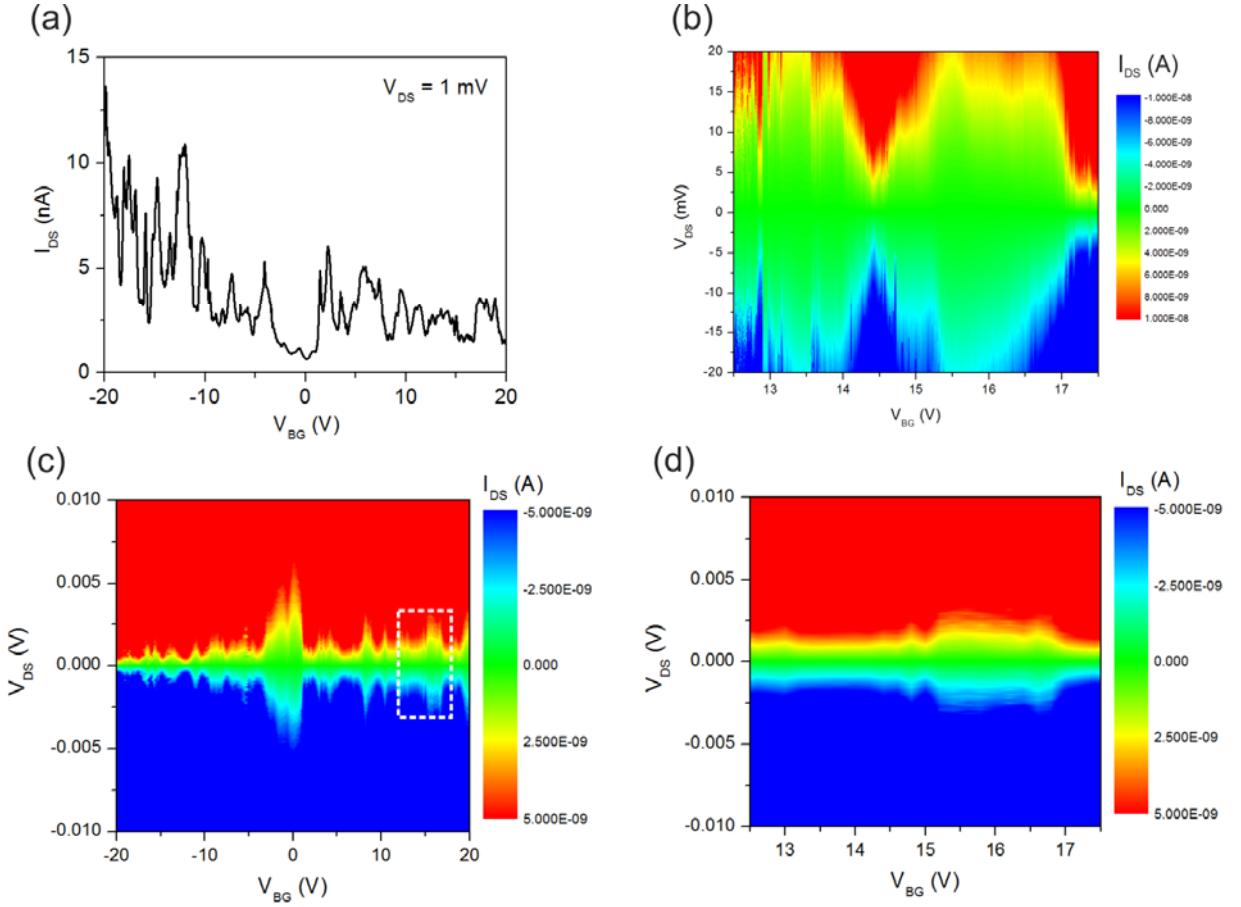

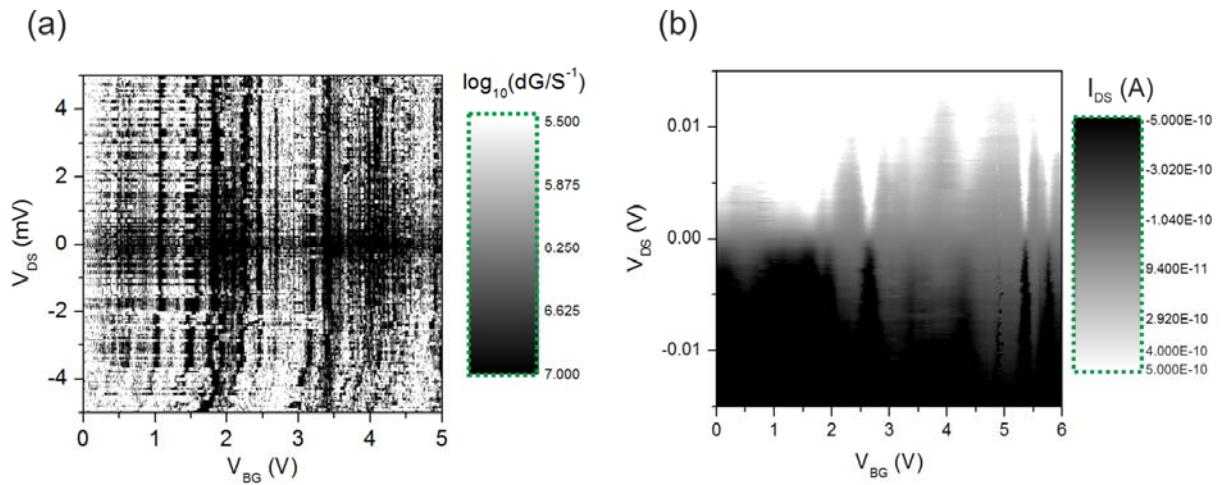

#### 3.3.1 Graphene nanoribbons