# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

# **UNIVERSITY OF SOUTHAMPTON**

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Optoelectronics Research Centre

# Silicon-germanium for photonic applications

by

Callum George Littlejohns

Thesis for the degree of Doctor of Philosophy

February 2015

### UNIVERSITY OF SOUTHAMPTON

# **ABSTRACT**

#### FACULTY OF PHYSICAL AND APPLIED SCIENCES

Optoelectronics Research Centre

**Doctor of Philosophy**

### SILICON-GERMANIUM FOR PHOTONIC APPLICATIONS

by Callum George Littlejohns

Germanium and silicon-germanium have become crucial materials in the silicon photonics field, enabling devices such as high speed photodetectors and high speed modulators to be realised.

In order to fabricate efficient and cost effective silicon photonic devices, high quality epitaxial germanium and silicon-germanium growth on silicon, or silicon-on-insulator, is of the utmost importance.

In this project, localised single crystal, defect free silicon-germanium on insulator islands have been grown using a rapid melt growth technique. Tailored tree-like structures have been used to modify the cooling rate of the structures during re-growth from the liquid phase. The resulting silicon-germanium composition profiles have been characterised using Raman spectroscopy.

Using these tailored tree-like structures, uniform composition silicongermanium strips have been grown, which is the first time this has been demonstrated using a rapid melt growth technique. Additionally, the ability to locally tune the composition of adjacent silicon-germanium strips has been shown. This enables the possibility of growing a whole range of uniform composition strips, using only a single growth step and a single anneal step, for, amongst others, wavelength division multiplexing applications.

Epitaxial growth of germanium on silicon by plasma enhanced chemical vapour deposition has also been studied. Single crystal layers with a defect density of approximately  $3.3 \times 10^8$  cm<sup>-2</sup> and root mean square surface roughness of 3.5 nm have been demonstrated. It has also been shown that the defect density, surface roughness and crystallinity are all improved with a two minutes, 600 °C anneal.

This material has been used to fabricate 12.5 Gbit/s, 0.1 A/W waveguide integrated, zero bias photodetectors for 1550 nm silicon photonics applications, and also, germanium-on-silicon waveguides for mid-infrared silicon photonics applications.

# **Table of contents**

| ABSTRACT                                             | i    |

|------------------------------------------------------|------|

| Table of contents                                    | iii  |

| List of figures                                      | ix   |

| DECLARATION OF AUTHORSHIP                            | xvii |

| Acknowledgements                                     | xxi  |

| Chapter 1: Introduction                              | 1    |

| 1.1 Silicon photonics                                | 1    |

| 1.1.1 Applications of silicon photonics              | 3    |

| 1.2 Silicon-germanium and germanium epitaxial growth | 3    |

| 1.3 Germanium photodetectors                         | 4    |

| 1.4 Thesis outline                                   | 4    |

| Chapter 2: Background and theory                     | 7    |

| 2.1 Properties of germanium and silicon-germanium    | 7    |

| 2.2 Germanium energy band structure                  | 8    |

| 2.3 Germanium and silicon-germanium epitaxial growth | 8    |

| 2.4 Epitaxial defect necking                         | 11   |

| 2.5 Light detection                                  | 11   |

| 2.5.1 Absorption coefficient                         | 12   |

| 2.5.2 p-n junctions                                  | 13   |

| 2.5.3 Photodetector performance characteristics      | 14   |

| 2.6 Techniques used                                  | 17   |

| 2.6.1 Chemical vapour deposition                     | 17   |

| 2.6.2 Inductively coupled plasma etching             | 19   |

| 2.6.3 Ion implantation                               | 21   |

| 2.6.4 Rapid thermal annealing                                  | 23 |

|----------------------------------------------------------------|----|

| 2.6.5 Metal sputtering                                         | 23 |

| 2.6.6 Raman spectroscopy                                       | 24 |

| 2.6.7 Auger electron spectroscopy                              | 27 |

| 2.6.8 X-ray diffraction spectroscopy                           | 28 |

| 2.6.9 Atomic force microscopy                                  | 28 |

| Chapter 3: Literature review                                   | 31 |

| 3.1 SiGe/Ge-on-silicon growth techniques                       | 31 |

| 3.1.1 Molecular beam epitaxy                                   | 31 |

| 3.1.2 Chemical vapour deposition                               | 33 |

| 3.1.3 Substrate patterning                                     | 36 |

| 3.2 SiGe/Ge-on-insulator fabrication techniques                | 37 |

| 3.2.1 Layer transfer using a donor wafer                       | 38 |

| 3.2.2 Ge condensation                                          | 39 |

| 3.2.3 Lateral Ge-on-insulator growth                           | 40 |

| 3.2.4 Rapid melt growth                                        | 41 |

| 3.3 Ge p-i-n photodetectors                                    | 48 |

| 3.3.1 Normal incidence photodetectors                          | 49 |

| 3.3.2 Waveguide integrated photodetectors                      | 51 |

| 3.3.3 Light coupling methods                                   | 56 |

| 3.4 Other photodetector designs                                | 57 |

| 3.4.1 Metal-semiconductor-metal photodetectors                 | 57 |

| 3.4.2 Avalanche photodetectors                                 | 57 |

| 3.4.3 Si defect photodetectors                                 | 58 |

| 3.5 Photodetectors summary                                     | 59 |

| 3.6 Literature review conclusions                              | 62 |

| Chapter 4: Ge-on-Si plasma enhanced chemical vapour deposition | 63 |

| 4.1 Motivation and applications                                | 63 |

| 4.2 Ge-on-Si growth process                         | 64  |

|-----------------------------------------------------|-----|

| 4.2.1 Pre-growth cleaning                           | 64  |

| 4.2.2 Ge growth                                     | 64  |

| 4.3 Characterisation                                | 66  |

| 4.3.1 Layer imaging                                 | 66  |

| 4.3.2 Crystal properties                            | 69  |

| 4.3.3 Surface roughness                             | 74  |

| 4.4 Ge on patterned SiO2 growth                     | 74  |

| 4.5 Ge PECVD growth summary                         | 76  |

| 4.6 Ge-on-Si waveguides for mid-IR wavelengths      | 78  |

| 4.6.1 Ge etch study                                 | 78  |

| 4.6.2 Device design                                 | 82  |

| 4.6.3 Measurement setup                             | 84  |

| 4.6.4 Loss measurements                             | 85  |

| 4.7 Ge-on-Si PECVD conclusions                      | 86  |

| Chapter 5: SiGe rapid melt growth                   | 87  |

| 5.1 Motivation and applications                     | 87  |

| 5.2 Fabrication process                             | 88  |

| 5.2.1 Regrowth mechanism                            | 93  |

| 5.3 Characterisation                                | 95  |

| 5.3.1 Raman spectroscopy                            | 96  |

| 5.3.2 Auger electron spectroscopy                   | 122 |

| 5.3.3 Transmission electron microscopy              | 124 |

| 5.3.4 Electron backscatter diffraction              | 125 |

| 5.4 Rapid melt growth from polycrystalline Si seeds | 126 |

| 5.5 Rapid melt growth conclusions                   | 128 |

| Chapter 6: Ge photodetectors                        | 129 |

| 6.1 Motivation and applications                     | 129 |

|                                                     |     |

| 6.2 Device design1                                 | 29 |

|----------------------------------------------------|----|

| 6.3 Process development                            | 32 |

| 6.3.1 Ge etch1                                     | 32 |

| 6.3.2 Rapid melt growth1                           | 33 |

| 6.3.3 Si etch                                      | 34 |

| 6.3.4 SiO2 etch                                    | 34 |

| 6.3.5 Metal sputtering1                            | 35 |

| 6.3.6 Metal etch                                   | 37 |

| 6.3.7 Transmission line measurements               | 38 |

| 6.4 Photodetector fabrication process              | 44 |

| 6.4.1 Wafer bowing1                                | 45 |

| 6.4.2 Summary of photodetector fabrication process | 49 |

| 6.5 Photodetector characterisation                 | 51 |

| 6.5.1 Measurement setup1                           | 51 |

| 6.5.2 DC performance                               | 53 |

| 6.5.3 AC performance                               | 54 |

| 6.6 4-channel photodetectors                       | 55 |

| 6.7 Ge photodetectors conclusions                  | 59 |

| Chapter 7: Conclusions and future work1            | 61 |

| 7.2 Conclusions1                                   | 61 |

| 7.1 Future work1                                   | 67 |

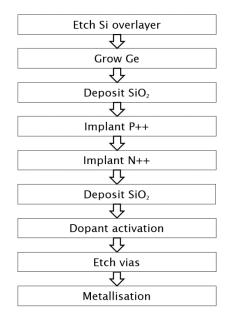

| Appendix A: PECVD photodetector process flow1      | 69 |

| Appendix B: RMG photodetector process flow1        | 71 |

| Appendix C: Scheil equation derivation1            | 73 |

| Appendix D: Complete mixing model derivation1      | 75 |

| References1                                        | 81 |

| Chapter 11                                         | 81 |

| Chapter 21                                         | 82 |

| Chapter 3 | 184 |

|-----------|-----|

| Chapter 4 | 193 |

| Chapter 5 | 198 |

| Chapter 6 | 202 |

| Chapter 7 | 205 |

# List of figures

| Fig. 1-1. Refractive index and absorption coefficient in silicon as a function                                           |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| of wavelength                                                                                                            | 3  |

| Fig. 2-1. Energy band diagram of Ge at 300 K, modified from [4]                                                          | 8  |

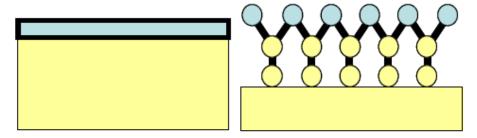

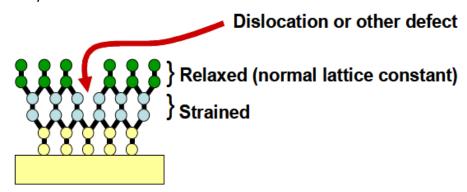

| Fig. 2-2. Cross-section and atomic view of Ge-on-Si growth, showing the wetting layer, reproduced from [7].              | 9  |

| Fig. 2-3. Cross section and atomic view of Ge-on-Si growth, below the critical thickness, reproduced from [7].           |    |

| Fig. 2-4. Atomic view of Ge-on-Si growth above the critical thickness, showing a misfit dislocation, reproduced from [7] | 10 |

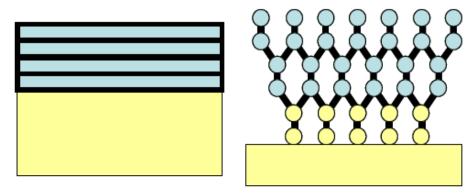

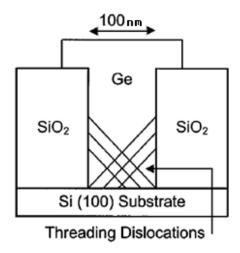

| Fig. 2-5. Cross-section diagram demonstrating the principles of epitaxial defect necking, reproduced from [9].           | 11 |

| Fig. 2-6. Optical absorption of a photon and consequent electron-hole pair generation, reproduced from [11].             | 12 |

| Fig. 2-7. Absorption spectra of Si and Ge at 300 K, modified from [12]                                                   | 13 |

| Fig. 2-8. A p-n junction in equilibrium, reproduced from [11].                                                           | 14 |

| Fig. 2-9. Schematic diagram of a PECVD reaction chamber, reproduced from [20]                                            | 18 |

| Fig. 2-10. Schematic diagram of ICP etch system, reproduced from [20]                                                    | 19 |

| Fig. 2-11. Processes involved in chemical etching during a plasma etch process, reproduced from [19].                    | 20 |

| Fig. 2-12. Fluxes of species in plasma etching, reproduced from [19]                                                     | 21 |

| Fig. 2-13. An ion implantation system, reproduced from [3]                                                               | 22 |

| Fig. 2-14. Diagram showing ion implantation, adapted from [3]                                                            | 22 |

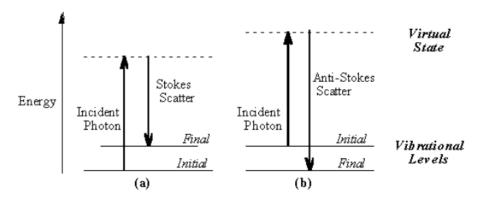

| Fig. 2-15. Energy level diagram for Raman scattering, reproduced from [23].                                              | 25 |

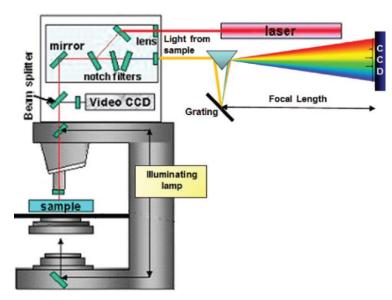

| Fig. 2-16. A Raman microscope, reproduced from [25].                                                                     | 26 |

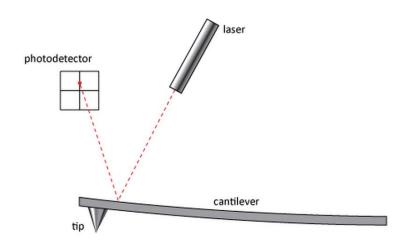

| Fig. 2-17. Simplified diagram of AFM, reproduced from [28]                                                               | 29 |

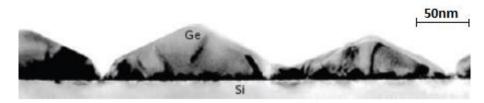

| Fig. 3-1. Stransky-Krastanov growth of Ge-on-Si at 550 °C in an ultrahigh                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| vacuum chemical vapour deposition reactor, reproduced from [6]31                                                                        |

| Fig. 3-2. Schematic showing growth of Ge by MBE in Si wells, reproduced from [9]                                                        |

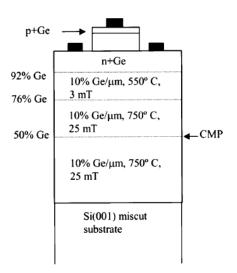

| Fig. 3-3. Schematic showing relaxed, graded SiGe buffer growth, reproduced from [11]                                                    |

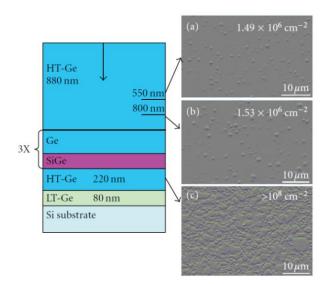

| Fig. 3-4. Schematic and optical images of a Ge-on-Si strained layer superlattice structure, reproduced from [19].                       |

| Fig. 3-5. Thick interfacial dislocation at coalescence point of ELO growth, reproduced from [23]                                        |

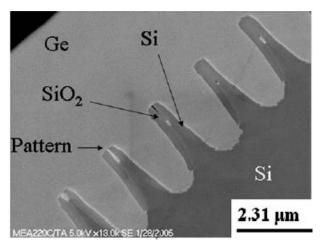

| Fig. 3-6. Cross-section SEM image of Ge on nanostructured Si substrate, reproduced from [24]                                            |

| Fig. 3-7. Layer transfer process using a donor wafer, reproduced from [28]38                                                            |

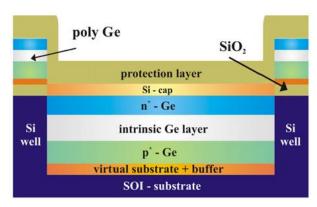

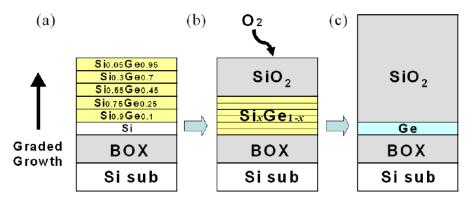

| Fig. 3-8. Graded Ge condensation growth method, reproduced from [33] 39                                                                 |

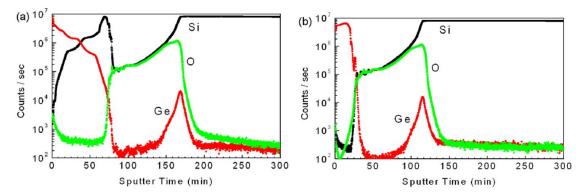

| Fig. 3-9. SIMS depth profiles of Ge condensation process, reproduced from [33]                                                          |

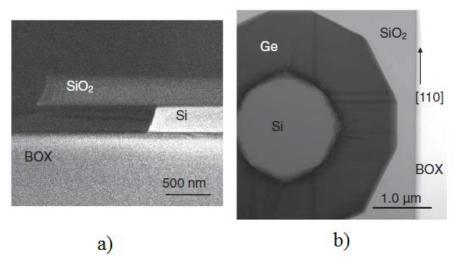

| Fig. 3-10. Lateral GOI growth, reproduced from [35]40                                                                                   |

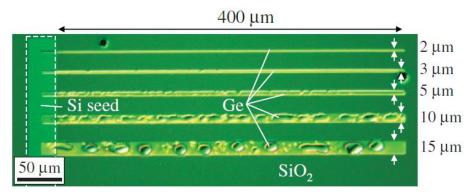

| Fig. 3-11. Optical micrograph of different width Ge strips grown by RMG, reproduced from [42]                                           |

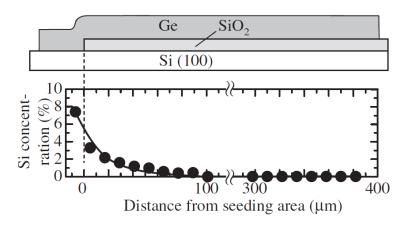

| Fig. 3-12. Si fraction obtained from Raman spectra as a function of distance from seeding area, for RMG Ge strips, reproduced from [42] |

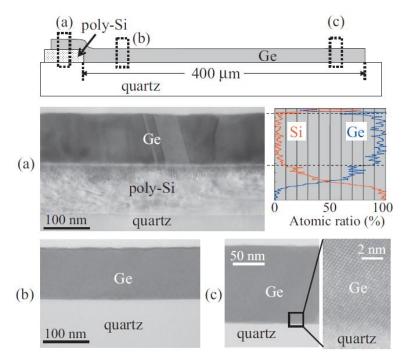

| Fig. 3-13. Ge RMG from a poly-Si seed, reproduced from [43]                                                                             |

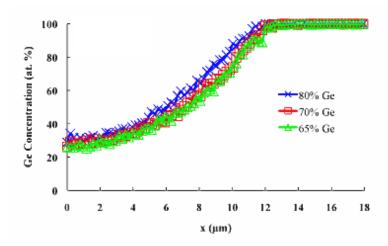

| Fig. 3-14. SiGe composition profiles, after RMG, of strips with different initial SiGe compositions, reproduced from [46]               |

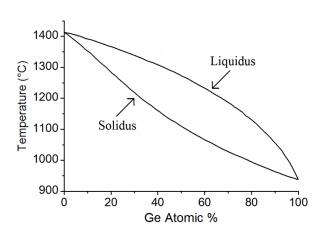

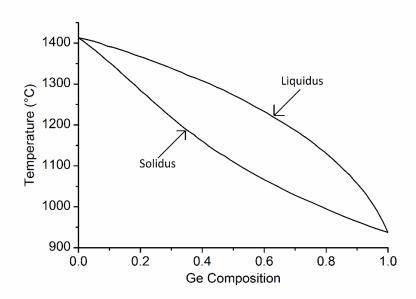

| Fig. 3-15. SiGe phase diagram – adapted from [53]45                                                                                     |

| Fig. 3-16. SiGe composition profiles for a variety of cooling rates and strip lengths, reproduced from [47]45                           |

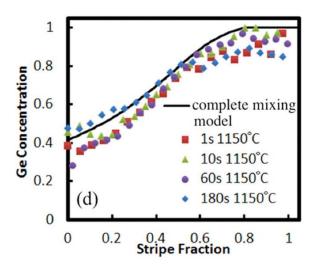

| Fig. 3-17. SiGe composition profiles after RMG at a range of anneal times, reproduced from [50]                                         |

| Fig. 3-18. Cross-sectional schematic of a typical normal incidence Ge photodetector, reproduced from [17]                               |

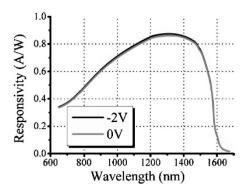

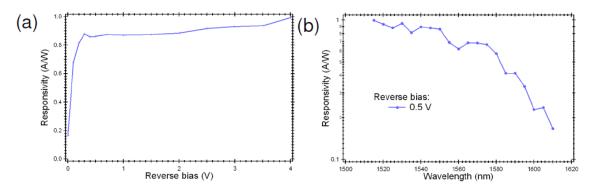

| Fig. 3-19. Responsivity of a Ge <i>p-i-n</i> photodetector at 0 V and 2 V reverse bias, reproduced from [76]                                                     | 50 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

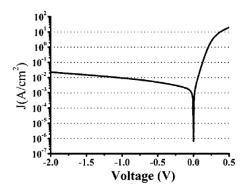

| Fig. 3-20. IV characteristics of a Ge <i>p-i-n</i> photodetector, reproduced from [76]                                                                           | 50 |

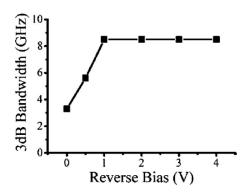

| Fig. 3-21. 3dB bandwidth of a <i>p-i-n</i> photodetector as a function of reverse bias, reproduced from [76]                                                     | 51 |

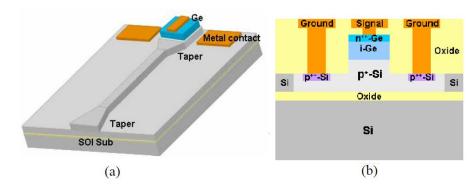

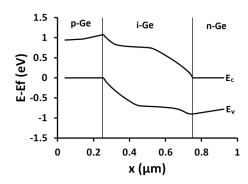

| Fig. 3-22. A typical waveguide integrated vertical Ge photodetector, reproduced from [81]                                                                        | 52 |

| Fig. 3-23. Responsivity of a waveguide coupled vertical Ge photodetector, reproduced from [84]                                                                   | 53 |

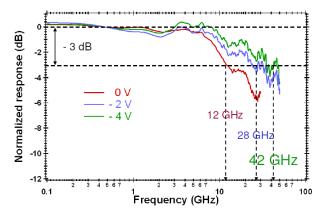

| Fig. 3-24. Normalised optical responses of a waveguide coupled vertical Ge photodetector, reproduced from [84].                                                  | 53 |

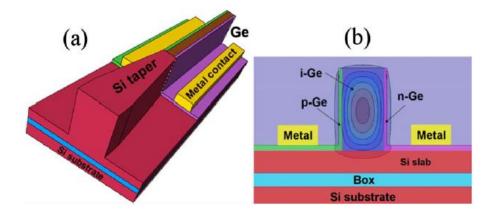

| Fig. 3-25. A typical waveguide integrated lateral Ge photodetector, reproduced from [95]                                                                         | 54 |

| Fig. 3-26. Eye diagrams of lateral Ge photodetectors at 10 Gbit/s, 20 Gbit/s, 30 Gbit/s and 40 Gbit/s, under 0 V bias and 1 V reverse bias, reproduced from [96] | 54 |

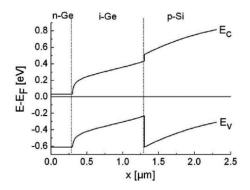

| Fig. 3-27. Band diagram for vertical heterojunction <i>p-i-n</i> Ge photodetector, reproduced from [21]                                                          | 55 |

| Fig. 3-28. Band diagram for lateral homojunction <i>p-i-n</i> Ge photodetector                                                                                   | 55 |

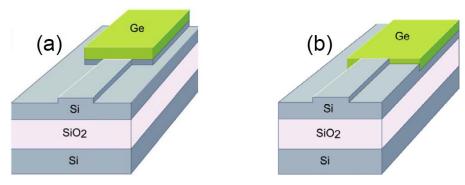

| Fig. 3-29. Methods of coupling light from a Si waveguide into a Ge photodetector, reproduced from [112].                                                         | 56 |

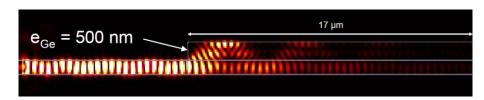

| Fig. 3-30. FDTD simulation of butt coupling into a Ge photodetector at 1.55 µm, reproduced from [112].                                                           | 56 |

| Fig. 3-31. FDTD simulation of evanescent coupling into a Ge photodetector at 1.55 µm, reproduced from [112].                                                     | 57 |

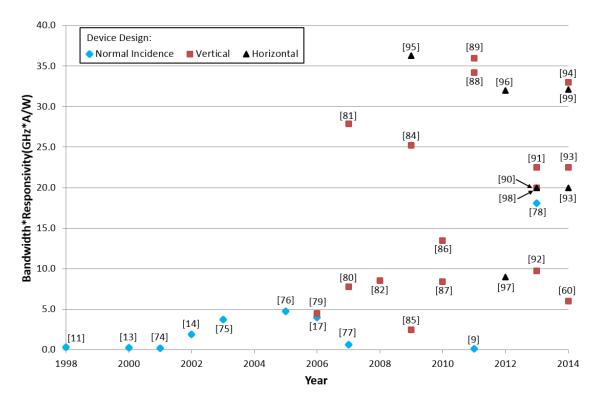

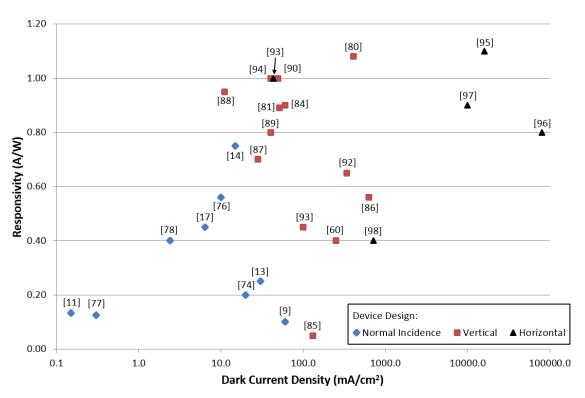

| Fig. 3-32. Ge photodetector performance comparison: Responsivity bandwidth product vs. year.                                                                     | 61 |

| Fig. 3-33. Ge photodetector performance comparison: Responsivity vs. dark current density                                                                        | 61 |

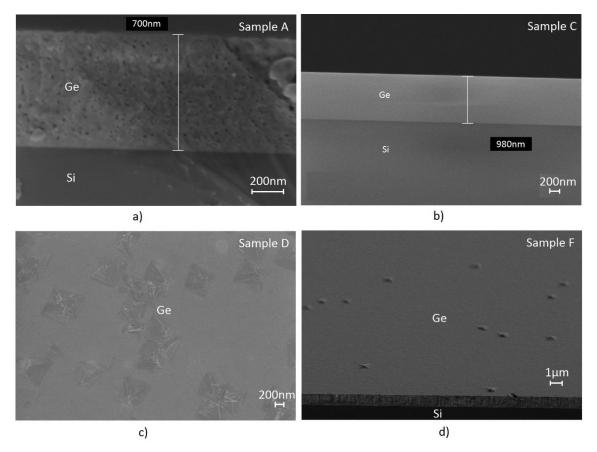

| Fig. 4-1. SEM images of PECVD Ge-on-Si                                                                                                                           | 67 |

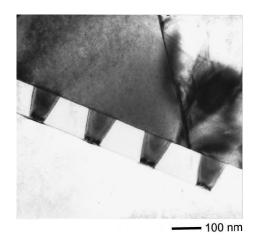

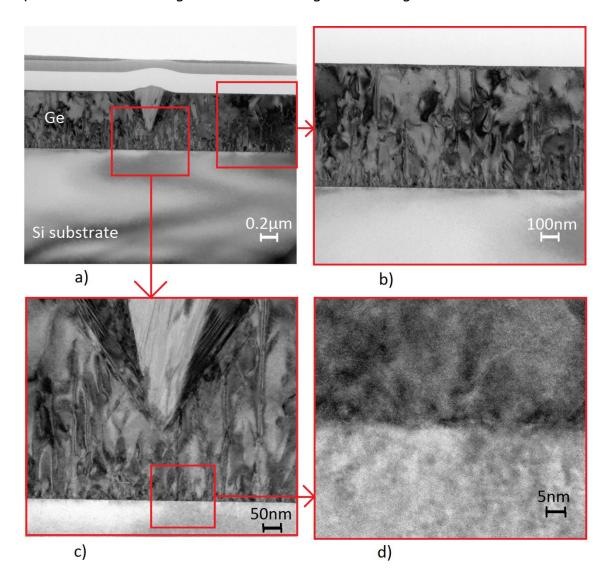

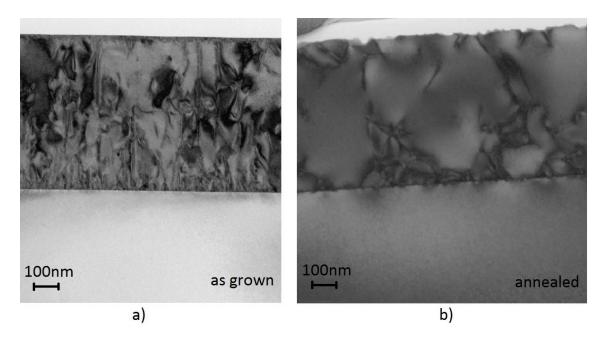

| Fig. 4-2. TEM images of sample G - as grown                                                                                     | 68 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4-3. TEM images of sample G showing the effects of annealing                                                               | 69 |

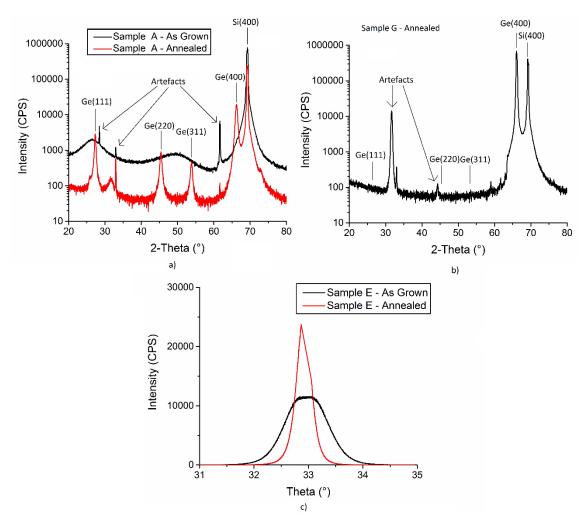

| Fig. 4-4. Theta:2-theta and rocking curve XRD spectra for various samples                                                       | 70 |

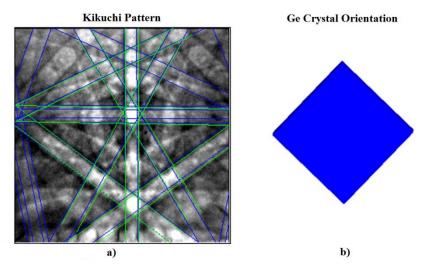

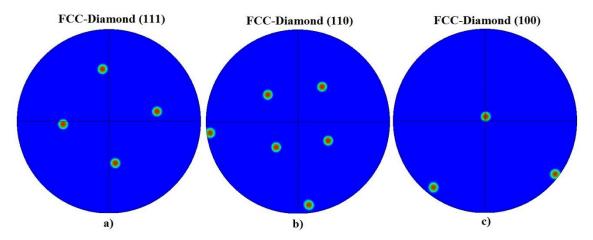

| Fig. 4-5. EBSD Kikuchi pattern of a single point, and equivalent crystal orientation – sample G, annealed                       | 72 |

| Fig. 4-6. Pole figures in various orientations – sample G, annealed                                                             | 73 |

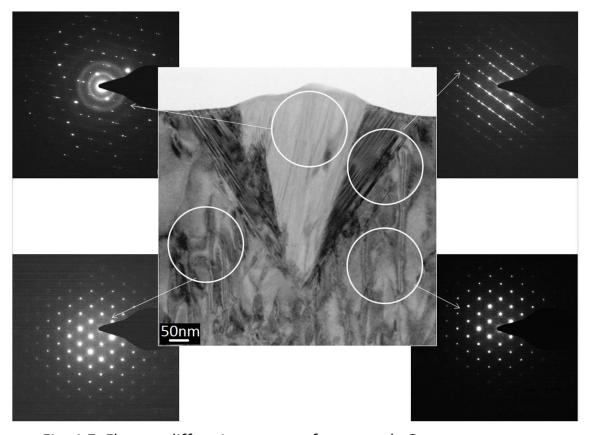

| Fig. 4-7. Electron diffraction patterns from sample G, as grown                                                                 | 73 |

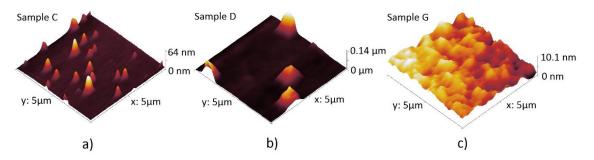

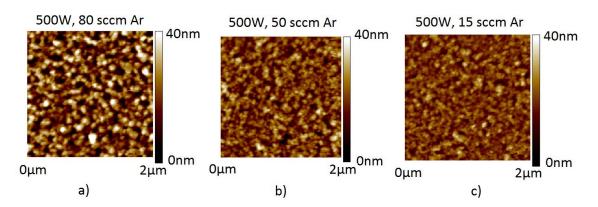

| Fig. 4-8. AFM surface roughness measurements.                                                                                   | 74 |

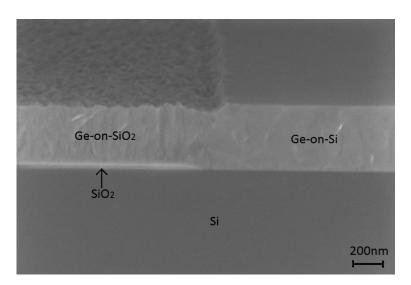

| Fig. 4-9. Cross-section SEM image of Ge grown on a patterned $SiO_2$ surface, using recipe C.                                   | 75 |

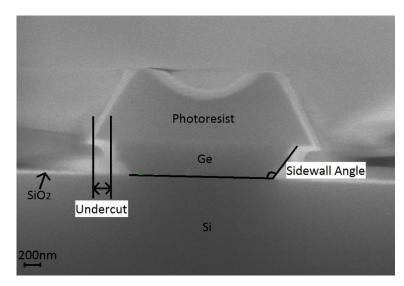

| Fig. 4-10. SEM image of Ge etch, showing undercut and sidewall angle measurements.                                              | 79 |

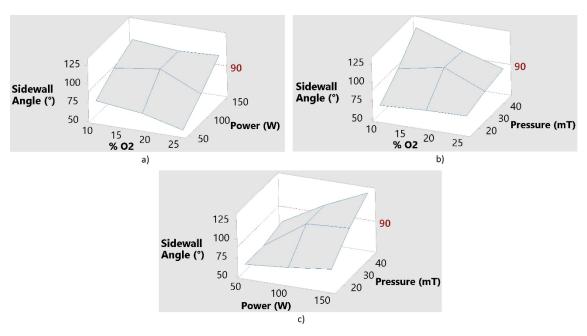

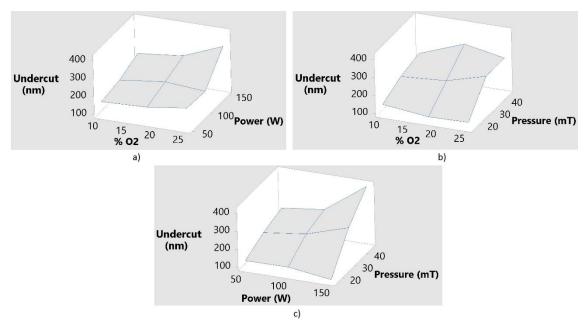

| Fig. 4-11. Surface plots of sidewall angle vs. process parameters                                                               | 79 |

| Fig. 4-12. Surface plots of undercut vs. process parameters                                                                     | 80 |

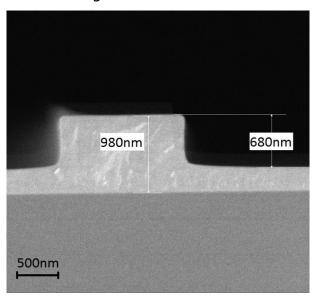

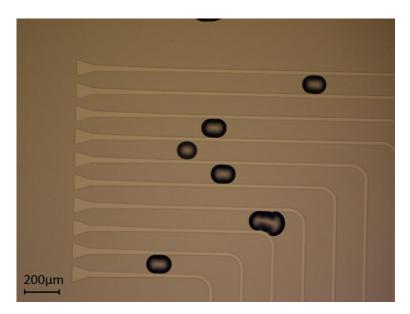

| Fig. 4-13. SEM image of Ge ICP etch                                                                                             | 81 |

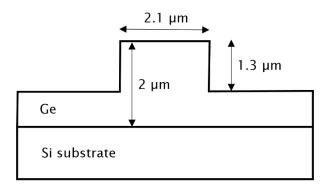

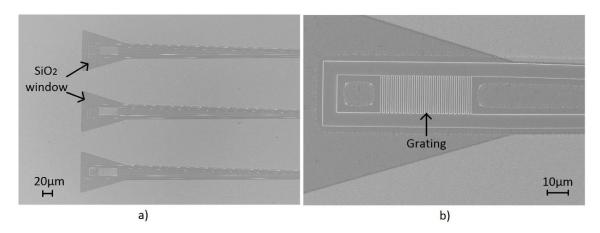

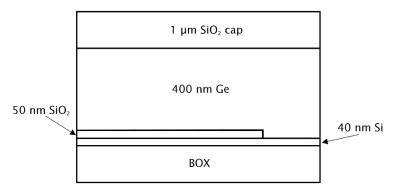

| Fig. 4-14. Schematic of Ge-on-Si mid-IR rib waveguide.                                                                          | 82 |

| Fig. 4-15. Optical microscope image of Ge growth on patterned $SiO_2$ surface, showing Ge delamination on some $SiO_2$ surfaces |    |

| Fig. 4-16. SEM image of Ge waveguides grown in windows defined in an SiO <sub>2</sub> layer.                                    |    |

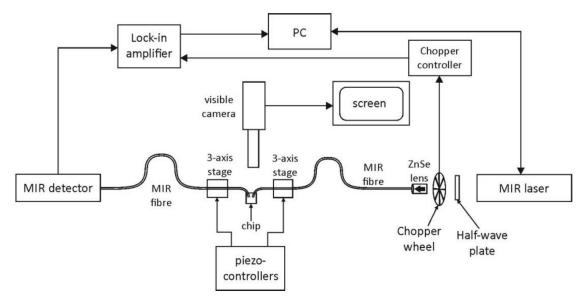

| Fig. 4-17. Measurement setup for mid-IR waveguide characterisation, reproduced from [56].                                       | 84 |

| Fig. 4-18. Propagation loss measurements for 2.1 µm wide PECVD Ge-on-Si waveguides.                                             | 86 |

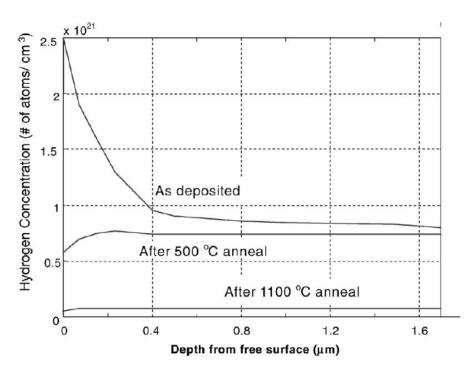

| Fig. 5-1. SIMS H composition analysis of SiH <sub>4</sub> based PECVD of SiO <sub>2</sub> , reproduced from [35].               | 89 |

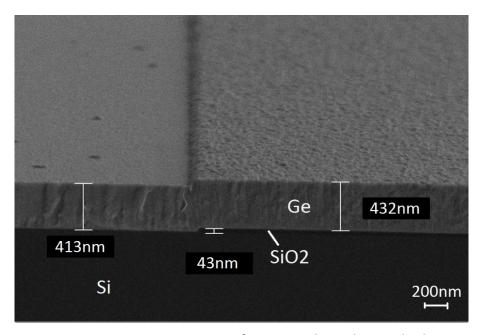

| Fig. 5-2. Cross-section SEM image of Ge growth at the seed edge                                                                 | 91 |

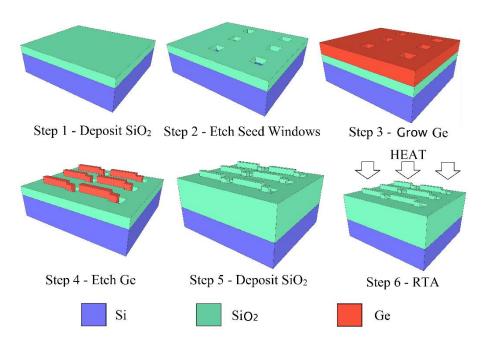

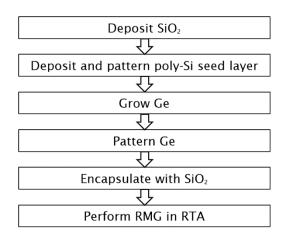

| Fig. 5-3. Summary of the SiGe RMG fabrication process.                                                                          | 92 |

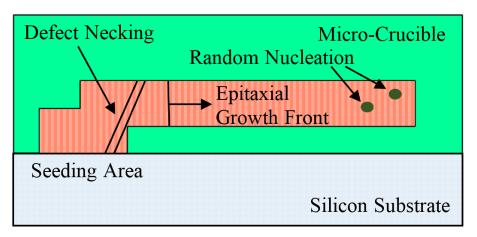

| Fig. 5-4. A cross-section schematic of the recrystallisation process during cooling.                                            | 93 |

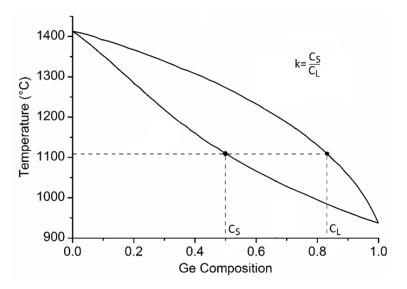

| Fig. 5-5. SiGe phase diagram - adapted from [40]                                                                                                   | 94  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

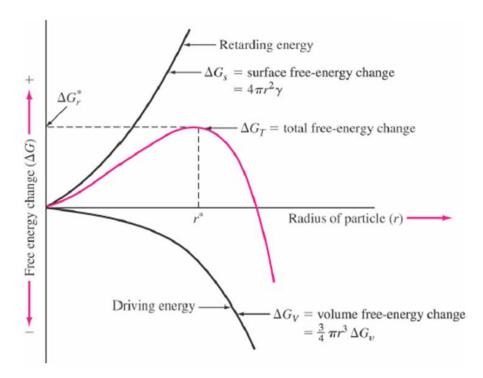

| Fig. 5-6. Energy change in random nucleation as a function of nucleus radius, reproduced from [43].                                                | 95  |

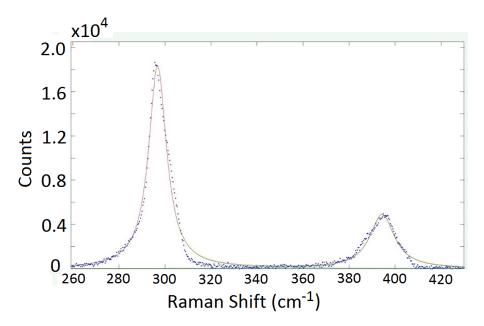

| Fig. 5-7. Example Raman spectrum showing fitted Lorentzian curves                                                                                  | 96  |

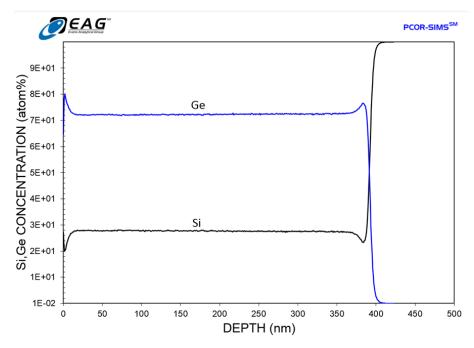

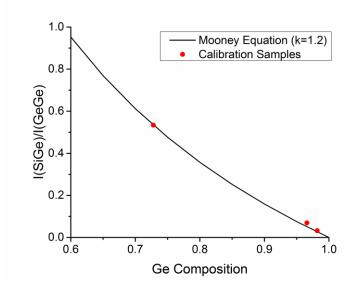

| Fig. 5-8. SIMS composition analysis of SiGe calibration sample                                                                                     | 98  |

| Fig. 5-9. Calculation of the Mooney equation constant, k                                                                                           | 98  |

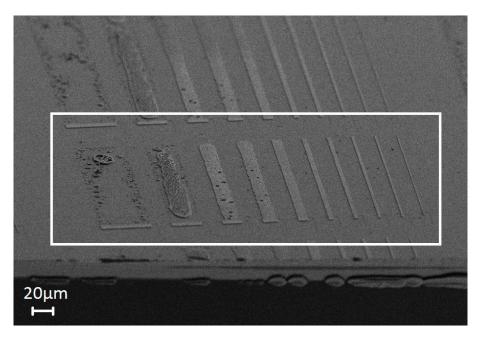

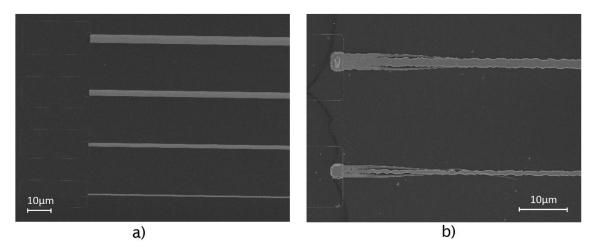

| Fig. 5-10. SEM image of RMG straight strips showing agglomeration at larg                                                                          | _   |

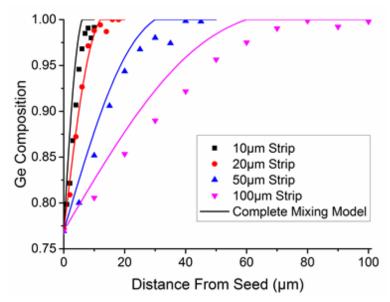

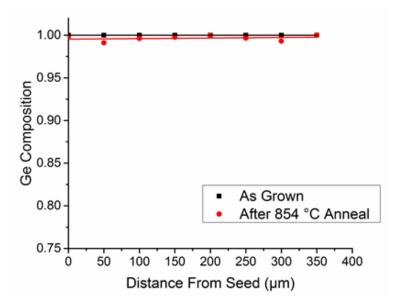

| Fig. 5-11. SiGe composition profiles for a range of straight strip lengths                                                                         | 100 |

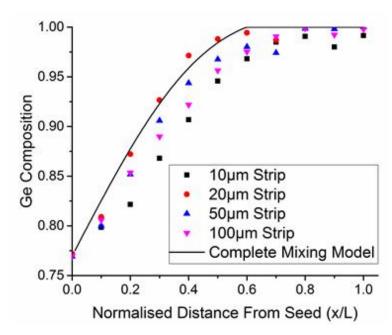

| Fig. 5-12. Normalised SiGe composition profiles of straight strips                                                                                 | 101 |

| Fig. 5-13. SiGe composition profile in a straight strip annealed below the of melting point.                                                       |     |

| Fig. 5-14. SEM images of straight SiGe strips after RCA-1 etching                                                                                  | 102 |

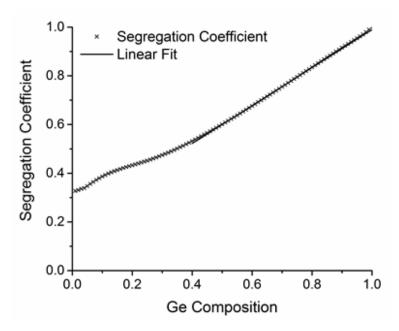

| Fig. 5-15. Calculating the segregation coefficient from the phase diagram.                                                                         | 103 |

| Fig. 5-16. Segregation coefficient as a function of solid Ge composition                                                                           | 104 |

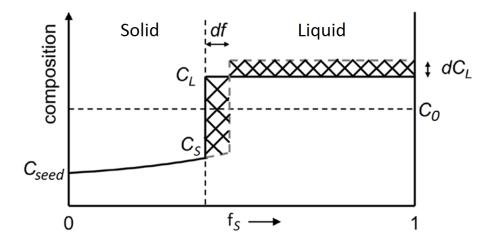

| Fig. 5-17. Composition profile evolution according to the Scheil equation, reproduced from [53].                                                   | 105 |

| Fig. 5-18. Derivation of the complete mixing model.                                                                                                | 106 |

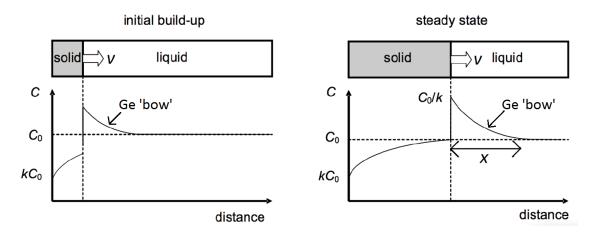

| Fig. 5-19. Steady-state solidification – adapted from [53]                                                                                         | 109 |

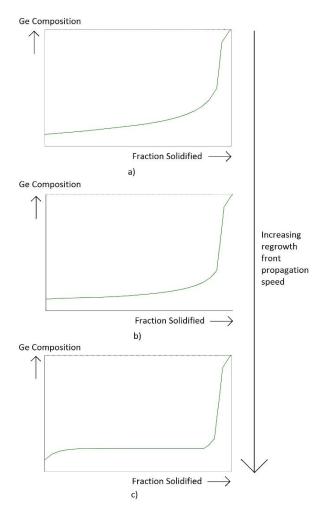

| Fig. 5-20. Simulations of Ge composition profiles using steady-state solidification [54].                                                          | 110 |

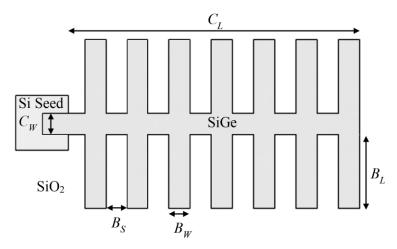

| Fig. 5-21. Schematic of a tailored tree-like structure                                                                                             | 112 |

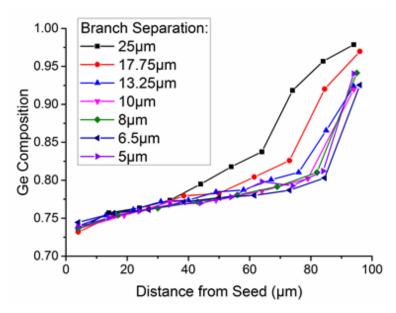

| Fig. 5-22. SEM image of a tailored tree-like structure                                                                                             | 112 |

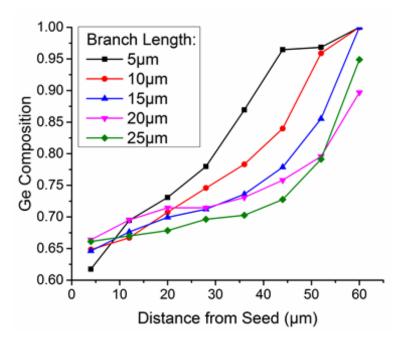

| Fig. 5-23. Ge composition as a function of distance from the seed for the central strip of tree-like structures with a range of branch separations | 113 |

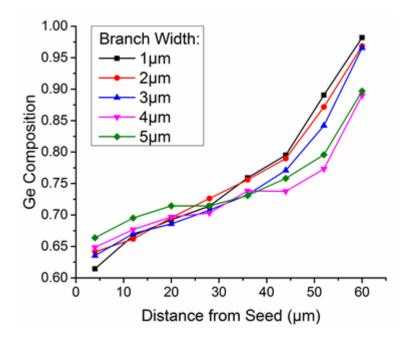

| Fig. 5-24. Ge composition as a function of distance from the seed for the central strip of tree-like structures with a range of branch lengths     | 114 |

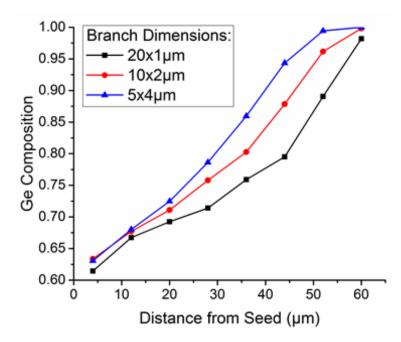

| Fig. 5-25. Ge composition as a function of distance from the seed for the central strip of tree-like structures with a range of branch widths      | 115 |

| Fig. 5-26. Ge composition as a function of distance from the seed for the central strip of tree-like structures with a fixed branch volume but different |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| branch dimensions                                                                                                                                        | 16 |

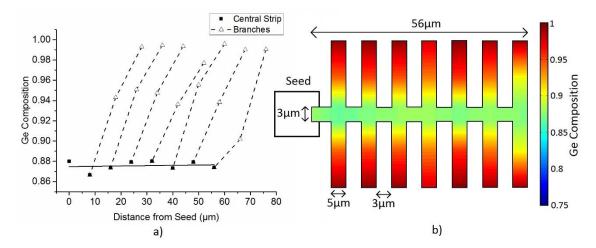

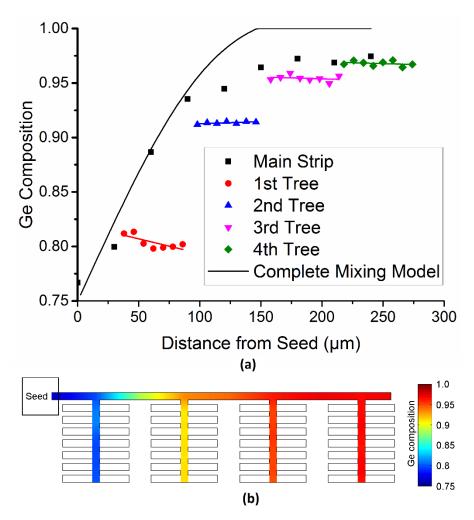

| Fig. 5-27. Composition profile of a tailored tree-like structure                                                                                         | 17 |

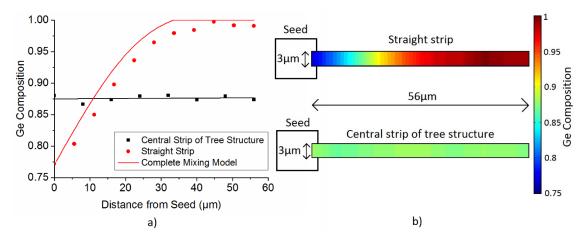

| Fig. 5-28. Comparison of composition profiles of straight strip and central strip of tailored tree-like structure                                        | 18 |

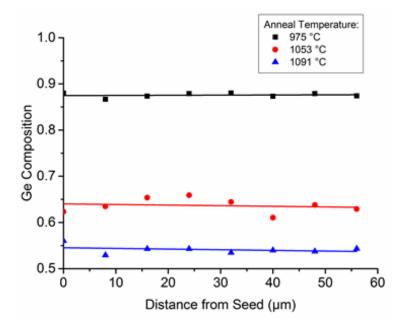

| Fig. 5-29. Composition profiles in the central strips of tailored tree-like structures annealed at a range of temperatures                               | 19 |

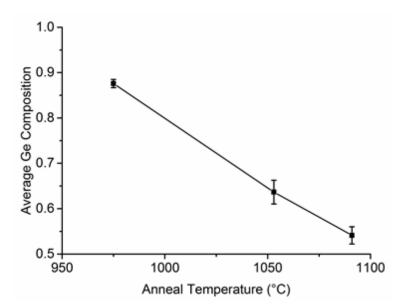

| Fig. 5-30. Average Ge composition along the central strip of a tailored tree-like structure as a function of anneal temperature                          | 20 |

| Fig. 5-31. Ge composition as a function of distance from the seed for a straight strip with a series of attached tree-like structures                    | 21 |

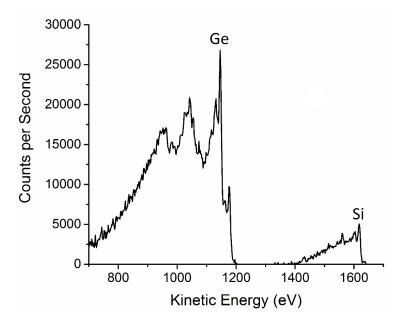

| Fig. 5-32. Example AES spectrum                                                                                                                          | 23 |

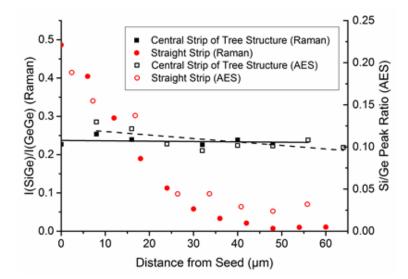

| Fig. 5-33. Comparison of Raman and AES data for a straight strip and the central strip of a tree-like structure                                          | 23 |

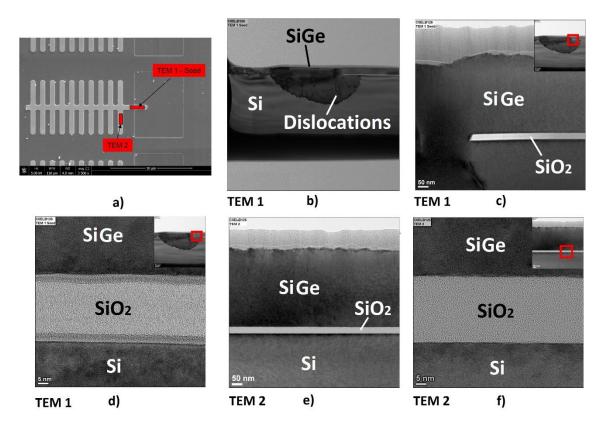

| Fig. 5-34. Cross-section TEM images of RMG SiGe in both the seed area and along a branch                                                                 | 25 |

| Fig. 5-35. EBSD scan of a tailored tree-like structure                                                                                                   | 26 |

| Fig. 5-36. Poly-Si seed RMG fabrication summary                                                                                                          | 27 |

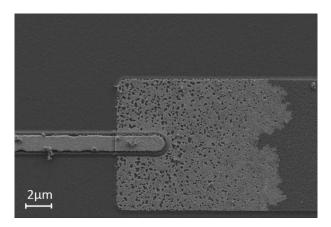

| Fig. 5-37. SEM image of a RMG SiGe straight strip from a poly-Si seed 1                                                                                  | 27 |

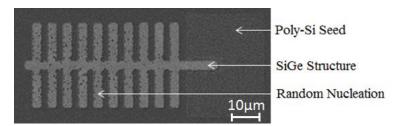

| Fig. 5-38. SEM image of RMG SiGe tree-like structure from a poly-Si seed 1                                                                               | 28 |

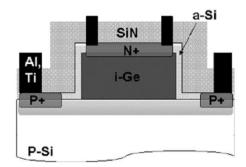

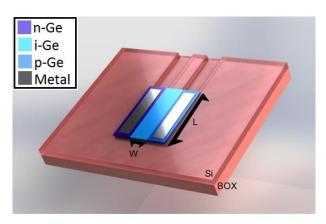

| Fig. 6-1. Schematic of photodetector design                                                                                                              | 31 |

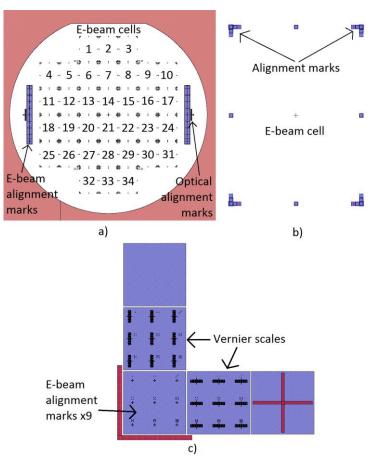

| Fig. 6-2. Photodetector wafer layout                                                                                                                     | 31 |

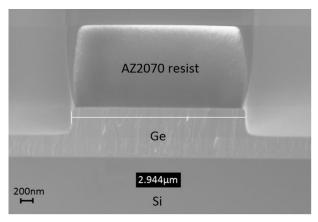

| Fig. 6-3. SEM image of Ge etch using 4 µm thick AZ2070 resist, written by ebeam lithography                                                              | 32 |

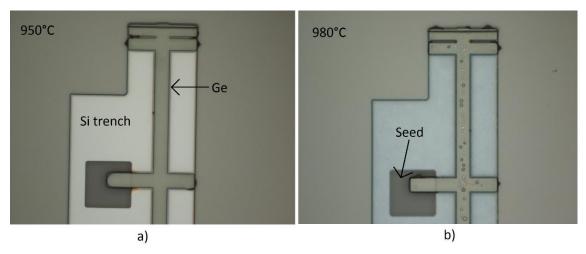

| Fig. 6-4. Optical microscope images of RMG Ge for photodetector device fabrication                                                                       | 33 |

| Fig. 6-5. Schematic of RMG in thinned SOI trenches                                                                                                       | 34 |

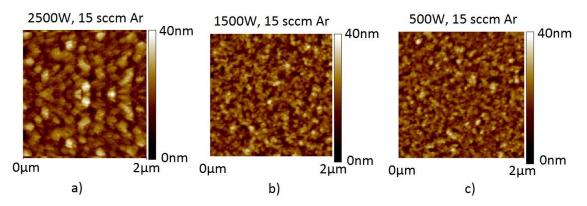

| Fig. 6-6. Cross-section SEM images of SiO <sub>2</sub> etch using Plasmatherm deep etching tool and ICP etching tool                                     | 35 |

| Fig. 6-7. AFM surface roughness plots of sputtered Al for various DC                                                                 |      |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

| powers1                                                                                                                              | 136  |

| Fig. 6-8. AFM surface roughness plots of sputtered Al for various Ar flows 1                                                         | 136  |

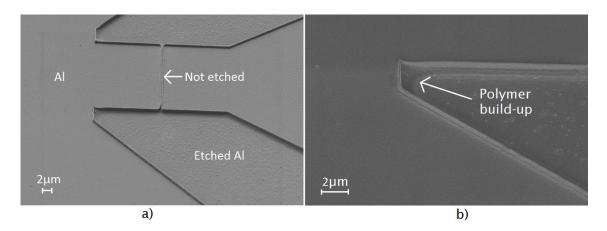

| Fig. 6-9. Al ICP etch using \$1813 photoresist                                                                                       | 137  |

| Fig. 6-10. Al ICP etch using PMMA e-beam resist                                                                                      | 138  |

| Fig. 6-11. Process flow for TLM test wafers                                                                                          | 138  |

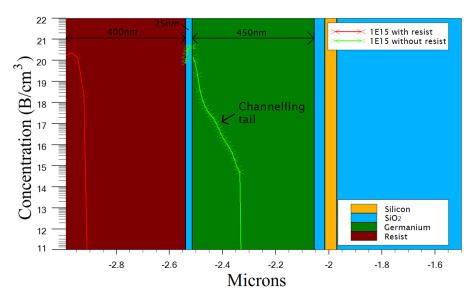

| Fig. 6-12. Silvaco Athena simulation of boron P++ implant                                                                            | 139  |

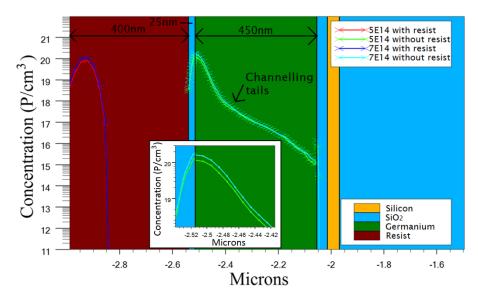

| Fig. 6-13. Silvaco Athena simulation of phosphorus N++ implant with different doses                                                  | l 40 |

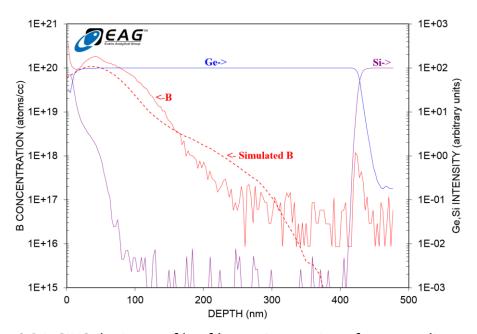

| Fig. 6-14. SIMS doping profile of boron P++ region after annealing at 600 °C                                                         | 141  |

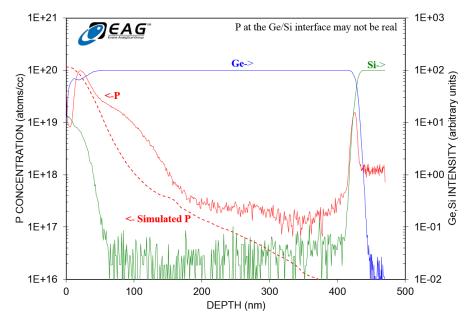

| Fig. 6 15. SIMS doping profile of phosphorus N++ region after annealing at 600 °C                                                    | 142  |

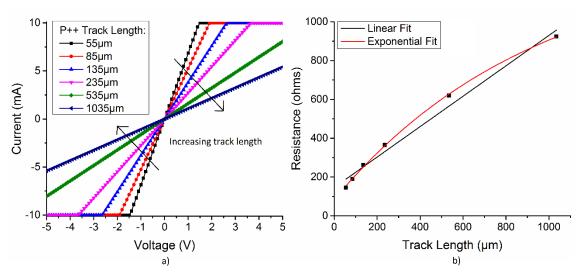

| Fig. 6-16. P++ TLM measurements 1                                                                                                    | 143  |

| Fig. 6-17. N++ TLM measurements                                                                                                      | 143  |

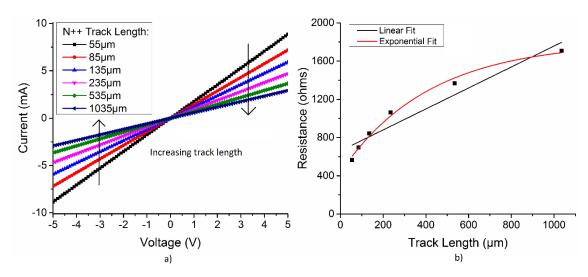

| Fig. 6-18. Contour plot of $Si_3N_4$ stress as a function of low frequency plasma percentage and $NH_3$ flow                         |      |

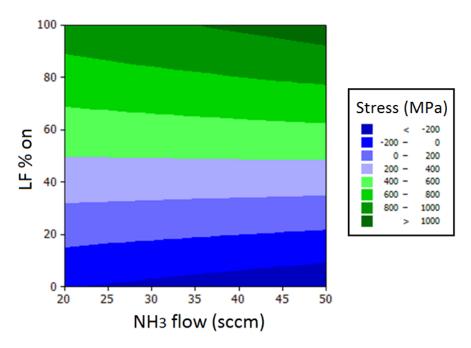

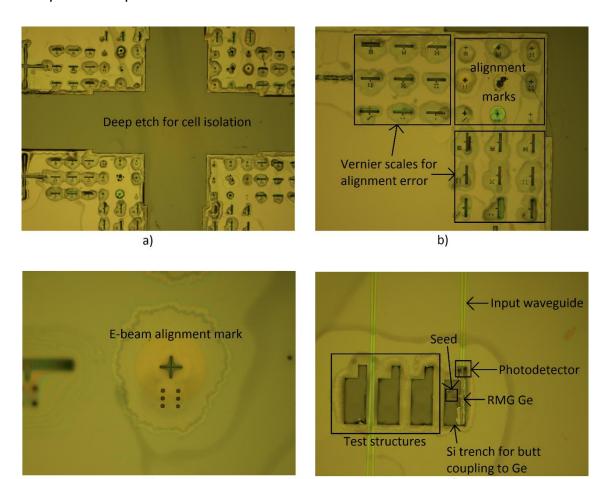

| Fig. 6-19. Microscope images of alignment mark damage after performing a deep etch to isolate each of the e-beam cells               | l 48 |

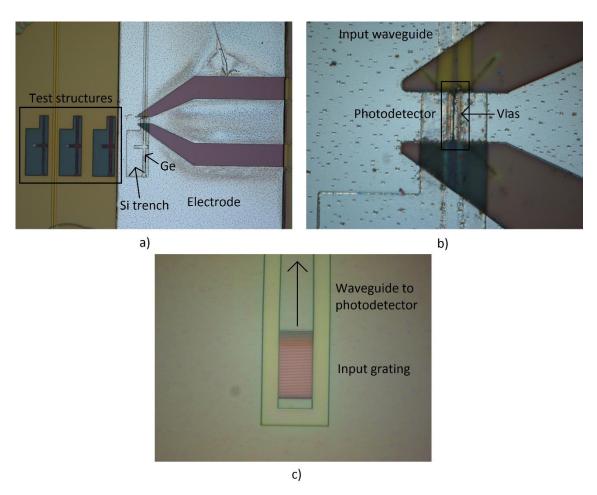

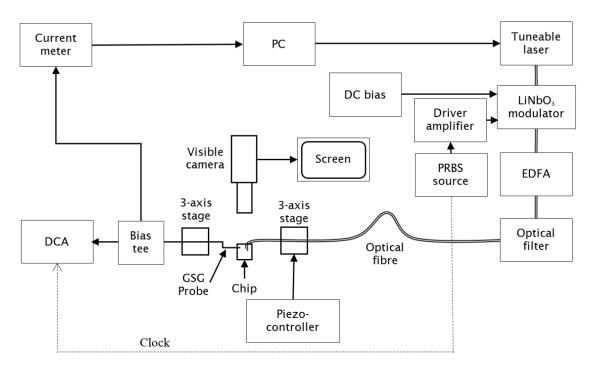

| Fig. 6-20. Microscope images of PECVD photodetectors                                                                                 | 150  |

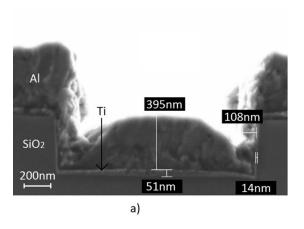

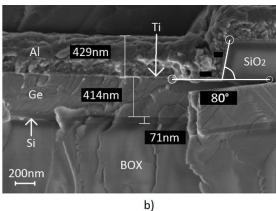

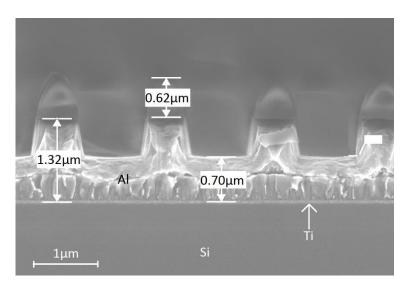

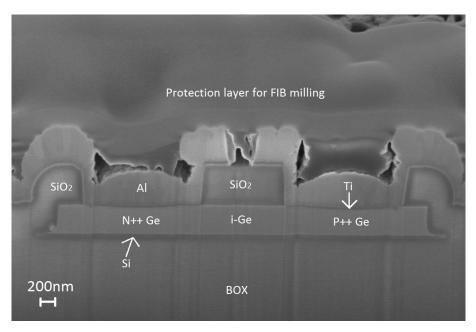

| Fig. 6-21. Cross-section SEM of a completed PECVD photodetector                                                                      | 151  |

| Fig. 6-22. Cross-section SEM of a completed PECVD photodetector, showing device dimensions                                           | 151  |

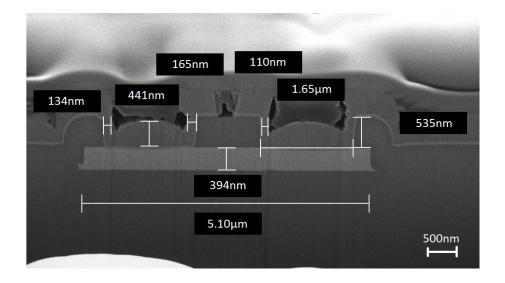

| Fig. 6-23. 1.55 µm photodetector device measurement setup                                                                            | 152  |

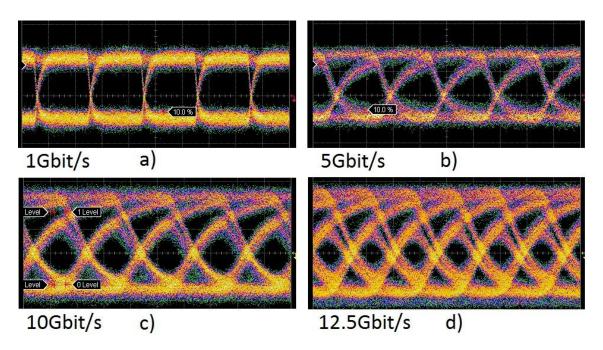

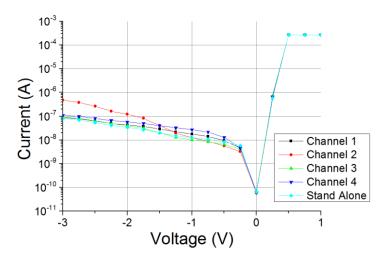

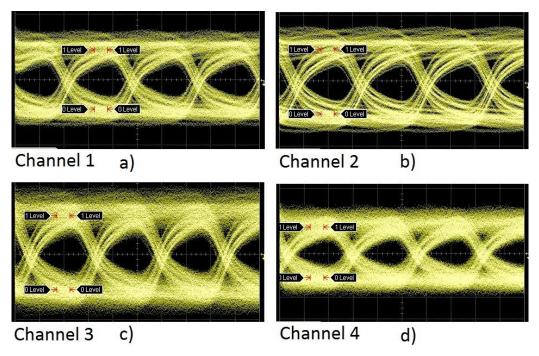

| Fig. 6-24. PECVD photodetector eye diagrams                                                                                          | 155  |

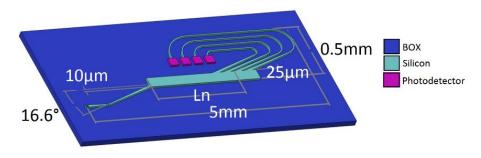

| Fig. 6-25. Schematic of the AMMI receiver, reproduced from [3]                                                                       | 156  |

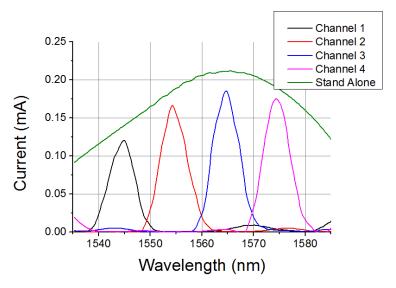

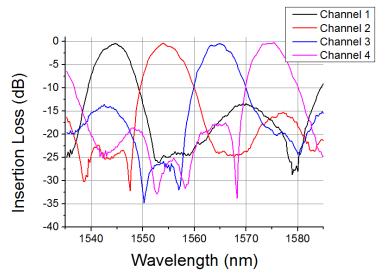

| Fig. 6-26. Measured current from the 4 photodetector channels and a standalone photodetector with the same configuration, reproduced |      |

| from [3]                                                                                                                             | 156  |

| from [3]                                                                                             | Fig. 6-27. Measured insertion loss of the 4-channel WDM device, reproduce | d     |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|

| photodetector, showing a dark current of 60 pA at 0 V, and 10-20 nA at -1 V, reproduced from [3]     | from [3]                                                                  | . 157 |

| -1 V, reproduced from [3]                                                                            | Fig. 6-28. IV curves for the 4-channel photodetectors and standalone      |       |

| Fig. 6-29. 12.5 Gb/s eye diagrams of 4-channel photodetectors operating at -1 V, reproduced from [3] | photodetector, showing a dark current of 60 pA at 0 V, and 10-20 nA at    |       |

| -1 V, reproduced from [3]                                                                            | -1 V, reproduced from [3].                                                | . 158 |

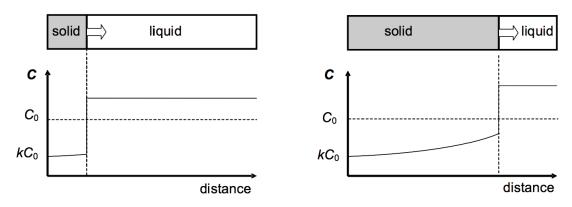

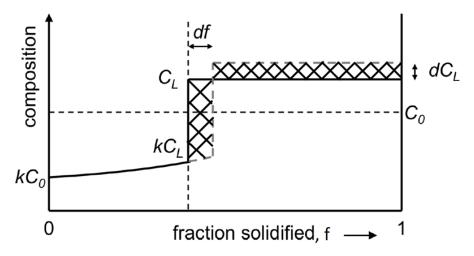

| Fig. C-1. Derivation of the Scheil equation                                                          | Fig. 6-29. 12.5 Gb/s eye diagrams of 4-channel photodetectors operating a | .t    |

|                                                                                                      | -1 V, reproduced from [3].                                                | . 158 |

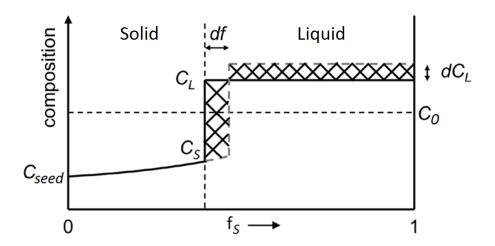

| Fig. D-1. Derivation of the complete mixing model                                                    | Fig. C-1. Derivation of the Scheil equation.                              | . 173 |

|                                                                                                      | Fig. D-1. Derivation of the complete mixing model.                        | . 175 |

|                                                                                                      |                                                                           |       |

# **DECLARATION OF AUTHORSHIP**

### I, CALLUM GEORGE LITTLEJOHNS

declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

### SILICON-GERMANIUM FOR PHOTONIC APPLICATIONS

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed:

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as:

### **Patents**

1. **C. G. Littlejohns**, F. Y. Gardes, G. T. Reed, "Melt-growth of single crystal alloy semiconductor structures and semiconductor assemblies incorporating such structures", 2014 (filed).

### **Journal Papers**

- 1. **C. G. Littlejohns,** M. Nedeljkovic, C. F. Mallinson, J. F. Watts, G. Z. Mashanovich, G. T. Reed, F. Y. Gardes, "Next generation device grade silicongermanium on insulator", *Scientific Reports*, vol. 5, pp. 8288, 2015.

- 2. G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, K. Li, M. Nedeljkovic, J. Soler Penades, A. Z. Khokhar, C. J. Mitchell, S. Stankovic, R. Topley, S. A. Reynolds, Y. Wang, B. Troia, V. M. N. Passaro, C. G. Littlejohns, T. Dominguez Bucio, P. R. Wilson, G. T. Reed, "Silicon photonic waveguides and devices for near- and mid-IR applications", *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 21, pp. 1-12, 2015.

- 3. M. Nedeljkovic, C. J. Mitchell, A. Z. Khokhar, S. A. Reynolds, D. J. Thomson, F. Y. Gardes, C. G. Littlejohns, G. T. Reed, G. Z. Mashanovich, "Mid-infrared thermo-optic modulators in SOI", *Photonics Technology Letters*, vol. 26, pp. 1352-1355, 2014.

4. **C. G. Littlejohns**, Y. Hu, F. Y. Gardes, D. J. Thomson, S. A. Reynolds, G. Z. Mashanovich, G. T. Reed, "50 Gb/s silicon photonics receiver with low insertion loss", *Photonics Technology Letters*, vol. 26, pp. 714-717, 2014.

### **Post-Deadline Conference Papers**

1. **C. G. Littlejohns**, M. Nedeljkovic, G. Z. Mashanovich, G. T. Reed, F. Y. Gardes, "Silicon-germanium composition engineering for next generation multilayer devices and systems", *IEEE Group IV Photonics*, Paris, France, 27-29 August 2014.

### **Invited Conference Papers**

- G. T. Reed, Y. Hu, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, J. Soler-Penades, M. Nedeljkovic, A. Khokar, P. Thomas, C. G. Littlejohns, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, D. J. Richardson, P. Petropoulos, P. Thomas, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, H. Chong, "Near infrared and the mid infrared silicon photonic devices", Nano Korea 2014 Symposium, Seoul, South Korea, 2-4 July 2014.

- 2. G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Khokar, P. Thomas, C. G. Littlejohns, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, X. Chen, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, H. Chong, "Silicon photonics", 7<sup>th</sup> ISTDM, Singapore, 2-4 June 2014.

- 3. Y. Hu, C. G. Littlejohns, J. Soler Penades, A. Z. Khokhar, S. Stankovic, S. A. Reynolds, C. J. Mitchell, F. Y. Gardes, D. J. Thomson, "Multichannel silicon photonic devices based on angled multimode interferometers", *Photonics North*, Montreal, Canada, 28-30 May 2014.

- 4. G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Z. Khokhar, P. Thomas, **C. G. Littlejohns**, A. Ahmed, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, H. M. H. Chong, "Silicon photonic devices for the near and mid-infrared wavelength ranges", *Mediterranean Photonics Conference*, Trani, Italy, 7-9 May 2014.

- 5. G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Khokhar, P. Thomas, **C. G. Littlejohns**, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, N. Owens, X. Chen, P. R. Wilson, L. Ke, T. Ben Masaud, A. Tarazona, H. M. H. Chong, "Recent results in silicon photonics at the University of Southampton", *Photonics West*, San Francisco, USA, 1-6 February 2014.

### **Conference Papers**

- 1. **C. G. Littlejohns**, F. Y. Gardes, M. Nedeljkovic, G. Z. Mashanovich, G. T. Reed, "Silicon diffusion engineering in rapid melt growth of silicon-germanium-on-insulator", *ECS and SMEQ Joint International Meeting*, Cancun, Mexico, 5-9 October 2014.

- 2. F. Y. Gardes, **C. G. Littlejohns**, T. Dominguez Bucio, J. Soler Penades, C. J. Mitchell, A. Z. Khokhar, G. T. Reed, G. Z. Mashanovich "Ge-on-Si and SiGeOI for future photonic integrated systems", *EMRS Fall Meeting*, Warsaw, Poland, 15-18 September 2014.

- 3. F. Y. Gardes, **C. G. Littlejohns**, J. Soler Penades, C. J. Mitchell, A. Z. Khokhar, G. T. Reed, G. Z. Mashanovich, "Germanium for photonic applications", 7<sup>th</sup> ISTDM, Singapore, 2-4 June 2014.

- 4. F. Y. Gardes, T. Dominguez Bucio, **C. G. Littlejohns**, G. T. Reed, K. Debnath, L. O'Faolain, "Group IV functionalization of low index waveguides", *Photonics North*, Montreal, Canada, 28-30 May 2014.

### **Conference Posters**

- 1. **C. G. Littlejohns**, M. Nedeljkovic, G. Z. Mashanovich, G. T. Reed, F. Y. Gardes, "Single crystal silicon-germanium-on-insulator growth for next generation devices and systems", *Zepler Institute Photonics Day*, Southampton, UK, 19 September 2014 (best poster runner-up prize).

- **2. C. G. Littlejohns**, Y. Hu, F. Y. Gardes, D. J. Thomson, S. A. Reynolds, R. W. Kelsall, L. J. M. Lever, "UKSP photodetectors", *UK Silicon Photonics Showcase Event*, Southampton, UK, 12 November 2013.

- 3. **C. G. Littlejohns**, F. Y. Gardes, G. Z. Mashanovich, G. T. Reed, "Germanium growth by liquid phase epitaxy", *Japanese Silicon Photonics International School*, Tokyo, Japan, 26-28 January 2013.

|--|

# Acknowledgements

This work would not have been possible without the guidance and support I have received from many others over the past few years. First and foremost I must thank my extremely patient and knowledgeable supervisors; Dr Frederic Gardes, Professor Graham Reed and Dr Goran Mashanovich. Without their seemingly endless expertise and enthusiastic teaching, this project would have been infinitely more difficult. Fred in particular has kept me motivated and inspired on a day-to-day basis, and has somehow managed to keep his sense of humour even with me knocking on his door twice a day! He has gathered the majority of the SEM images in this thesis, for which I am indebted. I am truly grateful to Dr David Thomson for always being available for help, particularly in the labs, for allowing me to move into his spare room, and for providing the only real competition in the office fantasy football league (honourable mentions go to Dr Goran Mashanovich and Dr Milos Nedeljkovic)! I would like to thank Dr Ali Khokhar for his never-ending support with e-beam lithography, and for always remaining so helpful and cheerful even as I piled extra work on his desk. He even spent some weekends writing my wafers so that I could finish my thesis on time. For this I am extremely grateful.

I would also like to thank all of the other members of the silicon photonics group, past and present, for their assistance with all things big and small; Dr Milos Nedeljkovic, Dr Youfang Hu, Dr Stevan Stankovic, Dr Rob Topley, Dr Xia Chen, Dr Nathan Owens, Dr Milan Milosevic, Dr Colin Mitchell, Scott Reynolds, Jordi Soler Penades, Thalia Dominguez Bucio, Paul Thomas, Arifa Ahmed, and Nathan Soper. In particular, I would like to express my gratitude to Dr Milos Nedeljkovic for his assistance with MATLAB, which saved me hours of time and effort, but also Jordi Soler Penades for his mid-IR waveguide designs and the measurements he performed for me, Thalia Dominguez Bucio for her help with the rapid melt growth mask designs, Dr Youfang Hu for his AMMI mask designs, and Scott Reynolds for his friendship, lifts to the office and CAD expertise.

A huge thank you must also go to the cleanroom technicians, in particular Dr Owain Clarke, Dr Stuart Pearce, Dr Kian Kiang and Mike Perry, who have provided endless support throughout my PhD. Their help and advice has proven to be priceless.

Parts of this project were carried out in collaboration with colleagues at other universities and companies, all of whom I would like to thank: Chris Mallinson and Professor John Watts at the University of Surrey for AES measurements, Chris Stephens at Thermofisher Scientific for EBSD measurements, Professor Russell Gwilliam and his team at the Ion Beam Centre in Surrey for ion implantation, and IHP in Germany for providing the SiGe composition calibration samples. I would also like to thank some people at the University of Southampton: Dr Mark Light for his help with XRD measurements, Dr Harold Chong for helping me settle into the University over the first few weeks and for always knowing the right person to speak to for assistance, and Glenys Howe and Lucyna Palmer for their help with everything over the last couple of years.

Finally, a very special thank you must of course go to my mum and dad, my brothers Ben and Euan, and the rest of my family for their unending love and support over the years. I would especially like to thank my little brother Euan for being a maths genius!

# **Chapter 1: Introduction**

The demand for increasing bandwidth and data rates in the communication and computing industries has led to the migration from electronic signals to optical signals at certain system levels. High data rates require high signal frequencies at which the skin effect becomes detrimental to the performance of copper interconnects. Optical signals are not susceptible to this effect, and because they use semiconductor or dielectric waveguides, they do not suffer from the resistive loss that dominates propagation loss in electrical lines [1]. High frequency, low loss signals, transmitted using optical fibres, revolutionised long distance communications in the 1990's, and have since become an integral part of the World Wide Web. However, optical signals have yet to replace electrical signals for short distance connections because of the higher costs of conventional optical systems. Nevertheless, the future need for on-chip optical interconnects has been discussed by Intel as early as 2004 [2].

This project is concerned with the development of low-cost, low thermal budget, epitaxial growth of germanium and silicon-germanium (SiGe) on silicon, and silicon-on-insulator (SOI) substrates, for use in the silicon photonics industry for, amongst other applications, high speed modulation and photodetection.

# 1.1 Silicon photonics

Silicon has dominated the electronics industry for decades, and is now also becoming the material of choice for parts of the photonics industry; an area that has traditionally been dominated by III-V semiconductors [3, 4]. One of the main advantages of silicon photonics is its compatibility with complementary metal oxide semiconductor (CMOS) technologies, therefore facilitating electronic and optical integration on the same wafer, in the same fabrication facility. This also enables the transfer of decades of knowledge of silicon processing techniques. Silicon is also an abundant material, and therefore available at low cost when compared with other semiconductor substrates. The challenge lies in reducing

### Chapter 1: Introduction

the fabrication costs associated with silicon photonics circuits, which will only be achieved through mass production.

Another potential benefit of migrating to optical systems is the reduction in power consumption. In electronic systems, the dominant energy dissipation is charging and discharging the capacitances of the interconnect wires. Furthermore, as the electronic interconnects become smaller to accommodate more transistors, their resistance is raised, further increasing the energy dissipation of the system. In optical interconnect systems these issues are not prevalent [5].

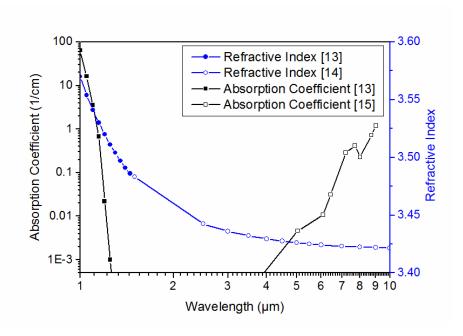

The refractive index (RI) of crystalline silicon at 1.55  $\mu$ m, the most commonly used communications wavelength, which corresponds to the minimum propagation loss in optical fibres, is 3.476 (see Fig. 1-1), compared with a refractive index of 1.443 for its native oxide (SiO<sub>2</sub>) [6]. This large refractive index contrast allows for high confinement of light and device miniaturisation, and is utilised by the most commonly used silicon photonics substrate: silicon-oninsulator.

The field has already yielded its first commercial products. In 2000, Bookham Technology (now Oclaro) commercially pioneered the first integrated silicon photonics product. They offered an arrayed waveguide grating (AWG) multiplexer, integrated with variable optical attenuators (VOA) [7]. In 2007, Luxtera released a CMOS photonics product [8] that contained 4 separate transceiver channels, each capable of transmitting 10 Gbit/s over 300 m. In 2012, Luxtera announced that this product had reached 1 million sales [9]. Luxtera have since developed an improved version of the product that is capable of transmitting 4 channels at 28 Gbit/s, powered by a single co-packaged laser [10]. These products offer a fully integrated solution, with on-chip waveguide level modulation and photodetection, along with associated electronics.

In 2012, IBM announced their first fully integrated CMOS silicon photonics transceiver [11]. Using 90 nm standard CMOS fabrication techniques, they were able to achieve 4 channels at 25 Gbit/s each, with an external light source.

In early 2013, Intel announced that it was shipping engineering samples of a 100 Gbit/s silicon photonics module, intended for links inside and between racks in data centres [12].

Fig. 1-1. Refractive index and absorption coefficient in silicon as a function of wavelength.

Data gathered from [13-15].

Further development looks set to accelerate with, in addition to the above, companies such as Kotura (recently acquired by Mellanox Technologies Ltd.), Genalyte, Oracle and HP all actively involved with silicon photonics research.

# 1.1.1 Applications of silicon photonics

The current mainstream target application for silicon photonics is short reach interconnects, for example from server to server in datacentres. Other envisioned applications include implantable medical chips, sensing, and fibre-to-the-home internet.

# 1.2 Silicon-germanium and germanium epitaxial growth

In order to achieve a complete library of silicon photonics circuit building blocks, it is necessary to incorporate germanium onto the substrate to fabricate the receiving element of the circuit. This therefore demands epitaxial germanium growth on silicon.

The most challenging obstacle for high quality germanium and silicongermanium epitaxial growth on silicon is caused by the 4.2% mismatch in lattice

### Chapter 1: Introduction

constants of the two materials. This mismatch leads to the formation of performance inhibiting defects in the epitaxial layer.

High quality germanium and silicon-germanium on silicon has been grown using a variety of techniques [16]. The majority of these techniques require high temperatures during the growth phase (> 600 °C), and are costly and complex. However, plasma enhanced chemical vapour deposition (PECVD) offers a low cost, low temperature growth method. In addition, rapid melt growth (RMG) offers the potential to grow localised high quality, single crystal germanium and silicon-germanium on insulator [17], using only a simple, non-critical growth step, and a single anneal step.

# 1.3 Germanium photodetectors

Silicon is transparent at 1.55 µm and therefore, as described above, germanium is often used for photodetection. Germanium, along with silicon, is a group IV material, and therefore avoids the contamination issues relating to III-V materials. It has the same diamond face centred cubic crystalline structure as silicon, but has a smaller bandgap, allowing it to absorb light at the communications wavelengths. Germanium also offers both higher electron mobility and higher hole mobility when compared with silicon, which ultimately allows for faster electronic devices. These properties make germanium the dominant material for silicon photonics integrated photodetectors [18-20].

### 1.4 Thesis outline

This thesis begins with a background discussion of germanium and silicongermanium epitaxial growth on silicon, followed by a summary of the principles of photodetection, as well as the important photodetector performance characteristics. The subsequent chapter reviews the current state-of-the-art in these fields.

There are then three chapters discussing the main areas of research carried out in this thesis. The first is a study of low cost, low temperature, germanium-on-silicon growth by plasma enhanced chemical vapour deposition. Using this technique, single crystal germanium is epitaxially grown on silicon at a

temperature of 400 °C, resulting in a defect density of approximately  $3.3 \times 10^8$  cm<sup>-2</sup> after an anneal at 600 °C for two minutes.

The second, and main area of research, is rapid melt growth of germanium and silicon-germanium on localised insulator islands. The main aim of this section is to develop a high quality localised silicon-germanium-on-insulator platform that will potentially enable the migration from conventional photonics silicon-on-insulator substrates, to silicon substrates typically used in the electronics industry. The use of the same substrate will greatly enhance the prospects of monolithic electronic-photonic integration. This can be achieved through the growth of localised silicon-germanium for modulation [21] and detection [22], connected by dielectric waveguides deposited on top of the active layer [23]. The challenge lies in developing a growth method that enables multiple silicon-germanium compositions to be grown for the realisation of multi-channel links, with the use of wavelength division multiplexing (WDM). In this chapter, single crystal, high quality, silicon-germanium-on-insulator is fabricated with a uniform composition using novel tailored tree-like structures.

The results gathered in these previous two chapters are subsequently utilised in the third and final research area: high speed germanium photodetectors. Zero bias, 12.5 Gbit/s waveguide integrated photodetectors are fabricated, with a responsivity, at a wavelength of 1550 nm, of approximately 0.1 A/W.

Finally the conclusions and potential future work are discussed

### Chapter 1: Introduction

# Chapter 2: Background and theory

### 2.1 Properties of germanium and silicon-germanium

Si, Ge and  $Si_{1-x}Ge_x$  alloys are all semiconducting materials with a diamond lattice structure based on that of a face-centred cubic unit cell. This enables epitaxial growth of one material onto the other for a plethora of applications in both photonics and electronics.

SiGe possesses full miscibility over its entire composition range which allows for the tuning of properties such as the bandgap and the lattice constant between those of bulk Si and bulk Ge.

Both Ge and SiGe have a higher hole and electron mobility than Si, meaning that they will ultimately lead to faster electronic devices, e.g. transistors [1]. In fact, Ge has the highest hole mobility of any known semiconductor [2]. It also has a major advantage over its III-V competitors in that it is a CMOS compatible material, and is in fact already part of the CMOS production line. This means that monolithic integration of Si, SiGe and Ge based electronics and photonics on the same substrate is possible. Table 2-1 compares some key properties of Si and Ge. The lower bandgap of Ge, when compared to Si, is critical for the fabrication of photodetectors as it results in an optically absorbing material at wavelengths where Si is transparent. The lattice constant is a key property for epitaxial growth as it determines the physical size of the crystal structure.

Table 2-1. Some key properties of Si and Ge, gathered from [3].

| Property                                                             | Silicon | Germanium |

|----------------------------------------------------------------------|---------|-----------|

| Bandgap (eV)                                                         | 1.11    | 0.66      |

| Electron mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 1400    | 3900      |

| Hole mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )     | 450     | 1900      |

| Lattice constant (nm)                                                | 0.5431  | 0.5658    |

# 2.2 Germanium energy band structure

A semiconductor, such as Ge, can be defined as either a direct bandgap material or an indirect bandgap material. In a direct bandgap material, an electron can move from the valance band to the conduction band if it gains sufficient energy to cross the bandgap. However, in an indirect bandgap material, in order for an electron to move from the valence band to the conduction band it needs to not only gain sufficient energy, but it also requires a change in momentum.

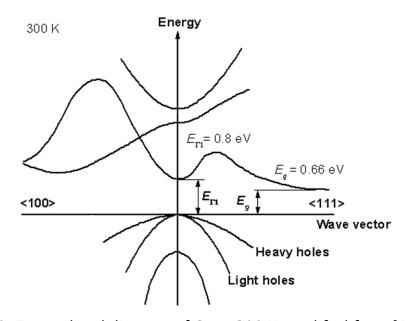

Ge is defined as an indirect bandgap material because its lowest energy bandgap,  $E_g = 0.66$  eV, is indirect. However, Ge also has a direct bandgap,  $E_{\Gamma I}$ , only 140 meV above at 0.8 eV, as shown in Fig. 2-1. For comparison the bandgap of Si is 1.11 eV (also indirect).

Fig. 2-1. Energy band diagram of Ge at 300 K, modified from [4].

# 2.3 Germanium and silicon-germanium epitaxial growth

Epitaxial growth of Ge and SiGe, on Si, is of vital importance for silicon photonics to enable fully integrated optical systems. A brief overview of epitaxial growth techniques and applications of Ge and SiGe on Si is given in Chapter 3.

If the lattice constants of two materials are the same, and both materials have the same crystal structure, then one material can be epitaxially grown on the other material without strain or dislocations. However, if there is a lattice constant mismatch between the two materials, as with Si and Ge, the epitaxial layer will become strained as its lattice constant adapts to that of the seed crystal. Equation 2-1 calculates the 4.2 % lattice constant mismatch between Si and Ge from the parameters listed in Table 2-1:

$$\frac{5.65791 \text{ Å} - 5.4311 \text{ Å}}{5.4311 \text{ Å}} \times 100 = 4.2 \%$$

Equation 2-1

As first discovered by Van Der Merwe in 1963 [5], if the epitaxial layer reaches a critical thickness, determined by the lattice mismatch, amongst other properties, the excess in strain energy leads to the formation of misfit dislocations. The elastic strain energy,  $E_{strain}$ , can be calculated using Equation 2-2:

$$E_{strain} = \lambda \left(\frac{\Delta a}{a}\right)^2 At$$

Equation 2-2

Where  $\lambda$  is the biaxial elastic modulus,  $\Delta a$  is the forced change in lattice constant, a is the unstrained lattice constant, A is the epitaxial film surface area and t is the film thickness. The critical thickness for defect free, compressively strained Ge-on-Si has been shown to be around 4-10 nm [6]. Once this critical thickness has been reached it is energetically favourable to form misfit dislocations to reduce the elastic strain energy. The growth evolution of Ge-on-Si is demonstrated in Fig. 2-2 through to Fig. 2-4.

Fig. 2-2 shows the initial wetting layer formed when Ge is grown on Si. As the Ge lattice is 4.2% bigger than the Si lattice the Ge is compressively strained.

Fig. 2-2. Cross-section and atomic view of Ge-on-Si growth, showing the wetting layer, reproduced from [7].

Fig. 2-3 shows the addition of a few more Ge monolayers. Total strain energy increases linearly with film thickness, as per Equation 2-2.

Fig. 2-3. Cross section and atomic view of Ge-on-Si growth, below the critical thickness, reproduced from [7].

Fig. 2-4 shows Ge-on-Si growth after the critical thickness has been reached. A misfit dislocation is formed that reduces the total elastic strain energy and allows a relaxed layer to be formed.

Fig. 2-4. Atomic view of Ge-on-Si growth above the critical thickness, showing a misfit dislocation, reproduced from [7].

Any subsequent layers grown on top of a film containing misfit dislocations will contain threading dislocations that propagate through the film. These dislocations can only terminate either at the surface, at high angle grain boundaries, at some material interfaces, or by annihilation with dislocations with an antiparallel Burgers vector (the Burgers vector represents the magnitude and direction of a lattice distortion) [8]. The density of these dislocations in the Ge layer, defined as the threading dislocation density (TDD) is an important measure of Ge-on-Si film quality. It is of vital importance to minimise the TDD of Ge-on-Si layers because these defects can degrade physical, optical, and electrical properties of the device material, which can lead to premature device failure and poor performance.

### 2.4 Epitaxial defect necking

Threading dislocations are terminated at the interface with an insulating material such as SiO<sub>2</sub>. This fact can be exploited for TDD reduction using a process called epitaxial defect necking, as shown in Fig. 2-5.

Fig. 2-5. Cross-section diagram demonstrating the principles of epitaxial defect necking, reproduced from [9].

In the (111) <110> diamond cubic slip system, misfit dislocations lie along the <110> directions and the slip plane is (111). Threading dislocations in the <110> directions make a 45° angle to the underlying Si (100) substrate. Therefore if the aspect ratio of the wells in the mask is greater than 1, crystallography dictates that threading dislocations will be blocked by the side-walls, resulting in a defect free Ge top surface. This is very similar to bulk Si Czochralski crystal growth [10].

The principles of epitaxial defect necking are used in the rapid melt growth work described in Chapter 5.

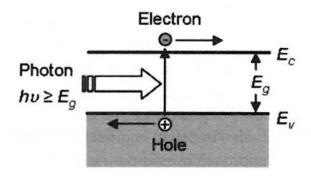

# 2.5 Light detection

When incident light falls upon the surface of a semiconductor, electrons are promoted from the valence band to the conduction band, providing the photons are of higher energy than the bandgap energy of the semiconductor, as shown in Fig. 2-6.

#### Chapter 2: Background and theory

Fig. 2-6. Optical absorption of a photon and consequent electron-hole pair generation, reproduced from [11].

$E_C$  is the conduction band energy,  $E_V$  is the valence band energy and  $E_g$  is the bandgap energy.

The photon energy, E, can be calculated using Planck's equation:

$$E = hv = \frac{hc}{\lambda}$$

Equation 2-3

Where h is Planck's constant (6.6262×10<sup>-34</sup> Js),  $\nu$  is the frequency, c is the speed of light in a vacuum (2.9979×10<sup>8</sup> m/s) and  $\lambda$  is the wavelength. Once the electrons are promoted to the conduction band they become mobile and can drift around the semiconductor under the influence of an electric field to produce a measurable current.

## 2.5.1 Absorption coefficient

The absorption coefficient,  $\alpha$ , describes a materials ability to absorb light at different wavelengths and can be calculated using the Beer-Lambert Law:

$$I = I_0 e^{-\alpha x}$$

Equation 2-4

Where I is the transmitted intensity,  $I_0$  is the incident intensity and x is the path length. Fig. 2-7 displays the absorption coefficient for both Si and Ge as a function of wavelength.

The inflection point on the Ge absorption spectrum, at a wavelength of approximately 1.55  $\mu m$ , is due to the shift from direct to indirect absorption.

Fig. 2-7. Absorption spectra of Si and Ge at 300 K, modified from [12].

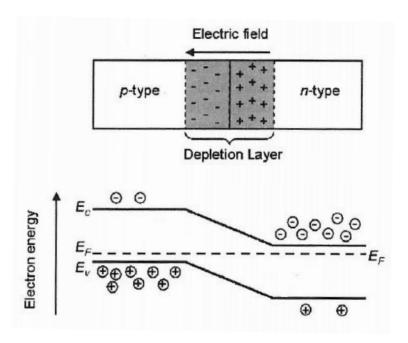

## 2.5.2 p-n junctions

The properties of a semiconductor can be altered with the introduction of a dopant, such as boron (B) or phosphorous (P). In an n-type region the dopants contribute mobile electrons that shift the Fermi level,  $E_F$ , (the energy level where the probability of occupation by an electron is 0.5) closer to the conduction band. Hence, there is a resultant surplus of electrons in the conduction band. Likewise, in a p-type region the dopants contribute mobile holes that shift the Fermi level closer to the valence band, resulting in surplus holes in the valence band.

When a *p*-type region and an *n*-type region are in contact with each other, the excess electrons in the *n*-type region diffuse across to the *p*-type region where they recombine with the abundant holes, and leave a positively charged impurity within the crystal structure of the *n*-type region. The opposite is true for holes in the *p*-type region. This results in a carrier depletion region, and a built in electric field which opposes the diffusion of carriers, causing equilibrium to be established. This is demonstrated in Fig. 2-8.

Fig. 2-8. A p-n junction in equilibrium, reproduced from [11].

a) Electric field across depletion layer caused by ionised donors, b) electron energy band diagram.

If a reverse bias is applied to the p-n junction then the depletion layer is extended as the potential barrier is increased, leading to reduced minority carrier diffusion.

Compared with an ordinary p-n junction, a p-i-n junction has an undoped layer in the centre of the device, leading to a bigger depletion region which enables more efficient collection of the photogenerated carriers in a detector. The introduction of an intrinsic region therefore generally leads to an improved photodetector.

## 2.5.3 Photodetector performance characteristics

In order to determine the relative performance of a photodetector, a number of important characteristics must be considered. This section defines these characteristics.

## 2.5.3.1 Quantum efficiency

The quantum efficiency,  $\eta$ , is defined as the number of electron-hole pairs generated per incident photon, as per Equation 2-5. It is dependent on the absorption coefficient of the material and is therefore wavelength dependent.

$$\eta = \frac{electrons/sec}{photons/sec} = \frac{I_p}{q} \cdot \frac{hv}{P_{out}}$$

Equation 2-5

Where  $I_p$  is the photogenerated current, q is the charge of an electron (1.6×10<sup>-19</sup> C) and  $P_{opt}$  is the incident optical power.

## 2.5.3.2 Responsivity

The responsivity, R, of a photodetector relates the incident optical power to the amount of generated photocurrent in units of A/W, as per Equation 2-6. Again, this is wavelength dependent and will be significantly higher at energies high enough to make direct band-band transitions possible.

$$R = \frac{I_p}{P_{opt}} = \eta \frac{q}{h\nu}$$

Equation 2-6

The responsivity is a much more useful characteristic than the quantum efficiency when comparing photodetectors, as it is dependent on the whole device rather than just the absorbing layer.

## 2.5.3.3 Optical bandwidth

The optical bandwidth is measured by illuminating the device with monochromatic light, intensity modulated at increasing frequency, and measuring the voltage drop across a 50  $\Omega$  load connected to the output. The optical bandwidth is then defined as the frequency at which the output voltage drops below half the maximum voltage (DC voltage). The bandwidth of a device is limited by a combination of four factors [13]:

- 1. Drift time of carriers across the depletion region.

- 2. Diffusion of carriers generated outside of the depletion region.

- 3. Capacitance of the junction.

#### 4. Access resistance and contact resistance.

The diffusion process is relatively slow so care must be taken to ensure that all the electron-hole pairs are generated in the depletion region. The drift time/velocity is related to the carrier mobility and the applied electric field. The carrier saturation velocity of Ge is of the order  $\sim 10^7$  cm/s [14]. Therefore, if the depletion region is approximately 1  $\mu$ m wide, and there is a strong electric field, the drift time will be picoseconds. This means that the drift time will be significantly shorter than the recombination time (the recombination time is expected to be of the order of tens of  $\mu$ s [15]), so the majority of carriers will be collected and contribute to the output current.

The capacitance, C, of a device can be approximated by its dimensions, as per Equation 2-7:

$$C = \frac{\varepsilon A}{d}$$

Equation 2-7

Where  $\varepsilon$  is the permittivity of the dielectric material, A is the cross sectional area of the doped regions acting as the plates and d is the depletion region width. It can be seen that increasing the width of the depletion region decreases the capacitance; however, this will also increase the drift time in the depletion region so a trade-off must occur in order to maximise the device speed.

The overall RC time constant is determined by the junction capacitance, the access resistance and contact resistance, and any load resistance applied to the device.

It is important to note that the electrical bandwidth of the photodetector is the frequency at which the optical power drops below half the maximum power. Electrical power is proportional to the square of the voltage, so in the decibel scale this appears as a factor of two difference between optical bandwidth and electrical bandwidth. Therefore, the 3 dB optical bandwidth is equivalent to the 6 dB point on the electrical response curve.

### 2.5.3.4 Dark current

The dark current,  $I_d$ , is the current flowing through the device when there is no input light source. Dark currents at room temperature have been shown by Ang

et al. [16] to be generated by Shockley-Read-Hall processes [17, 18]. In this mechanism, electron-hole pairs are generated via defect induced trap levels in the Ge forbidden gap, and then swept out of the device by the built-in electric field. It is therefore imperative to keep the number of defects in the Ge at a minimum to reduce the dark current of the resultant photodetector.

## 2.5.3.5 Other important characteristics

Another important characteristic that must always be considered is the overall cost for both the raw materials and fabrication of the device. This must be kept to a minimum by using simple fabrication techniques and low cost materials. Other important characteristics that cannot be measured quantitatively include CMOS compatibility and ease of integration with existing technology.

## 2.6 Techniques used

This section will briefly describe and explain the important physics behind the fabrication and characterisation tools used in this thesis.

## 2.6.1 Chemical vapour deposition

In chemical vapour deposition (CVD), a film is produced by chemical reactions that take place on the substrate surface. The input gases react to form solid byproducts, which are deposited on the surface of the substrate, and volatile gases that flow out of the reactor. In plasma enhanced chemical vapour deposition (PECVD), radio frequency (RF) power is applied across two electrodes inside the reaction chamber, which causes the input gases to dissociate and become ionised, forming a plasma. This allows deposition to take place at lower temperatures than more conventional CVD techniques. As described in "Silicon VLSI Technology" by Plummer *et al.* [19] there are 7 steps involved with PECVD:

- 1. Transport of the reactant gases into the chamber.

- 2. Dissociation of gases in the plasma.

- 3. Diffusion of the reactants from the plasma to the wafer surface.

- 4. Adsorption of the reactants on the wafer surface.

- 5. Surface processes, including migration to attachment sites and surface reaction.

#### Chapter 2: Background and theory

- 6. Desorption of by-products from the surface.

- 7. Transport of by-products away from the surface.

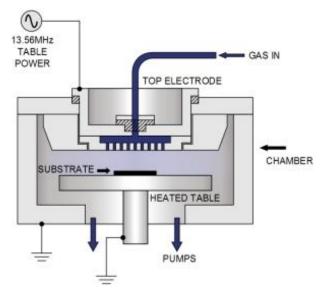

A PECVD reaction chamber is shown in Fig. 2-9.

Fig. 2-9. Schematic diagram of a PECVD reaction chamber, reproduced from [20].

Ge is formed by the decomposition of GeH<sub>4</sub> gas by the following reaction:

$$GeH_4 \rightarrow Ge + 2H_2$$

SiO<sub>2</sub> is formed by the reaction of SiH<sub>4</sub> with N<sub>2</sub>O, as per the following reaction:

$$SiH_4 + 2N_2O \rightarrow SiO_2 + 2N_2 + 2H_2$$

Often, in the above reactions, the gaseous by-products are incorporated into the deposited film. This is usually undesirable and can be rectified by a densification process whereby the substrate is heated to a few hundred degrees to allow the gases to diffuse from the film.

The major variables that affect PECVD growth are temperature, pressure, and gas flow rates. The temperature must be high enough for the chemical reactions to take place, but a temperature that is too high may have detrimental effects on features already developed on the substrate. As a general rule, a higher temperature leads to a higher growth rate. A higher growth rate can also typically be achieved by increasing the gas flow of the input gases. However, high growth rate usually leads to lower quality films with higher surface roughness [21]. A

low pressure is usually desirable since it leads to fewer contaminants in the film, but it must be kept high enough to allow the plasma to form.

## 2.6.2 Inductively coupled plasma etching

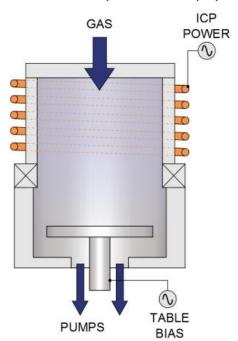

In inductively coupled plasma (ICP) etching, an RF (usually 13.56 MHz) current is delivered through a coil which is wrapped around the reaction chamber. This current induces a strong alternating magnetic field in the chamber, which in turn induces an alternating electric current which dissociates the input gases into a plasma, leaving reactive neutral chemical species and ions. RF power is also often applied across the electrodes in the reaction chamber, as shown in Fig. 2-10. The reactive neutral elements in the plasma are responsible for chemical etching and the ions are responsible for physical etching.

Fig. 2-10. Schematic diagram of ICP etch system, reproduced from [20].

Chemical etching is usually done by free radicals; that is chemical species that have incomplete bonding i.e. unpaired electrons. Typical free radicals used for chemical etching include F and  $CF_3$ , both of which can be formed by the reaction of free electrons in the plasma and  $CF_4$ , as per the reaction below:

$$e^- + CF_4 \rightarrow CF_3 + F + e^-$$

#### Chapter 2: Background and theory

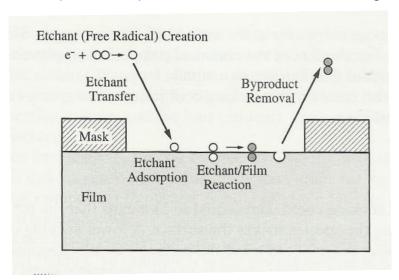

The unpaired electrons cause these free radicals to be highly reactive. As they are adsorbed onto the surface of the substrate, they react and form volatile products, which evaporate away from the surface as shown in Fig. 2-11.

Fig. 2-11. Processes involved in chemical etching during a plasma etch process, reproduced from [19].

Chemical etching is an isotropic process; that is, it etches in all directions, mainly due to an isotropic arrival angle, and the low sticking coefficient between the free radical and the substrate. However, it can also be a very selective process since certain free radicals only react with particular substrates.

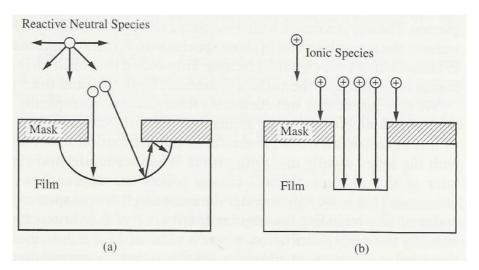

Physical etching is caused by the acceleration of the positive ions in the plasma towards the table, which holds the substrate. This accumulates charge on the substrate by absorbing the fast moving electrons that are accelerated towards it by the RF table power. When the ions strike the substrate, some atoms are etched from the surface. Since the ions tend to arrive normal to the surface of the substrate the etch profile is anisotropic; that is, it etches in one direction. However, this also means that there is no selectivity between materials that are etched. Fig. 2-12 shows a summary of chemical and physical etching.

The advantage of ICP etching over reactive ion etching (RIE) is that the plasma density, which is determined by the ICP power, can be controlled independently to the ion bombardment, which is determined by the table RF power. The high density plasma allows for a high ion flux, and therefore high etch rates at low pressure. This low pressure is advantageous in that there are less collisions between the ions that are bombarding the wafer, which results in an etch profile

that becomes more anisotropic because the majority of the ions are perpendicularly approaching the wafer.

Fig. 2-12. Fluxes of species in plasma etching, reproduced from [19]. a) Chemical, selective, isotropic etching, b) physical, non-selective anisotropic etching.

## 2.6.3 Ion implantation

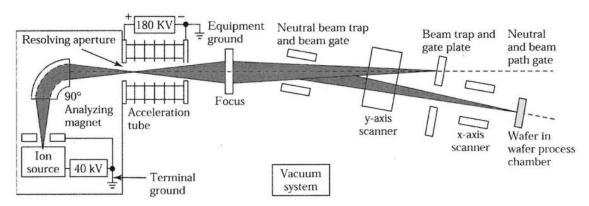

lon implantation is a commonly used technique to introduce impurities into a semiconductor in order to alter its properties. The main advantages of ion implantation, over dopant diffusion and in-situ doped growth, are its more precise control, which leads to improved reproducibility, and lower processing temperatures [3]. An ion implantation system is shown in Fig. 2-13. The ion source contains a filament which heats a source gas to break it up into charged ions, which are subsequently accelerated by the applied extraction voltage. The analysing magnet is adjusted so that only the ions with the desired mass-charge ratio are not filtered out (e.g. B<sup>+</sup> ions). These selected ions are then accelerated in the acceleration tube to the implantation energy, and collimated with the use of apertures. The beam is then scanned over the wafer with the use of electrostatic deflection plates. The whole process happens under low pressure to avoid ion scattering caused by collisions with gas molecules.

#### Chapter 2: Background and theory

Fig. 2-13. An ion implantation system, reproduced from [3].

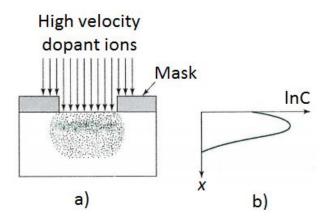

The energetic ions then lose their energy through collisions with the substrate electrons and nuclei, and come to rest within the substrate. The substrate can be selectively implanted with the use of a mask, as shown in Fig. 2-14. The average depth of the implant is controlled by the implantation energy.

Fig. 2-14. Diagram showing ion implantation, adapted from [3].

- a) Ion implantation for selective introduction of dopants using a mask,

- b) doping concentration profile as a function of depth.

Ion implantation inevitably causes lattice damage within the substrate due to the ion collisions. Therefore, this damage should be repaired with the use of a high temperature anneal, which simultaneously activates the implanted ions. Dopant activation is a process that locates the dopants in substitutional lattice sites so that they become electrically active. Interstitial dopant atoms are not electrically active.

### 2.6.4 Rapid thermal annealing