# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

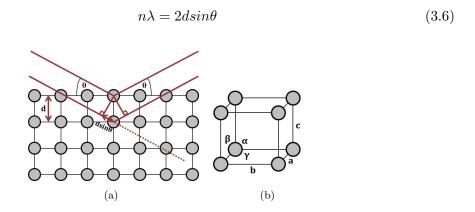

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

## UNIVERSITY OF SOUTHAMPTON

## FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

# Radiation Effects and Reliability of Dielectrics in CMOS Transistors and Resistive Memories

by

Katrina Anne Morgan

Thesis for the degree of Doctor of Philosophy

$\mathrm{June}\ 2015$

(C), University of Southampton, 2015.

"All brontosauruses are thin at one end, much, much thicker in the middle, and then thin again at the far end. That is my theory, it is mine and belongs to me, and I own it, and what it is too." - John Cleese, Monty Python's Flying Circus, Episode 31, 1972

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

## FACULTY OF PHYSICAL SCIENCES AND ENGINEERING Electronics and Computer Science

## Doctor of Philosophy

## RADIATION EFFECTS AND RELIABILITY OF DIELECTRICS IN CMOS TRANSISTORS AND RESISTIVE MEMORIES

by Katrina Anne Morgan

Many industries heavily rely upon advances in electronic devices. As development of electronics continues, new structures and new materials are being utilised. The reliability of these new technologies therefore need to meet the same high levels as the traditional technologies that they are replacing.

Industries such as space and nuclear in particular, face an additional challenge affecting the reliability of their electrical devices; radiation. Ionizing radiation in particular can damage dielectric layers in devices such as metal-oxide-semiconductor (MOS) transistors and resistive memories. In either case, controlling the radiation effects of dielectrics is essential for the reliability of these devices.

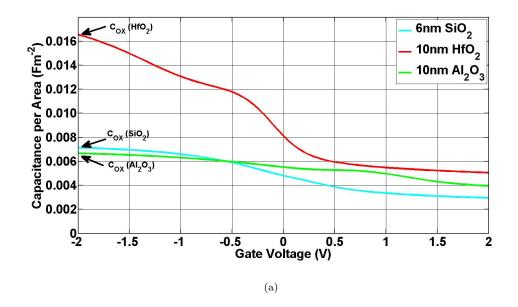

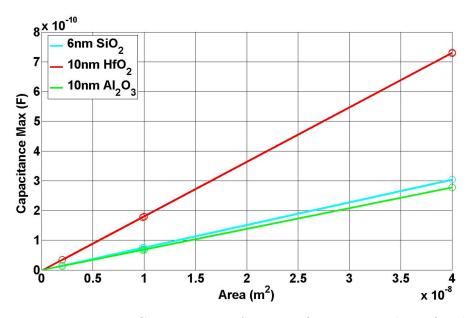

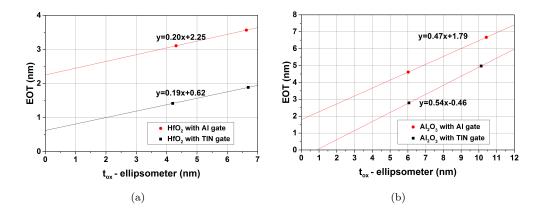

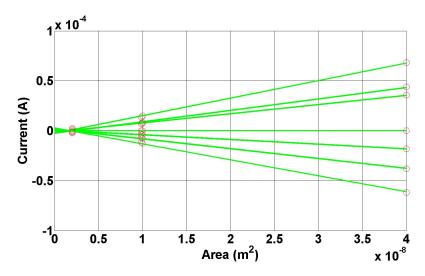

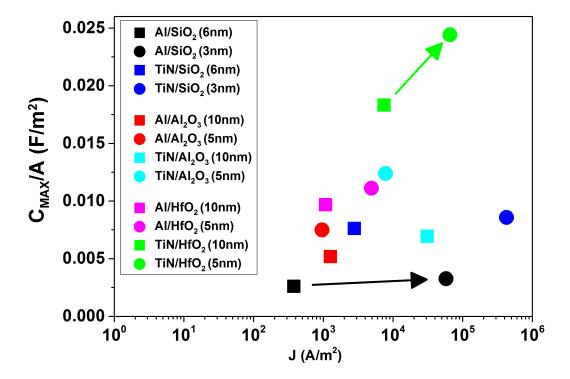

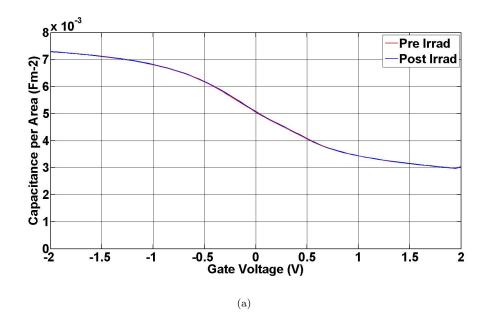

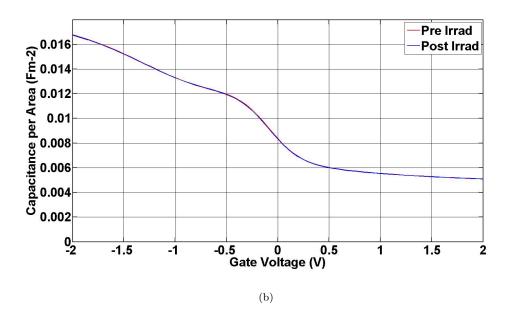

High-k MOS capacitors have been fabricated, analysed and irradiated and compared to a reference silicon dioxide MOS capacitor. Hafnium oxide and aluminium oxide were used for the dielectric layer, with Al and TiN used for the top electrode. C-V measurements indicated the high quality of the TiN/HfO<sub>2</sub>/Si structure in particular, with an interfacial equivalent oxide thickness (EOT) of less than half the total EOT of 1.9 nm. The TiN/HfO<sub>2</sub>/Si capacitor showed superior capacitance and leakage current properties when compared to silicon dioxide capacitors verifying the successful fabrication of high quality, high-k MOS capacitors. The ionizng radiation results showed a voltage shift of less than 100 mV up to 3 Mrad(Si) for the TiN/HfO<sub>2</sub>/Si capacitors. These radiation hardness levels are in the same order of magnitude as silicon dioxide structures. High-k dielectrics can therefore be used as a replacement for silicon dioxide gate oxides without decreasing the radiation hardness of the device, whilst simultaneously achieving reduced leakage current.

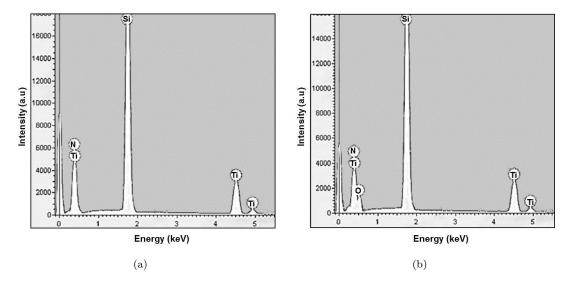

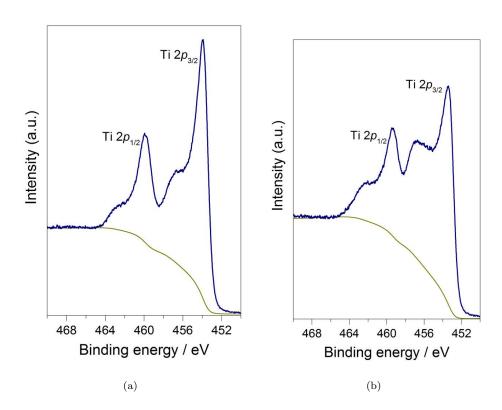

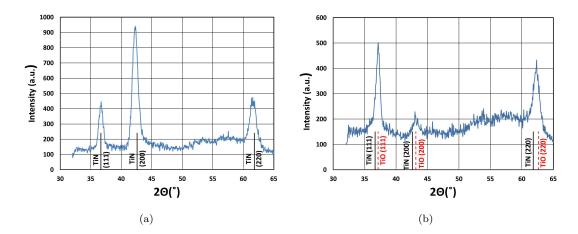

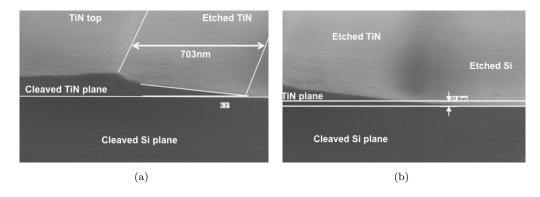

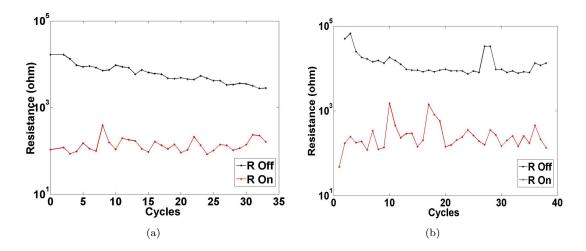

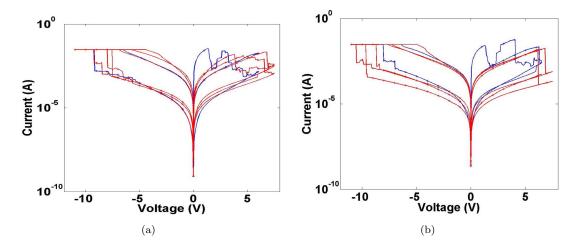

Two types of TiN/HfO $_x$ /TiN resistive memory cells have been fabricated where the top 200 nm TiN electrode has been deposited by two different sputtering methods; reactive, using a titanium target in a nitrogen environment, and non-reactive, using a titanium nitride target. Characterization of the materials shows that the reactive TiN is single-phase stoichiometric TiN with a sheet resistance of 7  $\Omega$ /square. The non-reactive TiN

has a sheet resistance of 300  $\Omega$ /square and was found to contain significant amounts of oxygen. The resistive switching behavior differs for both memory cells. The reactive stoichiometric TiN device results in bipolar switching with a  $R_{OFF}/R_{ON}$  ratio of 50. The non-reactive TiN results in unipolar switching with a  $R_{OFF}/R_{ON}$  ratio of more than  $10^3$ . These results show that an oxygen rich layer between the top electrode and insulator affects the  $R_{OFF}$  value. It supports the theory of oxygen vacancies leading to the formation of conductive filaments.

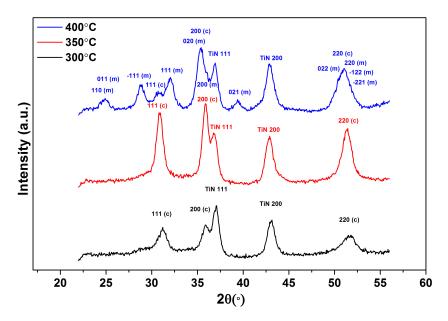

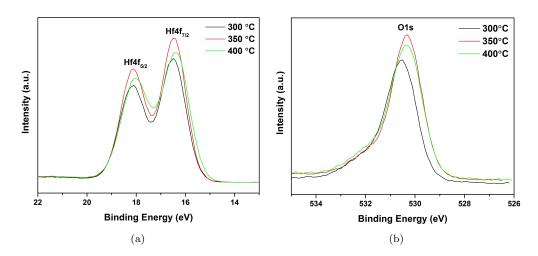

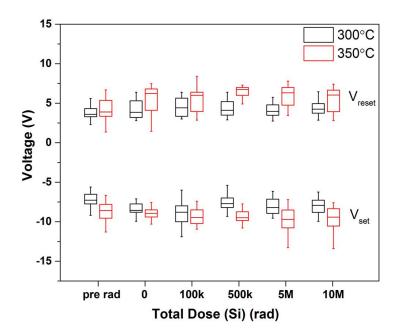

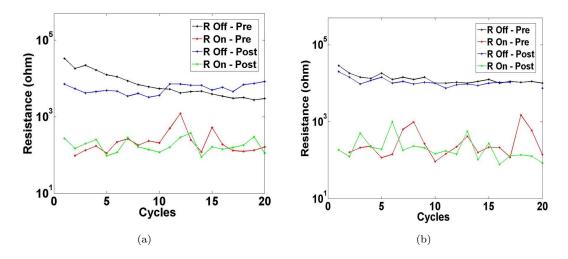

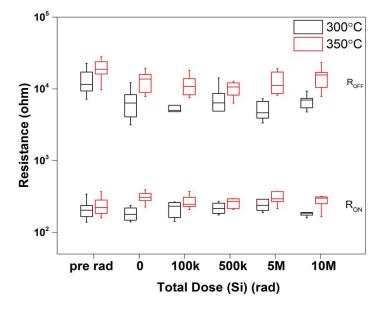

Resistive random access memory based on  $\text{TiN/HfO}_x/\text{TiN}$  has been fabricated, with the stoichiometry of the  $\text{HfO}_x$  layer altered through control of atomic layer deposition (ALD) temperature. Sweep and pulsed electrical characteristics were extracted before and after  $^{60}\text{Co}$  gamma irradiation. Monoclinic  $\text{HfO}_x$  deposited at 400 °C did not result in resistive switching. Deposition at 300 °C and 350 °C resulted in cubic  $\text{HfO}_x$  which switched successfully. Both stoichiometric  $\text{HfO}_2$  and sub-oxides  $\text{HfO}_{2-x}$  result in similar memory characteristics. All memory cells are shown to be radiation hard up to 10 Mrad(Si), independent of stoichiometry.

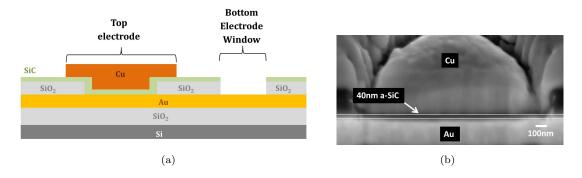

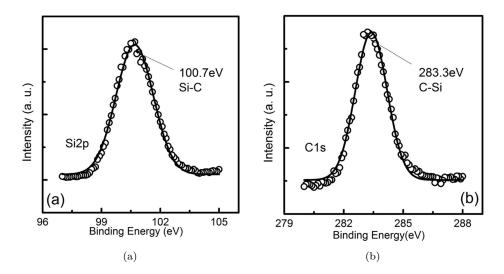

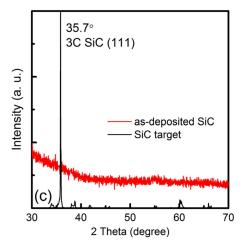

Amorphous silicon carbide Cu/a-SiC/Au resistive memory cells are measured using the pulsed voltage technique and exhibit the highest  $R_{OFF}/R_{ON}$  ratio recorded for any resistive memory. The switching kinetics are investigated and fitted to a numerical model, using thermal conductivity and resistivity properties of the dielectric. The SET mechanism of the Cu/a-SiC/Au memory cells is found to be due to ionic motion without thermal contributions, whereas the RESET mechanism is found to be due to thermally assisted ionic motion. The conductive filament diameter is extracted to be  $\Phi \sim 4$  nm. The high thermal conductivity and resistivity for the Cu/a-SiC/Au memory cells result in slow switching but with high thermal reliability and stability, showing potential for use in harsh environments. Radiation properties of SiC memory cells were investigated. No change was seen in DC sweep or pulsed switching nor in conductive mechanisms, up to 2 Mrad(Si) using  $^{60}$ Co gamma irradiation.

High-k metal gate MOS capacitors, valence change memory (VCM) and electrochemical metallization memory (ECM) cells have all shown high tolerance to ionizing radiation with negligible change seen in device parameters. This indicates that the radiation sensitive region within a memory circuit is the select device used to address the memory cell, such as transistors, and not the memory cell itself. In particular, within transistors, the gate oxide is essentially radiation hard, even when using high-k dielectrics, due to the thin layer. Therefore the areas within a circuit that are susceptible to ionizing radiation damage remain to be the buried oxides and isolation oxides.

## Declaration of Authorship

I, Katrina Anne Morgan , declare that the thesis entitled Radiation Effects and Reliability of Dielectrics in CMOS Transistors and Resistive Memories and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as shown in the List of Publications:

| Signed: | <br> | <br> |  |

|---------|------|------|--|

| 0       |      |      |  |

|         |      |      |  |

| Data    |      |      |  |

## List of Publications

## **Journal Publications**

- K. Morgan, R.Huang, K. Potter, C. Shaw, W. Redman-White, C. H. de Groot (2014) Total Dose Hardness of TiN/HfO<sub>x</sub>/TiN Resistive Random Access Memory, *IEEE Transactions on Nuclear Science*, 61(6), 2991-2996.

- K. Morgan, J. Fan, R.Huang, L. Zhong, R. Gowers, L. Jiang, C. H. de Groot (2015) Switching Kinetics of SiC Resistive Memory for Harsh Environments, *Applied Physics Letters*, (Submitted).

- K. Potter, K. Morgan, C. Shaw, P. Ashburn, W. Redman-White, C. H. de Groot (2014) Total Ionizing Dose Response of Fluorine implanted Silicon-On-Insulator Buried Oxide, *Microelectronics Reliability*, 54, 2339-2343.

- C. Shaw, K. Potter, K. Morgan, E. Chatzikyriakou, P. Ashburn, W. Redman-White, C. H. de Groot (2014) Total Dose Radiation Hardening of MOS Transistors by Fluorine Implantation, *IEEE Transactions of Nuclear Science*, (To be submitted).

## Conference Publications

- K. Morgan, R.Huang, K. Potter, C. Shaw, W. Redman-White, C. H. de Groot (2014) Total Dose Hardness of TiN/HfO<sub>x</sub>/TiN Resistive Random Access Memory Devices, Nuclear and Space Radiation Effects Conference (NSREC), Paris, France.

- K. Morgan, R.Huang, S. Pearce, C. H. de Groot (2014) The Effect of Atomic Layer Deposition Temperature on Switching Properties of HfO<sub>x</sub> Resistive RAM Devices, *IEEE International Symposium on Circuits and Systems (ISCAS)*, Melbourne, Australia, 432-435.

- K. Morgan, R.Huang, S. Pearce, L. Zhong, L. Jiang, C. H. de Groot (2014) Effect of Stoichiometry of TiN Electrode on the Switching Behavior of TiN/HfO<sub>x</sub>/TiN Structures for Resistive RAM Materials Research Society (MRS) Boston, USA.

## **Technical Reports**

K. Morgan, (2013) Radiation Hardness of High-k Dielectrics, AWE, Aldermaston, Hampshire, UK.

## Acknowledgements

Throughout my time here at Southampton, during the fours years spent working towards my PhD, I have had significant guidance and support from colleagues, friends and family. I would like to take this opportunity to thank all those who have helped me along the way.

I would like to express my gratitude to my supervisor, Prof. Kees De Groot, not only for giving me the chance to undertake this PhD, but also for giving me huge amounts of guidance throughout. I feel very fortunate to have had a supervisor such as Kees, who gave so much time for all my queries and work. I would also like to thank my other supervisors, Prof. Peter Ashburn and Prof. William Redman-White, for all their advice and feedback throughout the years.

The collaboration between University of Southampton and AWE would not have been possible if it were not for Chris Shaw and Kenneth Potter. Chris Shaw in particular has been a wonderful asset, providing me with ample opportunities to share my research with AWE and organising all of the logistics for the experimental work conducted at the radiation facility.

I would like to thank Dr. Ruomeng Huang, not only for his contributions experimentally for the  $HfO_x$  RRAM work, but also for his personal support he has provided me, pushing me forward in my research. Thanks to Dr. Le Zhong for providing me with TiN deposition and providing me with SiC resistive RAM devices. Thanks also must go to Dr. Liudi Jiang for the collaborative work regarding SiC resistive RAM, providing me with much support and guidance. I would also like to thank Junquing Fan for assisting me in conducting electrical measurements for the SiC work.

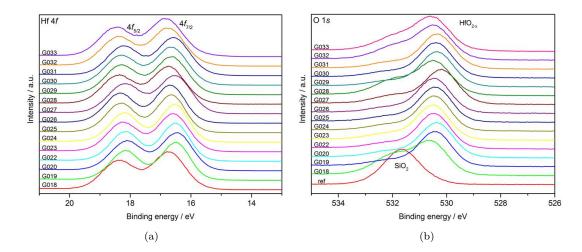

Special thanks go to Dr. Anna Regoutz and Dr. Owain Clark for their contributions for the  $\mathrm{HfO}_x$  DOE work. Both provided excellent knowledge on XPS and DOE and helped create a great collaborative environment. Further thanks must be extended to Dr. Owain Clark, who has assisted me greatly in the cleanroom throughout my 4 years of PhD. His level of commitment to research and willingness to help has benefited my research significantly, starting from day one. Similar thanks must go to Dr. Stuart Pearce. Not only has his development of TiN assisted my work, but his support in the cleanroom was invaluable to me. His charismatic outlook and supportive attitude has helped greatly whilst carrying out my PhD. I must also thank Mike Perry for his technical and personal support in the cleanroom and in particular, his perseverance with the ALD. His constant assistance was invaluable to my work.

The nano research group has been such a supportive environment throughout my time here. In particular, Dr. David Payne has not only provided support with MATLAB but has also become a dear friend of mine. His somewhat hidden, but optimistic attitude has helped me through the hard parts of my PhD, giving me perspective and lifting me up when I needed it. I also owe great amounts to Dr. Asa Asadollahbaik, for opening my eyes to the issues of gender equality and giving me the confidence and drive to get involved. I have been lucky enough to share my journey with two people who have become dear friends of mine; Eleni Chatzikyriakou and Zatil Hashim. Thank you both for your endless chats and laughs throughout these years. I must also thank Glenys Howe. Not only has she provided constant guidance and support, she is also a close friend of mine, one who is always there for me and others.

Further thanks must go to my closest friends and family for the endless support over the years. Lewis Carpenter, thank you for all the years you have pushed me and supported me both academically and personally. Without you, I would not be where I am today. Clare Linton, thank you for always making me see the silver lining and always being there for me. Sean Carey, thank you for the last six months. It has been a tough time coming to the end of my PhD, but your happiness and deeply caring attitude have made it so much easier. I must also thank my mum, dad, and sister for their endless support and love. Thank you for always believing in me. Thanks must also go to Philis and Sarah Cooper, for their ability to make me chuckle.

Finally, I would like to thank the two funding bodies who made this PhD possible by offering me a CASE scheme award; the Engineering and Physical Sciences Research Council (EPSRC) and AWE Ltd.

## List of Acronyms

**ALD** atomic layer deposition

APC automatic pressure control

**BEOL** back-end-of-line

BOX buried oxide

CBRAM conductive bridging random access memory

**CF** conductive filament

CMOS complementary metal oxide semiconductor

CPU central processing unit

**DOE** design of experiment

**DRAM** dynamic random access memory

ECM electrochemical metallization

**EDX** electron-dispersive X-ray dispersive Spectroscopy

EHP electron hole pair

EOT equivalent oxide thickness

EPR electron paramagnetic resonance

FEGSEM field emission scanning electron microscope

FeRAM ferroelectric memory

GADDs general area detector diffraction system

HfAA hafnium alkylamides

**HKMG** high k metal gate

**HRS** high resistance state

ICP inductively coupled plasma

**ITRS** international roadmap for semiconductors

LRS low resistance state

MOS metal oxide semiconductor

MOSFET metal oxide semiconductor field effect transistor

MRAM magnetic random access memory

MSE mean squared error

**nMOS** n type MOS

**NVM** non volatile memory

NOV neutral oxygen vacancy

**OIPT** Oxford instruments plasma technology

PCM programmable metallization cell

PCRAM phase change random access memory

**pMOS** p type MOS

RAM random access memory

RF radio frequency

**RIE** reactive ion etcher

RRAM resistive random access memory

**SCM** storage class memory

**SEM** scanning electron microscope

${f SiC}$  silicon carbide

$\mathbf{SiMOX}$  separation by implantation of oxygen

**SOI** silicon on insulator

SRAM static random access memory

**STI** shallow trench isolation

${\bf TEMAH}\ {\bf tetrakis} ({\bf ehtlmethlyamino}) {\bf hafnium}$

${f TID}$  total ionizing dose

$\mathbf{TMAl}$  triemthylaluminium

VCM valence change memory

$\mathbf{XPS}$  x-ray photoelectron spectroscopy

**XRD** x-ray diffraction

## Contents

| $\mathbf{D}_{0}$ | eclar                                  | ation of Authorship                                                   | V                 |

|------------------|----------------------------------------|-----------------------------------------------------------------------|-------------------|

| Li               | $\operatorname{st}$ of                 | Publications                                                          | vi                |

| A                | ckno                                   | wledgements                                                           | vii               |

| Li               | $\operatorname{st}$ of                 | Acronyms                                                              | ix                |

| 1                | Intr<br>1.1<br>1.2<br>1.3              | CMOS Logic and Memory                                                 | 1<br>1<br>6<br>7  |

| 2                | $Th\epsilon$                           | eory of Radiation Effects of Dielectrics                              | 9                 |

|                  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Dielectric Materials                                                  | 21                |

| 3                | Dev                                    | 1                                                                     | 49                |

|                  | 3.1<br>3.2<br>3.3                      | 1                                                                     | 49<br>69<br>75    |

| 4                | Rac                                    | diation Hardness of MOSFET High-k Dielectrics                         | 77                |

|                  | 4.1<br>4.2<br>4.3<br>4.4               | Capacitor Structure                                                   | 81<br>91          |

| 5                |                                        | tching Mechanics and Radiation Hardness of $HfO_x$ VCM Resistive mory | 99                |

|                  | 5.1<br>5.2<br>5.3<br>5.4               | Resistive Memory Cell Structure                                       | 100<br>103<br>106 |

|                  | 5.5                                    | -                                                                     | 115               |

xii CONTENTS

| 6  | Swit  | ching K    | inetics   | and     | Radiation     | Hardness          | of | $\mathbf{SiC}$ | $\mathbf{ECM}$ | Resistiv | $\mathbf{e}$ |

|----|-------|------------|-----------|---------|---------------|-------------------|----|----------------|----------------|----------|--------------|

|    | Mer   | nory       |           |         |               |                   |    |                |                |          | 117          |

|    | 6.1   | Switching  | g Kinetic | es of S | SiC Resistive | ${\bf Memory}\ .$ |    |                |                |          | . 118        |

|    | 6.2   | Irradiatio | on of SiC | Resis   | stive Memor   | y                 |    |                |                |          | . 125        |

|    | 6.3   | Summary    |           |         |               |                   |    |                |                |          | . 127        |

| 7  | Sum   | mary       |           |         |               |                   |    |                |                |          | 129          |

| Re | efere | ices       |           |         |               |                   |    |                |                |          | 133          |

## Chapter 1

## Introduction

## 1.1 CMOS Logic and Memory

Complementary Metal-Oxide-Semiconductor (CMOS) technology consists of using an array of alternating p-type and n-type Metal-Oxide-Semiconductor (MOS) transistors in the same substrate enabling construction of integrated circuits including microprocessors, power devices and semiconductor memories. MOS field effect transistors (MOS-FETs) are the most common transistor found in both digital and analogue circuits today [1]. The basic principle of a MOSFET was introduced by J.E. Lilienfeld in 1930 [2] and five years later O. Heil came up with the idea of using an electric field to alter the resistance in a semiconducting material [3]. W.B. Schockley and G. Pearson did further studies in the 1940's [4] but it wasn't until the 1960's when the idea became practically possible when D. Kahng and M.M. Atalla fabricated the first MOSFET [5].

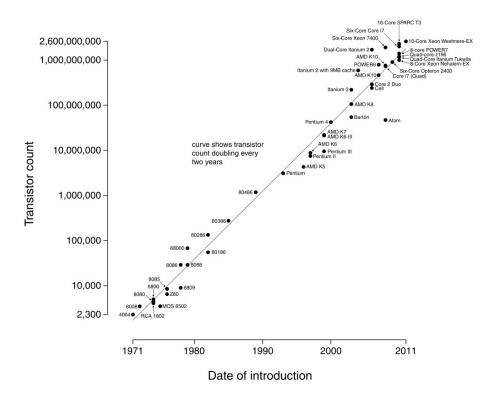

Since the first MOSFET was fabricated the size of the device has become increasingly smaller. In 1959 the integrated chip (IC) era began and since then the number of components per IC chip has been increasing exponentially [1]. G. Moore made a prediction that the number of transistors per chip will double approximately every two years as shown in Figure 1.1.

As the transistor count increases, the size of the transistors must decrease which has resulted in rapid scaling into deep sub micron regimes. Following Moore's Law, an International Technology Roadmap for Semiconductors (ITRS) has been created to predict the size of components in the future. For MOSFETs, the roadmap predictions, produced in 2007, are shown in Table 1.1 which shows a dramatic decrease in physical gate length. This physical gate length is the property of a MOSFET that is the vital parameter and the current size has only become possible with new fabrication techniques.

With the scaling of CMOS, the packing density needs to be high whilst keeping the individual MOSFETs electrically isolated. However the source and drain implants have

Figure 1.1: Microprocessor Transistor Counts from 1971 to 2011 and G. Moore's Prediction of increasing number of transistors per chip [6]

| Year                     | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|--------------------------|------|------|------|------|------|------|------|

| Physical Gate Length(nm) | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| Year                     | 2010 | 2012 | 2014 | 2016 | 2018 | 2020 | 2022 |

| Physical Gate Length(nm) | 10   | 14   | 11   | 0    | 7    | 5.6  | 4.5  |

Table 1.1: ITRS Roadmap for Semiconductors 2007 Edition: Prediction of Physical Gate Length of MOSFETs [7].

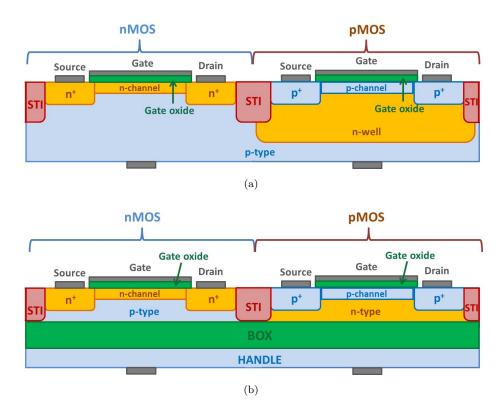

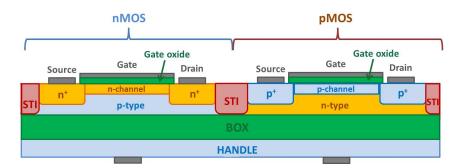

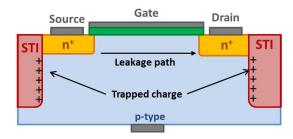

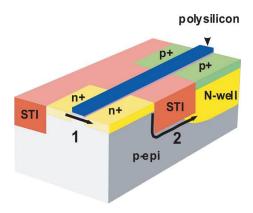

to be isolated from one another. This is done through the use of a field oxide which can be seen in Figure 1.2(a), labelled as the STI. Here the field oxide is separating the highly doped  $n^+$  drain region of an nMOSFET from the highly doped  $p^+$  source region of a pMOSFET. This oxide is named after the technique used to isolate the two implant areas which is called *Shallow Trench Isolation* or STI.

The use of bulk wafers for CMOS transistors, as shown in Figure 1.2(a), was a traditional method. For these, the bulk or substrate was made from one piece of semiconductor. However it was later realised that when the carriers are transported in the semiconducting material of a MOSFET, they only occupy the top 0.1-0.2  $\mu$ m. Over 99.9 percent of the semiconductor is used solely as a stable handle for the rest of the active device. This large area of inactive semiconducting material can give way to unwanted effects such as leakage currents [8].

The need for high performance and low power consumption was strong and it seemed a

Figure 1.2: Schematic Diagram of (a) bulk MOS technology with shallow trench isolation and (b) silicon-on-insulator technology.

new technology offered a solution [9]. In the 1990's, oxide properties improved, resulting in Silicon-on-Insulator (SOI). Figure 1.2(b) shows this has the same design as the bulk CMOS but with one exception; an additional layer of insulating material. This insulating material, an oxide known as the Buried Oxide or BOX, is located in the centre of the substrate which splits this large area of semiconducting material into two. The top layer of semiconductor is still used as the active part of the device, known as the body, whereas the bottom layer which is electrically isolated from the rest of the device, is used for mechanical stability only. This is known as silicon-on-insulator (SOI) and is shown in Figure 1.2(b) where the oxide layer and substrate handle are clearly labelled, with nMOS device on the left hand side and a pMOS device on the right hand side.

As predicted by the International Technology Roadmap for Semiconductors, the sizes of these components are dramatically decreasing and as a result of this scaling, one of the dimensions that has reached its operating limit, is the gate oxide thickness. To overcome this physical limit, high-k dielectrics are being utilized as a silicon dioxide replacement. The high-k allows thicker physical layers of oxides to be used, overcoming the scaling limitation, allowing the MOS transistor to be brought back in line with the ITRS roadmap predictions.

As CMOS industry moves away from silicon dioxide towards high-k dielectrics, another structural change is needed. This change is the top electrode, or gate contact, material.

High-k materials must be used in conjunction with metal gates, rather than the previous poly-silicon contacts. Poly-Si cannot be used as a gate material in combination with these high-k dielectrics, due to the resulting high threshold voltages and poor channel mobilities; therefore metal gates are used. From this, it can be seen that the structure of a high-k metal gate (HKMG) is needed to ensure high capacitive, low leakage MOS transistors.

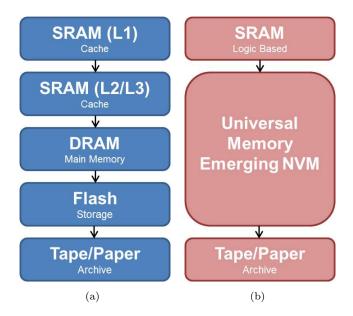

Transistors are used throughout computer architecture today, for both logic and memory. A computer can be split into two main units; a central processing unit (CPU) and memory. The CPU performs logic, arithmetic and control operations and the memory stores the instructions and data for the CPU. Traditionally a CPU is made up of thousands of transistors on one chip (microprocessor) and the memory is made up of traditional memory hierarchy, as depicted in Figure 1.3(a).

Figure 1.3: (a) Traditional memory hierarchy (b) Universal memory hierarchy, adapted from [10].

Traditional memory consists of two types of volatile memory; static random access memory (SRAM) and dynamic random access memory (DRAM). SRAM is normally stored on the logic processor, with level 1 (L1) being closest to the logic core, resulting in it being the fastest memory in the hierarchy. It is used to store instructions and data for future requests, also known as cache. The main memory is constructed from DRAM, which is typically separated from the logic processor and bridges the hard disk with SRAM. SRAM is constructed from 6 transistors arranged in a specific configuration whereas DRAM works by charging and discharging a capacitor alongside a select MOSFET. Both these volatile memories have low read and write times meant for high performance. In addition to these volatile memories, non-volatile memory (NVM) is needed to store the essential information that must be maintained without power. This is usually done using a floating gate MOSFET known as Flash, which comes in two

main designs; NOR and NAND. However, flash memory has reached physical limitations including dielectric thickness and applied voltages required due to the demand for higher electric fields needed for programming/erase operations, whilst retaining low leakage [11]. In the radiation environment, the large amounts of transistors in SRAM, DRAM and Flash also decrease overall radiation hardness of the traditional memory hierarchy.

New systems are being investigated as a replacement to this transitional memory hierarchy, known as universal storage class memory (SCM). In this universal memory hierarchy, as shown in Figure 1.3(b), emerging NVM cells offer high speed, scalable and cheap replacements for DRAM and Flash. This tackles many problems simultaneously including the lack of volatility of DRAM and the high power needs and scaling issues of Flash. In order for the emerging memory to act as a buffer between SRAM and hard disk, the requirements needed include being back-end-of-line (BEOL) compatible, with  $> 10^{15}$  endurance cycles, > 10 years retention and read/write times of < 10 ns [10].

The emerging SCM types include phase change memory (PCRAM), ferroelectric memory (FeRAM), magneto-resistive memory (MRAM) and resistive switching random access memory (RRAM) [12]. The most promising class of emerging non volatile memory is resistive switching based memory, RRAM. A comparison between traditional and emerging NVM memories is shown in Table 1.2. Due to excellent memory properties, including scaling down to sub-10nm dimensions, high density arrays, low power and simple device structures, RRAM is fast becoming a strong candidate for the next type of non-volatile memory.

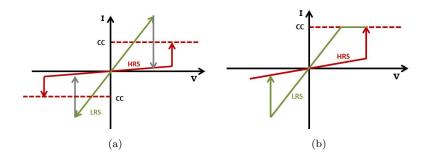

RRAM is based upon resistive switching whereby the resistance of the device is altered through an electrically induced change. RRAM cells consist of a simple metal-insulator-metal (MIM) cell where the insulator layer is often a mixed-conducting oxide, or a chalcogenide [12,13]. Switching cycles occur between a high resistance state (HRS) and a low resistance state (LRS).

|                          |                 | Tradition       | al Memor           | Emerging Memory     |                  |                         |              |               |

|--------------------------|-----------------|-----------------|--------------------|---------------------|------------------|-------------------------|--------------|---------------|

|                          | $\mathbf{DRAM}$ | $\mathbf{SRAM}$ | Flash              | Flash               | $\mathbf{FeRAM}$ | MRAM                    | PCRAM        | I RRAM        |

|                          |                 |                 | NOR                | $\mathbf{NAND}$     |                  |                         |              |               |

| Feature                  | 36              | 45              | 45                 | 16                  | 180              | 65                      | 45           | <5            |

| size (F) (nm)            |                 |                 |                    |                     |                  |                         |              |               |

| Read time                | 2  ns           | 0.2  ns         | 15  ns             | $0.1~\mathrm{ms}$   | 40  ns           | 35  ns                  | 12  ns       | 1  ns         |

| Write time               | 2  ns           | 0.2  ns         | 1 us               | $0.1 \mathrm{\ ms}$ | 65  ns           | 35  ns                  | 100  ns      | <1 ns         |

| Retention                | 4  ms           | n/a             | $>10 \mathrm{~yr}$ | >10 yr              | >10 yr           | $>10~{ m yr}$           | >10 yr       | $>10~{ m yr}$ |

| $_{ m time}$             |                 |                 |                    |                     |                  |                         |              |               |

| $\mathbf{V}_{write}$ (V) | 2.5             | 1               | 8-10               | 15-20               | 1.3 - 3.3        | 1.8                     | 3            | < 0.5         |

| $\mathbf{V}_{read}$ (V)  | 1.7             | 1               | 4.5                | 4.5                 | 1.3 - 3.3        | 1.8                     | 1.2          | < 0.2         |

| Write                    | $> 10^{16}$     | $> 10^{16}$     | $10^{5}$           | $10^{5}$            | $10^{14}$        | $10^{12}$               | $10^{9}$     | $> 10^{12}$   |

| endurance                |                 |                 |                    |                     |                  |                         |              |               |

| Write energy             | $4x10^{-15}$    | $5x10^{-16}$    | $10^{-10}$         | $4x10^{-16}$        | $3x10^{-14}$     | $2.5 \text{x} 10^{-12}$ | $6x10^{-12}$ | $< 10^{-12}$  |

| (J/bit)                  |                 |                 |                    |                     |                  |                         |              |               |

Table 1.2: Comparison of traditional and emerging memories [14].

## 1.2 Radiation Hardness of Logic and Memory

Events, such as the failure of the Telstar satellite in 1962, have shown that it is the semiconductor devices that are most prone to failure when irradiated [15]. The type of radiation will vary with different environments caused by a range of activities including fission reactors, high energy particle experiments such as CERN, space and nuclear industry. When a semiconductor device is irradiated there are two different types of damage mechanisms that can occur; Displacement damage and ionizing damage [16]:

- **Displacement Damage:** Atoms are moved from their lattice sites by incident radiation. This affects the crystals electronic characteristics. This depends on the energy and momentum that is transferred to the lattice atoms and is therefore dependent on the particle type (mass) and energy.

- Ionizing Damage: Incoming radiation ionizes the device and liberates charge carriers. These carries then travel around the device and become trapped resulting in areas of concentrated charge and therefore parasitic fields. This is independent on the type of radiation but depends on the absorbed energy through which ionization is the dominant absorption mechanism.

The two types of radiation damage can occur from a range of particles such as photons (in the form of X-rays,  $\gamma$ -rays etc), charged particles (such as electrons or protons), neutrons and atomic ions. In the nuclear and space environments, the main cause of displacement damage in semiconducting devices will be from the release of neutrons. One of the effects of displacement damage is the alteration of the minority carrier lifetime in the silicon substrate. For a bipolar device, which is a minority carrier device, the alteration in lifetime will heavily affect the device's gain [17]. However this reliance of the minority carrier lifetime in a MOS device is negligible and therefore MOS devices are relatively insusceptible to displacement damage. Increased junction leakage current is another effect the displacement damage can cause but due to the small dimensions of a MOS device this damage mechanism is not a primary concern. The other type of damage mechanism, ionizing damage, is a big problem for MOS devices and therefore it is this mechanism that this research will focus on.

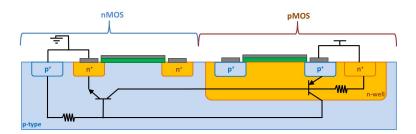

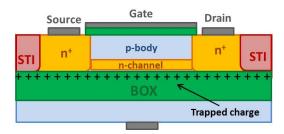

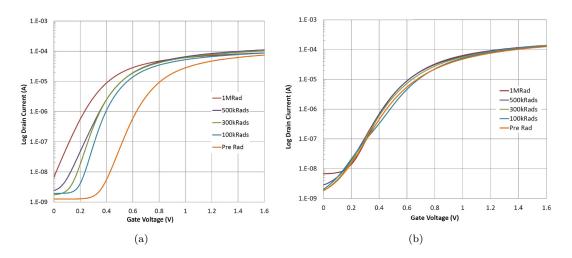

With the increasing density and scaling of MOSFET features sizes, the possibility of latchup increases. Latchup occurs when ionizing radiation causes a leakage path to form in the silicon, between two MOSFETs in a CMOS structure. This problem was overcome in the radiation industry by transferring to SOI technology. The n-well is no longer present and the active silicon area is heavily reduced, removing the potential leakage path [18]. However the presence of three oxide areas (the gate oxide, STI and BOX) have the potential to reduce the radiation hardness of MOSFETs today. With the move from silicon dioxide, to high-k gate oxides, the radiation tolerance is changed.

Therefore it is vital to investigate the radiation tolerance and effects of the new high-k MOS devices. With the memory occupying around half the chip in a processor today, the

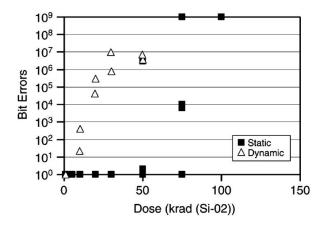

Figure 1.4: Error bit rates for flash memory (90nm node technology) for increasing total ionizing dose [19].

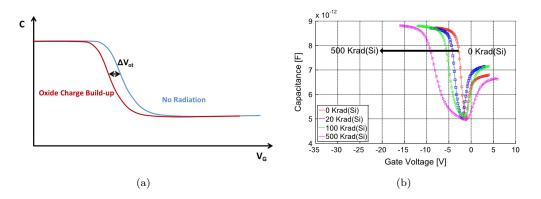

investment into radiation hardened memory is key for developers designing systems for use in radiation environments. Recently, with CMOS processes used to fabricate flash circuitry, high sensitivity to total ionizing dose has been repeatedly seen. The dynamic and static error rates are shown in Figure 1.4 for a 90 nm node flash memory cell whereby the number of errors increases rapidly with total ionizing dose [19]. More recently, improvements in voltage threshold distributions after radiation have been achieved with floating gate devices, although the demand for higher voltage CMOS devices elsewhere in the circuit suggests that ionizing radiation is still a major problem for semiconductor memories [10]. Fundamentally, semiconductor memories have poor radiation hardness levels.

New memories, such as RRAM, offer a potentially radiation hardened replacement for semiconductor memories. Not only does RRAM show superiority in terms of pre-radiation specifications, but also with simple structures and small device areas, RRAM could withstand high levels of ionizing radiation. Therefore it is of the uttermost importance that the radiation effects of resistive memory be investigated.

## 1.3 Thesis Outline

Due to scaling of devices towards smaller and smaller dimensions, high-k dielectrics are being utilised in MOS capacitor structures to overcome leakage issues, whilst RRAM is the potential replacement for semiconductor memories. Before using these new technologies in harsh environments such as space and nuclear, the radiation effects must be investigated, understood and controlled. The key area where ionizing radiation causes damage is within dielectric layers. Therefore this thesis will investigate the radiation effects and reliability of dielectrics for CMOS transistors and resistive memories.

Chapter 2 defines what is meant by the term dielectric. Following this, the ionizing radiation effects in dielectrics are discussed whereby a well known model of radiation mechanism in silicon dioxide MOS capacitors is explained. Using this, the radiation effects of MOS capacitors are described, followed by the effects seen in MOS transistors. Finally, resistive memory is discussed whereby a theory of switching is described followed by the potential radiation effects.

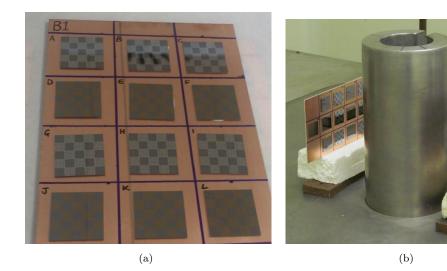

Chapter 3 describes the development of a high-k metal gate  $TiN/HfO_x$  stack. This chapter shows the material characterisation and process development used to control the stoichiometry and crystal structure of the hafnium oxide. Following this, techniques used to control of the TiN electrode stoichiometry are also discussed. The varied stoichiometries and material properties are utilised later for resistive memory in Chapter 5, whilst the fabrication of both TiN and  $HfO_x$  are used in Chapter 4, Chapter 5 and Chapter 6.

Chapter 4 presents the investigation into the radiation of high-k MOS capacitors. HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> MOS capacitors were fabricated along with TiN and Al gates. The pre-radiation properties are analysed allowing a comparison between the high-k and conventional silicon dioxide capacitors to be conducted. The MOS capacitors were measured before and after the ionizing radiation. A discussion of the radiation effects on high-k capacitors, compared to silicon dioxide capacitors is included.

Chapter 5 discusses the investigation into effects on switching properties and effects of radiation on  $TiN/HfO_x/TiN$  valence change memory cells. Firstly, the role of stoichiometry of the TiN electrode on switching properties are shown, followed by the role of stoichiometry of the  $HfO_x$  layer. The ionizing radiation effects on the memory cells with varied stoichiometry of the  $HfO_x$  layers are viewed and discussed.

Chapter 6 presents the work conducted on switching kinetics and radiation effects of SiC electrochemical memory cells. Cu/a-SiC/Au ECM memory cells have been measured using pulse voltage scheme and then irradiated. Firstly the switching kinetics of the SiC memory cells are studied, and the switching properties discussed. Following this, the ionizing radiation effects of the SiC memory cells is presented.

Chapter 7 summarises the key results of the work presented in this thesis and concludes with the identification of devices areas with high sensitivity to ionizing radiation.

## Chapter 2

# Theory of Radiation Effects of Dielectrics

Large amounts of research have been conducted into the ionizing radiation mechanism that occurs in silicon oxide MOS capacitor structure [20–22]. The model for  $SiO_2$  is often used as a basis for radiation effects that occur in other dielectrics and other structures due to the simple structure. The total ionizing dose effects in MOS oxides model is explained in Section 2.2.

Dielectric layers play a key part in the reliability of two types of electrical devices in particular; MOS transistors and resistive memory cells. Within the MOS transistor, three different dielectric areas are present, all of which are prone to radiation effects. The radiation mechanism that can occur in the different types of dielectric layers within a MOS transistor is discussed in Section 2.4.

Within a resistive memory cell, the dielectric layer is sandwiched between two electrodes and acts as the switching layer. The current theory of the switching mechanism is discussed in Section 2.5 followed by a discussion of possible radiation mechanisms.

## 2.1 Dielectric Materials

All materials can be defined as an insulator or a conductor. Charges have the ability to move freely around conductors, where as in insulators, these charges are attached to atoms or molecules. When insulators are put into an electric field, although not free to move around the material like in conductors, the charge can be displaced by microscopic distances, resulting in polarization.

In an atom, as the electrons and nucleus are pulled apart, their mutual attraction between each other will keep them together, until an equilibrium is reached. This results in

the polarization of the atom. The dipole moment of this atom,  $\overrightarrow{p}$  is given by Equation 2.1 and will align in the same direction of the electrical field.

$$\overrightarrow{p} = \alpha \stackrel{\rightarrow}{E} \tag{2.1}$$

The atomic polarizabilty,  $\alpha$  depends on the detailed structure of the atom.

When we consider an insulator in an electric field, the polarization is given by the dipole moment per unit volume,  $\overrightarrow{P}$ . In order to calculate the effect of polarization on the initial field, instead of adding all the infinitesimal contributions from all dipoles together, **bound charges** are used, named after the fact that electrons are attached to specific atoms or molecules and therefore cannot be removed. This bound charge is given by the net charge over a surface for uniform polarization, taking into account the charge within the insulator and on the surface. Therefore the field due to the polarization of the medium can be described as the field of the bound charge.

The total field within the medium is defined by the field resulting from the bound charge (field produced by polarization) plus the field due to everything else (known as **free charge**) as shown in Equation 2.2. This free charge can originate from defects like ions in the insulator, or from electrons from nearby conductors.

$$\rho = \rho_b + \rho_f \tag{2.2}$$

Inserting Equation 2.2 into Guass' Law and rearranging then gives Equation 2.3. Part of this equation can then be replaced by introducing the new term, electrical displacement  $\stackrel{\rightarrow}{D}$ , given by Equation 2.4.

$$\nabla \cdot (\epsilon_0 \stackrel{\rightarrow}{E} + \stackrel{\rightarrow}{P}) = \rho_f \tag{2.3}$$

The electrical displacement is a very useful term as it is dependent only on free charge and is not altered by the introduction of a dielectric.

$$\stackrel{\rightarrow}{D} \equiv \epsilon_0 \stackrel{\rightarrow}{E} + \stackrel{\rightarrow}{P} \tag{2.4}$$

The polarization term  $\overrightarrow{P}$  is defined in Equation 2.5 where  $\chi_e$  is the electrical susceptibility of a medium, whose value is dependent not only on the microscopic structure of the material but also external conditions such as temperature. The electrical susceptibility therefore describes how easily the material polarizes.

$$\stackrel{\rightarrow}{P} = \epsilon_0 \chi_e \stackrel{\rightarrow}{E} \tag{2.5}$$

Using this definition of polarization, the electrical displacement can now be rewritten as Equation 2.6, where the prefactor  $\epsilon$  is the permittivity of the material, as given by Equation 2.7. Equation 2.6 therefore shows how the electric field,  $\stackrel{\rightarrow}{E}$  is reduced by amount  $\epsilon$  due to the effect of polarization.

$$\stackrel{\rightarrow}{D} = \epsilon \stackrel{\rightarrow}{E} \tag{2.6}$$

$$\epsilon \equiv \epsilon_0 (1 + \chi_e) \equiv \epsilon_0 \epsilon_r \tag{2.7}$$

Removing the permittivity of free space,  $\epsilon_0$ , results in a dimensionless quantity,  $\epsilon_r$ . This is known as the relative permittivity or the dielectric constant of the material and is also given the term  $k_r$  [23]. This factor is a measurable term to indicate the amount the effective electric field is decreased due to the polarization of the medium.

From this definition, insulators that result in polarization when situated in an electric field, are referred to as dielectrics. As all insulators polarize in an electric field, all insulators are by definition dielectrics, although the two terms refer to two different physical mechanisms. The term dielectric refers to a medium which polarizes in an electric field whereas the term insulator refers to the ability for a material to resist the flow of electrons.

## 2.2 Ionizing Radiation Effects in Dielectrics

Radiation is a main concern for reliability of electronics for use in space and nuclear industries. In an radiative environment, the breakdown of dielectrics can be caused by defects within the dielectric reacting to the effects of radiation. The dielectric layers are greatly affected by ionizing radiation in particular, whereby charge is generated within the dielectric itself. It is the reaction between the defects and the charge that can lead to uncontrolled breakdown of the dielectric, resulting in device failure or error.

The ionizing irradiation degradation mechanism has been widely researched for silicon dioxide MOS capacitors. In order to gain a better understanding of defects and degradation mechanisms within other materials and structures, the silicon dioxide mechanism in a MOS capacitor can be viewed as similarities may exist. A brief overview of ionizing radiation terminology is explained first.

## 2.2.1 Ionizing Radiation

Ionizing radiation can be caused by photons, electrons, protons or atomic ions, as long as they have enough energy to liberate an electron from an atom, creating an ion or an

electron-hole pair (EHP) in the material of interest. For example, if a photon were to cause ionizing radiation in a piece of Silicon, the photon energy must be greater than the band gap of Silicon. Thus the energy needed will differ for material types whereby  $E_{\gamma} > 1.1$  eV for silicon and  $E_{\gamma} > 9$  eV for silicon dioxide [15].

The type of ionizing damage that occurs in insulators is referred to as Total Dose effects, also known as Total Ionizing Dose or TID effects. The total dose is the amount of energy deposited in any material by ionizing radiation and is given in units of Rad or Gray, where 1 Gray=100 Rad. The Rad is the unit that will be used where rad is the amount of energy absorbed per unit mass of material and so it can be seen that 1 rad=1 J/kg. The rad is material dependent and therefore the dose will be specified in rads with the material listed in brackets afterwards.

When materials are irradiated by ionizing radiation, electron-hole pairs are created. The number of electrons and holes generated in the material is directly proportional to the total dose, with an increasing number of electron-hole pairs for increased total dose. The type of ionizing radiation that is of particular importance in space and nuclear industry is gamma radiation at high TID levels.

The current theory of ionizing radiation effects, in a metal/silicon-dioxide/silicon structure, is presented here. This two-stage process describes how the defects, that occur in silicon dioxide from fabrication, react with the charge generated from ionizing radiation, leading to altered electrical characteristics. Multiple defects that exist in silicon dioxide have also been observed in many transitional oxides [24]. These similarities enables the comparison between silicon dioxide and transition metal oxides to be drawn, where the vast amount of research conducted on silicon dioxide defects and breakdown can be considered when considering breakdown in other dielectrics, e.g. high-k dielectrics.

#### 2.2.2 Defects in Dielectrics

There are three main defects found within a metal/silicon-dioxide/silicon structure and are given here:

- 1. Neutral Oxygen Vacancies

- 2. H<sub>2</sub> located at minimum energy sites

- 3. Silicon-Hydrogen bonds at the oxide/semiconductor interface

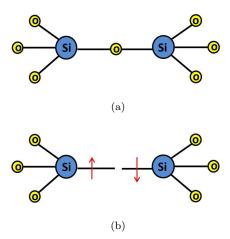

The neutral oxygen vacancy will be explained first. The basis of ideal SiO<sub>2</sub> consists of four oxygen atoms surrounding one silicon atom with highly-directional covalent bonds [25]. These oxygen atoms will then be bonded to one other silicon atom, so that every oxygen atom will be bonded to two silicon atoms, and every silicon atom will be bonded

to four oxygen atoms. This can be seen in Figure 2.1(a) where two silicon atoms, in blue, are connected to four oxygen atoms, in yellow. Please note the angle and bonds are not drawn to scale as this is just a picture representation of the silicon dioxide bonds.

In high temperature oxidation processes fabricating  $SiO_2$ , defects can occur when an oxygen atom does not form a bond with two silicon atoms [26]. This lack of an oxygen atom results in two Silicon atoms having an empty bond. These bonds are known as dangling bonds and each contain an unpaired electron of opposite spin. This defect is known as a neutral oxygen vacancy, or NOV, and is depicted in Figure 2.1(b) where the red arrows represent the unpaired electrons. It can also be represented by Equation 2.8 where the black dot represents the dangling bond, and the three lines represent the three individual bonds [27].

Figure 2.1: Picture Representation of (a) an ideal  $SiO_2$  bond and (b) a neutral oxygen vacancy, adapted from [27].

$$O_3 \equiv Si^{\bullet} \qquad Si^{\bullet} \equiv O_3$$

(2.8)

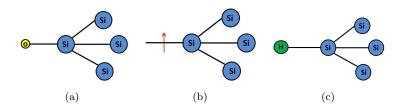

Another type of defect occurs due to hydrogen. Throughout the fabrication process, many steps use a hydrogen ambient, in water or gas form. These steps cannot be avoided and this level of hydrogen throughout device fabrication means it is nearly impossible to eliminate unwanted hydrogen [28]. When H<sub>2</sub> enters SiO<sub>2</sub>, it will sit at minimum energy sites throughout the oxide and remain there. The third type of defect occurs at the oxide/semiconductor interface. When oxides are fabricated, there are still around  $10^{13}$  cm<sup>2</sup> silicon bonds at the oxide/semiconductor interface that are not passivated with oxygen [22]. These silicon dangling bonds remain at the interface and are then passivated by hydrogen molecules. These hydrogen molecules are due to fabrications steps and diffuse into the oxides in the same manner as the molecular hydrogen described previously [29]. Figure 2.2(a) shows an ideal interface bond with the semiconductor on the right hand side and the oxide starting to form on the left hand side. Figure 2.2(b) shows the dangling silicon bond that occurs if there is no passivation by an oxygen atom

Figure 2.2: Silicon-silicon dioxide interface for (a) ideal silicon-silicon dioxide interface, (b) non-ideal Si dangling bond at silicon-silicon Dioxide interface and (c) non ideal Si-H Bond at silicon-silicon dioxide interface, adapted from [27].

and an unpaired electron is shown by the red arrow. Figure 2.2(c) shows the dangling bond which has been passivated by a hydrogen atom, leaving behind a Si-H bond.

The Si-H bond, the NOV and the molecular hydrogen are all defects that exist before the device is exposed to external or internal factors. It is *these* defects which later react with ionizing radiation, leading to device failure.

## 2.2.3 Ionizing Radiation Mechanism

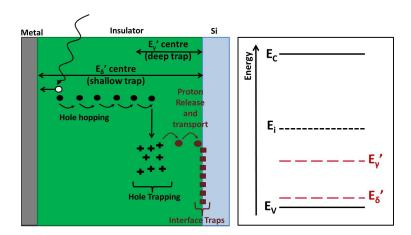

Figure 2.3 depicts the MOS structure, where the three sections represent the metal, the silicon dioxide and the silicon substrate. The black and white dots in Figure 2.3 represent an electron-hole pair that has been generated due to the incoming ionizing radiation. Due to the bias on the device, these electrons and holes will be transported through the oxide in opposite directions. Before this happens however, some of the electrons and holes will recombine. The number of electron-hole pairs that escape recombination is known as the yield. The amount of initial recombination, and therefore this final yield, is dependent on the oxide electric field strength and the energy of the incoming ionizing particle.

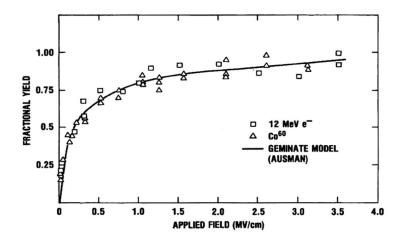

If the device was irradiated by a single ion, a strongly ionizing particle would generate a higher density of EHPs in its path. Due to the close proximity between the electrons and holes, the recombination would be high. For a weakly ionizing particle, recombination would be low due to the lower density of EHPs. The yield will be larger if the electric field strength is larger due to the EHPs being accelerated away from each other, reducing the chance of recombination. Figure 2.4 shows a plot of yield as a function of applied field for <sup>60</sup>Co gamma rays, 12MeV electrons and is compared to the geminate model [22].

$$N_h = Y(E)\kappa_q Dt_{OX} \tag{2.9}$$

The number of holes that remain in the oxide,  $N_h$ , can be found by Equation 2.9. This equation calculates the number of EHPs produced initially by the radiation and then takes into account the recombination, with the electric field strength and radiation type

Figure 2.3: Electron-hole pairs generated in oxide by ionizing radiation followed by hole transportation and trap formation in the oxide. Proton release can also occur followed by transportation towards the interface leading to interface trap formation in the oxide. The energies of different traps are shown. This is adapted from [30].

Figure 2.4: Fraction of holes that escape recombination as a function of applied electric field for gamma rays, electrons and compared to geminate model calculations [22].

dependencies. Y(E), the hole yield, takes into account the recombination with the field and radiation type dependencies [20].  $\kappa_g$  is the total pair generation rate which gives the initial EHP density generated per unit dose, for a certain material. Multiplying this by the total dose D will give the total EHP density generated. This will scale with oxide thickness and so the equation must be multiplied by  $t_{ox}$ .

The electrons and holes that escape recombination travel through the oxide at different rates, through different transport mechanisms and in opposite directions. In  $SiO_2$ , electrons are extremely mobile and get swept out of the oxide in the first few picoseconds. For a positive bias (on the metal), these electrons will be swept towards the metal as shown by Figure 2.3. The remaining holes then travel towards the oxide/semiconductor interface. This movement is slow and involves reactions with the defects in the oxide.

These reactions between the defects and holes result in two types of traps forming; oxide and interface traps.

Oxide traps occur when holes react with defects throughout the oxide bulk. The traps that occur, can be split into two types: shallow and deep traps. If a shallow trap is formed, the hole may hop through the oxide, towards the interface, between the shallow traps. If however the holes fall into a deep trap, they will become stuck here and contribute to a net positive charge in the oxide. This can be seen in Figure 2.3.

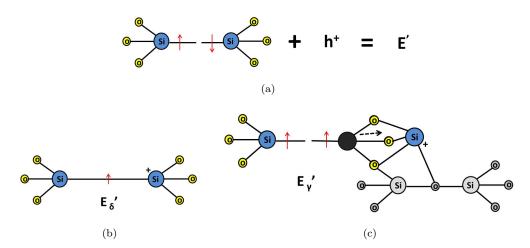

The shallow trap, shown in Figure 2.3 by  $E'_{\delta}$ , has an energy around 1 eV above the valence band in the oxide, allowing the holes to fall in and escape out of the trap easily. This, along with the positive bias on the electrode, facilitates the hopping towards the interface. The deep trap, shown in Figure 2.3 by  $E'_{\gamma}$ , has an energy around 3 eV above the valence band. When a hole falls into this trap, it cannot escape back into the valence band and so becomes trapped.

These two traps, or E centres, exist in different parts of the oxide, spatially. The shallow traps can be found throughout most of the bulk oxide, whereas the deeper traps are mostly found near the oxide/silicon interface. This is depicted in Figure 2.3, where the black arrows show the lateral area the traps are most likely to form. The deep traps act differently, depending on their location with respect to the interface [21]. If the deep trap is further away than 3 nm from the interface, the trap acts as a deep hole trap, where the hole forms a fixed positive charge,  $N_{OX}$ , known as a Fixed State. If however the trap is within 3 nm of the interface, the trap can emit or absorb charge from the silicon, known as a Switching State [31]. This is done through electron tunnelling and results in a neutral state but does not remove the trapped hole. This effect is an annealing effect which reduces the effect of the total fixed positive charge in the oxide, over time.

The event of a hole becoming trapped in a deep trap, causes a hydrogen ion (a proton), to be released. Due to the positive charge, this proton then travels towards the interface. The way in which the protons reach the interface was researched by Oldham and McLean [22], where they found the protons hopping distance was 0.26 nm. This matched the distance between the oxygen atoms in SiO<sub>2</sub>, and therefore it was verified that the protons hop between the oxygen atoms until they reach the interface. Once the protons reach the interface, a reaction occurs with the Si-H defects, and an interface trap is formed. This proton release, transport and interface trap formation can be seen in Figure 2.3.

This two-stage process whereby a hole becomes trapped, releasing a proton that then travels towards the interface, reacting with the Si-H bond, creating an interface trap has been verified by many different groups [32–38]. There are still a few other theories that some people prefer. A different theory suggest that the formation of interface traps occur from holes reacting with the Si-H bonds, not protons [39]. The dynamics however are not explained and this theory has been disproved by Oldham et al. [40]. Another theory is the interface traps are formed by neutral hydrogen instead of protons, but this

was shown to be very small, by Saks et al. [41]. Therefore the theory that will be used is the two-stage proton transport model, until proved otherwise [22].

The oxide trap formation is explained first, followed by explanation of interface trap formation.

Oxide traps form when the holes, generated by the radiation, come into the vicinity of neutral oxygen vacancies, as shown in Figure 2.5(a). When the hole becomes trapped in the NOV, the NOV structure relaxes back into a different state. This new relaxed structure, in which the hole is trapped, is the E' center. The NOV structure can relax into two different states and it is these two states that form the shallow and deep traps.

Figure 2.5: Defects in  $SiO_2$  (a) NOV and a hole react to give a E' centre (b) dimer shallow trap formation (c) puckered deep trap formation, adapted from [27].

The shallow trap,  $E'_{\delta}$ , is formed when the hole reacts with the NOV, and the NOV structure then relaxes into the state shown in Figure 2.5(b). The two previous silicon dangling bonds have now joined together and lengthened their bonds. The hole is trapped at one of the silicon sites and the two silicon atoms now share an unpaired electron. Due to the trapped hole, the charge of  $E'_{\delta}$  is positive. The shallow trap is also known as the  $Dimer\ E'$  center, or  $E'_{\delta}$ .

The deep trap,  $E_{\gamma}'$ , is formed when the hole reacts with the NOV, and the NOV structure then relaxes into the state shown in Figure 2.5(c). The black and black atom shows where the silicon atom was previously and the arrow shows where the silicon atom has now moved. In this structure one of the silicon atoms, with the unpaired electron, remains the same as shown on the left hand side of Figure 2.5(c). The other silicon atom however relaxes by passing through the plane of the three original oxygen atom. This silicon atoms then bonds itself to another oxygen atom from another site as shown by the grey arrangement of atoms. This silicon atom is now bonded to four oxygen atoms, and the newly bonded oxygen atom is now bonded to three silicon atoms. The hole has become

trapped and is located at the new oxygen bond. This structure has a positive charge also and is known as the *Puckered* E' center, or  $E'_{\gamma}$ . [21, 26, 42]

These E' centres are so named due to the unpaired electrons being consistent with observed signatures found using electron paramagnetic resonance (EPR) technique. These defects were then labelled E' [43,44]. It is these two different structures that the holes either hop between in the shallow traps, or become fixed charge, in the deep traps.

Long-term annealing effects however can occur, over hours or years, neutralizing or compensating the net positive fixed charge due to holes trapped at deep traps. This annealing is dependent on time, temperature and applied field and occurs through either tunnelling or thermal excitation. At room temperature, tunneling is the dominant mechanism but for increased temperatures, thermal excitation can take over. Many mechanisms were proposed however work by numerous groups have led to one accepted model; an electron tunnels to the neutral Si in a deep trap forming a dipole structure between the trapped electron and hole [22]. As the bias on the device is altered, the extra electron can tunnel between the substrate and the deep trap.

As mentioned before, the trapping of the hole in the deep trap can cause a proton to be released, which then travels on towards the interface, creating interface traps.

The holes produced by ionizing radiation have reacted with one of the defects, the NOV. The holes then become trapped and form the E' centres. The second defect, molecular hydrogen, then is activated once the E' centres are formed. Previous to irradiation, the molecular hydrogen sits at minimum energy sites throughout the oxide. When the E' centres are formed, these sites then become a lower energy site for the molecular hydrogen to react with. It is the reaction of the molecular hydrogen with the E' centres that releases a proton.

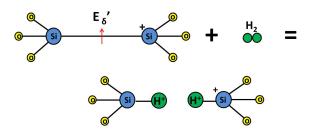

The molecular hydrogen has two different reactions with the two different E' centres. The  $E'_{\delta}$  centre reacts with the hydrogen and then acts as a proton sink. This is shown in Figure 2.6 where the hydrogen has caused the longer Si-Si bond to break, and the molecular hydrogen has separated into two protons, each proton passivating each dangling bond. The structure is stable in this state and the protons will not be released, hence this is said to be a proton sink.

Figure 2.6: Molecular hydrogen reacting with Dimer trap, adapted from [27].

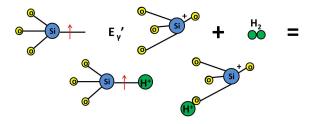

When the molecular hydrogen comes into the vicinity of the  $E'_{\gamma}$  centre, a proton source is created. This is shown in Figure 2.7 where the molecular hydrogen has separated with one of the protons passivating the dangling bond, whilst the other sits at one of the oxygen sites on the other silicon atom. This proton then travels between the oxygen atoms, until it reaches the interface. This is called a proton *source* due to the release of the proton.

Figure 2.7: Molecular hydrogen reacting with Puckered trap, adapted from [27].

The proton released from the puckered sites will hop through the oxygen atoms until they reach the interface. The proton reacts with the Si-H defects at the interface to form interface traps. The reaction that occurs is given by Equation 2.10, where the interface trap is given by the excited silicon atom,  $Si^*$ .

$$Si - H + H^+ \to Si^* + H_2$$

(2.10)

The molecular hydrogen diffuses away and the trivalent Si defect is left behind and is known as a  $P_b$  centre [28]. The interface state is amphoteric in nature whereby they are either positive or negative depending on the device bias. The interface traps lie on the oxide/silicon interface but the charge of the trap is determined by the silicon properties as the traps sit in the silicon band gap. The two different types of traps are known as donor and acceptor traps. Donor and acceptor traps differ in charge with respect to whether they are full or empty of electrons. A donor interface trap is one that is neutral when filled with an electron and positive when empty. An acceptor interface trap is negative when filled with an electron and neutral when empty. The definitions of donor and acceptor is given in Table 2.1. There is strong evidence that the donor interface traps are located in the lower half of the silicon band gap, whilst the acceptor interface traps are located in the upper half of the silicon band gap [15].

|       | Donor Charge | Acceptor Charge |

|-------|--------------|-----------------|

| Full  | neutral      | negative        |

| Empty | positive     | neutral         |

Table 2.1: Charge of Donor and Acceptor traps with different electron concentration

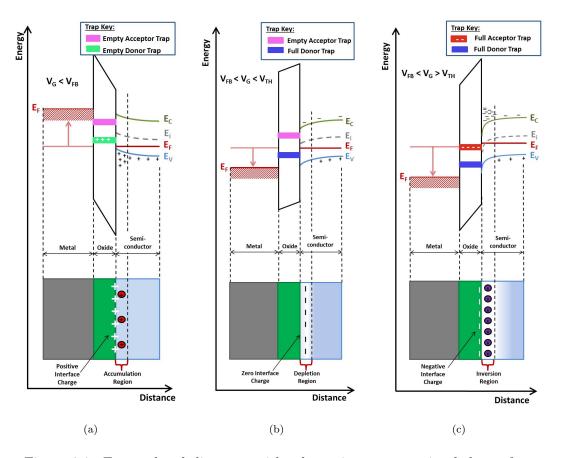

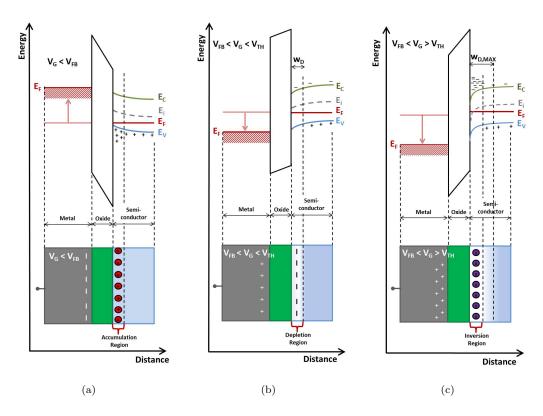

The position of the fermi level in the silicon, and therefore the bias of the device, determines whether the donor and interface traps are filled or empty, altering the overall charge at the interface. For a p-type MOS capacitor, for a negative bias, the device will be in accumulation. An accumulation region, full of majority carriers in the silicon is shown in the schematic representation of the device in the lower half of Figure 2.8(a). Figure 2.8(a) also shows the energy band diagram when the device is in accumulation, with the addition of the acceptor and donor trap levels shown by the pink and green stripes respectively. As the fermi level in the silicon at the interface is below both the acceptor and donor traps, neither contain any electrons. Looking at Table 2.1 it can be seen that when both are empty, the donor traps have a positive charge, and when the acceptor traps are empty they are neutral. The net charge is therefore a positive charge at the interface between the oxide and silicon as shown in the picture representation of the device layout in the bottom half of Figure 2.8(a).

Figure 2.8: Energy band diagrams with schematic representation below, of a p-type MOS capacitor with acceptor and donor interface traps in; (a) accumulation, with both interface traps empty resulting in a positive charge build-up at the interface (b) depletion, with the donor traps filled and the acceptor traps empty resulting in zero interfacial charge build-up (c) and inversion, with both the donor and acceptor interface traps filled resulting in an overall negative charge build-up at the interface.

As the voltage on the metal gate is increased, the device will go into depletion as shown by the schematic representation in the lower half of Figure 2.8(b). This will raise the fermi level in the silicon which can be seen in the energy diagram in Figure 2.8(b). The

donor traps are now fullwith electrons, shown by a blue band, as the fermi level is above the trap level, and therefore neutral in charge. The acceptor traps are still empty, shown by a pink band, and so are also neutral. Therefore the interface traps are neutral and there is no build-up of charge at the interface.

When the bias is increased further, the device will reach inversion whereby minority carriers are thermally generated, resulting in an inversion region in the silicon below the oxide/silicon interface. This is shown by the schematic representation of the device in the lower half of Figure 2.8(c). As the device reaches inversion and the fermi level is risen again, the acceptor traps become full with electrons, shown by the red band. This can be seen in Figure 2.8(c) where the fermi level is above the acceptor trap level. This will result in negative charge building up at the interface between the oxide and silicon.

Depending on the dopant of the substrate and the bias on the device, the interface traps will either be negative, neutral or positive. This will then either contribute or counteract the positive trapped oxide charge from the holes.

## 2.3 Irradiation of MOS Capacitors

In order to investigate radiation effects on MOS transistors, MOS capacitors are often utilised due their simple structure. Ideal MOS capacitor characteristics are explained first followed by the effects of radiation.

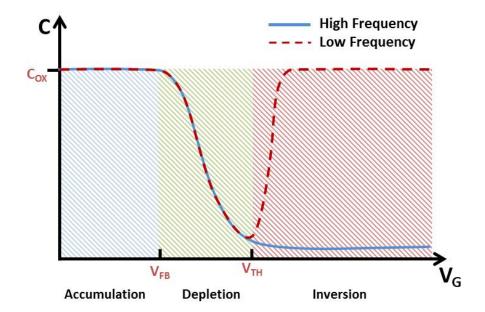

## 2.3.1 Ideal MOS Capacitor

The MOS capacitor structure can be used as a simplified model of a MOSFETs as the MOS capacitor structure exists within the MOSFET device. A layer of metal deposited on the back of the substrate is used to create an ohmic contact. This section will describe the modes of operation of a MOS capacitor. A p-type substrate will be considered unless stated otherwise, known as a nMOS capacitor. For an *ideal* MOS capacitor, a few assumptions must be made first. These assumptions are uniform doping of substrate, zero current flow in gate oxide and zero charge in gate oxide. An ideal MOS capacitor has four different modes of operation which are dependent upon the voltage applied to the gate. These are flatband, accumulation, depletion and inversion.

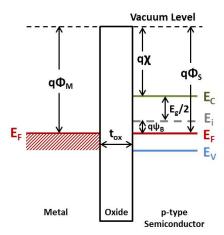

The first mode of operation is the 'Flatband' mode. This occurs when the device is in thermal equilibrium with 0 gate voltage applied. If the device is not in thermal equilibrium then a voltage must be applied to obtain the flat band mode, known as the flatband voltage  $V_{FB}$ . The Flatband name comes from the energy band diagram whereby the fermi level of each material is at the same level and therefore appears to be 'flat'. This can be seen in Figure 2.9 with the three vertical sections representing

the metal, oxide and semiconductor layers. For an intrinsic semiconductor the electron and hole concentrations are equal which is represented by the intrinsic fermi level,  $E_i$ , which will be exactly half way between the conduction band energy,  $E_C$  and the valence band energy,  $E_V$ . Figure 2.9 shows a nMOS Capacitor where the fermi level, in the semiconductor, is below  $E_i$  due to there being more holes in the valence band than there are electrons in the conduction band. For a pMOS capacitor, the fermi level in the semiconductor, is above  $E_i$  due to there being more electrons in the conduction band than there are holes in the valence band. In both of these capacitors there is no build up of charge in the semiconductor at the gate oxide/semiconductor interface. In other words the electron and hole densities are the same at the interface as they are in the main body of the semiconductor.

For a MOS capacitor not in thermal equilibrium, the flatband voltage required for zero band bending in the semiconductor to occur can be calculated. The required parameters include the metal work function,  $\phi_M$ , the semiconductor work function,  $\phi_S$ , half the semiconductor energy gap,  $\frac{E_g}{2}$ , the electron affinity,  $\chi$ , and the bulk potential,  $\psi_B$ . The flatband voltage for an ideal MOS capacitor is given by the difference between the metal and semiconductor work functions as shown in Equation 2.11.

Figure 2.9: Flatband energy band diagram for nMOS capacitor with parameters labelled.

$$V_{FB} = \phi_M - \phi_S = \phi_M - q\chi - \frac{E_g}{2} - \psi_B$$

(2.11)

The electron affinity and the energy gap are both constants that are material dependent. The bulk potential is the difference between  $E_i$  and  $E_F$ . This parameter is *not* constant but depends upon the doping concentration in the semiconductor  $N_a$  the intrinsic carrier concentration  $n_i$  and the temperature T. This can be seen in Equation 2.12 where k and q are the Boltzmann constant and electric charge respectively. Using Equation 2.11 and Equation 2.12, the flatband voltage can be calculated.

$$\psi_B = \frac{kT}{q} ln\left(\frac{N_a}{n_i}\right) \tag{2.12}$$

When a gate voltage is applied that is no longer equal to the  $V_{FB}$ , the flatband condition is no longer met. Depending on the magnitude and the polarity of the voltage applied, there are three more modes that the MOS Capacitor can be in. In order to explain these three modes, the nMOS Capacitor will be taken into consideration first.

The first mode, known as Accumulation, occurs when a voltage below the  $V_{FB}$  is applied to the gate, which is normally negative. The negative charge on the gate will attract the excess holes in the p-type substrate towards the oxide/semiconductor interface as shown in Figure 2.10(a). This process can also be illustrated using the energy band diagram. Here the negative gate voltage causes the metal fermi level to rise and this then causes the oxide energy band to tilt upwards towards the gate. This tilting of the oxide energy band in turn causes the band bending to occur in the semiconductor. This band bending now means that  $E_V$  is closer to  $E_F$  at the interface than it is in the bulk, causing the hole concentration to be larger at the interface. This build up of majority carriers forms the accumulation layer.

Figure 2.10: Charge build up and energy band diagram shown for an nMOS Capacitor in (a) accumulation (b) depletion and (c) inversion.

The second mode of operation occurs when a small positive applied voltage exceeds  $V_{FB}$  and is known as *Depletion*. The positive charge on the gate will cause the holes to

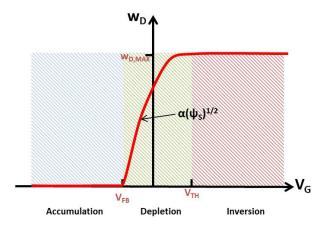

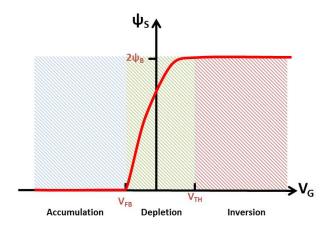

be pushed deeper into the substrate away from the interface. This results in a region, near the interface, that is depleted of mobile carriers leaving behind negatively charged acceptor ions. Figure 2.10(b) shows the depleted region in white under the oxide and also shows the negatively charged acceptor ions. The fermi level in the resulting energy band in the metal decreases which causes the oxide energy bands to tilt downwards towards the gate. Band bending then occurs in the opposite direction in the semiconductor when comparing it to accumulation. At the oxide/Semiconductor interface the  $E_V$  is further away from  $E_F$  when comparing to the  $E_V$ 's position deeper in the bulk. This results in holes being depleted away from the interface. With increasing applied voltage, the depletion region width increases and the minority carriers (electrons) will be attracted towards the interface. However in the depletion region the concentration of electrons is negligible. The depletion width is proportional to the square root of band bending (the surface potential,  $\psi_S$ , which is the change in potential from bulk to surface). This is shown in Figure 2.11.

Figure 2.11: Depletion width of a MOS capacitor plotted with respect to gate voltage. Increase in depletion width is proportional to the square root of the surface potential.

The third mode of operation is called strong inversion. If the gate voltage is increased even further, it will eventually reach the situation where the electron concentration at the oxide/semiconductor interface will be greater than or equal to the hole concentration of the bulk semiconductor. The semiconductor material under the interface has now become n-type and this region is known as the n-channel. The threshold voltage,  $V_{TH}$ , is reached when the surface potential (amount of band bending) is equal to twice the bulk potential,  $\psi_B$  resulting in the surface electron concentration becoming so large that the surface is now inverted, forming an n-channel. This is shown in Figure 2.12.

The n-channel can be seen in Figure 2.10(c). Compared to the energy band diagram for the depletion mode, the band bending for the inversion mode can be seen to be much larger, due to the metal's fermi level being lowered by a greater amount. This causes the hole concentration to decrease further at the interface and also causes the electron

Figure 2.12: Surface potential (amount of band bending) plotted against gate voltage. Threshold voltage reached when surface potential equals twice the bulk potential.

concentration to increase at the interface. The semiconductor band bending is so large that the fermi level in the semiconductor is now very close to  $E_C$  at the interface, causing the increased concentration of electrons. This is the formation of the n-channel.

The point of strong inversion,  $V_{TH}$ , is mathematically well defined and can be calculated by using Equation 2.13.

$$V_{TH} = 2\psi_B + \gamma \sqrt{2\psi_B} + V_{FB} + V_{ot} \tag{2.13}$$

$V_{FB}$  and  $\psi_B$  have already been calculated for the flatband voltage calculations using Equation 2.11 and Equation 2.12.  $V_{ot}$  represents the voltage shift caused by trapped oxide charge. The final parameter that needs to be inserted into Equation 2.13 is the body factor,  $\gamma$ . This body factor comes from an effect of the substrate (or body) bias. The body factor is given by Equation 2.14, where  $\epsilon_S$  and  $N_a$  are the permittivity and doping concentration of the substrate respectively, q is the electric charge and  $C_i$  is the oxide capacitance.

$$\gamma = \frac{\sqrt{2q\epsilon_S N_a}}{C_{OX}} \tag{2.14}$$

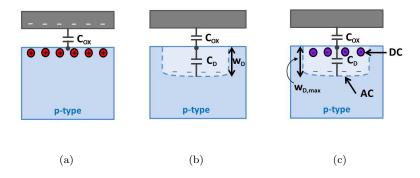

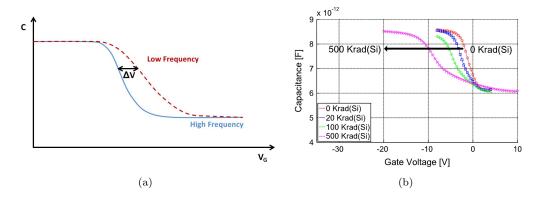

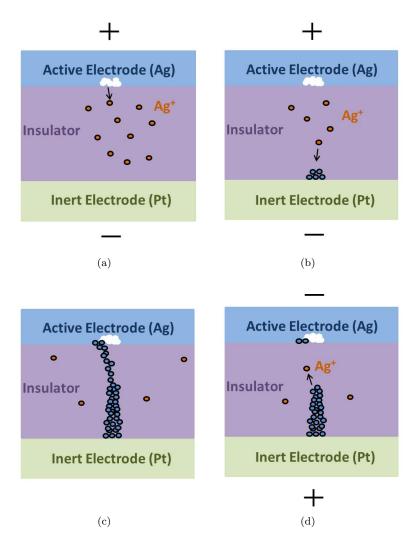

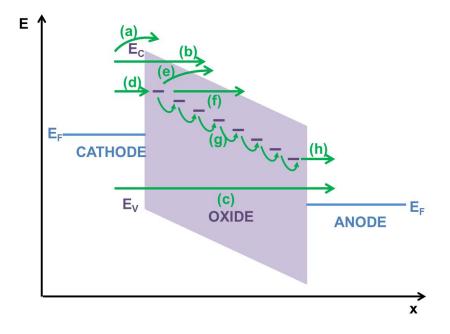

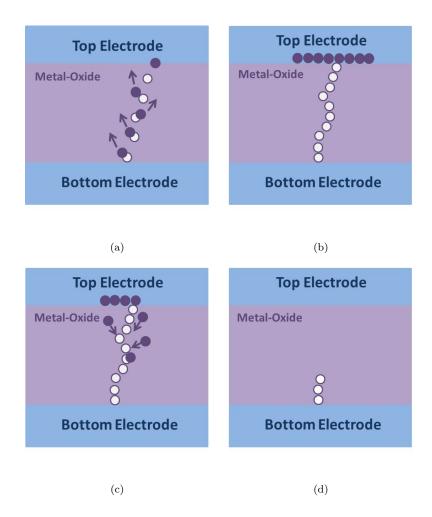

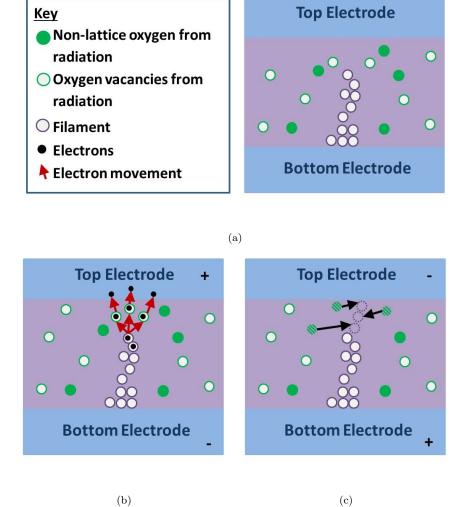

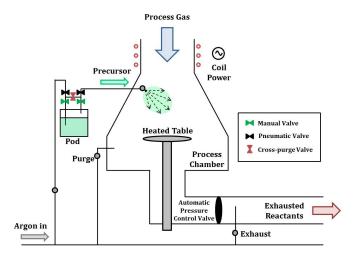

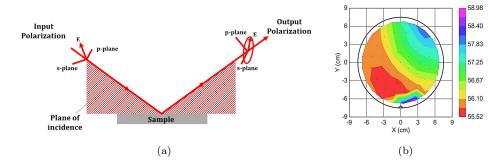

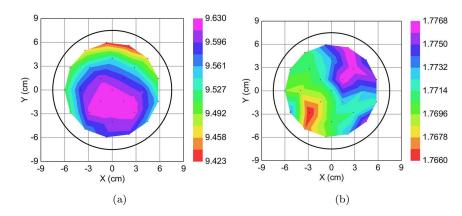

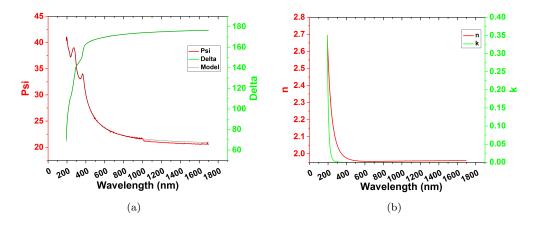

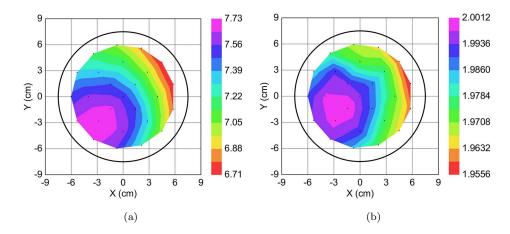

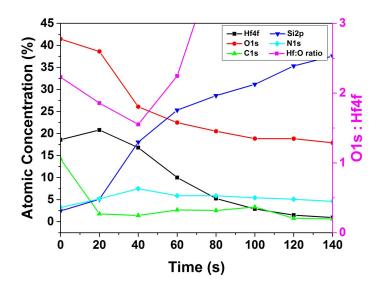

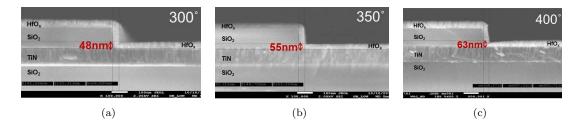

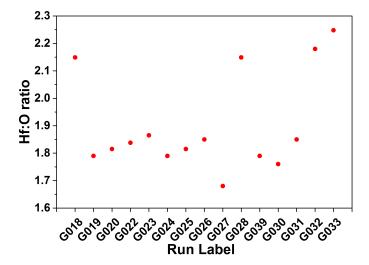

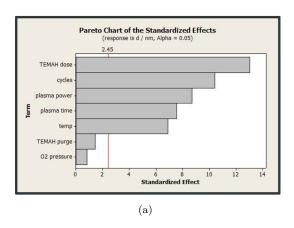

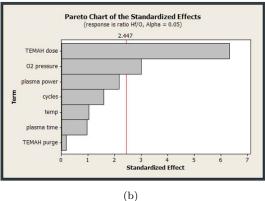

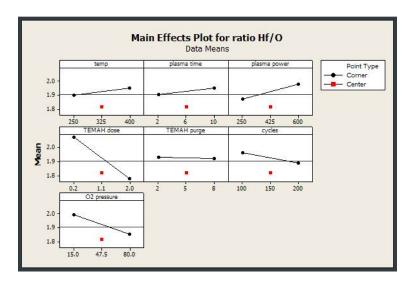

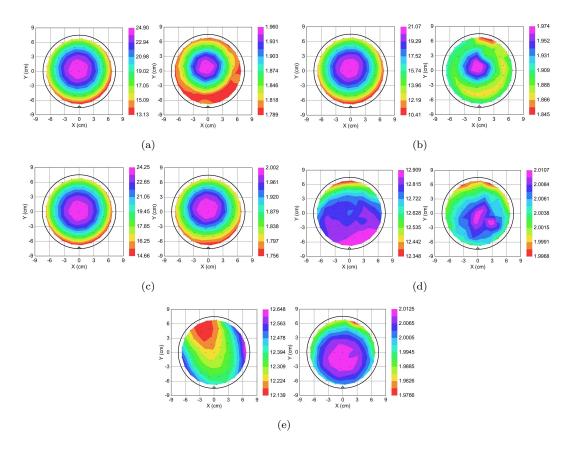

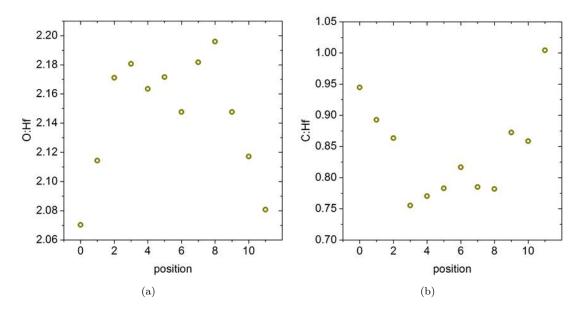

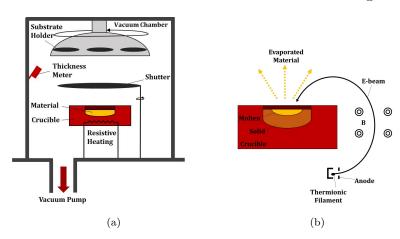

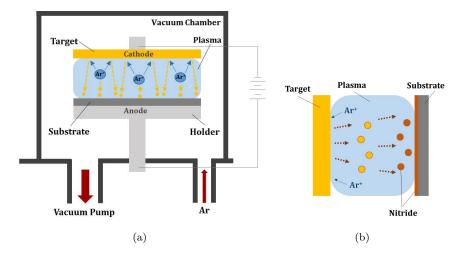

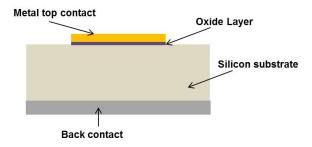

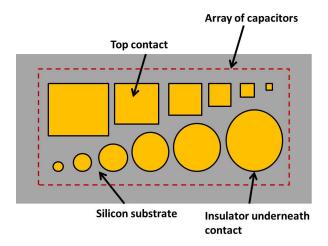

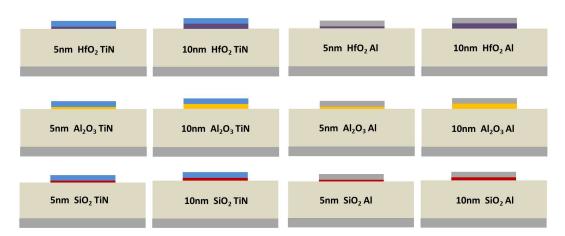

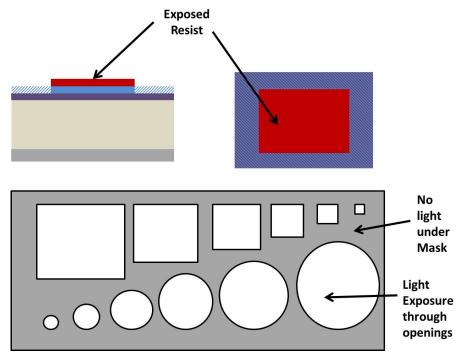

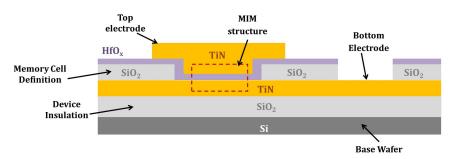

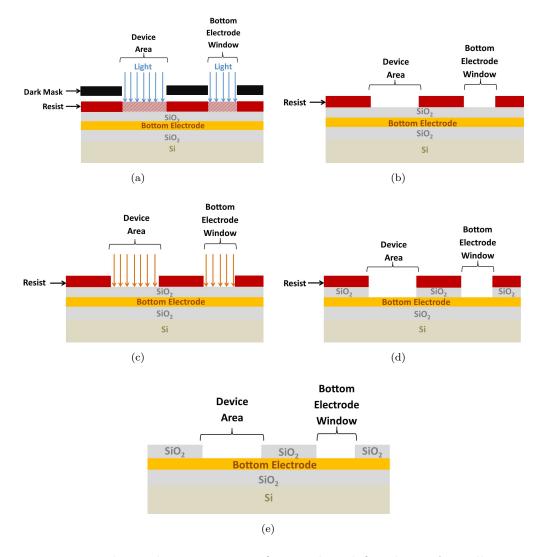

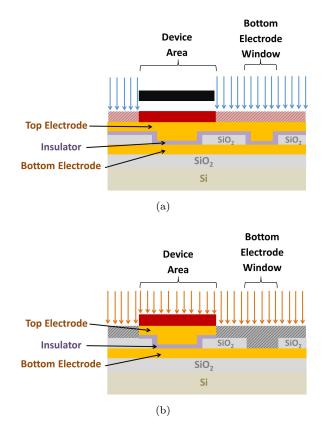

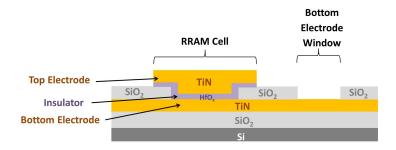

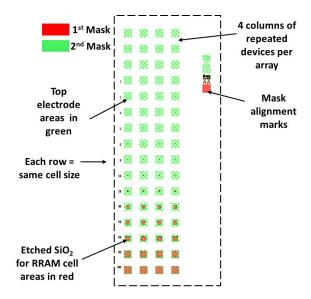

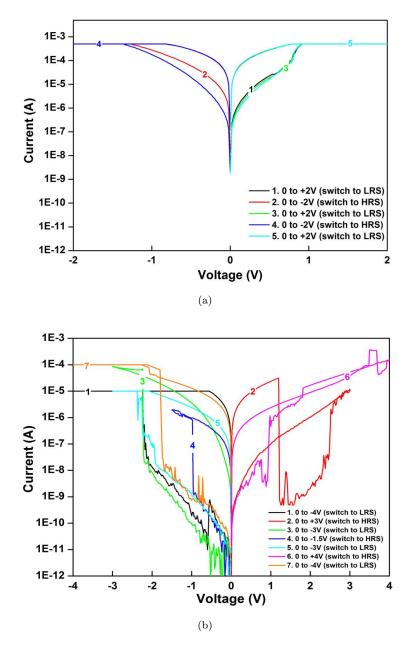

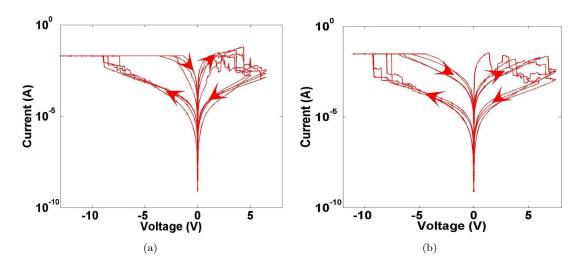

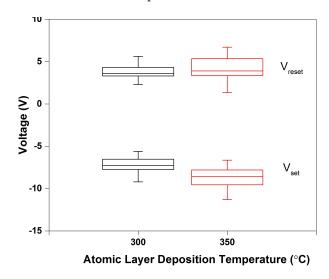

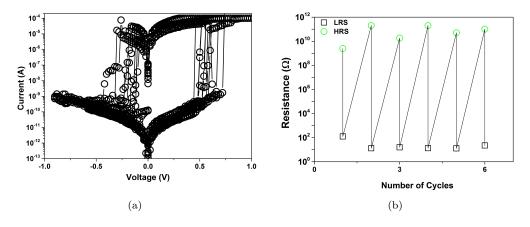

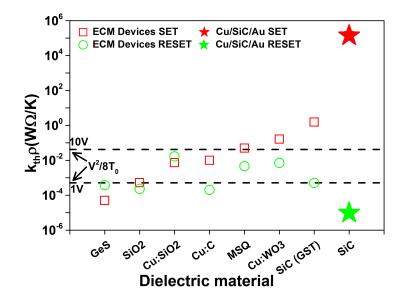

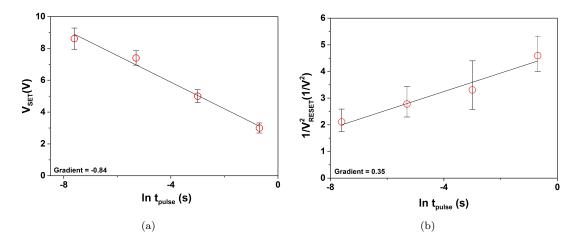

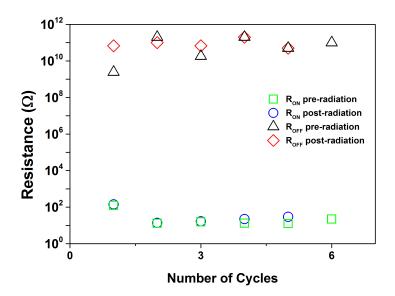

If the applied gate voltage is then increased further, above the threshold voltage, the depth of the depletion width under the interface will not increase further (this is true for the static, equilibrium case). When the electrons form at the interface, the high concentration and rapid increase with gate voltage shield the deeper parts of the bulk semiconductor from any additional charge that is applied to the gate. This leads to a maximum depletion depth which cannot be exceeded with increasing  $V_G$ . The equation for the maximum depletion depth,  $w_{D,max}$ , is given by Equation 2.15 where  $\epsilon_S$  and  $N_a$  are