University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

**System-Level Design Automation and Optimisation of

Network-on-Chips in Terms of Timing and Energy**

by

**Ji Qi**

Thesis for the degree of Doctor of Philosophy

September 2015

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

Doctor of Philosophy

SYSTEM-LEVEL DESIGN AUTOMATION AND OPTIMISATION OF

NETWORK-ON-CHIPS IN TERMS OF TIMING AND ENERGY

by **Ji Qi**

As system complexity constantly increases, traditional bus-based architectures are less adaptable to the increasing design demands. Specifically in on-chip digital system designs, Network-on-Chip (NoC) architectures are promising platforms that have distributed multi-core co-operation and inter-communication. Since the design cost and time cycles of NoC systems are growing rapidly with higher integration, system-level Design Automation (DA) techniques are used to abstract models at early design stages for functional validation and performance prediction. Yet precise abstractions and efficient simulations are critical challenges for modern DA techniques to improve the design efficiency. This thesis makes several contributions to address these challenges.

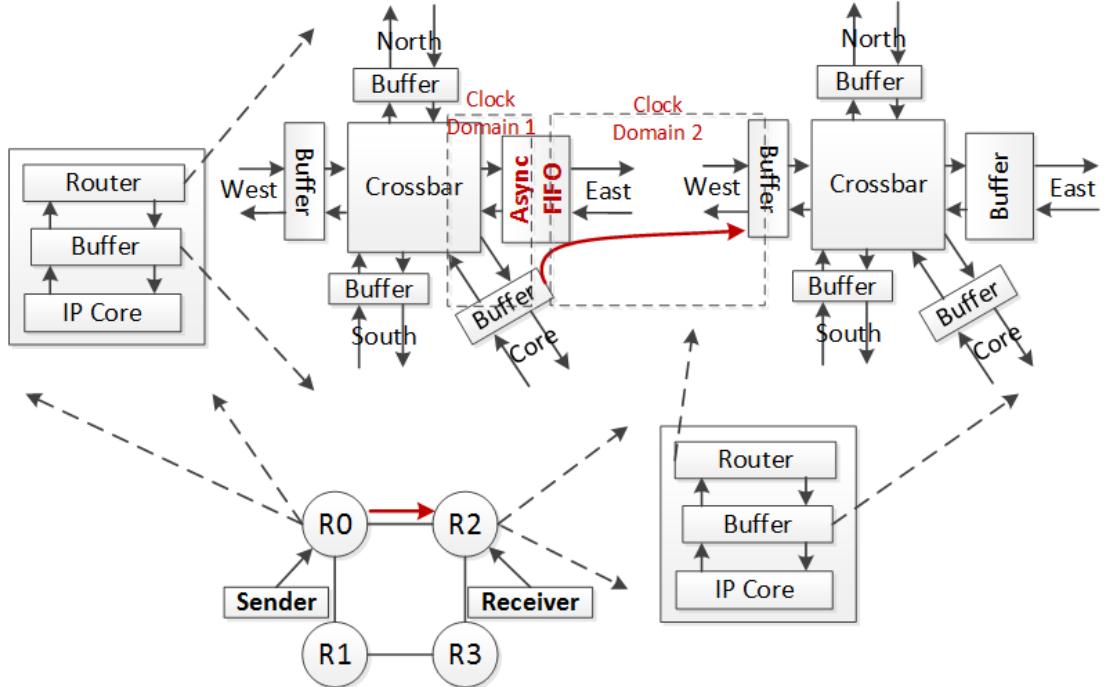

We have firstly extended a backbone simulator, NIRGAM, to offer accurate system-level models and performance estimates. A case study of developing a one-to-one transmission system using asynchronous FIFOs as buffers in both the NIRGAM simulator and a synthesised gate-level design is given to validate the model accuracy by comparing their power and timing performance.

Then we have made a second contribution to improve DA techniques by proposing a novel method to efficiently emulate non-rectangular NoC topologies in NIRGAM and generating accurate energy and timing performance. Our proposed method uses time-regulated models to emulate virtual non-rectangular topologies based on a regular Mesh. The performance accuracy of virtual topologies is validated by comparing with corresponding real NoC topologies.

The third contribution of our research is a novel task-mapping scheme that generates optimal mappings to tile-based NoC networks with accurate performance prediction and increased execution speed. A novel Non-Linear Programming (NLP) based mapping problem has been formulated and solved by a modified Branch and Bound (BB) algorithm. The proposed method predicts the performance of optimised mappings and compares it with NIRGAM simulations for accuracy validation.

# Contents

|                                                                 |              |

|-----------------------------------------------------------------|--------------|

| <b>Declaration of Authorship</b>                                | <b>xv</b>    |

| <b>Acknowledgements</b>                                         | <b>xvii</b>  |

| <b>Nomenclature</b>                                             | <b>xxi</b>   |

| <b>Abbreviations</b>                                            | <b>xxiii</b> |

| <b>1 Introduction</b>                                           | <b>1</b>     |

| 1.1 Introduction . . . . .                                      | 1            |

| 1.1.1 On-chip Network Architectures . . . . .                   | 1            |

| 1.1.2 Design Methodology of NoC Architectures . . . . .         | 2            |

| 1.1.3 Design Space Exploration of Current Methodology . . . . . | 5            |

| 1.2 Research Objectives . . . . .                               | 6            |

| 1.3 Research Contributions . . . . .                            | 8            |

| 1.4 Thesis Structure . . . . .                                  | 9            |

| <b>2 Literature Review</b>                                      | <b>11</b>    |

| 2.1 Network on Chip Basics . . . . .                            | 11           |

| 2.1.1 Basic Concepts . . . . .                                  | 11           |

| 2.1.1.1 Direct and Indirect Networks . . . . .                  | 13           |

| 2.1.1.2 Development of Network on Chip . . . . .                | 14           |

| 2.1.1.3 NoC Architectures . . . . .                             | 16           |

| 2.1.2 NoC Topology . . . . .                                    | 17           |

| 2.1.2.1 Popular Direct Network Topologies . . . . .             | 17           |

| 2.1.2.2 Popular Indirect Network Topologies . . . . .           | 19           |

| 2.1.3 Flow Control . . . . .                                    | 22           |

| 2.1.3.1 Basic Concepts . . . . .                                | 22           |

| 2.1.3.2 Switching Techniques . . . . .                          | 23           |

| 2.1.3.3 Virtual Channels . . . . .                              | 25           |

| 2.1.3.4 Quality of Service . . . . .                            | 27           |

| 2.1.4 Routing Algorithms . . . . .                              | 28           |

| 2.1.4.1 Basic Concepts . . . . .                                | 28           |

| 2.1.4.2 Deadlock, Livelock and Starvation . . . . .             | 29           |

| 2.1.4.3 Typical Classification of Routing Algorithms . . . . .  | 32           |

| 2.1.4.4 Deterministic and Adaptive Routing Algorithms . . . . . | 33           |

| 2.1.4.5 Source and Distributed Routing Algorithms . . . . .     | 36           |

| 2.1.4.6 Minimal and Non-minimal Routing Algorithms . . . . .    | 36           |

---

|          |                                                                      |           |

|----------|----------------------------------------------------------------------|-----------|

| 2.1.5    | Commercial Employment . . . . .                                      | 38        |

| 2.2      | System-level Design Automation . . . . .                             | 40        |

| 2.2.1    | Current Opinions . . . . .                                           | 40        |

| 2.2.2    | Major Performance Concerns in NoC Systems . . . . .                  | 43        |

| 2.2.2.1  | Energy . . . . .                                                     | 43        |

| 2.2.2.2  | Timing . . . . .                                                     | 44        |

| 2.2.2.3  | Other Factors . . . . .                                              | 45        |

| 2.3      | A Survey of NoC Application Mapping Techniques . . . . .             | 47        |

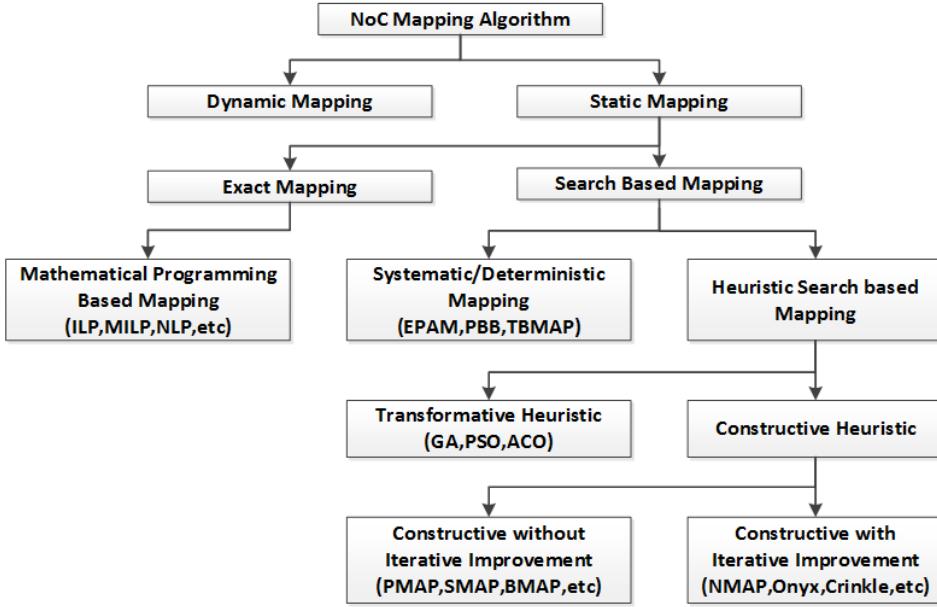

| 2.3.1    | The Classification of Mapping Techniques . . . . .                   | 47        |

| 2.3.2    | Dynamic Mapping Techniques . . . . .                                 | 49        |

| 2.3.3    | Static Mapping Techniques . . . . .                                  | 51        |

| 2.3.3.1  | Exact Mapping . . . . .                                              | 51        |

| 2.3.3.2  | Search Based Mapping . . . . .                                       | 54        |

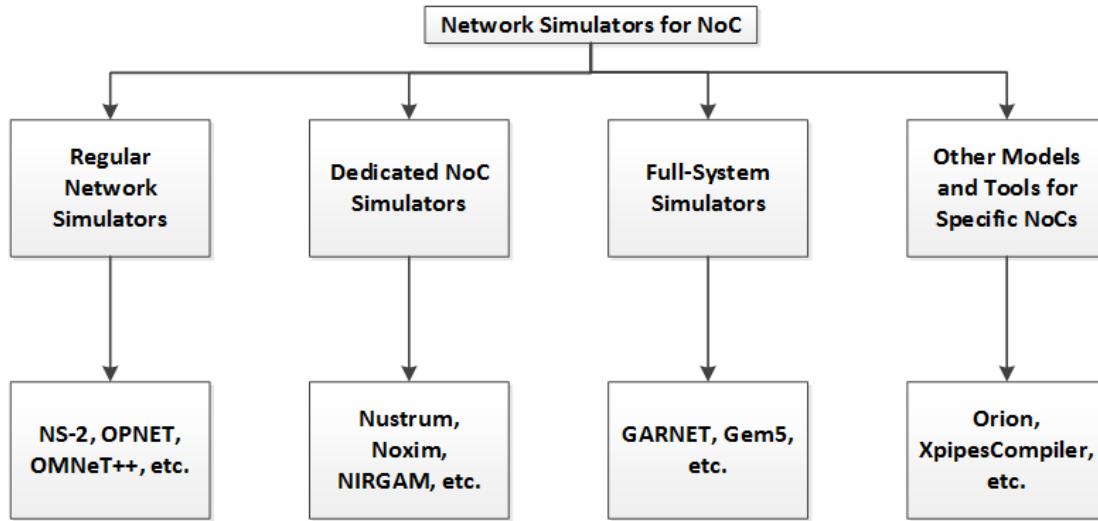

| 2.4      | A Survey of Current Network Simulators . . . . .                     | 61        |

| 2.4.1    | Emergence and Current Classification of Network Simulators . . . . . | 61        |

| 2.4.2    | Regular Network Simulators . . . . .                                 | 63        |

| 2.4.3    | Dedicated NoC Simulators . . . . .                                   | 64        |

| 2.4.4    | Full-system Simulators . . . . .                                     | 65        |

| 2.4.5    | Other Models and Tools for Specific NoC Simulations . . . . .        | 65        |

| 2.5      | Summary . . . . .                                                    | 66        |

| <b>3</b> | <b>System-Level Modelling of Networks on Chip</b> . . . . .          | <b>69</b> |

| 3.1      | Necessity of High-level Model Abstraction to NoC . . . . .           | 69        |

| 3.2      | Extended NIRGAM Simulator . . . . .                                  | 71        |

| 3.2.1    | Introduction to NIRGAM . . . . .                                     | 71        |

| 3.2.2    | Extended Work . . . . .                                              | 73        |

| 3.3      | Case Study: Asynchronous FIFO for NoC Buffer . . . . .               | 75        |

| 3.3.1    | Necessity and Motivation . . . . .                                   | 76        |

| 3.3.2    | Asynchronous FIFO Structure . . . . .                                | 77        |

| 3.3.3    | FIFO High-Level Modelling . . . . .                                  | 78        |

| 3.3.4    | FIFO Gate-Level Implementation . . . . .                             | 79        |

| 3.4      | Model Accuracy Analysis . . . . .                                    | 81        |

| 3.4.1    | Gate-level Asynchronous FIFO . . . . .                               | 81        |

| 3.4.1.1  | Experimental Setup . . . . .                                         | 81        |

| 3.4.1.2  | Result Analysis . . . . .                                            | 82        |

| 3.4.2    | Data Transmission System . . . . .                                   | 84        |

| 3.4.2.1  | Experimental Setup . . . . .                                         | 84        |

| 3.4.2.2  | Result Analysis . . . . .                                            | 87        |

| 3.4.3    | Result Analysis of Case Study . . . . .                              | 89        |

| 3.5      | Summary . . . . .                                                    | 90        |

| <b>4</b> | <b>Efficient Modelling of Non-rectangular Topologies</b> . . . . .   | <b>91</b> |

| 4.1      | Introduction and Motivation . . . . .                                | 92        |

| 4.2      | Non-rectangular NoC Architectures . . . . .                          | 94        |

| 4.2.1    | Significance of Non-rectangular Topological Modelling . . . . .      | 94        |

| 4.2.2    | Conventional Formation of Honeycomb Hexagonal Network . . . . .      | 97        |

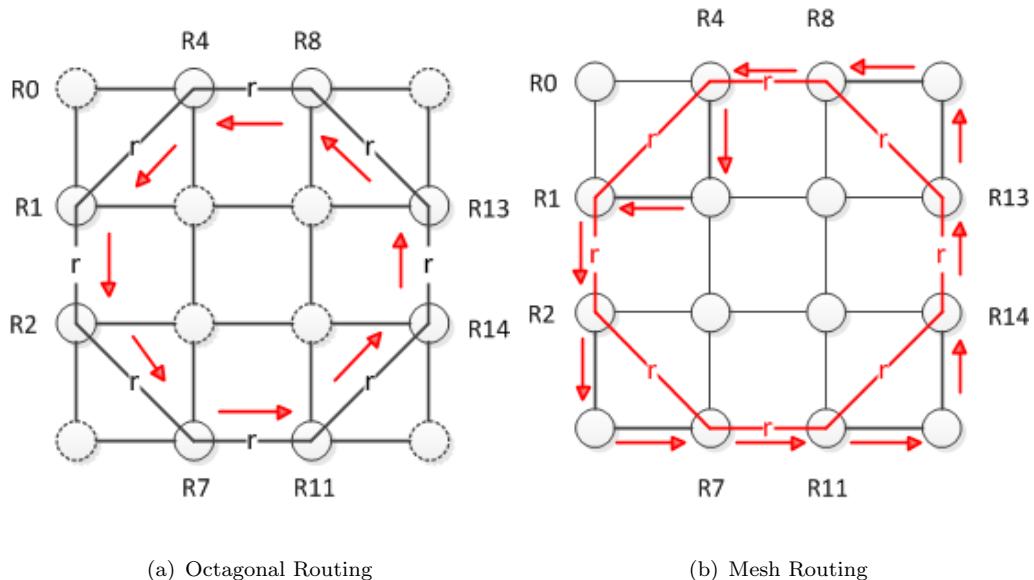

| 4.2.3    | Conventional Formation of Sparse-Octagonal Network . . . . .         | 98        |

---

|         |                                                        |            |

|---------|--------------------------------------------------------|------------|

| 4.3     | Proposed Design Methodology                            | 99         |

| 4.3.1   | Proposed Time Regulated Model                          | 100        |

| 4.3.2   | Example Topological Formation: Honeycomb Hexagon       | 101        |

| 4.3.3   | Example Topological Formation: Sparse-Octagon          | 104        |

| 4.4     | Experimental Results                                   | 106        |

| 4.4.1   | Specific Routings: Hexagonal and Irregular Routings    | 107        |

| 4.4.1.1 | Experimental Setup                                     | 107        |

| 4.4.1.2 | Theoretical Calculation                                | 108        |

| 4.4.1.3 | Result Analysis                                        | 110        |

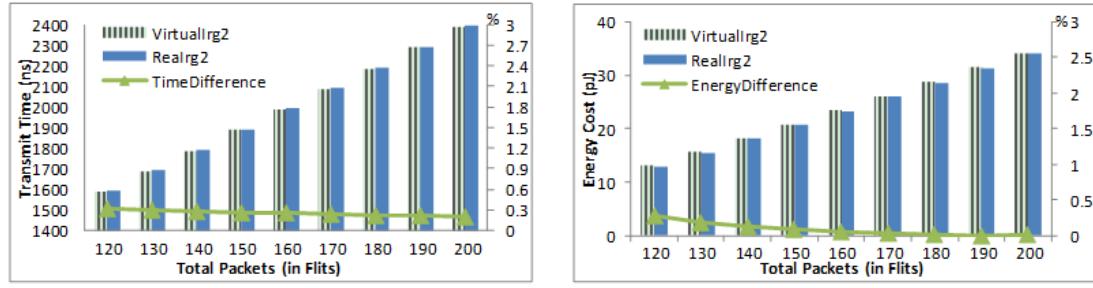

| 4.4.2   | Specific Routings: Octagonal Routing                   | 114        |

| 4.4.2.1 | Experimental Setup                                     | 114        |

| 4.4.2.2 | Result Analysis                                        | 115        |

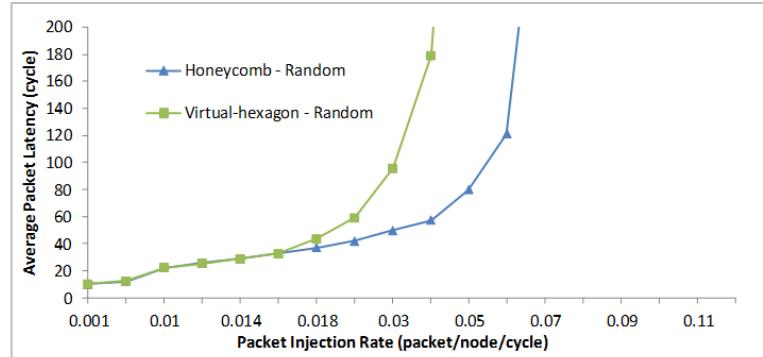

| 4.4.3   | Synthetic Traffic: Uniform Random                      | 116        |

| 4.4.3.1 | Experimental Setup                                     | 116        |

| 4.4.3.2 | Result Analysis                                        | 117        |

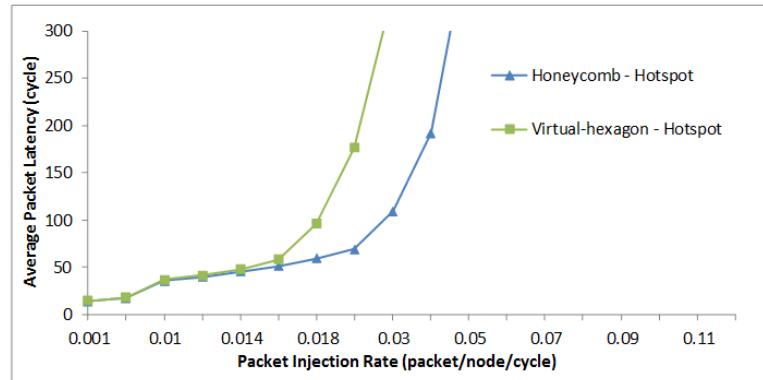

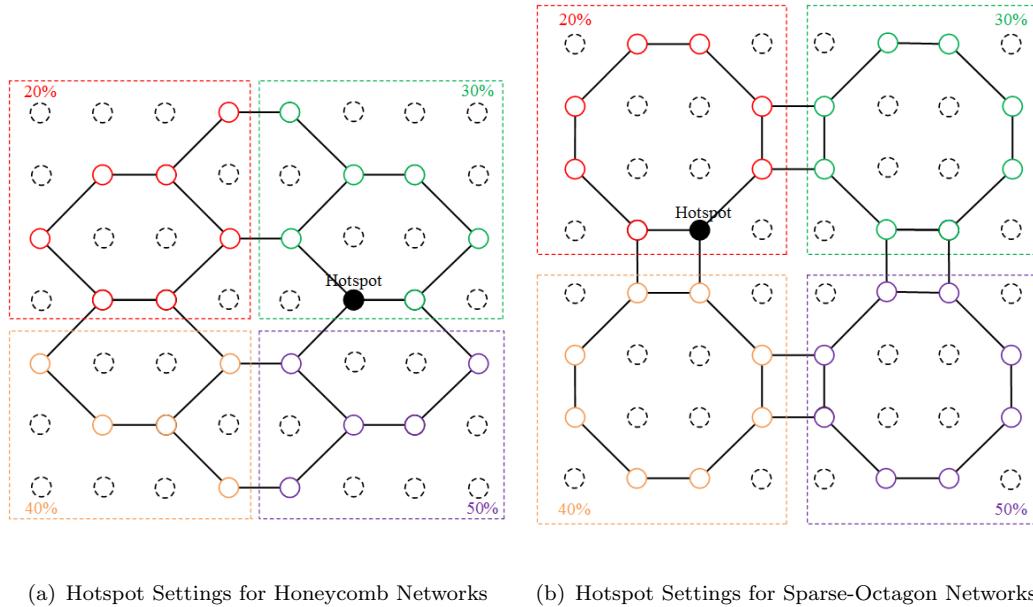

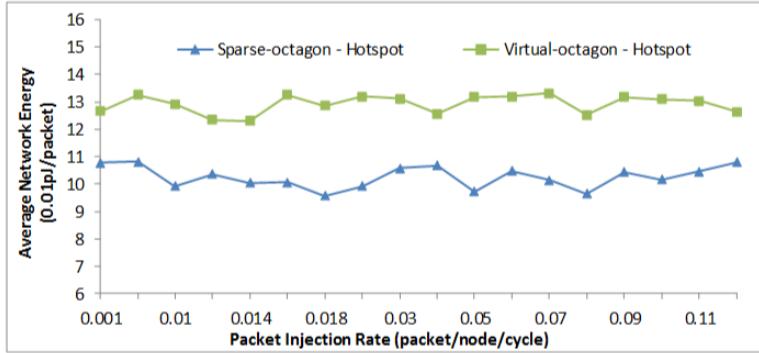

| 4.4.4   | Synthetic Traffic: Hotspot                             | 120        |

| 4.4.4.1 | Experimental Setup                                     | 120        |

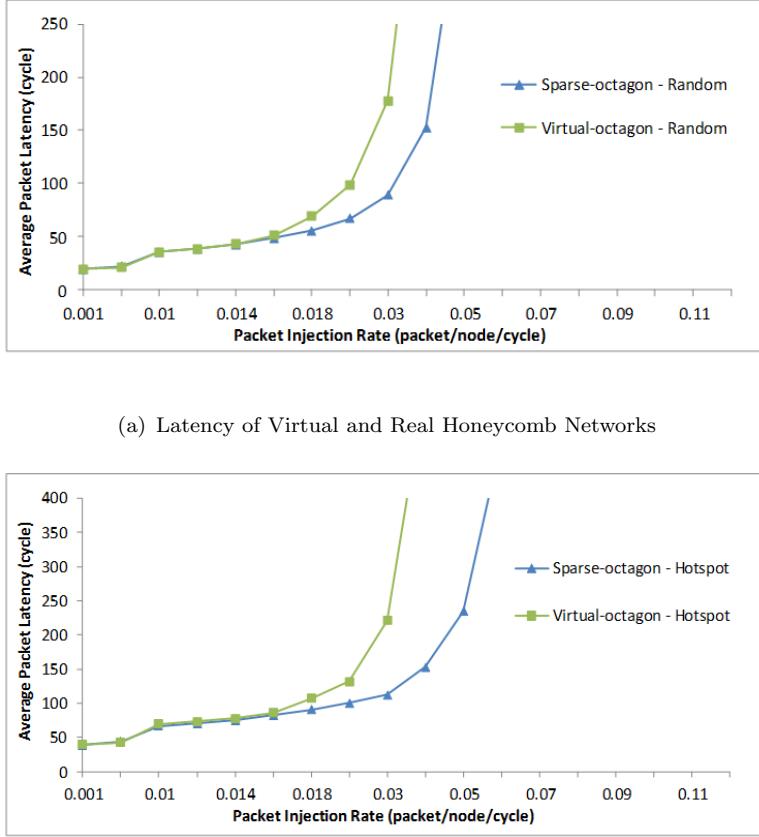

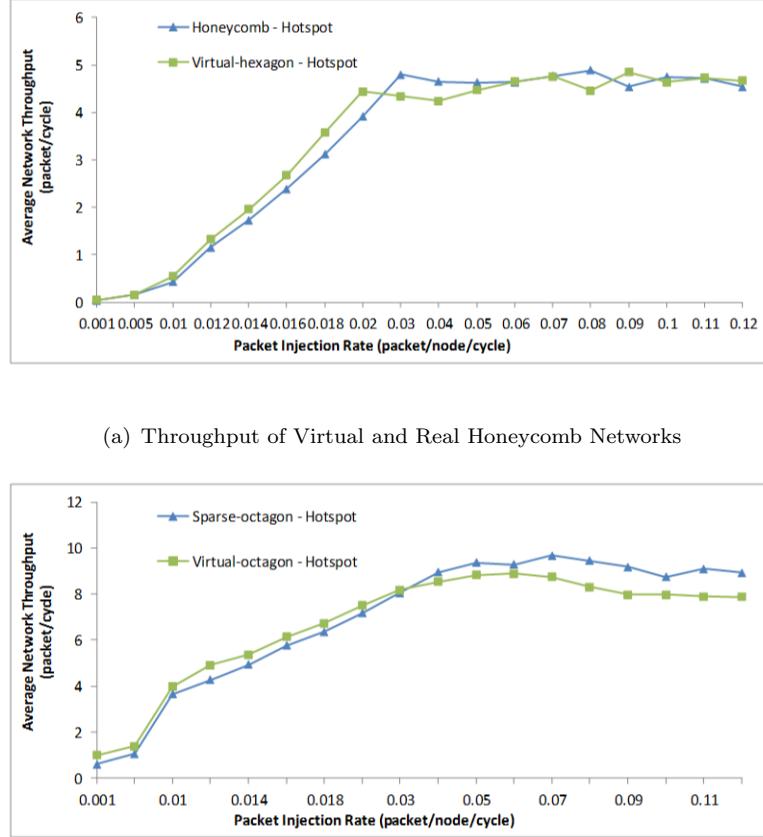

| 4.4.4.2 | Result Analysis                                        | 121        |

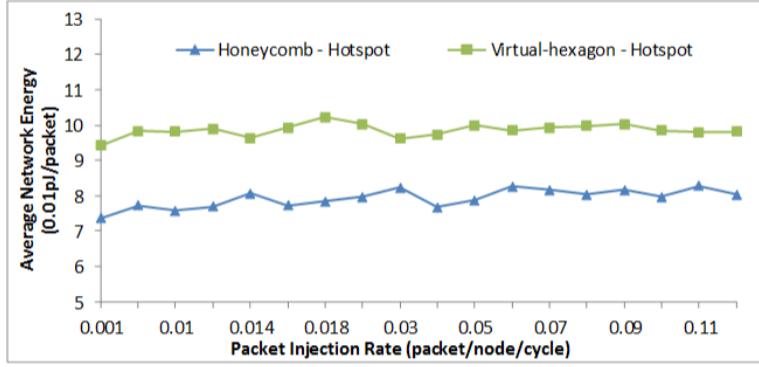

| 4.4.5   | Model Accuracy Discussion                              | 123        |

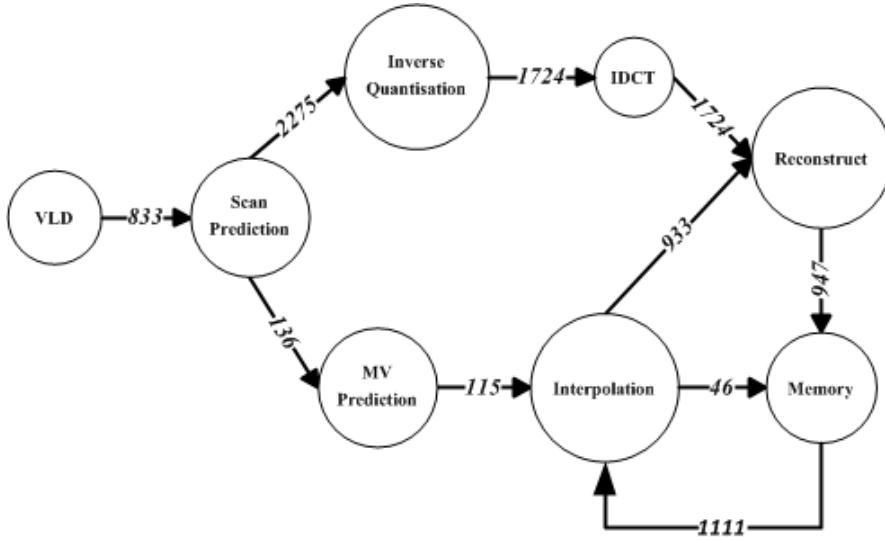

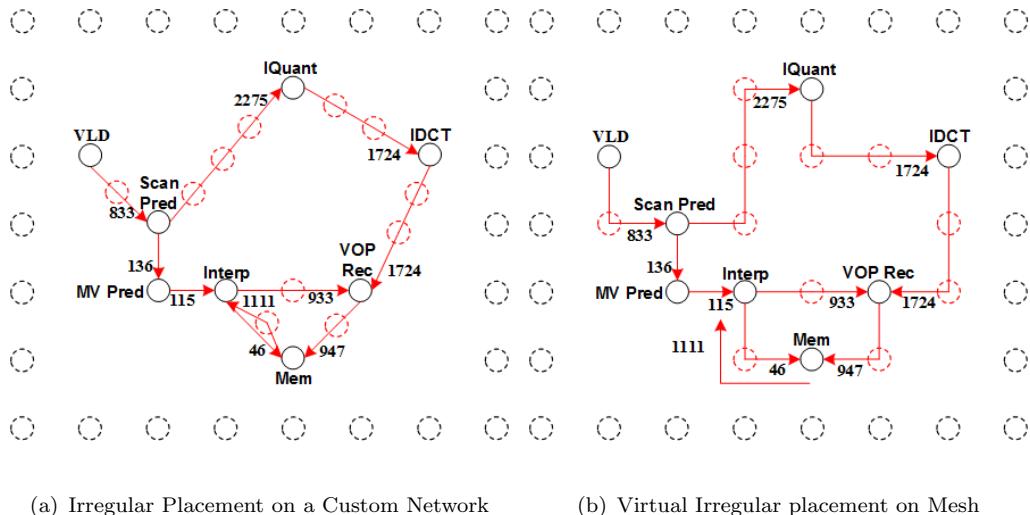

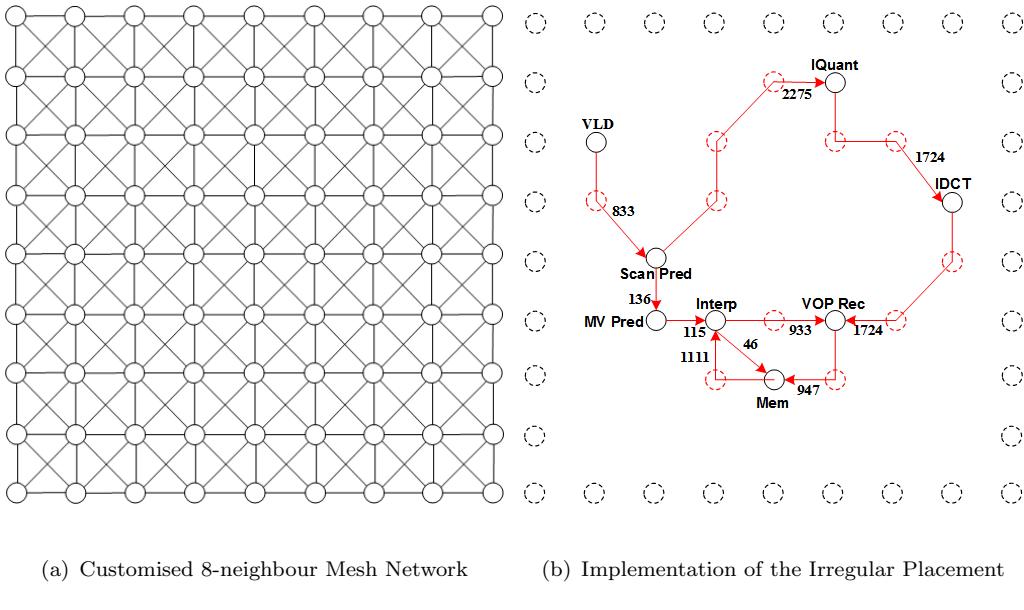

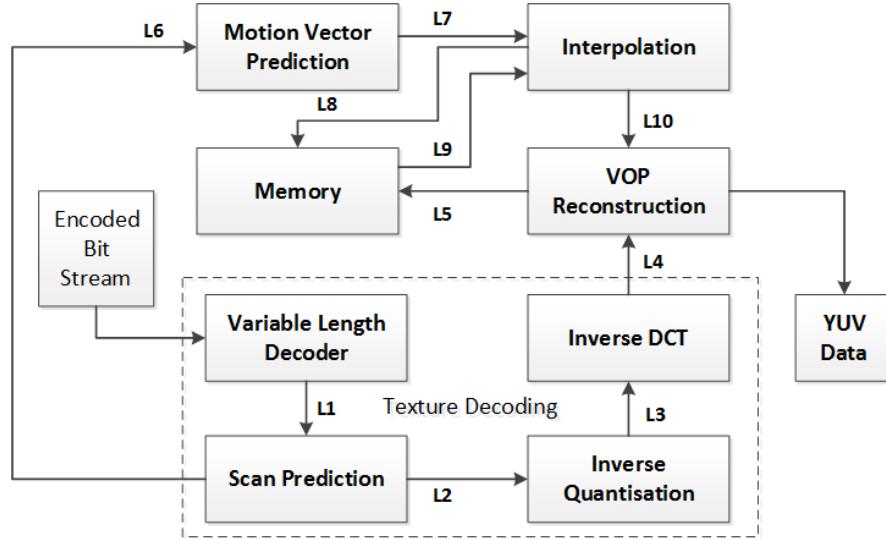

| 4.4.6   | Specific Application: MPEG-4 Decoder                   | 125        |

| 4.4.6.1 | Software Implementation                                | 125        |

| 4.4.6.2 | Experimental Setup                                     | 126        |

| 4.4.6.3 | Result Analysis                                        | 128        |

| 4.4.7   | Superiority of Our Method for Topological Modelling    | 129        |

| 4.5     | Summary                                                | 130        |

| 5       | <b>Application Mapping and Performance Prediction</b>  | <b>133</b> |

| 5.1     | Introduction and Necessity                             | 134        |

| 5.2     | Proposed Mapping Method and Performance Prediction     | 137        |

| 5.2.1   | Preliminaries                                          | 137        |

| 5.2.1.1 | The Architecture                                       | 137        |

| 5.2.1.2 | Energy and Timing Models                               | 139        |

| 5.2.2   | Problem Formulation of NLP Based Mapping               | 141        |

| 5.2.2.1 | Problem Definition                                     | 141        |

| 5.2.2.2 | Parameters and Variables                               | 142        |

| 5.2.2.3 | Objective Function                                     | 143        |

| 5.2.2.4 | Constraints                                            | 146        |

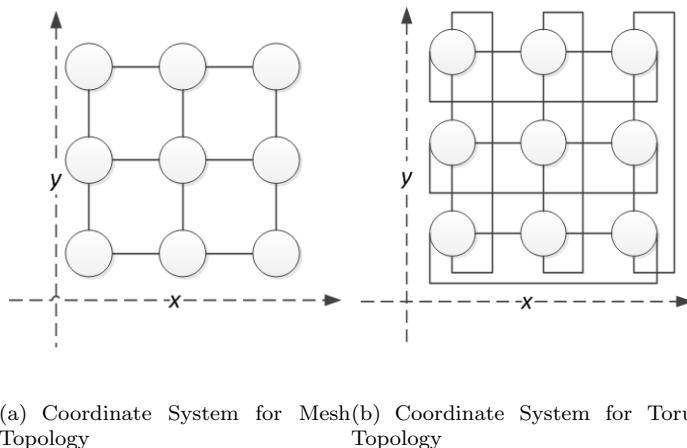

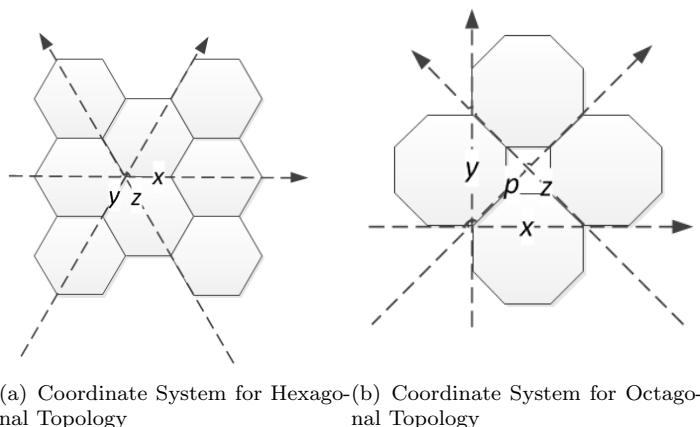

| 5.2.2.5 | Extension of Mapping Problem onto More Tile-based NoCs | 148        |

| 5.2.3   | Efficient Mapping                                      | 150        |

| 5.2.3.1 | Modified Branch and Bound Algorithm                    | 150        |

| 5.2.3.2 | Performance Prediction                                 | 156        |

| 5.2.3.3 | Statement                                              | 158        |

| 5.3     | Experimental Results                                   | 159        |

| 5.3.1   | Synthetic Applications                                 | 160        |

| 5.3.1.1 | Experimental Setup                                     | 160        |

| 5.3.1.2 | Functional Verification Analysis                       | 161        |

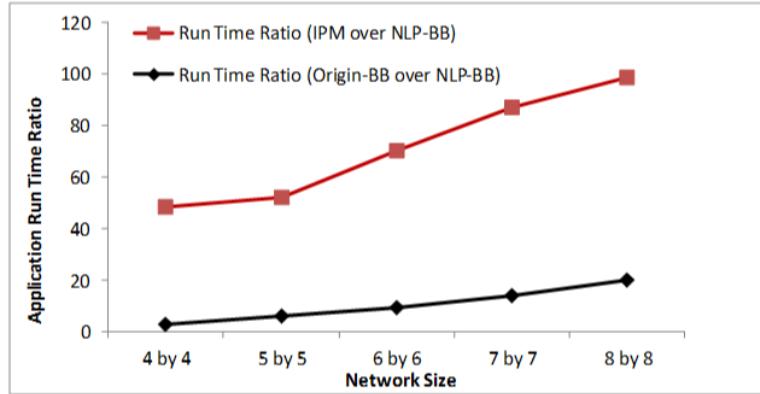

| 5.3.1.3 | Execution Efficiency Analysis                          | 162        |

|                   |                                                                                             |            |

|-------------------|---------------------------------------------------------------------------------------------|------------|

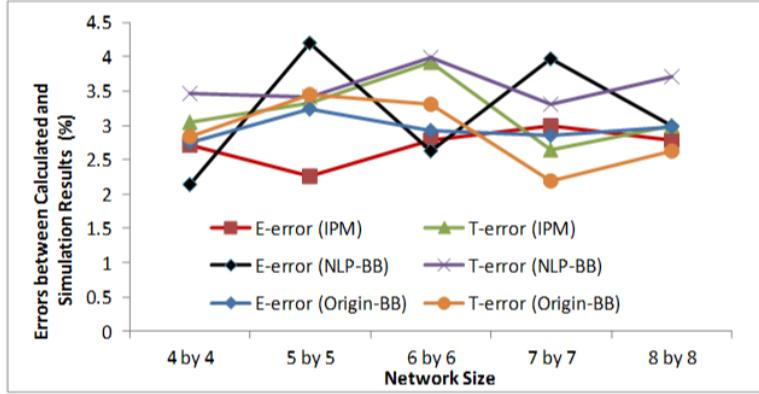

| 5.3.1.4           | Performance Accuracy Analysis                                                               | 163        |

| 5.3.2             | Real-World Media Application                                                                | 164        |

| 5.3.2.1           | Experimental Setup                                                                          | 164        |

| 5.3.2.2           | Functional Verification Analysis                                                            | 166        |

| 5.3.2.3           | Execution Efficiency Analysis                                                               | 166        |

| 5.3.2.4           | Performance Accuracy Analysis                                                               | 166        |

| 5.4               | Summary                                                                                     | 167        |

| <b>6</b>          | <b>Conclusions and Future Work</b>                                                          | <b>169</b> |

| 6.1               | Summary of the thesis                                                                       | 169        |

| 6.1.1             | Accurate Model Abstraction of System-Level NoC Architectures                                | 170        |

| 6.1.2             | Efficient Design Method of Application-Specific Network Topologies                          | 170        |

| 6.1.3             | Efficient Optimisation of Task-Mapping Performance Trade-offs in Terms of Timing and Energy | 171        |

| 6.2               | Future Work                                                                                 | 172        |

| <b>A</b>          | <b>Technology Parameters Used by Orion</b>                                                  | <b>175</b> |

| <b>References</b> |                                                                                             | <b>185</b> |

# List of Figures

|      |                                                                                               |    |

|------|-----------------------------------------------------------------------------------------------|----|

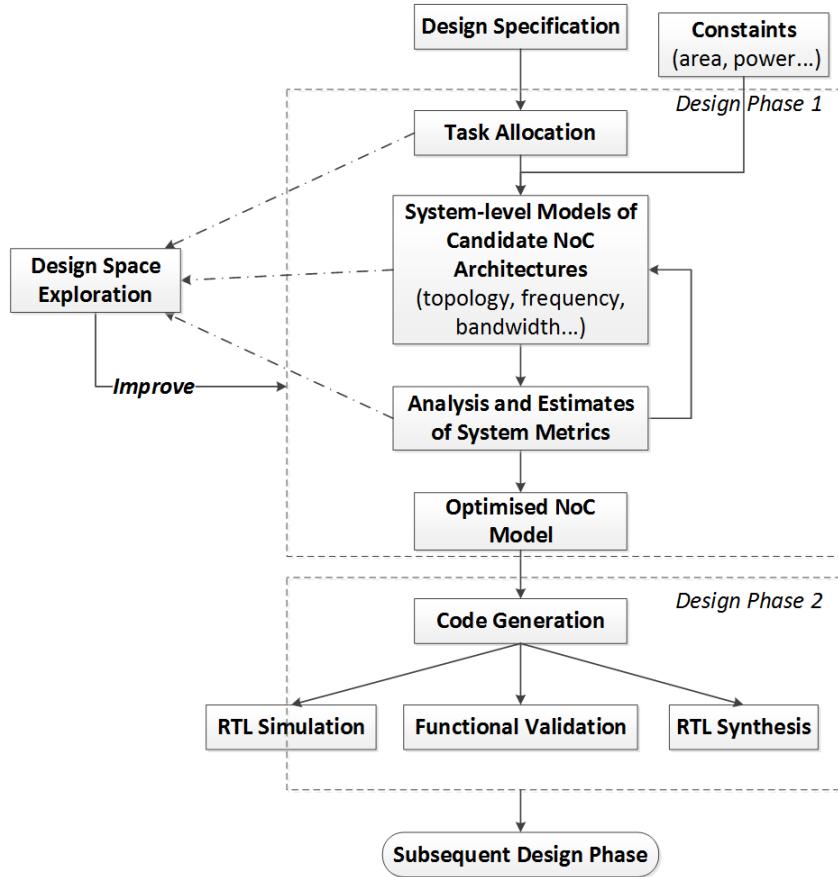

| 1.1  | Explore Design Space in Phase 1 of State-of-the-art Design Flow [1] . . . . .                 | 6  |

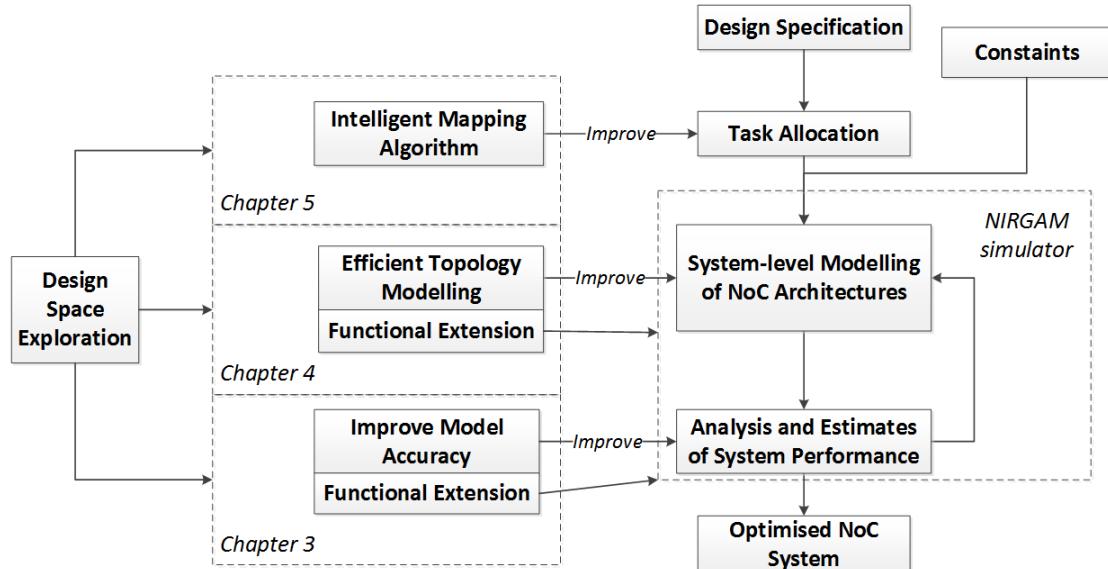

| 1.2  | Research Objectives . . . . .                                                                 | 7  |

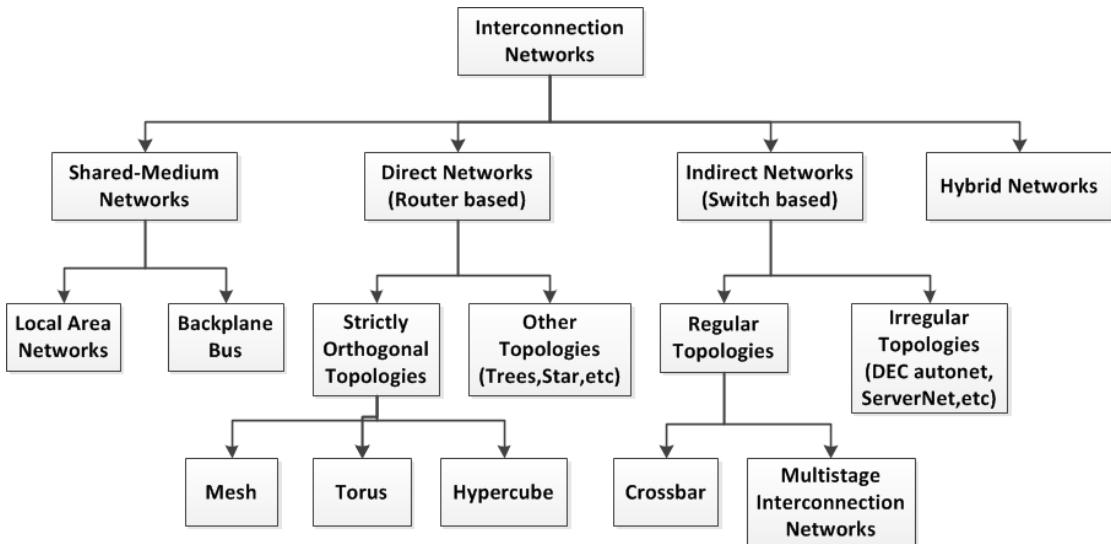

| 2.1  | Four Classifications of Interconnection Networks [2] . . . . .                                | 12 |

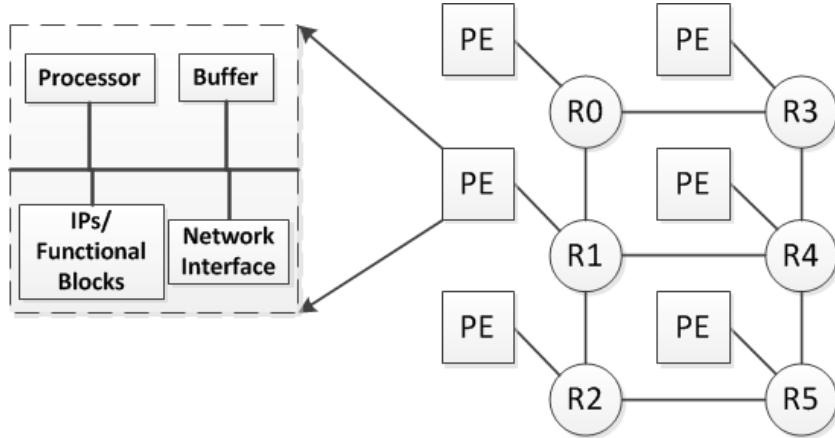

| 2.2  | A Typical Architecture of NoC [3] . . . . .                                                   | 16 |

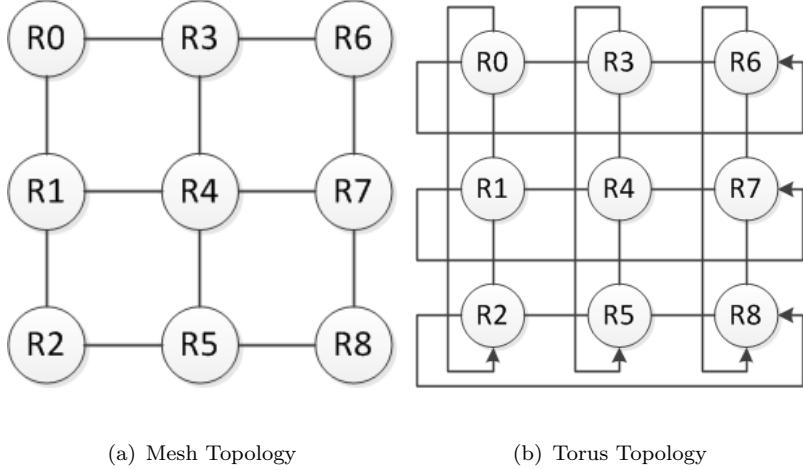

| 2.3  | Mesh and Torus Topologies [4] . . . . .                                                       | 18 |

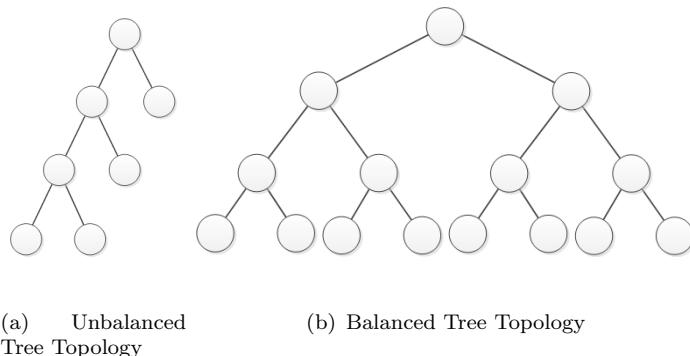

| 2.4  | Unbalanced and Balanced Binary Trees [5] [6] . . . . .                                        | 18 |

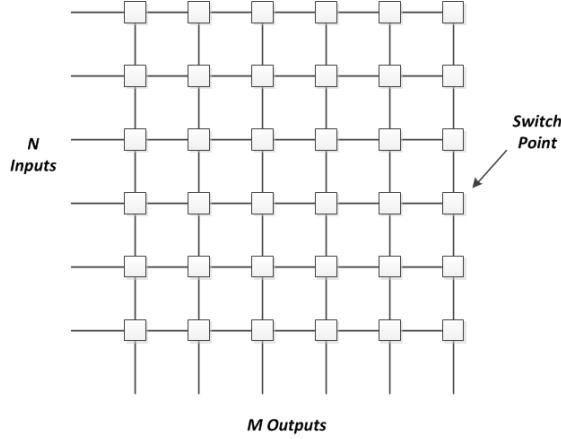

| 2.5  | An N by M Crossbar Topology [7] [8] . . . . .                                                 | 20 |

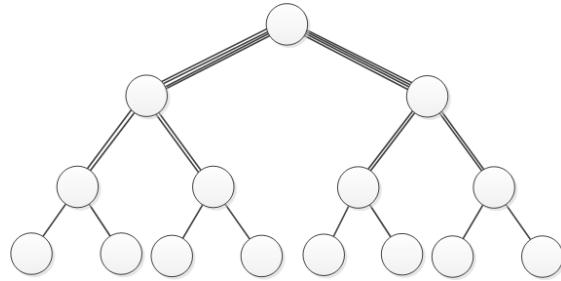

| 2.6  | A Simple Fat Tree Architecture [9] . . . . .                                                  | 20 |

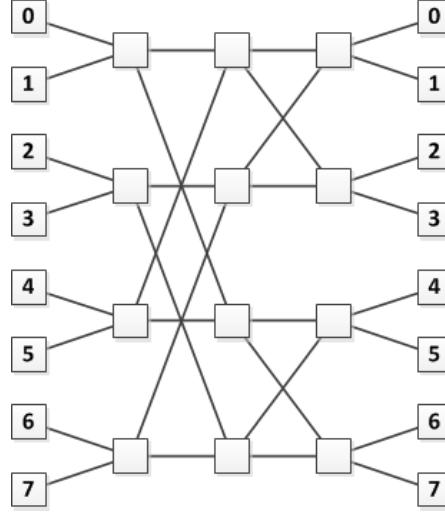

| 2.7  | A $2 - ary$ , $3 - fly$ Butterfly Architecture [10] . . . . .                                 | 21 |

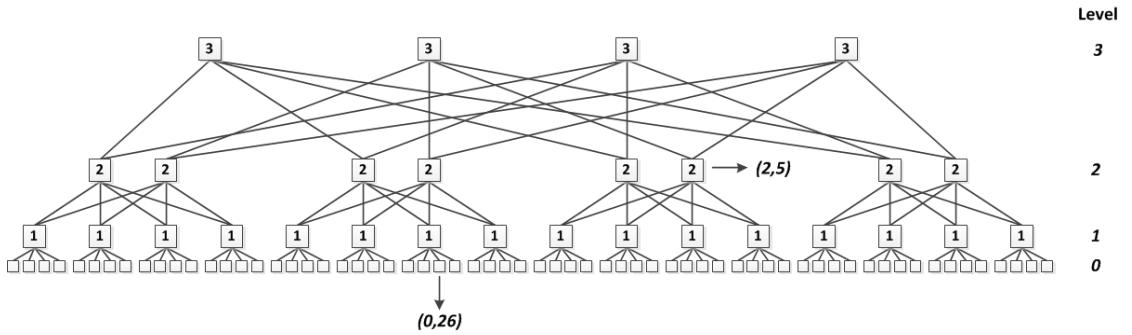

| 2.8  | Butterfly Fat Tree Architecture with $N=64$ PE Blocks [5] . . . . .                           | 21 |

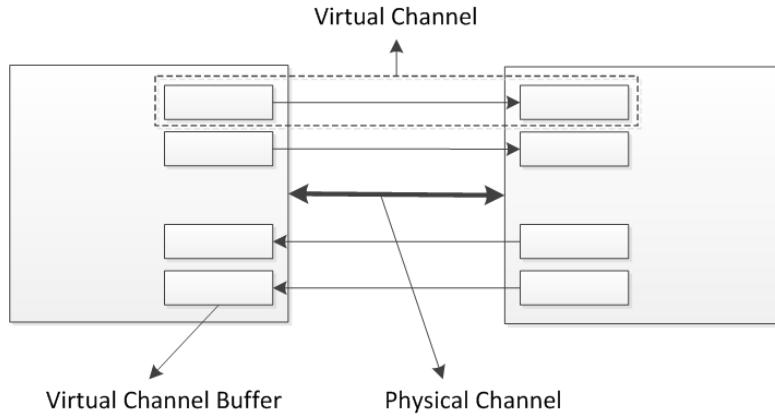

| 2.9  | Virtual Channels [8] . . . . .                                                                | 26 |

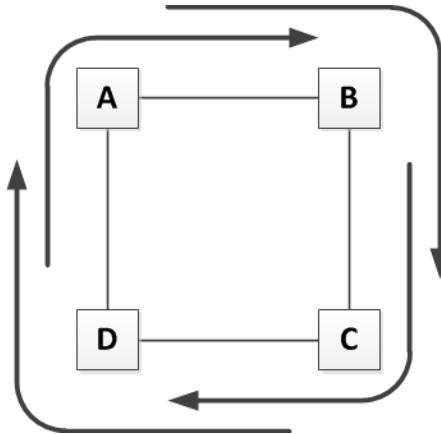

| 2.10 | Example of a Typical Network Deadlock [3] . . . . .                                           | 30 |

| 2.11 | Example of a Typical Network Livelock [10] . . . . .                                          | 30 |

| 2.12 | XY Routing Algorithm for 2D-Mesh - X First [11] . . . . .                                     | 34 |

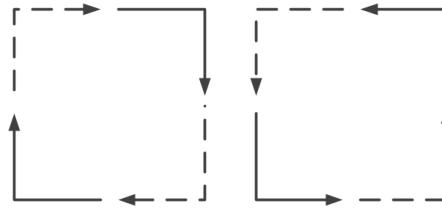

| 2.13 | Example Turn Model for Adaptive Routing [12] . . . . .                                        | 35 |

| 2.14 | Examples of OE Routing in 9 by 9 2D-Mesh [3] . . . . .                                        | 35 |

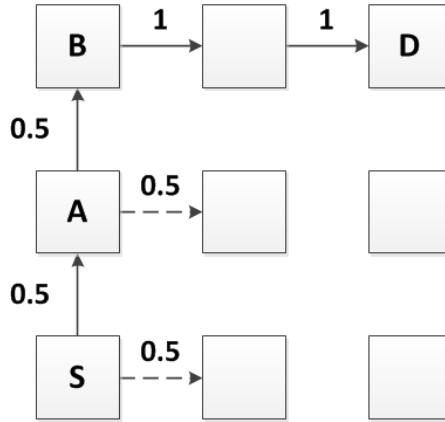

| 2.15 | PROM Example: Randomly Choose the Minimal Routing Path [13] . . . . .                         | 38 |

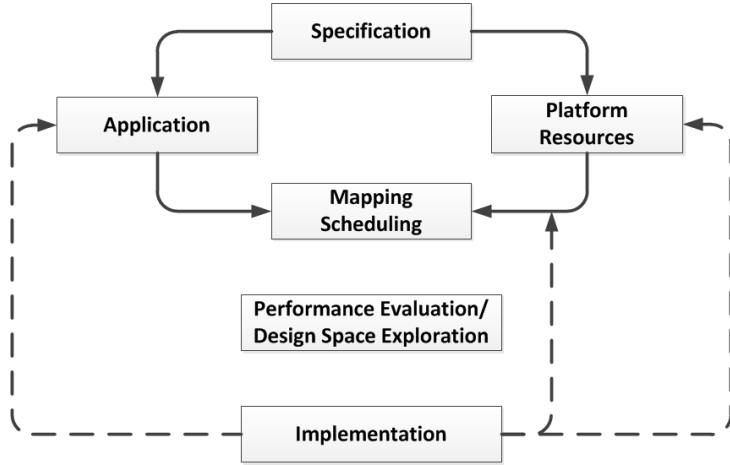

| 2.16 | Typical High-Level System Design Process [14] . . . . .                                       | 41 |

| 2.17 | The Classification of Mapping Algorithms [15] . . . . .                                       | 48 |

| 2.18 | The Classification of Current Network Simulators for NoC Simulations . . . . .                | 62 |

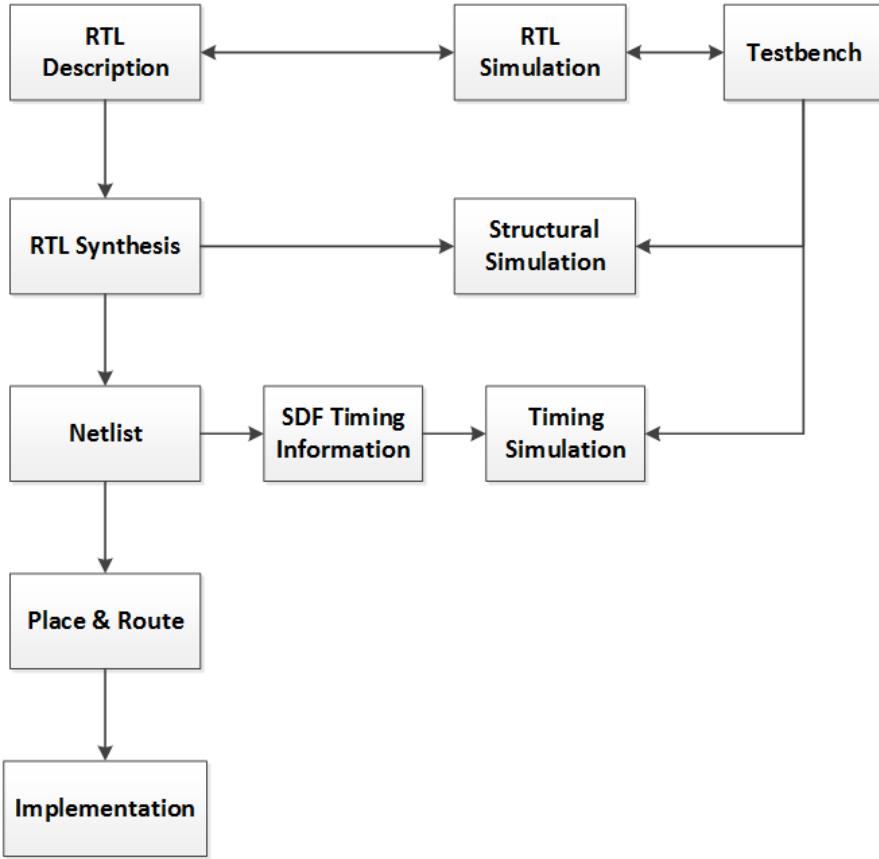

| 3.1  | Basic Digital Design Process . . . . .                                                        | 70 |

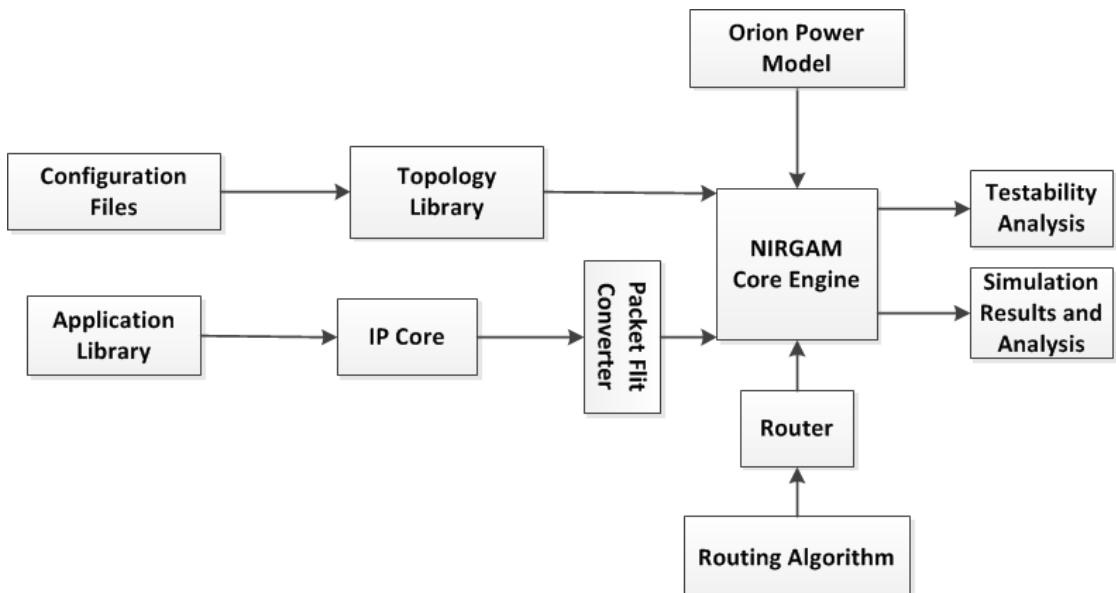

| 3.2  | The System Architecture of NIRGAM Simulator . . . . .                                         | 71 |

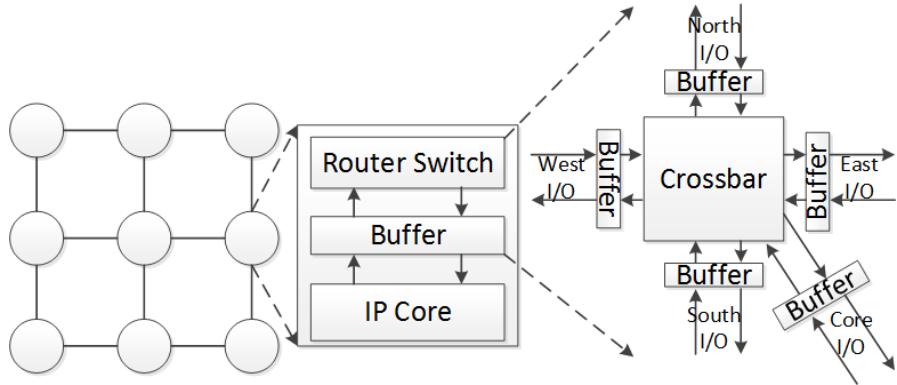

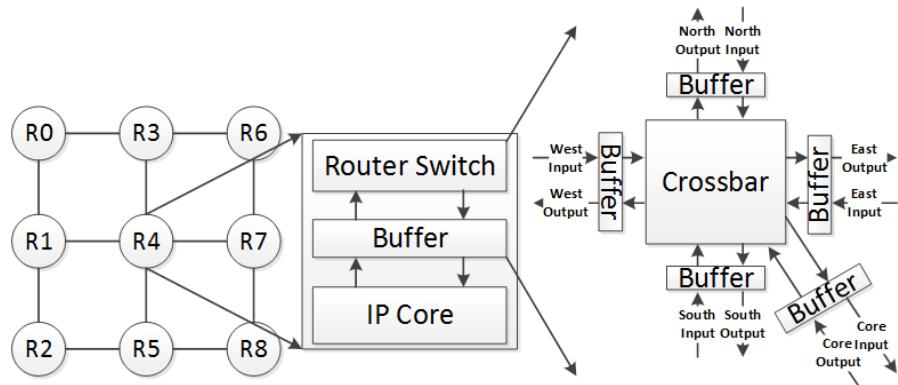

| 3.3  | Typical Mesh Network with Homogeneous Node Architecture . . . . .                             | 72 |

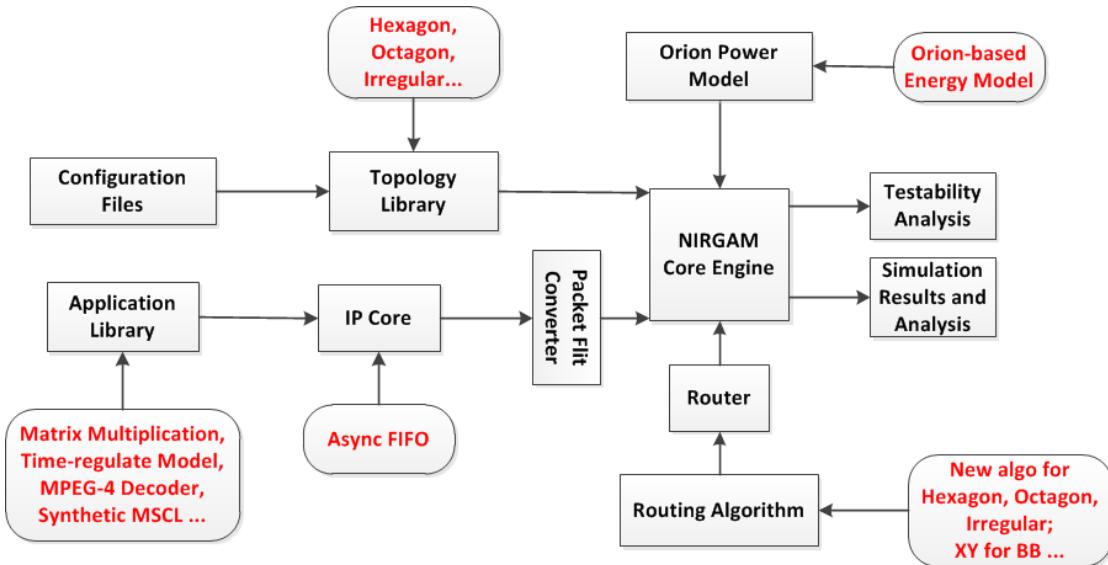

| 3.4  | The Extended NIRGAM Simulator . . . . .                                                       | 73 |

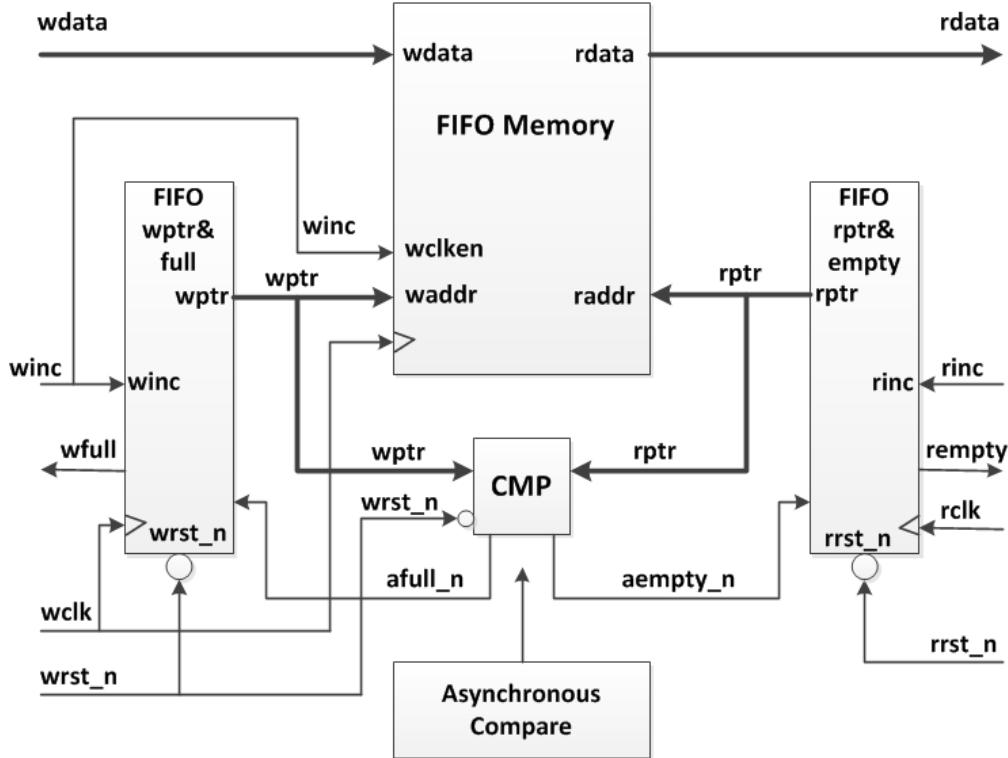

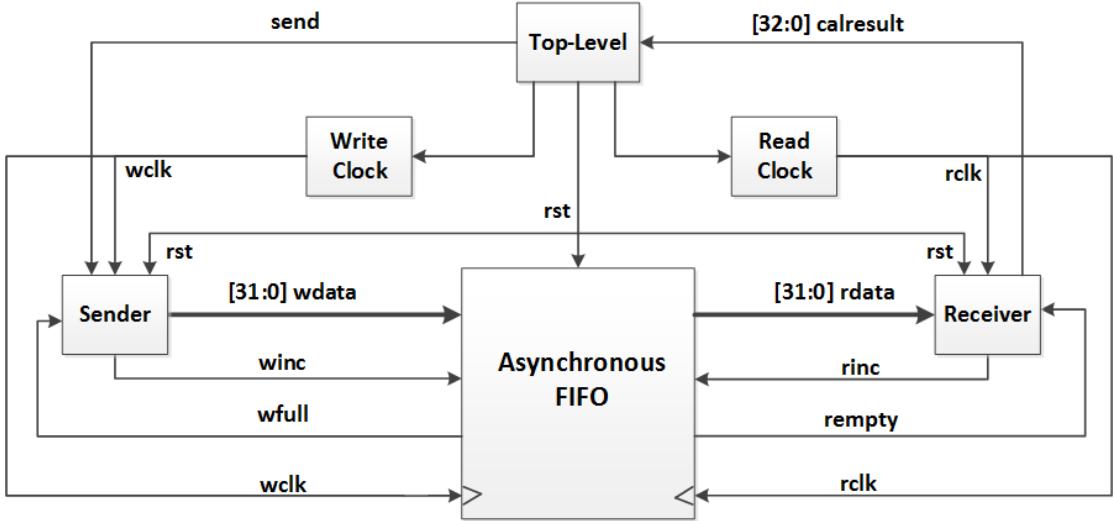

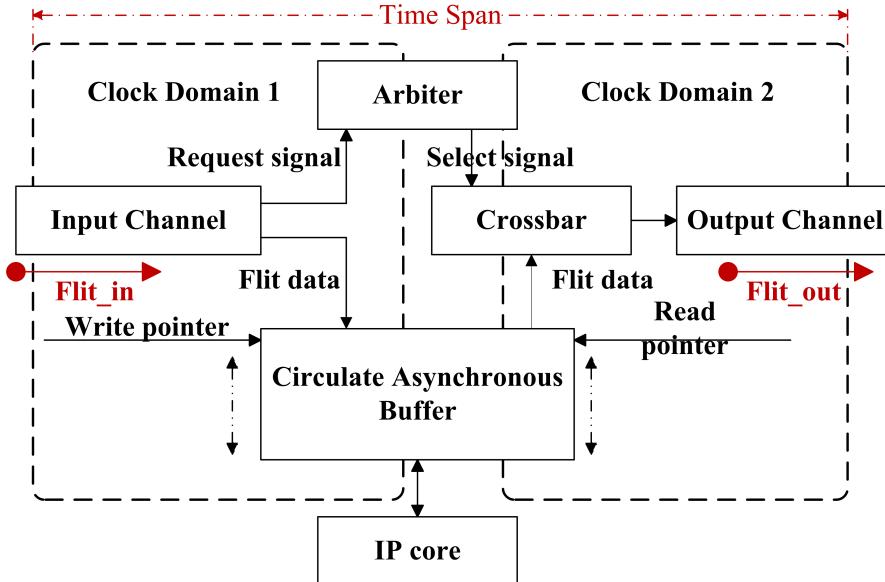

| 3.5  | The Applied Asynchronous FIFO Structure [16] . . . . .                                        | 78 |

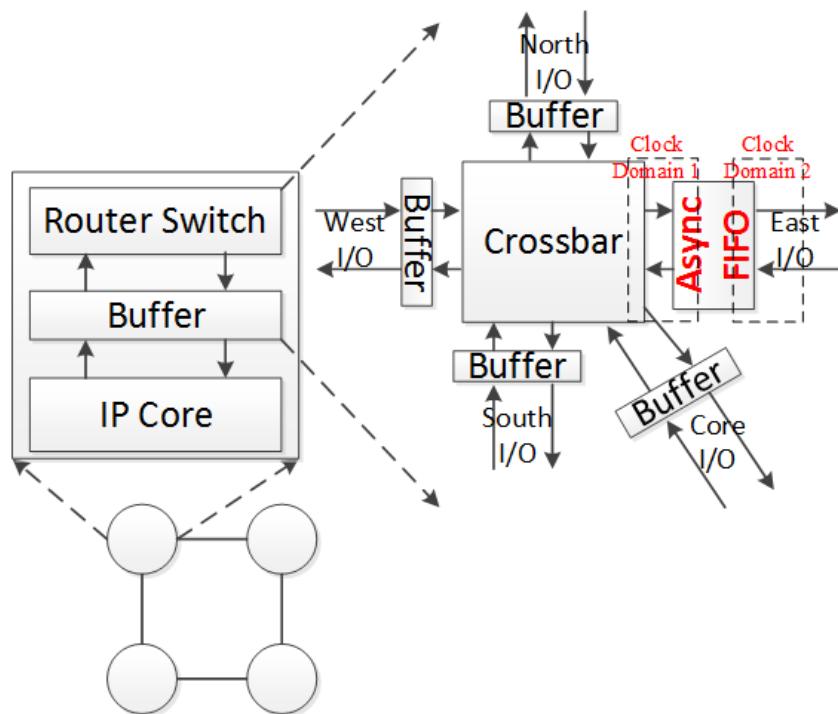

| 3.6  | System-Level Modelling of Asynchronous FIFO as NoC router Channel buffers in NIRGAM . . . . . | 79 |

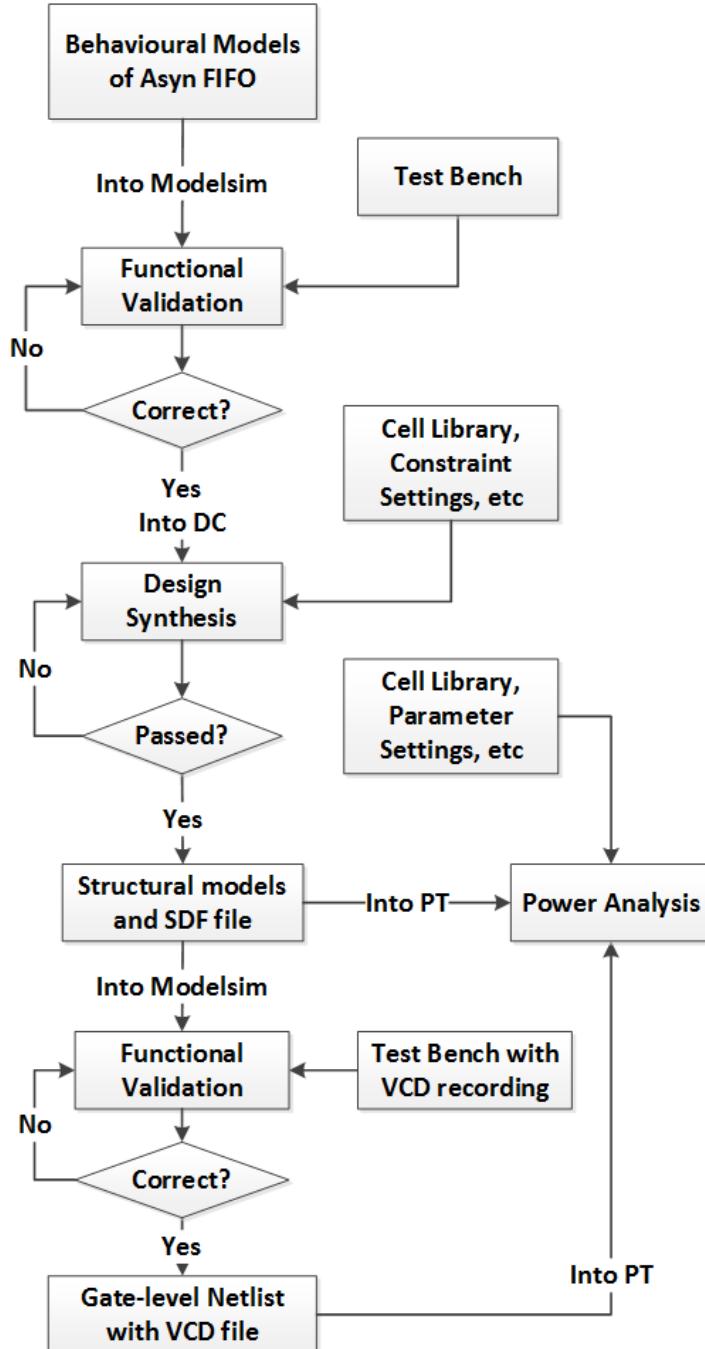

| 3.7  | Gate-Level Synthesis and Power Analysis Flow of Asynchronous FIFO . . . . .                   | 80 |

| 3.8  | Verilog Code for Jitter Insertion in Test Bench . . . . .                                     | 82 |

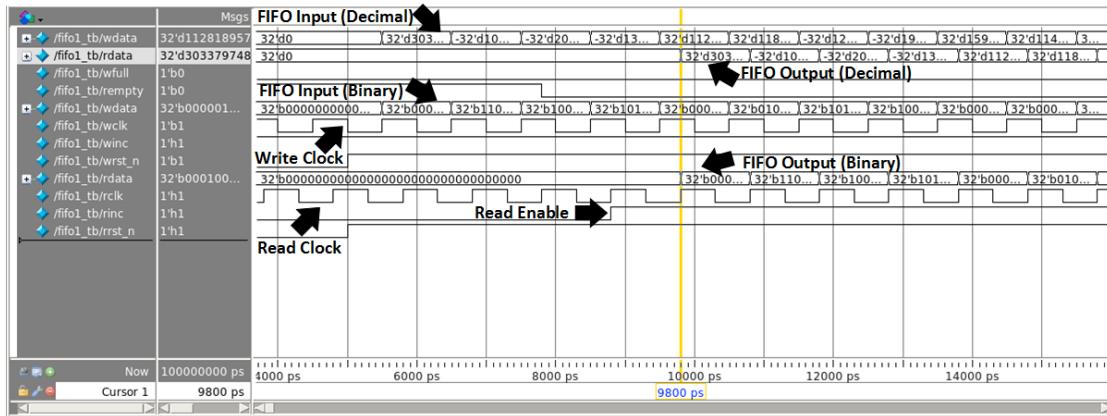

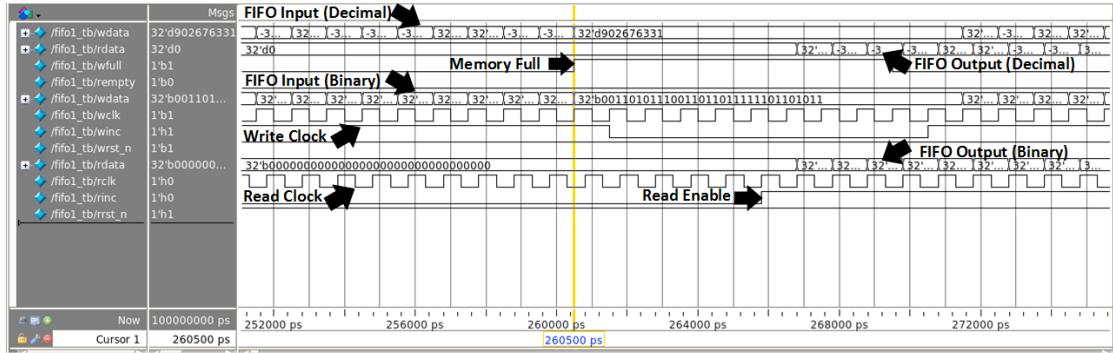

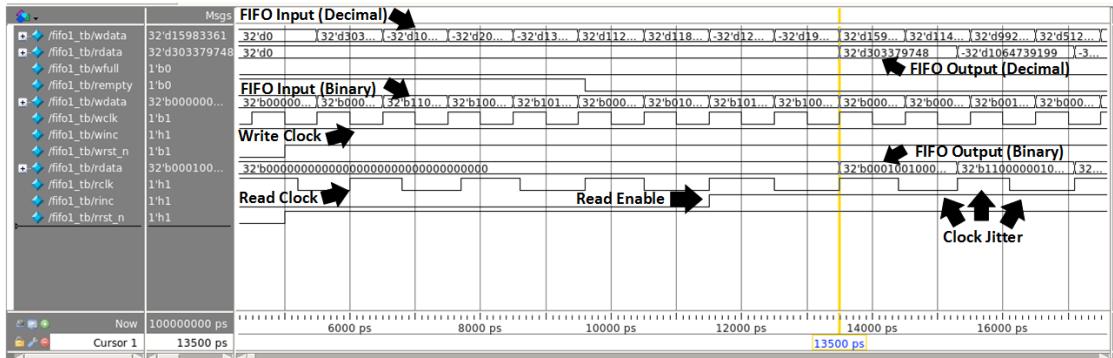

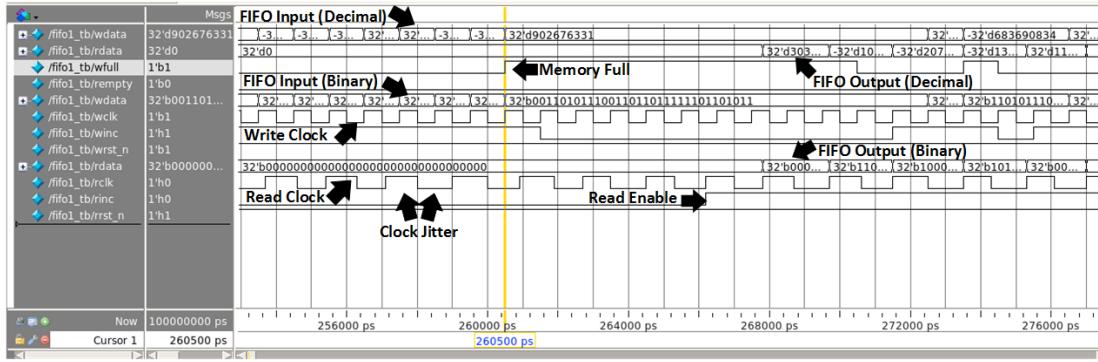

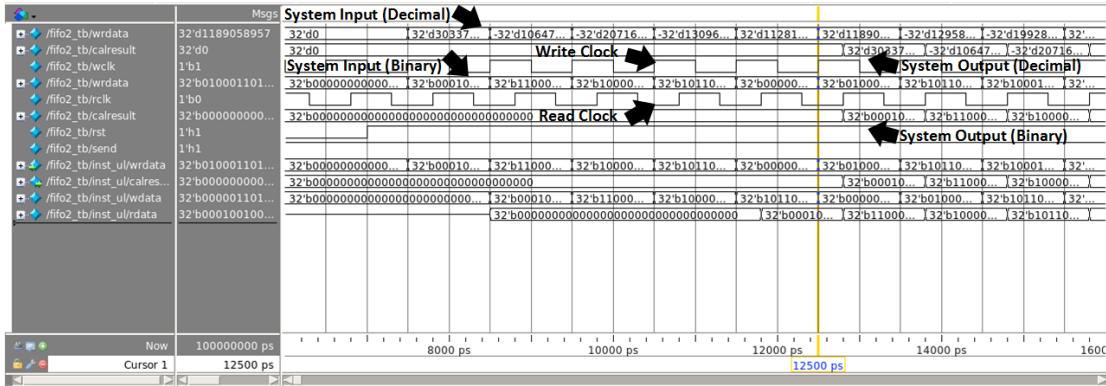

| 3.9  | Functional Verification of Asynchronous FIFO . . . . .                                        | 82 |

| 3.10 | Functional Verification of Asynchronous FIFO with full memory . . . . .                       | 83 |

| 3.11 | Functional Verification of Asynchronous FIFO with Clock Jitter . . . . .                      | 83 |

| 3.12 | Functional Verification of Asynchronous FIFO with Clock Jitter and Full Memory . . . . .      | 84 |

| 3.13 | High-Level Asynchronous Transmission System designed in NIRGAM . . . . .                      | 85 |

|      |                                                                                                                               |     |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 | Gate-Level Asynchronous Transmission System for Performance Comparison . . . . .                                              | 87  |

| 3.15 | Functional Verification and Power Cost of Gate-Level Asynchronous Transmission System . . . . .                               | 88  |

| 3.16 | Power Cost of System-Level Asynchronous Transmission System in NIRGAM . . . . .                                               | 88  |

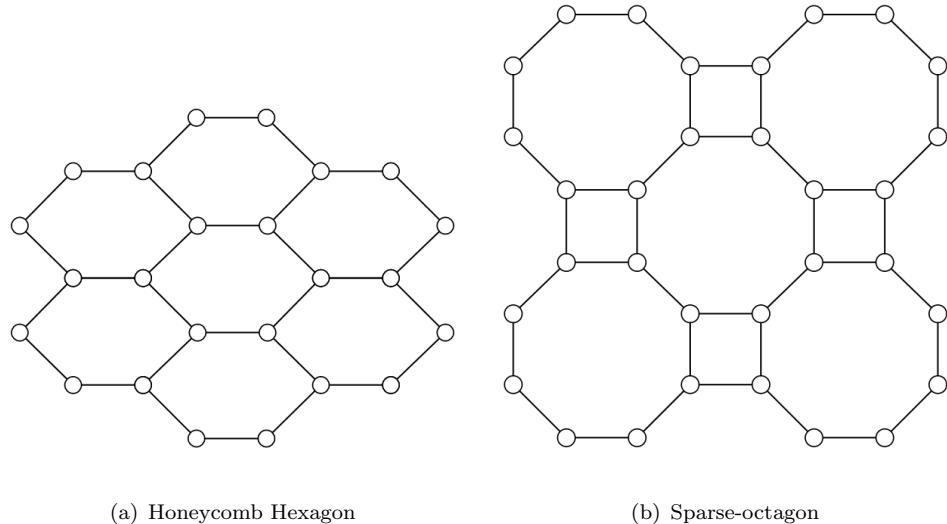

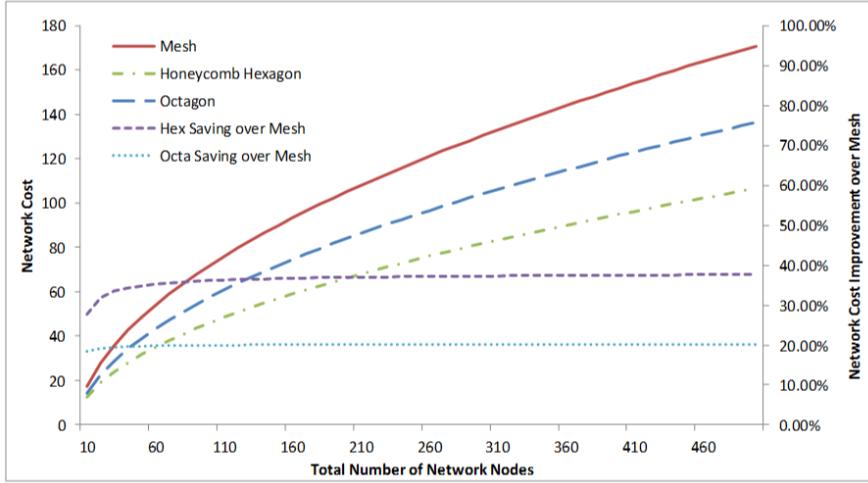

| 4.1  | The Exemplified Honeycomb and Sparse-octagon Topologies . . . . .                                                             | 95  |

| 4.2  | Network Cost Comparisons between Mesh and Non-rectangular Topologies                                                          | 96  |

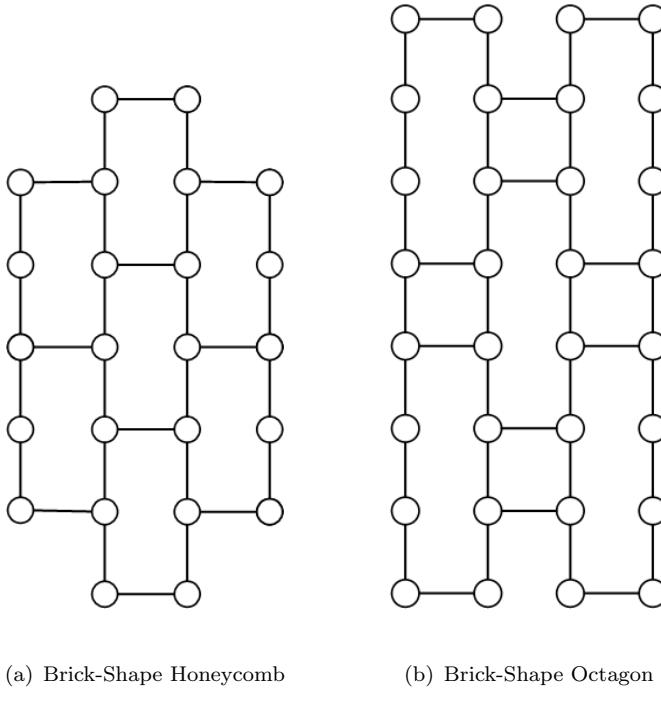

| 4.3  | Brick-Shape Transformations of Non-rectangular Topologies . . . . .                                                           | 96  |

| 4.4  | Conventional Formation of Honeycomb Topology . . . . .                                                                        | 98  |

| 4.5  | Conventional Formation of Sparse-Octagon Topology . . . . .                                                                   | 99  |

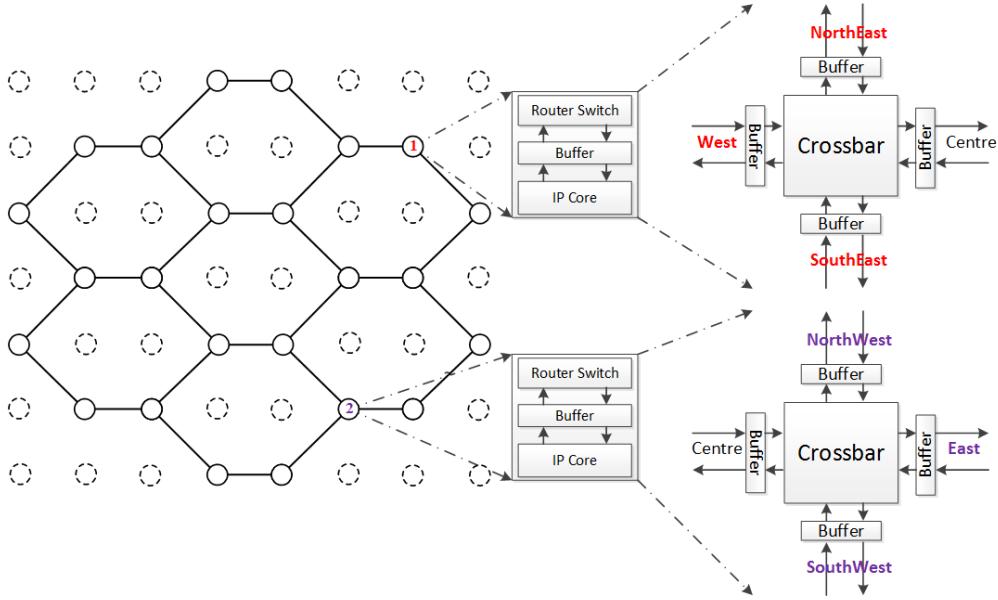

| 4.6  | The Node Architecture with Time-regulated Model Attached . . . . .                                                            | 100 |

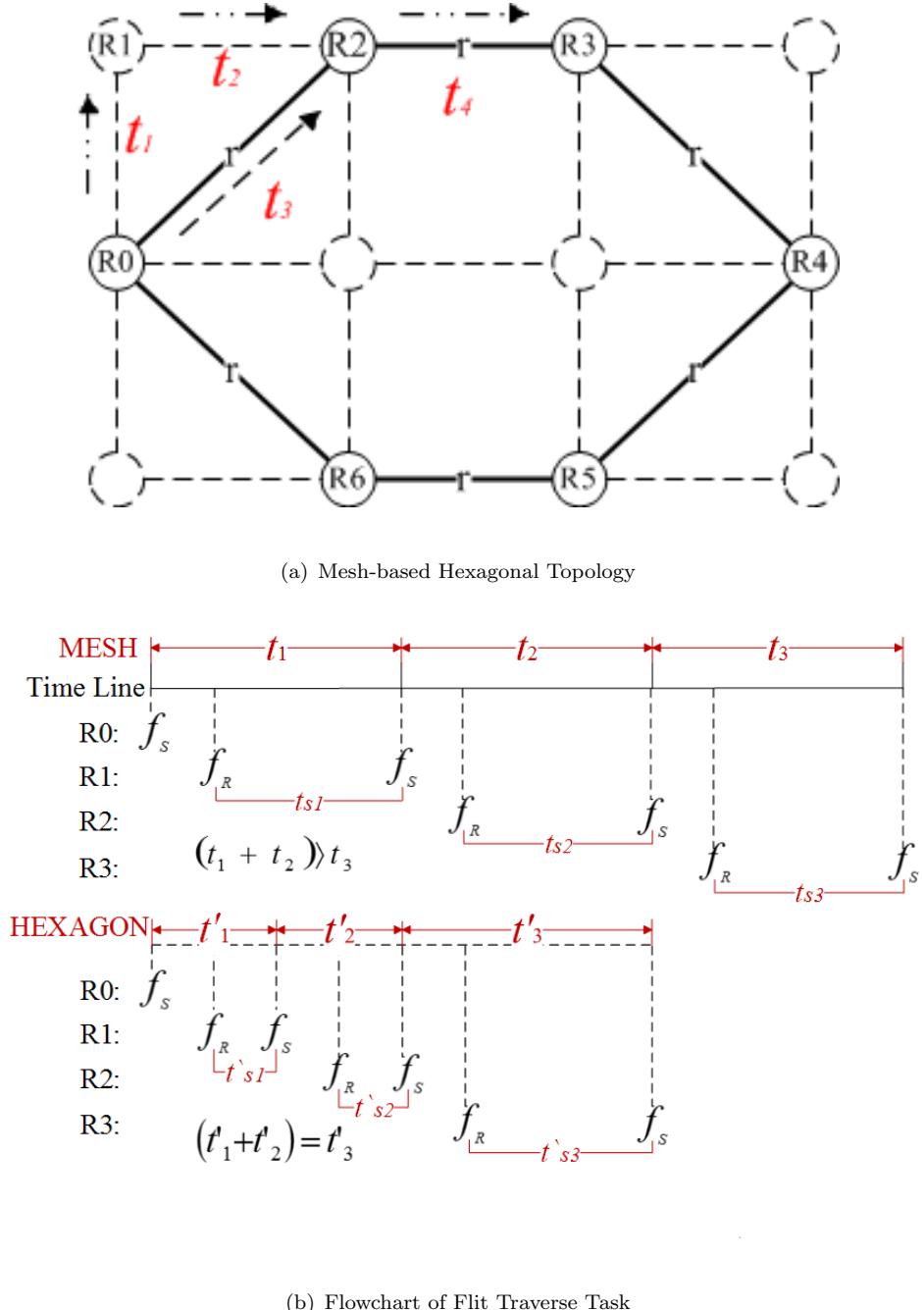

| 4.7  | Construction of Mesh-based Hexagonal Topology . . . . .                                                                       | 103 |

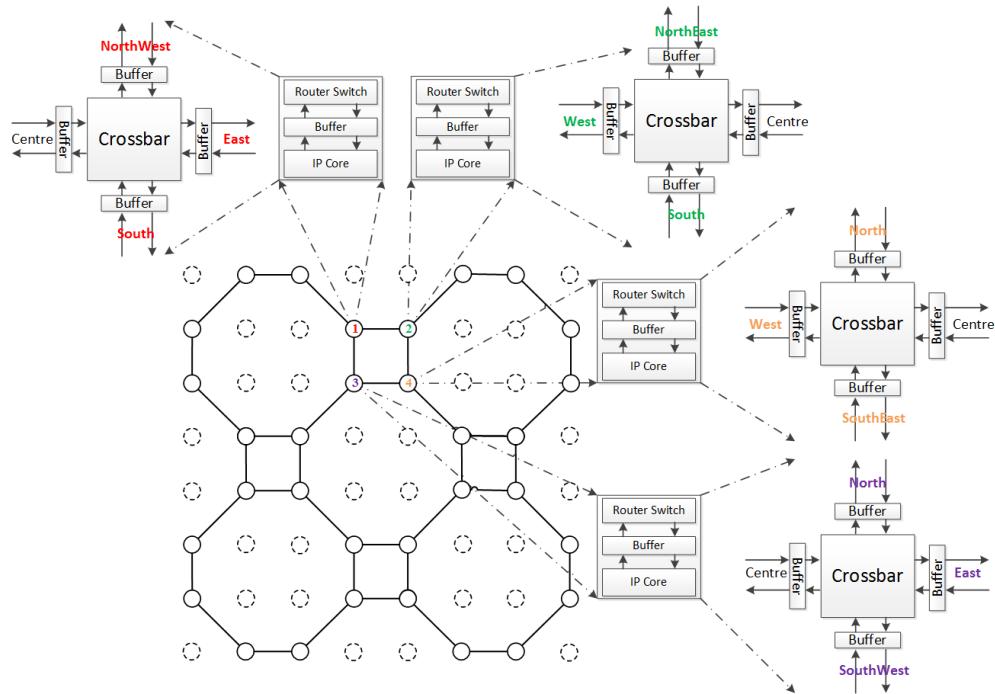

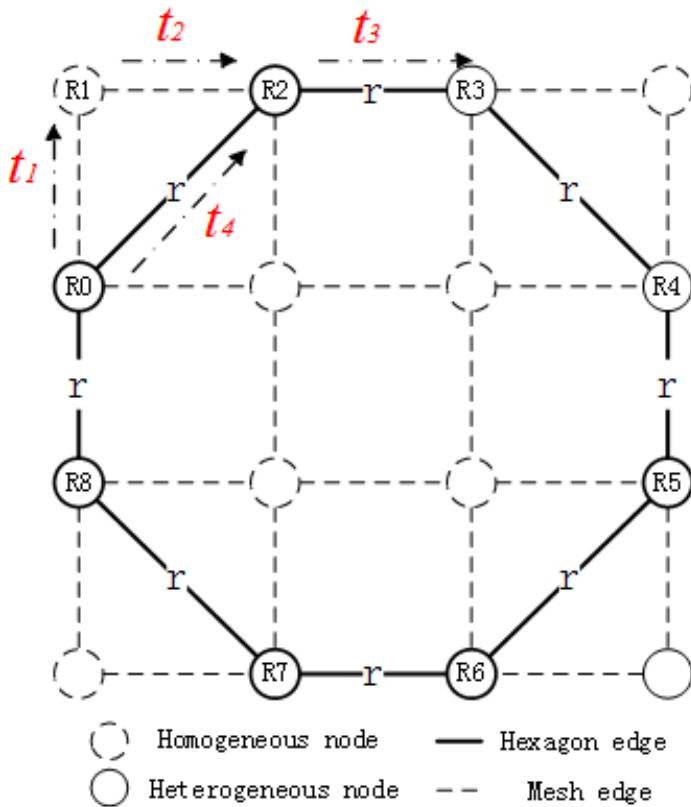

| 4.8  | Mesh-based Octagon Topology . . . . .                                                                                         | 105 |

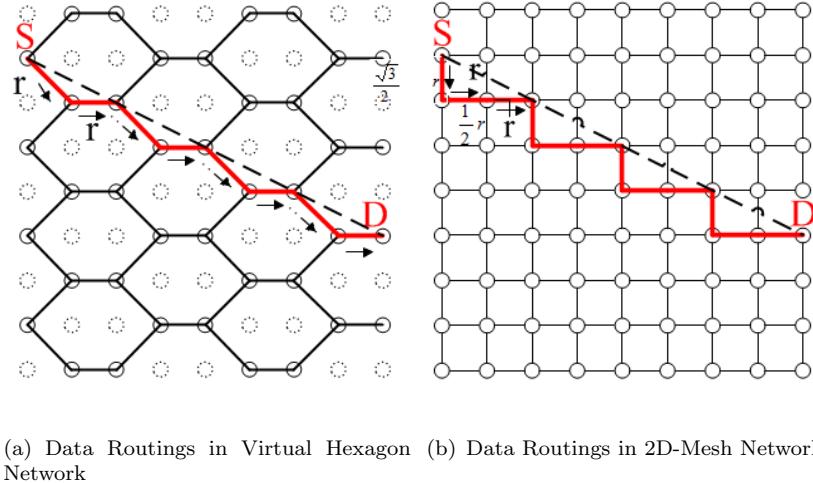

| 4.9  | Experimental Designs for Data Routing in Hexagonal and Mesh Networks                                                          | 109 |

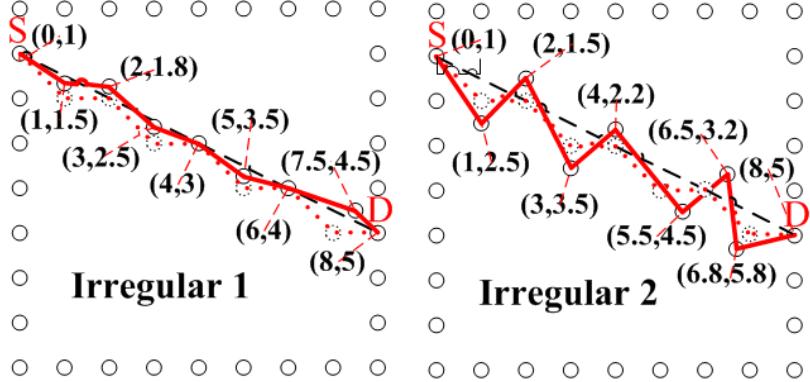

| 4.10 | Experimental Designs for Data Routing in Irregular Networks . . . . .                                                         | 110 |

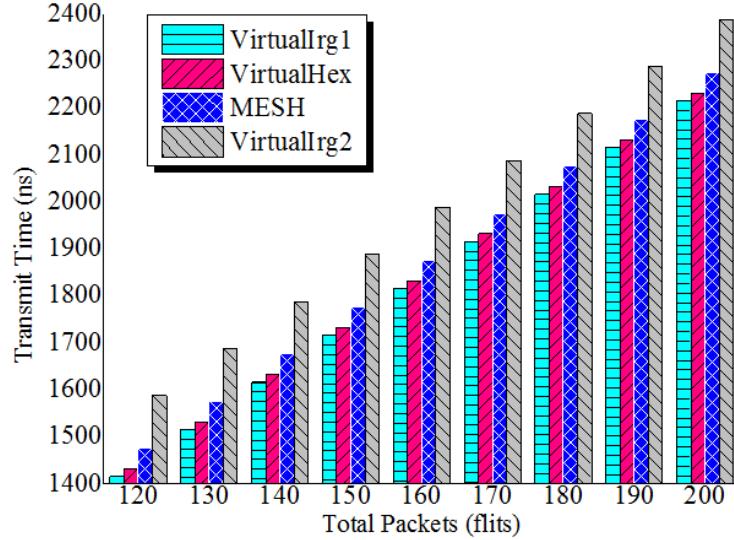

| 4.11 | Performance Comparison of Hexagon Topology and 2D-Mesh in terms of Overall Transmission Latency based on 9 by 9 Mesh. . . . . | 111 |

| 4.12 | Performance Comparison of Hexagon Topology and 2D-Mesh in terms of Energy Consumption based on 9 by 9 Mesh . . . . .          | 112 |

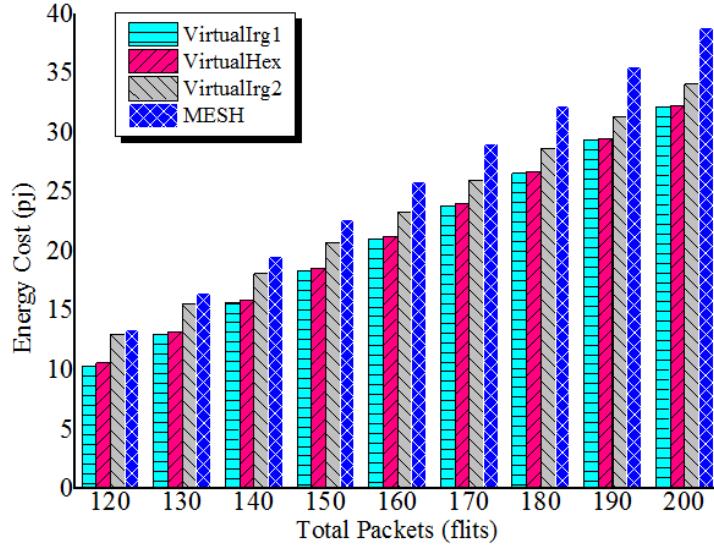

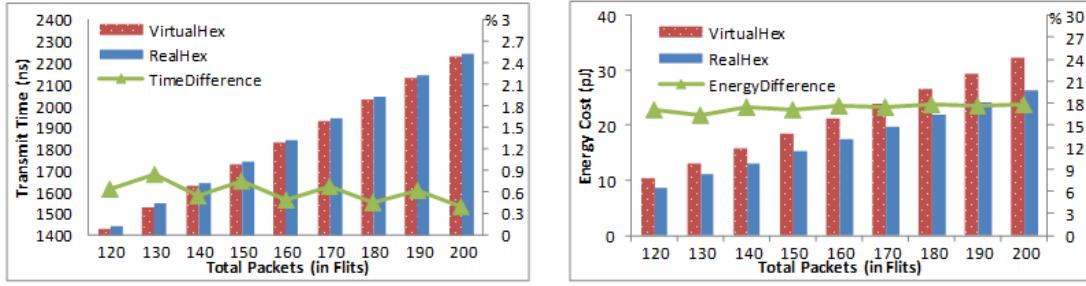

| 4.13 | Timing and Energy Comparisons of Data Routings in Virtual and Real Hexagonal Networks . . . . .                               | 112 |

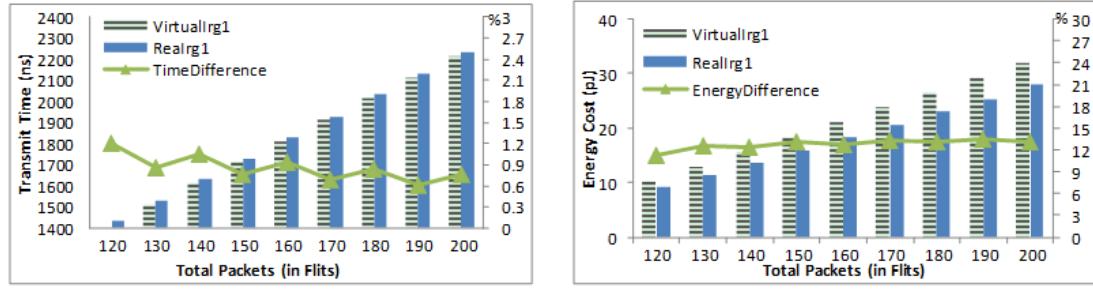

| 4.14 | Timing and Energy Comparisons of Data Routings in Virtual and Real Irregular 1 Networks . . . . .                             | 113 |

| 4.15 | Timing and Energy Comparisons of Data Routings in Virtual and Real Irregular 2 Networks . . . . .                             | 113 |

| 4.16 | Experimental Designs for Comparing Octagonal and 2D-Mesh Networks .                                                           | 114 |

| 4.17 | Latency Comparisons of Virtual and Real Non-rectangular Networks under Random Uniform Traffic . . . . .                       | 117 |

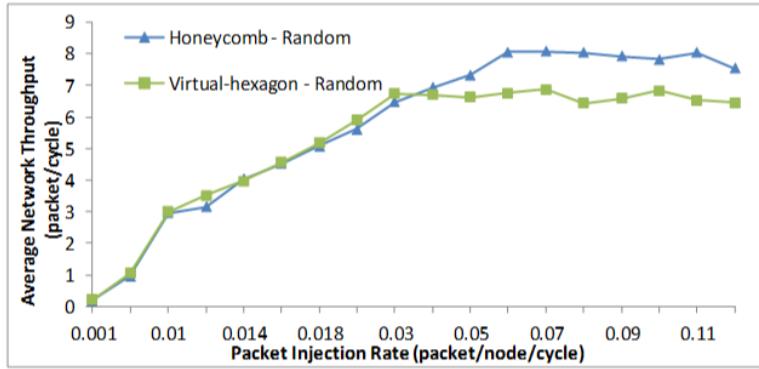

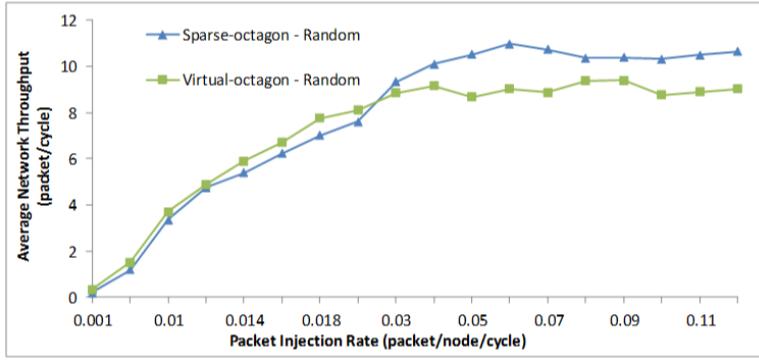

| 4.18 | Throughput Comparisons of Virtual and Real Non-rectangular Networks under Random Uniform Traffic . . . . .                    | 118 |

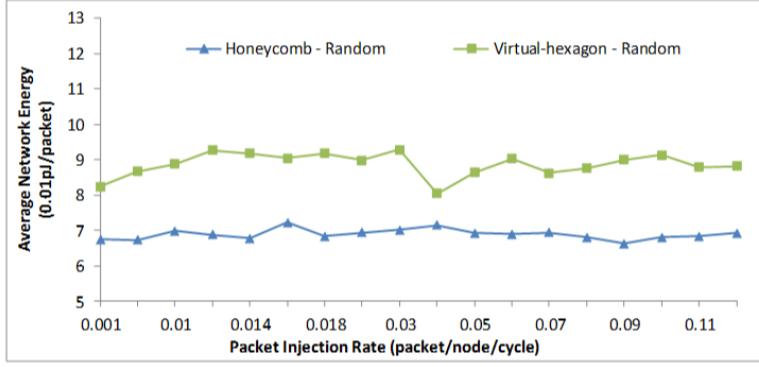

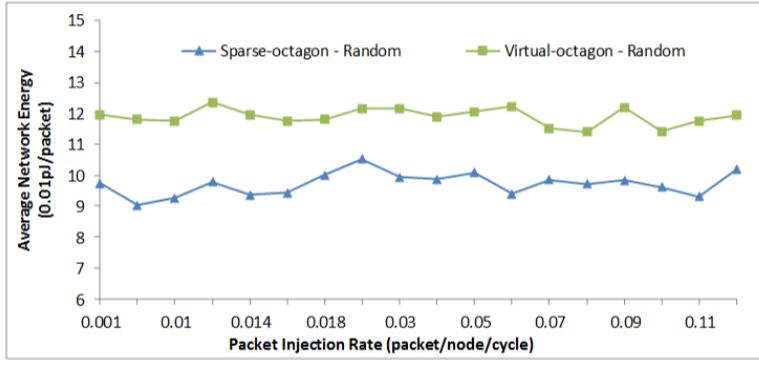

| 4.19 | Energy Comparisons of Virtual and Real Non-rectangular Networks under Random Uniform Traffic . . . . .                        | 120 |

| 4.20 | Hotspot Traffic Settings for Virtual and Real Non-rectangular Networks .                                                      | 121 |

| 4.21 | Latency Comparisons of Virtual and Real Non-rectangular Networks under Hotspot Traffic . . . . .                              | 122 |

| 4.22 | Throughput Comparisons of Virtual and Real Non-rectangular Networks under Hotspot Traffic . . . . .                           | 123 |

| 4.23 | Energy Comparisons of Virtual and Real Non-rectangular Networks under Hotspot Traffic . . . . .                               | 124 |

| 4.24 | MPEG-4 Decoder . . . . .                                                                                                      | 126 |

| 4.25 | Module placement of MPEG-4 Decoder for Irregular Routing . . . . .                                                            | 127 |

| 4.26 | Implementation of the Irregular Placement of MPEG-4 Decoder . . . . .                                                         | 128 |

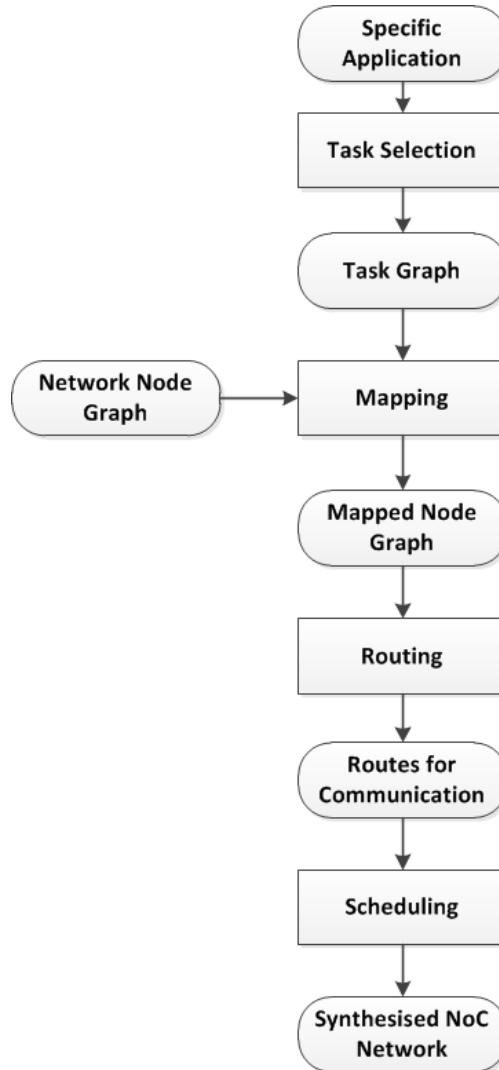

| 5.1  | Design Flow of Most Application-specific NoCs . . . . .                                                                       | 134 |

| 5.2  | Typical Structure of a 2D-Mesh Network Tile and Its Router Switch . . . . .                                                   | 137 |

| 5.3  | Coordinate Systems for Mesh and Torus Topologies . . . . .                                                                    | 149 |

|      |                                                                                                      |     |

|------|------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Coordinate Systems for Hexagon and Octagon Topologies . . . . .                                      | 149 |

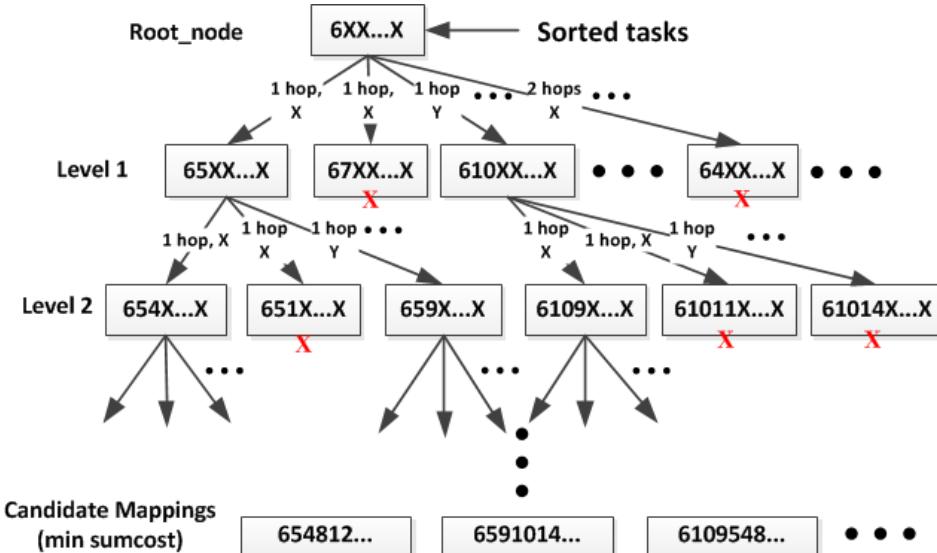

| 5.5  | Search Tree Example . . . . .                                                                        | 152 |

| 5.6  | Pseudo Code of Proposed Mapping Algorithm . . . . .                                                  | 155 |

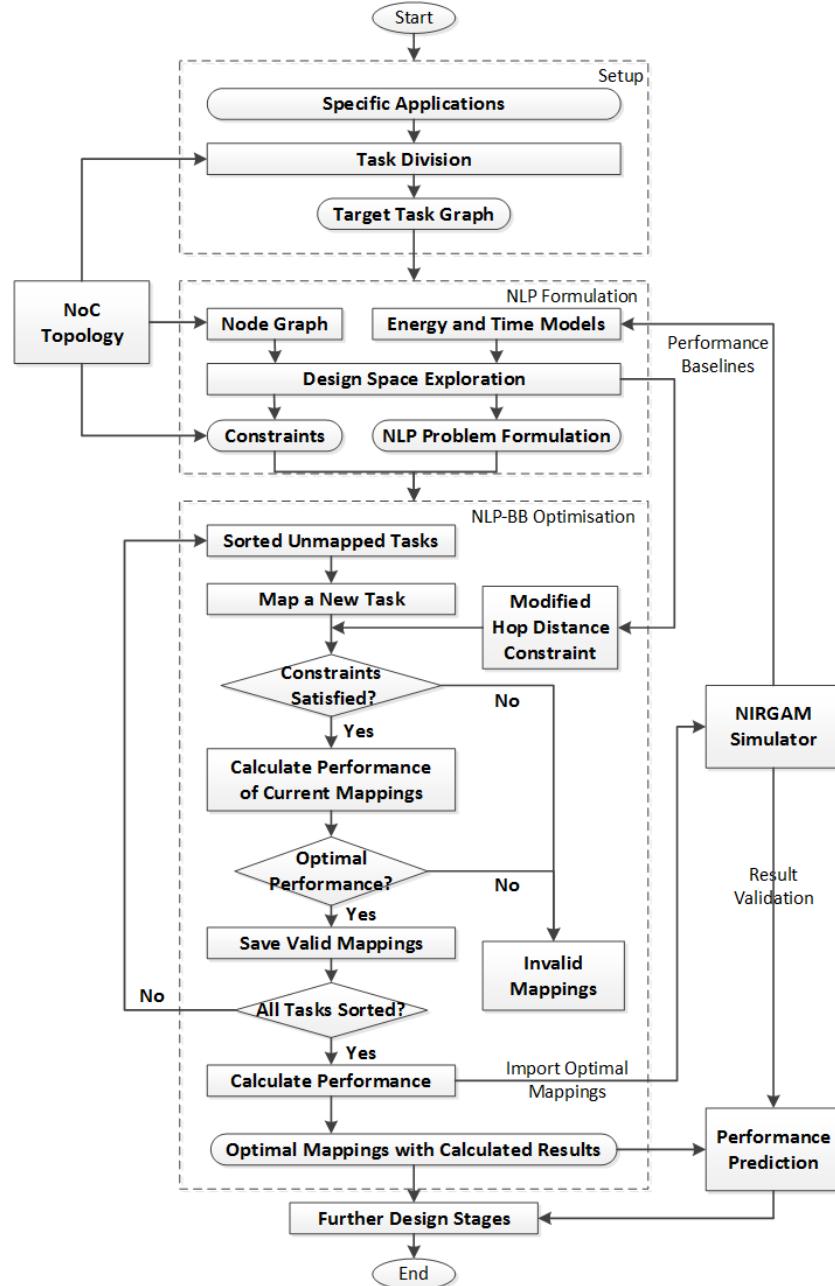

| 5.7  | Proposed Method of Performance Prediction . . . . .                                                  | 157 |

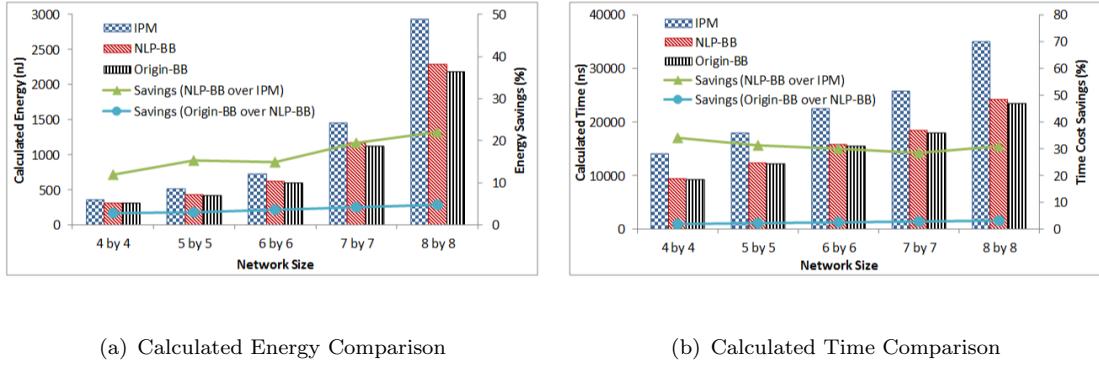

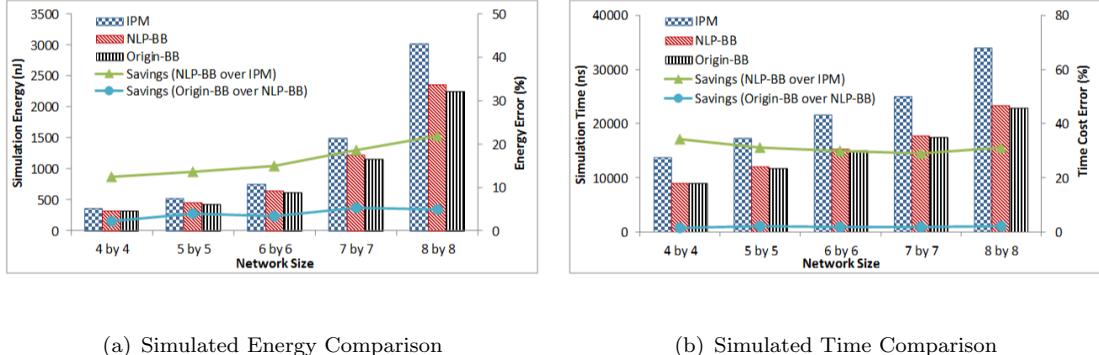

| 5.8  | Comparisons of Calculated Results by Different Algorithms for Synthetic Applications . . . . .       | 162 |

| 5.9  | Comparisons of Simulated Results by Different Algorithms for Synthetic Applications . . . . .        | 162 |

| 5.10 | Run Time Comparisons . . . . .                                                                       | 163 |

| 5.11 | Error Comparisons Between Calculated and Simulated Results of Different Mapping Algorithms . . . . . | 164 |

| 5.12 | Task Graph of MPEG-4 Decoder . . . . .                                                               | 165 |

# List of Tables

|     |                                                                                         |     |

|-----|-----------------------------------------------------------------------------------------|-----|

| 2.1 | Overview of Popular Routing Algorithms in NoC Design [4]                                | 33  |

| 3.1 | Comparison of Power Costs of Both Levels of Designs for 100,000-cycle Data Transmission | 89  |

| 4.1 | Comparisons of Octagonal and Mesh Routings                                              | 115 |

| 4.2 | Comparisons of Virtual and Real Octagonal Routings                                      | 115 |

| 4.3 | Performance Comparisons of MPEG-4 Decoding                                              | 128 |

| 4.4 | Comparison of Topology Design in Custom Way and by Our Method                           | 130 |

| 5.1 | Synthetic Benchmarks and Network Sizes                                                  | 161 |

| 5.2 | Runtime Records of Synthetic Applications Cost by Different Mapping Algorithms          | 163 |

| 5.3 | Number of Tasks for Each Link                                                           | 165 |

| 5.4 | Performance Results of Different Mapping Algorithms for MPEG-4 Decoding                 | 165 |

## Declaration of Authorship

I, **Ji Qi**, declare that the thesis entitled *System-Level Design Automation and Optimisation of Network-on-Chips in Terms of Timing and Energy* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: Section 1.3

Signed:.....

Date:.....

## Acknowledgements

I would like to sincerely appreciate my supervisor, Prof. Mark Zwolinski, for his patient and helpful guidance, support and supervision throughout my Ph.D research.

I am also grateful for the research facilities and environmental support provided by the School of Electronics and Computer Science (ECS), University of Southampton, throughout my time at Southampton. In addition, I wish to thank the people of the Electrical and Electronic Engineering (EEE) Group, including Yang, Wei, Alex, Ime, Kier and Fang, who have made Bay 1 such a memorable place to work in the past four years.

Finally, I would like to express my particular thanks to my parents and my girlfriend Lin, for their continuous love, support and encouragement. This thesis is dedicated to them, without whom none of this would be possible.

*To my parents, and beloved Lin...*

# Nomenclature

|                      |                                                                        |

|----------------------|------------------------------------------------------------------------|

| $b(e_{i,j})$         | Minimum Bandwidth of Communication from Tasks $t_i$ to $t_j$ [bit/sec] |

| $bw(l_{i,j})$        | Available Link Bandwidth Capacity of Nodes $n_i$ to $n_j$ [bit/sec]    |

| $comm(e_{i,j})$      | Communication Volume from $t_i$ to $t_j$ [bit]                         |

| $E_{bit}$            | Bit Energy [J]                                                         |

| $E_{B_{bit}}$        | Buffer Bit Energy [J]                                                  |

| $E_{bit}^{n_i, n_j}$ | Bit Energy from Nodes $n_i$ to $n_j$ [J]                               |

| $E_{C_{bit}}$        | Bit Energy between IP Core and Switch [J]                              |

| $E_{dst-C_{bit}}$    | Bit Energy between Switch and IP Core of Destination Node [J]          |

| $e_{i,j}$            | Communication from Tasks $t_i$ to $t_j$                                |

| $E_{L_{bit}}$        | Link Bit Energy [J]                                                    |

| $e(l_{i,j})$         | Communication Bit Energy from Nodes $n_i$ to $n_j$ [J]                 |

| $E_{S_{bit}}$        | Switch Bit Energy [J]                                                  |

| $E_{src-C_{bit}}$    | Bit Energy between IP Core and Switch of Source Node [J]               |

| $E_{W_{bit}}$        | Wire Bit Energy [J]                                                    |

| $hop_{n_i, n_j}$     | Hop Counts between Nodes $i$ and $j$                                   |

| $l_{i,j}$            | Link Routing Communication from Nodes $n_i$ to $n_j$                   |

| $n_{dst}$            | Destination Node of a Communication Routing Path                       |

| $n_i$                | Selected Network Node $i$                                              |

| $n_{src}$            | Source Node of a Communication Routing Path                            |

| $p_{i,j}$            | Potential Minimal Routing Path from Nodes $n_i$ to $n_j$               |

| $P_{i,j}$            | Communication Volume from Nodes $n_i$ to $n_j$ [bit]                   |

| $t_{dst}$            | Destination Task of a Communication Flow                               |

| $t_i$                | Selected IP Task $i$                                                   |

| $t(l_{i,j})$         | Bit Timing Cost from Nodes $n_i$ to $n_j$ [sec]                        |

| $t_{src}$            | Source Task of a Communication Flow                                    |

| $T_{bit}^{n_i, n_j}$ | Bit Timing Consumption from Nodes $n_i$ to $n_j$ [sec]                 |

# Abbreviations

|              |                                         |

|--------------|-----------------------------------------|

| <b>ACO</b>   | Ant Colony Optimisation                 |

| <b>ASIC</b>  | Application-Specific Integrated Circuit |

| <b>BB</b>    | Branch and Bound                        |

| <b>BBN</b>   | Bayesian's Belief Network               |

| <b>BC</b>    | Best Case                               |

| <b>BE</b>    | Best Effort                             |

| <b>BFT</b>   | Butterfly Fat Tree                      |

| <b>BLS</b>   | Binary Level Simulation                 |

| <b>CHMAP</b> | Chain Mapping                           |

| <b>CMAP</b>  | Constructive Mapping                    |

| <b>CMP</b>   | Chip Multi-Processors                   |

| <b>CPU</b>   | Central Processing Unit                 |

| <b>CSM</b>   | Core-Switching Mapping                  |

| <b>DA</b>    | Design Automation                       |

| <b>DC</b>    | Design Compiler                         |

| <b>DCS</b>   | Distributed Computing System            |

| <b>DOR</b>   | Dimension Order Routing                 |

| <b>DRSI</b>  | Double-Router to Single-IP              |

| <b>DSM</b>   | Dynamic Spiral Mapping                  |

| <b>DSP</b>   | Digital Signal Processing               |

| <b>DyAD</b>  | Dynamic Adaptive Deterministic          |

| <b>ECS</b>   | Electronic and Computer Science         |

| <b>EDA</b>   | Electronic Design Automation            |

| <b>EEE</b>   | Electrical and Electronic Engineering   |

| <b>EM</b>    | Euclidean Minimum                       |

| <b>EPAM</b>  | Energy- and Performance-Aware Mapping   |

| <b>ESL</b>   | Electronic System Level                 |

| <b>FC</b>    | Fixed Centre                            |

| <b>FDSM</b>  | Full Dynamic Spiral Mapping             |

| <b>FF</b>    | First Free                              |

| <b>FIFO</b>  | First-In First-Out                      |

| <b>flits</b> | flow control digits                     |

---

|               |                                                                |

|---------------|----------------------------------------------------------------|

| <b>GA</b>     | Genetic Algorithm                                              |

| <b>GS</b>     | Guaranteed Service                                             |

| <b>HDL</b>    | Hardware Description Language                                  |

| <b>HOL</b>    | Head-Of-Line                                                   |

| <b>IC</b>     | Integrated Circuit                                             |

| <b>IDCT</b>   | Inverse Discrete Cosine Transform                              |

| <b>ILP</b>    | Integer Linear Programming                                     |

| <b>inout</b>  | input/output                                                   |

| <b>IQuant</b> | Inverse Quantisation                                           |

| <b>ISS</b>    | Instruction Set Simulation                                     |

| <b>LBMAP</b>  | Link Based Mapping                                             |

| <b>LEC-DN</b> | Lower Energy Consumption based on Dependencies-Neighbourhood   |

| <b>LP</b>     | Linear Programming                                             |

| <b>LTS</b>    | Legal Turn Set                                                 |

| <b>MAC</b>    | Minimum Average Channel                                        |

| <b>MaXY</b>   | Miminally Adaptive XY                                          |

| <b>MB</b>     | Macroblock                                                     |

| <b>mCSM</b>   | many-to-many Core-Switching Mapping                            |

| <b>MILP</b>   | Mixed Integer Linear Programming                               |

| <b>MMC</b>    | Minimum Maximum Channel                                        |

| <b>MPSoC</b>  | Multi-Processor System on Chip                                 |

| <b>MSB</b>    | Most Significant Bit                                           |

| <b>MV</b>     | Motion Vector                                                  |

| <b>NF</b>     | Neighbour-aware Frontier                                       |

| <b>NI</b>     | Network Interface                                              |

| <b>NIRGAM</b> | Network-on-chip Interconnect Routing and Application Modelling |

| <b>NLP</b>    | Non-Linear Programming                                         |

| <b>NN</b>     | Nearest Neighbour                                              |

| <b>NoC</b>    | Network on Chip                                                |

| <b>NoWs</b>   | Networks of Workstations                                       |

| <b>OE</b>     | Odd-Even                                                       |

| <b>PBB</b>    | Performance-aware Branch and Bound                             |

| <b>PDSM</b>   | Partial Dynamic Spiral Mapping                                 |

| <b>PE</b>     | Processing Element                                             |

| <b>PL</b>     | Path Load                                                      |

| <b>PMAP</b>   | Physical Mapping                                               |

| <b>PSO</b>    | Particle Swarm Optimisation                                    |

| <b>PT</b>     | PrimeTime                                                      |

| <b>QoS</b>    | Quality of Service                                             |

| <b>RC</b>     | Random Frontier                                                |

| <b>RISC</b>   | Reduced Instruction Set Computing                              |

|               |                                            |

|---------------|--------------------------------------------|

| <b>RTL</b>    | Register-Transistor Level                  |

| <b>SA</b>     | Simulation Annealing                       |

| <b>SAF</b>    | Store-And-Forward                          |

| <b>SA-TA</b>  | Simulated Annealing with Timing Adjustment |

| <b>SBMAP</b>  | Sort Based Mapping                         |

| <b>SLS</b>    | Source Level Simulation                    |

| <b>SoC</b>    | System on Chip                             |

| <b>SRMI</b>   | Single-Router to Multiple-IP               |

| <b>SRSI</b>   | Single-Router to Single-IP                 |

| <b>SSM</b>    | Static Spiral Mapping                      |

| <b>TBMAP</b>  | Traffic-Balance Mapping                    |

| <b>UMA</b>    | Uniform Memory Access                      |

| <b>VC</b>     | Virtual Channel                            |

| <b>VCD</b>    | Value Change Dump                          |

| <b>VLD</b>    | Variable Length Decoder                    |

| <b>VOL</b>    | Video Object Layer                         |

| <b>VOP</b>    | Video Object Plane                         |

| <b>WC</b>     | Worst Case                                 |

| <b>WSN</b>    | Wireless Sensor Network                    |

| <b>WSNsim</b> | Wireless Sensor Network simulator          |

# Chapter 1

## Introduction

### 1.1 Introduction

#### 1.1.1 On-chip Network Architectures

As the integration of digital electronic circuits continues to scale up, an increasing number of transistors have been encapsulated on a single chip to build up larger and more complex systems. This higher systematic complexity brings about new design challenges that used to be ignored or given minor concern in the design process. For example, the consideration of leakage power cost becomes more essential in designing such highly complex on-chip systems. These new design challenges require researchers and designers to investigate effective solutions.

Moreover, the growing integration of digital systems also enables fast development of new patterns for data processing and mutual communication. Since the functionality and amount of processing data in these highly integrated systems has increased dramatically, the traditional bus-based architecture is hardly adaptable to tackle the enormous data requests with sufficient utilisation of available resources. Consequently, new patterns and architectures have been investigated to improve the efficiency and effectiveness of data processing in such systems. Multi-core processing and intercommunication is one promising pattern that processes data tasks in a parallel manner and implements functional systems as an interconnection network. This distributed pattern can better utilise available resources to process data more efficiently than traditional bus-based architectures, which leads to revolutionary improvements in system performance. It also prompts the advent of novel microprocessor structures that are applied in many computer fields, including on-chip systems, which can be named as *Distributed Computing Systems* (DCS) in general.

DCS architectures simultaneously distribute tasks onto many cores or functional modules, and collaboratively process them with frequent mutual communications. In

particular, such characteristics enable DCS to fulfil the huge amounts of data requests and high complexity of functional implementation in modern on-chip systems. However, researchers and developers have faced many new problems to take full advantage of DCS architectures and make full use of available resources for optimised system performance. A major challenge is the implementation of intercommunications in DCS architectures. Specifically, complex computations can be split and co-processed on many DCS sub-system units in a distributed or parallel mode, which alleviates the processing workload of each single unit. But the computational results at each unit have to be communicated with others for further processing and task accomplishment, which raises the data communication overheads in DCS. Compared to traditional bus-based architectures, it suggests a shift of modern on-chip architectural designs from a computation-centric to a communication-centric basis [6]. Hence, the intercommunications among DCS sub-systems has become very influential on overall system performance, which requires huge efforts to increase the efficiency.

*Multi-Processor Systems on Chip* (MPSoC) [17] and *Networks on Chip* (NoC) [18] are typical on-chip DCS architectures that are widely accepted as the potential solution to the problem of costly interconnection communications. In particular, NoC is considered as a central platform to suitably accommodate the communication requirements of future complex System-on-Chip (SoC) designs. This on-chip network paradigm employs routers interconnected by communication channels between pre-designed building blocks such as programmable RISC (Reduced Instruction Set Computing) cores, DSP (Digital Signal Processor) and memory blocks. The network holds a large number of functional components that tackle the high system complexity to perform versatile network functions while consuming tolerable production cost and design time cycles. Typical NoC architectures have received high research interest from researchers since the beginning of the last decade, to explore their potential for implementing complex on-chip systems with efficient network communications, high system performance and tolerable production costs.

### 1.1.2 Design Methodology of NoC Architectures

With the proposal of novel NoC architectures for highly integrated on-chip systems, their implementation methodology also needs to update for the fulfilment of efficient design flow. Due to the increased circuit integration, the *RTL (Register-Transistor-Level) synthesis* design flow no longer satisfied the demands of design productivity growth for complex on-chip systems. It is also proving increasingly difficult to bridge this productivity gap by simply increasing system abstractions for the design automation community [19]. This is because of the integration of transistors as well as the number of factors that must be considered are increased for NoC systems. Hence, researchers started to subsume *behavioural synthesis* into existing RTL synthesis and to tightly

couple the fresh synthesis flow with physical design to improve the design productivity. As per [20], such a **classic** design flow is as follows:

1. Investigate behavioural models for each link of the application design process.

2. Simulate applications on a test bench for testing the functional performance and environmental impact on developed models.

3. Validate the model performance and functionality on prototypes.

4. Deploy the application in a realistic environment and examine its practical performance.

This design method was believed to be a plausible solution for efficient development of NoC architectures and applications at the beginning of the last decade. However, as complex applications that required large-scale network resources with busy communications were implemented on NoC systems, potential demerits of this design flow for testing performance emerged. The tremendous costs of production overheads and overlong design cycles of iterative refinement for optimised NoC applications seemed formidable in this classic design flow, which led to low design productivity and tight time-to-market budget. Specifically, the cost for prototyping certain networks with complex applications by using the design flow was increasingly expensive but essentially needed by modern on-chip products. Additionally, the difficulty in making full use of available network resources for processing complex NoC applications is also growing and thus results in unaffordable design time cycles.

To overcome such demerits and further promote the design efficiency, alternative design methodologies started to investigate replacement of the classic design flow. New design methods are in demand not only to refine the design flow but also to balance the design cost and productivity for optimised system acquisitions. A new method that abstracts high-level behavioural models and establishes network platforms to emulate system performance at early design stages is a constructive attempt. This method introduced a higher level of functional modelling into the classic RTL design flow, which decides the suitable NoC components from a system perspective to avoid overmuch iterative refinement in subsequent levels of design flow and thus save design cycles. Apparently, the accuracy of captured high-level models will fundamentally determine the method's usefulness. As few existing Design Automation (DA) techniques were able to precisely simulate the entire performance of practical circumstances at this level during the last decade, the generated simulation results often showed large deviations to cause fatal errors in realistic scenarios, which led to this high-level method not being applicable enough for further implementation and manufacturing. But this system-level model abstraction was such a promising idea that it was believed to be the alternative design methodology for efficient NoC designs if more advanced DA techniques can be developed.

Researchers in [19] had detailed the major tasks and challenges of this **new** methodology for NoC implementation:

- In the initial step, an executable functional system specification needs to be derived to clarify what exactly the designed system needs to do. Simulation may be a significant tool to specify the main system functions.

- In the next step, a task graph of concurrent tasks has to be developed. Decisions on intercommunication requirements between those tasks are also necessary. This step is important to determine the specific resources needed for implementation.

- Once the task graph is produced, mapping the tasks onto NoC platforms is a must. In this step many boundary constraints, component resources and system problems are required to be tackled for an optimised architecture.

- If each task has been bound to a specific component resource, the system-level model abstraction is assembled and the model codes must be generated for functional validation and performance simulation.

- For an optimised NoC design, all these steps have to be considered together with functions and performance validated iteratively. The deployment of accurate estimation techniques is essential to help make design decisions and simulate model performance, which ensures an applicable design methodology.

As the technology of Computer-Aided Design (CAD) has advanced, it seems feasible to move the design process to higher abstraction levels [14] and precisely optimise system performance via software implementation. Accordingly, several research groups, such as [21] and [1], have gradually developed the refined design flow of NoC interconnects from system level to physical layout-level implementation in an automated way. Their work suggested that suitable high-level design and synthesis tools for NoC designs is a key element to benefit from NoC-based systems in nanometer-scale technologies [1]. Near the end of the last decade, such a design flow that applying advanced design automation techniques for NoCs started from system-level modelling to accelerate the design flow has been accepted by various researchers as a promising design methodology. Exploring the implications of the NoC paradigm at different levels for efficient synthesis designs of NoC interconnects are continually proposed [22], [23], [24]. In [1], a typical **state-of-the-art** design methodology of NoC systems from system-level modelling to physical-level implementation is given. The complete NoC design flow consists of *three* main phases:

1. In the first phase or Front-End Phase, key architectural features of NoC systems like network topology, traffic flow control and routing tables are determined. Design automation techniques are required in this phase to improve design efficiency.

2. In the second phase or Architectural Design Phase, the RTL codes of target NoC architectures are instantiated based on determined models, design specifications and parametric constraints.

3. In the third phase or Back-End Phase, the layout of generated NoC architectures is synthesised, placed and routed, and implemented. A number of simulations and emulations are given to validate system performance like clock, power and area.

### 1.1.3 Design Space Exploration of Current Methodology

The **state-of-the-art** design methodology of NoC systems introduced in [1] merely proved that it is currently feasible to completely automate NoC systems from high-level specification to physical-level implementation. The whole design methodology is far from perfect to efficiently customise desirable NoC systems. A wide design space has been left open at almost every step of the design flow for further exploration.

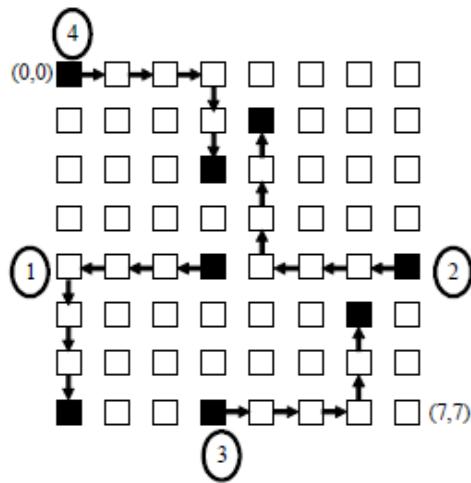

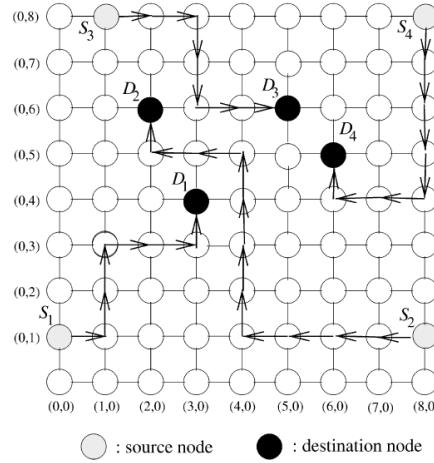

Specifically in the **first phase** of the given state-of-the-art design methodology, design objectives and resource constraints to desired NoC systems are initially specified, followed by the task allocation of NoC applications. The system-level modelling of candidate NoC architectures in which key network characteristics and parameters satisfy those conditions is then generated. In the topology generation, iterative analysis to all candidate networks with concerned metrics are performed based on pre-defined settings. Various traffic flows are routed on those network architectures for performance estimates in order to choose one particular architecture that optimises design objectives while satisfying all the constraints. The design steps of the front-end phase are given in Figure 1.1.

Since the accuracy and efficiency of *system-level model abstraction* are the most fundamental cornerstones in producing efficient and reliable NoC designs for contemporary complex applications, in this thesis we will explore potential design space at system level to carefully balance the modelling for improving the productivity of design flow. To be more specific, each step of *Design Phase 1* in Figure 1.1 explores its design space, investigating better design methods by utilising advanced modern design automation techniques. If the efficiency of all steps in design phase 1 is increased, a fully optimised system-level NoC model can be generated quickly with accurate performance and characteristic estimates, which will accelerate subsequent design phases to improve design cycles of the whole design flow. Moreover, as the design complexity of NoC systems grows to tackle the increasing computation requirements of various applications, finding optimised high-level models from a number of NoC candidates is more difficult and time-consuming. Design improvement in Phase 1 steps also enables a much faster searching process that saves more design cycles for the entire system implementation.

Figure 1.1: Explore Design Space in Phase 1 of State-of-the-art Design Flow [1]

Design space exploration in high-level modelling steps of the state-of-the-art design methodology raises several questions that further investigation will be conducted to solve them in this thesis:

- In the analysis step, are the performance estimates of system-level NoC models accurate enough to produce reliable optimised candidates for further design and implementation?

- In the high-level modelling step, are the NoC architectural and parametric models efficiently abstracted and flexible to represent desirable design specifications?

- In the task allocation step, can the current application tasks have better mapping schemes to balance the utilisation of available resources and optimised performance, such that both design efficiency and productivity are improved?

## 1.2 Research Objectives

Motivated by the fact that system level of the NoC design methodology has left wide design space open, this doctoral project aims to investigate advanced Electronic Design

Automation (EDA) techniques for efficiently developing accurate system-level models of NoC systems and optimised performance trade-offs in terms of energy and timing. The design space of each step in the initial phase of the state-of-the-art NoC design methodology is explored potential improvements to increase efficiency of the whole design flow. A better balance between model accuracy and design productivity is also considered. An extended simulator NIRGAM [25] is used in some design steps to help generate optimised models of NoC systems.

The expected improvements to current design methodology include to provide feasible task allocation schemes for versatile application requirements, accurate system-level behavioural models for efficient NoC design flow and reliable performance estimates in terms of energy and timing issues for optimised network candidates at early design stages. The developed techniques and methods at different design steps should be jointly applied to improve current design methodology for complex NoC applications. Figure 1.2 demonstrates the exact design space expected to explore at each step in the thesis.

Figure 1.2: Research Objectives

As shown from the figure, the detailed research objectives of the research project are categorised as follows:

### 1. Accurate Model Abstraction of System-Level NoC Architectures:

Before utilising EDA techniques for advanced NoC system designs and further performance evaluation, the accuracy of high-level behavioural models needs to be validated in Chapter 3 of the thesis. Functional and performance comparisons between high-level modelling and RTL synthesised designs using a traditional design method are helpful to improve the model accuracy. Since high-level models are developed in the NIRGAM simulator for accurate performance estimates, its

performance models need to be carefully calibrated with RTL synthesis technology library. Functional extension to the simulator is also expected if necessary.

## 2. Efficient Modelling of Various NoC Topologies:

After the accuracy of system-level models is improved, offering more candidate NoC architectures with optimised performance while meeting design requirements are considered to explore potential design space. Most existing NoC design methodologies merely abstract basic NoC network architectures at the system level owing to the easy implementation of modular structures in such topologies. High-level abstractions of other NoC architectures used in specific applications may be achievable in the current design methodology but lack efficient modelling method due to the difficulty and expensive design cost of their architectural implementation. Hence, in Chapter 4 we will explore an efficient method to model non-rectangular and irregular NoC architectures at system level. Again, the NIRGAM simulator will be used as a platform for such modelling, which may require extra functionality.

## 3. Optimised Task Mapping and Performance Trade-offs:

If both model accuracy and availability of system-level NoC architectures are improved, developing intelligent task mapping schemes for fast matching of optimised NoC systems is another space for improving the whole design methodology. Proper task mapping techniques with the optimisation of multiple design objectives are feasible to offer optimal trade-off performance for specific NoC applications. Due to the intrinsic nature of multi-objective problems, the optimisation techniques in high-level NoC designs are supposed to be application-specific, which leaves a large design space for performance improvement. Moreover, implementing specific task mappings for available NoC architectures may maximise the system performance, which offers optimal NoC matchings for various applications. Hence, we will explore potential design space of more intelligent and generalised mapping algorithms in Chapter 5.

### 1.3 Research Contributions

The contributions of this thesis are listed as follows:

- J. Qi, and M. Zwolinski, "Efficient Simulation and Modelling of Non-rectangular NoC Topologies," *Design, Automation and Test in Europe Conference and Exhibition (DATE)*, pp. 1-4, 2014.

- J. Qi, M. Zwolinski, V. Laxmi, and M.S. Gaur, "Area-efficient, Load-balancing, Non-rectangular Architectures for Networks on Chip," *Frontiers of Information Technology and Electronic Engineering*, (Under review).

- J. Qi, and M. Zwolinski, "NLP-based Application Mapping and Performance Prediction for Tile-based NoC Architectures," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, (Submitted).

## 1.4 Thesis Structure

Chapter 1 introduces background information for subsequent chapters. The concepts of on-chip networks and the development of its design methodology are included in the chapter. The motivation, research objectives and contributions of this project are given.

Chapter 2 discusses related research fields. Four areas of knowledge are mainly reviewed. The network on chip basics are initially proposed, followed by the opinions and concerns to current system-level designs of on-chip systems with advanced design automation techniques. Next, a survey of existing task mapping techniques for NoC systems is conducted. Finally a review of modern simulators for NoC designs is reported.

The next three chapters discuss the main contributions of this thesis. Chapter 3 presents research on the first objective, exploring the design space of improving high-level model accuracy for reliable system optimisation. A case study of developing asynchronous FIFOs as NoC router port buffers is undertaken to compare the performance accuracy of system-level abstract models with RTL synthesised designs. Models in the NIRGAM simulator are calibrated to achieve reliable simulation results. Other extensions and modifications to the simulator are also demonstrated.

Chapter 4 gives research towards the second objective, proposing an efficient method to emulate non-rectangular and irregular topologies at system level. This method models topological characteristics of different NoC architectures on a mesh network to accelerate the efficiency at this design step. A number of network topologies are supported by the proposed method, which enhances the functionality of the current NoC design methodology.

Chapter 5 introduces investigation of the third objective, exploring the design techniques for optimised task mapping allocation of specific applications to different networks under certain performance trade-offs. The proposed mapping algorithm provides better balance between the execution efficiency and mapping performance on various NoC architectures, improving the task allocation step with a more generalised and intelligent mapping algorithm that facilitates the yield of optimised NoC systems for further implementation.

The final Chapter 6 concludes the report and outlines plans for future work.

# Chapter 2

## Literature Review

Interconnection networks, like Multi-Processor System-on-Chip (MPSoC) or Network-on-Chip (NoC) systems, are increasingly popular in modern on-chip system designs for highly distributed communication demands. The efficient parallel computing and shared communication resources in such networks make them suitable to design complex on-chip systems with desirable performance. While enjoying these advanced features, a set of new problems such as data routing, flow control and topology [8] are also brought in and need to be tackled. Moreover, efficient and proper designs of such complex systems under tolerable time to market is harder to accomplish, which has also left large space for further exploration. In this case, comprehensive understandings of the NoCs and interconnection networks are an essential prerequisite for chip designers, which are initially introduced in this chapter from basic concepts to crucial characteristics. Next, investigation into existing opinions about system-level NoC modelling for performance estimation and optimisation at early design stages is conducted. Then, popular task mapping techniques for trade-off performance optimisation of NoC systems are surveyed to manifest current research progress at the task-allocation stage. Finally, a brief survey of modern network simulators for high-level modelling and performance estimation is presented in terms of their characteristics and extensibility, such that a backbone platform can be chosen for our further research.

### 2.1 Network on Chip Basics

#### 2.1.1 Basic Concepts

As the chip feature size is continuously scaled down, more functional components are integrated onto a single die. Traditional bus-based architectures with a single processing unit are no longer scalable to task computing requirements since the bus structure

becomes the performance bottleneck when more processors and functional units are integrated. The concept of network architectures is thus introduced and extensively adopted to loosen the bottleneck [2]. In modern chip design industries, multiprocessors dominate the parallel computing market and their architectures implement the interconnection networks with distributed control. According to [8] and [2], a network classification scheme is offered to categorise currently known interconnection networks into 4 major classes based mainly on the network topology, which are shared-medium networks, direct networks, indirect networks and hybrid networks (Figure 2.1). It is noteworthy that this classification focuses on existing networks and is not exhaustive. Other novel and innovative interconnection networks may constantly emerge as the technology further advances.

Figure 2.1: Four Classifications of Interconnection Networks [2]

As shown in Figure 2.1, the transmission medium in *shared-medium networks* is shared by all communicating components. An alternative to this approach, known as a *direct network*, has point-to-point links directly connecting each communicating unit to a subset of other communicating units in the network. In this case, any communication between non-neighbouring devices transmits data through several intermediate units. Instead, *indirect networks* connect those components by one or more switches that have point-to-point links to connect with each other. In this case, any communication between communicating units transmit data through switches. Finally, hybrid approaches are possible.

Since the primary investigation in this thesis focuses on improving NoC designs where low-power and efficient communications between wired-connection multiprocessors are mainly considered, concepts of direct, indirect and hybrid networks are reviewed later. The shared-medium network has a structural resemblance to a traditional bus structure and cannot mitigate the performance bottleneck of complex systems [8]. Most popular

existing network topologies for MPSoC and NoC systems stem from direct and indirect network classes. Network topologies and their characteristics currently evaluated in this thesis are introduced subsequently.

### 2.1.1.1 Direct and Indirect Networks

In the beginning, several network concepts are introduced based on the graph presentation used in [8].

- **Node Degree** is the number of connecting channels from one node to its neighbours.

- **Network Diameter** is the maximum distance between any two nodes in the network.

- **Regularity:** means all the nodes in a regular network have the same degree.

- **Network Symmetry:** means a network is symmetric if it looks the same from each node.

As per the classification in [8], a **direct network** is a kind of networks that each network node directly connects to other nodes. A node in a direct network normally contain independent processors, memories/buffers and other functional components. These components can be designed programmable and reusable, making the direct network scales well when the network size increases [8]. A *router* is a common component in each node of direct networks. It is used to handle data communication among nodes [8]. For this reason, a direct network is also called *a router-based network*. Each router has a number of port channels to directly connect to neighbouring node routers. In an **indirect network**, data communication between each node pair is via *switches*. Thus, an indirect networks is also called a *switch-based network* [2]. Each switch also has a number of port channels that either remain open or connected for data transmission. These ports of different switches are interconnected with each other to communicate different processors [8].

A direct networks can be characterised by its topology, routing, and switching mechanism [11]. The network *topology* indicates how nodes are interconnected by router channels and are modelled by a graph [10]. An ideal direct network topology connects every node directly to each other. But the cost of such a topology will be too high if the network size gets large. Hardware limitations also lead to a constrained number of physical connections that a direct network node may have [8]. Hence, most of existing direct networks connect each of their nodes via hopping among intermediate nodes. A network *Routing algorithm* determines the network path by which a data packet reaches its destination from its source on a network topology [10]. A data packet is a data

exchange unit for data transmission [8]. When a packet header reaches a node channel port, a *switching mechanism* is used to decide how and when the router should be set to forward the incoming data to its destination [8]. Buffer allocation and flow control techniques are important for an efficient switching mechanism. Enough available buffer space is needed to prevent drops of transmitted data. A flow control technique establishes a conversation between the source and destination nodes to arrange a data flow [10]. Both techniques are significant to the network performance.

Indirect networks can be modelled by a graph  $G(S, L)$ , where  $S$  is the set of switches and  $L$  is the set of unidirectional or bi-directional links between the switches [3]. The switches that connect to processors can be the source or destination for data routings [26]. Data transmission between a node pair in an indirect network needs to cross the link between the source and its connected switch, and the link between the last switch on the routing path and the destination [8]. An indirect network can also be characterised by its topology, routing, and switching mechanisms [11]. The topology determines how the node switches are interconnected by link channels and are modelled by a graph. Hardware limitations like the number of available pins and the available wiring area also constrain the number of physical connections an indirect network switch may have [10]. A suitable indirect network topology, routing or switching mechanism usually depends on specific hardware wiring and packaging constraints.

In modern chip design, researchers and developers usually consider direct and indirect networks as two different classes. However, recent developments in router architectures, algorithms, and switch designs have suggested a unified view of direct and indirect networks [8] [10]. In this view, direct networks can be considered as each switch in the network connecting to a node, while the switches of indirect networks can be considered as point-to-point links interconnected with one or more nodes. Hence, this unified view allows network design techniques, such as deadlock-free techniques, for one network class to be applicable to the other class. It is manifest that not all techniques can be directly used for both network classes. But such a unified view is a good attempt to properly describe some currently existing network topologies which have the characteristics of both network classes.

### 2.1.1.2 Development of Network on Chip

Before the emergence of Network on Chip concepts, Systems on Chip (SoC) are proposed as a typical kind of complex Integrated Circuit (ICs) which integrate major functional blocks of a digital electronic system onto a chip. Compared to traditional circuits, SoC implements a whole system on a chip to substantially improve the system performance and communication efficiency. However, its limitations are found as the IC technology continues to develop. One typical problem is the non-scalable global wire delay [6]. In former electronic circuits that the circuit scale is relatively small and the clock frequency

is not as high as in modern SoC integrated circuits, wires carry signals through the whole chip and all timing restraints are met. But in modern complex SoC systems, the wire delay increases linearly or even exponentially with the scaling of transistor size, which may cause the wire delays to exceed an entire clock cycle. Although First-In First-Out (FIFO) structures like Bi-FIFO, Global bus 1 and 2 and Crossbar Switch bus architectures have been developed to solve this wire delay problem [27], other problems such as ad-hoc hardware/software co-designs, functional validation of complex systems and the inconsistency between digital and analogue circuits still remain in SoC systems and are left for researchers and product developers to investigate their solutions.

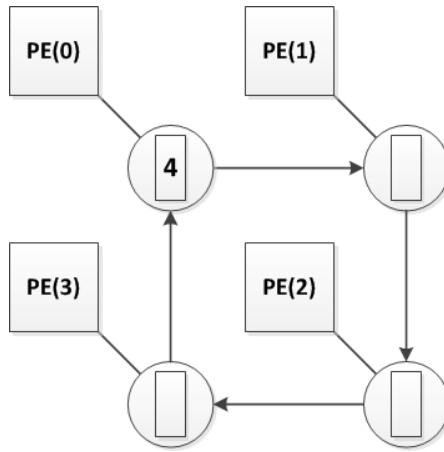

Several SoC systems, integrated with separated processing cores to co-operate in increasingly complex and diverse tasks, promote the advent of new architectures. One popular new architecture is called Multi-Processor System on Chip (MP-SoC) [28] [29]. It greatly improves the system performance compared to a SoC system with a single processing core. Moreover, new communication architectures for efficient mutual interconnection of SoCs are investigated with increasingly massive SoC cores. Among all the potential solutions, Network-on-chip (NoC) [18], in which the chip-level communication interconnects tens to hundreds of sub-systems, is a very promising and effective architecture based on MP-SoC. It forms a subclass of distributed interconnection systems and a special type of MP-SoC, wherein each processor has independent functions and mutually interconnects a network instead of top-level wiring to improve the architecture, performance and modularity. It can process specific application tasks with heavy workloads or tight time budgets that a single processor may not be able to afford. It is a promising architecture for fulfilling demands on large data and mutually independent operations like audio/video processing and network protocol processing [27]. Many proposals and discussions of Network-on-Chip (NoC) have been made since the beginning of the 21st century [18] [19] [30] [31] [32]. As shown in Figure 2.2, a typical NoC involves SoC sub-systems that have their independent microprocessors, buffers/caches, buses and other function units. One such sub-system in NoCs, usually denoted as a Processing Element (PE), communicates with other PEs via routers through the whole on-chip network. The Network Interface (NI) in each PE, acts on as a bridge, conveys data between the local sub-system and the interconnection network.

NoC has regular and well-controlled topologies constructed from multiple point-to-point links by switches or routers that can reduce the design complexity [3]. A high-level parallelism of data processing has been developed in NoC systems such that one complicated big task is disassembled into several less-complex sub-tasks and deployed to different node PEs to be simultaneously processed, which considerably increases processing efficiency. Moreover, designers may also design the parallelism of data processing at other levels to improve system performance. Three levels of design parallelism are usually categorised: the bit-level parallelism, operation-level parallelism

Figure 2.2: A Typical Architecture of NoC [3]

and task-level parallelism [27]. Among them, the task-level parallelism is most important to NoC architectures since it can be abstracted from a serial task and directly contributes to the performance improvement. Specifically, full usage of available network resources to implement proper task-level parallelism for complex and enormous data tasks can reduce design time cost. Besides, to the best of our knowledge, there is no a general tool that can properly abstract different levels of data-processing parallelism in NoC systems, leaving an open issue for further development of NoC modelling tools.

### 2.1.1.3 NoC Architectures

Modern NoC architectures basically consist of IP cores like microprocessors or Digital Signal Processors (DSP), on-chip memory and other functional blocks. Such PEs connected with routers, link the IP cores to neighbouring nodes to construct an NoC system [33]. Depending on different PE architectures, an NoC can be categorised into two classifications: *homogeneous* NoCs and *heterogeneous* NoCs. All the PEs in homogeneous NoCs have an identical internal structure, giving the same size of PE units and a symmetric chip, whereas the PEs in heterogeneous NoCs may have different unit structures. The size of its PE units is therefore diverse and the chip is asymmetric. Chip multi-processors may be homogeneous NoCs, as every PE is a processor [34]. Oppositely, MPSoCs may be designed to be heterogeneous because PEs may need different functions [35]. Each of these two kinds of NoC architecture has its merits and demerits [10]. A homogeneous NoC network has higher applicability and scalability for generic applications but less optimal performance for specific applications, while a heterogeneous NoC network performs optimal functions at the cost of prolonged design cycles for ad-hoc module designs.

According to a layer division proposed in [8], a network architecture can be divided into a *physical layer*, a *switching layer* and a *routing layer* from bottom to top. The **physical layer** describes how PEs are interconnected to each other. The **switching layer** decides