Received January 5, 2016, accepted January 26, 2016. Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2016.2523063

# Stochastic Computing Improves the Timing-Error Tolerance and Latency of Turbo Decoders: Design Guidelines and Tradeoffs

ISAAC PEREZ-ANDRADE, SHIDA ZHONG, ROBERT G. MAUNDER, BASHIR M. AL-HASHIMI, (Fellow, IEEE), AND LAJOS HANZO, (Fellow, IEEE)

Electronics and Computer Science, University of Southampton, Southampton, SO17 1BJ, U.K.

Corresponding author: L. Hanzo (lh@ecs.soton.ac.uk)

This work was supported in part by the European Research Council within the Beam-Me-Up Project, in part by the Engineering and Physical Sciences Research Council, Swindon, U.K., under Grant EP/J015520/1 and Grant EP/L010550/1, and in part by Technology Strategy Board, Swindon, U.K., under Grant TS/L009390/1. The work of I. Perez-Andrade was supported by the Consejo Nacional De Ciencia Y Tecnología, Mexico, within the Secretaría de Educación Pública y del Gobierno Mexicano.

The research data for this paper is available at http://dx.doi.org/10.5258/SOTON/375728

**ABSTRACT** Stochastic computing has been recently proposed for the hardware implementation of both low-density parity-check (LDPC) decoders and turbo decoders, which facilitate near-optimal error correction capabilities in wireless communication applications. Previous contributions have demonstrated that stochastic LDPC decoders offer an attractive tradeoff between their error correction capabilities, hardware performance, and timing-error tolerance. Motivated by this, we propose a pair of stochastic turbo decoder (STD) designs having significantly enhanced timing-error tolerance and significantly reduced processing latency. Moreover, we characterize the tradeoffs between chip area, energy efficiency, latency, throughput, and error correction capabilities of both the timing-error-tolerant STD and of the reduced-latency STD. We demonstrate that our proposed timing-error-tolerant STD operated at 1.20 V, with a clock period of 2.2 ns and in the presence of a three-standard deviation power supply variation of 7%, exhibits an unimpaired performance, compared with the state-of-the-art STD, operated at 1.20 V and 4 ns and with no power supply variations. This corresponds processing throughput improvement by a factor of 2.42 and energy consumption reduction by a factor of 4. Finally, we demonstrate that our proposed reduced-latency STD has a processing latency that is an order of magnitude lower than that of the state-of-the-art STD. This is despite reducing the chip area by a factor of 4, increasing the processing throughput by a factor of 65, while consuming only 0.005 times the energy of the state-of-the-art STD, when using binary phase-shift keying for communication over an additive white Gaussian noise channel having  $E_b/N_0 = 3$  dB.

**INDEX TERMS** ASIC, fault tolerance, low-latency, power supply variation, stochastic computing, timing errors, turbo decoder.

| NOMENCL     | ATURE                                   | JKLL    | JK-type riip riop                        |

|-------------|-----------------------------------------|---------|------------------------------------------|

| APP         | A Posteriori Probability                | LDPC    | Low-Density Parity-Check                 |

| ASIC        | Application Specific Integrated Circuit | LSB     | Least Significant Bit                    |

| AWGN        | Additive White Gaussian Noise           | LLR     | Logarithmic Likelihood Ratio             |

| BER         | Bit Error Ratio                         | LogBCJR | Logarithmic BCJR                         |

| BCJR        | Bahl-Cocke-Jelinek-Raviv                | LTE     | Long-Term Evolution                      |

| BPSK        | Binary Phase Shift Keying               | MCMTC   | Mission-Critical Machine-Type            |

| BS          | Bernoulli Sequence                      |         | Communication                            |

| CG          | Clock Gating                            | MSB     | Most Significant Bit                     |

| CRC         | Cyclic Redundancy Check                 | MUX     | Multiplexer                              |

| DC          | Decoding Cycle                          | NDS     | Noise-Dependent Scaling                  |

| DFF         | D-type Flip Flop                        | RCTFM   | Reduced-Complexity Tracking Forecast     |

| EM          | Edge Memory                             |         | Memory                                   |

| <b>FPGA</b> | Field-Programmable Gate Array           | RLSTD   | Reduced-Latency Stochastic Turbo Decoder |

|             |                                         |         |                                          |

IKEE

IK type Flip Flop

SNR Signal-to-Noise Ratio

SR Shift Register

STD Stochastic Turbo Decoder

TFM Tracking Forecast Memory

VLSI Very-Large-Scale Integration.

#### I. INTRODUCTION

Both Low-Density Parity-Check (LDPC) [1] codes and turbo codes [2] are widely used for error correction in wireless communications standards such as WiMAX [3], WiFi [4], DVB-S2 [5], CDMA2000 [6], UMTS [7] and LTE [8]. Traditional hardware implementations of LDPC decoders and turbo decoders rely on fixed-point binary arithmetic for representing and processing the probabilities of the received bits having the value 0 or 1. However, practical fixed-point LDPC and turbo decoder impose a high complexity owing to the interconnection and routing problems of fully-parallel designs [9], [10], or due to the large amount of memory of both partially-parallel and of fully-serial designs [11], [12]. Stochastic computing [13] has been proposed as a low-complexity design alternative to fixed-point binary arithmetic, where the probabilities are represented by streams of bits, known as Bernoulli Sequences (BSs) [13]. Only a single bit of each BS is processed per clock cycle and the specific fraction of bits having the logical value 1 determines the value of the probability represented. As a benefit of this, arithmetic operations in stochastic computing can be implemented using low-complexity digital circuits.

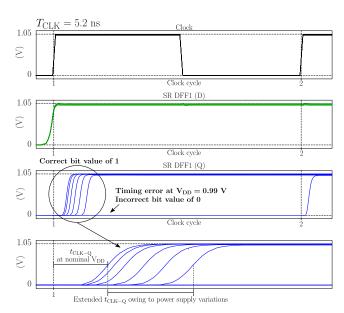

Timing errors in synchronous systems occur when the delay in a circuit path exceeds the clock period, owing to variations in the operating conditions of the system, such as the supply voltage or clock period. Furthermore, timing errors are more likely to occur when the supply voltage is reduced and the clock period is not adjusted accordingly, owing to the quadratic dependency of propagation delays on the supply voltage. As a result of this, the error correction capabilities of fixed-point LDPC decoders and turbo decoders in the presence of timing errors can be severely affected, unless sophisticated fault-tolerant design techniques are considered. More specifically, fixed-point implementations are particularly vulnerable to timing errors affecting the Most Significant Bit (MSB) of the fixed-point numbers, since this radically alters the represented bit value probabilities. By contrast, stochastic computing exhibits an inherent tolerance to processing errors. Since every bit of a BS has an identical significance, a processing error causing a single bit-flip will only result in a small change to the overall value of the probability represented. This represents a key advantage of the stochastic implementations of error correction decoders, particularly as Very-Large-Scale Integration (VLSI) technology scales reduce and the prevalence of timing errors increases, owing to the effects of IR-drop and L  $\cdot d_i/d_t$ , manufacturing imperfections and external factors such as crosstalk, electrostatic discharges and electromagnetic interference [14]-[18], among others.

However, stochastic decoders require a large number of clock cycles in order to achieve the same near-optimal error correction capability as their fixed-point implementation counterparts. Regretfully, this degrades their latency, throughput and energy efficiency. Owing to these impediments, stochastic decoders have been deemed unsuitable for practical low-latency next-generation Mission-Critical Machine-Type Communication (MCMTC) systems, such as those required by vehicular traffic safety and control, as well as industrial process automation and manufacturing [19]. In these applications, short emergency and control messages constituted by a low number of bits must be reliably transmitted with ultra-low latency, hence motivating the employment of error correction decoders having ultra-low processing latencies on the order of microseconds [19]. Motivated by this background, this paper proposes a pair of stochastic turbo decoder designs having significantly enhanced timing error tolerance and significantly reduced processing latency, as discussed in the following subsections.

#### A. RELATED WORK

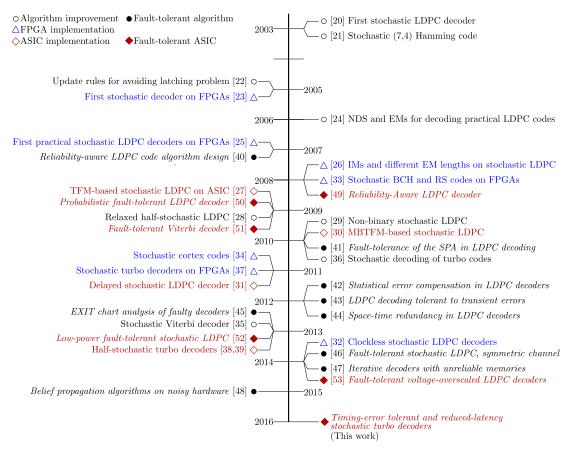

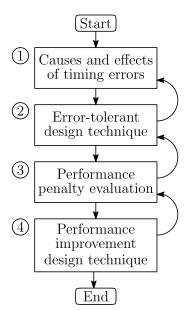

The following literature review is based on the fields of fault-tolerant design in iterative decoders and hardware implementation of stochastic iterative decoders, where Figure 1 summarizes some of the seminal contributions in these fields.

Stochastic computing has been recently proposed for the fully-parallel decoding of LDPC codes [20]-[32], Bose-Chaudhuri-Hocquenghem codes [33], Reed-Solomon codes [33], cortex codes [34], convolutional codes [35] and turbo codes [36]-[39]. Most of these contributions have focused on the employment of stochastic computing in traditional iterative decoding algorithms, where the main design objective has been to maximize the attainable error correction capabilities. In parallel to this, fault-tolerance in iterative decoders has mostly been explored from the algorithmic point of view in [40]-[48], with only few contributions [49]–[53] having considered the practical implications of fault-tolerant hardware design. Within these contributions, different approaches have been explored in order to improve the decoder's fault-tolerance. For example, hardware redundancy and voting units are employed in [49] for error detection and correction. Similarly, processing errors are corrected on the basis of probabilistic analyses in [50] and [51]. By contrast, our previous contribution [52] was the first one in the open literature to explore the inherent tolerance of stochastic LDPC decoders to timing errors, both in the presence of clock- and voltage-scaling.

Substantial research efforts have been invested in reducing the number of clock cycles required by stochastic decoders for achieving a near-optimal error correction performance. In particular, the authors of [24], [25], [27], and [30] considered the employment of Noise-Dependent Scaling (NDS) and Edge Memories (EMs) in stochastic LDPC decoders, reducing the number of clock cycles required to achieve near-optimal error correction performance from several thousands

FIGURE 1. Selected previous contributions in the field of hardware implementation of stochastic iterative decoders and fault-tolerant design for iterative decoders.

to as low as a few hundreds. By contrast, the fully-parallel Stochastic Turbo Decoder (STD) of [36] requires several thousands of processing cycles, despite the employment of NDS and EMs. This problem is partially overcome in [36] and [37] by further increasing the grade of processing parallelism. However, this significantly increases the hardware complexity of the STD, as it will be detailed is Section VIII. The authors of [38] and [39] proposed modified BS representations for the implementation of STDs. These contributions significantly reduced the number of clock cycles required without significantly increasing the hardware complexity of the design. However, these designs may be considered to represent partially-stochastic turbo decoders, since their operation is based on fixed-point arithmetic circuits, which do not benefit from the inherent tolerance of stochastic decoders to timing errors.

#### **B. CONTRIBUTIONS AND PAPER STRUCTURE**

The previous work mentioned in Section I-A has mainly focused on enhancing the error correction capabilities of stochastic decoders and separately of fault-tolerant iterative decoders. However, fault-tolerance in stochastic decoders has only been addressed in our previous work [52] for the case of stochastic LDPC decoders. Moreover, the above-mentioned contributions in the field of fault-tolerant iterative decoders

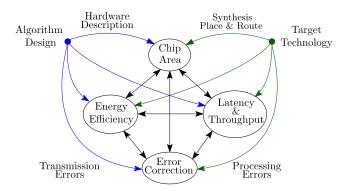

FIGURE 2. Relationship between different design trade-offs.

have failed to provide a comprehensive analysis of the various design trade-offs involved in the hardware implementation of error tolerant techniques, which is a common approach in performance-oriented design methodologies [54]. To elaborate further, the main design objective of these contributions is to enhance both the robustness and reliability of the decoders against processing errors. However, this is typically reported without considering the impact of fault-tolerant techniques on the associated hardware design trade-offs, such as the chip area, energy efficiency, latency, throughput and error correction capabilities, despite the strong dependence they have upon each other, as depicted in Figure 2. In this context,

a compelling Pareto-optimal design has a set of characteristics, where none of them can be further improved without degrading at least one of the others. In addition to this, the techniques introduced in [36] and [37] for reducing the number of processing cycles required by the STD impose a potentially excessive hardware complexity increase. As a result, the proposed STDs may not be suitable for practical next-generation low-latency MCMTC systems.

Against this background, we propose enhancements of the STD of [36] for improving its hardware characteristics. We first improve its tolerance to timing errors in the presence of power supply variations. More specifically, the first enhanced STD design proposes:

- 1.1) The employment of synchronizers for preventing the catastrophic cascading of metastability owing to timing errors.

- 1.2) The simultaneous decoding of two received frames for improving the processing throughput.

- 1.3) The employment of Tracking Forecast Memories (TFMs) [27] in STDs for the first time, in order to enhance their hardware implementation and decoding capabilities.

- 1.4) The inclusion of a pipelining stage for enhancing the decoding capabilities of the STD in the presence of power supply variations.

In parallel to this, we present a second improved STD design, which reduces the number of clock cycles required for achieving near-optimal error correction performance by an order of magnitude, without increasing the chip area. This is achieved by employing:

- 2.1) OR gates for performing approximate stochastic additions.

- 2.2) A reduced-complexity TFM design for overcoming the latching problem.

- 2.3) A single D-type Flip Flop (DFF) for estimating each decoded bit.

Moreover, we analyze the different trade-offs presented in Figure 2 for both of the improved STD designs.

The amalgam of those two STD designs yields significant performance enhancements, which substantially improve the appeal of STDs in practical next-generation timing-error-tolerant and low-latency MCMTC systems.

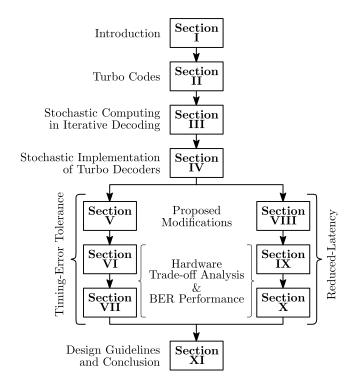

The remainder of this paper is structured as depicted in Figure 3. Section II reviews the operation of turbo decoders. Section III reviews the concept of stochastic computing in iterative decoding. Section IV details the hardware implementation of STDs. Note that experts of turbo decoders, stochastic computing and stochastic turbo decoding may wish to skip the comprehensive tutorials of Sections II to IV, respectively. Sections V to VII present the timing-error tolerant STD design. More specifically, Section V describes how to improve the STD's tolerance to timing errors, Section VI details its hardware implementation trade-offs, while Section VII characterizes its error correction performance in the presence of timing errors. Following this, Sections VIII to X portray our reduced-latency STD design.

FIGURE 3. Summary of paper structure.

More specifically, Section VIII details how to reduce the number of clock cycles required by the decoder, Section IX quantifies its error correction performance and Section X characterizes its hardware efficiency. Finally, Section XI presents our concluding remarks and offers design guidelines for STDs.

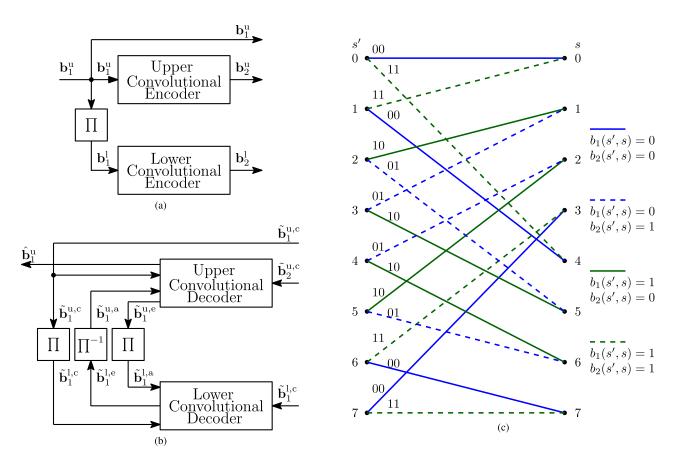

#### II. TURBO CODES

In this section, we review the concepts of turbo encoding and turbo decoding [2] presented in Figure 4. A turbo code comprises the parallel concatenation of two convolutional codes. As a result of this, a message frame comprising N bits  $\mathbf{b}_1^{\mathbf{u}} = [b_{1,k}^{\mathbf{u}}]_{k=1}^{N}$  can be turbo encoded with the aid of the two parallel concatenated convolutional encoders, as shown in Figure 4a. Each convolutional encoder operates in the same manner, with the upper convolutional decoder having the bits  $\mathbf{b}_1^{\mathbf{u}}$  for its input. However, these bits are reordered by the interleaver  $\Pi$  to provide  $\mathbf{b}_1^{\mathbf{l}}$ , which is then input into the lower encoder. Here, the superscripts 'u' and 'l' indicate relevance to the upper and lower convolutional encoders, respectively. However, these superscripts will be omitted, when the discussion applies equally to both convolutional encoders.

Each convolutional encoder operates on the basis of a trellis such as the 8-state Long-Term Evolution (LTE) trellis of Figure 4c. Here, each bit of  $\mathbf{b}_1$  triggers one of 16 different transitions among these states and the encoding of the first bit  $b_{1,1}$  commences from a particular previous state s'. If tailbiting [55] is employed, then this initial state is carefully selected such that it is equal to the final state s reached after encoding the final bit  $b_{1,N}$ . The simplified turbo encoder of

FIGURE 4. (a) Simplified turbo encoder. (b) Conventional structure of a turbo decoder. (c) State transition diagram of the LTE turbo code.

Figure 4a outputs a frame of systematic bits  $\mathbf{b}_1^{\mathrm{u}} = [b_{1,k}^{\mathrm{u}}]_{k=1}^N$  and two frames of parity bits  $\mathbf{b}_2^{\mathrm{u}} = [b_{2,k}^{\mathrm{u}}]_{k=1}^N$  and  $\mathbf{b}_2^{\mathrm{l}} = [b_{2,k}^{\mathrm{l}}]_{k=1}^N$ , which are provided by the upper and lower convolutional encoder, respectively. After their transmission over a wireless channel, the received frames  $\tilde{\mathbf{b}}_1^{\mathrm{u,c}} = [\tilde{b}_{1,k}^{\mathrm{u,c}}]_{k=1}^N$ ,  $\tilde{\mathbf{b}}_2^{\mathrm{u,c}} = [\tilde{b}_{2,k}^{\mathrm{u,c}}]_{k=1}^N$  and  $\tilde{\mathbf{b}}_2^{\mathrm{l,c}} = [\tilde{b}_{2,k}^{\mathrm{l,c}}]_{k=1}^N$  are entered into the turbo decoder, which is comprised of two convolutional decoders, as shown in Figure 4b. The upper convolutional decoder of Figure 4b employs the received frames  $\tilde{\mathbf{b}}_1^{\mathrm{u,c}}$ ,  $\tilde{\mathbf{b}}_2^{\mathrm{u,c}}$  and the frame of *a priori* soft bits  $\tilde{\mathbf{b}}_1^{\mathrm{u,a}}$  provided by the lower convolutional decoder, in order to provide the frame of extrinsic soft bits  $\tilde{\mathbf{b}}_1^{\mathrm{u,e}}$ . Following this, the extrinsic soft bits  $\tilde{\mathbf{b}}_1^{\mathrm{u,e}}$  are interleaved and passed to the lower convolutional decoder as the frame of a priori soft bits  $\tilde{\mathbf{b}}_{1}^{1,a}$ . The lower convolutional decoder employs the received frame  $\tilde{\mathbf{b}}_2^{1,c}$  and the interleaved received frame  $\tilde{\mathbf{b}}_1^{l,c}$  to provide the *extrinsic* soft bits  $\tilde{\mathbf{b}}_{1}^{1,e}$ , which are de-interleaved in the block  $\Pi^{-1}$ and passed as the frame of a priori soft bits  $\tilde{\mathbf{b}}_{1}^{\mathrm{u},\mathrm{a}}$  to the upper convolutional decoder. These soft bits express not only what the most likely value of the corresponding bits are, but also how likely these bit values are. More specifically, each soft bit  $\tilde{b}_{1,k}^{\text{u,c}}$  expresses the two probabilities  $P^c(b_{1,k}^{\text{u,c}} = 0)$ and  $P^{c}(b_{1,k}^{u,c} = 1)$ , where the subscripts and superscripts may be replaced for the case of the other soft bits in Figure 4b.

The convolutional decoders are iteratively operated on the basis of the Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm [56], which comprises Equations (1) to (6), as shown at the top of the next page. The BCJR algorithm employs (1) for calculating a branch metric  $\gamma_k(s', s)$  for each transition of Figure 4c from a previous state s' into the next state s. Here,  $P^{a}(b_{1,k} = b_1(s', s))$  is the probabilities that are expressed by the a priori soft bit  $\tilde{b}_{1k}^{a}$  provided by the other convolutional decoder. Note that at the start of the iterative decoding process,  $P^{a}(b_{1,k} = b_1(s', s)) = 0.5$  is assumed. The extrinsic branch metrics  $\gamma_k^{\rm e}(s',s)$  of (2) correspond to the received probability of the parity bit  $b_{2,k}$  provided by the other convolutional encoder. Following this, the state metrics  $\alpha_k(s)$  of (3) and  $\beta_k(s')$  of (4) are calculated for quantifying the probabilities associated with each of the 8 possible previous and next states of Figure 4c. Note that  $\alpha_{k-1}(s') = 1/8$  and  $\beta_k(s) = 1/8$ is assumed for all s' and s at the start of the iterative decoding process. If tailbiting [55] is employed, then  $\alpha_0(s') = \alpha_N(s')$ and  $\beta_N(s) = \beta_0(s)$  may be employed. Furthermore, (5) is employed for determining the probabilities  $P^{e}(b_{1,k} = 0)$ and  $P^{e}(b_{1,k} = 1)$ , which are expressed by the *extrinsic* soft bit  $\tilde{b}_{1,k}^e$ . Finally, (6) is employed for determining the a posteriori hard decision  $\hat{b}_{1,k}$ , pertaining to the bit  $b_{1,k}$ . This iterative process is repeated until an accurate estimation of the decoded frame  $\hat{\mathbf{b}}_1$  can be obtained or until the maximum affordable number of iterations has been reached.

$$\gamma_k(s',s) = P^{a}(b_{1,k} = b_1(s',s))P^{c}(b_{1,k} = b_1(s',s))P^{c}(b_{2,k} = b_2(s',s))$$

(1)

$$\gamma_k^{\mathbf{e}}(s', s) = P^{\mathbf{c}}(b_{2,k} = b_2(s', s))$$

(2)

$$\alpha_{k}(s) = P^{c}(b_{2,k} = b_{2}(s', s))$$

$$\alpha_{k}(s) = \frac{\sum_{\text{all } s'} \gamma(s', s)\alpha_{k-1}(s')}{\sum_{\text{all } (s', s)} \gamma(s', s)\alpha_{k-1}(s')}$$

(3)

$$\beta_{k-1}(s') = \frac{\sum\limits_{\text{all } s} \gamma(s', s)\beta_k(s)}{\sum\limits_{\text{all } (s', s)} \gamma(s', s)\beta_k(s)}$$

(4)

$$\beta_{k-1}(s') = \frac{\sum_{\substack{\text{all } (s',s) \\ \text{all } (s',s)}} \gamma(s',s)\beta_k(s)}{\sum_{\substack{\text{all } (s',s) \\ \text{all } (s',s)}} \gamma(s',s)\beta_k(s)}$$

$$P^{e}(b_{1,k} = j) = \frac{\sum_{\substack{\text{all } (s',s) \to (b_1(s',s) = j) \\ \text{all } (s',s) \to (b_1(s',s) = j)}} \sum_{\substack{\text{all } (s',s) \\ \text{all } (s',s) \\ \text{all } (s',s) \to (b_1(s',s) = j)}} \gamma_k^{e}(s',s)\alpha_{k-1}(s')\beta_k(s)$$

$$(5)$$

$$\hat{b}_{1,k} = \underset{j \in \{0,1\}}{\text{arg max}} \sum_{\text{all } (s',s) \to b_1(s',s) = j} \gamma_k(s',s) \alpha_{k-1}(s') \beta_k(s)$$

(6)

#### III. STOCHASTIC COMPUTING IN ITERATIVE DECODING

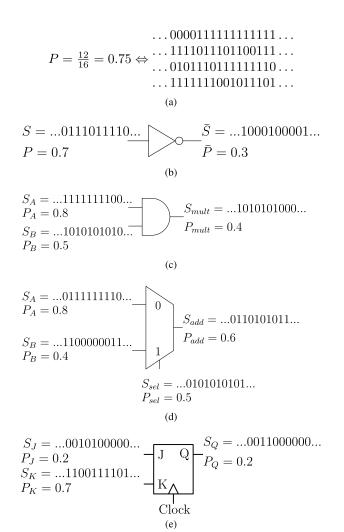

In stochastic computing, probabilities are represented by means of streams of bits known as Bernoulli Sequences (BSs) [13], which are generated by statistically independent processes and with only one bit of each Bernoulli Sequence (BS) being processed in each clock cycle that is referred to as a Decoding Cycle (DC) of stochastic decoders. The probability P represented by a BS is determined by the fraction of its bits having the value of 1. Owing to this, the same probability can be represented by different BSs having the same fraction of bits with the value 1, but in different positions. This is exemplified in Figure 5a, where the probability P = 0.75 is represented by different BSs, each having 12 out 16 bits with value 1. As an explicit benefit of this, stochastic computing offers an inherent tolerance to processing errors. To elaborate further, a single bit-flip caused by a processing error will only change the overall value of the represented probability by a fraction proportional to the length of the BS. In this way, if the BS is sufficiently long, the represented probability will not be significantly affected, if some of the bits are corrupted. As an example of this, if any of the 12 bits having the value of logical 1 of the BSs of Figure 5a is flipped to logical 0, the resultant BSs will represent the probability of P = 11/16 = 0.6875, which corresponds to an absolute error of 1/16.

#### A. STOCHASTIC ARITHMETIC

In stochastic computing, arithmetic combinations of the probabilities represented by two or more BSs can be implemented using low-complexity digital circuits. In particular, the binary complement  $\bar{P} = (1 - P)$  of a probability P can be obtained using a NOT gate, as exemplified in Figure 5b.

The multiplication  $P_{mult} = P_A \cdot P_B$  of two probabilities  $P_A$  and  $P_B$  can be performed using a bitwise logical AND of the two corresponding BSs  $S_A$  and  $S_B$ , as exemplified in Figure 5c. Similarly, the multiplication  $P_{mult} = \prod_{i=1}^{M} P_i$  of

the probabilities represented by M BSs can be performed with the aid of an M-input AND gate.

The weighted mean  $P_{add} = P_A \cdot (1 - P_{sel}) + P_B \cdot P_{sel}$  of two probabilities  $P_A$  and  $P_B$  can be obtained by using a two-input Multiplexer (MUX) to randomly select bits from the corresponding BSs  $S_A$  and  $S_B$ , with the aid of the BS  $S_{sel}$ , which represents the probability  $P_{sel} = 0.5$  for the case of a nonweighted mean, as exemplified in Figure 5d. The outgoing bit of the MUX will have the value of 1 only if the bit of the input selected by  $S_{sel}$  has the value of 1. More specifically, we have  $S_{add} = 1$  only if  $S_A = 1$  and  $S_{sel} = 0$  or  $S_B = 1$ and  $S_{sel} = 1$ . Similarly, the mean  $P_{add} = \left[\sum_{i=1}^{M} P_i\right]/M$  of M probabilities can be obtained using an M-input MUX to randomly select bits from the corresponding M BSs.

The division of the probability  $P_J$  by the probability  $P_K$  can be approximated by entering the corresponding BSs  $S_J$  and  $S_K$  into the J and K inputs of a JK-type Flip Flop (JKFF), respectively, as exemplified in Figure 5e. Here, the output O of the JKFF adopts the value of the input J if J and K disagree. By contrast, if J = 0 and K = 0, then Q retains the same value that it had in the previous clock cycle. If J = 1and K = 1, the output Q is toggled relative to its value in the previous clock cycle. The bits in the BS  $S_Q$  obtained at the output Q of the JKFF will adopt the value 1 with the probability  $P_Q = P_J/[P_J + P_K]$ , which approximates  $P_J/P_K$ if  $P_J \ll P_K$ . In the example presented in Figure 5e, the outgoing BS  $S_O$  represents the probability  $P_O = 0.2$ , whereas the resulting normalization gives  $0.2/(0.2+0.7) \approx 0.22$  and the approximated division gives  $0.2/0.7 \approx 0.28$ . Accurate stochastic computation realizations of division, integration, square and square operations can be obtained by combining the above-described basic stochastic arithmetic circuits, as detailed in [13], [57], and [58].

#### **B. LATCHING PROBLEM**

stochastic decoding of Low-Density Parity-Check (LDPC) codes, JKFFs are susceptible to the

**FIGURE 5.** Stochastic circuits for arithmetic operations: (a) Different BSs for P=0.75. (b) Complement. (c) Multiplication. (d) Scaled addition. (e) Approximate division and normalization.

latching problem, as detailed in [21]. This occurs when the bits of the BSs become stuck at 0 or 1 for several DCs, which severely affects the attainable error correction capability of the stochastic LDPC decoder [24]. This occurs when there is a high correlation among the bits of the BSs, owing to the short cycles in the factor graph of the LDPC code [21], [59]. A number of approaches have been proposed for overcoming the latching problem. For example, the employment of Noise-Dependent Scaling (NDS) was firstly proposed in [26]. This technique induces switching activity in order to help stochastic LDPC decoders become unstuck when they encounter the latching problem. This is particularly useful at high channel Signal-to-Noise Ratios (SNRs), where the probabilities represented by the soft bits received from the channel are very close to 0 or 1, causing the BSs to become stuck at 0 or 1, respectively. In this method, the probabilities received from the channel are scaled depending on the channel's noise power spectral density  $N_0$ . Assuming a Binary Phase Shift Keying (BPSK) transmission over an Additive White Gaussian Noise (AWGN) channel, a bit value probability P(b = 0) is converted into a scaled bit value probability P'(b=0) according to

$$P'(b=0) = \frac{1}{1 + \exp\left(\frac{\eta N_0}{\psi} \cdot \log \frac{1 - P(b=0)}{P(b=0)}\right)},\tag{7}$$

where  $\eta$  and  $\psi$  are parameters than can be chosen to optimize the Bit Error Ratio (BER) performance of the stochastic LDPC decoder.

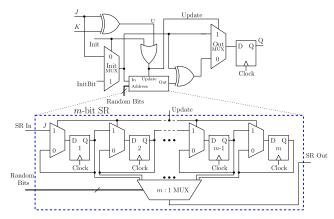

Another method of assisting stochastic LDPC decoders to become unstuck, when encountering the latching problem is replacing the JKFFs used for divisions by re-randomization units known as Edge Memories (EMs), which were firstly proposed in [24]. The EMs introduced in [24] consist of *m*-bit Shift Registers (SRs), which can be considered to behave as an *m*-length JKFF having a selectable output, as shown in the blue box printed using dashed lines in Figure 6.

FIGURE 6. EM employed for the re-randomization of BSs in stochastic decoding.

Just like a JKFF, the values stored by an SR-based EM are updated if the input bits J and K differ from each other  $J \neq K$ , whereupon the regenerative bit J is stored in the first D-type Flip Flop (DFF) of the SR and passed to the output DFFQ of the EM in analogy to the behavior of a JKFF, with the aid of the OutMUX. In this event, the signals U and Update of Figure 6 are asserted and the contents of the SR will be shifted by one position, with the oldest bit in the SR being discarded in order to ensure that only the m-most recent regenerative bits are stored. By contrast, when the J and Kinput bits are equal, one of the previous regenerative bits is randomly chosen from the SR and passed to the output DFFQ of the EM, in analogy to the behavior of a JKFF. This is achieved with the aid of an m : 1 MUX with pseudorandom selector bits that change in every DC, as shown in the lower part of Figure 6. Additionally, when J = K = 1, the outgoing bit of the SR is inverted with the aid of an XOR gate, before being provided to the output DFFQ, in analogy to the behavior of a JKFF. The SR-based EM of Figure 6 can be initialized prior the beginning of the decoding process by means of the Init signal. During the initialization phase, the assertion of the signal Init causes the InitMUX to feed the initialization bits InitBits into the SR. The values of

FIGURE 7. Block diagram of the fully-parallel STD.

InitBit can be chosen to optimize the BER performance of the decoder.

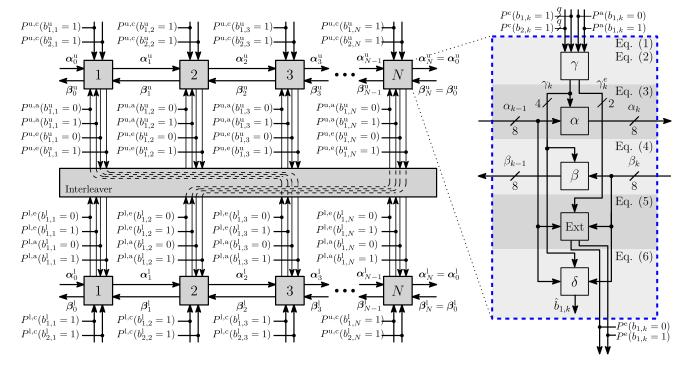

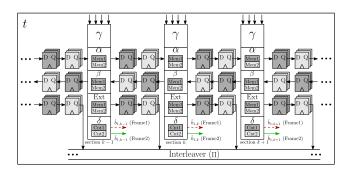

# IV. STOCHASTIC IMPLEMENTATION OF TURBO DECODERS

This section reviews the hardware implementation requirements of the Stochastic Turbo Decoder (STD), which is briefly summarized in [36] and is detailed in [60], although the latter is written in French. Therefore, this paper offers the first detailed treatment of the STD in English. In the fullyparallel stochastic decoding of turbo codes [36], [60], the block diagram in the blue box of Figure 7 is replicated for each bit decoded by each convolutional decoder of Figure 4b, with the two convolutional decoders being separated by a hard-wired interleaver, as shown in the left part of Figure 7. The STD of [36] and [60] adopts tailbiting [55] as described in Section II. This guarantees that the initial and final states of the trellis of each convolutional decoder are identical. Owing to this, the state metrics  $\alpha_N(s)$  output by the  $N^{th}$  block are provided as the inputs  $\alpha_0(s')$  of the first block in each convolutional decoder, as shown in Figure 7. Likewise, the state metrics  $\beta_0(s')$  output by the first block are provided as the inputs  $\beta_N(s)$  of the  $N^{th}$  block. The incoming edges  $\alpha_{k-1}$ ,  $\beta_k$ ,  $P^{a}(b_{1,k}=0)$  and  $P^{a}(b_{1,k}=1)$  of Figure 7 corresponds to one bit of a BS from a neighboring block. In a similar manner, the outgoing edges  $\alpha_k$ ,  $\beta_{k-1}$ ,  $P^e(b_{1,k}=0)$  and  $P^e(b_{1,k}=1)$ corresponds to an outgoing bit of a BS. By contrast, the incoming edges  $P^{c}(b_{1,k} = 1)$  and  $P^{c}(b_{2,k} = 1)$  correspond to q-bit fixed-point probabilities provided by the channel. The block diagram of Figure 7 processes and exchanges

one bit of each BS in each DC. Furthermore, each block of Figure 7 corresponds to the stochastic implementation of Equations (1) to (6). Building on this, the following sections present the stochastic hardware implementation requirements of Equations (1) to (6).

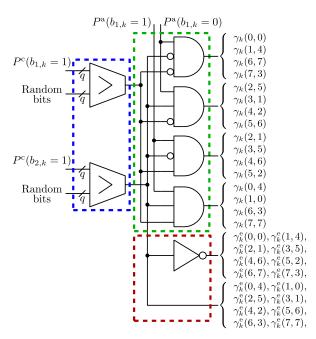

#### A. BRANCH METRICS

The module  $\gamma$  of Figure 7 performs the conversion of the q-bit fixed-point representations of the received channel probabilities  $P^c(b_{1,k} = 1)$  and  $P^c(b_{2,k} = 1)$  into BSs. In addition to this, this module generates BSs representing the branch metrics  $\gamma_k(s', s)$  and the extrinsic branch metrics  $\gamma_k^e(s', s)$ of (1) and (2), respectively. The conversion of the received channel probabilities into BSs is achieved with the aid of two q-bit fixed-point comparators and two q-bit pseudo-random numbers, as shown in the blue box of Figure 8. Here, q represents the number of quantization bits employed for representing the received channel probabilities and its value can be chosen based on the best trade-off between the advisable BER performance and the hardware requirements imposed, where q = 7 in the STD of [36] and [60], for example. In this structure,  $P^c(b_{1,k} = 1)$  and  $P^c(b_{2,k} = 1)$  remain constant throughout the decoding process and the pseudorandom numbers change in every DC. The outgoing bit of each comparator is set to 1, if the corresponding probability is greater than the pseudo-random number and 0 otherwise. Following their conversion to BSs, the received channel probabilities are employed for obtaining the branch metrics  $\gamma_k(s', s)$  of (1). This is achieved with the aid of four 3-input AND gates, as shown in the green box of Figure 8,

**FIGURE 8.** Stochastic realization of  $\gamma_k(s', s)$  and  $\gamma_k^e$  [60, Fig. 2.5].

corresponding to the four possible combinations of the systematic and parity bits  $b_1(s',s)$  and  $b_2(s',s)$  shown in Figure 4c. In addition to this, the *extrinsic* branch metrics  $\gamma_k^e(s',s)$  of (2) express the probabilities  $P^c(b_{2,k}=0)$  and  $P^c(b_{2,k}=1)$ , pertaining to the parity bit  $b_{2,k}$ . As a result of this, the stochastic realization of  $\gamma_k^e(s',s)$  can be implemented with two BSs for representing  $P^c(b_{2,k}=0)$  and  $P^c(b_{2,k}=1)$ , as shown in the red box of Figure 8. The BSs representing the *a priori* probabilities  $P^a(b_{1,k}=0)$  and  $P^a(b_{1,k}=1)$  are provided by the other convolutional decoder, but this will not yet have generated any output during the first DC. Therefore, the first bits of the BSs can be initialized with random binary values during the first DC.

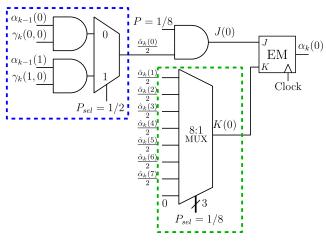

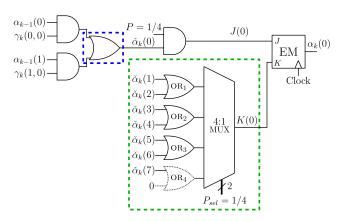

#### **B. STATE METRICS**

The modules  $\alpha$  and  $\beta$  of Figure 7 compute the forward recursion of (3) and the backward recursion of (4), respectively. This is achieved with the aid of AND gates, MUXs and EMs for the multiplication, addition and normalization of BSs, respectively, as shown in Figure 9. In the following discussion, the stochastic implementation of the state metrics is described for the forward recursion state metrics  $\alpha_k(s)$  of (3), for the case where s=0. The implementation of (3) for all other states  $s \in [1, 7]$  and of the backward recursion of (4) can be performed following the same principles. In the Long-Term Evolution (LTE) turbo decoder of [36] and [60], (3) can be modified as

$$\alpha_k(s) = \frac{\sum_{\text{all } s'} \gamma(s', s) \alpha_{k-1}(s')}{\sum_{\text{all } (s', s)} \gamma(s', s) \alpha_{k-1}(s')} = \frac{\hat{\alpha}_k(s)}{\sum_{s=0}^{7} \hat{\alpha}_k(s)},$$

(8)

**FIGURE 9.** Stochastic realization of  $\alpha_k$  (0) [60, Fig. 2.9].

where  $\hat{\alpha}_k(s) = [\sum_{s'=0}^7 \gamma(s',s)\alpha_{k-1}(s')]/2$  represents the nonnormalized forward recursion. According to the state transition diagram of Figure 4c, the state s=0 can only be reached from the previous states s'=0 and s'=1. Owing to this, the term  $\hat{\alpha}_k(0)$  of (8), is simply  $\hat{\alpha}_k(0) = [\gamma(0,0)\alpha_{k-1}(0) + \gamma(1,0)\alpha_{k-1}(1)]/2$ . Therefore, the stochastic implementation of  $\hat{\alpha}_k(0)$  can be performed by the circuit presented in the blue box of Figure 9, using a pair of 2-input AND gates and a 2-input MUX, as described in Section III-A. JKFFs may be employed for performing the division required for normalizing probabilities, although they are susceptible to the latching problem, as described in Section III-B. Owing to this, the STD of [36] and [60] employs the 32-bit SR-based EMs of Figure 6, as shown in Figure 9. Hence, Equation (8) can be expressed as

$$\alpha_k(s) = \frac{\hat{\alpha}_k(s)}{\hat{\alpha}_k(s) + \sum_{\bar{s} \in [0,7] \setminus \bar{s} = s} \hat{\alpha}_k(\bar{s})} = \frac{J(s)}{J(s) + K(s)}, \quad (9)$$

where  $J(s) = [\hat{\alpha}_k(s)]/8$ ,  $K(s) = [\sum_{\bar{s} \in [0,7] \setminus \bar{s} = s} \hat{\alpha}_k(\bar{s})]/8$  and  $\bar{s} \in [0, 7] \setminus \bar{s} = s$  denotes the exclusion of the state  $\bar{s} = s$  from the set of states  $\bar{s} \in [0, 7]$ . Here, K(s) can be implemented with the aid of stochastic computing using an 8-input MUX with 3 pseudo-random selector bits representing a probability of  $P_{sel} = 1/8$  and with one of the MUX inputs connected to logic 0, as shown in the green box of Figure 9. In addition to this, the factor of 8 division in the computation of J(s)can be performed using an AND gate to multiply  $\hat{\alpha}(s)$  with a BS representing the probability of 1/8. In the first DC, the inputs pertaining the BSs of  $\alpha_{k-1}(s')$  can be initialized based on the best trade-off between BER performance and latency. To elaborate further, our simulations of Section VII suggest that the decoding latency can be reduced when the bits of the BSs of the state metrics  $\alpha_{k-1}(s')$  and  $\beta_k(s)$  are initialized with random bit values. Moreover, the contents of the EM can be initialized as described in Section III-B during the first 32 DCs with a BS representing the probability P = 0.5. The resulting stochastic implementation of (3), for the case

of s = 0 is shown in Figure 9. Here, the inputs of the 8-input MUX are provided by structures similar to that shown in the blue box but corresponding to the other states,  $s \in [1, 7]$ .

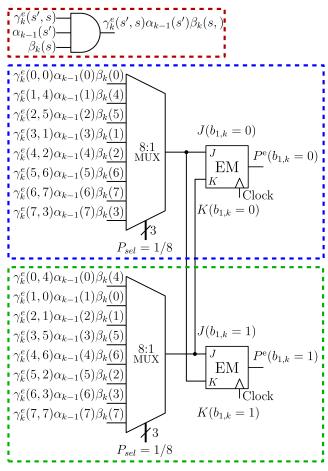

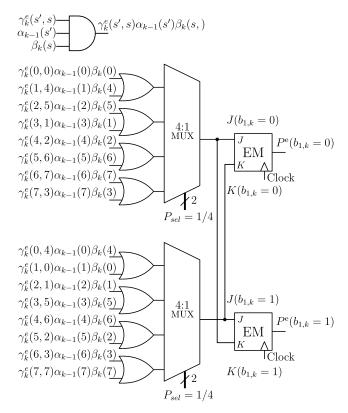

#### C. EXTRINSIC PROBABILITIES

The calculation of the *extrinsic* probabilities of (5) is performed by the module Ext of Figure 7. The stochastic implementation of (5) can be implemented using the circuit of Figure 10.

FIGURE 10. Stochastic realization of the calculation of the extrinsic probabilities in (5) [60, Fig. 2.11].

In the following discussion, the stochastic implementation of the *extrinsic* probabilities of (5) is described for the specific case where  $b_{1,k}(s',s)=0$ , as represented by the blue box in Figure 10. The implementation of (5) for the case where  $b_{1,k}(s',s)=1$  is represented by the green box in Figure 10 and can be performed following the same principles. In analogy to the discussion presented in Section IV-B, (5) can be modified for the case where  $b_{1,k}(s',s)=0$  as

$$P^{e}(b_{1,k} = 0) = \frac{J(b_{1,k} = 0)}{J(b_{1,k} = 0) + J(b_{1,k} = 1)},$$

(10)

where

$$J(b_{1,k} = 0) = \frac{\sum_{\text{all}(s',s) \to (b_1(s',s)=0)} \gamma_k^{\text{e}}(s',s) \alpha_{k-1}(s') \beta_k(s)}{8}$$

and  $J(b_{1,k}=1)=K(b_{1,k}=0)$  correspond to the set of state transitions engendered by the input bits  $b_{1,k}=0$  and  $b_{1,k}=1$ , respectively. According to the state transition diagram of Figure 4c, the input bit  $b_{1,k}=0$  triggers the set of transitions  $(s',s)=\{(0,0),(1,4),(2,5),(3,1),(4,2),(5,6),(6,7),(7,3)\}$ . As a result of this,  $J(b_{1,k}=0)$  can be expressed as

$$J(b_{1,k} = 0) = [\gamma_k^{e}(0,0)\alpha_{k-1}(0)\beta_k(0) + \gamma_k^{e}(1,4)\alpha_{k-1}(1)\beta_k(4) + \gamma_k^{e}(2,5)\alpha_{k-1}(2)\beta_k(5) + \gamma_k^{e}(3,1)\alpha_{k-1}(3)\beta_k(1) + \gamma_k^{e}(4,2)\alpha_{k-1}(4)\beta_k(2) + \gamma_k^{e}(5,6)\alpha_{k-1}(5)\beta_k(6) + \gamma_k^{e}(6,7)\alpha_{k-1}(6)\beta_k(7) + \gamma_k^{e}(7,3)\alpha_{k-1}(7)\beta_k(3)]/8.$$

(11)

Here,  $J(b_{1,k}=0)$  can be implemented with the aid of stochastic computing using a set of 8 3-input AND gates, one for each of the 8 multiplications of (11), and one 8-input MUX for the averaging of the 8 product terms of (11), as shown in the red and the blue box of Figure 10, respectively. In addition to this, the normalization of (11) can be performed using the EM structure of Figure 6 with the input bits  $J=J(b_{1,k}=0)$  and  $K=J(b_{1,k}=1)$ . Similarly to the initialization of the EMs of the state metrics, the contents of the EM in this module can be initialized during the first 32 DCs with a BS representing the probability P=0.5.

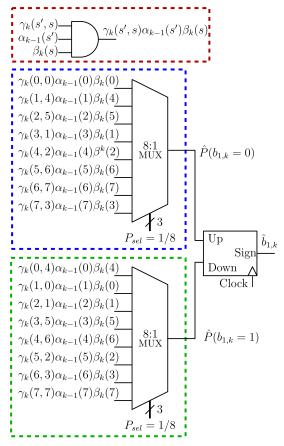

#### D. A POSTERIORI PROBABILITY

The estimation of the decoded bit  $\hat{b}_{1,k}$  of (6) is performed by the module  $\delta$  of Figure 7. This is achieved in stochastic computing with the aid of AND gates and 8-input MUXs, as shown in Figure 11. The circuit of Figure 11 calculates the term  $\hat{P}(b_{1,k}=0)$ , which is proportional to the probability of the bit having the value 0, as shown in the blue box of Figure 11. This can be obtained by analyzing (6) for the case where  $b_{1,k}(s',s)=0$  and with the aid of the state transition diagram of Figure 4c. In this way,  $\hat{P}(b_{1,k}=0)$  can be expressed as

$$\hat{P}(b_{1,k} = 0) = [\gamma_k(0,0)\alpha_{k-1}(0)\beta_k(0) + \gamma_k(1,4)\alpha_{k-1}(1)\beta_k(4) + \gamma_k(2,5)\alpha_{k-1}(2)\beta_k(5) + \gamma_k(3,1)\alpha_{k-1}(3)\beta_k(1) + \gamma_k(4,2)\alpha_{k-1}(4)\beta_k(2) + \gamma_k(5,6)\alpha_{k-1}(5)\beta_k(6) + \gamma_k(6,7)\alpha_{k-1}(6)\beta_k(7) + \gamma_k(7,3)\alpha_{k-1}(7)\beta_k(3)]/8, \quad (12)$$

The stochastic implementation of (12) can be performed with the aid of 8 3-input AND gates, one for each of the 8 multiplications of (12), and one 8-input MUX for the addition of the 8 product terms of (12), as shown in the red and the

FIGURE 11. Stochastic realization of the calculation of the APP [60, Fig. 2.12].

blue box of Figure 11, respectively. The same principle can be applied for the stochastic implementation of  $\hat{P}(b_{1,k} = 1)$ , which is proportional to the probability of the decoded bit being 1, as shown in the green box of Figure 11. Additionally, the estimation of the decoded bit  $\hat{b}_{1,k}$  can be performed with a signed up/down saturated counter, as shown in Figure 11. The up/down counter increments its value if the BS representing  $\hat{P}(b_{1,k} = 0)$  takes the value of 1 and decreases its value if the BS representing  $\hat{P}(b_{1,k} = 1)$  takes the value of 1. The counter will not change its value if  $\hat{P}(b_{1,k} = 0) = \hat{P}(b_{1,k} = 1)$ . Lastly, the counter saturates its value if either the maximum or the minimum count value has been reached. In the STD of [36] and [60], a 4-bit up/down counter with a maximum value of +7 and a minimum value of -8 is employed. The estimation of the decoded bit  $\hat{b}_{1,k}$  is performed in each DC by considering the sign bit of the saturated counter. In this way, if the value of the counter is  $\geq 0$ , the estimated decoded bit is  $\hat{b}_{1,k} = 0$  and 1 otherwise.

# V. TIMING-ERROR TOLERANT STOCHASTIC TURBO DECODER

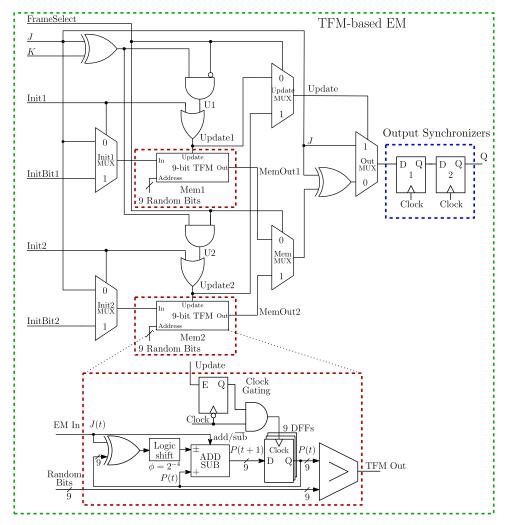

Timing errors in synchronous systems occur when the clock period is not sufficiently long for all the signals to propagate from the output of DFFs, through the combinational logic and to the input of other DFFs. This occurs when techniques such as voltage-scaling or clock-scaling are employed for reducing the energy consumption or increasing the throughput of the system. Furthermore, a reduction in the power supply, owing to voltage scaling or to power supply noise, increases the likelihood of occurrence of processing errors, as a result of the quadratic dependency of propagation delays on the power supply. Whenever a timing error occurs, there is a chance that the affected DFF might enter into a metastable state, in which the digital signals have an indeterminate value that does not correspond to either a logic 0 or 1. However, given sufficient time, the metastable state will randomly evolve to a stable but unpredictable logic value of 0 or 1 [61]. This effectively imposes an additional propagation delay on the affected signal, hence increasing the likelihood of timing errors and metastability occurring at the next DFF. In this way, a single metastable event can trigger subsequent metastability occurrences in successive DFFs, causing catastrophic propagation of metastability that destroys the operation of the entire circuit. Moreover, metastability might cause undesired glitches, logic inconsistency and late transitions [61], which may result in the corruption of the bits stored in the EMs in the context of stochastic decoders, hence severely degrading the error correction capability of the decoder, as our previous work on stochastic LDPC decoders demonstrated [52]. This motivates modifications to the STD of [36] and [60] in order to enhance its tolerance to timing errors by preventing the catastrophic propagation of metastabiliy. In the following sections, we present several novel enhancements to the STD of [36] and [60], which not only improve its tolerance to timing errors, but also significantly improves its latency, throughput, energy efficiency and error correction capabilities in the presence of timing errors caused by power supply variations. In addition to this, we describe how each of these enhancements affects each of the design trade-offs presented in Figure 2. Each of these enhancements is detailed in the following subsections, which will show that they may be implemented by replacing Figure 6 with Figure 12 and Figure 11 with Figure 14.

# A. OUTPUT SYNCHRONIZERS FOR MITIGATING THE CATASTROPHIC PROPAGATION OF METASTABILITY

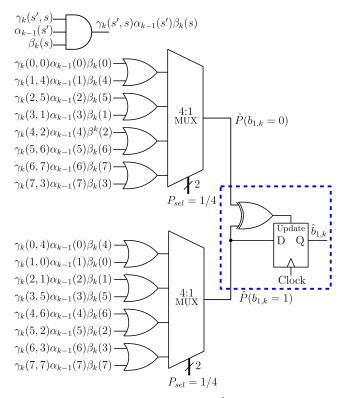

As mentioned above, variations in the power supply increase the likelihood of timing errors and metastability, which may catastrophically propagate through the system and destroy the entire operation of the STD. In order to reduce the probability of metastability cascading through the STD of [36] and [60] owing to timing errors caused by power supply variations, we propose the replacement of the single output DFFs of the STD's  $\alpha$ ,  $\beta$  and Ext blocks shown in Figures 7, 9 and 10, so that they employ the synchronizer circuits of Figure 12, which are comprised of two DFFs, labeled DFF1 and DFF2. Wherever combinational logic is present between two DFFs, the occurrence of metastability in the first DFF increases the likelihood of metastability occurring at the second DFF, potentially causing the catastrophic propagation

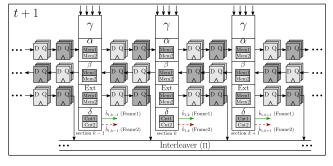

FIGURE 12. Modified TFM-based EM with output synchronizers, relying on two TFMs for concurrently decoding two frames and clock gating.

of metastability, as described above. However, since there is no combinational logic in the path between DFF1 and DFF2 of the synchronizers of Figure 12, the propagation delay associated with this path is negligible, when compared to the clock period. As a benefit of this, if DFF1 enters into a metastable state due to a timing error, the time available for its metastability to be resolved is maximized and the probability of metastability cascading to DFF2 is significantly reduced [62].

The employment of synchronizer circuits is a commonly used technique for preventing the propagation of metastability during the transfer of data between different clock domains in asynchronous systems [62]. However, in our timing analysis presented in Section VII-A, we demonstrate that timing errors will frequently occur if the nominal operating conditions of the STD are reduced below the recommended safety margins for the sake of improving either the throughput or the energy consumption. Timing errors may also occur due to power supply variations. In addition to this, in the stochastic decoding of turbo codes presented in [36] and [60],

up to  $250 \times 10^3$  DCs are needed before a reliable final decision can be obtained. More specifically, our analysis suggests that thousands of metastability events occur during the decoding of each frame, when the STD of [36] and [60] is operated continuously in the presence of power supply variations. This results in a high likelihood of timing errors and metastability occurring and cascading through the circuit, destroying the decoding process and severely affecting the error correction capabilities of the STD, unless synchronizers circuits are employed.

The introduction of the synchronizer circuits enhances the decoding capabilities of the STD in the presence of timing errors caused by power supply variations, as we will demonstrate in Section VII. However, this modification increases the chip area, latency and energy consumption of the STD and reduces its throughput, owing to the increased number of clock cycles required for exchanging each bit of the BSs, as we will show in Section VI. In order to mitigate this throughput reduction, Section V-B describes how the STD can be modified to decode two frames concurrently.

#### B. DECODING OF TWO FRAMES CONCURRENTLY

employment of the synchronizers described in Section V-A mitigates the probability of a single metastability event destroying the entire operation of the STD. However, this modification increases the chip area and increases the number of clock cycles required for exchanging each bit of the BSs, hence increasing both the latency as well as the energy consumption and reducing the throughput of the STD. Nonetheless, these additional clock cycles can be exploited for the concurrent decoding of a second received frame, in order to eliminate the throughput reduction. With this objective in mind, the STD can be modified to process information pertaining to alternate received frames in alternate clock cycles. This is achieved by modifying the EMs in the  $\alpha$ ,  $\beta$  and Ext blocks shown in Figures 7, 9 and 10 for simultaneously storing information pertaining to each of the two received frames. Note that while this eliminates the above-mentioned throughput reduction that is introduced by the synchronizers, this does not eliminate the above-mentioned latency, chip area and energy consumption increases, as we will show in Section VI. Instead, these disadvantages of introducing synchronizers will be eliminated using the techniques described in the following subsections.

The green box of Figure 12 shows how the EM structures of Figures 6, 9 and 10 can be modified for the simultaneous decoding of two frames, by including two independent sets of memories, labeled Mem1 and Mem2, as shown in the red boxes. In this configuration, each set of memories will store information related to a particular decoded frame. Along with the additional memory, we introduce a FrameSelect signal and the logic required for controlling which specific set of DFFs to use in each clock cycle. The FrameSelect signal alternately adopts values of 0 and 1 in alternate clock cycles, alternating the activation of Mem1 and Mem2 for their update and read operations, according to their control signals. More specifically, the contents of Mem1 and Mem2 can be updated or read according to the value of the control signals U1 and Update1, for the case of Mem1, and U2 and Update2 for the case of Mem2. When the FrameSelect signal has a logic value of 0 and  $J \neq K$ , the signals U1 and Update1 adopt the value of 1, whereupon the contents of Mem1 are updated according to the regenerative bit J. In this scenario, the Update signal adopts the value of Update1=1, owing to the UpdateMUX, whereupon the regenerative bit J is passed to the first DFF of the synchronizers through OutMUX. By contrast, when the FrameSelect signal has a logic value of 0 and J = K, the U1 and Update1 signals adopt the value of 0. In this case, the Update signal adopts the value of 0 and a randomly selected bit from Mem1 is xored with J and passed to the first DFF of the synchronizers through MemMUX and OutMUX. The operation of Mem2, for the case when FrameSelect=1, follows the same principle described above. Note that the initialization of each memory can be performed independently from each other and from the value adopted by Frame-Select. This is achieved using the signals Init1 and Init2, which directly dictate the value of Update1 and Update2 and control the initialization multiplexers Init1MUX and Init2MUX, corresponding to Mem1 and Mem2, respectively. Moreover, a memory can be initialized whilst the other memory is being employed during a decoding process. This allows one of the memories to be reset so that it can begin decoding a new frame, even if the other memory is still being used to decode a different frame. As described in Sections IV-B and IV-C, each memory is initialized before the beginning of each decoding process with a BS corresponding to a probability of 0.5.

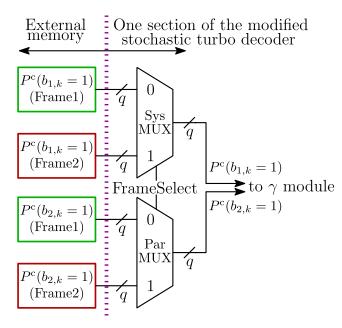

FIGURE 13. External set of systematic and probability probabilities for concurrently decoding two frames.

Along with the inclusion of the additional memories and control logic presented in Figure 12, the STD alternates between providing the corresponding systematic and the parity probabilities related to each of the two received frames. For the purpose of our investigation, we consider these sets of probabilities to be stored in a memory external to the decoder, which are selected according to the value of the FrameSelect signal, as shown in Figure 13. In this configuration, the set of MUXs labeled SysMUX in Figure 13 selects the between the systematic probabilities  $P^{c}(b_{1,k} = 1)$  of the received frames Frame1 and Frame2, when FrameSelect adopts the value of 0 and 1, respectively. Similarly, the received frame of parity probabilities  $P^{c}(b_{2,k} = 1)$  of Frame1 and Frame2 is selected with the aid of the ParMUX, when FrameSelect adopts the value of 0 and 1, respectively. In each clock cycle, the selected probabilities  $P^{c}(b_{1,k} = 1)$  and  $P^{c}(b_{2,k} = 1)$  are provided to the  $\gamma$  module of the corresponding section of the STD.

As described above, the synchronizers and additional EMs increase not only the chip area, but also the energy consumption of the STD. To overcome these problems, we recommend the employment of low-power design techniques. In our investigation, we employ Clock Gating (CG) for reducing the dynamic energy consumption of the Application

Specific Integrated Circuit (ASIC) implementation of the STD, as we will demonstrate in Section VI. More specifically, the dynamic energy consumption of the STD may be reduced by only enabling the clock signal of those specific DFFs, whose contents have to be updated in a particular clock cycle, as shown in Figure 12. More specifically, the clock signal is AND gated with the output of an active-low latch, which is driven by the Update signal, as shown in Figure 12. Moreover, the area used by the clock-gated SR-based EMs will be significantly reduced, as we will show in Section VI, since the feedback MUX used for each DFF in the SR of Figure 6 will no longer be required. Instead, the DFFs will update their contents only when their clock signal is enabled, maintaining their current value otherwise. Furthermore, the associated propagation delays of the EMs are reduced, owing to the reduced fanout load of the Update signals [52]. More specifically, the Update signal in the EM of Figure 6 has a fanout load of 32 Multiplexers, compared to a fanout load of a single latch in the clock-gated EMs of Figure 12.

Note however that CG does not mitigate the additional static energy consumption that is associated with the additional set of EMs. In order to overcome this static energy increase, the STD may employ other low-power design techniques, such as power gating or multiple- and variablethreshold transistor design, although this is achieved at the cost of increasing the complexity of the design. As an example of this, power gating may be employed for switching off specific blocks of the STD, when they are not being operated. However, state retention registers are required for restoring the state of the blocks upon power-up. Owing to this overhead, power gating is only effective, when specific blocks may be switched off for a significant amount of time. Motivated by this, our future work will conceive techniques for applying early-stopping to different blocks at different stages in the iterative decoding process. However, in the meantime, the low-power design techniques presented in this paper focus only on the reduction of the STD's dynamic energy consumption.

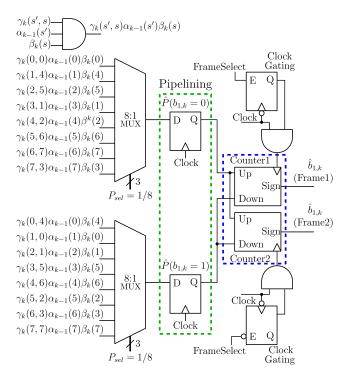

When decoding two frames concurrently, the STD is required to estimate two sets of decoded bits  $b_{1,k}$ . Owing to this, an additional up/down counter is introduced in the  $\delta$  module of Figures 7 and 11 for providing two independent decoded bits pertaining the two independent decoding process of Frame1 and Frame2, as shown in the blue boxes of Figure 14. In this configuration, two clock-gating latches are employed for updating the counters labeled Counter1 and Counter2. More specifically, the contents of Counter1 determines the decoded bit  $b_{1,k}$  of the decoded frame Frame 1 and is only updated when FrameSelect=1. By contrast, the decoded bit  $b_{1,k}$  for the case of the decoded frame Frame2 is determined when FrameSelect=0. As part of the tradeoff analysis of the hardware implementation of the STD presented in Section VI, we will demonstrate that the chip area, latency, throughput and energy consumption of the STD is not significantly affected by the introduction of the additional counter.

FIGURE 14. Modified stochastic realization of the calculation of the APP for concurrently decoding two frames.

#### C. TRACKING FORECAST MEMORY-BASED EDGE MEMORIES IN STOCHASTIC TURBO DECODERS

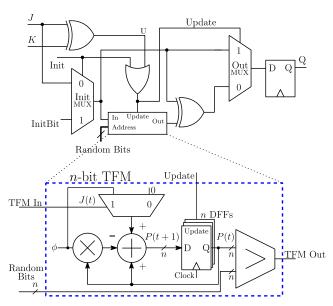

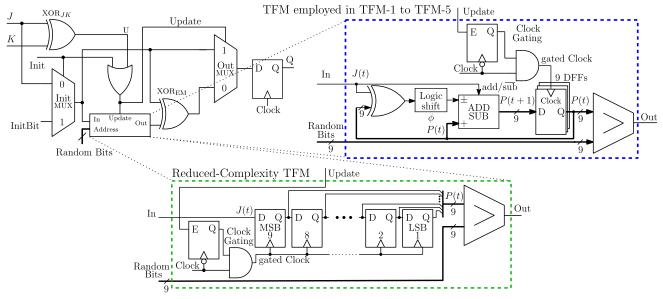

As described in Section V-B, the introduction of the additional EMs for the concurrent decoding of two received frames increases the chip area, latency and energy consumption of the STD. These problems can be overcome by the employment of Tracking Forecast Memory (TFM)based EMs, whilst enhancing the error correction capability of the STD in the presence of timing errors, as we will demonstrate in Sections VI and VII. The employment of SR-based [24], [26] and TFM-based [27], [30] EMs has been proposed in order to overcome the latching problem in stochastic LDPC decoders. However, in the STD of [36] and [60], only SR-based EMs have been previously employed. In this work, we demonstrate for the first time that the employment of TFM-based EMs, as shown in the lower part of Figure 12, is also beneficial in stochastic turbo decoding.

The TFM-based EM of Figure 15 was proposed in [27]. Here, the m-bit SR of Figure 6 is replaced by an n-bit TFM, which stores a fixed-point binary number to quantify a moving average probability of the regenerative bit J assuming the value 1. This is achieved by considering the previous bits of BSs, but placing special emphasis on the most recent bits, as detailed in [27]. More specifically, TFMs employ a decaying mechanism to ensure that only the most recent regenerative bits are considered for the calculation of the stored probability P(t+1), which is calculated with the aid of the relaxation parameter  $\phi$  for determining the significance given to the most recent regenerative bit J.

FIGURE 15. Architecture of TFM-based EMs, as proposed in [27].

As in the SR-based EM, when  $J \neq K$  in Figure 15, the fixed-point probability  $P(t + 1) \in [0, 1]$  of the TFM in time t + 1 is updated according to:

$$P(t+1) = (1 - \phi)P(t) + \phi J(t), \tag{13}$$

where  $\phi \in (0, 1)$  is the relaxation parameter, which can be chosen to optimize the BER performance of the stochastic LDPC decoder, and  $J(t) \in \{0, 1\}$  is the regenerative bit. By contrast, when J = K, the output of the TFM-based EM is determined by comparing the n-bit probability P(t) to an n-bit pseudo-random number. If the probability stored by the TFM is larger than or equal to the random number, the outgoing bit is set to 1, otherwise it is set to 0.

Considering that J can only take the value of 0 or 1 at any given time, (13) can be modified as follows:

$$P(t+1) = (1 - \phi)P(t) + \phi J(t)$$

$$= P(t) - \phi P(t) + \phi J(t)$$

$$= P(t) + \phi [J(t) - P(t)].$$

which can be further simplified as

$$P(t+1) = \begin{cases} P(t) - \phi P(t) & J(t) = 0\\ P(t) + \phi \bar{P}(t) & J(t) = 1, \end{cases}$$

(14)

where  $\bar{P}(t) = 1 - P(t)$  is the complementary probability of P(t). As a benefit of this, the two adders of the TFM of Figure 15 are substituted by a single adder/subtractor, where the complementary probability  $\bar{P}(t)$  can be obtained using XOR gates, if P(t) is stored as an unsigned fixed-point number. Meanwhile, the multiplication  $\phi \cdot P(t)$  can be readily implemented using a hard-wired logical shift, if the relaxation parameter  $\phi$  is chosen as a negative power of 2, as shown in the lower red box of Figure 12. According to (14), the complementary probability  $\bar{P}(t)$  is only necessary if J(t) = 1.

This functionality can be implemented with the aid MUXs and NOT gates, with the selector bits of the MUXs adopting the value of J, as described in [30]. Alternatively, the same functionality can be obtained with 2-input XOR gates, with one of the inputs adopting the value of J and the other input connected to the individual bits of P(t), as shown in the lower part of Figure 12. Additionally, the add/sub signal determines, whether an addition or a subtraction will be performed by the ADD/SUB block, when J = 1 and J = 0, respectively. The *n*-bit fixed-point comparator is employed for determining the outgoing bit when  $J \neq K$ , with TFMOut adopting the value of 1 if the probability stored in the TFM is larger than or equal to the *n*-bit pseudo-random number. Finally, at the start of the STD decoding process, each TFM is initialized to store the probability P = 0.5, which can be achieved in a single clock cycle by setting the Most Significant Bit (MSB) of each TFM to logic 1 and the rest of the bits to logic 0. This single clock cycle compares favorably to the 32 clock cycles required to initialize the SR Figure 6 with a given BS. The employment of TFMs in EMs effectively reduces the chip area requirements and energy consumption of the STDs, when compared to the employment of SRs in EMs in the STD of [36] and [60]. More specifically, for the proposed modifications, we recommend the employment of 9-bit TFMs, with a relaxation parameter  $\phi = 2^{-4}$ . As a result of this, the proposed TFM-based EMs can be realized by using only 9 DFFs, compared to the 32 DFFs required in the SR-based EMs of [36] and [60]. Moreover, the SR's 32 to 1 MUX of Figure 6 can be replaced with 9-bit fixedpoint comparators.

In addition to the advantages described above, TFMs are capable of tracking changes in the regenerative bit's probability more accurately than SRs, as detailed in [30]. This effectively reduces the number of DCs required for successfully decoding a frame when TFMs are employed, hence eliminating the potential latency increase resulting from the employment of the synchronizers of Section V-A Similarly, TFM-based EMs facilitate the use of lower clock periods than SR-based EMs, as Section VII will show. This may be attributed to the relatively low complexity of the TFMs, as well as to the relatively low fanout loads imposed on their Update signal. Owing to this, the proposed TFMs-based EMs offer a desirable trade-off between chip area, energy efficiency, latency, throughput and decoding performance, as Sections VI and VII will show. Figure 12 illustrates the resultant TFM-based EM circuit, relying on synchronizers, two sets of EMs and CG.

#### D. PIPELINING

The role of the  $\delta$  module of Figure 7 is to compute the APP and to make the final decision for the decoded bit  $\hat{b}_k$  output by the STD. Owing to this, the occurrence of a timing error within this module, caused by power supply variations, might lead to an incorrect decision for a decoded bit, hence severely affecting the error correction capability of the STD. Furthermore, our timing analysis presented in Section VII-A

revealed that timing errors are more likely to occur in the Ext and  $\delta$  modules of Figure 7, owing to their long critical paths. In order to overcome this problem, we propose the employment of a pipelining stage consisting of two DFFs placed in parallel, as shown in the green box of Figure 14. The additional DFFs break the combinational path that ends at the saturated counter. This reduces the time required for signals to propagate, hence reducing the occurrence of timing errors within the computation of the APP and improving the STD's error correction capability, as we will show in Section VII-B. Moreover, the employment of a pipeline stage does not impose a significant hardware overhead, as we will show in Section VI, since only two DFFs per decoded bit are employed. Similarly, the throughput and energy consumption of the STD are only slightly degraded, since the decision for the decoded bit  $\hat{b}_{1,k}$  is only delayed by one DC.

FIGURE 16. Data scheduling of the modified STD.

The data flow of the modified STD is illustrated in Figure 16, where each set of light-shaded and dark-shaded blocks and DFFs store information pertaining the decoding frames Frame1 and Frame2, respectively. In the upper part of Figure 16, the first set of memories Mem1 can represent either SR-based or TFM-based EMs. These EMs and the first DFF of the synchronizers will update their contents according to the bit of the BS resulting from the decoding process of Frame 1 at time t. In time t + 1, the contents of the second DFFs of the synchronizers will contain the stochastic bit generated at time t and pertaining Frame1, owing to the synchronizers shifting their contents to the following DFF, as shown in the dark-shaded DFF of the lower part of Figure 16. In this same manner, the contents of Mem2 and the first DFFs of the synchronizers will update their value according to the decoding process of Frame2 in time t + 1, as shown in the light-shaded DFFs of the lower part of Figure 16. Note that Counter1 is enabled one time instant after Mem1 is enabled, owing to the introduction of the pipelining stage. This is represented with a green solid line in the lower part of Figure 16. Alternatively, a red dashed line in Figure 16 represents either Counter1 or Counter2 in idle mode, in which their contents are not updated and no new estimation of  $\hat{b}_{1,k}$  is made for that particular frame.

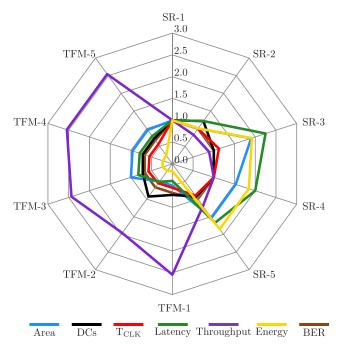

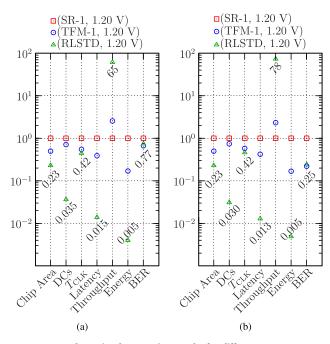

FIGURE 17. Hardware implementation results of the modified STD schemes. The presented results are normalized relative to SR-1, when  $V_{DD}=1.2\ V$  and  $E_b/N_0=3.0\ dB$ .

# VI. TRADE-OFF ANALYSIS OF THE HARDWARE IMPLEMENTATIONS OF THE TIMING-ERROR TOLERANT STOCHASIC TURBO DECODER

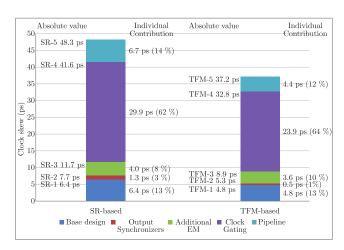

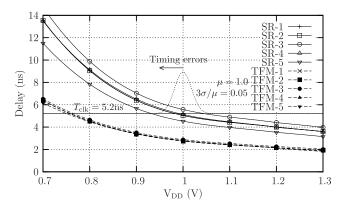

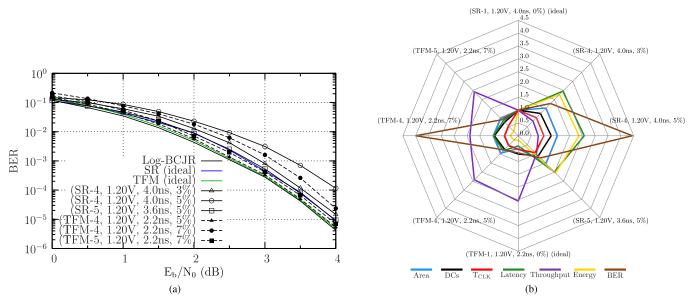

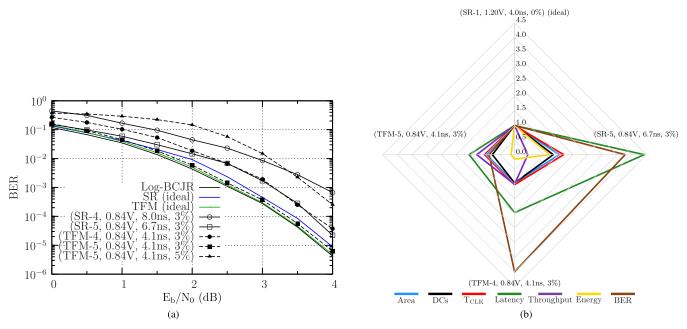

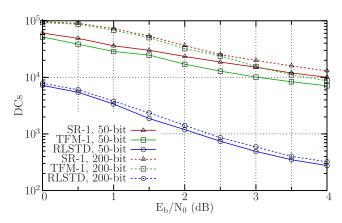

This section presents the different hardware trade-offs of various STD implementations. Table 1 characterizes the STD improvements of Section V in terms of diverse characteristics, including: the chip area per decoded bit, number of equivalent NAND gates, average number of DCs required for successfully decoding a frame, when employing early stopping, minimum clock period, latency, throughput and processing energy consumption per decoded bit, when using TSMC 90 nm technology. These results are obtained for the implementation of an 8-state, 50-bit, rate 1/3, tailbiting STD using an S-Random interleaver and the state-transition diagram of Figure 4c, as presented in [36]. Additionally, we employ NDS with  $\eta = 1$  and  $\psi = 2$ , as described in Section III-B. Each scheme presented in Table 1 and in Figure 17 corresponds to the successive inclusion of each of the improvements described in Section V, with SR-1 being the state-of-the-art STD of [36]. More specifically, SR-2 corresponds to the introduction of output synchronizers

| TABLE 1. Hardware implementation results of the STD when operated | at $E_b/N_0 = 3$ | .0 dB. |

|-------------------------------------------------------------------|------------------|--------|

|-------------------------------------------------------------------|------------------|--------|

| Scheme   | Improvement   | Chip area per decoded bit | Average<br>DCs     | V <sub>DD</sub> (V) | T <sub>CLK</sub> (ns) | Latency (μs) | Throughput (Kbps) | Energy (nJ/bit) |

|----------|---------------|---------------------------|--------------------|---------------------|-----------------------|--------------|-------------------|-----------------|

| CD 1     | B 1 1         | $0.0260 \; \mathrm{mm}^2$ | 14 103             | 1.20                | 4.0                   | 56           | 892               | 335             |

| SR-1     | Benchmark     | 8617 gates                | $14 \times 10^3$   | 0.84                | 8.0                   | 112          | 446               | 164             |

| SR-2     | Crmoheonizaea | $0.0260 \; \mathrm{mm}^2$ | $17 \times 10^{3}$ | 1.20                | 4.0                   | 68           | 735               | 337             |

| SK-2     | Synchronizers | 8744 gates                | 17 × 10°           | 0.84                | 8.0                   | 136          | 367               | 165             |

| SR-3     | Extra EMs     | $0.0495 \text{ mm}^2$     | $14 \times 10^3$   | 1.20                | 4.5                   | 126          | 793               | 643             |

| SK-3     | Extra EMS     | 15505 gates               | 14 × 10            | 0.84                | 8.6                   | 240          | 415               | 315             |

| SR-4     | Clock Gating  | $0.0397 \text{ mm}^2$     | $14 \times 10^3$   | 1.20                | 4.0                   | 112          | 892               | 620             |

| SIC-4    |               | 12853 gates               | 14 × 10            | 0.84                | 7.6                   | 212          | 469               | 303             |

| SR-5     | Pipeline      | $0.0397 \text{ mm}^2$     | $13 \times 10^{3}$ | 1.20                | 3.6                   | 93           | 1068              | 621             |

| SK-3     |               | 12933 gates               | 13 × 10            | 0.84                | 6.7                   | 174          | 574               | 304             |

| TFM-1    | TFM-based     | $0.0129 \text{ mm}^2$     | $10 \times 10^3$   | 1.20                | 2.2                   | 22           | 2272              | 55              |

| I FIVI-I |               | 4596 gates                | 10 × 10°           | 0.84                | 4.1                   | 41           | 1219              | 27              |

| TFM-2    | Synchronizers | $0.0129 \text{ mm}^2$     | $13 \times 10^{3}$ | 1.20                | 2.2                   | 28           | 1748              | 66              |

| 11.101-7 |               | 4724 gates                |                    | 0.84                | 4.1                   | 53           | 938               | 32              |

| TFM-3    | Extra EMs     | $0.0250 \; \mathrm{mm}^2$ | $10 \times 10^{3}$ | 1.20                | 2.3                   | 46           | 2173              | 88              |

| 11 W-3   |               | 8817 gates                | 10 × 10            | 0.84                | 4.2                   | 84           | 1190              | 45              |

| TFM-4    | Clock Gating  | $0.0250 \; \mathrm{mm}^2$ | $10 \times 10^{3}$ | 1.20                | 2.2                   | 44           | 2272              | 77              |

| 11 141-4 |               | 8516 gates                | 10 \ 10            | 0.84                | 4.1                   | 82           | 1219              | 37              |

| TFM-5    | Pipeline      | $0.0250 \; \mathrm{mm}^2$ | $10 \times 10^3$   | 1.20                | 2.2                   | 44           | 2272              | 77              |

| 11.01.5  | 1 ipenne      | 8531 gates                |                    | 0.84                | 4.1                   | 82           | 1219              | 37              |

into SR-1; SR-3 refers to the introduction of the additional set of EMs into SR-2 to enable the concurrent decoding of two frames; SR-4 corresponds to the introduction of CG into SR-3 and finally, SR-5 refers to the introduction of the pipelining stage into SR-4. The schemes TFM-1 to TFM-5 present the TFM-based STDs counterparts of SR-1 to SR-5, with TFM-5 being the modified STD employing all enhancements proposed in Section V.

The results of Table 1 were obtained from the physical layout generated by the automatic place and route of the above mentioned STDs using Cadence SoC Encounter. The results of chip area per decoded bit were obtained from the layout of the  $\gamma$ ,  $\alpha$ ,  $\beta$ , Ext and  $\delta$  modules of Figure 7, where the  $\gamma$  module includes q=7-bit fixed point comparators for converting the probabilities provided by the channel into BSs. Additionally, the results of Table 1 were obtained for the cases, where the supply voltage of the STDs is set to either 1.20 V or 0.84 V, in the absence of power supply variations. Both the critical clock period and the energy consumption of the STDs are obtained from Synopsys PrimeTime. The average number of DCs, latency, throughput and energy efficiency results were obtained from post-layout gate-level simulations, with extracted parasitics and annotated delays without timing errors, when allowing a maximum of 10<sup>5</sup> DCs and using early stopping, as described in Section II. We assume that a fully-parallel Cyclic Redundancy Check (CRC) [63] is employed in each DC for determining whether the frame of estimated decoded bits provided by the STDs contains any errors. Although the corresponding hardware characteristics are not considered in Table 1, they may be considered to have only a negligible effect, as detailed in [64]. We also assume that the different STDs operate at their critical clock period, for the case of BPSK communication over an AWGN channel and an SNR per bit of  $E_b/N_0=3.0~\mathrm{dB}$ . The notation (Scheme,  $V_{DD}$ ,  $T_{CLK}$ ) will be used in the following sections in order to simplify the discussion of the results. In addition to Table 1, Figure 17 presents the hardware implementation trade-offs associated with each scheme of Table 1, relative to the benchmark scheme SR-1, when the various different STDs operate at  $V_{DD}=1.2~\mathrm{V}$ . Note that similar trends were found for the case when  $V_{DD}=0.84~\mathrm{V}$ .

We begin our discussion by analyzing the impact of each enhancement in the hardware implementation of the STD. This is followed by a comparison of the different hardware implementation trade-offs of SR-based and TFM-based STDs.

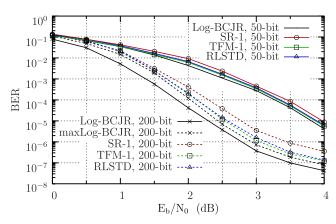

As discussed in Section V-A as well as confirmed in Table 1 and Figure 17, the employment of synchronizers increases the average number of DCs, latency and energy consumption and reduces the throughput of the STDs. This can be observed when comparing the SR-2 and TFM-2 schemes to the SR-1 and TFM-1 arrangements of Table 1 and Figure 17, respectively. More specifically, observe in the fourth column of Table 1 that SR-2 requires an average of  $17 \times 10^3$  DCs for successfully decoding a frame, compared to the  $14 \times 10^3$  required in SR-1, when these schemes are operated at  $E_b/N_0 = 3.0$  dB and achieve a BER of  $4.6 \times 10^{-4}$ , as we will show in Section VII-B. Likewise, TFM-2 requires an average

of  $13 \times 10^3$  DCs, compared to  $10 \times 10^3$  DCs required by TFM-1 to achieve a BER of  $2.8 \times 10^{-4}$  at  $E_b/N_0 = 3.0$  dB, which is the same BER that is achieved by the ideal floating-point Logarithmic BCJR (LogBCJR) implementation employing 8 iterations. These differences are explicitly visualized in Figure 17.

The inclusion of the additional EMs for concurrently decoding two frames increases the chip area, extends the latency of the STDs, increases the energy consumption, but facilitates an increased throughput, as observed for the schemes SR-3 and TFM-3 of Table 1 and Figure 17, when compared to SR-2 and TFM-2, respectively. As seen in Table 1, the average numbers of DCs required by schemes SR-3 and TFM-3 are identical to those of SR-1 and TFM-1, respectively. However, the latency of SR-3 and TFM-3 is increased, when compared to SR-2 and TFM-2, respectively. This may be attributed to the decoding process of SR-3 and TFM-3 is completed in alternate clock cycles. Despite the increased latency, SR-3 and TFM-3 exhibit an increased throughput, when compared to SR-2 and TFM-2, respectively, owing to the simultaneous decoding of two frames, as detailed in Section V-B. Similarly, SR-3 and TFM-3 exhibit an increased energy consumption owing to the additional EMs, when compared to SR-2 and TFM-2, respectively.

As detailed in Section V-B as well as observed in Table 1 and Figure 17, the employment of clock gating in SR-4 and TFM-4, reduces the chip area, the latency and the energy consumption and increases the throughput of the STDs, when compared to SR-3 and TFM-3, respectively. Particularly, the chip area reduction of SR-4 may be attributed to the elimination of the 32 MUXs needed in the SRs, as described in Section V-B. By contrast, only the equivalent number of NAND gates of TFM-4 is slightly reduced, when compared to TFM-3. Additionally, as explained in Section V-D, the inclusion of the pipelining stage does not significantly increase the area requirements of the STDs and does not extend the latency. As a result of this, the employment of clock gating and the pipelining stage facilitates lower clock periods, which is reflected in the improved latency, throughput and energy consumption of SR-4 and SR-5, when compared to SR-3, as well as of TFM-4 and TFM-5, when compared to TFM-3.