# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

User-Experience-Aware System Optimisation for Mobile Systems

by

Alexander S. Bischoff

Thesis for the degree of Doctor of Philosophy

January 2016

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING Electronics and Computer Science

#### Doctor of Philosophy

#### USER-EXPERIENCE-AWARE SYSTEM OPTIMISATION FOR MOBILE SYSTEMS

by Alexander S. Bischoff

This thesis considers the concept of Quality of Experience (QoE) in the context of mobile electronic consumer devices, such as smartphones. The modern smartphone is expected to deliver a high level of user experience across a wide variety of tasks, whilst remaining as power efficient as possible. Commonly, mobile devices undergo runtime optimisation to achieve the required level of performance, with the energy consumption being a secondary concern. In this thesis, we stress that it is vital to not focus on the raw performance of the device, but instead to concentrate on the needs and desires of the end user. This approach ensures that the end-user is satisfied at all times, and that the power consumption for a given level of user experience is minimised. Hence, we advocate user-experience-aware system optimisation.

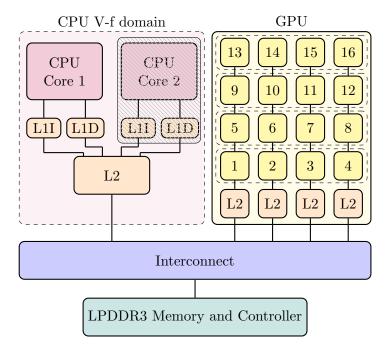

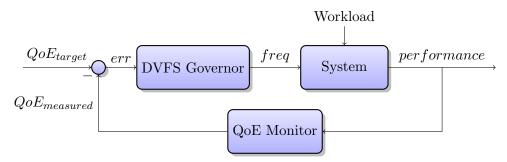

We introduce the concept of Quality of Experience, which has traditionally been used only in the telecommunications industry, to mobile system optimisation. We develop user experience models in the form of utility functions, and use these to translate lowlevel metrics into the delivered user experience. Upon these models we build simple, yet effective, QoE-aware Central Processing Unit (CPU) and Graphics Processing Unit (GPU) governing algorithms which adjust the performance and power consumption at runtime to meet user experience requirements. When creating our algorithms, we first analyse and characterise the operation of both CPU and GPU workloads. Specifically, we investigate how the level of compute-boundedness or memory-boundedness of CPU workloads affects frequency scalability, as well as determining how the available bandwidth and core count for a GPU affects the rendering performance. We combine both gem5-based simulation driven analysis and hardware-based verification in order to validate our QoE-aware governing algorithms. Additionally, we validate the operation of our algorithms using a variety of common mobile workloads. As part of this work, we have also extended the gem5 simulator to allow use to investigate the potential for finegrained Dynamic Voltage and Frequency Scaling (DVFS) adjustment, and use this as a platform to investigate the operation of the Linux CPUFreq governors used on modern mobile platforms.

# Contents

| D | eclar | ation of Authorship xii                                             |

|---|-------|---------------------------------------------------------------------|

| A | ckno  | wledgements                                                         |

| N | omei  | nclature xvi                                                        |

| 1 | Inti  | roduction                                                           |

|   | 1.1   | Research Statement                                                  |

|   | 1.2   | Research Questions                                                  |

|   | 1.3   | Experimental Setup                                                  |

|   | 1.4   | Thesis Outline                                                      |

| 2 | Lite  | erature Review 19                                                   |

|   | 2.1   | Measuring User Experience                                           |

|   | 2.2   | Optimising for User Experience                                      |

|   | 2.3   | Optimising for Performance and Energy Efficiency                    |

|   | 2.4   | Concluding Remarks                                                  |

| 3 | Une   | derstanding and Modelling User Experience 28                        |

|   | 3.1   | Quality of Experience                                               |

|   | 3.2   | Types of Workload                                                   |

|   | 3.3   | Determining System-Level QoE                                        |

|   | 3.4   | Measuring User Experience for CPUs and GPUs                         |

|   | 3.5   | Concluding Remarks                                                  |

| 4 | Cha   | aracterising CPU Efficiency 43                                      |

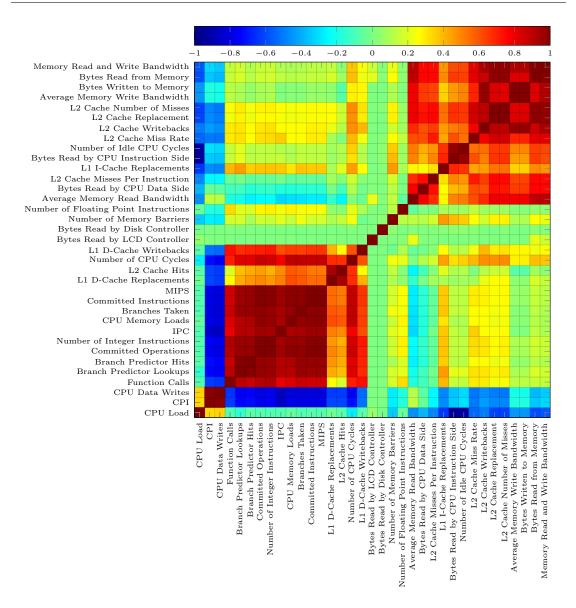

|   | 4.1   | Profiling CPU Traffic                                               |

|   | 4.2   | CPU Workload Frequency Sensitivity                                  |

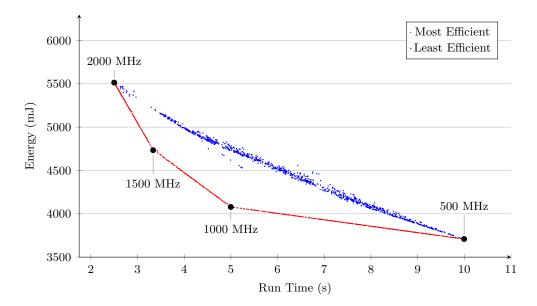

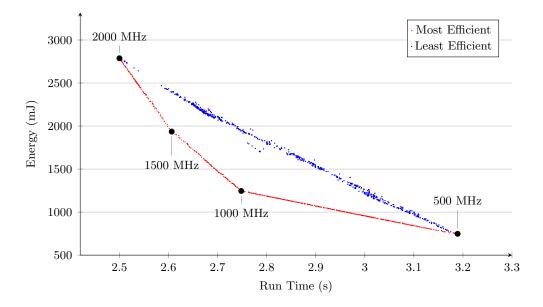

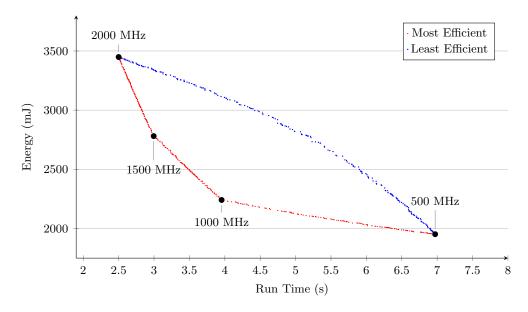

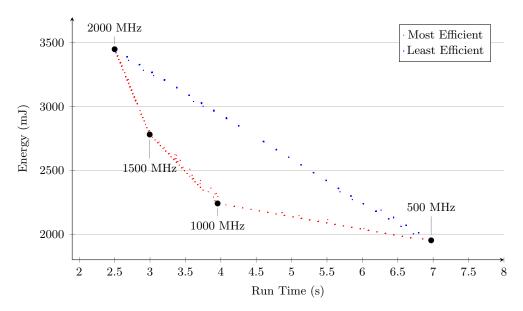

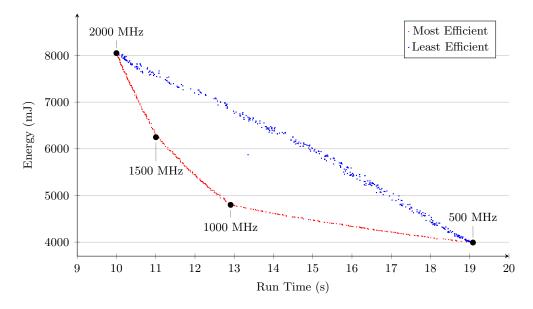

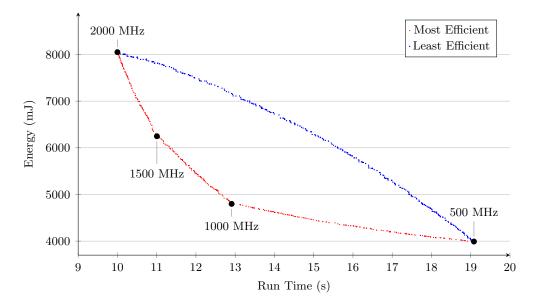

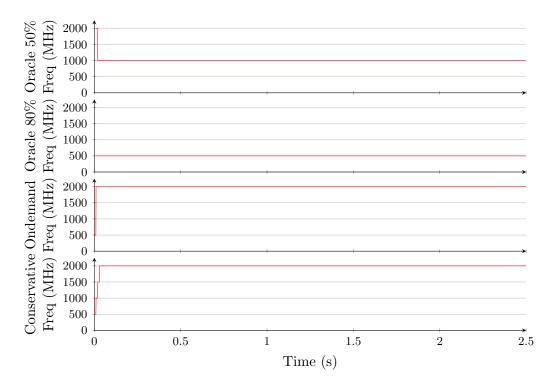

|   | 4.3   | Fine-Grained Workload Analysis                                      |

|   | 4.4   | Visualising the Pareto Frontier                                     |

|   | 4.5   | Concluding Remarks                                                  |

| 5 | Opt   | simising for CPU User Experience 7'                                 |

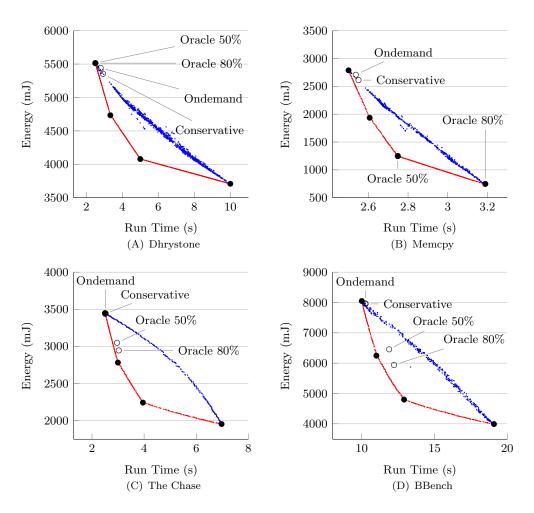

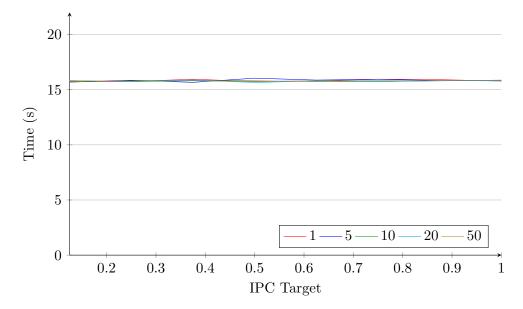

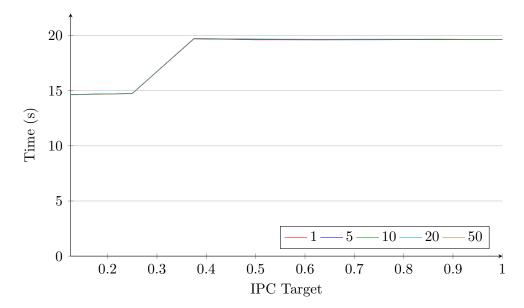

|   | 5.1   | CPUFreq Governor Analysis and Oracle Governing                      |

|   | 5.2   | Adjusting CPU DVFS based on QoE 8'                                  |

|   | 5.3   | Linking High- and Low-level Performance                             |

|   | 5.4   | Uniting CPU Efficiency, Application Performance and User Experience |

|   |       | on Real Hardware                                                    |

vi CONTENTS

|              | 5.5         | Concluding Remarks                                                |

|--------------|-------------|-------------------------------------------------------------------|

| 6            | Opt         | imising Complete System User Experience 109                       |

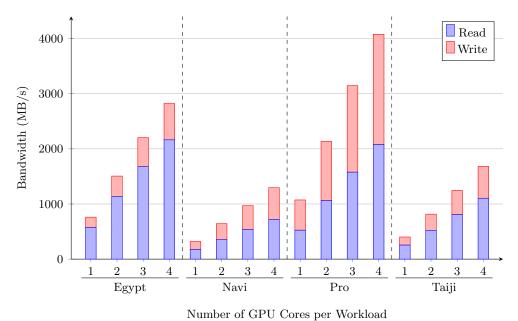

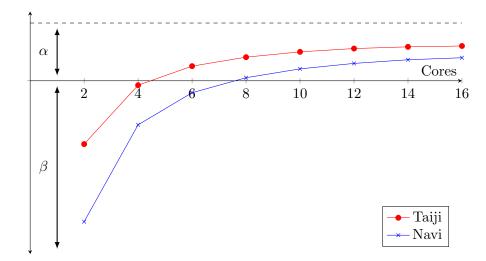

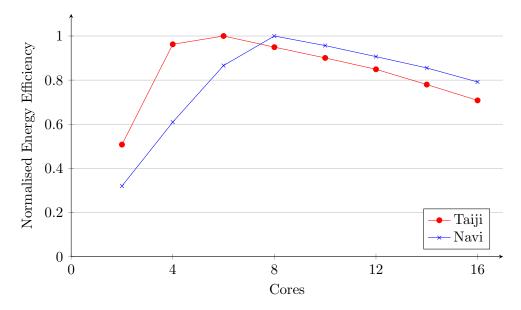

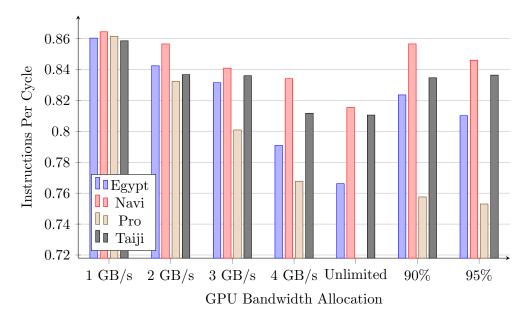

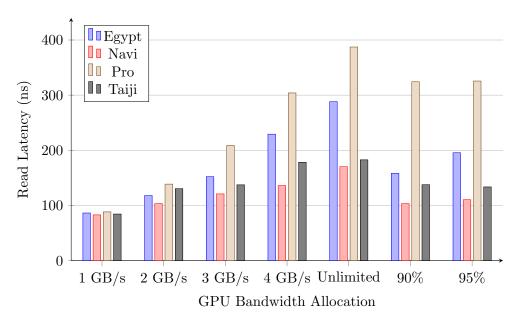

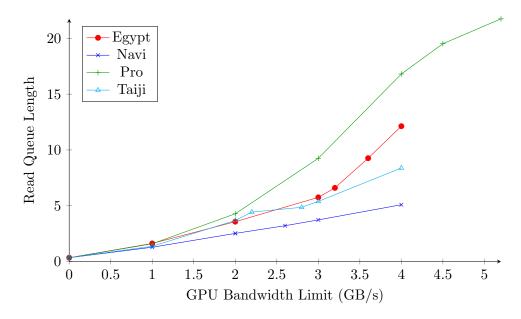

|              | 6.1         | Analysing and understanding the operation of the GPU              |

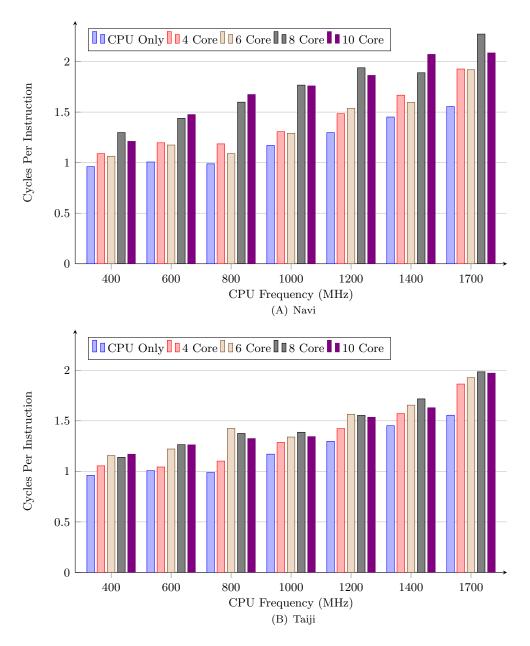

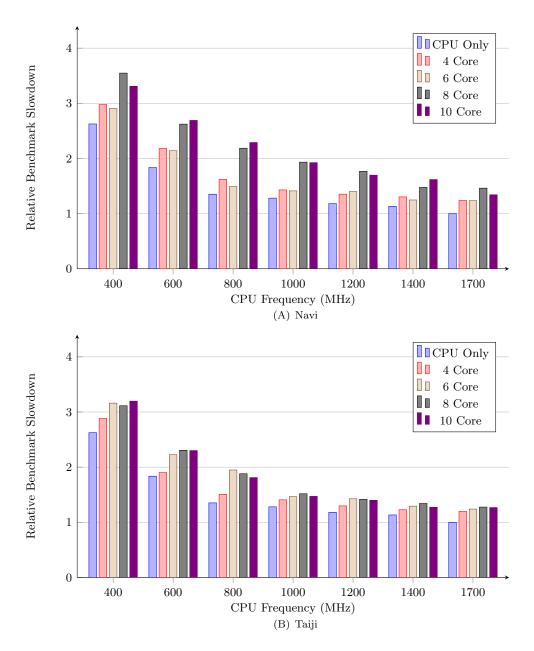

|              | 6.2         | Performance Trade-offs: Trading GPU for CPU                       |

|              | 6.3         | Picking the correct combination of CPU and GPU configurations 122 |

|              | 6.4         | GPU Governing                                                     |

|              | 6.5         | CPU and GPU Governing                                             |

|              | 6.6         | System Governing                                                  |

|              | 6.7         | Concluding Remarks                                                |

| 7            | Con         | clusions 147                                                      |

|              | 7.1         | Research Questions and Answers                                    |

|              | 7.2         | Future Work                                                       |

| A            | For         | king Infrastructure 161                                           |

|              | <b>A.</b> 1 | Comparing the Simulated Intervals                                 |

|              | A.2         | Forking Algorithm                                                 |

| $\mathbf{B}$ | Sou         | rce Code Listings 165                                             |

|              | B.1         | DVFS Governors                                                    |

|              | B.2         | Kernel                                                            |

| Re           | efere       | nces 175                                                          |

# List of Figures

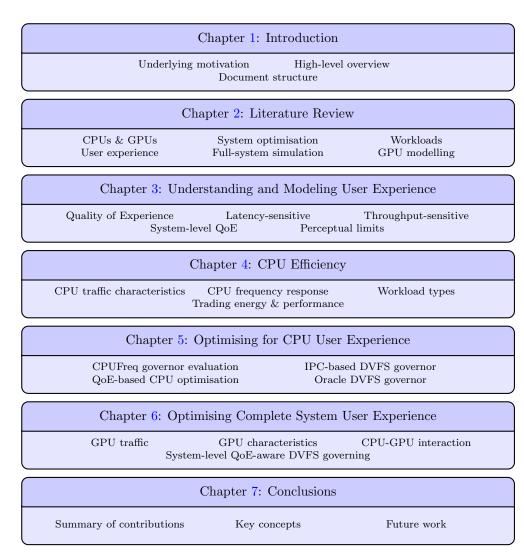

| 1.1<br>1.2 | Odroid XU3 by Hardkernel. Image from Pollin.de (2015)                                                                                                                                                               | 8<br>13 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

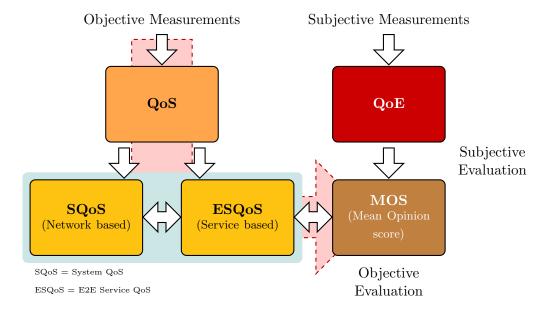

| 2.1        | Relationship between QoS, SQoS, ESQoS, QoE and MOS as presented by Soldani et at. (Soldani, 2010). Re-drawn from aforementioned publication.                                                                        | 16      |

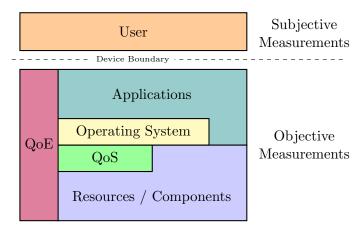

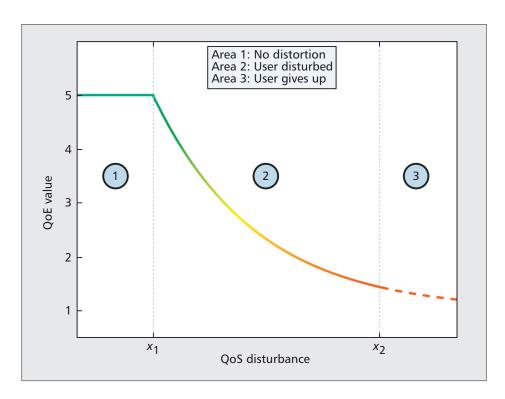

| 3.1<br>3.2 | Relationship between QoS, QoE, user requirements and system resources. General shape of the mapping curve between QoS and QoE as presented by Fiedler et al. (2010). The figure has been directly copied from their | 26      |

|            | publication without alteration                                                                                                                                                                                      | 30      |

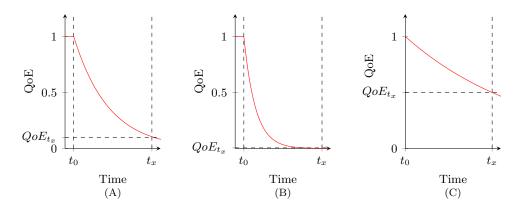

| 3.3        | Calculating QoE for a latency workload                                                                                                                                                                              | 32      |

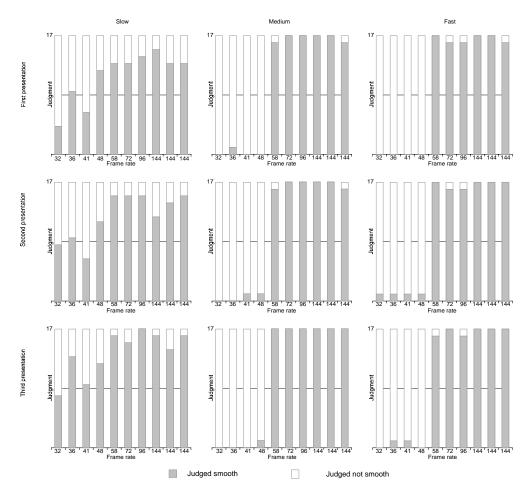

| 3.4        | Summed results of the judgements in the user experiment for each judgement attempt and each speed as presented by Krause et al. (2008). The                                                                         |         |

| 2 5        | figure has been directly copied from their publication without alteration.                                                                                                                                          | 33      |

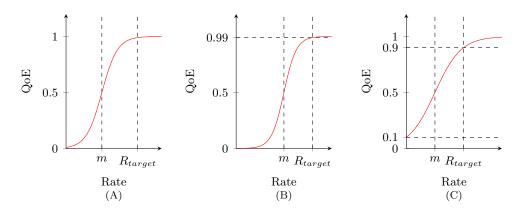

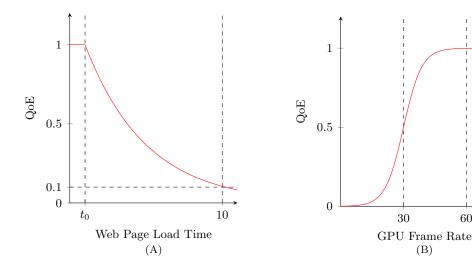

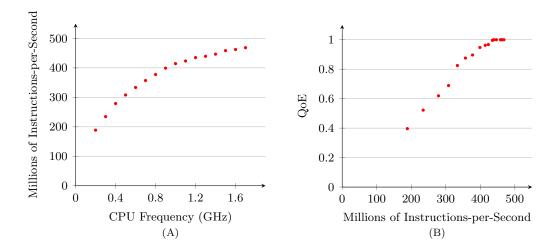

| 3.5<br>3.6 | Calculating QoE for a throughput workload                                                                                                                                                                           | 34      |

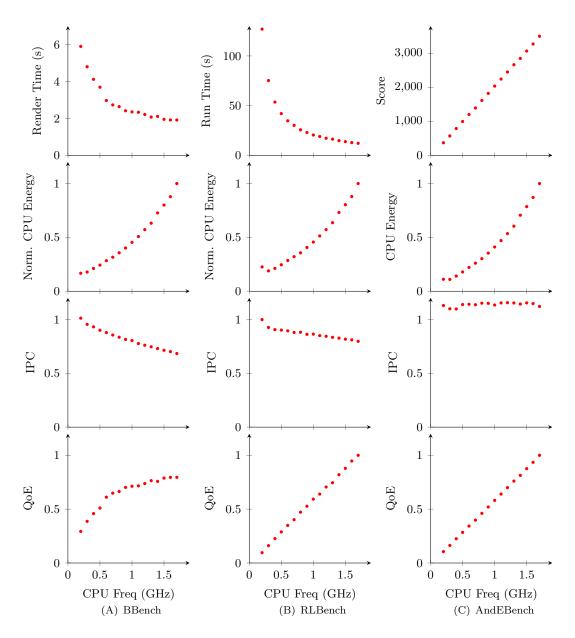

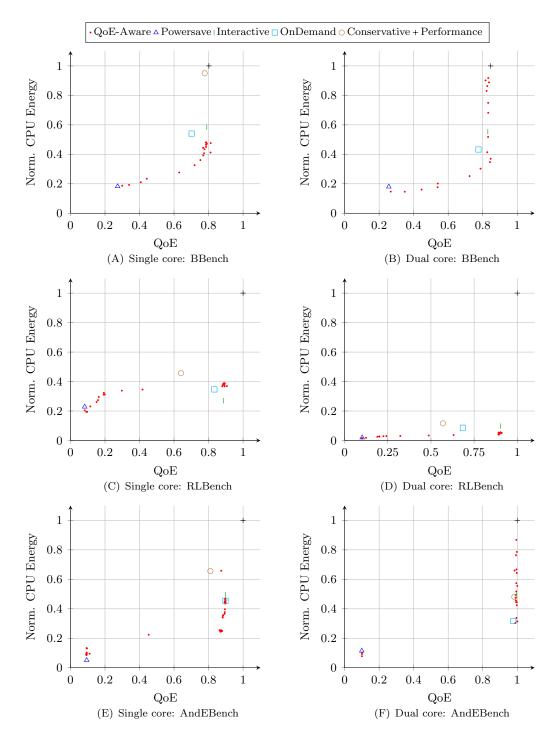

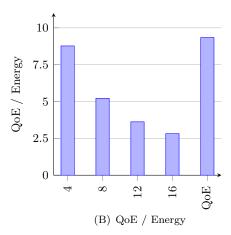

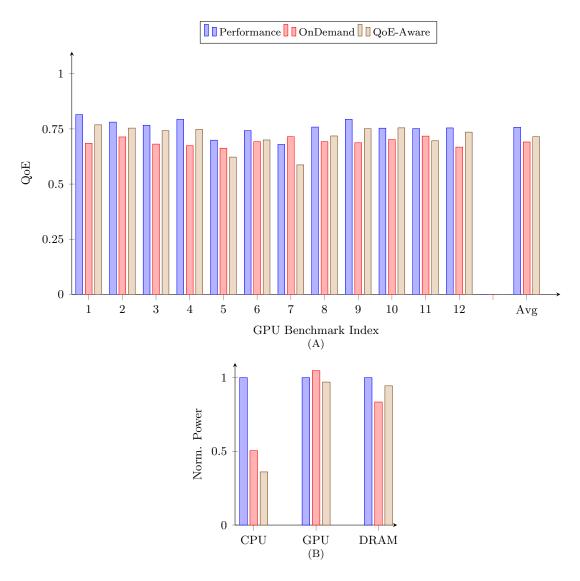

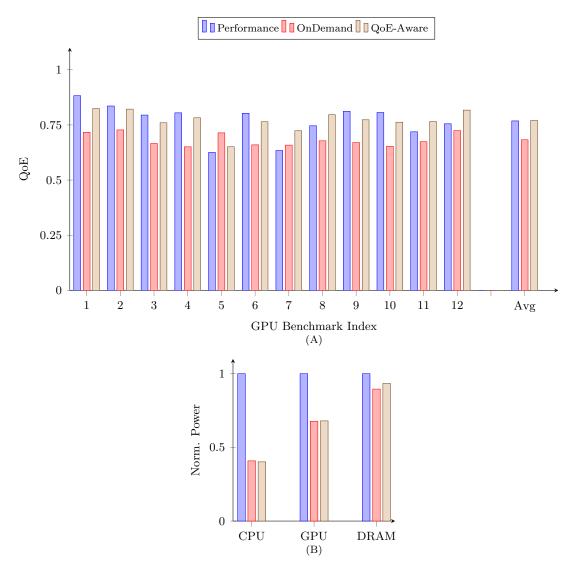

| 5.0        | and QoE for the GPU (right)                                                                                                                                                                                         | 38      |

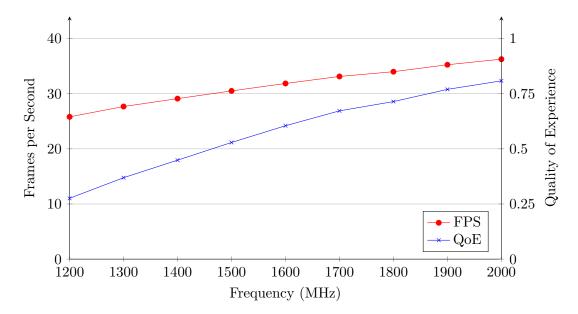

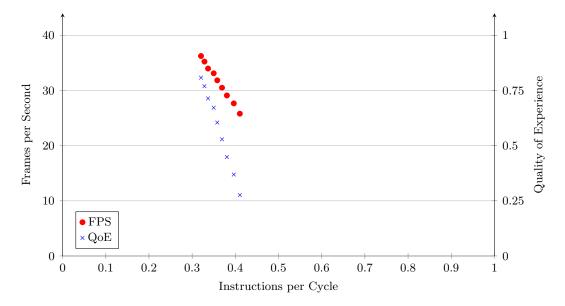

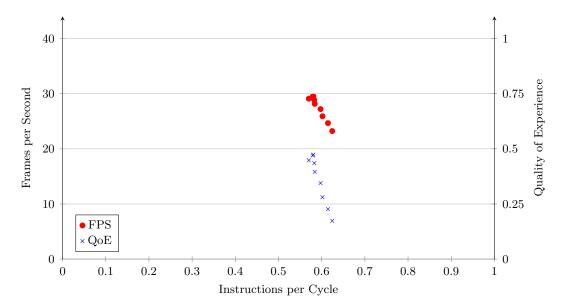

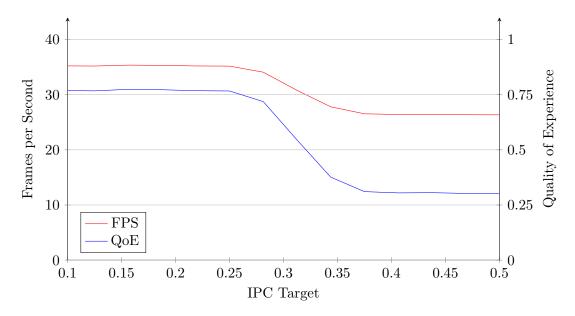

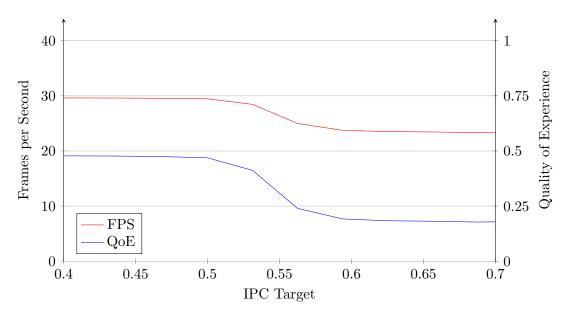

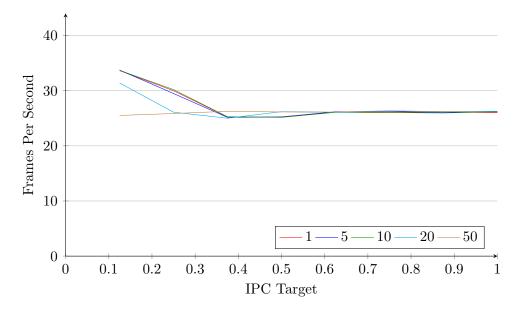

| 3.7        | The number of frames rendered per second and corresponding QoE when running The Chase on an Odroid XU3 as the frequency is varied                                                                                   | 40      |

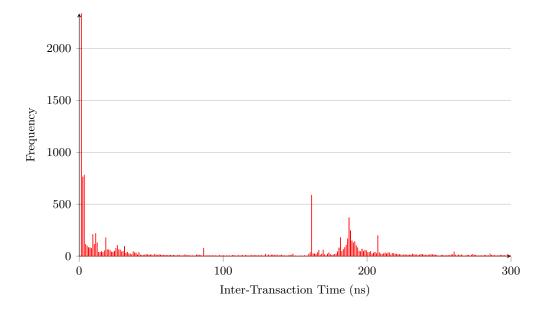

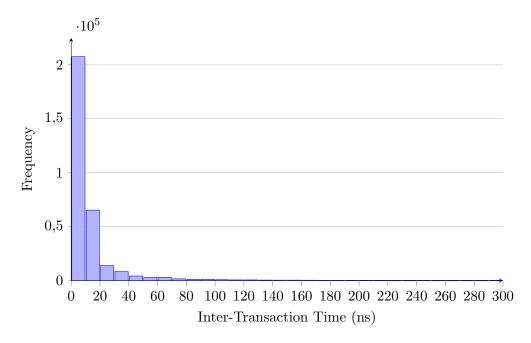

| 4.1        | Inter-Transaction Time (ITT) histogram for eon from SPEC2000 with                                                                                                                                                   |         |

| 1.1        | 150 ns memory latency, 1 ns bins                                                                                                                                                                                    | 45      |

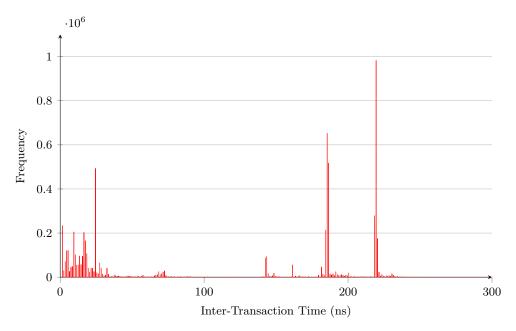

| 4.2        | ITT histogram for BBench, 1 ns bins, 1 second run-time                                                                                                                                                              | 45      |

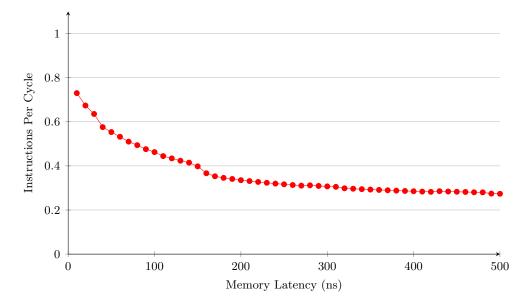

| 4.3        | IPC as memory latency varies for a 0.5s BBench run                                                                                                                                                                  | 46      |

| 4.4        |                                                                                                                                                                                                                     | 47      |

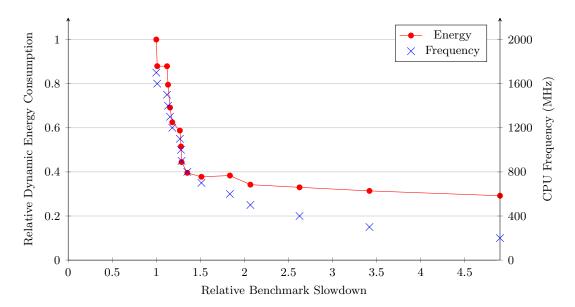

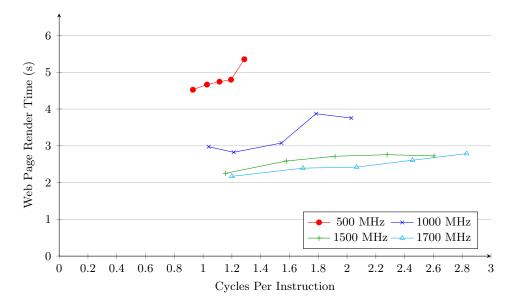

| 4.5        | CPI vs. geometric mean of web page render times for BBench as CPU                                                                                                                                                   | 4.0     |

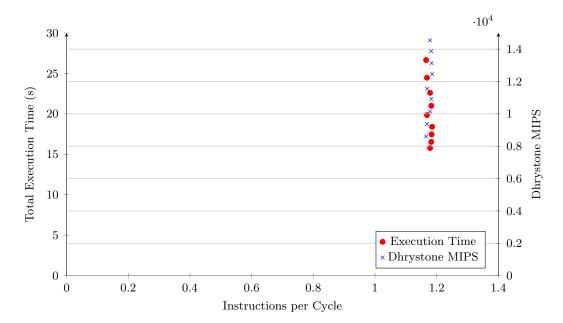

| 4.6        | frequency varies.                                                                                                                                                                                                   | 48      |

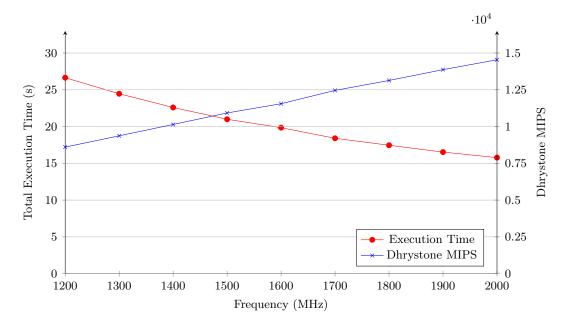

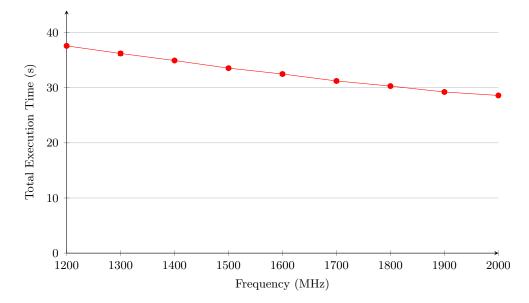

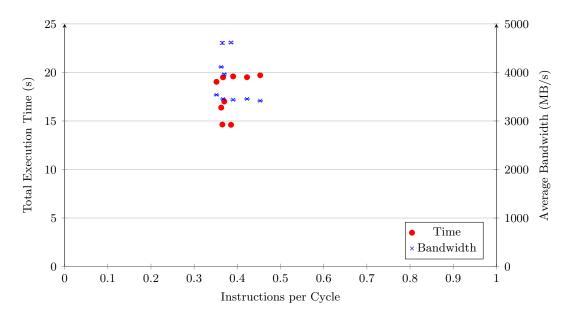

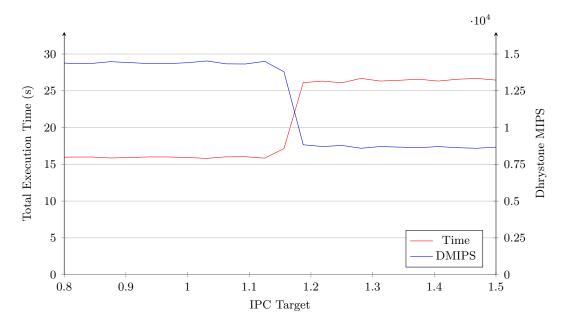

| 4.6        | Execution time and DMIPS for Dhrystone benchmark running on the Odroid XU3 as the CPU frequency is swept                                                                                                            | 49      |

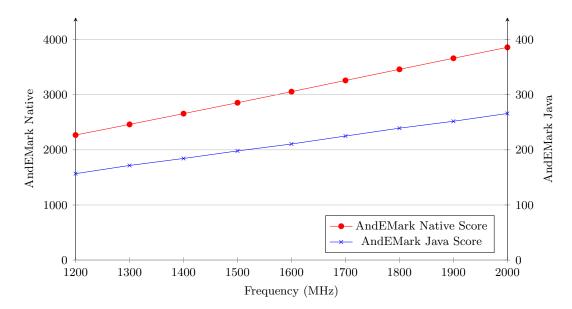

| 4.7        | AndEMark score for AndEBench benchmark running on the Odroid XU3                                                                                                                                                    | 10      |

|            | as the CPU frequency is swept                                                                                                                                                                                       | 50      |

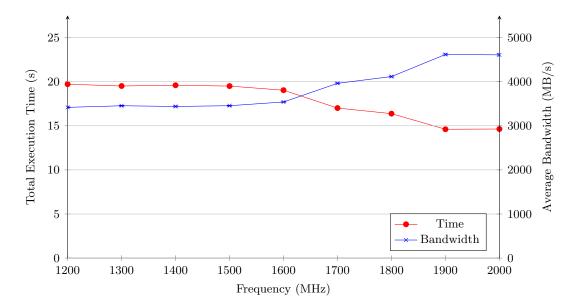

| 4.8        | Execution time for Memcpy benchmark running on the Odroid XU3 as                                                                                                                                                    |         |

| 4.0        | the CPU frequency is swept                                                                                                                                                                                          | 51      |

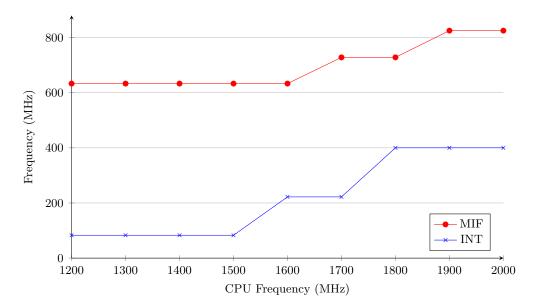

| 4.9        | Relationship between A15 CPU frequency and other clock sources for the Odroid XU3                                                                                                                                   | 52      |

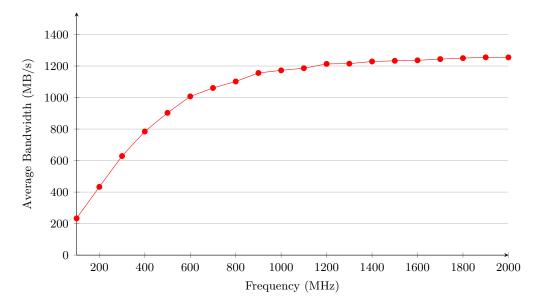

| 4.10       | Average memory bandwidth for Memcpy benchmark running on the gem5                                                                                                                                                   | 92      |

| _3         | simulator as the CPU frequency is swept.                                                                                                                                                                            | 53      |

| 4.11       | Execution time for RedLicense Labs SQLite benchmark running on the                                                                                                                                                  |         |

|            | Odroid XU3 as the CPU frequency is swept                                                                                                                                                                            | 54      |

viii LIST OF FIGURES

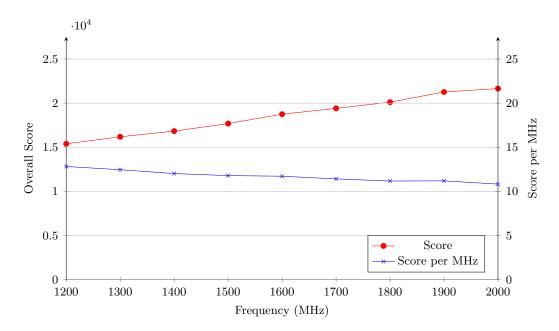

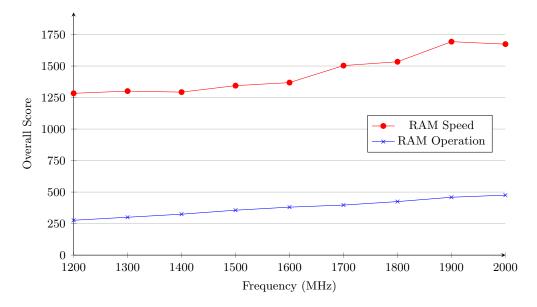

| Overall benchmark score and score per MHz for AnTuTu 4 benchmark            | . 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                             | . 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

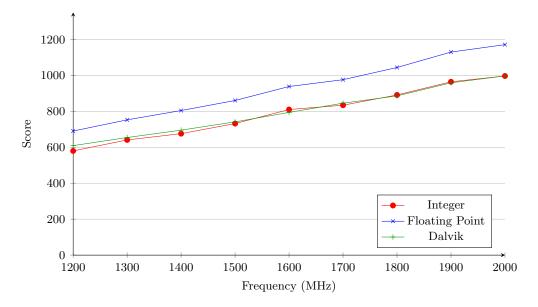

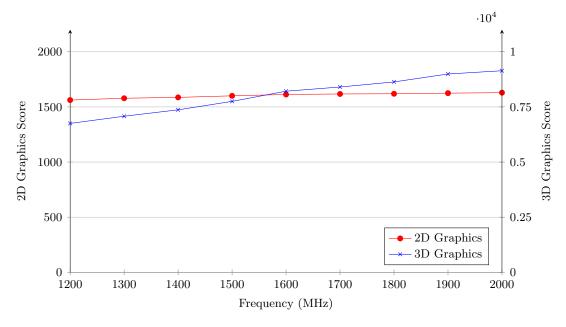

|                                                                             | . 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | . 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | . 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

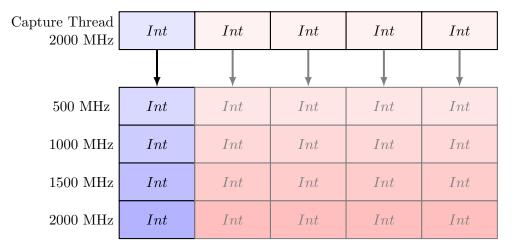

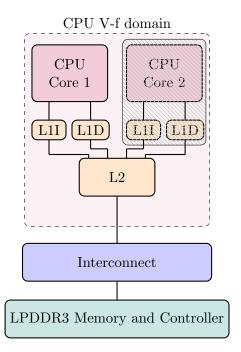

| Overview of the forking infrastructure                                      | . 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

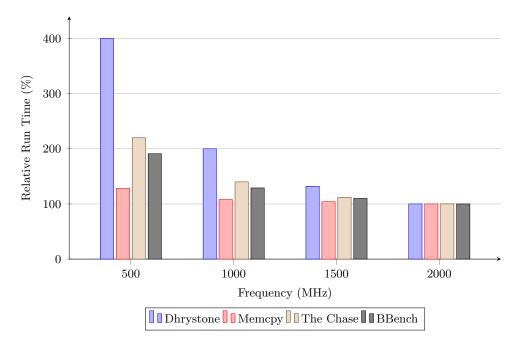

| Run time, relative to 2000 MHz, for all four workloads evaluated using      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| the gem5 forking infrastructure                                             | . 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

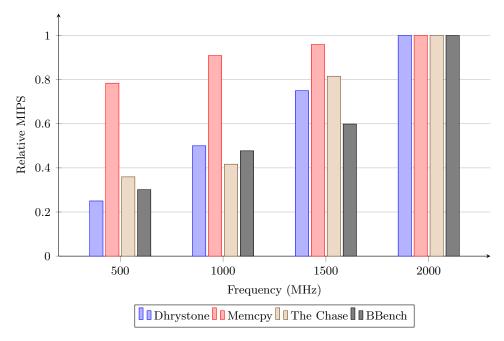

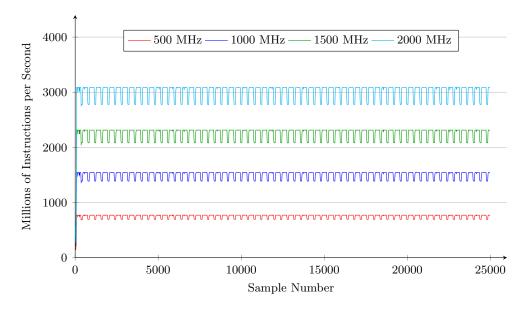

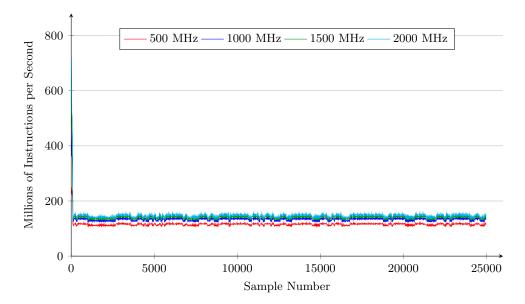

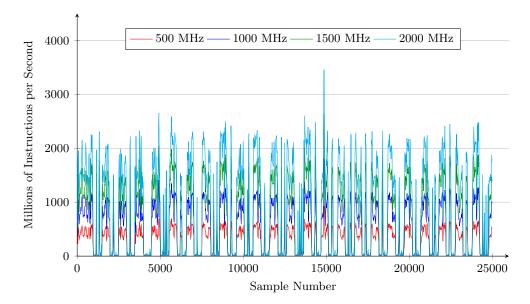

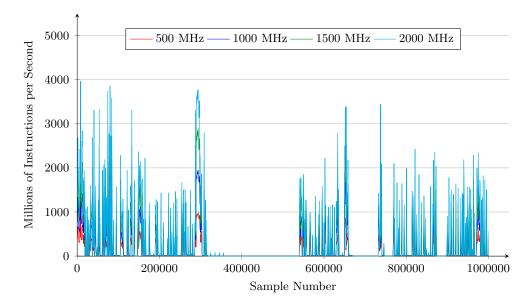

| Average MIPS relative to 2000 MHz for all four workloads evaluated using $$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | . 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | . 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             | or.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                             | . 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| • • • • • • • • • • • • • • • • • • • •                                     | . 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             | . 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             | . 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • •                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

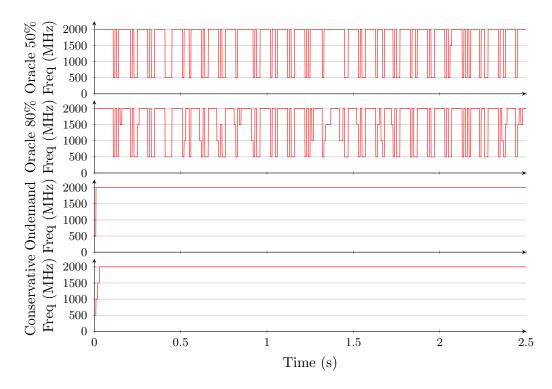

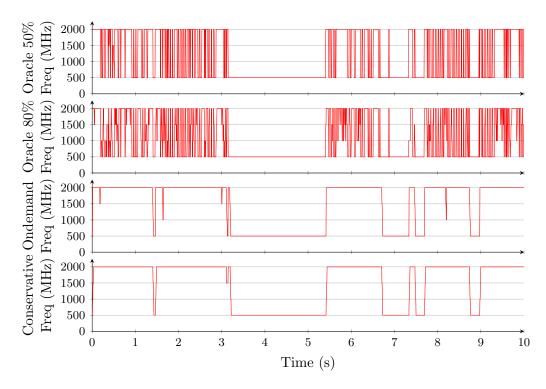

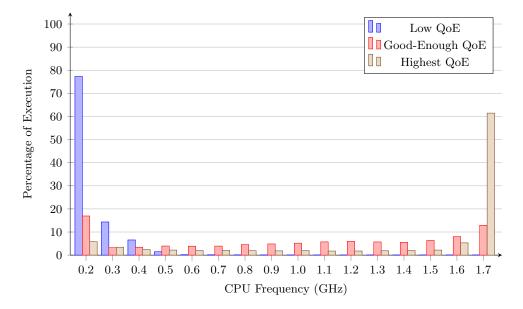

| Al. 11 f al. O I DVEC                                                       | 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

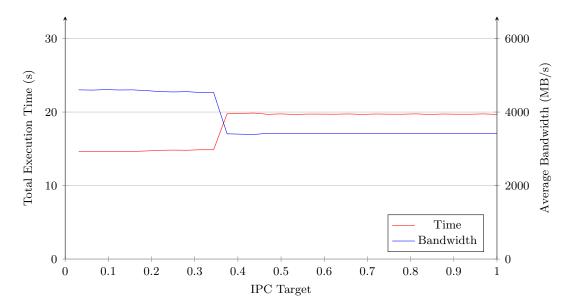

|                                                                             | . 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                             | . 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

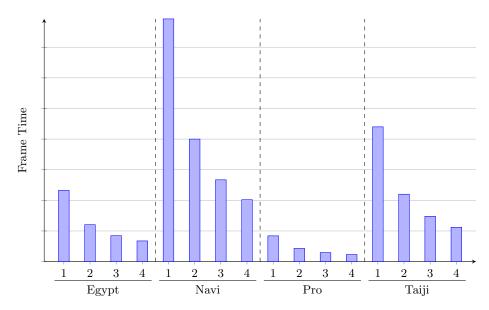

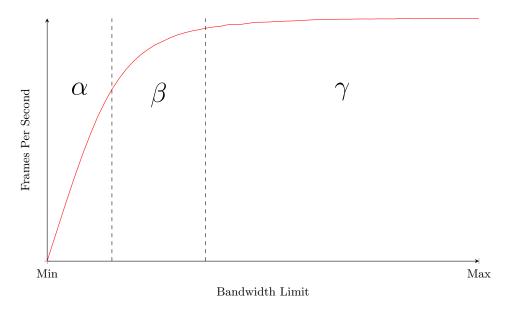

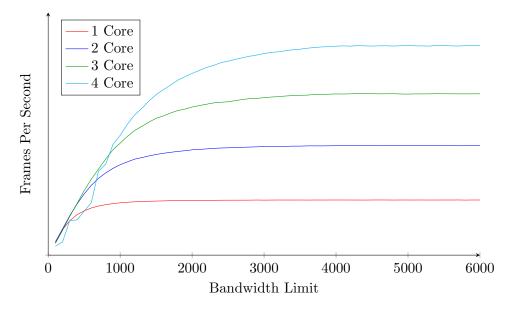

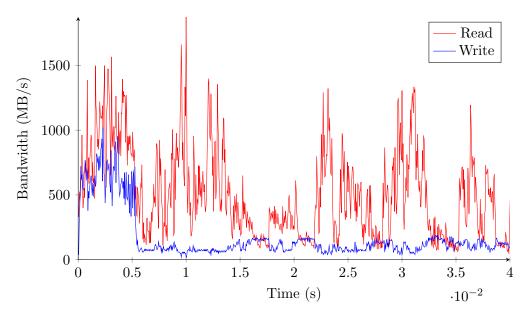

|                                                                             | . 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |