# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

Faculty of Engineering & Applied Science

Department of Electronics & Computer Science

# PNP POLYSILICON EMITTER BIPOLAR TRANSISTORS

by

Ian R.C. Post

A thesis submitted for the degree of Doctor of Philosophy

January 1992

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

## FACULTY OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

#### PNP Polysilicon Emitter Bipolar Transistors

by Ian R.C. Post

This thesis reports on an experimental and theoretical investigation of pnp polysilicon emitter bipolar transistors. The fabrication of transistors with shallow emitter junctions (<0.05 $\mu$ m) is described. Measurements of base current and emitter resistance are then made on devices both with and without a deliberately grown interfacial oxide layer at the polysilicon/silicon interface.

A simple electrical method of measuring the emitter/base junction depth in shallow bipolar devices is presented, based on the measured base sheet resistance with and without an emitter diffusion. Good agreement is achieved with analytical techniques, such as SIMS and spreading resistance, for deep emitter junctions (>0.1 $\mu$ m). However, the electrical method shows itself to be more accurate for shallow emitter junctions (<0.05 $\mu$ m). This method is a valuable characterisation tool, because it is only in shallow emitter devices that the full effect of the polysilicon/silicon interface on the base current is observed.

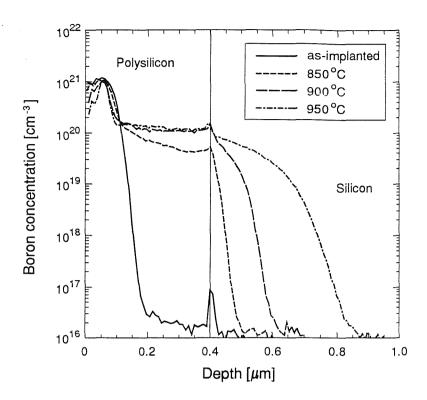

Investigations of boron diffusion in polysilicon and single-crystal silicon are undertaken, in an effort to characterise the necessary anneals required to produce shallow emitter junction *pnp* devices. It is shown that the enhancement of boron diffusivity in polysilicon, over that in single-crystal silicon, is only a factor of 50-220. This makes the attainment of shallow emitter *pnp* devices ( $<0.05\mu$ m) considerably more difficult than for typical arsenic doped *npn* devices, where the enhancement of diffusivity is typically  $10^4$ . Further problems are also described, such as boron precipitation in the as-implanted peak, which limits the maximum boron concentration in the polysilicon to  $1-2x10^{20}$  cm<sup>-3</sup>, and a low solid solubility, which limits the maximum electrically active boron concentration in the emitter to around  $1-2x10^{19}$  cm<sup>-3</sup>.

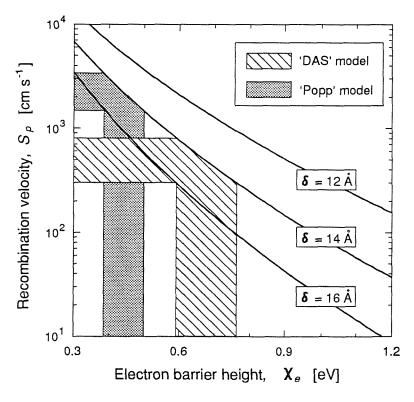

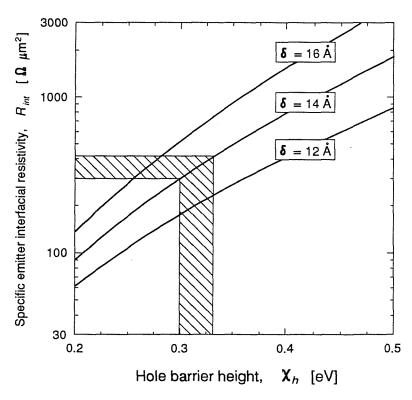

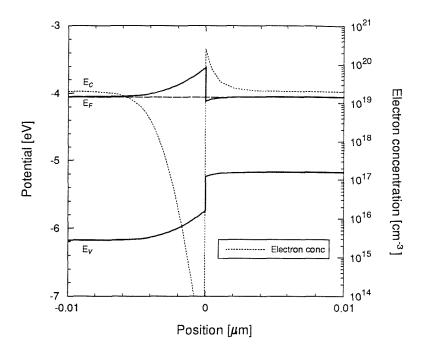

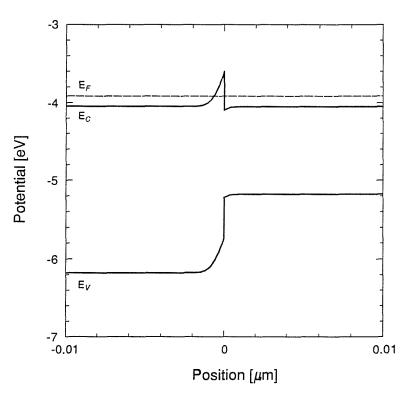

Using the shallow emitter pnp devices described above, the role of a deliberately grown interfacial oxide layer on the base current and emitter resistance is studied. Effective oxide barrier heights are extracted for these devices, which yield asymmetrical values of  $0.31\pm0.02$  eV for holes and either  $0.68\pm0.08$  eV or  $0.44\pm0.06$  eV for electrons, depending on which band-gap narrowing model is used ('DAS' or 'Popp'). This same procedure is also carried out for npn devices with identical interfacial oxide treatments, which also yield asymmetrical values of >0.72 eV for holes and  $0.40\pm0.01$  eV for electrons. The barrier heights obtained from pnp transistors are therefore inconsistent with those obtained from npn transistors. A new heterojunction tunnelling model is proposed for the polysilicon emitter, in which the interfacial 'oxide' layer is treated as a wide band-gap semiconductor. Using this model, the inconsistency in the measured barrier heights, and their asymmetry, can both be fully explained. Band-bending due to segregated dopant at the interface is central to this explanation.

#### **Acknowledgements**

First and foremost I would like to thank my supervisor, *Dr Peter Ashburn*, for his excellent supervision, encouragement, enthusiasm, suggestions, criticisms, cajoling, coaxing, attention to detail, etc., and without whom this thesis would only be a poor imitation of what you now see before you. Also thanks to *Peter Murkin* of STL (now BNR Europe) for help with the SUPREM analysis, and *Dr Alain Nouailhat* of CNET for very helpful insights and comments on my work.

Now that the serious part is over, many thanks to the 'Bipolar Boys'; Alan 'See yooz' Shafi for sharing the agony of thesis writing during the long night hours in the magic Faraway tower, Dilwyn 'Boyo' Williams for many enlightening discussions on life, the universe and epitaxial alignment, Dr Graham 'Mega Buck\$' Wolstenholme now acting as my agent in America, Dr Nasser 'Psst wanna buy a computer' Siabi for s{pply~ng the c%mput@r th&t I am n#w typ(\*ing on, and new boys Nick 'See you in a months time' Moisewitsch, and Haydn 'Stunt man' Gregory. Special mention must go to honorary 'bipolar boys' John 'Old man' Altrip, and I take this opportunity to wish him all the best in his well earned retirement, and Dr Rupert 'Bell ringer' Howes. Commiserations to my office mates, Hakan 'Turk man' Özdemir, Anna 'I love Philips' Durham and Didine 'Lurve machine' Berrezak for having to put up with me all these years. I'd also like to dis-acknowledge Julian Carter for being a complete and utter b\*\*\*\*\*\*.

A big vote of thanks to the clean room staff (Jean, Angie, Carol, Andrew, Richard, Tony, Ian, and John etc.) for help with the fabrication of my devices, and can I have my photolith done by today, after you've implanted my 13 wafers and etched the polysilicon. Miscellaneous grunts to Dr Greg 'Head banger' Parker, Dónal 'If you're buying one, mines a pint' Murphy, Jim 'Kipper ties are still in fashion' Smith, David 'Ditch' Leong, and I suppose I ought to acknowledge the SERC for keeping me in poverty for 2 years. To anyone I have forgot to mention - tough.

Finally, special mention must go to my parents for their constant encouragement throughout my long years of higher education. It is for their support that this thesis is dedicated to them.

Ian Post, Southampton University, 13<sup>th</sup> January 1992. To My Parents, Raymond and Dorothy Post

### **Table of Contents**

| Abstract. | • • • • • • • • • • • • • • • • • • • • |                                                        | i   |

|-----------|-----------------------------------------|--------------------------------------------------------|-----|

| Acknowle  | edgem                                   | ents                                                   | ii  |

| Table of  | conte                                   | nts                                                    | iii |

|           |                                         |                                                        |     |

| Chapter   | 1 -                                     | Introduction                                           | 1   |

|           | Refer                                   | ences                                                  | 5   |

|           |                                         |                                                        |     |

| Chapter   | 2 -                                     | Polysilicon Emitters for Bipolar Transistors: A Review |     |

|           |                                         | and Re-Evaluation of Theory and Experiment             |     |

| 2.1       | Introd                                  | luction                                                | 7   |

| 2.2       |                                         | w of current gain theories for polysilicon             |     |

|           |                                         | er transistors                                         |     |

| 2.3       | Theor                                   | -y                                                     | 12  |

|           | 2.3.1                                   | Base current of a shallow emitter bipolar transistor   | 12  |

|           |                                         | a) Metal contacted emitters                            | 13  |

|           |                                         | b) Polysilicon emitters                                | 14  |

|           | 2.3.2                                   | Recombination velocity model for polysilicon           |     |

|           |                                         | emitter bipolar transistors                            | 15  |

|           |                                         | a) Oxide tunnelling model                              | 16  |

|           |                                         | b) Pseudo-grain boundary mobility model                | 17  |

|           |                                         | c) Segregation model                                   | 18  |

|           | 2.3.3                                   | Extended emitter model                                 | 19  |

|           | 2.3.4                                   | Parameter values and minority carrier hole models      |     |

|           |                                         | in heavily doped n-type silicon                        | 19  |

| 2.4       | Exper                                   | rimental results                                       | 20  |

|           | 2.4.1                                   | Devices with interfacial oxides                        | 20  |

|           |                                         | a) Effect of an interface anneal                       | 20  |

|           |                                         | b) Temperature dependence of current gain              | 22  |

|           |                                         | c) Emitter resistance                                  |     |

|           | 2.4.2                                   | Devices without an interfacial oxide layer             |     |

|           |                                         | a) Segregation of dopant to the interface              |     |

|           |                                         | b) Hydrogen passivation                                |     |

|           |                                         | c) Polysilicon thinning                                |     |

|           |                                         | d) Temperature dependence of current gain              |     |

|           |                                         | e) Effect of an interface anneal                       |     |

| 2.5       | Mode                                    | elling a discontinuous interfacial oxide layer         |     |

|           |                                         | lusions                                                |     |

|           |                                         | ences                                                  |     |

| Chapter | 3 -                    | Electrical Method for Measuring the Emitter Depth of                                                                                                                   |    |  |  |

|---------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|         |                        | Shallow Bipolar Transistors                                                                                                                                            | 47 |  |  |

| 3.1     | Introd                 | luction                                                                                                                                                                | 47 |  |  |

| 3.2     | Theory                 |                                                                                                                                                                        |    |  |  |

| 3.3     | Accuracy               |                                                                                                                                                                        | 50 |  |  |

| 3.4     | Experimental procedure |                                                                                                                                                                        | 51 |  |  |

| 3.5     | Resul                  | ts and Discussion                                                                                                                                                      | 52 |  |  |

|         | 3.5.1                  | Emitter junction depth                                                                                                                                                 | 52 |  |  |

|         | 3.5.2                  | Modelling of collector currents                                                                                                                                        | 56 |  |  |

| 3.6     | Conc                   | usions                                                                                                                                                                 | 60 |  |  |

|         | Refer                  | ences                                                                                                                                                                  | 61 |  |  |

| Chapter | 4 –                    | Investigation of Boron Diffusion in Polysilicon and its Application to the Design of <i>pnp</i> Polysilicon Emitter Bipolar Transistors with Shallow Emitter Junctions |    |  |  |

| 4.1     | Intro                  | luction                                                                                                                                                                | 63 |  |  |

| 4.2     | Expe                   | imental procedure                                                                                                                                                      | 64 |  |  |

| 4.3     | Resul                  | ts                                                                                                                                                                     | 65 |  |  |

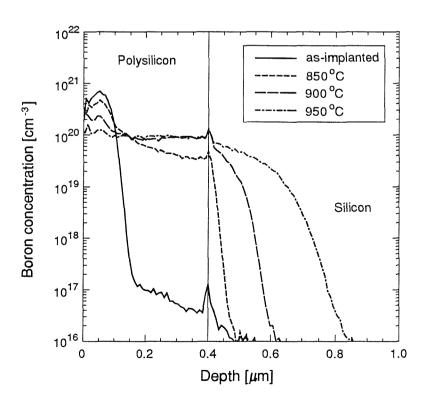

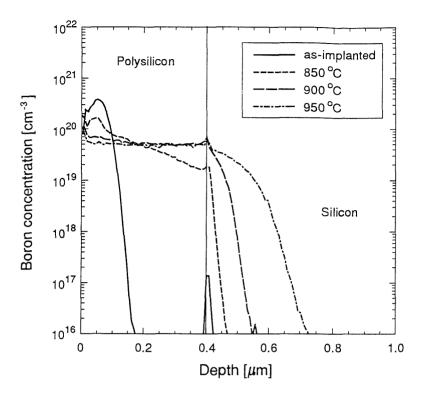

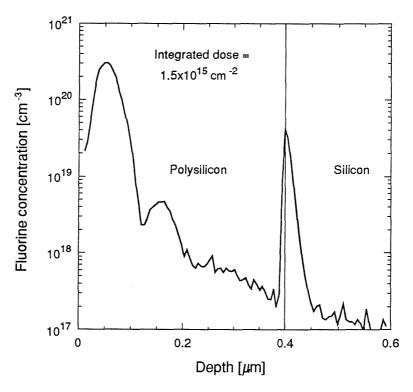

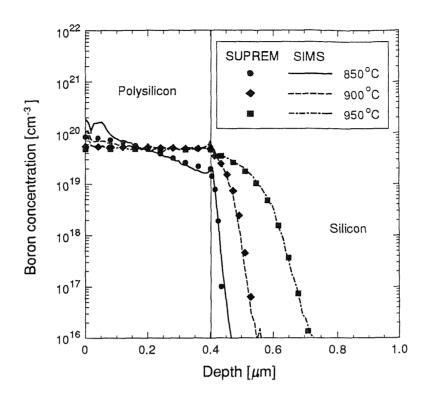

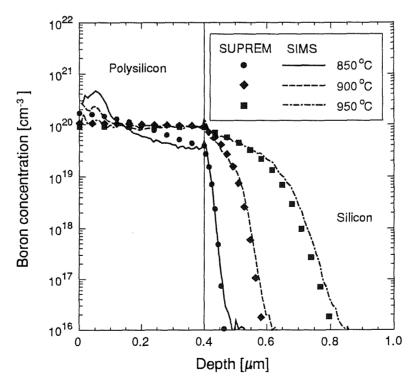

|         | 4.3.1                  | SIMS results                                                                                                                                                           | 65 |  |  |

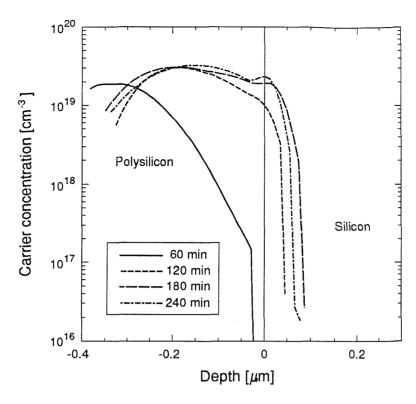

|         | 4.3.2                  | Spreading resistance results                                                                                                                                           | 68 |  |  |

|         | 4.3.3                  | Electrical results                                                                                                                                                     | 70 |  |  |

| 4.4     | Discu                  | ssion                                                                                                                                                                  | 73 |  |  |

| 4.5     | Conc                   | usions                                                                                                                                                                 | 82 |  |  |

|         | Refer                  | ences                                                                                                                                                                  | 83 |  |  |

| Chapter | 5 –                    | Analysis of the Role of the Interfacial Oxide in <i>pnp</i> and <i>npn</i> Polysilicon Emitter Transistors                                                             | 86 |  |  |

| 5.1     | Introd                 | luction                                                                                                                                                                |    |  |  |

|         |                        | imental procedure                                                                                                                                                      |    |  |  |

|         |                        | Theory                                                                                                                                                                 |    |  |  |

| 0.5     |                        | Effective recombination velocity and heavy                                                                                                                             |    |  |  |

|         | 0.0.1                  | doping parameters                                                                                                                                                      | 87 |  |  |

|         | 532                    | Tunnelling currents and resistances                                                                                                                                    |    |  |  |

| 54      |                        | ical results                                                                                                                                                           |    |  |  |

| 5.1     |                        | Base current                                                                                                                                                           |    |  |  |

|         |                        | Emitter resistance                                                                                                                                                     |    |  |  |

| 5.5     |                        | ssion                                                                                                                                                                  |    |  |  |

| 2.0     |                        | Extraction of oxide barrier heights                                                                                                                                    |    |  |  |

| 5.5.2 A heterojunction tunnelling model               | 99   |

|-------------------------------------------------------|------|

| 5.6 Conclusions                                       | 108  |

| References                                            | 109  |

| Chapter 6 – Conclusions and Further Work              | 112  |

| Appendices                                            | .115 |

|                                                       |      |

| Appendix 1 Derivation of $T_{block}$ expressions      | 115  |

| Appendix 2 Standard pnp processing details            | 120  |

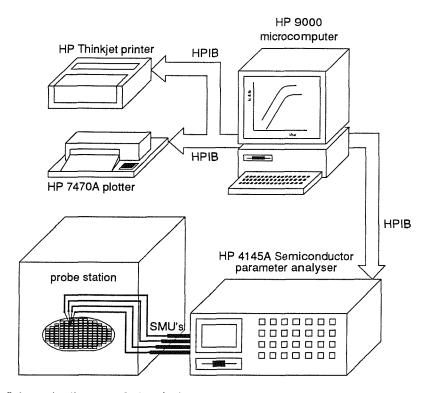

| Appendix 3 Electrical measurements set-up             | 127  |

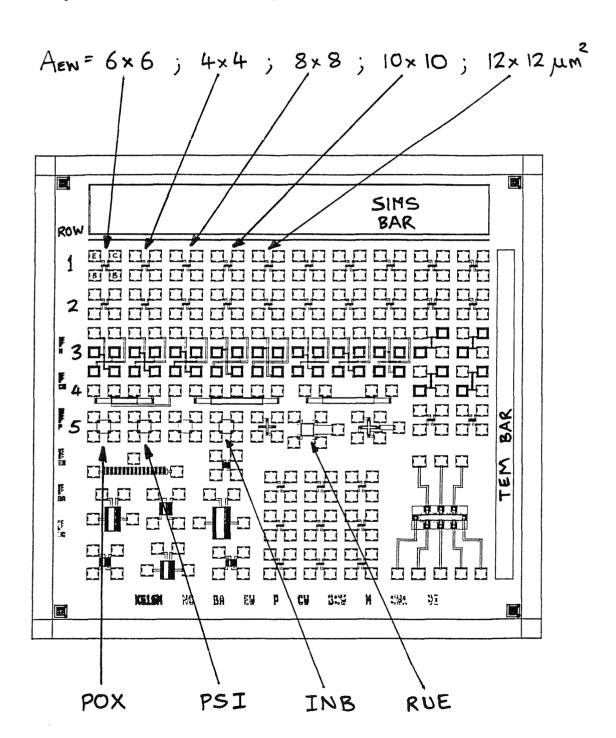

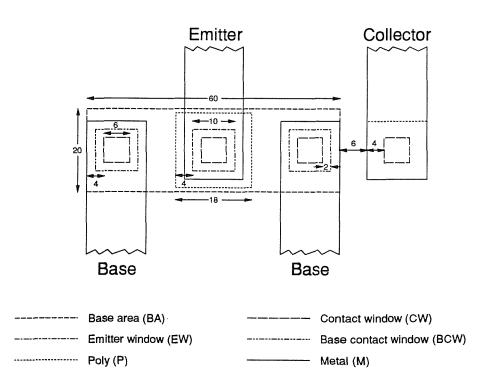

| Appendix 4 Mask set details                           | 129  |

| Appendix 5 HQUPETS input files for generating barrier |      |

| band diagrams                                         | 131  |

| Appendix 6 Published papers resulting from the work   |      |

| in this thesis                                        | 133  |

| Appendix 7 List of Symbols                            | 134  |

'Errors using inadequate data are much less than those using no data at all'

Charles Babbage 1792–1871.

Chapter 1

Introduction

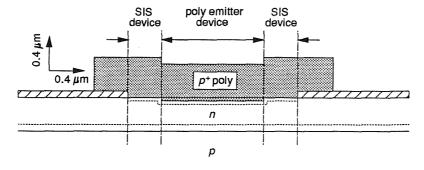

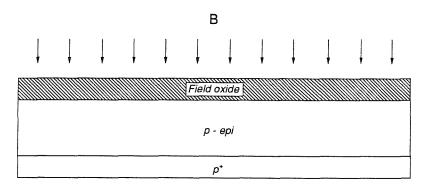

As the lateral dimensions of BiCMOS devices and circuits are scaled, the power supply voltage must also be similarly scaled in order to limit short-channel effects in the MOS transistors [1]. In conventional BiCMOS driver circuits this lowering of the supply voltage results in a large increase in gate delay [2], [3]. To combat this effect the use of vertical *pnp* transistors has recently been reported in so called complimentary BiCMOS driver circuits (CBiCMOS) [4], [5], which present a significant performance improvement over conventional BiCMOS circuits. This has lately fuelled interest in high performance vertical *pnp* polysilicon emitter bipolar transistors.

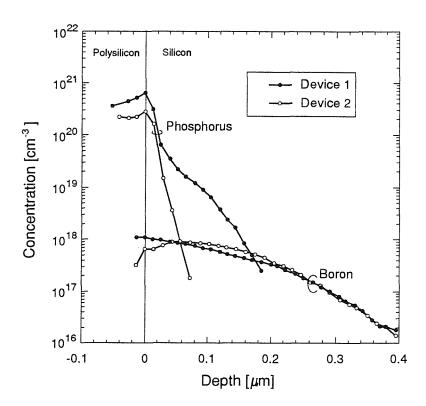

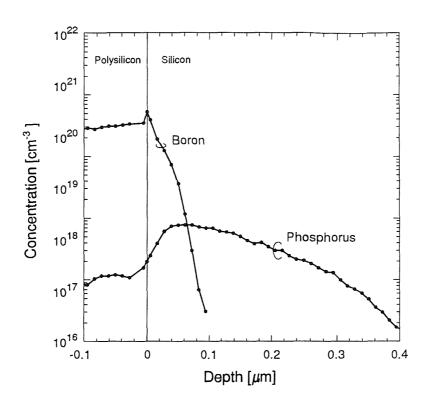

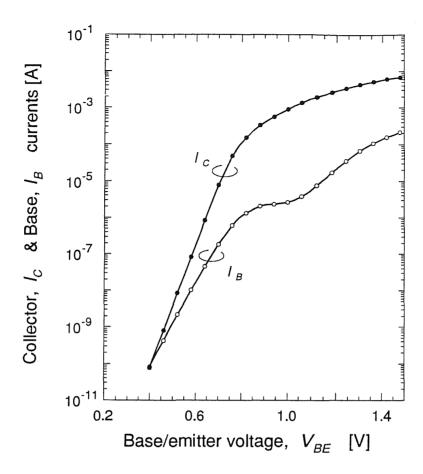

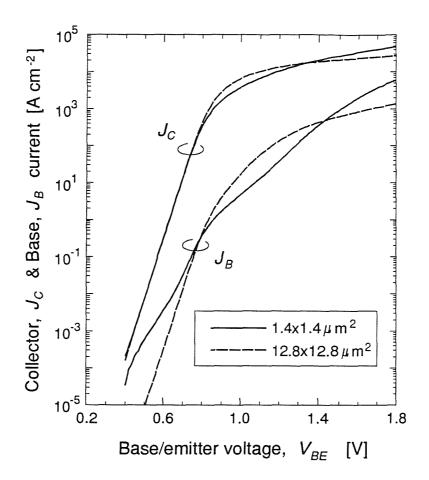

Lu et al. [6] and Warnock et al. [7] have recently reported the use of boron doped polysilicon for use as the emitters of bipolar transistors. Devices were produced without any deliberately grown oxide at the interface, and the polysilicon was doped by ion-implantation. This was followed by a furnace anneal at temperatures below 900°C, which was intended to uniformly dope the polysilicon and diffuse boron into the single-crystal silicon to produce shallow emitter junctions ( $\sim 0.03-0.05\mu m$ ). Modelling of the collector current of the resultant devices revealed that the band-gap narrowing and minority carrier mobility data of del Alamo et al. [8] provided a good fit to the measured collector current. The interfacial region of the polysilicon/silicon interface was characterised by a recombination velocity of  $1.4\times10^5$  cm s<sup>-1</sup> for minority carriers, and an emitter resistance of around  $300 \Omega \mu m^2$  for the majority carriers.

The vertical pnp polysilicon emitter transistors as analysed by Lu et al. [6] and Warnock et al. [7] have subsequently been employed in high-speed self-aligned processes [9]-[12] for use in complimentary bipolar circuits. Devices were produced with basewidths of 0.08µm, and a combination of furnace anneals at 800°C followed by rapid thermal anneals were used to produce shallow emitter depths of 0.02μm. Impressive high-frequency results were obtained for these pnp devices, namely a cut-off frequency,  $f_t$  of 27 GHz, a maximum oscillation frequency,  $f_{max}$  of 27 GHz, NTL gate delays of 36 ps, and ECL gate delays of 20 ps. This value of ECL gate delay was virtually the same as that obtained for a similar npn process. This somewhat surprising result can however, be explained by considering values of minority carrier mobility. At typical base doping concentrations of 10<sup>18</sup> cm<sup>-3</sup>, the minority carrier hole mobility is around 290 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [8], which is only marginally below the minority electron mobility value of 340 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [13]. This compares with a hole majority carrier mobility which is only half that of the majority carrier electron mobility for the same doping concentration. Moreover, the hole impact ionization rate is lower than that for electrons, which means that the collector doping in pnp devices can be raised above that for a corresponding *npn* device before junction break-down can compromise device performance. This increase in collector doping will suppress base push-out [14], enabling

the cut-off frequency to increase, which can be used to offset the reduced hole mobility. These results demonstrate that the intrinsic device limits for *pnp* transistors are quite comparable to those for corresponding *npn* devices.

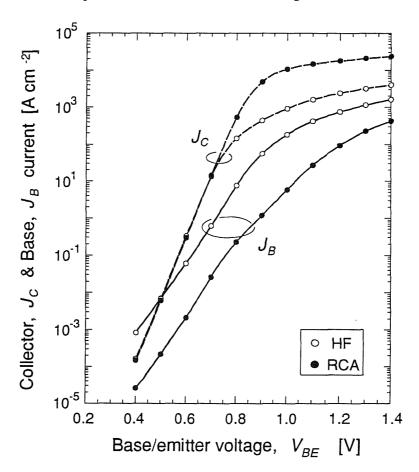

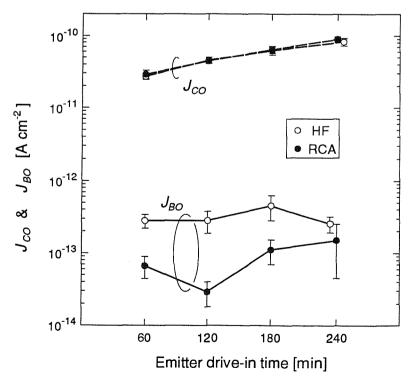

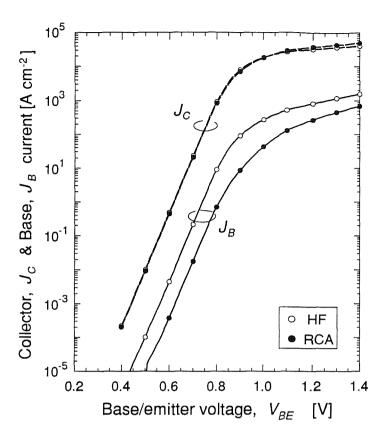

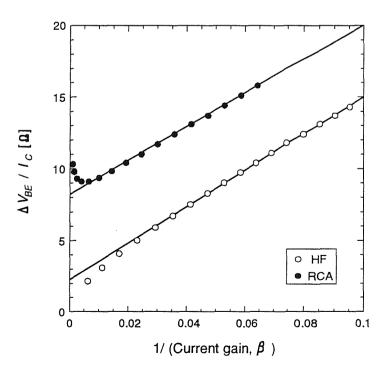

As an alternative to doping the polysilicon by ion-implantation, Maritan and Tarr [15] have investigated the use of boron *in-situ* doped polysilicon. Devices were analysed with either a dip etch in HF prior to polysilicon deposition (designed to remove any oxide at the interface), or a chemical clean which was designed to grow a uniform oxide layer approximately  $10-20\text{\AA}$  thick. Firstly, 'true' polysilicon emitter transistors were studied which received no emitter anneal after polysilicon deposition, so that the emitter/base junction resided at the polysilicon/silicon interface. The resulting base current characteristics of these devices were very non-ideal, as well as both the collector and base currents saturating at low forward bias. However, the devices with a deliberately grown interfacial oxide layer exhibited a base current suppression by over a factor of 18 compared to the devices which received a dip etch in HF. This gain enhancement, was however, achieved at the expense of a large increase in emitter resistance, with the deliberately grown oxide layer producing a resistance of 2500  $\Omega\mu m^2$  compared to 800  $\Omega\mu m^2$  for devices without a deliberately grown interfacial layer.

Maritan and Tarr [15] also produced devices which received an anneal of 900°C for 30 minutes after polysilicon deposition. This anneal considerably improved the ideality of the base current and improved the high current handling capability, and reduced the emitter resistance to acceptable values of  $100-200~\Omega\mu\text{m}^2$  for devices either with or without an interfacial oxide layer. However, this improvement in device performance was at the expense of a large increase in emitter depth ( $\geq 0.15\mu\text{m}$ ), which resulted in the base current blocking of the devices with chemically grown interfacial oxide layers diminishing to a factor of 2.5 below that for the HF device. These results are also confirmed by Ratanaphanyarat *et al.* [16], who directly compared emitter layers either fabricated from boron *in-situ* doped polysilicon or from boron ion-implanted polysilicon, followed by an anneal at 850°C for 15 minutes in dry nitrogen. They found that the use of ion-implantation enabled a shallower emitter/base junction depth of 0.06 $\mu$ m to be produced, compared to a junction depth of 0.08 $\mu$ m for the *in-situ* doped layers.

Laser *et al.* [17] attempted to model the devices of Maritan and Tarr [15] with deliberately grown interfacial oxide layers by using the one-band oxide model [18]. This model follows from the theoretical work of O'Neill [19], who explained the asymmetry in hole and electron barrier heights (as derived from modelling *npn* polysilicon emitter transistors [20]) as being due to tunnelling via states which are derived from the conduction band-edge. The hole barrier height is therefore assumed to be larger than the electron barrier height by an amount equal to the silicon band-gap.

Laser *et al.* [17] were unable to model the emitter resistance of these devices using the one-band oxide model, and had to artificially reduce the oxide thickness (equivalent to reducing the hole barrier height) in order to do so. Similarly, the modelled value of base current was a factor of 3 larger than the experimentally measured value. These results clearly contradict with the one-band oxide model, suggesting that the hole and electron barrier heights as derived from *npn* polysilicon emitter transistors are not applicable to *pnp* polysilicon emitter transistors.

The above results indicate that excellent high-frequency performance can be produced from *pnp* polysilicon emitter transistors, although they highlight two important areas where more work is required. Firstly, there are considerable problems in fabricating devices with shallow emitter junctions. Generally, for arsenic doped polysilicon emitter transistors, a wide range of anneals can be used to fabricate reproducible shallow emitter junctions [21]. However, this is much more difficult in *pnp* polysilicon emitter transistors. Both Lu *et al.* [6] and Warnock *et al.* [7] had to resort to a complicated combination of low temperature furnace anneals (800–880°C) and rapid thermal anneal to produce shallow emitter junctions. Furthermore, the *in-situ* doped polysilicon emitter transistors of Maritan and Tarr [15] had emitter junction depths of 0.15µm, which are too deep to exploit the gain enhancements due to blocking at the polysilicon/silicon interface.

Secondly, there exists much doubt about the precise physical mechanisms which control the base current of *pnp* polysilicon emitter transistors, especially for those with deliberately grown interfacial oxide layers. In *npn* polysilicon emitter transistors hole barrier heights of 1.1 eV and electron barrier heights of 0.4 eV have been extracted from the measured values of base current and emitter resistance [20]. However, Laser *et al.* [17] have shown that by using these barrier heights, they were unable to simultaneously model the base current and emitter resistance of *pnp* polysilicon emitter transistors. The work in this thesis has therefore been undertaken to address mainly these two problems, and is organised as follows:

Chapter 2 contains a critical review of the theories presented in the literature to explain the current gain enhancement of *npn* polysilicon emitter transistors. From these theories a simple analytical form is chosen which is then applied to a selection of experimental data from the literature, in an effort to identify the dominant current gain mechanisms as a function of fabrication conditions.

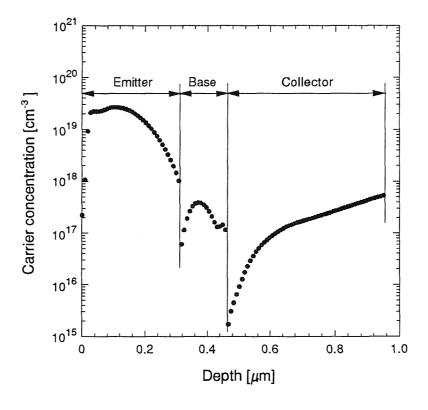

Chapter 3 outlines a simple electrical method for measuring the vertical base/collector and emitter/base junction depths of bipolar transistors, which are important parameters in characterising the electrical performance of devices. The electrical method is then validated by modelling the collector current from a selection of *npn* and *pnp* transistors.

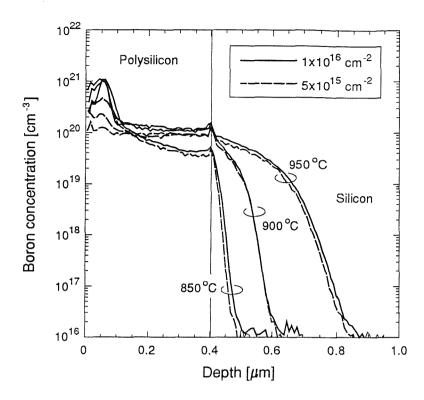

Chapter 4 investigates the diffusion properties of boron in polysilicon through the use of SIMS and SUPREM modelling, in an effort to characterise the necessary fabrication conditions to produce shallow emitter junctions.

Chapter 5 reports on the effects of a deliberately grown interfacial oxide layer on the base current and emitter resistance of *pnp* devices. Electron and hole barrier heights are extracted for these devices, and compared with barrier heights from *npn* devices with identical interfacial layer treatments. A methodology is then described to explain the experimental observations. Finally conclusions are drawn, and suggestions for further work made, in chapter 6.

#### References

- [1] C.G. Sodini, P.-K. Ko, and J.L. Moll, "The effect of high fields on MOS device and circuit performance", *IEEE Trans. Electron Devices*, vol. ED–31, pp. 1386–1393, 1984.

- [2] M. Fujishima, K. Asada, and T. Sugano, "Evaluation of delay-time degradation of low-voltage BiCMOS base on a novel analytical delay-time modeling", *IEEE J. Solid-State Circuits*, vol. 26, p. 25–31, 1991.

- [3] A. Wantanabe, T. Nagano, S. Shukuri, and T. Ikeda, "Future BiCMOS technology for scaled supply voltage", *International Electron Devices Meeting (IEDM) Tech. Dig. 1989*, pp. 429–432.

- [4] D. de Lang, E. Bladt, A. Van der Goor, and W. Josquin, "Integration of vertical pnp transistors in a double-polysilicon Bi-CMOS process", *Proc. Bipolar Circuits and Technology Meeting (BCTM) 1989*, pp. 190–193.

- [5] H.J. Shin, "Full-swing BiCMOS logic circuits with complementary emitter-follower driver configuration", *IEEE J. Solid-State Circuits*, vol. 26, p. 578–584, 1991.

- [6] P.-F. Lu, T.-C. Chen, M.J. Saccamango, "Modeling of currents in a vertical p-n-p transistor with extremely shallow emitter", *IEEE Electron Devices Lett.*, vol. 10, pp. 232–235, 1989.

- [7] J. Warnock, P.F. Lu, T.-C. Chen, and B. Meyerson, "Boron-doped emitters for high-performance vertical pnp transistors", *Proc. Bipolar Circuits and Technology Meeting* (BCTM) 1989, pp. 186–189.

- [8] J. del Alamo, S. Swirhun, and R.M. Swanson, "Simultaneous measurement of hole lifetime, hole mobility and band-gap narrowing in heavily doped n-type silicon", *International Electron Devices Meeting (IEDM) Tech. Dig. 1985*, pp. 290–294.

- [9] J. Warnock, P.-F. Lu, T.C. Chen, K.Y. Toh, J.D. Cressler, K.A. Jenkins, D.D. Tang, J. Burghartz, J.Y.C. Sun, C.T. Chuang, G.P. Li, and T.H. Ning, "A 27 GHz 20 ps PNP technology", *International Electron Devices Meeting (IEDM) Tech. Dig.* 1989, pp. 903–905.

- [10] J. Warnock, P.-F. Lu, J.D. Cressler, K.A. Jenkins, and J.Y.C. Sun, "35 GHz/35 psec ECL PNP technology", *International Electron Devices Meeting (IEDM) Tech. Dig. 1990*, pp. 301–304.

- [11] P.-F. Lu, J.D. Warnock, J.D. Cressler, K.A. Jenkins, and K.-Y. Toh, "The design and optimization of high-performance, double-poly self-aligned p-n-p technology", *IEEE Trans. Electron Devices*, vol. 38, pp. 1410–1418, 1991.

- [12] S. Ratanaphanyarat, J.B. Kuang, S.F. Chu, W. Rausch, M.J. Saccamango and M. Smadi, "25 GHz  $f_t$  / 27 GHz  $f_{max}$  pnp transistors for C-bipolar technology", *Electron. Lett.*, vol. 27, pp. 1224–1225, 1991.

- [13] S.E. Swirhun, Y.H. Kwark, and R.M. Swanson, "Measurement of electron lifetime, electron mobility and band-gap narrowing in heavily doped p-type silicon", *International Electron Devices Meeting (IEDM) Tech. Dig. 1986*, pp. 24–27.

- [14] C.T. Kirk, "A theory of transistor cut-off frequency fall-off at high current densities" *IRE Trans. Electron Devices*, vol. ED-9, pp. 164–174, 1962.

- [15] C.M. Maritan and N.G. Tarr, "Polysilicon emitter p—n—p transistors", *IEEE Trans. Electron Devices*, vol. 36, pp. 1139–1144, 1989.

- [16] S. Ratanaphanyarat, W. Rausch, M. Smadi, M.J. Saccamango, S.N. Mei, S.-F. Chu, P.A. Ronsheim and J.O. Chu, "Effect of emitter contact materials on high-performance vertical p—n—p transistors", *IEEE Electron Devices Lett.*, vol. 12, pp. 261–263, 1991.

- [17] A.P. Laser, K.M. Chu, D.L. Pulfrey, C.M. Maritan, and N.G. Tarr, "An investigation of pnp polysilicon emitter transistors", *Solid-State Electron.*, vol. 33, pp. 813–818, 1990.

- [18] K.M. Chu and D.L. Pulfrey, "An improved analytical model for the metal-insulator-semiconductor tunnel junction", *IEEE Trans. Electron Devices*, vol. 35, pp. 1056–1663, 1988.

- [19] A.G. O'Neill, "An explanation of the asymmetry in electron and hole tunnel currents through ultra-thin SiO<sub>2</sub> films", *Solid-State Electron.*, vol. 29, pp. 305–310, 1986.

- [20] P. Ashburn, D.J. Roulston, and C.R. Selvakumar, "Comparison of experimental and computed results on arsenic- and phosphorus-doped polysilicon emitter bipolar transistors", *IEEE Trans. Electron Devices*, vol. ED–34, pp. 1346–1353, 1987.

- [21] K. Park, S. Batra, S. Banerjee, G. Lux, and R. Manukonda, "Comparison of arsenic and boron diffusion in polycrystalline/single-crystal silicon systems", *J. Electrochem. Soc.*, vol. 138, pp. 545–549, 1991.

### Chapter 2

Polysilicon Emitters for Bipolar Transistors:

A Review and Re-Evaluation of

Theory and Experiment

#### 2.1 Introduction

In this chapter a critical review is presented of the theories proposed in the literature to explain the current gain enhancement of *npn* polysilicon emitter bipolar transistors. From these theories a simplified analytical formulation is chosen which models the blocking properties of the interface, including tunnelling through the interfacial oxide layer, reduced minority carrier mobility at the disordered interface, and the potential barrier created by segregated dopant, which can all give rise to an enhanced current gain. Also modelled are mechanisms which limit the extent of any gain enhancement, such as recombination in the single-crystal emitter, in the bulk polysilicon, and at the polysilicon/silicon interface. This model is then applied to a selection of experimental data in an effort to identify the dominant current gain mechanisms in polysilicon emitter transistors, as a function of a given set of fabrication conditions.

## 2.2 Review of current gain theories for polysilicon emitter transistors

The first reported use of polysilicon as an emitter contact to a bipolar transistor was by Takagi *et al.* [1] in 1972. The deposited polysilicon was *in-situ* doped, and was primarily used as a diffusion source for fabricating shallow emitter junctions. No mention was made of any gain enhancement of the transistors when compared to conventional metal contacted transistors.

Graul et al. [2] were the first to report a gain enhancement attributed directly to the inclusion of a polysilicon layer used to contact the emitter. They first deposited undoped polysilicon, which was then implanted with arsenic, followed by a high temperature drive-in. This was designed to uniformly dope the polysilicon, and also to diffuse arsenic into the single-crystal silicon to form a shallow emitter junction. The measured gain of the polysilicon emitter transistors were a factor of 5 larger than conventional metal contacted transistors. Moreover, the temperature dependence of the current gain was less sensitive to temperature for the polysilicon emitter transistors, than for the metal contacted transistors. Since the main source of a temperature dependence of current gain is the difference in band-gap narrowing between the emitter and base, Graul et al. [2] postulated that the temperature dependence was due to the band-gap narrowing in the polysilicon emitter being lower than that in the emitter of a conventional implanted transistor.

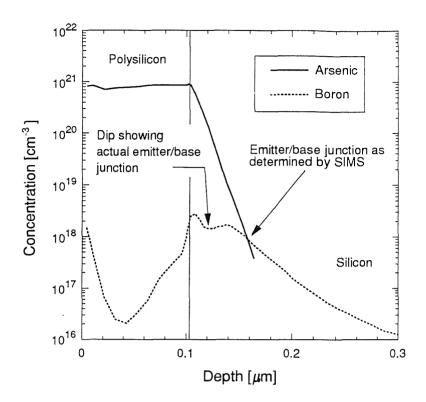

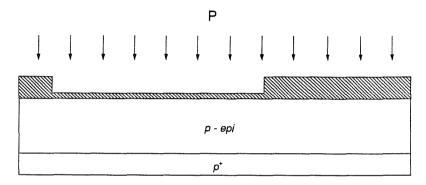

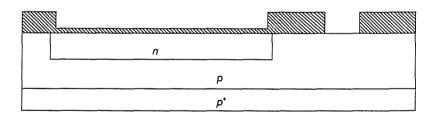

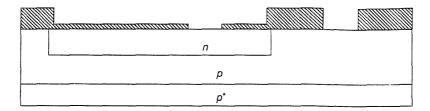

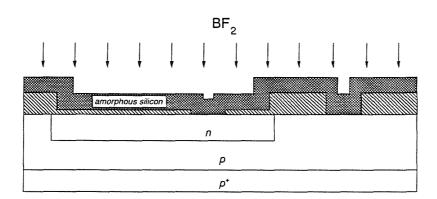

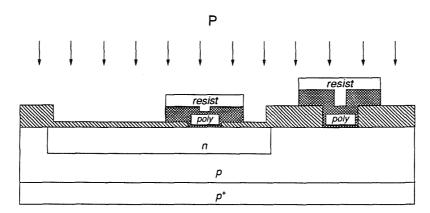

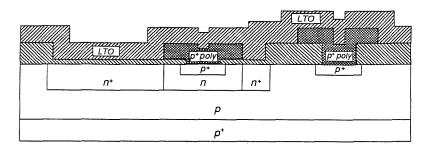

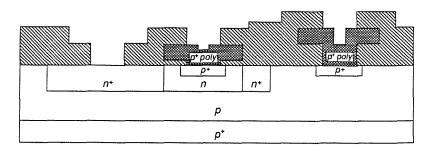

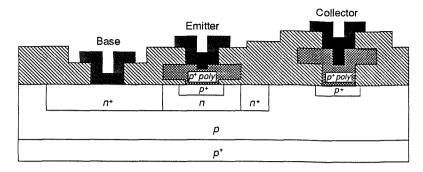

De Graaff and de Groot [3] fabricated conventional transistors up to and including the base fabrication. After the emitter windows were opened, a deliberately grown interfacial oxide layer of thickness between 20–60Å was grown. Phosphorus *in-situ* doped polysilicon was then deposited by LPCVD, followed by a high temperature

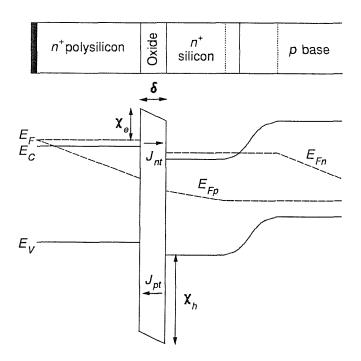

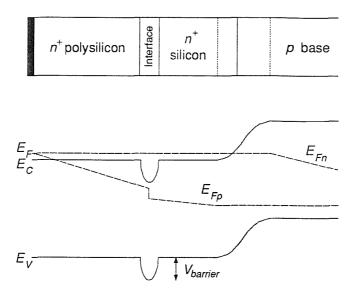

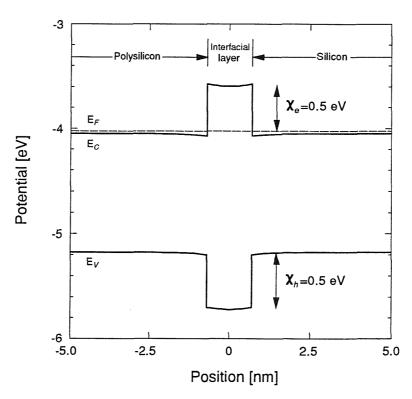

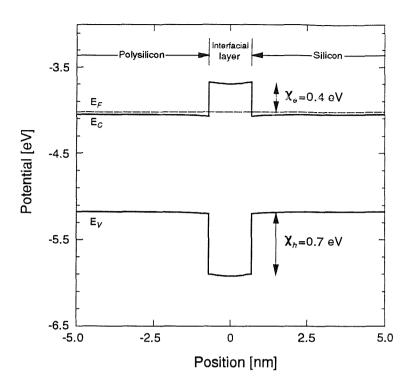

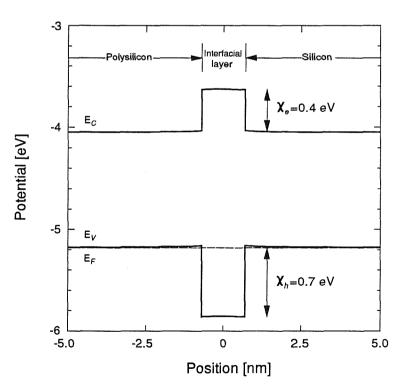

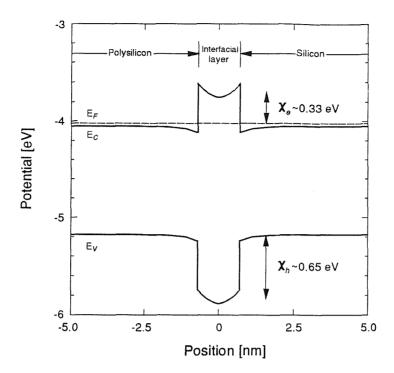

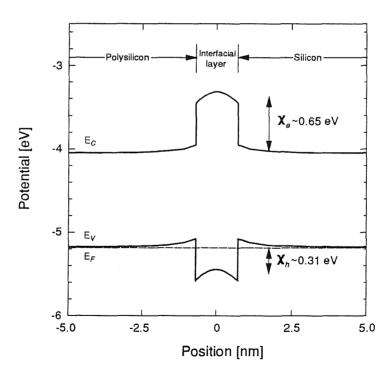

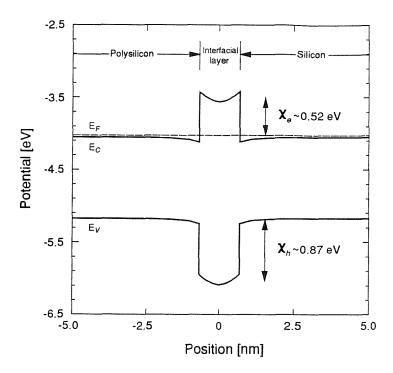

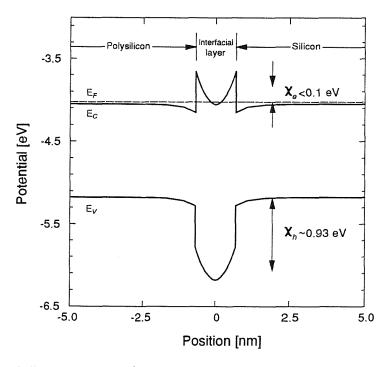

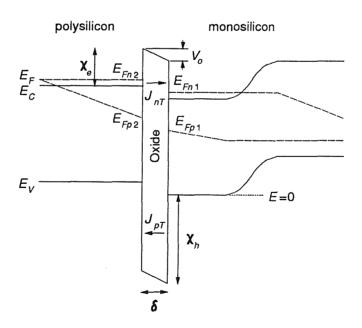

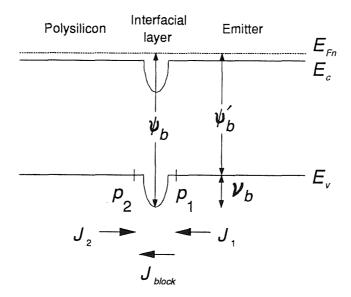

drive-in, which was used to activate the dopant in the polysilicon, and to form a shallow single-crystal emitter. Analysis of the base current showed that the incorporation of the interfacial oxide layer resulted in a suppression of the base current by a factor of around 10, although the base current became highly non-ideal. This reduction was explained by assuming that the injected minority carriers in the emitter are forced to tunnel through the interfacial oxide layer (see fig. 2.1), thereby impeding minority carrier flow. Similarly the majority carriers (which form the emitter current) also have to tunnel through the oxide (fig. 2.1), which can limit the maximum current carrying capability of the device. Furthermore, de Graaff and de Groot [3] estimated the tunnelling probability of holes to be 2–3 orders of magnitude lower than the tunnelling probability for electrons.

Fig. 2.1 Band diagram of the emitter/base structure of a polysilicon emitter transistor with an oxide layer at the polysilicon/silicon interface.

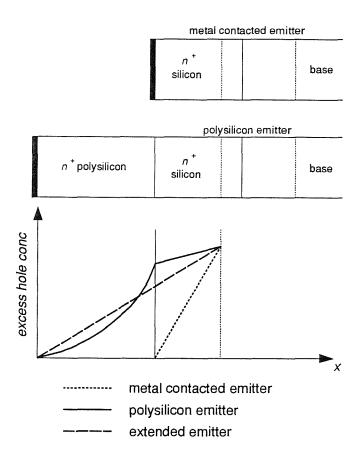

Ning and Isaac [4] fabricated transistors with conventional implanted emitters and then deposited arsenic *in-situ* doped polysilicon by LPCVD. They compared these transistors with conventional metal contacted devices, which ensured that any difference in base current could be attributed directly as a result of the emitter contact. The base current of the polysilicon contacted device was suppressed by a factor of 2 when compared to the metal contacted emitter. This increase in current gain was attributed to a lower minority carrier mobility in the polysilicon, when compared to single-crystal silicon. Solution of the current continuity and transport equations yields a minority carrier concentration which has a reduced gradient in the single-crystal emitter of the

polysilicon contacted device, compared to the metal contacted device (see fig. 2.2). Since the base current is directly proportional to the gradient of the minority carrier concentration at the edge of the emitter/base depletion region, the polysilicon contacted device will therefore have a reduced base current. This two-region model seems reasonable, if a little simplified, in that it would be expected that the amorphous nature of grain boundaries would enhance carrier scattering, and so the mobility in polysilicon, as a whole, would be less than single crystal silicon, doped to the same concentration.

Fig. 2.2 Minority hole concentration in the emitter for a metal contacted emitter transistor, an extended emitter transistor, and a polysilicon emitter transistor.

Also shown in fig. 2.2 is the minority carrier distribution of an extended emitter device, in which the  $n^+$  polysilicon is replaced by single-crystal silicon. This can arise in practice if complete epitaxial re-growth is induced during the emitter drive-in [5], [6]. It has many of the advantages of a polysilicon emitter, such as a shallow emitter/base junction, but the current gain is unaffected by the interface, and hence it behaves like a conventional bipolar transistor. For the purposes of this chapter this is a useful structure to consider, since a comparison of the gain of a polysilicon emitter, with that of an identical extended emitter, gives a measure of the gain enhancement or reduction resulting from the presence of the polysilicon/silicon interface.

Analysis of the microscopic structure of polysilicon reveals that it consists of crystalline regions (grains) separated by highly disordered amorphous regions (grain boundaries). Eltoukhy and Roulston [7], [8] have proposed theories which model the effects on minority carrier transport by individual grain boundaries. The grain boundaries are assumed to be infinitely thin, and characterised by a large concentration of interface states. The grain boundaries can affect minority carrier transport in two ways. Firstly, if the density of interface states are large enough (>10<sup>14</sup> cm<sup>-2</sup>) then they will act as efficient recombination centres, and the model will predict no improvement in current gain over that for a metal contacted emitter. For low densities of interface states (≤10<sup>12</sup> cm<sup>-2</sup>) recombination at the grain boundaries becomes negligible, and the minority carrier transport is dominated by scattering from the disordered region around the grain boundaries. This has the overall effect of lowering the minority carrier mobility in the polysilicon layer, and therefore reducing the base current. Eltoukhy and Roulston [7], [8] model the tunnelling through the interfacial layer in an analogous fashion to Stratton [9], and also analyse the effect that the interfacial layer has on the majority electron current by calculating the voltage drop across the interfacial oxide layer.

Yu et al. [10] have also proposed a unified tunnelling and transport model, and introduce the concept of an effective recombination velocity, which is a useful parameter for characterising the effects of various emitter contact technologies on the injected minority carrier concentration. The modelling of the grain boundaries is handled in a different way to that of Eltoukhy and Roulston [7], [8], in that they assume that the grain boundary has a finite thickness, in which the mobility of minority carriers is reduced, compared to that in the bulk of the grain. Recombination is assumed to occur only at the interface between the grain and grain boundary, but not actually in the grain boundary. Furthermore, recombination at the polysilicon/silicon interface is also modelled. Depending on whether the mobility degradation in the grain boundary, or the recombination at the grain/grain boundary interface dominates, the model will predict either a decrease or no improvement of base current, when compared to a device with a conventional metal contacted emitter.

An alternative explanation for the current gain enhancement in polysilicon emitter transistors has been proposed by Ng and Yang [11]–[13] to explain the observation that the current gain of polysilicon emitter transistors is dependent upon the amount of arsenic which segregates to the interface [14], [15]. Typically the concentration of arsenic at the polysilicon/silicon interface can be a factor of two or three larger than the concentration of arsenic in the bulk of the grains. Ng and Yang argued that if the segregated arsenic is electrically active then this could form a low-high-low barrier (see fig. 2.3). Typically the doping concentration changes so rapidly at the interface (greater than kT in a distance comparable to the mean free path) that the usual

Fig. 2.3 Band-diagram of polysilicon emitter with electrically active dopant segregation barrier at the polysilicon/silicon interface.

drift-diffusion theory for carrier transport is no longer valid, and thermionic emission has to be invoked. The resulting model can therefore explain the increase of gain of a polysilicon emitter transistor with segregated arsenic at the interface, as well as the reduced temperature dependence of the current gain, although the model does not predict any increase in emitter resistance.

The main assumption of the thermionic emission theory is that the segregated arsenic remains electrically active, for which there has been no direct experimental evidence, although Wong *et al.* [16] have argued indirectly that the segregated arsenic could be electrically active. Furthermore, rigourous analysis of the theory by Wolstenholme [17] indicates that the base current is proportional to the ratio of the *effective* doping densities in the polysilicon and at the interface, which includes the effects of band-gap narrowing. Since effective doping concentration tends to saturate to a constant value as the electrically active doping concentration increases [18], then this implies that the segregation barrier will be smaller than predicted in [11]–[13]. The analysis in this chapter will use both the original theory as proposed by Ng and Yang [11]–[13] (i.e. with no band-gap narrowing), and the extended theory as developed by Wolstenholme [17] (i.e. including the effects of band-gap narrowing).

The model to be used in this chapter (and described in detail in the next section) follows from that of Yu et al. [10], extended to include the thermionic emission barrier due to dopant segregation [17]. TEM evidence of the polysilicon suggests that the layer consists of columnar grains, and so the polysilicon will be assumed to consist of only one crystalline grain.

#### 2.3 Theory

#### 2.3.1 Base current of a shallow emitter bipolar transistor

The injection and recombination of minority carriers in the emitter of a bipolar transistor play a crucial role in determining device behaviour. Of particular importance to the polysilicon contacted emitter transistor is the limiting effect on the current gain by recombination in the heavily doped single-crystal emitter. It is therefore important to evaluate and model these effects. It is easier to analyse the emitter of a bipolar transistor in terms of the effective recombination velocity,  $S_p$  at the emitter contact. This is defined as,

$$J_{p}(W_{E}) = qS_{p}p(W_{E}) \tag{2.1}$$

where  $J_p(W_E)$  is the hole current density (for an npn device) at the emitter contact, and  $p(W_E)$  is the excess hole concentration at the emitter contact. The numerical value of  $S_p$  can be used to define the recombination and blocking properties of the interface. For example, in a metal contacted emitter all the minority carriers are forced to recombine at the contact. Hence  $p(W_E)$  is close to zero, and since  $J_p(W_E)$  is finite, then  $S_p$  takes a large value (typically  $\geq 10^6$  cm s<sup>-1</sup>). If the metal contact is replaced by a thick interfacial oxide layer then  $J_p(W_E) \rightarrow 0$  and so  $S_p \approx 0$ . For a typical polysilicon contact  $S_p$  will take an intermediate value between these two extremes.

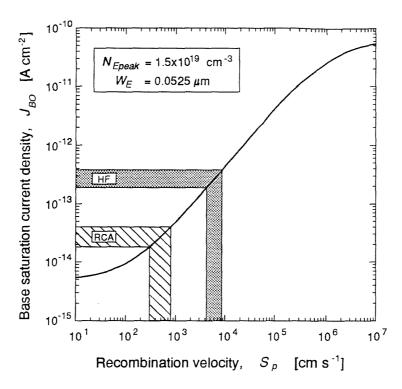

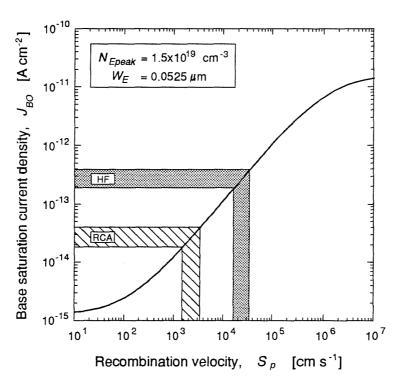

For typical emitter depths <0.2 $\mu$ m and peak electrical emitter concentrations  $\leq 10^{20}$  cm<sup>-3</sup>, then an analytical expression can be derived [19] which expresses the base saturation current density,  $J_{BO}$  as a function of the emitter contact effective recombination velocity,  $S_p$  and the recombination parameters in the emitter,

$$J_{BO} = \frac{q n_{io}^{2}}{G_{eff}(W_{E}) + N_{Eeff}(W_{E})/S_{p}} \left[ 1 + \int_{0}^{W_{E}} \frac{G_{eff}(W_{E}) - G_{eff}(x)}{\tau_{p}(x)N_{Eeff}(x)} dx + \frac{N_{Eeff}(W_{E})}{S_{p}} \int_{0}^{W_{E}} \frac{dx}{\tau_{p}(x)N_{Eeff}(x)} \right]$$

(2.2)

where  $\tau_p$  is the hole lifetime in the emitter,  $S_p$  is the effective recombination velocity at the emitter contact, and x=0 is defined as the edge of the emitter/base depletion region and  $x=W_E$  is the position of the polysilicon/silicon interface.  $G_{eff}(x)$  is the effective emitter Gummel number, and is defined as,

$$G_{eff}(x) = \int_0^x \frac{N_{Eeff}(x)}{D_p(x)} dx$$

(2.3)

$N_{Eeff}(x)$  is the 'effective' doping concentration in the emitter and is used to model heavy doping effects. It is defined by,

$$N_{Eeff}(x) = N_E(x) \exp\left(\frac{-\Delta E_g^{app}(x)}{kT}\right)$$

(2.4)

where  $N_E(x)$  is the electrically active doping profile in the emitter, and  $\Delta E_g^{app}(x)$  is the 'apparent' or 'device' band-gap narrowing in the emitter.

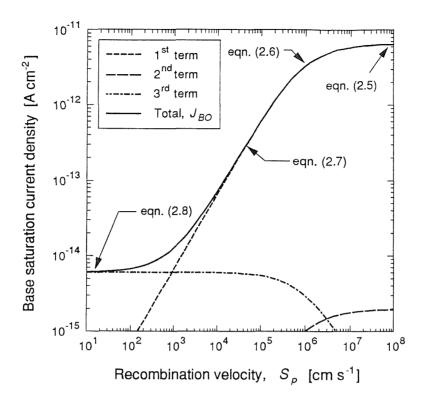

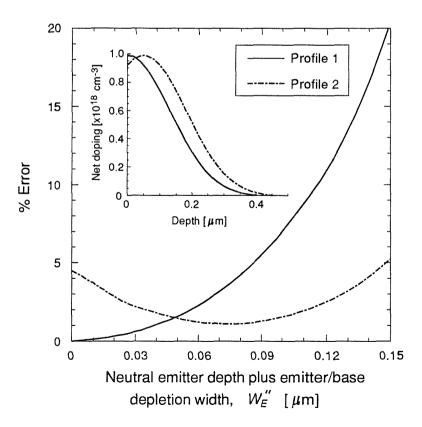

The first term in equation 2.2 is identical to that obtained by Shibib *et al.* [20] for transparent emitters (i.e. no recombination in the bulk of the emitter). The last two terms in brackets model the effect on the base current by recombination in the bulk emitter, although, for the vast majority of devices analysed in this chapter, recombination in the bulk emitter is negligible. The only notable exception to this is for devices with thick interfacial oxide layers. The three terms in equation 2.2 are illustrated in fig. 2.4 as a function of  $S_p$ , where it can be seen that equation 2.2 can be simplified for certain specific emitter contact technologies, as discussed below. In order to calculate predicted values of base current to compare with reported experimental values in the literature, equation 2.2 is used together with measured emitter profiles, where available. In cases where the emitter profile is not given, a Gaussian profile is assumed in the single-crystal emitter, the Gaussian being constructed using estimates of the emitter/base junction depth and the doping concentration at the polysilicon/silicon interface.

#### a) Metal contacted emitters

As stated previously, metal contacted emitters are characterised by a large effective recombination velocity. In this case the last two terms in brackets from equation 2.2 can be ignored (see fig. 2.4). Also since  $N_{Eeff}/S_p << G_{eff}(W_E)$  ( $S_p$  is large) then the base current of a shallow metal contacted emitter can be approximated to,

$$J_{BO} = \frac{q n_{io}^2}{\int_0^{W_E} N_{Eeff}(x)/D_p(x)dx} \qquad S_p \ge 10^6 \text{cm s}^{-1} \quad (2.5)$$

Fig. 2.4 Solution of equation 2.2 showing how the recombination velocity,  $S_p$  can be extracted from the measured base current,  $J_{BO}$ . Also shown are the simplifications that can be applied to equation 2.2 for certain ranges of  $S_p$ .

For this case recombination at the emitter contact is so large that the limiting factor is the supply of holes to the emitter contact. The base current is also proportional to the emitter depth, and so indicates that the base current will increase as the vertical dimensions of a metal contacted bipolar transistor are scaled.

#### b) Polysilicon emitters

If there is minimal blocking action of minority carriers at the polysilicon/silicon interface due to the 'break-up' of the interfacial layer, and/or a large density of recombination states exist at the interface, then typical values of effective recombination velocity,  $S_p$  are between  $10^5$  and  $10^6$  cm s<sup>-1</sup>. In this case  $N_{Eeff}/S_p \sim G_{eff}(W_E)$  and so equation 2.2 can be simplified to (see fig. 2.4),

$$J_{BO} = \frac{q n_{io}^2}{G_{eff}(W_E) + N_{Eeff}(W_E)/S_p} \qquad 10^5 < S_p < 10^6 \text{cm s}^{-1} (2.6)$$

This is the intermediate case where the recombination at the contact is large enough so that again the supply of holes to the emitter contact is a limiting factor, although the effective recombination velocity is small enough to provide some blocking action.

If the interface provides some greater blocking action due to reduced grain boundary mobility and/or the presence of an interfacial oxide, then the polysilicon contact can be characterised by an intermediate value of effective recombination velocity. In this case  $N_{Eeff}/S_p \gg G_{eff}(W_E)$  and so,

$$J_{BO} = \frac{q n_{io}^2 S_p}{N_{Eeff}(W_E)}$$

10<sup>3</sup> < S<sub>p</sub> < 10<sup>5</sup> cm s<sup>-1</sup> (2.7)

The base current is still dominated by recombination at the emitter contact, but this time the dependence on emitter depth is lost (and hence the base current will remain constant as the emitter depth is scaled). In the extreme that  $S_p$  becomes very small (eg. for a device with a thick interfacial oxide layer) then the third term in brackets in equation 2.2 become prominent. In this limit equation 2.2 reduces to,

$$J_{BO} = \int_0^{W_E} \frac{q \, n_{io}^2}{L_p^2(x) N_{Eeff}(x) / D_p(x)} dx \qquad S_p \le 10^2 \text{cm s}^{-1}(2.8)$$

The base current is now independent of the properties of the interface, and is completely dominated by recombination in the bulk of the emitter.

### 2.3.2 Recombination velocity model for polysilicon emitter bipolar transistors

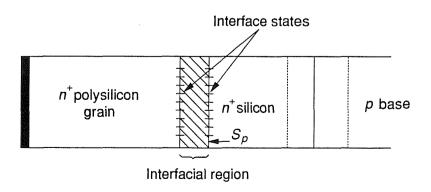

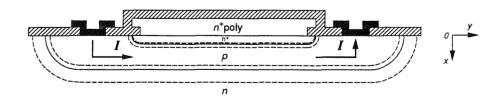

The general model to be used in this study for a polysilicon emitter transistor is shown schematically in fig. 2.5. It is assumed that the polysilicon layer consists of only one crystalline grain separated from the monosilicon substrate by an interfacial

Fig. 2.5 Schematic diagram of a polysilicon emitter transistor.

region of finite thickness, which will be described in detail further on. A density of interface traps are also assumed to exist at the two interfaces between the interface region and the polysilicon grain and the monosilicon substrate.

The effective recombination velocity,  $S_p$  which characterises the polysilicon contact, can in general be expressed as [10],

$$S_{p} = S_{I} + \left[ \frac{1}{T_{block}} + \frac{1}{S_{I} + S_{g}} \right]^{-1}$$

(2.9)

where  $S_I$  models the recombination of minority carriers via traps at the interface, and is given by,

$$S_I = \frac{1}{2} N_{it} c_p v_{th} {(2.10)}$$

and  $N_{ii}$  is the density of interface traps per unit area,  $c_p$  is the capture cross-section and  $v_{th}$  is the thermal velocity. The factor of 1/2 arises in equation 2.10, since it is assumed that the interface states are equally distributed between the left and right sides of the interface.

The parameter  $S_g$  describes the recombination of minority carriers in the bulk of the grain, and is given by [10],

$$S_{g} = a_{g} - \frac{b_{g}^{2}}{a_{g} + S_{M}} \tag{2.11}$$

where,

$$a_g = \frac{D_g}{L_g} \coth\left[\frac{W_p}{L_g}\right] \tag{2.12a}$$

$$b_g = \frac{D_g}{L_g} \operatorname{csch} \left[ \frac{W_p}{L_g} \right] \tag{2.12b}$$

and  $D_g$  and  $L_g$  are the diffusivity and diffusion length of minority carriers in the grain respectively,  $S_M$  is the effective recombination velocity at the metal contact, and  $W_p$  is the polysilicon thickness.

Depending on the dominant carrier blocking mechanism, the value of  $T_{block}$  can take one of three values (see Appendix 1):

#### a) Oxide tunnelling model

If a deliberately grown interfacial oxide layer is present, then the dominating

blocking mechanism will be the tunnelling of minority carriers through the oxide. This model will be termed the *oxide tunnelling model*, in which the blocking recombination velocity,  $T_{block}$  can be expressed as [10],

$$T_{block} = T_{tun} = \frac{A_{hi}^* T^2}{q N_v} \cdot \frac{\exp(-b_h)}{1 - c_h kT}$$

(2.13)

where,

$$b_h = \frac{4\pi\delta}{h} \sqrt{2m_{hi}^* \chi_h} \tag{2.14a}$$

$$c_h = \frac{2\pi\delta}{h} \sqrt{\frac{2m_{hi}^*}{\chi_h}} \tag{2.14b}$$

and  $\chi_h$  is the barrier height to holes,  $m_{hi}^*$  is the effective mass of holes in the oxide, and  $\delta$  is the oxide thickness.  $A_{hi}^*$  is the effective Richardson constant for holes in the oxide, and  $N_{\nu}$  is the effective density of states in the valence band, which are given by,

$$A_{hi}^* = \frac{4\pi q m_{hi}^* k^2}{h^3} \tag{2.15a}$$

$$N_{\nu} = 2 \left[ \frac{2\pi m_{\nu}^* kT}{h^2} \right]^{3/2} \tag{2.15b}$$

and  $m_{\nu}^{*}$  is the valence band effective density of states mass.

#### b) Pseudo-grain boundary mobility model

If no oxide is present at the interface, then the disordered nature of the interface can still block minority carrier injection. The interface can then be treated as a grain boundary of finite thickness, characterised by a reduction in carrier mobility. This model will be termed the *pseudo-grain boundary mobility model*, in which the blocking recombination velocity,  $T_{block}$  is given by,

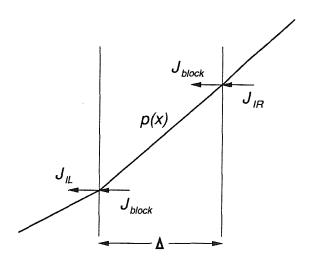

$$T_{block} = T_{pgb} = \frac{kT}{q} \cdot \frac{\mu_{pgb}}{\Delta}$$

(2.16)

where  $\Delta$  is the thickness of the pseudo-grain boundary, and  $\mu_{pgb}$  is the minority carrier mobility in the pseudo-grain boundary. A value for  $\Delta$  of 7Å [21] will be used throughout this chapter, which is consistent with the approximate thickness of a grain boundary in the bulk of the polysilicon. Typically,  $\mu_{pgb}$  can be several orders of magnitude less than the hole mobility in single-crystal silicon [22]. It is also likely that the amorphous nature of the interface, and the presence of impurities, such as carbon, could result in an increase in band-gap, and so lead to the blocking of minority carriers. However, due to the large uncertainty of the precise physical properties of the interfacial region, this mechanism will not be considered in this chapter.

#### c) Segregation model

An alternative blocking mechanism has been proposed by Ng and Yang [11]–[13] for interfaces with no deliberately grown oxide. The model assumes that the segregated dopant at the interface is electrically active, and that the minority carriers are dominated by thermionic emission over this electrical barrier. This model will be termed the segregation model, in which the blocking recombination velocity,  $T_{block}$  is given by,

$$T_{block} = T_{th} = \frac{A_h^* T^2}{\sigma N_{tot}} \cdot \frac{N_E}{N_{loc}}$$

(2.17)

where  $N_E$  is the electrically active doping density in the emitter, and  $N_{Int}$  is the electrically active doping density of the segregated dopant at the interface, and  $N_{\nu}$  is the effective density states in the valence band.  $A_h^*$  is the effective Richardson constant for holes in silicon, which is expressed as,

$$A_h^* = \frac{4\pi q \, m_{hth}^* k^2}{h^3} \tag{2.18}$$

and  $m_{hih}^*$  is the effective mass of holes thermionically emitted over the segregation barrier. It has been pointed out by Wolstenholme [17] that the doping densities in equation 2.17 should strictly be effective doping densities, which include the effects of band-gap narrowing. For this mechanism to dominate the base current, the barrier created by the segregated dopant must be greater than about 2kT. For a typical emitter doping concentration of  $10^{20}$  cm<sup>-3</sup>, this means that the segregated doping concentration must be greater than around  $8\times10^{20}$  cm<sup>-3</sup> for the original Ng and Yang model [11]–[13], or greater than  $10^{23}$ – $10^{24}$  cm<sup>-3</sup> for the extended model of Wolstenholme [17].

#### 2.3.3 Extended emitter model

An important device structure that is useful for direct comparisons with the polysilicon emitter is that of the extended emitter. This device has the same emitter structure and doping profile as the polysilicon emitter device, but with no interface. In other words  $T_{block} = \infty$  and  $S_I = 0$  in equation 2.9, so that  $S_p = S_g$ . The extended emitter can be used to clarify any blocking or recombination mechanisms at the interface. For example, if the base current of a polysilicon emitter is less than that of the identical extended emitter, then this is evidence of a blocking mechanism at the interface. Conversely, if the base current of the polysilicon emitter device is larger than that of an extended emitter device, then this is evidence of a recombination mechanism at the interface.

### 2.3.4 Parameter values and minority carrier hole models in heavily doped n-type silicon

Table 2.1 summarises the parameter values that will be used throughout this study, unless otherwise stated.

| Parameter                                                                  | Value                                              | Reference |

|----------------------------------------------------------------------------|----------------------------------------------------|-----------|

| Hole effective mass in the interfacial oxide layer $(m_{hi}^*)$            | $0.42m_{o}$                                        | [8]       |

| Hole effective mass for thermionic emission $(m_{hte}^*)$                  | 0.66 <i>m</i> <sub>o</sub>                         | [23]      |

| Valence band effective density of states mass $(m_{\nu}^*)$                | $0.81m_o$                                          | [24]      |

| Interface trap capture cross-<br>section x thermal velocity $(c_p v_{th})$ | 2x10 <sup>-9</sup> cm <sup>3</sup> s <sup>-1</sup> | [25]      |

| Grain boundary thickness (Δ)                                               | 7Å                                                 | [21]      |

| Recombination velocity at metal contact $(S_M)$                            | 10 <sup>6</sup> cm s <sup>-1</sup>                 | [10]      |

**Table 2.1** Parameter values used in this study.

In order to obtain predictions of effective recombination velocity and base current from doping profiles, it is necessary to use empirically fitted values for the minority carrier recombination and transport parameters such as hole lifetime  $\tau_p$ , hole mobility  $\mu_p$ , and band-gap narrowing,  $\Delta E_g^{app}$ . Values for these parameters, as a function of doping, will be taken from the work of del Alamo *et al.* [18],

$$\frac{1}{\tau_p} = (7.8 \times 10^{-13}) N_E + (1.8 \times 10^{-31}) N_E^2$$

(s) (2.19a)

$$\mu_p = 130 + \frac{370}{1 + (N_F/8 \times 10^{17})^{1.25}}$$

(cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) (2.19b)

$$\Delta E_g^{app} = 18.7 \times 10^{-3} \ln \left( \frac{N_E}{7 \times 10^{17}} \right)$$

(eV) (2.19c)

Unfortunately, there is still much disagreement in the literature over the precise form equation 2.19 should take, mainly because minority carrier transport parameters are extremely difficult to measure. However, the parameter set above are consistent in that the measurements were performed simultaneously on the same silicon samples, and so these will be used throughout this chapter.

#### 2.4 Experimental results

Over the past ten years or so, a considerable amount of experimental results on polysilicon emitter transistors have been published in the literature. In this section, approximately 8 or so key papers have been chosen which are representative of a broad cross-section of important experimental results. The results of these papers will be quoted in the form of raw experimental data (for example measured current densities and resistances etc.), and then any subsequent modeling will be performed using the simplified analytical equations outlined in section 2.3. This will allow a consistent comparison to be made between the predictions of the three blocking mechanisms and the reported experimental results.

#### 2.4.1 Devices with interfacial oxides

#### a) Effect of an interface anneal

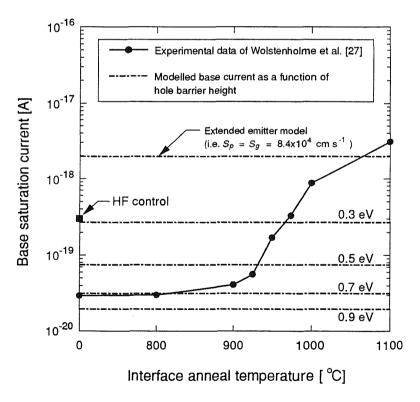

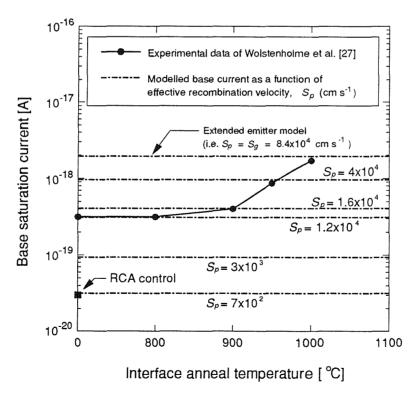

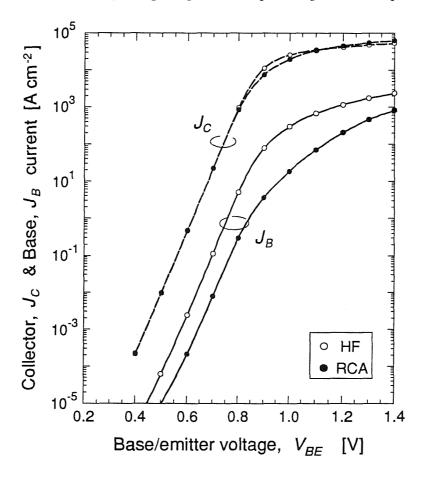

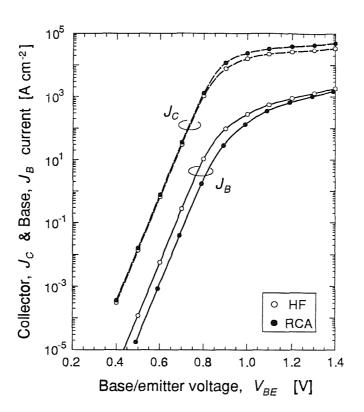

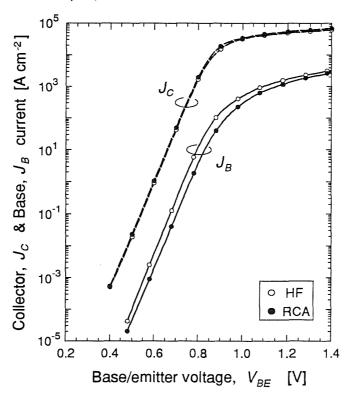

The analysis will begin by considering experimental results from devices with an interfacial oxide layer, which is generally grown using an oxidising chemical treatment. It has been well documented in the literature that such an interface treatment gives a significant improvement in the current gain. For example, Ashburn and Soerowirdjo [26] have shown that devices given an RCA clean prior to polysilicon deposition, had gains five times higher than those given an HF etch. A more detailed characterisation of the influence of the interfacial oxide on the current gain was carried out by Wolstenholme *et al.* [27]. In this experiment an interface anneal was carried out after polysilicon deposition, but prior to emitter implant, to thermally stress the interfacial

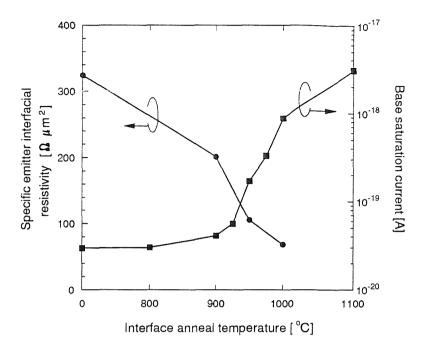

oxide. In this way, a range of interfacial oxide structures was obtained without significantly altering the emitter and base doping profiles. The results are shown in fig. 2.6 for devices given an RCA clean prior to polysilicon deposition. It is evident that a factor of 100 increase in base current is obtained as the temperature of the interface anneal is increased from 800 to 1100°C. These electrical results were correlated with high resolution TEM observations of the polysilicon/silicon interface which showed that an interfacial oxide was present, which broke up by increasing amounts as the interface anneal temperature was increased. For interface anneal temperatures of 900°C or below, the interfacial oxide was continuous and uniform, with a thickness of 14±2Å. In contrast, after an interface anneal at 950°C, a third of the interface had broken up, and the polysilicon had started to epitaxially align from the substrate, with these epitaxial regions extending typically 35Å into the polysilicon. An interface anneal at 1000°C lead to a further break-up of the interfacial oxide (70%, with epitaxial regions extending 40Å into the polysilicon), and an anneal at 1100°C produces an interface which consists entirely of oxide balls.

Fig. 2.6 Experimental data of Wolstenholme *et al.* [27] showing base saturation current as a function of interface anneal for devices with a deliberately grown interfacial oxide layer. The base current has been modelled by assuming that the dominant blocking mechanism is tunnelling through the interfacial oxide layer (i.e. *oxide tunnelling model* with  $\delta$ =14Å, and  $S_i$ =0). Also shown is the modelled base current using the *extended emitter model* ( $T_{block}$ = $\infty$ , and  $S_i$ =0).

Since interface anneals at 900°C and below produce a continuous interfacial oxide, it is possible to apply the *oxide tunnelling model* unambiguously to these results. Fig. 2.6 shows the modelled values of base current for different values of oxide barrier height, assuming that the devices are tunnelling-dominated (i.e.  $S_l$ =0 and  $T_{block}$ << $S_g$ ). It is evident that these devices can be modelled by an oxide barrier height of 0.7 eV. It is probably more realistic to assume that some form of recombination via interface traps is also acting in parallel with the tunnelling, and if this is the case then the barrier height of 0.7 eV must increase in order that a fit to the measured base current is still obtained. An upper limit for the interface state density can be obtained by modeling the base current under the assumption that the device is dominated by recombination at the interface (i.e.  $T_{block}$ =0). In this case, the control RCA device in fig. 2.6 can be modelled by an interface state density of 7.4×10<sup>11</sup> cm<sup>-2</sup>.

Also modelled in fig. 2.6 is the base current of an extended emitter device, in which no blocking or recombination at the interface is assumed to occur (i.e.  $T_{block} = \infty$  and  $S_r = 0$ ). As can be seen, a reasonable fit to the 1100°C interface anneal device is achieved, which implies that the interface has no effect on the base current of this device. This conclusion is consistent with the TEM analysis, which showed that the interfacial oxide had completely 'balled-up', such that 97% of the interface was oxide-free. There was also a substantial amount of epitaxial re-growth of the polysilicon. These experimental results show that the interfacial oxide plays a dominant role in controlling the current gain of polysilicon emitter transistors with deliberately grown interfacial oxide layers. Recent work by Ronsheim *et al.* [28], using depth-resolved secondary ion mass spectroscopy, has quantified this process, and shown that there exists a direct correlation between the amount of oxygen at the interface (expressed as atoms/cm²) and the base current of polysilicon emitter transistors.

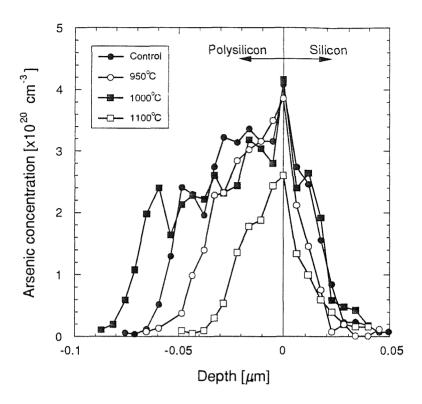

Rutherford back scattering (RBS) analysis has been used by Wolstenholme [17] to investigate the distribution of arsenic at the interface for the devices reported in fig. 2.6. The results of this analysis are shown in fig. 2.7, and indicate that the concentration of arsenic at the polysilicon/silicon interface remains unchanged for interface anneals up to a temperature of 1000°C. This therefore completely rules out the *segregation model* as a possible mechanism for explaining the experimental results in fig. 2.6.

#### b) Temperature dependence of current gain

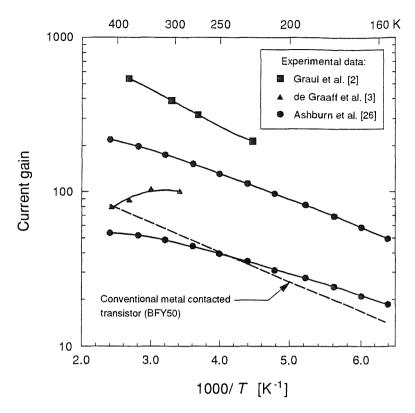

Further evidence supporting the *oxide tunnelling model* is obtained from measurements of the temperature dependence of the current gain. Several authors [2], [3], [26] have reported that polysilicon emitter transistors with a chemically grown interfacial oxide, have a gain which varies less strongly with temperature than observed

Fig. 2.7 Experimental data of Wolstenholme [17] showing Rutherford back scattering (RBS) arsenic profiles of the polysilicon/silicon interface for devices with a deliberately grown interfacial layer, subjected to various interface anneals.

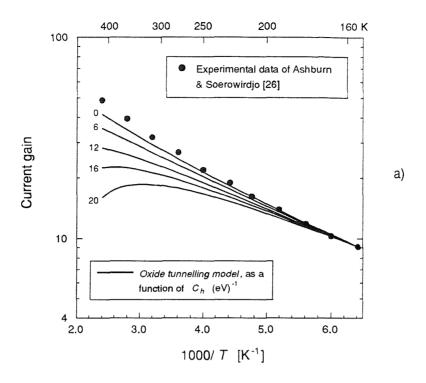

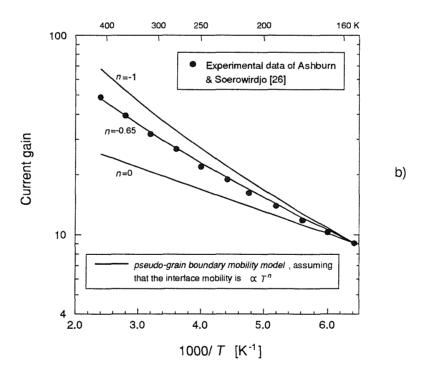

for conventional metal contacted transistors. Fig. 2.8 shows the current gain as a function of inverse temperature from the work of Graul *et al.* [2], de Graaff and de Groot [3] and Ashburn and Soerowirdjo [26]. Also shown in fig. 2.8 is the temperature dependence of current gain for a conventional metal contacted transistor (whereby the temperature dependence of the current gain is determined by the difference in band-gap narrowing in the base and emitter). It can be seen, especially for temperatures above 300K (i.e. for  $c_h kT \ge 0.2$  in equation 2.13), that the temperature dependence of current gain becomes less sensitive to temperature than conventional metal contacted transistors. In fact the results from de Graaff and de Groot [3] even show a negative temperature coefficient. Ashburn and Soerowirdjo [26] modelled the temperature dependence of gain, and showed that the *oxide tunnelling model* could explain the observed results for the whole temperature range in fig. 2.8.

#### c) Emitter resistance

The presence of a deliberately grown oxide layer at the polysilicon/silicon interface has been shown to block majority carrier flow, leading to an increase in emitter resistance [29]–[31]. This increased resistance can have serious consequences for circuit behaviour, most notably a reduction in output power, and also limitations on the output

Fig. 2.8 Experimental data of Graul *et al.* [2], de Graaff and de Groot [3], and Ashburn and Soerowirdjo [26] showing current gain as a function of inverse temperature for devices with a deliberately grown interfacial oxide layer. Also shown is the temperature dependence of a conventional metal contacted bipolar transistors, whereby the temperature dependence is attributed to the difference in band-gap narrowing between the base and emitter.

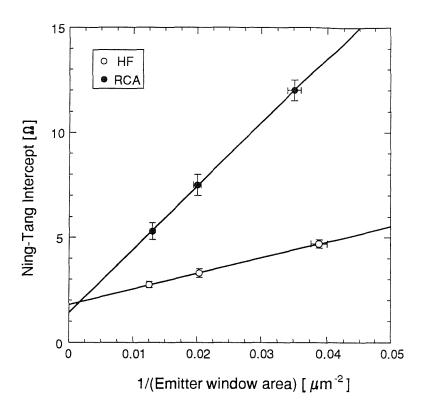

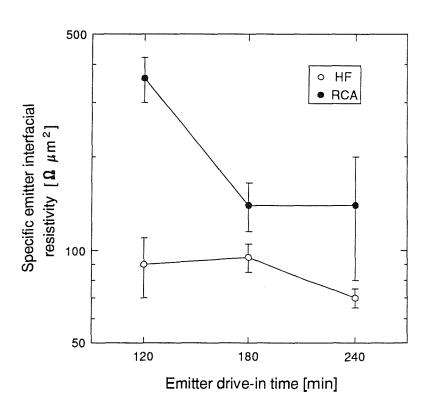

voltage swing of switching circuits. Measurements of specific emitter interfacial resistivity for devices with deliberately grown interfacial oxide layers typically range from 200 to 500  $\Omega\mu\text{m}^2$  [29]–[31]. This compares with generally far lower values of 10 to 200  $\Omega\mu\text{m}^2$  [29], [31], [32] for devices without deliberately grown interfacial oxide layers. By applying the *oxide tunnelling model* to the devices with interfacial layers, and assuming an average oxide thickness of 14Å and an electrically active polysilicon doping level of  $5\times10^{19}$  cm<sup>-3</sup>, implies a barrier height to electrons of around 0.3–0.4 eV (using the analytical expression for emitter resistance derived in [33]). Comparing this value with the barrier height for holes, which is around 0.7 eV (fig. 2.6), it can be clearly seen that there exists an asymmetry in oxide barrier heights for electrons and holes.

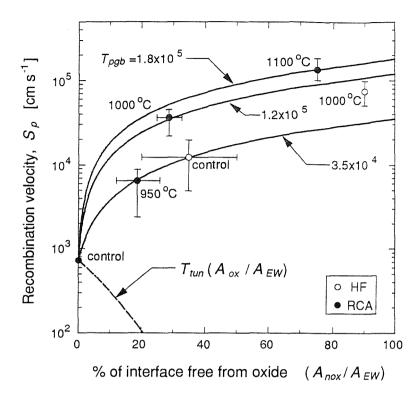

Wolstenholme *et al.* [31] have performed experiments on the 'balling-up' of the interfacial oxide from interface anneals, and then correlating this with measurements on emitter resistance, as shown in fig. 2.9. Also shown in fig. 2.9 is the base current data from fig. 2.6. Some important differences were observed when compared to the corresponding experiment used to study the effect of interface anneals on the base

Fig. 2.9 Experimental data of Wolstenholme *et al.* [27], [31] showing the specific emitter resistivity and base saturation current as a function of interface anneal temperature for devices with a deliberately grown interfacial oxide layer.

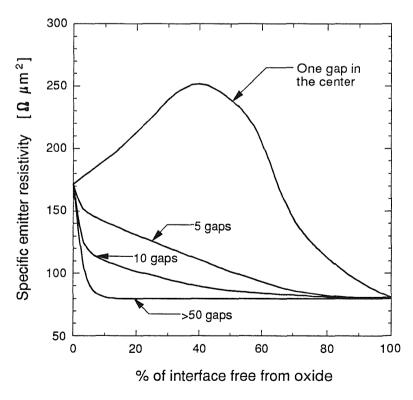

Fig. 2.10 Modelled specific emitter resistivity as a function of the percentage of the interface which is oxide-free for a device with a HF interfacial treatment, from the work of Hamel *et al.* [34]. It can be clearly seen that not only the amount of oxide, but its distribution along the interface will effect the emitter resistance.

current. Most notable was a substantial reduction in emitter resistance for the device given a 900°C interface anneal, compared to the control device, even though the TEM analysis showed that the interfacial layer for both devices was continuous and un-broken. Two-dimensional modeling by Hamel *et al.* [34], as shown in fig. 2.10, has recently shown that this result can be explained if a limited number of widely spaced small gaps in the oxide layer are produced in the 900°C interface anneal, even though nearly 99% of the oxide remains continuous (and so therefore these gaps would be difficult to observe by TEM). Since a large proportion of the interface remains intact, a reduction in base current is still obtained, as observed in fig. 2.9. These results show that an interface anneal is an important tool in adjusting the base current and emitter resistance of devices with deliberately grown interfacial oxide layers [35].

Measurement and modeling of the temperature dependence of emitter resistance, for devices with deliberately grown interfacial oxide layers, has been conducted by Yung et al. [36]. They found that the oxide tunnelling model could fit the observed temperature dependence, although the shape of the tunnelling barrier had to be changed from rectangular to triangular. Yung et al. [36] speculated that dopant pile-up at the interface was the physical cause of this change in barrier shape.

In summary, the *oxide tunnelling model* is successful in explaining the base current, emitter resistance, and the temperature dependence of these two quantities. Neither of the other two theories (*pseudo-grain boundary mobility model* and the *segregation model*) can explain both the reduction of base current and the increase in emitter resistance, as well as the temperature dependence of these quantities, for devices with interfacial oxide layers.

### 2.4.2 Devices without an interfacial oxide layer

For commercial applications, devices without a deliberately grown interfacial oxide layer are generally preferred because of the emitter resistance problem described above. However, it should be pointed out that an interfacial layer is invariably present at the polysilicon/silicon interface, even in devices given an HF etch prior to polysilicon deposition [27].

### a) Segregation of dopant to the interface

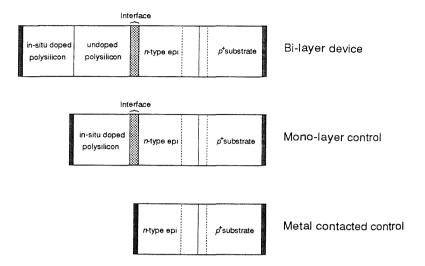

Confirmation of the role of the interface in controlling the gain comes from the work of Neugroschel *et al.* [14], who have fabricated bi-layer polysilicon diodes by first depositing undoped polysilicon and then capping the device with *in-situ* arsenic doped polysilicon, as shown in fig. 2.11(a). Drive-in conditions were carefully chosen so that the amount of arsenic segregated to the polysilicon/silicon interface could be

Fig. 2.11(a) Schematic diagram of a bi-layer device, mono-layer control device and metal contacted diodes as used by Neugroschel *et al.* [14].

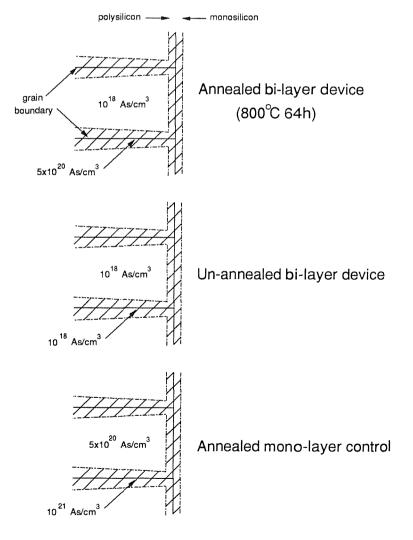

**Fig. 2.11(b)** Schematic diagram showing the arsenic concentration in the grains and grain boundaries of an annealed bi-layer device, an un-annealed bi-layer device and a mono-layer control as used by Neugroschel *et al.* [14].

varied. A long low temperature drive-in (eg. 64 hours at 800°C) was used to preferentially diffuse the arsenic along the grain boundaries, and dope the grain boundaries and interface to a concentration of around  $5 \times 10^{20}$  cm<sup>-3</sup>. However, the temperature of the drive-in was not high enough to diffuse arsenic into the bulk of the grains [37], which remained at a low concentration of  $\leq 10^{18}$  cm<sup>-3</sup>. This device was then compared to both an un-annealed bi-layer device (with a low arsenic concentration of  $\leq 10^{18}$  cm<sup>-3</sup> in the grains and at the interface), and to a control device with a single *in-situ* doped polysilicon layer (with an arsenic concentration of  $\sim 10^{21}$  cm<sup>-3</sup> at the interface and around  $5 \times 10^{20}$  cm<sup>-3</sup> in the grains). A schematic diagram showing the resulting doping concentrations in the polysilicon and at the interface for these three devices is shown in fig. 2.11(b).

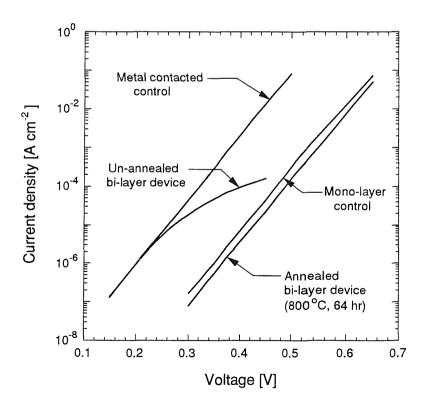

Fig. 2.12 shows the current-voltage characteristics for the annealed and un-annealed bi-layer devices, and the single polysilicon layer control device. Also shown is the characteristic for a metal contacted control with no polysilicon layer. The diode current can be assumed to consist only of a hole current (i.e. base current) since the minority electron current injected into the  $p^+$  substrate is small. If it is assumed that transport in the polysilicon layer dominates the hole current, then it would be expected that the current from both the annealed and un-annealed bi-layer devices would be the same, since they have near identical arsenic concentrations of  $\leq 10^{18}$  cm<sup>-3</sup> in the bulk of the

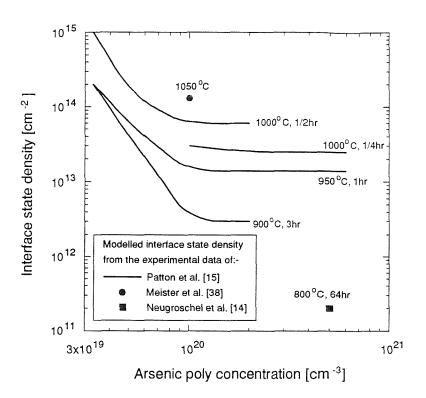

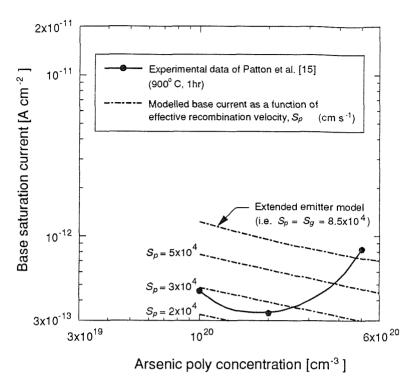

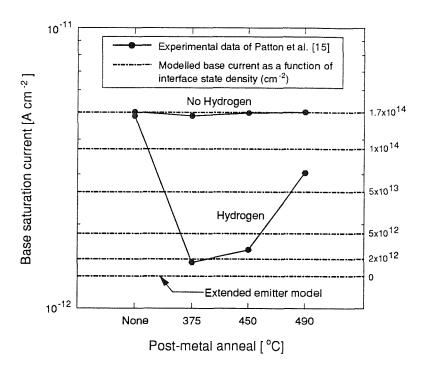

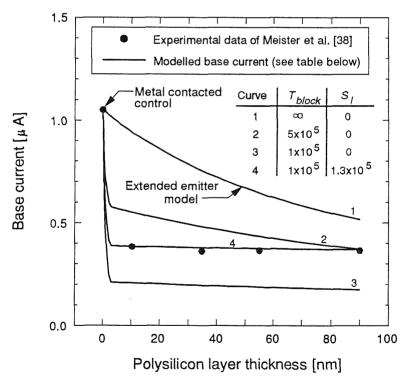

Fig. 2.12 Current-voltage characteristics of the diodes as analysed by Neugroschel *et al.* [14]. The devices shown are the metal contacted control, the single layer polysilicon control, and the annealed and un-annealed bi-layer devices.