# Design and implementation of a low-power hybrid capacitive MEMS oscillator

Cuong Do, Andreja Erbes, Jize Yan, Ashwin A. Seshia

Department of Engineering, University of Cambridge, Cambridge, United Kingdom.

Abstract—This paper reports on the design and implementation of a low power MEMS oscillator based on capacitively transduced silicon micromachined resonators. The analysis shows how design parameters of MEMS resonator impact on the power requirement of the oscillator, particularly with a view towards informing the impact of device and interface parasitics. The analysis is based on resonators fabricated in a 2-µm gap SOI-MEMS foundry process. The sustaining circuit, which is based on a Pierce topology, is fabricated in a standard 0.35µm process. An automatic gain control (AGC) is adopted to suppress the mechanical non-linearity so as to improve oscillator frequency stability. The 110-kHz MEMS and CMOS dies are assembled within a standard ceramic package and electrically integrated through wire bonds. The oscillator core consumes 400nA (900nA with parasitic readout loading) at 1.2-V dc supply while demonstrating a frequency stability of less than 0.5ppm. The work provides a thorough analysis and design guidelines for both MEMS and CMOS circuit design with a view towards minimizing overall power consumption. The implications of the results reported in this paper are towards enabling a new class of low power resonant MEMS sensors that utilize the oscillator as a front-end building block.

Keywords— MEMS; low-power oscillators; sensor interface circuits; Pierce topology; amplitude limiting control.

#### 1. Introduction

Micromachined resonant sensors have been researched for several decades due to the advantages inherent in chip-scale integration and dimensional scaling [1]. Semiconductor batch fabrication enables system integration and significantly reduced costs as compared to traditional resonant sensors. Recent technology breakthroughs in the areas of wafer-level vacuum packaging and passive temperature correction applied to MEMS-based timing and frequency references have addressed two of the significant technical challenges limiting translation to a potentially wide range of device applications

including the measurement of acceleration [2, 3], strain [4] and rotation rate [5, 6]. Central to the design of these devices is a micromechanical oscillator [7] whose physical parameters are functions of the measurands of interest. The micromechanical oscillator typically embeds the resonator in the feedback loop of a sustaining amplifier and a variety of circuit topologies may be employed for this purpose.

The minimization of power dissipation in sensors is of increasing interest in various applications such as consumer products and distributed wireless sensor nodes for environmental and infrastructure monitoring [8]. One of the under-stated advantages of resonant sensors is the potential for significantly reduced power dissipation has not been comprehensively addressed in previous studies [7, 9, 10]. The capacitive MEMS oscillator based on a Pierce topology [11] previously implemented for real-time clocks utilizing MEMS resonators [12, 13] with low-power consumption were demonstrated, though detailed design analysis was not provided. This paper reports on the comprehensive analysis and implementation of an oscillator circuit in standard CMOS as a low power front-end circuit interface for micromachined resonant sensors that addresses the power minimization criterion. The detailed analysis would help both the MEMS and circuit engineers to design a power-optimized capacitive MEMS oscillator based on the availability of the process.

The circuit is designed and fabricated in a 0.35µm foundry CMOS technology and integrated together in a hybrid two-chip format together with a 110kHz electro-statically actuated micromachined single-crystal silicon double-ended tuning fork (DETF) resonator. Double-ended tuning fork resonators operating in this frequency range have been previously integrated into a variety of device applications addressed above, and therefore the results reported in this paper potentially have wide device applicability. The CMOS read-out circuit is specifically designed with no additional bias control requirement apart from the supply voltage provided that can vary over a wide range from 1.1V to 3.3V.

The remainder of the paper is organized as follows: Section II describes the DETF device structure and its equivalent electrical model. Section III presents the oscillator design based on the developed model with a focus on low-power design considerations. Experimental results are presented in section IV. Finally, conclusions and future extensions of this research are discussed in Section V.

#### 2. Resonator model

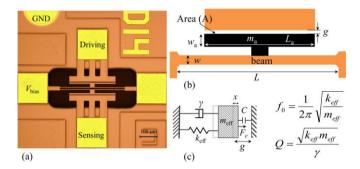

An optical micrograph of the DETF resonator used in this work is shown in Fig. 1(a). The device is designed and fabricated in a commercial foundry process using a silicon-on-insulator (SOI) MEMS process through MEMSCAP Inc., USA. The operating principle of DETF resonator has been discussed in previous papers [2, 14, 15].

Fig. 1. (a) Micrograph of the fabricated silicon DETF resonator. (b) Critical features of the MEMS device. (c) Spring-mass-damper equivalent of the MEMS resonator with electrostatic transduction.

The thickness of the SOI layer is  $t=25\mu m$ . A schematic of the device outlining critical dimensions and device features is shown in Fig. 1 (b). The dimensions of the tines are  $w=5\mu m$ ,  $L=420\mu m$  and the two tines are separated by a gap of  $8\mu m$ . The dimensions of the attached electrodes are  $w_a=10\mu m$ ,  $L_a=300\mu m$ . This resonator is capacitively actuated and sensed using a nominal designed gap ( $g=2\mu m$ ).

The Quality factor, Q, of the system is dependent on the damping coefficient,  $\gamma$ , of the resonator in a given operating environment. The fundamental mode resonant frequency is estimated by the expression [2]

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{k_{eff}}{m_{eff}}} = \frac{1}{2\pi} \sqrt{\frac{16E(w/L)^3}{\rho(w_a L_a + 0.375wL)}}$$

(1)

where E and  $\rho$  are Young modulus and density of the resonator material, which is silicon in this work, other parameters can be found in Fig. 1(b).

Capacitive driving and sensing is utilized for the resonator in this work. To bias and excite the resonator, a dc-bias voltage,  $V_{\text{bias}}$ , is applied to the body of the device, while an ac,  $v_{\text{ac}}$ , voltage applied to the driving electrode, where generally,  $V_{\text{bias}} >> v_{\text{ac}}$ . This voltage combination ( $V_{\text{bias}} + v_{\text{ac}}$ ) generates a

time-varying force that drives the beam into mechanical vibration. The electrostatic force is obtained from

$$F_{e}(x,t) = \frac{1}{2} (V_{bias} + v_{ac}(t))^{2} \frac{\partial C}{\partial x}$$

$$= \frac{1}{2} (V_{bias}^{2} + 2V_{bias}v_{ac}(t) + v_{ac}^{2}(t))^{2} \frac{\partial C}{\partial x}$$

(2)

where *C* is a capacitance between the driving and beam electrodes:

$$C(x) = \frac{\varepsilon_0 A}{g - x} \tag{3}$$

where  $\varepsilon_0$  is the permittivity of free space, A is the electrode area ( $A = L_a t$ ), g is the actuation gap, and x is the deflection of the moving electrode.

The electrostatic force in (2) consists of three frequency components: a dc-force due to term  $V_{bias}^2$ , a force at the excitation frequency due to the cross term  $2V_{bias}v_{ac}(t)$ , and a force at twice the excitation frequency due to square-term  $v_{ac}^2(t)$ . Assuming the deflection is very small compared to the actuation gap  $x \ll g$  and the forcing term at the excitation frequency dominates, we get

$$F_e(t) \cong V_{bias} \frac{\mathcal{E}_0 A}{\sigma^2} v_{ac}(t) \tag{4}$$

The time-varying capacitance between the beam and the electrodes through which a motional current is

$$i = -(V_{bias} + v_{ac}) \frac{\partial C}{\partial t} = -(V_{bias} + v_{ac}) \frac{\partial C}{\partial x} \frac{\partial x}{\partial t}$$

$$= -(V_{bias} + v_{ac}) \frac{\varepsilon_0 A}{(g - x)^2} \frac{\partial x}{\partial t} \cong -V_{bias} \frac{\varepsilon_0 A}{g^2} \frac{\partial x}{\partial t}$$

(5)

with  $V_{\text{bias}} >> v_{\text{ac}}$  and x << g,

The ac current through the capacitor in (5) is termed as the *motional current*. The minus sign on the right hand side denotes that the beam motional current flows in reverse with the applied ac signal input.

As be seen on both (4) and (5), a new variable can be defined, termed the electromechanical transduction factor [16],  $\eta = V_{bias} \frac{\mathcal{E}_0 A}{\rho^2}$ , for the time-varying capacitance of the system.

As the DETF resonator is symmetric, the electrostatic force and the motional output on the sensing pad (in-plane mode) are

$$F_{e}(t) = \eta v_{ac}(t)$$

$$i(t) = \eta \frac{\partial x}{\partial t}$$

(6)

The amplitude of vibration is highest at the resonance frequency where frequency of  $v_{ac}$  is coincident with the beam resonant frequency  $f_0$ . The forced vibration of the resonator shown in Fig.1(c) can be described as

$$m_{eff} \frac{\partial^2 x}{\partial t^2} + \gamma \frac{\partial x}{\partial t} + k_{eff} x = F_e(t)$$

(7)

Substituting  $F_e(t)$  and  $\frac{\partial x}{\partial t}$  in (6) into (7) gives

$$\frac{m_{eff}}{n^2} \frac{\partial i}{\partial t} + \frac{\gamma}{n^2} i + \frac{k_{eff}}{n^2} \int i dt = v_{ac}(t)$$

(8)

The behavior of motional current to ac actuation voltage in (8) is similarly found in a series RLC-circuit with equivalent parameters for motional resistance, motional inductance and motional capacitance as

$$R_{m} = \frac{\gamma}{\eta^{2}} = \frac{\sqrt{k_{eff} m_{eff}}}{Q \eta^{2}} = \frac{\sqrt{k_{eff} m_{eff}}}{Q} \frac{g^{4}}{V_{bias}^{2} \varepsilon_{0}^{2} A^{2}}$$

$$L_{m} = \frac{m_{eff}}{\eta^{2}}$$

$$C_{m} = \frac{\eta^{2}}{k_{eff}}$$

$$(9)$$

The spring-mass equivalent system in (7) of the beam resonator can now be represented by the electrical equivalent circuit as

$$L_{m}\frac{\partial i}{\partial t} + R_{m}i + \frac{1}{C_{m}}\int idt = v_{ac}(t)$$

(10)

The motional elements are governed by the stiffness and mass of the resonator, the electromechanical transduction factor and the damping factor of the resonator. This electrical model is an essential input to oscillator circuit design, presented in the next section. Additionally, the feed-through parasitic capacitor  $C_f$  that directly couples the drive and sense ports can be extracted through measurements. Proper grounding is required to reduce the feed-through coupling. Note that  $C_f$  is the feedthrough capacitance between drive and sense electrodes while  $C_d$  and  $C_s$  are parasitic capacitances associated with the drive and sense pads respectively. Furthermore, the designed nominal parameters are not very well-controlled during the fabrication process, especially the actuation gap, and therefore electrical parameters are generally extracted by the measured system response.

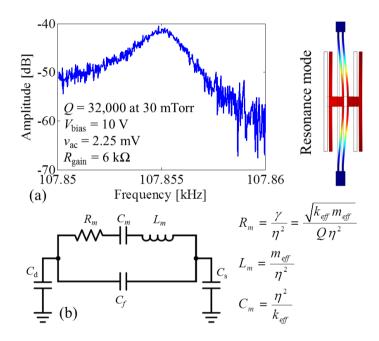

Fig. 2. (a) Measured admittance plot of the DETF resonator. (b) Equivalent electrical circuit model

Fig. 2(a) shows the measured transmission response of the resonator at  $V_{\rm bias} = 10 {\rm V}$  under vacuum conditions. The quality factor (Q) of the resonator is seen to be 32,000 at 30mTorr pressure and motion resistance  $R_{\rm m} = 1.1 {\rm M}\Omega$ . This translates to an actual effective electrical gap of about 3.1 $\mu$ m, which is much larger than that for the nominal design. The value of  $R_{\rm m}$  also increases considerably as  $V_{\rm bias}$  decreases.

TABLE I Equivalent circuit model parameters of the mems resonator at room temperature (25°C), Vbias=10V, P=30 mtorr.

| Model Parameters        | Value  | Unit |

|-------------------------|--------|------|

| $R_{ m m}$              | 1.1    | ΜΩ   |

| $L_{ m m}$              | 52,200 | Н    |

| $C_{ m m}$              | 41.7   | aF   |

| $C_{ m f}$              | 200    | fF   |

| Q                       | 32,000 |      |

| $f_0$                   | 107,85 | kHz  |

| $C_{ m d}$ , $C_{ m f}$ | 1      | pF   |

The extracted linear model parameters from measurement  $V_{\rm bias}$  =10V,  $P=30{\rm mTorr}$  are shown in Table I. The values of  $C_{\rm d}$  and  $C_{\rm s}$  are estimated based on the pad sizes and process parameters provided. The

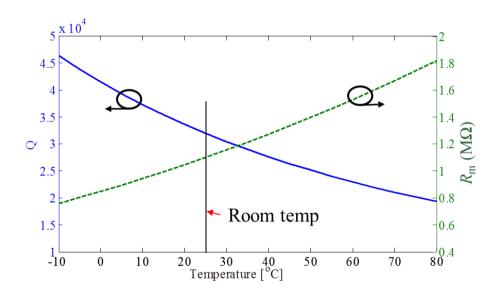

device parameters are normally functions of the bias voltage and environmental conditions including pressure and temperature [16]. Fig. 3 shows a simulation figure of quality factor, Q, and motion resistance,  $R_{\rm m}$ , versus temperature based on (1, 9) with some estimated values found in [17, 18]. It is predicted that the motion resistance could be changed from more than two times when temperature varies from -10°C to 80°C. Therefore, at different temperature, the model parameters in Table I should be updated accordingly.

Fig. 3. Simulation figure of Q and  $R_{\rm m}$  versus temperature. Assuming TCQ=3 [17] and TCE=-60ppm/ $^{\circ}$ C [18] and neglecting other temperature variant factors.

# 3. Oscillator design

## 3.1 Pierce topology

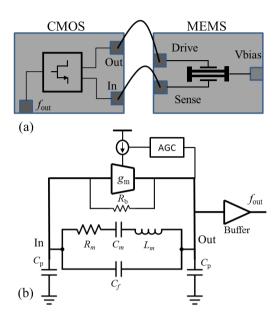

A feedback oscillator is constructed by connecting the resonator to a sustaining amplifier as shown in Fig. 4(a). The two conditions that must be satisfied for sustaining oscillation include, (i) the loop

gain should be higher than or equal to unity, (ii) the phase shift around the loop must be zero (or a multiple of 360°) [11, 16, 19]. A Pierce topology is employed due to its simplicity, stability and potential for power minimization with gain provided by a single transistor [11, 13].

Fig. 4. (a) Schematic of the bonding diagram between CMOS die and MEMS die. (b) Simplified block diagram of oscillator

The equivalent circuit representation of the resonator described here is only accurate in the linear region and must be appropriately modified when the resonator is driven into a non-linear regime [14]. However, at start-up, when the amplitude is small, the linear model is sufficient to evaluate the parameters to satisfy the critical condition for oscillation. A single MOS transistor can be employed to provide the required transconductance to form a three-point oscillator. A comprehensive and detailed analysis of the three-point oscillator can be found in the work of Vittoz [11].

In a two-die MEMS-CMOS oscillator as in this work, the total value of the capacitor  $C_p$  includes all parasitic and stray capacitances on both dies and is estimated to be approximately 2pF in this work. The critical transconductance required to sustain steady oscillation is

$$g_{m,crit} = R_m \omega_0^2 \frac{(C_p^2 + 2C_f C_p)^2}{C_p^2}$$

(11)

The parasitic capacitance  $C_p$  is unavoidable, and is particularly of concern when considering a hybrid integration of the MEMS and CMOS die. Fortuitously the Pierce configuration requires capacitive loading at the input and output nodes of the resonator/amplifier to form a three-point

oscillator [11]. However, a large value of  $C_p$  will require large  $g_{m,crit}$  and, consequently, large static power is dissipated. Therefore,  $C_p$  should be considered carefully so as to minimize power while satisfying Pierce oscillator criteria. The effective oscillation frequency output, which is lightly larger than the resonant frequency – frequency pulling-, also depends on  $C_p$  as

$$\frac{\Delta f}{f_m} = \frac{f_{out} - f_m}{f_m} = \frac{C_m}{2(C_f + \frac{C_p}{2})}$$

(12)

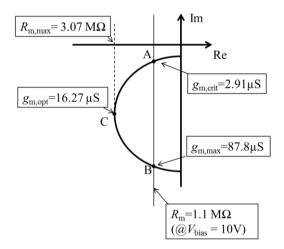

Fig. 5. Complex plane analysis of the oscillator follows the analysis of a three-point oscillator for the extracted parameters in Table I.

Good frequency stability requires small  $\Delta f$ , and hence a large value of  $C_p$  is preferred, but at the cost of increasing power consumption. This design dilemma is the classic trade-off between power consumption and stability for the oscillator.

The maximum negative resistance provided by the circuit when the value of transconductance  $g_m$  reaches the optimum value of  $g_{mopt}$  can be found as

$$g_{m,opt} = \omega_0 \left( 2C_p + \frac{C_p^2}{C_f} \right) \tag{13}$$

The maximum negative resistance,  $R_{m,max}$  provided by the Pierce oscillator must be larger than motional resistance of the resonator to allow oscillation. The following condition needs to be satisfied with sufficiently large margin.

$$\frac{QC_m}{C_f} > 2\left(1 + C_f \frac{2}{C_p}\right) \tag{14}$$

Based on the estimated model parameters, the complex plane representation of the three-point oscillator [11] for the above system is shown in Fig. 5. It is shown that at  $V_{\text{bias}} = 10\text{V}$ , the required value of  $g_{\text{m}}$  for the device parameters considered in this work is in the range (A to B) from 2.91 $\mu$ S to 87.8 $\mu$ S to meet the conditions for oscillation startup.

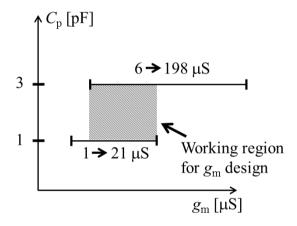

However, as the actual value of  $C_p$  is unknown, particularly with uncertainties due to the hybrid integration of MEMS and CMOS, it is desirable to evaluate the full range of the working region for  $g_m$  as shown in Fig. 6. If  $C_p$  is estimated to be around 1-3pF,  $g_m$  should be designed within the range from 6-21 $\mu$ S to guarantee oscillation startup.

Fig. 6. Working region for  $g_{\rm m}$  with  $C_{\rm p}$  is estimated in a range of 1 to 3 pF.

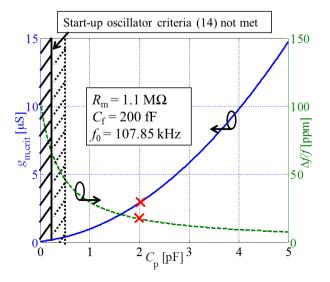

Fig. 7.  $g_{m,crit}$  and  $\Delta f/f_m$  versus  $C_p$ .

## 3.2 Power analysis and design consideration

By comparing parameters in (11), it is easy to spot that the dominating parameter that sets the power requirement is the operation frequency as it directly proportional to  $\omega_0^2$ . Therefore, scaling to high frequencies results in higher power consumption. As motion resistance,  $R_{\rm m}$ , is increased with temperature, Fig. 3, higher power is required at higher temperature condition.

In Fig. 7, the critical transconductance,  $g_{m,crit}$ , and frequency pulling are plotted as functions of  $C_p$  with all other parameters kept fixed as in Table I. It is seen that power dissipation can be reduced if the value of  $C_p$  decreases, but not lower than 0.5pF, where the start-up criteria not met. Therefore, in the monolithic integration of MEMS and CMOS [20],  $C_p$  can be minimized even further to reduce the power consumption. However,  $C_p$  should be big enough to satisfy the condition (14) with sufficient margin.

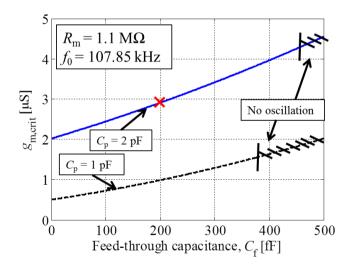

Fig. 8.  $g_{m,crit}$  versus  $C_f$  with different  $C_p$ .

The feed-through capacitance,  $C_f$ , is another crucial parameter that should be taken into account. There is a relationship between  $C_f$  and  $C_p$  that needs to be considered to ensure oscillator start up. For different values of  $C_p$ , the working range of  $C_f$  can be changed accordingly as shown in Fig. 8. The bigger the value of feed-through capacitance  $C_f$ , the higher the power is required to sustain oscillation.

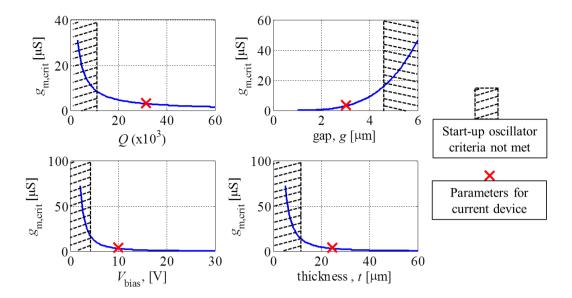

Fig. 9.  $g_{m,crit}$  versus quality factor Q, gap g, bias voltage  $V_{bias}$  and thickness t. In each case, all other parameters are kept fixed as in the extracted device parameters.

From Fig. 4 (b) and eq. (11), we can see that the primary source of power consumption is due to the motional resistance  $R_{\rm m}$  of the resonator.  $R_{\rm m}$  is proportional to  $g^4$  and inversely proportional to Q,  $V_{bias}^2$  and  $t^2$  (9). Fig. 9 shows the plots of  $g_{\rm m}$  versus quality factor Q, gap g, bias voltage  $V_{\rm bias}$  and thickness t. In each case, all other parameters are kept fixed. To reduce  $g_{\rm m,crit}$ , the biasing current and static power consumption, Q,  $V_{\rm bias}$  and t should be as high as possible whereas g should be as small as possible.

It is seen in Fig. 9 that for certain ranges of low quality factor, low bias voltage, high transconduction gap and process thickness, the oscillator will not be functional, no matter how large the  $g_{\rm m}$  is. The electrostatic gap, g, is the most crucial parameter for designing a low-power capacitive MEMS oscillator. For example, for the device under test in the work, if the gap spacing can be reduced down to only 80 nm as in [10], other parameters are kept fixed, the critical transconductance,  $g_{\rm m,crit}$ , as found in Fig. 5 reduced dramatically to  $1.5 \times 10^{-6}$  ( $\mu$ S), theoretically. This indicates that the power consumption can be substantially reduced when the gap spacing is decreased.

#### 3.3 ASIC circuit design

The oscillation start-up time reaches a minimum value when  $g_{\rm m} = g_{\rm mopt}$  [11]. It is also worth mentioning that to minimize the power consumption, operating the oscillator at the critical point (e.g.

point A in Fig. 5) is desirable. However, to minimize the start-up time and to extend the operation range, the start-up condition must be designed at the optimum point, C.

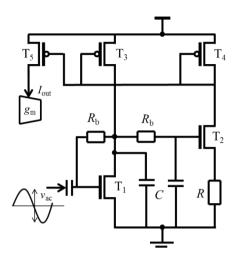

Fig. 10. Bias and automatic gain control (AGC) circuit

A bias and amplitude regulator circuit, Fig. 10, is designed based on previously established techniques [11, 21] for crystal oscillators. At the beginning, when the oscillator has not yet started up, the amplitude regulator behaves as a bias current reference circuit to provide the necessary start-up current for the Pierce core. The start-up transconductance  $g_{m,\text{start-up}}$  is set to be higher than the critical point and close to the optimal point (Fig. 5) to accelerate oscillation build-up. As the oscillation amplitude builds up, the reference current,  $I_{\text{out}}$ , generated by a regulator is reduced until the  $v_{\text{ac}}$  amplitude reaches a critical point where the loop gain approaches unity. At the stable oscillation condition, the oscillator is operating at the minimum current required to address the low power requirement. Furthermore, the ac drive voltage amplitude is also limited to reduce the impact of Duffing non-linearity in the resonator [14].

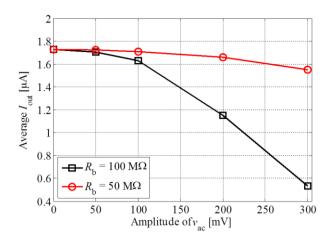

Fig. 11. Bias and automatic gain control (AGC) circuit at different value of  $R_b$  with capacitor C = 5 pF. The initial bias current is set at 1.75  $\mu$ A.

Fig. 11 shows an example of AGC current output versus amplitude input at different values of resistor  $R_b$ . The regulator requires an effective RC low-pass filter, therefore a high value of resistor  $R_b$  and capacitor C are expected. A higher regulated output range is expected at a higher corresponding value for the RC filter.

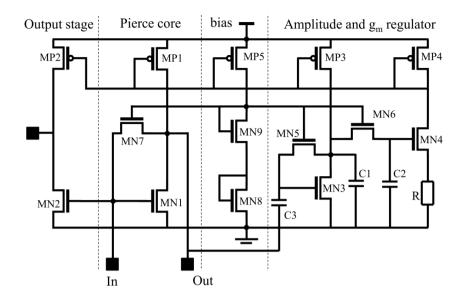

The transistor-level circuit schematic diagram for the oscillator is shown in Fig. 12. Resistor elements  $R_b$  in the Pierce core and regulator stage are implemented using sub-threshold nMOS devices (MN5, MN6, MN7) biased in the linear region to minimize layout area. Their values are set to be greater than 100 M $\Omega$  by the bias circuit. MN1 is a nMOS transistor providing the gain required for the oscillation startup while the  $g_m$  of MN1 is regulated by the transistor MP1. The initial drain current of MN1 is high to provide transconductance close to the  $g_{m,opt}$ , therefore, oscillation builds up. As the amplitude at the drain of MN1, which is the driving voltage on the resonator, rises, the current provided onto MN1 through MP1 is reduced by the AGC regulator. At a certain point, the regulated current reaches the critical point, where the loop gain approaches unity, and the output voltage amplitude is saturated and remains stable.

Fig. 12. Complete ASIC circuit diagram of the oscillator.

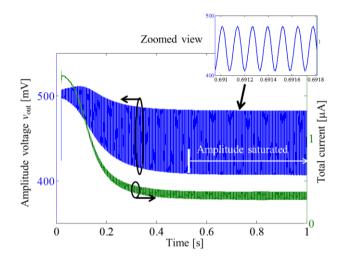

Fig. 13. Simulation results of amplitude voltage output and total current consumption of CMOS circuit in Fig. 12 with resonator model in Table I.

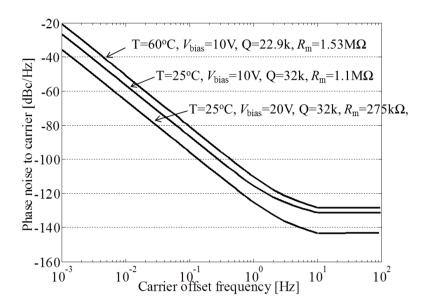

Figure 13 shows an example of simulation results of the circuit in Fig. 12 and the resonator model in Table I with topology as shown in Fig. 4. The initial  $g_m$  of MN1 is set at  $16\mu$ S. Simulations predict that at around half a second, the amplitude is saturated at about 80 mV and the total current is 330nA at 1.2V voltage supply. Fig. 14 plots the simulated phase noise [16] versus offset frequency for several values of temperature and bias voltage with data summarized in Table I, Figs 3,4,5,13. The feedback amplitude voltage is fixed at 80mV to keep the resonator operates in the expected linear region. At higher temperature, the quality factor, Q, is reduced, whereas the motion resistance,  $R_m$ , is increased (Fig. 3), therefore the stability is deteriorated. When the bias voltage is creased from 10V to 20V, the

motion resistance is reduced 4 times down to  $275k\Omega$ , the phase noise figure is improved by 10dBc/Hz. It is predicted that higher stability of the oscillator could be achieved by increasing bias voltage and/or low temperature environmental condition.

Fig. 14. Simulated phase noise of the oscillator under various values of temperature, T, bias voltage,  $V_{\text{bias}}$ , at  $V_{\text{Out}}$ =80mV. Q and  $R_{\text{m}}$  are changed with temperature as shown in Fig. 3.

# 4. Experimental results

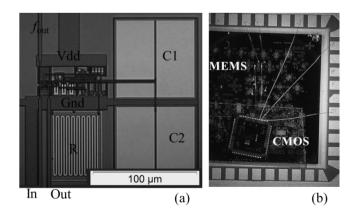

The oscillator circuit is realized in a standard 0.35µm CMOS process (Fig. 15 (a)) and electrically packaged together with DETF resonator on 44 pin leadless chip carrier, as shown in Fig. 15 (b), via bond-wires.

Fig. 15. (a) Micrograph of fabricated CMOS circuit. (b) Photo of the prototype package MEMS-CMOS oscillator on LCC 44 pins chip carrier.

Under vacuum conditions (pressure of 30mTorr), a minimum bias voltage ( $V_{\text{bias}} = 4\text{V}$ ) is required to maintain sustained oscillation. The oscillator can be operated on a power supply voltage (Vdd) range from 1.1V to 3.3V. The power dissipation of the circuit increases as Vdd is increased and  $V_{\text{bias}}$  is decreased.

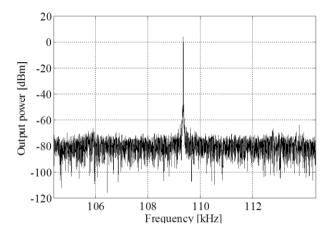

Fig. 16. Measured oscillator output spectrum

Fig. 16 shows the measured spectrum of the oscillator output. Note that the frequency is slightly different from the open loop measurement in Fig. 2 due to process variations resulting in different centre frequencies for the two resonators employed for these experiments.

At  $V_{\text{bias}} = 10\text{V}$ , Vdd = 1.2V, the oscillator is seen to dissipate ~ 900nA (with parasitics associated with the IO pads including ESD protection and chip carrier pad loading due to the nature of practical realization) at stable operation, which translates to a value of 400nA of oscillator core current dissipation for no external capacitive loading at the output buffer.

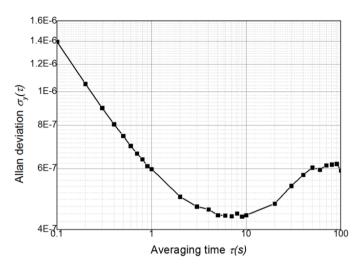

Fig. 17. Allan deviation plot for the Pierce oscillator.

A measured phase noise figure was not possible for the developed oscillator due to the unavailability of a commercial measurement system. Instead, a frequency counter (Agilent 53132A) was used to sample the oscillator output at fixed time intervals of 100ms spacing. The Allan deviation of the measured output frequency is calculated and is shown in Fig. 17. A short-term frequency stability of less than 0.5ppm is achieved for an averaging time t=10s.

TABLE II

CAPACITIVE MEMS OSCILLATOR COMPARISON

| C.M. HOLLIT & HARMING OBORRESHI ON COMMITMORE |              |          |         |        |          |

|-----------------------------------------------|--------------|----------|---------|--------|----------|

| Specs                                         | This<br>work | [3]      | [9]     | [13]   | [22]     |

| Frequency (Hz)                                | 110k         | 77k      | 77k     | 524k   | 32k      |

| Q                                             | 32k          | NA       | NA      | 52k    | 57k      |

| Resonator size(µm)                            | 430x200      | 505x435  | 505x435 | NA     | 120x120  |

| $R_{\rm m}$ (Ohm)                             | 1.1M         | 4M       | 4M      | 90k    | 1.94M    |

| Topology                                      | Pierce       | TIA      | Pierce  | Pierce | TIA      |

| AGC                                           | Yes          | Yes      | No      | Yes    | No       |

| Integration level                             | 2 dies       | PCB      | 2 dies  | 2 dies | 2 dies   |

| Power (W)                                     | 480n         | $100\mu$ | 21.6μ   | <288n  | $2.1\mu$ |

| Best Allan $\sigma_{\gamma}$ (mHz)            | 5            | 35       | 650     | NA     | NA       |

TIA: Transimpedance amplifier.

As shown in Table II the power consumption of this work is much lower than TIA topology previously reported in [3, 22] and comparable with the commercial oscillator product from SiTime [13]. The circuit reported in this work enables low-power operation for significantly higher motional resistance (1.1M $\Omega$  in this work compared with 90k $\Omega$ ) and capacitive parasitics than for the work reported in [13]. The results and analysis reported in this work show that significant reduction in power consumption is possible as tighter MEMS-CMOS integration (including fully monolithic integration) becomes available.

## 5. Conclusion and future work

In this paper, the modelling, comprehensive analysis and implementation of a low-power oscillator circuit for a capacitive SOI DETF resonator is presented. Detailed analysis and practical design considerations involved in hybrid integration of the capacitive resonator are provided to inform power optimization of the interface circuits.

The practical CMOS implementation is specifically designed for the device under test. The design is based on several factors including (i) the electrical model, (ii) measured feed-through capacitance and (iii) the nonlinear behavior of the resonator. It is designed for a maximum startup time and minimum power specification for the specified MEMS resonator. The comprehensive analysis verified by practical realization and experimental results provided in this paper provide a reference guideline for both MEMS and CMOS designers on evaluating practical considerations for the design of high-stability, power-optimized capacitive MEMS oscillators for a given process specification.

The MEMS-CMOS oscillator demonstrated a frequency stability of less than 0.5ppm while drawing 400nA at 1.2V. The fabricated circuit addresses the power requirements for resonant sensor applications where power optimization is critical.

Further research will focus on design optimization to improve the linearity of the resonator so as to improve the frequency stability and noise figure. Suitable circuit-level temperature compensation techniques are also being currently explored.

## **Acknowledgments**

This work was supported by the UK Engineering and Physical Sciences Research Council (Grant No. EP/K000314/1)

#### REFERENCES

[1] H. A. C Tilmans, M. Elwenspoek, and J. H. J. Fluitman. "Micro resonant force gauges." Sensors and Actuators A: Physical, vol.30, no. 1-2, pp 35-53, Jan. 1992.

- [2] A. A. Seshia, M. Palaniapan, T. A. Roessig, R. T. Howe, R. W. Gooch, T. R. Schimert, and S. Montague, "A vacuum packaged surface micromachined resonant accelerometer," J. Microelectromech. Syst., vol. 11, no. 6, pp. 784–793, Jun. 2002.

- [3] G. Langfelder, A. Caspani, and A. Tocchio, "Design criteria of low-power oscillators for consumer-grade MEMS resonant sensors," Industrial Electronics, IEEE Transactions on, vol. 61, pp. 567-574, 2014.

- [4] K. E. Wojciechowski, B. E. Boser and A. P. Pisano. "A MEMS resonant strain sensor operated in air." Micro Electro Mechanical Systems, 2004. 17th IEEE International Conference on MEMS, 2004.

- [5] A. A. Seshia, R. T. Howe, and S. Montague. "An integrated microelectromechanical resonant output gyroscope." Micro Electro Mechanical Systems, 2002. The Fifteenth IEEE International Conference on MEMS, 2002.

- [6] C.-W. Tsai, K.-h. Chen, C.-K. Shen, and J.-c. Tsai, "A MEMS doubly decoupled gyroscope with wide driving frequency range," Industrial Electronics, IEEE Transactions on, vol. 59, pp. 4921-4929, 2012.

- [7] A. A. Seshia, W. Low, S. A. Bhave, R. T. Howe and S. Montague, "Micromechanical Pierce oscillators for resonant sensing applications", Proceedings of the 5<sup>th</sup> International Conference on Modeling and Simulation of Microsystems, 2002.

- [8] C. L. Roozeboom, M. A. Hopcroft, W. S. Smith, J. Y. Sim, D. A. Wickeraad, P. G. Hartwell, et al., "Integrated multifunctional environmental sensors," *Microelectromechanical Systems, Journal of*, vol. 22, pp. 779-793, 2013.

- [9] A. Tocchio, A. Caspani, G. Langfelder, A. Longoni, and E. Lasalandra, "A Pierce oscillator for MEMS resonant accelerometer with a novel low-power amplitude limiting technique," in Frequency Control Symposium (FCS), 2012 IEEE International, 2012.

- [10] T. L. Naing, T. O. Rocheleau, E. Alon, and C.-C. Nguyen, "A 78-microwatt GSM phase noise-compliant pierce oscillator referenced to a 61-MHz wine-glass disk resonator," in European Frequency and Time Forum & International Frequency Control Symposium (EFTF/IFC), pp. 562-565, 2013.

- [11] E. Vittoz, M. G. R. Degrauwe, S. Bitz, "High-performance crystal oscillator circuits: theory and application", IEEE J. Solid-State Circuits, vol. 23, no. 3, pp. 774-783, Jun. 1988.

- [12] K. R. Cioffi and W. T. Su, "32KHz MEMS-based oscillator for low power application", Freq. Control Sym. And Exp., Proceedings of the 2005 IEEE International, p. 551-558, 2005

- [13] S. Zaliasl, J. C. Salvia, G. C. Hill, L. Chen, K. Joo, R. Palwai, et al., "A 3 ppm 1.5× 0.8 mm 2 1.0 μA 32.768 kHz MEMS-Based Oscillator," IEEE J. Solid-State Circuits, vol. 50, no. 1, pp. 291-302, 2015.

- [14] D. K. Agrawal, J. Woodhouse, A. A. Seshia, "Modeling nonlinearities in MEMS oscillators", Ultrasonics, Ferroelectrics and Frequency Control, IEEE Transactions on, vol. 60, no. 8, Aug. 2013.

- [15] C. Do, A. Erbes, J. Yan, and A. A. Seshia, Low power MEMS oscillators for sensor applications, in Proceedings of the 28th European Frequency and Time Forum (EFTF) conference, Neuchatel, Switzerland, June 23-26, 2014.

- [16] C.T-C. Nguyen and R. T. Howe, "An integrated CMOS micromechanical resonator high-Q oscillator," Solid-State Circuits, IEEE Journal of, vol. 34, pp. 440-455, 1999.

- [17] B. Kim, et al., "Temperature Dependence of Quality Factor in MEMS Resonators", J. Microelectromech. Syst., vol. 17, no. 3, pp. 755-765, Jun 2008.

- [18] M. Hopcroft, W. D. Nix, and T. W. Kenny, "What is the Young's Modulus of Silicon?." J. Microelectromech. Syst., vol. 19, no. 2, pp. 229-238, 2010.

- [19] Y.-W. Lin, S. Lee, S.-S. Li, Y. Xie, Z. Ren, and C.-C. Nguyen, "Series-resonant VHF micromechanical resonator reference oscillators," Solid-State Circuits, IEEE Journal of, vol. 39, pp. 2477-2491, 2004

- [20] A. Uranga, J. Verd, and N. Barniol, "CMOS-MEMS resonators: from devices to applications," Microelectronic Engineering, vol. 132, pp. 58-73, 2015.

- [21] E. Vittoz and J. Fellrath, "CMOS analog circuits based on weak inversion operation," IEEE J. Solid-State Circuits, vol. SC-12, pp.224–231, June 1977.

- [22] H. G. Barrow, T. L. Naing, R. Schneider, T. O. Rocheleau, V. Yeh, Z. Ren, and C. T. C. Nguyen, "A real-time 32.768-kHz clock oscillator using a 0.0154-mm 2 micromechanical resonator frequency-setting element," in Frequency Control Symposium (FCS) IEEE International, 2012.