#### UNIVERSITY OF SOUTHAMPTON

# System-Level Power Management using Online Machine Learning for Prediction and Adaptation

by Luis Alfonso Maeda-Nunez

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Physical Sciences and Engineering Electronics and Computer Science

2016-07-22

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF PHYSICAL SCIENCES AND ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

by Luis Alfonso Maeda-Nunez

Nowadays embedded devices have the need to be portable, battery powered and high performance. This need for high performance makes power management a matter of critical priority. Power management algorithms exist, but most of the approaches focus on an energy-performance trade-off oblivious to the applications running on the system. Others are application-specific and their solution cannot be applied to other applications.

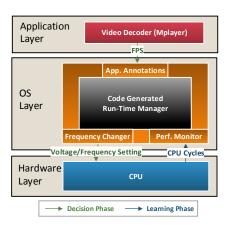

This work proposes Shepherd, a cross-layer runtime management system for reduction of energy consumption whilst offering soft real-time performance. It is cross-layer because it takes the performance requirements from the application, and learns to adjust the power management knobs to provide the expected performance at the minimum cost of energy. Shepherd is implemented as a Linux governor running at OS level, this layer offers a low-overhead interface to change the CPU voltage and frequency dynamically.

As opposed to the reactive behaviour of Linux Governors, Shepherd adapts to the application-specific performance requirements dynamically, and proactively selects the power state that fulfils these requirements while consuming the least power. Proactiveness is achieved by using AEWMA for adapting to the upcoming workload. These adaptations are facilitated using a model-free reinforcement learning algorithm, that once it learns the optimal decisions it starts exploiting them. This work enables Shepherd to work with different applications. A programming framework was designed to allow programmers to develop their applications to be power-aware, by enabling them to send their performance requirements and annotations to Shepherd and provide the cross-layer soft real-time performance desired.

Shepherd is implemented within the Linux Kernel 3.7.10, interfacing with the application and hardware to select an appropriate voltage-frequency control for the executing application. The performance of Shepherd is demonstrated on an ARM Cortex-A8 processor. Experiments conducted with multimedia applications demonstrate that Shepherd minimises energy consumption by up to 30% against existing Governors. Also, the framework has been used to adapt example applications to work with Shepherd, achieving 60% energy savings compared to the existing approaches.

# Contents

| $\mathbf{A}$ | ckno | wledgei | ments                                         | xvii |

|--------------|------|---------|-----------------------------------------------|------|

| 1            | Intr | oductio | on                                            | 1    |

|              | 1.1  | Resear  | ch Justification                              | . 2  |

|              |      | 1.1.1   | Power Consumption                             | . 2  |

|              |      | 1.1.2   | Low Power Design Techniques                   | . 3  |

|              |      |         | 1.1.2.1 Power Gating                          | . 4  |

|              |      |         | 1.1.2.2 Dynamic Voltage and Frequency Scaling | . 5  |

|              |      | 1.1.3   | Challenges of System Level Power Management   | . 6  |

|              | 1.2  | Resear  | ch Questions                                  | . 9  |

|              | 1.3  | Resear  | ch Contributions                              | . 9  |

|              | 1.4  | Resear  | ch Outputs                                    | . 10 |

|              | 1.5  | Docum   | nent Outline                                  | . 10 |

| 2            | Pov  | ver Mai | nagement in Microprocessors                   | 11   |

|              | 2.1  | Power   | consumption in Microprocessors                | . 13 |

|              |      | 2.1.1   | Dynamic Power                                 | . 14 |

|              |      |         | 2.1.1.1 Switching Power                       | . 15 |

|              |      |         | 2.1.1.2 Internal Power                        | . 16 |

|              |      | 2.1.2   | Static Power                                  | . 17 |

|              | 2.2  | Power   | Management Techniques: Knobs                  | . 18 |

|              |      | 2.2.1   | Multi-Vdd                                     | . 18 |

|              |      | 2.2.2   | Dynamic Voltage and Frequency Scaling (DVFS)  | . 18 |

|              |      | 2.2.3   | Power Gating (PG)                             | . 19 |

|              | 2.3  | Applica | ations and OS: Requirements                   | . 22 |

|              |      | 2.3.1   | Real-Time Systems                             | . 22 |

|              |      | 2.3.2   | Hard Real-Time versus Soft Real-Time          | . 23 |

|              | 2.4  | Power   | Management: Control                           | . 24 |

|              |      | 2.4.1   | Dynamic Power Management (DPM)                | . 24 |

|              |      |         | 2.4.1.1 Predictive Techniques                 | . 24 |

|              |      |         | 2.4.1.2 Stochastic Techniques                 | . 26 |

|              |      |         | 2.4.1.3 Machine Learning Techniques           |      |

|              |      |         | 2.4.1.4 Reinforcement Learning for DPM        | . 29 |

|              |      |         | 2.4.1.5 Other Predictive Techniques           |      |

|              |      | 2.4.2   | DVFS                                          |      |

|              |      |         | 2.4.2.1 Workload Detection                    | . 31 |

|              |      |         | 2.4.2.2 Online Learning                       |      |

vi CONTENTS

|   |     | 2.4.2.3 Offline Learning                                                 | 2 |

|---|-----|--------------------------------------------------------------------------|---|

|   |     | 2.4.2.4 Workload Prediction                                              | 4 |

|   |     | 2.4.2.5 Deadline Prediction                                              | 4 |

|   |     | 2.4.2.6 Application-specific DVFS                                        | 5 |

|   |     | 2.4.2.7 General Purpose DVFS                                             |   |

|   |     | 2.4.3 The Interplay of DPM and DVFS                                      |   |

|   |     |                                                                          | 8 |

|   | 2.5 | Discussion                                                               |   |

| 3 | Sys | tem-Level Power Management 4                                             | 3 |

|   | 3.1 | Run-Time Management                                                      | 3 |

|   |     | 3.1.1 Requriements                                                       | 4 |

|   |     | 3.1.1.1 Application adaptation for use with RTM 4                        | 7 |

|   |     | 3.1.2 Power Knobs                                                        | 7 |

|   |     | 3.1.3 Control                                                            | 8 |

|   |     | 3.1.3.1 Monitor Feedback                                                 | 8 |

|   |     | 3.1.4 Run-Time Management Algorithm                                      | 8 |

|   | 3.2 | Prediction Unit                                                          | 0 |

|   |     | 3.2.1 Motivation                                                         | 0 |

|   |     | 3.2.2 EWMA                                                               | 1 |

|   |     | 3.2.2.1 Optimisation and Results 5                                       | 2 |

|   |     | 3.2.3 AEWMA                                                              | 4 |

|   | 3.3 | Decision Unit                                                            | 7 |

|   |     | 3.3.1 Cost Function                                                      | 8 |

|   |     | 3.3.2 Learning Phase in Shepherd                                         | 0 |

|   | 3.4 | Discussion and Summary                                                   |   |

| 4 | Imp | plementation of Run-time Manager 6                                       | 5 |

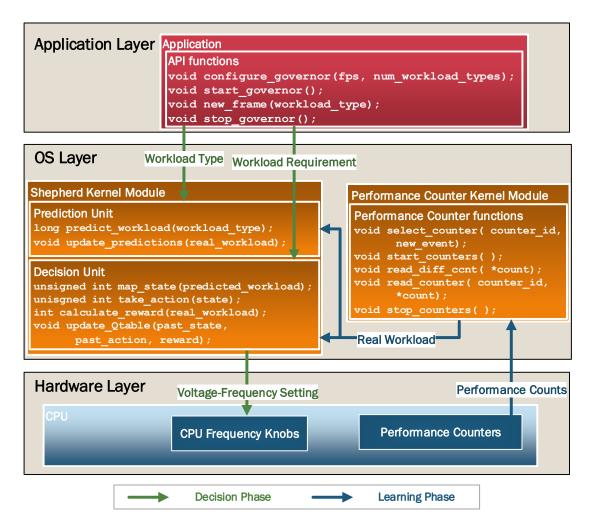

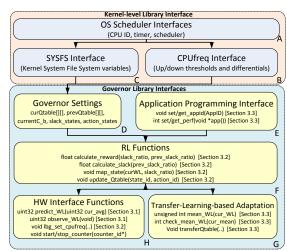

|   | 4.1 | Implementation as Linux Governor                                         | 5 |

|   |     | 4.1.1 Restrictions and optimisations for Linux Governor Implementation 6 | 7 |

|   | 4.2 | Implementation of Prediction Unit                                        | 8 |

|   | 4.3 | Implementation of Decision Unit                                          | 0 |

|   |     | 4.3.1 Implementation of Learning Phase in Shepherd                       | 1 |

|   |     | 4.3.2 Action Suitability for Exploiting Learning                         | 3 |

|   | 4.4 | Performance Counters Module                                              | 4 |

|   | 4.5 | An Application Programming Interface (API) for Shepherd                  | 5 |

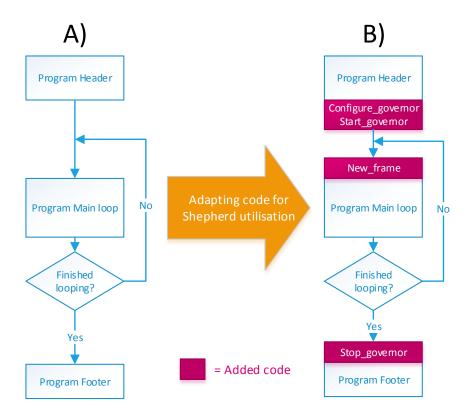

|   |     | 4.5.1 Design flow for application adapted to use Shepherd Governor $7$   | 7 |

|   | 4.6 | Discussion                                                               | 8 |

| 5 | Res | sults 7                                                                  | 9 |

|   | 5.1 | 1                                                                        | 9 |

|   | 5.2 | v                                                                        | 1 |

|   |     | *                                                                        | 2 |

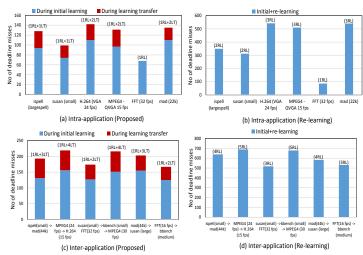

|   |     | 5.2.1.1 Shepherd on H.264 VGA                                            | 4 |

|   |     | 5.2.1.2 Shepherd on H.264 QVGA 8                                         | 5 |

|   |     | 5.2.1.3 Run-time Manager (RTM) on H.263 8                                | 6 |

|   |     | 5.2.1.4 Shepherd on MPEG2 8                                              | 6 |

CONTENTS vii

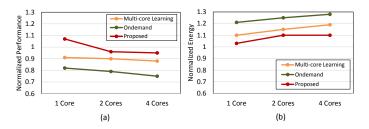

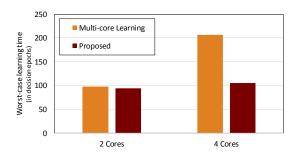

|                                               |                | 5.2.2             | Governor 5.2.2.1 | Shepherd<br>comparise<br>Comparise<br>Comparise | on<br>on versu | <br>s Dyn | <br>amic | Gove | erno | <br>rs . | <br> |  |  | 87<br>87     |

|-----------------------------------------------|----------------|-------------------|------------------|-------------------------------------------------|----------------|-----------|----------|------|------|----------|------|--|--|--------------|

|                                               | 5.3            |                   |                  | esults                                          |                |           |          |      |      |          |      |  |  |              |

|                                               | 5.4            | -                 |                  |                                                 |                |           |          |      |      |          |      |  |  |              |

|                                               | 5.5            |                   |                  | Summary                                         |                |           |          |      |      |          |      |  |  |              |

| 6                                             | <b>Con</b> 6.1 | clusion<br>Future |                  |                                                 |                |           |          |      |      |          | <br> |  |  | <b>93</b> 94 |

| Bibliography 97                               |                |                   |                  |                                                 |                |           | 97       |      |      |          |      |  |  |              |

| Appendix A - Sample Shepherd Output Files 107 |                |                   |                  |                                                 |                |           |          |      |      |          |      |  |  |              |

| Aı                                            | pen            | dix B -           | Publica          | tions                                           |                |           |          |      |      |          |      |  |  | 109          |

# List of Figures

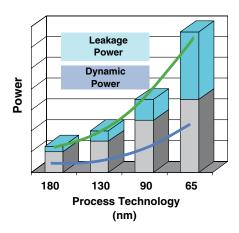

| 1.1  | Dynamic and Leakage Power trend[1]                                                                                                                                                                                           | 3  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

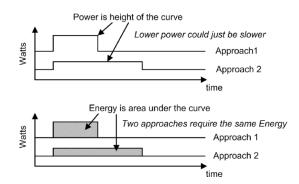

| 1.2  | Power vs Energy. Reproduced from [2]                                                                                                                                                                                         | 6  |

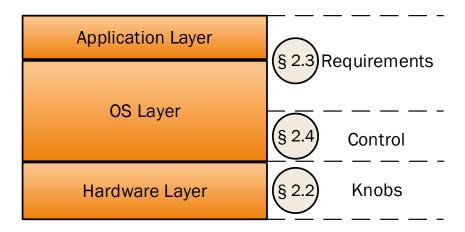

| 2.1  | Flowchart of an embedded system in a cross-layer approach. Analytical approach (left) and practical approach (right). Sections 2.2, 2.3 and 2.4 are described as per the figure                                              | 12 |

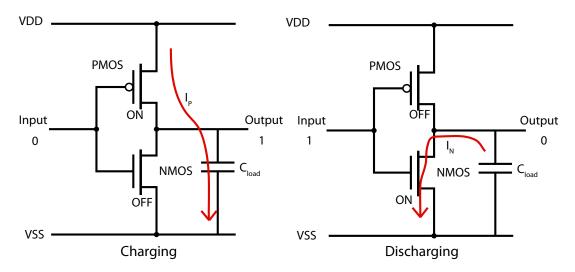

| 2.2  | A CMOS Inverter showing the charging and discharging of the capacitor $C_{load}$ . Based on [3]                                                                                                                              | 15 |

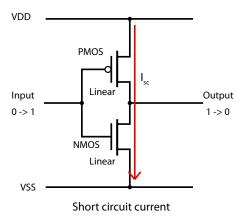

| 2.3  | A CMOS Inverter showing the short circuit current flowing from $V_{DD}$ to $V_{SS}$ . Based on [4]                                                                                                                           | 16 |

| 2.4  | Leakage Currents in a CMOS circuit (a). Taken from [2]. ITRS trends for leakage power dissipation (b). Based on [5]                                                                                                          | 18 |

| 2.5  | Definitions of power and times for a device with IDLE and SLEEP modes                                                                                                                                                        | 20 |

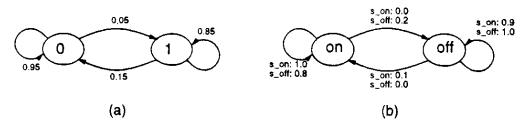

| 2.6  | Markov chain and Markov Decision Process model for DPM of StrongARM SA-1100, as presented by Benini et al. [6]                                                                                                               | 26 |

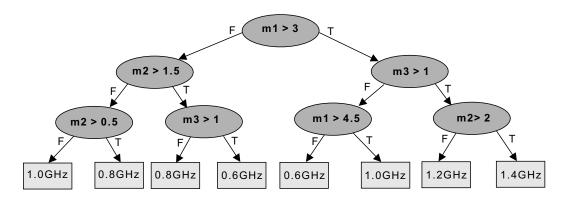

| 2.7  | Decision Tree example for selecting V-F settings. Taken from [7]                                                                                                                                                             | 33 |

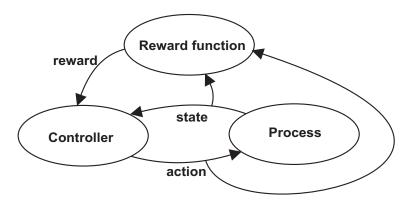

| 2.8  | Reinforcement Learning simple diagram. Taken from [8]                                                                                                                                                                        | 38 |

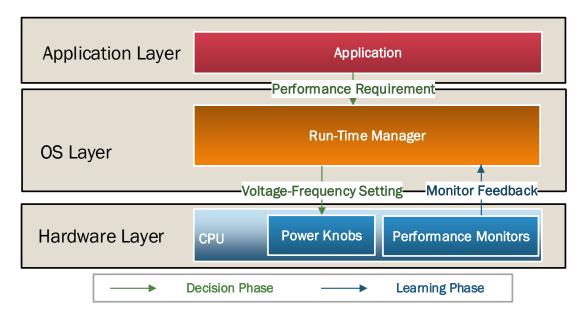

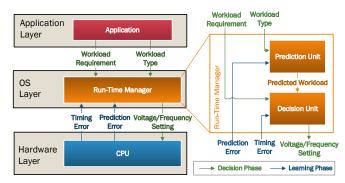

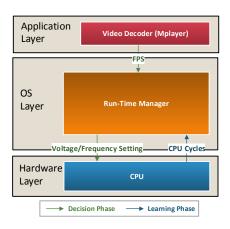

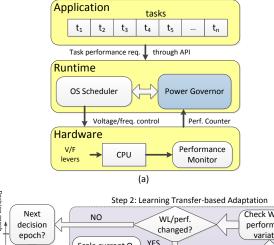

| 3.1  | Generic cross-layer RTM, where the arrows show the communication between the layers                                                                                                                                          | 44 |

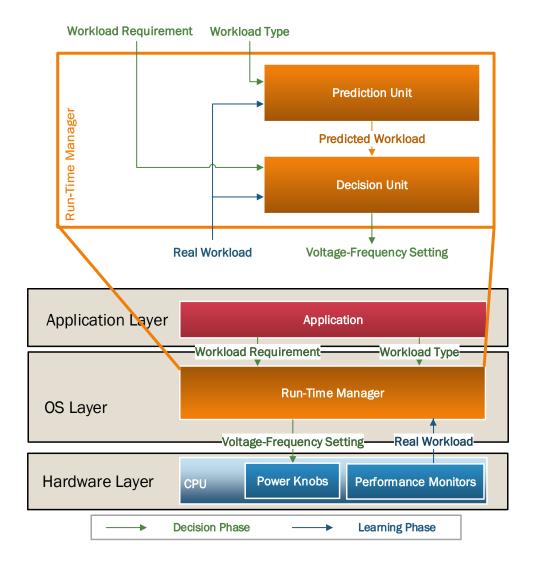

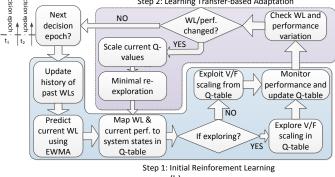

| 3.2  | Run-Time Management Unit in the cross-layer approach                                                                                                                                                                         | 49 |

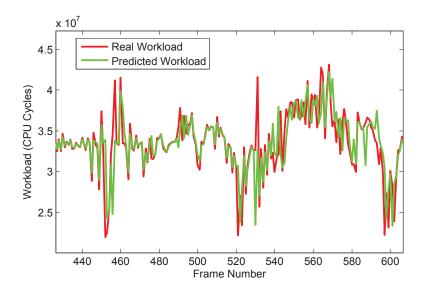

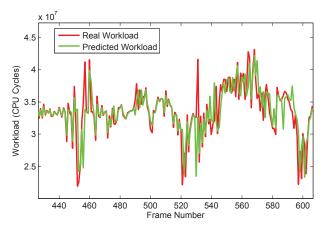

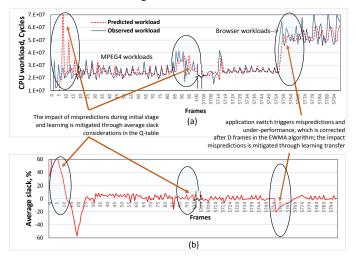

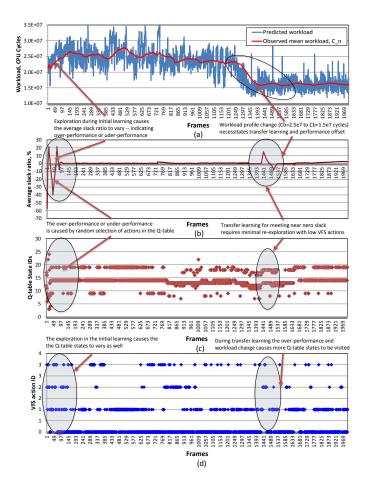

| 3.3  | Comparison of real workload vs. predicted on a sample video, from frames 430 to 615                                                                                                                                          | 52 |

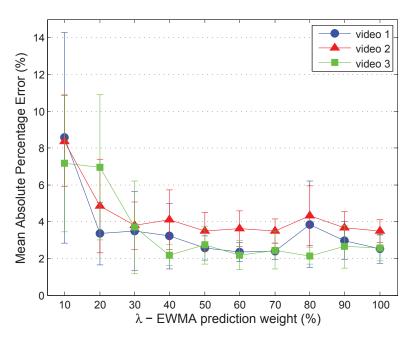

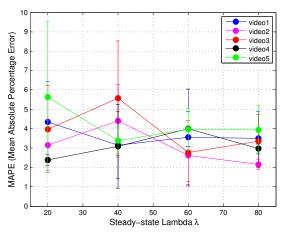

| 3.4  | Effect of weight for Exponential Weighted Moving Average (EWMA) on prediction error using dynamic workloads                                                                                                                  | 53 |

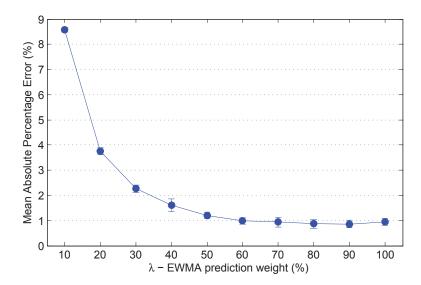

| 3.5  | Effect of weight for EWMA on prediction error using static workloads                                                                                                                                                         | 54 |

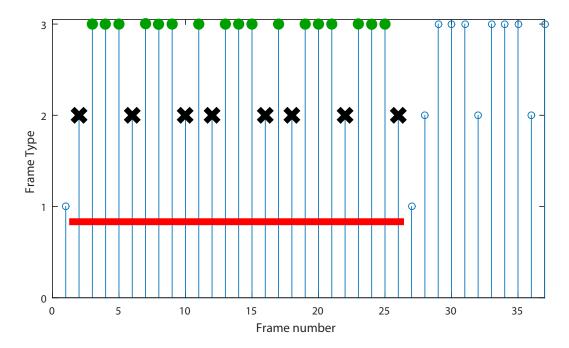

| 3.6  | Sample of video with frame types 1, 2 and 3. Red line represents the group of frames of type 2 (cross) and 3 (green filled circles) between frames type                                                                      | 01 |

|      | 1 (blue hollow circles) used to calculate local standard deviation                                                                                                                                                           | 55 |

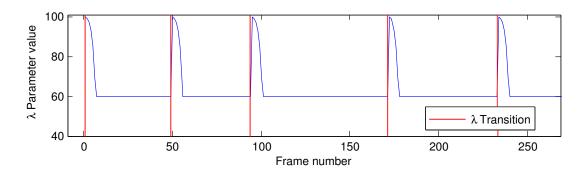

| 3.7  | AEWMA $\lambda$ parameter change at transitions                                                                                                                                                                              | 56 |

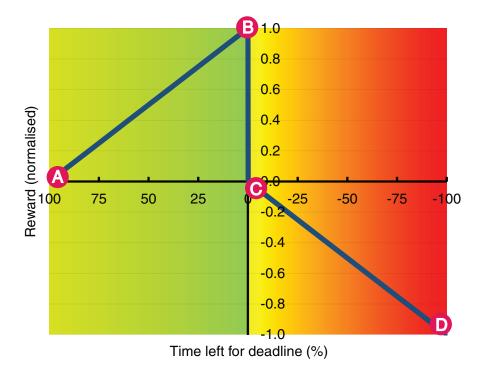

| 3.8  | Cost function of Q-Learning algorithm for Shepherd. This graph shows<br>the level of reward/punishment obtained for finishing the workload too<br>early (A), very close to the deadline without surpassing it (B), finishing |    |

|      | the workload shortly after the deadline (C) and finishing very late (D).                                                                                                                                                     |    |

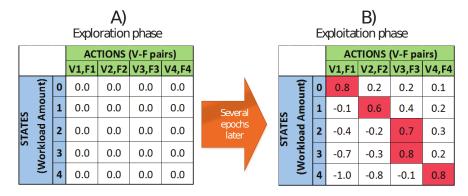

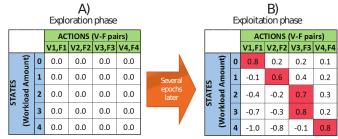

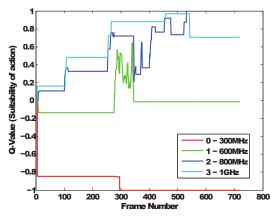

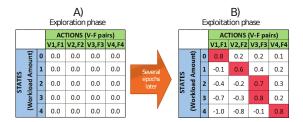

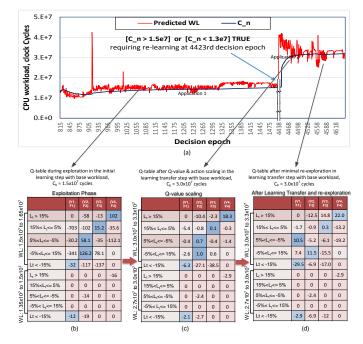

| 3.9  | Time left for deadline is calculated as $100 \frac{t_{deadline} - t_{finished}}{t_{deadline}}$ Q-Table during A) exploration and B) exploitation phases. The red boxes                                                       | 60 |

| J.J  | represent the best Action for each State                                                                                                                                                                                     | 61 |

| 3.10 |                                                                                                                                                                                                                              | ΟI |

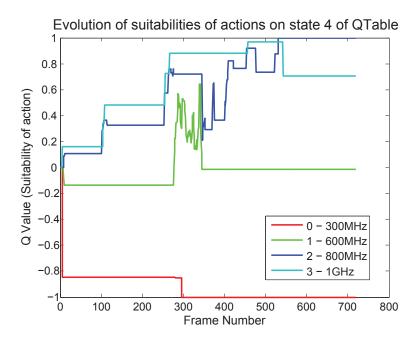

| 5.10 | Values of the different actions                                                                                                                                                                                              | 62 |

x LIST OF FIGURES

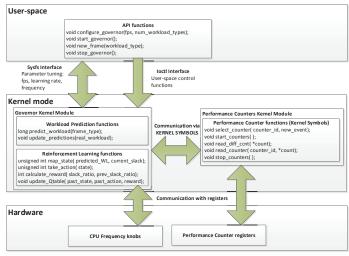

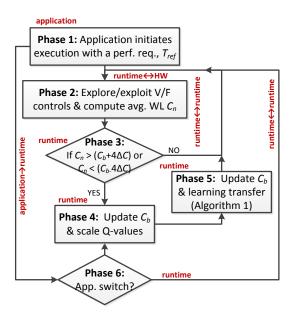

| 4.1 | Shepherd governor implementation                                           | 67 |

|-----|----------------------------------------------------------------------------|----|

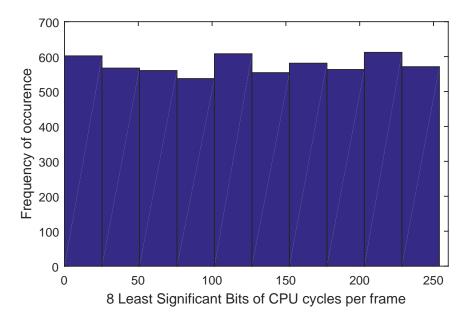

| 4.2 | Random number distribution generated from taking the 8 Least Signif-       |    |

|     | icant Bits (LSBs) from the CPU cycles measured per frame, over 5760        | 00 |

| 4.0 | frames                                                                     | 68 |

| 4.3 | Adaptation of program code for utilisation of the Shepherd Run-Time        |    |

|     | Manager                                                                    | 78 |

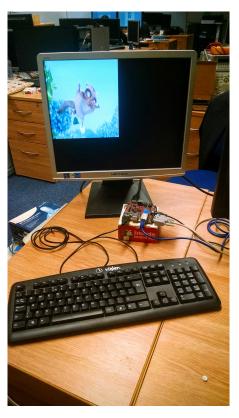

| 5.1 | BeagleBoard-xM[9] development board used for running the experiments       |    |

|     | of Shepherd                                                                | 80 |

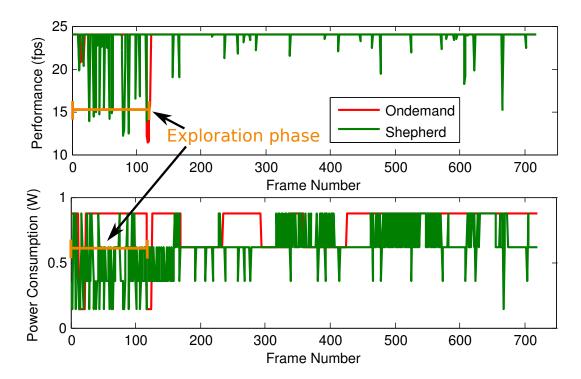

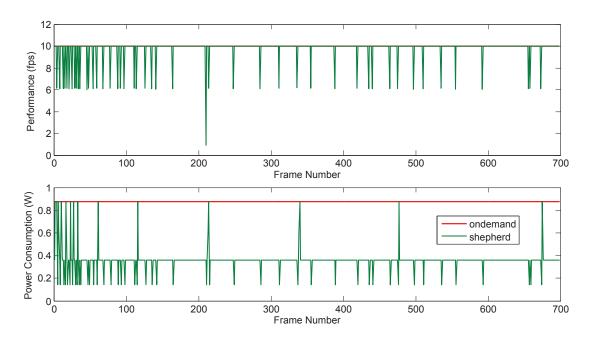

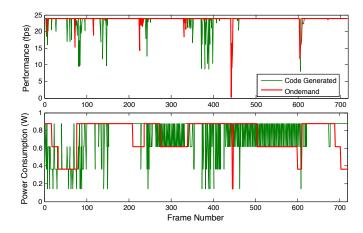

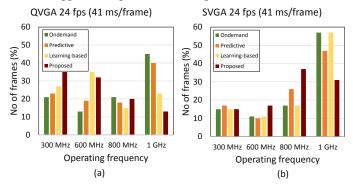

| 5.2 | Video Decoding experiment using Shepherd Governor running on BeagleBoar    | d- |

|     | xM                                                                         | 81 |

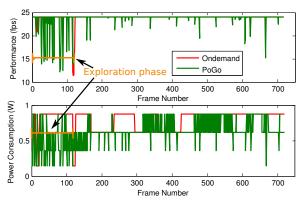

| 5.3 | Performance and Power Consumption of the governors Shepherd and On-        |    |

|     | demand for an H.264 Video                                                  | 83 |

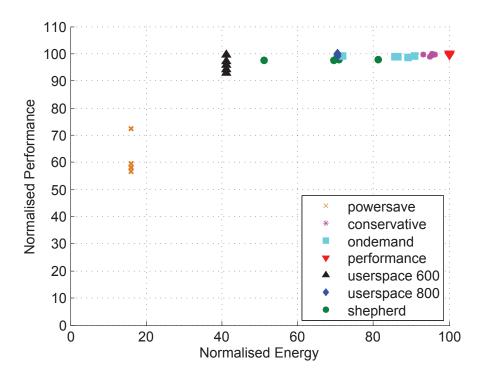

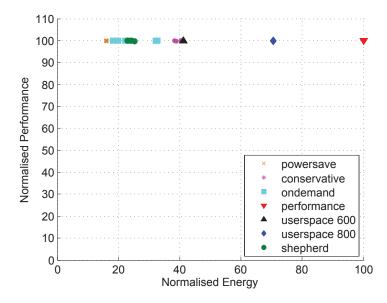

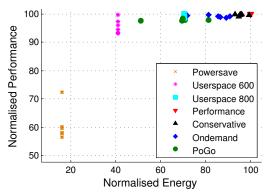

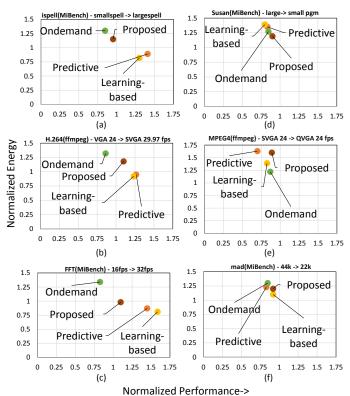

| 5.4 | Pareto graph comparing different governors vs. Shepherd by means of        |    |

|     | energy and performance running H264 VGA Video                              | 84 |

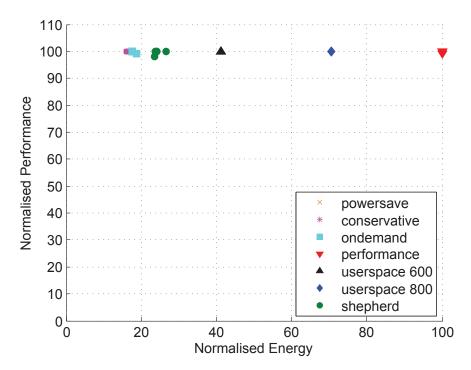

| 5.5 | Pareto graph comparing different governors vs. Shepherd by means of        |    |

|     | energy and performance running H264 QVGA Video                             | 85 |

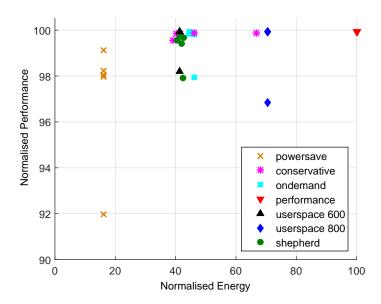

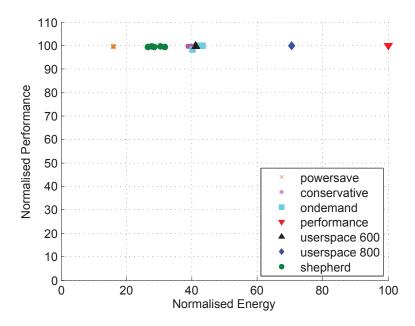

| 5.6 | Pareto graph comparing different governors vs. Shepherd by means of        |    |

|     | energy and performance running H263 Video                                  | 86 |

| 5.7 | Pareto graph comparing different governors vs. Shepherd by means of        |    |

|     | energy and performance running MPEG2 Video                                 | 86 |

| 5.8 | Pareto graph comparing different governors vs. Shepherd by means of        |    |

|     | energy and performance running MPEG4 Video                                 | 87 |

| 5.9 | Performance and Power Consumption of the governors Shepherd and On-        |    |

|     | demand for iFFT benchmark at 10 frames-per-second (fps) constraint $$ . $$ | 91 |

# List of Tables

| 1.1 | Semiconductor (CMOS)                                                                                                              | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Hard Real Time versus Soft Real Time comparison, as explained by Sally [10]                                                       | 24 |

| 2.2 | Symbols of Q-Learning algorithm                                                                                                   | 39 |

| 3.1 | Comparison of variation of the workload with and without grouping into frame types                                                | 53 |

| 3.2 | Comparison of variation of the workload with and without grouping into frame types                                                | 55 |

| 4.1 | Q-Values of State 3 of Q-Table from Listing 4.2                                                                                   | 74 |

| 5.1 | DM3730 Specifications (ARM Cortex-A8 processor) [11]                                                                              | 79 |

| 5.2 | Comparative table showing the paretos of energy and performance aver-                                                             |    |

|     | ages of every Linux governor compared to Shepherd. Numbers are normalised to 100. Ideal performance is 100, and ideal energy is 0 | 88 |

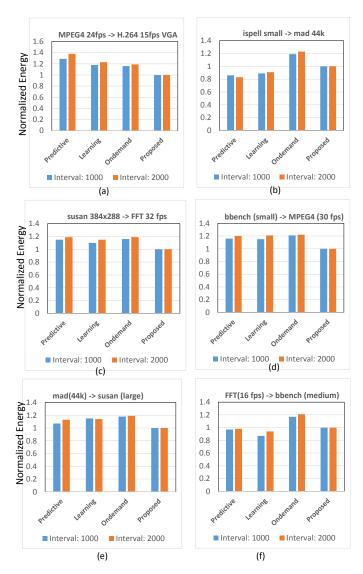

| 5.3 | FFT benchmark [12] performance vs. energy results. The governors aim to fulfil the objective                                      | 90 |

| 5.4 | FFT benchmark [12] performance vs. energy results. The governors aim                                                              | 90 |

|     | to fulfil the objective                                                                                                           | 90 |

| 5.5 | Inverse FFT benchmark [12] performance vs. energy results. The gover-                                                             |    |

|     | nors aim to fulfil the objective                                                                                                  | 90 |

| 5.6 | Inverse FFT benchmark [12] performance vs. energy results. The gover-                                                             |    |

|     | nors aim to fulfil the objective                                                                                                  | 91 |

## List of Acronyms

**CPU** Central Processing Unit

**GPU** Graphics Processing Unit

**DSP** Digital Signal Processor

FPGA Field-Programmable Gate Array

${f RF}$  Radio Frequency

CMOS Complementary Metal Oxide Semiconductor

**HW** Hardware

**OS** Operating System

IPS Instructions-Per-Second

WCET Worst - Case Execution Time

**TI** Texas Instruments

BBxM BeagleBoardxM

SoC System-on-Chip

SotA State-of-the-Art

**HDD** Hard Disk Drive

RTOS Real-Time Operating System

**GPOS** General Purpose Operating System

RTS Real-Time System

RT Real-Time

API Application Programming Interface

FPU Floating-Point Unit

xiv LIST OF TABLES

$\mathbf{SR}$  Service Requester

$\mathbf{SQ}$  Service Queue

SP Service Provider

MDP Markov Decision Process

SIMD Single-Instruction-Multiple-Data

LSB Least Significant Bit

PMU Performance Monitoring Unit

JTAG Joint Test Action Group

**FD** Frame-Dependent

FI Frame-Independent

V-F Voltage and Frequency

PM Power Management

**DVFS** Dynamic Voltage and Frequency Scaling

**DVS** Dynamic Voltage Scaling

**DPM** Dynamic Power Management

RTM Run-time Manager

$\mathbf{RTPM}$ Runtime Power Manager

**PG** Power Gating

ACPI Advanced Configuration and Power Interface

fps frames-per-second

ML Machine Learning

**RL** Reinforcement Learning

W Weight

EWMA Exponential Weighted Moving Average

AEWMA Adaptive Exponential Weighted Moving Average

MAPE Mean Absolute Percentage Error

${f ANN}$  Artificial Neural Network

LIST OF TABLES xv

${f FM}$  Frequency Mapper

$\alpha$  Learning Rate

S State

A Action

**PC** Program Counter

$\mathbf{CSV}$ Comma-Separated Values

#### Acknowledgements

I would like to thank first and foremost my parents, Alfonso and Aida, and my brothers Juan Carlos and Roberto, for their lifelong support in the good and the hardest times. You have taught me the most important things in life, and I would not be where I am without you. Not only am I proud to have you close, but deeply honoured to be a part of this family. I would like to thank also my supervisors Geoff Merrett and Bashir Al-Hashimi, as they have guided me through the long and winding road that is the PhD. I would like to thank my sponsor the National Council of Science and Technology (CONACYT) in Mexico, because without them I would not be able to do a postgraduate programme here. I would like to thank my friends which helped me through the difficult times, Isaac, Mauricio, Eryx, Domenico, Jean-Marie, Vasilis, Jaime. Finally, I would like to thank my colleagues who taught me valuable lessons on the PhD and life itself, Andy, Shida, Sheng, Anup, Rishad, Alex Wood, Matt, Davide, Asieh and Biswas. Thank you all for this wonderful experience.

## Chapter 1

## Introduction

In recent years the demand for portable devices has increased with requirements of very high performance and multi-functionality contained in relatively small devices. These devices include consumer electronics such as smartphones, tablets, cameras, etc. and reliable medical pervasive systems, in which their portability and mobility suggests that they use a constrained energy source such as a battery. For example, security cameras not only record video, but do object recognition, face detection and other computing intensive algorithms, while streaming the data to a server.

Besides the normal function of being able to make/receive calls, nowadays smartphones are expected to play and record HD video, surf the web, connect to social networks, transfer files wirelessly, provide location services and maps, play music and take pictures in a fast and reliable way, without draining the battery too quickly. The studies by Carroll and Heiser [13, 14] on smartphone power distribution suggest that appart from the antennas and the display, Central Processing Unit (CPU) contributes significantly to power consumption. As technology of smartphones evolves, average power does not imcrement substantially but maximum power does [14]. Therefore, not only battery life becomes a concern, but temperature increase, potentially reducing overall lifetime of the devices. Mahesri and Vardhan [15] performed a study on energy consumption for laptops, demonstrating that with intensive workloads CPU is the main source of power consumption. In addition, the energy costs are an increasing concern for data centres, these come from powering and cooling them[16]. Hence, the spectrum covering high performance needed in battery powered devices and their limited energy supply, as well as the server power and cooling; make energy efficiency a very important subject to address.

Addressing the energy problem, components of embedded devices have been improved. The efficiency of batteries has increased, providing more capacity, and incremented lifetime. Modern antennas can be powered down when idle. The introduction of multicore technology has reduced the load for a single CPU, allowing for several cores to perform

different tasks at the same time. Another technique for increasing the efficiency of embedded devices has been to distribute computation through the multicores, and to add application specific modules, or hardware accelerators; to the system. These accelerators include Graphics Processing Units (GPUs), Digital Signal Processors (DSPs), Floating-Point Units (FPUs), Field-Programmable Gate Arrays (FPGAs) hardware video codecs, camera interfaces, Radio Frequency (RF) transceivers, etc. The traditional CPU is then part of a larger System-on-Chip (SoC) with several internal modules. As mentioned by Carroll and Heiser [14], the use of hardware accelerators such as video decoders and GPUs has helped reduce the load for the CPU. But these technologies alone are not enough to fulfil the performance requirements with an acceptable battery life.

CPUs have been identified as one of the main sources of power consumption. Several technologies have been developed for semiconductors to make energy consumption more efficient. Some of these include the optimisation of the fabrication technology and the implementation of low power design techniques, the design of power efficient memory devices, and the reduction and variation of the power supply voltage and frequency. Section 1.1 provides an insight on these technologies, identifying the need for better optimisation.

#### 1.1 Research Justification

#### 1.1.1 Power Consumption

The CPU of an embedded device is a digital Complementary Metal Oxide Semiconductor (CMOS) circuit that consumes energy to stay active. Modern CPUs are part of a larger SoC, in which the latter includes other components such as GPUs and Hardware (HW) accelerators, each of these components consuming its share of en-Energy can be defined as the power consumption of the component per unit of time<sup>1</sup> [3]. This dissipated power comes from two sources, *Dynamic Power* (or switching power) and Leakage Power (or static power). Dynamic Power dissipation happens when the transistors inside a CMOS circuit are switched, allowing internal capacitances to charge/discharge and short-circuit currents move through the circuit. The Voltage, the load capacitance and the switching frequency determine the amount of Dynamic Power. Leakage Power dissipation does not depend on switching frequency but rather on the fabrication technology used, as the intrinsic parasitic currents of the transistors. As fabrication technology has reduced the size of transistors, Leakage Power has increased, exceeding switching power, as seen on Figure 1.1. Until recently, CPU design was more concerned with performance improvement and silicion area reduction for lower

<sup>&</sup>lt;sup>1</sup>A more detailed explanation on Power Consumption in CMOS is given in Section 2.1.

FIGURE 1.1: Dynamic and Leakage Power trend[1]

manufacturing costs, but power is now one of the major design constraints.

$$P(t) = I(t)V(t) \tag{1.1}$$

$$E = \int_{0}^{T} P(t)dt \tag{1.2}$$

#### 1.1.2 Low Power Design Techniques

Power minimisation is a major concern which has given rise to the development of power saving techniques. These techniques can be classified depending on the circuit abstraction level, from bottoms-up being: Logic and Technology level, Architecture and Circuit level and System level. These techniques can also be classified depending on whether they target more on either Dynamic or Leakage Power savings. Table 1.1 shows this classification with their target. It is fair to say that the techniques are not exclusive for Dynamic or Leakage, but they tend to save more power on their targets. A thorough explanation of these techniques is given in Section 2.1.

| Abstraction Level | Dynamic Power            | Leakage Power      |

|-------------------|--------------------------|--------------------|

| System level      | DVFS, Multi-Vdd          | Power Gating       |

| Architecture      | Clock Tree Optimisation, | Adaptive Voltage   |

| and               | Clock Gating,            | Scaling            |

| Circuit level     | Operand Isolation        | Scanng             |

| Logic             | Logic Resizing,          | $Multi-V_{th},$    |

| and               | Logic Restructuring      | Adaptive Body-Bias |

| Technology level  | Logic Restructuring      | Adaptive Dody-Dias |

Table 1.1: Common Low Power Design Techniques for CMOS

Architecture, Circuit, Logic and Technology level techniques are autonomous in the sense that no software control is needed for them to be triggered. System level techniques, however, require a controller for their optimisations to yield higher power savings. This control can be embedded on the Operating System (OS) (e.g. in Real-Time OSs), be developed as a driver (e.g. Linux Governors[17]), or manually set by the user. In any of these situations, this is software driven control. This control affects the performance of the SoC. For example, using Power Gating (PG) in a CPU effectively turns off its clock and voltage, leaving it unable to do any processing whilst powered down. Using Dynamic Voltage and Frequency Scaling (DVFS), the CPU clock and voltage are reduced, decreasing also both the power consumption and the Instructions-Per-Second (IPS), in which the latter can be seen as a reduction in performance. Multi-Vdd[1] is a high level design technique that requires having the system divided in several voltage domains, in which each of them can be either a CPU or a hardware accelerator, and each of them has its own voltage supply and clock. Depending on the application, the different domains can have their power when full performance is not needed from them. Further description of Multi-Vdd is explained in Section 2.2.1. As seen on these last three examples, performance and power are at a trade-off. This has been one of the fields of study since the system level techniques were developed.

#### 1.1.2.1 Power Gating

Power Gating (PG) allows for an SoC to effectively remove the voltage and clock of blocks that are not being used [2]. The strategy is to provide power modes to the blocks, low power mode and active mode. This is a very effective technique because it reduces both dynamic and leakage power. The implementation of PG includes the functional block to be gated, the controller, a power switching fabric, isolating logic and other components that are always on. The controller triggers a sequence that allows the state of the functional block to be saved (for after powering up again), as well as the stopping of the clocks together with the switching of the voltage supply. The saved state (or State Retention[2]) uses registers with reduced leakage power so when the functional block is off, only the always on logic power consumption is considerably low.

The complexity of using PG implicates time and energy required to power down/up the functional block, making it crucial to determine the situations in which to trigger PG for the system to provide the desired performance. The strategies developed to determine when to use PG are known as Dynamic Power Management (DPM). These strategies do not only include power management of the functional blocks inside the SoC, but the control of the low power modes of external peripherals (called in this text peripheral DPM). The main concern of DPM is the overhead for powering on/off. This overhead is composed by the higher power needed when the device is powering on/off, and the time it takes for this. Therefore the constraint is to determine whether it is

worth this overhead or not. The break-even time is defined as the minimum time the device needs to stay in low power mode for the energy consumed to be equal to that in the active mode for the same time. Some functional blocks/peripherals have different power states, the deeper sleep states have generally greater overheads [18]. Substantial research [6, 19–28] has been done for DPM to make more efficient decisions with less energy/time penalties. A survey of DPM strategies is presented in Section 2.4.1.

#### 1.1.2.2 Dynamic Voltage and Frequency Scaling

Dynamic Voltage and Frequency Scaling (DVFS) is a low power design technique that allows CPUs and other processing elements (DSPs, GPUs) to reduce their performance by lowering their voltage and frequency, therefore decreasing power consumption. The CPU is not shut down by DVFS, and therefore power reduction is not as drastic as with PG. Nonetheless, power savings are achievable when the task at hand does not require full speed of the CPU. The processing elements that use DVFS are powered by a programmable power supply, together with a System Clock (SysClock) Generator that provides a clock signal to the element. In order to run the CPU at a given frequency it will require a minimum voltage to run, and at higher frequencies higher supply voltages are needed. The sequence to use DVFS requires programming both the power supply and the clock generator at runtime[2]. This is further explained in Section 2.2.2.

As DVFS reduces performance when using lower frequencies, its use has to be controlled to allow demanding tasks to execute faster, if the task requires a given performance. DVFS is also used for thermal concerns, as high power consumption yields more heat. The main concern with DVFS is that reducing power consumption does not necessarily reduce energy consumption. Figure 1.2 shows how power is reduced from Approach 1 to Approach 2, but Energy consumption for both approaches (grey area below the curve) may not be necessarily reduced for the same workload. Care should be taken then to ensure that DVFS is used to target energy reduction, not only power. DVFS has also been used to for thermal optimisation [29]. This because reduction in power consumption directly correlates with temperature reduction, which enhances lifetime reliability of the system. Many modern commercial SoCs provide support for a discrete number of voltages and frequencies[2], usually paired together. These will be referred in this document as the Voltage and Frequency (V-F) pairs. The V-F pairs supported are SoC specific.

In order to have access to these system-level techniques, the industry specification called Advanced Configuration and Power Interface (ACPI) has been created[30]. ACPI sets the standard interface needed to facilitate communication of the hardware with the software and the OS. This interface allows for the OS to configure the power states of the SoC, as well as for the SoC to notify its available power levels, both sleep states

FIGURE 1.2: Power vs Energy. Reproduced from [2]

for DPM and voltage/frequency levels for DVFS. Next section analyses the challenges faced nowadays by the industry and academia to achieve better energy efficiency.

#### 1.1.3 Challenges of System Level Power Management

As mentioned before, System Level Power Management techniques control the power state of the processing elements. Therefore, the main challenges of using these techniques reside on how to efficiently reduce energy consumption without making a significant impact on performance. DPM and DVFS approaches are different in usage, as the strategies to optimise energy consumption are contrasting. The common strategy for DPM is to exploit large idle times, allowing the processing element to sleep more. On the contrary, the common strategy for DVFS is to exploit short idle times by reducing performance, maintaining the processor active at lower power consumption.

Operating Systems (OSs) play a major role in the control and efficiency of power management. Modern OSs are equipped with power controllers that take advantage of these idle times to provide lower energy consumption[17, 18]. Moreover, the scheduler will impact the power efficiency implicitly, as scheduling decisions will affect the amount of idle time between processes. Real-Time Operating Systems (RTOSs) are used for applications that have a strict constraint and therefore need to yield a defined amount of performance within a specific time frame. This creates the need for deterministic behaviour in which the workload and deadline are known beforehand, and therefore can be scheduled accordingly. Power management for RTOSs has been studied before [27, 31], where not only DPM and DVFS have been analysed separately but their interplay, allowing to decide whether to run as quick as possible then sleep or to run at lower frequencies.

The DPM - DVFS interplay can exist inside the same processing element e.g. CPU, with sleep states (DPM) and DVFS, for which the energy saving strategy should be a mix of both. The main challenge is to decide whether there are more energy savings running at maximum speed to reach idle period or to reduce speed given the current

workload. The current workload has to be known a priori. For example if the processing element were a CPU that requires to do intense video decoding, idle times may not make DPM feasible, whereas the DVFS strategies could work better. On the contrary if the application required has long idle times e.g. word processing, the DPM strategies may yield greater energy savings. An example of the interplay of DPM - DVFS is presented by Das et al. [32], where the approach is to decide whether to slowdown (using DVFS) or to run-to-idle (DPM) characterising the applications based on their break-even points (defined in Section 2.2.3).

General Purpose Operating Systems (GPOSs) (non-RTOSs)[33] do not explicitly have RTOS timing constraints, and therefore the approach for power management is targeted differently. The objective most commonly followed is to preserve a performance throughput. This throughput is measured with different metrics, yielding different results. Linux OS has in its kernel options for DVFS called governors, in which the performance objective is given as the idle time percentage of the CPU in periodic intervals, making frequency decisions to reach this target [18] i.e. if measured idle time is lower than the parameter, increase frequency, and vice versa. Some state of the art approaches use performance monitors to characterise the workload, and adjust frequency based on a usage factor calculated from the characterisation[22].

While the previous approaches are efficient for overall performance, they are oblivious to the applications running on the OS, potentially consuming more energy than required or providing lower performance than needed. Some approaches have created application specific algorithms to attack these shortcomings, some focused in video decoding [34, 35] and video games [36] for example. These approaches usually target real-time performance, resembling the behaviour of RTOSs. These approaches obtain performance constraints from the application running and based on the workload select the V-F pairs to keep that constraint. The energy efficiency of the algorithms is increased, but they remain application specific and are unable to run across different applications.

Moreover, the power control system of these approaches is embedded to the specific application, so replicating the code for another application is not trivial and may be time consuming. Added to this complexity, a recent survey [37] demonstrated that software developers have limited knowledge about energy efficiency, lack the knowledge about techniques to reduce energy consumption of software, and do not know how the software is using the energy. Therefore, a framework for programming different applications must exist to allow a power controller to provide energy efficiency across these applications. This framework should allow high level software developers to provide energy efficiency to their applications without the need to understand the complexity of the power management algorithms.

As mentioned before, modern SoCs integrate several modules (or components), in which some of the modules implement DVFS and others PG. Therefore, the strategies

for more efficient energy savings in the SoC depend on the low power hardware of the module. The OMAP processors by Texas Instruments[38] present an environment with both DVFS for some modules and PG for others. The strategy on interplay of both DPM (in Power Gating) and DVFS is different for each module. The PG modules e.g. WI-FI antennas, bus peripherals, memories, etc. can each be managed by analysing their usage rate, and whether or not a complex DPM algorithm may be required to control their power states. The DVFS modules e.g. CPU, DSP, GPU may be controlled using complex DVFS algorithms, with the power states of both PG and DVFS modules being controlled by a central power management system. The development of efficient the DPM and DVFS algorithms for the power management is imperative to provide significant power optimisations.

The challenges for system-level power management can be summarised then as:

- Power management techniques exist (PG, DVFS), and the algorithms to control these need to achieve a target performance.

- The power interfaces to communicate the hardware and software exist (ACPI), and the GPOSs have implemented algorithms to use them.

- State-of-the-Art for power management of GPOS is oblivious of the applications running, while State-of-the-Art for application specific power management is constrained to a single application.

- Software developers need a framework to take advantage of the power management algorithms running at OS level without the need for knowledge of the complexity of the algorithms.

#### 1.2 Research Questions

- 1. How can embedded devices save energy at system level in an unknown environment where workloads and applications vary, without losing performance?

- 2. How can this energy saving technique interact with its environment? How can it be used in real life?

- 3. How does the technique developed perform compared to existing State-of-the-Art?

#### 1.3 Research Contributions

The overall contribution of this research is the proposal for a new framework which optimises power consumption on embedded processors, enabling software developers to create power-aware applications. This contribution is divided into:

- 1. The design of a cross-layer Runtime Power Manager to optimise power consumption using DVFS embedded processors with an acceptable impact in performance. This Run-time Manager (RTM) uses Machine Learning (ML) optimisation algorithms for prediction and adapting of power states.

- 2. The design of a power-aware programming framework for:

- Converting general purpose applications into soft Real-Time (RT)

- Measuring performance as part of the Run-time Manager

- Allowing applications to become power-aware by communicating their performance constraints to the Run-time Manager

- 3. Evaluating the effectiveness of the Run-time Manager on DVFS. This includes the measurement of performance loss, power consumption, overheads, and comparisons with the State-of-the-Art.

#### 1.4 Research Outputs

This research has yielded three publications:

- "PoGo: An Application-Specific Adaptive Energy Minimisation Approach for Embedded Systems" published in HiPEAC 2015 [39]. I was the first author of this paper, doing all theoretical and experimental work and writing the majority of the paper.

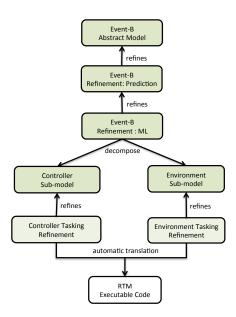

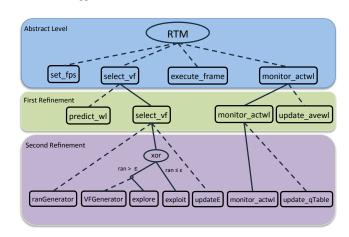

- "Towards automatic code generation of run-time power management for embedded systems using formal methods" published in MCSoC 2015 [40] I was the second author of this paper, taking the implementation from the PoGo paper, executing experiments on the real platform, and performing data analysis.

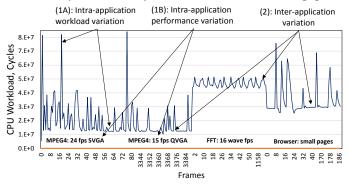

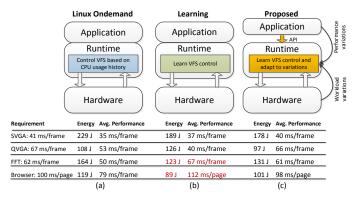

- "Learning transfer-based adaptive energy minimization in embedded systems" published at IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, August 2015 [41] My contributions for this paper include the aid in the literature review and the conceptualisation of the algorithm used.

#### 1.5 Document Outline

An overview of Power Management (PM) technologies has been given in this chapter, with the motivation on the role OSs play in the power saving of the devices. This Thesis is divided into 6 chapters. Chapter 2 gives a description of System-Level Power Management, providing an overview of the existing technologies, as well the State-of-the-Art techniques for optimising them. Chapter 3 proposes a global Run-time Manager (RTM) for Power Management (PM), with the theory behind efficient V-F selections. Chapter 4 describes how the design was developed for a real platform running Linux OS. Chapter 5 analyses the experiments run, highlighting the achievements of the proposed algorithm, and Chapter 6 provides Conclusions and Future Work.

## Chapter 2

# Power Management in Microprocessors

Power consumption in Complementary Metal Oxide Semiconductor (CMOS) circuits is a major concern nowadays, especially in embedded devices. For this reason, power management techniques have been developed to reduce power consumption by reducing the components' voltage. These techniques are known as power knobs, as they can be tuned, either automatically or manually. These power knobs include Power Gating (PG) and Dynamic Voltage and Frequency Scaling (DVFS), where the former completely shuts down a segment of hardware, and the latter reduces a processor's performance by reducing its frequency.

When addressing general purpose systems normally these run an Operating System (OS), on top of which run the applications. Depending on the context these applications and/or OSs may have performance requirements that the system must meet, whether it is a particular frame rate for video or an amount of computations per second. In other cases the system does not have these constraints, so any performance the system yields will suffice. This may seem well for the system, but there may be an impact in user experience [42]. Therefore, it is logical to take advantage of the opportunities that arise from knowing the performance constraints and the power knobs existing on the system.

It helps to see an embedded system as a cross-layered system. Let the system be a modern mobile phone. Analytically it can be divided into three layers:

• The physical or Hardware layer, where the processor resides, all of the electronic components and the battery. This layer includes the power management hardware it has embedded for reducing power consumption. In a modern mobile phone the hardware may have a quad-core ARM microprocessor, with 3G and Wi-Fi

antennas, battery, touchscreen, hardware accelerators and other peripherals. Each of these components consumes energy, which is provided by the battery (with limited energy).

- The Operating System layer, which is the overall manager of the system, controlling execution, scheduling tasks, memory management. It also controls the power states of the hardware. Depending on the system, the OS may be General Purpose or Real-Time. In the mobile phone example, the OS running may be general purpose e.g. Android, Linux, iOS, Windows Phone.

- The Application layer, where the user applications run. Here, applications running ask the OS for permission to run. Applications vary widely in their purpose, and therefore in their resource use, whether requiring some antennas for communication, intensive use of the processor for calculations, etc. Examples include text processors, video and audio applications, instant messaging, video games, etc.

Given that embedded devices are normally energy constrained, it is necessary to develop strategies to optimise energy consumption in order to extend the use time of the devices battery life. There are many components consuming energy in an embedded device (processor, screen, antennas, hardware accelerators, etc.). This work focuses in the power consumption of semiconductors, specifically of processors, the brain of the system. First, it is imperative to define what is power and energy consumption in a processor. Section 2.1 describes what power consumption is in semiconductors, setting up the need for better power saving techniques.

FIGURE 2.1: Flowchart of an embedded system in a cross-layer approach. Analytical approach (left) and practical approach (right). Sections 2.2, 2.3 and 2.4 are described as per the figure

Figure 2.1 presents the analytic division of an embedded system as a cross layer as defined before. Seen from a Power Management perspective, a Power Manager requires three things:

- The Power Knobs it will be manipulating. These knobs control the energy consumption of the processor, whether it is turning cores and modules on/off, reducing performance by reducing Voltage and Frequency (V-F), etc.

- The Control algorithm, which is the brain of the Power Manager. This algorithm takes decisions to modify the state of the Power Knobs. Depending on the application, normally the main objective of the Control algorithm is to reduce energy consumption of the processor with the least amount of performance penalties. This trade-off in energy and performance is regulated by the optimisation target.

- The Requirements provide the optimisation target to the Control. The Power Manager must aim to match the requirements which usually come in terms of a minimal performance requirement. In Real-Time Operating Systems (RTOSs) the application/task provides the performance requirement explicitly.

The elements required for the Power Manager can be mapped to the cross layer approach presented before, although the relationship is not necessarily one-to-one. The Control algorithm may be designed at any of the three layers, as an Application, as part of the OS or as a Hardware module. In the same way, the requirements may come from the Application running, or from the OS itself. This Chapter analyses all three elements of the Power Manager, with the Knobs available to the processor in Section 2.2, the Requirements and an overview of OSs in Section 2.3; and finally the Control algorithms for managing the knobs in Section 2.4, with a revision of the state-of-the-art of the algorithms available. Finally, the Discussion analyses the state-of-the-art approaches with their advantages and shortcomings. It addresses which improvements should be done to improve power optimisation.

## 2.1 Power consumption in Microprocessors

One of the major topics of concern when designing Integrated Circuits (IC) for battery-powered devices (WSNs) is the power consumption, as this will determine the active lifetime of the device before needing to replace or recharge the energy source. As technology has been developed, better energy storing cells have been designed, but this is not enough to fulfil the performance requirements. Therefore, some of the work is being done to reduce power consumption within the chip without compromising the performance constraint. The main objective of this project is to observe the power consumption of the OpenMSP430 and using low-power design techniques try to lower the power consumption overall. Therefore, the first step is to define power inside an IC and then the techniques that can be used to reduce its consumption.

The definition of *Power*, *Dynamic Power* and *Static Power* is based on [3]. The general definition of power is the energy consumed per unit of time. More specifically, the

energy E consumed is equal to the integral of the instantaneous power P(t) over an interval T (Equation 2.1). The average power is then the Energy E over the interval T (Equation 2.2). In electric circuits, the instantaneous power is defined as the product of the instantaneous current I(t) and the instantaneous voltage V(t) (Equation 2.3).

$$E = \int_0^T P(t)dt \tag{2.1}$$

$$P_{avg} = \frac{E}{T} = \frac{1}{T} \int_0^T P(t)dt \tag{2.2}$$

$$P(t) = I(t)V(t) \tag{2.3}$$

For the architecture used in this project, the voltage is constant (set to 1.08V in the constraints). Therefore the instantaneous power  $P_{total}(t)$  will be proportional to the sum of the currents of the transistors  $I_{total}(t)$  while maintaining a constant  $V_{DD}$ .

$$P_{total}(t) = V_{DD} \cdot I_{total}(t) \tag{2.4}$$

The equation for the energy in the capacitor is given at Equation 2.5

$$E_C = \frac{1}{2}CV_C^2 \tag{2.5}$$

Given these equations, the total power consumed in a CMOS based IC is divided into the Dynamic Power and the Static Power (Equation 2.6). The former refers to the energy drained during switching of the CMOS gates, whereas Static Power is consumed regardless of the switching frequency.

$$P_{total} = P_{dynamic} + P_{static} (2.6)$$

#### 2.1.1 Dynamic Power

Ideal CMOS gates consume no power, as their output is connected to the input of another CMOS gate (the gate of a transistor, which is activated by voltage, not current). However, real CMOS gates contain a parasitic load capacitance at the output of the gate due to small capacitances intrinsic to the MOS transistors. Another "real world" peculiarity is that the input voltage switching is not instantaneous, so short circuit currents emerge due to this factor. Power dissipation coming from these non-ideal characteristics is called *Dynamic Power*. The two forms of Dynamic Power are (Equation 2.7):

- Switching Power

- Internal Power, dissipated by short-circuit currents (as defined by Keating et al. [2] and in the Synopsys Manuals [4])

$$P_{dynamic} = P_{switching} + P_{short\ circuit} \tag{2.7}$$

#### 2.1.1.1 Switching Power

Switching Power results from the charging and discharging of the load capacitance  $C_{load}$ . Using Figure 2.2 as a reference of a CMOS inverter, when the input is 0 the PMOS transistor is  $ON^1$ , the capacitor  $C_{load}$  starts charging to  $V_{DD}$  (Charging in Figure 2.2). The output is 1. At this stage the NMOS transistor is OFF, so no current is flowing through it to  $V_{SS}$ . When the input is 1 (Discharging in Figure 2.2), the PMOS transistor is OFF (cutting  $V_{DD}$ ), the NMOS transistor is ON and the capacitor  $C_{load}$  starts discharging through it. Therefore, using Equation 2.5 the energy of the load capacitance is then:

$$E_{C_{load}} = \frac{1}{2}C_{load}V_{DD}^2 \tag{2.8}$$

As  $V_{DD}$  is constant, the integral of the voltage yields  $V_{DD}$ . The total energy delivered from the Power Supply is then shown on Equation 2.9 [3]. Half of this energy is stored in the capacitor. The other half of the energy is dissipated as heat from the PMOS, because when charging the capacitor the transistor has a voltage across and it has a current flowing through itself [3].

$$E_C = \int_0^\infty I(t) V_{DD} dt = \int_0^\infty C \frac{dV}{dt} V_{DD} dt = C V_{DD} \int_0^{V_{DD}} dV = C V_{DD}^2$$

(2.9)

Current is then driven through the PMOS only during the charging of  $C_{load}$ , so for this model, when  $C_{load}$ 's voltage is equal to  $V_{DD}$  the current is 0 (discarding leakage

<sup>&</sup>lt;sup>1</sup>A transistor is considered ON when it is in its saturation region, in which a channel has been produced from Source to Drain. It is considered OFF when the voltage at the Gate  $V_G$  is the same as the Source  $V_S$ , so no path is created [3].

FIGURE 2.2: A CMOS Inverter showing the charging and discharging of the capacitor  $C_{load}$ . Based on [3]

power). In the same manner, after the capacitor has completely discharged following the activation of the NMOS transistor, the current flowing through the transistor is 0. Therefore, Switching Power is dissipated only during capacitor charge. To calculate the switching power in a CMOS circuit, the number of times it has switched have to be counted. Supposing the switching frequency is  $f_{sw}$  and T is the time over which the average Power is to be calculated, the number of switching times is  $T \cdot f_{sw}$ . Using this, (2.2) and (2.9), the switching power  $P_{switching}$  is then [3]

$$P_{switching} = \frac{E}{T} = (T \cdot f_{sw}) \cdot \frac{CV_{DD}^2}{T} = f_{sw}CV_{DD}^2$$

(2.10)

The previous calculation is for a CMOS gate that keeps switching every clock cycle. Real gate inputs do not toggle that often (except for clock inputs). Therefore, an activity factor  $\alpha$  can be introduced based on switching probability for the device changing from 0 to 1 while the clock frequency  $f_{clk}$  is kept constant. The rearranged equation is then

$$P_{switching} = \alpha f_{clk} C V_{DD}^2 \tag{2.11}$$

#### 2.1.1.2 Internal Power

Internal Power is dissipated when there is a short circuit current driven from  $V_{DD}$  to  $V_{SS}$  passing through both the PMOS and NMOS transistors. As mentioned before, non-ideal switching delays exist during transitions in the CMOS gates. During switching from "0" to "1" and vice-versa, there is a moment in which both transistors are in the linear region, which neither of the transistors are saturated nor shut down, so there is a direct path from  $V_{DD}$  to  $V_{SS}$ , effectively creating a short circuit. The name Internal Power is given based on [4] and [43]. Figure 2.3 shows the short circuit current. This current is

FIGURE 2.3: A CMOS Inverter showing the short circuit current flowing from  $V_{DD}$  to  $V_{SS}$ . Based on [4]

considerably smaller than Switching current because it only happens during short linear periods of both transistors. In this case, it is also obvious that power will be dissipated depending on the switching activity ( $\alpha f_{clk}$ ). Also, as the transistors are in the linear

(ohmic) region, they behave as voltage dependent resistors. The current I(t) will depend on the voltage  $V_{DD}$  and the impedance dependent on  $V_{GS}$ .

As it can be seen, both types of Dynamic Power are dependent on the switching frequency of the gate and supply voltage  $V_{DD}$ . One approach could be to reduce  $V_{DD}$  (which in this case has been done, to a minimum of 1.08V), but this increases propagation delay. Therefore two options are possible, whether to reduce the general clock frequency, or the individual activity factor of the gates. The problem with reducing clock frequency is that although switching power is reduced, the energy required to complete a specific task will remain the same, as it will take the same number of clock cycles to be realised. Mathematically, using  $T_X$  as the time it takes to realise a particular task X, the switching count will be  $T_X \cdot f_c lk$ . Using 2.2 and 2.11, the switching energy will then be

$$E_{switching} = T_X \cdot P_{switching} = T_X \cdot \alpha f_{clk} C V_{DD}^2 = (T_X \cdot f_{clk}) \cdot \alpha C V_{DD}^2$$

(2.12)

and

$$T_X \cdot f_{clk} = k$$

where k is an adimensional constant (2.13)

$$\therefore E_{switching} = \alpha k C V_{DD}^2 \tag{2.14}$$

where, it is clearly seen that the Energy is not dependent on frequency.

#### 2.1.2 Static Power

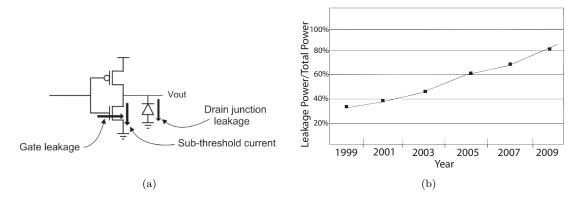

Static Power on the contrary does not depend on switching frequency but on the technology used. As the fabrication technology has been scaled down Static (or Leakage) Power has been increasing at the level that it equals and in some cases is grater than Dynamic Power [2], as shown on Figure 2.4(b). This means that even without switching, transistors dissipate energy only by being powered. Figure 2.4(a) shows three of the four leakage currents, which are (as stated on [2]):

**Sub-threshold Leakage:** Current flowing from drain to source when the transistor is in the weak inversion region. This is the most important source of leakage.

Gate Leakage: Current produced by the effect of tunnelling, where electrons flow through the Gate Oxide to the substrate, due to the reduced thickness of the oxide layer.

Gate Induced Drain Leakage: Current produced by the high field effect in the drain because of  $V_{DG}$  being high, which flows from drain to substrate.

Reverse Bias Junction Leakage: current produced by the creation of carrier pairs in the depletion regions.

As it can be seen from (2.15) (taken from [5]) (where K and n are constant, W is the width of the transistor,  $V_{th}$  is the threshold voltage,  $V_{DD}$  is the supply voltage and T

FIGURE 2.4: Leakage Currents in a CMOS circuit (a). Taken from [2]. ITRS trends for leakage power dissipation (b). Based on [5].

is the temperature), if  $V_{th}$  is reduced the subthreshold current increases exponentially. This happens with newer technologies, as the reduction in the technology size effectively reduces  $V_{th}$  [2]. As stated in the reference, current increases the temperature, and temperature increases  $I_{sub}$  exponentially, this problem is called thermal runaway. One way to reduce leakage power (as well as dynamic power) would be to reduce  $V_{DD}$ . As mentioned in section 2.1.1.2, reducing  $V_{DD}$  would increase propagation delay.

$$I_{sub} = KW e^{\frac{-V_{th}}{nT}} (1 - e^{\frac{-V_{DD}}{T}})$$

(2.15)

Therefore, it is imperative that low-power design techniques are implemented in future processor designs to counter the increased power consumption due to Dynamic and Static Power.

## 2.2 Power Management Techniques: Knobs

#### 2.2.1 Multi-Vdd

This technique is based on the premise that not all parts of the chip need to work at the same speed [44]. As mentioned in the introduction, the System-on-Chip (SoC) may contain several peripherals apart from the Central Processing Unit (CPU) cores that can run at different speeds. Therefore their supply voltage Vdd could be lowered and still meet timing requirements. Therefore its Dynamic (and Leakage) power could be lowered.

#### 2.2.2 **DVFS**

Another widely used technique for reducing power consumption is DVFS, or also commonly found in the literature as Dynamic Voltage Scaling (DVS). This technique aims

to reduce power by reducing the voltage supply of the device (or the core) at the expense of reducing the frequency of the clock signal. This reduction of frequency is done because of gate switching latency. By reducing the voltage it can be seen in Section 2.1 that overall power consumption gets reduced. By reducing the clock frequency the device reduces its performance as computations are directly dependent on the operating frequency, so this technique is most effective when maximum performance is not needed.

Then, in order to use DVFS effectively, techniques have been designed to reduce power with the aim of penalising performance at the very least. These include the simple detection of what the workload is at a particular moment, to predict what the workload will be in the future. Other techniques are aimed to particular types of applications such as multimedia and videogames, where performance constraints are fixed in order to provide a desired quality.

Depending on the device, the DVFS implementation may be defined as either a discrete compact number of voltage-frequency pairs e.g. Intel's XScale PXA270 processor [45]; or as an adaptable range of frequencies with an adaptable range of voltages, as the one implemented by Nakai et al. [46]. This review focuses more on the former, as future implementations of algorithms following this report will be based in voltage-frequency pairs (from now on called *V-F pairs* or *V-F setting*).

## 2.2.3 PG

Dynamic Power Management (DPM) is a technique widely employed in microprocessors and other electronic devices, such as Hard Disk Drives (HDDs) and other peripherals. The process of DPM consists of taking advantage of idle times of the device (e.g. processor, HDD) between workloads, by setting the device to an available low power mode. Low power modes vary among devices, e.g. IBM's Travelstar HDD has 5 low power modes (plus active power modes)[6], the microprocessor StrongARM SA-1100 [6] has 3 power modes: **ACTIVE**, **IDLE** and **SLEEP**.

Normally there is an important trade-off between the power consumption (or power saving) in a particular power mode and the time and power it takes to transition to/from that power mode, meaning that the deeper sleep level i.e. the more power savings, the longer the transition time there is. Therefore the decision to go to a low power state mode should be based on the idle time available for the device before a workload arrives. In most cases (but not all) the power consumption for doing the transition to a low power state is higher than the power consumed when idle. A term is then defined as the **Break-Even Time**  $T_{BE}$  which is the amount of time the device should spend in the low power mode plus the transition time, for the energy consumption to be the same as the device in IDLE mode [6]. For simple explanation of the terms it will be assumed that a device has 3 power modes: **ACTIVE**, **IDLE** and **SLEEP**.

In microprocessors, the SLEEP mode reduces power consumption compared to just being IDLE, as several modules and clocks of the processor get disabled when sleeping. Ideally as soon as a workload is finished and the processor stops being ACTIVE, it would enter SLEEP mode. In reality, there is a transition period between ACTIVE/IDLE to SLEEP as well as from SLEEP to ACTIVE. Some processors have several sleep modes. For example, Texas Instruments' DM3730 processor [47] has 5 power states: Active, Inactive, Retention with logic on in low-voltage, Retention with logic off, and Off. Normally, the deeper the sleep level in a processor, the higher the overhead is, both in terms of time and consequently energy. These overheads are important to decide if it is worth going to a SLEEP mode. The **Break Even Time** is the minimum time the processor needs to be asleep for it to be worth going into sleep mode.

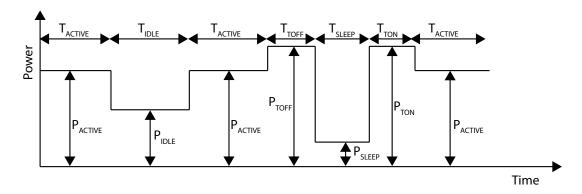

FIGURE 2.5: Definitions of power and times for a device with **IDLE** and **SLEEP** modes

In order to explain better what the Break Even Time  $T_{BE}$  is, Figure 2.5 shows the different powers and times under the different power modes and the transitions. Let  $P_{ACTIVE}$  be the power consumption when the processor is ACTIVE and the time at this state  $T_{ACTIVE}$ . In the same manner,  $P_{IDLE}$  is the power when the processor is IDLE, and the time at this state is  $T_{IDLE}$ . The energy consumed at ACTIVE and IDLE periods are  $E_{ACTIVE}$  and  $E_{IDLE}$  respectively:

$$E_{ACTIVE} = P_{ACTIVE}T_{ACTIVE}$$

$E_{IDLE} = P_{IDLE}T_{IDLE}$  (2.16)

For SLEEP mode there is a transition period  $T_{TR}$ , which is the sum of the time it takes to go to sleep  $T_{OFF}$  and to wake up  $T_{ON}$ , which in turn these transitions dissipate power,  $P_{OFF}$  and  $P_{ON}$  respectively. The sleep and wake up transitions are constant in terms of time and power, the energy it takes to transition  $E_{TR}$  is then fixed:

$$T_{TR} = T_{TOFF} + T_{TON} \qquad E_{TR} = T_{TOFF} P_{TOFF} + T_{TON} P_{TON} \qquad (2.17)$$

After the processor has gone to sleep, the power consumption  $P_{SLEEP}$  during the time  $T_{SLEEP}$  is the energy consumed  $E_{SLEEP}$ :

$$E_{SLEEP} = T_{SLEEP} P_{SLEEP} \tag{2.18}$$

Therefore, in order for the transition to the SLEEP mode to be worth it, it is necessary that the energy during sleeping  $E_{SLEEP}$  and the transition energy  $E_{TR}$  be less than the energy without going to sleep i.e. when being IDLE, this is  $E_{IDLE}$ :

$$E_{IDLE} \ge E_{TR} + E_{SLEEP} \tag{2.19}$$

The Break Even Time  $T_{BE}$  then substitutes the  $T_{IDLE}$ , so now  $T_{BE}$  needs to be calculated:

$$P_{IDLE}T_{BE} = \frac{E_{TR}}{T_{TR}}T_{TR} + P_{SLEEP}T_{SLEEP} \tag{2.20}$$

And as the  $T_{IDLE}$  is the time used for sleeping with the transitions,  $T_{SLEEP}$  becomes:

$$T_{IDLE} = T_{BE} = T_{TR} + T_{SLEEP} \rightarrow T_{SLEEP} = T_{BE} - T_{TR}$$

(2.21)

Substituting Equation 2.21 in Equation 2.20:

$$P_{IDLE}T_{BE} = \frac{E_{TR}}{T_{TR}}T_{TR} + P_{SLEEP}(T_{BE} - T_{TR})$$

(2.22)

Solving for  $T_{BE}$ :

$$T_{BE} = T_{TR} \frac{\frac{E_{TR}}{T_{TR}} - P_{SLEEP}}{P_{IDLE} - P_{SLEEP}}$$

$$(2.23)$$

Based on this concept, the determining factor for deciding to go to **SLEEP** is then to know if  $T_{IDLE} > T_{BE}$ . As in a microprocessor this value is not known *a priori*, different techniques have been developed to estimate what  $T_{IDLE}$  will be before really knowing it.

Benini et al. [6] provides a thorough review of different implementations of DPM techniques and their advantages. To provide some context for more complex techniques explained later, some of the basic DPM techniques of the reference are explained here. DPM techniques for microprocessors are mainly divided into Predictive and Stochastic Techniques.

# 2.3 Applications and OS: Requirements

Nowadays, high performance embedded systems are able to run applications that demand plenty of resources, intensive processing power, dedicated accelerators, internet for streaming, memory for running simultaneous applications, etc. It is a responsibility of the system not only to run these applications, but to provide a decent performance for each of them whilst doing it, with a finite power supply (battery) powering the system.

The simplest strategy to save energy would be to reduce V-F using DVFS. The problem is the reduction in performance, which in turn impacts user experience. Therefore, in order to reduce the energy consumption whilst preserving performance, a Power Manager is required to control the processor's power states. As opposed to setting a V-F manually, a dynamic Power Manager can control the V-F on the run, based on the OS, application and user needs. These needs or requirements allow the Power Manager to adapt and compensate for the situation.

The requirements needed from a Power Manager can come from a particular application or from the OS. There are two types of OSs, General Purpose Operating System (GPOS) and RTOS. In GPOS e.g. Windows, Linux, iOS, these requirements come from the OS, where the main optimisation constraint is the idle time, sampled at regular intervals. This approach allows to save energy, but as it is oblivious of the task or application being run, the Power Manager is not concerned in the user perceived performance. As opposed to GPOS, the main objective of RTOS is to provide a required performance to given tasks. In order to provide a performance that reduces energy consumption but does not compromise user experience, it is possible to take some elements from RTOSs for a Power Manager. Section 2.3.1 provides the definition of RTOS, an explanation as well as the types of existing RTOSs.

## 2.3.1 Real-Time Systems

The main objective of a Real-Time System (RTS) is to execute tasks within a time given. The system's tasks must not only deliver a result but deliver it timely[48]. The two main aspects of RTSs are to aim to meet the deadlines, and to behave in a predictable manner. In order to cope with several applications that require real-time scheduling, complex RTSs run in an RTOS.

The most important concepts in a Real-Time System are Deadlines, Latency, Jitter, Predictability, Worst Case, and Periodic Task. Taken from the book by Sally [10], they are described:

**Deadline** The time at which a task must be finished. This is the most important component of the real-time system, it is what makes it real-time. In hard real-time systems failing to meet the deadline can result in disastrous consequences.

In soft real-time systems the value of the task decreases when completed after the deadline.

- Latency The time between what should happen and when it does. Ideally latency should be zero, but in reality, hardware and software components take time (if infinitesimal) to move electric signals from one place to another. For example, a hardware interrupt caught in a pin of a processor activates a software interrupt. Even though this is almost instantaneous, there is a time taken between these two events i.e. latency.

- **Jitter** It is the variance of latency. In reality, latency between events varies in time. A non-deterministic task scheduler in the OS (e.g. Linux) cannot ensure that a task will start running at an exact given time with a given latency.

- **Predictability** Is the ability to know how much time will a task take to complete. A completely predictable system can repeat a process with no variation in the results nor in terms of the time taken. In reality, in order to make a real-time system predictable, jitter and latency are included when calculating the execution time (worst case).

- Worst Case Latency and jitter are factors in real-time systems. In order to make the system predictable, when determining the execution time of a task, a worst case scenario is calculated, which includes latency and jitter. Therefore, the task scheduler will know what is the longest time the task will take, in order to decide how to schedule it to meet its deadline.

- **Periodic Task** A task that executes at periodic (regular) intervals, and the interval of the task is always the same.

- **Priority Inversion** This happens when a task with low-priority holds a lock on a resource needed from a high-priority task, keeping the high-priority task from executing.

#### 2.3.2 Hard Real-Time versus Soft Real-Time

The two main types of RTSs are *Hard* and *Soft* RTSs. The former require all of the deadlines be met, if not, serious consequences may happen e.g. a lagging heart rate monitor. The Soft RTS on the other hand are more relaxed and can tolerate deadline misses. At a deadline miss, the value of the result at the end of the task is reduced, but it does not result in heavy consequences. Examples of this are media players, as a loss in performance translates into reduced frame rate. Table 2.1 shows a comparison between Hard and Soft Real-Time.

As mentioned, Hard and Soft RTSs are aimed at different situations. Observing a general purpose system, in order to increase power savings whilst maintaining performance, it