# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

Non-Neural Computing on the SpiNNaker Neuromorphic Computer

by

Kier J. Dugan

Thesis for the degree of Doctor of Philosophy

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING Electronics and Computer Science

#### Doctor of Philosophy

## NON-NEURAL COMPUTING ON THE SPINNAKER NEUROMORPHIC COMPUTER

by Kier J. Dugan

Moore's law scaling has slowed dramatically since the turn of the millennium, causing new generations of computer hardware to include more processor cores to offer more performance. Desktop computers, server machines, and even mobile phones are all multi-core devices now, and this trend has shown no signs of slowing soon. Eventually, computers will contain so many cores that they will be an *abundant resource*. Using this many processors requires new ways of thinking about software. Biology leads computer architecture here: mammalian brains contain *billions* of neurons embedded in a dense fabric of synapses—the human brain contains about  $10^{11}$  neurons and  $10^{15}$  synapses. Each neuron is essentially a small processing element in its own right.

Neuromorphic hardware draws inspiration from this and is typically used to support neural network simulations. SpiNNaker is one such platform, designed to support simulations containing up to  $10^9$  neurons and  $10^{12}$  synapses (about 1% of a human brain) in biological real-time. This is achieved by embedding a million ARM processors in a bespoke interconnection fabric which is non-deterministic, modelled after spiking neural networks, and predicated on the inherent fault-tolerance present in biological systems.

This thesis uses SpiNNaker as a test-bed for massively-parallel non-neural applications, showing how very fine-grain parallel software can be structured to solve real-world problems. First, we address the inherent non-determinism of the underlying platform, by designing a set of algorithms that discover the topology of an arbitrary SpiNNaker-like machine so that fine-grain parallel software can be mapped onto it. These algorithms are verified against various fault conditions, and remove a shortcoming present in the existing system. Secondly, we demonstrate a fine-grain parallel application, by solving two-dimensional heat-diffusion where each point of the problem grid is essentially a self-contained program. This software architecture is subject to various fault conditions to demonstrate the resilience of the approach.

### Contents

| D | Declaration of Authorship xix   |          |           |                                       |     |  |  |

|---|---------------------------------|----------|-----------|---------------------------------------|-----|--|--|

| A | cknov                           | wledge   | ements    |                                       | xxi |  |  |

| A | Acronyms and Abbreviations xxii |          |           |                                       |     |  |  |

| 1 | Intr                            | oducti   |           | 1                                     |     |  |  |

|   | 1.1                             | Perfor   |           | bstacles                              | 3   |  |  |

|   |                                 | 1.1.1    | Memory    | Bottlenecks                           | 3   |  |  |

|   |                                 | 1.1.2    | Instruct  | ion-level Parallelism                 | 4   |  |  |

|   |                                 | 1.1.3    | Power     |                                       | 7   |  |  |

|   |                                 | 1.1.4    | Reliabil  | ity                                   | 9   |  |  |

|   |                                 | 1.1.5    | When T    | Taken Collectively                    | 9   |  |  |

|   | 1.2                             | Parall   | el Softwa | re Structure                          | 9   |  |  |

|   |                                 | 1.2.1    | Scalabil  | ity                                   | 10  |  |  |

|   |                                 | 1.2.2    | Modellii  | ng                                    | 12  |  |  |

|   | 1.3                             | A Nev    | v Perspec | tive on Software                      | 12  |  |  |

|   |                                 | 1.3.1    | -         | ker—A Neuromorphic Computing Platform |     |  |  |

|   | 1.4                             | Contri   | ibutions  |                                       | 14  |  |  |

|   | 1.5                             | Organ    | isation   |                                       | 15  |  |  |

| 2 | Stat                            | te of tl | he Art    |                                       | 17  |  |  |

|   | 2.1                             | Conve    | ntional P | arallel Computing                     | 17  |  |  |

|   |                                 | 2.1.1    | Hardwa    | re Taxonomies                         | 17  |  |  |

|   |                                 |          | 2.1.1.1   | Single-Instruction Single-Data        | 18  |  |  |

|   |                                 |          | 2.1.1.2   | Single-Instruction Multiple-Data      | 19  |  |  |

|   |                                 |          | 2.1.1.3   | Multiple-Instruction Single-Data      | 20  |  |  |

|   |                                 |          | 2.1.1.4   | Multiple-Instruction Multiple-Data    | 20  |  |  |

|   |                                 |          | 2.1.1.5   | Single-Program Multiple-Data          | 22  |  |  |

|   |                                 |          | 2.1.1.6   | Multiple-Program Multiple-Data        | 23  |  |  |

|   |                                 |          | 2.1.1.7   | Non-uniform Memory Access             | 24  |  |  |

|   |                                 |          | 2.1.1.8   | General-Purpose GPU (GPGPU)           | 26  |  |  |

|   |                                 | 2.1.2    | Difficult | iies                                  | 27  |  |  |

|   |                                 |          | 2.1.2.1   | Resource Contention                   | 27  |  |  |

|   |                                 |          | 2.1.2.2   | Deadlock                              | 28  |  |  |

|   |                                 |          | 2.1.2.3   | Synchronisation                       | 29  |  |  |

|   |                                 |          | 2.1.2.4   | Cache Coherency                       | 30  |  |  |

|   |                                 |          | 2125      | Inter-Process Communication (IPC)     | 30  |  |  |

vi CONTENTS

|   |      |               | 2.1.2.6           | Load Imbalance                      | . 31 |

|---|------|---------------|-------------------|-------------------------------------|------|

|   |      | 2.1.3         | Commu             | nication                            | . 31 |

|   |      |               | 2.1.3.1           | Chip Multi-core Systems             | . 31 |

|   |      |               | 2.1.3.2           | Networks                            | . 32 |

|   |      |               | 2.1.3.3           | Intra-chip Networks                 |      |

|   |      |               | 2.1.3.4           | Inter-chip Networks                 |      |

|   |      |               | 2.1.3.5           | Cluster Computer Backbone Networks  |      |

|   |      | 2.1.4         | Software          | e and Frameworks                    |      |

|   |      |               | 2.1.4.1           | Asynchronous I/O                    |      |

|   |      |               | 2.1.4.2           | Multiple Threads                    |      |

|   |      |               | 2.1.4.3           | Multiple Processes                  |      |

|   | 2.2  | Neuro         |                   | Computing                           |      |

|   |      | 2.2.1         | -                 |                                     |      |

|   |      | 2.2.2         |                   | re                                  |      |

|   |      | 2.2.2         | 2.2.2.1           | BrainScaleS                         |      |

|   |      |               | 2.2.2.1 $2.2.2.2$ | TrueNorth                           |      |

|   |      |               | 2.2.2.2           | BlueHive                            |      |

|   |      |               | 2.2.2.4           | SpiNNaker                           |      |

|   |      | 2.2.3         |                   | 3                                   |      |

|   |      | 2.2.3         | 2.2.3.1           | NEURON                              |      |

|   |      |               | 2.2.3.1 $2.2.3.2$ | NEST                                |      |

|   |      |               | 2.2.3.2 $2.2.3.3$ |                                     |      |

|   |      |               |                   | Brian                               |      |

|   |      | 0.0.4         | 2.2.3.4           | PCSIM                               |      |

|   |      | 2.2.4         | 0 0               | ges                                 |      |

|   |      |               | 2.2.4.1           | Procedural                          |      |

|   | 0.0  | CL :NIN       | 2.2.4.2           | Declarative                         |      |

|   | 2.3  | Spinn         | aker in C         | Context                             | . 53 |

| 3 | Spil | NNake         | er                |                                     | 55   |

|   | 3.1  |               |                   | position                            |      |

|   | 0.1  | 3.1.1         |                   | NNaker Chip                         |      |

|   |      | 3.1.2         | _                 | Infrastructure                      |      |

|   |      | 0.1.2         | 3.1.2.1           | Communications NoC                  |      |

|   |      |               | 3.1.2.2           | Routing                             |      |

|   |      |               | 3.1.2.3           | Packet Types                        |      |

|   |      | 3.1.3         |                   | nip systems                         |      |

|   | 3.2  |               |                   | re                                  |      |

|   | 0.2  | 3.2.1         | _                 | ocess                               |      |

|   |      | 3.2.1 $3.2.2$ |                   | ng Applications                     |      |

|   | 3.3  |               | -                 | ion                                 |      |

|   | 0.0  |               |                   |                                     |      |

|   |      | 3.3.1         |                   | Systems                             |      |

|   |      | 3.3.2         |                   | ng with an Event-based Architecture |      |

|   | 9.4  | 3.3.3         |                   | t Time vs. Real-Time                |      |

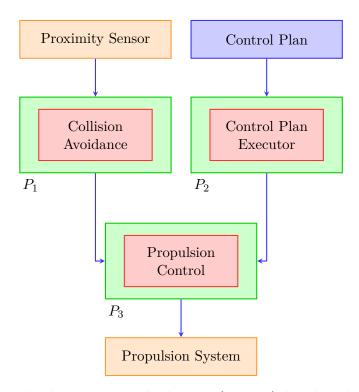

|   | 3.4  | mon-n         | eurai Sim         | ulations                            | . 79 |

| 4 | Svs  | tem C         | onfigurat         | tion                                | 81   |

| _ |      |               | _                 | ons                                 | . 83 |

CONTENTS vii

|   |     | 4.1.1    | Definition                                  |

|---|-----|----------|---------------------------------------------|

|   |     | 4.1.2    | Compilation                                 |

|   |     | 4.1.3    | Execution                                   |

|   | 4.2 | Contr    | ibutions                                    |

| 5 | Aut | to-disc  | overy Algorithms 93                         |

|   | 5.1 |          | em Statement                                |

|   | 5.2 |          | tions                                       |

|   | 5.3 |          | $rac{1}{2}$                                |

|   |     | 5.3.1    | Machine Model                               |

|   |     | 5.3.2    | Simulator Architecture                      |

|   |     | 5.3.3    | Fault Map Generation                        |

|   |     | 5.3.4    | Test Case                                   |

|   | 5.4 | Imple    | mentation                                   |

|   |     | 5.4.1    | SCAMP Modifications                         |

|   |     | 5.4.2    | Port Survey—The $\alpha$ -ping              |

|   |     | 5.4.3    | Test Case                                   |

|   | 5.5 | Labell   | ing Nodes and Building the Control Tree     |

|   |     | 5.5.1    | Depth-first Labelling                       |

|   |     |          | 5.5.1.1 Simulation                          |

|   |     |          | 5.5.1.2 Implementation                      |

|   |     | 5.5.2    | Lock-step Breadth-first Labelling           |

|   |     |          | 5.5.2.1 Simulation                          |

|   |     |          | 5.5.2.2 Implementation                      |

|   |     | 5.5.3    | Parallel Breadth-first Labelling            |

|   |     |          | 5.5.3.1 Simulation                          |

|   |     |          | 5.5.3.2 Implementation                      |

|   | 5.6 | Concl    | uding Remarks                               |

|   |     | 5.6.1    | Demonstration                               |

|   |     | 5.6.2    | Run-time Fault Detection                    |

|   |     | 5.6.3    | Review                                      |

| 6 | Nor | n-neura  | al Application 14'                          |

|   | 6.1 | Design   | n                                           |

|   | 6.2 | Simula   | ation                                       |

|   | 6.3 | Imple    | ${ m mentation}$                            |

|   |     | 6.3.1    | P2P Table Construction                      |

|   |     | 6.3.2    | Completing the Connectivity Model           |

|   |     | 6.3.3    | Reducing Packet Flux—The "Ping-pong" buffer |

|   |     | 6.3.4    | Downloading Data                            |

|   |     | 6.3.5    | Results                                     |

|   | 6.4 | Concl    | uding Remarks                               |

| 7 | Rel | iability | 16'                                         |

|   | 7.1 | •        | vare                                        |

|   |     | 7.1.1    | Cores                                       |

|   |     | 7.1.2    | Interrupts                                  |

viii CONTENTS

|    |      | 7.1.3    | Routing Subsystem                   | 168 |

|----|------|----------|-------------------------------------|-----|

|    |      | 7.1.4    | Packet Parity                       | 169 |

|    |      | 7.1.5    | Network Time Phase                  | 169 |

|    |      | 7.1.6    | Emergency Routing                   | 170 |

|    |      | 7.1.7    | Dropped Packet Re-injection         | 171 |

|    | 7.2  | Softwar  | re                                  | 172 |

|    |      | 7.2.1    | Problem Device Placement            | 172 |

|    |      | 7.2.2    | Inherently Robust Applications      | 172 |

|    |      |          | 7.2.2.1 Recovery                    | 173 |

|    |      | 7.2.3    | Real-time Fault Detection           | 174 |

| 8  | Con  | cluding  | g Observations                      | 175 |

|    | 8.1  | Contrib  | buting Back to SpiNNaker            | 175 |

|    |      | 8.1.1    | Non-neural Infrastructure           | 175 |

|    |      | 8.1.2    | Simplifying Application Development | 177 |

|    | 8.2  | Fault T  | Folerance Techniques                | 177 |

|    |      | 8.2.1    | Real-time Fault Discovery           | 177 |

|    |      | 8.2.2    | Orthogonal Encoding Schemes         | 178 |

|    | 8.3  | Paralle  | l Software Synthesis                | 178 |

|    |      | 8.3.1    | Functional Decomposition            | 178 |

|    |      | 8.3.2    | Massively Reconfigurable Computing  | 179 |

|    | 8.4  | Closing  | g Comments                          | 180 |

| A  | Pub  | olished  | Papers                              | 181 |

| В  | Boo  | ting Sc  | oftware on SpiNNaker                | 183 |

|    |      | _        | Load Files                          |     |

|    |      |          | Defining Sections in Code           |     |

|    |      |          | Linker symbols                      |     |

|    | B.2  |          | Boot-loader                         |     |

|    | B.3  |          | Images                              |     |

|    | B.4  |          | tracting APLX images                |     |

|    | B.5  |          | aker System Software                |     |

| Bi | hlio | graphy   |                                     | 193 |

|    | ع٠   | 5- ~P11J |                                     | 100 |

# List of Figures

| 1.1  | 40 years of microprocessor trend data (collated and plotted by Rupp [13]) showing the steady continuation of transistor scaling, but a levelling of |           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|      | clock frequency and single-threaded performance                                                                                                     | •         |

| 1.2  | Data cache latencies for various memory access patterns on various amounts of data (figure produced by Sutter [20]).                                |           |

| 1.3  | Two simple equations and the corresponding data-dependency graphs.                                                                                  |           |

| 1.4  | Intel Itanium instruction bundle format [21]                                                                                                        |           |

| 1.5  | Three stages of an out-of-order execution pipeline, based on Figure 4.72                                                                            |           |

|      | of Patterson and Hennessy [23].                                                                                                                     | 1         |

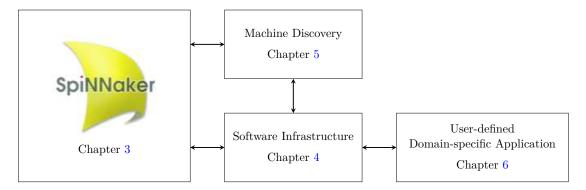

| 1.6  | High-level view of the tool-chain developed in the thesis, identifying how                                                                          |           |

|      | each chapter inter-relates.                                                                                                                         | 15        |

| 2.1  | Single-Instruction Single-Data (SISD) architecture.                                                                                                 | 18        |

| 2.2  | Single-Instruction Multiple-Data (SIMD) architecture                                                                                                | 19        |

| 2.3  | Multiple-Instruction Single-Data (MISD) architecture.                                                                                               | 20        |

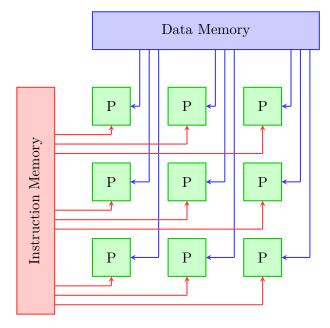

| 2.4  | Multiple-Instruction Multiple-Data (MIMD) architecture                                                                                              | 21        |

| 2.5  | Single-Program Multiple-Data (SPMD) architecture.                                                                                                   | 22        |

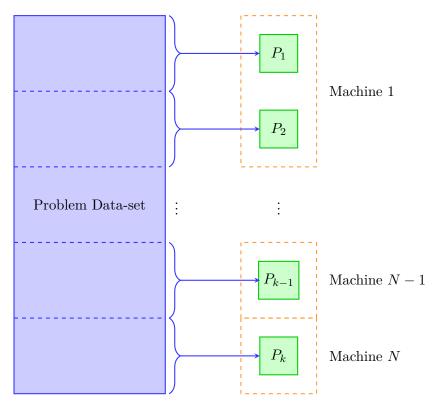

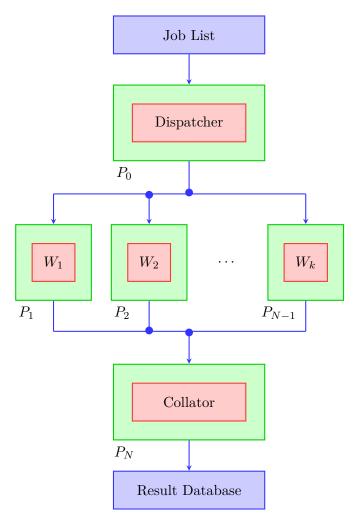

| 2.6  | Multiple-Program Multiple-Data (MPMD) job-based architecture                                                                                        | 23        |

| 2.7  | Multiple-Program Multiple-Data (MPMD) distributed architecture                                                                                      | 24        |

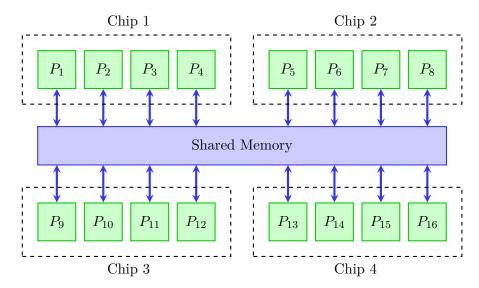

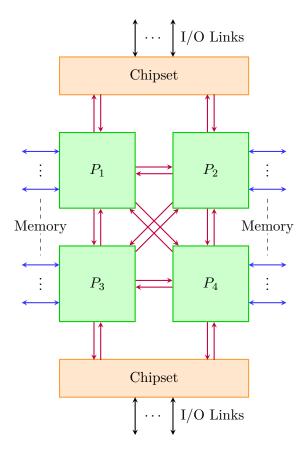

| 2.8  | Uniform Memory Access (UMA).                                                                                                                        | $2^{t}$   |

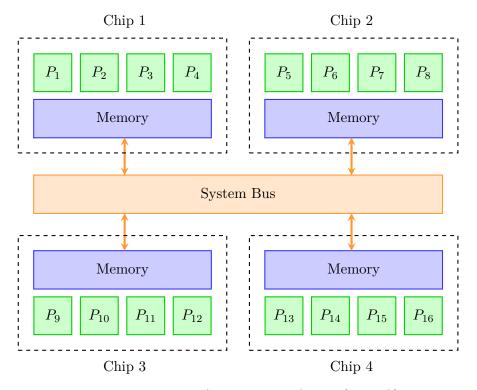

| 2.9  | Non-uniform Memory Access (NUMA)                                                                                                                    | $2^{\xi}$ |

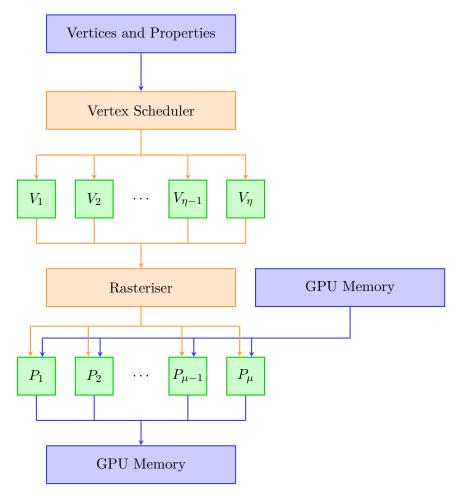

| 2.10 | Simplified block-diagram for a generic GPU (adapted from Figure 1 of Tarditi, Puri, and Oglesby [48]) with $\eta$ vertex processors and $\mu$ pixel |           |

|      | processors                                                                                                                                          | 26        |

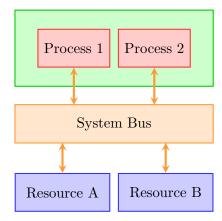

| 2.11 | Example architecture containing a single processor, running two pro-                                                                                | or        |

| 0.10 | ,                                                                                                                                                   | 27        |

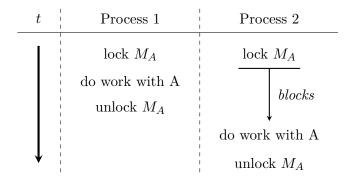

|      | 1                                                                                                                                                   | 28        |

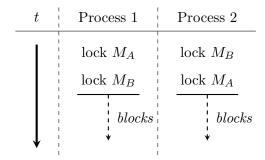

| 2.13 | Two processors using a pair of locks, $M_A$ and $M_B$ , to protect the two resources of Figure 2.11.                                                | 29        |

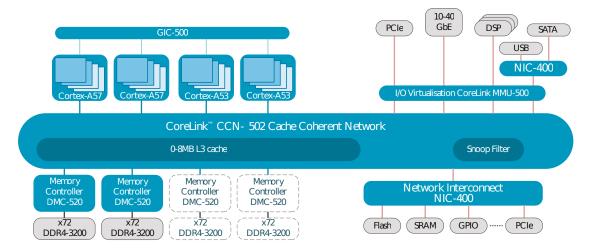

| 2.14 | ARM CoreLink <sup>TM</sup> CCN-502 system diagram showing an asymmetric multicore system (comprised of Cortex-A57 and Cortex-A53 processors) shar-  |           |

|      |                                                                                                                                                     | 32        |

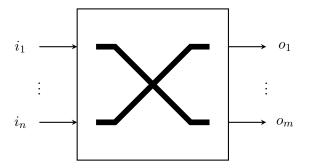

| 2.15 |                                                                                                                                                     | 33        |

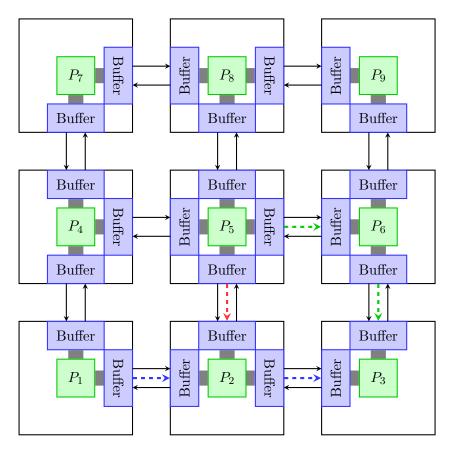

|      | Example of a network of crossbar switches with buffered I/O ports con-                                                                              |           |

|      |                                                                                                                                                     | 34        |

| 2.17 | A typical QPI use-case produced from Figure 6 of Intel Corporation [60].                                                                            |           |

|      | Memory connections are shown in blue and QPI connections are shown                                                                                  | ο.        |

|      | in purple                                                                                                                                           | 36        |

x LIST OF FIGURES

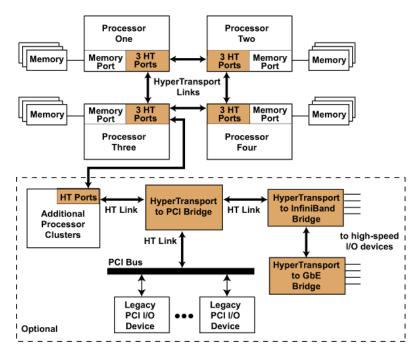

| 2.18              | An inter-processor use-case for HyperTransport showing how processors connect to each other and to system peripherals (Figure 11 of [61])                                                                        | 37  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

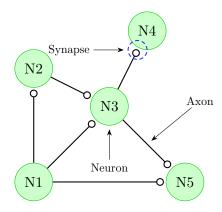

| 2 10              | A small neural network                                                                                                                                                                                           |     |

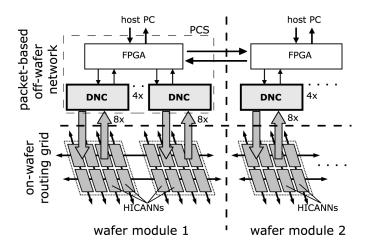

|                   | Logical structure of the BrainScaleS off-wafer hierarchical communication network (taken from [86]).                                                                                                             | 46  |

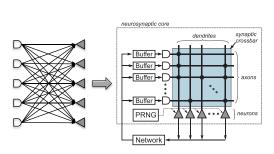

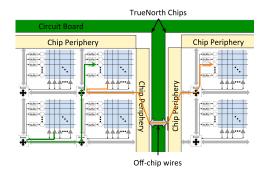

| 2.21              | Structural diagrams of the TrueNorth platform (taken from Akopyan, Sawada, Cassidy, et al. [88]).                                                                                                                |     |

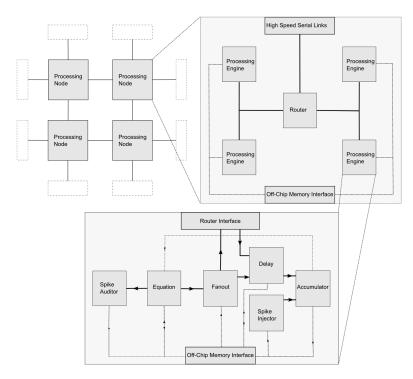

| 2.22              | BlueHive system-level diagram (taken from Moore, Fox, Marsh, et al. [89]).                                                                                                                                       |     |

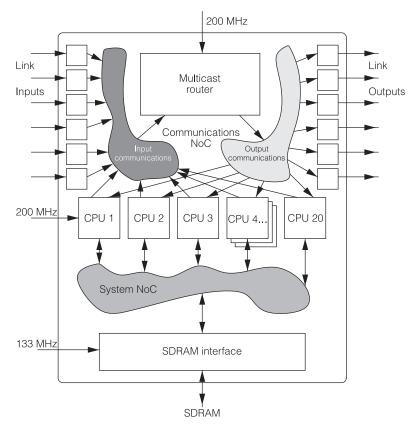

| 2.23              | SpiNNaker chip block diagram (taken from Plana, Furber, Temple, et al. [90])                                                                                                                                     | 48  |

| 3.1               | Detailed block diagram of the SpiNNaker chip (taken from the datasheet [115])                                                                                                                                    | 55  |

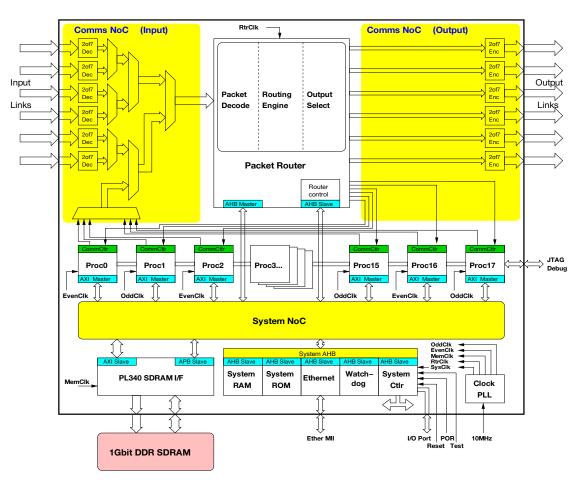

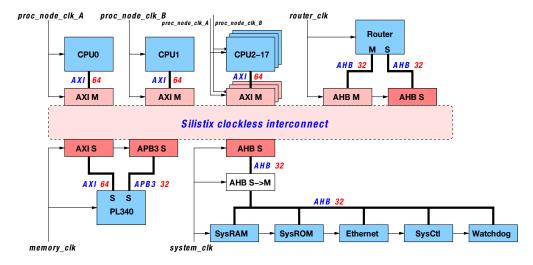

| 3.2               | Structure of the System NoC [117].                                                                                                                                                                               |     |

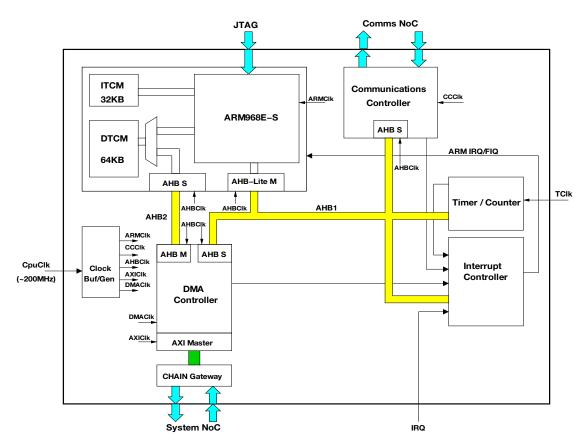

| 3.3               | Detailed block diagram of a SpiNNaker core subsystem [117]                                                                                                                                                       | 58  |

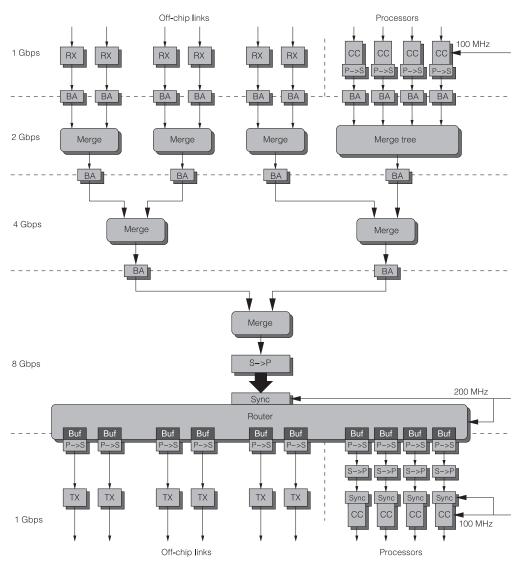

| 3.4               | Structure of the Communications NoC showing merge trees, bandwidth aggregators (BA), serial-to-parallel converters (S->P), and parallel-to-serial converters (P->S) [90]                                         |     |

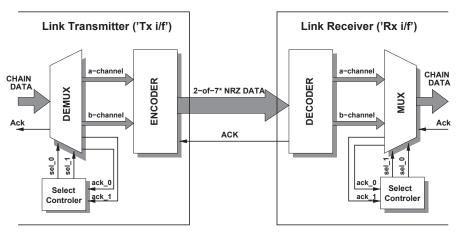

| 3.5               | SpiNNaker chip-to-chip communications [91].                                                                                                                                                                      |     |

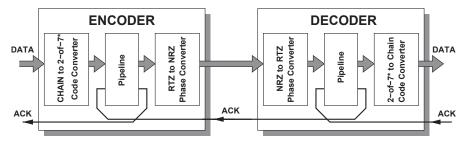

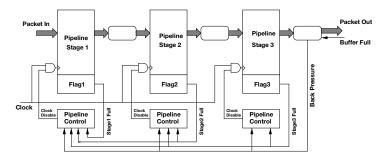

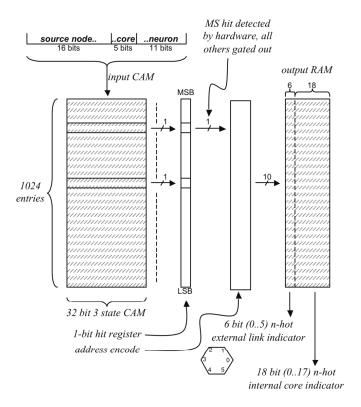

| 3.6               | SpinNaker router implementation [121]                                                                                                                                                                            | 62  |

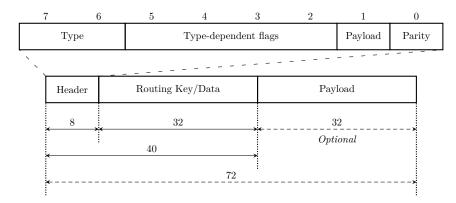

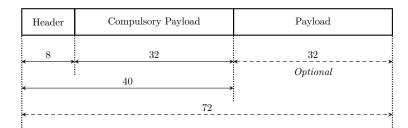

| 3.7               | SpiNNaker general packet format.                                                                                                                                                                                 |     |

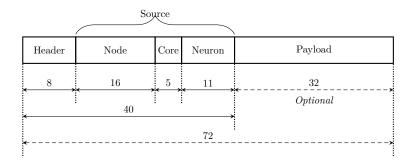

| $\frac{3.7}{3.8}$ | Nearest-neighbour (NN) packet.                                                                                                                                                                                   |     |

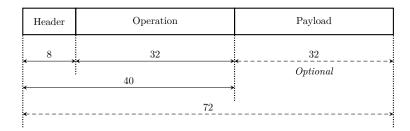

| 3.9               | Point-to-point (P2P) packet.                                                                                                                                                                                     |     |

|                   | Multicast (MC) packet.                                                                                                                                                                                           |     |

|                   | Mutlicast router content-addressable memory (CAM) [35]                                                                                                                                                           | 65  |

|                   | Fixed-route (FR) packet                                                                                                                                                                                          |     |

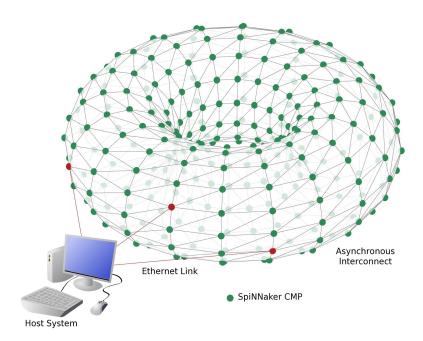

|                   | Connection diagram for a complete multi-chip SpiNNaker system showing                                                                                                                                            | 00  |

| 0.10              | external host connections.                                                                                                                                                                                       | 66  |

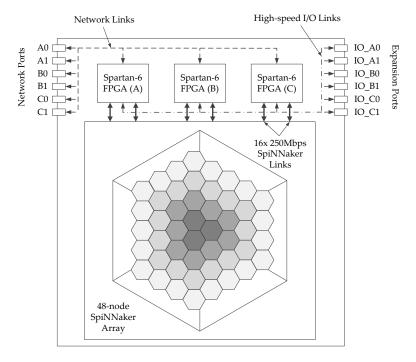

| 3 14              | Schematic view of a SpiNNaker-103 board showing inter-board connec-                                                                                                                                              | 00  |

| 0.11              | tions [2].                                                                                                                                                                                                       | 66  |

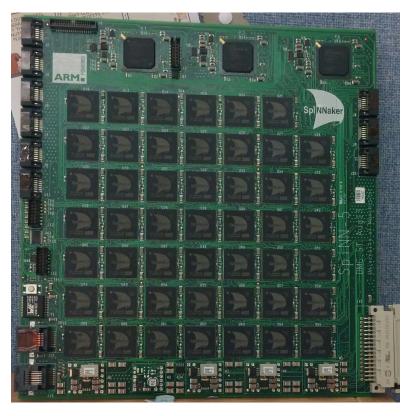

| 3.15              | A SpiNNaker-103 system, containing 48 chips and 864 processors                                                                                                                                                   | 67  |

|                   | A SpiNNaker-104 system comprised of 24 SpiNNaker-103 boards for a total of 1,152 chips and 20,736 processors.                                                                                                    |     |

| 3 17              | Connection pattern for a SpiNN-104 machine composed from 24 SpiNN-                                                                                                                                               | 00  |

| 0.1.              | 103 boards [124]                                                                                                                                                                                                 | 68  |

| 3.18              | Five SpiNNaker-105 cabinets forming the largest SpiNNaker system assembled to date. Each SpiNNaker-105 is built from five SpiNNaker-104 systems for a total of 5,760 chips and 103,680 processors. The system in |     |

|                   | this picture therefore contains 28,800 chips and 518,400 processors                                                                                                                                              | 69  |

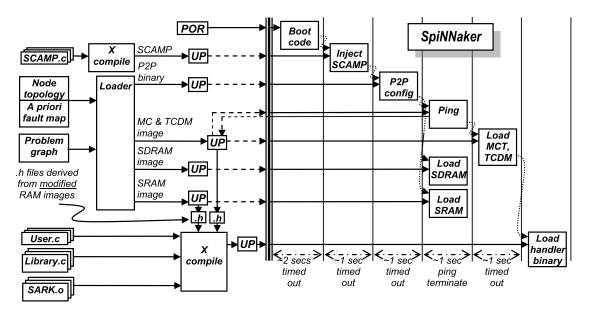

| 3.19              | Complete SpiNNaker boot sequence from power-up to starting an application [6].                                                                                                                                   | 69  |

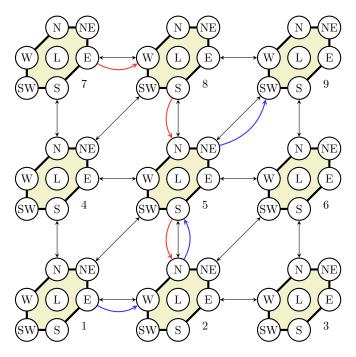

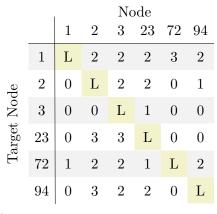

| 3.20              | Example P2P routes on a 3 × 3 SpiNNaker grid                                                                                                                                                                     | 71  |

|                   | Example P2P configuration for the system of Figure 3.20. The red and                                                                                                                                             | , _ |

| 0.41              | blue shading highlights entries relevant to the red and blue routes respec-                                                                                                                                      |     |

| 3.22              | tively. The yellow shading highlights node-local delivery Visual representation of how a biological network is mapped into a neural                                                                              | 72  |

|                   | network on SpiNNaker [35]                                                                                                                                                                                        | 75  |

LIST OF FIGURES xi

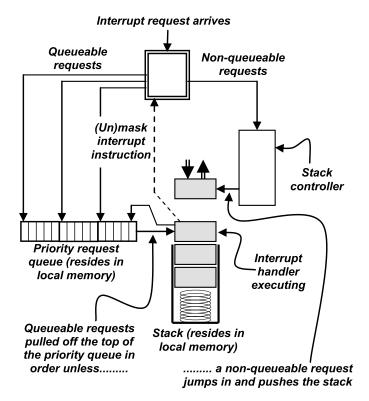

| 3.23          | Per-core interrupt handling process [6]                                                                                                          | . 76  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|

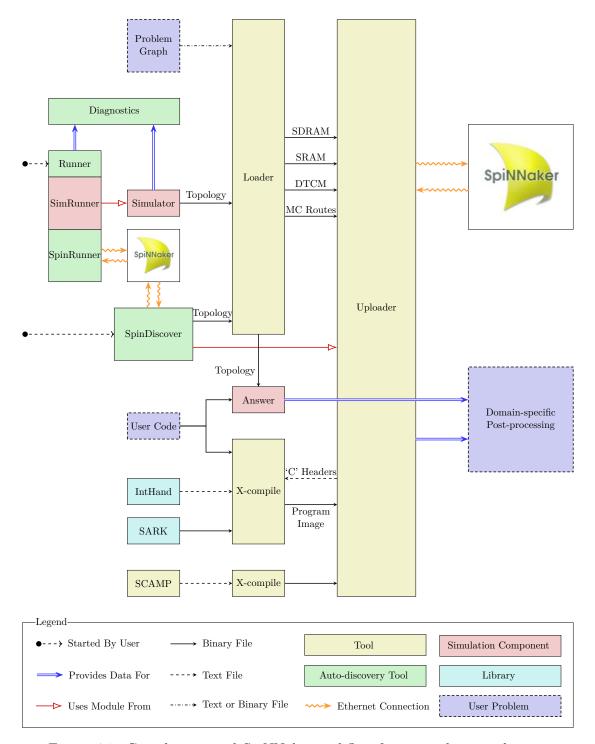

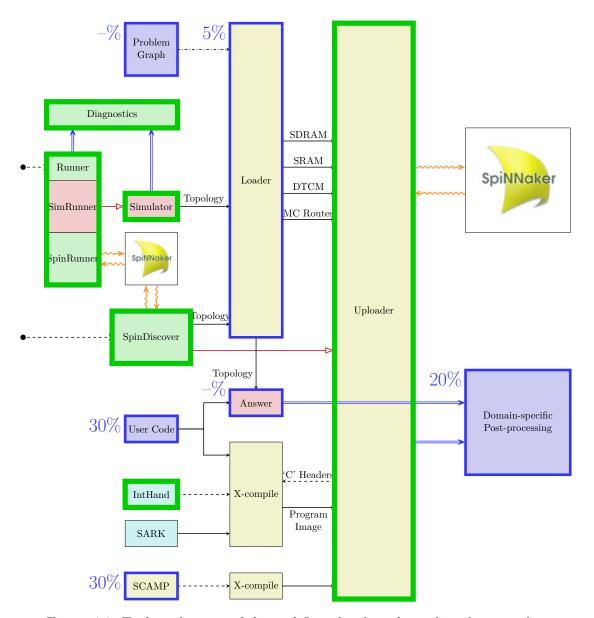

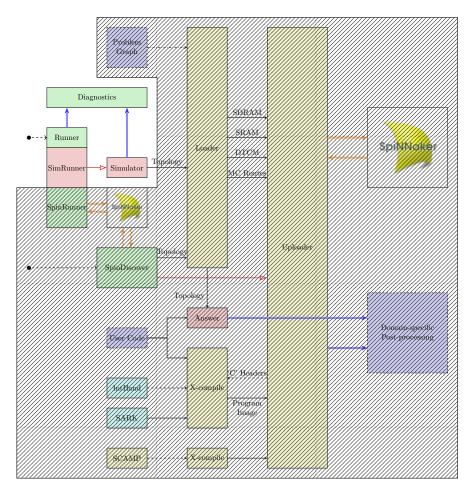

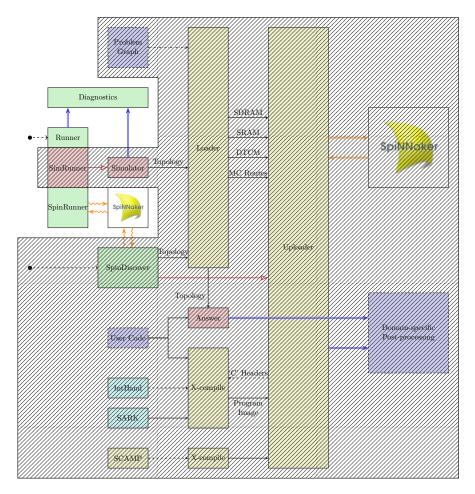

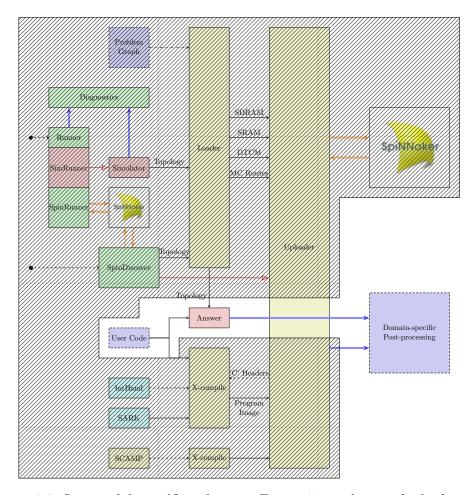

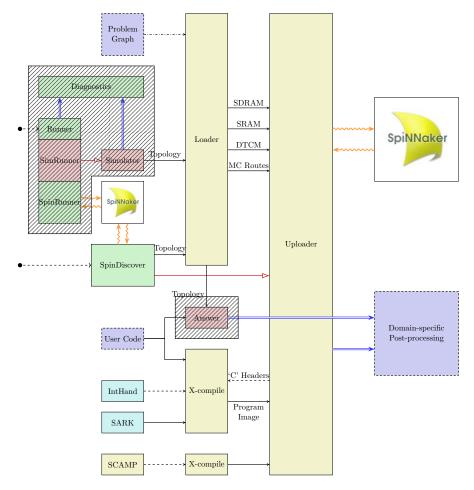

| 4.1           | Complete revised SpiNNaker tool-flow factoring the contributions of this thesis                                                                  | . 82  |

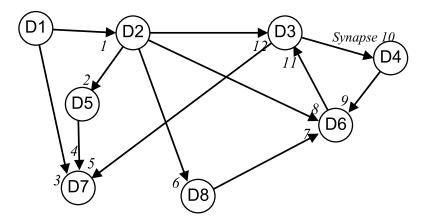

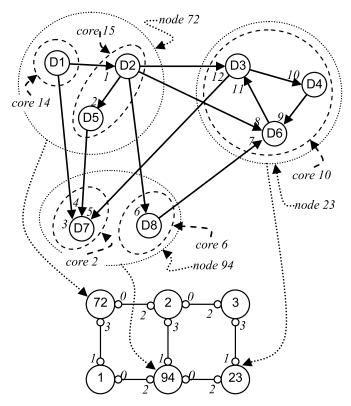

| 4.2           | Example problem graph [6].                                                                                                                       |       |

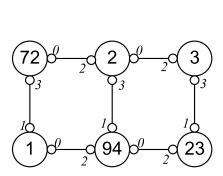

| 4.3           | Example SpiNNaker machine configuration [6]                                                                                                      |       |

| 4.4           | Mapping the example problem graph (Figure 4.2) to the example machine                                                                            | . 00  |

| 4.4           | topology (Figure 4.3a) [6]                                                                                                                       | . 85  |

| 4.5           | Data-structures for the mapping in Figure 4.4 [6].                                                                                               |       |

| 4.6           | Tools and stages of the tool-flow that have been directly created or mod-                                                                        | . 00  |

| 4.0           | ified by the work in this thesis                                                                                                                 | . 88  |

| 5.1           | Stages of the toolflow shown in Figure 4.1 required to design and simulate                                                                       | 0.4   |

|               | the behaviour of the auto-discovery algorithms.                                                                                                  |       |

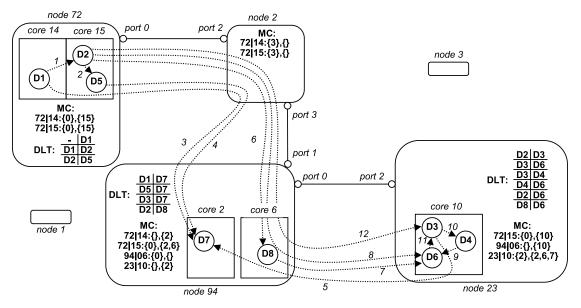

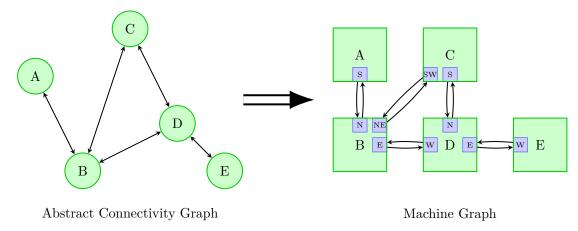

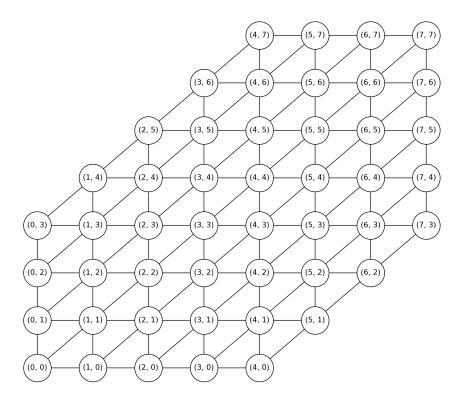

| 5.2           | Constructing a machine model from an abstract connectivity graph                                                                                 | . 95  |

| 5.3           | Abstract graph representing the connectivity of a SpiNN-103 system (Figure 3.15), showing the effect of the connectivity pattern of Figure 3.17. |       |

|               |                                                                                                                                                  |       |

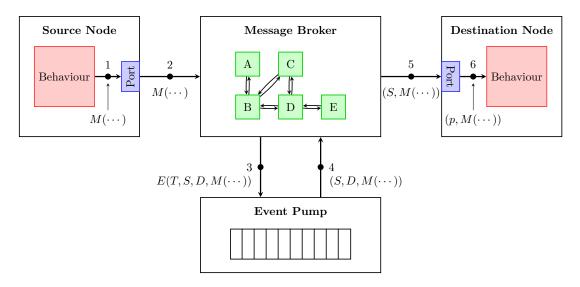

| 5.4           | Message delivery system in the simulator                                                                                                         | . 97  |

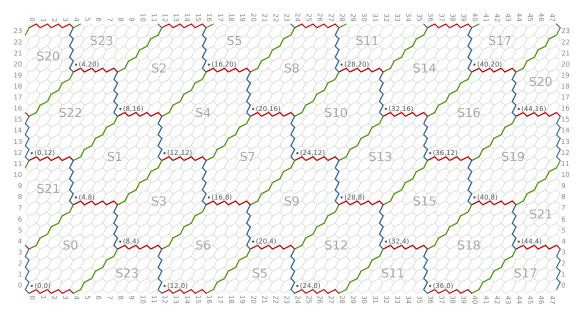

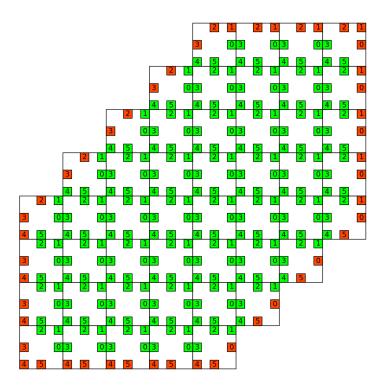

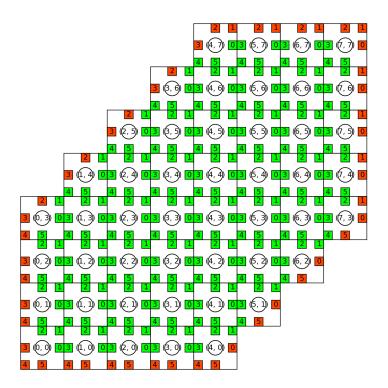

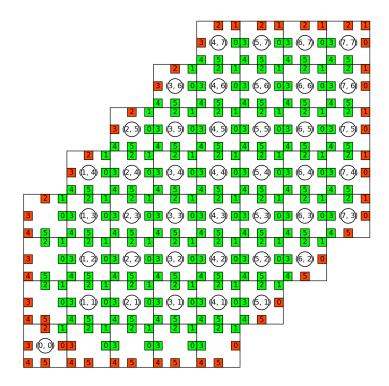

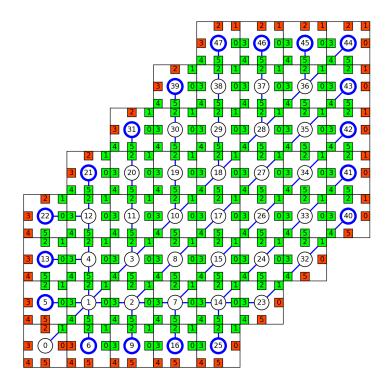

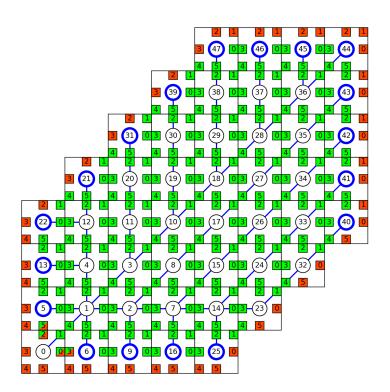

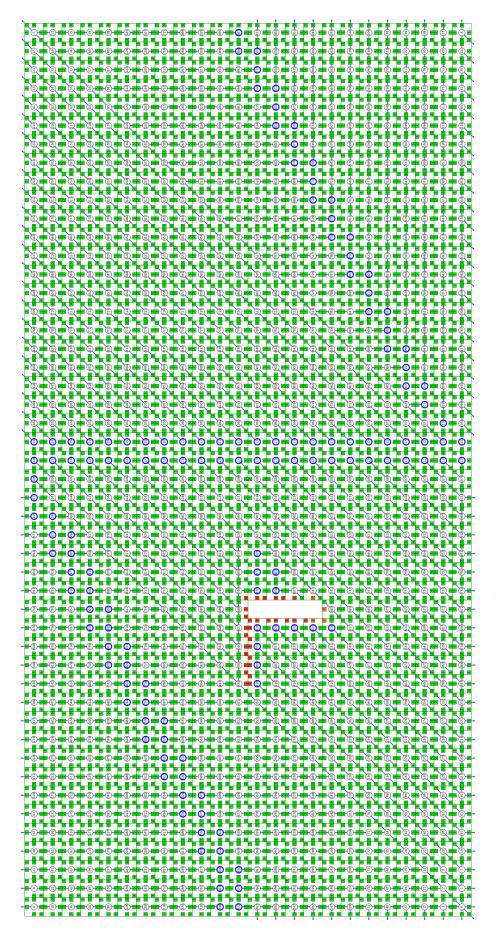

| 5.5           | Visualisation produced by the Runner infrastructure of the machine model resulting from the graph shown in Figure 5.3.                           | . 98  |

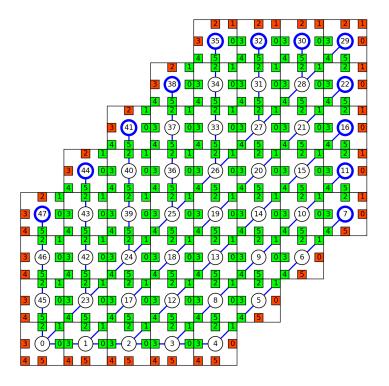

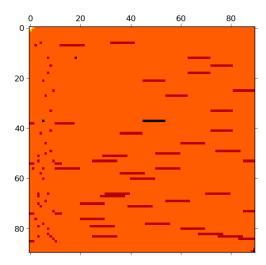

| 5.6           | Machine model state after P2P algorithm has been executed on various                                                                             |       |

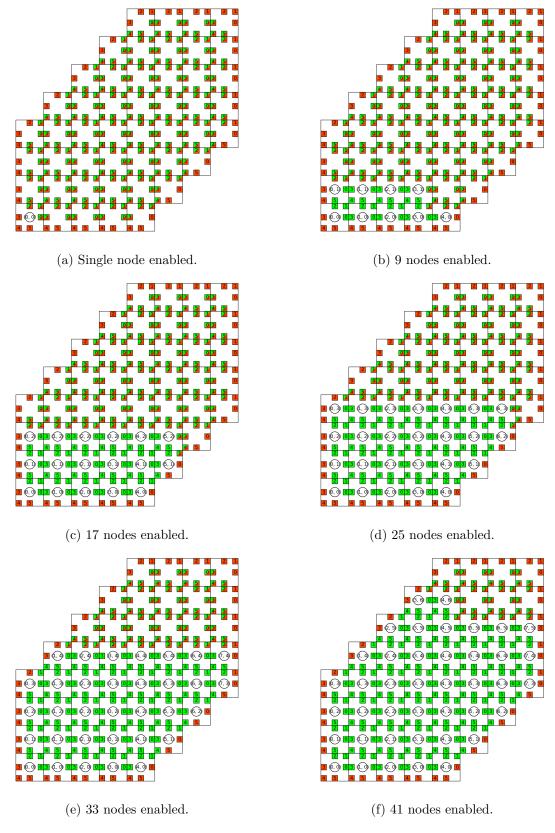

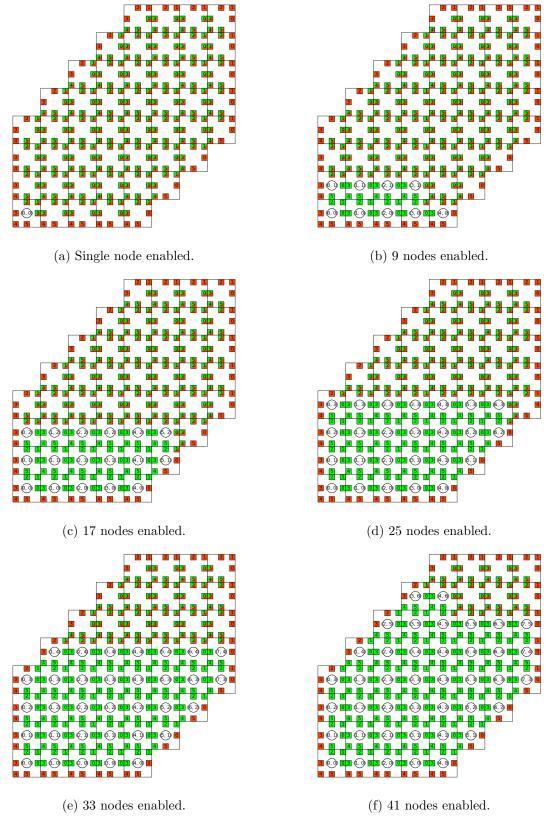

|               | fault maps limiting the number of discoverable nodes                                                                                             | . 100 |

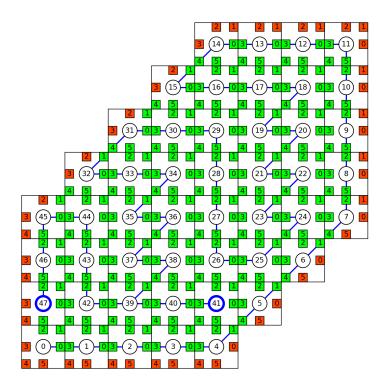

| 5.7           | Machine model state with all $48$ nodes enabled clearly showing the correct                                                                      |       |

|               | allocation of identifiers                                                                                                                        | . 101 |

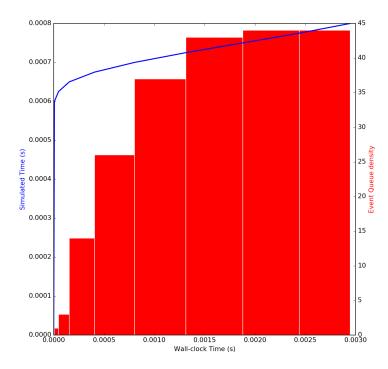

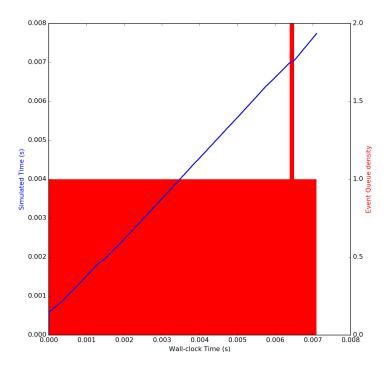

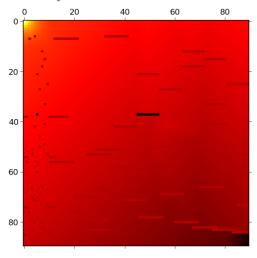

| 5.8           | Simulated time and event queue size as a function of wall-clock time for                                                                         |       |

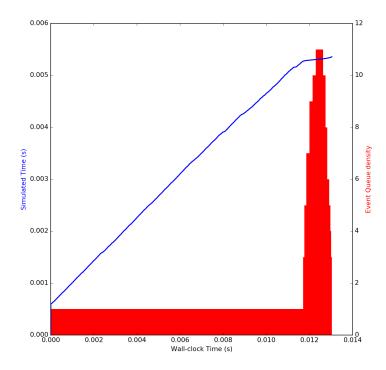

|               | the 48 node simulation run (Figure 5.7)                                                                                                          | . 102 |

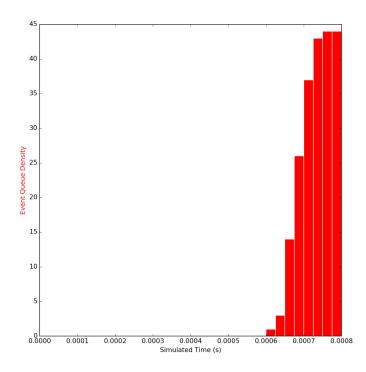

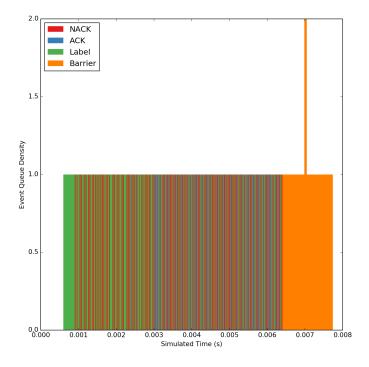

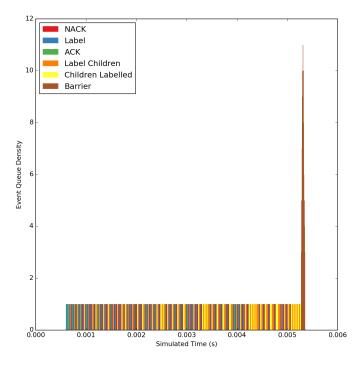

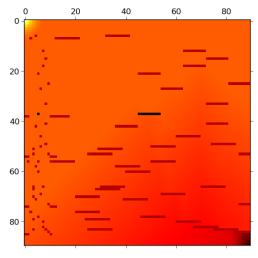

| 5.9           | Event queue size for each simulated time-step for the 48 node simulation run (Figure 5.7)                                                        | . 103 |

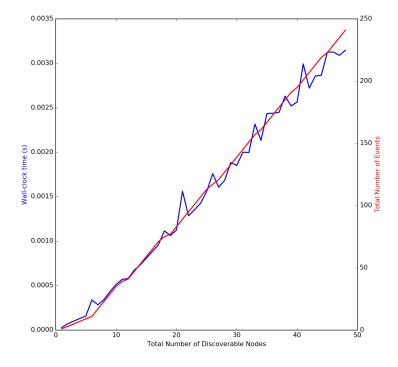

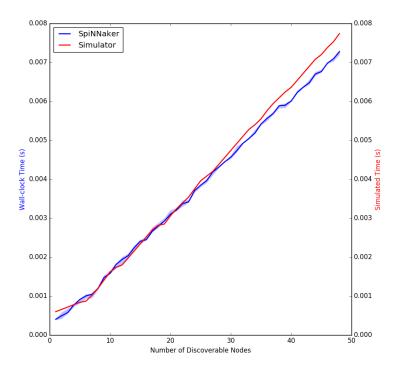

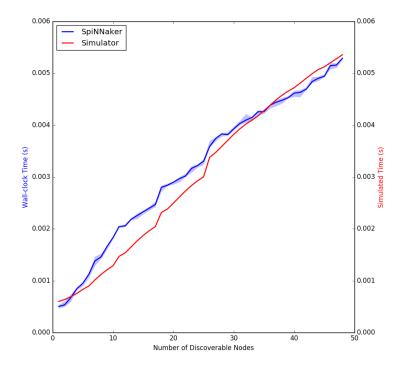

| 5.10          | Simulator wall-clock time and total number of events for increasing num-                                                                         |       |

|               | bers of enabled nodes                                                                                                                            | . 103 |

| 5.11          | Stages of the toolflow shown in Figure 4.1 required to implement and                                                                             |       |

|               | verify the auto-discovery algorithms on SpiNNaker.                                                                                               | . 104 |

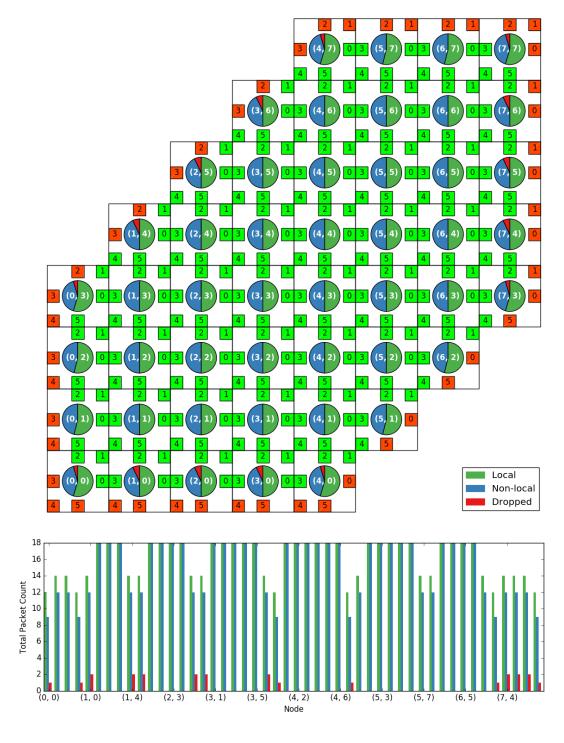

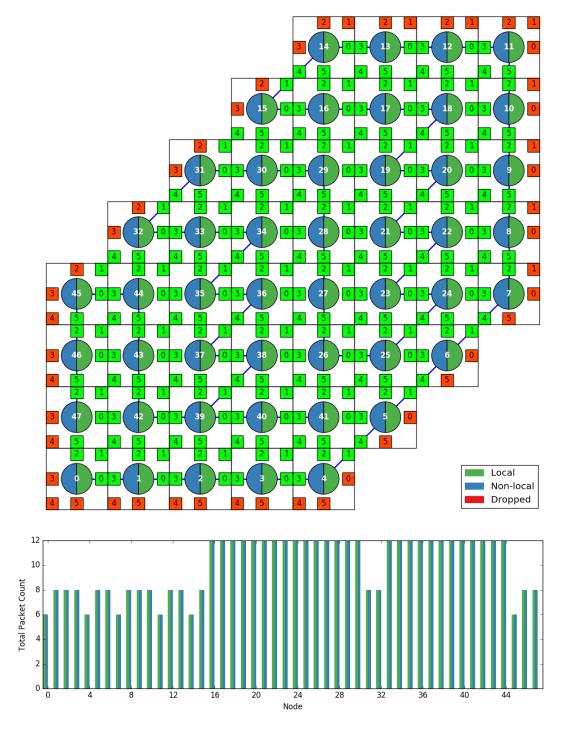

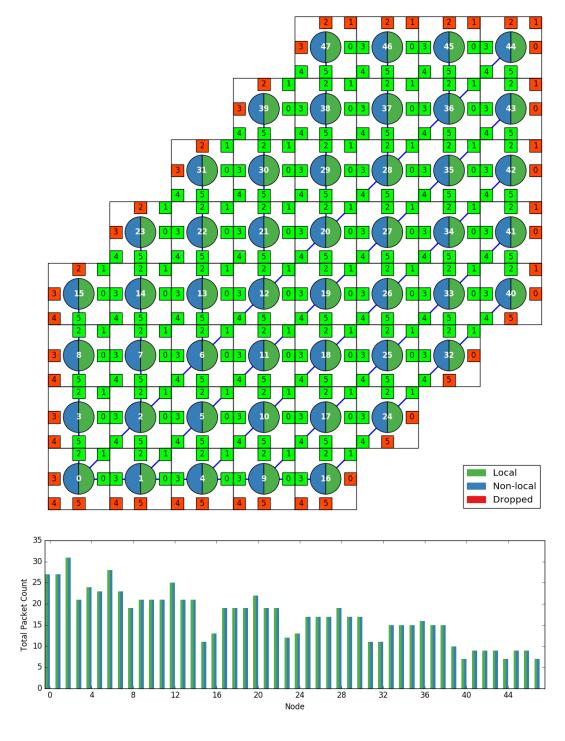

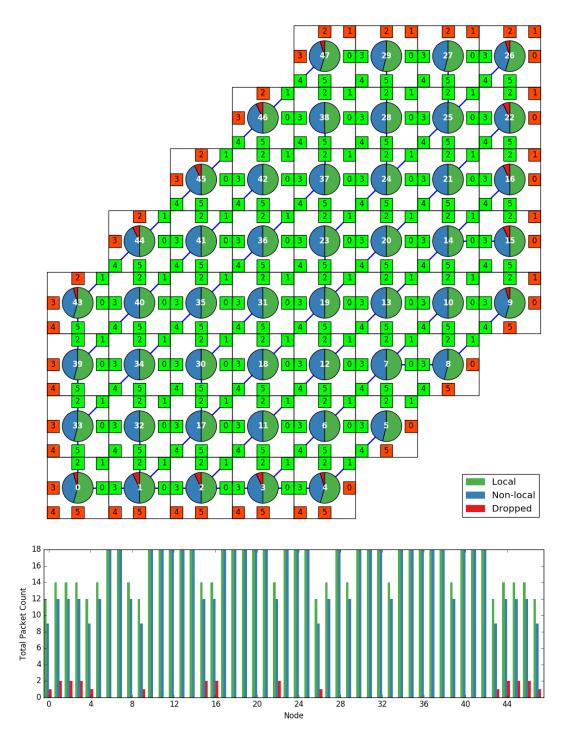

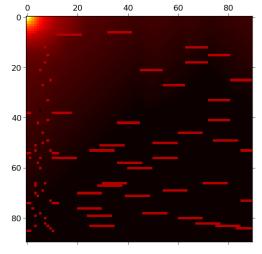

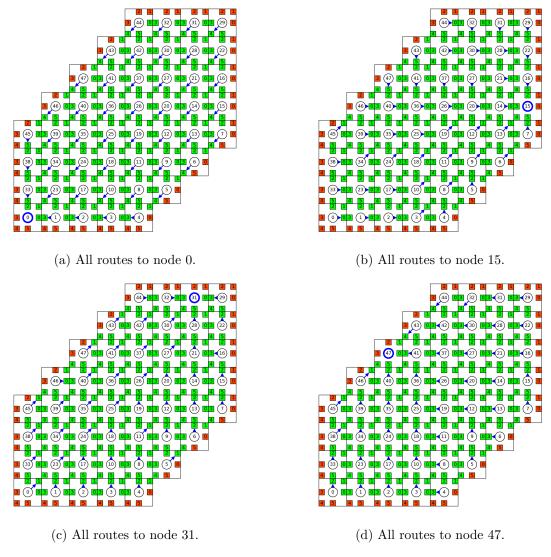

| 5.12          | Distribution of packets across a SpiNN-103 machine for the $\alpha$ -ping                                                                        | . 108 |

| 5.13          | Machine state downloaded from a SpiNN-103 machine after being subject                                                                            |       |

|               | to various fault-maps as with the simulator in Figure 5.6                                                                                        | . 110 |

| 5.14          | Distribution of packets across a SpiNN-103 machine for the P2P identifier                                                                        |       |

|               | assignment algorithm (Algorithm 5.1)                                                                                                             | . 111 |

| 5.15          | Simulation result demonstrating the potential issue with Algorithm 5.1.                                                                          | . 113 |

| 5.16          | Result from SpiNNaker implementation demonstrating the same potential $$                                                                         |       |

|               | issue with Algorithm 5.1 shown in Figure 5.15                                                                                                    | . 114 |

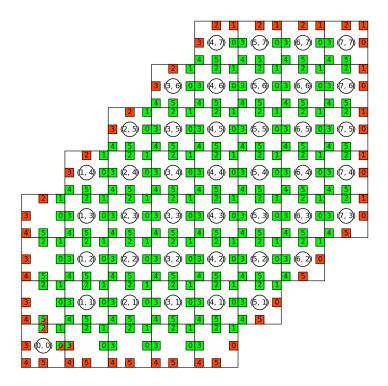

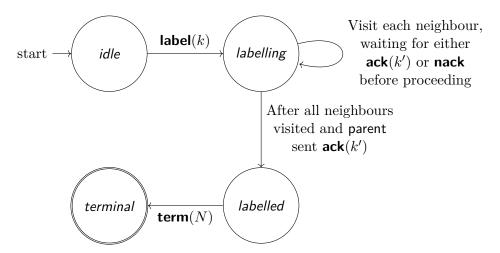

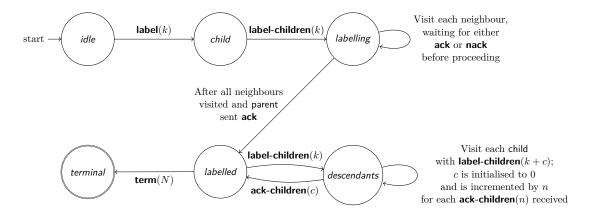

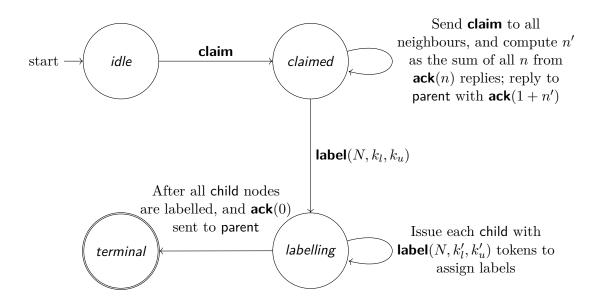

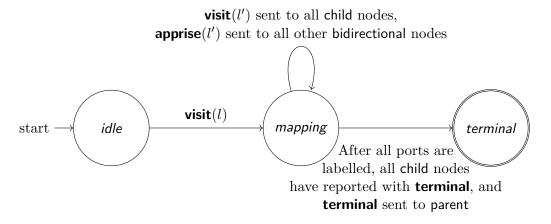

| 5.17          | State transition diagram for the depth-first discovery algorithm                                                                                 | . 115 |

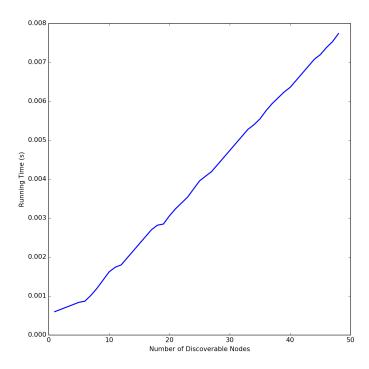

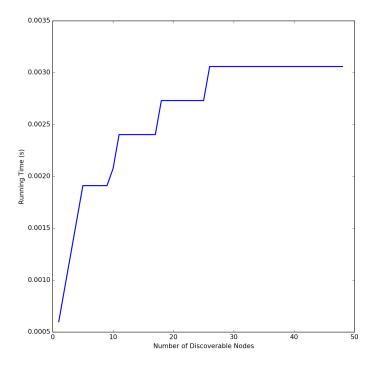

| 5.18          | Scaling of the depth-first discovery algorithm with machine size under simulation.                                                               | . 116 |

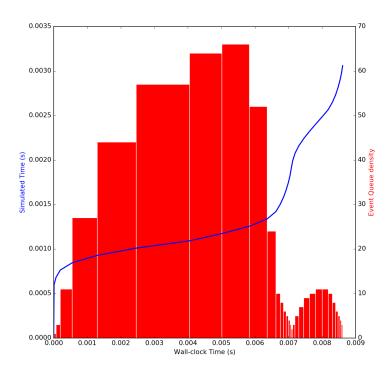

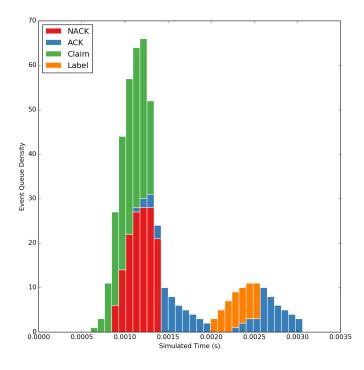

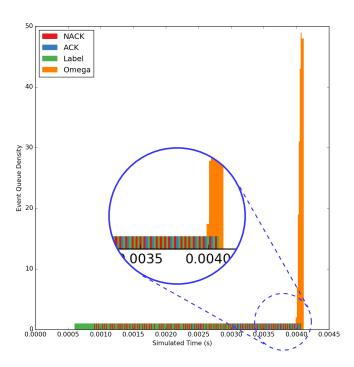

| 5 19          | Simulated time advancement and event queue density as a function of                                                                              |       |

| 0.10          | wall-clock time for the 48 node depth-first simulation run                                                                                       | . 117 |

| 5.20          | Distribution of event types (i.e., tokens) throughout the 48 node depth-                                                                         |       |

| J. <b>2</b> 0 | first simulation run.                                                                                                                            | . 117 |

|               |                                                                                                                                                  |       |

xii LIST OF FIGURES

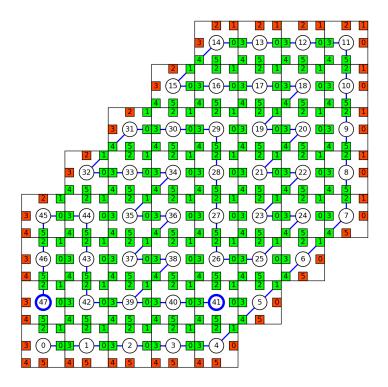

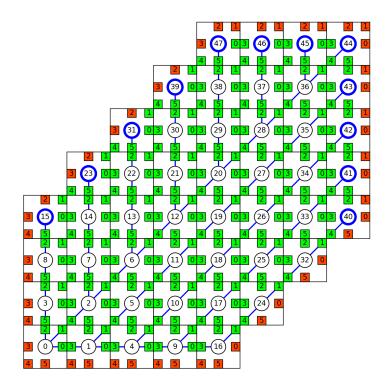

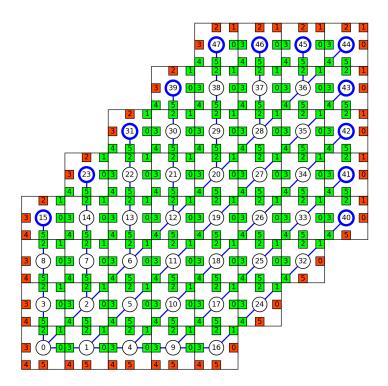

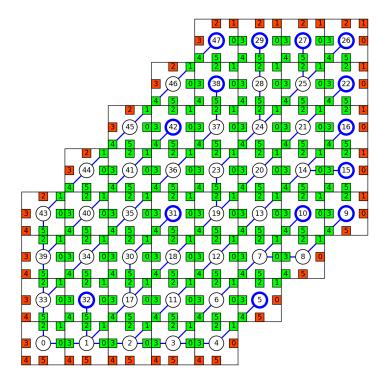

| 5.21 | Discovered machine model state after the 48 node simulation run, showing the embedded tree and the assigned node labels                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 5.22 | Resilience of the depth-first discovery simulation run against the same                                                                      |

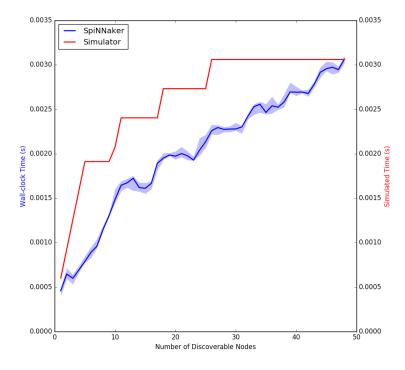

|      | fault pattern as in Figures 5.15 and 5.16                                                                                                    |

| 5.23 | Comparison of the running time predicted by the simulator and the mea-                                                                       |

|      | sured wall-clock time of 10 consecutive runs on SpiNN-103 hardware 120                                                                       |

| 5.24 | Packet distribution across the SpiNN-103 hardware for the 48 node run                                                                        |

|      | of the depth-first discovery run                                                                                                             |

| 5.25 | Discovered machine topology from the 48 node run on SpiNN-103 hardware                                                                       |

| 5.26 | Resilience against the fault pattern of a 48 node run on SpiNN-103 hard-                                                                     |

|      | ware                                                                                                                                         |

| 5.27 | State transition diagram for the lock-step breadth-first discovery algo-                                                                     |

|      | rithm                                                                                                                                        |

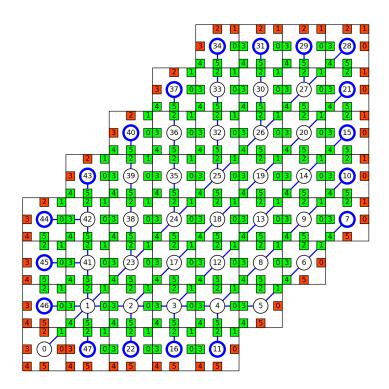

| 5.28 | Scaling of the breadth-first discovery algorithm with machine size under simulation                                                          |

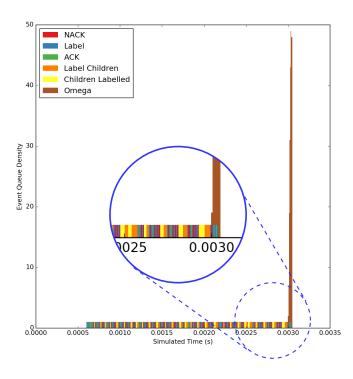

| 5.29 | Simulated time advancement and event queue density as a function of                                                                          |

|      | wall-clock time for the 48 node breadth-first simulation run. $\dots \dots 126$                                                              |

| 5.30 | Distribution of event types (i.e., tokens) throughout the 48 node breadth-                                                                   |

|      | first simulation run                                                                                                                         |

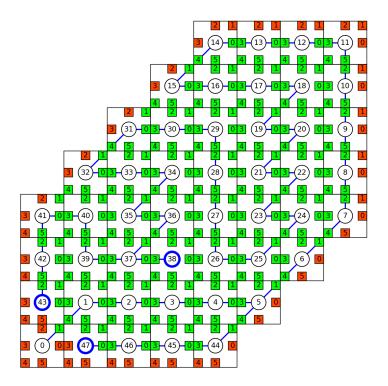

| 5.31 | Discovered machine model state after the 48 node breadth-first simulation                                                                    |

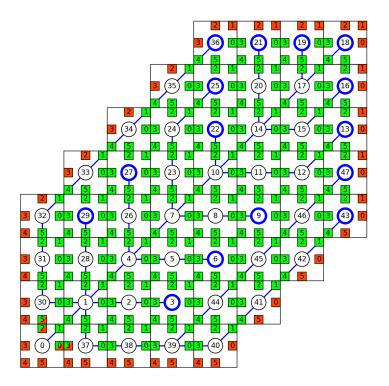

|      | run, showing the embedded tree and the assigned node labels 127                                                                              |

| 5.32 | Resilience of the breadth-first discovery simulation run against the same                                                                    |

| F 99 | fault pattern as in Figures 5.15 and 5.16                                                                                                    |

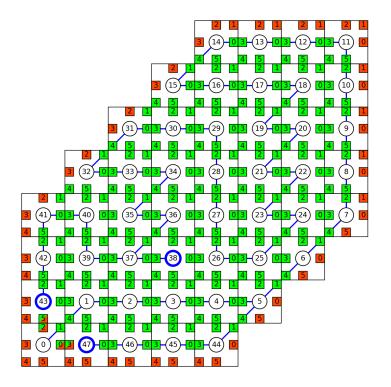

| 0.00 | Comparison of the running times predicted by the simulator and the measured wall-clock time of 10 consecutive runs on SpiNN-103 hardware for |

|      | the breadth-first discovery algorithm                                                                                                        |

| 5.34 | Packet distribution across the SpiNN-103 hardware for the 48 node run                                                                        |

| 0.0- | of the breadth-first discovery run                                                                                                           |

| 5.35 | Discovered machine topology from the 48 node breadth-first run on SpiNN-                                                                     |

|      | 103 hardware                                                                                                                                 |

| 5.36 | Resilience against the fault pattern of a 48 node breadth-first run on                                                                       |

|      | SpiNN-103 hardware                                                                                                                           |

|      | State transition diagram for the parallel breadth-first discovery algorithm. 132                                                             |

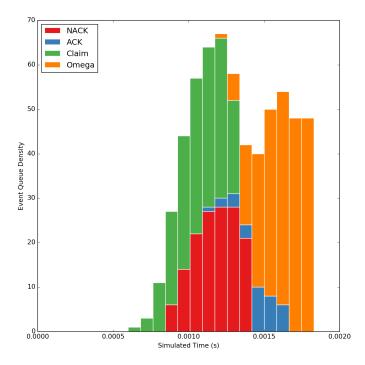

| 5.38 | Scaling of the parallel breadth-first discovery algorithm with machine size under simulation                                                 |

| 5.39 | Simulated time advancement and event queue density as a function of                                                                          |

|      | wall-clock time for the 48 node parallel breadth-first simulation run 134                                                                    |

| 5.40 | Distribution of event types (i.e., tokens) throughout the 48 node parallel                                                                   |

|      | breadth-first simulation run                                                                                                                 |

| 5.41 | Discovered machine model state after the 48 node parallel breadth-first                                                                      |

|      | simulation run, showing the embedded tree and the assigned node labels. 135                                                                  |

| 5.42 | Resilience of the parallel breadth-first discovery simulation run against                                                                    |

| F 40 | the fault pattern                                                                                                                            |

| 5.43 | Comparison of the running time predicted by the simulator and the measured wall-clock time of 10 consecutive runs on SpiNN-103 hardware for  |

|      | the parallel breadth-first discovery algorithm                                                                                               |

|      | the paramet stead the tibe abovery disortening                                                                                               |

LIST OF FIGURES xiii

| 5.44       | Packet distribution across the SpiNN-103 hardware for the 48 node run of the parallel breadth-first discovery run.                        | . 137        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5.45       | Discovered machine topology from the 48 node parallel breadth-first run on SpiNN-103 hardware.                                            | 138          |

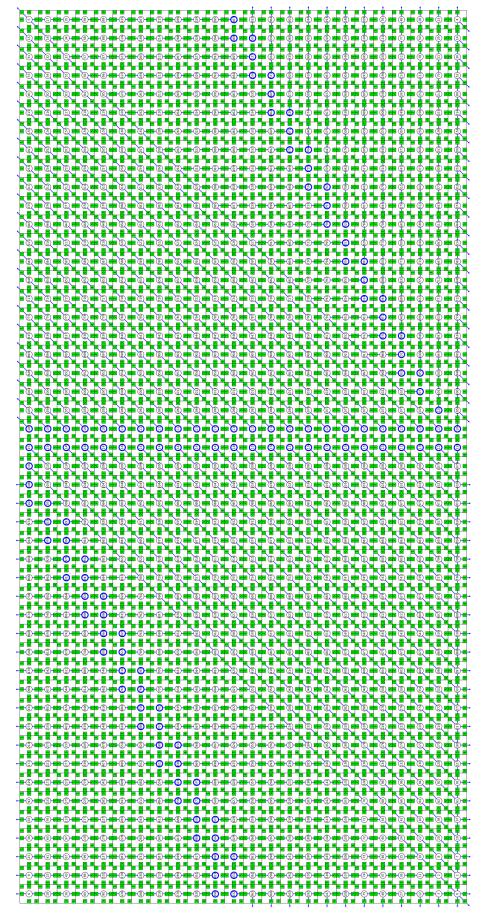

| 5.46       | Resilience against the fault pattern of a 48 node parallel breadth-first run on SpiNN-103 hardware.                                       |              |

| 5.47       | Complete survey of the SpiNN-104 hardware shown in Figure 3.16 using                                                                      |              |

| 5.48       | the lock-step breadth-first algorithm.  Survey of the same SpiNN-104 hardware but with a single inter-board                               |              |

| 5.49       | connection unplugged.  Depth-first algorithm designed in section 5.5.1 subject to an <b>omega</b> token injected at 4ms simulated time.   |              |

| 5.50       | Breadth-first algorithm designed in section 5.5.2 subject to an <b>omega</b> token injection at 3ms simulated time.                       |              |

| 5.51       | Parallel breadth-first algorithm designed in section 5.5.3 subject to an <b>omega</b> token injection after about 1ms simulated time.     |              |

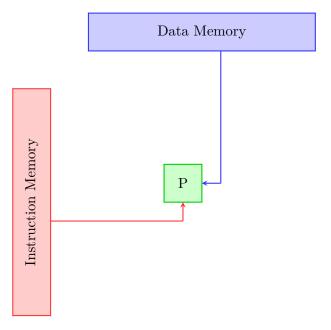

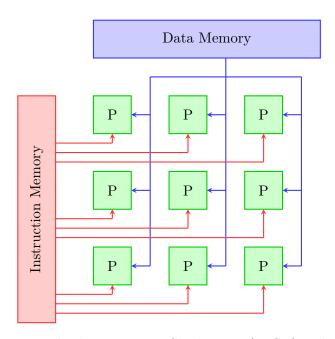

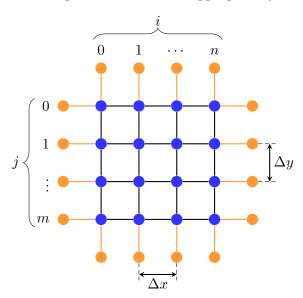

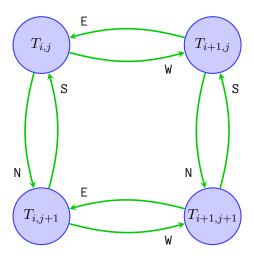

| 6.1        | Discretised problem grid showing problem nodes in blue and clamp nodes in orange.                                                         | 1.10         |

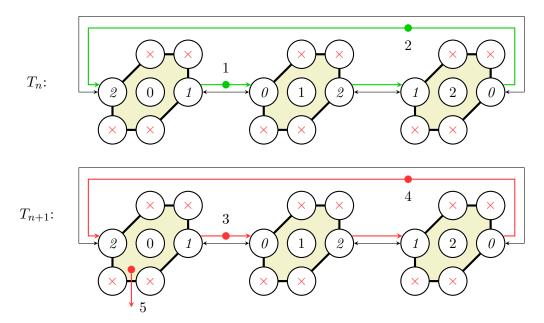

| 6.2        | in orange                                                                                                                                 | . 148<br>150 |

| 6.3        | Stages of the toolflow shown in Figure 4.1 used to verify the function of the heat diffusion application.                                 |              |

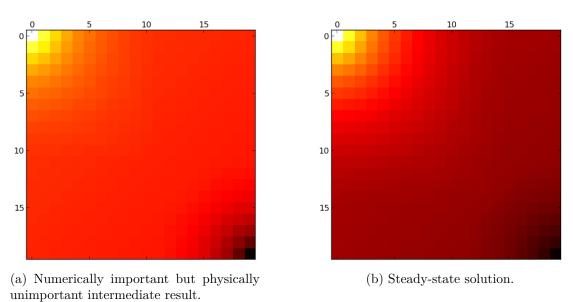

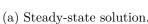

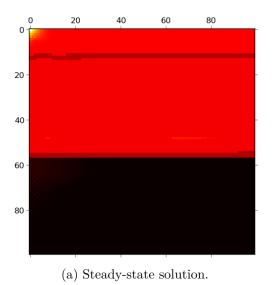

| 6.4        | Answer simulation result from a $20 \times 20$ grid.                                                                                      |              |

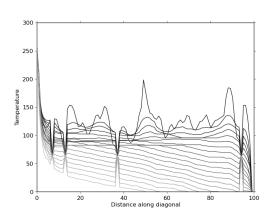

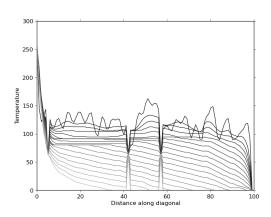

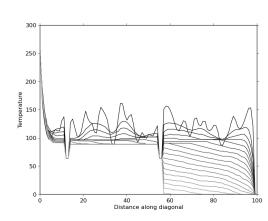

| 6.5        | Answer simulation result from a $90 \times 90$ grid with 5% of the simulated cores disabled.                                              |              |

| 6.6        | Stages of the toolflow shown in Figure 4.1 used to execute the heat diffusion application on SpiNNaker and collect the results            |              |

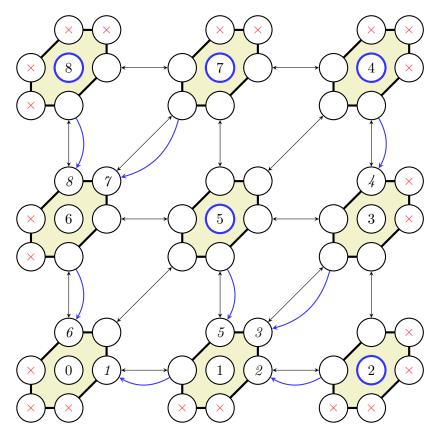

| 6.7<br>6.8 | State transition diagram for the P2P table construction algorithm Select slices through the P2P tables of all nodes in the SpiNN-103 sys- |              |

|            | tem. Each node shows the port it uses to communicate with the node highlighted with the thick blue circle.                                | . 157        |

| 6.9        | A $3 \times 3$ SpiNNaker mesh labelled by the parallel breadth-first discovery algorithm showing which neighbour identifiers are known    | . 158        |

| 6.10       | State transition diagram for the continuity algorithm                                                                                     |              |

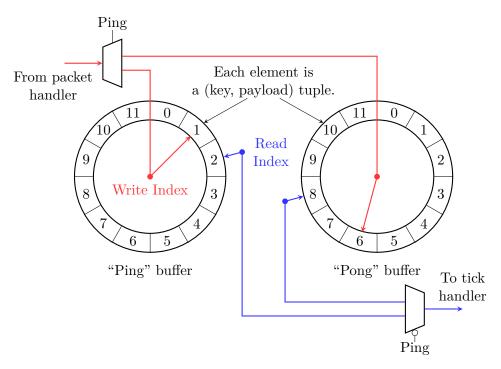

|            | Visual representation of a 12-element "ping-pong" buffer                                                                                  |              |

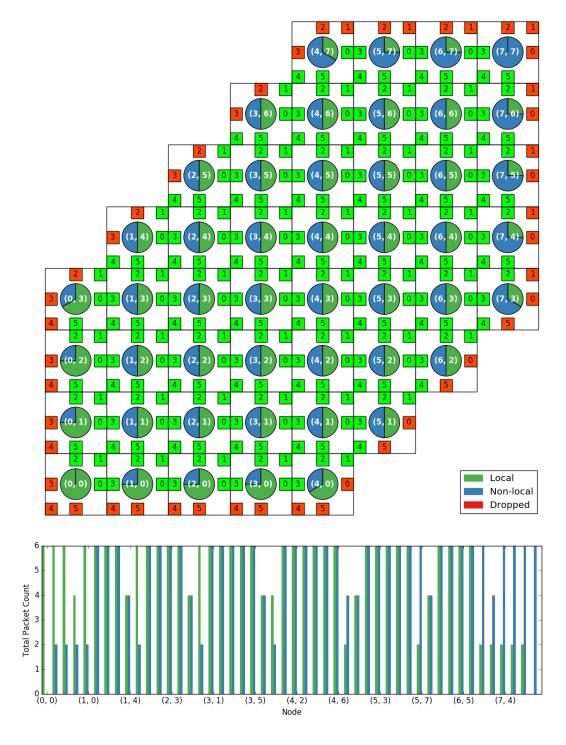

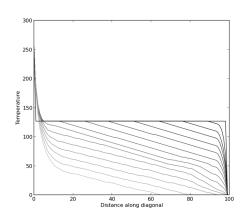

|            | SpiNNaker implementation results without any faults introduced                                                                            |              |

|            | SpiNNaker implementation results with 5% of problem devices disabled.                                                                     |              |

|            | SpiNNaker implementation results with 5% of cores disabled                                                                                |              |

|            | SpiNNaker implementation results with 5% of nodes disabled                                                                                |              |

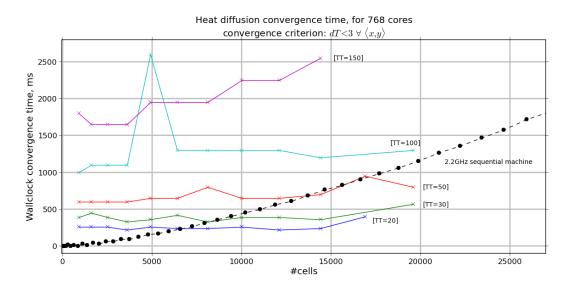

|            | Comparison of application run-times with various timer tick periods on a SpiNN-103 against a conventional serial desktop machine          |              |

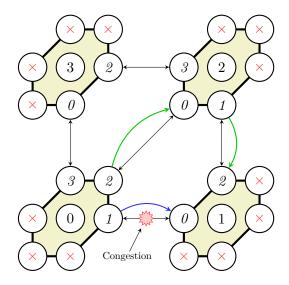

| 7.1        | Packet phase prevents packets from flowing around the network indefi-                                                                     |              |

| <b>7</b> 0 | nitely.                                                                                                                                   |              |

| 7.2        | Emergency routing around a heavily congested link                                                                                         | . 170        |

### List of Tables

| 1.1 | chitecture [21]. M-units primarily handle memory operations, I-units handle integer operations, and X-units handle extended length instructions of the form L+X. |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Flynn's computer organisation taxonomies                                                                                                                         |

| 2.2 | Cache contents for two processors demonstrating the need for cache coherence (reproduced from Figure 5.35 of Patterson and Hennessy [23]).                       |

|     | 30                                                                                                                                                               |

| 2.3 | Comparison of selected neuromorphic hardware platforms                                                                                                           |

| 3.1 | System memory map for each SpiNNaker chip [35]. Rows that are shaded indicate core-local resources, while the reset are node-local 57                            |

| B.1 | Description of the linker symbol attribute parts                                                                                                                 |

| B.2 | Boot commands and their operands as used by the Ethernet boot 188                                                                                                |

| В.3 | APLX commands and associated operands for the APLX table 188                                                                                                     |

| B.4 | Description of the APLX commands                                                                                                                                 |

# List of Listings

| 2.1 | Reading a file using the asynchronous API provided by Node.js 39                    |

|-----|-------------------------------------------------------------------------------------|

| 2.2 | Computing the sum of a set of numbers using a C++ worker thread. $$ 40              |

| 2.3 | Computing the sum of a set of numbers using a C++ packaged task. $$ 41              |

| 2.4 | Using OpenMP to unroll a sequential loop into multiple threads 42                   |

| 3.1 | Pseudo-code for a neuron update [129]                                               |

| B.1 | Sample scatter load file placing some_object.o in SECTION1 183                      |

| B.2 | Specifying a memory region to hold the heap memory                                  |

| B.3 | Mapping 'C' functions and variables to specific scatter load regions. $\dots$ . 185 |

| B.4 | Dividing source code into sections using the $\#pragma$ directive 185               |

| B.5 | Accessing the linker symbols from within 'C' and C++                                |

| B.6 | Accessing the linker symbols from within ARM Assembly 186                           |

| B.7 | APLX table construction in ARM Assembly                                             |

| B.8 | Scatter load file to appropriately construct an APLX image 190                      |

| B.9 | Scatter load file for applications linking against SARK 191                         |

#### Declaration of Authorship

I, Kier J. Dugan , declare that the thesis entitled *Non-Neural Computing on the SpiN-Naker Neuromorphic Computer* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: Brown, Mills, Reeve, et al. (2013) [1], Dugan, Brown, Reeve, et al. (2013) [2], Dugan, Reeve, and Brown (2013) [3], Dugan, Reeve, Brown, et al. (2014) [4], Brown, Mills, Dugan, et al. (2014) [5], Brown, Furber, Reeve, et al. (2014) [6], and Brown, Mills, Dugan, et al. (2015) [7].

| Signed: | <br> | <br> |  |

|---------|------|------|--|

| J       |      |      |  |

|         |      |      |  |

| Date:   | <br> | <br> |  |

#### Acknowledgements

This thesis is the result of many years of hard work, strange emotions, good times (when things worked), bad times (when they did not), and varied avenues of enquiry that I could not have predicted I would wander down.

My foremost thanks are extended to my supervisor, Dr. Jeff Reeve, who first convinced me to embark on the Ph.D. journey after a particularly successful final-year MEng group project, and has since tolerated my 'impeccable' time-planning. Although he is not responsible for the supervision of my work, I would also like to thank to Prof. Andrew Brown for his advice, input, and ability to always identify the elephant in the room. Dr. Rob Mills and I collaborated on several papers on work included in this thesis, and his advice and impromptu mini-lectures on complexity theory helped me get to grips with the massive scale of a machine as large as SpiNNaker. Prof. John Chad helped me appreciate just how similar neural systems and digital systems are, compelling me to ask, perhaps, a few too many questions.

Being a collaborative project, SpiNNaker presented many opportunities to discuss ideas with members of the teams based at the University of Manchester and at the University of Cambridge. I would like to thank Prof. Steve Furber, Dr. Steve Temple, and Dr. Luis Plana from the University of Manchester for their help with and advice on using the SpNNaker platform. I must also thank Prof. Simon Moore, Dr. Theo Markettos, Dr. Paul Fox, and Steve Marsh from the University of Cambridge, whose conversations led down interesting roads, improving my understanding of wherever it was we ended up.

Finally, I would like to thank my parents for putting up with me for the past *mumble* years, and my friends for also putting up with me. Especially whilst I have been working on my Ph.D.; they were amongst the unfortunate few who asked me how I was feeling.

### Acronyms and Abbreviations

AER Address-Event Representation

AHB Advanced High-performance Bus

API Application Programming Interface

CAM Content-Addressable Memory

CMP Chip Multi-Processor CPU Central Processing Unit

DDR Double Data-Rate

DI Delay Insensitive

DLT Device Look-up Table

EOP End-of-Packet

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FR Fixed Route

GPGPU General-Purpose GPU

GPU Graphical Processing Unit

HDL Hardware Description Language

IP Internet Protocol

IPC Inter-Process Communication

IRQ Interrupt Request

ITRS International Technology Roadmap for Semiconductors

LEMS Low-Entropy Model Specification

LIF Leaky Integrate-and-Fire

MC Multicast

MCT Multicast Table

MIMD Multiple-Instruction Multiple-Data MISD Multiple-Instruction Single-Data

MPI Message-Passing Interface

MPMD Multiple-Program Multiple-Data

NEST Neural Simulation Tool

NN Nearest Neighbour

NoC Network-on-Chip

NRZ Non-Return-to-Zero

NUMA Non-Uniform Memory Architecture

OOP Object-Oriented Programming

P2P Point-to-Point

POR Power-On Reset

POST Power-On Self-Test

RAID Redundant Array of Independent Disks

RAM Random-Access Memory ROM Read-Only Memory

RTL Register Transfer Language RTOS Real-Time Operating System

RTZ Return-To-Zero

SARK SpiNNaker Application Run-time Kernel

SCAMP SpiNNaker Command And Monitoring Program

SCP SpiNNaker Command Protocol SDP SpiNNaker Datagram Protocol

SDRAM Synchronous Dynamic Random Access Memory

SIMD Single-Instruction Multiple-Data SISD Single-Instruction Single-Data

SpiNNaker Spiking Neural-Network Architecture

SPMD Single-Program Multiple-Data

SRAM Static Random Access Memory

STDP Spike Timing-Dependent Plasticity

TCDM / DTCM Tightly-Coupled Data Memory

TCIM / ITCM Tightly-Coupled Instruction Memory

TCM Tightly-Coupled Memory

TCP Transmission Control Protocol

UDP User Datagram Protocol

UMA Uniform Memory Architecture

VLIW Very Long Instruction Word

WFI Wait For Interrupt

XML eXtensible Mark-up Language

### Chapter 1

### Introduction

For the past 50 years, Gordon Moore's 1965 prediction [8] has driven a rapid advance in electronic integrated circuit fabrication technology. Computers have seen a similarly rapid increase in capability because smaller transistors directly lead to an increase in clock speed. With greater clock speed and the ability to fit larger and larger numbers of transistors into a single die, processors were not only able to perform more operations per second, but also able to perform more complex operations.

Despite progress initially slowing ten years after the original prediction [9], planar transistor scaling remains in effect and has led to truly amazing feats of integration such as the Xilinx Virtex7 Ultrascale containing over 20bn transistors [10] and the Oracle SPARC M7 containing over 10bn transistors [11]. Continuing the trend further by scaling transistor gate lengths below 20nm will probably require advances in non-planar fabrication technology to compensate for worsening device parasitics and increased leakage currents [12].

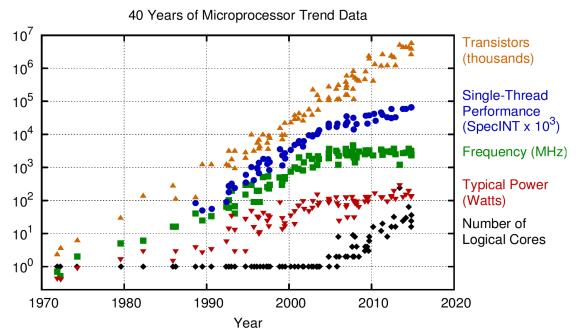

The direct correlation between smaller transistors and increased clock speed was a boon to the software industry and led to great advancements. However, as Figure 1.1 clearly shows, more recent transistor scaling has not brought with it a consequential increase in single-threaded performance. Chip manufacturers have begun to include multiple processor cores in a single package to compensate for the levelling of clock frequency. Observe from Figure 1.1 that frequency scaling slowed around the turn of the millennium, and that the number of cores began increasing around five years afterwards. This shift in system architecture requires new ways of thinking about software which focus on concurrent execution rather than conventional single-threaded programs [14].

Whilst modern desktop processors may contain 4–8 cores, some special-purpose architectures have gone further:

• Tilera's TILE64 [15] includes 64 32bit VLIW processors embedded in an  $8 \times 8$  mesh network that supports a range of static and dynamic routing functions. Each

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2015 by K. Rupp

Figure 1.1: 40 years of microprocessor trend data (collated and plotted by Rupp [13]) showing the steady continuation of transistor scaling, but a levelling of clock frequency and single-threaded performance.

processor is resident on a 'tile' which connects to this mesh with a 5-port crossbar-switch-based wormhole router. The caches of each processor tile are connected both to each other and to the system memory to provide overall system cache-coherence. Additionally, high-performance I/O devices allow the mesh to use DDR2 memories, and to be connected to 10-gigabit Ethernet and PCI-Express networks. Combined, these features make the TILE64 architecture particularly well-suited to processing high-speed sources of streaming data such as data-centre network routing.

- Centip3De designed by Fick, Dreslinski, Giridhar, et al. [16] at the University of Michigan combines 64 ARM Cortex-M3 processors into a 130nm stacked-3D package. Internally, the chip utilises through-silicon vias (TSVs) to communicate vertically between layers comprised solely of Cortex-M3 processors and layers comprised of 'cache-clusters' shared by up to four processors. A complete system may consist of four processor/cache layers (for up to 128) processors and up to three SDRAM layers (to a total of 256MB) Using near-threshold voltages (650mV–1.15V) and comparatively slow clock frequencies (10-80MHz) allow the devices to achieve 3,930 Dhrystone MIPS/W [17].

- Intel produced a prototype 'data-center-on-a-die' as a response to the trend of increasing core counts [18]. The chip embeds 24 pairs Pentium-class IA-32 processors in a 2D  $6 \times 4$  grid network. Each pair of processors share a 'message-passing

buffer' which works with the grid network to realise of a message-passing protocol that is primarily realised by hardware. A specific 'message-passing memory type' presents this protocol at the software-level, whilst the caches implement the communication at the hardware-level. Coherency between all the processors in the chip is maintained using the same system. Linux can be booted on each core as they each implement the IA-32 instruction set.

• Orcale's SPARC M7 [19] is similarly designed for the data-centre and includes 32 S4 cores capable of supporting 256 threads simultaneously. Each core has exclusive L1 instruction and data caches, but L2 caches are shared by four processors in a SPARC cache cluster (SCC). Within this cluster, a single instruction cache serves all four cores, and two data caches serve two pairs of cores. The SCC tiles are then embedded in the on-chip network which connects to various coherency systems, four memory controllers, and eight 'database analytic accelerator' engines. Overall, the chip contains 64MB of L3 cache partitioned eight ways to give each SCC an equal share, and has a total off-chip bandwidth of 1TB/s for memory, multi-socket coherency, and I/O interfaces.

#### 1.1 Performance Obstacles

#### 1.1.1 Memory Bottlenecks

Clock frequency is not the sole driving force behind increases in single-threaded performance. The persistent requirement for higher density memory chips typically drives advances in fabrication technology because the number of transistors on a memory chip is directly proportional to the amount of data it can store. However, such heavily populated chips often suffer from poor parasitic traits which cause the operating frequency of memory devices to lag behind that of same-generation processors. Additionally, high-density memories usually employ dynamic logic which further increases data density at the cost of increased read and write latency.

Modern processors use a multi-layered approach to mitigate this introduced latency. Processors normally access dynamic system memories through at least one layer of cache. Modern desktop processors have have two or three levels of cache of increasing size and latency, and decreasing bandwidth. L1 caches are physically closest to the processor, usually operate on the same clock frequency, and are capable of presenting the processor with data one-byte-at-a-time if requested, thus shielding the processor from the 'bursty' nature of system memory. Caches farther away from the processor and closer to system memory become more tolerant of bursts of data, effectively shielding the latency of subsequent reads from the processor.

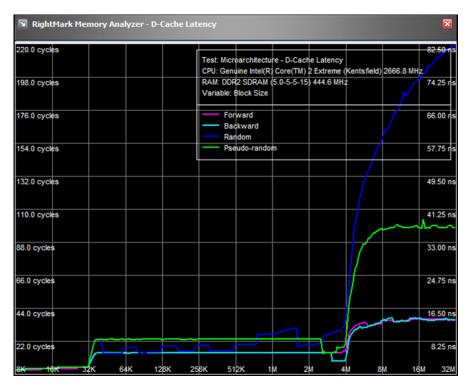

As a final defence against the comparatively high latencies of system memories, most systems use a prefetcher to perform speculative loads of addresses based on memory access patterns. If memory is being accessed in a predictable manner, system prefetchers will read additional data from the system memory so that it is already present in an appropriate level of cache before the processor requests it. Predictable accesses grant the prefetcher a sustainable lead on the processor and significantly reduce memory access times. Figure 1.2 shows how effective prefetchers can be when memory access patterns are predictable. Sutter [20] measured the data cache latencies for forward linear, reverse linear, pseudo-random, and random memory access patterns and clearly demonstrates that predictable accesses yield enormous performance increases over random accesses.

Figure 1.2: Data cache latencies for various memory access patterns on various amounts of data (figure produced by Sutter [20]).

Despite all of these techniques, Figure 1.2 still clearly shows that modern processors can consume data at a higher rate than it can be delivered. L1 caches and tightly-coupled memories are capable of delivering data in a small number of cycles, but large amounts of data causes high latency even when playing to the strengths of this multi-layered defence.

#### 1.1.2 Instruction-level Parallelism

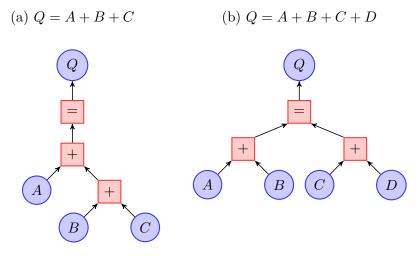

Many modern processors are capable of issuing several instructions simultaneously if they are independent and there is sufficient hardware to support them. As an example, consider equation (a) of Figure 1.3. Clearly the sum of A and B+C cannot be computed

until B+C is known. However, the value of A can be read into the register file whilst B+C is being computed. A multiple-issue processor would be capable of performing these parallel tasks to gain a performance boost. Some processors take this concept further and include multiple functional blocks of the same type. Such a processor would be capable of computing (b) in two cycles by computing A+B and C+D simultaneously, and then computing the sum of the results on the following cycle.

Figure 1.3: Two simple equations and the corresponding data-dependency graphs.

Static multiple issue is the simplest form of this technique, requiring that the compiler determines these potential optimisations a priori. The compiler constructs data-dependency graphs, such as in Figure 1.3, to determine exactly which instructions can be executed in parallel. Several instructions are then combined into a 'bundle' or an 'issue packet', more commonly known as a Very Long Instruction Word (VLIW), which is guaranteed by hardware to be dispatched simultaneously. Obviously, bundled instructions are subject to the constraints of the processor and two integer operations may only be executed in parallel if there are two integer arithmetic units present.

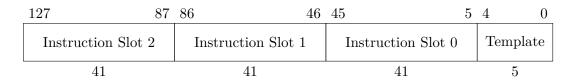

Figure 1.4: Intel Itanium instruction bundle format [21].

The Intel Itanium [21] is a mainstream VLIW processor which serves as a good demonstrator of how a VLIW architecture can dispatch instructions. Figure 1.4 shows that its VLIW format (called an *instruction bundle* in the Itanium nomenclature) is comprised of three instructions to be executed in parallel and then a *template* field providing some context for these instructions. Table 1.1 gives a small subset of the template codes used by the Itanium architecture, which map the instructions onto the various units within the processor. In addition to this mapping, the Itanium can enforce 'architectural stops'

| Template | Slot 0 | Slot 0                      | Slot 2                      |

|----------|--------|-----------------------------|-----------------------------|

| 0x00     | M-unit | I-unit                      | I-unit                      |

| 0x01     | M-unit | I-unit                      | $\underline{\text{I-unit}}$ |

| 0x02     | M-unit | $\underline{\text{I-unit}}$ | I-unit                      |

| 0x03     | M-unit | $\underline{\text{I-unit}}$ | $\underline{\text{I-unit}}$ |

| 0x04     | M-unit | L-unit                      | X-unit                      |

| 0x05     | M-unit | L-unit                      | $\underline{X}$ -unit       |

| 80x0     | M-unit | M-unit                      | I-unit                      |

| 0x09     | M-unit | M-unit                      | I-unit                      |

Table 1.1: First eight template instruction-mapping codes for the Intel Itanium architecture [21]. M-units primarily handle memory operations, I-units handle integer operations, and X-units handle extended length instructions of the form L+X.

(indicated by underlines in the table) if there are resource dependencies between subsequent instructions.

Dynamic multiple issue (more commonly known as superscalar) processors perform these optimisations at run-time rather than at compile-time. Clearly this requires more complex hardware as data-dependency must be detected as the instructions are presented for issue, but it carries a significant advantage over the VLIW approach: the hardware guarantees the correctness of the execution. VLIW processors will blindly execute the instructions as demanded by the compiler, so small architectural changes between hardware revisions can lead to performance degradations that can only be fixed by recompiling the software. Superscalar processors detect parallelism opportunities at run-time and are hence guaranteed to be correct.

Intel Hyper-Threading extends the superscalar concept by sharing function blocks between two copies of the architectural state [22]. This has the effect of each processor appearing as two 'logical processors' which both dispatch micro-operations to the shared compute resources. In addition to having a complete set of registers (including general-purpose) and a programmable interrupt controller, each copy of state also includes a 'return stack predictor' and an instruction translation look-aside buffer. Essentially, each copy appears as a complete processor from the software perspective.

Dynamic multiple-issue techniques are often further improved by allowing the processor to execute instructions in an order of its choosing. Out-of-order execution is common on larger processors and makes use of the data-dependency graphs already established by the multiple-issue hardware. As long as the processor can commit the results in the correct order—i.e., that of the input instruction stream—the end-result of the program is still correct. Consider again equation (a) of Figure 1.3, the overall sum cannot be computed until the result of B+C is known, but another instruction disjoint to this equation can be executed in parallel.

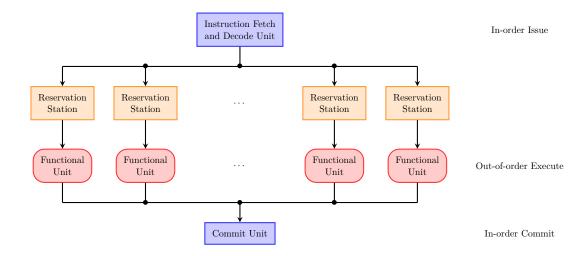

Figure 1.5: Three stages of an out-of-order execution pipeline, based on Figure 4.72 of Patterson and Hennessy [23].

Figure 1.5 shows the three stages of an out-of-order execution pipeline. Instructions flow into the fetch and decode unit in the order generated by the synthesis stage of the compiler. Operands and instructions are then dispatched to multiple functional units via their corresponding reservation stations which are queues that wait until all operands for an operation are available. Results from the functional units are then collated by the commit unit which both ensures the results are committed to the register file in the correct order, and distributes the results to the reservation stations waiting for operands. Continuing the earlier example: the commit unit would feed the result of B + C back to whichever reservation station has A + (B + C) queued.

#### 1.1.3 Power

Larger transistor counts naturally lead to an increased power requirement for modern processors. Austin, Blaauw, Mudge, et al. [24] present equations (1.1)–(1.5) to illustrate how processor design parameters affect the overall power dissipation. Of particular interest is equation (1.1) which shows two factors contributing to overall power dissipation:

$$P = \underbrace{ACV^2 f}_{\text{dynamic}} + \underbrace{VI_{\text{leak}}}_{\text{static}} \tag{1.1}$$

Dynamic power dissipation occurs while transistors are switching and is caused by the charging and discharging of the capacitive loads in the design. A is the proportion of gates actively switching and C is the total capacitive load of all gates. Clearly C is proportional to the number of transistors in the design, which is increasing with each new fabrication technology as explained earlier. Frequency, f, has largely plateaued in the

low-GHz range (i.e.,  $O(10^9)$ ). This leaves voltage, V, and A as two of the parameters that can be exploited to reduce dynamic power. However, the voltage cannot be scaled too low otherwise the clock frequency will drop correspondingly, as shown by equation  $(1.2)^1$ .

$$f_{\rm max} \propto \frac{(V - V_{\rm th})^{\alpha}}{V}$$

(1.2)

Static power is primarily described by the leakage current,  $I_{\text{leak}}$ , in equations (1.3)–(1.5). There are two contributions here: the *sub-threshold leakage current*,  $I_{\text{sub}}$ , and the gate-oxide leakage current,  $I_{\text{ox}}$ . Across both of these equations, the parameters  $K_1$ ,  $K_2$ , n,  $\beta$  must be determined experimentally for each fabrication technology level, W is the transistor gate width,  $V_{\theta}$  is the thermal voltage, and  $T_{\text{ox}}$  is the gate oxide thickness.  $V_{\theta}$  is typically 25mV at room temperature, but increases linearly as temperature increases.

$$I_{\text{leak}} = I_{\text{sub}} + I_{\text{ox}} \tag{1.3}$$

$$I_{\text{sub}} = K_1 W \exp\left(-\frac{V_{\text{th}}}{nV_{\theta}}\right) \cdot \left[1 - \exp\left(-\frac{V}{V_{\theta}}\right)\right]$$

(1.4)

$$I_{\text{ox}} = K_2 W \left(\frac{V}{T_{\text{ox}}}\right)^2 \cdot \exp\left(-\frac{\beta T_{\text{ox}}}{V}\right) \tag{1.5}$$

Austin, Blaauw, Mudge, et al. [24] note that equation (1.4) suggests two ways to reduce static power: firstly, to turn off the supply voltage, V, as often as possible, and secondly to increase the threshold voltage,  $V_{\rm th}$ . However, the latter would cause lower operating frequencies due to equation (1.2) just as reducing the supply voltage would. Austin et. al also note that while increasing the oxide thickness,  $T_{\rm ox}$ , in equation (1.5) is the obvious way to reduce the leakage current contribution, it is also not viable because oxide thickness must decrease with device scaling.

Increased power dissipation naturally requires improved cooling, which itself becomes complicated by the shrinking die-size of modern chips. The heat densities involved are high enough to make efficient cooling a difficult problem. Power must therefore be reduced inside the device by dynamically scaling the voltage and frequencies at runtime, or by power-gating large parts of the chips so that unused resources are simply not drawing any power.

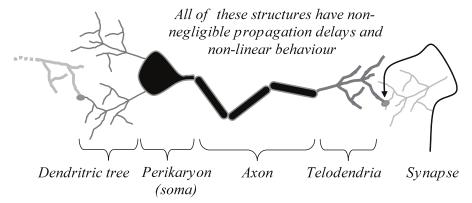

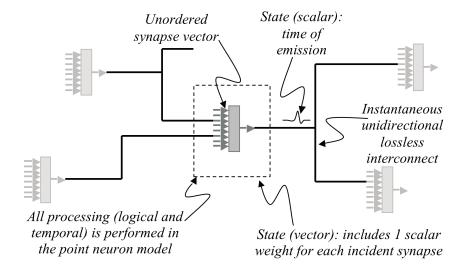

Esmaeilzadeh, Blem, St. Amant, et al. [25] constructed a model of power dissipation for CPU-like multi-core architectures (in contrast to GPU-like) and analysed the effects of the aggressive scaling given by  $ITRS^2$  projections. The authors determined that 8nm fabrication technologies would lead to over 50% of a chip being underutilised due to power constraints.