# University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

## **UNIVERSITY OF SOUTHAMPTON**

## FACULTY OF PHYSICAL SCIENCES AND ENGINEERING Electronics and Computer Science

## Interconnection Networks Performance Modelling for Multi-core Multi-Cluster Architecture

Ву

Norhazlina Hamid

Thesis for the degree of Doctor of Philosophy in Computer Science

June 2016

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

## FACULTY OF PHYSICAL SCIENCES AND ENGINEERING ELECTRONICS AND COMPUTER SCIENCE

#### **Doctor of Philosophy**

## Interconnection Networks Performance Modelling for Multi-core Multi-Cluster Architecture

#### Norhazlina Hamid

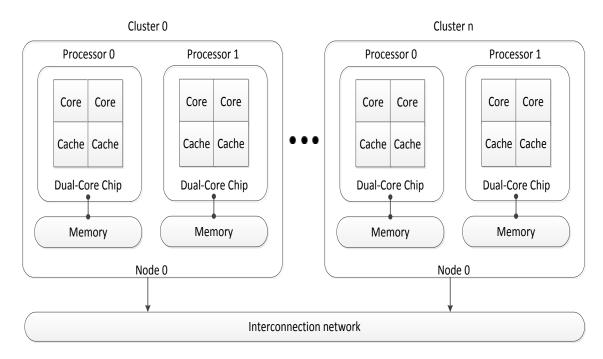

In High Performance Computing (HPC) system design and deployment there is an increasing trend towards networked parallel systems such as cluster computing systems. Cluster computing is typically built from a group of workstations connected by high-speed networks to form a single high-availability system. One of the driving forces behind high-performance clusters is the advent of multi-core clusters. The aim of the research reported here is to design a new architecture for large-scale multi-core cluster computing systems and to investigate the interconnection network performance of the new architecture.

Since the overall performance of cluster computing systems always depends on the efficiency of its communication networks, performance analysis of the interconnection networks is vital. A general problem in the network may arise from the fact that multiple messages can be in transmission at the same time, using the same network links.

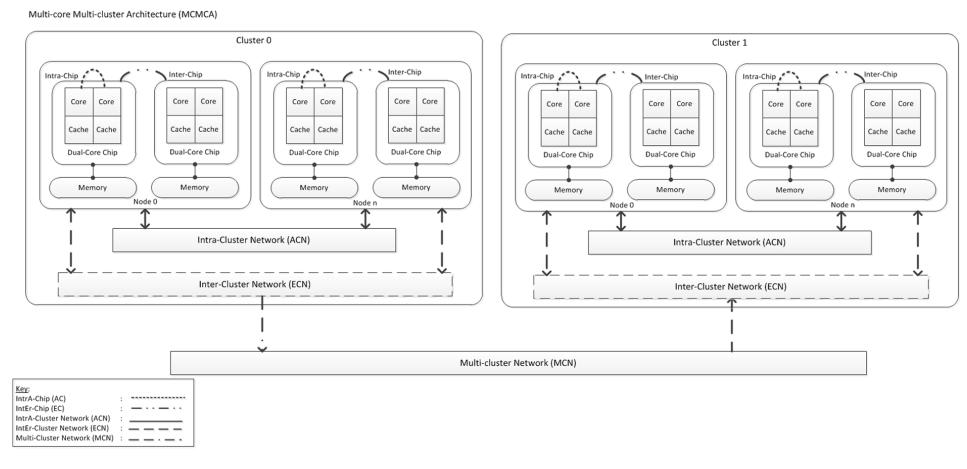

The contribution of this thesis is to develop a new architecture known as Multi-core Multi-cluster Architecture (MCMCA), composed of numbers of clusters where each cluster is a multi-core processor. Next, a simulation model is built to investigate the interconnection network performance of the new architecture, and the results are presented. The main performance metrics to be simulated are the latency and network throughput. The model is then used to evaluate the impact on scalability and cluster size of the interconnection network performance. Finally, analytical model including statistical analysis are used to validate the simulation results under various working conditions.

The analysis indicates that, from single-core to multi-core, there is a significant improvement in processor performance. To judge from the latency results, compared

i

to single-core cluster a multi-core cluster can improve the network performance. Another observation is that the architecture can achieve lower latency and higher throughput as the number of cores increases. The experiments also demonstrated that a multi-core cluster can scale better than a single-core cluster. The results comparison between the analytical model and those produced from the simulation experiments has shown that the derived simulation model provides a good basis for predicting the communication delay of the interconnection network performance of the Multi-Core Multi-Cluster Architecture (MCMCA).

## **Table of Contents**

| Table of Contents                                     | iii  |

|-------------------------------------------------------|------|

| List of algorithms                                    | ix   |

| List of figures                                       | xi   |

| List of tables                                        | XV   |

| Declaration of Authorship                             | xvii |

| Acknowledgements                                      | xix  |

| Definitions and Abbreviations                         | xxi  |

| Chapter 1Introduction                                 | 1    |

| 1.1 Research Motivation                               | 1    |

| 1.2 Research Objectives                               | 3    |

| 1.3 Published Papers                                  | 4    |

| 1.4 Thesis Structure                                  | 5    |

| Chapter 2 Literature Review                           | 7    |

| 2.1 Introduction                                      | 7    |

| 2.2 Computers and Processors                          | 7    |

| 2.3 Multi-core Processors                             | 9    |

| 2.3.1 Moore's 'Law' Changes with Multi-core Processor | 11   |

| 2.4 Cluster Computing                                 | 12   |

| 2.4.1 Cluster Interconnection Networks                | 14   |

| 2.5 Single-core Clusters                              | 15   |

| 2.6 Multi-core Clusters                               | 16   |

| 2.6.1 The Advantages of a Multi-core Cluster          | 18   |

| 2.6.2 Research Challenges                             | 19   |

| 2.7 Multi-cluster Architectures                                         |

|-------------------------------------------------------------------------|

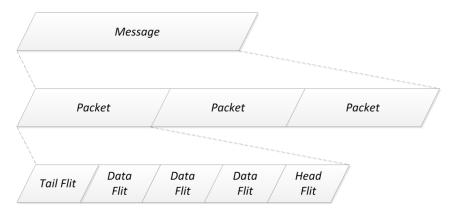

| 2.8 Message, Packet and Flits                                           |

| 2.9 Modelling and Simulation21                                          |

| 2.9.1 Modelling and Simulation Techniques22                             |

| 2.9.2 Simulation Model Structure                                        |

| 2.10Summary27                                                           |

| Chapter 3 The New Architecture29                                        |

| 3.1 Introduction29                                                      |

| 3.2 Multi-core Multi-cluster Architecture (MCMCA)29                     |

| 3.3 Appropriate characteristics for cluster architecture design31       |

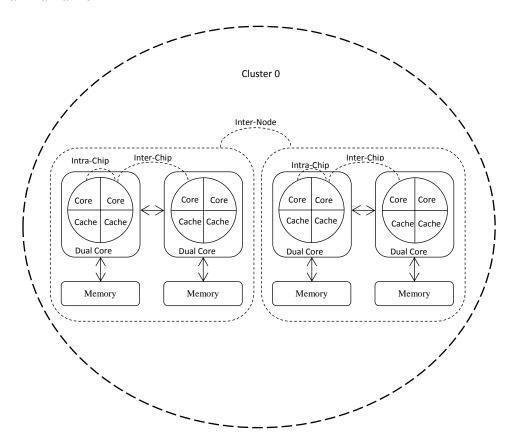

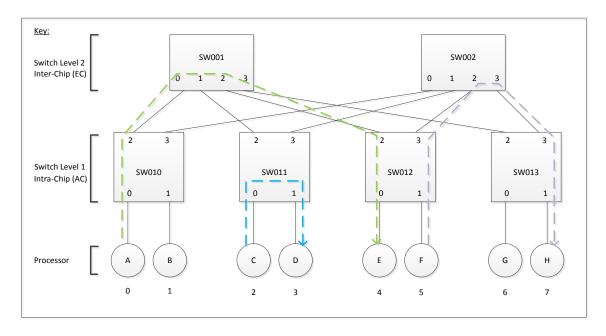

| 3.3.1 Intra-Chip network (AC)31                                         |

| 3.3.2 Inter-Chip network (EC)32                                         |

| 3.3.3 Intra-Cluster Network (ACN)33                                     |

| 3.3.4 Inter-Cluster Network (ECN) and Multi-Cluster Networ (MCN)        |

| 3.4 The MCMCA Queueing Network Model34                                  |

| 3.5 MCMCA Activity Diagrams                                             |

| 3.6 Simulation model to investigate interconnection network performance |

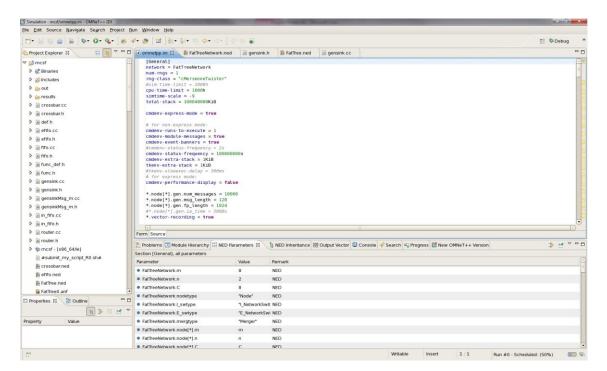

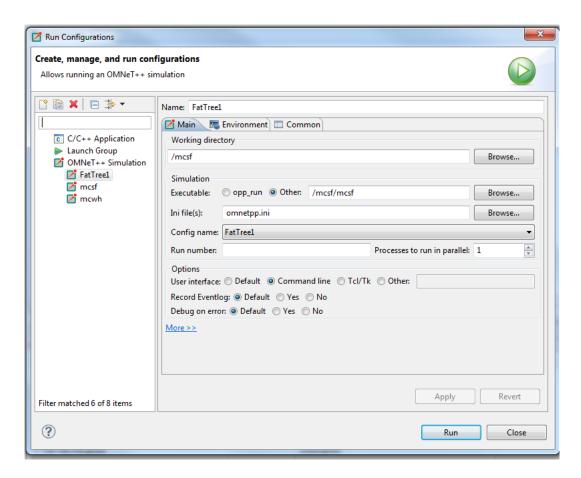

| 3.6.1 OMNeT++ Network Simulation Tool40                                 |

| 3.7 The MCMCA Simulation Model42                                        |

| 3.7.1 Experiments with a Single-core Cluster43                          |

| 3.7.2 Experiments with Multi-core Clusters46                            |

| 3.8 Summary48                                                           |

| Chapter 4 The Performance Model using Store-and-Forward Flow            |

| Control Mechanism49                                                     |

| 4.1 Introduction                              | 49             |

|-----------------------------------------------|----------------|

| 4.2 Store-and-Forward Flow Control Mechanism  | 51             |

| 4.3 Assumptions and Notations                 | 51             |

| 4.3.1 Assumptions                             | 51             |

| 4.3.2 Notations                               | 52             |

| 4.4 Evaluation Methodology                    | 53             |

| 4.4.1 Simulation Structures                   | 53             |

| 4.4.2 The Simulation Activity Diagram         | 57             |

| 4.4.3 Simulation Experimental Setup           | 57             |

| 4.5 The Analytical Model                      | 62             |

| 4.5.1 Preliminaries                           | 63             |

| 4.5.2 Average Message Latency of an           |                |

| Network                                       | 63             |

| 4.5.3 Average Message Latency of an Network   |                |

| 4.5.4 Average Message Latency of MCMCA        | 66             |

| 4.5.5 Implementation of the Analytical Model  | 66             |

| 4.6 Performance Evaluation (SQ4)              | 70             |

| 4.6.1 Latency and Throughput Performance on   | MCMCA71        |

| 4.6.2 The impact on cluster size              | 73             |

| 4.6.3 The impact on message length and scalab | oility75       |

| 4.7 Summary                                   | 77             |

| Chapter 5The Performance Model using Wormhol  | e Flow Control |

| Mechanism                                     | 79             |

| 5.1 Introduction                              | 79             |

| 5.2 Wormhole Flow Control Mechanism           | 80             |

| 5.3 Assumptions and Notations80                                 |

|-----------------------------------------------------------------|

| 5.4 The Simulation Model80                                      |

| 5.4.1 Simulation Structure80                                    |

| 5.4.2 The Experimental Setup82                                  |

| 5.5 The Analytical Model82                                      |

| 5.5.1 Preliminaries82                                           |

| 5.5.2 Average Message Latency of an Internal-Cluster  Network83 |

| 5.5.3 Average Message Latency of an External-Cluster  Network85 |

| 5.5.4 Average Message Latency of MCMCA87                        |

| 5.5.5 Implementation of the Analytical Model87                  |

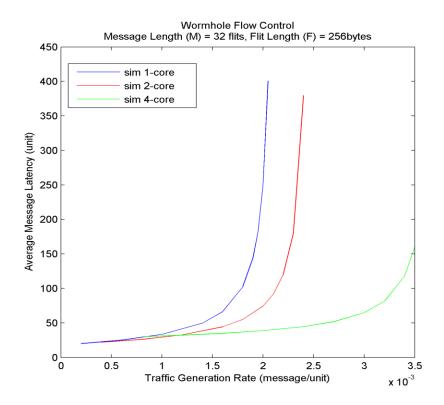

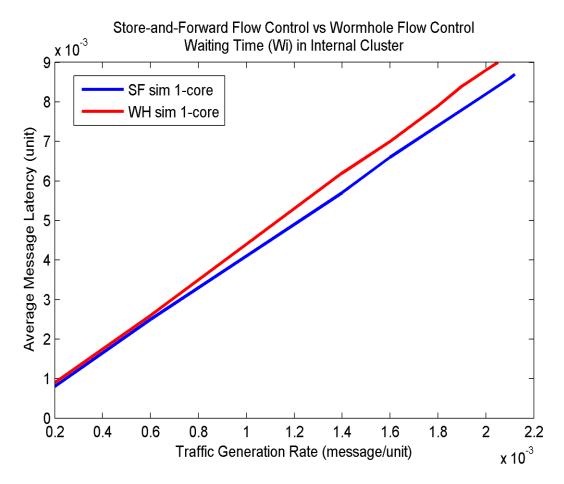

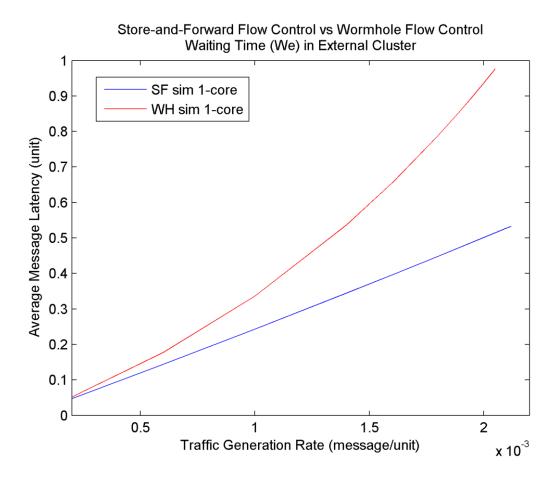

| 5.6 Performance Evaluation (SQ4)93                              |

| 5.6.1 Baseline experiment on MCMCA93                            |

| 5.6.2 Latency and throughput on MCMCA94                         |

| 5.6.3 The Impact on cluster size97                              |

| 5.6.4 The impact on message length and scalability100           |

| 5.7 Summary102                                                  |

| Chapter 6 Statistical Analysis105                               |

| 6.1 Introduction105                                             |

| 6.2 Analysis of Experimental Results105                         |

| 6.2.1 Normality test106                                         |

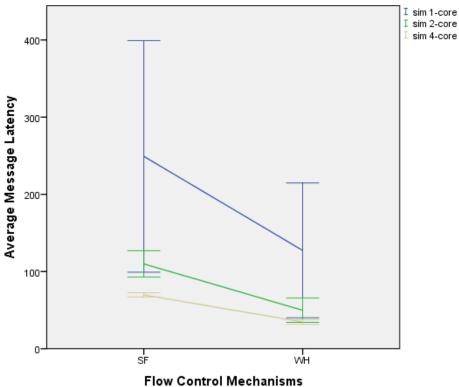

| 6.3 Mean Differences between Mechanisms110                      |

| 6.3.1 Discussion111                                             |

| 6.4 Mean Differences between Processor Core Performance 112     |

| 6.4.1 Discussion                                     | 114 |

|------------------------------------------------------|-----|

| 6.5 Summary                                          | 115 |

| Chapter 7 Conclusions, Contributions and Future Work | 117 |

| 7.1 Conclusions                                      | 117 |

| 7.2 Research Contributions                           | 120 |

| 7.3 Future Research Directions                       | 121 |

| 7.3.1 Limitations of the Research                    | 121 |

| 7.3.2 Specific Extensions                            | 123 |

| 7.4 Concluding Remarks                               | 124 |

| Appendix 2-A                                         | 125 |

| Appendix 3-A                                         | 127 |

| Appendix 3-B                                         | 155 |

| Appendix 4-A                                         | 161 |

| References                                           | 164 |

## List of algorithms

| Algorithm 4-1: Internal cluster switch connection (ISwitch) for store-and-forward flow |

|----------------------------------------------------------------------------------------|

| control mechanism59                                                                    |

| Algorithm 4-2: External cluster switch connection (ESwitch) for store-and-forward flow |

| control mechanism60                                                                    |

| Algorithm 4-3: Message probability in the internal cluster and external cluster62      |

| Algorithm 4-4: Process flow in calculating the communication latency of                |

| interconnection networks in MCMCA66                                                    |

| Algorithm 4-5: Pseudocode of process flow in calculating the communication latency of  |

| interconnection networks in MCMCA using MATLAB based on Store-and-Forward              |

| flow control67                                                                         |

| Algorithm 5-1: Process flow in calculating the communication latency of                |

| interconnection networks in MCMCA based on a wormhole flow-control mechanism           |

| 88                                                                                     |

| Algorithm 5-2: Pseudocode of process flow in calculating the communication latency of  |

| interconnection networks in MCMCA using MATLAB based on wormhole flow                  |

| control89                                                                              |

## List of figures

| Figure 2-1: Basic design of single-core processor                                     | 9             |

|---------------------------------------------------------------------------------------|---------------|

| Figure 2-2: Basic design of multi-core processor                                      | 10            |

| Figure 2-3: Cluster architecture (reproduced from (Baker et al., 2000)                | 13            |

| Figure 2-4: Illustration of a Single-core cluster basic structure                     | 16            |

| Figure 2-5: Illustration of Multi-core Clusters basic structure                       | 17            |

| Figure 2-6: Communication level in Multi-core cluster                                 | 18            |

| Figure 2-7: An illustration of the subdivision of a message into packets and of pack  | ets           |

| into flits (reproduced from (Dally & Towles, 2004))                                   | 21            |

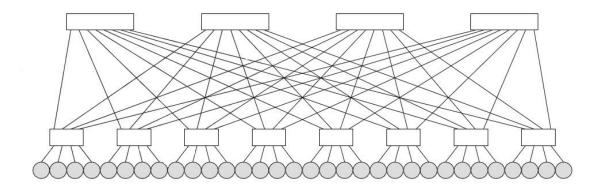

| Figure 2-8: An 8-port 2-tree constructed by proposed algorithm                        | 24            |

| Figure 2-9: The incorporate entities in MCMCA                                         | 28            |

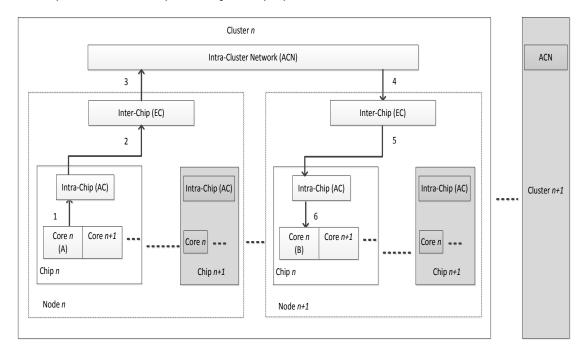

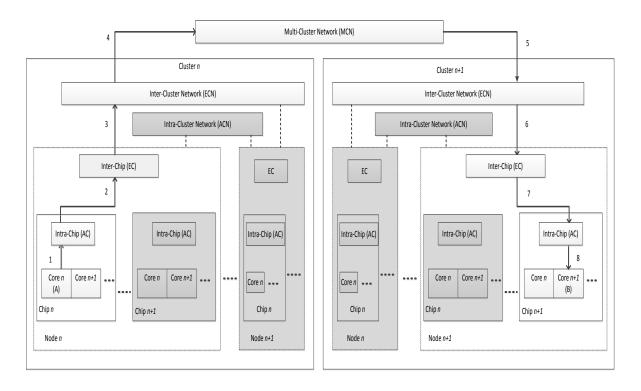

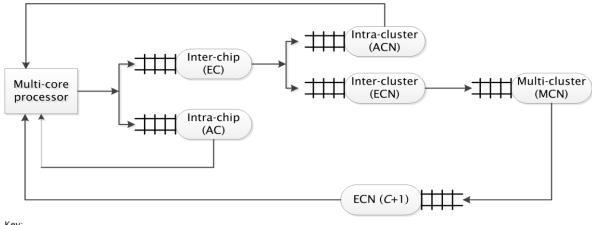

| Figure 3-1: Overview of the proposed Multi-Core Multi-Cluster Architecture (MCMCA     | <b>(</b> ) 30 |

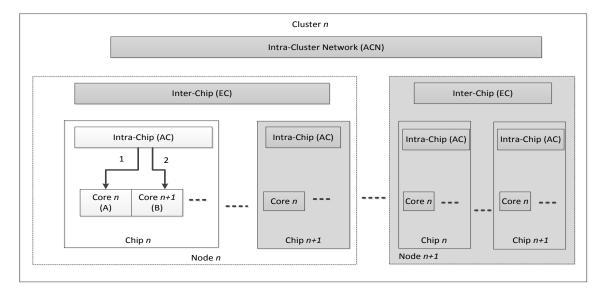

| Figure 3-2: Communication for message passing between two processor cores on t        | he            |

| same chip                                                                             | 32            |

| Figure 3-3: Communication for message passing across processors in different chip     | os,           |

| but within a node                                                                     | 32            |

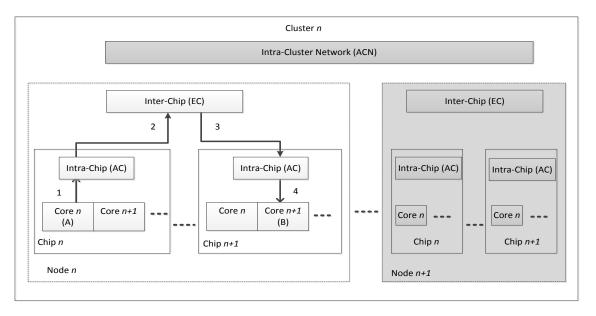

| Figure 3-4: Communication routes for messages passing between processors on           |               |

| different nodes, but within the same cluster                                          | 33            |

| Figure 3-5: Communication routes for transmitting messages between clusters           | 34            |

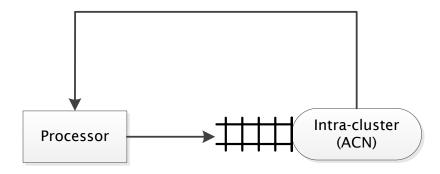

| Figure 3-6: Queuing network of single-core cluster                                    | 35            |

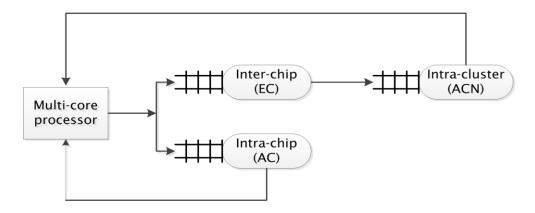

| Figure 3-7: Queuing network of multi-core cluster                                     | 36            |

| Figure 3-8: Queuing network of Multi-core Multi-cluster Architecture (MCMCA)          | 36            |

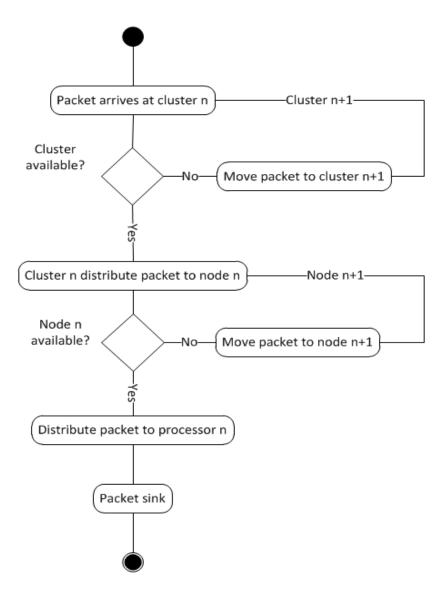

| Figure 3-9: Activity diagram of a packet traversing the cluster node of a single-core |               |

| processor                                                                             | 37            |

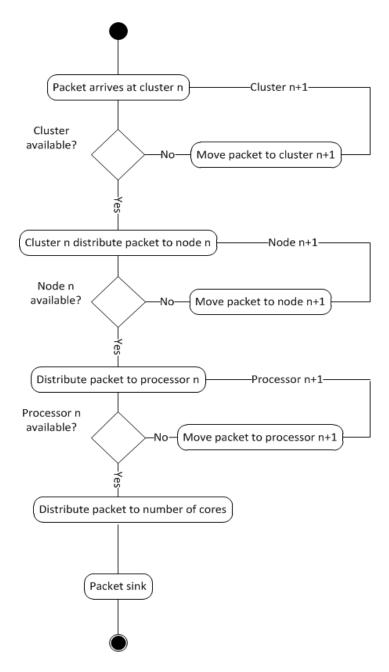

| Figure 3-10: Activity diagram of a packet traversing the cluster node of a multi-core | j             |

| processor                                                                             | 38            |

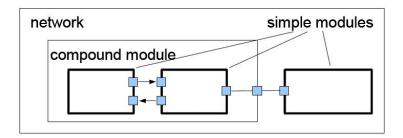

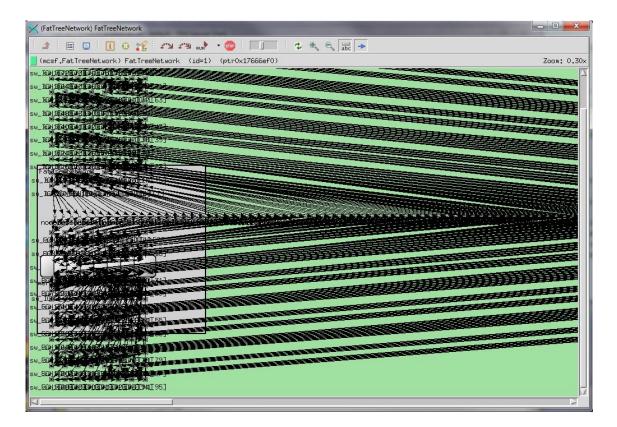

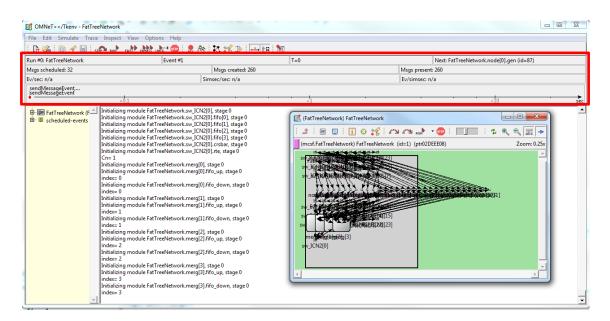

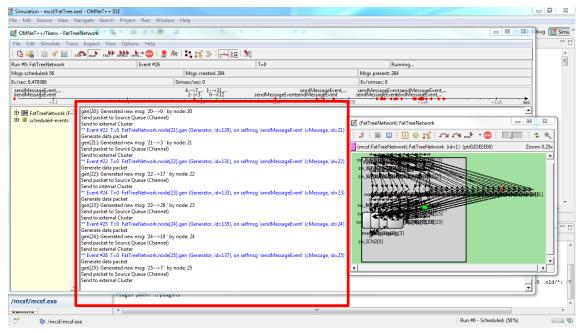

| Figure 3-11: Model Structure in OMNeT++ (Varga & Hornig, 2008)                        | 42            |

| Figure 3-12: Bahman's model for 8-cluster system with M=32                            | 44            |

| Figure 3-13: MCMCA model with $C=8$ , $M=32$ based on Store-and-Forward Flow Cont     | rol           |

|                                                                                       | 44            |

| Figure 3-14: Bahman's model for 8-cluster system with M=64                            | 45            |

| Figure 3-15: MCMCA model with $C=8$ , $M=64$ based on Store-and-Forward Flow Cont     | rol           |

|                                                                                       | 45            |

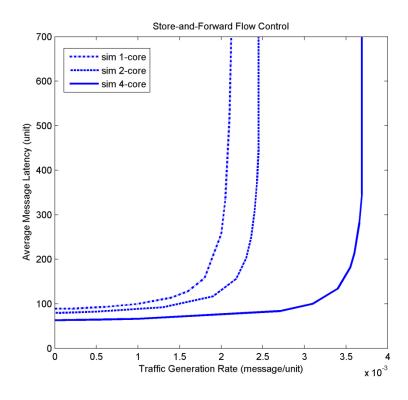

| Figure 3-16: MCMCA Simulation Results based on Store-and-Forward Flow Control         | 47            |

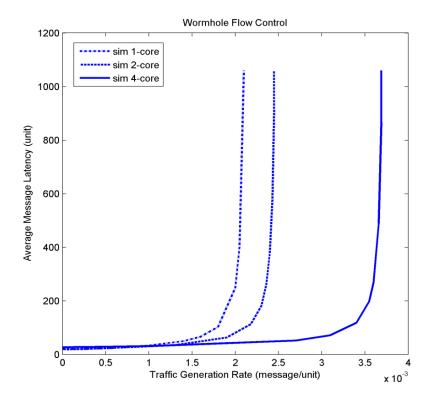

| Figure 3-17: MCMCA Simulation Results based on Wormhole Flow Control                  | 47            |

| Figure 4-1: Flow diagram of the Store-and-Forward flow control mechanism              |               |

| (reproduced from (Dally & Towles, 2004))                                              | 51            |

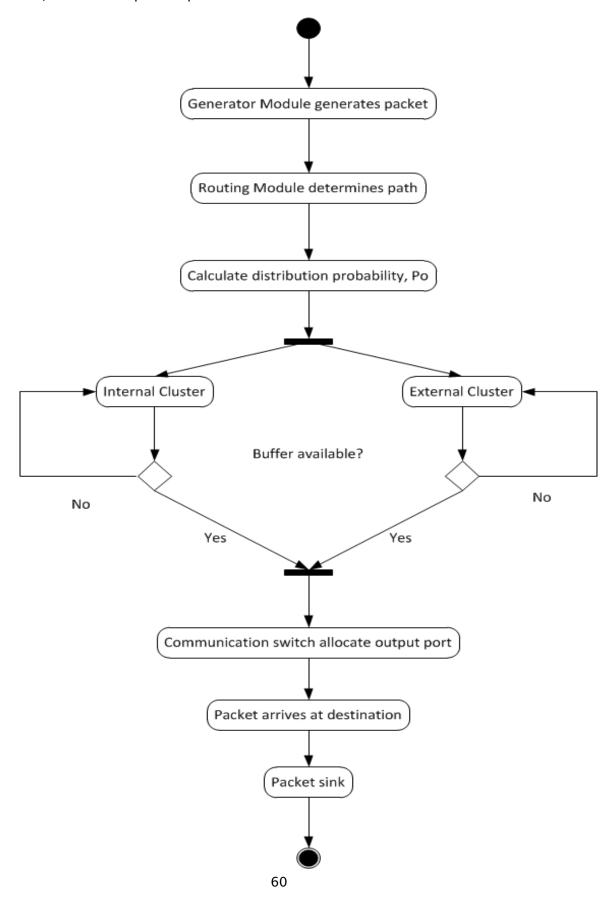

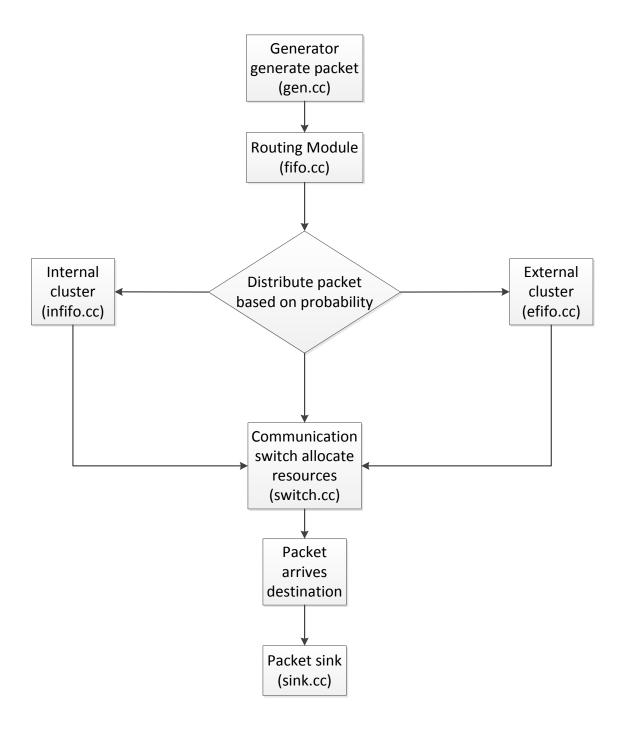

| Figure 4-2: Activity diagram of MCMCA simulation model                                 | 58     |

|----------------------------------------------------------------------------------------|--------|

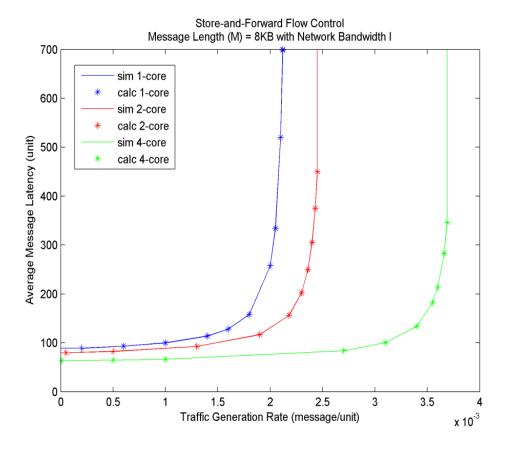

| Figure 4-3: Message latency and throughput results based on store-and-forward f        | low    |

| control mechanism with M=8KB using Network Bandwidth I                                 | 71     |

| Figure 4-4: Message latency and throughput results based on store-and-forward f        | low    |

| control mechanism with M=8KB using Network Bandwidth II                                | 72     |

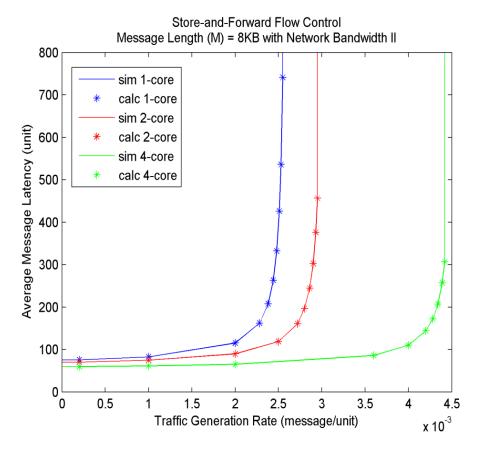

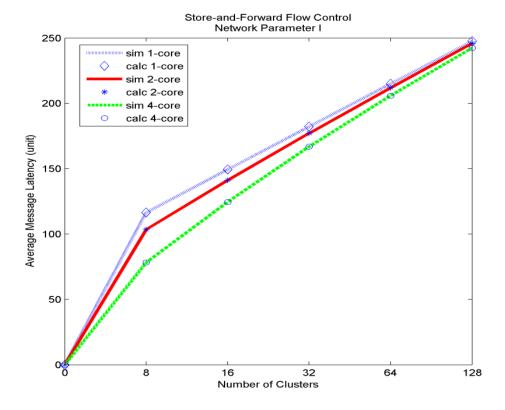

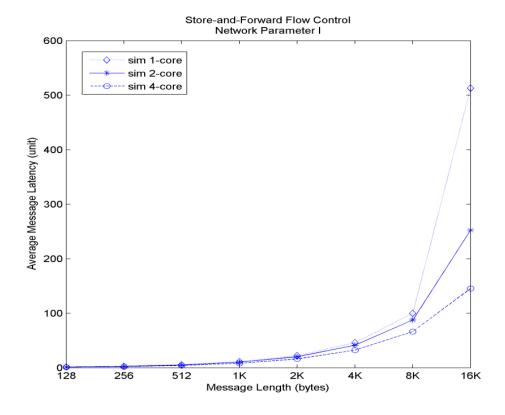

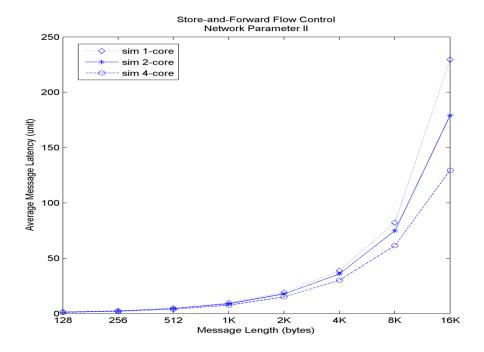

| Figure 4-5: Simulation results of the impact on the message latency with various       |        |

| number of clusters based on Network Parameter I                                        | 73     |

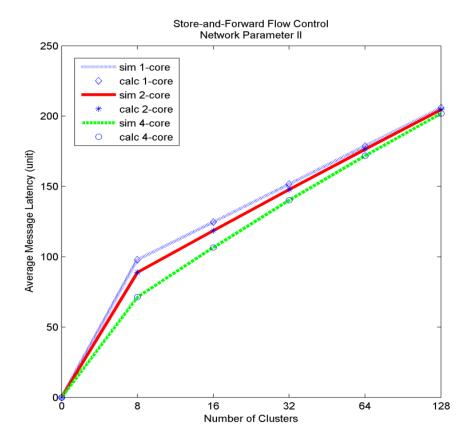

| Figure 4-6: Simulation results of the impact on the message latency with numbers       | s of   |

| clusters based on Network Parameter II                                                 | 74     |

| Figure 4-7: Simulation results of the impact on the message latency with various       |        |

| message lengths based on Network Parameter I                                           | 75     |

| Figure 4-8: Simulation results of the impact on the message latency with various       |        |

| message lengths based on Network Parameter II                                          | 76     |

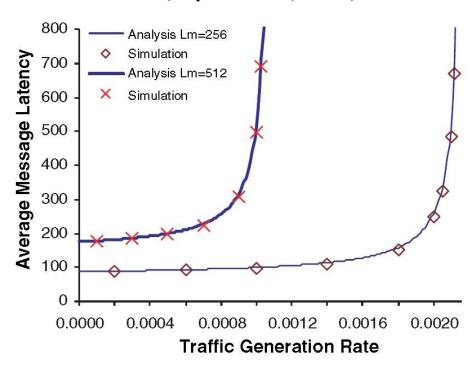

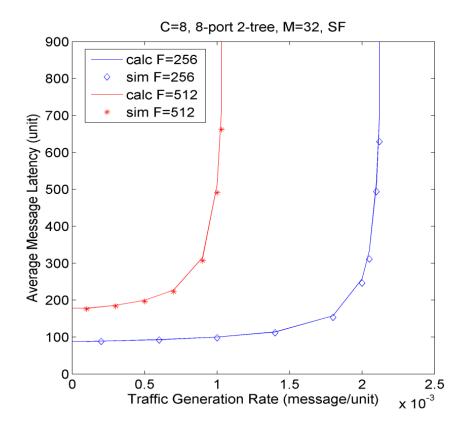

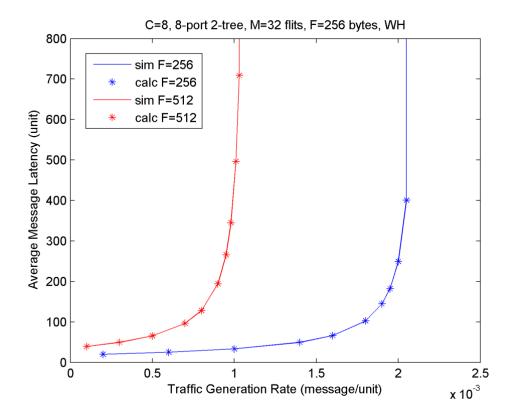

| Figure 5-1: MCMCA model with $C=8$ , $M=32$ flits, $F=256$ bytes based on Wormhole     | Flow   |

| Control                                                                                | 94     |

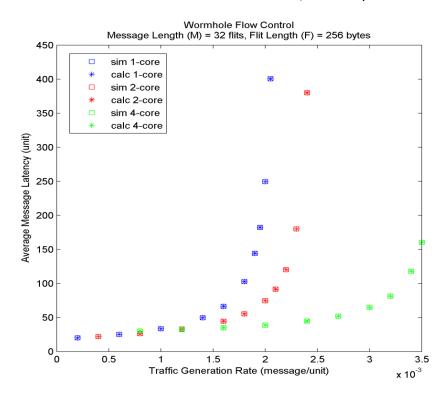

| Figure 5-2: Message latency and throughput simulation results based on Wormho          | le     |

| Flow Control Mechanism with M=32F, F=256 bytes                                         | 95     |

| Figure 5-3: Message latency and throughput simulation results compared to analy        | ytical |

| calculation results based on Wormhole Flow Control with M=32 flits, F=256 b            | ytes   |

|                                                                                        | 95     |

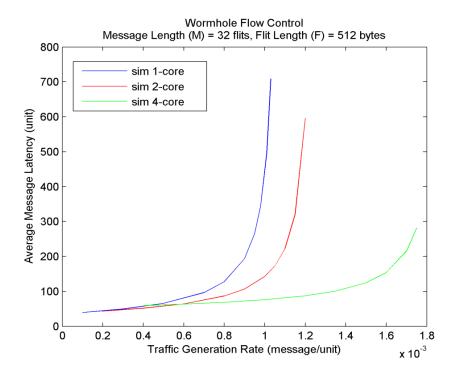

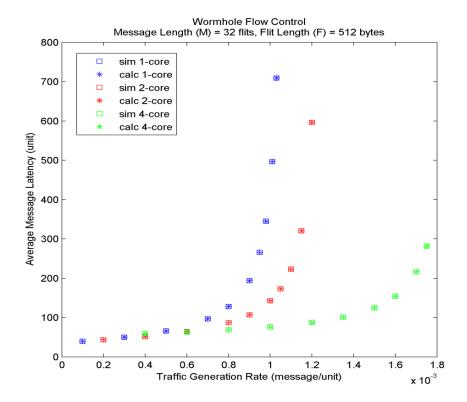

| Figure 5-4: Message latency and throughput simulation results based on Wormho          | le     |

| Flow Control Mechanism with M=32 flits, F=512 bytes                                    | 96     |

| Figure 5-5: Message latency and throughput simulation results compared to analy        | ytical |

| calculation results based on Wormhole Flow Control with M=32 flits, F=512 b            | ytes   |

|                                                                                        | 96     |

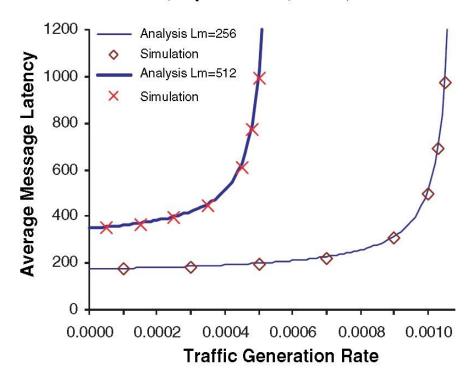

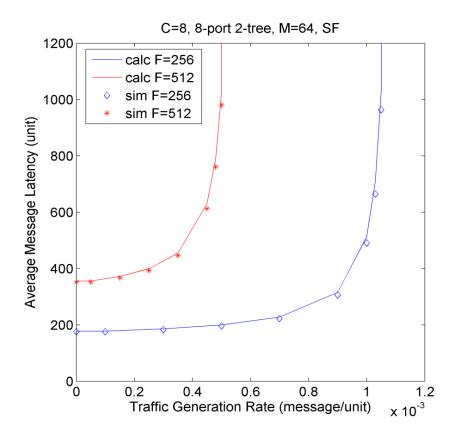

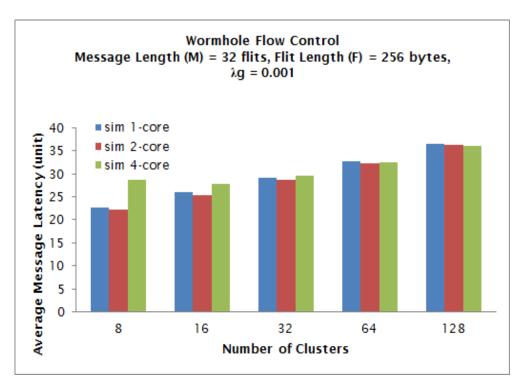

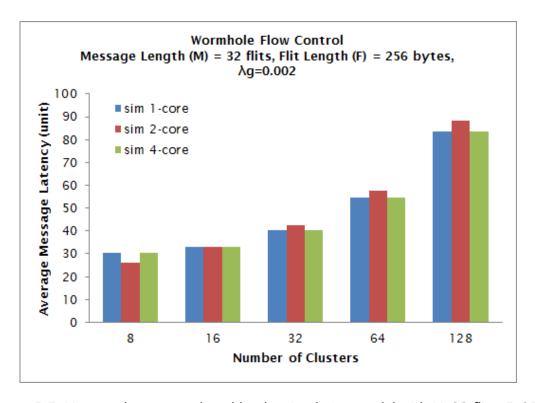

| Figure 5-6: Message latency predicted by the simulation model with $M=32$ flits, $F=1$ | =256   |

| bytes and $\lambda g$ =0.001                                                           | 98     |

| Figure 5-7: Message latency predicted by the simulation model with $M=32$ flits, $F=1$ | =256   |

| bytes and $\lambda g$ =0.002                                                           | 98     |

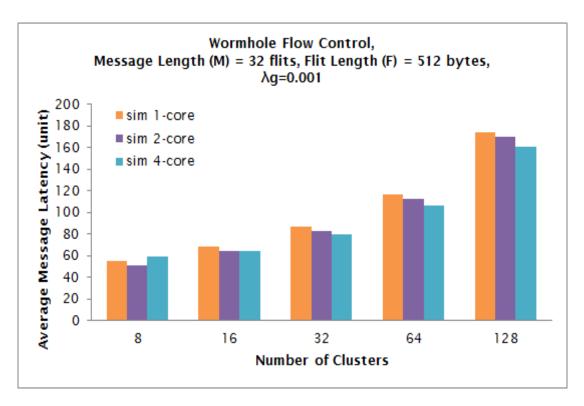

| Figure 5-8: Message latency predicted by the simulation model with $M=32$ flits, $F=1$ | =512   |

| bytes and $\lambda g$ =0.001                                                           | 99     |

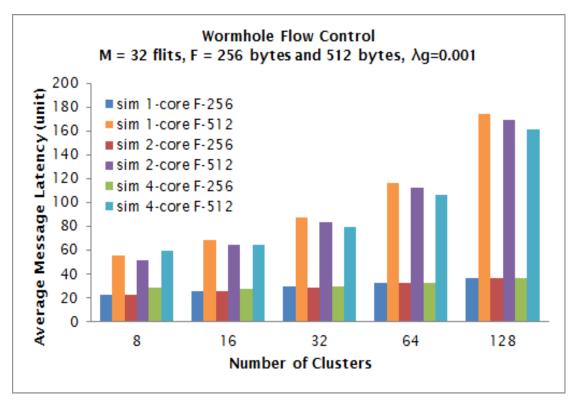

| Figure 5-9: Comparison of message latency with M=32 flits, F= 256 and 512 byte         | S      |

| predicted by the simulation model using $\lambda g$ =0.001                             | 99     |

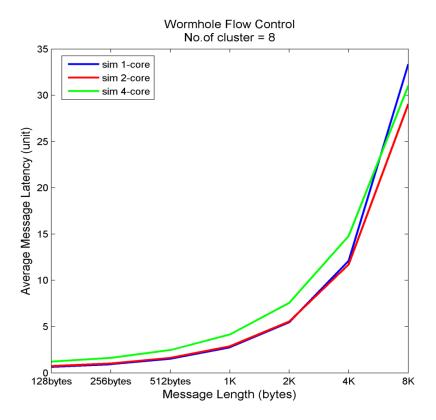

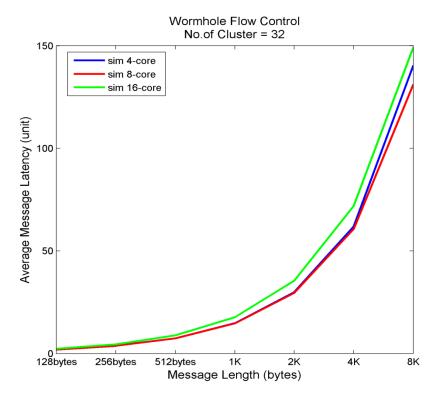

| Figure 5-10: Simulation results of the impact on the message latency with various      | 5      |

| message lengths based on Number of cluster = 8                                         | 101    |

| Figure 5-11: Simulation results of the impact on the message latency with various      | 5      |

| message lengths based on Number of cluster = 32                                        | 101    |

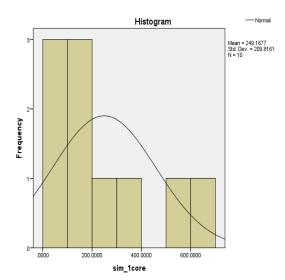

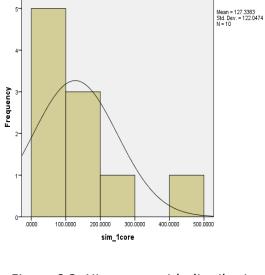

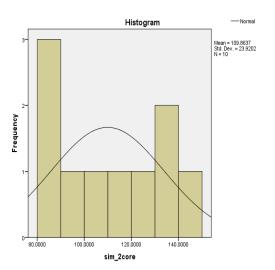

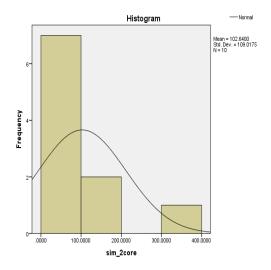

| Figure 6-1: Histogram with distribution curve plotted for store-and-forward flow control |

|------------------------------------------------------------------------------------------|

| mechanism with 1-core109                                                                 |

| Figure 6-2: Histogram with distribution curve plotted for wormhole flow control          |

| mechanism with 1-core109                                                                 |

| Figure 6-3: Histogram with distribution curve plotted for store-and-forward flow control |

| mechanism with 2-core109                                                                 |

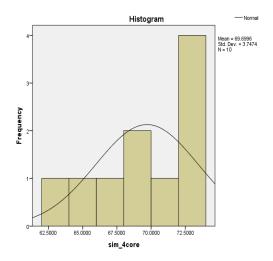

| Figure 6-4: Histogram with distribution curve plotted for wormhole flow control          |

| mechanism with 2-core109                                                                 |

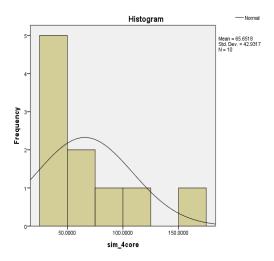

| Figure 6-5: Histogram with distribution curve plotted for store-and-forward flow control |

| mechanism with 4-core110                                                                 |

| Figure 6-6: Histogram with distribution curve plotted for wormhole flow control          |

| mechanism with 4-core110                                                                 |

| Figure 6-7: Error bar chart of average message latency between store-and-forward flow    |

| control and wormhole flow control111                                                     |

## List of tables

| Table 3-1: A comparison of OMNeT++ with other simulation tools                     | 41     |

|------------------------------------------------------------------------------------|--------|

| Table 3-2: Interconnection network parameters                                      | 43     |

| Table 3-3: Model cases for single-core clusters                                    | 43     |

| Table 3-4: Model cases for multi-core clusters                                     | 46     |

| Table 4-1: Notations used in MCMCA                                                 | 52     |

| Table 4-2: Interconnection Networks Parameter I                                    | 70     |

| Table 4-3: Simulation Input I                                                      | 70     |

| Table 4-4: Interconnection Networks Parameter II                                   | 73     |

| Table 4-5: Simulation Input II                                                     | 75     |

| Table 4-6: Simulation Input III                                                    | 75     |

| Table 5-1: Notations used in MCMCA for Wormhole Flow Control                       | 80     |

| Table 5-2: Interconnection Networks Parameters                                     | 93     |

| Table 5-3: Input Parameters                                                        | 93     |

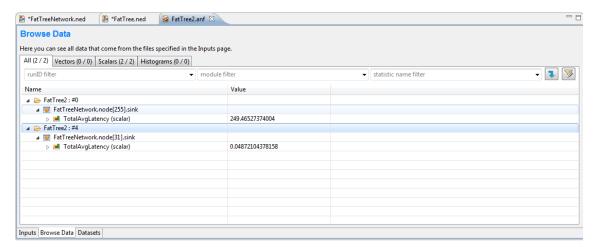

| Table 5-4: Baseline results comparison between MCMCA with 1-core with multi-cl     | uster  |

| model presented by Javadi et al. (2006)                                            | 94     |

| Table 5-5: Simulation Input for cluster sizes                                      | 97     |

| Table 5-6: Simulation Input for scalability                                        | 100    |

| Table 6-1: Descriptive Results for Store-and-Forward Flow Control                  | 106    |

| Table 6-2: Descriptive Results for Wormhole Flow Control                           | 106    |

| Table 6-3: SPSS Output for S-W tests of normality using Store-and-Forward Flow C   | ontrol |

| Mechanism                                                                          | 107    |

| Table 6-4: SPSS Output for S-W tests of normality using Wormhole Flow Control      |        |

| Mechanism                                                                          | 107    |

| Table 6-5: Descriptive Statistics for Skewness with Store-and-forward flow control | 108    |

| Table 6-6: Descriptive Statistics for Skewness with Wormhole flow control          | 108    |

| Table 6-7: The comparison of flow control mechanism performance using Mann-        |        |

| Whitney test                                                                       | 111    |

| Table 6-8: Comparison between processor core performance with two flow contro      | ol     |

| mechanism                                                                          | 113    |

| Table 6-9: Pairwise comparison between processor core performance for two flow     | /      |

| control mechanism                                                                  | 113    |

| Table 6-10: Comparison between processor core performance with Store-and-For       | ward   |

| flow control mechanism                                                             | 113    |

| Table 6-11: Pairwise comparison between processor core performance with Store      | -and-  |

| Forward flow control mechanism                                                     | 113    |

| Table 6-12: Comparison between processor core performance with V | Vormhole flow    |

|------------------------------------------------------------------|------------------|

| control mechanism                                                | 114              |

| Table 6-13: Pairwise comparison between processor core performan | ce with Wormhole |

| flow control mechanism                                           | 114              |

## **Declaration of Authorship**

#### I, Norhazlina Hamid,

declare that this thesis and the work presented in it are my own and have been generated by me as the result of my own original research.

## INTERCONNECTION NETWORKS PERFORMANCE MODELLING FOR MULTI-CORE MULTI-CLUSTER ARCHITECTURE

I confirm the following:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

- Either none of this work has been published before submission, or parts of this work have been published as:

- Hamid, N., Walters, R. J. and Wills, G. B. (2014), Performance evaluation of multi-core multi-cluster architecture, presented at *Emerging Software as a Service and Analytics, Barcelona, ES,03 - 05 Apr 2014*. Scitepress9pp, 46-54.

- 2. Hamid, N., Walters, R. J. and Wills, G. B. (2014), Analytical Calculation of Multi-Core Multi-Cluster Architecture (MCMCA), presented at *International Conference of Postgraduate in Education, Melaka, Malaysia, 17 18 Dec 2014.*

3. Hamid, N., Walters, R. J. and Wills, G. B. (2015), An Architecture for

Measuring Network Performance in Multi-Core Multi-Cluster Architecture

(MCMCA). In, International Journal of Computer Theory and

Engineering vol. 7, no. 1, pp. 57-61, February 2015.

4. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Performance evaluation of

multi-core multi-cluster architecture (MCMCA). In, Chang, Victor, Walters,

Robert John and Wills, Gary (eds.) Delivery and Adoption of Cloud

Computing Services in Contemporary Organizations. Hershey, US, IGI

Global.

5. Hamid, N., Walters, R. J. and Wills, G. B. (2015), An analytical model of

multi-core multi-cluster architecture (MCMCA). In Open Journal of Cloud

Computing (OJCC), 2, (1), 1-12.

6. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Simulation and

Mathematical Analysis of Multi-core Cluster Architecture, presented at 17th

International Conference on Computer Modelling and Simulation

(UKSim2015), Cambridge, United Kingdom, 27-29 March 2015.

7. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Interconnection Network

Performance of Multi-core Cluster Architecture, presented at 2<sup>nd</sup>

International Conference on Computer, Communication and Control

Technology (I4CT), Sarawak, Malaysia, 21-23 April 2015.

8. Hamid, N., Walters, R. J. and Wills, G. B. (2015), "Understanding the Impact

of the Interconnection Network Performance of Multi-core Cluster

Architectures," presented at 4th International Conference on Computer

Technology and Science (ICCTS), Bandar Seri Begawan, Brunei, 01-02 June

2015.

9. Hamid, N, Walters, R. J. and Wills, G. B., "Understanding the Impact of the

Interconnection Network Performance of Multi-core Cluster Architectures,"

Journal of Computers, vol. 11, no. 2, pp. 132-139, 2016.

Signed:

Date: 17 June 2016

xviii

## Acknowledgements

All praise to Allah SWT, the most Gracious, the most Compassionate. Alhamdulillah, I am given this golden opportunity, will and strength to pursue my PhD. I am absolutely delighted that I finally made it, and this chapter in my life is finally over!

Certainly, this PhD journey may never see the light without the support and encouragement from many wonderful and brilliant people who have helped me in various ways towards the completion of my study.

My sincere and deepest appreciation goes to my superb supervisors, Dr. Robert J. Walters and Dr. Gary B. Wills. Indeed, I am so grateful to have them as my supervisors who have taught me so many priceless lessons which I will never forget. A very big thank you to them for the guidance, advice, patience, and continuous support throughout my study. I am truly indebted for their tremendous effort to supervise me, together with the friendship forged throughout this journey. The success of this research would not be possible without their excellent supervision.

I would also like to extend my appreciation to my internal examiner, Mr.Lester Gilbert, and my external examiner, Professor Vassil Alexandrov. Their invaluable advice and constructive comments were certainly helpful in improving this thesis.

To my beloved family, I would like to thank them for all their prayers, love and encouragement. To my beloved parents, Dato' Haji Abdul Hamid Hamat, and Datin Hajah Wan Khuzaimah Wan Mamat, I would like to thank them for their continuous prayers, support, and unconditional love throughout all my pursuits. A big thank you too to my mother-in-law, Hasmah Jusoh, for her prayers while we were thousand miles away from her. I believe that it was the prayers of my loved ones who made me sustain my PhD journey.

A special dedication goes to the most loving, supportive and encouraging husband, Saipulbahri Mustapha, and my three lovely children, Arif Fikri, Sarah Alya and Adam Haris, for their patience, love, understanding, faith and support during this challenging yet rewarding period. I am truly blessed with a great family and am certainly looking forward to the arrival of my baby Viva in July 2016!

Thank you to my siblings, all my family members, my in-laws, my friends especially in PERJASA Group and DSG Group, and certainly the Malaysian community in Southampton, who have indirectly contributed to my success.

Thank you to all my friends at the ECS laboratory for their great help, and for motivating me to persevere and strive towards my goal. A special appreciation goes to Dr. Sei Ping Lau for his knowledge, time and continuous help in my simulation development which became an instrumental part of my thesis.

I would like to acknowledge the IRIDIS High Performance Computing Facility, and the associated support services at the University of Southampton, for the services and facilities offered to help with the completion of this work.

I would also like to acknowledge the Public Service Department of Malaysia for the scholarship awarded and the financial support to pursue my studies at this highly acclaimed University of Southampton, and fulfill my dream.

Last but not least, to all the many other amazing people I have met, who have contributed directly or indirectly towards this wonderful journey, from the bottom of my heart: Thank you, Thank you, and Thank You Very Much!

## **Definitions and Abbreviations**

| Analytical<br>Model           | A set of equations describing the performance of the cluster to support the simulation analysis.                                                                                                                                |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Average<br>message<br>latency | The average amount of time elapsed from the generation of a message until the last packet reaches the destination node.                                                                                                         |

| Bandwidth                     | The capacity of a network connection for supporting data transfers.                                                                                                                                                             |

| Blocking                      | A network is blocking if it cannot handle all switch requests that are a permutation of the inputs and outputs.                                                                                                                 |

| Buffered flow control         | Store a packet in a buffer, preventing the waste of channel bandwidth caused by dropping or misrouting packets.                                                                                                                 |

| Bufferless flow control       | Uses no buffering and simply allocates channel and bandwidth to competing packets.                                                                                                                                              |

| Chip                          | A complex and tiny modules that store computer memory or provide logic circuitry for processors.                                                                                                                                |

| Clock cycle                   | The time measured between two adjacent pulses of the oscillator and sets the tempo of the computer processor.                                                                                                                   |

| Clock rates                   | An indicator of the processor's speed and typically refers to the frequency.                                                                                                                                                    |

| Cluster<br>computing          | A form of computing in which a group of computers are linked together to act like a single entity.                                                                                                                              |

| Channel<br>bandwidth          | Transports messages between nodes and buffers, such as registers and memories, which allow messages to be held temporarily at the nodes.                                                                                        |

| Communication                 | The exchange of data between a source and a destination receiver in interconnection networks architecture.                                                                                                                      |

| Computer cluster              | A group of computers connected to each other by fast local area networks which work together to form a single computer.                                                                                                         |

| Computer                      | A piece of electronic equipment which, when given some data, will process that data in some pre-defined way to produce the required results (Willis & Kerridge, 1983).                                                          |

|                               | A complete system, composed of many interacting parts while computer systems are made of hardware and software (Sullivan, Lewis & Cook, 1988).                                                                                  |

| Computer<br>system network    | Essential elements for the computer network system to function include multiple servers, terminals, printers, network links, software, users, and support systems, including maintenance and repair, training, and spare parts. |

| Contention                    | Occurs when two or more messages want to use the same shared resource in the network.                                                                                                                                           |

| Control state                 | Tracks the resources allocated to the packet within the node and the state of the packet's traversal across the node.                                                                                                           |

| Core                          | A complete computational engine (Burger, 2005).                                                                                                                                                                                 |

Deadlock Occurs when resources are waiting on another set of resources to

complete a work cycle.

Deterministic

routing

The path a packet takes is only a function of its source and

destination.

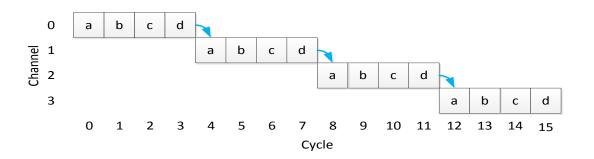

Flit Flow control digits are the basic units of bandwidth and storage

allocation used by most flow control mechanisms.

Flow control Determines how a network's resources - such as channel bandwidth.

buffer capacity and control state - are allocated to messages as they

progress along their route in the network.

The number of waves that pass a fixed place in a given amount of Frequency

time.

Hardware Parts of a computer that we can see and touch and the most

> important piece of hardware is a tiny rectangular chip inside our computer called the central processing unit (CPU), or microprocessor

(Karmakar, 2011).

High

Performance Computing (HPC)

Any computational activity requiring more than a single computer to

execute a task.

Homogeneous

network

A computer network composed of computers using similar

configurations.

Network

Interconnection A physical connection between the different components of a parallel

system.

Microprocessor A computer that has been made on a single chip of silicon about 4 to

6 millimetres square and ½ millimetre thick, and contains a minimum

of a few thousand transistors (Stevens, 1986).

Model A model is a representation of an actual system (J. Banks, 1998) or

process (Carson, 2005).

Modelling The process of identifying and abstracting relevant entities and

relationships from a system under study.

Model validation Substantiating that a computerized model, within its domain of applicability, behaves with satisfactory accuracy consistent with the

intended application of the model.

Model verification Ensuring that the computer program of the computerized model and

its implementation are correct.

**MCMCA** Simulation Model

A descriptive model to investigate the performance of multi-core

cluster system using simulation model.

Message A logically contiguous group of bits that are delivered from a source

node to a destination node.

Message Passing Interface (MPI) A library specification and standard for message-passing between multiple computers running a parallel program across distributed

memory.

Multi-cluster A multiple cluster system that is connected via the cluster

interconnection networks where each cluster system/node has

multiple processors (Shahhoseini, Naderi & Buyya, 2000).

| Multi-core<br>processor               | A single processor with two processing cores which means to place two or more processing cores on the same chip (Burger, 2005).                                                      |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-core<br>cluster                 | A cluster where all the nodes in the cluster have multi-core processors.                                                                                                             |

| Multi-core<br>multi-cluster           | An architecture built up of numbers of clusters where each cluster is composed of numbers of nodes consist a number of processors in a single chip, each with two or more cores.     |

| Network                               | Characterised by the media it uses to carry messages, the way the network links devices and the expansiveness of the network.                                                        |

| Network latency                       | A delay that happens as data packets transmits from one point to another over a network.                                                                                             |

| Node                                  | Consists a multiple processor chip.                                                                                                                                                  |

| Operating system (OS)                 | Software that manages the computer and the devices connected to it, for example Windows or Linux.                                                                                    |

| Packet                                | The basic unit of routing and sequencing.                                                                                                                                            |

| Personal<br>Computer (PC)             | A computer that is designed to be used by one person.                                                                                                                                |

| Processor                             | The logic circuitry that responds to and processes the basic instructions that drive a computer; in the simplest terms, the computer's brain (Rouse, 2006).                          |

| Poisson<br>distribution               | A probability distribution which expresses the probability of a number of procedures occurring in a fixed phase of time.                                                             |

| Random<br>number<br>generator         | A program written for and used in probability and statistics applications when large quantities of random digits are needed.                                                         |

| Routing<br>algorithm                  | Determines the path to be used for data transmission.                                                                                                                                |

| Scalability                           | An ability to radically change the size of something in order to meet<br>the additional requirements of a resource.                                                                  |

| Simulation                            | An imitation of a system as it progresses through time (Robinson, 2004) and contains a set of entities and relationships to fulfill a certain purpose (Wehrle, Gunes & Gross, 2010). |

| Simulation<br>model                   | The process of creating and analysing a digital prototype of a physical model to predict its performance in the real world.                                                          |

| Single-core processor                 | A processor with only one processing core.                                                                                                                                           |

| Single-core<br>cluster                | A cluster consists of numbers of single-core processor.                                                                                                                              |

| Single-core<br>multi-cluster          | An architecture built up of numbers of clusters where each cluster is composed of numbers of nodes that consist a number of single-core processors.                                  |

| Software                              | The instruction or programs that tell the hardware what to do.                                                                                                                       |

| Store-and-<br>forward flow<br>control | A packet switching mechanism whereby the message to be transmitted is partitioned into a sequence of packets.                                                                        |

Supercomputers Large mainframes used primarily for the analysis of scientific and

engineering problems (Sullivan et al., 1988).

System A construct or collection of different elements such as people,

machines, resources, that together produce results not obtainable by

the elements alone.

Throughput The rate at which traffic is delivered to the destination.

Topology The interconnection structure used to connect different processors

or processors and memory modules.

Transistor A semiconducting device that switches and amplifies electronic

signal.

Transmission The n

time

The network cycle time taken by a single packet to travel from one

node to another node in the simulator.

Up\*/Down\*

routing

An assignment of direction (up or down) to network channels where a spanning tree whose node (also called 'vertex') corresponds to a switch in the network, based on building a 'breadth-first search' (BFS)

spanning tree used in Autonet (M. D. Schroeder et al., 1991)

Workstations Type of computer that requires a moderate amount of computing

power and relatively high quality graphics capabilities.

Wormhole flow

control

A packet switching mechanism that works by dividing packets into a sequence of fixed-size units called 'flits', with channel and buffers

allocated to flits.

## **Chapter 1 Introduction**

The emergence of High Performance Computing (HPC), including Cluster computing, has improved the availability of high performance computers and high speed network technologies. High performance in this context is defined as a computational activity requiring more than a single computer to execute a task (Qian, 2010). The main target of HPC is better performance in computing and one of the aims is to leverage cluster computing to solve advanced computation problems (Hope & Lam, n.d.). Cluster computing is playing a major role in solving large-scale computing application problems as they need faster and more reliable systems, especially as they are often built using commodity-off-the-shelf (COTS) hardware components and commonly-used software (Hamid, Walters & Wills, 2015c).

The exponential growth in computing performance quickly led to more sophisticated computing platforms. This rapid growth increased the demand for faster computing performance: every new enhancement in processors leads to greater performance demands (Jin et al., 2011). Moore's Law predicted that the number of transistors on a processor would double approximately every two years, providing regular leaps in computing power (Moore, 1965). Over more than four decades, this has driven the impressive growth in computer speed and accessibility. However, Moore's Law has begun to show signs of failing, being replaced by the emergence of multi-core processors, which involves placing two or more processing cores within the same processor (Burger, 2005). This allows the processor to perform more work within a given clock cycle.

With the emergence of high-speed networks, High Performance Computing (HPC) has adopted network-based computing clusters as cost-effective platforms to achieve high performance, which has led the trend towards cluster systems with multi-cores: the multi-core cluster (Wu & Taylor, 2013). The multi-core cluster becomes more powerful due to the combination of faster processors, faster memory and faster interconnection (Bethel & Howison, 2012).

## 1.1 Research Motivation

Processor performance is often associated with high processor clock frequencies and increasing power dissipation. Every new performance enhancement in processors leads to greater performance demands. The demand for increasing performance continues and as single-core processors reach their physical limits of possible complexity and

speed, the movement towards multi-core processors begins. A multi-core processor means one processor with two or more complete computational engines (cores) within a single processor to enhance performance, reduce power consumption and permit simultaneous processing of multiple tasks (Al-Babtain, Al-Kanderi, Al-Fahad & Ahmad, 2013). Multi-core processors represent a major trend over the past decade and allow faster execution of applications by taking advantage of parallelism.

The Top 500 Supercomputer List published in June 2014 (Admin, 2014) showed that multi-core processors have been widely deployed in clusters of parallel computing, and more than 95% of the systems are using dual-core or quad-core processors. Another trend is reflected in the advances in multi-core processor technology that makes multi-core processors an excellent choice to use in clustered nodes (Soryani, Analoui & Zarrinchian, 2013). Many studies (Fengguang, Moore & Dongarra, 2009; Ichikawa & Takagi, 2009; Lei, Hartono & Panda, 2006; Ranadive, Kesavan, Gavrilovska & Schwan, 2008) have been carried out to improve the performance of multi-core clusters but few clearly distinguish a key issue: that of the performance of the interconnection networks. The existing multi-core cluster architectures are therefore unable to capture the potential performance and the characteristics of the traffic of the interconnection networks within the implementation of a multi-core cluster architecture. The cluster interconnection network is nonetheless critical for delivering efficiency and scalability for the applications, as it needs to handle the networking requirements of each processor core (Dally & Towles, 2004; Shainer et al., 2013). Even so, existing multi-core cluster architectures do not address the potential performance issues of the interconnection networks within multi-core clusters.

In a multi-core cluster architecture, multiple computing nodes are connected via the cluster interconnection network. The implementation of the architecture typically imposes higher latency for communication between processors located on different nodes compared with the processors located on the same nodes.

Apart from addressing the above concern, this thesis will expand the multi-core cluster architecture to a more scalable approach by applying multi-cluster architecture. Existing studies (Abdelgadir, Pathan & Ahmed, 2011) have found that having a good network bandwidth and a faster network will produce a better performance in relation to the scalability of the clusters. The conventional approach to improving cluster throughput is to add more processors, but there is a limit to the scalability of this approach: the infrastructure cannot provide effective memory access to unlimited numbers of processors and the interconnection network(s) become saturated (Shahhoseini et al., 2000). This thesis will identify the potential scalability of the multi-core cluster and will expand the architecture by employing a multi-cluster

architecture. The combination of multi-core cluster and multi-cluster architecture presents a novel architecture known as Multi-core Multi-cluster Architecture (MCMCA). The research described here is motivated by the fact that it is considered to be the first investigation of interconnection network performance of multi-core multi-cluster architecture.

Multi-core clusters allow for the faster execution of applications by taking advantage of the ability to work on multiple cores simultaneously. Several performance models of cluster systems have been proposed in (Alzeidi, Ould-Khaoua & Khonsari, 2008; Geyong, Yulei, Ould-Khaoua, Hao & Keqiu, 2009; Bahman Javadi, Abawajy & Akbari, 2008b; Sarbazi-Azad, Ould-Khaoua & Mackenzie, 2001; Yulei, Geyong, Keqiu & Javadi, 2012), but the evaluations are confined to a single-core processor in a cluster. In order to take advantage of a multi-core processor in a cluster system, it is important to have an in-depth understanding of the characteristics of multi-core clusters and their impact on application performance and behaviour.

This research also develops novel simulation models for predicting and investigating the MCMCA interconnection network performance. The main performance metrics to be simulated are the latency, network throughput and bandwidth. Latency is the time required for a packet to travel from a source node to a destination node; network throughput is the rate at which the networks sends or receives data, and bandwidths refers to the maximum rate at which a packet can be transferred. The model is then used to evaluate the impact of performance metrics on scalability and cluster size.

## 1.2 Research Objectives

The thesis objectives are to investigate and evaluate the interconnection network performance of multi-core multi-cluster architecture (MCMCA). The main research question is:

## RQ1: What is an appropriate architecture to investigate the communication latency of multi-core processors in multi-cluster?

Hence, this RQ1 addresses the following sub-research questions:

SQ1: What are the appropriate characteristics to be considered in designing cluster architecture?

SQ2: What is an appropriate simulation model to investigate interconnection network performance?

SQ3: How well does the MCMCA simulation model analyse cluster performance?

## RQ2: What is an appropriate flow control mechanism for communication latency modelling of the Multi-core Multi-cluster Architecture (MCMCA)?

Hence, this RQ2 addresses the following sub-research questions:

SQ4: What is the impact of the flow control mechanism in improving communication latency?

In order to achieve this goal, three research hypotheses are tested:

Hypotheses H1: Employing a multi-core processor in multi-cluster architecture will improve the performance of a cluster system.

Hypotheses H2: The proposed simulation model can be used to investigate the interconnection network performance in MCMCA.

Hypotheses H3: The common flow control mechanism can be employed to evaluate the impact of MCMCA on interconnection network performance

## 1.3 Published Papers

The research undertaken in this thesis has contributed in part or full to the following publications:

- 1. Hamid, N., Walters, R. J. and Wills, G. B. (2014), Performance evaluation of multi-core multi-cluster architecture, presented at *Emerging Software as a Service and Analytics, Barcelona, ES*, 03 05 Apr 2014. Scitepress9pp, 46-54.

- 2. Hamid, N., Walters, R. J. and Wills, G. B. (2014), Analytical Calculation of Multi-Core Multi-Cluster Architecture (MCMCA), presented at *International Conference of Postgraduate in Education, Melaka, Malaysia, 17 18 Dec 2014.*

- 3. Hamid, N., Walters, R. J. and Wills, G. B. (2015), An Architecture for Measuring Network Performance in Multi-Core Multi-Cluster Architecture (MCMCA). In, *International Journal of Computer Theory and Engineering* vol. 7, no. 1, pp. 57-61, February 2015.

- 4. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Performance evaluation of multi-core multi-cluster architecture (MCMCA). In, Chang, Victor, Walters, Robert John and Wills, Gary (eds.) *Delivery and Adoption of Cloud Computing Services in Contemporary Organizations*. Hershey, US, IGI Global.

- 5. Hamid, N., Walters, R. J. and Wills, G. B. (2015), An analytical model of multicore multi-cluster architecture (MCMCA). In *Open Journal of Cloud Computing* (OJCC), 2, (1), 1-12.

- 6. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Simulation and Mathematical Analysis of Multi-core Cluster Architecture, presented at 17<sup>th</sup> International Conference on Computer Modelling and Simulation (UKSim2015), Cambridge, United Kingdom, 27-29 March 2015.

- 7. Hamid, N., Walters, R. J. and Wills, G. B. (2015), Interconnection Network Performance of Multi-core Cluster Architecture, presented at 2<sup>nd</sup> International Conference on Computer, Communication and Control Technology (I4CT), Sarawak, Malaysia, 21-23 April 2015.

- 8. Hamid, N., Walters, R. J. and Wills, G. B. (2015), "Understanding the Impact of the Interconnection Network Performance of Multi-core Cluster Architectures," presented at 4<sup>th</sup> International Conference on Computer Technology and Science (ICCTS), Bandar Seri Begawan, Brunei, 01-02 June 2015.

- 9. Hamid, N, Walters, R. J. and Wills, G. B., "Understanding the Impact of the Interconnection Network Performance of Multi-core Cluster Architectures," *Journal of Computers*, vol. 11, no. 2, pp. 132-139, 2016.

## 1.4 Thesis Structure

This thesis is divided into seven chapters. This first chapter provides an overview of the research motivation, the research hypotheses and the research questions. The rest is organised as follows:

Chapter 2 presents a review of the literature on related research domains: multi core clusters. This chapter specifically highlights the importance of particular research topics and shows how they benefit the main contribution. This chapter also provides some background to modelling and simulation, including the simulation model structure.

**Chapter 3** introduces the new Multi-core Multi-cluster Architecture (MCMCA) and its interconnection network. The research methodology involved with baseline experimental results is also covered in this chapter.

**Chapter 4** presents the new simulation model with an analytical model as a validation for the simulation results based on a store-and-forward flow control mechanism.

**Chapter 5** presents the new simulation model with an analytical model as a validation to the simulation results based on a wormhole flow control mechanism.

Chapter 6 discusses the statistical analysis and findings of the performance model.

**Chapter 7** draws conclusions from the reported results, research limitations and also suggests a future direction for this research.

## **Chapter 2 Literature Review**

## 2.1 Introduction

In the early days of personal computing, personal computers (PCs) were stand-alone devices with single-user operating systems. User interaction occurred via text-based interfaces and only one program would run at a time. Over time, however, the exponential growth in computing performance quickly led to a more sophisticated computing platform.

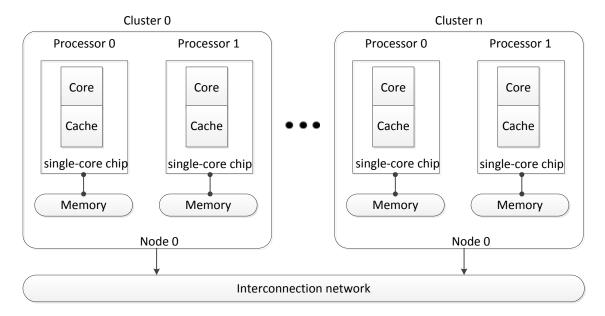

This chapter provides a background to the multi-core cluster that employs the characteristics of cluster computing and multi-core processors. Accordingly, this chapter starts in section 2.2 with an introduction to computers and processors, followed by an introduction to multi-core processing in section 2.3. This is followed in section 2.4 by an introduction to cluster computing. Since the multi-core cluster is a relatively new architecture (Wu & Taylor, 2013), it is important to have an in-depth understanding of the application behaviours and trends in order to obtain optimal performance. Thus section 2.5 provides reviews of the single-core cluster, to be compared with the multi-core cluster in section 2.6. Section 2.7 introduces the structure of multi-cluster architecture and section 2.8 introduces the differences between message, packet and flits. The background of the simulation model structure is presented in section 2.9 as an overview of the development of the new simulation model.

This chapter aims to clarify the apparent ambiguity by comparing multi-core clusters with traditional single-core clusters. Challenges and issues are identified, demonstrating why this study focuses on the issue of an interconnection network in a multi-core cluster.

## 2.2 Computers and Processors

A computer is a piece of electronic equipment which, when given some data, will process that data in some pre-defined way to produce the required results (Willis & Kerridge, 1983). Willis and Kerridge also state that a 'computer system' is a computer with software that makes the system more flexible in solving many different types of problem. A 'personal computer' (PC) is a computer system that is designed to be used by one person.

Every computer system has hardware components that perform four basic functions: input, output, processing and storage. In their book, Sullivan et al. (1988)

define a computer as a complete system composed of many interacting parts, while 'computer systems' are composed of hardware and software. 'Hardware' refers to the parts of a computer that we can see and touch, and the most important piece of hardware is the tiny rectangular chip inside the computer called the central processing unit (CPU), or microprocessor (Karmakar, 2011). Other hardware items are the monitor, keyboard, mouse, printer and devices such as a webcam. 'Software' refers to the instructions or programs that tell the hardware what to do (Kim & Bond, 2009). The operating system (OS) – for example Windows or Linux – is software that manages the computer and the devices connected to it. 'Workstations' refer to a type of computer that requires a moderate amount of computing power and relatively high-quality graphics capabilities, while 'supercomputers' are large 'mainframes', used primarily for the analysis of scientific and engineering problems (Sullivan et al., 1988). 'Mainframes' are very large computers that are built to perform complex and critical applications.

The 'processor' is the logic circuitry that responds to and processes the basic instructions that drive a computer; in the simplest terms, it is the computer's brain (Rouse, 2006). It is the part that translates instructions and performs calculations. Stevens (1986) mentioned that the term 'processor' has generally replaced the term 'central processing unit' (CPU), and the processor in a personal computer, or one embedded in a small device, is often called a 'microprocessor'. A microprocessor is a computer processor that has been made on a single chip of silicon about 4 to 6 millimetres square and ½ millimetre thick, and contains a minimum of a few thousand transistors (Stevens, 1986). A transistor is a semiconducting device that switches and amplifies electronic signal, which is also an essential component in CPU (Intel, 1997). Stevens also points out that most of the chips called microprocessors are not complete computers, but rather the central processing units (CPUs) of computers. Personal computer systems are usually built from CPU-only chips and the term 'microprocessor' is therefore applied to any chip that contains a whole CPU. Each generation of processors has grown smaller and faster, dissipating more heat and consuming more power (Schauer, 2008).

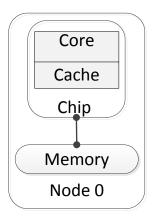

Processors were originally developed with only one core, as in Figure 2-1. A 'core' is a complete computational engine or the processing element in a processor (Varghese, McKee & Alexandrov, 2010). 'Single-core' denotes only one processing element within a single processor, and a 'multi-core' processor combines two or more processing elements in a single processor, on a single chip or multiple chips (Roy, 2008). A single-core processor can perform one task at a time whereas a multi-core processor can divide the work between two or more 'execution cores', allowing more work to be done within a given clock cycle (Burger, 2005). A 'clock cycle' is the time measured between two adjacent pulses of the oscillator and sets the tempo of the

computer processor. Thus a 'dual-core' processor contains two cores (such as the Intel Core Duo), a 'quad-core' processor contains four cores (e.g. AMD Phenom II X4) and a 'hexa-core' processor contains six cores (e.g. Intel Core i7 Extreme Edition 980X).

Figure 2-1: Basic design of single-core processor

## 2.3 Multi-core Processors

In 1965, Gordon Moore made his famous observation, the so-called 'Moore's Law', which predicted that the number of transistors per integrated circuit would double every year and that the speed would double every two years (Intel, 1997). Over more than four decades, this has driven the impressive growth in computer speed and accessibility.

In the past, the trend was to increase a processor's speed to get better performance. Transistor size had been reduced to increase the number of transistors that could be applied to processor functions and reduce the distance that signals must travel (Schauer, 2008). This allowed processor clock rates to soar. However, Lei, Qi and Panda (2007) have pointed out that nowadays it has become more difficult to speed up processors by increasing frequency. Frequency describes the number of waves that pass a fixed place in a given amount of time or the processor's speed (Stevens, 1986). As processor frequencies increase, the amount of heat produced by the processor increases (Pase & Eckl, 2005). The solution is to reduce the transistor size - because smaller transistors can operate at lower voltages, and this allows the processor to produce less heat. Unfortunately, David Geer (2005) demonstrated that, as a transistor gets smaller, it will be less able to block the flow of electrons. Also, smaller transistors keep using electricity even when they aren't switching, which wastes the power. However, transistors can't shrink forever, and chip manufacturers have struggled to cap power usage and heat generation which slow the processor performance (Chan, Ling & Aubanel, 2012). For these reasons, computer engineers are building a processor

with more processing cores, which means placing two or more processing cores on the same chip (Burger, 2005).

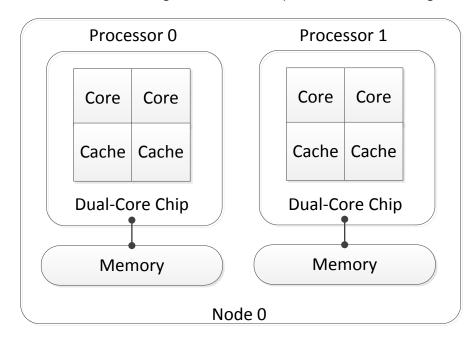

Multi-core processors are the solution to the deficiencies of single-core processors, as they increase bandwidth while decreasing power consumption (Burger, 2005). Multi-core processors have been developed to adhere to reasonable power consumption and heat dissipation. By dividing the workload among different cores, multi-core processors can speed up application performance by running at lower frequencies while minimising heat generation and the use of power (Lei et al., 2007). Multi-core processors do not necessarily run as fast as the highest-performing single-core models, but they improve overall performance by handling more work in parallel (Geer, 2005). Basic design of a multi-core processor is seen in Figure 2-2.

Figure 2-2: Basic design of multi-core processor

Despite such huge performance potential, many issues remain unsolved and need further attention – such as high-latency communication in interconnection networks (Rauber & Runger, 2010). Communication in this work refers to the exchange of data between a source and a destination receiver in interconnection networks architecture. Multiple cores on a single processor give rise to some problems and challenges, as follows (Hamid et al., 2015c; Karmakar, 2011; Lei et al., 2007; Schauer, 2008; Soryani et al., 2013):

• <u>Interconnection networks</u>: A faster network means a lower latency in network communication and memory transactions. Extra memory will be useless if the amount of time required for the memory request does not improve.

- Power and temperature: To reduce unnecessary power consumption and lessen

the heat, the design model must run the multiple cores at a lower frequency. It

must also ensure heat dissipation is distributed across the processor while

being careful not to form any hot spots.

- <u>Cache coherence</u>: Since each core has its own cache, the copy of the data in that cache may not always be the most up-to-date version. This may produce invalid results.

- <u>Multi-threading</u>: Programmers have to write applications with subroutines able to be run on different cores. This is to ensure that the full advantage of multi-core capabilities can be exploited.

- Improved memory system: Larger caches sizes are needed for multi-threaded multi-core processors.

- <u>Parallel programming</u>: Programmers need to learn how to write parallel programs that can be split up and be run concurrently on multiple cores.

- <u>Starvation</u>: If a program is not developed correctly for use in a multi-core processor, one or more cores may be starved for data. The thread would simply run in one of the cores while the other cores sit idle.

- Homogeneous vs heterogeneous cores: Homogeneous cores have the same cache sizes, equivalent frequencies, functions, etc., while each core in a heterogeneous system may have a different function, frequency, memory model etc.

## 2.3.1 Moore's 'Law' Changes with Multi-core Processor

For years, Moore's 'Law' has been the one of the guiding principles of computer architecture. Instead of increasing clock speeds, which allows software to automatically run faster, chip manufacturers have been increasing the number of cores on a single chip (Bethel & Howison, 2012). Multicore or many cores, again embodying Moore's 'Law', has become one of the important technologies in the electronic chip industry. It is foreseeable that hundreds of cores on a single chip will appear in the future (Holt, 2016). With the continuously increasing number of cores, it is important to fully harness the abundant computing resources with programming models that are still easy-to-use (Bethel & Howison, 2012). It is more difficult to speed up processors nowadays by increasing frequency.

The prevalence of multi-core processors beyond quad-cores forms the building block of high performance computing architectures (Chan et al., 2012). Multi-core processors have started to put pressure on the application development and programming language development. Taking advantage of multi-core processors requires that software is able to split the work among cores. The software must be

designed to support parallelism to use multi-core processors and to avoid stagnant performance (Lin-Dong, De-Yu, Qiang & Jin-Xin, 2014). Exploiting parallelism as the number of cores grows is a challenge (Donald & Martonosi, 2006). Thus, switching to multi-core processors chips grows the technological frontier asymmetrically by benefiting parallelized software.

Even after 50 years, Moore's 'Law' still leaves an impact and benefits in many ways (Intel, 2015). For the technological impact, Moore's observation transformed computing into a pervasive and affordable necessity. The technologies also created two important keys to technology development, performance and cost. Processing power has been increased and energy efficiency improved at a lower cost by applying multi-core processor technology, which has had an economic impact in the chip industry. These drivers have set the pace for innovation and development, but more research is being conducted into computing performance to investigate how the impact of multi-core processor compares to Moore's 'Law' prediction.

# 2.4 Cluster Computing

Cluster computing is a form of computing in which a group of computers are linked together to act like a single entity (Baker & Buyya, 1999a). Cluster computing was first developed in the 1960s by IBM (Admin, 1999) as an alternative way of connecting large mainframes to provide a more cost effective form of commercial parallelism (Buyya, Hai & Cortes, 2002). However, cluster computing only gained momentum after the convergence in the 1980s of high performance microprocessors, high-speed networks and standard tools for high performance distributed computing. The recent advances in these technologies are making clusters an appealing solution for cost-effective parallel computing, and have emerged as mainstream parallel platforms for high-performance, high-throughput and high-availability computing.

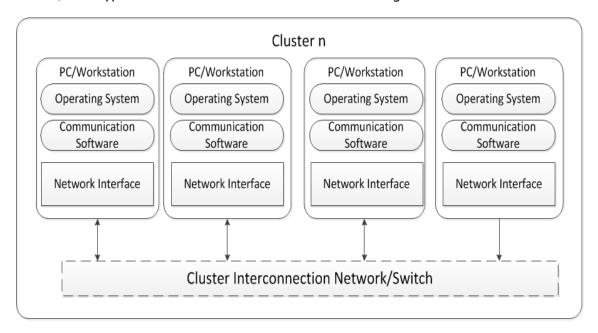

A computer cluster can be defined as "a collection of individual computers" (Baldassari, Kopec, Leshay, Truszkowski & Finkel, 2005) "connected to each other by fast local area networks" (Baker & Buyya, 1999b) which "work together to form a single computer" (Baker, Apon, Buyya & Jin, 2000). A computer cluster works as one to execute intensive computation that would be not feasible on a single computer. Each individual computer in a cluster represents a computer node. Computer nodes are capable of full independent operation and are employed individually for stand-alone workloads and applications (T. Sterling, Apon & Baker, 2000). The nodes may incorporate a single processor or multiple processors with memories and operating systems (Hamid, Walters & Wills, 2014). The key components of a cluster include multiple stand-alone computers (PCs, workstations or SMPs), high-performance

interconnects, parallel programming environments and applications (Baker & Buyya, 1999b). The typical architecture of a cluster is shown in Figure 2-3.

Figure 2-3: Cluster architecture (reproduced from (Baker et al., 2000)

There are many kinds of computer cluster, ranging from some which employ the world's largest computers to collections of personal computers. Clustering was among the first computer system architecture techniques to achieve significant improvements in overall performance, user access bandwidth and reliability (T. L. Sterling, 2002). In their 2002 paper, Buyya, Hai and Cortes described cluster computing as a fusion of the fields of parallel, high-performance, distributed, and high-availability computing. Despite the definition and stated key components, there are a number of important cluster features (Baker et al., 2000; Buyya et al., 2002; Goscinski, Hobbs & Silcock, 2001) that need to be noted, such as:

- Clusters are generally localized within a room or building.

- Clusters have a single administration.

- Clusters primarily focus only on compute-intensive problems and HPC.

- Clusters are typically homogeneous, based on a single processor and operating system.

- Clusters are static in nature, with fixed sets of processors and resources,

A cluster is deployed to increase performance and availability, and clusters are more cost-effective than a single computer. However, for all the benefits, there are challenges in cluster computing, as follows (Sadashiv & Kumar, 2011; Srinivas & Ramasubramaniam, 2011):

- <u>Middleware</u>: the need for a software environment that provides an illusion of a single system image, rather than a collection of independent computers.

- <u>Program</u>: applications that run on the clusters must be explicitly written so as to incorporate the division of tasks between nodes.

- <u>Elasticity</u>: providing a capability to adapt to changing potential requirements, for example the variance in real-time response time when the number of service requests changes dramatically.

- <u>Scalability</u>: an ability to scale up in order to meet the additional requirements of a resource. This can affect the performance of the system.

### 2.4.1 Cluster Interconnection Networks

An interconnection network is a physical connection between the different components of a parallel system, and it can be used with a multi-core cluster system. A network is characterised by the media it uses to carry messages, the way the network links devices, and the expansiveness size of the network (Sullivan et al., 1988). In multi-core cluster systems, the interconnection network is used to connect the nodes to each other (Peh, 2001) and is used to connect the processors to the memory modules. In a network, a node is a connection point, either a redistribution point or an end point for data transmissions (Rouse, 2006).