# Three-dimensional Finite Elements Method simulation of Total Ionizing Dose in 22 nm bulk nFinFETs

Eleni Chatzikyriakou, Kenneth Potter, William Redman-White, C.H. De Groot

Department of Electrical and Computer Science, University of Southampton

#### **Abstract**

Finite Elements Method simulation of Total Ionizing Dose effects on 22 nm bulk Fin Field Effect Transistor (FinFET) devices using the commercial software Synopsys Sentaurus TCAD are presented. The simulation parameters are extracted by calibrating the charge trapping model to experimental results on 400 nm SiO<sub>2</sub> capacitors irradiated under zero bias. The FinFET device characteristics are calibrated to the commercial 22 nm bulk technology. Irradiation simulations of the transistor performed with all terminals grounded reveal increased hardness up to a total dose of 1 MRad(SiO<sub>2</sub>).

Keywords: Total Ionizing Dose, Finite Elements Method, Synopsys, simulation, FinFET, Shallow Trench Isolation

#### 1. Introduction

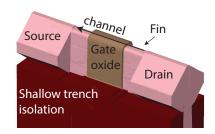

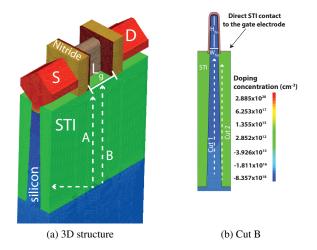

Exposure of deep sub-micron n-channel devices to ionizing radiation degrades electrical performance by inducing leakage paths due to positive charges gathering in the field oxides and at Si/SiO<sub>2</sub> interfaces. This creates off-state current through parasitic devices, that in extreme cases can impede the transistor from turning off leading to major faults and catastrophic failure in Integrated Circuits. We examine Total Ionizing Dose (TID) effects in FinFET devices. FinFETs have been adopted in commercial state-of-the-art transistor technologies at and beyond the 25 nm gate length as scaling alternatives to partially and fully depleted Silicon-on-Insulator technologies. The structure of a FinFET is shown in Figure 1. The active area of the transistor is shaped like a fin and wrapped by the gate which results in very good electrostatic control of the channel. The Source/Drain regions extend on the sides of the fin [1, 2, 3].

In Silicon-On-Insulator FinFETs, the TID effect has been shown to depend on the geometry of the fin [4, 5], while in bulk FinFET technologies its appearance is attributed mainly to charges gathering in the Shallow Trench Isolation (STI) neck region [6].

Microscopically, carriers generated in the oxide after irradiation are trapped at imperfections of the crystal structure (E'centers), while interface state creation from diffusion of hydrogen species can also affect device performance [7, 8]. The Sentaurus simulation tools can solve rate equations for both effects. However, bulk charge trapping has been identified before as being the main contributing factor in bulk FinFETs. [6, 9, 10].

In this work, the simple case of charge accumulation within the STI in bulk 22 nm nFinFETs under TID is presented.

Figure 1: Structure of a Fin Field Effect Transistor

### 2. Parameter extraction

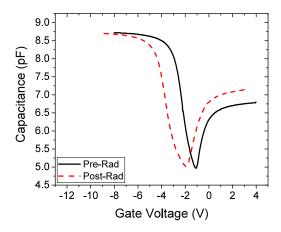

To derive the parameters for our simulations,  $400 \text{ nm SiO}_2$  capacitors were fabricated at the University of Southampton and subsequently irradiated using  $\text{Co}^{60}$  at a Dose Rate of  $38.6 \text{ Rad}(\text{SiO}_2)$ /s and a total dose of  $11.6 \text{ kRad}(\text{SiO}_2)$  [11]. The preand post- irradiation results are shown in Fig. 2. The analytically extracted mid-gap voltage shift is -1.5 V.

The simulator model was calibrated to the experimental prerad results using a doping concentration  $N_a = 6.4 \times 10^{14}~cm^{-3}$  and an Effective Oxide Thickness  $t_{ox} = 390~nm$ . A Schottky metal/oxide contact with workfunction of 4.2 eV was also used. The Schottky contact prevented voltage shifts when different amount of traps were defined in the oxide by fixing the electrostatic potential difference in the oxide to a value relative to the barrier height between the metal and silicon. A fixed oxide charge of  $N_{ot} = 6 \times 10^{15}~cm^{-3}$  was introduced to fit the simulated midgap voltage to the experimental results. Thermionic emission was included in the silicon/oxide interface to accurately describe the current through the heterointerface resulting from irradiation [12].

Carrier generation in the oxide is calculated using,

$$G_{ehp} = \dot{D} \cdot g_{SiO2} \cdot f_{y}(E) \tag{1}$$

Figure 2: Pre- and post- irradiation experimental results

with  $\dot{D}$ , the dose rate (rad(SiO<sub>2</sub>)/s),  $f_y$  the carrier yield and  $g_{SiO2}$  is the 'irradiation factor' given by

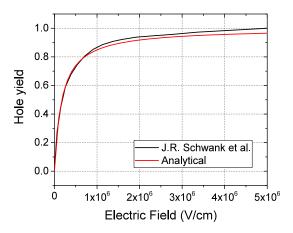

Figure 3: Hole yield as a function of electric field. The simulation parameters were fitted to Co<sup>60</sup> from [13].

$$g_{SiO2} = \frac{\rho}{w} \cdot 6.24 \cdot 10^{13} = 7.6 \cdot 10^{12} ehp \times cm^{-3} \times Rad (SiO_2)^{-1}$$

(2)

where  $\rho = 2.196$  is the density (g/cm<sup>-3</sup>) [14] and w = 18 eV is the energy required to create an electron-hole pair [15]. We are also taking into account that 1 Rad =  $6.24 \cdot 10^{13}$  eV/g.

The electron-hole pairs that are created are calculated using,

$$f_{y}(E) = \left(\frac{|E| + E_{1}}{|E| + E_{2}}\right)^{m} \tag{3}$$

where  $E_1$  and  $E_2$  and m are fitting parameters, and E the electric field (V/cm).

These carriers get transported out of the oxide through either the nearest electrode, or through the interface with the silicon.

Table 1: Simulation parameters for carrier generation and transport in the oxide

|                    |                   | Value             | Units                               |

|--------------------|-------------------|-------------------|-------------------------------------|

| m                  |                   | 0.9               |                                     |

| $E_1$              |                   | 0.1               | V/cm                                |

| $E_2$              |                   | $2 \times 10^{5}$ | V/cm                                |

| $\mu_{\mathrm{n}}$ | Electron mobility | 20                | $cm^2/V \cdot s$                    |

| $\mu_{ m p}$       | Hole mobility     | $10^{-5}$         | $\text{cm}^2/\text{V}\cdot\text{s}$ |

The transport of the electrons and holes is performed using the drift-diffusion model. The parameters for carrier generation and transport in the oxide are shown in Table 1. Mobility values were taken from [15]. The transport of holes in  $SiO_2$  occurs much slower than transport of electrons. This is translated to a lower mobility value and trapping mechanisms in defect sites.

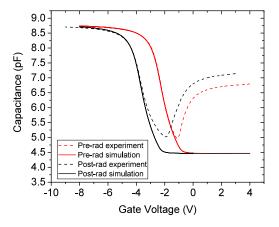

Figure 4: Pre- and post- irradiation results and simulations for  $400\ nm\ SiO_2$  capacitors

Microscopic studies on the types of defects capable of trapping positive charges in  $SiO_2$  have revealed a dimer configuration with a shallow activation energy  $\approx 1$  eV from the valence band edge ( $E_{\delta}$ 'center) at a concentration of 80% and bistable defects with an activation energy of  $\approx 4.5$  eV from the valence band edge ( $E_{\gamma}$ 'center) at a concentration of 20% [16].

These defects are simulated using effective trapping densities distributed uniformly throughout the oxide. The trapping mechanism is dominated by the drift motion of the holes. The simulated trapping rate is as follows:

$$\frac{dp_t^+}{dt} = p_t \left\{ \left( 1 - f_p \right) \left[ \sigma_p \frac{J_p}{q} - v_{th}^n \sigma_n n_1 \right] - f_p \left[ v_{th}^p \sigma_p p_1 - \sigma_n \frac{J_n}{q} \right] \right\}$$

(4)

where  $f_p$  is the occupational probability (within a range of 0 to 1) of the unoccupied trapping site  $p_t$  (either  $E_{\gamma}$ ' or  $E_{\delta}$ ' center),  $p_t^+$  is the density of the trapping sites occupied by holes (cm<sup>-3</sup>),  $\sigma_p = 6.8 \times 10^{-14}$  cm<sup>2</sup> is the capture cross section of a hole in the defect site and  $\sigma_n = 10^{-12}$  cm<sup>2</sup> is the capture cross section of an electron in the positively charged trapping site which causes the

trap to become annealed [17],  $v_{th}^n = 2.042 \times 10^7$  cm/s and  $v_{th}^p = 1.5626 \times 10^7$  cm/s are the thermal velocities of the electrons and holes respectively and  $J_{n,p}$  are the current densities (A/cm<sup>2</sup>).

$n_1$  and  $p_1$  are the effective densities of gap states (cm<sup>-3</sup>), given by,

$$n_1 = N_C exp \left\{ \frac{q \times \left( E_{trap} - E_C \right)}{kT} \right\}$$

(5)

$$p_1 = N_V exp \left\{ \frac{q \times \left( E_V - E_{trap} \right)}{kT} \right\}, \tag{6}$$

where  $E_{trap}$  is the activation energy of the trap,  $E_C$  and  $E_V$  are the conduction and valence band energies (eV),  $N_C$ =8.867×10<sup>18</sup> and  $N_V$ =1.931×10<sup>20</sup> the conduction and valence band density of states (cm<sup>-3</sup>).

The shallow  $E_{\delta}$ 'center gets annealed during or immediately following the radiation exposure. As the shallow traps get annealed, charges are trapped in deep hole trapping sites [18, 19]. Therefore, donor traps with an effective activation energy  $E_{trap} = E_V + 4$  eV were used in the simulations to account for the charge that did not get annealed at the time of the experimental measurement.

After transient simulation to a total dose of 11.6 kRad(SiO<sub>2</sub>), the device was solved in quasistationary with the traps frozen at their state. The full C-V pre- and post-irradiation results of the capacitor sample are shown in Figure 4. An effective trap density of  $p_t = 10^{18}$  cm<sup>-3</sup> was found. This value was used for the FinFET simulations.

## 3. FinFET simulations

The 3D structure of the FinFET is shown in figure 5. Structural parameters are in accordance to the Intel 22 nm bulk nFinFET High Performance technology node [1] with  $L_g=30$  nm,  $W_{\rm fin}=8$  nm,  $H_{\rm fin}=34$  nm and an effective oxide thickness of 0.9 nm. The trench depth of the STI is 120 nm.

Figure 5: Simulation model of the FinFET with locations of cuts for slices and 1D profile extraction  $\frac{1}{2}$

Table 2: FinFET device characteristics [1]

|                                  | Auth C. et al. | This work |

|----------------------------------|----------------|-----------|

| On-state voltage (V)             | 0.8            | 0.8       |

| Off-state current ( $nA/\mu m$ ) | 10             | 1.72      |

| Saturation current (mA/ $\mu$ m) | 1.26           | 1.29      |

| Threshold voltage (V)            | 0.18           | 0.11      |

The device simulation models include velocity saturation at the gate  $Si/SiO_2$  interface and the density gradient quantization model as calibrated in [20]. The final device characteristics compared to the commercial 22 nm bulk FinFET technology in [1] are presented in Table 2. The saturation current is measured at a gate bias,  $V_g=0.8\ V$ , and drain bias  $V_{ds}=0.8\ V$ . The off-state current is measured at  $V_g=0\ V$  and  $V_{ds}=0.05\ V$ .

There is a direct contact between the gate electrode and the  $SiO_2$  dielectric. This prevents unrealistic accumulation of trapped charge at the interface of the  $SiO_2$  with  $HfO_2$  by allowing the generated carriers to get transported out of the oxide. The carriers also escape through the hetero-interface of the oxide with the silicon.

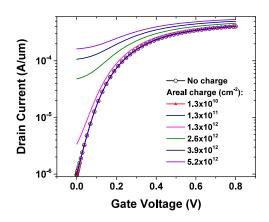

Initially, the device was solved with uniform fixed positive STI charges. Drain current  $(I_d)$  vs  $V_g$  curves with increasing charge density are shown in Figure 6. The densities indicated are areal charges projected to the Si/STI interface. Offstate current in the transistor starts increasing at  $1.3\times 10^{12}\ cm^{-2},$  while the transistor fails to turn off completely at a density of  $2.6\times 10^{12}\ cm^{-2}$  and beyond.

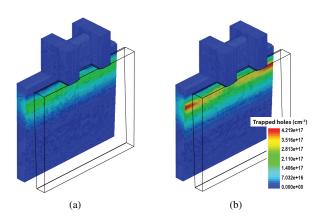

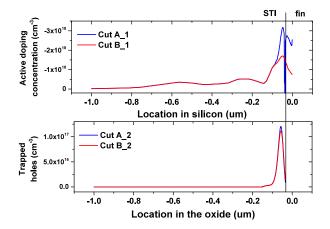

The simulation results with fixed STI charge were compared to radiation simulations where all terminals were unbiased. The density of trapped holes in the STI is shown in figure 7 for two total doses of 500 kRad(SiO<sub>2</sub>) and 1 Mrad(SiO<sub>2</sub>). Due to the absence of bias, the trapped charge is symmetric between the Source and Drain sides. Concentration is lower underneath the gate, where the parasitic electron channel from the Source to the Drain is expected to appear. The trapped charge profile re-

Figure 6: Simulation drain current - gate voltage results showing increasing the in off-state current of the transistor with increasing fixed areal oxide charge.

Figure 7: Trapped holes distribution in the STI at two total doses of (a) 500 kRad(SiO<sub>2</sub>) and (b) 1 MRad(SiO<sub>2</sub>)

flects the electric field in the oxide created due to the doping profile in silicon. This is also shown in figure 8. The negatively charged Boron impurity atoms attract holes with a higher intensity towards the top of the neck of the fin. The charge density has a peak located 25 nm below the STI surface. The areal trapped charge projected at the interface at that location is  $1.34\times10^9$  cm<sup>-2</sup> at 500 kRad(SiO<sub>2</sub>) and  $7.55\times10^{10}$  cm<sup>-2</sup> for 1 MRad(SiO<sub>2</sub>), which is lower than the areal charge required to invert the parasitic channel as was found during the fixed charge simulations presented in figure 6.

Figure 8: Doping profile and trapped charge distribution in the 1D cuts shown in figure 5.

### 4. Conclusions

Three-dimensional simulations of TID in bulk nFinFET devices using the commercial software Sentaurus device were presented. Based on previous studies on bulk FinFETs, hole trapping in the STI is the dominant cause of device degradation. Calibration of the charge trapping model to 400 nm SiO<sub>2</sub> capacitors revealed an effective bulk trap density of  $10^{18}~\rm cm^{-3}$ . The 22 nm bulk nFinFET device characteristics were calibrated to a

commercial transistor technology. Fixed oxide charge simulations were used to locate the areal charge at which inversion of the parasitic transistor occurred. The radiation simulations provided insight into the location and profile of the charge trapped in the STI. Increased hardness of this technology to TID was shown, which indicates its suitability for use in harsh environments of increased ionizing radiation. The simulation model can be extended to include the effects of interface trap formation.

## Acknowledgments

The authors acknowledge the support of the UK Engineering and Physical Sciences Research Council (EPSRC) award 1304067 as well as the use of the IRIDIS High Performance Computing Facility, and associated support services at the University of Southampton.

Data published in this paper are available from the University of Southampton repository at http://dx.doi.org/10.5258/SOTON/400301.

#### References

- C. Auth et al, A 22nm High Performance and Low-Power CMOS Technology Featuring Fully-Depleted Tri-Gate Transistors, Self-Aligned Contacts and High Density MIM Capacitors 980 (2003) (2012) 131–132.

- [2] C. Wu et al, High performance 22/20nm FinFET CMOS devices with advanced high-K/metal gate scheme, 2010 International Electron Devices Meeting (2010) 27.1.1–27.1.4doi:10.1109/IEDM.2010.5703430.

- [3] C.-H. Jan et al, A 22nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications, 2012 International Electron Devices Meeting (2012) 3.1.1–3.1.4doi:10.1109/IEDM.2012.6478969.

- [4] M. Gaillardin, P. Paillet, V. Ferlet-Cavrois, S. Cristoloveanu, O. Faynot, C. Jahan, High tolerance to total ionizing dose of Ω-shaped gate field-effect transistors, Applied Physics Letters 88 (22) (2006) 223511. doi:10.1063/1.2206097.

- [5] J.-J. Song, B. K. Choi, E. X. Zhang, R. D. Schrimpf, D. M. Fleetwood, C.-H. Park, Y.-H. Jeong, O. Kim, Fin Width and Bias Dependence of the Response of Triple-Gate MOSFETs to Total Dose Irradiation, IEEE Transactions on Nuclear Science 58 (6) (2011) 2871–2875. doi:10.1109/TNS.2011.2168977.

- [6] I. Chatterjee, E. X. Zhang, B. L. Bhuva, M. A. Alles, R. D. Schrimpf, D. M. Fleetwood, Y.-p. Fang, A. Oates, Bias Dependence of Total-Dose Effects in Bulk FinFETs, IEEE Transactions on Nuclear Science (December) (2013) 4476–4482.

- [7] H. P. Hjalmarson, R. L. Pease, S. C. Witczak, M. R. Shaneyfelt, J. R. Schwank, A. H. Edwards, C. E. Hembree, T. R. Mattsson, Mechanisms for Radiation Dose-Rate Sensitivity of Bipolar Transistors, IEEE Transactions on Nuclear Science 50 (6) (2003) 1901–1909. doi:10.1109/TNS.2003.821803.

- [8] H. P. Hjalmarson, R. L. Pease, R. A. B. Devine, Calculations of Radiation Dose-Rate Sensitivity of Bipolar Transistors, IEEE Transactions on Nuclear Science 55 (6) (2008) 3009–3015. doi:10.1109/TNS.2008.2007487.

- [9] I. Chatterje, E. X. Zhang, B. L. Bhuva, D. M. Fleetwood, Length and Fin Number Dependence of Ionizing Degradation in Bulk FinFETs (2013) 1–6.

- [10] I. Chatterjee, E. X. Zhang, B. L. Bhuva, R. a. Reed, M. L. Alles, N. N. Mahatme, D. R. Ball, R. D. Schrimpf, D. M. Fleetwood, D. Linten, E. Simoen, J. Mitard, C. Claeys, Geometry dependence of total-dose effects in bulk FinFETs, IEEE Transactions on Nuclear Science 61 (6) (2014) 2951–2958. doi:10.1109/TNS.2014.2367157.

- [11] K. Potter, K. Morgan, C. Shaw, P. Ashburn, W. Redman-White, C. De Groot, Total ionizing dose response of fluorine implanted Silicon-On-Insulator buried oxide, Microelectronics Reliability 54 (2014) 2339– 2343. doi:10.1016/j.microrel.2014.07.018.

- [12] K. Horio, Y. H., Numerical modeling of heterojunctions including the thermionic emission mechanism at the heterojunction interface, IEEE Transactions on Electron devices 37 (4).

- [13] J. Schwank, Basic mechanisms of radiation effects in the natural space radiation environment, Tech. rep., Sandia National Laboratotires (1994).

- [14] W. M. Haynes, CRC handbook of chemistry and physics: a readyreference book of chemical and physical data (2011).

- [15] H. Barnaby, M. McLain, I. Esqueda, X. J. C. X. J. Chen, Modeling Ionizing Radiation Effects in Solid State Materials and CMOS Devices, IEEE Transactions on Circuits and Systems I: Regular Papers 56 (August) (2009) 1870–1883. doi:10.1109/TCSI.2009.2028411.

- [16] R. D. S. Zhong-Yi Lu, C. J. Nicklaw, D.M. Fleetwood, S. Pantelides, Structure, Properties, and Dynamics of Oxygen Vacancies in Amorphous SiO<sub>2</sub>, Physical Review Letters 89 (2002) 285505. doi:10.1103/PhysRevLett.89.187201.

- [17] V. Ferlet-Cavrois, T. Colladant, P. Paillet, J. Leray, O. Musseau, J. Schwank, M. Shaneyfelt, J. Pelloie, J. du Port de Poncharra, Worst-case bias during total dose irradiation of SOI transistors, IEEE Transactions on Nuclear Science 47 (6) (2000) 2183–2188. doi:10.1109/23.903751.

- [18] W. Warren, D. Shaneyfelt, D. Fleetwood, J. Schwank, P. Winokur, D. R.A.B., Microscopic nature of border traps in MOS oxides, IEEE Transactions on Nuclear Science 41 (1994) 1817.

- [19] S. T. Pantelides, Z. Y. Lu, C. Nicklaw, T. Bakos, S. N. Rashkeev, D. M. Fleetwood, R. D. Schrimpf, The E center and oxygen vacancies in SiO<sub>2</sub>, Journal of Non-Crystalline Solids 354 (2008) (2008) 217–223. doi:10.1016/j.jnoncrysol.2007.08.080.

- [20] synopsys Inc., Device Monte Carlo Simulation Methodology of Twodimensional FinFET Slices.